(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2011-0135331

(43) 공개일자 2011년12월16일

(51) Int. Cl.

H01L 27/115 (2006.01) H01L 21/8247 (2006.01)

(21) 출원번호 10-2011-0041313

(22) 출원일자 2011년05월02일

심사청구일자 2011년05월02일

(30) 우선권주장

JP-P-2010-133057 2010년06월10일 일본(JP)

(71) 출원인

유니산티스 일렉트로닉스 싱가포르 프라이빗 리미티드

싱가포르 179098 싱가포르 노스 브릿지 로드 111

페닌슐라 플라자 넘버16-04

(72) 발명자

마스오카 후지오

일본 도쿄도 쥬오쿠 신카와 1쵸메 22-11 후지라이트 신카와 비루 2카이 니혼 유니산티스 에렉트로닉스 가부시키가이샤 나이

나카무라 히로키

일본 도쿄도 쥬오쿠 신카와 1쵸메 22-11 후지라이트 신카와 비루 2카이 니혼 유니산티스 에렉트로닉스 가부시키가이샤 나이

(74) 대리인

특허법인코리아나

전체 청구항 수 : 총 4 항

(54) 불휘발성 반도체 메모리 트랜지스터, 불휘발성 반도체 메모리, 및 불휘발성 반도체 메모리의 제조 방법

### (57) 요 약

(과제) 부유 게이트와 제어 게이트 사이의 용량을 크게 할 수 있음과 함께, 또한 제어 게이트와 섬 형상 반도체 사이의 기생 용량을 저감시키는, 섬 형상 반도체를 사용한 구조를 갖는 불휘발성 반도체 메모리, 및 그 제조 방법을 제공한다.

(해결 수단) 불휘발성 반도체 메모리를 구성하는 불휘발성 반도체 메모리 트랜지스터는, 기판측으로부터 소스 영역 (303), 채널 영역 (304) 및 드레인 영역 (302) 이 이 순서로 형성된 섬 형상 반도체 (301) 와, 채널 영역의 외주를 둘러싸도록, 터널 절연막 (305) 을 사이에 개재시켜 배치된 중공 기둥 형상의 부유 게이트 (306) 와, 당해 부유 게이트의 외주를 둘러싸도록, 인터폴리 절연막 (307) 을 사이에 개재시켜 배치된 중공 기둥 형상의 제어 게이트 (308) 를 구비하고 있다. 부유 게이트와, 제어 게이트의 상면, 하면 및 내측면 사이에는, 인터폴리 절연막이 개재 배치되어 있다.

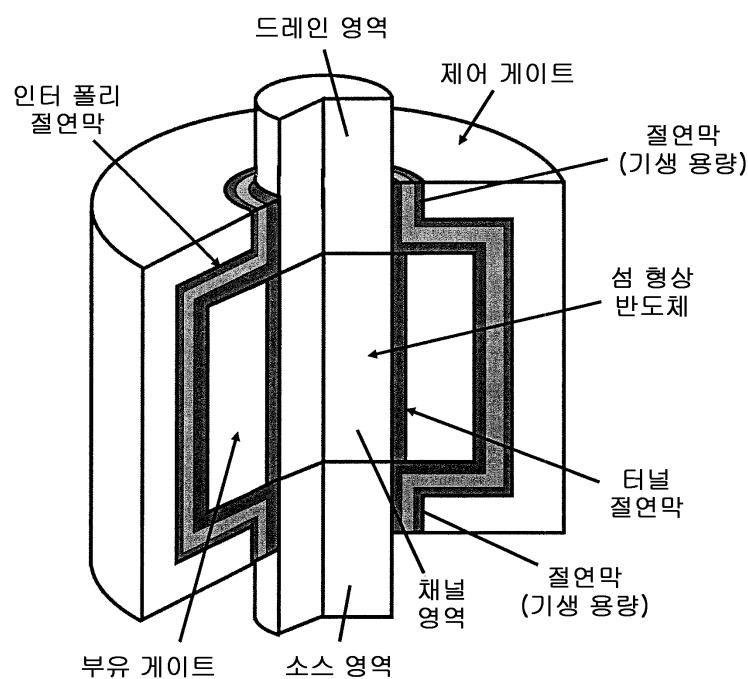

대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

기판측으로부터 소스 영역, 채널 영역 및 드레인 영역이 이 순서로 형성된 섬 형상 반도체와, 상기 채널 영역의 외주를 둘러싸도록, 터널 절연막을 사이에 개재시켜 배치된 중공 기둥 형상의 부유 게이트와, 상기 부유 게이트의 외주를 둘러싸도록, 인터폴리 절연막을 사이에 개재시켜 배치된 중공 기둥 형상의 제어 게이트를 구비하고, 상기 부유 게이트와, 상기 제어 게이트의 상면, 하면 및 내측면 사이에는, 인터폴리 절연막이 개재 배치되어 있는 것을 특징으로 하는 불휘발성 반도체 메모리 트랜지스터.

### 청구항 2

제 1 항에 있어서,

상기 부유 게이트의 하방에 위치하도록 상기 기판 상에 배치되며, 또한 상기 터널 절연막 및 인터폴리 절연막의 적어도 일방보다 두께가 두꺼운 제 1 절연막을 추가로 구비하고 있는 것을 특징으로 하는 불휘발성 반도체 메모리 트랜지스터.

### 청구항 3

제 1 항 또는 제 2 항에 기재된 불휘발성 반도체 메모리 트랜지스터를 구비하고,

상기 불휘발성 반도체 메모리 트랜지스터는, 상기 기판의 행렬 방향에 있어서의 행 방향으로 복수 배치되고,

상기 복수의 불휘발성 반도체 메모리 트랜지스터 중 적어도 하나의 당해 메모리 트랜지스터의 드레인 영역은, 상기 기판의 행렬 방향에 있어서의 열 방향으로 배선된 제 2 차 소스선에 전기적으로 접속되어 있는 것을 특징으로 하는 불휘발성 반도체 메모리.

### 청구항 4

상부에 하드 마스크가 형성된 섬 형상 반도체를 갖는 불휘발성 반도체 메모리 트랜지스터가 복수 배치되어 이루어지는 불휘발성 반도체 메모리의 제조 방법으로서,

상기 섬 형상 반도체는, 기판측으로부터 이 순서로 형성된 소스 영역, 채널 영역 및 드레인 영역을 구비하고, 상기 채널 영역의 근방에는, 부유 게이트와 제어 게이트가 상기 채널 영역측으로부터 이 순서로 배치되고,

기판에 제 1 차 소스선을 형성하는 공정과,

상기 제 1 차 소스선 상에 섬 형상 반도체를 형성하는 공정과,

상기 섬 형상 반도체 상에 상기 하드 마스크를 형성하는 공정과,

상기 섬 형상 반도체의 외주 벽면에 절연막 사이드 월을 형성하는 공정과,

상기 섬 형상 반도체의 저부, 및 상기 제 1 차 소스선 상에 절연막을 형성하는 공정과,

상기 절연막 상에 부유 게이트막을 형성하는 공정과,

상기 부유 게이트막을 에칭함으로써, 채널 영역의 근방에 부유 게이트를 형성하는 공정을 포함하는 것을 특징으로 하는 불휘발성 반도체 메모리의 제조 방법.

## 명세서

### 기술분야

[0001] 본 발명은 불휘발성 반도체 메모리 트랜지스터, 불휘발성 반도체 메모리, 및 불휘발성 반도체 메모리의 제조 방법에 관한 것이다.

## 배경기술

[0002] 제어 게이트와 전하 축적층을 갖고, 핫 일렉트론이나 Fowler-Nordheim 전류 등을 이용하여 전하 축적층에 대한 전하의 주입을 실시하는 플래시 메모리가 알려져 있다. 이 메모리 셀은, 전하 축적층의 전하 축적 상태에 따라 임계치 전압이 상이한 것을 이용하여, "1" 또는 "0"의 단위 데이터를 기록한다.

[0003] 전하 축적층에 대한 전자의 주입과 전하 축적층으로부터의 전자의 방출, 즉 단위 데이터의 기록과 소거를 효율적으로 실시하기 위해서, 부유(浮遊) 게이트와 제어 게이트 사이의 용량 결합의 관계가 중요하다. 부유 게이트와 제어 게이트 사이의 용량이 클수록, 제어 게이트의 전위를 효과적으로 부유 게이트에 전달할 수 있고, 이로써 기록, 소거가 용이해진다.

[0004] 부유 게이트와 제어 게이트 사이의 용량을 크게 하기 위해서, 도 57에 나타내는 Tri-Control Gate Surrounding Gate Transistor (TCG-SGT) Flash Memory Cell이 제안되었다 (예를 들어, 비특허문헌 1을 참조). 이 TCG-SGT 플래시 메모리 셀의 제어 게이트는, 부유 게이트의 측면에 추가하여, 부유 게이트의 상면, 하면을 덮는 구조를 갖기 때문에, 부유 게이트와 제어 게이트 사이의 용량을 크게 할 수 있어, 기록, 소거가 용이해진다.

[0005] 그러나, 도 57에 나타내는 TCG-SGT 플래시 메모리 셀의 제어 게이트의 상하 부위와, 섬 형상 반도체의 외주 벽면은, 절연막을 개재하여 근접하고 있기 때문에, 제어 게이트와 섬 형상 반도체 사이에 기생 용량이 발생한다. 이와 같은 제어 게이트와 섬 형상 반도체 사이의 기생 용량은, 트랜지스터의 동작 속도가 저하되는 원인이 되므로 불필요하다.

## 선행기술문헌

### 비특허문헌

[0006] (비특허문헌 0001) Takuya Ohba, Hiroki Nakamura, Hiroshi Sakuraba, Fujio Masuoka, "A novel tri-control gate surrounding gate transistor (TCG-SGT) nonvolatile memory cell for flash memory", Solid-State Electronics, Vol.50, No.6, pp.924-928, June 2006

## 발명의 내용

### 해결하려는 과제

[0007] 본 발명은, 상기 사정을 감안하여 이루어진 것으로서, 부유 게이트와 제어 게이트 사이의 용량을 크게 할 수 있음과 함께, 제어 게이트와 섬 형상 반도체 사이의 기생 용량을 저감시킬 수 있는, 섬 형상 반도체를 사용한 구조를 갖는 불휘발성 반도체 메모리 트랜지스터, 불휘발성 반도체 메모리, 및 불휘발성 반도체 메모리의 제조 방법을 제공하는 것을 목적으로 한다.

### 과제의 해결 수단

[0008] 상기 목적을 달성하기 위해서, 본 발명의 제 1 관점의 불휘발성 반도체 메모리 트랜지스터는, 기판측으로부터 소스 영역, 채널 영역 및 드레인 영역이 이 순서로 형성된 섬 형상 반도체와, 상기 채널 영역의 외주를 둘러싸도록, 터널 절연막을 사이에 개재시켜 배치된 중공(中空) 기둥 형상의 부유 게이트와,

[0009] 상기 부유 게이트의 외주를 둘러싸도록, 인터폴리 절연막을 사이에 개재시켜 배치된 중공 기둥 형상의 제어 게이트를 구비하고,

[0010] 상기 부유 게이트와, 상기 제어 게이트의 상면, 하면 및 내측면 사이에는, 인터폴리 절연막이 개재 배치되어 있는 것을 특징으로 한다.

[0011] 상기 부유 게이트의 하방에 위치하도록 상기 기판 상에 배치되며, 또한 상기 터널 절연막 및 인터폴리 절연막의 적어도 일방보다 두께가 두꺼운 제 1 절연막을 추가로 구비하고 있는 것이 바람직하다.

[0012] 또한, 상기 목적을 달성하기 위해서, 본 발명의 제 2 관점의 불휘발성 반도체 메모리는, 본 발명의 제 1 관점의

불휘발성 반도체 메모리 트랜지스터를 구비하고,

[0015] 상기 불휘발성 반도체 메모리 트랜지스터는, 상기 기판의 행렬 방향에 있어서의 행 방향으로 복수 배치되고,

[0016] 상기 복수의 불휘발성 반도체 메모리 트랜지스터 중 적어도 하나의 당해 메모리 트랜지스터의 드레인 영역은, 상기 기판의 행렬 방향에 있어서의 열 방향으로 배선된 제 2 차 소스선에 전기적으로 접속되어 있는 것을 특징으로 한다.

[0017] 또한, 상기 목적을 달성하기 위해서, 본 발명의 제 3 관점의 불휘발성 반도체 메모리 트랜지스터의 제조 방법은,

[0018] 상부에 하드 마스크가 형성된 섬 형상 반도체를 갖는 불휘발성 반도체 메모리 트랜지스터가 복수 배치되어 이루어지는 불휘발성 반도체 메모리의 제조 방법으로서,

[0019] 상기 섬 형상 반도체는, 기판측으로부터 이 순서로 형성된 소스 영역, 채널 영역 및 드레인 영역을 구비하고, 상기 채널 영역의 근방에는, 부유 게이트와 제어 게이트가 상기 채널 영역측으로부터 이 순서로 배치되고,

[0020] 기판에 제 1 차 소스선을 형성하는 공정과,

[0021] 상기 제 1 차 소스선 상에 섬 형상 반도체를 형성하는 공정과,

[0022] 상기 섬 형상 반도체 상에 상기 하드 마스크를 형성하는 공정과,

[0023] 상기 섬 형상 반도체의 외주 벽면에 절연막 사이드 월을 형성하는 공정과,

[0024] 상기 섬 형상 반도체의 저부, 및 상기 제 1 차 소스선 상에 절연막을 형성하는 공정과,

[0025] 상기 절연막 상에 부유 게이트막을 형성하는 공정과,

[0026] 상기 부유 게이트막을 에칭함으로써, 채널 영역의 근방에 부유 게이트를 형성하는 공정을 포함하는 것을 특징으로 한다.

### 발명의 효과

[0027] 본 발명에 의하면, 부유 게이트와 제어 게이트 사이의 용량을 크게 할 수 있음과 함께, 제어 게이트와 섬 형상 반도체 사이의 기생 용량을 저감시키는, 섬 형상 반도체를 사용한 구조를 갖는 불휘발성 반도체 메모리 트랜지스터, 불휘발성 반도체 메모리, 및 불휘발성 반도체 메모리의 제조 방법을 제공할 수 있다.

### 도면의 간단한 설명

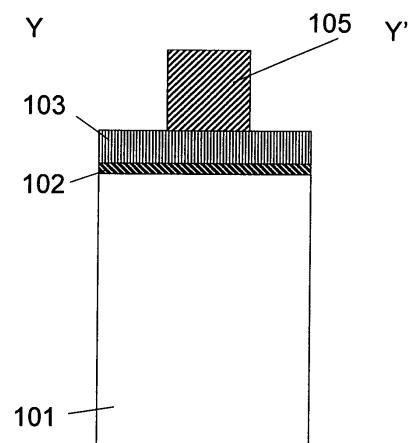

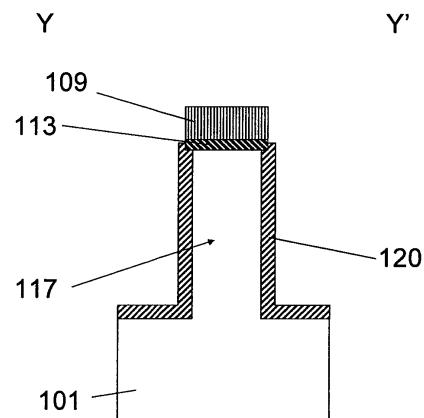

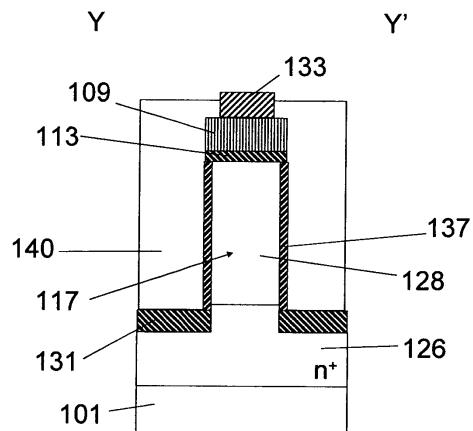

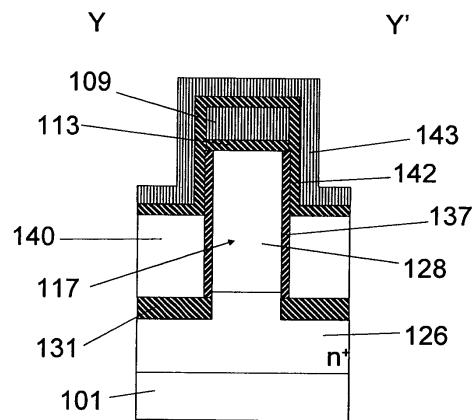

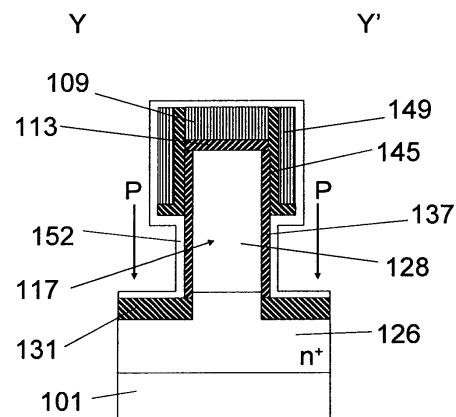

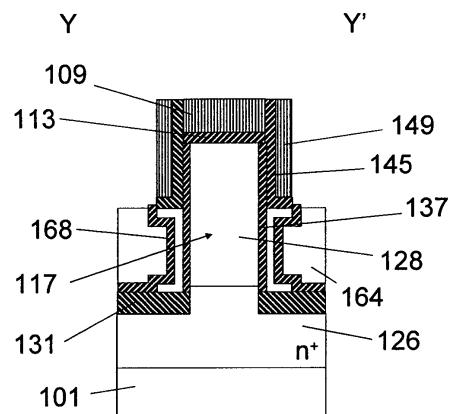

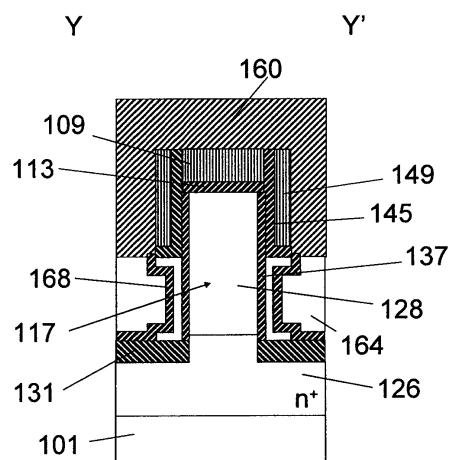

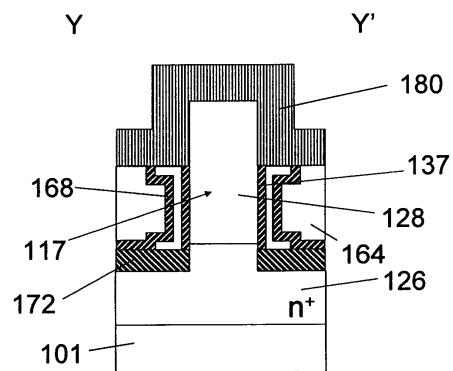

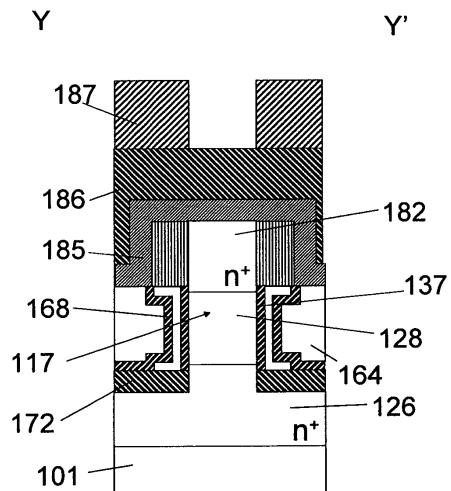

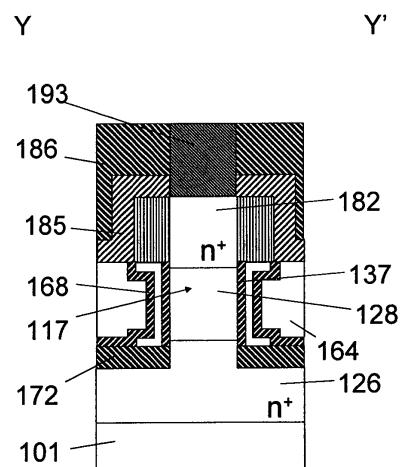

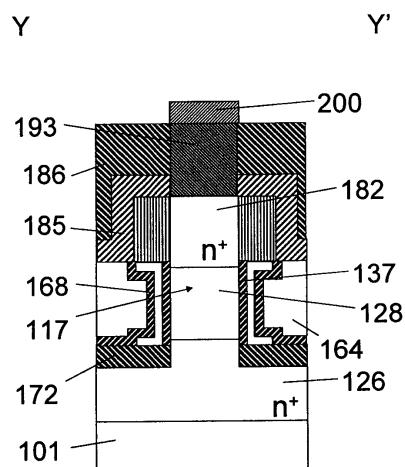

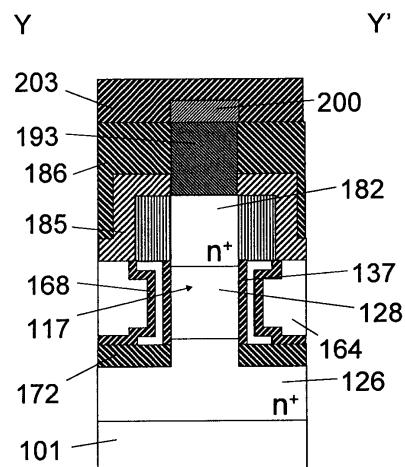

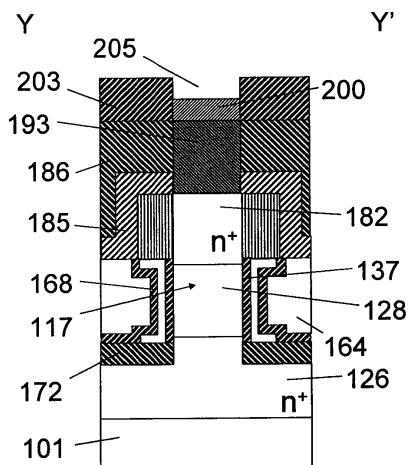

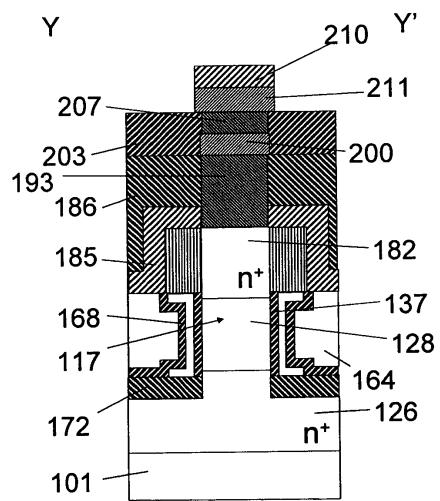

[0028] 도 1 은, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리 트랜지스터의 주요부를 나타내는 단면도.

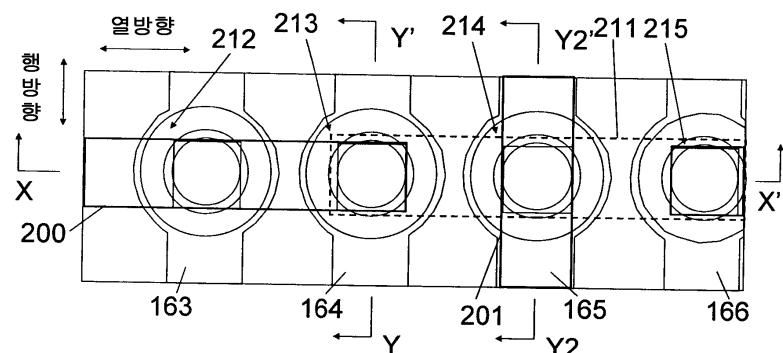

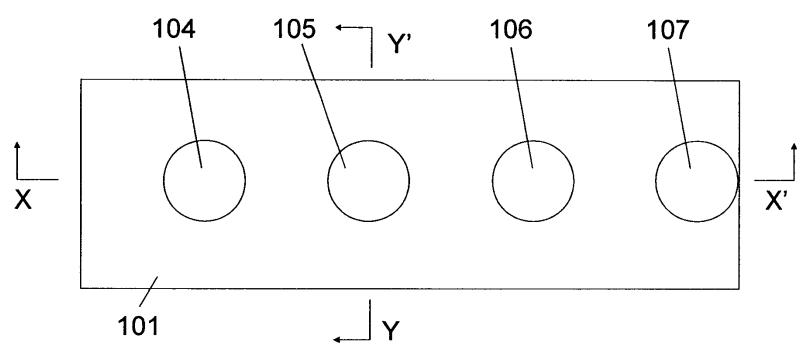

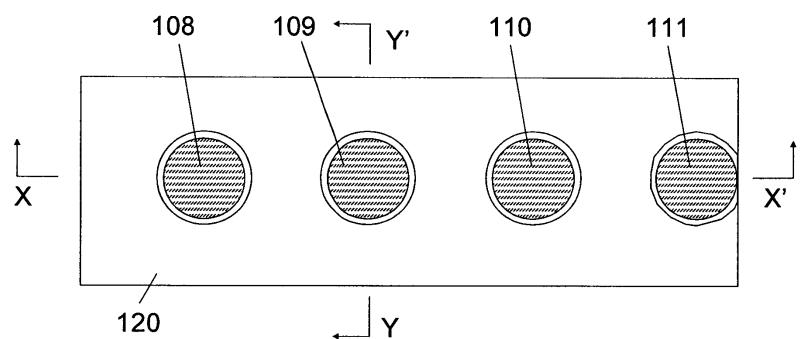

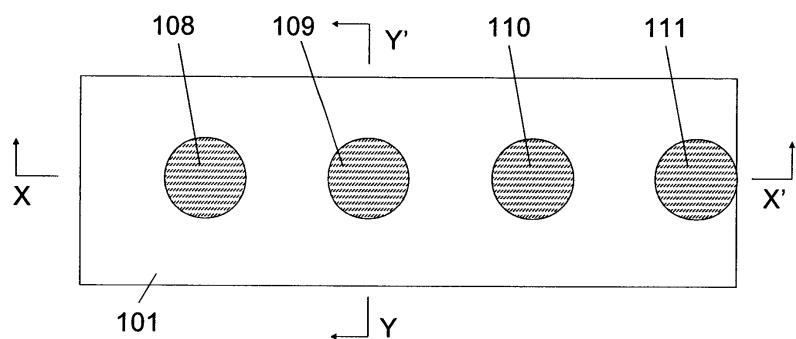

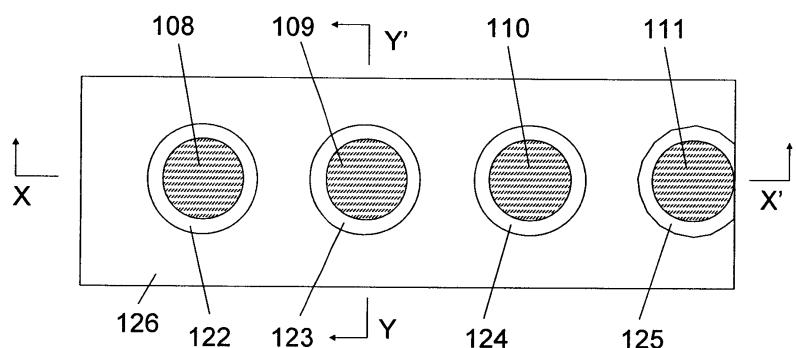

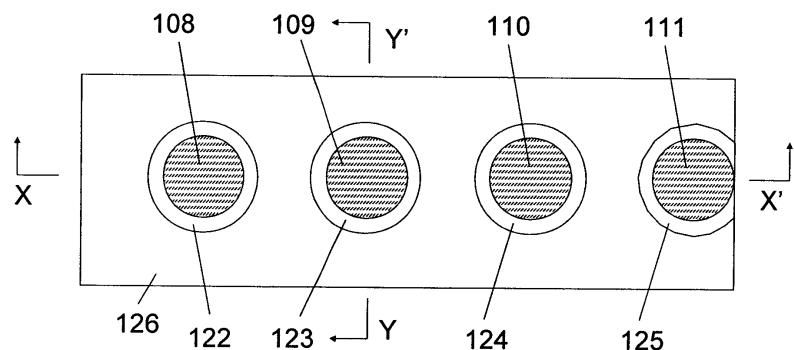

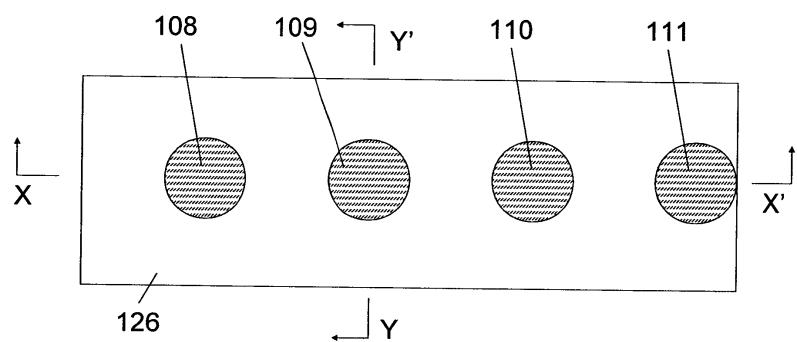

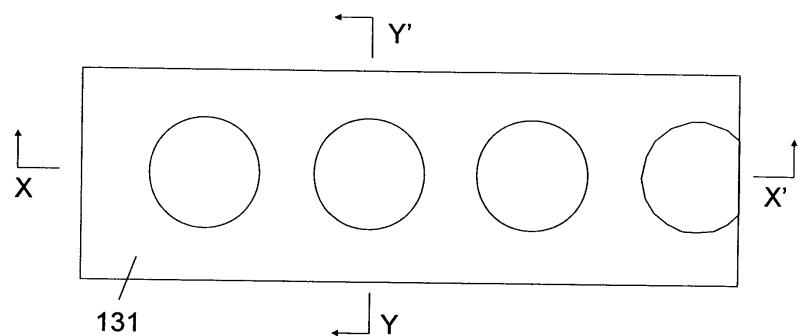

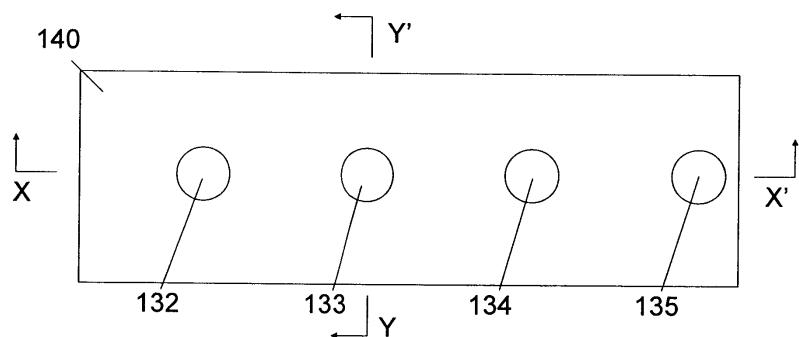

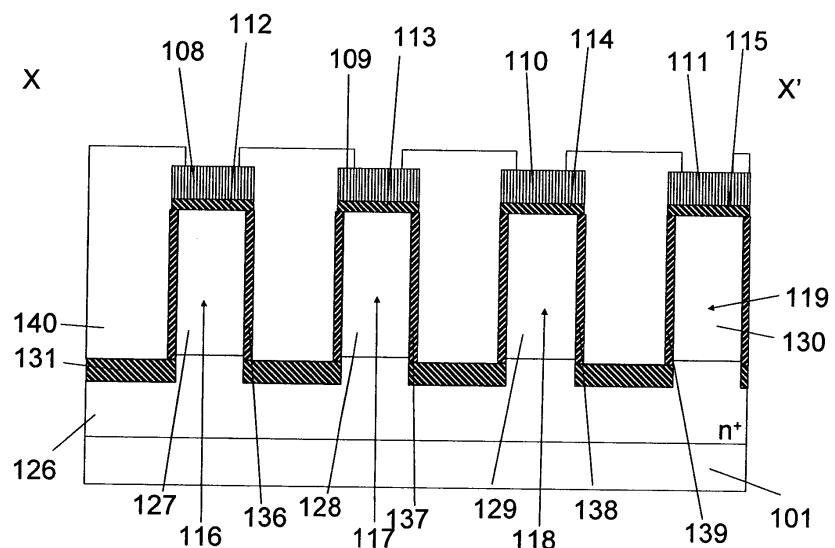

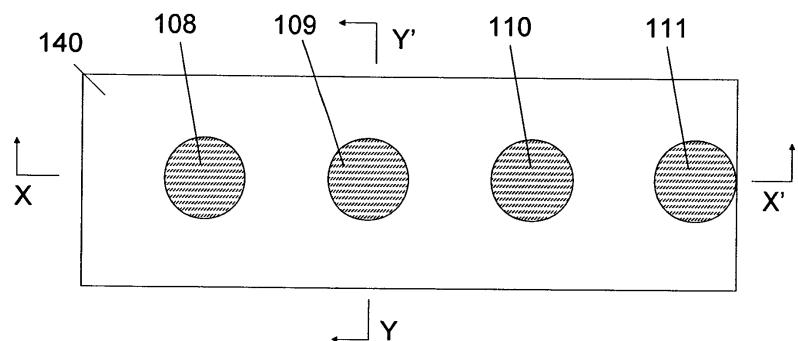

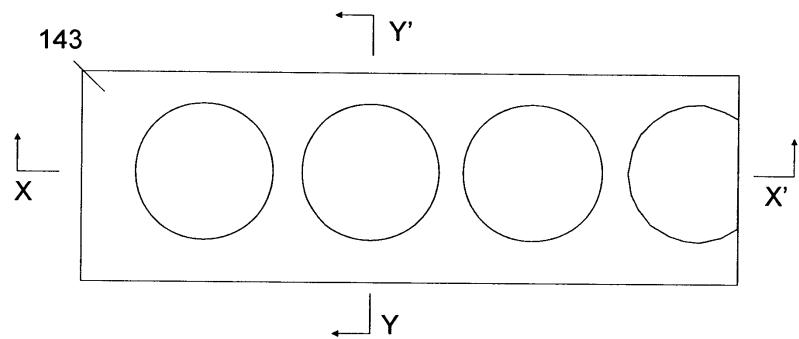

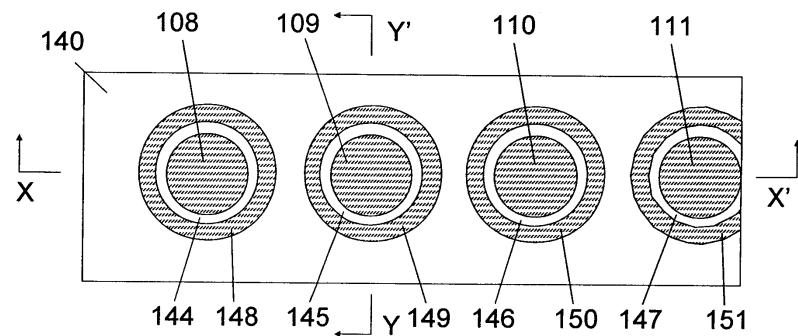

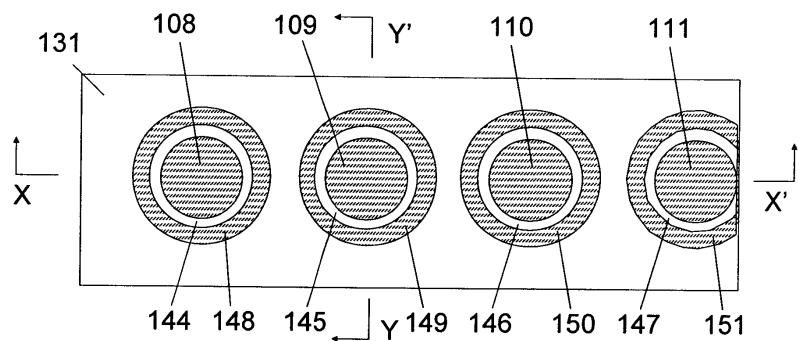

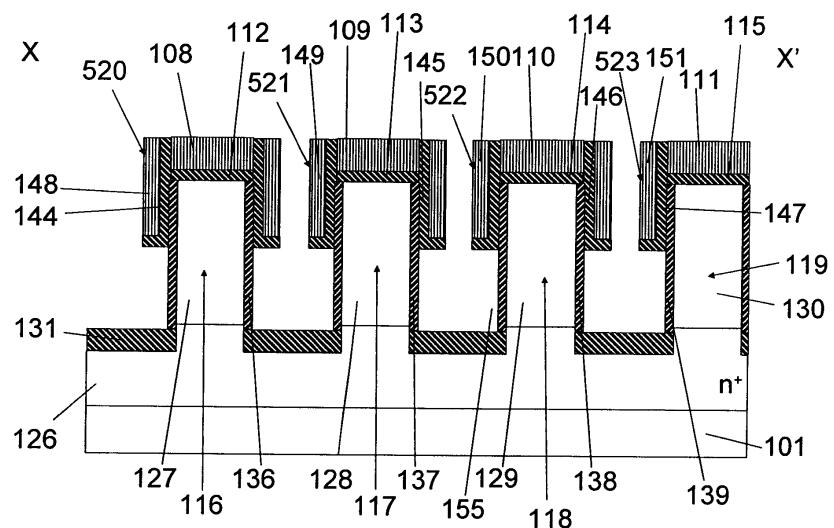

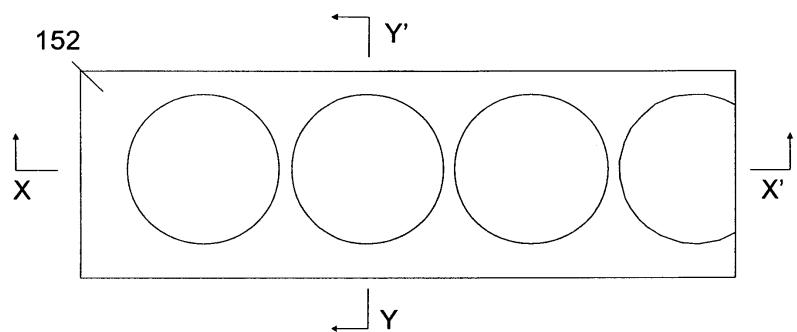

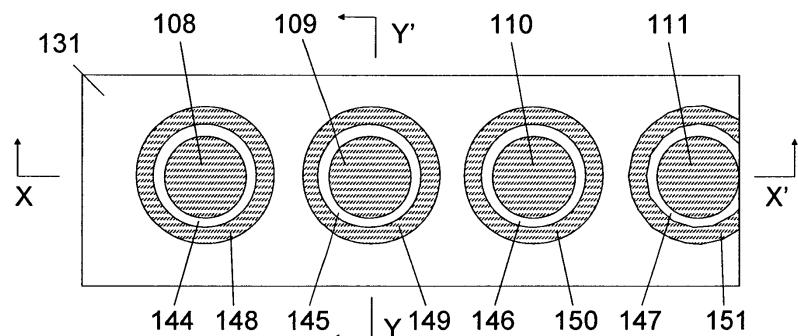

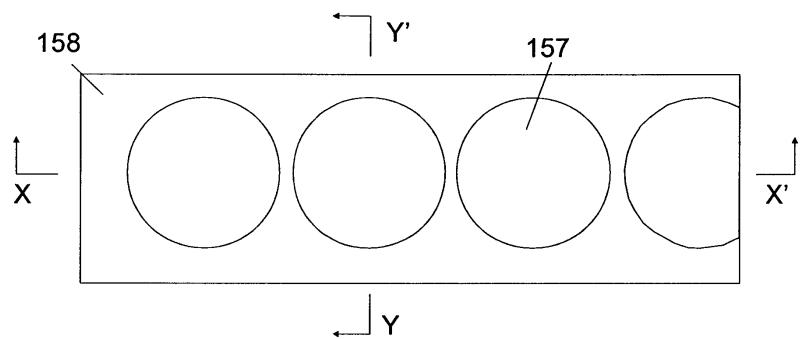

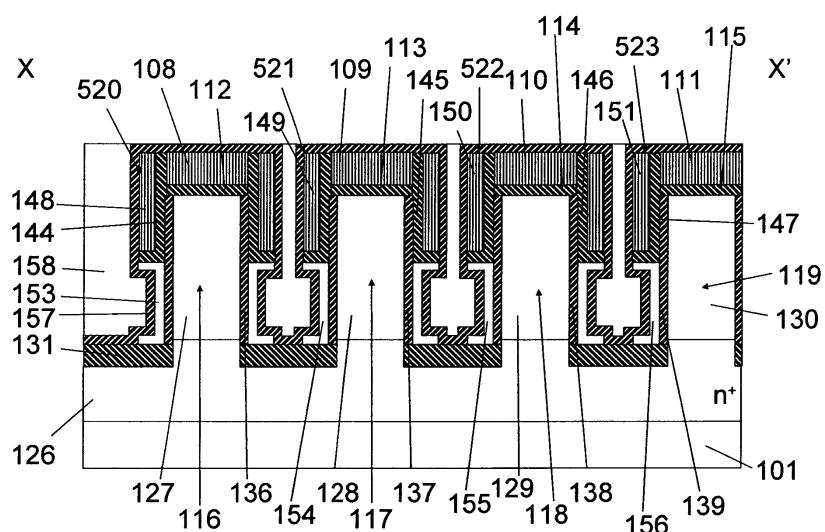

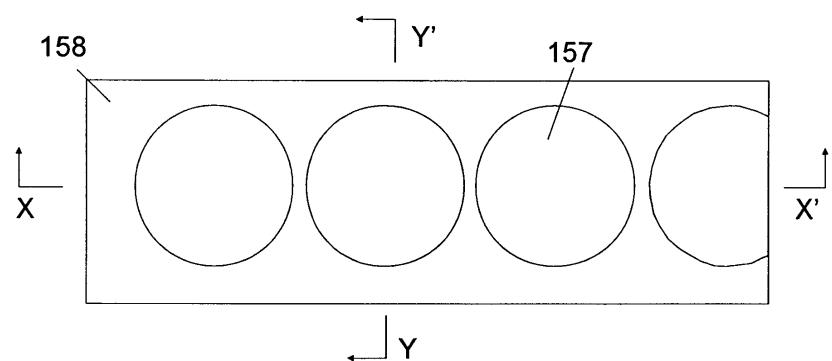

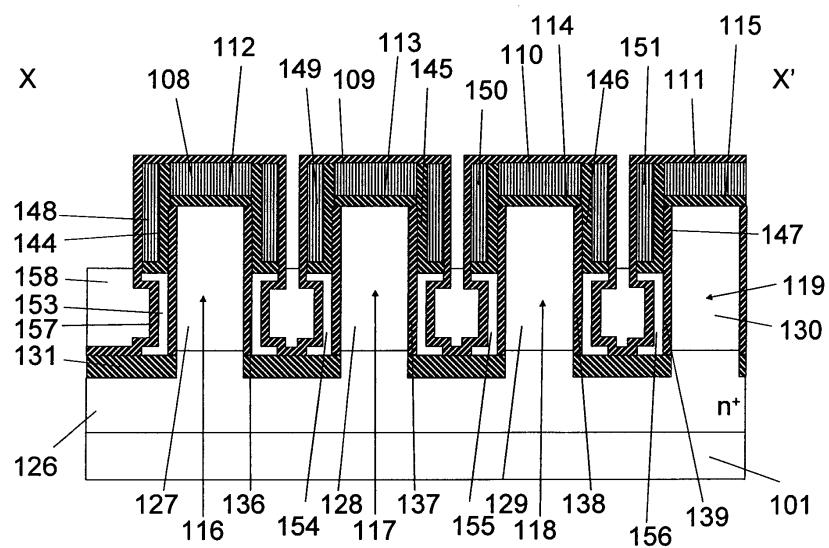

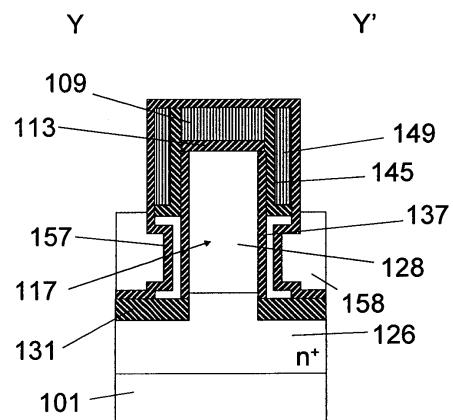

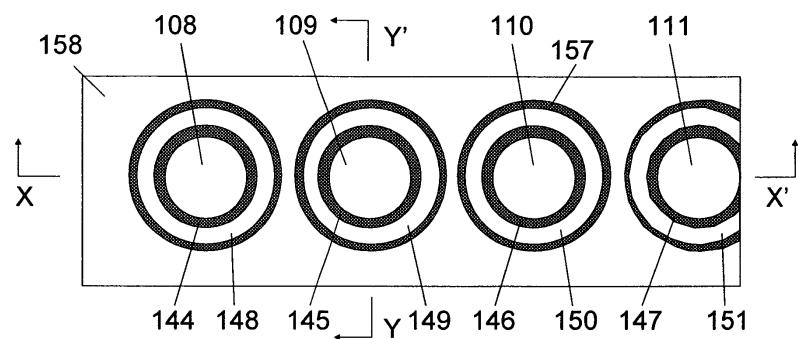

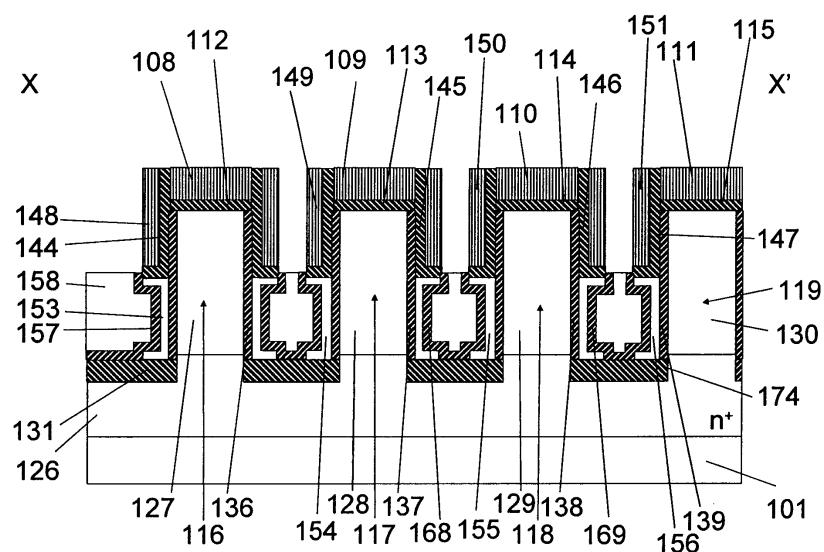

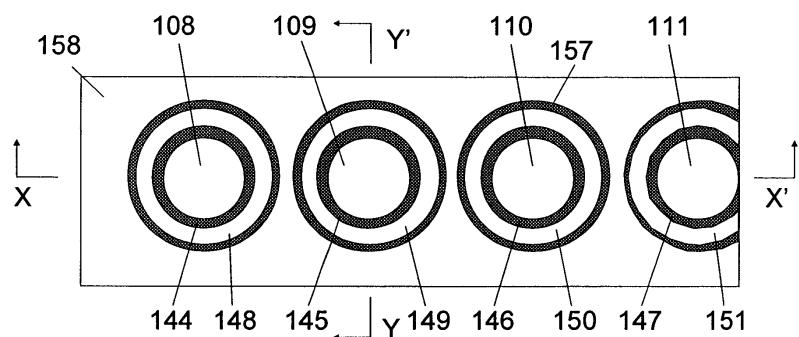

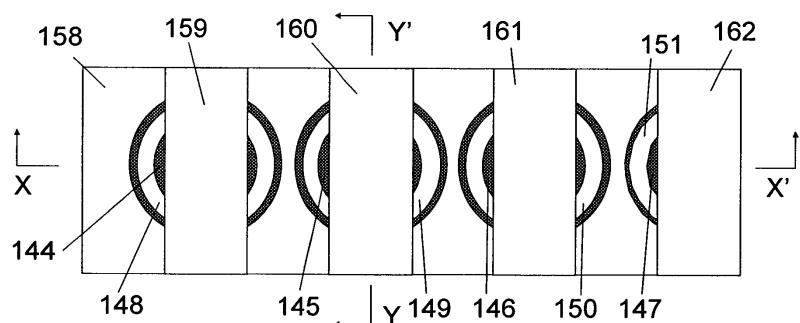

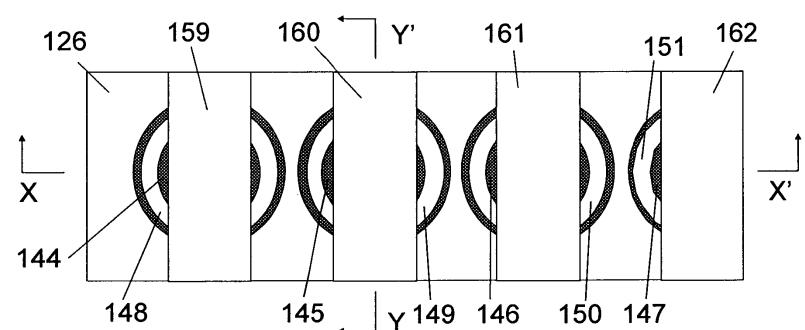

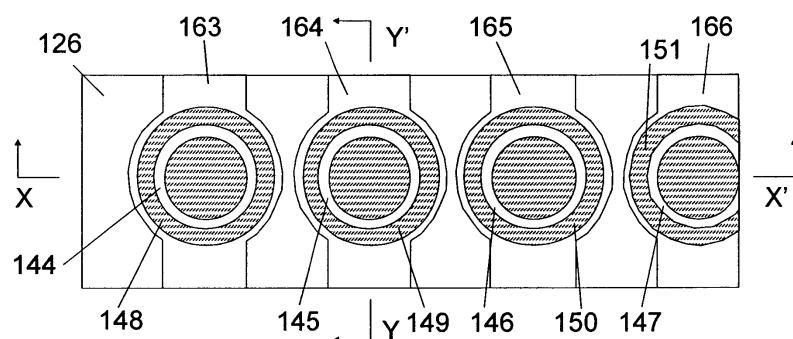

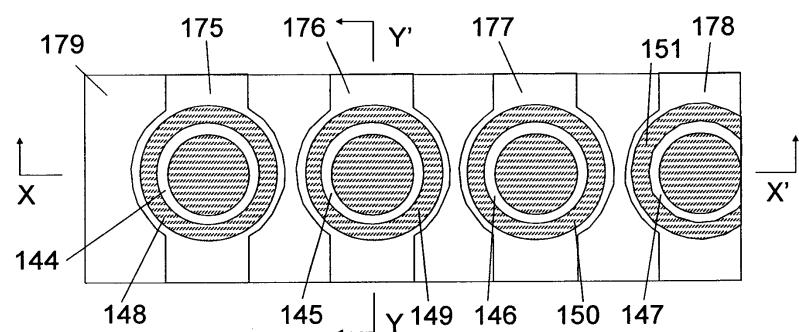

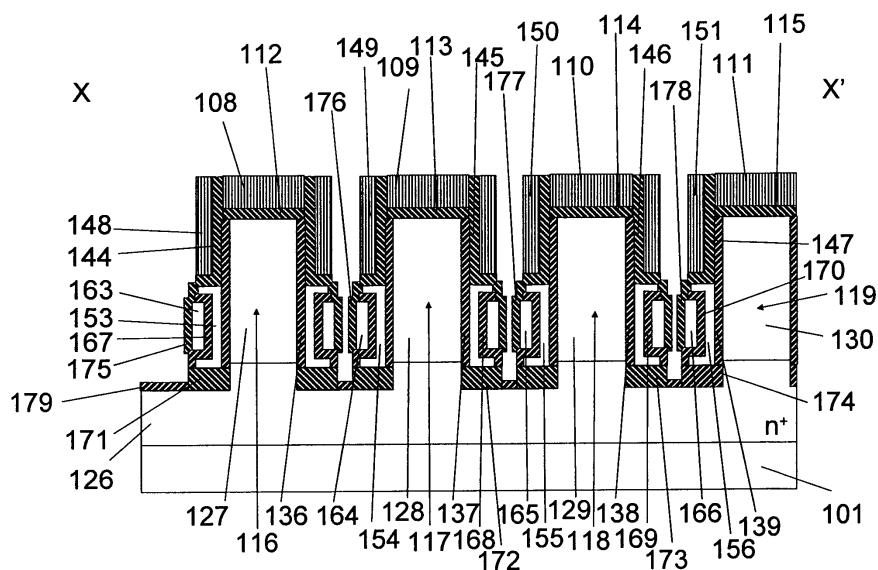

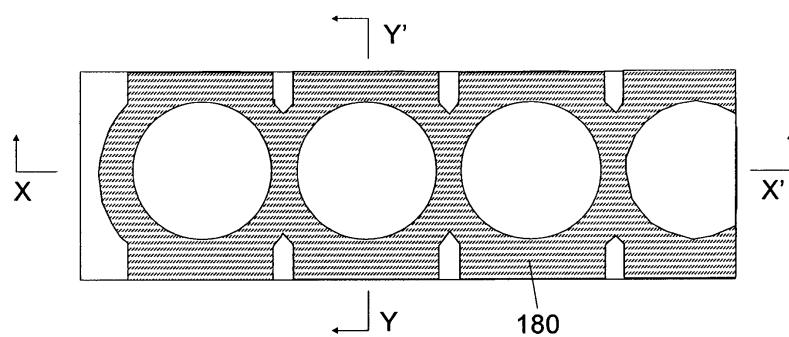

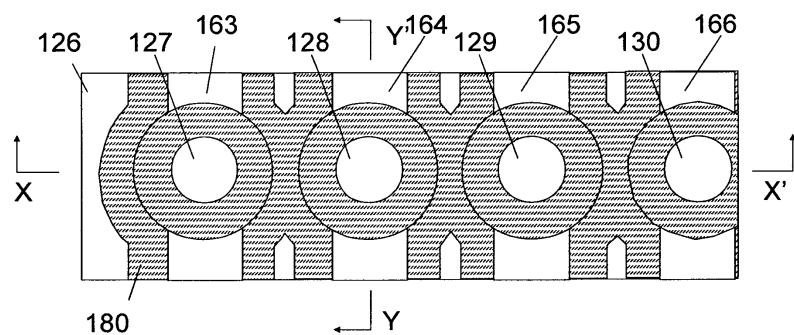

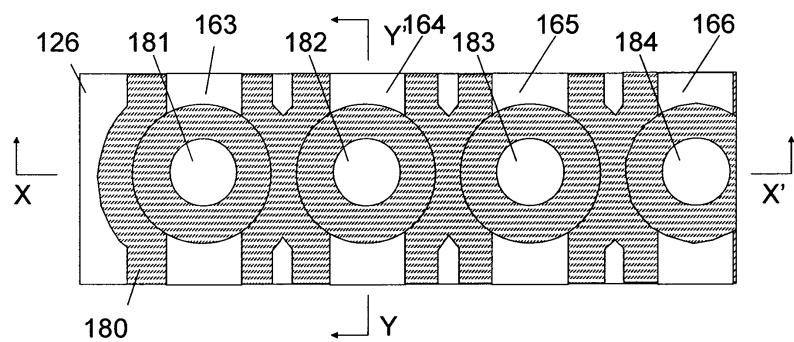

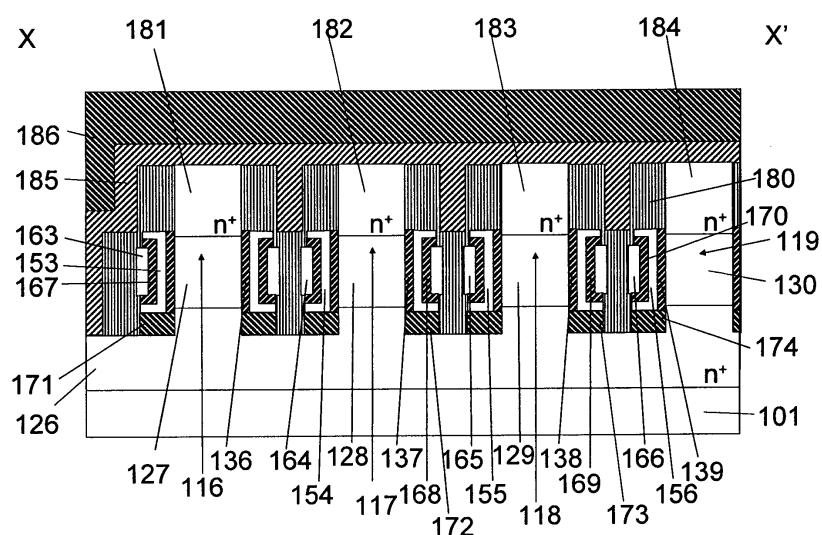

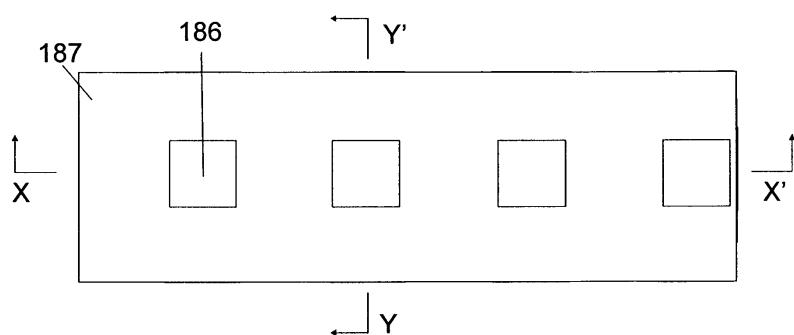

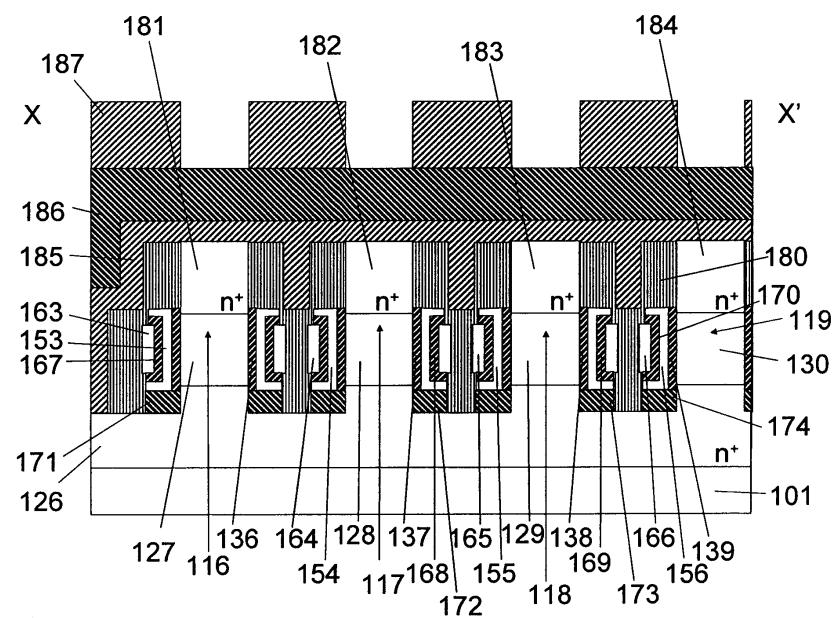

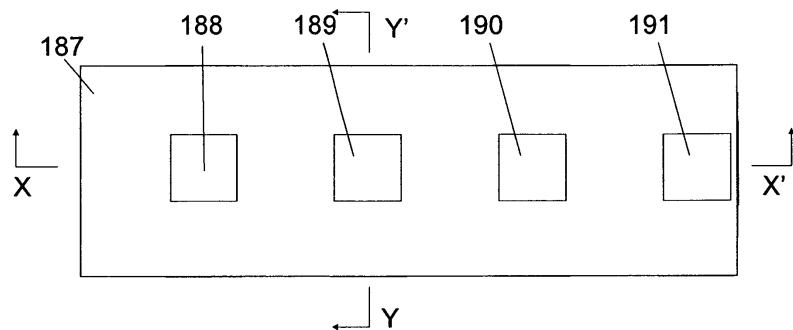

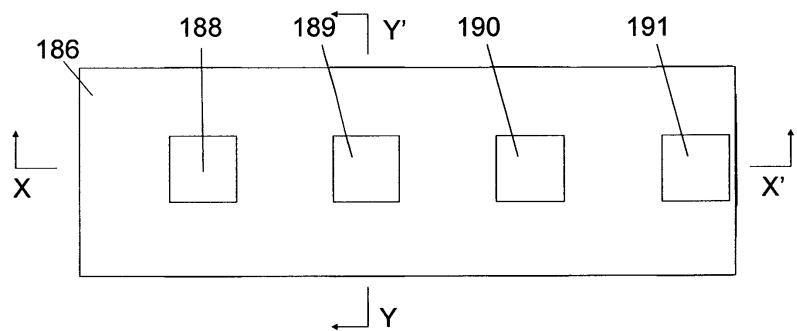

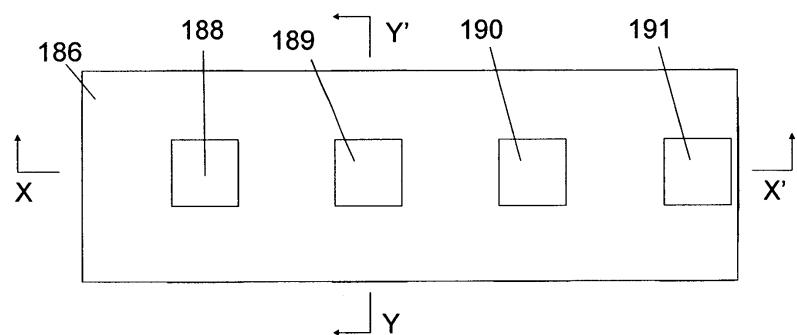

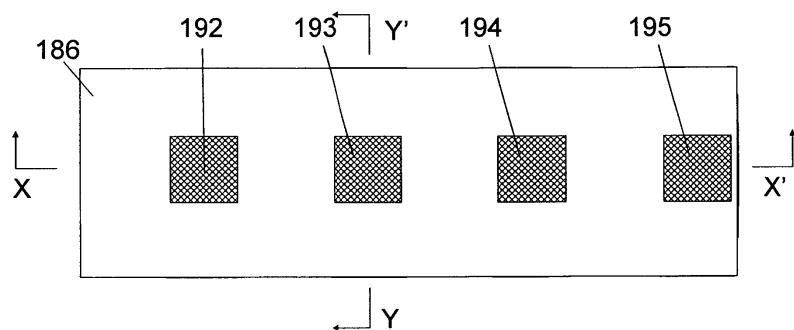

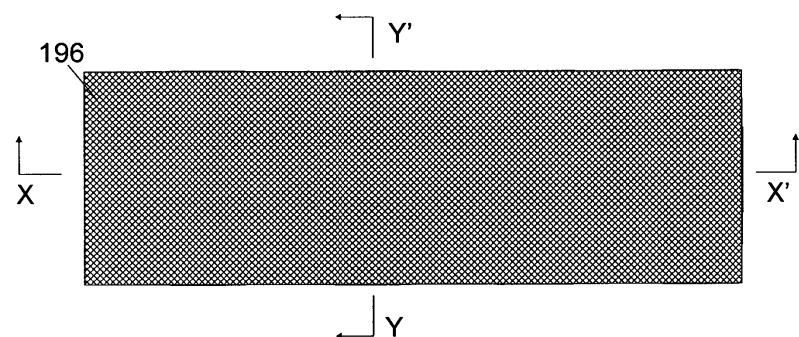

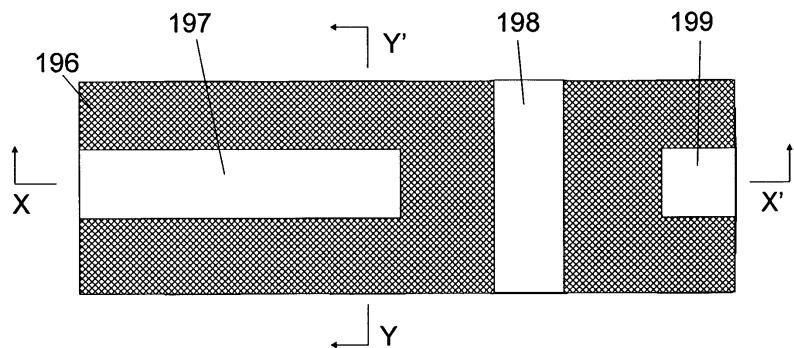

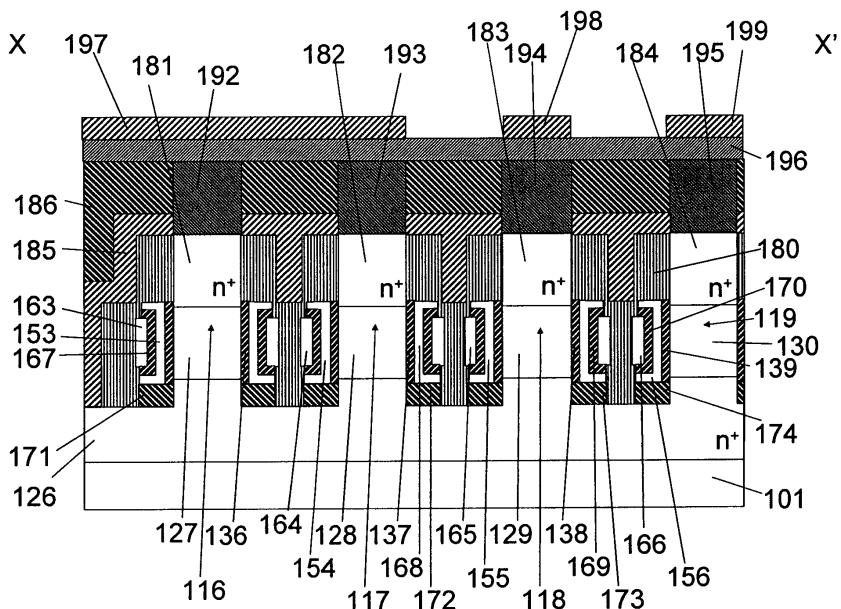

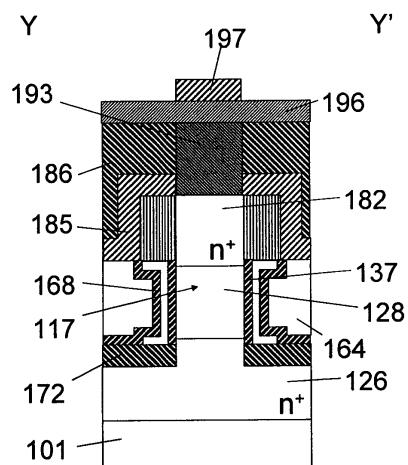

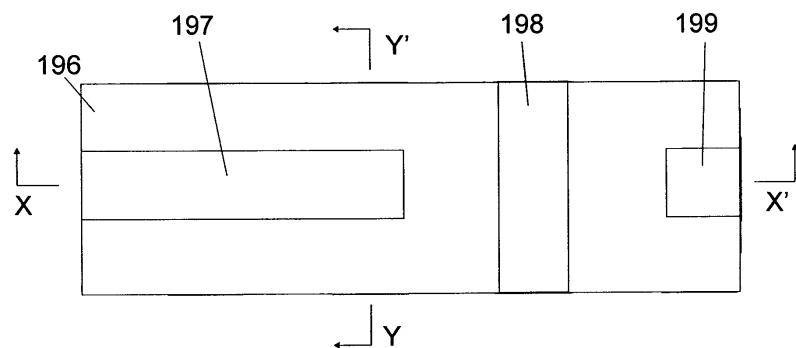

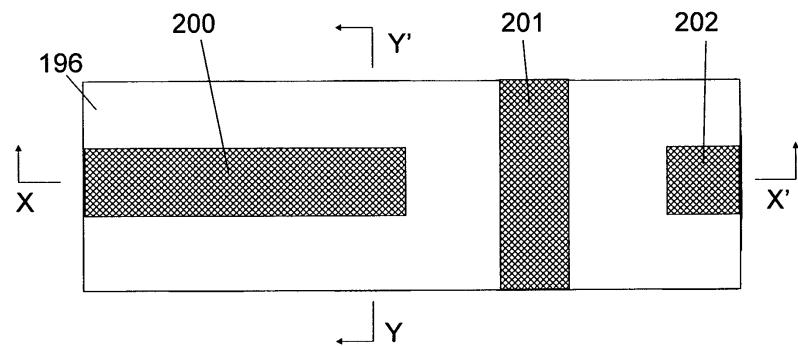

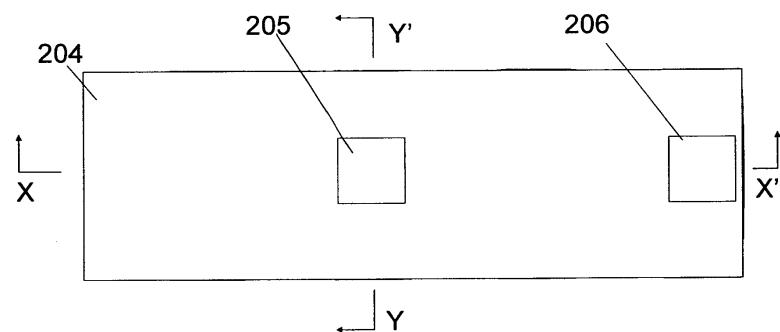

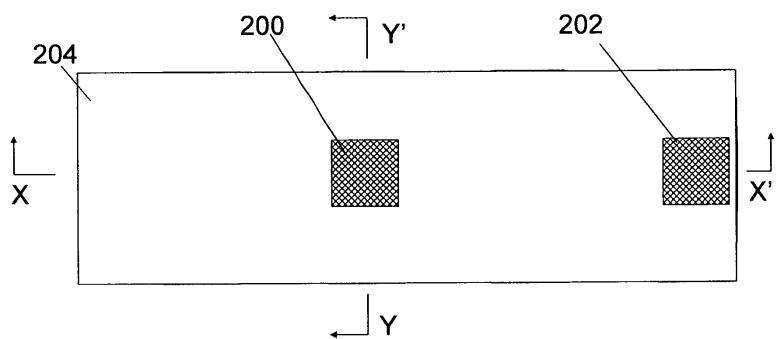

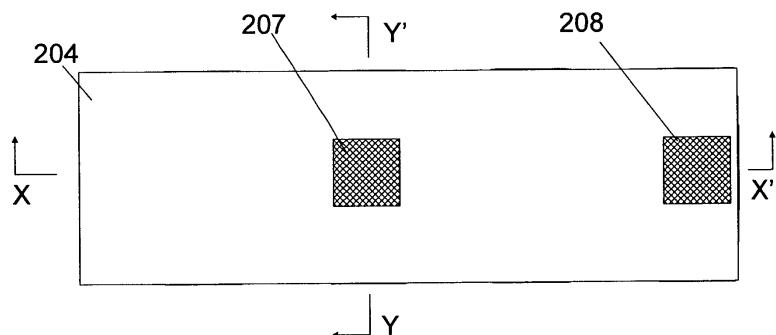

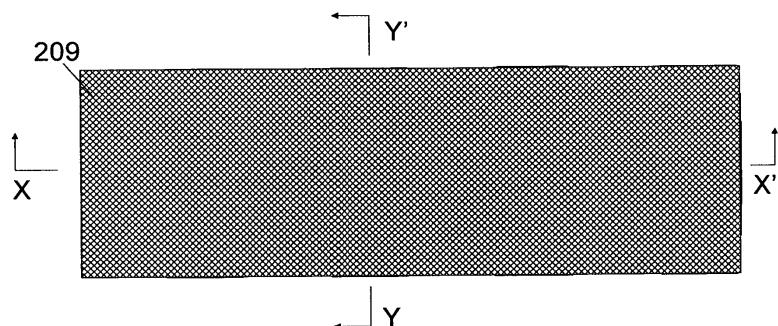

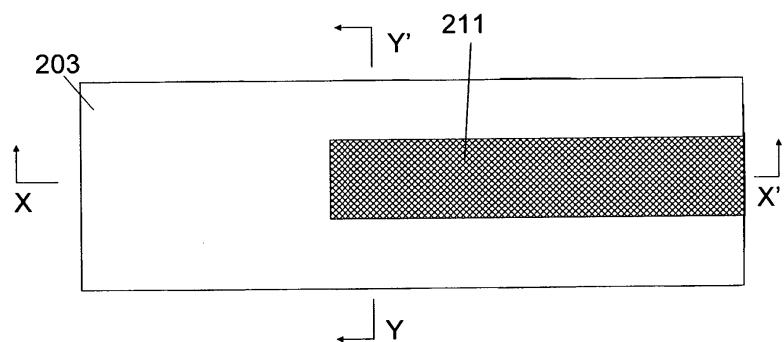

도 2a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 평면도.

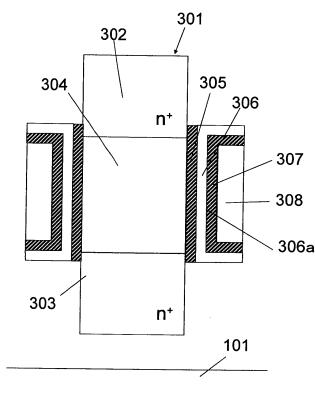

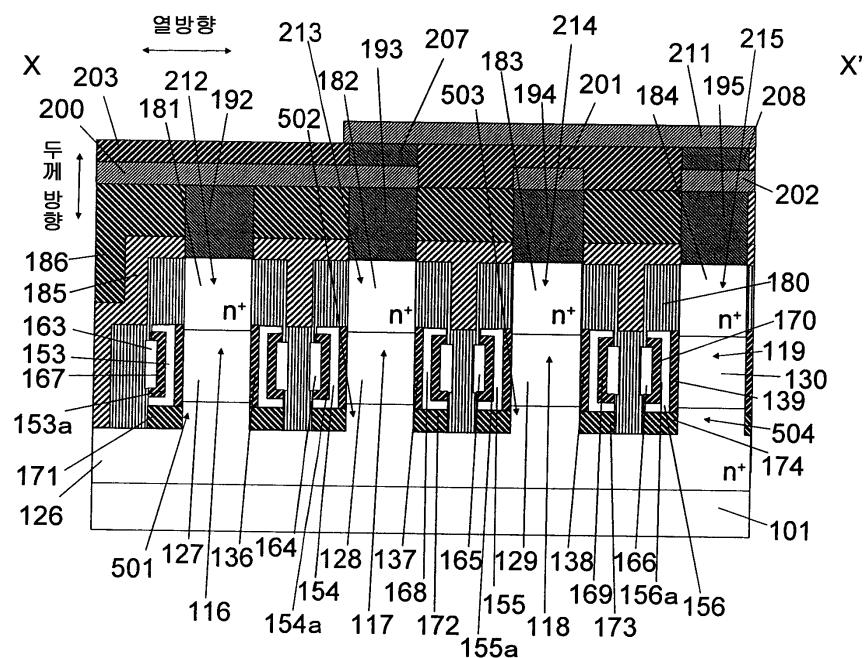

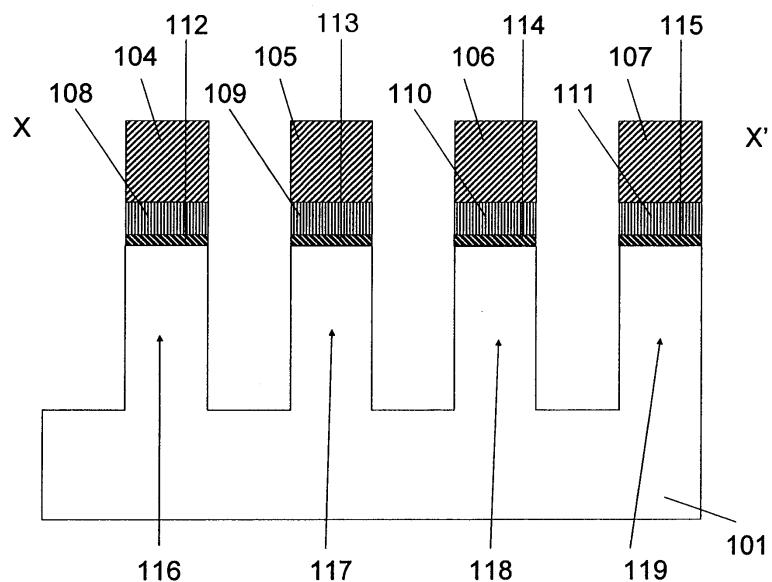

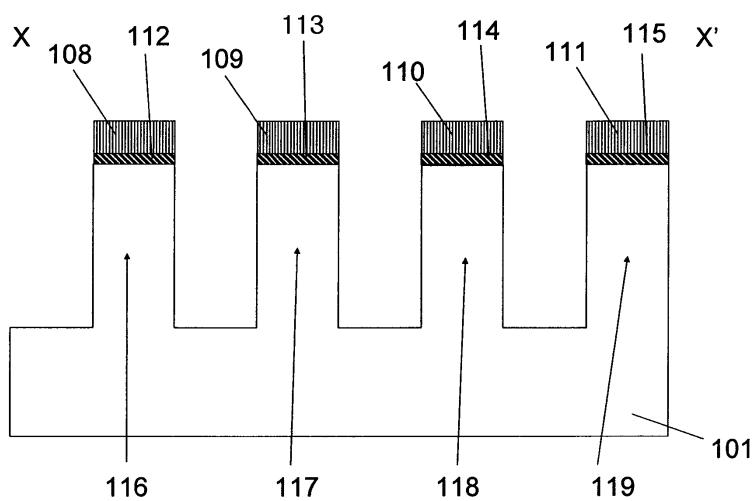

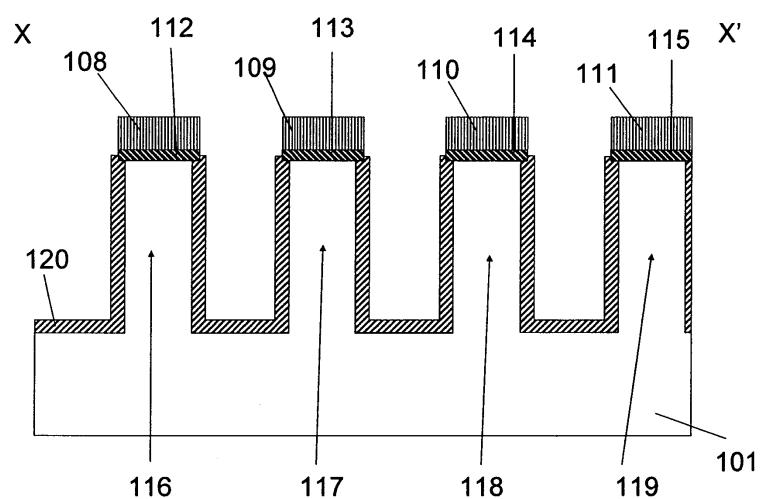

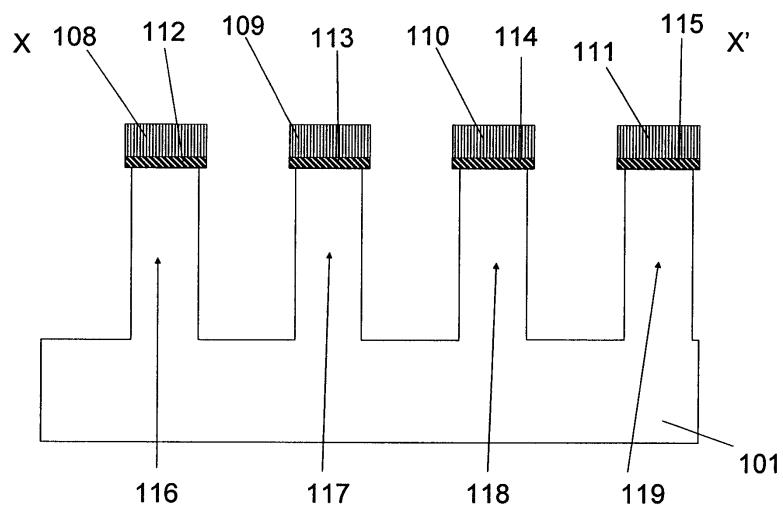

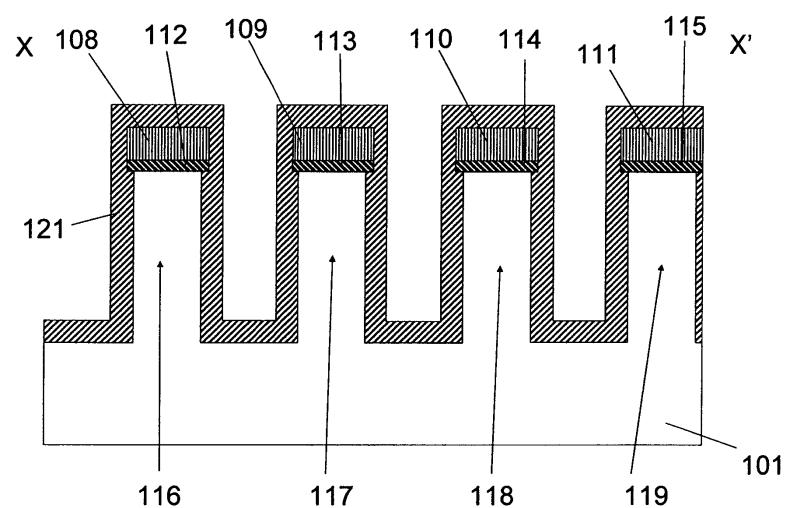

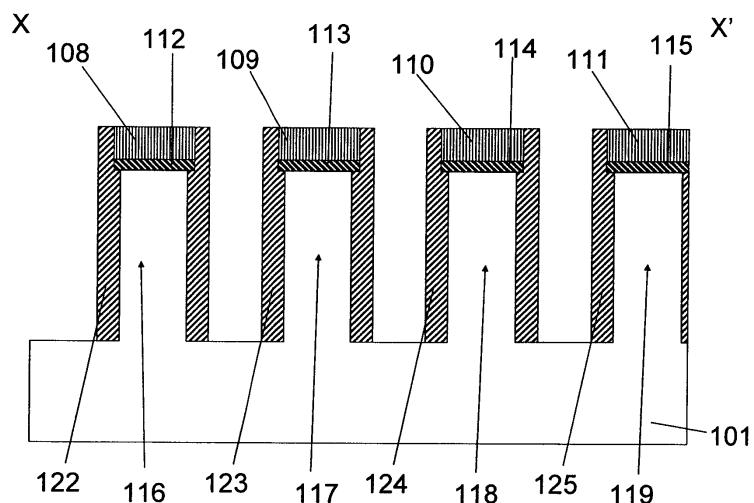

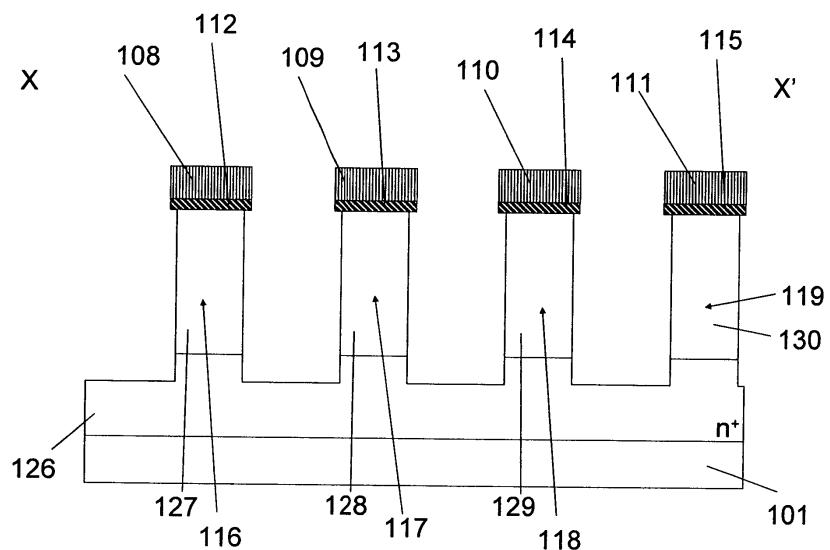

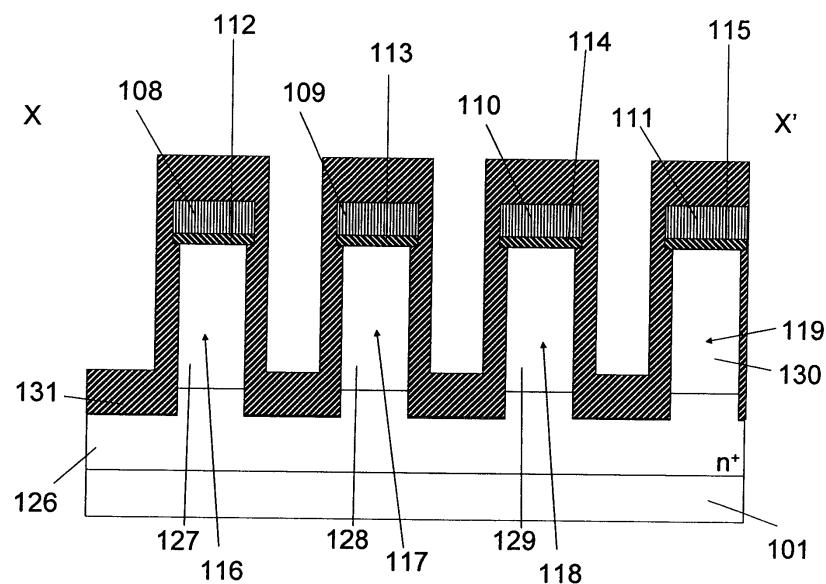

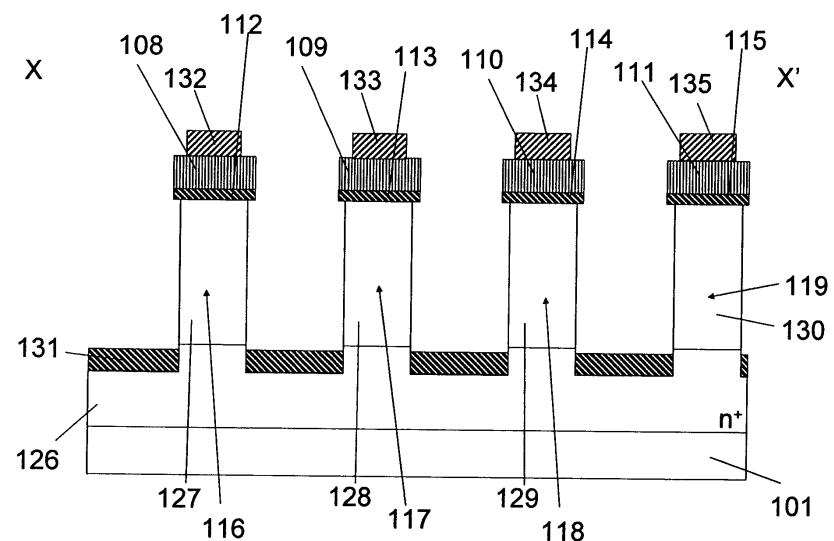

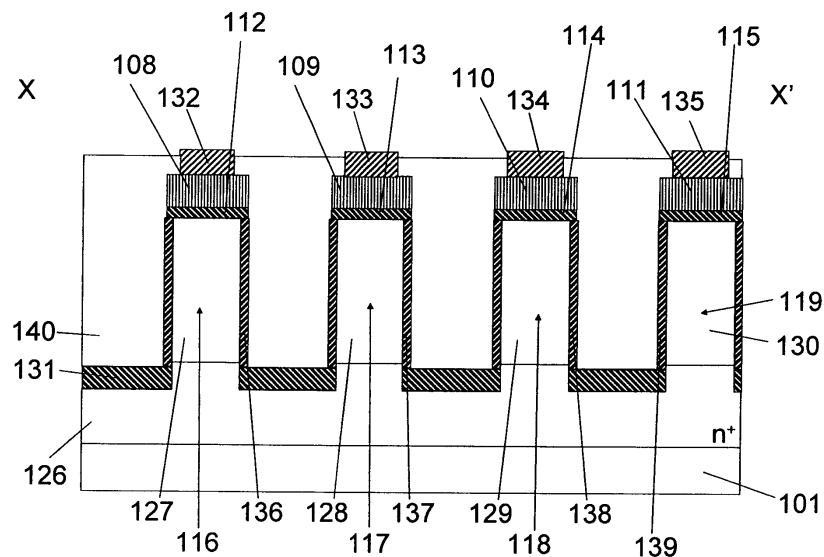

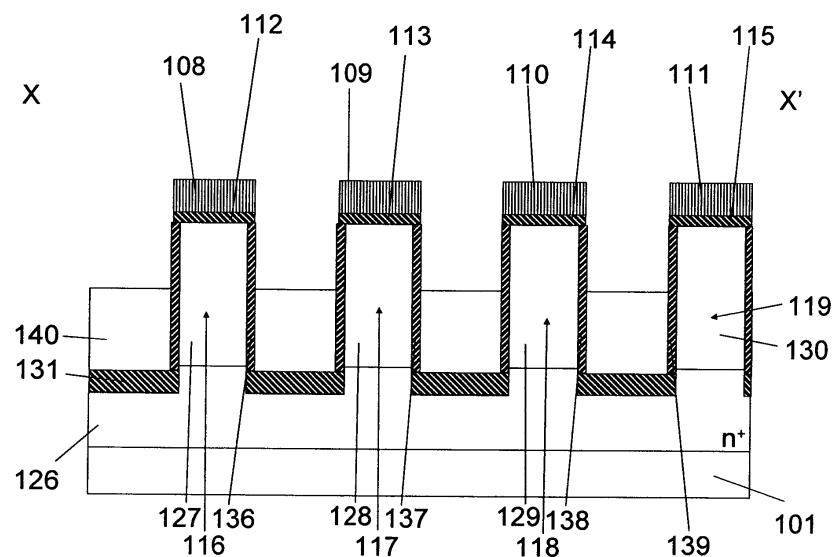

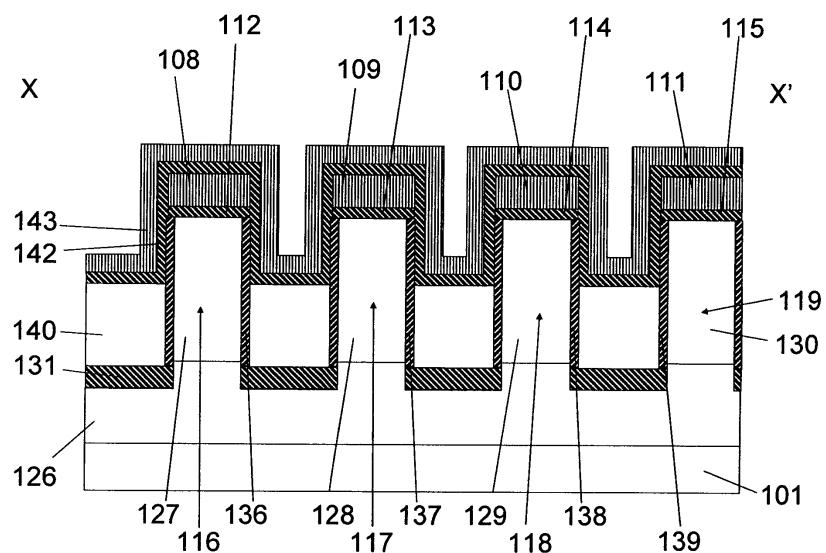

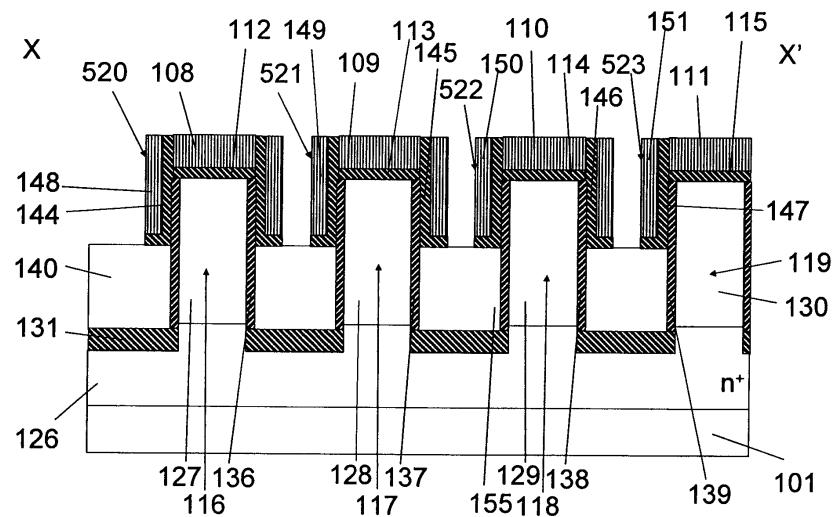

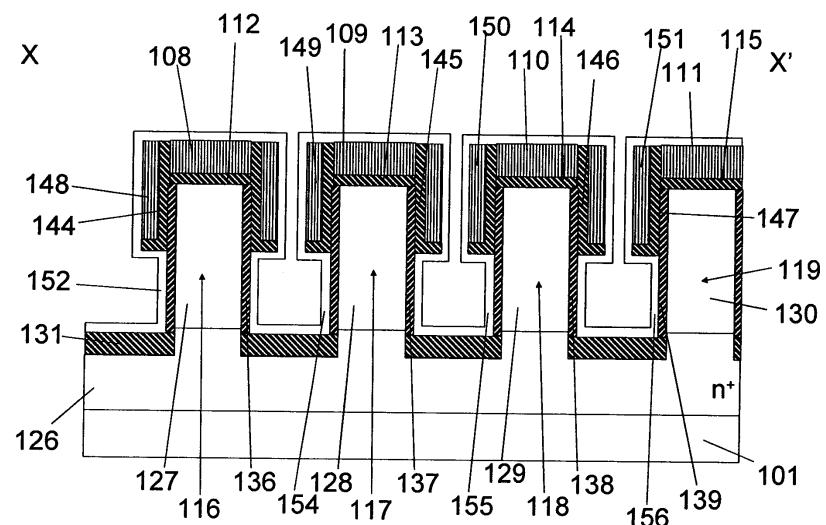

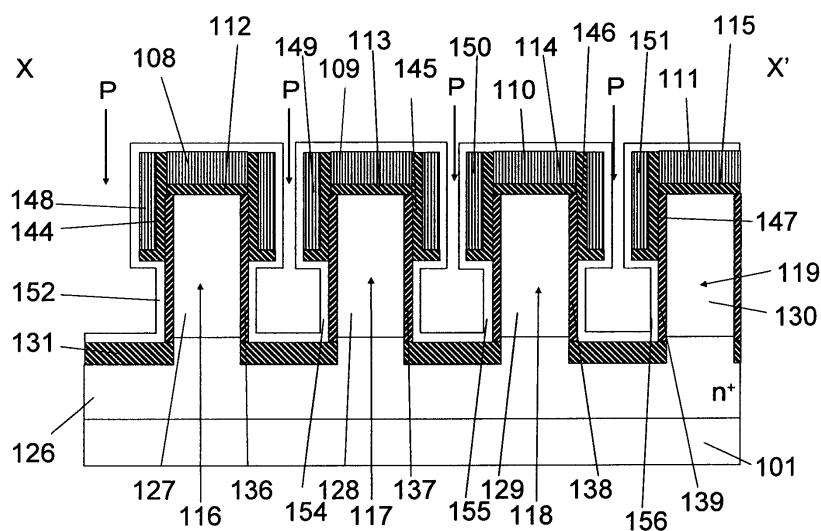

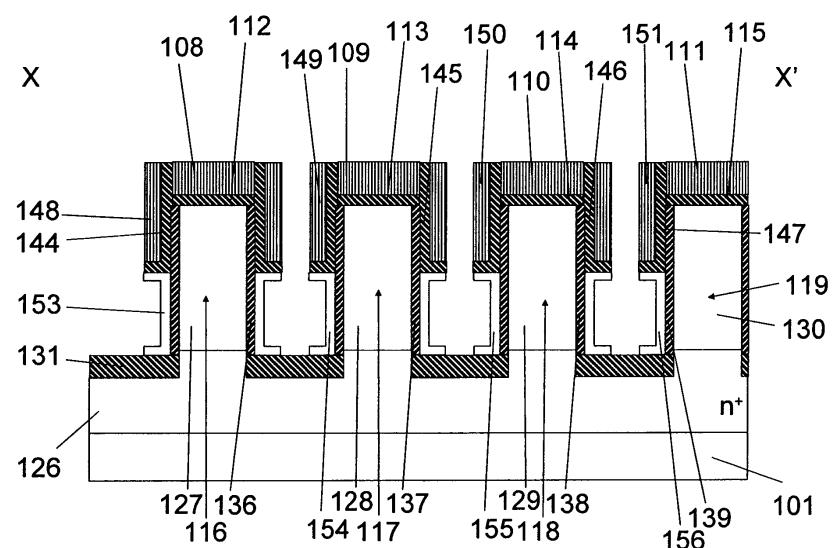

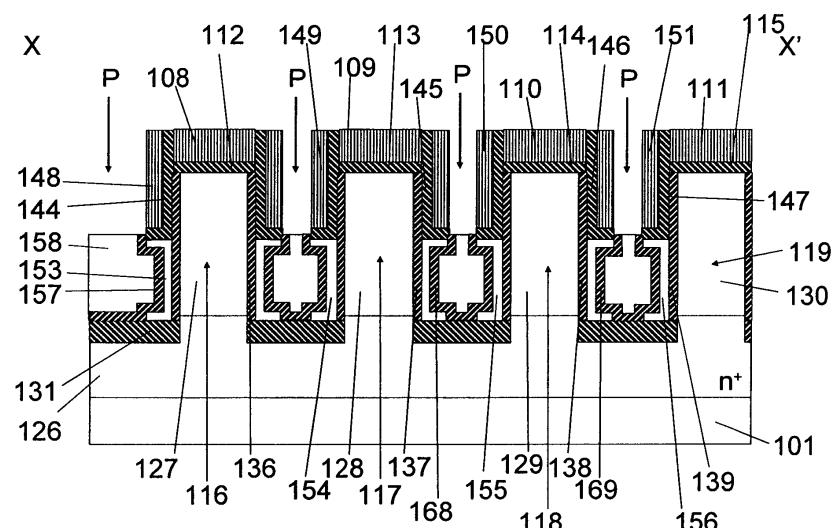

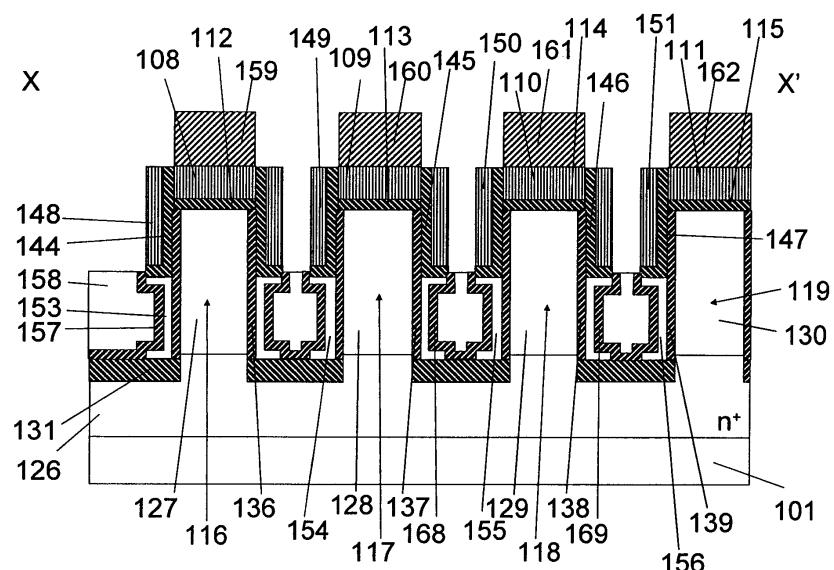

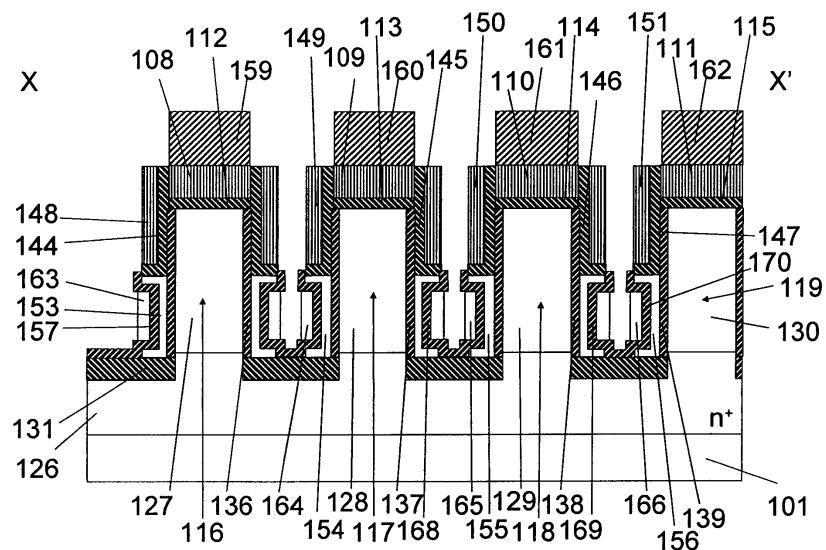

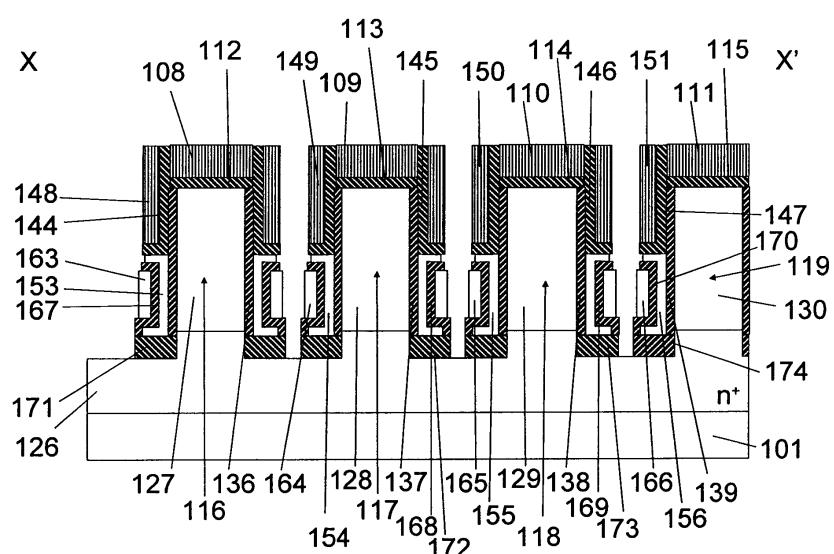

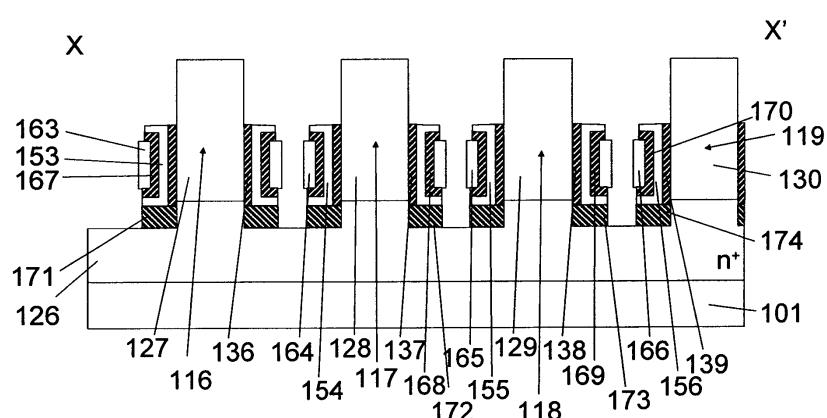

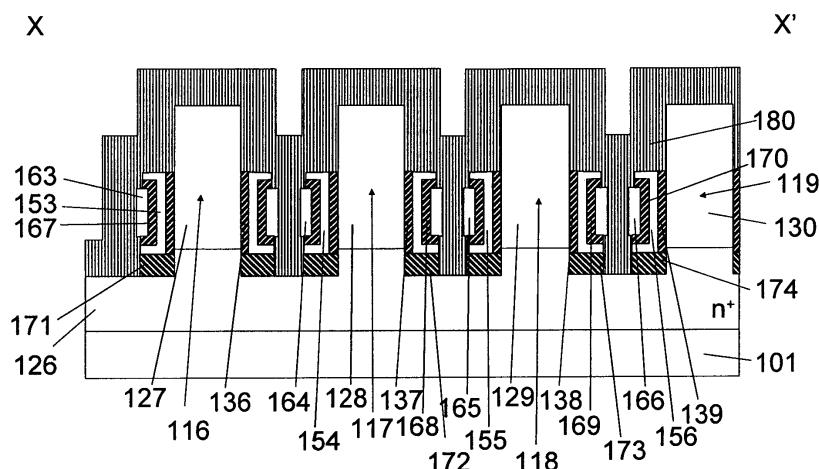

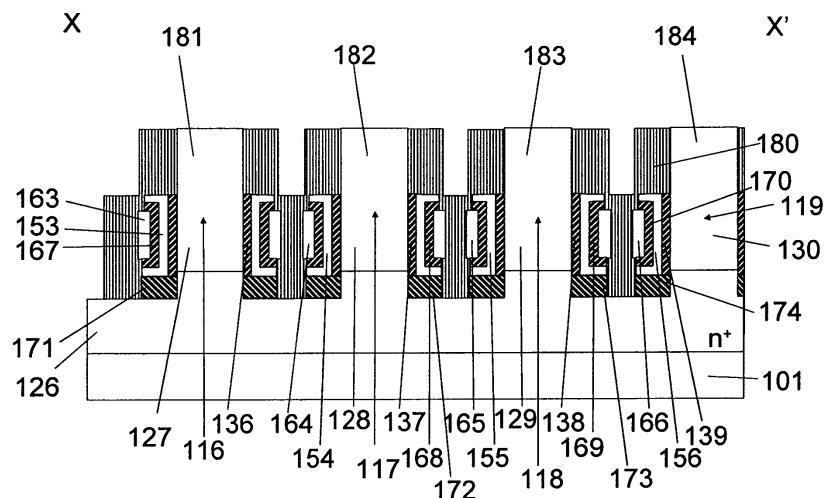

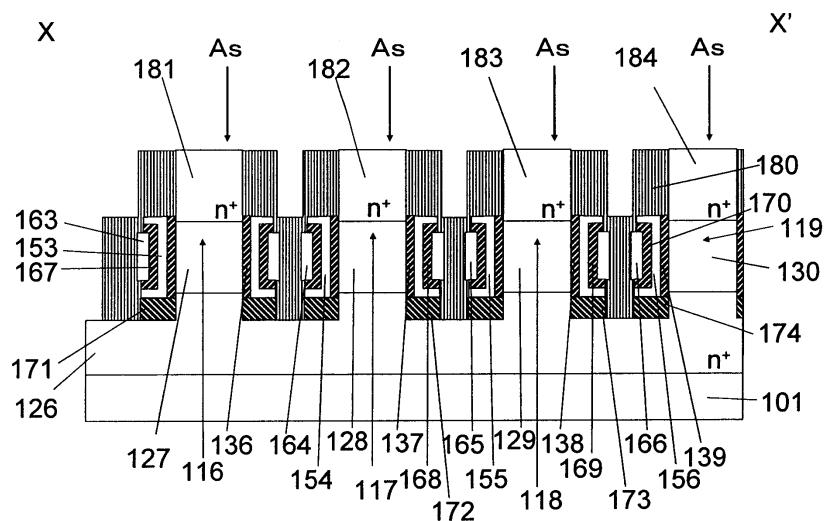

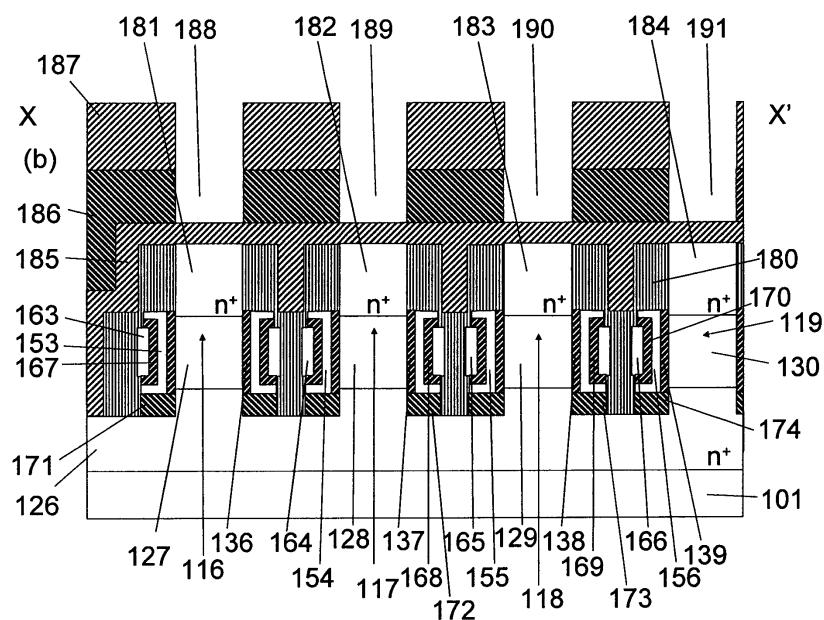

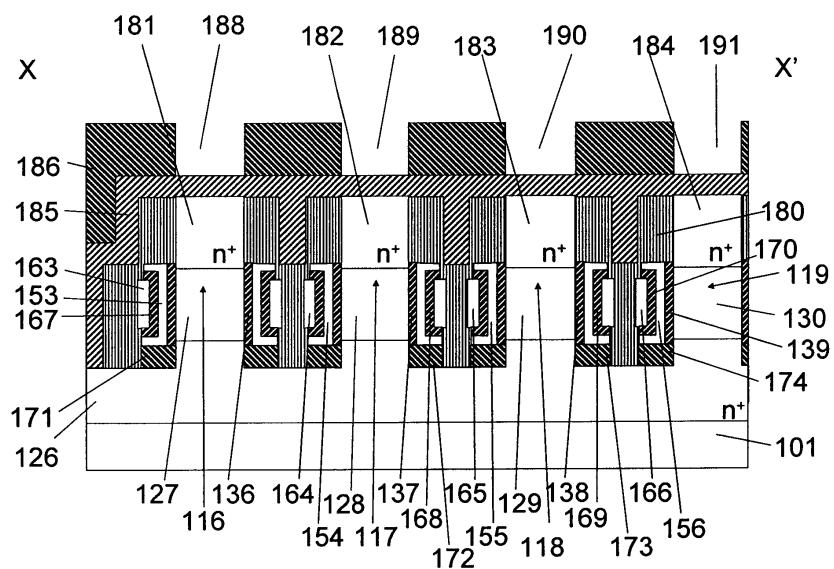

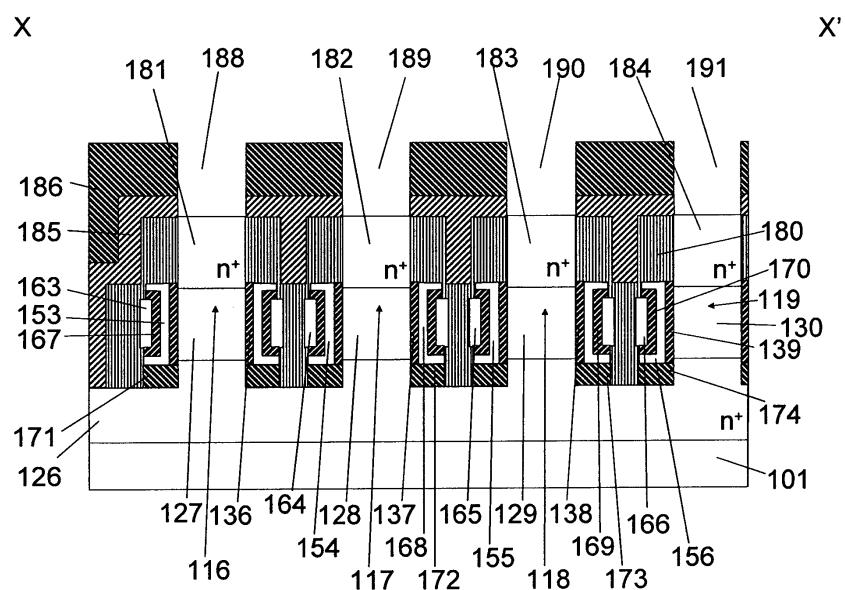

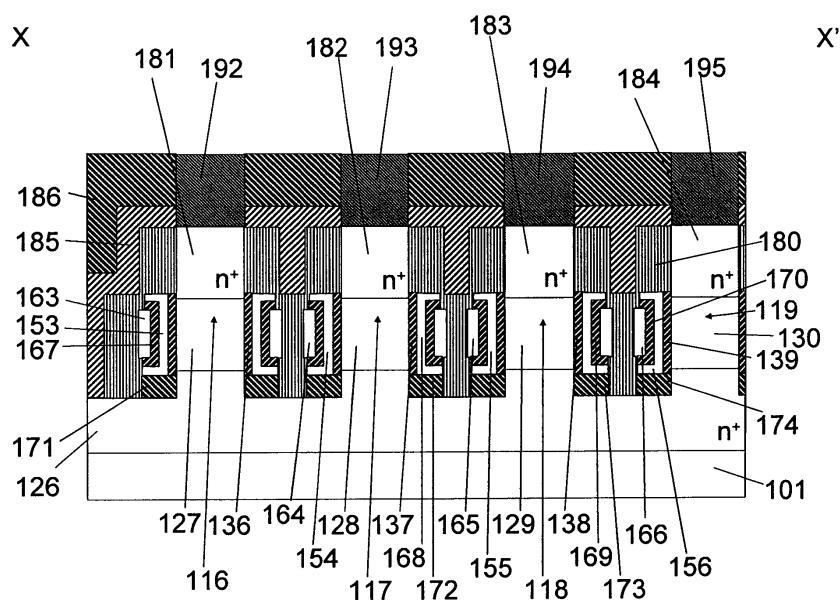

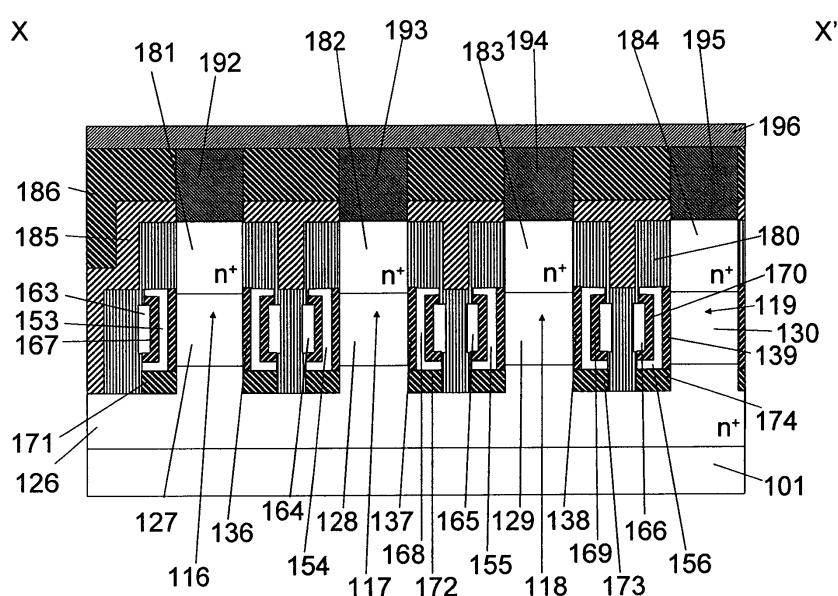

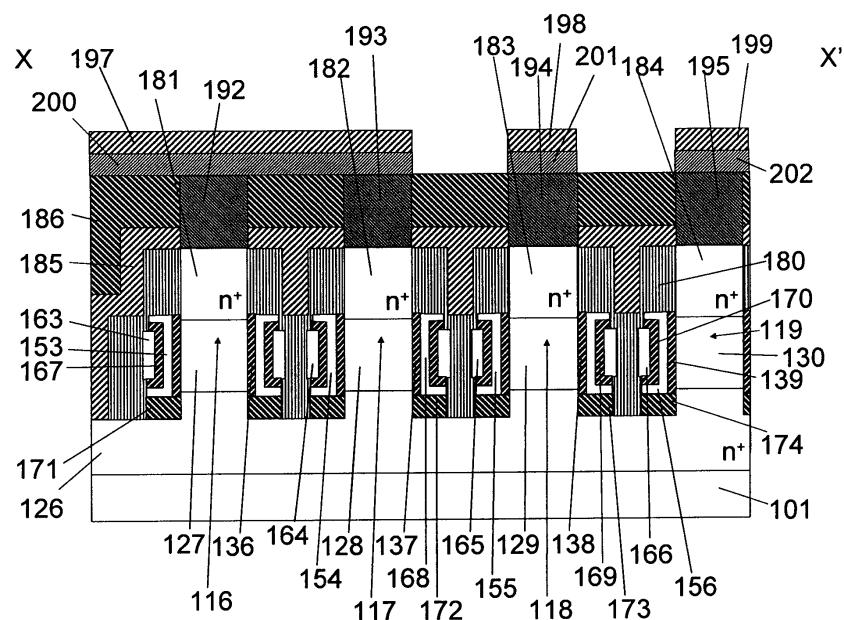

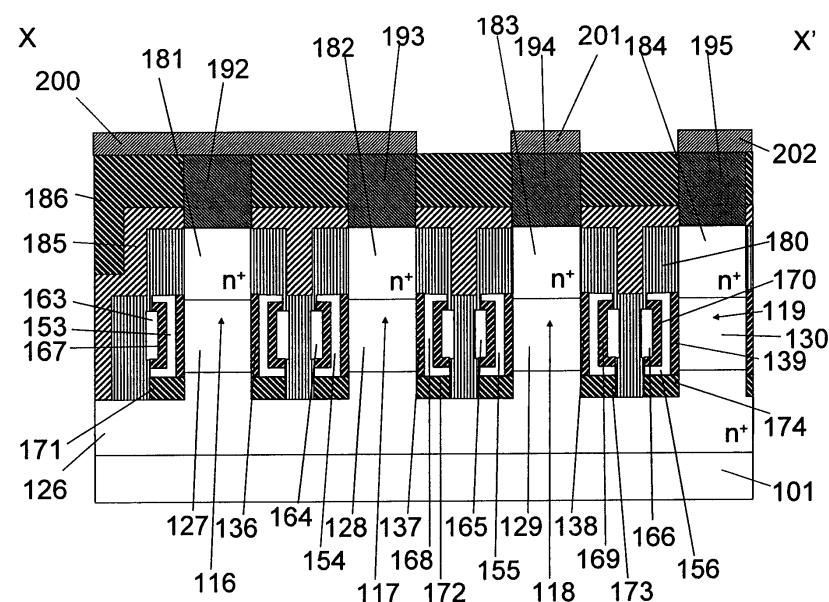

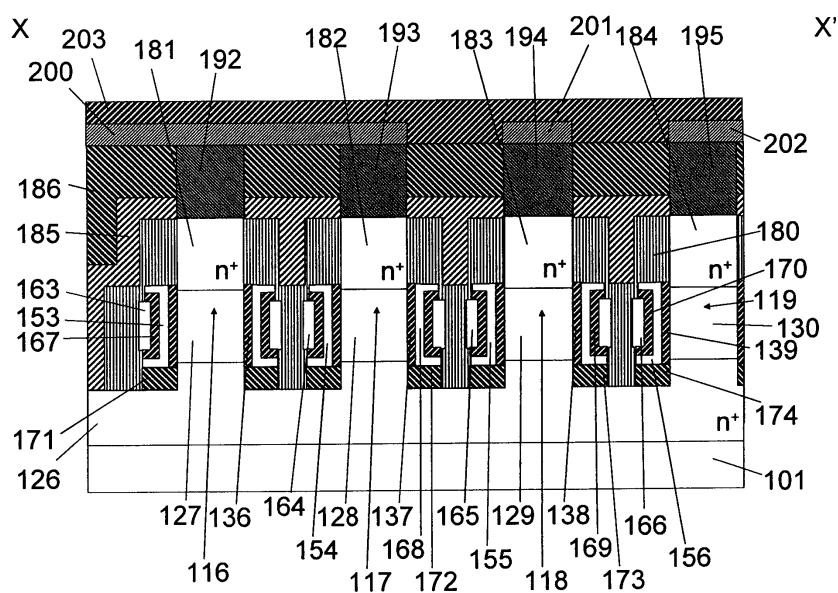

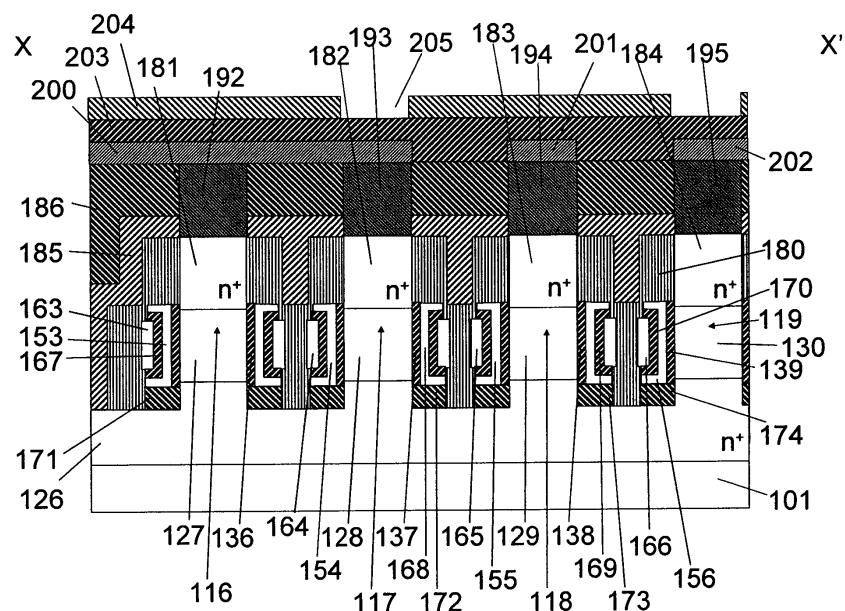

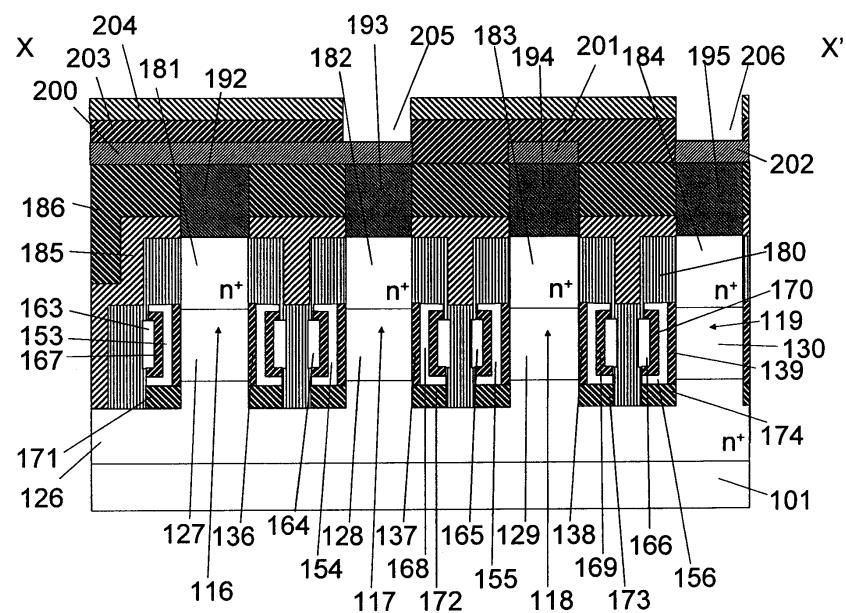

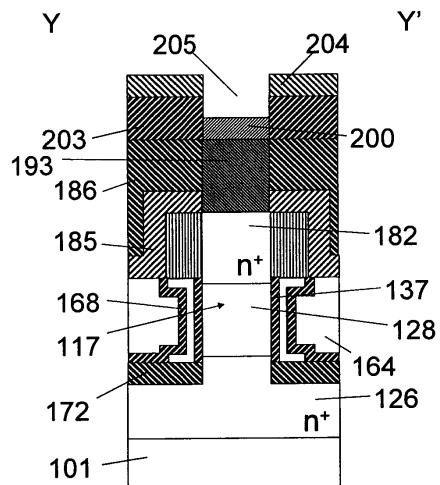

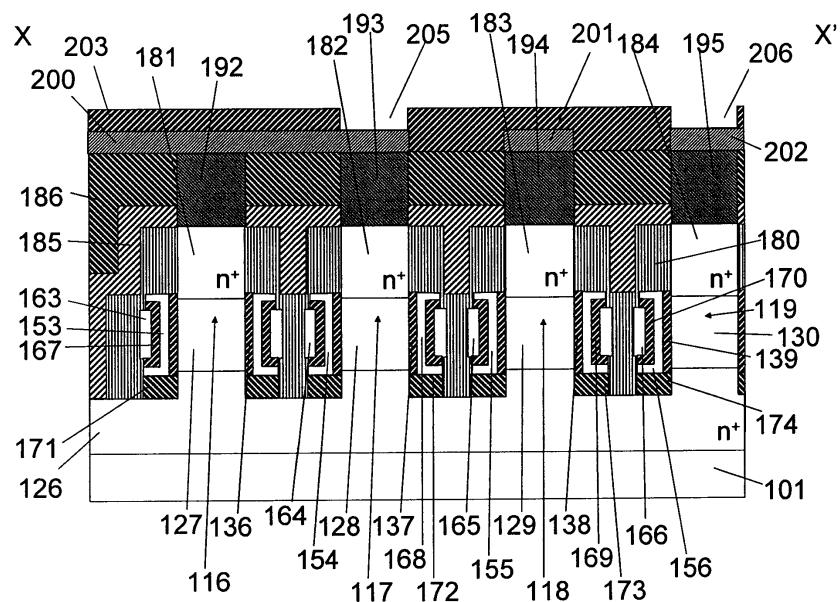

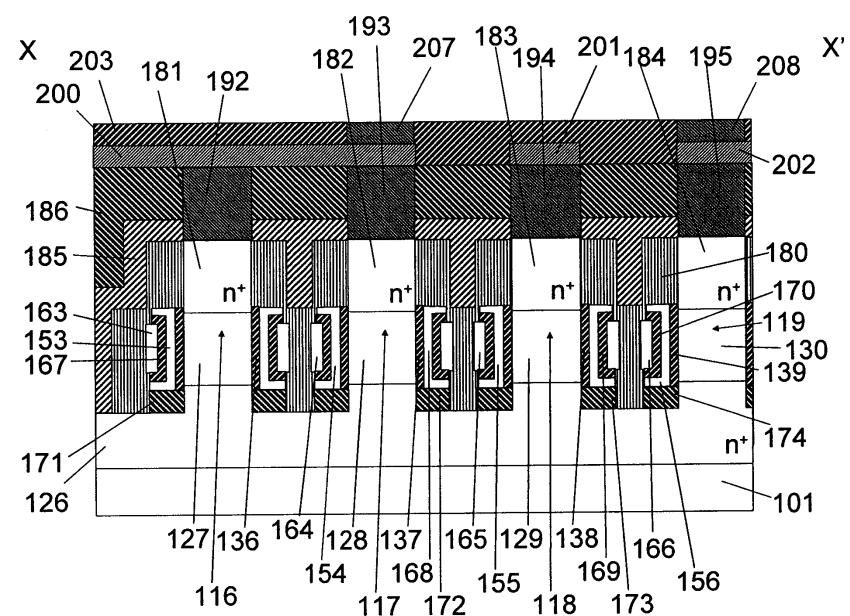

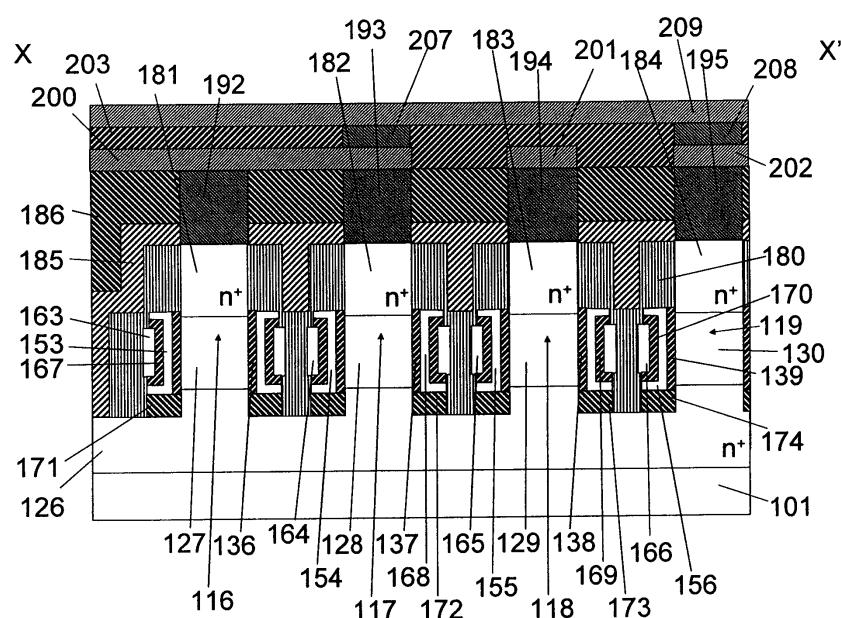

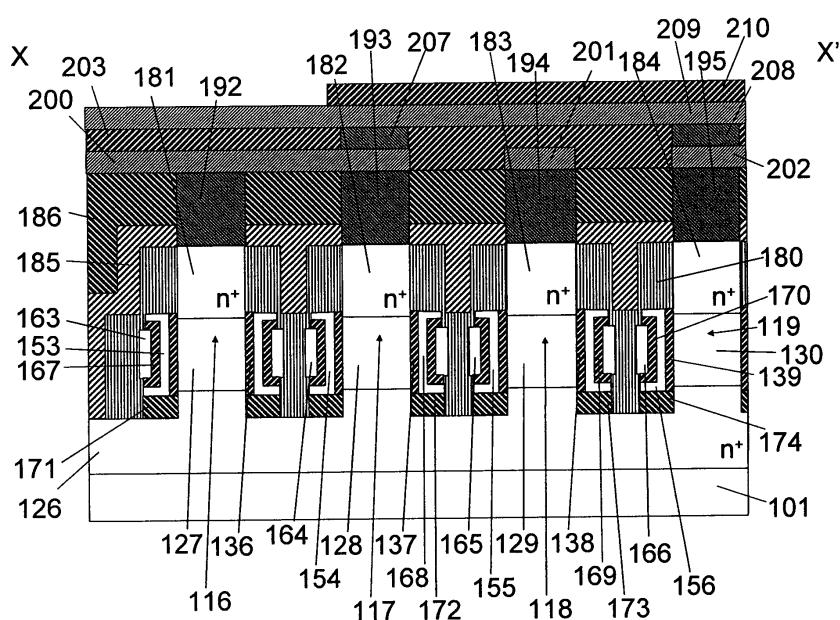

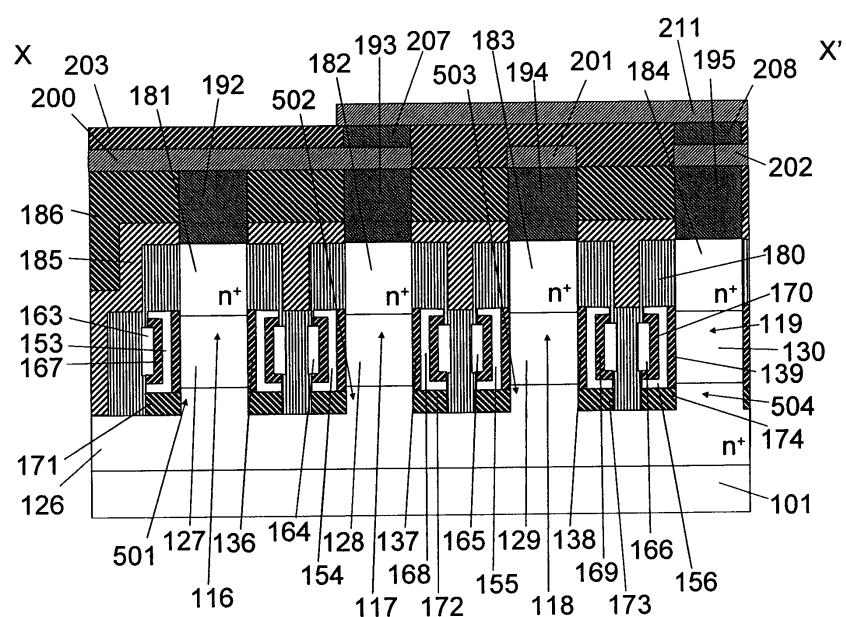

도 2b 는, 도 2a 의 X-X' 선에서의 단면도.

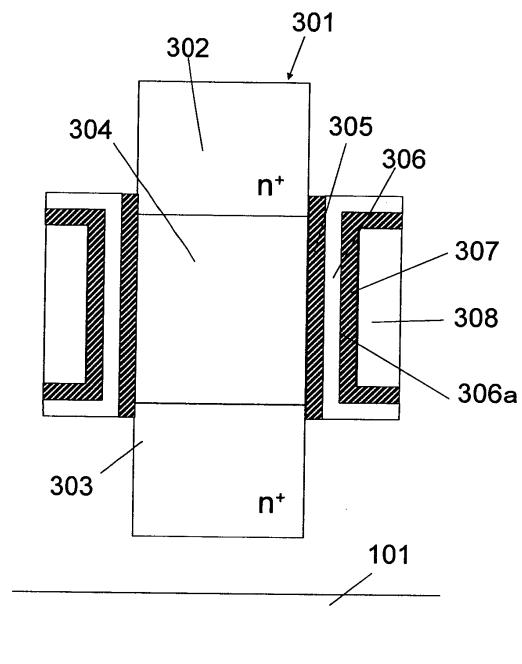

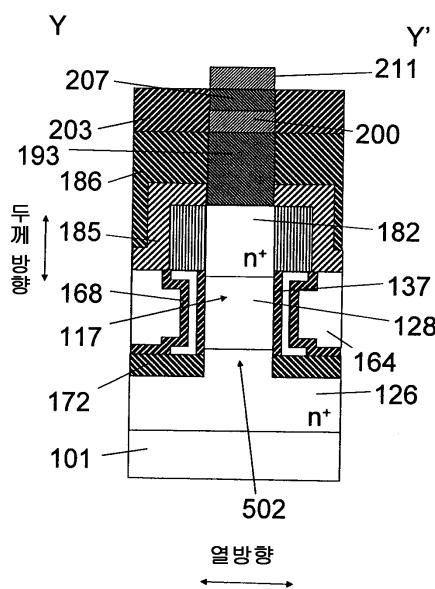

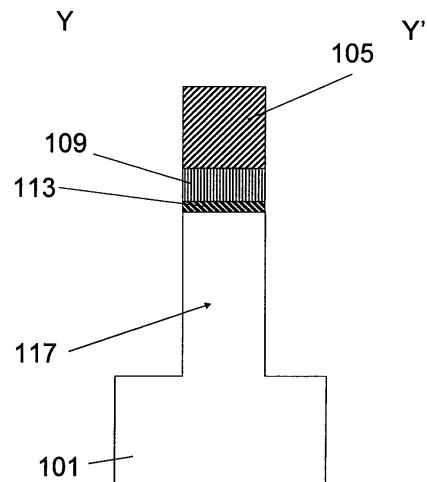

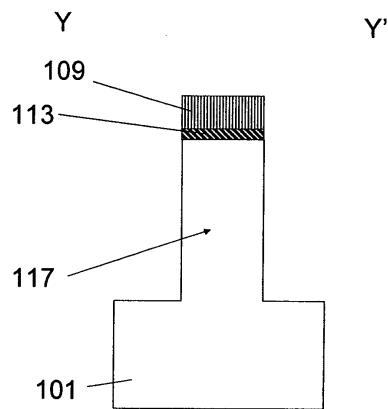

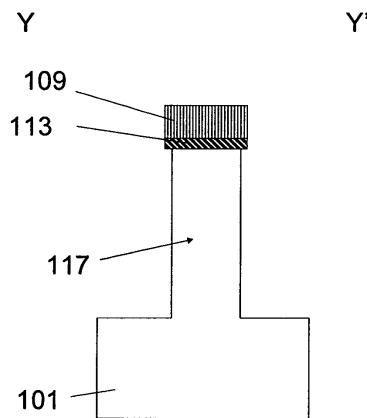

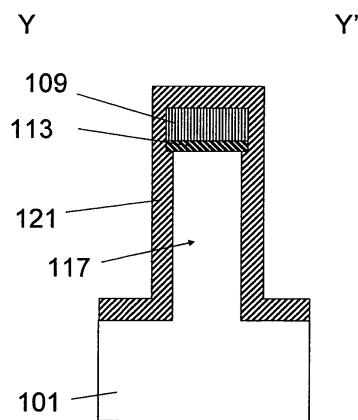

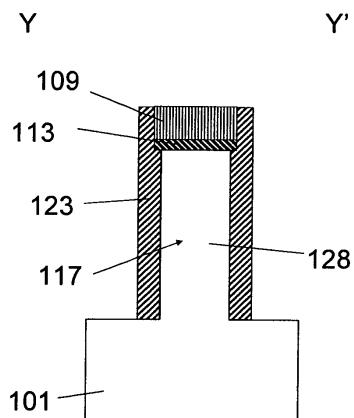

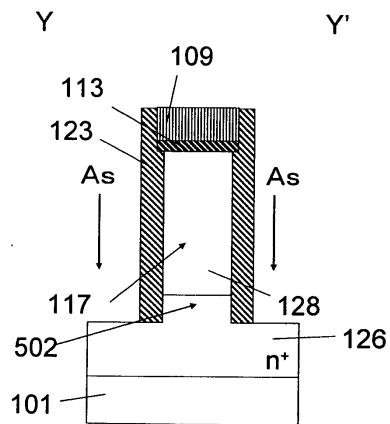

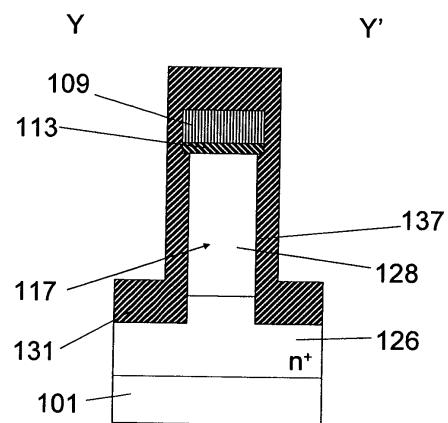

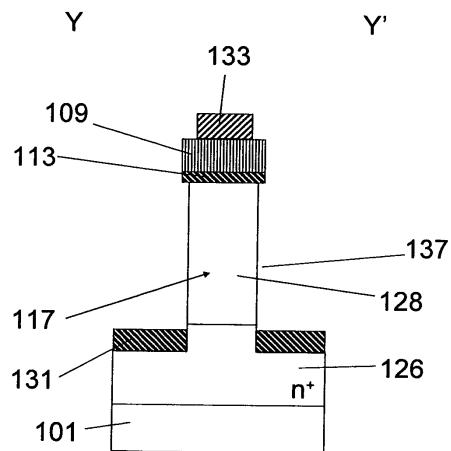

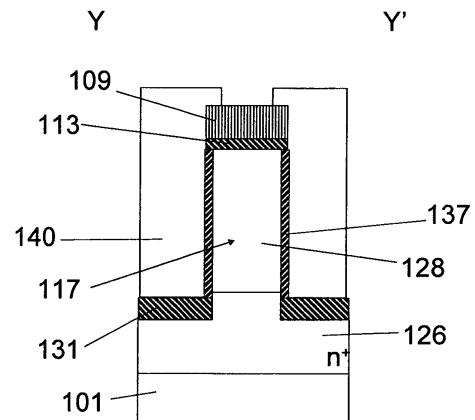

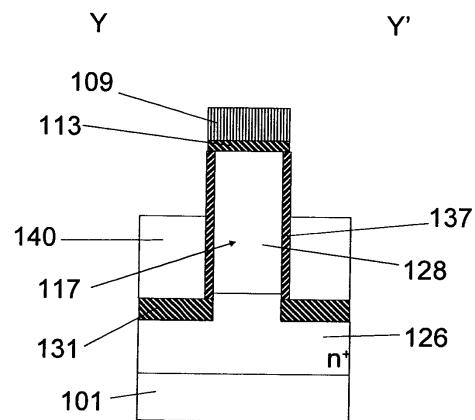

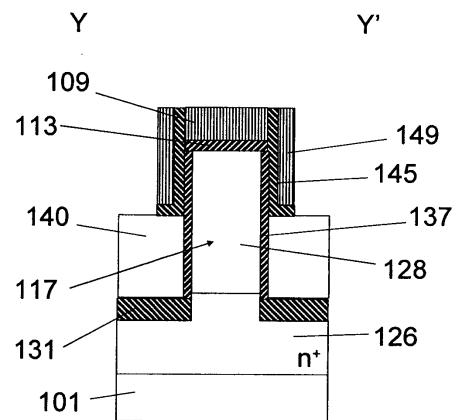

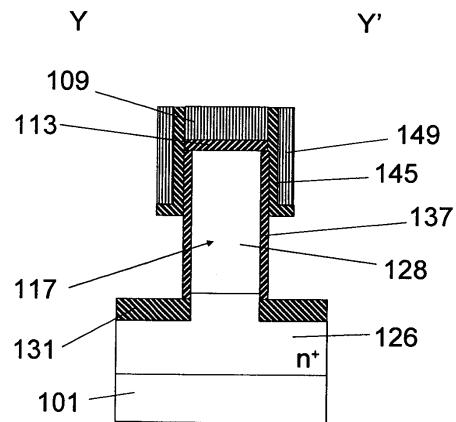

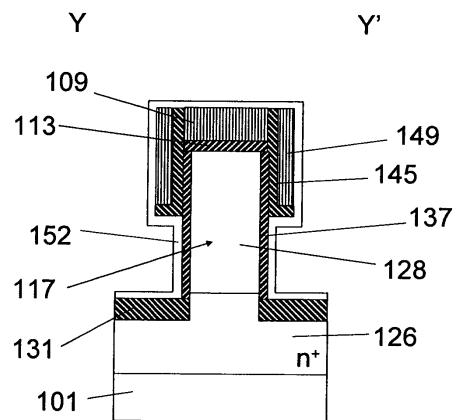

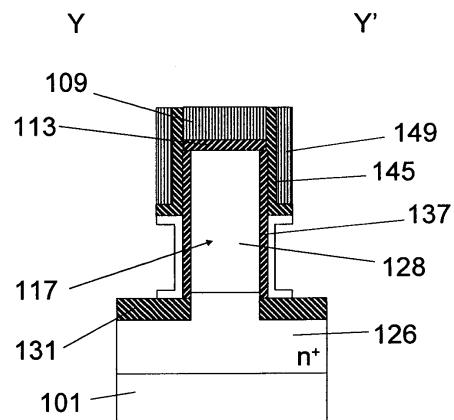

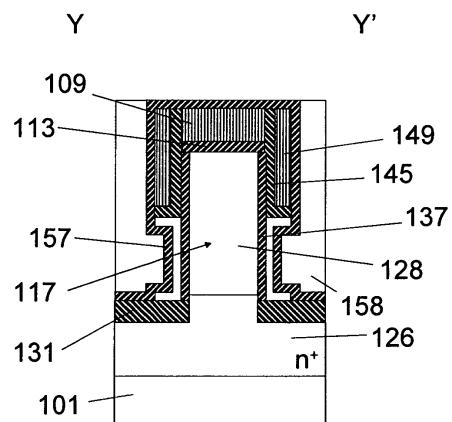

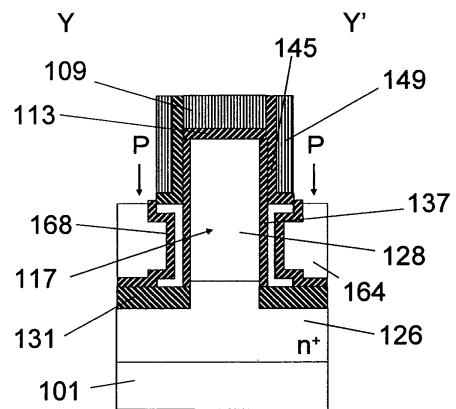

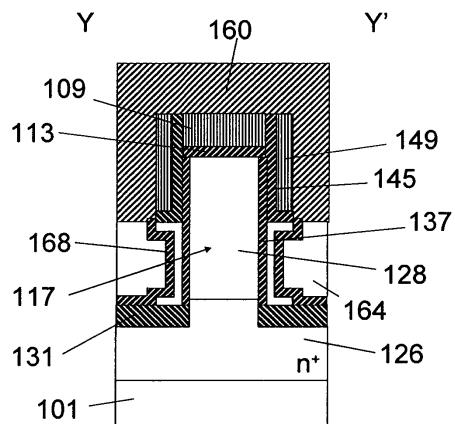

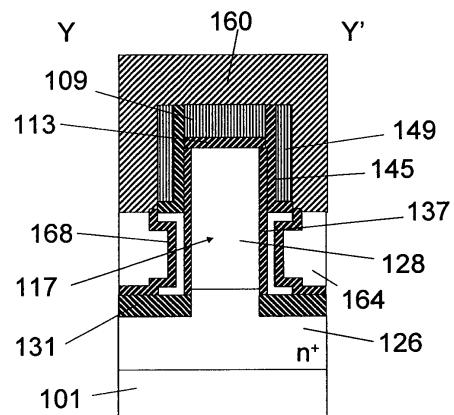

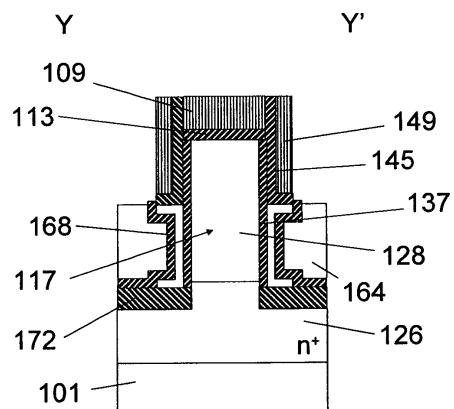

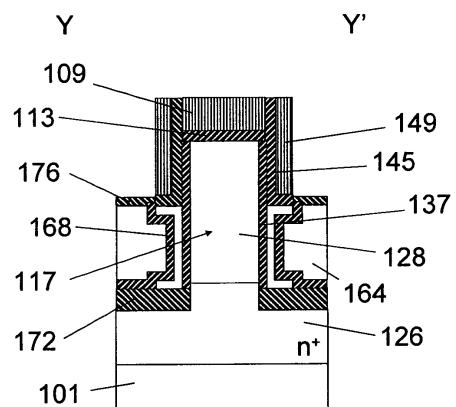

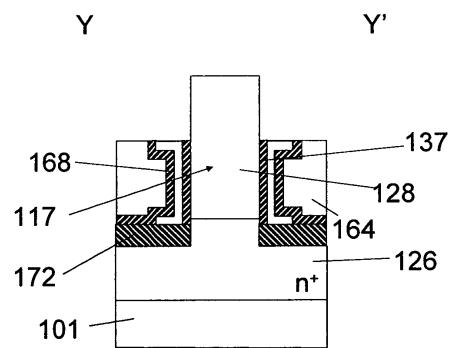

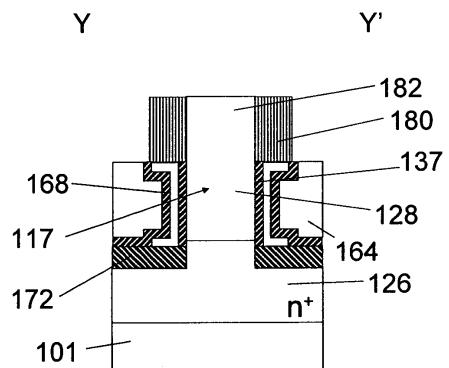

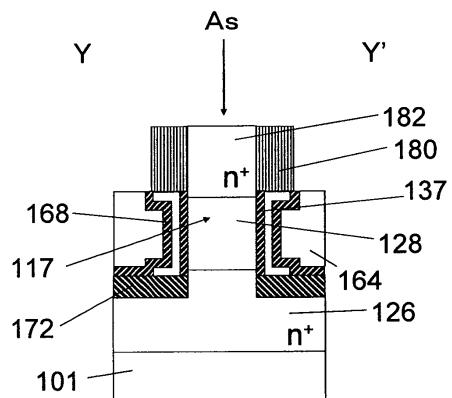

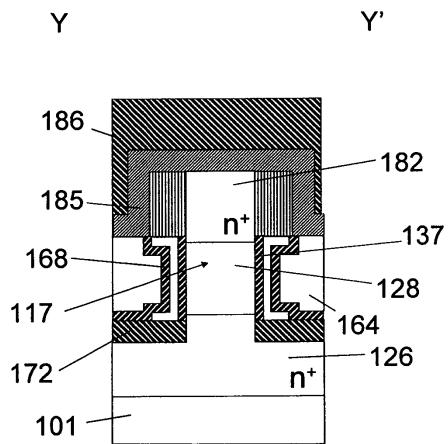

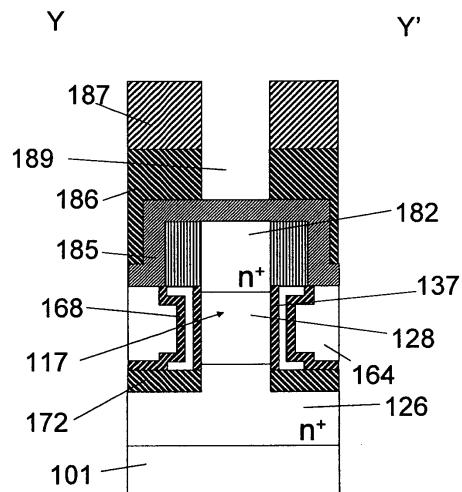

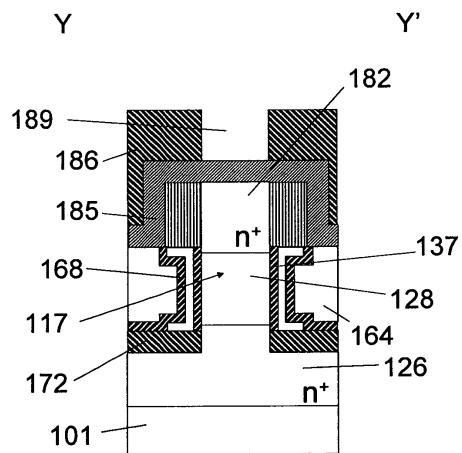

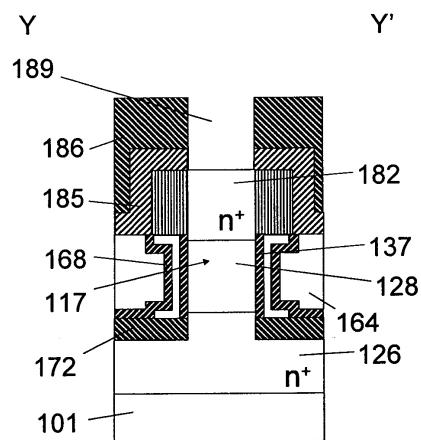

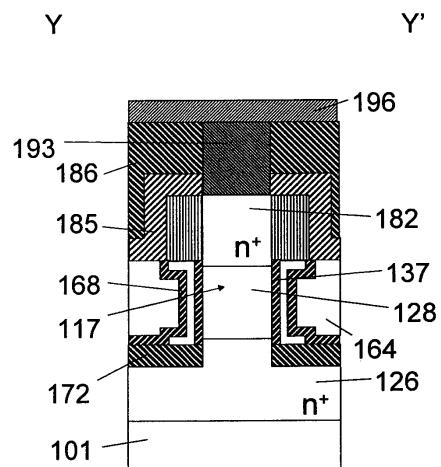

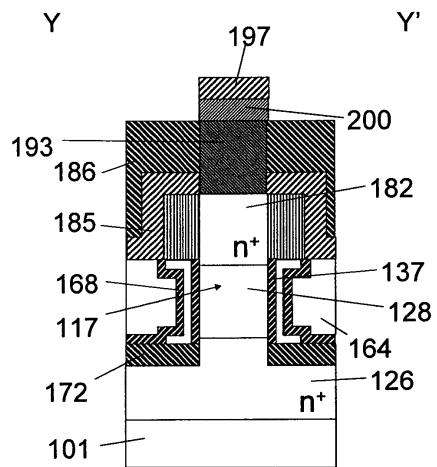

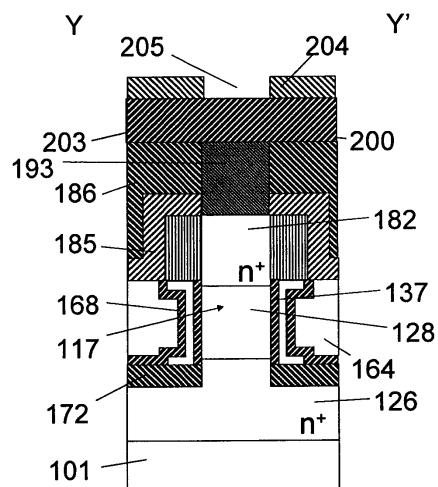

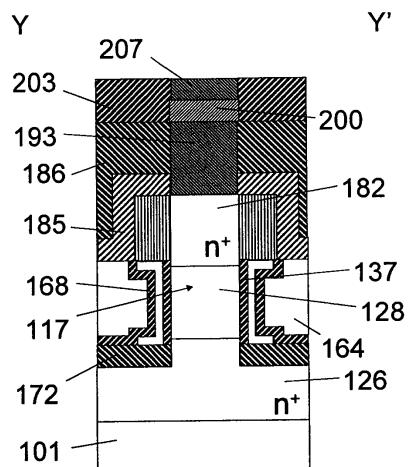

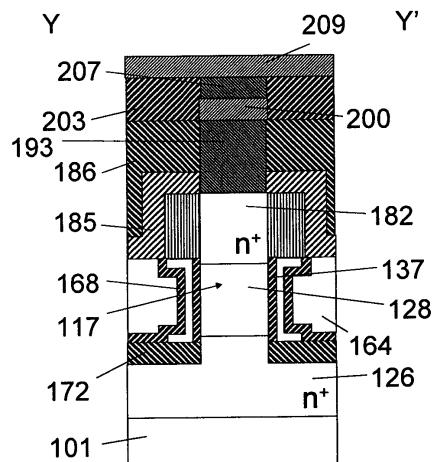

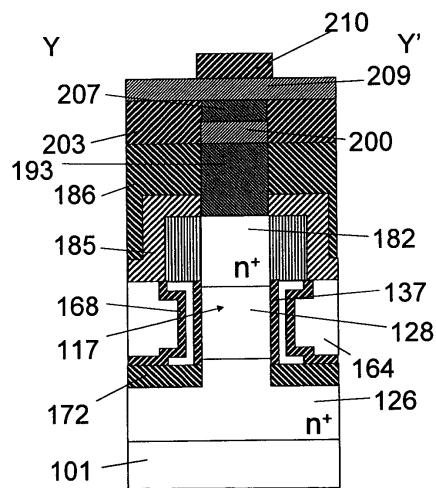

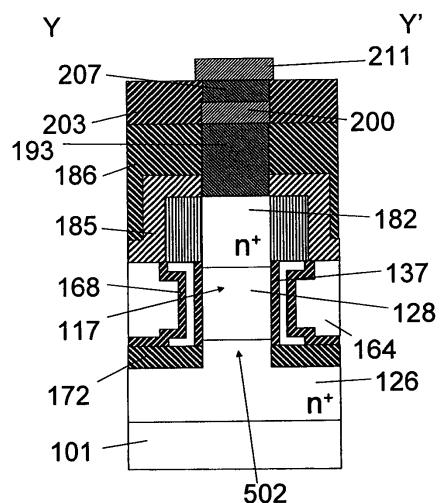

도 2c 는, 도 2a 의 Y-Y' 선에서의 단면도.

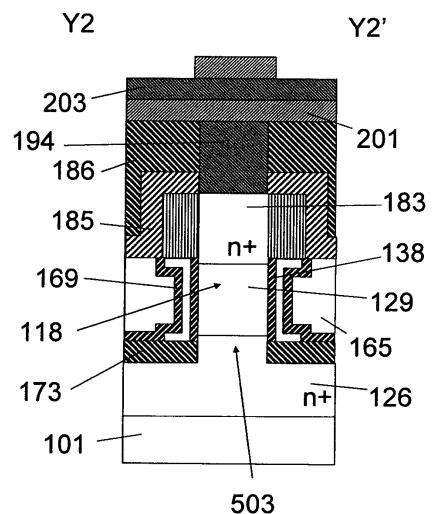

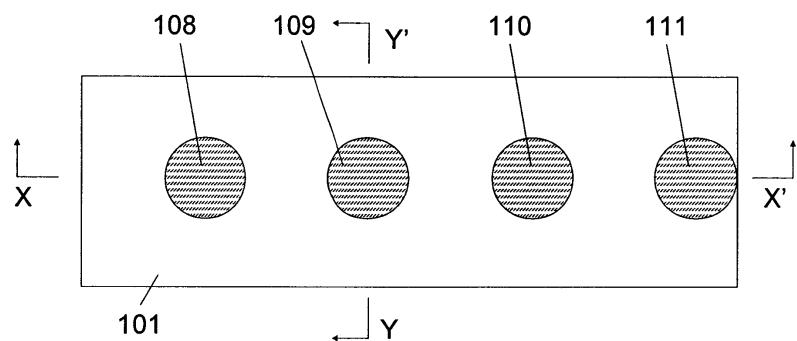

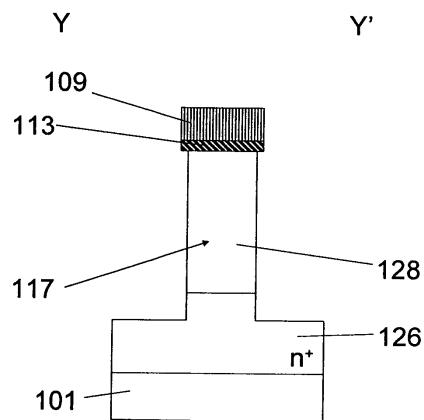

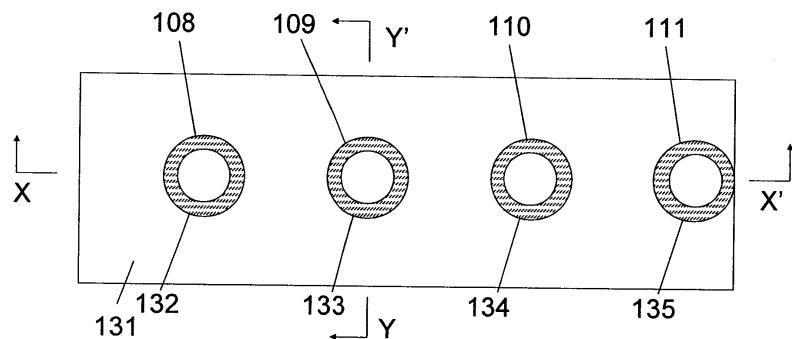

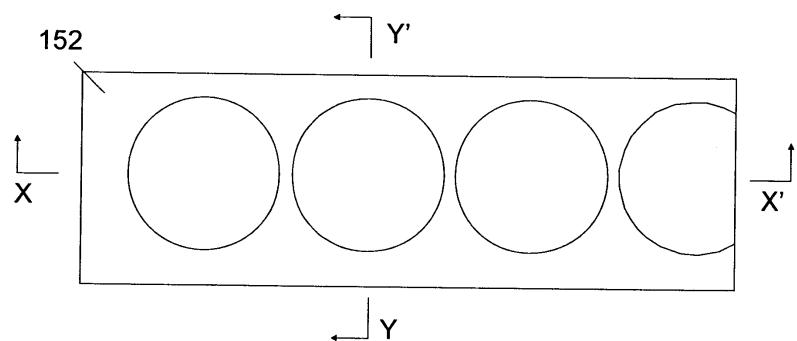

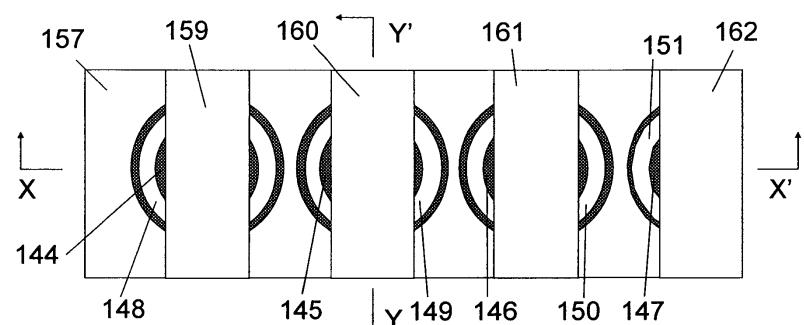

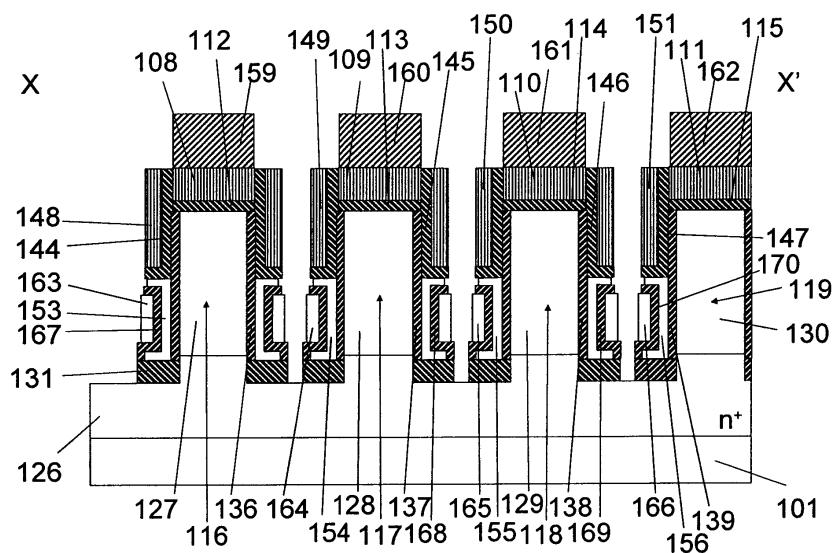

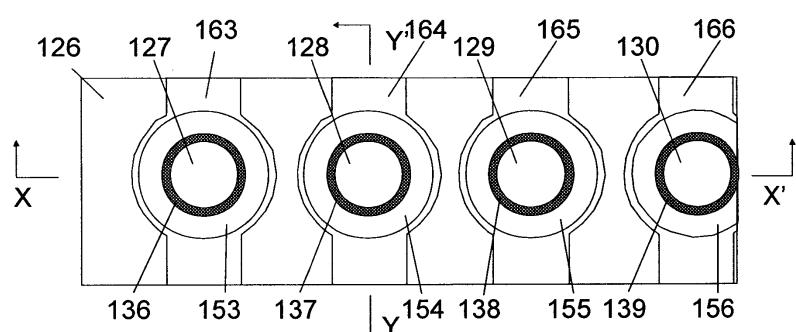

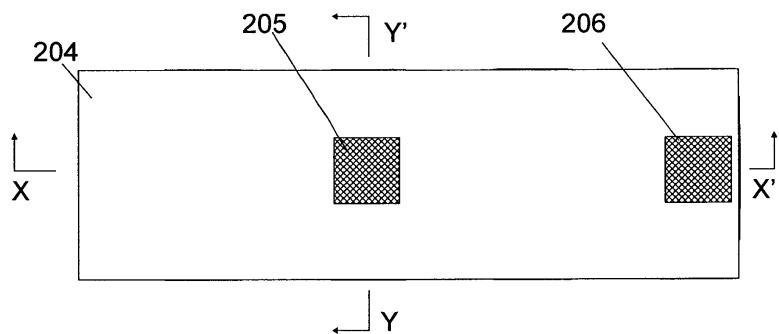

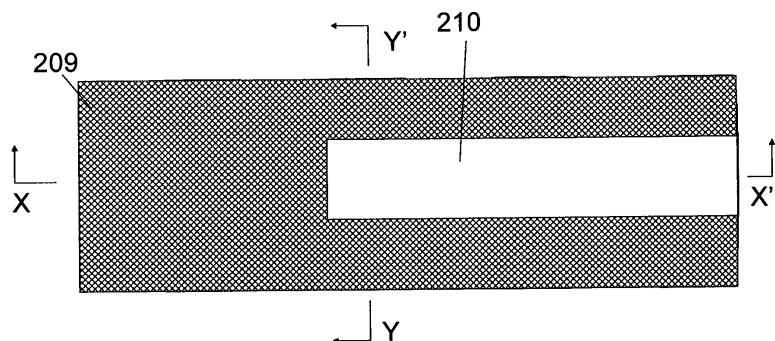

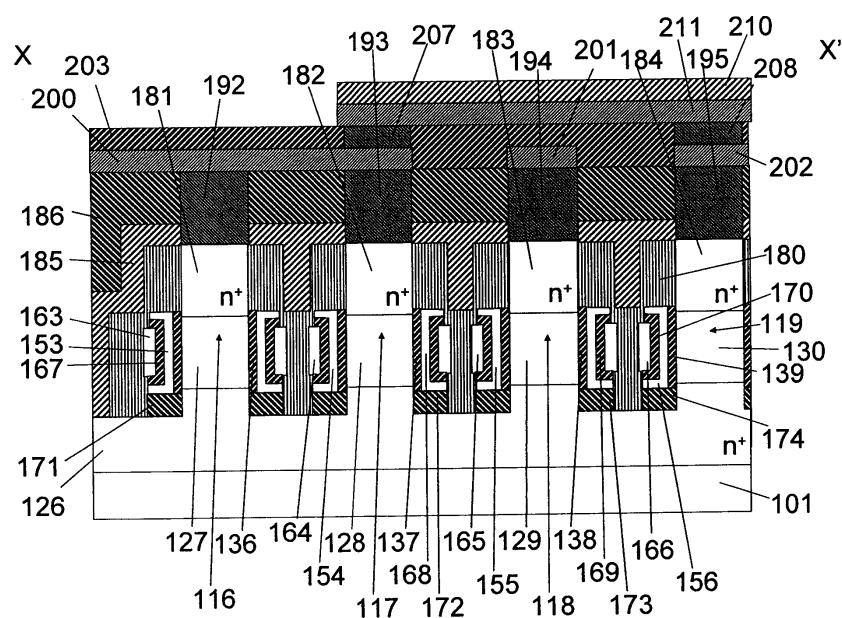

도 2d 는, 도 2a 의 Y2-Y2' 선에서의 단면도.

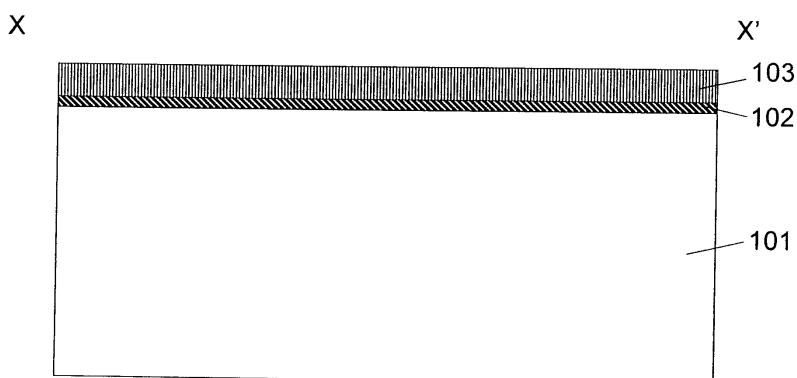

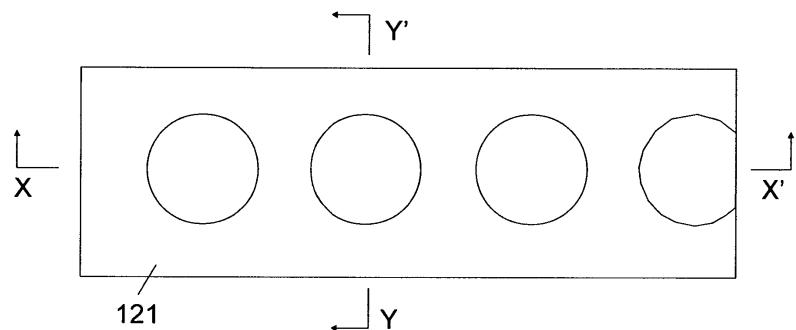

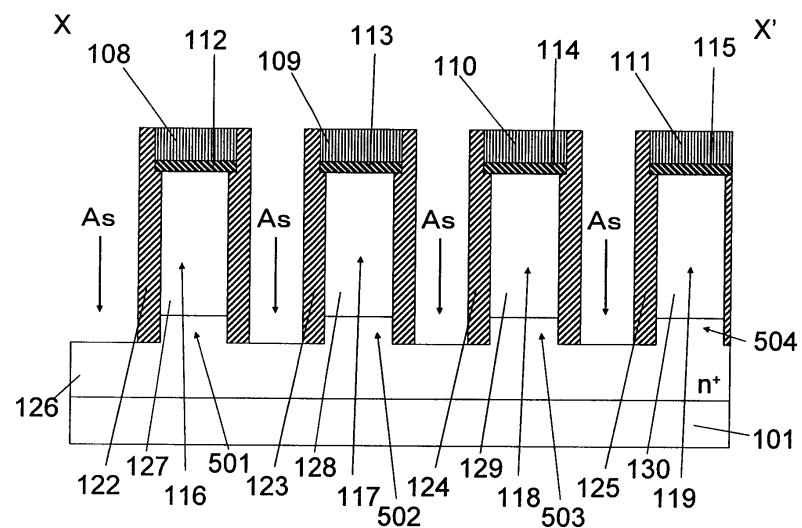

도 3a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 3b 는, 도 3a 의 X-X' 선에서의 단면도.

도 3c 는, 도 3a 의 Y-Y' 선에서의 단면도.

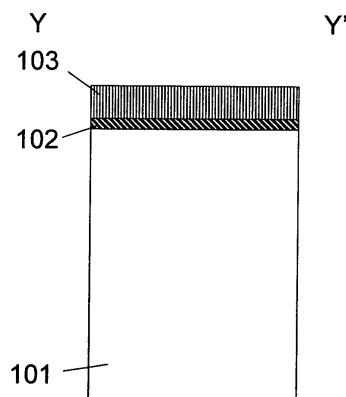

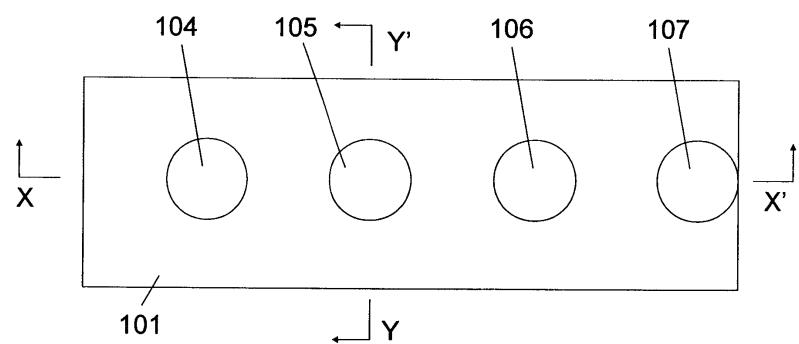

도 4a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 4b 는, 도 4a 의 X-X' 선에서의 단면도.

도 4c 는, 도 4a 의 Y-Y' 선에서의 단면도.

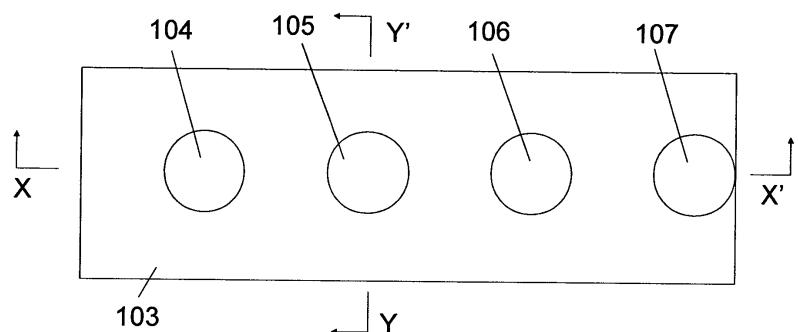

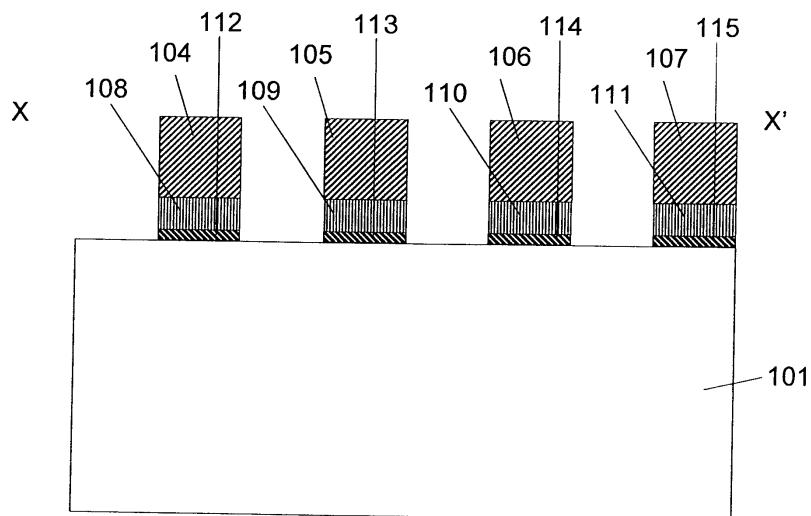

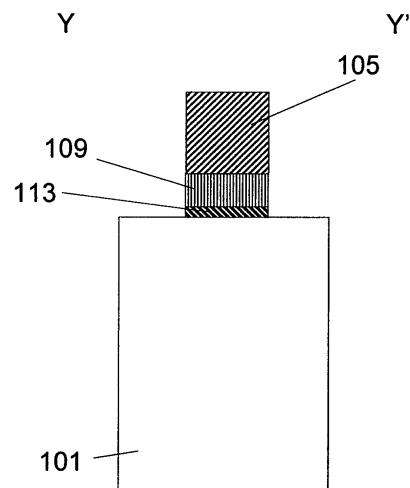

도 5a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 5b 는, 도 5a 의 X-X' 선에서의 단면도.

도 5c 는, 도 5a 의 Y-Y' 선에서의 단면도.

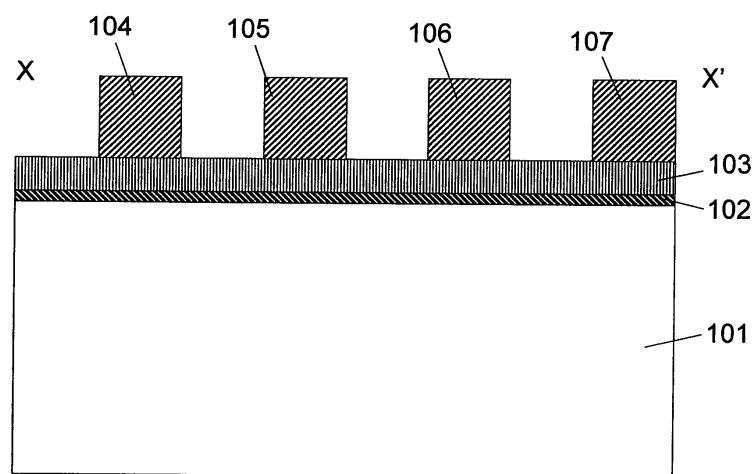

도 6a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 6b 는, 도 6a 의 X-X' 선에서의 단면도.

도 6c 는, 도 6a 의 Y-Y' 선에서의 단면도.

도 7a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 7b 는, 도 7a 의 X-X' 선에서의 단면도.

도 7c 는, 도 7a 의 Y-Y' 선에서의 단면도.

도 8a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 8b 는, 도 8a 의 X-X' 선에서의 단면도.

도 8c 는, 도 8a 의 Y-Y' 선에서의 단면도.

도 9a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 9b 는, 도 9a 의 X-X' 선에서의 단면도.

도 9c 는, 도 9a 의 Y-Y' 선에서의 단면도.

도 10a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 10b 는, 도 10a 의 X-X' 선에서의 단면도.

도 10c 는, 도 10a 의 Y-Y' 선에서의 단면도.

도 11a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 11b 는, 도 11a 의 X-X' 선에서의 단면도.

도 11c 는, 도 11a 의 Y-Y' 선에서의 단면도.

도 12a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 12b 는, 도 12a 의 X-X' 선에서의 단면도.

도 12c 는, 도 12a 의 Y-Y' 선에서의 단면도.

도 13a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 13b 는, 도 13a 의 X-X' 선에서의 단면도.

도 13c 는, 도 13a 의 Y-Y' 선에서의 단면도.

도 14a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 14b 는, 도 14a 의 X-X' 선에서의 단면도.

도 14c 는, 도 14a 의 Y-Y' 선에서의 단면도.

도 15a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 15b 는, 도 15a 의 X-X' 선에서의 단면도.

도 15c 는, 도 15a 의 Y-Y' 선에서의 단면도.

도 16a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 16b 는, 도 16a 의 X-X' 선에서의 단면도.

도 16c 는, 도 16a 의 Y-Y' 선에서의 단면도.

도 17a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 17b 는, 도 17a 의 X-X' 선에서의 단면도.

도 17c 는, 도 17a 의 Y-Y' 선에서의 단면도.

도 18a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 18b 는, 도 18a 의 X-X' 선에서의 단면도.

도 18c 는, 도 18a 의 Y-Y' 선에서의 단면도.

도 19a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 19b 는, 도 19a 의 X-X' 선에서의 단면도.

도 19c 는, 도 19a 의 Y-Y' 선에서의 단면도.

도 20a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 20b 는, 도 20a 의 X-X' 선에서의 단면도.

도 20c 는, 도 20a 의 Y-Y' 선에서의 단면도.

도 21a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 21b 는, 도 21a 의 X-X' 선에서의 단면도.

도 21c 는, 도 21a 의 Y-Y' 선에서의 단면도.

도 22a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 22b 는, 도 22a 의 X-X' 선에서의 단면도.

도 22c 는, 도 22a 의 Y-Y' 선에서의 단면도.

도 23a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 23b 는, 도 23a 의 X-X' 선에서의 단면도.

도 23c 는, 도 23a 의 Y-Y' 선에서의 단면도.

도 24a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 24b 는, 도 24a 의 X-X' 선에서의 단면도.

도 24c 는, 도 24a 의 Y-Y' 선에서의 단면도.

도 25a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 25b 는, 도 25a 의 X-X' 선에서의 단면도.

도 25c 는, 도 25a 의 Y-Y' 선에서의 단면도.

도 26a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 26b 는, 도 26a 의 X-X' 선에서의 단면도.

도 26c 는, 도 26a 의 Y-Y' 선에서의 단면도.

도 27a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 27b 는, 도 27a 의 X-X' 선에서의 단면도.

도 27c 는, 도 27a 의 Y-Y' 선에서의 단면도.

도 28a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 28b 는, 도 28a 의 X-X' 선에서의 단면도.

도 28c 는, 도 28a 의 Y-Y' 선에서의 단면도.

도 29a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 29b 는, 도 29a 의 X-X' 선에서의 단면도.

도 29c 는, 도 29a 의 Y-Y' 선에서의 단면도.

도 30a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 30b 는, 도 30a 의 X-X' 선에서의 단면도.

도 30c 는, 도 30a 의 Y-Y' 선에서의 단면도.

도 31a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 31b 는, 도 31a 의 X-X' 선에서의 단면도.

도 31c 는, 도 31a 의 Y-Y' 선에서의 단면도.

도 32a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 32b 는, 도 32a 의 X-X' 선에서의 단면도.

도 32c 는, 도 32a 의 Y-Y' 선에서의 단면도.

도 33a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 33b 는, 도 33a 의 X-X' 선에서의 단면도.

도 33c 는, 도 33a 의 Y-Y' 선에서의 단면도.

도 34a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 34b 는, 도 34a 의 X-X' 선에서의 단면도.

도 34c 는, 도 34a 의 Y-Y' 선에서의 단면도.

도 35a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 35b 는, 도 35a 의 X-X' 선에서의 단면도.

도 35c 는, 도 35a 의 Y-Y' 선에서의 단면도.

도 36a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 36b 는, 도 36a 의 X-X' 선에서의 단면도.

도 36c 는, 도 36a 의 Y-Y' 선에서의 단면도.

도 37a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 37b 는, 도 37a 의 X-X' 선에서의 단면도.

도 37c 는, 도 37a 의 Y-Y' 선에서의 단면도.

도 38a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 38b 는, 도 38a 의 X-X' 선에서의 단면도.

도 38c 는, 도 38a 의 Y-Y' 선에서의 단면도.

도 39a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 39b 는, 도 39a 의 X-X' 선에서의 단면도.

도 39c 는, 도 39a 의 Y-Y' 선에서의 단면도.

도 40a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 40b 는, 도 40a 의 X-X' 선에서의 단면도.

도 40c 는, 도 40a 의 Y-Y' 선에서의 단면도.

도 41a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 41b 는, 도 41a 의 X-X' 선에서의 단면도.

도 41c 는, 도 41a 의 Y-Y' 선에서의 단면도.

도 42a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 42b 는, 도 42a 의 X-X' 선에서의 단면도.

도 42c 는, 도 42a 의 Y-Y' 선에서의 단면도.

도 43a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 43b 는, 도 43a 의 X-X' 선에서의 단면도.

도 43c 는, 도 43a 의 Y-Y' 선에서의 단면도.

도 44a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 44b 는, 도 44a 의 X-X' 선에서의 단면도.

도 44c 는, 도 44a 의 Y-Y' 선에서의 단면도.

도 45a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 45b 는, 도 45a 의 X-X' 선에서의 단면도.

도 45c 는, 도 45a 의 Y-Y' 선에서의 단면도.

도 46a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 46b 는, 도 46a 의 X-X' 선에서의 단면도.

도 46c 는, 도 46a 의 Y-Y' 선에서의 단면도.

도 47a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 47b 는, 도 47a 의 X-X' 선에서의 단면도.

도 47c 는, 도 47a 의 Y-Y' 선에서의 단면도.

도 48a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 48b 는, 도 48a 의 X-X' 선에서의 단면도.

도 48c 는, 도 48a 의 Y-Y' 선에서의 단면도.

도 49a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 49b 는, 도 49a 의 X-X' 선에서의 단면도.

도 49c 는, 도 49a 의 Y-Y' 선에서의 단면도.

도 50a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 50b 는, 도 50a 의 X-X' 선에서의 단면도.

도 50c 는, 도 50a 의 Y-Y' 선에서의 단면도.

도 51a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 51b 는, 도 51a 의 X-X' 선에서의 단면도.

도 51c 는, 도 51a 의 Y-Y' 선에서의 단면도.

도 52a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 52b 는, 도 52a 의 X-X' 선에서의 단면도.

도 52c 는, 도 52a 의 Y-Y' 선에서의 단면도.

도 53a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 53b 는, 도 53a 의 X-X' 선에서의 단면도.

도 53c 는, 도 53a 의 Y-Y' 선에서의 단면도.

도 54a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 54b 는, 도 54a 의 X-X' 선에서의 단면도.

도 54c 는, 도 54a 의 Y-Y' 선에서의 단면도.

도 55a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 55b 는, 도 55a 의 X-X' 선에서의 단면도.

도 55c 는, 도 55a 의 Y-Y' 선에서의 단면도.

도 56a 는, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리의 제조 방법을 설명하기 위한 평면도.

도 56b 는, 도 56a 의 X-X' 선에서의 단면도.

도 56c 는, 도 56a 의 Y-Y' 선에서의 단면도.

도 57 은, 종래예의 SGT 플래시 메모리의 단면도.

### 발명을 실시하기 위한 구체적인 내용

[0029] 이하, 본 발명의 실시형태를 도면을 참조하면서 설명한다. 한편, 본 발명은, 이하에 나타내는 실시형태에 의해 한정되는 것은 아니다.

[0030] 도 1 에, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리 트랜지스터의 단면도를 나타낸다.

[0031] 도 1 에 나타내는 바와 같이, 이 불휘발성 반도체 메모리 트랜지스터는, 소스 영역 (303), 채널 영역 (304) 및 드레인 영역 (302) 이, 원기둥 형상의 섬 형상 반도체 (301) 를 구성하고, 실리콘 기판 (101) 측으로부터 이 순서로 형성되어 있다. 또한, 불휘발성 반도체 메모리 트랜지스터는, 채널 영역 (304) 의 외주를 둘러싸도록 배치된 중공 원기둥 형상의 부유 게이트 (306) 와, 당해 부유 게이트 (306) 의 외주에 위치하고, 부유 게이트 (306) 에 대향 (포위) 하도록 배치된 중공 원기둥 형상의 제어 게이트 (308) 를 구비하고 있다. 여기서, 부유 게이트 (306) 와 채널 영역 (304) 사이에는 터널 절연막 (305) 이 개재 배치되어 있다. 또한, 제어 게이트 (308) 와 부유 게이트 (306) 사이에는, 인터폴리 절연막 (307) 이 개재 배치되어 있다.

[0032] 도 1 에 나타내는 바와 같이, 부유 게이트 (306) 에는, 그 외주벽을 따라 원고리 형상의 오목부 (306a) 가 형성되어 있다. 그리고, 그 오목부 (306a) 에는, 중공 기둥 형상의 제어 게이트 (308) 가, 당해 제어 게이트 (308) 의 상면, 하면 및 내측면과의 사이에, 인터폴리 절연막 (307) 을 개재시킨 상태로 배치되어 있다. 이 배치 구성에 의해, 제어 게이트 (308) 의 크기 (체적) 에 비해, 제어 게이트 (308) 와 부유 게이트 (306) 사이에 두께가 얇으며, 또한 얕은 면적으로 유전체로서의 인터폴리 절연막 (307) 이 형성되게 되기 때문에, 부유 게이트 (306) 와 제어 게이트 (308) 사이의 용량 (정전 용량) 을 크게 할 수 있다. 게다가, 이 배치 구성에 의해, 제어 게이트 (308) 의 상면, 하면 및 내측면이 도전체인 부유 게이트 (306) 로 덮이게 되기 때문에, 제어 게이트 (308) 와 섬 형상 반도체 (301) 가 절연막을 개재하여 근접하는 경우가 없어져, 제어 게이트와 섬 형상 반도체 사이의 기생 용량을 실질적으로 0 (제로) 로 할 수 있다.

[0033] 도 2a, 도 2b, 도 2c, 도 2d 에, 각각 본 실시형태에 관련된 불휘발성 반도체 메모리의 평면도, 도 2a 의 X-X' 단면도, 도 2a 의 Y-Y' 단면도, 도 2a 의 Y2-Y2' 단면도를 나타낸다.

[0034] 도 2a 및 도 2b 에 나타내는 바와 같이, 이 불휘발성 반도체 메모리는, 도 1 에 나타낸 구조를 갖는 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 가, 복수 개 (동 도면에서는 4 개), 실리콘 기판 (101) 상의 행렬 방향에 있어서의 복수의 행 방향으로, 각각 일직선 형상, 또한, 대략 등각도 간격으로 정렬 배치되어 이루어지는 것이다.

[0035] 도 2a ~ 도 2d 에 나타내는 불휘발성 반도체 메모리에 있어서, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 열 방향의 1 열째에는, 불휘발성 반도체 메모리 트랜지스터 (212) 가 배치되어 있다.

[0036] 도 2a, 도 2b 에 나타내는 바와 같이, 이 불휘발성 반도체 메모리 트랜지스터 (212) 에서는, 소스 영역 (501), 채널 영역 (127) 및 드레인 영역 (181) 이 섬 형상 반도체 (116) 를 구성함과 함께, 실리콘 기판 (101) 측으로부터 이 순서로 형성되어 있다.

[0037] 불휘발성 반도체 메모리 트랜지스터 (212) 는, 채널 영역 (127) 의 외주를 둘러싸도록, 또한 당해 채널 영역

(127) 과의 사이에 터널 절연막 (136) 을 개재시켜 배치된 중공 기둥 형상의 부유 게이트 (153) 와, 부유 게이트 (153) 의 외주를 둘러싸도록, 또한 당해 부유 게이트 (153) 와의 사이에 인터폴리 절연막 (167) 을 개재시킨 상태로 배치된 중공 기둥 형상의 제어 게이트 (163) 를 구비하고 있다.

[0038] 도 2b 에 나타내는 바와 같이, 부유 게이트 (153) 는, 그 외주벽을 따라 원고리 형상의 오목부 (153a) 가 형성되어 있다. 그 오목부 (153a) 에는, 중공 기둥 형상의 제어 게이트 (163) 가, 당해 제어 게이트 (163) 의 상면, 하면 및 내측면과의 사이에 인터폴리 절연막 (167) 을 개재시킨 상태로 수용되어 있다.

[0039] 불휘발성 반도체 메모리 트랜지스터 (212) 에 있어서, 부유 게이트 (153) 의 하면에는, 터널 절연막 (136) 및 인터폴리 절연막 (167) 의 두께보다 두꺼운 제 1 절연막 (171) 이 배치되어 있다. 여기서는, 제 1 절연막 (171) 의 두께는, 터널 절연막 (136) 및 인터폴리 절연막 (167) 의 어느 두께보다 두껍다. 그러나 이것에 한정되지 않고, 제 1 절연막 (171) 은, 터널 절연막 (136) 및 인터폴리 절연막 (167) 의 적어도 일방의 두께보다 두꺼워도 상관없다.

[0040] 도 2a, 도 2b, 도 2c, 도 2d 에 나타내는 불휘발성 반도체 메모리에 있어서, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 열 방향의 2 열째에는, 불휘발성 반도체 메모리 트랜지스터 (213) 가 배치되어 있다.

[0041] 도 2a, 도 2b, 도 2c 에 나타내는 바와 같이, 이 불휘발성 반도체 메모리 트랜지스터 (213) 에서는, 소스 영역 (502), 채널 영역 (128) 및 드레인 영역 (182) 이 섬 형상 반도체 (117) 를 구성함과 함께, 실리콘 기판 (101) 측으로부터 이 순서로 형성되어 있다.

[0042] 불휘발성 반도체 메모리 트랜지스터 (213) 는, 채널 영역 (128) 의 외주를 둘러싸도록, 또한 당해 채널 영역 (128) 과의 사이에 터널 절연막 (137) 을 개재시킨 상태로 배치된 중공 기둥 형상의 부유 게이트 (154) 와, 부유 게이트 (154) 의 외주를 둘러싸도록, 또한 당해 부유 게이트 (154) 와의 사이에 인터폴리 절연막 (168) 을 개재시킨 상태로 배치된 중공 기둥 형상의 제어 게이트 (164) 를 구비하고 있다.

[0043] 도 2b, 도 2c 에 나타내는 바와 같이, 부유 게이트 (154) 는, 그 외주벽을 따라 원고리 형상의 오목부 (154a) 가 형성되어 있다. 그 오목부 (154a) 에는, 중공 기둥 형상의 제어 게이트 (164) 가, 당해 제어 게이트 (164) 의 상면, 하면 및 내측면과의 사이에 인터폴리 절연막 (168) 을 개재시킨 상태로 수용되어 있다.

[0044] 불휘발성 반도체 메모리 트랜지스터 (213) 에 있어서, 부유 게이트 (154) 의 하면에는, 터널 절연막 (137) 및 인터폴리 절연막 (168) 의 두께보다 두꺼운 제 1 절연막 (172) 이 배치되어 있다. 여기서는, 제 1 절연막 (172) 의 두께는, 터널 절연막 (137) 및 인터폴리 절연막 (168) 의 어느 두께보다 두껍다. 그러나 이것에 한정되지 않고, 제 1 절연막 (172) 은, 터널 절연막 (137) 및 인터폴리 절연막 (168) 의 적어도 일방의 두께보다 두꺼워도 상관없다.

[0045] 도 2a ~ 도 2d 에 나타내는 불휘발성 반도체 메모리에 있어서, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 열 방향의 3 열째에는, 불휘발성 반도체 메모리 트랜지스터 (214) 가 배치되어 있다.

[0046] 도 2a, 도 2b, 도 2d 에 나타내는 바와 같이, 이 불휘발성 반도체 메모리 트랜지스터 (214) 에서는, 소스 영역 (503), 채널 영역 (129) 및 드레인 영역 (183) 이 섬 형상 반도체 (118) 를 구성함과 함께, 실리콘 기판 (101) 측으로부터 이 순서로 형성되어 있다.

[0047] 불휘발성 반도체 메모리 트랜지스터 (214) 는, 채널 영역 (129) 의 외주를 둘러싸도록, 또한 당해 채널 영역 (129) 과의 사이에 터널 절연막 (138) 을 개재시킨 상태로 배치된 중공 기둥 형상의 부유 게이트 (155) 와, 부유 게이트 (155) 의 외주를 둘러싸도록, 또한 당해 부유 게이트 (155) 와의 사이에 인터폴리 절연막 (169) 을 개재시킨 상태로 배치된 중공 기둥 형상의 제어 게이트 (165) 를 구비하고 있다.

[0048] 도 2b, 도 2d 에 나타내는 바와 같이, 부유 게이트 (155) 는, 그 외주벽을 따라 원고리 형상의 오목부 (155a) 가 형성되어 있다. 그 오목부 (155a) 에는, 중공 기둥 형상의 제어 게이트 (165) 가, 당해 제어 게이트 (165) 의 상면, 하면 및 내측면과의 사이에 인터폴리 절연막 (169) 을 개재시킨 상태로 수용되어 있다.

[0049] 불휘발성 반도체 메모리 트랜지스터 (214) 에 있어서, 부유 게이트 (155) 의 하면에는, 터널 절연막 (138) 및 인터폴리 절연막 (169) 의 두께보다 두꺼운 제 1 절연막 (173) 이 배치되어 있다. 여기서는, 제 1 절연막 (173) 의 두께는, 터널 절연막 (138) 및 인터폴리 절연막 (169) 의 어느 두께보다 두껍다. 그러나 이것에 한정되지 않고, 제 1 절연막 (173) 은, 터널 절연막 (138) 및 인터폴리 절연막 (169) 의 적어도 일방의 두께보다 두꺼워도 상관없다.

[0050] 도 2a ~ 도 2d 에 나타내는 불휘발성 반도체 메모리에 있어서, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 열 방향의 4 열째에는, 불휘발성 반도체 메모리 트랜지스터 (215) 가 배치되어 있다.

[0051] 도 2a, 도 2b 에 나타내는 바와 같이, 이 불휘발성 반도체 메모리 트랜지스터 (215) 에서는, 소스 영역 (504), 채널 영역 (130) 및 드레인 영역 (184) 이 섬 형상 반도체 (119) 를 구성함과 함께, 실리콘 기판 (101) 측으로 부터 이 순서로 형성되어 있다.

[0052] 불휘발성 반도체 메모리 트랜지스터 (215) 는, 채널 영역 (130) 의 외주를 둘러싸도록, 또한 당해 채널 영역 (130) 과의 사이에 터널 절연막 (139) 을 개재시킨 상태로 배치된 중공 기둥 형상의 부유 게이트 (156) 와, 부유 게이트 (156) 의 외주를 둘러싸도록, 또한 당해 부유 게이트 (156) 와의 사이에 인터폴리 절연막 (170) 을 개재시킨 상태로 배치된 중공 기둥 형상의 제어 게이트 (166) 를 구비하고 있다.

[0053] 도 2b 에 나타내는 바와 같이, 부유 게이트 (156) 는, 그 외주벽을 따라 원고리 형상의 오목부 (156a) 가 형성되어 있다. 그 오목부 (156a) 에는, 중공 원기둥 형상의 제어 게이트 (166) 가, 당해 제어 게이트 (166) 의 상면, 하면 및 내측면과의 사이에 인터폴리 절연막 (170) 을 개재시킨 상태로 배치되어 있다.

[0054] 불휘발성 반도체 메모리 트랜지스터 (215) 에 있어서, 부유 게이트 (156) 의 하면에는, 터널 절연막 (139) 및 인터폴리 절연막 (170) 의 두께보다 두꺼운 제 1 절연막 (174) 이 배치되어 있다. 여기서는, 제 1 절연막 (174) 의 두께는, 터널 절연막 (139) 및 인터폴리 절연막 (170) 의 어느 두께보다 두껍다. 그러나 이것에 한정되지 않고, 제 1 절연막 (174) 은, 터널 절연막 (139) 및 인터폴리 절연막 (170) 의 적어도 일방의 두께보다 두꺼워도 상관없다.

[0055] 도 2a ~ 도 2d 에 나타내는 불휘발성 반도체 메모리에 있어서, 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 의 소스 영역 (501, 502, 503, 504) 은, 각각 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 의 섬 형상 반도체 (116, 117, 118, 119) 의 하방 부위에 형성됨과 함께, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 열 방향으로 배선된 제 1 차 소스선 (126) 에 전기적으로 접속되어 있다. 또한, 불휘발성 반도체 메모리 트랜지스터 (212, 213, 215) 의 드레인 영역 (181, 182, 184) 은, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 열 방향으로 배선된, 드레인 배선으로서의 제 1 차 메탈 배선 (200, 202) 에 전기적으로 접속되어 있다. 또한, 불휘발성 반도체 메모리 트랜지스터 (214) 의 드레인 영역 (183) 은, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 행 방향으로 배선된 제 2 차 소스선 (201) 에 전기적으로 접속되어 있다.

[0056] 도 2a ~ 도 2d 에 나타내는 불휘발성 반도체 메모리에 있어서, 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 의 부유 게이트 (153, 154, 155, 156) 의 하방에는, 각각 터널 절연막 (136, 137, 138, 139), 및 인터폴리 절연막 (167, 168, 169, 170) 의 두께보다 두꺼운 제 1 절연막 (171, 172, 173, 174) 이 배치되어 있다. 이로써, 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 에 있어서, 각각 부유 게이트 (153, 154, 155, 156) 와 제 1 차 소스선 (126) 사이의 기생 용량이 저감된다. 그 결과, 제어 게이트 (163, 164, 165, 166) 에 외부 전원 (도시 생략) 으로부터 인가된 전압이, 제 1 절연막 (171, 172, 173, 174) 이 배치되어 있지 않은 경우와 비교하여, 더욱 효율적으로 부유 게이트 (153, 154, 155, 156) 에 전달되게 된다. 이로써, 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 에 있어서, "1", "0" 등의 정보의 기록, 소거, 판독을 보다 확실하게 실시할 수 있게 된다.

[0057] 또한, 도 2a ~ 도 2d 에 나타내는 불휘발성 반도체 메모리에서는, 실리콘 기판 (101) 상에 있어서, 3 열째에 배치된 불휘발성 반도체 메모리 트랜지스터 (214) 의 드레인 영역 (183) 은, 컨택트 (194) 를 개재하여, 실리콘 기판 (101) 상의 행렬 방향에 있어서의 열 방향으로 배선된 제 2 차 소스선 (201) 에 접속되어 있다. 이 불휘발성 반도체 메모리 트랜지스터 (214) 는, 당해 트랜지스터 (214) 를 개재하여, 제 2 차 소스선 (201) 으로부터 제 1 차 소스선 (126) 에 전압을 인가하기 위해서 사용된다. 이 때문에, 불휘발성 반도체 메모리 트랜지스터 (214) 의 반복 패턴을 사용할 수 있다. 이와 같은 불휘발성 반도체 메모리 트랜지스터 (214) 의 반복 패턴을 사용함으로써, 노광의 해상도를 높일 수 있고, 제조시의 가공 형상을 균일하게 할 수 있다.

[0058] 이하에, 본 발명의 실시형태에 관련된 불휘발성 반도체 메모리가 구비하는 메모리 셀 어레이의 구조를 형성하기 위한 제조 공정의 일례를, 도 3 ~ 도 56 을 참조하여 설명한다.

[0059] 도 3a ~ 도 3c 를 참조하여, 실리콘 기판 (101) 상에 산화막 (102) 을 퇴적한다. 그 후, 산화막 (102) 상으로부터 질화막 (103) 을 퇴적한다.

[0060] 계속해서, 도 4a ~ 도 4c 를 참조하여, 질화막 (103) 상의 소정 위치에, 섬 형상 반도체 (301, 302, 303,

304) 를 형성하기 위한 레지스트 (104, 105, 106, 107) 를 형성한다.

[0061] 계속해서, 도 5a ~ 도 5c 를 참조하여, 반응성 이온 에칭 (RIE) 에 의해, 레지스트 (104, 105, 106, 107) 를 마스크로 하여 질화막 (103), 산화막 (102) 을 에칭한다. 이로써, 실리콘 기판 (101) 상에, 질화막 (108) 및 산화막 (112) 으로 이루어지는 하드 마스크, 질화막 (109) 및 산화막 (113) 으로 이루어지는 하드 마스크, 질화막 (110) 및 산화막 (114) 으로 이루어지는 하드 마스크, 질화막 (111) 및 산화막 (115) 으로 이루어지는 하드 마스크를 각각 형성한다.

[0062] 계속해서, 도 6a ~ 도 6c 를 참조하여, 추가로 반응성 이온 에칭에 의해, 레지스트 (104, 105, 106, 107) 를 마스크로 하여 실리콘 기판 (101) 을 에칭하고, 섬 형상 반도체 (116, 117, 118, 119) 를 형성한다.

[0063] 계속해서, 도 7a ~ 도 7c 를 참조하여, 레지스트 (104, 105, 106, 107) 를 박리한다.

[0064] 계속해서, 도 8a ~ 도 8c 를 참조하여, 섬 형상 반도체 (116, 117, 118, 119) 를 희생 산화하여, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면 및 섬 형상 반도체 (116, 117, 118, 119) 사이의 저면에 희생 산화막 (120) 을 형성한다.

[0065] 계속해서, 도 9a ~ 도 9c 를 참조하여, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면 및 섬 형상 반도체 (116, 117, 118, 119) 사이의 저면으로부터 희생 산화막 (120) 을 제거하여, 실리콘 기판 (101) 및 섬 형상 반도체 (116, 117, 118, 119) 의 실리콘 표면을 노출시킨다.

[0066] 계속해서, 도 10a ~ 도 10c 를 참조하여, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면 및 섬 형상 반도체 (116, 117, 118, 119) 사이의 저면에 산화막 (121) 을 퇴적한다.

[0067] 계속해서, 도 11a ~ 도 11c 를 참조하여, 산화막 (121) 을 에칭하고, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면에 산화막 사이드 월 (122, 123, 124, 125) 을 형성한다.

[0068] 계속해서, 도 12a ~ 도 12c 를 참조하여, 실리콘 기판 (101) 에 비소 (화살표 As 참조) 를 주입하고, 실리콘 기판 (101) 표면에 n 형 (제 2 도전형) 반도체인 제 1 차 소스선 (126) 을 형성함과 함께, 섬 형상 반도체 (116, 117, 118, 119) 의 하방 부위에, 제 1 차 소스선 (126) 과 모두 전기적으로 접속되도록 소스 영역 (501, 502, 503, 504) 을 형성한다. 이 때, 채널 영역 (127, 128, 129, 130) 이, 각각 소스 영역 (501, 502, 503, 504) 과, 질화막 (108) 및 산화막 (112), 질화막 (109) 및 산화막 (113), 질화막 (110) 및 산화막 (114), 질화막 (111) 및 산화막 (115) 사이에 형성된다.

[0069] 계속해서, 도 13a ~ 도 13c 를 참조하여, 산화막 사이드 월 (122, 123, 124, 125) 을 에칭에 의해 제거한다.

[0070] 계속해서, 도 14a ~ 도 14c 를 참조하여, 제 1 차 소스선 (126) 상, 및 질화막 (108, 109, 110, 111) 상에는 두께가 두꺼워지도록, 또한 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면에는 두께가 얇아지도록, 산화막 (131) 을 퇴적한다.

[0071] 계속해서, 도 15a ~ 도 15c 를 참조하여, 등방성 에칭에 의해, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면에 퇴적한 산화막 (131) 을 에칭한다. 이로써, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면의 산화막 (131) 을 에칭에 의해 제거한 후에도, 제 1 차 소스선 (126) 상에 산화막 (131) 이 잔존한다. 그리고, 질화막 (108, 109, 110, 111) 상에, 각각 산화막 (132, 133, 134, 135) 이 원반 형상으로 잔존한다. 이와 같이 산화막 (131) 이 산화막 (132, 133, 134, 135) 으로서 잔존하는 것은, 도 14a ~ 도 14c 를 참조하여, 제 1 차 소스선 (126) 상, 및 질화막 (108, 109, 110, 111) 상에는 두께가 두꺼워지도록 산화막 (131) 을 퇴적함과 함께, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면에는 두께가 얇아지도록 산화막 (131) 을 퇴적함과 함께, 이 산화막 (131) 을 어느 방향으로도 동일한 속도로 에칭이 진행되는 등방성 에칭을 사용하였기 때문이다. 그리고, 이 제 1 차 소스선 (126) 상에 남은 산화막 (131) 은, 얇어지는 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 에 있어서, 각각 제 1 절연막 (171, 172, 173, 174) (도 2b ~ 도 2d 참조) 이 되고, 부유 게이트 (153, 154, 155, 156) 와 제 1 차 소스선 (126) 사이의 용량의 저감에 기여하게 된다.

[0072] 계속해서, 도 16a ~ 도 16c 를 참조하여, 게이트 산화를 실시하고, 섬 형상 반도체 (116, 117, 118, 119) 의 외주 벽면에, 사이드 월 스페이서 형상으로 터널 절연막 (136, 137, 138, 139) 을 형성한다. 그 후, 원반 형상의 산화막 (132, 133, 134, 135) 의 선단까지 매설되도록, 질화막 (108, 109, 110, 111), 및 섬 형상 반도체 (116, 117, 118, 119) 사이에 폴리실리콘 (140) 을 퇴적한다. 그 후, CMP (Chemical Mechanical Polishing ; 화학 기계 연마) 에 의해 평탄화를 실시하고, 산화막 (132, 133, 134, 135) 의 선단부를

노출시킨다.

[0073] 계속해서, 도 17a ~ 도 17c 를 참조하여, 산화막 (132, 133, 134, 135) 을 에칭에 의해 제거한다.

[0074] 계속해서, 도 18a ~ 도 18c 를 참조하여, 폴리실리콘 (140) 을 에칭하고 소정 깊이까지 에치백하고, 게이트 길이를 결정한다.

[0075] 계속해서, 도 19a ~ 도 19c 를 참조하여, 폴리실리콘 (140) 상, 터널 절연막 (136, 137, 138, 139) 상, 및 질화막 (108, 109, 110, 111) 상으로부터, 산화막 (142) 을 퇴적한다. 그 후, 산화막 (142) 상으로부터 질화막 (143) 을 퇴적한다.

[0076] 계속해서, 도 20a ~ 도 20c 를 참조하여, 이방성 에칭에 의해 질화막 (143), 산화막 (142) 을 에칭한다. 그리고, 질화막 (143) 및 산화막 (142) 을, 섬 형상 반도체 (116, 117, 118, 119), 그리고 질화막 (108) 및 산화막 (112), 질화막 (109) 및 산화막 (113), 질화막 (110) 및 산화막 (114), 질화막 (111) 및 산화막 (115) 의 외주 벽면에, 사이드 월 형상으로 잔존시킨다. 이로써, 질화막 (148) (질화막 (143) 및 산화막 (144) (산화막 (142)) 으로 이루어지는 절연막 사이드 월 (520), 질화막 (149) 및 산화막 (145) 으로 이루어지는 절연막 사이드 월 (521), 질화막 (150) 및 산화막 (146) 으로 이루어지는 절연막 사이드 월 (522), 질화막 (151) 및 산화막 (147) 으로 이루어지는 절연막 사이드 월 (523) 이 형성된다.

[0077] 계속해서, 도 21a ~ 도 21c 를 참조하여, 폴리실리콘 (140) 을 에칭에 의해 제거한다. 이로써, 실리콘 기판 (101) 상에, 산화막 (131), 섬 형상 반도체 (116, 117, 118, 119) (터널 절연막 (136, 137, 138, 139)), 절연막 사이드 월 (520, 521, 522, 523) 로 둘러싸이는 공간이 형성된다.

[0078] 계속해서, 도 22a ~ 도 22c 를 참조하여, 산화막 (131), 섬 형상 반도체 (116, 117, 118, 119) (터널 절연막 (136, 137, 138, 139)), 절연막 사이드 월 (520, 521, 522, 523) 상으로부터, 부유 게이트막으로서의 폴리실리콘 (152) 을 퇴적한다. 폴리실리콘 (140) 을 에칭하였을 때에, 터널 절연막 (136, 137, 138, 139) 이 손상된 경우, 그 손상의 보충을 위해서, 여기서는, 폴리실리콘 (152) 의 퇴적 전에, 터널 절연막 (136, 137, 138, 139) 을 제거한 후, 새롭게 터널 절연막을 퇴적할 수도 있다.

[0079] 계속해서, 도 23a ~ 도 23c 를 참조하여, 폴리실리콘 (152) 에 인 (화살표 P 참조) 을 주입하고, 열처리를 실시하여 폴리실리콘 (152) 내에서 인을 확산시킨다.

[0080] 계속해서, 도 24a ~ 도 24c 를 참조하여, N+ 로 한 폴리실리콘 (152) 을, 절연막 사이드 월 (520, 521, 522, 523) 을 마스크로 하여 이방성 에칭을 실시하고, 섬 형상 반도체 (116, 117, 118, 119) (터널 절연막 (136, 137, 138, 139)) 의 외벽면에, 얻어지는 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 에 있어서의 부유 게이트 (153, 154, 155, 156) 를 형성한다. 부유 게이트 (153, 154, 155, 156) 는, 절연막 사이드 월 (520, 521, 522, 523) 의 하면과 제 1 차 소스선 (126) 상의 산화막 (131) 의 상면 사이에 형성된다.

[0081] 계속해서, 도 25a ~ 도 25c 를 참조하여, 제 1 차 소스선 (126) 상의 산화막 (131), 부유 게이트 (153, 154, 155, 156), 절연막 사이드 월 (520, 521, 522, 523), 및 질화막 (108, 109, 110, 111) 상으로부터, 인터폴리 절연막 (157) 을 형성한다. 그 후, 인터폴리 절연막 (157) 상에 폴리실리콘 (158) 을 퇴적하고, CMP 에 의해 표면의 평탄화를 실시한다. 여기서, 인터폴리 절연막 (157) 은, 산화막, 산화막, 질화막, 산화막의 적층 구조, 고(高)유전체막의 어느 것으로부터 형성되어 있어도 된다.

[0082] 계속해서, 도 26a ~ 도 26c 를 참조하여, 폴리실리콘 (158) 을 에칭하고 소정 깊이까지 에치백한다. 이 폴리실리콘이 얻어지는 불휘발성 반도체 메모리 트랜지스터 (212, 213, 214, 215) 에 있어서의 제어 게이트 (163, 164, 165, 166) 가 된다.

[0083] 계속해서, 도 27a ~ 도 27c 를 참조하여, 인터폴리 절연막 (157) 을 에칭하여, 질화막 (148, 149, 150, 151), 산화막 (144, 145, 146, 147), 및 질화막 (108, 109, 110, 111) 상의 인터폴리 절연막 (157) 을 제거한다.

[0084] 계속해서, 도 28a ~ 도 28c 를 참조하여, 폴리실리콘 (158) 에 인 (화살표 P 참조) 을 주입하고, 당해 폴리실리콘 (158) 을 p 형 (제 1 도전형) 실리콘으로 한다.

[0085] 계속해서, 도 29a ~ 도 29c 를 참조하여, 질화막 (108, 109, 110, 111) 상에, 제어 게이트 (163, 164, 165, 166) 를 형성하기 위한 레지스트 (159, 160, 161, 162) 를 열 방향으로 연장되도록 형성한다.

[0086] 계속해서, 도 30a ~ 도 30c 를 참조하여, 절연막 사이드 월 (520, 521, 522, 523), 레지스트 (159, 160, 161, 162) 를 마스크로 하여 폴리실리콘 (158) 을 에칭함으로써, 제어 게이트 (163, 164, 165, 166) 를 열 방향으로

형성한다. 그러면, 중공 기둥 형상의 부유 게이트 (153, 154, 155, 156) 가, 인터폴리 절연막 (157) 을 사이에 개재시켜, 중공 기둥 형상의 제어 게이트 (163, 164, 165, 166) 의 상면, 하면 및 내측면에 대향하는 구조가 형성된다.

[0087] 계속해서, 도 31a ~ 도 31c 를 참조하여, 인터폴리 절연막 (157) 을 예칭하고, 제어 게이트 (163, 164, 165, 166) 의 상면, 및 산화막 (131) 의 상면에 위치하는 부분을 제거하고, 인터폴리 절연막 (167, 168, 169, 170) 을 형성한다. 그 후, 산화막 (131) 의 노출 부분을 예칭하고, 제 1 절연막 (171, 172, 173, 174) 을 형성한다.

[0088] 계속해서, 도 32a ~ 도 32c 를 참조하여, 질화막 (108, 109, 110, 111) 상의 레지스트 (159, 160, 161, 162) 를 박리한다.

[0089] 계속해서, 도 33a ~ 도 33c 를 참조하여, 제어 게이트 (163, 164, 165, 166), 인터폴리 절연막 (167, 168, 169, 170), 부유 게이트 (153, 154, 155, 156) 의 각 표층부의 산화를 실시하여, 부유 게이트 (153, 154, 155, 156), 제어 게이트 (163, 164, 165, 166), 제 1 차 소스선 (126) 상에 산화막 (175, 176, 177, 178, 179) 을 형성한다.

[0090] 계속해서, 도 34a ~ 도 34c 를 참조하여, 질화막 (108, 109, 110, 111), 질화막 (148, 149, 150, 151) 을 박리함과 함께, 산화막 (112, 113, 114, 115), 산화막 (144, 145, 146, 147), 산화막 (175, 176, 177, 178, 179) 을 박리한다.

[0091] 계속해서, 도 35a ~ 도 35c 를 참조하여, 섬 형상 반도체 (116, 117, 118, 119), 및 제 1 차 소스선 (126) 을 덮도록 질화막 (180) 을 퇴적한다. 이 공정 전에, 섬 형상 반도체의 상층부에 비소를 주입해도 된다.

[0092] 계속해서, 도 36a ~ 도 36c 를 참조하여, 질화막 (180) 을 예칭하고, 섬 형상 반도체 (116, 117, 118, 119) 의 측벽에 사이드 월 형상으로 잔존시킨다.

[0093] 계속해서, 도 37a ~ 도 37c 를 참조하여, 섬 형상 반도체 (116, 117, 118, 119) 의 상층부에 비소 (화살표 As 참조) 를 주입하고, n 형 반도체인 드레인 영역 (181, 182, 183, 184) 을 형성한다. 이 후, 저저항화를 위해서, 금속 재료를 사용하여 섬 형상 반도체나 제어 게이트나 제 1 차 소스선에 실리사이드 공정을 실시해도 된다.

[0094] 계속해서, 도 38a ~ 도 38c 를 참조하여, 섬 형상 반도체 (116, 117, 118, 119), 및 질화막 (180) 을 덮도록, 절연성 재료를 사용하여 컨택트 스토퍼 (185) 를 퇴적함과 함께, 추가로 그 상층에 충간막 (186) 을 퇴적한 후, CMP 에 의해 평탄화한다.

[0095] 계속해서, 도 39a ~ 도 39c 를 참조하여, 충간막 (186) 상의 소정 위치에, 컨택트 구멍 (188, 189, 190, 191) (도 40 참조) 의 형성을 위한 레지스트 (187) 를 형성한다.

[0096] 계속해서, 도 40a ~ 도 40c 를 참조하여, 레지스트 (187) 를 마스크로 하여 충간막 (186) 을 예칭하고, 컨택트 구멍 (188, 189, 190, 191) 을 형성하고, 컨택트 스토퍼 (185) 의 표면을 노출시킨다.

[0097] 계속해서, 도 41a ~ 도 41c 를 참조하여, 레지스트 (187) 를 박리한다.

[0098] 계속해서, 도 42a ~ 도 42c 를 참조하여, 컨택트 구멍 (188, 189, 190, 191) 의 저부에 위치하는 컨택트 스토퍼 (185) 를 예칭에 의해 제거한다.

[0099] 계속해서, 도 43a ~ 도 43c 를 참조하여, 컨택트 구멍 (188, 189, 190, 191) 내에, 도전성 물질을 사용하여 컨택트 (192, 193, 194, 195) 를 형성하고, 섬 형상 반도체 (116, 117, 118, 119) 의 드레인 영역 (181, 182, 183, 184) 과 전기적으로 접속한다.

[0100] 계속해서, 도 44a ~ 도 44c 를 참조하여, 금속 재료를 사용하여, 충간막 (186), 및 컨택트 (192, 193, 194, 195) 상에 메탈 (196) 을 퇴적한다.

[0101] 계속해서, 도 45a ~ 도 45c 를 참조하여, 메탈 (196) 상에 제 1 차 메탈 배선 (200, 202) 과 제 2 차 소스선 (201) 의 형성을 위한 레지스트 (197, 198, 199) 를 형성한다.

[0102] 계속해서, 도 46a ~ 도 46c 를 참조하여, 레지스트 (197, 198, 199) 를 마스크로 하여 메탈 (196) 을 예칭하고, 제 1 차 메탈 배선 (200, 202) 과 제 2 차 소스선 (201) 을 형성한다. 이 때, 제 2 차 소스선 (201) 은 열 방향으로 배선된다.

[0103] 계속해서, 도 47a ~ 도 47c 를 참조하여, 레지스트 (197, 198, 199) 를 박리한다.

[0104] 계속해서, 도 48a ~ 도 48c 를 참조하여, 제 1 차 메탈 배선 (200, 202), 제 2 차 소스선 (201), 및 충간막 (186) 상에, 절연성 재료를 사용하여 충간막 (203) 을 퇴적한다.

[0105] 계속해서, 도 49a ~ 도 49c 를 참조하여, 충간막 (203) 상에, 비아 구멍 (205, 206) (도 50 참조) 형성을 위한 레지스트 (204) 를 형성한다.

[0106] 계속해서, 도 50a ~ 도 50c 를 참조하여, 레지스트 (204) 를 마스크로 하여 충간막 (203) 을 에칭하고, 제 1 차 메탈 배선 (200, 202) 의 일부가 노출되도록 비아 구멍 (205, 206) 을 형성한다.

[0107] 계속해서, 도 51a ~ 도 51c 를 참조하여, 레지스트 (204) 를 박리한다.

[0108] 계속해서, 도 52a ~ 도 52c 를 참조하여, 비아 구멍 (205, 206) 내에, 도전성 재료를 사용하여 비아 (207, 208) 를 형성한다.

[0109] 계속해서, 도 53a ~ 도 53c 를 참조하여, 충간막 (203) 및 비아 (207, 208) 상에, 도전성 재료를 사용하여 메탈 (209) 을 퇴적한다.

[0110] 계속해서, 도 54a ~ 도 54c 를 참조하여, 메탈 (209) 상의 소정 위치에 제 2 차 메탈 배선 (211) (도 55 참조) 을 형성하기 위한 레지스트 (210) 를 형성한다.

[0111] 계속해서, 도 55a ~ 도 55c 를 참조하여, 레지스트 (210) 를 마스크로 하여 메탈 (209) 을 에칭하고, 제 2 차 메탈 배선 (211) 을 형성한다. 이 제 2 차 메탈 배선 (211) 은, 비아 (207, 208) 를 개재하여 제 1 차 메탈 배선 (200, 202) 과 전기적으로 접속되어 비트라인이 된다.

[0112] 계속해서, 도 56a ~ 도 56c 를 참조하여, 레지스트 (210) 를 박리한다. 이로써, 도 2a ~ 도 2d 에 나타내는 불휘발성 반도체 메모리가 완성된다.

[0113] 또한 상기 실시형태에서는, 소스 영역 (303), 채널 영역 (304) 및 드레인 영역 (302) 을 갖는 섬 형상 반도체 (301) 는 원기둥 형상으로 하였다. 본 발명의 작용 효과가 얻어지는 한, 예를 들어 사각기둥 형상이어도 되고, 또한 원기둥 형상 이외의, 단면이 육각형 형상, 팔각형 형상 등의 다각형 형상의 기둥 형상이어도 된다. 또한, 섬 형상 반도체 (301) 는 두께 방향의 단면의 면적이 거의 동일한 형상으로 하였지만, 본 발명의 작용 효과가 얻어지는 한, 예를 들어 두께 방향의 중앙부에서 단면의 면적이 작은 형상으로 해도 물론 된다.

[0114] 상기 실시형태에서는, 부유 게이트 (306), 제어 게이트 (308), 부유 게이트 (306) 와 채널 영역 (304) 사이의 터널 절연막 (305), 제어 게이트 (308) 와 부유 게이트 (306) 사이의 인터폴리 절연막 (307) 은, 모두 중공 원기둥 형상으로 하였다. 본 발명의 작용 효과가 얻어지는 한, 예를 들어 중공 원기둥 형상이어도 되고, 또한 단면이 육각형 형상, 팔각형 형상 등의 다각형 형상의 중공 기둥 형상이어도 된다. 또한, 부유 게이트 (306), 제어 게이트 (308), 터널 절연막 (305), 인터폴리 절연막 (307) 은, 모두 두께 방향의 단면의 면적이 거의 동일한 형상으로 하였지만, 본 발명의 작용 효과가 얻어지는 한, 예를 들어 두께 방향의 중앙부에서 단면의 면적이 작은 형상으로 해도 물론 된다.

[0115] 상기 실시형태에서는, 부유 게이트 (306), 제어 게이트 (308), 부유 게이트 (306) 와 채널 영역 (304) 사이의 터널 절연막 (305), 제어 게이트 (308) 와 부유 게이트 (306) 사이의 인터폴리 절연막 (307) 은, 모두 섬 형상 반도체 (301) 의 외주를 연속적으로 둘러싸는 중공 기둥 형상으로 하였다. 부유 게이트 (306), 제어 게이트 (308), 부유 게이트 (306) 와 채널 영역 (304) 사이의 터널 절연막 (305), 제어 게이트 (308) 와 부유 게이트 (306) 사이의 인터폴리 절연막 (307) 은, 불연속인 중공 기둥 형상, 예를 들어 복수의 판 형상체가 협동하여 섬 형상 반도체 (301) 의 외주를 둘러싸는 형상이어도 된다 (제어 게이트 (308) 에 대해서는, 구성 요소인 복수의 판 형상체는, 서로 전기적으로 접속되어 있는 것이 바람직하다). 이와 같은 불연속인 중공 기둥 형상이어도 본 발명에서 말하는 중공 기둥 형상에 포함된다.

[0116] 또한 본 발명은, 본 발명의 광의의 정신과 범위를 일탈하지 않고, 여러 가지 실시형태 및 변형이 가능하게 되는 것이다. 또한 상기 서술한 실시형태는, 본 발명의 일 실시예를 설명하기 위한 것이며, 본 발명의 범위를 한정하는 것은 아니다.

### 부호의 설명

[0117] 101 실리콘 기판

- 102 산화막

- 103 질화막

- 104 ~ 107 레지스트

- 108 ~ 111 질화막

- 112 ~ 115 산화막

- 116 ~ 119 섬 형상 반도체

- 120 희생 산화막

- 121 산화막

- 122 ~ 125 산화막 사이드 월

- 126 제 1 차 소스선

- 127 ~ 130 채널 영역

- 131 ~ 135 산화막

- 136 ~ 139 터널 절연막

- 140 폴리실리콘

- 142 산화막

- 143 질화막

- 144 ~ 147 산화막

- 148 ~ 151 질화막

- 152 폴리실리콘

- 153 ~ 156 부유 게이트

- 157 인터폴리 절연막

- 158 폴리실리콘

- 159 ~ 162 레지스트

- 163 ~ 166 제어 게이트

- 167 ~ 170 인터폴리 절연막

- 171 ~ 174 제 1 절연막

- 175 ~ 179 산화막

- 180 질화막

- 181 ~ 184 드레인 영역

- 185 컨택트 스토퍼

- 186 충간막

- 187 레지스트

- 188 ~ 191 컨택트 구멍

- 192 ~ 195 컨택트

- 196 메탈

- 197 ~ 199 레지스트

- 200 제 1 차 메탈 배선

- 201 제 2 차 소스선

- 202 제 1 차 메탈 배선

- 203 층간막

- 204 레지스트

- 205, 206 비아 구멍

- 207, 208 비아

- 209 메탈

- 210 레지스트

- 211 제 2 차 메탈 배선

- 212 ~ 215 불휘발성 반도체 메모리 트랜지스터

- 301 섬 형상 반도체

- 302 드레인 영역

- 303 소스 영역

- 304 채널 영역

- 305 터널 절연막

- 306 부유 게이트

- 307 인터폴리 절연막

- 308 제어 게이트

- 501 ~ 504 소스 영역

- 520 ~ 523 절연막 사이드 월

도면

도면1

도면2a

도면2b

도면2c

도면2d

도면3a

도면3b

도면3c

도면4a

도면4b

도면4c

도면5a

도면5b

도면5c

도면6a

도면6b

도면6c

도면7a

도면7b

도면7c

도면8a

도면8b

도면8c

도면9a

도면9b

도면9c

도면10a

도면10b

도면10c

도면11a

도면11b

도면11c

도면12a

도면12b

도면12c

도면13a

도면13b

도면13c

도면14a

도면14b

도면14c

도면15a

도면15b

도면15c

도면16a

도면16b

도면16c

도면17a

도면17b

도면17c

도면18a

도면18b

도면18c

도면19a

도면19b

도면19c

도면20a

도면20b

도면20c

도면21a

도면21b

## 도면21c

### 도면22a

### 도면22b

도면22c

### 도면23a

### 도면23b

도면23c

도면24a

도면24b

도면24c

도면25a

도면25b

도면25c

도면26a

도면26b

도면26c

도면27a

도면27b

## 도면27c

### 도면28a

## 도면28b

도면28c

도면29a

도면29b

도면29c

### 도면30a

### 도면30b

도면 30c

### 도면31a

### 도면31b

도면31c

도면32a

도면32b

도면32c

도면33a

도면33b

도면33c

도면34a

도면34b

도면34c

도면35a

도면35b

도면 35c

### 도면36a

### 도면36b

도면 36c

### 도면37a

### 도면37b

### 도면37c

### 도면38a

### 도면38b

도면38c

도면39a

도면39b

도면39c

도면40a

도면40b

도면40c

도면41a

도면41b

도면41c

도면42a

도면42b

도면42c

도면43a

도면43b

도면43c

도면44a

도면44b

도면44c

도면45a

도면45b

도면45c

도면46a

도면46b

### 도면46c

### 도면47a

### 도면47b

도면47c

도면48a

도면48b

도면48c

도면49a

도면49b

도면49c

도면50a

도면50b

도면50c

### 도면51a

### 도면51b

도면51c

도면52a

도면52b

도면52c

도면53a

도면53b

도면53c

도면54a

도면54b

도면54c

도면55a

도면55b

도면55c

도면56a

도면56b

도면56c

도면57