(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4462269号

(P4462269)

(45) 発行日 平成22年5月12日(2010.5.12)

(24) 登録日 平成22年2月26日(2010.2.26)

(51) Int.Cl.

F 1

G02B 6/122 (2006.01)

G02B 6/42 (2006.01)G02B 6/12

G02B 6/42

B

請求項の数 10 (全 15 頁)

(21) 出願番号 特願2006-537601 (P2006-537601)

(86) (22) 出願日 平成16年9月29日 (2004.9.29)

(86) 国際出願番号 PCT/JP2004/014226

(87) 国際公開番号 WO2006/035499

(87) 国際公開日 平成18年4月6日 (2006.4.6)

審査請求日 平成19年3月20日 (2007.3.20)

(73) 特許権者 000004455

日立化成工業株式会社

東京都新宿区西新宿2丁目1番1号

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 松岡 康信

日本国東京都国分寺市東恋ヶ窪一丁目28

○番地 株式会社日立製作所 中央研究所

内

(72) 発明者 宮倉 正人

日本国東京都国分寺市東恋ヶ窪一丁目28

○番地 株式会社日立製作所 中央研究所

内

審査官 吉田 英一

最終頁に続く

(54) 【発明の名称】光電気集積回路素子およびそれを用いた伝送装置

## (57) 【特許請求の範囲】

## 【請求項 1】

四辺を有する基板と、

前記基板上に搭載されたLSIパッケージと、

前記LSIパッケージの一辺に配置されたI/O端子と電気的に接続された第1の光電変換素子と、

前記LSIパッケージの前記一辺に対向する辺に配置されたI/O端子と電気的に接続された第2の光電変換素子と、

前記LSIパッケージの前記一辺に隣接する辺に配置されたI/O端子と電気的に接続された第3の光電変換素子と、

前記LSIパッケージの前記隣接する辺に対向する辺に配置されたI/O端子と電気的に接続された第4の光電変換素子と、

前記第1および第3の光電変換素子が、それぞれ第1および第3の光導波路を介して光学的に接続された第1および第3のコネクタ設置溝を有するとともに、前記第2および第4の光電変換素子が、それぞれ第2および第4の光導波路を介して光学的に接続された第2および第4のコネクタ設置溝とを有し、

前記第1および第3のコネクタ設置溝が、前記基板の一側辺に配列されていること特徴とする光電気集積回路素子。

## 【請求項 2】

前記第1および第3の光電変換素子は信号増幅用集積回路と面受光ダイオードを有し、

10

20

前記第2および第4の光電変換素子は駆動用集積回路と面発光ダイオードを有すること特徴とする請求項1記載の光電気集積回路素子。

【請求項3】

前記第2の光電変換素子と前記第4の光電変換素子とは、駆動用集積回路と面発光ダイオードと有し、前記面発光ダイオードから発せられた光を前記第1および第3のコネクタ設置溝のそれぞれに接続された光導波路に伝送すること特徴とする請求項1記載の光電気集積回路素子。

【請求項4】

前記第1および第3のコネクタ設置溝は、前記基板の側邊に掛かるように配置されること特徴とする請求項1記載の光電気集積回路素子。

10

【請求項5】

前記第1の光導波路と前記第3の光導波路とは、前記基板内に設けられた同じ層に形成され、互いに交差する方向に配置されていること特徴とする請求項2記載の光電気集積回路素子。

【請求項6】

前記第1の光導波路と前記第3の光導波路とは、それぞれが前記基板内に設けられた異なる層に形成され、互いに交差する方向に配置されていること特徴とする請求項2記載の光電気集積回路素子。

【請求項7】

前記第2および第4のコネクタ設置溝が、前記一側邊に対向する側邊に配列されていること特徴とする請求項1記載の光電気集積回路素子。

20

【請求項8】

前記第1および第3の光電変換素子は、信号增幅用集積回路と面受光ダイオードとを有し、前記第2および第4の光電変換素子は、駆動用集積回路と面発光ダイオードを有すること特徴とする請求項7記載の光電気集積回路素子。

【請求項9】

前記第2および第4のコネクタ設置溝は、前記基板の側邊に掛かるように配置されること特徴とする請求項7記載の光電気集積回路素子。

【請求項10】

四辺を有する基板と、

30

前記基板上に搭載されたL S Iパッケージと、

前記L S Iパッケージの一辺に配置されたI / O端子と電気的に接続された第1の光電変換素子と、

前記L S Iパッケージの前記一辺に対向する辺に配置されたI / O端子と電気的に接続された第2の光電変換素子と、

前記L S Iパッケージの一辺に隣接する辺に配置されたI / O端子と電気的に接続された第3の光電変換素子と、

前記L S Iパッケージの前記隣接する辺に対向する辺に配置されたI / O端子と電気的に接続された第4の光電変換素子と、

前記基板の外部に接続される光ファイバを接続するコネクタ設置溝とを有し、

40

前記第1の光電変換素子は、光導波路を介して光学的に前記コネクタ設置溝に接続され、

前記第3の光電変換素子は、光導波路を介して前記基板の外部に接続されること特徴とする光電気集積回路素子。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、伝送装置内においてボード間で送受信される大容量光信号を一括処理する光電気集積回路素子と、その実装構成及びそれを用いた伝送装置に関する。

【背景技術】

50

## 【0002】

近年情報通信分野において、光を用いて大容量のデータを高速でやりとりする通信トラフィックの整備が急速に行われつつあり、これまで基幹、メトロ、アクセス系といった数km以上の比較的長い距離について光ファイバ網が展開されてきた。今後はさらに、伝送装置間（数m～数百m）、或いは装置内（数cm～数十cm）といった極めて近距離についても、大容量データを遅延なく処理するため、信号配線を光化する事が有効である。伝送装置内の光配線化に関して、例えばルータ／スイッチ装置では、イーサなど外部から光ファイバを通して高周波信号をラインカードに入力する。このラインカードは1枚のバックプレーンに対して数枚で構成されており、各ラインカードへの入力信号はさらにバックプレーンを介してスイッチカードに集められ、スイッチカード内のLSIにて処理した後、再度バックプレーンを介して各ラインカードに出力している。ここで、現状の装置では各ラインカードから現状300Gbit/s以上の信号がバックプレーンを介してスイッチカードに集まる。これを現状の電気配線で伝送するには、伝播損失の関係で配線1本あたり1～3Gbit/s程度に分割する必要があるため、100本以上の配線数が必要となる。さらに、これら高周波線路に対して波形成形回路や、反射、或いは配線間クロストークの対策が必要である。今後、さらにシステムの大容量化が進み、Tbit/s以上の情報を処理する装置になると、従来の電気配線では配線本数やクロストーク対策等の課題がますます深刻となってくる。これに対し、装置内ラインカード～バックプレーン～スイッチカードのボード間の信号伝送線路を光化することによって、10Gbps以上の高周波信号を低損失で伝播可能となるため、配線本数が少なくすむ事と、高周波信号に対してても上記の対策が必要無くなるため有望である。これに関し、上記各ラインカードからの大容量信号を一括処理するスイッチカード内のLSIパッケージ内に、光電変換素子を搭載した光電気集積回路素子の開発がなされている。10

## 【0003】

例えば、LEOS2003(Lasers and Electro-Optics Society, 2003, volume:1, 26-30, Oct, 2003)のOpto-Electronics Packaging Techniques for Interconnection（非特許文献1参照）にて光電気集積回路素子に関しての報告がされている。これを図16に示す。ここでは、バンプアレイ18を有する同一パッケージ基板11の中央にLSI162とその四方に光電変換素子12が搭載されており、これに直接ファイバコネクタ15を接続することにより光結合する構成となっている。このように、LSI162の近くまで光配線化することにより、LSI162のI/O端子と光電変換素子12のI/O端子間を接続する高周波電気線路24を比較的短く出来るため、高周波信号の伝播損失を緩和できる。さらに、この構造では同一パッケージ基板11上でLSI162の四方に光電変換素子12を配置することにより、パッケージの集積性を向上している。20

## 【0004】

【非特許文献1】「オプト・エレクトロニクス・パッケージング・フォー・インターフェクション(Opto-Electronics Packaging Techniques for Interconnection・)」、LEOS2003(Lasers and Electro-Optics Society, volume:1, 26-30, Oct, 2003)、2003年10月、第1巻、p. 26-30

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0005】

しかし前記光電気集積回路素子では、光電変換素子12に直接ファイバコネクタ15を接続する構造となっており、光電変換素子12のサイズがファイバコネクタ15のサイズに依存し大きくなってしまうため、LSI162のI/O数に対して素子12の集積度に限界がある。また、光電変換素子12には発光または受光ダイオードと、それを駆動するためのICが搭載され、このダイオードの特性は温度によって大きく影響する。そこで、放熱フィンを用いてモジュールを冷却する事が有効であるが、前記構造では光電変換素子12の直上に光コネクタ15が接続されるため、放熱フィン取り付けによる冷却が困難である。このため、ダイオード自体の発熱又はICからの熱の回り込みによってダイオード4050

特性の劣化を引き起こす恐れがある。

【0006】

さらに、前記光電気集積回路素子について、LSI162の四方に配置された光電変換素子12に各々接続されたファイバ16は、バックプレーン側の光コネクタに接続する。その際、ファイバは強度と光の放射損失を考慮して、大きい曲げ半径をとりながらボード上を迂回させて引き回す必要があるため、配線が困難である。さらに同様のパッケージを数個配置すると、このボード上光配線の引き回しが益々困難となる。

【0007】

上記のファイバコネクタ直接接続による光電変換素子の集積度限界及び放熱の問題を回避する手段として、ファイバ芯自身をパッケージ基板に直接埋め込み、コネクタ部を光電変換素子とは別の場所に設ける方策が考えられる。しかしながらこの方法では、ファイバ芯をパッケージ基板に固定する際に通常使用される接着剤が、パッケージ基板をボードに搭載する時のリフロー熱(>250)に耐えられず、軟化や剥がれ等の問題を引き起こす恐れがある。また、実装の順序を変えてパッケージ基板をボードに搭載後、基板にファイバを取り付け、その後光電変換素子を搭載しても良いが、パッケージ基板をボードに搭載した状態で、高精度が必要な光結合部を形成することは実装上非常に困難であるため、実用的では無い。

10

【0008】

これに対し、パッケージ基板に光路として耐熱性の高い光導波路を形成し、基板端にコネクタを設けることにより、光電変換素子とコネクタ部を高周波信号の損失を抑制しつつ物理的に遠ざけることが可能となる。これによって、光電変換素子のサイズを小さく出来ると共に、LSIと光電変換素子の放熱フィンを共通化することが可能であるため、素子の集積度限界及び放熱の問題を回避できる。

20

【0009】

しかしながら前記構造においても、パッケージ基板上LSIの四方に配置された光電変換素子に各々接続された光導波路と、バックプレーン側の光コネクタとのボード上光配線引き回しの課題は残る。また、ここでは光電気集積回路素子とバックプレーン側光コネクタとの光接続はファイバを想定している。しかし、ボード上に光導波路を形成した場合、それとパッケージ基板端の4方向から入出力する光導波路との接続においては、基板をボード搭載する時に、ベクトルがそれぞれ違う光導波路同士の光結合を一度に満足する必要がある。このため、角度ずれなどによって高精度な光結合を満足できないといった新たな課題が出てくる。

30

【0010】

本発明の目的は、同一基板上でLSIの四方に配置された光電変換素子を高集積で実装すると共に、発熱による発光又は受光ダイオードの特性劣化を回避し、さらにボード上の光配線の引き回しを簡便にした光電気集積回路素子及びそれを用いた伝送装置を提供することにある。

【課題を解決するための手段】

【0011】

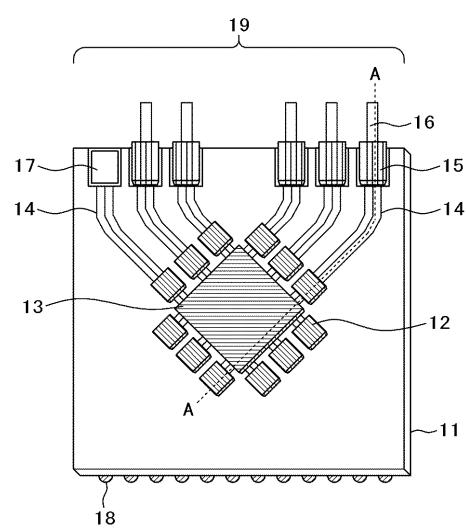

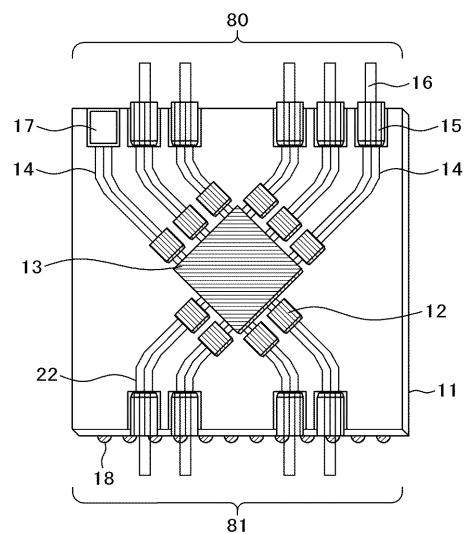

本発明では上記課題を解決するために、図1に示すような四角形のパッケージ基板11上にLSIパッケージ13が搭載され、そのLSIパッケージ13の二辺以上の周辺に光電変換素子12が各々搭載され、第1、第2の光電変換素子はそのLSIパッケージ13のI/O端子と電気接続される一の辺と、それとは異なる辺のI/O端子と電気接続されるようそれぞれ設けられ、前記第1の光電変換素子の光信号入出力端と外部とを結ぶ第一の光導波路と、前記第2の光電変換素子の光入出力端と外部とを結ぶ第二の光導波路とは前記パッケージ基板11の同じ端面の全てで終端していることを特徴とする光電気集積回路素子とする。このように、パッケージ基板11に光路として光導波路を形成し、光電変換素子の光信号入出力端と外部とを結ぶ光導波路14を同じ基板端19で終端することにより、前述したように光電変換素子12とファイバコネクタ部15を高周波信号の損失を抑制しつつ物理的に遠ざけることが可能となる。これによって、光電変換素子12のサイ

40

50

ズを小さく出来ると共に、LSIパッケージ13と光電変換素子12の放熱フィンを共通化することが可能のため、光電変換素子12の集積度限界及び放熱の問題を回避できる。

【0012】

また、前記第一の光導波路と、第二の光導波路とを前記パッケージ基板11の同じ端面の全てで終端することにより、図11に示すように、基板終端部分の光コネクタ15からボード端光コネクタ112までのファイバ16を直線的に配線可能となり、ボード111上の光配線の引き回しを簡便にできる。また図12のように、前述したボード111上に光導波路22を形成した場合の、それとパッケージ基板端の4方向から入出力する光導波路14との接続においても、光導波路同士は基板端の1辺(1ベクトル)で光結合すれば良いため、角度ずれの無い高精度な光結合が実現可能となる。

10

【0013】

さらに、基板の外部と接続する光I/Oを基板端の1辺に集約することにより、他の3辺の基板端の近傍に電気線路113を介してメモリパッケージ114等の周辺チップを搭載できるため、ボード111内におけるパッケージ高集積化に対しても効果がある。

【0014】

また、図10に示すように、四角形のパッケージ基板11上にLSIパッケージ13が搭載され、そのLSIパッケージ13の二辺以上の周辺に光電変換素子12が各々搭載され、第1、第2の光電変換素子はそのLSIパッケージ13のI/O端子と電気接続される一の辺と、それとは異なる辺のI/O端子と電気接続されるようそれぞれ設けられ、前記第1の光電変換素子の光信号入出力端と外部とを結ぶ第一の光導波路と、前記第2の光電変換素子の光入出力端と外部とを結ぶ第二の光導波路とは前記基板の4つの端面のうちの任意のいずれか2つの、それぞれ同じ端面の全てで終端していることを特徴とする光電気集積回路素子とする。

20

また、図8のように、第一の光導波路14と、第二の光導波路22とは基板11の4つの端面のうちの、隣り合った2つのそれぞれ同じ端面の全てで終端していることを特徴とする光電気集積回路素子とする。これにより、ボード上に2つの前記集積回路素子を搭載した場合において、各々の基板の4つの端面のうちの一端面同士で集積回路素子間を光接続し、各々の基板のもう一方の端面でバックプレーン側ボード端光コネクタと直線的に光配線可能である。

また、図10に示すように、第一の光導波路14と、第二の光導波路22とは基板11の4つの端面のうちの、基板中心に対して対向した2つのそれぞれ同じ端面の全てで終端していることを特徴とする光電気集積回路素子とする。これにより、イーサなどボードのフロント部から入出力される光信号を同光電気集積回路素子にて処理後、バックプレーンに入出力する構成においても、本発明構造によって前述した内容と同様の効果が得られる。

30

【0015】

また、図8のように第一の光導波路14と、第二の光導波路22とが基板11上で互いに交差していることを特徴とする光電気集積回路素子とする。前述した、本発明構造による効果は図7または図9のように第一の光導波路14と、第二の光導波路22を交差しなくても実現可能であるが、さらに図8のように光導波路同士を基板上で互いに交差することにより、導波路曲げによる光の放射損失抑制や光配線部分の省スペース化により、集積回路素子基板の小面積化ができるため有効である。なお、電気配線では同層で配線同士を交差すると短絡してしまうが、光配線の場合はこの場合においても干渉等の影響は殆ど無いと考えられる。

40

また図1のように、LSIパッケージ13及びそのI/O端子と電気接続されるようそれぞれ設けられた光電変換素子12と、パッケージ基板の端面19との位置関係が平行に対し傾いていることを特徴とする光電気集積回路素子とする。これにより、図4に示すようなLSIパッケージ13及び光電変換素子12と基板の端面との位置関係が平行な場合と比べて、光導波路14の曲げ半径を緩和できるため、曲げ部分からの光の放射による損失を抑制可能である。

50

また、図6、図7のように第一の光導波路と、第二の光導波路とが前記基板の厚さ方向に対してそれぞれ同層または2層にて構成されていることを特徴とする光電気集積回路素子とする。

#### 【0016】

さらに図1に示すように、パッケージ基板11にボードと電気接続するためのポールグリッドアレイ18又はピングリッドアレイ端子を具備していることを特徴とする光電気集積回路素子とする。

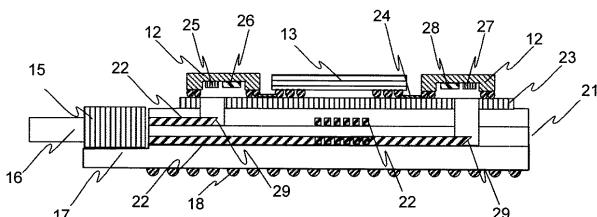

また図2に示すように、光電変換素子12は少なくとも1つの駆動用IC28と面発光ダイオード27で構成されていることを特徴とする光電気集積回路素子とする。

さらに、図2のように光電変換素子は少なくとも1つの信号增幅用IC26と面受光ダイオード25で構成されていることを特徴とする光電気集積回路素子とする。 10

また図1のように、光導波路14の基板端面19の終端部分と外部とが光ファイバコネクタ15を介して光接続されていることを特徴とする光電気集積回路素子とする。

また図15に示すように、光電気集積回路素子151を用いて、ボード間の高周波信号配線を光配線152で構成し、これを伝送装置とする。

#### 【発明の効果】

#### 【0017】

本発明の実施例によれば、同一基板上でLSIの四方に配置された光電変換素子を高集積で実装すると共に、発熱による発光又は受光ダイオードの特性劣化を回避し、さらにボード上の光配線の引き回しを簡便にした光電気集積回路素子及びそれを用いた伝送装置を提供できる。 20

#### 【発明を実施するための最良の形態】

#### 【0018】

以下に、図面を用いて実施の形態を詳細に述べる。

#### 【実施例1】

#### 【0019】

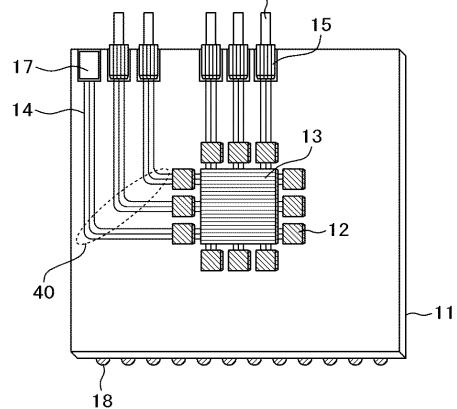

図1は、本発明の第一の実施例である光電気集積回路素子の上面図である。ここでは、パッケージ基板11上に形成したそれぞれの光導波路14の光入出力部が、パッケージ基板11の同じ端面19の全てで終端している例を示す。また、図2に本発明の第一の実施例である光電気集積回路素子の断面図を示す。図2の例では、パッケージ基板21に光導波路22が2層構成で形成されている。それぞれの光導波路22の外部との光入出力部は、パッケージ基板の同じ端面の全てで終端されており、この部分の溝部17に設置した光コネクタ15を介して光接続される。また、これら光導波路22の他端にはミラー部29が形成されており、光導波路内の伝播光がミラー部29で折り返され、基板上にフリップチップ実装された光電変換素子12内の面受光ダイオード25または面発光ダイオード27と光接続される。また、基板上に搭載するLSIパッケージ13と光電変換素子12は高周波電気配線層23上に形成された線路24を介して電気接続されている。 30

#### 【0020】

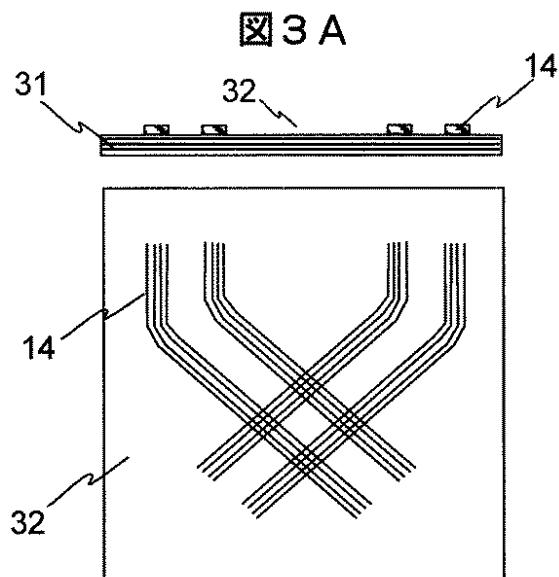

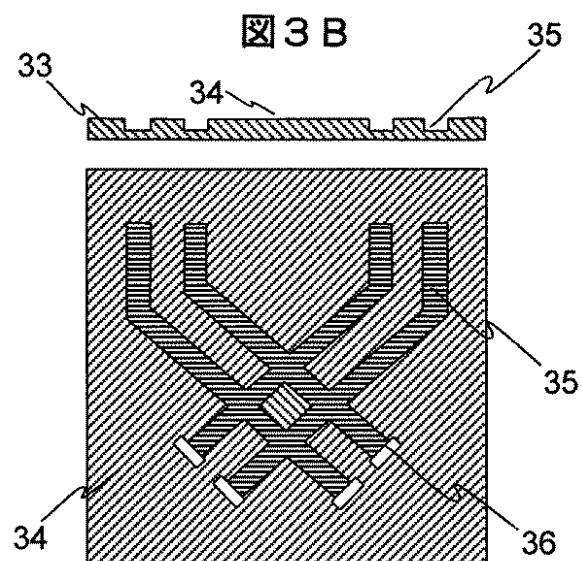

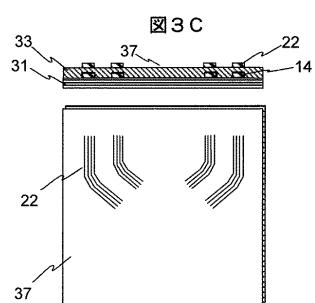

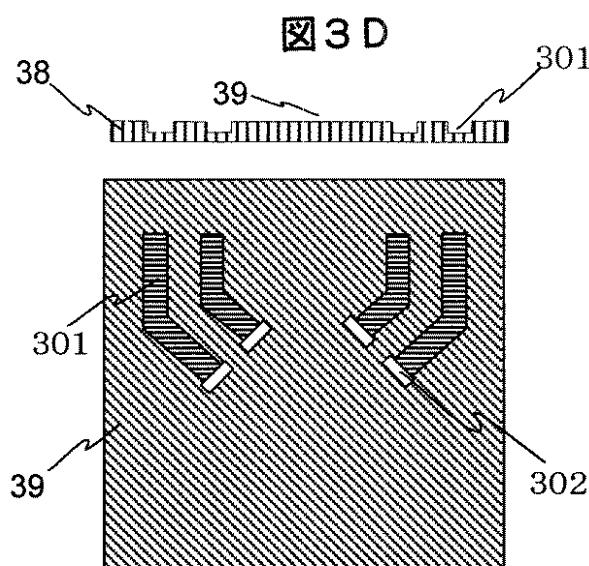

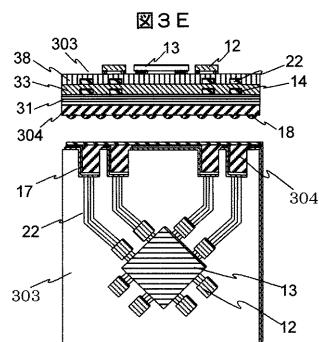

次に、この光電気集積回路素子の作成方法の一例について図3を用いて簡単に説明する。まず、図3Aのように積層基板(1)31の表面32に、材料がポリマ又は石英である光導波路14を塗布または貼付け、エッチングなどによりパタン形成する。ここで、図3Aのようにそれぞれの光導波路14は同層で交差されている。次に図3Bのように積層基板(2)33の裏面34にエッチングまたは切削等により基板溝部35を形成後、光入射窓36をそれぞれ図に示す位置に形成する。ここで、基板溝部35の深さは図3Aで示した光導波路14の厚さよりも深くする。なお、光入射窓36は基板を完全に割り貫きそのまま、もしくは割り貫き部に使用光の波長に透明な樹脂を埋め込んでも良い。次に、図3Cのように積層基板(2)33の表面37に図3Aでの説明同様、光導波路22を形成する。その後、先ほどの積層基板(1)31の表面32と積層基板(2)33の裏面34とをアライメントマーク等を用いて貼り合わせる。次に図3Dに示すように、これまでと同様に積層基板(3)38の裏面39に基板溝部301及び光入射窓302を形成する。こ 40 50

ここで基板(3)表面303には高周波電気線路パターンを形成する。次に、積層基板(1)31と貼り合わせた積層基板(2)33の表面37と積層基板(3)38の裏面39とを先程と同様のアライメントマーク等を用いて貼り合せる。その後、図3Eのように積層基板(1)～(3)の端部にコネクタ設置溝を切削等によって形成した後、さらに積層基板(1)～(3)をベース基板304に貼り付ける事によりパッケージ基板が完成される。また、同パッケージ基板の最上層である積層基板(3)38の表面303の高周波電気線路パターンにLSIパッケージ13及び光電変換素子12をフリップチップ実装することにより、光電気集積回路素子が完成される。なお、ここではLSIパッケージ13又は光電変換素子12の電気I/Oとパッケージ基板の電気I/Oであるバンプアレイ18との電気接続については言及しなかったが、実際は積層基板(1)～(3)の表裏面に電気配線パターンが形成されており、さらに各層間についてもビアホールを介して電気接続されている。また、それら電気配線パターンは、層間で光導波路14部を避けるようにファンアウトしても良いし、クラッド部などのコア部以外であれば電気ビアが光導波路を貫通していても良い。

#### 【0021】

次に、図1に示す例では、LSIパッケージ13及び光電変換素子12と、パッケージ基板11の端面19との位置関係が平行に対し傾いているが、図4に示すようにLSIパッケージ13及び光電変換素子12と基板の端面との位置関係が平行であっても本発明構造による効果は同じである。但し、前述したように光導波路曲げ部40からの光の放射による損失を考慮すると、図1のようにLSIパッケージ13及び光電変換素子12と、パッケージ基板11の端面19に対し平行より傾けた方が、光導波路14の曲げ半径又は角度を緩和できるため、より好ましい。

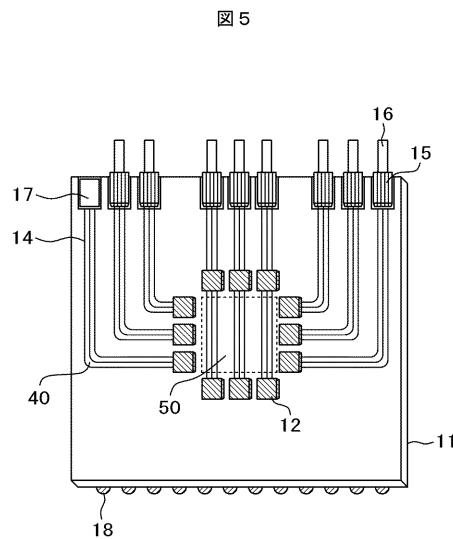

#### 【0022】

また、図3に示す例では光導波路14同士が基板上で互いに交差しているが、図5のように光導波路同士を交差しなくても本発明構造による効果は実現可能である。但し、前述したように、図3のような導波路同士を基板上で互いに交差した方が、導波路曲げによる光の放射損失抑制や光配線部分の省スペース化により、集積回路素子基板の小面積化ができるため有効である。

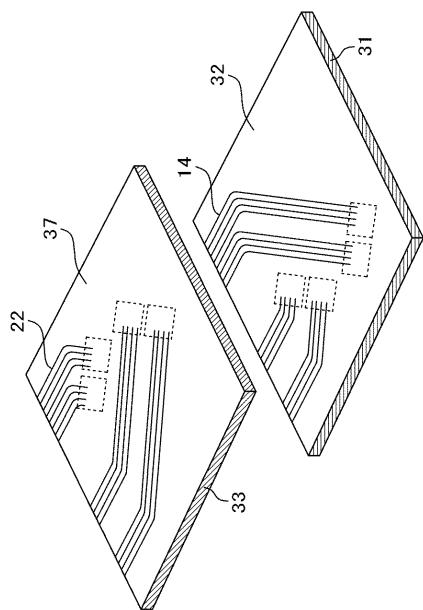

さらに、図3の例では積層基板(1)31上に光導波路14を、積層基板(2)33上の光導波路22をそれぞれ2層構成で形成しており、積層基板(2)33上の光導波路22は、同層基板上でそれぞれ交差している。これに対し図6に示すように、基板端光入力部60に近い方の光電変換素子搭載位置A61に配線する光導波路、及び遠い方の光電変換素子搭載位置B62に接続する光導波路を、それぞれ単層基板上に長さを交互に変えながらレイアウトしても良い。また、図7に示すように、積層基板(1)31上に光導波路14と積層基板(2)33上の光導波路22をそれぞれの同層基板上で交差せずに2層構成としても、本発明構造による効果は同じである。

#### 【実施例2】

#### 【0023】

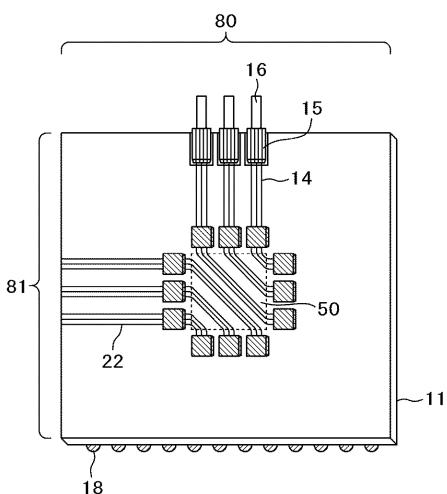

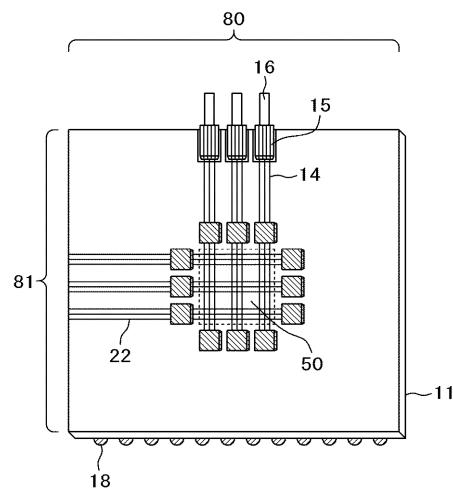

図8は、本発明の第二の実施例である光電気集積回路素子の上面図である。ここでは、パッケージ基板11上に形成したそれぞれの光導波路の光入出力部が、パッケージ基板11の4つの端面のうちの、隣り合った2つのそれぞれ同じ端面の全てで終端している例を示す。図8のように、パッケージ基板11上に搭載した第1の光電変換素子の光信号入出力端と外部とを結ぶ第一の光導波路14はバックプレーン側基板端光入出力部80のファイバコネクタ15に終端し、第2の光電変換素子の光入出力端と外部とを結ぶ第二の光導波路22は基板端光入出力部80と隣り合った基板端の光入出力部81で終端している。この例では、ボード上に2つの光電気集積回路素子を搭載した場合における光接続方法に對して有効である。

#### 【0024】

なお、図8に示す例ではパッケージ基板11上のLSI搭載部50にて光導波路14と光導波路22が互いに交差しているが、図9のように光導波路同士を交差しなくても本発

10

20

30

40

50

明構造による効果は同じである。

【実施例 3】

【0025】

図10は、本発明の第三の実施例である光電気集積回路素子の上面図である。ここでは、パッケージ基板111上に形成したそれぞれの光導波路の光入出力部が、パッケージ基板111の4つの端面のうちの、基板中心に対して対向した2つのそれぞれ同じ端面の全てで終端している例を示す。図10のように、パッケージ基板111上に搭載した第1の光電変換素子の光信号入出力端と外部とを結ぶ第一の光導波路14はバックプレーン側基板端光入出力部80のファイバコネクタ15に終端し、第2の光電変換素子の光入出力端と外部とを結ぶ第二の光導波路22は、基板端光入出力部80と基板中心に対して対向した基板端の光入出力部81のファイバコネクタ18に終端している。この例では、イーサなどボードのフロント部から入出力される光信号を同光電気集積回路素子にて処理後、バックプレーンに入出力する構成において、光配線の直線的引回しが可能のため有効である。

10

【実施例 4】

【0026】

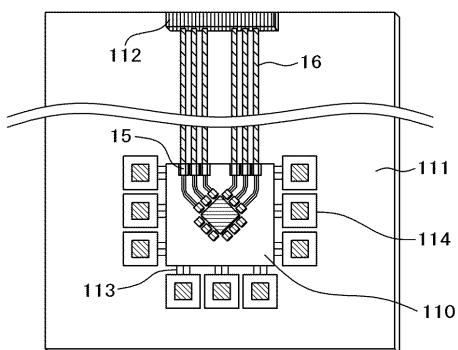

図11は本発明の第四の実施例である図1の光電気集積回路素子を搭載し、光接続したボードの上面図である。図11のように、データボード111上に図1で説明した光電気集積回路素子110を搭載し、同集積回路素子110の基板終端部分の光コネクタ15からボード端光コネクタ112までのファイバ16を直線的に配線し、ボード111上の光配線の引き回しを簡便にしている。また、同集積回路素子110の外部と接続する光I/O部以外の3辺の基板端の近傍に、電気線路113を介してメモリパッケージ114等の周辺チップを搭載している。これにより、前述したようにボード111内におけるパッケージ高集積化に対しても効果がある。

20

【実施例 5】

【0027】

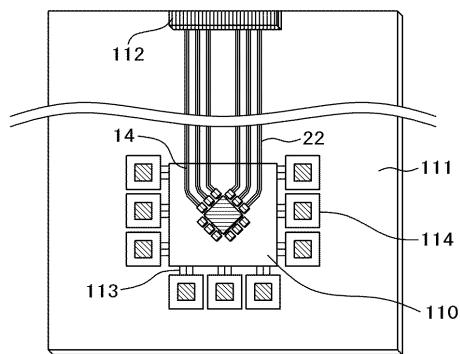

図12は本発明の第五の実施例である光電気集積回路素子を搭載し、光導波路同士で光接続したボードの上面図である。図12のように、データボード111上に、光電気集積回路素子110を搭載することにより、同集積回路素子110の基板終端部分の光導波路14とデータボード111に形成された光導波路22とをボード端光コネクタ112まで直線的に配線している。これにより、前述したように基板終端部分及びデータボードに形成した光導波路同士は基板端の1辺(1ベクトル)で光結合すれば良いため、角度ずれの無い高精度な光結合が実現可能となる。

30

【実施例 6】

【0028】

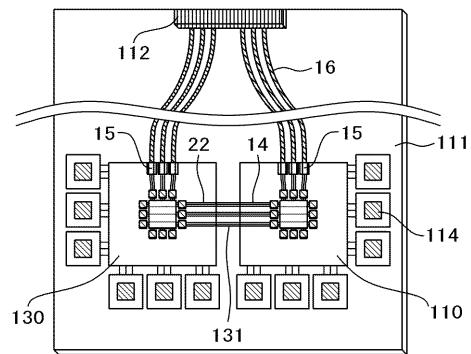

図13は本発明の第六の実施例である図8の光電気集積回路素子を搭載し、集積回路素子間、及び集積回路素子とボード端を光接続したボードの上面図である。図13のように、データボード111上に、光電気集積回路素子110ともう1つの光電気集積回路素子130を搭載し、集積回路素子110の基板終端部分の光導波路14と集積回路素子130の基板終端部分の光導波路22とをデータボード111に形成された光導波路131で光接続する。さらに、それぞれの集積回路素子のもう一方の基板終端部分の光コネクタ15とボード端光コネクタ112をファイバ16にて直線的に配線する構成としている。これにより、光電気集積回路素子を2つ並べて搭載した場合においても、実施例1及び5でそれぞれ説明した両方の効果が得られる。

40

【実施例 7】

【0029】

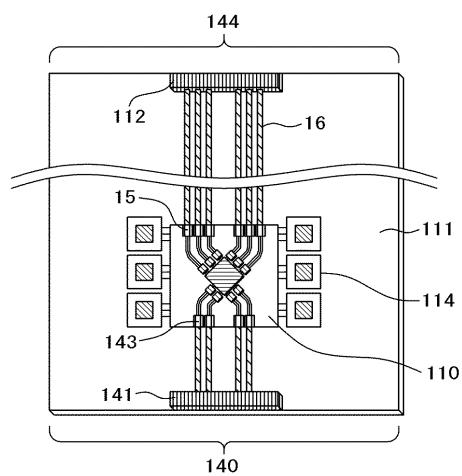

図14は本発明の第七の実施例である図10の光電気集積回路素子を搭載し、光接続したボードの上面図である。図14のように、データボード111上に図10で説明した光電気集積回路素子110を搭載し、同集積回路素子110の一方の基板終端部分の光コネクタ15とバックプレーン側ボード端144の光コネクタ112とをファイバ16にて直線的に配線する。また同様に、同集積回路素子110のもう一方の基板終端部分の光コネ

50

クタ 143 とフロント側ボード端 140 の光コネクタ 141 とをファイバ 142 にて直線的に配線する。この構成により実施例 3 で説明した効果が得られる。

【実施例 8】

【0030】

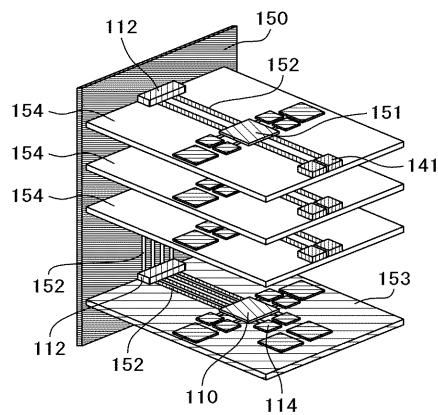

図 15 は本発明の第八の実施例である光電気集積回路素子を用いた光伝送装置の斜視図である。図 15 のように、バックプレーン 150 にそれぞれ接続されたラインカード 154 には実施例 7 と同様の構成を適用し、イーサなどボードのフロント部から光コネクタ 141 を介して入出力される光信号を光電気集積回路素子 151 にて処理後、バックプレーン側の光コネクタ 112 と光接続している。さらに、各ラインカード 154 からの光信号はバックプレーンの光配線 152 を介してスイッチカード 153 に集められる。このスイッチカードには実施例 4 と同様の構成を適用し、ボード上光配線 152 にて光電気集積回路素子 110 とボード端光コネクタ 112 まで直線的に光接続され、集積回路素子 110 で処理した光信号を再度各ラインカード 154 に入出力する機能をもつ。

【産業上の利用可能性】

【0031】

本発明は、伝送装置内においてボード間で送受信される大容量光信号を一括処理する光電気集積回路素子と、その実装構成及びそれを用いた伝送装置に適用できる。

【図面の簡単な説明】

【0032】

【図 1】本発明の第一の実施例である、光電気集積回路素子の上面図。

20

【図 2】本発明の第一の実施例である、光電気集積回路素子の断面図。

【図 3 A】本発明の第一の実施例である、光電気集積回路素子の作成方法の一例を説明するための図。

【図 3 B】本発明の第一の実施例である、光電気集積回路素子の作成方法の一例を説明するための図。

【図 3 C】本発明の第一の実施例である、光電気集積回路素子の作成方法の一例を説明するための図。

【図 3 D】本発明の第一の実施例である、光電気集積回路素子の作成方法の一例を説明するための図。

【図 3 E】本発明の第一の実施例である、光電気集積回路素子の作成方法の一例を説明するための図。

30

【図 4】本発明の第一の実施例である光電気集積回路素子の、L S I パッケージ及び光電変換素子が基板端に対し平行な位置関係における上面図。

【図 5】本発明の第一の実施例である光電気集積回路素子の、光導波路同士を交差しない構造の上面図。

【図 6】本発明の第一の実施例である光電気集積回路素子の、光導波路を单層基板に形成した斜視構造図。

【図 7】本発明の第一の実施例である光電気集積回路素子の、光導波路を同層基板上で交差せず各々 2 層で形成した斜視構造図。

【図 8】本発明の第二の実施例である、光電気集積回路素子の上面図。

40

【図 9】本発明の第二の実施例である光電気集積回路素子の、光導波路同士を交差しない構造の上面図。

【図 10】本発明の第三の実施例である、光電気集積回路素子の上面図。

【図 11】本発明の第四の実施例である、図 1 の光電気集積回路素子を搭載し光接続したボードの上面図。

【図 12】本発明の第五の実施例である、光電気集積回路素子を搭載し光導波路同士で光接続したボードの上面図。

【図 13】本発明の第六の実施例である図 8 の光電気集積回路素子を搭載し、集積回路素子間、及び集積回路素子とボード端を光接続したボードの上面図。

【図 14】本発明の第七の実施例である図 10 の光電気集積回路素子を搭載し、光接続し

50

たボードの上面図。

【図15】本発明の第八の実施例である光電気集積回路素子を用いた光伝送装置の斜視図。

【符号の説明】

【0033】

11, 21...パッケージ基板、12...光電変換素子、13...LSIパッケージ、14, 22, 131...光導波路、15, 143...ファイバコネクタ、16, 142...ファイバ、17...コネクタ設置溝、18...バンプアレイ、19, 60, 80, 81...基板端光入出力部、23...高周波電気配線層、24...高周波電気線路、25...面受光ダイオード、26...信号増幅IC、27...面発光ダイオード、28...駆動用IC、29...光導波路ミラー部、31...積層基板(1)、32...積層基板(1)表面、33...積層基板(2)、34...積層基板(2)裏面、35, 301...基板溝部、36, 302...光入出射窓、37...積層基板(2)表面、38...積層基板(3)、39...積層基板(3)裏面、303...積層基板(3)表面、304...ベース基板、40...光導波路曲げ部、50...LSI搭載部、61...光電変換素子搭載位置A、62...光電変換素子搭載位置B、110, 130, 151...光電気集積回路素子、111...データボード、112, 141...ボード端光コネクタ、113...電気線路、114...メモリパッケージ、140...フロント側ボード端、144...バックプレーン側ボード端、150...バックプレーン、152...光配線、153...スイッチカード、154...ラインカード、162...LSI。

【図1】

図1

【図2】

図2

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4】

図4

〔 図 5 〕

【図6】

【 図 7 】

【 四 8 】

【図9】

【図 1 0】

図 1 0

【図 1 1】

図 1 1

【図 1 2】

図 1 2

【図 1 3】

図 1 3

【図14】

図14

【図15】

図15

---

フロントページの続き

(56)参考文献 特開2002-101051(JP,A)

特開平08-110435(JP,A)

特開2003-344695(JP,A)

特開平07-084148(JP,A)

特開平11-125752(JP,A)

Takashi Mikawa, Hideto Furuyama, Seiki Hiramatsu, Masao Kinoshita, and Osamu Ibaragi , Over 10 Gbps/ch Compact Active Interposer Module for High-speed and High-density Chip Level Optical Interconnects , Lasers and Electro-Optics Society, 2003. LEOS 2003. The 16th Annual Meeting of the IEEE , 2003年10月27日 , Vol. 1 , p. 368 - 369

S. Hiramatsu, M. Kinoshita, T. Mikawa, O. Ibaragi, H. Nanai, T. Yoshida, S. Suzuki , Optical Path Redirected Three-dimensional Lightguide Connectors for High-speed Interconnection Modules , Electronic Components and Technology Conference, 2004. Proceedings. 54th , 2004年 6月 1日 , Vol. 2 , p. 1530 - 1536

(58)調査した分野(Int.Cl., DB名)

G02B 6/122

G02B 6/42