# (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3577195号 (P3577195)

最終頁に続く

(45) 発行日 平成16年10月13日(2004.10.13)

(24) 登録日 平成16年7月16日 (2004.7.16)

弁理士 酒井 將行

| (51) Int.C1. <sup>7</sup> | F I                    |          |                    |         |          |

|---------------------------|------------------------|----------|--------------------|---------|----------|

| HO1L 21/824               | HO1L                   | 27/10    | 621C               |         |          |

| HO1L 21/768               | HO1L                   | 21/90    | D                  |         |          |

| HO1L 27/108               | HO1L                   | 27/10    | 881B               |         |          |

| HO1L 29/78                | HO1L                   | 27/10 e  | 881F               |         |          |

|                           | HO1L                   | 29/78    | 3 O 1 M            |         |          |

|                           |                        |          |                    | 請求項の数 5 | (全 30 頁) |

| (21) 出願番号                 | 特願平9-125257            | (73) 特許権 | <b>對</b> 503121103 |         |          |

| (22) 出願日                  | 平成9年5月15日(1997.5.15)   |          | 株式会社ルネ             | サステクノロジ |          |

| (65) 公開番号                 | 特開平10-321815           |          | 東京都千代田             | 区丸の内二丁目 | 4番1号     |

| (43) 公開日                  | 平成10年12月4日 (1998.12.4) | (74) 代理人 | 100064746          |         |          |

| 審査請求日                     | 平成15年9月24日 (2003.9.24) |          | 弁理士 深見             | 久郎      |          |

|                           |                        | (74) 代理人 | 100085132          |         |          |

|                           |                        |          | 弁理士 森田             | 俊雄      |          |

|                           |                        | (74) 代理人 | 100083703          |         |          |

|                           |                        |          | 弁理士 仲村             | 義平      |          |

|                           |                        | (74) 代理人 | 100096781          |         |          |

|                           |                        |          | 弁理士 堀井             | 豊       |          |

|                           |                        | (74) 代理人 |                    |         |          |

|                           |                        |          | 弁理士 野田             | 久登      |          |

|                           |                        | (74) 代理人 | 100109162          |         |          |

(54) 【発明の名称】半導体装置およびその製造方法

# (57)【特許請求の範囲】

### 【請求項1】

半導体領域の主表面にチャネル領域を挟むように間隔を隔てて形成された 1 対の第 1 および第 2 のソース / ドレイン領域と、

前記チャネル領域上に形成されたゲート電極と、

前記ゲート電極上に形成された絶縁膜からなる第1のエッチングストッパ層と、

前記第1のエッチングストッパ層上に形成された第1の層間絶縁膜と、

前記第1の層間絶縁膜および前記第1のエッチングストッパ層の前記第1のソース / ドレイン領域上に位置する領域に形成されたビット線用開口と、

前記第1の層間絶縁膜および前記第1のエッチングストッパ層の前記第2のソース/ドレ 10 イン領域上に位置する領域に形成された第1のキャパシタ用開口と、

前記第1のキャパシタ用開口を介して前記第2のソース/ドレイン領域に接続されるとともに、前記第1のキャパシタ用開口を充填するように形成され、底面の平面積よりも上面の平面積の方が大きいプラグ電極と、

前記第1の層間絶縁膜上および前記プラグ電極の前記第1の層間絶縁膜に隣接する領域上 に形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成され、前記ビット線用開口を介して前記第1のソース / ドレイン領域に接続されたビット線と、

前記プラグ電極の上面に電気的に接続された垂直方向に延びるキャパシタコンタクト部と、前記キャパシタコンタクト部の上部と一体的に形成された水平方向に延びるキャパシタ

下部電極とを有する導電層とを備え、

前記導電層のキャパシタコンタクト部は、第2の絶縁膜を介して前記ビット線の上面および側面を覆うように形成されており、

前記第1の層間絶縁膜上と前記第2の絶縁膜上とに形成された絶縁膜からなる第2のエッ チングストッパ層と、

前記第2のエッチングストッパ層上に形成された第2の層間絶縁膜と、

<u>前記第1のキャパシタ用開口に達するように、前記第2の層間絶縁膜と前記第2のエッチ</u>ングストッパ層とに形成された第2のキャパシタ用開口とをさらに備え、

前記第2の層間絶縁膜と前記第2の絶縁膜との間に位置する前記第2のエッチングストッパ層の、前記第2のキャパシタ用開口側の端部が除去されて、前記ビット線の上部側端部の上方に位置する領域に凹部が形成され、

前記キャパシタコンタクト部は、前記第2のキャパシタ用開口内および前記凹部内に充填 されて前記ビット線の上方に延びるように形成されており、前記キャパシタ下部電極は、 前記第2の層間絶縁膜の上面に沿って延びるように形成されている、半導体装置。

### 【請求項2】

前記第2の絶縁膜は、

前記ビット線の上面上に接触して形成された上部絶縁膜と、

前記ビット線の側面と前記上部絶縁膜の側面とに接触して形成されたサイドウォール絶縁膜とを含み、

前記ビット線の上面は前記プラグ電極の上面よりも上方に位置している、請求項<u>1</u>に記載 20の半導体装置。

#### 【請求項3】

前記キャパシタ下部電極の表面は凹凸形状を有している、請求項1に記載の半導体装置。

#### 【請求項4】

前記第2の絶縁膜は酸化膜である、請求項1~3のいずれか1項に記載の半導体装置。

#### 【請求項5】

半導体領域の主表面に、1対の第1および第2のソース/ドレイン領域とゲート電極とを形成する工程と、

前記ゲート電極を覆うように第1のシリコン窒化膜を形成する工程と、

前記第1のシリコン窒化膜上にシリコン酸化膜からなる第1の層間絶縁膜を形成する工程 30と、

前記第1のシリコン窒化膜をエッチングストッパ層として、前記第1の層間絶縁膜の前記第1のソース/ドレイン領域の上方に位置する領域をエッチングすることにより第1の開口を形成する工程と、

前記第1の開口内の前記第1のシリコン窒化膜をエッチングすることにより、前記第1の層間絶縁膜の上面から前記第1のソース/ドレイン領域にまで達する第1のキャパシタ用開口を形成する工程と、

前記第1のキャパシタ用開口を充填するとともに、前記第1のソース / ドレイン領域に電気的に接続するようにプラグ電極を形成する工程と、

前記第1のシリコン窒化膜をエッチングストッパ層として、前記第1の層間絶縁膜の前記 40 第2のソース/ドレイン領域の上方に位置する領域をエッチングすることにより第2の開口を形成する工程と、

前記第2の開口内の前記第1のシリコン窒化膜をエッチングすることにより前記第1の層間絶縁膜の上面から前記第2のソース/ドレイン領域にまで達するビット線用開口を形成する工程と、

前記ビット線用開口を介して前記第2のソース/ドレイン領域に電気的に接続されるとと もに前記第1の層間絶縁膜上に延びるビット線を形成する工程と、

前記ビット線の上面および側面を覆うように第2の絶縁膜を形成する工程と、

前記第1の層間絶縁膜と前記第2の絶縁膜とを覆うように第2のシリコン窒化膜を形成する工程と、

10

30

40

50

前記第2のシリコン窒化膜上にシリコン酸化膜からなる第2の層間絶縁膜を形成する工程と、

前記第2のシリコン窒化膜をエッチングストッパ層として、前記第2の層間絶縁膜の前記 プラグ電極の上方に位置する領域をエッチングすることにより第3の開口を形成する工程 と、

前記第3の開口内の前記第2のシリコン窒化膜をエッチングすることにより、前記第2の 層間絶縁膜の上面から前記プラグ電極の上面にまで達する第2のキャパシタ用開口を形成 するとともに、前記第2のキャパシタ用開口の前記ビット線の上部側端部の上方に位置す る領域に凹部を形成する工程と、

前記凹部および前記第2のキャパシタ用開口を充填するキャパシタコンタクト部と、前記第2の層間絶縁膜の上面上に延びるキャパシタ下部電極とを有する導電層を形成する工程とを備えた、半導体装置の製造方法。

#### 【発明の詳細な説明】

[0001]

# 【発明の属する技術分野】

この発明は、一般に、半導体装置およびその製造方法に関し、より特定的には、コンタクトホールを有する半導体装置およびその製造方法に関する。

### [00002]

### 【従来の技術】

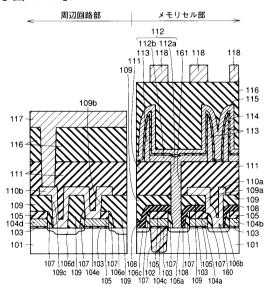

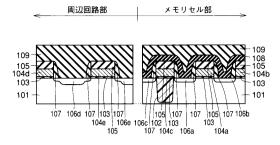

従来、半導体装置の1種である半導体メモリとして、DRAM(Dynamic Random Access Memory)が知られている。図35は、従来のDRAMを示した断面図である。図35を参照して、まず従来のDRAMの断面構造について説明する

# [0003]

従来のDRAMのメモリセル部では、シリコン基板101の主表面上の所定領域に分離領域102が設けられている。また、分離領域102によって囲まれた活性領域において、ソース/ドレイン領域106a、106bおよび106cが形成されている。ソース/ドレイン領域106aと106bとの間に位置するチャネル領域上にはゲート酸化膜103を介してゲート電極104aが形成されている。また、ゲート電極104aと所定の間隔を隔ててゲート電極104bおよび104cが形成されている。ゲート電極104a~104cの上部表面を覆うようにTEOS酸化膜105が形成されている。また、ゲート電極104a~104cの側表面とTEOS酸化膜105の側表面とに接触するようにサイドウォール酸化膜107が形成されている。

# [0004]

また、TEOS酸化膜105およびサイドウォール酸化膜107ならびにソース/ドレイン領域106a~106cを覆うようにシリコン窒化膜108が形成されている。シリコン窒化膜108上には層間絶縁膜109が形成されている。シリコン窒化膜108および層間絶縁膜109の、ソース/ドレイン領域106b上に位置する領域にはビット線用コンタクトホール160が形成されている。そのビット線用コンタクトホール160を介してソース/ドレイン領域106bに電気的に接続するとともに、層間絶縁膜109の上部表面上に延在するようにビット線110aが形成されている。

#### [0005]

また、ビット線110aおよび層間絶縁膜109の上には層間絶縁膜111が形成されている。シリコン窒化膜108、層間絶縁膜109および111の、ソース / ドレイン領域106a上に位置する領域にはキャパシタ用コンタクトホール161が形成されている。キャパシタ用コンタクトホール161を介してソース / ドレイン領域106aに電気的に接続するとともに層間絶縁膜111の上部表面上に延在するようにドープト多結晶シリコン膜112が形成されている。ドープト多結晶シリコン膜112は、ソース / ドレイン領域106aに電気的に接続するとともにコンタクトホール161を充填する垂直部分112aと、その垂直部分112aと一体的に形成されるとともにキャパシタ下部電極を構成

(4)

する水平部分112bとを含んでいる。

### [0006]

また、水平部分112bの両側端面に接触するとともに垂直方向に延びるように、ドープト多結晶シリコン膜からなるサイドウォール113が形成されている。このサイドウォール113を書からなるサイドウォール113を表面とサイドウォール113の表面を覆うように、キャパシタ誘電体膜114を介して、キャパシタ上部電極115が形成されている。キャパシタ上部電極115は、ドープト多結晶シリコン膜からなる。キャパシタ下部電極112b,113と、キャパシタ誘電体膜114と、キャパシタ上部電極115とによってキャパシタが構成される。そのようなキャパシタを覆うように層間絶縁膜116が形成されている。層間絶縁膜116の上部表面上には所定の間隔を隔ててメタル配線118が形成されている。

#### [0007]

一方、周辺回路部では、シリコン基板101の主表面に所定の間隔を隔ててソース/ドレイン領域106dと106eが形成されている。ソース/ドレイン領域106dと106eとの間に位置するチャネル領域上にはゲート酸化膜103を介してゲート電極104eが形成されている。また、ゲート電極104eからソース/ドレイン領域106dを隔てた領域上にはゲート酸化膜103を介してゲート電極104dが形成されている。ゲート電極104dおよび104eの上部表面上にはそれぞれTEOS酸化膜105が形成されている。また、ゲート電極104dおよび104eの側表面とTEOS酸化膜105の側表面とに接触するようにサイドウォール酸化膜107が形成されている。

#### [00008]

ソース / ドレイン領域 1 0 6 d 、 1 0 6 e と、サイドウォール酸化膜 1 0 7 とTEOS酸化膜 1 0 5 とを覆うように層間絶縁膜 1 0 9 が形成されている。層間絶縁膜 1 0 9 の、ソース / ドレイン領域 1 0 6 d 上に位置する領域とゲート電極 1 0 4 e 上に位置する領域とには、それぞれコンタクトホールが形成されている。それらのコンタクトホール内で、ソース / ドレイン領域 1 0 6 d とゲート電極 1 0 4 e とに電気的に接続するように配線層 1 1 0 b が形成されている。なお、配線層 1 1 0 b は、ソース / ドレイン領域 1 0 6 d またはゲート電極 1 0 4 e の一方のみに接続していてもよい。配線層 1 1 0 b を覆うように層間絶縁膜 1 1 1 が形成されており、さらにその層間絶縁膜 1 1 1 を覆うように層間絶縁膜 1 1 1 を覆うように層間絶縁膜 1 1 6 が形成されている。層間絶縁膜 1 1 1 6 の、配線層 1 1 0 b の側端部上に位置する領域には、コンタクトホールが形成されている。そのコンタクトホールを介して配線層 1 1 0 b に電気的に接続するとともに、層間絶縁膜 1 1 6 上に沿って延びるようにメタル配線 1 1 7 が形成されている。

# [0009]

上記のような従来のDRAMのメモリセル部全体の平面レイアウト図が図36に示されている。図36を参照して、従来のDRAMのメモリセル部では、ゲート電極104a~104cが、所定の間隔を隔てて互いに平行に延びるように形成されている。また、ゲート電極104a~104cとほぼ直交する方向に、ビット線110aが所定の間隔を隔ててほぼ平行に延びるように形成されている。ビット線110aは、活性領域170のソース/ドレイン領域106bに、ビット線用コンタクトホール160を介して接続されている。また、活性領域170のソース/ドレイン領域106aにはキャパシタ用コンタクトホール161を介してキャパシタ下部電極を構成するドープト多結晶シリコン膜112が接続されている。

# [0010]

図 3 7 ~ 図 5 3 は、図 3 5 に示した従来の D R A M の製造プロセスを説明するための断面図である。以下、図 3 7 ~ 図 5 3 を参照して、従来の D R A M の製造プロセスについて説明する。

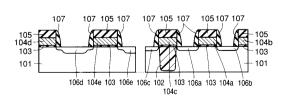

### [0011]

まず、図37に示すように、シリコン基板101のメモリセル部の主表面上に分離領域102を形成する。また、シリコン基板101の主表面に所定の間隔を隔ててゲート酸化膜

. .

20

30

103を形成する。そのゲート酸化膜103上にそれぞれゲート電極104a、104b および104cを形成する。また、周辺回路部においても、ゲート酸化膜103上にそれ ぞれゲート電極104dおよび104eを形成する。ゲート電極104a~104eをマ スクとして、不純物をシリコン基板101にイオン注入することによって、ソース/ドレイン領域106a~106eを形成する。

#### [0012]

また、ゲート電極104a~104eの上部表面上にそれぞれTEOS酸化膜105を形成する。また、ゲート電極104a~104eの側表面とTEOS酸化膜105の側表面とに接触するようにサイドウォール酸化膜107を形成する。周辺回路部のサイドウォール酸化膜107をマスクとして再びソース/ドレイン領域106dおよび106eに不純物をイオン注入することによって、LDD構造のソース/ドレイン領域106dおよび106eを完成させる。

### [0013]

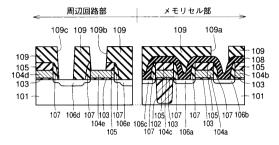

次に、図38に示すように、メモリセル部の全体を覆うようにエッチングストッパ層としてのシリコン窒化膜108を形成する。シリコン窒化膜108および周辺回路部の全体を覆うようにシリコン酸化膜からなる層間絶縁膜109を形成する。

### [0014]

この後、写真製版技術とドライエッチング技術とを用いて図39に示されるようなコンタクトホール109a~109cを形成する。メモリセル部のコンタクトホール109aの形成時のエッチングの際には、シリコン窒化膜108がエッチングストッパ層となる。この後、コンタクトホール109a内に位置するシリコン窒化膜108をエッチング除去することによって、図40に示されるような層間絶縁膜109の上面からソース/ドレイン領域106bにまで達するビット線用コンタクトホール160が形成される。この後、図41に示すように、タングステンポリサイド層などからなる配線層110を形成する。そして、その配線層110をパターニングすることによって、図42に示されるような、メモリセル部のビット線110aと周辺回路部の配線層110bとを形成する。

# [0015]

次に、図43に示すように、全体を覆うように層間絶縁膜111を形成する。そして、図44に示すように、層間絶縁膜111上に多結晶シリコン膜150を形成した後その多結晶シリコン膜150上にTEOS酸化膜151を形成する。その後、TEOS酸化膜151の所定領域に開口151aを形成する。

# [0016]

また、TEOS酸化膜151および開口151aを覆うようにTEOS酸化膜(図示せず)を形成した後、そのTEOS酸化膜151を異方性エッチングすることによって、図45に示されるようなサイドウォール膜152を形成する。そのサイドウォール膜152をマスクとして下層の多結晶シリコン膜150をエッチングすることにより、開口151aよりも2つのサイドウォール152の厚み分だけ径の小さい開口150aを形成することができる。そしてこのような開口150aを用いて下層の層間絶縁膜111および109を異方性エッチングすることによって、図46に示されるようなキャパシタ用コンタクトホール161を形成する。

# [0017]

その後、キャパシタ用コンタクトホール161内にレジスト153を埋込む。このレジスト153は、後のプロセスで多結晶シリコン膜150をエッチングにより除去する際にキャパシタ用コンタクトホール161の底部に位置するシリコン基板101の表面を保護するために設けられている。このようなレジスト153を設けた状態で、多結晶シリコン膜150を除去する。そして、図47に示すように、キャパシタ用コンタクトホール161内を埋込むとともに層間絶縁膜111の上部表面上に沿って延びるドープト多結晶シリコン膜112を形成する。ドープト多結晶シリコン膜112上にBPSG酸化膜154を形成する。

# [0018]

40

20

30

40

50

この後、写真製版技術とドライエッチング技術とを用いて、BPSG酸化膜154およびドープト多結晶シリコン膜112をパターニングすることによって、図48に示されるようなメモリセル部の形状が得られる。そして、BPSG酸化膜154および層間絶縁膜111を覆うように図49に示すようなドープト多結晶シリコン膜113を形成する。その後ドープト多結晶シリコン膜113を異方性エッチングすることによって、図50に示すようなドープト多結晶シリコン膜からなるサイドウォール113aを形成する。この後BPSG酸化膜154を除去することによって、図51に示されるような形状が得られる。【0019】

次に、図52に示すように、ドープト多結晶シリコン膜112およびサイドウォール113aならびに層間絶縁膜111を覆うように、キャパシタ誘電体膜114とキャパシタ上部電極となるドープト多結晶シリコン膜115とを形成する。その後キャパシタ誘電体膜114とドープト多結晶シリコン膜115とをパターニングすることによって、図53に示されるようなキャパシタ構造が得られる。

[0020]

この後、図35に示したように、周辺回路部の層間絶縁膜111上とメモリセル部のキャパシタ上部電極115上に層間絶縁膜116を形成する。そして周辺回路部の層間絶縁膜116および111の、配線層110b上に位置する領域に、コンタクトホールを形成する。その後、そのコンタクトホール内を埋込むとともに層間絶縁膜116の上部表面上に沿って延びるメタル配線117を形成する。また、メモリセル部においても、層間絶縁膜116上に所定の間隔を隔ててメタル配線118を形成する。このようにして、従来のDRAMが形成されていた。

[0021]

【発明が解決しようとする課題】

図35に示した従来のDRAMでは、半導体装置の高集積化に伴って、メモリセル部の面積の縮小化が必要になってきている。この場合、非常に狭い活性領域にキャパシタ用コンタクトホール161およびビット線用コンタクトホール160を形成する必要がある。従来ではこのような要求を満たすために、自己整合的にコンタクトホールを開口する技術が要求される。このような自己整合的コンタクト開口法の1つとして、従来、シリコン窒化膜をエッチングストッパとして用いたコンタクト開口法が知られている。

[0022]

図35に示した従来の構造では、ビット線用コンタクトホール160を形成する際に上記のようなシリコン窒化膜による自己整合的コンタクト開口法を用いている。具体的には、図38に示すように、シリコン窒化膜108を形成した後その上にシリコン酸化膜からなる層間絶縁膜109を形成する。そして、図39に示すようにシリコン窒化膜108をエッチングストッパ層として、ソース/ドレイン領域106bの上方に位置する層間絶縁膜109の部分をエッチングすることにより自己整合的にコンタクトホール109aを形成する。その後、コンタクトホール109a内の窒化膜108を除去することによって、図40に示すようなビット線コンタクトホール160が形成される。従来では、ビット線用コンタクトホール160を形成するために上記のようなシリコン窒化膜108を用いた自己整合的コンタクト開口法を用いていた。

[0023]

しかしながら、このようなシリコン窒化膜108をエッチングストッパ層として用いた開口法は、図39に示すコンタクトホール109aのように、その深さがあまり大きくないものにのみ適用可能である。これは以下の理由による。すなわち、シリコン酸化膜とシリコン窒化膜との選択比(シリコン酸化膜のエッチングレート)は理論的には30程度であるが、シリコン窒化膜108の段差部では平坦部よりエッチングが速く進行する。このため、段差部においては、シリコン酸化膜に対するシリコン窒化膜の選択比が10~15程度に減少する。

[0024]

このような選択比の場合に、たとえばキャパシタ用コンタクト161のように深さが大き

い(アスペクト比が大きい)コンタクトホールをシリコン窒化膜108をエッチングストッパ層として開口しようとすると、プロセスマージンの関係からシリコン窒化膜108がエッチングされる時間が長くなる。このため、キャパシタ用コンタクトホール161のように深さの深いコンタクトホールを開口しようとすると、下地のシリコン窒化膜108の段差部が完全に削られ、さらにゲート電極104c上に位置するTEOS酸化膜105が削られてゲート電極104cが露出する。この場合に、キャパシタ用コンタクトホール161内にキャパシタ下部電極となるドープト多結晶シリコン膜112を形成すると、そのドープト多結晶シリコン膜112とゲート電極104cとがショートを起こすという不都合が生じる。したがって、従来では、深さのあまり深くないビット線用コンタクトホール160の形成のみにシリコン窒化膜108を用いた自己整合的開口法を採用し、キャパシタ用コンタクトホール161の形成には、図44~図46に示した径縮小プロセスを用いていた。

#### [0025]

しかしながら、上記のような径縮小プロセスは、シリコン窒化膜ストッパを用いた自己整合的開口法に比べて工程数が多くなり、製造プロセスが複雑化するという問題点があった。また、メモリセルサイズの縮小に伴ってキャパシタ用コンタクトホール161のコンタクト径も縮小化が要求されるが、図35に示したような深さの深いかつコンタクト径の小さいコンタクトホールを形成するのは技術的に困難になってきているという問題点もあった。

### [0026]

また、メモリセル部の縮小化に伴って、図36に示す隣接するビット線160a間の間隔も狭くなってきている。ビット線110a間の間隔が狭くなると、ビット配線容量(Cb)が大きくなり、そのため、データの読出および書込に遅延が生じ、その結果高速なアクセスが困難になるという問題点もあった。図36に示した従来の構造では、隣接するビット線110a間に、ドープト多結晶シリコン膜112の垂直部112aが位置している。しかし、この垂直部112aの外径は小さいため、隣接するビット線110a間のビット配線容量を低減するまでには至らなかった。

#### [0027]

この発明は、上記のような課題を解決するために成されたものであり、

この発明の1つの目的は、半導体装置において、キャパシタ用コンタクトホールを容易に 製造し得るとともにビット配線容量を低減することが可能な構造を提供することである。

# [0028]

この発明のもう1つの目的は、半導体装置の製造方法において、キャパシタ用コンタクトホールを自己整合的に形成するとともにビット配線容量を低減し得る構造を容易に製造することである。

### [0031]

# 【課題を解決するための手段】

請求項<u>1</u>における半導体装置は、1対の第1および第2のソース / ドレイン領域と、ゲート電極と、第1のエッチングストッパ層と、第1の層間絶縁膜と、ビット線用開口と、第1のキャパシタ用開口と、プラグ電極と、第1の絶縁膜と、ビット線と、</u>導電層とを備えている。第1および第2のソース / ドレイン領域は、半導体領域の主表面にチャネル領域を挟むように間隔を隔てて形成されており、ゲート電極はチャネル領域上に形成されている。第1のエッチングストッパ層上に形成されており、絶縁膜からなる。第1の層間絶縁膜は第1のエッチングストッパ層の第1のソース / ドレイン領域上に近置する領域に形成されている。第1のキャパシタ用開口は、第1の層間絶縁膜および第1のエッチングストッパ層の第2のソース / ドレイン領域上に位置する領域に形成されている。プラグ電極は、第1のキャパシタ用開口を介して第2のソース / ドレイン領域に接続されるとともに、第1のキャパシタ用開口を充填するように形成されている。また、プラグ電極の底面の平面積よりも上面の平面積の方が大きくなるように形成されている。

20

30

40

30

40

50

第1の絶縁膜は、第1の層間絶縁膜上およびプラグ電極の第1の層間絶縁膜に隣接する領域上に形成されている。ビット線は、第1の絶縁膜上に形成され、ビット線用開口を介して第1のソース / ドレイン領域に接続されている。 導電層は、プラグ電極の上面に電気的に接続された垂直方向に延びるキャパシタコンタクト部と、そのキャパシタコンタクト部の上部と一体的に形成された水平方向に延びるキャパシタ下部電極とを有する。 導電層のキャパシタコンタクト部は、第1の絶縁膜を介してビット線の上面および側面を覆うように形成されている。

# [0032]

請求項1に記載の半導体装置では、ビット線用開口が形成される第1の層間絶縁膜および 第1のエッチングストッパ層に、第1のキャパシタ用開口を形成し、その第1のキャパシ タ用開口にプラグ電極を充填するように構成することにより、ビット線用開口と同じアス ペクト比で第1のキャパシタ用開口を形成することができ、その結果、第1のエッチング ストッパ層を用いた自己整合的開口法を第1のキャパシタ用開口の形成に適用することが できる。これにより、径縮小プロセスによって第1のキャパシタ用開口を形成する場合に 比べて製造プロセスを簡略化することができるとともに、セルサイズが縮小化された場合 にも容易に形成することができる。また、プラグ電極の上面に電気的に接続される導電層 のキャパシタコンタクト部の一部を、ビット線の上面および側面を覆うように形成するこ とによって、隣接するビット線間にキャパシタコンタクト部が位置することになる。これ により、従来の通常のコンタクト径を有するコンタクト部がビット線間に配置された構成 に比べて、隣接するビット線間を遮る部分の面積が大きくなる。このため、隣接するビッ ト線間のビット線配線容量が大きくなるのを有効に防止することができる。その結果、デ ータの読出および書込動作が遅延するのも防止することができ、高速なアクセスが可能と なる。また、<u>前述の</u>半導体装置では、第2のソース/ドレイン領域に接続されるプラグ電 極の底面の平面積よりも、キャパシタ下部電極に接続されるプラグ電極の上面の平面積の 方が大きくなるように形成されている。このため、プラグ電極の上面に接続するようにキ ャパシタ下部電極を形成する際に、重ね合わせずれの余裕を大きく取ることができ、その 結果キャパシタ下部電極の形成プロセスが容易になる。

また、請求項1に記載の半導体装置は、第2のエッチングストッパ層と、第2の層間絶縁膜と、第2のキャパシタ用開口とをさらに備えるように構成する。第2のエッチングストッパ層は、第1の層間絶縁膜上と第1の絶縁膜上とに形成されており、絶縁膜からなる。第2の層間絶縁膜は、第2のエッチングストッパ層上に形成されている。第2のキャパシタ用開口は、第1のキャパシタ用開口に達するように、第2の層間絶縁膜と第2のエッチングストッパ層とに形成されている。また、第2の層間絶縁膜と第1の絶縁膜との間に位置する第2のエッチングストッパ層の、第2のキャパシタ用開口側の端部が除去されて、ビット線の上部側端部の上方に位置する領域に凹部が形成されている。キャパシタコンタクト部は、第2のキャパシタ用開口内および凹部内に充填されてビット線の上方にの延びるように形成されている。また、キャパシタ下部電極は、第2の層間絶縁膜の上面に沿って延びるように形成されている。請求項1の構成では、このように第2のキャパシタ用開口のビット線の上部側端部の上方に位置する領域に凹部を形成し、その凹部内および第2のキャパシタ用開口内にキャパシタコンタクト部を形成することができる。

### [0033]

請求項<u>2</u>は、上記請求項<u>1</u>の構成において、第1の絶縁膜が、ビット線の上面上に接触して形成された<u>第2</u>絶縁膜と、ビット線の側面と<u>第2の</u>絶縁膜の側面とに接触して形成されたサイドウォール絶縁膜とを含むように構成する。そして、ビット線の上面はプラグ電極の上面よりも上方に位置する。このように構成することによって、ビット線の側面と上面とを覆うキャパシタ下部電極を容易に形成することができる。

### [0034]

請求項<u>3</u>は、上記請求項<u>1~3のいずれか</u>の構成において、キャパシタ下部電極の表面が 凹凸形状を有するように構成する。このように構成することによって、キャパシタ下部電 (9)

極の表面積が増加し、その結果、キャパシタ容量を増大させることができる。

### [0035]

請求項4は、上記請求項1の構成において、第2の絶縁膜が酸化膜であることが望ましい

### [0037]

請求項5の製造方法は、以下のような工程を備えている。半導体領域の主表面に、1対の 第1および第2のソース/ドレイン領域とゲート電極とを形成する。そのゲート電極を覆 うように第1のシリコン窒化膜を形成する。第1のシリコン窒化膜上にシリコン酸化膜か らなる第1の層間絶縁膜を形成する。第1のシリコン窒化膜をエッチングストッパ層とし て、第1の層間絶縁膜の第1のソース/ドレイン領域の上方に位置する領域をエッチング することにより第1の開口を形成する。その第1の開口内の第1のシリコン窒化膜をエッ チングすることにより、第1の層間絶縁膜の上面から第1のソース/ドレイン領域にまで 達する第1のキャパシタ用開口を形成する。第1のキャパシタ用開口を充填するとともに 、第1のソース/ドレイン領域に電気的に接続するようにプラグ電極を形成する。第1の シリコン窒化膜をエッチングストッパ層として、第1の層間絶縁膜の第2のソース/ドレ イン領域の上方に位置する領域をエッチングすることにより第2の開口を形成する。その 第2の開口内の前記第1のシリコン窒化膜をエッチングすることにより第1の層間絶縁膜 の上面から第2のソース/ドレイン領域にまで達するビット線用開口を形成する。ビット 線用開口を介して第2のソース/ドレイン領域に電気的に接続されるとともに第1の層間 絶縁膜上に延びるビット線を形成する。ビット線の上面および側面を覆うように第1の絶 縁膜を形成する。第1の層間絶縁膜と第1の絶縁膜とを覆うように第2のシリコン窒化膜 を形成する。その第2のシリコン窒化膜上にシリコン酸化膜からなる第2の層間絶縁膜を 形成する。第2のシリコン窒化膜をマスクとして第2の層間絶縁膜のプラグ電極の上方に 位置する領域をエッチングすることにより第3の開口を形成する。第3の開口内の第2の シリコン窒化膜をエッチングすることにより、第2の層間絶縁膜の上面からプラグ電極の 上面にまで達する第2のキャパシタ用開口を形成するとともに、第2のキャパシタ用開口 の、ビット線の上部側端部の上方に位置する領域に、凹部を形成する。凹部および第2の キャパシタ用コンタクトを充填するキャパシタコンタクト部と、第2の層間絶縁膜の上面 上に延びるキャパシタ下部電極とを有する導電層を形成する。

[0038]

請求項<u>5</u>に記載の製造方法によれば<u>ビ</u>ット線用開口が形成される膜と同じ第1のシリコン窒化膜および第1の層間絶縁膜に第1のキャパシタ用開口を形成するので、第1のキャパシタ用開口の形成時に第1のシリコン窒化膜をエッチングストッパ層とした自己整合開口法を用いることができる。これにより、第1のキャパシタ用開口を径縮小プロセスを簡略化することができるとともに、セルサイズが縮小されたとしても容易に第1のキャパシタ用開口を形成することが可能とカックト部を充填することによって、容易に、ビット線の側面および上面を覆うキャパシタコンタクト部を形成することができる。これにより、隣接するビット線間にキャパシタコンタクト部が介在する形となり、従来の通常のコンタクト部に比べて隣接するビット線間をシールドする部分の面積が大きくなる。このため、ビット配線容量を従来に比べて大きくすることができる。その結果、メモリセルからのデータの読出およびメモリセルへのデータの書込速度の遅延を防止し得る半導体装置を容易に製造することができる。

[0039]

【発明の実施の形態】

(実施の形態1)

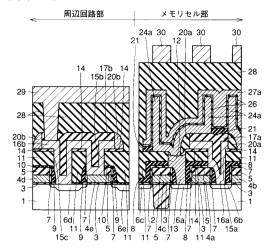

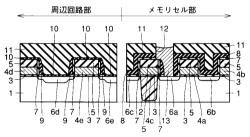

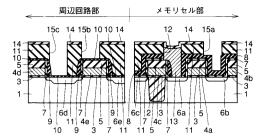

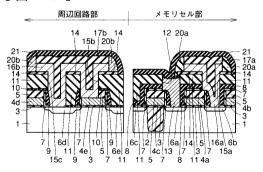

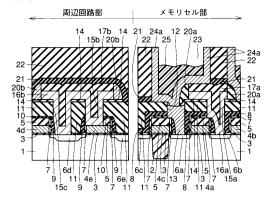

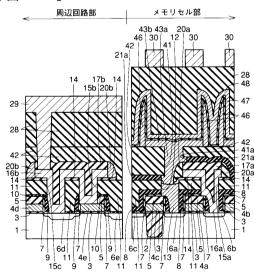

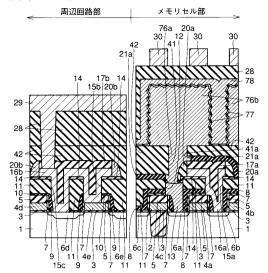

図1は、本発明の実施の形態1によるDRAMを示した断面構造図である。図1を参照して、この実施の形態1によるDRAMのメモリセル部では、シリコン基板1の主表面の所定領域に分離領域2が形成されている。分離領域2は、トレンチ溝を形成した後そのトレンチ溝に酸化膜を埋込むように形成されている。この分離領域2は、通常のLOCOS分

20

30

40

離酸化膜を用いたものでもよい。分離領域2によって囲まれた活性領域には、所定の間隔を隔ててソース / ドレイン領域6 a、 6 b および6 c が形成されている。ソース / ドレイン領域6 a と 6 b との間に位置するチャネル領域上にはゲート酸化膜3を介してゲート電極4 a が形成されている。また、ゲート電極4 a と所定の間隔を隔ててゲート電極4 b および4 c が形成されている。

#### [0040]

ゲート電極4a、4bおよび4cの上部表面上にはTEOS酸化膜5が形成されている。また、ゲート電極4a~4cとTEOS酸化膜5を覆うように10~20nm程度の厚みを有するTEOS酸化膜7が形成されている。また、そのTEOS酸化膜7を覆うように30~50nm程度の厚みを有するシリコン窒化膜8が形成されている。シリコン窒化膜8上にはBPSG酸化膜またはPSG酸化膜からなる層間絶縁膜11が形成されている。層間絶縁膜11およびシリコン窒化膜8の、ソース/ドレイン領域6a上に位置する領域には、キャパシタ用コンタクトホール12が形成されている。また、シリコン窒化膜8および層間絶縁膜11のソース/ドレイン領域6b上に位置する領域には、ビット線用コンタクトホール15aが形成されている。

#### [0041]

キャパシタ用コンタクトホール12内には多結晶シリコン膜からなるプラグ電極13が充填されている。また、層間絶縁膜11を覆うように30nm程度の厚みを有するTEOS酸化膜14が形成されている。TEOS酸化膜14の、プラグ電極13上に位置する領域とビット線用コンタクトホール15a上に位置する領域とには、それぞれ開口部が形成されている。ビット線用コンタクトホール15a内でソース/ドレイン領域6bに電気的に接続されるとともに、TEOS酸化膜14の上部表面上に沿って延びるようにビット線16aが形成されている。ビット線16aの上部表面上には100~200 程度の厚みを有するTEOS酸化膜17aが形成されている。TEOS酸化膜17aの側表面とビット線16aの側表面とに接触するようにTEOS酸化膜からなるサイドウォール酸化膜20aが形成されている。

# [0042]

プラグ電極13の上面に電気的に接続するとともに、サイドウォール酸化膜20aおよびTEOS酸化膜17aの上部表面上に沿って延びるように、多結晶シリコン膜からなるキャパシタ下部電極24aが形成されている。キャパシタ下部電極24aはその両側端部で垂直方向に延びる筒状構造を有するように形成されている。また、隣接するキャパシタ下部電極24a間にはシリコン窒化膜21が形成されている。キャパシタ下部電極24aを覆うようにキャパシタ誘電体膜26が形成されている。また、キャパシタ接電体膜26とシリコン窒化膜21とを覆うように多結晶シリコン膜からなるキャパシタ上部電極27aが形成されている。また、キャパシタ上部電極27aが形成されている。また、キャパシタ上部電極27aを覆うようにTEOS酸化膜またはBPSG酸化膜などからなる層間絶縁膜28が形成されている。層間絶縁膜28の上部表面上には、所定の間隔を隔ててメタル配線30が形成されている。

### [0043]

一方、周辺回路部では、シリコン基板 1 の主表面に所定の間隔を隔ててソース / ドレイン領域 6 d および 6 e が形成されている。ソース / ドレイン領域 6 d と 6 e との間に位置するチャネル領域上にはゲート酸化膜 3 を介してゲート電極 4 e が形成されている。ゲート電極 4 e からソース / ドレイン領域 6 d を隔てた領域上にはゲート酸化膜 3 を介してゲート電極 4 d が形成されている。ゲート電極 4 d および 4 e の上部表面上には、TEOS酸化膜 5 が形成されている。また、ゲート電極 4 d および 4 e の側表面と、TEOS酸化膜 5 の側表面とに接触するように 1 0 ~ 2 0 n m程度の厚みを有するTEOS酸化膜 7 が形成されている。また、TEOS酸化膜 7 の側部には、シリコン窒化膜からなるサイドウォール絶縁膜 9 が形成されている。このサイドウォール酸化膜 9 は、LDD(Light1 y Doped Drain )構造を有するソース / ドレイン領域 6 d および 6 e を形成するために用いる。

# [0044]

40

20

20

30

40

50

TEOS酸化膜5上にはシリコン窒化膜からなる絶縁膜10が形成されている。なお、絶縁膜10は、TEOS酸化膜により形成してもよい。また、全面を覆うように層間絶縁膜11が形成されている。層間絶縁膜11上にはTEOS酸化膜14が形成されている。ソース/ドレイン領域6dおよびゲート電極4e上に位置する、層間絶縁膜11およびTEOS酸化膜14には、それぞれコンタクトホールが形成されている。それらのコンタクトホールを介してソース/ドレイン領域6dおよびゲート電極4eに電気的に接続するように配線層16bが形成されている。なお、配線層16bは、ソース/ドレイン領域6dまたはゲート電極4eの一方のみに接続していてもよい。配線層16bの上部表面を覆うようにTEOS酸化膜17bが形成されている。配線層16bの側表面とTEOS酸化膜17bの側表面とに接触するように、TEOS酸化膜からなるサイドウォール酸化膜20bが形成されている。

[0045]

また、サイドウォール酸化膜20bおよびTEOS酸化膜17bを覆うように層間絶縁膜28が形成されている。層間絶縁膜28およびTEOS酸化膜17bの、配線層16bの側端部上に位置する領域には、コンタクトホールが形成されている。そのコンタクトホールを介して配線層16bに電気的に接続するとともに、層間絶縁膜28の上部表面上に沿って延びるようにメタル配線29が形成されている。

[0046]

なお、メモリセル部におけるゲート電極 4 a ~ 4 c と、周辺回路部のゲート電極 4 d および 4 e とは、同一の層をパターニングすることによって形成される。また、メモリセル部のビット線 1 6 a と周辺回路部の配線層 1 6 b とは同一の層をパターニングすることによって形成される。

[0047]

ここで、実施の形態1によるDRAMでは、キャパシタ下部電極24aとソース / ドレイン領域6aとの間にプラグ電極13を介在させている。そしてそのプラグ電極13は、ビット線用コンタクトホール15aと同様のアスペクト比(深さ)を有するキャパシタ用コンタクトホール12内を充填するように形成されている。したがって、後述する製造プロセスで説明するように、この実施の形態1の構造では、キャパシタ用コンタクトホール12をビット線用コンタクトホール15aと同様の小さいアスペクト比で形成することができる。このため、キャパシタ用コンタクトホール12を、シリコン窒化膜8をエッチングストッパとして用いた自己整合的開口法によって形成することができる。その結果、図44~図46を用いて説明した従来の径縮小プロセスを用いてキャパシタ用コンタクトホール161を形成する場合に比べて、製造プロセスをより簡略化することができる。また、シリコン窒化膜8を用いた自己整合的開口法を用いれば、メモリセルサイズが縮小化された場合にも、容易にキャパシタ用コンタクトホール12を形成することができる。

[0048]

また、この実施の形態1の構造では、ソース/ドレイン領域6aに接続されるプラグ電極13の底面の平面積よりも、キャパシタ下部電極24aに接続されるプラグ電極13の上面の平面積の方が大きくなるように形成されている。このため、プラグ電極13の上面に接続するようにキャパシタ下部電極24aを形成する際に、重ね合わせずれの余裕を大きく取ることができ、その結果キャパシタ下部電極24aの形成プロセスが容易になるという効果を奏する。

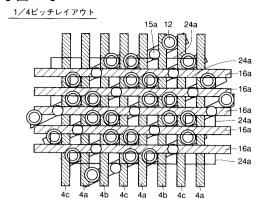

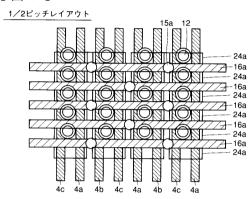

[0049]

さらに、この実施の形態1による構造では、キャパシタ下部電極24aが、サイドウォール酸化膜20aおよびTEOS酸化膜17aを介して、ビット線16aの側表面と上部表面とを覆うように形成されている。図1に示したメモリセル部全体の平面レイアウト図が図2および図3に示されている。図2は、1/4ピッチの場合のレイアウト図であり、図3は1/2ピッチの場合のレイアウト図である。図1~図3を参照して、この実施の形態1の構造では、ビット線16aの側部とそれに隣接するビット線16aの側部との間にキャパシタ下部電極24aが介在されている。そのため、隣接するビット線16aの側部間

20

30

50

をキャパシタ下部電極24aが遮る構造になり、キャパシタ下部電極24aにシールド効果を持たせることができる。これにより、隣接するビット線16a間のビット配線容量を低減することができる。また、キャパシタ下部電極24aはビット線16aの上部表面上にも形成されているので、隣接するビット線16aの上部表面間のビット配線容量をも低減することができる。このように、ビット線16a間のビット配線容量を低減することができるので、データの書込および読出動作が遅くなるのを有効に防止することができる。

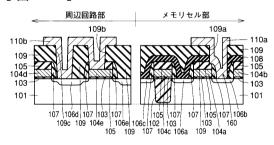

図 4 ~ 図 2 0 は、図 1 に示した D R A M の製造プロセスを説明するための断面構造図である。図 4 ~ 図 2 0 を参照して、以下に実施の形態 1 による D R A M の製造プロセスについて説明する。

### [0051]

[0050]

まず、図4に示すように、シリコン基板1のメモリセル部の主表面の所定領域に、分離領域2を形成する。この分離領域2は、トレンチ溝に酸化膜を埋込むトレンチ分離領域であってもよいし、LOCOS酸化膜を用いた分離領域であってもよい。また、シリコン基板1の主表面上に、所定の間隔を隔ててゲート酸化膜3を形成するとともに、そのゲート酸化膜3上にそれぞれゲート電極4a~4eを形成する。ゲート電極4a~4eは、多結晶シリコン膜とその多結晶シリコン膜上に形成したタングステンシリサイド膜との2層構造を有するように構成してもよい。ゲート電極4a~4eをマスクとして、シリコン基板1に不純物をイオン注入することによって、ソース/ドレイン領域6a~6eを形成する。

# [0052]

また、ゲート電極4a~4eの上部表面上にTEOS酸化膜5を形成する。また、全面を覆うように10~20nm程度の厚みを有するTEOS酸化膜7を形成した後、そのTEOS酸化膜7上に30~50nm程度の厚みを有するシリコン窒化膜8を形成する。この後、周辺回路部に位置するシリコン窒化膜8を異方性エッチングすることによって、図5に示されるような、シリコン窒化膜からなるサイドウォール9を形成する。そしてこのサイドウォール9をマスクとして周辺回路部のシリコン基板1の表面に不純物をイオン注入することによって、LDD構造を有するソース/ドレイン領域6dおよび6eを形成する

# [0053]

また、周辺回路部のTEOS酸化膜5の上部表面上に、シリコン窒化膜からなる絶縁膜を5~10nm程度の膜厚で形成する。なお、この絶縁膜10はTEOS酸化膜によって形成してもよい。

### [0054]

この後、図6に示すように、BPSG酸化膜またはPSG酸化膜からなる層間絶縁膜11を形成した後、ソース/ドレイン領域6a上に位置する層間絶縁膜11の領域にキャパシタ用コンタクトホール12は、まずシリコン窒化膜8をエッチングストッパ層として、たとえば、CHF3 /CF4 のエッチャントを用いて選択比10~20以上で層間絶縁膜11をエッチングすることにより形成する。これにより、自己整合的にキャパシタ用コンタクトホール12が形成される。さらに、キャパシタ用コンタクトホール12内に位置するシリコン窒化膜8を層間絶縁膜11に対して選択的にエッチングできる条件で異方性エッチングする。この異方性エッチングは、たとえば、F系ガスをエッチャントとして選択比10程度で行なう。さらに、ソース/ドレイン領域6a上のTEOS酸化膜7を希フッ酸などを用いて除去する。この希フッ酸は、たとえば1/50希釈HFを用いる。これにより、図7に示されるような、層間絶縁膜11の上面からソース/ドレイン領域6aに至るキャパシタ用コンタクトホール12が完成される。

### [0055]

この後、そのキャパシタ用コンタクトホール12内を埋込むとともに層間絶縁膜11の上部表面上に沿って延びる多結晶シリコン膜(図示せず)を形成した後、その多結晶シリコン膜をドライエッチングすることによって、プラグ電極13を形成する。このプラグ電極

30

40

50

13は、キャパシタ用コンタクトホール12内を充填するように形成する。

### [0056]

次に、図8に示すように、プラグ電極13の上面上および層間絶縁膜11の上面上に30 nm程度の厚みを有するTEOS酸化膜14を形成する。

#### [0057]

次に、図9に示すように、シリコン窒化膜8 および絶縁膜10をエッチングストッパ層として、層間絶縁膜11 およびTEOS酸化膜14をエッチングすることによって、ビット線用コンタクトホール15 b および15 c とを自己整合的に形成する。このビット線用コンタクト15 a の自己整合的開口法で用いるエッチングは、たとえば、 $CHF_3$  /  $CF_4$  のエッチャントを用いて選択比10~20以上で行なう。

### [0058]

この後、ビット線用コンタクトホール15a内に位置するシリコン窒化膜8と、配線用コンタクトホール15bおよび15c内に位置する絶縁膜10とを、層間絶縁膜11に対してシリコン窒化膜8および絶縁膜10を選択的にエッチングできる条件で異方性エッチングする。これにより、図10に示されるような、ビット線用コンタクトホール15aと、配線用コンタクトホール15bおよび15cとが完成される。

#### [0059]

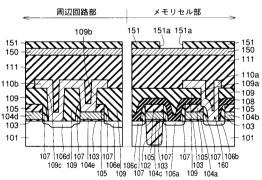

その後、50~100 n m程度の厚みを有する多結晶シリコン膜と、50~100 n m程度の厚みを有するチタンシリサイド膜とからなる導電層(図示せず)、および、その上に 100~20 n m程度の厚みを有する TEOS酸化膜(図示せず)を形成した後、その TEOS酸化膜および導電層をパターニングする。これによって、図 10 に示されるような、ビット線 16 a およびその上の TEOS酸化膜 17 a と、配線層 16 b およびその上の TEOS酸化膜 17 b とが形成される。

### [0060]

次に、図11に示すように、全面を覆うようにTEOS酸化膜19を50~100nm程度の厚みで形成した後、そのTEOS酸化膜19をドライエッチングすることによって、図12に示されるような、TEOS酸化膜からなるサイドウォール酸化膜20aおよび20bを形成する。

# [0061]

この後、図13に示すように、50nm程度の厚みでシリコン窒化膜21を形成する。この後、図14に示すように、シリコン窒化膜21上にBPSG酸化膜またはTEOS酸化膜からなる絶縁膜22を形成した後、シリコン窒化膜21をエッチングストッパ層とする自己整合的コンタクト開口法によって、キャパシタホール23を形成する。キャパシタホール23の形成は、たとえば、CHF3 / CF4 をエッチャントとして、選択比を10~20以上に設定したエッチングを用いて行なう。

# [0062]

そのキャパシタホール 2 3 内に位置するシリコン窒化膜 2 1 を絶縁膜 2 2 に対して選択的にエッチングできる等方性エッチングによって除去する。この等方性エッチングは、たとえば熱リン酸を用いて選択比が 5 0 程度で行なう。これにより、図 1 5 に示すような構造が得られる。さらに、プラグ電極 1 3 の上面を 1 / 1 0 0 希釈 H F などの希フッ酸を用いてクリーニングする。

### [0063]

この後、図16に示すように、多結晶シリコン膜24を100nm程度の膜厚で形成した後、フォトレジスト25をキャパシタホール23内に埋込む。そして、層間絶縁膜22上に位置する多結晶シリコン膜24をドライエッチングにより除去することによって、図17に示すような筒状のキャパシタ下部電極24aの形状が得られる。この後、層間絶縁膜22を等方性エッチングにより除去することによって、図18に示されるような構造が得られる。この層間絶縁膜22のエッチングは、たとえば、10:1の希釈HFによって行なう。

#### [0064]

次に、全面を覆うようにキャパシタ誘電体膜26および多結晶シリコン膜27を形成する。キャパシタ誘電体膜26としては、たとえば、シリコン酸化窒化膜を用いてもよいし、Ta2O5 膜などの高誘電体膜を用いてもよい。図19に示した状態から、パターニングを行なうことによって、図20に示すような多結晶シリコン膜からなるキャパシタ上部電極27aを形成することができる。

#### [0065]

この後、図1に示すように、全面にTEOS酸化膜またはBPSG酸化膜などからなる層間絶縁膜28を形成した後、その層間絶縁膜28のメモリセル部の上部表面上にメタル配線30を所定の間隔を隔てて形成する。また、周辺回路部に位置する層間絶縁膜28およびTEOS酸化膜17bにコンタクトホールを形成した後、そのコンタクトホール内で配線層16bに電気的に接続されるとともに層間絶縁膜28の上部表面上に沿って延びるメタル配線層29を形成する。このようにして、図1に示した実施の形態1によるDRAMが完成される。

#### [0066]

#### (実施の形態2)

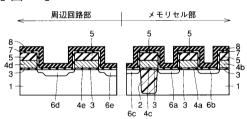

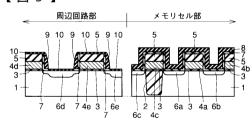

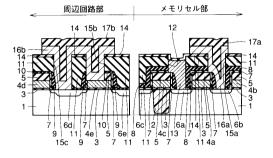

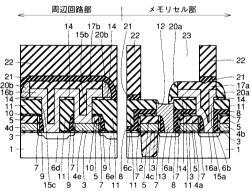

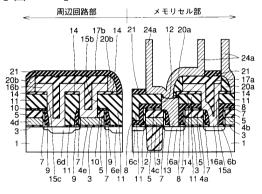

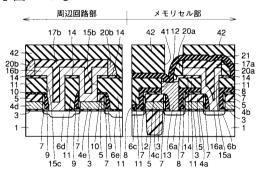

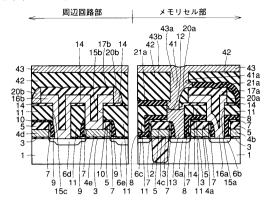

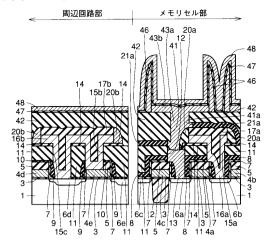

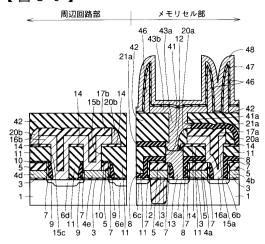

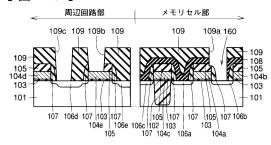

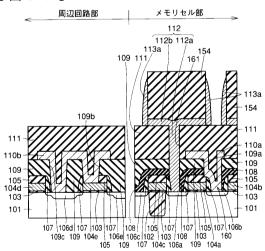

図21は、本発明の実施の形態2によるDRAMを示した断面図である。図21を参照して、この実施の形態2によるDRAMでは、プラグ電極13およびビット線16aについては実施の形態1による構造と同様の構造を有している。しかし、この実施の形態2では、キャパシタ構造が実施の形態1による構造とは異なる。

### [0067]

具体的には、この実施の形態2の構造では、プラグ電極13の上部表面に直接キャパシタ下部電極部43bが接続されているのではなく、キャパシタ下部電極部43bとプラグ電極13との間にキャパシタコンタクト部43aが介在されている。キャパシタコンタクト部43aとキャパシタ下部電極43bとは一体的に形成されている。

### [0068]

また、シリコン窒化膜21 a は、層間絶縁膜11の上部表面上と、TEOS酸化膜17 a の上部表面上とに形成されている。また、シリコン窒化膜21 a 上にはTEOS酸化膜と、BPSG酸化膜またはPSG酸化膜との積層膜からなる層間絶縁膜42が形成されている。層間絶縁膜42と、シリコン窒化膜21 a と、サイドウォール酸化膜20 a と、TEOS酸化膜14とによって、第2のキャパシタ用コンタクトホール41が形成されている。また、第2のキャパシタ用コンタクトホール41の、ビット線16 a の側端部上に位置する領域には凹部41 a が形成されている。その第2のキャパシタ用コンタクトホール41 およびその凹部41 a を充填するようにキャパシタコンタクト部43 a が形成されている。

### [0069]

そしてそのキャパシタコンタクト部43aの上部と一体的に、層間絶縁膜42の上部表面上に沿って延びるキャパシタ下部電極部43bが形成されている。またキャパシタ下部電極部43bの両側端部に接触するように、上方に向かって延びる多結晶シリコン膜からなるサイドウォール46が形成されている。キャパシタ下部電極部43bとサイドウォール46とによってキャパシタ下部電極が構成される。キャパシタ下部電極部43bおよびサイドウォール46を覆うようにキャパシタ誘電体膜46が形成されており、そのキャパシタ誘電体膜46を覆うように多結晶シリコン膜からなるキャパシタ上部電極48が形成されている。

#### [0070]

また、周辺回路部では、TEOS酸化膜17bとサイドウォール酸化膜20bとを覆うように層間絶縁膜42が形成されており、その層間絶縁膜42上に層間絶縁膜28が形成されている。層間絶縁膜28、42およびTEOS酸化膜17bの所定領域にはコンタクトホールが設けられており、そのコンタクトホールを介して、配線層16bに電気的に接続するようにメタル配線29が形成されている。

20

30

4(

20

30

40

50

### [0071]

ここで、この実施の形態2では、上述した実施の形態1と同様、ビット線用コンタクトホ ール 1 5 a と同じアスペクト比で第 1 のキャパシタ用コンタクトホール 1 2 を形成するこ とができるので、その第1のキャパシタ用コンタクトホール12の形成の際に、シリコン 窒化膜8を用いた自己整合的コンタクト開口法を用いることができる。さらに、キャパシ タ用コンタクトホールを、第1のキャパシタ用コンタクトホール12とその上方の第2の キャパシタ用コンタクトホール41との2段階に分けることによって、第2のキャパシタ 用コンタクトホール41のアスペクト比を小さくすることができる。これにより、第2の キャパシタ用コンタクトホール41も、シリコン窒化膜21aをエッチングストッパ層と した自己整合的開口法によって形成することができる。

[0072]

このように、この実施の形態2では、第1のキャパシタ用コンタクトホール12と第2の キャパシタ用コンタクトホール41との両方をシリコン窒化膜8および21aを用いた自 己整合的開口法によって形成することができるので、従来の径縮小プロセスによってキャ パシタ用コンタクトホールを形成する場合に比べて、製造方法を簡素化することができる 。また、メモリセルサイズが縮小化されたとしても容易に第1のキャパシタ用コンタクト ホール12および第2のキャパシタ用コンタクトホール41を形成することができる。

[0073]

また、この実施の形態2の構造では、キャパシタコンタクト部43aが、サイドウォール 酸化膜20aおよびTEOS酸化膜17aを介して、ビット線16aの側面および上面を 覆うように形成されているので、隣接するビット線16a間のビット配線容量を低減する ことができる。これにより、メモリセルからのデータの読出およびメモリセルへのデータ の書込速度の低下を防止することができ、アクセス速度を向上させることができる。

[0074]

また、この実施の形態2の構造では、上記した実施の形態1と同様、ソース/ドレイン領 域 6 a に接続されるプラグ電極13の底面の平面積よりも、キャパシタ下部電極24 a に 接続されるプラグ電極13の上面の平面積の方が大きくなるように形成されている。この ため、プラグ電極13の上面に接続するようにキャパシタ下部電極24aを形成する際に 、重ね合わせずれの余裕を大きく取ることができ、その結果キャパシタ下部電極24aの 形成プロセスが容易になるという効果を奏する。

[0075]

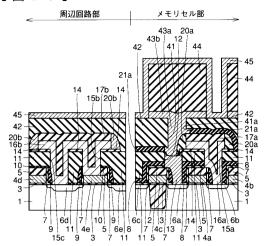

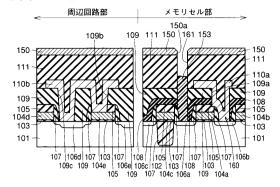

図 2 2 ~ 図 3 0 は、図 2 1 に示した実施の形態 2 による D R A M の製造プロセスを説明す るための断面図である。以下に、図22~図30を用いて実施の形態2による製造プロセ スについて説明する。

[0076]

まず、図4~図13に示した実施の形態1による製造プロセスと同様のプロセスを用いて 、シリコン窒化膜21までを形成する。この後、周辺回路部に位置するシリコン窒化膜2 1を除去することによって、図22に示されるような形状が得られる。

[0077]

次に、図23に示すように、BPSG酸化膜またはPSG酸化膜と、その上のTEOS酸 化膜との積層膜からなる層間絶縁膜42を形成する。その場合のTEOS酸化膜は10~ 20nm程度の厚みで形成する。その後、層間絶縁膜42のプラグ電極13の上方に位置 する領域を、下層のシリコン窒化膜21をエッチングストッパ層としてエッチングする。 この場合のエッチングは、CHF3 / CF4 をエッチャントとして、選択比を10~ 2 0 以上として行なう。これにより、キャパシタ用コンタクトホール 4 1 が自己整合的に 形成される。

[0078]

この後、シリコン窒化膜21を層間絶縁膜42に対して選択的にエッチングすることが可 能な等方性エッチングを用いて、シリコン窒化膜21をエッチングする。この等方性エッ チングは、たとえば熱リン酸を用いて選択比50程度で行なう。このような等方性エッチ

30

50

ングによって、形成されるシリコン窒化膜 2 1 a は、図 2 4 に示すように、層間絶縁膜 4 2 に対して大きく後退した形状になる。つまり、ビット線 1 6 a の側端部上方に凹部 4 1 a が形成された形状になる。この後、プラグ電極 1 3 の上面を希フッ酸などでクリーニングする。このクリーニングは、たとえば 1 / 1 0 0 希釈 H F を用いて行なう。

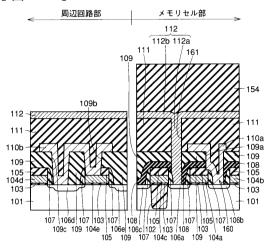

### [0079]

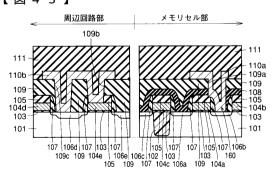

この後、図25に示すように、多結晶シリコン膜43を形成する。この多結晶シリコン膜43は、第2のキャパシタ用コンタクトホール41およびその凹部41aを埋込むとともに、層間絶縁膜42の上部表面上に延びるように形成する。その後、多結晶シリコン膜43上に50~100nm程度の厚みを有するBPSG酸化膜(図示せず)を形成した後、そのBSPG酸化膜と多結晶シリコン膜43とをパターニングすることによって、図26に示されるようなキャパシタコンタクト部43aと、キャパシタ下部電極部43bと、そのキャパシタ下部電極部43b上のBPSG酸化膜44とが得られる。

# [0800]

この後、層間絶縁膜42およびBPSG酸化膜44を覆うように、50~100nm程度の厚みを有する多結晶シリコン膜45を形成する。その多結晶シリコン膜45を異方性エッチングすることによって、図27に示されるような、キャパシタ下部電極を構成する、多結晶シリコン膜からなるサイドウォール46が形成される。このサイドウォール46と、キャパシタ下部電極部43bとによって、筒状のキャパシタ下部電極が構成される。この後、BPSG酸化膜44を気相HFを用いて、下層の層間絶縁膜42とキャパシタ下部電極(46,43b)とに対して高選択比のエッチング(選択比1000程度)を行なう。これにより、BPSG酸化膜44を除去し、図28に示された構造が得られる。

#### [0081]

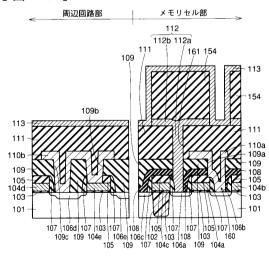

次に、図29に示すように、キャパシタ下部電極部43bおよびサイドウォール46を覆うようにキャパシタ誘電体膜47を形成した後、そのキャパシタ誘電体膜47を覆うように多結晶シリコン膜からなるキャパシタ上部電極48を形成する。キャパシタ誘電体膜としては、シリコン酸化窒化膜などの誘電体膜や、Ta₂ O₅ 膜などの高誘電体膜を用いる。この後、キャパシタ上部電極48とキャパシタ誘電体膜47とをパターニングすることによって、図30に示されるような形状のキャパシタ上部電極48が得られる。

# [0082]

この後、図21に示したように、キャパシタ上部電極48を覆うように層間絶縁膜28を形成した後、その層間絶縁膜28の上部表面上のメモリセル部にメタル配線30を所定の間隔を隔てて形成する。また、周辺回路部の層間絶縁膜28、42およびTEOS酸化膜17bにコンタクトホールを形成した後、そのコンタクトホールを介して配線層16bに電気的に接続するようにメタル配線29を形成する。このようにして、実施の形態2によるDRAMが形成される。

### [0083]

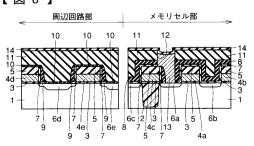

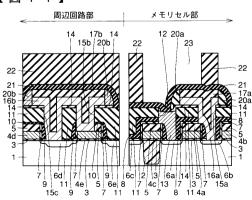

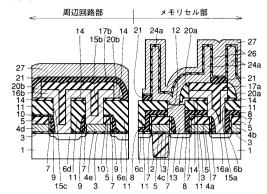

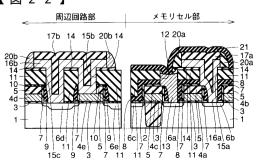

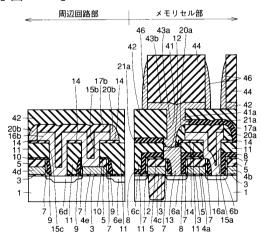

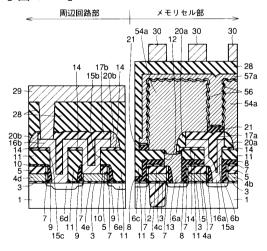

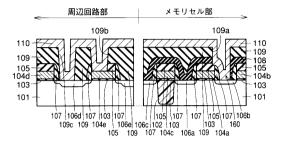

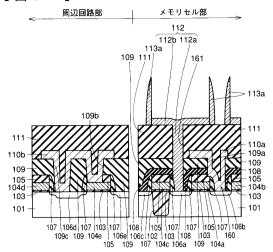

### (実施の形態3)

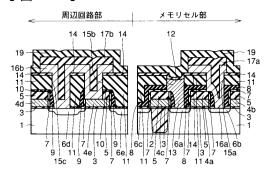

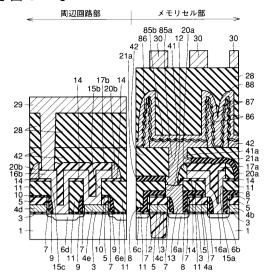

図31は、本発明の実施の形態3によるDRAMを示した断面図である。図31を参照して、この実施の形態3では、キャパシタ下部電極54aを、上述した実施の形態1および2の筒状構造ではなく、単純スタック型の構造にしている。さらに、キャパシタ下部電極54aの表面を凹凸を有するように粗面化している。これにより、キャパシタ下部電極54aの表面積が増加し、その結果キャパシタ容量を増加させることができる。なお、キャパシタ下部電極54a上にはキャパシタ誘電体膜56を介してキャパシタ上部電極57aが形成されている。

#### [0084]

表面に凹凸を有するキャパシタ下部電極 5 4 a は以下の方法により形成する。すなわち、高真空(~10 <sup>6</sup> Torr)下においてジシラン(Si<sub>2</sub> H<sub>6</sub> )やシラン(Si H<sub>4</sub> )ガスを流すことによって、多結晶シリコン膜上に選択的に多結晶シリコン粒を選択成長させる。これにより、図 3 1 に示すような凹凸形状を有するキャパシタ下部電極 5 4 a を形成することが可能となる。

#### [0085]

なお、この実施の形態3の構造においても、上述した実施の形態1と同様、プラグ電極13を介してキャパシタ下部電極54aがソース/ドレイン領域6aに電気的に接続される構造を有している。このため、実施の形態1と同様、キャパシタ用コンタクトホール12をビット線用コンタクトホール15aと同じアスペクト比で形成することができ、その結果、シリコン窒化膜8をエッチングストッパ層とする自己整合的開口法によって、キャパシタ用コンタクトホール12を形成することができる。これにより、キャパシタ用コンタクトホールを径縮小プロセスによって形成する場合に比べて、製造プロセスを簡略化することができる。また、キャパシタ下部電極54aがビット線16aの側部および上部を、サイドウォール酸化膜20aおよびTEOS酸化膜17aを介して覆うように形成されているので、隣接するビット線16a間のビット配線容量を低減することができる。これにより、動作速度の低下を防止することができる。

#### [0086]

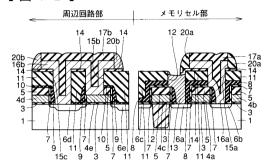

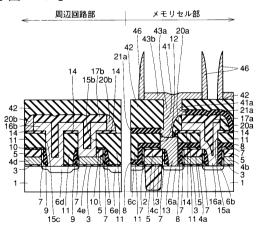

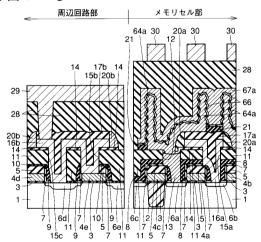

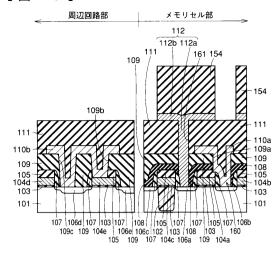

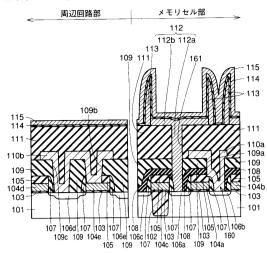

(実施の形態4)

図32は、本発明の実施の形態4によるDRAMを示した断面図である。図32を参照して、この実施の形態4は、図1に示した実施の形態1と基本的には同じ構造を有している。この実施の形態3の構造が実施の形態1と異なるのは、実施の形態3ではキャパシタ下部電極64aの表面が凹凸形状を有していることである。この凹凸形状を有するキャパシタ上部電極64aを覆うようにキャパシタ誘電体膜66を介してキャパシタ上部電極67aが形成されている。このようにキャパシタ下部電極64aの表面を粗面化して凹凸形状に形成することによって、キャパシタ容量を増大させることができる。キャパシタ下部電極64aの表面を粗面化する方法は、上記した実施の形態3の方法と同様な方法を用いる

### [0087]

この実施の形態 4 による構造も、基本的には実施の形態 1 の構造と同様の構造を有しているので、実施の形態 1 と同様、キャパシタ用コンタクトホールの形成プロセスを容易にすることができるとともに、読出および書込動作の速度が低下するのを防止することができる。

# [0088]

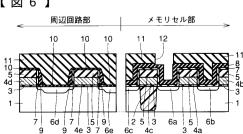

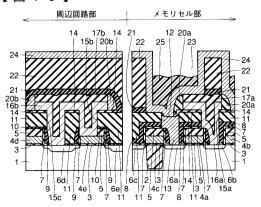

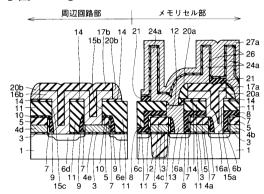

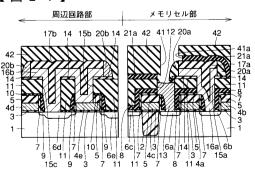

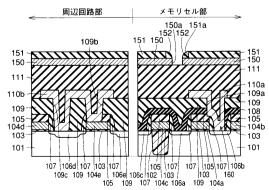

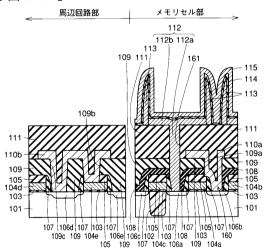

(実施の形態5)

図33は、本発明の実施の形態5によるDRAMを示した断面図である。図33を参照して、この実施の形態5では、図21に示した実施の形態2のキャパシタ部分の構造の変形例である。具体的には、この実施の形態5では、キャパシタコンタクト部76aの上方に位置するキャパシタ下部電極部76bが、筒状構造ではなく単純スタック型の構造を有している。そしてそのキャパシタ下部電極部76bの表面は凹凸形状に形成されている。そのキャパシタ下部電極部76bを覆うようにキャパシタ誘電体膜77を介してキャパシタ上部電極78が形成されている。このようにキャパシタ下部電極部76bの表面を凹凸形状に形成することによって、キャパシタ容量を増大することができる。

# [0089]

また、この実施の形態5では、上述した実施の形態2と同様、キャパシタコンタクト部76aがビット線16aの側面および上面を覆うように形成されているので、ビット線16a間のビット配線容量を低減することができ、その結果、データの読出および書込動作速度を向上させることができる。また、プラグ電極を設けることによって、第1のキャパシタ用コンタクトホール12と第2のキャパシタ用コンタクトホール41とをアスペクト比が小さくなるようにすることができる。これにより、第1のキャパシタ用コンタクトホール12と第2のキャパシタ用コンタクトホール41とを、窒化膜8および21aをそれぞれ用いた自己整合的開口法によって形成することができる。これにより、径縮小プロセスによってキャパシタ用コンタクトホールを形成する場合に比べて製造プロセスを簡略化することができる。

# [0090]

20

30

20

50

(実施の形態6)

図34は、本発明の実施の形態6によるDRAMを示した断面図である。図34を参照し て、この実施の形態6では、図21に示した実施の形態2とほぼ同様の構造を有している 。ただし、この実施の形態6では、キャパシタコンタクト部85aと一体的に形成された キャパシタ下部電極部85bの表面と、多結晶シリコン膜からなるサイドウォール86の 表面とが凹凸形状を有するように形成されている。そして、そのキャパシタ下部電極部8 5 b およびサイドウォール 8 6 を覆うようにキャパシタ誘電体膜 8 7 を介してキャパシタ 上部電極88が形成されている。このようにキャパシタ下部電極を構成するキャパシタ下 部電極部85bおよびサイドウォール86の表面を凹凸形状に形成することによって、キ ャパシタ容量を増大させることができる。

[0091]

また、この実施の形態6では、実施の形態2の構造と同様、第1のキャパシタ用コンタク トホール12および第2のキャパシタ用コンタクトホール41をともに、シリコン窒化膜 8 および 2 1aを用いた自己整合的開口法により形成することができる。これにより、製 造プロセスを簡略化することができる。また、隣接するビット線16a間の配線容量も低 減することができ、これにより動作速度を向上させることができる。

[0092]

【発明の効果】

以上のように、請求項1~3に記載の半導体装置によれば、製造プロセスを簡略化するこ とができるとともにビット配線容量を低減することができる。また、請求項4に記載の半 導体装置では、さらにキャパシタ容量を増大することができる。また、請求項5に記載の 半導体装置では、キャパシタ用コンタクトホールを容易に形成することができる。さらに 、請求項6および7に記載の半導体装置の製造方法では、キャパシタ用コンタクトホール を、シリコン窒化膜を用いた自己整合的開口法によって容易に形成することができるとと もに、ビット配線容量を低減し得る半導体装置を容易に製造できる。

【図面の簡単な説明】

- 【図1】本発明の実施の形態1によるDRAMを示した断面図である。

- 【図2】図1に示したDRAMのメモリセル部の1/4ピッチのレイアウト図である。

- 【図3】図1に示したDRAMのメモリセル部の1/2ピッチのレイアウト図である。

- 【図4】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面 30 図である。

- 【図5】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面 図である。

- 【図6】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面 図である。

- 【図7】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面

- 【図8】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面 図である。

- 【図9】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面 40 図である。

- 【図10】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断 面図である。

- 【図11】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断 面図である。

- 【図12】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断

- 【図13】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断 面図である。

- 【図14】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断

30

50

面図である。

- 【図15】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面図である。

- 【図16】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面図である。

- 【図17】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面図である。

- 【図18】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断面図である。

- 【図19】図1に示した実施の形態1によるDRAMの製造プロセスを説明するための断 面図である。

- 【図 2 0 】図 1 に示した実施の形態 1 による D R A M の製造プロセスを説明するための断面図である。

- 【図21】本発明の実施の形態2によるDRAMを示した断面図である。

- 【図22】図21に示した実施の形態2によるDRAMの製造プロセスを説明するための断面図である。

- 【図23】図21に示した実施の形態2によるDRAMの製造プロセスを説明するための断面図である。

- 【図24】図21に示した実施の形態2によるDRAMの製造プロセスを説明するための 断面図である。

- 【図 2 5 】図 2 1 に示した実施の形態 2 による D R A M の製造プロセスを説明するための断面図である。

- 【図 2 6 】図 2 1 に示した実施の形態 2 による D R A M の製造プロセスを説明するための断面図である。

- 【図27】図21に示した実施の形態2によるDRAMの製造プロセスを説明するための 断面図である。

- 【図28】図21に示した実施の形態2によるDRAMの製造プロセスを説明するための 断面図である。

- 【図29】図21に示した実施の形態2によるDRAMの製造プロセスを説明するための 断面図である。

- 【 図 3 0 】図 2 1 に示した実施の形態 2 による D R A M の製造プロセスを説明するための 断面図である。

- 【図31】本発明の実施の形態3によるDRAMを示した断面図である。

- 【図32】本発明の実施の形態4によるDRAMを示した断面図である。

- 【図33】本発明の実施の形態5によるDRAMを示した断面図である。

- 【図34】本発明の実施の形態6によるDRAMを示した断面図である。

- 【図35】従来のDRAMを示した断面図である。

- 【 図 3 6 】図 3 5 に示した従来のDRAMのメモリセル部の1/2ピッチのレイアウト図である。

- 【図37】図35に示した従来のDRAMの製造プロセスを説明するための断面図である 40

- 【図38】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

- 【図39】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

- 【図40】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

- 【図41】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

- 【図42】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

20

【図43】図35に示した従来のDRAMの製造プロセスを説明するための断面図である。

【図44】図35に示した従来のDRAMの製造プロセスを説明するための断面図である。

【図45】図35に示した従来のDRAMの製造プロセスを説明するための断面図である。

【図46】図35に示した従来のDRAMの製造プロセスを説明するための断面図である。

【図47】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

【図48】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

【図49】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

【図50】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

【図51】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

【図52】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

【図53】図35に示した従来のDRAMの製造プロセスを説明するための断面図である

### 【符号の説明】

1 シリコン基板、6 a , 6 b ソース / ドレイン領域、8 , 2 1 a シリコン窒化膜、1 1 層間絶縁膜、1 2 第 1 のキャパシタ用コンタクトホール、1 3 プラグ電極、1 5 a ビット線用コンタクトホール、1 6 a ビット線、1 7 a TEOS酸化膜、2 0 a サイドウォール酸化膜、2 4 a キャパシタ下部電極、2 6 キャパシタ誘電体膜、2 7 a キャパシタ上部電極。

【図1】

【図2】

【図3】

【図4】

【図7】

【図5】

【図8】

【図6】

### 【図9】

# 【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

【図16】

# 【図17】

# 【図18】

# 【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

周辺回路部

メモリセル部

### 【図38】

# 【図39】

### 【図40】

【図41】

【図42】

# 【図44】

【図43】

【図45】

# 【図46】

# 【図47】

# 【図49】

# 【図48】

【図50】

【図51】

【図52】

【図53】

# フロントページの続き

# (72)発明者 新川田 裕樹

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

# 審査官 正山 旭

# (56)参考文献 特開平09-064306(JP,A)

特開平09-017978(JP,A)

特開平05-226609(JP,A)

特開平06-283681(JP,A)

特開平09-102588(JP,A)

特開平09-064297(JP,A)

特開平09-321238(JP,A)

# (58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H01L 27/108

H01L 21/8242

H01L 21/768

H01L 29/78