US 20050024948A1

## (19) United States (12) Patent Application Publication (10) Pub. No.: US 2005/0024948 A1

### (10) Pub. No.: US 2005/0024948 A1 (43) Pub. Date: Feb. 3, 2005

### Kanamitsu et al.

#### (54) SEMICONDUCTOR DEVICE AND DATA PROCESSING SYSTEM

(75) Inventors: Michitaro Kanamitsu, Ome (JP); Yoshinori Takase, Tokyo (JP)

> Correspondence Address: MILES & STOCKBRIDGE PC 1751 PINNACLE DRIVE SUITE 500 MCLEAN, VA 22102-3833 (US)

- (73) Assignces: Hitachi, Ltd.; Hitachi ULSI Systems Co., Ltd.

- (21) Appl. No.: 10/928,195

- (22) Filed: Aug. 30, 2004

#### **Related U.S. Application Data**

(63) Continuation of application No. 10/623,527, filed on Jul. 22, 2003, now abandoned, which is a continuation of application No. 10/013,538, filed on Dec. 13, 2001, now Pat. No. 6,603,680.

- (30) Foreign Application Priority Data

- Dec. 26, 2000 (JP) ..... 2000-394935

#### Publication Classification

- (51) Int. Cl.<sup>7</sup> ...... G11C 11/34

#### (57) ABSTRACT

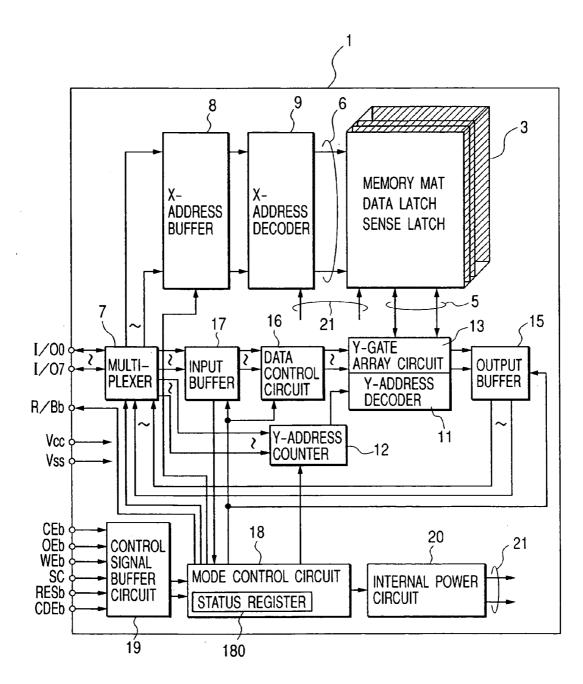

The present invention provides a semiconductor device such as a multi-valued flash memory or the like, which is capable of shortening a processing time required to set write control information to a sense latch. The semiconductor device is capable of electrically writing multi-value information therein. Bit lines are connected to the right and left input/ output terminals of a sense latch, and data latches are connected to the respective bit lines. A decoder is provided which decodes write data supplied from outside to thereby generate write control information. The write control information is latched in each of the sense latch and data latches, and the latched control information is set as information indicative of go/no-go of the application of a write voltage, which corresponds to each value in a multivalue. A write operation based on the data latched in the sense latch is first controlled, and the write control information for the sense latches are internally transferred from the data latches in turn subsequently and successively write-controlled.

FIG. 3

| OPERATING<br>MODE   | COMMAND |

|---------------------|---------|

| READ                | 00H     |

| WRITE               | 1FH     |

| ADDITIONAL<br>WRITE | 10H     |

| ERASE               | 20H     |

|      | DESIGNATION   | DEFINITION             |

|------|---------------|------------------------|

| I/07 | Ready / Busy  | "Voн"=Ready "VoL"=Busy |

| I/06 | Reserved      |                        |

| I/05 | Erase Check   | "Voh"=Fail "Vol"=Pass  |

| I/04 | Program Check | "Voh"=Fail "Vol"=Pass  |

| I/03 | Reserved      |                        |

| I/02 | Reserved      |                        |

| I/01 | Reserved      |                        |

| I/00 | Reserved      |                        |

STATUS REGISTER

.

| WRITE | I/ | ⁄0 | DLL | DLR |  |  |

|-------|----|----|-----|-----|--|--|

| DATA  | 4  | 0  |     | DLN |  |  |

| 01    | 0  | 1  | 0   | 1   |  |  |

| 00    | 0  | 0  | 0   | 0   |  |  |

| 10    | 1  | 0  | 1   | 0   |  |  |

| 11    | 1  | 1  | 1   | 1   |  |  |

INPUT WRITE DATA

OPERATING VOLTAGE

FIG. 20(B)

| DATA LATCH PROCESSING       | CONTENTS OF OPERATION<br>(SENSE LATCH DATA ON<br>SELECTED MAT SIDE) |

|-----------------------------|---------------------------------------------------------------------|

| "01" WRITE DATA             | A+B                                                                 |

| "00" WRITE DATA             | A+B                                                                 |

| "10" WRITE DATA             | Ā+B                                                                 |

| "00" ERRATIC DETECTION DATA | A+B                                                                 |

| "10" ERRATIC DETECTION DATA | A·B                                                                 |

| "11" DISTURB DETECTION DATA | А·В                                                                 |

A: UPPER DATA B: LOWER DATA

FIG. 22

| A<br>UPPER | B<br>LOWER | A+B | A+B | Ā+B | A+B | A・B | А•В |

|------------|------------|-----|-----|-----|-----|-----|-----|

| 0          | 1          | 0   | 1   | 1   | 0   | 0   | 0   |

| 0          | 0          | 1   | 0   | 1   | 1   | 0   | 0   |

| 1          | 0          | 1   | 1   | 0   | 0   | 1   | 0   |

| 1          | 1          | 1   | 1   | 1   | 0   | 0   | 1   |

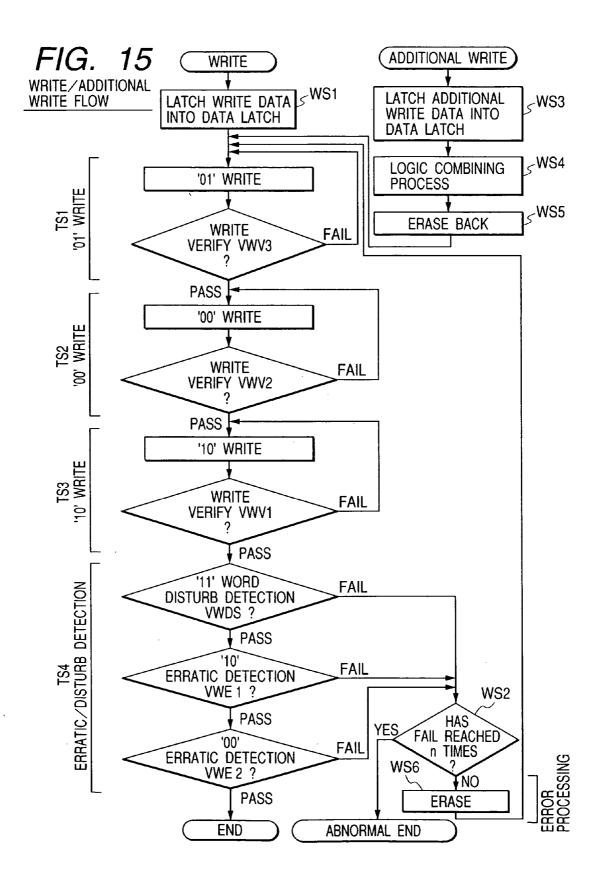

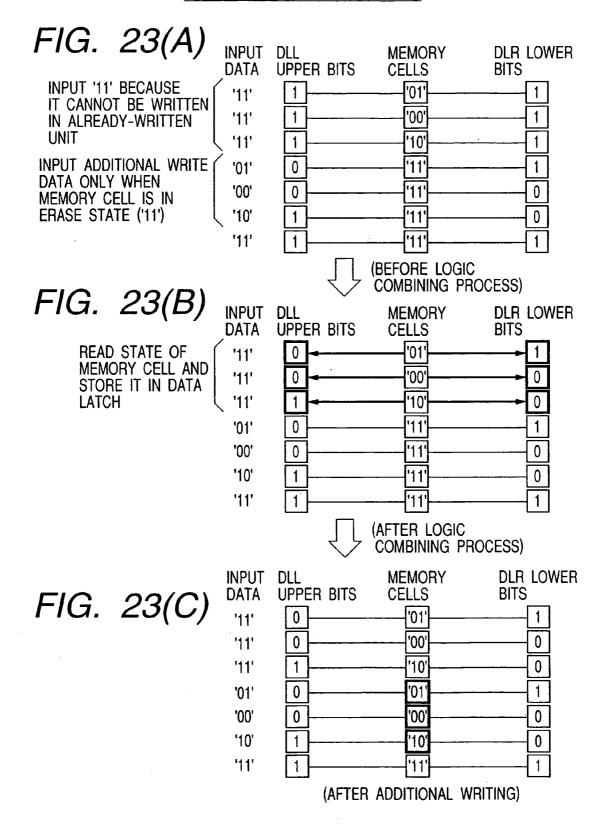

### CONCEPT OF ADDITIONAL WRITING

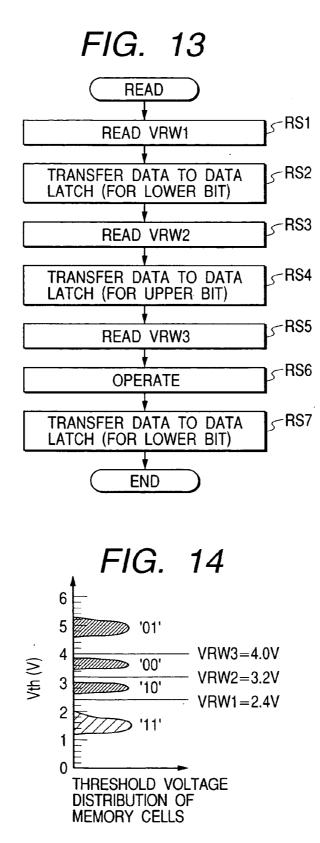

LOWER BIT :  $a0 \cdot (b1 \oplus b3)$ UPPER BIT :  $\overline{a1} \oplus \overline{b2}$

> a0: ADDITIONAL WRITE DATA (LOWER BIT) a1 : ADDITIONAL WRITE DATA (UPPER BIT) b1 : MEMORY READ DATA (VRW1 (2.4V) READ) b2: MEMORY READ DATA (VRW2 (3.2V) READ) b3: MEMORY READ DATA (VRW3 (4.0V) READ)  $\oplus: \mathsf{EXCLUSIVE}\ \mathsf{OR}$

| STATE OF<br>MEMORY<br>CELL | ADDITIONAL<br>WRITE DATA | a1 | a0 | b1 | b2 | b3 |

|----------------------------|--------------------------|----|----|----|----|----|

| 01                         | 11                       | 1  | 1  | 1  | 1  | 1  |

| 00                         | 11                       | 1  | 1  | 1  | 1  | 0  |

| 10                         | 11                       | 1  | 1  | 1  | 0  | 0  |

| 11                         | 01                       | 0  | 1  | 0  | 0  | 0  |

| <u>,</u> 11                | 00                       | 0  | 0  | 0  | 0  | 0  |

| 11                         | 10                       | 1  | 0  | 0  | 0  | 0  |

| 11                         | 11                       | 1  | 1  | 0  | 0  | 0  |

| ao                                      | aO                                   | a0                    | a0                                                                     | a0                                                                                                                                                                                                   | -∕(∕a0+(b1⊕ b3))                                                                                                                                                                   | ∕(∕⁄a0+(b1⊕ b3))                                                                                                                                                                        | ∕(∕a0+(b1⊕ b3))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /(∕a0+(b1⊕ b3))                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ∕(∕a0+(b1⊕ b3))                                                                                                                                                                                                                                                                                                                                                                                                           | LOWER BIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------|--------------------------------------|-----------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /a0                                     | ⁄a0                                  | /a0                   | ⁄a0                                                                    | ⁄a0                                                                                                                                                                                                  | ∕a0+(b1⊕b3)                                                                                                                                                                        | ∕a0+(b1⊕b3)                                                                                                                                                                             | ∕a0+(b1⊕ b3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ∕a0+(b1⊕ b3)                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ∕a0+(b1⊕ b3)                                                                                                                                                                                                                                                                                                                                                                                                              | LOWE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| G-BLF                                   |                                      | b1                    | e                                                                      | ∕a0+(b1⊕b3)                                                                                                                                                                                          | ∕a0+(b1⊕ b3)                                                                                                                                                                       |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2                                       | b3                                   | p3                    | 8) b1⊕b                                                                |                                                                                                                                                                                                      | ,                                                                                                                                                                                  | b2                                                                                                                                                                                      | b2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | b2                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| T                                       | ∕b3                                  | ∕b3                   | b1⊕∕b3                                                                 |                                                                                                                                                                                                      |                                                                                                                                                                                    | /b2                                                                                                                                                                                     | /b2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | p2                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| G-BLL                                   |                                      |                       | $\sim$                                                                 |                                                                                                                                                                                                      |                                                                                                                                                                                    |                                                                                                                                                                                         | ∕b2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ∕a1⊕∕                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                           | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| at at                                   | ⁄a1                                  | /a1                   | ⁄a1                                                                    | ⁄a1                                                                                                                                                                                                  | /a1                                                                                                                                                                                | /a1                                                                                                                                                                                     | ∕a1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ⁄a1                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L                                                                                                                                                                                                                                                                                                                                                                                                                         | UPPER BIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ليسمعا                                  |                                      |                       |                                                                        |                                                                                                                                                                                                      |                                                                                                                                                                                    | _                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (1⊕∕b2)                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                         |                                      |                       |                                                                        |                                                                                                                                                                                                      |                                                                                                                                                                                    |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ///                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ADDITIONAL WRITE<br>DATA INPUT (STEP 1) | VRW3 READ (STEP 4)                   | VRW1 READ (STEP 6)    | OPERATION 1 (STEP 8)                                                   | OPERATION 2 (STEP 11)                                                                                                                                                                                | DL SENSE (STEP 12)                                                                                                                                                                 | VRW2 READ (STEP 16)                                                                                                                                                                     | DATA TRANSFER (STEP18)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OPERATION 3 (STEP 19)                                                                                                                                                                                                                                                                                                                                                                                                                                              | DL SENSE (STEP 21)                                                                                                                                                                                                                                                                                                                                                                                                        | J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                         | DLL G-BLL SL G-BLR DLR<br>a1 /a1 /a0 | a1 /a1 /b3 b3 /a0 /a0 | a1 /a1 G-BLL SL G-BLR DLR<br>a1 /a1 /b3 b3 /a0<br>a1 /a1 /b3 b3 b1 /a0 | DILG-BLLSLG-BLRDLRa1/a1/a1/a0a1/a1/b3b3/a0a1/a1/b3b3/a0a1/a1/b3b1/a0a1/a1/b1/b3b1a1/a1/b1/b3b1a1/a1/b1/b3b1a1/a1/b1/b3b1a1/a1/b1/b3b1a1/a1/b1/b3b1a2/a1/b1/b3b1a3/a1/b1/b3b1a4/a1/b1/b3b1a5/a1/b1/a0 | DILG-BLLSLG-BLRDLRa1/a1/a1/a0a1/a1/b3b3/a0a1/a1/b3b3/a0a1/a1/b1( $\oplus$ /b3)b1( $\oplus$ b3/a0a1/a1/b1( $\oplus$ /b3)b1( $\oplus$ b3/a0a1/a1/b1( $\oplus$ /b3)b1( $\oplus$ b3/a0 | DLG-BLLSLG-BLRDLRa1/a1/a1/a0a0a1/a1/b3b3b3a0a1/a1/b3b3b1/a0a0a1/a1/b3b1/a0a0a1/a1/b1/b3b1/a0a0a1/a1/b1/b3b1b3a0a1/a1/a1/a0+(b1)/a0a0a1/a1/a0+(b1)/a0+(b1)a0a0a1/a1/a0+(b1)/a0+(b1)b1)a0 | DL       G-BL       SL       G-BLR       DLR         a1       /a1       /a1       /a0       a0         a1       /a1       /b3       b3       /a0       a0         a1       /a1       /b3       b3       /a0       a0         a1       /a1       /b3       b3       /a0       a0         a1       /a1       /b1       /b3       b1       /a0       a0         a1       /a1       /a0+(b1       /a0       a0       a0         a1       /a1       /a0+(b1       /a0       a0       a0         a1       /a1       /a0+(b1       b3)       /a0+(b1       b3)       //a0+(b1         a1       /a1       /b2       b2       /a0+(b1       b3)       //a0+(b1       b3)       //a0+(b1 | all $G-BLI$ $SL$ $G-BLR$ $DLR$ al/al/al/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/bl/blbl/alalal/al/al/al/alalal/al/al/al/al/alalal/al/bl/bl/blbl/blal/al/bl/bl/al/al/alal/al/bl/bl/bl/al//alal/al/bl/bl/bl/bl/loal/al/bl/bl/al/al//alal/al/bl/bl/bl/al//alal/al/bl/bl/bl/al//alal/al/bl/bl/bl/al//alal/al/bl/bl/bl/al//alal/al/bl/bl/bl/al//alal/al/bl/bl/al/al//alal/al/bl/bl/bl/al//alal/al/bl/bl/bl/al//alal/al/bl/bl/bl/al//alal/ | alG-BLLGLG-BLRDLRal/al/al/al/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/al/blblalal/al/al/al/al(blal/al/al/al/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/al/alal/al/blbl/alal/al/blbl/alal/al/blbl/alal/al/blbl/alal/al/blb | al $G-BLI$ $G-BLR$ $DLI$ al/al/al/al/alal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/blbl/alalal/al/al/blblalal/al/al/al/alalal/al/al/blbl/al+(blal/al/blbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(blal/al/bbbb/al+(bl(/al+(bb))/al+(blbb/al+(bl(/al+(bb))/al+(bl/al+(bl/al+(bl(/al+(bb))/al+(bl/al+(bl/al+(bl(/al+(bb))/al+(bl/al+(bl/al+(bl(/al+(bb))/al+(bl/al+(bl/al+(bl(/al+(bb))/al+(bl/al+(bl/al+(bl(/al+(bb))/al+(bl/al+(bl/al+(bl(/al+(bb))/al+(bl </td |

| READ SEQUENCE         VRW1 READ         VRW2 READ         VRW2 READ         SIEP 4           SIEP         SIEP 1         SIEP 2         SIEP 3         SIEP 4           In         0         1         1         0         1         1         0           In         0         0         1         1         0         0         1         1         0         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         0         1         1         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                     |     |     |          |            |              |          |   |   |   |            |          |                       | ·            |          | _        |      |            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|------------|--------------|----------|---|---|---|------------|----------|-----------------------|--------------|----------|----------|------|------------|

| SECUENCE         VRWI READ         STEP 1         STEP 2         STEP 3         STEP 4           STEP 1         STEP 1         STEP 2         STEP 3         STEP 4         STEP 4< |     |     |          |            |              |          |   |   |   |            |          | æ                     | DLR          | (0)1     | 0(1)     | 0(1) | 1(0)       |

| SECUENCE         VRWI READ         STEP 1         STEP 2         STEP 3         STEP 4           STEP 1         STEP 1         STEP 2         STEP 3         STEP 4         STEP 4< |     |     |          |            |              |          |   |   |   |            | 0        | н<br>Ц<br>Ц<br>Ц<br>Ц | G-BLR        | 0        | 1        | -    | 0          |

| SECUENCE         VRWI READ         STEP 1         STEP 2         STEP 3         STEP 4           STEP 1         STEP 1         STEP 2         STEP 3         STEP 4         STEP 4< |     |     |          |            |              |          |   |   |   |            | L.       | - DI                  | SL(R)        | -        | 0        | 0    | 0          |

| SECUENCE         VRWI READ         STEP 1         STEP 2         STEP 3         STEP 4           STEP 1         STEP 1         STEP 2         STEP 3         STEP 4         STEP 4< |     |     |          |            |              |          |   |   |   |            | STE      | L H H                 | SL(L)        | 0        | +        |      | -          |

| SECUENCE         VRWI READ         STEP 1         STEP 2         STEP 3         STEP 4           STEP 1         STEP 1         STEP 2         STEP 3         STEP 4         STEP 4< |     |     |          |            |              |          |   |   |   |            |          | ATA<br>DLB            |              |          | 0        | _    | 0          |

| SECUENCE         VRWI READ         VRW2 READ         STEP 4           STEP 1         STEP 2         STEP 3         STEP 4           STEP 1         STEP 2         STEP 3         STEP 4           VRW1 READ         SL(f) - DLR         VRW2 READ         DATA TRANSFER           VRW1 READ         SL(f) - DLR         VRW2 READ         SL(f) - DLL           VRW1 READ         DATA TRANSFER         VRW2 READ         SL(f) - DLL           D 0 1 1 1         0 0 1 1 1 1         0 0 1 1 1 1         0 0 1 1 1 1         0 0 1 1 1 1           D 0 1 1 1         0 0 1 1 1 1         0 0 1 1 1 1 1         0 0 1 1 1 1         0 0 1 1 1 1         0 0 1 1 1 1           STEP 5         STEP 6         STEP 7         STEP 7         STEP 8         STEP 9           VRW3 READ         G-BLL <r< td="">         DLR -G-BLR         OP 0 1 1 1 1         0 0 1 1         0 0 0 1           VRW3 READ         G-BLL<r< td="">         DLR -G-BLR         SOFEARID         OR CRATION         OL 0 0 0         OL 0 0           VRW3 READ         G-BLR         DLR -G-BLR         SOFEARID         OR 0 0 1 1         O 0 0 0         OL 0 0         OL 0 0           VRW3 READ         G-BLR         DLR -G-BLR         SOFEARID         SOFEARID         OR 0 0 0</r<></r<>                            |     |     |          |            |              |          |   |   |   |            |          | 500                   | DLL          | (E)      | (1)0     | 6    | <u>(0)</u> |

| SEQUENCE         VRWI         READ         STEP 2         STEP 2         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           D0         0         1         1         0         0         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         0         0         1         1         1         1         1         1         1                                                                                                                                                                            |     |     |          |            |              |          |   |   |   |            |          | R                     | DLR          | 0        | 0        |      | 0          |

| SEQUENCE         VRWI         READ         STEP 2         STEP 2         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           D0         0         1         1         0         0         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         0         0         1         1         1         1         1         1         1                                                                                                                                                                            |     |     |          |            |              |          |   |   |   |            |          | LEA                   | G-BLR        | 0        | -        |      | 0          |

| SEQUENCE         VRWI         READ         STEP 2         STEP 2         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           D0         0         1         1         0         0         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         0         0         1         1         1         1         1         1         1                                                                                                                                                                            |     |     |          |            |              |          |   |   |   |            | 6        | A C                   | SL(R)        | 1        | 0        | 0    | 0          |

| SEQUENCE         VRWI         READ         STEP 2         STEP 2         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           D0         0         1         1         0         0         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         0         0         1         1         1         1         1         1         1                                                                                                                                                                            |     |     |          |            |              |          |   |   |   |            | STE      | JAT.                  | SL(L)        | 0        | -        | -    | -          |

| SEQUENCE         VRWI         READ         STEP 2         STEP 2         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         STEP 4           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           VRWI         READ         SL(R) - DLR         VRW2         READ         SL(L) - DLL           D0         0         1         1         0         0         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         0         0         1         1         1         1         1         1         1                                                                                                                                                                            |     |     |          |            |              |          | f |   |   |            |          | E E                   |              | 0        | 0        | 0    | 0          |

| SEQUENCE       VRWI       READ       STEP 2       STEP 3       STEP 4         VRWI       READ       SL(R) - DLR       VRW2       READ       STEP 4         VRWI       READ       SL(R) - DLR       VRW2       READ       STEP 4         VRWI       READ       SL(R) - DLR       VRW2       READ       SL(1) - DLL         VRW1       READ       SL(R) - DLR       VRW2       READ       SL(1) - DLL         VRW1       READ       SL(R) - DLR       VRW2       READ       SL(1) - DLL         0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       1       1       0       0       0       0       0       0                                                                                                                                                                                                                                                                     |     |     |          |            |              |          |   |   |   |            |          | Ы                     | DLL          | 0        | 0        | -    | -          |

| SEQUENCE         VRW1         READ         VRW1         READ         VRW1         READ         VRW2                                                                     |     |     |          | В          | DLR          | 1        | 1 | 1 | 0 |            |          |                       | DLR          | -        | -        |      |            |

| SEQUENCE         VRW1         READ         VRW1         READ         VRW1         READ         VRW2                                                                     |     |     | _        | SFE        |              | -        | 1 | 0 | 0 |            | 8        | N<br>BLR              | G-BLR        | 0        | ţ        |      | 0          |

| SEQUENCE         VRW1         READ         VRW1         READ         VRW1         READ         VRW2                                                                     |     |     | <u>d</u> | DLI        | SL(R)        | 1        |   | 0 | 0 | Z          | Ш        | 0-E                   | _SL(R)       | 1        | 0        | 0    | 0          |

| SEQUENCE         VRW1         READ         VRW1         READ         VRW1         READ         VRW2                                                                     |     |     | SI       | † ₽        | SL(L)        | 0        | 0 |   | - |            | S        | RA),                  | SL(L)        | 0        | -        | -    |            |

| SEQUENCE         VRW1         READ         VRW1         READ         VRW1         READ         VRW2                                                                     |     | 9   |          | ATA<br>ATA |              | 0        | 0 |   | - | BA         |          | OPE<br>(SL(           |              | 0        | 0        | 0    | 0          |

| SEQUENCE       VRW1 READ       STEP 2       STEP 2       STEP 2         STEP 1       STEP 2       STEP 2       STEP 2       STEP 2         STEP 1       STEP 2       STEP 2       STEP 2       STEP 3         VRW1 READ       SL(R) - DLR       DATA TRANSFER       NRW2 RE       STEP 3         VRW1 READ       SL(R) - DLR       DATA TRANSFER       NRW2 RE         0       0       1       1       0       0       1         0       0       1       1       0       0       1       1       0         1       1       0       0       1       1       1       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                        |     | R   |          | SD         |              | 0        | 0 | - | - | B          |          | _                     | DLL          | 0        | 0        | -    | -          |

| SEQUENCE       VRW1 READ       STEP 2       STEP 2       STEP 2         STEP 1       STEP 2       STEP 2       STEP 2       STEP 2         STEP 1       STEP 2       STEP 2       STEP 2       STEP 3         VRW1 READ       SL(R) - DLR       DATA TRANSFER       NRW2 RE       STEP 3         VRW1 READ       SL(R) - DLR       DATA TRANSFER       NRW2 RE         0       0       1       1       0       0       1         0       0       1       1       0       0       1       1       0         1       1       0       0       1       1       1       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                        |     | W2  | ·        |            |              | -        | - | - | 0 | 8          |          | œ                     |              |          | -        | -    |            |

| ) SEQUENCE     VRW1 READ     STEP 1     STEP 2       VRW1 READ     VRW1 READ     SLP 1     STEP 2       VRW3 READ     SLP 1     STEP 2       VRW3 READ     SLP 2     STEP 2       VRW3 READ     CLEAR     STEP 2       VRW3 READ     CLEAR     STEP 2       VRW3 READ     CLEAR     DD 1       VRW3 READ     CLEAR       VRW3 READ     O       VRW3 READ <t< td=""><td>:</td><td>片</td><td>-</td><td>EAD</td><td>G-BLR</td><td></td><td>-</td><td>0</td><td>0</td><td>EA  </td><td>~</td><td>SFE</td><td>G-BLR</td><td>-</td><td>-</td><td>-</td><td>0</td></t<>                                                                                                                     | :   | 片   | -        | EAD        | G-BLR        |          | - | 0 | 0 | EA         | ~        | SFE                   | G-BLR        | -        | -        | -    | 0          |

| ) SEQUENCE     VRW1 READ     STEP 1     STEP 2       VRW1 READ     VRW1 READ     SLP 1     STEP 2       VRW3 READ     SLP 1     STEP 2       VRW3 READ     SLP 2     STEP 2       VRW3 READ     CLEAR     STEP 2       VRW3 READ     CLEAR     STEP 2       VRW3 READ     CLEAR     DD 1       VRW3 READ     CLEAR       VRW3 READ     O       VRW3 READ <t< td=""><td></td><td></td><td>à</td><td>HE I</td><td>SL(R)</td><td>-</td><td>-</td><td>0</td><td>0</td><td>E<br/>E</td><td>Ш</td><td>ANG-E</td><td><u>SL(R)</u></td><td></td><td>0</td><td>0</td><td>0</td></t<>                                                                                                          |     |     | à        | HE I       | SL(R)        | -        | - | 0 | 0 | E<br>E     | Ш        | ANG-E                 | <u>SL(R)</u> |          | 0        | 0    | 0          |

| ) SEQUENCE     VRW1 READ     STEP 1     STEP 2       VRW1 READ     VRW1 READ     SLP 1     STEP 2       VRW3 READ     SLP 1     STEP 2       VRW3 READ     SLP 2     STEP 2       VRW3 READ     CLEAR     STEP 2       VRW3 READ     CLEAR     STEP 2       VRW3 READ     CLEAR     DD 1       VRW3 READ     CLEAR       VRW3 READ     O       VRW3 READ <t< td=""><td></td><td></td><td>SI</td><td>2W5</td><td><u>SL(L)</u></td><td>0</td><td>0</td><td>-</td><td></td><td>MA<br/>MA</td><td>S</td><td>† E</td><td><u>SL(L)</u></td><td><math>\vdash</math></td><td></td><td>-</td><td>-</td></t<>                                                                                  |     |     | SI       | 2W5        | <u>SL(L)</u> | 0        | 0 | - |   | MA<br>MA   | S        | † E                   | <u>SL(L)</u> | $\vdash$ |          | -    | -          |

| ) SEQUENCE         VRW1       READ         VRW3       READ         VR       VR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |          | Y          |              | 0        | 0 | - |   |            |          | AT/                   |              | 0        | 0        | 0    | 0          |

| SEQUENCE         VRW1         READ           VRW1         READ         VRW1         READ           VRW1         READ         SIEP1         SIEP2           SIEP1         SIEP1         SIEP1         SIEP2           VRW1         READ         DATA         TRANSFE           0         0         1         1         0           1         1         0         1         1           0         1         1         0         1         1           1         1         0         1         1         1         1           1         1         1         0         1         1         1         1         1           1         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                         |     |     |          |            |              |          |   |   |   |            | L        |                       |              | 0        | 0        | -    | -          |

| 0     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     - <td></td> <td></td> <td></td> <td>œ</td> <td></td> <td>-</td> <td>-</td> <td>-</td> <td>0</td> <td></td> <td></td> <td></td> <td></td> <td>-</td> <td>-</td> <td></td> <td>0</td>                                                                                                                                                                                                                                                                               |     |     |          | œ          |              | -        | - | - | 0 |            |          |                       |              | -        | -        |      | 0          |

| 0     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     - <td></td> <td></td> <td></td> <td>SFE</td> <td>G-BLR</td> <td>-</td> <td>-</td> <td>1</td> <td>0</td> <td></td> <td>9</td> <td></td> <td></td> <td>0</td> <td>0</td> <td>0</td> <td>_</td>                                                                                                                                                                                                                                                                      |     |     |          | SFE        | G-BLR        | -        | - | 1 | 0 |            | 9        |                       |              | 0        | 0        | 0    | _          |

| 0     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     - <td></td> <td></td> <td><u>d</u></td> <td>AN D</td> <td><u>SL(R)</u></td> <td>-</td> <td>-</td> <td>-</td> <td>0</td> <td></td> <td>Ъ</td> <td>BLF</td> <td><u>SL(R)</u></td> <td>-</td> <td>0</td> <td>0</td> <td>0</td>                                                                                                                                                                                                                                       |     |     | <u>d</u> | AN D       | <u>SL(R)</u> | -        | - | - | 0 |            | Ъ        | BLF                   | <u>SL(R)</u> | -        | 0        | 0    | 0          |

| 0     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     - <td></td> <td></td> <td>E S</td> <td></td> <td>SL(L)</td> <td>0</td> <td></td> <td>0</td> <td>-</td> <td></td> <td>ST</td> <td>80</td> <td><u>SL(L)</u></td> <td></td> <td></td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                          |     |     | E S      |            | SL(L)        | 0        |   | 0 | - |            | ST       | 80                    | <u>SL(L)</u> |          |          | -    | -          |

| 0     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     - <td></td> <td>P</td> <td></td> <td>L(R</td> <td></td> <td>0</td> <td>0</td> <td>0</td> <td>-</td> <td></td> <td></td> <td>00</td> <td></td> <td>0</td> <td>0</td> <td>0</td> <td>0</td>                                                                                                                                                                                                                                                                         |     | P   |          | L(R        |              | 0        | 0 | 0 | - |            |          | 00                    |              | 0        | 0        | 0    | 0          |

| 0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0 <td></td> <td></td> <td></td> <td>ഗ്വ</td> <td></td> <td> </td> <td></td> <td></td> <td></td> <td></td> <td><u> </u></td> <td></td> <td></td> <td>0</td> <td>0</td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                                       |     |     |          | ഗ്വ        |              |          |   |   |   |            | <u> </u> |                       |              | 0        | 0        | -    | -          |

| 0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0 <td></td> <td>PW1</td> <td></td> <td>-</td> <td>-</td> <td></td>                                                                                                                                                                                                                                                                                  |     | PW1 |          |            |              |          |   |   |   |            |          |                       |              |          | -        | -    |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     | AD       | G-BLR      |              | -        | ţ | 0 |   |            | AD       | G-BLR                 |              | 0        | 0        | 0    |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ю   |     | ЦЦ       | SL(R)      | <u> </u>     | -        | - | 0 |   | ١ <u>ٿ</u> | E E      | SL(R)                 | -            | 0        | 0        | 0    |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R   |     | M1       | SL(L)      | 0            | 0        | 0 | - |   | ST         | 3W3      | SL(L)                 |              |          |          | -    |            |

| OLL     DLL     DLL     OLL     OLL <td>ğ</td> <td></td> <td></td> <td>K</td> <td></td> <td>9</td> <td>0</td> <td>0</td> <td></td> <td></td> <td></td> <td>A<br/>H</td> <td></td> <td>0</td> <td><u> </u></td> <td></td> <td></td>                                                                                                                  | ğ   |     |          | K          |              | 9        | 0 | 0 |   |            |          | A<br>H                |              | 0        | <u> </u> |      |            |