등록특허 10-2097838

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2020년05월27일

(11) 등록번호 10-2097838

(24) 등록일자 2020년03월31일

- (51) 국제특허분류 (Int. Cl.)

*H01M 4/02* (2006.01) *H01M 10/05* (2010.01)

*H01M 10/058* (2010.01) *H01M 4/13* (2010.01)

*H01M 4/134* (2010.01) *H01M 4/38* (2006.01)

- (21) 출원번호 10-2014-7020881

- (22) 출원일자(국제) 2013년01월24일

심사청구일자 2018년01월24일

- (85) 번역문제출일자 2014년07월24일

- (65) 공개번호 10-2014-0135691

- (43) 공개일자 2014년11월26일

- (86) 국제출원번호 PCT/US2013/022868

- (87) 국제공개번호 WO 2013/112670

국제공개일자 2013년08월01일

- (30) 우선권주장

13/357,320 2012년01월24일 미국(US)

(56) 선행기술조사문헌

JP2010146732 A\*

US20110129732 A1

JP2012516941 A

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 19 항

심사관 : 김유희

(54) 발명의 명칭 미세구조화된 전극 구조

(57) 요약

에너지 저장 장치에서 이용하기 위한 구조가 개시되며, 이 구조는 기준 평면으로부터 대체로 수직으로 연장되는 백본 시스템과, 백본들의 측면들에 의해 지지되는 미세구조화된 애노드적 활성 재료층들의 집합체를 포함하고, 미세구조화된 애노드적 활성 재료층들 각각은 적어도 0.1의 체적 공극률과 적어도 1 마이크로미터의 두께를 갖는다.

대 표 도

(72) 발명자

샤, 니라브 에스.

미국 94566 캘리포니아주 플레젠톤 알렌 플레이스

4726

라마서브라마니안, 무랄리

미국 94539 캘리포니아주 프레몬트 에스. 모레이

스트리트 43970

리스트 3세, 하롤드 제이.

미국 94507 캘리포니아주 알라모 알라모 컨트리 셔

클 2528

월콕스, 제임스 디.

미국 94566 캘리포니아주 플레젠톤 카미노 브라조

스 2220

---

암스트롱, 마이클 제이.

미국 94526 캘리포니아주 덴빌 알리칸테 코트 202

브루스카, 브라이언 이.

미국 95377 캘리포니아주 트래시 잭슨 애비뉴 2749

캐슬린, 크리스토퍼 지.

미국 94089 캘리포니아주 서니베일 투손 애비뉴

1250

라우츨란, 로리 제이.

미국 95070 캘리포니아주 사라토가 라도이카 드라

이브 12508

## 명세서

### 청구범위

#### 청구항 1

에너지 저장 장치에서 이용하기 위한 전기화학적 스택으로서,

상기 스택은 캐소드 전류 콜렉터들 및 캐소드적 활성 재료층들을 포함하는 캐소드 구조들의 집합체 (population), 세퍼레이터 층들, 및 애노드적 활성 재료층들 사이에 배치된 백본 애노드 전류 콜렉터들을 포함하는 애노드 구조들의 집합체를 적층된 형태로 포함하고, 상기 세퍼레이터 층들은 상기 캐소드 구조들의 집합체의 부재들의 상기 캐소드적 활성 재료층들과 상기 애노드 구조들의 집합체의 부재들의 애노드적 활성 재료층들 사이에 배치되고,

상기 백본 애노드 전류 콜렉터들은 상기 애노드적 활성 재료층들의 전기 전도도보다 큰 전기 전도도를 갖고,

상기 캐소드 전류 콜렉터들, 캐소드적 활성 재료층들, 세퍼레이터 층들, 백본 애노드 전류 콜렉터들 및 애노드적 활성 재료층들의 적층 방향은 기준 평면에 평행하고, 캐리어 이온들은 2차 전지가 충전 및 방전됨에 따라 상기 기준 평면에 평행한 상기 캐소드적 활성 재료층들과 상기 애노드적 활성 재료층들 사이의 이동 방향을 갖고,

상기 애노드 구조들의 집합체의 상기 부재들 각각은 상기 기준 평면에 직교하는 방향에서 측정된 1000 마이크로미터 내지 10,000 마이크로미터의 높이  $H_A$ , 정면, 상기 애노드 구조 부재의 상기 백본 애노드 전류 콜렉터에 인접한 배면, 상기 정면으로부터 상기 배면까지 측정된 두께  $T$ , 및 적어도 0.1의 공극 체적률(void volume fraction)을 갖는 애노드적 활성 재료층들을 포함하고, 상기 정면 및 배면은 상기 기준 평면에 수직이고, 상기 두께  $T$ 는 적어도 1 마이크로미터이고 상기 기준 평면에 평행한 방향에서 측정되고, 상기 애노드적 활성 재료층들은 섬유성 또는 다공성의 애노드적 활성 재료를 포함하고, 상기 기준 평면에 평행한 방향에서 측정된 상기 애노드적 활성 재료층들의 집합체의 적어도 2개의 부재 사이의 직선 거리  $D_L$ 은 상기 집합체에 대한  $H_A$ 의 최대값보다 큰, 전기화학적 스택.

#### 청구항 2

제1항에 있어서, 상기 캐리어 이온들은 리튬 이온들인, 전기화학적 스택.

#### 청구항 3

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 100 마이크로미터 이상이지만 5,000 마이크로미터 미만의 높이  $H_A$ 를 갖는, 전기화학적 스택.

#### 청구항 4

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 0.1 이상이지만 0.8 미만의 공극 체적률을 갖는 다공성 실리콘 층을 포함하는, 전기화학적 스택.

#### 청구항 5

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 0.25 이상이지만 0.6 미만의 공극 체적률을 갖는 다공성 실리콘 층을 포함하는, 전기화학적 스택.

#### 청구항 6

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 1 내지 200 마이크로미터의 두께  $T$ 를 갖는 다공성 실리콘 층을 포함하는, 전기화학적 스택.

#### 청구항 7

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 10 내지 80 마이크로미터의 두께  $T$ 를 갖는 다공성 실리콘 층을 포함하는, 전기화학적 스택.

**청구항 8**

제1항에 있어서, 상기 전기화학적 스택 내의 애노드 구조들의 수는 적어도 10개인, 전기화학적 스택.

**청구항 9**

제1항에 있어서, 상기 전기화학적 스택 내의 애노드 구조들의 수는 적어도 20개인, 전기화학적 스택.

**청구항 10**

제1항에 있어서, 상기 전기화학적 스택 내의 애노드 구조들의 수는 적어도 100개인, 전기화학적 스택.

**청구항 11**

제1항에 있어서, 상기 백본 애노드 전류 콜렉터는 상기 애노드 구조들의 집합체의 각각의 부재에 대한 상기 애노드적 활성 재료층의 상기 배면과 접촉하는, 전기화학적 스택.

**청구항 12**

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재의 백본 애노드 전류 콜렉터는 금속을 포함하는, 전기화학적 스택.

**청구항 13**

제12항에 있어서, 상기 금속은 알루미늄, 구리, 니켈, 코발트, 티타늄 및 텉스텐으로 이루어진 그룹으로부터 선택된 적어도 하나의 금속을 포함하는, 전기화학적 스택.

**청구항 14**

제1항에 있어서, 상기 애노드적 활성 재료층의 전기 전도도에 대한 상기 백본 애노드 전류 콜렉터의 전기 전도도의 비율은 상기 애노드 구조들의 집합체의 각 부재에 대해 적어도 100:1인, 전기화학적 스택.

**청구항 15**

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 10nm 미만의 기공 치수를 갖는 미세다공성 재료인 다공성 실리콘 층을 포함하는, 전기화학적 스택.

**청구항 16**

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 10nm 내지 50nm의 기공 치수를 갖는 중간다공성 재료인 다공성 실리콘 층을 포함하는, 전기화학적 스택.

**청구항 17**

제1항에 있어서, 상기 애노드 구조들의 집합체의 각각의 부재는 50nm 초과의 기공 치수를 갖는 거대다공성 재료인 다공성 실리콘 층을 포함하는, 전기화학적 스택.

**청구항 18**

제1항의 전기화학적 스택들 중 적어도 2개를 포함하는 2차 전지로서, 상기 전기화학적 스택들은 상기 기준 평면에 직교하는 병향으로 서로에 대하여 적층되는, 2차 전지.

**청구항 19**

에너지 저장 장치에서 이용하기 위한 전기화학적 스택으로서,

상기 스택은 캐소드 전류 콜렉터들 및 캐소드적 활성 재료층들을 포함하는 캐소드 구조들의 집합체, 미세다공성 세퍼레이터 재료(microporous separator material)를 포함하는 세퍼레이터 층들, 및 애노드적 활성 재료층들 사이에 배치된 백본 애노드 전류 콜렉터들을 포함하는 애노드 구조들의 집합체를 적층된 형태로 포함하고, 상기 세퍼레이터 층들은 상기 캐소드 구조들의 집합체의 부재들의 상기 캐소드적 활성 재료층들과 상기 애노드 구조들의 집합체의 부재들의 애노드적 활성 재료층들 사이에 배치되고,

상기 백본 애노드 전류 콜렉터들은 상기 애노드적 활성 재료층들의 전기 전도도보다 큰 전기 전도도를 갖고, 상기 캐소드 전류 콜렉터들, 캐소드적 활성 재료층들, 세퍼레이터 층들, 백본 애노드 전류 콜렉터들 및 애노드적 활성 재료층들의 적층 방향은 기준 평면에 평행하고, 캐리어 이온들은 2차 전지가 충전 및 방전됨에 따라 상기 기준 평면에 평행한 상기 캐소드적 활성 재료층들과 상기 애노드적 활성 재료층들 사이의 이동 방향을 갖고, 상기 애노드 구조들의 집합체의 상기 부재들 각각은 상기 기준 평면에 직교하는 방향에서 측정된 1000 내지 10,000 마이크로미터의 높이  $H_A$ , 정면, 상기 애노드 구조 부재의 상기 백본 애노드 전류 콜렉터에 인접한 배면, 상기 정면으로부터 상기 배면까지 측정된 두께  $T$ , 및 적어도 0.1의 공극 체적률을 갖는 애노드적 활성 재료층들을 포함하고, 상기 정면 및 배면은 상기 기준 평면에 수직이고, 상기 두께  $T$ 는 적어도 1 마이크로미터이고 상기 기준 평면에 평행한 방향에서 측정되고, 상기 애노드적 활성 재료층들은 섬유성 또는 다공성의 애노드적 활성 재료를 포함하고, 상기 기준 평면에 평행한 방향에서 측정된 상기 애노드적 활성 재료층들의 집합체의 적어도 2개의 부재 사이의 직선 거리  $D_L$ 은 상기 집합체에 대한  $H_A$ 의 최대값보다 크고,

상기 애노드 구조들의 집합체의 상기 부재들의 애노드적 활성 재료층들은 상기 세퍼레이터 층을 포함하는 절연성 재료로 둘러싸인, 전기화학적 스택.

#### 청구항 20

삭제

#### 청구항 21

삭제

#### 청구항 22

삭제

#### 청구항 23

삭제

#### 청구항 24

삭제

#### 청구항 25

삭제

#### 청구항 26

삭제

#### 청구항 27

삭제

#### 청구항 28

삭제

#### 청구항 29

삭제

#### 청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

청구항 33

삭제

청구항 34

삭제

청구항 35

삭제

청구항 36

삭제

청구항 37

삭제

청구항 38

삭제

청구항 39

삭제

청구항 40

삭제

청구항 41

삭제

청구항 42

삭제

청구항 43

삭제

청구항 44

삭제

청구항 45

삭제

청구항 46

삭제

## 청구항 47

삭제

## 발명의 설명

## 기술 분야

- [0001] 본 발명은 대체로 에너지 저장 장치에서 사용하기 위한 구조에 관한 것으로, 이러한 구조를 포함하는 에너지 저장 장치, 및 이러한 구조와 에너지 장치를 생성하기 위한 방법에 관한 것이다.

- [0002] 흔들 의자(rocking chair) 또는 삽입 2차 전지는, 리튬, 나트륨 또는 칼륨 이온 등의 캐리어 이온이 전해질을 통해 애노드 전극과 캐소드 전극 사이에서 이동하는 에너지 저장 장치의 유형이다. 2차 전지는 단일의 배터리 셀, 또는 전기적으로 결합되어 배터리를 형성하는 2개 이상의 배터리 셀을 포함할 수 있고, 각각의 배터리 셀은, 애노드 전극, 캐소드 전극, 및 전해질을 포함한다.

- [0003] 흔들 의자 배터리 셀에서, 애노드 및 캐소드 양쪽 모두는 캐리어 이온이 삽입되고 추출되는 재료를 포함한다. 셀이 방전됨에 따라, 캐리어 이온은 애노드로부터 추출되어 캐소드에 삽입된다. 셀이 충전됨에 따라, 역 과정이 발생한다: 캐리어 이온이 캐소드로부터 추출되어 애노드에 삽입된다.

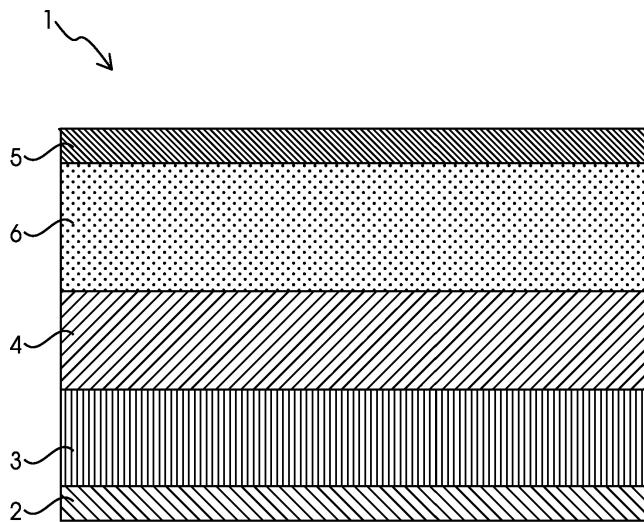

- [0004] 도 1은 비수성 리튬-이온 배터리 등의, 기존의 에너지 저장 장치의 전기화학적 스택의 단면도를 도시한다. 전기화학적 스택(1)은 캐소드 전류 콜렉터(2)를 포함하고, 그 상부에 캐소드 층(3)이 조립된다. 이 층은 미세다공성 세퍼레이터(4)로 덮이고, 그 위에 애노드 전류 콜렉터(5)와 애노드 층(6)의 어셈블리가 놓여진다. 이 스택은 때때로 애노드 전류 콜렉터(5) 위의 (도시되지 않은) 또 다른 세퍼레이터 층으로 덮이고, 롤링(roll)되어 캔(can)에 스터핑(stuff)되고, 비수성 전해질로 채워져 2차 전지를 조립한다.

- [0005] 애노드 및 캐소드 전류 콜렉터들은 각각의 활성 전기화학적 전극들로부터 전류를 모아(pool) 배터리 외부 환경으로의 전류 전달을 가능케 한다. 애노드 전류 콜렉터의 일부는 애노드 활성 재료와 물리적으로 접촉하는 반면 캐소드 전류 콜렉터의 일부는 캐소드 활성 재료와 접촉한다. 전류 콜렉터는 전기화학적 반응에 참여하지 않으므로 애노드 및 캐소드에 대한 각각의 전기화학적 전위 범위에서 전기화학적으로 안정적인 재료로 제약된다.

- [0006] 전류 콜렉터가 전류를 배터리 외부 환경으로 가져가기 위하여, 전류 콜렉터는 통상적으로, 대개 집합적으로 컨택트라 불리는, 탭, 태그, 팩키지 피드-쓰루(package feed-through) 또는 하우징 피드-쓰루에 접속된다. 컨택트의 한 끝은 하나 이상의 전류 콜렉터에 접속되는 반면, 다른 끝은 배터리 외부 환경으로의 전기 접속을 위해 배터리 팩키징을 관통한다. 용접, 압착, 또는 초음파 접합에 의해 애노드 컨택트는 애노드 전류 콜렉터에 접속되고 캐소드 컨택트는 캐소드 전류 콜렉터에 접속되거나, 도전성 접착제에 의해 제 위치에서 접착된다.

- [0007] 충전 프로세스 동안에, 리튬은 리튬 이온으로서 캐소드 층(3)을 떠나 세퍼레이터(4)를 통해 이동하여 애노드 층(6)으로 간다. 이용되는 애노드 재료에 따라, 리튬 이온은 개재(intercalate)되거나(예를 들어, 합금을 형성하지 않고 애노드 재료의 매트릭스에 안착하거나) 합금을 형성한다. 방전 프로세스 동안에, 리튬은 애노드 층(6)을 떠나, 세퍼레이터(4)를 통해 캐소드 층(3)으로 관통해 간다. 전류 도전체는 배터리 컨택트(미도시)로부터 전극들로 또는 그 반대로 전자를 도통시킨다.

- [0008] 배터리, 연료 전지, 및 전기화학적 커패시터 등의 기존의 에너지 저장 장치는 통상적으로 도 1에 나타낸 바와 같은 2차원 박판형 아키텍처(예를 들어, 평면형 또는 나선형으로 감겨진 라미네이트)를 가지며, 각각의 라미네이트의 표면적은 대략적으로 그 기하학적 풋프린트와 같다(다공성 및 표면 거칠기 무시).

- [0009] 배터리 용량과 활성 재료 활용을 향상시키는 방편으로서 문헌에서 3차원 배터리가 제안되었다. 2차원 박판형 배터리 아키텍처에 비해 더 큰 표면적 및 더 높은 에너지를 제공하기 위해 3차원 아키텍처가 이용될 수 있다는 것이 제안되었다. 작은 기하학적 면적으로부터 얻어질 수 있는 증가된 에너지량으로 인해 3차원 에너지 저장 장치를 제작하는데에는 이점이 있다. 예를 들어, Rust 등의 WO 2008/089110와 Long 등의 "Three-Dimensional Battery Architectures", Chemical Reviews, (2004), 104, 4463-4492를 참조한다.

- [0010] 에너지 밀도, 안정성, 충전/방전률, 및 2차 전지의 사이클 수명을 향상시키기 위한 방편으로서, 새로운 애노드 및 캐소드 재료도 역시 제안되었다. 리튬 배터리에서 실리콘, 알루미늄, 또는 주석 애노드 등의 이들 새로운

고용량 재료들 중 일부는, 리튬 삽입 및 추출 동안에 그 기존의 전자적 전류 콜렉터로부터의 분해와 박리를 야기하는 상당한 체적 팽창을 가진다. 예를 들어, 탄소 전극에 대한 대체로서 이용하기 위해 실리콘 애노드가 제안되었는데, 그 이유는 실리콘 애노드는 리튬 배터리 응용에서 리튬에 대한 호스트 재료의 상당히 더 큰 단위 체적당 에너지를 제공하는 용량을 갖기 때문이다. 예를 들어, Konishi ike 등의 미국 특허 공개 제2009/0068567 호; Kasavajjula 등의 "Nano- and Bulk-Silicon-Based Insertion Anodes for Lithium-Ion Secondary Cells", Journal of Power Sources 163 (2007) 1003-1039를 참조한다. 애노드에 리튬이 삽입될 때 리튬 실리사이드의 형성은 애노드의 크랙 형성과 분쇄로 이어질 수 있는 상당한 체적 변화를 초래한다. 그 결과, 배터리가 반복적으로 방전 및 충전됨에 따라 배터리의 용량이 감소될 수 있다.

[0011] 반복된 충전 및 방전 사이클의 결과로서 실리콘 애노드가 겪는 상당한 체적 변화에 의해 제기되는 해결과제를 극복하기 위해 다양한 전략들이 제안되었다. 예를 들어, Bourderau 등은 아몰퍼스 실리콘을 개시하고 있다 (Bourderau 등의 "Amorphous Silicon As A Possible Anode Material For Li-Ion Batteries", Journal of Power Sources 81-82 (1999) 233-236). Li 등은 실리콘 나노와이어를 개시하고 있다(Li 등의 "The Crystal Structural Evolution Of Nano-Si Anode Caused By Lithium Insertion And Extraction At Room Temperature", Solid State Ionics 135 (2000) 181-191). NL1015956에서, Sloe Yao Kan은 배터리를 위한 다공성 실리콘 전극을 개시하고 있다. Shin 등도 역시, 배터리를 위한 다공성 실리콘 전극을 개시하고 있다(Shin 등의 "Porous Silicon Negative Electrodes For Rechargeable Lithium Batteries", Journal of Power Sources 139 (2005) 314-320).

[0012] 몰딩되거나 기타의 방식으로 소정 형상으로 형성되고 입자성 재료의 응집체의 형상을 유지하기 위해 도전체 또는 바인더에 의존하는 입자성 전극에 비해 성능(무게측정 및 체적측정 에너지 밀도, 레이트 등)을 향상시키기 위한 대안으로서 모놀리식 전극, 즉, 바인더를 이용하지 않고 그 형상을 유지하는 많은 전극 재료를 포함하는 전극이 제안되었다. 모놀리식 애노드는, 예를 들어, 단일의 실리콘 덩어리(예를 들어, 단결정 실리콘, 다결정 실리콘, 또는 아몰퍼스 실리콘)를 포함할 수 있거나, 소결되거나 기타의 방식으로 처리되어 함께 애노드 재료를 퓨징하고 임의의 바인더를 제거하는 응집된 입자성 덩어리를 포함할 수도 있다. 하나의 이러한 실시예에서, 리튬-이온 배터리에 대한 모놀리식 애노드 재료로서 실리콘 웨이퍼가 채용될 수 있고, 여기서, 웨이퍼의 한 측은 세페레이터를 통해 제1 캐소드 요소에 결합되는 반면, 다른 측은 그와 대향하는 제2 캐소드 요소에 결합된다. 이러한 구조에서, 중요한 기술적 해결과제 중 하나는, 배터리 내부의 가용 공간을 효율적으로 이용하면서 전류를 모으고 전류를 모놀리식 전극으로부터 배터리 외부로 운반하는 능력이다.

[0013] 비활성 컴포넌트의 무게와 부피를 줄여 배터리를 더욱 효율적으로 팩킹함으로써 종래의 배터리의 에너지 밀도도 역시 증가될 수 있다. 현재의 배터리들은 비교적 두꺼운 전류 콜렉터를 이용하는데, 그 이유는, 전류 콜렉터를 형성하는 호일(foil)이 활성 재료 적용 프로세스를 견디기에 충분히 강하도록 최소한의 두께 요건으로 이용되기 때문이다. 전류 수집을 처리 제약으로부터 분리하기 위해 발명이 이루어진다면 성능상의 이점이 기대될 수 있다.

## 발명의 내용

### 해결하려는 과제

[0014] 다양한 접근법에도 불구하고, 배터리 용량을 개선하고 활성 재료를 활용하는 것에 대한 필요성이 남아 있다.

### 과제의 해결 수단

[0015] 본 발명의 다양한 양태들 중에는, 배터리, 연료 전지, 및 전기화학적 커뮤니케이터 등의 에너지 저장 장치에서 이용하기 위한 3차원 구조의 제공이 있다. 이러한 3차원 구조는, 백본 구조의 측면 상에 미세구조화된 애노드적 활성 재료(anodically active material)의 층을 포함하고, 이 층은 애노드적 활성 재료가 충전 상태와 방전 상태 사이에서 사이클할 때 애노드적 활성 재료에서의 상당한 체적 변화를 수용하는 공극률(void fraction)을 포함한다. 유익하게도, 이러한 3차원 구조는 수직으로 적층된 2개 이상의 배터리 셀 내에 병합될 수 있음으로써, 배터리 셀 내의 애노드적 활성 재료와 캐소드 재료 사이의 최단 거리는 배터리 셀들의 적층 방향에 직교하는 방향에서 측정된다(예를 들어, 3차원 카테시안(X-Y-Z) 좌표에서, 적층 방향이 Z 방향이면, 애노드적 활성 재료와 캐소드 재료 사이의 최단 거리는 X 또는 Y 방향에서 측정된다). 이러한 3차원 에너지 저장 장치는 종래의 장치보다 단위 기하학적 면적당 더 높은 에너지 저장과 회수를 생성할 수 있다. 이들은 또한, 애노드와 캐소드 사이의 전자 및 이온 전달을 위한 수송 거리를 최소화 또는 감소시키는 등에 의해, 저장된 에너지의 특정한 양에 대

해 2차원 에너지 저장 장치보다 높은 에너지 회수율을 제공할 수 있다. 이들 장치들은, 장치를 위해 이용가능한 기하학적 면적이 제한되어 있고 및/또는 에너지 밀도 요건이 박판형 장치로 달성될 수 있는 것보다 높은 경우의 응용에 대해 및 소형화에 대해 더욱 적합할 수 있다.

[0016] 따라서, 요약하면, 본 발명의 한 양태는 에너지 저장 장치에서 이용하기 위한 구조이다. 이 구조는 미세구조화된 애노드적 활성 재료층들의 집합체(population)를 포함하고, (a) 이 집합체의 부재들은 섬유성 또는 다공성의 애노드적 활성 재료를 포함하며 기준 평면에 실질적으로 수직인 표면과, (ii) 기준 평면에 평행한 방향에서 측정된 적어도 1 마이크로미터의 두께와, 기준 평면에 직교하는 방향에서 측정된 적어도 50 마이크로미터의 높이와, 적어도 0.1의 공극 체적률을 가진다. 또한, 집합체의 적어도 2개의 부재들 사이의, 기준 평면에 평행한 방향에서 측정된 직선 거리는 집합체 내의 임의의 층의 최대 높이보다 크다.

[0017] 본 발명의 또 다른 양태는 일련의 측면(lateral surface)을 포함하는 백본망을 포함하는 에너지 저장 장치에서 이용하기 위한 구조이다. 측면은 기준 평면에 대해 실질적으로 수직이며, 기준 평면에 실질적으로 수직인 방향에서 측정된 적어도 50 마이크로미터의 높이를 가진다. 이 구조는 측면에 의해 지지되는 미세구조화된 애노드적 활성 재료층들의 집합체를 더 포함하고, 기준 평면에 평행한 방향으로 측정된 집합체 내의 측면들 중 적어도 2개 사이의 최대 직선 거리는 일련의 측면들 중 임의의 측면의 최대 높이보다 크다. 미세구조화된 애노드적 활성 재료층들은, 정면, 배면, 및 섬유성 또는 다공성의 애노드적 활성 재료를 포함하고, 미세구조화된 애노드적 활성 재료층들은 적어도 0.1의 공극 체적률과 정면과 배면 사이의 적어도 1 마이크로미터의 두께를 가진다. 각각의 이러한 미세구조화된 애노드적 활성 재료층의 배면은 이러한 미세구조화된 애노드적 활성 재료층을 지지하는 백본의 측면에 근접해 있다. 각각의 이러한 미세구조화된 애노드적 활성 재료층의 정면은 이러한 미세구조화된 애노드적 활성 재료층을 지지하는 백본의 측면으로부터 멀리 있다. 미세구조화된 애노드적 활성 재료층들의 집합체의 부재로 구성된 섬유들은 기준 평면에 부착되고 이러한 섬유를 포함하는 집합체 부재의 배면으로의 섬유들의 부착 지점에서 기준 평면에 실질적으로 평행한 중심축을 가진다. 미세구조화된 애노드적 활성 재료층들의 집합체의 부재로 구성된 공극(pore)들은 기준 평면에 실질적으로 평행한 주축(major axis)을 갖는 공극 개구를 가진다.

[0018] 본 발명의 또 다른 양태는 에너지 저장 장치에서 이용하기 위한 전기화학적 스택이다. 전기화학적 스택은, 적층된 구조로, 캐소드 구조, 세퍼레이터 층 및 애노드 구조를 포함하고, 세퍼레이터 층은 애노드 구조와 캐소드 구조 사이에 배치되며, 전기화학적 스택 내의 캐소드 구조, 세퍼레이터 층, 및 애노드 구조의 적층의 방향은 기준 평면에 평행하다. 애노드 구조는 미세구조화된 애노드적 활성 재료층들의 집합체를 포함하고, (a) 이 집합체의 부재들은 섬유성 또는 다공성의 애노드적 활성 재료를 포함하고 (i) 기준 평면에 실질적으로 수직인 표면과, (ii) 기준 평면에 평행한 방향에서 측정된 적어도 1 마이크로미터의 두께와, (iii) 기준 평면에 직교하는 방향에서 측정된 적어도 50 마이크로미터의 높이와, (iv) 적어도 0.1의 공극 체적률을 가진다. 추가적으로, 집합체의 적어도 2개의 부재들 사이의, 기준 평면에 평행한 방향에서 측정된 직선 거리는 집합체의 부재의 최대 높이보다 크다.

[0019] 본 발명의 또 다른 양태는 에너지 저장 장치에서 이용하기 위한 전기화학적 스택이다. 전기화학적 스택은, 애노드 구조, 캐소드 구조, 및 애노드 구조와 캐소드 구조 사이에 다공성 유전 재료를 포함하는 세퍼레이터 층들의 집합체를 포함한다. 애노드 구조, 캐소드 구조, 및 세퍼레이터 층은 기준 평면에 실질적으로 평행한 방향으로 적층되고, 각각의 애노드 구조는 (a) 측면 - 측면은 기준 평면에 실질적으로 수직이고, 기준 평면의 표면에 실질적으로 수직인 방향에서 측정된 적어도 50 마이크로미터의 높이를 가짐 - 을 갖는 백본, 및 (b) 측면에 의해 지지되는 미세구조화된 애노드적 활성 재료층을 포함한다. 집합체의 적어도 2개의 부재들 사이의, 기준 평면에 평행한 방향에서 측정된 직선 거리는 집합체의 부재의 최대 높이보다 크다. 미세구조화된 애노드적 활성 재료층은, 배면, 정면, 및 섬유성 또는 다공성의 애노드적 활성 재료를 포함한다. 미세구조화된 애노드적 활성 재료층은 또한 적어도 0.1의 공극 체적률과 배면과 정면 사이의 적어도 1 마이크로미터의 두께를 가지며, (i) 각각의 이러한 미세구조화된 애노드적 활성 재료층의 배면은 이러한 미세구조화된 애노드적 활성 재료층을 지지하는 백본의 측면에 근접하고, (ii) 각각의 이러한 미세구조화된 애노드적 활성 재료층의 정면은 이러한 미세구조화된 애노드적 활성 재료층을 지지하는 백본의 측면으로부터 멀리 있고, (iii) 미세구조화된 애노드적 활성 재료층들의 집합체의 부재로 구성된 섬유들은 이러한 섬유들을 포함하는 부재의 배면에 부착되고 이 배면에 실질적으로 수직인 중심축을 가지며, (iv) 미세구조화된 애노드적 활성 재료층들의 집합체의 부재로 구성된 공극들은 기준 평면에 실질적으로 평행한 주축을 갖는 공극 개구를 가진다.

[0020] 본 발명의 또 다른 양태는, 캐리어 이온, 비수성 전해질 및 전기화학적 스택을 포함하는 에너지 저장 장치이며, 캐리어 이온은, 리튬, 나트륨 또는 칼륨 이온이고, 전기화학적 스택은, 적층된 구조로, 캐소드 구조, 세퍼레이

터 층 및 애노드 구조를 포함하고, 세퍼레이터 층은 애노드 구조와 캐소드 구조 사이에 배치된다. 전기 화학적 스택 내의 캐소드 구조, 세퍼레이터 층, 및 애노드 구조의 적층 방향은 기준 평면에 평행하다. 애노드 구조는 미세구조화된 애노드적 활성 재료층들의 집합체를 포함하고, (a) 이 집합체의 부재들은 섬유성 또는 다공성의 애노드적 활성 재료를 포함하고 (i) 기준 평면에 수직인 표면과, (ii) 기준 평면에 평행한 방향에서 측정된 적어도 1 마이크로미터의 두께와, (iii) 기준 평면에 직교하는 방향에서 측정된 적어도 50 마이크로미터의 높이와, (iv) 적어도 0.1의 공극 체적률을 가진다. 집합체의 적어도 2개의 부재들 사이의, 기준 평면에 평행한 방향에서 측정된 직선 거리는 미세구조화된 애노드적 활성 재료층들의 집합체의 임의의 부재의 최대 높이 보다 크다.

[0021] 본 발명의 또 다른 양태는, 캐리어 이온, 비수성 전해질, 및 적어도 2개의 전기화학적 스택을 포함하는 2차 전지이며, 캐리어 이온은, 리튬, 나트륨 또는 칼륨 이온이다. 전기화학적 스택들 각각은, 적층된 구조로, 캐소드 구조, 세퍼레이터 층 및 애노드 구조를 포함한다. 세퍼레이터 층은 애노드 구조와 캐소드 구조 사이에 배치되고, 각각의 이러한 전기화학적 스택 내의 캐소드 구조, 세퍼레이터 층, 및 애노드 구조의 적층의 방향은 기준 평면에 평행하다. 애노드 구조는 미세구조화된 애노드적 활성 재료층들의 집합체를 포함하고, (a) 이 집합체의 부재들은 섬유성 또는 다공성의 애노드적 활성 재료를 포함하고 (i) 기준 평면에 수직인 표면과, (ii) 기준 평면에 평행한 방향에서 측정된 적어도 1 마이크로미터의 두께와, (iii) 기준 평면에 직교하는 방향에서 측정된 적어도 50 마이크로미터의 높이와, (iv) 적어도 0.1의 공극 체적률을 가진다. 추가적으로, 전기화학적 스택들은 기준 평면에 직교하는 방향으로 서로에 관해 적층된다.

[0022] 다른 목적과 특징들은 이하에서 부분적으로 자명하고 부분적으로 지적될 것이다.

### 도면의 간단한 설명

[0023] 도 1은 리튬-이온 배터리 등의 기존의 2차원 에너지 저장 장치의 전기화학적 스택의 셀의 일반 단면도이다.

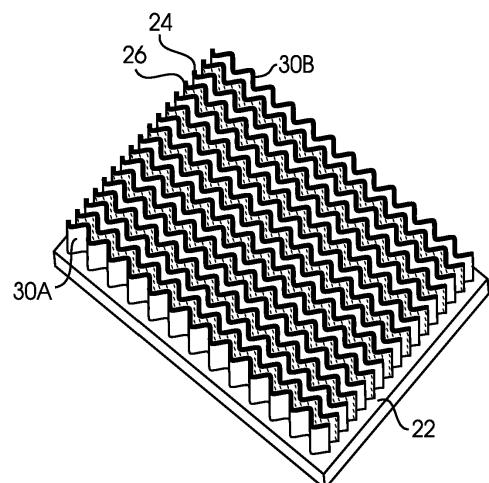

도 2는 이러한 2차 전지 등의 본 발명의 3차원 에너지 저장 장치의 2개 셀의 개략도이다.

도 3은 도 2의 라인 3-3을 따라 취해진 실리콘을 포함하는 애노드적 활성 재료층의 부분 단면도이다.

도 4a 내지 도 4e는 애노드와 캐소드 구조가 본 발명의 소정 실시예들에 따라 조립될 수 있는 일부 형상들의 개략적 도면이다.

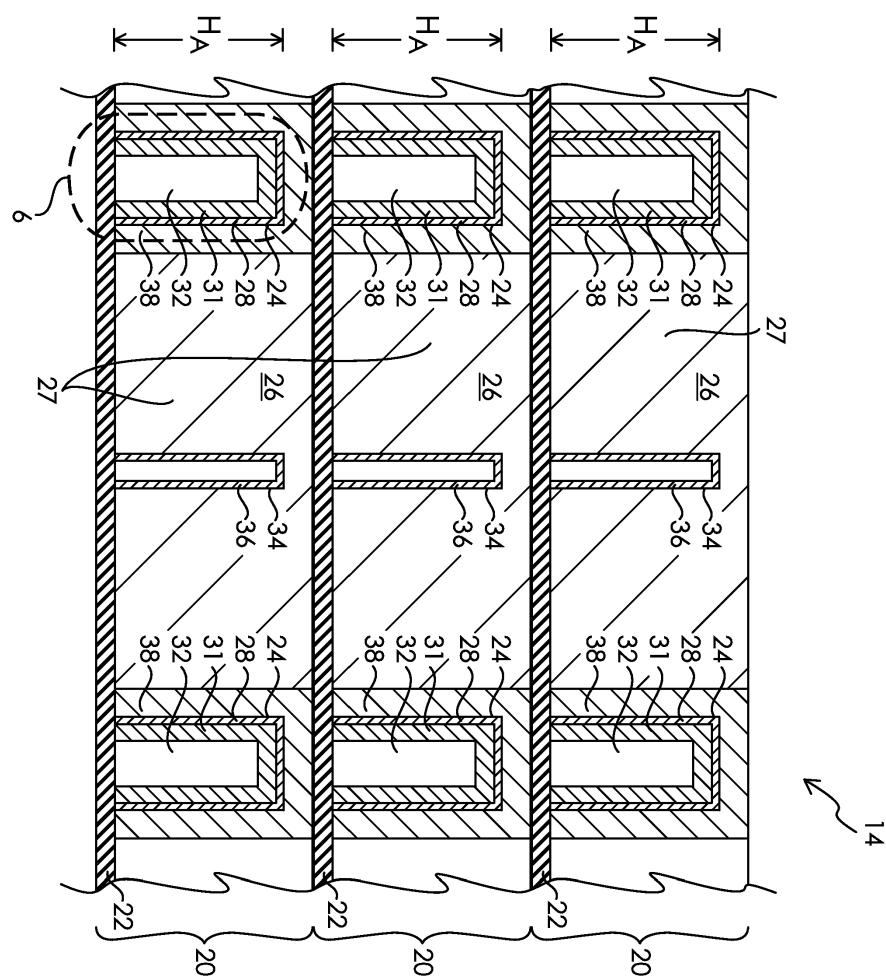

도 5는 각각이 전기화학적 스택을 포함하는 3개 다이의 부분 단면도이다.

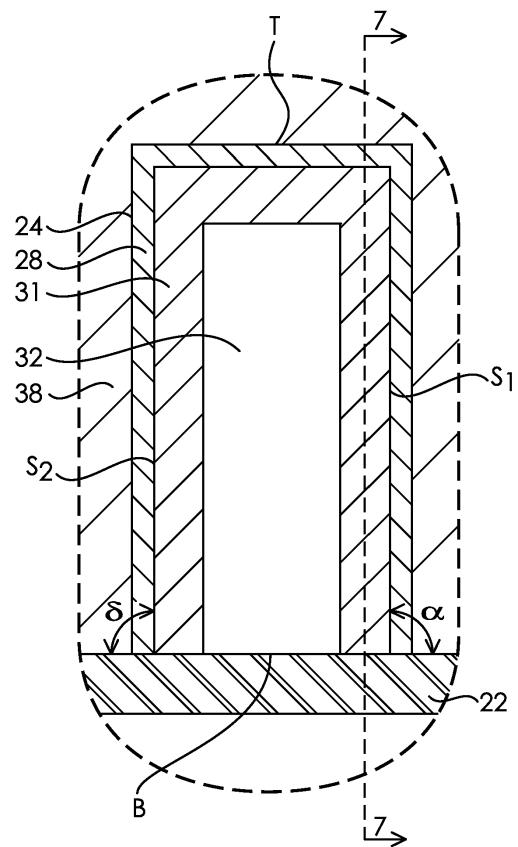

도 6은 도 5의 다이들 중 하나의 애노드 구조의 도면이다.

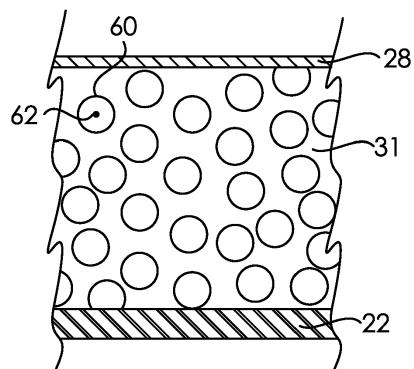

도 7은 도 6의 라인 7-7을 따라 취해진 다공성 실리콘을 포함하는 애노드적 활성 재료층의 부분 단면도이다.

도 8은 본 발명의 애노드 백본 및 캐소드 지지 구조를 제작하는 단계를 위한 시재료의 개략도이다.

도 9는 본 발명의 프로세스의 한 실시예에 따라 형성된 예시적인 애노드 백본 및 캐소드 지지 구조의 개략도이다.

도 10은 본 발명의 2차 전지의 개략도이다.

도 11은 본 발명의 대안적 실시예에 따른 에너지 저장 장치의 3차원 전기화학적 스택의 개략도이다.

도 12는 본 발명의 대안적 실시예에 따른 에너지 저장 장치의 3차원 전기화학적 스택의 부분 개략도이다.

도 13은 본 발명의 대안적 실시예에 따른 에너지 저장 장치의 맞물린 3차원 전기화학적 스택의 개략도이다.

도 14는 예 1에서 설명된 바와 같이 준비된 실리콘 백본 상의 다공성 실리콘 층의 사진이다.

도면들 전체에 걸쳐 대응하는 참조 문자는 대응하는 부분을 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0024] 본 발명의 다양한 양태들 중에서, 배터리, 커패시터, 및 연료 전지 등의 에너지 저장 장치의 전기화학적 스택 내에 병합될 때 특별한 이점을 제공하는 3차원 구조가 주목될 수 있다. 예를 들어, 이러한 구조는, 애노드, 캐소드, 및/또는 세퍼레이터가 본질적으로 비-박판형(non-laminar)인 2차 전지 내에 병합될 수 있다. 유익하게도, 이러한 비-박판형 애노드 구조와 캐소드 구조를 위한 표면적은, 전극을 지지하는 베이스의 기하학적 풋프린트를 1.5배, 2배, 2.5배, 또는 심지어 3배 이상 초과할 수 있다. 한 바람직한 실시예에서, 이러한 구

조는, 리튬, 나트륨, 및 칼륨 이온으로부터 선택된 캐리어 이온이 애노드와 캐소드 사이에서 이동하는 2차 전지 내에 병합된다.

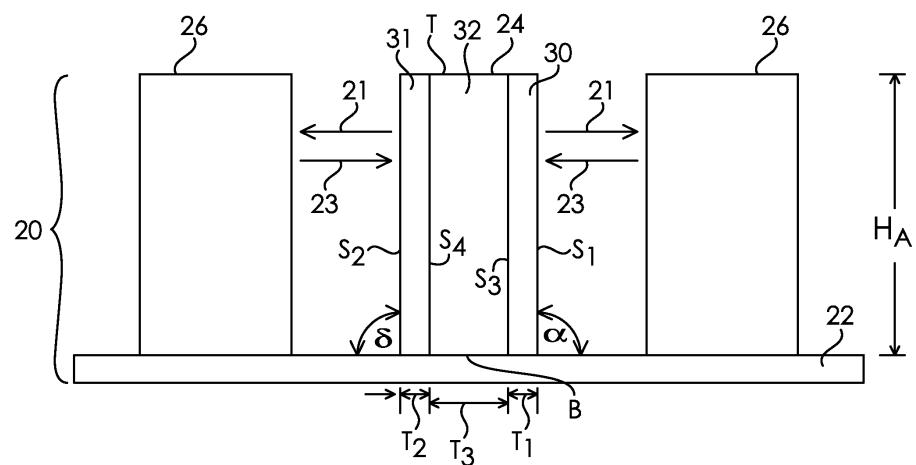

[0025] 도 2는 본 발명의 한 실시예에 따른 3차원 배터리의 2개 셀들의 전기화학적 스택을 개략적으로 도시한다. 예시의 용이성을 위해, 각각의 셀(20)에 대해 단 하나의 애노드 구조(24)와 2개의 캐소드 구조(26)가 도 2에 도시되어 있고 단 2개의 셀만이 도 2에 나타나 있지만; 실제로는, 각각의 셀의 전기화학적 스택은 통상적으로 공통의 기준 평면으로부터 수직으로 연장되는 일련의 애노드 및 캐소드 구조를 포함하고, 셀당 애노드와 캐소드 구조의 개수, 및 배터리 내의 셀들의 개수는 응용마다 다르다. 예를 들어, 한 실시예에서, 전기화학적 스택 내의 애노드 구조의 개수는 적어도 10이다. 추가의 예로서, 한 실시예에서, 전기화학적 스택 내의 애노드 구조의 개수는 적어도 50이다. 추가의 예로서, 전기화학적 스택 내의 애노드 구조의 개수는 적어도 100이다.

[0026] 각각의 셀(20)의 전기화학적 스택은, 도시된 바와 같이, 베이스(22), 애노드 구조(24) 및 캐소드 구조(26)를 포함한다. 각각의 애노드 구조(24)는 공통 기준 평면인 (예시된) 베이스(22)의 표면으로부터 수직으로(즉, 도 2에 나타낸 카테시안 좌표계의 축들로 예시된 바와 같이 Z방향으로) 돌출되고, 베이스(22)에 근접한 하부면(B), 베이스(22)로부터 면 상부면(T), 및 상부면(T)으로부터 하부면(B)으로 연장되는 측면( $S_1$ ,  $S_2$ )을 가진다. 측면( $S_1$ )은 베이스(22)의 표면을 각도  $\alpha$ 로 교차하고, 측면( $S_2$ )은 베이스(22)의 표면을 각도  $\delta$ 로 교차한다. 바람직한 실시예에서,  $\alpha$ 와  $\delta$ 는 대략 동일하고 약  $80^\circ$  내지  $100^\circ$ 이다. 예를 들어, 한 실시예에서,  $\alpha$ 와  $\delta$ 는 대략 동일하고  $90^\circ \pm 5^\circ$ 이다. 특히 바람직한 실시예에서,  $\alpha$ 와  $\delta$ 는 실질적으로 같고 대략  $90^\circ$ 이다. 교차 각도 와는 독립적으로, 측면들( $S_1$  및  $S_2$ ) 각각의 표면적의 대다수(표면들  $S_1$  및  $S_2$  내의 임의의 공극은 무시)는 기준 평면, 이 실시예에서는 베이스(22)의 표면에 실질적으로 수직인 것이 일반적으로 선호되고; 달리 말하면, 측면들( $S_1$  및  $S_2$ ) 각각의 표면적의 대다수(표면들  $S_1$  및  $S_2$  내의 임의의 공극은 무시)는 약  $80^\circ$  내지  $100^\circ$ 의 각도, 더 바람직하게는  $90^\circ \pm 5^\circ$ 의 각도로 기준 평면(예시된 바와 같이, 베이스(22)의 표면)을 교차하는 평면(또는 평면들) 내에 놓여 있는 것이 일반적으로 선호된다. 또한, 상부면(T)은 측면들( $S_1$  및  $S_2$ )(표면들  $S_1$  및  $S_2$  내의 임의의 공극은 무시)에 실질적으로 수직이고, 기준 평면, 이 실시예에서는 베이스(22)의 표면에 실질적으로 평행한 것이 일반적으로 선호된다. 예를 들어, 하나의 현재 선호되는 실시예에서, 베이스(22)는 실질적으로 평면형 표면을 갖고 애노드 구조(24)는 기준 평면, 즉, 이 실시예에서는 베이스(22)의 평면형 표면에 실질적으로 평행한 상부면(T)을 가지며, 측면들( $S_1$  및  $S_2$ )(표면들  $S_1$  및  $S_2$  내의 임의의 공극은 무시)은 기준 평면, 즉, 이 실시예에서는 베이스(22)의 평면형 표면에 실질적으로 수직이다.

[0027] 예시된 바와 같이, 각각의 애노드 구조(24)는, (기준 평면인 예시된 베이스(22)의 평면형 표면에 평행한 방향으로 표면  $S_3$ 으로부터  $S_4$ 까지 측정된) 두께  $T_3$ 을 갖는 애노드 백본(32)과, 각각 (기준 평면인 예시된 베이스(22)의 평면형 표면에 평행한 방향으로 표면  $S_1$ 로부터  $S_3$ 까지 측정된) 두께  $T_1$  및 (기준 평면인 예시된 베이스(22)의 평면형 표면에 평행한 방향으로 표면  $S_2$ 로부터  $S_4$ 까지 측정된) 두께  $T_2$ 와 (기준 평면에 직교하는 방향에서 측정된) 높이  $H_A$ 를 갖는 애노드적 활성 재료층들(30, 31)을 포함한다. 충전 프로세스 동안에, 리튬(또는 기타의 캐리어)은 캐소드 구조(26)를 떠나 일반적으로 리튬 이온으로서 세퍼레이터(미도시)를 통해 화살표(23)의 방향으로 이동하여 애노드적 활성 재료층들(30, 31) 내로 간다. 이용되는 애노드적 활성 재료에 따라, 리튬 이온은 개재되거나(예를 들어, 합금을 형성하지 않고 애노드 재료의 매트릭스에 안착하거나) 합금을 형성한다. 방전 프로세스 동안에, 리튬 이온(또는 기타의 캐리어 이온)은 애노드적 활성 재료층들(30, 31)을 떠나 일반적으로 세퍼레이터(미도시)를 통해 화살표(21)의 방향으로 이동하여 캐소드(26) 내로 간다. 도 2에 나타낸 바와 같이, 2개의 셀들은 수직으로(즉, 예시된 바와 같이 Z 방향으로) 배열되어 있고 개개의 셀의 애노드적 활성 재료층과 캐소드 재료 사이의 최단 거리는, 기준 평면, 즉, 이 실시예에서는 베이스(22)의 실질적으로 평면형 표면에 평행하고(즉, 예시된 바와 같이 X-Y 평면에 있고), 셀들의 적층 방향(즉, 예시된 Z 방향)에 직교하는 방향에서 측정된다. 또 다른 실시예에서, 2개의 셀들은 수평으로(즉, 도 2에 나타낸 X-Y 평면으로) 배열되어 있고 개개의 셀의 애노드적 활성 재료층과 캐소드 재료 사이의 최단 거리는, 기준 평면, 즉, 이 실시예에서는 베이스(22)의 실질적으로 평면형 표면에 평행한 방향에서(즉, 예시된 바와 같이 X-Y 평면에서) 측정되고, 셀들의 적층 방향도 역시 기준 평면에 평행하다(즉, 도 2에 나타낸 X-Y 평면 내에 있다).

[0028] 애노드 백본(32)은 애노드적 활성 재료층들(30, 31)에 대한 기계적 안정성을 제공한다. 통상적으로, 애노드 백본(32)은 (기준 평면의 표면, 즉, 예시된 베이스(22)의 실질적으로 평면형 표면에 평행한 방향으로 배면( $S_3$ )으로부터 배면( $S_4$ )까지 측정된) 적어도 1 마이크로미터의 두께  $T_3$ 을 가질 것이다. 애노드 백본(32)은 상당히 더

두께율 수도 있지만, 일반적으로는 100 마이크로미터를 초과하는 두께를 갖지 않을 것이다. 예를 들어, 한 실시예에서, 애노드 백본(32)은 약 1 내지 약 50 마이크로미터의 두께를 가질 것이다. 일반적으로, 애노드 백본은, (기준 평면, 즉, 예시된 베이스(22)의 실질적으로 평면형 표면에 수직인 방향에서 측정될 때) 적어도 약 50 마이크로미터, 더욱 일반적으로는 적어도 약 100 마이크로미터의 높이를 가질 것이다. 그러나, 일반적으로, 애노드 백본(32)은 통상적으로 약 10,000 마이크로미터보다 크지 않은, 더욱 일반적으로는 약 5000 마이크로미터보다 크지 않은 높이를 가질 것이다. 예로서, 한 실시예에서, 애노드 백본(32)은 약 5 내지 약 50 마이크로미터의 두께와 약 50 내지 약 5000 마이크로미터의 높이를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드 백본(32)은 약 5 내지 약 20 마이크로미터의 두께와 약 100 내지 약 1,000 마이크로미터의 높이를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드 백본(32)은 약 5 내지 약 20 마이크로미터의 두께와 약 100 내지 약 2,000 마이크로미터의 높이를 가질 것이다.

[0029] 응용에 따라, 애노드 백본(32)은 도전성 또는 절연성일 수 있다. 예를 들어, 한 실시예에서, 애노드 백본(32)은 도전성이고 애노드적 활성 재료층들(30, 31)에 대한 전류 콜렉터를 포함할 수 있다. 하나의 이러한 실시예에서, 애노드 백본은, 적어도 약  $10^3$  Siemens/cm의 전도도를 갖는 전류 콜렉터를 포함한다. 추가의 예로서, 하나의 이러한 실시예에서, 애노드 백본은, 적어도 약  $10^4$  Siemens/cm의 전도도를 갖는 전류 콜렉터를 포함한다. 추가의 예로서, 하나의 이러한 실시예에서, 애노드 백본은, 적어도 약  $10^5$  Siemens/cm의 전도도를 갖는 전류 콜렉터를 포함한다. 다른 실시예들에서, 애노드 백본(32)은 비교적 비도전성이다. 예를 들어, 한 실시예에서, 애노드 백본(32)은 10 Siemens/cm 미만의 전기 전도도를 가진다. 추가의 예로서, 한 실시예에서, 애노드 백본(32)은 1 Siemens/cm 미만의 전기 전도도를 가진다. 추가의 예로서, 한 실시예에서, 애노드 백본(32)은  $10^{-1}$  Siemens/cm 미만의 전기 전도도를 가진다.

[0030] 애노드 백본(32)은, 금속, 반도체, 유기물, 세라믹, 및 유리와 같은, 성형될 수 있는 임의의 재료를 포함할 수도 있다. 현재 바람직한 재료는 실리콘 및 게르마늄 등의 반도체 재료를 포함한다. 그러나, 대안으로서, 알루미늄, 구리, 니켈, 코발트, 티타늄, 및 텉스텐 등의 금속 또는 탄소-기반의 유기 재료도 역시 애노드 백본 구조 내에 병합될 수 있다. 하나의 실시예에서, 애노드 백본(32)은 실리콘을 포함한다. 실리콘은, 예를 들어, 단결정 실리콘, 다결정 실리콘, 아몰퍼스 실리콘 또는 이들의 조합일 수 있다.

[0031] 애노드적 활성 재료층들(30, 31)은 미세구조화되어 상당한 공극 체적률을 제공해 충전 및 방전 프로세스 동안에 리튬 이온(또는 기타의 캐리어 이온)이 애노드적 활성 재료층들(30, 31) 내에 병합되거나 이를 떠날 때 체적 팽창 및 수축을 수용한다. 일반적으로, 애노드적 활성 재료층의 공극 체적률은 적어도 0.1이다. 그러나, 통상적으로, 애노드적 활성 재료층의 공극 체적률은 0.8보다 크지 않다. 예를 들어, 한 실시예에서, 애노드적 활성 재료층의 공극 체적률은 약 0.15 내지 약 0.75이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층의 공극 체적률은 약 0.2 내지 약 0.7이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층의 공극 체적률은 약 0.25 내지 약 0.6이다.

[0032] 미세구조화된 애노드적 활성 재료층의 조성과 그 형성 방법에 따라, 미세구조화된 애노드적 활성 재료층들은 거대다공성(macroporous), 미세다공성(microporous) 또는 중간다공성(mesoporous) 재료층들, 또는 거대다공성과 중간다공성의 조합이나 중간다공성과 거대다공성의 조합과 같은 이들의 조합을 포함할 수 있다. 미세다공성 재료는, 통상적으로, 10 nm 미만의 공극 크기, 10 nm 미만의 벽 크기, 1-50 마이크로미터의 공극 깊이, 및 일반적으로 "스폰지같고" 불규칙 외관과 평활하지 않은 벽과 분기형 공극을 특징으로 하는 공극 형태를 특징으로 한다. 중간다공성 재료는, 통상적으로, 10-50 nm의 공극 크기, 10-50 nm의 벽 크기, 1-100 마이크로미터의 공극 깊이, 및 일반적으로 다소 명확하거나 수지상의(well defined or dendritic) 공극인 분기형 공극을 특징으로 하는 공극 형태를 특징으로 한다. 거대다공성 재료는, 통상적으로, 50 nm보다 큰 공극 크기, 50 nm보다 큰 벽 크기, 1-500 마이크로미터의 공극 깊이, 및 다양한(varied), 똑바른(straight), 분기형(branched), 또는 수지상(dendritic)이고 평활(smooth)하거나 거친(rough)-벽일 수 있는 공극 형태를 특징으로 한다. 추가적으로, 공극 체적은 개방된 또는 폐쇄된 공극 또는 이들의 조합을 포함할 수 있다. 한 실시예에서, 공극 체적은 개방 공극을 포함, 즉, 애노드적 활성 재료층은 애노드적 활성 재료층의 정면(도 2에 예시된 표면 S<sub>1</sub>, S<sub>2</sub>)에 개구를 갖는 공극을 포함하고, 공극 개구는 세퍼레이터와 캐소드적 활성 재료쪽으로 향하며 이를 통해 리튬 이온(또는 기타의 캐리어 이온)이 애노드적 활성 재료층에 들어가거나 이를 떠나는데; 예를 들어, 리튬 이온은 캐소드적 활성 재료를 떠나 일반적으로 화살표(23)로 표시된 방향으로 애노드적 활성 재료까지 이동한 후에 공극 개구를 통해 애노드적 활성 재료에 들어갈 수 있다. 또 다른 실시예에서, 공극 체적은 폐쇄 공극을 포함할 수 있는데,

즉, 애노드적 활성 재료층은 애노드적 활성 재료에 의해 에워싸인 공극을 포함한다. 일반적으로, 개방 공극은 캐리어 이온에 대한 더 큰 계면 표면적을 제공할 수 있는 반면, 폐쇄 공극은 고체 전해질 계면("SEI")에 덜 민감한 경향이 있으며, 동시에, 각각은 캐리어 이온의 진입시에 애노드적 활성 재료층의 팽창을 위한 공간을 제공한다. 따라서, 소정 실시예들에서, 애노드적 활성 재료층이 개방 및 폐쇄 공극의 조합을 포함하는 것이 선호된다.

[0033] 애노드적 활성 재료층(30, 31)은 리튬 등의 캐리어 이온을 흡수 및 방출할 수 있는 애노드적 활성 재료를 포함한다. 이러한 재료는, 흑연 등의 탄소 재료, 또는 금속류 중 임의의 것, 반금속, 합금, 산화물 및 리튬과 합금을 형성할 수 있는 화합물을 포함한다. 애노드 재료를 구성할 수 있는 금속 또는 반금속의 구체적인 예로서는, 주석, 납, 마그네슘, 알루미늄, 봉소, 갈륨, 실리콘, 인듐, 지르코늄, 게르마늄, 비스무트, 카드뮴, 안티몬, 금, 은, 아연, 비소, 하프늄, 이트륨, 및 팔라듐이 포함된다. 하나의 예시적인 실시예에서, 애노드적 활성 재료층들(30, 31)은, 알루미늄, 주석, 실리콘, 또는 이들의 산화물, 이들의 질화물, 이들의 불화물, 또는 이들의 다른 합금을 포함한다. 또 다른 실시예에서, 애노드적 활성 재료층들(30, 31)은 미세구조화된 실리콘 또는 그 합금을 포함한다. 하나의 특히 바람직한 실시예에서, 애노드적 활성 재료층들(30, 31)은 다공성 실리콘 또는 그 합금, 실리콘 또는 그 합금의 섬유(예를 들어, 나노와이어), 다공성 실리콘 또는 그 합금과 실리콘 또는 그 합금의 섬유(예를 들어, 나노와이어)의 조합, 또는 적어도 0.1의 공극 체적률을 갖는 다른 형태의 미세구조화된 실리콘 또는 그 합금을 포함한다. 본 특허 출원에서 이 단락 및 다른 곳에 인용된 실시예 및 예들 각각에서, 애노드적 활성 재료층은 모놀리식 또는 입자 응집체(particulate agglomerate)일 수 있다.

[0034] 일반적으로, 애노드적 활성 재료층들(30, 31)은 각각 정면( $S_1, S_2$ ), 각각 배면( $S_3, S_4$ ), 및 (베이스(22)의 표면에 평행한 방향에서 측정된) 각각 적어도 1 마이크로미터의 두께( $T_1, T_2$ )를 가진다. 그러나, 통상적으로, 애노드적 활성 재료층들(30, 31)은 각각, 200 마이크로미터를 초과하지 않는 두께를 가질 것이다. 예를 들어, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 1 내지 약 100 마이크로미터의 두께를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 2 내지 약 75 마이크로미터의 두께를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 10 내지 약 100 마이크로미터의 두께를 가진다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 5 내지 약 50 마이크로미터의 두께를 가진다. 추가의 예로서, 한 이러한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 1 내지 약 100 마이크로미터의 두께를 갖고, 미세구조화된 실리콘 및/또는 니켈 실리사이드 등의 그 합금을 포함한다. 추가적으로, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 1 내지 약 50 마이크로미터의 두께를 가질 것이고, 미세구조화된 실리콘 및/또는 니켈 실리사이드 등의 그 합금을 포함한다. 일반적으로, 애노드적 활성 재료층들(30, 31)은, (기준 평면, 즉, 예시된 베이스(22)의 실질적으로 평면형 표면에 수직인 방향에서 측정될 때) 적어도 약 50 마이크로미터, 더욱 일반적으로는 적어도 약 100 마이크로미터의 높이  $H_A$ 를 가질 것이다. 그러나, 일반적으로, 애노드적 활성 재료층들(30, 31)은 통상적으로 약 10,000 마이크로미터보다 크지 않은, 더욱 일반적으로는 약 5000 마이크로미터보다 크지 않은 높이  $H_A$ 를 가질 것이다. 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 1 내지 약 200 마이크로미터의 두께와 약 50 내지 약 5000 마이크로미터의 높이를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 1 내지 약 50 마이크로미터의 두께와 약 100 내지 약 1,000 마이크로미터의 높이를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 5 내지 약 20 마이크로미터의 두께와 약 100 내지 약 1,000 마이크로미터의 높이를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 10 내지 약 100 마이크로미터의 두께와 약 100 내지 약 1,000 마이크로미터의 높이를 가질 것이다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 약 5 내지 약 50 마이크로미터의 두께와 약 100 내지 약 1,000 마이크로미터의 높이를 가질 것이다.

[0035] 한 실시예에서, 미세구조화된 애노드적 활성 재료층들(30, 31)은 다공성 알루미늄, 주석, 또는 실리콘 또는 그 합금을 포함한다. 다공성 실리콘층들은, 예를 들어, 양극산화(anodization)에 의해, 에칭(예를 들어, 단결정 실리콘의 (100) 표면 상에 금, 백금, 또는 금/팔라듐을 피착하고 그 표면을 불화 수소산과 과산화수소의 혼합물로 에칭)에 의해, 또는 패터닝된 화학적 에칭 등의 당업자에게 공지된 다른 방법에 의해 형성될 수 있다. 추가적으로, 애노드적 활성 재료층은 일반적으로 적어도 약 0.1의 그러나 0.8미만의 공극률과 약 1 내지 약 100 마이크로미터의 두께를 가질 것이다. 예를 들어, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 다공성 실리콘을 포함하고, 약 5 내지 약 100 마이크로미터의 두께를 가지며, 약 0.15 내지 약 0.75의 공극률을 가진다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 다공성 실리콘을 포함하고, 약 10 내지 약

80 마이크로미터의 두께를 가지며, 약 0.15 내지 약 0.7의 공극률을 가진다. 추가의 예로서, 한 이러한 실시예에서, 애노드적 활성 재료층들(30, 31)은 다공성 실리콘을 포함하고, 약 20 내지 약 50 마이크로미터의 두께를 가지며, 약 0.25 내지 약 0.6의 공극률을 가진다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 다공성 실리콘 합금(니켈 실리사이드 등)을 포함하고, 약 5 내지 약 100 마이크로미터의 두께를 가지며, 약 0.15 내지 약 0.75의 공극률을 가진다. 상기 실시예들 각각에서, 애노드적 활성 재료층의 두께는 통상적으로 공극 깊이를 초과할 것이다. 달리 말하면, 공극의 베이스(예를 들어, 애노드 백본(32)에 근접한 기공의 표면(도 2 참조))는 애노드적 활성 재료층과 애노드 백본 사이의 경계(즉, 도 2에 도시된 표면  $S_3$  및  $S_4$ )에서 발생하지 않을 것이고; 대신에, 애노드적 활성 재료층과 애노드 백본 사이의 경계는 공극의 베이스로부터 더 큰 깊이(예를 들어, 도 2의 화살표 23의 방향에서 측정된 더 큰 거리)에서 발생할 것이다.

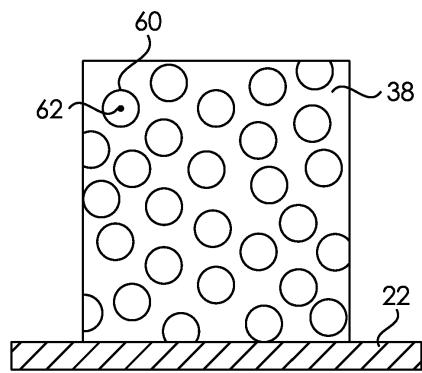

[0036] 상당한 공극-대-공극 편차가 있을 수 있지만, 다공성 실리콘(또는 그 합금)의 공극은 주로 화학적 또는 전기화학적 에칭 프로세스의 방향인 주축(때때로 중심축이라고 함)을 가진다. 이제 도 3을 참조하면, 애노드적 활성 재료층(32)이 다공성 실리콘을 포함하면, 공극(60)은, 측면( $S_1$ )(도 2 참조)에 주로 수직이고 기준 평면, 이 실시예에서는, 베이스(22)의 평면형 표면에 대체로 평행한 주축(62)을 가질 것이다. 특히, 셀들이 도 2에 나타낸 바와 같이 수직으로 적층되면, 공극들의 주축은 셀들의 적층 방향에 대체로 직교한다(즉, 공극들의 주축들은, 적층 방향이 도 2에 나타낸 Z방향일 때 X-Y 평면에 놓인다).

[0037] 또 다른 실시예에서, 미세구조화된 애노드적 활성 재료층들(30, 31)은, 알루미늄, 주석, 또는 실리콘, 또는 그 합금의 섬유들을 포함한다. 개개의 섬유들은, 약 5 nm 내지 약 10,000 nm의 직경(두께 치수)와, 미세구조화된 애노드적 활성 재료층들(30, 31)의 두께에 대체로 대응하는 길이를 가질 수 있다. 실리콘의 섬유들(나노와이어)은, 예를 들어, 화학적 증착 또는 VLS(vapor liquid solid) 성장 및 SLS(solid liquid solid) 성장 등의 공지된 기타의 기술에 의해 형성될 수 있다. 추가적으로, 애노드적 활성 재료층은 일반적으로 적어도 약 0.1의 그러나 0.8미만의 공극률과 약 1 내지 약 200 마이크로미터의 두께를 가질 것이다. 예를 들어, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 실리콘 나노와이어를 포함하고, 약 5 내지 약 100 마이크로미터의 두께를 가지며, 약 0.15 내지 약 0.75의 공극률을 가진다. 추가의 예로서, 한 이러한 실시예에서, 애노드적 활성 재료층들(30, 31)은 실리콘 나노와이어를 포함하고, 약 10 내지 약 80 마이크로미터의 두께를 가지며, 약 0.15 내지 약 0.7의 공극률을 가진다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 실리콘 나노와이어를 포함하고, 약 20 내지 약 50 마이크로미터의 두께를 가지며, 약 0.25 내지 약 0.6의 공극률을 가진다. 추가의 예로서, 한 실시예에서, 애노드적 활성 재료층들(30, 31)은 실리콘 합금(니켈 실리사이드 등)의 나노와이어를 포함하고, 약 5 내지 약 100 마이크로미터의 두께를 가지며, 약 0.15 내지 약 0.75의 공극률을 가진다.

[0038] 상당한 섬유-대-섬유 편차가 있을 수 있지만, 알루미늄, 주석 또는 실리콘(또는 이들의 합금)의 나노와이어는(미세구조화된 애노드적 활성 재료층으로의 나노와이어의 부착점에서) 애노드 백본에 주로 수직이고 백본을 지지하는 베이스의 표면에 평행한 주축(때때로 중심축이라 함)을 가진다(도 2 참조). 특히, 셀들이 도 2에 나타낸 바와 같이 수직으로 적층될 때, 섬유들의 주축은 셀들의 적층 방향에 대체로 직교한다.

[0039] 또 다른 실시예에서, 미세구조화된 애노드적 활성 재료층들(30, 31)은, 실리콘 또는 그 합금과 다공성 실리콘 또는 그 합금의 나노와이어를 포함한다. 이러한 실시예에서, 애노드적 활성 재료층은, 다공성 실리콘 및 실리콘 나노와이어와 연계하여 앞서 설명된 바와 같이, 일반적으로 적어도 약 0.1 그러나 0.8 미만인 공극률과 약 1 내지 약 100 마이크로미터의 두께를 가질 것이다.

[0040] 다시 도 2를 참조하면, 베이스(22)는 강성 백플레인(rigid backplane)으로서 역할하고 광범위한 재료들 중 임의의 재료로 구성될 수 있다. 예를 들어, 베이스(22)는, 세라믹, 유리, 중합체 또는 전체 구조에 충분한 강성을 제공하는 광범위한 재료들 중 임의의 재료를 포함할 수 있다. 한 실시예에서, 베이스(22)는 절연성으로; 예를 들어, 베이스(22)는 10 Siemens/cm 미만의 전기 전도도를 가질 수 있다. 한 실시예에서, 베이스(22)는 실리콘-온-인슐레이터(silicon-on-insulator) 구조를 포함할 수 있다. 일부 실시예에서, 그러나, 베이스(22)는 전기화학적 스택이 형성된 후에 제거될 수 있다.

[0041] 이제 도 4a 내지 도 4e를 참조하면, 애노드 구조(24)와 캐소드 구조(26)는 동일한 기준 평면, 이 실시예에서는 베이스(22)의 평면형 표면으로부터 돌출되고, 주기적으로 교대하고 있다. 추가로, 도 4a 내지 도 4e들 각각에서, 각각의 애노드 구조(24)는 도 2와 연계하여 더 상세히 설명되는 바와 같이 미세구조화된 애노드적 활성 재료층(30)들의 집합체를 지지하기 위해 그 하부면과 상부면 사이에 적어도 하나의 측면을 포함한다. 예를 들어, 애노드 구조(24)가 기둥(pillars) 형상일 때(도 4a), 미세구조화된 애노드적 활성 재료층은 적어도 부분적으로

연장되고, 바람직하게는 측면의 둘레에 대해 완전히 연장된다. 추가 예로서, 애노드 구조(24)가, 예를 들어, 도 4b 내지 도 4e에 예시된 바와 같이 2개의(또는 그 이상의) 측면을 가질 때, 애노드적 활성 재료층은, 측면들 중 적어도 하나를 적어도 부분적으로 덮고, 바람직하게는 완전히 덮는다. 추가로, 집합체 내의 미세구조화된 애노드적 활성 재료층들 각각은(베이스(22)에 수직인 방향에서 측정되는) 높이를 가지며, 층들은, 집합체의 층들 중 적어도 2개 사이의, 예를 들어, 층들(30A 및 30B) 사이의, 베이스(22)의 평면형 표면에 실질적으로 평행한 방향으로 측정된 직선 거리( $D_L$ )가 집합체 내의 층들 중 임의의 층의 최대 높이보다 크도록 배치된다(즉, 직선 거리( $D_L$ )만큼 분리되고 집합체 내의 애노드적 활성 재료층들 모두 중에서 최대 높이를 갖는 애노드적 활성 재료층의 높이  $H_A$ 를 초과하는, 애노드적 활성 재료층들의 집합체 중 적어도 한 쌍의 애노드적 활성 재료층이 존재한다). 예를 들어, 한 실시예에서, 집합체 내의 층들 중 적어도 2개 사이의, 예를 들어, 층들(30A 및 30B) 사이의 직선 거리( $D_L$ )는 집합체 내의 층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다. 추가 예로서, 한 실시예에서, 집합체 내의 다수의 층들 사이의 직선 거리( $D_L$ )는 집합체 내의 층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다.

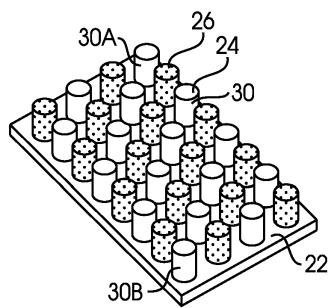

[0042] 도 4a는 기둥 형상의 애노드 구조(24)와 캐소드 구조(26)를 갖는 3차원 어셈블리를 도시한다. 기둥들 각각은 베이스(22)로부터 수직으로 돌출하는 측면(미도시)을 갖는 백본(backbone)을 포함한다. 백본들 각각의 측면은 애노드적 활성 재료층(30)을 지지하고, 층(30)들은, 집합체의 층들 중 적어도 2개 사이의 직선 거리, 예를 들어, 층들(30A 및 30B) 사이의 직선 거리가 집합체 내의 층들 중 임의의 층의 최대 높이보다 크도록 배치된다. 예를 들어, 한 실시예에서, 집합체의 애노드적 활성 재료층들 중 적어도 한 쌍(즉, 집합체 내의 2개의 애노드적 활성 재료층들의 임의의 가능한 쌍들 중 적어도 한 쌍)의 부재들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다. 추가 예로서, 한 실시예에서, 집합체의 다수의 애노드적 활성 재료층들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다.

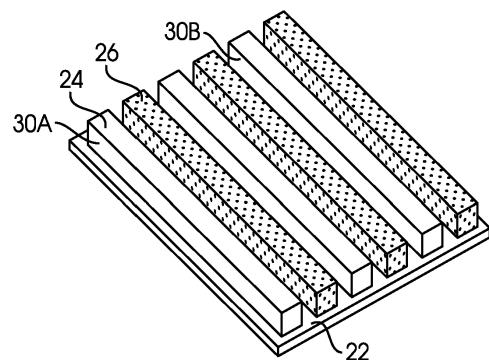

[0043] 도 4b는 플레이트(plate) 형상의 캐소드 구조(26)와 애노드 구조(24)를 갖는 3차원 어셈블리를 도시한다. 플레이트들 각각은 베이스(22)로부터 수직으로 돌출하는 측면(미도시)을 갖는 백본을 포함한다. 백본들 각각의 측면은 애노드적 활성 재료층(30)을 지지하고, 층(30)들은, 집합체의 층들 중 적어도 2개 사이의 직선 거리, 예를 들어, 층들(30A 및 30B) 사이의 직선 거리가 집합체 내의 층들 중 임의의 층의 최대 높이보다 크도록 배치된다. 예를 들어, 한 실시예에서, 집합체의 애노드적 활성 재료층들 중 적어도 한 쌍(즉, 집합체 내의 2개의 애노드적 활성 재료층들의 임의의 가능한 쌍들 중 적어도 한 쌍)의 부재들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다. 추가 예로서, 한 실시예에서, 집합체의 다수의 애노드적 활성 재료층들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다.

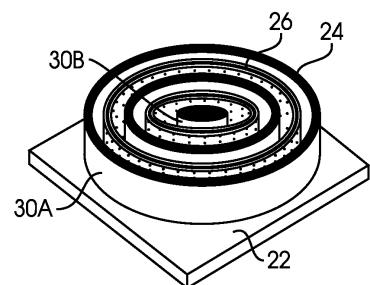

[0044] 도 4c는 동심원(concentric circle) 형상의 캐소드 구조(26)와 애노드 구조(24)를 갖는 3차원 어셈블리를 도시한다. 동심원들 각각은 베이스(22)로부터 수직으로 돌출하는 측면(미도시)을 갖는 백본을 포함한다. 백본들 각각의 측면은 애노드적 활성 재료층(30)을 지지하고, 층(30)들은, 집합체의 층들 중 적어도 2개 사이의 직선 거리, 예를 들어, 층들(30A 및 30B) 사이의 직선 거리가 집합체 내의 층들 중 임의의 층의 최대 높이보다 크도록 배치된다. 예를 들어, 한 실시예에서, 집합체의 애노드적 활성 재료층들 중 적어도 한 쌍(즉, 집합체 내의 2개의 애노드적 활성 재료층들의 임의의 가능한 쌍들 중 적어도 한 쌍)의 부재들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다. 추가 예로서, 한 실시예에서, 집합체의 다수의 애노드적 활성 재료층들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료층들 중 임의의 층의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 십지어 10배만큼 크다.

[0045] 도 4d는 파동(wave) 형상의 캐소드 구조(26)와 애노드 구조(24)를 갖는 3차원 어셈블리를 도시한다. 파동들 각각은 베이스(22)로부터 수직으로 돌출하는 측면(미도시)을 갖는 백본을 포함한다. 백본들 각각의 측면은 애노드적 활성 재료층(30)을 지지하고, 층(30)들은, 집합체의 층들 중 적어도 2개 사이의 직선 거리, 예를 들어, 층

들(30A 및 30B) 사이의 직선 거리가 집합체 내의 충들 중 임의의 충의 최대 높이보다 크도록 배치된다. 예를 들어, 한 실시예에서, 집합체의 애노드적 활성 재료충들 중 임의의 쌍(즉, 집합체 내의 2개의 애노드적 활성 재료충들의 가능한 쌍들 중 임의의 쌍)의 2개 부재들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료충들 중 임의의 충의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 심지어 10배만큼 크다. 추가 예로서, 한 실시예에서, 집합체의 다수의 애노드적 활성 재료충들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료충들 중 임의의 충의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 심지어 10배만큼 크다.

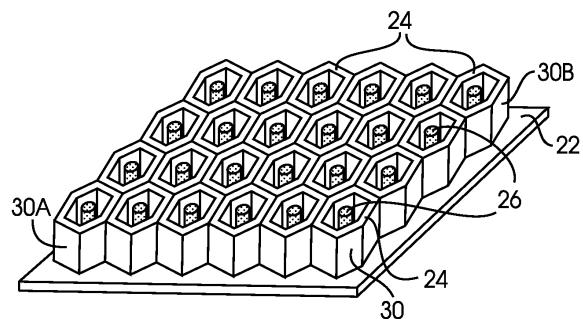

[0046] 도 4e는 벌집(honeycomb) 패턴의 캐소드 구조(26)와 애노드 구조(24)를 갖는 3차원 어셈블리를 도시한다. 캐소드 구조(26)는 벌집 구조의 각각의 단위 셀의 중심에서 기둥 형상으로 있고, 벌집 구조의 각각의 단위 셀의 벽들은 베이스(22)로부터 수직으로 돌출하는 측면(미도시)을 갖는 상호접속된 백본망(시스템)을 포함한다. 백본망(시스템)의 측면들은 애노드적 활성 재료충(30)을 지지하고, 충(30)들은, 집합체의 충들 중 적어도 2개 사이의, 예를 들어, 충들(30A 및 30B) 사이의 직선 거리가 집합체 내의 충들 중 임의의 충의 최대 높이보다 크도록 배치된다. 예를 들어, 한 실시예에서, 집합체의 애노드적 활성 재료충들 중 임의의 쌍(즉, 집합체 내의 2개의 애노드적 활성 재료충들의 가능한 쌍들 중 임의의 쌍)의 2개 부재들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료충들 중 임의의 충의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 심지어 10배만큼 크다. 추가 예로서, 한 실시예에서, 집합체의 다수의 애노드적 활성 재료충들 사이의 직선 거리( $D_L$ )는 집합체 내의 애노드적 활성 재료충들 중 임의의 충의 최대 높이보다 적어도 2배, 일부 실시예에서는, 상당히 더 많이, 예를 들어, 적어도 5배 또는 심지어 10배만큼 크다. 대안적 실시예에서, 3차원 어셈블리는 벌집 구조이지만, 애노드 구조와 캐소드 구조의 상대적 위치는 도 4e에 도시된 실시예에 비해 뒤바뀌는데, 즉, 대안적 실시예에서, 애노드 구조는 (애노드적 활성 재료충들을 지지하는 측면을 갖는) 기둥 형상이고, 각각의 단위 셀의 벽들은 캐소드적 활성 재료를 포함한다.

[0047] 애노드 구조의 지오메트리와는 독립적으로, 한 실시예에서, 전기변색 스택은 부재로서 적어도 20개의 애노드적 활성 재료충들을 갖는 미세구조화된 애노드적 활성 재료충들의 집합체를 포함한다. 예를 들어, 한 실시예에서, 집합체는 적어도 50개의 부재를 포함한다. 추가의 예로서, 한 실시예에서, 집합체는 적어도 100개의 부재를 포함한다. 다른 실시예들에서, 집합체는 적어도 150개, 적어도 200개, 또는 심지어 적어도 500개의 부재를 포함할 수 있다.

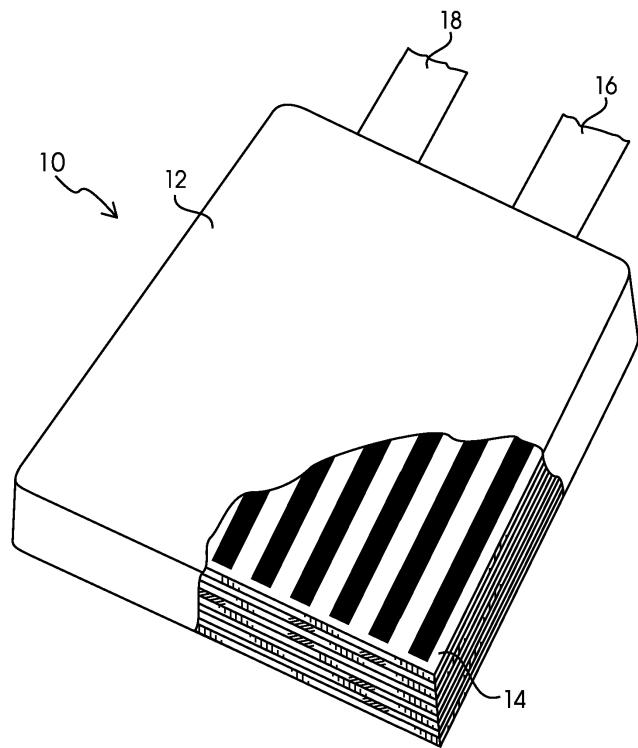

[0048] 이제 도 5를 참조하면, 다이 스택(14)은 3개의 다이를 포함하고, 각각의 다이(20)는 베이스(22)와 베이스(22)로부터 돌출된 교대하는 일련의 애노드 구조(24) 및 캐소드 구조(26)를 포함하는 전기화학적 스택을 포함한다. 각각의 애노드 구조(24)는, 애노드 백본(32), 미세구조화된 애노드적 활성 재료충(31), 및 애노드 전류 콜렉터(28)를 포함한다. 애노드 구조(24)의 각각의 애노드적 활성 재료충(31)은 (베이스(22)에 직교하는 방향에서 측정된) 높이  $H_A$ 를 가진다. 각각의 캐소드 구조(26)는, 캐소드 재료(27), 캐소드 전류 콜렉터(34), 및 캐소드 백본(36)을 포함한다. 세퍼레이터(38)는 각각의 애노드 구조(24)와 각각의 캐소드 구조(26) 사이에 위치한다. 한 실시예에서, 베이스(22)는 제거되고 애노드 구조(24)와 캐소드 구조(26)는 베이스(22)에 평행한 공통 기준 평면으로부터 돌출된다.

[0049] 예시의 용이성을 위해, 각각의 다이(20)에 대해 단 2개의 애노드 구조(24)와 단 1개의 캐소드 구조(26)만이 도 5에 도시되어 있고 단 3개의 다이만이 도 5에 도시된 수직 스택에 나타나 있지만; 실제로는, 각각의 다이는 통상적으로 교대하는 일련의 애노드 구조와 캐소드 구조를 포함하는 전기화학적 스택을 포함하고, 전기화학적 스택당 애노드 구조 및 캐소드 구조의 개수와 수직 스택 내의 다이의 개수는 응용마다 다르다. 이동 전화 및 컴퓨터 등의 휴대형 전자장치용의 리튬 이온 배터리의 경우, 예를 들어, 각각의 다이는 약 20개 내지 약 500개의 애노드 구조와 거의 동일한 개수의 캐소드 구조를 포함할 수 있다. 예를 들어, 한 실시예에서, 각각의 다이는 적어도 20개의, 적어도 50개의, 적어도 100개의, 적어도 150개의, 적어도 200개의, 또는 심지어 적어도 500개의 애노드 구조와 거의 동일한 개수의 캐소드 구조를 포함할 수 있다. 다이의 크기는 또한, 응용에 따라 상당히 달라질 수 있다. 이동 전화 및 컴퓨터 등의 휴대형 전자 장치용의 리튬 배터리 이온의 경우, 예를 들어, 각각의 다이는 50 mm (L) x 50 mm (W) x 5 mm (H)의 크기를 가질 수 있다. 추가적으로, 한 실시예에서, 다이들은 바람직하게는, 다이의 전기화학적 스택 내에서의 애노드 구조, 세퍼레이터 충, 및 캐소드 구조의 적층 방향과 직교하는 방향으로 서로에 관해 적층되는데; 달리 말하면, 각각의 다이는 바람직하게는 개개의 다이의 각각의 베이스(22)의 실질적으로 평면형 표면(또는 공통 기준 평면)에 직교하는 방향으로 적층된다. 한 대안적 실시예에서, 다이들은, 다이의 전기화학적 스택 내에서의 애노드 구조, 세퍼레이터 충, 및 캐소드 구조의 적층 방향과

평행한 방향으로 서로에 관해 적층되는데; 달리 말하면, 각각의 다이는 바람직하게는 개개의 다이의 각각의 베이스(22)의 실질적으로 평면형 표면(또는 공통 기준 평면)과 평행한 평면 내에 놓인 방향으로 적층된다.

[0050] 베이스(22)는 강성 백플레이으로서 역할하고 광범위한 재료들 중 임의의 재료로 구성될 수 있다. 앞서 언급된 바와 같이, 베이스(22)는, 세라믹, 유리, 종합체 또는 전체 구조에 충분한 강성과 전기 절연을 제공하는 광범위한 기타 재료들 중 임의의 재료를 포함할 수 있다. 한 실시예에서, 베이스(22)는 제거되거나 기타의 방식으로 생략되고(소정 구조 또는 수단이 제공되어 애노드와 캐소드 구조 사이의 전기 단락을 방지한다고 가정) 애노드 및 캐소드 구조는 공통 베이스 대신에 공통 기준 평면으로부터 돌출된다.

[0051] 애노드 구조(24)의 전체 크기는, 부분적으로는 응용에 따라, 부분적으로는 제조 관심사에 따라 달라질 수 있다. 이동 전화 및 컴퓨터 등의 휴대형 전자 장치용 리튬 이온 배터리의 경우, 예를 들어, 각각의 애노드 구조(24)는 적어도 약 50 마이크로미터, 더 일반적으로는 적어도 약 100 마이크로미터의 (베이스(22)에 수직인 방향에서 측정된) 높이를 가질 것이다. 그러나, 일반적으로, 애노드 구조(들)은 통상적으로 약 10,000 마이크로미터보다 크지 않은, 더 일반적으로는 약 5,000 마이크로미터보다 크지 않은 높이를 가질 것이다. 추가적으로, 동일한 전기화학적 스택(20)의 애노드적 활성 재료층(31)의 적어도 한 쌍(미도시) 사이의 직선 거리는 바람직하게는, 동일한 전기화학적 스택 내의 애노드적 활성 재료층들의 집합의 부재들의 최대 높이  $H_A$ 를 초과한다.

[0052] 다시 도 5를 참조하면, 각각의 애노드 구조(24)는, 애노드 백본(32)과 접촉하여 그 위에 놓인 애노드적 활성 재료층(31)과 접촉하여 그 위에 놓인 애노드 전류 콜렉터층(28)을 포함한다. 캐리어 이온들은 이러한 전기화학적 스택 내의 애노드적 활성 재료와 캐소드적 활성 재료 사이에서 이동하므로, 이들은 세퍼레이터와 애노드적 활성 재료층 사이에 위치한 애노드 전류 콜렉터층(28)을 통과한다. 이 실시예에서, 애노드 전류 콜렉터층(28)은, 세퍼레이터로부터 애노드적 활성 재료층으로의 캐리어 이온의 이동을 용이하게 하기 위한 캐리어 이온에 대한 충분한 이온 투과성 및 전류 콜렉터로서 역할하는 것을 가능하기 위한 충분한 전기 전도도를 갖는 이온적으로 투과가능한 도전체를 포함한다.

[0053] 애노드적 활성 재료 층과 세퍼레이터 사이에 위치해 있으므로, 애노드 전류 콜렉터층은 애노드 전류 콜렉터로부터의 전류를 애노드적 활성 재료층의 표면에 걸쳐 분산시킴으로써 더욱 균일한 캐리어 이온 수송을 용이하게 할 수 있다. 이것은, 결국, 캐리어 이온의 보다 균일한 삽입과 추출을 용이하게 할 수 있음으로써 사이클링 동안에 애노드적 활성 재료 내의 스트레스를 감소시키는데; 애노드 전류 콜렉터층은 전류를 세퍼레이터쪽으로 향한 애노드 활성 재료층의 표면에 분산시키므로, 캐리어 이온에 대한 애노드 활성 재료층의 반응성은 캐리어 이온 농도가 최대인 곳에서 최대가 될 것이다.

[0054] 이 실시예에서, 애노드 전류 콜렉터층은, 이온적으로 및 전기적으로 전도성인 이온적으로 투과가능한 도전체 재료를 포함한다. 달리 말하면, 애노드 전류 콜렉터층은, 이온적으로 투과가능한 도전체층의 한 측 상의 바로 인접한 활성 전극 재료층과 전기화학적 스택 내의 애노드 전류 콜렉터층의 다른 측 상의 바로 인접한 세퍼레이터 층 사이에서의 캐리어 이온의 이동을 용이하게 하는 캐리어 이온에 대한 두께, 전기 전도도, 및 이온 전도도를 가진다. 상대적인 기반으로, 애노드 전류 콜렉터층은 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때 그 이온 컨덕턴스보다 큰 전기적 컨덕턴스를 가진다. 예를 들어, 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 통상적으로 적어도 1,000:1일 것이다. 추가의 예로서, 한 이러한 실시예에서, 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 통상적으로 적어도 1,000:1일 것이다. 추가의 예로서, 한 이러한 실시예에서, 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 10,000:1이다. 추가의 예로서, 한 이러한 실시예에서, 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 50,000:1이다. 추가의 예로서, 한 이러한 실시예에서, 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 100,000:1이다.

[0055] 한 실시예에서 및 2차 전지의 충전 또는 방전시와 같은 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 애노드 전류 콜렉터층은 인접하는 세퍼레이터 층의 이온 컨덕턴스와 필적하는 이온 컨덕턴스를 가진다. 예를 들어, 한 실시예에서, 애노드 전류 콜렉터층은, 장치에 에너지를 저장하는 인가

된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때 세퍼레이터 층의 이온 컨덕턴스의 적어도 50%인(즉, 각각 0.5:1의 비율) (캐리어 이온에 대한) 이온 컨덕턴스를 가진다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1:1이다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1.25:1이다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1.5:1이다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 ((애노드 전류 콜렉터층) 캐리어 이온에 대한) 이온 컨덕턴스에 대한 애노드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 2:1이다.

[0056] 한 실시예에서, 애노드 전류 콜렉터층은 또한 애노드적 활성 재료층의 전기적 컨덕턴스보다 상당히 큰 전기적 컨덕턴스를 가진다. 예를 들어, 한 실시예에서, 애노드적 활성 재료층의 전기적 컨덕턴스에 대한 애노드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 100:1이다. 추가의 예로서, 일부 실시예에서, 애노드적 활성 재료층의 전기적 컨덕턴스에 대한 애노드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 500:1이다. 추가의 예로서, 일부 실시예에서, 애노드적 활성 재료층의 전기적 컨덕턴스에 대한 애노드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1000:1이다. 추가의 예로서, 일부 실시예에서, 애노드적 활성 재료층의 전기적 컨덕턴스에 대한 애노드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 5000:1이다. 추가의 예로서, 일부 실시예에서, 애노드적 활성 재료층의 전기적 컨덕턴스에 대한 애노드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 10,000:1이다.

[0057] 이 실시예에서 애노드 전류 콜렉터층의 두께(즉, 애노드 전류 콜렉터층이 끼워져 있는 세퍼레이터와 애노드적 활성 재료층 사이의 최단 거리)는 전기화학적 스택에 대한 층의 조성과 성능 명세에 의존할 것이다. 일반적으로, 애노드 전류 콜렉터층이 이온적으로 투과가능한 도전체층일 때, 이 층은 적어도 약 300 옹스트롱의 두께를 가질 것이다. 예를 들어, 일부 실시예에서, 이 층은 약 300-800 옹스트롱 범위의 두께를 가질 수 있다. 그러나, 더욱 일반적으로는, 이 층은 약 0.1 마이크로미터보다 큰 두께를 가질 것이다. 일반적으로, 이온적으로 투과가능한 도전체층은 약 100 마이크로미터보다 크지 않은 두께를 가질 것이다. 따라서, 예를 들어, 한 실시예에서, 애노드 전류 콜렉터층은 약 0.1 내지 약 10 마이크로미터 범위의 두께를 가질 것이다. 추가의 예로서, 일부 실시예에서, 애노드 전류 콜렉터층은 약 0.1 내지 약 5 마이크로미터 범위의 두께를 가질 것이다. 추가의 예로서, 일부 실시예에서, 애노드 전류 콜렉터층은 약 0.5 내지 약 3 마이크로미터 범위의 두께를 가질 것이다. 일반적으로, 애노드 전류 콜렉터층의 두께가 거의 균일한 것이 선호된다. 예를 들어, 한 실시예에서, 애노드 전류 콜렉터층이 약 25% 미만의 두께 불균일성을 갖는 것이 선호되며, 두께 불균일성은 층의 최대 두께 - 층의 최소 두께를 평균 층 두께로 나눈 양으로서 정의된다. 소정 실시예에서, 두께 편차는 훨씬 작다. 예를 들어, 일부 실시예에서, 애노드 전류 콜렉터층은 약 20% 미만의 두께 불균일성을 가진다. 추가의 예로서, 일부 실시예에서, 애노드 전류 콜렉터층은 약 15% 미만의 두께 불균일성을 가진다. 일부 실시예에서, 이온적으로 투과가능한 도전체층은 약 10% 미만의 두께 불균일성을 가진다.

[0058] 한 바람직한 실시예에서, 애노드 전류 콜렉터층은 이온 투과율과 전기 전도도에 기여하는 전기 도전 성분과 이온 도전 성분을 포함하는 이온적으로 투과가능한 도전층이다. 통상적으로, 전기 도전 성분은, 메쉬나 패터닝된 표면 형태의 연속적인 전기 도전 재료(연속적 금속 또는 금속 합금 등), 막, 또는 연속적인 전기 도전 재료(연속적 금속 또는 금속 합금 등)를 포함하는 복합 재료를 포함할 것이다. 추가로, 이온 도전 성분은 통상적으로 공극들, 예를 들어, 메쉬의 틈새, 재료층을 포함하는 패터닝된 금속이나 금속 합금 사이의 공간, 금속막 내의 공극, 또는 캐리어 이온에 대한 충분한 확산성을 갖는 고체 이온 도전체를 포함할 것이다. 소정 실시예들에서, 이온적으로 투과가능한 도전체층은, 피착된 다공성 재료, 이온-수송 재료, 이온-반응성 재료, 복합 재료, 또는 물리적으로 다공성의 재료를 포함한다. 다공성, 예를 들어, 이온적으로 투과가능한 도전체층은 적어도 약 0.25의 공극률을 가질 수 있다. 그러나, 일반적으로, 공극률은 통상 약 0.95를 초과하지 않을 것이다. 더 일반적으로는, 이온적으로 투과가능한 도전체층이 다공성일 때, 공극률은 약 0.25 내지 약 0.85의 범위에 있을 수 있

다. 일부 실시예에서, 예를 들어, 이온적으로 투과가능한 도전체층이 다공성일 때, 공극률은 약 0.35 내지 약 0.65의 범위에 있을 수 있다.

[0059] 도 5에 나타낸 실시예에서, 애노드 전류 콜렉터층(28)은 애노드적 활성 재료층(31)에 대한 유일한 애노드 전류 콜렉터이다. 달리 말하면, 이 실시예에서 애노드 백본(32)은 애노드 전류 콜렉터를 포함하지 않는다. 그러나, 소정의 다른 실시예에서, 애노드 백본(32)은 선택사항으로서 애노드 전류 콜렉터를 포함할 수 있다.

[0060] 각각의 캐소드 구조(26)는, 캐소드 활성 재료의 혼합물을 포함한 다양한 캐소드 활성 재료(27) 중에서 임의의 것을 포함할 수 있다. 예를 들어, 리튬-이온 배터리의 경우,  $\text{LiCoO}_2$ ,  $\text{LiNi}_{0.5}\text{Mn}_{1.5}\text{O}_4$ ,  $\text{Li}(\text{Ni}_x\text{Co}_y\text{Al}_2)\text{O}_2$ ,  $\text{LiFePO}_4$ ,  $\text{Li}_2\text{MnO}_4$ ,  $\text{V}_2\text{O}_5$ , 및 몰리브덴 산황화물 등의 캐소드 재료를 포함할 수 있다. 예를 들어, 전기영동 피착, 전착, 동시-피착(co-deposition) 또는 슬러리 피착을 포함한 다양한 기술들 중 임의의 기술에 의해, 캐소드 활성 재료가 피착되어 캐소드 구조를 형성할 수 있다. 하나의 예시적인 실시예에서, 전술된 캐소드 활성 재료들 중 하나, 또는 그들의 조합이, 입자 형태로, 전기영동적으로 피착된다. 또 다른 예시적인 실시예에서,  $\text{V}_2\text{O}_5$  등의 캐소드 활성 재료가 전착된다. 또 다른 예시적인 실시예에서, 전술된 캐소드 활성 재료들 중 하나, 또는 그들의 조합이, 입자 형태로, 폴리아닐린 등의 도전성 매트릭스에서 동시-피착된다. 또 다른 예시적인 실시예에서, 전술된 캐소드 활성 재료들 중 하나, 또는 그들의 조합이, 입자 형태로, 슬러리 피착된다. 피착 방법과는 독립적으로, 캐소드 활성 재료층은 통상적으로 1 마이크론 내지 1 mm의 두께를 가질 것이다. 소정 실시예에서, 총 두께는 5 마이크론 내지 200 마이크론이고, 소정 실시예에서, 총 두께는 10 마이크론 내지 150 마이크론이다.

[0061] 각각의 캐소드 구조(26)는, 도 5에 나타낸 실시예에서는 캐소드 지지물(36) 위에 놓인 캐소드 전류 콜렉터(34)를 더 포함한다. 캐소드 전류 콜렉터(34)는 애노드 전류 콜렉터에 대해 앞서 식별된 임의의 금속을 포함할 수 있는데; 예를 들어, 한 실시예에서, 캐소드 전류 콜렉터(34)는, 알루미늄, 탄소, 크롬, 금, 니켈, NiP, 팔라듐, 백금, 로듐, 루테늄, 실리콘 및 니켈의 합금, 티타늄, 또는 이들의 조합을 포함한다(*Journal of the Electrochemical Society*, 152(11) A2105-A2113 (2005)에서, A. H. Whitehead 및 M. Schreiber에 의한 "Current collectors for positive electrodes of lithium-based batteries"를 참조한다). 추가의 예로서, 한 실시예에서, 캐소드 전류 콜렉터층(34)은 금, 또는 금 실리사이드 등의 금의 합금을 포함한다. 추가의 예로서, 한 실시예에서, 캐소드 전류 콜렉터층(34)은 니켈, 또는 니켈 실리사이드 등의 니켈의 합금을 포함한다.

[0062] 마찬가지로, 캐소드 지지물(36)은 애노드 백본에 대해 앞서 식별된 임의의 재료를 포함할 수 있다. 현재 바람직한 재료는 실리콘 및 게르마늄 등의 반도체 재료를 포함한다. 그러나, 대안으로서, 백금, 로듐, 알루미늄, 금, 니켈, 코발트, 티타늄, 텉스텐, 및 그 합금 등의 금속 또는 탄소-기반의 유기 재료도 역시 캐소드 지지 구조 내에 병합될 수 있다. 통상적으로, 캐소드 지지물은 적어도 약 50 마이크로미터, 더 일반적으로는 적어도 약 100 마이크로미터의 높이와, 이용되는 제작 방법에 의해 허용되는 (최소치를 포함한) 두께 범위 중 임의의 두께를 가질 것이다. 그러나, 일반적으로, 캐소드 지지물(36)은 통상적으로 약 10,000 마이크로미터보다 크지 않은, 더욱 일반적으로는 약 5000 마이크로미터보다 크지 않은 높이를 가질 것이다. 추가로, 이러한 실시예에서, 캐소드 전류 콜렉터(34)는 약 0.5 내지 약 50 마이크로미터 범위의 두께를 가질 것이다.

[0063] 대안적 실시예에서, 캐소드 전류 콜렉터층 및 캐소드 활성 재료층의 위치는 도 5에 도시된 바와 같은 그들의 위치에 관해 뒤바뀐다. 달리 말하면, 일부 실시예에서, 캐소드 전류 콜렉터층은 세페레이터 층과 캐소드적 활성 재료층 사이에 위치한다. 이러한 실시예에서, 바로 인접한 캐소드적 활성 재료층에 대한 캐소드 전류 콜렉터는 애노드 전류 콜렉터층과 연계하여 설명된 조성과 구조를 갖는 이온적으로 투과가능한 도전체를 포함; 즉, 캐소드 전류 콜렉터층은 이온적으로 및 전기적으로 도전성의 이온적으로 투과가능한 도전체 재료의 층을 포함한다. 이 실시예에서, 캐소드 전류 콜렉터층은, 캐소드 전류 콜렉터층의 다른 층 상의 바로 인접한 캐소드적 활성 재료 층과 전기화학적 스택 내의 캐소드 전류 콜렉터층의 다른 층 상의 바로 인접한 세페레이터 층 사이에서의 캐리어 이온의 이동을 용이하게 하는 캐리어 이온에 대한 두께, 전기 전도도, 및 이온 전도도를 가진다. 상대적인 기반으로, 이 실시예에서, 캐소드 전류 콜렉터층은 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때 그 이온 컨덕턴스보다 큰 전기적 컨덕턴스를 가진다. 예를 들어, 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1,000:1일 것이다. 추가의 예로서, 한 이러한 실시예에서, 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 5,000:1이다. 추가의 예로서, 한 이러한 실시예에서, 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전

시키는 인가된 부하가 있을 때, 적어도 10,000:1이다. 추가의 예로서, 한 이러한 실시예에서, 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 50,000:1이다. 추가의 예로서, 한 이러한 실시예에서, 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 전기적 컨덕턴스의 비율은, 각각 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 100,000:1이다.

[0064] 2차 전지의 충전 또는 방전시와 같은 이 실시예에서 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 캐소드 전류 콜렉터층은 인접하는 세퍼레이터 층의 이온 컨덕턴스와 필적하는 이온 컨덕턴스를 가진다. 예를 들어, 한 실시예에서, 캐소드 전류 콜렉터층은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때 세퍼레이터 층의 이온 컨덕턴스의 적어도 50%인(즉, 각각 0.5:1의 비율) (캐리어 이온에 대한) 이온 컨덕턴스를 가진다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1:1이다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1.25:1이다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 (캐리어 이온에 대한) 이온 컨덕턴스에 대한 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1.5:1이다. 추가의 예로서, 일부 실시예에서, 세퍼레이터 층의 ((캐소드 전류 콜렉터층) 캐리어 이온에 대한) 이온 컨덕턴스에 대한 캐소드 전류 콜렉터층의 (캐리어 이온에 대한) 이온 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 2:1이다.

[0065] 캐소드 전류 콜렉터층이 캐소드적 활성 재료층과 세퍼레이터 층 사이에 있는 이 실시예에서, 캐소드 전류 콜렉터는 캐소드적 활성 재료층의 전기적 컨덕턴스보다 상당히 큰 전기적 컨덕턴스를 갖는 이온적으로 투과가능한 도전체층을 포함한다. 예를 들어, 한 실시예에서, 캐소드적 활성 재료층의 전기적 컨덕턴스에 대한 캐소드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 100:1이다. 추가의 예로서, 일부 실시예에서, 캐소드적 활성 재료층의 전기적 컨덕턴스에 대한 캐소드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 500:1이다. 추가의 예로서, 일부 실시예에서, 캐소드적 활성 재료층의 전기적 컨덕턴스에 대한 캐소드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 1000:1이다. 추가의 예로서, 일부 실시예에서, 캐소드적 활성 재료층의 전기적 컨덕턴스에 대한 캐소드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 5000:1이다. 추가의 예로서, 일부 실시예에서, 캐소드적 활성 재료층의 전기적 컨덕턴스에 대한 캐소드 전류 콜렉터층의 전기적 컨덕턴스의 비율은, 장치에 에너지를 저장하는 인가된 전류 또는 장치를 방전시키는 인가된 부하가 있을 때, 적어도 10,000:1이다.

[0066] 이 실시예에서 캐소드 전류 콜렉터층의 두께(즉, 캐소드 전류 콜렉터층이 끼워져 있는 세퍼레이터와 캐소드적 활성 재료층 사이의 최단 거리)는 전기화학적 스택에 대한 층의 조성과 성능 명세에 의존할 것이다. 일반적으로, 캐소드 전류 콜렉터층이 이온적으로 투과가능한 도전체층일 때, 이 층은 적어도 약 300 옹스트롱의 두께를 가질 것이다. 예를 들어, 일부 실시예에서, 이 층은 약 300-800 옹스트롱 범위의 두께를 가질 수 있다. 그러나, 더욱 일반적으로는, 이 층은 약 0.1 마이크로미터보다 큰 두께를 가질 것이다. 일반적으로, 캐소드 전류 도전체는 통상 약 100 마이크로미터보다 크지 않은 두께를 가질 것이다. 따라서, 예를 들어, 한 실시예에서, 캐소드 전류 콜렉터층은 약 0.1 내지 약 10 마이크로미터 범위의 두께를 가질 것이다. 추가의 예로서, 일부 실시예에서, 캐소드 전류 콜렉터층은 약 0.1 내지 약 5 마이크로미터 범위의 두께를 가질 것이다. 일반적으로, 캐소드 전류 콜렉터층의 두께가 거의 균일한 것이 선호된다. 예를 들어, 한 실시예에서, 이온적으로 투과가능한 도전체층(캐소드 전류 도전체)이 약 25% 미만의 두께 불균일성을 갖는 것이 선호되며, 두께 불균일성은 층의 최대 두께 - 층의 최소 두께를 평균 층 두께로 나눈 양으로서 정의된다. 소정 실시예에서, 두께 편차는 훨씬 작다. 예를 들어, 일부 실시예에서, 캐소드 전류 콜렉터층은 약 20% 미만의 두께 불균일성을 가진다. 추가의 예로서, 일부 실시예에서, 캐소드 전류 콜렉터층은 약 15% 미만의 두께 불균일성을 가진다. 일부

실시예에서, 캐소드 전류 콜렉터층은 약 10% 미만의 두께 불균일성을 가진다.

[0067] 한 바람직한 실시예에서, 캐소드 전류 콜렉터층은, 애노드 전류 콜렉터와 연계하여 설명된 바와 같이 이온 투과율과 전기 전도도에 기여하는 전기 도전 성분과 이온 도전 성분을 포함하는 이온적으로 투과가능한 도전층이다. 통상적으로, 전기 도전 성분은, 메쉬나 패터닝된 표면 형태의 연속적인 전기 도전 재료(연속적 금속 또는 금속 합금 등), 막, 또는 연속적인 전기 도전 재료(연속적 금속 또는 금속 합금 등)를 포함하는 복합 재료를 포함할 것이다. 추가로, 이온 도전 성분은 통상적으로 공극들, 예를 들어, 메쉬의 틈새, 재료층을 포함하는 패터닝된 금속이나 금속 합금 사이의 공간, 금속막 내의 공극, 또는 캐리어 이온에 대한 충분한 확산성을 갖는 고체 이온 도전체를 포함할 것이다. 소정 실시예들에서, 이온적으로 투과가능한 도전체층은, 피착된 다공성 재료, 이온-수송 재료, 이온-반응성 재료, 복합 재료, 또는 물리적으로 다공성의 재료를 포함한다. 다공성, 예를 들어, 이온적으로 투과가능한 도전체층은 적어도 약 0.25의 공극률을 가질 수 있다. 그러나, 일반적으로, 공극률은 통상 약 0.95를 초과하지 않을 것이다. 더 일반적으로는, 이온적으로 투과가능한 도전체층이 다공성일 때, 공극률은 약 0.25 내지 약 0.85의 범위에 있을 수 있다. 일부 실시예에서, 예를 들어, 이온적으로 투과가능한 도전체층이 다공성일 때, 공극률은 약 0.35 내지 약 0.65의 범위에 있을 수 있다.

[0068] 한 실시예에서, 전극 전류 콜렉터층(즉, 애노드 전류 콜렉터층 또는 캐소드 전류 콜렉터층)으로 구성된 이온적으로 투과가능한 도전체층은 세퍼레이터 층과 전극 활성 재료층 사이에 위치한 메쉬를 포함한다. 메쉬는 전기 도전 재료의 메쉬 스트랜드(mesh strand)에 의해 정의된 틈새를 가진다. 예를 들어, 전극 활성 재료층이 애노드적 활성 재료층일 때, 메쉬는 탄소, 코발트, 크롬, 구리, 니켈, 티타늄, 또는 이들 중 하나 이상의 합금의 스트랜드를 포함할 수 있다. 추가의 예로서, 전극 활성 재료층이 캐소드적 활성 재료층일 때, 메쉬는, 알루미늄, 탄소, 크롬, 금, NiP, 팔라듐, 로듐, 루테늄, 티타늄, 또는 이들의 하나 이상의 합금의 스트랜드를 포함할 수 있다. 일반적으로, 메쉬는 적어도 약 2 마이크로미터의 두께를 가질 것이다(메쉬의 스트랜드는 적어도 약 2 마이크로미터의 직경을 가진다). 하나의 예시적인 실시예에서, 메쉬는 적어도 약 4 마이크로미터의 두께를 가진다. 또 다른 예시적인 실시예에서, 메쉬는 적어도 약 6 마이크로미터의 두께를 가진다. 또 다른 예시적인 실시예에서, 메쉬는 적어도 약 8 마이크로미터의 두께를 가진다. 상기 실시예들 각각에서, 메쉬의 개방 면적률(즉, 메쉬 스트랜드들 사이의 틈새들을 구성하는 메쉬의 비율)은 바람직하게는 적어도 0.5이다. 예를 들어, 상기 실시예들 각각에서, 메쉬의 개방 면적률은 적어도 0.6일 수 있다. 추가의 예로서, 상기 실시예들 각각에서, 메쉬의 개방 면적률은 적어도 0.75일 수 있다. 추가의 예로서, 상기 실시예들 각각에서, 메쉬의 개방 면적률은 적어도 0.8일 수 있다. 그러나, 일반적으로, 상기 실시예들 각각에서, 전극 활성 재료층의 두께에 대한 메쉬의 스트랜드들 사이의 평균 거리의 비율은 각각 단지 100:1이다. 예를 들어, 상기 실시예들 각각에서, 전극 활성 재료층의 두께에 대한 메쉬 스트랜드들 사이의 평균 거리의 비율은 각각 단지 50:1이다. 추가의 예로서, 상기 실시예들 각각에서, 전극 활성 재료층의 두께에 대한 메쉬 스트랜드들 사이의 평균 거리의 비율은 단지 25:1이다. 유의하게도, 메쉬의 하나 또는 양쪽 끝은 용접되거나 기타의 방식으로 금속 템이나 다른 커넥터에 접속되어 수집된 전류가 배터리 외부 환경으로 운반될 수 있게 한다.

[0069] 한 실시예에서, 전극 전류 콜렉터층으로 구성된 이온적으로 투과가능한 도전체층(즉, 애노드 전류 콜렉터층 또는 캐소드 전류 콜렉터층)은 앞서 설명된 바와 같이 금속 또는 그 합금의 메쉬를 포함하고, 메쉬의 스트랜드들 사이의 틈새들은 개방되어, 전해질이 침투할 수 있는 다공성 재료로 채워지거나, 캐리어 이온이 확산할 수 있는 비다공성 재료를 포함할 수 있다. 다공성 재료로 채워질 때, 다공성 재료는 통상적으로 적어도 약 0.5의 공극률을 가질 것이고, 일부 실시예에서, 공극률은 적어도, 0.6, 0.7 또는 심지어 적어도 약 0.8일 것이다. 예시적인 다공성 재료로는,  $\text{SiO}_2$ ,  $\text{Al}_2\text{O}_3$ ,  $\text{SiC}$ , 또는  $\text{Si}_3\text{N}_4$  등의 입자성 세라믹의 응집체, 및 폴리에틸렌, 폴리프로필렌, 폴리메틸메타크릴레이트 및 그 공중합체 등의 입자성 중합체의 응집체가 포함된다. 메쉬의 틈새에 배치될 수 있는 예시적인 비다공성 재료로는,  $\text{Na}_3\text{Zr}_2\text{Si}_2\text{PO}_{12}$  (NASICON),  $\text{Li}_{2+2x}\text{Zn}_{1-x}\text{GeO}_4$  (LISICON) 등의 고체 이온 도전체, 및 리튬 인 산화질화물(LiPON)이 포함된다.

[0070] 한 실시예에서, 전극 전류 콜렉터층(즉, 애노드 전류 콜렉터층 또는 캐소드 전류 콜렉터층)으로 구성된 이온적으로 투과가능한 도전체층은 바로 인접한 세퍼레이터 층 또는 바로 인접한 전극 활성 재료층(즉, 바로 인접한 애노드적 활성 재료층 또는 바로 인접한 캐소드적 활성 재료층)의 표면 상에 피착되거나 기타의 방식으로 형성된 도전체 라인을 포함한다. 이 실시예에서, 도전체 라인은 메쉬 캠포넌트와 연계하여 앞서 식별된 금속들(또는 그 합금들) 중 임의의 것을 포함할 수 있다. 예를 들어, 이온적으로 투과가능한 도전체층은 세퍼레이터 층과 애노드적 활성 재료층 사이에 위치하고, 도전체 라인은, 탄소, 코발트, 크롬, 구리, 니켈, 티타늄, 또는 이들 중 하나 이상의 합금을 포함할 수 있다. 이온적으로 투과가능한 도전체층이 세퍼레이터 층과 캐소드적 활성 재료층 사이에 위치하면, 도전체 라인은, 알루미늄, 탄소, 크롬, 금, NiP, 팔라듐, 로듐, 루테늄, 티타늄, 또는

이들 중 하나 이상의 합금을 포함할 수 있다. 일반적으로, 도전성 라인은 적어도 약 2 마이크로미터의 두께를 가질 것이다. 하나의 예시적인 실시예에서, 도전성 라인은 적어도 약 4 마이크로미터의 두께를 가진다. 또 다른 예시적인 실시예에서, 도전성 라인은 적어도 약 6 마이크로미터의 두께를 가진다. 또 다른 예시적인 실시예에서, 도전성 라인은 적어도 약 8 마이크로미터의 두께를 가진다. 상기 실시예들 각각에서, 전극 활성 재료층의 두께에 대한 도전성 라인들 사이의 평균 거리의 비율은 각각 단지 100:1이다. 예를 들어, 상기 실시예들 각각에서, 전극 활성 재료층의 두께에 대한 도전성 라인들 사이의 평균 거리의 비율은 각각 단지 50:1이다. 추가의 예로서, 상기 실시예들 각각에서, 전극 활성 재료층의 두께에 대한 도전성 라인들 사이의 평균 거리의 비율은 각각 단지 25:1이다. 유익하게도, 도전성 라인들의 하나 이상의 끝은 용접되거나 기타의 방식으로 금속 템이나 다른 커넥터에 접속되어 수집된 전류가 배터리 외부 환경으로 운반될 수 있게 한다.

[0071] 한 실시예에서, 전극 전류 콜렉터층으로 구성된 이온적으로 투과가능한 도전체층(즉, 애노드 전류 콜렉터층 또는 캐소드 전류 콜렉터층)은 앞서 설명된 바와 같이 금속 또는 그 합금의 도전성 라인을 포함하고, 코팅된 재료의 표면 상의 공간들은 개방되어, 전해질이 침투할 수 있는 다공성 재료로 채워지거나, 캐리어 이온이 확산할 수 있는 비다공성 재료를 포함할 수 있다. 다공성 재료로 채워질 때, 다공성 재료는 통상적으로 적어도 약 0.5의 공극률을 가질 것이고, 일부 실시예에서, 공극률은 적어도 0.6, 0.7 또는 심지어 적어도 약 0.8일 것이다. 예시적인 다공성 재료로는,  $\text{SiO}_2$ ,  $\text{Al}_2\text{O}_3$ ,  $\text{SiC}$ , 또는  $\text{Si}_3\text{N}_4$  등의 입자성 세라믹의 응집체, 및 폴리에틸렌, 폴리프로필렌, 폴리메틸메타크릴레이트 및 그 공중합체 등의 입자성 중합체의 응집체가 포함된다. 도전성 라인들 사이에 배치될 수 있는 예시적인 비다공성 재료로는,  $\text{Na}_3\text{Zr}_2\text{Si}_2\text{PO}_{12}$  (NASICON),  $\text{Li}_{2+2x}\text{Zn}_{1-x}\text{GeO}_4$  (LISICON) 등의 고체 이온 도전체, 및 리튬 인 산화질화물(LiPON)이 포함된다.

[0072] 한 실시예에서, 전극 전류 콜렉터층(즉, 애노드 전류 콜렉터층 또는 캐소드 전류 콜렉터층)으로 구성된 이온적으로 투과가능한 도전체층은 다공성 금속층 등의 다공성 층이나 막을 포함한다. 예를 들어, 전극 활성 재료층이 애노드적 활성 재료층일 때, 다공성 층은, 탄소, 코발트, 크롬, 구리, 니켈, 티타늄, 또는 이들 중 하나 이상의 합금의 다공성 층을 포함할 수 있다. 추가의 예로서, 전극 활성 재료층이 캐소드적 활성 재료층일 때, 다공성 층은, 알루미늄, 탄소, 크롬, 금, NiP, 팔라듐, 로듐, 루테늄, 티타늄, 또는 이들의 하나 이상의 다공성 층을 포함할 수 있다. 이러한 다공성 층들의 형성을 위한 예시적인 피착 기술로는, 무전해 피착(electroless deposition), 전착(electro deposition), 스퍼터링 등의 진공 피착 기술, 치환 도금(displacement plating), 화학적 증착 및 물리적 증착 등의 증착 기술, 선택된 에칭에 후속하는 동시-피착, 및 바인더를 이용한 금속 입자의 슬러리 코팅이 포함된다. 일반적으로, 이러한 다공성 층의 공극률은 적어도 0.25인 것이 선호된다. 예를 들어, 한 실시예에서, 다공성 금속층의 공극률은, 적어도 0.4, 적어도 0.5, 적어도 0.6, 적어도 0.7 및 약 0.75 까지 이를 것이다. 원하는 전기적 컨덕턴스를 제공하기 위해, 층은 통상적으로 적어도 약 1 마이크로미터의 두께를 가질 것이다. 일부 실시예에서, 층은 적어도 2 마이크로미터의 두께를 가질 것이다. 일부 실시예에서, 층은 적어도 5 마이크로미터의 두께를 가질 것이다. 그러나, 일반적으로, 층은 20 마이크로미터를 초과하지 않는 두께를 가질 것이고, 더 일반적으로는 약 10 마이크로미터를 초과하지 않는다. 선택사항으로서, 이러한 금속층이나 막은 PVDF(polyvinylidene fluoride) 또는 기타의 중합체 또는 세라믹 재료 등의 바인더를 포함할 수 있다.

[0073] 역시 또 다른 대안적 실시예에서, 전극 전류 콜렉터층(즉, 애노드 전류 콜렉터층 또는 캐소드 전류 콜렉터층)으로 구성된 이온적으로 투과가능한 도전체층은 금속-충진형 이온 도전성 중합체 복합막을 포함한다. 예를 들어, 이온적으로 투과가능한 도전체층은, 폴리에틸렌 산화물 등의 이온적으로 도전성막이나, 알루미늄, 탄소, 금, 티타늄, 로듐, 팔라듐, 크롬, NiP, 또는 루테늄 등의 도전성 원소 또는 이들의 합금을 포함하는 젤 중합체 전해질을 포함할 수 있다. 그러나, 통상적으로, 고체 이온 도전체는 비교적 낮은 이온 전도도를 가지므로, 층들은 원하는 이온 컨덕턴스를 제공하기 위해 비교적 얇아야 할 필요가 있다. 예를 들어, 이러한 층들은 약 0.5 마이크로미터 내지 약 10 마이크로미터 범위의 두께를 가질 수 있다.

[0074] 역시 또 다른 대안적 실시예에서, 전극 전류 콜렉터층(즉, 애노드 전류 콜렉터층 또는 캐소드 전류 콜렉터층)으로 구성된 이온적으로 투과가능한 도전체층은, 금속이나 금속 합금, 바람직하게는 리튬과 금속간 화합물을 형성하지 않는 것의 다공성 층을 포함한다. 이 실시예에서, 예를 들어, 이온적으로 투과가능한 도전체층은, 구리, 니켈, 및 크롬 또는 이들의 합금으로 구성된 그룹으로부터 선택된 적어도 하나의 금속을 포함할 수 있다. 예를 들어, 하나의 이러한 실시예에서, 전극 전류 콜렉터층은, 다공성 구리, 다공성 니켈, 구리 또는 니켈의 다공성 합금, 또는 이들의 조합을 포함할 수 있다. 추가의 예로서, 한 이러한 실시예에서, 전극 전류 콜렉터층은, 다공성 구리, 또는 다공성 구리 실리사이드 등의 그 합금을 포함한다. 추가의 예로서, 한 이러한 실시예에서, 전극 전류 콜렉터층은, 다공성 니켈, 또는 다공성 니켈 실리사이드 등의 그 다공성 합금을 포함한다. 이 단락에

기재된 상기 실시예들 각각에서, 전극 전류 콜렉터층의 두께(즉, 바로 인접한 전극 활성 재료층과 바로 인접한 세퍼레이터 층 사이의 최단 거리)는 일반적으로 적어도 약 0.1 마이크로미터일 것이고, 통상적으로는 약 0.1 내지 10 마이크로미터 범위 내에 있을 것이다. 이 단락에서 인용된 상기 실시예들 각각에서, 전극 전류 콜렉터층은 약 0.25 내지 약 0.85 범위의, 소정 실시예에서는 약 0.35 내지 약 0.45 범위의 공극률을 갖는 다공성일 수 있다.

[0075] 하나의 바람직한 실시예에서, 애노드 전류 콜렉터층은 치환 도금 단계를 포함하는 프로세스에 의해 형성된다. 이 실시예에서, 애노드적 활성 재료층은 바람직하게는 실리콘을 포함하고, 이 층은 실리콘 부분을 용해하기 위한 용해 성분과 금속의 이온을 포함하는 용액과 접촉한다. 실리콘은 용해되고, 용액 내의 금속은 실리콘의 용해에 의해 제공된 전자들에 의해 감소되며, 금속은 애노드적 활성 재료층 상에 피착되고, 어닐링되어 금속-실리콘 합금층을 형성한다. "용해 성분"이란 반도체 재료의 용해를 촉진하는 성분을 말한다. 용해 성분은, 불화물, 염화물, 과산화물, 수산화물, 과망간산염 등을 포함한다. 선호되는 용해 성분은 불화물 및 수산화물이다. 가장 선호되는 용해 성분은 불화물이다. 금속은 앞서 언급된 금속들 중 임의의 것일 수 있고, 니켈 및 구리가 선호된다. 유익하게도, 결과적인 층은 다공성일 것이고, 약 0.15 내지 약 0.85의 공극률을 가진다. 추가로, 결과적인 이온적으로 투과가능한 도전체층의 두께는 제어되어 약 100 나노미터 내지 3 마이크로미터가 되도록 제어될 수 있는데; 원한다면, 더 두꺼운 층이 형성될 수 있다.

[0076] 다시 도 5를 참조하면, 세퍼레이터 층(38)은 각각의 애노드 구조(24)와 각각의 캐소드 구조(26) 사이에 위치한다. 세퍼레이터 층(38)은, 예를 들어, 미세다공성 폴리에틸렌, 폴리프로필렌,  $TiO_2$ ,  $SiO_2$ ,  $Al_2O_3$  등을 포함하는 2차 전지 세퍼레이터로서 종래에 이용되는 임의의 재료를 포함할 수 있다(Chemical Reviews 2004, 104, 4419-4462에서, P. Arora 및 J. Zhang의, "Battery Separators"). 이러한 재료는, 예를 들어, 입자성 세퍼레이터 재료의 전기영동 피착, 입자성 세퍼레이터 재료의 (스핀 또는 스프레이 코팅을 포함한) 슬러리 피착, 또는 이온적으로 도전성의 입자성 세퍼레이터 재료의 스퍼터 코팅에 의해 피착될 수 있다. 세퍼레이터 층(38)은, 예를 들어, 약 5 내지 100 마이크로미터의 두께(인접하는 애노드 구조와 인접하는 캐소드 구조를 분리하는 거리)와 약 0.25 내지 약 0.75의 공극률을 가질 수 있다.

[0077] 동작시, 세퍼레이터에는 비수성 전해질 2차 전지를 위해 종래에 이용된 임의의 비수성 전해질을 포함하는 비수성 전해질이 침투할 수 있다. 통상적으로, 비수성 전해질은 유기 용매에 용해된 리튬 염을 포함한다. 예시적인 리튬 염으로는,  $LiClO_4$ ,  $LiBF_4$ ,  $LiPF_6$ ,  $LiAsF_6$ ,  $LiCl$ , 및  $LiBr$  등의 무기 리튬 염; 및  $LiB(C_6H_5)_4$ ,  $LiN(SO_2CF_3)_2$ ,  $LiN(SO_2CF_3)_3$ ,  $LiNSO_2CF_3$ ,  $LiNSO_2CF_5$ ,  $LiNSO_2C_4F_9$ ,  $LiNSO_2C_5F_{11}$ ,  $LiNSO_2C_6F_{13}$ , 및  $LiNSO_2C_7F_{15}$  등의 유기 리튬 염을 포함한다. 리튬 염을 용해하는 예시적인 유기 용매로는, 환상 에스테르(cyclic ester), 사슬 에스테르(chain ester), 환상 에테르, 및 사슬 에테르가 포함된다. 환상 에스테르의 구체적인 예로는, 프로필렌 카보네이트, 부틸렌 카보네이트,  $\gamma$ -부틸로락톤, 비닐렌 카보네이트, 2-메틸- $\gamma$ -부틸로락톤, 아세틸- $\gamma$ -부틸로락톤, 및  $\gamma$ -발레로락톤이 포함된다. 사슬 에스테르의 구체적 예로서는, 디메틸 카보네이트, 디에틸 카보네이트, 디부틸 카보네이트, 디프로필 카보네이트, 메틸 에틸 카보네이트, 메틸 부틸 카보네이트, 메틸 프로필 카보네이트, 에틸 부틸 카보네이트, 에틸 프로필 카보네이트, 부틸 프로필 카보네이트, 알킬 프로피오네이트, 디알킬 말로네이트, 및 알킬 아세테이트가 포함된다. 환상 에테르의 구체적인 예로서는, 테트라하이드로푸란, 알킬테트라하이드로푸란, 디알킬테트라하이드로푸란, 알콕시테트라하이드라푸란, 디알콕시테트라하이드라푸란, 1,3-디옥솔란, 알킬-1,3-디옥솔란, 1,4-디옥솔란이 포함된다. 사슬 에테르의 구체적인 예로서는, 1,2-디메톡시에탄, 1,2-디에톡시에탄, 디에틸 에테르, 에틸렌 글리콜 디알킬 에테르, 디에틸렌 글리콜 디알킬 에테르, 트리에틸렌 글리콜 디알킬 에테르, 및 테트라에틸렌 글리콜 디알킬 에테르가 포함된다.

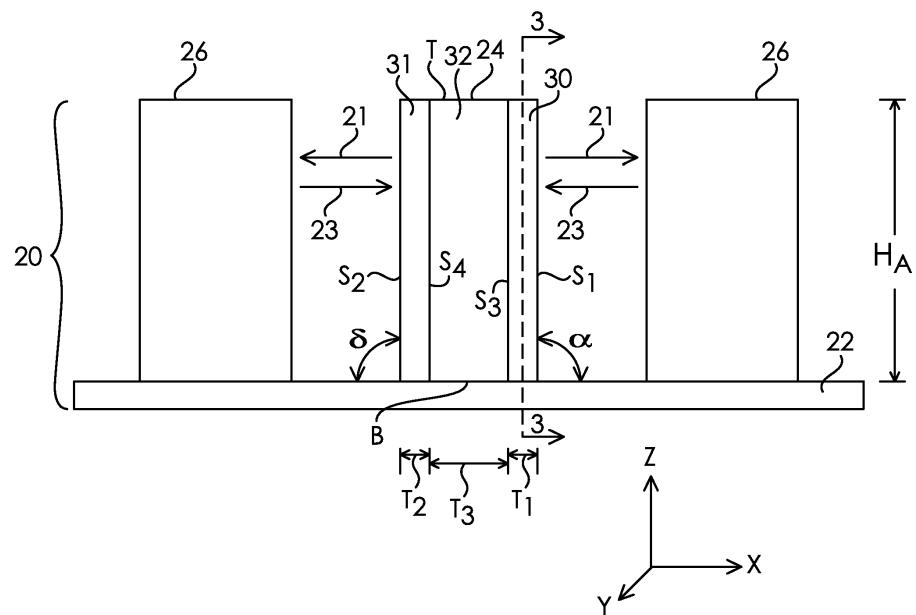

[0078] 이제 도 6을 참조하면, 애노드 구조(24)는, 베이스(22)에 근접한 하부면(B), 베이스(22)로부터 면 상부면(T), 및 상부면(T)으로부터 하부면(B)으로 연장되는 측면( $S_1$ ,  $S_2$ )을 포함한다. 측면( $S_1$ )은 베이스(22)의 표면을 각도  $\alpha$ 로 교차하고, 측면( $S_2$ )은 베이스(22)의 표면에 관해 각도  $\delta$ 로 베이스(22)의 표면을 교차한다. 바람직한 실시예에서,  $\alpha$ 와  $\delta$ 는 대략 동일하고 약  $80^\circ$  내지  $100^\circ$ 이다. 예를 들어, 한 실시예에서,  $\alpha$ 와  $\delta$ 는 대략 동일하고  $90^\circ \pm 5^\circ$ 이다. 특히 바람직한 실시예에서,  $\alpha$ 와  $\delta$ 는 실질적으로 동일하고 대략  $90^\circ$ 이다. 교차 각도  $\alpha$ 와는 독립적으로, 측면들( $S_1$  및  $S_2$ ) 각각의 표면적의 다수는 기준 평면, 이 실시예에서는, 베이스(22)의 표면에 실질적으로 수직인 것이 일반적으로 선호되는데; 달리 말하면, 측면들( $S_1$  및  $S_2$ ) 각각의 표면적의 다수는 약  $80^\circ$  내지  $100^\circ$ 의 각도, 더 바람직하게는  $90^\circ \pm 5^\circ$ 의 각도로 기준 평면(예시된 바와 같이, 베이스(22)의 표면)을 교차하는 평면(또는 평면들) 내에 놓여 있는 것이 일반적으로 선호된다. 또한, 상부면(T)은 측면들( $S_1$

및  $S_2$ )에 실질적으로 수직이고 베이스(22)의 표면에 실질적으로 평행한 것이 일반적으로 선호된다. 예를 들어, 하나의 현재 선호되는 실시예에서, 베이스(22)는 실질적으로 평면형 표면을 갖고 애노드 구조(24)는 베이스(22)의 평면형 표면에 실질적으로 평행한 상부면(T)을 가지며 측면들( $S_1$  및  $S_2$ )은 베이스(22)의 평면형 표면에 실질적으로 수직이다.

[0079] 이제 도 7을 참조하면, 다공성층(31)은 공극(60)과 공극축(62)을 갖는 애노드적 활성 재료를 포함한다. 선호되는 실시예에서, 애노드적 활성 재료는 다공성 실리콘 또는 니켈 실리사이드 등의 실리콘의 합금을 포함한다. 공극(60)의 크기, 형상 및 대칭성은 다양할 수 있지만, 공극축(62)은 (i) 측면( $S_1$ )에 근접한 다공성층(31)의 영역에서 측면( $S_1$ )에 주로 수직이고, (ii) 측면( $S_2$ )에 근접한 다공성층(31)의 영역에서 측면( $S_2$ )에 주로 수직이며, (iii) 상부면(T)에 근접한 다공성층(31)의 영역에서 상부면(T)에 주로 수직일 것이다(도 6 참조). 따라서, 측면( $S_1$  및  $S_2$ )이 베이스(22)의 표면에 실질적으로 수직일 때, 공극축(62)은 (i) 측면( $S_1$  및  $S_2$ )에 근접한 다공성층(31)의 영역에서 베이스(22)의 표면에 주로 평행하고, (iii) 상부 표면(T)에 근접한 다공성 층(31)의 영역에서 베이스(22)의 표면에 주로 수직이다(도 6 참조). 추가로, 한 실시예에서, 상부(T) 부근의 다공성층(31)의 영역에서의 공극 크기, 벽 크기, 공극 깊이, 및 공극 형태는, 표면( $S_1$  및  $S_2$ ) 부근의 다공성층(31)의 영역에서의 벽 크기, 공극 깊이, 및 공극 형태와는 상이할 수 있다.

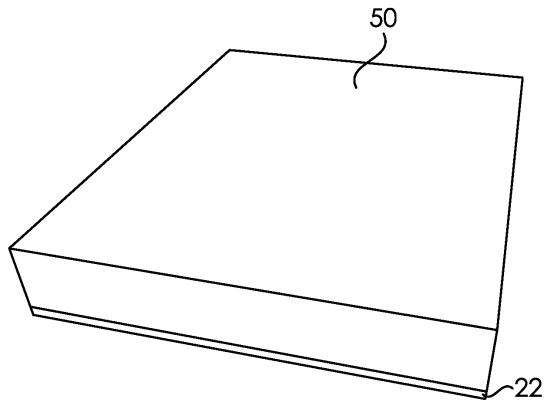

[0080] 도 8 및 도 9는 본 발명의 애노드 백본 및 캐소드 지지물을 제작하기 위한 프로세스의 한 실시예의 개략도를 도시한다. 이제 도 8을 참조하면, 실리콘 웨이퍼(50)는 종래의 수단에 의해 베이스(22)에 부착된다. 베이스는 기판과 동일한 크기를 가지거나, 기판보다 더 크거나 더 작은 크기를 가질 수도 있다. 예를 들어, 웨이퍼(50) 및 베이스(22)는 함께 애노드적 접합되거나, 접착제를 이용하여 접합되거나, 제 위치에서(*in situ*) 중합체층이 형성될 수도 있다. 앞서 언급된 바와 같이, 베이스(50)는, 유리, 세라믹, 중합체 또는 후속 처리 단계들에서 충분한 강성을 제공하는 기타의 재료의 층을 포함할 수 있다. 대안으로서, 실리콘-온-인슐레이터 웨이퍼가 시재료로서 이용될 수도 있다.

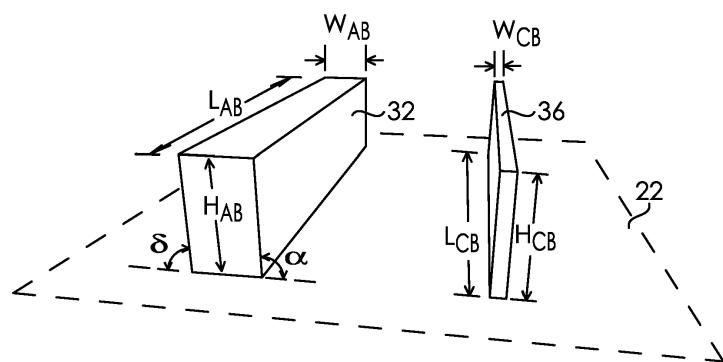

[0081] 이제 도 9를 참조하면, 포토레지스트가 웨이퍼(50) 상에 패터닝되어 원하는 백본 구조를 제공하고 화학적으로 에칭되어 애노드 백본 및 캐소드 지지물을 제공한다. 결과적인 애노드 백본(32)은 길이  $L_{AB}$ , 높이  $H_{AB}$ , 및 폭  $W_{AB}$ 를 가지며, 여기서, 높이  $H_{AB}$ 는 베이스(22)의 표면에 수직인 방향에서 측정되고, 길이  $L_{AB}$  및 폭  $W_{AB}$ 는 베이스(22)의 표면에 평행한 방향으로 측정되는데; 통상적으로,  $W_{AB}$ 는 적어도 5 마이크로미터일 것이고,  $H_{AB}$ 는 적어도 50 마이크로미터일 것이며,  $L_{AB}$ 는 적어도 1000 마이크로미터일 것이다. 결과적인 캐소드 지지물(36)은 길이  $L_{CB}$ , 높이  $H_{CB}$ , 및 폭  $W_{CB}$ 를 가지며, 여기서, 높이  $H_{CB}$ 는 베이스(22)의 표면과 길이  $L_{CB}$ 와 폭  $W_{CB}$ 에 수직인 방향에서 측정된다.

[0082] 예시된 실시예에서 애노드 백본과 캐소드 지지물이 형성된 후에, 캐소드 지지물은 마스킹되고 애노드 백본(32)은 앞서 설명된 바와 같이 애노드 백본(32) 상에 적어도 0.1의 공극 체적률을 갖는 미세구조화된 실리콘의 층을 형성하도록 처리된다. 그 다음, 캐소드는 언마스킹되고 애노드 전류 콜렉터가 애노드적 활성 재료층 상에 형성되고 캐소드 전류 콜렉터가 캐소드 지지물 상에 형성된다. 캐소드 재료가 캐소드 전류 콜렉터 상에 선택적으로 피착된 후에, 세파레이터는 캐소드 재료와 애노드 전류 콜렉터 사이에 피착될 수 있고, 각각의 전류 콜렉터는 배터리 텁에 접속되고, 전체 어셈블리는 종래의 배터리 파우치(pouch) 내에 삽입되고, 리튬 염, 및 유기 탄산염(프로필렌 탄산염 + 에틸렌 탄산염)의 혼합물 포함하는 종래의 리튬 배터리 전해질로 채워지고, 전기적 접속을 형성하기 위하여 파우치 바깥으로 연장되는 와이어를 갖는 진공 씰러(sealer)를 이용하여 씰링(seal)된다. 하나의 대안적 실시예에서, 전술된 바와 같이 조립된 하나 이상의 애노드 및 하나 이상의 캐소드를 각각이 포함하는 2개 이상의 다이가 스택 내에 위치하고 전체 어셈블리가 배터리를 형성하기 위해 종래의 배터리 파우치 등에 삽입되기 이전에 배터리 텁에 전기적으로 접속된다.

[0083] 이제 도 10을 참조하면, 본 발명의 3차원 배터리(10)의 한 실시예는, 배터리 케이스(battery enclosure; 12), 다이 스택(14), 및 다이 스택(14)을 외부 에너지 공급원이나 소비자(미도시)에 전기적으로 접속하기 위한 텁(16, 18)을 포함한다. 이동 전화 및 컴퓨터 등의 휴대형 전자장치용의 리튬 이온 배터리의 경우, 예를 들어, 배터리 케이스(12)는 파우치 또는 기타의 종래의 배터리 케이스일 수 있다. 다이 스택(14)은 수 개의 다이를 포함하고, 각각의 다이는 일련의 맞물린 애노드들 및 캐소드들을 갖는 배터리 셀을 포함하며, 애노드들은 텁(16)에 전기적으로 접속되고, 캐소드들은 텁(18)에 전기적으로 접속된다. 수직 스택 내의 다이의 개수는 중요

하지 않고, 예를 들어, 1 내지 50의 범위일 수 있으며, 스택 내의 2 내지 20개 다이가 통상적이다.

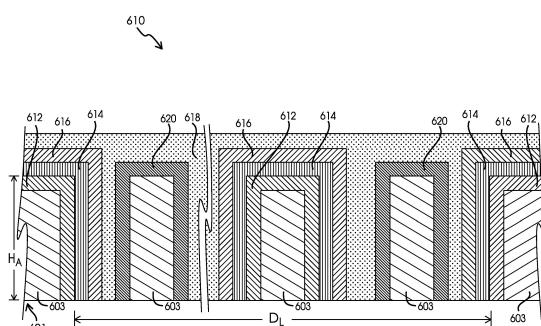

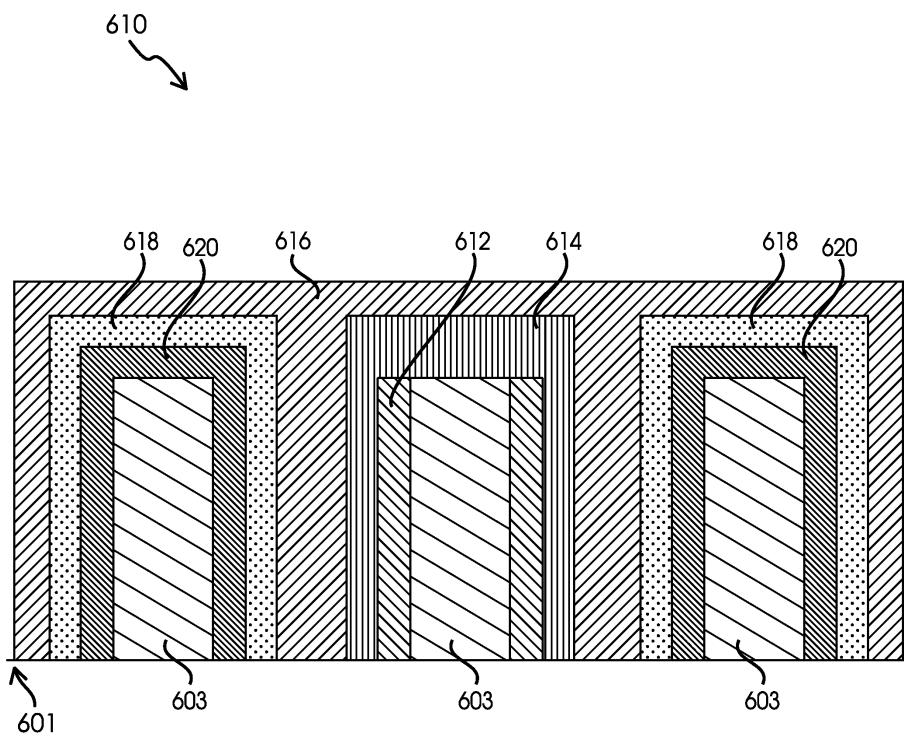

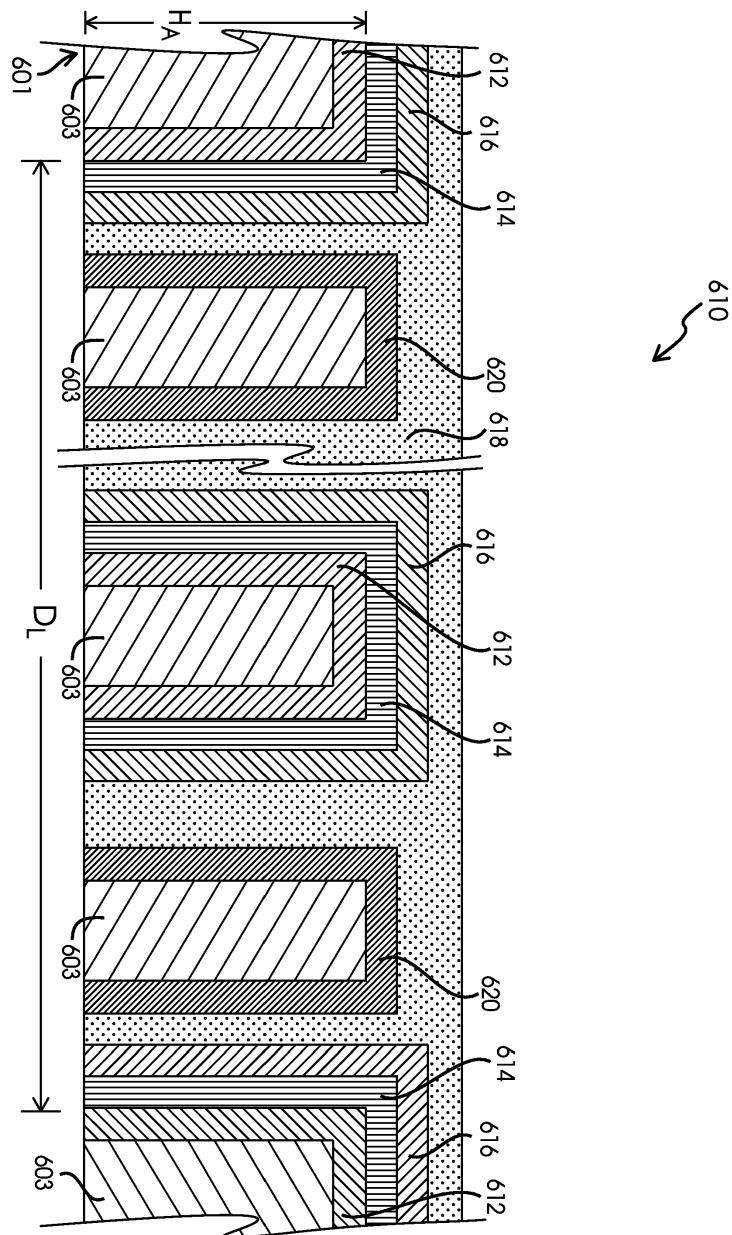

[0084] 이제 도 11을 참조하면, 한 실시예에서, 전기화학적 스택(610)은 기준 평면(601)과 기준 평면(601)으로부터 대체로 수직으로 돌출된 백본(603)을 포함한다. 전기화학적 스택(610)의 캐소드 요소들은 캐소드 전류 콜렉터층(620) 및 캐소드 활성 재료층(618)을 포함한다. 전기화학적 스택(610)의 애노드 요소들은, 애노드적 활성 재료층(612)과 애노드적 전류 콜렉터층으로서도 역할하는 이온적으로 투과가능한 도전체층(614)을 포함한다. 바람직하게는, 이온적으로 투과가능한 도전체층(614)은 백본(603)의 상부, 즉, 기준 평면(601)으로부터 먼 백본의 표면에서, 백본(603)의 측면들(상부와 기준 평면(601) 사이의 표면들) 상의 이온적으로 투과가능한 층의 두께보다 큰 두께를 갖는데; 예를 들어, 한 실시예에서, 백본의 상부에서의 이온적으로 투과가능한 도전체의 두께는 측면 상의 이온적으로 투과가능한 도전체의 두께의 110% 내지 2,000%이다. 추가의 예로서, 한 실시예에서, 백본의 상부에서의 두께는 측면 상의 이온적으로 투과가능한 도전체의 두께의 200% 내지 1,000%이다. 한 실시예에서, 백본의 상부에서의 이온적으로 투과가능한 도전체의 투과율은 측면 상의 이온적으로 투과가능한 도전체보다 캐리어 이온(예를 들어, 리튬 이온)에 대해 덜 투과적이고, 심지어 캐리어 이온에 대해 비투과성일 수도 있다. 세퍼레이터 층(616)은 이온적으로 투과가능한 도전체층(614)과 캐소드적 활성 재료층(618) 사이에 있다. 캐소드 전류 콜렉터층(620)은 캐소드 컨택트(미도시)에 전기적으로 접속되고 이온적으로 투과가능한 도전체층(614)은 애노드 컨택트(미도시)에 전기적으로 접속된다. 예시의 용이성을 위해, 단 하나의 애노드 백본과 단 2개의 캐소드 백본만이 도 11에 도시되지만; 실제로는, 전기화학적 스택은 통상적으로 교대하는 일련의 애노드와 캐소드 백본을 포함할 것이고, 스택당 개수는 응용에 따라 다르다.

[0085] 이제 도 12를 참조하면, 한 실시예에서, 전기화학적 스택(610)은 기준 평면(601)과 기준 평면(601)으로부터 대체로 수직으로 돌출된 백본(603)을 포함한다. 전기화학적 스택(610)의 캐소드 요소들은 캐소드 전류 콜렉터층(620) 및 캐소드 활성 재료층(618)을 포함한다. 전기화학적 스택(610)의 애노드적 요소들 각각은, (기준 평면(601)으로부터 이에 직교하는 방향으로 측정된) 높이  $H_A$ 를 갖는 애노드적 활성 재료층(612)과 애노드적 전류 콜렉터층으로서도 역할하는 이온적으로 투과가능한 도전체층(614)을 포함한다. 세퍼레이터 층(616)은 이온적으로 투과가능한 도전체층(614)과 캐소드적 활성 재료층(618) 사이에 있다. 이 실시예에서, 애노드적 활성 재료층(612)은 백본(603)의 상부와 측면 상에 있고 캐소드적 활성 재료(618)는 백본(603)의 상부와 측면에 근접해 있다. 그 결과, 전기화학적 스택(610)을 포함하는 에너지 저장 장치의 충전 및 방전 동안에, 캐리어 이온은 기준 평면(601)에 관하여 2개 방향으로 동시에 이동하는데; 캐리어 이온은 기준 평면(601)에 대체로 평행한 방향으로 이동하고(백본(603)의 측면 상의 애노드적 활성 재료(612)에 들어가거나 이를 떠나고), 및 기준 평면(601)에 대체로 직교하는 방향으로 이동한다(백본(603)의 상부면에서 애노드적 활성 재료(612)에 들어가거나 이를 떠난다). 캐소드 전류 콜렉터층(620)은 캐소드 컨택트(미도시)에 전기적으로 접속되고 이온적으로 투과가능한 도전체층(614)은 애노드 컨택트(미도시)에 전기적으로 접속된다. 예시의 용이성을 위해, 단 3개의 애노드 백본과 단 2개의 캐소드 백본이 도 12에 도시되어 있고, 이 도면은 부분적인 것으로서, 절단된 부분은, 도면에 도시된 절단선 좌측의 애노드적 요소와 캐소드적 요소는 도면에 도시된 절단선 우측의 2개의 애노드적 및 하나의 캐소드적 요소에 바로 인접하지 않는다는 것을 나타내지만; 실제로는, 전기화학적 스택은 통상적으로 교대하는 일련의 애노드 및 캐소드 백본을 포함하고, 스택당 개수는 앞서 설명된 바와 같이 응용마다 다르다. 예시된 바와 같이, 전기화학적 스택(610)은, 전기화학적 스택(610)으로 구성된 애노드적 활성 재료층들의 집합체의 부재들에 대한 최대  $H_A$ 를 초과하는 직선 거리  $D_L$ 만큼 서로로부터 분리된 적어도 한 쌍의 애노드적 활성 재료층(612)을 포함한다(달리 말하면, 집합체 내의 애노드적 활성 재료층들 모두 중에서 최대 높이를 갖는 애노드적 활성 재료층의 높이  $H_A$ 를 초과하는 직선 거리  $D_L$ 만큼 분리된 전기화학적 스택(610)으로 구성된 애노드적 활성 재료층들의 집합체 내의 적어도 한 쌍의 애노드적 활성 재료층이 존재한다). 따라서, 예를 들어, 직선 거리  $D_L$ 만큼 서로로부터 분리된 애노드적 활성 재료층(612)의 쌍의 2개의 예시된 부재들은 전기화학적 스택(610)으로 구성된 집합체의 하나 이상의 개재하는 캐소드적 활성 재료층(618) 및 애노드적 활성 재료층(612)에 의해 서로로부터 분리될 수 있다(예를 들어, 도 4a, 4b, 4c, 4d, 및 4e와 그 연관된 설명을 참조).

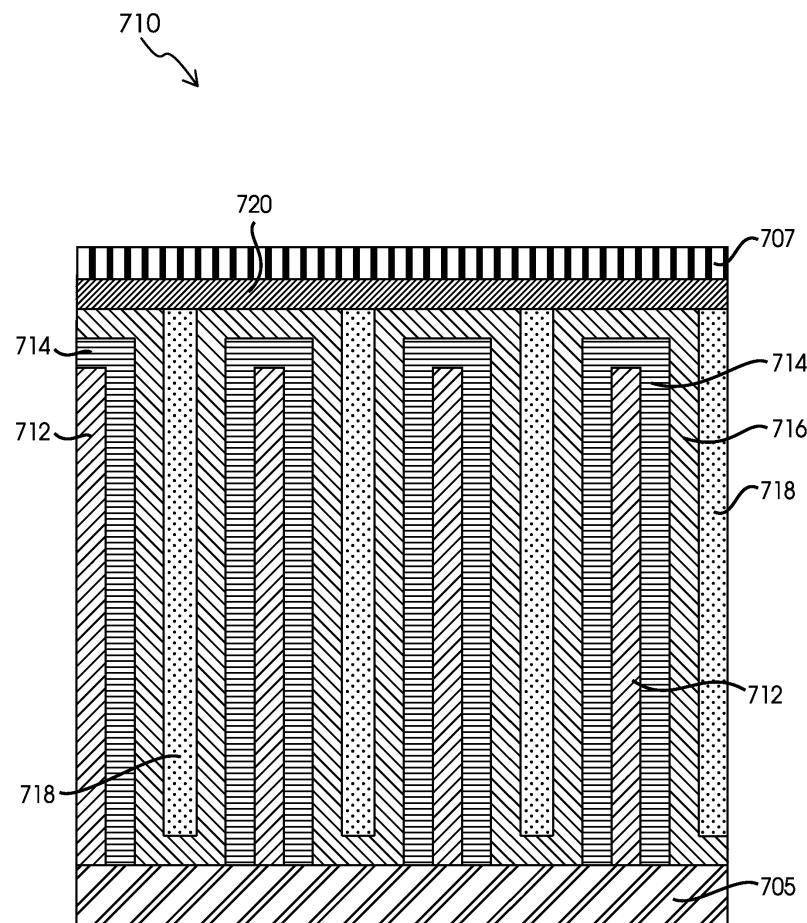

[0086] 이제 도 13을 참조하면, 한 실시예에서, 전기화학적 스택(710)은 맞물린 애노드적 활성 재료층(712)과 캐소드적 활성 재료층(718)을 포함한다. 전기화학적 스택(710)의 캐소드적 요소는 캐소드 전류 콜렉터층(720)을 더 포함하고, 전기화학적 스택의 애노드적 요소는 애노드 전류 콜렉터로서 기능하는 이온적으로 투과가능한 도전체층(714)을 포함한다. 세퍼레이터(716)는 이온적으로 투과가능한 도전체층(714)과 캐소드적 활성 재료층(718) 사이에 있다. 지지층(705, 707)은 맞물린 애노드적 활성 재료층(712)에 대한 기계적 지지를 제공한다. 도 12에는 도시되어 있지 않지만, 한 실시예에서, 애노드적 활성 재료층(712)과 캐소드적 활성 재료층(718)은, 도 2와

연계하여 예시되고 설명된 바와 같이, 백본에 의해 지지될 수도 있다.

[0087] 이하의 비-제한적 예들은 본 발명을 더 설명하기 위해 제공된다.

[0088] 예들

[0089] 예 1

[0090]  $100\mu\text{m}/1\mu\text{m}/675\mu\text{m}$ (장치층/절연층/백킹층)의 층 두께를 갖는 실리콘 온 인슐레이터(SOI) 웨이퍼가 샘플로서 이용되었다.  $2000\text{ \AA}$  실리콘 이산화물의 하드 마스크층이 장치 실리콘층의 상부에 스퍼터 피착되었다. 그 다음, 이 웨이퍼는  $5\mu\text{m}$ 의 레지스트로 스픈 코팅되었고 마스크로 패터닝되어,  $100\mu\text{m}$ 의 벌집 벽 두께와  $200\mu\text{m}$ 의 캡 두께를 갖는 벌집 형상의 구조를 얻었다. 그 다음, 포토레지스트가 포토마스크로서 이용되어 이온 밀링(ion milling)에 의해 실리콘 이산화물을 제거하였다.

[0091] 실리콘 이산화물과 포토레지스트의 조합이, 불화물 플라즈마에서의 깊은 반응성 이온 에칭(DRIE; Deep Reactive Ion Etching)을 이용한 실리콘 제거를 위한 마스크로서 이용되었다. DRIE는, 산화물층에 계속 남아 있는, 벌집 구조 캡들 내의 장치층을 구성하는 실리콘이 완전히 제거될 때까지 수행되었다. 이용된 오버에칭 시간은 트렌치 바닥(floor)에서 실리콘들의 섬(island)을 제거하기 위하여 총 DRIE 시간의 10%였다. 임의의 상부 포토레지스트가 아세톤 스트립핑에 의해 제거되었다.

[0092] 회석된 (5:1) 베퍼링된 산화물 에칭(BOE):수용액에서 1분 동안 샘플을 담금으로써 상부 마스킹 산화물층이 제거되었다. 용해 시간은, 트렌치의 하부의 절연 산화물층이 완전히 에칭 제거되지 않도록 조정되었다.

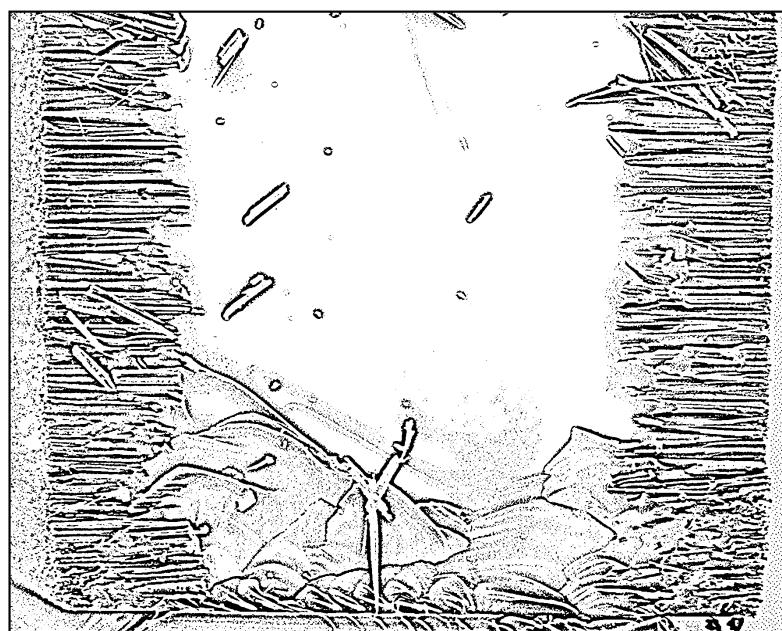

[0093] 그 다음, 실리콘 샘플은 증발 챔버 내에 삽입되었고,  $100\text{ \AA}$ 의 Au가 샘플 표면 상에 피착되었다. 이 프로세스의 결과, 벌집구조의 상부, 그 측벽 뿐만 아니라 하부 산화물층에 Au가 있다. 이 때 접착성 테이프 마스크에 의해 실리콘 백킹층이 보호되었다. 이 샘플은 후속해서 다공성 실리콘 층을 형성하기 위해  $30^\circ\text{C}$ 에서 플루오르화 수소산(4%)과 과산화수소(30%)의 체적으로 1:1 용액에 침지되었다. 다공성 실리콘 깊이는 에칭 시간을 변동시킴으로써 조정되었다. 다공성 실리콘의 대략적 형성 속도는  $750 - 1000\text{ nm/분}$ 이었다. 타겟 공극 깊이  $30\mu\text{m}$ 에 도달할 때, 부분들이 제거되었고 건조되었다. 결과적인 다공성 실리콘층은 약 0.3의 공극 체적률을 가졌다.

[0094] 그 다음, 샘플은 건조되었고, 단면 사진촬영되었다. 도 14에 나타낸 바와 같이, 건조되고 단면화된 샘플의 공극들은 주로 베이스 산화물층에 평행한 방향으로 배향되어 있다.

[0095] 예 2

[0096]  $100\mu\text{m}/1\mu\text{m}/675\mu\text{m}$ (장치층/절연층/백킹층)의 층 두께를 갖는 실리콘 온 인슐레이터(SOI) 웨이퍼가 샘플로서 이용되었다.  $1000\text{ \AA}$ 의 Pd가 장치층의 상부에 스퍼터 피착되었고  $2000\text{ \AA}$ 의 실리콘 이산화물의 하드 마스크층이 후속되었다. 그 다음, 이 웨이퍼는  $5\mu\text{m}$ 의 레지스트로 스픈 코팅되었고 마스크로 패터닝되어, 도 3에 도시된 바와 같이 서로로부터 격리된 2개의 맞물린 빗(comb)을 갖는 빗 형상의 구조를 얻었다. 2개의 맞물린 빗은 또한, 격리될 수 있고 처리를 위한 및 최종 배터리를 위한 컨택트 패드로서 역할할 수 있는 랜딩 패드를 각 측 상에 가진다. 그 다음, 포토레지스트가 포토마스크로서 이용되어 이온 밀링에 의해 실리콘 이산화물 및 팔라듐을 제거하였다.

[0097] 실리콘 이산화물, 포토레지스트, 및 Pd의 조합이, 불화물 플라즈마에서의 깊은 반응성 이온 에칭(DRIE)을 이용한 실리콘 제거를 위한 마스크로서 이용되었다. DRIE는, 산화물층에 계속 남아 있는, 마스크 캡들 내의 장치층을 구성하는 실리콘이 완전히 제거될 때까지 수행되었다. 이용된 오버에칭 시간은 트렌치 바닥에서 실리콘들의 섬을 제거하기 위하여 총 DRIE 시간의 10%였다. 임의의 상부 포토레지스트가 아세톤 스트립핑에 의해 제거되었다. 이 시점에서, 2개의 빗들이 DRIE에 의해 전기적으로 격리되었다.

[0098] 회석된 (5:1) 베퍼링된 산화물 에칭(BOE) 용액에서 1분 동안 샘플을 담금으로써 상부 마스킹 산화물층이 제거되었다. 용해 시간은, 트렌치의 하부의 절연 산화물층이 완전히 에칭 제거되지 않도록 조정되었다.

[0099] 빗 모양 구조들의 격리된 쌍 중 하나는 팔라듐 도전체를 통해 전기적으로 접속되었고 전기영동 레지스트 조(electrophoretic resist bath)에 침지되었다. 시판중인 전기영동 레지스트가 이용되었고(Shipley EAGLE), 빗(comb)은  $50\text{ V}$ 에서  $120\text{초}$  동안에 전기영동적으로 피착되어 레지스트 코팅을 형성하였다. 다이가  $120^\circ\text{C}$ 에서  $30\text{ 분}$ 간 소성(bake)되어 레지스트를 경화시켰다. 이 레지스트는 후속 금속 피착 단계 동안에 보호층으로서 역할한다.

- [0100] 그 다음, 실리콘 샘플은 중발 챔버 내에 삽입되었고, 100 Å의 Au가 샘플 표면 상에 피착되었다. 이 Au 피착 프로세스의 결과, 빗의 상부, 그 측벽, 및 하부 산화물층 상에 Au가 있다. 그러나, 포토레지스트가 빗들 중 하나 상에 존재하는 것은 Au가 2개의 빗구조들 중 단 하나 상의 실리콘과 접촉하게 한다. 이 때 접착성 테이프 마스크에 의해 실리콘 백킹층이 역시 보호되었다. 이 샘플은 후속해서 다공성 실리콘 층을 형성하기 위해 30 °C에서 플루오르화 수소산(49 %)과 과산화수소(30 %)의 체적으로 1:1 용액에 침지되었다. 다공성 실리콘 깊이는 에칭 시간을 변동시킴으로써 조정되었다. 다공성 실리콘의 대략적 형성 속도는 750 - 1000 nm/분이었다. 타겟 공극 깊이 30  $\mu\text{m}$ 에 도달할 때, 부분들이 제거되었고 견조되었다. 결과적인 다공성 실리콘층은 약 0.3의 공극 체적률을 가졌다.

- [0101] 전기영동 레지스트가 패터닝되어 있지 않은 빗-세트에만 다공성 실리콘이 형성되었다. 그러면 다공성 실리콘 세트는 리튬 이온 배터리 내의 애노드로서 이용될 수 있다. 전기영동 레지스트는 후속해서 아세톤에서 15분간 스트립핑되었다.

- [0102] 예 3

- [0103] 100 $\mu\text{m}$ /1 $\mu\text{m}$ /675 $\mu\text{m}$ (장치층/절연층/백킹층)의 층 두께를 갖는 실리콘 온 인슐레이터(SOI) 웨이퍼가 샘플로서 이용되었다. 1000 Å의 Pd가 장치층의 상부에 스퍼터 피착되었고 2000 Å의 실리콘 이산화물의 하드 마스크층이 후속 되었다. 그 다음, 이 웨이퍼는 5 $\mu\text{m}$ 의 레지스트로 스픈 코팅되었고 마스크로 패터닝되어, 도 3에 도시된 바와 같이 서로로부터 격리된 2개의 맞물린 빗(comb)을 갖는 빗 형상의 구조를 얻었다. 2개의 맞물린 빗들은 또한, 격리될 수 있고 처리를 위한 및 최종 배터리를 위한 컨택트 패드로서 역할할 수 있는 랜딩 패드를 각 측 상에 가진다. 그 다음, 포토레지스트가 포토마스크로서 이용되어 이온 밀링에 의해 실리콘 이산화물 및 팔라듐을 제거하였다.

- [0104] 실리콘 이산화물, 포토레지스트, 및 Pd의 조합이, 불화물 플라즈마에서의 깊은 반응성 이온 에칭(DRIE)을 이용한 실리콘 제거를 위한 마스크로서 이용되었다. DRIE는, 산화물층에 계속 남아 있는, 마스크 캡들 내의 장치층을 구성하는 실리콘이 완전히 제거될 때까지 수행되었다. 이용된 오버에칭 시간은 트렌치 바닥에서 실리콘들의 섬(island)을 제거하기 위하여 총 DRIE 시간의 10%였다. 임의의 상부 포토레지스트가 아세톤 스트립핑에 의해 제거되었다. 이 시점에서, 2개의 빗들이 DRIE에 의해 전기적으로 격리되었다.

- [0105] 희석된 (5:1) 베퍼링된 산화물 에칭(BOE) 용액에서 1분 동안 샘플을 담금으로써 상부 마스킹 산화물층이 제거되었다. 용해 시간은, 트렌치의 하부의 절연 산화물층이 완전히 에칭 제거되지 않도록 조정되었다.

- [0106] 빗 모양 구조들의 격리된 쌍 중 하나는 팔라듐 도전체를 통해 전기적으로 접속되었고 전기영동 레지스트 조 (electrophoretic resist bath)에 침지되었다. 시판중인 전기영동 레지스트가 이용되었고(Shipley EAGLE), 빗 (comb)은 50 V에서 120초 동안에 전기영동적으로 피착되어 레지스트 코팅을 형성하였다. 다이가 120 °C에서 30 분간 소성되어 레지스트를 경화시켰다.

- [0107] 그 다음, 실리콘 샘플은 중발 챔버 내에 삽입되었고, 20 Å의 Au가 샘플 표면 상에 피착되었다. 이 Au 피착 프로세스의 결과, 빗, 그 측벽 뿐만 아니라 하부 산화물층 상에 Au가 있다. 그러나, 포토레지스트가 빗들 중 하나 상에 존재하는 것은 Au로 하여금 2개의 빗구조들 중 단 하나 상의 실리콘과 접촉하게 한다. 이 때 접착성 테이프 마스크에 의해 실리콘 백킹층이 보호되었다. 샘플은 후속해서 아세톤에서 15분간 침지되어 전기영동 레지스트를 전기영동 레지스트 상부의 중발된 Au와 함께 제거하였다. 이것은 Au 나노클러스터를 2개의 격리된 빗들 중 하나에 대해 격리시킨다.

- [0108] 그 다음, 실리콘 나노와이어들이 CVD 방법에 의해 빗구조들 중 하나의 상부 상에서 성장되었다. 샘플은 CVD 챔버 내에 삽입되어 550°C로 가열되었다. 실란 가스가 챔버 내에 도입되었고 반응기 압력은 10 Torr로 유지되었다. 실리콘 나노와이어는 Au가 피착되어 있는 표면 상에서 성장되었다. 피착 속도는 4  $\mu\text{m}/\text{hr}$ 이었고; 피착은 20  $\mu\text{m}$ 의 타겟 나노와이어 두께까지 이루어졌다. Au는 실리콘 웨이브셋(waveset)들 중 단 하나와 접촉하였기 때문에, 와이어들은 이 웨이브셋을 벗어나 바깥쪽으로, 하부 산화물층과 평행한 방향으로 성장을 시작했다. 결과적인 실리콘 나노와이어층은 약 0.5의 공극 체적률을 가졌다.

- [0109] 예 4

- [0110] 100 $\mu\text{m}$ /1 $\mu\text{m}$ /675 $\mu\text{m}$ (장치층/절연층/백킹층)의 층 두께를 갖는 실리콘 온 인슐레이터(SOI) 웨이퍼가 샘플로서 이용되었다. 1000 Å의 Pd가 장치층의 상부에 스퍼터 피착되었고 2000 Å의 실리콘 이산화물의 하드 마스크층이 후속 되었다. 그 다음, 이 웨이퍼는 5 $\mu\text{m}$ 의 레지스트로 스픈 코팅되었고 마스크로 패터닝되어, 도 3에 도시된 바와

같이 서로로부터 격리된 2개의 맞물린 빗(comb)을 갖는 빗 형상의 구조를 얻었다. 2개의 맞물린 빗은 또한, 격리될 수 있고 처리를 위한 및 최종 배터리를 위한 컨택트 패드로서 역할 수 있는 랜딩 패드를 각 측 상에 가진다. 그 다음, 포토레지스트가 포토마스크로서 이용되어 이온 밀링에 의해 실리콘 이산화물 및 팔라듐을 제거하였다.

[0111] 실리콘 이산화물, 포토레지스트, 및 Pd의 조합이, 불화물 플라즈마에서의 깊은 반응성 이온 에칭(DRIE; Deep Reactive Ion Etching)을 이용한 실리콘 제거를 위한 마스크로서 이용되었다. DRIE는, 산화물층에 계속 남아 있는, 마스크 캡들 내의 장치층을 구성하는 실리콘이 완전히 제거될 때까지 수행되었다. 이용된 오버에칭 시간은 트렌치 바닥의 실리콘들의 섬(island)을 제거하기 위하여 총 DRIE 시간의 10%였다. 임의의 상부 포토레지스트가 아세톤 스트립핑에 의해 제거되었다. 이 시점에서, 2개의 빗들이 DRIE에 의해 전기적으로 격리되었다.

[0112] 제2 포토레지스트가 웨이퍼의 대부분 상에 인가되었고, 제2 마스크를 이용하여 노출되어 빗 패턴들 각각 상의 소영역 개구를 노출하였다. 이것은 후속해서 이온 밀링에 의해 실리콘 이산화물을 제거하고 Pd 층을 노출하는데 이용되었다.

[0113] 애노드로서 역할하는 빗구조가 DMSO 내의 HF/H<sub>2</sub>O(2M/2.5M)을 포함하는 용액 내에 침지되었고, 애노드 전위가 Pt 카운터 전극에 관해 인가되었다. 애노드적으로 산화되어 다공성 실리콘을 형성할 실리콘 빗은 개방된 비아 내의 Pd를 통해 접속되었다. 전류 밀도는 3 mA/cm<sup>2</sup>에 유지되었고, 양극산화 프로세스가 60분간 실행되어 ~20 μm의 기공 깊이를 산출하였다. 결과적인 다공성 실리콘층은 약 0.4의 공극 체적률을 가졌다. 이 프로세스는 다공성 실리콘 형성을 2개의 빗 구조들 중 하나만으로 제약했다.

[0114] 예 5

[0115] 100μm/1μm/675μm(장치층/절연층/백킹층)의 층 두께를 갖는 실리콘 온 인슐레이터(SOI) 웨이퍼가 샘플로서 이용되었다. 1000 Å의 Pd가 장치층의 상부에 스퍼터 피착되었고 2000 Å의 실리콘 이산화물의 하드 마스크층이 후속되었다. 그 다음, 이 웨이퍼는 5μm의 레지스트로 스판 코팅되었고 마스크로 패터닝되어, 서로로부터 격리된 2개의 맞물린 빗(comb)을 갖는 빗 형상의 구조를 얻었다. 2개의 맞물린 빗들은 또한, 격리될 수 있고 처리를 위한 및 최종 배터리를 위한 컨택트 패드로서 역할할 수 있는 랜딩 패드를 각 측 상에 가진다. 그 다음, 포토레지스트가 포토마스크로서 이용되어 이온 밀링에 의해 실리콘 이산화물 및 팔라듐을 제거하였다.

[0116] 실리콘 이산화물, 포토레지스트, 및 Pd의 조합이, 불화물 플라즈마에서의 깊은 반응성 이온 에칭(DRIE)을 이용한 실리콘 제거를 위한 마스크로서 이용되었다. DRIE는, 산화물층에 계속 남아 있는, 마스크 캡들 내의 장치층을 구성하는 실리콘이 완전히 제거될 때까지 수행되었다. 이용된 오버에칭 시간은 트렌치 바닥의 실리콘들의 섬(island)을 제거하기 위하여 총 DRIE 시간의 10%였다. 임의의 상부 포토레지스트가 아세톤 스트립핑에 의해 제거되었다. 이 시점에서, 2개의 빗들이 DRIE에 의해 전기적으로 격리되었다.

[0117] 이 시점에서, 샘플은 열적으로 산화되어 모든 노출된 실리콘 표면의 상부에 0.25μm의 SiO<sub>2</sub> 층을 형성하였다. 이 SiO<sup>2</sup>는 실리콘의 전기화학적 에칭을 위한 마스크로서 역할하도록 피착되었다. 후속해서, 50 Å의 Au층이 스퍼터 피착 기술을 이용하여 산화물층의 상부에 피착되었다. 이 Au층의 두께는 완전한 막이 아니라 섬(island)의 형태로 Au를 얻기 위하여 최적화되었다. 그 다음, 섬 형태의 이 Au는 그 아래의 열적 산화물층을 에칭하기 위한 마스킹층으로서 이용되었다.

[0118] 제2 포토레지스트가 웨이퍼의 대부분 상에 인가되었고, 제2 마스크를 이용하여 노출되어 빗 패턴들 각각 상의 랜딩 패드 영역을 노출하였다. 이것은 후속해서 습식 화학적 에칭에 의해 Au와 SiO<sub>2</sub>층을 제거하는데 이용되었다. Au는 상용 KI/I<sub>2</sub> 용액을 이용하여 제거되었고, SiO<sub>2</sub> 층은 베퍼링된 산화물 에칭 용액을 이용하여 제거되어 후속하는 전기적 컨택트를 위해 Pd 상부층을 노출하였다.

[0119] 그 다음, 샘플이 아세톤에 침지되어 포토레지스트를 벗겨 내었고, 후속해서 1:25 BOE: 수용액에 침지되었다. BOE 용액은 Au 입자 아래의 빗의 측벽 내의 SiO<sub>2</sub>층을 공격하여 Au의 패턴을 산화물 내로 전사한다. 90초 후에 에칭이 정지되었고, 이것은 산화물을 에칭하고 Si를 노출하기에 충분하면서, Au 아래의 산화물층을 언더컷팅하지 않는다. 헹굼과 건조 후에, 샘플이 전기화학적 용해를 위해 준비되었다.

[0120] 이전 단계에서 노출된 컨택트 패드가 이용되어 실리콘 애노드 에칭 프로세스 동안에 샘플에 대한 전기 접속을 형성하였다. 이것은, Pt 카운터 전극을 이용하여, 동작 전극으로서 접속되었고, 전기화학적으로 구동되어 접속된 빗 구조의 노출된 영역으로부터 실리콘을 용해하였다. 샘플은, 체적으로 1 파트(part) 에탄올, 1 파트 49%

HF, 및 10 파트 물을 포함하는 용액에 담구어졌고;  $15 \text{ mA/cm}^2$ 의 전류 밀도에서 애노드로서 구동되었다. 노출된 실리콘은 용해되어, 약 0.5의 공극 체적률을 갖고 섬유와 공극들을 포함하는 Au 나노클러스터 분포를 복제한 미세구조화된 실리콘층을 남겼다.

[0121] 예 6

[0122]  $100\mu\text{m}/1\mu\text{m}/675\mu\text{m}$ (장치층/절연층/백킹층)의 층 두께를 갖는 실리콘 온 인슐레이터(SOI) 웨이퍼가 샘플로서 이용되었다.  $1000\text{\AA}$ 의 Pd가 장치층의 상부에 스퍼터 피착되었고  $2000\text{\AA}$ 의 실리콘 이산화물의 하드 마스크층이 후속되었다.

[0123] 그 다음, 이 웨이퍼는  $5\mu\text{m}$ 의 레지스트로 스픈 코팅되었고 마스크로 패터닝되어, 도 3에 도시된 바와 같이 서로로부터 격리된 2개의 맞물린 빗(comb)을 갖는 빗 형상의 구조를 얻었다. 설계는, 각각의 구조가 전기적 컨택트를 형성하기에 적합한 랜딩 패드에서 터미네이트되는 2개의 독립된 빗형상 구조를 야기하는 구조를 보여준다. 그 다음, 이 패턴에서의 포토레지스트가 포토마스크로서 이용되어 이온 밀링에 의해 실리콘 이산화물 및 팔라듐을 제거하였다.

[0124] 실리콘 이산화물, 포토레지스트, 및 Pd의 조합이, 불화물 플라즈마에서의 깊은 반응성 이온 에칭(DRIE; Deep Reactive Ion Etching)을 이용한 실리콘 제거를 위한 마스크로서 이용되었다. DRIE는, 산화물층에 계속 남아 있는, 마스크 캡들 내의 장치층을 구성하는 실리콘이 완전히 제거될 때까지 수행되었다. 이용된 오버에칭 시간은 트렌치 바닥의 실리콘의 섬(island)들을 제거하기 위하여 총 DRIE 시간의 10%였다. 임의의 상부 포토레지스트가 아세톤 스트립핑에 의해 제거되었다. 이 시점에서, 2개의 빗들이 DRIE에 의해 전기적으로 격리된다.

[0125] 회석된 (5:1) 베퍼링된 산화물 에칭(BOE) 용액에서 1분 동안 샘플을 담금으로써 상부 마스킹 산화물층이 후속해서 제거되었다. 용해 시간은, 트렌치의 하부의 절연 산화물층이 완전히 에칭 제거되지 않도록 조정되었다.

[0126] 빗 모양 구조들의 격리된 쌍 중 하나는 팔라듐 도전체를 통해 전기적으로 접속되었고 전기영동 레지스트 조(electrophoretic resist bath)에 침지되었다. 시판중인 전기영동 레지스트가 이용되었고(Shipley EAGLE), 빗(comb)은  $50\text{ V}$ 에서 120초 동안에 전기영동적으로 피착되어 레지스트 코팅을 형성하였다. 다이가  $120\text{ }^\circ\text{C}$ 에서 30분간 소성(bake)되어 레지스트를 경화시켰다.

[0127] 그 다음, 실리콘 샘플은 증발 챔버 내에 삽입되었고,  $20\text{ \AA}$ 의 Au가 샘플 표면 상에 피착되었다. 이 Au 피착 프로세스의 결과, 별집구조의 상부 뿐만 아니라 그 측벽 외에도 하부 산화물층에 Au가 있다. 그러나, 포토레지스트가 빗들 중 하나 상에 존재하는 것은 Au로 하여금 2개의 빗구조들 중 단 하나 상의 실리콘과 접촉하게 한다. 이 때 접착성 테이프 마스크에 의해 실리콘 백킹층이 보호되었다. 샘플은 후속해서 아세톤에서 15분간 침지되어 전기영동 레지스트를 전기영동 레지스트의 상부 상의 증발된 Au와 함께 제거하였다. 이것은 Au 나노클러스터를 2개의 격리된 빗들 중 하나에 대해 격리시켰다.

[0128] 그 다음, 실리콘 나노와이어들이 CVD 방법에 의해 빗구조들 중 하나의 상부 상에서 성장되었다. 샘플은 CVD 챔버 내에 삽입되어  $550\text{ }^\circ\text{C}$ 로 가열되었다. 실란 가스가 챔버 내에 도입되었고 반응기 압력은  $10\text{ Torr}$ 로 유지되었다. 실리콘 나노와이어는 Au가 피착되어 있는 표면 상에서 성장되었다. 피착 속도는  $4\text{ }\mu\text{m/hr}$ 이었고; 피착은  $20\text{ }\mu\text{m}$ 의 타겟 나노와이어 두께까지 이루어졌다. 결과적인 실리콘 나노와이어층은 약 0.5의 공극 체적률을 가졌고 리튬-이온 배터리를 위한 애노드로서 역할했다.

[0129] 실리콘 나노와이어가 부착되지 않은 빗이 리튬 이온 배터리 캐소드 재료를 이용하여 전기영동적으로 피착되었다. 전기영동 피착 용액은, 캐소드 재료( $\text{LiCoO}_2$ ), 15 wt% 카본 블랙(carbon black), 및 아세톤 용액 내의 150 ppm의 요오드를 포함했다. 용액 혼합물은 입자들을 균일하게 분산시키기 위하여 하룻밤 동안 교반(stir)되었다. Pd 컨택트 패드는 캐소드 피착을 위한 전기 접속용 단자로서 이용되었다. Pt 카운터 전극이 이용되었다. 샘플은 100V의 전압에서 3분간 피착되어  $40\mu\text{m}$  두께의 캐소드 구조를 피착했다.

[0130] 그 다음, 샘플은 스픈 코터로 전송되어 그 곳에서 거대다공성 세퍼레이터가 배터리에 인가되었다. 이 경우 거대다공성 세퍼레이터는, 2 체적 퍼센트의 PVDF 바인더와 함께 아세톤 내에 분산된 미세 유리 분말( $< 2\mu\text{m}$  직경)의 조합이었다. 이 슬러리는 다이 상에 코팅되었고 과도 슬러리는 스픈 오프(spin off)되어 세퍼레이터 층을 충진 및 평탄화되었다. 건조 프로세스의 결과, 용매가 증발했고 거대다공성 세퍼레이터 층을 형성하였다.

[0131] 그 다음, 컨택트 패드가 이용되어 배터리에 대한 접속점으로서 역할하는 Au 와이어를 와이어본딩하였다. 전체의 어셈블리가 종래의 배터리 파우치 내에 삽입되었고, 리튬 염을 포함하는 종래의 리튬 배터리 전해질과, 유기 탄산염의 혼합물(프로필렌 탄산염 + 에틸렌 탄산염)로 채워졌다. 그 다음 파우치는 전기 접속을 형성하기 위하

여 파우치 바깥으로 연장되는 와이어와 진공 셀러를 이용하여 셀링되었다.

[0132] 예 7

[0133] 5개 다이가 서로의 상부에 적층되었고, 각 다이로부터의 접속 패드로부터의 라인들 각각은 각 전극을 위한 텁에 접속되었다는 점을 제외하고는, 예 6의 프로세스가 반복되었다.

[0134] 전체의 어셈블리가 종래의 배터리 파우치 내에 삽입되었고, 리튬 염을 포함하는 종래의 리튬 배터리 전해질과, 유기 탄산염의 혼합물(프로필렌 탄산염 + 에틸렌 탄산염)로 채워졌다. 그 다음 파우치는 전기 접속을 형성하기 위하여 파우치 바깥으로 연장되는 와이어와 진공 셀러를 이용하여 셀링되었다.

[0135] 상기에 비추어, 본 발명의 수 개 목적이 달성되고 기타의 유익한 결과들이 얻어진다는 것을 알 수 있을 것이다.

[0136] 본 발명 또는 그 양호한 실시예(들)의 요소를 도입할 때, 관사 "한(a)", "한(an)", "그 하나(the)", 및 "상기 (said)"는 하나 이상의 요소들이 존재한다는 것을 의미하기 위한 것이다. 용어 "포함하는(comprising)", "내포하는(including)", 및 "갖는(having)"은 내포적(inclusive)인 것으로서, 열거된 요소들 이외의 추가적인 요소가 있을 수도 있다는 것을 의미하기 위한 것이다.

[0137] 본 발명의 범위로부터 벗어나지 않고 상기 항목들, 조성들 및 방법들에서 다양한 변경이 이루어질 수 있기 때문에, 상기 설명에 포함되고 첨부된 도면에 도시된 모든 내용은 제한적 의미가 아니라 예시적인 의미로서 해석되어야 한다.

## 도면

### 도면1

종래 기술

## 도면2

### 도면3

도면4a

도면4b

도면4c

도면4d

## 도면4e

## 도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 1, 19

【변경전】

상기 기준 평면에 대체로 평행한

【변경후】

상기 기준 평면에 평행한