(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6754157号

(P6754157)

(45) 発行日 令和2年9月9日(2020.9.9)

(24) 登録日 令和2年8月25日(2020.8.25)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 27/146

D

H04N 5/355 (2011.01)

H01L 27/146

A

H04N 5/369 (2011.01)

H04N 5/355

H04N 5/369

請求項の数 8 (全 32 頁)

(21) 出願番号

特願2015-209533 (P2015-209533)

(22) 出願日

平成27年10月26日(2015.10.26)

(65) 公開番号

特開2017-84892 (P2017-84892A)

(43) 公開日

平成29年5月18日(2017.5.18)

審査請求日

平成30年8月31日(2018.8.31)

前置審査

(73) 特許権者 316005926

ソニーセミコンダクタソリューションズ株

式会社

神奈川県厚木市旭町四丁目14番1号

(74) 代理人 100121131

弁理士 西川 孝

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100168686

弁理士 三浦 勇介

(72) 発明者 柳田 剛志

東京都港区港南1丁目7番1号 ソニー株

式会社内

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の単位画素が配置されている画素アレイ部の前記単位画素が、

第1の光電変換部と、

前記第1の光電変換部の受光面よりも小さい受光面の第2の光電変換部と

を備え、

前記第2の光電変換部の光が入射する側にスリット形状の遮光膜が形成され、2×2の4画素のそれぞれの画素上の前記遮光膜は異なる4方向のスリット形状で形成されている

撮像装置。

## 【請求項 2】

前記第2の光電変換部上には、入射される光を集光するためのレンズは形成されていない

請求項1に記載の撮像装置。

## 【請求項 3】

隣接する光電変換部への光の漏れ込みを防ぐ遮光壁が、光電変換部間に備えられる

請求項1または2に記載の撮像装置。

## 【請求項 4】

前記スリット形状の前記遮光膜が配置された前記4画素は、同色である

請求項1乃至3のいずれかに記載の撮像装置。

## 【請求項 5】

10

20

裏面型のイメージセンサである

請求項 1 乃至 4 のいずれかに記載の撮像装置。

【請求項 6】

表面型のイメージセンサである

請求項 1 乃至 4 のいずれかに記載の撮像装置。

【請求項 7】

前記遮光膜は、前記第 2 の光電変換部上に形成されている配線層の下側または上側に形成されている

請求項 6 に記載の撮像装置。

【請求項 8】

10

前記遮光膜は、アモルファスシリコン膜、ポリシリコン膜、Ge 膜、GaN 膜、CdTe 膜、GaAs 膜、InP 膜、CuInSe<sub>2</sub>膜、Cu<sub>2</sub>S、CIGS 膜、非導体構造のカーボン膜、黒色レジスト膜、有機光電変換膜、または金属膜である

請求項 1 乃至 7 のいずれかに記載の撮像装置。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、撮像装置に関する。詳しくは、ダイナミックレンジを拡大できるようにした撮像装置に関する。

【背景技術】

20

【0002】

従来、様々な方式の撮像装置のダイナミックレンジ拡大技術が存在する。例えば、異なる感度で時分割に撮影し、時分割に撮影した複数の画像を合成する時分割方式が知られている。

【0003】

また、例えば、感度が異なる受光素子を設け、感度が異なる受光素子でそれぞれ撮影した複数の画像を合成することによりダイナミックレンジを拡大する空間分割方式が知られている（例えば、特許文献 1、2 参照）。

【0004】

さらに、例えば、各画素内にフォトダイオードから溢れた電荷を蓄積するメモリを設け、1 回の露光期間に蓄積できる電荷量を増やすことによりダイナミックレンジを拡大する画素内メモリ方式が知られている（例えば、特許文献 3 参照）。

30

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特許第 3071891 号公報

【特許文献 2】特開 2006-253876 号公報

【特許文献 3】特許第 4317115 号公報

【発明の概要】

【発明が解決しようとする課題】

40

【0006】

しかしながら、時分割方式や空間分割方式では、分割数を増やすことによりダイナミックレンジを拡大することができる一方、分割数が増えると、アーチファクトの発生や解像度の低下等による画質の劣化が発生する。

【0007】

また、画素内メモリ方式では、メモリの容量が限られるため、拡大できるダイナミックレンジに限界があった。

【0008】

本技術は、このような状況に鑑みてなされたものであり、画質を劣化させずに、撮像装置のダイナミックレンジを拡大できるようにするものである。

50

**【課題を解決するための手段】**

**【0009】**

本技術の一側面の撮像装置は、複数の単位画素が配置されている画素アレイ部の前記単位画素が、第1の光電変換部と、前記第1の光電変換部の受光面よりも小さい受光面の第2の光電変換部とを備え、前記第2の光電変換部の光が入射する側にスリット形状の遮光膜が形成され、2×2の4画素のそれぞれの画素上の前記遮光膜は異なる4方向のスリット形状で形成されている。

**【0010】**

前記第2の光電変換部上には、入射される光を集光するためのレンズは形成されていないようにすることができる。

10

**【0011】**

隣接する光電変換部への光の漏れ込みを防ぐ遮光壁が、光電変換部間に備えられるようになることができる。

**【0012】**

前記スリット形状の前記遮光膜が配置された前記4画素は、同色であるようにすることができます。

**【0014】**

裏面型のイメージセンサであるようにすることができます。

**【0015】**

表面型のイメージセンサであるようにすることができます。

20

**【0016】**

前記遮光膜は、前記第2の光電変換部上に形成されている配線層の下側または上側に形成されているようにすることができます。

**【0017】**

前記遮光膜は、アモルファスシリコン膜、ポリシリコン膜、Ge膜、GaN膜、CdTe膜、GaAs膜、InP膜、CuInSe<sub>2</sub>膜、Cu<sub>2</sub>S、CIGS膜、非導体構造のカーボン膜、黒色レジスト膜、有機光電変換膜、または金属膜であるようにすることができます。

**【0018】**

本技術の一側面の撮像装置においては、複数の単位画素が配置されている画素アレイ部の単位画素に、第1の光電変換部と、第1の光電変換部の受光面よりも小さい受光面の第2の光電変換部とが備えられている。また第2の光電変換部の光が入射する側にスリット形状の遮光膜が形成され、2×2の4画素のそれぞれの画素上の前記遮光膜は異なる4方向のスリット形状で形成されている。

30

**【発明の効果】**

**【0019】**

本技術の一側面によれば、画質を劣化させずに、撮像装置のダイナミックレンジを拡大できる。

**【0020】**

なお、ここに記載された効果は必ずしも限定されるものではなく、本開示中に記載されたいずれかの効果であってもよい。

40

**【図面の簡単な説明】**

**【0021】**

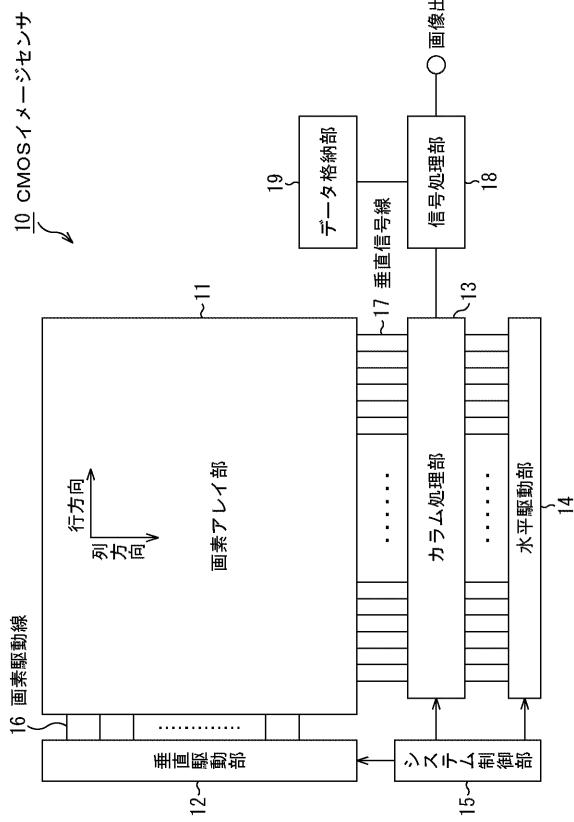

**【図1】**本技術が適用されるCMOSイメージセンサの構成の概略を示すシステム構成図である。

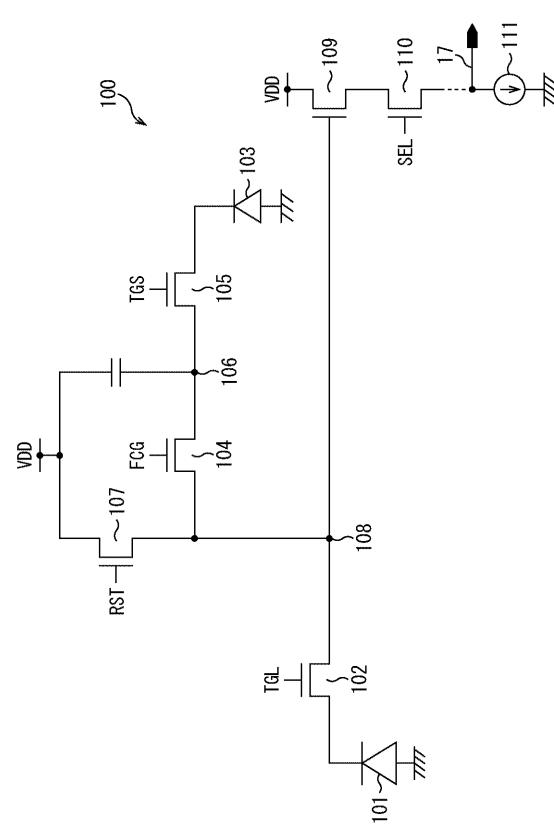

**【図2】**単位画素の構成例を示す回路図である。

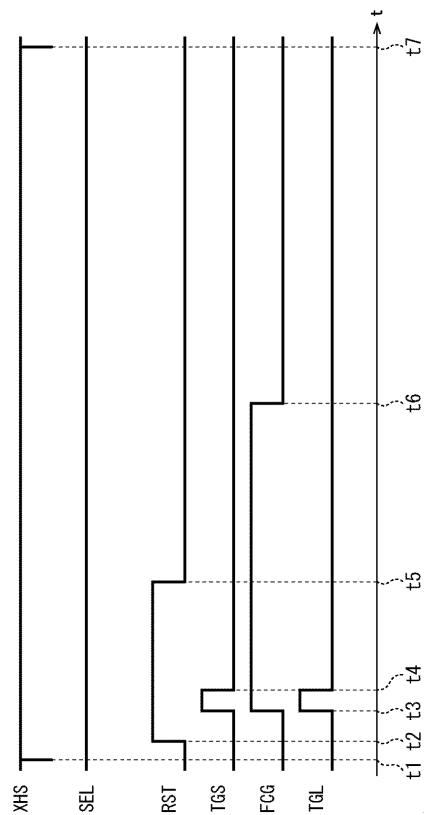

**【図3】**単位画素の露光開始時の動作を説明するためのタイミングチャートである。

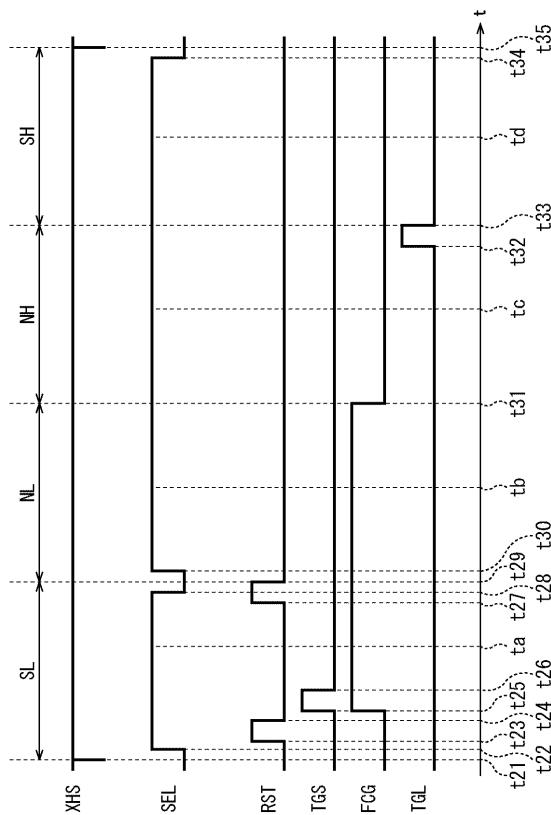

**【図4】**単位画素の読み出し時の動作を説明するためのタイミングチャートである。

**【図5】**信号処理の説明に供する入射光量 - 出力の特性図である。

**【図6】**画素の第1の構成について説明するための図である。

**【図7】**画素の第2の構成について説明するための図である。

50

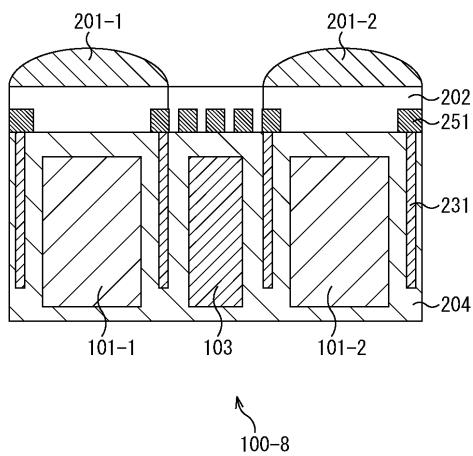

- 【図 8】画素の第 3 の構成について説明するための図である。

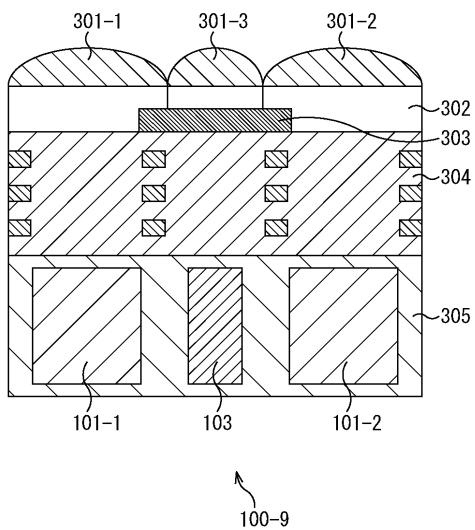

- 【図 9】画素の第 4 の構成について説明するための図である。

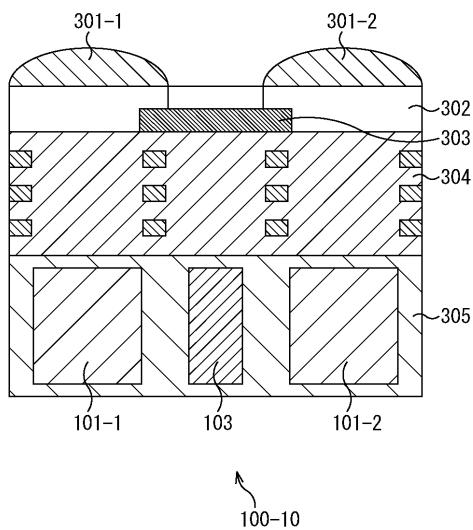

- 【図 10】画素の第 5 の構成について説明するための図である。

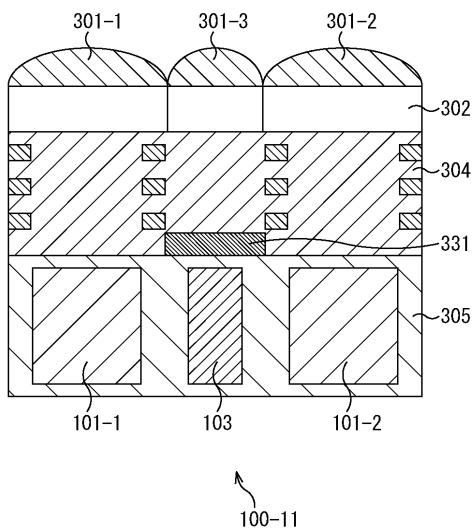

- 【図 11】画素の第 6 の構成について説明するための図である。

- 【図 12】画素の第 7 の構成について説明するための図である。

- 【図 13】画素の第 8 の構成について説明するための図である。

- 【図 14】画素の第 9 の構成について説明するための図である。

- 【図 15】画素の第 10 の構成について説明するための図である。

- 【図 16】画素の第 11 の構成について説明するための図である。

- 【図 17】画素の第 12 の構成について説明するための図である。 10

- 【図 18】画素の第 13 の構成について説明するための図である。

- 【図 19】画素の第 14 の構成について説明するための図である。

- 【図 20】画素の第 15 の構成について説明するための図である。

- 【図 21】画素の第 16 の構成について説明するための図である。

- 【図 22】異感度の画素配置について説明するための図である。

- 【図 23】色配置について説明するための図である。

- 【図 24】遮光膜の配置について説明するための図である。

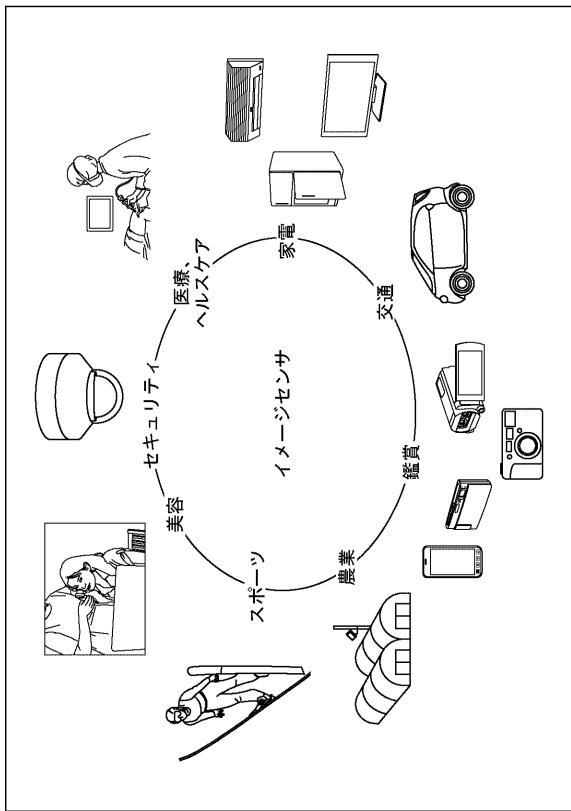

- 【図 25】撮像装置の使用例を示す図である。

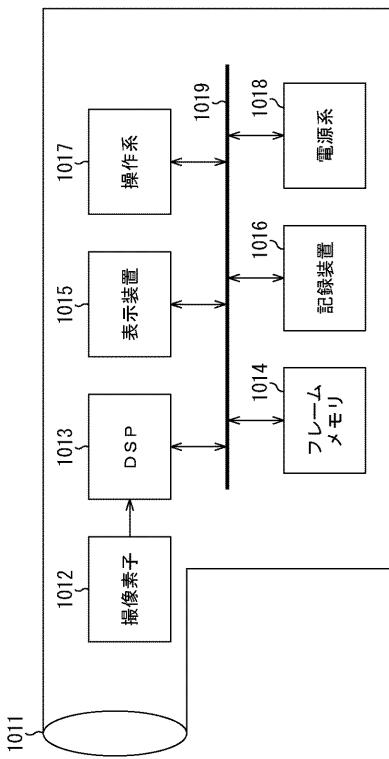

- 【図 26】撮像装置の構成を示す図である。

## 【発明を実施するための形態】 20

## 【0022】

以下に、本技術を実施するための形態（以下、実施の形態という）について説明する。

なお、説明は、以下の順序で行う。

1. 本技術が適用される撮像装置

2. 単位画素の構成（第 1 乃至第 16 の構成）

3. 第 1、第 2 光電変換部の配置について

4. 变形例

5. 撮像装置の使用例

## 【0023】

## &lt;本技術が適用される撮像装置&gt;

図 1 は、本技術が適用される撮像装置、例えば X - Y アドレス方式撮像装置の一種である C M O S イメージセンサの構成の概略を示すシステム構成図である。ここで、C M O S イメージセンサとは、C M O S プロセスを応用して、または、部分的に使用して作成されたイメージセンサである。 30

## 【0024】

本適用例に係る C M O S イメージセンサ 10 は、図示せぬ半導体基板（チップ）上に形成された画素アレイ部 11 と、当該画素アレイ部 11 と同じ半導体基板上に集積された周辺回路部とを有する構成となっている。周辺回路部は、例えば、垂直駆動部 12、カラム処理部 13、水平駆動部 14 及びシステム制御部 15 から構成されている。

## 【0025】

C M O S イメージセンサ 10 は更に、信号処理部 18 及びデータ格納部 19 を備えている。信号処理部 18 及びデータ格納部 19 については、本 C M O S イメージセンサ 10 と同じ基板上に搭載しても構わないし、本 C M O S イメージセンサ 10 とは別の基板上に配置するようにしても構わない。また、信号処理部 18 及びデータ格納部 19 の各処理については、本 C M O S イメージセンサ 10 とは別の基板に設けられる外部信号処理部、例えば、D S P (Digital Signal Processor) 回路やソフトウェアによる処理でも構わない。 40

## 【0026】

画素アレイ部 11 は、受光した光量に応じた電荷を生成しがつ蓄積する光電変換部を有する単位画素（以下、単に「画素」と記述する場合もある）が行方向及び列方向に、すなわち、行列状に 2 次元配置された構成となっている。ここで、行方向とは画素行の画素の

配列方向（すなわち、水平方向）を言い、列方向とは画素列の画素の配列方向（すなわち、垂直方向）を言う。単位画素の具体的な回路構成や画素構成の詳細については後述する。

#### 【0027】

画素アレイ部11において、行列状の画素配列に対して、画素行ごとに画素駆動線16が行方向に沿って配線され、画素列ごとに垂直信号線17が列方向に沿って配線されている。画素駆動線16は、画素から信号を読み出す際の駆動を行うための駆動信号を伝送する。図1では、画素駆動線16について1本の配線として示しているが、1本に限られるものではない。画素駆動線16の一端は、垂直駆動部12の各行に対応した出力端に接続されている。

10

#### 【0028】

垂直駆動部12は、シフトレジスタやアドレスデコーダなどによって構成され、画素アレイ部11の各画素を全画素同時あるいは行単位等で駆動する。すなわち、垂直駆動部12は、当該垂直駆動部12を制御するシステム制御部15と共に、画素アレイ部11の各画素の動作を制御する駆動部を構成している。この垂直駆動部12はその具体的な構成については図示を省略するが、一般的に、読み出し走査系と掃出し走査系の2つの走査系を有する構成となっている。

#### 【0029】

読み出し走査系は、単位画素から信号を読み出すために、画素アレイ部11の単位画素を行単位で順に選択走査する。単位画素から読み出される信号はアナログ信号である。掃出し走査系は、読み出し走査系によって読み出し走査が行われる読み出し行に対して、その読み出し走査よりも露光時間分だけ先行して掃出し走査を行う。

20

#### 【0030】

この掃出し走査系による掃出し走査により、読み出し行の単位画素の光電変換部から不要な電荷が掃き出されることによって当該光電変換部がリセットされる。そして、この掃出し走査系による不要電荷の掃き出す（リセットする）ことにより、所謂電子シャッタ動作が行われる。ここで、電子シャッタ動作とは、光電変換部の電荷を捨てて、新たに露光を開始する（電荷の蓄積を開始する）動作のことを言う。

#### 【0031】

読み出し走査系による読み出し動作によって読み出される信号は、その直前の読み出し動作または電子シャッタ動作以降に受光した光量に対応するものである。そして、直前の読み出し動作による読み出しタイミングまたは電子シャッタ動作による掃出しタイミングから、今回の読み出し動作による読み出しタイミングまでの期間が、単位画素における電荷の露光期間となる。

30

#### 【0032】

垂直駆動部12によって選択走査された画素行の各単位画素から出力される信号は、画素列ごとに垂直信号線17の各々を通してカラム処理部13に入力される。カラム処理部13は、画素アレイ部11の画素列ごとに、選択行の各画素から垂直信号線17を通して出力される信号に対して所定の信号処理を行うとともに、信号処理後の画素信号を一時的に保持する。

40

#### 【0033】

具体的には、カラム処理部13は、信号処理として少なくとも、ノイズ除去処理、例えばCDS（Correlated Double Sampling；相関二重サンプリング）処理や、DDS（Double Data Sampling）処理を行う。例えば、CDS処理により、リセットノイズや画素内の増幅トランジスタの閾値ばらつき等の画素固有の固定パターンノイズが除去される。カラム処理部13にノイズ除去処理以外に、例えば、AD（アナログ - デジタル）変換機能を持たせ、アナログの画素信号をデジタル信号に変換して出力することも可能である。

#### 【0034】

水平駆動部14は、シフトレジスタやアドレスデコーダなどによって構成され、カラム処理部13の画素列に対応する単位回路を順番に選択する。この水平駆動部14による選

50

査走査により、カラム処理部13において単位回路ごとに信号処理された画素信号が順番に出力される。

#### 【0035】

システム制御部15は、各種のタイミング信号を生成するタイミングジェネレータなどによって構成され、当該タイミングジェネレータで生成された各種のタイミングを基に、垂直駆動部12、カラム処理部13、及び、水平駆動部14などの駆動制御を行う。

#### 【0036】

信号処理部18は、少なくとも演算処理機能を有し、カラム処理部13から出力される画素信号に対して演算処理等の種々の信号処理を行う。データ格納部19は、信号処理部18での信号処理に当たって、その処理に必要なデータを一時的に格納する。

10

#### 【0037】

< 単位画素100の回路構成 >

図2は、図1の画素アレイ部11に配置される単位画素100の構成例を示す回路図である。

#### 【0038】

単位画素100は、第1光電変換部101、第1転送ゲート部102、第2光電変換部103、第2転送ゲート部104、第3転送ゲート部105、電荷蓄積部106、リセットゲート部107、FD(フローティングディフュージョン)部108、増幅トランジスタ109、及び、選択トランジスタ110を含むように構成される。

20

#### 【0039】

また、単位画素100に対して、図1の画素駆動線16として、複数の駆動線が、例えば画素行毎に配線される。そして、図1の垂直駆動部12から複数の駆動線を介して、各種の駆動信号TGL、TGS、FCG、RST、SELが供給される。これらの駆動信号は、単位画素100の各トランジスタがN MOSトランジスタなので、高レベル(例えば、電源電圧VDD)の状態がアクティブ状態となり、低レベルの状態(例えば、負電位)が非アクティブ状態となるパルス信号である。

#### 【0040】

第1光電変換部101は、例えば、PN接合のフォトダイオードからなる。第1光電変換部101は、受光した光量に応じた電荷を生成し、蓄積する。

30

#### 【0041】

第1転送ゲート部102は、第1光電変換部101とFD部108との間に接続されている。第1転送ゲート部102のゲート電極には、駆動信号TGLが印加される。駆動信号TGLがアクティブ状態になると、第1転送ゲート部102が導通状態になり、第1光電変換部101に蓄積されている電荷が、第1転送ゲート部102を介してFD部108に転送される。

#### 【0042】

第2光電変換部103は、第1光電変換部101と同様に、例えば、PN接合のフォトダイオードからなる。第2光電変換部103は、受光した光量に応じた電荷を生成し、蓄積する。

#### 【0043】

第1光電変換部101と第2光電変換部103を比較すると、第1光電変換部101の方が受光面の面積が広く、感度が高く、第2光電変換部103の方が受光面の面積が狭く、感度が低い。このように、単位画素100内には、感度の異なる2つの光電変換部が備えられている。すなわちこの場合、第1光電変換部101は、高感度画素として機能し、第2光電変換部103は、低感度画素として機能する。

40

#### 【0044】

第2転送ゲート部104は、電荷蓄積部106とFD部108との間に接続されている。第2転送ゲート部104のゲート電極には、駆動信号FCGが印加される。駆動信号FCGがアクティブ状態になると、第2転送ゲート部104が導通状態になり、電荷蓄積部106とFD部108のポテンシャルが結合する。

50

## 【0045】

第3転送ゲート部105は、第2光電変換部103と電荷蓄積部106との間に接続されている。第3転送ゲート部105のゲート電極には、駆動信号TGSが印加される。駆動信号TGSがアクティブ状態になると、第3転送ゲート部105が導通状態になり、第2光電変換部103に蓄積されている電荷が、第3転送ゲート部105を介して、電荷蓄積部106、或いは、電荷蓄積部106とFD部108のポテンシャルが結合した領域に転送される。

## 【0046】

また、第3転送ゲート部105のゲート電極の下部は、ポテンシャルが若干深くなっている。第2光電変換部103の飽和電荷量を超え、第2光電変換部103から溢れた電荷を電荷蓄積部106に転送するオーバーフローパスが形成されている。なお、以下、第3転送ゲート部105のゲート電極の下部に形成されているオーバーフローパスを、単に第3転送ゲート部105のオーバーフローパスと称する。

10

## 【0047】

電荷蓄積部106は、例えば、キャパシタからなり、第2転送ゲート部104と第3転送ゲート部105との間に接続されている。電荷蓄積部106の対向電極は、電源電圧VDDを供給する電源VDDの間に接続されている。電荷蓄積部106は、第2光電変換部103から転送される電荷を蓄積する。

## 【0048】

リセットゲート部107は、電源VDDとFD部108との間に接続されている。リセットゲート部107のゲート電極には、駆動信号RSTが印加される。駆動信号RSTがアクティブ状態になると、リセットゲート部107が導通状態になり、FD部108の電位が、電源電圧VDDのレベルにリセットされる。

20

## 【0049】

FD部108は、電荷を電圧信号に電荷電圧変換して出力する。

## 【0050】

増幅トランジスタ109は、ゲート電極がFD部108に接続され、ドレイン電極が電源VDDに接続されており、FD部108に保持されている電荷を読み出す読出し回路、所謂ソースフォロワ回路の入力部となる。すなわち、増幅トランジスタ109は、ソース電極が選択トランジスタ110を介して垂直信号線17に接続されることにより、当該垂直信号線17の一端に接続される定電流源111とソースフォロワ回路を構成する。

30

## 【0051】

選択トランジスタ110は、増幅トランジスタ109のソース電極と垂直信号線17との間に接続されている。選択トランジスタ110のゲート電極には、選択信号SELが印加される。選択信号SELがアクティブ状態になると、選択トランジスタ110が導通状態になり、単位画素100が選択状態となる。これにより、増幅トランジスタ109から出力される画素信号が、選択トランジスタ110を介して、垂直信号線17に出力される。

## 【0052】

なお、以下、各駆動信号がアクティブ状態になることを、各駆動信号がオンするともいい、各駆動信号が非アクティブ状態になることを、各駆動信号がオフするともいう。また、以下、各ゲート部又は各トランジスタが導通状態になることを、各ゲート部又は各トランジスタがオンするともいい、各ゲート部又は各トランジスタが非導通状態になることを、各ゲート部又は各トランジスタがオフするともいう。

40

## 【0053】

<単位画素100の動作>

次に、図3及び図4のタイミングチャートを参照して、単位画素100の動作について説明する。まず、図3のタイミングチャートを参照して、単位画素100の露光開始時の動作について説明する。この処理は、例えば、画素アレイ部11の画素行毎、又は、複数の画素行毎に、所定の走査順で行われる。なお、図3には、水平同期信号XHS、駆動信

50

号 S E L、R S T、T G S、F C G、T G L のタイミングチャートが示されている。

**【0054】**

まず、時刻 t 1において、水平同期信号 X H S が入力され、単位画素 1 0 0 の露光処理が開始する。

**【0055】**

次に、時刻 t 2において、駆動信号 R S T がオンし、リセットゲート部 1 0 7 がオンする。これにより、F D 部 1 0 8 の電位が、電源電圧 V D D のレベルにリセットされる。

**【0056】**

次に、時刻 t 3において、駆動信号 T G L、F C G、T G S がオンし、第 1 転送ゲート部 1 0 2、第 2 転送ゲート部 1 0 4、第 3 転送ゲート部 1 0 5 がオンする。これにより、電荷蓄積部 1 0 6 と F D 部 1 0 8 のポテンシャルが結合する。また、第 1 光電変換部 1 0 1 に蓄積されている電荷が、第 1 転送ゲート部 1 0 2 を介して、結合した領域に転送され、第 2 光電変換部 1 0 3 に蓄積されている電荷が、第 3 転送ゲート部 1 0 5 を介して、結合した領域に転送される。そして、結合した領域がリセットされる。

10

**【0057】**

次に、時刻 t 4において、駆動信号 T G L、T G S がオフし、第 1 転送ゲート部 1 0 2、第 3 転送ゲート部 1 0 5 がオフする。これにより、第 1 光電変換部 1 0 1 及び第 2 光電変換部 1 0 3 への電荷の蓄積が開始され、露光期間が開始する。

**【0058】**

次に、時刻 t 5において、駆動信号 R S T がオフし、リセットゲート部 1 0 7 がオフする。

20

**【0059】**

次に、時刻 t 6において、駆動信号 F C G がオフし、第 2 転送ゲート部 1 0 4 がオフする。これにより、電荷蓄積部 1 0 6 は、第 2 光電変換部 1 0 3 から溢れ、第 3 転送ゲート部 1 0 5 のオーバーフローパスを介して転送されてくる電荷の蓄積を開始する。

**【0060】**

そして、時刻 t 7において、水平同期信号 X H S が入力される。

**【0061】**

( 単位画素 1 0 0 の読み出し時の動作 )

次に、図 4 のタイミングチャートを参照して、単位画素 1 0 0 の画素信号の読み出し時の動作について説明する。この処理は、例えば、画素アレイ部 1 1 の画素行毎、又は、複数の画素行毎に、図 3 の処理が行われてから所定の時間後に所定の走査順で行われる。なお、図 4 には、水平同期信号 X H S、駆動信号 S E L、R S T、T G S、F C G、T G L のタイミングチャートが示されている。

30

**【0062】**

まず、時刻 t 2 1において、水平同期信号 X H S が入力され、単位画素 1 0 0 の読み出し期間が開始する。

**【0063】**

次に、時刻 t 2 2において、選択信号 S E L がオンし、選択トランジスタ 1 1 0 がオンする。これにより、単位画素 1 0 0 が選択状態になる。

40

**【0064】**

次に、時刻 t 2 3において、駆動信号 R S T がオンし、リセットゲート部 1 0 7 がオンする。これにより、F D 部 1 0 8 の電位が、電源電圧 V D D のレベルにリセットされる。

**【0065】**

次に、時刻 t 2 4において、駆動信号 R S T がオフし、リセットゲート部 1 0 7 がオフする。

**【0066】**

次に、時刻 t 2 5において、駆動信号 F C G、T G S がオンし、第 2 転送ゲート部 1 0 4 及び第 3 転送ゲート部 1 0 5 がオンする。これにより、電荷蓄積部 1 0 6 と F D 部 1 0 8 のポテンシャルが結合するとともに、第 2 光電変換部 1 0 3 に蓄積されている電荷が、

50

結合した領域に転送される。これにより、露光期間中に第2光電変換部103及び電荷蓄積部106に蓄積された電荷が、結合した領域に蓄積される。

【0067】

この時刻t25において、画素信号の読み出しが開始され、露光期間が終了する。

【0068】

次に、時刻t26において、駆動信号TGSがオフし、第3転送ゲート部105がオフする。これにより、第2光電変換部103からの電荷の転送が停止する。

【0069】

次に、時刻t26と時刻t27の間の時刻taにおいて、電荷蓄積部106とFD部108のポテンシャルが結合した領域の電位に基づく信号SLが、増幅トランジスタ109及び選択トランジスタ110を介して垂直信号線17に出力される。信号SLは、露光期間中に第2光電変換部103で生成され、第2光電変換部103及び電荷蓄積部106に蓄積された電荷に基づく信号である。10

【0070】

また、信号SLは、露光期間中に第2光電変換部103及び電荷蓄積部106に蓄積された電荷が、電荷蓄積部106とFD部108のポテンシャルが結合した領域に蓄積された状態における結合した領域の電位に基づく信号となる。従って、信号SLの読み出し時に電荷を電荷電圧変換する容量は、電荷蓄積部106とFD部108を合わせた容量となる。

【0071】

なお、以下、信号SLのことを、低感度データ信号SLとも称する。20

【0072】

次に、時刻t27において、駆動信号RSTがオンし、リセットゲート部107がオンする。これにより、電荷蓄積部106とFD部108のポテンシャルが結合した領域がリセットされる。

【0073】

次に、時刻t28において、選択信号SELがオフし、選択トランジスタ110がオフする。これにより、単位画素100が非選択状態になる。

【0074】

次に、時刻t29において、駆動信号RSTがオフし、リセットゲート部107がオフする。30

【0075】

次に、時刻t30において、選択信号SELがオンし、選択トランジスタ110がオンする。これにより、単位画素100が選択状態になる。

【0076】

次に、時刻t30と時刻t31の間の時刻tbにおいて、電荷蓄積部106とFD部108のポテンシャルが結合した領域の電位に基づく信号NLが、増幅トランジスタ109及び選択トランジスタ110を介して垂直信号線17に出力される。この信号NLは、電荷蓄積部106とFD部108のポテンシャルが結合した領域がリセットされた状態における結合した領域の電位に基づく信号となる。40

【0077】

なお、以下、信号NLのことを、低感度リセット信号NLとも称する。

【0078】

次に、時刻t31において、駆動信号FCGがオフし、第2転送ゲート部104がオフする。

【0079】

次に、時刻t31と時刻t32の間の時刻tcにおいて、FD部108の電位に基づく信号NHが、増幅トランジスタ109及び選択トランジスタ110を介して垂直信号線17に出力される。信号NHは、リセットされた状態におけるFD部108の電位に基づく信号となる。50

**【0080】**

なお、以下、信号N Hのことを、高感度リセット信号N Hとも称する。

**【0081】**

次に、時刻t 3 2において、駆動信号T G Lがオンし、第1転送ゲート部1 0 2がオンする。これにより、露光期間中に第1光電変換部1 0 1で生成され、蓄積された電荷が、第1転送ゲート部1 0 2を介してF D部1 0 8に転送される。

**【0082】**

次に、時刻t 3 3において、駆動信号T G Lがオフし、第1転送ゲート部1 0 2がオフする。これにより、第1光電変換部1 0 1からF D部1 0 8への電荷の転送が停止する。

**【0083】**

次に、時刻t 3 3と時刻t 3 4の間の時刻t dにおいて、F D部1 0 8の電位に基づく信号S Hが、増幅トランジスタ1 0 9及び選択トランジスタ1 1 0を介して垂直信号線1 7に出力される。信号S Hは、露光期間中に第1光電変換部1 0 1で生成され、蓄積された電荷に基づく信号である。

**【0084】**

また、信号S Hは、露光期間中に第1光電変換部1 0 1に蓄積された電荷がF D部1 0 8に蓄積された状態におけるF D部1 0 8の電位に基づく信号となる。従って、信号S Hの読み出し時に電荷を電荷電圧変換する容量は、F D部1 0 8の容量となり、時刻t aにおける低感度データ信号S Lの読み出し時より小さくなる。

**【0085】**

なお、以下、信号S Hのことを、高感度データ信号S Hとも称する。

**【0086】**

次に、時刻t 3 4において、選択信号S E Lがオフし、選択トランジスタ1 1 0がオフする。これにより、単位画素1 0 0が非選択状態になる。

**【0087】**

次に、時刻t 3 5において、水平同期信号X H Sが入力され、単位画素1 0 0の画素信号の読み出し期間が終了する。

**【0088】**

(ノイズ除去処理及び演算処理に関する説明)

上述した単位画素1 0 0からは、低感度データ信号S L、低感度リセット信号N L、高感度リセット信号N H、及び、高感度データ信号S Hの順に、垂直信号線1 7に対して信号が出力される。そして、後段の信号処理部、例えば、図1に示すカラム処理部1 3や信号処理部1 8において、低感度データ信号S L、低感度リセット信号N L、高感度リセット信号N H、及び、高感度データ信号S Hに対して所定のノイズ除去処理及び信号処理が行われる。以下、後段のカラム処理部1 3におけるノイズ除去処理及び信号処理部1 8における演算処理の例について説明する。

**【0089】**

(ノイズ除去処理)

最初に、カラム処理部1 3によるノイズ除去処理について説明する。

**【0090】**

(ノイズ除去処理の処理例)

まず、ノイズ除去処理の処理例について説明する。

**【0091】**

カラム処理部1 3は、低感度データ信号S Lと低感度リセット信号N Lとの差分をとることにより、低感度差分信号S N Lを生成する。従って、

低感度差分信号S N L = 低感度データ信号S L - 低感度リセット信号N L

となる。

**【0092】**

次に、カラム処理部1 3は、高感度データ信号S Hと高感度リセット信号N Hとの差分をとることにより、高感度差分信号S N Hを生成する。従って、

10

20

30

40

50

高感度差分信号  $S_{NH}$  = 高感度データ信号  $S_H$  - 高感度リセット信号  $N_H$

となる。

【0093】

このように、低感度の信号  $S_L$ 、 $N_L$  に対しては、画素内の増幅トランジスタの閾値ばらつき等の画素固有の固定パターンノイズは除去されるもののリセットノイズは除去されない DDS 处理が行われる。高感度の信号  $S_H$ 、 $N_H$  については、リセットノイズや画素内の増幅トランジスタの閾値ばらつき等の画素固有の固定パターンノイズが除去される CDS 处理が行われる。

【0094】

(画素信号の演算処理の処理例)

10

次に画素信号の演算処理の処理例について説明する。

【0095】

信号処理部 18 は、低感度差分信号  $S_{NL}$  が所定の範囲内となったときに、低感度差分信号  $S_{NL}$  と高感度差分信号  $S_{NH}$  の比を画素毎、複数画素毎、色毎、共有画素単位内の特定画素毎、もしくは全画素一律にゲインとして算出してゲインテーブルを生成する。そして、信号処理部 18 は、低感度差分信号  $S_{NL}$  と当該ゲインテーブルの積を低感度差分信号  $S_{NL}$  の補正值として算出する。

【0096】

ここで、ゲインを  $G$ 、低感度差分信号  $S_{NL}$  の補正值（以下、補正低感度差分信号と称する）を  $S_{NL}'$  とすると、ゲイン  $G$  及び補正低感度差分信号  $S_{NL}'$  は、次式（1）、（2）に基づいて求めることができる。

20

【0097】

$$G = S_{NH} / S_{NL} = (C_{fd} + C_{fc}) / C_{fd} \quad \dots \quad (1)$$

$$S_{NL}' = G \times S_{NL} \quad \dots \quad (2)$$

【0098】

ここで、 $C_{fd}$  は FD 部 108 の容量値、 $C_{fc}$  は電荷蓄積部 106 の容量値である。

従って、ゲイン  $G$  は、容量比と等価である。

【0099】

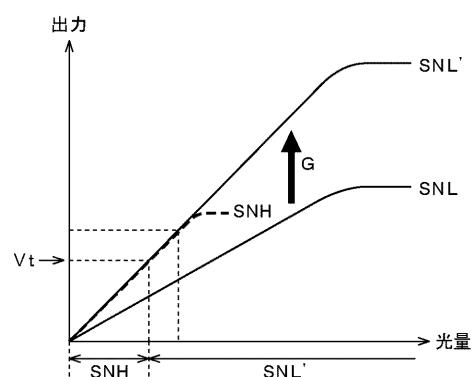

図 5 は、入射光量に対する低感度差分信号  $S_{NL}$ 、高感度差分信号  $S_{NH}$ 、及び、補正低感度差分信号  $S_{NL}'$  の関係を示している。

30

【0100】

次に、信号処理部 18 は、図 5 に示すように、予め設定された所定の閾値  $V_t$  を用いる。閾値  $V_t$  は、光応答特性において、高感度差分信号  $S_{NH}$  が飽和前かつ光応答特性がリニアな領域において予め設定される。

【0101】

そして、信号処理部 18 は、高感度差分信号  $S_{NH}$  が所定の閾値  $V_t$  を超えない場合、当該高感度差分信号  $S_{NH}$  を処理対象画素の画素信号  $S_N$  として出力する。すなわち、 $S_{NH} < V_t$  の場合、画素信号  $S_N =$  高感度差分信号  $S_{NH}$  となる。

【0102】

一方、信号処理部 18 は、高感度差分信号  $S_{NH}$  が所定の閾値  $V_t$  を超える場合、低感度差分信号  $S_{NL}$  の補正低感度差分信号  $S_{NL}'$  を処理対象画素の画素信号  $S_N$  として出力する。すなわち、 $V_t > S_{NH}$  の場合、画素信号  $S_N =$  補正低感度差分信号  $S_{NL}'$  となる。

40

【0103】

以上のような演算処理を行うことにより、低照度時の信号から高照度時の信号へより滑らかに切り替えることが出来る。

【0104】

また、CMOS イメージセンサ 10 では、低感度の第 2 光電変換部 103 に対して電荷蓄積部 106 を設けることにより、低感度データ信号  $S_L$  が飽和するレベルを引き上げることができる。これにより、ダイナミックレンジの最小値を保持したまま、ダイナミック

50

レンジの最大値を大きくすることができ、ダイナミックレンジを拡大することができる。

#### 【0105】

例えば、車載向けのイメージセンサにおいて、LED光源のように点滅する被写体を、点滅するタイミングによって撮像できないLEDフリッカという現象が発生する場合がある。このLEDフリッカは、例えば、従来のイメージセンサのダイナミックレンジが低く、被写体毎に露光時間を調整する必要があるために生じる。

#### 【0106】

すなわち、従来のイメージセンサは、様々な照度の被写体に対応するため、低照度の被写体に対しては露光時間を長く、高照度の被写体に対しては露光時間を短くしている。これにより、低いダイナミックレンジでも様々な照度の被写体に対応することが可能になる。一方、露光時間に関わらず読み出し速度は一定であるため、読み出し時間よりも短い単位で露光時間を設定する場合、露光時間以外に光電変換部に入射した光は、光電変換されて電荷になるものの、読み出されることなく破棄される。

#### 【0107】

一方、CMOSイメージセンサ10では、上述したようにダイナミックレンジを拡大することができ、露光時間を長く設定することができるため、LEDフリッカの発生を抑制することができる。また、CMOSイメージセンサ10では、上述したように時分割方式や空間分割方式で分割数を増やした場合に発生するアーチファクトの発生や解像度の低下を防止することができる。

#### 【0108】

##### < 単位画素の構成 >

次に、上記したように、高感度の第1光電変換部101と低感度の第2光電変換部103を有する単位画素100の構成についてさらに説明を加える。以下に、単位画素100の断面図を示し、単位画素100の構成について説明を加える。

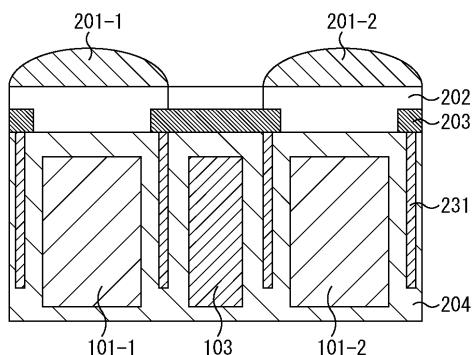

#### 【0109】

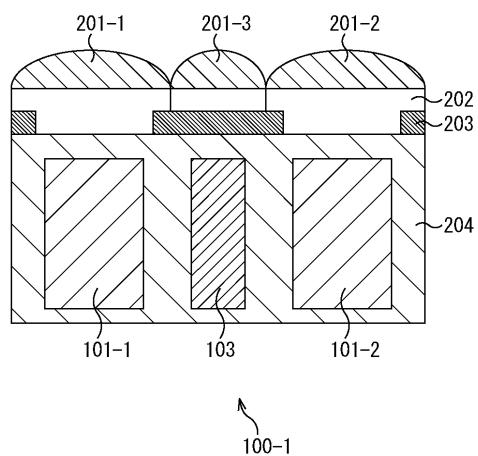

##### ( 単位画素の第1の構成 )

図6は、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100の断面図である。図6に示した単位画素100は、第1の構成であることを示すために、以下、単位画素100-1と記述する。

#### 【0110】

単位画素100-1は、図中上側から、オンチップレンズ201、カラーフィルタ202、遮光膜203、およびシリコン基板204が積層され、シリコン基板204には、第1光電変換部101と第2光電変換部103が形成されている。

#### 【0111】

なお、図示はしていないが、例えば、オンチップレンズ201の上側には、カバーガラスなどが積層され、シリコン基板204の下側には、配線層や支持基板が積層されている。以下の説明において必要な部分を適宜図示し、説明を加え、その他の部分については、適宜図示や説明を省略する。

#### 【0112】

図6では、第1光電変換部101-1、第1光電変換部101-2、および第2光電変換部103を図示している。また、これら3箇所の光電変換部上に、それぞれオンチップレンズ201-1乃至201-3が形成されている。

#### 【0113】

遮光膜203は、第2光電変換部103上にのみ形成されている。遮光膜203は、光を吸収、反射する機能を有する膜である。遮光膜203は、金属膜で形成され、光を反射する膜として形成されていても良いし、光の一部を吸収し、一部を透過する膜として形成されていても良いし、光を吸収する光吸収膜として形成されていても良い。

#### 【0114】

遮光膜203は、例えば、アモルファスシリコン膜、ポリシリコン膜、ゲルマニウム(Ge)膜、窒化ガリウム(GaN)膜、テルル化カドミウム(CdTe)膜、ヒ化ガリウム(HgI<sub>2</sub>)膜等である。

10

20

30

40

50

ム ( GaAs ) 膜、リン化インジウム ( InP ) 膜、CuInSe<sub>2</sub>膜、Cu<sub>2</sub>S膜、CIGS膜、非導体構造のカーボン膜、黒色レジスト膜、有機光電変換膜などとされる。

#### 【0115】

なお、以下に説明する第2乃至第16の構成においても、遮光膜が第2光電変換部103上に設けられている形態を示すが、それらの形態においても、遮光膜は、上記した材料で形成されるようにすることができる。なお、上記した遮光膜の材料は、一例であり、限定を示すものではない。

#### 【0116】

このように、低感度の第2光電変換部103上に遮光膜203を形成することで、オンチップレンズ201-3を透過してきた光が、遮光膜203に吸収され、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の感度が、さらに低下することになるため、低感度の光電変換部としての性能は向上し、ダイナミックレンジを拡大することができる。10

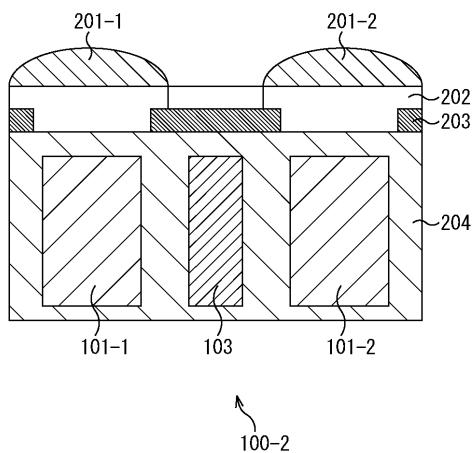

#### 【0117】

##### (単位画素の第2の構成)

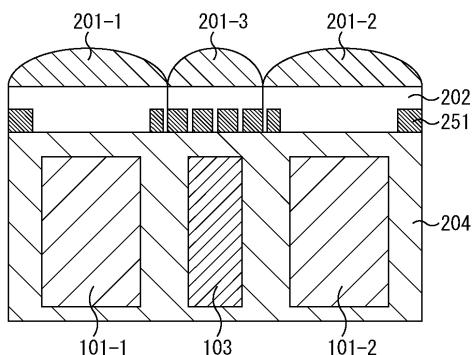

次に、単位画素100の第2の構成について説明する。図7は、図6に示した単位画素100-1と同じく、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100-2の断面図である。

#### 【0118】

図7に示した単位画素100-2と、図6に示した単位画素100-1を比較するに、単位画素100-2は、単位画素100-1から第2光電変換部103上に形成されているオンチップレンズ201-3を削除した構成となされている点が異なり、他の部分は同一である。単位画素100-1と同様の構成を有する部分には、同様の符号を付し、その説明を省略する。以下、他の部分も同様に、適宜同様の部分に関しては説明を省略する。20

#### 【0119】

第2光電変換部103上にオンチップレンズ201-3を形成しない構成とすることで、第2光電変換部103に光が集光されない状態で入射される構成となり、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の感度が、さらに低下し、低感度の光電変換部のダイナミックレンジを拡大させることが可能となる。

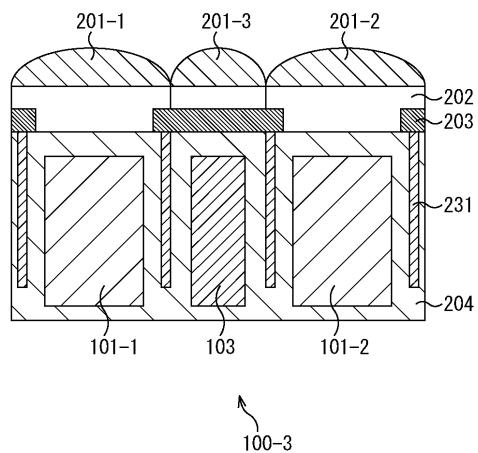

#### 【0120】

##### (単位画素の第3の構成)

次に、単位画素100の第3の構成について説明する。図8は、図6に示した単位画素100-1と同じく、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100-3の断面図である。

#### 【0121】

図8に示した単位画素100-3と、図6に示した単位画素100-1を比較するに、単位画素100-3は、単位画素100-1に遮光壁231を追加した構成となされている点が異なり、他の部分は同一である。

#### 【0122】

遮光壁231は、画素間に設けられており、図8に示した単位画素100-3においては、第1光電変換部101-1と第2光電変換部103の間、第1光電変換部101-2と第2光電変換部103の間にそれぞれ設けられている。このように、遮光壁231は、画素分離領域に設けられている。また遮光壁231は、受光面側から形成された絶縁膜で形成された溝で囲まれるように形成することができる。40

#### 【0123】

また遮光壁231は、トレンチを形成し、そのトレンチ内に、負の固定電荷膜と酸化膜を組み合わせて形成されるようにしても良いし、負の固定電荷膜、酸化膜、および金属を組み合わせて形成されるようにしても良い。

#### 【0124】

遮光壁231は、隣接する光電変換部への光の漏れ込みを防ぐために設けられている。

50

遮光壁 231 を設けることで、混色などが発生することを低減させることが可能となる。

#### 【0125】

このような構成とした場合においても、低感度の第2光電変換部103上に遮光膜203を形成することで、オンチップレンズ201-3を透過してきた光が、遮光膜203に吸収され、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の感度が、さらに低下し、ダイナミックレンジを拡大させることができるとなる。また遮光壁231を設けることで、混色などの発生を低減させることができるとなる。

#### 【0126】

(単位画素の第4の構成)

次に、単位画素100の第4の構成について説明する。図9は、図7に示した単位画素100-2と同じく、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100-4の断面図である。

10

#### 【0127】

図9に示した単位画素100-4と、図7に示した単位画素100-2を比較するに、単位画素100-4は、単位画素100-2に遮光壁231を追加した構成となされている点が異なり、他の部分、例えば、第2光電変換部103上のオンチップレンズ201-3が形成されていない点などは同一である。また、遮光壁231を追加した構成は、図8に示した単位画素100-3と同様の構成である。

#### 【0128】

このような構成とした場合においても、低感度の第2光電変換部103上に遮光膜203を形成することで、遮光膜203に入射された光が吸収され、第2光電変換部103に入射される光量が減少し、さらにオンチップレンズが形成されていないために、さらに第2光電変換部103に入射される光量が減少するため、第2光電変換部103の感度が、さらに低下する構成となる。よって、低感度の光電変換部のダイナミックレンジを拡大させることができるとなる。また遮光壁231を設けることで、混色などの発生を低減させることができるとなる。

20

#### 【0129】

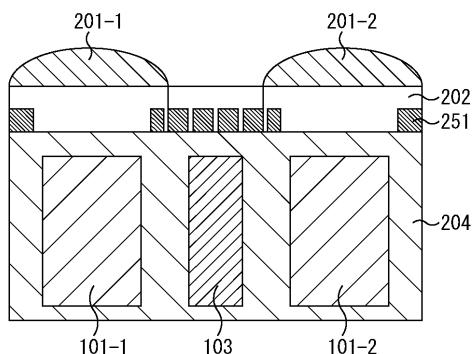

(単位画素の第5の構成)

次に、単位画素100の第5の構成について説明する。図10は、図6に示した単位画素100-1と同じく、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100-5の断面図である。

30

#### 【0130】

図10に示した単位画素100-5と、図6に示した単位画素100-1を比較するに、単位画素100-5の遮光膜251は、単位画素100-1の遮光膜203と異なる形状をしている点が異なり、他の部分は同一である。単位画素100-5の遮光膜251は、スリットがある形状に形成されている。スリットに該当する部分には、遮光膜251が形成されていないようにしても良いし、スリットではない部分の遮光膜251よりも薄く形成されているようにしても良い。

#### 【0131】

遮光膜251をスリット形状とすることで、第2光電変換部103を偏光画素として用いることができる。

40

#### 【0132】

例えば、第2光電変換部103が車載され、道路表面を含む画像を撮像する場合、道路表面から反射された光は、道路の表面に平行な偏光となる。このような偏光を除去した撮影を行う場合には、道路表面と平行となる方向に遮光膜251のスリットを形成することで、道路表面で反射された光を選択的に遮止し、他の被写体からの光を受光することができる。

#### 【0133】

このように、遮光膜251の形状をスリット形状とすることで、第2光電変換部103への光の量を少なくさせるだけでなく、不要な光を除去することも可能な構成とすること

50

ができる。

【0134】

このように、遮光膜251を偏光子としても用いるようにした場合、遮光膜251の材料として、上記した材料の他に、金属を用いることも可能である。なお偏光子に遮光膜を使用することで、偏光子を金属で形成した場合より、効率よく直接、間接光を減光できる構成とすることができます。

【0135】

このような構成とした場合においても、低感度の第2光電変換部103上に遮光膜251を形成することで、第2光電変換部103に入射される光量が減少し、低感度化によるダイナミックレンジの拡大を実現することができる。また、遮光膜251をスリット形状とすることで、遮光膜251を偏光子として用いることができ、反射光などの不要な光の影響を除去することができる。10

【0136】

(単位画素の第6の構成)

次に、単位画素100の第6の構成について説明する。図11は、図7に示した単位画素100-2と同じく、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100-6の断面図である。

【0137】

図11に示した単位画素100-6と、図7に示した単位画素100-2を比較するに、単位画素100-6の遮光膜251は、単位画素100-2の遮光膜203と異なる形状をしている点が異なり、他の部分、例えば、第2光電変換部103上にオンチップレンズ201-3が形成されていない点などは同一である。単位画素100-6の遮光膜251は、図10に示した単位画素100-5と同じく、スリット形状に形成されている。20

【0138】

遮光膜251をスリット形状とすることで、単位画素100-5(図10)と同じく、第2光電変換部103への光の量を少なくさせるだけでなく、不要な光を除去することも可能な構成とすることができます。

【0139】

このような構成とした場合においても、低感度の第2光電変換部103上に遮光膜251を形成することで、第2光電変換部103に入射される光量が減少し、低感度化によるダイナミックレンジの拡大を実現することができる。また第2光電変換部103上にオンチップレンズを形成しないことで、第2光電変換部103に入射される光量がより減少し、低感度化によるダイナミックレンジの拡大を実現することができる。また、遮光膜251をスリット形状とすることで、遮光膜251を偏光子として用いることができ、反射光などの不要な光の影響を除去することができる。30

【0140】

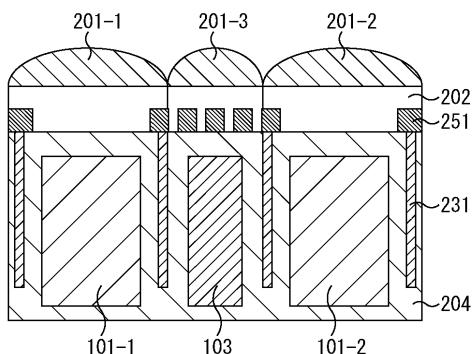

(単位画素の第7の構成)

次に、単位画素100の第7の構成について説明する。図12は、図8に示した単位画素100-3と同じく、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100-7の断面図である。40

【0141】

図12に示した単位画素100-7と、図8に示した単位画素100-3を比較するに、単位画素100-7は、遮光膜251がスリット形状に形成されている点が異なり、他の部分、例えば、画素間に遮光膜231が設けられている点などは同一である。

【0142】

このような構成とした場合においても、低感度の第2光電変換部103上に遮光膜251を形成することで、第2光電変換部103に入射される光量が減少し、低感度化によるダイナミックレンジの拡大を実現することができる。また、遮光膜251をスリット形状とすることで、遮光膜251を偏光子として用いることができ、反射光などの不要な光の影響を除去することができる。また遮光壁231を設けることで、混色などの発生を低減50

させることが可能となる。

**【0143】**

(単位画素の第8の構成)

次に、単位画素100の第8の構成について説明する。図13は、図9に示した単位画素100-4と同じく、CMOSイメージセンサ10が裏面型のイメージセンサである場合の単位画素100-8の断面図である。

**【0144】**

図13に示した単位画素100-8と、図9に示した単位画素100-4を比較するに、単位画素100-8は、遮光膜251がスリット形状に形成されている点が異なり、他の部分、例えば、単画素間に遮光膜231が設けられ、第2光電変換部103上にオンチップレンズが形成されていない点などは同一である。

10

**【0145】**

このような構成とした場合においても、低感度の第2光電変換部103上に遮光膜251を形成することで、第2光電変換部103に入射される光量が減少し、低感度化によるダイナミックレンジの拡大を実現することができる。また第2光電変換部103上にオンチップレンズを形成しないことで、第2光電変換部103に入射される光量がより減少し、低感度化によるダイナミックレンジの拡大を実現することができる。

**【0146】**

また、遮光膜251をスリット形状として用いることができ、反射光などの不要な光の影響を除去することができる。また遮光壁231を設けることで、混色などの発生を低減させることができる。

20

**【0147】**

(単位画素の第9の構成)

図14は、CMOSイメージセンサ10が表面型のイメージセンサである場合の単位画素100-9の断面図である。

**【0148】**

図14に示した単位画素100-9は、図中上側から、オンチップレンズ301、カラーフィルタ302、遮光膜303、配線層304、およびシリコン基板305が積層され、シリコン基板305には、第1光電変換部101と第2光電変換部103が形成されている。

30

**【0149】**

なお、図示はしていないが、例えば、オンチップレンズ201の上側には、カバーガラスなどが積層されている。以下の説明において必要な部分を適宜図示し、説明を加え、その他の部分については、適宜図示や説明を省略する。

**【0150】**

図14では、第1光電変換部101-1、第1光電変換部101-2、および第2光電変換部103を図示している。また、これら3箇所の光電変換部上に、それぞれオンチップレンズ301-1乃至301-3が形成されている。

**【0151】**

遮光膜303は、第2光電変換部103上にのみ形成されている。遮光膜303は、例えば、アモルファスシリコン膜、ポリシリコン膜、Ge膜、GaN膜、CdTe膜、GaAs膜、InP膜、CuInSe2膜、Cu2S、CIGS膜、非導体構造のカーボン膜、黒色レジスト膜、有機光電変換膜で形成される。また、後述するように、遮光膜303が、スリット形状で形成される場合、金属で形成されるようにすることも可能である。なお、上記した遮光膜の材料は、一例であり、限定を示すものではない。

40

**【0152】**

このように、表面型のイメージセンサにおいても、低感度の第2光電変換部103上に遮光膜303を形成することで、オンチップレンズ301-3を透過してきた光が、遮光膜303に吸収され、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の感度が、さらに低下することになるため、ダイナミックレンジは拡

50

大することになる。

#### 【0153】

##### (単位画素の第10の構成)

次に、単位画素100の第10の構成について説明する。図15は、図14に示した単位画素100-9と同じく、CMOSイメージセンサ10が表面型のイメージセンサである場合の単位画素100-10の断面図である。

#### 【0154】

図15に示した単位画素100-10と、図14に示した単位画素100-9を比較するに、単位画素100-10は、単位画素100-9から第2光電変換部103上に形成されているオンチップレンズ301-3を削除した構成となされている点が異なり、他の部分は同一である。

10

#### 【0155】

第2光電変換部103上にオンチップレンズ301-3を形成しない構成とすることで、第2光電変換部103に光が集光されない状態で入射される構成となり、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の低感度化によるダイナミックレンジを拡大させることが可能となる。

#### 【0156】

##### (単位画素の第11の構成)

次に、単位画素100の第11の構成について説明する。図16は、図14に示した単位画素100-9と同じく、CMOSイメージセンサ10が表面型のイメージセンサである場合の単位画素100-11の断面図である。

20

#### 【0157】

図16に示した単位画素100-11と、図14に示した単位画素100-9を比較するに、単位画素100-9の遮光膜303は、配線層304の図中上側（オンチップ301側）に形成されているのに対して、単位画素100-11の遮光膜は、配線層304の図中下側（シリコン基板305側）に形成されている点が異なり、他の部分は同一である。

#### 【0158】

再度図14を参照するに、単位画素100-9の遮光膜303は、配線層304の上側であり、カラーフィルタ302の層内に形成されている。これに対して、図15に示した単位画素100-11の遮光膜331は、配線層304の下側であり、シリコン基板305の上側の配線層304内に形成されている。このように、遮光膜が形成される位置は、配線層304の上側でも良いし、下側でも良い。

30

#### 【0159】

このように、表面型のイメージセンサにおいても、低感度の第2光電変換部103上に遮光膜303を形成することで、オンチップレンズ301-3を透過してきた光が、遮光膜303に吸収され、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の感度が、さらに低下し、ダイナミックレンジを拡大させることが可能となる。

#### 【0160】

##### (単位画素の第12の構成)

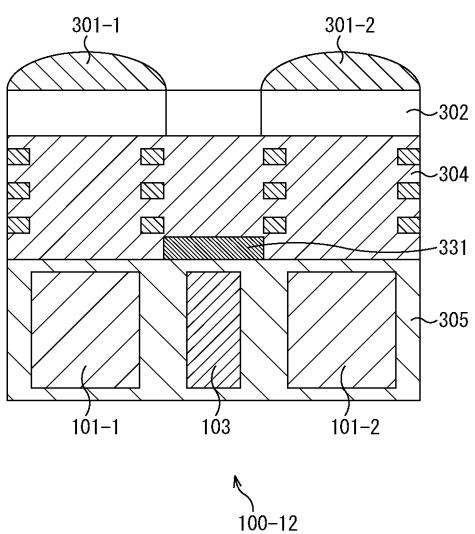

次に、単位画素100の第12の構成について説明する。図17は、図16に示した単位画素100-11と同じく、CMOSイメージセンサ10が表面型のイメージセンサである場合の単位画素100-12の断面図である。

40

#### 【0161】

図17に示した単位画素100-12と、図16に示した単位画素100-11を比較するに、単位画素100-12は、単位画素100-11から第2光電変換部103上に形成されているオンチップレンズ301-3を削除した構成となされている点が異なり、他の部分は同一である。

#### 【0162】

第2光電変換部103上にオンチップレンズ301-3を形成しない構成とすることで、第2光電変換部103に光が集光されない状態で入射される構成となり、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の低下化のダイナミックレンジを拡大させることが可能となる。

#### 【0163】

(単位画素の第13の構成)

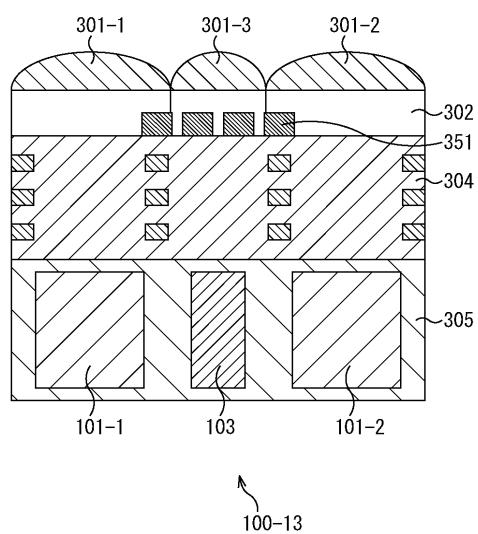

次に、単位画素100の第13の構成について説明する。図18は、図14に示した単位画素100-9と同じく、CMOSイメージセンサ10が表面型のイメージセンサである場合の単位画素100-13の断面図である。

#### 【0164】

図18に示した単位画素100-13と、図14に示した単位画素100-9を比較するに、単位画素100-13の遮光膜351は、単位画素100-9の遮光膜303と異なる形状をしている点が異なり、他の部分は同一である。単位画素100-13の遮光膜351は、スリット形状に形成され、カラーフィルタ302の層内に形成されている。

#### 【0165】

遮光膜351をスリット形状とすることで、遮光膜351を偏光子として用いることができ、第2光電変換部103を偏光画素として用いることができる。

#### 【0166】

このような構成とした場合においても、低感度の第2光電変換部103上に遮光膜351を形成することで、第2光電変換部103に入射される光量が減少し、低感度化によるダイナミックレンジの拡大を実現することができる。また、遮光膜351をスリット形状とすることで、遮光膜351を偏光子として用いることができ、反射光などの不要な光の影響を除去することができる。

#### 【0167】

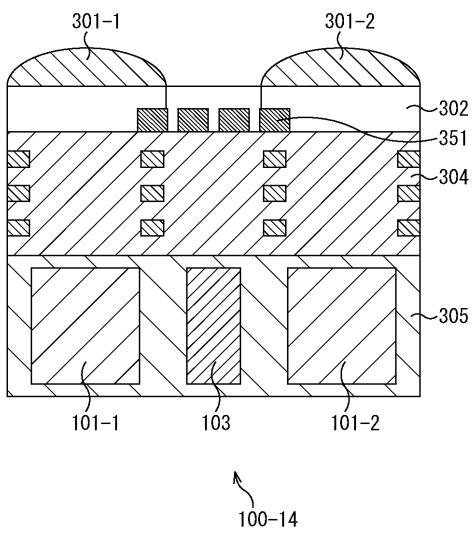

(単位画素の第14の構成)

次に、単位画素100の第14の構成について説明する。図19は、図18に示した単位画素100-13と同じく、CMOSイメージセンサ10が表面型のイメージセンサである場合の単位画素100-14の断面図である。

#### 【0168】

図19に示した単位画素100-14と、図18に示した単位画素100-13を比較するに、単位画素100-14は、単位画素100-13から第2光電変換部103上に形成されているオンチップレンズ301-3を削除した構成となされている点が異なり、他の部分は同一である。単位画素100-14の遮光膜351は、スリット形状で形成され、カラーフィルタ302の層内に形成されている。

#### 【0169】

第2光電変換部103上にオンチップレンズ301-3を形成しない構成とすることで、第2光電変換部103に光が集光されない状態で入射される構成となり、第2光電変換部103に入射される光量が減少する。このため、第2光電変換部103の感度が、さらに低下することになるため、ダイナミックレンジを拡大させることができ、反射光などの不要な光の影響を除去することができる。

#### 【0170】

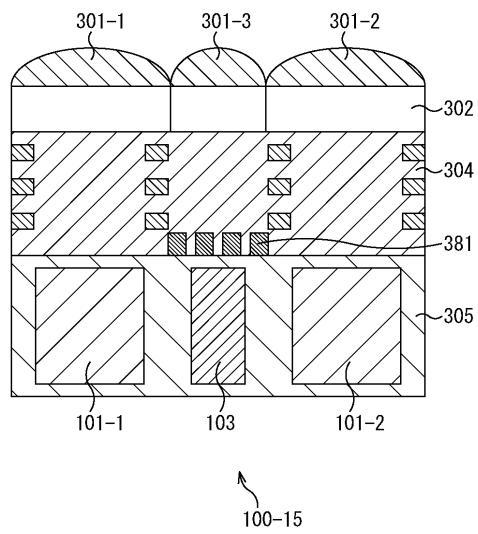

(単位画素の第15の構成)

次に、単位画素100の第15の構成について説明する。図20は、図18に示した単位画素100-13と同じく、CMOSイメージセンサ10が表面型のイメージセンサである場合の単位画素100-15の断面図である。

#### 【0171】

図20に示した単位画素100-15と、図18に示した単位画素100-13を比較するに、単位画素100-13の遮光膜351は、配線層304の図中上側に形成されているのに対して、単位画素100-15の遮光膜381は、配線層304の図中下側に形

10

20

30

40

50

成されている点が異なり、他の部分は同一である。すなわち、単位画素 100 - 15 の遮光膜 381 は、配線層 304 の下側にスリット形状で形成されている。

#### 【0172】

このような構成の表面型のイメージセンサにおいても、低感度の第2光電変換部 103 上に遮光膜 381 を形成することで、オンチップレンズ 301 - 3 を透過してきた光が、遮光膜 381 に吸収され、第2光電変換部 103 に入射される光量が減少する。このため、第2光電変換部 103 の低感度化によるダイナミックレンジを拡大させることができるとなる。また、遮光膜 381 をスリット形状とすることで、遮光膜 351 を偏光子として用いることができ、反射光などの不要な光の影響を除去することが可能となる。

#### 【0173】

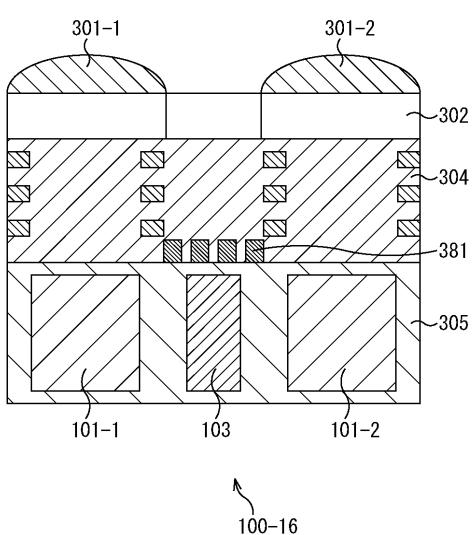

##### (単位画素の第 16 の構成)

次に、単位画素 100 の第 16 の構成について説明する。図 21 は、図 20 に示した単位画素 100 - 15 と同じく、CMOS イメージセンサ 10 が表面型のイメージセンサである場合の単位画素 100 - 16 の断面図である。

#### 【0174】

図 21 に示した単位画素 100 - 16 と、図 20 に示した単位画素 100 - 15 を比較するに、単位画素 100 - 16 は、単位画素 100 - 15 から第2光電変換部 103 上に形成されているオンチップレンズ 301 - 3 を削除した構成となされている点が異なり、他の部分は同一である。すなわち、端画素 100 - 16 の遮光膜 381 は、配線層 304 の下側にスリット形状で形成されている。

#### 【0175】

第2光電変換部 103 上にオンチップレンズ 301 - 3 を形成しない構成とすることで、第2光電変換部 103 に光が集光されない状態で入射される構成となり、第2光電変換部 103 に入射される光量が減少する。このため、第2光電変換部 103 の低感度化によるダイナミックレンジを拡大させることができるとなる。また、遮光膜 381 をスリット形状とすることで、遮光膜 381 を偏光子として用いることができ、反射光などの不要な光の影響を除去することが可能となる。

#### 【0176】

第 1 乃至第 16 の構成として示したように、低感度の第2光電変換部 103 上に、光を吸収する機能を有する膜を形成し、第2光電変換部 103 に入射される光の量を減少させることで、低感度化によるダイナミックレンジを拡大させることができるとなる。

#### 【0177】

また、遮光膜をスリット形状とすることで、偏光子として用いることができ、偏光子を設けることで反射光の影響（不要な光の影響）を除去し、低感度化によるダイナミックレンジを拡大することを同時に実現することができる。

#### 【0178】

また偏光子に遮光膜を使用することで、偏光子を金属で形成した場合より、効率よく直接、間接光を減光できる構成とすることができる。

#### 【0179】

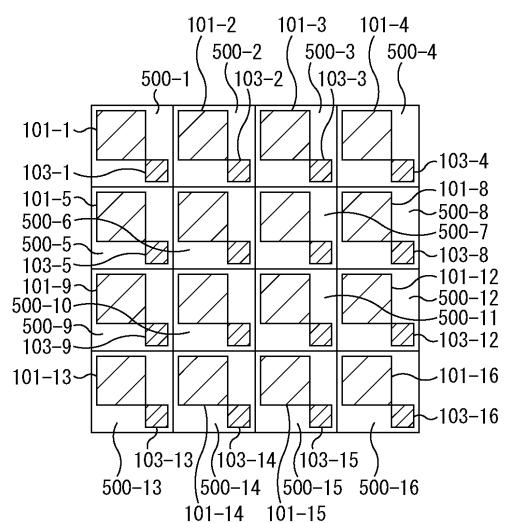

##### <第 1 、 第 2 光電変換部の配置について>

第 1 光電変換部 101 と第 2 光電変換部 103 を含む単位画素 100 は、例えば、図 22 に示すように配置されている。図 22 においては、単位画素 500 とし、単位画素 500 は、上記した単位画素 100 - 1 乃至 100 - 18 のいずれかであるとして説明を続ける。

#### 【0180】

図 22 では、 $4 \times 4$  の 16 個の単位画素 500 - 1 乃至 500 - 16 が配置されている例を示した。各単位画素 500 は、第 1 光電変換部 101 と第 2 光電変換部 103 を含む。例えば、単位画素 500 - 1 は、第 1 光電変換部 101 - 1 と第 2 光電変換部 103 - 1 を含む。

#### 【0181】

10

20

30

40

50

第1光電変換部101と第2光電変換部103は、受光面の大きさにより異なる感度となるように構成されている。すなわち、図22に示したように、第1光電変換部101の受光面は、第2光電変換部103の受光面よりも大きくなるように構成されている。

#### 【0182】

図22に示した例では、例えば、第1光電変換部101-1の右斜め下に第2光電変換部103-1が配置されている。図示はしていないが、第1光電変換部101-1の右横に第2光電変換部103-1が配置されるようにしても良い。また、他の配置関係でも良い。

#### 【0183】

単位画素500内で、第1光電変換部101と第2光電変換部103が配置されていない部分には、信号処理回路などを配置するようにしても良い。すなわち、異なる受光面積の第1光電変換部101と第2光電変換部103が、単位画素500内に配置されることで、余剰な領域が発生するが、その余剰な領域に信号処理回路などを配置することで、領域を有効利用するようにしても良い。

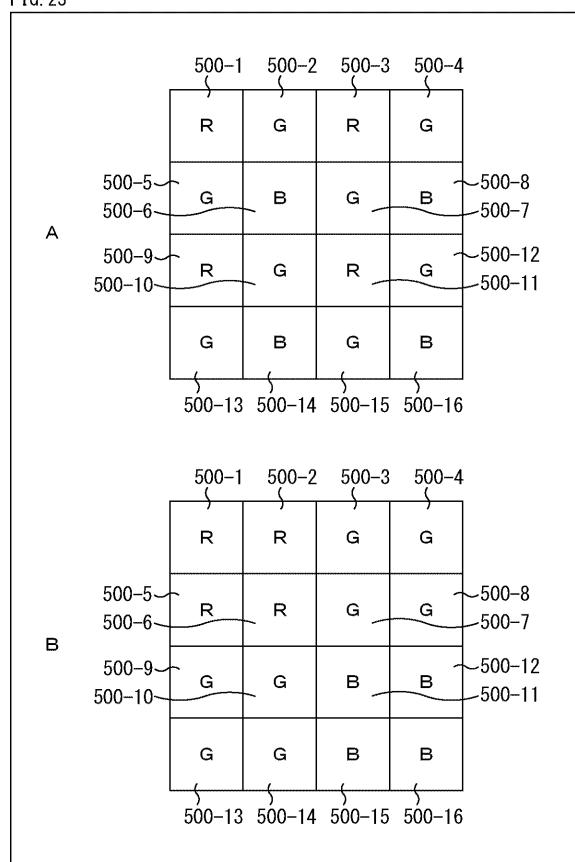

#### 【0184】

単位画素500上に配置されるカラーフィルタ202(302)の色は、例えば、ベイヤ-配列とすることができる。図23Aに示すように、単位画素500-1を赤色(R)、単位画素500-2を緑色(G)、単位画素500-5を緑色(G)、単位画素500-6を青色(B)とする色配置にすることができる。

#### 【0185】

このような色配置とされた場合、図22と図23Aを再度参照するに、例えば、単位画素500-1には、第1光電変換部101-1と第2光電変換部103-1が配置され、カラーフィルタ202(302、以下、202を例に挙げて説明する)の色は、赤色(R)である。このように、同一の単位画素500内に配置されている第1光電変換部101と第2光電変換部103は、同一のカラーフィルタ202の色とされている。

#### 【0186】

図23Bに示すように、4画素を同色としたベイヤ-配列としても良い。図23Bにおいては、単位画素500-1、単位画素500-2、単位画素500-5、単位画素500-6が赤色(R)、単位画素500-3、単位画素500-4、単位画素500-7、単位画素500-8が緑色(G)、単位画素500-9、単位画素500-10、単位画素500-13、単位画素500-14が緑色(G)、単位画素500-11、単位画素500-12、単位画素500-15、単位画素500-16が緑色(G)とされている。

#### 【0187】

ここでは、色配置として、ベイヤ-配列を例に挙げて説明したが、他の色配置であっても本技術を適用できる。

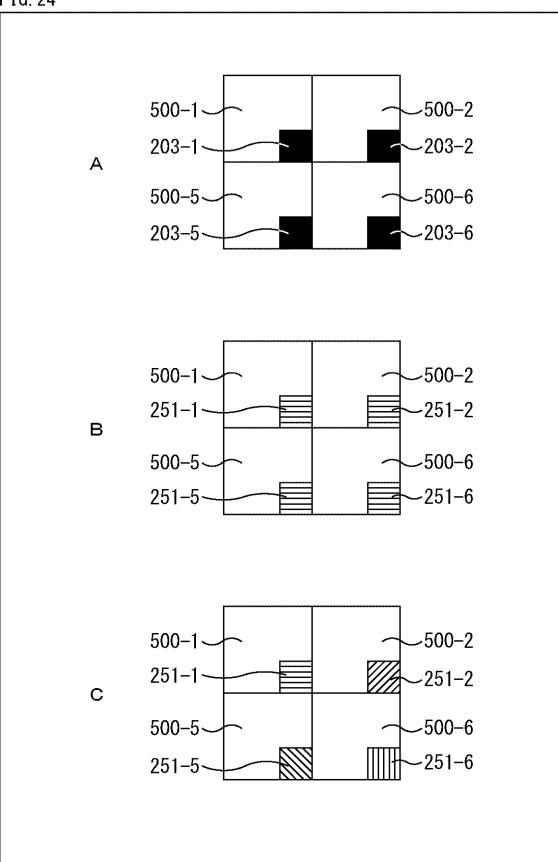

#### 【0188】

第2光電変換部103上には、上記したように、遮光膜が形成されている。遮光膜としては、図6などに示したスリット形状ではない遮光膜203(以下、ベタ形状の遮光膜203と記述する)と、図10などに示したスリット形状の遮光膜251がある。

#### 【0189】

なおここでは、ベタ形状の遮光膜として、遮光膜203(図6)を例に挙げて説明するが、遮光膜303(図14)、遮光膜331(図16)に対しても、以下の説明は適用される。また、スリット形状の遮光膜として、遮光膜251(図10)を例に挙げて説明するが、遮光膜351(図18)、遮光膜381(図20)に対しても、以下の説明は適用される。

#### 【0190】

ベタ形状の遮光膜203が形成されている場合、例えば、図24Aに示したように遮光膜203は形成される。図24Aでは、図22に示した4×4の16個の単位画素500-1乃至500-16のうちの左上側に配置されている4画素だけ図示してあるが、他の

10

20

30

40

50

画素も同様に遮光膜 203 が形成されている。

**【0191】**

図 24A に示すように、単位画素 500 内の第 2 光電変換部 103 上には、ベタ形状の遮光膜 203 が形成されている。例えば、図 24A に示した単位画素 500-1 内の右下に、第 2 光電変換部 103 が形成され、その第 2 光電変換部 103-1 が形成されている領域に、遮光膜 203-1 が形成される。

**【0192】**

なお、図 24A に示したように、遮光膜 203 は、画素外周領域でウェル (WELL) に接続されているように形成されるようにすることができる。

**【0193】**

スリット形状の遮光膜 251 が形成されている場合、例えば、図 24B に示したように遮光膜 251 が形成される。図 24B に示すように、単位画素 500 内の第 2 光電変換部 103 上には、スリット形状の遮光膜 251 が形成されている。

**【0194】**

図 24B に示したスリットの方向は、図中横方向であり、4 画素とも同方向のスリットとされている。このように、第 2 光電変換部 103 上に設けられる遮光膜 251 のスリットは、全て同一の方向を有しているように形成することができる。

**【0195】**

遮光膜 251 のスリットの方向を、画素毎に変えるようにしても良い。図 24C は、単位画素 500 内の第 2 光電変換部 103 上に、スリット形状の遮光膜 251 が形成されている場合であり、画素毎に異なる方向のスリットが形成されている場合の遮光膜 251 を示している。

**【0196】**

図 24C に示した単位画素 500-1 内の第 2 光電変換部 103-1 上に形成されている遮光膜 251-1 のスリットは、図中、横方向に形成されている。単位画素 500-2 内の第 2 光電変換部 103-2 上に形成されている遮光膜 251-2 のスリットは、図中、左斜め下方向に形成されている。

**【0197】**

単位画素 500-5 内の第 2 光電変換部 103-5 上に形成されている遮光膜 251-5 のスリットは、図中、右斜め下方向に形成されている。単位画素 500-6 内の第 2 光電変換部 103-6 上に形成されている遮光膜 251-6 のスリットは、図中、縦方向に形成されている。

**【0198】**

図 24C に示した例では、4 方向のスリットが形成されている場合を示している。図示していない他の画素も、 $2 \times 2$  の 4 画素内で、それぞれの画素上の遮光膜 251 は、異なる 4 方向のスリット形状で形成されている。なおここでは、4 方向を例に挙げて説明したが、さらに他の方向が追加されたり、2 方向または 3 方向など、遮光膜 251 のスリットの方向は、4 方向に限定されるわけではない。

**【0199】**

このように、画素毎にスリットの方向を変える、換言すれば、隣接する第 2 光電変換部 103 上に形成された遮光膜 251 のスリット方向が異なるようにすることで、異なる方向からの偏光を沮止することが可能となる。

**【0200】**

また、このように、画素毎にスリットの方向が変わるように形成した場合、例えば、図 24C に示した 4 画素単位で、それぞれ異なる方向のスリットが形成される場合、単位とされる 4 画素は同一色としても良い。すなわち、図 23B に示したように、4 画素が同一色とされたペイヤ - 配列とされ、同一色とされている 4 画素内の画素同士は異なる方向のスリットとされている構成としても良い。

**【0201】**

< 变形例 >

10

20

30

40

50

以上の説明では、1画素内に感度が異なる2つの光電変換部を設ける例を示したが、1画素内に3つ以上の感度が異なる光電変換部を設けることも可能である。また感度の違いは、遮光膜の材料の違いや膜厚の違いなどで調整することも可能である。

#### 【0202】

また、上記した実施の形態では、単位画素が行列状に配置されているCMOSイメージセンサに適用した場合を例に挙げて説明したが、本技術は、CMOSイメージセンサへの適用に限定されるものではない。すなわち、本技術は、単位画素が行列状に2次元配置されているX-Yアドレス方式の撮像装置全般に対して適用可能である。

#### 【0203】

さらに、本技術は、可視光の入射光量の分布を検知して画像として撮像する撮像装置への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する撮像装置全般に対して適用可能である。10

#### 【0204】

なお、撮像装置はワンチップとして形成された形態であってもよいし、撮像部と、信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

#### 【0205】

<撮像装置の使用例>

図25は、上述の撮像装置の使用例を示す図である。

#### 【0206】

上述した撮像装置は、例えば、以下のように、可視光や、赤外光、紫外光、X線等の光をセンシングする様々なケースに使用することができる。20

#### 【0207】

- ・デジタルカメラや、カメラ機能付きの携帯機器等の、鑑賞の用に供される画像を撮影する装置

- ・自動停止等の安全運転や、運転者の状態の認識等のために、自動車の前方や後方、周囲、車内等を撮影する車載用センサ、走行車両や道路を監視する監視カメラ、車両間等の測距を行う測距センサ等の、交通の用に供される装置

- ・ユーザのジェスチャを撮影して、そのジェスチャに従った機器操作を行うために、TVや、冷蔵庫、エアーコンディショナ等の家電に供される装置30

- ・内視鏡や、赤外光の受光による血管撮影を行う装置等の、医療やヘルスケアの用に供される装置

- ・防犯用途の監視カメラや、人物認証用途のカメラ等の、セキュリティの用に供される装置

- ・肌を撮影する肌測定器や、頭皮を撮影するマイクロスコープ等の、美容の用に供され装置

- ・スポーツ用途等向けのアクションカメラやウェアラブルカメラ等の、スポーツの用に供される装置

- ・畑や作物の状態を監視するためのカメラ等の、農業の用に供される装置

#### 【0208】

図26は、本技術を適用した電子機器の一例である撮像装置(カメラ装置)1001の構成例を示すブロック図である。40

#### 【0209】

図26に示すように、撮像装置1001は、レンズ群1011などを含む光学系、撮像素子1012、カメラ信号処理部であるDSP1013、フレームメモリ1014、表示装置1015、記録装置1016、操作系1017、及び、電源系1018等を有している。そして、DSP1013、フレームメモリ1014、表示装置1015、記録装置1016、操作系1017、及び、電源系1018がバスライン1019を介して相互に接続された構成となっている。

#### 【0210】

50

20

30

40

50

レンズ群 1011 は、被写体からの入射光（像光）を取り込んで撮像素子 1012 の撮像面上に結像する。撮像素子 1012 は、レンズ群 1011 によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。

#### 【0211】

表示装置 1015 は、液晶表示装置や有機 E L (electro luminescence) 表示装置等のパネル型表示装置から成り、撮像素子 1012 で撮像された動画または静止画を表示する。記録装置 1016 は、撮像素子 1012 で撮像された動画または静止画を、メモリカードやビデオテープや D V D (Digital Versatile Disk) 等の記録媒体に記録する。

#### 【0212】

操作系 1017 は、ユーザによる操作の下に、本撮像装置 1001 が持つ様々な機能について操作指令を発する。電源系 1018 は、D S P 1013、フレームメモリ 1014、表示装置 1015、記録装置 1016、及び、操作系 1017 の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

#### 【0213】

このような撮像装置 1001 は、ビデオカメラやデジタルスチルカメラ、更には、スマートフォン、携帯電話機等のモバイル機器向けカメラモジュールに適用される。そして、この撮像装置 1001 において、撮像素子 1012 として、上述した各実施形態に係る撮像装置を用いることができる。これにより、撮像装置 1001 の画質を向上させることができる。

#### 【0214】

本明細書において、システムとは、複数の装置により構成される装置全体を表すものである。

#### 【0215】

なお、本明細書に記載された効果はあくまで例示であって限定されるものではなく、また他の効果があってもよい。

#### 【0216】

なお、本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

#### 【0217】

なお、本技術は以下のよう構成も取ることができる。

##### (1)

複数の単位画素が配置されている画素アレイ部の前記単位画素が、

第 1 の光電変換部と、

前記第 1 の光電変換部より感度が低い第 2 の光電変換部と

を備え、

前記第 2 の光電変換部の光が入射する側に、遮光膜が形成されている

撮像装置。

##### (2)

前記第 2 の光電変換部上には、入射される光を集光するためのレンズは形成されていない

前記(1)に記載の撮像装置。

##### (3)

隣接する光電変換部への光の漏れ込みを防ぐ遮光壁が、光電変換部間に備えられる

前記(1)または(2)に記載の撮像装置。

##### (4)

前記遮光膜は、スリット形状である

前記(1)乃至(3)のいずれかに記載の撮像装置。

##### (5)

隣接する第 2 の光電変換部上に形成されている前記遮光膜のスリットの方向は、異なる

方向とされている

10

20

30

40

50

前記(4)に記載の撮像装置。

(6)

裏面型のイメージセンサである

前記(1)乃至(5)のいずれかに記載の撮像装置。

(7)

表面型のイメージセンサである

前記(1)乃至(5)のいずれかに記載の撮像装置。

(8)

前記遮光膜は、前記第2の光電変換部上に形成されている配線層の下側または上側に形成されている

10

前記(7)に記載の撮像装置。

(9)

前記遮光膜は、アモルファスシリコン膜、ポリシリコン膜、Ge膜、GaN膜、CdTe膜、GaAs膜、InP膜、CuInSe<sub>2</sub>膜、Cu<sub>2</sub>S、CIGS膜、非導体構造のカーボン膜、黒色レジスト膜、有機光電変換膜、または金属膜である

前記(1)乃至(8)のいずれかに記載の撮像装置。

【符号の説明】

【0218】

10 CMOSイメージセンサ, 11 画素アレイ部, 12 垂直駆動部, 13

カラム処理部, 14 水平駆動部, 15 システム制御部, 16 画素駆動線,

17 垂直信号線, 18 信号処理部, 19 データ格納部, 100 単位画素

, 101 第1光電変換部, 102 第1の転送ゲート部, 103 第2光電変換

部, 104 第2転送ゲート部, 105 第3転送ゲート部, 106 電荷蓄積部

, 107 リセットゲート部, 108 FD部, 109 増幅トランジスタ, 1

10 選択トランジスタ, 151 第4転送ゲート部, 203, 251, 303, 3

31, 351, 381 遮光膜

20

【図 1】

FIG. 1

【図 2】

FIG. 2

【図 3】

FIG. 3

【図 4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

100-4

【図10】

FIG. 10

100-5

【図11】

FIG. 11

100-6

【図12】

FIG. 12

100-7

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

FIG. 15

【図16】

FIG. 16

【図 17】

FIG. 17

【図 18】

FIG. 18

【図 19】

FIG. 19

【図 20】

FIG. 20

【図21】

FIG. 21

【図22】

FIG. 22

【図23】

FIG. 23

【図24】

FIG. 24

【図 25】

FIG. 25

【図 26】

FIG. 26

---

フロントページの続き

(72)発明者 名取 太知

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 高橋 裕嗣

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 丸山 俊介

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 丸山 康

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 田邊 顕人

(56)参考文献 特表2011-526105 (JP, A)

特開2013-175494 (JP, A)

特開2012-009539 (JP, A)

特開2014-175553 (JP, A)

特開2010-109295 (JP, A)

特開2005-086083 (JP, A)

特開2015-153859 (JP, A)

特開平05-175471 (JP, A)

特開平10-074926 (JP, A)

特開平03-117284 (JP, A)

特開2005-086082 (JP, A)

特開2004-193762 (JP, A)

特開2007-135200 (JP, A)

特開平09-162381 (JP, A)

特開2012-038981 (JP, A)

特開2011-243996 (JP, A)

特開2014-229810 (JP, A)

米国特許出願公開第2011/0175981 (US, A1)

特開2011-199643 (JP, A)

特開2015-065270 (JP, A)

特開2005-116568 (JP, A)

特開2004-032059 (JP, A)

特開2001-267543 (JP, A)

特開2014-225667 (JP, A)

特開2015-095879 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/355

H04N 5/369