(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2011-0071710

(43) 공개일자 2011년06월29일

(51) Int. Cl.

G11C 11/15 (2006.01) H01L 27/115 (2006.01)

(21) 출원번호 10-2009-0128344

(22) 출원일자 2009년12월21일

심사청구일자 없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

한국과학기술원

대전 유성구 구성동 373-1

(72) 발명자

김광석

경기도 성남시 분당구 삼평동 이지더원아파트

204-702

이택동

대전광역시 유성구 과학로 335 한국과학기술원 신

소재공학과

(뒷면에 계속)

(74) 대리인

리엔목특허법인

전체 청구항 수 : 총 28 항

(54) 수직 자기터널접합과 이를 포함하는 자성소자 및 그 제조방법

### (57) 요 약

수직 MTJ(Magnetic Tunnel Junction)와 이를 포함하는 자성소자 및 그 제조방법에 관해 개시되어 있다. 개시된 수직 MTJ는 상부 및 하부 자성층 중 어느 한 자성층에 자유층을 포함하고, 터널링층과 자유층 사이에 분극 강화층(PEL)과 교환 차단층(EBL)이 적층되어 있다. 상기 교환 차단층은 비정질의 비자성층일 수 있다. 상기 분극 강화층은 Fe층, 체심입방(bcc) 구조를 갖는 Fe계 합금층, FeCoB계 비정질 합금층 및 L21 타입 헤슬러(Heusler) 합금층 중 어느 하나일 수 있다. 상기 비정질 비자성층은 지르코늄 베이스 비정질 합금층, 티타늄 베이스 비정질 합금층, 팔라듐 베이스 비정질 합금층 및 알루미늄 베이스 비정질 합금층 중 어느 하나일 수 있다. 또한, 상기 비정질 비자성층은 전체적으로는 비정질이지만, 국소적으로는 나노 결정구조를 갖는 것일 수 있다.

### 대 표 도 - 도3

(72) 발명자

김우진

대전광역시 유성구 과학로 335 한국과학기술원 신

소재공학과

서준애

경기 화성시 기산동 464 행림마을 삼성래미안1차아

파트 107-1501

김기원

경기 수원시 영통구 영통동 황골마을2단지 한국아

파트 211-2008

김선옥

대전광역시 유성구 과학로 335 한국과학기술원 신

소재공학과

---

## 특허청구의 범위

### 청구항 1

하부 자성층;

상기 하부 자성층 상에 형성된 터널링층; 및

상기 터널링층 상에 형성된 상부 자성층을 포함하고,

상기 상부 및 하부 자성층 중 어느 한 자성층은 스핀 분극 전류에 의해 자화 방향이 바뀌고 수직 자기이방성을 나타내는 자유층을 포함하고,

상기 터널링층과 상기 자유층 사이에 분극 강화층(PEL)과 교환 차단층(EBL)이 적층되어 있는 수직 MTJ.

### 청구항 2

제 1 항에 있어서,

상기 교환 차단층은 비자성층인 수직 MTJ.

### 청구항 3

제 1 항에 있어서,

상기 교환 차단층의 두께는 0.2nm~1nm인 수직 MTJ.

### 청구항 4

제 1 항에 있어서,

상기 분극 강화층은 Fe층, 체심입방(bcc) 구조를 갖는 Fe계 합금층, FeCoB계 비정질 합금층 및 L21 타입 헤슬러(Heusler) 합금층 중 어느 하나인 수직 MTJ.

### 청구항 5

제 2 항에 있어서,

상기 교환 차단층은 비정질 비자성층인 수직 MTJ.

### 청구항 6

제 5 항에 있어서,

상기 비정질 비자성층은 지르코늄 베이스 비정질 합금층, 티타늄 베이스 비정질 합금층, 팔라듐 베이스 비정질 합금층 및 알루미늄 베이스 비정질 합금층 중 어느 하나인 수직 MTJ.

### 청구항 7

제 5 항에 있어서,

상기 비정질 비자성층은 Ta, Mo, W, Nb 및 V 중 어느 하나의 층 또는 이들의 합금층인 수직 MTJ.

### 청구항 8

제 5 항에 있어서,

상기 비정질 비자성층은 전체적으로는 비정질이지만, 국소적으로는 나노 결정구조를 갖는 수직 MTJ.

### 청구항 9

제 5 항에 있어서,

상기 비정질 비자성층은 Cr, Cu, Ta, Mo, W, Nb 및 V 중 어느 하나의 층 또는 이들의 합금층인 수직 MTJ.

#### 청구항 10

제 6 항 또는 제 7 항에 있어서,

상기 분극 강화층은 비정질의 FeCoB계 합금층인 수직 MTJ.

#### 청구항 11

제 9 항에 있어서,

상기 분극 강화층은 Fe계 합금층인 수직 MTJ.

#### 청구항 12

제 6 항에 있어서,

상기 지르코늄 베이스 비정질 합금층은 Zr-Ti-Al-TM층 및 Zr-Al-TM층 중 어느 하나인 수직 MTJ.

#### 청구항 13

제 6 항에 있어서,

상기 티타늄 베이스 비정질 합금층은 Ti-Ni-Sn-Be-Zr층 및 Ti-Ni-Cu층 중 어느 하나인 수직 MTJ.

#### 청구항 14

제 6 항에 있어서,

상기 팔라듐 베이스 비정질 합금층은 Pd-Cu-Ni-P층 및 Pd-Cu-B-Si층 중 어느 하나인 수직 MTJ.

#### 청구항 15

제 6 항에 있어서,

상기 알루미늄 베이스 비정질 합금층은 Al-Ni-Ce층 및 Al-V-Fe층 중 어느 하나인 수직 MTJ.

#### 청구항 16

제 1 항에 있어서,

상기 상부 및 하부 자성층 중에서 상기 자유층을 포함하지 않는 자성층은 상기 터널링층과 접촉되는 다른 분극 강화층을 포함하는 수직 MTJ.

#### 청구항 17

제 16 항에 있어서,

상기 터널링층과 상기 자유층 사이의 분극 강화층과 상기 다른 분극 강화층은 동일한 물질이거나 다른 물질인 수직 MTJ.

#### 청구항 18

스위칭 소자와 이에 연결되고 정보를 저장하는 스토리지 노드를 포함하는 자기 메모리 소자에 있어서,

상기 스토리지 노드는 청구항 1의 수직 MTJ인 자기 메모리 소자.

#### 청구항 19

MTJ를 자기 헤드에 포함하는 MPM에 있어서, 상기 MTJ는 청구항 1의 수직 MTJ인 MPM.

#### 청구항 20

MTJ를 이용하여 논리연산을 수행하는 자성 논리소자(logic device)에 있어서,

상기 MTJ는 청구항 1의 수직 MTJ인 자성 논리소자.

## 청구항 21

하부층 상에 하부 자성층을 형성하는 단계;

상기 하부 자성층 상에 터널링층을 형성하는 단계; 및

상기 터널링층 상에 상부 자성층을 형성하는 단계를 포함하고,

상기 하부 자성층을 형성하는 단계와 상기 상부 자성층을 형성하는 단계 중 어느 한 단계는 스픈 분극 전류에 의해 자화 방향이 바뀌고 수직 자기이방성을 나타내는 자유층을 형성하는 단계를 포함하고,

상기 터널링층과 상기 자유층 사이에 분극 강화층(PEL)과 교환 차단층(EBL)을 적층하는 수직 MTJ의 제조방법.

## 청구항 22

제 21 항에 있어서,

상기 자유층을 포함하지 않는 자성층을 형성하는 단계에서 상기 터널링층과 접촉되는 다른 분극 강화층을 형성하는 수직 MTJ의 제조방법.

## 청구항 23

제 21 항에 있어서,

상기 교환 차단층은 비정질 비자성층으로 형성하는 수직 MTJ의 제조방법.

## 청구항 24

제 21 항에 있어서,

상기 분극 강화층은 Fe층, 체심입방(bcc) 구조를 갖는 Fe계 합금층, FeCoB계 비정질 합금층 및 L21 타입 헤슬러(Heusler) 합금층 중 어느 하나로 형성하는 수직 MTJ 제조방법.

## 청구항 25

제 23 항에 있어서,

상기 비정질 비자성층은 지르코늄 베이스 비정질 합금층, 티타늄 베이스 비정질 합금층, 팔라듐 베이스 비정질 합금층 및 알루미늄 베이스 비정질 합금층 중 어느 하나인 수직 MTJ의 제조방법.

## 청구항 26

제 23 항에 있어서,

상기 비정질 비자성층은 Ta, Mo, W, Nb 및 V 중 어느 하나의 층 또는 이들의 합금층인 수직 MTJ의 제조방법.

## 청구항 27

제 26 항에 있어서,

상기 비정질 비자성층은 전체적으로는 비정질이지만, 국소적으로는 나노 결정구조를 갖는 수직 MTJ의 제조방법.

## 청구항 28

제 23 항에 있어서,

상기 비정질 비자성층은 Cr, Cu, Ta, Mo, W, Nb 및 V 중 어느 하나의 층 또는 이들의 합금층인 수직 MTJ의 제조방법.

## 명세서

### 발명의 상세한 설명

### 기술 분야

[0001] 본 발명의 일 실시예는 자성소자에 관한 것으로써, 보다 자세하게는 수직 MTJ(Magnetic Tunnel Junction)와 이를 포함하는 자성소자와 그 제조방법에 관한 것이다.

### 배경기술

[0002] MTJ에서의 터널자기저항(tunneling magnetoresistance)(이하, TMR)현상을 이용하는 MRAM(Magnetic Random Access Memory)은 비휘발성을 갖고, 고속동작이 가능하며, 고집적을 기대할 수 있는 차세대 비휘발성 메모리이다.

[0003] 기존의 자기장(magnetic field)으로 정보를 저장하는 통상의 MRAM의 경우, 사이즈 축소(scability)에 어려움이 있다.

[0004] 그러나 최근 소개되고 있는 스핀 전류(spin current)의 스핀 트랜스퍼 토크(spin transfer torque)에 의해 정보를 저장하는 STT-MRAM(spin transfer torque MRAM)의 경우, 사이즈 축소의 어려움을 해결할 수 있을 것으로 평가되고 있다.

[0005] 그러나 STT-MRAM은 자성층은 사이즈가 작기 때문에, 자성층은 열적 요동(thermal fluctuation) 현상을 겪을 수 있다.

[0006] 자성층의 열적 안정성은  $K_u V / K_B T$ 에 비례한다. 따라서 자기 이방성 에너지(magnetic anisotropy,  $K_u$ )가 클수록 그리고 부피(V)가 클수록 열적으로 안정하게 된다.

[0007] 이에 따라 50nm이하의 셀 사이즈를 갖는 고 집적 MRAM에서는 큰 자기 이방성 에너지(high  $K_u$ )를 갖는 수직 자기 이방성(Perpendicular Magnetic Anisotropy, PMA) 물질이 사용된다.

[0008] PMA 물질을 이용하여 MTJ구조를 제작할 경우, PMA 물질의 스핀 분극(spin polarization) 값이 수평 자기이방성(in-plane magnetic anisotropy, IMA) 물질, 예를 들면 CoFeB보다 낮다. 따라서 PMA 물질/터널링막(tunnel barrier)/PMA 물질의 구조에서는 큰 TMR을 기대하기 어려운 것으로 알려져 있다.

[0009] 이에, PMA 물질의 큰 자기이방성에너지(high  $K_u$ )를 이용하면서 큰 TMR을 확보하기 위해 분극 강화층(Polarization Enhancing Layer, PEL)을 PMA 물질과 터널링막 사이에 삽입하는 기술이 최근 소개되었다.

### 발명의 내용

#### 해결 하고자하는 과제

[0010] 본 발명의 일 실시예는 PMA 물질을 포함하는 MTJ를 제공한다.

[0011] 본 발명의 일 실시예는 이러한 MTJ를 포함하는 자성소자를 제공한다.

[0012] 본 발명의 일 실시예는 그러한 MTJ 및 자성소자의 제조방법을 제공한다.

#### 과제 해결수단

[0013] 본 발명의 일 실시예에 의한 MTJ는 상부 및 하부 자성층 중 어느 한 자성층에 자유층을 포함하고, 터널링층과 자유층 사이에 분극 강화층(PEL)과 교환 차단층(EBL)이 적층되어 있다. 상기 교환 차단층은 비정질의 비자성층일 수 있다.

[0014] 상기 분극 강화층은 Fe층, 체심입방(body-centered cubic, bcc) 구조를 갖는 Fe계 합금층, FeCoB계 비정질 합금층 및 L21 타입 헤슬러(Heusler) 합금층 중 어느 하나일 수 있다.

[0015] 상기 비정질 비자성층은 지르코늄 베이스 비정질 합금층, 티타늄 베이스 비정질 합금층, 팔라듐 베이스 비정질 합금층 및 알루미늄 베이스 비정질 합금층 중 어느 하나일 수 있다. 또한, 상기 비정질 비자성층은 전체적으로는 비정질이지만, 국소적으로는 나노 결정구조를 갖는 것일 수 있다.

[0016] 상기 상부 및 하부 자성층 중에서 상기 자유층을 포함하지 않는 자성층은 상기 터널링층과 접촉되는 다른 분극 강화층을 포함할 수 있다.

[0017] 본 발명의 일 실시예에 의한 자성소자는 스위칭 소자와 이에 연결되고 정보를 저장하는 스토리지 노드를 포함하는 자기 메모리 소자로써, 상기 스토리지 노드는 적어도 상기 교환 차단층을 포함하는 수직 MTJ일 수 있다.

- [0018] 본 발명의 다른 실시예에 의한 자성소자는 MTJ를 자기 헤드에 포함하는 MPM으로써, 상기 MTJ는 적어도 상기 교환 차단층을 포함하는 수직 MTJ일 수 있다.

- [0019] 본 발명의 또 다른 실시예에 의한 자성소자는 MTJ를 이용하여 논리연산을 수행하는 자성 논리소자(logic device)로써, 상기 MTJ는 적어도 상기 교환 차단층을 포함하는 수직 MTJ일 수 있다.

- [0020] 본 발명의 일 실시예에 의한 수직 MTJ의 제조방법은 하부층 상에 하부 자성층을 형성하는 단계, 상기 하부 자성층 상에 터널링층을 형성하는 단계 및 상기 터널링층 상에 상부 자성층을 형성하는 단계를 포함하고, 상기 하부 자성층을 형성하는 단계와 상기 상부 자성층을 형성하는 단계 중 어느 한 단계는 스핀 분극 전류에 의해 자화방향이 바뀌고 수직 자기이방성을 나타내는 자유층을 형성하는 단계를 포함하고, 상기 터널링층과 상기 자유층 사이에 분극 강화층(PEL)과 교환 차단층(EBL)을 적층한다.

- [0021] 이러한 제조방법에서 상기 자유층을 포함하지 않는 자성층을 형성하는 단계에서 상기 터널링층과 접촉되는 다른 분극 강화층을 형성할 수 있다.

- [0022] 상기 교환 차단층은 비정질 비자성층으로 형성할 수 있다.

- [0023] 상기 분극 강화층은 Fe층, 체심입방구조를 갖는 Fe계 합금층, FeCoB계 비정질 합금층 및 L21 타입 헤슬러(Heusler) 합금층 중 어느 하나로 형성할 수 있다.

## 효과

- [0024] 본 발명의 일 실시예에 의한 MTJ를 이용하면, 스위칭 시간을 줄일 수 있다. 곧, MTJ의 스핀 토크 스위칭(spin torque switching)이 빨라질 수 있다. 또한, MTJ의 상태 반전에 필요한 스핀 전류를 줄일 수 있다. 이에 따라 본 발명의 일 실시예에 의한 MTJ를 포함하는 자성소자, 예컨대 자기 메모리 소자의 동작속도를 증가시킬 수 있고, 동작에 필요한 전류는 줄일 수 있다. 아울러 분극 강화층을 구비하는 바, 큰 TMR을 얻을 수 있다.

## 발명의 실시를 위한 구체적인 내용

- [0025] 이하, 본 발명의 일 실시예에 의한 MTJ와 이를 포함하는 자성소자와 그 제조방법을 첨부된 도면들을 참조하여 상세하게 설명한다. 이 과정에서 도면에 도시된 층이나 영역들의 두께는 명세서의 명확성을 위해 과장되게 도시된 것이다.

- [0026] 먼저, 본 발명의 일 실시예에 의한 수직 MTJ를 설명한다.

- [0027] 이에 앞서, 도 1 및 도 2를 살펴본다.

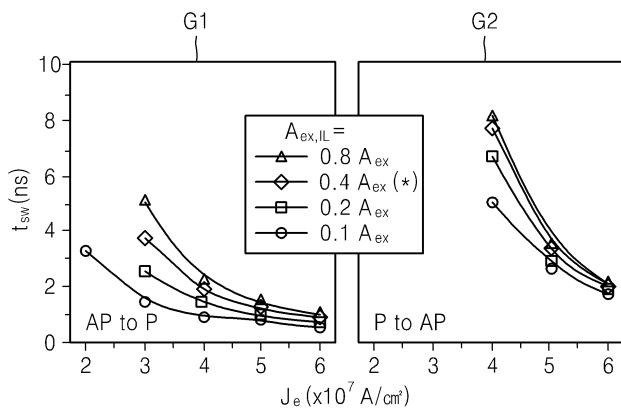

- [0028] 도 1은 분극 강화층(Polarization Enhancing Layer)과 PMA 물질의 교환 상호작용(exchange interaction)과 스위칭 시간(switching time) 사이의 관계를 보여준다.

- [0029] 도 1에서 가로축은 스핀전류밀도(Je)를 나타내고, 세로축은 스위칭 시간을 나타낸다.

- [0030] 도 1에서 제1 그래프 군(G1)은 수직 MTJ의 분극 강화층과 PMA 물질 사이의 교환 상호작용(Aex)이 주어진 값일 때, 수직 MTJ의 자화방향이 고정된 자성층의 자화방향과 스핀전류에 따라 자화방향이 자유롭게 변화될 수 있는 자유층의 자화방향이 반평행에서 평행으로 반전될 때의 스위칭 시간을 보여준다. 제2 그래프 군(G2)은 상기 주어진 교환 상호작용에서 상기 각 층의 자화방향이 평행에서 반평행으로 반전될 때의 스위칭 시간을 보여준다.

- [0031] 제1 및 제2 그래프 군(G1, G2)에서 제1 그래프( $\Delta$ )는 교환 상호작용이  $0.8A_{ex}$ 일 때, 스핀전류에 따른 스위칭 시간을 나타내고, 제2 그래프( $\diamond$ )는 교환 상호작용이  $0.4A_{ex}$  일 때, 제3 그래프( $\square$ )는 교환 상호작용이  $0.2A_{ex}$ 일 때, 제4 그래프( $\circ$ )는 교환 상호작용이  $0.1A_{ex}$ 일 때, 스핀전류에 따른 스위칭 시간을 나타낸다.

- [0032] 도 1을 참조하면, 분극 강화층과 PMA 물질의 교환 상호작용의 세기, 곧 교환 필드(exchange field)의 세기가 커질수록, 스핀 토크(spin torque)에 의한 스위칭 시간이 많이 걸리는 것을 알 수 있다. 이것은 교환 상호작용(Aex)의 세기가 약할수록 수직 MTJ에서 스핀 토크에 의한 스위칭이 더 잘 일어나는 것을 의미한다. 상기 수직 MTJ는 PMA 물질을 포함하는 MTJ를 의미한다.

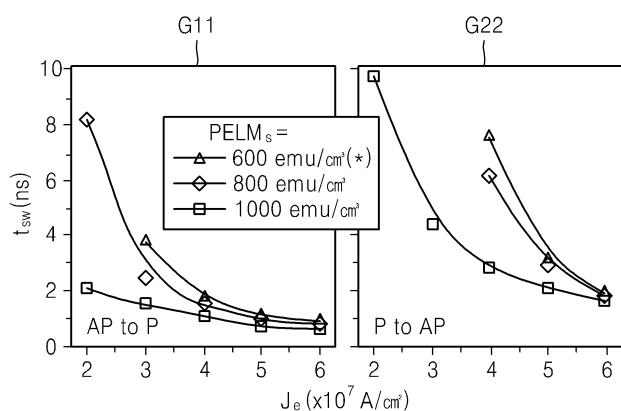

- [0033] 도 2는 PMA물질/분극 강화층/터널링막/분극 강화층/PMA물질의 구조에서 분극 강화층의 포화 자화(saturation magnetization,  $M_s$ )에 따른 스핀 토크 스위칭 특성을 보여준다.

- [0034] 도 2에서 가로축은 스핀전류밀도(Je)를 나타내고, 세로축은 스위칭 시간을 나타낸다.

- [0035] 도 2에서 제1 그래프 군(G11)은 수직 MTJ의 분극 강화층의 Ms가 주어진 값일 때, 수직 MTJ의 자화방향이 고정된 자성층의 자화방향과 스픈전류에 따라 자화 방향이 자유롭게 변화될 수 있는 자유층의 자화방향이 반평행에서 평행으로 반전될 때의 스위칭 시간을 보여준다. 또한, 제2 그래프 군(G22)은 상기 주어진 Ms 값에서 상기 각 층의 자화방향이 평행에서 반평행으로 반전될 때의 스위칭 시간을 보여준다.

- [0036] 제1 및 제2 그래프 군(G11, G22)에서 제1 그래프( $\triangle$ )는 분극 강화층의 Ms 값이  $600\text{emu}/\text{cm}^3$ 일 때, 스픈전류에 따른 스위칭 시간을 나타내고, 제2 그래프( $\diamond$ )는 분극 강화층의 Ms 값이  $800\text{emu}/\text{cm}^3$ 일 때, 제3 그래프( $\square$ )는 분극 강화층의 Ms 값이  $1000\text{emu}/\text{cm}^3$ 일 때, 스픈전류에 따른 스위칭 시간을 나타낸다.

- [0037] 도 2를 참조하면, 분극 강화층의 Ms 값이 커질수록 스픈 토크 스위칭이 빨라지는 것을 알 수 있다. 따라서 Ms 값이 큰 분극 강화층이 스픈 토크 스위칭에 더 유리함을 알 수 있다.

- [0038] 도 1 및 도 2를 결과를 참조하면, Ms 값이 큰 분극 강화층을 사용하고, 이러한 분극 강화층과 PMA 물질 사이의 교환 상호작용을 줄일 수 있는 수직 MTJ 구조에서 스픈 토크 스위칭이 더 잘 일어날 것으로 보인다.

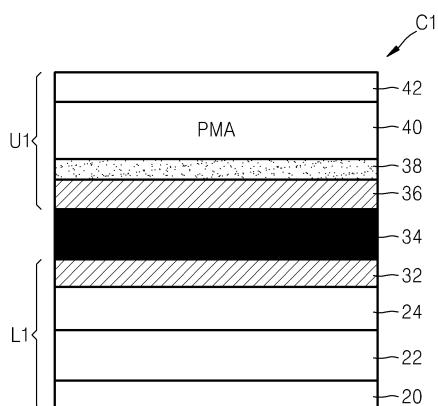

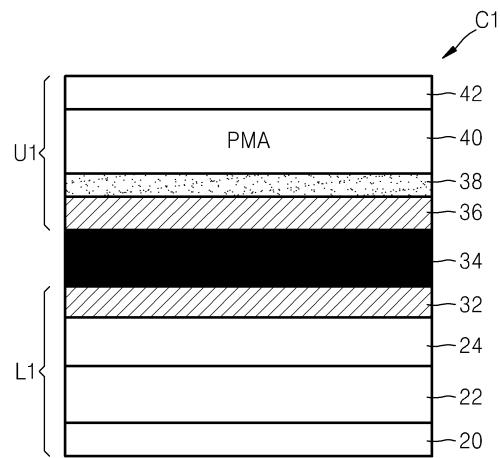

- [0039] 도 3은 도 1 및 도 2의 결과를 바탕으로 하여 형성한 것으로, 본 발명의 일 실시예에 의한 수직 MTJ 구조를 보여준다.

- [0040] 도 3을 참조하면, 제1 MTJ(C1)는 순차적으로 적층된 하부 자성층(L1), 터널링층(34) 및 상부 자성층(U1)을 포함한다. 하부 자성층(L1)은 씨드층(20)과 그 위에 순차적으로 적층된 피닝층(22), 핀드층(24) 및 제1 PEL(32)을 포함할 수 있다. 피닝층(22)과 핀드층(24)은 PMA 물질층일 수 있다. 제1 PEL(32)에 의해 스픈전류는 스픈특성을 잃지 않고 상부 자성층(U1)에 전달될 수 있다. 터널링층(34)은, 예를 들면 MgO층 또는 알루미늄 산화물층(예,  $\text{Al}_2\text{O}_3$ )일 수 있다. 상부 자성층(U1)은 터널링층(34) 상에 형성된 제2 PEL(36)과 그 위에 순차적으로 적층된 교환 차단층(exchange blocking layer, EBL)(38), PMA 물질의 자유층(free magnetic layer)(40) 및 캡핑층(42)을 포함할 수 있다. 제2 PEL(36)은 제1 PEL(32)과 동일한 물질일 수 있다. 제2 PEL(36)은 분극 강화층이다. 따라서 스픈전류에 의한 자유층(40)의 스픈 분극률을 높일 수 있고, 이에 따라 TMR이 커질 수 있다. 또한, 제2 PEL(36)은 큰 Ms 값을 갖는다. 따라서 도 2에서 설명한 바와 같이 스픈 토크에 의한 스위칭이 빨라질 수 있다. 교환 차단층(38)은 자유층(40)과 제2 PEL(36) 사이의 교환 상호작용(Aex)을 차단하거나 감소시킨다. 곧, 교환 차단층(38)은 자유층(40)과 제2 PEL(36) 사이의 교환 필드(exchange field)를 차단하거나 그 세기를 감소시킨다. 따라서 도 1에서 설명한 바에 따라 스픈 토크에 의한 자유층(40)의 스위칭은 더욱 빨라질 수 있다. 자유층(40)과 제2 PEL(36) 사이의 교환 상호작용이 차단되거나 감소될 경우, 자유층(40)에 의한 제2 PEL(36)의 자화 구속력이 사라지거나 약화되기 때문에, 교환 차단층(38)이 존재하지 않을 때보다 작은 값의 스픈 분극 전류를 사용하더라도 제2 PEL(36)의 수직 자화 상태를 반전시킬 수 있고, 결국 자유층(40)의 자화 상태를 반전시킬 수 있다. 자유층(40)의 자화 상태는 정보를 의미하므로, 교환 차단층(38)이 존재함으로써 정보를 기록하기 위한 혹은 스픈 토크 스위칭을 위한 스픈 분극 전류를 줄일 수 있다. 캡핑층(42)은 자유층(40) 혹은 제1 MTJ(C1)의 표면을 보호하기 위한 보호막일 수 있다.

- [0041] 자유층(40)은 수직 자기 이방성 물질층일 수 있다. 예를 들면, 자유층(40)은 FePt, CoPt 등과 같이 L10 구조(L10 structure)의 결정화된 구조(ordered structure)를 갖는 물질층일 수 있다. 자유층(40)은 또한 Co/Pt층, Co/Ni층 또는 Co/Pd층과 같은 다층 시스템(multilayer system) 혹은 다층의 적층구조를 갖는 물질층일 수도 있다. Co/Pt층은 Co층과 Pt층이 순차적으로 적층된 물질층을 의미하고, Co/Ni층과 Co/Pd층도 마찬가지다. 자유층(40)은 또한 Tb, Gd 등과 같은 희토류(Rare-Earth)와 Fe, Co, Ni 등과 같은 전이금속을 포함하는 합금층일 수도 있다. 자유층(40)으로 사용되는 이러한 PMA 물질들은 대부분  $10^6 \sim 10^8 \text{ emu/cc}$  정도의 충분한  $K_u$  값을 갖고 있다. 피닝층(22) 및/또는 핀드층(24)은 자유층(40)과 동일한 물질일 수 있다.

- [0042] 제2 PEL(36)은 Ms가 큰 Fe층, 체심입방구조를 갖는 Fe계 합금층, FeCoB계 비정질 합금층 또는 L21 타입 헤슬러(Heusler) 합금층일 수 있다. 제2 PEL(36)은 자유층(40)의 스트레이 필드(stray field) 및 자유층(40)과의 교환 필드에 의해 수직 자화를 나타낸다. 그러므로 제2 PEL(36)은 상기 스트레이 필드 또는 상기 교환 필드에 의해 수직 자화될 수 있을 정도의 두께를 가질 수 있다. 제2 PEL(36)의 두께는 열처리 온도 및 시간에 따라서, 자유층(40)으로 사용되는 PMA 물질의 이방성상수, Ms 및 두께에 따라서 달라질 수 있다. 제2 PEL(36)의 두께는 0.3~3nm 정도일 수 있지만, 이 범위로 한정되지 않을 수도 있다.

- [0043] 제2 PEL(36)이 Fe계 합금층일 때, 제2 PEL(36)은, 예를 들면 철(Fe)에 10% 이하로 바나듐(V)과 몰리브덴(Mo)

등을 함유하여 Ms를 제어할 수 있는 합금층(예: FeV층, FeMo층 등)일 수 있고, FeCo층이나 FeNi층일 수도 있다.

[0044] 제2 PEL(36)이 FeCoB계 비정질 합금층일 때, 제2 PEL(36)은, 예를 들면 Fe가 풍부한(Fe rich) FeCoB층(Fe:40% 이상, B:10-30%) 또는 Co가 풍부한(Co rich) FeCoB층(Co:40% 이상, B:10-30%)일 수 있다.

[0045] 제2 PEL(36)이 L21 타입 허슬러 합금층일 때, 제2 PEL(36)은, 예를 들면  $Co_2MnSi$ 층,  $Co_2SiAl$ 층,  $Co_2Cr_{(1-x)}Fe_{(x)}Al$ 층 또는  $Co_2FeAl_{(1-x)}Si_{(x)}$ 층일 수 있다.

[0046] 상술한 제2 PEL(36)의 물질층들은 제1 PEL(32)의 물질층으로 사용될 수도 있다. 이때, 제1 및 제2 PEL(32, 36)은 동일한 물질층이거나 다른 물질층일 수 있다. 예를 들면, 제1 및 제2 PEL(32, 36)은 모두 Fe계 합금층일 수 있고, 제1 PEL(32)은 Fe계 합금층인 반면, 제2 PEL(36)은 FeCoB계 합금층일 수도 있다.

[0047] 제1 MTJ(C1)에 스핀 분극 전류가 인가되면  $K_u$ 가 작고 Ms가 큰 제2 PEL(36)이 먼저 여기(excite)되어 스위칭되면서 자유층(40)의 스위칭을 돋게되고 그 결과 스핀분극 전류밀도( $J_c$ )를 낮출 수 있다.

[0048] 제2 PEL(36)의  $K_u$ 가 작기 때문에, 보다 작은 스핀 분극 전류에서 제2 PEL(36)을 여기시키기 위해서는 Ms가 크고, 자유층(40)과 제2 PEL(36) 사이의 교환 필드는 작은 것이 유리하다. 자유층(40)과 제2 PEL(36) 사이에 구비된 교환 차단층(38)은 자유층(40)과 제2 PEL(36) 사이의 교환 필드를 차단하거나 줄이는 역할을 하므로, 자유층(40)의 스위칭에 필요한 스핀분극 전류밀도를 더욱 낮출 수 있다.

[0049] 이러한 역할을 하는 교환 차단층(38)은 0.2nm~1nm 정도의 두께를 갖는 비자성층일 수 있다. 교환 차단층(38)으로 사용되는 물질층은 제2 PEL(36)로 사용되는 물질층에 따라 달라질 수 있다. 예를 들면, 제2 PEL(36)이 비정질의 FeCoB계 합금층일 때, 교환 차단층(38)은 비정질의 비자성층일 수 있다. 이때, 교환 차단층(38)은 지르코늄 베이스 비정질 합금층(Zr based amorphous alloy layer), 티타늄 베이스 비정질 합금층(Ti based amorphous alloy layer), 팔라듐 베이스 비정질 합금층(Pd based amorphous alloy layer) 또는 알루미늄 베이스 비정질 합금층(Al based amorphous alloy layer)일 수 있다. 상기 지르코늄 베이스 비정질 합금층은, 예를 들면 Zr-Ti-Al-TM층 또는 Zr-Al-TM층일 수 있다. 여기서 "TM"은 전이금속(Transition Metal)을 나타낸다. 상기 티타늄 베이스 비정질 합금층은, 예를 들면 Ti-Ni-Sn-Be-Zr층 또는 Ti-Ni-Cu층일 수 있다. 상기 팔라듐 베이스 비정질 합금층은, 예를 들면 Pd-Cu-Ni-P층 또는 Pd-Cu-B-Si층일 수 있다. 상기 알루미늄 베이스 비정질 합금층은, 예를 들면 Al-Ni-Ce층 또는 Al-V-Fe층일 수 있다.

[0050] 또한, 제2 PEL(36)이 비정질의 FeCoB계 합금층일 때, 교환 차단층(38)으로 사용될 수 있는 비정질의 비자성층은 Ta, Mo, W, Nb 및 V 중 어느 하나의 층 또는 이들의 합금층일 수 있다. 이러한 층들은 전체적으로는 비정질이지만, 국소적으로는 나노 결정구조를 가질 수 있다.

[0051] 한편, 제2 PEL(36)이 Fe계 합금층일 때, 교환 차단층(38)은 Cr, Cu, Ta, Mo, W, Nb 및 V 중 어느 하나의 층 또는 이들의 합금층을 사용하는 비정질 비자성층일 수 있다.

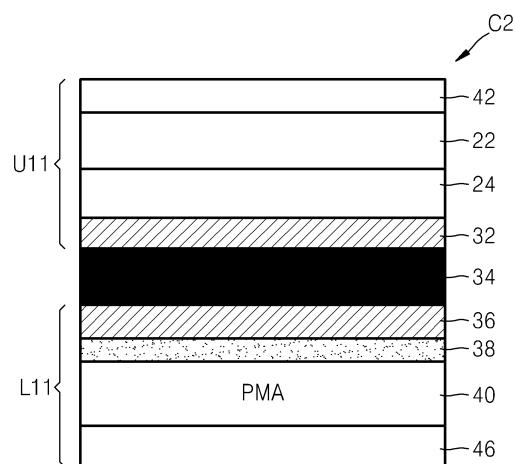

[0052] 도 4는 본 발명의 다른 실시예에 의한 제2 MTJ(C2)를 보여준다.

[0053] 도 3의 제1 MTJ(C1)가 펀드층(24)을 기준으로 볼 때, 펀드층(24)이 자유층(40) 아래에 존재하는 바텀 펀드층을 갖는 구조라면, 도 4의 제2 MTJ(C2)는 펀드층(24)이 자유층(40) 위에 존재하는 탑 펀드층을 갖는 구조이다. 도 4의 설명에서 도 3에서 설명한 부재에 대해서는 동일한 참조번호를 사용하고 그에 대한 설명은 생략한다.

[0054] 도 4를 참조하면, 제2 MTJ(C2)는 순차적으로 적층된 하부 자성층(L11), 터널링층(34) 및 상부 자성층(U11)을 포함한다. 하부 자성층(L11)은 씨드층(46)과 그 위에 순차적으로 적층된 자유층(40), 교환 차단층(38) 및 제2 PEL(36)을 포함한다. 씨드층(46)은 자유층(40)의 성장에 적합한 물질층일 수 있다. 씨드층(46)은 도 3의 씨드층(20)과 동일하거나 다를 수 있다. 상부 자성층(U11)은 제1 PEL(32)과 그 위에 순차적으로 적층된 펀드층(24), 피泞층(22) 및 캡핑층(42)을 포함한다.

[0055] 다음에는 본 발명의 일 실시예에 의한 수직 MTJ를 포함하는 자성소자를 설명한다.

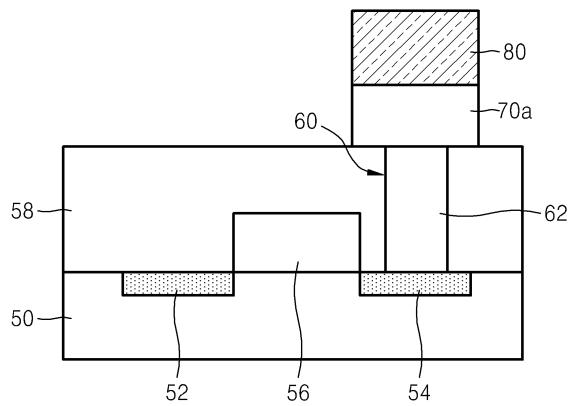

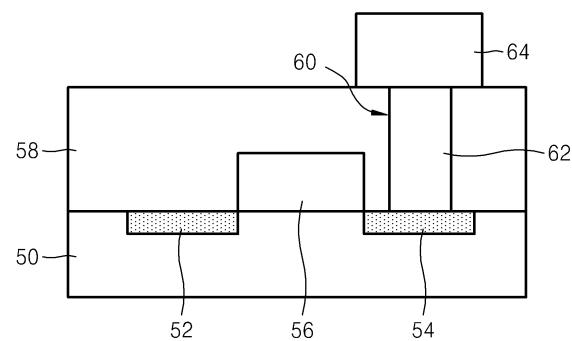

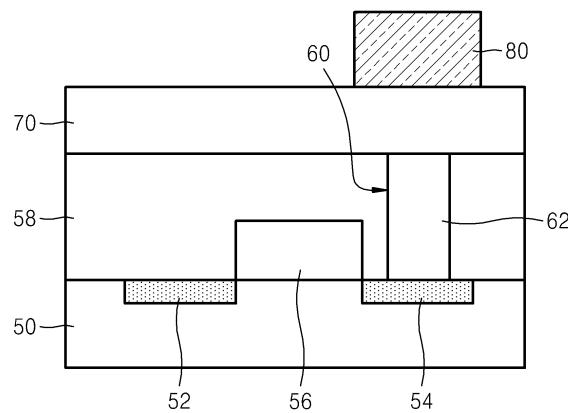

[0056] 도 5는 본 발명의 일 실시예에 의한 수직 MTJ를 포함하는 자기 메모리 소자(MRAM)를 보여준다.

[0057] 도 5를 참조하면, 기판(50)에 제1 및 제2 불순물 영역(52, 54)과 게이트(56)를 갖는 트랜지스터가 존재한다. 기판(50)은 P형 또는 N형 실리콘 기판을 비롯해서 반도체 트랜지스터가 형성될 수 있는 모든 기판일 수 있다. 상기 트랜지스터는 스위칭 소자의 일 예에 불과하다. 따라서 상기 트랜지스터 대신에 다이오드가 구비될 수도 있다. 제1 및 제2 불순물 영역(52, 54)은 기판(50)과 반대되는 타입의 불순물이 도핑된 영역일 수 있다. 제1 및

제2 불순물 영역(52, 54) 중 하나는 소스 영역이고, 나머지는 드레인 영역일 수 있다. 게이트(56)는 제1 및 제2 불순물 영역(52, 54) 사이의 기판(50) 상에 존재한다. 게이트(56)는 게이트 절연막과 게이트 전극 등을 포함할 수 있다. 기판(50) 상에 상기 트랜지스터를 덮는 충간 절연층(58)이 존재한다. 충간 절연층(58)에 제2 불순물 영역(54)이 노출되는 콘택홀(60)이 형성되어 있고, 콘택홀(60)은 도전성 플러그(62)로 채워져 있다. 충간 절연층(58) 상에 도전성 플러그(62)의 상부면을 덮는 수직 MTJ(64)가 존재한다. MTJ(64)는 데이터가 저장되는 스트리지 노드일 수 있다. MTJ(64)는 도 3의 제1 MTJ(C1) 또는 도 4의 제2 MTJ(C2)일 수 있다. 도전성 플러그(62)와 MTJ(64) 사이에 다른 도전성 부재가 더 구비될 수도 있다.

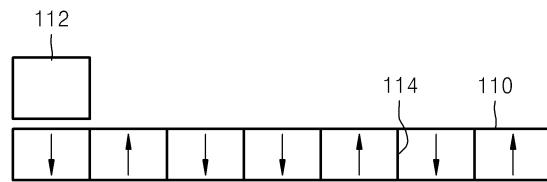

[0058] 본 발명의 실시예들에 의한 MTJ는 도 5의 자기 메모리 소자외에 MTJ를 필요로 하는 다른 자성소자에도 적용될 수 있다. 예를 들면, 본 발명의 실시예들에 의한 MTJ는 수직 자기기록헤드에도 적용될 수 있다. 본 발명의 실시예들에 의한 MTJ는 도 6에 도시한 바와 같이 MPM(Magnetic Packet Memory)의 자구벽 이동 기록매체(110)에 데이터를 기록하거나 기록된 데이터를 읽기 위한 자기 헤드(112)에 적용될 수도 있다. 도 6에서 참조번호 114는 자구벽을 나타내고, 수직 화살표는 기록매체(110)의 각 도메인의 수직 자기분극, 곧 각 도메인에 기록된 데이터를 나타낸다. 또한, MTJ를 이용하여 논리연산을 수행하는 자성 논리소자의 MTJ에 도 3 또는 도 4의 MTJ를 적용할 수 있을 것이다.

[0059] 다음에는 본 발명의 일 실시예에 의한 MTJ를 포함하는 자기 메모리 소자의 제조방법을 도 7 및 도 8을 참조하여 설명한다.

[0060] 도 7을 참조하면, 도 5의 트랜지스터를 덮는 충간 절연층(58) 상에 도전성 플러그(62)의 상부면을 덮는 MTJ층(70)을 형성한다. MTJ층(70)의 층 구성은 도 3의 제1 MTJ(C1) 또는 도 4의 제2 MTJ(C2)와 동일할 수 있다. 따라서 MTJ층(70)에 대한 자세한 설명은 생략한다. 계속해서, MTJ층(70)의 소정 영역 상에 마스크(80)를 형성한다. 마스크(80)는 감광막 패턴일 수 있다. 마스크(80)는 적어도 도전성 플러그(60)를 포함하는 위치에 형성한다. 마스크(80)는 MTJ가 형성될 영역을 한정한다. 마스크(80)를 형성한 다음, 마스크(80) 둘레의 MTJ층(70)을 식각한다. 식각은 충간 절연층(70)이 노출될 때까지 실시할 수 있다. 이러한 식각으로 도 8에 도시한 바와 같이 충간 절연층(58) 상에 MTJ(70a)가 형성된다. MTJ(70a)는 도 3의 제1 MTJ(C1) 또는 도 4의 제2 MTJ(C2)일 수 있다. 상기 식각 후, 마스크(80)를 제거한다.

[0061] 상기한 설명에서 많은 사항이 구체적으로 기재되어 있으나, 그들은 발명의 범위를 한정하는 것이라기보다, 바람직한 실시예의 예시로서 해석되어야 한다. 때문에 본 발명의 범위는 설명된 실시예에 의하여 정하여 질 것이 아니고 특히 청구범위에 기재된 기술적 사상에 의해 정하여져야 한다.

### 도면의 간단한 설명

[0062] 도 1은 PMA물질/분극 강화층/터널링막/분극 강화층/PMA물질의 구조에서 분극 강화층과 PMA물질 사이의 교환 상호작용의 세기에 따른 스핀 토크 스위칭 특성을 나타낸 그래프이다.

[0063] 도 2는 PMA물질/분극 강화층/터널링막/분극 강화층/PMA물질의 구조에서 분극 강화층의 포화 자화(saturation magnetization)에 따른 스핀 토크 스위칭 특성을 나타낸 그래프이다.

[0064] 도 3은 본 발명의 일 실시예에 의한, PMA 물질을 포함하는 MTJ 구조를 보여주는 단면도이다.

[0065] 도 4는 본 발명의 다른 실시예에 의한, PMA 물질을 포함하는 MTJ 구조를 보여주는 단면도이다.

[0066] 도 5는 본 발명의 실시예들에 의한 MTJ를 포함하는 자성소자의 일 예를 보여주는 단면도이다.

[0067] 도 6은 본 발명의 실시예들에 의한 MTJ가 적용된 자성소자의 다른 예를 보여주는 단면도이다.

[0068] 도 7 및 도 8은 본 발명의 실시예들에 의한 MTJ를 포함하는 MRAM의 제조방법을 단계별로 나타낸 단면도들이다.

[0069] <도면의 주요 부분에 대한 부호설명>

[0070] 20, 46: 씨드층 22: 피닝층

[0071] 24: 핀드층 32, 36: 제1 및 제2 PEL

[0072] 34: 터널링층 38: 교환 차단층

[0073] 40: 자유층 42: 캡핑층

[0074] 50: 기판 52, 54: 제1 및 제2 불순물 영역

|        |                     |                 |

|--------|---------------------|-----------------|

| [0075] | 56: 케이트             | 58: 층간 절연층      |

| [0076] | 60: 콘택홀             | 62: 도전성 플러그     |

| [0077] | 64, 70a: MTJ        | 70: MTJ 층       |

| [0078] | 80: 마스크             | 110: 기록매체       |

| [0079] | 112: 자기 헤드          | 114: 자구벽        |

| [0080] | C1, C2: 제1 및 제2 MTJ | L1, L11: 하부 자성층 |

| [0081] | U1, U11: 상부 자성층     |                 |

## 도면

### 도면1

### 도면2

도면3

도면4

도면5

도면6

도면7

도면8