(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-14940

(P2011-14940A)

(43) 公開日 平成23年1月20日(2011.1.20)

|                  |           |                     |

|------------------|-----------|---------------------|

| (51) Int.Cl.     | F 1       | テーマコード (参考)         |

| <b>H01G 2/24</b> | (2006.01) | H01G 1/04 5 E O O 1 |

| <b>H01G 4/12</b> | (2006.01) | H01G 4/12 4 4 5     |

|                  |           | H01G 4/12 3 4 6     |

|                  |           | H01G 4/12 3 5 8     |

|                  |           | H01G 4/12 3 6 4     |

審査請求 有 請求項の数 8 O L (全 16 頁)

|            |                              |          |                               |

|------------|------------------------------|----------|-------------------------------|

| (21) 出願番号  | 特願2010-234837 (P2010-234837) | (71) 出願人 | 000003067                     |

| (22) 出願日   | 平成22年10月19日 (2010.10.19)     |          | T D K 株式会社                    |

| (62) 分割の表示 | 特願2008-39111 (P2008-39111)   |          | 東京都中央区日本橋一丁目13番1号             |

|            | の分割                          | (74) 代理人 | 100088155                     |

| 原出願日       | 平成20年2月20日 (2008.2.20)       |          | 弁理士 長谷川 芳樹                    |

|            |                              | (74) 代理人 | 100113435                     |

|            |                              |          | 弁理士 黒木 義樹                     |

|            |                              | (74) 代理人 | 100124062                     |

|            |                              |          | 弁理士 三上 敬史                     |

|            |                              | (74) 代理人 | 100145012                     |

|            |                              |          | 弁理士 石坂 泰紀                     |

|            |                              | (72) 発明者 | 井口 俊宏                         |

|            |                              |          | 東京都中央区日本橋一丁目13番1号 T D K 株式会社内 |

最終頁に続く

(54) 【発明の名称】セラミック電子部品、セラミック電子部品の製造方法、及びセラミック電子部品の梱包方法

## (57) 【要約】

【課題】内部電極層の積層方向を判別可能なセラミック電子部品を提供する。

【解決手段】セラミック電子部品1のチップ素体2は、互いに対向する2つの端面2a, 2bと、両端面2a, 2bに垂直で互いに対向する第1の側面1c及び第2の側面1dと、両端面2a, 2b及び第1並びに第2の側面2c, 2dに垂直で互いに対向する第3の側面2e及び第4の側面2fとを有すると共に、第1のセラミックで形成され、内部に内部電極層7が設けられている。識別層5, 6は、チップ素体2の第1の側面2cと第2の側面2dとにそれぞれ設けられ、第1のセラミックとは異なる第2のセラミックにより形成され、チップ素体2の第1～第4の側面2c～2fとは色が異なる。第1のセラミックと第2のセラミックとは、それぞれBaTiO<sub>3</sub>を主成分とすると共に、BaTiO<sub>3</sub>におけるBサイト原子に対するAサイト原子のモル比率が異なる。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

互いに対向する 2 つの面と、前記 2 つの面に垂直で互いに対向する第 1 の側面並びに第 2 の側面と、前記 2 つの面及び前記第 1 並びに前記第 2 の側面に垂直で互いに対向する第 3 の側面並びに第 4 の側面とを有すると共に、第 1 のセラミックで形成され、内部に導体が配置されたチップ素体と、

前記チップ素体の前記 2 つの面にそれぞれ形成された外部電極と、

前記チップ素体の前記第 1 の側面と前記第 2 の側面との少なくとも一方の側面に設けられ、前記第 1 のセラミックとは異なる第 2 のセラミックにより形成され、前記第 1 のセラミックで形成された前記第 3 及び第 4 の側面とは色が異なる識別層と、

10

を備え、

前記識別層は、前記少なくとも一方の側面の全面を覆うように設けられ、

前記第 1 のセラミックと前記第 2 のセラミックとは、それぞれ  $BaTiO_3$  を主成分とすると共に、 $BaTiO_3$  における B サイト原子に対する A サイト原子のモル比率が異なることを特徴とするセラミック電子部品。

20

## 【請求項 2】

前記第 2 のセラミックは、前記第 1 のセラミックよりも、 $BaTiO_3$  における B サイト原子に対する A サイト原子のモル比率が大きいことを特徴とする請求項 1 に記載のセラミック電子部品。

## 【請求項 3】

前記第 2 のセラミックは、前記第 1 のセラミックよりも、 $BaTiO_3$  における B サイト原子に対する A サイト原子のモル比率が小さいことを特徴とする請求項 1 に記載のセラミック電子部品。

30

## 【請求項 4】

複数の第 1 のセラミックグリーン層が積層され、内部に電極パターンが設けられた積層体を形成する積層体形成工程と、

前記積層体において積層方向に互いに対向する面の少なくともいずれか一方に、前記第 1 のセラミックグリーン層とは異なると共に、焼成後の色が前記第 1 のセラミックグリーン層の焼成後の色と異なる材料を用いて第 2 のセラミックグリーン層を形成する識別層形成工程と、

30

前記第 2 のセラミックグリーン層が形成された前記積層体を切断して、互いに対向する 2 つの面と、前記 2 つの面に垂直で互いに対向する第 1 の側面並びに第 2 の側面と、前記 2 つの面及び前記第 1 並びに前記第 2 の側面に垂直で互いに対向すると共に前記第 1 のセラミックグリーン層で構成された第 3 の側面及び第 4 の側面とを有し、前記第 1 の側面と前記第 2 の側面との少なくとも一方の側面に前記識別層形成工程において形成された前記第 2 のセラミックグリーン層が設けられた積層体チップを形成するチップ形成工程と、

前記積層体チップを焼成して、第 1 のセラミックで形成されたチップ素体であって、前記少なくとも一方の側面に第 2 のセラミックで形成された識別層が設けられたチップ素体を形成する焼成工程と、

40

前記チップ素体の前記 2 つの面に外部電極を形成する外部電極形成工程と、

を備え、

前記第 1 のセラミックグリーン層と前記第 2 のセラミックグリーン層とは、それぞれ  $BaTiO_3$  を主成分とすると共に、 $BaTiO_3$  における B サイト原子に対する A サイト原子のモル比率が異なることを特徴とするセラミック電子部品の製造方法。

## 【請求項 5】

前記第 2 のセラミックグリーン層は、前記第 1 のセラミックグリーン層よりも、 $BaTiO_3$  における B サイト原子に対する A サイト原子のモル比率が大きいことを特徴とする請求項 4 に記載のセラミック電子部品の製造方法。

## 【請求項 6】

前記第 2 のセラミックグリーン層は、前記第 1 のセラミックグリーン層よりも、 $BaTiO_3$  における B サイト原子に対する A サイト原子のモル比率が大きいことを特徴とする請求項 4 に記載のセラミック電子部品の製造方法。

50

iO<sub>3</sub>におけるBサイト原子に対するAサイト原子のモル比率が小さいことを特徴とする請求項4に記載のセラミック電子部品の製造方法。

【請求項7】

請求項1～3のいずれか1項に記載のセラミック電子部品を複数準備する準備工程と、前記第3又は前記第4の側面と前記識別層との色の違いに基づいて、前記セラミック電子部品における前記内部電極層の積層方向を判別する判別工程と、前記判別工程において判別した前記積層方向が同じ向きを向くように、複数の前記セラミック電子部品を配置して梱包する梱包工程と、を備えることを特徴とするセラミック電子部品の梱包方法。

【請求項8】

前記判別工程において、前記第3の側面と前記識別層との色の違いは、明度の差を測定することにより判別することを特徴とする請求項7に記載のセラミック電子部品の梱包方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、セラミック電子部品、その製造方法及び梱包方法に関する。

【背景技術】

【0002】

直方体状に形成されたチップ素体と、チップ素体の内部に対向するように配置された複数の導体層と、チップ素体の端面にそれぞれ形成された外部電極と、を備えるセラミック電子部品がある。このセラミック電子部品は、製造されると、梱包材に形成された複数の凹部にそれぞれ収容される（下記特許文献1参照）。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開昭61-217317号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

梱包されたセラミック電子部品を実装する際には、梱包材の凹部から露出したセラミック電子部品の上側の側面を吸着搬送装置により吸着して、セラミック電子部品を梱包材から取り出し、実装基板上に載置する。そして、吸着した側面が上になった状態で実装基板にセラミック電子部品が実装される。この場合、導体層の対向方向が、実装基板に対して平行な場合と垂直な場合とでは、導体層と外部の導体部品との間の電気容量や、導体層による磁界等が異なる。

【0005】

よって、実装基板に対するセラミック電子部品の導体層の対向方向によってその電気的特性が異なり、電気的特性がばらつくので問題がある。また、チップ素体の内部に複数の導体層が対向して配置されている場合に限らず、チップ素体の内部に導体が形成されたセラミック電子部品は、その導体の配置方向によって電気的特性がばらつくので問題がある。そこで、導体の配置方向が揃うように基板に実装するために、導体の配置方向を揃えて梱包することが求められている。

【0006】

しかしながら、完成したセラミック電子部品において、チップ素体の内部に配置された導体は、セラミック及び外部電極に覆われているので、その方向を視認することができない。特に、外部電極が形成された端面が正方形の場合は、チップ素体のどの側面も同形状であるので、導体の配置方向を形状により判別することができない。

【0007】

そこで本発明は、チップ素体の内部に配置された導体の配置方向を判別可能なセラミック

10

20

30

40

50

ク電子部品、その製造方法、及び導体の配置方向を揃えて梱包することが可能なセラミック電子部品の梱包方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明のセラミック電子部品は、互いに対向する2つの面と、2つの面に垂直で互いに対向する第1の側面並びに第2の側面と、2つの面及び第1並びに第2の側面に垂直で互いに対向する第3の側面並びに第4の側面とを有すると共に、第1のセラミックで形成され、内部に導体が配置されたチップ素体と、チップ素体の2つの面にそれぞれ形成された外部電極と、チップ素体の第1の側面と第2の側面との少なくとも一方の側面に設けられ、第1のセラミックとは異なる第2のセラミックにより形成され、第1のセラミックで形成された第3及び第4の側面とは色が異なる識別層と、を備えることを特徴とする。

10

【0009】

本発明のセラミック電子部品では、チップ素体は第1のセラミックで形成され、第1の側面と第2の側面との少なくとも一方の側面には第1のセラミックとは異なる第2のセラミックにより形成された識別層が設けられている。この第2のセラミックで形成された識別層は、第1のセラミックで形成されたチップ素体の第3及び第4の側面とは色が異なる。従って、導体の配置方向と平行な側面と垂直な側面とのいずれか一方の側面に識別層が設けられているか分かれば、識別層により導体の配置方向を容易に判別することができる。

20

【0010】

本発明のセラミック電子部品は、好ましくは、識別層は、少なくとも一方の側面の全面を覆うように形成されている。この場合、識別層の色をより確認しやすくなる。

【0011】

本発明のセラミック電子部品は、好ましくは、第1のセラミックと第2のセラミックとは、焼成の度合いが異なることにより、色が異なる。この場合、第1のセラミックとは色の異なる第2のセラミックの識別層をチップ素体の側面に容易に設けることができる。

30

【0012】

本発明のセラミック電子部品は、好ましくは、第1のセラミックと第2のセラミックとは、それぞれ含まれる粒子の粒径が異なる。この場合、第1のセラミックとは色の異なる第2のセラミックの識別層をチップ素体の側面に容易に設けることができる。

【0013】

本発明のセラミック電子部品は、好ましくは、第1のセラミックと第2のセラミックとは、それぞれ含まれる添加物が異なる。この場合、第1のセラミックとは色の異なる第2のセラミックの識別層をチップ素体の側面に容易に設けることができる。

【0014】

本発明のセラミック電子部品は、第1のセラミックと第2のセラミックとは、それぞれ含まれる材料の組成比が異なる。この場合、第1のセラミックとは色の異なる第2のセラミックの識別層をチップ素体の側面に容易に設けることができる。

【0015】

本発明に係るセラミック電子部品の製造方法は、複数の第1のセラミックグリーン層が積層され、内部に電極パターンが設けられた積層体を形成する積層体形成工程と、積層体において積層方向に互いに対向する面の少なくともいずれか一方に、第1のセラミックグリーン層とは異なると共に、焼成後の色が第1のセラミックグリーン層の焼成後の色と異なる材料を用いて第2のセラミックグリーン層を形成する識別層形成工程と、第2のセラミックグリーン層が形成された積層体を切断して、互いに対向する2つの面と、2つの面に垂直で互いに対向する第1の側面並びに第2の側面と、2つの面及び第1並びに第2の側面に垂直で互いに対向すると共に第1のセラミックグリーン層で構成された第3の側面及び第4の側面とを有し、第1の側面と第2の側面との少なくとも一方の側面に識別層形成工程において形成された第2のセラミックグリーン層が設けられた積層体チップを形成するチップ形成工程と、積層体チップを焼成して、第1のセラミックで形成されたチップ

40

50

素体であって、少なくとも一方の側面に第2のセラミックで形成された識別層が設けられたチップ素体を形成する焼成工程と、チップ素体の2つの面に外部電極を形成する外部電極形成工程と、を備えることを特徴とする。

#### 【0016】

本発明のセラミック電子部品の製造方法では、識別層形成工程において、チップ素体の母体となる積層体の互いに対向する面の少なくともいずれか一方に識別層となる第2のセラミックグリーン層を形成し、その後、切断してチップ状にし、焼成する。これにより、容易に、第1の側面と第2の側面との少なくとも一方の側面に第2のセラミックにより形成された識別層が設けられたチップ素体を形成することができる。この第2のセラミックで形成された識別層は、第1のセラミックで形成されたチップ素体の第3及び第4の側面とは色が異なる。また、チップ素体の内部に設けられた導体の配置方向と垂直な側面と平行な側面とのいずれか一方の側面に設けられている。従って、識別層により導体の配置方向を簡易に判別することができる。

10

#### 【0017】

本発明のセラミック電子部品は、第1のセラミックグリーン層と第2のセラミックグリーン層とは、それぞれ含まれる粒子の粒径が異なる。この場合、第1のセラミックとは色の異なる第2のセラミックの識別層をチップ素体の側面に容易に設けることができる。

#### 【0018】

本発明のセラミック電子部品は、第1のセラミックグリーン層と第2のセラミックグリーン層とは、それぞれ含まれる添加物が異なる。この場合、第1のセラミックとは色の異なる第2のセラミックの識別層をチップ素体の側面に容易に設けることができる。

20

#### 【0019】

本発明のセラミック電子部品は、第1のセラミックグリーン層と第2のセラミックグリーン層とは、それぞれ含まれる材料の組成比が異なる。この場合、第1のセラミックとは色の異なる第2のセラミックの識別層をチップ素体の側面に容易に設けることができる。

#### 【0020】

本発明に係るセラミック電子部品の梱包方法は、上記のセラミック電子部品を複数準備する準備工程と、第3又は第4の側面と識別層との色の違いに基づいて、セラミック電子部品における内部電極層の積層方向を判別する判別工程と、判別工程において判別した積層方向が同じ向きを向くように、複数のセラミック電子部品を配置して梱包する梱包工程と、を備えることを特徴とする。

30

#### 【0021】

本発明のセラミック電子部品の梱包方法では、導体の配置方向と平行な側面と垂直な側面とのいずれか一方の側面に識別層が設けられているか分かれば、判別工程において、識別層により導体の配置方向を判別することができる。続いて、梱包工程において、導体の配置方向が同じ向きを向くように、複数のセラミック電子部品を配置して梱包することができる。

#### 【0022】

本発明に係るセラミック電子部品の梱包方法では、好ましくは、判別工程において、第3の側面と識別層との色の違いは、明度の差を測定することにより判別する。この場合、精度よく色の違いを判別することができるので、精度よく内部電極層の積層方向を判別することができる。

40

#### 【発明の効果】

#### 【0023】

本発明によれば、導体の配置方向を判別可能なセラミック電子部品、その製造方法、及び導体の配置方向を揃えて梱包することが可能なセラミック電子部品の梱包方法を提供することができる。

#### 【図面の簡単な説明】

#### 【0024】

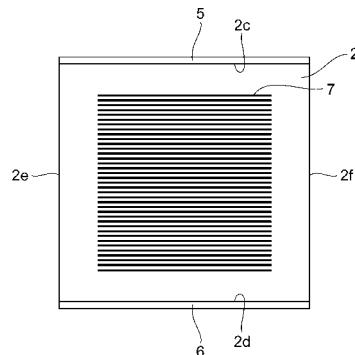

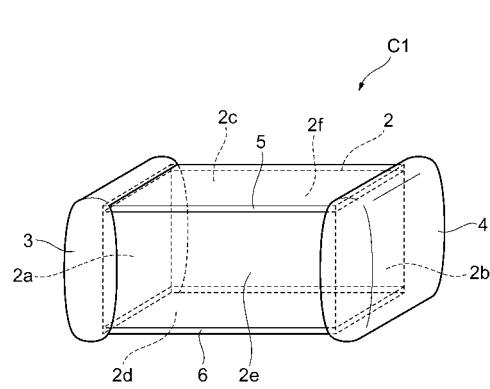

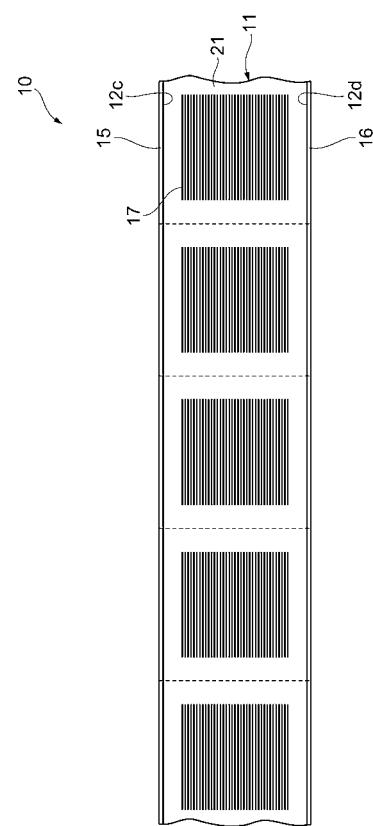

【図1】本実施形態に係るセラミック電子部品の斜視図である。

50

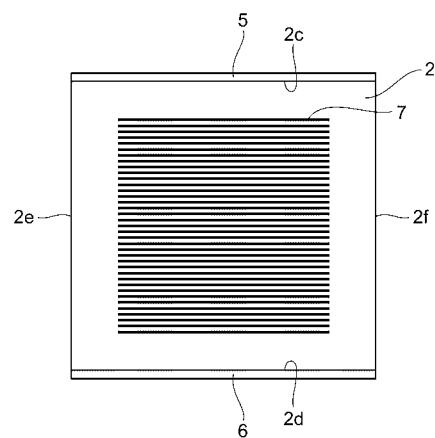

【図2】本実施形態に係るセラミック電子部品の断面図である。

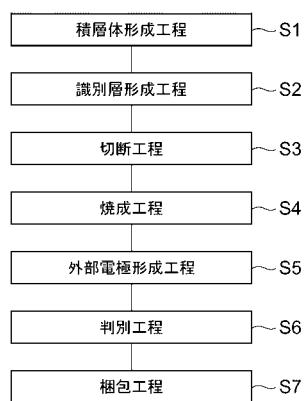

【図3】本実施形態に係るセラミック電子部品の製造方法及び梱包方法の手順を示すフロー図である。

【図4】本実施形態に係るセラミック電子部品の製造方法において形成される積層体の断面図である。

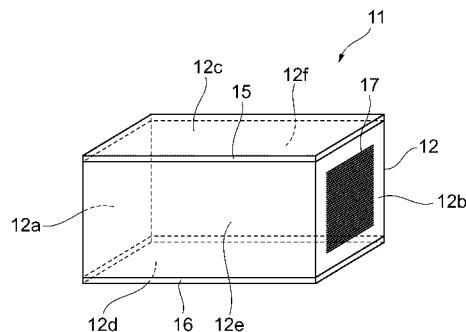

【図5】本実施形態に係るセラミック電子部品の製造方法において形成される積層体チップの斜視図である。

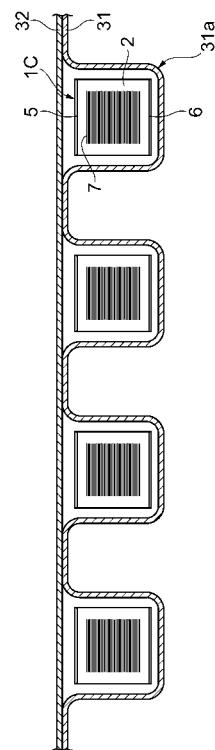

【図6】本実施形態に係るセラミック電子部品の梱包状態を示す断面図である。

【図7】本実施形態に係るセラミック電子部品の実施例を示す図である。

【発明を実施するための形態】

10

【0025】

以下、添付図面を参照して、本発明を実施するための最良の形態を詳細に説明する。なお、図面の説明において同一の要素に同一の符号を付し、重複する説明を省略する。

【0026】

図1は、本実施形態に係るセラミック電子部品の斜視図である。本実施形態に係るセラミック電子部品C1は、積層型のチップコンデンサである。セラミック電子部品C1は、略直方体形状で、高さ2.5mm程度、幅2.5mm程度、奥行3.2mm程度の大きさであり、高さ方向の寸法と幅方向の寸法が実質的に同一であり、外部電極が形成される端面が正方形である。

【0027】

セラミック電子部品C1は、略直方体形状のチップ素体2と、チップ素体2の両端面2a, 2bにそれぞれ形成された第1及び第2の外部電極3, 4と、チップ素体2の互いに対向する第1の側面2c及び第2の側面2dにそれぞれ設けられた識別層5, 6とを備える。

【0028】

チップ素体2において、両端面2a, 2bは互いに対向し、第1の側面2c及び第2の側面2dは互いに対向すると共に両端面2a, 2bと垂直である。そして、チップ素体2は、両端面2a, 2b及び第1並びに第2の側面2c, 2dに垂直で互いに対向する第3の側面2e及び第4の側面2fを備える。識別層5, 6は、チップ素体1の第1の側面2cと第2の側面2dとの全面をそれぞれ覆っている。

20

【0029】

第1の外部電極3は、チップ素体2の端面2aに形成され、端面2aの全面を覆い、識別層5, 6及び第3並びに第4の側面2e, 2fの一部まで覆っている。第2の外部電極4は、チップ素体2の端面2bに形成され、端面2bの全面を覆い、識別層5, 6及び第3並びに第4の側面2e, 2fの一部まで覆っている。

30

【0030】

図2を参照して、チップ素体2及び識別層5, 6について説明する。図2は、本実施形態に係るセラミック電子部品の断面図である。図2に示す断面図は、セラミック電子部品C1の両端面2a, 2bと平行な断面である。この断面は、本実施形態では、正方形である。

40

【0031】

チップ素体2は、セラミック(第1のセラミック)で形成され、内部に複数の内部電極層7が形成されている。チップ素体2を形成する第1のセラミックは、例えば、 $BaTiO_3$ を主成分とし、 $MgO$ 、 $Y_2O_3$ 、 $MnO$ 、 $V_2O_5$ 、及び $BaSiO_3$ 又は $CaSiO_3$ 等の添加物を加えて構成される。

【0032】

複数の内部電極層7は、間に第1のセラミックで形成された第1のセラミック層を挟んで、複数積層されている。複数の内部電極層7は、端面2a側にずれて端面2aに内部電極層7の端面が露出するように配置された内部電極層7と、端面2b側にずれて端面2bに内部電極層7の端面が露出するように配置された内部電極層7とが、交互に積層されて

50

いる。端面 2 a 側にされた内部電極層 7 の端面が、第 1 の外部電極 3 と電気的且つ機械的に接続され、端面 2 b 側にされた内部電極層 7 の端面が、第 2 の外部電極 4 と電気的且つ機械的に接続されている。

【0033】

複数の内部電極層 7 のうち最も第 1 の側面 2 c 側に位置する内部電極層 7 と第 1 の側面 2 c との間の寸法は、300 μm 程度である。複数の内部電極層 7 のうち最も第 2 の側面 2 d 側に位置する内部電極層 7 と第 2 の側面 2 d との間の寸法は、300 μm 程度である。

【0034】

複数の内部電極層 7 の第 3 の側面 2 e 側の端面が揃って配置され、その端面と第 3 の側面 2 e との間の寸法は、200 μm 程度である。複数の内部電極層 7 の第 4 の側面 2 f 側の端面が揃って配置され、その端面と第 4 の側面 2 f との間の寸法は、200 μm 程度である。すなわち、チップ素体 2 において第 1 ~ 第 4 の側面 2 c ~ 2 f は、第 1 のセラミックで構成されている。

【0035】

識別層 5, 6 の厚さ寸法は、30 μm 程度である。識別層 5, 6 は、第 1 のセラミックとは異なる第 2 のセラミックで形成されている。これにより、識別層 5, 6 は、チップ素体 2 の第 1 ~ 第 4 の側面 2 c ~ 2 f とは色が異なる。

【0036】

例えば、第 1 のセラミックと第 2 のセラミックとは、それぞれ含まれる粒子の粒径が異なる。第 2 のセラミックの材料となるセラミック粒子の平均粒径や B E T 径を第 1 のセラミックの材料となるセラミック粒子の平均粒径や B E T 径より小さくし、焼結度合いをより高めることにより、第 1 のセラミックより第 2 のセラミックの色を暗くする。この場合、第 2 のセラミックにおいて焼結したセラミック粒子の平均粒径は、第 2 のセラミックにおいて焼結したセラミック粒子の平均粒径より小さく、第 2 のセラミックの密度は第 1 のセラミックの密度より高い。また、第 2 のセラミックの材料となるセラミック粒子の平均粒径や B E T 径を第 1 のセラミックの材料となるセラミック粒子の平均粒径や B E T 径より大きくし、第 1 のセラミックより第 2 のセラミックの色を明るくしてもよい。

【0037】

また、第 1 のセラミックと第 2 のセラミックとは、それぞれ含まれる添加物が異なるように構成されていてもよい。例えば、第 1 と第 2 のセラミックのいずれか一方に、他方に含まれていない添加物であって、バンドギャップ中のエネルギー準位を変化させて色を異ならせる添加物や、焼結の度合いが異なることにより色が異なる添加物等を加えてよい。

【0038】

また、第 1 のセラミックと第 2 のセラミックとは、それぞれ含まれる材料の組成比が異なるように構成されていてもよい。例えば、第 1 と第 2 のセラミックのいずれか一方に、色を異ならせる添加物や焼結の度合いが異なる添加物を他方より多く加えてよい。

【0039】

セラミック電子部品 C 1 において、複数の内部電極層 7 は、チップ素体 1 の内部に配置された導体である。複数の内部電極層 7 は、チップ素体 1 の中心を通り端面 2 a、第 1 の側面 2 c、及び第 2 の側面 2 e に平行な 3 つの面に対してそれぞれ対称に配置されている。この導体の配置方向は、内部電極層 7 の積層方向により示すことができる。本実施形態では、内部電極層 7 の積層方向は、識別層 5, 6 に垂直な方向である。

【0040】

以上説明した本実施形態に係るセラミック電子部品 C 1 では、チップ素体 2 は第 1 のセラミックで形成され、第 1 の側面 2 c と第 2 の側面 2 d とには第 1 のセラミックとは異なる第 2 のセラミックにより形成された識別層 5, 6 がそれぞれ設けられている。この第 2 のセラミックで形成された識別層 5, 6 は、第 1 のセラミックで形成されたチップ素体 2 の第 1 ~ 第 4 の側面 2 c ~ 2 f とは色が異なる。この識別層 5, 6 は、複数の内部電極層

10

20

30

40

50

7の積層方向と垂直な第1及び第2の側面2c, 2dに設けられているので、識別層5, 6により内部電極層7の積層方向を判別することができる。すなわち、チップ素体2の内部に設けられた導体の配置方向を判別することができる。

【0041】

また、識別層5, 6は、第1及び第2の側面2c, 2dの全面を覆うように形成されているので、識別層5, 6と第3及び第4の側面2e, 2fの色の違いが確認しやすい。

【0042】

また、第1のセラミックと第2のセラミックとは、それぞれ含まれる主成分の粒子の粒径が異なる。これにより、容易に、第1のセラミックとは色の異なる第2のセラミックの識別層5, 6をチップ素体1の側面に設けることができる。また、第1と第2のセラミックは、成分及びその組成比が同じなので、チップ素体2の第1及び第2の側面2c, 2dと識別層5, 6との間の剥離を抑制することができる。

10

【0043】

また、第1のセラミックと第2のセラミックとは、それぞれ含まれる添加物が異なるように構成されていてもよい。また、第1のセラミックと第2のセラミックとは、それぞれ含まれる材料の組成比が異なるように構成されていてもよい。これにより、上記の場合と同様に、容易に、第1のセラミックとは色の異なる第2のセラミックの識別層5, 6をチップ素体1の側面に設けることができる。また、第1と第2のセラミックは、主成分が同じなので、チップ素体2の第1及び第2の側面2c, 2dと識別層5, 6との間の剥離を抑制することができる。また、第1のセラミックと第2のセラミックとは、材料の一部が異なるか、又は、一部の添加量が異なることにより、色が異なる。よって、容易に識別層5, 6を形成できる。

20

【0044】

引き続いて、本実施形態に係るセラミック電子部品C1の製造方法及び梱包方法について説明する。図3は、本実施形態に係るセラミック電子部品の製造方法及び梱包方法の手順を示すフロー図である。本実施形態に係るセラミック電子部品の製造方法は、積層体形成工程S1、識別層形成工程S2、切断工程S3、焼成工程S4、及び外部電極形成工程S5を含む。この工程S1~S5により上述したセラミック電子部品C1が複数形成される(準備工程)。各工程について説明する。

30

【0045】

積層体形成工程S1では、図4に示すように、複数の第1のセラミックグリーン層21が積層され、内部に複数の電極パターン17が設けられた積層体を形成する。まず、PETフィルム上に第1のセラミックグリーン層21を形成する。第1のセラミックグリーン層21は、第1のセラミックとなるグリーン層である。第1のセラミックグリーン層21は、主成分に添加物を加え、バインダ樹脂(例えば有機バインダ樹脂等)、溶剤、可塑剤等を更に加えて混合分散することにより得られたセラミックスラリーをPETフィルム上に塗布後、乾燥することによって形成される。例えば、第1のセラミックグリーン層21の主成分はBaTiO<sub>3</sub>であり、添加物はMgO、Y<sub>2</sub>O<sub>3</sub>、MnO、V<sub>2</sub>O<sub>5</sub>、BaSiO<sub>3</sub>、及びCaSiO<sub>3</sub>等である。

【0046】

次に、第1のセラミックグリーン層21の上面に複数の電極パターン17を形成する。電極パターン17は、第1のセラミックグリーン層21の上面に電極ペーストを印刷後、乾燥することにより形成される。電極ペーストは、例えばNi、Ag、Pdなどの金属粉末にバインダ樹脂や溶剤等を混合したペースト状の組成物である。印刷手段として、例えばスクリーン印刷などを用いる。

40

【0047】

この電極パターン17が形成された第1のセラミックグリーン層21を複数積層する。電極パターン17が形成された複数の第1のセラミックグリーン層21を挟んで、電極パターン17が形成されていない複数の第1のセラミックグリーン層21を上下それぞれに積層する。これにより、積層体が形成される。

50

## 【0048】

続いて、識別層形成工程S2において、識別層5, 6となる第2のセラミックグリーン層15, 16を形成する。第2のセラミックグリーン層15, 16は、積層体の積層方向に互いに対向する面12c, 12dにそれぞれ形成される。

## 【0049】

第2のセラミックグリーン層15, 16は、第2のセラミックとなるグリーン層である。第2のセラミックグリーン層15, 16は、BaTiO<sub>3</sub>を主成分とし、MgO、Y<sub>2</sub>O<sub>3</sub>、MnO、V<sub>2</sub>O<sub>5</sub>、及びBaSiO<sub>3</sub>又はCaSiO<sub>3</sub>等の添加物を加えて、更に、バインダ樹脂（例えば有機バインダ樹脂等）、溶剤、可塑剤等を加えて混合分散することにより得たセラミックスラリーを面15, 16上に塗布後、乾燥することによって形成される。なお、セラミックスラリーをPETフェイルム上に塗布後、乾燥させて、シート状にしたものを、積層体に積層してもよい。

10

## 【0050】

ただし、第2のセラミックグリーン層15, 16は、第1のセラミックグリーン層21とは異なるセラミックグリーン層である。第2のセラミックグリーン層15, 16は、焼成後の色が、第1のセラミックグリーン層21の焼成後の色と異なる。色を異ならせるために、例えば、第1のセラミックグリーン層21と第2のセラミックグリーン層15, 16とは、それぞれ含まれる粒子の粒径を異ならせる。また、第1のセラミックグリーン層21と第2のセラミックグリーン層15, 16とを、それぞれ含まれる添加物が異なるように構成してもよい。また、第1のセラミックグリーン層21と第2のセラミックグリーン層15, 16とを、それぞれ含まれる材料の組成比が異なるように構成してもよい。

20

## 【0051】

次に、切断工程S3において、第2のセラミックグリーン層15, 16が形成された積層体10を切断して、図5に示すように、積層体チップ11を形成する。積層体チップ11は、互いに対向する2つの端面12a, 12bと、2つの端面12a, 12bに垂直で互いに対向する第1の側面12c及び第2の側面12dと、2つの端面12a, 12b及び第1並びに第2の側面12c, 12dと垂直で互いに対向する第3の側面12eと第4の側面12fとを有する。

30

## 【0052】

2つの端面12a, 12bには、電極パターンの端部が露出している。また、第1の側面12cと第2の側面12dとは、識別層形成工程S2により形成された第2のセラミックグリーン層15, 16で構成されている。

30

## 【0053】

次に、焼成工程S4において、第1のセラミックグリーン層21及び第2のセラミックグリーン層15, 16に含まれるバインダを除去し、焼成する。焼成により、積層体チップ11の第1のセラミックグリーン層21は、第1のセラミックとなり、第2のセラミックグリーン層15, 16は、第2のセラミックで形成された識別層5, 6となり、内部電極パターン17は、内部電極層7となる。

## 【0054】

すなわち、焼成により、識別層5, 6が設けられたチップ素体2が形成される。チップ素体2の第1～第4の側面2c～2dは、識別層5, 6とは色が異なる。例えば、第1のセラミックは第2のセラミックのセラミック粒子のBET径をいずれか一方を他方より大きく又は小さくする。セラミック粒子が小さい方が、大きい方よりも低温で焼結が進むので、色を暗くすることができる。

40

## 【0055】

また、例えば、第1のセラミックは第2のセラミックの材料のいずれか一方のセラミックにSiO<sub>2</sub>化合物若しくはTiO<sub>2</sub>を添加することにより、他方のセラミックより一方のセラミックを暗くすることができる。又は、一方のセラミックにSiO<sub>2</sub>化合物若しくはTiO<sub>2</sub>を多く添加することにより、他方のセラミックより一方のセラミックを暗くすることができる。すなわち、SiO<sub>2</sub>化合物、TiO<sub>2</sub>等の添加物により、セラミックが焼け易くなる為に、より焼

50

成が進み、明度 L が低下する。

【0056】

また、例えば、第1のセラミック又は第2のセラミックの材料のいずれか一方のセラミックにBaO、MgO、若しくは $Re_2O_3$ （希土類酸化物）を添加することにより、他方のセラミックより一方のセラミックを明るくすることができる。又は、一方のセラミックにBaO、MgO、若しくは $Re_2O_3$ （希土類酸化物）を多く添加することにより、他方のセラミックより一方のセラミックを明るくすることができる。すなわち、BaO、MgO、 $Re_2O_3$ 等の添加物により、セラミックが焼けにくくなる為に、より明るくなり、明度 L があがる。

【0057】

また、例えば、第1のセラミック又は第2のセラミックの材料のいずれか一方のセラミックに $V_2O_5$ を添加することにより、他方のセラミックより一方のセラミックを暗くすることができる。又は、一方のセラミックに $V_2O_5$ を多く添加することにより、他方のセラミックより一方のセラミックを暗くすることができる。これは、Vを添加することでBaTiO<sub>3</sub>のバンド構造が変化することに起因するものである。

10

【0058】

次に、外部電極形成工程 S 5において、チップ素体 2 の両端面 2 a, 2 b に、第1の外部電極 3 と第2の外部電極 4 とがそれぞれ形成される。これにより、内部電極層 7 が第1の外部電極 3 又は第2の外部電極 4 に電気的に接続される。以上説明した各工程によって、複数のセラミック電子部品 C 1 が完成する。

20

【0059】

引き続いて、本実施形態に係るセラミック電子部品の梱包方法について説明する。本実施形態に係るセラミック電子部品の梱包方法は、準備工程、判別工程 S 6、及び梱包工程 S 7 を含む。まず、準備工程として、上述した工程 S 1 ~ S 5 を実施し、複数のセラミック電子部品 C 1 を準備する。

20

【0060】

次に、判別工程 S 6において、第3又は第4の側面 2 e, 2 f と識別層 5, 6 との色の違いに基づいて、セラミック電子部品 C 1 における内部電極層 7 の積層方向を判別する。セラミック電子部品 C 1 における外部電極 3, 4 が形成された端面を除く側面のうち、隣り合う2つの側面の色を、測色機器を用いて測定する。その明度 L の差に基づいて、測定した側面が識別層 5, 6 か第3又は第4の側面 2 e, 2 f か識別する。

30

【0061】

例えば、測色機器として、分光色差計を用いることができる。この分光色差計により L \* a \* b \* 表色系 (JIS Z8729) の明度 L を測定する。その明度 L の差に基づいて、測定した側面が識別層 5, 6 か第3又は第4の側面 2 e, 2 f か識別する。測定した側面が識別層 5, 6 であれば、測定した面は内部電極層の積層方向と垂直な面である。測定した側面が第3又は第4の側面 2 e, 2 f であれば、測定した面は、内部電極層の積層方向と平行な面である。

30

【0062】

次に、梱包工程 S 7において、判別した内部電極層の積層方向が同じ向きを向くように、図 6 に示すように、複数のセラミック電子部品 C 1 を配置して梱包する。梱包材は、梱包材 3 1 及び梱包材 3 2 からなる。梱包材 3 1 には、断面が四角形状の凹部 3 1 a が2次元に配列して複数形成されている。この凹部 3 1 にそれぞれセラミック電子部品 C 1 が収容される。

40

【0063】

セラミック電子部品 C 1 は、識別層 5, 6 が凹部 3 1 の深さ方向に対して垂直となるように、凹部 3 1 に収容される。すなわち、セラミック電子部品 C 1 は、その内部電極層 7 の積層方向が凹部 3 1 の深さ方向と平行となるように、凹部 3 1 に収容される。その後、梱包材 3 2 により、凹部 3 1 a の開口部が覆われて、梱包が完了する。

【0064】

以上説明した本実施形態に係るセラミック電子部品の製造方法では、識別層形成工程 S

50

1において、チップ素体1の母体となる積層体の互いに対向する面12c, 12dに識別層5, 6となる第2のセラミックグリーン層15, 16をそれぞれ形成し、その後、切削してチップ状にし、焼成する。これにより、容易に、第1の側面2cと第2の側面2dとに第2のセラミックにより形成された識別層5, 6が設けられたチップ素体2を形成することができる。この第2のセラミックで形成された識別層5, 6は、第1のセラミックで形成されたチップ素体2の第3及び第4の側面2e, 2fとは色が異なる。そして、識別層5, 6は、内部電極層7の積層方向に垂直である。従って、識別層5, 6により内部電極層7の積層方向を簡易に判別することができる。

#### 【0065】

本実施形態に係るセラミック電子部品の梱包方法では、まずセラミック電子部品C1を準備する。内部電極層7の積層方向と垂直な側面に識別層5, 7が設けられているので、判別工程S6において、識別層5, 6により内部電極層6の積層方向を判別することができる。続いて、梱包工程S7において、内部電極層7の積層方向が同じ向きを向くように、複数のセラミック電子部品C1を配置して梱包することができる。

10

#### 【0066】

これにより、実装時に、内部電極層7の積層方向を揃えて基板に実装することができる。セラミック電子部品C1及び基板上の電子部品における電気的特性のばらつきを抑制することができる。

#### 【0067】

また、本実施形態に係るセラミック電子部品の梱包方法では、判別工程S6において、第3又は4の側面2e, 2fと識別層5, 6との色の違いは、L\*a\*b\*表色系の明度Lの差を測定することにより判別する。これにより、精度よく色の違いを判別することができる。精度よく内部電極層の積層方向を判別することができる。

20

#### 【0068】

また、焼成後に第1のセラミックと第2のセラミックとなる第1のセラミックグリーン層と第2のセラミックグリーン層とは、それぞれ含まれる主成分の粒子のBET径が異なる。これにより、容易に、第1のセラミックとは色の異なる第2のセラミックの識別層5, 6をチップ素体1の側面に設けることができる。また、第1と第2のセラミックは、成分及びその組成比が同じなので、チップ素体2の第1及び第2の側面2c, 2dと識別層5, 6との間の剥離を抑制することができる。

30

#### 【0069】

また、第1のセラミックと第2のセラミックとなる第1のセラミックグリーン層と第2のセラミックグリーン層とは、それぞれ含まれる添加物が異なるように構成されていてよい。また、第1のセラミックと第2のセラミックとなる第1のセラミックグリーン層と第2のセラミックグリーン層とは、それぞれ含まれる材料の組成比が異なるように構成されていてよい。これにより、上記の場合と同様に、容易に、第1のセラミックとは色の異なる第2のセラミックの識別層5, 6をチップ素体1の側面に設けることができる。また、第1と第2のセラミックは、主成分が同じなので、チップ素体2の第1及び第2の側面2c, 2dと識別層5, 6との間の剥離を抑制することができる。

30

#### 【0070】

また、一般的に、セラミック電子部品のチップ素体は、内部電極層の積層方向と垂直な第1及び第2の側面が凸状になり、積層方向と平行な第3及び第4の側面が凹状になる。よって、第1又は第2の側面を実装基板側にして実装した場合と、第3又は第4の側面を実装基板側にして実装した場合とでは、セラミック電子部品の設置状態が異なる。実装基板側の側面が第1又は第2の側面の場合と第3又は第4の側面となる場合とが混在すると、設置精度がばらつくことになり、問題である。

40

#### 【0071】

それに対して、本実施形態に係るセラミック電子部品の梱包方法によれば、内部電極層7の積層方向が揃って梱包される。これにより、梱包材から取り出したセラミック電子部品C1について、内部電極層7の積層方向を変えずに実装することにより、セラミック電

50

子部品 C 1 の設置精度のばらつきを抑制することができる。

【 0 0 7 2 】

また、梱包材からセラミック電子部品 C 1 を取り出すときには、負圧を利用してセラミック電子部品 C 1 を吸着して取り出す。この際に、梱包材の開口部側の側面を吸着して取り出すので、その側面が凸状である方が凹状である場合より吸着し易い。本実施形態のセラミック電子部品の梱包方法では、梱包材の開口部側には、第 1 又は第 2 の側面 2 c , 2 d が位置しているので、凸状の第 1 又は第 2 の側面 2 c , 2 d を吸着することとなる。よって、容易に吸着搬送を行うことができる。

【 0 0 7 3 】

本発明は、上記実施形態に限定されるものではなく、種々の変形が可能である。例えば、上記本実施形態に係るセラミック電子部品 C 1 は、チップコンデンサとしたが、これに限られず、積層型の圧電体、バリスタ、インダクタ等でもよい。また、上記実施形態に係るセラミック電子部品 C 1 は、複数の導体（内部電極層 7 ）が積層されていることとしたが、導体は 1 つでもよい。

10

【 0 0 7 4 】

また、例えば、上記本実施形態に係るセラミック電子部品 C 1 は、識別層 5 , 6 をチップ素体 2 の第 1 の側面 2 c 及び第 2 の側面 2 d にそれぞれ設けることとしたが、これに限らない。第 1 の側面 2 c と第 2 の側面 2 d とのいずれか一方に設けてもよい。また、チップ素体 2 において積層方向と平行で互いに対向する側面に、識別層 5 , 6 を設けてもよい。また、識別層は、第 1 ~ 第 4 の側面のいずれか一部に設けられていてもよい。

20

【 0 0 7 5 】

（実施例）

引き続いて、実施例について説明する。上述した本実施形態に係るセラミック電子部品の製造方法により製造したセラミック電子部品を実施例 1 ~ 1 2 とし、上述した本実施形態に係るセラミック電子部品の製造方法において識別層形成工程を省き、識別層のないセラミック電子部品を比較例 1 とする。

30

【 0 0 7 6 】

図 7 には、比較例 1 及び実施例 1 ~ 1 2 のセラミックグリーン層を構成する材料と、分光色差計による測定結果を L \* a \* b \* 表色系により示す。用いた分光色差計は、日本電色工業株式会社製の微小面分光色差計 VSS 400 である。

30

【 0 0 7 7 】

図 7 において、比較例 1 については、第 1 のセラミックグリーン層の材料を示す。図 7 において実施例 1 ~ 1 2 については、第 2 のセラミックグリーン層の材料、すなわち、識別層の材料を示す。実施例 1 ~ 1 2 の第 3 及び第 4 の側面を構成する第 1 のセラミックグリーン層の材料は、比較例 1 の第 1 のセラミックの材料と同じである。

【 0 0 7 8 】

比較例 1 においては、識別層の明度 L 8 0 . 9 と第 3 又は第 4 の側面の明度 L 8 0 . 2 との差は、0 . 7 であった。これは、誤差程度の差であり、明度に基づいて識別層の判別はできなかった。

40

【 0 0 7 9 】

実施例 1 は、比較例 1 より BaTiO<sub>3</sub> の B E T を大きくし、実施例 2 は、比較例 1 より BaTiO<sub>3</sub> の B E T を小さくした。実施例 1 においては、識別層の明度 L 7 5 . 3 と第 3 又は第 4 の側面の明度 L 8 0 . 9 との差は、- 5 . 6 であった。この場合、明度に基づく識別層の判別ができた。実施例 2 においては、識別層の明度 L 8 8 . 9 と第 3 又は第 4 の側面の明度 L 8 0 . 7 との差は、8 . 2 であった。この場合、明度に基づく識別層の判別ができた。

【 0 0 8 0 】

実施例 3 は、比較例 1 より BaTiO<sub>3</sub> の B サイト原子に対する A サイト原子のモル比率を小さくし、実施例 4 は、比較例 1 より BaTiO<sub>3</sub> の B サイト原子に対する A サイト原子のモル比率を大きくした。実施例 3 においては、識別層の明度 L 7 3 . 7 と第 3 又は第 4 の側面の

50

明度 L 80 . 6 との差は、 - 6 . 9 であった。この場合、明度に基づく識別層の判別ができた。実施例 4 においては、識別層の明度 L 89 . 0 と第 3 又は第 4 の側面の明度 L 80 . 4 との差は、 8 . 7 であった。この場合、明度に基づく識別層の判別ができた。

【 0 0 8 1 】

実施例 5 は、比較例 1 より MgO の添加量を多くし、実施例 6 は、比較例 1 より MgO の添加量を少なくした。実施例 6 においては、識別層の明度 L 73 . 2 と第 3 又は第 4 の側面の明度 L 81 . 2 との差は、 - 8 . 0 であった。この場合、明度に基づく識別層の判別ができた。実施例 6 においては、識別層の明度 L 89 . 0 と第 3 又は第 4 の側面の明度 L 80 . 2 との差は、 8 . 8 であった。この場合、明度に基づく識別層の判別ができた。

【 0 0 8 2 】

実施例 7 は、比較例 1 より Y<sub>2</sub>O<sub>3</sub> の添加量を多くし、実施例 8 は、比較例 1 より Y<sub>2</sub>O<sub>3</sub> の添加量を少なくした。実施例 7 においては、識別層の明度 L 71 . 9 と第 3 又は第 4 の側面の明度 L 80 . 3 との差は、 - 8 . 3 であった。この場合、明度に基づく識別層の判別ができた。実施例 8 においては、識別層の明度 L 87 . 9 と第 3 又は第 4 の側面の明度 L 80 . 7 との差は、 7 . 2 であった。この場合、明度に基づく識別層の判別ができた。

【 0 0 8 3 】

実施例 9 は、比較例 1 より V<sub>2</sub>O<sub>5</sub> の添加量を多くし、実施例 10 は、比較例 1 より V<sub>2</sub>O<sub>5</sub> の添加量を少なくした。実施例 9 においては、識別層の明度 L 65 . 3 と第 3 又は第 4 の側面の明度 L 80 . 6 との差は、 - 15 . 3 であった。この場合、明度に基づく識別層の判別ができた。実施例 10 においては、識別層の明度 L 90 . 3 と第 3 又は第 4 の側面の明度 L 80 . 6 との差は、 9 . 7 であった。この場合、明度に基づく識別層の判別ができた。

【 0 0 8 4 】

実施例 11 は、比較例 1 より (Ba,Ca)SiO<sub>3</sub> の添加量を多くし、実施例 12 は、比較例 1 より (Ba,Ca)SiO<sub>3</sub> の添加量を少なくした。実施例 11 においては、識別層の明度 L 73 . 7 と第 3 又は第 4 の側面の明度 L 80 . 2 との差は、 - 6 . 6 であった。この場合、明度に基づく識別層の判別ができた。実施例 12 においては、識別層の明度 L 89 . 0 と第 3 又は第 4 の側面の明度 L 80 . 2 との差は、 8 . 8 であった。この場合、明度に基づく識別層の判別ができた。

【 0 0 8 5 】

以上のように、識別層の明度と第 3 又は第 4 の側面の明度との差が、 1 以上あれば、比較的正確に識別層の判別を行うことができる。

【 符号の説明 】

【 0 0 8 6 】

C 1 ... セラミック電子部品、 2 ... チップ素体、 2 a , 2 b ... 端面、 2 c ... 第 1 の側面、 2 d ... 第 2 の側面、 2 e ... 第 3 の側面、 2 f ... 第 4 の側面、 3 ... 第 1 の外部電極、 4 ... 第 2 の外部電極、 5 , 6 ... 識別層、 7 ... 内部電極層（導体）、 11 ... 積層体チップ、 15 , 16 ... 第 2 のセラミックグリーン層、 17 ... 電極パターン、 21 ... 第 1 のセラミックグリーン層。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

| 条件    | 材料                           |                            |       | 添加物 [mol%] |                               |     | 識別層の厚さ<br>(Ba <sub>x</sub> C <sub>y</sub> )<br>[SiO <sub>2</sub> ] |                                                          |      | △*** |      |      | 判定   |      |       |   |

|-------|------------------------------|----------------------------|-------|------------|-------------------------------|-----|--------------------------------------------------------------------|----------------------------------------------------------|------|------|------|------|------|------|-------|---|

|       | BaTiO <sub>3</sub><br>[mol%] | BET<br>[m <sup>2</sup> /g] | A/B   | MgO        | Y <sub>2</sub> O <sub>3</sub> | MnO | V <sub>2</sub> O <sub>5</sub>                                      | (Ba <sub>x</sub> C <sub>y</sub> )<br>[SiO <sub>2</sub> ] | L    | a    | b    | L    | a    | b    | L     |   |

| 比較例1  | 100                          | 3.5                        | 1.004 | 2.0        | 2.0                           | 0.2 | 0.06                                                               | 3.0                                                      | 80.9 | 17.9 | 28.1 | 80.2 | 17.3 | 27.9 | 0.7   |   |

| 実施例1  | 100                          | 4.0                        | 1.004 | 2.0        | 2.0                           | 0.2 | 0.06                                                               | 3.0                                                      | 75.3 | 19.7 | 29.7 | 80.9 | 18.0 | 27.9 | -5.6  | O |

| 実施例2  | 100                          | 3.0                        | 1.004 | 2.0        | 2.0                           | 0.2 | 0.06                                                               | 3.0                                                      | 85.9 | 19.9 | 27.9 | 80.7 | 17.9 | 28.6 | 8.2   | O |

| 実施例3  | 100                          | 3.5                        | 1.001 | 2.0        | 2.0                           | 0.2 | 0.06                                                               | 3.0                                                      | 73.7 | 16.8 | 27.9 | 80.6 | 17.3 | 27.9 | -6.9  | O |

| 実施例4  | 100                          | 3.5                        | 1.006 | 2.0        | 2.0                           | 0.2 | 0.06                                                               | 3.0                                                      | 83.0 | 15.8 | 26.8 | 80.4 | 17.9 | 28.2 | 8.7   | O |

| 実施例5  | 100                          | 3.5                        | 1.004 | 2.2        | 2.0                           | 0.2 | 0.06                                                               | 3.0                                                      | 73.2 | 19.8 | 27.6 | 81.2 | 18.1 | 28.7 | -8.0  | O |

| 実施例6  | 100                          | 3.5                        | 1.004 | 1.8        | 2.0                           | 0.2 | 0.06                                                               | 3.0                                                      | 85.0 | 15.6 | 28.5 | 80.2 | 17.9 | 28.4 | 8.6   | O |

| 実施例7  | 100                          | 3.5                        | 1.004 | 2.0        | 2.2                           | 0.2 | 0.06                                                               | 3.0                                                      | 71.9 | 15.6 | 29.8 | 80.3 | 17.3 | 28.6 | -8.3  | O |

| 実施例8  | 100                          | 3.5                        | 1.004 | 2.0        | 1.8                           | 0.2 | 0.06                                                               | 3.0                                                      | 87.9 | 17.0 | 30.4 | 80.7 | 18.2 | 28.0 | 7.2   | O |

| 実施例9  | 100                          | 3.5                        | 1.004 | 2.0        | 2.0                           | 0.2 | 0.09                                                               | 3.0                                                      | 65.3 | 19.7 | 25.7 | 80.6 | 17.8 | 28.7 | -15.3 | O |

| 実施例10 | 100                          | 3.5                        | 1.004 | 2.0        | 2.0                           | 0.2 | 0.03                                                               | 3.0                                                      | 90.3 | 15.6 | 26.1 | 80.6 | 17.3 | 28.3 | 9.7   | O |

| 実施例11 | 100                          | 3.5                        | 1.004 | 2.0        | 2.0                           | 0.2 | 0.06                                                               | 3.5                                                      | 73.7 | 20.4 | 29.4 | 80.2 | 17.3 | 27.9 | -6.6  | O |

| 実施例12 | 100                          | 3.5                        | 1.004 | 2.0        | 2.0                           | 0.2 | 0.06                                                               | 2.5                                                      | 89.0 | 16.2 | 30.0 | 80.2 | 17.3 | 27.9 | 8.8   | O |

---

フロントページの続き

(72)発明者 吉井 彰敏

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 五島 亮

秋田県にかほ市平沢字前田151 TDK-MCC株式会社内

(72)発明者 長谷部 和幸

秋田県にかほ市平沢字前田151 TDK-MCC株式会社内

Fターム(参考) 5E001 AB03 AE02 AE03 AE04 AG00 AJ04