(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6165127号

(P6165127)

(45) 発行日 平成29年7月19日(2017.7.19)

(24) 登録日 平成29年6月30日(2017.6.30)

(51) Int.Cl.

H01L 21/02 (2006.01)

B23K 20/00 (2006.01)

F 1

H01L 21/02 B

B23K 20/00 310M

B23K 20/00 310L

請求項の数 9 (全 16 頁)

(21) 出願番号 特願2014-259115 (P2014-259115)

(22) 出願日 平成26年12月22日 (2014.12.22)

(65) 公開番号 特開2016-119415 (P2016-119415A)

(43) 公開日 平成28年6月30日 (2016.6.30)

審査請求日 平成28年7月19日 (2016.7.19)

(73) 特許権者 315017775

三菱重工工作機械株式会社

滋賀県栗東市六地蔵130番地

(74) 代理人 110002147

特許業務法人酒井国際特許事務所

(72) 発明者 内海 淳

東京都港区港南二丁目16番5号 三菱重工業株式会社内

(72) 発明者 後藤 崇之

東京都港区港南二丁目16番5号 三菱重工業株式会社内

(72) 発明者 鈴木 賀典

東京都港区港南二丁目16番5号 三菱重工業株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及び半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基材の接合面に導電材及び絶縁材がそれぞれ露出した一対の基板を備え、前記基板同士を常温接合した半導体装置であって、

一対の前記接合面の間に、単独では非導電性を示すと共に前記導電材と結合して導電性を示す接合中間層を備え、前記接合中間層は、非導電性を保持しつつ前記基板の前記絶縁材同士を接合する絶縁接合部と、導電性を有し、前記基板の前記導電材同士を接合する導電接合部と、を備えることを特徴とする半導体装置。

## 【請求項 2】

前記基板の前記絶縁材同士は、前記接合中間層を介して接合されることを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

前記接合中間層は、非晶質半導体材料で形成されることを特徴とする請求項1または2に記載の半導体装置。

## 【請求項 4】

少なくとも一方の基板は、前記接合面における前記絶縁材の高さ位置が前記導電材よりも低く形成されることを特徴とする請求項1から3のいずれか一項に記載の半導体装置。

## 【請求項 5】

半導体基材の接合面に導電材及び絶縁材がそれぞれ露出した一対の基板同士を常温接合して製造した半導体装置の製造方法であって、

前記基板の接合面をそれぞれ活性化させる工程と、活性化された前記接合面の少なくとも一方に、単独では非導電性を示すと共に前記導電材と結合して導電性を示す接合中間層を形成する工程と、

前記接合中間層を介して、一対の前記基板同士を圧接する工程と、を備え、

前記半導体材料に高速原子ビームを照射して、前記半導体材料をスパッタリングすることにより、一方の前記基板の接合面に前記接合中間層を形成した後、該接合面に形成された接合中間層に高速原子ビームを照射して、該接合中間層を形成する前記半導体材料の一部をスパッタリングすることにより、他方の前記基板の接合面に前記接合中間層を形成することを特徴とする半導体装置の製造方法。

【請求項 6】

10

半導体基材の接合面に導電材及び絶縁材がそれぞれ露出した一対の基板同士を常温接合して製造した半導体装置の製造方法であって、

前記基板の接合面をそれぞれ活性化させる工程と、

活性化された前記接合面の少なくとも一方に、単独では非導電性を示すと共に前記導電材と結合して導電性を示す接合中間層を形成する工程と、

前記接合中間層を介して、一対の前記基板同士を圧接する工程と、を備え、

少なくとも一方の前記基板は、前記接合面における前記絶縁材の高さ位置が前記導電材よりも低く形成され、前記接合中間層は、前記基板同士を圧接する際に前記導電材により破断され、該導電材同士が直接的に接合されることを特徴とする半導体装置の製造方法。

【請求項 7】

20

少なくとも一方の前記基板は、前記接合面における前記絶縁材の高さ位置が前記導電材よりも低く形成され、前記接合中間層は、前記基板同士を圧接する際に前記導電材により破断され、該導電材同士が直接的に接合されることを特徴とする請求項 5 に記載の半導体装置の製造方法。

【請求項 8】

前記接合中間層は、半導体材料の蒸着やスパッタリング、または、化学気相成長により形成されることを特徴とする請求項 5 から 7 のいずれか一項に記載の半導体装置の製造方法。

【請求項 9】

一対の前記基板を圧接した後に、該基板を所定の温度で加熱する工程を備えたことを特徴とする請求項 5 から 8 のいずれか一項に記載の半導体装置の製造方法。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の基板を接合して形成される半導体装置、及び、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体デバイスの高集積化に関し、同種もしくは異種の半導体デバイスを積層化する 3 次元集積化技術が注目されている。この 3 次元集積化技術においては、電極や配線となる導電材と絶縁材とが露出した基板の接合面同士を接合する技術が重要となる。一般に、2 枚の基板の接合技術として、常温接合が知られている。常温接合とは、接合する 2 枚の基板の接合面を真空雰囲気で活性化し、活性化された接合面同士を圧接することで接合する技術である。常温接合では、熱処理を必要とせず、接合材（基板）同士を直接接合することができる。このため、熱処理に伴う基板の膨張等の変形を抑えることができ、接合時に、2 枚の基板のアライメントを正確に行うことができるという利点がある。

40

【0003】

ところで、上記した常温接合では、導電材としての金属類同士を直接接合することはできるものの、絶縁材として一般的に用いられている酸化膜や窒化膜などを直接接合することはできない。このため、従来、接合面に付着された極微量金属を利用して、導電材と絶

50

縁材とを同時に接合（ハイブリッド接合）できる常温接合方法が提案されている（例えば、特許文献1参照）。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第4162094号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、基板の接合面には、微細な導電材（電極）が多数形成されているため、従来の接合方法では、接合面に付着された金属により、近接した導電材（電極）間でリーク電流が発生し、デバイスの動作上の問題が懸念された。

10

【0006】

本発明は、上記に鑑みてなされたものであって、導電材間のリーク電流の発生を防止しつつ、導電材と絶縁材とを同時に接合可能とする半導体装置、及び、半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

上述した課題を解決し、目的を達成するために、本発明は、半導体基材の接合面に導電材及び絶縁材がそれぞれ露出した一対の基板を備え、基板同士を常温接合した半導体装置であって、一対の接合面の間に、単独では非導電性を示すと共に導電材と結合して導電性を示す接合中間層を備えることを特徴とする。

20

【0008】

この構成によれば、一対の接合面の間に接合中間層を備えるため、導電材及び絶縁材をそれぞれ同時に接合することができる。さらに、接合中間層は、単独では非導電性を示すと共に導電材と結合して導電性を示すため、導電材間の導電性を確保しつつ、絶縁材間の非導電性を確保できる。このため、導電材間のリーク電流の発生を防止でき、半導体装置の安定した動作を実現できる。

【0009】

また、基板の絶縁材同士は、接合中間層を介して接合されても良い。この構成によれば、絶縁材同士を強固に接合することができる。

30

【0010】

また、接合中間層は、非晶質半導体材料で形成されても良い。この構成によれば、半導体材料を蒸着、スパッタリングまたは化学気相成長により、単独では非導電性を示すと共に導電材と結合して導電性を示す性質を有する接合中間層を基板の接合面に簡単に形成することができる。

【0011】

また、少なくとも一方の基板は、接合面における絶縁材の高さ位置が導電材よりも低く形成されても良い。この構成によれば、基板同士を圧接した際に、この圧接荷重が導電材にかかるため、この導電材により接合中間層が破断される。このため、導電材同士が直接的に接合されることにより、導電材間の接合において良好な電気特性及び接合強度を得ることが可能となる。

40

【0012】

また、本発明は、半導体基材の接合面に導電材及び絶縁材がそれぞれ露出した一対の基板同士を常温接合して製造した半導体装置の製造方法であって、基板の接合面をそれぞれ活性化させる工程と、活性化された接合面の少なくとも一方に、単独では非導電性を示すと共に導電材と結合して導電性を示す接合中間層を形成する工程と、接合中間層を介して、一対の基板同士を圧接する工程と、を備えたことを特徴とする。この構成によれば、導電材及び絶縁材をそれぞれ同時に接合するハイブリッド接合を容易に実現することができる。

50

## 【0013】

また、接合中間層は、半導体材料の蒸着やスパッタリングまたは化学気相成長により形成されても良い。この構成によれば、基板の接合面に接合中間層を簡単に形成することができる。

## 【0014】

また、半導体材料に高速原子ビームを照射して、半導体材料をスパッタリングすることにより、一方の基板の接合面に接合中間層を形成した後、該接合面に形成された接合中間層に高速原子ビームを照射して、該接合中間層を形成する半導体材料の一部をスパッタリングすることにより、他方の基板の接合面に接合中間層を形成しても良い。この構成によれば、作業手順を簡素化し、各基板の接合面に接合中間層を簡単に形成することができる。

## 【0015】

また、少なくとも一方の基板は、接合面における絶縁材の高さ位置が導電材よりも低く形成され、接合中間層は、基板同士を圧接する際に導電材により破断され、該導電材同士が直接的に接合されても良い。この構成によれば、導電材同士が直接的に接合されることにより、導電材間の接合において良好な電気特性及び接合強度を得ることが可能となる。

## 【0016】

また、一対の基板を圧接した後に、該基板を所定の温度で加熱する工程を備えてよい。この構成によれば、導電材間の接合強度及び電気特性の向上を図ることができる。

## 【発明の効果】

## 【0017】

本発明によれば、導電材間のリーク電流の発生を防止しつつ、導電材と絶縁材とを同時に接合することができる。

## 【図面の簡単な説明】

## 【0018】

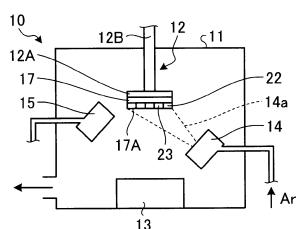

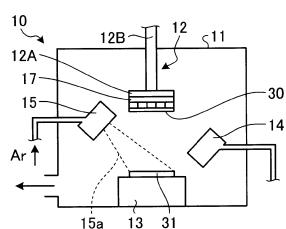

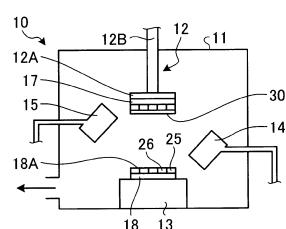

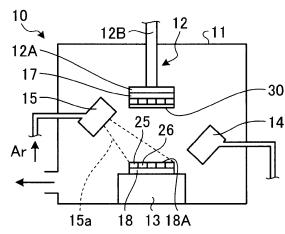

【図1】図1は、本実施形態に係る半導体装置が接合される常温接合装置の構成を模式的に示す断面図である。

【図2】図2は、接合前の第1ウェハと第2ウェハの構成を模式的に示す断面図である。

【図3】図3は、第1ウェハと第2ウェハとを接合して形成された半導体装置の構成を模式的に示す断面図である。

【図4】図4は、第1ウェハと第2ウェハが接合した状態を模式的に示す断面図である。

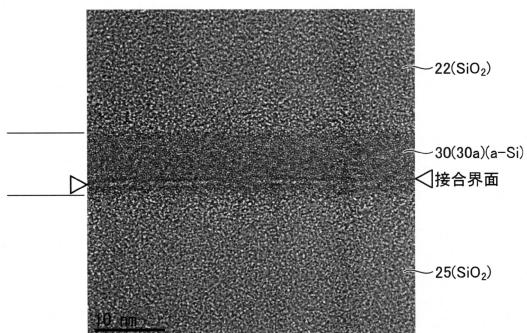

【図5】図5は、絶縁層としてのSiO<sub>2</sub> / SiO<sub>2</sub>の接合界面を示す透過型電子顕微鏡写真である。

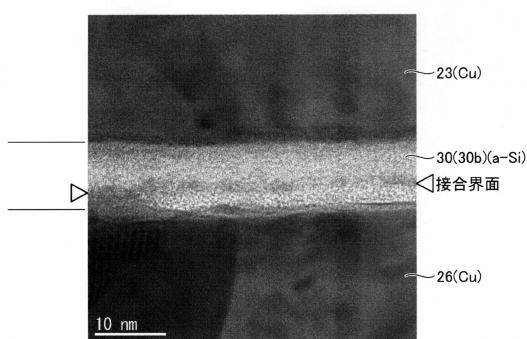

【図6】図6は、接合電極としてのCu / Cuの接合界面を示す透過型電子顕微鏡写真である。

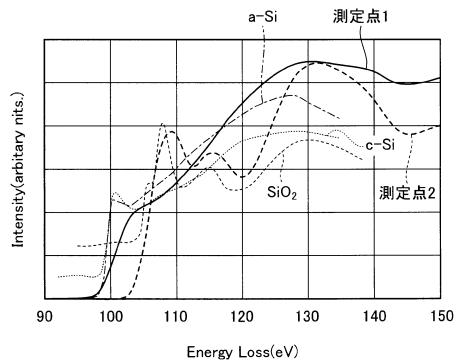

【図7】図7は、測定点におけるSi-L吸収端のEELSスペクトルを示すグラフである。

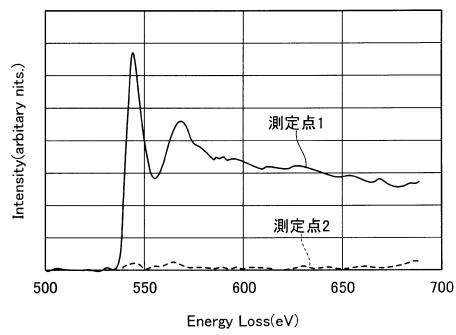

【図8】図8は、測定点におけるO-K吸収端のEELSスペクトルを示すグラフである。

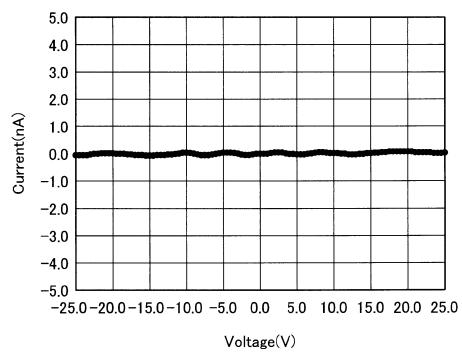

【図9】図9は、SiO<sub>2</sub> / SiO<sub>2</sub>間ににおける電流と電圧との関係を示すグラフである。

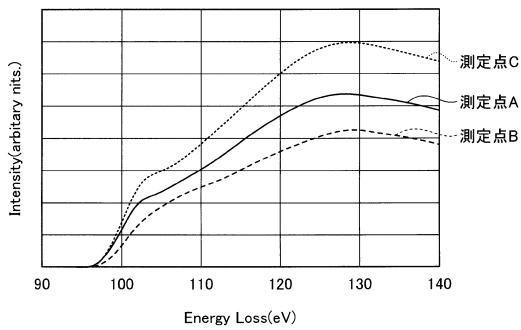

【図10】図10は、測定点におけるSi-L吸収端のEELSスペクトルを示すグラフである。

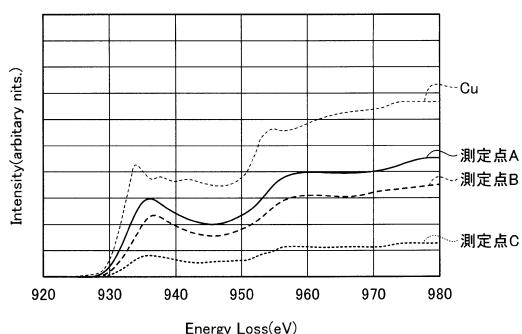

【図11】図11は、測定点におけるCu-L吸収端のEELSスペクトルを示すグラフである。

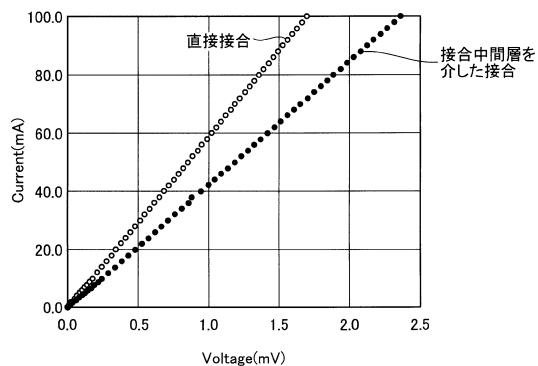

【図12】図12は、Cu / Cu間ににおける電流と電圧との関係を示すグラフである。

【図13-1】図13-1は、第1ウェハと第2ウェハとを接合する工程を示す工程説明図である。

【図13-2】図13-2は、第1ウェハと第2ウェハとを接合する工程を示す工程説明図である。

10

20

30

40

50

【図13-3】図13-3は、第1ウェハと第2ウェハとを接合する工程を示す工程説明図である。

【図13-4】図13-4は、第1ウェハと第2ウェハとを接合する工程を示す工程説明図である。

【図13-5】図13-5は、第1ウェハと第2ウェハとを接合する工程を示す工程説明図である。

【図13-6】図13-6は、第1ウェハと第2ウェハとを接合する工程を示す工程説明図である。

【図14-1】図14-1は、第1ウェハと第2ウェハとを接合する別の工程を示す工程説明図である。

【図14-2】図14-2は、第1ウェハと第2ウェハとを接合する別の工程を示す工程説明図である。

【図14-3】図14-3は、第1ウェハと第2ウェハとを接合する別の工程を示す工程説明図である。

【図14-4】図14-4は、第1ウェハと第2ウェハとを接合する別の工程を示す工程説明図である。

【図15-1】図15-1は、別の実施形態に係る第1ウェハと第2ウェハの接合前の構成を模式的に示す断面図である。

【図15-2】図15-2は、別の実施形態に係る第1ウェハと第2ウェハとを接合した状態の構成を模式的に示す断面図である。

【発明を実施するための形態】

【0019】

以下に、本発明に係る実施形態について、図面を参照して説明する。なお、以下の実施形態によりこの発明が限定されるものではない。また、以下の実施形態における構成要素には、当業者が置換可能かつ容易なもの、あるいは実質的に同一のものが含まれる。

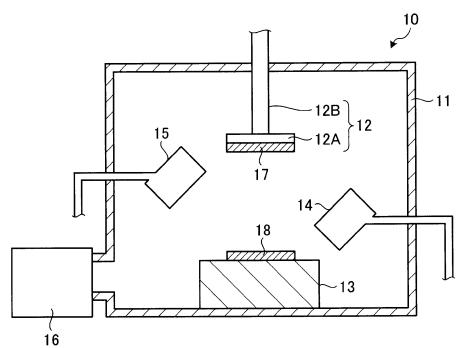

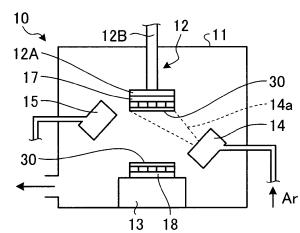

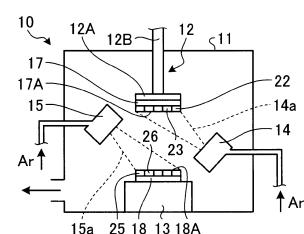

【0020】

図1は、本実施形態に係る半導体装置が接合される常温接合装置の構成を模式的に示す断面図である。常温接合装置10は、図1に示すように、真空チャンバ11と、この真空チャンバ11内に設置される上側ステージ12、下側ステージ13と、高速原子ビーム源(FAB: Fast Atom Beam)14, 15と、真空排気装置16とを備えている。

【0021】

真空チャンバ11は内部を環境から密閉する容器であり、真空排気装置16は、真空チャンバ11の内部から気体を排出する。これにより、真空チャンバ11の内部は、真空雰囲気となる。さらに、真空チャンバ11は、この真空チャンバ11の内部空間と外部とを連通させ、または、分離するゲート(不図示)を備える。

【0022】

上側ステージ12は、円板状に形成された静電チャック12Aと、この静電チャック12Aを鉛直方向に上下させる圧接機構12Bとを備えている。静電チャック12Aは、円板の下端に誘電層を備え、その誘電層に電圧を印加し、静電力によってその誘電層に第1ウェハ(基板)17を吸着して支持する。圧接機構12Bは、ユーザの操作により、静電チャック12Aを真空チャンバ11に対して鉛直方向に平行移動させる。

【0023】

下側ステージ13は、その上面に第2ウェハ(基板)18を支持するステージであり、図示されていない移送機構を備えている。その移送機構は、ユーザの操作により下側ステージ13を水平方向に平行移動させ、下側ステージ13を鉛直方向に平行な回転軸を中心回転移動させる。また、下側ステージ13は、その上端に誘電層を備え、その誘電層に電圧を印加し、静電力によってその誘電層に第2ウェハ18を吸着して支持する機構を備えても良い。

【0024】

高速原子ビーム源14, 15は、ウェハの表面の活性化に用いられる中性原子ビーム(

10

20

30

40

50

例えば、アルゴン Ar 原子)を出射する。一方の高速原子ビーム源 14 は、上側ステージ 12 に支持される第 1 ウェハ 17 に向けて配置され、他方の高速原子ビーム源 15 は、下側ステージ 13 に支持される第 2 ウェハ 18 に向けて配置される。中性原子ビームが照射されることにより、第 1 ウェハ 17 及び第 2 ウェハ 18 の活性化が行われる。また、高速原子ビーム源 14, 15 の代わりに、他の活性化手段(例えば、イオンガンまたはプラズマ)が各ウェハの活性化に用いられても良い。

【0025】

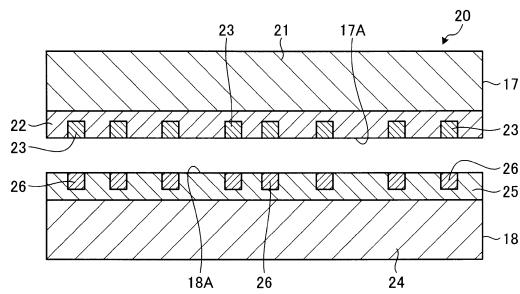

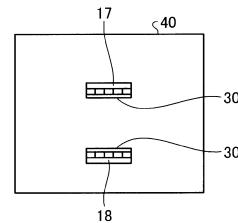

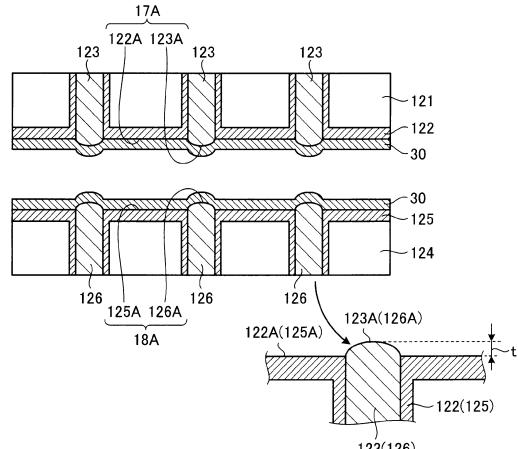

次に、常温接合装置 10 を用いて常温接合される半導体装置 20 について説明する。図 2 は、接合前の第 1 ウェハと第 2 ウェハの構成を模式的に示す断面図であり、図 3 は、第 1 ウェハと第 2 ウェハとを接合して形成された半導体装置の構成を模式的に示す断面図である。第 1 ウェハ 17 は、図 2 に示すように、第 1 半導体基材 21 上に積層して形成された第 1 絶縁層(絶縁材) 22 と、この第 1 絶縁層 22 に形成された第 1 接合電極(導電材) 23 とを備える。第 1 絶縁層 22 及び第 1 接合電極 23 は、それぞれ第 1 ウェハ 17 の表面 17A に露出して形成され、この表面 17A が接合面として機能する。また、第 2 ウェハ 18 は、第 2 半導体基材 24 上に積層して形成された第 2 絶縁層(絶縁材) 25 と、この第 2 絶縁層 25 に形成された第 2 接合電極(導電材) 26 とを備える。第 2 絶縁層 25 及び第 2 接合電極 26 は、それぞれ第 2 ウェハ 18 の表面 18A に露出して形成され、この表面 18A が接合面として機能する。これらの表面 17A, 18A は平坦面に形成され、表面 17A, 18A 同士は密接される。

【0026】

第 1 半導体基材 21 及び第 2 半導体基材 24 は、例えば、単結晶シリコン(Si)が用いられるが、他にも単結晶ゲルマニウム(Ge)、ヒ化ガリウム(GaAs)やシリコンカーバイド(SiC)などの材料を用いることもできる。また、第 1 半導体基材 21 及び第 2 半導体基材 24 は、同種の材料だけでなく、異種の材料を用いても良い。

【0027】

第 1 絶縁層 22 及び第 2 絶縁層 25 は、表面 17A, 18A 側に、半導体基材の酸化物や窒化物で形成される。具体的には、半導体基材として単結晶シリコン(Si)が用いられている場合には、第 1 絶縁層 22 及び第 2 絶縁層 25 としてシリコン酸化膜(SiO<sub>2</sub>)やシリコン窒化膜(Si<sub>3</sub>N<sub>4</sub>)が、酸化炉、窒化炉、または、化学気相成長(CVD: Chemical Vapor Deposition)装置などでの成膜にて形成される。本実施形態では、シリコン酸化膜(SiO<sub>2</sub>)が形成されているものとする。また、第 1 接合電極 23 及び第 2 接合電極 26 は、導電性の優れた材料、例えば銅(Cu)により形成されている。この第 1 接合電極 23 及び第 2 接合電極 26 には、配線材が接続されて電子回路や各種素子が形成される。

【0028】

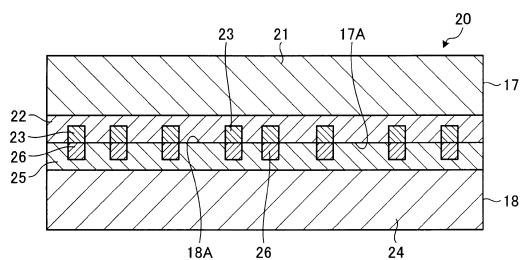

第 1 ウェハ 17 と第 2 ウェハ 18 とを接合する場合には、図 2、図 3 に示すように、接合面としての表面 17A, 18A をお互いに対向させ、上記した常温接合装置 10 を用いて常温接合がなされる。この場合、第 1 ウェハ 17 の第 1 接合電極 23 と、第 2 ウェハ 18 の第 2 接合電極 26 とが接合され、第 1 ウェハ 17 の第 1 絶縁層 22 と、第 2 ウェハ 18 の第 2 絶縁層 25 とが接合される。常温接合では、第 1 接合電極 23 及び第 2 接合電極 26 の金属類同士は接合できるものの、第 1 絶縁層 22 及び第 2 絶縁層 25 はシリコン酸化膜(SiO<sub>2</sub>)やシリコン窒化膜(Si<sub>3</sub>N<sub>4</sub>)であるため、これらを直接接合することはできない。このため、本構成では、図 4 に示すように、第 1 ウェハ 17 の表面 17A と第 2 ウェハ 18 の表面 18A との間に、接合電極と絶縁層とを同時に接合するための接合中間層 30 が設けられている。

【0029】

接合中間層 30 は、第 1 ウェハ 17 の表面 17A と第 2 ウェハ 18 の表面 18A とを接合するための薄膜であり、非晶質半導体材料(例えば、アモルファスシリコン)によって形成されている。発明者の研究によれば、非晶質半導体材料(例えば、アモルファスシリコン)は、単独(単体)では非導電性を示すが、金属類等と結合することにより導電性を

10

20

30

40

50

示すことが判明した。このため、非晶質半導体材料を接合中間層30として用いることにより、第1絶縁層22と第2絶縁層25との間の非導電性(絶縁性)を保持しつつ第1絶縁層22と第2絶縁層25とを強固に接合することができる。さらに、第1接合電極23と第2接合電極26との間の電気特性の劣化がなく、第1接合電極23と第2接合電極26との間の導電性を確保することができる。すなわち、接合中間層30は、非導電性(絶縁性)を保持しつつ第1絶縁層22と第2絶縁層25とを接合する領域(絶縁接合部30a)と、導電性を有し、第1接合電極23と第2接合電極26とを接合する領域(導電接合部30b)とを備えて形成される。

#### 【0030】

次に、接合中間層30を具体的に説明する。図5は、絶縁層としての $\text{SiO}_2$  /  $\text{SiO}_2$ の接合界面を示す透過型電子顕微鏡写真であり、図6は、接合電極としての $\text{Cu}$  /  $\text{Cu}$ の接合界面を示す透過型電子顕微鏡写真である。透過型電子顕微鏡(TEM: Transmission Electron Microscope)は、観察対象に電子線をあて、それを透過してきた電子が作り出す干渉像を拡大して観察する形式の電子顕微鏡である。

#### 【0031】

図5に示すように、第1絶縁層22及び第2絶縁層25としての $\text{SiO}_2$  /  $\text{SiO}_2$ の接合界面には、接合中間層30(絶縁接合部30a)としてアモルファスシリコン層が形成されている。また、図6に示すように、第1接合電極23と第2接合電極26としての $\text{Cu}$  /  $\text{Cu}$ の接合界面には、同様に、接合中間層30(導電接合部30b)としてアモルファスシリコン層が形成されている。これら接合中間層30は、いずれも厚さが7~9nm程度に形成されており、接合中間層30と $\text{SiO}_2$ もしくは $\text{Cu}$ との間にボイド(空隙)の存在は見られず十分な密着状態が得られている。

#### 【0032】

接合中間層30は、単結晶シリコンのスパッタリングにより、絶縁層( $\text{SiO}_2$ )及び接合電極( $\text{Cu}$ )の接合面に形成されたものであり、単結晶シリコンから非晶質(アモルファス)シリコンに状態を変えて形成されている。発明者は、接合中間層30内の測定点1及び絶縁層( $\text{SiO}_2$ )内の測定点2の2か所について、電子エネルギー損失分光法(EELS: Electron Energy-Loss Spectroscopy)による界面近傍の状態分析を行った。電子エネルギー損失分光法とは、電子が薄片試料を透過する際に原子との相互作用により失うエネルギーを測定することによって、物質の構成元素や電子構造を分析する手法である。

#### 【0033】

図7は、測定点における $\text{Si}$ -L吸収端のEELSスペクトルを示すグラフであり、図8は、測定点におけるO-K吸収端のEELSスペクトルを示すグラフである。この図7においては、比較のために、単結晶シリコン(c-Si)、アモルファスシリコン(a-Si)、及びシリコン酸化膜( $\text{SiO}_2$ )における同エネルギー域のスペクトルを示している。図7に示すように、接合中間層30内の測定点1における $\text{Si}$ -L吸収端のEELSスペクトルは、単結晶シリコンもしくはアモルファスシリコンに近く、 $\text{SiO}_2$ の特徴的なピークは見られなかった。また、O-K吸収端におけるEELSスペクトルでは、接合中間層30には、酸素原子Oの存在はほとんど確認されなかった。このため、接合中間層30は $\text{Si}$ 酸化物を含むものではなく、さらに、図5に示す高分解能像から、第1絶縁層22と第2絶縁層25との間に形成される接合中間層30(絶縁接合部30a)は、アモルファスシリコンであると考えられる。

#### 【0034】

続いて、 $\text{SiO}_2$  /  $\text{SiO}_2$ 間に形成された接合中間層30(絶縁接合部30a)の電気特性を測定した。図9は、 $\text{SiO}_2$  /  $\text{SiO}_2$ 間ににおける電流と電圧との関係を示すグラフである。この図9に示すように、アモルファスシリコンは、単結晶シリコンと比べて電気特性が大きく異なり、単独では電気を通さない非導電性を有することが確認できた。ここで、非導電性とは、抵抗率が $10^5 \cdot \text{cm}$ 以上の状態をいう。

#### 【0035】

また、接合中間層30を介して接合された $\text{SiO}_2$  /  $\text{SiO}_2$ の接合強度を測定した。

10

20

30

40

50

接合強度の測定は、接合した  $\text{SiO}_2 / \text{SiO}_2$  の試料を  $12\text{ mm} \times 12\text{ mm}$  のサイズのチップにカットし、このチップを引張試験することにより行った。試験に際しては、チップを治具に固定し、この治具への引張荷重を変更しつつ、チップが破断する際の荷重を測定した。引張試験では、破断は生じたものの、この破断はチップと治具とが接着界面で剥離したことにより生じ、 $\text{SiO}_2 / \text{SiO}_2$  の接合は保持されていた。破断したときの引張強度は  $25\text{ MPa}$  以上であったため、接合中間層 30 による接合界面の強度はこれ以上と考えられる。

#### 【0036】

このように、アモルファスシリコン（非晶質半導体材料）を接合中間層 30 として用いた構成では、第 1 絶縁層 22 と第 2 絶縁層 25 との間の非導電性（絶縁性）を保持しつつ第 1 絶縁層 22 と第 2 絶縁層 25 とを強固に接合することができるという結果を得た。10

#### 【0037】

次に、 $\text{Cu} / \text{Cu}$  間に形成された接合中間層 30（導電接合部 30b）について、電子エネルギー損失分光法による界面近傍の状態分析を行った。測定点としては、接合中間層 30 と  $\text{Cu}$  との境界近傍に位置する測定点 A、接合中間層 30 内の厚み方向中央に位置する測定点 B、及び、測定点 A と測定点 B との厚み方向の間に位置する測定点 C の 3 つである。図 10 は、測定点における  $\text{Si-L}$  吸収端の EELS スペクトルを示すグラフであり、図 11 は、測定点における  $\text{Cu-L}$  吸収端の EELS スペクトルを示すグラフである。この図 11 においては、比較のために、銅（ $\text{Cu}$ ）の同エネルギー域のスペクトルを示している。20

#### 【0038】

図 10 に示すように、接合中間層 30 内の測定点 A ~ C における  $\text{Si-L}$  吸収端における EELS スペクトルは、いずれも同じような形状であり、シリコンが単独で存在していることを示している。また、図 11 に示すように、 $\text{Cu-L}$  吸収端の EELS スペクトルでは、接合中間層 30 内のいずれの測定点 A ~ C でも銅の存在が認められる。

#### 【0039】

さらに、 $\text{Cu} / \text{Cu}$  間に形成された接合中間層 30 の電気特性を測定した。図 12 は、 $\text{Cu} / \text{Cu}$  間における電流と電圧との関係を示すグラフである。この図 12 に示すように、接合中間層 30 を介して接合された場合であっても、電圧と電流との間には直線的な関係が得られ、 $\text{Cu} / \text{Cu}$  間においてオーミックな（オームの法則に従った）接続が得られていると考えられる。また、 $\text{Cu} / \text{Cu}$  間を直接接合した際の抵抗値が  $20\text{ (m)}$  以下であったのに対し、接合中間層 30 を介した接合では、 $25\text{ (m)}$  以下となり、ほぼ同程度の結果であった。この点は、 $\text{SiO}_2 / \text{SiO}_2$  間の接合中間層では非導電性を示していたことと比較すると大きく異なる。これは、上述したように、部分的には微量であるが、接合中間層 30（導電接合部 30b）の全域に銅が存在しているためと考えられ、第 1 接合電極 23 と第 2 接合電極 26 との圧接時に、接合中間層 30 のアモルファスシリコンと各電極の銅とが結合したためと考えられる。30

#### 【0040】

このように、アモルファスシリコン（非晶質半導体材料）を接合中間層 30 として用いた構成では、第 1 接合電極 23 と第 2 接合電極 26 との間の導電性を確保できるという結果を得た。従って、本実施形態の半導体装置 20 は、接合電極 23, 26 及び絶縁層 22, 25 がそれぞれ露出した表面 17A, 18A の間に接合中間層 30 を備えるため、接合電極 23, 26 及び絶縁層 22, 25 をそれぞれ同時に接合するハイブリッド接合を実現できる。さらに、接合中間層 30 は、単独では非導電性を示すと共に接合電極 23, 26 と結合して導電性を示すため、第 1 接合電極 23 と第 2 接合電極 26 との間の導電性を確保しつつ、第 1 絶縁層 22 と第 2 絶縁層 25 との間の非導電性を確保できる。このため、第 1 接合電極 23 と第 2 接合電極 26 との間を流れる電流が第 1 絶縁層 22 と第 2 絶縁層 25 との間を流れることを防止できるため、リーク電流の発生を防止することができ、半導体装置 20 の安定した動作を実現できる。40

#### 【0041】

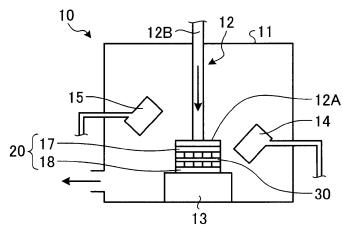

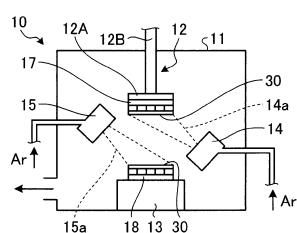

次に、半導体装置 20 の製造手順について説明する。図 13-1 ~ 図 13-6 は、第 1 ウェハと第 2 ウェハとを接合する工程を示す工程説明図である。前提として、第 1 ウェハ 17 と第 2 ウェハ 18 は、それぞれ表面 17A, 18A に接合電極 23, 26 及び絶縁層 22, 25 がそれぞれ露出した状態に、別の作業工程によって事前に製造されている。

#### 【0042】

図 13-1 に示すように、第 1 ウェハ 17 が常温接合装置 10 の真空チャンバ 11 内に搬送され、この第 1 ウェハ 17 は、表面 17A が鉛直下方を向くように、上側ステージ 12 の静電チャック 12A に支持される。真空チャンバ 11 内は真空雰囲気に維持されている。この状態で、高速原子ビーム源 14 から第 1 ウェハ 17 の表面 17A に向けて、アルゴンビーム 14a を出射する。このアルゴンビーム 14a は、第 1 ウェハ 17 の表面 17A に照射され、該表面 17A が活性化される。 10

#### 【0043】

続いて、図 13-2 に示すように、真空チャンバ 11 内にペアウェハ 31 が搬送され、このペアウェハ 31 は下側ステージ 13 の上面に載置される。ペアウェハ 31 は、単結晶シリコンで形成されており、接合中間層 30 を生成する際のスパッタ源として用いられる。この状態で、高速原子ビーム源 15 からペアウェハ 31 に向けて、アルゴンビーム 15a を出射する。これにより、ペアウェハ 31 はスパッタリングされ、ペアウェハ 31 から弾き出されたシリコン原子が上昇し、第 1 ウェハ 17 の表面 17A 上に接合中間層 30 が成膜される。本実施形態では、アルゴンビーム 15a の照射を所定時間（例えば 10min）行い、第 1 ウェハ 17 の表面 17A 上に厚さ 1nm ~ 50nm 程度の接合中間層 30 を形成する。この接合中間層 30 は、上述したように、アモルファス（非晶質）シリコンである。 20

#### 【0044】

続いて、図 13-3 に示すように、真空チャンバ 11 からペアウェハ 31 を搬出し、その代わりに第 2 ウェハ 18 が真空チャンバ 11 内に搬送される。この第 2 ウェハ 18 は、表面 18A が鉛直上方を向くように、下側ステージ 13 の上面に載置される。続いて、図 13-4 に示すように、高速原子ビーム源 15 から第 2 ウェハ 18 の表面 18A に向けて、アルゴンビーム 15a を出射する。このアルゴンビーム 15a は、第 2 ウェハ 18 の表面 18A に照射され、該表面 18A が活性化される。 30

#### 【0045】

続いて、図 13-5 に示すように、高速原子ビーム源 14 から第 1 ウェハ 17 の表面に形成された接合中間層 30 に向けて、アルゴンビーム 14a を出射する。この場合、接合中間層 30 を形成するアモルファスシリコンの一部がスパッタ源として機能する。アルゴンビーム 14a の照射により、接合中間層 30 がスパッタリングされ、接合中間層 30 から弾き出されたシリコン原子が上昇し、第 2 ウェハ 18 の表面 18A 上にも接合中間層 30 が成膜される。本実施形態では、アルゴンビーム 14a の照射を所定時間（例えば 10min）行い、第 2 ウェハ 18 の表面 18A 上に厚さ 1nm ~ 50nm 程度の接合中間層 30 を形成する。この接合中間層 30 も、上述したように、アモルファス（非晶質）シリコンである。本実施形態では、第 1 ウェハ 17 の表面に形成された接合中間層 30 をスパッタ源として使用するため、第 2 ウェハ 18 の表面 18A 用に別途スパッタ源を用意する必要が無いと共に、真空チャンバ 11 内へのスパッタ源の出し入れが低減するため、作業手順を簡素化し、第 1 ウェハ 17 及び第 2 ウェハ 18 の各表面 17A, 18A に接合中間層 30 を簡単に形成することができる。 40

#### 【0046】

続いて、第 1 ウェハ 17 と第 2 ウェハ 18 とのアライメントを行った後、図 13-6 に示すように、上側ステージ 12 の圧接機構 12B を動作させることで、第 1 ウェハ 17 を支持した静電チャック 12A を鉛直下方に下降させ、第 1 ウェハ 17 と第 2 ウェハ 18 とを圧接する。これにより、第 1 ウェハ 17 の表面 17A と第 2 ウェハ 18 の表面 18A とが接合中間層 30 を介して接合され、半導体装置 20 が形成される。続いて、真空チャンバ 11 内で半導体装置 20（第 1 ウェハ 17 及び第 2 ウェハ 18）を所定温度（例えば 500

0 ~ 400 程度)で加熱する。これにより、第1接合電極23及び第2接合電極26の銅Cuと、接合中間層30のアモルファスシリコンとの合金化が促進され、第1接合電極23と第2接合電極26との接合がより強固となり、電気特性が向上する。

#### 【0047】

以上説明したように、本実施形態の半導体装置20の製造方法は、第1ウェハ17の表面17Aと第2ウェハ18の表面18Aをそれぞれ活性化させる工程と、活性化された表面17A, 18Aに接合中間層30を形成する工程と、接合中間層30を介して、第1ウェハ17と第2ウェハ18とを圧接する工程とを備えたため、接合電極23, 26及び絶縁層22, 25をそれぞれ同時に接合するハイブリッド接合を容易に実現することができる。

10

#### 【0048】

さらに、本実施形態では、ペアウェハ31にアルゴンビーム15aを照射して、ペアウェハ31をスパッタリングすることにより、第1ウェハ17の表面17Aに接合中間層30を形成した後、この表面17Aに形成された接合中間層30にアルゴンビーム14aを照射して、接合中間層30を形成するアモルファスシリコンの一部をスパッタリングすることにより、第2ウェハ18の表面18Aに接合中間層30を形成するため、作業手順を簡素化し、第1ウェハ17及び第2ウェハ18の各表面17A, 18Aに接合中間層30を簡単に形成することができる。

#### 【0049】

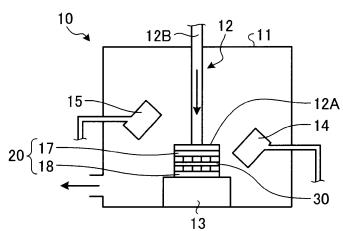

次に、半導体装置20の別の製造手順について説明する。図14-1～図14-4は、第1ウェハと第2ウェハとを接合する別の工程を示す工程説明図である。この場合においても、前提として、第1ウェハ17と第2ウェハ18は、それぞれ表面17A, 18Aに接合電極23, 26及び絶縁層22, 25がそれぞれ露出した状態に、別の作業工程によって事前に製造されている。

20

#### 【0050】

図14-1に示すように、第1ウェハ17が常温接合装置10の真空チャンバ11内に搬送され、この第1ウェハ17は、表面17Aが鉛直下方を向くように、上側ステージ12の静電チャック12Aに支持される。同様に、第2ウェハ18が真空チャンバ11内に搬送され、この第2ウェハ18は、表面18Aが鉛直上方を向くように、下側ステージ13の上面に載置される。真空チャンバ11内は真空雰囲気に維持されている。この状態で、高速原子ビーム源14, 15からそれぞれ第1ウェハ17の表面17A, 第2ウェハ18の表面18Aに向けて、アルゴンビーム14a, 15aを出射する。このアルゴンビーム14a, 15aは、第1ウェハ17の表面17A, 第2ウェハ18の表面18Aにそれぞれ照射され、該表面17A, 18Aが活性化される。

30

#### 【0051】

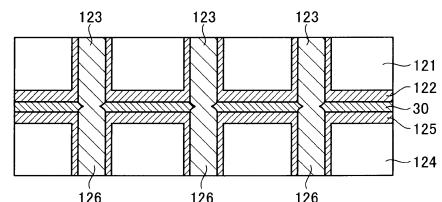

続いて、図14-2に示すように、表面17A, 18Aが活性化された第1ウェハ17及び第2ウェハ18は、真空チャンバ11から成膜チャンバ40に移送される。この場合、第1ウェハ17及び第2ウェハ18は、外気(酸素)に触れないように、真空の搬送路によって搬送されることが好ましい。成膜チャンバ40は、第1ウェハ17の表面17A及び第2ウェハ18の表面18Aに上記した接合中間層30を成膜するためのチャンバであり、成膜チャンバ40内には、化学気相成長装置(不図示)が配置されている。化学気相成長法は、第1ウェハ17及び第2ウェハ18を所定条件で加熱した状態で、第1ウェハ17の表面17A及び第2ウェハ18の表面18Aに、シリコンを含む原料ガスを供給し、これら表面17A, 18Aでの化学反応により接合中間層30を形成するものである。この化学気相成長法においても、接合中間層30はアモルファス(非晶質)シリコンにより形成される。この構成では、接合中間層30を別途形成することができるため、接合工程の処理時間の短縮化を図ることができる。

40

#### 【0052】

続いて、図14-3に示すように、接合中間層30が形成された第1ウェハ17及び第2ウェハ18を真空チャンバ11内に搬送する。そして、第1ウェハ17は、接合中間層

50

30が鉛直下方を向くように、上側ステージ12の静電チャック12Aに支持され、第2ウェハ18は、接合中間層30が鉛直上方を向くように、下側ステージ13の上面に載置される。真空チャンバ11内は真空雰囲気に維持されている。この状態で、高速原子ビーム源14, 15からそれぞれ第1ウェハ17, 第2ウェハ18に形成された接合中間層30, 30に向けて、アルゴンビーム14a, 15aを出射する。このアルゴンビーム14a, 15aは、第1ウェハ17, 第2ウェハ18の接合中間層30, 30の表面にそれぞれ照射され、該接合中間層30, 30の表面が活性化される。

#### 【0053】

続いて、第1ウェハ17と第2ウェハ18とのアライメントを行った後、図14-4に示すように、上側ステージ12の圧接機構12Bを動作させることで、第1ウェハ17を支持した静電チャック12Aを鉛直下方に下降させ、第1ウェハ17と第2ウェハ18とを圧接する。これにより、第1ウェハ17の表面17Aと第2ウェハ18の表面18Aとが接合中間層30を介して接合され、半導体装置20が形成される。続いて、真空チャンバ11内で半導体装置20(第1ウェハ17及び第2ウェハ18)を所定温度(例えば50 ~ 400)で加熱する。これにより、第1接合電極23及び第2接合電極26の銅Cuと、接合中間層30のアモルファスシリコンとの合金化が促進され、第1接合電極23と第2接合電極26との接合がより強固となり、電気特性が向上する。

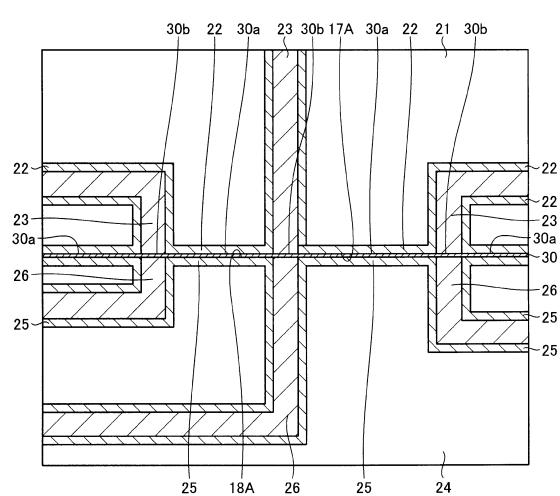

#### 【0054】

次に、別の実施形態について説明する。図15-1は、別の実施形態に係る第1ウェハと第2ウェハの接合前の構成を模式的に示す断面図であり、図15-2は、別の実施形態に係る第1ウェハと第2ウェハとを接合した状態の構成を模式的に示す断面図である。上記した構成では、第1ウェハ17の表面17A、及び、第2ウェハ18の表面18Aは、それぞれ平坦面に形成され、これら表面17A, 18A同士は密接するように形成されていた。これに対し、この別の実施形態では、図15-1に示すように、表面17Aには、第1半導体基材121上に積層された第1絶縁層122と第1接合電極123とが露出しており、第1絶縁層122の表面122Aの高さ位置が第1接合電極123の表面123Aの高さ位置よりも低く形成されている。この高さ位置の差tは、接合中間層30と同程度の1nm ~ 100nm程度に設定されている。同様に、表面18Aには、第2半導体基材124上に積層された第2絶縁層125と第2接合電極126とが露出しており、第2絶縁層125の表面125Aの高さ位置が第2接合電極126の表面126Aの高さ位置よりも低く形成されている。この高さ位置の差tは、接合中間層30と同程度の1nm ~ 100nm程度に設定されている。この他の構成については、上記した実施形態の構成と同様であるため説明を省略する。

#### 【0055】

この構成によれば、第1ウェハ17と第2ウェハ18とを圧接した際に、この圧接荷重が第1接合電極123及び第2接合電極126にかかるため、図15-2に示すように、接合中間層30は、第1接合電極123と第2接合電極126とにより破断され、第1接合電極123と第2接合電極126同士が直接的に接合される。これにより、第1接合電極123と第2接合電極126との間の接合において良好な電気特性及び接合強度を得ることが可能となる。

#### 【0056】

以上、本発明の実施形態について説明したが、本発明は、上記実施形態に限定されるものではない。例えば、上記実施形態では、接合中間層30を第1ウェハ17及び第2ウェハ18の表面17A, 18Aの両方に形成したが、一方に形成してもよい。また、上記実施形態では、第1接合電極123及び第2接合電極126をそれぞれ第1絶縁層122及び第2絶縁層125よりも突となる形状としたが、第1接合電極123または第2接合電極126の一方であっても良い。また、上記実施形態では、接合中間層30をスパッタリングまたは化学気相成長法によって形成する構成を説明したが、蒸着によって接合中間層30を形成しても良い。蒸着は、真空容器の中で、蒸着材料(例えばシリコン)を加熱し、気化または昇華して、離れた位置に置かれた基板の表面に付着させて薄膜を形成するも

10

20

30

40

50

のである。この方法によっても、接合中間層 30 はアモルファス（非晶質）シリコンにより形成される。この構成では、接合中間層 30 を別途形成することができるため、接合工程の処理時間の短縮化を図ることができる。

【符号の説明】

【0057】

|               |             |    |

|---------------|-------------|----|

| 1 0           | 常温接合装置      |    |

| 1 1           | 真空チャンバ      |    |

| 1 2           | 上側ステージ      |    |

| 1 2 A         | 静電チャック      | 10 |

| 1 2 B         | 圧接機構        |    |

| 1 3           | 下側ステージ      |    |

| 1 4 , 1 5     | 高速原子ビーム源    |    |

| 1 4 a , 1 5 a | アルゴンビーム     |    |

| 1 7           | 第1ウェハ（基板）   |    |

| 1 7 A         | 表面（接合面）     |    |

| 1 8           | 第2ウェハ（基板）   |    |

| 1 8 A         | 表面（接合面）     |    |

| 2 0           | 半導体装置       |    |

| 2 1 , 1 2 1   | 第1半導体基材     | 20 |

| 2 2 , 1 2 2   | 第1絶縁層（絶縁材）  |    |

| 2 3 , 1 2 3   | 第1接合電極（導電材） |    |

| 2 4 , 1 2 4   | 第2半導体基材     |    |

| 2 5 , 1 2 5   | 第2絶縁層（絶縁材）  |    |

| 2 6 , 1 2 6   | 第2接合電極（導電材） |    |

| 3 0           | 接合中間層       |    |

| 3 1           | ペアウェハ       |    |

| 4 0           | 成膜チャンバ      |    |

| 1 2 2 A       | 表面          |    |

| 1 2 3 A       | 表面          |    |

| 1 2 5 A       | 表面          | 30 |

| 1 2 6 A       | 表面          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13-1】

【図13-2】

【図13-3】

【図13-4】

【図13-5】

【図13-6】

【図14-3】

【図14-4】

【図14-1】

【図14-2】

【図15-1】

【図15-2】

---

フロントページの続き

(72)発明者 井手 健介

東京都港区港南二丁目16番5号 三菱重工業株式会社内

審査官 儀同 孝信

(56)参考文献 特開2012-238729 (JP, A)

特開平10-256263 (JP, A)

特開平06-084733 (JP, A)

特開平10-092702 (JP, A)

特開平01-133341 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

B23K 20/00