(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-47608

(P2004-47608A)

(43) 公開日 平成16年2月12日(2004.2.12)

(51) Int.Cl.<sup>7</sup>

H01L 21/336

H01L 21/28

H01L 21/3205

H01L 21/768

H01L 29/417

F 1

H01L 29/78

H01L 21/28

H01L 29/50

H01L 21/88

H01L 21/90

301P

301S

M

Q

C

テーマコード(参考)

4M104

5F033

5F140

審査請求 未請求 請求項の数 15 O L (全 13 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2002-201127(P2002-201127)

平成14年7月10日(2002.7.10)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100068814

弁理士 坪井 淳

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】不要なシリサイドの形成を回避するとともに接合リーケ電流の低減が可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板の表面内に配設された、素子領域を分離する素子分離絶縁膜を含む。素子領域の半導体基板上には、ゲート絶縁膜を介してゲート電極が配設される。半導体基板の表面内には、ゲート電極の下の領域を挟むように1対のソース／ドレイン領域が形成される。シリサイド膜は、ソース／ドレイン領域の表面上に配設され、素子分離絶縁膜上まで延在する。素子分離絶縁膜上とシリサイド膜上とには、層間絶縁膜が配設される。コンタクトホールは、層間絶縁膜を貫通してシリサイド膜に達し、一端及び他端がシリサイド膜上及び素子分離絶縁膜上にそれぞれ位置する。また、コンタクトホールは底部で且つ素子分離絶縁膜の上部において一端がシリサイド膜の端部と接する溝部を有する。配線層がコンタクトホールの内部に配設される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体基板と、

前記半導体基板の表面内に配設された、素子領域を分離する素子分離絶縁膜と、

前記素子領域の前記半導体基板上にゲート絶縁膜を介して配設されたゲート電極と、

前記ゲート電極の下の領域を挟むように前記半導体基板の表面内に形成された1対のソース／ドレイン領域と、

前記ソース／ドレイン領域の表面上に配設され、且つ前記素子分離絶縁膜上まで延在し、且つ前記半導体基板の表面より上方に位置する上面を有する、シリサイド膜と、

前記素子分離絶縁膜上と前記シリサイド膜上とに配設された層間絶縁膜と、

前記層間絶縁膜を貫通素子して前記シリサイド膜に達し、且つ一端及び他端が前記シリサイド膜上及び前記分離絶縁膜上にそれぞれ位置し、且つ底部で且つ前記素子分離絶縁膜の上部において一端が前記シリサイド膜の端部と接する溝部を有する、コンタクトホールと、

前記コンタクトホールの内部に配設された配線層と、

を具備することを特徴とする半導体装置。

**【請求項 2】**

前記溝部は、前記コンタクトホールの他端と共に通の端部を有することを特徴とする請求項1に記載の半導体装置。

**【請求項 3】**

前記ソース／ドレイン領域のそれぞれの端部が前記素子分離絶縁膜と接することを特徴とする請求項1または2に記載の半導体装置。

**【請求項 4】**

前記溝部と前記ソース／ドレイン領域との間には、前記素子分離絶縁膜の一部が介在することを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

**【請求項 5】**

前記溝部の内部は前記配線層と同一の材料により充填されていることを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

**【請求項 6】**

前記ゲート電極と前記シリサイド膜との間の前記半導体基板表面上に配設され、且つ前記シリサイド膜と実質的に同じ高さを有する、シリコン膜をさらに具備することを特徴とする請求項1乃至5のいずれかに記載の半導体装置。

**【請求項 7】**

前記シリコン膜は、導電性であることを特徴とする請求項6に記載の半導体装置。

**【請求項 8】**

前記ソース／ドレイン領域は、第1拡散領域と、シリコン膜の下の領域の前記半導体基板の表面内に形成され且つ前記第1拡散領域より低い不純物濃度を有する第2拡散領域と、を具備することを特徴とする請求項6または7に記載の半導体装置。

**【請求項 9】**

前記素子分離絶縁膜の端部と前記溝部の一端との間の距離は、5nm乃至50nmであることを特徴とする請求項1乃至8のいずれかに記載の半導体装置。

**【請求項 10】**

半導体基板の表面内に、素子領域を分離する素子分離絶縁膜を形成する工程と、

前記素子領域の前記半導体基板の表面内に、1対のソース／ドレイン領域を形成する工程と、

前記ソース／ドレイン領域の相互間の前記半導体基板上に、ゲート絶縁膜及びゲート電極を具備するゲート構造を形成する工程と、

前記ソース／ドレイン領域上から前記素子分離絶縁膜上まで延在するようにシリサイド膜を形成する工程と、

前記素子分離絶縁膜上と前記シリサイド膜上とに層間絶縁膜を形成する工程と、

10

20

30

40

50

前記層間絶縁膜を選択的にエッチングすることにより、底面が前記シリサイド膜に達し且つ一端及び他端が前記シリサイド膜上及び前記素子分離絶縁膜上にそれぞれ位置するコンタクトホールを形成するとともに、前記素子分離絶縁膜の上部において一端が前記シリサイド膜の端部と接する溝部を形成する工程と、

前記コンタクトホールを導電膜で埋め込む工程と、

を具備することを特徴とする半導体装置の製造方法。

#### 【請求項 1 1】

前記シリサイド膜を形成する工程は、

前記ソース / ドレイン領域上に、前記ゲート構造の端部から前記素子分離絶縁膜上まで延在するようにシリコン膜を形成する工程と、

前記シリコン膜の一部をシリサイド化する工程と、

を具備することを特徴とする請求項 1 0 に記載の半導体装置の製造方法。

#### 【請求項 1 2】

前記シリコン膜を形成後、前記シリコン膜に不純物を注入することにより、前記シリコン膜を導電化させる工程をさらに具備することを特徴とする請求項 1 1 に記載の半導体装置の製造方法。

#### 【請求項 1 3】

前記溝部は、前記シリサイド膜をマスクとして自己整合的に形成されることを特徴とする請求項 1 0 乃至 1 2 のいずれかに記載の半導体装置の製造方法。

#### 【請求項 1 4】

前記溝部の一端と前記素子分離絶縁膜の端部との間には、自己整合的に前記素子分離絶縁膜の一部が残存することを特徴とする請求項 1 0 乃至 1 3 のいずれかに記載の半導体装置の製造方法。

#### 【請求項 1 5】

前記シリコン膜の膜厚は、5 nm 乃至 50 nm であることを特徴とする請求項 1 0 乃至 1 4 のいずれかに記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【0 0 0 1】

##### 【発明の属する技術分野】

本発明は半導体装置に関し、特にソース、ドレイン拡散層の一部にシリサイド膜が形成されたM I S (Metal Insulator Semiconductor) 型F E T (Field Effect Transistor) 素子に関する。

##### 【0 0 0 2】

##### 【従来の技術】

M I S 型F E T 等のトランジスタを有する半導体装置は、トランジスタが形成される領域（以下、トランジスタ領域と称する）、及びコンタクトが形成される領域（以下、コンタクト領域と称する）を有する。コンタクトは、トランジスタと配線とを電気的に接続する。トランジスタ領域とコンタクト領域との境界は、所定の余裕を持って形成される。この余裕は、フォトリソグラフィ工程における露光の際に、マスクパターンのズレによる不具合を回避するために設けられる。なお、以下、M I S 型F E T には、M O S (Metal Oxide Semiconductor) 型F E T が含まれる。

##### 【0 0 0 3】

近時、半導体装置の微細化が進んでいる。これに伴い、トランジスタ領域及びコンタクト領域が半導体装置の面積を占める割合が増加している。これらの領域の割合が増加することにより、トランジスタ領域とコンタクト領域の境界部に、余裕を持たせることが困難となっている。このため、余裕を持たせることなくトランジスタのゲート電極やソース及びドレイン電極にコンタクトを形成する技術が要求される。この技術は、いわゆるボーダレスコンタクトと呼ばれる。

##### 【0 0 0 4】

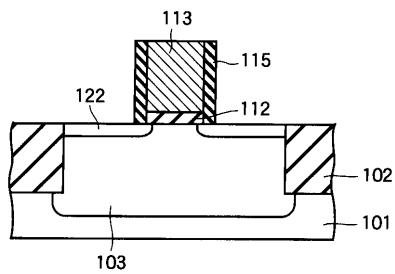

図9～図12は、ボーダレスコンタクトを用いた、トランジスタの従来の製造工程を順に

10

20

30

40

50

示している。

【0005】

図9に示すように、半導体基板101の表面内に、シリコン酸化膜による素子分離絶縁膜102、ウェル拡散層103が形成される。次に、ゲート絶縁膜112、ゲート電極113、第1側壁絶縁膜115からなるゲート構造が形成される。次に、不純物が注入されることにより、ウェル拡散層103の表面に第2拡散領域122が形成される。

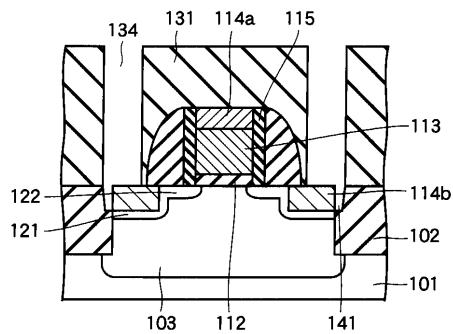

【0006】

次に、図10に示すように、第1側壁絶縁膜115の周囲に第2側壁絶縁膜116が形成される。次に、不純物が注入されることにより、第1拡散領域121が形成される。次に、公知のサリサイド工程を用いて、ゲート電極113及び第1拡散領域121の表面にシリサイド膜114a、114bがそれぞれ形成される。

【0007】

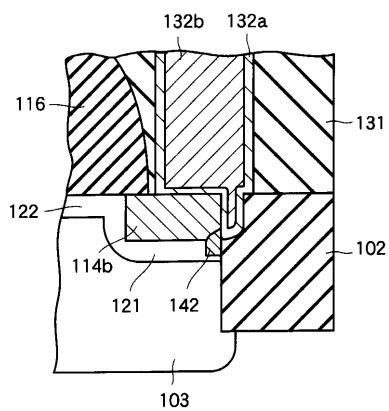

次に、図11に示すように、半導体基板1上の全面に、シリコン酸化膜等の層間絶縁膜131が形成される。次に、フォトリソグラフィ工程及びRIE(Reactive Ion Etching)等の異方性エッティングにより、コンタクトホール134が形成される。このエッティングの際、コンタクトホール134の位置に対応する位置に開口を有するマスクが用いられる。

【0008】

次に、図12に示すように、コンタクトホール134の内壁上に、チタン膜、窒化チタン膜からなる積層膜が形成される。次に、この積層膜を介してコンタクトホール134がタンゲステン膜により埋め込まれる。この結果、コンタクト132が形成される。次に、配線層133が適宜形成される。

【0009】

【発明が解決しようとする課題】

ところで、リソグラフィ工程及びエッティングの際に、マスクの位置にズレが生じることがある。このズレが発生した結果、コンタクトホール134を形成する工程において、マスクの開口が素子分離絶縁膜102上に亘る場合がある。

【0010】

ここで、上記したようにコンタクトホール134はエッティングにより形成される。また、層間絶縁膜131及び素子分離絶縁膜102は、ともにシリコン酸化膜により構成される。このため、コンタクトホール134を形成するためのエッティングの際、素子分離絶縁膜102が一部除去される場合が生じる。この結果、場所によって、図11に示すように溝141が形成されてしまうことがある。

【0011】

シリコン酸化膜に対応するRIEの選択比では、コバルトからなるシリサイド膜114bはエッティングされない。したがって、典型的には、溝141は素子分離絶縁膜102のうち、シリサイド膜112bとの界面に形成される。

【0012】

図13は、図12の実線で囲む領域を拡大した図である。図13に示すように、図12に示す工程において、コンタクトホール134内に、積層膜132a及びタンゲステン膜134bが形成される。しかし、溝141が形成されていると、この溝141内にも積層膜132a及びタンゲステン膜132bからなるコンタクト132が形成されてしまう。

【0013】

特に、溝141の深さが深くなり、第1拡散領域121とウェル拡散層103との接合面に達する場合がある。この場合、溝141内に形成されたコンタクト134により、この部分でショートが発生し、半導体装置の動作不良が生じる。

【0014】

また、溝141の深さがそれほど深くない場合でも、図13に示すように、溝141が第1拡散領域121の側面に達する場合がある。この場合、積層膜132a中のチタンと第1拡散領域121中のシリコンとによりチタンシリサイド142が形成されてしまう。す

10

20

30

40

50

ると、第1拡散領域121とウェル拡散層103との間で、シリサイド142を介して流れるリーク電流が増大する。この結果、半導体装置の動作不良が生じる。

【0015】

また、半導体装置の微細化に伴い、第1拡散領域121の深さが浅くなっている。このため、シリサイド膜114bの底面と、第1拡散領域121とウェル拡散層103との間の接合面と、の距離が小さくなる。すると、上記したようにシリサイド142が形成されなくても、シリサイド膜114bからの接合リーク電流が増大する。

【0016】

さらに、これらの問題は、エッチングの条件等により、発生にはらつきがある。このため、半導体素子の歩留りが低下する問題がある。

10

【0017】

また、素子の微細化が進行し、ゲート長が100nm以下になると、第2拡散領域122の形成の際に以下のような問題が生じる。すなわち、第2拡散領域122の形成には、上記したようにイオン注入工程が用いられる。しかし、ゲート長が100nm以下においては単純にイオン注入工程の加速エネルギーを低下させるだけでは、この領域のシート抵抗が著しく上昇してしまう。この結果、トランジスタの駆動能力が劣化してしまう問題が生じる。この問題を回避するため、注入する不純物原子の数（ドーズ量）を増やす方法が考えられる。しかし、この方法によっても実際にシリコン中で活性化する不純物の量はほとんど増大しない。このため、上記問題を解決することはできない。さらに、この問題を解決できないばかりか、第2拡散領域122の拡散深さを増大させる結果を招く。すると、素子特性の劣化（特に短チャネル効果の発生）を招く問題が生じる。

20

【0018】

また、コンタクトホール134の形成の際、エッチングの時間等を調整することにより、溝141の形成を回避することが試みられている。しかし、それぞれの素子分離絶縁膜102において、上記問題を回避することは、エッチングの制御性等により困難である。

【0019】

また、図10に示す工程後、素子分離絶縁膜102上から、ゲート電極113上のシリサイド114a上までシリコン窒化膜等のライナー材を形成する方法も考えられる。こうすることによって、コンタクトホール134の形成時に、素子分離絶縁膜102が不要にエッチングされることを回避する試みがなされている。しかしながら、層間絶縁膜131及び素子分離絶縁膜102に用いられる材料との関係を考慮すると、これらの材料とライナー材との間の選択比を十分大きく取ることはできない。このため、上記問題を解決するには至っていない。

30

【0020】

なお、上記した例では、PMOS素子について説明しているが、NMOS素子についても同様の問題が生じる。

【0021】

本発明は、上記課題を解決するためになされたものであり、その目的とするところは、不要なシリサイドが形成されることを回避するとともに、接合リーク電流の低減が可能な半導体装置及びその製造方法を提供しようとするものである。

40

【0022】

【課題を解決するための手段】

本発明は、上記課題を解決するために以下に示す手段を用いている。

【0023】

本発明の第1の視点による半導体装置は、半導体基板と、前記半導体基板の表面内に配設された、素子領域を分離する素子分離絶縁膜と、前記素子領域の前記半導体基板上にゲート絶縁膜を介して配設されたゲート電極と、前記ゲート電極の下の領域を挟むように前記半導体基板の表面内に形成された1対のソース／ドレイン領域と、前記ソース／ドレイン領域の表面上に配設され、且つ前記素子分離絶縁膜上まで延在し、且つ前記半導体基板の表面より上方に位置する上面を有する、シリサイド膜と、前記素子分離絶縁膜上と前記シ

50

リサイド膜上とに配設された層間絶縁膜と、前記層間絶縁膜を貫通して前記シリサイド膜に達し、且つ一端及び他端が前記シリサイド膜上及び前記素子分離絶縁膜上にそれぞれ位置し、且つ底部で且つ前記素子分離絶縁膜の上部において一端が前記シリサイド膜の端部と接する溝部を有する、コンタクトホールと、前記コンタクトホールの内部に配設された配線層と、を具備することを特徴とする。

## 【0024】

本発明の第2の視点による半導体装置の製造方法は、半導体基板の表面内に、素子領域を分離する素子分離絶縁膜を形成する工程と、前記素子領域の前記半導体基板の表面内に、1対のソース／ドレイン領域を形成する工程と、前記ソース／ドレイン領域の相互間の前記半導体基板上に、ゲート絶縁膜及びゲート電極を具備するゲート構造を形成する工程と、前記ソース／ドレイン領域上から前記素子分離絶縁膜上まで延在するようにシリサイド膜を形成する工程と、前記素子分離絶縁膜上と前記シリサイド膜上とに層間絶縁膜を形成する工程と、前記層間絶縁膜を選択的にエッチングすることにより、底面が前記シリサイド膜に達し且つ一端及び他端が前記シリサイド膜上及び前記素子分離絶縁膜上にそれぞれ位置するコンタクトホールを形成するとともに、前記素子分離絶縁膜の上部において一端が前記シリサイド膜の端部と接する溝部を形成する工程と、前記コンタクトホールを導電膜で埋め込む工程と、を具備することを特徴とする。

## 【0025】

更に、本発明に係る実施の形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の発明が抽出され得る。例えば、実施の形態に示される全構成要件から幾つかの構成要件が省略されることで発明が抽出された場合、その抽出された発明を実施する場合には省略部分が周知慣用技術で適宜補われるものである。

## 【0026】

## 【発明の実施の形態】

以下に本発明の実施の形態について図面を参照して説明する。なお、以下の説明において、略同一の機能及び構成を有する構成要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

## 【0027】

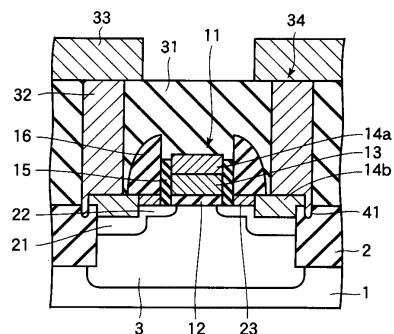

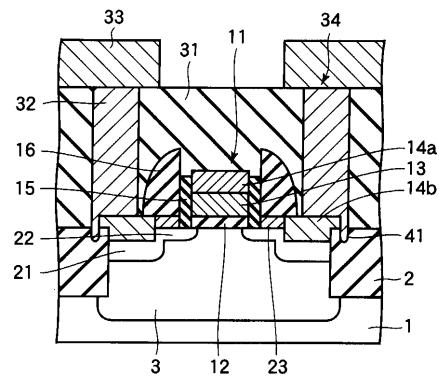

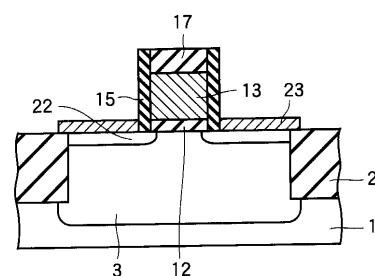

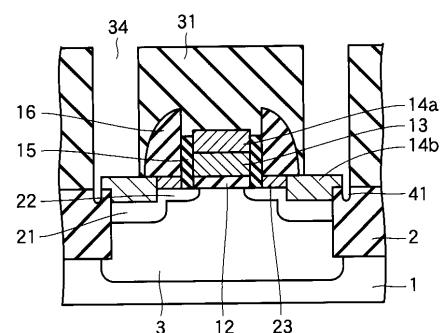

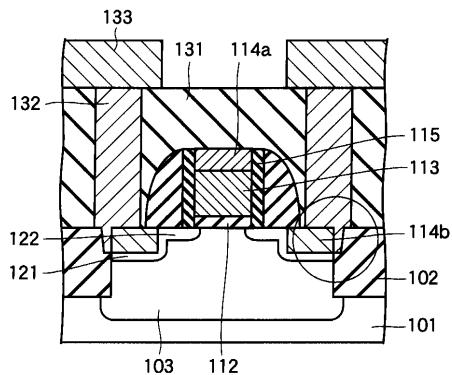

図1は、本発明の実施形態に係る半導体装置を概略的に示す断面図である。なお、以下の説明において、P型のMISトランジスタについて説明するが、N型のトランジスタについても、不純物の導電型を適宜変更することにより同様に形成することができる。

## 【0028】

図1に示すように、例えばN型の半導体基板1の表面内に、複数の素子分離絶縁膜2が形成される。半導体基板1として例えばシリコンが用いられる。素子分離絶縁膜2により、素子領域が相互に分離される。素子分離絶縁膜2として、例えばシリコン酸化膜が用いられる。素子分離絶縁膜2は、上面に溝部41を有する。この溝部41については、後に詳述する。

## 【0029】

素子領域の半導体基板1の表面内にN型のウェル拡散層3が形成される。ウェル拡散層3上にMISトランジスタ11が形成される。トランジスタ11は、ゲート絶縁膜12、ゲート電極13、シリサイド膜14a、14b、第1側壁絶縁膜15、第2側壁絶縁膜16、第1拡散層21、第2拡散層22を具備する。

## 【0030】

ゲート電極13は、ゲート絶縁膜12を介してウェル拡散層3上に設けられる。ゲート絶縁膜12は、例えばシリコン酸化膜により構成され、ゲート電極13は、例えば多結晶シリコンにより構成される。ゲート電極13の上部に、シリサイド膜14aが形成される。このシリサイド膜14aとして、例えばコバルトシリサイド(CoSi2)が用いられる。シリサイド膜14bの上面は、半導体基板1の表面より上方に位置する。

## 【0031】

10

20

30

40

50

第1側壁絶縁膜15により、ゲート絶縁膜12、ゲート電極13、シリサイド膜14aの側面が覆われる。第1側壁絶縁膜15は、例えばシリコン窒化膜により構成される。第1側壁絶縁膜15の周囲には、第2側壁絶縁膜16が形成される。第2側壁絶縁膜16は、例えばシリコン酸化膜により構成される。

#### 【0032】

P型の第1拡散領域(ソース／ドレイン・コンタクト領域)21は、ウェル拡散層3の表面内において、例えば素子分離絶縁膜2から、第1側壁絶縁膜15の近傍まで形成される。ウェル拡散層3の表面内に、P型の第2拡散領域(ソース／ドレイン・エクステンション領域)22が形成される。第2拡散領域22は、例えば第1拡散領域21の端部からゲート電極13の端部まで形成され、第1拡散領域21より浅く形成される。また、第2拡散領域22は、第1拡散領域より低い不純物濃度を有する。10

#### 【0033】

第1拡散領域21、第2拡散領域22の表面には、シリコン膜23が形成される。シリコン膜23は、半導体基板1と第2側壁絶縁膜16との間に設けられ、例えば第1側壁絶縁膜15の端部から第2側壁絶縁膜16の端部近傍まで亘る。

#### 【0034】

第1拡散領域21の表面上には、シリサイド膜14bが形成される。シリサイド膜14bは素子分離絶縁膜2の上まで延在し、溝部41の端部からシリコン膜23の端部まで亘る。シリサイド膜14bは、シリサイド膜14aと同様に例えばコバルトを用いて形成される。20

#### 【0035】

半導体基板1上の全面には、層間絶縁膜31が設けられる。層間絶縁膜31は、例えばシリコン酸化膜により構成される。層間絶縁膜31内に、コンタクトホール34が形成される。コンタクトホール34は、底面がシリサイド膜14bまで達する。コンタクトホール34の一端はシリサイド膜14b上に位置し、他端は素子分離絶縁膜2の上に位置する。コンタクトホール34は、溝部53とつながっている。

#### 【0036】

コンタクトホール34内には、例えばアルミニウム、銅等により構成された導電膜が設けられる。この結果、コンタクト32が形成されている。導電膜は、溝部41内にも設けられる。層間絶縁膜31上には、コンタクト32と接続された配線層33が設けられる。30

#### 【0037】

溝部53の一端はシリサイド膜14bの端部と接し、他端はコンタクトホール34の他端と共に通とされている。また、溝部41は、素子分離絶縁膜2の端部から所定距離だけ離した位置に形成される。すなわち、溝部41と第1拡散領域21の端部との間には、素子分離絶縁膜2が介在する。

#### 【0038】

溝部41の端部と素子分離絶縁膜2の端部との距離は、例えば5nm～50nm、望ましくは、10nm～30nmとすることができる。この値は、例えば素子のデザインルールが100nm、ゲート電極13のゲート長が40nm、シリサイド膜14bの膜厚が30nmの場合、20nmとすることができる。このような距離とすることにより、後述する所望の効果を得られる。なお、溝部41の端部と素子分離絶縁膜2の端部との距離は、後述する方法により、任意の値に設定することができる。40

#### 【0039】

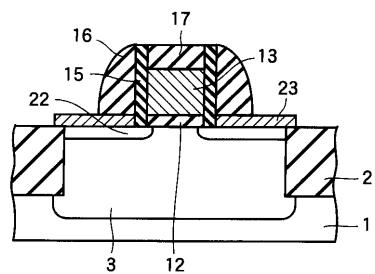

次に、上記構成の半導体装置の製造工程を説明する。図2～図7は、図1に示す半導体装置の製造工程を順に示す断面図である。

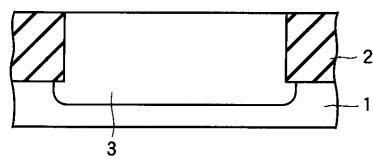

#### 【0040】

図2に示すように、半導体基板1の表面にフォトリソグラフィ工程及びエッティング技術を用いて溝が形成される。エッティング技術として、例えばRIE等の異方性エッティングが用いられる。溝の内部にシリコン酸化膜等の絶縁膜を埋め込むことにより、素子分離絶縁膜2が形成される。次に、N型の不純物が半導体基板1にイオン注入される。この不純物と50

して、例えばリンを用いることができる。次に、半導体基板1を熱処理することにより不純物が拡散し、ウェル拡散層3が形成される。

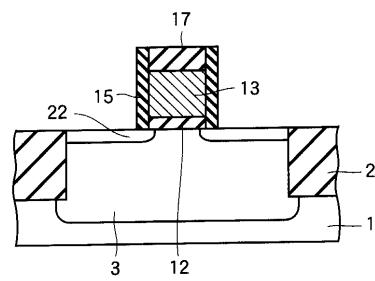

#### 【0041】

次に、図3に示すように、半導体基板1(ウェル拡散層3)の露出している表面上にゲート絶縁膜材が形成される。ゲート絶縁膜材の形成には、例えば熱酸化等の技術を用いることができる。次にゲート絶縁膜材上に多結晶シリコン材、シリコン窒化膜材が堆積される。次に、リソグラフィ工程及びエッティング技術を用いて、シリコン窒化膜材、多結晶シリコン材、ゲート絶縁膜材がエッティングされる。この結果、ゲート絶縁膜12、ゲート電極13、シリコン窒化膜17からなるゲート構造が形成される。

#### 【0042】

次に、半導体基板1上の全面に、シリコン窒化膜等の絶縁膜が、例えばCVD(Chemical Vapor Deposition)法により堆積される。次に、RIE等のエッティング技術を用いて、この絶縁膜がエッティングされる。この結果、第1側壁絶縁膜15が形成される。次に、シリコン窒化膜17及び第1側壁絶縁膜15をマスクとして、半導体基板1の表面にP型不純物が注入される。P型不純物として、例えばホウ素(B)、フッ化ホウ素(BF<sub>2</sub>)を用いることができる。このイオン注入は低エネルギーの条件により行われる。例えば、不純物としてホウ素を用いる場合、エネルギーは500eV程度以下であり、フッ化ホウ素を用いる場合、2.5keV程度以下である。不純物が注入された結果、第2拡散領域22が形成される。

#### 【0043】

次に、図4に示すように、第2拡散領域22の表面上にシリコン膜23が選択成長により形成される。このシリコン膜23は、第1側壁絶縁膜15から素子分離絶縁膜2の上面の一部分まで延在する。シリコン膜23の形成は、例えば、低温の条件でアモルファスシリコンを堆積した後、このアモルファスシリコンを、600程度で熱処理して結晶化させることにより形成することができる。このとき、単結晶化した領域以外のアモルファスシリコン膜は、ケミカルドライエッティング等のエッティング手法によって選択的に除去することができる。このような工程により単結晶シリコン膜を選択的に形成する方法は、例えば特願平11-375404により提案されているので、そちらを参照願いたい。

#### 【0044】

シリコン膜23の膜厚および素子分離絶縁膜2上への張り出し量は、任意に設定することができる。この設定は、例えばアモルファスシリコン膜の膜厚、結晶化熱処理温度、時間を調節することにより可能である。このような調節により、本実施形態が適用される半導体装置に応じて、シリコン膜23の形成を最適化することができる。例えば、各構成部分を上記した寸法、すなわち、素子のデザインルールが100nm、ゲート長が40nm、シリサイド膜の膜厚が30nmの場合、シリコン膜23の膜厚を20nm程度とすればよい。この結果、素子分離絶縁膜2上へ張り出したシリコン膜23の長さを、20nm程度とすることができる。後の工程で、この張り出したシリコン膜23がシリサイド化され、シリサイド膜をマスクとして溝部41が形成される。この結果、溝部41の端部と素子分離絶縁膜2の端部との距離を、20nmとすることができる。

#### 【0045】

特願平11-375404で提案されている方法を採用することにより、以下の利点を得ることができる。まず、単結晶シリコン膜をCVD法により選択的に成長させる場合、高温(900以上)の条件下でシリコン表面をクリーニングする必要がある。この高温の熱処理により、第2拡散領域22に低エネルギーで注入された不純物が拡散してしまう。この結果、第2拡散領域22の底部が、所望以上に深い位置に形成されてしまう。しかし、提案された方法によれば高温での処理が不要となる。このため、この問題を回避できる。さらに、注入されたホウ素が外方拡散によって失われることも防止できる。

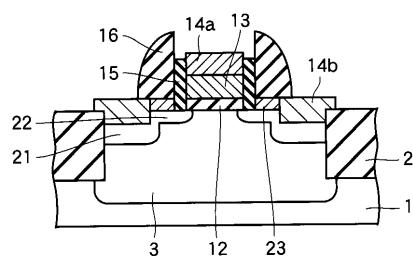

#### 【0046】

次に、図5に示すように、半導体基板1上の全面にシリコン酸化膜等の絶縁膜が、例えばCVD法により堆積される。次に、エッティング技術を用いて、この絶縁膜がエッティングさ

10

20

30

40

50

れる。この結果、第2側壁絶縁膜16が形成される。

#### 【0047】

次に、図6に示すように、シリコン窒化膜17が、例えば加熱したリン酸等を用いて除去される。次に、半導体基板1の全面に、第2側壁絶縁膜16をマスクとしてP型の不純物が注入される。この不純物として例えばホウ素を用いることができる。次に、半導体基板1を、例えば1050程度の条件下で、極短時間、熱処理する。この結果、第1拡散領域21が形成されるとともに、ゲート電極13がP型の導電性を有することとなる。また、同時に、第2拡散領域22の表面のP型不純物が、シリコン膜23のうち第1側壁絶縁膜15近傍の領域に熱拡散する。この結果、この領域がP型の導電性を有することとなる。

10

#### 【0048】

次に、図7に示すように、ゲート電極13及びシリコン膜23の表面の自然酸化膜が、ウェットエッティングにより除去される。ウェットエッティングの薬液として、例えば希フッ酸溶液等を用いることができる。次に、公知のサリサイド工程を用いて、シリコン酸化膜23及び半導体基板1の表面の一部がシリサイド化される。この結果、ゲート電極13及び第2拡散領域22の表面にシリサイド膜14a、14bがそれぞれ形成される。

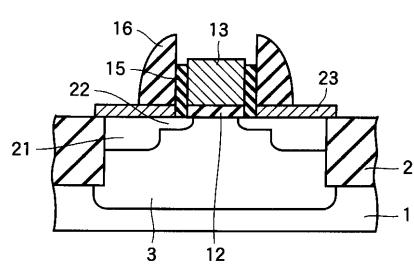

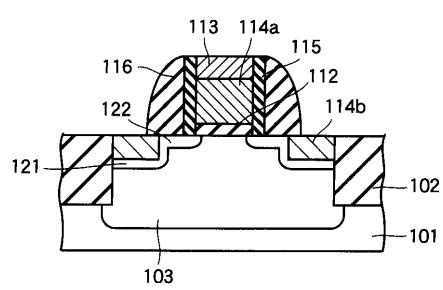

#### 【0049】

次に、図8に示すように、半導体基板1上の全面にシリコン酸化膜等の絶縁膜が、例えばCVD法により堆積される。次に、この絶縁膜の表面が、例えばCMP(Chemical Mechanical Polishing)等により平坦化される。この結果、層間絶縁膜31が形成される。次に、フォトリソグラフィ工程及びRIE等の異方性エッティングにより、コンタクトホール34が形成される。

20

#### 【0050】

従来技術の説明において記載したように、シリサイド膜14bが形成される領域とコンタクトホール34が形成される領域との間には、マスクの合わせズレに対する余裕を取らない。このため、コンタクトホール34の形成の際、マスクの開口の端部が素子分離絶縁膜2上に位置する場合がある。しかし、シリサイド膜14bが素子分離絶縁膜2まで延在しているため、この部分がエッティングされない。このため、マスクの開口において、素子分離絶縁膜2のうちシリサイド膜14bが形成されていない領域が除去される。この結果、溝部41がシリサイド膜14bをマスクとして、自己整合的に形成される。

30

#### 【0051】

次に、図1に示すように、コンタクトホール34の内部に、チタン膜、窒化チタン膜、タンゲステン膜からなるコンタクト32が形成される。すなわち、チタン膜、窒化チタン膜からなる積層膜32aがコンタクトホール34の内壁に沿って形成され、この積層膜を介してコンタクトホール34がタンゲステン膜により埋め込まれる。コンタクト32の形成には、例えばCVD法、スパッタリングが用いられる。コンタクトホール34を埋め込む際、溝部41が形成されている場合、この溝部41内もコンタクトホール34と同様に埋め込まれる。次に、公知の方法により配線層33が形成される。

#### 【0052】

本発明の実施形態によれば、シリサイド膜14bが素子分離絶縁膜2まで、所定距離、延在する。このため、コンタクトホール34の形成の際、素子分離絶縁膜2に溝部41が形成された場合でも、溝部41が第1拡散領域21と接することを回避できる。このため、従来例に示す、異常成長したシリサイド142が形成されることを防止できる。したがって、シリサイド142が原因による接合リーケ電流の発生を回避できる。

40

#### 【0053】

また、シリサイド膜14bの底面と、第1拡散領域21とウェル拡散層3との間の接合面と、の距離が選択成長させたシリコン膜23の膜厚分、離間する。このため、シリサイド膜による接合リーケ電流に起因する不良の発生も抑制することができる。

#### 【0054】

また、近時、素子の微細化によって問題となるソース／ドレイン・エクステンション領域

50

の寄生抵抗の増加が問題となっている。しかし、本実施形態によれば、第2側壁絶縁膜16の下に、P型のシリコン膜23が形成される。この部分は導電膜として機能し、ドレイン電流を流す働きをする。このため、上記寄生抵抗を大幅に低減することが可能となる。したがって、トランジスタの駆動能力を向上できる。

#### 【0055】

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

#### 【0056】

##### 【発明の効果】

以上、詳述したように本発明によれば、不要なシリサイドが形成されることを回避とともに、接合リーケ電流の低減が可能な半導体装置及びその製造方法を提供できる。

##### 【図面の簡単な説明】

【図1】本発明の実施形態に係る半導体装置を概略的に示す断面図。

【図2】図1に示す半導体装置の製造工程を概略的に示す断面図。

【図3】図2に続く工程を概略的に示す断面図。

【図4】図3に続く工程を概略的に示す断面図。

【図5】図4に続く工程を概略的に示す断面図。

【図6】図5に続く工程を概略的に示す断面図。

【図7】図6に続く工程を概略的に示す断面図。

【図8】図7に続く工程を概略的に示す断面図。

【図9】半導体装置の従来の製造工程を概略的に示す断面図。

【図10】図9に続く工程を概略的に示す断面図。

【図11】図10に続く工程を概略的に示す断面図。

【図12】図11に続く工程を概略的に示す断面図。

【図13】図12の一部を拡大して示す図。

##### 【符号の説明】

1 ... 半導体基板、

2 ... 素子分離絶縁膜、

3 ... ウェル拡散層、

11 ... トランジスタ、

12 ... ゲート絶縁膜、

13 ... ゲート電極、

14 a、b ... シリサイド膜、

15 ... 第1側壁絶縁膜、

16 ... 第2側壁絶縁膜、

17 ... シリコン窒化膜、

21 ... 第1拡散領域(ソース/ドレイン・コンタクト領域)、

22 ... 第2拡散領域(ソース/ドレイン・エクステンション領域)、

23 ... シリコン膜、

31 ... 層間絶縁膜、

32 ... コンタクト、

33 ... 配線層、

34 ... コンタクトホール。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

H 0 1 L 29/78

F I

H 0 1 L 29/78 3 0 1 R

テーマコード(参考)

(74)代理人 100070437

弁理士 河井 将次

(72)発明者 飯沼 俊彦

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

F ターム(参考) 4M104 BB01 BB14 BB18 BB19 BB30 DD02 DD07 DD43 DD78 DD84

FF14 FF16 FF22 GG09 GG10 GG14 HH20

5F033 HH04 HH25 JJ18 JJ19 JJ33 KK01 KK25 MM07 NN06 NN07

QQ37 QQ70 QQ73 TT08 XX15 XX31

5F140 AA14 AA24 BA01 BC06 BE07 BF04 BF11 BF18 BG09 BG12

BG14 BG37 BG43 BG52 BG53 BH08 BH15 BJ08 BJ11 BJ17

BJ25 BJ27 BJ28 BK02 BK13 BK19 BK25 BK29 BK30 BK34

CB04 CB08 CB10 CC03 CE07 CF07