(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4460741号

(P4460741)

(45) 発行日 平成22年5月12日(2010.5.12)

(24) 登録日 平成22年2月19日(2010.2.19)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 29/739 (2006.01)H01L 29/78 652K

H01L 29/78 301G

H01L 29/78 301J

H01L 29/78 653A

H01L 29/78 655A

請求項の数 24 (全 17 頁) 最終頁に続く

(21) 出願番号

特願2000-294316 (P2000-294316)

(22) 出願日

平成12年9月27日 (2000.9.27)

(65) 公開番号

特開2002-110980 (P2002-110980A)

(43) 公開日

平成14年4月12日 (2002.4.12)

審査請求日

平成18年1月25日 (2006.1.25)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100070437

弁理士 河井 将次

最終頁に続く

(54) 【発明の名称】電力用半導体素子及びその製造方法

(57) 【特許請求の範囲】

## 【請求項 1】

電力用半導体素子であって、

第1導電型ベース層と、

前記第1導電型ベース層の一方の表面に選択的に形成された第2導電型ベース層と、

前記第2導電型ベース層の表面に選択的に形成された第1導電型エミッタ層と、

前記第1導電型ベース層の一方及び他方の表面の1つに選択的に形成されたコレクタ層と、

前記コレクタ層上に形成された第1の主電極と、

前記第1導電型エミッタ層上及び前記第2導電型ベース層上に形成された第2の主電極と、

第1絶縁部と第2絶縁部とを含み、前記第1導電型エミッタ層と前記第1導電型ベース層間の前記第2導電型ベース層の表面に直接接触させて形成されたゲート絶縁膜と、

前記第1絶縁部と前記第2絶縁部の上方に形成されたゲート電極と、を具備し、

前記第2絶縁部のキャパシタンスの容量は、前記第1絶縁部のキャパシタンスの容量よりも小さいことを特徴とする電力用半導体素子。

## 【請求項 2】

前記第1絶縁部は、前記第1導電型エミッタ層に近い位置に形成され、前記第2絶縁部は、前記第1導電型ベース層に近い位置に形成されていることを特徴とする請求項1記載の電力用半導体素子。

## 【請求項 3】

前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きいことを特徴とする請求項2記載の電力用半導体素子。

## 【請求項 4】

前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さいことを特徴とする請求項2記載の電力用半導体素子。

## 【請求項 5】

前記第2絶縁部の厚さは勾配を持ち、前記第1導電型エミッタ側の厚さは、前記第1導電型ベース層側の厚さよりも小さいことを特徴とする請求項2記載の電力用半導体素子。

## 【請求項 6】

前記ゲート電極は、前記第1導電型エミッタ層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれているトレンチ構造を有することを特徴とする請求項1乃至5のいずれか1つに記載の電力用半導体素子。

10

## 【請求項 7】

電力用半導体素子の製造方法であって、

第1導電型ベース層を形成すること、

前記第1導電型ベース層の一方の表面に第2導電型ベース層を選択的に形成することと

、

前記第2導電型ベース層の表面に第1導電型エミッタ層を選択的に形成することと、

前記第1導電型ベース層の一方及び他方の表面の1つにコレクタ層を選択的に形成すること、

20

前記コレクタ層上に第1の主電極を形成することと、

前記第1導電型エミッタ層上及び前記第2導電型ベース層上に第2の主電極を形成することと、

第1絶縁部と第2絶縁部とを含み、前記第1導電型エミッタ層と前記第1導電型ベース層間の前記第2導電型ベース層の表面に直接接触させてゲート絶縁膜を形成することと、

前記第1絶縁部と前記第2絶縁部の上方にゲート電極を形成することと、を具備し、

前記第2絶縁部のキャパシタンスの容量は、前記第1絶縁部のキャパシタンスの容量よりも小さいことを特徴とする電力用半導体素子の製造方法。

30

## 【請求項 8】

前記第1絶縁部は、前記第1導電型エミッタ層に近い位置に形成され、前記第2絶縁部は、前記第1導電型ベース層に近い位置に形成されていることを特徴とする請求項7記載の電力用半導体素子の製造方法。

## 【請求項 9】

前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きいことを特徴とする請求項8記載の電力用半導体素子の製造方法。

## 【請求項 10】

前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さいことを特徴とする請求項8記載の電力用半導体素子の製造方法。

40

## 【請求項 11】

前記第2絶縁部の厚さは勾配を持ち、前記第1導電型エミッタ側の厚さは、前記第1導電型ベース層側の厚さよりも小さいことを特徴とする請求項8記載の電力用半導体素子の製造方法。

## 【請求項 12】

前記ゲート電極は、前記第1導電型エミッタ層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれているトレンチ構造を有することを特徴とする請求項7乃至11のいずれか1つに記載の電力用半導体素子の製造方法。

## 【請求項 13】

50

電力用半導体素子であって、

第1導電型ベース層と、

前記第1導電型ベース層の一方の表面に選択的に形成された第2導電型ベース層と、

前記第2導電型ベース層の表面に選択的に形成された第1導電型ソース層と、

前記第1導電型ベース層の一方及び他方の表面の1つに選択的に形成されたドレイン層と、

前記ドレイン層上に形成された第1の主電極と、

前記第1導電型ソース層上及び前記第2導電型ベース層上に形成された第2の主電極と、

第1絶縁部と第2絶縁部とを含み、前記第1導電型ソース層と前記第1導電型ベース層間の前記第2導電型ベース層の表面に直接接触させて形成されたゲート絶縁膜と、

前記第1絶縁部と前記第2絶縁部の上方に形成されたゲート電極と、を具備し、

前記第2絶縁部のキャパシタンスの容量は、前記第1絶縁部のキャパシタンスの容量よりも小さいことを特徴とする電力用半導体素子。

**【請求項14】**

前記第1絶縁部は、前記第1導電型ソース層に近い位置に形成され、前記第2絶縁部は、前記第1導電型ベース層に近い位置に形成されていることを特徴とする請求項13記載の電力用半導体素子。

**【請求項15】**

前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きいことを特徴とする請求項14記載の電力用半導体素子。

**【請求項16】**

前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さいことを特徴とする請求項14記載の電力用半導体素子。

**【請求項17】**

前記第2絶縁部の厚さは勾配を持ち、前記第1導電型ソース側の厚さは、前記第1導電型ベース層側の厚さよりも小さいことを特徴とする請求項14記載の電力用半導体素子。

**【請求項18】**

前記ゲート電極は、前記第1導電型ソース層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれているトレンチ構造を有することを特徴とする請求項13乃至17のいずれか1つに記載の電力用半導体素子。

**【請求項19】**

電力用半導体素子の製造方法であって、

第1導電型ベース層を形成することと、

前記第1導電型ベース層の一方の表面に第2導電型ベース層を選択的に形成することと、

前記第2導電型ベース層の表面に第1導電型ソース層を選択的に形成することと、

前記第1導電型ベース層の一方及び他方の表面の1つにドレイン層を選択的に形成することと、

前記ドレイン層上に第1の主電極を形成することと、

前記第1導電型ソース層上及び前記第2導電型ベース層上に第2の主電極を形成することと、

第1絶縁部と第2絶縁部とを含み、前記第1導電型ソース層と前記第1導電型ベース層間の前記第2導電型ベース層の表面に直接接触させてゲート絶縁膜を形成することと、

前記第1絶縁部と前記第2絶縁部の上方にゲート電極を形成することと、を具備し、

前記第2絶縁部のキャパシタンスの容量は、前記第1絶縁部のキャパシタンスの容量よりも小さいことを特徴とする電力用半導体素子の製造方法。

**【請求項20】**

前記第1絶縁部は、前記第1導電型ソース層に近い位置に形成され、前記第2絶縁部は

10

20

30

40

50

、前記第1導電型ベース層に近い位置に形成されていることを特徴とする請求項19記載の電力用半導体素子の製造方法。

【請求項21】

前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きいことを特徴とする請求項20記載の電力用半導体素子の製造方法。

【請求項22】

前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さいことを特徴とする請求項20記載の電力用半導体素子の製造方法。

【請求項23】

前記第2絶縁部の厚さは勾配を持ち、前記第1導電型ソース側の厚さは、前記第1導電型ベース層側の厚さよりも小さいことを特徴とする請求項20記載の電力用半導体素子の製造方法。

10

【請求項24】

前記ゲート電極は、前記第1導電型ソース層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれているトレンチ構造を有することを特徴とする請求項19乃至23のいずれか1つに記載の電力用半導体素子の製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

20

本発明は、インバータなど電力変換装置を構成する電力半導体素子のなかで、IGBT、パワーMOSFETに係り、特に負荷短絡耐量を向上させた素子構造に関する。

【0002】

【従来の技術】

近年のパワーエレクトロニクス分野における電源機器の小型化、高性能化への要求を受けて、電力用半導体素子では、高耐圧化、大電流化と共に、低損失化、高破壊耐量化、高速化に対する性能改善が注力されている。特に高耐圧化、高電流化という点で、300V程度以上の耐圧を有する電力用半導体素子としてパワーMOSFETよりも低オン電圧を得ることができるIGBTが用いられている。

【0003】

30

この種のIGBTとしては、ゲートを平板状に設けたプレーナ構造およびゲートを構内に埋め込み形成したトレンチ構造の2種類が広く知られている。

【0004】

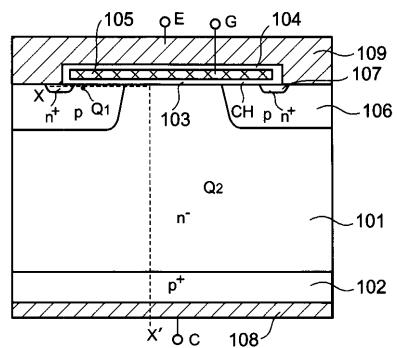

図11は、この種のプレーナ構造を有するIGBTの構成を示す断面図である。このIGBTでは、高抵抗のn型ベース層101の表面に高濃度のp型コレクタ層102が形成され、他方の面には、選択的にp型ベース層106が形成され、さらに、p型ベース層106内には、n型エミッタ層107が選択的に形成されている。

【0005】

n型ベース層101上とp型ベース層106上の一

部およびn型エミッタ層107上的一

部にゲート酸化膜103が設けられている。また、エミッタ電極109が、p型ベース層

106とn型エミッタ層107に設けられる。ゲート電極105は、ゲート酸化膜103

と層間絶縁膜104によってエミッタ電極109およびn型ベース層101およびp型ベ

ース層106と絶縁されている。

40

【0006】

n型ベース層101、p型ベース層106、n型エミッタ層107、ゲート電極105によ

って、CHをチャネル領域とする電子注入用MOSFETが構成されている。さらに、

n型エミッタ層107とp型ベース層106上には両方に接するようにエミッタ電極109

が設けられている。

【0007】

上記構造において従来のプレーナ構造のIGBTでは、n型エミッタ層107とp型ベ

ース層106と絶縁されている。

50

ス層 106 は、それぞれ不純物の注入および熱拡散によって形成されるために、それらの不純物分布はガウス分布に準じる分布となることから、チャネル領域 CH に沿った不純物濃度分布をみると n 型エミッタ層 107 と p 型ベース層 106 との接合付近に p 型不純物濃度の最高値があり、p 型ベース層 106 と n 型ベース層 101 の接合付近に近づくほど徐々に p 型不純物濃度が下がっていく。

#### 【0008】

次に IGBT の動作を説明する。プレーナ構造の IGBT とトレンチ構造の IGBT は、動作原理は同様であるので以下では、プレーナ構造の IGBT の動作を説明する。

#### 【0009】

コレクタ電極 108 に正電圧、エミッタ電極 109 に負電圧が印加されているとき、エミッタ電極 109 より正となる正電圧をゲート電極 105 に印加すると、p 型ベース層 106 のゲート電極 105 に接した表面が n 型に反転し、電子 e が n 型エミッタ層 107 から反転層を介して n 型ベース層 101 に注入されて p 型コレクタ層 102 に達する。これによつて n 型ベース層 101 と p 型コレクタ層 102 が順バイアスされて、p 型コレクタ層 102 から正孔 h が n 型ベース層 101 に注入される。このように、n 型ベース層 101 に電子 e と正孔 h の両方が注入され、n 型ベース層 101 領域で電導率変調が起こつてオン電圧が低減される。すなわち、素子が導通状態になる。

#### 【0010】

一方、ターンオフするには、ゲート電極 105 にエミッタ電極 109 に対して負の電圧が印加される。これにより、ゲート電極 105 に接した p 型ベース層 106 の表面に形成されていた反転層が消失して、電子注入が停止する。一方、n 型ベース層 101 内に蓄積されていた正孔 h は、その一部が p 型ベース層 106 を介してエミッタ電極 109 に排出され、残りの正孔 h が電子 e と再結合して消滅し、素子はターンオフする。

#### 【0011】

ここで素子が負荷短絡状態になった場合、素子は導通状態でコレクタ電極 108 に電源電圧が印加される。これによつて素子には大きな短絡ピーク電流 (I<sub>cp</sub>) が流れ、ある一定時間 (t<sub>sc</sub>) で素子は破壊する。従来の IGBT では、チャネル密度を大きくするとオン電圧を低減することができたが、一方でチャネル密度の増加は電流を流し易くなる結果、短絡ピーク電流 (I<sub>cp</sub>) を大きくし負荷短絡耐量 (t<sub>sc</sub>) が小さくなるという問題があつた。

#### 【0012】

##### 【発明が解決しようとする課題】

以上述べたように、従来の半導体素子では、負荷短絡耐量が小さいという問題がある。

#### 【0013】

本発明は上記事情を考慮してなされたもので、低いオン電圧を維持しつつ高い負荷短絡耐量を同時に実現し得る電力用半導体素子及びその製造方法を提供することにある。

#### 【0014】

##### 【課題を解決するための手段】

上記の目的を達成するためには、本発明の第 1 の態様は、電力用半導体素子であつて、第 1 導電型ベース層と、前記第 1 導電型ベース層の一方の表面に選択的に形成された第 2 導電型ベース層と、前記第 2 導電型ベース層の表面に選択的に形成された第 1 導電型エミッタ層と、前記第 1 導電型ベース層の一方及び他方の表面の 1 つに選択的に形成されたコレクタ層と、前記コレクタ層上に形成された第 1 の主電極と、前記第 1 導電型エミッタ層上及び前記第 2 導電型ベース層上に形成された第 2 の主電極と、第 1 絶縁部と第 2 絶縁部とを含み、前記第 1 導電型エミッタ層と前記第 1 導電型ベース層間の前記第 2 導電型ベース層の表面に直接接触させて形成されたゲート絶縁膜と、前記第 1 絶縁部と前記第 2 絶縁部の上方に形成されたゲート電極と、を具備し、前記第 2 絶縁部のキャパシタンスの容量は、前記第 1 絶縁部のキャパシタンスの容量よりも小さい。

また、本発明の第 2 の態様は、第 1 の態様において、前記第 1 絶縁部は、前記第 1 導電型エミッタ層に近い位置に形成され、前記第 2 絶縁部は、前記第 1 導電型ベース層に近い

10

20

30

40

50

位置に形成されている。

また、本発明の第3の態様は、第2の態様において、前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きい。

【0015】

また、本発明の第4の態様は、第2の態様において、前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さい。

また、本発明の第5の態様は、第2の態様において、前記第2絶縁部の厚さは勾配を持ち、前記第1導電型エミッタ側の厚さは、前記第1導電型ベース層側の厚さよりも小さい。

また、本発明の第6の態様は、第1乃至第5のいずれか1つの態様において、前記ゲート電極は、前記第1導電型エミッタ層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれている。

【0016】

また、本発明の第7の態様は、電力用半導体素子の製造方法であって、第1導電型ベース層を形成することと、前記第1導電型ベース層の一方の表面に第2導電型ベース層を選択的に形成することと、前記第2導電型ベース層の表面に第1導電型エミッタ層を選択的に形成することと、前記第1導電型ベース層の一方及び他方の表面の1つにコレクタ層を選択的に形成することと、前記コレクタ層上に第1の主電極を形成することと、前記第1導電型エミッタ層上及び前記第2導電型ベース層上に第2の主電極を形成することと、第1絶縁部と第2絶縁部とを含み、前記第1導電型エミッタ層と前記第1導電型ベース層間の前記第2導電型ベース層の表面に直接接触させてゲート絶縁膜を形成することと、前記第1絶縁部と前記第2絶縁部の上方にゲート電極を形成することと、を具備し、前記第2絶縁部のキャパシタンスの容量は、前記第1絶縁部のキャパシタンスの容量よりも小さい。

また、本発明の第8の態様は、第7の態様において、前記第1絶縁部は、前記第1導電型エミッタ層に近い位置に形成され、前記第2絶縁部は、前記第1導電型ベース層に近い位置に形成されている。

また、本発明の第9の態様は、第8の態様において、前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きい。

また、本発明の第10の態様は、第8の態様において、前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さい。

また、本発明の第11の態様は、第8の態様において、前記第2絶縁部の厚さは勾配を持ち、前記第1導電型エミッタ側の厚さは、前記第1導電型ベース層側の厚さよりも小さい。

また、本発明の第12の態様は、第7乃至第11のいずれか1つの態様において、前記ゲート電極は、前記第1導電型エミッタ層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれているトレンチ構造を有する。

また、本発明の第13の態様は、電力用半導体素子であって、第1導電型ベース層と、前記第1導電型ベース層の一方の表面に選択的に形成された第2導電型ベース層と、前記第2導電型ベース層の表面に選択的に形成された第1導電型ソース層と、前記第1導電型ベース層の一方及び他方の表面の1つに選択的に形成されたドレイン層と、前記ドレイン層上に形成された第1の主電極と、前記第1導電型ソース層上及び前記第2導電型ベース層上に形成された第2の主電極と、第1絶縁部と第2絶縁部とを含み、前記第1導電型ソース層と前記第1導電型ベース層間の前記第2導電型ベース層の表面に直接接触させて形成されたゲート絶縁膜と、前記第1絶縁部と前記第2絶縁部の上方に形成されたゲート電極と、を具備し、前記第2絶縁部のキャパシタンスの容量は、前記第1絶縁部のキャパシタンスの容量よりも小さい。

また、本発明の第14の態様は、第13の態様において、前記第1絶縁部は、前記第1

10

20

30

40

50

導電型ソース層に近い位置に形成され、前記第2絶縁部は、前記第1導電型ベース層に近い位置に形成されている。

【0017】

また、本発明の第15の態様は、第14の態様において、前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きい。

また、本発明の第16の態様は、第14の態様において、前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さい。

また、本発明の第17の態様は、第14の態様において、前記第2絶縁部の厚さは勾配を持ち、前記第1導電型ソース側の厚さは、前記第1導電型ベース層側の厚さよりも小さい。

10

また、本発明の第18の態様は、第13乃至第17のいずれか1つの態様において、前記ゲート電極は、前記第1導電型ソース層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれているトレンチ構造を有する。

【0018】

また、本発明の第19の態様は、電力用半導体素子の製造方法であって、第1導電型ベース層を形成することと、前記第1導電型ベース層の一方の表面に第2導電型ベース層を選択的に形成することと、前記第2導電型ベース層の表面に第1導電型ソース層を選択的に形成することと、前記第1導電型ベース層の一方及び他方の表面の1つにドレイン層を選択的に形成することと、前記ドレイン層上に第1の主電極を形成することと、前記第1導電型ソース層上及び前記第2導電型ベース層上に第2の主電極を形成することと、第1絶縁部と第2絶縁部とを含み、前記第1導電型ソース層と前記第1導電型ベース層間の前記第2導電型ベース層の表面に直接接触させてゲート絶縁膜を形成することと、前記第1絶縁部と前記第2絶縁部の上方にゲート電極を形成することと、を具備し、前記第2絶縁部のキャパシタンスの容量は、前記第1絶縁部のキャパシタンスの容量よりも小さい。

20

【0019】

また、本発明の第20の態様は、第19の態様において、前記第1絶縁部は、前記第1導電型ソース層に近い位置に形成され、前記第2絶縁部は、前記第1導電型ベース層に近い位置に形成されていることを特徴とする請求項19記載の電力用半導体素子の製造方法。

30

また、本発明の第21の態様は、第20の態様において、前記第2絶縁部の厚さは、前記第1絶縁部の厚さよりも大きい。

また、本発明の第22の態様は、第20の態様において、前記第2絶縁部の比誘電率は、前記第1絶縁部の比誘電率よりも小さい。

また、本発明の第23の態様は、第20の態様において、前記第2絶縁部の厚さは勾配を持ち、前記第1導電型ソース側の厚さは、前記第1導電型ベース層側の厚さよりも小さい。

また、本発明の第24の態様は、第19乃至第23のいずれか1つの態様において、前記ゲート電極は、前記第1導電型ソース層の表面から前記第2導電型ベース層を貫通して前記第1導電型ベース層の途中の深さまで達するように形成されたトレンチの内部に前記第1絶縁部と前記第2絶縁部とを介して埋め込まれているトレンチ構造を有する。

40

【0020】

【発明の実施の形態】

以下、図面を参照しながら本発明の実施の形態（以下、実施形態という）を説明する。

【0021】

（第1の実施形態）

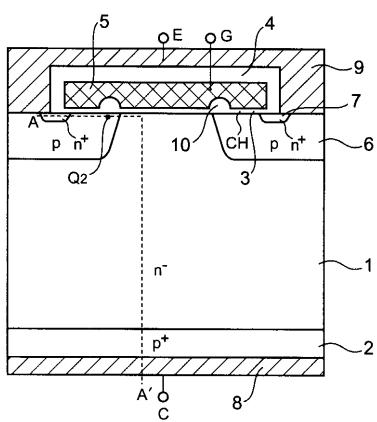

図1は、本発明の第1の実施形態である電力用半導体素子の断面図である。以下、電力用半導体素子の一例としてプレーナ構造を有するIGBTを用いて説明する。以下の全ての実施形態では第1導電型層としてn型、第2導電型層としてp型を用いる。

【0022】

50

図中、1は高抵抗のn型ベース層を示しており、このn型ベース層1の一方の面には、高不純物濃度のp型コレクタ層2が形成されている。

【0023】

また、ゲート絶縁膜3およびゲート絶縁膜3と同じ材質ではあるが厚さの異なるゲート絶縁膜10を介してゲート電極5が形成されている。n型ベース層1の表面にはp型ベース層6が形成されている。このp型ベース層6の表面には、高不純物濃度のn型エミッタ層7が形成されている。

【0024】

また、上記p型ベース層6は、不純物の注入および熱拡散によって形成されることから、不純物濃度分布はガウス分布に準じる分布になっており、チャネル領域CHにおいても同様である。

10

【0025】

n型ベース層1、p型ベース層6、n型エミッタ層7、ゲート絶縁膜3、ゲート絶縁膜10およびゲート電極5によって、ゲート絶縁膜3およびゲート絶縁膜10とp型ベース層6の界面にチャネルCHが形成されn型エミッタ層7からn型ベース層1に電子を注入するMOSFETを構成している。

【0026】

p型コレクタ層2上にはコレクタ電極8が設けられている。また、n型エミッタ層7およびp型ベース層6上にはエミッタ電極9が設けられている。n型エミッタ層7とp型ベース層6はこのエミッタ電極9によって短絡している。また、ゲート電極5上には層間絶縁膜4が設けられていて、エミッタ電極9と接しないようになっている。

20

【0027】

次にこのIGBTの動作を以下に説明する。ターンオン時には、エミッタ電極9とコレクタ電極8との間にコレクタ電圧VCEが印加された状態で、エミッタ電極9とゲート電極5との間に所定の正のゲート電圧VGEを印加すると、チャネル領域CHがn型に反転しチャネルが形成される。このチャネルを通じてエミッタ電極9から電子がn型ベース層1に注入される。この注入された電子によりp型コレクタ層2とn型ベース層1との間が順バイアスされ、正孔がp型コレクタ層2よりn型ベース層1に注入される。この結果、伝導度変調によりn型ベース層1の抵抗が大幅に低減して通電する。

【0028】

30

一方ターンオフするには、ゲート電極5にエミッタ電極9に対して負の電圧が印加される。これによって、p型ベース層6とゲート絶縁膜3およびゲート絶縁膜10に接した位置に形成されていた反転層が消失して、電子注入が停止する。一方、n型ベース層1内に蓄積されていた正孔hは、その一部がp型ベース層6を介してエミッタ電極9に排出され、残りの正孔hが電子eと再結合して消滅し、素子はターンオフする。

【0029】

ここで素子が負荷短絡状態になった場合、素子は導通状態でコレクタ電極8に電源電圧が印加され、これによって素子には短絡ピーク電流(Icp)が流れ、ある一定時間(tsc)で素子は破壊する。負荷が短絡してから素子破壊に至るまでの時間が負荷短絡耐量(tsc)である。

40

【0030】

ここで、このIGBTの短絡ピーク電流が大きくなると負荷短絡耐量は小さくなることが確認されている。この理由は短絡ピーク電流による熱破壊である。本発明による新構造のIGBTでは、短絡ピーク電流とほぼ同じ静特性で電流の飽和値を小さくすることによって負荷短絡耐量を大きくすることができる。

【0031】

以下に上記した本発明の構成により負荷短絡耐量が向上する理由を述べる。

【0032】

一般に、オン状態にあるIGBTにさらにコレクタ電圧VCEを増大すると、それに伴つてp型ベース層6のチャネル部分CHの点Q2での電位も上昇し、ゲート電位と点Q2で

50

のベース電位との電位差がしきい値電圧よりも小さくなり反転層を維持することが出来なくなつて空乏化（ピンチオフ）し抵抗が無限大となり、IGBTの電流は飽和する。しきい値電圧は、ゲート絶縁膜のキャパシタンスの容量と反比例の関係があり、キャパシタンス容量が増大するにつれ、しきい値電圧は低下する。

【0033】

本実施形態ではチャネル部分CHにおいて、しきい値電圧は、上記のしきい値電圧とゲート絶縁膜のキャパシタンスの関係よりゲート絶縁膜3に接するp型ベース層6領域よりもゲート絶縁膜3の膜厚よりも厚い膜厚を有するゲート絶縁膜10に接するp型ベース層6領域の点Q2で決まり、したがつて、ピンチオフもこのゲート絶縁膜10に接するp型ベース層6領域の点Q2で起る。

10

【0034】

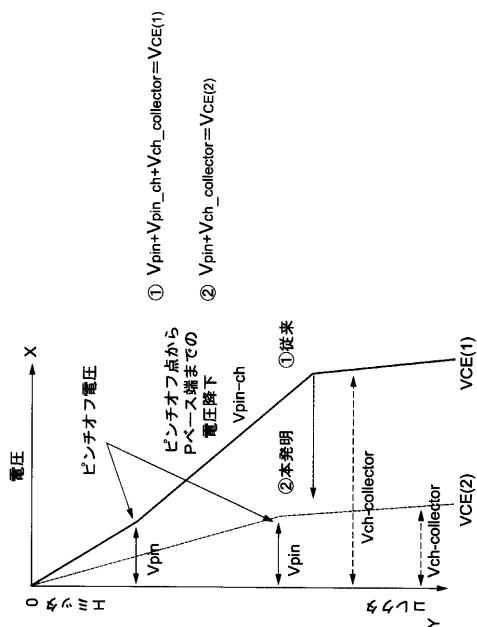

次に従来のIGBTの電流の飽和値よりも本発明のIGBTの電流の飽和値が小さくなることを示す。図7は、縦軸にn型エミッタ層7とエミッタ電極9の境界を原点にとりエミッタ電極9からコレクタ電極8への距離を示し、横軸にエミッタ電極9を基準（接地）とした電圧分布を、図11（従来技術のプレーナIGBT）のX-Xと図1（本発明のプレーナIGBT）のA-Aのぞれぞれに対して示している。

【0035】

この図7より、従来のIGBTは、ピンチオフする電圧 $V_{pin}$ と、ピンチオフ点Q1からn型ベース層101までのチャネル部分の抵抗による電圧 $V_{pin-ch}$ と、n型ベース層101とp型コレクタ層102間の電圧 $V_{ch-coll}$ とを合わせたもの（ $V_{pin} + V_{pin-ch} + V_{ch-coll} = V_{CE(1)}$ ）がコレクタ電圧 $V_{CE}$ であり、IGBTの飽和の電流値はこのコレクタ電圧 $V_{CE}$ の二乗で変換する。

20

【0036】

本発明は、ピンチオフ点をゲート絶縁膜10に接するp型ベース層6領域の点Q2にシフトさせることにより、ピンチオフ点Q2からn型ベース層1との間のチャネル部分の抵抗による電圧 $V_{pin-ch}$ を取り除くことにより、コレクタ電圧が、ピンチオフ電圧 $V_{pin}$ と、n型ベース層1とp型コレクタ層3間の電圧 $V_{ch-coll}$ との足し合わせになるようにしている（ $V_{pin} + V_{ch-coll} = V_{CE(2)}$ ）。

【0037】

したがつて、本発明のコレクタ電圧 $V_{CE}$ は従来のコレクタ電圧 $V_{CE}$ よりも小さく、これによって、本発明によるIGBTの飽和の電流値も従来のIGBTでの飽和の電流値にくらべて小さくなる。

30

【0038】

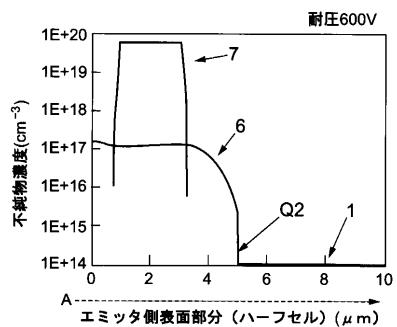

図8は、ゲート酸化膜下の不純物濃度分布を示す図であり、n型エミッタ層7、p型ベース層6、n型ベース層1の不純物濃度を示している。図に示すように、p型ベース層6の不純物濃度は、エミッタ側表面においてエミッタ側にピークを持つガウス分布に準じる分布になっている。

【0039】

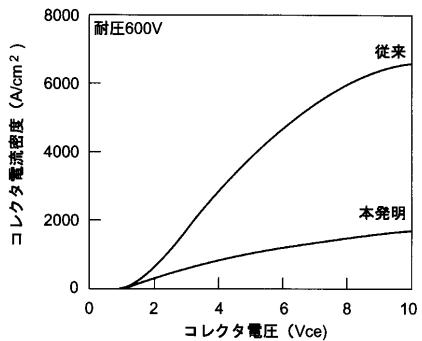

図9は、上記のシミュレーションの結果である。具体的には、従来のIGBTでは、p型ベース層107上のゲート絶縁膜103の膜厚が1000オングストロームで、この時の飽和電流値が6800A/cm<sup>2</sup>であるのに対して、本発明では、p型ベース層6上のゲート酸化膜3を従来のIGBTでのゲート酸化膜103の膜厚と同じ1000オングストロームの膜厚に保ちつつ、ゲート絶縁膜10の膜厚を1μmにした場合、この時の飽和電流値は1700A/cm<sup>2</sup>となった。研究の結果、この飽和電流値に対応する負荷短絡耐量（tsc）（短絡ピーク電流Icpが流れてから素子の短絡保護回路の動作が開始するまでの所要時間）は10μs以上得られることを確認した。

40

【0040】

したがつて、負荷短絡耐量とIGBTの電流の飽和値との関係から、本発明の電流の飽和値を小さくする方法によって、負荷短絡耐量を大きくすることが出来る。

【0041】

50

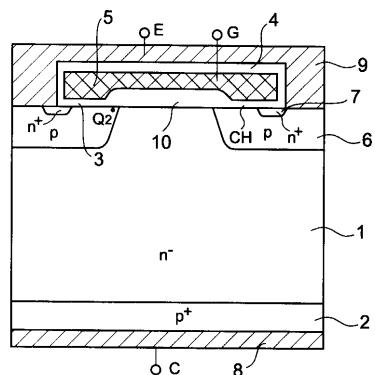

## (第2の実施形態)

図2は、本発明の第2の実施形態である電力用半導体素子の断面図である。本実施形態と前述した第1の実施形態を示す図1との違いは、n型ベース層1の表面に接するゲート絶縁膜が、第1の実施形態の図1ではゲート絶縁膜3であったが、本実施形態では、ゲート絶縁膜3よりも膜厚の厚いゲート絶縁膜10であるところである(テラス型ゲート)。図2のプレーナIGBTの動作は、前述した図1のプレーナIGBTの動作と比べて基本的には同じであり、しきい値電圧はゲート絶縁膜10と接するp型ベース層6領域内で決まるところから、ピンチオフは、このゲート絶縁膜10と接するp型ベース層6の領域内のQ2で起こる。

## 【0042】

10

本実施形態では、n型ベース層1領域内に接するゲート絶縁膜をゲート絶縁膜10にすることによりゲート絶縁膜のキャパシタンス容量が、n型ベース層1領域内にゲート絶縁膜3を有する図1に比べて小さくすることができることにより、ターンオン、ターンオフに要する時間を図1よりも短くすることができる。また、製造工程もより容易である。

## 【0043】

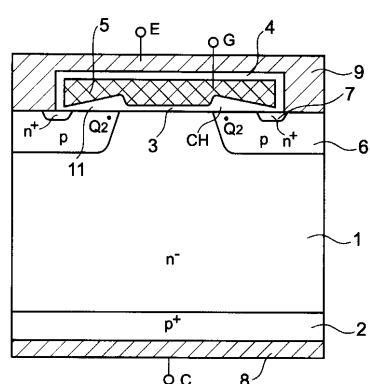

## (第3の実施形態)

図3は、本発明の第3の実施形態である電力用半導体素子の断面図である。本実施形態と前述した第1の実施形態を示す図1との違いは、図1のゲート絶縁膜3が、本実施形態の図3での勾配をもつゲート酸化膜11に対応している点である。このゲート絶縁膜11は、p型ベース層6とn型ベース層1との接合部分上にあるゲート絶縁膜の膜厚を、n型エミッタ層7とp型ベース層6との接合部分上にあるゲート絶縁膜の膜厚よりも厚く、n型エミッタ層7とp型ベース層6との接合部分に近づくにつれゲート絶縁膜の膜厚が徐々に薄くなるよう勾配がついていることが特徴である。

20

## 【0044】

図3のプレーナIGBTの動作は、前述した第1の実施形態における図1のプレーナIGBTの動作とくらべて基本的には同じである。本実施形態においては、ゲート絶縁膜11はp型ベース層6とn型ベース層1の接合に近づくにつれ膜厚は厚くなることから、しきい値電圧もp型ベース層6とn型ベース層1の接合に近づくにつれ徐々に高くなる。したがって、前述した図1のプレーナIGBTと同様に点Q2でピンチオフがおこり、前述した第1の実施形態における負荷短絡耐量が向上する理由と同様の理由により、負荷短絡耐量を向上することができる。

30

## 【0045】

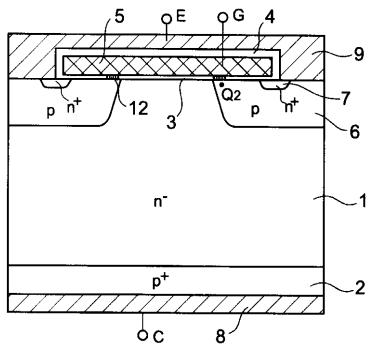

## (第4の実施形態)

図4は、本発明の第4の実施形態である電力用半導体素子の断面図である。図4と第1の実施形態の図1との違いは、図1においては、ゲート絶縁膜3とゲート絶縁膜10との材質が同じであり、したがって、比誘電率も同じであるが、本実施形態の図4においては、ゲート絶縁膜3とゲート絶縁膜12とは材質が異なり、したがって、比誘電率も異なる。本実施形態のゲート絶縁膜の例として、例えば、ゲート絶縁膜3に五酸化タンタル( $Ta_2O_5$ )(比誘電率22)あるいは、窒化シリコン( $Si_3N_4$ )(比誘電率7)を用いて、ゲート絶縁膜12に二酸化シリコン( $SiO_2$ )(比誘電率3.9)を用いることである。これによって、2つのゲート絶縁膜の膜厚がゲート絶縁膜3とゲート絶縁膜12と同じであっても、2つのゲート絶縁膜のキャパシタンス容量は異なることになる。しきい値電圧は、ゲート絶縁膜キャパシタンス容量がゲート絶縁膜3にくらべ小さいゲート絶縁膜12によってきまり、ピンチオフは、ゲート絶縁膜12と接するp型ベース層6のチャネル領域CH点Q2において起こる。

40

## 【0046】

したがって、前述した第1の実施形態における負荷短絡耐量が向上する理由と同様の理由により、負荷短絡耐量を向上することができる。

## 【0047】

## (第5の実施形態)

50

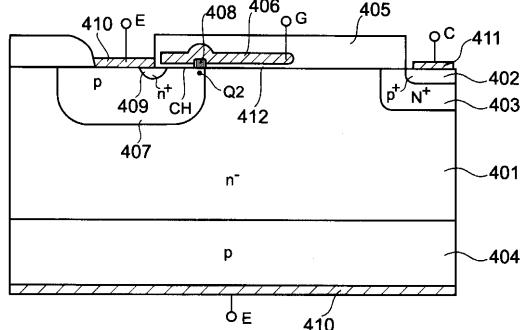

図5は、本発明の第5の実施形態である電力用半導体素子（横型IGBT）の断面図である。図5中、401は高抵抗のn型ベース層であり、このn型ベース層401の一方の面には、p型基板層404が形成されており、このp型基板層404上にはエミッタ電極410が設けられている。また、n型ベース層401の他方の面には、選択的にp型ベース層407が形成されており、このp型ベース層407の表面には選択的に高不純物濃度のn型エミッタ層409が形成される。また、前記n型ベース層401の他方の面には、選択的にn型バッファ層403が形成されており、このn型バッファ層403の表面には選択的に高不純物濃度のp型コレクタ層402が形成され、このp型コレクタ層402に接してコレクタ電極411が形成されている。

## 【0048】

前記p型ベース層407上的一部、p型ベース層408上、n型ベース層401上的一部およびn型バッファ層上にゲート絶縁膜412が、さらにp型ベース層407上的一部分には、ゲート絶縁膜408が設けられている。このゲート絶縁膜408は、ゲート絶縁膜412と膜厚あるいは比誘電率が異なることによりゲート絶縁膜のキャパシタンス容量が異なっている。ゲート絶縁膜412およびゲート絶縁膜408上にはゲート電極406が設けられている。このゲート電極406上には層間絶縁膜405が設けられており、それに開口されたコンタクトホールを介して前記n型エミッタ層409上的一部およびp型ベース層407上的一部にコンタクトするようにエミッタ電極410が設けられている。なお、前記ゲート電極406は、ゲート絶縁膜412とゲート絶縁膜408と層間絶縁膜405によって、エミッタ電極410、コレクタ電極411、n型ベース層401およびp型ベース層407とは、絶縁されている。

## 【0049】

図5の横形IGBTの動作は、前述した第1の実施形態における図1のプレーナIGBTの動作とくらべて基本的には同じである。本実施形態においては、ゲート絶縁膜408下のp型ベース層407のチャネル部分CH点Q2でしきい値電圧が決まる。したがって、前述した図1のプレーナIGBTと同様に点Q2でピンチオフがおこり、前述した第1の実施形態における負荷短絡耐量が向上する理由と同様の理由により、負荷短絡耐量を向上することができる。

## 【0050】

## (第6の実施形態)

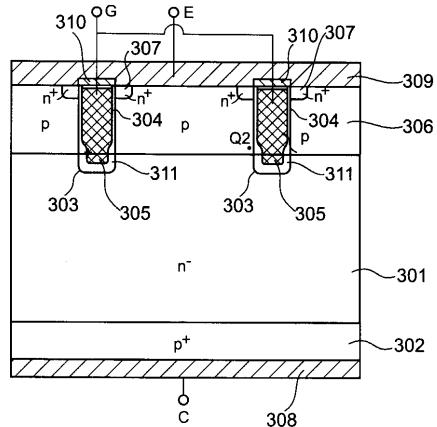

図6は、本発明の第6の実施形態である電力用半導体素子（トレンチIGBT）の断面図である。

## 【0051】

図中、301は高抵抗のn型ベース層を示しており、このn型ベース層301の一方の面には、高不純物濃度のp型コレクタ層302が形成されている。

## 【0052】

また、トレンチ303の内部には、ゲート絶縁膜304およびゲート絶縁膜311を介してゲート電極305が埋め込み形成されている。各トレンチ303で挟まれた領域のn型ベース層301の表面には高不純物濃度のp型ベース層306が形成されている。

## 【0053】

このp型ベース層306の表面には高不純物濃度のn型エミッタ層307が形成されている。n型ベース層301、p型ベース層306、n型エミッタ層307、ゲート絶縁膜304、ゲート絶縁膜311およびゲート電極305によって、トレンチ303に接したp型ベース層306の表面にチャネルCHが形成されn型エミッタ層307からn型ベース層301に電子を注入するMOSFETを構成している。

## 【0054】

p型コレクタ層302上にはコレクタ電極308が設けられている。また、n型エミッタ層307およびp型ベース層306上にはエミッタ電極309が設けられている。n型エミッタ層307とp型ベース層306はこのエミッタ電極309によって短絡している。また、ゲート電極305上には層間絶縁膜310が設けられていて、エミッタ電極309

10

20

30

40

50

と接しないようになっている。

【0055】

次にこのIGBTの動作を以下に説明する。ターンオン時には、エミッタ電極309とコレクタ電極308との間にコレクタ電圧V<sub>CE</sub>が印加された状態で、エミッタ電極309とゲート電極305との間に所定の正のゲート電圧V<sub>GE</sub>を印加すると、チャネル領域がn型に反転しチャネルCHが形成される。このチャネルCHを通じてエミッタ電極309から電子がn型ベース層301に注入される。この注入された電子によりp型コレクタ層302とn型ベース層301との間が順バイアスされ、正孔がp型コレクタ層302よりn型ベース層301に注入される。この結果、伝導度変調によりn型ベース層301の抵抗が大幅に低減して通電する。

10

【0056】

一方ターンオフするには、ゲート電極305にエミッタ電極309に対して負の電圧が印加される。これによって、p型ベース層306のゲート電極305に接した位置に形成されていた反転層が消失して、電子注入が停止する。一方、n型ベース層内に蓄積されていた正孔hは、その一部がp型ベース層306を介してエミッタ電極309に排出され、残りの正孔hが電子eと再結合して消滅し、素子はターンオフする。

【0057】

ここで素子が負荷短絡状態になった場合、素子は導通状態でコレクタ電極308に電源電圧が印加され、これによって素子には短絡ピーク電流(I<sub>cp</sub>)が流れ、ある一定時間(t<sub>sc</sub>)で素子は破壊する。負荷が短絡してから素子破壊に至るまでの時間が負荷短絡耐量(t<sub>sc</sub>)である。

20

【0058】

ここで、このIGBTの短絡ピーク電流が大きくなると負荷短絡耐量は小さくなることが確認されている。この理由は短絡ピーク電流による熱破壊である。本発明による新構造のIGBTでは、短絡ピーク電流とほぼ同じ静特性での電流の飽和値を小さくすることによって負荷短絡耐量を大きくすることができる。

【0059】

以下、本発明で負荷短絡耐量が向上する理由を述べる。

【0060】

一般に、オン状態にあるIGBTにさらにコレクタ電圧V<sub>CE</sub>を増大すると、それに伴ってp型ベース層306のチャネル部分CHの点Q2での電位も上昇し、ゲート電位と点Q2でのベース電位との電位差が閾値電圧よりも小さくなり反転層を維持することが出来なくなつて空乏化(ピンチオフ)し抵抗が無限大となり、IGBTの電流は飽和する。本実施形態では、チャネル部分CHにおいて閾値電圧は、第1の実施形態と同様の理由により、ゲート絶縁膜311で決まる。したがって、ピンチオフもこのゲート絶縁膜311に接するp型ベース層306の点Q2で起こる。

30

【0061】

次に従来のIGBTの電流の飽和値よりも本発明のIGBTの電流の飽和値が小さくなることを示す。

【0062】

本発明は、ピンチオフ点をゲート絶縁膜311に接するp型ベース層306にシフトさせることによりピンチオフ点からn型ベース層307との間のチャネル部分の抵抗による電圧V<sub>pin-ch</sub>を取り除くことにより、コレクタ電圧が、ピンチオフ電圧V<sub>pin</sub>と、n型ベース層301とp型コレクタ層302間の電圧V<sub>ch-coll</sub>との足し合わせになるようにしている(V<sub>pin</sub> + V<sub>ch-coll</sub> = V<sub>CE(2)</sub>)。したがって、本発明のコレクタ電圧V<sub>CE</sub>は従来のコレクタ電圧V<sub>CE</sub>よりも小さく、これによって、本発明によるIGBTの飽和の電流値も従来のIGBTでの飽和の電流値に較べて小さくなる。よって、負荷短絡耐量は向上する。

40

【0063】

(第7の実施形態)

50

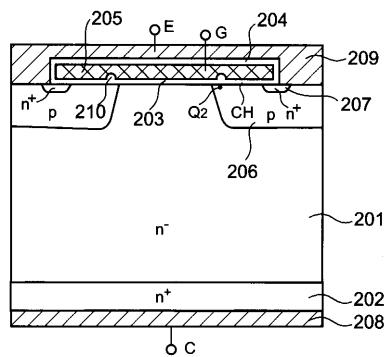

図10は、本発明の第7の実施形態である電力用半導体素子（パワーMOSFET）の断面図である。

【0064】

図10のパワーMOSFETは、前述した図1のプレーナIGBTとくらべて、p型不純物で形成されたコレクタ層2の代わりに、n型不純物で形成されたドレイン層202になり、コレクタ電極8がドレイン電極208となり、n型エミッタ層7がn型ソース層207となり、エミッタ電極9がソース電極209となっている点が異なり、その他は同じである。

【0065】

一般に、オン状態にあるパワーMOSFETにさらにドレイン電圧VSDを増大すると、それに伴ってp型ベース層206のチャネル部分CHの点Q2での電位も上昇し、ゲート電位と点Q2でのベース電位との電位差が閾値電圧よりも小さくなり反転層を維持することが出来なくなって空乏化（ピンチオフ）し抵抗が無限大となり、パワーMOSFETの電流は飽和する。本実施形態では、チャネル部分CHにおいて閾値電圧は、第1の実施形態と同様の理由により、ゲート絶縁膜210で決まる。したがって、ピンチオフもこのゲート絶縁膜210に接するp型ベース層206の点Q2で起こる。

【0066】

次に従来のパワーMOSFETの電流の飽和値よりも本発明のパワーMOSFETの電流の飽和値が小さくなることを示す。

【0067】

本発明は、ピンチオフ点をゲート絶縁膜210に接するp型ベース層206にシフトさせることによりピンチオフ点からn型ソース層207との間のチャネル部分の抵抗による電圧 $V_{pin-ch}$ を取り除くことにより、コレクタ電圧を、ピンチオフ電圧 $V_{pin}$ と、n型ベース層201とp型ドレイン層202間の電圧 $V_{ch-coll}$ との足し合わせになるようにしている（ $V_{pin} + V_{ch-coll} = V_{CE(2)}$ ）。したがって、本発明のドレイン電圧VSDは従来のドレイン電圧VSDよりも小さく、これによって、本発明によるパワーMOSFETの飽和の電流値も従来のパワーMOSFETでの飽和の電流値にくらべて小さくなる。よって、負荷短絡耐量は向上する。

【0068】

【発明の効果】

上述したように本発明によれば、低いオン電圧を維持しつつ、負荷短絡時に生じる短絡ピーク電流を抑えることによって高い負荷短絡耐量を実現し得る電力用半導体素子及びその製造方法を提供することができる。

【図面の簡単な説明】

【図1】本発明の電力用半導体素子の第1の実施形態に係わるプレーナIGBTを示す断面図である。

【図2】本発明の電力用半導体素子の第2の実施形態に係わるプレーナIGBTを示す断面図である。

【図3】本発明の電力用半導体素子の第3の実施形態に係わるプレーナIGBTを示す断面図である。

【図4】本発明の電力用半導体素子の第4の実施形態に係わるプレーナIGBTを示す断面図である。

【図5】本発明の電力用半導体素子の第5の実施形態に係わるプレーナIGBTを示す断面図である。

【図6】本発明の電力用半導体素子の第6の実施形態に係わるプレーナIGBTを示す断面図。

【図7】図11に示す従来のプレーナIGBTのX-X'に沿った電圧分布と、図1に示す本発明のプレーナIGBTのA-A'に沿った電圧分布とを対比して示す図である。

【図8】ゲート絶縁膜下の不純物濃度分布を示す図である。

【図9】図1のトレンチIGBTのコレクタ電圧対コレクタ電流静特性をシミュレーション

10

20

30

40

50

ンした結果と、従来のプレーナIGBTのコレクタ電圧対コレクタ電流静特性をシミュレーションした結果とを対比して示す図である。

【図10】本発明の電力用半導体素子の第7の実施形態に係わるプレーナIGBTを示す断面図である。

【図11】従来のプレーナIGBTを示す断面図である。

【符号の説明】

- 1 n型ベース層

- 2 p型コレクタ層

- 3 ゲート絶縁膜

- 4 層間絶縁膜

- 5 ゲート電極

- 6 p型ベース層

- 7 n型エミッタ層

- 8 コレクタ電極

- 9 エミッタ電極

- 10 ゲート絶縁膜

- 11 ゲート絶縁膜

- 12 ゲート絶縁膜

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/78 6 5 5 Z

(72)発明者 服部 秀隆

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

審査官 後谷 陽一

(56)参考文献 特表2004-500716 (JP, A)

特開2001-111050 (JP, A)

特開平02-290077 (JP, A)

特開平04-154171 (JP, A)

特開平08-181309 (JP, A)

特開平09-036352 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 29/739