(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property

Organization

International Bureau

(10) International Publication Number

WO 2019/016036 A1

(43) International Publication Date

24 January 2019 (24.01.2019)

(51) International Patent Classification:

**C25D 11/04** (2006.01) **C23F 1/00** (2006.01)

**C25D 11/10** (2006.01) **C25D 1/00** (2006.01)

**C25D 11/12** (2006.01) **C25D 3/12** (2006.01)

VEN [BE/BE]; KU Leuven R&D Waastraat 6 box 5105, 3000 Leuven (BE).

(21) International Application Number:

PCT/EP2018/068683

(72) Inventors: **ZANKOWSKI, Stanislaw Piotr**; C/O IMEC VZW, patent department Kapeldreef 75, 3001 Heverlee (BE). **VEREECKEN, Philippe M.**; C/O IMEC VZW, patent department Kapeldreef 75, 3001 Leuven (BE).

(22) International Filing Date:

10 July 2018 (10.07.2018)

(74) Agent: **EGO, Christophe** et al.; Leuvensesteenweg 203, 3190 Boortmeerbeek (BE).

(25) Filing Language:

English

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA,

(26) Publication Language:

English

(30) Priority Data:

17181782.8 18 July 2017 (18.07.2017) EP

(71) Applicants: IMEC VZW [BE/BE]; Kapeldreef 75, 3001 Leuven (BE). KATHOLIEKE UNIVERSITEIT LEU-

(54) Title: TRANSFORMING A VALVE METAL LAYER INTO A TEMPLATE COMPRISING A PLURALITY OF SPACED (NANO)CHANNELS AND FORMING SPACED STRUCTURES THEREIN

FIG 1

(57) Abstract: A method is provided for transforming at least part of a valve metal layer into a template comprising a plurality of spaced (nano)channels. The method comprises a first anodization step, thereby forming a porous layer of valve metal oxide comprising a plurality of (nano)channels; a protective treatment, thereby inducing hydrophobic surfaces to (nano)channel walls and (nano)channel bottoms; a second anodization step after the protective treatment; and an etching step. A method is provided for forming a plurality of spaced structures inside the (nano)channels of the template. These methods may relate to the formation of a layer of functional material on an electrically conductive substrate and/or to the fabrication of solid-state battery cells and batteries.

---

SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN,

TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

**(84) Designated States** (*unless otherwise indicated, for every kind of regional protection available*): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

**Declarations under Rule 4.17:**

— *of inventorship (Rule 4.17(iv))*

**Published:**

— *with international search report (Art. 21(3))*

**TRANSFORMING A VALVE METAL LAYER INTO A TEMPLATE COMPRISING A PLURALITY OF SPACED (NANO)CHANNELS AND FORMING SPACED STRUCTURES THEREIN**

5 **Field**

[0001] The present disclosure relates to methods for transforming a metal layer into a template comprising a plurality of spaced channels, e.g. nanochannels, and to templates obtainable by such methods. The present disclosure relates to methods for forming a plurality of spaced structures, e.g. nanostructures, inside the plurality of spaced (nano)channels of such a template, and to devices 10 comprising such plurality of spaced (nano)structures.

**State of the art**

[0002] Solid-state batteries, and more in particular thin film solid-state batteries are attractive energy storage devices. Solid-state batteries are based on solid-state battery cells typically 15 comprising a stack of a first current collector layer, a first electrode layer (e.g. a positive active material layer or cathode layer), a solid electrolyte layer, a second electrode layer (e.g. a negative active material layer or anode layer) and a second current collector layer. The batteries may further be encapsulated, such as for example in a polymer package.

[0003] In the example of solid-state Li ion insertion battery cells, the current collector layers 20 may comprise a metal foil, such as a foil of aluminum, nickel or copper and the active cathode layer may for example comprise lithiated transition metal oxides or salts, such as lithium manganese oxide (LMO), lithium cobalt oxide (LCO) or lithium iron phosphate (LPO). The anode layer may for example comprise carbon, silicon, spinel lithium titanium oxide (LTO) or metallic lithium. The solid-state electrolyte may comprise glassy, ceramic, crystalline or polymer lithium-containing 25 materials. Due to the high electric and ionic resistivity of the active materials, the anode and cathode layer thicknesses are limited to less than 5 micrometers. This results in a limited energy and power density of the thin film solid-state battery cells.

[0004] To overcome these limitations, three-dimensional electrode structuring has been proposed to increase the surface area of the electrodes, thus increasing the amount of the active 30 materials present in a unit area of a battery cell. In such three-dimensional approach, one of the main manufacturing challenges is conformal coating of battery materials on the three-dimensional electrode surfaces. Another challenge is the need for advanced, preferably low-cost, methods for manufacturing the three-dimensional electrode structures.

[0005] A three-dimensional electrode structure may for example comprise or consist of a 35 plurality of electrically conductive nanowires oriented along a same direction and being closely spaced, for example with a spacing between neighboring nanowires smaller than the nanowire

length, such as for example a spacing that is a factor of 1.2 to 10 smaller than the nanowire length. A known, relatively cheap method for manufacturing such plurality of electrically conductive nanowires comprises electroplating of a metal in a porous anodic aluminum oxide (AAO) template formed by anodization of an aluminum foil. Up to 100 micrometer thick porous aluminum oxide 5 templates can be produced. However, the pores or channels of the templates produced by anodization of aluminum foils are always covered with an insulating aluminum oxide barrier layer having a thickness of tens to hundreds of nanometers. This barrier layer needs to be removed from the channel bottoms to enable subsequent formation of the plurality of electrically conductive nanowires by electroplating.

10 [0006] Various methods are known for removing the barrier layer from the channel bottoms, without separation of the template from the underlying remaining part (non-anodized part) of the aluminum foil. For example, the voltage used in the anodization process may be gradually reduced during the final stage of anodization. This results in a reduction of the interpore distance and of the pore size at a bottom of the channels, with a barrier layer of smaller thickness, for example 1 nm or 15 less. Such barrier layer thickness is sufficiently small to allow electroplating of a metal inside the channels or pores. However, this approach results in nanowires poorly connected to the substrate, through long (hundreds of nanometers long) root-like, thin (a few nm in diameter) nanowires. This may result in poor mechanical stability of the nanowires network, prone to delamination from the substrate.

20 [0007] Another known method for removing the barrier layer from the channel bottoms of the template comprises thinning the barrier layer by immersing the template in a  $H_3PO_4$  solution that slowly etches the barrier layer. This, however, results in excessive pore widening, resulting in nanowires formed in such a template that have a rather large diameter and that fill most of the volume. This limits the volume remaining available for the active electrode material to be coated 25 thereon, eventually limiting the energy density of the electrode.

[0008] Yet another method for removing the barrier layer from the channel bottoms of the template comprises separation of the template from the underlying remaining part (non-anodized part) of the aluminum foil. According to this method, the aluminum foil is removed, e.g. dissolved, after formation of the porous template. This results in a fragile, free standing template with an 30 exposed barrier layer at one side and open pores at another side. The exposed barrier layer is then removed, for example by single-side etching in a diluted  $H_3PO_4$  solution, and a thin metal layer is deposited to act as a working electrode for subsequent electrodeposition of metallic nanowires in the template. However, the fragility of the free-standing template makes this method hard to implement in large-scale manufacturing.

35 [0009] Hence, there is a need for a method that allows removing the barrier layer from the channel bottoms of a porous anodic template for subsequent formation therein of a plurality of

spaced nanowires e.g. by electroplating, wherein pore widening is avoided at one hand, wherein pore narrowing is avoided on the other hand, and wherein the method is suitable for implementation in large-scale manufacturing.

**[0010]** In a method for fabricating solid-state batteries having a three-dimensional electrode structure, there is a need for forming an active electrode material layer on the three-dimensional electrode structure. The active electrode material layer is preferably formed by a process that allows conformal deposition. A known method that can advantageously be used is electroplating. For example, in case of Li ion insertion electrodes, manganese oxide ( $MnO_x$  with  $1 \leq x \leq 2$ ) may be used as a cathode precursor material, which is then further transformed into an active lithium manganese oxide (LMO) electrode material upon conversion with lithium (lithiation).

**[0011]** In large-scale manufacturing of commercial batteries, a hot acidic bath containing  $MnSO_4$  and  $H_2SO_4$  is typically used for the synthesis of  $MnO_x$ . However, due to the acidic nature of the bath, electrodeposition cannot be carried out on most metals, due to their inherent oxidation and dissolution in an acidic environment upon application of an anodic current. The only metals suitable for anodic deposition of  $MnO_2$  from acidic baths are the noble metals such as Pt or Au or metals forming a stable, dense passive oxide layer on their surface, such as titanium. However, these metals are either very expensive (noble metals) or very difficult to electrodeposit (titanium).

**[0012]** Other methods for the fabrication of manganese oxide cathode precursors use neutral manganese baths based on organic complexes of  $Mn^{2+}$ , such as acetates or citrates. These baths, having a pH close to 7, can be used to electroplate  $MnO_x$  precursors on less noble metals, such as Ni. However, due to the near-neutral pH of such baths and due to the presence of dissolved oxygen, these solutions are not stable and, upon time,  $MnO_x$  precipitates are formed in the bath. This substantially limits the applicability of these baths for large-scale manufacturing, where stability of the baths is important from an economical and industrial point of view. The change in composition of the bath may also lead to changes in electroplating kinetics, resulting in poor reproducibility.

**[0013]** Further, in a method for fabricating solid-state batteries an annealing step (lithiation step) is typically done after deposition of the cathode precursor material on the electrode structure, to thereby activate (lithiate) the cathode precursor material and form an active (lithiated) cathode material. When using a non-noble metal such as for example a transition metal for forming the electrode structure, such annealing step may lead to an undesired thermal degradation (e.g. due to oxidation or another chemical reaction) of the electrode structure.

**[0014]** Hence, there is a need for a method that allows forming a layer of active electrode material on a broad range of metals, wherein the method is preferably a low-cost process suitable for large-scale manufacturing and wherein the method allows substantially conformal deposition. Further, there is a need for a method with a reduced risk of degradation of the electrode material during subsequent processing, such as annealing.

**Summary**

[0015] It is an object of embodiments of the present disclosure to provide anodization based methods for transforming at least part of a metal layer, more in particular at least part of a valve metal layer, into a template comprising a plurality of spaced channels, e.g. a plurality of spaced nanochannels, wherein barrier layers resulting from the anodization process may be removed with no or limited pore widening at one hand and with no or limited pore narrowing on the other hand. It is an object of embodiments of the present disclosure to provide templates obtainable by such methods.

[0016] It is a further object of the present disclosure to provide methods for forming a plurality of spaced structures, e.g. nanostructures, within the plurality of spaced channels, e.g. nanochannels, of such templates, wherein the plurality of spaced structures has a good mechanical stability. It is a further object of the present disclosure to provide methods for forming a plurality of spaced electrically conductive structures, e.g. electrically conductive nanostructures, within the plurality of spaced channels, e.g., nanochannels, of such templates, wherein a good electrical contact is established between the plurality of spaced electrically conductive structures and an underlying electrically conductive substrate. It is an object of the present disclosure to provide devices comprising such plurality of spaced structures.

[0017] The above objectives are at least partially accomplished by methods and devices according to the present disclosure.

[0018] According to a first aspect, the present disclosure is related to a method for transforming at least part of a valve metal layer into a template comprising a plurality of spaced channels aligned longitudinally along a first direction. A method according to the first aspect of the present disclosure comprises a first anodization step anodizing at least part of the valve metal layer in the thickness direction and thereby forming a porous layer of valve metal oxide comprising a plurality of channels, each channel having channel walls aligned longitudinally along the first direction and having a channel bottom, the channel bottoms being coated with a first insulating metal oxide barrier layer as a result of the first anodization step; next a protective treatment inducing hydrophobic surfaces to the channel walls and channel bottoms; a second anodization step after the protective treatment, thereby substantially removing the first insulating metal oxide barrier layer from the channel bottoms and inducing anodization only at the bottoms of the plurality of channels and creating a second insulating metal oxide barrier layer at the channel bottoms; and an etching step in an acidic etching solution or in a basic etching solution, thereby removing the second insulating metal oxide barrier layer from the channel bottoms. The plurality of spaced channels may for example comprise a plurality of spaced nanochannels.

**[0019]** In the context of the present disclosure, a valve metal is a metal selected from the group of aluminum, tungsten, titanium, tantalum, hafnium, niobium, vanadium and zirconium. In the context of the present disclosure, a valve metal layer is a layer comprising a valve metal or a valve metal alloy. A valve metal layer may be a single layer or it may be a layer stack comprising at least

5 two valve metal layers. In preferred embodiments of a method of the first aspect of the present disclosure a valve metal layer comprising a layer of aluminum, an aluminum alloy, titanium, a titanium alloy, tantalum or a tantalum alloy may be used.

**[0020]** In embodiments of a method of the first aspect, performing the protective treatment may comprise annealing at a temperature in the range between 300°C and 550°C.

10 **[0021]** In embodiments of a method of the first aspect, performing the protective treatment may comprise depositing a protective layer over the channel walls and over the channel bottoms. In such embodiments, the second anodization step additionally removes the protective layer only from the channel bottoms.

15 **[0022]** It is an advantage of embodiments of the method of the first aspect of the present disclosure that it allows removing a barrier layer from the channel bottoms of a template formed by anodization, wherein the barrier layer can be removed with a limited pore widening at one hand and with a limited pore narrowing on the other hand. This results in a template comprising a plurality of spaced channels having a diameter that is substantially constant along their entire length, i.e. up to the bottom.

20 **[0023]** It is an advantage of a limited pore narrowing that it allows forming afterwards a plurality of structures inside the plurality of channels with a good mechanical stability, a limited risk of delamination from an underlying substrate, and with a good electrical and mechanical contact with the underlying substrate, for example an electrically conductive underlying substrate.

25 **[0024]** It is an advantage of a limited pore widening that it may result in a template comprising a plurality of spaced channels having a diameter (corresponding to a final pore diameter) that is smaller than, e.g. substantially smaller than, a spacing between neighboring channels (wherein the spacing is defined here as a distance between facing channel walls). This has as an advantage that it allows forming afterwards a plurality of structures inside the plurality of channels of the template that take in a reduced volume as compared to prior art templates wherein pore widening results in

30 channels being spaced at a distance that is typically smaller than their diameter. It is an advantage of a plurality of structures taking in a reduced volume that an increased volume remains available between the structures, e.g. for deposition of an additional layer or additional layers. For example, a plurality of structures formed inside the plurality of channels may be used as a current collector in electrochemical devices such as for example electrochemical sensors, batteries, supercapacitors,

35 fuel cells, (photo)electrolyzers or chemical reactors. The increased volume available between the structures may then for example be utilized for providing a layer of functional material, such as a

layer of active electrode material or an electrolyte material, the present disclosure not being limited thereto.

**[0025]** It is an advantage of a method of the first aspect of the present disclosure that it is relatively simple. It does not require sophisticated equipment or vacuum equipment and it is therefore potentially low-cost. It is suitable for implementation in large-scale manufacturing.

**[0026]** It is an advantage of a method of the first aspect of the present disclosure that the use of an anodization based process for forming the template allows for a good control of a diameter of the plurality of spaced channels and a distance between neighboring channels by controlling a voltage or a current used during anodization. It is an advantage of a method of the first aspect of the present disclosure that the use of an anodization based process for forming the template allows for a good control of a depth of the plurality of spaced channels by controlling a duration of the first anodization step.

**[0027]** In embodiments of a method of the first aspect wherein performing the protective treatment comprises depositing a protective layer on the channel walls and on the channel bottoms, the protective layer may for example comprise hydrophobic silane or a polymer that is resistant to the etching solution, such as for example polystyrene, poly(methyl 2-methylpropanoate) or poly(dimethylsiloxane).

**[0028]** In embodiments of a method of the first aspect of the present disclosure the etching solution may be an aqueous solution, which is advantageous in that the template may be formed without the use of organic solvents, resulting in an environmentally friendly method. The aqueous etching solution may for example be an acidic etching solution comprising phosphoric acid, sulfuric acid, oxalic acid or chromic acid or a combination thereof. Alternatively, the etching solution may be a basic etching solution e.g. comprising ammonia, hydrogen peroxide, potassium hydroxide or a combination thereof.

**[0029]** In embodiments of a method of the first aspect the etching solution may further comprise a surface tension adjusting agent, which is advantageous in that the surface tension adjusting agent may facilitate penetration of the etching solution inside the plurality of channels towards the channel bottoms. The surface tension adjusting agent may for example be selected from ethyl alcohol, isopropyl alcohol, acetone and sodium dodecyl sulphate, the present disclosure not being limited thereto.

**[0030]** Embodiments of a method of the first aspect of the present disclosure may further comprise providing ultrasonic waves during the second anodization step, which is advantageous in that it may facilitate removal of the first insulating metal oxide barrier layer and, if present, removal of the protective layer, from the channel bottoms during the second anodization step. It may further facilitate removal of the second insulating metal oxide barrier layer from the channel bottoms during the etching step. Embodiments of a method of the first aspect of the present disclosure may comprise

providing ultrasonic waves during the first anodization step. Embodiments of a method of the first aspect of the present disclosure may comprise providing ultrasonic waves during both the first anodization step and the second anodization step.

**[0031]** In embodiments of a method of the first aspect of the present disclosure the first anodization step may anodize only a part of the valve metal layer in the thickness direction, to thereby form the template and defining a substrate supporting the template, wherein the substrate comprises a remaining, non-anodized part of the valve metal layer. This is advantageous in that it allows forming good templates from a free-standing metal layer such as a free-standing metal foil, e.g. a free-standing aluminum foil. In such embodiments, the need for providing a separate substrate supporting the valve metal layer may be reduced, which may lead to a reduced cost. It is a further advantage of using a free-standing layer of metal that it allows anodizing the layer at two opposite sides or surfaces, thus allowing the formation of a stack comprising a first porous layer of valve metal oxide (first template), a non-anodized valve metal layer (substrate) and a second porous layer of valve metal oxide (second template). Such a stack comprising a first template and a second template at opposite substrate sides may for example be used advantageously for forming a plurality of spaced (nano)structures in a fabrication process of solid-state batteries comprising a stack of battery cells. It is an advantage that in such embodiments a single substrate provides support for nanostructures (the nanostructures e.g. having the function of a current collector) at both sides of the substrate, thus reducing the volume occupied by substrate material per battery cell.

**[0032]** In other embodiments of a method of the first aspect of the present disclosure the valve metal layer may be provided on an electrically conductive substrate. In this context, “electrically conductive substrate” also includes any substrate comprising an electrically conductive layer at an exposed surface thereof. In such embodiments, the first anodization step may anodize the valve metal layer throughout the layer in the thickness direction, to thereby form a porous layer of valve metal oxide comprising a plurality of channels, each channel having channel walls aligned longitudinally along the first direction and having a channel bottom, the channel bottoms being located at an interface between the valve metal layer and the underlying electrically conductive layer or substrate. In such embodiments, the etching step exposes the electrically conductive layer at the channel bottoms. The electrically conductive layer may for example be a titanium nitride layer, a titanium layer, a nickel layer, an indium tin oxide layer, a gold layer or a platinum layer, the present disclosure not being limited thereto.

**[0033]** According to a second aspect, the present disclosure is related to a template comprising a plurality of spaced channels aligned longitudinally along a first direction, wherein the template is obtainable by a method according to an embodiment of the first aspect of the present disclosure.

**[0034]** In general, features of the second aspect of the present disclosure provide similar advantages as discussed above in relation to the first aspect of the present disclosure.

**[0035]** It is an advantage of embodiments of the template of the second aspect of the present disclosure that the plurality of spaced channels may have a diameter that is substantially constant along their entire length, i.e. up to the bottom, and that they may have a channel bottom free of any barrier layer, i.e. exposing an underlying substrate. This has as an advantage that it allows forming afterwards a plurality of structures inside the plurality of channels with a good mechanical stability, a limited risk of delamination from an underlying substrate, and with a good electrical and mechanical contact with the underlying substrate, for example an electrically conductive underlying substrate.

**[0036]** It is an advantage of embodiments of the template of the second aspect of the present disclosure that the plurality of spaced channels may have a diameter that is smaller than, e.g. substantially smaller than, a spacing between neighboring channels (wherein the spacing is defined here as a distance between facing channel walls). This has as an advantage that it allows forming afterwards a plurality of structures inside the plurality of channels of the template that take in a reduced volume as compared to prior art templates wherein pore widening results in channels being spaced at a distance that is typically smaller than their diameter. It is an advantage of a plurality of structures taking in a reduced volume that an increased volume remains available between the structures, e.g. for deposition of an additional layer or additional layers. For example, a plurality of structures formed inside the plurality of channels may be used as a current collector in electrochemical devices such as electrochemical sensors, batteries, supercapacitors, fuel cells, (photo)electrolyzers or chemical reactors. The increased volume available between the structures may then for example be utilized for providing a layer of functional material, such as for example a layer of active electrode material or an electrolyte material, the present disclosure not being limited thereto.

**[0037]** In embodiments of a template of the second aspect of the present disclosure, the first direction may be at an angle in the range between 60° and 90°, for example between 80° and 90°, with respect to a surface of the valve metal layer from which the template is formed. For example, the first direction may be substantially orthogonal to a surface of the valve metal layer.

**[0038]** In embodiments of a template of the second aspect of the present disclosure, the template may further comprise a plurality of interconnecting channels oriented along a second direction different from the first direction, wherein the interconnecting channels form a connection between neighboring spaced channels oriented along the first direction. The second direction may for example be substantially orthogonal to the first direction. It is an advantage of a template comprising such interconnecting channels that it allows forming afterwards a plurality of interconnected structures inside the plurality of channels of the template. Such plurality of interconnected structures may for example form a mesh-shaped structure.

**[0039]** According to a third aspect, the present disclosure is related to a method for forming a plurality of spaced structures on a substrate. A method according to the third aspect of the present disclosure comprises transforming at least part of a valve metal layer into a template comprising a plurality of spaced channels aligned longitudinally along a first direction according to an embodiment of the first aspect of the present disclosure, thereby forming the template and defining the substrate, and depositing a solid functional material within the channels of the template to thereby form the plurality of spaced structures inside the plurality of spaced channels. This results in a plurality of spaced structures being aligned longitudinally along the first direction. The method may further comprise removing the template by etching. Examples of spaced electrically conductive structures that may be formed using a method of the third aspect of the present disclosure are pillars, nanopillars, wires, nanowires, tubes (or ‘hollow’ wires), nanotubes, meshes and nanomeshes.

**[0040]** In the context of the third aspect of the present disclosure, a functional material or functional material layer is a material or material layer that satisfies or provides a defined functionality and/or has defined properties, adjusted for a device in which it is integrated.

**[0041]** In embodiments of a method of the third aspect of the present disclosure, depositing the solid functional material within the channels of the template may comprise depositing an electrically conductive material, a semiconductor material, an electrically insulating material or a combination thereof.

**[0042]** In embodiments, depositing the solid functional material within the channels of the template may comprise filling the channels with the solid functional material, e.g. completely filling the channels in a lateral direction orthogonal to the first direction. In embodiments, depositing the solid functional material within the channels may comprise depositing a layer of solid functional material on the channel walls, thereby only partially filling the channels in a lateral direction with the solid functional material and leaving openings inside.

**[0043]** In embodiments of a method of the third aspect of the present disclosure, depositing the solid functional material within the channels of the template may comprise depositing an electrically conductive material by galvanostatic or potentiostatic electrodeposition or plating, to thereby form a plurality of spaced electrically conductive structures. In such embodiments, a good, low-resistance electrical contact may be established between the plurality of spaced electrically conductive structures and an underlying electrically conductive substrate. The electrical contact may for example have a contact resistance lower than 1 Ohm cm<sup>2</sup>.

**[0044]** In general, features of the third aspect of the present disclosure provide similar advantages as discussed above in relation to the previous aspects of the present disclosure.

**[0045]** It is an advantage of a method of the third aspect of the present disclosure that it allows forming a plurality of spaced structures on a substrate with a good mechanical stability, a limited risk of delamination from the underlying substrate, and a good mechanical contact with the

underlying substrate. It is an advantage of a method of the third aspect of the present disclosure that it allows forming a plurality of spaced electrically conductive structures with a good electrical contact to an underlying electrically conductive substrate, such as for example with a contact resistance lower than 1 Ohm cm<sup>2</sup>. It is an advantage of a method of the third aspect of the present disclosure that it allows forming a plurality of spaced structures, e.g. electrically conductive structures, taking in a relatively limited volume, thereby leaving an increased volume available in between the plurality of spaced structures, for example for deposition of an additional layer, e.g. an additional layer of functional material, such as e.g. a layer of active electrode material.

5 [0046] It is an advantage of a method of the third aspect of the present disclosure that it may be relatively simple. It does not require sophisticated equipment or vacuum equipment and is therefore potentially low-cost. It is suitable for implementation in large-scale manufacturing.

10 [0047] It is an advantage of a method of the third aspect of the present disclosure that it allows for a good control of a diameter and a length (height) of the plurality of spaced structures, e.g. electrically conductive structures, and of a distance between neighboring structures. It is an advantage that this further enables for example a good control of the energy density and power density of a battery cell having a current collector comprising such a plurality of spaced electrically conductive structures.

15 [0048] In embodiments of the method of the third aspect of the present disclosure the electrically conductive material deposited within the channels of the template to thereby form the plurality of spaced electrically conductive structures may be a transition metal, which is advantageous in that it may result in a reduced cost. It is an advantage that this further allows reducing a cost of battery cells having a current collector comprising such plurality of spaced electrically conductive transition metal structures. In embodiments of the third aspect of the present disclosure the transition metal may for example be selected from nickel, copper and chromium.

20 [0049] According to a fourth aspect, the present disclosure is related to an entity comprising a substrate with a plurality of spaced structures thereon, the plurality of spaced structures being aligned longitudinally along a first direction and being obtainable by a method according to an embodiment of the third aspect of the present disclosure.

25 [0050] In general, features of the fourth aspect of the present disclosure provide similar advantages as discussed above in relation to the previous aspects of the present disclosure.

[0051] In embodiments of an entity of the fourth aspect of the present disclosure the first direction may be at an angle in the range between 60 and 90, for example between 80 and 90, with respect to a surface of the substrate. For example, the first direction may be substantially orthogonal to a surface of the substrate.

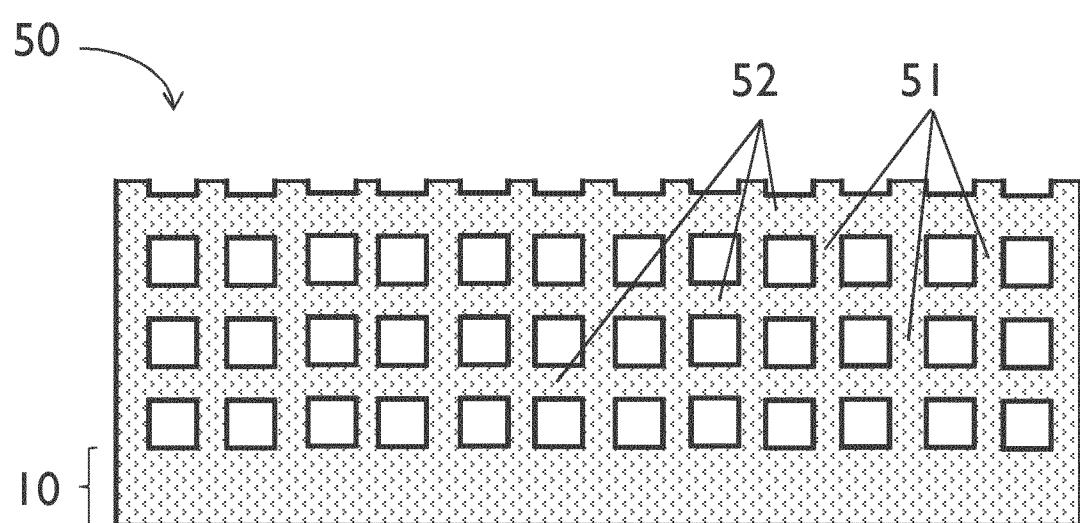

30 [0052] In embodiments of an entity of the fourth aspect of the present disclosure, the entity may further comprise a plurality of interconnecting structures oriented along a second direction different

from the first direction, wherein the interconnecting structures form a connection between neighboring spaced structures oriented along the first direction, thereby forming for example a mesh-shaped structure. The second direction may for example be substantially orthogonal to the first direction, the present disclosure not being limited thereto,

5 [0053] In embodiments of the fourth aspect of the present disclosure the plurality of spaced structures and, if present, the plurality of interconnecting structures, may comprise an electrically conductive material, a semiconductor material, an electrically insulating material or a combination thereof.

10 [0054] According to a fifth aspect, the present disclosure is related to a device comprising an entity according to the fourth aspect of the present disclosure. In embodiments of the fifth aspect of the present disclosure the device may for example be an electrochemical device, such as e.g. an electrochemical sensor, a battery, a supercapacitor, a fuel cell, an electrolyzer, a photo-electrolyzer or a chemical reactor, the present disclosure not being limited thereto.

15 [0055] In general, features of the fifth aspect of the present disclosure provide similar advantages as discussed above in relation to the previous aspects of the present disclosure.

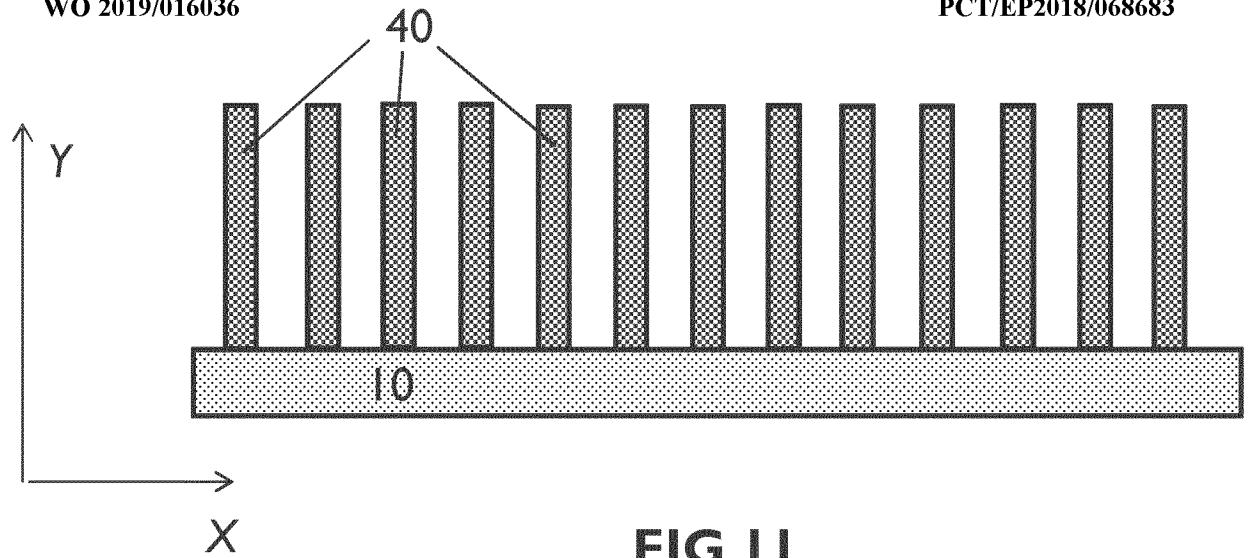

20 [0056] According to a sixth aspect, the present disclosure is related to a method for forming a layer of a functional material on an electrically conductive substrate, such as for example on a transition metal substrate. A method according to the sixth aspect of the present disclosure comprises depositing an interlayer on the substrate, wherein the interlayer comprises a transition metal oxide, a noble metal or a noble-metal oxide, and wherein the interlayer has a thickness in the range between 0.5 nm and 30 nm, for example in the range between 0.5 nm and 10 nm; depositing a functional material precursor layer on the interlayer; and activating the functional material precursor layer by annealing to thereby form the layer of functional material.

25 [0057] In embodiments of the method of the sixth aspect of the present disclosure the layer of functional material may for example be a layer of active electrode material. In such embodiments depositing the functional material precursor layer comprises depositing an electrode material precursor layer. The annealing step for activating the electrode material precursor layer may be done in the presence of an ion containing precursor, such as for example a lithium containing precursor, a sodium containing precursor or a magnesium containing precursor, the present disclosure not being limited thereto. In embodiments of the sixth aspect of the present disclosure the electrode material may be a cathode material or an anode material. The functional material precursor layer may be a layer of cathode precursor material, for example comprising manganese oxide, manganese dioxide, cobalt oxide, manganese nickel oxide or iron phosphate, or it may be a layer of anode precursor material.

30 [0058] In general, features of the sixth aspect of the present disclosure provide similar advantages as discussed above in relation to the previous aspects of the present disclosure.

**[0059]** It is an advantage of providing an interlayer in accordance with a method of the sixth aspect of the present disclosure that it results in a reduced risk of degradation of the underlying electrically conductive substrate material, such as for example a reduced risk of oxidation of the electrically conductive substrate material. The electrically conductive substrate may for example be 5 used as a current collector of a battery cell. It is an advantage of providing an interlayer in accordance with a method of the sixth aspect of the present disclosure that it results in a reduced risk of degradation (e.g. oxidation) of the current collector material, for example under the influence of the step of activating the layer of electrode precursor material by annealing.

**[0060]** It is a further advantage of providing an interlayer in accordance with a method of the 10 sixth aspect of the present disclosure that it may result in a reduced risk of degradation of the underlying electrically conductive substrate material, e.g. current collector material, under the influence of an electrochemical deposition process, as may for example be used for depositing the functional material precursor layer. Such electrochemical deposition process may for example comprise deposition in an acidic bath, for example for depositing the layer of electrode precursor 15 material (electrode material precursor layer), the present disclosure not being limited thereto.

**[0061]** In embodiments of the sixth aspect of the present disclosure depositing the functional material precursor layer, e.g. layer of electrode precursor material, may comprise anodic electrodeposition from an acidic solution or from a basic solution, which is advantageous in that anodic electrodeposition is a low-cost process suitable for large scale manufacturing. In some 20 embodiments, the use of an acidic solution may advantageously offer a good stability of the electrodeposition bath.

**[0062]** It is an advantage of a method of the sixth aspect of the present disclosure that it allows forming a functional material layer, such as a layer of active electrode material, on a broad range of metals, including for example relatively cheap transition metals. This further allows for example 25 reducing a cost of battery cells having a current collector structure comprising such plurality of spaced electrically conductive transition metal structures.

**[0063]** It is an advantage of a method of the sixth aspect of the present disclosure that it allows conformally forming a layer of functional material on a large variety of metal substrates, including transition metal substrates, for example on three-dimensional transition metal substrates. More in 30 particular, it is an advantage of a method of the sixth aspect of the present disclosure that it allows conformally forming a layer of active cathode material on a large variety of metal substrates, including transition metal substrates, for example on three-dimensional transition metal substrates. This is advantageous as compared to fabrication methods wherein an active anode material is formed on a three-dimensional substrate in that it allows fabricating solid-state battery cells with an 35 improved energy density and power density. This is related to a generally lower capacity of cathode materials as compared to anode materials. Therefore, three-dimensional structuring of a cathode

layer has a more advantageous effect on the capacity, energy density and power density of a battery cell as compared to an approach wherein only the anode layer is three-dimensionally structured and not the cathode layer.

**[0064]** In embodiments of the sixth aspect of the present disclosure the electrically conductive substrate may be a three-dimensional substrate comprising a plurality of spaced electrically conductive structures being substantially aligned along a first direction, which is advantageous in that it results in a substantially increased electrode surface area as compared to flat substrates, which may further lead to substantially higher charging rates of solid-state battery cells comprising such three-dimensional electrode structure. In embodiments of the sixth aspect of the present disclosure the electrically conductive substrate may further comprise a plurality of electrically conductive interconnecting structures oriented along a second direction different from the first direction, such as for example substantially orthogonal to the first direction, wherein the electrically conductive interconnecting structures form a connection between neighboring electrically conductive structures oriented along the first direction.

**[0065]** Examples of spaced electrically conductive structures are pillars, nanopillars, wires, nanowires, tubes (or 'hollow' wires), nanotubes, meshes and nanomeshes. It is advantageous that such structures enable the formation of flexible battery cells, due to a reduced mechanical stress upon bending.

**[0066]** In embodiments of the sixth aspect of the present disclosure wherein the interlayer comprises a transition metal oxide, depositing the interlayer may for example comprise electrodeposition in a solution having a pH in the range of 7 to 12. The use of a neutral or basic solution for depositing the interlayer on the substrate, e.g. transition metal substrate, is advantageous in that it allows forming the interlayer with a reduced risk of degradation of the substrate, e.g. transition metal substrate, under the influence of the interlayer deposition process. It is an advantage of using an electrodeposition process for depositing the interlayer that it is suitable for low-cost large-scale manufacturing. The transition metal oxide may for example comprise chromium oxide, nickel oxide, titanium oxide or manganese oxide.

**[0067]** According to a seventh aspect, the present disclosure is related to a method for fabricating a solid-state battery cell. A method according to the seventh aspect of the present disclosure comprises forming a plurality of spaced electrically conductive structures on a substrate according to a method of the third aspect of the present disclosure; forming a first layer of active electrode material on the plurality of electrically conductive structures, wherein the first layer of active electrode material conformally coats surfaces of the plurality of electrically conductive structures; depositing a solid electrolyte layer over the first layer of active electrode material; and forming a second layer of active electrode material over the solid electrolyte layer, wherein one of the first layer of active electrode material and the second layer of active electrode material forms a

cathode layer and the other one forms an anode layer of the solid-state battery cell. The plurality of spaced electrically conductive structures may form a first current collector of the solid-state battery cell. The method may further comprise depositing a second current collector or collector layer over the second layer of active electrode material.

5 **[0068]** In embodiments of the method of the seventh aspect of the present disclosure forming the first layer of active electrode material on the plurality of electrically conductive structures may be done according to an embodiment of the sixth aspect of the present disclosure.

**[0069]** In general, features of the seventh aspect of the present disclosure provide similar advantages as discussed above in relation to the previous aspects of the present disclosure.

10 **[0070]** It is an advantage of a method of the seventh aspect of the present disclosure that a substantial part of the fabrication steps may be done by means of a simple, low-cost electrochemical deposition process. More in particular, the anodization steps in the method for forming a template, the step of depositing an electrically conductive material within the template and the step of depositing an electrode material precursor layer may be done by means of an electrochemical 15 deposition process. It is an advantage that these steps may be done in the same equipment. It is an advantage of a method of the seventh aspect of the present disclosure that the electrochemical deposition processes may be performed in an aqueous solution without organic solvents, resulting in an environmental-friendly fabrication method.

20 **[0071]** According to an eighth aspect, the present disclosure is related to a method for fabricating a solid-state battery cell. A method according to the eighth aspect of the present disclosure comprises: forming a plurality of spaced electrically conductive structures on a substrate; forming a first layer of active electrode material on the plurality of spaced electrically conductive structures in accordance with an embodiment of the sixth aspect of the present disclosure, wherein the first layer of active electrode material conformally coats surfaces of the plurality of spaced 25 electrically conductive structures; depositing a solid electrolyte layer over the first layer of active electrode material; and forming a second layer of active electrode material over the solid electrolyte layer, wherein one of the first layer of active electrode material and the second layer of active electrode material forms a cathode layer and the other one forms an anode layer of the solid-state battery cell. The plurality of spaced electrically conductive structures may form a first current 30 collector layer of the solid-state battery cell. The method may further comprise depositing a second current collector layer over the second layer of active electrode material.

**[0072]** In general, features of the eighth aspect of the present disclosure provide similar advantages as discussed above in relation to the previous aspects of the present disclosure.

35 **[0073]** According to a ninth aspect, the present disclosure is related to a method for fabricating a solid-state battery. A method according to the ninth aspect of the present disclosure comprises: fabricating a plurality of solid-state battery cells in accordance with an embodiment of the seventh

or the eighth aspect of the present disclosure; and forming a stack of the plurality of solid-state battery cells with a solid electrolyte being provided in between neighboring solid-state battery cells.

**[0074]** In general, features of the ninth aspect of the present disclosure provide similar advantages as discussed above in relation to the previous aspects of the present disclosure,

5 **[0075]** According to a tenth aspect, the present disclosure is related to a solid-state battery cell. A solid-state battery cell according to the tenth aspect of the present disclosure comprises a plurality of spaced electrically conductive structures; a first layer of active electrode material conformally coating surfaces of the plurality of spaced electrically conductive structures; a solid electrolyte layer over the first layer of active electrode material; a second layer of active electrode material over the

10 solid electrolyte layer, wherein one of the first layer of active electrode material and the second layer of active electrode material forms a cathode layer and the other one forms an anode layer of the solid-state battery cell; and a 0.5 nm to 10 nm thick interlayer between the plurality of electrically conductive structures and the first layer of active electrode material, wherein the interlayer comprises a transition metal oxide, a noble metal or a noble-metal oxide. In embodiments

15 of the tenth aspect of the present disclosure the plurality of spaced electrically conductive structures may form a first current collector layer of the solid-state battery cell. The solid-state battery cell may further comprise a second current collector layer over the second layer of active electrode material.

**[0076]** In general, features of the tenth aspect of the present disclosure provide similar

20 advantages as discussed above in relation to the previous aspects of the present disclosure.

**[0077]** According to an eleventh aspect, the present disclosure is related to a solid-state battery comprising at least one, for example a plurality of, e.g. a stack of, solid-state battery cells according to the tenth aspect of the present disclosure.

**[0078]** In general, features of the eleventh aspect of the present disclosure provide similar

25 advantages as discussed above in relation to the previous aspects of the present disclosure.

**[0079]** Particular and preferred aspects of the disclosure are set out in the accompanying independent and dependent claims. Features from the dependent claims may be combined with features of the independent claims and with features of other dependent claims as appropriate and not merely as explicitly set out in the claims.

30 **[0080]** The above and other characteristics, features and advantages of the present disclosure will become apparent from the following detailed description, taken in conjunction with the accompanying drawings, which illustrate, by way of example, the principles of the disclosure. This description is given for the sake of example only, without limiting the scope of the disclosure. The reference figures quoted below refer to the attached drawings.

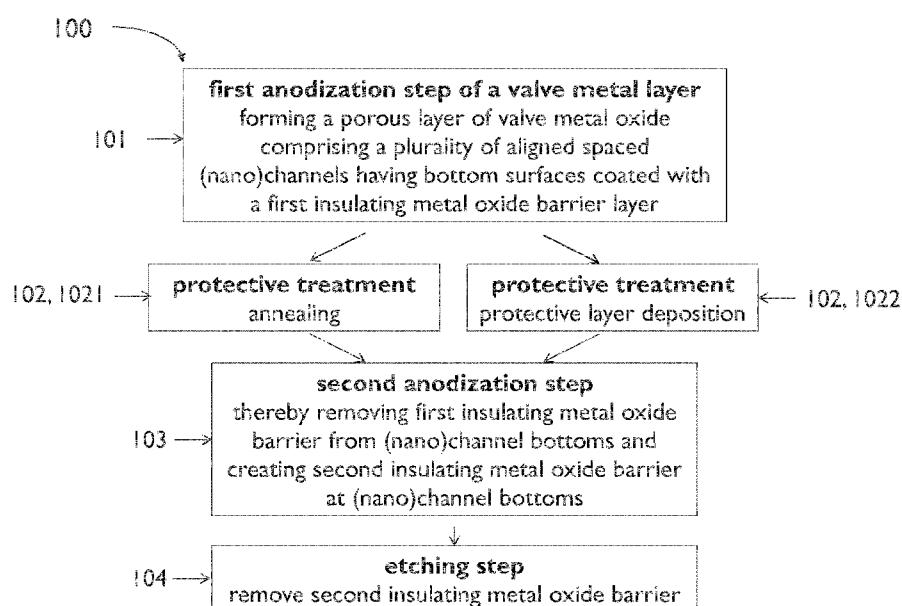

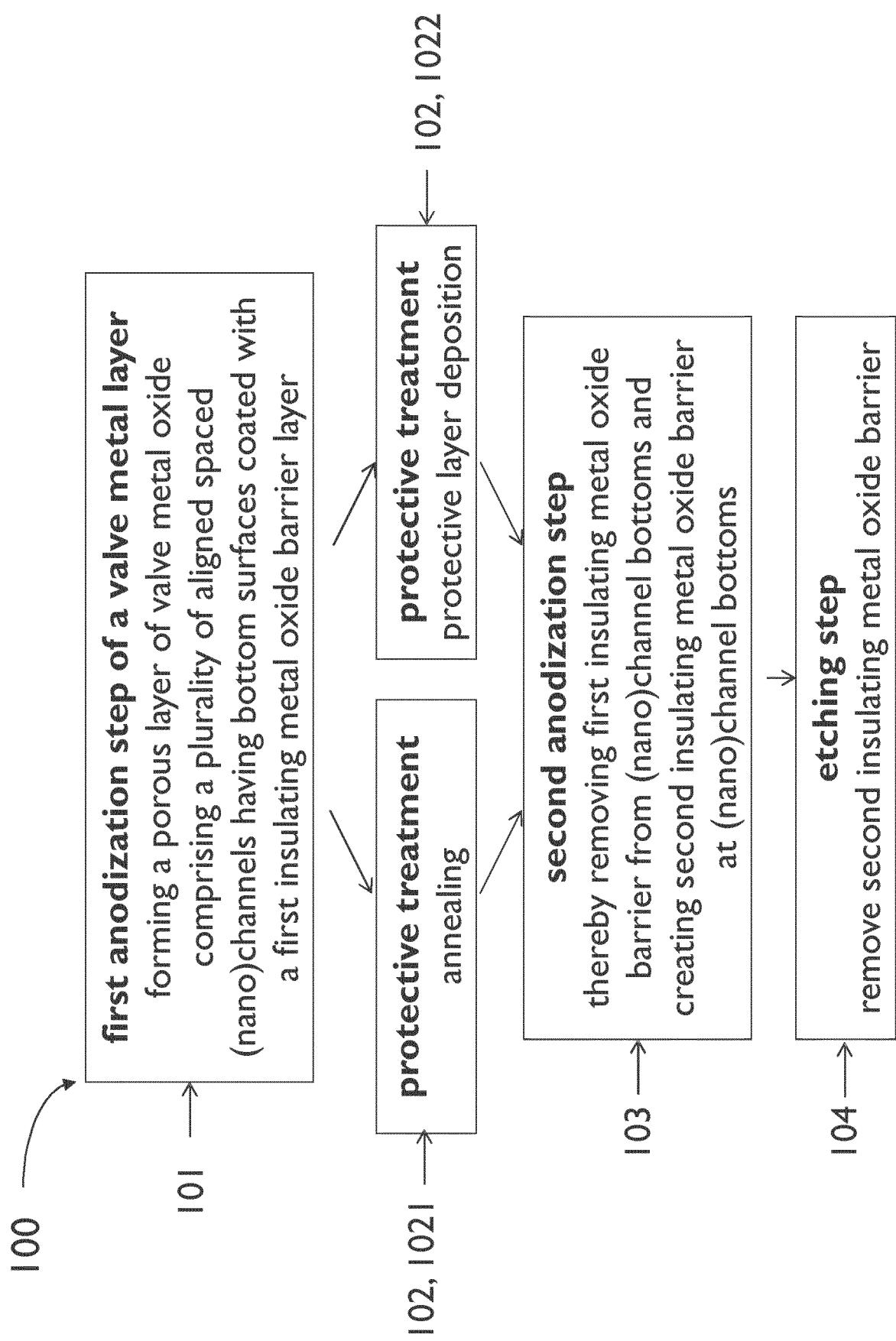

**[0081]** FIG 1 illustrates an exemplary process sequence of a method for transforming at least part of a valve metal layer into a template comprising a plurality of spaced (nano)channels according to an embodiment of the first aspect of the present disclosure.

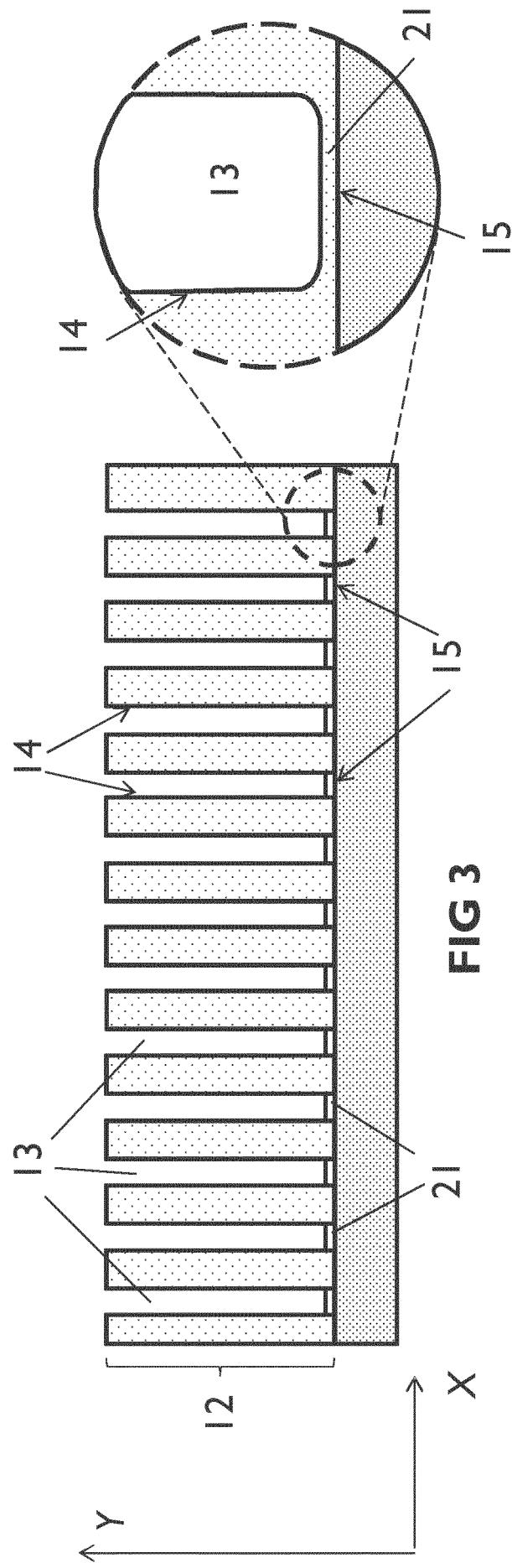

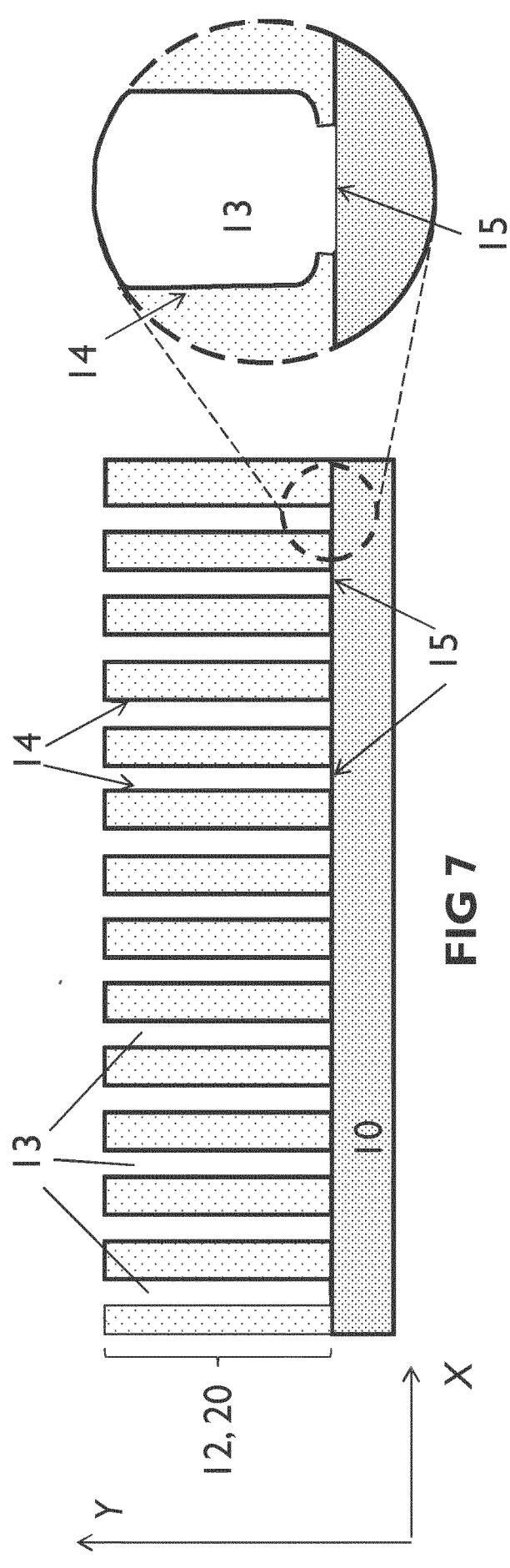

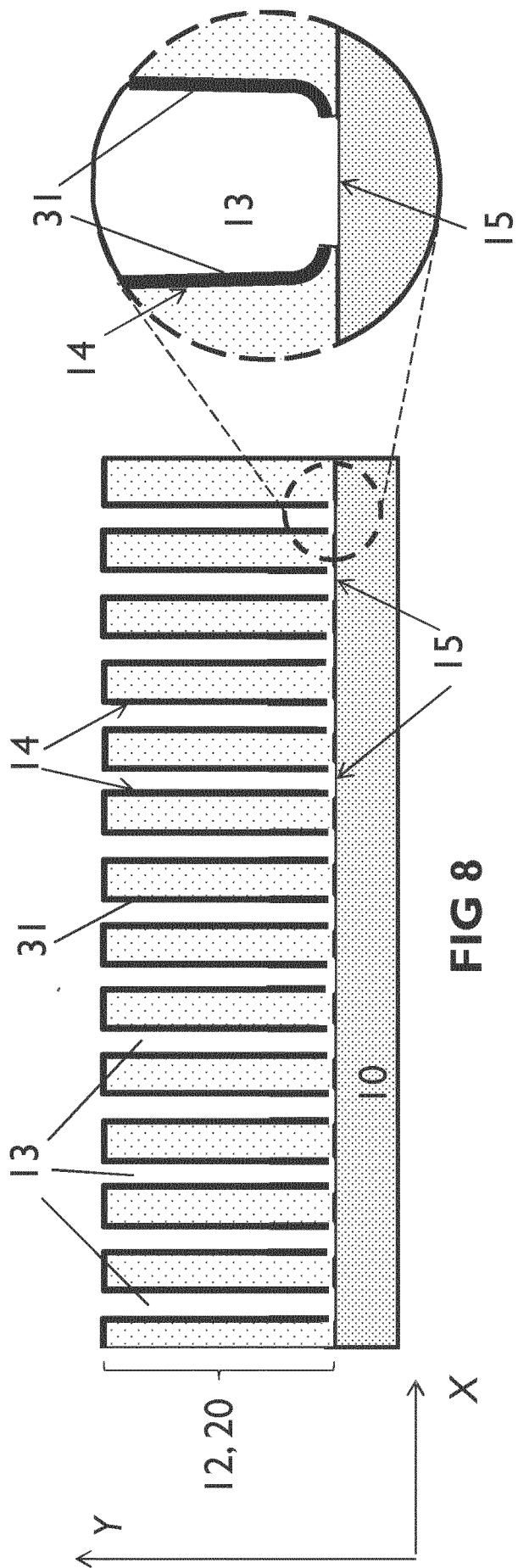

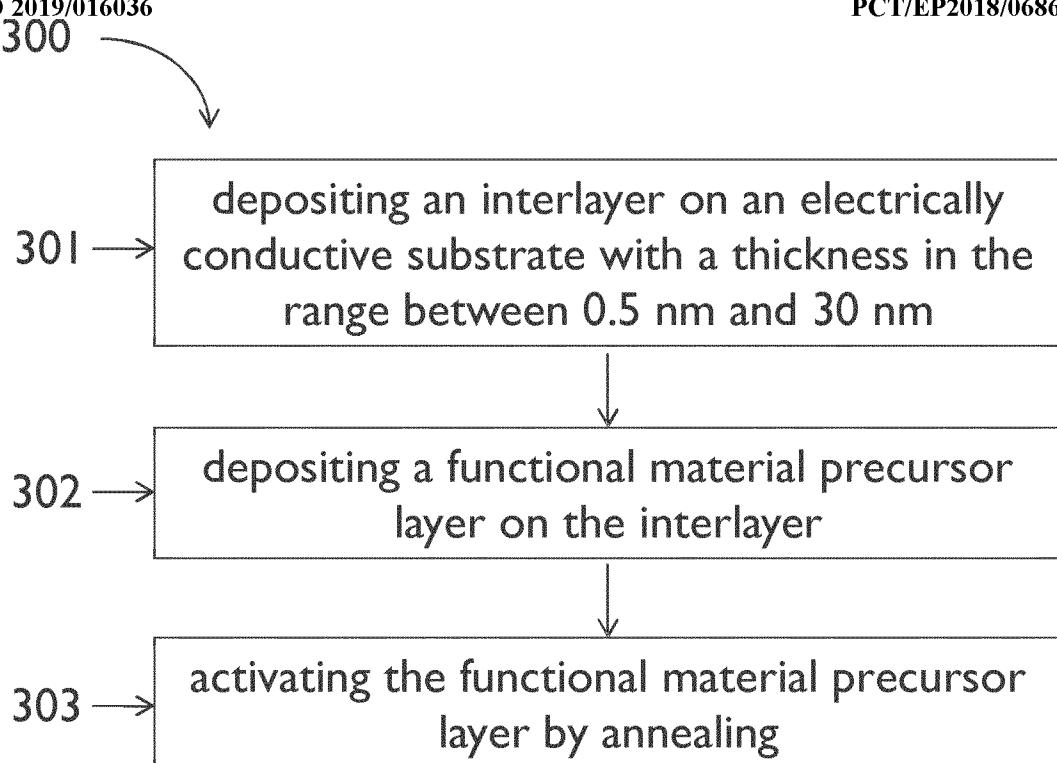

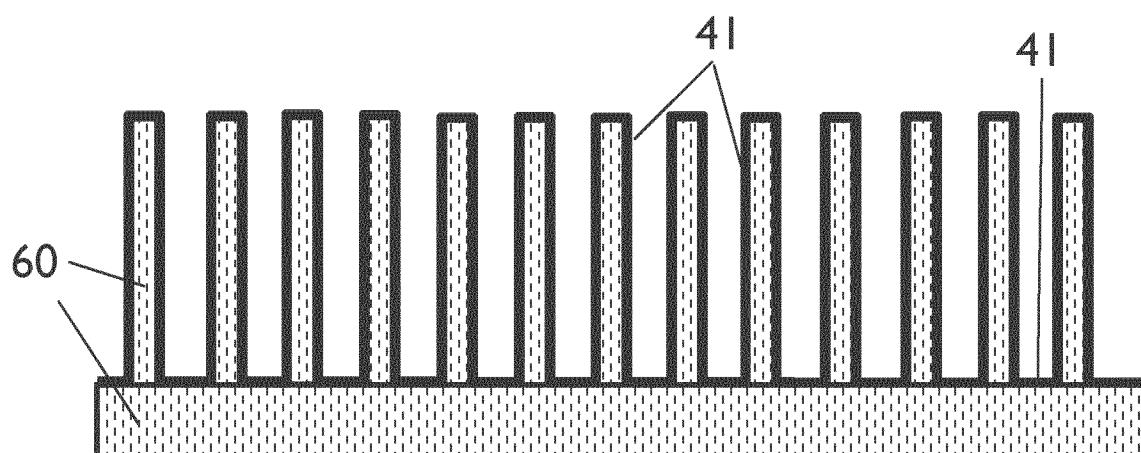

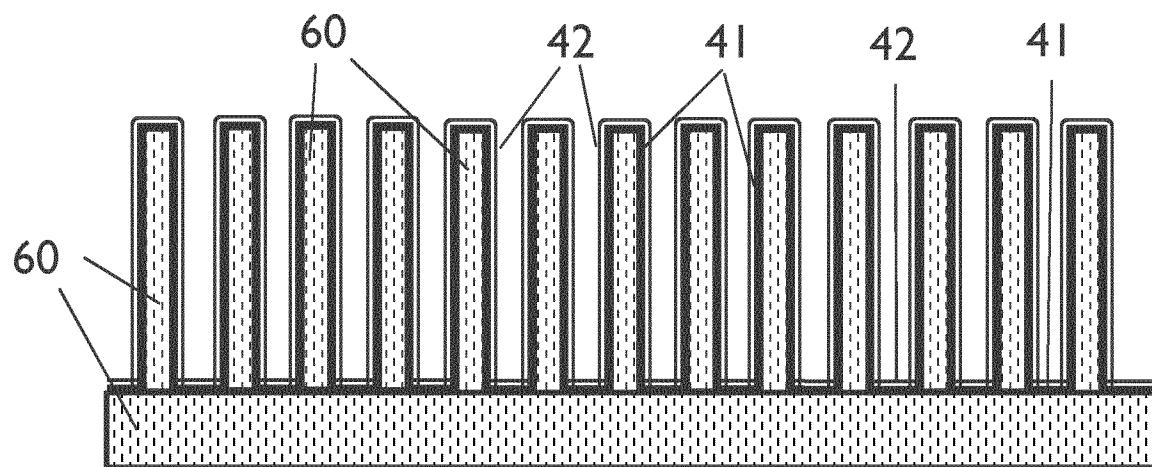

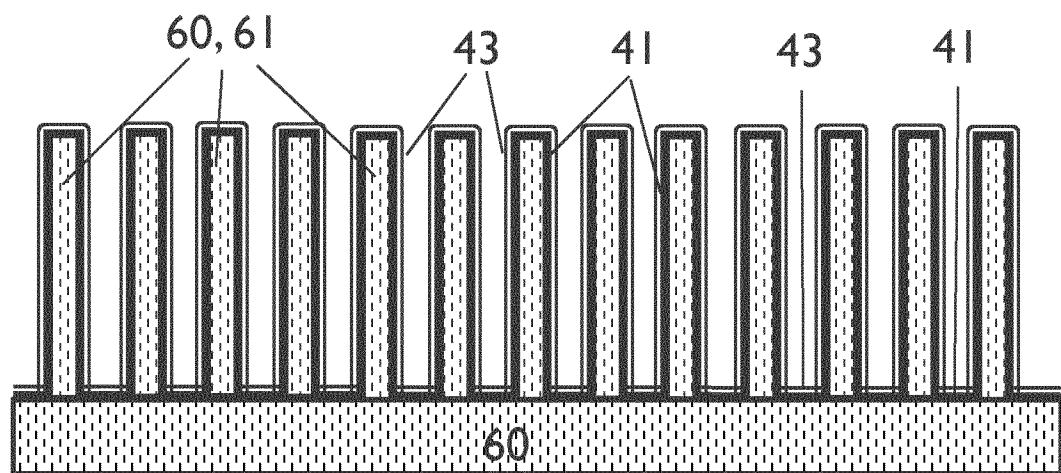

5 **[0082]** FIG 2 to FIG 8 schematically show cross sections illustrating results of successive steps of the process sequence of FIG 1.

**[0083]** FIG 7 and FIG 8 schematically show a cross section of examples of a template according to an embodiment of the second aspect of the present disclosure.

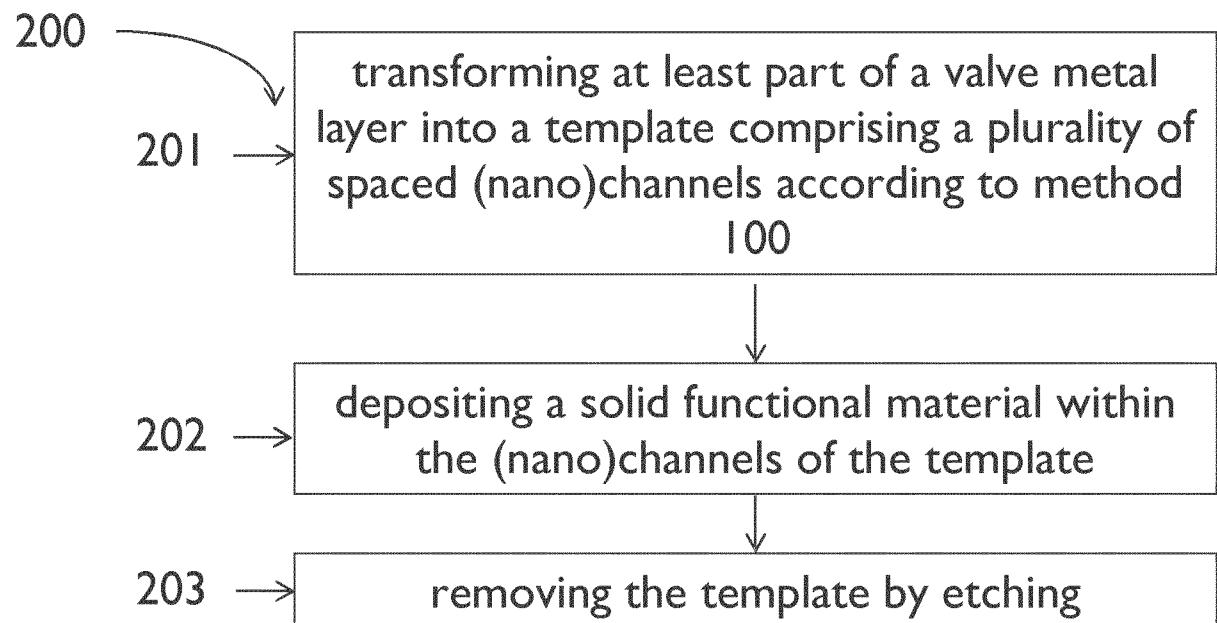

10 **[0084]** FIG 9 illustrates an exemplary process sequence of a method for forming a plurality of spaced (nano)structures on a substrate according to an embodiment of the third aspect of the present disclosure.

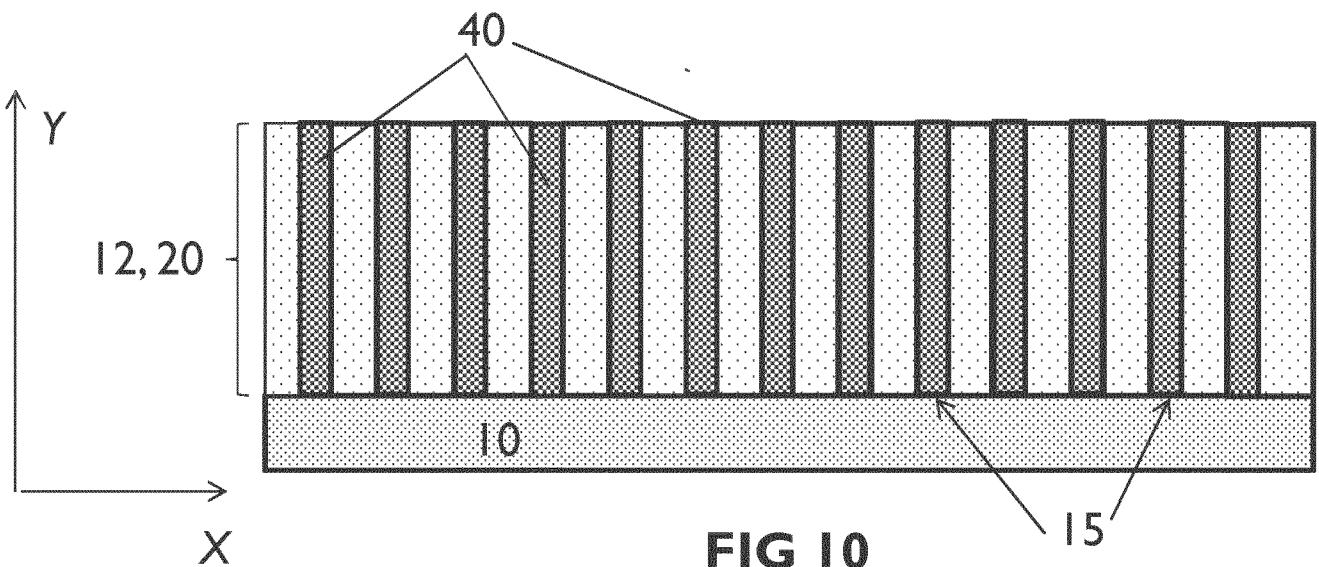

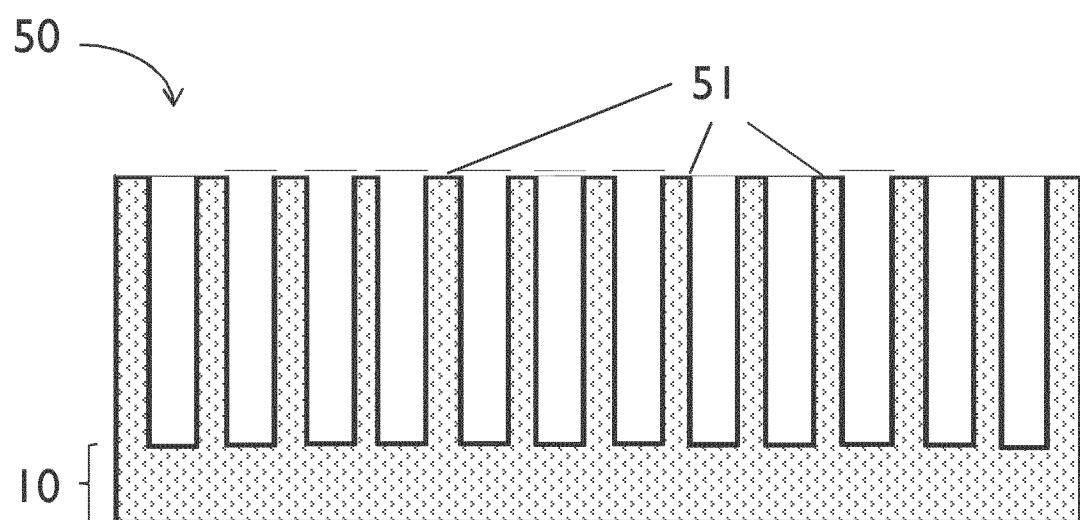

**[0085]** FIG 10 and FIG 11 schematically show cross sections illustrating results of successive steps of the process sequence of FIG 9.

**[0086]** FIG 11 schematically shows a cross section of an example of an entity according to an embodiment of the fourth aspect of the present disclosure.

15 **[0087]** FIG 12(a) and FIG 12(b) schematically show a cross section of an example of an entity according to an embodiment of the fourth aspect of the present disclosure.

**[0088]** FIG 13 illustrates an exemplary process sequence of a method for forming a layer of functional material on an electrically conductive substrate according to an embodiment of the sixth aspect of the present disclosure.

20 **[0089]** FIG 14 to FIG 16 schematically show cross sections illustrating results of successive steps of the process sequence of FIG 13.

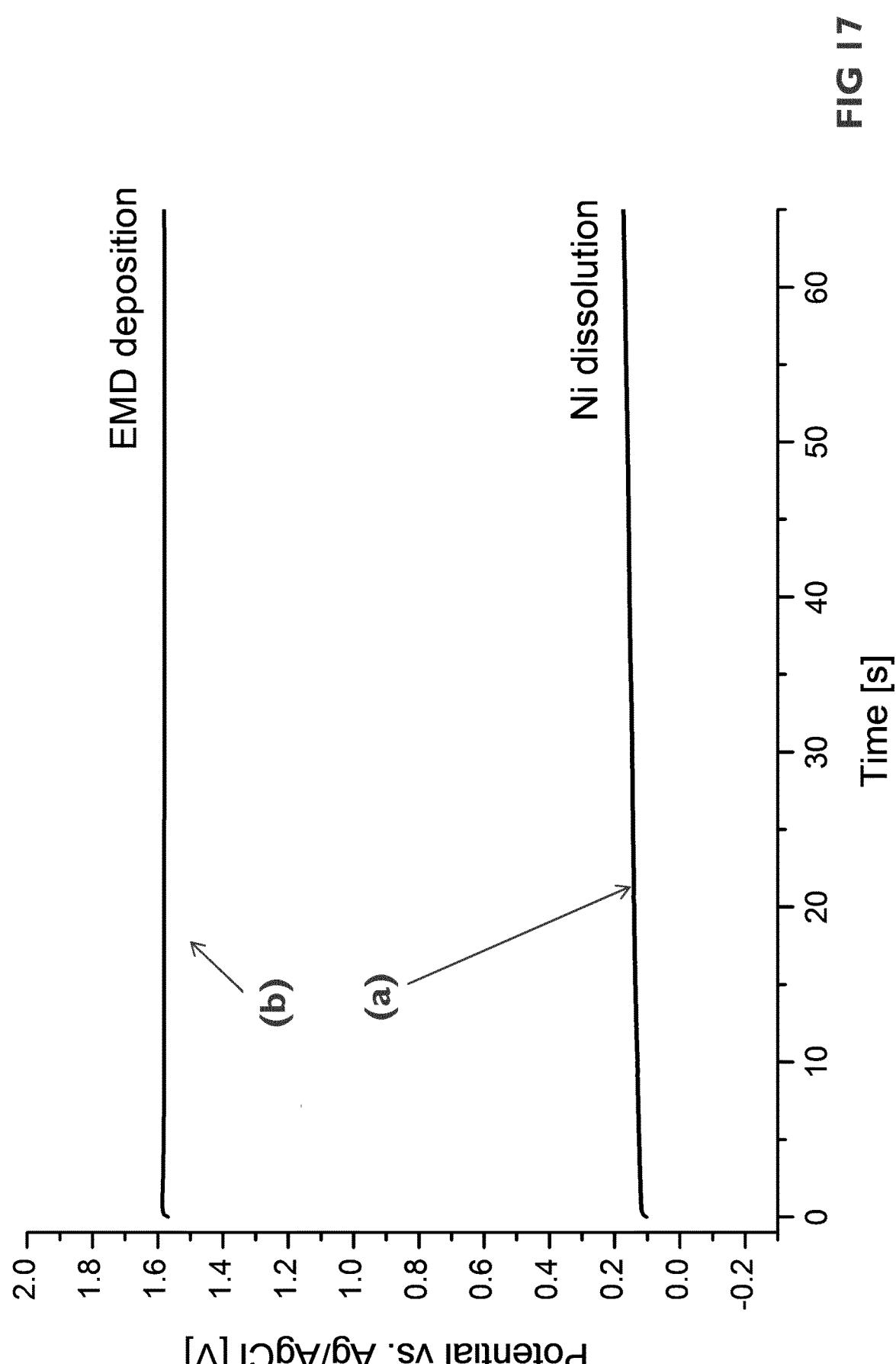

25 **[0090]** FIG 17 shows potential transients as measured during galvanostatic deposition of a  $MnO_x$  cathode precursor layer on Ni nano-mesh samples. The curves labeled (a) corresponds to samples without an interlayer being provided, whereas the curve labeled (b) corresponds to samples covered with an interlayer in accordance with an embodiment of the third aspect of the present disclosure.

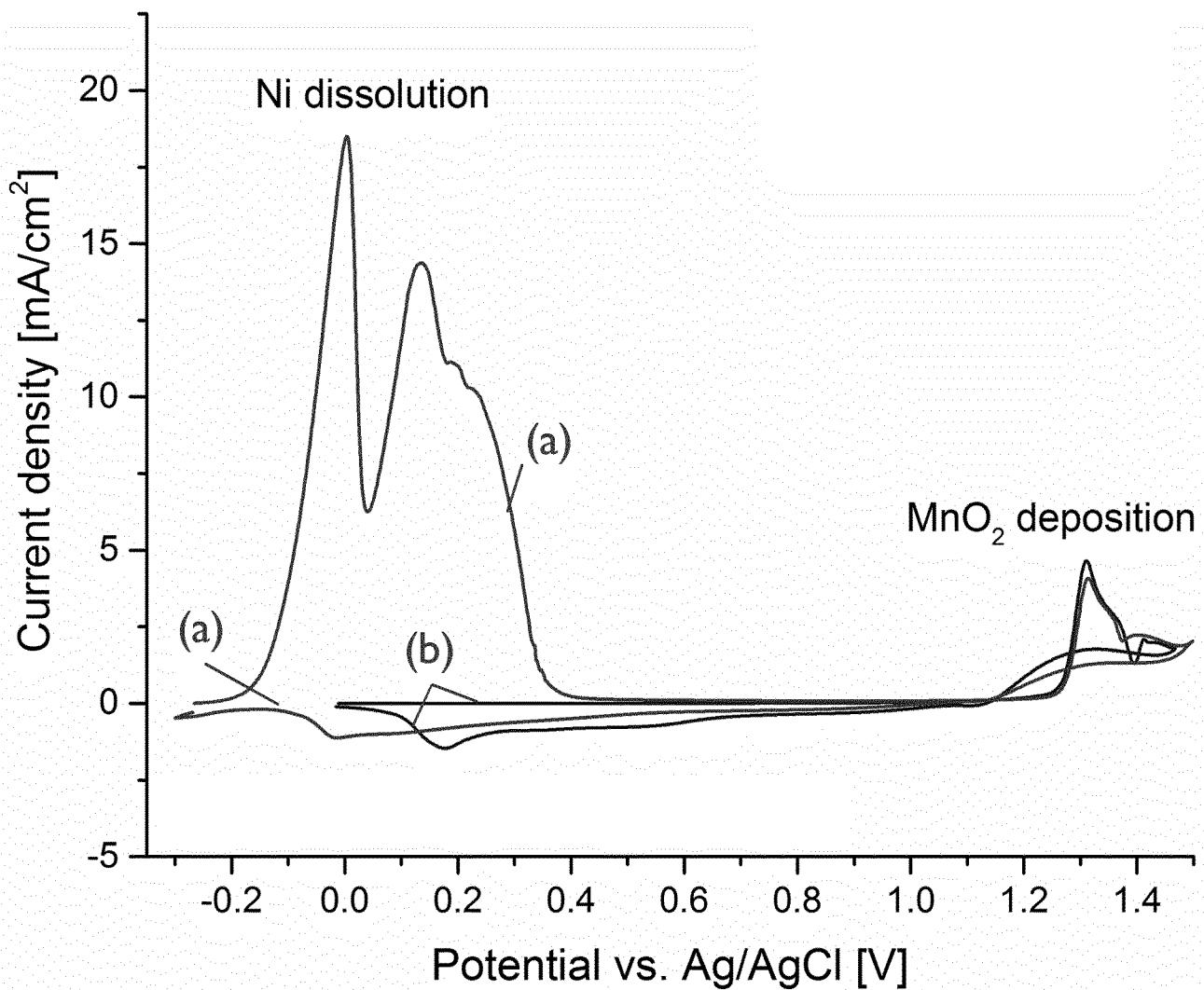

30 **[0091]** FIG 18 shows results of a cyclic voltammetry experiment on a structure comprising a nickel substrate with a  $MnO_x$  layer deposited thereon. Curves labeled (a) correspond to a structure without an interlayer being provided, whereas curves labeled (b) correspond to a structure having an interlayer provided thereon before deposition of the  $MnO_x$  layer, in accordance with an embodiment of the third aspect of the present disclosure.

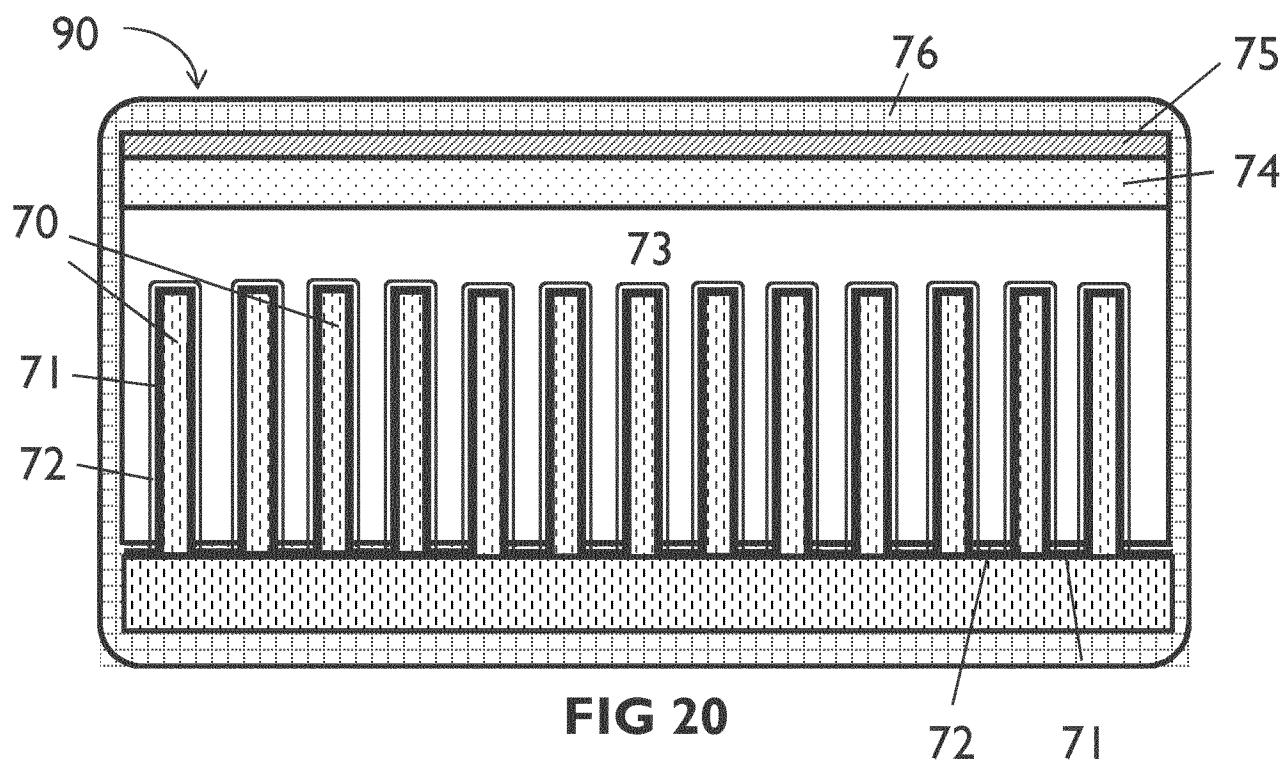

**[0092]** FIG 19 schematically shows a cross section of an example of a solid-state battery cell according to an embodiment of the tenth aspect of the present disclosure.

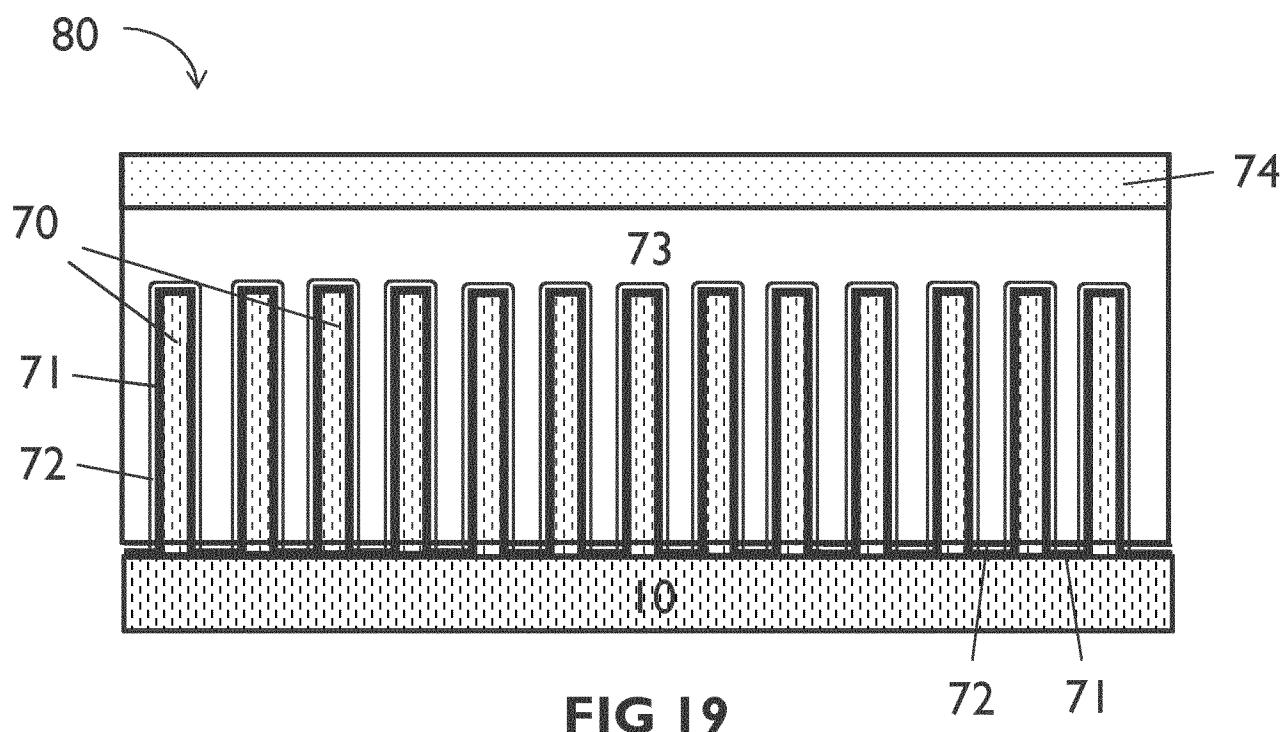

35 **[0093]** FIG 20 schematically shows a cross section of an example of a solid-state battery according to an embodiment of the eleventh aspect of the present disclosure.

**[0094]** In the different figures, the same reference signs refer to the same or analogous elements.

**Detailed description**

**[0095]** The present disclosure will be described with respect to particular embodiments and with reference to certain drawings but the disclosure is not limited thereto but only by the claims.

5 The drawings described are only schematic and are non-limiting. In the drawings, the size of some of the elements may be exaggerated and not drawn on scale for illustrative purposes. The dimensions and the relative dimensions do not correspond to actual reductions to practice of the disclosure.

**[0096]** The terms first, second, third and the like in the description and in the claims, are used 10 for distinguishing between similar elements and not necessarily for describing a sequence, either temporally, spatially, in ranking or in any other manner. It is to be understood that the terms so used are interchangeable under appropriate circumstances and that the embodiments of the disclosure described herein are capable of operation in other sequences than described or illustrated herein.

**[0097]** It is to be noticed that the term “comprising”, used in the claims, should not be 15 interpreted as being restricted to the means listed thereafter; it does not exclude other elements or steps. It is thus to be interpreted as specifying the presence of the stated features, integers, steps or components as referred to, but does not preclude the presence or addition of one or more other features, integers, steps or components, or groups thereof. Thus, the scope of the expression “a device comprising means A and B” should not be limited to devices consisting only of components 20 A and B. It means that with respect to the present disclosure, the only relevant components of the device are A and B.

**[0098]** Reference throughout this specification to “one embodiment” or “an embodiment” means that a particular feature, structure or characteristic described in connection with the embodiment is included in at least one embodiment of the present disclosure. Thus, appearances of 25 the phrases “in one embodiment” or “in an embodiment” in various places throughout this specification are not necessarily all referring to the same embodiment, but may. Furthermore, the particular features, structures or characteristics may be combined in any suitable manner, as would be apparent to one of ordinary skill in the art from this disclosure, in one or more embodiments.

**[0099]** Similarly it should be appreciated that in the description of exemplary embodiments of 30 the disclosure, various features of the disclosure are sometimes grouped together in a single embodiment, figure, or description thereof for the purpose of streamlining the disclosure and aiding in the understanding of one or more of the various inventive aspects. This method of disclosure, however, is not to be interpreted as reflecting an intention that the claimed disclosure requires more features than are expressly recited in each claim. Rather, as the following claims reflect, inventive 35 aspects lie in less than all features of a single foregoing disclosed embodiment. Thus, the claims

following the detailed description are hereby expressly incorporated into this detailed description, with each claim standing on its own as a separate embodiment of this disclosure.

**[0100]** Furthermore, while some embodiments described herein include some but not other features included in other embodiments, combinations of features of different embodiments are meant to be within the scope of the disclosure, and form different embodiments, as would be understood by those in the art. For example, in the following claims, any of the claimed embodiments can be used in any combination.

**[0101]** In the description provided herein, numerous specific details are set forth. However, it is understood that embodiments of the disclosure may be practiced without these specific details.

10 In other instances, well-known methods, structures and techniques have not been shown in detail in order not to obscure an understanding of this description.

**[0102]** The following terms are provided solely to aid in the understanding of the disclosure.

**[0103]** In the context of the present disclosure, a battery cell is a structure comprising two electrode layers with an electrolyte layer in between, i.e. a structure comprising a stack of a first electrode layer (first layer of active electrode material) / electrolyte layer / second electrode layer (second layer of active electrode material). The first electrode layer and the second electrode layer are of opposite polarity. A battery may comprise a single battery cell or it may comprise a plurality of, e.g. at least two, battery cells. A battery may comprise two or more battery cells connected in series or in parallel, or a combination of series and parallel connected battery cells. A battery further comprises a first current collector layer and a second collector layer, the first current collector layer and the second current collector layer being of opposite polarity.

**[0104]** In the context of the present disclosure, an ion insertion battery cell is a battery cell comprising electrodes that can accept or release cations or anions during operation of the battery cell. Ion insertion battery cells can rely on the insertion/extraction of only one cation element, 25 multiple cation elements, only anions or a mixture of anion and cation elements. An ion insertion battery cell further comprises an electrolyte that allows for ionic conduction of the respective ion used, while being (electro)chemically stable with regard to the used electrode materials.

**[0105]** In a rechargeable battery cell, each of the electrodes has a first polarity during the discharge (i.e. battery operation) and a second, opposite polarity during charging. Technically speaking however, the negative electrode is the anode during the discharge and the cathode during charging. Vice versa, the positive electrode is the cathode during discharge and the anode when charging the battery. In the context of the present disclosure, the terminology of the discharge (i.e. battery operation) is used. Herein further, with anode the negative electrode is meant and with cathode the positive electrode is meant. Through the disclosure, when referred to 'anode material' 30 it is meant the negative electrode material and when referred to 'cathode material' it is meant the positive electrode material.

**[0106]** In the context of the present disclosure, an active electrode material is a material that is a component of a battery electrode layer. In the active electrode material, the actual electrochemical transformation (change in valence or oxidation state of the atoms) takes place, which gives rise to storage of chemical energy in the electrode. An electrode layer is typically composed of the active electrode material and supporting material.

**[0107]** In the context of the present disclosure, the term ‘anodization’ when applied to a valve metal (such as for example aluminum) or to a valve metal layer refers to an electrochemical process comprising applying a potential or a current between the valve metal layer (the material to be anodized) functioning as a working electrode at one hand and a counter-electrode at the other hand, in the presence of an acid electrolyte. This method leads to the formation of a porous layer of valve metal oxide comprising plurality of pores or channels, e.g. a cluster of channels, arranged in an orderly fashion (e.g. hexagonally) perpendicularly to the surface of the layer. This cluster may be referred to as an array, due to the orderly nature of the arrangement.

**[0108]** In the context of the present disclosure, a valve metal is a metal that can be oxidized by means of an anodization process (anodic oxidation) to thereby form a stable valve metal oxide. More in particular, in the context of the present disclosure, a valve metal is a metal selected from the group of aluminum, tungsten, titanium, tantalum, hafnium, niobium, vanadium and zirconium. In the context of the present disclosure, a valve metal layer is a layer comprising a valve metal or a valve metal alloy (or a ‘doped’ valve metal). An example of an aluminum alloy that may for example be used in the context of the present disclosure is a copper doped aluminum layer, e.g. with a doping concentration in the range between 1% and 10%, the present disclosure not being limited thereto.

**[0109]** In the context of the present disclosure, when referring to a substrate, the substrate may be a planar substrate or a non-planar, e.g. three-dimensional (3D) substrate. In the context of the present disclosure, a 3D substrate may for example comprise a plurality of 3D features, 3D structures, such as 3D micro- or nano-structures, such as for example a plurality of micro-pillars or nano-pillars, a plurality of microwires or nanowires or 3D (nano)meshes, (nano)tubes and/or other porous structures, such as for example porous anodized alumina. The 3D features may be present in a regular pattern, such as for example a regular array pattern, or they may be randomly distributed over the substrate.

**[0110]** In the context of the present disclosure, a plurality of spaced channels refers to a plurality of channels that are separated in space from one another, i.e. that are located at a distance from each other. The plurality of spaced channels may be either completely separated from each other, e.g. by a surrounding medium, or they may be interconnected, for example partially interconnected, e.g. by a plurality of interconnecting channels through a surrounding medium. The plurality of

interconnecting channels may for example have a longitudinal orientation substantially orthogonal to a longitudinal orientation of the plurality of spaced channels.

**[0111]** In the context of the present disclosure, a template comprising a plurality of spaced channels aligned longitudinally along a direction may refer to a template comprising a plurality of channels being completely separated from each other or to a template comprising a plurality of channels that are interconnected, for example partially interconnected by a plurality of interconnecting channels. The interconnecting channels may be oriented in a direction substantially orthogonal to the longitudinal direction of the plurality of spaced channels. In the context of the present disclosure, a template comprising a plurality of spaced channels aligned longitudinally along a direction may refer to a template comprising two or more regions positioned subsequently along the longitudinal direction, wherein at least a first region comprises a plurality of completely separated (non-interconnected) spaced channels and wherein at least a second region comprises a plurality of interconnected spaced channels (being interconnected by interconnecting channels).

**[0112]** In the context of the present disclosure, a plurality of spaced structures, e.g. nanostructures, aligned longitudinally along a direction refers to a plurality of structures, e.g. nanostructures, that are located at a distance from each other. The plurality of (nano)structures may for example comprise (nano)pillars, (nano)wires, (nano)meshes or (nano)tubes. The plurality of structures, e.g. nanostructures, may be either completely separated from each other, e.g. by a surrounding medium such as air or a solid material different from the (nano)structure material, or they may be interconnected, for example partially interconnected, e.g. by a plurality of interconnecting structures, e.g. interconnecting nanostructures. The plurality of interconnecting (nano)structures may for example have a longitudinal orientation substantially orthogonal to a longitudinal orientation of the plurality of spaced (nano)structures. The interconnecting (nano)structures are typically made of the same material as the spaced (nano)structures themselves.

25 In the context of the present disclosure, a plurality of spaced (nano)structures aligned longitudinally along a direction may refer to structure comprising two or more regions positioned subsequently along the longitudinal direction, wherein at least a first region comprises a plurality of spaced, completely separated (non-interconnected) (nano)structures and wherein at least a second region comprises a plurality of spaced, interconnected (nano)structures (for example being interconnected by interconnecting (nano)structures).

**[0113]** In the context of the present disclosure, a functional material or functional material layer is a material or material layer that satisfies or provides a defined functionality and/or has defined properties, adjusted for a device in which it is integrated. A functional material may for example comprise a metal, a metal alloy, a semiconductor, an oxide, a metal hydride, a ceramic material, a metal-organic crystal, a polymer, or an organic supramolecular solid, the present disclosure not being limited thereto. It provides a defined functionality or property, such as for example a high

electrical conductivity, catalytic activity towards chemical reactions, electrochemical activity towards ion insertion, high optical absorbance, iridescence, photoluminescence, high magnetic anisotropy, or piezoelectricity, the present disclosure not being limited thereto. This is adjusted for the final device or intended field of application in which it is used. A functional material or a 5 functional material layer may for example have the functionality of an electrode, a current collector, a catalyst, an energy storage material, a light absorber, a photonic crystal, a light emitter, an information storage medium, an ion trap, or a gas absorber, the present disclosure not being limited thereto.

**[0114]** The disclosure will now be described by a detailed description of several embodiments 10 of the disclosure. It is clear that other embodiments of the disclosure can be configured according to the knowledge of persons skilled in the art without departing from the technical teaching of the disclosure, the disclosure being limited only by the terms of the appended claims.

**[0115]** According to a first aspect, the present disclosure is related to a method for transforming 15 at least part of a valve metal layer into a template comprising a plurality of spaced (nano)channels aligned longitudinally along a first direction. An example of a method according to an embodiment of the first aspect of the present disclosure is schematically illustrated in FIG 1, showing a flow chart comprising an exemplary process sequence and in FIG 2 to FIG 8, schematically showing cross sections illustrating results of successive steps of the process sequence of FIG 1.

**[0116]** As illustrated in the example shown in FIG 1, a method 100 according to an embodiment 20 of the first aspect of the present disclosure comprises a first anodization step 101 of at least part of a valve metal layer, the first anodization step 101 resulting in the formation of a porous layer of valve metal oxide comprising a plurality of aligned spaced (nano)channels having bottom surfaces coated with a first insulating metal oxide barrier. The plurality of (nano)channels formed as a result of the first anodization step are substantially aligned longitudinally along a first direction. The 25 plurality of (nano)channels each have (nano)channel walls substantially aligned longitudinally along the first direction and a (nano)channel bottom substantially parallel with a surface of the valve metal layer. As a result of the first anodization step the surfaces of the (nano)channel bottoms are covered with a first insulating metal oxide barrier layer, for example a first valve metal oxide barrier layer.

**[0117]** In embodiments of the first aspect of the present disclosure the valve metal layer may 30 be a free-standing layer, for example a flexible free-standing layer such as a metal foil, or the valve metal layer may be provided on a substrate, for example on a rigid substrate or on a flexible substrate. FIG 2 illustrates an example of an embodiment wherein the valve metal layer 11 is a free-standing layer, but the present disclosure is not limited thereto. The first anodization step 101 may 35 result in a structure as schematically shown in FIG 3. It illustrates formation of a porous layer 12 of anodized metal comprising a plurality of spaced (nano)channels 13 that are substantially aligned

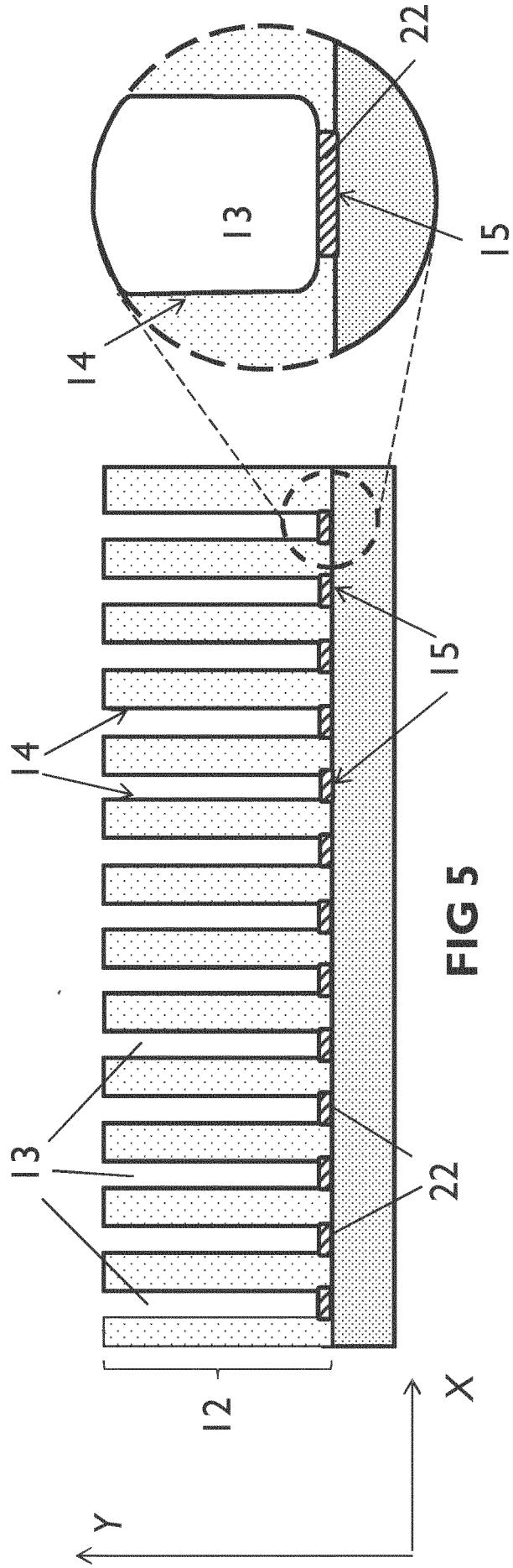

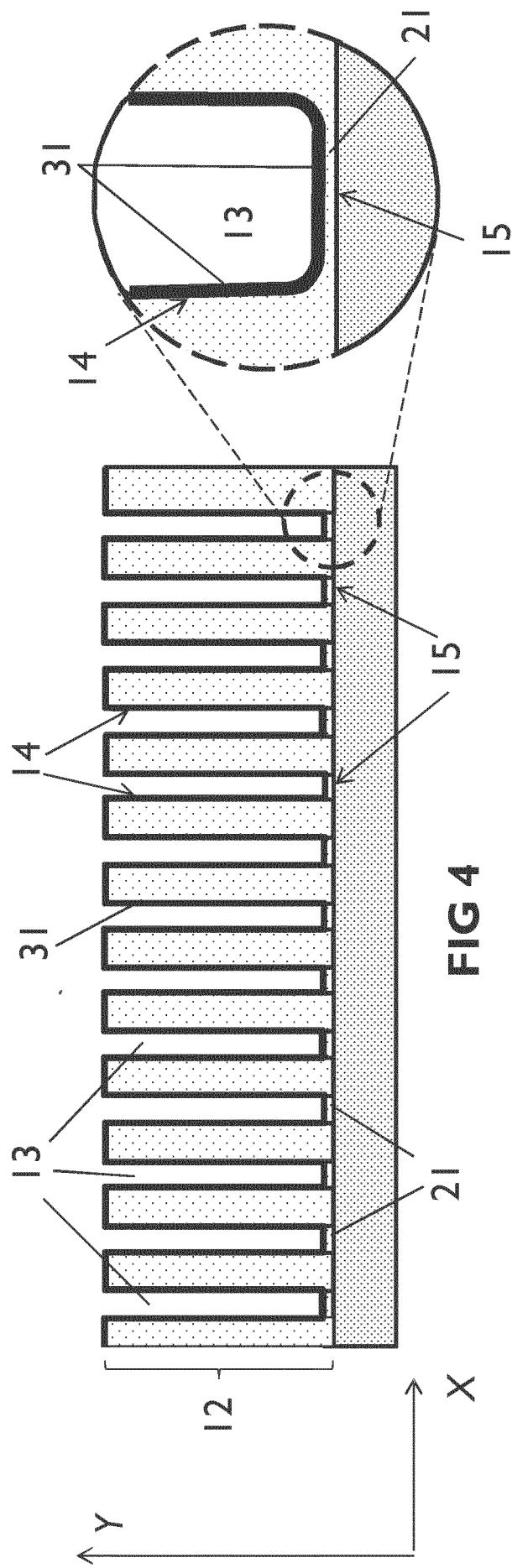

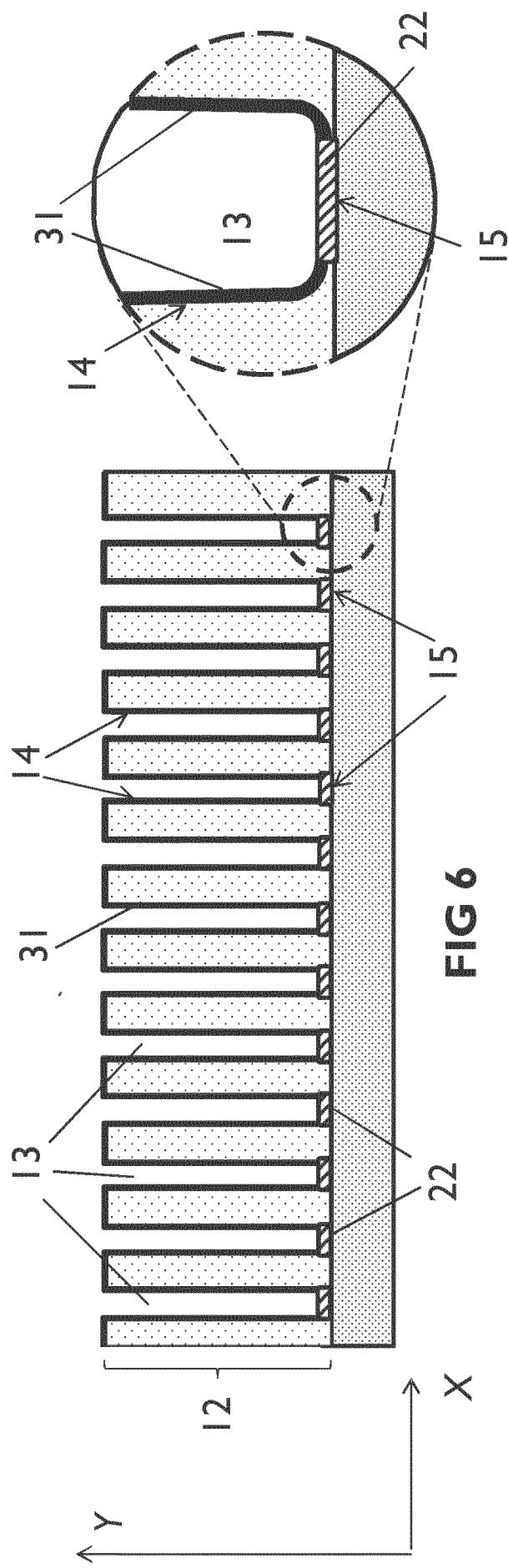

longitudinally along a first direction. In embodiments of the present disclosure the first direction may correspond to a thickness direction of the valve metal layer, i.e. it may be substantially orthogonal to a surface of the valve metal layer, as schematically illustrated in the example shown in FIG 3. However, the present disclosure is not limited thereto, and the first direction may be at an angle, for example at an angle in the range between 60° and 90°, with respect to a surface of the valve metal layer. FIG 3 illustrates an example wherein the first direction is orthogonal to the surface of the valve metal layer 11. In other words, the first direction corresponds to a thickness direction  $Y$  of the valve metal layer 11. The plurality of (nano)channels 13 each have (nano)channel walls 14 substantially aligned longitudinally along the thickness direction  $Y$  and a (nano)channel bottom 15. As a result of the first anodization step 101 the surface of the (nano)channel bottoms 15 is covered with a first insulating metal oxide barrier layer 21, as shown more in detail in the inset of FIG 3.

**[0118]** In the example illustrated in FIG 3 the porous layer 12 comprising the plurality of channels 13 is formed only in a part of the valve metal layer. However, the present disclosure is not limited thereto. For example, in embodiments according to the first aspect wherein the valve metal layer 11 is provided on a substrate (not illustrated) the porous layer 12 comprising the plurality of (nano)channels 13 may also be formed throughout the valve metal layer 11, thereby exposing the underlying substrate at the channel bottoms.

**[0119]** In embodiments of the present disclosure (not illustrated) the first anodization step may comprise complete immersion of a free-standing valve metal layer 11 in an anodizing solution. In such embodiments, the first anodization step may result in the formation of a first porous layer of valve metal oxide comprising a plurality of spaced (nano)channels at a first side of the valve metal layer and simultaneously in the formation of a second porous layer of valve metal oxide comprising a plurality of spaced (nano)channels at a second, opposite side of the valve metal layer. In between the first porous layer and the second porous layer a non-anodized valve metal layer remains.

**[0120]** A method 100 according to embodiments of the first aspect of the present disclosure comprises, after the first anodization step 101, performing a protective treatment 102 (FIG 1). The protective treatment induces hydrophobic surfaces to the (nano)channel walls 14 and (nano)channel bottoms 15, i.e. it results in (nano)channels 13 having hydrophobic (nano)channel wall surfaces and hydrophobic (nano)channel bottom surfaces.

**[0121]** In embodiments of the first aspect of the present disclosure, performing the protective treatment may comprise annealing 102, 1021 (FIG 1), such as for example annealing at a temperature in the range between 300°C and 550°C. The annealing may be done in an inert atmosphere, such as for example in nitrogen or argon, or in air. Annealing may be done under ambient pressure or at a reduced pressure, such as in vacuum.

**[0122]** In embodiments of the first aspect of the present disclosure, performing the protective treatment may comprise depositing 102, 1022 (FIG 1) a protective layer over the (nano)channel walls and over the (nano)channel bottoms. This is schematically illustrated in FIG 4, showing a protective layer 31 being provided on the (nano)channel walls 14 and on the first insulating metal oxide barrier layer 21 that is present on the (nano)channel bottoms 15. The protective layer 31 is also formed on an upper surface of the porous layer 12.

**[0123]** In embodiments the protective layer may be a layer comprising hydrophobic silane, e.g. formed by vapor deposition, for example in air or in vacuum, for example at a temperature in the range between 80°C and 120°C. In other embodiments the protective layer may be a polymer layer, 10 e.g. formed by application of polymer solution onto the pore walls and bottoms of the template and drying. Such a protective polymer layer may for example be formed by immersing the sample in 1% to 20% solution of polystyrene or PMMA (poly(methyl 2-methylpropanoate)) or PDMS (poly(dimethylsiloxane)), dissolved in acetone, in toluene or in a chlorinated solvent such as dichloromethane and spin coating the excess of the solution, followed by drying at a temperature 15 e.g. in the range between 20°C and 60°C, e.g. in air or in vacuum.

**[0124]** In embodiments of the first aspect of the present disclosure, performing the protective treatment may comprise both depositing 102, 1022 (FIG 1) a protective layer 31 over, e.g. directly on, the (nano)channel walls and over the (nano)channel bottoms and annealing 102, 1021 (FIG 1).

**[0125]** The protective treatment results in the formation of hydrophobic surfaces on the 20 (nano)channel walls and (nano)channel bottoms. Such a hydrophobic surface may advantageously provide protection against wetting, e.g. against wetting by an etchant used in subsequent process steps, and therefore it may provide protection against etching.

**[0126]** A method 100 according to embodiments of the first aspect of the present disclosure comprises, after the protective treatment 102, 1021, 1022, a second anodization step 103 (FIG 1). 25 The second anodization step may for example be done using similar anodization conditions as used for the first anodization step, preferably for a relatively short period, such as for example 1 minute to 30 minutes. In embodiments of the first aspect of the present disclosure, this second anodization step affects the (nano)channel bottoms only and induces hydrophilic surfaces at the (nano)channel bottoms only. In embodiments wherein a protective layer 31 has been deposited (FIG 1, step 1022; 30 FIG 4), the second anodization step 103 results in removal of the protective layer 31 from the bottom of the plurality of spaced (nano)channels. The second anodization step thus results in the formation of hydrophilic, unprotected (nano)channel bottoms (e.g. not protected against wetting). The second anodization step further results in removal of the first insulating metal oxide barrier layer 21 from the (nano)channel bottoms. The second anodization step leaves the plurality of (nano)channel walls 35 substantially unaffected, i.e. the plurality of (nano)channel walls remain substantially protected. The second anodization step results in further anodization only at the bottoms of the plurality of

(nano)channels and creates a second (unprotected) insulating metal oxide barrier layer at the (nano)channel bottoms.

[0127] FIG 5 schematically illustrates a cross section of the structure as may be obtained after having performed the second anodization step in a method according to an embodiment of the first 5 aspect of the present disclosure wherein the protective treatment comprises annealing. More in particular, FIG 5 illustrates the first metal oxide barrier layer 21 being removed from the channel bottoms 15 and being replaced by a second metal oxide barrier layer 22 at the channel bottoms 15 as a result of the second anodization step 103.