(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4607405号

(P4607405)

(45) 発行日 平成23年1月5日(2011.1.5)

(24) 登録日 平成22年10月15日(2010.10.15)

(51) Int.Cl.

F 1

G06F 13/36 (2006.01)

G06F 12/10 (2006.01)G06F 13/36 310E

G06F 12/10 505Z

G06F 12/10 559

請求項の数 2 (全 18 頁)

(21) 出願番号 特願2001-520657 (P2001-520657)

(86) (22) 出願日 平成12年8月18日 (2000.8.18)

(65) 公表番号 特表2003-508850 (P2003-508850A)

(43) 公表日 平成15年3月4日 (2003.3.4)

(86) 國際出願番号 PCT/US2000/022833

(87) 國際公開番号 WO2001/016772

(87) 國際公開日 平成13年3月8日 (2001.3.8)

審査請求日 平成19年6月26日 (2007.6.26)

(31) 優先権主張番号 09/385,209

(32) 優先日 平成11年8月30日 (1999.8.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 591003943

インテル・コーポレーション

アメリカ合衆国 95052 カリフォルニア州・サンタクララ・ミッション・カレッジ・ブーレバード・2200

(74) 代理人 100064621

弁理士 山川 政樹

(72) 発明者 ネイヤー, ラマン

アメリカ合衆国・97123・オレゴン州

ヒルズボロ・サウスイースト エアリアル・ストリート・7106

(72) 発明者 モラン, ダグラス・アール

アメリカ合衆国・97007・オレゴン州

ビバートン・サウスウエスト 189ティエイチ・アベニュー・7949

最終頁に続く

(54) 【発明の名称】ローカルI/Oバスに近接するブリッジでの入出力(I/O)アドレス変換

## (57) 【特許請求の範囲】

## 【請求項1】

1つまたは複数のI/Oポートを介してシステム・メモリおよびI/Oコントローラに結合するように構成され、1つまたは複数のI/Oポートを介してコンピュータ・システムのメイン・メモリとの間でデータ転送を可能にする第1インターフェース・ユニットと、

アクセラレーテッド・グラフィックス・ポート(AGP)バスを介して周辺装置との間でのデータ転送を可能にするためにバス制御信号およびアドレスを供給するアクセラレーテッド・グラフィックス・ポート(AGP)ユニットと、そして

前記第1インターフェース・ユニットおよび前記AGPインターフェース・ユニットと結合されたアドレス変換ユニットと

を具備し、

前記アドレス変換ユニットは、グラフィックス・アドレス再配置デーブル(GART)を含むスタティック・ランダム・アクセス・メモリ(SRAM)にアクセスすることによって、前記AGPバスで受け取ったインバウンドAGPトランザクションに関連するグラフィックス・アドレスを変換し、

前記GARTは、コンピュータ・システムのメイン・メモリ内のページの物理的アドレスと、そしてグラフィックス・アクセラレータからのトラフィックがシステム・バス315とコヒーレントである必要があるかどうかを示すコヒーレント・ビットとを含むことを特徴とするグラフィックス拡張ブリッジ。

10

20

## 【請求項 2】

1つまたは複数の入出力( I / O )ポートとアクセラレーテッド・グラフィックス・ポート( A G P )バスとの間でのバス・プロトコル・ブリッジング機能を提供し、ローカル・メモリ内に格納されたグラフィックス・アドレス再配置テーブル( G A R T )に基づいて、インバウンド・トランザクションに関連する仮想アドレスを、コンピュータ・システムのメイン・メモリ内の物理的アドレスに変換するように構成されたグラフィックス拡張ブリッジと、そして

グラフィックス拡張ブリッジに結合され、コンピュータ・システムのシステム・バスおよびメモリ・バスに結合するように構成され、グラフィックス拡張ブリッジのためにメイン・メモリとの間でのデータ転送を実行するように構成されたシステム・メモリおよび I / O コントローラと

を具備し、

前記 G A R T は、グラフィックス・アクセラレータからのトラフィックがシステム・バス 3 1 5 とコヒーレントである必要があるかどうかを示すコヒーレント・ビットを含む、

ことを特徴とするチップセット。

## 【発明の詳細な説明】

## 【0001】

(著作権表示)

本明細書に含まれる資料は著作権保護の対象となる。著作権者は、この特許開示が米国特許商標局の特許ファイルまたは記録中に見出されるとき、それが何人によって複製されることに対しても異議はないが、そうでない場合は、その著作権に対するすべての権利を何であれ留保する。

20

## 【0002】

(発明の背景)

## 発明の分野

本発明は、一般にバス・プロトコル・ブリッジングに関する。より詳細には、本発明は、連続する論理アドレス空間を不連続かもしれないアドレス空間に再マップすることなど、ブリッジでの入出力( I / O )アドレス変換に関する。

## 【0003】

## 関連技術の説明

30

入出力( I / O )周辺装置は、一般に、システム・メモリ( メイン・メモリ )の大きな連続するビューとともに示された場合により効率的に動作する。これにより、このような装置が、注目するデータを含むメモリの広い領域にランダム・アクセスを行うことが可能となる。メモリの連続するビューは、ディスプレイ装置にシーンをレンダリングするために、テクスチャ・マップ全体を取り出さなければならないことが多いグラフィックス・カードにとって特に重要である。本願では、大規模な連続するアドレス空間を認識する、 I / O 周辺装置がその中で動作するアドレス空間を「仮想アドレス空間」と呼ぶ。

## 【0004】

いずれにしても、周辺装置は、ホスト・コンピュータ・システムのメイン・メモリとは異なるアドレス空間を利用するので、周辺装置によって供給される仮想アドレスを、対応するメイン・メモリ内の不連続かもしれないアドレスにマップする「アドレス変換」と呼ばれるプロセスが必要である。

40

## 【0005】

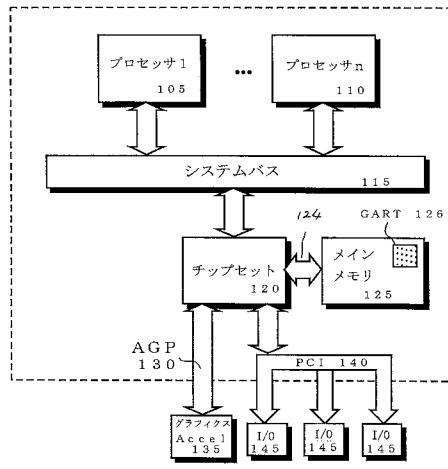

次に、アドレス変換のための現在の技法の例を図 1 を参照しながら説明する。図 1 は、グラフィックス・アドレスの物理アドレスへの変換を示す、汎用コンピュータ・システム 1 0 0 の高レベルブロック図である。コンピュータ・システム 1 0 0 は、1つまたは複数のプロセッサ 1 0 5 および 1 1 0 などの処理手段、チップセット 1 2 0 、メイン・メモリ 1 2 5 、メモリ・バス 1 2 4 、アクセラレーテッド・グラフィックス・ポート( A G P )バス 1 3 0 、および P C I バス 1 4 0 を含む。この例では、メイン・メモリは、グラフィックス・アクセラレータ 1 3 5 などの周辺装置によって使用される仮想アドレスを、メイン

50

・メモリ125中の物理アドレスにマップするためのエントリを含むグラフィックス・アドレス再配置テーブル( G A R T )を含む。

#### 【 0 0 0 6 】

チップセット120は、A G Pバス130、P C Iバス140、およびメモリ・バス124の間のブリッジング機能を提供する。ブリッジング機能の一部として、チップセット120は、インバウンド読取りおよび書き込みトランザクション(例えば、グラフィックス・アクセラレータ135から発信された読取りおよび書き込みトランザクション)中に含まれるグラフィックス・アドレスを、G A R T 1 2 6を用いて、対応するメイン・メモリ125中の物理アドレスに変換する。したがって、図1に従って構成されたコンピュータ・システムでは、テクスチャ・マップなどのグラフィックス・データの処理は、メイン・メモリ125に複数のアクセスを必要とする。まず、チップセット120は、実行されるトランザクション中で指定されたグラフィックス・アドレスに対応するG A R T 1 2 6からエントリを取り出さなければならない。次いで、所望の物理アドレスがチップセット120によって決定された後、チップセット120は、トランザクションによって指定されたデータを読み書きするために、メイン・メモリ125に第2のアクセスを実行しなければならない。

#### 【 0 0 0 7 】

A G Pの大きな利点の1つは、コンピュータ・システムの残りの部分からA G Pがビデオ・サブシステムを分離し、したがってI / O帯域幅を介する競合がP C Iほどではないことである。しかし、上述の説明より、A G Pトランザクションの変換が現在処理されている方式に関連するいくつかの非効率が存在することは明らかであろう。まず、動的ランダム・アクセス・メモリ( D R A M )から一般に構成されるメイン・メモリ125へのアクセスは、例えば静的ランダム・アクセス・メモリ( S R A M )へのアクセスと比較して相対的に低速である。第2に、アドレス変換のためのメイン・メモリ125アクセスは、プロセッサ105または110から発信され、システム・バス115を介して受け取られるアクセス要求、またはP C Iバス140上で受け取られるアクセス要求などの他のアクセス要求と競合しなければならない。その結果、A G P変換は競合するトラフィックによってスローダウンする。最後に、変換ユニット(図示せず)が複数のタイプのトラフィック、例えばシステム・バス・トラフィック、P C Iトラフィック、およびA G Pトラフィックを処理する場合、様々なタイプのインバウンド・トランザクションおよびアウトバウンド・トランザクションの間の変換ユニットについての競合をアビトリエーション論理が解決することが必要となるので、この状況はさらに悪化する。

#### 【 0 0 0 8 】

したがって、I / Oトランザクションの実行をスピードアップし、アドレス変換論理の単純な実装を提供する、I / Oアドレスを変換するための技法を提供することが望ましい。加えて、システム・バス・トラフィックまたは他のI / O装置からのトラフィックなどの他のタイプのトラフィックから分離する装置中で、必要なI / Oアドレス変換を実行することが有利である。

#### 【 0 0 0 9 】

(発明の簡潔な概要)

40

入出力( I / O )拡張ブリッジでのアドレス変換を実行するための方法および装置を説明する。I / O拡張ブリッジは、第1インターフェース・ユニット、第2インターフェース・ユニット、およびアドレス変換ユニットを含む。第1インターフェース・ユニットは、1つまたは複数のI / Oポートを介して、システム・メモリとI / Oコントローラに結合するように構成される。第1インターフェース・ユニットは、コンピュータ・システムのメイン・メモリとの間で、1つまたは複数のI / Oポートを介してデータを転送できる。第2インターフェース・ユニットは、周辺装置との間で、バスを介してデータを転送するための、バス制御信号およびアドレスを供給する。アドレス変換ユニットは、第1インターフェース・ユニットおよび第2インターフェース・ユニットに結合される。アドレス変換ユニットは、コンピュータ・システムのメイン・メモリ内のページの物理アドレスを含

10

20

30

40

50

むローカル・メモリにアクセスすることによって、第2インターフェースで受け取ったトランザクションに関連するアドレスを変換する。

【0010】

本発明の他の特徴および利点は、添付の図面および詳細な説明から明らかとなろう。

【0011】

本発明を、限定的なものではなく、例示的なものとして添付の図面に示す。同一の参照番号は、類似の要素を指す。

【0012】

(発明の詳細な説明)

I/O拡張ブリッジでのアドレス変換を実行するための方法および装置を説明する。本発明の実施形態は、I/O拡張ブリッジなどのI/O変換装置をシステム・バス・トランザクションなどの他のタイプのトラフィックから分離することによって、I/Oトランザクションの実行をスピードアップする、I/Oアドレスを変換するための技法を提供することを試みる。本発明の一特徴によれば、GARTは、メモリ・バスを通らずに、ローカルSRAM中に格納することができる。インターフェースはローカルであり、かつ、GARTエントリを取り出すためのアクセスが他のタイプのトラフィックと競合する必要がないので、トランザクションをより高速に完了することができ、変換装置の実装を単純にすることができる。

10

【0013】

以下の説明では、説明の目的で、本発明の完全な理解を与えるために多数の特定の細部を説明する。しかし、本発明をこれらの特定の細部の一部を用いずに実施できることは当業者には明らかであろう。他の場合には、周知の構造および装置をブロック図形式で示す。

20

【0014】

本発明は、以下で説明する様々なステップを含む。本発明のステップは、ハードウェア構成要素によって実行することができ、あるいは、汎用プロセスもしくは特殊目的プロセッサ、または命令によってプログラムされた論理回路にこのステップを実行させるために使用することのできるマシン実行可能命令で実施することができる。あるいは、このステップは、ハードウェアおよびソフトウェアの組み合わせによって実行することもできる。

【0015】

重要なことであるが、本発明の実施形態は、様々なAGPおよびPCIライクのトランザクションを変換するための、様々なグラフィックス拡張ブリッジ(GXB)にとってローカルにアクセス可能なアクセラレーテッド・グラフィックス・ポート(AGP)およびグラフィックス・アドレス再配置テーブル(GART)に関連して説明するが、本明細書で説明する方法および装置は、他のタイプのI/OトランザクションおよびI/O拡張ブリッジ、あるいはI/Oバスの装置がメイン・メモリの連続するビューを必要とする他のタイプのバスにも等しく適用することができる。例えば、本明細書で説明する技法は、VESAローカル・バス(VLB)および/または周辺構成要素相互接続(PCI)バスに関するトランザクションに関連して有用であると考えられる。

30

【0016】

用語

40

本発明の様々な実施形態を実装することができる例示的環境を説明する前に、本願全体を通して使用する、いくつかの用語を簡潔に説明する。

【0017】

用語「バス」は、一般に、情報が2つ以上の装置の間を流れる物理的通信媒体またはチャネルを指す。装置をその上に2つだけ有するバスは、本明細書で使用する「ポート」と見ることもあるが、バスという用語は、このようなポートも包含するものとする。

【0018】

用語「プロセッサ・バス」、「システム・バス」、または「ホスト・バス」は、一般に、コンピュータ・システムのバスの階層中の最高レベルのバスを指す。このバスは、一般にシステム・チップセットによって使用され、コンピュータ・システムの1つまたは複数の

50

プロセッサに情報が送受信される。

【0019】

メモリ・バスは、メモリ・サブシステムを、システム・チップセットおよびプロセッサに接続するバスを指す。重要なことであるが、一部のコンピュータ・システムでは、プロセッサ・バスおよびメモリ・バスは、同じバスとすることができます。

【0020】

「ローカルI/Oバス」は、一般に、メモリ、システム・チップセット、および／またはコンピュータ・システムのプロセッサに様々なタイプの周辺装置を接続するために使用される高速入出力(I/O)バスである。例えば、ビデオ・カード、ディスク記憶装置、高速ネットワーク・インターフェース、パフォーマンス・クリティカルな他の周辺装置は、一般にこの種類のバスに結合される。共通ローカルI/Oバスは、VESAローカル・バス(VLB)、周辺構成要素相互接続(PCIE)バス、およびアクセラレーテッド・グラフィックス・ポート(AGP)バスを含む。やはり、この開示では、I/OポートまたはAGPなどの、3つ以上の装置が共用するために設計されたバスと、2つだけの装置が使用するために設計されたポートのどちらもバスとする。

10

【0021】

「アクセラレーテッド・グラフィックス・ポート」(AGP)は、3Dグラフィックスおよびビデオ・イメージの高速で高品質な表示の目的で設計されている、Accelerated Graphics Port Interface Specification, Revision 2.0, May 4, 1998およびそれに続く改訂に記載されている高性能バス仕様である。

20

【0022】

「PCIEトランザクション」は、一般に、AGPバスに対して発行されるAGPセマンティクスを有するPCIEトランザクションを指す。

【0023】

本明細書で仕様するように、「ブリッジ」は、一般に、例えば2つのバスを接続し、一方のバスの装置が他のバスの装置と通信できるようにすると共にその逆をも可能にするために、チップセットで具体化された論理および回路を指す。一例として、コンピュータ・システムで見つかる1つの共通ブリッジは、PCI-ISAブリッジであり、一般にシステム・チップセットの一部である。PCIバスは、PCI拡張ブリッジ(PXB)と呼ばれる、プロセッサ・バスへのブリッジも有することができる。

30

【0024】

本願では、「トランザクション」は、1つまたは複数の要求(アドレス)フェーズおよびデータ・フェーズを含む。トランザクションは、一般に、開始アドレス、トランザクション・タイプ、および転送すべきデータ量の表示を含む。

【0025】

特定のトランザクションの指示は、プロセッサの予測から決定される。したがって、「インバウンド・トランザクション」は、一般に、ビデオ・カード、ディスク記憶装置、または高速ネットワーク・インターフェースなどの周辺装置によって、コンピュータ・システムに向けて送られる読み取り要求または書き込み要求を指し、「アウトバウンド・トランザクション」は、一般に、コンピュータ・システムによって周辺装置に向けて送られる読み取り要求または書き込み要求を指す。

40

【0026】

(入出力アドレス変換)

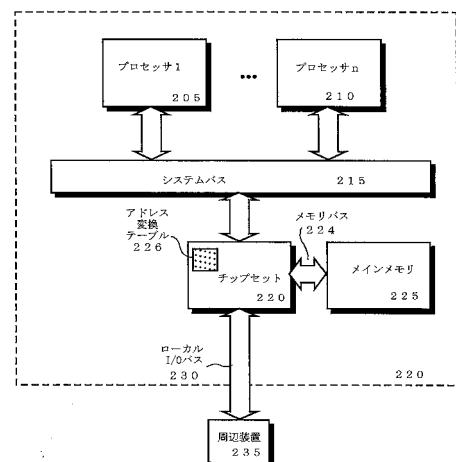

本発明の様々な特徴は、I/O拡張ブリッジでアドレス変換を実行することに関連して一般に有用であると考えられる。本発明のこの広範な態様を説明する目的で、次に、本発明の一実施形態を実現することのできる例示的コンピュータ・システム・アーキテクチャを、図2を参照しながら説明する。図2は、本発明の一実施形態による方法の1つまたは複数のステップを実行することができ、本発明による一実施形態による装置がその中に常駐することができる汎用コンピュータ・システム200を示す。コンピュータ・システム2

50

00は、1つまたは複数のプロセッサ205および210、チップセット220、メイン・メモリ225、メモリ・バス224、およびローカルI/Oバス230などの処理手段を含む。この実施形態によれば、チップセット220は、アドレス変換テーブル226を含む。アドレス変換テーブルは、周辺装置235から受け取った仮想アドレスを、メイン・メモリ225中の物理アドレスに変換するエントリ(図示せず)を含む。以下でさらに説明するように、チップセット220は、様々なチップセット機能、例えばシステム・バス・アービトリエーション、I/Oアドレス変換などを配置させることのできる1つまたは複数の集積回路を含むことができる。この例では、チップセット220は、ローカルI/Oバス230とシステム・バス215およびローカルI/Oバス230とメモリ・バス224の双方の間でブリッジとして働く。そのブリッジ動作の一部として、チップセット220は、ローカル・アドレス変換テーブル226にアクセスして、周辺装置235によって利用される連続するI/Oアドレス空間を、メイン・メモリ225の物理アドレス空間にマップする。重要なことであるが、以下でさらに説明するように、アドレス変換テーブル226をチップセット220にローカルに(例えば専用オンチップまたはオフチップSRAM中に)配置することによって、周辺装置235からのインバウンド・トランザクションをより効率的に実行することができる。

10

#### 【0027】

##### グラフィックス・アドレス変換

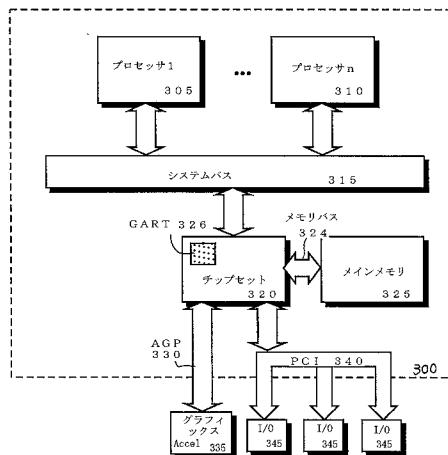

本発明の様々な特徴は、AGP互換グラフィックス装置によって利用されるグラフィックス・アドレス空間などのグラフィックス・アドレス空間から、メイン・メモリ225の物理アドレス空間にアドレス変換を実行するために特に有用であると考えられる。図3は、本発明の一実施形態による、改善された仮想アドレス変換技法を実装することのできる汎用コンピュータ・システム300を示す高レベル・ブロック図である。コンピュータ・システム300は、1つまたは複数のプロセッサ305および310、チップセット320、メイン・メモリ225、メモリ・バス324、アクセラレーテッド・グラフィックス・ポート(AGP)バス330、およびPCIバス340などの処理手段を含む。図の実施形態では、チップセット320はグラフィックス・アドレス再配置テーブル(GART)326を含む。GART326は、グラフィックス・アクセラレータ335から受け取った仮想アドレスをメイン・メモリ325の物理アドレスに変換するための情報を含むGARTエントリ(以下で説明する)を含む。

20

#### 【0028】

この実施形態によれば、GART326は、メモリ・バス324を通じてメイン・メモリ325中で見つけられるのではなく、チップセット320にローカルにアクセス可能となる。チップセット320は、AGPバス330、PCIバス340、およびメモリ・バス324との間のブリッジング機能を果たしている。ブリッジング機能の一部として、チップセット320は、インバウンド読み取りおよび書き込みトランザクション(例えば、グラフィックス・アクセラレータ335から発信された読み取りおよび書き込みトランザクション)中に含まれるグラフィックス・アドレスを、ローカルGART326を用いて、対応するメイン・メモリ325中の物理アドレスに変換する。図2を参照して上記で説明したのと同様に、チップセット320中にGART326を位置付けることによって、グラフィックス・アクセラレータ335などの、周辺装置からのインバウンド・トランザクションをより効率的に処理し、実行することができる。重要なことであるが、メイン・メモリ325(例えばDRAM)からデータを取り出すのにおよそ300~500ナノ秒が必要であるのに対して、ローカルSRAMからの取出しは、約30ナノ秒以下で実行することができる。

30

#### 【0029】

##### 例示的チップセット

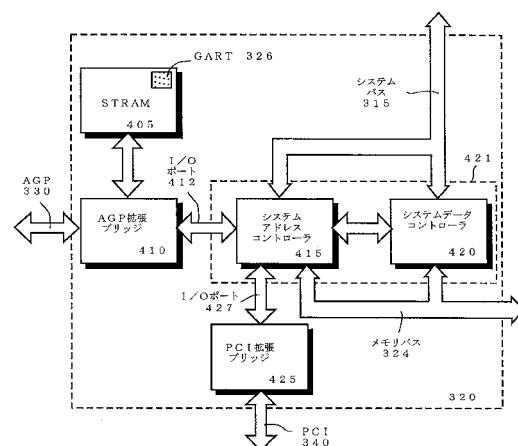

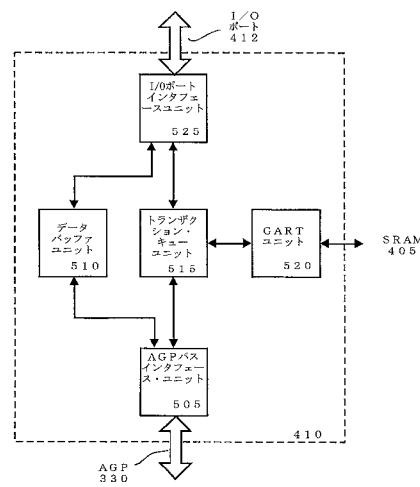

本発明を利用することができる例示的環境を簡潔に説明したので、次に例示的チップセット実装を、図4を参照しながら説明する。図4は、本発明の一実施形態による、複数のユニット(例えばチップ)間の機能の例示的割り振りを示す。この例では、チップセット3

20は、システム・アドレス・コントローラ (SAC) 415、システム・データ・コントローラ (SDC) 420、PCI拡張ブリッジ (PXB) 425、グラフィックス拡張ブリッジ (GXB) 410、および静的RAM (SRAM) 405を含む。

#### 【0030】

SAC415は、システム・バス315のアドレス部分と制御部分（図示せず）に接続される。SACは、システム・バス315アクセスを翻訳し、適切なI/Oポートまたはメイン・メモリ325に向けて送ることを担当する。SACは、インバウンド・トラフィックに対して経路指定エージェントとしても働き、インバウンド・トラフィックをピアI/Oポート412または427、メイン・メモリ325、またはシステム・バス315に向けて送る。

10

#### 【0031】

SDCは、システム・バス315上のデータ信号（図示せず）に接続され、メモリ・バス324およびSAC415によってメイン・メモリ325にも接続する。システム・バス315からメイン・メモリ325に、I/Oポート412または427の一方からメモリに、あるいはピア・ツー・ピアでI/Oポート412または427に転送される場合でも、すべての転送に関するデータはSDCを通過する。SAC415とSDC420の間の接続により、システム・バス315へ、ならびにI/Oポート412または427への同時データ転送が可能となり、それによって各システム・エージェントに対する利用可能な帯域幅を最大にすることができる。代替方法実施形態では、SAC420およびSDCの機能は、単一のシステム・メモリおよびI/Oコントローラ421に組み合わせることができ、または追加の集積回路を介して分散させることもできる。

20

#### 【0032】

PXB425は、F16バスなどのI/Oポート427と、PCIバス340の間のバス・プロトコル・ブリッジング機能を提供する。単一のPXB425は、一般に、1つのI/Oポート427に接続し、2つの33MHz、32ビットPCIバスを形成する。あるいは、PXB425は、単一の64ビットPCIバスをサポートすることもできる。コンピュータ・システムは、複数のPXBを含むことができる（一般には1～4個）。

#### 【0033】

GXB410は、I/Oポート412とAGPバス330の間のバス・プロトコル・ブリッジング機能を提供することによって、I/Oポート412、例えば2つのF16バスと、AGPバス330の間のブリッジを形成する。このようにして、GXB410は、コンピュータ・システムに高性能な専用グラフィックス・ポートを加える。複数のGXBをコンピュータ・システム中でインスタンス化して、複数の多重グラフィックス・ポート・ワーカステーションを形成することができる。GXB410の主要機能は、I/Oポート412とAGPバス330の間のブリッジを形成することである。簡単に言えば、GXB410は、I/Oポート412からアウトバウンド・トランザクションを受諾し、内部にそれを格納し、次いで適切な信号プロトコルを使用して、AGPバス330に対してそれを送ることによってこのことを行う。逆に言えば、GXB410は、AGPバス330に発行されたインバウンド・トランザクションを受諾し、それをこの場合も内部に格納し、インバウンド・トランザクションに関連するグラフィックス・アドレスに変換し、変換後インバウンド・トランザクションをI/Oポート412に発行する。以下にさらに詳細に説明するように、GXB410は、オンチップまたはオフチップSRAM405中に格納されたGART326にアクセスすることによってアドレス変換を実行する。図4のチップセット・アーキテクチャにより、いくつかの利点が達成される。第1に、GXB410はシステム・バス315および関連するシステム・トラフィックから分離し、それによってGXB410のリソースについての競合の源がなくなり、関連するアービトリエーション論理の必要がなくなる。第2に、GART326はGXB410中に常駐するので、アドレス変換処理はメイン・メモリトラフィックとは干渉せず、メモリ・バス324はより効率的に使用される。加えて、GART326にアクセスするローカルSRAMは、GXB410がメモリ・バス324を介して進まなければならない場合よりも約10倍高速になる

30

40

50

したがって、最終結果として、AGPバス330上のトランザクションを処理するためのプロトコル・ブリッジが改善される。この改善されたプロトコル・ブリッジは、前述の、現在のブリッジング技法よりも単純であり、高速であり、かつ効率的である。GX B 4 1 0の例示的な内部区分化を以下で説明する。

#### 【0034】

重要なことであるが、最近の集積化の波を考えて、GX B 4 1 0構成要素のうちの1つまたは複数を単一の集積回路（IC）上に統合できることを企図する。加えて、代替実施形態では、GX B 4 1 0構成要素のうちの1つまたは複数を、単一の集積回路上のプロセッサおよび/またはメモリで統合することもできる。

#### 【0035】

##### グラフィックス拡張ブリッジ機能区分化

次に、特定のユニットへの、GX B 4 1 0の様々な機能の例示的区分化を、図5Aを参照しながら説明する。図5Aは、本発明の一実施形態によるグラフィックス拡張ブリッジの機能単位間の高レベル相互接続を示す概略ブロック図である。この例では、GX B 4 1 0は、AGPバス・インターフェース・ユニット505、データ・バッファ・ユニット510、トランザクション・キュー・ユニット515、GARTユニット520、およびI/Oポート・インターフェース・ユニット525を含む。AGPバス・インターフェース・ユニット505は、66MHz、32ビットPCIバスに基づくことができる。実際には、実装を容易にするために、AGPバス・インターフェース・ユニット505を、コアPCIバスと、AGP機能を追加する増分論理にさらに分割することができる。AGP側では、AGPバス・インターフェース・ユニット505は、インバウンド・トランザクションとアウトバウンド・トランザクションとの間でAGPバス330所有権を管理するためのアービトリエーション論理（図示せず）を含む。加えて、バス制御信号およびアドレスが、AGPバス・インターフェース・ユニット505によって供給され、AGPバス330を介したAGPデータ転送が可能となる。AGPバス・インターフェース・ユニット505は、必要などんなイントラ・ストリーム記録も実行し、かつ、トランザクションを処理するためにトランザクション・キュー・ユニット515中で十分なリソースが利用可能となるまでトランザクションを保持するために、内部トランザクション・キューおよびデータ・バッファ（図示せず）を維持することもできる。

#### 【0036】

以下でさらに詳細に説明するように、トランザクション・キュー・ユニット515は、インバウンド・トランザクションおよびアウトバウンド・トランザクションについての、1つまたは複数の内部トランザクション・キューを実装する。様々なデータ・バッファリングの必要をサポートするために、GX B 4 1 0中にバッファ・スペースも実装することができる。例えば、データ・バッファ・ユニット510は、GX B 4 1 0内にデータを一時的に格納するためのデータ・バッファを含むことができる。このデータ・バッファは、各指示でのトランザクション・タイプごとに別々のバッファとして実装することができ、または共通バッファとして実装することができる。

#### 【0037】

前述のように、現在のグラフィックス・アドレス変換機構では、GART126はメイン・メモリ125中に格納される。したがって、そのような実装では、GART機能はメイン・メモリ125の近くで実行される。それとは対照的に、本実施形態によれば、GART機能は、GARTユニット520によってGX B 4 1 0内で実行される。一実施形態によれば、GARTユニットは、プッシュ・モデルを実装し、有効なトランザクションがトランザクション・キューの1つにあるときはいつでも、トランザクションを変換する。これに関して、GARTユニット520は、トランザクション・キューからインバウンド・トランザクションを受諾し、必要に応じてそのトランザクションを変換することを担当する。ここで示す実施形態では、GARTユニット520は、GART326を含むローカル・オフチップSRAM405に結合される。あるいは、GART326は、オンチップSRAM中に格納することもできる。GARTユニット520は、SRAM405の内容

10

20

30

40

50

をプログラムすることも担当する。S R A M 4 0 5 は、無効として初期化するか、またはどんなアクセスが開始する前にもプログラムすべきである。例えば新しいアプリケーションが開始するごとに動的にS R A M 4 0 5 をプログラムするように、G A R T ユニット5 2 0 に指示することができる。プログラミングは、システム・バス3 1 5 からプログラミング・アクセス要求を発行することによって達成することができる。

【0 0 3 8】

I / O ポート・インターフェース・ユニット5 2 5 は、1つまたは複数のI / O ポートを介する要求およびデータ転送を使用可能にすることによって、1つまたは複数のI / O ポートに対するインターフェースを提供する。例えば、一実施形態によれば、I / O ポート・インターフェース・ユニット5 2 5 は、2つのF 1 6 バスとインターフェースをとる。I / O ポート・インターフェース・ユニット5 2 5 は、可用性およびストリーム優先度に基づいてトランザクション・キュー・ユニット5 1 5 中に維持されるインバウンド・トランザクション・キューからトランザクションを削除し、適切なI / O ポート4 1 2 を通じてトランザクションを送信する。要求が書込みである場合、データがデータ・バッファ・ユニット5 1 0 の中の適切なバッファから読み取られ、送信もされる。アウトバウンド・トランザクションについては、トランザクション・キュー・ユニット5 1 5 中の適切なアウトバウンド・トランザクション・キューにエントリが加えられる。必要な場合、アウトバウンド・トランザクションに関連するデータは、データ・バッファ・ユニット5 1 0 中の適切なバッファに送られる。

【0 0 3 9】

この説明では、トランザクションと、それに関係するデータは、別々の単位に区分される。しかし、様々な他の代替方法実施形態を企図することができる。例えば、一実施形態によれば、関係するデータ・バッファおよびトランザクションは、グループ化することができる。したがって、本明細書で開示される事柄は、G X B 機能の特定の区分化に基づく実施形態に本発明を限定するものとして解釈すべきではない。

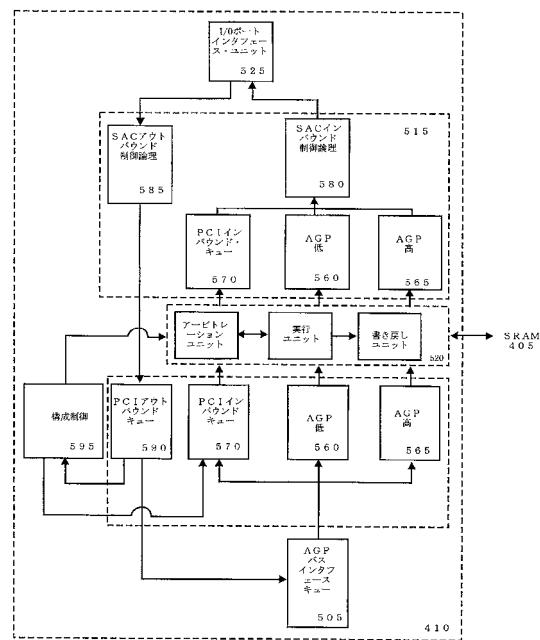

【0 0 4 0】

図5 B は、本発明の一実施形態によるグラフィックス拡張ブリッジ4 1 0 のより詳細なビューを示す概略ブロック図である。この例によれば、A G P 仕様の精神において、高および低A G P およびP C I ストリームが、I / O ポート・インターフェース・ユニット5 2 5 まで、別々の構造として維持される。トランザクション・キュー・ユニット5 1 5 は、A G P 低優先度キュー5 6 0 、A G P 高優先度キュー5 6 5 、P C I インバウンド・キュー5 7 0 、S A C インバウンド制御論理5 8 0 、S A C アウトバウンド制御論理5 8 5 、P C I アウトバウンド・キュー5 9 0 を含む。A G P バス・インターフェース・ユニット5 0 5 は、A G P バス3 3 0 からインバウンドA G P トランザクションを受け取り、それを適切なキュー5 6 0 、5 6 5 、または5 7 0 に加える。例えば、A G P バス3 3 0 からのインバウンドP C I トランザクションは、A G P バス・インターフェース・ユニット5 0 5 によってP C I インバウンド・キュー5 7 0 に発送される。

【0 0 4 1】

S A C アウトバウンド制御論理5 8 5 は、I / O ポート4 1 2 からアウトバウンド・トランザクションを受け取り、それをP C I アウトバウンド・キュー5 9 0 上に待ち行列化する。P C I アウトバウンド・キュー5 9 0 は、A G P バス・インターフェース・ユニット5 0 5 によってアンロードされる。重要なことであるが、アウトバウンド・トランザクションはアドレス変換を必要としないので、G A R T ユニット5 2 0 を介して進む必要がない。

【0 0 4 2】

この実施形態によれば、G A R T ユニット6 2 0 は、アービトレーション・ユニット5 3 0 、実行ユニット5 3 5 、および書戻しユニット5 4 0 を含む。アービトレーション・ユニット5 3 0 は、(1) A G P およびP C I アクセスと、構成制御ユニット5 9 5 から来るS R A M アクセス(プログラミング・アクセス)との間のアービトレーション、(2) S R A M アドレス(G A R T 索引)の生成という2つの主要な機能を実行する。アービト

10

20

30

40

50

レーション・ユニット530のアービトレーション機能は、トランザクション・キュー560、565、および570の先頭のトランザクションのうちのどのトランザクションを次に変換するかを決定するものである。トランザクション・キュー560、565、および570中のインバウンド・トランザクションに関連する仮想アドレス（一実施形態では40ビット幅である）は、SRAM405に直接供給するには広過ぎる。したがって、アービトレーション・ユニット530のSRAMアドレス生成関数（GART指標生成関数）は、アービトレーションを得たトランザクションの仮想アドレスに基づいてSRAMアドレスを決定する。次いで、アービトレーション・ユニット530は、SRAMオペレーションのための適切な制御信号（例えば書き込みまたは読み取り）をアサートすべき実行ユニット535と通信することができる。このようにして、実行ユニット535は、アドレスをさらに処理する必要がなく、直ちにSRAMサイクルを発行することができる。あるいは、アービトレーション・ユニット530は、SRAMアドレスで実行ユニット535を提供することもでき、実行ユニット535は、全パケットをアセンブルし、それをSRAM405に発行することができる。

#### 【0043】

理想的には、SRAM405は、パイプライン・モードで動作すべきであり、クロックごとに、アービトレーション・ユニット530は、変換すべき次のトランザクションについてのアドレスを供給し、次のトランザクションの可用性を実行ユニット535に通信することができるべきである。

#### 【0044】

一実施形態では、実行ユニット535は、適切な時にSRAM制御信号をアサートし、データアサートすることによって、様々なSRAMオペレーションを開始し、制御する。代替実施形態では、実行ユニット535は、アービトレーション・ユニット530からの着信SRAMアドレスを処理し、それをSRAM405に送ることによってそれを実行することを含む実行ステージを実行することができる。実行ユニット535がGARTエントリを受け取ったとき、アドレス変換を実行するためにGARTエントリを使用し、またはそれを廃棄する。GARTエントリに対応するインバウンド・トランザクション・アドレスがGARTアパーチャ内にある場合、GARTエントリを使用してアドレス変換が実行される。しかし、インバウンド・トランザクション・アドレスがGARTアパーチャの外にある場合（例えば物理アドレスである場合）、GARTエントリは飛ばされ、変換は実行されない。代替実施形態では、実行ユニット535は、古い変換を保持し、または変換索引バッファを使用して、アドレス変換を行うことができる。いずれにしても、「変換後アドレス」、例えば元のインバウンド・トランザクション・アドレスまたは物理アドレスは、書戻しユニット540に供給される。

#### 【0045】

書戻しユニット540は、SRAMデータを受け取り、実行ユニット535によって供給された情報を使用し、構成制御ユニット595は、データをフォーマットしてそれを正しい宛先（例えばトランザクション・キュー・ユニット515の中のキューのエントリ）に発送する。例えば、ここで示す実施形態によれば、書戻しユニット540は、インバウンド・トランザクションの仮想アドレスを、実行ユニットによって供給される変換後アドレスで上書きすることを担当する。

#### 【0046】

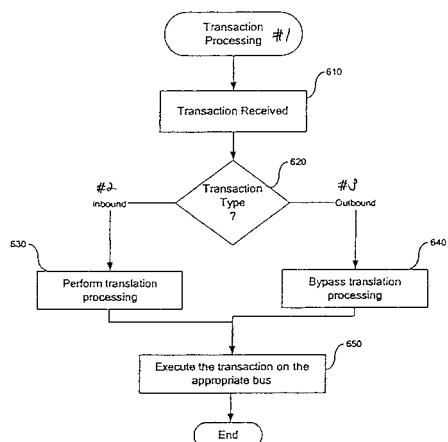

##### 高レベル・トランザクション処理

図6は、本発明の一実施形態によるトランザクション処理を概念的に示す高レベルの流れ図である。この例では、ステップ610で、トランザクションを受け取る。その後、ステップ620で、トランザクション・タイプに基づいて、アドレス変換を実行するかどうかの決定を行う。トランザクションがインバウンド・トランザクション（例えば、AGPバス330から受け取ったトランザクション）である場合、トランザクション処理はステップ630に進む。そうでない場合、トランザクションがアウトバウンド・トランザクション（例えば1つまたは複数のI/Oポート412から受け取ったトランザクション）であ

10

20

30

40

50

る場合、処理はステップ 640 に進む。ステップ 630 で変換処理を実行する。便宜上、GART エントリを SRAM 410 から予測的に取り出すことができるが、すべてのインバウンド・トランザクションが変換されるわけではない。例えば、AGP 範囲外の仮想アドレス（例えば GART アパーチャ）を指定するインバウンド・トランザクションは、変換されないことになる。ステップ 640 では、アウトバウンド・トランザクションは変換処理を迂回する。最後に、ステップ 650 では、適切なバスのトランザクションを実行する（例えば、1つまたは複数の I/O ポート 412 に対してインバウンド・トランザクションを実行し、AGP バス 330 に対してアウトバウンド・トランザクションを実行する）。

#### 【0047】

10

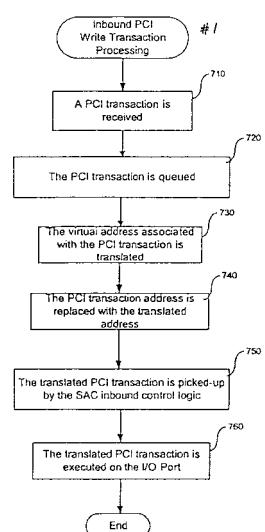

##### インバウンド PCI 書込みトランザクション処理

好みしくは、図 5B に示すように、GX B410 は、AGP バス 330 上で受け取った AGP トランザクションおよび PCI トランザクションの両方を処理し、下位互換性のレベルを提供するように構成される。GX B410 を通過する処理は、PCI、低優先度 AGP、および高優先度 AGP ストリームのそれぞれに対して非常に類似している。したがって、例示的な PCI トランザクションの処理だけを本明細書で説明する。

#### 【0048】

20

図 7 は、本発明の一実施形態によるインバウンド PCI 書込みトランザクション処理を示す流れ図である。ここで説明する例では、ステップ 710 で、PCI サイクルは、AGP バス 330 上で動作して PCI トランザクションを GX B410 に送り、その後に PCI トランザクションに関連するデータが続く。ステップ 720 では、PCI トランザクションを PCI インバウンド・バッファ 570 中にバッファリングする。アビトレーションを得ると、以下でさらに詳細に説明するように、PCI トランザクションに関連する仮想アドレスをメイン・メモリ 325 中の物理アドレスに変換する（ステップ 730）。PCI トランザクションの仮想アドレスは、ステップ 740 で、変換後アドレスで上書きされる。GART エントリの検索の予測的な性質のために、変換を実行すべきでないとき、変換後アドレスを仮想アドレスと同じにすることができる。いずれにしても、ステップ 750 で、トランザクションを適切な I/O ポート 412 に対して実行することができるまで、変換後 PCI トランザクションを SAC インバウンド・バッファ 580 中にバッファリングする。最後に、I/O ポート 412 に対して書込みサイクルを実行することによって、変換後 PCI トランザクションを実行する。

30

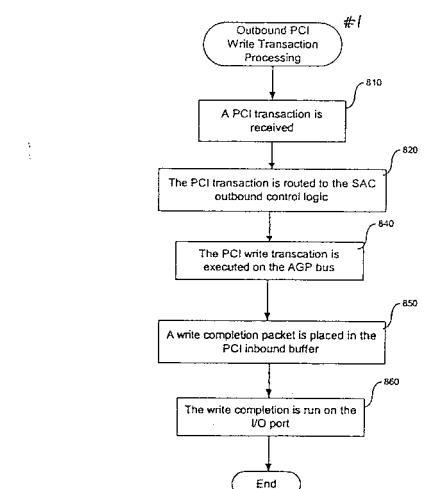

#### 【0049】

30

##### アウトバウンド PCI 書込みトランザクション処理

前述のように、アウトバウンド・トランザクションを GX B410 で変換する必要はない。このことをさらに示すために、次に、アウトバウンド PCI 書込みトランザクションに関連する処理を図 8 を参照しながら説明する。この例によれば、I/O ポート 412 に対して書込み要求を実行し、PCI 要求が受け取られ、SAC アウトバウンド制御論理 585 に発送される（ステップ 810 および 820）。PCI 要求に関連するデータは、データ・バッファ・ユニット 510 に転送される。ステップ 840 では、アビトレーション時間スロットを得ると、AGP バス 330 に対して書込みサイクルを実行することによって、アウトバウンド PCI 書込みトランザクションを実行する。アウトバウンド PCI 書込みトランザクションが首尾よく完了した後に、書込み完了表示を供給することができる（ステップ 850 および 860）。

40

#### 【0050】

##### アドレス変換の概要

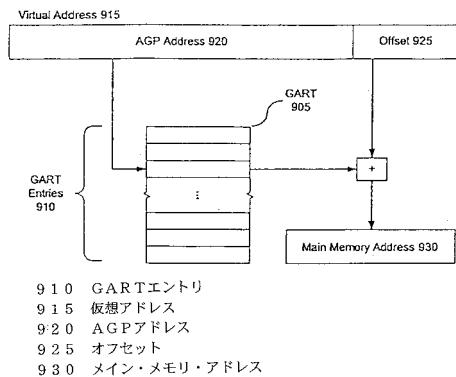

図 9 は、本発明の一実施形態による物理アドレス空間変換に対するグラフィックス（仮想）を概念的に示す。簡潔には、この例では、仮想アドレス 915 は、AGP アドレス 920 およびオフセット 925 を含む。仮想アドレス 915 は、例えばグラフィックス・アクセラレータ 335 が利用する、連続する論理アドレス空間中のアドレスを表す。AGP アドレス 920、その一部、または AGP アドレス 920 から導出される他の情報は、GA

50

R T 9 0 5 からの適切なエントリを取り出すために使用される。G A R T エントリ内に含まれる情報は、仮想アドレス 9 1 5 に対応する物理アドレスを含むメイン・メモリ 3 2 5 中の物理ページを識別する。G A R T エントリで識別される物理ページは、仮想アドレス 9 1 5 からのオフセット 9 2 5 と共に組み合わされ、メイン・メモリ・アドレス 9 3 0 が形成される。

#### 【 0 0 5 1 】

##### 複数ページ・サイズのサポート

一実施形態によれば、G X B 4 1 0 は、メイン・メモリ 3 2 5 中の 2 つの異なるページ・サイズをサポートする。仮想アドレス 9 1 5 の変換は、対応する物理アドレスがその中に常駐するページ・サイズに依存する。一実施形態では、G A R T アパー・チャ内にあるすべてのページに対して固定ページ・サイズ（例えば 4 K バイトまたは 4 M バイト）が使用され、ページ・サイズの表示は、システム・ブート中に G X B 4 1 0 中の制御レジスタ中に格納される。現在、A G P プログラミング・モデルは、G A R T エントリに対して 4 K バイト・ページを用いて設計される。より大きなページ・サイズ（例えば 2 M バイト、4 M バイトなど）を使用可能にすることによって、G X B 4 1 0 は、高性能コンピュータ・システムと互換となる。

#### 【 0 0 5 2 】

上記で、G A R T アパー・チャ中のすべてのページは 1 つのサイズまたは別のサイズであるが、代替実施形態では、G A R T アパー・チャは、異なるサイズのページを同時に含むことができる。この実施形態では、以下で説明するように、アドレス変換を動的に制御する必要がある。

#### 【 0 0 5 3 】

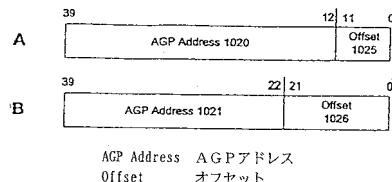

図 1 0 A に、メイン・メモリ内の 4 K バイト・ページ中に常駐するデータを参照するために利用することができる、例示的な仮想アドレス・フォーマットを示す。この実施形態によれば、仮想アドレス 9 1 5 は 4 0 ビット幅である。A G P アドレス 1 0 2 0 は 2 8 ビットを有し、オフセット 1 0 2 5 は 1 2 ビットを有する。

#### 【 0 0 5 4 】

図 1 0 B に、メイン・メモリ内の 4 M バイト・ページ中に常駐するデータを参照するために利用することができる、例示的な仮想アドレス・フォーマットを示す。この実施形態によれば、仮想アドレス 9 1 5 はやはり 4 0 ビット幅である。しかし、A G P アドレス 1 0 2 1 は 1 8 ビットに減少し、オフセット 1 0 2 5 は 2 2 ビットに増加する。様々な他のページ・サイズも収容できるものとする。

#### 【 0 0 5 5 】

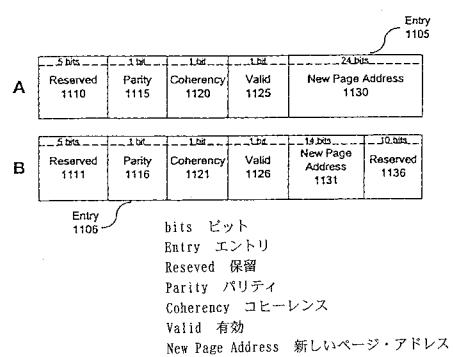

図 1 1 A に、メイン・メモリ内の 4 K バイト・ページへのアドレス変換をサポートするための、例示的な G A R T エントリ・フォーマット 1 1 0 5 を示す。この例では、エントリ 1 1 0 5 は 3 2 ビット幅で、パリティ・ビット 1 1 1 5 、コヒーレンス・ビット 1 1 2 0 、有効ビット 1 1 2 5 、新しいページ・アドレス 1 1 3 0 、および予約済み領域 1 1 1 0 を含む。各エントリは、1 つの 4 K バイト・ページをカバーする。2 5 6 k エントリ、または 4 K バイト・ページについての合計 1 G B の変換可能スペースを保持するのに 1 メガバイトで十分である。

#### 【 0 0 5 6 】

パリティ・ビット 1 1 1 5 は、G A R T エントリ 1 1 0 5 全体をカバーする。パリティ・ビット 1 1 1 5 はハードウェアで生成することができ、パリティ・ビット 1 1 1 5 を含む 1 の合計数が、偶数または奇数になるように計算することができる。

#### 【 0 0 5 7 】

コヒーレント・ビット 1 1 2 0 は、グラフィックス・カードからのトラフィックがシステム・バス 3 1 5 とコヒーレントである必要があるかどうかを示す。コヒーレンスは以下でさらに論じる。

#### 【 0 0 5 8 】

有効ビット 1 1 2 5 は、S R A M 4 0 5 がこのエントリに関する有効データを含むかどうか

10

20

30

40

50

かを示す。データがこのエントリに関して有効であることを有効ビット 1125 が示す場合、アドレス変換のためにこのエントリを使用することができる。

【0059】

この例では、この新しいページ・アドレス 1130 は 24 ビット幅である。この新しいページ・アドレス 1130 は、所望の物理アドレスを含むメイン・メモリ 325 中の 4K バイト物理ページの開始アドレスを含む。

【0060】

図 11B に、メイン・メモリ内の 4M バイト・ページへのアドレス変換をサポートするための、例示的な GART エントリ・フォーマットを示す。この例では、上記と同様に、エントリ 1106 は 32 ビット幅で、パリティ・ビット 1116、コヒーレンス・ビット 1121、有効ビット 1126、新しいページ・アドレス 1131、および予約済み領域 1111 および 1136 を含む。各エントリは、4M バイト・ページをカバーする。

【0061】

上記と同様に、パリティ・ビット 1116 は、GART エントリ 1106 全体をカバーし、パリティ・ビット 1116 を含む 1 の合計数が、偶数または奇数になるように計算することができる。

【0062】

コヒーレンス・ビット 1121 は、グラフィックス・カードからのトラフィックがシステム・バス 315 とコヒーレントである必要があるかどうかを示す。コヒーレンスは以下で 20 さらに論じる。

【0063】

有効ビット 1126 は、SRAM 405 が当該のエントリに関する有効データを含むかどうかを示す。データがこのエントリに関して有効であることを有効ビット 1126 が示す場合、アドレス変換のためにこのエントリを使用することができる。

【0064】

この例では、この新しいページ・アドレス 1131 は 14 ビット幅である。この新しいページ・アドレス 1131 は、所望の物理アドレスを含むメイン・メモリ 325 中の 4M バイト物理ページの開始アドレスを含む。

【0065】

代替実施形態では、ビットおよびフィールドの相対的位置決めを図 11A および図 11B の例で示したものとは異なるものとすることができる。やはり、代替実施形態では、エントリ・フォーマットは、宛先ページ・サイズ（例えば 4K バイトまたは 4M バイト）を示すためのページ・モードビットも含むことができ、アドレス変換プロセスの動的制御を実現することができる。このようにして複数の異なるページ・サイズを同時にサポートすることができる。

【0066】

（コヒーレンス）

グラフィックス・カード（例えばグラフィックス・アクセラレータ 335）からのトラフィックは、システム・バス 325 とコヒーレントにしたいこともあり、そうでないこともある。一実施形態によれば、コヒーレンスはページごとに選択可能である。この開示では、「コヒーレンス」とは、1 つまたは複数のプロセッサ 305 および 310 がアドレスに関するキャッシュをスヌープすることができるよう、そのアドレスがシステム・バス 325 上に出現することを意味する。テクスチャ・マップまたは他のイメージ・データが、プロセッサによって、書き込み結合 (WC) とマークされた場合、そのデータはコヒーレントではない。プロセッサの WC バッファ中でヒットする、システム・バス 325 に対するアドレスはスヌープされない。あるいは、アプリケーションは、メイン・メモリ 325 中のデータがプロセッサによって使用されなかった（例えば、データがディスクから来た）ことを認識し、システム・バス 325 帯域幅を使用せずにデータを取り出すようにグラフィックス・カードに要求し、したがって強制的にアクセスを非コヒーレントにすることができる。

10

20

30

40

50

**【 0 0 6 7 】**

前述と同様に、A G P範囲中にヒットするすべてのA G Pタイプ・アクセスについて、アドレスがコヒーレントであるかどうかを判定するG A R Tエントリごとのビットが存在する。A G P範囲外のA G Pタイプ・アクセスについて、情報（例えば1ビット・コヒーレンス標識）をG X B 4 1 0の構成レジスタから読み取り、コヒーレンスを判定することができる。重要なことであるが、コヒーレンスまたは非コヒーレンスは、A G Pプロトコルを使用するアクセスだけに当てはまる。P C Iプロトコルを使用するアクセスは、変換テーブルにヒットするかどうかに関わらず、常にコヒーレントに行われる。

**【 0 0 6 8 】**

上記の明細書において、本発明の特定の実施形態を参照しながら本発明を説明した。しかし、本発明のより広範な精神および範囲から逸脱することなく、それに対して様々な修正形態および変更を行えることは明らかであろう。したがって、この明細書および図面は、限定的な意味ではなく、例示的な意味とみなすべきである。

10

**【図面の簡単な説明】**

【図1】 グラフィックス・アドレス変換のための従来技術の手法を示すブロック図である。

【図2】 本発明の一実施形態による入出力アドレス変換を示すブロック図である。

【図3】 本発明の一実施形態によるグラフィックス・アドレス変換を示すブロック図である。

【図4】 本発明の実施形態を実装することができる例示的チップセットを示すブロック図である。

20

【図5 A】 本発明の一実施形態によるグラフィックス拡張ブリッジの機能単位間の高レベル相互接続を示す単純化したブロック図である。

【図5 B】 本発明の一実施形態によるグラフィックス拡張ブリッジのより詳細なビューを示す単純化したブロック図である。

【図6】 本発明の一実施形態によるトランザクション処理を概念的に示す高レベル流れ図である。

【図7】 本発明の一実施形態によるインバウンドP C I書込みトランザクション処理を示す流れ図である。

【図8】 本発明の一実施形態によるアウトバウンドP C I書込みトランザクション処理を示す流れ図である。

30

【図9】 本発明の一実施形態によるグラフィックス（仮想）-物理アドレス空間変換を概念的に示す図である。

【図10】 メイン・メモリ内の4 Kバイト・ページ中に常駐するデータを参照するためを利用することができる例示的仮想アドレス・フォーマットを示す図である。

【図11】 メイン・メモリ内の4 Kバイト・ページへのアドレス変換をサポートするための例示的G A R Tエントリ・フォーマットを示す図である。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6】

# 1 トランザクション処理

# 2 インバウンド

# 3 アウトバウンド

6 1 0 トランザクションを受け取った

6 2 0 トランザクション・タイプ?

6 3 0 変換処理を実行する

6 4 0 変換処理を迂回する

6 5 0 適切なバスに対してトランザクションを実行する

【図7】

# 1 インバウンドPCI書き込みトランザクション処理

7 1 0 PCIトランザクションを受け取る

7 2 0 PCIトランザクションを待ち行列化する

7 3 0 PCIトランザクションに関連する仮想アドレスを変換する

7 4 0 PCIトランザクション・アドレスを変換後アドレスで置換する

7 5 0 変換後PCIトランザクションをSACインバウンド制御論理でピックアップする

7 6 0 変換後PCIトランザクションをI/Oポートに対して実行する

【図 8】

- # 1 アウトバウンド PCI 書込みトランザクション処理

8 1 0 PCI トランザクションを受け取る

8 2 0 PCI トランザクションをSACアウトバウンド制御論理に向けて発送する

8 4 0 PCI 書込みトランザクションをAGPバスに対して実行する

8 5 0 書込み完了パケットをPCIインバウンド・バッファ中に配置する

8 6 0 書込み完了をI/Oポートに対して実行する

【図 9】

【図 10】

【図 11】

---

フロントページの続き

(72)発明者 クロス, レナード・ダブリュ

アメリカ合衆国・97229・オレゴン州・ポートランド・ノースウェスト 124ティエイチ

プレイス・3701

審査官 木村 貴俊

(56)参考文献 米国特許第05905509(US, A)

特開平11-167523(JP, A)

特開平11-073386(JP, A)

国際公開第99/034293(WO, A1)

国際公開第99/041671(WO, A1)

(58)調査した分野(Int.Cl., DB名)

G06F 3/06- 3/08、12/08-12/12

13/10-13/378