(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6582175号

(P6582175)

(45) 発行日 令和1年10月2日(2019.10.2)

(24) 登録日 令和1年9月13日(2019.9.13)

(51) Int.CI.

HO2M 3/28 (2006.01)

F 1

HO2M 3/28

R

請求項の数 2 (全 12 頁)

(21) 出願番号 特願2016-49373 (P2016-49373)

(22) 出願日 平成28年3月14日 (2016.3.14)

(65) 公開番号 特開2017-169256 (P2017-169256A)

(43) 公開日 平成29年9月21日 (2017.9.21)

審査請求日 平成30年11月2日 (2018.11.2)

早期審査対象出願

(73) 特許権者 392026888

京都電機器株式会社

京都府京都市下京区東洞院通上珠数屋町上

る富田町382番地

(74) 代理人 110001069

特許業務法人京都国際特許事務所

(72) 発明者 辻本 正志

京都府宇治市横島町十六19-1 京都電

機器株式会社内

(72) 発明者 藤吉 敏一

京都府宇治市横島町十六19-1 京都電

機器株式会社内

(72) 発明者 伏谷 周一

京都府宇治市横島町十六19-1 京都電

機器株式会社内

最終頁に続く

(54) 【発明の名称】 DC-DCコンバータ装置

(57) 【特許請求の範囲】

## 【請求項 1】

直流電源と、一次巻線及び二次巻線を有するトランスと、主スイッチング素子を含み、前記直流電源から供給された直流電圧をスイッチングして前記一次巻線に交流電圧を印加するスイッチング回路と、前記二次巻線に接続された、複数の整流用ダイオードを含む整流回路と、該整流回路の出力端に接続された、リクトルを含む平滑回路と、を具備し、前記一次巻線に印加された交流電圧によって前記二次巻線に誘起された交流電圧を前記整流回路及び前記平滑回路により平滑化して負荷に供給するDC-DCコンバータ装置において、

a) 前記整流回路と前記平滑回路との間に介挿され、該整流回路に並列に接続されたスナバ回路と、

b) 前記主スイッチング素子と後記スナバ用スイッチング素子とをそれぞれオン・オフ動作させる駆動制御部と、

を備え、前記スナバ回路は、

a1) スナバ用コンデンサと順方向接続であるスナバ用の第1のダイオードとの直列回路であり、前記整流回路に並列に接続された第1の直列回路と、

a2) スナバ用スイッチング素子と限流用リクトルとの直列回路であり、前記第1のダイオードに並列に接続された第2の直列回路と、

a3) 前記スナバ用スイッチング素子と前記限流用リクトルとの接続点と、前記第1の直列回路の高電圧側端部との間に、該接続点から該高電圧側端部に向かって順方向に接続

10

20

された第2のダイオードと、

を含み、

前記駆動制御部は、前記スナバ用の第1のダイオードを通して前記スナバ用コンデンサを充電したあと、前記主スイッチング素子がオフ状態であるときに所定期間、前記スナバ用スイッチング素子をオン動作させることで、前記スナバ用コンデンサに溜まった電荷を前記第2の直列回路を通して放出することを特徴とするDC-D Cコンバータ装置。

【請求項2】

請求項1に記載のDC-D Cコンバータ装置であって、

前記駆動制御部は、前記主スイッチング素子をオン・オフ動作させるサイクルを複数実行する毎に、前記スナバ用スイッチング素子をオン動作させることを特徴とするDC-D Cコンバータ装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トランスによって一次側回路と二次側回路とが電気的に絶縁されたDC-D Cコンバータ装置に関し、さらに詳しくは、スイッチング時に発生するサージ電圧を抑制するスナバ回路を二次側回路に設けたDC-D Cコンバータ装置に関する。

【背景技術】

【0002】

DC-D Cコンバータ装置は、小型・軽量でありながら高効率であるという特徴を有しており、近年、様々な電子機器や装置の電源として広く利用されている。 20

【0003】

一般的なDC-D Cコンバータ装置は、トランスを用いて一次側回路と二次側回路とが電気的に絶縁された構成を有しており、一次側回路には、直流電源から供給される直流電圧をスイッチングするスイッチング回路が設けられている。そのスイッチング回路におけるスイッチング動作によって、トランスの一次巻線に交流電圧が印加される。一次巻線に交流電圧が印加されることで、トランスの巻数比に応じた電圧が二次巻線に誘起される。そして、二次巻線に誘起された交流電圧がダイオードブリッジなどの整流回路により整流されたあと、フィルタ回路により平滑され、直流出力電圧、直流出力電流として負荷に供給される。 30

【0004】

二次側回路の整流回路はトランスから出力された交流電圧を整流している。この整流回路のダイオードがオン状態からオフ状態に移行するとき、二次側回路にはトランスの漏れインダクタンスと上記ダイオードの逆回復時間及び該ダイオードの寄生容量に起因して発生するサージ電圧が発生する。このサージ電圧が整流回路のダイオードの耐電圧を超えると、ダイオードが破損に至るおそれがある。そのため、サージ電圧が大きいと、それだけ耐電圧の大きなダイオードを整流回路に用いる必要がありコストが高くなる。

【0005】

こうしたことから、サージ電圧を抑制するために二次側回路にスナバ回路を設けたDC-D Cコンバータ装置が従来知られている。 40

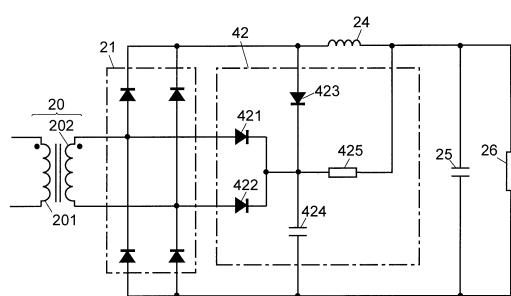

図5は、特許文献1に記載のDC-D Cコンバータ装置における二次側回路の構成図である。トランス20の一次巻線201は図示しない一次側回路に接続され、二次巻線202は二次側回路に含まれるダイオードブリッジ構成の整流回路21に接続され、整流回路21の後段には、リアクトル24とコンデンサ25とから成るLCフィルタが接続されている。このコンデンサ25の両端が出力端であり、出力端に負荷26が接続されている。

【0006】

スナバ回路42は、トランス20の二次巻線202の両端にそれぞれアノードが接続されたダイオード421、422と、それらダイオード421、422の共通のカソードと整流回路21の高電圧側出力との間に接続されたダイオード423と、その共通のカソードと整流回路21の低電圧側出力との間に接続されたコンデンサ424と、その共通のカソード

10

20

30

40

50

ソードとリアクトル 2 4 の出力側端との間に接続された抵抗 4 2 5 と、から構成される。

【0007】

このDC - DCコンバータ装置が動作し始めると、上述したようにトランス 2 0 の二次巻線 2 0 2 の両端には方形波電圧が現れる。スナバ回路 4 2 において、ダイオード 4 2 1 、4 2 2 のアノードはそれぞれ二次巻線 2 0 2 の両端に接続されており、コンデンサ 4 2 4 にはダイオード 4 2 1 又は 4 2 2 を通して電流が流入し該コンデンサ 4 2 4 は充電される。そのため、コンデンサ 4 2 4 の両端電圧は二次巻線 2 0 2 の両端に発生する方形波電圧の波高値にほぼ固定される。即ち、コンデンサ 4 2 4 は基本的に定電圧源として機能する。

【0008】

トランス 2 0 の漏れインダクタンスと整流回路 2 1 内のダイオードの逆回復時間、及びそのダイオードの寄生容量に起因して、整流回路 2 1 の高電圧側出力と低電圧側出力との間にサージ電圧が発生すると、ダイオード 4 2 3 を通してコンデンサ 4 2 4 にサージ電流が流入する。このため、上記サージ電圧はコンデンサ 4 2 4 の充電電圧にクランプされ、該コンデンサ 4 2 4 に充電される。この充電によってコンデンサ 4 2 4 の電圧が上昇すると、ダイオード 4 2 3 によりコンデンサ 4 2 4 の放電が阻止されると共に、その電圧上昇分のエネルギーは抵抗 4 2 5 を介して平滑用のコンデンサ 2 5 に放出される。これによって、スナバ回路 4 2 はサージ電圧を抑制することができ、放電阻止スナバとして動作する。

【0009】

上記DC - DCコンバータ装置は、該装置が固定電圧出力電源であるなど、出力端電圧が略一定であるときに有用な回路である。しかしながら、出力電圧を大きく可変する必要がある場合には不向きである。何故なら、コンデンサ 4 2 4 の両端電圧は二次巻線 2 0 2 の両端に発生する方形波電圧の波高値でほぼ決定されるので、出力電圧が 0 V 近くまで下げられると、コンデンサ 4 2 4 の放電のための抵抗 4 2 5 両端の電位差が大きくなり、該抵抗 4 2 5 での発熱が問題となるからである。

【0010】

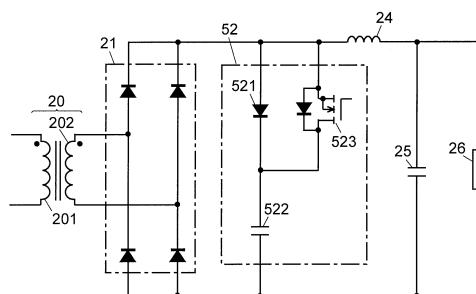

これに対し、出力電圧の可変幅を広げることができるDC - DCコンバータ装置が特許文献 2 に開示されている。図 6 はこのDC - DCコンバータ装置における二次側回路の構成図である。この構成では、図 5 に示した例と同様のダイオードブリッジ構成である整流回路 2 1 と、リアクトル 2 4 とコンデンサ 2 5 とから成るLCフィルタとの間に設けられたスナバ回路 5 2 は、放電阻止用のダイオード 5 2 1 とコンデンサ 5 2 2 との直列回路と、該ダイオード 5 2 1 と並列に接続された回生用のスイッチング素子 5 2 3 とを含む。スイッチング素子 5 2 3 は、図示しない一次側回路のスイッチング回路に含まれるスイッチング素子がいずれもオフ状態であるとき、つまりはデッドタイムである期間中の一部でオンするように駆動される。

【0011】

このDC - DCコンバータ装置では、図 5 に示した回路と同様に、整流回路 2 1 の高電圧側ラインと低電圧側ラインとの間にサージ電圧が発生すると、ダイオード 5 2 1 を通してコンデンサ 5 2 2 にサージ電流が流入し、コンデンサ 5 2 2 は充電される。一方、充電されたコンデンサ 5 2 2 の放電は回生用のスイッチング素子 5 2 3 を通して行われる。即ち、整流回路 2 1 が環流動作期間であるときにスイッチング素子 5 2 3 がオンされると、リアクトル 2 4 の定電流作用によりコンデンサ 5 2 2 に蓄えられていたエネルギーはスイッチング素子 5 2 3 を通して放出される。スイッチング素子 5 2 3 のオン抵抗はごく小さいので、この抵抗の発熱による損失は殆どない。

【0012】

しかしながら、図 6 に示したDC - DCコンバータ装置では次のような問題がある。

上述のように、整流回路 2 1 の高電圧側出力と低電圧側出力との間にサージ電圧が発生し、ダイオード 5 2 1 を通じてコンデンサ 5 2 2 の電圧にクランプされ、その後、ダイオード 5 2 1 が放電阻止状態であるとき、トランス 2 0 の漏れインダクタンスとダイオードの寄生容量による振動電圧が整流回路 2 1 の高電圧側出力と低電圧側出力と間に減衰振動

10

20

30

40

50

として現れる場合がしばしばある。この場合、コンデンサ522の両端電圧が整流回路21の両端電圧よりも大きくなつた状態であるときにスイッチング素子523がオンされると、コンデンサ522からスイッチング素子523を通して整流回路21内のダイオードの寄生容量側へと電流が流れてしまう場合があり、その分、電源の効率が低下することになる。また、上記電流の経路には電流を制限する回路部品が存在しないため、瞬間に大きな電流が流れてしまい、その電流経路上の各回路部品にダメージを与えるおそれがある。

【先行技術文献】

【特許文献】

【0013】

10

【特許文献1】特開2013-74767号公報

【特許文献2】国際公開第2010/067629号

【発明の概要】

【発明が解決しようとする課題】

【0014】

本発明は上記課題を解決するためになされたものであり、広い可変幅の出力電圧に対応しつつ、サージ電圧が発生した際にそのスパイク状の電圧部分のみを吸収することでエネルギー損失の少ないサージ電圧抑制を行うことが可能なスナバ回路を備えたDC-DCコンバータ装置において、スナバ回路中のコンデンサの両端電圧がその前段の整流回路の両端電圧よりも高くなつた場合でも、該コンデンサから整流回路に大きな電流が流れることを回避し、効率の改善と回路部品へのダメージの低減を図ることをその目的としている。

20

【課題を解決するための手段】

【0015】

上記課題を解決するためになされた本発明は、直流電源と、一次巻線及び二次巻線を有するトランスと、主スイッチング素子を含み、前記直流電源から供給された直流電圧をスイッチングして前記一次巻線に交流電圧を印加するスイッチング回路と、前記二次巻線に接続された、複数の整流用ダイオードを含む整流回路と、該整流回路の出力端に接続された、リクトルを含む平滑回路と、を具備し、前記一次巻線に印加された交流電圧によって前記二次巻線に誘起された交流電圧を前記整流回路及び前記平滑回路により平滑化して負荷に供給するDC-DCコンバータ装置において、

30

a)前記整流回路と前記平滑回路との間に介挿され、該整流回路に並列に接続されたスナバ回路と、

b)前記主スイッチング素子と後記スナバ用スイッチング素子とをそれぞれオン・オフ動作させる駆動制御部と、

を備え、前記スナバ回路は、

a1)スナバ用コンデンサと順方向接続であるスナバ用の第1のダイオードとの直列回路であり、前記整流回路に並列に接続された第1の直列回路と、

a2)スナバ用スイッチング素子と限流用リクトルとの直列回路であり、前記第1のダイオードに並列に接続された第2の直列回路と、

a3)前記スナバ用スイッチング素子と前記限流用リクトルとの接続点と、前記第1の直列回路の高電圧側端部との間に、該接続点から該高電圧側端部に向かって順方向に接続された第2のダイオードと、

40

を含み、

前記駆動制御部は、前記スナバ用の第1のダイオードを通して前記スナバ用コンデンサを充電したあと、前記主スイッチング素子がオフ状態であるときに所定期間、前記スナバ用スイッチング素子をオン動作させることで、前記スナバ用コンデンサに溜まった電荷を前記第2の直列回路を通して放出することを特徴としている。

【0016】

本発明に係るDC-DCコンバータ装置では、トランスの一次巻線に接続される一次側回路の構成は特に問わず、例えば上記スイッチング回路は4個の主スイッチング素子を用

50

いたフルブリッジ回路でも、2個の主スイッチング素子を用いたハーフブリッジ回路でもよく、さらにはプシュプル回路やフォワード回路であってもよい。

【0017】

本発明に係るDC - DCコンバータ装置において、整流用ダイオードのターンオフ及び該ダイオードの寄生容量に起因するサージ電圧が整流用ダイオードに発生すると、サージ電流が第1の直列回路に流れスナバ用コンデンサにサージ電流が流入する。これにより、サージ電流はスナバ用コンデンサに充電され、整流回路の両端電圧は所定のレベルでクランプされる。駆動制御部は、トランスの一次巻線に交流電圧を印加するために主スイッチング素子をオン・オフ駆動するが、主スイッチング素子を全てオフしているデッドタイムの期間中に所定時間だけ、スナバ用スイッチング素子をオン動作させる。スナバ用スイッチング素子がオン状態になると、スナバ用コンデンサに充電されていたサージ電圧に由来するエネルギーが第2の直列回路を通して放出される。

【0018】

スナバ用スイッチング素子がターンオンされるときにスナバ用コンデンサの両端電圧が整流回路の両端電圧よりも低ければ、スナバ用コンデンサから放出されたエネルギーによる電流は負荷に回生される。一方、スナバ用スイッチング素子がターンオンされるときにスナバ用コンデンサの両端電圧が整流回路の両端電圧よりも高いと、スナバ用コンデンサから放出されたエネルギーによる電流の少なくとも一部は第2の直列回路から整流回路内のダイオードの寄生容量に流れようとする。しかしながら、この第2の直列回路中には限流用リクトルが配置されているため、整流回路内のダイオードの寄生容量に流れる電流は制限される。それによって、過大な電流が整流回路に流れることを回避することができる。その後、スナバ用スイッチング素子がターンオフされると、限流用リクトルはそれまでに蓄積されていたエネルギーに基づく電流を流し続けようとする。この電流は第2のダイオードを通して負荷へと回生される。そのため、スナバ用コンデンサから放出されたエネルギーの一部は負荷に回生され、有効に利用されることになる。

【0019】

なお、本発明に係るDC - DCコンバータ装置において、駆動制御部は、デッドタイム毎にスナバ用スイッチング素子をオンさせる必要はなく、例えば、所定回数のデッドタイム毎に1回だけスナバ用スイッチング素子をオンさせるようにしてもよい。例えばデッドタイム毎にスナバ用スイッチング素子をオンさせるようにすると、そのオン時間（上記所定時間）をかなり短くする必要がある場合もあるが、複数回のデッドタイム毎に1回、スナバ用スイッチング素子をオンさせるようにすれば、1回のオン時間を或る程度長くすることができ、それによって制御を容易にできる。

【発明の効果】

【0020】

本発明に係るDC - DCコンバータ装置によれば、スナバ用コンデンサに蓄積されたエネルギーは有効に負荷に回生される。また、主スイッチング素子を全てオフしているデッドタイムの期間中、サージ電流の流入によってスナバ用コンデンサの両端電圧が整流回路の両端電圧よりも高くなった状態で該コンデンサに蓄えられた電荷を放出するためにスナバ用スイッチング素子がオンされたときにも、スナバ回路から整流回路に流れる過大な電流を抑制することができる。それによって、電源効率を改善することができると共に、整流回路に含まれるダイオード等の回路部品にダメージが与えられることを防止することができる。さらにまた、そうした過大な電流を抑制する際に限流用リクトルに蓄積されたエネルギーも有効に負荷へと回生されるため、一層、電源効率の改善に繋がる。

【図面の簡単な説明】

【0021】

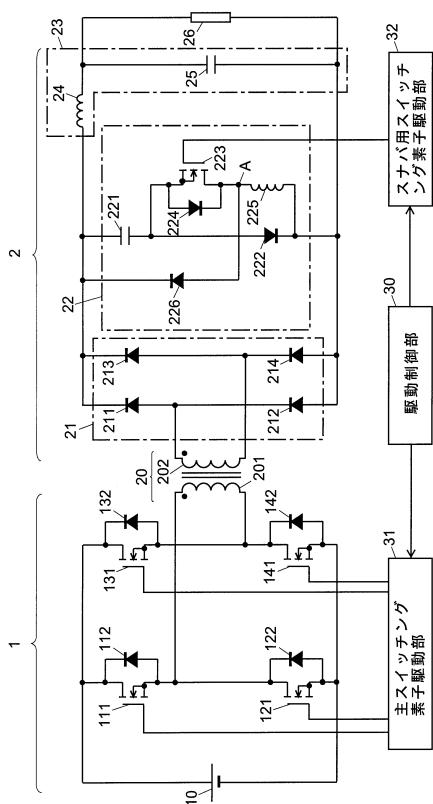

【図1】本発明の一実施例であるDC - DCコンバータ装置の構成図。

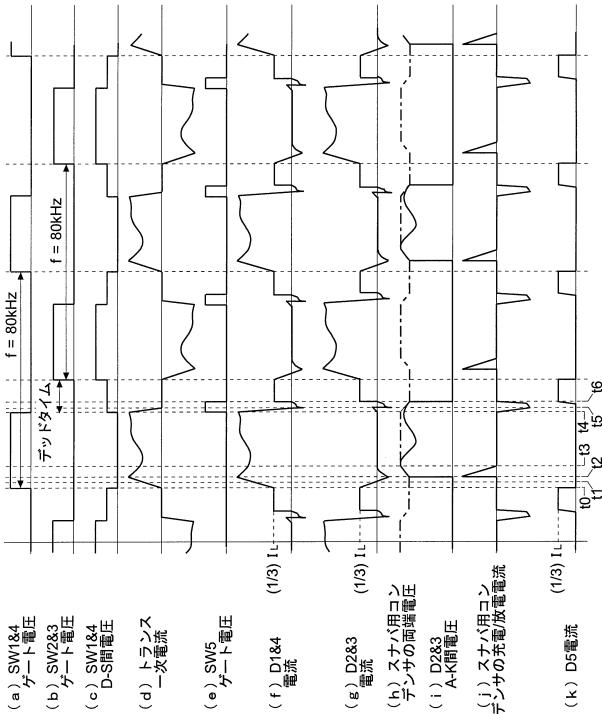

【図2】本実施例のDC - DCコンバータ装置における基本的な動作タイミング及び波形図。

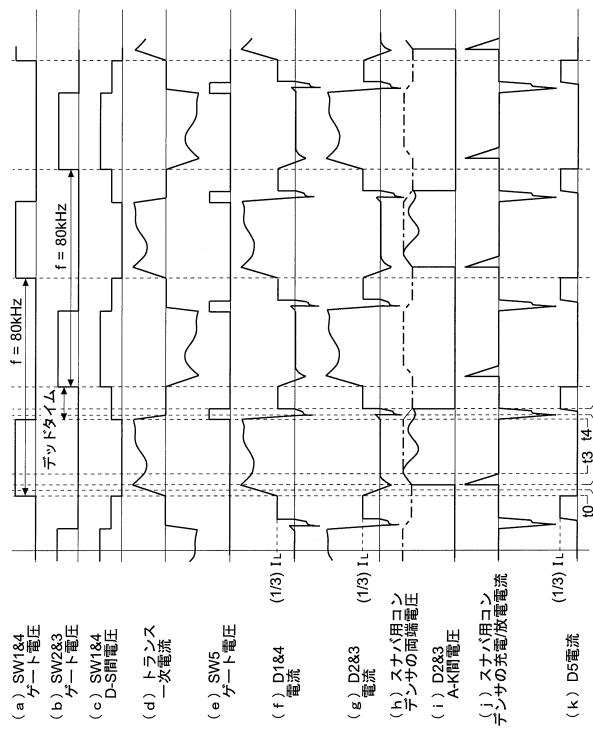

【図3】本実施例のDC - DCコンバータ装置において、限流用リクトルが機能せず、

10

20

30

40

50

オフ状態にあるダイオードの寄生容量に流れる電流が抑制されない場合の波形図。

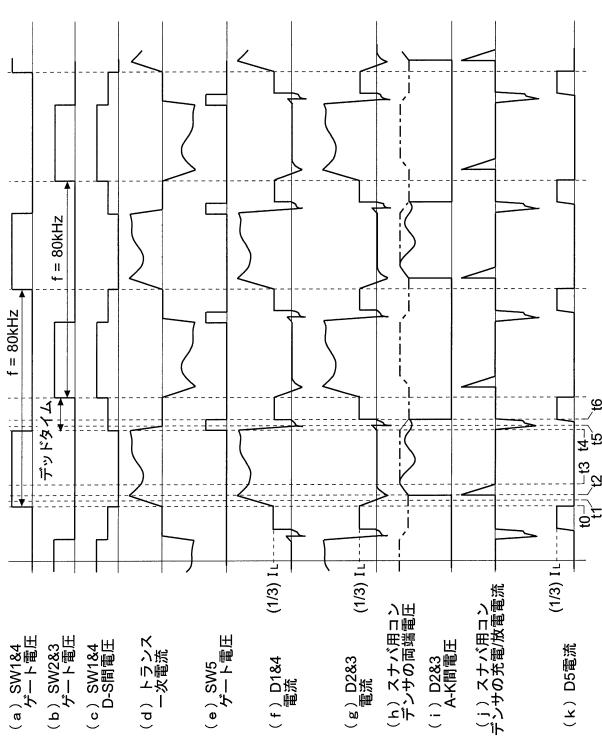

【図4】本実施例のDC-DCコンバータ装置において、限流用リクトルが機能し、オフ状態にあるダイオードの寄生容量に流れる電流が抑制される場合の波形図。

【図5】従来のDC-DCコンバータ装置の一例の構成図。

【図6】図5とは異なる従来のDC-DCコンバータ装置の一例の構成図。

【発明を実施するための形態】

【0022】

本発明の一実施例であるDC-DCコンバータ装置について、添付図面を参照して説明する。

図1は本実施例のDC-DCコンバータ装置の構成図、図2は本実施例のDC-DCコンバータ装置における動作タイミング及び波形図である。

【0023】

絶縁されたトランス20の一次巻線201に接続されている一次側回路1は、直流電源10と、複数(4個)のパワーMOSFET等の第1乃至第4の主スイッチング素子111、121、131、141を含むフルブリッジ構成であるスイッチング回路と、を有し、第1～第4の主スイッチング素子111、121、131、141にはそれぞれ逆並列にダイオード112、122、132、142が接続されている。トランス20の一次巻線201は、第1の主スイッチング素子111と第2の主スイッチング素子121との接続点と、第3の主スイッチング素子131と第4の主スイッチング素子141との接続点と、の間に接続されている。第1～第4の主スイッチング素子111～141は、駆動制御部30からの制御信号に基づいて主スイッチング素子駆動部31により生成される駆動信号によりそれぞれオン・オフ制御される。

【0024】

トランス20の二次巻線202に接続された二次側回路2は、整流回路21、スナバ回路22、LCフィルタ回路23、を含む。即ち、トランス20の二次巻線202の両端は、4個のダイオード211、212、213、214をフルブリッジ構成した整流回路21に接続されており、この整流回路21により整流された出力電圧は、リクトル24とコンデンサ25とを含む平滑回路であるLCフィルタ回路23に入力され、該LCフィルタ回路23で平滑化されて負荷26に出力される。整流回路21とLCフィルタ回路23との間には、整流回路21のダイオード211～214の両端に発生するサージ電圧を抑制するスナバ回路22が設けられている。なお、この4個のダイオード211、212、213、214にはそれぞれ、図示しない寄生容量が含まれる。

【0025】

スナバ回路22は、スナバ用コンデンサ221とスナバ用の第1のダイオード222とが直列に接続された第1の直列回路と、第1のダイオード222の両端(アノード-カソード端子)間に接続された、スナバ用スイッチング素子223と限流用リクトル225とが直列に接続された第2の直列回路と、スナバ用スイッチング素子223と限流用リクトル225との接続点Aと整流回路21の高電圧側ラインとの間に、前者から後者に向けて順方向に接続された第2のダイオード226と、を含む。なお、図1中、スナバ用スイッチング素子223のソース-ドレイン間に接続されているダイオード224は該スイッチング素子223のボディダイオードである。このスナバ用スイッチング素子223は、駆動制御部30からの制御信号に基づいてスナバ用スイッチング素子駆動部32により生成される駆動信号によりオン・オフ制御される。

【0026】

駆動制御部30は後述する特徴的な動作を実施するために、CPUや制御用プログラムが格納されたメモリ(例えばフラッシュROM)などを備えるようにすることができる。

【0027】

次に、図2を参照し、本実施例のDC-DCコンバータ装置における電力変換動作を説明する。

なお、図2では、主スイッチング素子111、121、131、141、スナバ用スイ

10

20

30

40

50

ツーピング素子 223 をそれぞれ SW1、SW2、SW3、SW4、SW5 と称し、ダイオード 211、212、213、214、226 をそれぞれ D1、D2、D3、D4、D5 と称する。

【0028】

駆動制御部 30 からの指示に基づき主スイッチング素子駆動部 31 は、フルブリッジ回路の異なるアームに含まれる 2 個の主スイッチング素子 111、141 のゲート端子に図 2 (a) に示す駆動信号を与える。同様に異なるアームに含まれる 2 個の主スイッチング素子 121、131 のゲート端子に図 2 (b) に示す駆動信号を与える。ここでは一例として、スイッチング制御の 1 サイクルは 80 kHz であり、第 2、第 3 の主スイッチング素子 121、131 に与えられる駆動信号は、第 1、第 4 の主スイッチング素子 111、141 に与えられる駆動信号に対して 180° だけ位相が遅れている。これら駆動信号がハイレベルであるときに第 1～第 4 の主スイッチング素子 111～141 はオン状態となる。つまり、第 1、第 4 の主スイッチング素子 111、141 の組と第 2、第 3 の主スイッチング素子 121、131 の組とは、いずれもがオフ状態である所定のデッドタイムを挟んで交互にオン状態となる。もちろん、1 サイクルの周波数はこれに限らない。

【0029】

図 2 の (c) は第 1、第 4 の主スイッチング素子 111、141 のドレイン - ソース間電圧、(d) はトランス 20 の一次巻線 201 に流れる電流、(e) はスナバ用スイッチング素子駆動部 32 からスナバ用スイッチング素子 223 のゲート端子に印加される電圧、(f) は整流回路 21 のダイオード 211、214 に流れる電流、(g) は整流回路 21 のダイオード 212、213 に流れる電流、(h) はスナバ用コンデンサ 221 の両端電圧、(i) はダイオード 212、213 のアノード - カソード間電圧、(j) はスナバ用コンデンサ 221 の充電 / 放電電流、(k) は第 2 のダイオード 226 に流れる電流、をそれぞれ示す波形である。

【0030】

時刻  $t_0$  の直前には、第 1～第 4 の主スイッチング素子 111～141 は全てオフ状態であり、このとき、それ以前に平滑用リアクトル 24 に蓄積されているエネルギーに基づいて、整流回路 21 の各ダイオード 211～214 と第 2 のダイオード 226 にはそれぞれ平滑用のリアクトル 24 に流れる電流  $I_L$  の略 1/3 の電流が流れている (図 2 (f)、(g)、(k) 参照)。

【0031】

時刻  $t_0$  において第 1、第 4 の主スイッチング素子 111、141 のゲート端子に印加される駆動信号が立ち上がって該主スイッチング素子 111、141 が共にターンオンすると、トランス 20 の一次巻線 201 には所定方向 (図 1 中では上から下向き) に電流が流れ始める。図 2 (d) はこのときの電流の向きを正極性で示している。トランス 20 の二次巻線 202 の両端には巻数比に応じた電圧が誘起され、図 2 (f) に示すように、ダイオード 211、214 に流れる電流は  $I_L$  / 3 から増加し始める。これと反対に、図 2 (g) に示すように、ダイオード 212、213 に流れる電流は  $I_L$  / 3 から減少し始める。時刻  $t_0$  においてダイオード 211、214 に流れる電流は  $I_L$  に達する一方、ダイオード 212、213 に流れる電流はゼロとなり、該ダイオード 212、213 はカットオフ状態となる。

【0032】

ただし、オフしようとしているダイオード 212、213 についてはリカバリー時間が存在するために、少しの間 (時刻  $t_2$  になるまで)、ダイオード 211、214 に流れる電流は増加し続け、ダイオード 212、213 に流れる電流はゼロ以下まで減少し続ける。ダイオード 212、213 の電流がゼロ以下になるということは、カソードからアノードに向けて電流が逆流することを意味する。そのため、ダイオード 211～214 にリカバリー電流 (短絡電流) が流れると共に、トランス 20 の漏れインダクタンスにエネルギーが蓄積される。

【0033】

10

20

30

40

50

スナバ回路 2 2 が設けられていない場合、時刻  $t_2 \sim t_3$  の期間中に、ダイオード 2 1 2、2 1 3 が逆電流阻止能力を回復し始めると、トランス 2 0 の漏れインダクタンスのエネルギーと上記ダイオード 2 1 1 ~ 2 1 4 の寄生容量とに起因する大きな振動サージ電圧が発生する。これに対し、本実施例の DC - DC コンバータ装置では、整流回路 2 1 の両端間（高電圧側ラインと低電圧側ラインとの間）にサージ電圧が発生すると、第 1 のダイオード 2 2 2 を介してスナバ用コンデンサ 2 2 1 に充電電流が流れ（図 2 ( j ) 参照）、それにより該コンデンサ 2 2 1 の両端電圧は充電された分だけ上昇する。即ち、転流に伴い発生する振動サージ電圧のスパイク状の部分はスナバ用コンデンサ 2 2 1 に吸収され（図 2 ( h ) 参照）、整流回路 2 1 のダイオード 2 1 1、2 1 4 の両端電圧は図 2 ( i ) に示すように、立ち上がり直後が略平坦にクランプされる。これにより、サージ電圧がダイオード 2 1 1 ~ 2 1 4 に印加されることを回避することができる。

10

#### 【 0 0 3 4 】

上述したようにサージ電圧がスナバ用コンデンサ 2 2 1 に吸収され、時刻  $t_3$  において、ダイオード 2 1 2、2 1 3 に流れる電流はゼロに戻る。他方、ダイオード 2 1 1、2 1 4 に流れる電流は  $I_L$  になる。しかしながら、電流  $I_L$  には上述したトランス 2 0 の漏れインダクタンスとダイオード 2 1 1 ~ 2 1 4 の寄生容量に起因する減衰振動波形が重畠する。この電流は LC フィルタ回路 2 3 により平滑されて負荷 2 6 に供給される。ここで、スナバ用コンデンサ 2 2 1 の充電電圧は第 1 のダイオード 2 2 2 の極性のために放電が阻止されるので、クランプされた電圧に保持される。また、整流回路 2 1 のダイオード 2 1 2、2 1 3 の両端電圧には、電流  $I_L$  と同様に、上記漏れインダクタンスとダイオード 2 1 1 ~ 2 1 4 の寄生容量に起因する減衰振動波形が重畠される。

20

#### 【 0 0 3 5 】

時刻  $t_4$  において、第 1、第 4 の主スイッチング素子 1 1 1、1 4 1 のゲート端子に印加される駆動信号が立ち下がって該主スイッチング素子 1 1 1、1 4 1 が共にターンオフすると、第 1 ~ 第 4 の主スイッチング素子 1 1 1 ~ 1 4 1 が全てオフした状態、つまりデッドタイム期間となる。このデッドタイム期間中の所定時間、図 2 ( e ) に示すようなスナバ用スイッチング素子駆動部 3 2 からの駆動信号によってスナバ用スイッチング素子 2 2 3 がオン状態になると、第 1 のダイオード 2 2 2 に並列である、スイッチング素子 2 2 3 及び限流用リクトル 2 2 5 を介した電流経路が形成される。それによって、スナバ用コンデンサ 2 2 1 に蓄えられたサージ電圧に起因するエネルギーは該コンデンサ 2 2 1 からリクトル 2 4 の定電流作用によって電流  $I_L$  として放出され、スナバ用スイッチング素子 2 2 3、限流用リクトル 2 2 5、LC フィルタ回路 2 3 に含まれる平滑用リクトル 2 4 等を含む経路を介して負荷 2 6 に回生される。これによって、スナバ用コンデンサ 2 2 1 の充電電圧は下がる。

30

#### 【 0 0 3 6 】

ただし、スナバ用スイッチング素子 2 2 3 がオン状態になったときにスナバ用コンデンサ 2 2 1 の両端電圧と整流回路 2 1 の両端間の振動電圧との差が大きい場合、スナバ用コンデンサ 2 2 1 に蓄えられたエネルギー由来の電流の少なくとも一部が整流回路 2 1 に含まれるダイオード 2 1 1 ~ 2 1 4 の寄生容量に流れてしまう。仮に限流用リクトル 2 2 5 がない（短絡されている）とすると、瞬間に大きな電流がダイオード 2 1 1 ~ 2 1 4 に流れ、これらにダメージを与えるおそれがある。これに対し、本実施例の DC - DC コンバータ装置では、限流用リクトル 2 2 5 がスナバ用スイッチング素子 2 2 3 と直列に接続され、上述した第 2 の直列回路を構成している。それによって、整流回路 2 1 に含まれるダイオード 2 1 1 ~ 2 1 4 に流れる電流を減らし、これら回路部品にダメージを与えることを回避することができる。

40

#### 【 0 0 3 7 】

時刻  $t_6$  において、スナバ用スイッチング素子 2 2 3 がターンオフされると該スイッチング素子 2 2 3 を通した電流の流れは阻止される。このとき、限流用リクトル 2 2 5 にはエネルギーが蓄積されていて該エネルギーに基づいた電流をそれまでと同じ方向に流し続けるとする。この電流はスイッチング素子 2 2 3 を通ることはできないが、その代わりに

50

、第2のダイオード226を通して整流回路21の高電圧側ラインに流れる。これにより、この電流は平滑用リアクトル24等を通して負荷26に回生され、サージ電圧に由来するエネルギーを有効に利用することができる。

【0038】

本実施例のDC-DCコンバータ装置において、上記限流用リアクトル225の有無による波形の比較を図3及び図4に示す。図3は限流用リアクトル225を短絡して機能させず、オフ状態であるダイオード211～214の寄生容量に流れる電流が抑制できない場合の波形図である。一方、図4は限流リアクトル225が機能し、オフ状態であるダイオード211～214の寄生容量に流れる電流を抑制している場合の波形図である。

【0039】

図3の時刻t4において、スナバ用スイッチング素子223がオン状態になり、時刻t5におけるスナバ用コンデンサ221の両端電圧と整流回路21の両端間の振動電圧との差が大きい場合、図3(f)、(g)、(j)の波形より、スナバ用コンデンサ221からダイオード211～214の寄生容量に大きな電流が流れていることが分かる。これに対し、図4における同一時刻の図4(f)、(g)、(j)の波形より、限流用リアクトル225の作用によって、スナバ用コンデンサ221からダイオード211～214の寄生容量に流れる電流が抑制されていることが分かる。

【0040】

なお、上記実施例のDC-DCコンバータ装置では、図2に示すように、1サイクル(この例では80kHzの周波数)中に1回、スナバ用スイッチング素子223を所定時間、つまり時刻t4からt6までの期間だけオンさせてスナバ用コンデンサ221に充電された余分なエネルギーを放出しているが、これは必ずしも1サイクルに1回行う必要はない。そこで、例えば、主スイッチング素子111～141をオン・オフ動作させるサイクルを決める信号を分周(例えば1/2分周、1/4分周)した信号に基づいてスナバ用スイッチング素子223をオンさせるタイミングを決めるようにしてよい。これにより、主スイッチング素子111～141をオン・オフ動作させるサイクルは80kHzでも、スナバ用スイッチング素子223がオンするサイクルは40kHz或いは20kHzなどとなる。

【0041】

このように、スナバ用スイッチング素子223をオンするサイクルを延ばす場合には、1回のエネルギー放出によって放出すべきエネルギー量が増えるから、その分だけオン時間(時刻t4からt6までの期間)を長くすればよい。このオン時間が短すぎると却って該オン時間の正確な制御が難しくなることがあるが、エネルギー放出のサイクルを長くしてオン時間を延ばすと、該オン時間の正確な制御が容易になる。

【0042】

また、上記実施例は本発明の一例にすぎず、本発明の趣旨の範囲で適宜変形、修正、追加を行っても本願特許請求の範囲に包含されることはある。

例えば、上記実施例では一次側回路はフルブリッジ回路であるが、これはハーフブリッジ回路でも、さらにプシュブル回路やフォワード回路であってもよい。

【符号の説明】

【0043】

1…一次側回路

10…直流電源

111、121、131、141…主スイッチング素子

112、122、132、142…ダイオード

2…二次側回路

20…トランス

201…一次巻線

202…二次巻線

21…整流回路

211、212、213、214…ダイオード

10

20

30

40

50

- 2 2 ... スナバ回路

2 2 1 ... スナバ用コンデンサ

2 2 2 ... 第1のダイオード

2 2 3 ... スナバ用スイッチング素子

2 2 4 ... ダイオード(ボディダイオード)

2 2 5 ... 限流用リクトル

2 2 6 ... 第2のダイオード

2 3 ... L C フィルタ回路

2 4 ... 平滑用リクトル

2 5 ... 平滑用コンデンサ

2 6 ... 負荷

3 0 ... 駆動制御部

3 1 ... 主スイッチング素子駆動部

3 2 ... スナバ用スイッチング素子駆動部

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 木村 智

京都府宇治市槇島町十六 19 - 1 京都電機器株式会社内

(72)発明者 岡本 景太

京都府宇治市槇島町十六 19 - 1 京都電機器株式会社内

審査官 久保 正典

(56)参考文献 特開2015-070716 (JP, A)

特開2005-137178 (JP, A)

国際公開第2013/076752 (WO, A1)

特開2016-052222 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 1/00 - 3/44