(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-530360

(P2004-530360A)

(43) 公表日 平成16年9月30日(2004.9.30)

(51) Int.C1.<sup>7</sup>H01P 1/213

H01P 1/20

H01P 1/205

F 1

H01P 1/213

H01P 1/20

H01P 1/205M

Z

J

テーマコード(参考)

5J006

審査請求 未請求 予備審査請求 有 (全 97 頁)

(21) 出願番号 特願2002-581616 (P2002-581616)

(86) (22) 出願日 平成14年4月2日 (2002.4.2)

(85) 翻訳文提出日 平成15年10月8日 (2003.10.8)

(86) 國際出願番号 PCT/IB2002/001030

(87) 國際公開番号 WO2002/084781

(87) 國際公開日 平成14年10月24日 (2002.10.24)

(31) 優先権主張番号 60/283,093

(32) 優先日 平成13年4月11日 (2001.4.11)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 09/904,631

(32) 優先日 平成13年7月13日 (2001.7.13)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 09/912,753

(32) 優先日 平成13年7月24日 (2001.7.24)

(33) 優先権主張国 米国(US)

(71) 出願人 503370192

キヨウセラ ワイヤレス コーポレイション

アメリカ合衆国 カリフォルニア 921

21, サンディエゴ, キャンパス

ポイント ドライブ 10300

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】チューナブルマルチブレクサ

## (57) 【要約】

本発明は、CDMA通信デバイスにおいて利用するためのチューナブル強誘電性マルチブレクサを提供する。チューナブル強誘電性キャパシタは、マルチブレクサで利用されるいくつかの共振器の共振周波数をチューニングし、かつ、マルチブレクサの周波数応答の形状をチューニングするために利用される。低損失強誘電性材料および構成が提供される。チューナブルマルチブレクサは、同様であり、固定チューニングされたマルチブレクサより小さい挿入損失を有する。

【選択図】図12

**【特許請求の範囲】****【請求項 1】**

第1の制御信号を生成する第1の制御信号ジェネレータと、

第1のキャパシタと、

第1の共振器と、

ここで、該第1のキャパシタおよび該第1の共振器は、第1の共振周波数を有する第1の電磁気信号フィルタとして構成され、

該第1の共振周波数を調節する該第1のキャパシタの容量を該第1の制御信号に応答して調節する、該第1のキャパシタの近位に位置する第1の強誘電性材料部分と、

第2の制御信号を生成する第2の制御信号ジェネレータと、

第2のキャパシタと、

第2の共振器と、

ここで、該第2のキャパシタおよび該第2の共振器は、第2の共振周波数を有する第2の電磁気信号フィルタとして構成され、

該第2の共振周波数を調節する該第2のキャパシタの容量を該第2の制御信号に応答して調節する、該第2のキャパシタの近位に位置する第2の強誘電性材料部分とを含み、

各キャパシタのQ値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、約80より大きくなる、

チューナブルマルチプレクサ。

10

20

**【請求項 2】**

各キャパシタの前記Q値は、約180より大きい、請求項1に記載のマルチプレクサ。

**【請求項 3】**

各キャパシタの前記Q値は、約350より大きい、請求項1に記載のマルチプレクサ。

**【請求項 4】**

前記Q値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、0.25GHzと7.0GHzとの間の周波数範囲で約80より大きくなる、請求項1に記載のマルチプレクサ。

**【請求項 5】**

前記Q値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、約0.8GHzと7.0GHzとの間の周波数範囲で約80より大きくなる、請求項4に記載のマルチプレクサ。

30

**【請求項 6】**

前記Q値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、約0.25GHzと2.5GHzとの間の周波数範囲で約80より大きくなる、請求項4に記載のマルチプレクサ。

**【請求項 7】**

前記Q値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、約0.8GHzと2.5GHzとの間の周波数範囲で約80より大きくなる、請求項6に記載のマルチプレクサ。

40

**【請求項 8】**

前記Q値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、0.25GHzと7.5GHzとの間の周波数範囲で約180より大きくなる、請求項1に記載のマルチプレクサ。

**【請求項 9】**

前記Q値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、約0.8GHzと2.5GHzとの間の周波数範囲で約180より大きくなる、請求項8に記載のマルチプレクサ。

**【請求項 10】**

前記Q値は、摂氏約-50度と摂氏約100度との間の温度範囲で作動する場合に、約0

50

.3 pF と 3.0 pFとの間の範囲で容量に対して約 80 より大きくなる、請求項 1 に記載のマルチプレクサ。

【請求項 11】

前記 Q 値は、摂氏約 -50 度と摂氏約 100 度との間の温度範囲で作動する場合に、約 0.5 pF と 1.0 pF との間の範囲で容量に対して約 80 より大きくなる、請求項 10 に記載のマルチプレクサ。

【請求項 12】

前記 Q 値は、摂氏約 -50 度と摂氏約 100 度との間の温度範囲で作動する場合に、約 0.3 pF と 3.0 pF との間の範囲で容量に対して約 180 より大きくなる、請求項 1 に記載のマルチプレクサ。

10

【請求項 13】

前記 Q 値は、摂氏約 -50 度と摂氏約 100 度との間の温度範囲で作動する場合に、約 0.5 pF と 1.0 pF との間の範囲で容量に対して約 180 より大きくなる、請求項 12 に記載のマルチプレクサ。

【請求項 14】

前記第 1 の共振周波数は、約 1850 MHz から約 1910 MHz の範囲の間にあり、第 2 の共振周波数は、約 1930 MHz から約 1990 MHz の範囲の間にあり、請求項 1 に記載のマルチプレクサ。

【請求項 15】

前記第 1 の共振周波数は、約 1750 MHz から約 1780 MHz の範囲の間にあり、第 2 の共振周波数は、約 1840 MHz から約 1870 MHz の範囲の間にあり、請求項 1 に記載のマルチプレクサ。

【請求項 16】

第 3 の制御信号を生成する第 3 の制御信号ジェネレータと、

第 3 のキャパシタと、

第 3 の共振器と、

ここで、該第 3 のキャパシタおよび該第 3 の共振器は、第 3 の共振周波数において共振するように構成される第 3 の電磁気信号フィルタとして構成され、該第 3 の共振周波数は、前記第 1 の共振周波数にほぼ等しく、

該第 3 の共振周波数を調節する該第 3 のキャパシタの容量を該第 3 の制御信号に応答して調節する、該第 3 のキャパシタの近位に位置する第 3 の強誘電性材料部分と、

第 4 の制御信号を生成する第 4 の制御信号ジェネレータと、

第 4 のキャパシタと、

第 4 の共振器と、

ここで、該第 4 のキャパシタおよび該第 4 の共振器は、第 4 の共振周波数を有する第 4 の電磁気信号フィルタとして構成され、該第 4 の共振周波数は、前記第 2 の共振周波数にほぼ等しく、

該第 4 の共振周波数を調節する該第 4 のキャパシタの容量を該第 4 の制御信号に応答して調節する、該第 4 のキャパシタの近位に位置する第 4 の強誘電性材料部分とをさらに含む、請求項 1 に記載のマルチプレクサ。

40

【請求項 17】

第 1 の制御信号を生成する第 1 の制御信号ジェネレータと、

第 1 のキャパシタと、

第 1 のボリュメトリック共振器と、

ここで、該第 1 のキャパシタおよび該第 1 の共振器は、第 1 の共振周波数を有する第 1 の電磁気信号フィルタとして構成され、

該第 1 の共振周波数を調節する該第 1 のキャパシタの容量を該第 1 の制御信号に応答して調節する、該第 1 のキャパシタの近位に位置する第 1 の強誘電性材料部分と、

第 2 の制御信号を生成する第 2 の制御信号ジェネレータと、

第 2 のキャパシタと、

50

第2のボリュメトリック共振器と、

ここで、該第2のキャパシタおよび該第2の共振器は、第2の共振周波数を有する第2の電磁気信号フィルタとして構成され、

該第2の共振周波数を調節する該第2のキャパシタの容量を該第2の制御信号に応答して調節する、該第2のキャパシタの近位に位置する第2の強誘電性材料部分とを含む、チューナブルマルチプレクサ。

【請求項18】

前記第1の共振周波数は、約1850MHzから約1910MHzの範囲の間であり、前記第2の共振周波数は、約1930MHzから約1990MHzの範囲の間である、請求項17に記載のマルチプレクサ。

10

【請求項19】

各共振器は、ストライプライン共振器を含む、請求項17に記載のマルチプレクサ。

【請求項20】

各共振器は、モノブロック共振器を含む、請求項17に記載のマルチプレクサ。

【請求項21】

各共振器は、同軸誘電性ロード(loaded)共振器を含む、請求項17に記載のマルチプレクサ。

【請求項22】

各キャパシタのQ値は、約80より多い、請求項17に記載のマルチプレクサ。

【請求項23】

各キャパシタのQ値は、約180より多い、請求項17に記載のマルチプレクサ。

20

【請求項24】

各キャパシタのQ値は、約350より多い、請求項17に記載のマルチプレクサ。

【請求項25】

前記第1の共振周波数は、約1850MHzから約1910MHzの範囲の間であり、前記第2の共振周波数は、約1930MHzから約1990MHzの範囲の間である、請求項17に記載のマルチプレクサ。

【請求項26】

第5の制御信号を生成する第5の制御信号ジェネレータと、

第5のキャパシタと、

30

前記マルチプレクサに応答して該第1の周波数を調節する該第5のキャパシタの容量を該第5の制御信号に応答して調節する、該第5のキャパシタの近位に位置する第5の強誘電性材料部分と、

第6の制御信号を生成する第6の制御信号ジェネレータと、

第6のキャパシタと、

該マルチプレクサに応答して該第2の共振周波数を調節する該第6のキャパシタの容量を該第6の制御信号に応答して調節する、該第6のキャパシタの近位に位置する第6の強誘電性材料部分と

をさらに含む、請求項17に記載のマルチプレクサ。

【請求項27】

電池と、

トランシーバと、

ユーザインターフェイスと、

該電池および該トランシーバをカプセル化する筐体であって、該筐体にユーザインターフェイス外部を提示するように適応される、筐体と、

第1の制御信号を生成する第1の制御信号ジェネレータと、

第1のキャパシタと、

第1の共振器と、

ここで、該第1のキャパシタおよび該第1の共振器は、第1の共振周波数を有する第1の電磁気信号フィルタとして構成され、

40

50

該第1の共振周波数を調節する該第1のキャパシタの容量を該第1の制御信号に応答して調節する、該第1のキャパシタの近位に位置する第1の強誘電性材料部分と、

第2の制御信号を生成する第2の制御信号ジェネレータと、

第2のキャパシタと、

第2の共振器と、

ここで、該第2のキャパシタおよび該第2の共振器は、第2の共振周波数を有する第2の電磁気信号フィルタとして構成され、

該第2の共振周波数を調節する該第2のキャパシタの容量を該第2の制御信号に応答して調節する、該第2のキャパシタの近位に位置する第2の強誘電性材料部分とを含む、無線通信デバイス。

10

【請求項28】

ボリュメトリック共振器

をさらに含む、請求項29に記載の無線通信デバイス。

【請求項29】

ストライプライン共振器

をさらに含む、請求項30に記載の無線通信デバイス。

【請求項30】

モノブロック共振器

をさらに含む、請求項30に記載の無線通信デバイス。

【請求項31】

同軸誘電性ロード共振器

をさらに含む、請求項32に記載の無線通信デバイス。

【請求項32】

各キャパシタのQ値は、約80より大きい、請求項29に記載の無線通信デバイス。

【請求項33】

各キャパシタのQ値は、約180より大きい、請求項29に記載の無線通信デバイス。

【請求項34】

各キャパシタのQ値は、約350より大きい、請求項29に記載の無線通信デバイス。

【請求項35】

前記第1の共振周波数は、約1850MHzから約1910MHzの範囲の間であり、前記第2の共振周波数は、約1930MHzから約1990MHzの範囲の間である、請求項29に記載の無線通信デバイス。

30

【請求項36】

前記第1の共振周波数は、約1750MHzから約1780MHzの範囲の間であり、前記第2の共振周波数は、約1840MHzから約1870MHzの範囲の間である、請求項29に記載の無線通信デバイス。

【請求項37】

第3の制御信号を生成する第3の制御信号ジェネレータと、

第3のキャパシタと、

第3の共振器と、

ここで、該第3のキャパシタおよび該第3の共振器は、第3の共振周波数において共振するように構成される第3の電磁気信号フィルタとして構成され、該第3の共振周波数は、前記第1の共振周波数にほぼ等しく、

該第3の共振周波数を調節する該第3のキャパシタの容量を該第3の制御信号に応答して調節する、該第3のキャパシタの近位に位置する第3の強誘電性材料部分と、

第4の制御信号を生成する第4の制御信号ジェネレータと、

第4のキャパシタと、

第4の共振器と、

ここで、該第4のキャパシタおよび該第4の共振器は、第4の共振周波数を有する第4の電磁気信号フィルタとして構成され、該第4の共振周波数は、前記第2の共振周波数にほ

40

50

ば等しく、

該第4の共振周波数を調節する該第4のキャパシタの容量を該第4の制御信号に応答して調節する、該第4のキャパシタの近位に位置する第4の強誘電性材料部分とをさらに含む、請求項29に記載の無線通信デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願)

本出願は、2001年4月11日に出願され、参考として本明細書で援用される米国仮出願第60/283,093号の利益を主張する。

10

【0002】

さらに、本出願は、2001年7月13日に出願され、参考として本明細書で援用される米国出願「Tunable Ferro-electric Filter」に関する。

【背景技術】

【0003】

(背景)

(関連技術の説明)

バンドパスフィルタなどのフィルタは、通信およびエレクトロニクスにおいての多数の出願を有する。例えば、無線通信において、所与の周波数帯域は、多くの無線ユーザを収容する。それほど多くのユーザを収容するためには、提供される周波数割り当てが混雑しているために、厳密なバンドパスフィルタリング要件が達成されなければならない。

20

【0004】

現在、無線ハンドセットは、固定チューニングされたバンドパスフィルタ(BPF)を用いて、それらのフィルタリング規格を満たす。このようなフィルタの設計は、それらが最小の可能なパスバンド挿入損失(I.L.)を達成しなければならず、同時に、特定化された大きな帯域外除去を達成するために、複雑化されている。特定の例として、PCS CDMAハンドセットを考慮してみる。PCS送信(TX)帯域は、-3.5dBの帯域内I.L.のみを有するとともに(米国において1850から1910MHz)、受信(RX)帯域(1930~1990MHz範囲)において、少なくとも38.0dBの帯域外除去を有する。

30

【0005】

さらに、このBPFは、高さについて、最大制限を有する上記の規格を満たさなければならない。今日のハンドセットの典型的な高さ制限は、例えば、4.0mm以下である。上記の要求している電気的な要件であって、最小の可能なサイズおよび高さを有する要件を満たすために、個々の同軸共振器素子またはモノブロック構造から構築される高次(>2次)固定チューニングされたフィルタは、常に必要とされる。さらに、帯域外除去規格を満足させるために、トランスマッショングゼロが常に要求され、帯域エッジにてI.L.を増加させる。セラミックおよび製造耐久性についての変動のために、ベンダーは、個別に、製造中に固定チューニングされたフィルタの特性を調整しなければならず、コストをより高くする。

40

【0006】

さらに、一つより多い周波数帯域がサポートされている場合(例えば米国、韓国およびインドではPCS帯域をサポートしている)、複数の固定チューニングされたBPFが必要であり、余分なスイッチを必要とし、さらなる損失を生じさせる。これは、電力増幅器および用いられた低雑音増幅器が、上記の複数の帯域を介して動作するのに十分な帯域幅を有する場合でさえ、当てはまる。

【0007】

チューナブルBPFにより、任意の特定の時間にて必要とされるバスバンドより広い帯域幅をカバーしたいくつかの帯域を介する一つのBPFの使用、または、より低次のフィルタの使用が可能になる。チューナブルBPFに可変性を提供するために、可変容量を提供

50

できるコンポーネントが、通常、用いられる。

【0008】

いくつかの構造は、現在、可変キャパシタを実現するように用いられる。例えば、移動可能な平行板は、家庭のラジオのチューナーとして、長年、用いられてきた。しかし、このようなプレートは、あまりにも、かさ高く、うるさく、現在の用途のために使用するには非実用的である。

【0009】

別の代替物、電気バラクターは、印加電圧に応答して容量 (capacitance) を調節する半導体デバイスである。バラクターは、通常、うるさく、損失が大きく、特に 500 MHz より大きい印加では、うるさく、損失が大きいので、高性能が要求される高周波数の低損失用途に対しては非効率である。

【0010】

別の代替物、マイクロエレクトロメカニカルスイッチ（またはシステム）（MEMS）は、付与された制御信号に応答してキャパシタ間でスイッチングし得る微小のスイッチングデバイスである。しかし、それは、コストがかかり、製造することが困難であり、信頼性が立証されていない。たいていの場合、それは、システムが、有限の（かつ小さい）数の固定キャパシタの間を選択しなければならないという点で、個別のチューニングを提供する。

【0011】

強誘電体チューナブルキャパシタは、試用されてきた別の代替物である。強誘電体 (f-e) 材料は、材料の一つの種類であり、通常、セラミック希土酸化物であり、顕著な特徴は、それらの比誘電率 ( ) 、および結果として、電気誘電率 ( ) が、印加されたゆっくりと変化する (DC または低周波数の) 電界に応答して、変化する。材料の比誘電率 ( ) と電気誘電率 ( ) との関係は、以下の

$$= 0$$

として与えられる。

【0012】

ここで、 $\epsilon_0$  は、真空の電気誘電率である。以下、f-e 属性を有する数百の公知の材料がある。通常の f-e 材料において、ほぼ 3:1 程度のファクタだけの範囲を得ることができる。このこのような変化を生じさせるために必要とされる DC 電圧は、DC 制御電圧が印加される f-e 材料の寸法に依存する。キャパシタの容量がキャパシタ導体に隣接した誘電体の比誘電率に依存するために、それらの可変比誘電率の結果として、f-e 材料を用いてチューナブルキャパシタを作ることができる。通常、チューナブル f-e キャパシタは、平行板（オーバーレイ）、インターデジタル（IDC）またはギャップキャパシタとして実現される。

【0013】

公知の f-e の可変キャパシタにおいて、チタン酸バリウムストロンチウム  $Ba_x Sr_1-x TiO_3$  (BSTO) 等の適切な f-e 材料の層は、キャパシタの一方または両方の導体に隣接して配置される。f-e 材料に印加される電界の強度および選択された f-e 材料の固有特性に依存して、容量が変化する。通常、f-e フィルムのキュリー温度  $T_c$  の下では、f-e 材料は、強誘電状態であり、変化する電界に対するその応答において、ヒステリシスを示す。 $T_c$  より上では、f-e 材料は、常誘電状態であり、ヒステリシスを示さない。したがって、概して、常誘電状態に動作するように、 $T_c$  が予想される動作温度より低い f-e 材料を選択し、強誘電状態のヒステリシスの影響を避ける。

【0014】

しかし、従来の f-e 可変キャパシタは、ハンドセット等の挿入 - 損失 - 感知用途での使用に対しては、あまりにも損失が大きいことが証明されている。さらに、これらのデバイスは、予測不可能に、実行する場合が多く、f-e チューナブルフィルタの最適な設計、構築および使用を妨げる。

【0015】

10

20

30

40

50

デュプレクサは、T × および R × 周波数をそれらの個別の信号バスに分離する C D M A 技術にて用いられる。デュプレクサは、通常、二つのバンドパスフィルタを含む。それぞれのフィルタは、通過されるべき T × または R × 周波数信号のいずれかを選択する。フィルタは、一方の端にて接続され、共通のポートを形成する。この共通ポートは、通常、送信信号を送り、受信信号を受け取るために、アンテナまたはダイプレクサに接続される。

【 0 0 1 6 】

厳密な挿入損失および帯域外除去要件は、例えば、無線ハンドセット等の、損失感知用途に使用するためにデュプレクサの設計に影響を与える第 1 の要件である。他の電気的および機械的な規格、例えばサイズおよび高さ要件等もまた満足されなければならない。

【 0 0 1 7 】

したがって、当該分野において、低い I . L . および高い帯域外除去に関する所望の周波数範囲を越えるチューニング範囲を提供できる改良されたチューナブル f - e フィルタ、および、同一のものを設計する方法が必要となる。次いで、これらのフィルタは、チューナブルデュプレクサを作るために使用され得る。

【 発明の開示 】

【 課題を解決するための手段 】

【 0 0 1 8 】

( 要旨 )

C D M A 無線ハンドセットにおいて、厳密な挿入損失および帯域外除去要件が、概して、デュプレクサの使用のために、高次（3 次より大きい）フィルタを要求する。帯域内挿入損失要件は、概して、任意の所与の時間にて動作のために用いられる周波数より広い周波数を越えて適用する。デュプレクサの使用のための固定チューニングされたフィルタが、同一のパスバンドを超えるチューニングによって用いられるチューナブルフィルタより広いパスバンドを有さなければならないことを意味する。チューナブルフィルタがより小さい（チューナブル）パスバンドを有し得るので、それは、より低次であり得る（場所を取り得ない）か、より少ない挿入損失を有し得るか、または両方であり得る。

【 0 0 1 9 】

これは、可変性の追加がデュプレクサの挿入損失をあまり大きく増加させない場合にのみ、当てはまる。本発明は、低い挿入損失を維持しながら、強誘電体チューナブルキャパシタ、デュプレクサをチューナブルにするキャパシタおよび共振器回路を提供する。

【 0 0 2 0 】

したがって、同一のパスバンドをカバーできる固定チューニングされたバンドパスフィルタより小さく、かつ、より小さい挿入損失を有する、低挿入損失のチューナブルデュプレクサが提供される。無線ハンドセットのスペース節約は、他の所望の機能および特性を提供するように用いられ得、または、それは、ハンドセットのサイズおよび重さを単に低減するように用いられ得る。さらに、挿入損失の節約は、結果的に、より長い通話時間およびバッテリ使用期間を生じさせる。

【 発明を実施するための最良の形態 】

【 0 0 2 1 】

( 詳細な説明 )

異なる図面の同一の参照符号の使用は類似または同一の部材を表示する。

【 0 0 2 2 】

電気信号処理システム、例えば通信システム等の使用および用途のためのチューナブルバンドパスフィルタ（ B P F ）を設計する場合、帯域外除去およびパスバンド挿入損失（ I . L . ）要件の両方、およびサイズ、重さ並びに他の機械的、環境的、固定チューニングされた B P F に課された電気的要件を通常満たさなければならないか、越えなければならない。

【 0 0 2 3 】

したがって、チューナブル B P F が、固定チューニングされた B P F の代わりに置き換えられることが商業的に実施されるためには、チューナブル B P F の性能は、電気的および

10

20

30

40

50

機械的要件のほとんど全ての点において置き換わる固定チューニングされたBPFの性能に勝っているべきである。無線ハンドセット等の用途を要求する点で、パスバンドI.L.は、ハンドセットの他のコンポーネント上にまさにより大きな負担を置くことを防ぐよう最小化されなければならない。チューナブルBPFが、それが置き換わることになる固定チューニングされたBPFより大きなI.L.を有する場合、追加されたI.L.は、全体のシステム性能上の余りにも大きな負担であることが分かり得る。追加された負担は、通常、增幅器等のアクティブデバイス上にて最大となる。增幅器は、現存する固定帯域幅フィルタの影響を超える増加したパスバンド損失の影響を克服するために、より大きな利得およびパワー出力を有さなければならない。

## 【0024】

10

「パスバンド」を定義するものの多くの定義が用いられ得る。通常、パスバンドはポイントによって定義され、このポイントでは、バンドパスフィルタ応答が、中間帯域、または帯域中心挿入損失(I.L.)より下の3.0dBに落ちる。しかし、任意の固定フィルタ応答は、パスバンドを定義するように用いられ得る。より高次(より多くの共振器)バンドパスフィルタは、通常、特定の帯域外除去要件と整合することが要求される。しかし、フィルタ次数を増加させることは、I.L.を増加させる。フィルタ次数とI.L.との間の有用な基本的な関係は、以下の式によって与えられる。

## 【0025】

## 【数1】

20

$$IL_0 = (4.34 * Q_i / Q_u) * \sum_{i=1}^N g_i \quad (1)$$

Nはフィルタ次数であり、

Q<sub>u</sub>は用いられる共振器の無負荷のQであり、

Q<sub>i</sub> = f<sub>0</sub> / BW (BWは3dBパスバンドであり、f<sub>0</sub>は中間帯域周波数である)、および、

g<sub>i</sub>は、所与のトポロジ(Chebyshev vs. Butterworth)についてのフィルタ素子値(filter element value)である。

## 【0026】

30

概して、Chebyshev応答は、それが所与のフィルタ次数のButterworthフィルタによって与えられる除去応答と比較すると急勾配の除去応答を与えるため、好適である。さらに、Chebyshev BPFのリップルを増加させることは、帯域外除去をさらに増加させる。式(1)からわかるように、所与のフィルタ次数Nについて、より大きなパスバンドは、結果として、BWが増加するにつれてQ<sub>i</sub>が減少するより低いI.L.を生じさせる。このより低いI.L.は、減らされた選択性を犠牲にする。選択性を再度獲得するためには、フィルタ次数Nは、I.L.を犠牲にして増加されなければならない。バンドパスフィルタ設計の当業者は、式(1)が表わすのは、最もものが所与のシステム要件およびフィルタ次数に役立つということを認める。高次フィルタ(所与の無負荷のQのより多い共振器)を用いることは、I.L.を素早く増加させる。なぜなら、g<sub>i</sub>値は、合計すべきより多くの値(増加したN)があるとともに、次第に、大きさ(magnitude)が大きくなるからである。式(1)は、特に帯域端が近づけられるとI.L.をさらに増加させる実施損失を無視することに留意する。

40

## 【0027】

一次または二次バンドパスフィルタを用いることはI.L.を低減させることが式(1)から理解され得る。これらのより低次にて、g<sub>i</sub>係数の数(N)およびg<sub>i</sub>の大きさの両方が減少する。これらの低次フィルタでは、最小の可能なI.L.を与えるように最小の損失(最高Q<sub>u</sub>)を有する共振器から構築されるべきである。結果として生じる一次または二次のバンドパスフィルタは、常に、比較可能な高次の固定チューニングされたバンドパスフィルタ設計より、所与の共振器のサイズおよびタイプ(すなわち所与のQ<sub>u</sub>)

50

の低い  $I \cdot L_0$  を有する。可変性により、低次の狭帯域 BPF がより広い帯域の、固定チューニングされた BPF と置き換わることが可能になる。チューナブル狭帯域低次 BPF は、関心のある帯域全体をカバーでき、狭帯域幅の有する限界を克服する。これは、所望のチャネル（情報）帯域幅が全体のシステム帯域幅より狭いことを仮定する。

【0028】

固定チューニングされた BPF が、単一の信号の送信および受信のために必要とされるよりも大きいシステム帯域幅をカバーする場合、チューナブル BPF は、固定チューニングされた BPF と置き換わる最高の機械を有する。例えば、米国 CDMA PCS 帯域内の動作のためのハンドセット内の固定チューニングされた BPF はまた、このような BW をカバーする。これはまた、米国 cellular CDMA および多くの他の標準に当てはまることが理解される。本明細書中にて教示された技術、方法およびデバイスは、米国 CDMA PCS に加えて、多くの標準に適用可能である。米国 CDMA PCS が実例としてのみ議論される。

【0029】

米国 PCS 帯域において、60 MHz は、 $T_x$  (1850 ~ 1910 MHz) に割り当てられ、60 MHz は、 $R_x$  (1930 ~ 1990 MHz) に割り当てられる。CDMA 標準は、完全デュプレックスシステムであり、ハンドセットが同時に送受信することを意味する。これを成し遂げるために、デュプレクサフィルタは、帯域を分離し、干渉を防ぐために必要とされる。PCS 帯域が 60 MHz 幅である一方、個別の CDMA チャネルは単に 1.25 MHz 幅である。しかし、現在のシステムアーキテクチャは、CDMA PCS バンドパスフィルタおよびマルチプレクサ（デュプレクサを含む）に、システムが、60 MHz 帯域の任意の領域において、任意の 1.25 MHz チャネルの動作を可能にし、かつ適応しなければならない場合は、BW 60 MHz を有するようにする。

【0030】

チューナブル PCS 帯域フィルタは、より小さい物理領域を占めるより単純なトポロジのより低次の BPF を提供しながら、最悪の場合の除去規格を満たすことにより、この状況を変え得る。このようなより低次のフィルタは、必ず、式(1)により、より低い  $I \cdot L_0$  を提供する。

【0031】

高次の固定チューニングされた BPF をより低次のチューナブル BPF に効率良く取り替えるために、三つのファクタが考慮される。第1に、低次の BPF の帯域幅（すなわち  $Q_1$ ）および選択されたトポロジは、最悪の場合の除去規格が満たされるようなものでなければならない。 $Q_1 = f_0 / BW$  なので、3 dB 帯域幅 (BW) が減少すると、 $I \cdot L_0$  が増加する。したがって、BW が  $f_0$  に対してあまりにも小さい場合、結果として生じる BPF は、許容不可能なほど高い  $I \cdot L_0$  を有し、BW と  $I \cdot L_0$  との間にトレードオフを必要とする。実際の設計について、低次のチューナブル BPF は、最小で可能な  $I \cdot L_0$  を、最悪の場合に必要とされる除去を満たすことと一貫させるべきである。いくつかのトポロジは、それらが本来、低い側（送信帯域下）ゼロまたは高い側（送信帯域上）ゼロを提供する点において好適である。図10に示されるようなトポロジは、BPF  $Q_1$  がより小さい（帯域幅がより大きいので）か、または、リップル（対応する Chelychlev BPF の  $g_1$  の観点から明示される）がより低いか、または両方であるために、より低いパスバンド  $I \cdot L_0$  を提供できる。送信ゼロは、ある周波数範囲を超える余分に必要とされる除去を提供する。

【0032】

第2に、低次のチューナブルフィルタは、固定チューニングされたフィルタと同様に、全体の BW をカバーするために、チューナブルでなければならない。最後に、低次のチューナブルフィルタ内に用いられるチューナブルキャパシタは、結果として生じるフィルタが規格を満足するか、または越える  $I \cdot L_0$  を有するように、十分に低い損失を有する。チューナブル一次または二次バンドパスフィルタは、より高次の ( $N > 2$ ) 固定チューニングされたバンドパスフィルタ設計と比較して最小の追加損失を有するが、チューナブルコ

10

20

30

40

50

ンポーネント（可変  $f - e$  キャパシタ）は速いチューニングメカニズムを有し、利用可能なチューニング電圧を用いて、全体のバンドパス範囲をカバーするようにチューナブルでなければならない。

### 【0033】

キャパシタの全損失、 $L_t$  は、チューナブルであろうとなかろうと、それが蓄えられたエネルギーに対する消費されたエネルギーの割合によって与えられる。エネルギーは、電界にて蓄えられ、抵抗にて消費される、すなわち、 $L_t = (\text{消費されたエネルギー}) / (\text{蓄えられたエネルギー})$  である。この損失の逆数が  $Q$  値、 $Q$  である。キャパシタに関して、 $L_t$  は、量 ( $* R_s * C$ ) によって与えられ得、 $R_s$  は角振動数であり、 $R_s$  はキャパシタの合計直列抵抗であり、 $C$  は容量である。

10

### 【0034】

共振器回路の  $f - e$  キャパシタによって与えられる全損失を決定することの重要性は、以下の式から理解され得る。 $L_c = 1 / Q_c$  および  $1 / Q_T = 1 / Q_c + 1 / Q_u$  であり、 $L_c$  = キャパシタの損失；

$Q_T = f - e$  キャパシタおよび共振器または組み合わされたインダクタの合計  $Q$ ；

$Q_c$  = キャパシタの  $Q$ ；および

$Q_u$  = 無負荷の共振器の  $Q$  または並列共振器回路を作成するために用いられるインダクタの  $Q$ 。

### 【0035】

$Q_c$  が増加すると、それは、次第に、 $Q_T$  への影響が減少する。 $Q_c$  が無限である場合、それは  $Q_T$  に影響を与えない。これは、実用するために、 $Q_c$  がほぼ  $10 * Q_u$  となる場合、当てはまる。逆もまた真である。 $Q_u$  は  $Q_c$  に対して次第に高くなると、 $Q_u$  は、 $Q_T$  への影響を次第に減少させる。いずれの場合においても、最高に実用的な  $Q_c$  が望まれる。

20

### 【0036】

PCS 帯域の使用に有用な例では、 $1.0 \text{ pF}$  に対して、 $2.0 \text{ GHz}$  にて  $Q_c = 250$  を有するチューナブルキャパシタは、 $R_s$  が  $.32$  (オーム) であることが必要である。損失を最小にする（低い  $R_s$  を得る）ためには、可能であれば、現在の全ての損失メカニズムを計上し、かつ、これらの損失メカニズムの排除することを必要とする。

30

### 【0037】

$f - e$  デバイスについて、全損失は、以下のように、それぞれの電源寄与を合計することにより、左右される。

$$L_t = L_{geom} + L_{attach} + L_{metal} + L_{sub} + L_{rad} + L_{meas} + L_{f-e};$$

ここで  $L_{geom}$  は、キャパシタのトポロジから導出され、

$L_{attach}$  はデバイス取り付けによる損失であり、

$L_{metal}$  は、全金属損失であり、

$L_{sub}$  は、基本的な基板損失であり（存在する場合）、

$L_{rad}$  は、望まれる放射損失および望まれない放射損失の両方であり、

$L_{meas}$  は、測定誤差から生じる全損失であり、

$L_{f-e}$  は、 $f - e$  損失タンジェントである。

40

### 【0038】

この損失割り当ては、第 1 に、所望の動作周波数で、 $f - e$  キャパシタが用いられる様で  $L_{f-e}$  (または  $f - e$  tan) の正確な値を得られるように用いられ得る。 $L_{f-e}$  を正確に得るために、ちょうど説明された他の損失寄与源の全てを排除するか、または抑制しなければならない。例えば、 $L_{geom}$  は、トポロジに応じて変動し、オーバーレイキャパシタに対しては最良であり、ギャップキャパシタに対してはより悪く、IDC キャパシタに対してはかなり悪い。この損失は低減され得、制御され得るが、それはデバイスに固有である。結果として、所与の  $f - e$  キャパシタのトポロジの選択は、 $f - e$  キャパシタから達成できる最良の可能な  $Q_c$  に影響を与える。電磁場 (EM) ソフトウェ

50

アは、所望のジオメトリのベースライン損失を確立でき、損失なしの f - e 膜を仮定する。このベースライン損失は、所与のジオメトリの最良の（最小の）損失を表示する。

#### 【 0 0 3 9 】

概して、ギャップキャパシタは、製造するのが最も容易である。IDCは、次に容易であり、オーバーレイキャパシタは、これら三つの中で最も困難である。IDCと比較すると、ギャップキャパシタは、単位断面毎に、より良いQを有するが、より低い容量を有する（図1aのW）。IDCの容量は、単位断面毎に、多数のフィンガー（finger）の使用によってより大きくなる。しかし、多くの通信フィルタ用途のために、大きな容量（C 4.0 pF）が必要とされない。したがって、ギャップキャパシタは、しばしば、十分な容量を提供できる。たいていのf - e 膜のの本来高い値が、単位断面、W毎に、従来のギャップキャパシタと比較すると、比較的に高い容量を提供するのに役立つ。

#### 【 0 0 4 0 】

Lattachは、例えば半田、銀塗料、またはワイヤボンディング等の個別のデバイス取り付け技術から生じる。これらの取り付け損失は、大きくなり得、予測不可能で在り得る。最小の損失は、共振器または他のRF回路へのf - e キャパシタの直接の製造によって達成され、したがってこの損失コンポーネントを排除しない場合、最小化する。

#### 【 0 0 4 1 】

独立型のf - e キャパシタの本来の損失は、ほとんど影響しない。ずっと大きな影響であることが、f - e キャパシタの回路への取り付けから生じる任意に追加された損失である。f - e キャパシタが損失無しであるとしても、大きな損失の接続が用いられる場合、全体の影響は、損失のあるf - e デバイスの影響である。例えば、2.0 GHzでQ 250が1.0 pFの容量に望まれる場合、合計直列抵抗Rsは、0.32オームでなければならない。したがって、任意のさらなる損失がこのキャパシタのQをさらに低減する。この追加的な損失が実際の容量外であることは見当違いである。マウンティングによるもの等の、不可避な損失メカニズムでさえ、例えば、システム上のその影響の見地からキャパシタの有効なQを低下させる。

#### 【 0 0 4 2 】

最小の追加損失について、f - e キャパシタと共振器との間の接続は、最小の追加された抵抗を提供する。したがって、電流およびf - e キャパシタに関連する電荷は最小の追加損失となる。半田付け、ワイヤボンディングまたは銀塗料またはペースト（これらに限定されるわけではない）等の従来のボンディングまたはマウンティング技術は、このような低い損失、制御可能なボンドを提供しない。

#### 【 0 0 4 3 】

このようなボンディング方法の使用から生じる追加された予測不可能な損失は、f - e キャパシタが、共振器チューニング目的またはf - e 膜の特性化のために用いられるかどうかに関わらず、実現されるQを劣化させる。したがって、最良の性能（最小の損失）のために、f - e キャパシタ構造は、チューニングが予定される共振器上または共振器と共に直接製造されるべきであるか、または、他の不可欠なRF回路上に直接製造されるべきである。直接の製造によってのみ、f - e チューニング素子から共振器への電磁（EM）源（電流）に対する最小の損失遷移が存在し得る。共振器上への、または共振器と一緒に直接のf - e キャパシタ製造の所望の影響は、鋭い角の欠如または遷移によって、増強され得る。

#### 【 0 0 4 4 】

Lmetalに対するファクタは、金属の表面粗さ（SR）、皮膜深さに比較される金属厚、s、および導電率である。SRは、LおよびS帯域（1~4 GHz）における動作周波数に対して約10マイクロインチニ乗平均平方根（rms）未満である場合に、ファクタとして有効に除去され得る。金属厚は、厚さが1.5 s以上である場合にファクタとして低減され得るか、または厚さ5 sである場合に有効に除去される。電極コンタクトについて、金属厚（tm）は約1.5 sであり得る。電磁共振器について、進行波または定常波がサポートされなければならない場合、すなわち、注目する金属が波長の検

10

20

30

40

50

出可能な割合（約10%以上）である場合に、金属厚は約5s以上により近づくべきである。

#### 【0045】

導電率はAu、Cu、またはAgについて最も良い。したがって、L<sub>metal</sub>はファクタとして低減かつ制御され得るが除去されない。しかし、その効果は、当業者に周知の式によってか、または一般に使用される回路シミュレータ（EaglewareまたはTouchstoneなど）において利用可能なライン計算器ツールによって計算され得る。さらに、正確な製造制御は、L<sub>metal</sub>の幾何的ばらつきを制限し得る。

#### 【0046】

L<sub>sub</sub>によって表される損失寄与は、対象の動作周波数において0.001未満、好ましくは0.0005未満の損失タンジェントを有する低損失基板を選択することによって最小限にされ得る。適切な材料は、>99%純度のアルミナを含み、これは損失/コストの有益さについて現在最も良い選択である。サファイアまたはMgOは、より損失タンジェントが低いという点でアルミナよりも良いが、より高価である。これらの材料はすべて、バッファ層を用いなくてもf-e薄膜を受容し、かつさらなる研磨をほとんどあるいは全く行わなくても受容可能な表面粗さを有する。半導体基板は、導電率が比較的高いので良い選択ではない。損失タンジェント、表面粗さおよび価格に加えて、適切な基板は脆性であるべきでなく、より広い面積のウェハとして製造され得、かつ高価な前処理を用いずに容易にメタライズされ得る。

#### 【0047】

L<sub>sub</sub>を複合基板（f-e膜+基板）の総損失から切り離すことは、電磁界または回路シミュレーションソフトウェアによって達成され得る。例えば、ソネット、モメンタム、またはIE3Dが使用され得る。このように、L<sub>sub</sub>は著しく低減され、かつ正確に計算され得る。

#### 【0048】

L<sub>rad</sub>は、適切な遮蔽および設計によって除去され得、かつしたがって、通常ファクタではない。なお、広範囲のフィルタ、特にブレーナーフィルタ（コームラインまたはヘアピンなど）、は放射結合に依存して所望の性能を達成する。これらの場合、不要な浮遊結合は、除去されないかもしれないが、低減されることを確実にすべきである。

#### 【0049】

L<sub>meas</sub>は著しく回路損失エラーを付加し得る。なぜなら、小さな付加損失がテスト中のデバイス（DUT：device-under-test）またはシステムの測定されたQを著しく低減し、したがってDUTの固有のQを不明瞭にする。材料における比誘電率および損失タンジェントを測定するための従来の方法は、当業者に周知のキャビティ撮動法である。しかし、L帯域において、キャビティの大きさは非常に大きい。f-e膜などの膜厚1.5μmを有する薄膜（バルクとは対照的に）を特性化すると、測定誤差がひどくなり問題が非常に難しくなる。さらに、f-eキャパシタ（またはフィルタ）を、それがどのように使用されるかにほとんど同様のやり方で特性化すべきである。f-e化合物または膜を特性化する好適な方法はマイクロストリップ共振器法によるものである。

#### 【0050】

f-e膜特性を決定し、かつf-eキャパシタを特性化するためには、マイクロストリップ法は、例えばf-e膜特性化のためのストリップラインまたは他のボリュメトリック法よりも、以下の理由で好まれる。

#### 【0051】

1)マイクロストリップ回路は上部カバーを有さないブレーナーシステムであり、したがって上部カバーとしての堅い基板を接合する必要がない。したがって、例えば、ストリップラインにおいて必要とされるような接地面（上から下）の連続性も必要でない。

#### 【0052】

2)好ましくはギャップキャパシタ、またはIDC、は容易に製造および測定され得る。

#### 【0053】

10

20

30

40

50

3 ) マイクロストリップ共振器の特性化に関して大量の知識が存在する。

【 0 0 5 4 】

4 ) 例えば、誘電キャビティに必要とされるような複雑な固定または製造またはその両方が必要でない。

【 0 0 5 5 】

高 Q 回路を共振器法を使用して測定すべきである。なぜなら、広帯域測定は R F / マイクロ波周波数におけるオーム以下の抵抗性損失を任意の正確さで正確に分解し得ないからである。同じ理由のために、 L R C メータは良い選択ではない。

【 0 0 5 6 】

無線周波数における測定は、 f - e キャパシタに対して、正しく R s を得、そしてその結果 Q を得るために必要とされる。なぜなら、低い周波数測定（特に、約 1 0 0 M H z 以下の周波数）は、注目する容量をシャントする大きな並列抵抗 R p によって支配されるからである。R p の支配は、注目する容量の比較的小さな値（4 . 0 ~ 5 . 0 p F ）と共に、低周波数における信頼性のある Q ( および従って R s ) 測定の妨げとなる。

【 0 0 5 7 】

損失を測定するために使用される場合、ウェハプローブステーションは注意深く使用されなければならない。なぜなら、 R F / マイクロ波周波数における抵抗性および誘導性損失を検量するのは困難だからである。接地接続を伴うプローブ先端はまた、 D U T 上の配置およびそこに適用される圧力に影響されやすい。その結果、個々のデバイス損失測定を必要としない方法で所望のパラメータの直接測定を可能にする共振器テスト回路を使用することがより良い。

【 0 0 5 8 】

したがって、共振器回路の測定について、ネットワークアナライザは好適な選択である。測定損失を最小限にし、かつ最も正確な測定を達成するために、 D U T に対する損失を検量し、ネットワークアナライザの全 2 ポート検量を使用すべきである。最後に、測定データの適切な分析が、テスト中のキャパシタの Q または損失を正確に抽出するために必要である。適切な分析の概要は、「 Data Reduction Method for Q Measurements of Strip-Line Resonators 」、 I E E E Transactions in MTT 、 S . Toncich および R . E . Collin 、第 4 0 卷、 No . 9 、 1 9 9 2 年 9 月、 1 8 3 3 ~ 1 8 3 6 頁に記載され、その内容は本明細書中に参考として援用される。

【 0 0 5 9 】

上記検討の結果を使用して上記損失の各々を最小限にするか、除去するか、または制限すると、総損失は以下のように表され得る。

【 0 0 6 0 】

$$L_t = L_{geom} + L_{metal} + L_{f-e} + L_{miss}$$

上記のように、 L \_ g e o m および L \_ m e t a l の両方は、分析的に定量および取り除かれる。 L \_ g e o m は、損失のない f - e 材料を仮定する回路の正確な電磁的なシミュレーションから決定され得る。 L \_ m e t a l は、導電率、 S R ( 適用可能な場合 ) 、および皮膜深さを仮定する金属損失についての式を使用して決定され得る。最後の項である L \_ m i s s は、他の損失メカニズムの不完全な除去、または有限な境界からまたは L \_ m e t a l および L \_ g e o m の不完全な除去、あるいはその両方の組み合わせを表す。したがって、 L \_ m i s s は低減できないエラー項を表す。 f - e 膜 / コンポーネント性質を正確に測定するためには、 L \_ m i s s は前記したように最小化および制限されるべきである。

【 0 0 6 1 】

最後に、アルミニウムへの L \_ f - e の影響を低減するために、 f - e 膜がチューニングのために必要とされる領域にのみ配置され、他のどこにも配置されないように、 f - e 膜の選択的堆積が用いられなければならない。

【 0 0 6 2 】

すべての損失メカニズムを説明し、かつ、これらの損失を消去するか、または限度内にと

どめるプロセスは、 $f - e$  損失を決定するだけでなく、低損失チューニング可能フィルタの正しい設計ガイドラインもまた確立する。 $L_{f-e}$  を知ることは、 $f - e$  膜を用いて任意のタイプの最適設計を行うために必要な $f - e$  膜のベースラインを設計者に与える。これを知ることは、例えば、損失正接をチューニング可能性と有効にトレードオフすべき場合に必要である。簡単に言うと、正確な製作および測定技術は、均一の $f - e$  膜損失特性および用途をもたらす。

#### 【 0 0 6 3 】

損失を最小化する上述の技術が所与のものであるとして、 $f - e$  キャパシタの3つのタイプの好適な実施形態が、次に述べられ得る。これらの設計は、L帯域(1~2GHz)において使用するためのものであるが、本発明の教示は、他の周波数帯域の $f - e$  キャパシタを設計するために用いられ得ることを理解されたい。10

#### 【 0 0 6 4 】

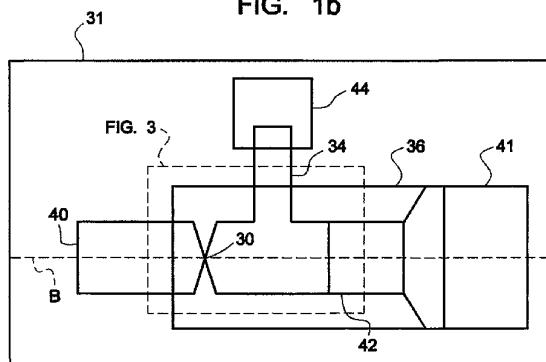

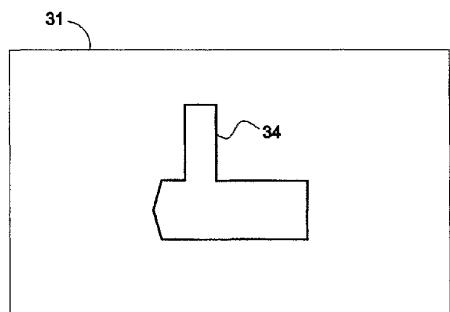

無線ハンドセットのセルラー帯域(800~1000MHz)およびL帯域(1~2GHz)において使用するための好適な $f - e$  チューニング可能ギャップキャパシタ10が1aおよび1bに示される。ギャップキャパシタ10は、好適には、5.0マイクロインチ RMSよりも小さいSRを有する、99%以上の純度の、0.5~1.0mm厚さのアルミナ、MgOまたはサファイア基板12上に形成される。あるいは、ギャップキャパシタは、任意の数の共振器構造の前面または背面または側壁に直接パターニングされ得る。実施例は、同軸、モノブロックまたはストリップライン共振器である。このようなキャパシタは、共振器へのその電気的接続点に可能な限り近くなるように製作されるべきである。20

#### 【 0 0 6 5 】

基板12は、他の要件に依存して金属グラウンド平面14を有し得る。しかしながら、好適な実施形態は、グラウンド平面を用いずに浮遊容量を最小化することである。好適には、BSTO、あるいは他の適切な、または最大容量およびチューニング範囲を得るために好適な $f - e$  材料で形成された、厚さが約0.1~2.0ミクロンの、 $f - e$  層16が基板12上に堆積される。より好適には、層16は、0.5~1.0ミクロンの厚さである。Ba/Srフラクションの他の成分とのドーピング、合金、混合、および/またはアニールは、所望のチューニング特性および損失(tan $\delta$ )、従って、Qも決定する。30

#### 【 0 0 6 6 】

一般に、チューニング特性は、最小チューニング電圧を有する最低限必要とされるチューニング範囲を満たすことが好ましい。好適には、他のエレメントがドーピングされたか、または前処理または後処理アニーリングを行ったか否かに関わらず、室温での作業の場合の $Ba_xSr_{1-x}TiO_3$ の組成において $x = 0.5$ である。BSTOを除く他の $f - e$  材料がウェルとして用いられ得ることを理解されたい。 $f - e$  層16上に形成された金属層18は、好適には、3.0~5.0ミクロンの幅のギャップ20を規定する。好適には、金属層18は、0.5~6.0ミクロンの厚さである。より好適には、金属層18は、1.5~2.5ミクロンの厚さである。ギャップ20は、要件および処理用機器に依存してこの範囲よりも幅広いか、または狭くなり得ることが理解されたい。PCS帯域における最小の追加的損失について、生じた容量は、0ボルトDCにおいて約0.6pF~1.5pFであるが、セルラーCDMA帯域については、約1.0pF~3.0pFであり得る。キャパシタの幅W17は、さらに、用いられる特定の $f - e$  膜および所望のギャップ20に依存して $f - e$  容量を決定する。この幅は、通常、0.25mm~2.0mmであり得る。容量は、通常、0.6~3.0pFである。生じたキャパシタは、既存の最悪の場合のCDMA PCS帯域BPF損失仕様を満たすために、2.0GHzにおいて、少なくとも160のQを提供すべきである。40

#### 【 0 0 6 7 】

$f - e$  膜からの追加的損失を最小化するために、選択的堆積が用いられなければならない。すなわち、 $f - e$  膜は、上述のように、チューニングのために必要とされる場所にのみ堆積され、他のどこにも堆積されない。図1aに示されるように、例えば、図1aのギャップキャパシタ20において、ギャップ20の周囲の狭い領域 $D_{f-e}$ において所望の $f$ 50

- e 膜 1 6 が堆積され得る。D<sub>f - e</sub> は、製作時に、ギャップ 2 0 が f - e 膜にわたって繰り返しパターニングされ得る（マスク位置合わせの許容誤差を見越して）ことを確実にし、かつ、チューニングプロセスのためにギャップ 2 0 の下の必要とされる領域を覆うために十分な大きさである。L 帯域 P C S フィルタについては、D<sub>f - e</sub> = 0 . 2 ~ 0 . 5 mm が適切であり、0 . 2 mm が好適である。動作周波数が大きくなると、D<sub>f - e</sub> は小さくなり得る。動作周波数が小さくなると、D<sub>f - e</sub> は大きくなり得る。

#### 【 0 0 6 8 】

f - e 膜の特性、およびその製作は、キャパシタ損失全体に重要な影響を及ぼす。f - e 膜損失を軽減および最小化するための複数の技術が存在する。f - e 膜の 1 つの特徴は、f - e 膜の損失およびチューニング可能性が、通常、逆の関係を有することである。すなわち、これらは、通常、互いにトレードオフされなければならない。大抵の場合、f - e チューニング範囲が大きいほど、f - e 損失が大きい。

#### 【 0 0 6 9 】

従って、f - e 材料が約 3 ~ 1 の チューニング範囲を達成し得る場合であっても、所与のフィルタアプリケーションには、少しのチューニングしか許容され得ない。この場合、少しのチューニングが選択され、損失が少ないと利益がある。例えば、米国の P C S C D M A 帯域において、トランジットバンドは、1 8 5 0 M H z ~ 1 9 1 0 M H z 、または約 4 % である。従って、f - e 材料は、3 ~ 1 よりもかなり小さいチューニング可能性を有し得る。

#### 【 0 0 7 0 】

例えば、0 V D C バイアスでの 0 . 6 p F f - e ギャップキャパシタは、P C S 伝送帯域にわたってチューニングするために、3 3 % のチューニング（0 . 6 p F から 0 . 4 p F に下げる）を必要とする。実際のチューニング範囲は、B P F トポロジ、およびこのB P F がチューニングされなければならない帯域に依存する。この実施例において 3 3 % のチューニングを提供することが必要とされるチューニング電圧は、f - e 厚さ、および f - e 膜特性を含む f - e キャパシタジオメトリーに依存する。

#### 【 0 0 7 1 】

周波数チューニング可能性への チューニング可能性の効果は、整合回路のトポロジによって決定される。この効果は、f - e 材料を選択する際にも考慮されなければならない。しかしながら、f - e 損失の f - e の チューニング可能性へのトレードオフの正確な特性決定がなされない場合、設計者が最適な f - e 材料の選択を開始することさえできない。このトレードオフの正確な特性決定は、設計者が最適な f - e 材料を選択することを可能にする（最低損失を提供する一方で、チューニング要件を満たす）。

#### 【 0 0 7 2 】

ギャップキャパシタの L<sub>g e o m</sub> に関して、損失に主に寄与するのは、ギャップによって形成される 4 つの隅である。これらの損失は、これらの隅を丸くすることによって低減され得る。

#### 【 0 0 7 3 】

ギャップおよびインターデジタルキャパシタと比較して、オーバーレイキャパシタは、最低 L<sub>g e o m</sub> を有する。オーバーレイキャパシタは、平行板ジオメトリの実施例であり、ここで、プレート寸法（長さおよび幅）は、プレート間隔よりもはるかに大きい。このようなジオメトリが所与のものであるとして、プレート間の電界のほとんどは、エッジに沿うフリンジ部分を除いて均一である。このようなフリンジ効果は、当該分野において周知のように保護帯域の使用によって著しく低減され得る。従って、平行板キャパシタからのジオメトリ損失は、かなり低い。さらに、平行板ジオメトリは、小さい制御電圧振動から、高チューニングとともに高容量を提供し得る。

#### 【 0 0 7 4 】

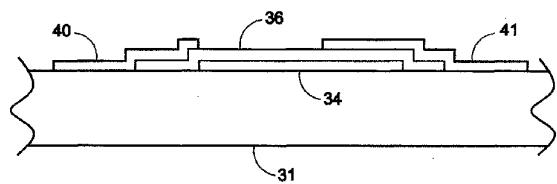

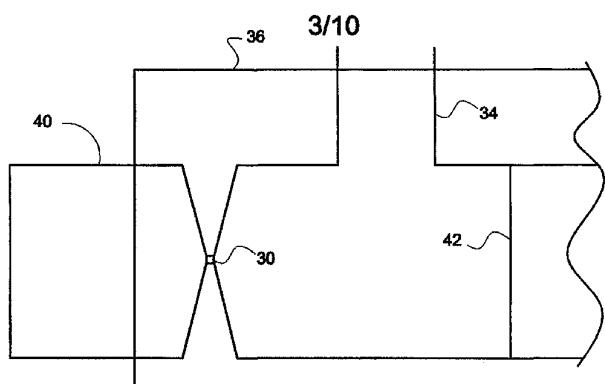

好適なオーバーレイキャパシタ 3 0 が、図 2 a、2 b、2 c および 3 に示されており、このオーバーレイキャパシタ 3 0 は、L<sub>g e o m</sub> への寄与を最小にする。キャパシタ 3 0 は、2 5 m i l のアルミナ基板 3 1 上に直接配置される。第一の金属層 3 4 は、基板 3 1 に

10

20

30

40

50

結合する。金属層 3 4 の形状がまた、図 2 b に図示される。強誘電性層 3 6 が金属層 3 4 の上に存在する。オーバーレイキャパシタ 3 0 を形成するために、強誘電性層 3 6 上に形成された金属パッド 4 0 が第一の金属層 3 4 の部分にオーバーラップする。図 3 は、オーバーラップしている部分の拡大図を示す。金属パッド 4 0 および金属層 3 4 の両方は、適切な容量のオーバーレイキャパシタ 3 0 を形成するテーパー領域を有する。さらなる金属パッド 4 1 は、金属層 3 4 にオーバーラップして、DC 遮断キャパシタ 4 2 を形成する。金属パッド 4 1 は、テーパーにされて、DC 遮断キャパシタ 4 2 のために適切な容量を形成する。

#### 【 0 0 7 5 】

最も可能性が高い、用いられる  $f - e$  フィルムの高い比誘電率 ( $k$ ) のために、オーバーレイキャパシタ 3 0 は、領域において極めて小さくあり、それでも、 $1.5 \text{ pF}$  の容量 ( $C_{f-e}$ ) を提供し得る。結合バイアスパッド 4 4 は、高値 ( $500 \sim 1000 \text{ k}$ ) チップ抵抗の付着のために提供される。 $f - e$  フィルムは、オーバーレイキャパシタ 3 0 の下だけではなく、遮断キャパシタ 4 2 にも堆積されることに留意のこと。しかしながら、DC 遮断キャパシタ 4 2 の容量 ( $C_{DC}$ ) についての影響は、 $C_{DC} = 180 \text{ pF}$  および  $C_{f-e} = 1.5 \text{ pF}$  であれば、最大の  $V_{DC}$  バイアス (好ましくは、 $10 \text{ V DC}$ ) の下であっても、無関係である。これは、DC 遮断キャパシタが、容量が  $f - e$  チューニングによって低減される場合であっても十分に高い容量を有し、依然として  $C_{f-e}$  上に最小の効果を有するからである。

#### 【 0 0 7 6 】

$0.7 C_{f-e} = 1.5 \text{ pF}$ 、 $f - e$  は約  $1000$  であるような実施形態において、オーバーラップされたキャパシタ 3 0 は、約  $7.0 \mu\text{m} \times 7.0 \mu\text{m}$  であり、 $f - e$  フィルム厚は、約  $1.0 \mu\text{m}$  である。金属層 3 4 は、 $\text{Pt}$  であり得、 $0.5 \mu\text{m}$  の厚さを有し得る。金属パッド 4 0 および 4 1 は、 $\text{Ag}$  であり、約  $1.5 \sim 2.5 \mu\text{m}$  の厚さを有し得る。

#### 【 0 0 7 7 】

オーバーレイキャパシタの  $L_{gap}$  は、ギャップキャパシタのもの未満であるが、 $r_f$  領域の全てが  $f - e$  フィルムに集中されているので、オーバーレイキャパシタの  $L_{f-e}$  は、より高くあり得る。ギャップキャパシタでは、 $r_f$  領域は、部分的に空気中にあり、部分的に  $f - e$  領域内にあり、部分的に基板内にある。同じ理由で、オーバーレイキャパシタは、ギャップキャパシタよりも所与の印加電圧に対してより大きい容量チューナブル可能性を有する。

#### 【 0 0 7 8 】

所与の断面領域に対して、IDC は、ギャップキャパシタより高い容量を提供し得る。しかしながら、ギャップ間隔を含む  $L_{gap}$  への主要な寄与に伴い、より損失性が高い。同様に、損失は、フィンガー ( $finger$ ) 幅が減少するにつれて増加する。フィンガー長も、フィンガー長が増加するときの損失増加に伴う損失に影響する。特に、微小小片 ( $microstrip$ ) (最も一般的) では、半端なモード損失としての IDC の実現は、このような構造で優勢である。さらに、さらなる鋭いコーナーから導入された損失に起因して、フィンガーの数が増加するにつれて損失は増加する。フィンガーの数を増加させることは、典型的には、IDC の容量を増加させるために用いられることに留意のこと。 $f - e$  領域における多くの研究は、狭いフィンガー幅およびギャップ (それぞれについて、 $5.0 \mu\text{m}$ ) を有する IDC (複数) を用いて、 $f - e$  フィルムを特徴付けた。これは、このような IDC 構造は高い  $L_{gap}$ 、それに伴う、それ自体で低い  $Q$  を与えるので、問題がある。典型的には、任意の  $L_{f-e}$  がなくても、約  $1.0 \text{ pF}$  に対して  $2.0 \text{ GHz}$  で  $Q = 200$  である。これは、 $L_{f-e}$  を測定することを極めて困難にする。ブロードバンド測定技術の広げられたの使用は、上記のように、任意の  $L_{f-e}$  測定をさらに混乱させる。

#### 【 0 0 7 9 】

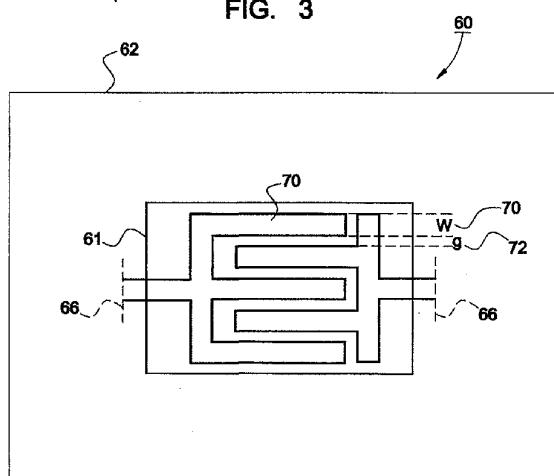

$L_{gap}$  への寄与を最小にする、好適な IDC キャパシタ 6 0 が図 4 に図示される。こ

10

20

30

40

50

れは、約 0.2 ~ 1.5 mm 厚の、99% アルミナ、MgO、サファイアまたは他の適切な基板 62 上に形成される。f-e 層 64 は、基板 62 上に形成される。入力ポート 66 および出力ポート 68 は、IDC キャパシタ 60 に結合する。1.5 ~ 3.0 ミクロン厚さを有し、f-e 層 64 上に堆積される金属層 70 は、約 5.0 ミクロンのギャップ間隔 72、約 150 ミクロンまたは可能な限りこれより大きいフィンガー幅 70 を形成する。

#### 【0080】

チューナブルバンドパスフィルタを構築するための一般的な方法論がここで記載され得る。第一工程として、設計者は、要求される帯域外拒絶を達成するために、チューナブルフィルタの 3 dB のバンド幅をフィルタ次数とトレードオフしなければならない。周知のように、フィルタ次数が増加されるにつれて、そのロールオフ (roll off) 速度が増加され、要求される拒絶仕様を達成することがより容易になる。ロールオフは、3 dB 帯域幅 (BW) を規定する 3 dB ポイントのいずれかを開始するときにモデル化される。このため、BW は減少するので、それは、さらに、要求される拒絶仕様を達成することがより容易になる。

#### 【0081】

最小の損失に対して、最も低いオーダーが所望される。典型的には、これは、2 次 BPF になる。低次 BPF は、より少ない調整可能な共振器を用いて製造および調整することがより簡単になるというさらなる利点を有する。

#### 【0082】

Chelychev プロトタイプ BPF が Butterworth を超えて好適であるのは、これは、設計者に、帯域外拒絶と共にパスバンドリップルをトレードオフするためにより柔軟性を与えるからである。設計者は、トランスミッションゼロが対応するパスバンドエッジでのフィルタの複雑さ、費用、および損失を増加させるとときに余分なトランスミッションゼロを付加することなく、バンド幅調節によって最も悪い場合の拒絶仕様を満たすために努力するべきである。しかしながら、人は、この場合に高いまたは低いサイドトランスミッションゼロを自然に発生するトポロジを開発し得る。

#### 【0083】

しかしながら、BW を過度に狭めることは、上記のように、挿入損失を増加させる。このため、全部の特定された条件の中から要求される拒絶仕様と一致する最も狭い BW が選択されるべきである。選択された BW が受け入れられない挿入損失を提供する場合、BW は、増加されるべきであり、おそらくまた、フィルタ次数の増加または増加されたパスバンドリップル (受け入れ可能な場合) を要求する。さらなる高いまたは低いサイドトランスミッションゼロが、所望であれば加えられ得る。

#### 【0084】

チューナブル BPF は、制御回路を必要とする。これは、付加的な支出であり、固定調整された BPF (複数) を要求しない。このため、所望の調整可能なフィルタ設計は、低減された挿入損失、より小さいサイズ、またはこの支出をオフセットするために固定調整された BPF の利益を超える他の利益を提供するべきである。低減された挿入損失およびより小さいサイズを達成するために、たかだか 1 または 2 のステージ調整可能なフィルタを使用することが好ましい。しかしながら、本発明の原理は、任意のオーダーの調整可能な f-e フィルタ設計するために利点があるように使用され得ることが理解される。

#### 【0085】

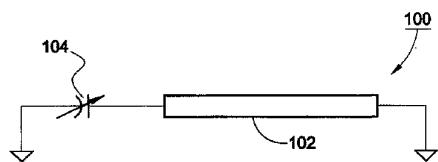

フィルタ次数に対する選択および拒絶要求を満足する BW が与えられて、共振器に対する最も可能性が高い  $Q_u$  が、要求された I.L.、与えられたサイズおよび高さ制限を一致させるまたは超えるために用いられるべきである。 $Q_u$  を規定するために、トポロジが図 5 に示される基本ステージ 100 に対して選択されるべきである。各ステージ 100 は、f-e キャパシタ 104 に結合された共振器 102 によって形成される。f-e キャパシタ 104 は、本明細書に記載された形態の一つを想定し得る。共振器 102 は、接地された 4 分の 1 波長共振器として示されるが、開回路半波長共振器も使用され得る。さらに、共振器は、他の適切な電気的な長さであり得る。

## 【0086】

基礎ステージ100は、チューナブルEM共振器であると考えられ得る。f-eキャパシタ104は、それらの接続の性質によって決定されるように、共振器102と直列に、または、シャントに(in shunt)接続され得る。図6に示されるように、f-eキャパシタ104は、共振器102とシャントに接続され、これにより、f-eキャパシタ104の $Q_{f-e}$ は、固定チューニングされたEM共振器102のQに影響する。ボルメトリック共振器(例えば、同軸、ストリップラインおよびモノブロック)が好ましい。なぜなら、これらは、平面状(すなわち、マイクロストリップ、代替物)と比べて最小の値段で、最大 $Q_u$ および最小のエリアおよび高さを提供するからである。

## 【0087】

チューナブルキャパシタがボルメトリック共振器と直列に、または、シャントに配置されるかどうかは、接続の形態によって決定されることが多い(1つの配置のみが可能であることもある)。チューナブルキャパシタが直列にまたはシャントに配置されるかどうかを決定する際の別のキーとなる特徴は、追加損失が最小であることと、より割合は低いが、チューニング範囲である。シャント接続は、典型的に、直列接続よりも物理的にコンパクトなチューナブルフィルタを製造する。通常、同様に達成することがより容易である。(モノブロック、同軸またはストリップライン等の)電磁接続共振器が(小さなアーチャを通して接続されるのではなく)それら全体の範囲に沿って接続される場合に、直列接続は、より良いチューニングを提供し得る。製作の面からも、直列接続は、これらの場合により自然な選択である。

## 【0088】

上記のように、取り付け損失は、f-eキャパシタ104が共振器102または他のRF回路によって統合されない場合に重要であり得る。一度、f-eキャパシタ104に対するトポロジが選択されると、その $Q_c$ は、上記のように導かれ得る。基礎ステージ100全体に対する $Q_T$ は、次いで、 $1/Q_T = 1/Q_c + 1/Q_u$ によって決定される。ここで、 $Q_u$ は、共振器102の負荷無しQであり、 $Q_c$ は、f-eキャパシタのQである。

## 【0089】

基礎ステージ100に対する $Q_T$ が与えられると、設計者は、式(1)を用いて、必要なI.L.が達成される、または、越えられるかどうかを判定し得る。I.L.があまりにも高い場合、設計者は、 $Q_c$ または $Q_u$ のいずれか、あるいは、 $Q_c$ または $Q_u$ の両方を増加させることによってより低いI.L.を獲得し得る。 $Q_c$ または $Q_u$ のいずれもさらに増加できない場合、それらは、最終的に $Q_T$ を制限する。さらに、より低い損失のトポロジに切り替えることによってのみ、I.L.をさらに減少し得る。例えば、マイクロストリップ共振器の代わりにボルメトリック共振器が所与のフットプリント(エリア)に対して用いられる場合に、 $Q_u$ が増加され得る。

## 【0090】

CDMA無線ハンドセット、横方向電磁波(TEM(transverse electric from magnetic)波)ボルメトリック共振器が好ましい。このようなボルメトリック共振器は、最も共通して実現されている3つの名前を挙げると、セラミックロード同軸共振器、スラブライン(slabline)(モノブロック)またはストリップラインのうちのいずれかであり得る。(通常、f。のBW 10%として定義される)標準的に狭帯域トポロジは、同軸かストリップライン共振器かのいずれかによって製作された上部をキャパシティブに接続した(TCC(top capacitive coupled))BPFを用いて実現され得る。図8に示されるTCCトポロジは、f-eチューニングの役に立つ。なぜなら、このトポロジが(直列のf-eチューニングを伴うTCCトポロジよりも小さいフットプリントを有して)最大限にコンパクトに実現するからである。また、シャント1/4波共振器は、共振近くで並列LCチューニング回路として挙動する。

## 【0091】

モノブロックBPFのステップインピーダンスの実現が同様に用いられ得る。モノブロッ

10

20

30

40

50

ク共振器は、通常、それらの全体の長さに沿って E M 接続されており、それらの設計の直接の結果である。それらは、直列 f - e チューニングに役に立つ。それらの電気的な長さは、 f - e チューニングキャパシタの選択配置およびパターニングによってチューニングされ得る。（誘電負荷導波共振器あるいは（遮蔽包囲を有する、または、有しない）誘電パックを含むがこれらに限定されない）非 T E M 共振器は、同様に用いられ得る。

#### 【 0 0 9 2 】

しかし、高さの制限は、ボルメトリック共振器からの達成可能な  $Q_u$  を制限し得る。このような高さを制限したシステムにおけるボルメトリック同軸共振器の代替物は、ストリップライン共振器を用いることである。ここで、ストリップライン共振器は、（ある点）まで中央コンダクタを広くして、全高さを固定したままで  $Q_u$  を改善し得る。この実施形態はさらに利点を有する。すなわち、ストリップライン共振器端部の上部カバーを f - e キャパシタの位置の前に置くことによって、ギャップキャパシタまたは I D C 等の平らな f - e キャパシタを組み込んで効率良く実現され得る。この様態で、平らな f - e キャパシタは、上部カバーを越えて延びるストリップライン共振器の底部カバーを形成する基板の一部に形成される。

#### 【 0 0 9 3 】

特定の共振器が実現されているにもかかわらず、共振器の  $Q_u$  がさらに増加することを高さの制限が防ぐ場合、  $Q_c$  は、例えば、 I D C の f - e キャパシタを、ギャップまたは上を覆う f - e キャパシタで置き換えることによって、増加される必要がある。

#### 【 0 0 9 4 】

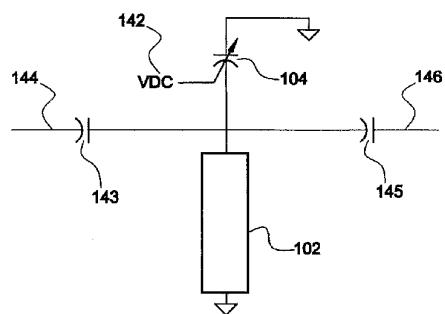

多くの用途に対して、図 6 に示されるように、1つのステージバンドパスフィルタ 1 4 0 が良好である。図 5 に関して説明されたように、バンドパスフィルタ 1 4 0 は、 f - e キャパシタ 1 0 4 および共振器 1 0 2 を含む。 f - e キャパシタ 1 0 4 に加えられた可変 D C 電圧 1 4 2 は、フィルタ 1 4 0 をチューニングする。フィルタリングされた R F 信号は、入力ポート 1 4 4 にかけられ、出力ポート 1 4 6 で出力される。入力ポート 1 4 4 および出力ポート 1 4 6 は、相互転換可能であることに留意されたい。キャパシタ 1 4 3 は、入力ポート 1 4 4 と共振器 1 0 2 との間で共に定義される。別のキャパシタ 1 4 5 は、出力ポート 1 4 6 と共振器 1 0 2 との間で定義される。 f - e キャパシタ 1 0 4 は、それがギャップ、オーバーレイまたは I D C キャパシタのいずれかにかかわらず、上記の様態で損失を最小にするように構築される。同様に、共振器 1 0 2 は、短 1 / 4 波長共振器か 1 / 2 波長オープン回路共振器かのいずれかであり得、  $Q_u$  を最大化するように選択される。

#### 【 0 0 9 5 】

より高い  $Q_u$  は、より小さなフットプリントおよびより低いコストで、同軸共振器、誘電ロード波長ガイド、モノブロック、または、ストリップライン共振器等のボルメトリック共振器によって提供される。あるいは、マイクロストリップ共振器等のより広いエリアの平らな共振器は、規格および価格の制約が許す場合に用いられ得る。大部分のマイクロストリップ共振器回路は、薄膜プロセスによって堅い基板上に製作される。それらは、より薄い金属厚さを達成し、 E M フィールドの一部がマイクロストリップ上位のエア領域であるために、より大きなサイズである。

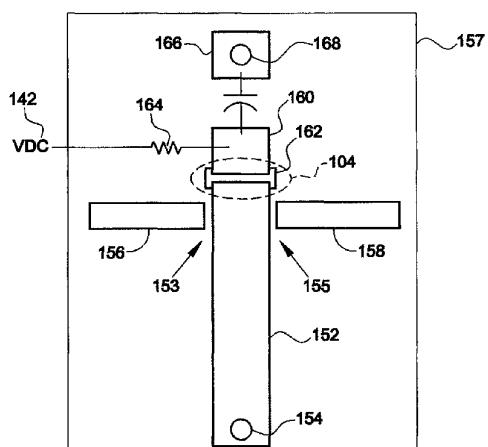

#### 【 0 0 9 6 】

次に図 7 に戻って、バンドパスフィルタ 1 4 0 の平らな実現 1 5 0 が図示される。共振器 1 0 2 は、ビア 1 5 4 を通して接地されたマイクロストリップライン 1 5 2 によって形成される。マイクロストリップライン 1 5 2 がまた、適切な損失無し（ lossless ）接地面（図示せず）で終り、ビア 1 5 4 の必要性を無くすことに留意されたい。キャパシタ 1 5 3 および 1 5 5 は、入力マイクロストリップライン 1 5 6 および出力マイクロストリップライン 1 5 8 と共振器マイクロストリップライン 1 5 2 との間のギャップによって形成される。キャパシタ 1 5 5 および 1 5 7 の容量を実用的な大きさ（約 0.2 pF ）にして、平らな構造を維持しつつ入力および出力カップリングを最大化することが望ましい。マイクロストリップラインは、最大のマイクロストリップ共振器  $Q$  を提供するために好

10

20

30

40

50

ましい厚さ（約1.0mm）で、99.5%の純粋なアルミナ、MgOまたはサファイアの基板157の上に形成される。f-eキャパシタ104は、f-e層162をパッド160およびマイクロストリップライン152の下にして、パッド160およびマイクロストリップライン152によってギャップキャパシタとして形成される。

【0097】

可変DC電圧源は、レジスタ164を通してパッド160をバイアスする。DCブロックキングキャパシタは、パッド160とパッド166との間に配置される。ここで、パッド166は、接地するためのビア168を含む。パッド166はまた、適切な損失無し接地プレート（図示せず）で終り、ビア168の必要性を無くすことに留意されたい。

【0098】

図7に示すように、共振器がシャントされる場合、DCブロックキャパシタが必要とされる。DCブロックキャパシタの容量は、 $C_{f-e}$ 上の負荷の影響を最小限にするため、理想的には、少なくとも $100C_{f-e}$ である。DCブロックキャパシタのQは、理想的には、対象となる帯域において、40以上である。ギャップキャパシタおよびマイクロストリップ共振器は、任意に選択されることが理解される。本明細書に記載の形態は、いずれも、本発明の教示内容と矛盾することなく採用され得る。

【0099】

図7のバンドパスフィルタは、理想的には、本明細書に記載されるように、f-e膜を特徴付けるため、テスト回路として用いられ得る。従って、図7のバンドパスフィルタは、以下の利点を提供する。

【0100】

1) f-eキャパシタは、特に、ギャップキャパシタまたはIDCとして実現される場合、用いられる状態に製造され得る。

【0101】

2) f-eギャップキャパシタが示されるが、IDCも用いられ得る。ギャップキャパシタは、より単純なジオメトリを有する。ギャップキャパシタは、IDCと比較して、製造がより容易であり、ジオメトリの損失がより低い。ギャップキャパシタはまた、オーバーレイキャパシタよりも製造が容易である。

【0102】

3) 薄膜処理技術を用いて回路が製造されるので、ジオメトリは、正確に制御および測定され得る。

【0103】

4) 金属の厚さが、プロフィロメトリ（profilometry）によって正確に測定され得る。金属のタイプは、所望の通りに選択され得る（Au、AgまたはCu）。

【0104】

5) 高いQのマイクロストリップ回路は、回路の固定された共振器部分を完成させる。

【0105】

6) f-eキャパシタは、共振器内で直接製造される。はんだ付け、ボンディングなどに起因するさらなる損失はない。共振器からf-eキャパシタへのトランジションは、均一であるか、または、所望される場合には、テーパー状であってもよい。

【0106】

7) 広い面積の接地平面およびWilsonテスト取り付け具（保持するためのジョーを有し、回路上部および底部を接地させる）が用いられる場合、バイアホールは必要とされない。固い基板にバイアを開けることによって、大幅にコストが追加され、このようなテスト回路の製造できる数が低減される。

【0107】

8) この回路は、EMソフトウェアで正確にモデリングされ得る。

【0108】

9) この回路は、f-e膜なしに製造され得、シミュレーションとの関連で回路の（当然、より高いf。における）基本的な損失が決定される。

10

20

30

40

50

## 【0109】

100) 低損失基板を用いることによって、回路全体に対する影響が最小限になる。

## 【0110】

110) 測定された  $f_e$  および  $I_L$  の結果が、  $f_e$  膜誘電率および  $\tan \delta$  を抽出するために用いられ得る。

## 【0111】

120) 図7の回路は、  $f_e$  キャップが示されている、ベース基板にアーチャが開けられた状態で製造され得る。次に、個々の  $f_e$  キャップがアーチャの上に位置され得、圧力で所定の位置に保持され、  $f_e$  キャップがスタンドアロンコンポーネントとしてテストされることを可能にする。

10

## 【0112】

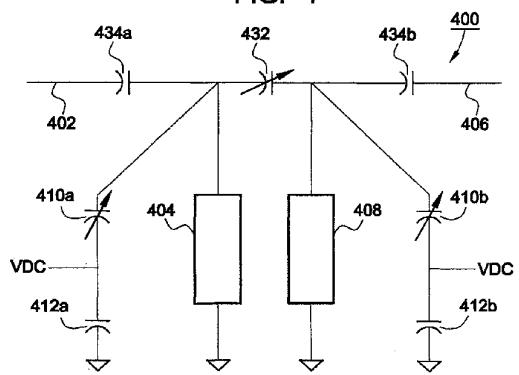

次に、図8aを参照すると、2段TCCチューナブルBPF400が示されている。図5に関して説明したように、バンドパスフィルタ400のそれぞれの段は、共振器404および408、ならびに  $f_e$  キャパシタ410aおよび410bを含む。共振器404および408は、4分の1波長短絡共振器として示されているが、2分の1波長開回路共振器であってもよい。

## 【0113】

$f_e$  キャパシタ410aおよび410bに印加される可変DC電圧は、バンドパスフィルタ400をチューニングする。強誘電性キャパシタ410aおよび410bは、この例においては共振器が短絡しているので、DCブロックキャパシタ412aおよび412bを介して接地される。

20

## 【0114】

RF信号は、入力ポート402で受信され、出力ポート406で出力される。入力ポート402と出力ポート406とは交換可能であることに留意されたい。図6に関して説明されたキャパシタ143および145と機能的に類似する、入力キャパシタ434aおよび出力キャパシタ434bに加えて、さらなるキャパシタ432が、インピーダンスおよびアドミタンスインバータとして、共振器404と共振器408との間に設けられて、所望のBPF応答を作成し得る。キャパシタ432が、別個の素子であってもよいし、共振器404と共振器408とを結合するアーチャを通じて実現されてもよいことが理解される。

30

## 【0115】

図8aおよび8bに示されるチューナブル2段フィルタ400および450は、ある所とのバスバンド  $I_L$  について、より良好な除去を行わせるように用いられ得るハイまたはローサイドゼロを作成する基本的なトポロジを有する。共振器間の全長にわたる結合の場合、バスバンド  $I_L$  および帯域外除去は、強誘電性キャパシタがバスバンドに渡ってバンドパスフィルタをチューニングするにつれて変化する。生じるあらゆるひずみを、特に除去帯域において、最小限にするため、キャパシタ432は、  $f_e$  キャパシタであってもよい。キャパシタ413および419をチューニングすることによって、ゼロに周波数をチューナブルバスバンドに従ってトラックさせ得る。

40

## 【0116】

共振器404と共振器408との間を結合する  $f_e$  キャパシタのバイアシングおよびチューニングを容易にするため、図8bに示すように、キャパシタ432の代わりに、  $f_e$  キャパシタ437aおよび437bが用いられてもよい。キャパシタ437aおよび437bは、理想的には、キャパシタ432の容量の2倍の容量を有する。この実施形態において、強誘電性キャパシタ410a、410b、437aおよび437bは全て、1つのDCチューニング電圧VDCを用いてチューニングされ得る。

40

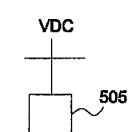

## 【0117】

$f_e$  キャパシタ用の1つのDCチューニング電圧VDCは、図9に示すように構成され得る。図9において、VDCはディバイダネットワーク505に結合されている。ディバイダネットワーク505は、  $f_e$  キャパシタ437aおよび437bの両方に結合され

50

ている。ディバイダネットワーク 505 は、f-e キャパシタ 437a および 437b に適切なチューニング範囲を提供して、上述したように、ゼロがパスバンドに従ってトラックするように構成され得る。

【0118】

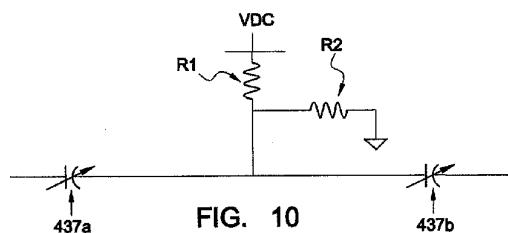

ディバイダネットワーク 505 は、図 10 に示すように構成され得る。図 10 において、 $V_{DC}$  は、 $R_1$  に結合される。 $R_1$  は  $R_2$  に結合され、キャパシタ 437a および 437b の両方に結合される。 $R_2$  はまた、接地される。 $R_1$  および  $R_2$  は、上述したように、ゼロがパスバンドに従ってトラックするように選択される。

【0119】

あるいは、キャパシタ 437a および 437b の両方をチューニングするために、別の電圧が用いられてもよい。

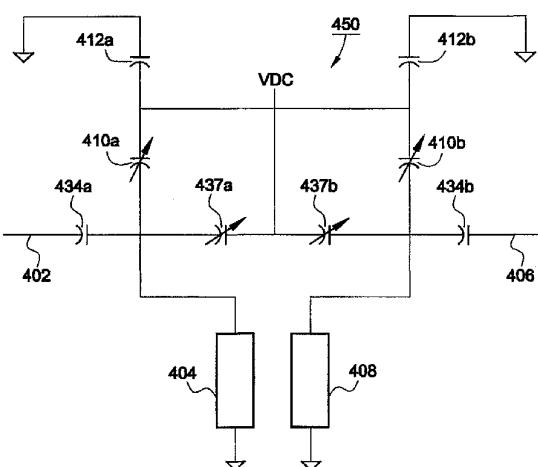

【0120】

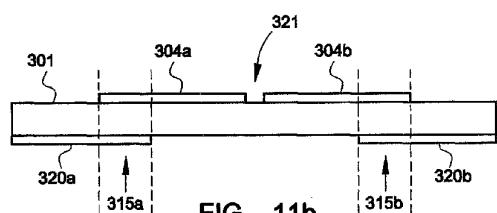

次に、図 11a を参照すると、同軸モノブロック共振器 302a および 302b を用いるチューナブル 2 段フィルタ 300 が示されている。他のタイプの共振器が用いられてもよいことに留意されたい。共振器 302a および 302b は、開回路であってもよいし、短絡されていてもよい。共振器 302a および 302b は、基板 301 の第 1 の表面に取り付けられる。基板 301 の第 1 の表面上に形成されたパッド 304a および 304b は、リード 305a および 305b を介して、共振器 302a および 302b に結合される。基板 301 の第 1 の表面上に形成されたパッド 306a および 306b は、パッド 304a および 304b に結合されて、強誘電性キャパシタ 310a および 310b のための所望のギャップを作る。パッド 304a および 304b、ならびに、306a および 306b の下にある強誘電性層 312a および 312b は、強誘電性ギャップキャパシタ 310a および 310b を完成させる。図面は、縮尺が調整されていないことに留意されたい。典型的な例として、ギャップの間隔は、より明瞭にするために広げられている。

【0121】

基板 301 の第 2 の表面上には送信ライン 320a および 320b がある。これらの送信ラインは、信号 RF の入力および信号 RF の出力のための入力ポート 320a および出力ポート 320b として使用される。入力キャパシタ 315a および出力キャパシタ 315b は、図 11b に示されるように、その間に基板 301 を備えて、送信ライン 320a および 320b と、パッド 304a および 304b との間に形成される。図 11b は、図 11a に示したフィルタ 300 の一部の断面図である。断面は線 B に沿っている。

【0122】

さらに、キャパシタ 321 は、パッド 304a および 304b の分離によって、ギャップキャパシタとして形成される。キャパシタ 321 によって提供された結合は、代替的には、キャパシタ 321 の必要性はなく、同軸共振器 302a と同軸共振器 302b との間の開口結合を介して提供されてもよいことに留意されたい。同軸共振器 302a および 302b は別の構造として示されたが、それらは、空間を節約し、任意の開口結合を可能にするために共通の壁を共有し得ることが理解される。さらに、それらの間に、空間がなくても、壁がなくてもよい。すなわち、それらは、相互に結合されたモノブロック共振器であってもよい。キャパシタ 321 によって提供された結合が開口結合を介して実装される実施形態において、パッド 304a および 304b は、十分な間隔で分離され、それらの間の任意のギャップ容量を最小化する。バイアス電圧  $V_{DC}$  は、レジスタ 340a および 340b を介して結合され、強誘電体キャパシタ 310a および 310b を同調する。強誘電体ギャップキャパシタ 310a および 310b のそれぞれは、DC ブロックキャパシタ 341a および 341b を介してグランドに接続されている。

【0123】

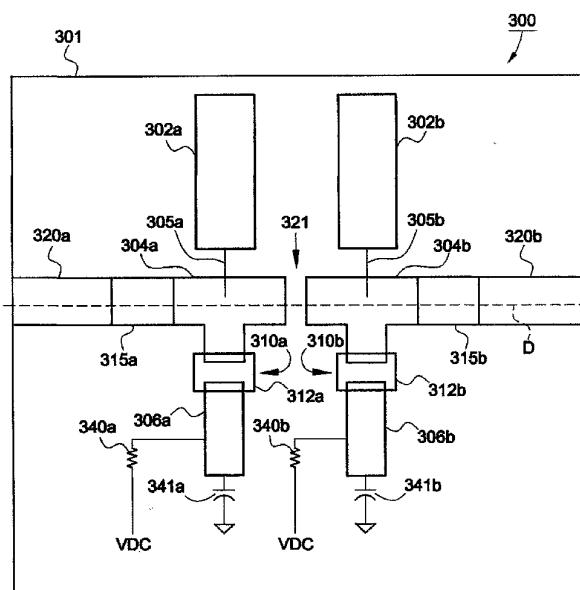

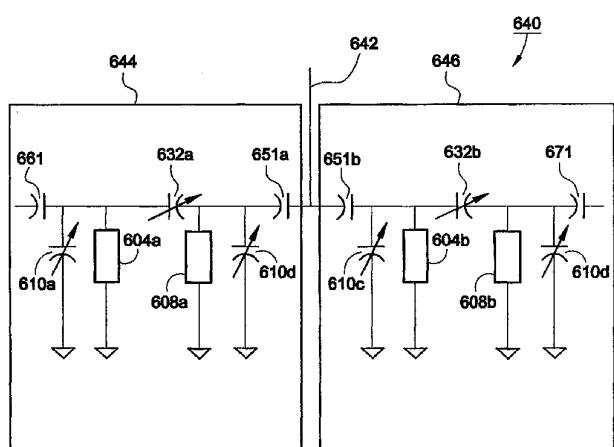

フィルタ 400 および 450 は、図 12 に示されるように、デュプレクサ 640 の送信部および受信部として機能するように適応され得る。デュプレクサは、マルチプレクサの特別の場合であることに留意されたい。デュプレクサは、2 つの帯域に関連して使用される一方で、マルチプレクサは、2 つ以上の帯域に関連して使用される。あるいは、マルチプ

10

20

30

40

50

レクサは、2つの帯域より多くの帯域を用いる場合に使用するものとして定義され得る。どちらにしても、簡潔さのためにデュプレクサの観点で説明していたとしても、本発明は、一般的にマルチプレクサにおいて使用され得ることが理解されるべきである。

#### 【0124】

デュプレクサ640は、共通ポート642を介してアンテナまたはダイプレクサに結合している。送信部644は、図9、10および11に関連して説明されたように構成された2段チューナブルフィルタを含む。したがって、送信部644は、強誘電体キャパシタ610aおよび610bにそれぞれ結合された共振器604aおよび608aを有する。共振器604a、604b、608aおよび608bは、3例を挙げれば、同軸、ストリップラインまたはモノブロック共振器として実現され得る。Tx部およびRx部は、一般的に、同じトポロジ、例えば、モノブロックで製造される。しかし、所望な場合、Tx部およびRx部に異なるトポロジを使用してもよい。例えば、要件または選択に応じて、Tx部がストリップラインであり、Rx部がモノブロックであってもよい。

10

#### 【0125】

モノブロック共振器として実現された場合、それは、全体の長さにそってEM結合され得る。キャパシタ632aによって提供された結合とともに、このEM結合を用いて、Rx帯域に位置するハイサイド阻止ゼロを作成する。理想的には、そのゼロは、PCSCDMAのTxチャンネルと対になるRxチャンネルを含むRx帯域の一部に位置する。このトポロジは、最大Rx帯域阻止とともに最小のTx帯域I.L.を提供する。

20

#### 【0126】

DCブロックキャパシタおよびDC同調電圧源は図示されていない。強誘電体キャパシタ632aは図8aにおいて実装されたように図示される。しかし、図8bに示されるように、2つの直列結合f-eキャパシタとしてキャパシタ2C2のそれぞれを実装することが好ましいと理解される。キャパシタ610aおよび610bに対するDC帰還路は、短絡共振器604aおよび608aを介している。

20

#### 【0127】

受信部646は同様に構成される。モノブロック結合およびTx帯域阻止に関する同じ注釈が、Txフィルタに対するRx帯域阻止に関する注釈と同様に、これに適用される。しかし、受信部646の共振器604bおよび608bの電子的な長さは、送信部のそれと異なって選択される。このように、その部が同調するパスバンドは分離され、f-e同調キャパシタ610cおよび610dの容量値は、キャパシタ610aおよび610bの容量値と同じままである。

30

#### 【0128】

例えば、全米CDMA PCS帯域において、送信部(TX)部644は、1850から1910MHzまでのパスバンドを介して送信するように同調される必要がある。同様に、受信部(RX)部446は、1930から1990MHzまでのパスバンドを介して受信するように同調される必要がある。全米PCS帯域がここで説明されるが、同じ概念が、他の無線帯域(例えば、セルラー帯域(800MHzから1000MHz)、他のPCS帯域、3-G CDMA帯域、および任意の部分帯域を含む)に適用される。

40

#### 【0129】

TxおよびRx帯域の同調電圧範囲は、この場合には、同じではない。なぜなら、必要とされる同調範囲が60MHzであったとしても(全米PCS帯域)、TxおよびRxの部分帯域幅がわずかに異なるからである。このため、Tx帯域が1850MHzで始まる一方で、Rx帯域が1930MHzで始まる。したがって、別の同調電圧が、等しい値のf-eキャパシタを用いた場合に必要とされる。

#### 【0130】

別の実施形態では、Tx帯域用の共振器604aおよび608aは、Rx帯域用の共振器604bおよび608bと同じ電気的長さを有する。この場合、TxおよびRx帯域を調整するために使用されたf-eキャパシタの容量値は異なり、それにより必要な周波数分離を提供する。

50

## 【0131】

F-E キャパシタ 610a ~ d は、個々の共振器を同様に調整するために使用され得る。従来の固定された帯域幅設計では、各フィルタまたはデュプレクサは、電気的規格を満たすために、100%のベンダーによる選別および調整を必要とする。電気的に調整可能な f-e キャパシタの使用は、この目的のために開発され、誘電率変化、製造許容差、および温度変化を補償し得る。この調整は、付与された調整容量範囲を犠牲にし、理想的には、各共振器に対する（制御）電圧を独立して調整することによって実行される。このアプローチは、DC 制御電圧を発生させる制御回路についての要求を増加させる。

## 【0132】

別の実施形態では、PCS 構成デュプレクサは、キャパシタ 651a、651b、661 10 および 671 を形成するためにギャップ結合を使用し得る。キャパシタ 651a、651b、661、および 671 は、典型的には、米国 PCS CDMA 帯域用の 0.25PF ~ 0.3PF の範囲にある。これらのキャパシタは、BPF またはデュプレクサのインピーダンスを正確な入力および出力インピーダンス（典型的には 50 オーム）に変換する。

## 【0133】

さらなるインピーダンス整合回路は、示されたように、キャパシタ 651a および 651b のみを用いるのではなくコモンポート 642 において必要とされ得る。Tx および Rx 部分が正確に特定されたインピーダンス（典型的には 50 ）において終端される場合、特定の用途に対するシステム要求は、どれくらいの電圧定常波比（VSWR）が、ポート 20 642 を調べるために検査されなければならないかを決定する。

## 【0134】

フィルタまたはデュプレクサ（またはマルチプレクサ）は、周波数選択インピーダンス変換ネットワークである。このように、標準的な 50 オーム以外の値におよびその値から、入力と出力ポートとの間のインピーダンスレベルを変換するように設計され得る。これを留意すると、キャパシタ 661 および 671 は、必要に応じて、値のより広い範囲を取り得る。キャパシタは、任意の場合において正確な容量を与えるように選択されなければならない。

## 【0135】

一実施形態では、共振器 604a、604b、608a、および 608b のセラミックの誘電率（DK）は、38.6 である。伝送部 644 の共振器 604a および 608b は、232 ミルの電気的長さを有する一方で、受信部 646 の共振器 604b および 608b は、221 ミルの電気的長さを有する。f-e キャパシタ 610a ~ d は、0.66 pF の容量および 180 の Q を有する。

## 【0136】

別の実施形態では、高さ 4.0 mm、 $Z_{oe} = 18.95$  、 $Z_{oo} = 13.80$  、中心導電体の直径 36.24 ミル、および 64.68 ミルの中心導電体の両端の間隔を有する、 $DK = 38.6$  であるセラミックを用いて製造されたものブロックフィルタが使用される。

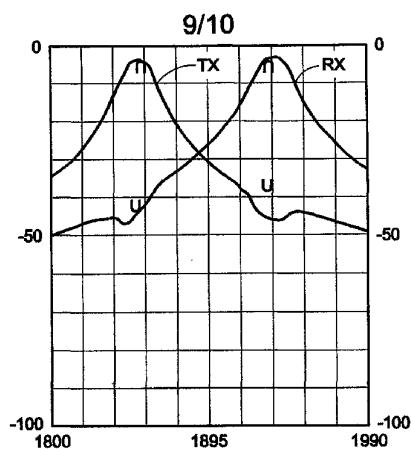

## 【0137】

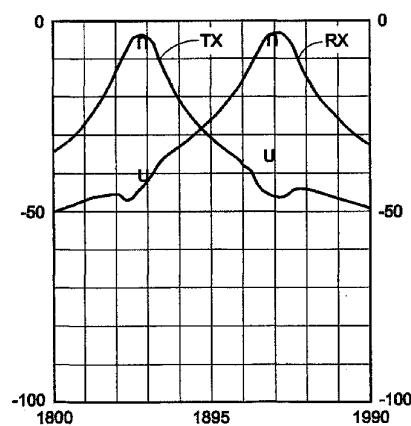

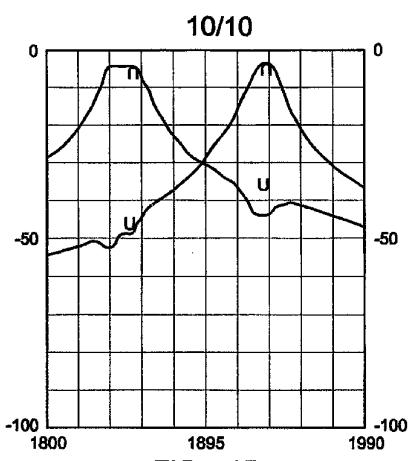

このような PCS 構成部 644 および 646 等のための生成した周波数応答が図 13 に示される。図 14 は、f-e キャパシタ 610a ~ d の Q が 450 まで増加した場合の生成した周波数応答を示す。図 13 および図 14 の応答は、キャパシタ間の EN 結合のない 4.0 mm の同軸共振器に基づく。

## 【0138】

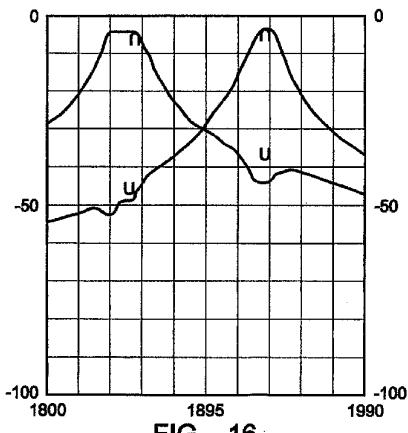

別の実施形態では、キャパシタ 651a、651b、661、および 671 は、250 以上の Q 因子を有する別個のオーバーレイキャパシタとしてインプリメントされ得る。この実施形態では、伝送部 644 の共振器 604a および 608b は、233.179 ミルの電気的長さを有する一方で、受信部 646 の共振器 604b および 608b は、222.32 ミルの電気的長さを有し得る。強誘電体キャパシタ 610a ~ d が 0.66 pF のキ 50

ヤパシタおよび 180 の Q 因子を有する場合、生成した P C S 構成デュプレクサの周波数応答が図 15 に示される。同様に、強誘電体キャパシタ 610 a ~ d の Q 因子が 450 まで増加する場合、周波数応答が図 16 に示されたように存在する。図 13 ~ 図 16 は、例示的なデュプレクサの周波数応答の例である。

#### 【0139】

任意のこれらの実施形態では、増加されたパスバンド I . L . が許容される限り、f - e キャップの Q が低くなり得る。最悪の場合のパスバンド I . L . に対する仕様が T x 帯域に対して -3.5 dB である場合、2.0 GHz において約 80 の関連した Q と共に  $C_{f-e} = 0.66 \text{ pF}$  を使用し得、依然としてその仕様を満たしている。f - e キャパシタの Q は、L attach 等の製造損失を説明するためにより高くなる必要があり得る。

10

#### 【0140】

好適な解決策は、調整要求を満たしつつ、可能な最大の f - e キャパシタの Q を獲得することである。これは、T x および R x 帯域の両方で最小の I . L . 0 を提供する。より小さい  $C_{f-e}$  は、1900 MHz において BPF またはデュプレクサのより小さい負荷を生じる。 $C_{f-e}$  の低限界は、調整範囲によって課される。図 12 ~ 図 16 に示された実施形態では、(図 8 a のキャパシタ 432 の)  $C_{f-e} = 0.33 \text{ pF}$  と共に(図 8 a のキャパシタ 410 a および 410 b の)最小デルタ( )  $C_{f-e} = 0.25 \text{ pF}$  が EM 結合モノブロック設計において必要とされ、 $C_{f-e}$  (図 8 a のキャパシタ 410 a および 410 b の) = 0.34 pF が、非 EM 結合設計において必要とされる。低パスバンド I . L . は、典型的には、ハンドセット等の電力に敏感な用途において特に好適である。なぜなら、低パスバンド I . L . は、電力増幅器等の他のコンポーネントに関する少ない要求を行う。次いで、これは、バッテリ寿命または通話時間に正の影響を与える。

20

#### 【0141】

一例としてモノブロック設計を使用することは、2:1 の  $C_{f-e}$  調整範囲が、所与の f - e フィルム、DC 調整電圧、および f - e キャパシタトポロジに対して達成可能である場合、 $C_{f-e} (0 \text{ V DC}) = 0.5 \text{ pF}$  は、必要とされた  $C_{f-e} = 0.25 \text{ pF}$  を達成する最小  $C_{f-e}$  である。 $C_{f-e} (0 \text{ V DC}) = 0.375 \text{ pF}$  で開始することを望む場合、必要とされた  $C_{f-e} = 0.25 \text{ pF}$  を達成するために 3:1 の調整範囲を必要とする。

30

#### 【0142】

本発明は、特定の実施形態を参照しながら説明してきたが、この説明は本発明の用途の一例に過ぎず、限定するものとして考えるべきではない。その結果、開示された実施形態の特徴の種々の適用および組み合わせは、特許請求の範囲に含まれたような本発明の範囲内にある。

#### 【図面の簡単な説明】

#### 【0143】

【図 1 a】図 1 a は、強誘電体のギャップキャパシタの平面図である。

【図 1 b】図 1 b は、線 A に沿って切り取られた図 1 a の強誘電体ギャップキャパシタの断面図である。

【図 2 a】図 2 a は、付随の DC ブロッキングキャパシタを伴う、強誘電体オーバーレイキャパシタの平面図である。

40

【図 2 b】図 2 b は、図 2 a のオーバーレイキャパシタの第 1 の金属層の平面図である。

【図 2 c】図 2 c は、図 2 a の線 B に沿って切り取られた図 2 a のオーバーレイキャパシタの断面図である。

【図 3】図 3 は、図 2 a の領域 C の拡大図を例示する。

【図 4】図 4 は、強誘電体インターデジタルキャパシタの平面図である。

【図 5】図 5 は、チューナブル強誘電体キャパシタに接続された共振器の模式図である。

【図 6】図 6 は、シングルポールチューナブルフィルタの模式図である。

【図 7】図 7 は、図 6 のシングルポールフィルタの平面回路実施の図である。

【図 8 a】図 8 a は、チューニングによって引き起こされる周波数応答ゆがみを補償する

50

ように構成されている、強誘電体キャパシタを有するダブルポールチューナブルフィルタの模式図である。

【図 8 b】図 8 b は、チューニングによって引き起こされる周波数応答ゆがみを補償するように構成されている、二つの強誘電体キャパシタを有するダブルポールチューナブルフィルタの模式図である。

【図 9】図 9 は、分周器ネットワークおよび直流電源の模式図であり、この分周器ネットワークおよび直流電源は、図 8 b に図示された、チューニングによって引き起こされる周波数応答ゆがみを補償するように構成された二つの強誘電体キャパシタをチューニングするように用いられる。

【図 10】図 10 は、図 9 に示された分周器ネットワークの一つの実施を図示する。 10

【図 11 a】図 11 a は、図 8 a に示されたチューナブルフィルタの平面図である。

【図 11 b】図 11 b は、線 D に沿って切り取られた図 11 のチューナブルフィルタの断面図である。

【図 12】図 12 は、チューナブルデュプレクサの模式図である。

【図 13】図 13 は、チップキャパシタ入力および出力が接続し、かつ、f - e キャパシタ  $Q = 180$  であるチューナブルデュプレクサの周波数応答図である。

【図 14】図 14 は、チップキャパシタ入力および出力が接続し、かつ、f - e キャパシタ  $Q = 450$  であるチューナブルデュプレクサの周波数応答図である。

【図 15】図 15 は、統合されたギャップキャパシタ入力および出力が接続し、かつ、f - e キャパシタ  $Q = 180$  であるチューナブルデュプレクサの周波数応答図である。 20

【図 16】図 16 は、統合されたギャップキャパシタ入力および出力が接続し、かつ、f - e キャパシタ  $Q = 450$  であるチューナブルデュプレクサの周波数応答図である。

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

24 October 2002 (24.10.2002)

PCT

(10) International Publication Number

WO 02/084781 A1

(51) International Patent Classification: H01P 1/213. (72) Inventor: TONICH, Stoney, Slavko; 11155 Spooner Court, San Diego, CA 92131 (US).

(21) International Application Number: PCT/IB02/01030

(81) Designated States (national): AL, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EL, ES, IT, GB, GD, GE, GH, GM, IIR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, ME, MN, MW, MX, MZ, NO, NZ, OM, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(22) International Filing Date: 2 April 2002 (02.04.2002)

(25) Filing Language: English

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), European patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BH, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(26) Publication Language: English

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), European patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BH, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(30) Priority Data: 60/283,093 11 April 2001 (11.04.2001) US 09/904,631 13 July 2001 (13.07.2001) US 09/912,753 24 July 2001 (24.07.2001) US 09/927,732 8 August 2001 (08.08.2001) US 09/927,136 10 August 2001 (10.08.2001) US

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), European patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BH, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(71) Applicant: KYOCERA WIRELESS CORPORATION

[US/US]; 10300 Campus Point Drive, San Diego, CA 92121 (US).

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), European patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BH, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report

[Continued on next page]

(54) Title: TUNABLE MULTIPLEXER

WO 02/084781 A1

(57) Abstract: The present invention provides a tunable ferroelectric multiplexer for use in CDMA communication devices. Tunable ferroelectric capacitors are used to tune the resonant frequencies of several resonators used in a multiplexer and to tune the frequency response shape of the multiplexer. A low loss ferroelectric material and configuration is provided. The tunable multiplexer is smaller and has less insertion loss than a fixed tuned multiplexer.

---

**WO 02/084781 A1**

*before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments*

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WO 02/084781

PCT/IB02/01030

Tunable Multiplexer

Related Application

5 This application claims the benefit of U.S. Provisional Application 60/283,093, filed April 11, 2001, which is hereby incorporated by reference.

In addition, this application relates to U.S. application

10 "Tunable Ferro-electric Filter," filed on July 13, 2001, which is hereby incorporated by reference.

**BACKGROUND**Description of Related Art

15 Filters, such as bandpass filters, have numerous applications in communications and electronics. For example, in wireless communications a given frequency band must accommodate many wireless users. To accommodate so many users, stringent bandpass filtering requirements must be achieved because of the crowded frequency allocations

20 provided.

At present, wireless handsets use fixed-tuned bandpass filters (BPFs) to meet their filtering specifications. The design of such filters is complicated because they must achieve the lowest possible passband insertion loss (I.L.)

25 while simultaneously achieving a specified large out-of-band rejection. As a specific example, consider PCS CDMA handsets. The PCS transmit (TX) band should have no more than -3.5 dB I.L. in-band (1850 to 1910 MHz in the U.S.) while having at least a 38.0 dB out-of-band rejection in the receive (RX) band

30 (1930 to 1990 MHz range).

Further, this BPF must meet these specifications with a maximum constraint on height. A typical height constraint in

WO 02/084781

PCT/IB02/01030

present day handsets, for example, is 4.0 mm or less. To meet these demanding electrical requirements yet possess the smallest possible size and height, high order (> 2<sup>nd</sup> order) fixed-tuned filters constructed from either individual coaxial resonator elements or monoblock structures are usually necessary. In addition, to satisfy out-of-band rejection specifications, a transmission zero is usually required, increasing I.L. at the band edge. Because of variations in ceramics and fabrication tolerances, vendors must individually adjust the characteristics of fixed-tuned filters during their manufacture, driving costs higher.

Moreover, if more than one frequency band were to be supported (e.g., supporting the PCS bands in the U.S., Korea, and India) multiple fixed-tuned BPFs would be necessary, requiring extra switches and introducing additional loss. This is true, even if the power amplifier and low noise amplifier used have sufficient bandwidth to operate over these multiple bands.

A tunable BPF would allow the use of one BPF over several bands, or of a lower order filter to cover a bandwidth wider than a required passband at any particular time. To provide the tunability in a tunable BPF, a component capable of providing a variable capacitance is typically used.

Several structures are presently used to implement a variable capacitor. For example, movable parallel plates have been used for many years as the tuner in home radios. However, such plates are far too bulky, noisy, and impractical for use in modern applications.

Another alternative, the electronic varactor, is a semiconductor device that adjusts capacitance responsive to an applied voltage. Because the varactor is typically noisy and lossy, particularly in applications above 500 MHz, it is

WO 02/084781

PCT/IB02/01030

ineffective for high-frequency, low-loss applications where high performance is required.

Another alternative, a micro-electro-mechanical-switch (or system) (MEMS) is a miniature switching device that may 5 switch between capacitors responsive to an applied control signal. It, however, is costly, difficult to manufacture and of unproven reliability. In most cases, it provides discrete tuning, in that a system must select between a finite (and small) number of fixed capacitors.

10 Ferroelectric tunable capacitors are another alternative that has been attempted. Ferroelectric (f-e) materials are a class of materials, typically ceramic rare-earth oxides, whose prominent feature is that their dielectric constant ( $\kappa$ ), and as a consequence, the electric permittivity ( $\epsilon$ ) changes in 15 response to an applied slowly varying (DC or low frequency) electric field. The relationship of the dielectric constant ( $\kappa$ ) and the electric permittivity ( $\epsilon$ ) of a material is given as follows:

$$\epsilon = \kappa \epsilon_0$$

20 where  $\epsilon_0$  is the electric permittivity of a vacuum. At present, there are several hundred known materials that possess f-e properties. In a typical f-e material, one can obtain a range in  $\kappa$  by a factor of as much as approximately 3:1. The required DC voltage to generate such a change in  $\kappa$  25 depends on the dimensions of the f-e material over which a DC control voltage is applied. As a result of their variable dielectric constant, one can make tunable capacitors using f-e materials, because the capacitance of a capacitor depends on the dielectric constant of the dielectric proximate the 30 capacitor conductors. Typically, a tunable f-e capacitor is realized as a parallel plate (overlay), interdigital (IDC), or a gap capacitor.

WO 02/084781

PCT/IB02/01030

In known f-e variable capacitors, a layer of an appropriate f-e material, such as barium strontium titanate,  $\text{Ba}_x\text{Sr}_{1-x}\text{TiO}_3$  (BSTO) is disposed adjacent to one or both conductors of a capacitor. Depending upon the strength of the electric field applied to the f-e material and the intrinsic properties of the f-e material selected, the capacitance changes. Typically, below the Curie temperature,  $T_c$ , of the f-e film, the f-e material is in the ferroelectric state and will exhibit hysteresis in its response to a changing electric field. Above  $T_c$ , f-e material is in the paraelectric state and will not exhibit hysteresis. Thus, one generally picks an f-e material whose  $T_c$  is lower than the expected operating temperature so as to operate in the paraelectric state, avoiding the hysteresis effects of the ferroelectric state.

However, conventional f-e variable capacitors have proven to be too lossy for use in insertion-loss-sensitive applications such as handsets. Moreover, these devices often perform unpredictably, preventing optimal design, construction, and use of f-e tunable filters.

Duplexers are used in CDMA technology to separate the Tx and the Rx frequencies into their respective signal paths. Duplexers typically comprise two bandpass filters. Each filter selects either the Tx or the Rx frequency signal to be passed. The filters are coupled at one end, forming a common port. This common port is typically coupled to an antenna or a diplexer for sending transmit signals and receiving receive signals.

Strict insertion loss and out-of-band rejection requirements are the primary requirements that influence the design of duplexers for use in loss sensitive applications, such as, for example, in wireless handsets. Other electrical and mechanical specification must also be satisfied, such as, for example, size and height requirements.

WO 02/084781

PCT/IB02/01030

Accordingly, there is a need in the art for improved tunable f-e filters capable of providing a tuning range over a desired frequency range with low I.L. and high out-of-band rejections and methods for designing the same. These filters 5 could then be used to make tunable duplexers.

**SUMMARY**

In CDMA wireless handsets, strict insertion loss and out-of-band rejection requirements generally mandate high order (> 10 3<sup>rd</sup> order) filters for use in duplexers. The in band insertion loss requirements generally apply over a frequency broader than that used for operation at any given time. This means that a fixed tuned filter for use in a duplexer must have a broader passband than would a tunable filter used by tuning 15 over that same passband. Because the tunable filter could have a smaller (tunable) passband, it could be lower order (taking up less space) or it could have less insertion loss, or both.

This is only true though, if adding tunability does not 20 increase the insertion loss of the duplexer too much. The invention provides for a ferro-electric tunable capacitor and capacitor and resonator circuit that makes a duplexer tunable, while maintaining low insertion loss.

Thus, a low insertion loss tunable duplexer which is 25 smaller and has less insertion loss than a fixed tuned bandpass filter that could cover the same passband is provided. The space savings in a wireless handset can be used to provide other desired functions and properties, or it can be used to simply reduce the size and weight of the handset. Additionally, the savings in insertion loss result in a longer 30 talk time and battery life.

**BRIEF DESCRIPTION OF THE DRAWINGS**

FIG. 1a is a plan view of a ferro-electric gap capacitor.

WO 02/084781

PCT/IB02/01030

FIG. 1b is a cross-sectional view of the ferro-electric gap capacitor of FIG. 1a taken along line A.

FIG. 2a is a plan view of a ferro-electric overlay capacitor, along with an accompanying DC blocking capacitor.

5 FIG. 2b is a plan view of the first metal layer in the overlay capacitor of FIG. 2a.

FIG. 2c is a cross-sectional view of the overlay capacitor of FIG. 2a taken along line B in Fig. 2a.

Figure 3 illustrates an enlarged view of area C in Figure

10 2a.

Figure 4 is a plan view of a ferro-electric interdigital capacitor.

Figure 5 is a schematic of a resonator coupled to a tunable ferro-electric capacitor.

15 Figure 6 is a schematic of a single pole tunable filter.

Figure 7 is a planar circuit implementation of the single pole filter of Figure 6

Figure 8a is a schematic of a double pole tunable filter having a ferro-electric capacitor configured to compensate for

20 frequency response distortions induced by tuning.

Figure 8b is a schematic of a double pole tunable filter having a two ferro-electric capacitors configured to compensate for frequency response distortions induced by tuning.

25 Figure 9 is a schematic of a divider network and direct current voltage source used to tune the two ferro-electric capacitors configured to compensate for frequency response distortions induced by tuning shown in Fig. 8b.

WO 02/084781

PCT/IB02/01030

Figure 10 shows one implementation of the divider network shown in Fig. 9.

Figure 11a is a plan view of the tunable filter shown in Fig. 8a.

5 Figure 11b is a cross-sectional view of the tunable filter shown in Fig. 11a, taken along line D.

Figure 12 is a schematic of a tunable duplexer.

Figure 13 is a frequency response graph of a tunable duplexer with chip capacitor input and output coupling and f-e capacitor  $Q = 180$ .

10 Figure 14 is a frequency response graph of a tunable duplexer with chip capacitor input and output coupling and f-e capacitor  $Q = 450$ .

15 Figure 15 is a frequency response graph of a tunable duplexer with integrated gap capacitor input and output coupling and f-e capacitor  $Q = 180$ .

Figure 16 is a frequency response graph of a tunable duplexer with integrated gap capacitor input and output coupling and f-e capacitor  $Q = 450$ .

20 Use of the same reference symbols in different figures indicates similar or identical items.

#### DETAILED DESCRIPTION

In designing a tunable bandpass filter (BPF) for use and 25 application in electronic signal processing systems, such as, for example, communications systems, one must usually meet or exceed both out-of-band rejection and pass band insertion loss (I.L.) requirements as well as size, weight and other

WO 02/084781

PCT/IB02/01030

mechanical, environmental and electrical requirements imposed on fix-tuned BPF's.

Thus, for a tunable BPF to be a commercially viable replacement for a fixed-tuned BPF, its performance should exceed that of the fixed-tuned BPF it is replacing in terms of most or all of the electrical and mechanical requirements. In demanding applications such as wireless handsets, passband I.L. must be minimized to prevent placing an even greater burden on other components in the handset. If a tunable BPF has I.L. greater than the fixed-tuned BPF it is to replace, the added I.L. may prove to be too great a burden on the overall system performance. The added burden would usually be greatest on active devices like amplifiers. The amplifiers would have to have greater gain and power output to overcome the effects of increased passband loss over that of existing fixed bandwidth filters.

Many definitions of what defines a "pass band" may be used. Typically the pass band is defined by the points where the bandpass filter response falls to 3.0dB below the mid-band, or band-center insertion loss ( $I.L_0$ ). However, any fixed filter response can be used to define the pass band. Higher order (more resonators) bandpass filters are typically required to meet a specific out-of-band rejection requirement. But increasing the filter order will increase the  $I.L_0$ . A useful basic relationship between filter order and  $I.L_0$  is given by the following equation:

$$I.L_0 = (4.34 * Q_r / Q_u) * \sum_{i=1}^N g_i \quad (1)$$

where N is the filter order,

$Q_u$  is the unloaded Q of the resonators used,

WO 02/084781

PCT/IB02/01030

$Q_1 = f_0/BW$  (BW is the 3 dB passband and  $f_0$  is the midband frequency), and

$g_i$  are the filter element values for a given topology (Chebyshev vs. Butterworth).

5 Generally, a Chebyshev response is preferable as it gives a steeper rejection response compared to that given by a Butterworth filter for a given filter order. Additionally, increasing the ripple in a Chebychev BPF further increases out of band rejection. As can be seen from equation (1), for a 10 given filter order  $N$ , a larger passband results in lower  $I.L_0$ . as  $Q_1$  will decrease as BW increases. This lower  $I.L_0$ . comes at the expense of decreased selectivity. To regain selectivity, 15 the filter order  $N$  must be increased, at the expense of  $I.L_0$ . One of ordinary skill in the art of bandpass filter design 20 will appreciate that equation (1) represents the best one can do for a given system requirement and filter order. Using a higher order filter (more resonators of a given unloaded  $Q$ ) quickly increases  $I.L_0$ ., because the  $g_i$  values get progressively larger in magnitude, even as there are more of 25 them to sum (increased  $N$ ). Note that equation (1) neglects implementation losses, which further increase  $I.L_0$ , especially as the band edge is approached.

It can be seen from equation (1) that using a first or 25 second order bandpass filter reduces  $I.L_0$ . At these lower orders, both the number ( $N$ ) of the  $g_i$  coefficients decreases as well as the magnitudes of the  $g_i$ . These low-order filters should be constructed from resonators that have the lowest loss (highest  $Q_u$ ) so as to give the minimum  $I.L_0$ . possible. The resulting 1<sup>st</sup> or 2<sup>nd</sup> order bandpass filter will always have 30 lower  $I.L_0$ . for a given resonator size and type (i.e., for a given  $Q_u$ ) than the comparable fixed-tuned bandpass filter design of higher order. Tunability allows the low order narrowband BPF able to replace a wider band, fix-tuned BPF. A

WO 02/084781

PCT/IB02/01030

tunable narrowband low order BPF can cover the entire band of interest, overcoming the limitation of having a narrow bandwidth. This assumes that the desired channel (information) bandwidth is narrower than the total system bandwidth.

5 Tunable BPFs have the best chance of replacing fixed-tuned BPFs in those cases where the fixed-tuned BPF covers a system bandwidth that is greater than that required for transmission or reception of a single channel. For example, a fixed-tuned BPF in a handset for operation in the U.S. CDMA

10 PCS band covers such a BW. It will be understood that this is also true of U.S. cellular CDMA and many other standards. The techniques, methods and devices taught herein are applicable to many standards besides U.S. CDMA PCS. U.S. CDMA PCS is discussed as an example only.

15 In the U.S. PCS band, 60 MHz is allocated for Tx (1850 to 1910 MHz) and 60 MHz for Rx (1930 to 1990 MHz). The CDMA standard is a full duplex system, meaning the handset must simultaneously transmit and receive. To accomplish this, a duplexer filter is needed to separate the bands and prevent

20 interference. While the PCS band is 60 MHz wide, the individual CDMA channel is only 1.25 MHz wide. Current system architecture, however, forces CDMA PCS bandpass filters and multiplexers (including duplexers) to have a  $BW \geq 60$  MHz as the system must allow for and accommodate operation of any

25 1.25 MHz channel in any region of the 60 MHz band.

30 A tunable PCS band filter could alter this situation by meeting the worst case rejection specifications while providing a lower order BPF of simpler topology that occupies a smaller physical area. Such a lower order filter would necessarily provide lower  $I.L_0$ . by virtue of equation (1).

To effectively replace a high-order fixed-tuned BPF with a low-order tunable BPF, three factors should be considered.

WO 02/084781

PCT/IB02/01030

First, the bandwidth (i.e.  $Q_1$ ) of the low-order BPF and the chosen topology must be such that the worst case rejection specification is met. Because  $Q_1 = f_0/\text{BW}$ , as the 3dB bandwidth (BW) decreases, the I.L. increases. Thus, if BW is too small relative to  $f_0$ , the resulting BPF will have an unacceptably high I.L., requiring a tradeoff between BW and I.L. For practical designs, a low-order tunable BPF should have the lowest possible I.L. consistent with meeting the worst-case required rejection. Some topologies are preferred in that they naturally provide a low side (below the transmission band) zero or a high side (above the transmission band) zero. A topology such as that shown in Fig. 10 is capable of providing a lower passband I.L. because the BPF  $Q_1$  is smaller (because bandwidth is greater) or the ripple (manifested in the  $g_1$  terms of the corresponding Chebychev BPF) is lower or both. The transmission zero provides the extra required rejection over a certain frequency range.

Second, the low-order tunable filter must be tunable to cover the entire BW, just as with a fixed-tuned filter. Finally, the tunable capacitor used within the low-order tunable filter should be of sufficiently low loss so the resulting filter has an I.L. that meets or exceeds specifications. Although a tunable 1<sup>st</sup> or 2<sup>nd</sup> order bandpass filter will be of minimum added loss compared to a higher order ( $N > 2$ ) fixed-tuned bandpass filter design, the tunable component (variable f-e capacitor) must have a fast tuning mechanism and be tunable to cover the entire bandpass range, using the available tuning voltage.

The total loss of a capacitor,  $L_t$ , whether tunable or not, is given by a ratio of its dissipated to stored energy, where the energy is stored in the electric field and dissipated in resistance, i.e.,  $L_t = (\text{dissipated energy})/(\text{stored energy})$ . The inverse of this loss is the quality factor,  $Q$ . For a capacitor,  $L_t$  may be given by the quantity  $(\omega * R_s * C)$ , where  $\omega$  is

WO 02/084781

PCT/IB02/01030

the frequency in radians,  $R_s$  is the total series resistance of the capacitor, and  $C$  is the capacitance.

The importance of determining the total loss given by an f-e capacitor in a resonant circuit can be seen from the 5 following equations:  $L_c = 1/Q_c$  and  $1/Q_T = 1/Q_c + 1/Q_u$ , where,

$L_c$  = the loss of the capacitor;

$Q_T$  = the total Q of the f-e capacitor and the resonator or inductor combined;

$Q_c$  = the Q of the capacitor; and

10  $Q_u$  = the Q of the unloaded resonator or alternatively, the Q of an inductor used to create a parallel resonant circuit.

As  $Q_c$  increases, it will affect the  $Q_T$  less and less. If  $Q_c$  is infinite, it has no affect on  $Q_T$ . For practical purposes, this is also true if  $Q_c$  is approximately  $10*Q_u$ . The 15 converse is true too. As  $Q_u$  becomes higher and higher relative to  $Q_c$ ,  $Q_u$  has less and less effect on  $Q_T$ . In either case, the highest practical  $Q_c$  is desired.

For a useful example for use in the PCS band, for a 1.0 pF tunable capacitor to have a  $Q_c = 250$  at 2.0 GHz requires 20 that  $R_s$  be  $.32 \Omega$  (ohms). To minimize loss (obtain a low  $R_s$ ), requires an accounting of all loss mechanisms present and an elimination of these loss mechanisms if possible.

For f-e devices, the total loss is governed by summing each source contribution as follows:

25  $L_t = L_{geom} + L_{attach} + L_{metal} + L_{sub} + L_{rad} + L_{meas} + L_{f-e}$ ;

where  $L_{geom}$  is derived from the topology of the capacitor,

$L_{attach}$  is loss due to device attachment,

$L_{metal}$  is the total metal loss,

WO 02/084781

PCT/IB02/01030

$L_{\text{sub}}$  is the base substrate loss (if present),

$L_{\text{rad}}$  is the radiation loss, both desired and undesired,

$L_{\text{meas}}$  is the total loss arising from measurement errors,

and

5  $L_{\text{f-e}}$  is the f-e loss tangent:

This loss allocation can first be used to obtain an accurate value of  $L_{\text{f-e}}$  (or  $f\text{-e} \tan \delta$ ) at the desired operating frequency in the manner in which the f-e capacitor will be used. To correctly derive  $L_{\text{f-e}}$ , one must eliminate or constrain

10 all of the other loss contribution sources just described.

For example,  $L_{\text{geom}}$  will vary according to topology, being best for an overlay capacitor, worse for a gap capacitor, and much worse for an IDC capacitor. Although this loss can be reduced and controlled, it is inherent to a device. Consequently, the

15 choice of topology for a given f-e capacitor will affect the best possible  $Q_a$  attainable from the f-e capacitor.

Electromagnetic (EM) software can establish a baseline loss for a desired geometry, assuming a lossless f-e film. This baseline loss represents the best (lowest) loss for a given

20 geometry.

In general, a gap capacitor is easiest to fabricate. An IDC is next easiest, and an overlay capacitor is hardest of these three. Compared to an IDC, the gap capacitor will have a better  $Q$  but lower capacitance per unit cross section ( $W$  in

25 Fig. 1a). The IDC's capacitance is greater due to the use of a number of fingers per unit cross section. For many

communication filter applications, however, large capacitance ( $C \geq 4.0 \text{ pF}$ ) is not needed. Thus, a gap capacitor often can provide adequate capacitance. The inherently high value of  $\kappa$

30 for most f-e films helps provide relatively high capacitance

WO 02/084781

PCT/IB02/01030

per unit cross section,  $W$ , compared to a conventional gap capacitor.

$L_{attach}$  arises from discrete device attachment techniques, including, for example, solder, silver paint, or wire bonding. 5 These attachment losses may be large and unpredictable. The lowest losses are achieved by direct fabrication of the f-e capacitor to the resonator or other RF circuitry, thus minimizing if not eliminating this loss component.

The inherent loss of a stand-alone f-e capacitor is of 10 little consequence. What is of much greater consequence is any added loss arising from the attachment of the f-e capacitor to a circuit. Even if the f-e capacitor were lossless, should a large loss connection be used, the overall 15 effect is that of a lossy f-e device. For example, if a  $Q \geq 250$  at 2.0 GHz is desired for a capacitance of 1.0 pF, then the total series resistance  $R_s$  must be  $\leq 0.32$  ohm. Any additional loss will thus further reduce the  $Q$  of this 20 capacitor. That this additional loss is external to the actual capacitor is irrelevant. Even unavoidable loss mechanisms, such as those due to mounting, for example, lower the effective  $Q$  of the capacitor from the perspective of its 25 effect on the system.

For minimum added loss, the connection between the f-e capacitor and the resonator should provide the lowest added 25 resistance. Thus, the electric currents and charges associated with the f-e capacitor should see a minimum added loss. Conventional bonding or mounting techniques, such as (but not limited to) soldering, wire bonding or silver paint or paste do not provide for such a low loss, controllable 30 bond.

The added, unpredictable loss arising from the use of such bonding methods degrade the realized  $Q$  regardless of

WO 02/084781

PCT/IB02/01030

whether or not the f-e capacitor is being used for resonator tuning purposes or characterization of an f-e film. Thus, for best performance (lowest loss) the f-e capacitor structure should be directly fabricated onto or with the resonator it is 5 meant to tune or onto other essential RF circuitry. Only by direct fabrication can there be a minimum loss transition for electromagnetic (EM) sources (currents) from the f-e tuning elements to the resonator. The desirable effects of direct f-e capacitor fabrication onto or with a resonator can be enhanced 10 by the lack of sharp corners or transitions.

Factors for  $L_{\text{metal}}$  include the surface roughness (SR) of the metal, metal thickness as compared to skin depth,  $\delta_s$ , and conductivity. SR may be effectively eliminated as a factor if SR is less than approximately 10 micro inches root mean square (rms) for operating frequencies in the L and S band (1-4 GHz). 15 The metal thickness may be reduced as a factor if the thickness is  $1.5\delta_s$  or greater, or effectively eliminated if the thickness is  $\geq 5\delta_s$ . For electrode contacts, metal thickness ( $t_m$ ) can be approximately  $1.5\delta_s$ . For the case of 20 electromagnetic resonators, where a travelling or standing wave must be supported, i.e., where the metal in question extends for an appreciable fraction of a wavelength (about 10% or greater), the metal thickness should be closer to about  $5\delta_s$  or greater.