Filed April 6, 1964

316 Sheets-Sheet 1

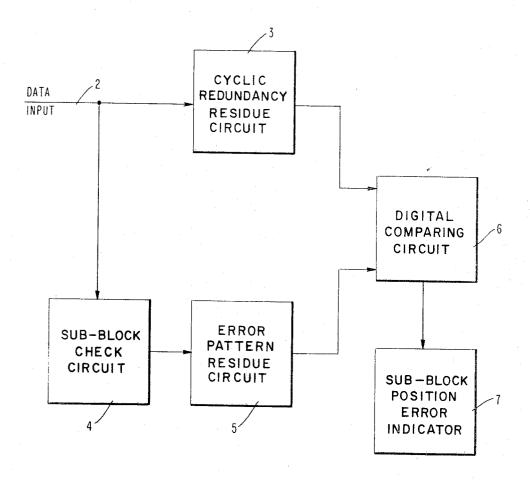

FIG. 1

INVENTOR DAVID T. BROWN

ΒY

Bernard M. Goldman ATTORNEY

Filed April 6, 1964

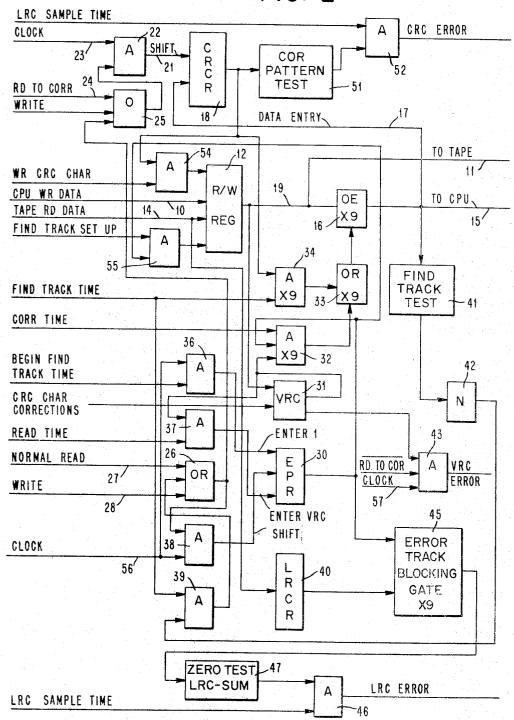

FIG. 2

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 6

Filed April 6, 1964

316 Sheets-Sheet 7

Filed April 6, 1964

316 Sheets-Sheet 8

Filed April 6, 1964

316 Sheets-Sheet 9

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 12

Filed April 6, 1964

316 Sheets-Sheet 13

Filed April 6, 1964

FIG. 13

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 17

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 21

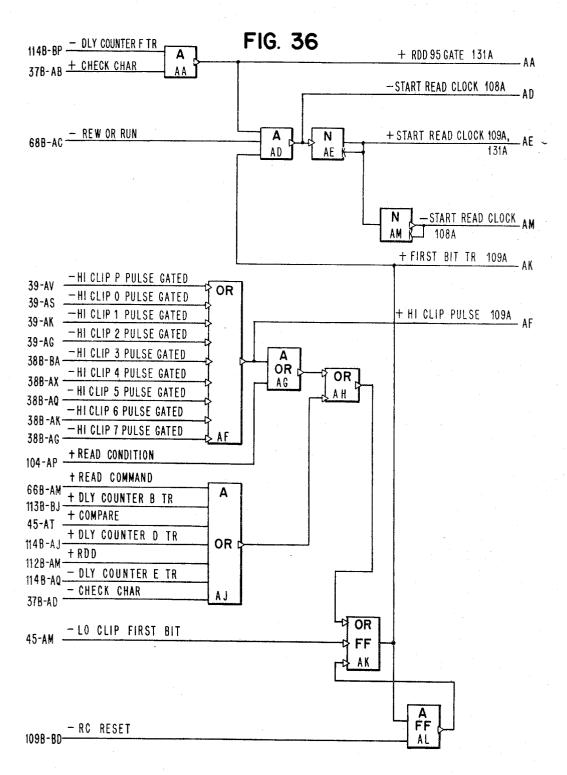

#### FIG.19A

Filed April 6, 1964

316 Sheets-Sheet 22

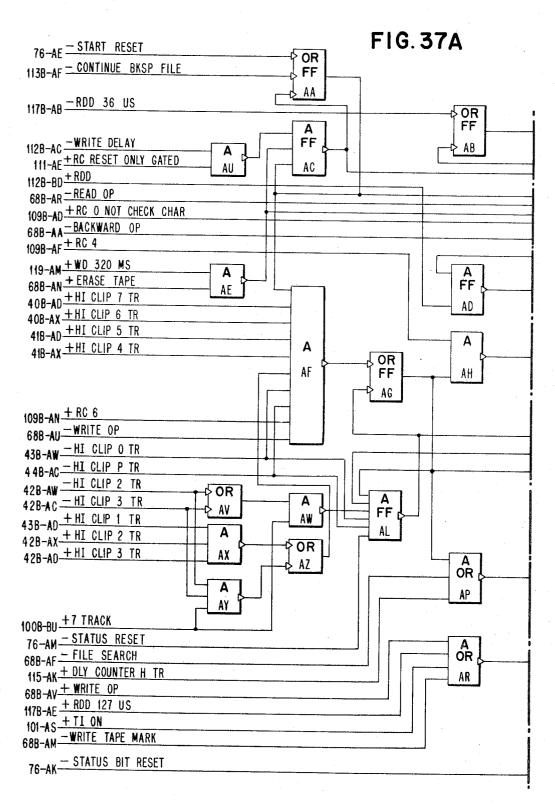

# FIG.19B

Filed April 6, 1964

316 Sheets-Sheet 23

## FIG.20A

Filed April 6, 1964

316 Sheets-Sheet 24

FIG.20B

Filed April 6, 1964

316 Sheets-Sheet 25

# FIG. 21A

Filed April 6 , 1964

FIG. 21B

Filed April 6 , 1964

Filed April 6, 1964

Filed April 6 , 1964

316 Sheets-Sheet 29

# FIG.23A

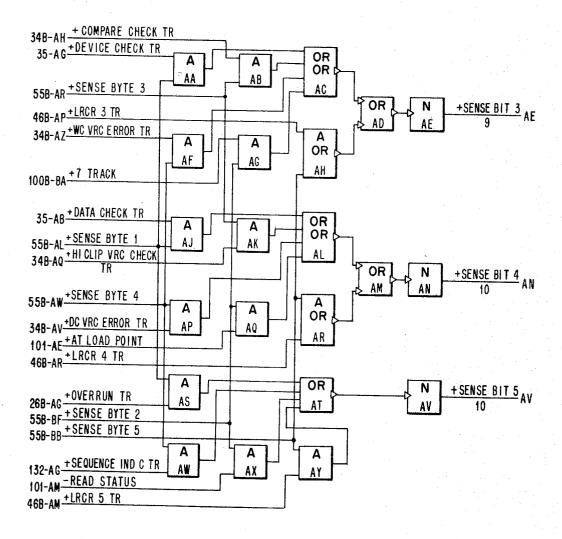

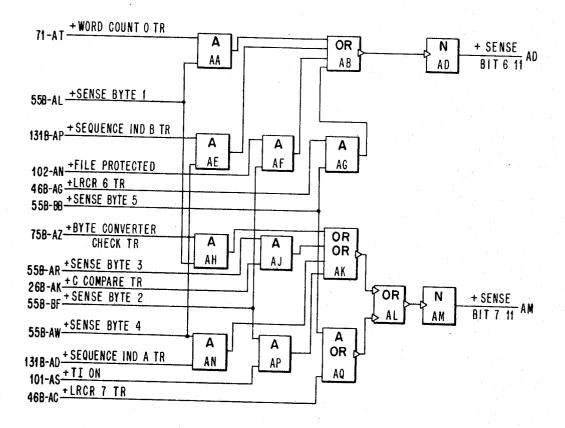

Filed April 6 , 1964

316 Sheets-Sheet 30

FIG.23B

Filed April 6, 1964

Filed April 6 , 1964

FIG. 24 B

Filed April 6 , 1964

316 Sheets-Sheet 33

#### FIG.25A

Filed April 6 , 1964

FIG.25B

Filed April 6 , 1964

Filed April 6 , 1964

ERROR DETECTION AND CORRECTION SYSTEM

| Filed | April | 6  | 1064   |

|-------|-------|----|--------|

| rited | Whit  | ю. | . 1904 |

316 Sheets-Sheet 37

| Filed April 6 , 1964                                                                                                                                                                                                                                                 |                                                                                 |                                                                          | 316                                                                                         | Sheets-Sheet 37                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| -CORR R-W BUS 7 BIT 22A DL +CORR R-W BUS 7 BIT 14,15, AA 12,22A,28A,28B,33B                                                                                                                                                                                          |                                                                                 | - CORR R-W BUS 6 BIT 22A<br>+ CORR R-W BUS 6 BIT 22A,<br>28A, 28B, 33B   | - CORR R-W BUS 5 BIT 22A<br>+ CORR R-W BUS 5 BIT 13,15,<br>16, 28A, 28B, 33B                | -CORR R-W BUS 4 BIT 22A<br>+CORR R-W BUS 4 BIT 15,<br>22A, 28A, 28B, 33B |

| R-W GATE-7  R-W GATE-7  A DG DH DK OR N  A DG DH DK DK OR N  A DG DH DK |                                                                                 | R-W GATE-6                                                               | R-W GATE -5                                                                                 | R-W GATE-4                                                               |

| 32-BB +EPR 7 BIT EX<br>28A-AA -CRCR 7 BIT<br>25B-BJ -R-W VRC ERROR                                                                                                                                                                                                   | 48B-AX + R-W REG 7 TR<br>48B-AK - R-W REG 7 TR<br>33D-AC + GATE CRCR TO R-W BUS | 32-BC + EPR 6 BIT EX<br>28A-AB + R-W REG 6 BIT<br>18B-AP - R-W REG 6 BIT | 32-BD +EPR 5 BIT EX<br>28A-AC -CRCR 5 BIT<br>48B-AT +R-W REG 5 BIT<br>48B-AV -R-W REG 5 BIT | 32-BE                                                                    |

16.27A

ERROR DETECTION AND CORRECTION SYSTEM

Filed April 6, 1964

|         | -CORR R-W BUS 3 BIT 22A<br>+CORR R-W BUS 3 BIT 22A,<br>28B,33B      | -CORR R-W BUS 2 BIT 22A<br>+CORR R-W BUS 2 BIT 22A,<br>28A, 28B, 33B                        | + CORR R-W BUS # BIT 17,                                                                         | + CORR R-W BUS 0 BIT 47,                                                                          | +CORR R-W BUS P BIT<br>28A,28B,33B                                                 |

|---------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|         | R-W GATE-3                                                          | R-W GATE-2                                                                                  | R-W GATE-4                                                                                       | R-W GATE - 0                                                                                      | R-W GATE - P                                                                       |

| FIG.27B | 298-KA + EPR 3 BIT<br>288-AE - CRCR 3 BIT<br>19B-AH - R W REG 3 BIT | 32-BF +EPR 2 BIT EX<br>28B-AF +CRCR 2 BIT<br>49B-AC +R-W REG 2 BIT<br>49B-AE -R-W REG 2 BIT | 28B-AG + EPR 1 BIT EX<br>28B-AG - CRCR 1 BIT<br>19B-AL + R-W REG 1 BIT<br>19B-AS - R-W REG 1 BIT | 28B-AH — CRCR 0 BIT EX<br>28B-AH — CRCR 0 BIT<br>20B-AB + R-W REG 0 BIT<br>20B-AC — R-W REG 0 BIT | 32-BJ +EPR P BIT EX 28B-AJ +CRCR P BIT 20B-AD +R-W REG P BIT 20B-AG -R-W REG P BIT |

Filed April 6, 1964

316 Sheets-Sheet 39

### FIG.28A

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 41

### FIG.29A

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 43

# FIG.30

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 45

#### FIG. 32

Filed April 6, 1964

316 Sheets-Sheet 46

### FIG.33A

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 50

### FIG.34A

Filed April 6, 1964

316 Sheets-Sheet 51

### FIG.34B

Filed April 6, 1964

316 Sheets-Sheet 52

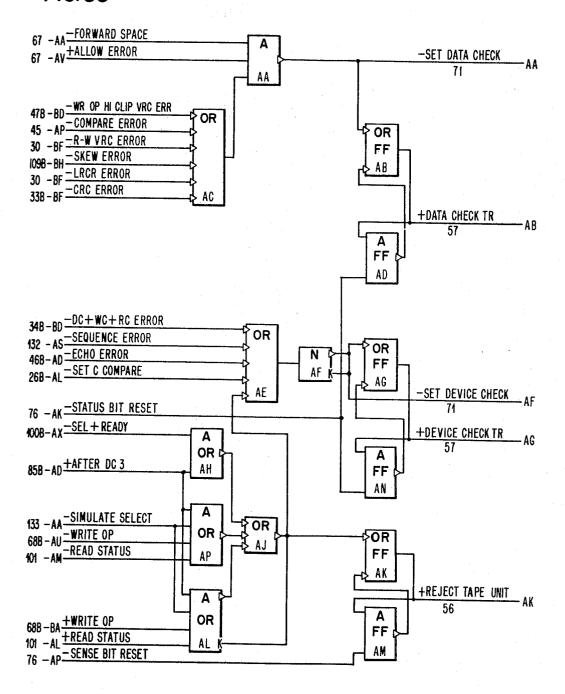

#### FIG. 35

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

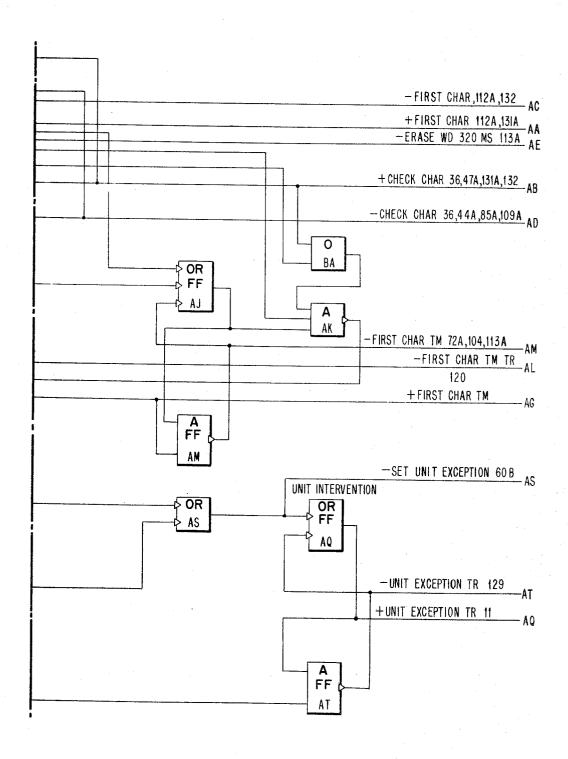

FIG. 37B

Filed April 6, 1964

316 Sheets-Sheet 56

# FIG.38A

Filed April 6, 1964

316 Sheets-Sheet 57

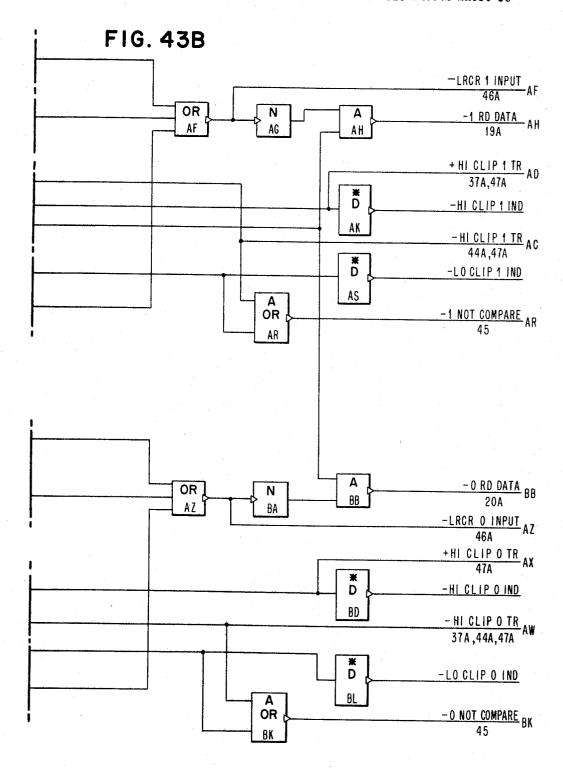

### FIG.38B

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 61

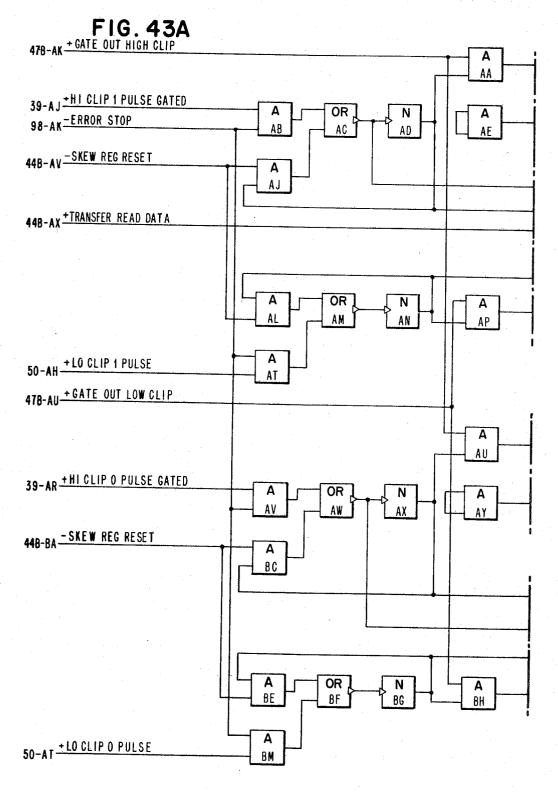

# FIG. 41A

Filed April 6, 1964

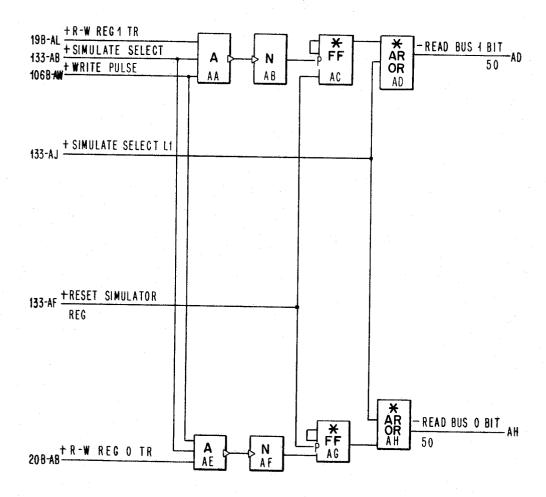

FIG. 41B

Filed April 6, 1964

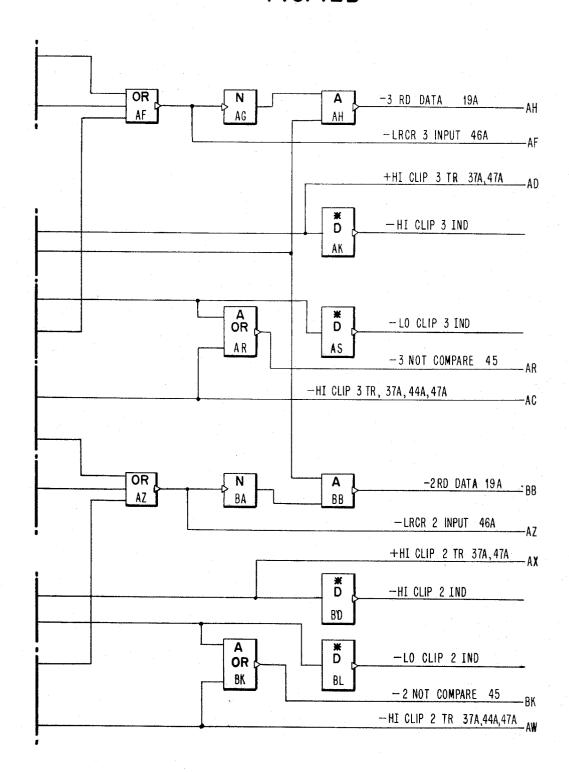

FIG. 42A

Filed April 6, 1964

FIG. 42B

Filed April 6, 1964

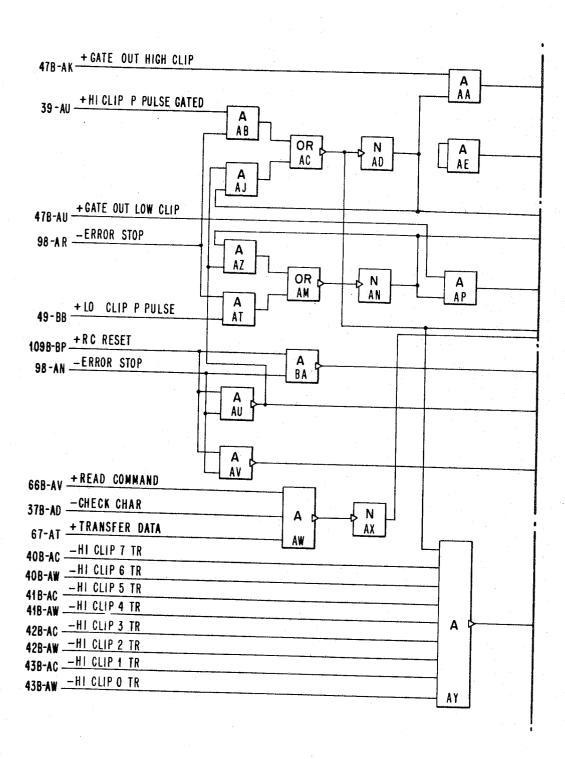

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 67

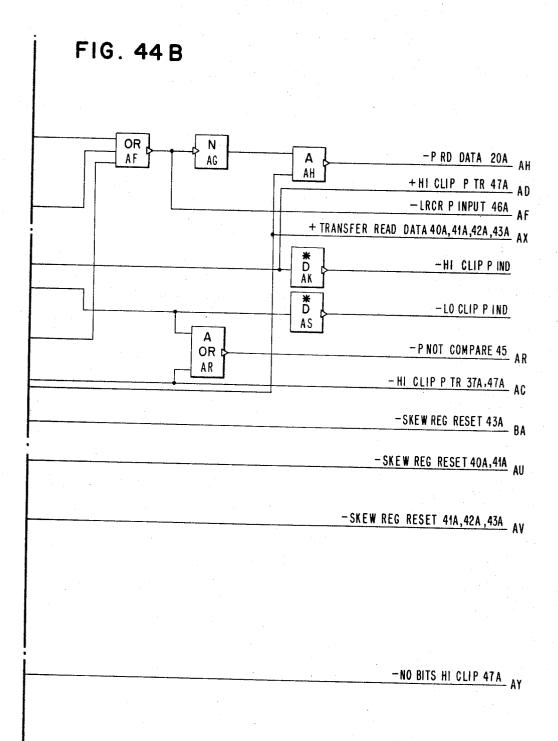

# FIG. 44A

Filed April 6, 1964

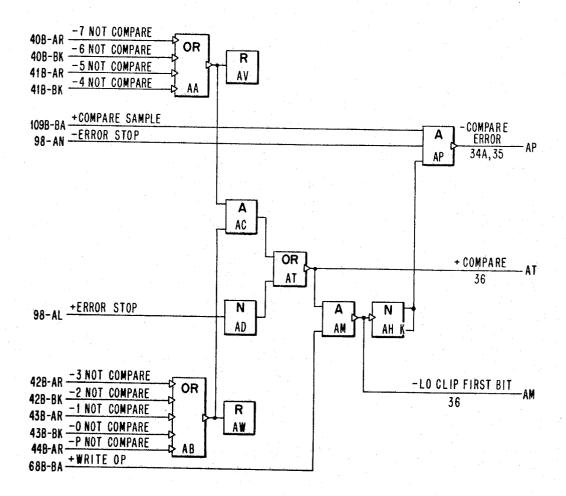

Filed April 6, 1964

316 Sheets-Sheet 69

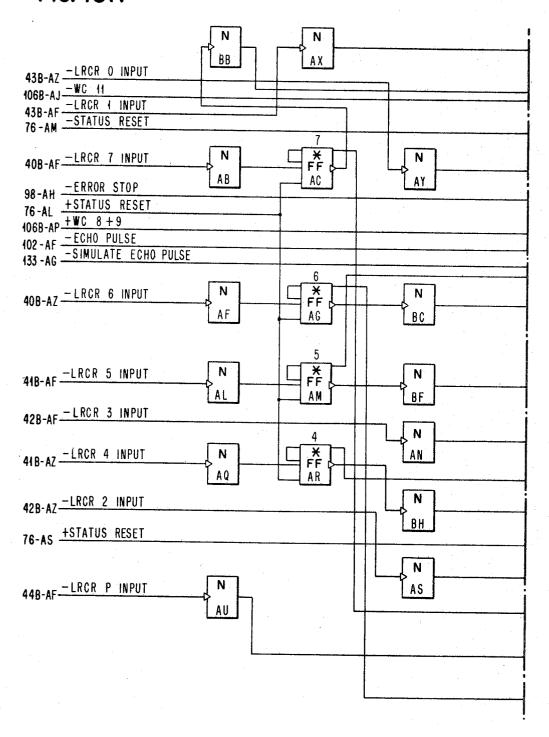

# FIG. 45

Filed April 6, 1964

316 Sheets-Sheet 70

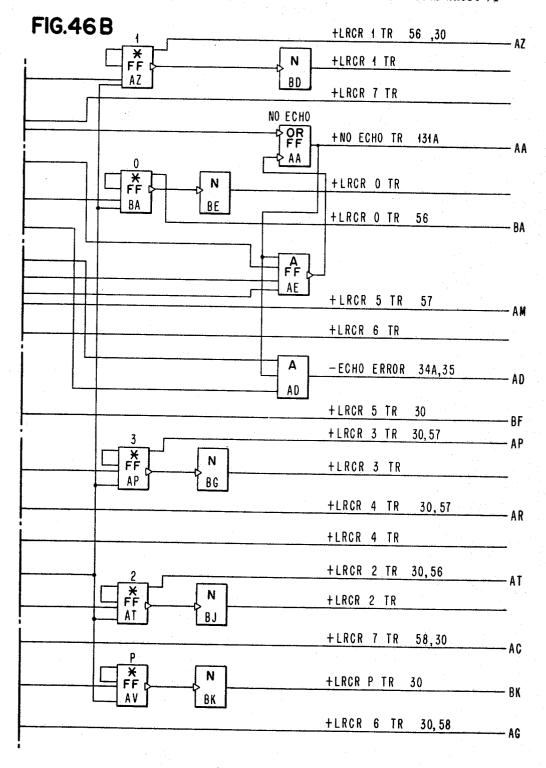

#### FIG.46A

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 75

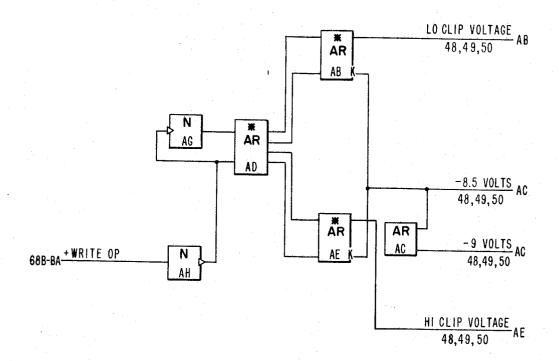

### FIG. 49

Filed April 6, 1964

316 Sheets-Sheet 76

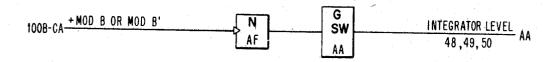

## FIG. 50

Filed April 6, 1964

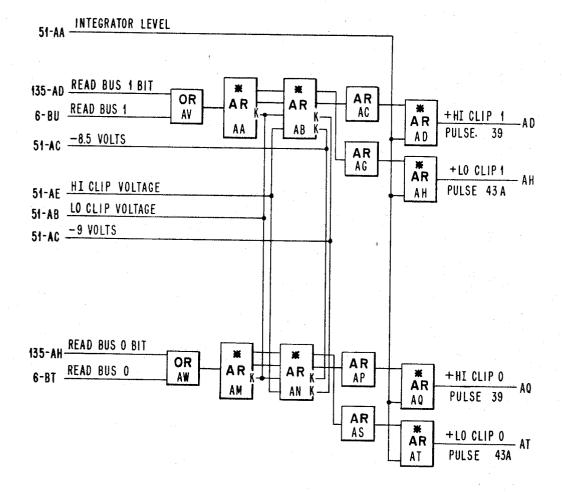

FIG. 51

Filed April 6, 1964

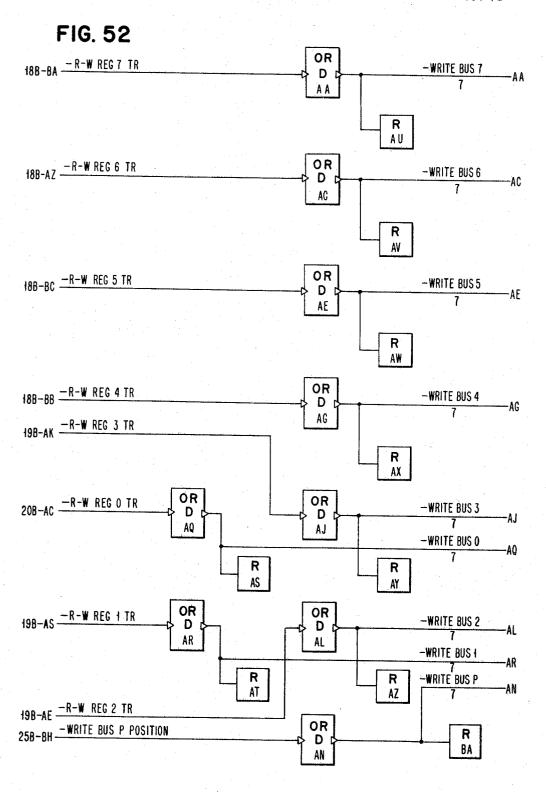

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 81

## FIG. 54A

Filed April 6, 1964

FIG. 54B

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 35

## **FIG.56**

Filed April 6, 1964

FIG. 57

Filed April 6, 1964

FIG. 58

Filed April 6, 1964

FIG. 59

Filed April 6, 1964

316 Sheets-Sheet 89

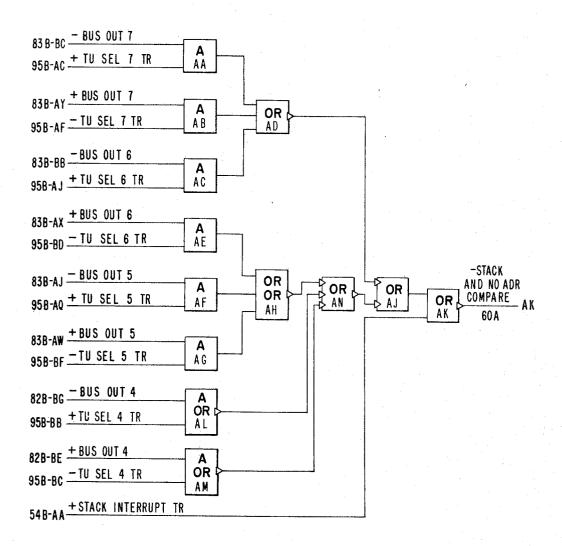

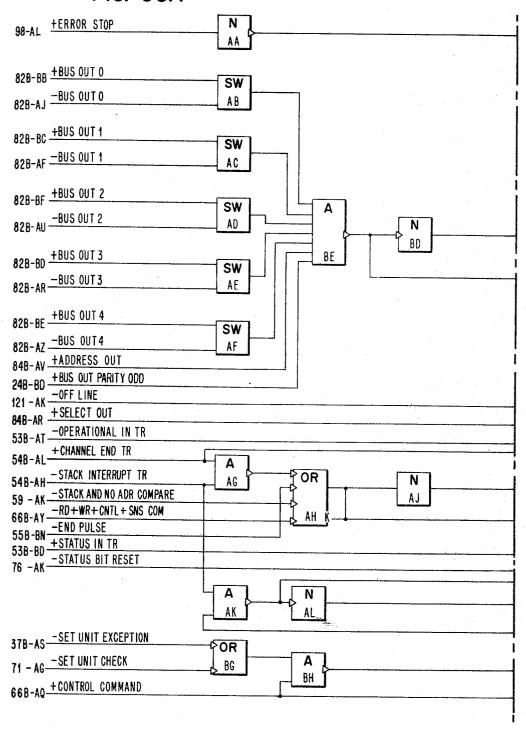

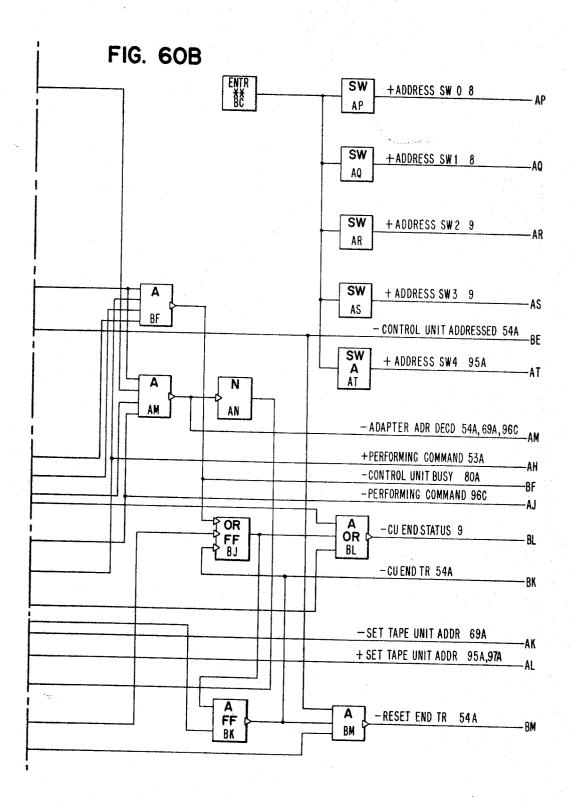

## FIG. 60A

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

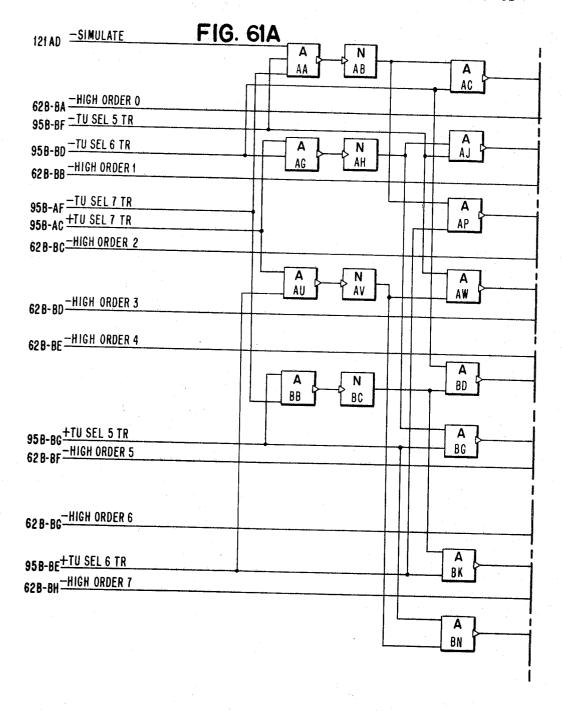

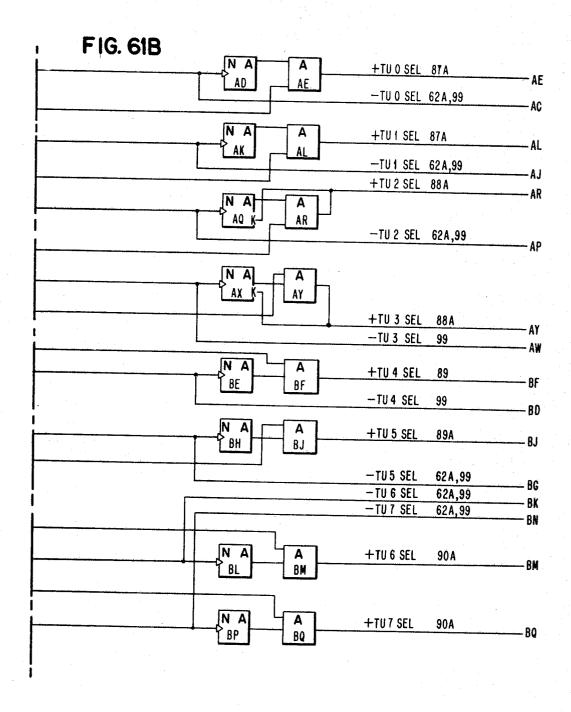

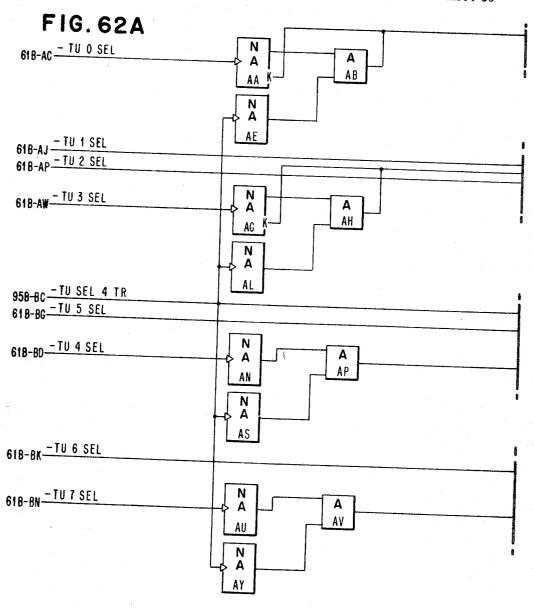

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 95

## FIG.63

Filed April 6, 1964

316 Sheets-Sheet 96

### FIG. 64A

Filed April 6, 1964

316 Sheets-Sheet 97

## FIG.64B

Filed April 6, 1964

316 Sheets-Sheet 98

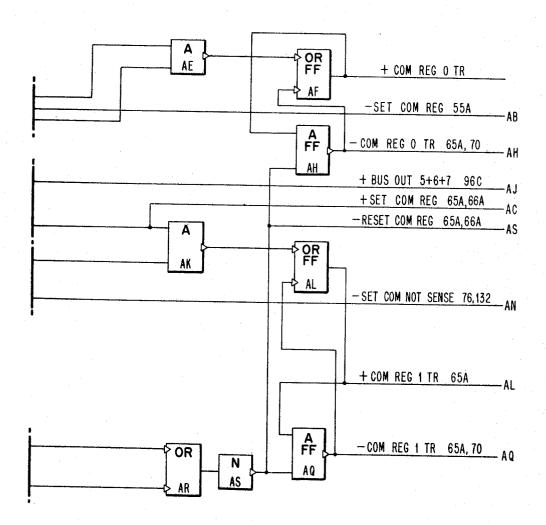

## FIG. 65A

Filed April 6, 1964

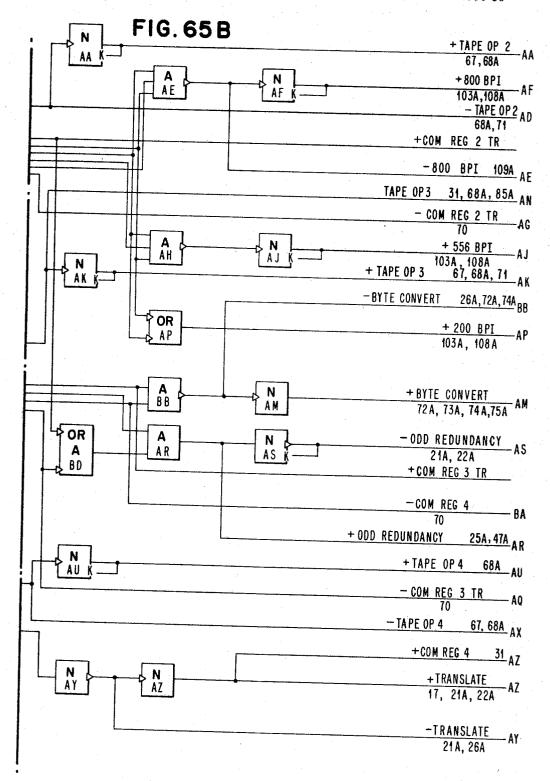

Filed April 6, 1964

316 Sheets-Sheet 100

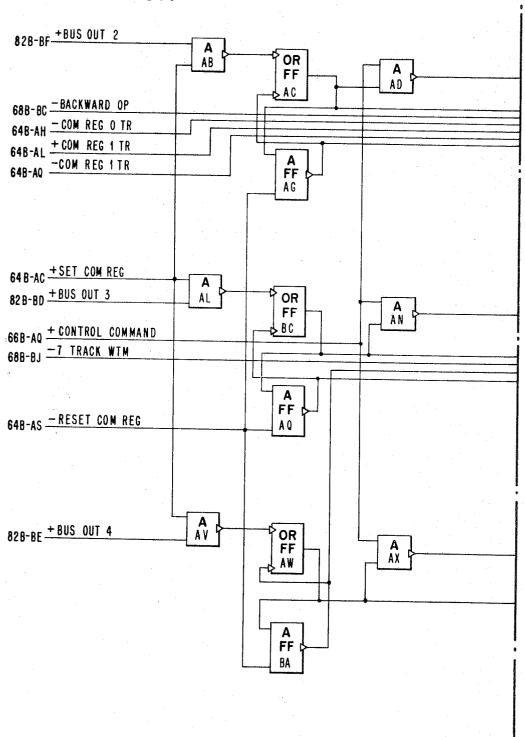

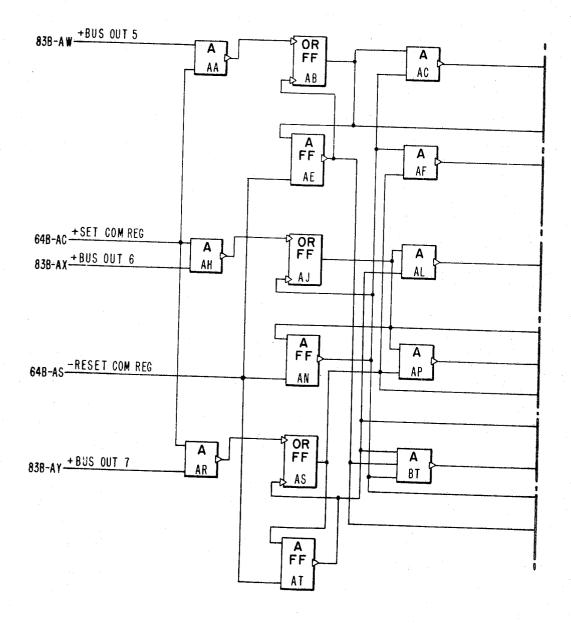

# FIG. 66A

Filed April 6, 1964

FIG. 66B

Filed April 6, 1964

Filed April 6, 1964

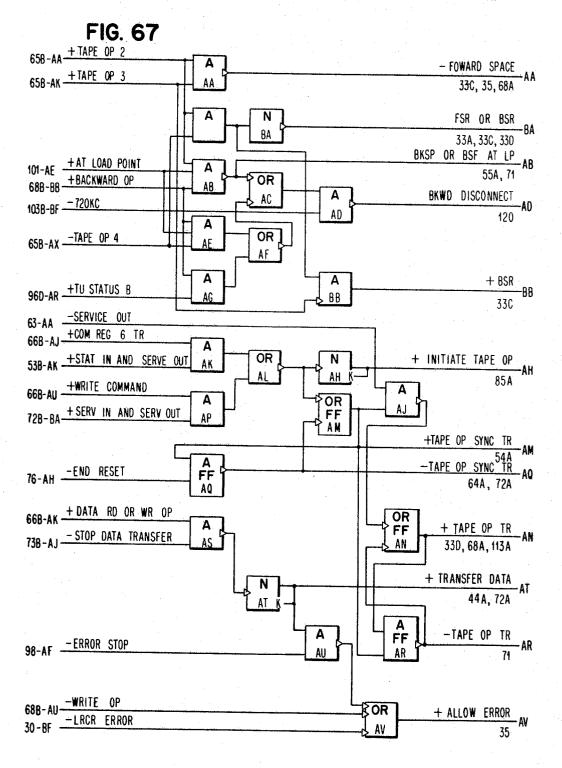

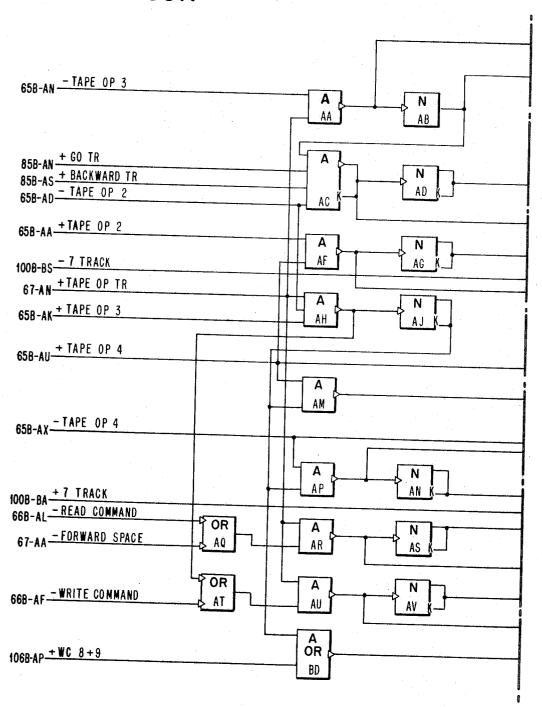

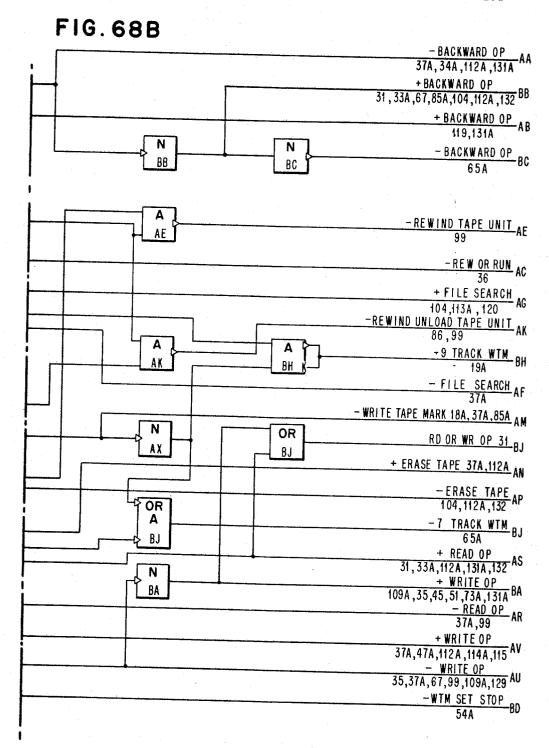

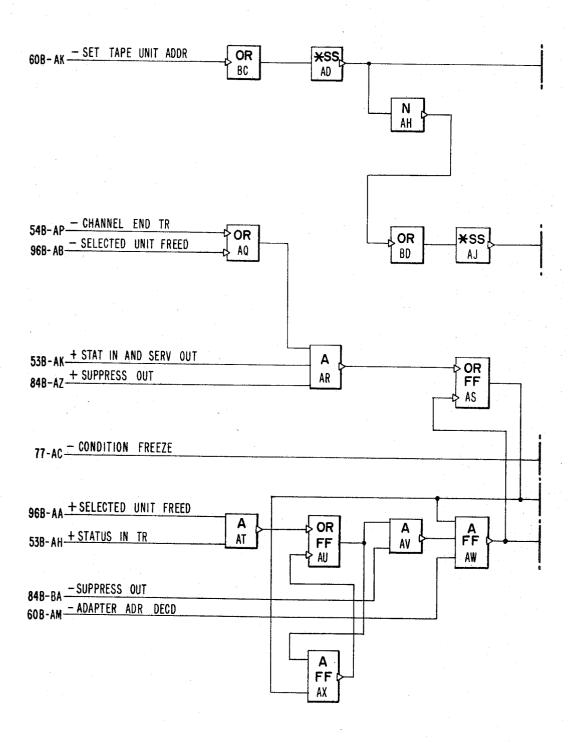

FIG. 68A

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 105

## FIG. 69A

Filed April 6, 1964

FIG. 69B

Filed April 6, 1964

316 Sheets-Sheet 107

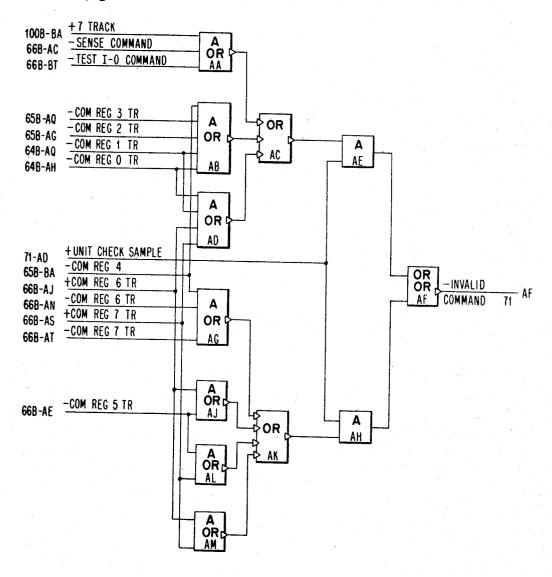

### FIG. 70

Filed April 6, 1964

316 Sheets-Sheet 108

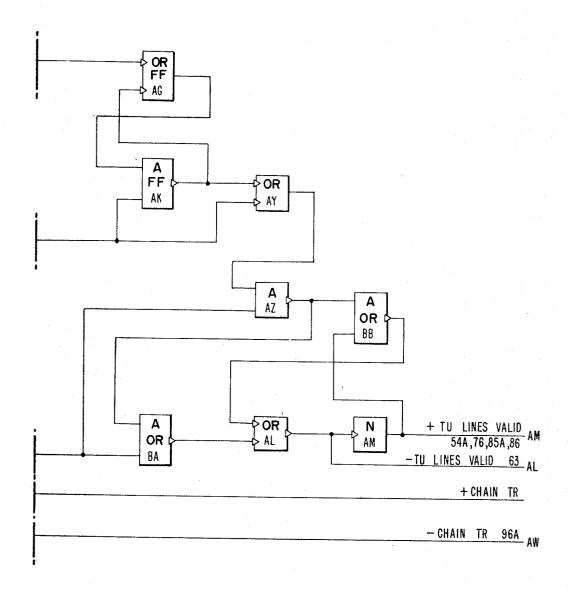

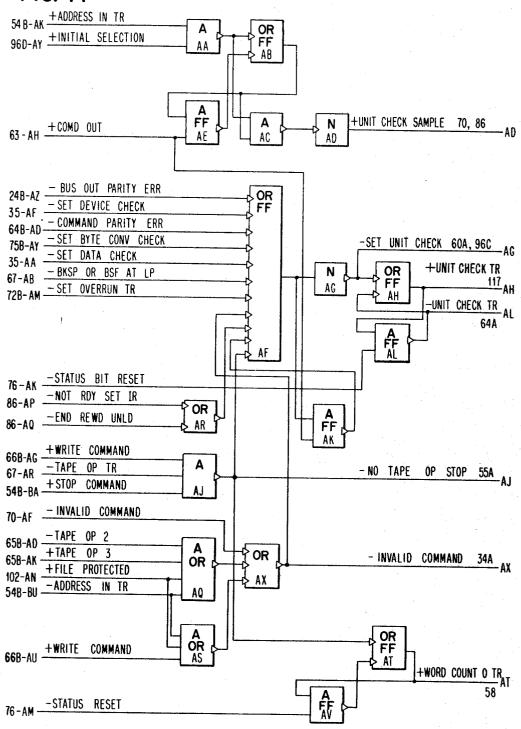

#### FIG. 71

Filed April 6, 1964

Filed April 6, 1964

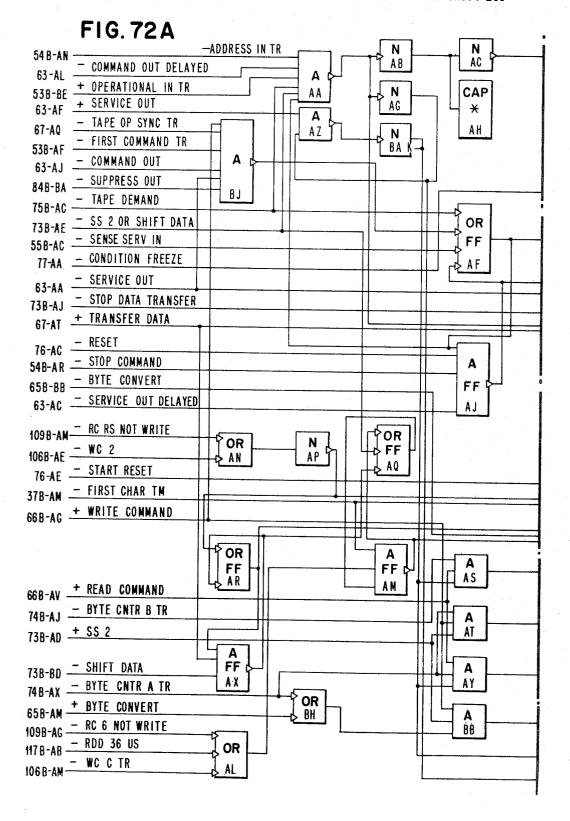

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 113

# FIG. 74A

Filed April 6, 1964

FIG. 74B

Filed April 6, 1964

316 Sheets-Sheet 115

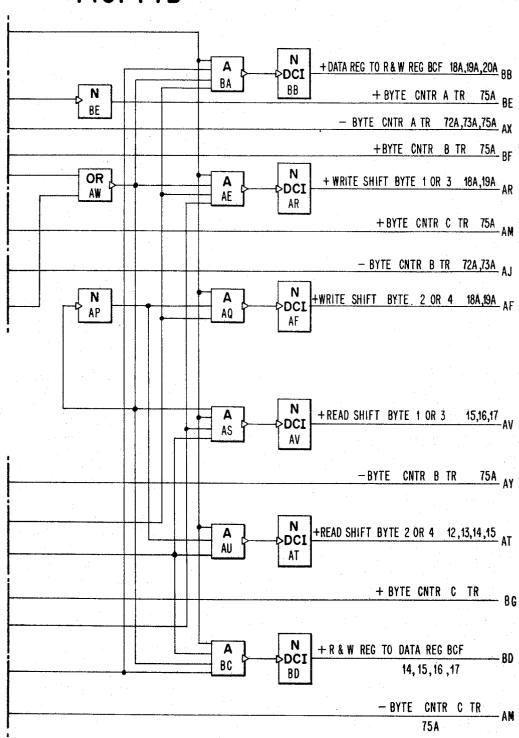

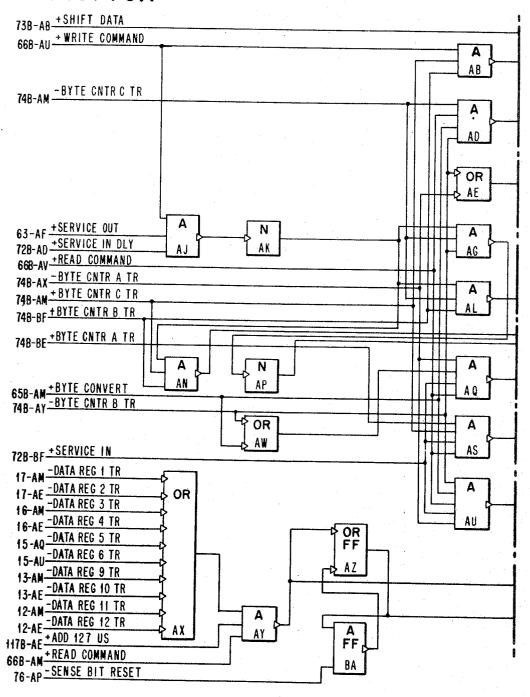

# FIG. 75A

Filed April 6, 1964

Filed April 6, 1964

FIG. 77

Filed April 6, 1964

316 Sheets-Sheet 119

### FIG. 78

Filed April 6, 1964

316 Sheets-Sheet 120

## FIG. 79

Filed April 6, 1964

316 Sheets-Sheet 121

## FIG.80A

Filed April 6, 1964

316 Sheets-Sheet 122

# FIG.80B

Filed April 6, 1964

FIC OI

316 Sheets-Sheet 123

**FIG.81**

Filed April 6, 1964

316 Sheets-Sheet 124

# FIG.82A

Filed April 6, 1964

316 Sheets-Sheet 125

# FIG.82B

Filed April 6, 1964

316 Sheets-Sheet 126

# FIG.83A

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 132

## FIG. 86

Filed April 6, 1964

FIG. 87A

Filed April 6, 1964

FIG. 87B

Filed April 6, 1964

316 Sheets-Sheet 135

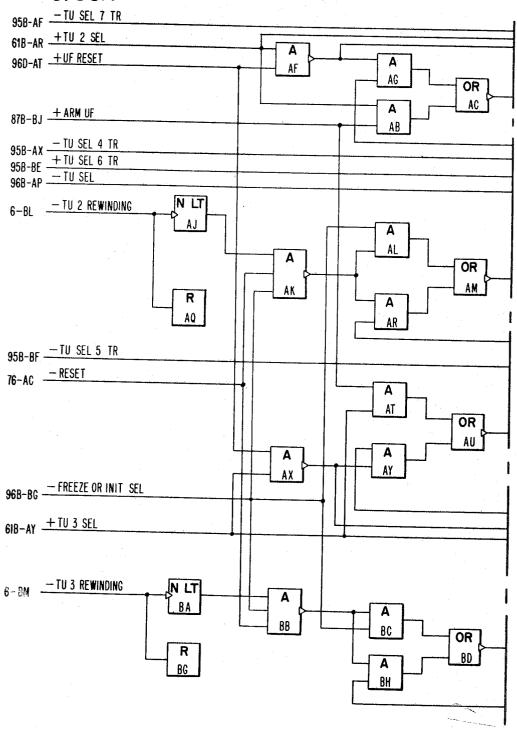

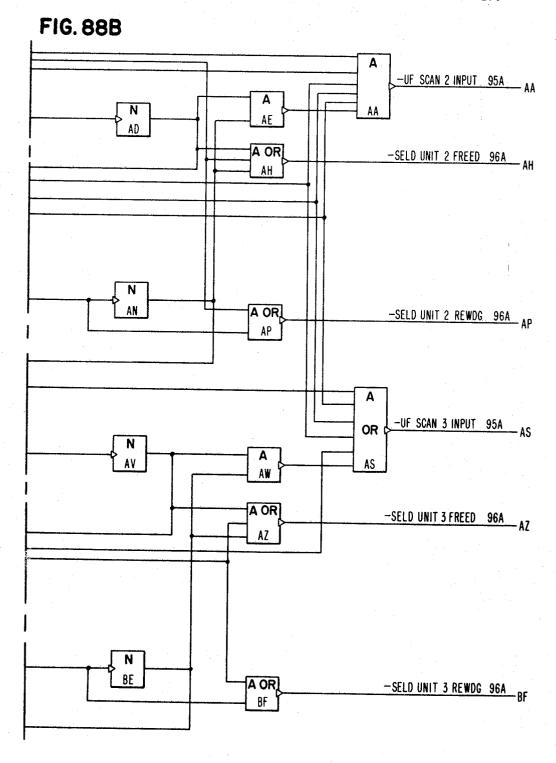

## FIG. 88A

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 137

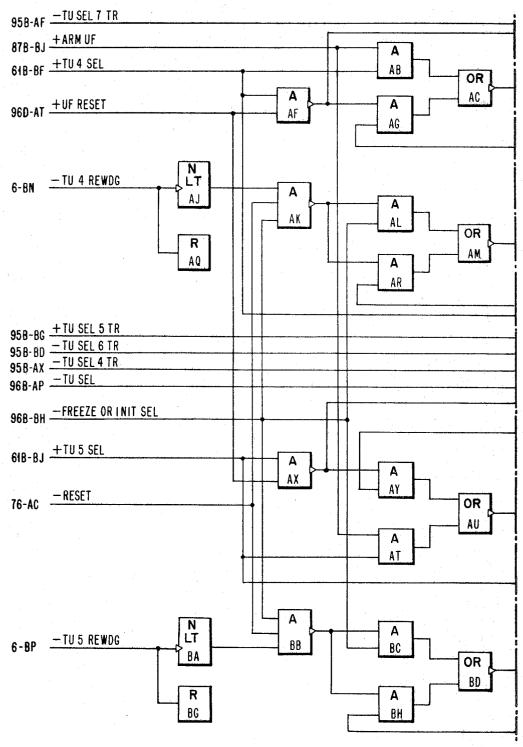

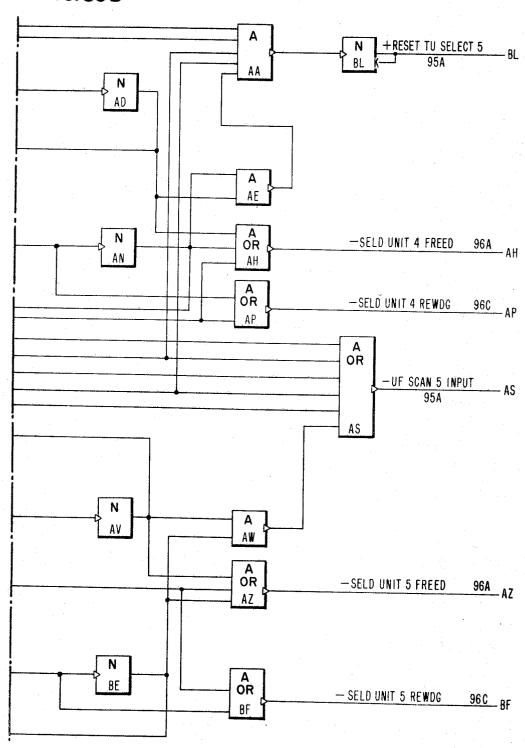

## FIG.89A

Filed April 6, 1964

316 Sheets-Sheet 138

# FIG.89B

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 141

## FIG.91A

Filed April 6, 1964

316 Sheets-Sheet 142

# FIG. 91B

Filed April 6, 1964

316 Sheets-Sheet 143

# FIG. 92A

Filed April 6, 1964

FIG.92B

Filed April 6, 1964

316 Sheets-Sheet 145

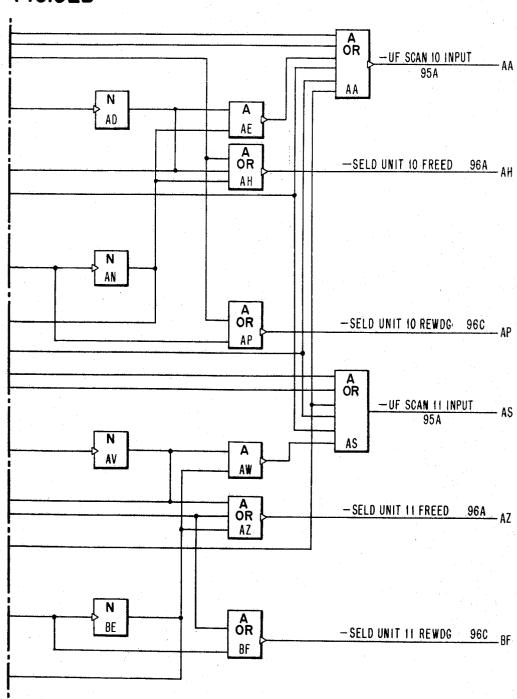

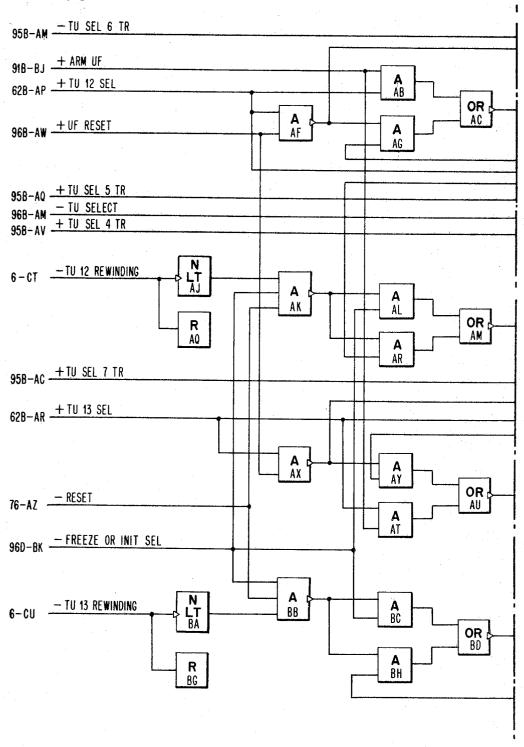

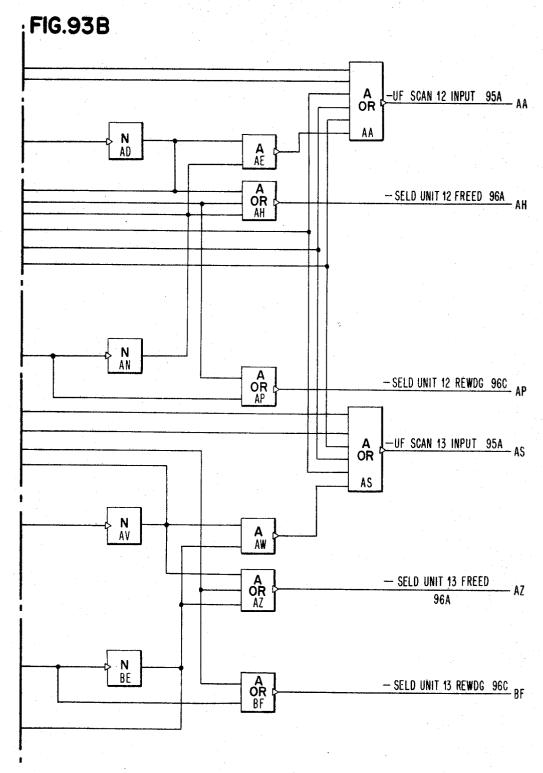

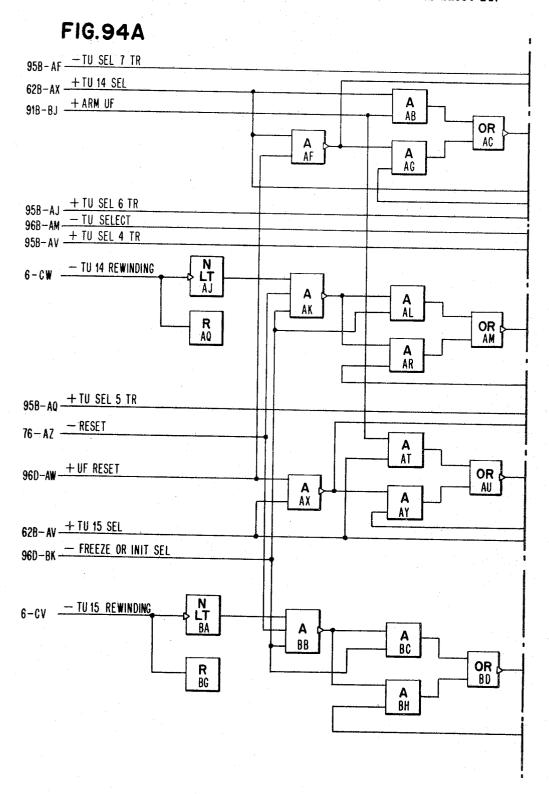

### FIG.93A

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

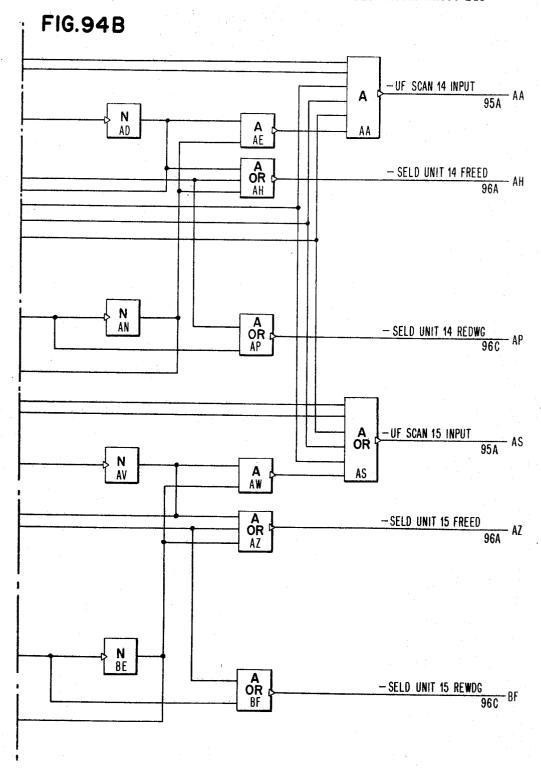

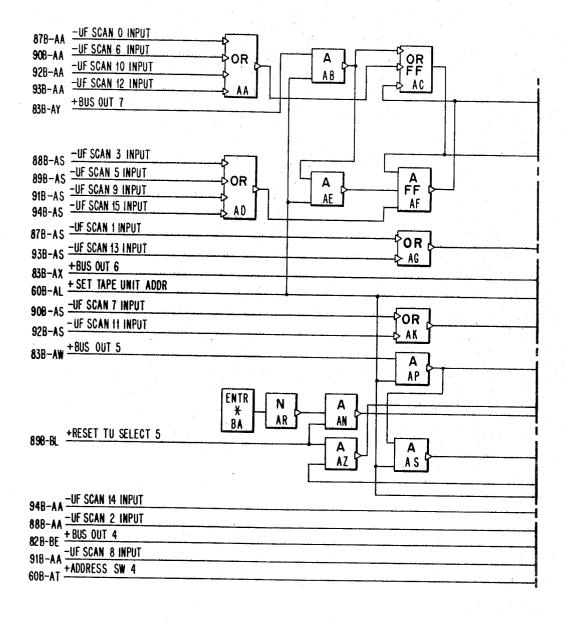

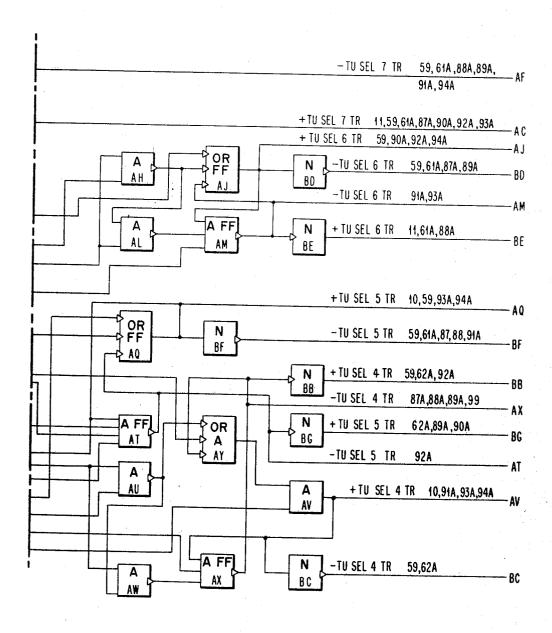

316 Sheets-Sheet 149

#### FIG. 95A

Filed April 6, 1964

316 Sheets-Sheet 150

FIG. 95B

Filed April 6, 1964

316 Sheets-Sheet 151

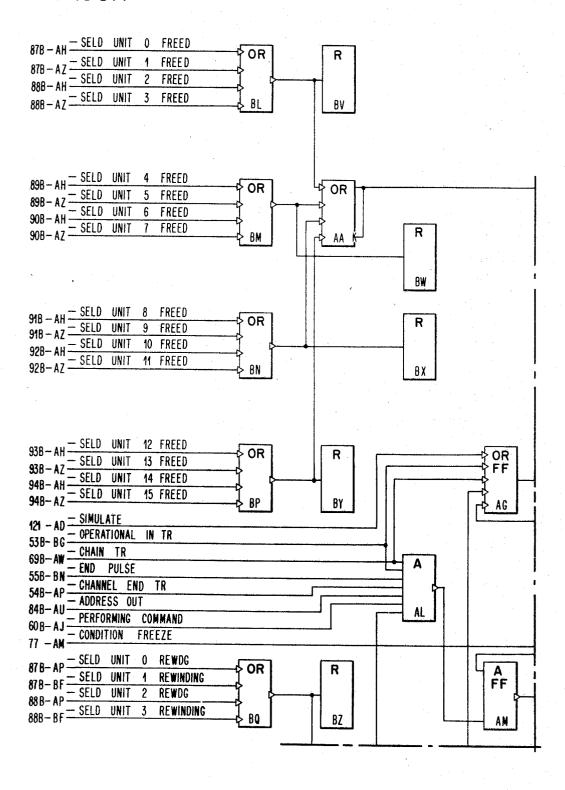

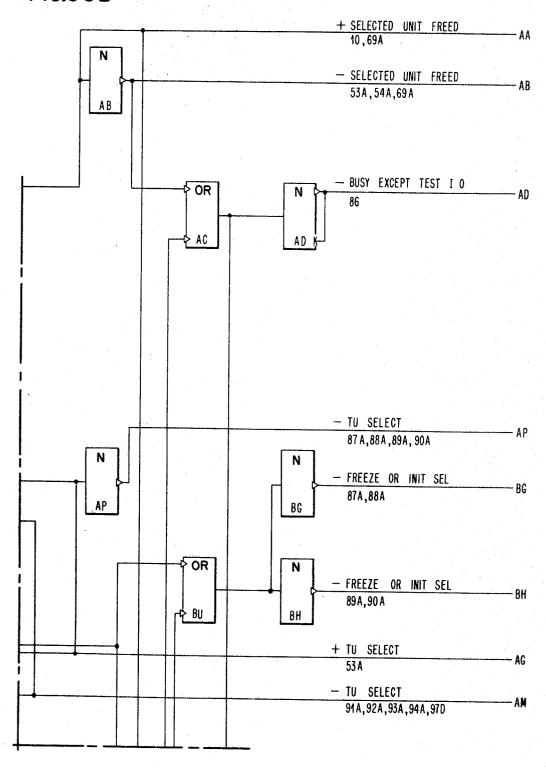

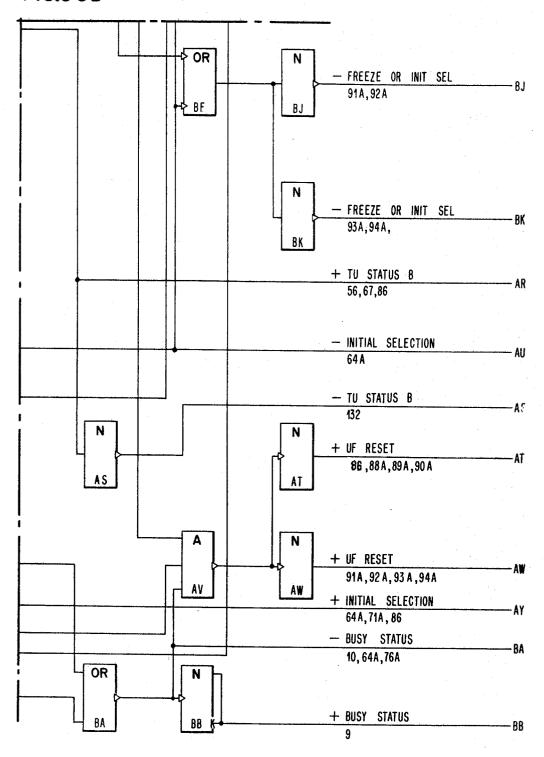

### FIG.96A

Filed April 6, 1964

316 Sheets-Sheet 152

# FIG.96B

Filed April 6, 1964

316 Sheets-Sheet 153

#### FIG.96C

Filed April 6, 1964

316 Sheets-Sheet 154

## FIG.96D

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 157

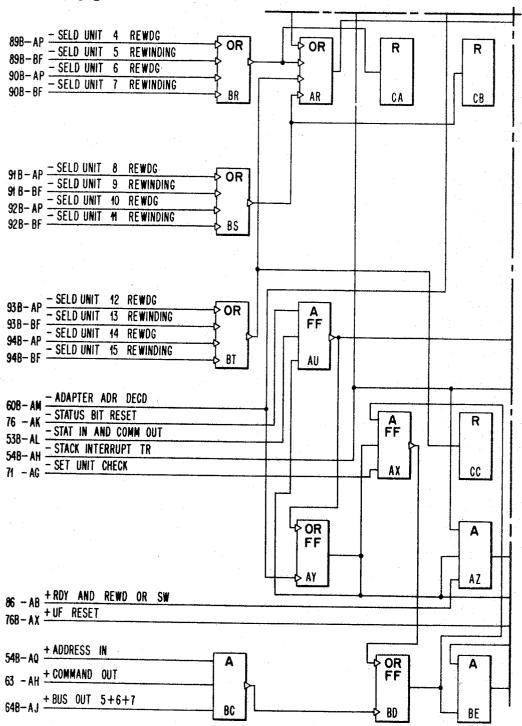

Filed April 6, 1964

Filed April 6, 1964

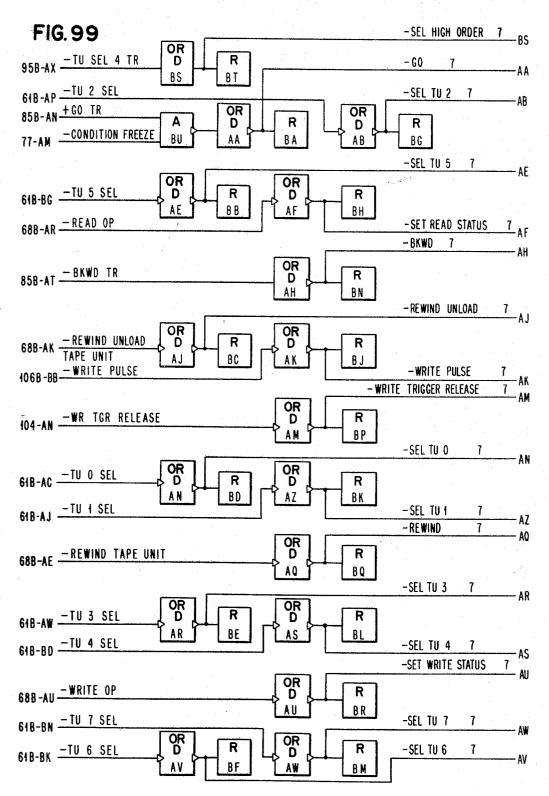

FIG. 98

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 161

# FIG.100A

Filed April 6, 1964

316 Sheets-Sheet 162

## **FIG.100B**

Filed April 6, 1964

316 Sheets-Sheet 163

# FIG. 101

Filed April 6, 1964

316 Sheets-Sheet 164

# FIG.102

Filed April 6, 1964

316 Sheets-Sheet 165

# FIG. 103A

Filed April 6, 1964

316 Sheets-Sheet 166

## FIG. 103B

Filed April 6, 1964

316 Sheets-Sheet 167

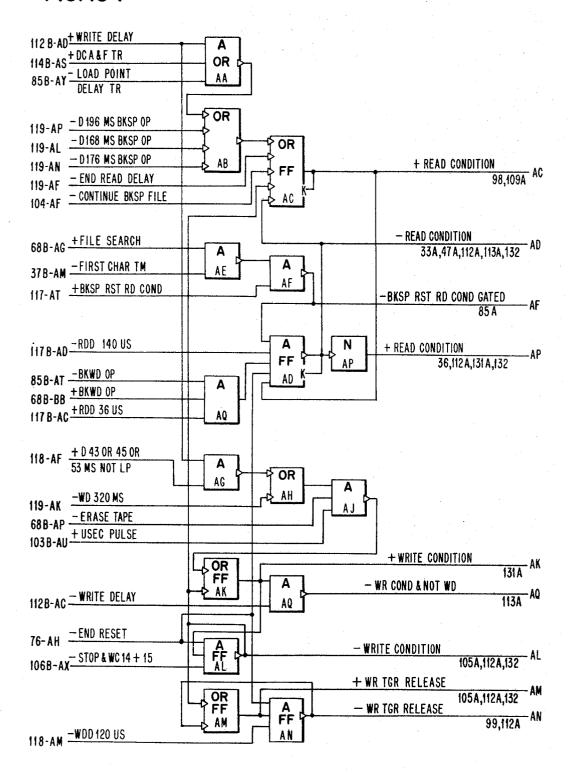

#### FIG. 104

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 170

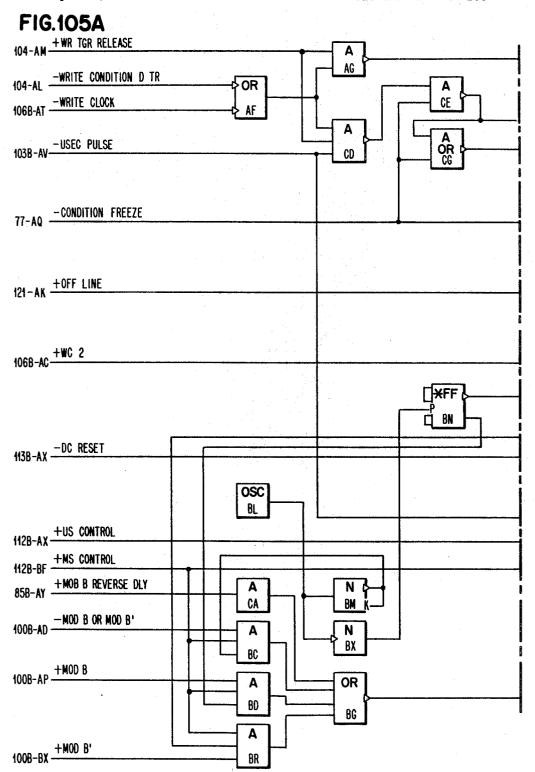

# FIG. 106A

Filed April 6, 1964

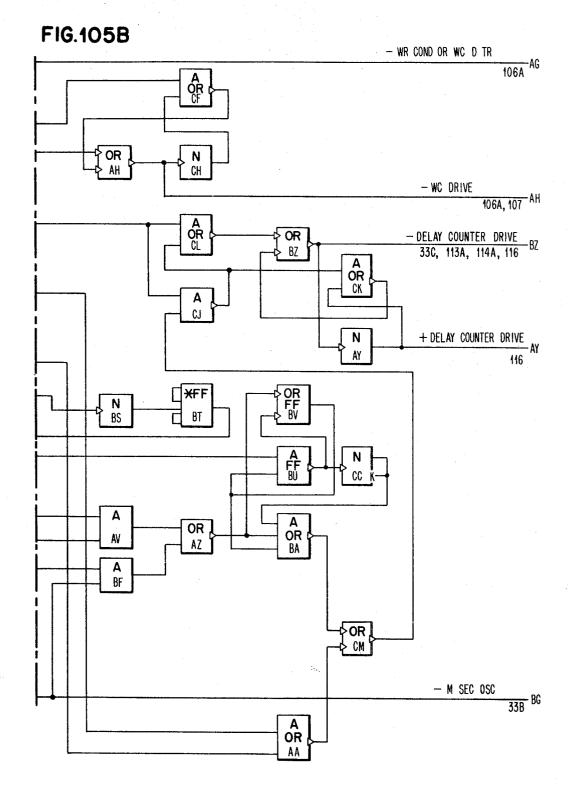

FIG. 106B

Filed April 6, 1964

316 Sheets-Sheet 172

# FIG. 107

Filed April 6, 1964

316 Sheets-Sheet 173

# FIG.108A

Filed April 6, 1964

316 Sheets-Sheet 174

# FIG.108B

Filed April 6, 1964

316 Sheets-Sheet 175

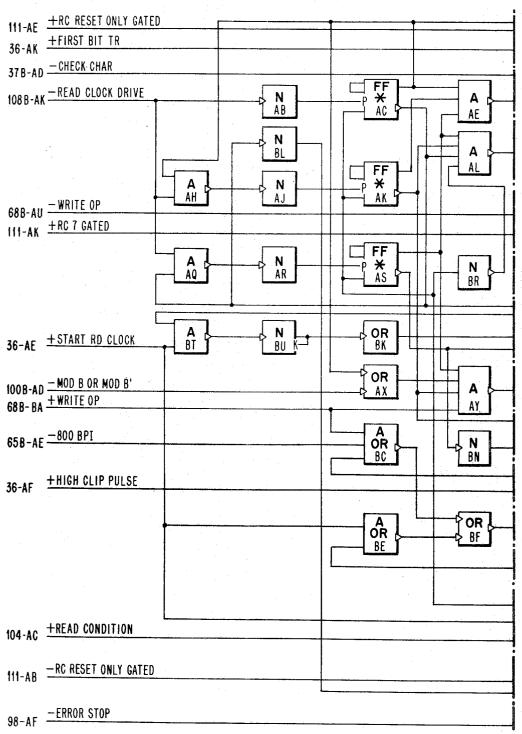

## FIG. 109A

Filed April 6, 1964

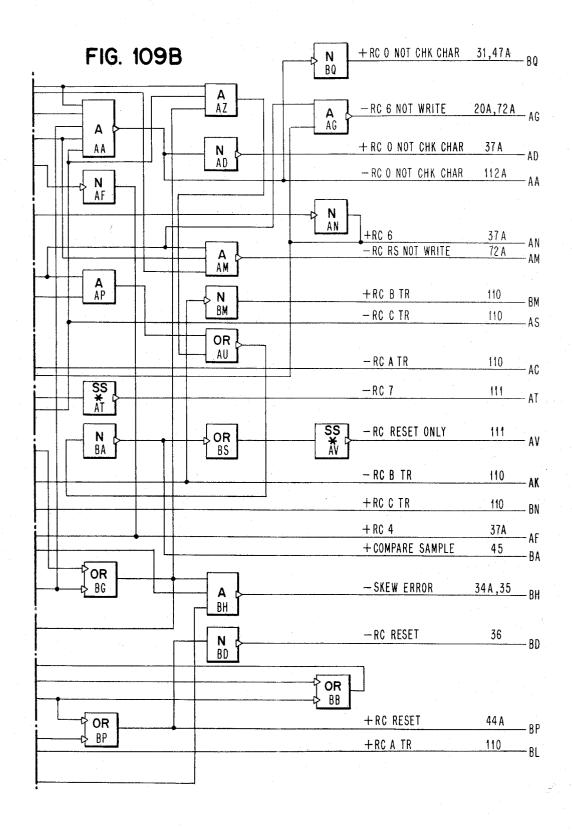

Filed April 6, 1964

316 Sheets-Sheet 177

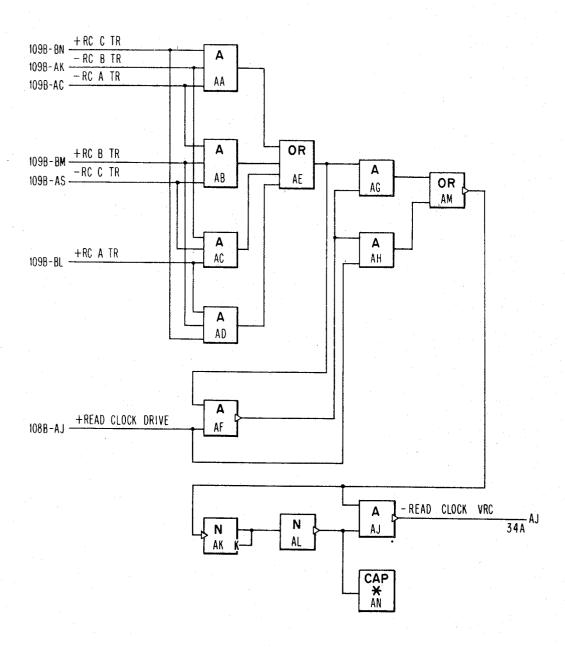

# FIG. 110

Filed April 6, 1964

316 Sheets-Sheet 178

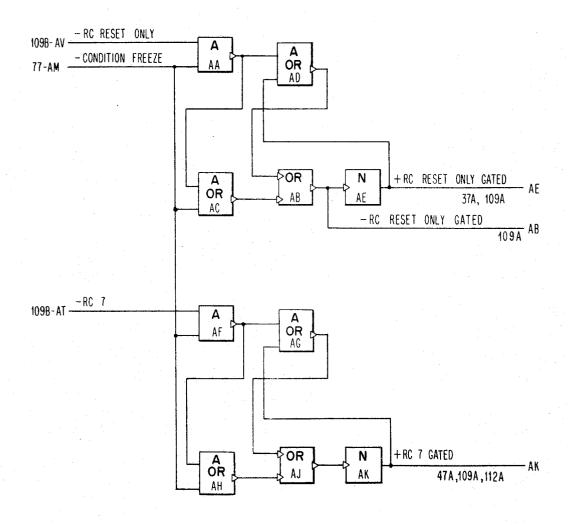

# FIG.111

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 180

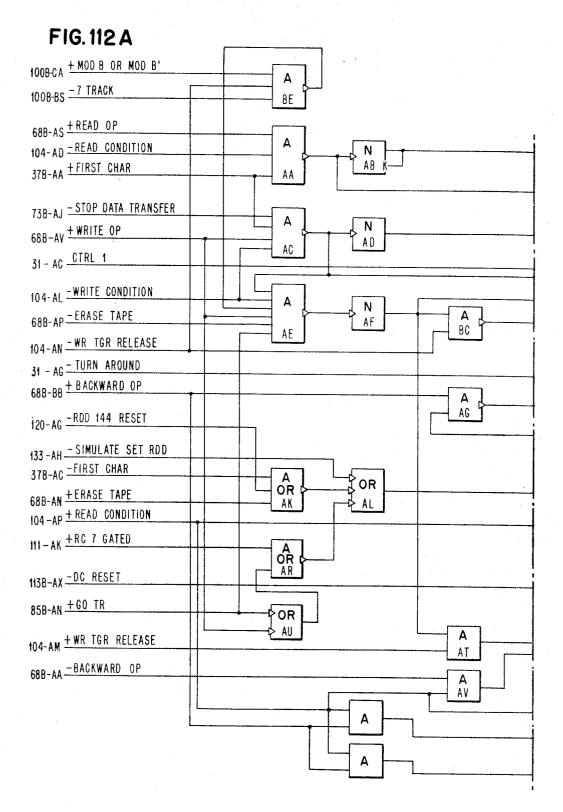

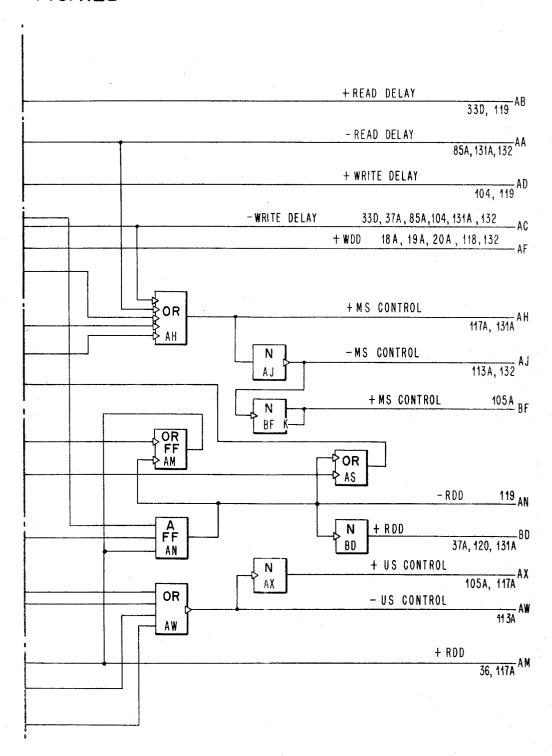

#### FIG. 112B

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 183

# **FIG.114A**

Filed April 6, 1964

FIG.114B

Filed April 6, 1964

316 Sheets-Sheet 185

Filed April 6, 1964

316 Sheets-Sheet 186

Filed April 6, 1964

316 Sheets-Sheet 187

### FIG.117A

Filed April 6, 1964

316 Sheets-Sheet 188

## FIG.117B

Filed April 6, 1964

316 Sheets-Sheet 189

Filed April 6, 1964

316 Sheets-Sheet 190

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 194

## FIG.122B

Filed April 6, 1964

316 Sheets-Sheet 195

Filed April 6, 1964

316 Sheets-Sheet 196

Filed April 6, 1964

316 Sheets-Sheet 197

Filed April 6, 1964

316 Sheets-Sheet 198

Filed April 6, 1964

316 Sheets-Sheet 199

Filed April 6, 1964

316 Sheets-Sheet 200

# FIG.128A

Filed April 6, 1964

316 Sheets-Sheet 201

# FIG.128B

Filed April 6, 1964

316 Sheets-Sheet 202

Filed April 6, 1964

316 Sheets-Sheet 203

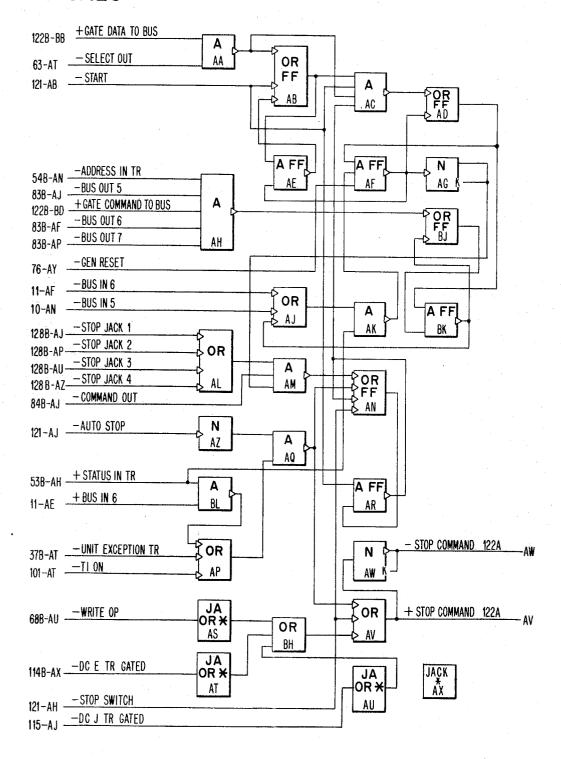

# FIG. 130A

Filed April 6, 1964

316 Sheets-Sheet 204

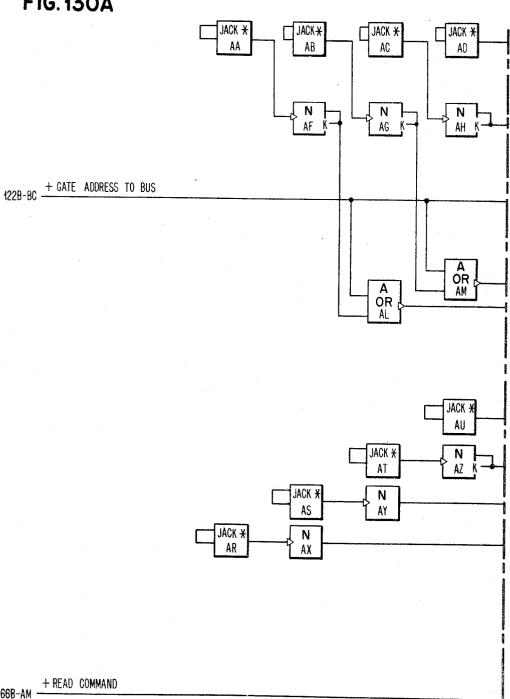

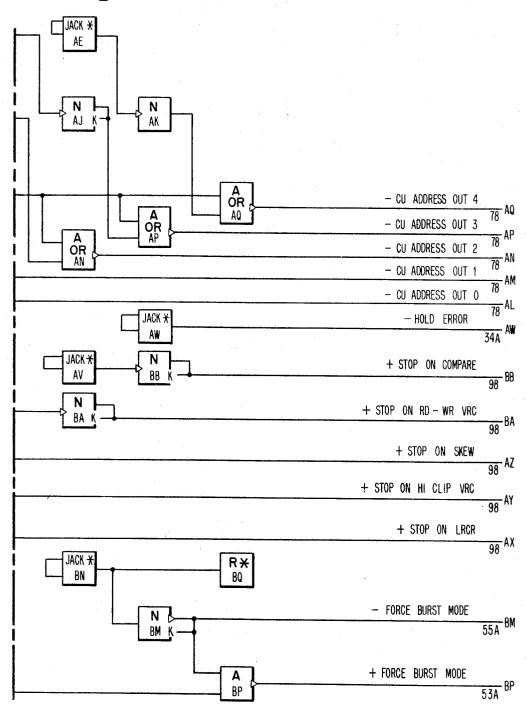

## **FIG.130B**

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 207

Filed April 6, 1964

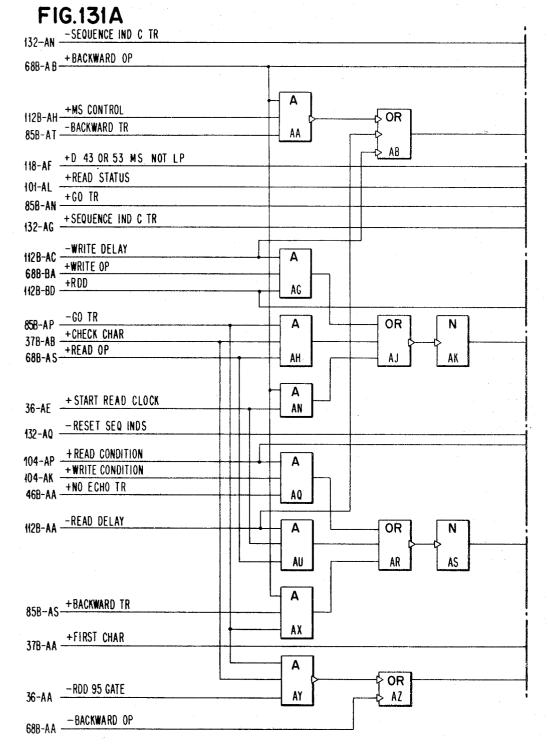

316 Sheets-Sheet 208

Filed April 6, 1964

316 Sheets-Sheet 209

Filed April 6, 1964

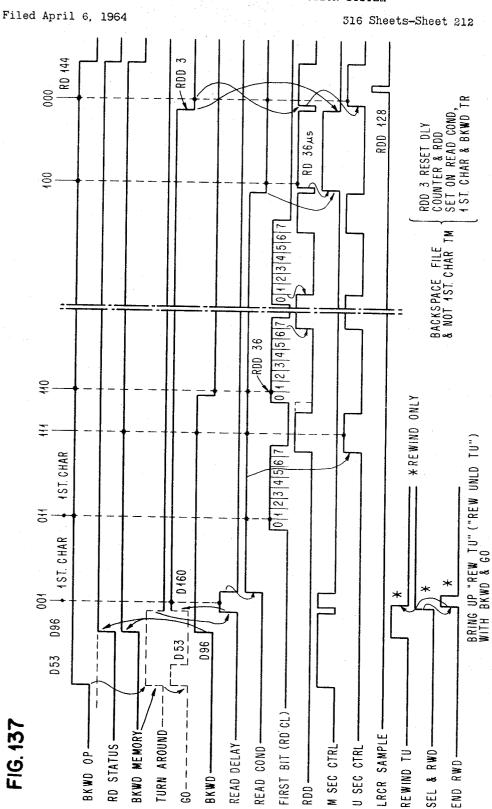

FIG. 135

Filed April 6, 1964

316 Sheets-Sheet 211

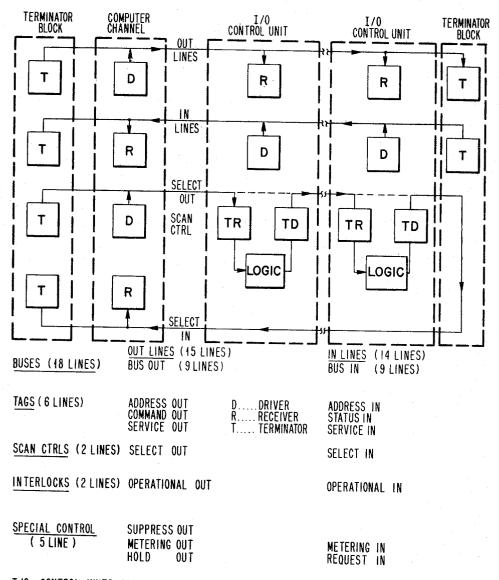

### FIG. 136

I/O CONTROL UNITS CONNECT IN SERIES TO SELECT OUT AND SELECT IN

I/O CONTROL UNITS CONNECT IN PARALLEL TO ALL OTHER INTERFACE LINES

Filed April 6, 1964

316 Sheets-Sheet 213

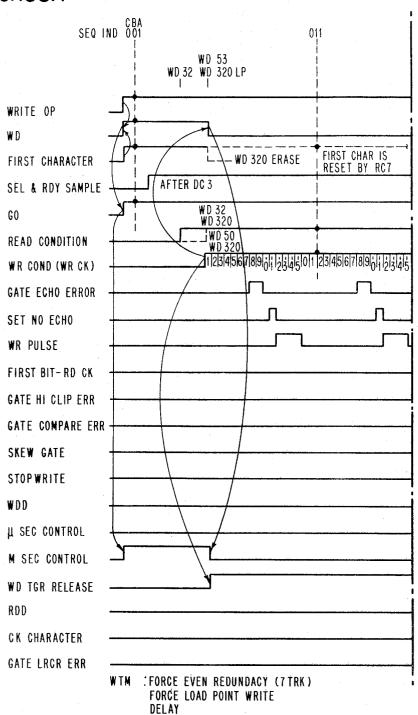

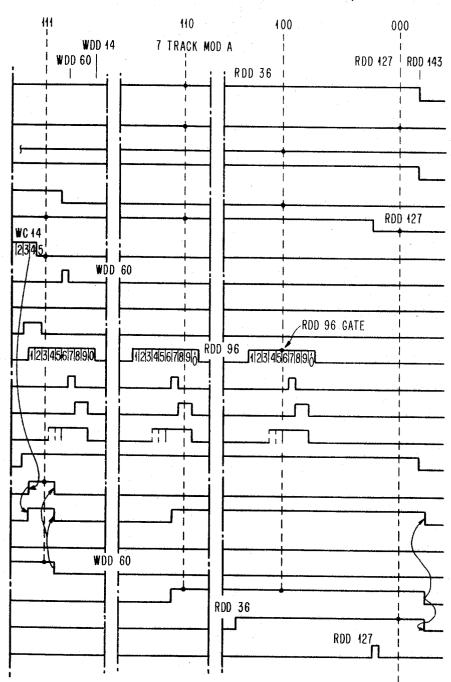

### FIG.138A

Filed April 6, 1964

316 Sheets-Sheet 214

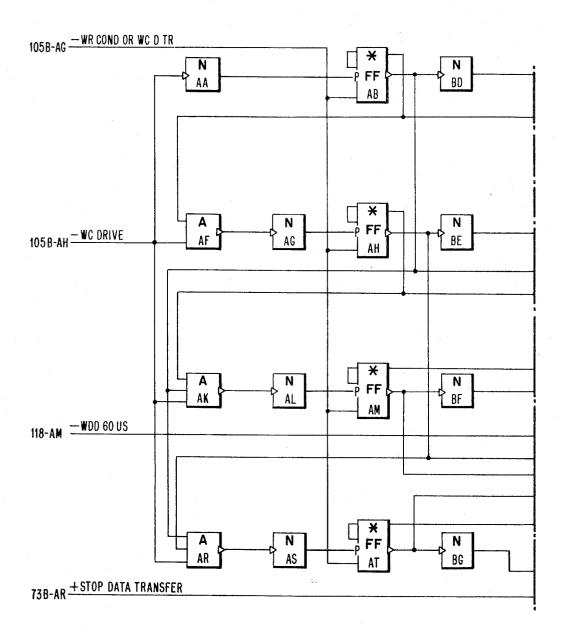

FIG.138B

GO IS RESET BY:

WDD 60 д SEC

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

FIG. 140

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 220

# FIG.143

Filed April 6, 1964

316 Sheets-Sheet 221

# FIG.144

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

DATA REG TGR'S ARE LOCATED ON FIGS. 12,13,14,15,16,17

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 228

## **FIG.150B**

Filed April 6, 1964

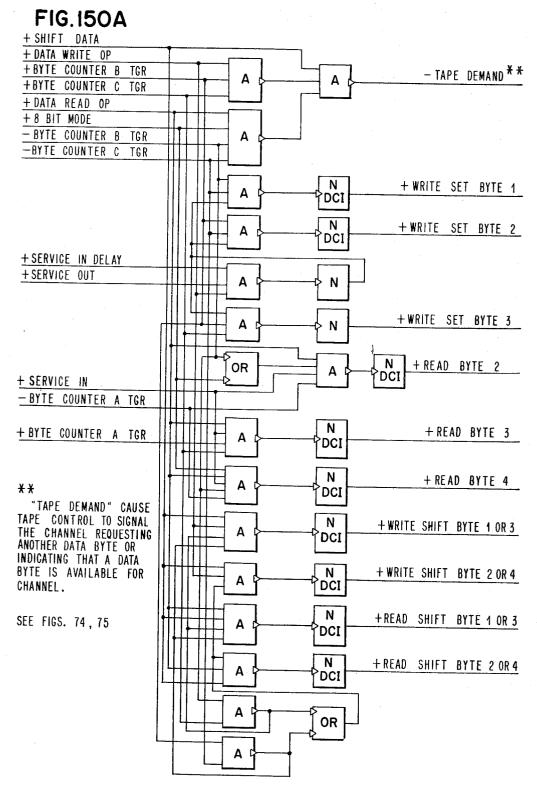

| [6.13]                               |   |   |     |   |    | WRITE | TE       |    |    |    |             |          |                                  |

|--------------------------------------|---|---|-----|---|----|-------|----------|----|----|----|-------------|----------|----------------------------------|

| DATA REGISTER POSITIONS              | - | 2 | 3   | 4 | S  | 9     | 7        | 8  | 60 | 10 | <del></del> | 12       |                                  |

| BYTE 1 FROM INTERFACE (8-BIT CODE)   |   |   |     |   | 0  |       | 2        | 23 | 4  | 2  | 9           | 7        | "WRITE SET BYTE 1" ACTIVE        |

| BYTE 1 TO R-W REG (BCD)              |   |   |     |   | 11 |       | <u></u>  | A  | ∞  | 4  | 2           | <b>~</b> | "WRITE SHIFT BYTE 1 OR 3" ACTIVE |

| BYTE 2 FROM INTERFACE (8-BIT CODE)   | 4 | 3 | 2   | - |    |       |          |    | 0  | 7  | 9           | 5        | "WRITE SET BYTE 2" ACTIVE        |

| BYTE 2 TO R-W REG (BCD)              | æ | ⋖ | 80  | 4 | 2  | 1     |          |    | 1/ | 1  | 1/          | 1        | "WRITE SHIFT BYTE 2 OR 4" ACTIVE |

| BYTE 3 FROM INTERFACE (8-BIT CODE)   | 8 | 7 | 9   | 5 | 4  | 2     | 2        | -  | 1  | 1  | //          |          | "WRITE SET BYTE 3" ACTIVE        |

| BYTE 3 TO R-W REG (BCD)              |   |   |     |   |    |       | <b>6</b> | A  | 8  | 4  | 2           | _        | "WRITE SHIFT BYTE 1 OR 3" ACTIVE |

| BYTE 4 TO R-W REG (BCD) * *          | œ | ⋖ | 80  | 4 | 2  | -     |          |    |    |    |             |          | "WRITE SHIFT BYTE 2 OR 4" ACTIVE |

| * DATA REG IS FULL                   |   |   |     |   |    |       |          |    |    |    |             |          |                                  |

| ** DATA REG IS EMPTY                 |   |   |     |   |    |       |          |    |    |    |             |          |                                  |

|                                      | _ | - | -   | - |    | READ  | <u>.</u> |    |    |    |             |          |                                  |

| DATA REGISTER POSITIONS              |   | 2 | 3   | 4 | 22 | 9     | 7        | 80 | 6  | 0  | =           | 12       |                                  |

| BYTE 1 FROM R-W REG (BCD)            |   |   |     |   |    |       | 80       | ⋖  | 8  | 4  | 2           | <b>—</b> | "READ SHIFT BYTE 1 OR 3"ACTIVE   |

| BYTE 2 FROM R-W REG (BCD) *          | 8 | Æ | , ∞ | 4 | 2  | -     |          |    |    |    |             |          | "READ SHIFT BYTE 2 OR 4" ACTIVE  |

| BYTE I TO INTERFACE (8-BIT CODE)     |   |   |     |   | 0  | -     | 2        | 2  | 4  | 5  | 9           | ~        | "READ BYTE 2" ACTIVE             |

| BYTE 3 FROM R-W REG (BCD)            |   |   |     |   |    |       | 8        | A  | 8  | 4  | 2           |          | "READ SHIFT BYTE 1 OR 3" ACTIVE  |

| BYTE 2 TO INTERFACE (8-BIT CODE)     | 4 | 2 | 9   | _ |    | 77    |          |    | 0  | -  | 2           | w.       | 'READ BYTE 3" ACTIVE             |

| BYTE 4 FROM R-W REG (BCD)            | ω | A | ∞   | 4 | 2  | -     |          |    |    |    |             |          | "READ SHIFT BYTE 2 OR 4" ACTIVE  |

| BYTE 3 TO INTERFACE (8-BIT CODE) * * | 0 | - | 2   | 3 | 4  | 5     | 9        | ~  |    |    |             |          | "READ BYTE 4" ACTIVE             |

Filed April 6, 1964

316 Sheets-Sheet 230

\* DATE REG 12 TGR SETS R-W REG 7 TGR; DATA REG 10 TGR SETS R-W REG 5 TGR

\* \* SEE FIG. 21

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 232

# FIG.154A

| COLLATING<br>SEQUENCE | GRAP<br>8 BIT | HICS<br>BCD  |    |   |          | BIT | CO | DE |   |    |          | BCD |   |   |   |   |  |  |  |

|-----------------------|---------------|--------------|----|---|----------|-----|----|----|---|----|----------|-----|---|---|---|---|--|--|--|

|                       | 0 011         | 000          | 0  | 4 | 2        | 3   | 4  | 5  | တ | 7  | В        | A   | 8 | 4 | 2 | 1 |  |  |  |

| 00                    | BLANK         | BLANK        | 0  | 1 | 0        | 0   | 0  | 0  | 0 | 0  | 0        | 0   | 0 | 0 | 0 | 0 |  |  |  |

| 01                    |               |              | 0  | 1 | 0        | 0   | 1  | 0  | 1 | 1  | 1        | 1   | 1 | 0 | 1 | 1 |  |  |  |

| 02                    | <b>4</b>      | п)           | 0  | 1 | 0        | 0   | 1  | 1  | 0 | 0  | 1        | 1   | 1 | 1 | 0 | 0 |  |  |  |

| 03                    | (             | Ε            | 0  | 1 | 0        | 0   | 1  | 1  | 0 | 1_ | 1        | 1   | 1 | 1 | 0 | 1 |  |  |  |

| 04                    | +             | <            | 0  | 1 | 0        | 0   | 1  | 1  | 1 | 0  | 1        | 1   | 1 | 1 | 1 | 0 |  |  |  |

| 05                    | GM            | GM           | 0  | 1 | 0        | 0   | 1  | 1  | 1 | 1  | 1        | 1   | 1 | 1 | 1 | 1 |  |  |  |

| 06                    | å             | &+           | 0  | 1 | 0        | 1   | 0  | 0  | 0 | 0  | 1        | 1   | 0 | 0 | 0 | 0 |  |  |  |

| 07                    | \$            | \$           | 0  | 1 | 0        | 1   | 1  | 0  | 1 | 1  | 1        | 0   | 1 | 0 | 1 | 1 |  |  |  |

| 08                    | *             | *            | 0  | 1 | 0        | 1   | 1  | 1  | 0 | 0  | 1        | 0   | 1 | 1 | 0 | 0 |  |  |  |

| 09                    | )             | ]            | 0  | 1 | 0        | 1   | 1  | 1  | 0 | 1  | 1        | 0   | 1 | 1 | 0 | 1 |  |  |  |

| 10                    | . <i>j</i>    | ;            | 0  | 1 | 0        | 1   | 1  | 1  | 1 | 0  | 1        | 0   | 1 | 1 | 1 | 0 |  |  |  |

| 11                    | MC            | MC           | 0  | 1 | 0        | 1   | 1  | 1  | 1 | 1  | 1        | 0   | 1 | 1 | 1 | 1 |  |  |  |

| 12                    | -             | _            | 0  | 1 | 1        | 0   | 0  | 0  | 0 | 0  | 1        | 0   | 0 | 0 | 0 | 0 |  |  |  |

| 13                    | 1             | 1            | 0  | 1 | 1        | 0   | 0  | 0  | 0 | 1  | 0        | 1   | 0 | 0 | 0 | 1 |  |  |  |

| 14                    | ,             | ,            | 0  | 1 | 1        | 0   | 1  | 0  | 1 | 1  | 0        | 1   | 1 | 0 | 1 | 1 |  |  |  |

| 15                    | %             | %(           | 0  | 1 | 1        | 0   | 1  | 1  | 0 | 0  | 0        | 1   | 1 | 1 | 0 | 0 |  |  |  |

| 16                    | <u>ws</u>     | <u>ws</u>    | 0  | 1 | 1        | 0   | 1  | 1  | 0 | 1  | 0        | 1   | 1 | 1 | 0 | 1 |  |  |  |

| 17                    | <b>†</b>      | ١            | 0  | 1 | 1        | 0   | 1  | 1  | 1 | 0  | 0        | 1   | 1 | 1 | 1 | 0 |  |  |  |

| 18                    | SM            | SM           | 0  | 1 | 1        | 0   | 1  | 1  | 1 | 1  | 0        | 1   | 1 | 1 | 1 | 1 |  |  |  |

| 19                    | 15            | ъ            | 0  | 1 | 1        | 1   | 1  | 0  | 1 | 0  | 0        | 1   | 0 | 0 | 0 | 0 |  |  |  |

| 20                    | #             | *.           | 0  | 1 | 1        | 1   | 1  | 0  | 1 | 1  | 0        | 0   | 1 | 0 | 1 | 1 |  |  |  |

| 21                    | @             | @'           | 0  | 1 | 1        | 1   | 1  | 1  | 0 | 0  | 0        | 0   | 1 | 1 | 0 | 0 |  |  |  |

| 22                    | ٧             | ;            | 0  | 1 | 1        | 1   | 1  | 1  | 0 | 1  | 0        | 0   | 1 | 1 | 0 | 1 |  |  |  |

| 23                    | =             | >            | 0  | 1 | 1        | 1   | 1  | 1  | 1 | 0  | 0        | 0   | 1 | 1 | 1 | 0 |  |  |  |

| 24                    | TM            | TM           | 0  | 1 | 1        | 1   | 1  | 1  | 1 | 1  | 0        | 0   | 1 | 1 | 1 | 1 |  |  |  |

| 25                    | b             | ð            | 1  | 1 | 0        | 0   | 0  | 0  | 0 | 0  | 1        | 1   | 1 | 0 | 1 | 0 |  |  |  |

| 26                    | Α             | Α            | 1  | 1 | 0        | 0   | 0  | 0  | 0 | 1  | 1        | 1   | 0 | 0 | 0 | 1 |  |  |  |

| 27                    | В             | В            | 1  | 1 | 0        | 0   | 0  | 0  | 1 | 0  | 1        | 1   | 0 | 0 | 1 | 0 |  |  |  |

| 28                    | С             | C            | 1  | 1 | 0        | 0   | 0  | 0  | 1 | 1  | 1        | 1   | 0 | 0 | 1 | 1 |  |  |  |

| 29                    | D             | D            | 1  | 1 | 0        | 0   | 0  | 1  | 0 | 0  | 1        | 1   | 0 | 1 | 0 | 0 |  |  |  |

| 30                    | E             | E            | 1  | 1 | 0        | 0   | 0  | 1  | 0 | 1  | 1        | 1   | 0 | 1 | 0 | 1 |  |  |  |

| 31                    | F             | F            | 1  | 1 | 0        | 0   | 0  | 1  | 1 | 0  | 1        | 1   | 0 | 1 | 1 | 0 |  |  |  |

| 32                    | G             | G            | 1  | 1 | 0        | 0   | 0  | 1  | 1 | 1  | 1        | 1   | 0 | 1 | 1 | 1 |  |  |  |

| 33                    | Н             | H            | 1  | 1 | 0        | 0   | 1  | 0  | 0 | 0  | 1        | 1   | 1 | 0 | 0 | 0 |  |  |  |

| 34                    | ''            | ' <u> </u>   | 1  | 1 | 0        | 0   | 1  | 0  | 0 | 1  | 1        | 1   | 1 | 0 | 0 | 1 |  |  |  |

| 35                    | - i           | <del>-</del> | 1  | 1 | 0        | 1   | 0  | 0  | 0 | 0  | 1        | 0   | 1 | 0 | 1 | 0 |  |  |  |

| 36                    | J             | J            | 1  | 1 | 0        | 1   | 0  | 0  | 0 | 1  | 1        | 0   | 0 | 0 | 0 | 1 |  |  |  |

| 30                    |               |              | l' | Ľ | <u> </u> | Ľ   |    | Ľ  |   | Ľ  | <u> </u> | U   | L | U | 0 |   |  |  |  |

Filed April 6, 1964

FIG.154B

| 37 | K  | K  | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |  |

|----|----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| 38 | L  | L  | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |  |

| 39 | М  | M  | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |  |

| 40 | N  | N  | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |  |

| 41 | 0  | 0  | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |  |

| 42 | Р  | Р  | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |  |

| 43 | Q  | Q  | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |  |

| 44 | R  | R  | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |  |

| 45 | RM | RM | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |  |

| 46 | S  | S  | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |  |

| 47 | T  | T  | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |  |

| 48 | U  | U  | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |  |

| 49 | ٧  | ٧  | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |  |

| 50 | W  | W  | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |  |

| 51 | χ  | X  | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |  |

| 52 | Y  | Υ  | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |  |

| 53 | Z  | Z  | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |  |

| 54 | 0  | 0  | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |  |

| 55 | 1  | 1  | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |  |

| 56 | 2  | 2  | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |  |

| 57 | 3  | 3  | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |  |

| 58 | 4  | 4  | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |  |

| 59 | 5  | 5  | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |  |

| 60 | 6  | 6  | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |  |

| 61 | 7  | 7  | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |  |

| 62 | 8  | 8  | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |  |

| 63 | 9  | 9  | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |  |

Filed April 6, 1964

316 Sheets-Sheet 234

## FIG.155

Filed April 6, 1964

316 Sheets-Sheet 235

FIG. 156

8-BIT CODE INPUT CHARACTERS

(8-BIT BYTES)

1 1 1 0 0 1 1 0 1

0 1 0 1 0 1 0 0

BCD OUTPUT CHARACTERS

(6-BIT BYTES)

1 1 1 1 0 0

1 1 0 1 0 1

0 1 0 1 0 1

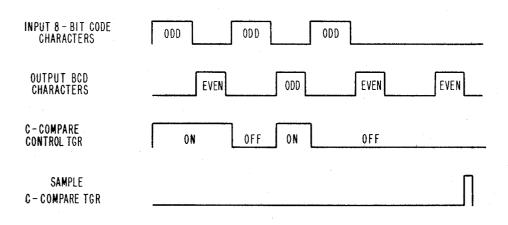

C-COMPARE CIRCUTS IN A SPECIFIC WRITE OPERATION

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 238

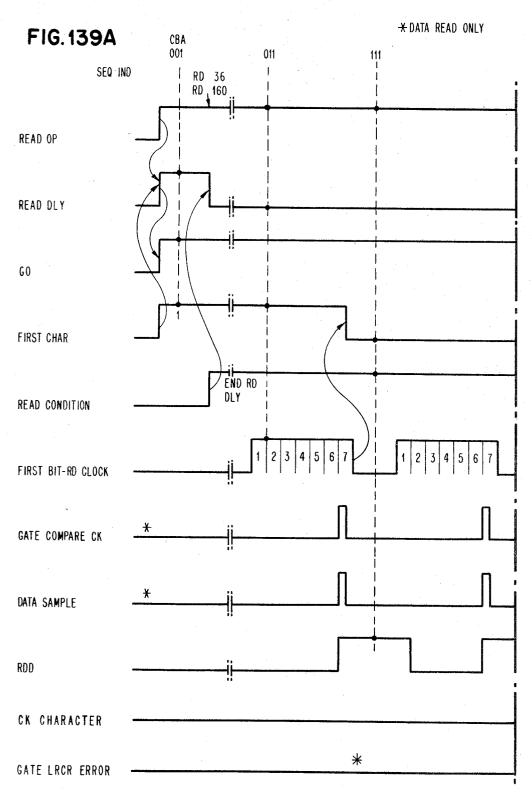

## FIG. 159A

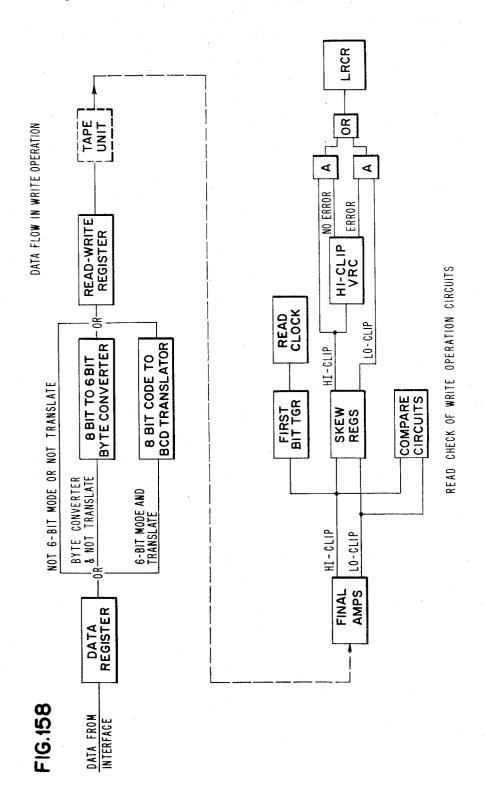

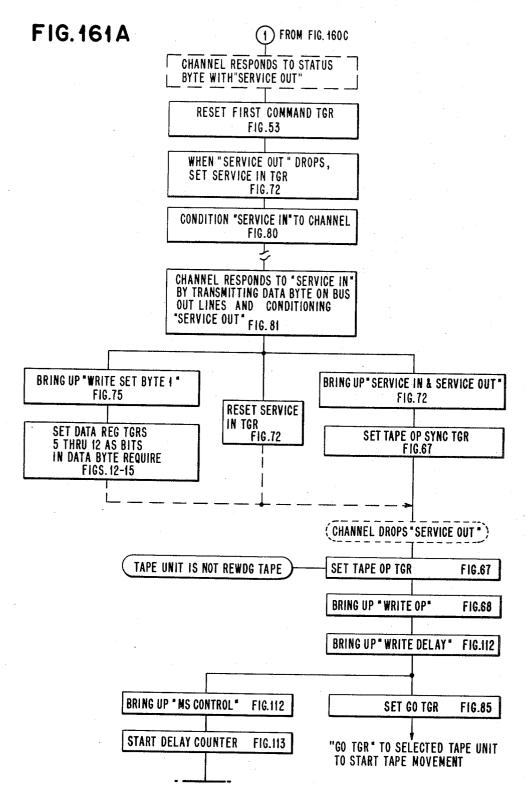

# INITIAL SELECTION SEQUENCE FIG.160

CHANNEL REQUESTS THAT TAPE CONTROL AND A SELECTED TAPE UNIT PERFORM A WRITE OPERATION.

# CONDITION TAPE CONTROL TO EXECUTE WRITE OPERATION FIG.161

CHANNEL TRANSFERS A CHARACTER ACROSS INTERFACE LINES TO TAPE CONTROL TAPE CONTROL STORES THE CHARACTER IN THE DATA REGISTER.

SET TAPE OP TGR.

SET GO TGR.

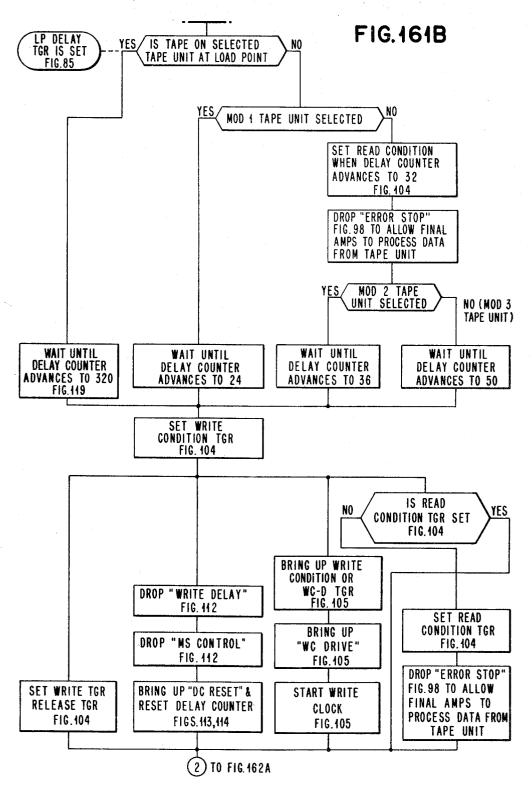

DELAY COUNTER ADVANCES THROUGH WRITE DELAY.

SET WRITE CONDITION AND READ CONDITION TGRS.

SET WRITE TGR RELEASE TGR.

START WRITE CLOCK.

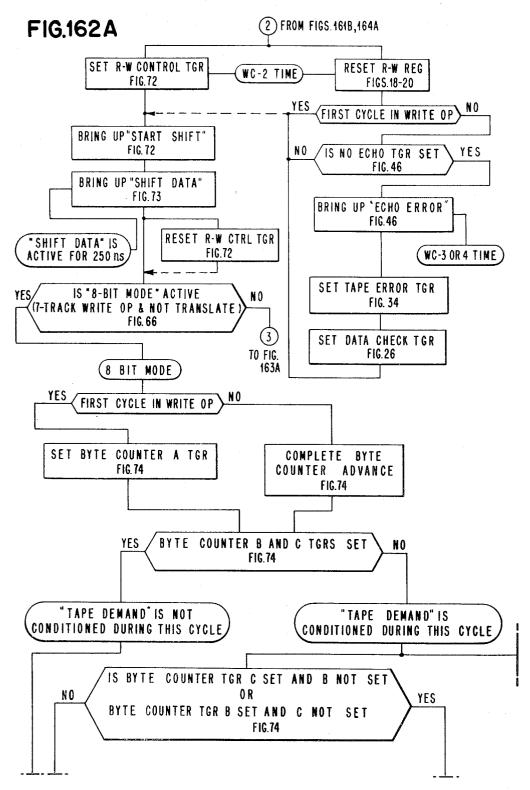

# START WRITE CLOCK CYCLE FIG.163

ON ALL OTHERS EXCEPT THE FIRST WRITE CLOCK CYCLE IN THE OPERATION, CHECK STATUS OF NO ECHO TGR.

RESET R-W REG. SET R-W CONTROL TGR.

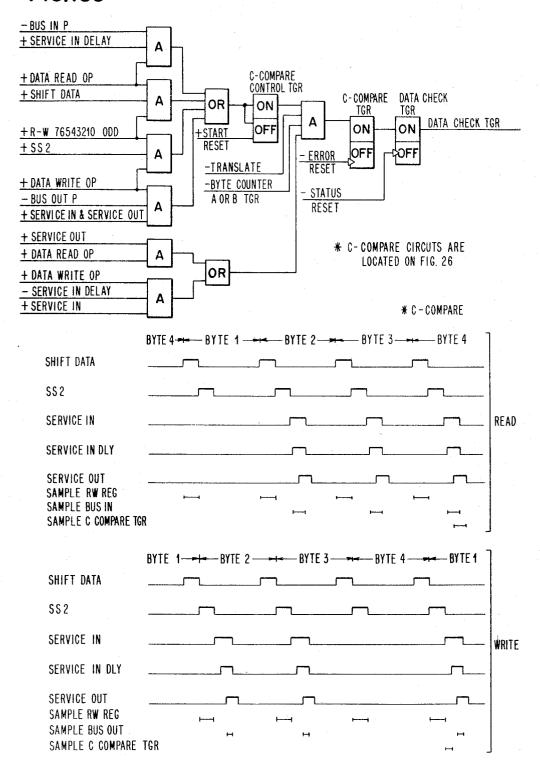

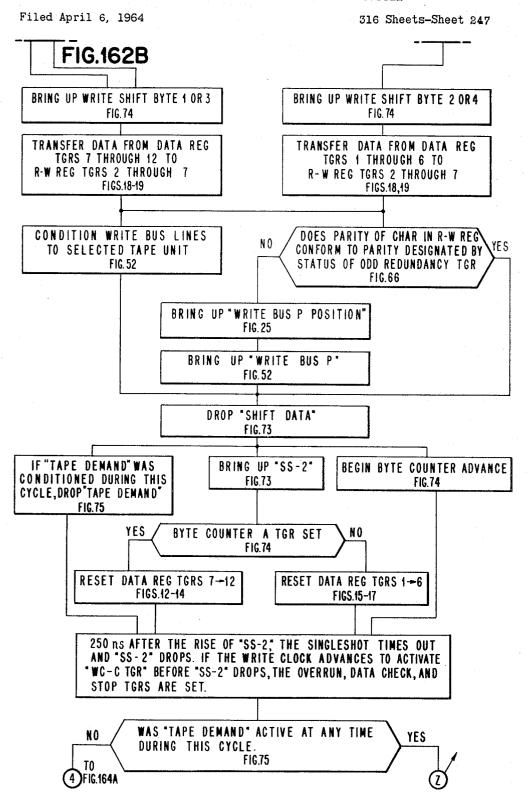

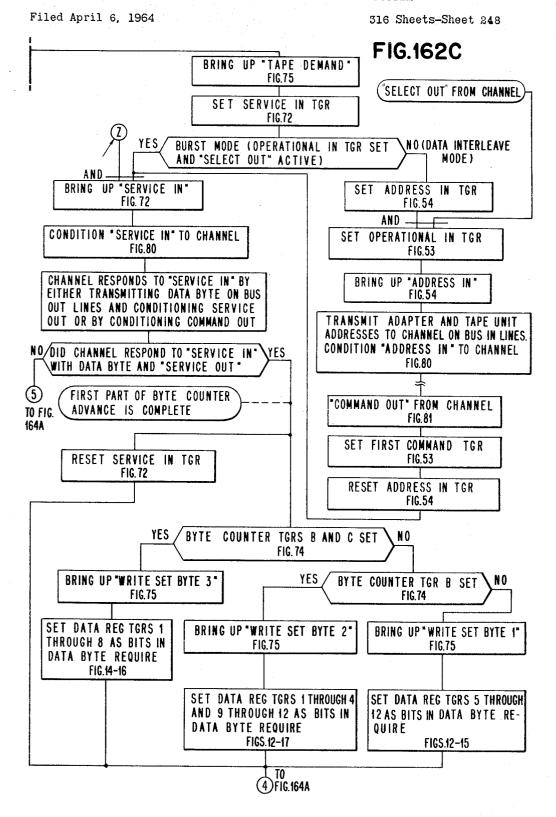

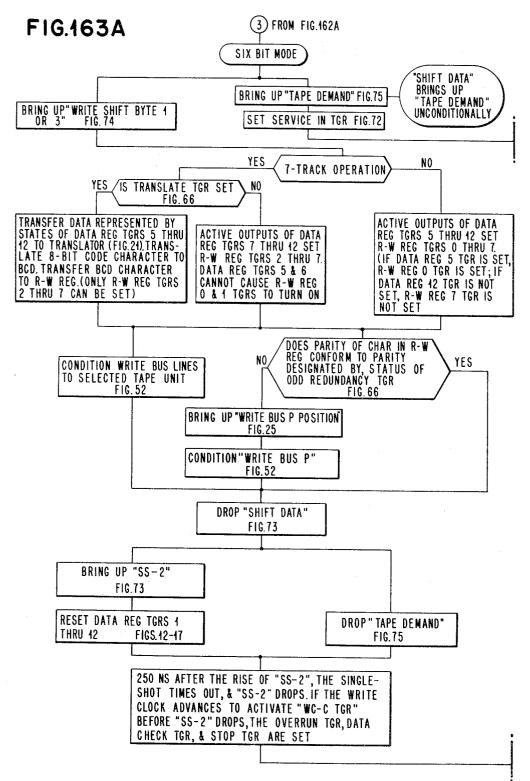

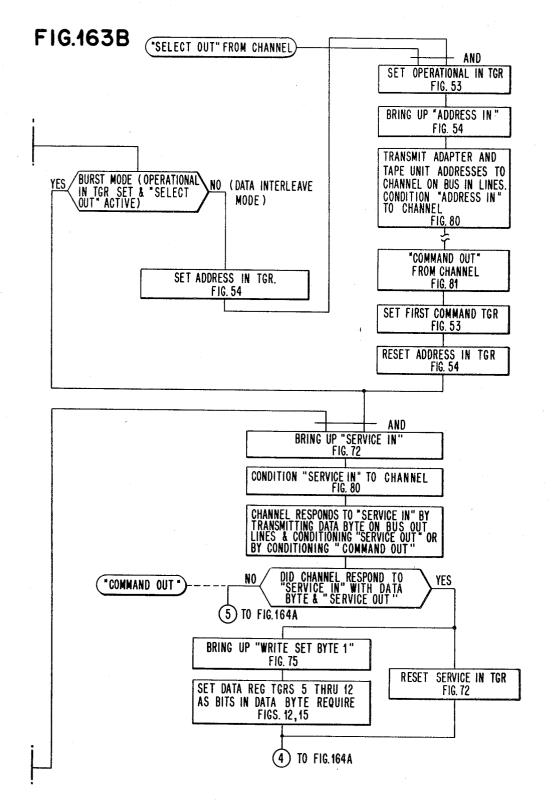

#### SHIFT CYCLE FIGS 162 163

TRANSFER BITS IN CHARACTER IN DATA REG TO R-W REG.

IN 6-BIT MODE, SET SERVICE IN TGR. "SERVICE IN"

INITIATES ACTIONS TO REQUEST ANOTHER

CHARACTER FROM CHANNEL.

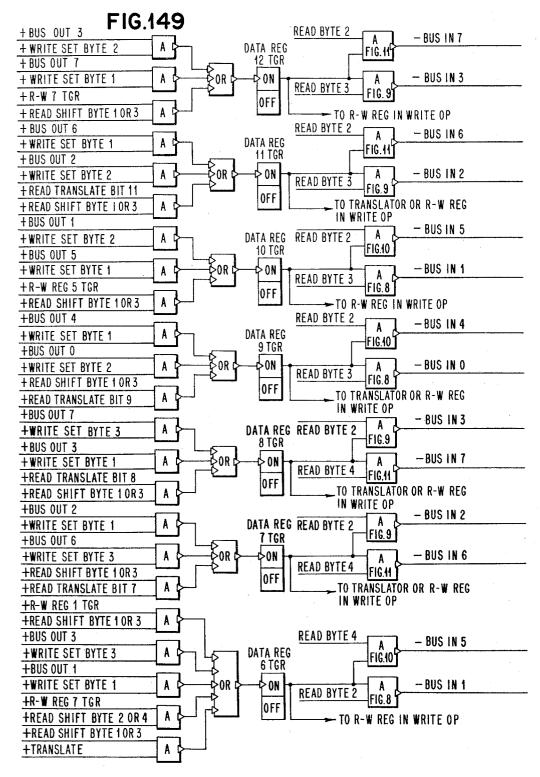

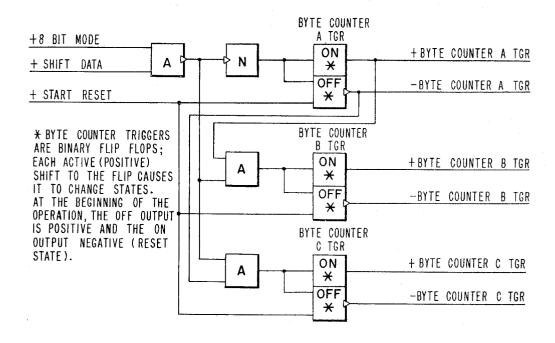

IN 8-BIT MODE, ADVANCE BYTE COUNTER. IF COUNTER INDICATES THAT ANOTHER CHANNEL CHARACTER IS REQUIRED, SET SERVICE IN TGR.

CHANNEL RESPONDS TO THE REQUEST FOR DATA BY CONDITIONING EITHER THE "SERVICE OUT" OR "COMMAND OUT" INTERFACE LINE. IF CHANNEL CONDITIONS "SERVICE OUT", IT ALSO TRANSFERS ANOTHER CHARACTER TO TAPE CONTROL. TAPE CONTROL STORES THE CHARACTER IN THE DATA REGISTER. IF CHANNEL CONDITIONS "COMMAND OUT", IT DOES NOT TRANSFER A CHARACTER TO TAPE CONTROL; TAPE CONTROL SETS THE STOP TGR.

Filed April 6, 1964

316 Sheets-Sheet 239

FIG. 159B

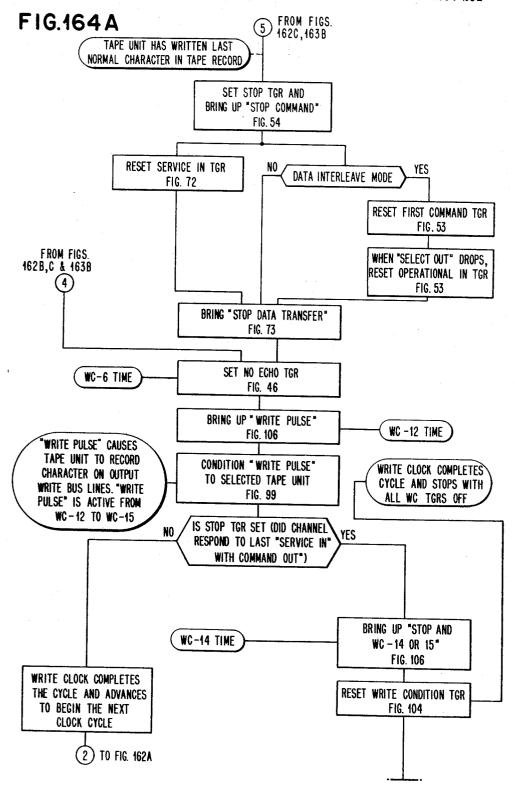

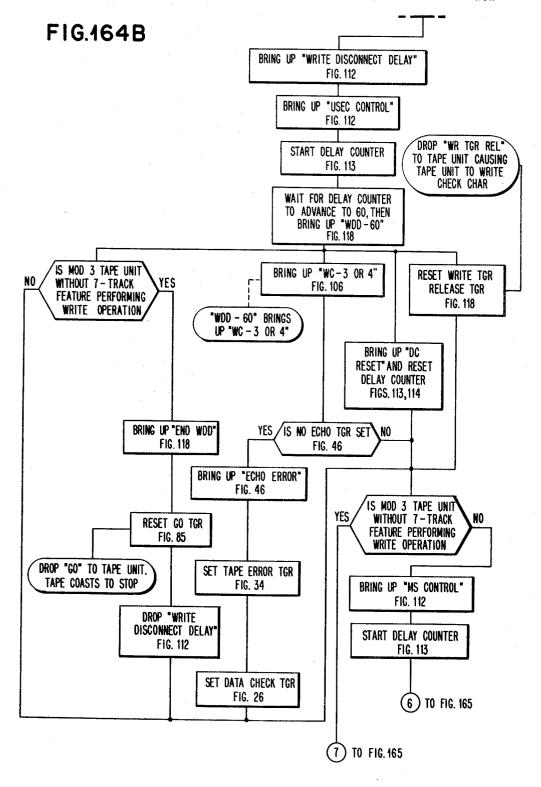

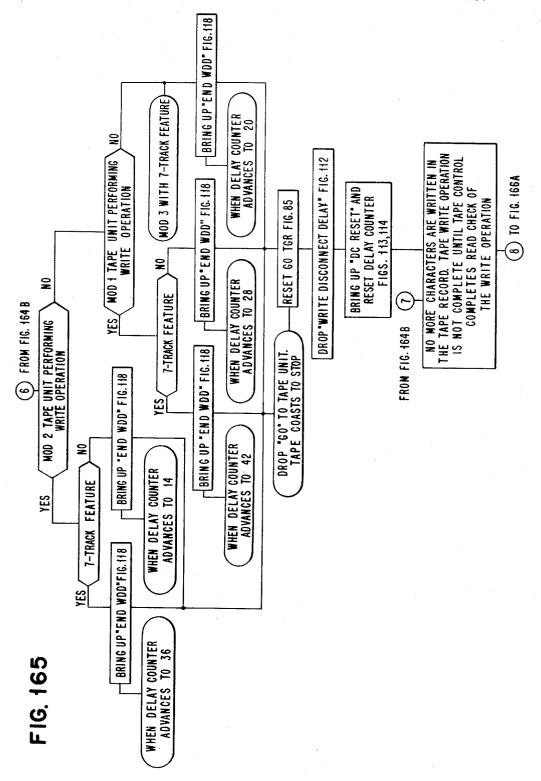

COMPLÉTE WRITE CLOCK CYCLE FIGS.164-165

SET NO ECHO TGR.

CONDITION DATA LINES AND "WRITE PULSE" TO

TAPE UNIT, TAPE UNIT WRITES THE CHARACTER.

IF STOP TGR IS NOT SET, WRITE CLOCK ADVANCES

TO 15, THEN BEGINS ANOTHER CYCLE.

IF STOP TGR IS SET:

RESET WRITE CONDITION TGR.

START DELAY COUNTER.

RESET WRITE TGR RELEASE TGR, TAPE

UNIT WRITES A CHECK CHARACTER.

RESET GO TGR.

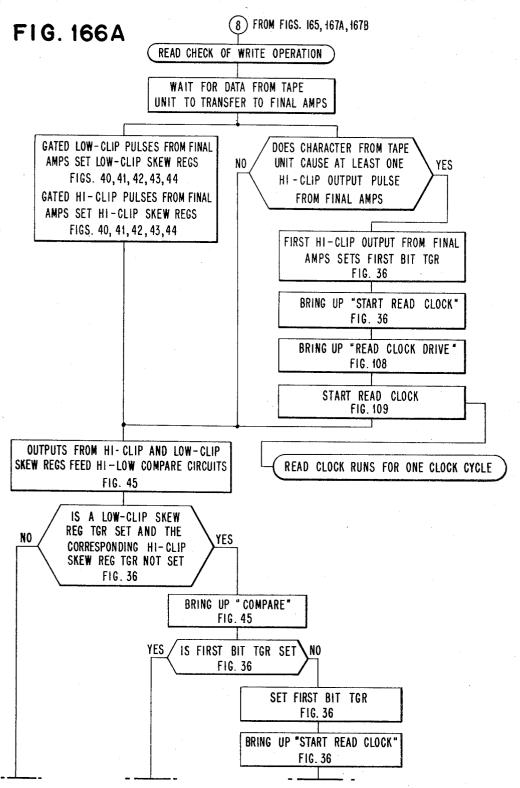

READ CHECK OF WRITE OPERATION

TAPE CONTROL PERFORMS THE READ CHECK OPERATION

AT THE SAME TIME THAT IT EXECUTES ACTIONS THAT

CAUSE THE TAPE UNIT TO WRITE THE TAPE RECORD.

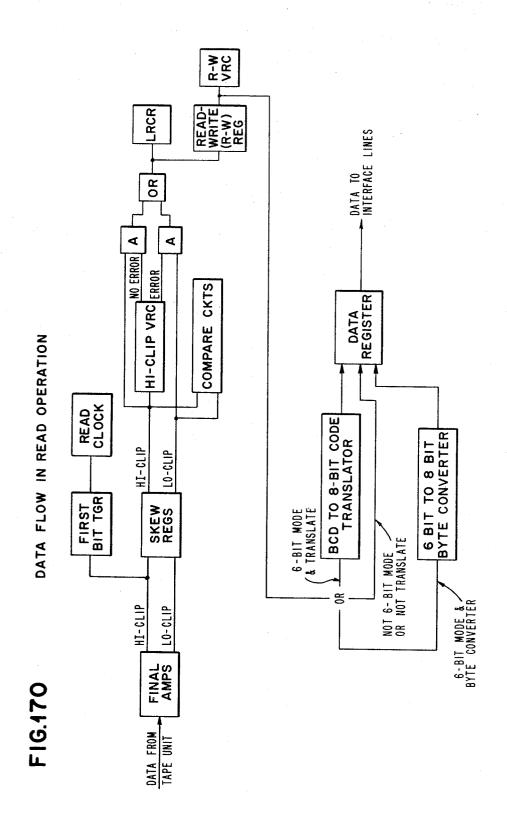

RECEIVE INPUT CHARACTER FROM Tape Unit Fig.166

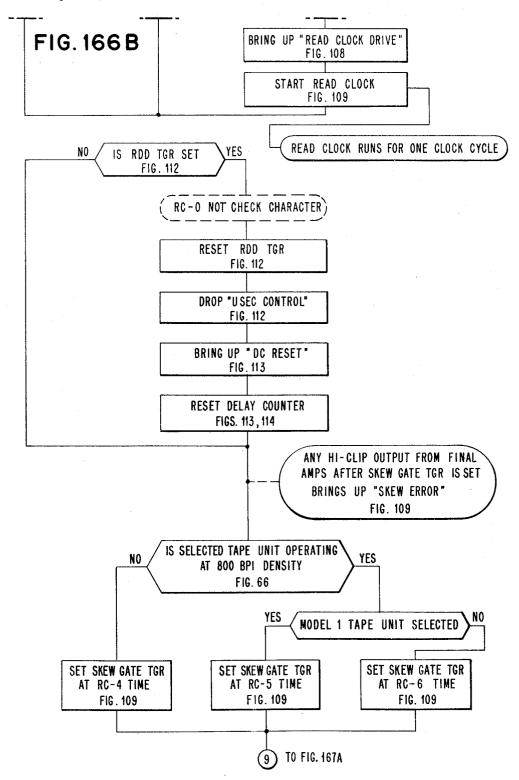

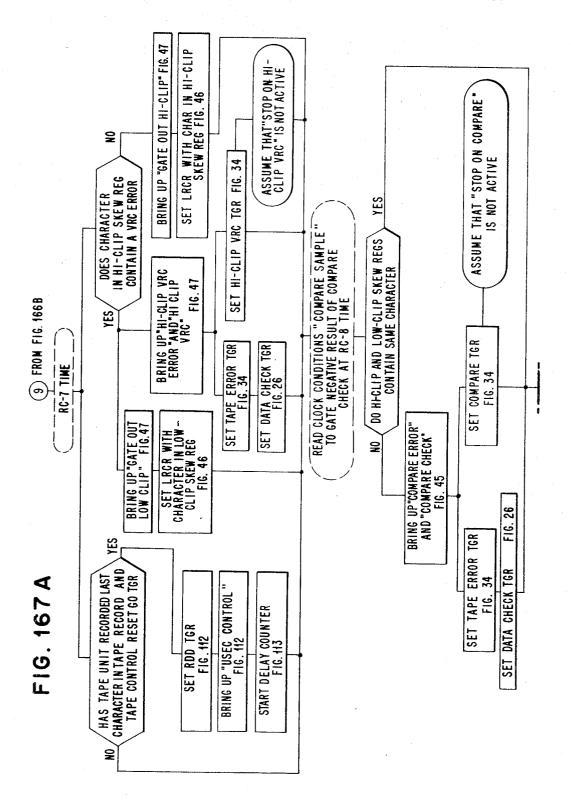

PROCESS TAPE CHARACTER THROUGH FINAL AMPS TO SKEW REGS. SET FIRST BIT TGR; START READ CLOCK. IF RDD TGR IS SET, RESET RDD TGR; DELAY COUNTER STOPS.

Filed April 6, 1964

316 Sheets-Sheet 240

FIG. 159C

#### READ CLOCK CYCLE FIGS. 166-167

SET SKEW GATE TGR.

IF TAPE UNIT HAS WRITTEN CHECK CHARACTER,

SET RDD TGR; START DELAY COUNTER.

PERFORM HI-CLIP VRC AND COMPARE CHECKS.

SET LRCR.

RESET FIRST BIT TGR; READ CLOCK STOPS; RESET

SKEW GATE TGR.

RESET SKEW REGS.

WAIT FOR NEXT CHARACTER FROM TAPE UNIT.

IF NEXT TAPE CHARACTER PRODUCES AN OUTPUT

FROM FINAL AMPS BEFORE DELAY COUNTER ADVANCES TO 36, TAKE ANOTHER READ CLOCK CYCLE.

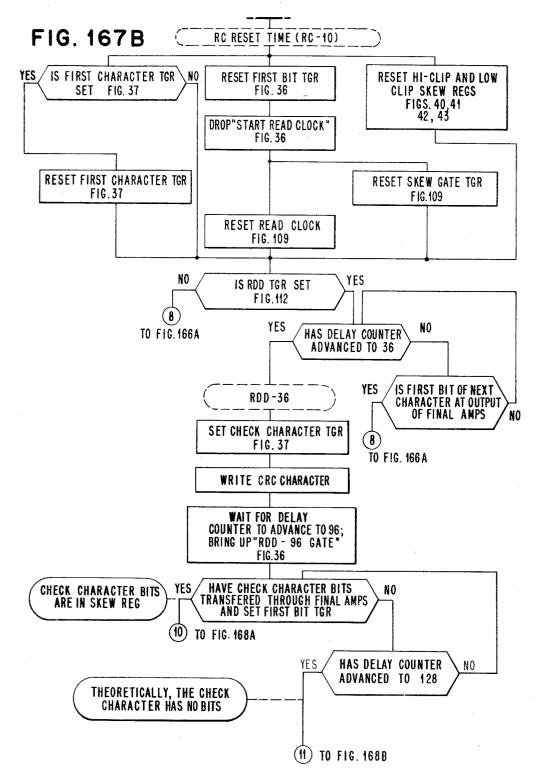

IF DELAY COUNTER ADVANCES TO 36 BEFORE

ANOTHER HI-CLIP OUTPUT FROM FINAL AMPS

IS SENSED, SET CHECK CHARACTER TGR. PROCESS

CHECK CHARACTER BITS TO SKEW REGS.

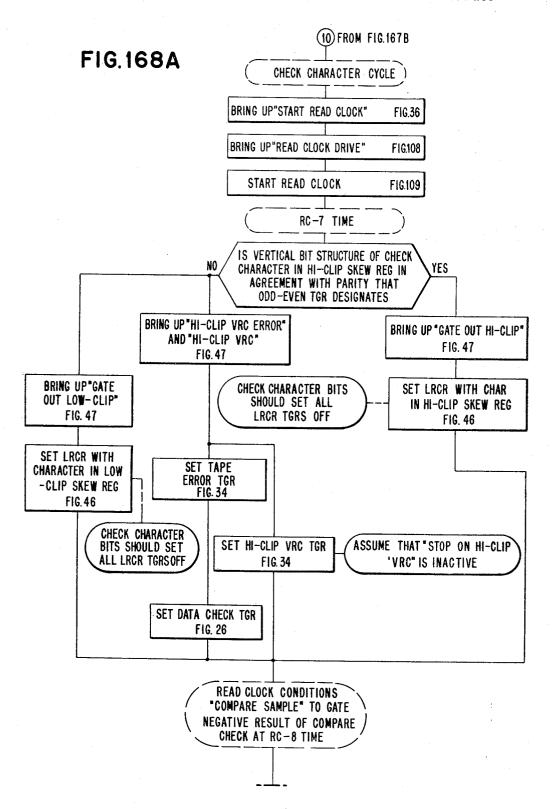

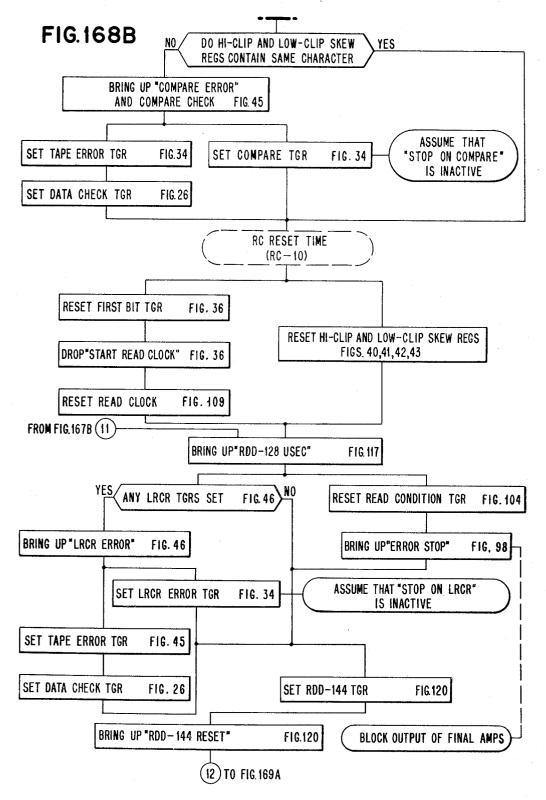

#### CHECK CHARACTER CYCLE FIG.168

SET FIRST BIT TGR AFTER DELAY COUNTER AD-VANCES TO 96; START READ CLOCK. PERFORM HI-CLIP VRC AND COMPARE CHECKS. SET LRCR. RESET FIRST BIT TGR; READ CLOCK STOPS. RESET SKEW REGISTERS. PERFORM LRCR CHECK AND RESET READ CON-DITION TGR WHEN DELAY COUNTER ADVANCES TO 128.

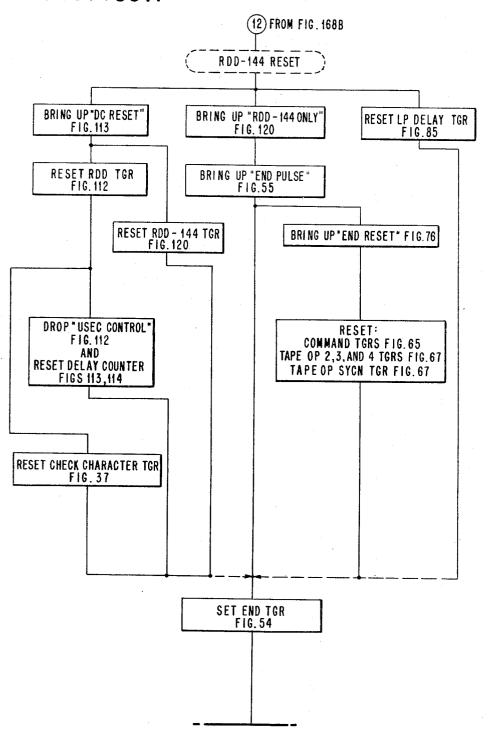

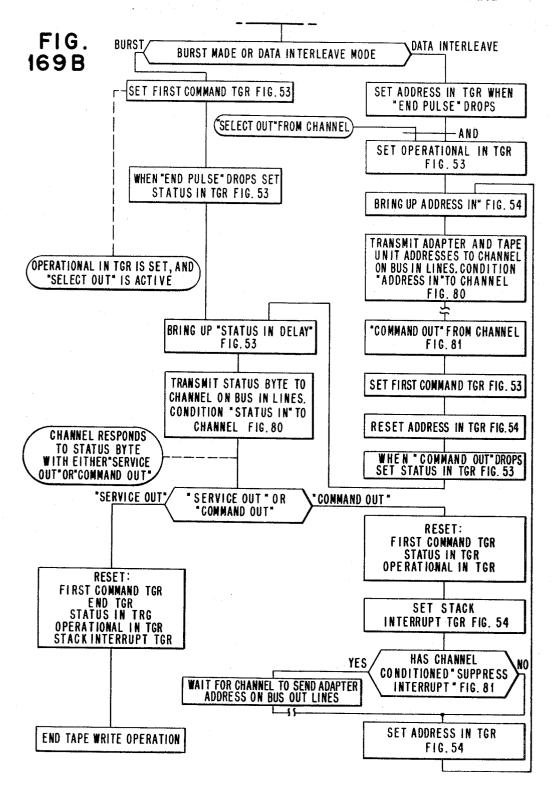

#### END OPERATION FIG.169

RESET TAPE CONTROL CIRCUITS ACTIVATED TO PERFORM THE WRITE OPERATION.

SET END TGR.

TRANSMIT STATUS BYTE TO CHANNEL.

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

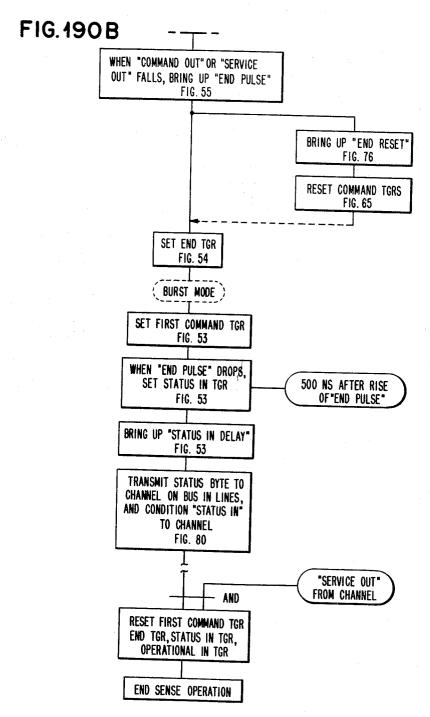

FIG. 169A

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 263

# FIG. 171A

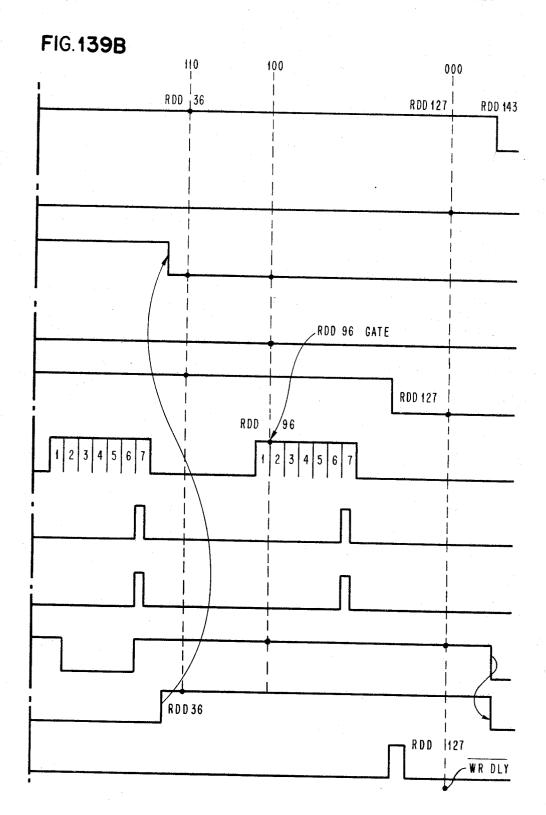

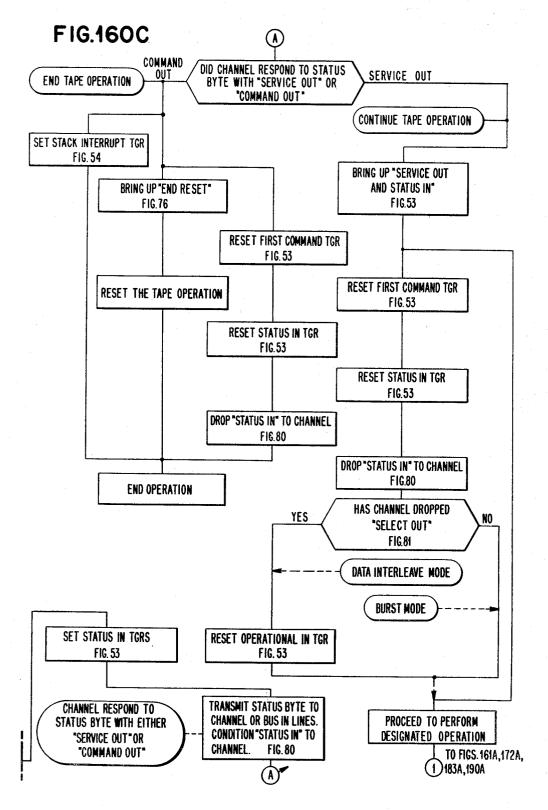

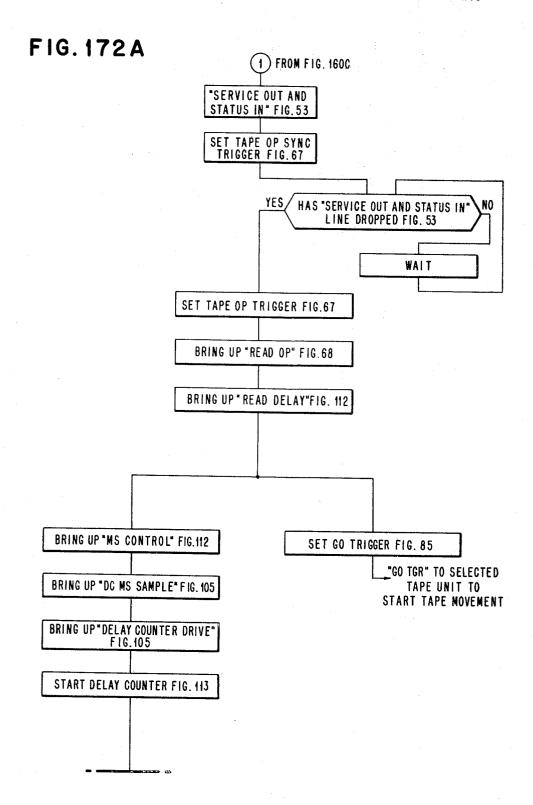

INITIAL SELECTION SEQUENCE FIG. 160 CHANNEL REQUESTS THAT TAPE CONTROL AND A SELECTED TAPE UNIT PERFORM A READ OPERATION.

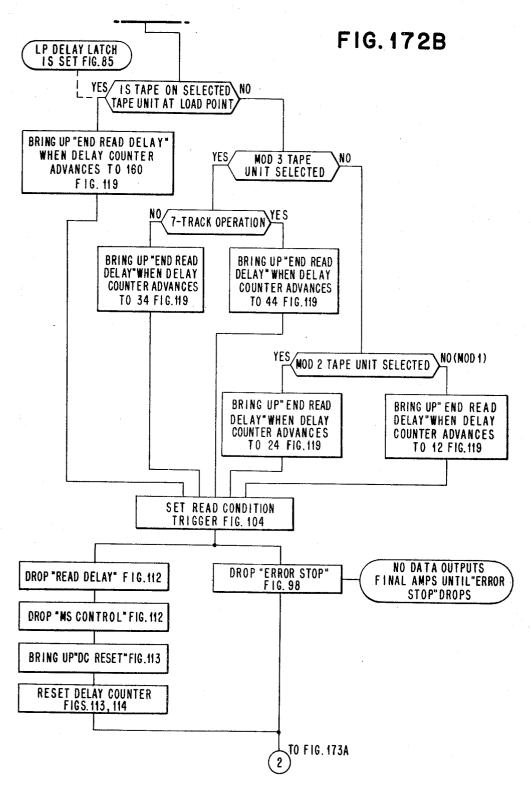

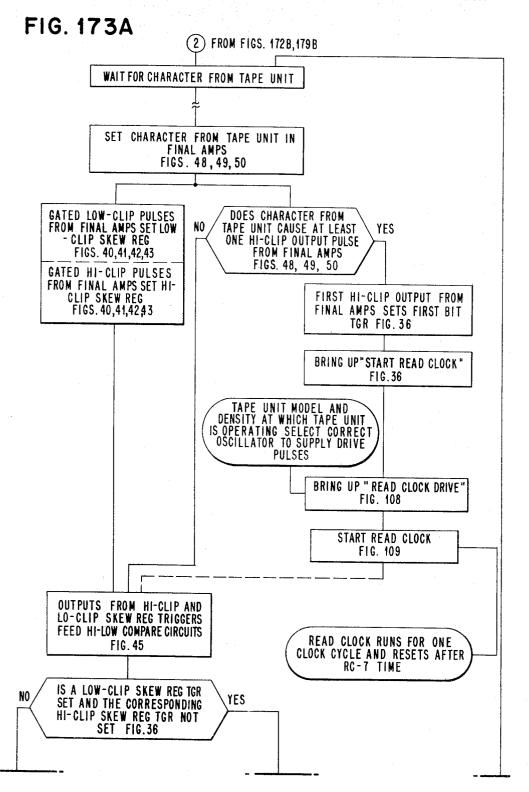

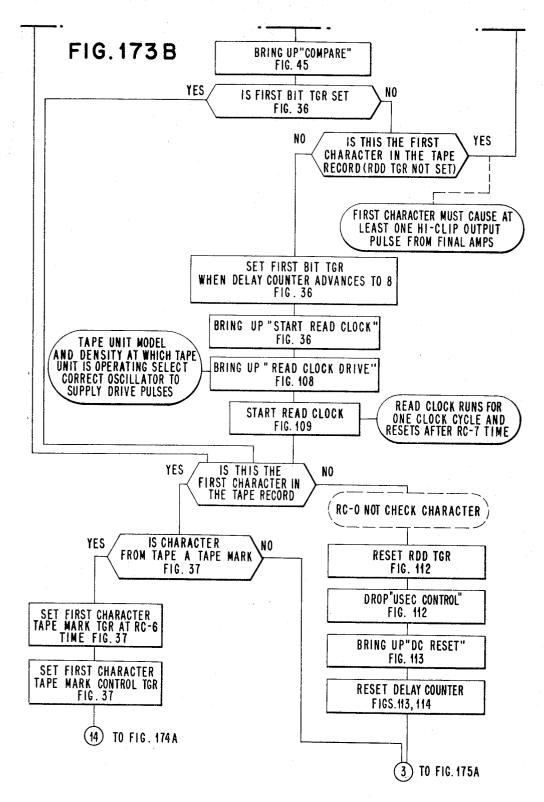

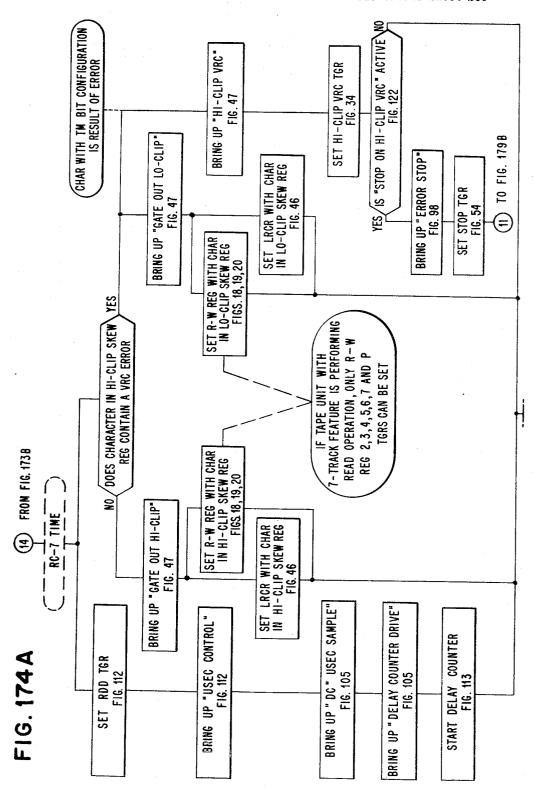

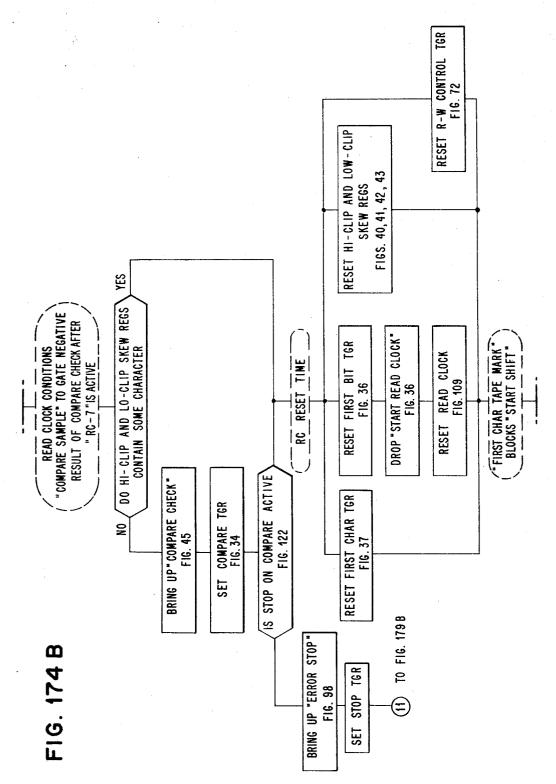

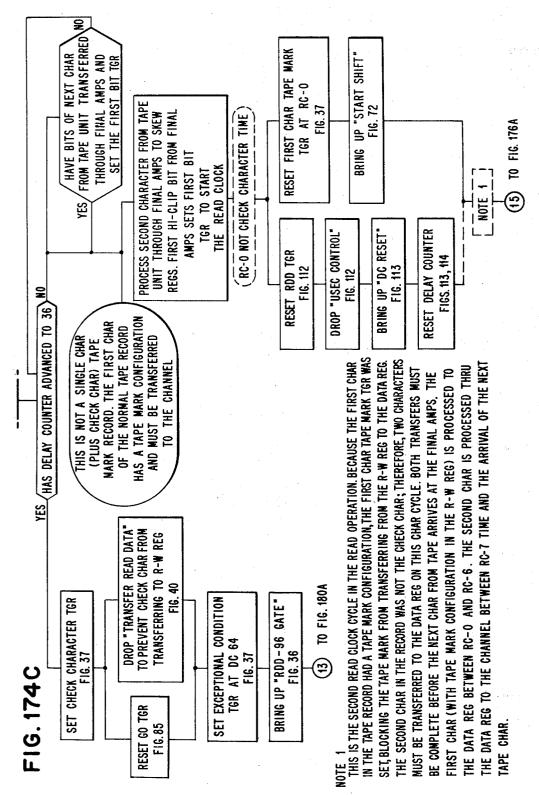

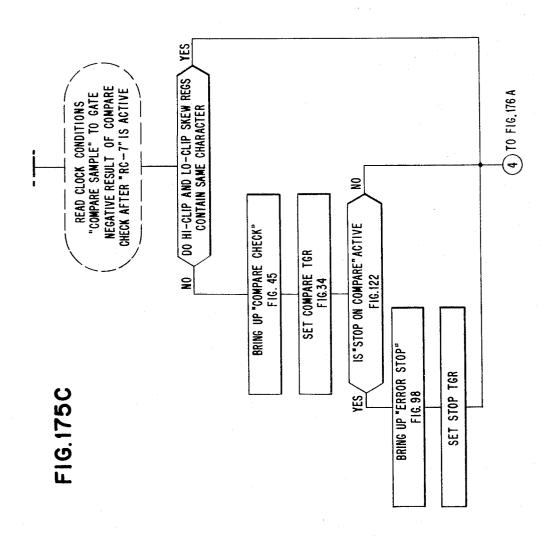

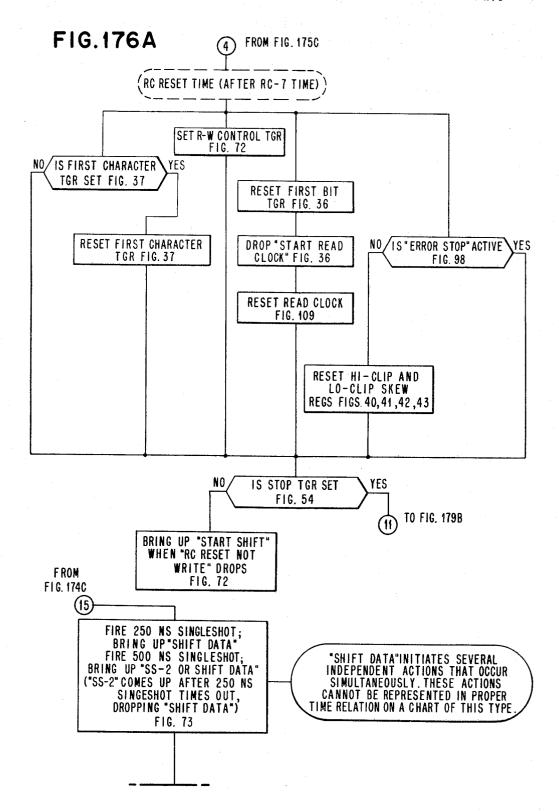

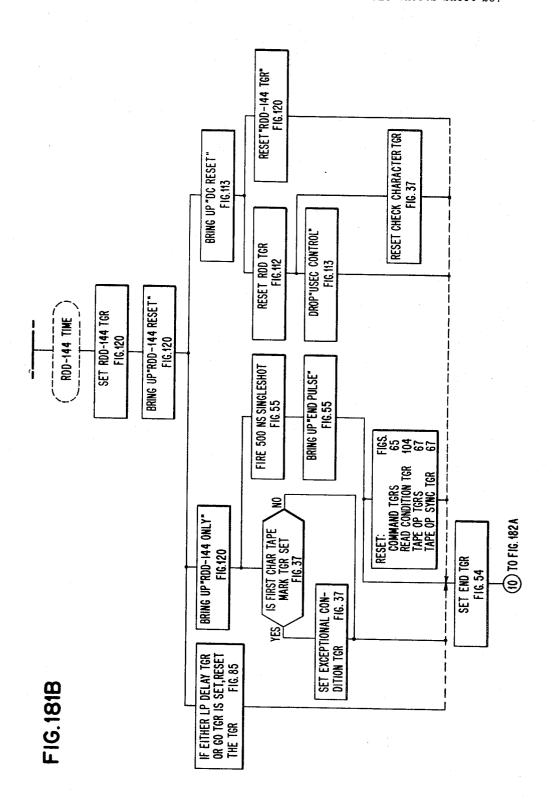

CONDITION TAPE CONTROL TO **EXECUTE READ OPERATION** FIG. 172 SET TAPE OP TGR. SET GO TGR. DELAY COUNTER ADVANCES THROUGH READ FIRST CHARACTER TAPE MARK DELAY. FIG. 174 SET READ CONDITION TGR. SET FIRST CHARACTER TAPE MARK TGR. PERFORM NORMAL READ CLOCK CYCLE CHECKS ON TAPE MARK CHARACTER, AND PROCESS RECEIVE INPUT CHARACTER FROM TAPE UNIT TAPE MARK CHARACTER R-W REG AND LRCR. RESET SKEW REGISTERS, FIRST BIT TGR, AND FIG.173 READ CLOCK. PROCESS TAPE CHARACTER THROUGH FINAL SET RDD TGR; START DELAY COUNTER. AMPS TO SKEW REGS. HOLD TAPE MARK CHARACTER IN R-W REG SET FIRST BIT TGR; START READ CLOCK. UNTIL NEXT CHARACTER FROM TAPE RESET RDD TGR; DELAY COUNTER STOPS. UNIT ARRIVES. TAPE SECOND CHARACTER NOT CHECK CHARACTER CHAR FIG. 174 OR BEGIN READ CLOCK CYCLE. TAKE FORCED SHIFT CYCLE TO PROCESS FIRST CHARACTER (IN R-W REG) TO DATA REG AND TO CHANNEL (IF TRANSFER TO CHANNEL IS REQUIRED). PROCESS SECOND CHARACTER (IN SKEW REGISTERS) AT NORMAL READ CLOCK TIMES. NORMAL READ CLOCK CYCLE FIGS.175,176 SECOND CHARACTER CHECK PERFORM HI-CLIP VRC AND COMPARE CHARACTER CHECKS. FIG. 174 SET LRCR AND R-W REGISTERS. SET EXCEPTIONAL CONDITION TGR. RESET SKEW REGISTERS, FIRST BIT TGR. AND READ CLOCK.

Filed April 6, 1964

316 Sheets-Sheet 264

### FIG.171B

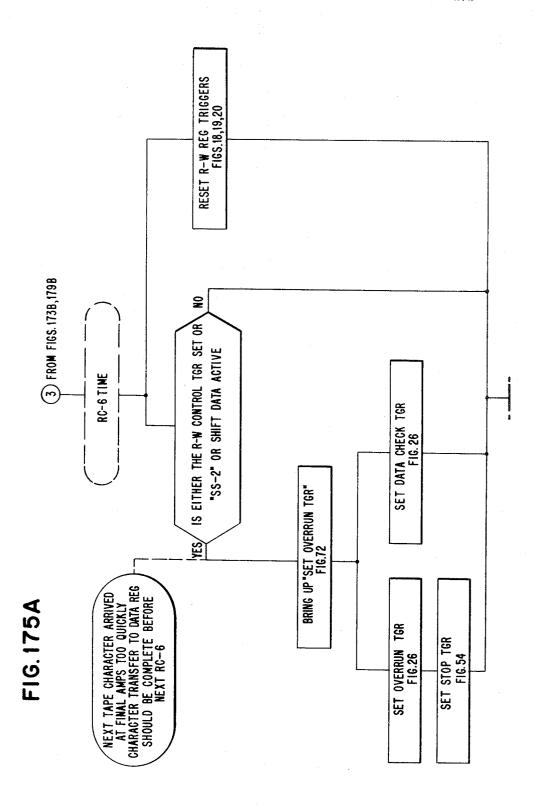

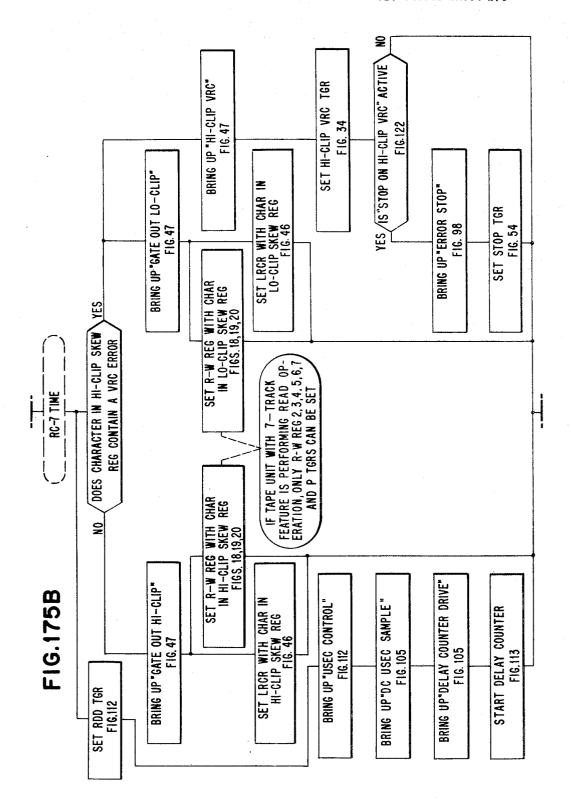

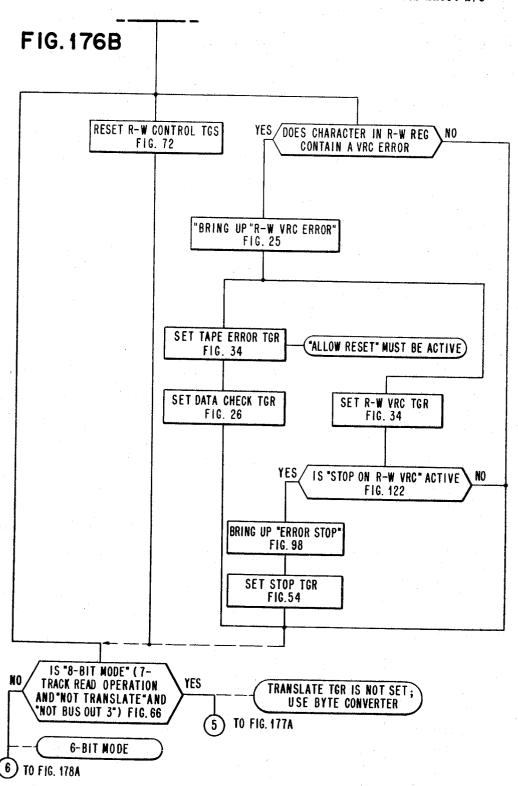

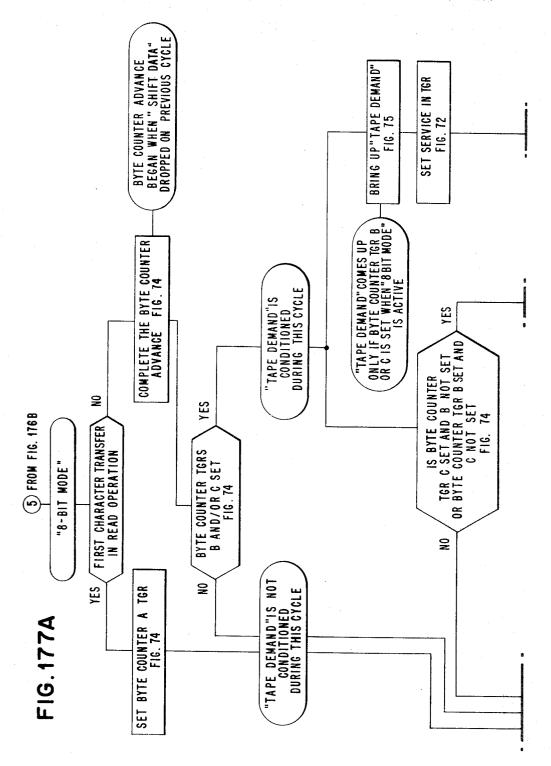

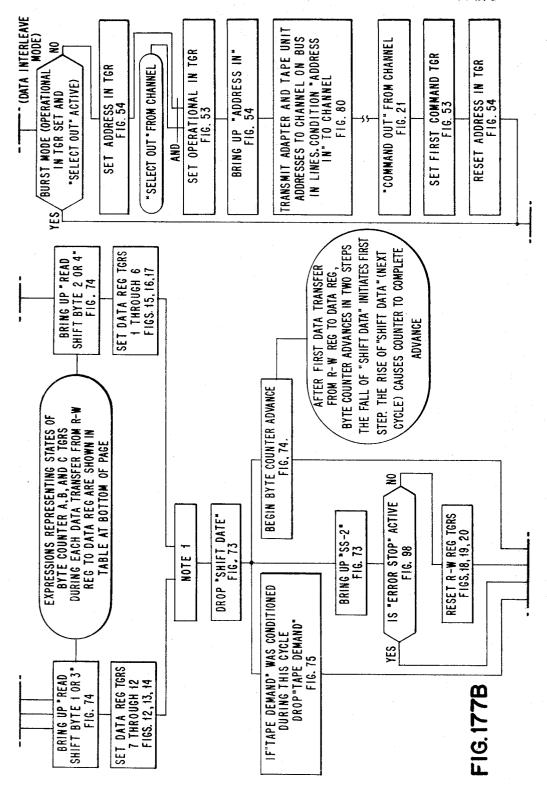

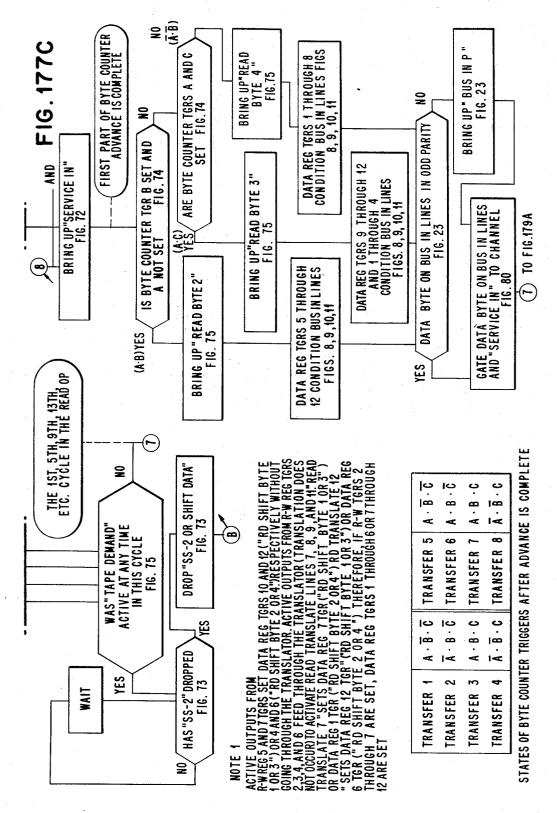

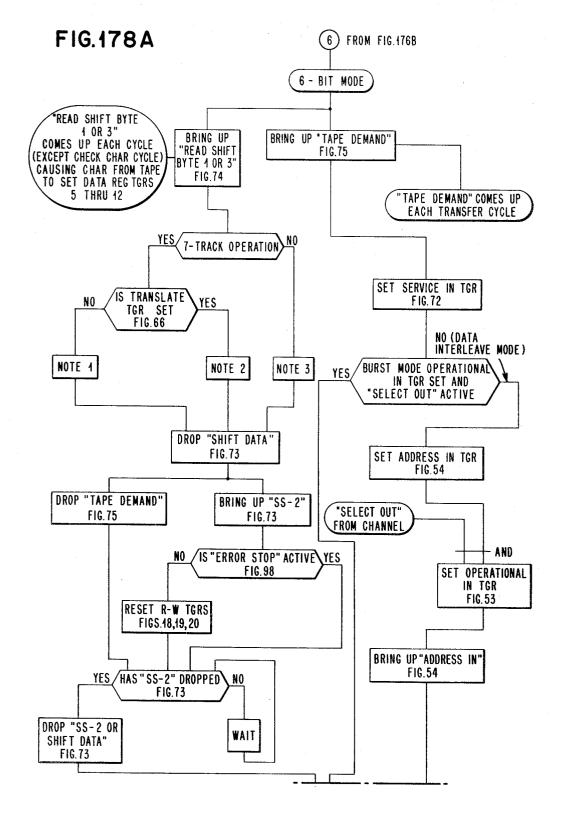

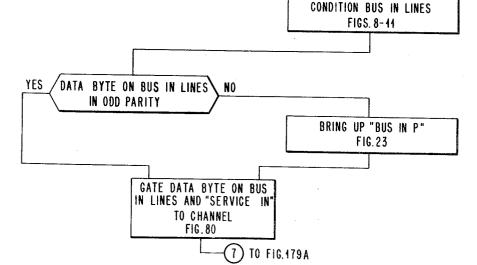

### SHIFT CYCLE FIGS.176,177,178

PERFORM VRC CHECK ON CHARACTER IN R-W REG.

TRANSFER CHARACTER IN R-W REG TO DATA REGISTER.

IN 6-BIT MODE, TRANSFER DATA REGISTER CHARACTER TO

CHANNEL.

IN 8-BIT MODE, ADVANCE BYTE COUNTER. IF COUNTER INDICATES THAT A TRANSFER IS REQUIRED, TRANSFER A DATA REGISTER CHARACTER TO CHANNEL.

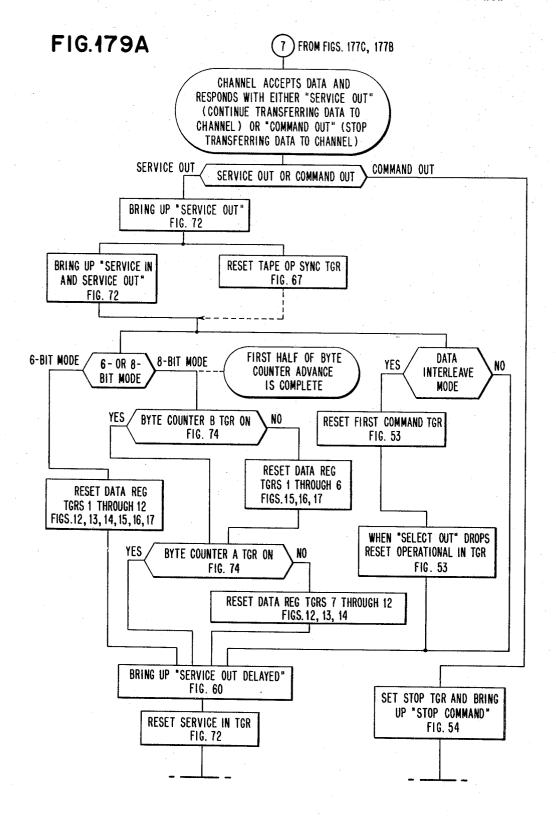

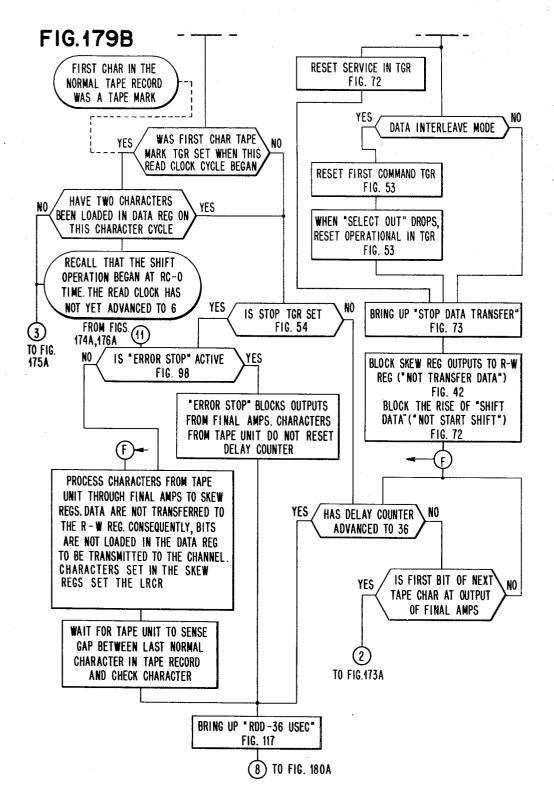

### CHANNEL RESPONSE FIG.179

IF CHANNEL RESPONDS WITH SERVICE OUT AND NEXT CHARACTER FROM TAPE UNIT IS NOT CHECK CHARACTER, PROCESS NEXT CHARACTER TO CHANNEL.

IF CHANNEL RESPONDS WITH "COMMAND OUT TAPE CONTROL DOES NOT TRANSMIT MORE CHARACTERS TO CHANNEL. WAIT FOR CHECK CHARACTER.

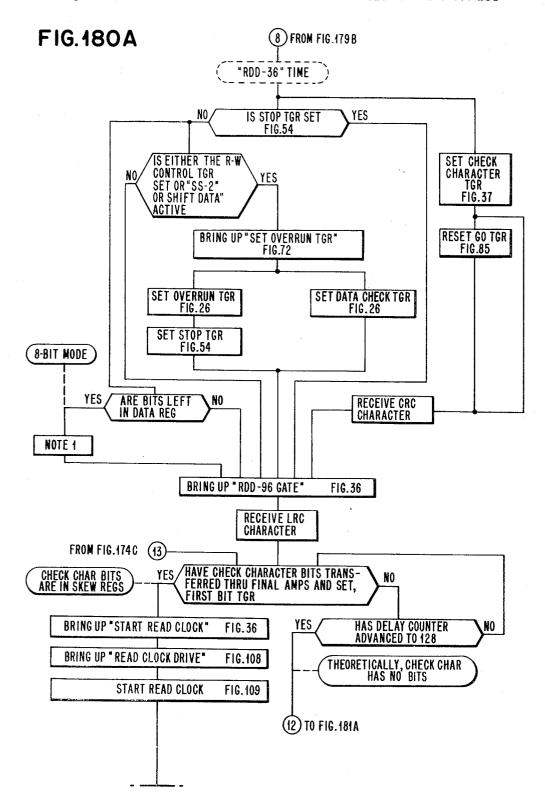

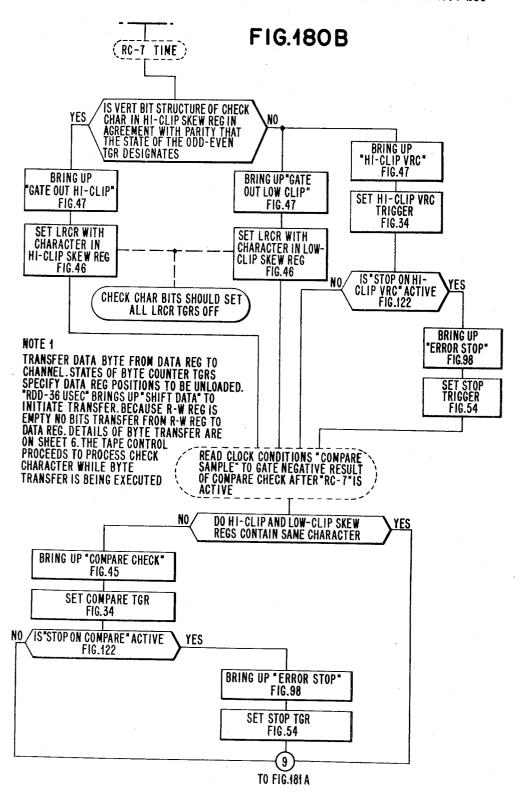

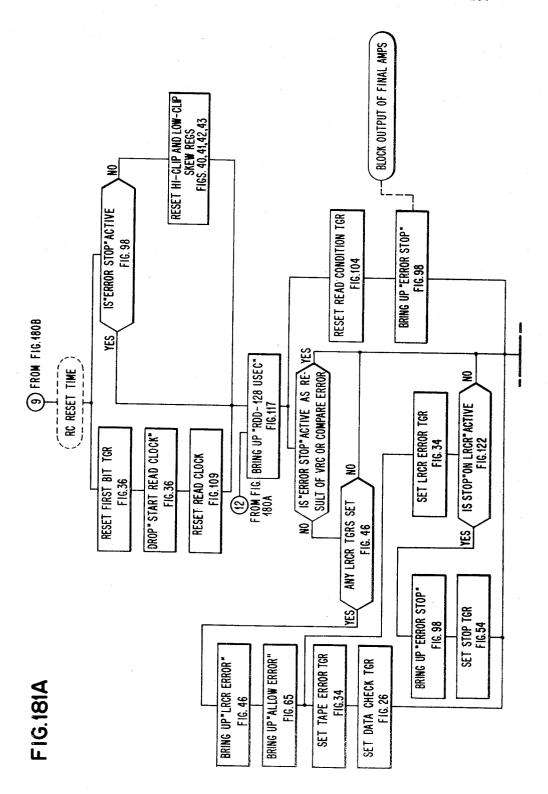

## CHECK CHARACTER CYCLE

FIGS. 179,180,181

SET CHECK CHARACTER TGR. RESET GO TGR.

PROCESS CHECK CHARACTER THROUGH FINAL AMPS TO SKEW REGS.

PERFORM HI-CLIP VRC AND COMPARE CHECKS.

SET LRCR. RESET SKEW REGS, FIRST BIT TGR, AND READ CLOCK.

PERFORM LRCR CHECK.

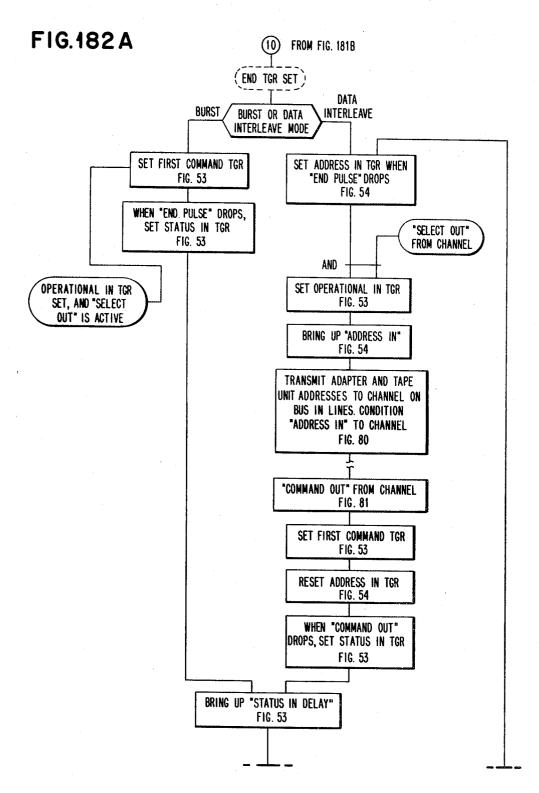

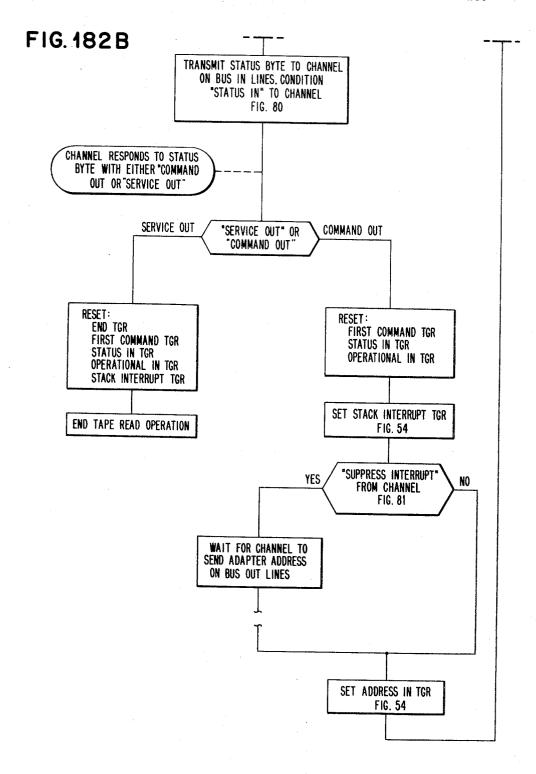

### END OPERATION FIGS. 181, 182

RESET TAPE CONTROL CIRCUITS ACTIVATED TO

PERFORM THE READ OPERATION. SET END TGR FIG. 181

TRANSMIT STATUS BYTE TO CHANNEL FIG. 182

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

316 Sheets-Sheet 281

#### FIG.178B NOTE 4 ACTIVE OUTPUTS FROM R-W REG 0,1,5 & 7 TGRS TRANSMIT ADAPTER & TAPE SET DATA REG TGRS 5,6,10 & 12 RESPECTIVELY. RECALL, HOWEVER, THAT DATA FROM TAPE DID NOT UNIT ADDRESSES TO CHAN ON BUS IN LINES. SET R-W REG O & 1 TGRS; ZEROS ARE INSERTED IN DATA REG POSITIONS 5 & 6. ACTIVE OUTPUTS CONDITION "ADDRESS IN" TO CHAN FIG. 80 FROM R-W REG TGRS 2,3,4 & 6 FEED THRU THE TRANSLATOR (TRANSLATION DOES NOT OCCUR) TO ACTIVATE READ TRANSLATE LINES 7, 8,9 & 41. "READ TRANSLATE 7" SETS DATA REG "COMMAND OUT" FROM CHANNEL 7 TGR THEREFORE, IF R-W REG TGRS 2 THRU 7 FIG. 84 ARE SET, DATA REG TGRS 7 THRU 12 ARE SET. THE CHAR GATED TO THE INTERFACE HAS ZEROS IN THE TWO HIGH ORDER POSITIONS ONLY DATA REG 5 THRU 12 TGRS ARE USED IN THE 6-BIT SET FIRST COMMAND TGR MODE. FIG. 53 NOTE 2 "TRANSLATE" SETS DATA REG 6 TGR. ONLY ACTIVE OUTPUTS FROM R-W REG TGRS 5 & 7 SET DATA REG TGRS 10 & 12 RESPECTIVELY. OUTPUTS FROM R-W REG TGRS RESET ADDRESS IN TGR FIG. 54 FEED THE BCD TO 8-BIT TRANSLATOR. THE TRANSLATOR CONVERTS DATA AND PRODUCES INPUT "READ TRANSLATE" LINES TO THE DATA REG. "READ TRANSLATE" LINES SET DATA REG AND BRING UP "SERVICE IN" 5,7,8,9 & 12 TGRS. FIG.72 NOTE 3 GATE CHARACTER REPRESENTED BY STATES BRING UP "READ BYTE 2" OF R-W REG TGRS TO DATA REG POSITIONS 5 THRU 12 (IF R W REG O TGR IS SET, SET FIG.75 DATA REG 5 TGR; IF R-W REG 7 TGR IS SET, SET DATA REG 12 TGR.) DATA REG TGRS 5 THRU 12

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

Filed April 6, 1964

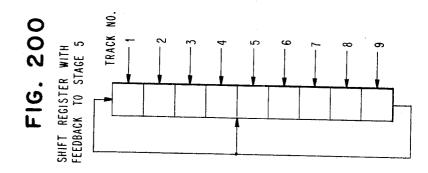

CRC REGISTER IN FIG. 200 (WITH INTERMEDIATE FEEDBACK TO STAGE 5)

Filed April 6, 1964

Filed April 6, 1964

FIG. 201

FIG. 202

1

#### 3,508,194

ERROR DETECTION AND CORRECTION SYSTEM

David T. Brown, Wappingers Falls, N.Y., assignor to

International Business Machines Corporation, New

York, N.Y., a corporation of New York

Filed Apr. 6, 1964, Ser. No. 357,368 Int. Cl. G08b 29/00; G06f 11/00

U.S. Cl. 340—146.1

10 Claims

# ABSTRACT OF THE DISCLOSURE

Locating any tape track having an error in a data 15 block. The bit positions in a byte are in respectively different tape tracks. To locate any track having from one to all bit positions erroneous, a first cyclic storage means (CRC shift register) receives all of the bits of every byte 20 in parallel, including a CRC redundancy byte, for an entire block. A second cyclic storage means (EP shift register) serially receives the output from a byte redundancy check (VRC) circuit which checks the parity 25 for each byte in the block. Each storage means has at least end-around feedback. The CRC shift register is also used to generate and write the CRC byte at the end of a tape block. After a block is read, the two cyclic storage 30 means should have bit patterns which correspond in a predetermined manner if no error occurred in the block. An error is indicated by non-correspondence. Then the pattern of one storage means is moved relative to the 35 pattern in the other until the patterns correspond. The track in the block having the erroneous bits is determined by the number of bit positions of relative movement needed to obtain correspondence between the patterns. 40 A diagonal redundancy byte is effective as the cyclic redundancy byte where the number of tape tracks is a prime number, such as 1, 2, 3, 5, 7, 11, 13, etc.

| INDEX                                                |        |   |

|------------------------------------------------------|--------|---|

| SECTION TITLE:                                       | Column |   |

| (I) CRC Error Detection and Correction.              | 7      |   |

| (II) Mathematical Description of Cyclic Correction   | 14     | i |

| (III) Embodiment Introduction                        | 17     |   |

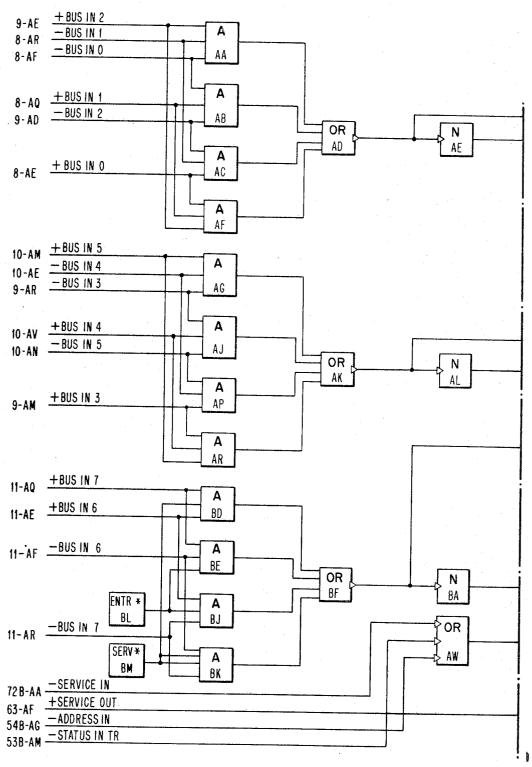

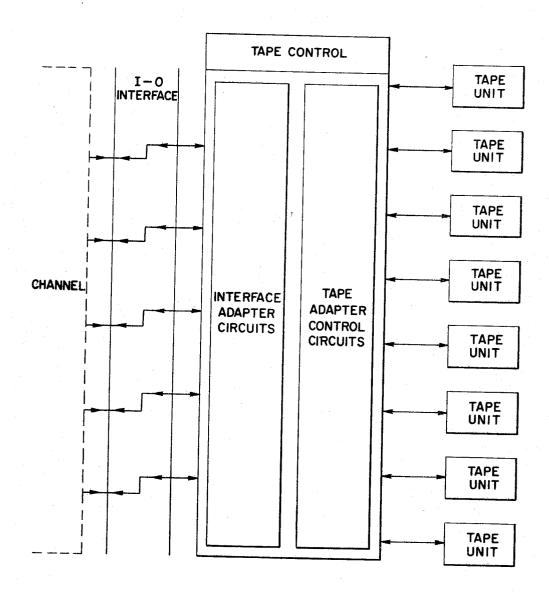

| (A) I/O channel interface                            | 19     |   |

| (B) Non-cyclic error detection                       | 38     |   |

| (C) Data transfer circuits                           | 42     |   |

| (D) Tape control write operation                     | 48     |   |

| (E) Tape control read operation without cyclic error |        |   |

| correction                                           | 55     |   |

| (F) Tape motion control without data transfer        | 62     |   |

| (G) Cyclic error detection circuits                  | 69     |   |

| (H) Cyclic error correction circuits                 | 73     |   |

| (J) Read operation with cyclic error correction      | 77     |   |

| (IV) Drawing Element Definitions                     | 82     |   |

|                                                      |        |   |

2

This invention relates generally to error detection and correction systems. In particular, this invention relates to an error detection and correction system utilizing cyclic redundancy and is particularly pertinent to systems having a prime number of bits in a byte.

The term "byte" herein means a sub-word which is a fixed number of data bits handled as a matter of convenience by the hardware of a data system. Although the bits of a byte generally are transferred in parallel, they may be transferred serially in some situations.

This invention provides an error detection and correction system which has unique characteristics over prior error detection and correction systems. For example, it has been previously known to use a longitudinal redundancy check byte at the end of the data block and to use byte redundancy (character redundancy) for each byte in the block. This has been done for a number of years to obtain error detection for data read from magnetic tape. Also, it has been well known that either odd or even parity, or a fixed number of 1-bits check may be utilized as an effective form of byte redundancy (character redundancy).

Error check circuits do not provide error correction. Generally all error correction systems require error detection means in a form which can locate one or more erroneous bits. The location of any erroneous binary bit position permits error correction by inversion since a binary bit can only have two states; and if one state is determined to be erroneous, the other binary state must be correct.

Cyclic redundancy for error detection has been described generally in an article by D. T. Brown and W. W. Peterson, "Cyclic Codes for Error Detection," published in Proceedings of the I.R.E., No. 49 (January 1961). Cyclic error detection and correction is also treated in a book by W. W. Peterson "Error-Correcting Codes," Wiley & Sons (1961), and references cited in the book. The book and its references primarily are mathematical treatises on cyclic redundancy detection and correction for bit serial operation only. However, parallel bit operation for cyclic redundancy error detection is disclosed in other prior art which, however, does not disclose any error correction system utilizing cyclic redundancy. Error correction utilizing a combination of 55 longitudinal redundancy and byte redundancy is described and claimed in the prior art such as Patent No. 3,273,120, issued Sept. 13, 1966 to R. V. McFadden, D. R. Dustin, C. P. Rauf, and G. G. Unger, entitled 60 "Error Correction System By Retransmission of Erroneous Data." This last reference discloses how an er-

50

roneous bit in a data block read from tape can be corrected after the track in error has been determined by rereading the tape and utilizing the byte redundancy during the rereading to determine the particular byte having the error and reinserting a bit lost by drop out.

Prior error correction systems utilizing longitudinal redundancy to determine an erroneous bit position in a byte of a data block have the difficulty that longitudinal redundancy is only capable of detecting 50 percent of the possible error pattern which can exist in any common bit position of a block of data. This invention describes and claims means by which a common bit position having an error in a data block can be located for much greater than 50 percent of such error patterns. Depending upon the particular design of the invention, it can locate in excess of 95 percent of the possible error patterns that can exist in any given common bit position of a data block.

It is an object of this invention to provide means for controlling and communicating data with a high order of reliability.

It is an object of this invention to provide means for controlling a storage device to provide a high order of reliability in communicating data from the storage device.

It is another object of this invention to provide control means for a storage medium enabling error correction of data read from the storage medium.

It is another object of this invention to provide a control means for one or more tape drives capable of writing tape with a format which enables error correction of tape data.

It is another object of this invention to provide control means for one or more tape drives which can correct all of the bit errors occurring at least within any single track of a tape block.

It is a further object of this invention to provide cyclically-operating error detection during the reading of tape.

It is a further object of this invention to provide means for error correcting the data read from tape by utilizing cyclic-redundancy error-checking means.

It is a further object of this invention to provide a data format which utilizes a cyclic redundancy check character written either before, after, or within a data block.

This invention pertains to finding a common bit posi- 55 tion having an error in any byte of a data block derived from any source, such as core memory, film memory, etc. This invention utilizes a storage means having wraparound feedback for either generating or detecting cyclic 60 redundancy with a data block; cyclic redundancy alone is used to locate an erroneous bit position in a byte of a block. Finding an erroneous bit position in a byte of a data block is a partial location of an error in a data block. 65 In many magnetic tape systems, the bit positions in a byte are represented by the different tape tracks. The invention utilizes two cyclic storage means which are each capable of developing separate error patterns that have a 70 particular bit correlation, in the absence of any error in a block. One cyclic storage means receives the data in the block, which may include redundancy. The other register receives an input from a byte redundancy check 75

circuit which examines each byte in the block. Each cyclic storage means can be any one of number of circuits capable of moving data internally while receiving data, such as a delay line or a circuit capable of step-shifting bits such as a shift register. The two cyclic storage means are designated a cyclic redundancy check (CRC) storage means and error pattern (EP) storage means. Thus the CRC storage means can receive all of the bits of a data block, while the EP storage means receives the byte redundancy indication for each byte of the block. After a block is read with a cyclic redundancy byte, these two cyclic storage means should have patterns which correlate in a predetermined manner if no error occurred in the block. However, if an error did occur, the bit position in any byte having the error can be determined by moving the pattern of one of the storage means relative to the pattern of the other storage means until a particular predetermined correlation is obtained between the bit patterns. In this case the number of bit positions of relative movement needed to obtain a predetermined correlation relates to an erroneous bit position in any byte of the block. This particular means for determining the location of an erroneous bit position of any byte in the data block has been found to be particularly effective in cases where  $^{30}$  the number of bit positions in a byte is a prime number, such as 1, 2, 3, 5, 7, 11, 13, etc.

The foregoing and other objects, features and advantages of the invention will be apparent from the following more particular description of the preferred embodiments of the invention, as illustrated in the accompanying drawings.

# DESCRIPTIVE TABLE OF DRAWINGS

|                                                         | Figure  |

|---------------------------------------------------------|---------|

| Pitle description of drawing:                           | number  |

| General Partial Error Location System                   | 1       |

| Error Correction System                                 | 2       |

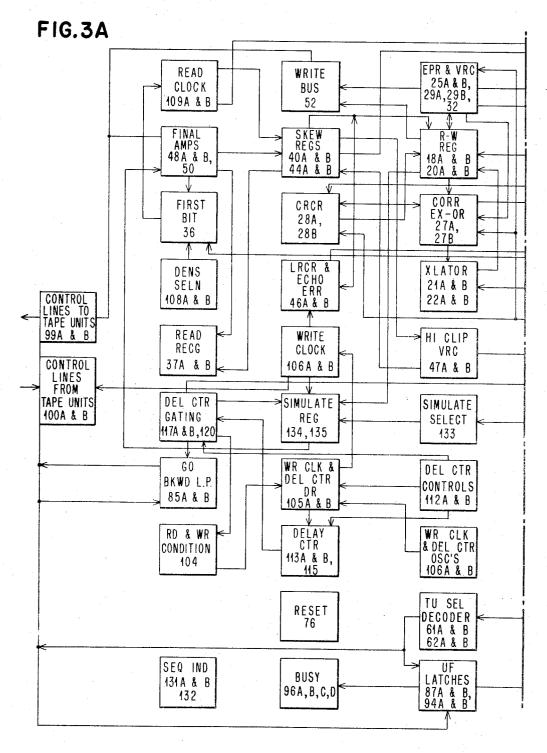

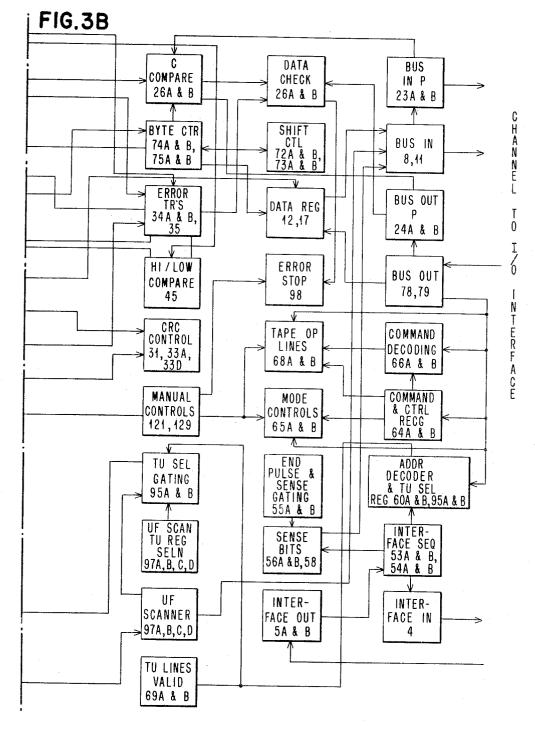

| Tape Control System                                     | 3A & B  |

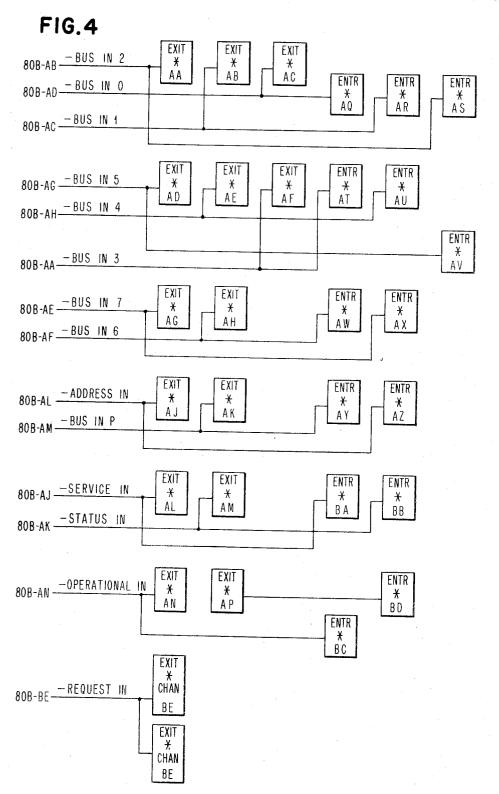

| Interface In                                            | 4       |

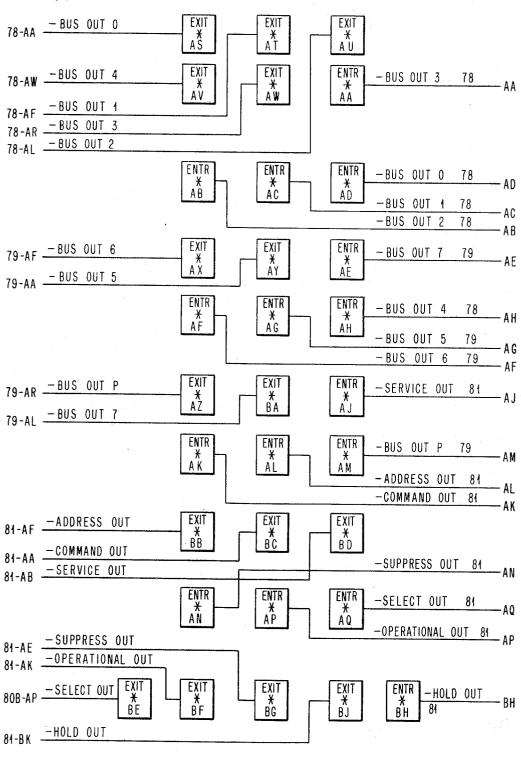

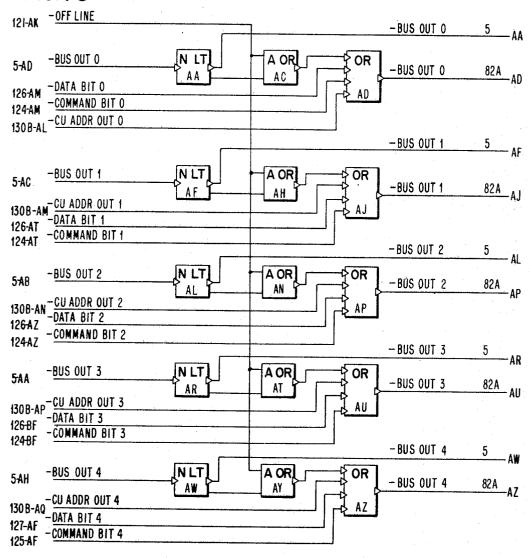

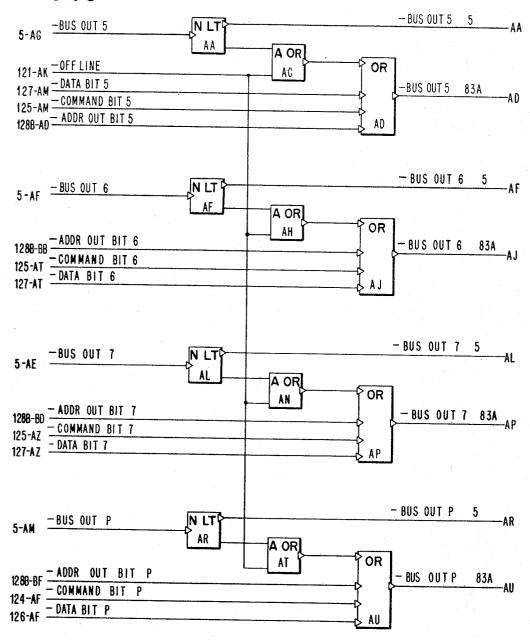

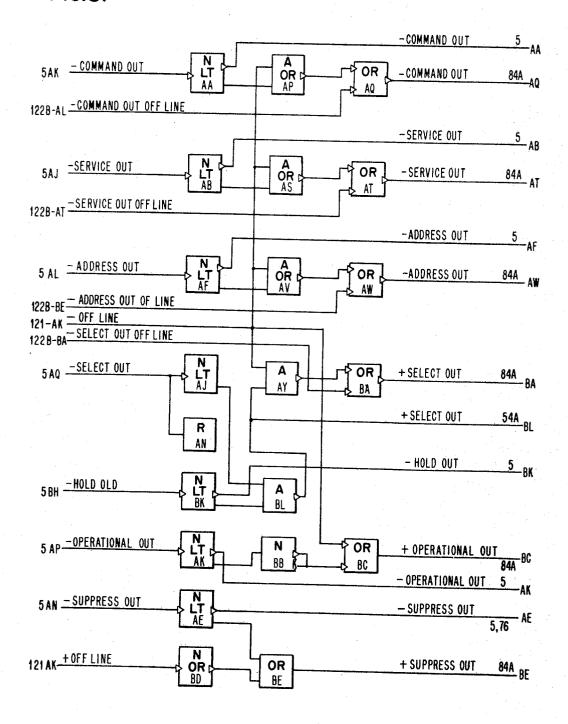

| Interface Out                                           | 5       |

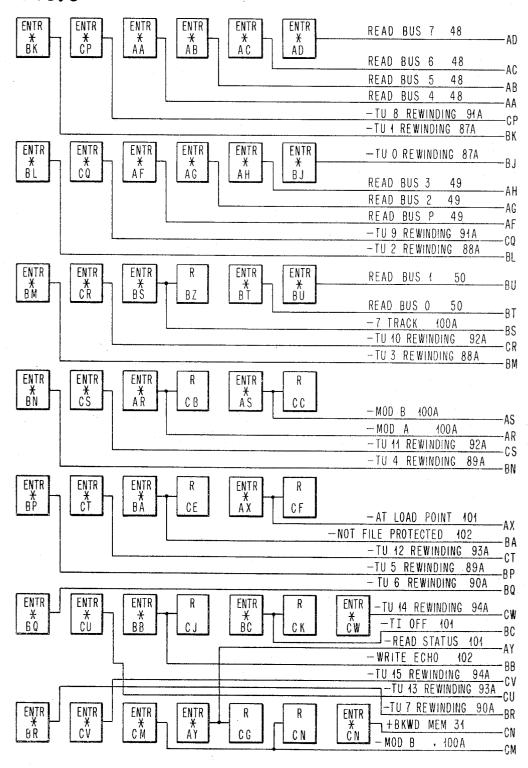

| Tape Unit Read Lines                                    | 6       |

| Tape Unit Write Lines                                   | 7       |

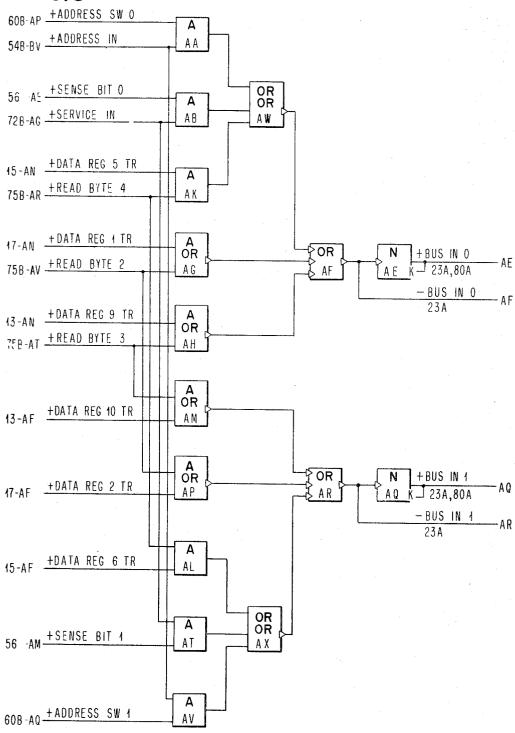

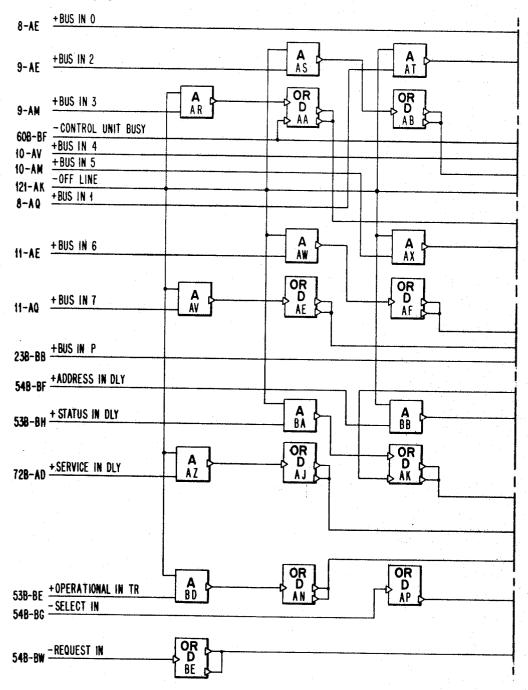

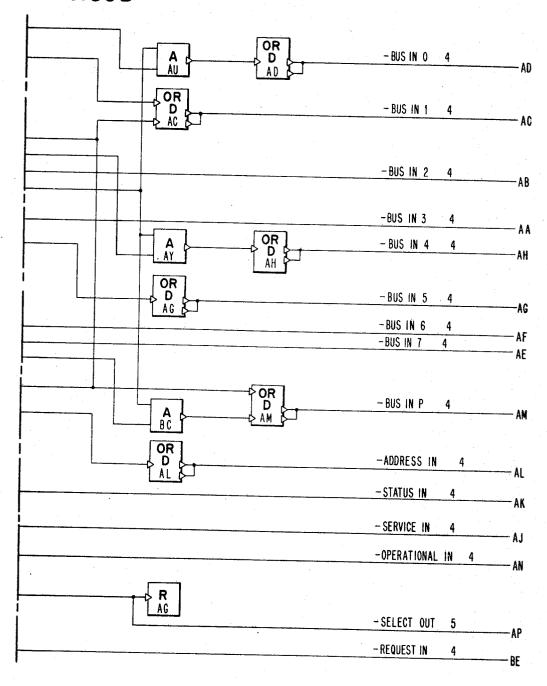

| Bus In 0 and 1                                          | 8       |

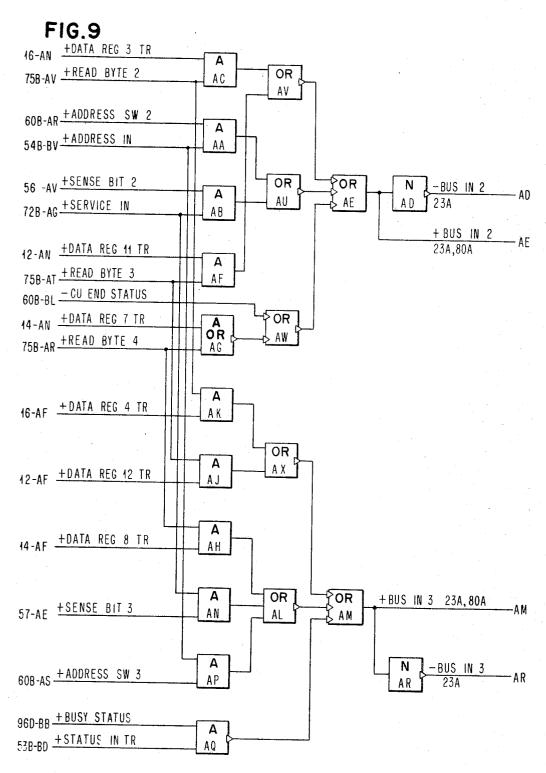

| Bus In 2 and 3.                                         | 9       |

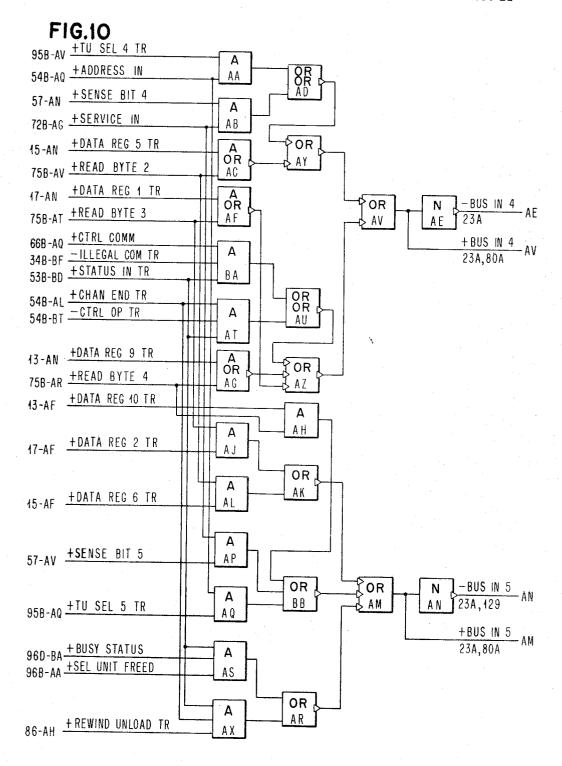

| Bus In 4 and 5                                          | 10      |

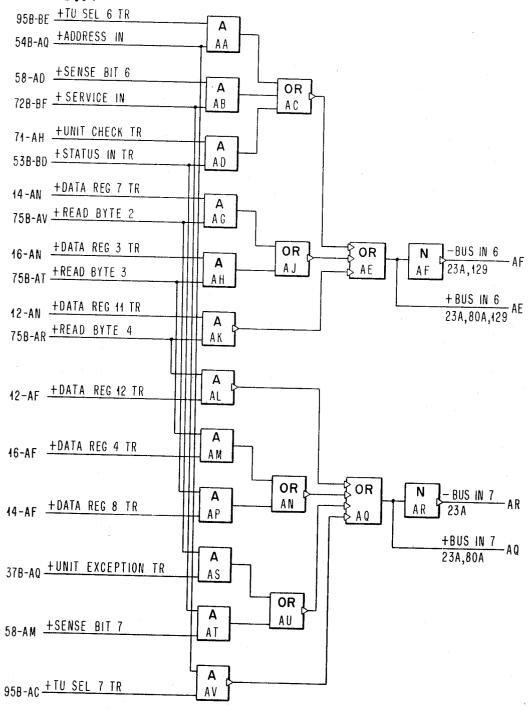

| Bus In 6 and 7                                          | 11      |

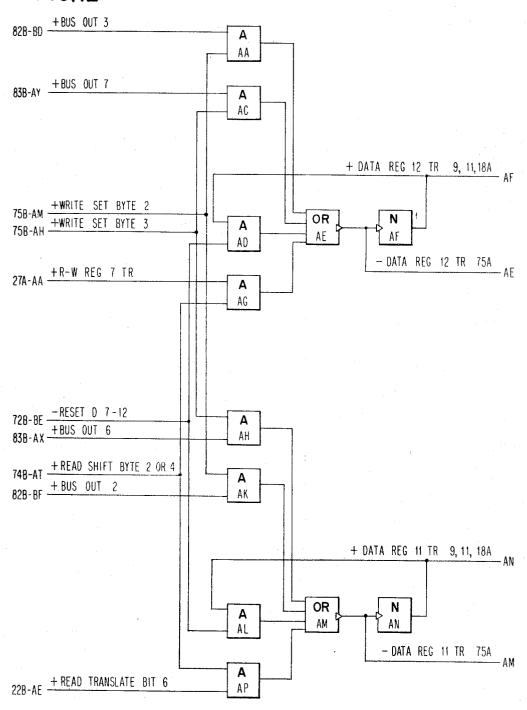

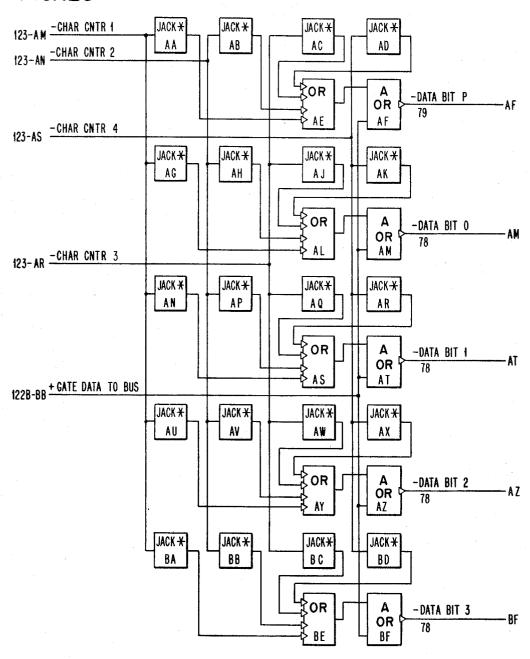

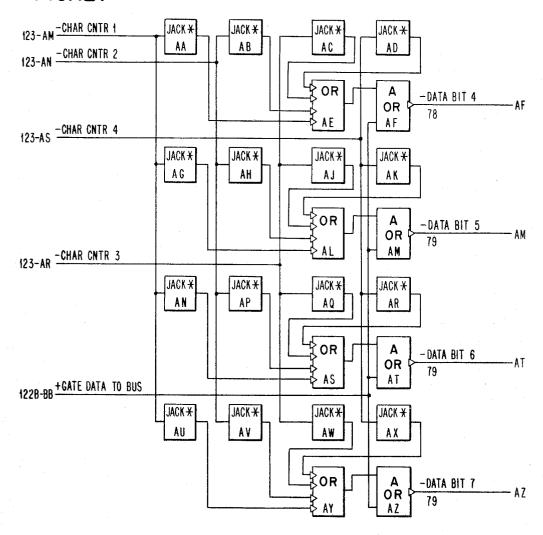

| Data Register Positions 12, 11                          | 12      |

| Data Register Positions 10, 9                           | 13      |

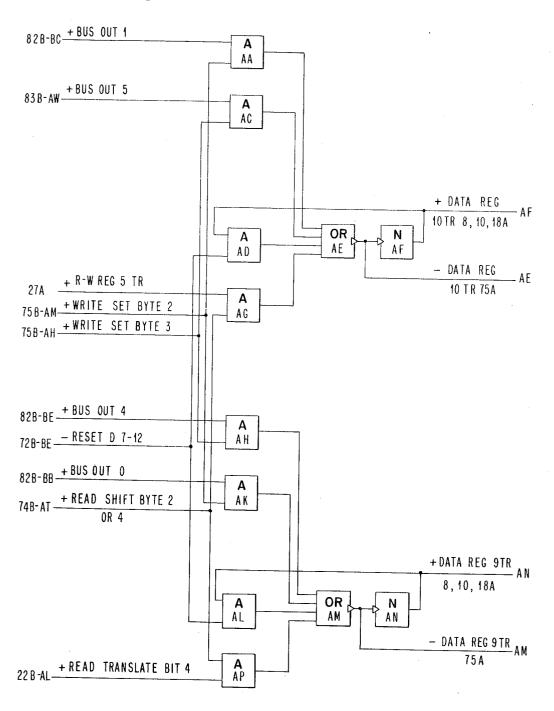

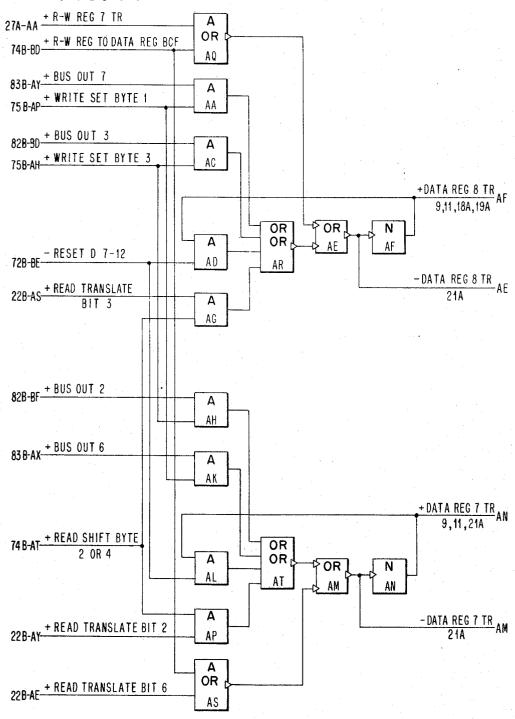

| Data Register Positions 8, 7                            | 14      |

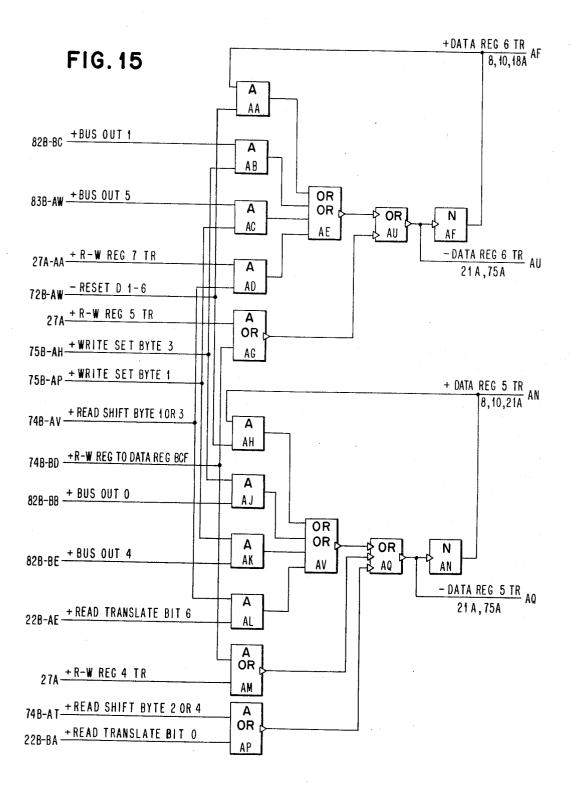

| Data Register Positions 6, 5                            | 15      |

| Data Register Positions 4, 3                            | 16      |

| Data Register Positions 2, 1                            | 17      |

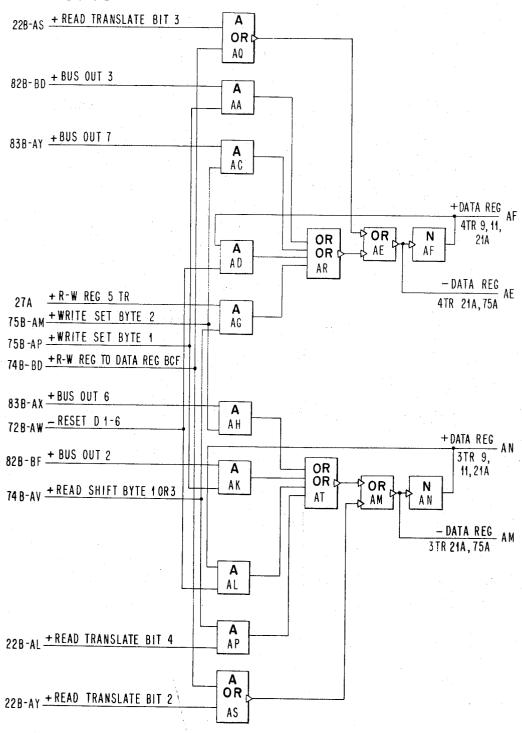

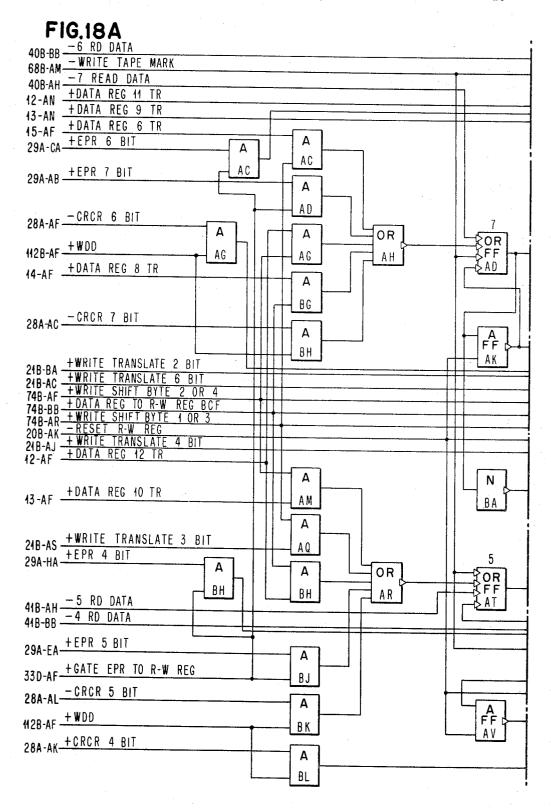

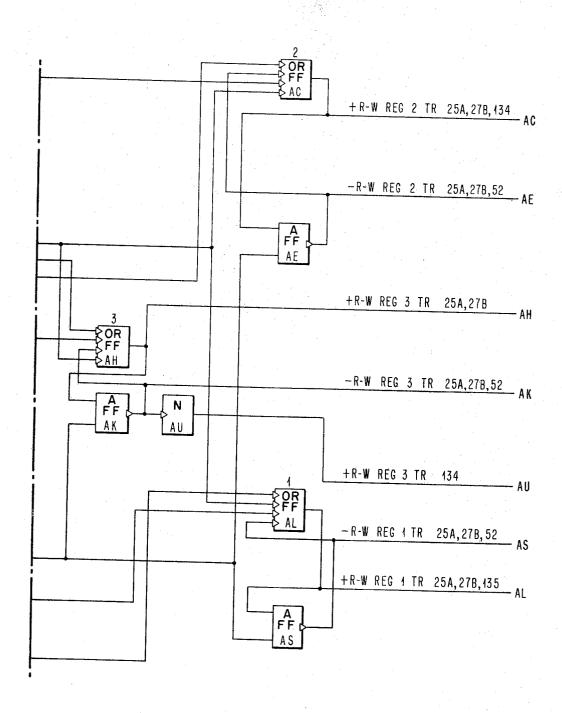

| R-W (Read-Write) Register Positions 4, 5, 6, 7          | 18A & B |

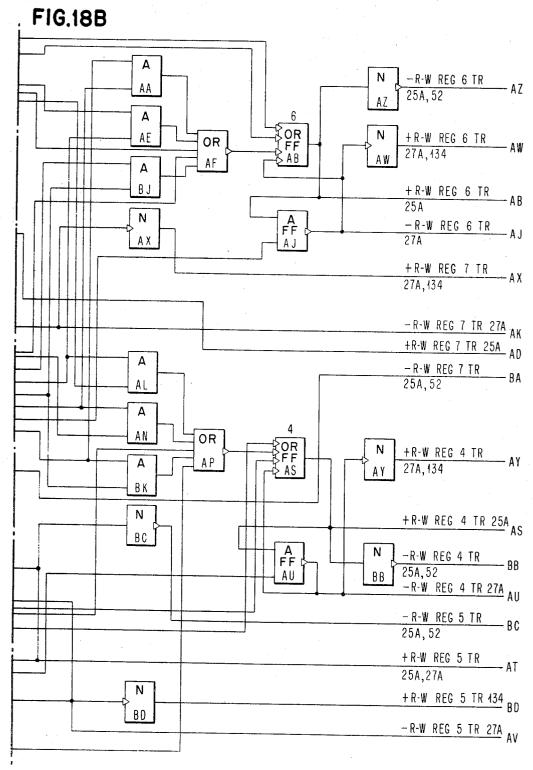

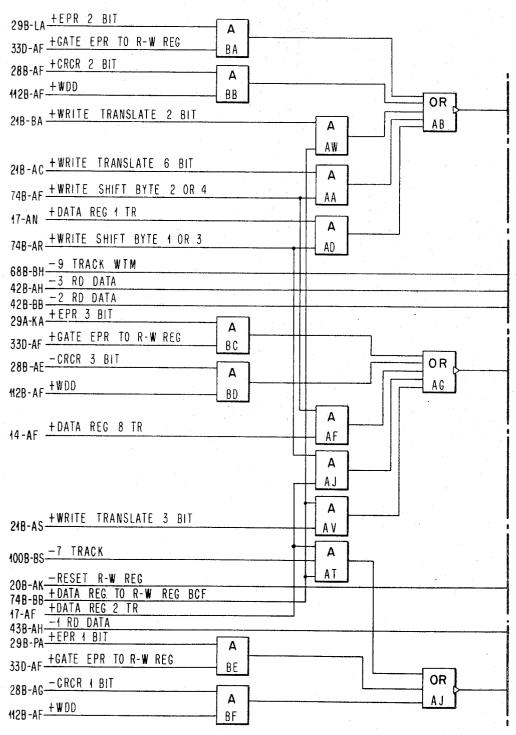

| R-W Register Positions 1, 2, 3                          | 19A & B |

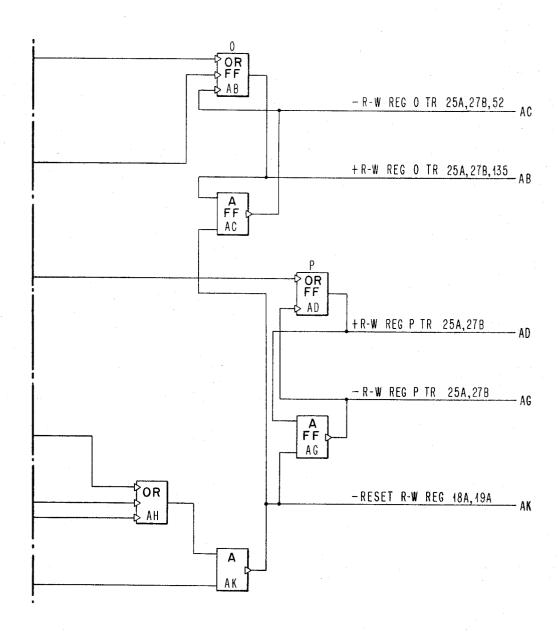

| R-W Register Positions OP                               | 20A & B |

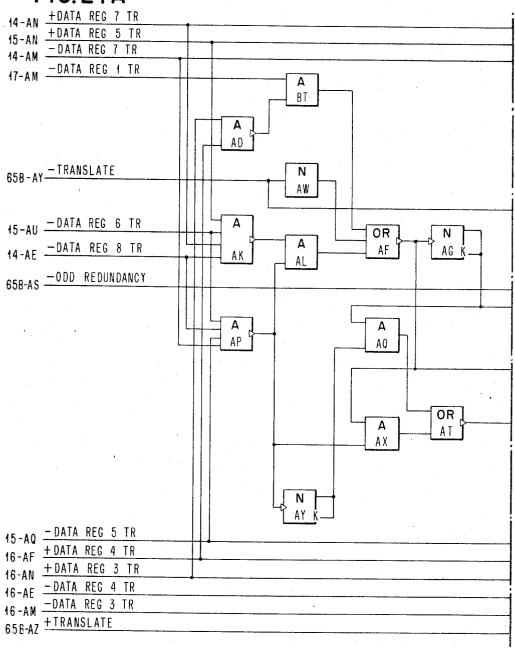

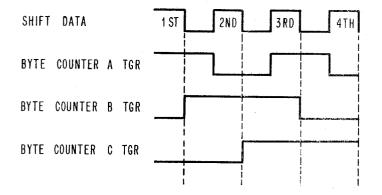

| 8 Bit to BCD (Binary Coded Decimal) Translator 2, 3, 4, | 21A & B |

| 6, Bits.                                                |         |

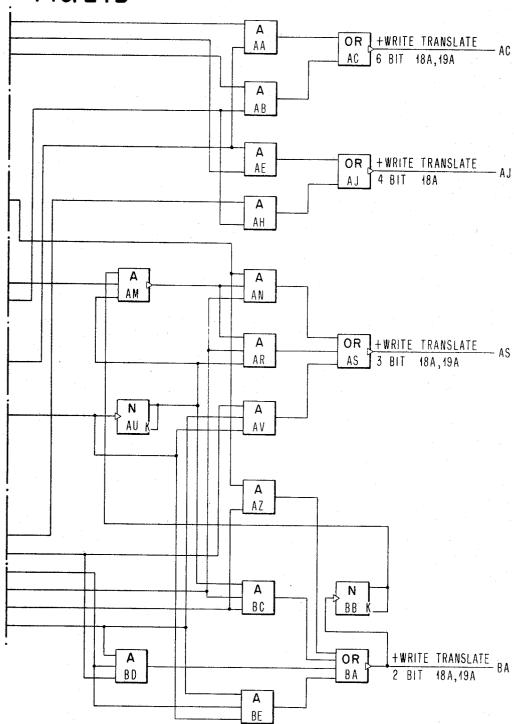

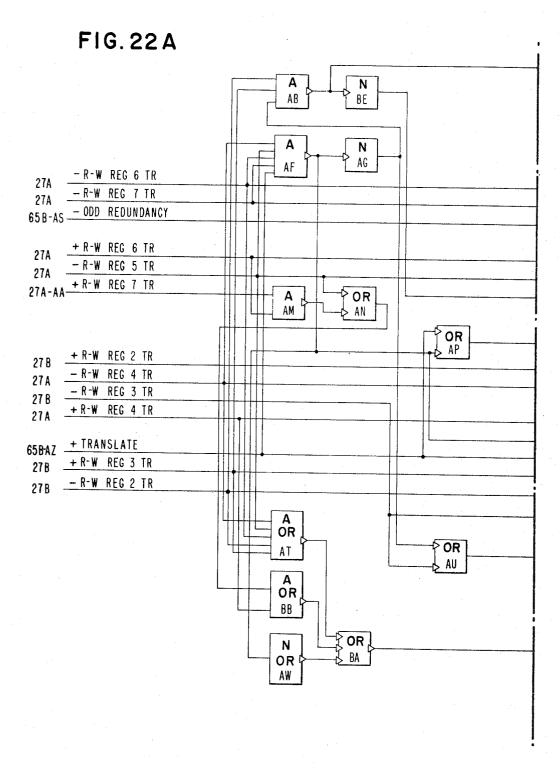

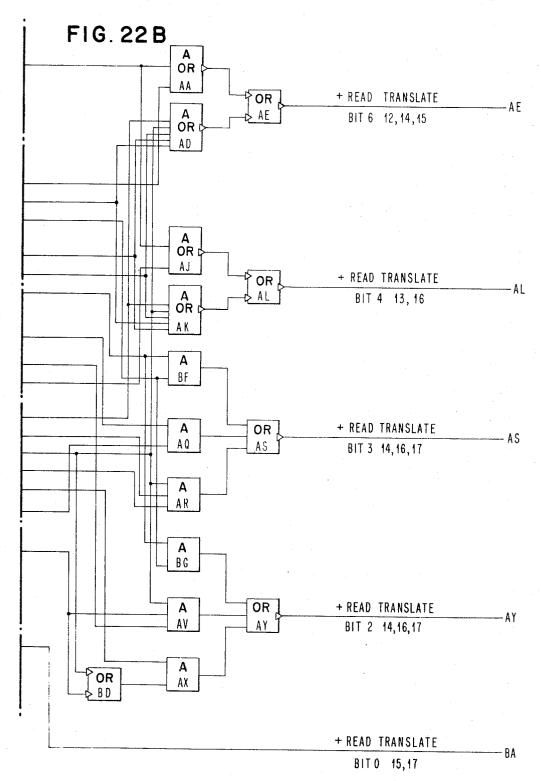

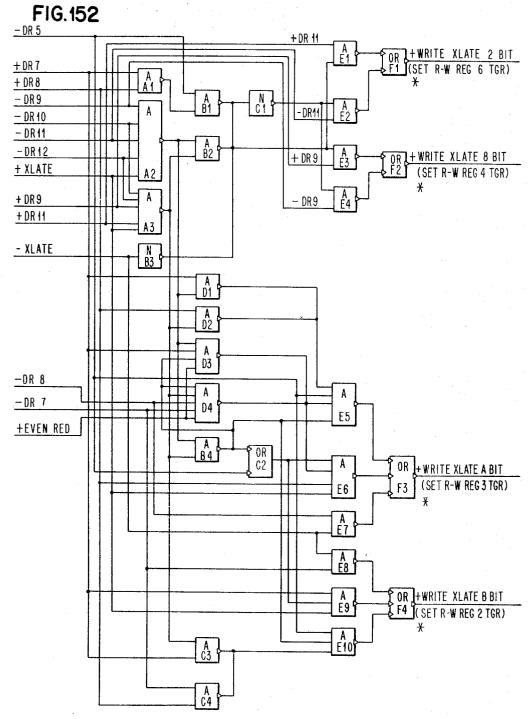

| BCD to 8 Bit Translator 0, 2, 3, 4, 6 Bits              | 22A & B |

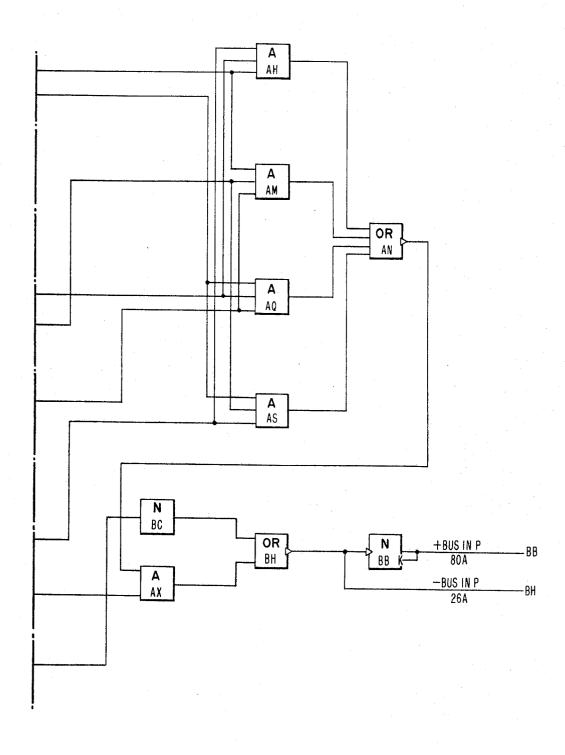

| Bus In P                                                | 23A & B |

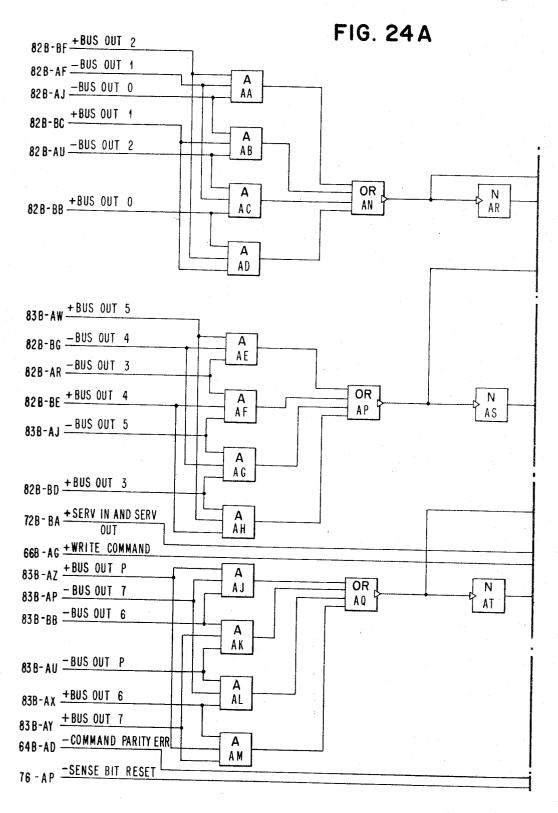

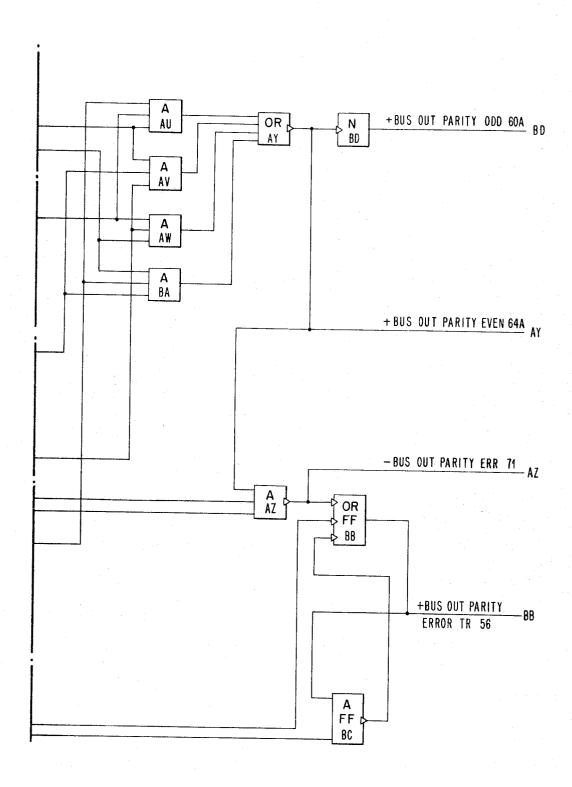

| Bus Out Parity                                          | 24A & B |

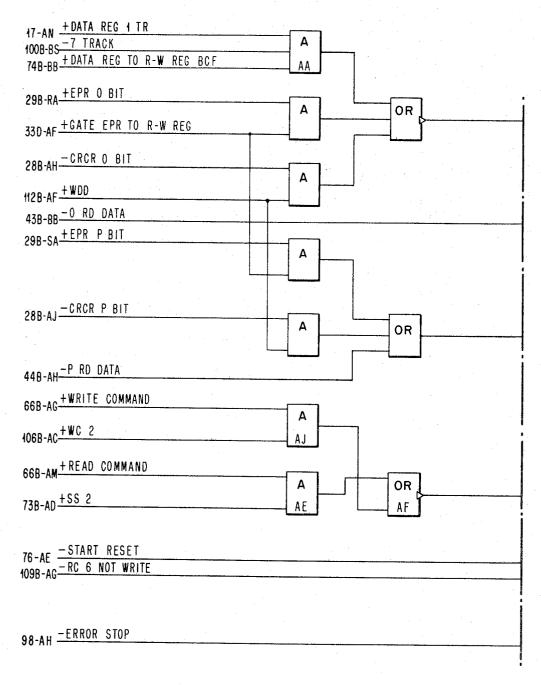

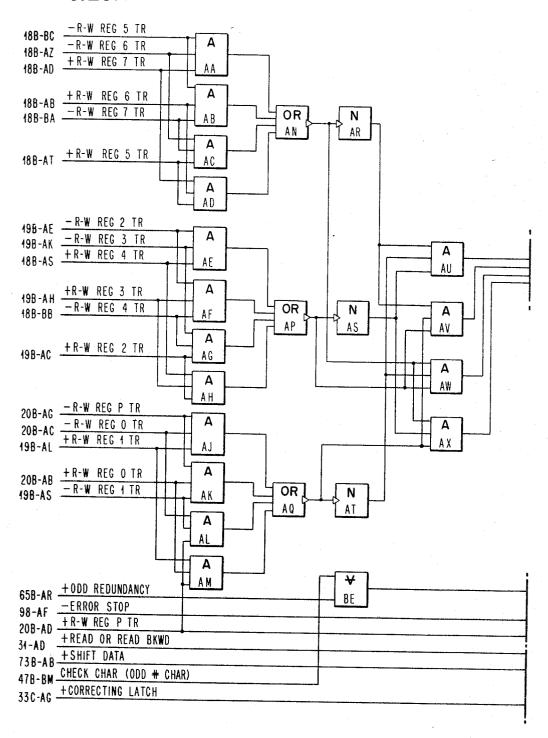

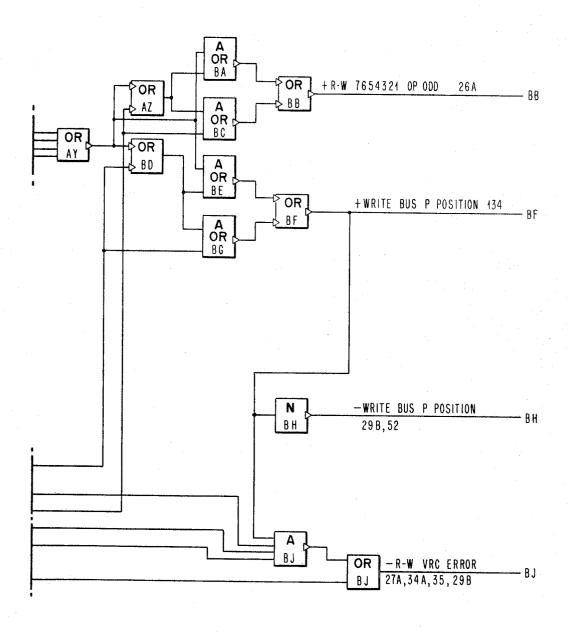

| R-W VRC (Vertical Redundancy Check)                     | 25A & B |

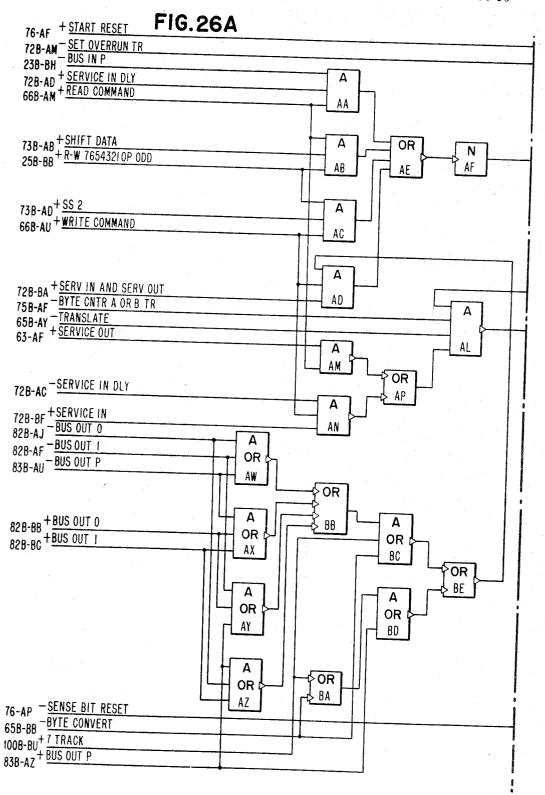

| C Compare Data Check and Overrun                        | 26A & B |

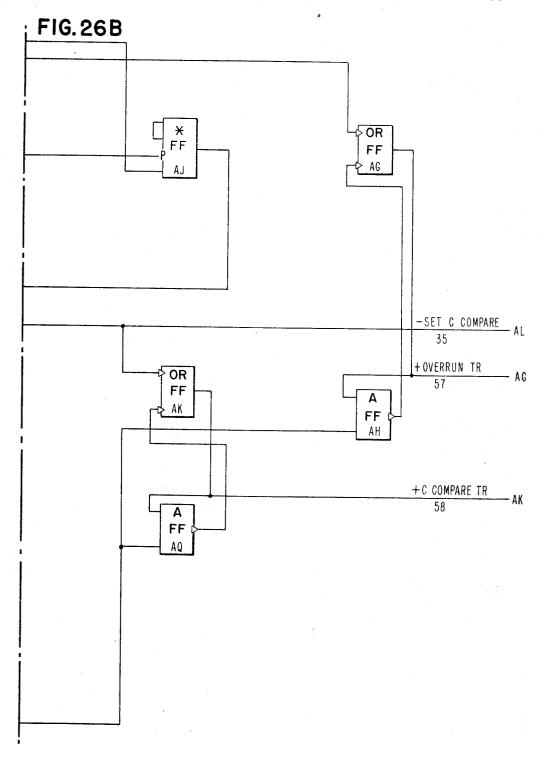

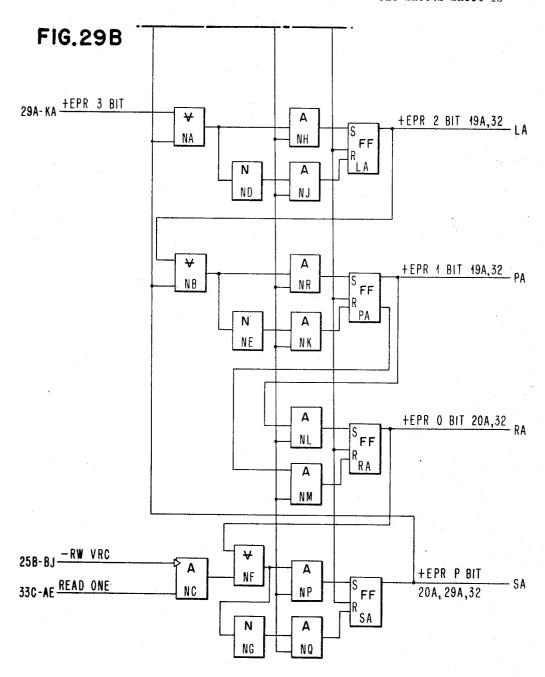

| R-W Correction Gate Bits 7-4                            | 27A     |

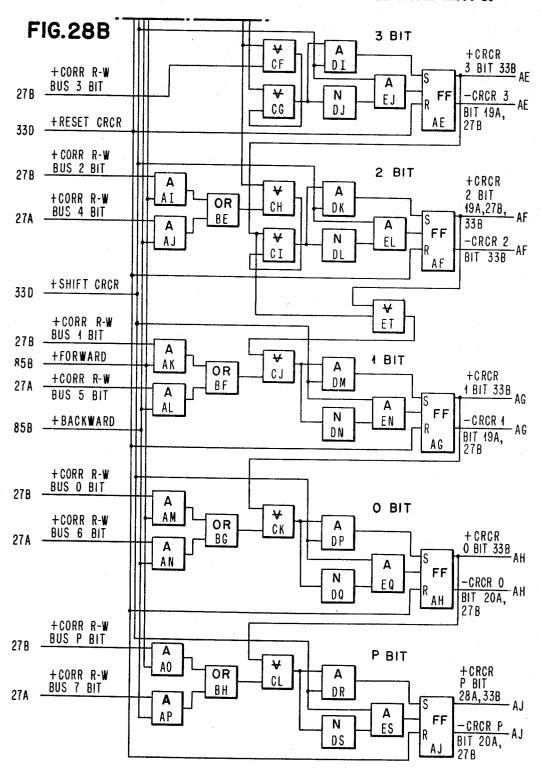

| R-W Correction Gate Bits 3. P.                          | 27B     |

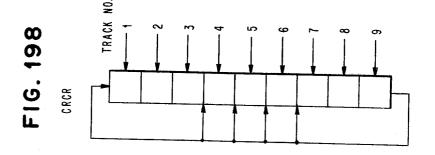

| CRCR (Cyclic Redundancy Check Register) Bits 7-4        | 28A     |

| CRCR Bits 3-P                                           | 28B     |

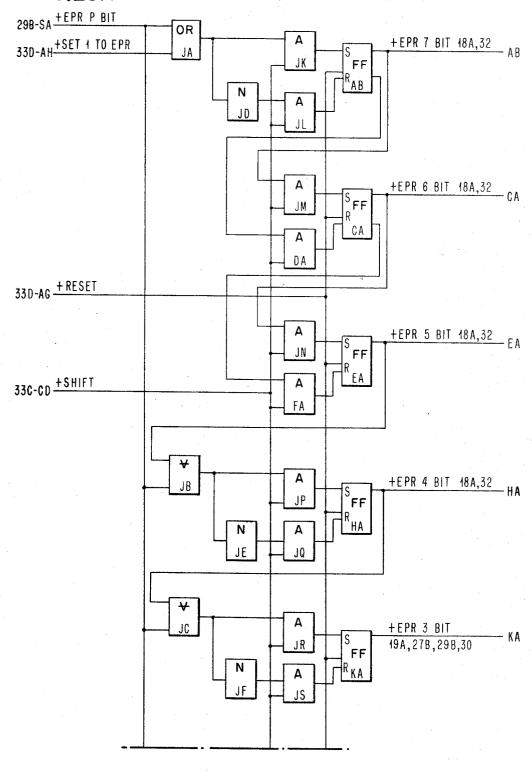

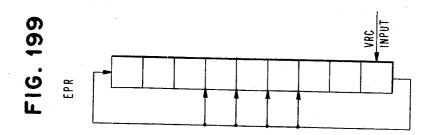

| EPR (Error Pattern Register) Bits 7-3                   | 29 A    |

| EPR Bits 2-P                                            | 29B,    |

|                                                         |         |

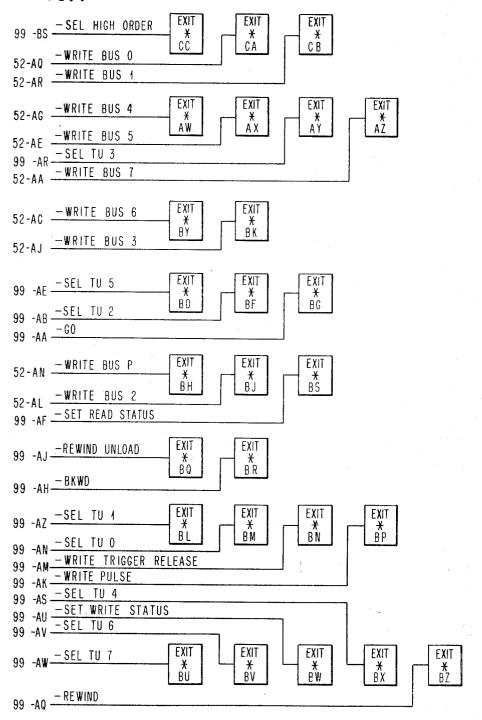

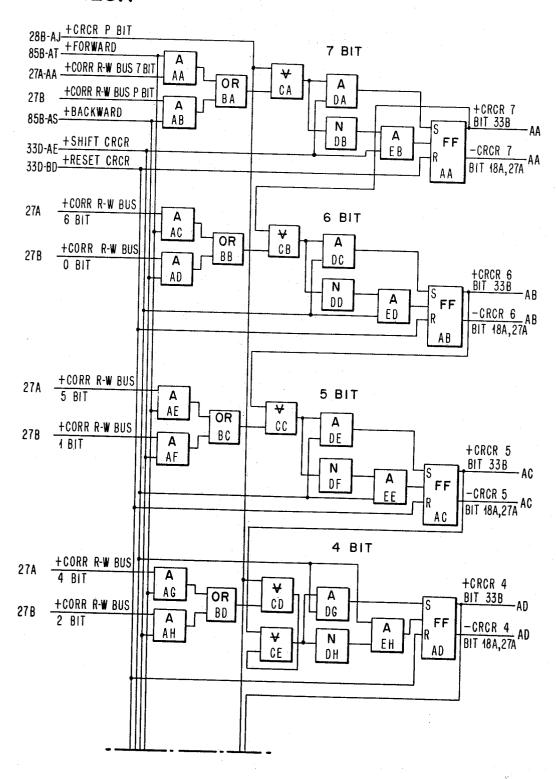

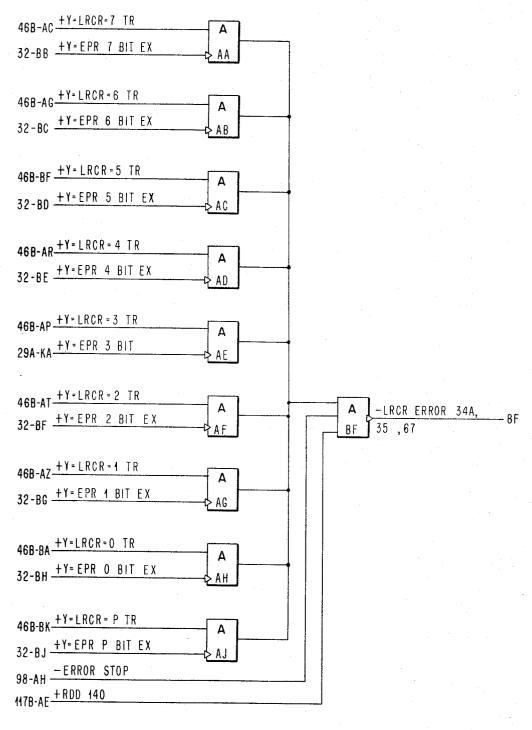

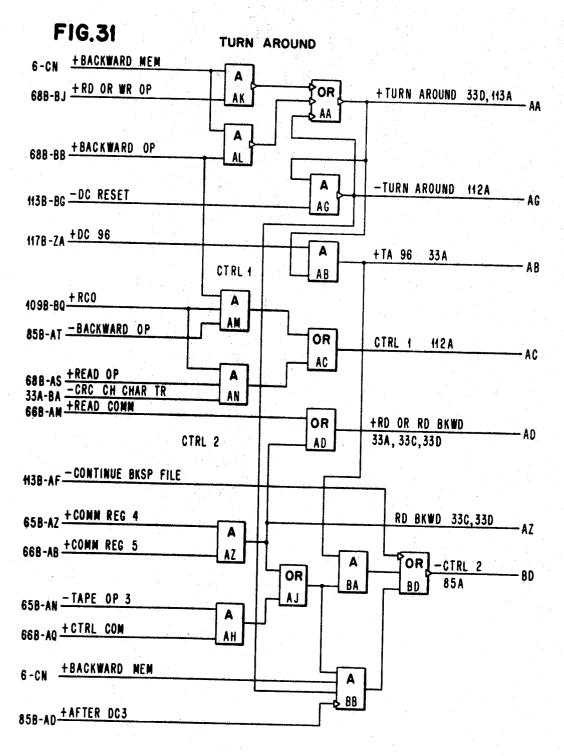

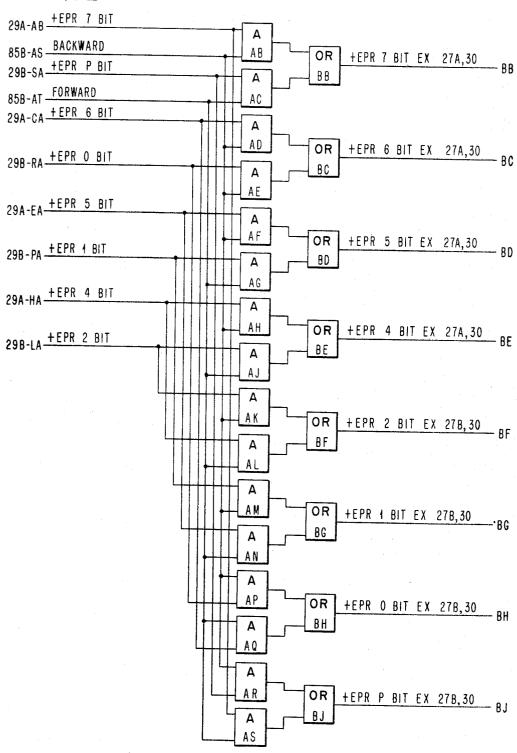

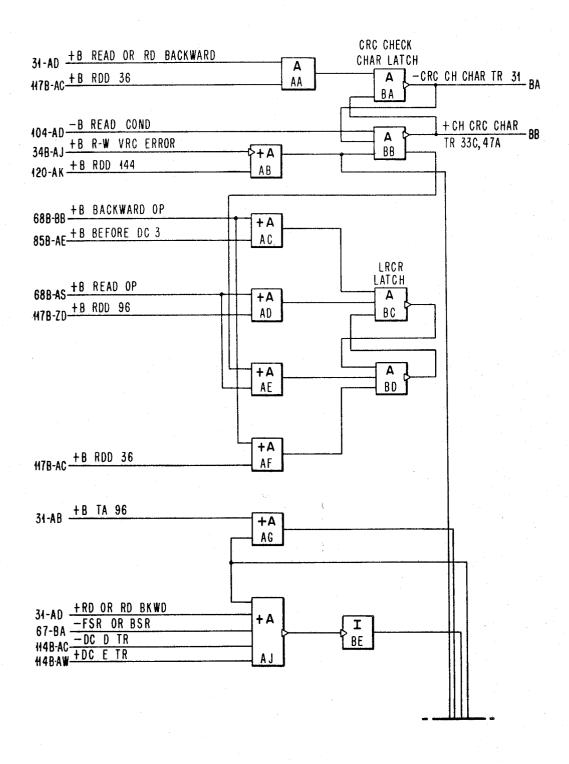

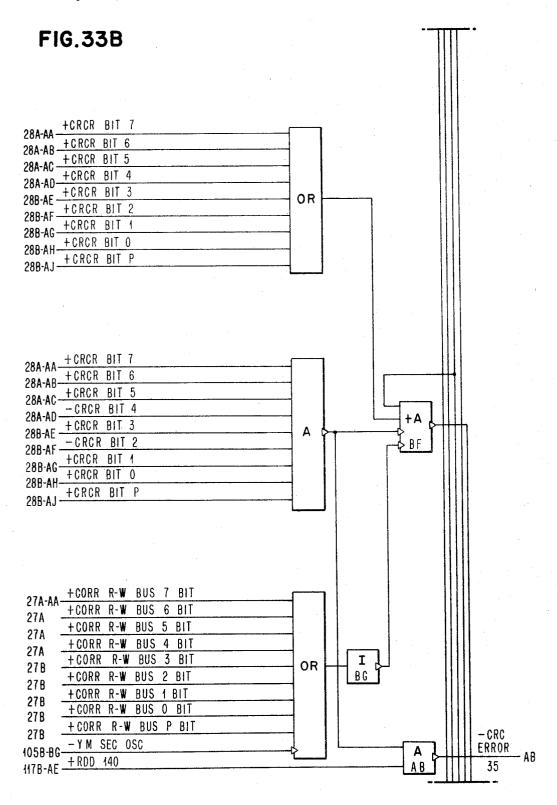

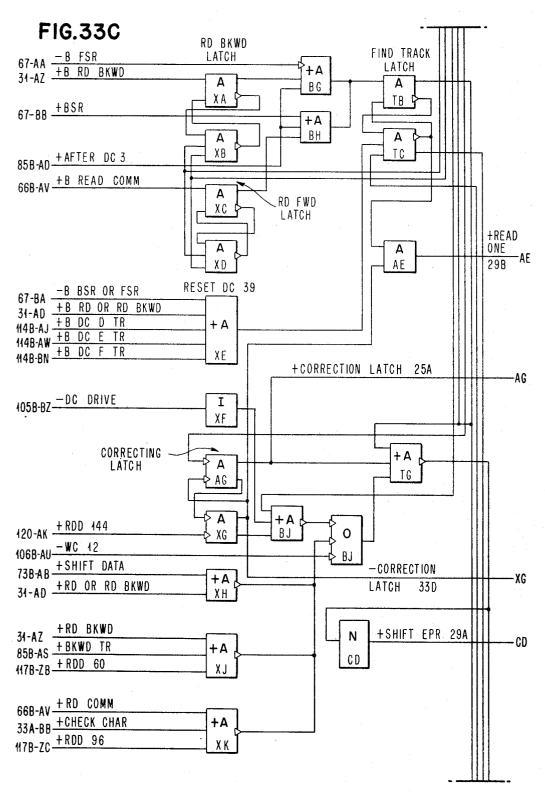

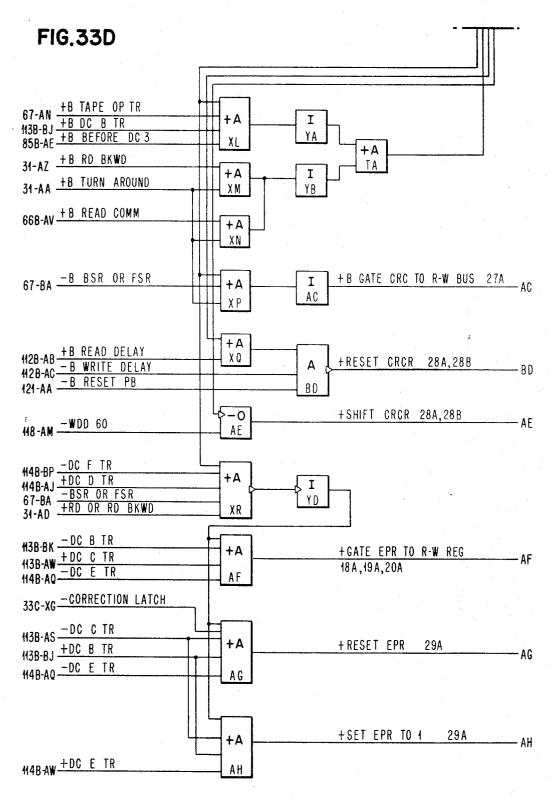

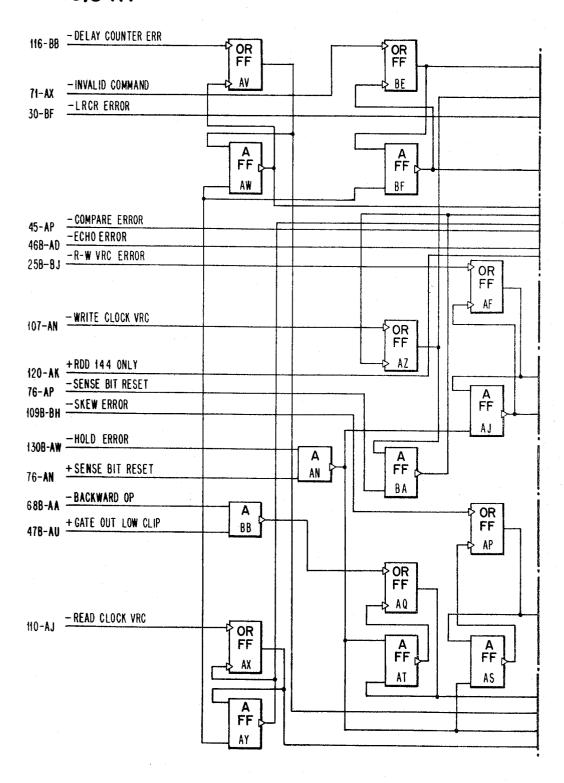

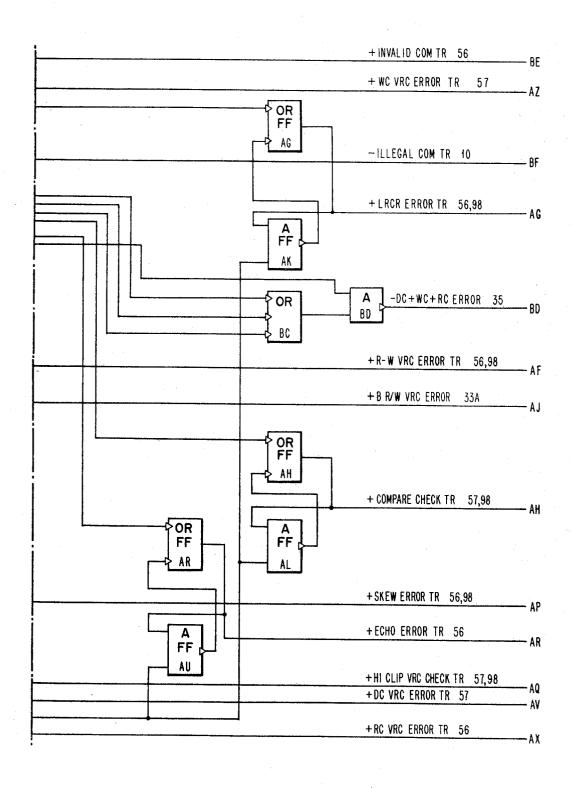

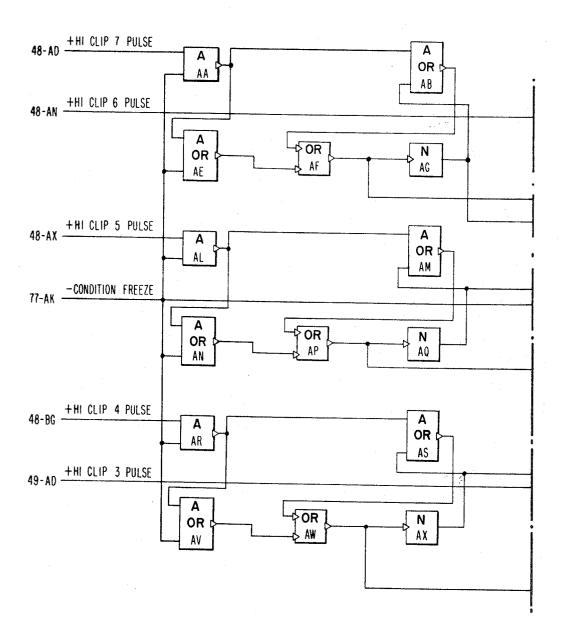

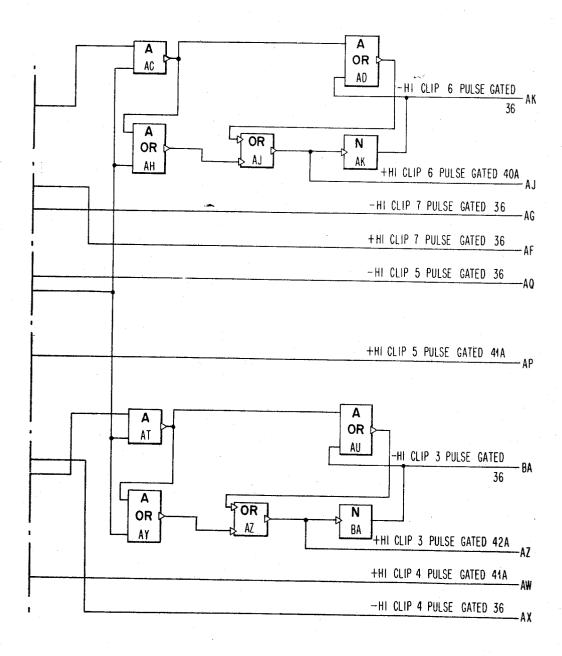

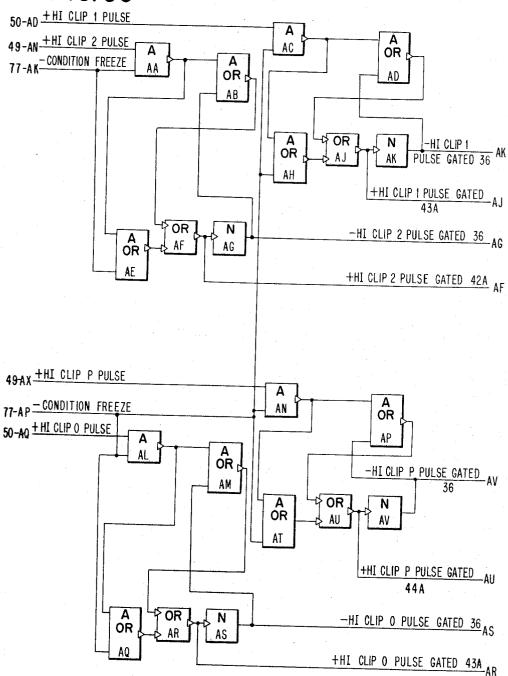

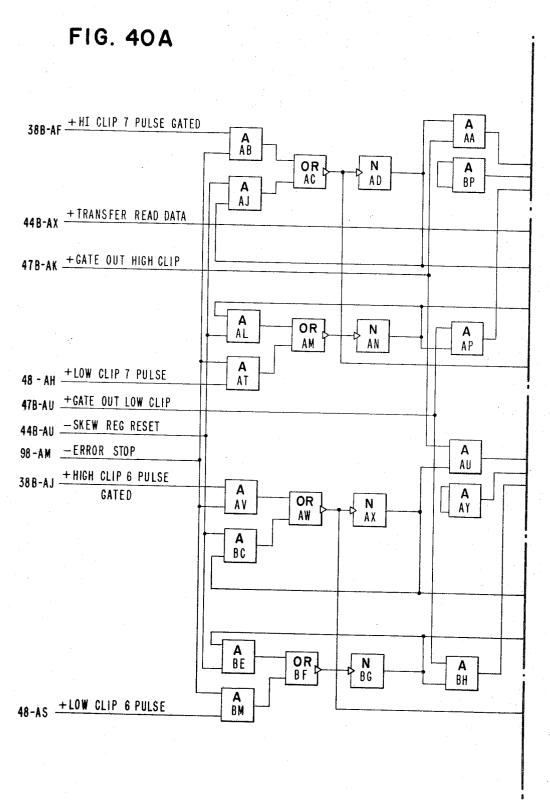

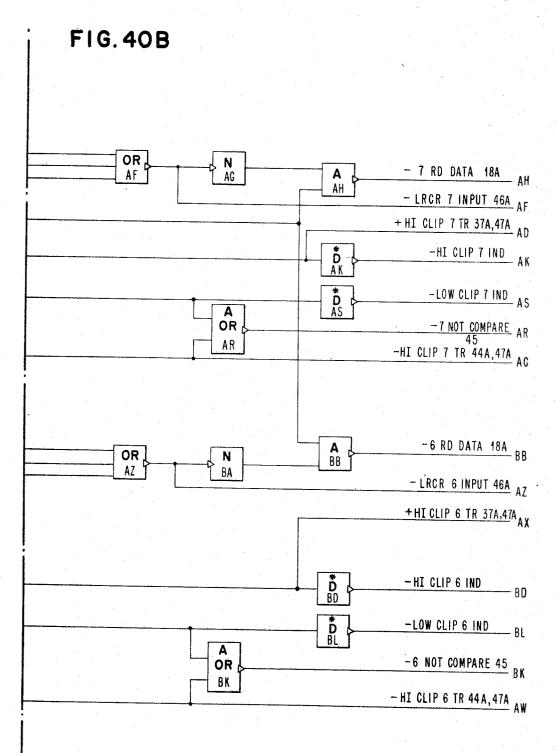

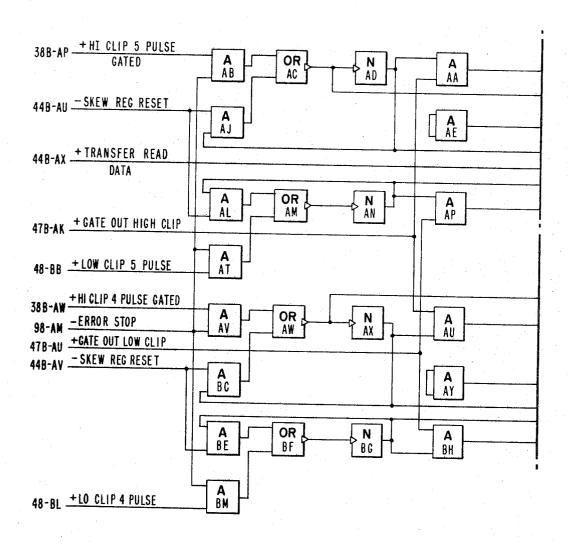

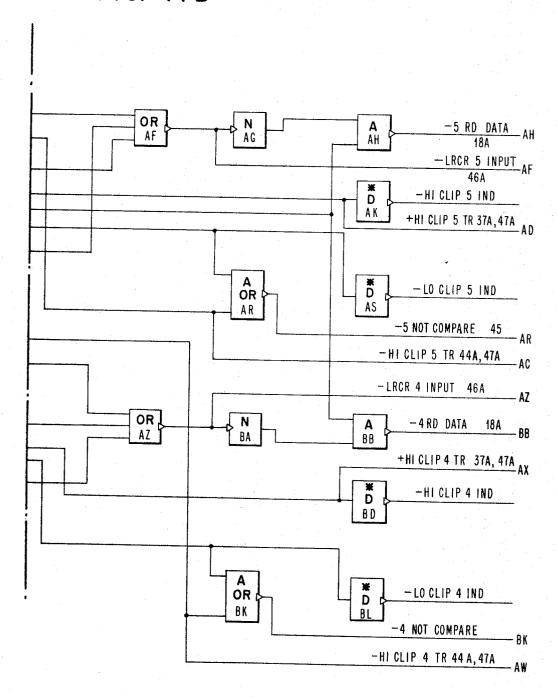

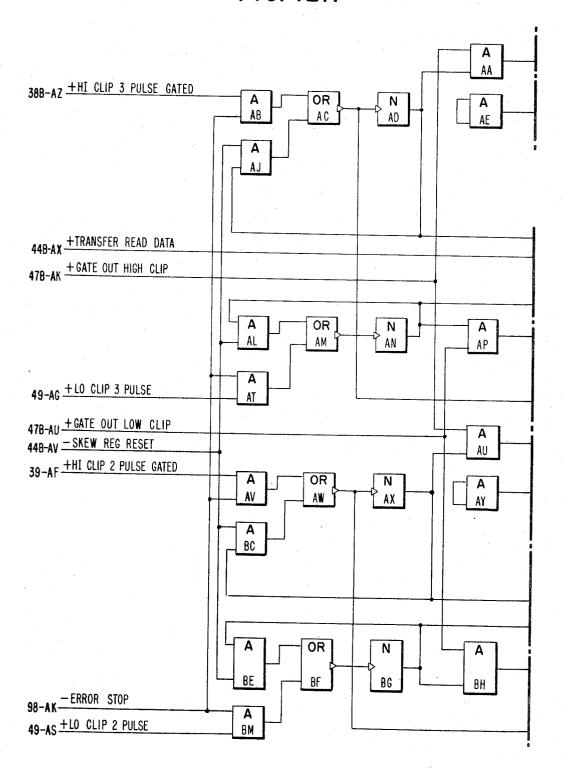

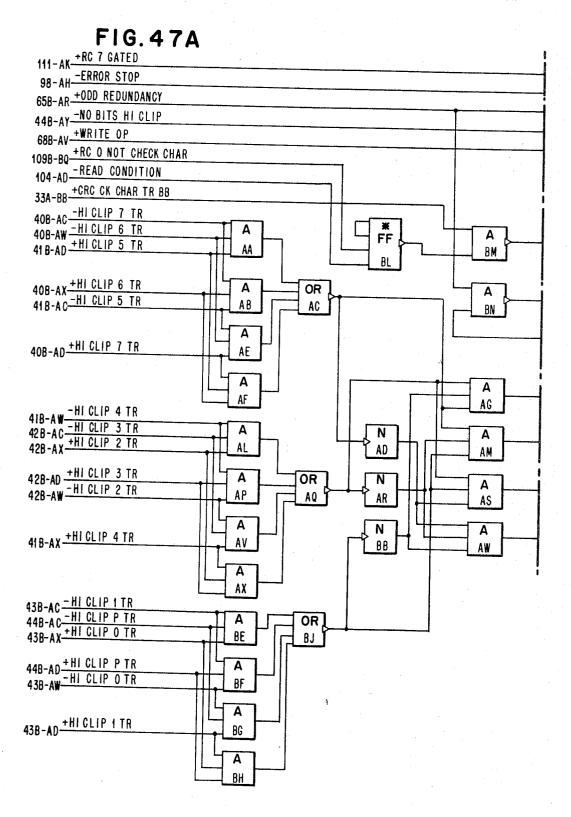

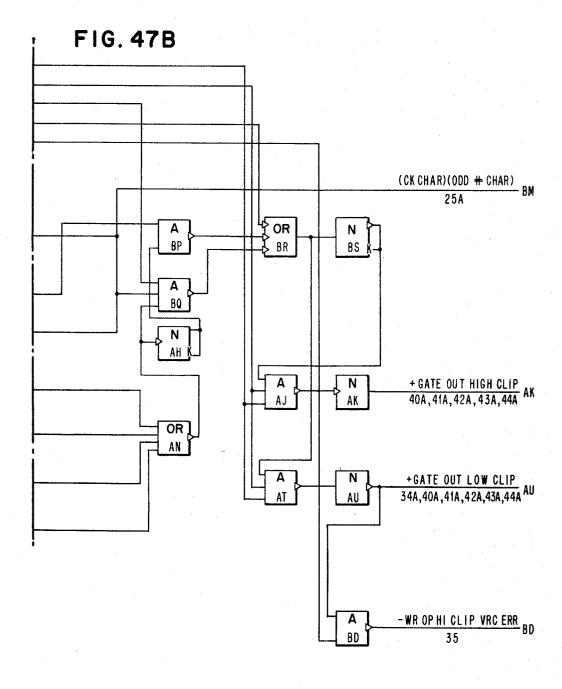

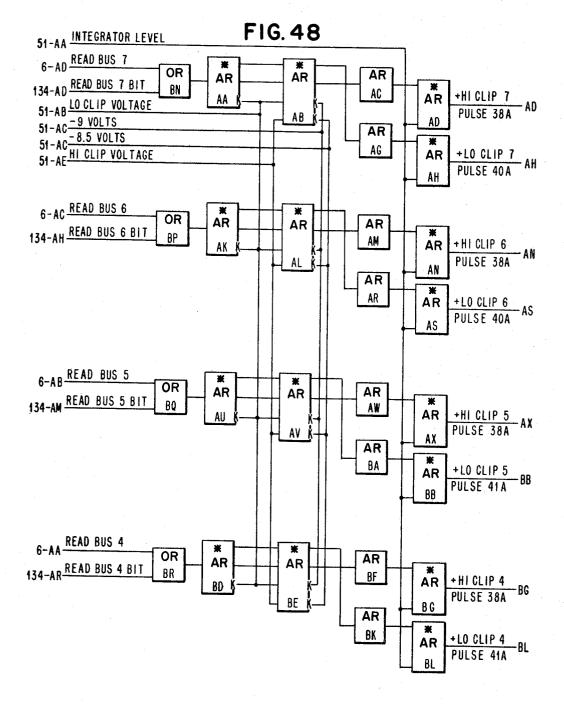

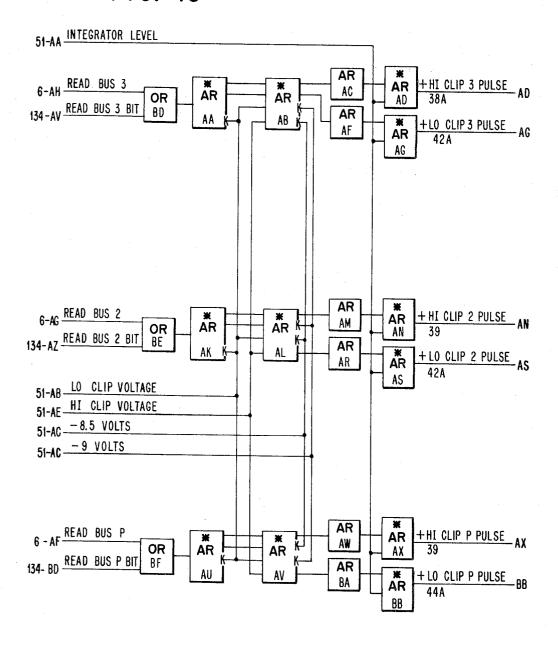

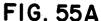

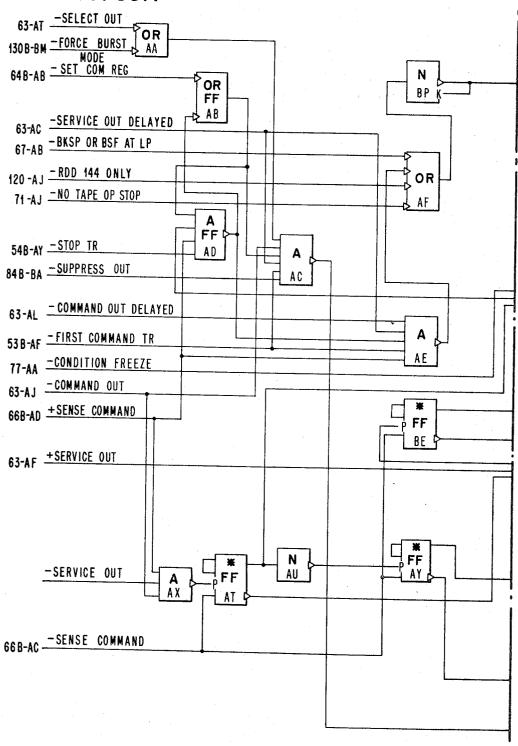

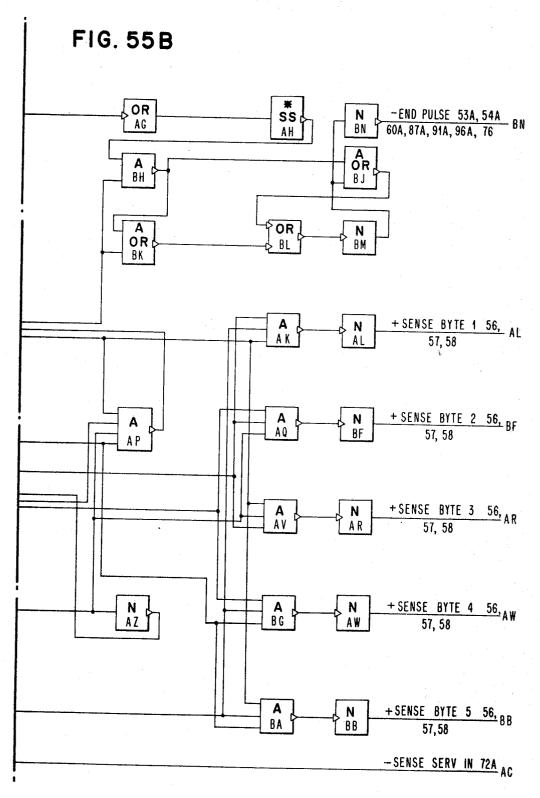

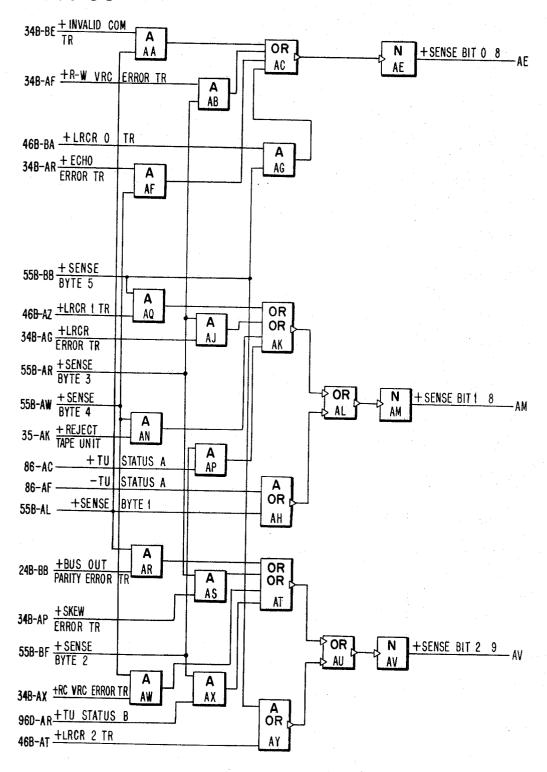

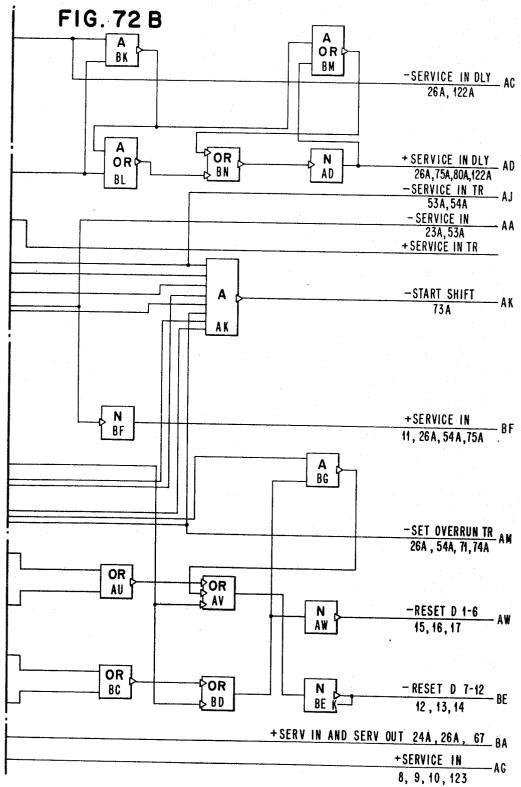

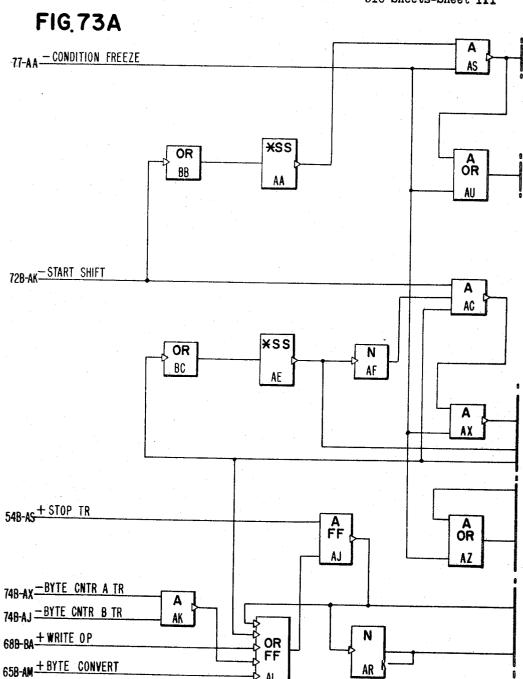

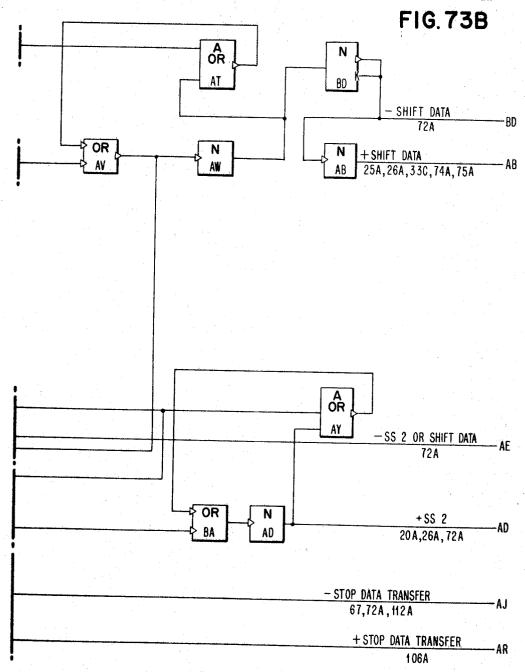

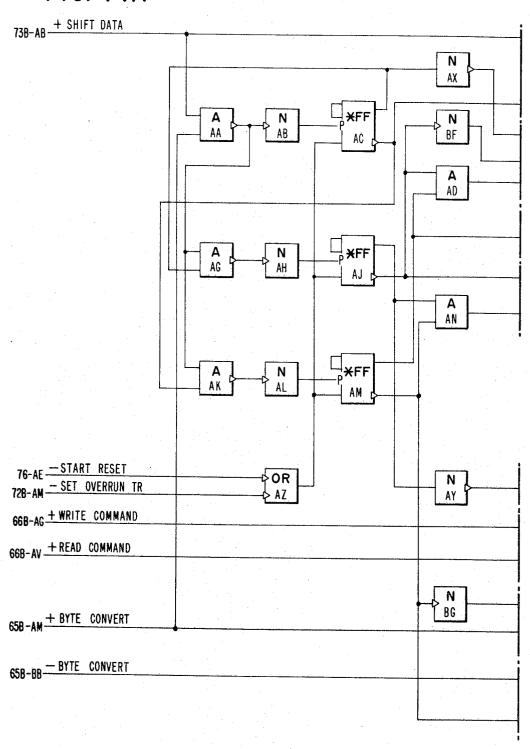

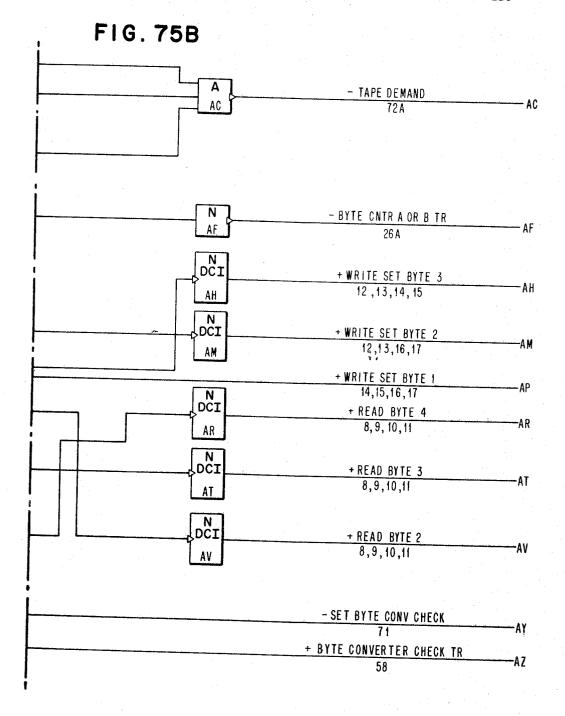

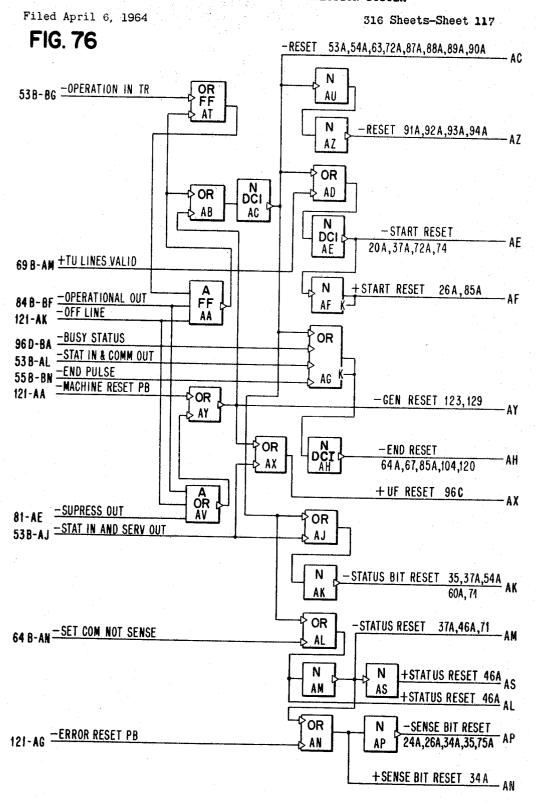

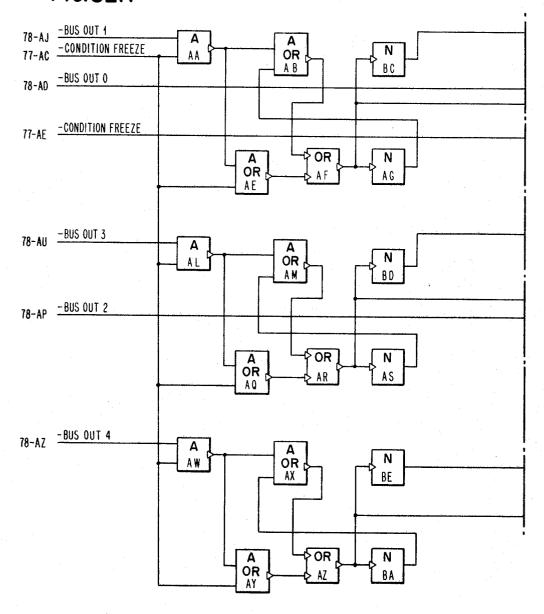

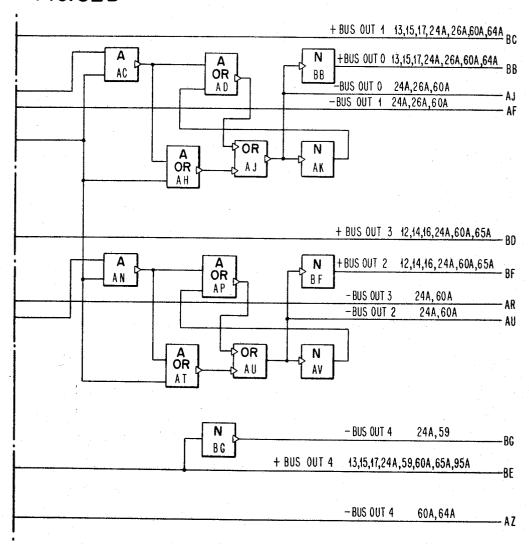

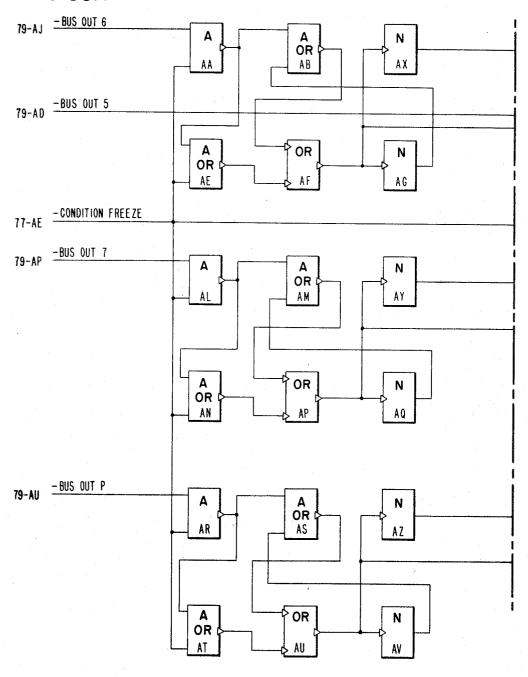

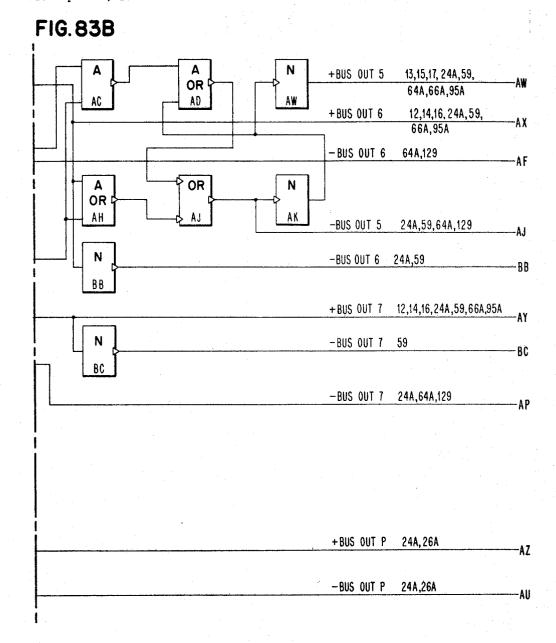

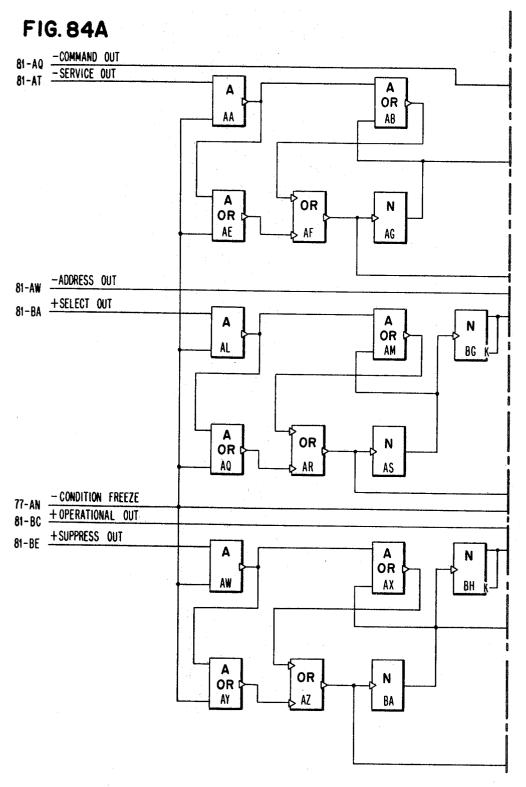

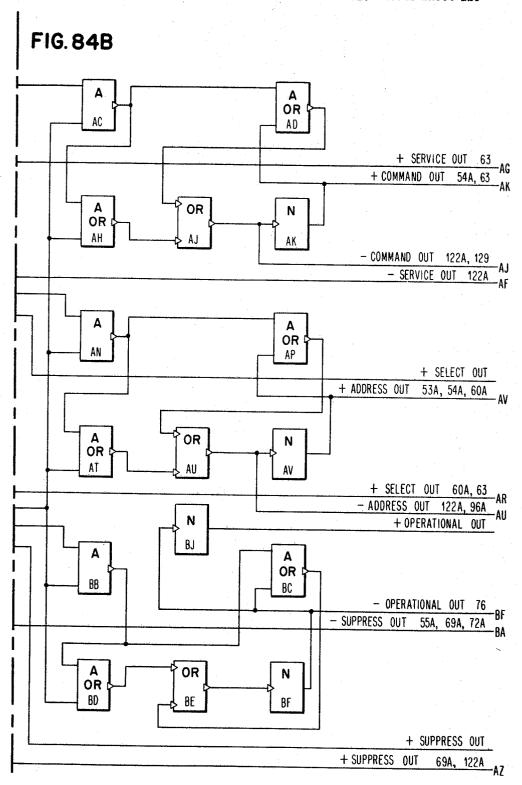

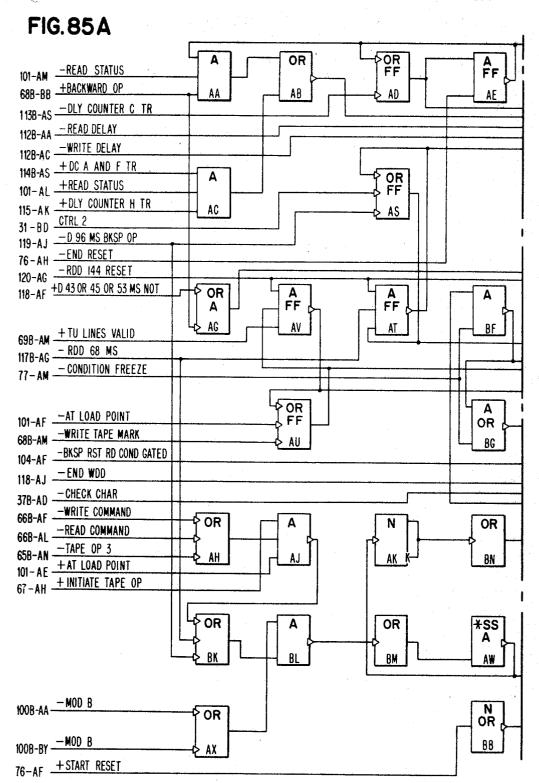

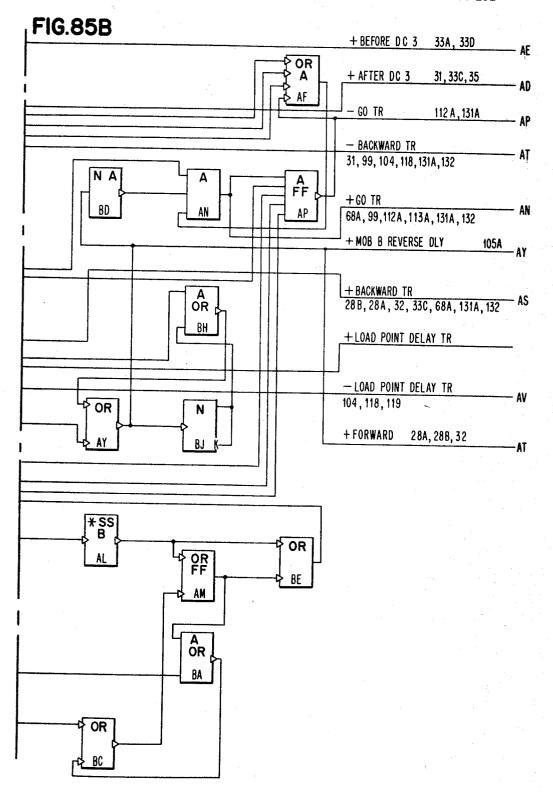

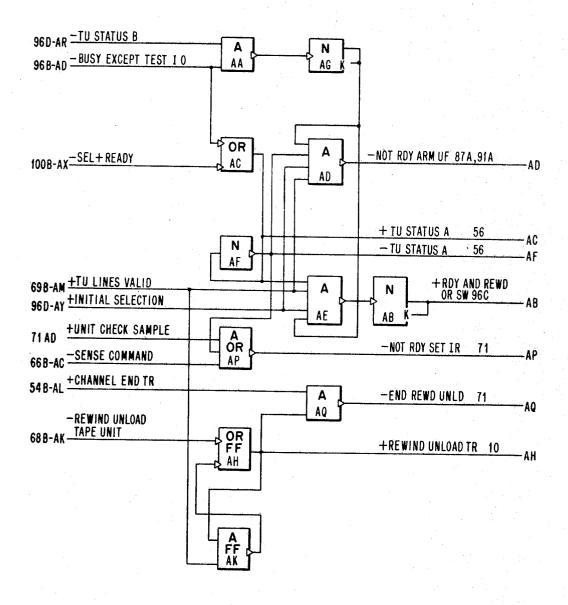

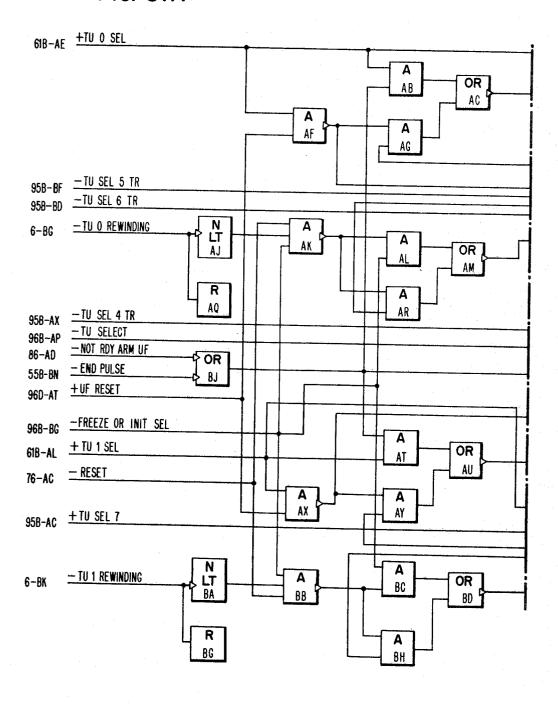

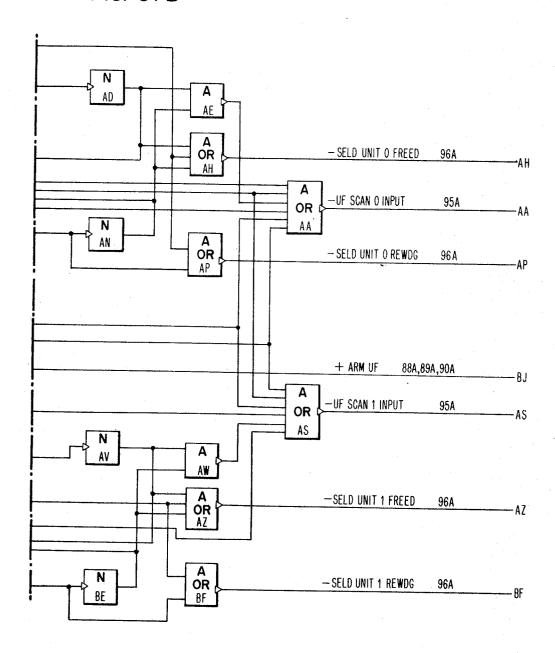

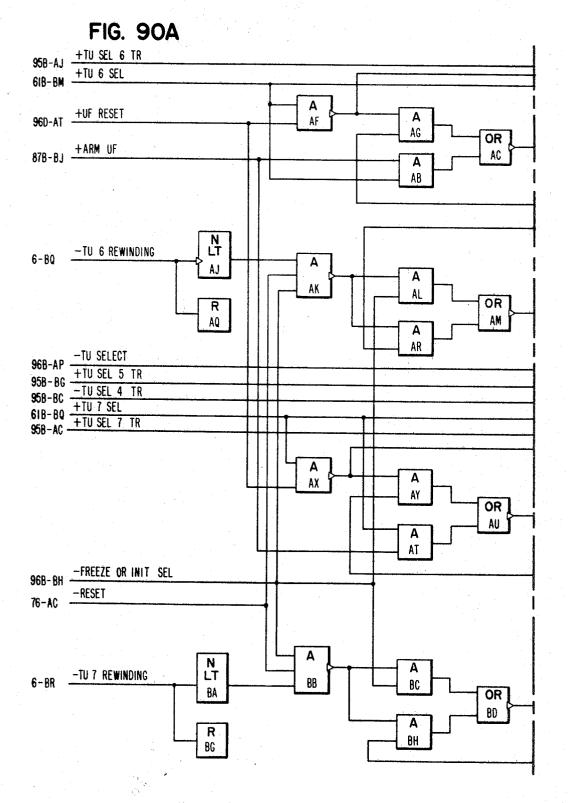

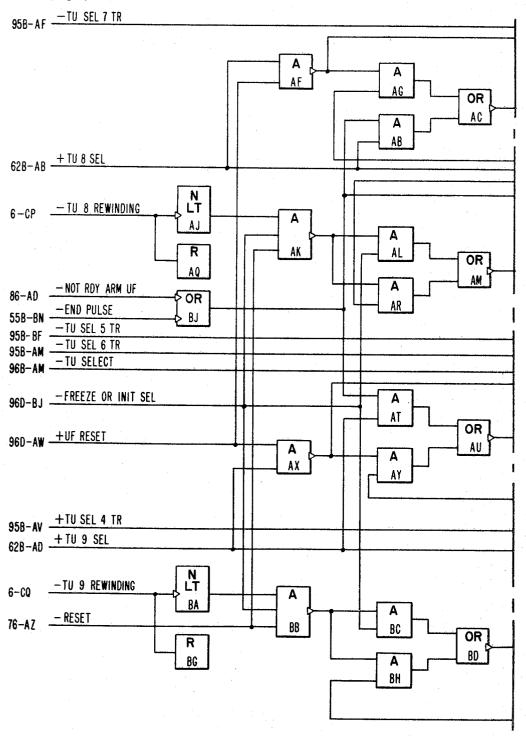

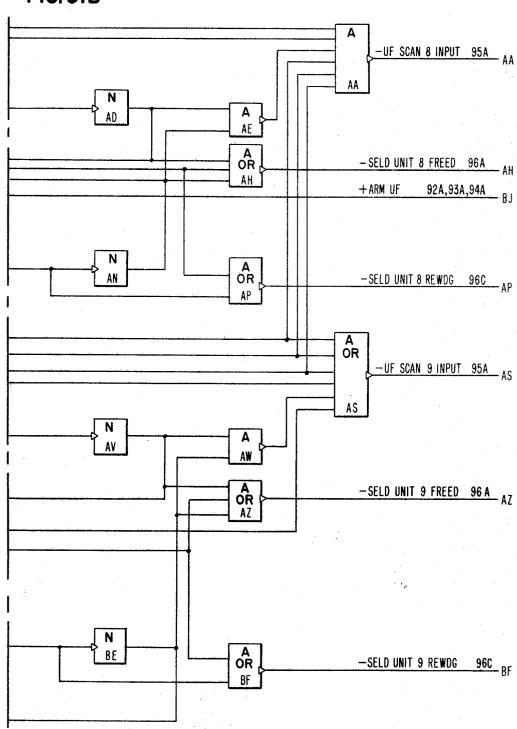

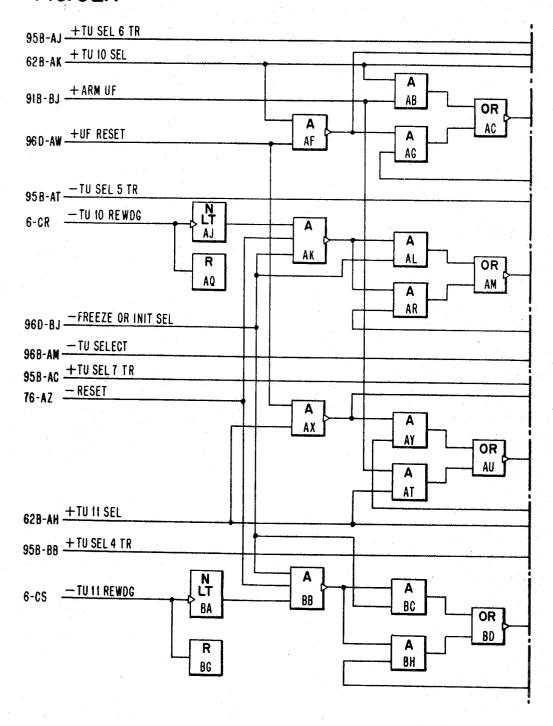

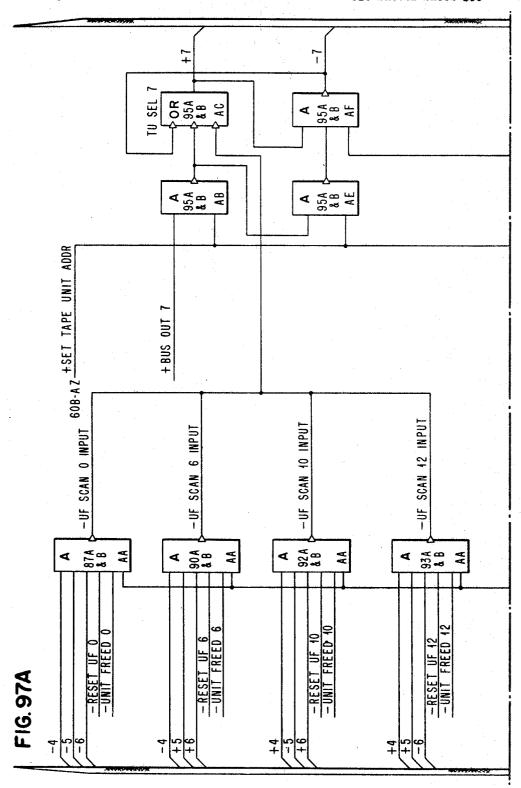

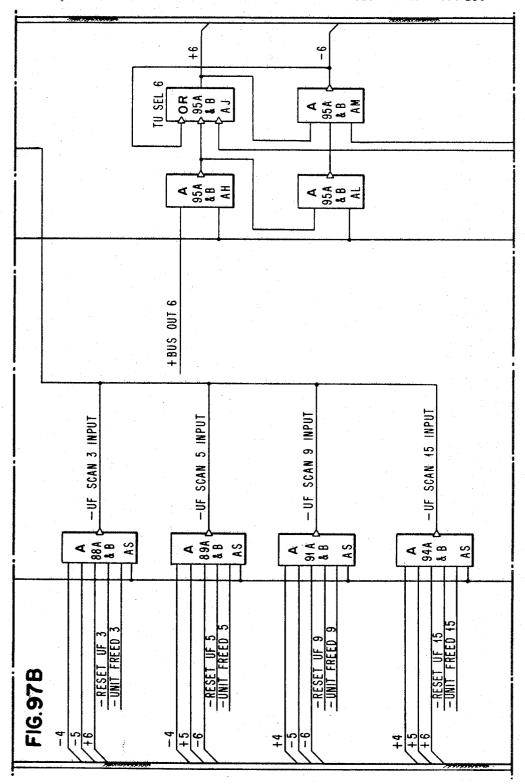

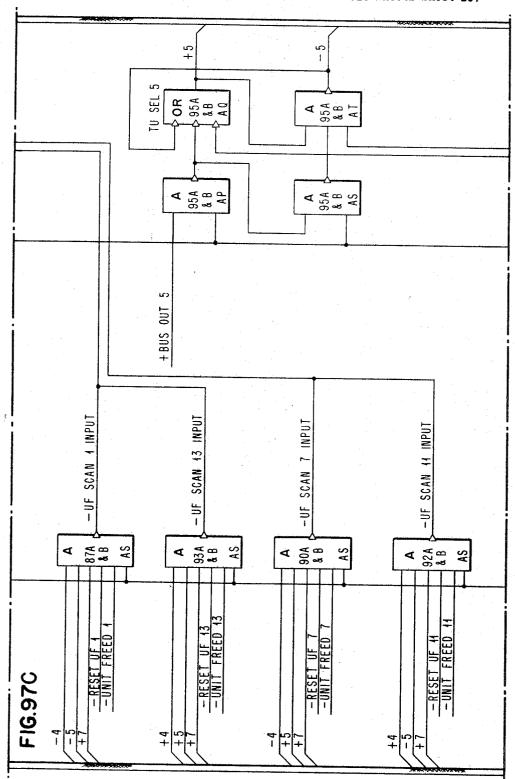

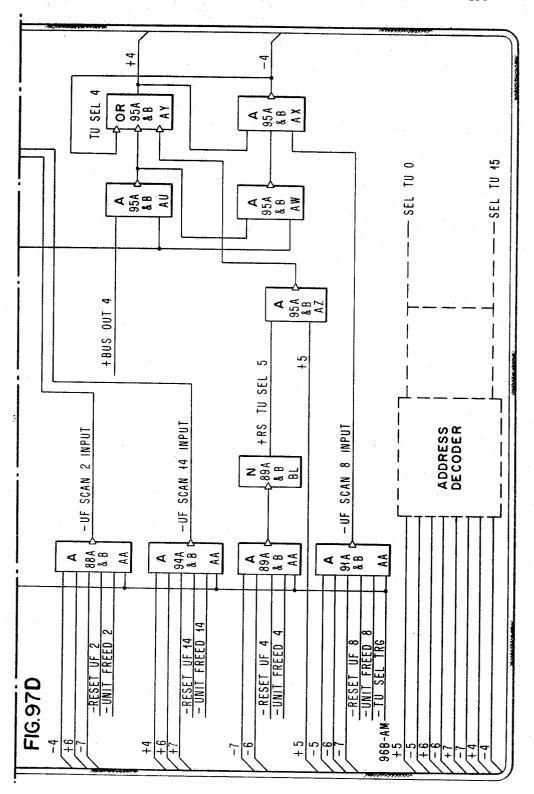

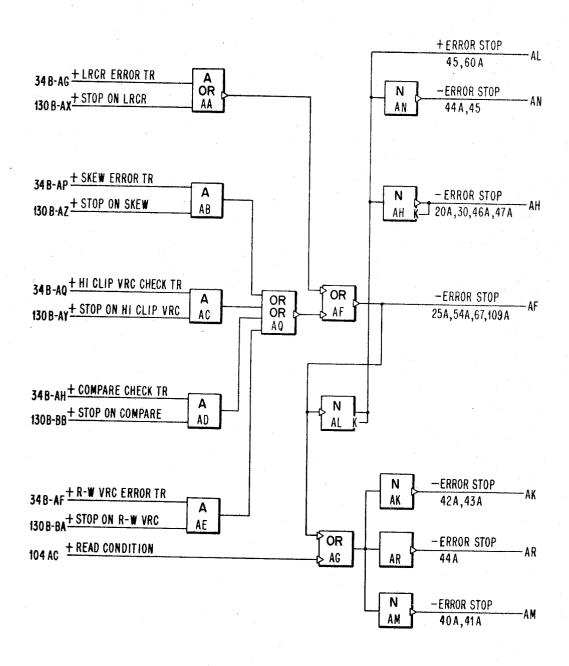

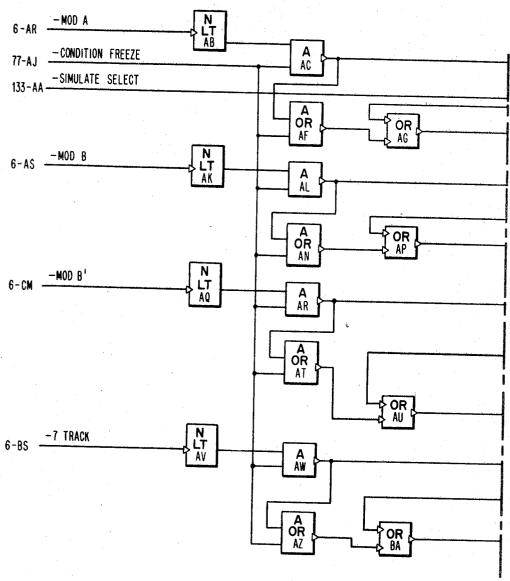

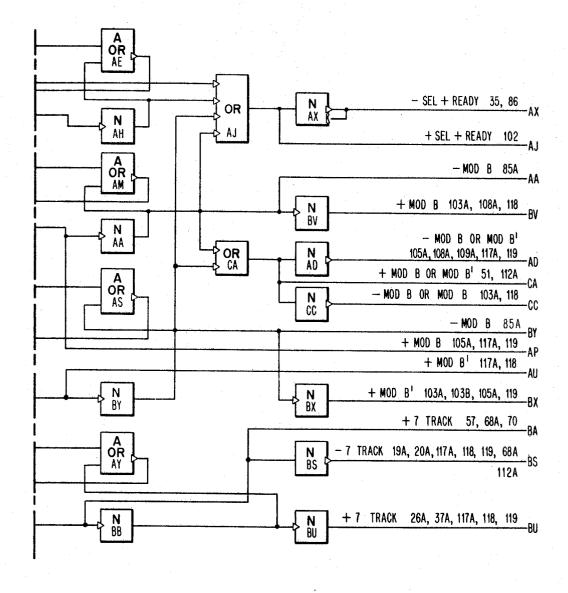

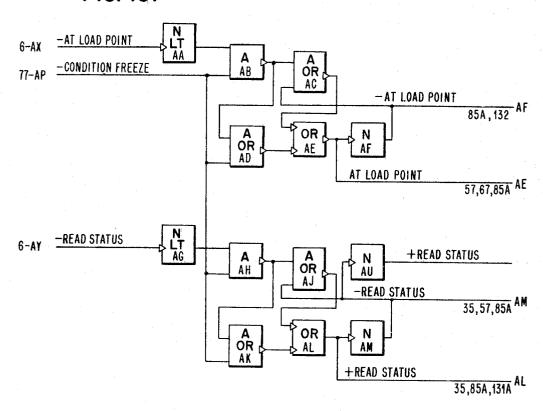

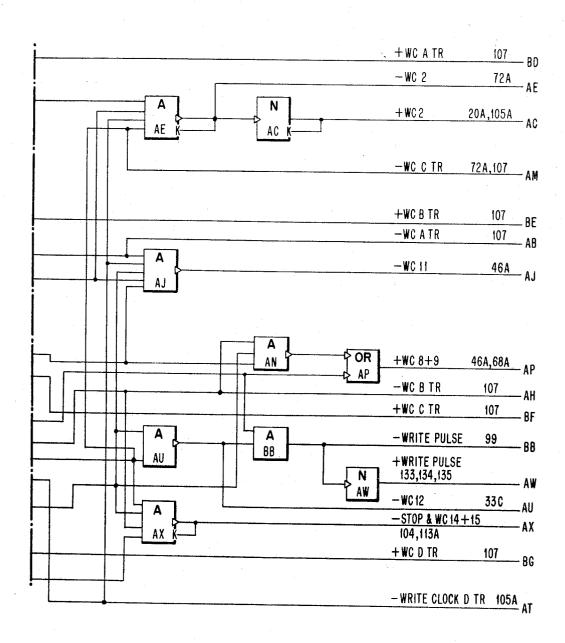

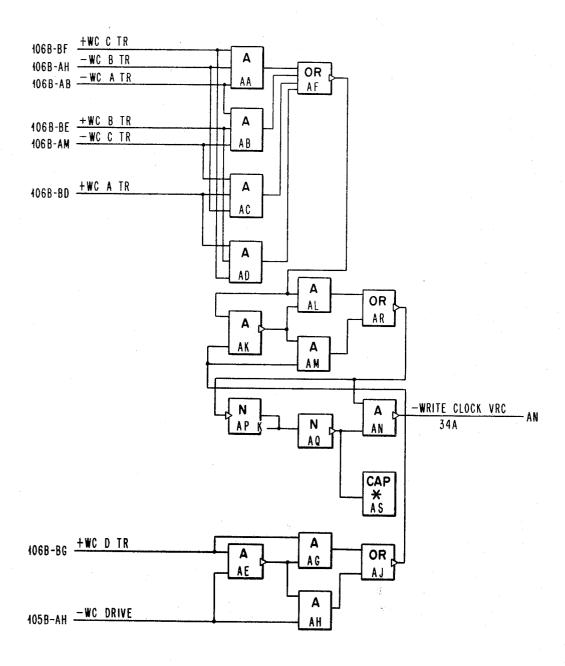

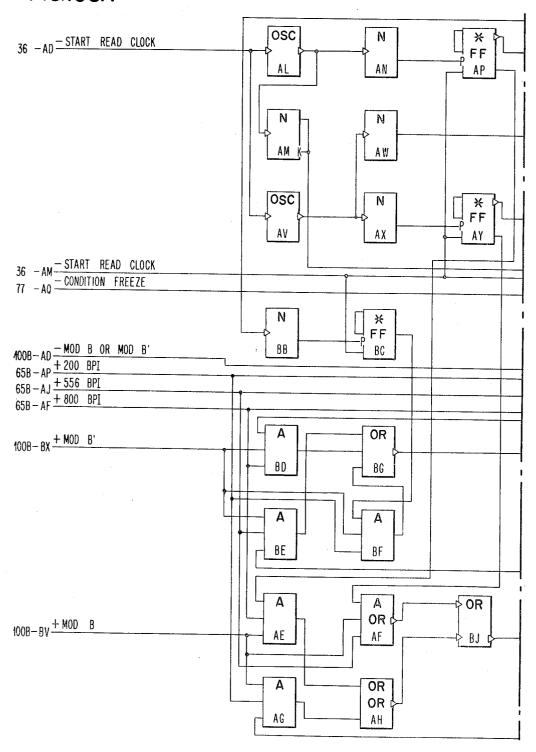

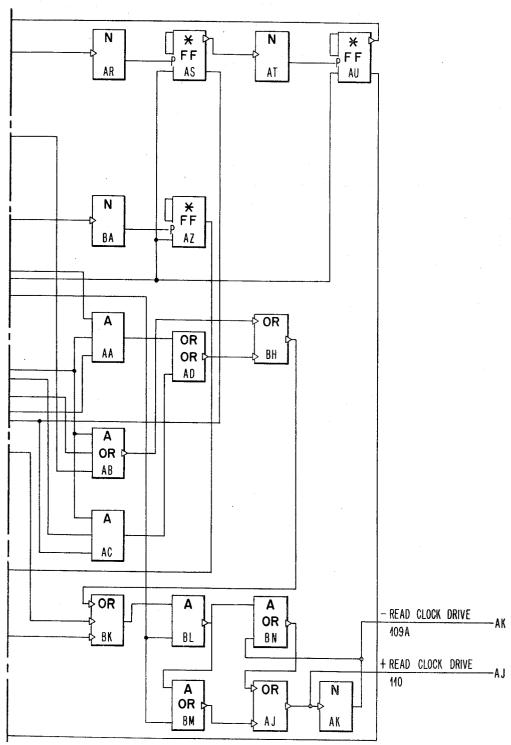

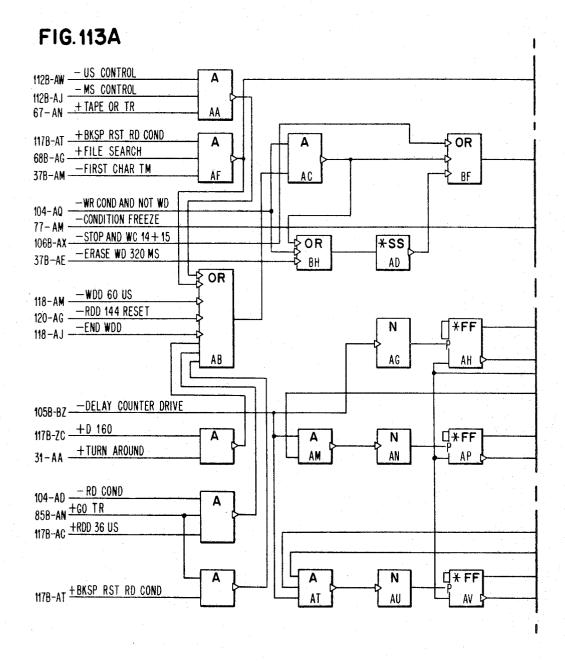

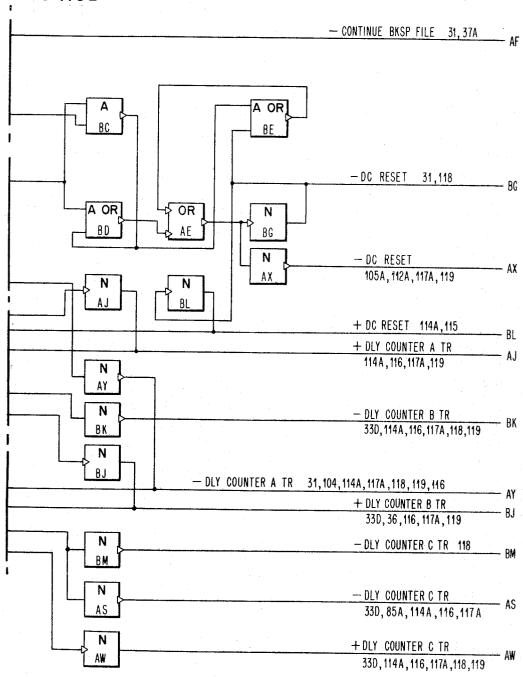

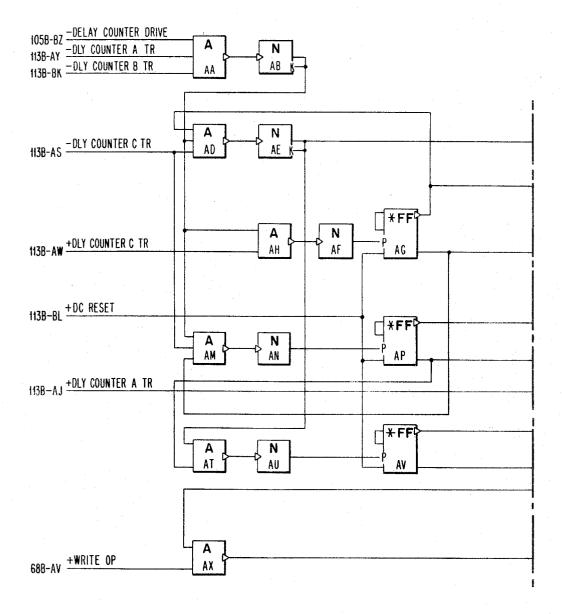

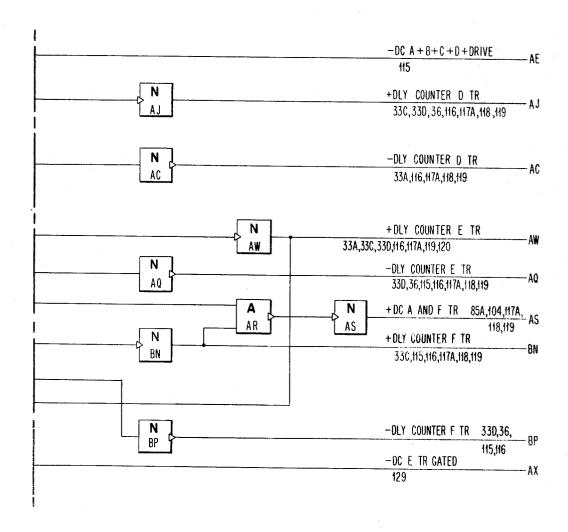

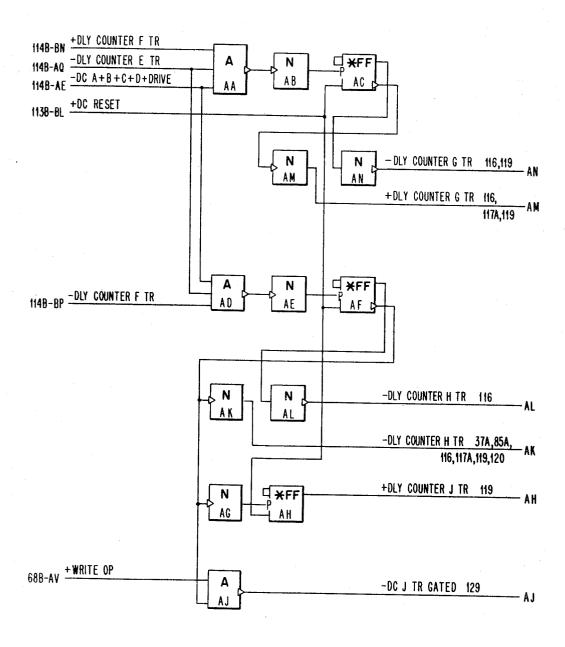

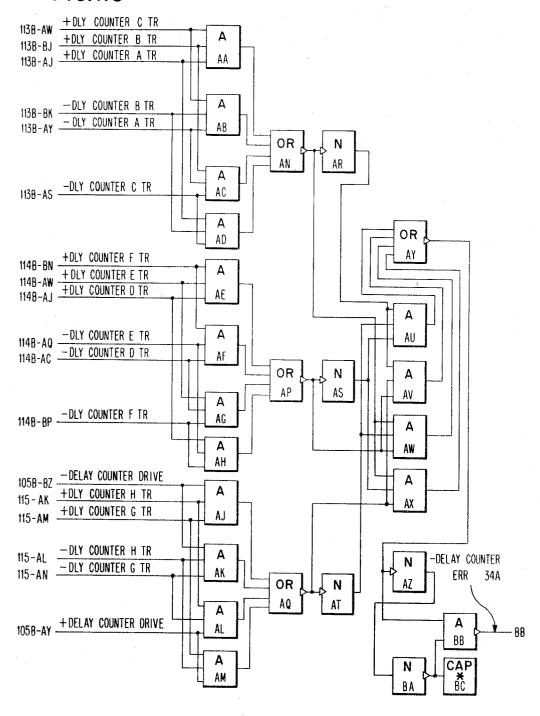

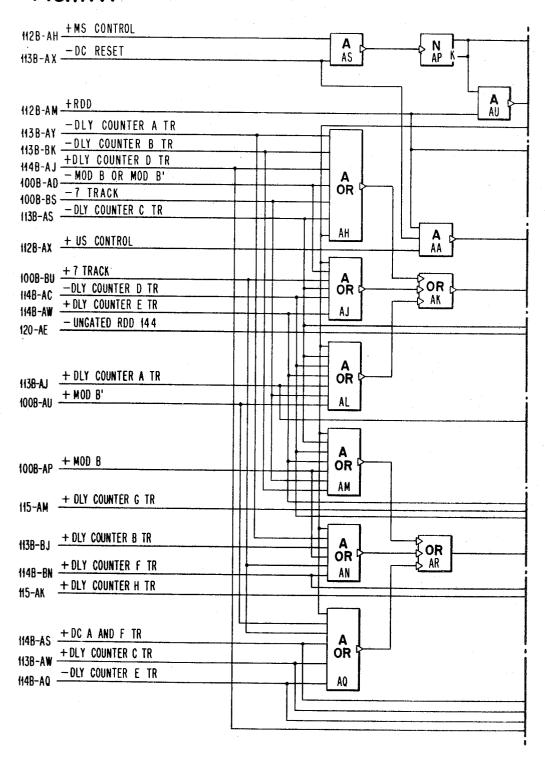

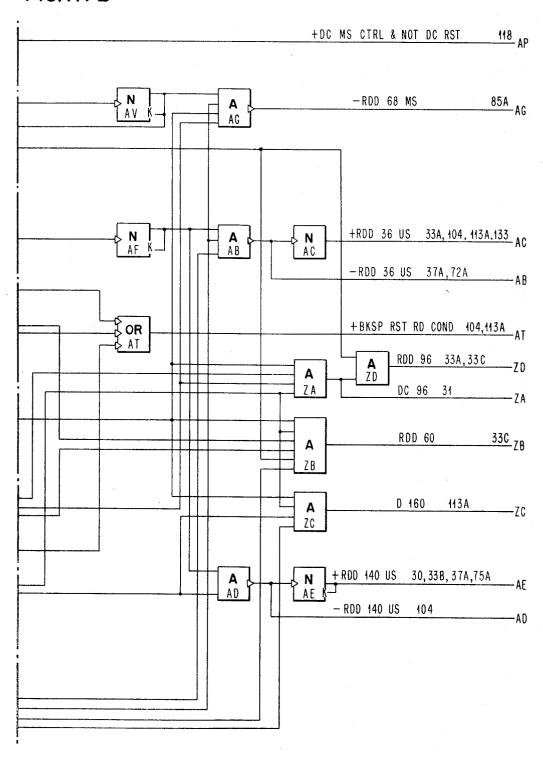

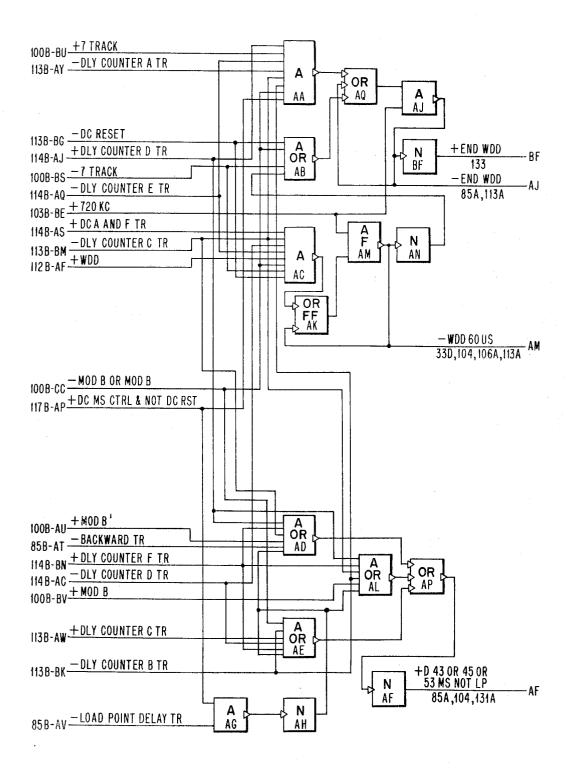

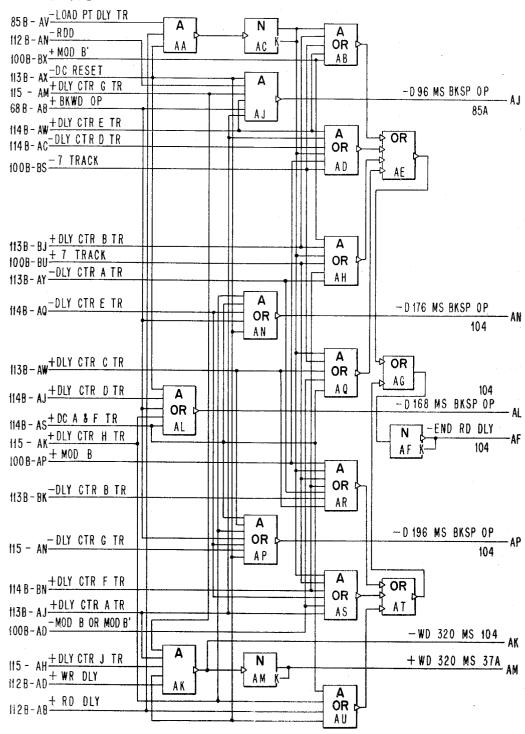

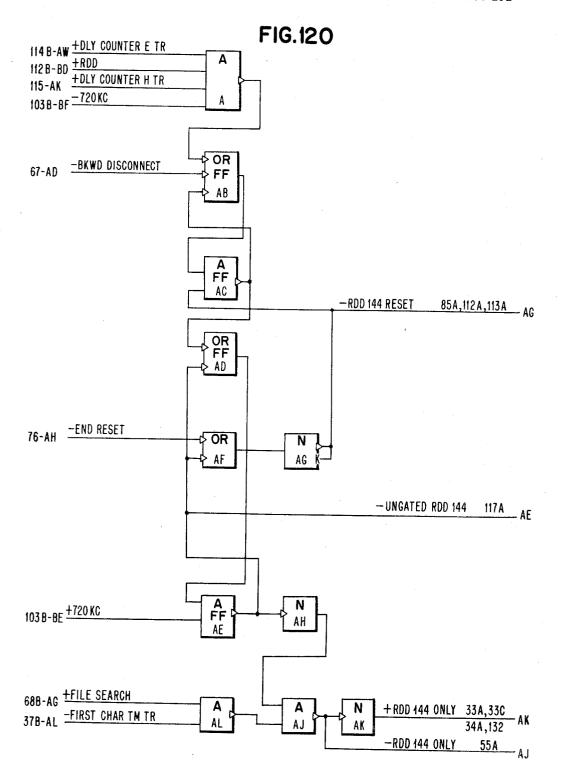

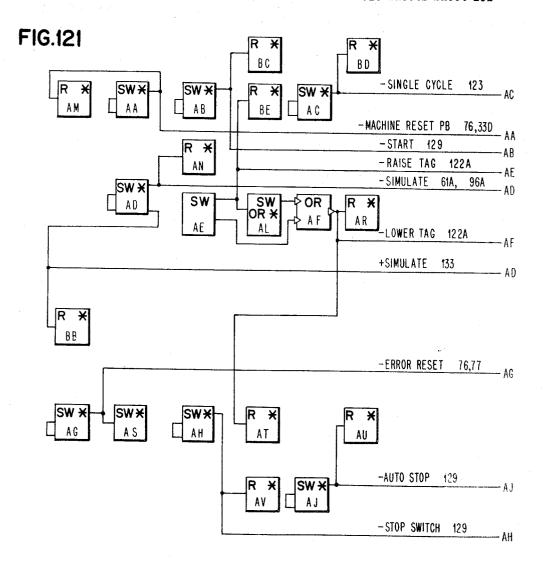

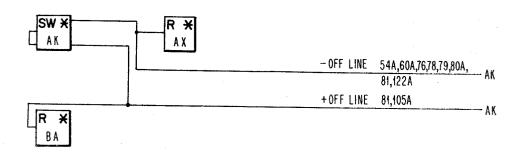

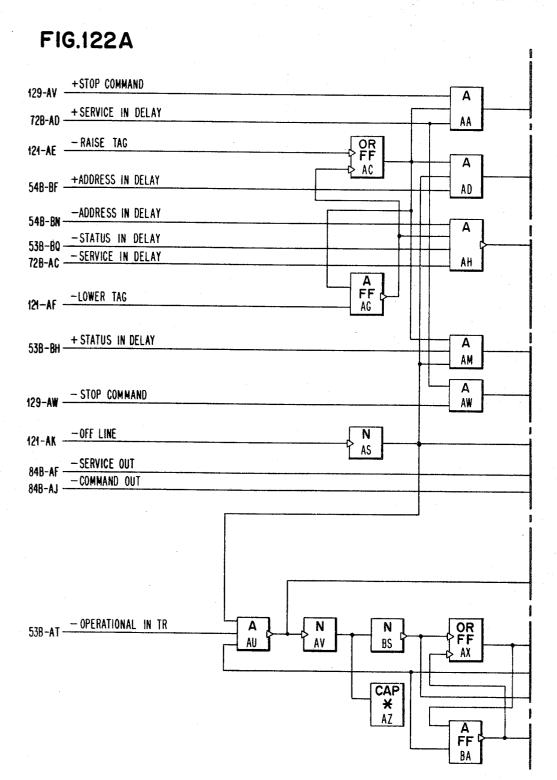

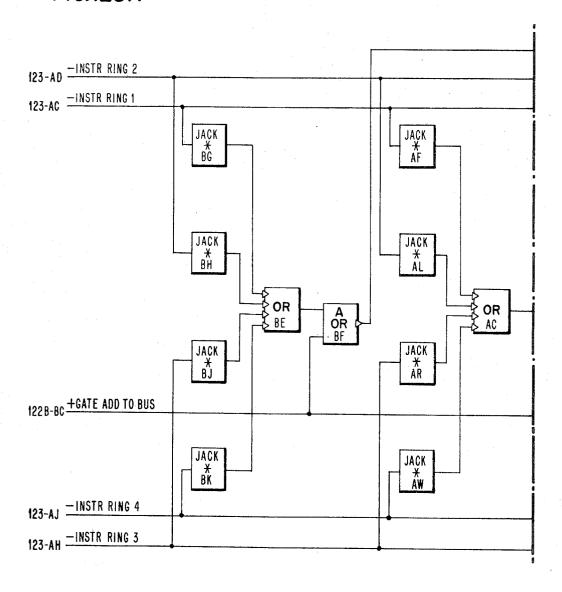

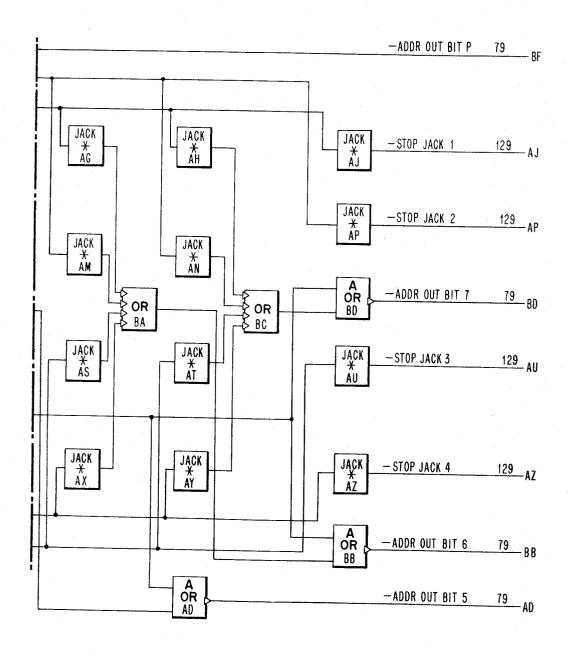

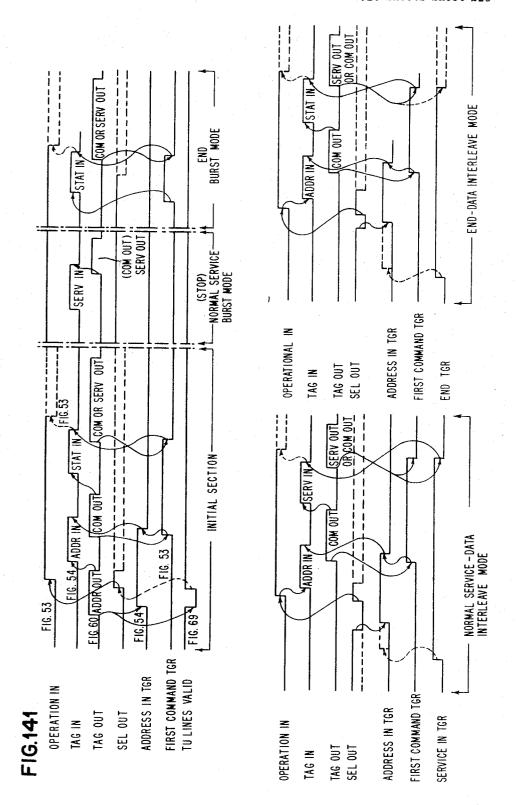

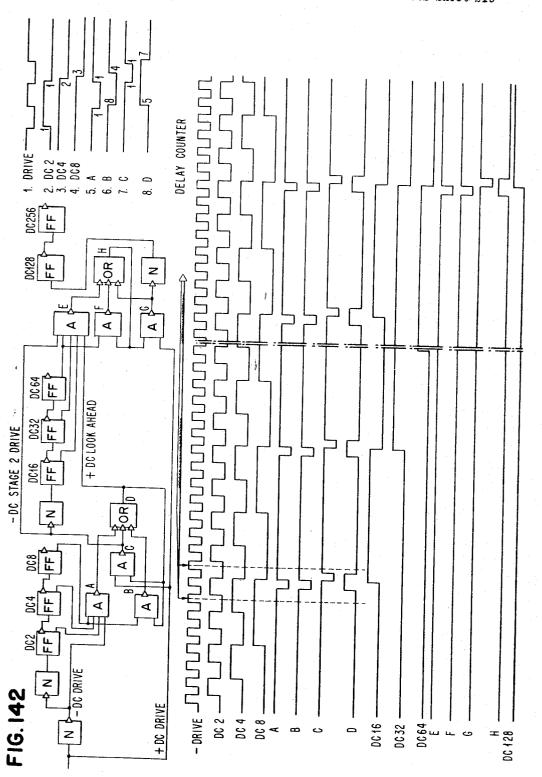

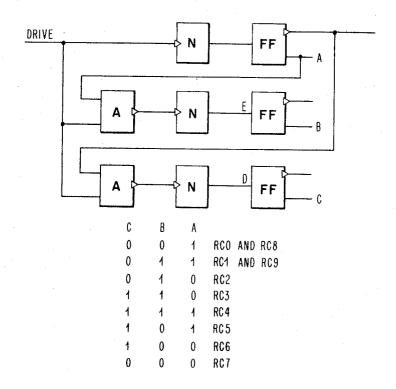

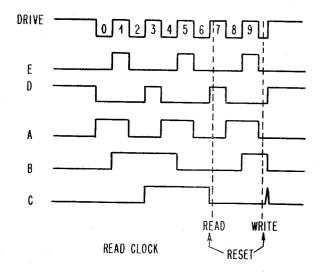

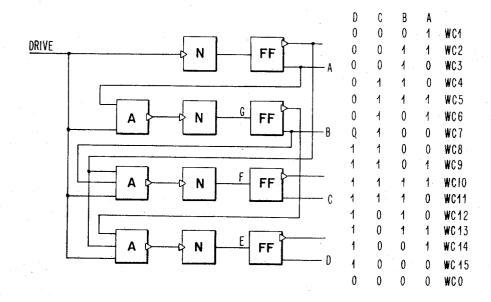

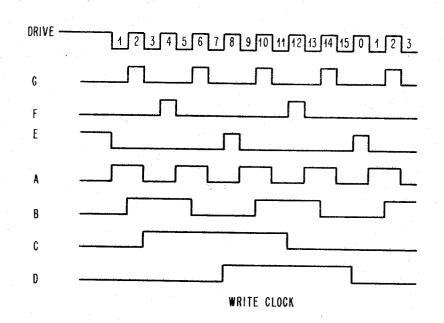

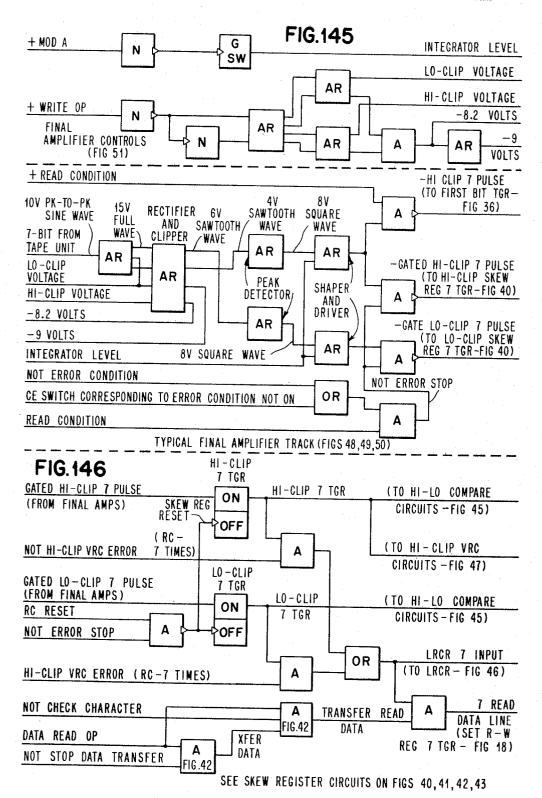

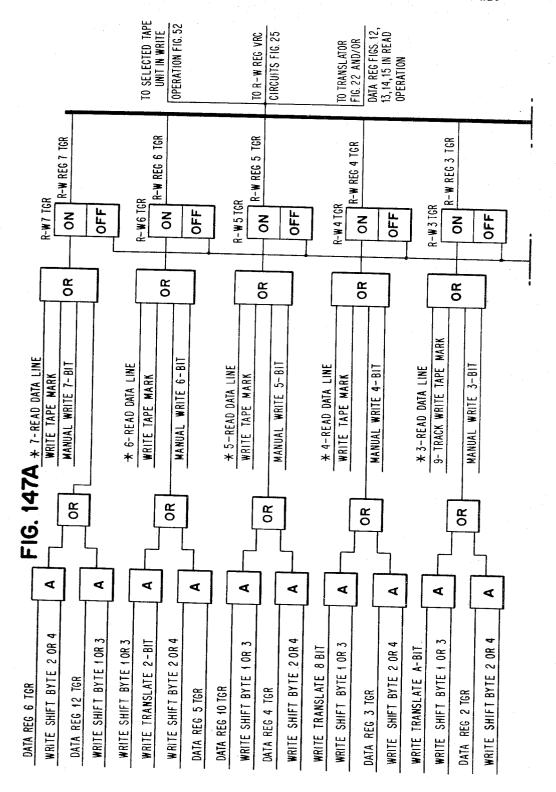

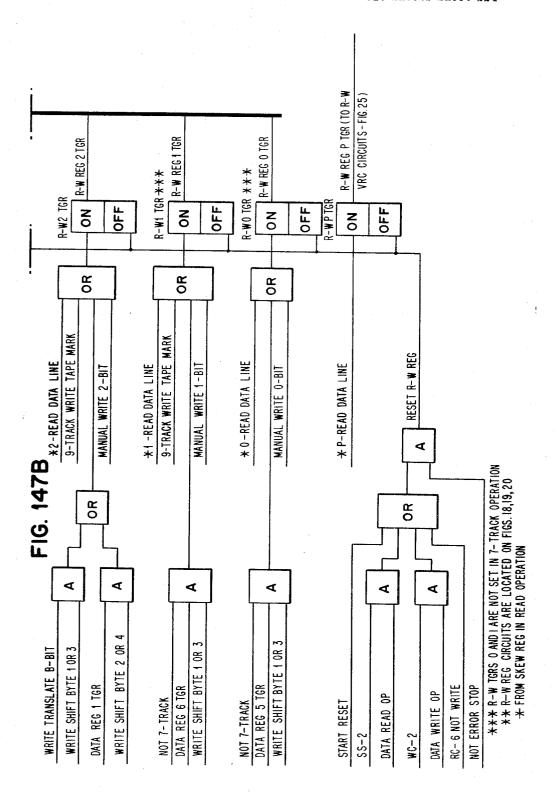

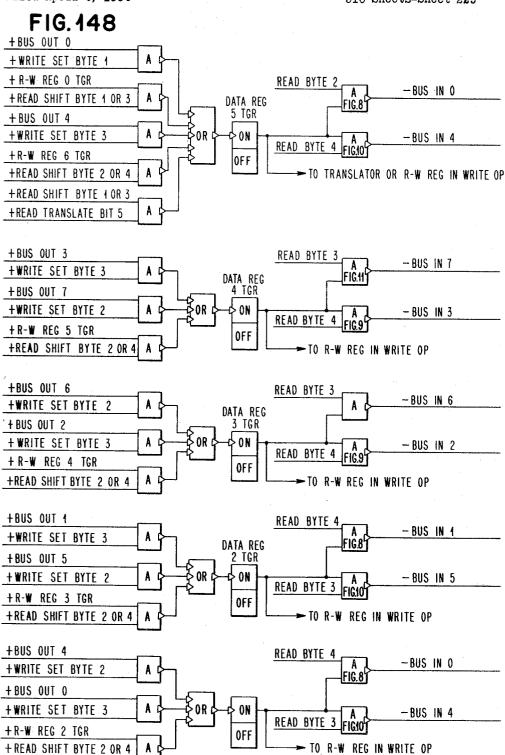

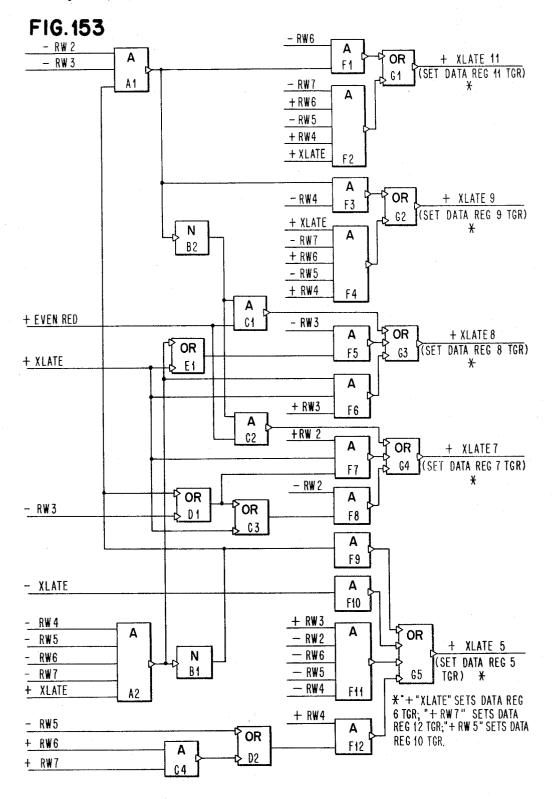

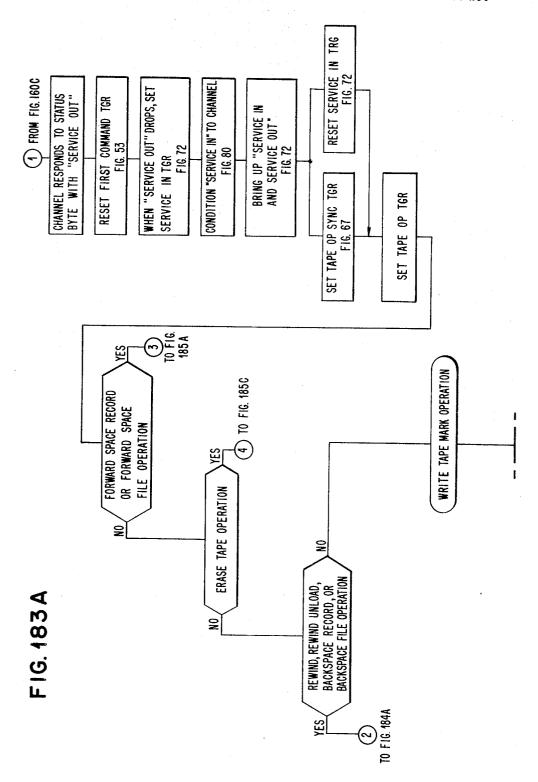

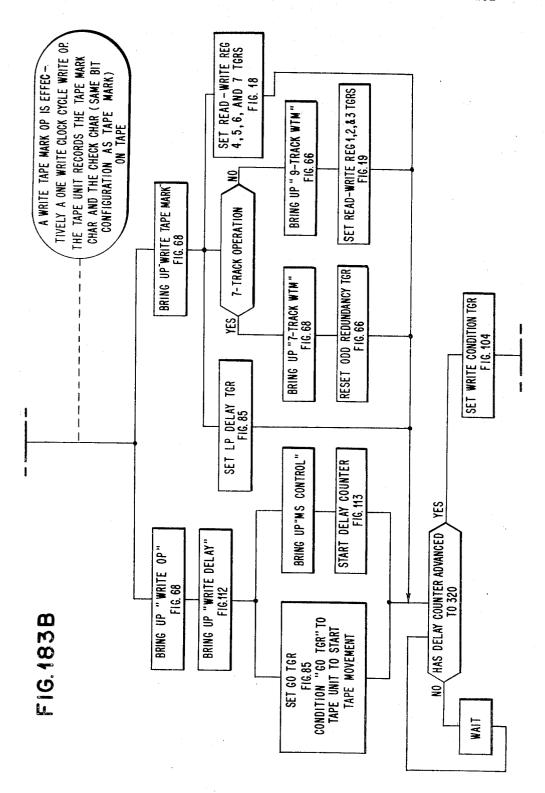

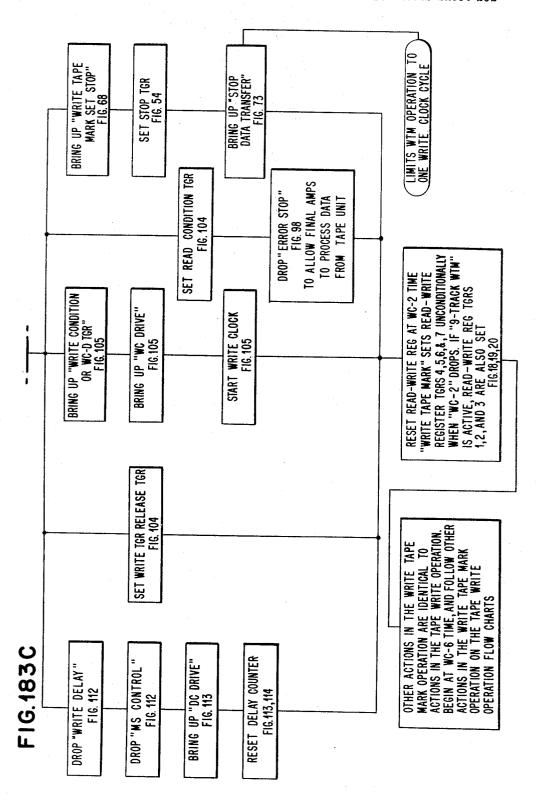

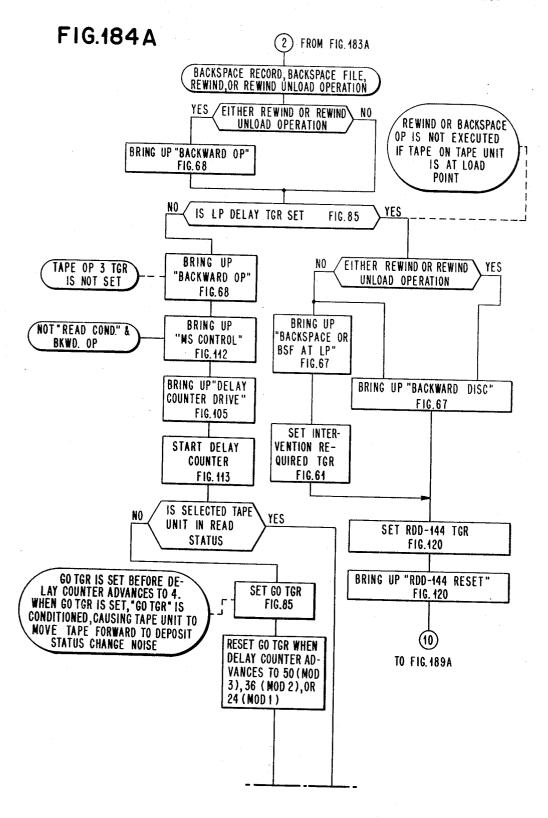

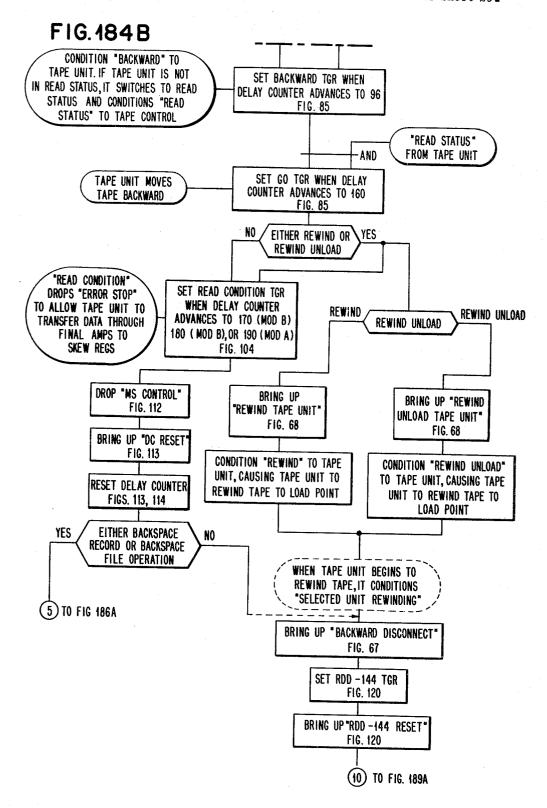

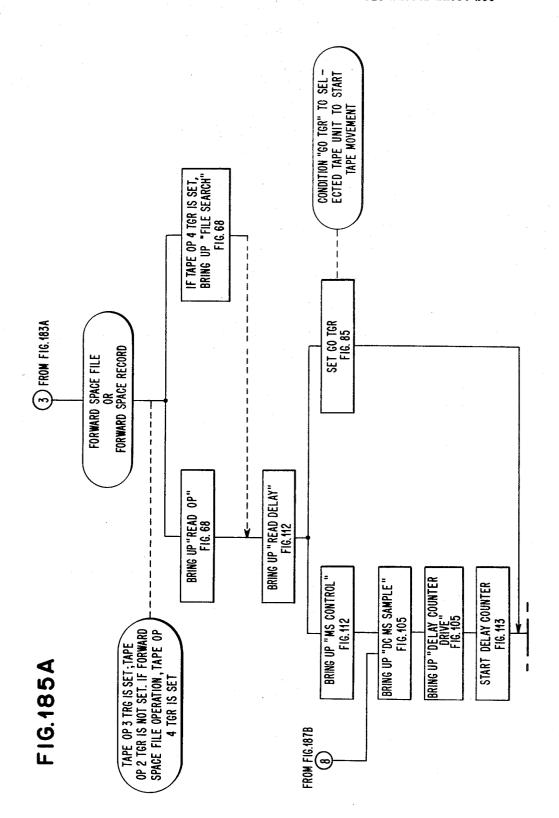

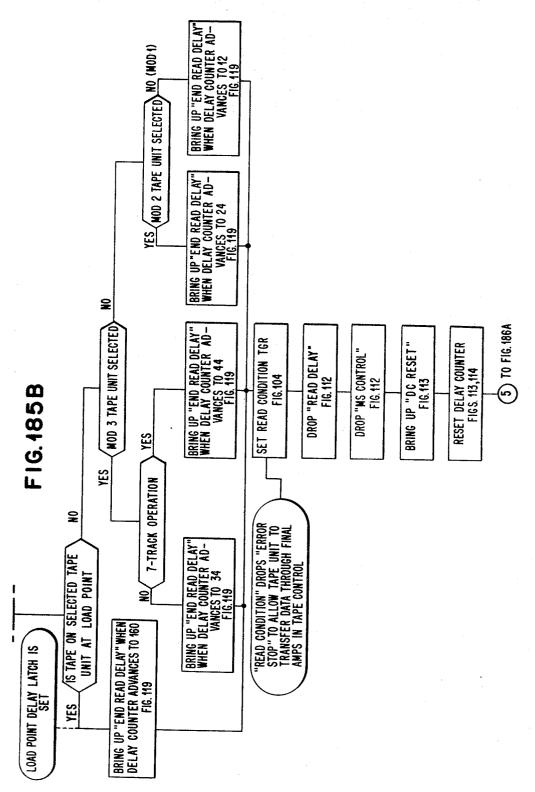

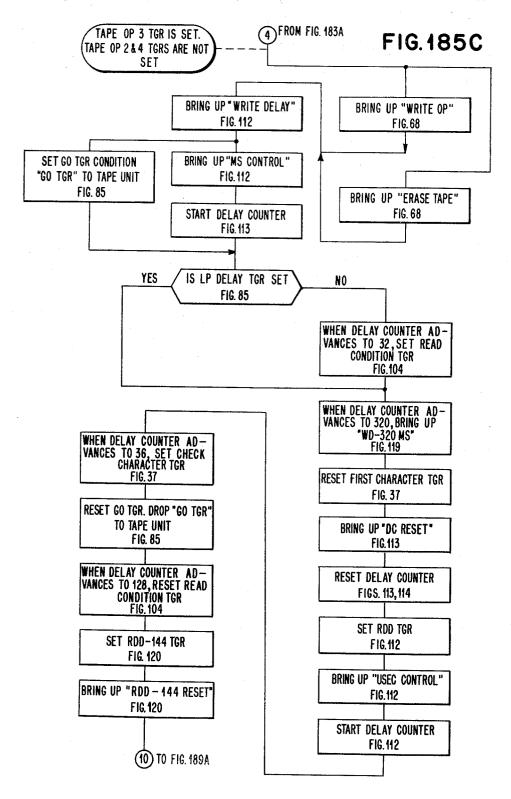

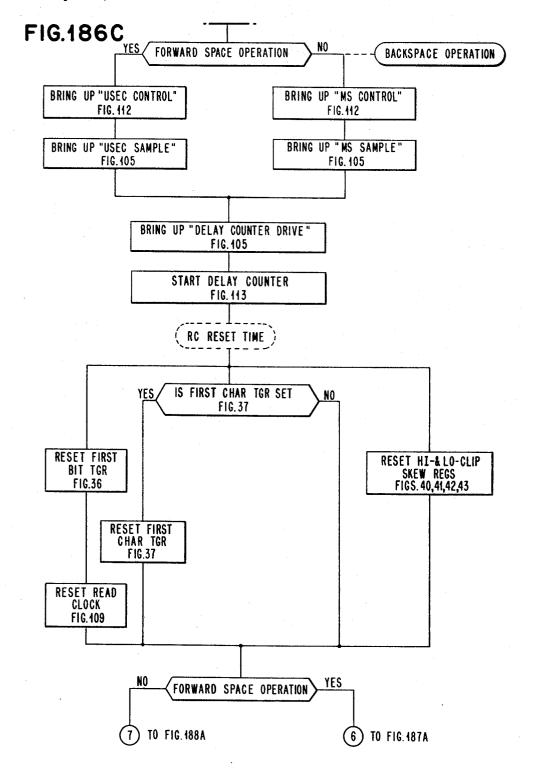

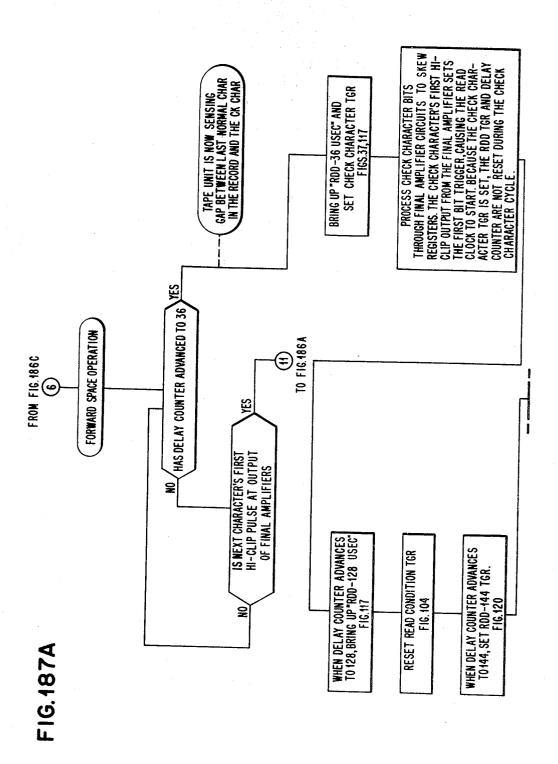

#### DESCRIPTIVE TABLE OF DRAWINGS-Continued DESCRIPTIVE TABLE OF DRAWINGS-Continued Figure Title description of drawing: number Title description of drawing: LRC (Longitudinal Redundancy Check) Sample...... Write Clock VRC GRC (Cyclic Redundancy Check) Control 1..... Density Selection 108A & B Read Clock 109A & B Read Clock VRC 110 31 5 EPR Twist to Read Backward..... 32 GRC Character Latches 33A CRC Pattern Test\_\_\_\_\_ 33B RC 7+RC Reset Gate 111 GRC Control Latches.... 33C Delay Counter Controls...... 112A & B CRC Control 2.... 33D Delay Counter A B C Triggers\_\_\_\_\_\_113A & B 10 Error Triggers.... 34A & B Delay Counter D E F Triggers 114A & B Error Triggers 35 Delay Counter G H J Triggers.... First Bit..... 36 Delay Counter VRC.... 116 Read Recognition 37A & B Delay Counter Gating \_\_\_\_\_\_ 117A & B Delay Counter Gating D43+45+53 WDD 60 End WDD \_\_\_ 118 Hi Clip Pulse Freeze Registers 7, 6, 5, 4, 3................. 38A & B Hi Clip Pulse Freeze Registers 2, 1, O P. 39 15 Delay Counter Gating End RD, Dly D96, D168, D170, D196 and WD 320\_\_\_\_\_ 119 Delay Counter Gating RDD 144\_\_\_\_\_ 120 Manual Control Switches 12<sub>1</sub> Off Line Tag Out Generation 122A & B Skew Register Position P 44A & B Hi Lo Compare 45 Instruction Ring and Character Counter 123 Manual Controls Command Bits P 0 1 2 3 124 Manual Controls Command Bits 4 5 6 7 125 Hi Clip Register VRC 47A & B Manual Controls Data Bits P 0 1 2 3 126 Final Amplifier, 7, 6, 5, 4..... Manual Controls Data Bits 4 5 6 7. 127 Manual Controls Tape Unit Address and Stop Jacks\_\_\_\_ 128A & B Final Amplifier 3, 2, P Final Amplifier 0, 1 Off Line Start Stop and Record Length Controls. 25 Final Amplifier Controls..... 51 Off Line Control Unit Address Jacks Stop on Error Jacks\_\_ 130A & B Write Bus Sequence Indicator C Interface Sequence 54A & B Simulate Select\_\_\_\_\_ 133 Simulate Register 7 6 5 4 3 2 P End Pulse + Sense Gating 55A & B 134 30 Simulate Register 1 0 Sense Bit 0, 1, 2\_\_\_\_\_ 135 Sense Bit 3, 4, 5..... 57 Multiple Control Unit Connection to Computer Channel. 136 Backward Read Operation Timing Sense Bit 6, 7\_\_\_\_\_ 137 Address Compare 59 Address Decoder and CU (Control Unit) End........... 60A & B Write Operation Timing 138A & B Read Operation Timing 139A & B Tape Control—System Relation TU 8-15 Select 62A & B Interface Sequences 141 Tags Out\_\_\_\_\_ Delay Counter\_\_\_\_ 142 64A & B Command Register 0, 1\_\_\_\_\_ Read Clock 143 Command Register 2, 3, 4, Mode Sets\_\_\_\_\_65A & B Write Clock.... 144 Command Register 5, 6, 7 and Command Decoding\_\_\_\_\_ 66A & B Final Amplifiers 145 Tape Operation Sync and Backward Disconnect..... 67 Typical Skew Register Position 146 Tape Operation Lines 68A & B TU Lines Valid and Chain TR. 69A & B Read-Write Register 147A & B Data Registers.... 148 Invalid Command Decoding 70 Data Registers\_\_\_\_ 140 Unit Check 71 Byte Counter\_\_\_\_\_ 150A & B Eight Bit Mode Data Register Operation 151 Shift Control 73A & B 45 Eight Bit to BCD Translator 152 Byte Counter 74A & B Byte Counter and Byte Counter Check 75A & B BCD to Eight Bit Translator 153 Eight Bit Code-BCD Relations...... 154A & B Resets\_\_\_\_ 76 C-Compare\_\_\_\_ 155 Freeze Generation 77 C-Compare Circuits in a Specific Write Operation 156 Interface Terminators 0 1 2 3 4 LRCR Circuits.... 157 50 Interface Terminators 5 6 7 P. 79 Date Flow in Write Operation\_\_\_\_ Simplified Tape Control Write Operation\_\_\_\_\_159A, B & C Interface Terminators Initial Selection Sequence\_\_\_\_\_160A, B & C Freeze Gate Bus Out 0010203+4...... 82A & B Tape Write Operation (1 of 9) Freeze Gate Bus Out 5 6 7 P\_\_\_\_\_83A & B Tape Write Operation (2 of 9)\_\_\_\_\_\_162A, B & C Tape Write Operation (3 of 9) 163A & B Go Backward LP 85A & B Tape Write Operation (4 of 9) 164A & B Tape Write Operation (5 of 9) Select and Ready Status\_\_\_\_\_ Tape Write Operation (6 of 9) 166A & B Tape Write Operation (7 of 9) 167A & B Unit Freed Register 4 5...... 89A & B Tape Write Operation (8 of 9) 168A & B Unit Freed Register 6 7...... 90A & B Tape Write Operation (9 of 9) 169A & B Data Flow in Read Operation\_\_\_\_ Unit Freed Register 8 9\_\_\_\_\_ 91A & B Simplified Tape Control Read Operation 171A & B Unit Freed Register 12 13\_\_\_\_\_ 93A & B Tape Read Operation (1 of 11) 172A & B Unit Freed Register 14 15\_\_\_\_\_ 94A & B Tape Read Operation (2 of 11) 173A & B Tape Read Operation (3 of 11) 174A, B & C Tape Read Operation (4 of 11) 175A, B & C Tape Unit Select Triggers\_\_\_\_\_ 95A & B Busy\_\_\_\_\_\_96A, B, C & D Tape Read Operation (5 of 11) 176A & B Tape Read Operation (6 of 11) 177A, B & C Tape Unit Select Register and Unit Freed Scanner\_\_97A, B, C & D Error Stop\_\_\_\_\_ Control Lines to Tape\_\_\_\_\_ 98 Tape Read Operation (7 of 11)\_\_\_\_\_\_ 178A & B Control Lines from Tape 100A & B Tape Read Operation (8 of 11) 179A & B 101 70 Control Lines from Tape Tape Read Operation (9 of 11) \_\_\_\_\_\_ 180A & B Control Lines from Tape Tape Read Operation (10 of 11) 181A & B USEC (microsecond) Pulse 103A & B Tape Read Operation (11 of 11)\_\_\_\_\_\_\_ 182A & B Read + Write Condition 104 Motion Control (1 of 7)\_\_\_\_\_\_183A, B & C WC and DC Drive 105A & B Motion Control (2 of 7) \_\_\_\_\_\_184A & B Write Clock 106A & B

#### DESCRIPTIVE TABLE OF DRAWINGS-Continued

|                                                           | Figure   |

|-----------------------------------------------------------|----------|

| Title description of drawing:                             | number   |

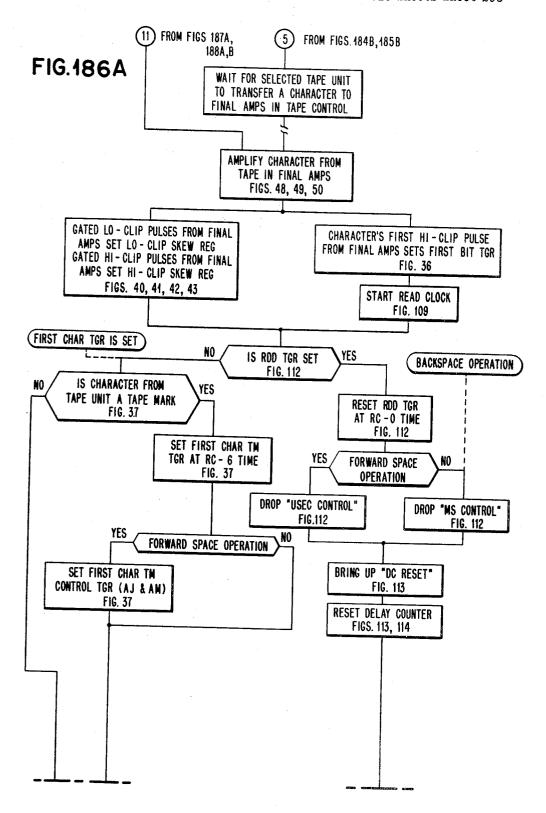

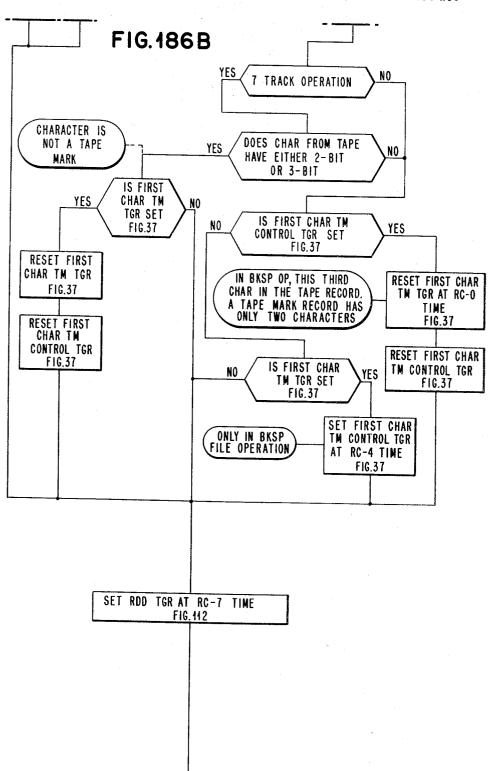

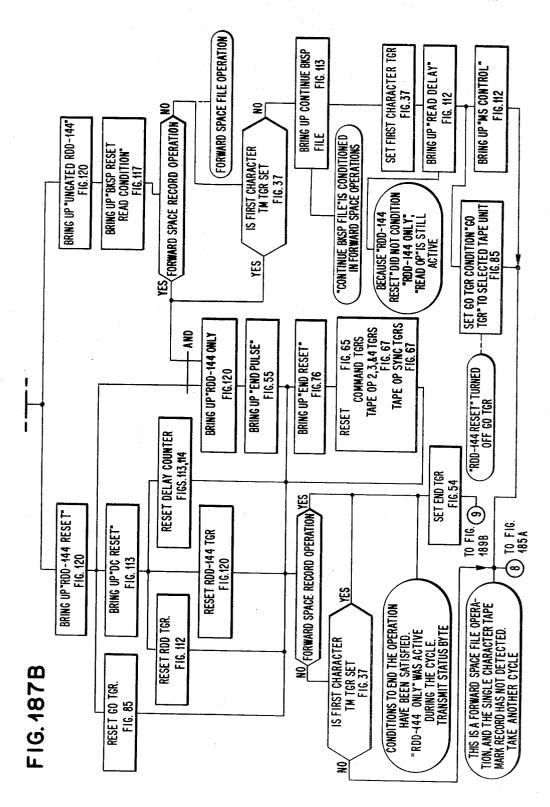

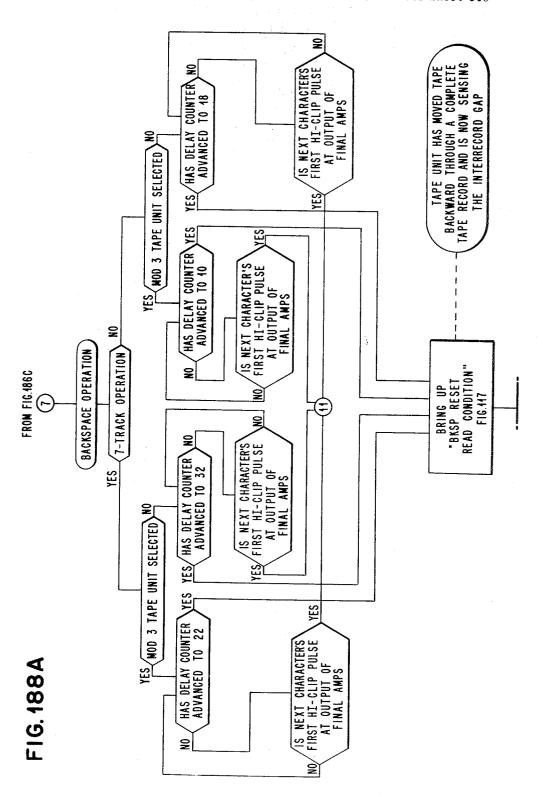

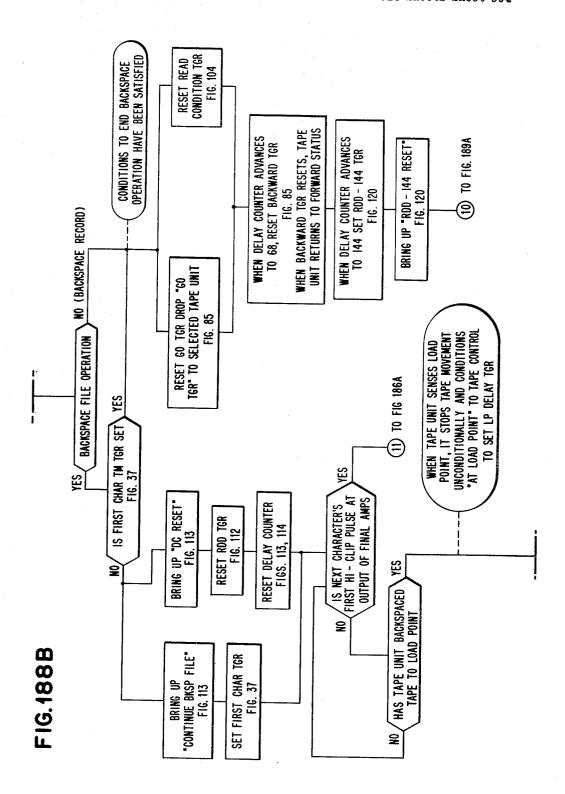

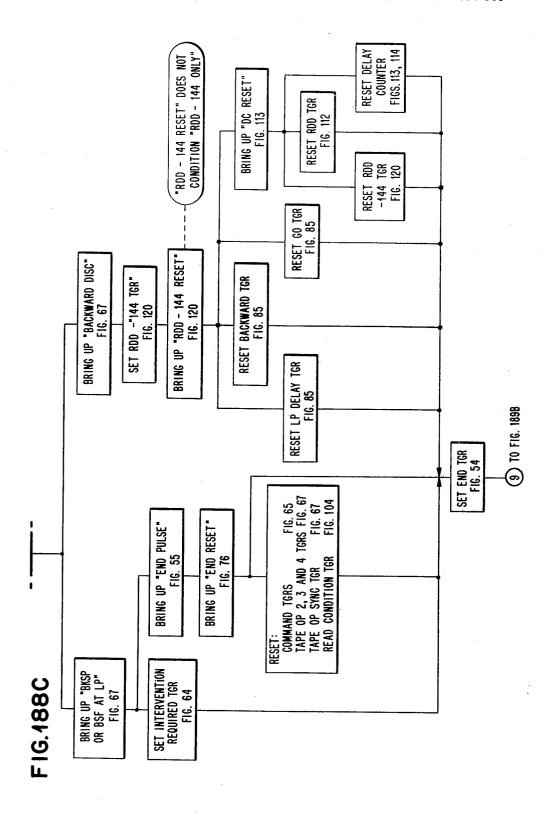

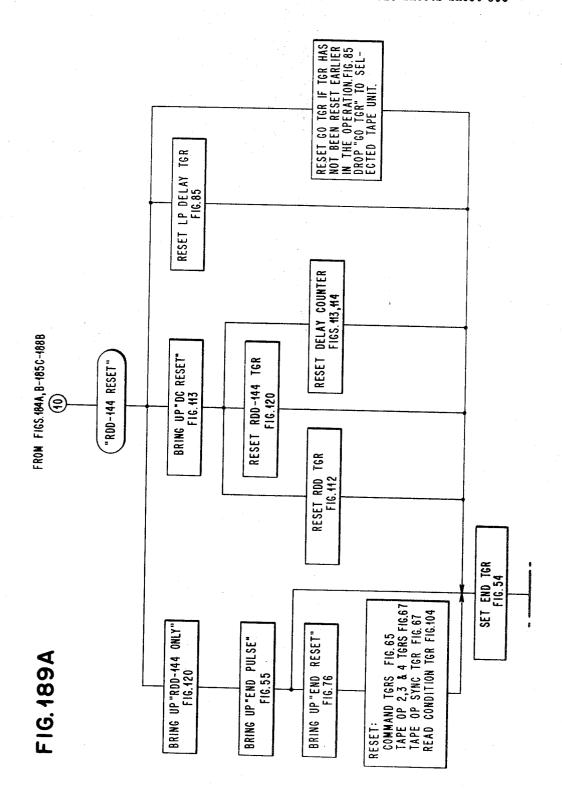

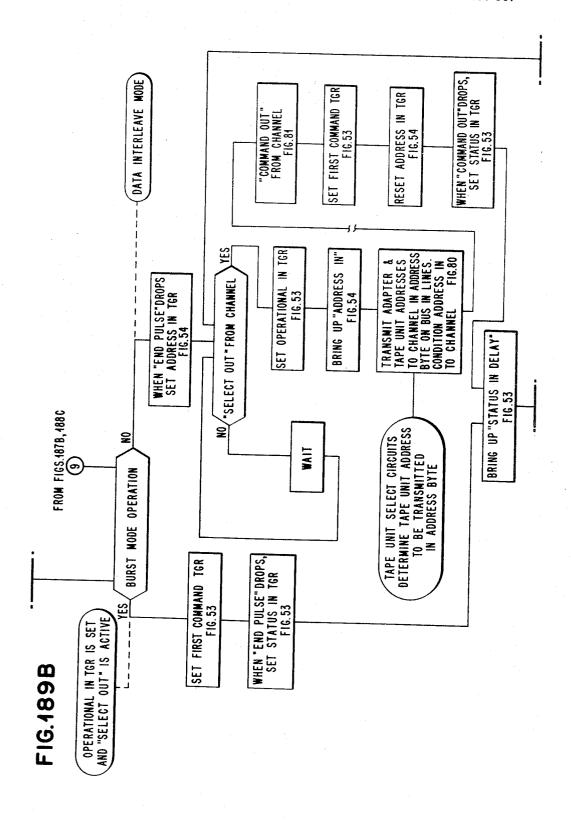

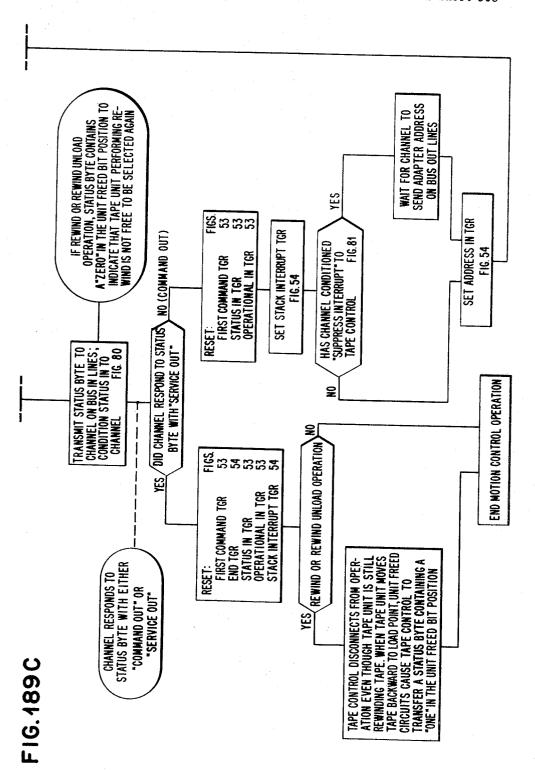

| Motion Control (4 of 7)1864                               | 1, B & C |

| Motion Control (5 of 7)                                   | 187A & B |

| Motion Control (6 of 7)188A                               |          |

| Motion Control (7 of 7)189A                               | , В & С  |

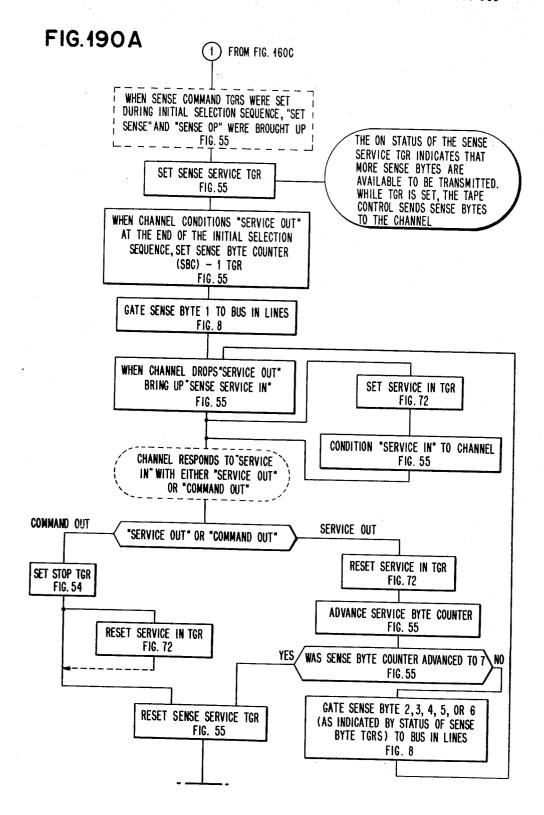

| Burst Mode Sense Operation1                               | 10A & B  |

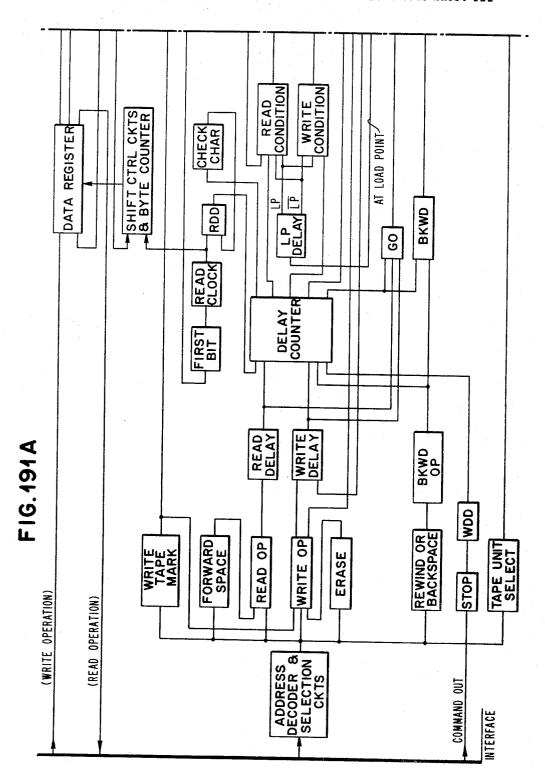

| Unit Data and Control Diagram1                            | 91A & B  |

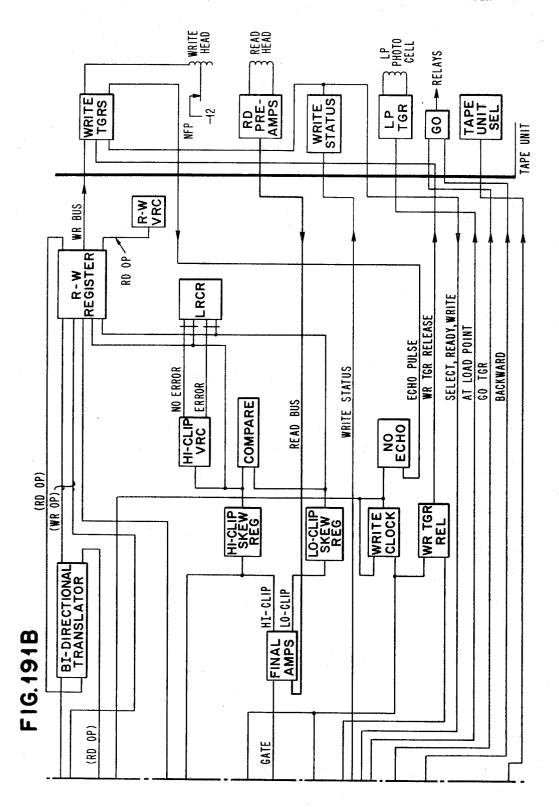

| Cyclic Redundancy Check Register Block Diagram            | 192      |

| Error Pattern Register Block Diagram                      | 193      |

| CRC Register Operation without Internal Feedback          | 194      |

| Data Block Format with CRC Byte                           | 195      |

| Data Block Format with CRC Byte and LRC Byte              | 196      |

| Operation of CRC Register in FIGURE 200                   | 197      |

| CRCR Block Diagram with Multiple Internal Feedback Paths. | 198      |

| EPR Block Diagram with Multiple Internal Feedback Paths.  | 199      |

| CRCR Block Diagram with One Internal Feedback Path.       | 200      |

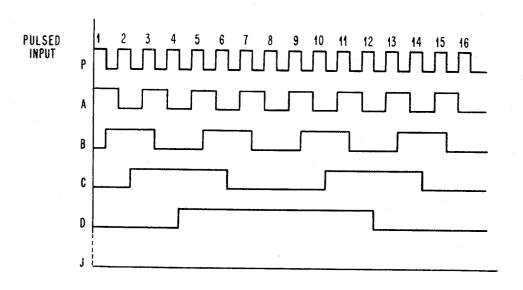

| Parity Checked Counter Circuit                            | 201      |

| Waveforms for a Parity Checked Counter                    | 202      |

An overall reference designation for each block (box) may be obtained by combining the figure number (without the word "Figure") with the two-letter identification found in each block (box). For example "21BT" is the reference designation for the upper left hand box on FIG-URE 21A containing the letters "BT." This reduces verbosity otherwise needed on the drawings and in the de-  $^{35}$ scription of the detailed embodiment. Each input lead coming from a drawing having a different figure number is labeled with the overall reference designation of the box on the drawing from which the lead comes. Each output lead going to a figure having a different number is labeled with the two reference letters of the box on the drawing from which the lead comes. In addition, each such output lead has a functional label, and also is 45 labeled with each figure number to which the lead goes.

The term "byte" defined in the second paragraph of this application is often used interchangeably with the term "character." However, "byte" has a broader mean- 50 ing than "character," since the latter is generally associated with a binary coding defining a particular symbol, such as a letter of the alphabet or a decimal digit. The term "byte"" includes a "character" but also includes 55groups of bits which are not intended to have any common symbolic meaning. For example, bit positions 9 through 16 of a binary number can be a "byte" but they are not a "character." Unfortunately prior usage of the term "character" has permitted its usage for bytes that have no symbolic meaning, such as a "check character." The latter usage will be continued herein because of its conventionality, but "byte" will be used herein in most other situations.

#### (I) CRC error detection and correction

FIGURE 1 shows the outline of an error location sys- 70 tem. Data is received in a data input bus 2. The block data is broken into sub-blocks of equal size. There is a sub-block check circuit 4 which gives an output when the sub-block is detected to be in error. Each sub-block 75

is written with redundancy in such a way that if an error occurs, the check circuit will detect the fact. The error indication is sent to the error pattern residue circuit 5 called the EPR. The data itself is sent to the cyclic redundancy residue circuit 3 called the CRCR. After the total block of data has been read, a check character, to be called the cyclic redundancy check or CRC, enters on the data input 2. This is checked by a sub-block check circuit and is sent to the cyclic redundancy residue circuit. After the data block and the check character have been received, the digital comparing circuit 6 which has inputs both from the cyclic redundancy residue circuit and from the error pattern residue circuit now can determine the sub-block error position. This is entered into the sub-block position error indicator 7.

In the embodiment of FIGURE 2 described herein a sub-block is a byte of 9 bits. The sub-block check circuit is a parity checker 31. The CRCR 18 and the EPR 30 blocks are shift registers with feedback connections. The data input can be considered to be the read-write register 12. The sub-block check circuit is the VRC checker 31. The cyclic redundancy residue circuit is the CRCR 18. The error pattern residue circuit is the EPR 30. The digital comparing circuit is the find track test 41. This is used in a conjunction with controls which shift the CRCR during the sub-block position error time. The sub-block error indicator in this case is the EPR 30 which is shifted with the CRCR 18.

### Tape control operation with CRC error correction

The following paragraphs describe a method of doing error correction on a magnetic tape and refer to FIG-URE 2. The method of writing, reading, and reading with correction is described. Then variations on these basic operations are described for the read backward operation. There are a number of ways of implementing this, several are mentioned with the descriptions.

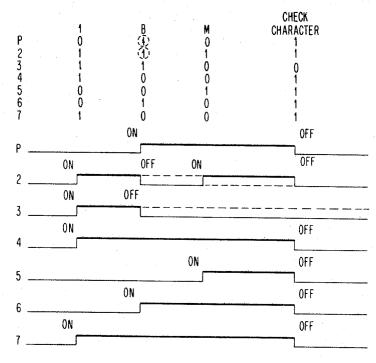

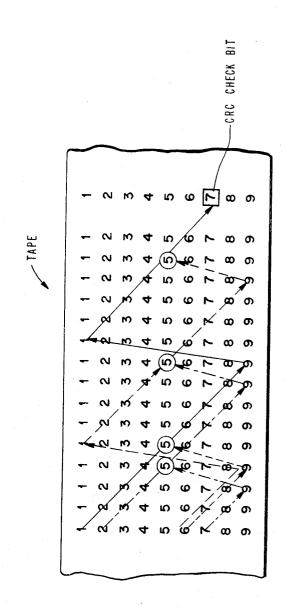

The operation of writing is broken into two parts. The first part consists of writing data in bytes. The data is received in a tape control unit and transmitted to the tape in bytes. Each byte has a parity bit appended for error detection. Other methods of writing characters which have error detection redundancy such as having a predetermined number of 1's and 0's are also suitable. As each character is sent to the tape drive from R/W register 12, it is also sent to a register 18 in FIGURE 2 called the CRCR (cyclic redundancy check register). Data is entered in this register in such a way as to Exclusive-OR with the present contents of the register and to shift one position. FIGURES 192 and 198 represent a simplified block form of a CRCR. FIGURE 192 shows a diagonal redundancy register which has end-around feedback but no intermediate feedback, and it receives and Exclusive OR's the bits in the diagonal order shown in FIGURE 194. In FIGURES 198, 199, and 200, there also are intermediate feedback connections on the register to modify the contents during the shift operation to receive and Exclusive OR's the bits in a cyclic order, such as shown in FIGURE 197.

CRCR 18 is shown in detail in FIGURES 28A and B.

9

When the last byte of a data block is received in the tape control unit, it is sent to the tape and also to the CRCR. Then the CRCR is given one extra shift. The contents of the CRCR are then transferred to a read-write register 12 by use of AND gate 54. This is done in such a way that certain bit positions of the CRCR are complemented. The contents of the read-write register are then written onto tape as a CRC check byte after the end of the data block (see FIGURES 194 or 195) at a time known as WDD 60. 10 A check character known as the LRC is written on the tape after the CRC byte in FIGURE 195 at time WDD 120.

The LRC has the following property: It insures that  $^{15}$ there are an even number of ones written on tape in every track. For example, the 4 bit of the LRC character is chosen so that throughout the block there will be exactly an even number of ones in the four track. The LRC 20 is calculated over the total block written and the CRC byte which was written. The purpose of complementing certain bits of the CRC as it was transferred to the readwrite register is to insure odd redundancy for the LRC 25 byte. This property is valuable during the read backward operation. The way this works is explained in a special section on the operation of the shift register.

During the write operation there is a read-while-write 30 feature. Data is read on a tape head into the tape control and the block is checked for proper VRC (byte redundancy) and LRC. The LRC is calculated in 40 from data on line 14. At the end of the block write operation if a 35 will contain a pattern of ones and zeros related to the VRC error was detected or if a LRC error was detected by circuitry 45, 46, 47 an error signal is sent to the computer signaling that the write operation was not done properly. In this manner, a number of information bytes, 40 normal mode of operating is to backspace over the block a CRC check character byte, and an LRC check character byte have now been written onto tape, as shown in FIGURE 195.

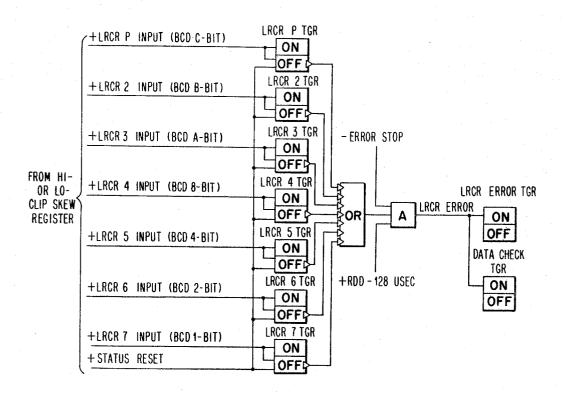

The operation of reading is done as follows. The read 45 command is given and the tape starts to move. The data read from tape enters the tape control unit from the tape unit and is transferred to read-write register 12 in FIGURE 2 on line 4. From the read-write register 12, it 50 is transferred through Exclusive OR 16 to the CRCR 18 in the same way as it was done during write. A VRC (Vertical Redundancy Check) is calculated on the data by VRC circuit 31. If the data is calculated to be in 55 error, a one is inserted into another register called the error pattern register or EPR 30 by use of AND 37. The error pattern register (EPR) 30 is similar to CRCR 18 except that it has only one input for the read-write VRC  $\,_{60}$ error. See FIGURES 191A and B and 192 for simplified block representations of a CRCR and an EPR. The EPR is shifted at the same time the CRCR is. The shifting of the EPR is done by condition OR 26. This feeds AND 65 38 which gives a pulse to shift the EPR. The CRCR is shifted by the output of OR 26 feeding OR 25 to AND 22 which gives a pulse out to shift the CRCR.

gate 43 is sampled to send an error signal to the CPU.

Each character or byte of data read from tape actuates a read clock and is transferred under control of read clock timing pulses. At the end of the read operation, the 75 cycle between operations.

read clock is reset and a delay counter called RDD is turned on. The RDD counter is reset and restarted each time a byte of data is read. If the counter called RDD is

10

not reset by a following data byte, it reaches count RDD 36, and a latch called first check character is turned on. If this latch is turned on, it is assumed that the next byte to be read will be the CRC character. When the CRC character is read into register 12, it is sent to the CRC register as the data was. However, the redundancy (or VRC) of this character may not be the same as for the data. Hence, the VRC check is modified to take this possibility into account. This is done by the line check character correction. The CRC character is not sent to the CPU (computer). A short time later, the delay counter sequence provides a pulse at RDD 96, and a second check character latch is sent. It is assumed the next character to be received will be the LRCR character. This character is not sent to the CRC register. Like the CRC it is not sent to the CPU. It is sent to the LRCR 40. This is the end of the normal read operation. At this time the LRC register is sampled for error by circuits 45, 46, 47,

the CRC register is sampled by circuits 51 and 52 to de-

termine if an error occurred, and the read-write VRC

latch is sampled to determine if there was a read-write

VRC error during the reading of this block. If any of

these errors occurred, an error signal is sent to the CPU

by means of a computer channel.

If an error did occur, the CRCR 18 and the EPR 30 pattern of errors that occurred. Due to the special nature of these registers it is possible to use their contents to determine the track in which the error occurred. The just read and to reread it, correcting those characters which have a VRC error by complementing the bit in those characters corresponding to the track which was determined to have the error. The time at which the track in error is determined could be anytime between the completion of the first block read operation, and the receiving of data during the next read operation.

In FIGURE 2 the calculation of track in error is done before the beginning of the second data read operation during the time in which the tape was picking up speed to again read the block. A variation on this technique would be to do the track calculation at the end of the first read operation and to store the track calculated to be in error. If the track in error were stored in the CPU the error detection track location circuitry could be used on other tape drives and/or other records on the same tape drive before correction was attempted on the original record in error. When it was desired to correct the original record in error, the track calculated to be in error could be transmitted back to the tape adapter along with status information which would set the tape adapter into an error correcting mode. The storage of the track in error could also have been done in the tape control in a If there is a VRC error from circuit 31, the AND 70 special memory. The CPU would have special instructions to retrieve the track in error information when the record in error was reread. The track in error calculation may also be done during the backspace or during a special 11

In the embodiment of FIGURE 2 track in error information is discarded if the correction cycle is not attempted immediately. That is, the sequence of operation must be-the record is read and error detected, a backspace operation is done and then a read operation is done on which the error correction is attempted. The latter is done through the use of several control latches. When a backspace operation is done after a block read with an error, a special latch 41 (called find track latch) is turned on. The contents of the EPR and the CRCR are  $_{10}$ retained. At the beginning of the next block read (which will be the read for error correction), read-write register 12 is reset, the contents of the EPR is transferred to the read-write register through use of gate 55, and a one is inserted into the top position of the EPR register by means 15 of AND gate 37. At this time the CRCR and the EPR registers are shifted through use of AND circuit 34 into OR 26 into AND 38 to shift the EPR and OR 26 to OR 25 to AND 22 to shift the CRCR. After each shift the contents of the CRCR are compared bit position for bit 20 position with the contents of the read-write register. The comparison is done by entering the CRCR 18 contents into the Exclusive OR gate 16 through use of AND gate 34 and OR 33. The output of the Exclusive OR's 16 go to the find track test circuit 41 which gives an output if the 25 CRCR and the contents of the read-write register 12 match bit for bit. If there is an exact match, a latch called the correcting latch (within block 41) is turned on and the shifting is stopped. When the find track test 41 turns on, the inverter 42 will give a 0 output. This will degate AND 30 39 and the EPR and CRC will get no more shift pulses. Then the contents of the EPR will indicate the track in error by means of the position of the single one bit in the EPR. The CRC register is reset.

At this time a rereading of the tape data block can 35 begin. Data is now entered into the read-write register under the control of the read clock just as in the normal read operation. However, if a read-write VRC error is found for a byte of data, the bit corresponding to the track which the EPR says is in error will be comple- 40 mented. This is done as follows. The VRC 31 energizes AND 32 which gates the EPR 30 to the OR 33 to the correction Exclusive OR's 16. Since the EPR has only one 1 in a position corresponding to the track in error the output of the Exclusive OR's 16 will be the same as  $_{45}$ the input except for the track in which the EPR has a 1. In this track the read-write register bit will be complemented. The byte as corrected is sent to the CPU 15 and to the CRC register 18. Nevertheless, the input to the LRC register is the uncorrected data.

When all the data of the tape block has been read, the CRC character is also read. Its VRC may be different from that of the data. However, it is predictable. The CRC is sent to the CRC register but not to the CPU. Then the LRC character is read into the LRCR but not 55 the CRCR. This is the end of the read with correction cycle. Now it is time to sample for error. The CRC register is tested by circuit 52 to be sure that it has the pattern corresponding to no error. The LRC register is sampled to see that it is all zeros except possibly in the position in 60 which error correction took place. This is done by blocking the sampling of the track calculated to be in error (as held in the EPR 30) using the ERROR track blocking gate 45. This is sampled by AND 46 and zero tested by circuit 47. If either of these indicate error, an error 65 signal is sent to the CPU.

There are several exceptions to the general mode of operation. One exception is when no track is calculated to be in error. In this case at the beginning of the read, 8 shifts take place without a match between the CRCR and the contents of the read-write register which at that time is that the CRCR register is either all zeros or a special setting. In both of these settings when the CRCR is shifted, its setting is identical to its previous setting. That

12

is, if all zeros are shifted it will be all zeros or if the other special setting is shifted it will be identical to itself before shifting. No track calculation is attempted in these situations. For the case where no track in error is calculated, the CRC and the EPR are reset and the read proceeds as it does during a normal read, that is, the VRC errors are entered into the EPR and the data is entered into the CRC register. No correction, of course, being attempted.

It should be noted that the tape as written with these two check characters could be read on a tape control which was not fitted for error correction. During the check character reading time, it would read both check characters into its LRC register but ignore the information in the CRC character. If the time alloted for entry of check characters is specified to be long enough for the CRC and the LRC to enter the adapter there will be a compatibility between tapes written with and without CRC check character.

There is a tape read operation known as read backward or sometimes backward read. In this operation the tape is read in the opposite direction to that which it was written. In this case, the check characters are read first and then the data which comes in the reverse order of that which it was written. The tape error correction scheme just outlined will work about the same for read backward as it does for read. There are several special situations which must be considered, however.

First, since the data is going into the CRCR and shifted in a certain direction during the normal read and write, the data shifting must be modified during the backward read. This can be done by shifting the CRCR in the opposite of its normal shifting direction during backward read. Another way to accomplish the same result is to twist the data lines going into the CRCR so that those which normally went into the top go into the bottom and those which normally went into the bottom go into the top. A very important factor is that the CRCR itself must by symmetric, that is, feedback connections are symmetrically arranged around the center position of the register.

The input lines to the shift register are shown with circuitry for twisting in FIGURES 28A and B. When this is done, it is also necessary to twist the lines at the output of EPR for correction. This is on FIGURE 32. The reason for this is that when the EPR is matched with the CRC, the number of shifts necessary to get a match relates to the tracks in their twisted manner rather than the way they go to the CPU. Hence, in order to correct the proper track it is necessary to twist the output of EPR lines the same as the inputs to the CRC were twisted

Another important factor in read backward is obtaining the check character properly. Since the LRC character is not sent into the CRC register, it is necessary to know which of the characters received is the LRC and which is the CRC. If only one check character is received, this is difficult to do. Hence, provision is made to guarantee the LRC character is never all zeros. This is done by changing the VRC of the CRC character during the write operation. This has the effect of causing the LRC character to have odd redundancy, thus the first character read during the read backward will be the LRC character. It is not entered into the CRC register. All other characters read will be read into the CRC register. During a read backward operation it is not possible to predict the VRC of the CRC character. Hence, either this must be given by the CPU or through memory in the tape control or this error signal must not be sampled. The latter course has been taken in this embodiment. The backward read is identical to the forward read except for these special considerations. Since the CRC character is not sampled for error, in read backward it is not possible to correct errors which include the CRC character. If the VRC of the CRC had been known, it would be possible to corAfter a read backward operation in which errors are detected, a forward space operation is done. This operation will not be a read, it will be simply a forward space. At the beginning of the next backward read operation, the track in error is calculated. Error correction is attempted on the data read.

A number of variations on this general operating procedure is possible. One would be: when an error is found during read backward, the correction is automatically done during the next forward read. Another would be: to provide several kinds of instructions such as, a normal read command and a read with correction command. In this case a CPU would give a normal read command until an error is detected. Then the track in error would be located. The next time, the CPU would give a read with correction command; and data in the block would be corrected in the track calculated.