# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01L 27/115** (2017.01) **H01L 21/8247** (2006.01)

(21) 출원번호 **10-2013-0089833**

(22) 출원일자 **2013년07월29일** 심사청구일자 **2018년07월27일**

(65) 공개번호 **10-2015-0014577**

(43) 공개일자 **2015년02월09일**

(56) 선행기술조사문헌 KR100744566 B1\* (뒷면에 계속) (45) 공고일자 2020년02월10일

(11) 등록번호 10-2074942

(24) 등록일자 2020년02월03일

(73) 특허권자

## 삼성전자 주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

## 이명재

경기 화성시 동탄반석로 277, 111동 702호 (석우 동, 예당마을우미린제일풍경채)

#### 조성호

경기 과천시 관문로 143, 1102동 303호 (중앙동, 래미안에코팰리스)

(뒷면에 계속)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 13 항

심사관: 고연화

## (54) 발명의 명칭 비휘발성 메모리 트랜지스터 및 이를 포함하는 소자

#### (57) 요 약

비휘발성 메모리 트랜지스터 및 이를 포함하는 소자에 관해 개시되어 있다. 개시된 비휘발성 메모리 트랜지스터는 채널과 게이트전극 사이에 이온종 이동층을 구비할 수 있다. 상기 이온종 이동층 내에서 이온종이 이동됨에 따라, 상기 메모리 트랜지스터의 문턱전압이 변화될 수 있다. 그 결과, 상기 메모리 트랜지스터는 멀티-레벨(multi-level) 특성을 가질 수 있다. 상기 이온종 이동층은 바이폴라 메모리층을 포함할 수 있다. 상기 메모리트랜지스터는, 예컨대, 시냅스 소자(synapse device)나 뇌신경모사 소자(neuromorphic device)에 적용될 수 있다.

## 대 표 도 - 도14

## (72) 발명자

## 김호정

경기 수원시 영통구 영통로90번길 4-27, 109동 70 1호 (망포동, 늘푸른벽산아파트)

### 박영수

경기도 용인시 수지구 성복1로164번길 20 112동 1502호 (성복동,버들치마을성복자이1차아파트)

#### 서형석

경기 용인시 기흥구 삼성2로 97, 기숙사 B318 (농 서동, 삼성종합기술원)

## 유인경

경기 용인시 수지구 신봉2로 26, 113동 802호 (신 봉동, LG신봉자이1차아파트) (56) 선행기술조사문헌 KR1020100007467 A\*

US20060223251 A1

JP2003188350 A JP2007528616 A

KR1020120021539 A

\*는 심사관에 의하여 인용된 문헌

## 명 세 서

## 청구범위

## 청구항 1

채널요소;

상기 채널요소에 대응하는 위치에 구비된 게이트전극;

상기 채널요소와 상기 게이트전극 사이에 구비된 게이트절연층;

상기 게이트절연층과 상기 게이트전극 사이에 구비된 이온종 이동층; 및

상기 채널요소를 사이에 두고 이격된 소오스 및 드레인;을 포함하고,

상기 게이트전극에 인가된 전압에 따라 상기 이온종 이동층 내에서 이온종이 이동되고, 상기 이온종 이동에 따라 문턱전압이 변화되어 적어도 16개의 레벨을 포함하는 멀티-레벨(multi-level) 특성을 가지며,

상기 이온종 이동층은 다층 구조를 갖는 비휘발성 메모리 트랜지스터.

#### 청구항 2

제 1 항에 있어서,

상기 이온종 이동층은 가변 저항 물질(variable resistance material) 또는 바이폴라(bipolar) 메모리층을 포함하는 비휘발성 메모리 트랜지스터.

#### 청구항 3

삭제

## 청구항 4

삭제

## 청구항 5

삭제

# 청구항 6

제 1 항에 있어서,

상기 이온종 이동층은 음(-)의 이온종을 포함하고, 상기 이온종 이동층 내에서 상기 음(-)의 이온종의 농도가 상기 게이트절연층 측으로 증가할수록 상기 문턱전압이 증가하도록 구성된 비휘발성 메모리 트랜지스터.

## 청구항 7

제 1 항에 있어서,

상기 이온종 이동층은 양(+)의 이온종을 포함하고, 상기 이온종 이동층 내에서 상기 양(+)의 이온종의 농도가 상기 게이트절연층 측으로 증가할수록 상기 문턱전압이 감소하도록 구성된 비휘발성 메모리 트랜지스터.

#### 청구항 8

삭제

## 청구항 9

제 1 항에 있어서,

상기 게이트절연층과 상기 이온종 이동층 사이에 구비된 도전층을 더 포함하는 비휘발성 메모리 트랜지스터.

#### 청구항 10

삭제

#### 청구항 11

삭제

## 청구항 12

삭제

#### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

청구항 1에 기재된 비휘발성 메모리 트랜지스터를 포함하는 시냅스 소자(synapse device).

## 청구항 16

제 15 항에 있어서,

상기 비휘발성 메모리 트랜지스터의 게이트전극은 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)에 연결되고,

상기 비휘발성 메모리 트랜지스터의 소오스는 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)에 연결된 시냅스 소자.

#### 청구항 17

제 15 항에 있어서,

복수의 상기 비휘발성 메모리 트랜지스터가 복수의 열 및 복수의 행을 이루도록 배열된 시냅스 소자.

### 청구항 18

제 17 항에 있어서, 상기 시냅스 소자는,

복수의 제1 배선; 및

상기 복수의 제1 배선과 교차하는 복수의 제2 배선;을 포함하고,

상기 복수의 제1 배선과 상기 복수의 제2 배선의 교차점 각각에 상기 비휘발성 메모리 트랜지스터가 구비된 시냅스 소자.

## 청구항 19

제 18 항에 있어서,

상기 복수의 제1 배선은 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)에 연결되고,

상기 복수의 제2 배선은 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)에 연결된 시냅스 소자.

### 청구항 20

청구항 15 내지 19 중 어느 하나에 기재된 시냅스 소자를 포함하는 뇌신경모사 소자(neuromorphic device).

#### 청구항 21

제 20 항에 있어서,

상기 시냅스 소자와 연결된 CMOS 뉴런 회로를 더 포함하는 뇌신경모사 소자.

#### 청구항 22

청구항 1의 비휘발성 메모리 트랜지스터의 동작방법에 있어서,

상기 게이트전극에 전압을 인가하여 상기 이온종 이동층 내에서 이온종을 이동시키는 단계; 및

상기 비휘발성 메모리 트랜지스터를 턴-온(turn-on) 시키는 단계;를 포함하는 비휘발성 메모리 트랜지스터의 동작방법.

#### 청구항 23

삭제

#### 발명의 설명

## 기 술 분 야

[0001] 비휘발성 메모리 트랜지스터 및 이를 포함하는 소자에 관한 것이다.

## 배경기술

- [0002] 비휘발성 메모리소자로 플래시 메모리(flash memory)가 많이 사용되고 있다. 플래시 메모리는 터널 절연층 (tunnel insulation layer)을 통해 플로팅 게이트(floating gate)에 전자를 채우거나 그로부터 전자를 제거함으로써, 데이터를 저장한다. 그런데, 플래시 메모리는 전자의 터널 주입(tunnel injection)을 이용하기 때문에, 동작전압이 10~20 V 정도로 높은 단점이 있다. 또한, 플로팅 게이트에 트랩(trap) 되는 전자의 수가 제한적이기 때문에, 멀티-비트(multi-bit) 특성을 구현하기 어려운 문제가 있다. 예컨대, 20~30 nm 정도의 선폭을 갖는 플로팅 게이트에는 불과 수십 개 정도의 전자가 트랩될 수 있다.

- [0003] 위와 같은 플래시 메모리의 문제점들을 극복하기 위해, 낮은 동작전압을 가지면서 작은 사이즈에서도 충분히 큰 멀티-레벨(multi-level) 특성을 가질 수 있는 비휘발성 소자가 요구된다.

## 발명의 내용

#### 해결하려는 과제

- [0004] 멀티-레벨(multi-level) 혹은 멀티-밸류(multi-value) 특성을 갖는 비휘발성 메모리 트랜지스터를 제공한다.

- [0005] 낮은 동작전압을 갖는 비휘발성 메모리 트랜지스터를 제공한다.

- [0006] 전압 인가에 의해 특성(ex, 문턱전압)이 점진적으로/연속적으로 변화되는 비휘발성 메모리 트랜지스터를 제공한다.

- [0007] 상기 비휘발성 메모리 트랜지스터를 포함하는 소자/회로를 제공한다.

- [0008] 상기 비휘발성 메모리 트랜지스터를 적용한 시냅스 소자(synapse device)를 제공한다.

- [0009] 상기 비휘발성 메모리 트랜지스터 및 이를 포함하는 소자/회로의 동작방법을 제공한다.

#### 과제의 해결 수단

[0010] 일 측면(aspect)에 따르면, 채널요소; 상기 채널요소에 대응하는 위치에 구비된 게이트전국; 상기 채널요소와 상기 게이트전국 사이에 구비된 게이트절연충; 상기 게이트절연충과 상기 게이트전국 사이에 구비된 이온종 이동충; 및 상기 채널요소를 사이에 두고 이격된 소오스 및 드레인;을 포함하고, 상기 게이트전국에 인가된 전압에 따라 상기 이온종 이동층 내에서 이온종이 이동되고, 상기 이온종 이동에 따라 문턱전압이 변화되어 멀티-레벨(multi-level) 특성을 갖는 비휘발성 메모리 트랜지스터가 제공된다.

- [0011] 상기 이온종 이동층은 가변 저항 물질(variable resistance material)을 포함할 수 있다.

- [0013] 상기 이온종 이동층은 PCMO(PrCaMnO), Ti 산화물, Ta 산화물, Ni 산화물, Zn 산화물, W 산화물, Co 산화물, Nb 산화물, TiNi 산화물, LiNi 산화물, InZn 산화물, V 산화물, SrZr 산화물, SrTi 산화물, Cr 산화물, Fe 산화물, Cu 산화물, Hf 산화물, Zr 산화물, Al 산화물 및 이들의 혼합물 중 적어도 어느 하나를 포함할 수 있다.

- [0014] 상기 이온종 이동층은, 예컨대, PCMO를 포함할 수 있다.

- [0015] 상기 이온종 이동층은 음(-)의 이온종을 포함할 수 있고, 상기 이온종 이동층 내에서 상기 음(-)의 이온종의 농도가 상기 게이트절연층 측으로 증가할수록 상기 문턱전압이 증가하도록 구성될 수 있다.

- [0016] 상기 이온종 이동층은 양(+)의 이온종을 포함할 수 있고, 상기 이온종 이동층 내에서 상기 양(+)의 이온종의 농도가 상기 게이트절연층 측으로 증가할수록 상기 문턱전압이 감소하도록 구성될 수 있다.

- [0017] 상기 이온종 이동층은 상기 이온종으로 산소 이온 및/또는 산소 공공(vacancy)을 포함할 수 있다.

- [0018] 상기 게이트절연층과 상기 이온종 이동층 사이에 구비된 도전층을 더 포함할 수 있다.

- [0019] 상기 비휘발성 메모리 트랜지스터는 16 레벨 이상의 멀티-레벨(multi-level) 특성을 가질 수 있다.

- [0020] 상기 이온종 이동층은 단층 구조를 가질 수 있다.

- [0022] 다른 측면에 따르면, 채널요소; 상기 채널요소에 대응하는 위치에 구비된 게이트전극; 상기 채널요소와 상기 게이트전극 사이에 구비된 게이트절연층; 상기 게이트절연층과 상기 게이트전극 사이에 구비된 바이폴라 메모리층; 및 상기 채널요소를 사이에 두고 이격된 소오스 및 드레인;을 포함하는 비휘발성 메모리 트랜지스터 가 제공된다.

- [0023] 상기 게이트절연층과 상기 바이폴라 메모리층 사이에 구비된 전극층을 더 포함할 수 있다.

- [0024] 다른 측면에 따르면, 전술한 비휘발성 메모리 트랜지스터를 포함하는 시냅스 소자(synapse device)가 제공된다.

- [0025] 상기 비휘발성 메모리 트랜지스터의 게이트전극은 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)에 연결될 수 있고, 상기 비휘발성 메모리 트랜지스터의 소오스는 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)에 연결될 수 있다.

- [0026] 복수의 상기 비휘발성 메모리 트랜지스터가 복수의 열 및 복수의 행을 이루도록 배열될 수 있다.

- [0027] 상기 시냅스 소자는 복수의 제1 배선; 및 상기 복수의 제1 배선과 교차하는 복수의 제2 배선;을 포함할 수 있고, 상기 복수의 제1 배선과 상기 복수의 제2 배선의 교차점 각각에 상기 비휘발성 메모리 트랜지스터가 구비될 수 있다.

- [0028] 상기 복수의 제1 배선은 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)에 연결될 수 있고, 상기 복수의 제2 배선은 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)에 연결될 수 있다.

- [0029] 다른 측면에 따르면, 전술한 시냅스 소자를 포함하는 뇌신경모사 소자(neuromorphic device)가 제공된다.

- [0030] 상기 뇌신경모사 소자는 상기 시냅스 소자와 연결된 CMOS(complementary metal-oxide-semiconductor) 뉴런 회로를 더 포함할 수 있다.

- [0031] 다른 측면에 따르면, 전술한 비휘발성 메모리 트랜지스터의 동작방법에 있어서, 상기 게이트전국에 전압을 인가 하여 상기 이온종 이동층 내에서 이온종을 이동시키는 단계; 및 상기 비휘발성 메모리 트랜지스터를 턴-온 (turn-on) 시키는 단계;를 포함하는 비휘발성 메모리 트랜지스터의 동작방법이 제공된다.

- [0032] 상기 이온종을 이동시키는 단계에서 상기 이온종 이동층에 인가하는 전압은 약 ±5.0 V 이내의 저전압일 수 있다.

#### 발명의 효과

[0033] 멀티-레벨(multi-level) 특성을 갖는 비휘발성 메모리 트랜지스터를 구현할 수 있다. 저전압으로 동작될 수 있

는 비휘발성 메모리 트랜지스터를 구현할 수 있다. 저전압 영역에서 동작되면서 작은 사이즈로도 충분히 많은 멀티-레벨(multi-level) 특성을 나타내는 비휘발성 메모리 트랜지스터를 구현할 수 있다.

[0034] 상기 비휘발성 메모리 트랜지스터를 이용하여 다양한 전자소자 및 논리소자를 구현할 수 있다. 예컨대, 상기 비휘발성 메모리 트랜지스터를 이용하여 시냅스 소자 및 뇌신경모사 소자(neuromorphic device)를 구현할 수 있다.

### 도면의 간단한 설명

[0035] 도 1은 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터를 보여주는 단면도이다.

도 2는 본 발명의 다른 실시예에 따른 비휘발성 메모리 트랜지스터를 보여주는 단면도이다.

도 3은 본 발명의 다른 실시예에 따른 비휘발성 메모리 트랜지스터를 보여주는 단면도이다.

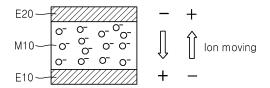

도 4는 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터에 사용될 수 있는 이온종 이동층의 저항 변화 특성을 측정하기 위한 셀 구조를 보여주는 단면도이다.

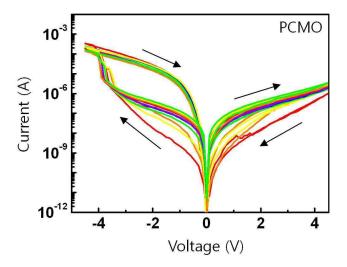

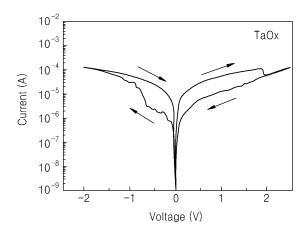

도 5 및 도 6은 도 4의 구조에서 이온종 이동층의 인가 전압에 따른 저항 변화 특성을 보여주는 그래프이다.

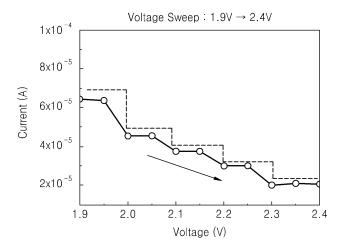

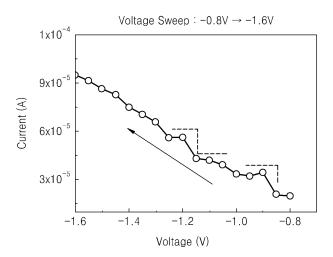

도 7 및 도 8은 도 4의 구조에 대한 전압 스윕(voltage sweep)에 따른 전류 변화를 보여주는 그래프이다.

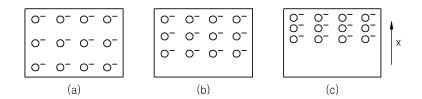

도 9a 내지 도 9c는 이온종 이동층의 다양한 이온 분포를 예시적으로 보여주는 단면도이다.

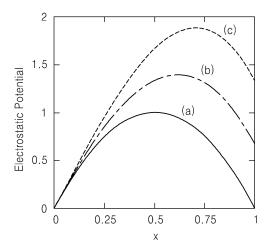

도 10은 도 9a 내지 도 9c의 이온 분포 변화에 따른 이온종 이동층의 정전위(electrostatic potential) 변화를 보여주는 그래프이다.

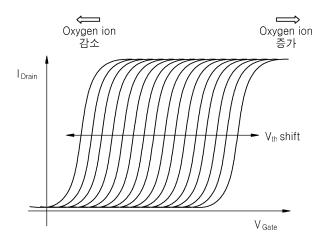

도 11은 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터의 이온종 이동층의 이온종 이동에 따른 문턱전압 변화를 보여주는 그래프이다.

도 12는 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터의 이온종 이동층의 이온종 이동에 따른 문턱전압 변화를 보여주는 시뮬레이션 결과이다.

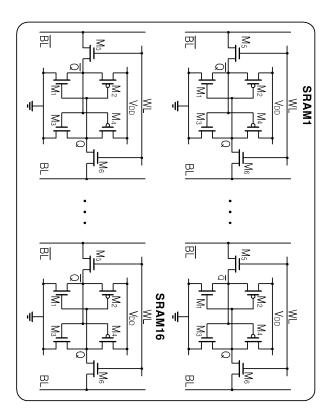

도 13은 종래의 SRAM(static random access memory)으로 16 레벨의 소자를 구성한 예를 보여주는 회로도이다.

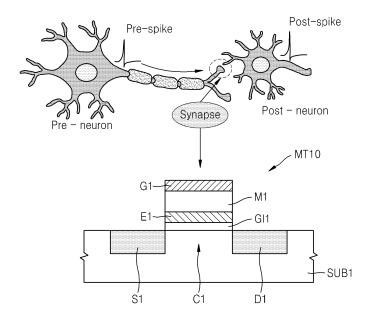

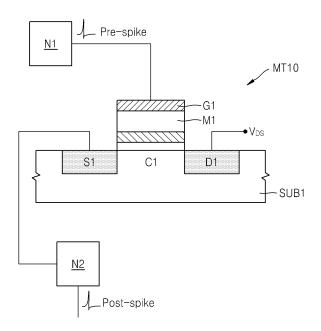

도 14는 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터를 시냅스 소자에 적용하는 경우를 보여주는 개념 도이다.

도 15는 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터를 포함하는 시냅스 소자를 보여주는 단면도이다.

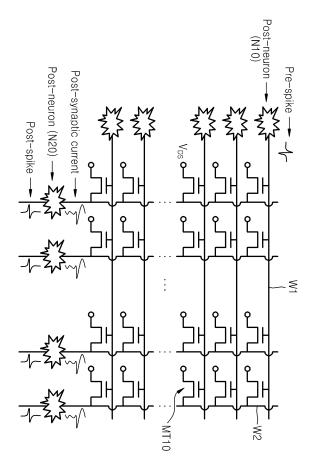

도 16은 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터를 포함하는 시냅스 어레이 소자를 보여주는 회로 도이다.

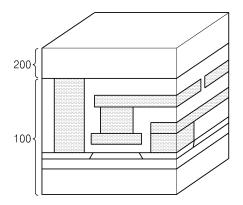

도 17은 본 발명의 실시예에 따른 시냅스 소자를 포함하는 뇌신경모사 소자(neuromorphic device)를 보여주는 사시도이다

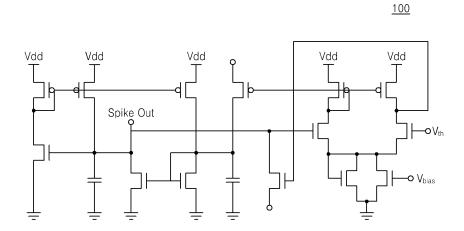

도 18은 도 17의 CMOS(complementary metal-oxide-semiconductor) 뉴런 회로의 구성을 예시적으로 보여주는 회로도이다.

## 발명을 실시하기 위한 구체적인 내용

[0036] 이하, 본 발명의 실시예들에 따른 비휘발성 메모리 트랜지스터, 이를 포함하는 소자 및 이들의 동작방법을 첨부된 도면을 참조하여 상세하게 설명한다. 첨부된 도면에 도시된 층이나 영역들의 폭 및 두께는 명세서의 명확성을 위해 다소 과장되게 도시된 것이다. 상세한 설명 전체에 걸쳐 동일한 참조번호는 동일한 구성요소를 나타낸다.

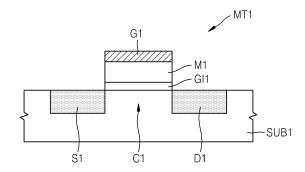

[0037] 도 1은 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터(MT1)를 보여주는 단면도이다.

[0038] 도 1을 참조하면, 채널요소(C1)가 구비되고, 채널요소(C1)에 대응하는 게이트전극(G1)이 구비될 수 있다. 채널요소(C1)와 게이트전극(G1) 사이에 게이트절연충(GI1)이 구비될 수 있다. 게이트절연충(GI1)과 게이트전극(G1) 사이에 이온종 이동충(ionic species moving layer or ionic species movable layer)(M1)이 구비될 수 있다. 채널요소(C1) 상에 게이트절연충(GI1), 이온종 이동충(M1) 및 게이트전극(G1)이 순차로 구비될 수 있다. 또한, 채널요소(C1)를 사이에 두고 서로 이격된 소오스(S1) 및 드레인(D1)이 구비될 수 있다. 소오스(S1) 및 드레인

(D1)은 채널요소(C1)의 양단에 접촉될 수 있다. 소오스(S1), 드레인(D1) 및 채널요소(C1)는 기판(SUB1) 내에 구비될 수 있다. 예컨대, 게이트전극(G1) 양측의 기판(SUB1) 영역 내에 소정의 불순물을 주입하여 소오스(S1) 및 드레인(D1)을 형성할 수 있고, 소오스(S1)와 드레인(D1) 사이의 기판(SUB1) 영역이 채널요소(채널영역)(C1)으로 정의될 수 있다. 기판(SUB1)은, 예컨대, 실리콘(Si) 기판일 수 있다.

- [0039] 이온종 이동층(M1)은 소정의 이온종(ionic species)을 가질 수 있다. 예컨대, 상기 이온종은 산소 이온(oxygen ion) 및/또는 산소 공공(oxygen vacancy)을 포함할 수 있다. 이온종 이동층(M1)의 양단(상하 양단) 사이에 인가된 전압에 따라, 이온종 이동층(M1) 내에서 상기 이온종이 이동될 수 있다. 상기 이온종의 이동에 따라, 본 실시예에 따른 비휘발성 메모리 트랜지스터(MT1)의 문턱전압이 변화될 수 있다. 이와 관련해서, 비휘발성 메모리트랜지스터(MT1)는 멀티-레벨(multi-level) 특성을 가질 수 있다. 예컨대, 비휘발성 메모리트랜지스터(MT1)는 16 레벨 이상의 멀티-레벨(multi-level) 특성을 가질 수 있다.

- [0040] 이온종 이동층(M1)은 저항성(resistive) 메모리 물질을 포함할 수 있다. 이 경우, 이온종 이동층(M1)은 산화물 저항체(oxide resistor)를 포함할 수 있다. 상기 산화물 저항체는 금속 산화물 저항체일 수 있고, 인가 전압에 따라 저항이 변하는 가변 저항 물질(variable resistance material)일 수 있다. 상기 가변 저항 물질은 바이폴라(bipolar) 메모리 물질일 수 있다. 구체적인 예로, 이온종 이동층(M1)은 PCMO(PrCaMnO), Ti 산화물, Ta 산화물, Ni 산화물, Zn 산화물, W 산화물, Co 산화물, Nb 산화물, TiNi 산화물, LiNi 산화물, InZn 산화물, V 산화물, SrZr 산화물, SrTi 산화물, Cr 산화물, Fe 산화물, Cu 산화물, Hf 산화물, Zr 산화물, Al 산화물 및 이들의 혼합물 중 적어도 어느 하나를 포함할 수 있다. 이 물질들은 형성 조건에 따라 유니폴라(mipolar) 또는 바이폴라(bipolar) 특징을 가질 수 있다. 본 실시예에서는 위 물질들의 바이폴라(bipolar) 특징을 이용할 수 있다. 또한, 상기한 물질들은 그 조성비에 따라 특성이 크게 변화될 수 있다. 따라서, 위 물질들은 저항 변화특성 및/또는 바이폴라 특성을 나타낼 수 있는 조성비를 갖는 것으로 해석되어야 한다. 일례로, Al 산화물의 경우, Al<sub>2</sub>O<sub>3</sub>와 같이 화학양론적 조성을 갖는 산화물은 유전체(절연체) 특성을 갖고, 저항 변화 특성 및/또는 바이폴라 특성을 나타내지 않을 수 있다. 따라서, 상기한 Al 산화물은 저항 변화 특성 및/또는 바이폴라 특성을 나타낼 수 있는 비화학양론적 조성을 갖는 것으로 해석될 수 있다. 이는 전술한 다른 물질에 대해서도 유사하게 적용될 수 있다. 한편, 이온종 이동층(M1)의 두께는 10~100nm 정도, 예컨대, 20~80nm 정도일 수 있다.

- [0041] 도 1에서 게이트전극(G1)에 인가된 전압과 기판(SUB1)의 몸체부(body)에 인가된 전압의 차이(이하, 전압차)에 의해 이온종 이동층(M1)의 상하 양단 사이에 전압이 인가될 수 있다. 상기 전압차에 해당하는 전압은 게이트절 연층(GI1)과 이온종 이동층(M1)에 분산되어 인가될 수 있다. 이온종 이동층(M1)에 인가된 전압에 의해 이온종 이동층(M1) 내에서 이온종이 이동될 수 있다. 기판(SUB1)의 몸체부(body)에 소정의 전압이 일정하게 인가되고 있다고 가정하면, 게이트전극(G1)에 인가된 전압에 의해 이온종 이동층(M1) 내에서 이온종이 이동된다고 할 수 있다. 다른 측면에서 설명하면, 이온종 이동층(M1)의 상하 양단 사이에 인가된 전기장(electric field)에 의해 이온종 이동층(M1)의 이온종이 이동될 수 있다. 상기 전기장은 게이트전극(G1)에 인가된 전압에 의해 발생할 수 있다.

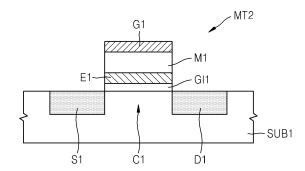

- [0042] 본 발명의 다른 실시예에 따르면, 게이트절연충(GI1)과 이온종 이동충(M1) 사이에 "도전충"을 더 구비시킬 수 있다. 그 일례가 도 2에 도시되어 있다.

- [0043] 도 2를 참조하면, 비휘발성 메모리 트랜지스터(MT2)는 게이트절연층(GI1)과 이온종 이동층(M1) 사이에 구비된 도전층(E1)을 더 포함할 수 있다. 도전층(E1)은 일종의 전극층일 수 있고, 금속이나 금속화합물 등으로 형성될 수 있다. 이온종 이동층(M1)은 두 개의 전극(E1, G1) 사이에 구비된 것으로 볼 수 있다. 이와 같이 도전층(E1)을 구비시킨 경우, 이온종 이동층(M1)에 대한 전압 인가(또는 전기장 인가)가 용이해질 수 있다. 따라서, 이온종 이동층(M1)의 이온종 이동이 용이해질 수 있다.

- [0044] 도 1 및 도 2의 이온종 이동층(M1) 내에서 이온종(예컨대, 산소 이온 및/또는 산소 공공)이 이동함에 따라, 이온종 이동층(M1)의 정전위(electrostatic potential)가 달라질 수 있고, 그에 따라, 비휘발성 메모리 트랜지스터(MT1, MT2)의 문턱전압이 변화될 수 있다. 다시 말해, 이온종 이동층(M1) 내에서 이온종이 이동함에 따라, 이온종 이동층(M1)의 이온종 분포가 변화되고, 채널요소(C1)에 대한 이온종 이동층(M1)의 전기적 영향이 변화될수 있다. 그 결과, 비휘발성 메모리 트랜지스터(MT1, MT2)의 문턱전압이 변화될수 있다. 상기 이온종이 음(-)의 이온종인 경우, 이온종 이동층(M1) 내에서 상기 음(-)의 이온종의 농도가 게이트절연층(GI1) 측으로 증가할수록 문턱전압은 증가할수 있다. 상기 이온종이 양(+)의 이온종인 경우, 이온종 이동층(M1) 내에서 상기 양(+)의 이온종의 농도가 게이트절연층(GI1) 측으로 증가할수록 문턱전압은 감소할 수 있다. 이온종 이동층(M1) 내에서 상기 이온종의 이동은 점진적으로(continuous-like or gradually) 그리고 가역적으로 이루어질 수 있다.

따라서, 비휘발성 메모리 트랜지스터(MT1, MT2)의 문턱전압도 점진적으로 그리고 가역적으로 변화될 수 있다. 다른 측면에서 설명하면, 이온종 이동층(M1)의 상하 양단 사이에 인가된 전기장(electric field)에 의해 이온종 이동층(M1)의 이온종이 이동할 수 있고, 그 결과, 이온종 이동층(M1) 내에 내부 전계(internal electric field)가 유발 또는 변화될 수 있다. 이온종 이동에 따라, 상기 내부 전계의 세기도 달라질 수 있다. 상기 내부 전계는 점진적으로 그리고 가역적으로 변화될 수 있다. 이러한 내부 전계의 변화에 의해 비휘발성 메모리 트랜지스터(MT1, MT2)의 문턱전압이 변화될 수 있다. 또한, 상기 이온종의 이동에 따라, 이온종 이동층(M1)의 소정 영역의 캐패시턴스(capacitance)가 변화될 수 있고, 이러한 캐패시턴스의 변화에 의해 문턱전압이 변화되는 것으로 여길 수도 있다. 이온종 이동층(M1)의 이온종 이동에 따른 문턱전압의 변화에 대해서는 추후에 보다 상세히 설명한다.

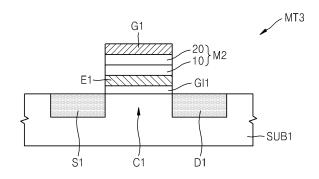

- [0045] 본 발명의 다른 실시예에 따르면, 도 1 및 도 2의 구조에서 이온종 이동층(M1)을 다층 구조로 형성할 수 있다. 그 일례가 도 3에 도시되어 있다. 도 3은 도 2의 이온종 이동층(M1)이 다층 구조를 갖는 경우이다.

- [0046] 도 3을 참조하면, 비휘발성 메모리 트랜지스터(MT3)는 다층 구조의 이온종 이동층(M2)을 포함할 수 있다. 이온종 이동층(M2)은, 예컨대, 이중층 구조를 가질 수 있다. 이 경우, 이온종 이동층(M2)은 제1 물질층(10) 및 제2 물질층(20)을 포함할 수 있다. 제1 물질층(10) 내에 산소 이온 및/또는 산소 공공(vacancy)이 존재할 수 있다. 이러한 제1 물질층(10)은 제2 물질층(20)에 대하여 "산소공급층"(oxygen supplying layer)으로 작용할 수 있다. 제1 물질층(10)은 "산소저장층"(oxygen reservoir layer)이라고 할 수도 있다. 제2 물질층(20)은 제1 물질층(10)과 유사하게 산소 이온 및/또는 산소 공공(vacancy)을 포함할 수 있다. 제2 물질층(20)은 제1 물질층(10)과 산소 이온 및/또는 산소 공공(vacancy)을 주고 받으며, 이온종 이동층(M1)의 저항 변화를 유도하는 층일 수 있다. 이런 점에서, 제2 물질층(20)은 "산소교환층"(oxygen exchange layer)이라 할 수 있다. 제2 물질층(20)의 산소 농도는 제1 물질층(10)의 산소 농도보다 높을 수 있다.

- [0047] 도 4는 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터에 사용될 수 있는 이온종 이동층의 저항 변화 특성을 측정하기 위한 셀 구조를 보여준다.

- [0048] 도 4를 참조하면, 이온종 이동층(M10)이 두 전극(이하, 제1 및 제2 전극)(E10, E20) 사이에 구비되어 있다. 이온종 이동층(M10)은 다량의 산소 이온을 가질 수 있다. 산소 이온은 제1 및 제2 전극(E10, E20) 사이에 인가된 전압에 의해 이동할 수 있다. 예컨대, 제1 전극(E10)에 양(+)의 전압이 인가되고, 제2 전극(E20)에 음(-)의 전압이 인가되면, 산소 이온들은 제1 전극(E10) 측으로 어느 정도 이동할 수 있다. 반대로, 제1 전극(E10)에 음(-)의 전압이 인가되고, 제2 전극(E20)에 양(+)의 전압이 인가되면, 산소 이온들은 제2 전극(E20) 측으로 어느 정도 이동할 수 있다. 만약, 동일한 전압 신호가 반복해서 두 전극(E10, E20) 사이에 인가되면, 상기 신호가 인가된 횟수만큼 산소 이온들이 어느 한 방향으로 점진적으로(누적하여) 이동할 수 있다. 이온종 이동층(M10)의 산소 공공(vacancy)(미도시)은 산소 이온과 반대 방향으로 이동할 수 있다. 산소 이온은 음(-)의 전하를 갖는다고할 수 있고, 산소 공공은 양(+)의 전하를 갖는다고 할 수 있다.

- [0049] 도 5 및 도 6은 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터에 사용될 수 있는 이온종 이동층의 인가 전압에 따른 저항 변화 특성을 보여주는 그래프이다. 도 5 및 도 6은 도 4의 구조에 대한 전압-전류 특성 변화를 보여준다. 도 5는 도 4의 이온종 이동층(M10)이 PCMO층인 경우이고, 도 6은 도 4의 이온종 이동층(M10)이 TaOx층인 경우이다. 도 5는 온/오프(ON/OFF) 동작, 즉, 세트/리세트(set/reset) 동작을 반복하면서 측정한 결과를 보여주고, 도 6은 한 번의 온/오프(ON/OFF) 스윕(sweep) 동작에 대한 결과를 보여준다.

- [0050] 도 5를 참조하면, 저항 변화 그래프의 커런트(current) 레벨이 여러 개로 나눠지는 것을 확인할 수 있다. 이는 이온종 이동층(M10)이 멀티-레벨 특성을 가질 수 있다는 것을 의미한다. 또한, PCMO층의 저항 변화는 약 ±4.0 V 이내의 범위 내에서 이루어지는 것을 알 수 있다.

- [0051] 도 6을 참조하면, TaOx층의 저항 변화가 ±2.5V 이내의 전압 범위 내에서 이루어지는 것을 알 수 있다. 이는 이 온종 이동층(M10)의 저항 변화가 ±2.5 V 이내의 저전압 범위에서 이루어질 수 있음을 의미한다.

- [0052] 도 7 및 도 8은 도 4의 구조에 대한 전압 스윕(voltage sweep)에 따른 전류 변화를 보여주는 그래프이다. 도 7은 두 전극(E10, E20) 사이의 전압을 1.9 V에서 2.4 V로 증가시키면서 전류 변화를 측정한 결과이고, 도 8은 두 전극(E10, E20) 사이의 전압을 -0.8 V에서 -1.6 V로 증가(절대값 증가)시키면서 전류 변화를 측정한 결과이다.

- [0053] 도 7 및 도 8을 참조하면, 전압 스윕(voltage sweep)에 따라 전류가 점진적으로 감소하거나 증가하는 것을 알수 있다. 이는 전압 스윕(voltage sweep) 방향에 따라, 도 4 구조의 저항이 점차 증가하거나 감소할 수 있음을

의미한다.

- [0054] 도 9a 내지 도 9c는 이온종 이동층(M10)의 다양한 이온 분포를 예시적으로 보여주는 단면도이다. 도 9a에서 도 9c로 갈수록 산소 이온이 위쪽으로(즉, 상면측으로) 축적되는 것을 알 수 있다. 이온종 이동층(M10) 내에서 산소 이온의 분포가 달라진다는 것은 소정 영역에서 산소 이온의 밀도가 변화된다는 것을 의미한다. 이온종 이동층(M10)에 인가된 전압에 따라, 이온종 이동층(M10)의 이온 분포가 점진적으로 변화될 수 있다.

- [0055] 도 10은 도 9a 내지 도 9c의 이온 분포 변화에 따른 이온종 이동층(M10)의 정전위(electrostatic potential) 변화를 보여주는 그래프이다. 도 10의 (a), (b), (c) 그래프는 각각 도 9a, 도 9b 및 도 9c에 대응된다. 도 10의 결과로부터, 이온 분포 변화에 따라 정전위가 점진적으로 변화되는 것을 확인할 수 있다.

- [0056] 도 11은 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터의 이온종 이동층의 이온종 이동에 따른 문턱전압 변화를 보여주는 그래프이다.

- [0057] 도 11을 참조하면, 이온종 이동층(도 1 및 도 2의 M1)의 채널영역에 가까운 부분(여기서는, 하단부)에 산소 이온이 많아질수록 문턱전압은 양(+)의 방향으로 점진적으로 증가할 수 있다. 이는 이온종 이동층(M1)의 채널영역에 가까운 부분에 산소 이온이 많아질수록 채널영역에 양(+)의 전하가 축적될 수 있고, 결과적으로, n-채널을 형성하는데 더 높은 전압이 요구되기 때문이다. 도 11에서 산소 이온의 다소(많고 적음)는 산소 공공의 다소(많고 적음)와 반대이다. 그러므로, 이온종 이동층(M1)의 채널영역에 가까운 부분(여기서는, 하단부)에 산소 공공의 약이 적어질수록 문턱전압은 양(+)의 방향으로 점진적으로 증가할 수 있다. 산소 이온이나 산소 공공이 점진적으로 이동함에 따라, 문턱전압도 그에 대응하여 점진적으로 변화될 수 있고, 이러한 이온종의 이동 및 문턱전압 변화는 "비휘발성"을 가질 수 있다. 즉, 전압을 인가하여 이온종을 이동시키면, 상기 전압을 제거하여도, 최종 상태가 지속적으로 유지될 수 있다.

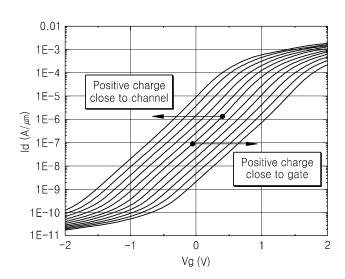

- [0058] 도 12는 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터의 이온종 이동층의 이온종 이동에 따른 문턱전압 변화를 보여주는 시뮬레이션(simulation) 결과이다. 양(+)의 이온종을 채널영역 쪽으로 이동시키면서 또는 게이 트전극 쪽으로 이동시키면서 게이트전압(Vg)-드레인전류(Id) 특성을 평가하였다.

- [0059] 도 12를 참조하면, 양(+)의 이온종(즉, positive charge)이 게이트전극에 가까이 이동할수록 메모리 트랜지스터의 문턱전압은 점차 증가하였다. 양(+)의 이온종이 채널영역에 가까이 이동할수록 문턱전압은 점차 감소하였다.이러한 결과는 도 11의 그래프와 유사하다. 또한, 도 12의 그래프에서는 소정의 게이트전압, 예컨대, 1V의 게이트전압에서 멀티-레벨(multi-level)의 드레인전류가 출력되는 것을 알 수 있다. 문턱전압의 변화에 따라, 멀티-레벨의 드레인전류가 출력될 수 있다.

- [0060] 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터는 낮은 동작전압(예컨대, 약 ±5.0 V 이내의 동작전압)을 가지면서 동시에 작은 사이즈에서도 충분히 큰 멀티-레벨(multi-level) 특성을 나타낼 수 있다. 즉, 도 5 및 도 6에서 설명한 바와 같이, 이온종 이동층의 저항 변화는 약 ±4.0 V 이내 또는 약 ±2.5 V 이내의 저전압 범위에서 이루어질 수 있으므로, 상기 비휘발성 메모리 트랜지스터는 낮은 전압 범위에서 동작될 수 있다. 또한, 이온종 이동층의 이온종을 점진적으로 이동시킴으로써, 도 11 및 도 12에서 설명한 바와 같이, 메모리 트랜지스터의 문턱전압이 점진적으로 변화되기 때문에, 16 레벨 이상의 멀티-레벨(multi-level) 특성을 용이하게 구현할 수 있다.

- [0061] 플래시 메모리의 경우, 전자의 터널 주입(tunnel injection)을 이용하기 때문에, 동작전압이 10~20 V 정도로 높은 단점이 있다. 또한, 플로팅 게이트에 트랩(trap) 되는 전자의 수가 제한적이기 때문에, 멀티-비트(multibit) 특성을 구현하기 어려운 문제가 있다. 그러나, 본 발명의 실시예에 따르면, 상기한 플래시 메모리의 문제 점들을 극복하고, 저전압 영역에서 동작되면서 작은 사이즈로도 충분히 큰 멀티-레벨(multi-level) 특성을 나타 내는 비휘발성 소자를 구현할 수 있다.

- [0062] 도 13은 종래의 SRAM(static random access memory)으로 16 레벨(4 bit)의 소자를 구성한 예를 보여주는 회로 도이다.

- [0063] 도 13을 참조하면, 종래의 SRAM으로 16 레벨(4 비트)의 소자를 구성하려면, 16개의 SRAM이 필요하고, 이와 더불어 주변회로(미도시)가 요구된다. 그리고, 각각의 SRAM은 6개의 트랜지스터를 포함한다. 따라서, 종래의 SRAM으로 16 레벨(4 비트)의 소자를 구성하려면, 최소 96개의 트랜지스터가 요구된다.

- [0064] 그러나, 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터는, 하나의 트랜지스터만으로 16 레벨 이상의 멀티-레벨을 구현할 수 있다. 따라서, 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터를 사용하여 소정의

회로를 구성할 경우, 필요한 단위 소자의 수를 획기적으로 줄일 수 있고, 회로의 구성을 단순화할 수 있으며, 전체 시스템의 사이즈를 크게 줄일 수 있다.

- [0065] 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터는 다양한 전자장치 및 논리소자 등에 여러 가지 목적으로 사용될 수 있다. 특히, 상기 비휘발성 메모리 트랜지스터는 시냅스(synapse) 소자/회로에 적용될 수 있다. 시냅스는 뇌신경 세포 간을 연결하는 연접부로, 학습과 기억에 중요한 역할을 한다. 시냅스를 통해 전달 신호가 흐를 때마다 시냅스가 강화되는 것과 마찬가지로, 본 실시예의 비휘발성 메모리 트랜지스터의 게이트전국에 전압이 가해지면 이온종 이동층의 전기적 특성이 변화되면서 트랜지스터의 문턱전압이 점진적으로(누적하여) 변화될수 있다. 또한, 문턱전압의 변화는 "비휘발성"을 가질 수 있다. 따라서, 본 발명의 실시예들에 따른 비휘발성 메모리 트랜지스터는 시냅스 소자/회로에 적용될 수 있다. 상기 비휘발성 메모리 트랜지스터는 16 레벨 이상의 멀티-레벨 특성을 가질 수 있고, 또한 저전압 범위에서 동작할 수 있기 때문에, 이를 이용하여 시냅스 소자/회로를 구성할 경우, 소자/회로의 크기를 크게 줄일 수 있고 소비 전력을 낮출 수 있다. 또한, 저전압에서 동작되기 때문에, 신뢰성을 높일 수 있다.

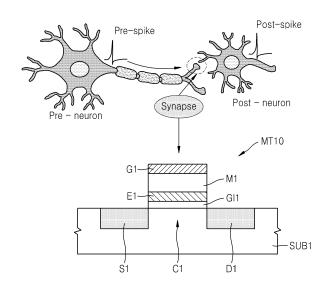

- [0066] 도 14는 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터(MT10)를 시냅스 소자에 적용하는 경우를 보여주는 개념도이다.

- [0067] 도 14를 참조하면, 프리-뉴런(pre-neuron)과 포스트-뉴런(post-neuron) 사이의 연결부인 시냅스를 회로적으로 구성할 때, 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터(MT10)를 적용할 수 있다. 프리-뉴런(pre-neuron)은 프리-스파이크(pre-spike) 신호를 시냅스에 입력할 수 있고, 시냅스는 소정의 시냅틱 신호(synaptic signal)를 포스트-뉴런(post-neuron)으로 전달할 수 있으며, 포스트-뉴런(post-neuron)은 포스트-스파이크 (post-spike) 신호를 발생할 수 있다. 시냅스가 프리-뉴런(pre-neuron)과 포스트-뉴런(post-neuron)을 연결하는 것과 유사하게, 비휘발성 메모리 트랜지스터(MT10)는 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)와 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)를 연결하는 역할을 할 수 있다. 이러한 구성을 회로적으로 도시하면 도 15와 같을 수 있다.

- [0068] 도 15를 참조하면, 비휘발성 메모리 트랜지스터(MT10)의 게이트전극(G1)은 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)(N1)에 연결될 수 있다. 비휘발성 메모리 트랜지스터(MT10)의 소오스(S1)는 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)(N2)에 연결될 수 있다. 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)(N1)로부터 프리-스파이크(pre-spike) 신호가 게이트전극(G1)에 인가될 수 있고, 소오스(S1)를 통해 포스트-시냅틱 전류(post-synaptic current)가 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)(N2)로 흐를 수 있다. 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)(N2)로부터 포스트-스파이크(post-spike) 신호가 발생할 수 있다. 한편, 트랜지스터(MT10)의 드레인(D1)에는 소정의 전압(VDS)이 일정하게 인가될 수 있다. 즉, 소정의 정전압(constant voltage)(VDS)이 드레인(D1)에 인가될 수 있다.

- [0069] 게이트전극(G1)에 프리-스파이크(pre-spike) 신호가 반복해서 인가됨에 따라, 트랜지스터(MT10)의 문턱전압이 양(+)의 방향 또는 음(-)의 방향으로 점진적으로 변화될 수 있고, 문턱전압의 변화가 소정의 임계점을 넘어가면, 프리-스파이크(pre-spike) 신호에 의해 트랜지스터(MT10)가 턴-온(turn-on) 될 수 있다. 이때, 소오 스(S1)를 통해 포스트-시냅틱 전류(post-synaptic current)가 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)(N2)로 흐를 수 있다.

- [0070] 도 16은 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터(MT10)를 적용한 시냅스 어레이 소자를 보여주는 회로도이다.

- [0071] 도 16을 참조하면, 복수의 비휘발성 메모리 트랜지스터(MT10)가 복수의 열 및 복수의 행을 이루도록 배열될 수 있다. 복수의 제1 배선(W1)이 배열될 수 있고, 이와 교차하는 복수의 제2 배선(W2)이 배열될 수 있으며, 제1 배선(W1)과 제2 배선(W2)의 교차점에 메모리 트랜지스터(MT10)가 구비될 수 있다. 복수의 제1 배선(W1)은 메모리트랜지스터(MT10)의 게이트전극에 연결될 수 있고, 복수의 제2 배선은 메모리트랜지스터(MT10)의 소오스에 연결될 수 있다. 제1 배선(W1)은 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)(N10)에 연결될 수 있고, 제2 배선(W2)은 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)(N20)에 연결될 수 있다. 한편, 메모리트랜지스터(MT10)의 드레인에는 소정의 전압(VDS)이 인가될 수 있다.

- [0072] 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit)(N10)로부터 제1 배선(W1)을 통해 메모리 트랜지스터 (MT10)의 게이트전극에 프리-스파이크(pre-spike) 신호가 인가될 수 있다. 메모리 트랜지스터(MT10)의 소오스를 통해 포스트-시냅틱 전류(post-synaptic current)가 포스트-시냅틱 뉴런 회로(post-synaptic neuron

circuit)(N20)로 흐를 수 있다. 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit)(N20)로부터 포스트-스파이크(post-spike) 신호가 발생할 수 있다.

- [0073] 도 17은 본 발명의 실시예에 따른 시냅스 소자를 포함하는 뇌신경모사 소자(neuromorphic device)를 예시적으로 보여주는 사시도이다.

- [0074] 도 17을 참조하면, 뇌신경모사 소자(neuromorphic device)는 CMOS 뉴런 회로(complementary metal-oxide-semiconductor neuron circuit)(100)와 이와 연결된 시냅스 소자(200)를 포함할 수 있다. CMOS 뉴런 회로(10 0)는 소정의 기판(예컨대, Si 기판)에 구비될 수 있다. CMOS 뉴런 회로(100)는 프리-시냅틱 뉴런 회로(pre-synaptic neuron circuit) 및 포스트-시냅틱 뉴런 회로(post-synaptic neuron circuit) 등을 포함할 수 있다. 시냅스 소자(200)는 본 발명의 실시예에 따른 것으로, 예컨대, 도 16에서 설명한 바와 같은 어레이 구조를 가질수 있다. 편의상, 여기서는, 시냅스 소자(200)를 단순하게 도시하였다. 도 17의 뇌신경모사 소자(neuromorphic device)의 구조는 예시적인 것이고, 이는 매우 다양하게 변화될 수 있다.

- [0075] 도 17의 CMOS 뉴런 회로(100)는, 예컨대, 도 18에 도시된 바와 같은 회로 구성을 가질 수 있다. CMOS 뉴런 회로 (100)의 구성은 잘 알려진바, 이에 대한 자세한 설명은 생략한다.

- [0076] 본 발명의 실시예들에 따른 비휘발성 메모리 트랜지스터는 다양한 전자소자, 논리소자 등에 적용될 수 있다. 예 컨대, 전술한 바와 같이, 상기 비휘발성 메모리트랜지스터는 시냅스 소자(synapse device)에 적용될 수 있고, 상기 시냅스 소자는 뇌신경모사 소자(neuromorphic device)에 적용될 수 있다. 이와 관련된 응용 분야로는 동시 통역 등이 있을 수 있다. 또한, 상기 비휘발성 메모리 트랜지스터는 하나의 단위 유닛으로 멀티-레벨(multilevel)을 동시에 연산하는 멀티-밸류 로직(multi-valued logic)에 응용될 수 있다. 이 경우, 연산 속도를 증가시킬 수 있고, 소자의 사이즈를 감소시킬 수 있다. 멀티-밸류(multi-value)를 필요로 하는 회로 구성에 있어서, 하이브리드(hybrid) CMOS/multi-value circuits으로 아날로그 컴퓨테이션(analog computation)을 수행하는 소자에 이용 가능하다. 또한, 인공지능(artificial intelligence) 기능을 갖는 회로 또는 칩, 신경 네트워크 (neural network)로 동작하는 회로 또는 칩, 기존 디지털 방식의 정보 처리 한계를 극복하기 위한 기술, 뉴런과 같은(neuron-like) 동작이 가능한 회로 또는 칩, 메모리와 스위칭이 동시에 가능한 소자 등에 본 발명의 실시예에 따른 비휘발성 메모리 트랜지스터를 적용할 수 있다.

- [0077] 한편, 본 발명의 실시예에 다른 비휘발성 메모리 트랜지스터의 동작방법을 간략히 정리하면 다음과 같다. 상기 비휘발성 메모리 트랜지스터의 동작방법은 게이트전극에 전압을 인가하여 이온종 이동층 내에서 이온종을 이동시키는 단계와, 상기 비휘발성 메모리 트랜지스터를 턴-온(turn-on) 시키는 단계를 포함할 수 있다. 이때, 상기 이온종을 이동시키는 단계에서 상기 이온종 이동층에 인가하는 전압은 약 ±5.0 V 이내의 저전압일 수 있다. 보다 구체적으로 설명하면, 도 1 내지 도 3 및 도 14의 구조에서 게이트전극(G1)에 소정의 전압을 인가하여 이온종 이동층(M1, M2) 내에서 이온종을 이동시킬 수 있다. 이러한 이온종 이동에 의해 메모리 트랜지스터(MT1, MT2, MT3, MT10)의 문턱전압이 변화될 수 있다. 상기 전압을 게이트전극(G1)에 반복해서 인가하여, 상기 문턱전압을 점진적으로 변화시킬 수 있다. 예컨대, 상기 문턱전압을 양(+)의 방향 또는 음(-)의 방향으로 점진적으로 변화시킬 수 있다. 상기 문턱전압의 변화가 소정의 임계점을 넘어가면, 상기 전압에 의해 메모리 트랜지스터 (MT1, MT2, MT3, MT10)가 턴-온(turn-on) 될 수 있다. 이에 따라, 소오스(S1)를 통해 소정의 신호(전류/전압신호)가 출력될 수 있다. 그러나 여기서 설명한 동작방법은 예시적인 것이고, 적용 분야 및 목적에 따라 다양하게 변화될 수 있다.

- [0078] 상기한 설명에서 많은 사항이 구체적으로 기재되어 있으나, 그들은 발명의 범위를 한정하는 것이라기보다, 구체적인 실시예의 예시로서 해석되어야 한다. 예들 들어, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자라면, 도 1 내지 도 3의 비휘발성 메모리 트랜지스터의 구성은 다양하게 변형될 수 있음을 알 수 있을 것이다. 구체적인 예로, 게이트절연층(GI1)과 게이트전극(G1) 사이에 이온종 이동층(M1, M2) 및 도전층(E1) 이외에 다른 물질층이 더 구비될 수 있고, 소오스/드레인(S1, D1) 및 채널요소(C1)의 구성도 다양하게 변형될 수 있음을 알수 있을 것이다. 또한, 도 15 내지 도 17의 시냅스 소자 및 이를 포함하는 장치의 구성도 다양하게 변형될 수 있음을 알 수 있을 것이다. 때문에 본 발명의 범위는 설명된 실시예에 의하여 정하여 질 것이 아니고 특허 청구범위에 기재된 기술적 사상에 의해 정하여져야 한다.

## 부호의 설명

[0079] <도면의 주요 부분에 대한 부호의 설명>

C10 : 채널요소(채널영역) D1 : 드레인

E1 : 도전층 E10, E20 : 전극

G1 : 게이트전극 GI1 : 게이트절연층

M1, M2, M10 : 이온종 이동층 MT1, MT2, MT3 : 메모리 트랜지스터

N1, N10 : 프리-시냅틱 회로 N2, N20 : 포스트-시냅틱 회로

S1 : 소오스 SUB1 : 기판

100 : CMOS 뉴런 희로 200 : 시냅스 소자

# 도면

# 도면1

# 도면2

# *도면5*

# 도면8

# 도면11