(12)发明专利

(10)授权公告号 CN 104798249 B

(45)授权公告日 2019.04.09

(21)申请号 201380059282.6

(72)发明人 D·恩雅尔

(22)申请日 2013.11.12

(74)专利代理机构 上海专利商标事务所有限公司 31100

(65)同一申请的已公布的文献号

申请公布号 CN 104798249 A

代理人 袁逸

(43)申请公布日 2015.07.22

(51)Int.Cl.

H01P 5/16(2006.01)

(30)优先权数据

13/678,277 2012.11.15 US

(56)对比文件

EP 0374427 A1,1989.10.24,

JP 2000124712 A,2000.04.28,

JP 2000307314 A,2000.11.02,

CN 102637938 A,2012.08.15,

Fernando Noriega等.《Designing LC

Wilkinson power splitters》.《RF Design》

.2002,第25卷(第8期),18-24.

(85)PCT国际申请进入国家阶段日

2015.05.13

审查员 赵峻

(86)PCT国际申请的申请数据

PCT/US2013/069753 2013.11.12

权利要求书2页 说明书5页 附图6页

(87)PCT国际申请的公布数据

W02014/078334 EN 2014.05.22

(73)专利权人 高通股份有限公司

地址 美国加利福尼亚州

(54)发明名称

具有灵活输出间距的紧凑功率分配器/合成器

(57)摘要

公开了一种具有灵活端口间距的紧凑功率分配器/合成器(300)。在一示例性实施例中，一种装置包括具有第一、第二和第三端口的三端口电路和配置成将该第二和第三端口耦合到接地的匹配电路(306)。该匹配电路包括连接在第一端口与第二端口之间的第一传输线(302)、连接在该第一端口与第三端口之间的第二传输线(304)、连接在该第二端口与第一节点之间的第一匹配电路(402)、连接在该第一节点与该第三端口之间的第二匹配电路(404)、以及连接在该第一节点与接地之间的第三匹配电路(406)。

1. 一种电子设备,包括:

具有耦合到第二和第三端口的第一端口的三端口电路;以及

串联连接在所述第二和第三端口之间的匹配电路,所述匹配电路配置成将所述第二和第三端口耦合到接地,所述设备形成双向功率合成器/分配器。

2. 如权利要求1所述的电子设备,其特征在于,所述匹配电路包括:

耦合在所述第二端口与第一节点之间的第一匹配电路;

耦合在所述第一节点与所述第三端口之间的第二匹配电路;以及

耦合在所述第一节点与接地之间的第三匹配电路。

3. 如权利要求2所述的电子设备,其特征在于,进一步包括:

耦合在所述第一端口与所述第二端口之间的第一传输线;以及

耦合在所述第一端口与所述第三端口之间的第二传输线。

4. 如权利要求3所述的电子设备,其特征在于,所述第一和第二传输线及所述第一、第二和第三匹配电路配置成提供在所述第一端口处所见的、匹配于选定的特性阻抗值的组合阻抗值。

5. 如权利要求4所述的电子设备,其特征在于,所述选定的特性阻抗值被设为50欧姆。

6. 如权利要求3所述的电子设备,其特征在于,所述第一、第二和第三匹配电路配置成调节所述第一和第二传输线的尺寸。

7. 如权利要求2所述的电子设备,其特征在于,所述第一和第二匹配电路配置成增大所述第二和第三端口之间的间距。

8. 如权利要求3所述的电子设备,其特征在于,所述第一和第二传输线及所述第一、第二和第三匹配电路配置成提供所述第二端口处所见的、匹配于选定的特性阻抗值的组合阻抗值。

9. 如权利要求8所述的电子设备,其特征在于,所述选定的特性阻抗值被设定为50欧姆。

10. 如权利要求1所述的电子设备,其特征在于,所述设备形成双向无源功率合成器/分配器。

11. 如权利要求10所述的电子设备,其特征在于,所述双向无源功率合成器/分配器配置成用于收发机中。

12. 一种电子设备,包括:

用于提供具有耦合到第二和第三端口的第一端口的三端口电路的装置;以及

串联连接在所述第二端口和第三端口之间的用于匹配的装置,所述用于匹配的装置配置成将所述第二和第三端口耦合到接地,所述设备形成双向功率合成器/分配器。

13. 如权利要求12所述的电子设备,其特征在于,所述用于匹配的装置包括:

用于耦合所述第二端口与第一节点的装置;

用于耦合所述第一节点与所述第三端口的装置;以及

用于将接地耦合到所述第一节点的装置。

14. 如权利要求13所述的电子设备,其特征在于,进一步包括:

用于在所述第一和第二端口之间耦合第一传输线的装置;以及

用于在第一和第三端口之间耦合第二传输线的装置。

15. 如权利要求14所述的电子设备,其特征在于,所述第一传输线、所述第二传输线、所述用于耦合第二端口和所述第一节点的装置、所述用于耦合第一节点和所述第三端口的装置、以及所述用于耦合接地的装置配置成提供在所述第一端口处所见的、匹配于选定的特性阻抗值的组合阻抗值。

16. 如权利要求14所述的电子设备,其特征在于,所述用于耦合第二端口和所述第一节点的装置、所述用于耦合第一节点和所述第三端口的装置、以及所述用于耦合接地的装置配置成调节所述第一和第二传输线的尺寸。

17. 如权利要求14所述的电子设备,其特征在于,所述用于耦合第二端口和所述第一节点的装置、所述用于耦合第一节点和所述第三端口的装置配置成增大所述第二和第三端口之间的间距。

18. 如权利要求14所述的电子设备,其特征在于,所述第一传输线、所述第二传输线、所述用于耦合第二端口和所述第一节点的装置、所述用于耦合第一节点和所述第三端口的装置、以及所述用于耦合接地的装置配置成提供在所述第二端口处所见的、匹配于选定的特性阻抗值的组合阻抗值。

19. 如权利要求12所述的电子设备,其特征在于,所述设备形成双向无源功率合成器/分配器。

20. 如权利要求19所述的电子设备,其特征在于,所述双向无源功率合成器/分配器配置成用于收发机中。

## 具有灵活输出间距的紧凑功率分配器/合成器

### 背景技术

[0001] 领域

[0002] 本申请一般涉及模拟前端的操作和设计，并且尤其涉及在模拟前端中使用的功率分配器/合成器的操作和设计。

[0003] 背景

[0004] 具有多个天线的波束成形收发机一般被用以在工作于毫米波长的无线链路上发射和接收信号，例如，在60GHz发射和接收信号。几乎所有波束成形收发机都利用功率分配器/合成器网络。在信号发射(Tx)期间，该分配器/合成器网络被用以在多个天线之间划分发射信号的功率。在信号接收(Rx)期间，该分配器/合成器网络被用以组合从多个天线接收的信号的功率。

[0005] 一种常规功率分配器/合成器被称为Wilkinson功率分配器/合成器。Wilkinson功率分配器/合成器是能够在Tx和Rx功能之间被共享、没有功耗、具有良好线性度和良好噪声性能的无源网络。遗憾的是，与Wilkinson功率分配器/合成器相关联的一个问题在于其使用了较大的电路面积。与Wilkinson功率分配器/合成器相关联的另一问题在于，其电路实现一般会使得端口引脚相距较近，这会导致布局复杂度增大。

[0006] 相应地，将会期望有简单且低成本的功率分配器/合成器，其具有与Wilkinson功率分配器/合成器相当的性能，但是利用更小的电路面积并且提供更大的灵活性以减小布局复杂度。

[0007] 附图简述

[0008] 通过参照以下结合附图考虑的描述，本文中所描述的以上方面将变得更易于明了，在附图中：

[0009] 图1示出了包括功率分配器/合成器的示例性实施例的宽带直接转换接收机；

[0010] 图2示出了常规Wilkinson功率分配器/合成器的详细示图；

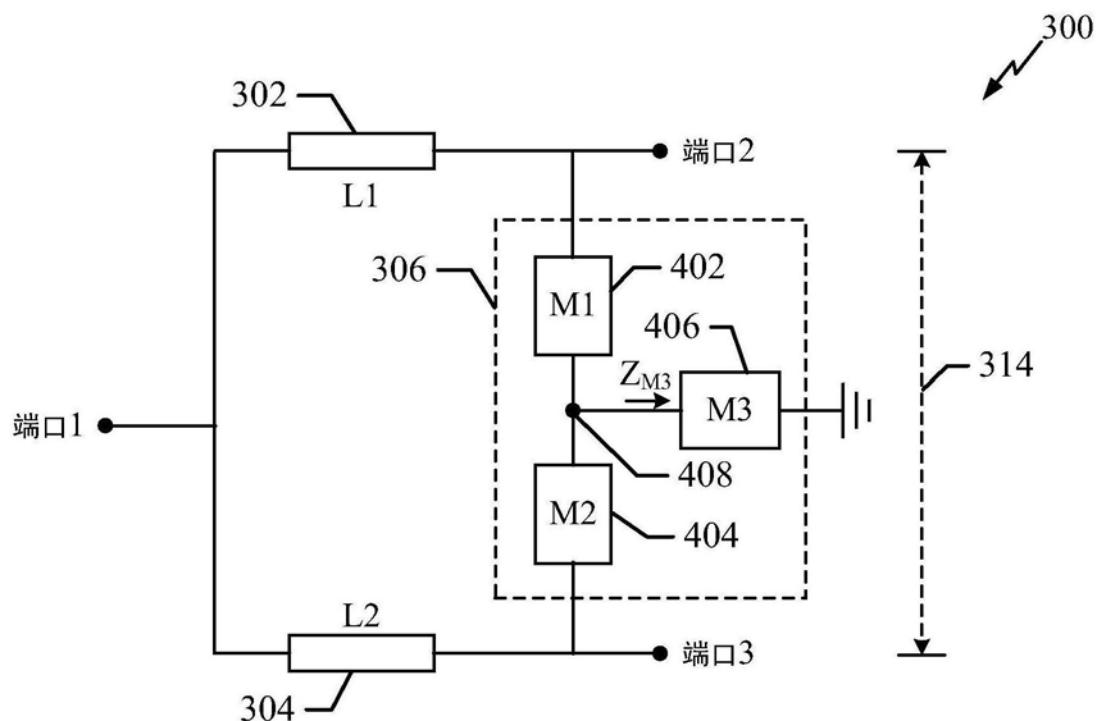

[0011] 图3示出了分配器/合成器的示例性实施例；

[0012] 图4示出了图3中所示的分配器/合成器的详细示例性实施例；

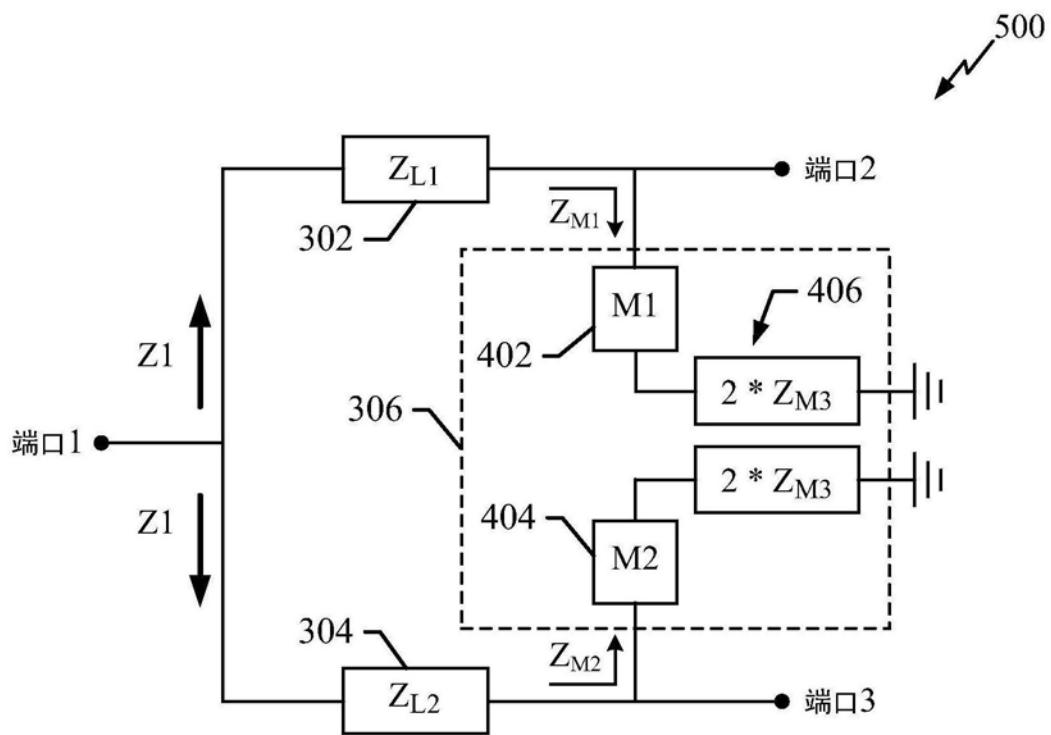

[0013] 图5示出了图4中所示的分配器/合成器的示例性偶模表示；

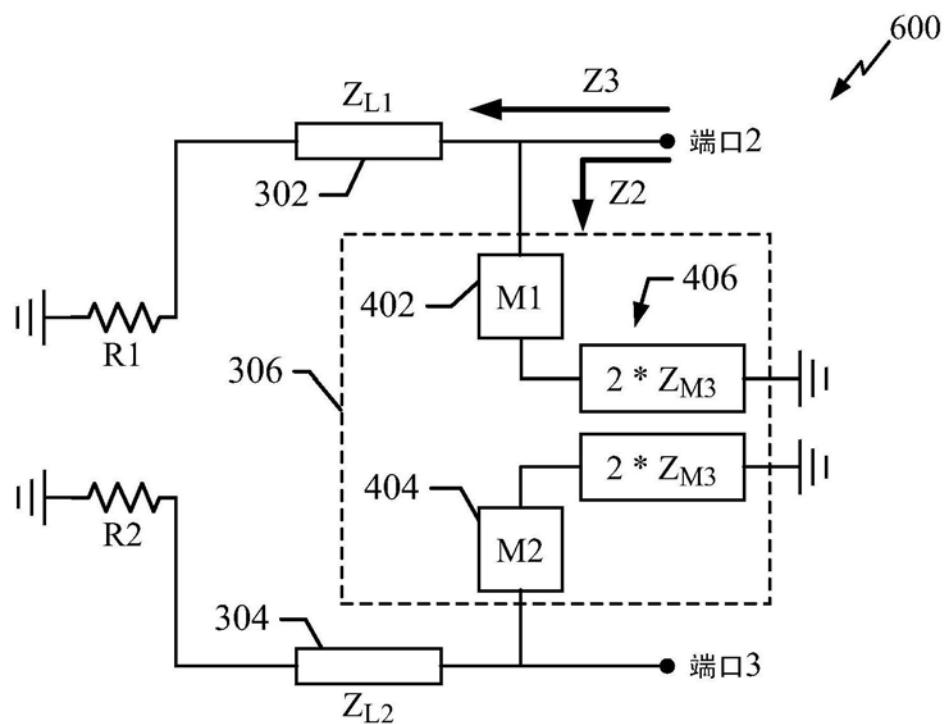

[0014] 图6示出了图4中所示的分配器/合成器的示例性偶模表示；

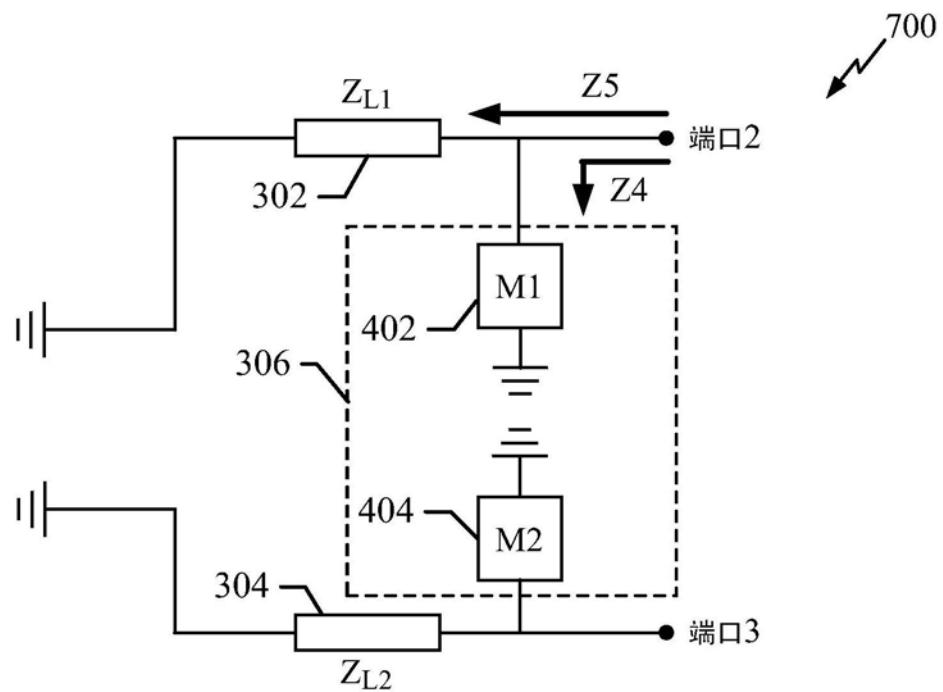

[0015] 图7示出了图4中所示的分配器/合成器的示例性奇模表示；

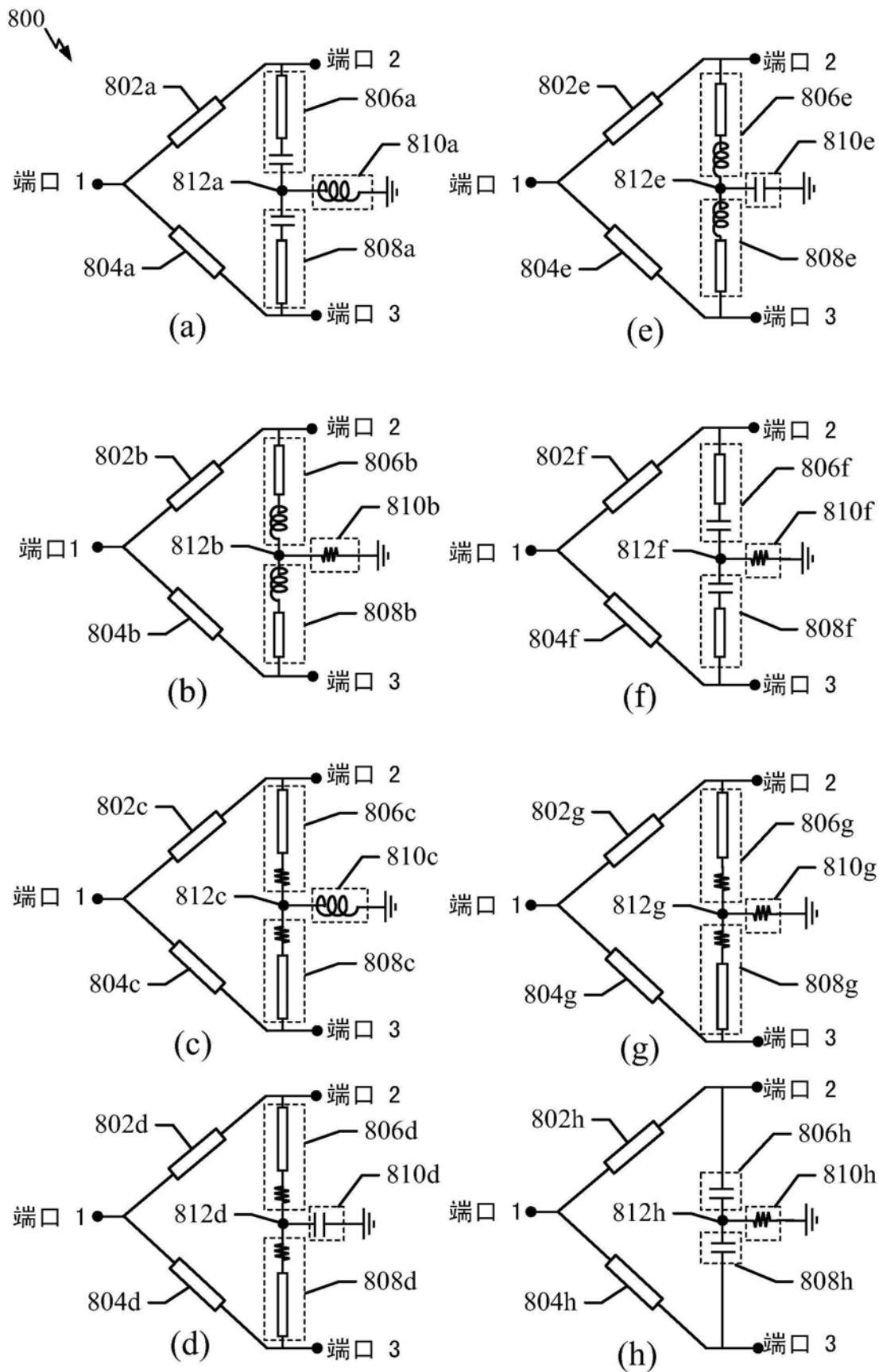

[0016] 图8示出了分配器/合成器配置的示例性实施例；并且

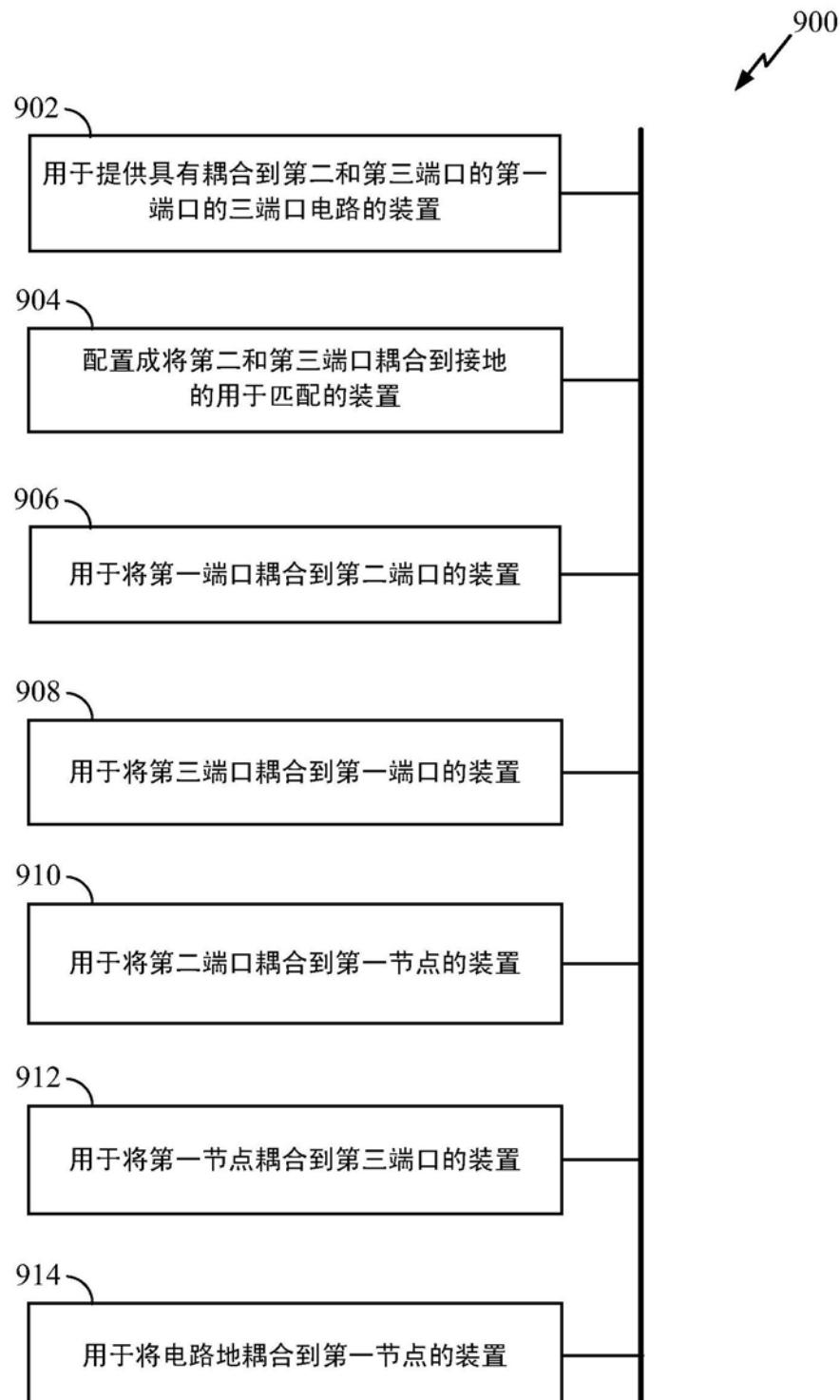

[0017] 图9示出了分配器/合成器设备的示例性实施例。

[0018] 详细描述

[0019] 下面结合附图阐述的详细描述旨在作为对本发明的示例性实施例的描述，而非旨在代表可在其中实践本发明的仅有实施例。贯穿本描述使用的术语“示例性”意指“用作示例、实例或解说”，并且不应一定解释成优于或胜于其它示例性实施例。本详细描述包括具体细节以提供对本发明的示例性实施例的透彻理解。对于本领域技术人员将显而易见的是，没有这些具体细节也可实践本发明的示例性实施例。在一些实例中，公知的结构和设备

以框图形式示出以免湮没本文中给出的示例性实施例的新颖性。

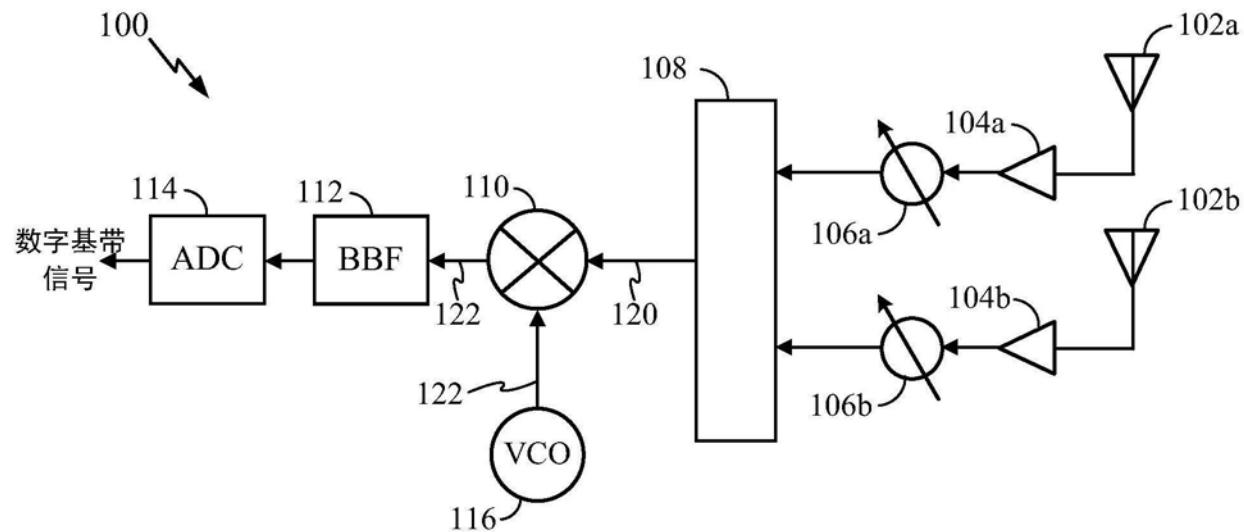

[0020] 图1示出了在无线设备中使用的采用RF波束成形的宽带直接转换接收机100。多个天线102(a-b)各自接收被输入到低噪声放大器104(a-b)的宽带RF信号。这些LNA 104的输出被输入到移相器106(a-b), 移相器106(a-b)用与期望的波束图型/方向相关联的选定相移量将这些接收到的RF信号进行相移。通过提供恰当的相移, 移相器106能够生成选自多个可能的波束图型/方向的选定波束图型/方向。

[0021] 从诸移相器106输出的这些经移相的信号由新颖的分配器/合成器108组合以生成RF宽带经波束成形信号120。经波束成形信号120被输入到混频器110, 混频器110使用由压控振荡器(VCO)116生成的本振(LO)信号122来执行下变频。混频器110生成基带经波束成形信号122, 该信号122由基带滤波器(BBF)112滤波并由模数滤波器(ADC)114数字化以生成能由该无线设备作进一步处理的数字BB信号。

[0022] 在各种示例性实施例中, 此新颖的分配器/合成器108被配置成与常规分配器/合成器相比使用更小的电路面积并提供更大的灵活性来实现减小的布局复杂度。还应当注意, 分配器/合成器108也操作以处理反向流动(诸如在信号传送期间)的信号。由此, 在传送期间, 分配器/合成器108接收发射信号作为输入, 并且将该发射信号的功率划分给连接到多个移相器的多个输出。这些移相器接着提供选定的相移量以形成期望的发射波束图型。

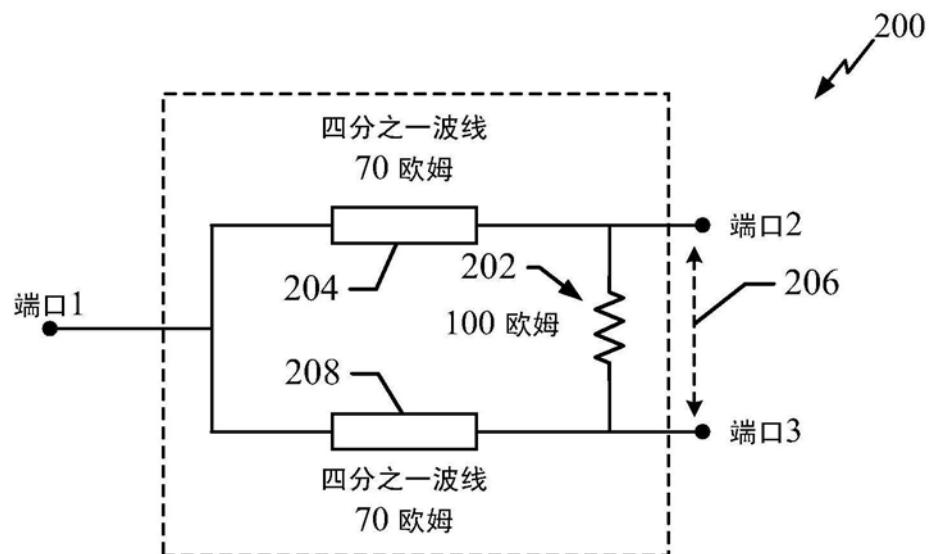

[0023] 图2示出了常规Wilkinson功率分配器/合成器200。例如, 分配器/合成器200可被用于图1中所示的接收机100中。分配器/合成器200包括以100欧姆电阻器202连接在一起的两个节点(端口2、端口3)。电阻器202一般很小, 这意味着两个节点(端口2、端口3)之间的间距206通常很小。在许多实现中, 使这些节点(端口2、端口3)非常靠近可能不可行, 并且因此分配器/合成器200的实现提供的灵活性较小, 这导致了布局复杂度增大。

[0024] 分配器/合成器200还包括提供70欧姆的特性阻抗的传输线204、208。传输线204、208的阻抗与尺寸之间存在关系。例如, 随着传输线204的阻抗变得更大, 传输线204所要求的电路面积也会增加。因此, 由于利用70欧姆传输线和小电阻器202, 分配器/合成器200具有电路面积大和布局复杂度增大的缺点。相应地, 在各种示例性实施例中, 新颖的功率分配器/合成器108与Wilkinson分配器/合成器200相比具有更小的电路面积并提供更大的灵活性来实现减小的布局复杂度。

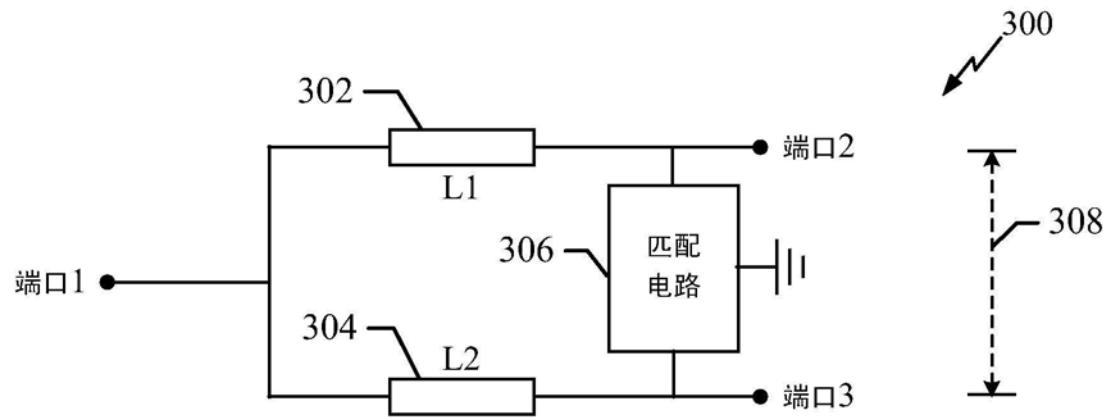

[0025] 图3示出了分配器/合成器300的示例性实施例。分配器/合成器300是可配置的, 以与图2中所示的常规Wilkinson分配器/合成器200相比利用更小的电路面积并且提供增加的灵活性来实现减小的布局复杂度。分配器/合成器300包括连接在第一端口(端口1)和第二端口(端口2)之间的第一传输线302。分配器/合成器300还包括连接在端口1和第三端口(端口3)之间的第二传输线304。分配器/合成器300还包括耦合在端口2和端口3之间的匹配电路306。匹配电路306还被耦合到接地。由此, 分配器/合成器300包括具有第一、第二和第三端口的三端口电路, 和配置成将该第二和第三端口耦合到接地的匹配电路。

[0026] 在一示例性实施例中, 匹配电路306允许端口2与端口3之间有增大的间距308, 藉此提供了增加的布局灵活性。进一步, 传输线302、304和匹配电路306的阻抗是可调节的, 这允许减小传输线302和304的尺寸, 藉此得到了与图2中所示的分配器/合成器200相比更小的总体电路。

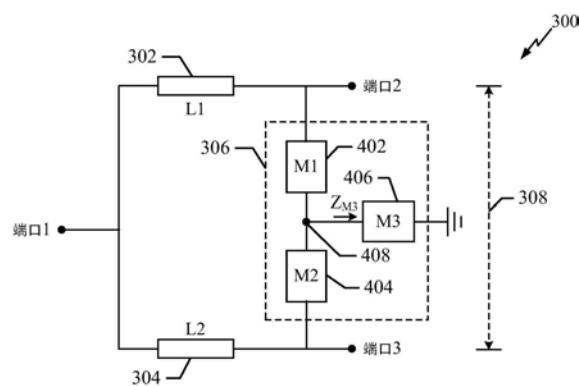

[0027] 图4示出了分配器/合成器300的详细示例性实施例。分配器/合成器300是可配置

的,以与图2中所示的常规Wilkinson分配器/合成器200相比使用更小的电路面积并且提供增加的灵活性来实现减小的布局复杂度。传输线302具有长度(L1)和特性阻抗(Z<sub>L1</sub>)。传输线304具有长度(L2)和特性阻抗(Z<sub>L2</sub>)。匹配电路306包括串联连接在端口2与端口3之间的第一匹配电路(M1)402和第二匹配电路(M2)404。第三匹配电路(M3)406连接在第一节点408与接地之间。第三匹配电路406具有定义为(Z<sub>M3</sub>)的输入阻抗值。

[0028] 在一示例性实施例中,第一402和第二404匹配电路的实现提供了端口2与端口3之间增大的间距314,藉此提供了增加的布局灵活性。传输线302、304和匹配电路402、404和406的阻抗也可被调节以减小传输线302和304的尺寸,藉此得到了与图2中所示的分配器/合成器200相比更小的总体电路。为获得减小的电路尺寸而对分配器/合成器300的阻抗作出的调节能够基于以下提供的偶模和奇模分析的结果来执行。

#### [0029] 偶模分析

[0030] 图5示出了分配器/合成器300的针对端口1的示例性偶模表示500。在该表示中,传输线302、304和匹配电路402、404和406的阻抗被配置使得其组合起来匹配端口1处所见的阻抗(Z1)。如图5中所解说的,匹配电路M3406被划分开以提供组合起来形成输入阻抗Z<sub>M3</sub>的两个单独的阻抗。

[0031] 在一示例性实施例中,以上这些阻抗被设置使得阻抗Z1等于100欧姆,并且由此在端口1处所见的组合阻抗将会是50欧姆。应当注意,阻抗值的范围可被用以获得在端口1处所见的不同于50欧姆的组合阻抗。通过调节匹配电路M1402、M2404和M3406的阻抗,就有可能调节传输线302、304的尺寸,而同时达成期望的端口1阻抗。例如,可以通过调节匹配电路402、404和406的阻抗来减小传输线302、304的尺寸以达成端口1处期望的组合阻抗。结果,传输线302、304可被设置成提供较小的阻抗并具有相应的较小的尺寸。

[0032] 图6示出了新颖的分配器/合成器300的针对端口2和3的示例性偶模表示600。参见端口2,传输线302、304和匹配电路402、404和406的阻抗被配置使得在端口2处所见的阻抗(Z2和Z3)形成并联组合以获得期望的阻抗值。例如,若端口2处期望的阻抗是50欧姆,那么阻抗Z2和Z3的并联组合被如下地设置成50欧姆。

#### [0033] 50=Z<sub>2II</sub> Z<sub>3</sub> (Z<sub>2</sub>和Z<sub>3</sub>的并联组合)

[0034] 由此,可以通过调节匹配电路402、404和406的阻抗来减小传输线302、304的尺寸以达成端口2处期望的组合阻抗。结果,传输线302、304可被设置成提供较小的阻抗并具有相应较小的尺寸。

#### [0035] 奇模分析

[0036] 图7示出了新颖的分配器/合成器300的针对端口2和3的示例性奇模表示700。参见端口2,匹配电路406被设置成具有零阻抗并且因此用短接到地来代替。传输线302、304和匹配电路402、404的阻抗被配置使得在端口2处所见的阻抗(Z4和Z5)形成并联组合以获得期望的阻抗值。例如,若端口2处期望的阻抗是50欧姆,那么阻抗Z4和Z5的并联组合被如下地设置成50欧姆。

#### [0037] 50=Z<sub>4II</sub> Z<sub>5</sub> (Z<sub>4</sub>和Z<sub>5</sub>的并联组合)

[0038] 因此,新颖的分配器/合成器300可通过调节匹配电路402、404和406的阻抗以减小传输线302、304的阻抗、并藉此减小传输线302和304的所要求芯片面积的方式来被配置。分配器/合成器300还被配置成增加端口2和3之间的端口间距以提供与图2中所示的分配器/

合成器200相比更大的布局灵活性。

[0039] 图8示出了分配器/合成器配置800的示例性实施例。在每个配置中，端口1藉由传输线802耦合到端口2，并且端口1藉由传输线804耦合到端口3。第一匹配电路806被耦合在端口2与节点812之间，并且第二匹配电路808被耦合在端口3与节点812之间。第三匹配电路810被耦合在节点812与接地之间。

[0040] 在各种配置中，匹配电路802、808和810包括传输线、电感器、电容器和/或电阻器。例如，匹配电路806a包括传输线和电容器，匹配电路806b包括传输线和电感器，而匹配电路806c包括传输线和电阻器。应当注意，匹配电路806和808并非需要包括传输线。例如，匹配电路806h和808h仅包括电容器。

[0041] 图8中所示的所有新颖的分配器/合成器可通过调节匹配电路806、808和810的阻抗以减小传输线802和804所需要的芯片面积并且增大端口2和3之间的端口间距以提供与图2中所示的分配器/合成器200相比更大的布局灵活性的方式来被配置。

[0042] 图9示出了分配器/合成器设备900的示例性实施例。例如，设备900适于用作图4中所示的分配器/合成器300或者图1中所示的分配器/合成器108。在一方面，设备900由配置成提供如本文所描述的功能的一个或多个模块来实现。例如，在一方面，每个模块包括硬件和/或执行软件的硬件。

[0043] 设备900包括第一模块，其包括用于提供使第一端口耦合到第二和第三端口的三端口电路的装置(902)，在一方面，该装置(902)包括功率分配器/合成器300。

[0044] 设备900包括第二模块，其包括用于匹配的装置(904)，该装置(904)配置成将第二和第三端口耦合到接地，在一方面，该装置(904)包括匹配电路306。

[0045] 设备900用于匹配的装置904包括第三模块，该第三模块包括用于将第一端口耦合到第二端口的装置(906)，在一方面，该装置(906)包括传输线302。

[0046] 设备900用于匹配的装置904还包括第四模块，该第四模块包括用于将第三端口耦合到第一端口的装置(908)，在一方面，该装置(908)包括传输线304。

[0047] 设备900用于匹配的装置904还包括第五模块，该第五模块包括用于将第二端口耦合到第一节点的装置(910)，在一方面，该装置(910)包括匹配电路402。

[0048] 设备900用于匹配的装置904还包括第六模块，该第六模块包括用于将第一节点耦合到第三端口的装置(912)，在一方面，该装置(912)包括匹配电路404。

[0049] 设备900用于匹配的装置904还包括第七模块，该第七模块包括用于将接地耦合到第一节点的装置(914)，在一方面，该装置(914)包括匹配电路406。

[0050] 本领域技术人员将理解，信息和信号可使用各种不同技术和技艺中的任何一种来表示或处理。例如，贯穿上面描述始终可能被述及的数据、指令、命令、信息、信号、位(比特)、码元、和码片可由电压、电流、电磁波、磁场或磁粒子、光场或光粒子、或其任何组合来表示。还应注意晶体管的类型和技术可被替换、重新安排或以其他方式修改以达成相同的结果。例如，可以把示为利用PMOS晶体管的电路修改为使用NMOS晶体管，反之亦然。由此，本文中所公开的放大器可以使用各种晶体管类型和技术来实现，并且不受限于附图中所示的这些晶体管类型和技术。例如，可以使用诸如BJT、GaAs、MOSFET之类的晶体管类型或任何其他的晶体管技术。

[0051] 本领域技术人员将进一步领会，结合本文所公开的实施例描述的各种解说性逻辑

框、模块、电路、和算法步骤可被实现为电子硬件、计算机软件、或两者的组合。为清楚地解说硬件与软件的这一可互换性，各种解说性组件、块、模块、电路、和步骤在上面是以其功能性的形式作一般化描述的。此类功能性是被实现为硬件还是软件取决于具体应用和施加于整体系统的设计约束。技术人员可针对每种特定应用以不同方式来实现所描述的功能性，但此类实现决策不应被解读为致使脱离本发明的示例性实施例的范围。

[0052] 结合本文所公开的实施例描述的各种解说性逻辑块、模块、和电路可用设计成执行本文所描述的功能的通用处理器、数字信号处理器(DSP)、专用集成电路(ASIC)、现场可编程门阵列(FPGA)或其他可编程逻辑器件、分立门或晶体管逻辑、分立硬件组件、或其任何组合来实现或执行。通用处理器可以是微处理器，但在替换方案中，该处理器可以是任何常规的处理器、控制器、微控制器、或状态机。处理器还可以被实现为计算设备的组合，例如DSP与微处理器的组合、多个微处理器、与DSP核心协同的一个或更多个微处理器、或任何其他此类配置。

[0053] 结合本文所公开的实施例描述的方法或算法的各个步骤可直接用硬件、由处理器执行的软件模块或两者的组合来实现。软件模块可驻留在随机存取存储器(RAM)、闪存、只读存储器(ROM)、电可编程ROM(EPROM)、电可擦式可编程ROM(EEPROM)、寄存器、硬盘、可移动盘、CD-ROM、或本领域中所知的任何其他形式的存储介质中。示例性存储介质被耦合到处理器以使得该处理器能从/向该存储介质读和写信息。替换地，存储介质可以被整合到处理器。处理器和存储介质可驻留在ASIC中。ASIC可驻留在用户终端中。替换地，处理器和存储介质可作为分立组件驻留在用户终端中。

[0054] 在一个或多个示例性实施例中，所描述的功能可在硬件、软件、固件或其任何组合中实现。如果在软件中实现，则各功能可以作为一条或多条指令或代码存储在计算机可读介质上或藉其进行传送。计算机可读介质包括非瞬态计算机存储介质和通信介质两者，其包括促成计算机程序从一地到另一地的转移的任何介质。非瞬态存储介质可以是能被计算机访问的任何可用介质。作为示例而非限定，这样的计算机可读介质可包括RAM、ROM、EEPROM、CD-ROM或其它光盘存储、磁盘存储或其它磁存储设备、或能被用来携带或存储指令或数据结构形式的期望程序代码且能被计算机访问的任何其它介质。任何连接也被正当地称为计算机可读介质。例如，如果软件是使用同轴电缆、光纤电缆、双绞线、数字订户线(DSL)、或诸如红外、无线电、以及微波之类的无线技术从web网站、服务器、或其它远程源传送而来，则该同轴电缆、光纤电缆、双绞线、DSL、或诸如红外、无线电、以及微波之类的无线技术就被包括在介质的定义之中。如本文中所使用的盘(disk)和碟(disc)包括压缩碟(CD)、激光碟、光碟、数字多用碟(DVD)、软盘和蓝光碟，其中盘(disk)往往以磁的方式再现数据，而碟(disc)用激光以光学方式再现数据。上述的组合也应被包括在计算机可读介质的范围内。

[0055] 提供了对所公开的示例性实施例的描述是为了使得本领域任何技术人员皆能够制作或使用本发明。对这些示例性实施例的各种修改对于本领域技术人员将是显而易见的，并且本文中定义的一般原理可被应用于其他实施例而不会脱离本发明的精神或范围。因此，本发明并非意在被限定于本文中所示出的示例性实施例，而是应当被授予与本文中所公开的原理和新颖性特征相一致的最广义的范围。

图1

图2现有技术

图3

图4

图5

图6

图7

图8

图9