(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6185062号

(P6185062)

(45) 発行日 平成29年8月23日(2017.8.23)

(24) 登録日 平成29年8月4日(2017.8.4)

(51) Int.Cl.

F 1

|                    |                  |      |       |      |

|--------------------|------------------|------|-------|------|

| <b>H01L 29/78</b>  | <b>(2006.01)</b> | H01L | 29/78 | 652K |

| <b>H01L 29/06</b>  | <b>(2006.01)</b> | H01L | 29/78 | 652P |

| <b>H01L 29/12</b>  | <b>(2006.01)</b> | H01L | 29/78 | 652T |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | H01L | 29/78 | 653A |

|                    |                  | H01L | 29/06 | 301F |

請求項の数 11 (全 22 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-524304 (P2015-524304)  |

| (86) (22) 出願日 | 平成25年7月11日 (2013.7.11)        |

| (65) 公表番号     | 特表2015-529017 (P2015-529017A) |

| (43) 公表日      | 平成27年10月1日 (2015.10.1)        |

| (86) 國際出願番号   | PCT/US2013/050046             |

| (87) 國際公開番号   | W02014/018273                 |

| (87) 國際公開日    | 平成26年1月30日 (2014.1.30)        |

| 審査請求日         | 平成28年7月1日 (2016.7.1)          |

| (31) 優先権主張番号  | 13/558, 218                   |

| (32) 優先日      | 平成24年7月25日 (2012.7.25)        |

| (33) 優先権主張国   | 米国 (US)                       |

| (31) 優先権主張番号  | 13/572, 492                   |

| (32) 優先日      | 平成24年8月10日 (2012.8.10)        |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                           |

|-----------|-------------------------------------------------------------------------------------------|

| (73) 特許権者 | 501315784<br>パワー・インテグレーションズ・インコーポレーテッド<br>アメリカ合衆国 95138 カリフォルニア州・サンホゼ・ヘリヤー アベニュー<br>・5245 |

| (74) 代理人  | 100100181<br>弁理士 阿部 正博                                                                    |

| (72) 発明者  | パーササラサイ ヴィジェイ<br>アメリカ合衆国 94087 カリフォルニア州 サニーベイル、ニューファウンドランド ドライヴ 1442                      |

最終頁に続く

(54) 【発明の名称】テープ付けされた酸化物の堆積／エッチング

## (57) 【特許請求の範囲】

## 【請求項 1】

テープ付けされたフィールドプレート誘電体領域を半導体ウエハに形成する方法であつて、

前記半導体ウエハ内に溝をエッチングすることであつて、前記溝が側壁をもつ、溝を工ツチングすること、

前記側壁を含め、前記半導体ウエハ上に第1の厚さの第1の絶縁層を堆積させること、

第1の量の前記第1の絶縁層をエッチングすることであつて、前記溝の上部に隣接した前記溝の垂直面上の前記第1の絶縁層の第1の上部が除去されて、前記第1の上部に隣接していた前記溝の垂直面が露出する、前記第1の絶縁層をエッチングすること、

前記半導体ウエハ上に第2の厚さの第2の絶縁層を堆積させることであつて、前記第2の絶縁層が前記溝の側壁上で除去されていない前記第1の絶縁層と重なり、前記第2の絶縁層が除去された前記第1の上部に代わり堆積され、前記第1の上部が除去された前記溝の垂直面に重なる、第2の絶縁層を堆積させること、および、

第2の量の前記第2の絶縁層をエッチングすることであつて、前記溝の前記側壁上の前記第1の絶縁層上の前記第2の絶縁層の第2の上部が除去される、前記第2の絶縁層を工ツチングすること、

前記半導体ウエハ上に第3の厚さの第3の絶縁層を堆積させること、および、

第3の量の前記第3の絶縁層をエッチングすることであつて、前記第3の絶縁層の第3の上部が除去され、前記第3の量の前記第3の絶縁層をエッチングすることによって、前

10

20

記第3の上部に隣接していた前記第1の絶縁層の少なくとも一部と、前記第3の上部に隣接していた前記第2の絶縁層の少なくとも一部と、を露出させる、前記第3の絶縁層をエッティングすること、

を含む方法。

【請求項2】

前記第2の量の前記第2の絶縁層をエッティングすることが、前記第2の上部に隣接していいた、前記第1の絶縁層の少なくとも一部を露出させる、

請求項1の方法。

【請求項3】

前記第1の厚さと前記第2の厚さとが、略同一である、

請求項1の方法。

【請求項4】

前記第3の絶縁層と前記第2の絶縁層とが、同じ材料である、

請求項3の方法。

【請求項5】

前記第1の厚さは、前記第1の絶縁層が上に堆積されている表面の傾きに実質的に無関係である、

請求項1の方法。

【請求項6】

前記溝をエッティングする前に、前記溝の位置を規定するハードマスクをパターン形成することであって、前記ハードマスクをパターン形成することが、ハードマスク材料を堆積させることを含む、ハードマスクをパターン形成すること、

をさらに含む、請求項1の方法。

【請求項7】

前記ハードマスクが、多結晶シリコンで作られている、

請求項6の方法。

【請求項8】

前記ハードマスクを堆積させる前に、前記半導体ウエハの前記表面に保護層を堆積させること、

をさらに含む、請求項7の方法。

【請求項9】

前記保護層が、酸化物である、

請求項8の方法。

【請求項10】

前記溝内の前記第1の絶縁層と前記第2の絶縁層との上に導電性材料を堆積させることであって、前記導電性材料が、前記第1の絶縁層と前記第2の絶縁層とにより、前記溝の前記側壁と直接接触しないように分離されている、導電性材料を堆積させること、

をさらに含む、請求項1の方法。

【請求項11】

前記第1の絶縁層をエッティングすることと、前記第2の絶縁層をエッティングすることとが、異方性エッティングを使用して行われる、

請求項1の方法。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願の相互参照)

本出願は、2012年7月25日に出願された米国特許出願第13/558,218号、および2012年8月10日に出願された米国特許出願第13/572,492号の優先権を主張し、両米国特許出願の開示内容の全体が、事実上、以下に完全に記載されてい

10

20

30

40

50

るものとして、参照により援用される。

#### 【0002】

##### (技術分野)

本開示は、概して、高電圧半導体のフィールドプレート誘電体の製造に関し、より具体的には、本開示は、高電圧半導体装置のテーパ付けされたフィールドプレート誘電体の製造に関する。

#### 【背景技術】

##### 【0003】

電子装置は、動作に電力を使用する。電力は、一般に、壁の差込口を通して、高電圧の交流 (A C ; alternating current) として伝送される。典型的には電力変換装置または電源と呼ばれる装置を使用して、エネルギー変換素子により高電圧 A C 入力を、適切に調節された直流電流 (D C ; direct current) 出力に変換できる。電力変換装置の一種がスイッチング電力変換装置であり、スイッチング電力変換装置は、高効率であり、寸法が小さく、重さが軽いことから、現在の多くの電子装置に電力供給するために一般的に使用されている。タブレットコンピュータ、スマートフォンおよび L E D 光源などの電子装置に電力供給する多くのスイッチング電力変換装置は、高電圧を扱える電力半導体装置に依存する。例えば、携帯電話の充電装置内の半導体装置は、絶縁破壊なしに最大 6 0 0 V のピーク電圧を扱うことが必要とされる場合がある。これらの高電圧装置のいくつかは、半導体のより広い領域に電界を広げることにより高電圧を扱い、これにより電界が絶縁破壊閾値を上回ることを防ぐ。電界の広がりに寄与するよう 10 に、フィールドプレートが使用される場合がある。

##### 【0004】

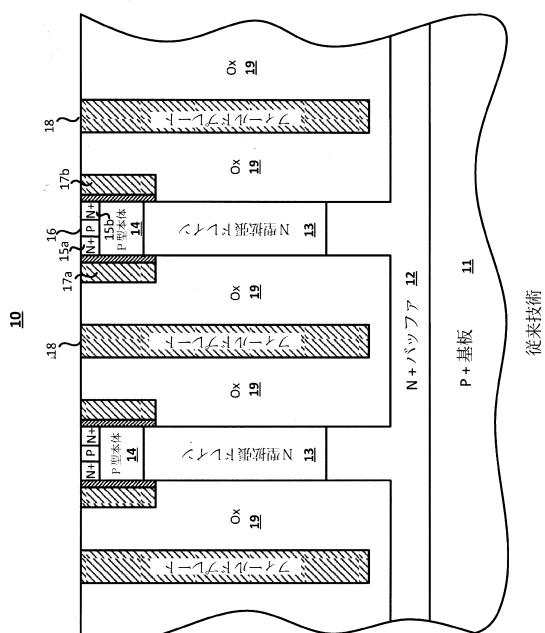

高電圧トランジスタの一種が、縦型薄シリコン (V T S ; vertical thin silicon) 高電圧電界効果トランジスタ (H V F E T ; high-voltage field effect transistor) である。例えば、図 1 は、ウエハ 1 1 に構築された一実施例の V T S H V F E T 1 0 を示す。V T S H V F E T 1 0 は、シリコン柱に、ソース領域 1 5 a および 1 5 b 、本体領域 1 4 ならびにドレイン領域 1 2 および 1 3 (長いドレイン拡張部を含む) を含む。ゲート 1 7 a および 1 7 b に印加される電位は、本体領域 1 4 のチャネルを調節し得、ソース領域 1 5 a および 1 5 b とドレイン領域 1 2 および 1 3 との間の導電を制御し得る。本体領域 1 4 の電位は、本体接点 1 6 によって制御され得る。H V F E T 1 0 は、さらに、フィールドプレート誘電体 1 9 によりシリコン柱から分離されたフィールドプレート 1 8 を有する。フィールドプレート 1 8 は、大幅な電圧降下を拡張ドレイン領域内に広げる(すなわち、電界を広げる)ことにより、絶縁破壊電圧の増大を可能にする。

##### 【0005】

以下の図を参照しながら、本発明の非限定的かつ非網羅的な実施形態について説明する。図中、類似した参照符号は、別段の指定がない限り、異なる図にわたって類似した部分を参照する。

##### 【0006】

図 1 ~ 1 0 は、複数の段階での、堆積およびエッティングによるテーパ付けされた酸化物の形成を示す。図 1 1 ~ 2 3 は、複数の段階での、厚い酸化物を堆積させることによるテーパ付けされた酸化物の形成を示す。

##### 【図面の簡単な説明】

##### 【0007】

【図 1】図 1 は、フィールドプレートをもつ例示的な H V F E T を示す。

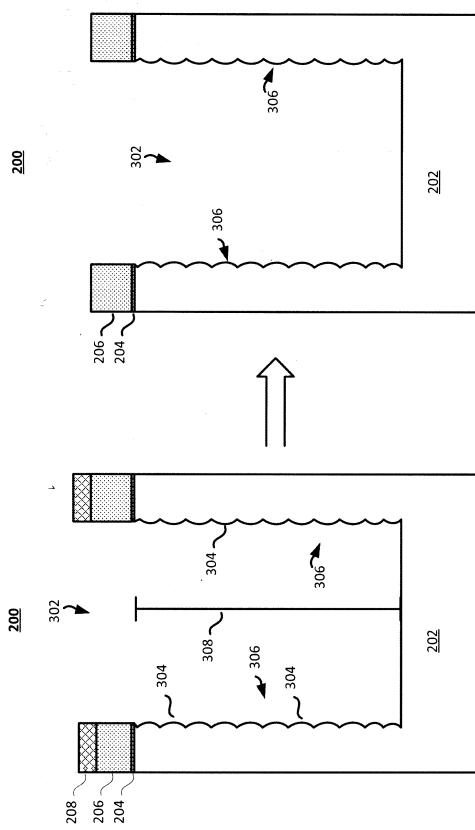

【図 2】図 2 A ~ 2 C は、テーパ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、ハードマスクの形成過程を示す。

【図 3】図 3 A および 3 B は、テーパ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、溝のエッティングを示す。

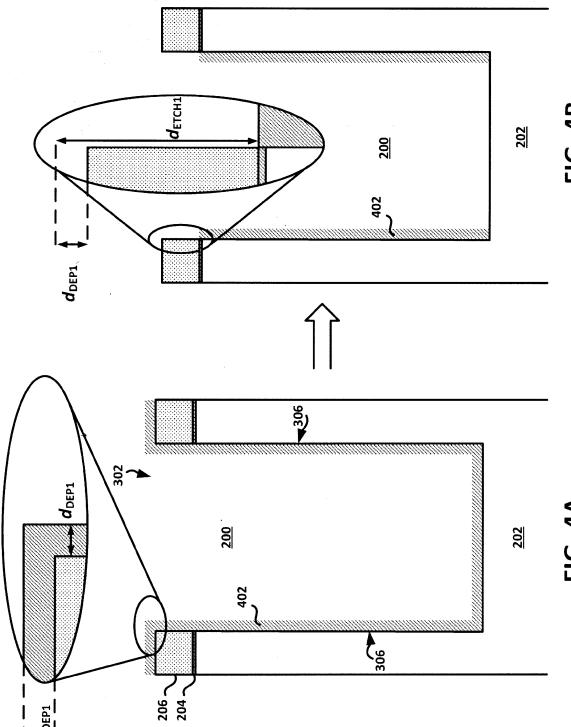

【図 4】図 4 A および 4 B は、テーパ付けされたフィールドプレート誘電体領域を形成す 40

10

20

30

40

50

る例示的な処理工程に従った、絶縁層の堆積およびエッティングの1サイクル目を示す。

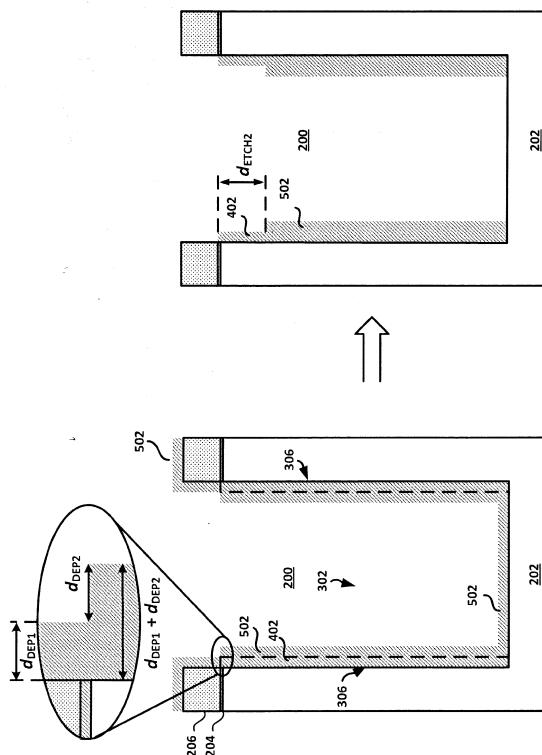

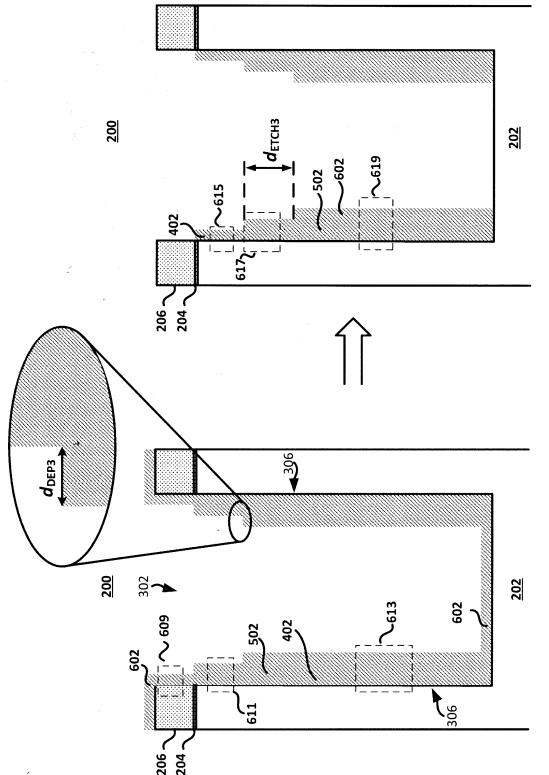

【図5】図5Aおよび5Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、絶縁層の堆積およびエッティングの2サイクル目を示す。

【図6】図6Aおよび6Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、絶縁層の堆積およびエッティングの3サイクル目を示す。

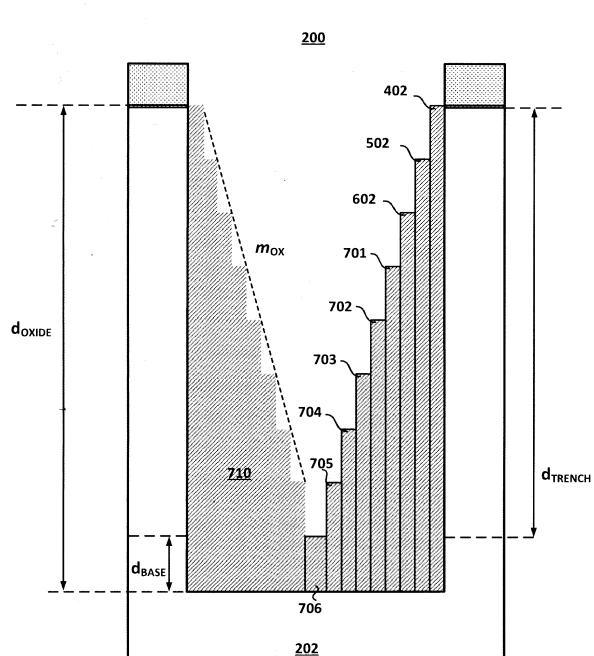

【図7】図7は、例示的な処理工程に従って、導電性材料を受容して例示的なテープ付けされたフィールドプレートを形成する準備が整った、テープ付けされたフィールドプレート誘電体領域を示す。

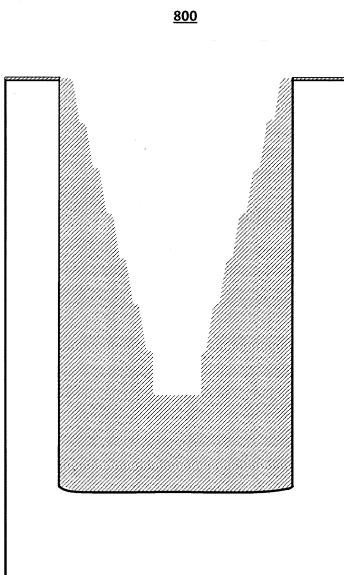

【図8】図8は、外形の異なる、他のテープ付けされたフィールドプレート誘電体領域の断面を示す。 10

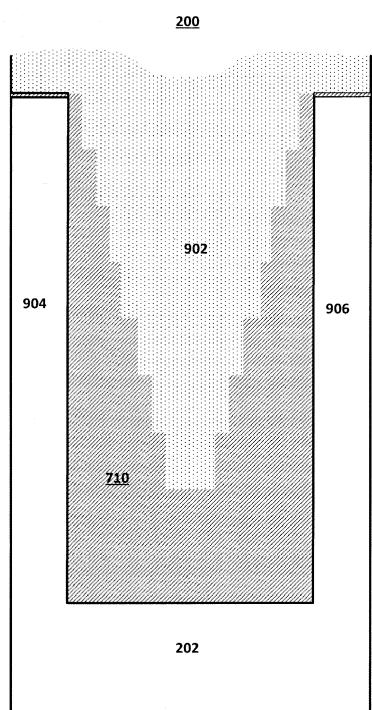

【図9】図9は、テープ付けされたフィールドプレート誘電体領域を形成するためにテープ付けされたフィールドプレート誘電体領域によって形成されるテープ付けされた領域に堆積された導電性材料を示す。

【図10】図10は、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程の流れ図を示す。

【図11】図11は、フィールドプレートをもつ他の例示的なHVFET構造を示す。

【図12】図12Aおよび12Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、テープ付けされたフィールドプレートおよびフィールドプレート誘電体領域のための溝をエッティングするためのマスクの形成過程を示す。

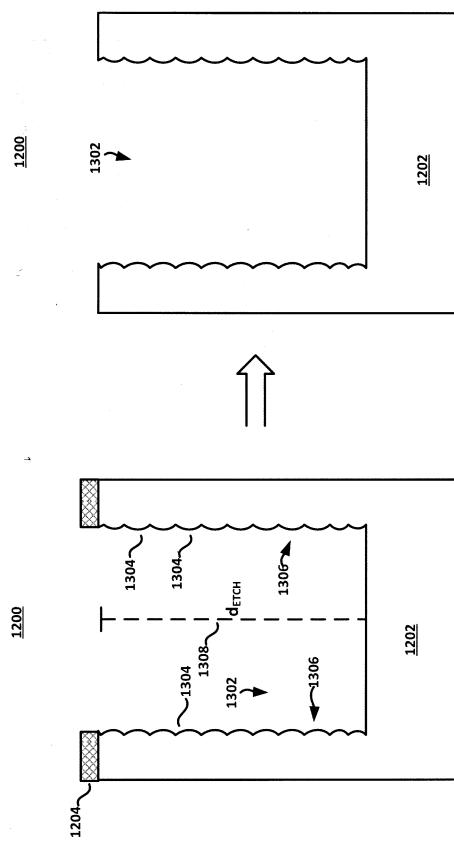

【図13】図13Aおよび13Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、溝のエッティングを示す。 20

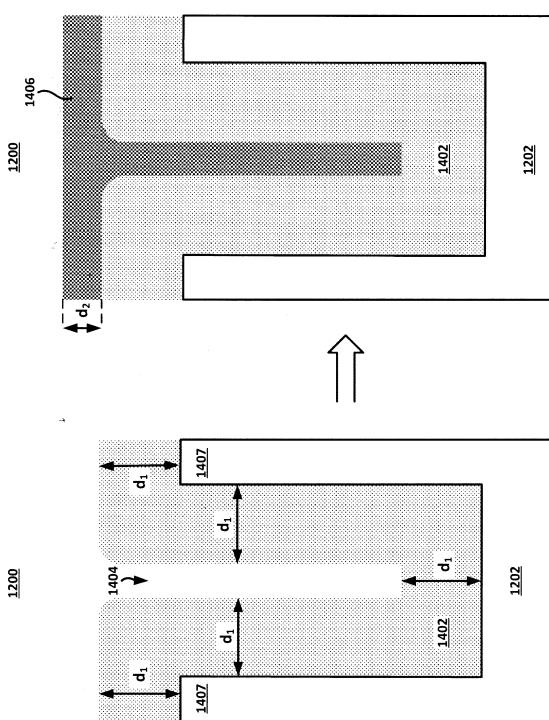

【図14】図14Aおよび14Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、第1の絶縁層の堆積、および、マスク層による絶縁層内の隙間の充填を示す。

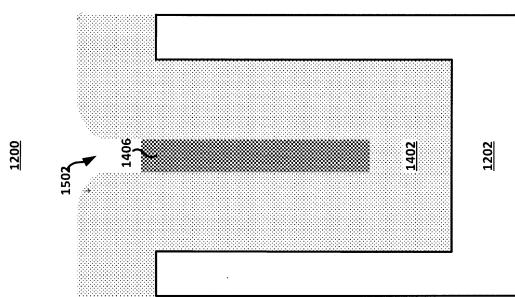

【図15】図15は、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、マスク層のエッティングを示す。

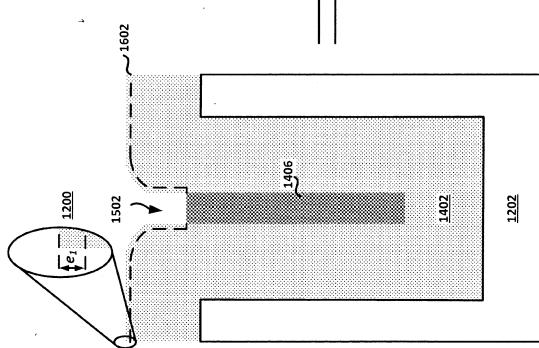

【図16】図16Aおよび16Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、絶縁層の等方性エッティングを示す。

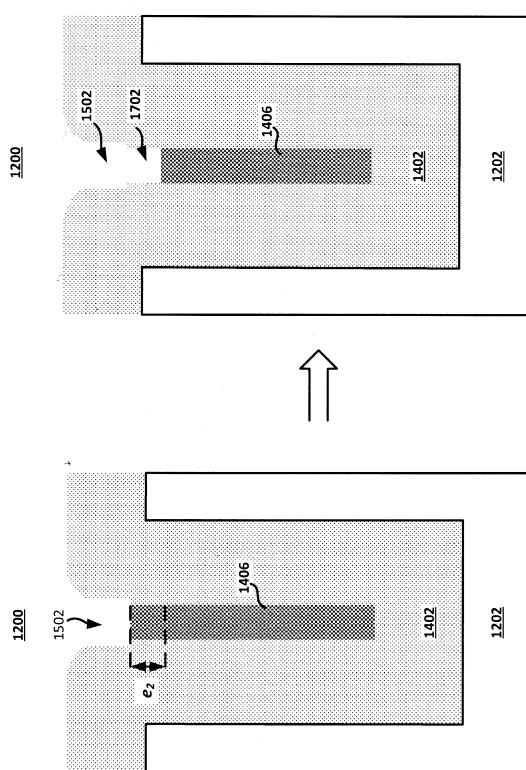

【図17】図17Aおよび17Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、マスク層のエッティングの2サイクル目を示す。 30

【図18】図18Aおよび18Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、絶縁層の等方性エッティングの2サイクル目を示す。

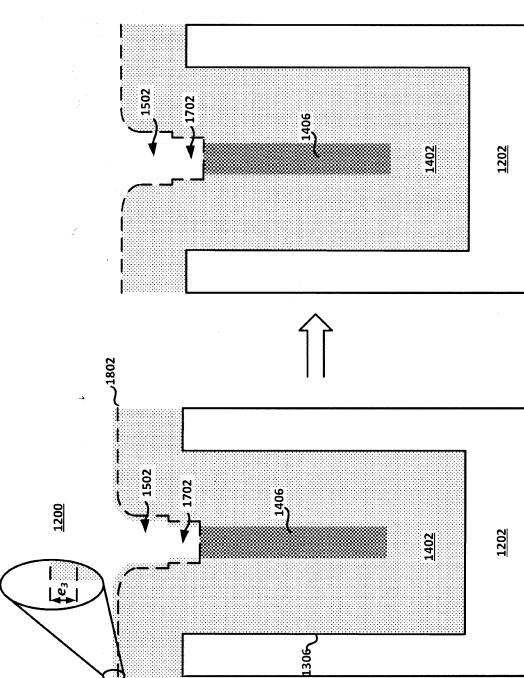

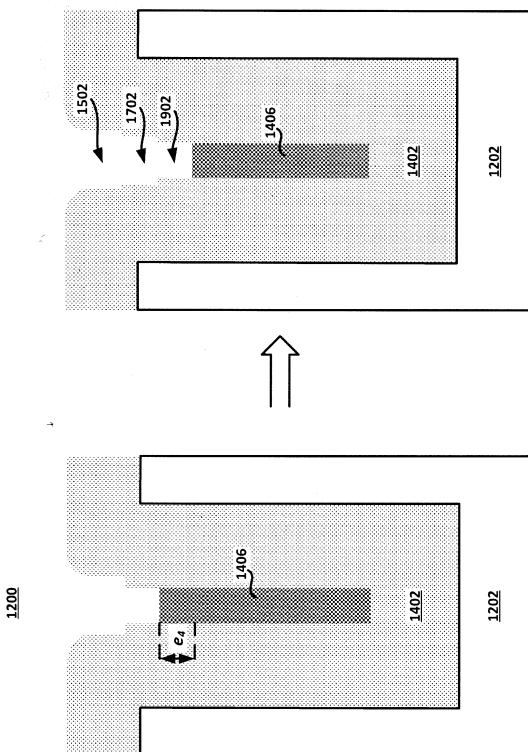

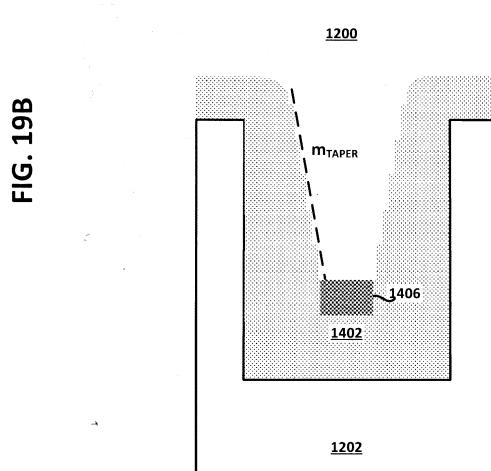

【図19】図19Aおよび19Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、マスク層のエッティングの3サイクル目を示す。

【図20】図20は、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従って、絶縁層のエッティングおよびマスク層のエッティングをさらに何度か繰り返した後の、テープ付けされたフィールドプレート誘電体領域を示す。

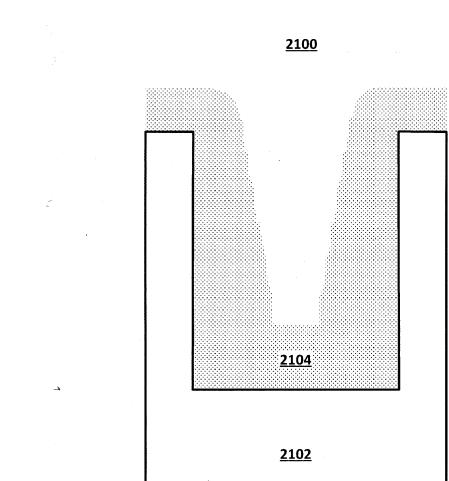

【図21】図21は、理想よりも劣る外形をもつ、テープ付けされたフィールドプレート誘電体領域を示す。

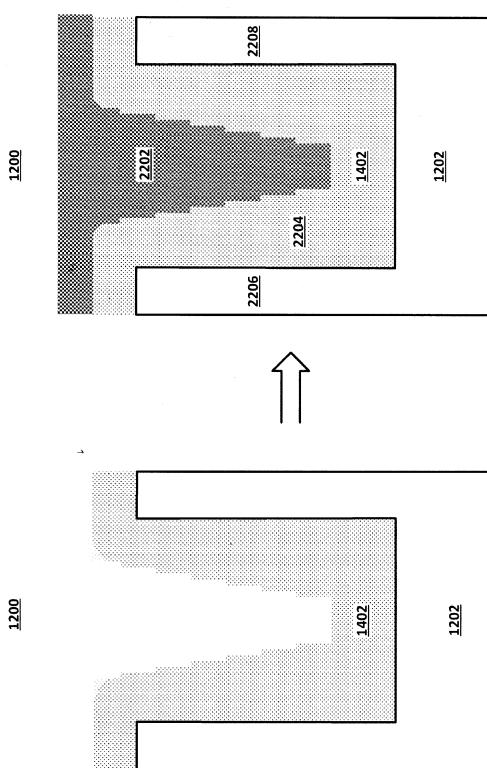

【図22】図22Aおよび22Bは、テープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程に従った、テープ付けされたフィールドプレートを形成するために使用される導電性材料の堆積を示す。 40

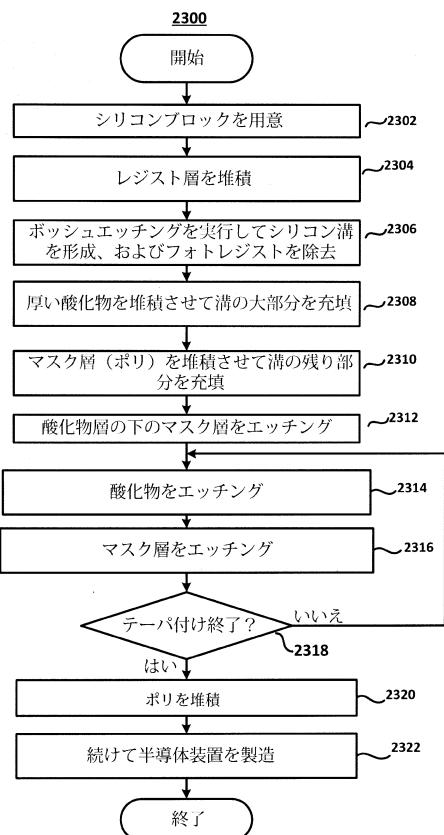

【図23】図23は、テープ付けされたフィールドプレート誘電体を形成する、他の例示的な処理工程の流れ図を示す。

#### 【発明を実施するための形態】

##### 【0008】

以下の説明では、本発明を十分に理解できるように、多くの具体的な詳細事項が記載されている。しかし、本発明を実施する際に具体的な詳細事項を利用する必要があるわけではないことが、当業者には明らかとなるであろう。他の例では、本発明が理解しにくくなないように、よく知られた材料または方法は、詳細には説明されていない。 50

## 【0009】

本明細書中で「一実施形態」、「実施形態」、「一例」または「例」についての言及は、実施形態または例に関連して説明されている特定の特徴、構造または特性が、本発明の少なくとも1つの実施形態に含まれることを意味する。従って、本明細書中の様々な場所に出現する「一実施形態において」、「実施形態において」、「一例」または「例」という語句は、必ずしもすべてが同じ実施形態または実施例を参照しているわけではない。さらに、特定の特徴、構造または特性は、1以上の実施形態または実施例において、任意の適切な組み合わせおよび/または部分的組み合せとして組み合わされてもよい。特定の特徴、構造または特性は、説明されている機能を提供する、集積回路、電子回路、結合論理回路または他の適切な構成要素に含まれていてもよい。さらに、本明細書と共に提供される図は、当業者への説明を目的としており、必ずしも一定の縮尺で描かれているわけではないことが理解されるべきである。

10

## 【0010】

前述のとおり、図1は、フィールドプレート18と、フィールドプレート18の深さに沿って実質的に同じ厚さもつフィールドプレート誘電体19とを示す。信頼性の高い装置を最適に構築するには、拡張ドレイン領域13に沿って一定した電界に保つことが適切であり得る。一定した電界の柱を保つため、拡張ドレイン領域13において濃度勾配のあるドーピング分布が必要であり得る。特に、ドレイン領域13における濃度勾配のあるドーピングは、深さに沿って、VTS装置10の表面に近づくにつれて徐々に減少してもよい。このようにして、VTS装置10は、拡張ドレイン領域13と酸化物19との間を空乏状態にすることができる。VTS装置10は、最大絶縁破壊電圧に耐えることができる。しかし、濃度勾配のあるドーピング分布とすることによる1つの欠点は、VTS装置10の表面に近いほど薄いドーピングとなり得ることにより、抵抗率がより大きくなり、効率がより下がり得ることである。

20

## 【0011】

図に示され、以下で説明するように、装置の深さに沿って、フィールドプレート誘電体の厚さが異なっている。特に、酸化物の厚さは、表面で最小であり、装置10の深さに沿って底部に達するまで増大するので、VTS装置10の表面付近で拡張ドレイン領域13のドーピングを増大させることができるとなる。その結果、VTS装置10の抵抗率は、最大3分の1~4分の1に低減し得る。一例において、オン抵抗率は、VTS装置10のドレインヒソースとの間が実質的に0ボルトであるときの、半導体の材料および設計に基づいて内在する抵抗として規定されてもよい。半導体装置の効率を高めるため、装置が導通しているときの電力損失を低減させるように抵抗率が低減され得ると理解されてもよい。一例において、フィールドプレート誘電体の様々な厚さは、テープ付けにより実現される。このようにして、ドーピングの定分布が、実現されてもよい。

30

## 【0012】

半導体基板にテープ付けされたフィールドプレート誘電体を形成する例示的な処理工程が、以下に説明されている。この例示的な処理工程は、例えば、ショットキーダイオード、HVFET、JFET、IGBT、バイポーラトランジスタなど、様々な種類の装置を形成する処理工程と合わせて有用であり得る。テープ付けされたフィールドプレート誘電体の製造が、例示的な処理工程の様々な段階を示す図に関連して説明されている。説明を簡単にするため、例示的な処理工程は、1つのフィールドプレート誘電体領域の製造について説明されている。しかし、図には、基板の一部のみが図示されていることが理解されるべきである。実際には、テープ付けされたフィールドプレート誘電体領域を有するフィールドプレートを備える多くの装置（例えば、HVFET）が、基板中に並列に形成されてもよい。

40

## 【0013】

図2Aは、基板200を示し、基板200は、ウエハ202、保護層204、およびマスク層206を含む。ウエハ202は、例えば、例として、シリコン、炭化ケイ素、ダイヤモンド、ガリウムヒ素、アルミニウムガリウムヒ素、りん化インジウム、窒化ガリウム

50

などの種々の材料で作られていてもよい。ウエハ202は、また、ヘテロ構造を形成するように複数の異なる材料で作られていてもよい。ウエハ202は、また、基部ウエハ（例えば、シリコンウエハ）と、基部ウエハの上に成長させた他の層（例えば、エピタキシャル成長層）とで形成されていてもよい。一例において、ウエハ202は、厚さが700～1000 μmであってもよい。

#### 【0014】

示されるように、処理中の欠陥および損傷からウエハ202の表面を保護するため、保護層204をウエハ202の表面に堆積させる。例示的な処理工程のいくつかの変形例において、保護層204およびマスク層206は、任意選択的であってもよい。より単純な処理工程では、テープ付けされた酸化物が、マスク層206を使用せずに形成されてもよく、シリコン柱自体が、酸化物に対するハードマスクとして使用されてもよい。ウエハ202としてシリコンウエハを使用する例示的な処理工程の変形例において、保護層204は、例えば、厚さ約200 Aの熱成長酸化物であってもよい。

10

#### 【0015】

マスク層206は、ハードマスク（例えば、多結晶シリコン、窒化物など）であってもよい。マスク層206は、フィールドプレート誘電体を形成するのに使用されることとなる絶縁材料とは異なるエッチング特性をもつように選択されてもよい。フィールドプレート誘電体とは異なるエッチング特性をもつマスク層206を選択することにより、マスク層206よりもフィールドプレート誘電体材料に対して高い選択性を示すエッチング剤が使用されてもよく、これにより、マスク層206が、テープ付けされたフィールドプレート誘電体の形成過程の全体を通して使用されることが可能となる。例えば、ポリシリコンが、マスク層206として使用されてもよい。フィールドプレート誘電体材料が酸化物であることが予定される場合、酸化物対シリコンのエッチング選択性が10：1または20：1であるようなエッチングレシピを選択できる。一例において、マスク層206は、約2～5 μmの厚さであってもよいが、フィールドプレート誘電体材料をエッチングするに使用されるエッチングレシピの選択性に応じて、他の厚さであってもよい。

20

#### 【0016】

図2Bは、マスク層208が堆積されて、溝と、半導体装置が位置することとなるシリコン柱（これらの柱は、おおよそ、マスク層208の残留部分の下方に存在することとなる）に隣接したフィールドプレート誘電体との位置を規定するようパターン形成された後の基板200を示す。マスク層208フォトレジストマスクである。他の実施例では、保護層204およびマスク層が使用されなくてもよく、フォトレジスト層が、シリコンウエハ202の表面に直接堆積されてもよい。

30

#### 【0017】

図2Cは、マスク層206および保護層204がエッチングされて、マスク層208で規定されたとおりに溝がエッチングされることとなる領域でウエハ202の表面を露出させた後の基板200を示す。一例において、ウエハ202の露出された部分は、 $d_{\text{EXP}} = 0.5 \text{ E} \text{D}$ であり、約10～12 μmの幅であってもよい。

#### 【0018】

図3Aは、溝302が形成された後の基板200を示す。一例において、深掘り反応性イオンエッチング（DRIE；deep reactive ion etch）ステップが使用され、その結果、溝302の側壁306に波形の凹凸304が形成される。溝302は、深さ308までエッチングされてもよく、一例において、約60 μmの深さであってもよい。溝302をエッチングするため、波形の凹凸を形成しない他のエッチング技術が使用されてもよいことが理解されるべきである。

40

#### 【0019】

図3Bは、マスク層208が除去された後の基板200を示す。マスク層208を除去することは、様々な工程で実現されてもよい。例えば、マスク層208がフォトレジストマスクである場合、プラズマアッシング工程が使用されてもよい。他の実施例では、窒化物または酸化物が使用される場合、リン酸またはフッ化水素酸、それぞれのエッチング工

50

程が使用されてもよい。図4Aは、絶縁層402が堆積された後の基板200を示す。前述のとおり、フィールドプレート誘電体は、1以上の絶縁層402を備える。絶縁層402を堆積させる処理工程は、垂直面(例えば、側壁306)および水平面(例えば、溝302の底部およびマスク層206上)の両方での露出された表面において、およそ $d_{DEP_1}$ の厚さの絶縁材料が存在するように、等角であってもよい。絶縁層402は、二酸化ケイ素、窒化ケイ素、りん化ホウ素ケイ酸塩ガラスなどであってもよい。例えば、低圧化学蒸着、高密度プラズマ、プラズマ化学蒸着などの処理工程を使用して、絶縁層402を堆積させてもよい。厚さ $d_{DEP_1}$ は、処理工程での温度、時間および光に応じて決定されてもよい。他の実施例において、 $d_{DEP_1}$ は、約0.5μmである。

## 【0020】

図4Bは、高異方性エッチングで厚さ $d_{ETCH_1}$ ぶんの絶縁層402をエッチングした後の基板200を示す。言い換えると、基板の水平面は、垂直面より実質的に多くエッチングされる。例えば、エッチングの指向性とも呼ばれ得る垂直対水平のエッチング比は、100対1であってもよい。一例において、 $d_{ETCH_1}$ は、垂直方向に4μmの距離であってもよい。絶縁層402をエッチングするのに使用されるエッチングレシピは、絶縁層402のエッチング速度がマスク層206またはウエハ202のエッチング速度よりもはるかに大きくなるように選択されてもよい。エッチングレシピの選択性が十分大きい場合、テープ付けされたフィールドプレート誘電体を形成する処理工程の全体で、同じマスク層206が使用されてもよい。さらに、半導体ウエハ202とマスク層206と(例えば、シリコンウエハとポリシリコンマスクと)に同じ材料が使用される場合、絶縁層402をエッチングするためのエッチングレシピは、溝302の底部における半導体ウエハ202の露出された部分と、半導体ウエハ202の表面におけるマスク層206との両方の上にある絶縁層402の材料に対して、類似の選択性を有していてもよい。例えば、少なくとも10:1、また、さらには20:1という選択性が使用されてもよい。

## 【0021】

図4Bに示すように、 $d_{ETCH_1}$ は、 $d_{DEP_1}$ より大きくてよく、そうすれば、水平面上の絶縁層402の部分(例えば、マスク層206の上面および溝302の底部)が、完全に除去されることとなる。しかし、溝302の側壁306に描かれているよう、垂直面上の絶縁層402の部分は、約 $d_{ETCH_1}$ ぶん、または、場合によっては、 $d_{ETCH_1}$ 未満の大きさぶん下方にエッチングされることとなる。言い換えると、垂直面の絶縁層402の上部(深さが $d_{ETCH_1}$ に比例する)のみが除去される(例えば、溝302内の側壁306上の絶縁層402の部分)。

## 【0022】

図4Aでは、波形の凹凸304が見えていないことに注意されたい。波形の凹凸は、絶縁層402の堆積前に、溝302の側壁から除去されてもよい。例えば、ウエハ202がシリコンである場合、波形の凹凸を消去するため、熱酸化工程が使用されてもよく、熱酸化物を除去してより滑らかな側壁を残すため、酸化物除去工程が使用されてもよい。代替的に、例示的な処理工程の変形例において、波形の凹凸が残存していてもよい。例示的な処理工程の他の変形例において、使用される溝エッチング技術に起因して波形の凹凸が存在しなくてもよく、または、波形の凹凸が容易には見えない程度に、または大きく影響しない程度に、波形の凹凸が十分小さくてもよい。

## 【0023】

図5Aは、基板202に絶縁層502が堆積された後の基板200を示す。絶縁層502は、以前に絶縁層402が除去されていない溝302の側壁306上で、絶縁層402に重ねて堆積されてもよい。絶縁層502を堆積させる処理工程は、垂直面および水平面の両方に、およそ $d_{DEP_2}$ の厚さの絶縁材料502が堆積されるように、等角であってもよい。絶縁層502は、絶縁層402と同じ厚さまで、同じ技術を使用して堆積された、同じ材料であってもよい。一代替例において、絶縁層402に比べて、絶縁層502は、異なる材料であってもよく、異なる技術を使用して堆積されてもよく、または、異なる

10

20

30

40

50

厚さをもっていてもよい。絶縁層402が除去されていない側壁306の部分は、この時点で、合計の厚さがおよそ $d_{DEP_1} + d_{DEP_2}$ の絶縁材料を有していてもよい。しかし、溝302の底部で露出されたウエハ202の部分は、厚さがおよそ $d_{DEP_2}$ だけの絶縁材料を有している。一例において、絶縁層402の厚さ $d_{DEP_1}$ は、絶縁層502の厚さ $d_{DEP_2}$ と実質的に同じである。他の実施例において、絶縁層402および502の厚さ $d_{DEP_1}$ および $d_{DEP_2}$ は異なる。

#### 【0024】

図5Bは、異方性エッティング（例えば、図4Bに関連して説明された、絶縁層402をエッティングするのに使用されるエッティングと同じエッティング）を使用して、厚さ $d_{ETC_{H2}}$ ぶんの絶縁層502と、ある程度の絶縁層402と、をエッティングした後の基板200を示す。特に、マスク206の側壁上および溝302の側壁上（絶縁層402上）の、絶縁層502の上部がすでにエッティングされている。この時点で、絶縁層402の柱上に絶縁層502の柱が存在する。

10

#### 【0025】

図6Aは、基板202に絶縁層602が堆積された後の基板200を示す。絶縁層602を堆積させる処理工程は、垂直面および水平面の両方に、およそ $d_{DEP_3}$ の厚さの絶縁材料602が堆積されるように、等角であってもよい。絶縁層602は、絶縁層402または絶縁層502と同じ技術を使用して同じ厚さまで堆積された、同じ材料であってもよい。一代替例において、絶縁層402または絶縁層502に比べて、絶縁層602は、異なる材料であってもよく、異なる技術を使用して堆積されてもよく、または、異なる厚さであってもよい。絶縁層402および502が除去されていない側壁306の部分は、この時点で、合計の厚さがおよそ $d_{DEP_1} + d_{DEP_2} + d_{DEP_3}$ の絶縁材料を有していてもよい。しかし、溝302の底部で露出されたウエハ202の部分は、厚さがおよそ $d_{DEP_3}$ だけの絶縁材料を有する。示されるように、第1の領域609は、絶縁層602の部分のみを含み、絶縁材料は、厚さ $d_{DEP_3}$ である。第2の領域611は、絶縁層402および602の部分を含み、領域611の側壁306に沿った絶縁材料の合計の厚さは、 $d_{DEP_1} + d_{DEP_3}$ である。第3の領域613は、絶縁層402、502、および602の部分を含み、領域613の側壁306に沿った絶縁材料の合計の厚さは、 $d_{DEP_1} + d_{DEP_2} + d_{DEP_3}$ に等しい。

20

#### 【0026】

図6Bは、異方性エッティング（例えば、図4Bに関連して説明された、絶縁層402をエッティングするのに使用されるエッティングと同じエッティング）を使用して、厚さ $d_{ETC_{H3}}$ ぶんの絶縁層602（ならびに、ある程度の絶縁層402および絶縁層502）をエッティングした後の基板200を示す。この時点で、絶縁層402の柱上に存在する絶縁層502の柱上に、絶縁層602の柱が存在する。示されるように、第1の領域615は、絶縁層402のみを含み、第1の領域615中の絶縁材料は、厚さが $d_{DEP_1}$ である。第2の領域617は、側壁306に沿った絶縁層402および502の部分を含み、領域617における絶縁材料の合計の厚さは、 $d_{DEP_1} + d_{DEP_2}$ である。第3の領域619は、絶縁層402、502、および602の部分を含み、領域619における側壁306に沿った絶縁材料の合計の厚さは、 $d_{DEP_1} + d_{DEP_2} + d_{DEP_3}$ に等しい。

30

#### 【0027】

図の組、図4A～4B、図5A～5Bおよび図6A～6Bの任意の1つに描かれ、関連して説明された、誘電体を堆積およびエッティングする処理工程は、溝302を充填するために必要な回数だけ繰り返されてもよい。例えば、図7に示すように、図7に示す溝を充填するのに9サイクルの堆積およびエッティングが使用された。具体的に、9サイクルは、前述の絶縁層402、502および602と、絶縁層701～706を生成する追加の6サイクルとに関連付けられる。堆積厚がすべて略同一（例えば、 $d_{DEP_1} = d_{DEP_2} = d_{DEP_3} = d_{DEP_X}$ ）であり、エッティング量がすべて略同一（例えば、 $d_{ETC_{H1}} = d_{ETC_{H2}} = d_{ETC_{H3}} = d_{ETC_{HX}}$ ）である場合、テーパ付けされたフィールドプロート誘電体領域の傾き $m_{ox}$ は、 $d_{ETC_{HX}} / d_{DEP_X}$ によって近似されてもよい

40

。

**【0028】**

例示的な処理工程の他の変形例において、テープ付けされたフィールドプレート誘電体領域の外形は、異なっていてもよい。例えば、異なる厚さの絶縁層を使用すること、および、異なる量の絶縁層をエッティングすることにより、テープ付けされたフィールドプレート誘電体領域の外形が制御されてもよい。一実施例において、テープ付けされたフィールドプレート誘電体領域の外形は、テープ付けされたフィールドプレート誘電体領域の外形に沿った複数の異なる傾きを有することとなる。

**【0029】**

テープ付けされたフィールドプレート誘電体領域は、1つの段が堆積／エッティングサイクルの各々を表すように、明確に画定された段を有するように描かれてきた。しかし、実際には、明確に画定された段が存在しなくてもよいことが理解されるべきである。例えば、テープ付けされたフィールドプレート誘電体領域の外形は、より直線的な形状を有していてもよい。図8は、図7に示す外形ほど理想的ではない、テープ付けされたフィールドプレート誘電体における他の例示的な外形を有する基板800を示す。

**【0030】**

図9は、テープ付けされたフィールドプレート誘電体領域710によって充填されていない溝302の残りの部分（符号なし）を充填する導電性材料902の堆積後の基板200を示す。導電性材料902は、例えば、アモルファスシリコン、多結晶シリコン、金属などの、任意の数の材料であってもよい。導電性材料902に半導体を使用する場合、導電性材料902は、それが堆積されているときにその場でドーピングされてもよい。次に、導電性材料902の上部が、化学機械研磨（CMP；chemical mechanical polishing）またはエッチバック工程を使用して平坦化されてもよい。次に、テープ付けされたフィールドプレートを形成する導電性材料902の残留部分に、電気接点が作られてもよい。

**【0031】**

テープ付けされたフィールドプレート誘電体およびテープ付けされたフィールドプレートが形成されたら、基板200の活性領域（例えば、シリコン柱904および906）に能動素子を形成する半導体装置製造工程が実施されてもよい。例えば、シリコン柱904および906にHVFETを形成するため、VTS HVFET処理工程が使用されてもよい。

**【0032】**

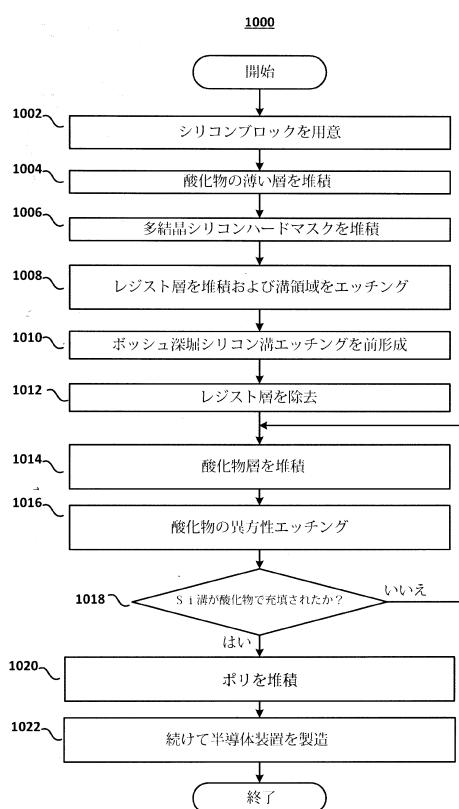

図10は、半導体基板にテープ付けされたフィールドプレート誘電体領域を形成する例示的な処理工程1000（図2～9に関連する前述の例示的な処理工程と同様）の流れ図を示す。工程1002において、シリコンウエハが用意される。シリコンウエハは、例えば、シリコンのエピタキシャル成長層を有するように形成された、ドーピングに違いのある層を有していてもよい。工程1004において、処理時の損傷および残骸からシリコンウエハの表面を保護する保護層を形成するため、シリコンウエハの表面に酸化物の薄い層を成長させる。工程1006において、多結晶シリコンハードマスクが堆積される（例えば、図2A参照）。テープ付けされたフィールドプレートを囲むテープ付けされたフィールドプレート誘電体領域の形成過程の全体を通して、多結晶シリコンハードマスクが使用されてもよい。多結晶シリコンよりも酸化物（または他の絶縁材料）のエッティングに対して高い選択性を示すエッティングレシピが利用しやすい場合があるので、ハードマスクには多結晶シリコンが好ましい場合がある。次に、工程1008において、フォトリソグラフィ工程を使用して、ハードマスクが、パターン形成およびエッティングされてもよい（例えば、図2Bおよび2C参照）。ハードマスクは、この時点で、傾斜したフィールドプレートのための溝がエッティングされることとなる領域を規定する。工程1010において、傾斜したフィールドプレートのための溝を画定する（例えば、図3A参照）ため、DRIE（またはボッシュエッティング）工程が実行される。例示的な処理工程1000のいくつかの変形例において、工程1008および1010が、1つの工程に組み合わされてもよい

10

20

30

40

50

。工程 1012において、工程 1008または1010の後に残されたすべてのフォトマスクが、プラズマアッティング工程を使用して除去される（例えば、図 3B 参照）。工程 1014において、工程 1010で形成された溝の側壁および底部を含めて、基板の垂直面および水平面に、酸化物層が堆積される（例えば、図 4A、5A および 6A 参照）。工程 1016において、工程 1014で堆積された酸化物を、ある厚さぶん除去するため、異方性エッティングが実行される（例えば、図 4B、5 および 6B 参照）。エッティングは異方性（すなわち、実質的に異方性）なので、ウエハの水平面の酸化物が完全に除去される一方で、垂直側面の酸化物の最上部のみが除去される。そのため、溝の側壁に堆積された酸化物の多く（例えば、最上部を除く、側壁上のすべての酸化物）が、残ることとなる。工程 1018において、テープ付けされたフィールドプレート（例えば、図 7 参照）を形成する材料を受容するため、溝が酸化物で十分に充填されているかどうか決定される。例えば、これは、すでに実行された酸化物の堆積 / エッティングサイクル数に基づいて決定されてもよい。他の例として、酸化物エッティング工程 1016 の後、溝の中央底部に閾値厚さの酸化物が残るまで、工程 1014 および 1016 のサイクルが繰り返されてもよい。工程 1020において、溝内にテープ付けされたフィールドプレート誘電体が形成された後、テープ付けされたフィールドプレートを形成するため、溝内に多結晶シリコンが堆積される（例えば、図 9 参照）。フィールドプレートとウエハの表面とが共面となることを確実にするため、平坦化工程が必要とされてもよい。工程 1022において、傾斜したフィールドプレートを収容する溝に隣接したシリコン柱に HVFET を形成するため、半導体処理手順が実行される。

10

20

#### 【0033】

例示的な処理工程 1000 は、特定の材料および層に関連して説明されてきたが、いくつかの層は、任意選択的であってもよく、ウエハおよび層の材料は、さまざまであってもよいことが理解されるべきである。

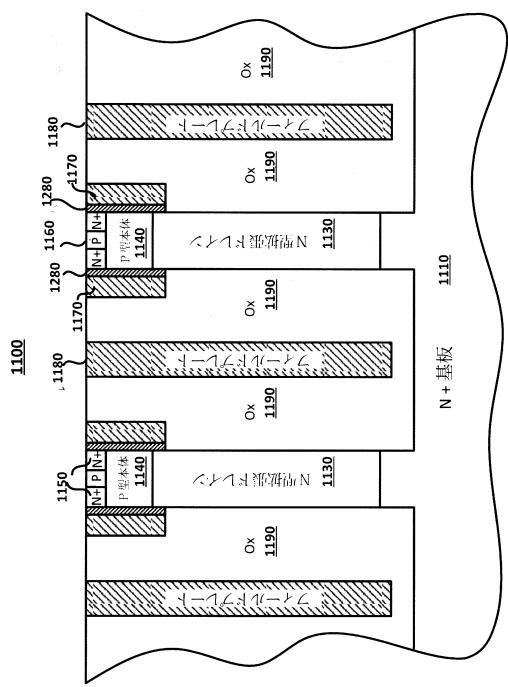

#### 【0034】

図 11 は、ウエハ（N+ 基板）1110 に構築された、例示的な VTS HVFET 1100 を示す。VTS HVFET 1100 は、ソース領域 1150（N+）、本体領域 1140（P型本体）、および 1130（N型拡張ドレイン領域）を含み、シリコン柱内に長いドレイン拡張部を含む。ゲート 1170 に印加される電位が、本体領域 1140 内のチャンネルを調節してもよく、ソース領域 1150 とドレイン領域との間の導電を制御してもよい。HVFET 1100 は、また、フィールドプレート誘電体 1190（Ox）によりシリコン柱から分離されるフィールドプレート 1180 を有する。フィールドプレート 1180 は、大幅な電圧降下を拡張ドレイン領域内のより広い領域に広げる（すなわち、電界を広げる）ことにより、絶縁破壊電圧の増大を可能にする。

30

#### 【0035】

フィールドプレート誘電体 1190 は、フィールドプレート 1180 の深さに沿って、実質的に同じ厚さである。信頼性の高い装置を最適に構築するためには、拡張ドレイン領域 1130 に沿って一定した電界を保つことが適切であり得る。一定した電界を保つためには、拡張ドレイン領域 1130 に、濃度勾配のあるドーピング分布が必要であり得る。特に、ドレイン領域 1130 の濃度勾配のあるドーピングは、深さに沿って、VTS 装置 1100 の表面に近づくにつれて徐々に減少してもよい。このようにして、VTS 装置 1100 が最大絶縁破壊電圧に耐えられるように、VTS 装置 1100 は、拡張ドレイン領域 1130 と酸化物 1190 との間を空乏状態にすることができる。しかし、濃度勾配のあるドーピング分布とすることの 1 つの欠点は、VTS 装置 1100 の表面に近いほど薄いドーピングとなり得ることにより、抵抗率がより大きくなり、効率が下がり得ることである。

40

#### 【0036】

図 12A は、ウエハ 1202 を含む基板 1200 を示す。ウエハ 1202 は、例えば、例として、シリコン、炭化ケイ素、ダイヤモンド、ガリウムヒ素、アルミニウムガリウムヒ素、りん化インジウム、窒化ガリウムなどの、種々の材料で作られていてもよい。ウエ

50

ハ1202は、また、ヘテロ構造を形成するため、複数の異なる材料で作られていてよい。ウエハ1202は、また、基部ウエハ（例えば、シリコンウエハ）と、シリコンウエハに重ねて成長させた他の層（例えば、エピタキシャル成長層）とで形成されていてよい。

#### 【0037】

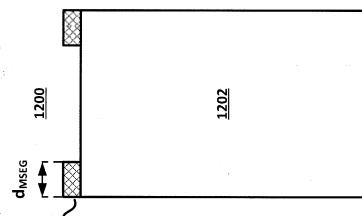

図12Bは、マスク層1204が堆積されて、溝と、半導体装置が位置することとなるシリコン柱（これらの柱は、おおよそ、マスク層1204の残留部分の下方に存在することとなる）に隣接するフィールドプレート誘電体との位置を規定するようにパターン形成された後の基板1200を示す。マスク層1204は、ハードマスクまたはソフトマスクであってもよい。一例において、ソフトマスクは、フォトレジスト層であってもよい。例示的な処理工程のいくつかの変形例において、マスク層1204の堆積およびパターン形成前に、ウエハ1202の表面上に保護層が堆積されてもよい。保護層は、処理中に欠陥および損傷からウエハ1202の表面を保護し得る。例示的な処理工程が保護層を使用しない場合（図12Bに示すように）、ウエハ1202の表面から損傷を除去するため、または欠陥を取り除くため、ウエハ1202の表面に関わる他の処理を実行する前に修復工程が使用されてもよい。例えば、ウエハ1202にシリコンウエハが使用される場合、保護層（図示せず）は、例えば、厚さが約200Åの熱成長酸化物であってもよい。一例において、マスク層1204部分は、 $1 \sim 3 \mu\text{m}$ の長さ $d_{MSEG}$ を有していてもよい。

10

#### 【0038】

図13Aは、溝1302が形成された後の基板1200を示す。一例において、深掘り反応性イオンエッティング（DRIE）工程が使用され、その結果、溝1302の側壁1306に波形の凹凸1304が形成される。溝1302は、深さ $d_{ETCH}1308$ までエッティングされてもよく、一例において、約 $60 \mu\text{m}$ の深さであってもよい。波形の凹凸を形成しない、他のエッティング技術も使用可能であることが理解されるべきである。

20

#### 【0039】

図13Bは、マスク層1204が除去された後の基板1200を示す。マスク層1204を除去することは、様々な工程で実現されてもよい。例えば、マスク層1204がフォトレジストマスクである場合、プラズマアッシング工程が使用されてもよい。他の実施例において、マスク層1204に窒化物または酸化物が使用される場合、リン酸またはフッ化水素酸、それぞれのエッティング工程が使用されてもよい。

30

#### 【0040】

図14Aは、絶縁層1402が堆積された後の基板1200を示す。絶縁層1402を堆積させる処理工程は、厚さ約 $d_1$ の絶縁材料が垂直側壁1306、溝1302の底部、およびシリコン柱1407上に存在するように、等角であってもよい。絶縁層1402は、さらに、隙間1404を形成することとなる。絶縁層1402は、二酸化ケイ素、窒化ケイ素、りん化ホウ素ケイ酸塩ガラスなどを含んでもよい。絶縁層1402を堆積させるため、例えば、低圧化学蒸着、高密度プラズマ、プラズマ化学蒸着などの処理工程が使用されてもよい。一例において、 $d_1$ は、 $0.5 \mu\text{m}$ から $10 \mu\text{m}$ の間であってもよく、隙間1404は、幅が約 $10 \mu\text{m}$ であってもよい。

40

#### 【0041】

図14Aでは、波形の凹凸1304が見えていないことに注意されたい。絶縁層1402の堆積前に、溝1302の側壁1306から波形の凹凸が除去されてもよい。例えば、ウエハ1202がシリコンである場合、波形の凹凸を消去するため、熱酸化工程が使用されてもよく、熱酸化物を除去してより滑らかな側壁を残すため、酸化物除去工程が使用されてもよい。代替的に、例示的な処理工程の変形例において、波形の凹凸が残存していてよい。例示的な処理工程の他の変形例において、使用される溝エッティング技術に起因して波形の凹凸が存在しなくてもよく、または、波形の凹凸が容易には見えない程度に、または大きく影響しない程度に、波形の凹凸が十分小さくてもよい。

#### 【0042】

図14Bは、基板1200に充填マスク層1406が堆積された後の基板1200を示

50

す。充填マスク層 1406 の厚さ  $d_2$  は、隙間 1404 が完全に充填されることを確実にするように選択されてもよい。例示的な処理工程の他の変形例において、マスク層 1406 は、隙間 1404 を完全には充填しなくてもよい。特に、絶縁層 1402 および充填マスク層 1406 に想定されるローフィングに起因して、隙間 1404 が狭められて、隙間 1404 の一部を未充填のまま残してもよい（図示せず）。一例において、充填マスク層 1406 の材料よりも絶縁層 1402 の材料のエッティングに対して高い選択性を示すエッティングレシピが利用できるように、充填マスク層 1406 の材料は、絶縁層 1402 の材料とは異なるエッティング特性を有しているべきである。例えば、絶縁層 1402 が酸化物である場合、マスク層 1406 は、多結晶シリコンであってもよい。

## 【0043】

10

図 15 は、隙間 1404 の一部（領域 1502 で示される）を再形成するため、マスク層 1406 が平坦化エッティングを受けて、絶縁層 1402 の上面と絶縁層 1402 の側壁の一部とから充填マスク層 1406 を除去した後の基板 1200 を示す。一例において、図 15 は、テープ付けされたフィールド誘電体領域を形成するため、絶縁層 1402 をエッティングすることと充填マスク 1406 をエッティングすることとを交互に行うサイクルに進む前の、基板 1200 の始点を示す。

## 【0044】

20

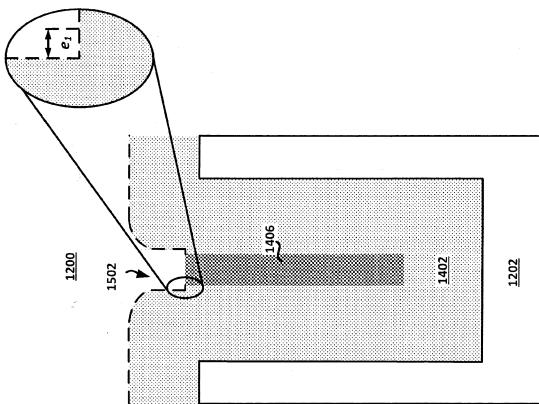

図 16A および 16B は、量  $e_1$  の絶縁層 1402 が等方性エッティングされる前および後の基板 1200 を示しており、等方性エッティングは、エッティングが実行されている面の傾きに関わらず略同一量の材料がエッティングされることを意味する。言い換えると、水平面からエッティングされる絶縁層 1402 の量が、垂直面からエッティングされる絶縁層 1402 の量と略同一である。エッティング中に図 16A から図 16B へと除去される絶縁層 1402 の量を近似的に示す線 1602 により、エッティングの等方性の性質が描かれている。線 1602 からわかるように、除去される厚さ  $e_1$  の絶縁材料は、絶縁層 1402 の表面全域で略一定である。絶縁層 1402 に対するエッティングが適切に選択された場合（その結果、充填マスク層 1406 よりも絶縁層 1402 に対して高い選択性を示すようにエッティングが選択されてもよい）、マスク層 1406 は、ほとんどエッティングされないはずである。例えば、絶縁層 1402 が酸化物であり、さらに、充填マスク層 1406 が多結晶シリコンである場合、この等方性エッティングを実行するため、水溶性のフッ化水素酸中のエッティング工程が使用されてもよい。領域 1502 に隣接した絶縁層 1402 の側壁が露出されたので、領域 1502 の幅は約  $2 \times e_1$  ぶん増加したことに注意されたい。

30

## 【0045】

図 17A および 17B は、厚さ  $e_2$  ぶんの充填マスク層 1406 をエッティングする前および後の基板 1200 を示す。充填マスク層 1406 をエッティングすることにより、領域 1502 の下方に、絶縁材料 1402 の新たに露出された側壁により画定される領域 1702 が形成される。領域 1702 および領域 1502 の初期幅は、いずれも隙間 1404 の幅（図 14A）によって定まるので、領域 1702 は、領域 1502 より狭く、領域 1502 が最初に形成されたとき（図 15 参照）に有していた幅と略同一の幅をもつ。

## 【0046】

40

図 18A および 18B は、厚さ  $e_3$  ぶんの絶縁層 1402 が等方性エッティングされる前および後の基板 1200 を示しており、等方性エッティングにより、エッティングが実行されている面の傾きに関わらず、略同一量の材料がエッティングされることが可能となる。言い換えると、水平面からエッティングされる絶縁層 1402 の量は、垂直面からエッティングされる絶縁層 1402 の量と略同一である。エッティングの等方性の性質が、エッティング中に図 18A から図 18B へと除去される絶縁層 1402 の量を近似的に示す線 1802 で描かれている。線 1802 からわかるように、除去される絶縁材料の量は、絶縁層 1402 の表面全域で略一定である。絶縁層 1402 に対するエッティングが適切に選択された場合、マスク層 1406 は、ほとんどエッティングされないはずである（例えば、図 16A および 16B に関する説明されたのと同じエッティング）。領域 1502 および 1702 に隣接した絶縁層 1402 の側壁が露出されたので、領域 1502 の幅が、さらに約  $2 \times e_3$

50

(すなわち、領域 1502 の初期幅から全体で  $2 \times e_3 + 2 \times e_1$  ) ぶん増加したこと、および領域 1702 の幅が約  $2 \times e_3$  (すなわち、領域 1702 の初期幅から全体で  $2 \times e_3$  ) ぶん増加したことに注意されたい。言い換えると、絶縁層 1402 の内部側壁と側壁 1306との間に、厚さ  $e_3$  ぶん少ない絶縁層 1402 が存在する。

#### 【0047】

図 19A および 19B は、厚さ  $e_4$  ぶんの充填マスク層 1406 をエッティングする前および後の基板 1200 を示す。充填マスク層 1406 をエッティングすることにより、領域 1502 および 1702 の下方に、絶縁材料 1402 の新たに露出された側壁により画定される領域 1902 が形成される。領域 1902、1702、および 1502 の初期幅は、すべて隙間 1404 の幅 (図 14A) によって定まるので、領域 1902 は、領域 1702 より狭く、領域 1502 および 1702 が最初に形成されたときに有していた幅 (図 15 および図 17 をそれぞれ参照) と略同一の幅をもつ。

10

#### 【0048】

絶縁層 1402 およびマスク層 1406 をエッティングすることの繰り返しは、絶縁層 1402 の所望のテープが達成されるまで続いててもよい。例えば、2つのエッティング (絶縁層および充填マスク層) を交互に行う処理工程は、所望のテープを生成するために知られている、ある所定の繰り返し数だけ続いててもよい。他の例として、2つのエッティングを交互に行う処理工程は、マスク層 1406 が消滅するまで、または、ある閾値未満の厚さをもつようになるまで続いててもよい。交互に行うエッティングのそれぞれの繰り返しが、既存の領域 (例えば、領域 1502、1702 および 1902) を、ある量だけ広げ、隙間 1404 の幅 (図 14A) に近似した幅をもつ新しい領域を形成する。そのため、繰り返しを増やすことにより、溝 1302 の上部のテープ (図 13A) が広がり、さらに、溝 1302 内のより深い所に新しい「段」が追加される。

20

#### 【0049】

図 20 は、マスク層 1406 および絶縁層 1402 をエッティングすることの、合計 6 回の繰り返しの後の基板 1200 を示す。絶縁層 1402 のすべてのエッティングが、略同一量の絶縁層 1402 (すなわち、 $x$  をエッティングの繰り返し数としたとき  $e_1 = e_3 = e_2 \times - 1$ ) を除去し、さらに、マスク層 1406 のすべてのエッティングが、略同一量のマスク層 1406 (すなわち、 $x$  をエッティングの繰り返し数としたとき  $e_2 = e_4 = e_2 \times$ ) を除去する場合、絶縁層 1402 のテープの傾き  $m_{T A P E R}$  は、約  $e_1 / e_2$  であつてもよい。

30

#### 【0050】

例示的な処理工程の他の変形例において、絶縁層 1402 の外形は、異なっていてもよい。例えば、異なる繰り返し段階において異なる量の絶縁層 1402 およびマスク層 1406 をエッティングすることにより、絶縁領域の外形が制御されてもよい。一実施例において、絶縁層 1402 の外形は、露出された絶縁層 1402 の側壁に沿って複数の異なる傾きをもつこととなる。

#### 【0051】

絶縁材料は、1つの段が堆積 / エッティングサイクルの各々を表すように、明確に画定された段を有するように描かれてきた。しかし、実際には、明確に画定された段が存在しなくてよいことが理解されるべきである。例えば、絶縁領域の外形は、より直線的な形状を有していてもよい。図 21 は、図 20 に示す外形ほど理想的ではない、テープ付けされたフィールドプレート誘電体において他の例示的な外形をもつ基板 2100 を示す。

40

#### 【0052】

図 22A は、交互に行うエッティング工程のすべての繰り返しが終了し、さらに、充填マスク層 1406 の残留部分がすべて除去された後の基板 1200 を示す。例示的な処理工程の変形例において、すべての充填マスク層 1406 が、代替例のエッティング工程の繰り返し中にエッティングされてもよいことが理解されるべきである。また、例示的な処理工程の他の変形例は、絶縁層 1402 中のテープによって形成される溝への導電性材料の堆積後に形成されるフィールドプレートの一部となるように、充填マスク層 1406 のうちの

50

任意の残留部分を残してもよい(図22B参照)。

**【0053】**

図22Bは、絶縁層1402によって充填されていない、または、テーパの形成過程中にエッチングされた溝1302の残りの部分(符号なし)を充填する導電性材料2202の堆積後の基板1200を示す。導電性材料2202は、例えば、アモルファスシリコン、多結晶シリコン、金属などの、任意の数の材料であってもよい。導電性材料2202として半導体を使用する場合、導電性材料2202は、それが堆積されているときに、その場でドーピングされてもよい。次に、導電性材料2202の上部が、化学機械研磨(CMP)またはエッチバック工程を使用して平坦化されてもよい。次に、テーパ付けされたフィールドプレートを形成する導電性材料2202の残留部分に、電気接点が形成されてもよい。フィールドプレートが形成されると、絶縁層1402が、テーパ付けされたフィールドプレート誘電体領域2204となる。

10

**【0054】**

テーパ付けされたフィールドプレート誘電体2204が形成され、さらに、ウエハ1202の表面が(必要とされる場合に)平坦化されると、基板1200の活性領域(例えば、シリコン柱2206および2208)に能動素子を形成するため、半導体装置製造工程が実施されてもよい。例えば、シリコン柱2206および2208にHVFETを形成するため、VTS HVFET処理工程が使用されてもよい。

**【0055】**

図23は、半導体処理工程において、テーパ付けされたフィールドプレート誘電体領域を形成する、例えば、処理工程2300(図12~22に関連した前述の例示的な処理工程と同様)の流れ図を示す。工程2302において、シリコンウエハが用意される。シリコンウエハは、例えば、シリコンのエピタキシャル成長層を有するように形成された、ドーピングに違いのある層を有していてもよい(例えば、図12A参照)。工程2304において、フォトレジストマスクがパターン形成される(例えば、図12B参照)。フォトレジストマスクは、テーパ付けされたフィールドプレートとテーパ付けされたフィールドプレート誘電体領域とを収容する溝の、位置および大きさを規定する。工程2306において、テーパ付けされたフィールドプレートのための溝を画定するDRIE(または、ボッシュエッチング)工程が実行され(例えば、図13A参照)、あらゆる残りのフォトレジストが取り除される(例えば、図13B参照)。工程2308において、基板の垂直面および水平面上に酸化物層が堆積される(例えば、図14A参照)。堆積された酸化物は、溝の大部分を充填するが、溝の中央の隙間を空けたまま残す。工程2310において、ウエハ上と、工程2308での酸化物の堆積によって形成される隙間内とに、ポリシリコンマスク層が堆積される(例えば、図14B参照)。工程2312において、隙間内で酸化物層の側壁の一部を露出するため、多結晶シリコンマスクのエッチングが実行される(例えば、図15参照)。工程2314において、工程2308で堆積された酸化物を、ある厚さぶん除去するため、等方性酸化物エッチングが実行される(例えば、図16Aおよび18A参照)。エッチングが等方性(すなわち、実質的に等方性)であるので、酸化物層の露出された表面のすべてが、略同一量ぶんエッチングされるはずである。工程2316において、隙間内で工程2308を経た酸化物層の側壁の新たな部分を露出するため、多結晶シリコンマスクが、さらなる量のぶんエッチングされる(例えば、図17Bおよび19B参照)。工程2318において、酸化物層のテーパ付けが終了したかどうか決定される(例えば、図20参照)。例えば、これは、すでに実行された酸化物エッチング/ポリエッティングの繰り返し数に基づいて決定されてもよい。他の例として、工程2314および2316の繰り返しは、閾値厚さのポリが残る(または、ポリがまったく残らなくなる)まで繰り返されてもよい。工程2320において、溝内にテーパ付けされたフィールドプレート誘電体が形成された後、テーパ付けされたフィールドプレートを形成するため、多結晶シリコンが溝内に堆積される(例えば、図22B参照)。フィールドプレートとウエハの表面とが共面となることを確実にするため、平坦化工程が必要とされてもよい。工程2322において、傾斜したフィールドプレートを収容する溝に隣接したシリコン柱

20

30

40

50

に H V F E T を形成するため、M O S F E T 处理手順が実行される。

【 0 0 5 6 】

例示的な処理工程 2 3 0 0 が、特定の材料および層に関連して説明されてきたが、いくつかの層は、任意選択的であってもよく、ウエハおよび層の材料は、さまざまであってもよいことが理解されるべきである。

【 0 0 5 7 】

本発明の示されている例についての上記の説明は、要約で説明されている事項も含めて、網羅的であることとも、開示されている形態そのものに制限することも意図されてはいない。本発明の特定の実施形態、および本発明の例は、本明細書において例示を目的として、説明されており、本発明のより広い趣旨および範囲から逸脱することなく、様々な同等な変更が可能である。特に、具体的で例示的な、電圧、電流、周波数、出力範囲値、時間などは、説明のために提示されていること、ならびに、他の実施形態および実施例において、本発明の教示に従って他の値が使用されてもよいことが理解される。10

【 0 0 5 8 】

前述の詳細な説明を考慮に入れて、本発明の例に対してこれらの変更が行われ得る。後述の請求項で使用される用語は、本発明を、明細書および請求項に開示されている特定の実施形態に限定するように解釈されてはならない。むしろ、範囲は、確立された請求項の解釈の原則に従って解釈される後述の請求項によって、完全に決定される。そのため、本明細書および図は、限定するものではなく例示的なものとみなされる。

【 図 1 】

【図3】

【図4】

【図5】

【図6】

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図 1 1】

【図 1 2】

FIG. 12B

FIG. 12A

FIG. 11

FIG. 12A

【図 1 3】

FIG. 13B

FIG. 13A

【図 1 4】

FIG. 14B

FIG. 14A

【図15】

【図16】

FIG. 15

FIG. 15

FIG. 16A

FIG. 16B

【図17】

FIG. 17B

FIG. 17A

【図18】

FIG. 18B

FIG. 18A

【図19】

【図20】

FIG. 19B

$$m_{TAPER} = \frac{e_1}{e_2}$$

FIG. 20

【図21】

FIG. 21

【図22】

FIG. 22A

FIG. 22B

【図23】

FIG. 23

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| H 0 1 L | 29/06 | 3 0 1 V |

| H 0 1 L | 29/78 | 6 5 8 F |

(72)発明者 バネルジー スジット

アメリカ合衆国 9 5 1 3 5 カリフォルニア州 サンノゼ、 フォックスボロ プレイス 3 2

4 3

(72)発明者 グラボウスキ ウェイン ビー

アメリカ合衆国 9 4 0 2 4 カリフォルニア州 ロスアルトス、 ミラヴェイユ アヴェニュー

1 3 9 0

審査官 綿引 隆

(56)参考文献 米国特許出願公開第2 0 0 7 / 0 0 6 9 2 5 7 ( U S , A 1 )

特開2 0 0 2 - 2 9 9 6 1 9 ( J P , A )

特開2 0 1 1 - 0 4 0 6 8 2 ( J P , A )

(58)調査した分野(Int.Cl. , DB名)

|         |             |

|---------|-------------|

| H 0 1 L | 2 1 / 3 3 6 |

| H 0 1 L | 2 9 / 0 6   |

| H 0 1 L | 2 9 / 4 2 3 |

| H 0 1 L | 2 9 / 7 8   |