## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4794158号 (P4794158)

(45) 発行日 平成23年10月19日(2011.10.19)

(24) 登録日 平成23年8月5日(2011.8.5)

| (51) Int.Cl.<br>GO9G 3/20<br>GO9G 3/30<br>GO9G 3/36<br>GO2F 1/133<br>G11C 19/00 | (2006. 01)<br>(2006. 01)<br>(2006. 01)<br>(2006. 01)<br>(2006. 01)                                | F I<br>G09G<br>G09G<br>G09G<br>G09G<br>G09G | 3/20<br>3/20                                 | 622E<br>623H<br>611A<br>621A<br>J<br>請求項の数 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (全 50 頁)                                        | 最終頁に続く           |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------|

| (21) 出願番号<br>(22) 出願日<br>(65) 公開番号<br>(43) 公開日<br>審查請求日                         | 特願2004-339730 (P20<br>平成16年11月25日 (20<br>特開2006-146091 (P20<br>平成18年6月8日 (2006<br>平成19年11月15日 (20 | 004.11.25)<br>006-146091A)<br>6.6.8)        | (73) 特許権<br>(74) 代理人<br>(72) 発明者<br>(72) 発明者 | 弁理士 宮園<br>千田 みちる<br>大て電機株式会社<br>「大なでででは、<br>大なでででは、<br>大なでででは、<br>大なでででは、<br>大なででは、<br>大なでは、<br>大なでは、<br>大なでは、<br>大なでは、<br>大なでは、<br>大なでは、<br>大なでは、<br>大なでは、<br>大なでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>はないでは、<br>とないでは、<br>とないでは、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とない。<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とないでも、<br>とない。<br>とないでも、<br>とないでも、<br>とないでも、<br>とをも、<br>とをも、<br>とをも、<br>とをも、<br>とをも、<br>とをも、<br>とをも、<br>とを | 京阪本通2丁目<br>博一<br>京阪本通2丁目<br>驻内<br>京阪本通2丁目<br>全内 | 5番5号 三<br>5番5号 三 |

|                                                                                 |                                                                                                   |                                             |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 最                                               | 終頁に続く            |

# (54) 【発明の名称】表示装置

# (57)【特許請求の範囲】

# 【請求項1】

第1電位とクロック信号線の間に直列に接続される第1トランジスタと第2トランジスタとを有し、前記第2トランジスタと前記第1トランジスタのゲートには第1信号と第3信号がそれぞれ入力される第1回路部と、

前記第1電位と第2電位の間に直列に接続される第3トランジスタおよび第4トランジスタと、前記第1電位と前記クロック信号線の間に直列に接続される第5トランジスタおよび第6トランジスタと、を有し、

<u>前記第4トランジスタと前記第5トランジスタのゲートには、前記第2トランジスタを介</u> して前記クロック信号線からクロック信号が供給され、

前記第6トランジスタは、前記第1信号が入力される前記第2トランジスタのオン状態の期間と重ならないオン状態の期間が得られる第2信号がゲートに供給され、オンすることにより、シフト信号を出力するとともに前記第3トランジスタのゲートに前記クロック信号を供給し、前記第3トランジスタは、前記クロック信号に応じてシフト出力信号を出力する第2回路部と

を含むシフトレジスタ回路部が複数段設けられており、

前記第1トランジスタ乃至第6トランジスタは同一の導電型を有し、

スキャン方向を切り替えるためのスキャン方向切替回路部と、

前記第3信号を所定段の前段の前記シフトレジスタ回路部のシフト出力信号とし、

前記第1信号と前記第2信号が、それぞれ前記スキャン方向に対して所定段の次段の前記

シフトレジスタ回路部のシフト信号および所定段の前段の前記シフトレジスタ回路部のシフト信号となるよう、前記スキャン方向に応じていずれのシフト信号を前記第1信号および前記第2信号とするかを切り替える入力信号切替回路部を含む表示装置。

## 【請求項2】

前記第3トランジスタのゲートとソースとの間には、容量が接続されており、

前記第1信号および前記第2信号は、前記第3トランジスタのゲート電位である、請求項1に記載の表示装置。

## 【請求項3】

前記第3トランジスタのソースまたはドレインは、第2電位側に接続されている、請求項2に記載の表示装置。

# 【請求項4】

前記第3トランジスタのソースまたはドレインは、前記第1電位と第2電位とが周期的に切り替わる周期信号を供給する周期信号線に接続されている、請求項2に記載の表示装置

## 【請求項5】

前記シフトレジスタ回路部は、複数段設けられているとともに、前記周期信号線は、第1周期信号線と第2周期信号線とを含み、

前記第3トランジスタのドレインには、前記第1周期信号線と前記第2周期信号線とが1 段毎に交互に接続されている、請求項4に記載の表示装置。

## 【請求項6】

前記入力信号切替回路部は、前記第 2 トランジスタのゲートにソースまたはドレインが接続される第 7 トランジスタおよび第 8 トランジスタを含むとともに、

前記第6トランジスタのゲートにソースまたはドレインが接続される第9トランジスタおよび第10トランジスタを含み、

前記第7トランジスタと前記第9トランジスタのゲートには、前記スキャン方向が順方向であるときに該トランジスタをオン状態とする信号が、前記第8トランジスタと前記第1 0トランジスタのゲートには、前記スキャン方向が逆方向であるときに該トランジスタをオン状態とする信号が、それぞれ入力され、

第1の方向にスキャンする場合には、前記第7トランジスタがオンすることにより前記第2トランジスタのゲートに前記第1信号が供給されるとともに、前記第10トランジスタがオンすることにより前記第6トランジスタのゲートに前記第2信号が供給され、

前記第1の方向とは反対の第2の方向にスキャンする場合には、前記第8トランジスタがオンすることにより前記第2トランジスタのゲートに前記第1信号が供給されるとともに、前記第9トランジスタがオンすることにより前記第6トランジスタのゲートに前記第2信号が供給される、請求項1~5のいずれか1項に記載の表示装置。

### 【請求項7】

前記第1トランジスタは、前記第1信号に応答してオンする前記第2トランジスタがオン状態の期間にはオフ状態になるとともに、前記第5トランジスタは、前記第2信号に応答してオンする前記第6トランジスタがオン状態の期間にはオフ状態になる、請求項1~6のいずれか1項に記載の表示装置。

# 【請求項8】

前記第 5 トランジスタは、前記第 4 トランジスタがオン状態のときに、前記第 3 トランジスタをオフ状態にする機能を有する、請求項 1 ~ 7 のいずれか 1 項に記載の表示装置。

## 【請求項9】

前記第1トランジスタ、前記第2トランジスタ、前記第5トランジスタおよび前記第6トランジスタの少なくとも1つは、互いに電気的に接続された2つのゲート電極を有する、請求項1~8のいずれか1項に記載の表示装置。

### 【請求項10】

前記第 5 トランジスタのゲートと前記第 2 トランジスタとの間には、第 1 ダイオードが接続されており、前記第 3 トランジスタのゲートと前記第 6 トランジスタとの間には、第 2

10

20

30

40

ダイオードが接続されている、請求項1~9のいずれか1項に記載の表示装置。

## 【請求項11】

前記第1ダイオードは、ダイオード接続された第11トランジスタを含むとともに、前記 第2ダイオードは、ダイオード接続された第12トランジスタを含み、

前記第11トランジスタおよび前記第12トランジスタは、前記第1トランジスタ、前記第2トランジスタ、前記第3トランジスタ、前記第4トランジスタ、前記第5トランジスタおよび前記第6トランジスタと同じ導電型のトランジスタである、請求項10に記載の表示装置。

## 【請求項12】

前記シフトレジスタ回路は、ゲート線を駆動するためのシフトレジスタ回路、および、ドレイン線を駆動するためのシフトレジスタ回路の少なくとも一方に適用されている、請求項1~11のいずれか1項に記載の表示装置。

# 【発明の詳細な説明】

## 【技術分野】

### [0001]

この発明は、表示装置に関し、特に、シフトレジスタ回路を有する表示装置に関する。

### 【背景技術】

## [0002]

従来、抵抗負荷型のインバータ回路が知られている(たとえば、非特許文献 1 参照)。また、従来では、上記した抵抗負荷型のインバータ回路を含むシフトレジスタ回路が知られている。なお、シフトレジスタ回路は、たとえば、液晶表示装置や有機 E L 表示装置のゲート線やドレイン線を駆動する回路に用いられる。

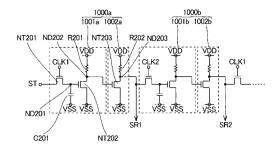

### [0003]

図18は、従来の抵抗負荷型のインバータ回路を含むシフトレジスタ回路の回路図である。図18を参照して、従来のシフトレジスタ回路1000aは、第1回路部1001a と第2回路部1002aとによって構成されている。また、2段目のシフトレジスタ回路 1000bは、第1回路部1001bと第2回路部1002bとによって構成されている

## [0004]

1段目のシフトレジスタ回路1000aを構成する第1回路部1001aは、nチャネルトランジスタNT201およびNT202と、容量C201と、抵抗R201とを含む。以下、従来技術の説明においては、nチャネルトランジスタNT201およびNT202と称する。トランジスタNT201のソースは、ノードND201に接続されているとともに、ドレインには、スタート信号STが入力される。このトランジスタNT201のゲートには、クロック信号CLK1が供給される。また、トランジスタNT202のソースは、負側電位VSSに接続されているとともに、ドレインは、ノードND202に接続されている。また、容量C201の一方の電極は、ノードND201に接続されているとともに、他方の電極は、負側電位VSSに接続されている。また、抵抗R201の一方端子は、正側電位VDDに接続されているとともに、他方端子は、ノードND202に接続されている。そして、トランジスタNT202と抵抗R201とによって、インバータ回路が構成されている。

## [0005]

また、1段目のシフトレジスタ回路1000aを構成する第2回路部1002aは、nチャネルトランジスタNT203と、抵抗R202とを含む。以下、従来技術の説明においては、nチャネルトランジスタNT203は、トランジスタNT203と称する。トランジスタNT203のソースは、負側電位VSSに接続されているとともに、ドレインは、ノードND203に接続されている。また、抵抗R202の一方端子は、正側電位VDDに接続されているとともに、他方端子は、ノードND203に接続されている。そして、トランジスタNT203と抵抗R202とによって、インバータ回路が構成されている

10

20

30

#### [0006]

また、2段目以降のシフトレジスタ回路も、上記した1段目のシフトレジスタ回路1000aと同様の回路構成を有する。なお、後段のシフトレジスタ回路の第1回路部は、前段のシフトレジスタ回路の出力ノードに接続されるように構成されている。また、奇数段に配置された第1回路部のトランジスタNT201のゲートには、上記したようにクロック信号CLK1が供給されるとともに、偶数段に配置された第1回路部のトランジスタNT201のゲートには、クロック信号CLK2が供給される。

## [0007]

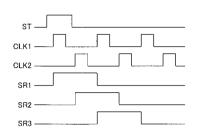

図19は、図18に示した従来のシフトレジスタ回路の動作を説明するための波形図である。次に、図18および図19を参照して、従来のシフトレジスタ回路の動作について説明する。

[00008]

まず、スタート信号 S T が H レベルになる。この後、クロック信号 C L K 1 が H レベルになる。この際、1段目のシフトレジスタ回路 1 0 0 0 a において、トランジスタNT 2 0 1 がオン状態になるとともに、ノードND 2 0 1 の電位が H レベルに上昇するので、トランジスタNT 2 0 2 がオン状態になる。これにより、ノードND 2 0 2 の電位が L レベルに降下することによりトランジスタNT 2 0 3 がオフ状態になるので、ノードND 2 0 3 の電位が H レベルに上昇して 1段目のシフトレジスタ回路 1 0 0 0 a から H レベルの出力信号 S R 1 が出力される。なお、クロック信号 C L K 1 が H レベルである期間には、容量 C 2 0 1 に H レベルの電位が蓄積される。

[0009]

次に、クロック信号CLK1がLレベルになる。この際、1段目のシフトレジスタ回路1000aのトランジスタNT201がオフ状態になる。この後、スタート信号STがLレベルになる。ここで、1段目のシフトレジスタ回路1000aにおいて、トランジスタNT201がオフ状態になったとしても、ノードND201の電位が容量C201に蓄積されたHレベルの電位によりHレベルに保持されているので、トランジスタNT202がオン状態に保持される。このため、ノードND202の電位がHレベルに上昇しないので、トランジスタNT203がオフ状態に保持される。これにより、1段目のシフトレジスタ回路1000aからHレベルの出力信号SR1が出力され続ける。

[0010]

次に、クロック信号 C L K 2 が H レベルになる。これにより、 2 段目のシフトレジスタ 1 0 0 0 b には、 1 段目のシフトレジスタ回路 1 0 0 0 a の H レベルの出力信号 S R 1 が 入力されるので、上記した 1 段目のシフトレジスタ回路 1 0 0 0 a と同様の動作が行われる。これにより、 2 段目のシフトレジスタ回路 1 0 0 0 b から H レベルの出力信号 S R 2 が出力される。

[0011]

この後、クロック信号 C L K 1 が再度 H レベルになる。この際、1 段目のシフトレジスタ回路 1 0 0 0 a において、トランジスタ N T 2 0 1 がオン状態になるとともに、ノード N D 2 0 1 の電位が L レベルに降下する。このため、トランジスタ N T 2 0 2 がオフ状態になるとともに、ノード N D 2 0 2 の電位が H レベルに上昇するので、トランジスタ N T 2 0 3 がオン状態になる。これにより、ノード N D 2 0 3 の電位が H レベルから L レベルに降下するので、1 段目のシフトレジスタ回路 1 0 0 0 a から L レベルの出力信号 S R 1 が出力される。上記のような動作によって、各段のシフトレジスタ回路からタイミングのシフトした H レベルの出力信号 (SR1、SR2、SR3…)が順次出力される。

【非特許文献 1 】岸野正剛著「半導体デバイスの基礎」、オーム社出版、 1 9 8 5 年 4 月 2 5 日、pp. 1 8 4 - 1 8 7

【発明の開示】

【発明が解決しようとする課題】

[0012]

しかしながら、図18に示した従来のシフトレジスタ回路では、1段目のシフトレジス

20

10

30

40

20

30

40

50

タ回路1000aにおいて、Hレベルの出力信号SR1を出力する場合、トランジスタNT202がオン状態に保持されるので、抵抗R201およびトランジスタNT202を介してVDDとVSSとの間に貫通電流が流れるという不都合があった。また、Lレベルの出力信号SR1を出力する場合、トランジスタNT203がオン状態に保持されるので、抵抗R202およびトランジスタNT203を介してVDDとVSSとの間に貫通電流が流れるという不都合もあった。このように、VDDとVSSとの間には常に貫通電流が流れるという不都合がある。また、2段目以降のシフトレジスタ回路についても1段目のシフトレジスタ回路1000aと同様の構成を有するので、VDDとVSSとの間に貫通電流が流れるという不都合がある。したがって、上記した従来のシフトレジスタ回路を液晶表示装置や有機EL表示装置のゲート線やドレイン線を駆動する回路に用いた場合には、液晶表示装置や有機EL表示装置の消費電力が増加するという問題点があった。

[0013]

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、消費電力が増加するのを抑制することが可能なシフトレジスタ回路を有する表示装置を提供することである。

【課題を解決するための手段および発明の効果】

[0014]

上記目的を達成するために、この発明の一の局面による表示装置は、第1電位側に接続された第1トランジスタと、クロック信号線に接続され、第1信号に応答してオンする第3トランジスタと、第1電位側に接続された第4トランジスタと、第3トランジスタのゲートと第1電位との間に接続された第4トランジスタと、第3トランジスタのゲートとクロック信号線との間に接続され、第1信号が入力される第2トランジスタのオン状態の期間と重ないオン状態の期間が得られる第2信号に応答してオンすることにより第3トランジスタのゲートにクロック信号を供給する第6トランジスタとを有する第2回路部とを含むシトレジスタ回路部と、スキャン方向を切り替えるためのスキャン方向切替回路部と、スキャン方向に応じて、第2トランジスタのゲートおよび第6トランジスタのゲートにそれぞれ供給される第1信号および第2信号を切り替えるための入力信号切替回路部とを含むシフトレジスタ回路を備えている。

[0015]

この一の局面による表示装置では、上記のように、第1信号に応答してオンする第2ト ランジスタと、第1の信号が入力される第2トランジスタのオン状態の期間と重ならない オン状態の期間が得られる第2信号に応答してオンすることにより第3トランジスタのゲ ートにクロック信号を供給する第6トランジスタとを設けることによって、たとえば、第 1信号に応答してオンする第2トランジスタがオンするときに第5トランジスタがオンす るように構成すれば、第5トランジスタと、第2信号に応答してオンする第6トランジス タとが同時にオン状態になることがないので、第5トランジスタおよび第6トランジスタ を介して第1電位とクロック信号線との間に貫通電流が流れるのを抑制することができる 。この場合、第5トランジスタがオンするときに第4トランジスタがオンするように構成 すれば、第2信号に応答してオンする第6トランジスタによりゲートにクロック信号が供 給される第3トランジスタと、第4トランジスタとが同時にオン状態になることがないの で、第3トランジスタおよび第4トランジスタを介して貫通電流が流れるのを抑制するこ とができる。また、第1信号に応答してオンする第2トランジスタがオンするときに第1 トランジスタがオフするように構成すれば、第1トランジスタと第2トランジスタとが同 時にオン状態になることがないので、第1トランジスタおよび第2トランジスタを介して 第1電位とクロック信号線との間に貫通電流が流れるのを抑制することができる。このよ うにシフトレジスタ回路部における貫通電流の発生を抑制することができるので、シフト レジスタ回路部を含む表示装置の消費電力が増加するのを抑制することができる。また、 スキャン方向に応じて第2トランジスタおよび第6トランジスタにそれぞれ供給される第 1 信号および第 2 信号を切り替えるための入力信号切替回路部を設けることによって、ス

20

30

40

50

キャン方向を切り換えた場合にも、第2トランジスタが第1信号に応答してオンするように、かつ、第6トランジスタが第2信号に応答してオンするように制御することができる。これにより、上記と同様、第2トランジスタがオンするときに第1トランジスタがオフになるとともに、第2トランジスタがオンするときに第4トランジスタおよび第5トランジスタがオンになるように構成すれば、スキャン方向を切り換えた場合にも、上記と同様、シフトレジスタ回路部における貫通電流の発生を抑制することができる。その結果、双方向スキャン機能を有する表示装置の消費電力が増加するのを抑制することができる。

## [0016]

上記一の局面による表示装置において、好ましくは、シフトレジスタ回路部は、複数段設けられており、第1信号は、スキャン方向に対して所定段の次段のシフトレジスタ回路部のシフト信号であり、第2信号は、スキャン方向に対して所定段の前段のシフトレジスタ回路部のシフト信号である。このように構成すれば、所定段の次段のシフトレジスタ回路部のシフト信号とはオン状態の期間が重ならないので、所定段の次段のシフトレジタ回路部のシフト信号に応答してオンする第2トランジスタとのオン状態の期間が重なることがない。これにより、容易に、第1信号に応答してオンする第2トランジスタがオン状態であるときに、第2信号に応答してオンする第6トランジスタがオン状態であるときに、第1信号に応答してオンする第6トランジスタがオン状態であるときに、第1信号に応答してオンする第6トランジスタがオン状態であるときに、第1信号に応答してオンする第2トランジスタがオフ状態になるように制御することができる。

## [0017]

上記一の局面による表示装置において、好ましくは、第3トランジスタのゲートとソースとの間には、容量が接続されており、第1信号および第2信号は、第3トランジスタのゲート電位である。このように構成すれば、容量が接続された第3トランジスタのゲート・ソース間電圧を維持するように、第3トランジスタのソース電位の上昇または低下に伴って第3トランジスタのゲート電位を上昇または低下させることができる。これにより、確実に第3トランジスタをオン状態に保持することができる。

# [0018]

上記第3トランジスタのゲートとソースとの間に容量が接続されている構成において、第3トランジスタのドレインは、第2電位側に接続されていてもよい。このように構成すれば、第3トランジスタが第2電位の信号に応答してオンする場合に、容易に、第3トランジスタのゲート電位を、第2電位よりも高くまたは低くすることができる。

### [0019]

上記第3トランジスタのゲートとソースとの間に容量が接続されている構成において、第3トランジスタのドレインは、第1電位と第2電位とが周期的に切り替わる周期信号を供給する周期信号線に接続されている。このように構成すれば、第3トランジスタがオン状態のときにソース電位を第1電位から第2電位に変動させることができるので、その電位の変動分だけ第3トランジスタのゲート電位を上昇または低下させることができる。すなわち、第3トランジスタのドレインが第2電位側に接続されている場合の第3トランジスタのゲートとソースとの間の容量による第3トランジスタのゲート電位の上昇または低下に加えて、ソース電位を第1電位から第2電位に変動させるときの変動分だけ第3トランジスタのゲート電位をより高くまたは低くすることができる。これにより、第3トランジスタのドレインが固定的な電位である第2電位側に接続されている場合に比べて、より確実に、第3トランジスタをオン状態に保持することができる。

### [0020]

この場合、好ましくは、シフトレジスタ回路部は、複数段設けられているとともに、周期信号線は、第1周期信号線と第2周期信号線とを含み、第3トランジスタのドレインには、第1周期信号線と第2周期信号線とが1段毎に交互に接続されている。このように構成すれば、隣接するシフトレジスタ回路部において、所定段のシフトレジスタ回路部および所定段の次段のシフトレジスタ回路部の各々の第3トランジスタがクロック信号に応答

20

30

40

50

してオンするタイミングに合わせて第3トランジスタのソース電位を第1電位から第2電位に変動させることができ、かつ、所定段のシフトレジスタ回路部および所定段の次段のシフトレジスタ回路部の各々の第3トランジスタがクロック信号に応答してオフ状態による直前まで第3トランジスタのソース電位を第2電位に保持することができる。これにより、第3トランジスタがクロック信号に応答してオフする直前までの間に第3トランジスタのゲート電位が第1電位になることに起因して、第3トランジスタのゲート電位が変動するとができる。この場合、所定段の第3トランジスタのがつト電位が所定段の次段のシフトレジスタ回路部の第6トランジスタに入り、第6トランジスタの動作が不安定になるのを抑制することができる。また、第6トランジスタの動作が不安定になることにより第6トランジスタがオンするタイミングが遅れるのを抑制することができるので、第6トランジスタを介して第3トランジスタのがっトにクロック信号が入力される際のタイミングが遅れるのを抑制することができる

[0021]

上記一の局面による表示装置において、好ましくは、入力信号切替回路部は、第2トランジスタのゲートに接続される第7トランジスタおよび第10トランジスタを含むととりに、第6トランジスタのゲートに接続される第9トランジスタがオンすることにより第6トランジスタのゲートに第1信号が供給されるとともに、第10トランジスタがオンすることにより第6トランジスタのゲートに第2信号が供給され、第1の方向とは反対の第2の方向にスキャンする場合には、第8トランジスタがオンすることにより第2トランジスタがオンすることにより第2とにより第3トランジスタがオンすることにより第3の方向にスキャンする場合にオンする第7トランジスタおよび第10トランジスタとによりにスキャンする場合にオンする第8トランジスタおよび第10トランジスタとにより、容易にスキャンする場合にオンする第8トランジスタおよび第6トランジスタとにより、容易に、スキャン方向に応じて、第2トランジスタおよび第6トランジスタにそれぞれ供給される第1信号および第2信号を切り替えることができる。

[0022]

上記一の局面による表示装置において、好ましくは、第1トランジスタは、第1信号に応答してオンする第2トランジスタがオン状態の期間にはオフ状態になるとともに、第5トランジスタは、第2信号に応答してオンする第6トランジスタがオン状態の期間にはオフ状態になる。このように構成すれば、容易に、第1トランジスタと第2トランジスタとが同時にオン状態になるのを防止することができるとともに、第5トランジスタと第6トランジスタとが同時にオン状態になるのを防止することができる。これにより、容易に、第1トランジスタおよび第2トランジスタを介して貫通電流が流れるのを抑制することができる。

[0023]

上記一の局面による表示装置において、好ましくは、第 5 トランジスタは、第 4 トランジスタがオン状態のときに、第 3 トランジスタをオフ状態にする機能を有する。このように構成すれば、容易に、第 3 トランジスタと第 4 トランジスタとが同時にオン状態になるのを防止することができる。これにより、容易に、第 3 トランジスタおよび第 4 トランジスタを介して貫通電流が流れるのを抑制することができる。

[0024]

上記一の局面による表示装置において、好ましくは、少なくとも第1トランジスタ、第 2トランジスタ、第3トランジスタ、第4トランジスタ、第5トランジスタおよび第6ト ランジスタは、同じ導電型のトランジスタである。このように構成すれば、第1~第6ト ランジスタを形成する際に、イオン注入工程の回数およびイオン注入マスクの枚数が増加 するのを抑制することができる。これにより、製造プロセスが複雑化するのを抑制することができるとともに、製造コストが増大するのを抑制することができる。

#### [0025]

上記一の局面による表示装置において、好ましくは、第1トランジスタ、第2トランジスタ、第5トランジスタおよび第6トランジスタの少なくとも1つは、互いに電気的に接続された2つのゲート電極を有する。このように構成すれば、第1トランジスタ、第2トランジスタ、第5トランジスタおよび第6トランジスタの少なくとも1つに印加される電圧を、2つのゲート電極により各ゲート電極に対応するソース・ドレイン間に分配することができる。この場合、第1トランジスタ、第2トランジスタ、第5トランジスタおよび第6トランジスタ、第1トランジスタ、第2トランジスタの少なくとも1つの各ゲート電極に対応するソース・ドレイン間に印加される電圧を小さくすることができるので、第1トランジスタ、第2トランジスタ、第5トランジスタの少なくとも1つに大きい電圧が印加されることに起因する特性の劣化を抑制することができる。これにより、シフトレジスタ回路部を含む表示装置のスキャン特性が低下するのを抑制することができる。

#### [0026]

上記一の局面による表示装置において、好ましくは、第5トランジスタのゲートと第2トランジスタとの間には、第1ダイオードが接続されており、第3トランジスタのゲートと第6トランジスタとの間には、第2ダイオードが接続されている。

## [0027]

この場合、好ましくは、第1ダイオードは、ダイオード接続された第11トランジスタを含むとともに、第2ダイオードは、ダイオード接続された第12トランジスタを含み、第11トランジスタおよび第12トランジスタは、第1トランジスタ、第2トランジスタ、第3トランジスタ、第4トランジスタ、第5トランジスタおよび第6トランジスタと同じ導電型のトランジスタである。このように構成すれば、第1ダイオードおよび第2ダイオードを設けたとしても、イオン注入工程の回数およびイオン注入マスクの枚数が増加するのを抑制することができる。これにより、第1ダイオードおよび第2ダイオードを設けることに起因して、製造プロセスが複雑化し、かつ、製造コストが増大するという不都合が発生するのを抑制することができる。

### [0028]

上記一の局面による表示装置において、好ましくは、シフトレジスタ回路は、ゲート線を駆動するためのシフトレジスタ回路、および、ドレイン線を駆動するためのシフトレジスタ回路の少なくとも一方に適用されている。このように構成すれば、ドレイン線を駆動するためのシフトレジスタ回路の少なくとも一方において、容易に、消費電力が増加することを抑制することができる。また、ドレイン線を駆動するためのシフトレジスタ回路とゲート線を駆動するためのシフトレジスタ回路との両方に適用すれば、消費電力が増加することをより抑制することができる

【発明を実施するための最良の形態】

# [0029]

以下、本発明の実施形態を図面に基づいて説明する。

# [0030]

### (第1実施形態)

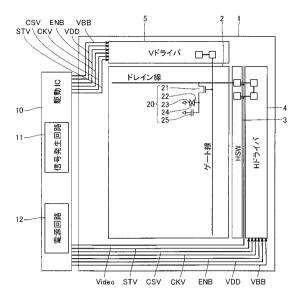

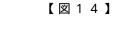

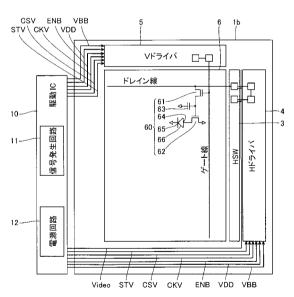

図1は、本発明の第1実施形態による液晶表示装置を示した平面図である。図2は、図1に示した第1実施形態による液晶表示装置のVドライバ内部の回路図である。

## [0031]

まず、図1を参照して、この第1実施形態では、基板1上に、表示部2が設けられている。この表示部2には、画素20がマトリクス状に配置されている。なお、図1では、図面の簡略化のため、1つの画素20のみを図示している。各々の画素20は、nチャネルトランジスタ21(以下、トランジスタ21という)、画素電極22、画素電極22に対向配置された各画素20に共通の対向電極23、画素電極22と対向電極23との間に挟持された液晶24、および、補助容量25によって構成されている。そして、トランジスタ21のソースは、画素電極22および補助容量25に接続されているとともに、ドレイ

10

20

30

40

ンは、ドレイン線に接続されている。このトランジスタ21のゲートは、ゲート線に接続されている。

# [0032]

また、表示部 2 の一辺に沿うように、基板 1 上に、表示部 2 のドレイン線を駆動(スキャン)するための水平スイッチ(HSW) 3 およびHドライバ 4 が設けられている。また、表示部 2 の他の辺に沿うように、基板 1 上に、表示部 2 のゲート線を駆動(スキャン)するためのVドライバ 5 が設けられている。なお、図 1 の水平スイッチ 3 には、 2 つのスイッチのみを図示しているが、実際は画素数に応じた数のスイッチが配置されている。また、図 1 のHドライバ 4 およびVドライバ 5 には、それぞれ、シフトレジスタ回路部を 2 つのみ図示しているが、実際は画素数に応じた数のシフトレジスタ回路部が配置されている。

### [0033]

また、基板1の外部には、駆動IC10が設置されている。この駆動IC10は、信号発生回路11および電源回路12を備えている。駆動IC10からHドライバ4へは、ビデオ信号Video、スタート信号STV、スキャン方向切替信号CSV、クロック信号CKV、イネーブル信号ENB、正側電位VDDおよび負側電位VBBが供給される。また、駆動IC10からVドライバ5へは、スタート信号STV、スキャン方向切替信号CSV、クロック信号CKV、イネーブル信号ENB、正側電位VDDおよび負側電位VBBが供給される。

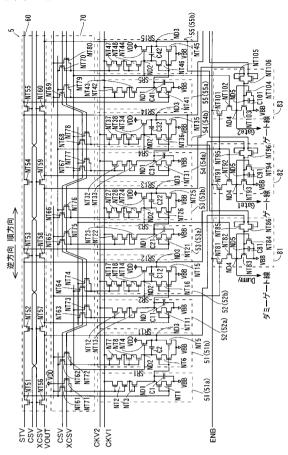

# [0034]

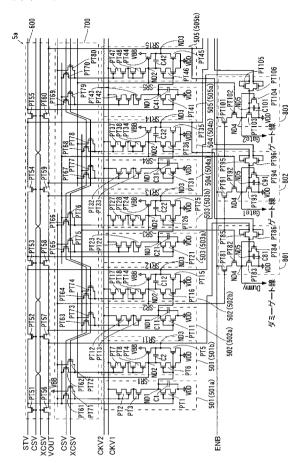

また、図2を参照して、第1実施形態では、Vドライバ5の内部に、複数段のシフトレジスタ回路部51~55と、スキャン方向切替回路部60と、入力信号切替回路部70と、複数段の論理合成回路部81~83とが設けられている。なお、図2では、図面の簡略化のため、5段分のシフトレジスタ回路部51~55および3段分の論理合成回路部81~83のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

# [0035]

そして、1段目のシフトレジスタ回路部51は、第1回路部51aと第2回路部51bとによって構成されている。第1回路部51aは、nチャネルトランジスタNT1およびNT2と、ダイオード接続されたnチャネルトランジスタNT3と、容量C1とを含む。なお、nチャネルトランジスタNT1およびNT2は、それぞれ、本発明の「第1トランジスタ」および「第2トランジスタ」の一例であり、nチャネルトランジスタNT3は、本発明の「第1ダイオード」および「第11トランジスタ」の一例である。また、第2回路部51bは、nチャネルトランジスタNT4、NT5、NT6およびNT7と、ダイオード接続されたnチャネルトランジスタNT8と、容量C2とを含む。なお、nチャネルトランジスタNT8と、容量C2とを含む。なお、nチャネルトランジスタNT7は、それぞれ、本発明の「第3トランジスタ」の一例である。また、nチャネルトランジスタNT8は、本発明の「第2ダイオード」および「第12トランジスタ」の一例である。以下、nチャネルトランジスタNT1~NT8と称する。

# [0036]

ここで、第1実施形態では、1段目のシフトレジスタ回路部51に設けられたトランジスタNT1~NT8は、すべてn型のMOSトランジスタ(電界効果型トランジスタ)からなるTFT(薄膜トランジスタ)により構成されている。また、第1実施形態では、トランジスタNT1、NT2、NT6、NT7およびNT8は、互いに電気的に接続された2つのゲート電極を有する。

### [0037]

また、第1回路部51aにおいて、トランジスタNT1のソースは、負側電位VBBに接続されているとともに、ドレインは、ノードND1に接続されている。また、容量C1の一方の電極は、負側電位VBBに接続されているとともに、他方の電極は、ノードND

10

20

30

40

1に接続されている。

## [0038]

ここで、第1実施形態では、トランジスタNT2のソースは、トランジスタNT3を介してノードND1に接続されているとともに、ドレインは、クロック信号線(CKV1)に接続されている。

# [0039]

また、第2回路部51bにおいて、トランジスタNT4のソースは、ノードND3に接続されているとともに、ドレインは、正側電位VDDに接続されている。このトランジスタNT4のゲートは、ノードND2に接続されている。また、トランジスタNT5のソースは、負側電位VBBに接続されているとともに、ドレインは、ノードND3に接続されている。このトランジスタNT5のゲートは、第1回路部51aのノードND1に接続されている。また、トランジスタNT6のソースは、負側電位VBBに接続されているとともに、ドレインは、ノードND2に接続されている。このトランジスタNT6のゲートは、第1回路部51aのノードND1に接続されている。

### [0040]

ここで、第1実施形態では、トランジスタNT6は、トランジスタNT5がオン状態のときに、トランジスタNT4をオフ状態にするために設けられている。また、第1実施形態では、トランジスタNT7のソースは、トランジスタNT8を介してノードND2に接続されているとともに、ドレインは、クロック信号線(CKV1)に接続されている。また、第1実施形態では、容量C2は、トランジスタNT4のゲートとソースとの間に接続されている。

### [0041]

また、2段目以降のシフトレジスタ回路部52~55は、上記した1段目のシフトレジスタ回路部51と同様の回路構成を有する。具体的には、2段目以降のシフトレジスタ回路部52~55は、それぞれ、1段目のシフトレジスタ回路部51の第1回路部51aと同様の回路構成を有する第1回路部52a~55aと、第2回路部51bと同様の回路構成を有する第2回路部52b~55bとによって構成されている。

### [0042]

2 段目のシフトレジスタ回路部5 2 は、1 段目のシフトレジスタ回路部5 1 のトランジスタNT1~NT8に対応するnチャネルトランジスタNT11~NT18と、容量C1 およびC2に対応する容量C11およびC12とを含む。なお、nチャネルトランジスタNT11、NT12、NT14、NT15、NT16およびNT17は、それぞれ、本発明の「第1トランジスタ」、「第2トランジスタ」、「第3トランジスタ」、「第4トランジスタ」、「第5トランジスタ」はよび「第6トランジスタ」の一例である。また、nチャネルトランジスタNT13は、本発明の「第1ダイオード」および「第11トランジスタ」の一例であり、nチャネルトランジスタNT18は、本発明の「第2ダイオード」および「第12トランジスタNT11~NT18は、それぞれ、トランジスタNT11~NT18と称する。

## [0043]

また、3段目のシフトレジスタ回路部53は、1段目のシフトレジスタ回路部51のトランジスタNT1~NT8に対応するnチャネルトランジスタNT21~NT28と、容量C1およびC2に対応する容量C21およびC22とを含む。なお、nチャネルトランジスタNT21、NT22、NT24、NT25、NT26およびNT27は、それぞれ、本発明の「第1トランジスタ」、「第2トランジスタ」、「第3トランジスタ」、「第4トランジスタ」、「第4トランジスタ」、「第4トランジスタ」の一例である。また、nチャネルトランジスタNT23は、本発明の「第1ダイオード」および「第11トランジスタ」の一例であり、nチャネルトランジスタNT28は、本発明の「第2ダイオード」および「第12トランジスタNT21~NT28と称する。

# [0044]

50

10

20

30

20

30

40

50

また、4段目のシフトレジスタ回路部 5 4 は、1段目のシフトレジスタ回路部 5 1のトランジスタN T 1 ~ N T 8 に対応する n チャネルトランジスタN T 3 1 ~ N T 3 8 と、容量 C 1 および C 2 に対応する容量 C 3 1 および C 3 2 とを含む。なお、 n チャネルトランジスタN T 3 1、 N T 3 2、 N T 3 4、 N T 3 5、 N T 3 6 および N T 3 7 は、それぞれ、本発明の「第 1 トランジスタ」、「第 2 トランジスタ」、「第 3 トランジスタ」、「第 4 トランジスタ」、「第 5 トランジスタ」および「第 6 トランジスタ」の一例である。また、 n チャネルトランジスタN T 3 3 は、本発明の「第 1 ダイオード」および「第 1 1 トランジスタ」の一例であり、 n チャネルトランジスタN T 3 8 は、本発明の「第 2 ダイオード」および「第 1 2 トランジスタ」の一例である。以下、 n チャネルトランジスタN T 3 1 ~ N T 3 8 と称する。

[0045]

[0046]

そして、2段目のシフトレジスタ回路部52のトランジスタNT12およびNT17と、4段目のシフトレジスタ回路部54のトランジスタNT32およびNT37とは、クロック信号線(CKV2)に接続されている。また、3段目のシフトレジスタ回路部53のトランジスタNT22およびNT27と、5段目のシフトレジスタ回路部55のトランジスタNT42およびNT47とは、クロック信号線(CKV1)に接続されている。すなわち、シフトレジスタ回路部51~55には、クロック信号線(CKV1)とクロック信号線(CKV2)とが1段毎に交互に接続されている。

[0047]

また、スキャン方向切替回路部 60 は、 n チャネルトランジスタNT 51 ~ NT 60 を含む。以下、 n チャネルトランジスタNT 51 ~ NT 60 は、それぞれ、トランジスタNT 51 ~ NT 60 と称する。

[0048]

ここで、第 1 実施形態では、スキャン方向切替回路部 6 0 を構成するトランジスタN T 5 1 ~ N T 6 0 は、すべて n 型の M O S トランジスタからなる T F T により構成されている。

[0049]

また、トランジスタNT51~NT55は、この順番でソース/ドレインの一方とソース/ドレインの他方とが互いに接続されている。また、トランジスタNT51、NT53およびNT55のゲートには、スキャン方向切替信号線(CSV)が接続されているとともに、トランジスタNT52およびNT54のゲートには、反転スキャン方向切替信号線(XCSV)が接続されている。すなわち、トランジスタNT51~NT55のゲートには、スキャン方向切替信号線(CSV)と反転スキャン方向切替信号線(XCSV)とが1つずつ交互に接続されている。

[0050]

また、トランジスタNT56~NT60は、この順番でソース/ドレインの一方とソース/ドレインの他方とが互いに接続されている。トランジスタNT56、NT58およびNT60のゲートには、反転スキャン方向切替信号線(XCSV)が接続されているとともに、トランジスタNT57およびNT59のゲートには、スキャン方向切替信号線(C

20

30

40

50

SV)が接続されている。すなわち、トランジスタNT56~NT60のゲートには、反転スキャン方向切替信号線(XCSV)とスキャン方向切替信号線(CSV)とが1つずつ交互に接続されている。

### [0051]

なお、スキャン方向が順方向の場合には、スキャン方向切替信号線CSVがHレベル(VDD)になるように、かつ、反転スキャン方向切替信号XCSVがLレベル(VBB)になるように制御される。このため、スキャン方向が順方向の場合には、トランジスタNT51、NT53、NT55、NT57およびNT59がオン状態になるように、かつ、トランジスタNT52、NT54、NT56、NT58およびNT60がオフ状態になるように制御される。また、スキャン方向が逆方向の場合には、スキャン方向切替信号線CSVがLレベル(VBB)になるように、かつ、反転スキャン方向切替信号XCSVがHレベル(VDD)になるように制御される。このため、スキャン方向が逆方向の場合には、トランジスタNT51、NT53、NT55、NT57およびNT59がオフ状態になるように、かつ、トランジスタNT52、NT55、NT57およびNT59がオフ状態になるように制御される。

### [0052]

また、1段目のシフトレジスタ回路部51のトランジスタNT1のゲートが、スキャン方向切替回路部60のトランジスタNT51のソース/ドレインの他方(トランジスタNT52のソース/ドレインの一方)に接続されているとともに、1段目のシフトレジスタ回路部51のノードND3が、スキャン方向切替回路部60のトランジスタNT56のソース/ドレインの他方(トランジスタNT57のソース/ドレインの一方)に接続されている。

# [0053]

また、2段目のシフトレジスタ回路部52のトランジスタNT11のゲートが、スキャン方向切替回路部60のトランジスタNT57のソース/ドレインの他方(トランジスタNT58のソース/ドレインの一方)に接続されているとともに、2段目のシフトレジスタ回路部52のノードND3が、スキャン方向切替回路部60のトランジスタNT52のソース/ドレインの他方(トランジスタNT53のソース/ドレインの一方)に接続されている。

# [0054]

また、3段目のシフトレジスタ回路部53のトランジスタNT21のゲートが、スキャン方向切替回路部60のトランジスタNT53のソース/ドレインの他方(トランジスタNT54のソース/ドレインの一方)に接続されているとともに、3段目のシフトレジスタ回路部53のノードND3が、スキャン方向切替回路部60のトランジスタNT58のソース/ドレインの他方(トランジスタNT59のソース/ドレインの一方)に接続されている。

# [0055]

また、4段目のシフトレジスタ回路部54のトランジスタNT31のゲートが、スキャン方向切替回路部60のトランジスタNT59のソース/ドレインの他方(トランジスタNT60のソース/ドレインの一方)に接続されているとともに、4段目のシフトレジスタ回路部54のノードND3が、スキャン方向切替回路部60のトランジスタNT54のソース/ドレインの他方(トランジスタNT55のソース/ドレインの一方)に接続されている。

# [0056]

また、5段目のシフトレジスタ回路部55のトランジスタNT41のゲートが、スキャン方向切替回路部60のトランジスタNT55のソース/ドレインの他方に接続されているとともに、5段目のシフトレジスタ回路部55のノードND3が、スキャン方向切替回路部60のトランジスタNT60のソース/ドレインの他方に接続されている。

### [0057]

各段のシフトレジスタ回路部51~55とスキャン方向切替回路部60とを上記のよう

に接続することによって、スキャン方向に応じて、所定段のシフトレジスタ回路部の第1回路部にスキャン方向に対して前段のシフト出力信号(SR11~SR15)が入力されるように制御される。ただし、初段のシフトレジスタ回路部51の第1回路部51 aには、スタート信号STVが入力される。

## [0058]

また、入力信号切替回路部70は、 n チャネルトランジスタNT61~NT80を含む。なお、 n チャネルトランジスタNT61、NT63、NT65、NT67およびNT69は、本発明の「第7トランジスタ」の一例であり、 n チャネルトランジスタNT62、NT64、NT66、NT68およびNT70は、本発明の「第10トランジスタ」の一例である。また、 n チャネルトランジスタNT71、NT73、NT75、NT77およびNT79は、本発明の「第8トランジスタ」の一例であり、 n チャネルトランジスタNT72、NT74、NT76、NT78およびNT80は、本発明の「第9トランジスタ 」の一例である。以下、 n チャネルトランジスタNT61~NT80は、それぞれ、トランジスタNT61~NT80と称する。

### [0059]

ここで、第1実施形態では、入力信号切替回路部70を構成するトランジスタNT61~NT80は、すべてn型のMOSトランジスタからなるTFTにより構成されている。

### [0060]

また、第1実施形態では、スキャン方向切替信号線(CSV)に接続された n チャネル トランジスタと、ゲートが反転スキャン方向切替信号線(XCSV)に接続されたnチャ ネルトランジスタとは、各段毎に2つずつ設けられている。具体的には、1段目に、ゲー トがスキャン方向切替信号線(CSV)に接続されたトランジスタNT61およびNT6 2 と、ゲートが反転スキャン方向切替信号線(XCSV)に接続されたトランジスタNT 71およびNT72とが設けられている。トランジスタNT61およびNT71のソース /ドレインの一方は、1段目のシフトレジスタ回路部51のトランジスタNT2のゲート に接続されている。トランジスタNT61のソース / ドレインの他方は、2段目のシフト レジスタ回路部52のノードND2に接続されているとともに、トランジスタNT71の ソース / ドレインの他方は、正側電位 V D D に接続されている。また、トランジスタ N T 6 2 および N T 7 2 のソース / ドレインの一方は、 1 段目のシフトレジスタ回路部 5 1 の トランジスタNT7のゲートに接続されている。トランジスタNT62のソース/ドレイ ンの他方は、スタート信号STVが供給されるスキャン方向切替回路部60のトランジス タNT51のソース/ドレインの他方(トランジスタNT52のソース/ドレインの一方 )およびトランジスタNT1のゲートに接続されているとともに、トランジスタNT72 のソース/ドレインの他方は、2段目のシフトレジスタ回路部52のノードND2に接続 されている。

# [0061]

また、2段目には、ゲートがスキャン方向切替信号線(CSV)に接続されたトランジスタNT63およびNT64と、ゲートが反転スキャン方向切替信号線(XCSV)に接続されたトランジスタNT73およびNT74とが設けられている。トランジスタNT63およびNT73のソース / ドレインの一方は、2段目のシフトレジスタ回路部52のトランジスタNT12のゲートに接続されている。トランジスタNT63のソース / ドレインの他方は、3段目のシフトレジスタ回路部53のノードND2に接続されているとともに、トランジスタNT73のソース / ドレインの他方は、1段目のシフトレジスタ回路部51のノードND2に接続されている。また、トランジスタNT64およびNT74のソース / ドレインの一方は、1段目のシフトレジスタ回路部52のトランジスタNT17のゲートに接続されている。トランジスタNT64のソース / ドレインの他方は、1段目のシフトレジスタ回路部51のノードND2に接続されているとともに、トランジスタNT

## [0062]

10

20

30

20

30

40

50

また、3段目には、ゲートがスキャン方向切替信号線(CSV)に接続されたトランジスタNT65およびNT66と、ゲートが反転スキャン方向切替信号線(XCSV)に接続されたトランジスタNT75およびNT76とが設けられている。トランジスタNT65およびNT75のソース/ドレインの一方は、3段目のシフトレジスタ回路部53のトランジスタNT22のゲートに接続されている。トランジスタNT65のソース/ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されているとともに、トランジスタNT75のソース/ドレインの他方は、2段目のシフトレジスタ回路部52のノードND2に接続されている。また、トランジスタNT66およびNT76のソース/ドレインの一方は、3段目のシフトレジスタ回路部53のトランジスタNT27のゲートに接続されている。トランジスタNT66のソース/ドレインの他方は、2段目のシフトレジスタ回路部52のノードND2に接続されているとともに、トランジスタNT76のソース/ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されている。

# [0063]

また、4段目には、ゲートがスキャン方向切替信号線(CSV)に接続されたトランジスタNT67およびNT68と、ゲートが反転スキャン方向切替信号線(XCSV)に接続されたトランジスタNT77およびNT78とが設けられている。トランジスタNT67およびNT77のソース/ドレインの一方は、4段目のシフトレジスタ回路部54のトランジスタNT32のゲートに接続されている。トランジスタNT67のソース/ドレインの他方は、5段目のシフトレジスタ回路部55のノードND2に接続されているともに、トランジスタNT77のソース/ドレインの他方は、3段目のシフトレジスタ回路部53のノードND2に接続されている。また、トランジスタNT68およびNT78のソース/ドレインの一方は、4段目のシフトレジスタ回路部54のトランジスタNT37のゲートに接続されている。トランジスタNT68のソース/ドレインの他方は、3段目のシフトレジスタ回路部53のノードND2に接続されているとともに、トランジスタNT78のソース/ドレインの他方は、5段目のシフトレジスタ回路部55のノードND2に接続されている。

## [0064]

また、5段目には、ゲートがスキャン方向切替信号線(CSV)に接続されたトランジスタNT69およびNT70と、ゲートが反転スキャン方向切替信号線(XCSV)に接続されたトランジスタNT79およびNT80とが設けられている。トランジスタNT69およびNT79のソース/ドレインの一方は、5段目のシフトレジスタ回路部55のトランジスタNT69のソース/ドレインの他方は、図示しない6段目のシフトレジスタ回路部のノードND2に接続されているとともに、トランジスタNT79のソース/ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されている。また、トランジスタNT70およびNT80のソース/ドレインの一方は、5段目のシフトレジスタ回路部55のトランジスタNT47のゲートに接続されている。トランジスタNT70のソース/ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されているとともに、トランジスタNT80のソース/ドレインの他方は、図示しない6段目のシフトレジスタ回路部のノードND2に接続されている。

### [0065]

入力信号切替回路部70を構成するトランジスタNT61~NT80を上記のように構成することによって、スキャン方向が順方向の場合には、トランジスタNT61~NT70がオン状態になるように、かつ、トランジスタNT71~NT80がオフ状態になるように制御される。また、各段のシフトレジスタ回路部51~55と入力信号切替回路部70とを上記のように接続することによって、スキャン方向に応じて、所定段のシフトレジスタ回路部の第1回路部にスキャン方向に対して次段のシフト信号(SR1~SR5)が入力されるように、かつ、所定段のシフトレジスタ回路部の第2回路部にスキャン方向に対して前段のシフト信号(SR1~SR5)が入力されるように制御される。ただし、初

20

30

40

50

段のシフトレジスタ回路部 5 1 の第 1 回路部 5 1 a には、スタート信号 S T V が入力される。なお、シフト信号 S R 1 ~ S R 5 は、本発明の「第 1 信号」および「第 2 信号」の一例である。

## [0066]

また、論理合成回路部 8 1 ~ 8 3 は、それぞれ、ダミーゲート線( D u m m y )、 1 段目のゲート線( G a t e 1 )および 2 段目のゲート線( G a t e 2 )に接続されている。

### [0067]

ダミーゲート線(Dummy)に接続される論理合成回路部81は、nチャネルトランジスタNT81~NT84と、ダイオード接続されたnチャネルトランジスタNT85およびNT86と、容量C81とを含む。以下、nチャネルトランジスタNT81~NT86は、それぞれ、トランジスタNT81~NT86と称する。

### [0068]

ここで、第1実施形態では、論理合成回路部81を構成するトランジスタNT81~NT86は、すべてn型のMOSトランジスタからなるTFTにより構成されている。

## [0069]

また、トランジスタNT81のドレインは、イネーブル信号線(ENB)に接続されているとともに、ソースは、トランジスタNT82のドレインに接続されている。トランジスタNT82のソースは、ノードND4(ダミーゲート線)に接続されている。トランジスタNT81のゲートは、2段目のシフトレジスタ回路部52のシフト信号SR2が出力されるノードND2に接続されているとともに、トランジスタNT82のゲートは、3段目のシフトレジスタ回路部53のシフト信号SR3が出力されるノードND2に接続されている。

# [0070]

また、トランジスタNT83のソースは、負側電位VBBに接続されているとともに、ドレインは、ノードND4(ダミーゲート線)に接続されている。このトランジスタNT83のゲートは、ノードND5に接続されている。また、トランジスタNT84のソースは、負側電位VBBに接続されているとともに、ドレインは、ノードND5に接続されている。このトランジスタNT84のゲートは、ノードND4(ダミーゲート線)に接続されている。また、容量C81の一方の電極は、負側電位VBBに接続されているとともに、他方の電極は、ノードND5に接続されている。また、ノードND5は、トランジスタNT85を介して、1段目のシフトレジスタ回路部51のシフト出力信号SR11が出力されるノードND3に接続されているとともに、トランジスタNT86を介して、4段目のシフトレジスタ回路部54のシフト出力信号SR14が出力されるノードND3に接続されている。

# [0071]

また、1段目のゲート線(Gate1)に接続される論理合成回路部82は、ダミーゲート線(Dummy)に接続される論理合成回路部81と同様の回路構成を有する。具体的には、1段目のゲート線(Gate1)に接続される論理合成回路部82は、ダミーゲート線(Dummy)に接続される論理合成回路部81のトランジスタNT81~NT86に対応するnチャネルトランジスタNT91~NT96は、それぞれ、トランジスタNT91~NT96は、それぞれ、トランジスタNT91~NT96と称する。

## [0072]

なお、1段目のゲート線(Gate1)に接続される論理合成回路部82において、トランジスタNT91のゲートは、3段目のシフトレジスタ回路部53のシフト信号SR3が出力されるノードND2に接続されているとともに、トランジスタNT92のゲートは、4段目のシフトレジスタ回路部54のシフト信号SR4が出力されるノードND2に接続されている。また、ノードND5は、トランジスタNT95を介して、2段目のシフトレジスタ回路部52のシフト出力信号SR12が出力されるノードND3に接続されているとともに、トランジスタNT96を介して、5段目のシフトレジスタ回路部55のシフ

20

30

40

50

ト出力信号SR15が出力されるノードND3に接続されている。

## [0073]

また、2段目のゲート線(Gate2)に接続される論理合成回路部83は、ダミーゲート線(Dummy)に接続される論理合成回路部81と同様の回路構成を有する。具体的には、2段目のゲート線(Gate2)に接続される論理合成回路部83は、ダミーゲート線(Dummy)に接続される論理合成回路部81のトランジスタNT81~NT86に対応するnチャネルトランジスタNT101~NT106と、容量C81に対応する容量C101とを含む。以下、nチャネルトランジスタNT101~NT106は、それぞれ、トランジスタNT101~NT106と称する。

## [0074]

なお、2段目のゲート線(Gate2)に接続される論理合成回路部83において、トランジスタNT101のゲートは、4段目のシフトレジスタ回路部54のシフト信号SR4が出力されるノードND2に接続されているとともに、トランジスタNT102のゲートは、5段目のシフトレジスタ回路部55のシフト信号SR5が出力されるノードND2に接続されている。また、ノードND5は、トランジスタNT105を介して、3段目のシフトレジスタ回路部53のシフト出力信号SR13が出力されるノードND3に接続されているとともに、トランジスタNT106を介して、図示しない6段目のシフトレジスタ回路部のシフト出力信号が出力されるノードND3に接続されている。

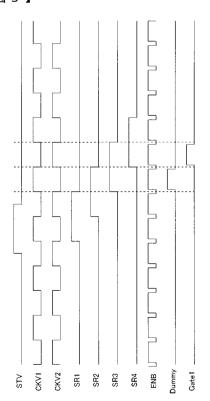

## [0075]

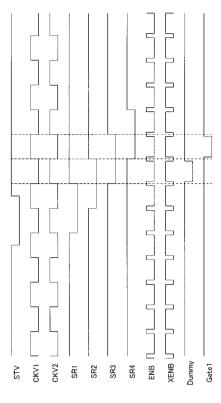

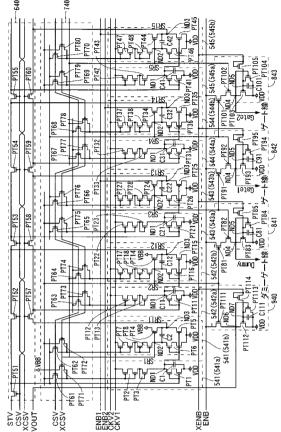

図3は、本発明の第1実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図2および図3を参照して、第1実施形態による液晶表示装置のVドライバの動作について説明する。

# [0076]

まず、図2中の順方向に沿って、各段のゲート線にタイミングのシフトした出力信号が 順次出力される場合(順方向スキャンの場合)について説明する。この順方向スキャンの 場合には、スキャン方向切替信号CSVがHレベルに保持されるとともに、反転スキャン 方向切替信号XCSVがLレベルに保持される。これにより、スキャン方向切替回路部6 0において、スキャン方向切替信号CSVがゲートに入力されるトランジスタNT51、 NT53、NT55、NT57およびNT59がオン状態に保持されるとともに、反転ス キャン方向切替信号XCSVがゲートに入力されるトランジスタNT52、NT54、N T56、NT58およびNT60がオフ状態に保持される。また、入力信号切替回路部7 0 において、スキャン方向切替信号 CSVがゲートに入力されるトランジスタNT61~ NT70がオン状態に保持されるとともに、反転スキャン方向切替信号XCSVがゲート に入力されるトランジスタNT71~NT80がオフ状態に保持される。そして、初期状 態では、各段のシフトレジスタ回路部51~55のノードND2から出力されるシフト信 号 S R 1 ~ S R 5 と、ノード N D 3 から出力されるシフト出力信号 S R 1 1 ~ S R 1 5 と がLレベルになっている。また、ダミーゲート線および各段のゲート線のそれぞれに論理 合成回路部 8 1 ~ 8 3 のノード N D 4 から出力される出力信号 D u m m y 、 G a t e 1 お よびGate2がLレベルになっている。この状態で、図3に示すように、スタート信号 STVをHレベルに上昇させる。これにより、スキャン方向切替回路部60のオン状態の トランジスタNT51を介して1段目のシフトレジスタ回路部51のトランジスタNT1 のゲートにHレベルのスタート信号STVが入力されるので、トランジスタNT1がオン 状態になる。この後、1段目のシフトレジスタ回路部51のトランジスタNT2およびN T7のドレインに入力されるクロック信号CKV1がHレベル(VDD)に上昇する。

### [0077]

この際、第1実施形態では、1段目のシフトレジスタ回路部51のトランジスタNT2のゲートに、入力信号切替回路部70のオン状態のトランジスタNT61を介して、2段目のシフトレジスタ回路部52から出力されるLレベルのシフト信号SR2が入力されている。これにより、トランジスタNT2がオフ状態になっている。このため、トランジスタNT1がオン状態であっても、トランジスタNT1およびNT2を介してクロック信号

線(CKV1)と負側電位VBBとの間に貫通電流が流れることはない。

## [0078]

また、1段目のシフトレジスタ回路部51のトランジスタNT1がオン状態でトランジスタNT2がオフ状態であるので、トランジスタNT1を介して負側電位VBBからLレベルの電位が供給されることによりノードND1の電位がLレベルに低下する。これにより、1段目のシフトレジスタ回路部51のノードND1にゲートが接続されるトランジスタNT5およびNT6がオフ状態になる。

## [0079]

また、Hレベルのスタート信号STVは、スキャン方向切替回路部60のオン状態のトランジスタNT51および入力信号切替回路部70のオン状態のトランジスタNT62を介して、1段目のシフトレジスタ回路部51のトランジスタNT7のゲートにも入力される。これにより、トランジスタNT7がオン状態になっている。

### [0800]

この際、第1実施形態では、トランジスタNT7がオン状態であっても、トランジスタNT6がオフ状態であるので、トランジスタNT6およびNT7を介してクロック信号線(CKV1)と負側電位VBBとの間に貫通電流が流れることはない。

## [0081]

また、Hレベルのクロック信号CKV1が、トランジスタNT7およびNT8を介して入力されることにより、1段目のシフトレジスタ回路部51のノードND2の電位がHレベルに上昇する。これにより、トランジスタNT4がオン状態になるとともに、正側電位VDDからトランジスタNT4を介してノードND3にHレベル(VDD)の電位が供給される。

## [0082]

この際、第1実施形態では、トランジスタNT4がオン状態であっても、トランジスタNT5がオフ状態であるので、トランジスタNT4およびNT5を介して正側電位VDDと負側電位VBBとの間に貫通電流が流れることはない。

### [0083]

また、正側電位VDDからトランジスタNT4を介してノードND3にHレベル(VDD)の電位が供給されることにより、ノードND3の電位がVDD側に上昇する。この際、1段目のシフトレジスタ回路部51のノードND2の電位は、容量C2によってトランジスタNT4のゲート・ソース間電圧が維持されるように、ノードND3の電位の上昇に伴ってブートされることにより上昇する。これにより、ノードND2の電位がVDDよりもしきい値電圧(Vt)以上の所定の電圧(V )分高い電位まで上昇する。したがって、1段目のシフトレジスタ回路部51のノードND2からVDD+Vt以上の電位(VDD+V )を有するHレベルのシフト信号SR1が出力される。また、同時に、1段目のシフトレジスタ回路部51のノードND3からHレベル(VDD)のシフト出力信号SR11が出力される。

## [0084]

そして、1段目のシフトレジスタ回路部51のHレベル(VDD)のシフト出力信号SR11は、ダミーゲート線に繋がる論理合成回路部81のトランジスタNT85を介して、トランジスタNT83のゲートに入力される。これにより、トランジスタNT83がオン状態になる。このとき、論理合成回路部81のトランジスタNT81のゲートには、2段目のシフトレジスタ回路部52からLレベルのシフト信号SR2が入力されているとともに、トランジスタNT82のゲートには、3段目のシフトレジスタ回路部53からLレベルのシフト信号SR3が入力されている。これにより、論理合成回路部81のトランジスタNT81およびNT82が両方ともオフ状態になっている。このため、トランジスタNT83を介して負側電位VBBからLレベル(VBB)の電位が供給されることにより、論理合成回路部81のノードND4からLレベル(VBB)の出力信号Dummyがダミーゲート線に続けて出力される。

## [0085]

50

10

20

30

20

30

40

50

また、1段目のシフトレジスタ回路部51のHレベル(VDD)のシフト出力信号SR11は、スキャン方向切替回路部60のオン状態のトランジスタNT57を介して、2段目のシフトレジスタ回路部52のトランジスタNT11のゲートにも入力される。これにより、トランジスタNT11がオン状態になる。また、1段目のシフトレジスタ回路部51のHレベル(VDD+V))のシフト信号SR1は、入力信号切替回路部70のオン状態のトランジスタNT64を介して、2段目のシフトレジスタ回路部52のトランジスタNT17がオン状態になる。また、2段目のシフトレジスタ回路部52のトランジスタNT17がオン状態になる。また、2段目のシフトレジスタ回路部52のトランジスタNT12のゲートには、3段目のシフトレジスタ回路部53のノードND2から出力されたLレベルのシフト信号SR3が入力される。これにより、トランジスタNT12がオフ状態になっている。この後、2段目のシフトレジスタ回路部52のトランジスタNT12およびNT17のドレインに入力されるクロック信号CKV2の電位がHレベル(VDD)に上昇する。

[0086]

この際、シフト信号SR1は、VDDよりもしきい値電圧(Vt)以上の所定の電圧(V)分高い電位(VDD+V)になっている。このシフト信号SR1を2段目のシフトレジスタ回路部52のトランジスタNT17のゲートに入力する場合、トランジスタNT64のゲート電位がスキャン方向切替信号CSVの電位(VDD)に等しいので、トランジスタNT17のゲート電圧がVDD-Vtに充電される。この後、クロック信号CKV2がHレベル(VDD)に立ち上がるので、トランジスタNT17のゲート電圧は、ゲート・ソース間電圧を保持したまま、さらにVDDとVBBの電位差分上昇する。

[0087]

この後、上記した1段目のシフトレジスタ回路部51の動作と同様の動作が2段目のシフトレジスタ回路部52においても行われる。すなわち、2段目のシフトレジスタ回路部52のノードND2からVDD+Vt以上の電位(VDD+V)を有するHレベルのシフト信号SR2が出力される。また、同時に、2段目のシフトレジスタ回路部52のノードND3からHレベル(VDD)のシフト出力信号SR12が出力される。

[0088]

そして、2段目のシフトレジスタ回路部52のHレベル(VDD+V >VDD+Vt)のシフト信号SR2は、ダミーゲート線に繋がる論理合成回路部81のトランジスタNT81のゲートに入力される。また、Hレベルのシフト信号SR2(VDD+V )は、入力信号切替回路部70のオン状態のトランジスタNT61を介して1段目のシフトレジスタ回路部51のトランジスタNT2のゲートに入力されるとともに、入力信号切替回路部70のオン状態のトランジスタNT3段目のシフトレジスタ回路部53のトランジスタNT27のゲートに入力される。この際、トランジスタNT61およびNT27のゲートに入力される。この際、トランジスタNT61およびNT27のゲート電圧がVDD・Vtに充電される。また、2段目のシフトレジスタ回路部52のHレベル(VDD)のシフト出力信号SR12は、スキャン方向切替回路部60のオン状態のトランジスタNT53を介して3段目のシフトレジスタ回路部53のトランジスタNT95を介して3段目のゲート線に繋がる論理合成回路部52のトランジスタNT95を介してトランジスタNT93のゲートに入力される。

[0089]

そして、ダミーゲート線に繋がる論理合成回路部81のトランジスタNT81は、Hレベル(VDD+V )のシフト信号SR2がゲートに入力されることによりオン状態になる。このとき、論理合成回路部81のトランジスタNT82がオフ状態に保持されるとともに、トランジスタNT83がオン状態に保持されている。このため、トランジスタNT83を介して負側電位VBBから供給されるLレベル(VBB)の電位により、論理合成回路部81のノードND4の電位がLレベル(VBB)に保持される。したがって、Lレベル(VBB)の出力信号Dummyが論理合成回路部81のノードND4からダミーゲート線に続けて出力される。

20

30

40

50

#### [0090]

また、1段目のシフトレジスタ回路部51のトランジスタNT2は、トランジスタNT61を介してHレベルのシフト信号SR2がゲートに入力されることによりオン状態になる。この際、トランジスタNT61のゲート電位がスキャン方向切替信号CSVの電位(VDD)に等しいので、トランジスタNT2のゲート電圧がVDD・Vtに充電される。そして、シフト信号SR2がHレベル(VDD+V)に上昇するのと同時に、トランジスタNT2およびNT7のドレインに入力されるクロック信号CKV1がLレベルに低下する。この際、1段目のシフトレジスタ回路部51のノードND1の電位がLレベルに保持される。これにより、1段目のシフトレジスタ回路部51のトランジスタNT5およびNT6がオフ状態になる。

[0091]

また、1段目のシフトレジスタ回路部51のトランジスタNT7のドレインにLレベルのクロック信号CKV1が入力される場合には、ダイオード接続されたトランジスタNT8によりLレベルのクロック信号CKV1が1段目のシフトレジスタ回路部51のノードND2側に逆流されない。これにより、1段目のシフトレジスタ回路部51のノードND2の電位がHレベル(VDD+V )に保持されるので、ノードND2からHレベル(VDD+V )のシフト信号SR1が続けて出力される。また、1段目のシフトレジスタ回路部51のノードND2の電位がHレベル(VDD+V )に保持されることにより、トランジスタNT4がオン状態に保持されるので、1段目のシフトレジスタ回路部51のノードND3からHレベル(VDD)のシフト出力信号SR11が続けて出力される。

[0092]

また、 3 段目のシフトレジスタ回路部のトランジスタNT27は、トランジスタNT66を介してゲートにHレベル(VDD・Vt)のシフト信号SR2が入力されることによりオン状態になるとともに、トランジスタNT21は、ゲートにHレベル(VDD)のシフト出力信号SR12が入力されることによりオン状態になる。このとき、 3 段目のシフトレジスタ回路部のトランジスタNT22のゲートに、 4 段目のシフトレジスタ回路部 5 4 のLレベルのシフト信号SR4が入力されている。これにより、トランジスタNT22がオフ状態になっている。

[0093]

この後、スタート信号STVの電位がLレベルに低下することによって、1段目のシフトレジスタ回路部51のトランジスタNT1およびNT7がオフ状態になるとともに、トランジスタNT5およびNT6がオフ状態に保持される。これにより、1段目のシフトレジスタ回路部51のノードND2の電位がHレベル(VDD+V )に保持されるとともに、ノードND3の電位がHレベル(VDD)に保持される。このため、1段目のシフトレジスタ回路部51において、ノードND2からHレベル(VDD+V )のシフト信号SR1が続けて出力されるとともに、ノードND3からHレベル(VDD)のシフト出力信号SR11が続けて出力される。

[0094]

この後、3段目のシフトレジスタ回路部53のトランジスタNT22およびNT27のドレインに入力されるクロック信号CKV1がHレベルに上昇する。これにより、上記した1段目のシフトレジスタ回路部51の動作と同様の動作が3段目のシフトレジスタ回路部53においても行われる。すなわち、3段目のシフトレジスタ回路部53のノードND2からVDD+Vt以上の電位(VDD+V)を有するHレベルのシフト信号SR3が出力されるとともに、3段目のシフトレジスタ回路部53のノードND3からHレベル(VDD)のシフト出力信号SR13が出力される。

[0095]

そして、3段目のシフトレジスタ回路部53のHレベル(VDD+V > VDD+V t) のシフト信号SR3は、ダミーゲート線に繋がる論理合成回路部81のトランジスタNT82と、1段目のゲート線に繋がる論理合成回路部82のトランジスタNT91のゲートとに入力される。また、Hレベルのシフト信号SR3は、入力信号切替回路部70のオ

20

30

40

50

ン状態のトランジスタNT63を介して2段目のシフトレジスタ回路部52のトランジスタNT12のゲートに入力されるとともに、入力信号切替回路部70のオン状態のトランジスタNT68を介して4段目のシフトレジスタ回路部54のトランジスタNT37のゲートに入力される。この際、トランジスタNT63およびNT68のゲート電位がスキャン方向切替信号CSVの電位(VDD)に等しいので、トランジスタNT12およびNT37のゲート電圧がVDD・Vtに充電される。また、3段目のシフトレジスタ回路部53のHレベル(VDD)のシフト出力信号SR13は、スキャン方向切替回路部60のオン状態のトランジスタNT59を介して4段目のシフトレジスタ回路部54のトランジスタNT31のゲートに入力されるとともに、2段目のゲート線に繋がる論理合成回路部83のトランジスタNT105を介してトランジスタNT103のゲートに入力される。

[0096]

そして、ダミーゲート線に繋がる論理合成回路部81において、トランジスタNT81およびNT82のゲートにそれぞれ入力されるシフト信号SR2およびSR3が両方ともHレベル(VDD+V))になることにより、トランジスタNT81およびNT82が両方ともオン状態になる。これにより、イネーブル信号線(ENB)からトランジスタNT81およびNT82を介してイネーブル信号ENBが供給される。このイネーブル信号ENBが供給される。このイネーブル信号ENBがは、シフト信号SR1およびSR2が両方ともHレベルになった時点ではLレベルがのり、その後わずかな期間後にLレベルからHレベルに電位が切り替わる。これにより、ダミーゲート線に繋がる論理合成回路部81のノードND4の電位がHレベルに上昇するので、論理合成回路部81からダミーゲート線にHレベルの出力信号Dummyが出力される。すなわち、イネーブル信号ENBがLレベルの間は、出力信号Dummyの電位が 日レベルに上昇するのに伴って、出力信号Dummyの電位がHレベルに上昇するのに伴って、出力信号Dummyの電位がHレベルに上昇される。

[0097]

この際、ダミーゲート線に繋がる論理合成回路部81のノードND4の電位(出力信号 Dummyの電位)がHレベルに上昇するのに伴って、ノードND4にゲートが接続されたトランジスタNT84がオン状態になる。これにより、トランジスタNT84を介して負側電位VBBからLレベルの電位がトランジスタNT83のゲートに供給されるので、トランジスタNT83がオフ状態になる。このため、トランジスタNT81およびNT82が両方ともオン状態になった場合にも、トランジスタNT83がオフ状態になるので、上記のようにダミーゲート線に繋がる論理合成回路部81のノードND4の電位が上昇される。また、トランジスタNT81、NT82およびNT83を介して、イネーブル信号線(ENB)と負側電位VBBとの間に貫通電流が流れるのが抑制される。

[0098]

また、この際、ダミーゲート線に繋がる論理合成回路部81において、トランジスタNT81およびNT82のゲートに、それぞれ、VDDよりもしきい値電圧(Vt)以上の所定の電圧(V )分高い電位(VDD+V )のHレベルのシフト信号SR2およびSR3が入力されるので、論理合成回路部81のノードND4に現れる電位がVDDからトランジスタNT81およびNT82のしきい値電圧(Vt)分低下された電位になるのが抑制される。このため、論理合成回路部81からダミーゲート線に出力されるHレベルの出力信号Dummyの電位が低下するのが抑制される。

[0099]

また、1段目のゲート線に繋がる論理合成回路部82では、トランジスタNT91のゲートに3段目のシフトレジスタ回路部53のHレベル(VDD+V)のシフト信号SR3が入力されるとともに、トランジスタNT92のゲートに4段目のシフトレジスタ回路部54のLレベルのシフト信号SR4が入力されている。また、トランジスタNT93のゲートには、2段目のシフトレジスタ回路部52のHレベル(VDD)のシフト出力信号SR12が入力されている。これにより、1段目のゲート線に繋がる論理合成回路部82では、トランジスタNT91およびNT93がオン状態になるとともに、トランジスタNT92がオフ状態になる。このため、1段目のゲート線に繋がる論理合成回路部82にお

20

30

40

50

いて、トランジスタNT93を介して負側電位VBBから供給されるLレベル(VBB)の電位により、ノードND4の電位がLレベル(VBB)に保持される。これにより、Lレベル(VBB)の出力信号Gate1が論理合成回路部82のノードND4から1段目のゲート線に続けて出力される。

## [0100]

また、2段目のシフトレジスタ回路部52では、トランジスタNT12のゲートに3段目のシフトレジスタ回路部53のHレベルのシフト信号SR3が入力されることにより、トランジスタNT12がオン状態になる。この際、クロック信号CKV1の電位がHレベルにあり、クロック信号CKV2の電位がLレベルにある。この際、2段目のシフトレジスタ回路部52のノードND1の電位がLレベルに保持されるので、トランジスタNT15およびNT16がオフ状態に保持される。また、2段目のシフトレジスタ回路部52において、トランジスタNT17のゲート電位がLレベルにあるので、トランジスタNT17はオフしている。したがって、2段目のシフトレジスタ回路部52のノードND2の電位がHレベル(VDD+V))のシフト信号SR2が続けて出力される。また、2段目のシフトレジスタ回路部52において、トランジスタNTNT16がオフ状態に保持されることにより、ノードND2の電位がHレベル(VDD)に保持される。これにより、2段目のシフトレジスタ回路部52からHレベル(VDD)のシフト出力信号SR12が続けて出力される。

# [0101]

また、1段目のシフトレジスタ回路部51では、Hレベル(VDD-Vt)のシフト信号SR2がゲートに入力されるトランジスタNT2がオン状態に保持されるとともに、そのトランジスタNT2を介してHレベルのクロック信号CKV1が入力される。この際、トランジスタNT1がオフ状態であるので、1段目のシフトレジスタ回路部51のノードND1の電位がHレベルに上昇する。

## [0102]

そして、1段目のシフトレジスタ回路部51のノードND1の電位がHレベルに上昇することにより、トランジスタNT5およびNT6がオン状態になる。この際、トランジスタNT7がオフ状態であるので、トランジスタNT6を介して負側電位VBBからLレベル(VBB)の電位が供給されるとともに、1段目のシフトレジスタ回路部51のノードND2の電位がLレベルに低下する。また、1段目のシフトレジスタ回路部51のオートの電位がLレベルに低下する。また、1段目のシフトレジスタ回路部51のオードND2の電位がLレベルに低下することにより、トランジスタNT4がオフ状態になる。これにより、1段目のシフトレジスタ回路部51において、トランジスタNT5を介して負側電位VBBからLレベルの電位が供給されることにより、「日日のシフトレジスタ回路部51において、フトレジスタNT5を介して負側電位VBBからLレベルに低下する。また、1段目のシフトレジスタNT5を介しても側ではがLレベルに低下する。また、1段目のシフトレジスタロ路部51の大の電位がHレベルに低下する。また、1段目のシフトレジスタNT5を介していたのででがHレベルに低下する。また、1段目のシフトレジスタNT5を記していて、次にトランジスタNT1がオン状態になるまでノードND1の電位がHレベルに保持される。これにより、次にトランジスタNT1がオン状態になるまでノードND1の電位がHレベルに保持される。これにより、次にトランジスタNT1がオン状態になるまでトランジスタNT5およびNT6がオン状態に保持される。

### [0103]

上記したシフト信号SR1の電位がLレベルに低下する前に、イネーブル信号ENBの電位がHレベルからLレベルに低下する。これにより、ダミーゲート線に繋がる論理合成回路81では、トランジスタNT81およびNT82を介してLレベルの電位が供給されることにより、ノードND4の電位がLレベルに低下する。このため、論理合成回路部81からダミーゲート線に出力される出力信号Dummyの電位がLレベルに低下する。

# [0104]

そして、4段目のシフトレジスタ回路部54では、トランジスタNT37のゲートにH レベル(VDD-Vt)のシフト信号SR3が入力されるとともに、トランジスタNT3

20

30

40

50

1のゲートにHレベル(VDD)のシフト出力信号SR13が入力されている。また、トランジスタNT32のゲートには、5段目のシフトレジスタ回路部55からLレベルのシフト信号SR5が入力されている。この状態で、トランジスタNT32およびNT37のドレインに入力されるクロック信号CKV2の電位がHレベルに上昇する。これにより、上記した1段目のシフトレジスタ回路部51の動作と同様の動作が4段目のシフトレジスタ回路部54のメードND2からVDD+Vt以上の電位(VDD+V)を有するHレベルのシフト信号SR4が出力されるとともに、4段目のシフトレジスタ回路部54のノードND3からHレベル(VDD)のシフト出力信号SR14が出力される。

# [0105]

そして、ダミーゲート線に繋がる論理合成回路部81において、Hレベル(VDD)のシフト出力信号SR14がトランジスタNT86を介してトランジスタNT83のゲートに入力される。これにより、トランジスタNT83がオン状態になる。このため、トランジスタNT83を介して負側電位VBBからLレベルの電位が供給されるので、ノードND4の電位がLレベルに固定される。これにより、論理合成回路部81からダミーゲート線に出力される出力信号Dummyの電位がLレベルに固定される。なお、Hレベル(VDD)のシフト出力信号SR14がトランジスタNT83のゲートに入力された際、容量でVBBからLレベルの電位が供給されるまで、ノードND5の電位(トランジスタNT83のゲート電位)がHレベルに保持される。このため、次にトランジスタNT84がオン状態になるまでトランジスタNT83がオン状態に保持されるので、論理合成回路部81からダミーゲート線に出力される出力信号Dummyの電位がLレベルに固定された状態で保持される。

### [ 0 1 0 6 ]

また、1段目のゲート線に繋がる論理合成回路部82では、トランジスタNT91のゲ ートにHレベル(VDD+V )のシフト信号SR3が入力されるととともに、トランジ スタNT92のゲートにHレベル(VDD+V )のシフト信号SR4が入力される。こ れにより、トランジスタNT91およびNT92が両方ともオン状態になるので、イネー ブル信号線(ENB)からトランジスタNT91およびNT92を介してイネーブル信号 ENBが供給される。このイネーブル信号ENBは、シフト信号SR1およびSR2が両 方ともHレベルになった時点ではLレベルであり、その後わずかな期間後にLレベルから Hレベルに電位が切り替わる。これにより、1段目のゲート線に繋がる論理合成回路部8 2のノードND4の電位がHレベルに上昇するので、論理合成回路部81から1段目のゲ ート線にHレベルの出力信号Gate1が出力される。すなわち、イネーブル信号ENB がLレベルの間は、出力信号Gate1の電位が強制的にLレベルに保持されるとともに 、イネーブル信号ENBの電位がLレベルからHレベルに上昇するのに伴って、出力信号 Gate1の電位がHレベルに上昇される。したがって、イネーブル信号ENBがLレベ ルの際、論理合成回路部81からダミーゲート線に出力される出力信号Dummyも強制 的にLレベルに保持されているので、出力信号DummyがHレベルからLレベルに立ち 下がるタイミングと、出力信号Gate1がLレベルからHレベルに立ち上がるタイミン グとが重なるのが抑制される。

### [0107]

この後、上記した1~4段目のそれぞれのシフトレジスタ回路部51~54と同様の動作が、5段目のシフトレジスタ回路部55においても行われる。また、上記したダミーゲート線および1段目のゲート線にそれぞれ繋がる論理合成回路部81および82と同様の動作が、2段目のゲート線に繋がる論理合成回路部83においても行われる。すなわち、5段目のシフトレジスタ回路部55からシフト信号SR5が出力され、かつ、シフト信号SR4およびSR5が2段目のゲート線に繋がる論理合成回路部83に入力されるとともに、イネーブル信号ENBがHレベルになることによって、論理合成回路部83から2段目のゲート線にHレベルの出力信号Gate2が出力される。

20

30

40

50

## [0108]

上記したように、第1実施形態では、各段のシフトレジスタ回路部51~55からHレベルのシフト信号SR1~SR5が出力されるタイミングがシフトする。これにより、スキャン方向に対して所定段の次段のシフト信号(第1信号)と、スキャン方向に対して所定段の前段のシフト信号(第2信号)とが同時にHレベルになることがない。

# [0109]

このようにして、第1実施形態による液晶表示装置の各段のゲート線が、順次、駆動( 走査)される。そして、上記の動作が最後のゲート線の走査が終了されるまで繰り返され る。その後、再度、1段目のシフトレジスタ回路部51から上記の動作が繰り返し行われ る。

# [0110]

次に、図2中の逆方向に沿って、各段のゲート線にタイミングのシフトした出力信号が 順次出力される場合(逆方向スキャンの場合)には、スキャン方向切替信号CSVがLレ ベルに保持されるとともに、反転スキャン方向切替信号XCSVがHレベルに保持される 。これにより、スキャン方向切替回路部60において、スキャン方向切替信号CSVがゲ ートに入力されるトランジスタNT51、NT53、NT55、NT57およびNT59 がオフ状態に保持されるとともに、反転スキャン方向切替信号XCSVがゲートに入力さ れるトランジスタNT52、NT54、NT56、NT58およびNT60がオン状態に 保持される。また、入力信号切替回路部70において、スキャン方向切替信号CSVがゲ ートに入力されるトランジスタNT61~NT70がオフ状態に保持されるとともに、反 転スキャン方向切替信号XCSVがゲートに入力されるトランジスタNT71~NT80 がオン状態に保持される。そして、逆方向スキャン時には、上記した順方向スキャン時と 同様の動作が、図2中の逆方向に沿って各段のシフトレジスタ回路部と、各段のゲート線 に繋がる論理合成回路部とにおいて行われる。この際、スキャン方向に対して所定段の次 段のシフトレジスタ回路部から所定段のシフトレジスタ回路部にシフト信号(第1信号) を入力する場合や、所定段の前段のシフトレジスタ回路部から所定段のシフトレジスタ回 路部にシフト信号(第2信号)およびシフト出力信号を入力する場合には、上記したスキ ャン方向切替回路部60のオン状態のトランジスタNT52、NT54、NT56、NT 5 8 および N T 6 0 と、入力信号切替回路部 7 0 のオン状態のトランジスタ N T 7 1 ~ N T80とを介して行われる。

## [0111]

第1実施形態では、上記のように、スキャン方向に対して所定段の次段のシフト信号( 第1信号)に応答してオンするトランジスタ(トランジスタNT2、NT12、NT22 NT32およびNT42)と、スキャン方向に対して所定段の前段のシフト信号(第2 信号)に応答してオンするトランジスタ(トランジスタNT7、NT17、NT27、N T 3 7 および N T 4 7 )とを設けることによって、シフト信号(第 1 信号)とシフト信号 (第2信号)とのHレベルの期間が重なることがないので、シフト信号(第1信号)に応 答してオンするトランジスタ(トランジスタNT2、NT12、NT22、NT32およ びNT42)と、シフト信号(第2信号)に応答してオンするトランジスタ(トランジス タNT7、NT17、NT27、NT37およびNT47)とが同時にオン状態になるこ とがない。この場合、スキャン方向が順方向であれば、たとえば2段目(所定段)のシフ トレジスタ回路部 5 2 において、 3 段目 ( 次段 ) のシフト信号 5 R 3 ( 第 2 信号 ) に応答 してオンするトランジスタNT12がオンすることによりトランジスタNT16がオンす るので、トランジスタNT16と、1段目(前段)のシフト信号SR1(第1信号)に応 答してオンするトランジスタNT17とが同時にオン状態になることがない。これにより トランジスタNT16およびNT17を介して負側電位VBBとクロック信号線(CK V2)との間に貫通電流が流れるのを抑制することができる。

# [0112]

また、1段目(前段)のシフト信号SR1(第1信号)に応答してオンするトランジスタNT17がオンすることによりトランジスタNT14がオンするとともに、3段目(次

20

30

40

50

段)のシフト信号SR3(第2信号)に応答してオンするトランジスタNT12がオンすることによりトランジスタNT15がオンするので、トランジスタNT14とトランジスタNT14とトランジスタNT15とが同時にオン状態になることがない。これにより、トランジスタNT14およびNT15を介して負側電位VBBと正側電位VDDとの間に貫通電流が流れるのを抑制することができる。また、トランジスタNT11が1段目(前段)のシフト出力信号SR11に応答してオンするので、トランジスタNT11と、3段目(次段)のシフト信号SR3に応答してオンするトランジスタNT12とが同時にオン状態になることもない。これにより、トランジスタNT11およびNT12を介して負側電位VBBとクロック信号線(CKV2)との間に貫通電流が流れるのも抑制することができる。また、1段目のシフトレジスタ回路部51および3段目以降のシフトレジスタ回路部53~55においても、2段目のシフトレジスタ回路部52と同様、貫通電流が流れるのを抑制することができる。

[0113]

さらに、第1実施形態では、スキャン方向に応じて、NT2、NT12、NT22、NT32およびNT42と、トランジスタNT7、NT17、NT27、NT37およびNT47とにそれぞれ供給されるシフト信号(スキャン方向に対して所定段の次段のシフト信号(第1信号)およびスキャン方向に対して所定段の前段のシフト信号(第2信号))を切り替えるための入力信号切替回路部70を設けることによって、スキャン方向を切り換えた場合にもシフトレジスタ回路部51~55における貫通電流の発生を抑制することができる。これにより、第1実施形態では、双方向スキャン機能を有する表示装置の消費電力が増加するのを抑制することができる。

[0114]

また、第1実施形態では、トランジスタNT2、NT12、NT22、NT32およびNT42を、スキャン方向に対して所定段の次段のシフト信号(第1信号)に応答してオンするように、かつ、トランジスタNT7、NT17、NT27、NT37およびNT47を、スキャン方向に対して所定段の前段のシフト信号(第2信号)に応答してオンするように構成することによって、スキャン方向に対して所定段のかりフト信号(第2信号)とのHレベルの期間が重なることがないので、容易に、シフト信号(第1信号)に応答してオンするトランジスタNT2、NT12、NT32およびNT42)がオン状態であるときに、シフト信号(第2信号)に応答してオンするトランジスタ(トランジスタ バー37、NT37およびNT47)がオフ状態となるように制御することができる。また、シフト信号(第2信号)に応答してオンするトランジスタ(トランジスタ(トランジスタ)ンジスタNT7、NT17、NT27、NT37およびNT47)がオン状態であるときに、シフト信号(第2信号)に応答してオンするトランジスタ(トランジスタ)ときる。

[0115]

また、第1実施形態では、トランジスタNT4、NT14、NT24、NT34およびNT44のゲートとソースとの間に、それぞれ、容量C2、C12、C22、C32およびC42を接続することによって、たとえば、2段目のシフトレジスタ回路部52において、容量C12が接続されたトランジスタNT14のゲート・ソース間電圧を維持するように、トランジスタNT14のソース電位の上昇または低下に伴ってトランジスタNT14のゲート電位を上昇または低下させることができる。これにより、確実にトランジスタNT14をオン状態に保持することができる。

[0116]

また、第1実施形態では、順方向にスキャンする場合にオンするトランジスタNT51、NT53、NT55、NT57およびNT59と、逆方向にスキャンする場合にオンするトランジスタNT52、NT54、NT56、NT58およびNT60とを含むように入力信号切替回路部70を構成するとともに、入力信号切替回路部70を構成するトラン

ジスタ(NT51~NT60)を介してシフトレジスタ回路部(51~55)にシフト信号(SR1~SR5)を入力することによって、容易に、スキャン方向に対して次段のシフト信号(第1信号)が第1回路部(51a~55a)に入力されるように、かつ、スキャン方向に対して前段のシフト信号(第2信号)が第2回路部(51b~55b)に入力されるように制御することができる。

# [0117]

また、第1実施形態では、Vドライバ5を構成するトランジスタを、すべて同じ導電型(n型)のトランジスタにすることによって、Vドライバ5のトランジスタを形成する際に、イオン注入工程の回数およびイオン注入マスクの枚数が増加するのを抑制することができる。これにより、製造プロセスが複雑化するのを抑制することができるとともに、製造コストが増大するのを抑制することができる。

## [0118]

また、第1実施形態では、1段目のシフトレジスタ回路部51において、トランジスタ N T 1、N T 2、N T 6、N T 7 およびN T 8を、互いに電気的に接続された2つのゲート電極を有するように構成することによって、トランジスタN T 1、N T 2、N T 6、N T 7 およびN T 8に印加される電圧を、2つのゲート電極により各ゲート電極に対応するソース・ドレイン間に分配することができる。この場合、トランジスタN T 1、N T 2、N T 6、N T 7 およびN T 8の各ゲート電極に対応するソース・ドレイン間に印加される電圧を小さくすることができるので、トランジスタN T 1、N T 2、N T 6、N T 7 およびN T 8に大きい電圧が印加されることに起因する特性の劣化を抑制することができる。また、2段目以降のシフトレジスタ回路部52~55においても、同様の効果を得ることができる。これにより、シフトレジスタ回路部51~55を含む表示装置のスキャン特性が低下することを抑制することができる。

### [0119]

また、第1実施形態では、1段目のシフトレジスタ回路部51において、トランジスタNT6のゲートとトランジスタNT2との間に、ダイオード接続されたトランジスタNT3を設けるとともに、トランジスタNT4のゲートとトランジスタNT7との間に、ダイオード接続されたトランジスタNT8を設けることによって、トランジスタNT6がオンまたはオフするときに発生するノイズがトランジスタNT2に伝わるのをトランジスタNT3により遮断することができるとともに、トランジスタNT4がオンまたはオフするときに発生するノイズがトランジスタNT7に伝わるのをトランジスタNT8により遮断することができる。また、2段目以降のシフトレジスタ回路部52~55においても、同様の効果を得ることができる。

# [0120]

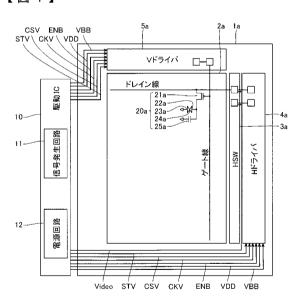

## (第2実施形態)

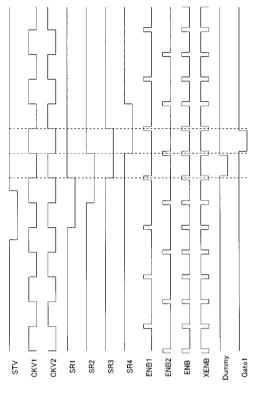

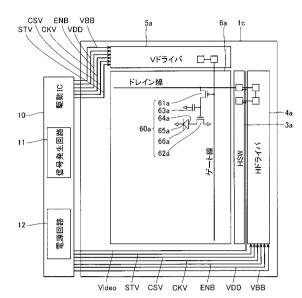

図4は、本発明の第2実施形態による液晶表示装置を示した平面図である。図5は、図4に示した第2実施形態による液晶表示装置のVドライバ内部の回路図である。図4および図5を参照して、この第2実施形態では、上記第1実施形態のVドライバをpチャネルトランジスタで構成する場合について説明する。

## [0121]

まず、図4を参照して、この第2実施形態では、基板1a上に、表示部2aが設けられている。この表示部2aには、画素20aがマトリクス状に配置されている。なお、図4では、図面の簡略化のため、1つの画素20aのみを図示している。各々の画素20aは、pチャネルランジスタ21a(以下、トランジスタ21aという)、画素電極22a、画素電極22aに対向配置された各画素20aに共通の対向電極23a、画素電極22aと対向電極23aとの間に挟持された液晶24a、および、補助容量25aによって構成されている。そして、トランジスタ21aのソースは、ドレイン線に接続されているとともに、ドレインは、画素電極22aおよび補助容量25aに接続されている。このトランジスタ21aのゲートは、ゲート線に接続されている。

# [0122]

50

10

20

30

また、表示部2aの一辺に沿うように、基板1a上に、表示部2aのドレイン線を駆動 (スキャン)するための水平スイッチ(HSW)3aおよびHドライバ4aが設けられている。また、表示部2aの他の辺に沿うように、基板1a上に、表示部2aのゲート線を駆動 (スキャン)するためのVドライバ5aが設けられている。なお、図4の水平スイッチ3aには、2つのスイッチのみを図示しているが、実際は画素数に応じた数のスイッチが配置されている。また、図4のHドライバ4aおよびVドライバ5aには、それぞれ、シフトレジスタ回路部を2つのみ図示しているが、実際は画素数に応じた数のシフトレジスタ回路部が配置されている。また、基板1aの外部には、上記第1実施形態と同様、信号発生回路11および電源回路12を含む駆動IC10が設置されている。

# [0123]

また、図5を参照して、第2実施形態では、Vドライバ5aの内部に、複数段のシフトレジスタ回路部501~505と、スキャン方向切替回路部600と、入力信号切替回路部700と、複数段の論理合成回路部801~803とが設けられている。なお、図5では、図面の簡略化のため、5段分のシフトレジスタ回路部501~505および3段分の論理合成回路部801~803のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

## [0124]

そして、1段目のシフトレジスタ回路部501は、第1回路部501aと第2回路部501bとによって構成されている。第1回路部501aは、pチャネルトランジスタPT1およびPT2と、ダイオード接続されたpチャネルトランジスタPT3と、容量C1とを含む。なお、pチャネルトランジスタPT1およびPT2は、それぞれ、本発明の「第1トランジスタ」の一例であり、pチャネルトランジスタ」の一例であり、pチャネルトランジスタPT4、PT5、PT6およびPT1と、ダイオード接続されたpチャネルトランジスタPT4、PT5、PT6およびPT7と、ダイオード接続されたpチャネルトランジスタPT8と、容量C2とを含む。なの「第3トランジスタ」、「第4トランジスタ」、「第5トランジスタ」および「第6トランジスタ」の一例である。また、pチャネルトランジスタPT8は、本発明の「第2ダイオード」および「第12トランジスタ」の一例である。以下、pチャネルトランジスタPT1~PT8は、それぞれ、トランジスタPT1~PT8と称する。

### [0125]

ここで、第2実施形態では、第1回路部501aおよび第2回路部501bに設けられたトランジスタPT1~PT8は、すべてp型のMOSトランジスタからなるTFTにより構成されている。また、第2実施形態では、トランジスタPT1、PT2、PT6、PT7およびPT8は、互いに電気的に接続された2つのゲート電極を有する。

## [0126]

そして、1段目のシフトレジスタ回路部501を構成するトランジスタPT1~PT8は、それぞれ、図2に示した第1実施形態の1段目のシフトレジスタ回路部51のトランジスタNT1~NT8に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタPT1のソースは、正側電位VDDに接続されているとともに、トランジスタPT4のドレインは、負側電位VBBに接続されている。また、トランジスタPT5およびPT6のソースは、正側電位VDDに接続されている。

## [0127]

また、2段目以降のシフトレジスタ回路部502~505は、上記した1段目のシフトレジスタ回路部501と同様の回路構成を有する。具体的には、2段目以降のシフトレジスタ回路部502~505は、それぞれ、1段目のシフトレジスタ回路部501の第1回路部501aと同様の回路構成を有する第1回路部502a~505aと、第2回路部501bと同様の回路構成を有する第2回路部502b~505bとによって構成されている。

# [0128]

10

20

30

20

30

40

50

2 段目のシフトレジスタ回路部 5 0 2 は、1 段目のシフトレジスタ回路部 5 0 1 のトランジスタPT 1 ~ PT 8 に対応する p チャネルトランジスタPT 1 1 ~ PT 1 8 と、容量 C 1 および C 2 に対応する容量 C 1 1 および C 1 2 とを含む。なお、 p チャネルトランジスタPT 1 1、 PT 1 2、 PT 1 4、 PT 1 5、 PT 1 6 および PT 1 7 は、それぞれ、本発明の「第 1 トランジスタ」、「第 2 トランジスタ」、「第 3 トランジスタ」、「第 4 トランジスタ」、「第 5 トランジスタ」および「第 6 トランジスタ」の一例である。また、 p チャネルトランジスタPT 1 3 は、本発明の「第 1 ダイオード」および「第 1 1 トランジスタ」の一例であり、 p チャネルトランジスタPT 1 8 は、本発明の「第 2 ダイオード」および「第 1 2 トランジスタPT 1 1 ~ PT 1 8 は、それぞれ、トランジスタPT 1 1 ~ PT 1 8 と称する。

[0129]

[0130]

また、4段目のシフトレジスタ回路部 5 0 4 は、1段目のシフトレジスタ回路部 5 0 1 のトランジスタ P T 1 ~ P T 8 に対応する p チャネルトランジスタ P T 3 1 ~ P T 3 8 と、容量 C 1 および C 2 に対応する容量 C 3 1 および C 3 2 とを含む。なお、 p チャネルトランジスタ P T 3 1、 P T 3 2、 P T 3 4、 P T 3 5、 P T 3 6 および P T 3 7 は、それぞれ、本発明の「第 1 トランジスタ」、「第 2 トランジスタ」、「第 3 トランジスタ」、「第 4 トランジスタ」、「第 5 トランジスタ」および「第 6 トランジスタ」の一例である。また、 p チャネルトランジスタ P T 3 3 8 は、本発明の「第 1 ダイオード」および「第 1 1 トランジスタ」の一例である。以下、 p チャネルトランジスタ P T 3 1 ~ P T 3 8 は、それぞれ、トランジスタ P T 3 1 ~ P T 3 8 と称する。

[0131]

また、5段目のシフトレジスタ回路部505は、1段目のシフトレジスタ回路部501のトランジスタPT1~PT8に対応するpチャネルトランジスタPT41~PT48と、容量C1およびC2に対応する容量C41およびC42とを含む。なお、pチャネルトランジスタPT41、PT42、PT45、PT46およびPT47は、それぞれ、本発明の「第1トランジスタ」、「第2トランジスタ」、「第3トランジスタ」、「第4トランジスタ」、「第5トランジスタ」および「第6トランジスタ」の一例である。また、pチャネルトランジスタPT43は、本発明の「第1ダイオード」および「第11トランジスタ」の一例であり、pチャネルトランジスタPT48は、本発明の「第2ダイオード」および「第12トランジスタ」の一例である。以下、pチャネルトランジスタPT41~PT48と称する。

[0132]

また、スキャン方向切替回路部 6 0 0 は、 p チャネルトランジスタ P T 5 1 ~ P T 6 0 を含む。以下、 p チャネルトランジスタ P T 5 1 ~ P T 6 0 は、それぞれ、トランジスタ P T 5 1 ~ P T 6 0 と称する。

[0133]

ここで、第2実施形態では、スキャン方向切替回路部600を構成するトランジスタPT51~PT60は、すべてp型のMOSトランジスタからなるTFTにより構成されて

いる。

## [0134]

そして、スキャン方向切替回路部600を構成するトランジスタPT51~PT60は、それぞれ、図2に示した第1実施形態のスキャン方向切替回路部60のトランジスタNT51~NT60に対応した位置に接続されている。

### [0135]

また、入力信号切替回路部700は、 p チャネルトランジスタPT61~PT80を含む。なお、 p チャネルトランジスタPT61、 P T63、 P T65、 P T67およびPT69は、 本発明の「第7トランジスタ」の一例であり、 p チャネルトランジスタPT62、 P T64、 P T66、 P T68およびPT70は、 本発明の「第10トランジスタ」の一例である。また、 p チャネルトランジスタPT71、 P T73、 P T75、 P T77およびPT79は、 本発明の「第8トランジスタ」の一例であり、 p チャネルトランジスタ P T72、 P T74、 P T76、 P T78および P T80は、 本発明の「第9トランジスタ」の一例である。以下、 p チャネルトランジスタPT61~ P T80は、 それぞれ、 トランジスタPT61~ P T80と称する。

### [0136]

ここで、第2実施形態では、入力信号切替回路部700を構成するトランジスタPT6 1~PT80は、すべてp型のMOSトランジスタからなるTFTにより構成されている

# [0137]

そして、入力信号切替回路部700を構成するトランジスタPT61~PT80は、それぞれ、図2に示した第1実施形態の入力信号切替回路部70のトランジスタNT61~NT80に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタPT71のソース/ドレインの他方は、負側電位VBBに接続されている。

### [0138]

また、論理合成回路部801~803は、それぞれ、ダミーゲート線、1段目のゲート 線および2段目のゲート線に接続されている。

### [0139]

ダミーゲート線に接続される論理合成回路部801は、 p チャネルトランジスタ P T 8 1 ~ P T 8 4 と、ダイオード接続された p チャネルトランジスタ P T 8 5 および P T 8 6 と、容量 C 8 1 とを含む。以下、 p チャネルトランジスタ P T 8 1 ~ P T 8 6 は、それぞれ、トランジスタ P T 8 1 ~ P T 8 6 と称する。

### [0140]

ここで、第2実施形態では、論理合成回路部801を構成するトランジスタPT81~ PT86は、すべてp型のMOSトランジスタからなるTFTにより構成されている。

## [0141]

そして、ダミーゲート線に接続される論理合成回路部801を構成するトランジスタPT81~PT86は、それぞれ、図2に示した第1実施形態のダミーゲート線に接続される論理合成回路部81のトランジスタNT81~NT86に対応した位置に接続されている。ただし、トランジスタPT83のソースは、正側電位VDDに接続されている。

# [0142]

また、1段目のゲート線に接続される論理合成回路部802は、ダミーゲート線に接続される論理合成回路部801と同様の回路構成を有する。具体的には、1段目のゲート線に接続される論理合成回路部802は、ダミーゲート線に接続される論理合成回路部801のトランジスタPT81~PT86に対応するpチャネルトランジスタPT91~PT96と、容量C81に対応する容量C91とを含む。以下、pチャネルトランジスタPT91~PT96は、それぞれ、トランジスタPT91~PT96と称する。

# [0143]

そして、1段目のゲート線に接続される論理合成回路部802を構成するトランジスタ PT91~PT96は、それぞれ、図2に示した第1実施形態の1段目のゲート線に接続 10

20

30

40

される論理合成回路部82のトランジスタNT91~NT96に対応した位置に接続されている。ただし、トランジスタPT93のソースは、正側電位VDDに接続されている。

## [0144]

また、2段目のゲート線に接続される論理合成回路部803は、ダミーゲート線に接続される論理合成回路部801と同様の回路構成を有する。具体的には、2段目のゲート線に接続される論理合成回路部801のトランジスタPT81~PT86に対応するpチャネルトランジスタPT101~PT106と、容量C81に対応する容量C101とを含む。以下、pチャネルトランジスタPT101~PT106と称する

[0145]

そして、2段目のゲート線に接続される論理合成回路部803を構成するトランジスタPT101~PT106は、それぞれ、図2に示した第1実施形態の2段目のゲート線に接続される論理合成回路部803のトランジスタNT101~NT106に対応した位置に接続されている。ただし、トランジスタPT103のソースは、正側電位VDDに接続されている。

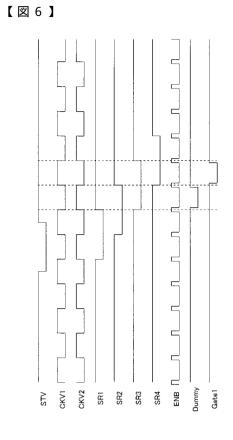

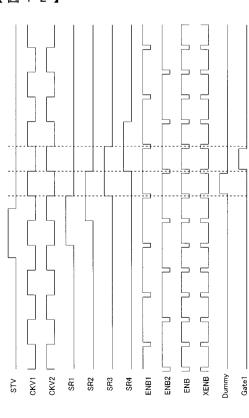

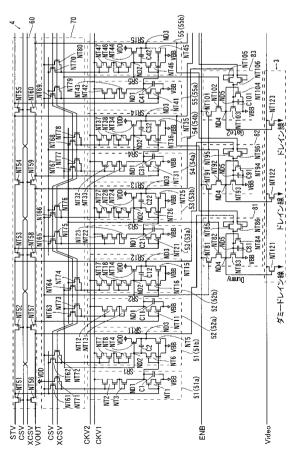

## [0146]

図6は、本発明の第2実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図5および図6を参照して、第2実施形態によるVドライバ5 a の動作を説明する。この第2実施形態のVドライバ5 a では、図3に示した第1実施形態のスタート信号STV、クロック信号CKV1、クロック信号CKV2およびイネーブル信号ENBのHレベルとLレベルとを反転させた波形の信号を、それぞれ、スタート信号STV、クロック信号CKV2およびイネーブル信号ENBとして入力する。これにより、第2実施形態のシフトレジスタ回路部501~505からは、第1実施形態のシフトレジスタ回路部51~55からのシフト信号SR1~SR5のHレベルとLレベルとを反転させた波形を有する信号が出力される。また、第2実施形態の論理合成回路部81~83から出力される出力信号Dummy、Gate1およびGate2のHレベルとLレベルとを反転させた波形を有する信号が出力される。この第2実施形態のVドライバ5aのこれ以外の動作は、上記した第1実施形態のVドライバ5と同様である。

[0147]

なお、第2実施形態では、トランジスタPT4、PT14、PT24、PT34およびPT44のゲートとソースとの間に、それぞれ、容量C2、C12、C22、C32およびC42を接続することによって、以下のような動作が行われる。たとえば、2段目のシフトレジスタ回路部502において、容量C12が接続されたトランジスタPT14のゲート・ソース間電圧を維持するように、トランジスタPT14のソース電位の低下に伴ってトランジスタPT14のゲート電位(シフト信号SR2の電位)が低下する。すなわち、トランジスタPT14のゲート電位(シフト信号SR2の電位)がVBBよりもしきい値電圧(Vt)以上の所定の電圧(V )分低い電位まで降下するので、スキャン方向が順方向の場合、1段目のトランジスタPT2カのが1を有するシフト信号SR2が供給される。これにより、トランジスタPT2カよびPT27のソース電位が、それぞれ、VBBからトランジスタPT2およびPT27のしきい値電圧(Vt)分だけ上昇するのが抑制される。

[0148]

また、第2実施形態では、上記のように構成することによって、Vドライバ5aの消費電流の増加を抑制することができるなどの上記第1実施形態と同様の効果を得ることができる。

[0149]

(第3実施形態)

10

20

30

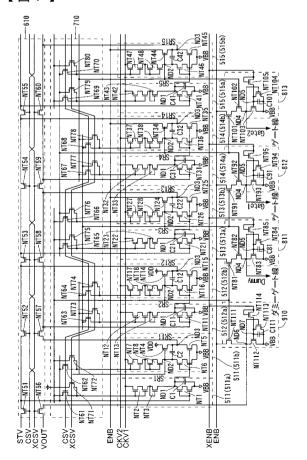

図7は、本発明の第3実施形態による液晶表示装置のVドライバ内部の回路図である。 図7を参照して、この第3実施形態では、上記第1実施形態の構成において、3段目以降 のシフトレジスタ回路部のシフト出力信号が出力されるノードに接続されたトランジスタ のドレインに、正側電位に代えてイネーブル信号を供給する場合について説明する。

## [0150]

すなわち、この第3実施形態では、図7に示すように、複数段のシフトレジスタ回路部511~515と、スキャン方向切替回路部610と、入力信号切替回路部710と、複数段の論理合成回路部811~813とが設けられている。なお、図7では、図面の簡略化のため、5段分のシフトレジスタ回路部511~515および3段分の論理合成回路部811~813のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

[0151]

そして、1段目のシフトレジスタ回路部511は、図2に示した第1実施形態の1段目のシフトレジスタ回路部51の第1回路部51aおよび第2回路部51bと同様の回路構成を有する第1回路部511aおよび第2回路部511bによって構成されている。また、2段目のシフトレジスタ回路部512は、図2に示した第1実施形態の2段目のシフトレジスタ回路部52の第1回路部52aおよび第2回路部52bと同様の回路構成を有する第1回路部512aおよび第2回路部512bによって構成されている。

[0152]

ここで、第3実施形態では、3段目のシフトレジスタ回路部513、4段目のシフトレジスタ回路部514および5段目のシフトレジスタ回路部515のそれぞれに、イネーブル信号線(ENB)が接続されている。

[0153]

具体的には、3段目のシフトレジスタ回路部513は、第1回路部513aと第2回路部513bとによって構成されている。第1回路部513aおよび第2回路部513bは、それぞれ、図2に示した第1実施形態の3段目のシフトレジスタ回路部53の第1回路部53aおよび第2回路部53bと同様の回路構成を有する。そして、この第3実施形態では、トランジスタNT24のドレインに、イネーブル信号線(ENB)が接続されている。

[0154]

また、4段目のシフトレジスタ回路部514は、第1回路部514aと第2回路部514bとによって構成されている。第1回路部514aおよび第2回路部514bは、それぞれ、図2に示した第1実施形態の4段目のシフトレジスタ回路部54の第1回路部54aおよび第2回路部54bと同様の回路構成を有する。そして、この第3実施形態では、トランジスタNT34のドレインに、イネーブル信号線(ENB)が接続されている。

[0155]

また、5段目のシフトレジスタ回路部515は、第1回路部515aと第2回路部515bとによって構成されている。第1回路部515aおよび第2回路部515bは、それぞれ、図2に示した第1実施形態の5段目のシフトレジスタ回路部55の第1回路部55aおよび第2回路部55bと同様の回路構成を有する。そして、この第3実施形態では、トランジスタNT44のドレインに、イネーブル信号線(ENB)が接続されている。

[0156]

また、第3実施形態のスキャン方向切替回路部610は、図2に示した第1実施形態のスキャン方向切替回路部60と同様の回路構成を有する。ただし、第3実施形態では、トランジスタNT56のソース/ドレインの他方と、トランジスタNT57のソース/ドレインの一方とが接続されていない。

[0157]

また、第3実施形態の入力信号切替回路部710は、図2に示した第1実施形態の入力信号切替回路部70と同様の回路構成を有する。

[0158]

10

20

30

20

30

40

50

また、第3実施形態のダミーゲート線に接続される論理合成回路部811は、トランジスタNT81~NT84と、ダイオード接続されたトランジスタNT85と、容量C81とを含む。すなわち、第3実施形態の論理合成回路部811は、図2に示した第1実施形態の論理合成回路部81の回路構成において、ダイオード接続されたトランジスタNT86が設けられていない回路構成を有する。また、第3実施形態の論理合成回路部811のノードND5は、トランジスタNT85を介して、反転イネーブル信号線(XENB)に接続されている。

## [0159]

また、1段目のゲート線に接続される論理合成回路部812は、トランジスタNT91~NT94と、ダイオード接続されたトランジスタNT95と、容量C91とを含む。すなわち、第3実施形態の論理合成回路部812は、図2に示した第1実施形態の論理合成回路部82の回路構成において、ダイオード接続されたトランジスタNT96が設けられていない回路構成を有する。また、第3実施形態の論理合成回路部812のノードND5は、トランジスタNT95を介して、反転イネーブル信号線(XENB)に接続されている。

## [0160]

また、 2 段目のゲート線に接続される論理合成回路部 8 1 3 は、トランジスタNT 1 0 1 ~ NT 1 0 4 と、ダイオード接続されたトランジスタNT 1 0 5 と、容量 C 1 0 1 とを含む。すなわち、第 3 実施形態の論理合成回路部 8 1 3 は、図 2 に示した第 1 実施形態の論理合成回路部 8 3 の回路構成において、ダイオード接続されたトランジスタNT 1 0 6 が設けられていない回路構成を有する。また、第 3 実施形態の論理合成回路部 8 1 3 の J ードND 5 は、トランジスタNT 1 0 5 を介して、反転イネーブル信号線(X E N B)に接続されている。

### [0161]

また、第3実施形態では、複数段のシフトレジスタ回路部511~515と、スキャン方向切替回路部610と、入力信号切替回路部710と、複数段の論理合成回路部811~813とに加えて、回路部910が設けられている。この回路部910は、nチャネルトランジスタNT111~NT113と、ダイオード接続されたnチャネルトランジスタNT111~NT114と、容量C111とを含む。以下、nチャネルトランジスタNT111~NT114と称する。

# [0162]

ここで、第3実施形態では、回路部910を構成するトランジスタNT111~NT1 14は、すべてn型のMOSトランジスタからなるTFTにより構成されている。

### [0163]

そして、トランジスタNT111のドレインは、イネーブル信号線(ENB)に接続されているとともに、ソースは、ノードND6に接続されている。このトランジスタNT111のゲートは、2段目のシフトレジスタ回路部512のノードND2に接続されている。トランジスタNT112のソースは、負側電位VBBに接続されているとともに、ドレインは、ノードND6に接続されている。このトランジスタNT112のゲートは、ノードND7に接続されている。このトランジスタNT112のゲートは、ノードND7に接続されている。このトランジスタNT113のゲートは、ノードND7に接続されている。容量C111の一方の電極は、負側電位VBBに接続されているとともに、他方の電極は、ノードND7に接続されている。また、ノードND6は、スキャン方向切替回路部610のトランジスタNT56のソース/ドレインの他方に接続されている。また、ノードND7は、トランジスタNT114を介して、反転イネーブル信号線(XENB)に接続されている。

### [0164]

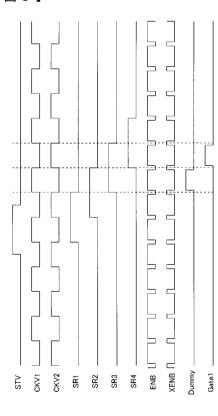

図8は、本発明の第3実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図7および図8を参照して、第3実施形態による液晶表示装置のVドライバの動作について説明する。

20

30

40

50

### [0165]

この第3実施形態のVドライバの動作は、基本的には、上記第1実施形態のVドライバ5の動作と同様である。ただし、この第3実施形態のVドライバでは、上記第1実施形態と異なり、3段目以降のシフトレジスタ回路部513~515のシフト出力信号SR13~SR15が出力されるノードND3に接続されたトランジスタNT24、NT34およびNT44のドレインに、正側電位VDDに代えてイネーブル信号ENBを供給する。また、各段の論理合成回路部811~813の負側電位VBBと、出力信号を出力するノードND4との間に接続されたトランジスタNT83、NT93およびNT103のゲートに、反転イネーブル信号XENBを入力する。

# [0166]

具体的には、 1 段目および 2 段目のシフトレジスタ回路部 5 1 1 および 5 1 2 (図 7 参 照)における動作は、図2に示した第1実施形態の1段目および2段目のシフトレジスタ 回路部51および52における動作と同様である。そして、3段目のシフトレジスタ回路 部 5 1 3 では、 2 段目のシフトレジスタ回路部 5 1 2 からトランジスタNT 2 7 のゲート にHレベルのシフト信号SR2が入力されるとともに、トランジスタNT21のゲートに Hレベル(VDD)のシフト出力信号SR12が入力される。また、トランジスタNT2 2のゲートには、4段目のシフトレジスタ回路部514からLレベルのシフト信号SR4 が入力される。これにより、トランジスタNT21およびNT27がオン状態になるとと もに、トランジスタNT22がオフ状態になる。このため、トランジスタNT21を介し て負側電位VBBからLレベルの電位が供給されることにより、ノードND1の電位がL レベルに低下する。これにより、トランジスタNT25およびNT26がオフ状態になる 。この状態で、トランジスタNT27のドレインに入力されるクロック信号CKV1がL レベルからHレベルに上昇する。これにより、3段目のシフトレジスタ回路部513のノ ードND2の電位がHレベルに上昇するので、トランジスタNT24がオン状態になる。 このとき、トランジスタNT24のドレインにLレベルのイネーブル信号ENBが供給さ れるので、トランジスタNT24のソース電位(ノードND3の電位)がLレベルに保持 される。

# [0167]

この後、第3実施形態では、イネーブル信号ENBの電位がLレベルからHレベルに上昇する。これにより、3段目のシフトレジスタ回路部513のノードND3の電位がHレベルに上昇する。この際、3段目のシフトレジスタ回路部513のノードND2の電位は、容量C22によってトランジスタNT24のゲート・ソース間電圧が維持されるよりに、ノードND3の電位の上昇に伴ってブートされることにより上昇する。これによりに、3段目のシフトレジスタ回路部513のノードND2の電位がVDDよりもしきい値電上に、ソカードND2の電位(VDD+V)とりしまりもしきい値電上昇する。なお、このときのノードND2の電位(VDD+V)は、上記第1実施形態にそりて、3段目のシフトレジスタ回路部513のノードND2からVDD+Vt以上の電位で、3段目のシフトレジスタ回路部513のノードND2からVDD+Vt以上の電位で、3段目のシフトレジスタ回路部513と同様の動作により、上記第1実施形態のシフトレジスタ回路部513と同様の動作により、上記第1実施形態のシフトレジスタ回路部から出力される日レベル(VDD+V)のシフト信号SR4およびSR5が出力される。

# [0168]

そして、3段目のシフトレジスタ回路部513のHレベルのシフト信号SR3は、トランジスタNT63を介して2段目のシフトレジスタ回路部512のトランジスタNT12のゲートに入力されるとともに、トランジスタNT68を介して4段目のシフトレジスタ回路部514のトランジスタNT37のゲートに入力される。この際、トランジスタNT63およびNT68のゲート電位がスキャン方向切替信号CSVの電位(VDD)に等しいので、トランジスタNT12およびNT37のゲート電圧がVDD-Vtに充電される

。この後、クロック信号 C K V 2 が H レベル( V D D )に立ち上がるので、トランジスタ N T 1 2 および N T 3 7 のゲート電圧は、ゲート・ソース間電圧を保持したまま、さらに V D D と V B B の電位差分上昇する。

### [0169]

また、3段目のシフトレジスタ回路部513のHレベル(VDD+V )のシフト信号SR3は、1段目のゲート線に繋がる論理合成回路部812のトランジスタNT91のゲートにも入力される。また、1段目のゲート線に繋がる論理合成回路部812のトランジスタNT92のゲートには、4段目のシフトレジスタ回路部514のHレベル(VDD+V )のシフト信号SR4が入力される。これにより、1段目のゲート線に繋がる論理合成回路部812において、トランジスタNT91のドレインに入力されるイネーブル信号ENBの電位がHレベル(VDD)の電位に上昇した場合に、トランジスタNT92のしきい信電圧(Vt)分低下したHレベルの電位になるのが抑制される。上記のようにして、2段目以降のゲート線に繋がる論理合成回路部813においても、イネーブル信号ENBの電位がHレベル(VDD)に上昇するのに伴って、ノードND4の電位が上昇する場合に、ノードND4に生じるHレベルの電位が大きく低下するのが抑制される。

## [0170]

また、第3実施形態では、論理合成回路部811~813から各段のゲート線に出力する出力信号の電位をLレベルに固定する際、反転イネーブル信号XENBを用いて電位を固定する。たとえば、1段目のゲート線に繋がる論理合成回路部812において、共にオン状態になっているトランジスタNT91およびNT92を介してHレベルのイネーブル信号ENBが供給されることにより、1段目のゲート線に出力する出力信号Gate1がHレベルになっている。この後、イネーブル信号ENBの電位がLレベルに低下するとともに、反転イネーブル信号XENBの電位がHレベルに上昇する。これにより、Lレベルのイネーブル信号ENBがトランジスタNT91およびNT92を介して供給されることにより、1段目のゲート線に出力される出力信号Gate1の電位がLレベルに低下する

# [0171]

また、1段目のゲート線に繋がる論理合成回路部812において、反転イネーブル信号 XENBの電位がHレベルに上昇することにより、Hレベルの反転イネーブル信号 XENBが論理合成回路部812のダイオード接続されたトランジスタNT95を介してトランジスタNT93のゲートに入力される。これにより、トランジスタNT93がオン状態になる。そして、トランジスタNT93を介して負側電位 VBBからノードND4側へLレベルの電位が供給される。これにより、論理合成回路部812から1段目のゲート線に出力される出力信号 Gate1の電位がLレベルに固定される。

## [0172]

そして、1段目のゲート線に繋がる論理合成回路部812において、トランジスタNT93のゲートにHレベルの反転イネーブル信号XENBが供給される際に容量C91が充電される。これにより、トランジスタNT93のゲート電位(ノードND5の電位)は、次にトランジスタNT94がオン状態になることによりトランジスタNT94を介して負側電位VBBからLレベルの電位が供給されるまでHレベルに保持される。このため、次にトランジスタNT94がオン状態になるまでトランジスタNT93がオン状態に保持されるので、トランジスタNT93を介して負側電位VBBから供給されるLレベルの電位により、出力信号Gate1がLレベルに固定された状態で保持される。上記のようにして、各段の論理合成回路部811~813において、反転イネーブル信号XENBを用いて出力信号の電位がLレベルに固定される。

### [0173]

第3実施形態によるVドライバの上記以外の動作は、上記第1実施形態のVドライバ5の動作と同様である。

# [0174]

50

10

20

30

第3実施形態では、上記のように、シフトレジスタ回路部513~515のシフト出力信号SR13~SR15が出力されるノードND3に接続されたトランジスタNT24、NT34およびNT44のドレインに、正側電位VDDと負側電位VBBとが周期的に切り替わるイネーブル信号ENBを供給することによって、たとえば、3段目のシフトレジスタ回路部513において、トランジスタNT24がオン状態のときにソース電位をVBBからVDDに変動させることができるので、その電位の変動分(V )だけトランジスタNT24のゲート電位を上昇させることができる。これにより、トランジスタNT24のドレインが固定的な負側電位VBB側に接続されている場合に比べて、より確実にトランジスタNT24をオン状態に保持することができる。

### [0175]

なお、第3実施形態のその他の効果は、上記第1実施形態と同様である。

### [0176]

### (第4実施形態)

図9は、本発明の第4実施形態による液晶表示装置のVドライバ内部の回路図である。 図9を参照して、この第4実施形態では、上記第3実施形態のVドライバをpチャネルト ランジスタで構成する場合について説明する。

## [0177]

すなわち、この第4実施形態では、図9に示すように、複数段のシフトレジスタ回路部521~525と、スキャン方向切替回路部620と、入力信号切替回路部720と、複数段の論理合成回路部821~823と、回路部920とが設けられている。なお、図9では、図面の簡略化のため、5段分のシフトレジスタ回路部521~525および3段分の論理合成回路部821~823のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

### [0178]

そして、1段目のシフトレジスタ回路部521は、図5に示した第2実施形態の1段目のシフトレジスタ回路部501の第1回路部501aおよび第2回路部501bと同様の回路構成を有する第1回路部521aおよび第2回路部521bによって構成されている。また、2段目のシフトレジスタ回路部522は、図5に示した第2実施形態の2段目のシフトレジスタ回路部502の第1回路部502aおよび第2回路部502bによって構成されている。路構成を有する第1回路部522aおよび第2回路部522bによって構成されている。

# [0179]

ここで、第4実施形態では、3段目のシフトレジスタ回路部523、4段目のシフトレジスタ回路部524および5段目のシフトレジスタ回路部525のそれぞれに、イネーブル信号線(ENB)が接続されている。

# [0180]

具体的には、3段目のシフトレジスタ回路部523は、第1回路部523aと第2回路部523bとによって構成されている。第1回路部523aおよび第2回路部523bは、それぞれ、図5に示した第2実施形態の3段目のシフトレジスタ回路部503の第1回路部503aおよび第2回路部503bと同様の回路構成を有する。そして、この第4実施形態では、トランジスタPT24のドレインに、イネーブル信号線(ENB)が接続されている。

### [0181]

また、4段目のシフトレジスタ回路部524は、第1回路部524aと第2回路部524bとによって構成されている。第1回路部524aおよび第2回路部524bは、それぞれ、図5に示した第2実施形態の4段目のシフトレジスタ回路部504の第1回路部504aおよび第2回路部504bと同様の回路構成を有する。そして、この第4実施形態では、トランジスタPT34のドレインに、イネーブル信号線(ENB)が接続されている。

## [0182]

また、5段目のシフトレジスタ回路部525は、第1回路部525aと第2回路部52

20

10

30

40

5 bとによって構成されている。第1回路部525 aおよび第2回路部525 bは、それぞれ、図5に示した第2実施形態の5段目のシフトレジスタ回路部505の第1回路部505 aおよび第2回路部505 bと同様の回路構成を有する。そして、この第4実施形態では、トランジスタPT44のドレインに、イネーブル信号線(ENB)が接続されている。

## [0183]

また、第4実施形態のスキャン方向切替回路部620は、図5に示した第2実施形態のスキャン方向切替回路部600と同様の回路構成を有する。ただし、第4実施形態では、トランジスタPT56のソース/ドレインの他方と、トランジスタPT57のソース/ドレインの一方とが接続されていない。

## [0184]

また、第4実施形態の入力信号切替回路部720は、図5に示した第2実施形態の入力信号切替回路部700と同様の回路構成を有する。

# [0185]

また、第4実施形態のダミーゲート線に接続される論理合成回路部821は、トランジスタPT81~PT84と、ダイオード接続されたトランジスタPT85と、容量C81とを含む。すなわち、第4実施形態の論理合成回路部821は、図5に示した第2実施形態の論理合成回路部801の回路構成において、ダイオード接続されたトランジスタPT86が設けられていない回路構成を有する。また、第4実施形態の論理合成回路部821のノードND5は、トランジスタPT85を介して、反転イネーブル信号線(XENB)に接続されている。

### [0186]

また、1段目のゲート線に接続される論理合成回路部822は、トランジスタPT91~PT94と、ダイオード接続されたトランジスタPT95と、容量C91とを含む。すなわち、第4実施形態の論理合成回路部822は、図5に示した第2実施形態の論理合成回路部802の回路構成において、ダイオード接続されたトランジスタPT96が設けられていない回路構成を有する。また、第4実施形態の論理合成回路部822のノードND5は、トランジスタPT95を介して、反転イネーブル信号線(XENB)に接続されている。

## [0187]

また、2段目のゲート線に接続される論理合成回路部823は、トランジスタPT101~PT104と、ダイオード接続されたトランジスタPT105と、容量C101とを含む。すなわち、第4実施形態の論理合成回路部823は、図5に示した第2実施形態の論理合成回路部803の回路構成において、ダイオード接続されたトランジスタPT106が設けられていない回路構成を有する。また、第4実施形態の論理合成回路部823のノードND5は、トランジスタPT105を介して、反転イネーブル信号線(XENB)に接続されている。

## [0188]

また、第4実施形態の回路部920は、pチャネルトランジスタPT111~PT113と、ダイオード接続されたpチャネルトランジスタPT1114と、容量C1111とを含む。以下、pチャネルトランジスタPT1114は、それぞれ、トランジスタPT111~PT1114は、それぞれ、トランジスタPT111~PT1114と称する。

## [0189]

そして、回路部920を構成するトランジスタPT111~PT114は、それぞれ、図7に示した第3実施形態のトランジスタNT111~NT114に対応した位置に接続されている。ただし、トランジスタPT112のソースは、正側電位VDDに接続されている。

# [0190]

図10は、本発明の第4実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図9および図10を参照して、第4実施形態による液晶表

10

20

30

40

示装置のVドライバの動作を説明する。

## [0191]

この第4実施形態のVドライバでは、図8に示した第3実施形態のスタート信号STV、クロック信号CKV1、クロック信号CKV2、イネーブル信号ENBおよび反転イネーブル信号XENBのHレベルとLレベルとを反転させた波形の信号を、それぞれ、スタート信号STV、クロック信号CKV1、クロック信号CKV2、イネーブル信号ENBおよび反転イネーブル信号XENBとして入力する。これにより、第4実施形態のシフトレジスタ回路部521~525からは、それぞれ、第3実施形態のシフトレジスタ回路部511~515からのシフト信号SR1~SR5のHレベルとLレベルとを反転させた波形を有する信号が出力される。また、第4実施形態の論理合成回路部821~823からは、第3実施形態の論理合成回路部811~813から出力される出力信号Dummy、Gate1およびGate2のHレベルとLレベルとを反転させた波形を有する信号が出力される。この第4実施形態のVドライバの動作は、上記した第3実施形態のVドライバの動作と同様である。

### [0192]

第4実施形態では、上記のように構成することによって、Vドライバの消費電流の増加を抑制することができるなどの上記第3実施形態と同様の効果を得ることができる。

#### [0193]

なお、第4実施形態では、シフトレジスタ回路部513~515のシフト出力信号SR13~SR15が出力されるノードND3に接続されたトランジスタPT24、PT34およびPT44のドレインに、正側電位VDDと負側電位VBBとが周期的に切り替わるイネーブル信号ENBを供給することによって、以下のような動作が行われる。たとえば、3段目のシフトレジスタ回路部523において、トランジスタPT24がオン状態のときにソース電位がVDDからVBBに変動するので、その電位の変動分(V))だけトランジスタPT24のゲート電位が降下する。これにより、トランジスタPT24のドレインが固定的な負側電位VBB側に接続されている場合に比べて、より確実にトランジスタPT24をオン状態に保持することができる。

### [0194]

## (第5実施形態)

図11は、本発明の第5実施形態による液晶表示装置のVドライバ内部の回路図である。図11を参照して、この第5実施形態では、上記第3実施形態の構成において、3段目以降のシフトレジスタ回路部のシフト出力信号が出力されるノードに接続されたトランジスタのドレインに、タイミングの異なる2つのイネーブル信号を1つずつ交互に供給する場合について説明する。

# [0195]

すなわち、この第5実施形態では、図11に示すように、複数段のシフトレジスタ回路部531~535と、スキャン方向切替回路部630と、入力信号切替回路部730と、論理合成回路部831~833と、回路部930とが設けられている。なお、図11では、図面の簡略化のため、5段分のシフトレジスタ回路部531~535および3段分の論理合成回路部831~833のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

### [0196]

そして、1段目のシフトレジスタ回路部531は、図2に示した第1実施形態の1段目のシフトレジスタ回路部51の第1回路部51aおよび第2回路部51bと同様の回路構成を有する第1回路部531aおよび第2回路部531bによって構成されている。また、2段目のシフトレジスタ回路部532は、図2に示した第1実施形態の2段目のシフトレジスタ回路部52の第1回路部52aおよび第2回路部52bと同様の回路構成を有する第1回路部532aおよび第2回路部532bによって構成されている。

# [0197]

ここで、第5実施形態では、3段目以降のシフトレジスタ回路部533~535に、イ

10

20

30

40

ネーブル信号 E N B 1 が供給されるイネーブル信号線とイネーブル信号 E N B 2 が供給されるイネーブル信号線とが1つずつ交互に接続されている。なお、イネーブル信号 E N B 1 は、本発明の「第1 周期信号」の一例であり、イネーブル信号 E N B 1 が供給されるイネーブル信号線は、本発明の「第1 周期信号線」の一例である。また、イネーブル信号 E N B 2 は、本発明の「第2 周期信号」の一例であり、イネーブル信号 E N B 2 が供給されるイネーブル信号線は、本発明の「第2 周期信号線」の一例である。

#### [0198]

具体的には、3段目のシフトレジスタ回路部533は、第1回路部533aと第2回路部533bはお533bとによって構成されている。第1回路部533aおよび第2回路部533bは、それぞれ、図2に示した第1実施形態の3段目のシフトレジスタ回路部53の第1回路部53aおよび第2回路部53bと同様の回路構成を有する。そして、この第5実施形態では、トランジスタNT24のドレインに、イネーブル信号線(ENB1)が接続されている。

## [0199]

また、4段目のシフトレジスタ回路部534は、第1回路部534aと第2回路部534bとによって構成されている。第1回路部534aおよび第2回路部534bは、それぞれ、図2に示した第1実施形態の4段目のシフトレジスタ回路部54の第1回路部54aおよび第2回路部54bと同様の回路構成を有する。そして、この第5実施形態では、トランジスタNT34のドレインに、イネーブル信号線(ENB2)が接続されている。

### [0200]

また、5段目のシフトレジスタ回路部535は、第1回路部535aと第2回路部535bとによって構成されている。第1回路部535aおよび第2回路部535bは、それぞれ、図2に示した第1実施形態の5段目のシフトレジスタ回路部55の第1回路部55aおよび第2回路部55bと同様の回路構成を有する。そして、この第5実施形態では、トランジスタNT44のドレインに、イネーブル信号線(ENB1)が接続されている。

#### [0201]

また、第5実施形態のスキャン方向切替回路部630は、トランジスタNT51~NT55と、トランジスタNT57~NT60とを含む。すなわち、第5実施形態のスキャン方向切替回路部630は、図7に示した第3実施形態のスキャン方向切替回路部610の回路構成において、トランジスタNT56が設けられていない回路構成を有する。

#### [0202]

また、第5実施形態の入力信号切替回路部730は、図7に示した第3実施形態の入力信号切替回路部710と同様の回路構成を有する。

#### [0203]

また、第5実施形態の論理合成回路部831~833は、それぞれ、図7に示した第3 実施形態の論理合成回路部811~813と同様の回路構成を有する。

## [0204]

また、第5実施形態の回路部930は、図7に示した第3実施形態の回路部910と同様の回路構成を有する。

#### [0205]

図12は、本発明の第5実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図11および図12を参照して、第5実施形態による液晶表示装置のVドライバの動作について説明する。

## [0206]

この第5実施形態のVドライバの動作は、基本的には、上記第3実施形態のVドライバの動作と同様である。ただし、この第5実施形態のVドライバでは、上記第3実施形態と異なり、3段目以降の各段のシフトレジスタ回路部533~535のシフト出力信号SR13~SR15が出力されるノードND3に接続されたトランジスタNT24、NT34およびNT54のドレインに、タイミングの異なるイネーブル信号ENB1およびENB2を交互に供給する。

10

20

30

40

10

20

30

40

50

#### [0207]

具体的には、1段目および2段目のシフトレジスタ回路部531および532(図11 参照)における動作は、図7に示した第3実施形態による1段目および2段目のシフトレ ジスタ回路部511および512における動作と同様である。そして、3段目のシフトレ ジスタ回路部533では、2段目のシフトレジスタ回路部532からトランジスタNT2 7のゲートにHレベルのシフト信号 SR2 が入力されるとともに、トランジスタNT2 1 のゲートにHレベル(VDD)のシフト出力信号SR12が入力される。また、トランジ スタNT22のゲートには、4段目のシフトレジスタ回路部534からLレベルのシフト 信号SR4が入力される。これにより、トランジスタNT21およびNT27がオン状態 になるとともに、トランジスタNT22がオフ状態になる。このため、トランジスタNT 2 1 を介して負側電位 V B B から L レベルの電位が供給されることにより、ノード N D 1 の電位がLレベルに低下する。これにより、トランジスタNT25およびNT26がオフ 状態になる。この状態で、トランジスタNT27のドレインに入力されるクロック信号C KV1がLレベルからHレベルに上昇する。これにより、3段目のシフトレジスタ回路部 5 3 3 の ノード N D 2 の電位が H レベルに上昇するので、トランジスタ N T 2 4 がオン状 態になる。このとき、トランジスタNT24のドレインにLレベルのイネーブル信号EN B1が供給されているので、トランジスタNT24のソース電位(ノードND3の電位) がLレベルに保持される。

#### [0208]

この後、第5実施形態では、イネーブル信号ENB1の電位がLレベルからHレベルに上昇する。これにより、3段目のシフトレジスタ回路部533のノードND3の電位がHレベルに上昇する。この際、3段目のシフトレジスタ回路部533のノードND2の電位は、容量C22によってトランジスタNT24のゲート・ソース間電圧が維持されるように、ノードND3の電位の上昇に伴ってブートされることにより上昇する。これにより、3段目のシフトレジスタ回路部533のノードND2の電位がVDD+Vは)まで上昇する。なお、このときのノードND2の電位(VDD+V)は、上記第1実施形態において上昇した後のノードND2の電位(VDD+V)よりもさらに高い電位となる。そして、3段目のシフトレジスタ回路部533のノードND2からVDD+Vは以上の電位(VDD+V)を有するHレベルのシフト信号SR3が出力される。

#### [0209]

また、4段目のシフトレジスタ回路部534では、トランジスタNT68を介して3段目のシフトレジスタ回路部533からトランジスタNT37のゲートにHレベルのシフト信号SR3が入力されるとともに、トランジスタNT31のゲートにHレベル(VDD)のシフト出力信号SR13が入力される。また、トランジスタNT32のゲートにはフトランジスタNT67を介して5段目のシフトレジスタ回路部535からLレベルのシフト信号SR5が入力される。これにより、トランジスタNT31およびNT37がオン状態になるとともに、トランジスタNT32がオフ状態になる。このため、トランジスタNT31を介して負側電位VBBからLレベルの電位が供給されることにより、ノードND1の電位がLレベルに低下する。これにより、トランジスタNT35およびNT36がオフ状態になる。この後、トランジスタNT37のドレインに入力されるクロック信号CKV2がLレベルからHレベルに上昇するので、トランジスタNT34がオン状態になる。このとき、トランジスタNT34のドレインにLレベルのイネーブル信号ENB2が供給されているので、トランジスタNT34のソース電位(ノードND3の電位)がLレベルに保持される。

#### [0210]

この後、第5実施形態では、イネーブル信号ENB2の電位がLレベルからHレベルに 上昇する。これにより、4段目のシフトレジスタ回路部534のノードND3の電位がH レベルに上昇する。この際、4段目のシフトレジスタ回路部534のノードND2の電位

10

20

30

40

50

は、容量 C 3 2 によってトランジスタN T 3 4 のゲート - ソース間電圧が維持されるように、ノードN D 3 の電位の上昇に伴ってブートされることにより上昇する。これにより、4 段目のシフトレジスタ回路部 5 3 4 のノードN D 2 の電位が V D D よりもしきい値電圧 (V t )以上の所定の電圧 (V )分高い電位 (V D D + V > V D D + V t )まで上昇する。そして、4 段目のシフトレジスタ回路部 5 3 4 のノードN D 2 から V D D + V t 以上の電位 (V D D + V )を有する H レベルのシフト信号 S R 4 が出力される。

[0211]

5 段目のシフトレジスタ回路部535および6 段目以降のシフトレジスタ回路部においても、上記の3 段目および4 段目のシフトレジスタ回路部533および534による動作と同様の動作を行う。すなわち、5 段目のシフトレジスタ回路部535では、クロック信号 CKV1をHレベルに上昇させることによりノードND2の電位を上昇させた後、イネーブル信号 ENB1をHレベルに上昇させることにより、ノードND2の電位をさらに上昇させてHレベル(VDD+V > VDD+Vt)の電位にする。そして、5 段目の次段のシフトレジスタ回路部では、クロック信号 CKV2をHレベルに上昇させることにより、ノードND2の電位を上昇させた後、イネーブル信号 ENB2をHレベルに上昇させることにより、ノードND2の電位をさらに上昇させてHレベル(VDD+V > VDD+Vt)の電位にする。この動作を各段のシフトレジスタ回路部で交互に行う。これにより、各段のシフトレジスタ回路部から出力されるシフト信号の電位を、順次、Hレベル(VDD+V > VDD+Vt)に上昇させる。

[0212]

この第5実施形態のVドライバの上記以外の動作は、上記した第3実施形態のVドライバの動作と同様である。

[0213]

第5実施形態では、上記のように、3段目以降の各段のシフトレジスタ回路部533~535のシフト出力信号SR13~SR15が出力されるノードND3に接続されたトランジスタNT24、NT34およびNT54のドレインに、タイミングの異なるイネーブル信号ENB1およびENB2を交互に供給することによって、たとえば、3段目のシフトレジスタ回路部513と同様、トランジスタNT24のドレインが固定的な正側電位VDD側に接続されている場合に比べて、トランジスタNT24のゲート電位(VDD+V > VDD+Vt)をより高くすることができるので、より確実に、トランジスタNT24をオン状態に保持することができる。

[0214]

また、第5実施形態では、タイミングの異なる2つのイネーブル信号ENB1およびE NB2を用いることによって、たとえば、隣接するシフトレジスタ回路部533および5 3 4 において、シフトレジスタ回路部 5 3 3 のトランジスタNT 2 4 およびシフトレジス 夕回路部 5 3 4 のトランジスタNT 3 4 の各々がクロック信号CKV 1 およびCKV2に 応答してオンするタイミングに合わせてトランジスタNT24およびNT34のソース電 位をVBBからVDDに変動させることがでる。また、シフトレジスタ回路部533のト ランジスタNT24およびシフトレジスタ回路部534のトランジスタNT34の各々が クロック信号CKV1およびCKV2に応答してオフ状態になる直前までトランジスタN T24およびNT34のソース電位をVDDに保持することができる。これにより、トラ ン ジ ス タ N T 2 4 お よ び N T 3 4 の 各 々 が ク ロ ッ ク 信 号 C K V 1 お よ び C K V 2 に 応 答 し てオフする直前までの間にトランジスタNT24およびNT34のソース電位がVBBに なることに起因して、トランジスタNT24およびNT34のゲート電位が変動するとい う不都合が発生するのを抑制することができる。この場合、トランジスタNT24(NT 34)のゲート電位が、次段のシフトレジスタ回路部534(535)のトランジスタN T37(NT47)に入力される場合に、トランジスタNT37(NT47)の動作が不 安定になるのを抑制することができる。また、トランジスタNT37(NT47)の動作 が不安定になることによりトランジスタNT37(NT47)がオンするタイミングが遅 れるのを抑制することができるので、トランジスタNT37(NT47)を介してトランジスタNT34(NT44)のゲートにクロック信号が入力される際のタイミングが遅れるのを抑制することができる。

#### [0215]

なお、第5実施形態のその他の効果は、上記第3実施形態と同様である。

#### [0216]

(第6実施形態)

図13は、本発明の第6実施形態による液晶表示装置のVドライバ内部の回路図である。図13を参照して、この第6実施形態では、上記第5実施形態のVドライバをpチャネルトランジスタで構成する場合について説明する。