(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5010660号

(P5010660)

(45) 発行日 平成24年8月29日(2012.8.29)

(24) 登録日 平成24年6月8日(2012.6.8)

(51) Int.Cl.

F 1

|                    |                  |                   |             |

|--------------------|------------------|-------------------|-------------|

| <b>H01L 21/76</b>  | <b>(2006.01)</b> | <b>H01L 21/76</b> | <b>L</b>    |

| <b>H01L 29/78</b>  | <b>(2006.01)</b> | <b>H01L 29/78</b> | <b>301R</b> |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | <b>H01L 29/78</b> | <b>301D</b> |

| <b>H01L 29/732</b> | <b>(2006.01)</b> | <b>H01L 29/72</b> | <b>P</b>    |

| <b>H01L 21/331</b> | <b>(2006.01)</b> | <b>H01L 21/76</b> | <b>S</b>    |

請求項の数 5 (全 22 頁)

(21) 出願番号

特願2009-220903 (P2009-220903)

(22) 出願日

平成21年9月25日(2009.9.25)

(65) 公開番号

特開2011-71304 (P2011-71304A)

(43) 公開日

平成23年4月7日(2011.4.7)

審査請求日

平成23年9月7日(2011.9.7)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 月原 徹也

東京都港区芝浦一丁目1番1号 株式会社

東芝内

審査官 松本 陶子

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、前記埋め込み層よりも前記第2の導電型の不純物濃度が低い所定の厚さの前記第2の導電型の半導体層と、が積層された基板と、

前記基板に、前記埋め込み層の形成位置よりも深く形成され、前記基板内の素子形成領域内を区画するトレンチと、

前記トレンチの内壁に沿って形成される側壁酸化膜と、前記側壁酸化膜で被覆された前記トレンチ内を埋める埋め込み膜と、を含む素子分離絶縁膜と、

前記素子分離絶縁膜で区画される素子形成領域に形成される半導体素子と、

を備え、

前記トレンチは、前記基板表面から所定の境界深さまでの第1のトレンチと、前記境界深さから底部までの前記第1のトレンチよりも小さい開口径を有する第2のトレンチによって構成され、

前記半導体素子は、

前記素子形成領域の前記半導体層の表面に形成される所定の導電型の不純物拡散層からなるソース領域と、

前記素子形成領域の前記半導体層の表面に前記ソース領域から離れて形成され、所定の導電型の不純物拡散層からなるドレイン領域と、

前記ソース領域と前記ドレイン領域との間で、前記半導体層上にゲート絶縁膜を介して

10

20

形成されるゲート電極と、

前記ドレイン領域から前記ゲート電極の下部にかけて、前記ドレイン領域に隣接して形成され、前記ドレイン領域の不純物濃度よりも低い濃度の不純物拡散層からなる前記第2の導電型のドリフト領域と、

前記ソース領域に接続されるソース電極と、

前記ドレイン領域に接続されるドレイン電極と、

を有し、

前記トレンチの境界深さは前記半導体層内にあり、

前記第2のトレンチの側壁の周囲にのみ前記埋め込み層に接続される第1の拡散層が形成されることを特徴とする半導体装置。

10

【請求項2】

第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、前記埋め込み層よりも前記第2の導電型の不純物濃度が低い所定の厚さの前記第2の導電型の半導体層と、が積層された基板と、

前記基板に、前記埋め込み層の形成位置よりも深く形成され、前記基板内の素子形成領域内を区画するトレンチと、

前記トレンチの内壁に沿って形成される側壁酸化膜と、前記側壁酸化膜で被覆された前記トレンチ内を埋める埋め込み膜と、を含む素子分離絶縁膜と、

前記素子分離絶縁膜で区画される素子形成領域に形成される半導体素子と、

を備え、

20

前記トレンチは、前記基板表面から所定の境界深さまでの第1のトレンチと、前記境界深さから底部までの前記第1のトレンチよりも小さい開口径を有する第2のトレンチによって構成され、

前記半導体素子は、

前記素子形成領域内の前記第2の導電型の半導体層の表面から前記埋め込み層にかけて形成されるコレクタ領域と、

前記素子形成領域内の前記コレクタ層の形成位置とは異なる前記半導体層の表面に形成される前記第1の導電型のベース領域と、

前記ベース領域内に形成される前記第2の導電型のエミッタ領域と、

前記コレクタ領域に接続されるコレクタ電極と、

30

前記ベース電極に接続されるベース電極と、

前記エミッタ領域に接続されるエミッタ電極と、

を有し、

前記トレンチの境界深さは前記埋め込み層よりも下の前記半導体基板内にあり、

前記第1のトレンチの側壁の周囲にのみ前記埋め込み層に接続される第1の拡散層が形成されることを特徴とする半導体装置。

【請求項3】

前記素子分離絶縁膜の下部に前記第1の導電型の第2の拡散層が形成されることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、所定の厚さの前記第2の導電型の半導体層とが積層された基板上に、ストップ膜とマスク膜とを形成する工程と、

前記マスク膜上にレジストを塗布し、形成するトレンチの部分が開口するようにパターニングを行ってレジストパターンを形成する工程と、

前記レジストパターンを前記マスク膜に転写する工程と、

前記パターンが形成されたマスク膜を用いて、前記埋め込み層よりも浅くなるように前記半導体層をエッチングし、第1のトレンチを形成する工程と、

酸化処理を行って、前記第1のトレンチの側壁に第1の側壁酸化膜を形成する工程と、

前記マスク膜を用いて、前記埋め込み層よりも下部の前記半導体基板内の所定の深さま

40

50

でエッティングし、第2のトレンチを形成する工程と、

酸化処理を行って、前記第2のトレンチの側壁に第2の側壁酸化膜を形成するとともに、前記埋め込み層中の前記第2の導電型の不純物が拡散した拡散層を形成する工程と、

前記第1および第2のトレンチ内に絶縁膜を埋め込み、前記基板内の所定の素子形成領域を囲む素子分離絶縁膜を形成する工程と、

前記素子分離絶縁膜で囲まれた前記素子形成領域内にLDMOSを形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

#### 【請求項5】

第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、所定の厚さの前記第2の導電型の半導体層とが積層された基板上に、ストップ膜とマスク膜とを形成する工程と

10

、

前記マスク膜上にレジストを塗布し、形成するトレンチの部分が開口するようにパターニングを行ってレジストパターンを形成する工程と、

前記レジストパターンを前記マスク膜に転写する工程と、

前記パターンが形成されたマスク膜を用いて、前記埋め込み層よりも深くなるように前記半導体層、前記埋め込み層および前記半導体基板をエッティングし、第1のトレンチを形成する工程と、

酸化処理を行って、前記第1のトレンチの側壁に第1の側壁酸化膜を形成するとともに、前記埋め込み層中の前記第2の導電型の不純物が拡散した拡散層を形成する工程と、

前記マスク膜を用いて、前記第1のトレンチの底面よりも下部の前記半導体基板を所定の深さまでエッティングし、第2のトレンチを形成する工程と、

20

酸化処理を行って、前記第2のトレンチの側壁に第2の側壁酸化膜を形成する工程と、

前記第1および第2のトレンチ内に絶縁膜を埋め込み、前記基板内の所定の素子形成領域を囲む素子分離絶縁膜を形成する工程と、

前記素子分離絶縁膜で囲まれた前記素子形成領域内に高周波半導体素子を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

30

本発明は、半導体装置およびその製造方法に関する。

##### 【背景技術】

##### 【0002】

従来、埋め込み層を有する半導体装置の素子分離方法として、ディープトレンチ素子分離(Deep Trench Isolation; 以下、DTIという)を用いた技術が知られている。このDTIは以下のようにして形成される。まず、P型の半導体基板の所定の位置に、イオン注入法を用いて高濃度にN型不純物が拡散された埋め込み層を形成する。ここで、埋め込み層の周縁部から半導体基板に向けて、埋め込み層よりもN型不純物濃度が低い不純物領域が形成されている。ついで、埋め込み層の表面が露出した状態の半導体基板上にN型の半導体層をエピタキシャル成長させる。その後、N型の半導体層の上面に素子分離用のディープトレンチを形成するための開口部を有するマスクを形成し、エッティングによって不純物領域よりも深く、半導体基板に到達するディープトレンチを形成する。このディープトレンチは、埋め込み層に接する位置に形成される。ついで、850~1,200℃での熱酸化によって、ディープトレンチの少なくとも内表面を覆う絶縁膜を形成した後、CVD(Chemical Vapor Deposition)法でディープトレンチの内部を埋め込むように酸化シリコン膜を形成し、CMP(Chemical Mechanical Polishing)法によって半導体層の上面の不必要的膜を除去するとともに平坦化する。以上のようにして、DTIが形成される(たとえば、特許文献1参照)。

40

##### 【0003】

しかしながら、従来技術では、ディープトレンチは、埋め込み層に接する位置に形成さ

50

れるため、ディープトレンチの形成後の状態では、埋め込み層はディープトレンチ内で露出した状態にある。そのため、ディープトレンチの側壁を酸化する際に、埋め込み層のN型不純物がディープトレンチ側壁に外方拡散され、ディープトレンチ側壁にN-層が形成される。埋め込み層よりも下部に形成されるN-層は、埋め込み層の不純物濃度勾配を緩和する作用があり、また、空乏層が延びるため、素子分離耐圧の改善に効果がある。一方、埋め込み層よりも上部に形成されるN-層は、空乏層の伸びを抑え、素子内部の耐圧を低下させてしまう。

#### 【0004】

また、ディープトレンチを必要とする半導体装置には、LDMOS (Lateral Double Diffusion Metal-Oxide-Semiconductor) などの高耐圧半導体装置のほかに、LDMOSのように高い素子間耐圧を必要としない高周波向け半導体装置がある。しかし、従来では、これらの半導体装置の特性を区別することなく上記のような方法でディープトレンチを形成した後に、ディープトレンチで区画される領域に高耐圧半導体素子や高周波半導体素子などの半導体素子を形成していた。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

【特許文献1】特開2003-297845号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

本発明は、形成する素子に要求される素子間耐圧や素子内部耐圧に応じた素子分離絶縁膜を有する半導体装置およびその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

本発明の一態様によれば、第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、前記埋め込み層よりも前記第2の導電型の不純物濃度が低い所定の厚さの前記第2の導電型の半導体層と、が積層された基板と、前記基板に、前記埋め込み層の形成位置よりも深く形成され、前記基板内の素子形成領域内を区画するトレンチと、前記トレンチの内壁に沿って形成される側壁酸化膜と、前記側壁酸化膜で被覆された前記トレンチ内を埋める埋め込み膜と、を含む素子分離絶縁膜と、前記素子分離絶縁膜で区画される素子形成領域に形成される半導体素子と、を備え、前記半導体素子は、前記素子形成領域の前記半導体層の表面上に形成される所定の導電型の不純物拡散層からなるソース領域と、前記素子形成領域の前記半導体層の表面上に前記ソース領域から離れて形成され、所定の導電型の不純物拡散層からなるドレイン領域と、前記ソース領域と前記ドレイン領域との間で、前記半導体層上にゲート絶縁膜を介して形成されるゲート電極と、前記ドレイン領域から前記ゲート電極の下部にかけて、前記ドレイン領域に隣接して形成され、前記ドレイン領域の不純物濃度よりも低い濃度の不純物拡散層からなる前記第2の導電型のドリフト領域と、前記ソース領域に接続されるソース電極と、前記ドレイン領域に接続されるドレイン電極と、を有し、前記トレンチは、前記基板表面から所定の境界深さまでの第1のトレンチと、前記境界深さから底部までの前記第1のトレンチよりも小さい開口径を有する第2のトレンチによって構成され、前記トレンチの境界深さは前記半導体層内にあり、前記第2のトレンチの側壁の周囲にのみ前記埋め込み層に接続される第1の拡散層が形成されることを特徴とする半導体装置が提供される。

また、本発明の一態様によれば、第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、前記埋め込み層よりも前記第2の導電型の不純物濃度が低い所定の厚さの前記第2の導電型の半導体層と、が積層された基板と、前記基板に、前記埋め込み層の形成位置よりも深く形成され、前記基板内の素子形成領域内を区画するトレンチと、前記トレンチの内壁に沿って形成される側壁酸化膜と、前記側壁酸化膜で被覆された前記トレンチ内を埋める埋め込み膜と、を含む素子分離絶縁膜と、前記素子分離絶縁膜で区画される素子

10

20

30

40

50

形成領域に形成される半導体素子と、を備え、前記トレンチは、前記基板表面から所定の境界深さまでの第1のトレンチと、前記境界深さから底部までの前記第1のトレンチよりも小さい開口径を有する第2のトレンチによって構成され、前記半導体素子は、前記素子形成領域内の前記第2の導電型の半導体層の表面から前記埋め込み層にかけて形成されるコレクタ領域と、前記素子形成領域内の前記コレクタ層の形成位置とは異なる前記半導体層の表面に形成される前記第1の導電型のベース領域と、前記ベース領域内に形成される前記第2の導電型のエミッタ領域と、前記コレクタ領域に接続されるコレクタ電極と、前記ベース電極に接続されるベース電極と、前記エミッタ領域に接続されるエミッタ電極と、を有し、前記トレンチの境界深さは前記埋め込み層よりも下の前記半導体基板内にあり、前記第1のトレンチの側壁の周囲にのみ前記埋め込み層に接続される第1の拡散層が形成されることを特徴とする半導体装置が提供される。

#### 【0008】

また、本発明の一態様によれば、第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、所定の厚さの前記第2の導電型の半導体層とが積層された基板上に、ストップ膜とマスク膜とを形成する工程と、前記マスク膜上にレジストを塗布し、形成するトレンチの部分が開口するようにパターニングを行ってレジストパターンを形成する工程と、前記レジストパターンを前記マスク膜に転写する工程と、前記パターンが形成されたマスク膜を用いて、前記埋め込み層よりも浅くなるように前記半導体層をエッチングし、第1のトレンチを形成する工程と、酸化処理を行って、前記第1のトレンチの側壁に第1の側壁酸化膜を形成する工程と、前記マスク膜を用いて、前記埋め込み層よりも下部の前記半導体基板内の所定の深さまでエッチングし、第2のトレンチを形成する工程と、酸化処理を行って、前記第2のトレンチの側壁に第2の側壁酸化膜を形成するとともに、前記埋め込み層中の前記第2の導電型の不純物が拡散した拡散層を形成する工程と、前記第1および第2のトレンチ内に絶縁膜を埋め込み、前記基板内の所定の素子形成領域を囲む素子分離絶縁膜を形成する工程と、前記素子分離絶縁膜で囲まれた前記素子形成領域内にLDMOSを形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

#### 【0009】

さらに、本発明の一態様によれば、第1の導電型の半導体基板上に、第2の導電型の埋め込み層と、所定の厚さの前記第2の導電型の半導体層とが積層された基板上に、ストップ膜とマスク膜とを形成する工程と、前記マスク膜上にレジストを塗布し、形成するトレンチの部分が開口するようにパターニングを行ってレジストパターンを形成する工程と、前記レジストパターンを前記マスク膜に転写する工程と、前記パターンが形成されたマスク膜を用いて、前記埋め込み層よりも深くなるように前記半導体層、前記埋め込み層および前記半導体基板をエッチングし、第1のトレンチを形成する工程と、酸化処理を行って、前記第1のトレンチの側壁に第1の側壁酸化膜を形成するとともに、前記埋め込み層中の前記第2の導電型の不純物が拡散した拡散層を形成する工程と、前記マスク膜を用いて、前記第1のトレンチの底面よりも下部の前記半導体基板を所定の深さまでエッチングし、第2のトレンチを形成する工程と、酸化処理を行って、前記第2のトレンチの側壁に第2の側壁酸化膜を形成する工程と、前記第1および第2のトレンチ内に絶縁膜を埋め込み、前記基板内の所定の素子形成領域を囲む素子分離絶縁膜を形成する工程と、前記素子分離絶縁膜で囲まれた前記素子形成領域内に高周波半導体素子を形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

#### 【発明の効果】

#### 【0010】

本発明によれば、形成する素子に要求される素子間耐圧や素子内部耐圧に応じた素子分離絶縁膜を有する半導体装置およびその製造方法を提供することができるという効果を奏する。

#### 【図面の簡単な説明】

#### 【0011】

【図1】図1は、第1の実施の形態による半導体装置の構造を模式的に示す断面図である

10

20

30

40

50

。

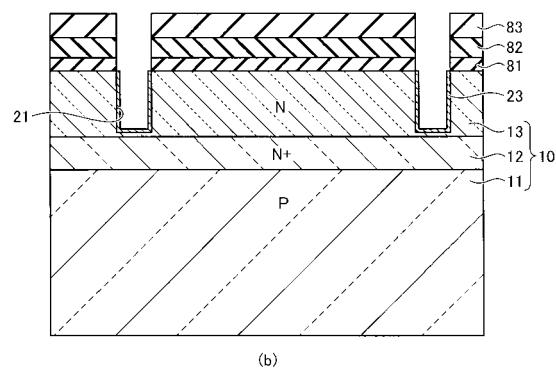

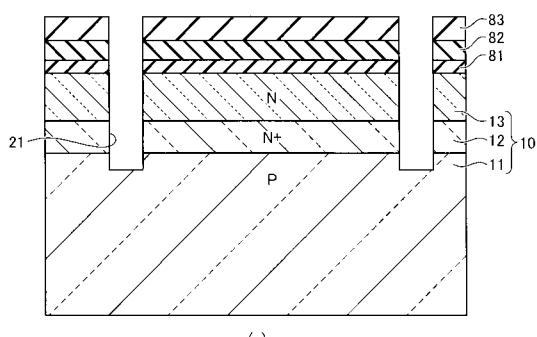

【図2-1】図2-1は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その1）。

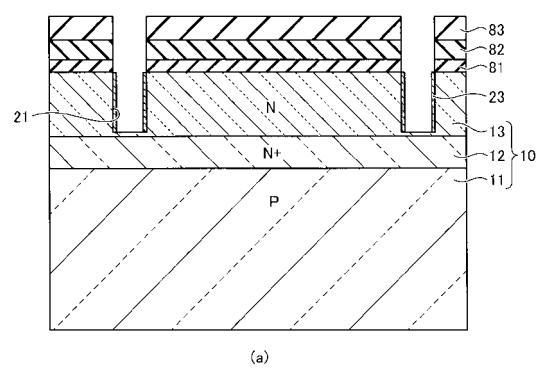

【図2-2】図2-2は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その2）。

【図2-3】図2-3は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その3）。

【図2-4】図2-4は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その4）。

【図2-5】図2-5は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その5）。 10

【図2-6】図2-6は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その6）。

【図2-7】図2-7は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その7）。

【図2-8】図2-8は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その8）。

【図3】図3は、ディープトレンチの構成の違いによる素子間耐圧および素子内部耐圧の一例を示す図である。

【図4】図4は、第2の実施の形態による半導体装置の構造を模式的に示す断面図である 20

。

【図5-1】図5-1は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その1）。

【図5-2】図5-2は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その2）。

【図5-3】図5-3は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その3）。

【図5-4】図5-4は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その4）。

【図5-5】図5-5は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その5）。 30

【図5-6】図5-6は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その6）。

【図5-7】図5-7は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である（その7）。

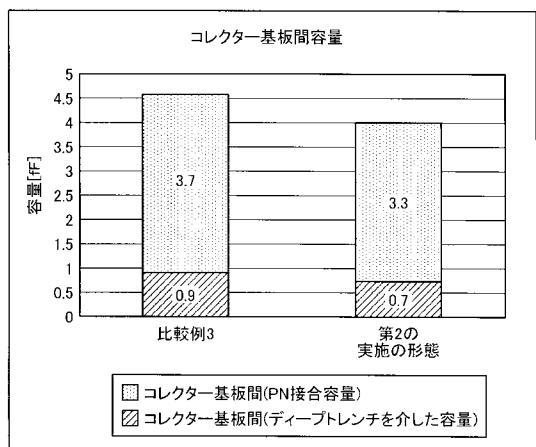

【図6】図6は、ディープトレンチの構成の違いによるコレクタ-基板間の容量の一例を示す図である。

#### 【発明を実施するための形態】

##### 【0012】

以下に添付図面を参照して、本発明の実施の形態にかかる半導体装置およびその製造方法を詳細に説明する。なお、これらの実施の形態により本発明が限定されるものではない。また、以下の実施の形態で用いられる半導体装置の断面図は模式的なものであり、層の厚みと幅との関係や各層の厚みの比率などは現実のものとは異なる。さらに、以下で示す膜厚は一例であり、これに限定されるものではない。 40

##### 【0013】

##### (第1の実施の形態)

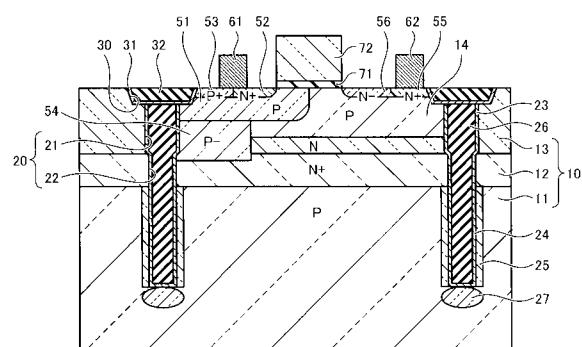

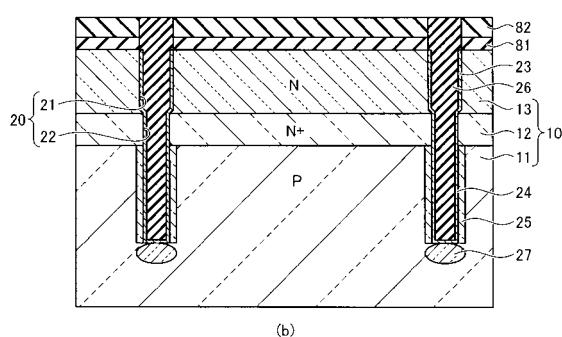

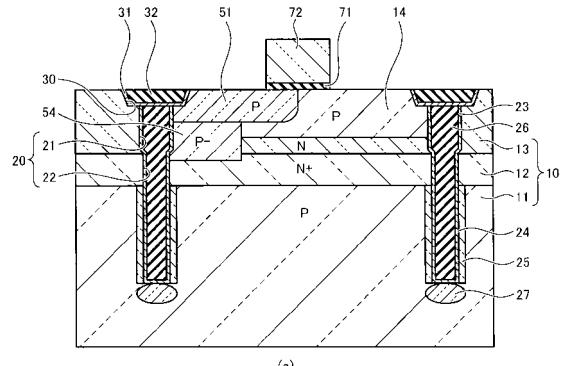

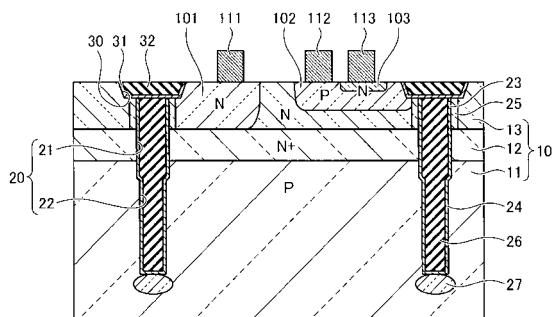

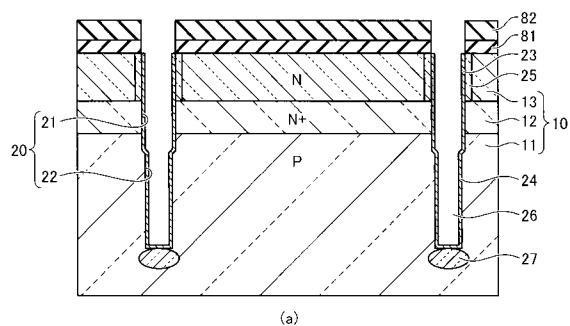

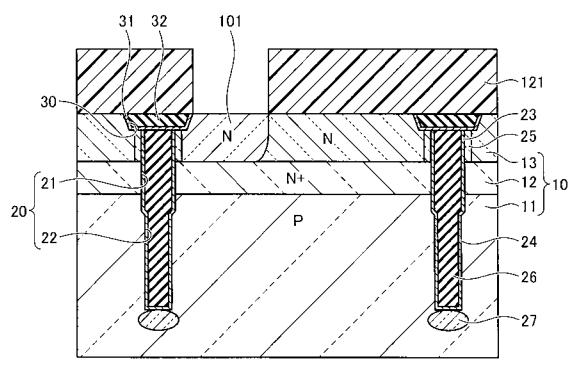

図1は、第1の実施の形態による半導体装置の構造を模式的に示す断面図である。ここでは、N+型埋め込み層12が形成されたP型のシリコン基板11の素子分離絶縁膜としてのディープトレンチ膜26で区画された素子形成領域内にLDMOSが形成された構造の半導体装置を例に挙げて説明する。 50

## 【0014】

基板10としては、N+型埋め込み層12が所定の深さに形成されたP型のシリコン基板11が用いられる。この基板10は、P型のシリコン基板11上に、N型不純物が導入されたシリコン層からなるN+型埋め込み層12と、N+型埋め込み層12よりもN型不純物の濃度が低いシリコン層からなるN型半導体層13とが形成された構造を有している。

## 【0015】

この基板10の所定の領域には、N+型埋め込み層12の下層のシリコン基板11まで到達する所定の深さのディープトレンチ20が、平面視上たとえば額縁状に形成されており、ディープトレンチ20にはシリコン酸化膜やシリコン膜などが埋め込まれ、ディープトレンチ膜26を形成している。このディープトレンチ膜26で区画される領域が素子形成領域となる。また、ディープトレンチ20の底部の下側のシリコン基板11には、P型不純物が導入されたP型拡散層27が形成される。このP型拡散層27は、素子形成領域を電気的に分離する機能を有する。

## 【0016】

ディープトレンチ膜26の上部には、シリコン基板10の表面から浅い位置における隣接する領域間を絶縁する分離膜であるシャロートレンチ30が形成され、シャロートレンチ30の側面および底面には基板10を酸化して得られるシャロートレンチ側壁酸化膜31が形成され、シャロートレンチ30内にはシリコン酸化膜などからなるシャロートレンチ膜32が形成されている。

## 【0017】

素子形成領域内のN型半導体層13の表面から所定の深さにはP型ウェル14が形成され、このP型ウェル14にLDMOSが形成されている。このP型ウェル14において、ソースが形成される領域には、P型のベース領域51が形成され、そのP型のベース領域51の表面には、N+型ソース領域52とP+型ソース領域53とが互いに接するようになされ、さらに、N+型ソース領域52とP+型ソース領域53との表面上にソース電極61が形成されている。また、ベース領域51からN+型埋め込み層12にかけて、P-型拡散層54が形成される。

## 【0018】

一方、P型ウェル14のドレインが形成される領域には、N+型のドレイン領域55が形成され、ドレイン領域55の表面にはドレイン電極62が形成される。ドレイン領域55とベース領域51との間には、ドレイン領域55に隣接して、N-型のドリフト領域56が形成されている。さらに、ソース電極61とドレイン電極62との間のベース領域51およびP型ウェル14上には、ゲート絶縁膜71を介してゲート電極72が形成されている。

## 【0019】

ここで、基板10に形成されるディープトレンチ20について説明する。第1の実施の形態によるディープトレンチ20は、N+型埋め込み層12よりも上の位置を境に開口径が異なっている。この図では、N+型埋め込み層12とN型半導体層13との境界付近で開口径が異なる境界を有しており、この境界よりも上側で開口径が大きく、この境界以下で開口径が小さくなっている。以下では、ディープトレンチ20の開口径が大きい部分を第1のディープトレンチ21といい、開口径が小さい部分を第2のディープトレンチ22という。

## 【0020】

第1のディープトレンチ21の側面を被覆するように、第1の側壁酸化膜23が形成され、第2のディープトレンチ22の側面と底面を被覆するように、第2の側壁酸化膜24が形成される。また、これらの側壁酸化膜23, 24で被覆されたディープトレンチ20内には、TEOS (Tetraethyl orthosilicate) 膜が埋め込まれている。さらに、第2のディープトレンチ22の周囲には、N+型埋め込み層12を拡散源としたN型拡散層25が形成される。しかし、第1のディープトレンチ21の周囲には、N型拡散層25は形

10

20

30

40

50

成されていない。

#### 【0021】

このように、N+型埋め込み層12を拡散源とするN型拡散層25は、N+型埋め込み層12の上部のN型半導体層13には形成されないので、N+型埋め込み層12の上部では、所望の不純物プロファイルを形成することができる。また、N+型埋め込み層12の下部のシリコン基板11にのみN型拡散層25は形成されるので、N+型埋め込み層12の不純物濃度勾配が緩和され、また空乏層が伸びる。その結果、素子間耐圧を改善するとともに、素子内部耐圧を向上させることができる。

#### 【0022】

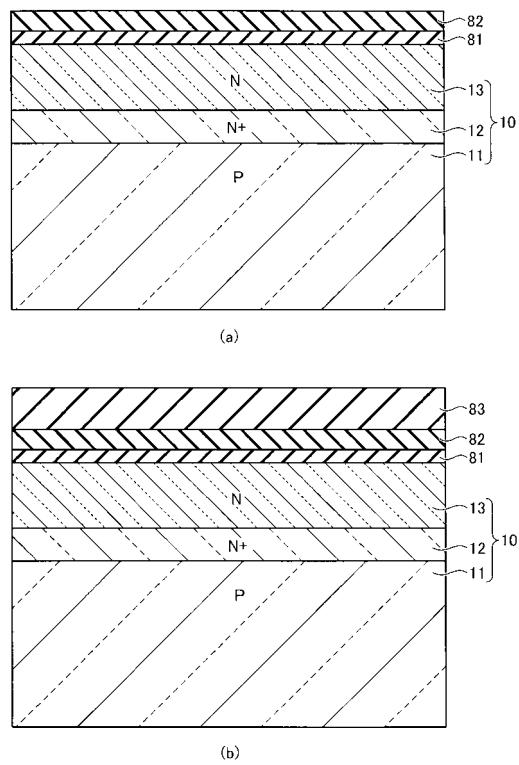

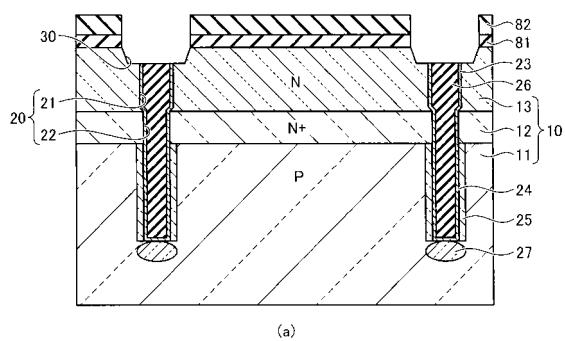

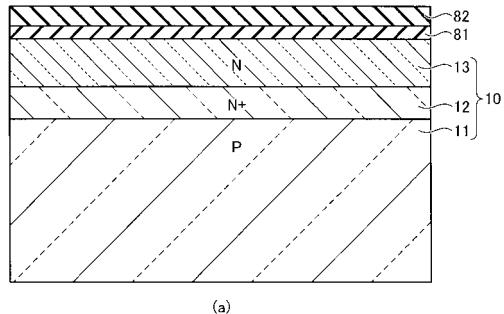

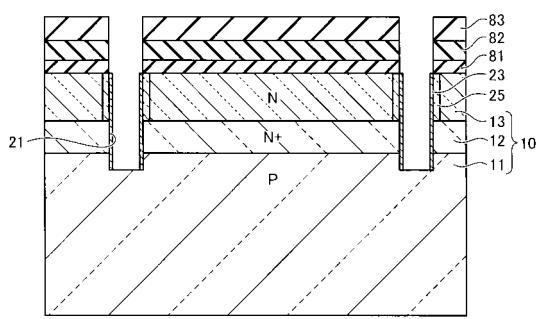

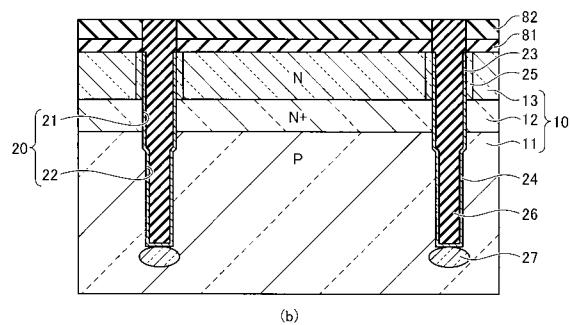

つぎに、このような構造の半導体装置の製造方法について説明する。図2-1～図2-8は、第1の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である。まず、図2-1(a)に示されるように、基板10として、基板10表面から5μmの深さにN+型埋め込み層12を形成したP型シリコン基板11を用いる。具体的には、P型シリコン基板11上に、N+型埋め込み層12および厚さ5μmのN型半導体層13が順に形成された基板10を用いる。この基板10上に、酸化技術を用いて15nmの厚さのSiO膜からなるバッファ酸化膜81を形成し、その後、LPCVD(Low Pressure CVD)法によって200nmの厚さのSiN膜からなるストップ膜82を形成する。バッファ酸化膜81は、後工程において、素子形成領域の保護膜として使用し、ストップ膜82は、後工程の酸化膜のCMP処理時のストップ膜82として利用する。

#### 【0023】

ついで、図2-1(b)に示されるように、ストップ膜82上の全面にCVD法によってSiO系のマスク膜83を成膜する。このマスク膜83は、後の工程でのディープトレンチ20を形成する際のRIE(Reactive Ion Etching)のマスクとして使用する。そのため、このマスク膜83の厚さは、ディープトレンチ20を形成する際の溝をRIEでエッチングすることができる厚さに設定される。ここでは、1,000nmの厚さに堆積されるものとする。

#### 【0024】

その後、図2-2(a)に示されるように、マスク膜83上に図示しないレジストを塗布し、リソグラフィ技術を用いて、ディープトレンチ20の形成領域を決定するためのパターニングを行う。ここでは、0.7μmの開口幅を有し、概略矩形の額縁状のディープトレンチ20を形成するためのパターニングを行うものとする。ついで、パターニングされたレジストをマスクとして、マスク膜83、ストップ膜82およびバッファ酸化膜81を、RIE法を用いてN型半導体層13に達するまでエッチングする。アッシングによってレジストを除去した後、パターニングされたマスク膜83をマスクとして、基板10をRIE法によってエッチングする。このときの基板10のエッチング量は、N+型埋め込み層12に達しない深さとし、ここでは、基板10(N型半導体層13)の表面から4μmとする。これによって、第1のディープトレンチ21が形成される。なお、これによって、マスク膜83の厚さは200nm程度となる。

#### 【0025】

ついで、図2-2(b)に示されるように、酸化技術によって、第1のディープトレンチ21の内面に露出しているシリコンを酸化して、第1のディープトレンチ21の側壁および底面に、50nmの厚さの第1の側壁酸化膜23を形成する。この第1の側壁酸化膜23は、素子分離のための絶縁膜として使用する。この第1の側壁酸化膜23を形成する時点では、第1のディープトレンチ21の底面の位置は、N+型埋め込み層12の形成位置よりも上に位置しているので、N+型埋め込み層12は露出していない。そのため、酸化によって、N+型埋め込み層12を構成するN型の不純物による外方拡散は発生しない。つまり、第1のディープトレンチ21の内壁の側面には、N+型埋め込み層12が拡散源となるN型拡散層25は形成されず、シリコン酸化膜のみによって構成される第1の側壁酸化膜23が形成される。

#### 【0026】

10

20

30

40

50

その後、図2-3(a)に示されるように、RIE法を用いて全面エッティングを行う。具体的には、RIE法によってエッチバックを行い、第1のディープトレンチ21の底部に形成された第1の側壁酸化膜23を除去し、第1のディープトレンチ21の側面にのみ第1の側壁酸化膜23をサイドウォールとして残す。

#### 【0027】

ついで、図2-3(b)に示されるように、200nm程度残されたマスク膜83をマスクとして、RIE法によって、自己整合的に第2のディープトレンチ22を第1のディープトレンチ21の下部に形成する。この第2のディープトレンチ22の深さは、第1のディープトレンチ21の深さ(4μm)と合わせて、10μmとなるようにする。これによつて、第1のディープトレンチ21と第2のディープトレンチ22とによって構成されるディープトレンチ20が形成される。10

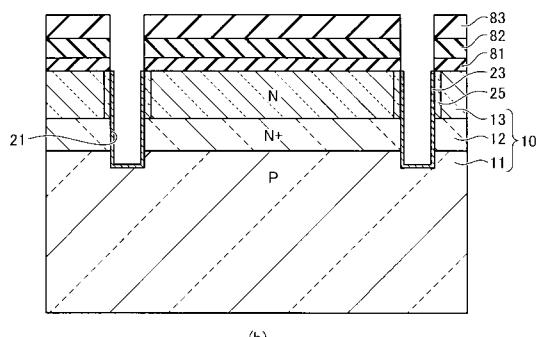

#### 【0028】

第2のディープトレンチ22を形成した後、図2-4(a)に示されるように、酸化技術によって、第2のディープトレンチ22の内面(側面と底面)に50nmの厚さの第2の側壁酸化膜24を形成する。この酸化処理では、N+型埋め込み層12は、第2のディープトレンチ22の形成によって表面に露出している状態であるので、酸化処理時に外方拡散が発生する。その結果、第2のディープトレンチ22の内壁には、N+型埋め込み層12を拡散源としたN型拡散層25が形成される。しかし、N+型埋め込み層12よりも上部の第1のディープトレンチ21の側壁は、第1の側壁酸化膜23(サイドウォール)によって表面が保護されているため、シリコンまでは拡散されない。これによつて、ディープトレンチ20において、第2のディープトレンチ22の側面の周囲にのみN型拡散層25が形成される。その後、ディープトレンチ20の底部に、素子分離の耐圧を向上させるために、イオン注入を行つてP型拡散層27を形成する。ここでは、ホウ素(B)を注入してP型拡散層27を形成する。20

#### 【0029】

ついで、図2-4(b)に示されるように、ディープトレンチ20を形成したマスク膜83上の全面に、LPCVD法によって500nmの厚さのTEOS膜を形成する。これによつて、マスク膜83上にTEOS膜が成膜されるとともに、ディープトレンチ20内にTEOS膜が埋め込まれる。その後、マスク膜83上に形成されたTEOS膜をCMP法によつて除去し、平坦化する。さらに、RIE法によつて、ストップ膜82をストップとして、TEOS膜をエッティングする。具体的には、TEOS膜をストップ膜82よりもエッティングされやすい条件で、ストップ膜82の表面が露出するまでエッティングを行う。これによつて、ディープトレンチ20内にTEOS膜からなるディープトレンチ膜26が形成される。30

#### 【0030】

その後、ストップ膜82上にシャロートレンチ30加工のマスク材となる図示しないマスク材絶縁膜をたとえば100nmの厚さで形成し、マスク材絶縁膜上に図示しないレジストを塗布し、リソグラフィ技術によつてアクティブ領域を分離するシャロートレンチ30を形成するためのパターニングを行う。

#### 【0031】

ついで、図2-5(a)に示されるように、このパターニングしたレジストをマスクとして、マスク材絶縁膜、ストップ膜82およびバッファ酸化膜81をRIE法によつてエッティングし、シャロートレンチ形成用のパターンをマスク材絶縁膜に転写する。レジストをアッシングで除去した後、マスク材絶縁膜をマスクとして、基板10(N型半導体層13)をエッティングし、シャロートレンチ30を形成する。この深さは、0.4μmとする。なお、N+型埋め込み層12の上面から基板10の表面までは、5μm程度あるので、このシャロートレンチ30の深さは十分に浅い。このとき、ディープトレンチ20内のTEOS膜もシャロートレンチ30の加工時に同時にエッティングされるので、ディープトレンチ20の上部にもシャロートレンチ30が形成される。40

#### 【0032】

10

20

30

40

50

ついで、図2-5(b)に示されるように、シャロートレンチ30の側壁を保護することを目的に酸化技術によって50nmの厚さのシャロートレンチ側壁酸化膜31を形成する。その後、LPCVD法によってシャロートレンチ30内をTEOS膜で埋め込む。成膜後に発生する段差は、CMP法によってストップ膜82をストップとして平坦化する。CMP処理の後、不要となったストップ膜82を、熱磷酸などを用いたウェットエッティング法によって除去する。これによって、シャロートレンチ30内にシャロートレンチ膜32が形成される。以上によって、ディープトレンチ膜26とシャロートレンチ膜32とによって区画された基板10上の領域が素子形成領域となる。そして、イオン注入法によって、素子形成領域内にBなどのP型不純物を打ち込み、活性化させて、N型半導体層13の下面よりも浅い領域にP型ウェル14を形成する。

10

#### 【0033】

この後、素子形成領域上へのLDMOSの形成が行われる。まず、図2-6(a)に示されるように、ディープトレンチ膜26を形成した基板10上の全面にレジスト84を塗布し、リソグラフィ技術によって、ソース領域形成領域付近に開口部を有するようにパターニングを行う。そして、イオン注入法によって、基板10表面からN+型埋め込み層12にかけてBなどのP型不純物を導入し、活性化させてP-型拡散層54を形成する。

#### 【0034】

レジスト84をアッシングなどの方法で除去した後、図2-6(b)に示されるように、基板10上の全面にレジスト85を塗布し、ベース領域51に開口部を有するようにリソグラフィ技術によってパターニングを行う。そして、イオン注入法によって、基板10表面からP型ウェル14内の所定の深さにかけてBなどのP型不純物を導入し、活性化させ、ベース領域51を形成する。このとき、ベース領域51のP型不純物濃度は、P-型拡散層54よりも高くなるように調節される。

20

#### 【0035】

レジスト85をアッシングなどの方法で除去した後、基板10上に絶縁膜とポリシリコン膜などの導電性材料膜とを積層する。導電性材料膜上に図示しないレジストを塗布し、ゲート電極形状にパターニングを行った後、RIE法などの方法でレジストをマスクとしてエッティングを行う。これによって、図2-7(a)に示されるように、基板10上にゲート絶縁膜71とゲート電極72とが形成される。ここでは、ゲート絶縁膜71とゲート電極72お積層体は、P型ウェル14とベース領域51との境界をまたぐように形成される。

30

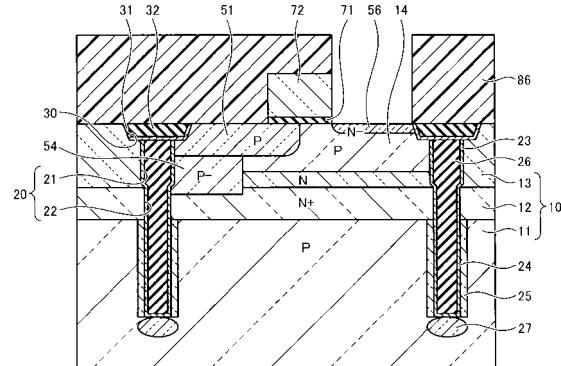

#### 【0036】

ついで、図2-7(b)に示されるように、ゲート電極72を形成した基板10上にレジスト86を塗布し、ドリフト領域56およびドレイン領域55が開口するようにリソグラフィ技術によってパターニングを行う。そして、イオン注入法によって、基板10表面から所定の深さまでPなどのN型不純物を導入し、活性化させ、ドリフト領域56を形成する。

#### 【0037】

レジスト86をアッシングなどの方法で除去した後、図2-8(a)に示されるように、基板10上にレジスト88を塗布し、ドレイン領域55およびN+型ソース領域52が開口するように、リソグラフィ技術によってパターニングを行う。そして、イオン注入法によって、基板10表面から所定の深さまでPなどのN型不純物を導入し、活性化させ、ドレイン領域55およびN+型ソース領域52を形成する。このときのN型不純物濃度は、ドリフト領域56よりも高くなるように調節される。

40

#### 【0038】

レジスト88をアッシングなどの方法で除去した後、図2-8(b)に示されるように、基板10上にレジスト88を塗布し、P+型ソース領域53が開口するように、リソグラフィ技術によってパターニングを行う。そして、イオン注入法によって、基板10表面から所定の深さまでBなどのP型不純物を導入し、活性化させ、P+型ソース領域53を形成する。

50

## 【0039】

レジスト88をアッシングなどの方法で除去した後、たとえばレジストを基板10上に塗布し、ドレイン領域55の一部と、N+型ソース領域52とP+型ソース領域53の一部が開口するようにリソグラフィ技術によってパターニングを行う。そして、導電性材料膜を開口部内に形成し、レジストを除去する。これによって、図1に示されるように、ソース電極61およびドレイン電極62が形成される。以上によって、LDMOSが製造される。

## 【0040】

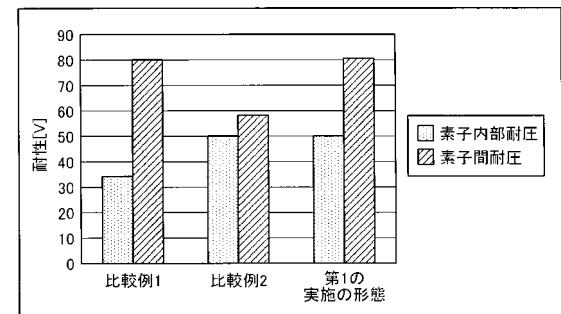

図3は、ディープトレンチの構成の違いによる素子間耐圧および素子内部耐圧の一例を示す図である。ここでは、最小寸法が0.13μmのデバイス製造技術を用いて形成されたLDMOSを用いて測定を行っている。比較例1は、特許文献1のように、ディープトレンチの側壁に酸化膜を形成する際に、ディープトレンチの側壁に沿ってN+型埋め込み層を拡散源とするN型拡散層が形成された場合を示し、比較例2は、比較例1の場合でN型拡散層の外方拡散を抑える条件で酸化を行った場合を示している。また、縦軸は耐圧[V]を示している。

10

## 【0041】

比較例1では、N+型埋め込み層の不純物が拡散することによって、N+型埋め込み層の不純物濃度勾配を緩和し、N+型埋め込み層の下部では空乏層が伸びることで、素子間耐圧が改善するが、N+型埋め込み層の上部では空乏層の伸びが抑えられるため、素子内部耐圧が低下している。また、比較例2では、酸化条件によってN+型埋め込み層の外方拡散を抑制している結果、比較例1とは逆に、素子内部耐圧は向上しているが、素子間耐圧が低下してしまっている。

20

## 【0042】

一方、第1の実施の形態では、ディープトレンチ20を、N+型埋め込み層12よりも上の第1のディープトレンチ21と、その下部に形成され、N+型埋め込み層12よりも深い位置に底部を有する第2のディープトレンチ22と、を別々形成した。具体的には、第1のディープトレンチ21の側壁に沿って第1の側壁酸化膜23のみを形成し、その後に、第2のディープトレンチ22の側壁に沿って第2の側壁酸化膜24を形成するとともに、その外側にN+型埋め込み層12を拡散源とするN型拡散層25を形成した。これによつて、比較例1のように素子間耐圧を改善するとともに、比較例2のように素子内部耐圧も向上させることができるという効果を有する。

30

## 【0043】

また、ディープトレンチ20の形成時において、第1のディープトレンチ21の底部がN+型埋め込み層12の上面よりも上の位置となるようにして第1のディープトレンチ21を形成したので、第1のディープトレンチ21の側壁に第1の側壁酸化膜23を形成する際に、N+型埋め込み層12のN型不純物が第1のディープトレンチ21の周囲に拡散することがない。さらに、第2のディープトレンチ22を形成後に、酸化処理を行つても、第1のディープトレンチ21の側壁には第1の側壁酸化膜23が形成されているので、N+型埋め込み層12のN型不純物が第1のディープトレンチ21の側壁の周囲に拡散することもない。

40

## 【0044】

また、第1のディープトレンチ21を形成したマスク膜83を用いて、第2のディープトレンチ22を形成するようにしたので、第1と第2のディープトレンチ21, 22を形成するために別個のリソグラフィ工程を行うことなく、従来のディープトレンチ20の製造工程に最小限の工程の追加のみで、ディープトレンチ20の側面に形成される不純物層の制御が可能となる。

## 【0045】

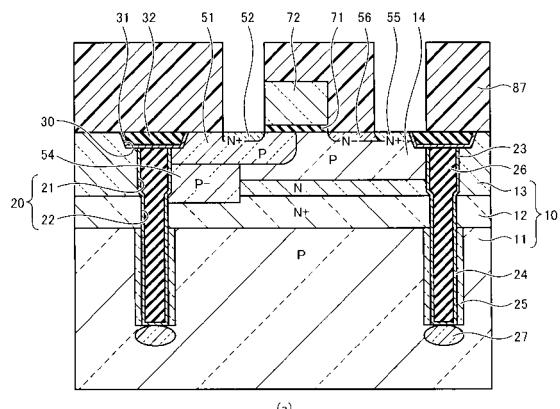

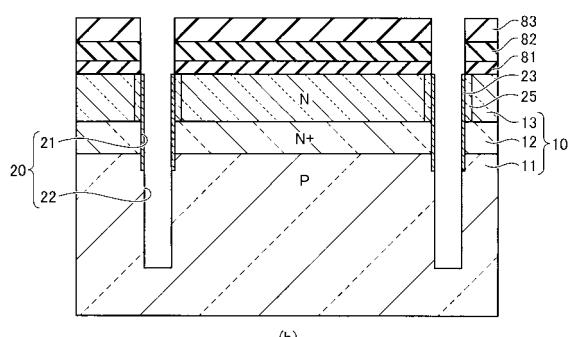

## (第2の実施の形態)

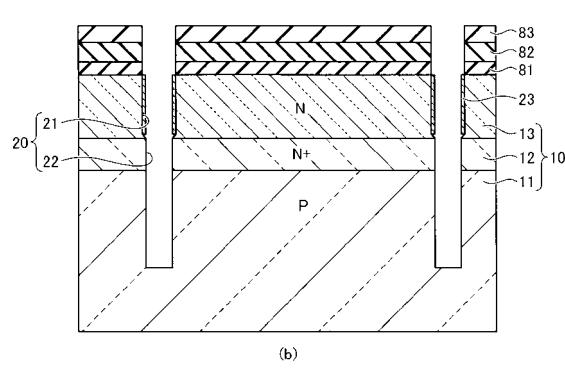

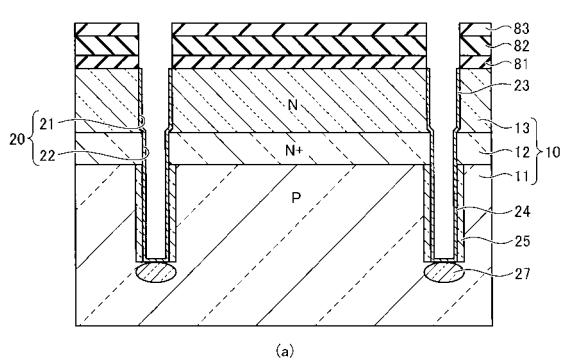

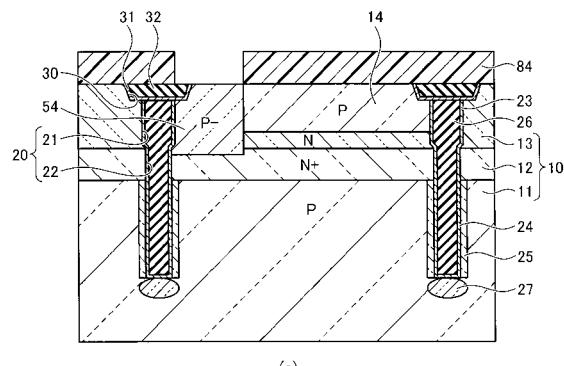

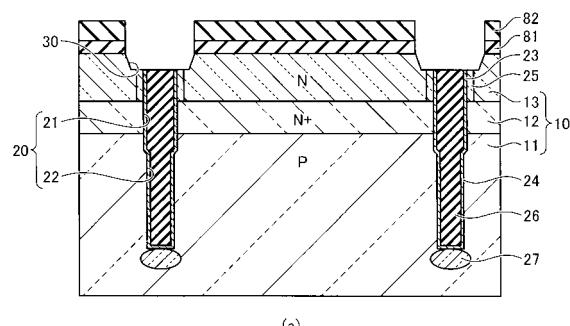

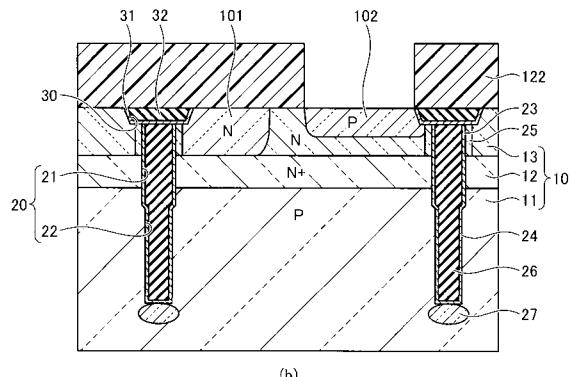

図4は、第2の実施の形態による半導体装置の構造を模式的に示す断面図である。ここでは、N+型埋め込み層12が形成されたP型のシリコン基板11のディープトレンチ2

50

0膜で区画された素子形成領域内に高周波半導体装置が形成された構造の半導体装置を例に挙げて説明する。

#### 【0046】

基板10としては、N+型埋め込み層12が所定の深さに形成されたP型のシリコン基板11が用いられる。この基板10は、第1の実施の形態と同様に、P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13とが形成された構造を有しているが、N型半導体層13の厚さが第1の実施の形態とは異なり、薄くなっている。たとえば、N型半導体層13の厚さ（基板10の表面からN+型埋め込み層12の上面までの距離）は、第1の実施の形態では5μm程度であるのに対して、第2の実施の形態では1μm程度である。

10

#### 【0047】

この基板10の所定の領域には、N+型埋め込み層12の下層のシリコン基板11まで到達する所定の深さのディープトレンチ20が、平面視上たとえば額縁状に形成されており、ディープトレンチ20にはシリコン酸化膜やシリコン膜などが埋め込まれ、ディープトレンチ膜26を形成している。このディープトレンチ膜26で区画される領域が素子形成領域となる。また、ディープトレンチ20の底部の下側のシリコン基板11には、素子形成領域を電気的に分離するP型不純物が導入されたP型拡散層27が形成される。

#### 【0048】

ディープトレンチ膜26の上部には、シャロートレンチ30が形成され、シャロートレンチ30の側面および底面には基板10を酸化して得られるシャロートレンチ側壁酸化膜31が形成され、シャロートレンチ30内にはシリコン酸化膜などからなるシャロートレンチ膜32が形成されている。

20

#### 【0049】

素子形成領域内には、高周波半導体装置としてNPNバイポーラトランジスタが形成されている。具体的には、素子形成領域内のN型半導体層13には、N+型埋め込み層12に達するN型のコレクタ領域101が形成されている。また、N型半導体層13の上部には、コレクタ領域101の形成位置とN型半導体層13によって分離されるP型のベース領域102が形成されている。また、ベース領域102の上部にはN型のエミッタ領域103が形成されている。そして、コレクタ領域101、ベース領域102およびエミッタ領域103上には、それぞれ、コレクタ電極111、ベース電極112およびエミッタ電極113が形成されている。

30

#### 【0050】

ここで、基板に形成されるディープトレンチ20について説明する。第2の実施の形態によるディープトレンチ20は、N+型埋め込み層12よりも下の位置を境に開口径が異なっている。この図では、N+型埋め込み層12よりも下のシリコン基板11内で開口径が異なる境界を有しており、この境界よりも上側で開口径が大きく、この境界以下で開口径が小さくなっている。以下では、ディープトレンチ20の開口径が大きい部分を第1のディープトレンチ21といい、開口径が小さい部分を第2のディープトレンチ22という。

40

#### 【0051】

第1のディープトレンチ21の側面を被覆するように、第1の側壁酸化膜23が形成され、第2のディープトレンチ22の側面と底面を被覆するように、第2の側壁酸化膜24が形成される。また、これらの側壁酸化膜23, 24で被覆されたディープトレンチ20内には、TEOS膜が埋め込まれている。さらに、第1のディープトレンチ21の周囲には、N+型埋め込み層12を拡散源としたN型拡散層25が形成される。しかし、第2のディープトレンチ22の周囲には、N型拡散層25は形成されていない。

#### 【0052】

このように、N+型埋め込み層12を拡散源とするN型拡散層25は、N+型埋め込み層12の下部のP型シリコン基板11には形成されないので、N+型埋め込み層12の下部では、空乏層の伸びが抑えられる。その結果、素子間耐圧は、第1の実施の形態に比し

50

て劣る。しかし、N+型埋め込み層12の上部では、空乏層の伸びが生じるので、素子内部の耐圧を向上させることができる。

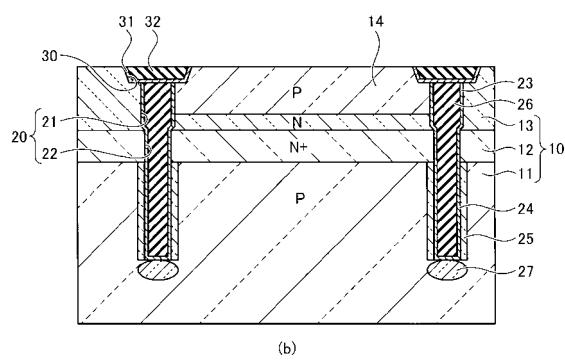

#### 【0053】

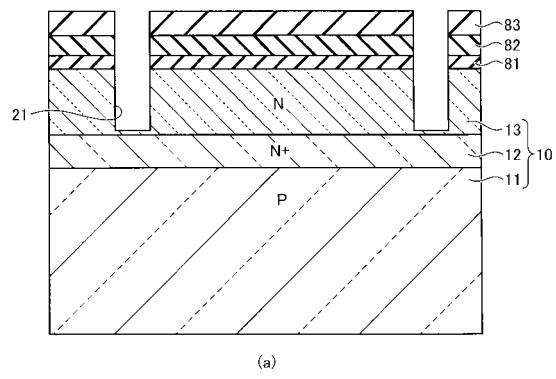

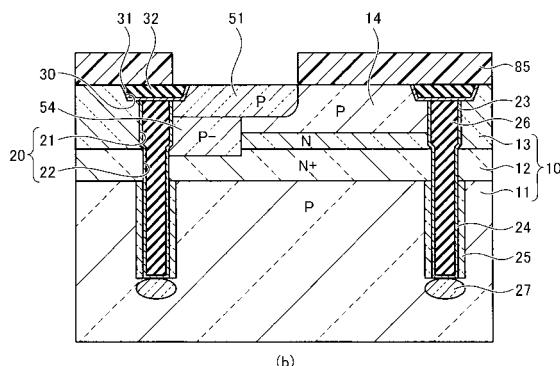

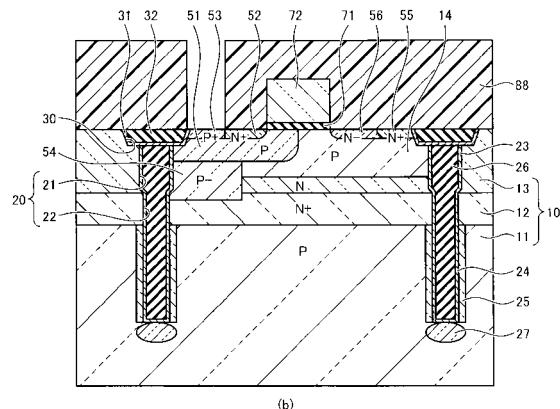

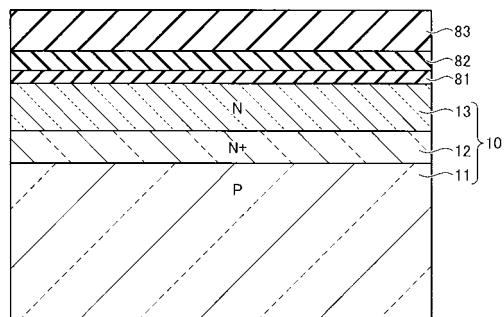

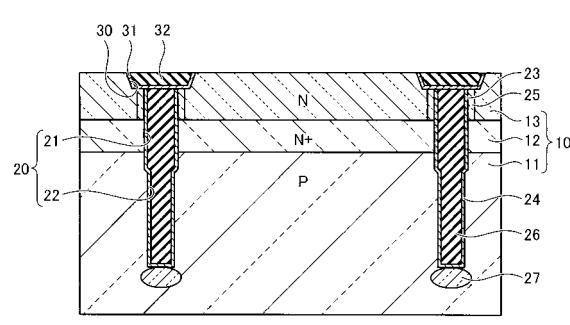

つぎに、このような構造の半導体装置の製造方法について説明する。図5-1～図5-7は、第2の実施の形態による半導体装置の製造方法の手順の一例を模式的に示す図である。まず、図5-1(a)に示されるように、基板10として、基板表面から1μmの深さにN+型埋め込み層12を形成したP型シリコン基板11を用いる。具体的には、P型シリコン基板11上に、N+型埋め込み層12および厚さ1μmのN型半導体層13が順に形成された基板10を用いる。この基板10上に、酸化技術を用いて15nmの厚さのSiO膜からなるバッファ酸化膜81を形成し、その後、LPCVD法によって200nmの厚さのSiN膜からなるストップ膜82を形成する。バッファ酸化膜81は、後工程において、素子形成領域の保護膜として使用し、ストップ膜82は、後工程の酸化膜のCMP処理時のストップ膜82として利用する。10

#### 【0054】

ついで、図5-1(b)に示されるように、ストップ膜82上の全面にCVD法によってSiO系のマスク膜83を成膜する。このマスク膜83は、後の工程でのディープトレンチ20を形成する際のRIEのマスクとして使用する。そのため、ディープトレンチ20を形成する際の溝をRIEでエッチングすることができる厚さに設定される。ここでは、1,000nmの厚さに堆積されるものとする。20

#### 【0055】

その後、図5-2(a)に示されるように、マスク膜83上に図示しないレジストを塗布し、リソグラフィ技術を用いて、ディープトレンチ20の形成領域を決定するためのパターニングを行う。ここでは、ディープトレンチ20の開口幅を0.7μmとする。ついで、パターニングされたレジストをマスクとして、マスク膜83、ストップ膜82およびバッファ酸化膜81を、RIE法を用いてN型半導体層13に達するまでエッチングする。アッシングによってレジストを除去した後、パターニングされたマスク膜83をマスクとして、N型半導体層13、N+型埋め込み層12およびP型シリコン基板11をRIE法によってエッチングする。このときの基板10のエッチング量は、N+型埋め込み層12の底部(下面)よりも深い深さとし、ここでは、基板10(N型半導体層13)の表面から2μmとする。これによって、第1のディープトレンチ21が形成される。なお、これによって、マスク膜83の厚さは200nm程度となる。30

#### 【0056】

ついで、図5-2(b)に示されるように、酸化技術によって、第1のディープトレンチ21の内面に露出しているシリコンを酸化して、第1のディープトレンチ21の側壁および底面に、50nmの厚さの第1の側壁酸化膜23を形成する。この第1の側壁酸化膜23は、素子分離のための絶縁膜として使用する。この第1の側壁酸化膜23を形成する時点で、第1のディープトレンチ21の内壁には、N+型埋め込み層12が露出しているので、酸化によってN+型埋め込み層12を構成するN型の不純物による外方拡散が発生する。その結果、第1のディープトレンチ21の側面の内部には、基板10の酸化によって第1の側壁酸化膜23が形成されるとともに、第1のディープトレンチ21の側面の外周には、N+型埋め込み層12を拡散源とするN型拡散層25が形成される。40

#### 【0057】

その後、図5-3(a)に示されるように、RIE法を用いて全面エッチングを行う。具体的には、RIE法によってエッチバックを行い、第1のディープトレンチ21の底部に形成された第1の側壁酸化膜23を除去し、第1のディープトレンチ21の側面にのみ第1の側壁酸化膜23をサイドウォールとして残す。

#### 【0058】

ついで、図5-3(b)に示されるように、200nm程度残されたマスク膜83をマスクとして、RIE法によって、自己整合的に第2のディープトレンチ22を第1のディープトレンチ21の下部に形成する。この第2のディープトレンチ22の深さは、第1の50

ディープトレンチ21の深さ(2μm)と合わせて、5μmとなるようにする。これによつて、第1のディープトレンチ21と第2のディープトレンチ22とによって構成されるディープトレンチ20が形成される。

#### 【0059】

第2のディープトレンチ22を形成した後、図5-4(a)に示されるように、酸化技術によつて、第2のディープトレンチ22の内面(側面と底面)に50nmの厚さの第2の側壁酸化膜24を形成する。N+型埋め込み層12は、第2のディープトレンチ22の形成によつて表面に露出していない状態であるので、この酸化処理では、N+型埋め込み層12を構成するN型の不純物による外方拡散は発生しない。つまり、第2のディープトレンチ22の内壁の側面には、N+型埋め込み層12を拡散源とするN型拡散層25は形成されず、基板10のプロファイルが維持され、シリコン酸化膜のみによつて構成される第2の側壁酸化膜24が形成される。その後、ディープトレンチ20の底部に、素子分離の耐圧を向上させるために、BなどのP型不純物のイオン注入を行つてP型拡散層27を形成する。

#### 【0060】

ついで、図5-4(b)に示されるように、ディープトレンチ20を形成したマスク膜83上の全面に、LPCVD法によつて500nmの厚さのTEOS膜を形成する。これによつて、マスク膜83上にTEOS膜が成膜されるとともに、ディープトレンチ20内にTEOS膜が埋め込まれる。その後、マスク膜83上に形成されたTEOS膜をCMP法によつて除去し、平坦化する。さらに、RIE法によつて、ストップ膜82をストップとして、TEOS膜をエッティングする。具体的には、TEOS膜をストップ膜82よりもエッティングされやすい条件で、ストップ膜82の表面が露出するまでエッティングを行う。これによつて、ディープトレンチ20内にTEOS膜からなるディープトレンチ膜26が形成される。

#### 【0061】

その後、ストップ膜82上にシャロートレンチ30加工のマスク材となる図示しないマスク材絶縁膜をたとえば100nmの厚さで形成し、マスク材絶縁膜上に図示しないレジストを塗布し、リソグラフィ技術によつてアクティブ領域を分離するシャロートレンチ30を形成するためのパターニングを行う。

#### 【0062】

ついで、図5-5(a)に示されるように、このパターニングしたレジストをマスクとして、マスク材絶縁膜、ストップ膜82およびバッファ酸化膜81をRIE法によつてエッティングし、シャロートレンチ形成用のパターンをマスク材絶縁膜に転写する。レジストをアッシングで除去した後、マスク材絶縁膜をマスクとして、基板10(N型半導体層13)をエッティングし、シャロートレンチ30を形成する。この深さは、0.3μmとする。なお、N+型埋め込み層12の上面から基板10の表面までは、1μm程度があるので、このシャロートレンチ30の深さは十分に浅い。このとき、ディープトレンチ20内のTEOS膜もシャロートレンチ30の加工時に同時にエッティングされるので、ディープトレンチ20の上部にもシャロートレンチ30が形成される。

#### 【0063】

ついで、図5-5(b)に示されるように、シャロートレンチ30の側壁を保護することを目的に酸化技術によつて50nmの厚さのシャロートレンチ側壁酸化膜31を形成する。その後、LPCVD法によつてシャロートレンチ30内をTEOS膜で埋め込む。成膜後に発生する段差は、CMP法によつてストップ膜82をストップとして平坦化する。CMP処理の後、不要となつたストップ膜82を、熱磷酸などを用いたウェットエッティング法によつて除去する。これによつて、ディープトレンチ膜26とシャロートレンチ膜32とによつて区画された基板10上の領域が素子形成領域となる。

#### 【0064】

この後、素子形成領域上への高周波半導体素子の形成が行われる。まず、図5-6(a)に示されるように、ディープトレンチ膜26を形成した基板10上の全面にレジスト1

10

20

30

40

50

21を塗布し、リソグラフィ技術によって、コレクタ領域101に開口部を有するようにパターニングを行う。そして、イオン注入法によって、基板10表面からN+型埋め込み層12にかけてPなどのN型不純物を導入し、活性化させてコレクタ領域101を形成する。

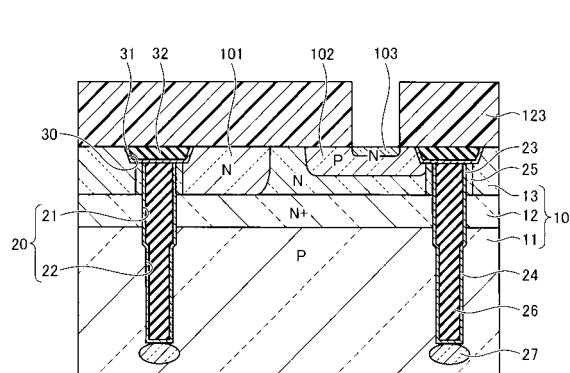

#### 【0065】

レジスト121をアッシングなどの方法で除去した後、図5-6(b)に示されるように、基板10上の全面にレジスト122を塗布し、ベース領域102に開口部を有するようにリソグラフィ技術によってパターニングを行う。そして、イオン注入法によって、基板10表面からN型半導体層13内の所定の深さにかけてBなどのP型不純物を導入し、活性化させ、ベース領域102を形成する。このとき、ベース領域102は、コレクタ領域101から所定の距離をおいて形成される。10

#### 【0066】

レジスト122をアッシングなどの方法で除去した後、図5-7に示されるように、基板10上の全面にレジスト123を塗布し、ベース領域102内に開口部を有するようにリソグラフィ技術によってパターニングを行う。そして、イオン注入法によって、基板10表面からベース領域102内の所定の深さにかけてPなどのN型不純物を導入し、活性化させ、エミッタ領域103を形成する。

#### 【0067】

レジスト123をアッシングなどの方法で除去した後、基板10上の全面に導電性材料膜を形成し、さらにその上にレジストを塗布する。リソグラフィ技術によって、コレクタ領域101、ベース領域102およびエミッタ領域103上にそれぞれコレクタ電極111、ベース電極112およびエミッタ電極113を形成するためのパターンを形成する。その後、RIE法によって、レジストをマスクとして導電性材料膜のエッチングを行う。これによって、図4に示されるように、コレクタ電極111、ベース電極112およびエミッタ電極113が、それぞれコレクタ領域101、ベース領域102およびエミッタ領域103上に形成される。以上によって、高周波半導体装置としてのNPNトランジスタが製造される。20

#### 【0068】

図6は、ディープトレンチの構成の違いによるコレクタ-基板間の容量の一例を示す図である。ここでは、最小寸法が0.13μmのデバイス製造技術を用いて形成された高周波半導体層値を用いて測定を行っている。また、コレクタ-基板間の容量は、コレクタ領域101-シリコン基板11間のPN接合による第1の容量と、ディープトレンチ20を介した第2の容量とに分類することができる。比較例3は、特許文献1のように、ディープトレンチ20の側壁に酸化膜を形成する際に、最終的な深さまでディープトレンチを形成し、N+型埋め込み層を露出させた状態で酸化処理を行って、N+型埋め込み層を拡散源とするN型拡散層がディープトレンチの側壁に沿って形成された場合を示している。30

#### 【0069】

第2の実施の形態によるディープトレンチ20では、N+型埋め込み層12よりも下部のN型拡散層25の形成が抑制されているので、空乏層の伸びが抑えられる。その結果、比較例3に比較して容量が低下し、高周波特性の改善が可能となるという効果を有する。40

#### 【0070】

なお、上述した説明では、P型の半導体基板にN+型埋め込み層12を有する場合を例に挙げて説明したが、逆にN型の半導体基板にP型の埋め込み層を有するものに、上述した実施の形態を適用してもよい。また、半導体基板としては、シリコン基板11に限られず、他のガリウムヒ素などの半導体基板を用いることができる。

#### 【符号の説明】

#### 【0071】

10...基板、11...P型シリコン基板、12...N+型埋め込み層、13...N型半導体層、14...P型ウェル、20...ディープトレンチ、21...第1のディープトレンチ、22...第2のディープトレンチ、23...第1の側壁酸化膜、24...第2の側壁酸化膜、25...N50

型拡散層、26…ディープトレンチ膜、30…シャロートレンチ、31…シャロートレンチ側壁酸化膜、32…シャロートレンチ膜、51，102…ベース領域、52…N+型ソース領域、53…P+型ソース領域、54…P-型拡散層、55…N+型ドレイン領域、56…ドリフト領域、61…ソース電極、62…ドレイン電極、71…ゲート絶縁膜、72…ゲート電極、101…コレクタ領域、103…エミッタ領域、111…コレクタ電極、112…ベース電極、113…エミッタ電極。

【図1】

【図2-1】

【図2-2】

【図2-3】

【図2-4】

【図2-5】

【図2-6】

(a)

(b)

【図2-7】

(a)

(b)

【図2-8】

(a)

(b)

【図3】

【図4】

【図5-1】

(a)

(b)

【図5-2】

(a)

【図5-3】

(a)

(b)

(b)

【図5-4】

(a)

(b)

【図5-5】

(a)

(b)

【図5-6】

(a)

(b)

【図5-7】

【図6】

---

フロントページの続き

(56)参考文献 特開平05-218064(JP,A)

特開昭59-056740(JP,A)

特開2006-108646(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

H01L 21/331

H01L 29/732

H01L 29/78

H01L 21/336