【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第3区分

【発行日】平成23年2月24日(2011.2.24)

【公表番号】特表2003-514299(P2003-514299A)

【公表日】平成15年4月15日(2003.4.15)

【出願番号】特願2001-536680(P2001-536680)

【国際特許分類】

G 06 F 12/08 (2006.01)

G 06 F 9/38 (2006.01)

【F I】

|        |       |         |

|--------|-------|---------|

| G 06 F | 12/08 | 5 0 3 E |

| G 06 F | 12/08 | 5 0 7 Z |

| G 06 F | 12/08 | 5 2 5 E |

| G 06 F | 9/38  | 3 5 0 A |

| G 06 F | 9/38  | 3 5 0 B |

【誤訳訂正書】

【提出日】平成22年12月21日(2010.12.21)

【誤訳訂正1】

【訂正対象書類名】明細書

【訂正対象項目名】全文

【訂正方法】変更

【訂正の内容】

【書類名】明細書

【発明の名称】インデックスおよび任意選択的ウェイ一致に基づいてデータをフォワードするストアバッファ

【特許請求の範囲】

【請求項1】各々が、(i)ストアメモリ動作のストアアドレスの少なくともインデックス部と、(ii)前記ストアメモリ動作がデータキャッシュ内でヒットしているかどうかを示すヒット表示と、(iii)前記ストアメモリ動作に対応するストアデータとをストアするように構成された複数のエントリを含むバッファと、

前記バッファに結合された回路とを含み、前記回路は、(i)前記データキャッシュを探索するロードメモリ動作のロードアドレスのインデックス部と、(ii)前記ロードメモリ動作が前記データキャッシュ内でヒットしているかどうかを示すロードヒット信号とを受けるように結合されるとともに、前記複数のエントリのうちの第1のエントリにストアされた前記インデックス部が前記ロードアドレスの前記インデックス部と一致しかつ前記第1のエントリ内の前記ヒット表示がヒットを示し、かつさらに前記ロードヒット信号がヒットを示すことに応じて、前記第1のエントリのストアデータが前記第1のエントリからフォワードされるように構成される、装置。

【請求項2】前記回路は、前記ロードアドレスの前記インデックス部が前記ストアアドレスの前記インデックス部と一致することに応じて、フォワード信号をアサートするように構成される、請求項1に記載の装置。

【請求項3】前記回路は、さらに前記ヒット表示がヒットを示すことに応じて、前記フォワード信号をアサートするように構成される、請求項2に記載の装置。

【請求項4】前記回路は、その後前記ロードヒット信号を受け、前記ロードヒット信号が前記ロードアドレスが前記データキャッシュ内でミスしていると示すことに応じて、フォワード取消信号をアサートするように構成される、請求項3に記載の装置。

【請求項5】前記複数のエントリの各々は、前記データキャッシュにおいて前記ストアメモリ動作がヒットするウェイを示すストアウェイ表示をストアするように構成され

る、請求項 4 に記載の装置。

【請求項 6】 前記回路はさらに、前記データキャッシュにおいて前記ロードメモリ動作がヒットするウェイを示すロードウェイ表示を受けるように結合されるとともに、前記第 1 のエントリにストアされた前記ストアウェイ表示が前記ロードウェイ表示と一致しないことに応じて前記フォワード取消信号をアサートするように構成される、請求項 5 に記載の装置。

【請求項 7】 前記複数のエントリの各々は、前記データキャッシュにおいて前記ストアメモリ動作がヒットするウェイを示すストアウェイ表示をストアするように構成される、請求項 1 に記載の装置。

【請求項 8】 前記回路はさらに、前記データキャッシュにおいて前記ロードメモリ動作がヒットするウェイを示すロードウェイ表示を受けるように結合されるとともに、さらに前記ロードウェイ表示および前記第 1 のエントリにストアされた前記ストアウェイ表示が一致することに応じて、前記ストアデータがフォワードされるように構成される、請求項 7 に記載の装置。

【請求項 9】 データキャッシュと、

前記データキャッシュに結合されたロード／ストアユニットとを含み、前記ロード／ストアユニットは、複数のエントリを含むバッファを含み、前記複数のエントリは各々、(i)ストアメモリ動作のストアアドレスの少なくともインデックス部と、(ii)前記ストアメモリ動作が前記データキャッシュ内でヒットしているかどうかを示すヒット表示と、(iii)前記ストアメモリ動作に対応するストアデータとをストアするように構成され、前記ロード／ストアユニットは、前記データキャッシュをロードアドレスを用いて探索し、それに応じて前記データキャッシュからヒット信号を受けるように構成されるとともに、前記ロードアドレスのインデックス部が前記複数のエントリの第 1 のエントリにストアされた前記インデックス部と一致していることに応じてかつさらに前記第 1 のエントリ内の前記ヒット表示がヒットを示し前記ヒット信号がヒットを示すことに応じて、ストアデータを、前記第 1 のエントリからフォワードすると決定するように構成される、プロセッサ。

【請求項 10】 前記ロード／ストアユニットは、前記データキャッシュに対しフォワードデータ信号をアサートするように構成され、前記データキャッシュは、前記ストアデータを前記データキャッシュから読出したキャッシュデータの代わりにフォワードするように構成される、請求項 9 に記載のプロセッサ。

【請求項 11】 前記ロード／ストアユニットは、前記ロードアドレスの前記インデックス部が前記第 1 のエントリにストアされたインデックス部と一致することに応じて、前記フォワードデータ信号をアサートするように構成される、請求項 10 に記載のプロセッサ。

【請求項 12】 前記ロード／ストアユニットは、さらに前記第 1 のエントリ内の前記ヒット表示がヒットを示すことに応じて前記フォワードデータ信号をアサートするように構成される、請求項 11 に記載のプロセッサ。

【請求項 13】 前記ロード／ストアユニットは、前記ヒット信号がミスを示すことに応じてフォワード取消信号をアサートするように構成される、請求項 12 に記載のプロセッサ。

【請求項 14】 前記フォワード取消信号を受けるように結合された 1 以上のリザベーションステーションをさらに含み、前記 1 以上のリザベーションステーションは、前記フォワード取消信号に応じて前記ロードのためにフォワードされた前記ストアデータを無効にするように構成される、請求項 13 に記載のプロセッサ。

【請求項 15】 前記複数のエントリの各々は、前記データキャッシュにおいて前記ストアメモリ動作がヒットするウェイを示すストアウェイ表示をストアするように構成される、請求項 13 に記載のプロセッサ。

【請求項 16】 前記データキャッシュは、前記データキャッシュにおいて前記ロードメモリ動作がヒットするウェイを示すロードウェイ表示を前記ロード／ストアユニット

に与えるように構成され、前記ロード／ストアユニットは、前記第1のエントリ内の前記ストアウェイ表示が前記ロードウェイ表示と一致しないことに応じて前記フォワード取消信号をアサートするように構成される、請求項15に記載のプロセッサ。

【請求項17】 前記複数のエントリの各々は、前記データキャッシュにおいて前記ストアメモリ動作がヒットするウェイを示すストアウェイ表示をストアするように構成される、請求項9に記載のプロセッサ。

【請求項18】 前記データキャッシュは、前記データキャッシュにおいて前記ロードメモリ動作がヒットするウェイを示すロードウェイ表示を前記ロード／ストアユニットに与えるように構成され、前記ロード／ストアユニットは、さらに前記第1のエントリにストアされた前記ストアウェイ表示が前記ロードウェイ表示と一致することに応じて、ストアデータを前記第1のエントリからフォワードすると決定するように構成される、請求項17に記載のプロセッサ。

【請求項19】 方法であって、

データキャッシュをロードアドレスを用いて探索するステップと、

前記ロードアドレスのインデックス部をバッファにストアされたストアアドレスのインデックス部と比較するステップと、

前記ストアアドレスに対応するストアデータを、前記ロードアドレスに対応するロードメモリ動作のためにフォワードするステップとを含み、前記フォワードするステップは、前記比較により前記ロードアドレスの前記インデックス部が前記ストアアドレスの前記インデックス部と一致していると判断されたことに応じてかつさらに前記ロードアドレスおよび前記ストアアドレス双方がデータキャッシュ内でヒットしていることに応じて行なわれる、方法。

【請求項20】 前記フォワードするステップは、前記比較により前記ロードアドレスの前記インデックス部が前記ストアアドレスの前記インデックス部と一致していると判断されたことに応じて、フォワードデータ信号をアサートするステップを含む、請求項19に記載の方法。

【請求項21】 前記アサートするステップは、さらに前記ストアアドレスが前記データキャッシュにおいてヒットしていることに応じて行なわれる、請求項20に記載の方法。

【請求項22】 前記フォワードするステップはさらに、前記ロードアドレスが前記データキャッシュ内でミスしていることに応じてフォワード取消信号をアサートするステップを含む、請求項21に記載の方法。

【請求項23】 前記方法はさらに、前記バッファにストアされたストアウェイ表示を前記ロードアドレスに対応するロードウェイ表示と比較するステップを含み、前記ストアウェイ表示は、前記データキャッシュにおいて前記ストアアドレスがヒットするウェイを示し、前記ロードウェイ表示は、前記データキャッシュにおいて前記ロードアドレスがヒットするウェイを示し、前記方法はさらに、前記比較によりストアウェイ表示が一致しないと判断されたことに応じて、前記フォワード取消信号をアサートするステップを含む、請求項22に記載の方法。

【請求項24】 前記方法はさらに、前記バッファにストアされたストアウェイ表示を前記ロードアドレスに対応するロードウェイ表示と比較するステップを含み、前記ストアウェイ表示は、前記データキャッシュにおいて前記ストアアドレスがヒットするウェイを示し、前記ロードウェイ表示は、前記データキャッシュにおいて前記ロードアドレスがヒットするウェイを示し、前記方法はさらに、さらに前記比較によりストアウェイ表示が一致すると判断されたことに応じて、前記ストアデータをフォワードするステップを含む、請求項19に記載の方法。

【発明の詳細な説明】

【0001】

【発明の分野】

本発明は、プロセッサの分野に関し、より特定的にはデータをストアバッファから従属

するロードのためにフォワードすることに関する。

#### 【0002】

##### 【関連技術の説明】

プロセッサは典型的に、ストアメモリ動作をストアするためのバッファを用いる。このストアメモリ動作は、実行済みである（たとえばストアアドレスが既に生成されている、ストアデータがあるかもしれない）が、まだ投機的であるためメモリ（またはこのプロセッサが用いるデータキャッシュ）に記憶させる準備が整っていないものである。本明細書で用いている「メモリ動作」という用語は、プロセッサおよびメモリ間のデータ転送（この転送はキャッシュ内で行なわれる可能性がある）を指定する動作を意味する。ロードメモリ動作は、メモリからプロセッサへのデータ転送を指定し、ストアメモリ動作はプロセッサからメモリへのデータ転送を指定する。本明細書においては、ロードメモリ動作をより簡潔に「ロード」と呼ぶこともあり、同様に、ストアメモリ動作を「ストア」と呼ぶこともある。メモリ動作は、プロセッサが用いる命令セット次第で、メモリオペランドに直接アクセスして定められた機能（たとえば算術演算、論理など）を果たすための命令内で暗示されていることもあり、データ転送のみを行なう明示命令のこともある。一般的に、メモリ動作は、このメモリ動作の1以上のオペランドから生成されたアドレスを介して関係する記憶場所を指定する。本明細書ではこのアドレスのことを一般的に「データアドレス」と呼ぶ、または、（対応するメモリ動作がロードであれば）ロードアドレスと呼び、（対応するメモリ動作がストアであれば）ストアアドレスと呼ぶ。他方、命令そのもののメモリ内での場所を示すアドレスは「命令アドレス」と呼ぶ。

#### 【0003】

ストアは、後に続くロードが実行される際にバッファ内で待ち行列に入れられていることがある、そのため、典型的にプロセッサはバッファを検査して、ロードが読出す1以上のバイトを更新するストアがバッファ内で待ち行列に入れられているかどうか判断する（すなわちこのロードがストアに従属するのかまたはストアに「ヒット」するのか判断）。一般的には、ロードアドレスをストアアドレスと比較してロードがストアにヒットしているかどうか判断する。ヒットが検出されれば、このロードのためにストアデータをキャッシュデータの代わりにフォワードする。したがって、ヒットを、キャッシュからデータにアクセスするのに要する時間と同じまたはそれより短い時間で検出することが望ましい。

#### 【0004】

ロードの待ち時間（たとえば、あるロードを実行してからこのロードによって読出されたデータを使用できるようになるまでの時間）を最短にすることは、多くのプロセッサの性能にとって重要である。あいにく、アドレスの比較は、アドレスのビット数が比較的多い（たとえば32ビット、または32ビットを超えて64ビットまでが一般的になりつつある）ため、時間のかかる作業である。したがって、ロードがバッファ内のストアにヒットしているかどうか判断するのに要する時間を短縮化することが、プロセッサの性能を高めることになる。なぜなら、この短縮化がロードの待ち時間の短縮になり得るからである。その代わりとしては、アドレスを比較するのにかかる時間が減少すれば、所与のサイクル時間および所与のロード待ち時間に対するタイミングの制約を満たしやすくなる。

#### 【0005】

仮想アドレス指定およびアドレス変換を用いると、ロードアドレスをバッファ内のストアアドレスと照合する間に経過する時間を短縮するというさらなる問題が生じ得る。仮想アドレス指定を用いる場合、ロードおよびストアの実行により生成されるデータアドレスは、（たとえばページング変換方式によって）物理アドレスに変換される仮想アドレスである。複数の仮想アドレスが所与の物理アドレスに対応しているかもしれないため（「別名（エイリアス）」と呼ばれる）、ロードおよびストアの物理データアドレスを比較して確実にバッファから正確な転送を行なう（または行なわない）ようにする。不都合なことにロードの物理アドレスは、典型的に変換索引バッファ（TLB）から生成されるため、キャッシュアクセスがほぼ完了するまで利用できないことが多く、バッファ内のストアにヒットしていることを迅速だが正確なやり方で検出するという問題がさらに悪化する。

**【 0 0 0 6 】****【発明の概要】**

上記の問題は主として、本明細書で説明するようにストアデータをロードのためにフォワードする装置により解決される。この装置は、ストアメモリ動作に対応する情報をストアするように構成されたバッファと、バッファにおいて示されたストアの1つにヒットするロードを検出する回路とを含む。より具体的には、この回路は、ロードアドレスのインデックス部をバッファにストアされているストアアドレスのインデックス部と比較する。これらのインデックスが一致しかつロードおよびストア双方がデータキャッシュ内でヒットしていれば、ロードおよびストアは同じキャッシュラインにアクセスしている。このキャッシュライン内の1以上のバイトがストアにより更新されロードにより読み出されるならば、ストアデータはそのロードのためにフォワードされる。好都合なことに、この比較的小規模のロードおよびストアインデックス比較は速やかに完了する。加えて、(すべてではないにしても)ほとんどのインデックスが典型的には物理(変換されていない)ビットなので、比較は、変換されているロードアドレスよりも前に実施することができ、比較の正確性に大きな影響はない。

**【 0 0 0 7 】**

ある実施例では、上記回路は、ロードおよびストアインデックスが一致しかつストアがデータキャッシュ内でヒットしていれば、データを投機的にフォワードする。次に、ロードがキャッシュ内でヒット/ミスしていると判断されると、このフォワードィングが、ロードのヒット/ミス表示を用いて検査される。セットアソシアティブの実施例では、ロードのヒットのウェイをストアのヒットのウェイと比較してフォワードィングの正確度をさらに検査する。

**【 0 0 0 8 】**

概して、ある装置が意図されている。この装置は、バッファとバッファに結合された回路とを含む。バッファは複数のエントリを含み、複数のエントリは各々、(i)ストアメモリ動作のストアアドレスの少なくともインデックス部と、(ii)ストアメモリ動作がデータキャッシュ内でヒットしているかどうか示すヒット表示と、(iii)このストアメモリ動作に対応するストアデータとをストアするように構成される。回路は、(i)データキャッシュを検索するロードメモリ動作のロードアドレスのインデックス部と、(ii)ロードメモリ動作がデータキャッシュ内でヒットしているかどうか示すロードヒット信号とを受けるように結合される。この回路は、ストアデータを、複数のエントリのうち第1のエントリから、第1のエントリにストアされたインデックス部がロードアドレスのインデックス部に一致することに応じて、かつさらに、第1のエントリのヒット表示がヒットを示しロードヒット信号がヒットを示すことに応じて、フォワードするように構成される。

**【 0 0 0 9 】**

さらに、データキャッシュとデータキャッシュに結合されたロード/ストアユニットとを含むプロセッサが意図されている。ロード/ストアユニットは、複数のエントリを含むバッファを備え、複数のエントリは各々、(i)ストアメモリ動作のストアアドレスの少なくともインデックス部と、(ii)ストアメモリ動作がデータキャッシュ内でヒットしているかどうか示すヒット表示と、(iii)このストアメモリ動作に対応するストアデータとをストアするように構成される。ロード/ストアユニットは、ロードアドレスを用いてデータキャッシュを探索し、それに応じてデータキャッシュからヒット信号を受けるように構成される。加えて、ロード/ストアユニットは、ストアデータを、複数のエントリのうち第1のエントリから、ロードアドレスのインデックス部が第1のエントリにストアされたインデックス部に一致することに応じて、かつさらに、第1のエントリのヒット表示がヒットを示しヒット信号がヒットを示すことに応じて、フォワードすると決定する。

**【 0 0 1 0 】**

さらに、ある方法が意図されている。データキャッシュはロードアドレスを用いて検索される。ロードアドレスのインデックス部がバッファにストアされたストアアドレスのインデックス部と比較される。ストアアドレスに対応するストアデータが、ロードアドレス

に対応するロードメモリ動作のためにフォワードされる。このフォワーディングは、比較によりロードアドレスのインデックス部がストアアドレスのインデックス部と一致すると判断されたことに応じて、かつさらに、ロードアドレスおよびストアアドレス双方がデータキャッシュ内でヒットしていることに応じて、行なわれる。

#### 【 0 0 1 1 】

本発明の上記以外の目的および利点は、以下の詳細な説明を読み添付の図面を参照することによって明らかになるであろう。

#### 【 0 0 1 2 】

本発明には種々の変形および代替形が可能であり、本発明の具体的な実施例が図面において例示され本明細書において詳細に説明されている。しかしながら、図面およびその詳細な説明は本発明を開示された特定の形態に限定することを意図したものではなく、反対に、前掲の特許請求の範囲において定められた本発明の精神および範囲に含まれるすべての変形、等価物および代替形を包含することを意図している。

#### 【 0 0 1 3 】

##### 【好ましい実施例の詳細な説明】

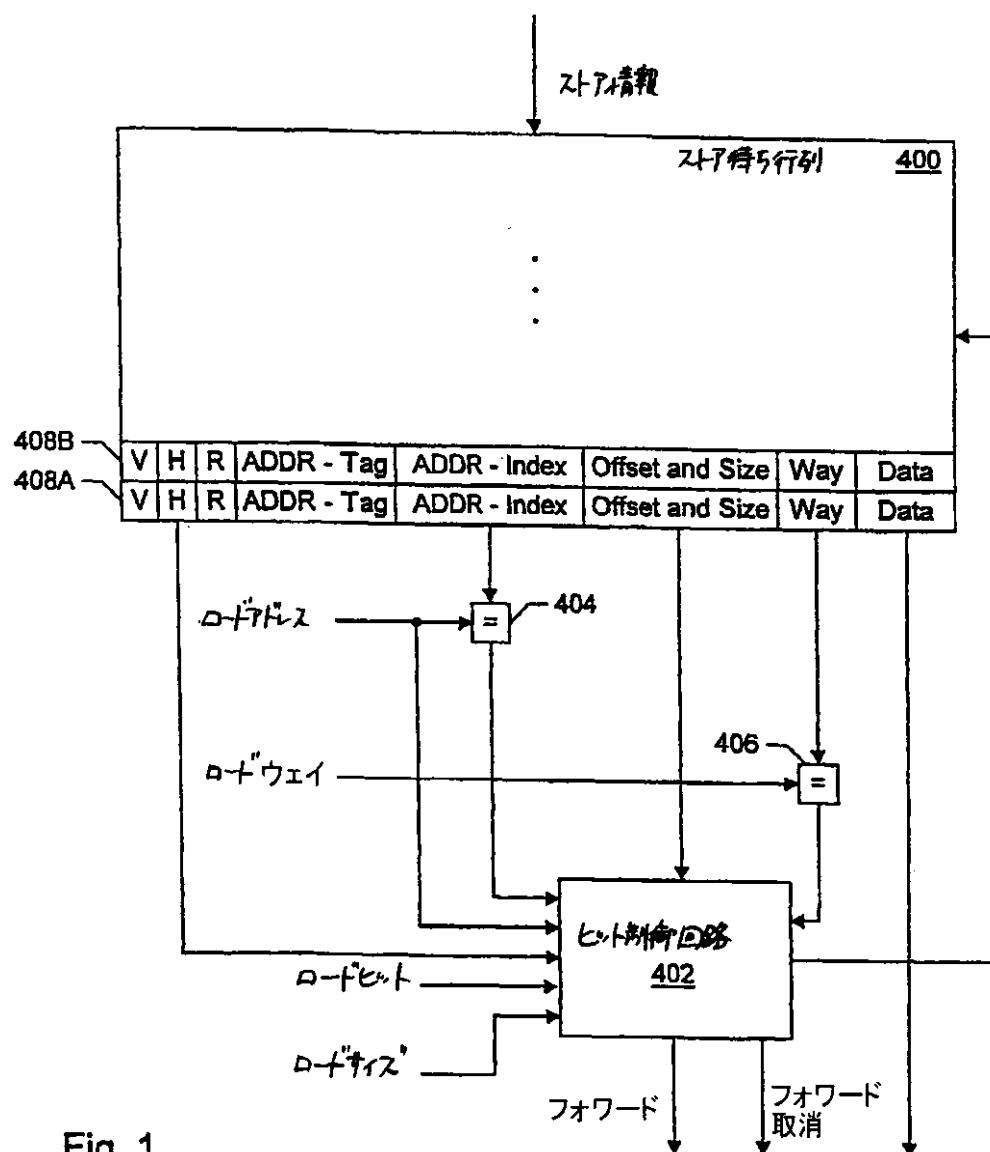

次に図1を参照して、ストア待ち行列400、ヒット制御回路402ならびに比較器404および406の一実施例のブロック図が示される。この図1に示した装置は、ストアに関連する情報をストアがデータキャッシュ（および／またはメモリ）に与えられるまで保持するデータキャッシュを有するプロセッサにおいて用いることができ、さらに、ストアにヒットするロードを検出しストアデータをストア待ち行列400からロードのためにフォワードするのに用いることができる。他の実施例も可能であり意図されている。図1の実施例では、ストア待ち行列400は、実行されたストアに対応するストア情報を受けるように結合され、さらにヒット制御回路402ならびに比較器404および406に結合される。比較器404および406はさらに、ヒット制御回路402に結合される。ヒット制御回路402は、フォワード信号およびフォワード取消信号を与えるように結合される。

#### 【 0 0 1 4 】

概して、図1に示した装置は、ストア待ち行列400において示されているストアにヒットするロードを検出し、そのロードのためにストアに対応するデータを（データキャッシュからのキャッシュデータの代わりに）ストア待ち行列400からフォワードするように構成される。この装置は、ロードアドレス全体をストア待ち行列400にストアされたストアアドレスと比較するのではなく、ロードアドレスのインデックス部（「ロードインデックス」）をストアアドレスのインデックス部（「ストアインデックス」）と比較する。アドレスの一部を比較するため、この比較はより速やかに行なわれ、結果として、ロードがストア待ち行列400に示されたストアにヒットするかどうか判断するのに要する時間が短縮される。ロードおよびストア双方がデータキャッシュにおいてヒットしかつインデックス部が一致すれば、ロードおよびストアはデータキャッシュ内の同じキャッシュラインにアクセスしている。データキャッシュがダイレクトマッピングの場合、ロードおよびストアは同じキャッシュラインにアクセスしている。データキャッシュがセットアソシアティブの場合、ストアのヒットのウェイおよびロードのヒットのウェイを比較して、ロードおよびストアが同じキャッシュラインにアクセスしているかどうか判断することができる。ロードがヒットでありストアがミスである（またはその逆）の場合、ロードおよびストアは同じキャッシュラインにアクセスしていない（インデックス部はどれも仮想でないと仮定）。したがって、ロードはストアにヒットしておらず、ストアデータをストア待ち行列400からフォワードする必要はない。ロードおよびストア双方がミスの場合、ロードおよびストアは同じキャッシュラインにアクセスしているかもしれない。しかしながら、データキャッシュは、ロードがミスの場合データをキャッシュからロードのためにフォワードしておらず、したがって、ストアデータをストア待ち行列400からフォワードする必要はない。ロードを、データキャッシュがロードが読み出したキャッシュラインで満たされた後に（または満たすデータをキャッシュに書込んでいる間に）再び試みてもよく

、そのキャッシュラインへのストアがキャッシュを満たす間にヒットとなる可能性がある。こうして、再度ロードを試みる間に、ロードがストアにヒットすることが検出される可能性がある。

#### 【 0 0 1 5 】

典型的に、仮想アドレスから物理アドレスへの変換は、ページの粒度に対して実施される。最下位アドレスビットは、ページに対するオフセットを形成しこの変換では変更されない。最上位アドレスビットは仮想から物理に変換される。たとえば、32ビットの仮想アドレスおよび4キロバイトのページサイズを用いた実施例では、下位12ビットがページオフセットであり上位20ビットが変換される。これ以外のページサイズが意図されている。典型的には、アドレスのインデックス部の（すべてではないにしても）ほとんどの部分は、ページオフセット内にあるため、仮想から物理へのアドレス変換中に変更されることはない。したがって、ロードがストアにヒットするかどうか検出する際の正確度に対するエイリアスの影響を、減じるまたは排除することができる。さらに、仮想ロードアドレスを比較において用い、物理ストアアドレス（メモリなどに与えるために用いられる）をストア待ち行列400にストアしてもよい。インデックス部の1以上のビットが仮想-物理変換において変更されるならば、仮想ビットもストアすればよい。したがって、仮想ロードアドレスと比較するために仮想ストアアドレスをストアするのに追加する記憶量は最小でよい（たとえば変換されかつインデックスの一部でもあるビット）。

#### 【 0 0 1 6 】

図1に示した実施例を、セットアソシアティブデータキャッシュを用いたプロセッサで使用してもよい。ダイレクトマッピングデータキャッシュを用いる実施例では、ウェイ表示および関連する比較器はない。より具体的には、ストア待ち行列400が複数のエントリを含む。たとえば、図1にはエントリ408Aおよび408Bが示されており、ストア待ち行列400はさらなるエントリ（図示せず）を含み得る。各エントリ408は、ストアメモリ動作に対応する情報をストアするように構成されている。ストア待ち行列400は、ストアに対応する情報をこのストアの実行の際に受取り、この情報を、ストアがリタイア（終了処理）されてデータキャッシュおよび/またはメモリに与えられてしまうまで保持する。ここに示されている実施例では、ひとつのエントリは、有効表示（V）、ヒット表示（H）、リタイア表示（R）、アドレスタグ部（ADDR - Tag）、アドレスインデックス部（ADDR - Index）、オフセットおよびサイズ情報（Offset and Size）、ウェイ表示（Way）、およびデータ（Data）を含む。有効表示は、エントリが有効かどうか（たとえばストアがエントリ内の情報で表わされているかどうか）示す。ヒット表示は、ストアがデータキャッシュ内でヒットしているかどうか示す。リタイア表示は、ストアがリタイアされている（したがって、データキャッシュおよび/またはメモリに与えるのに適切である）かどうか示す。この有効、ヒットおよびリタイア表示に対しては適切な表示を用いればよい。たとえば、各表示は、セットされると一方の状態を示しクリアされると他方の状態を示すビットを含み得る。以下の説明（下記図5および6に示された実施例の説明を含む）では、有効、ヒットおよびリタイア表示のことを、有効、ヒットおよびリタイアビットと呼ぶ。しかしながら、他の実施例でこの符号化を逆にしたり他の符号化を用いることもある。アドレスタグ部はタグとしてデータキャッシュにストアされるアドレスの部分であり、アドレスインデックス部はインデックスとしてデータキャッシュが用いる部分である。オフセットおよびサイズ情報は、ストアにより更新されてキャッシュライン内にあるバイトを示す。ウェイ表示は、ヒットビットがセットされた場合（ストアのヒットを示す）、（セットアソシアティブの実施例において）ストアがデータキャッシュでヒットするウェイを示す。最後に、ここでのデータは、データキャッシュおよび/またはメモリに与えられるストアデータである。

#### 【 0 0 1 7 】

比較器404は、ストア待ち行列400の各エントリからストアインデックスを受けるように結合され、かつ、実行されているロードのロードインデックスを受けるように結合される。比較器404は、ロードおよびストアインデックスを比較し、一致が検出される

とヒット制御回路 402 に対し信号をアサートする。比較器 404 はこのように、ストア待ち行列 400 の各エントリに対する比較器回路を表わしており、各比較器回路が出力信号をヒット制御回路 402 に与える。同様に、比較器 406 はストア待ち行列 400 の各エントリにストアされたウェイ表示を受けるように結合され、かつ、ロードウェイ表示を受けるように結合される。比較器 406 は、ロードおよびストアのウェイ表示を比較し、一致が検出されるとヒット制御回路 402 に対し信号をアサートする。比較器 406 はこのように、ストア待ち行列 400 の各エントリに対する比較器回路を表わしており、各比較器回路が出力信号をヒット制御回路 402 に与える。なお、所望されれば比較器 404 および 406 を連想記憶装置 (CAM) 構成としてストア待ち行列 400 に組み込んでもよい。

#### 【0018】

ヒット制御回路 402 は、各エントリからのヒットビットおよび実行されているロードについてのヒット信号を受けるように結合される。ロードインデックスおよびストア待ち行列 400 に示されたストアのストAINDEX およびストアはヒットであり、ロードおよびこのストアはヒットであり、ロードおよびこのストアのウェイ表示は一致し、ヒット制御回路 402 により、データがストア待ち行列 400 からロードのためにフォワードされる。より具体的には、ヒット制御回路 402 は、ストア待ち行列 400 に、ヒットしているエントリのエントリ番号の表示で知らせ、ストア待ち行列 400 は、このエントリからのデータを、データキャッシュからのキャッシュデータの代わりにフォワードするために与える。

#### 【0019】

なお、ロードアドレスは、ロードによるデータキャッシュの探索の開始時に、比較のために利用でき、ロードヒット信号は、データキャッシュの探索の終了近くまで（たとえばロードアドレスが変換されてキャッシュタグと比較された後）決定されない。さらに、ロードのウェイ表示も、ヒット信号が決定されるまで決定されない。したがって、この実施例において、ヒット制御回路 402 は、ロードインデックスおよびストAINDEX の一致、ならびに、ストアのヒットビットがストアがヒットであると示すことに応じて、ストア待ち行列 400 からのデータフォワードを合図する（かつストア待ち行列 400 にデータをフォワードさせる）ように構成される。ヒット制御回路 402 は、図 1 に示したフォワード信号をアサートしてデータフォワーディングを知らせる。次に、ロードのために、ヒット信号およびウェイ表示を求める。ヒット制御回路 402 は、ロードがストアにヒットしていることを、ロードウェイ表示をストアウェイ表示と比較しヒット信号がアサートされてヒットを示していることを確認することにより、確かめる。ウェイ表示が一致しかつロードのヒット信号がヒットを示しているならば、ヒット制御回路 402 は、フォワーディングが正しいと判断する。他方、フォワーディングが誤りである場合、ヒット制御回路 402 は、図 1 に示したフォワード取消信号をアサートして、フォワードされたストアデータを受けたプロセッサの部分に、フォワードが誤りであると知らせる。ある具体的な実施例では、データのフォワードを第 1 のクロックサイクルで行ない、フォワードの取消しを第 1 のクロックサイクルに続く第 2 のクロックサイクルで行なう。

#### 【0020】

上記は、図 1 に示した装置の、1 つのロードが実行される場合の動作について説明したものである。しかしながら、複数のロードが同時に実行される実施例も意図されている。上記のように各ロードを同時に処理することができる。

#### 【0021】

ロードおよびストAINDEX (ならびにデータアドレスのヒットウェイ) を比較して、ロードおよびストアが同じキャッシュラインにアクセスしていると判断する。さらなる情報を用いて、ロードが読み出した少なくとも 1 バイトがストアにより更新されていると判断する。たとえば、アドレスのオフセット部分ならびにロードおよびストアに影響されるサイズ (すなわちバイト数) を用いることができる。オフセットおよびサイズ情報は、設計上の選択によって、何らかの適切なフォーマットで与えて符号化することができる。たとえば、オフセットおよびサイズ情報は、バイトイネーブルマスクを含み、ここで各バ

イトの 1 ビットがキャッシュラインにある。このビットがセットされると、対応するバイトがアクセスされる。ロードおよびストアに対するバイトイネーブルマスクの各ビットの論理和をとり、このバイトがロードにより読出されかストアにより書込まれるかどうか判断する。バイトイネーブルマスクを、キャッシュラインの一部のために生成してもよく（たとえばキャッシュが 1 キャッシュラインあたり複数のバンクを有する場合）、バンク選択のために用いるオフセットの部分を、バイトイネーブルマスクビットの論理和に加え、ロードおよびストアアドレス間で比較する。ロードおよびストアアドレスのオフセットの部分を、インデックス比較に加えて、比較器 404 を用いて比較する。ヒット制御回路 402 は、（上記のインデックス比較、ヒットビットおよびウェイ表示に加えて）オフセットおよびサイズ情報を用いて、ストア待ち行列 400 にストアされたデータをロードのためにフォワードするかどうか判断する。

#### 【 0022 】

なお、ロードの実行中にストア待ち行列 400 の 2 以上のエントリがヒットする場合がある。ヒット制御回路 402 は、ヒットしているエントリに対応するストアのうち、プログラム順序で最も新しい（最後に実行された）ストアを求め、データをそのエントリからフォワードする。また、ロードが読出した 1 以上のバイトを、ロードがヒットしたストアが、ロードが読出した 1 以上の他のバイトについては更新しない場合がある。その場合、データキャッシュは、ストアデータをキャッシュデータと組合せて、ロードが読出したバイトを与える。複数のストアが、あるロードが読出したバイトのうち異なるバイトを与える場合、このロードをリタイアして再び試みる。複数のストアのうち 1 以上をリタイアしてデータキャッシュに与え、これらストアにより更新されロードによって読出されたバイトを、データキャッシュから与える。その代わりとして、図 1 の装置は、異なるストアからのバイトを組合せてロードデータを与えてよい。所望に応じ、これ以外の実施例において上記のモデルを他のやり方で処理してもよい。

#### 【 0023 】

なお、ここで示されている比較器 406 は、ストア待ち行列 400 にストアされたウェイ表示をロードのウェイ表示と比較しているが、これに代わる実施例では、ロードのためにデータをフォワードするのに用いるエントリからウェイ表示を読出し（このフォーディングがインデックス比較およびデータキャッシュにおけるストアヒットに基づく場合）、読出されたウェイ表示をロードウェイ表示と比較してロードおよびストアが同じウェイでヒットしているかどうか検査する。

#### 【 0024 】

本明細書で用いているアドレスのインデックス部（または簡潔に「インデックス」）は、このアドレスに対応するデータをストアするのに適切な 1 以上のキャッシュエントリを選択するために用いる部分である。加えて、データアドレスは、データキャッシュ内で、このデータアドレスが識別するデータがそのデータキャッシュにストアされている場合に「ヒットする」。データアドレスは、データキャッシュ内で、このデータアドレスが識別するデータがそのデータキャッシュにストアされている場合に「ミスする」。さらに、セットアソシティブデータキャッシュは、所与のインデックスに対応するキャッシュラインをストアするのに適切な複数のキャッシュエントリを含む。各エントリはそのインデックスに対しては異なるウェイである。

#### 【 0025 】

図 2 は、ロード／ストアユニット内でストア待ち行列 400 を用いるプロセッサの実施例を示す。その代わりとして、このプロセッサおよびロード／ストアユニットは、図 4-6 に関連して説明する待ち行列構成を用いてよい。図 1 の装置または図 4-6 の実施例を用いるこれ以外のプロセッサの実施例も意図されている。

#### 【 0026 】

##### プロセッサ概観

次に図 2 を参照して、プロセッサ 10 の一実施例のブロック図が示される。これ以外の実施例が可能であり意図されている。図 2 に示すように、プロセッサ 10 は、プリフェッ

チ / プリデコードユニット 12 と、分岐予測ユニット 14 と、命令キャッシュ 16 と、命令アライメントユニット 18 と、複数のデコードユニット 20A - 20C と、複数のリザベーション（保留、reservation）ステーション 22A - 22C と、複数の機能ユニット 24A - 24C と、ロード / ストアユニット 26 と、データキャッシュ 28 と、レジスタファイル 30 と、リオーダ (reorder) バッファ 32 と、MR ROM ユニット 34 と、バスインターフェイスユニット 37 を含む。本明細書において特定の参照番号およびこれに続く文字で示されている構成要素はまとめて、参照番号のみを用いて表わす。例として、デコードユニット 20A - 20C はまとめてデコードユニット 20 と示す。

#### 【 0027 】

プリフェッч / プリデコードユニット 12 は、バスインターフェイスユニット 37 から命令を受けるように結合され、かつさらに、命令キャッシュ 16 および分岐予測ユニット 14 に結合される。同様に、分岐予測ユニット 14 は、命令キャッシュ 16 に結合される。さらに、分岐予測ユニット 14 は、デコードユニット 20 および機能ユニット 24 に結合される。命令キャッシュ 16 はさらに、MR ROM ユニット 34 および命令アライメントユニット 18 に結合される。命令アライメントユニット 18 は、デコードユニット 20 に結合される。各デコードユニット 20A - 20C は、ロード / ストアユニット 26 およびリザベーションステーション 22A - 22C にそれぞれ結合される。リザベーションステーション 22A - 22C はさらに、それぞれの機能ユニット 24A - 24C に結合される。加えて、デコードユニット 20 およびリザベーションステーション 22 は、レジスタファイル 30 およびリオーダバッファ 32 に結合される。機能ユニット 24 はまた、ロード / ストアユニット 26 、レジスタファイル 30 およびリオーダバッファ 32 に結合される。データキャッシュ 28 は、ロード / ストアユニット 26 およびバスインターフェイスユニット 37 に結合される。バスインターフェイスユニット 37 はさらに、L2キャッシュへのL2インターフェイスおよびバスに結合される。最後に、MR ROM ユニット 34 は、デコードユニット 20 に結合される。

#### 【 0028 】

命令キャッシュ 16 は、命令をストアするために設けられた高速キャッシュメモリである。命令は、命令キャッシュ 16 からフェッчされデコードユニット 20 にディスパッチされる。ある実施例において、命令キャッシュ 16 は、64キロバイトまでの命令を、64のバイトライン（1バイトは8バイナリビットを含む）を有する2ウェイセットアソシアティブ構成内にストアするように構成される。その代わりとして、これ以外の所望の構成およびサイズを用いてもよい。例として、命令キャッシュ 16 を、フルアソシアティブ、セットアソシアティブまたはダイレクトマッピング構成として実現してもよい。

#### 【 0029 】

命令は、プリフェッч / プリデコードユニット 12 により、命令キャッシュ 16 にストアされる。命令を、要求される前に、命令キャッシュ 16 からプリフェッч方法に従いプリフェッчしてもよい。プリフェッч / プリデコードユニット 12 は、種々のプリフェッч方法を用いることができる。プリフェッч / プリデコードユニット 12 は、命令を命令キャッシュ 16 に転送する際、命令の各バイトにつき3つのプリデコードビットすなわちスタートビット、エンドビットおよび機能ビットを生成する。プリデコードビットは、各命令の境界を示すタグを形成する。プリデコードタグは、以下でより具体的に説明するように、所与の命令をデコードユニット 20 が直接デコードできるかどうか、または、命令をMR ROM ユニット 34 が制御するマイクロコード手続を呼出すことにより実行するかどうかといった、さらなる情報も伝える。さらに、プリフェッч / プリデコードユニット 12 を、分岐命令を検出し分岐命令に対応する分岐予測情報を分岐予測ユニット 14 にストアするように構成してもよい。これ以外の実施例において何らかの適切なプリデコード方法を用いてもよい。

#### 【 0030 】

次に、可変バイト長命令セットを用いるプロセッサ 10 のある実施例においてプリデコードタグを符号化することについて説明する。可変バイト長命令セットは、異なる命令が

異なる数のバイトを占める命令セットである。プロセッサ10の一実施例で用いる可変バイト長命令セットの一例として×86命令セットを挙げる。

#### 【0031】

ここで例として挙げる符号化では、所与のバイトがある命令の第1のバイトである場合、このバイトに対しスタートビットがセットされる。このバイトが命令の最終バイトである場合、このバイトに対しエンドビットがセットされる。デコードユニット20が直接デコードできる命令のことを「高速経路」命令と呼ぶ。残りの×86命令のことを、ある実施例ではMRROM命令と呼ぶ。高速経路命令については、機能ビットは、命令に含まれる各プレフィックスバイトに対しセットされ、これ以外のバイトに対してはクリアされる。その代わりとして、MRROM命令については、機能ビットは、各プレフィックスバイトに対しクリアされ、これ以外のバイトに対してはセットされる。命令の種類を、エンドバイトに対応する機能ビットを調べることによって決定できる。この機能ビットがクリアされている場合、命令は高速経路命令である。逆に、この機能ビットがセットされている場合、命令はMRROM命令である。したがって、ある命令の演算コードの場所は、デコードユニット20により直接デコードされる命令内の、命令の第1のクリアの機能ビットに関連するバイトとして、求めることができる。たとえば、2つのプレフィックスバイト、Mod R/Mバイト、および中間バイトを含む高速経路命令は、以下のようなスタート、エンドおよび機能ビットを有する。

#### 【0032】

|         |           |

|---------|-----------|

| スタートビット | 1 0 0 0 0 |

| エンドビット  | 0 0 0 0 1 |

| 機能ビット   | 1 1 0 0 0 |

MRROM命令は、デコードユニット20がデコードするには複雑すぎると判断される命令である。MRROM命令は、MRROMユニット34を呼出すことによって実行される。より具体的には、MRROM命令がある場合、MRROMユニット34は、この命令を解析し規定された高速経路命令のサブセットに発行して所望の動作を実施する。MRROMユニット34は、この高速経路命令のサブセットをデコードユニット20にディスパッチする。

#### 【0033】

プロセッサ10は、条件付分岐命令に続く命令を投機的にフェッチするために分岐予測を用いる。分岐予測ユニット14は、分岐予測動作を行なうために含まれている。ある実施例では、分岐予測ユニット14は、命令キャッシュ16内の1つのキャッシュラインの16バイト部分につき2つまでの分岐ターゲットアドレスおよび対応する分岐発生/分岐非発生(taken/not taken)予測をキャッシュする分岐ターゲットバッファを用いる。この分岐ターゲットバッファは、たとえば2048のエントリまたはこれ以外の適切な数のエントリを含む。プリフェッチ/プリデコードユニット12は、特定のラインがプリデコードされたときに最初の分岐ターゲットを求める。続いて、キャッシュラインに対応する分岐ターゲットの更新が、キャッシュライン内で命令を実行したことによって発生する。命令キャッシュ16は、フェッチされている命令アドレスを示し、分岐予測ユニット14は、どの分岐ターゲットアドレスを選択して分岐予測を形成するか判断する。デコードユニット20および機能ユニット24は、分岐予測ユニット14に更新情報を与える。デコードユニット20は、分岐予測ユニット14が予測しなかった分岐命令を検出する。機能ユニット24は、分岐命令を実行し、予測された分岐方向が誤りかどうか判断する。分岐方向が「テイクン(発生)」となるのは、後続の命令が分岐命令のターゲットアドレスからフェッチされる場合である。逆に、分岐方向が「ノットテイクン(非発生)」であるのは、後続の命令が分岐命令に続く記憶場所からフェッチされる場合である。分岐命令予測誤りが検出されると、誤って予測された分岐に続く命令が、プロセッサ10の多様なユニットから廃棄される。これに代わる構成では、分岐予測ユニット14は、デコードユニット20および機能ユニット24ではなくリオーダバッファ32に結合されて、リオーダバッファ32から分岐予測誤り情報を受ける。分岐予測ユニット14は種々の適切な分岐予測アルゴリズムを用いることができる。

**【 0 0 3 4 】**

命令キャッシュ 16 からフェッチされた命令は、命令アライメントユニット 18 に送られる。命令が命令キャッシュ 16 からフェッチされると、対応するプリデコードデータがスキャンされ、命令アライメントユニット 18 に（かつ MROM ユニット 34 に）、フェッチされた命令に関する情報が与えられる。命令アライメントユニット 18 は、スキャンデータを用いて各デコードユニット 20 に命令を整列させる。ある実施例において、命令アライメントユニット 18 は、3 組の 8 命令バイトからの命令をデコードユニット 20 に整列させる。デコードユニット 20 A は、現在デコードユニット 20 B および 20 C が受けている命令に（プログラム順序で）先行する命令を受ける。同様に、デコードユニット 20 B は、現在デコードユニット 20 C が受けている命令にプログラム順序で先行する命令を受ける。

**【 0 0 3 5 】**

デコードユニット 20 は、命令アライメントユニット 18 から受けた命令をデコードするように構成される。レジスタオペランド情報が検出され、レジスタファイル 30 およびリオーダバッファ 32 に送られる。さらに、命令が 1 以上のメモリ動作の実施を要求するものであれば、デコードユニット 20 は、このメモリ動作をロード／ストアユニット 26 に送る。各命令は、機能ユニット 24 に対する 1 組の制御値にデコードされ、これらの制御値が、オペランドアドレス情報および命令に含まれた変位または即値データとともに、リザベーションステーション 22 に送られる。ある特定の実施例では、各命令は、2 つまでの動作にデコードされ、機能ユニット 24 A - 24 C により別々に実行される。

**【 0 0 3 6 】**

プロセッサ 10 は、命令順変更（アウトオブオーダ、out-of-order）実行をサポートし、そのため、リオーダバッファ 32 を用いて、レジスタの読み出しおよび書き動作の当初のプログラムシーケンスを追跡し、レジスタ再命名を実施し、投機的な命令が実行され分岐予測誤りが修復されるようにし、的確な例外にし易くする。リオーダバッファ 32 内の一時記憶場所を、レジスタを更新して投機的レジスタ状態をストアすることを含む命令のデコードの際に確保しておく。分岐予測が誤りであれば、予測誤り経路に沿い投機的に実行された命令の結果を、バッファにおいて、レジスタファイル 30 への書き込み前に無効化することができる。同様に、特定の命令が結果として例外をもたらした場合、その特定の命令に続く命令を廃棄する。このようにして、例外は「的確」となる（すなわち例外を生じさせる特定の命令に続く命令は、その命令の前に完了しない）。なお、特定の命令は、プログラム順序でその特定の命令に先行する命令よりも先に実行される場合、投機的に実行される。先行する命令は、分岐命令または例外発生命令であり、その場合、リオーダバッファ 32 は投機的結果を廃棄する。

**【 0 0 3 7 】**

デコードユニット 20 の出力で与えられた命令制御値および即値または変位データは直接それぞれのリザベーションステーション 22 に送られる。ある実施例では、各リザベーションステーション 22 が、対応する機能ユニットに発行されるのを待っている 6 つまでのペンドイング命令についての命令情報（すなわち命令制御値、オペランド値、オペランダタグおよび／または即値データ）を保持できる。なお、図 2 の実施例では、各リザベーションステーション 22 は専用の機能ユニット 24 と関連付けられている。したがって、リザベーションステーション 22 および機能ユニット 24 により 3 つの専用「発行位置」が形成される。言換えれば、発行位置 0 がリザベーションステーション 22 A および機能ユニット 22 A により形成される。整列してリザベーションステーション 22 A にディスパッチされる命令を、機能ユニット 24 A が実行する。同様に、発行位置 1 は、リザベーションステーション 22 B および機能ユニット 24 B により形成され、発行位置 2 は、リザベーションステーション 22 C および機能ユニット 24 C により形成される。

**【 0 0 3 8 】**

特定の命令をデコードしたときに、必要なオペランドがレジスタ場所であった場合、レジスタアドレス情報が同時にリオーダバッファ 32 およびレジスタファイル 30 に送られ

る。当業者であれば、 $\times 86$  レジスタファイルが 8 つの 32 ビット実レジスタを含む（すなわち典型的には EAX、EBX、ECX、EDX、EBP、ESI、EDI および ESP と呼ばれる）ことがわかるであろう。 $\times 86$  プロセッサーアーキテクチャを用いたプロセッサ 10 の実施例では、レジスタファイル 30 は、各 32 ビット実レジスタに対する記憶場所を含む。さらなる記憶場所が ROM ユニット 34 が使用するためにレジスタファイル 30 内に含まれている。リオーダバッファ 32 に含まれる一時記憶場所は、こうしたレジスタの内容を変更してアウトオブオーダ（命令順変更）実行が行なえるようにするためのものである。リオーダバッファ 32 の一時記憶場所が、各命令に対して確保され、これは、デコードの際に実レジスタのうち 1 つの内容を変更するものと決定される。したがって、特定のプログラムの実行中の種々のポイントで、リオーダバッファ 32 は、所与のレジスタの投機的に実行された内容を含む 1 以上の場所を含み得る。所与の命令のデコードに続いて、リオーダバッファ 32 が所与の命令においてオペランドとして用いられたレジスタに割当てられた以前のひとつまたは複数の場所を有すると判断されれば、リオーダバッファ 32 は、対応するリザベーションステーションに、1) 最後に割当てられた場所の値、または 2) その値を、最終的には以前の命令を実行する機能ユニットが生成していない場合は、最後に割当てられた場所のタグを転送する。リオーダバッファ 32 が、所与のレジスタのために確保された場所を有していれば、オペランド値（またはリオーダバッファタグ）が、レジスタファイル 30 からではなくリオーダバッファ 32 から与えられる。リオーダバッファ 32 において必要とされるレジスタのために確保された場所がなければ、その値は直接レジスタファイル 30 から取込まれる。オペランドが記憶場所に対応していれば、オペランド値がロード／ストアユニット 26 を通してリザベーションステーションに与えられる。

#### 【 0039 】

ある具体的な実施例において、リオーダバッファ 32 は、同時にデコードされた命令を 1 単位としてストアし操作するように構成される。この構成のことを本明細書では「ライン指向」と呼ぶ。いくつかの命令をまとめて処理することにより、リオーダバッファ 32 内で用いるハードウェアを単純化することができる。たとえば、この実施例に含まれるライン指向リオーダバッファは、デコードユニット 20 が 1 以上の命令をディスパッチするときは常に、3 つの命令（各デコードユニット 20 から 1 つずつ）に関する命令情報に十分な記憶を割当てる。対照的に、従来のリオーダバッファでは、実際にディスパッチされる命令の数に応じて、可変量の記憶が割当てられる。この可変量の記憶を割当てるには比較的多数の論理ゲートが必要である。同時にデコードされた命令の各々が実行されたとき、命令結果は同時にレジスタファイル 30 にストアされる。したがって、記憶は、同時にデコードされる命令の別の組に割当てるために空いている。さらに、1 命令当たり用いられる制御論理回路の量は減少する。なぜなら、制御論理は同時にデコードされるいくつかの命令に対して償却されるからである。特定の命令を識別するリオーダバッファタグを、2 つのフィールド、すなわちラインタグおよびオフセットタグに分割できる。ラインタグは、特定の命令を含む同時にデコードされた命令の組を識別し、オフセットタグは、この組内のどの命令が特定の命令に対応するか識別する。なお、命令結果をレジスタファイル 30 にストアし対応する記憶を空けることを、命令を「リタイアする」という。さらに、プロセッサ 10 の種々の実施例においていかなるリオーダバッファ構成を用いてもよい。

#### 【 0040 】

先に述べたように、リザベーションステーション 22 は、命令を、その命令が対応する機能ユニット 24 によって実行されるまでストアする。ある命令が実行のために選択されるのは、(i) その命令のオペランドが既に与えられている場合、および(ii) 同じリザベーションステーション 22A - 22C にありプログラム順序で当該命令に先行している命令のためのオペランドがまだ与えられていない場合である。なお、ある命令を機能ユニット 24 の 1 つが実行すると、その命令の結果は直接、その結果を待っているリザベーションステーション 22 に送られ、同時にその結果が送られてリオーダバッファ 32 を更新する（この技術を一般に「結果フォワーディング」と呼ぶ）。ある命令は、実行のために

選択されて機能ユニット 24A - 24C に送られるが、これは、関連する結果がフォワードされるクロックサイクル中に行なわれる。この場合、リザベーションステーション 22 は、フォワードされた結果を機能ユニット 24 に送る。命令が複数の動作にデコードされて機能ユニット 24 により実行される実施例では、この動作は別々にスケジューリングされる。

#### 【0041】

ある実施例において、各機能ユニット 24 は、加算および減算という整数算術演算、シフト、ローテート、論理演算ならびに分岐演算を行なうように構成されている。これらの動作（演算）は、デコードユニット 20 が特定の命令のためにデコードした制御値に応じて行なわれる。なお、浮動小数点ユニット（図示せず）を用いて浮動小数点演算に対応してもよい。浮動小数点ユニットは、コプロセッサとして動作し、MR ROM ユニット 34 またはリオーダバッファ 32 から命令を受けた後にリオーダバッファ 32 と連絡してその命令を完了する。加えて、機能ユニット 24 は、ロード／ストアユニット 26 が実行するコードおよびストアメモリ動作のためにアドレス生成を行なうように構成されていてもよい。ある特定の実施例で、各機能ユニット 24 は、アドレスを生成するためのアドレス生成ユニットおよび残余の機能を果たすための実行ユニットを含む。これら 2 つのユニットは、1 クロックサイクルにおいて異なる命令または動作に対し独立して動作する。

#### 【0042】

各機能ユニット 24 はまた、条件付分岐命令の実行に関連する情報を分岐予測ユニット 14 に与える。分岐予測が誤っている場合、分岐予測ユニット 14 は、既に命令処理パイプラインに入っている誤って予測された分岐に続く命令をフラッシュし、命令キャッシュ 16 またはメインメモリから必要な命令をフェッチする。なお、こうした状況下では、当初のプログラムシーケンスにおいて予測誤り分岐命令後に発生した命令の結果は廃棄され、これは、投機的に実行され一時的にロード／ストアユニット 26 およびリオーダバッファ 32 にストアされているものを含む。なお、分岐実行結果は、機能ユニット 24 がリオーダバッファ 32 に与えるもので、これは、機能ユニット 24 に分岐の予測誤りを示す。

#### 【0043】

機能ユニット 24 が生成した結果は、レジスタ値が更新されればリオーダバッファ 32 に送られ、記憶場所の内容が変更されればロード／ストアユニット 26 に送られる。結果をレジスタにストアするのであれば、リオーダバッファ 32 は、命令がデコードされたときにレジスタの値のために確保しておいた場所に結果をストアする。複数の結果バス 38 が、機能ユニット 24 およびロード／ストアユニット 26 から結果をフォワードするために含まれている。結果バス 38 は、発生した結果、および、実行されている命令を識別するリオーダバッファタグを送る。

#### 【0044】

ロード／ストアユニット 26 は、機能ユニット 24 およびデータキャッシュ 28 間のインターフェイスを与える。ある実施例において、ロード／ストアユニット 26 は、データキャッシュ 28 にまだアクセスしていないペンドィング中のロードまたはストアのデータおよびアドレス情報のための記憶場所を有する第 1 のロード／ストアバッファと、既にデータキャッシュ 28 にアクセスしているロードおよびストアのデータおよびアドレス情報のための記憶場所を有する第 2 のロード／ストアバッファとを含むように構成されている。たとえば、第 1 のバッファは 12 の場所を含み、第 2 のバッファは 32 の場所を含む。デコードユニット 20 は、ロード／ストアユニット 26 へのアクセスを調停する。第 1 のバッファが一杯であるとき、デコードユニットは、ペンドィング中のロードまたはストア要求情報のための場所がロード／ストアユニット 26 にできるまで、待機しなければならない。ロード／ストアユニット 26 はまた、ロードメモリ動作の、ペンドィング中のストアメモリ動作に対する従属性検査も行ない、データコヒーレンシ（一貫性）が確実に維持されるようにする。メモリ動作は、プロセッサ 10 およびメインメモリサブシステム間のデータ転送である。メモリ動作は、メモリにストアされたオペランドを用いる命令の結果である、または、データ転送を行なわせるが他の動作は行なわせないロード／ストア命令

の結果である。加えて、ロード／ストアユニット26は、セグメントレジスタなどの特殊レジスタおよび×86プロセッサーアーキテクチャが定めるアドレス変換メカニズムに関する他のレジスタのための特殊レジスタ記憶を含む。

#### 【0045】

データキャッシュ28は、ロード／ストアユニット26およびメインメモリサブシステム間で転送されているデータを一時的にストアするために設けられた高速キャッシュメモリである。ある実施例では、データキャッシュ28には、2ウェイセットアソシアティブ構成において64キロバイトまでのデータをストアする容量がある。データキャッシュ28を、セットアソシアティブ構成、フルアソシアティブ構成、ダイレクトマッピング構成およびその他の構成の適切な大きさを含む、種々の特殊メモリ構成で実現できることがわかるであろう。

#### 【0046】

×86プロセッサーアーキテクチャを用いたプロセッサ10の特定の実施例では、命令キヤッシュ16およびデータキャッシュ28は、線形的にアドレス指定され物理的にタグ付けされる。線形アドレスは、命令が特定するオフセットおよび×86アドレス変換メカニズムのセグメント部が特定するベースアドレスから形成される。任意選択として、線形アドレスをメインメモリへのアクセスのために物理アドレスに変換してもよい。線形-物理変換は、×86アドレス変換メカニズムのページング部によって指定されている。物理アドレスは、物理タグと比較されてヒット／ミス状態が判断される。

#### 【0047】

バスインターフェイスユニット37は、コンピュータシステム内でバスを介してプロセッサ10とこれ以外の構成要素との間で連絡が行なえるように構成されている。たとえば、このバスは、Digital Equipment Corporationが開発したEV-6バス互換のものでもよい。その代わりとして、パケットに基づいたもの、単方向リンクまたは双向リンクなどを含む適切な相互接続構成を用いてもよい。任意選択のL2キャッシュインターフェイスを用いてレベル2キャッシュに対するインターフェイスを設けてもよい。

#### 【0048】

##### ロード／ストアユニット

次に、ロード／ストアユニット26のある実施例についてより詳細に説明する。これ以外の実施例が可能であり意図されている。図3は、プロセッサ10のある実施例に従う、ロード／ストアユニット26、リオーダバッファ32、データキャッシュ28、バスインターフェイスユニット(BIU)37、デコードユニット20A、リザベーションステーション22Aおよび機能ユニット24Aを示し、相互接続を強調している。他の実施例において、所望に応じてさらなる、代替のまたはこれに代わる相互接続を用いてもよい。デコードユニット20B-20C、リザベーションステーション22B-22C、機能ユニット24B-24Cおよび図3に示した他のユニット間の相互接続も図3に示したものと同様である。

#### 【0049】

デコードユニット20Aは、命令アライメントユニット18から命令を受けてその命令をデコードする。デコードユニット20Aは、デコードした命令をリザベーションステーション22Aに与え、リザベーションステーション22Aは、デコードされた命令を、この命令が実行のために選択されるまでストアする。加えて、この命令がロードまたはストアメモリ動作を指定していれば、デコードユニット20Aは、L/Sライン46Aを介してロード／ストアユニット26に信号を送る。ロード／ストアユニット26はデコードユニット20B-20Cからも同様の信号を受ける。L/Sライン46Aは、デコードされている命令が指定しているのはロードメモリ動作なのか、ストアメモリ動作なのかまたは双方なのかを示す。たとえば、L/Sライン46Aは、ロードラインおよびストアラインを含み得る。何のメモリ動作も指定されていない場合、双方のラインの信号はデアサートされる。ロードライン上の信号は、ロードメモリ動作が指定された場合にアサートされ、同様に、ストアライン上の信号はストアメモリ動作が指定された場合にアサートされる。

ロードメモリ動作およびストアメモリ動作双方が指定されていれば、これらの信号双方がアサートされる。L/Sライン46A上の信号に応答して、ロード/ストアユニット26は、含まれているロード/ストアバッファにエントリを割当てて、対応するメモリ動作をストアする。

#### 【0050】

上記に加え、デコードユニット20Aは、リオーダバッファ32に、デコードされている命令に関する情報を与える。リオーダバッファ32は、この情報（同様の情報が他のデコードユニット20B-20Cから与えられる）を受け、これに応じてリオーダバッファエントリを割当てる。割当てられたリオーダバッファエントリは、命令タグバス48でロード/ストアユニット26に送られるリオーダバッファタグにより識別される。命令タグバス48は、可能な命令各々（たとえばこの実施例では3つありこれらはそれぞれデコードユニット20A-20Cからのものである）に対するタグを送るように構成される。これに代えて、前述のライン指向構成を用いる実施例では、リオーダバッファ32を、ラインのラインタグを送るように構成し、ロード/ストアユニット26が、特定のロードまたはストアを信号で知らせる発行位置のオフセットタグで、ラインタグを増大してもよい。

#### 【0051】

リオーダバッファ32はさらに、命令のレジスタオペランドに対する従属性検査を実施するように構成されてもよい。レジスタオペランドは、デコードユニット20が送る命令情報において識別される。ストアメモリ動作については、ストアデータは、ロード/ストアユニット26がストアアドレスに加えて受けるソースオペランドである。したがって、リオーダバッファ32は、各ストアメモリ動作に対しストアデータを生成した命令を求め、ストアデータ/タグバス50で、ストアデータ（ストアメモリ動作のディスパッチの際にリオーダバッファ32またはレジスタファイル30で利用できる場合）、または、そのストアデータに対するストアデータタグを送る。ストアメモリ動作に対応する命令が、レジスタの内容をメモリにストアするという明示ストア命令であれば、ストアデータを生成する命令の命令タグ（利用できるならばストアデータ）が送られる。他方、命令がストアメモリ動作を暗示動作として含む場合は、命令そのものがストアデータを生成する。こうした場合、リオーダバッファ32は、この命令の命令タグをストアデータタグとして与える。

#### 【0052】

図3では簡潔にするために示していないが、リザベーションステーション22Aは、リオーダバッファ32から、命令のオペランドタグおよび/またはデータも受ける。リザベーションステーション22Aは、オペランドタグおよび/またはデータを入手し、結果バス38から残りのオペランドデータ（オペランドタグが識別するもの）が送られるのを待つ。ある命令がそのオペランドを受けると、機能ユニット24Aはそれを実行することができる。より具体的にいえば、ここに示している実施例では、機能ユニット24Aは、実行ユニット（EXU）40およびアドレス生成ユニット（AGU）42を含む。実行ユニット40は、命令動作を行ない（たとえば算術演算および論理演算）、結果を生成し、その結果が結果バス38A（結果バス38の1つ）でロード/ストアユニット26、リザベーションステーション22およびリオーダバッファ32に転送される。AGU42は、データアドレスを生成しこのデータアドレスは命令が指定した1つまたは複数のメモリ動作で使用され、AGU42はこのデータアドレスをアドレスバス44Aを介してロード/ストアユニット26に送る。なお、AGU42および実行ユニット40が結果バス38Aを共有し機能ユニット24Aがアドレス生成およびその他命令実行動作を実施する実行ユニットのみを含む実施例を用いてもよい。ロード/ストアユニット26はさらに、他の機能ユニット24B-24C内の実行ユニットおよびAGUからの結果バスおよびアドレスバスを受けるように結合される。

#### 【0053】

ここで示している実施例ではAGU42を用いているため、リザベーションステーション22Aはある命令のアドレス生成部を選択し、AGU42がこれを実行するが、これは

、アドレスを形成するオペランドは既に受けているが命令が指定するさらなるオペランドをまだ受けていないときに行なわれる。A G U 4 2 は、発生したアドレスを、ロード／ストアユニット2 6 に、アドレスバス4 4 A で、データアドレスを生成した命令の命令タグとともに送る。これに応じて、ロード／ストアユニット2 6 は、アドレスバス4 4 A で受けたタグを、ロード／ストアバッファにストアされた命令タグと比較して、データアドレスが対応するのはロードなのかストアなのかを判断する。

#### 【 0 0 5 4 】

ロード／ストアユニット2 6 は、結果バス3 8 で与えられた結果タグをモニタして、ストアメモリ動作のストアデータを入手する。結果タグがロード／ストアユニット内のストアデータタグと一致していれば、ロード／ストアユニット2 6 は、対応するデータを入手し、このデータを対応するストア命令と関連付ける。

#### 【 0 0 5 5 】

ロード／ストアユニット2 6 は、データキャッシュインターフェイスを介してデータキャッシュ2 8 に結合される。ロード／ストアユニット2 6 は、メモリ動作を選択して、データキャッシュインターフェイスを介してデータキャッシュ2 8 を探索し、データキャッシュインターフェイスから探索結果を受ける。一般的に、特定のメモリ動作に対するデータキャッシュの「探索」は、その特定のメモリ動作のデータアドレスをデータキャッシュ2 8 に送りデータキャッシュ2 8 によりデータアドレスがヒットしているかどうかを判断することを含む。データキャッシュ2 8 は、探索結果（たとえばヒット／ミス表示）をロード／ストアユニット2 6 に返す。加えて、特定のメモリ動作がロードでありヒットしていれば、データキャッシュ2 8 は対応するロードデータを結果バス3 8 D でリザベーションステーション2 2 、リオーダバッファ3 2 およびロード／ストアユニット2 6 にフォワードする。ある実施例において、データキャッシュ2 8 は、2つのポートを含みこれに応じて2つまでの探索を同時に受ける。データキャッシュ2 8 は、たとえばバンク構成を用いてもよく、この構成では、キャッシュラインが少なくとも2つのバンクにわたりストアされ、2つの探索が、異なるバンクにアクセスしている限り同時に処理される。ある特定の実施例では、データキャッシュ2 8 は8つのバンクを用いる。データキャッシュインターフェイスの種々の実施例について以下でさらに詳しく説明する。

#### 【 0 0 5 6 】

データキャッシュ2 8 は、ミスであった探索に応じてキャッシュラインを割当るように構成され、バスインターフェイスユニット3 7 と連絡してミスのキャッシュラインをフェッチする。加えて、データキャッシュ2 8 は、取戻した変更されているキャッシュラインを、メインメモリ更新のためにバスインターフェイスユニット2 7 に送る。

#### 【 0 0 5 7 】

バスインターフェイスユニット3 7 は、データキャッシュ2 8 に結合されまたスヌープインターフェイス5 2 を介してロード／ストアユニット2 6 にも結合される。バスインターフェイスユニット3 7 がスヌープインターフェイス5 2 を用いて、バスから受けるスヌープ動作に応じてコヒーレンシ（coherency）動作を行なう必要があるかどうかが判断される。一般的に、「スヌープ動作」は、バス上で、このバスに接続されたキャッシュに対するメモリのコヒーレンシを保つために（たとえばプロセッサ内で）行なわれる動作である。コヒーレンシが適切に保たれていれば、特定の記憶場所に対応しキャッシュの1つにストアされているデータのコピーは、他のキャッシュ各々にストアされたコピーと一致している。スヌープ動作は、明示動作である、または、特定の記憶場所のアドレスに対して実施される動作の暗示部分である。一般的に、スヌープ動作は、スヌープされるアドレス（「スヌープアドレス」）を指定し、かつ、アドレスがキャッシュにストアされている場合はキャッシュラインの所望の状態を指定する。バスインターフェイスユニットは、スヌープインターフェイス5 2 を介してスヌープ要求をデータキャッシュ2 8 およびロード／ストアユニット2 6 に送り、スヌープ動作を行なう。

#### 【 0 0 5 8 】

リオーダバッファ3 2 は、命令のリタイアを管理する。リオーダバッファ3 2 は、リタ

イインターフェイス 54 を介してロード／ストアユニット 26 と連絡をとり、リタイアされているかこれからリタイアされようとしている命令を識別する。たとえば、ある実施例では、ストアは、リタイアされるまでデータキャッシュ 28（またはメインメモリ）を更新しない。加えて、いくつかのロード命令を非投機的実行に制限してもよい。リオーダバッファ 32 は、リタイアインターフェイス 54 を介してロード／ストアユニット 26 に、リタイアされているまたはリタイア可能なメモリ動作を示す。このように、デコードユニット 20 が各命令のためにリオーダバッファ 32 に与える命令情報は、この命令がロードまたはストア動作を含むかどうかを示す。ロード／ストアユニット 26 は、特定のメモリ動作がリタイアされたときにロギングされているという肯定応答をリオーダバッファ 32 に返し、リオーダバッファ 32 はこれに続いて対応する命令をリタイアさせる。

#### 【 0059 】

ロード／ストアバッファは一杯になることがあるため、ロード／ストアユニット 26 は、フロー制御メカニズムを用い、デコードユニット 20 で、後続のメモリ動作を、その後続のメモリ動作のために十分なエントリがロード／ストアバッファにおいて（先のメモリ動作の完了によって）空になるまで、停止させる。たとえば、ロード／ストアユニット 26 は、空いているエントリの数のカウントをデコードユニット 20 に一斉に送り、デコードユニットは、このカウントが、デコードされている命令のメモリ動作に利用できるエントリが不十分であることを示す場合、停止する。ある特定の実施例に従うと、同時にデコードユニット 20 によりデコードされている命令は、ロックステップ（lockstep）でリザベーションステーション 22 に移動する。（図 2 に関して先に述べたようにラインが命令のためにリオーダバッファ 32 に割当てられる）このような実施例では、デコードユニット 20 は、同時にデコードされる命令の組内ですべてのメモリ動作に対して十分なエントリが利用できるまで停止する。これに代わるものとして、ロード／ストアユニット 26 が、後続のメモリ動作をバッファエントリが利用できるようになるまで停止させるための停止信号を用いてもよい。何らかの適切なフロー制御メカニズムを用いればよい。

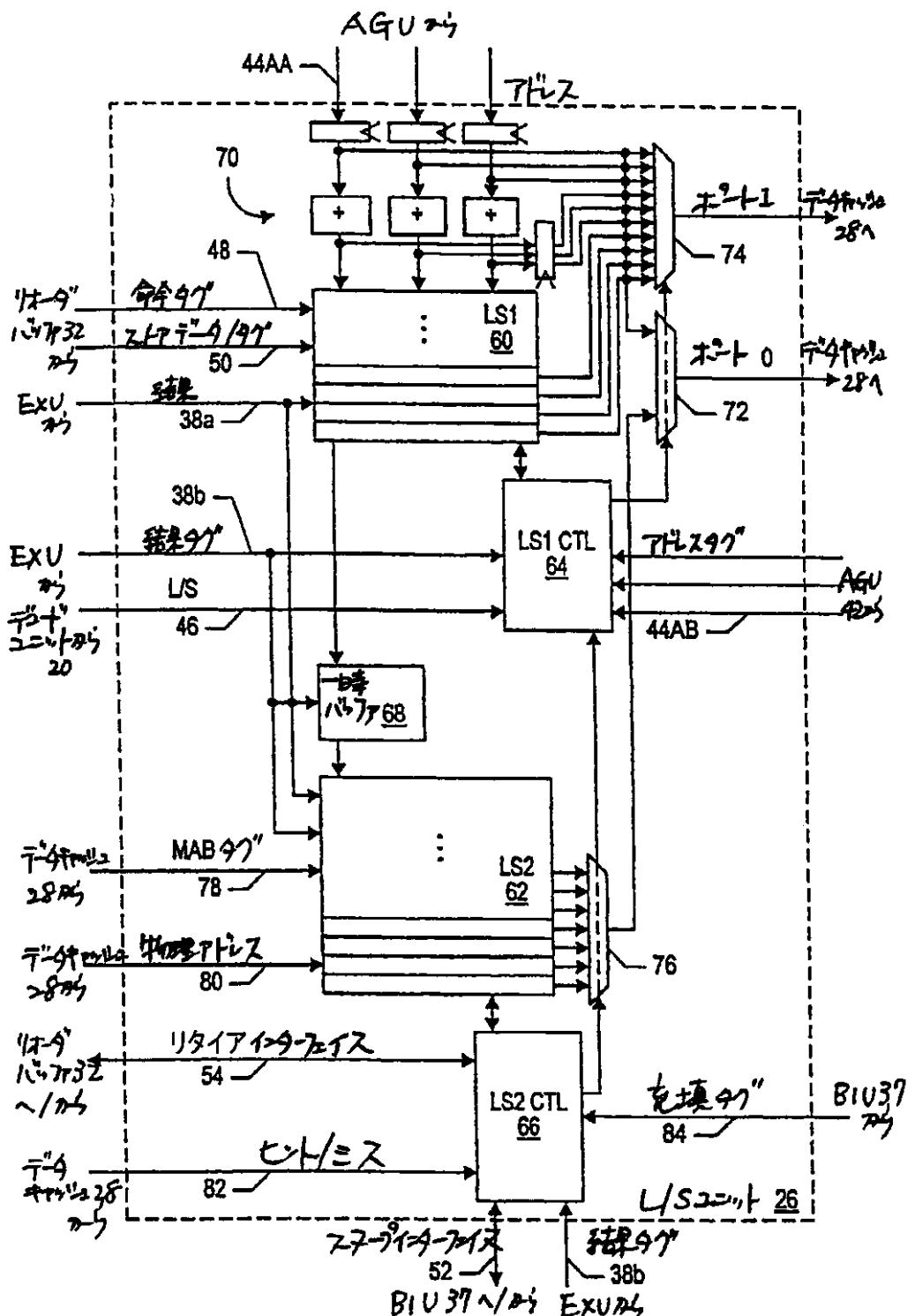

#### 【 0060 】

次に図 4 を参照して、ロード／ストアユニット 26 のある実施例のブロック図が示される。これ以外の実施例が可能であり意図されている。図 4 に示した実施例では、ロード／ストアユニット 26 は、第 1 のロード／ストアバッファ（LS1 バッファ）60、第 2 のロード／ストアバッファ（LS2 バッファ）62、LS1 制御回路 64、LS2 制御回路 66、一時バッファ 68、セグメント加算器 70、ポート 0 マルチプレクサ（mux）72、ポート 1 マルチプレクサ 74、および LS2 再探索マルチプレクサ 76 を含む。セグメント加算器 70 は、機能ユニット 24A - 24C 内の AGU42 からデータアドレスを受けるように結合される。（たとえば図 3 に示したアドレスバス 44A の一部、アドレスバス 44AA は、機能ユニット 24A 内の AGU42 からのデータアドレスを送る。）マルチプレクサ 70 および 72 は、AGU42 からのデータアドレスおよびセグメント加算器 70 の出力を受けるように結合され、LS1 バッファ 60 にも結合される。マルチプレクサ 72 はまた、LS2 再探索マルチプレクサ 76 からの入力を受ける。さらに、LS1 バッファ 60 は、セグメント加算器 70、LS1 制御回路 64、一時バッファ 68、命令タグバス 48、ストアデータ／タグバス 50 および結果バス 38a（結果バス 38 の結果データ部分）に結合される。LS1 制御回路 64 は、マルチプレクサ 72 および 74 ならびに LS2 制御回路 66 に結合される。さらに、LS1 制御回路 64 は、AGU42 からのアドレスタグ（たとえば図 3 に示したアドレスタグバス 44A の一部、アドレスタグバス 44AB は、機能ユニット 24A 内の AGU42 からのアドレスタグを送る）、結果タグバス 38b を介して結果タグ（結果バス 38 の結果タグ部分）、および L/S ライン 46（デコードユニット 20A からの L/S ライン 46A を含む）を受けるように結合される。一時バッファ 68 および LS2 バッファ 62 は、結果バス 38a および結果タグバス 38b に結合される。LS2 バッファ 62 はさらに、MAB タグバス 78 上のミスアドレスバッファ（MAB）タグを受け、データキャッシュ 28 からの、物理アドレスバス 80 上の物理アドレスを受けるように結合される。LS2 バッファ 62 はさらに、マルチプレ

クサ76、LS2制御回路66および一時バッファ68に結合される。LS2制御回路66はさらに、マルチプレクサ76、リタイアインターフェイス54、結果タグバス38b、スヌープインターフェイス52、データキャッシュ28からのヒット/ミス信号82、およびバスインターフェイスユニット37からの充填タグバス84に結合される。

#### 【0061】

一般的に、ロード/ストアユニット26は、プリキャッシュバッファ(LS1バッファ60)およびポストキャッシュバッファ(LS2バッファ62)を含む。メモリ動作は、プロセッサ10内でディスパッチの際にLS1バッファ60に割当てられ、選択されてデータキャッシュ28の探索が行なわれるまでLS1バッファ60内にある。データキャッシュ28の探索に続き、メモリ動作は、探索状態(たとえばヒット/ミスなど)にかかわらず、LS2バッファ62に移される。

#### 【0062】

ミスしたメモリ動作は、その後LS2再探索マルチプレクサ76およびポート0マルチプレクサ72を通して選択して、データキャッシュ28を再び探索すればよい。本明細書で用いる「再探索」という用語は、特定の動作に対する第1の探索の後に第2のまたは後続の試みとしてキャッシュを探索することを指す。加えて、ストアメモリ動作を、ストアがリタイアの状態になるまでLS2バッファ62内に保持しておいてよい。

#### 【0063】

L/Sライン46上の信号に応答して、LS1制御回路64は、LS1バッファ60内のエントリを識別されたロードおよびストアメモリ動作に割当てる。LS1制御回路64の制御により、LS1バッファ60はそれぞれの命令タグおよびストアデータ/タグ(適用できる場合)を割当てられたエントリに受ける。次に、対応するデータアドレスをAGUから受けて(LS1制御回路64が受けたアドレスタグにより識別される)、割当てられたエントリにストアする。

#### 【0064】

メモリ動作はそのアドレスを受けるとデータキャッシュ28を探索できるようになる。LS1制御回路64は、メモリ動作を求めてLS1バッファエントリをスキャンしてデータキャッシュ28を探索し、ポート0マルチプレクサ72およびポート1マルチプレクサ74のために選択制御を生成する。したがって、ここで示している実施例では、1クロックサイクル当り2つまでのメモリ動作がデータキャッシュ28を探索することができる。ある具体的な実施例に従うと、LS1制御回路64は、データキャッシュ28を探索するためにプログラム順序でメモリ動作を選択する。よって、LS1制御回路64を、LS1バッファ60内の最も古いメモリ動作に対するスキャンに制限するように構成してもよい。メモリ動作の「プログラム順序」とは、命令のフェッチおよび実行が一度に1つずつ行なわれる場合の命令の実行順序である。さらに、投機的にフェッチされた命令のプログラム順序とは(たとえば分岐予測に従ったもの)、上記のようにこの投機が正しいと仮定した上で命令が実行される順序である。命令がプログラム順序で他の命令に先行する場合、前者の命令は他の命令よりも古いといえる。逆に、命令がプログラム順序で他の命令の後続命令の場合、前者の命令は他の命令よりも新しいといえる。なお、他の実現化例では、所望に応じ順序を崩してメモリ動作を選択しデータキャッシュ28を探索してもよい。

#### 【0065】

LS1制御回路64は、メモリ動作を選択して、データアドレスを受けたときにデータキャッシュ28を探索するように構成される。(この実施例ではメモリ動作がLS1制御回路64によりスキャンされているエントリ内にあると仮定する。)AGU42から受けたアドレスタグがそうでなければ選択可能なメモリ動作の命令タグに一致していれば、LS1制御回路64は、マルチプレクサ72および74の一方を介してAGU42から受けた対応するデータアドレスを選択する。

#### 【0066】

データアドレスは、ロード/ストアユニット26に与えられたときに選択され探索が行なわれるが、データアドレスは、セグメント加算器70の1つにも与えられる。この実施

例では、セグメント加算器 70 は、 $\times 8$  6 アドレス指定方法のセグメント化部分を処理するために設けられている。 $\times 8$  6 命令セットアーキテクチャを用いない実施例では、セグメント加算器 70 がなくてもよい。一般的に、AGU 42 はメモリ動作に対応する論理アドレスを生成する。この論理アドレスは、命令のアドレスオペランドの加算により生成されるアドレスである。 $\times 8$  6 アーキテクチャでは、2段の変換方法が定められており、セグメント化方法により論理アドレスから線形アドレスに、次にページング方法により物理アドレスに変換される。AGU 42 は命令のアドレスオペランドを加算するため、AGU が与えるデータアドレスは論理アドレスである。しかしながら、現代の命令コードは一般的に「フラットアドレス指定モード」を用いており、このモードでは、セグメントベースアドレス（論理アドレスに加算されて線形アドレスを形成するもの）は、ゼロにプログラミングされる。したがって、ロード/ストアユニット 26 は、セグメントベースアドレスがゼロである（したがって論理および線形アドレスが等しい）と推定し、論理アドレスを選択してデータキャッシュ 28 を探索する。セグメント加算器 70 は、メモリ動作のために選択されたセグメントのセグメントベースアドレスを加算し、線形アドレスをマルチブレクサ 72 および 74 ならびに LS1 バッファ 60 に送って記憶させる。特定のメモリ動作に対するセグメントベースアドレスが非ゼロであり、メモリ動作を選択して論理アドレスを受けた際にデータキャッシュ 28 を探索するのであれば、LS1 制御回路 64 は、先行するアクセスを取消して（ロードデータが フォワード されないように）、対応する線形アドレスを対応するセグメント加算器 70 の出力から選択してデータキャッシュ 28 を探索する。これ以外の代替実施例では、AGU 42 がセグメントベースアドレスを受け線形アドレスを生成してもよい。さらに他の実施例では、フラットアドレス指定モードを要求してセグメントベースアドレスを無視してもよい。

#### 【 0067 】

マルチブレクサ 72 および 74 は、LS1 バッファ 60 内のエントリからデータアドレスを受けるようにも結合される。メモリ動作に対応するデータアドレスは、AGU 42 から受けた際にメモリ動作に割当てられる LS1 エントリにストアされる。データアドレスが、メモリ動作選択に際してエントリから選択され、データキャッシュ 28 が探索される。なお、データアドレスに加え、他の情報をマルチブレクサ 70 および 72 を介してデータキャッシュ 28 に送ってもよい。たとえば、メモリ動作がロードであるかストアであるかを示すものを送ってもよい。メモリ動作の命令タグを送って、ロードメモリ動作のためのロードデータとともに結果バス 38D で転送することができる。この動作（適切なデータをマルチブレクサする）のサイズを送ることもできる。設計上の選択に応じて所望の情報を送ることができる。

#### 【 0068 】

ストアデータはストアメモリ動作のために与えられ、ストアメモリ動作は LS1 バッファ 60 にある。これに応じて、LS1 制御回路 64 は結果タグバス 38b をモニタする。LS1 バッファ 64 内のストアデータタグに一致するタグが与えられると、結果バス 38a のうち対応する結果バスからの対応するストアデータが、一致するストアデータタグを有するエントリ内に取り込まれる。

#### 【 0069 】

LS1 制御回路 64 は、LS1 バッファ 60 から、メモリ動作を、メモリ動作のデータキャッシュ 28 探索に応じて除去する。ある具体的な実施例では、メモリ動作は、データキャッシュ 28 の探索のために選択された後のサイクルで除去される。当該後のサイクルを用いて、メモリ動作が AGU 42 の 1 つによりデータアドレスの生成が行なわれた際に選択された場合は、データアドレスを LS1 バッファ 60 に伝搬してもよい。他の実施例では、メモリ動作が選択されたサイクル中にメモリ動作を除去することを選択してもよい。メモリ動作は選択された後のサイクルで除去されるため、LS1 制御回路 64 は、LS1 バッファ 60 内の最も古い 4 つのエントリをスキャンしてメモリ動作を選択してデータキャッシュ 28 を探索するように構成される（先行するクロックサイクルでは 2 つまでのエントリを選択し現在のクロックサイクルでは 2 つまでのエントリを選択できる）。

## 【0070】

LS1バッファ60から除去されたメモリ動作は、一時バッファ68に移される。一時バッファ68を設けて、LS1バッファ60からエントリを読み出しこれらをLS2バッファ62に書込む際のタイミング上の制約を緩和してもよい。したがって、一時バッファ68は、設計上好都合であるに過ぎず、全く任意的選択である。メモリ動作が一時バッファ68に移された後のクロックサイクルで、メモリ動作はLS2バッファ62に移される。ストアデータは、ストアメモリ動作が一時バッファ68に保持されているクロックサイクル中に結果バス38上で与えられるので、一時バッファ68は、結果タグバス38b上の結果タグをモニタし、LS1バッファ60がデータを収集するのと同じやり方で結果バス38aからデータを収集する。

## 【0071】

このように、データキャッシュ28を探索したメモリ動作は、LS2バッファ62に与えられる。この実施例では、すべてのメモリ動作が、データキャッシュ28の最初の探索後にLS2バッファ62に与えられる。ストアは、データキャッシュ28に与えられるまでLS2バッファ62に保持される（すなわちデータキャッシュ28を更新できるようになるまで）。一般的に、ストアは、投機的でなくなったときに与えられる。ある実施例では、ストアは、リタイアに応じて（リタイアインターフェイス54を介して示される）またはその後いずれかの時点で与えられる。ロードは、この実施例でもリタイアまでLS2バッファ62に保持される。ロードヒットは、スヌープのためLS2バッファ62内に留まる。ロードミスは、少なくともロードがアクセスするキャッシュラインがデータキャッシュ28に送られるまではLS2に保持される。キャッシュライン（またはロードデータを含むその一部分）がキャッシュの更新にスケジューリングされていることに応じて、ロードミスはデータキャッシュ28の再探索にスケジューリングされる。再探索の際、ロードミスはロードヒットとなり（かつロードデータはデータキャッシュ28によりフォワードされる）、ヒットとしてリタイアまで保持される。

## 【0072】

LS2制御回路66は、データキャッシュ28を探索したメモリ動作のためにLS2バッファ62内にエントリを割当てる。加えて、LS2制御回路66は、データキャッシュ28から、ヒット/ミス信号82の各探索について、探索状態情報を受ける。ヒット/ミス情報は、探索状態が与えられたメモリ動作に対応するLS2バッファエントリにストアされる。ある実施例では、データキャッシュ28は、データキャッシュへのアクセスと並行して仮想アドレスを物理アドレスに変換しようと試みるアドレス変換回路を含む。アドレス変換回路で変換を行なうことができなければ、変換が行なわれるまで探索はミスであると識別される（たとえばメインメモリ内のソフトウェア管理変換テーブルを探索することによって）。ある具体的な実現化例では、データキャッシュ28内のアドレス変換回路は、32エントリレベル1TLBと、4ウェイセットアソシアティブ、256エントリレベル2TLBとを含む、2レベル変換索引バッファ(TLB)構成を有する。

## 【0073】

メモリ動作のデータアドレスをデータキャッシュ28が変換することができれば、対応する物理アドレスが物理アドレスバス28で与えられる。LS2制御回路は、対応するエントリが仮想アドレスを物理アドレスで上書きするようにする。しかしながら、再探索におけるインデックス付けのためにいくつかの仮想アドレスビットは別に保持しておき、ストアデータは、データキャッシュ28に対する仮想インデックス付けおよび物理的タグ付けが行なわれる実施例においては与えられる。

## 【0074】

データキャッシュ28にミスするメモリ動作に対し、データキャッシュ28はエントリを含まれているミスアドレスバッファ内に割当てる。ミスアドレスバッファは、ミスアドレスを、バスインターフェイスユニット37に送るために待ち行列に入れ、インターフェイスユニット37はアドレスをL2キャッシュからまたはメインメモリからフェッチする。ミスアドレスバッファ内のエントリを識別するタグ(MABタグ)が、ミスした各メモ

リ動作に対しM A Bタグバス78上に与えられる。なお、データキャッシュ28は、ミスアドレスバッファエントリをキャッシュラインに基づいて割当てる。したがって、後続の、同じキャッシュラインに対するミスは、同じM A Bタグを受け、さらなるミスアドレスバッファエントリが割当てられないようとする。

#### 【0075】

次に、バスインターフェイスユニット37は、ミスのキャッシュラインをフェッチし、このキャッシュラインを充填データとしてデータキャッシュ28に戻す。バスインターフェイスユニット37はまた、キャッシュラインに対応するM A Bタグを充填タグとして充填タグバス84上に置く。LS2制御回路66は、充填タグをLS2バッファ62内のM A Bタグと比較する。ロードメモリ動作についてM A Bタグの一一致が生じれば、そのロードを選択してデータキャッシュ28を再探索する。2以上の一致が検出されれば、最も古い一致ロードを、後続のクロックサイクル中に選択される他のメモリ動作とともに選択する。M A Bタグに一致するストアはヒットとしてマークされるが、データを与える試みを行なう前に非投機となるのを待つ。

#### 【0076】

ある実施例では、データのキャッシュラインは、複数のパケットを用いて戻される。各ロードメモリ動作は、どのパケットにアクセスしているかを記録し（またはそのパケットはロードアドレスの適切なアドレスビットから区別される）、バスインターフェイスユニット37は、充填タグとともに戻されているパケットを識別する。このように、戻されるパケットにアクセスするロードのみを選択して再探索を行なう。

#### 【0077】

バスインターフェイスユニット37は、充填データよりも前に充填タグを与えて、ロードが再探索のために選択されポート0を介してデータキャッシュ28に送られて、データキャッシュ28にデータのパケットが届くのと同時にデータ転送段に達するようとする。アクセスされたデータをこうして転送することができる。

#### 【0078】

ストアがデータキャッシュ28の探索後にLS2バッファ62に送られ後続のロードがLS1バッファ60からデータキャッシュ28を探索しそこからデータをフォワーディングできるようになっているため、古いストアと同じ記憶場所にアクセスしている新しいロードは、古いストアがデータをデータキャッシュ28に与える前に、データキャッシュ28を探索することができる。ロードの正しい結果とは、その古いストアに対応するストアデータを受けることである。したがって、LS2制御回路66は、探索アドレスをモニタし、このアドレスへの古いストアがLS2バッファ62内にあるかどうか判断する。一致が検出されストアデータをLS2バッファ62内で利用できるのであれば、LS2制御回路66はデータキャッシュ28に信号で知らせフォワーディングのためにLS2バッファから与えられるデータを選択し、選択されたデータを与える。他方、一致が検出されストアデータをLS2バッファ62内で利用することができなければ、データキャッシュ28からのデータフォワーディングは取消される。ロードはLS2バッファ62に送られ、ストアデータを利用できるようになるまで探索のために選択される。ストアからロードへのフォワードについてのさらなる詳細事項については以下に示す。

#### 【0079】

一般的に、LS2制御回路66は、LS2バッファ62内のエントリをスキャンしメモリ動作を選択してデータキャッシュ28を再探索するように構成されている。ロードミスを選択し、データがデータキャッシュ28に戻されることに応じて再探索を行なう。古いストアにヒットしたロードを選択し、現在再探索を行なっていないならば再探索を行なう。ストアを選択し、リタイアされたことに応じて再探索を行なう。複数のメモリ動作を選択できる場合、LS2制御回路66は、複数のメモリ動作のうち最も古いものを選択する。LS2制御回路66は、ポート0を使用している（ポート0マルチプレクサ72を介して）ならば、LS1制御回路64に信号で知らせ、制御回路64は、ポート0マルチプレクサ72を通してLS2入力を選択し、そのクロックサイクルでポート0上のLS1バッ

ファ 6 0 からのメモリ動作の選択を不能にする。

【 0 0 8 0 】

LS 2 制御回路 6 6 はさらに、スヌープインターフェイス 5 2 を介してバスインターフェイスユニット 3 7 からスヌープ要求を受けるように結合される。一般的に、LS 2 バッファ 6 2 内のメモリ動作はスヌープされる。なぜなら、このメモリ動作は既にデータキャッシュ 2 8 を探索しておりスヌープ動作に応じて訂正作業が必要だからである。たとえば、ロードヒット（従属する命令にデータを フォワード 濟み）は、廃棄されて再び実行されなければならない。ストアは、探索から変更の必要があるキャッシュ状態をストアしている。対照的に、LS 1 バッファ 6 0 内のメモリ動作は、データキャッシュ 2 8 を探索しておらずしたがってスヌープの必要はない。

【 0 0 8 1 】

LS 2 制御回路 6 6 は、スヌープ要求を受け、LS 2 バッファエントリをスヌープ要求に対して調べて、スヌープインターフェイス 5 2 を介してバスインターフェイスユニット 3 7 に応答する。加えて、LS 2 制御回路 6 6 は、スヌープに応じて LS 2 バッファエントリ内で更新を行なってもよい。

【 0 0 8 2 】

一般的に、バッファは、2 以上の情報項目を後で検索するためにストアするのに用いられる記憶素子である。バッファは、複数のレジスタ、ラッチ、フリップフロップまたは他のクロックされた記憶装置を含む。その代わりとして、バッファが、適切に配列された1組のランダムアクセスメモリ (RAM) セルを含んでいてもよい。バッファは多数のエントリに分割され、各エントリは、バッファの設計対象である1つの情報項目をストアするように設計されている。エントリは、適切な方法で割当および割当解除可能である。たとえば、バッファは、シフト先入れ先出し (FIFO) バッファとして動作してもよく、この場合、エントリは、古いエントリが削除されるときにシフトダウンされる。それに代えて、ヘッドおよびテールポインタを用いてバッファ内の最も古いおよび最も新しいエントリを示してもよく、エントリは、削除されるまでバッファの特定の記憶場所に保持される。図 1 に示したストア待ち行列 4 0 0 は、一種のバッファである。本明細書で用いる「制御回路」という用語は、入力に対し動作を行なってこれに応じて出力を生成し上記の動作を実現する、組合せ論理回路、クロックト記憶回路および／またはステートマシンの組合せのことをいう。

【 0 0 8 3 】

なお、ある実施例では、ロード／ストアユニット 2 6 は、LS 1 からのストア探索と同じポート上の古いストアのデータ提供と重畠しようとする。これが実施される理由は、ストア探索ではヒット／ミスについてデータキャッシュタグを検査しているだけでデータ記憶内のデータの検索または更新の試みがされていないからである。さらに、上記の説明では、すべてのメモリ動作が LS 2 バッファ 6 2 内にあるものとして実施例の説明をしているが、これ以外の実施例ではこのような方法で動作が行なわれないかもしれない。たとえば、ロードヒットは実施例によっては LS 2 バッファ 6 2 内にストアされないことがある。例として、こうした実施例は厳密なメモリ順序が望まれない場合に用いられる。

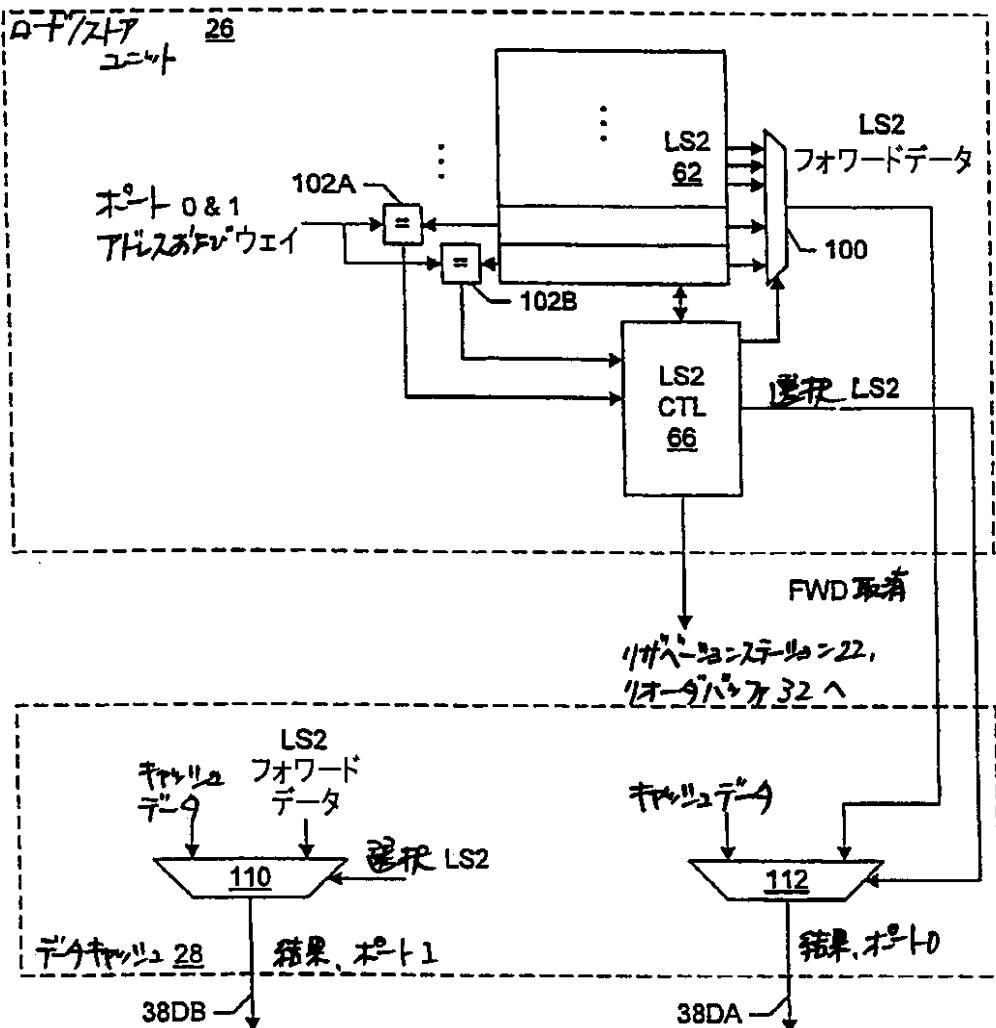

【 0 0 8 4 】

ストア - ロードフォワーディング

図 5 は、ロード／ストアユニット 2 6 およびデータキャッシュ 2 8 の一部の一実施例を示す。これ以外の実施例が可能であり意図されている。図 5 の実施例では、ロード／ストアユニット 2 6 は、LS 2 バッファ 6 2 、LS 2 制御回路 6 6 、データ フォワード マルチプレクサ 1 0 0 、ならびにアドレスおよび ウェイ 比較器 1 0 2 A - 1 0 2 B を含む。加えて、図 5 に示した実施例では、データキャッシュ 2 8 は、ポート 1 データマルチプレクサ 1 1 0 およびポート 0 データマルチプレクサ 1 1 2 を含む。LS 2 バッファ 6 2 は、データ フォワード マルチプレクサ 1 0 0 、比較器 1 0 2 A - 1 0 2 B および LS 2 制御回路 6 6 に結合される。LS 2 制御回路 6 6 はさらに、マルチプレクサ 1 0 0 、1 1 0 および 1 1 2 に結合される。LS 2 制御回路 6 6 はさらに、比較器 1 0 2 A - 1 0 2 B に結合され

る。比較器 102A - 102B は、データキャッシュ 28 のポート 0 および 1 上に与えられたデータアドレスおよび ウェイ を受けるように結合される。マルチブレクサ 112 は、結果を結果バス 38DA に与えるように結合され、同様に、マルチブレクサ 110 は、結果を結果バス 38DB に与えるように結合される。結果バス 38DA - 38DB は、図 3 に示す結果バス 38D の一実施例を成す。

#### 【0085】

一般的に、ロード / ストアユニット 26 は、ロードメモリ動作の探索が LS2 バッファ 62 にストアされた古いストアメモリ動作にヒットする場合を処理するように構成される。ロード / ストアユニット 26 は、LS1 バッファ 60 からデータキャッシュ 28 を探索するメモリ動作のデータアドレスのインデックス部を、LS2 バッファ 62 内のメモリ動作のデータアドレスのインデックス部と比較する。これらのインデックスが一致しメモリ動作がデータキャッシュ 28 内でデータキャッシュ 28 と同じ ウェイ にヒットしていれば、探索しているメモリ動作は LS2 バッファ 62 内のストアにヒットしている。探索しているロードが LS2 バッファ 62 内のストアにヒットしておりストアデータが LS2 バッファ 62 で利用できるのであれば、ストアデータはデータキャッシュ 28 に送られてキャッシュにあるロードデータの代わりに フォワード される。他方、探索しているロードが、ストアデータが利用できない LS2 バッファ 62 内のストアにヒットするかもしれない。このような場合、データキャッシュ 28 からのデータ フォワード は取消され、ロード記憶動作を選択して、ストアデータが利用できるようになるまで LS2 バッファ 62 からの再探索を行なう。最終的に、ストアデータは LS2 内で利用できるようになり、バッファから、ロードによる再探索中に フォワード される、または、ストアがデータキャッシュ 28 を更新しデータがデータキャッシュ 28 からロードによる再探索中に フォワード される。

#### 【0086】

一般的に、ストアデータが記憶場所から「利用可能」であるのは、このストアデータが実際にその記憶場所にストアされている場合である。その後のある時点でデータが記憶場所にストアされるかもしれないがまだそこにストアされていない場合、データは、「利用可能でない」、「まだ利用可能でない」または「利用できない」。たとえば、ストアデータは、そのストアデータがストアデータのソースから LS2 バッファエントリにまだ転送されていない場合は、LS2 バッファエントリにおいて利用可能でない。ストアデータのソースとは、実行によりストアデータを発生させる命令であり、ストアが対応する命令と同じ命令である（メモリオペランドを宛先として指定する命令）、またはより古い命令である。ストアデータタグは、ストアデータのソースを識別し、よって、実行ユニット 40 からの結果タグと比較されてストアデータを収集する。

#### 【0087】

上記のように、ロードアドレスおよび ウェイ 表示が、LS2 バッファ 62 内のストアアドレスおよび ウェイ 表示と比較され、古いストアにヒットするロードが検出される。したがって、比較器 102 のような比較器が設けられる。比較器 102 は、データキャッシュ 28 の各ポート上のアドレスおよび ウェイ 表示を LS2 バッファ 62 内にストアされたデータアドレスおよび ウェイ 表示と比較するために設けられる。さらに、所望されれば、比較器 102 を LS2 バッファ 62 に CAM 構成として組込んでよい。

#### 【0088】

ストアエントリ上のロードヒットが検出され対応するストアデータが利用可能の場合、LS2 制御回路 66 は、データ フォワード マルチブレクサ 100 を用いてストアデータを選択し、そのデータをポート 0 マルチブレクサ 112 またはポート 1 マルチブレクサ 110 のいずれかに、ヒットが検出されたポートに基づいて与える。したがって、データ フォワード マルチブレクサ 100 は、各ポートに 1 つずつ、1 組の独立したマルチブレクサを含む。加えて、LS2 制御回路 66 は、データキャッシュ 28 に対して対応する信号をアサートし、データキャッシュ 28 が、ヒットしているロードに対しデータキャッシュ 28 から読み出されたキャッシュデータの代わりに フォワード されたデータを選択できるようにする。

## 【 0 0 8 9 】

さらに、この実施例は、LS2バッファ62を用いるものとして示されているが、他の実施例も意図されている。この他の実施例においては、上記のストアフォワードメカニズムが、従来のストア待ち行列とともに実施され、このストア待ち行列は、データキャッシュ28を既に探索しているストアメモリ動作のみをストアする。（たとえばストア待ち行列400をある特定の実施例で用いることができる）。またさらに、ここで示されているマルチプレクサ110および112はデータキャッシュ28内にあるが、この回路を所望に応じてロード／ストアユニット26内で用いてもよい。加えて、ここで示されているマルチプレクサ100はLS2バッファ62からデータを選択してフォワードするものであるが、マルチプレクサ100を省いて、読出エントリ番号をデータを読出したLS2バッファ62に与えてもよい。これは、LS2バッファ62が個別クロックド記憶装置（たとえばレジスタ）ではなくRAM構成の場合である。

## 【 0 0 9 0 】

さらに、ある具体的な実現化例では、ロード／ストアユニット26が、従属性リンクファイルを用いて、対応するストアデータが利用可能でないストアにヒットするロードが検出されたときにデータのフォワードを加速してもよい。このようなロードの検出に応じて、ロード／ストアユニット26は、ロードのために従属性リンクファイルにエントリを割当てる。従属性リンクファイルエントリは、ストアにヒットしたロードを識別するロード識別子（たとえばリオーダバッファ32がロードに対応する命令に割当てた命令タグ）およびロードがヒットしたストアに対応するストアデータのソースを識別するストアデータ識別子（たとえばストアデータタグ）をストアする。次に、ロード／ストアユニット26は、従属性リンクファイル内にストアされたストアデータタグに対し、結果バス38をモニタする。ストアデータが結果バス38の1つに与えられていることが検出されると、ロード／ストアユニット26は、データキャッシュ28に、対応する結果バスからのデータをデータキャッシュ28からの結果バスにフォワードさせる。加えて、対応するエントリからのロード識別子が結果タグとしてフォワードされる。なお、従属性リンクファイルは、全く任意選択の性能の向上のためのものである。従属性リンクファイルを用いない実施例も意図されている。

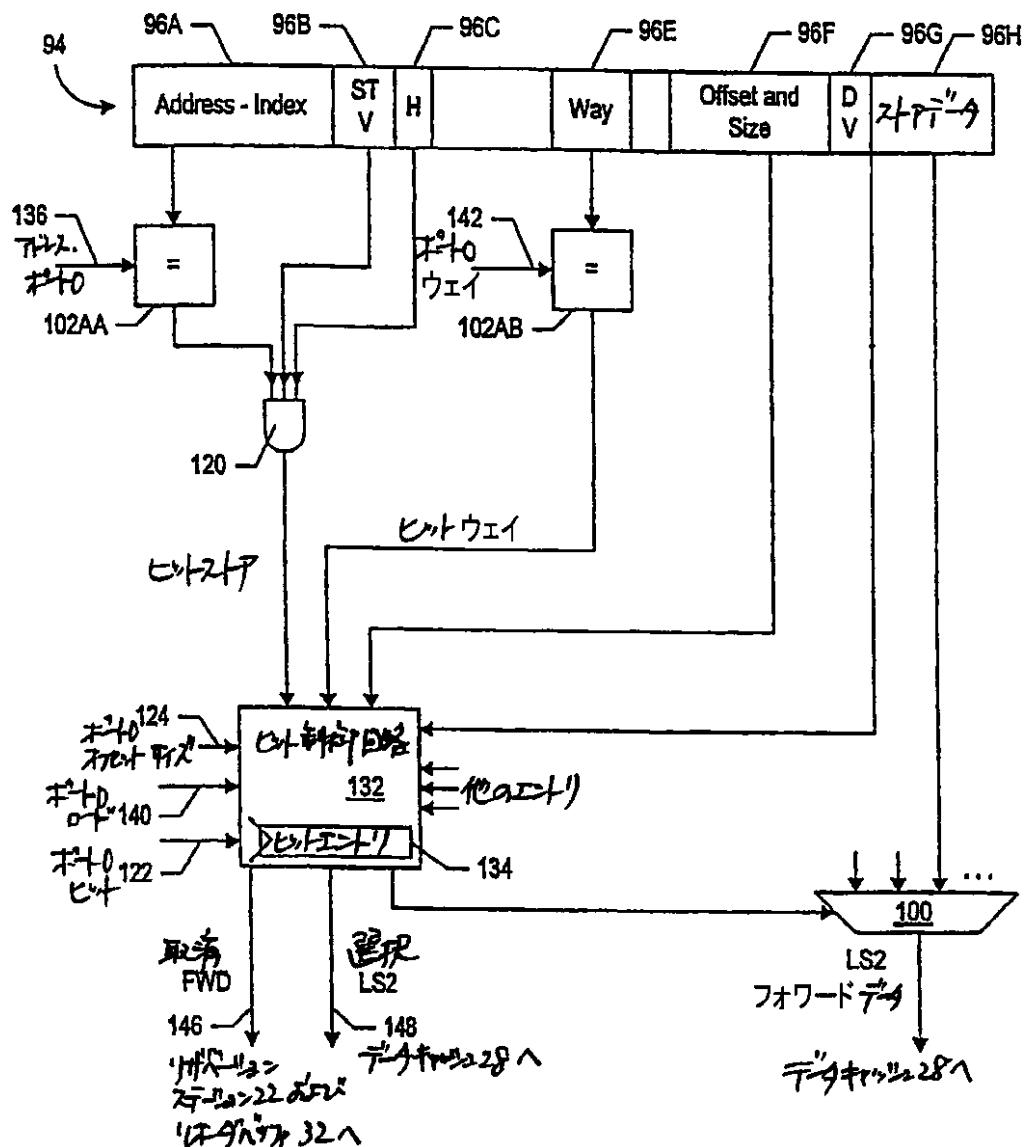

## 【 0 0 9 1 】

次に図6を参照して、LS2制御回路66およびLS2エントリ94の一実施例の一部のブロック図が示される。これ以外の実施例および特定の実現化例が意図されている。図6の実施例は、比較器102AA、比較器102AB、ANDゲート120、ヒット制御回路132、およびデータ転送マルチプレクサ100を含む。ヒット制御回路132はヒットエントリレジスタ134を含む。比較器102AAは、ポート0からデータアドレスの少なくともインデックス部を受け（参照番号136）、かつ、エントリ94のアドレス・インデックスフィールド96Aにストアされたデータアドレスのインデックス部を受けるように結合される。比較器102AAは、出力をANDゲート120に与え、ANDゲート120はさらに、エントリ94からストア有効ビット（STVフィールド96B）およびヒットビット（Hフィールド96C）を受けるように結合される。ANDゲート120の出力は、ヒットストア信号としてヒット制御回路132に結合され、ヒット制御回路132はさらに、ポート0ロード信号（参照番号140）、ポート0ヒット信号（参照番号122）およびポート0オフセットおよびサイズ情報（参照番号124）を受ける。比較器102ABは、ウェイフィールド96Eの内容を受けるように結合され、かつ、ポート0ウェイ表示（参照番号142）を受けるように結合される。比較器102ABは、出力をヒットウェイ信号としてヒット制御回路132に与えるように結合される。ヒット制御回路132はさらに、データ有効フィールド96Gからデータ有効ビットを受け、オフセットおよびサイズフィールド96Fからオフセットおよびサイズ情報を受けるように結合される。ヒット制御回路132は、他のエントリに対応する、同様のヒットストア、ヒットウェイ、データ有効ならびにオフセットおよびサイズ信号を受ける。ヒット制御回路132は、リザベーションステーション22およびリオーダバッファ32に取消しデータ

FWD信号を与え（参照番号146）、データキャッシュ28にLS2信号を選択する（参照番号148）ように結合される。加えて、ヒット制御回路132は、選択制御をマルチプレクサ100に与えるように結合される。マルチプレクサ100は、ストアデータフィールド96Hからのストアデータ（および他のLS2バッファエントリからのストアデータ）を受けるように結合される。

#### 【0092】

一般に、図6に示した論理では、エントリ94内のストアに対するポート0上のロードのヒットを検出する。ポート1およびエントリ94について、ならびに他のエントリに対する上記ポート双方について、同様の論理を用いることができる。より具体的には、比較器102AAは、ポート0上のデータアドレスのインデックス部をアドレス-インデックスフィールド96Cのインデックスと比較する。これらのインデックスが一致していれば、比較器102AAはその出力信号をアサートする。ANDゲート120は、比較器102AAの出力信号を受け、この出力信号をストア有効ビットおよびヒットビットと組合せる。ストア有効ビットは、エントリ94がストアメモリ動作に対応する情報をストアしているかどうかを示し（なぜならエントリ94および他のLS2バッファエントリはロードおよびストアいずれかに対応する情報をストアしている可能性があるため）、ヒットビットは、ストアがデータキャッシュ28を探索したときにデータキャッシュ28内でヒットしているかどうかを示す。したがって、ANDゲート120が与えるヒットストア信号は、アサートされたときに、ロードインデックスが、データキャッシュ28内でヒットであるストアインデックスにヒットしたことを示す。

#### 【0093】

ヒット制御回路132は、エントリ94に対応するヒットストア信号、ポート0に対応する他のヒットストア信号、およびポート0ロード信号140を組合せて、ポート0上にメモリ動作のためのデータフォワード信号を生成する。この実施例では、ヒット制御回路132は、ロードについて2つの場合を検出する。すなわち（i）ヒットストア信号がアサートされ対応するデータ有効ビット96Gがセットされる。（ii）ヒットストア信号がアサートされ対応するデータ有効ビット96Gがクリアされる。アサートされるヒットストア信号がない場合、またはポート0上のメモリ動作がロードでない場合、ヒット制御回路132は、そのメモリ動作には使用されない。この実施例では、同様のヒット制御回路を用いてポート1上のメモリ動作を行なうことができる。

#### 【0094】

（i）の場合、ヒット制御回路132は、データフォワードマルチプレクサ100に対しマルチプレクサ選択信号を生成し、これにより、データフォワードマルチプレクサ100は、アサートされたヒットストア信号に対応するLS2バッファエントリのストアデータフィールド96Hからのストアデータを選択する。たとえば、ANDゲート120が生成したヒットストア信号がアサートされる場合、ヒット制御回路132は、マルチプレクサ100が、エントリ94からストアデータフィールド96Hからのストアデータを選択するようにし、ポート0マルチプレクサ112に対応する選択LS2信号148をアサートする。選択されたデータは、データキャッシュ28によりフォワードされるが、これは図5について先に説明したとおりである。（ii）の場合、ヒット制御回路132は、転送（FWD）取消信号146をリザベーションステーション22およびリオーダバッファ32に対してアサートして、これらの構成要素に、そのクロックサイクル中ポート0上のロードに対してフォワードされたデータを無視するよう伝える。

#### 【0095】

このように、ヒット制御回路132は、エントリ94からのデータを、エントリ94内のストアインデックスおよびロードインデックスの一一致に基づいて、かつ、ストアがデータキャッシュ28内でヒットであることにに基づいて、フォワードする。特に、ロードがデータキャッシュ28内でヒットしているかどうかまたはロードおよびストアが同じウェイでヒットしているかどうか判断されていないことがある。この情報は、ロードの探索が終了するまで利用できないかもしれない。このような事態は、この実施例では後続のクロッ

クサイクルで生じる。したがって、ヒット制御回路 132 は、ヒットエントリレジスタ 134 内で、フォワードされたデータがもとあった LS2 バッファ 62 のエントリ番号を収集する。次のクロックサイクル中に、ヒット制御回路 132 は、LS2 バッファ 62 からのデータフォワードが正しいかどうか判断する。データフォワードが正しいのは、ロードがデータキャッシュ 28 内でヒットし（ポート 0 ヒット信号 122 で通知される）、ヒットエントリレジスタ 134 により識別されたエントリ内のロードおよびストアのウェイ表示が一致する場合（たとえば比較器 102AB がポート 0 のウェイ表示およびウェイフィールド 96E からのウェイ表示が一致することを検出した場合、エントリ 94 がヒットエントリレジスタ 134 によって示されている場合）である。フォワーディングが誤りであれば、ヒット制御回路 132 は、フォワード取消信号 146 をアサートして、リザベーションステーション 22 および / またはリオーダバッファ 32 に、以前にフォワードされたポート 0 上のデータを無視するよう知らせる。ヒット制御回路 132 は、別のデータフォワード取消信号 146 を与えてフォワーディングを取消すようにしてもよい。これは、（上記のように）データが利用可能でないため、および、ストア（データはここからフォワードされた）と異なるウェイのミスまたはヒットであるロードに対する誤ったフォワーディングのためである。この信号は、同じロードに対して異なる時間にアサートし得る。

#### 【 0096 】

図 1 に関して先に述べたように、ヒット制御回路 132 はさらに、LS2 バッファ 62 からのストアデータをロードのためにフォワードすべきかどうかをロードおよびストアに対する（キャッシュライン内の）オフセットおよびサイズ情報を用いて判断し、ロードが読出す少なくとも 1 バイトをストアにより更新するかどうか決定する。オフセットおよびサイズ情報は上記のようにどのような適切なフォーマットで与えてもよい（たとえばアドレスビットおよびバイトイネーブルマスクの組合せ）。なお、ヒット制御回路 132 がロードおよびストアアドレスのオフセットの一部を比較する場合、その部分を、所望される場合はインデックス部に加えて比較器 102AA で比較することができる。

#### 【 0097 】

さらに、ヒット制御回路 132 は、所与のロードについて 2 以上のストアのヒットを検出してもよい。ヒット制御回路 132 は、データフォワードのためにロードよりも古い、最も新しいストアを求める。それに代えて、各 LS2 バッファエントリが、所与のアドレスを更新する LS2 バッファ 62 内の最後のストアを識別するバッファ表示のうちの最終を含んでいてもよい。AND ゲート 120 内で L1B 表示を用いて、ヒットストア信号が、LS2 バッファ 62 内の最も新しいストアを除いてアサートされないようにする。このように、複数のヒットの優先順位をつけないようにする。ストアは LS2 バッファ 62 内に置かれているため、その L1B ビットをセットし、同じアドレスへの古いストアの L1B ビットをクリアしてもよい。

#### 【 0098 】

なお、ここで示している比較器 102AB は、LS2 バッファエントリ 94 にストアされたウェイ表示をロードのウェイ表示と比較するが、代替実施例においては、ロードのためにデータをフォワードするのに用いるエントリからのウェイ表示を読出して（フォワーディングがインデックス比較およびストアのデータキャッシュでのヒットに基づいている場合）、読出されたウェイ表示をロードウェイ表示と比較して、ロードおよびストアが同じウェイでヒットしていることを確認する。ウェイ表示を、ヒットエントリレジスタ 134 と同様のレジスタにストアして、将来の比較に備えることができる。

#### 【 0099 】

さらに、ロードが読出した 1 以上のバイトが、ロードが読出した 1 以上の他のバイトについてロードがヒットしたストアによって、更新されないことがある。このような場合、データキャッシュは、ストアデータをキャッシュデータと併合して、ロードが読出したバイトを与える。複数のストアが、ロードが読出したバイトのうち異なるバイトを与えるとき、このロードをリタイアさせて再探索する。複数のストアのうち 1 つ以上のストアをリタイアさせてデータキャッシュに与えてもよく、これらのストアが更新しロードが読出し

たバイトをデータキャッシュから与えてもよい。その代わりとして、図6の装置が、異なるストアからのバイトを併合してロードデータを与える。これ以外の実施例では、所望に応じて上記の方法を他のやり方で処理する。

#### 【0100】

なお、図6に示した論理は例示にすぎない。適切な組合せ論理（ここで示している論理のブール等価物を含む）を用いることができる。なお、エントリ94はLS2バッファエントリの一例である。エントリ94は、設計上の選択に応じて図6に示したものとの上にさらなる情報をストアしてもよい。

#### 【0101】

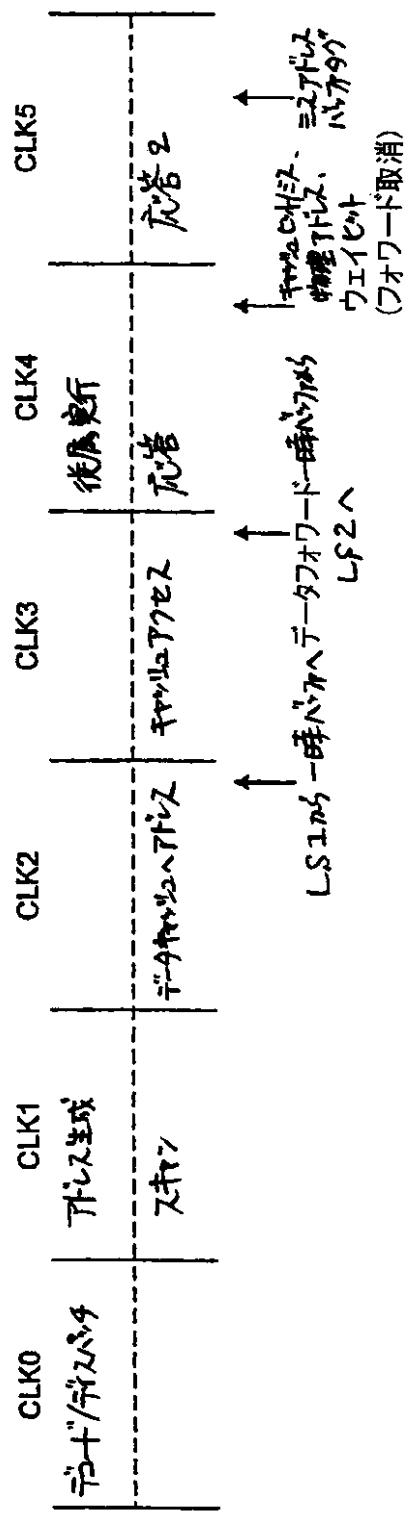

次に図7を参照して、LS1バッファ60からデータキャッシュ28を探索するメモリ動作のパイプラインの例を示すタイミング図が示されている。異なるパイプラインを用いたこれ以外の実施例が可能であり意図されている。図7において、クロックサイクルは垂直方向の実線で区切られている。水平方向の点線も示されている。プロセッサ10の他の部分に関連するパイプライン段を示して、他の構成要素のロード/ストアユニット26へのインターフェイスを示している。

#### 【0102】

クロックサイクルCLK0は、メモリ動作を指定する命令のデコード/ディスパッチサイクルである。クロックサイクルCLK0において、この命令をデコードするデコードユニット20は、メモリ動作に関しロード/ストアユニット26に信号を送る。LS1制御回路64は、対応する命令に対するデコード/ディスパッチ段においてメモリ動作のためにLS1バッファエントリを割当てる。加えて、デコードユニット20は、デコードされた命令を対応するリザベーションステーション22に送る。

#### 【0103】

クロックサイクルCLK1において、アドレス生成ユニットは、このメモリ動作のためにデータアドレスを生成し、このデータアドレスをロード/ストアユニット26に送る。このクロックサイクル中に、メモリ動作が、LS1制御回路64による（与えられたデータアドレスにより行なう）スキャンに加わり、データキャッシュ28を探索するために選択される。このようにして、メモリ動作はLS1パイプラインのスキャンパイプライン段にある。

#### 【0104】

クロックサイクルCLK2において、データアドレスはデータキャッシュ28に送られる。クロックサイクルCLK2内の矢印で示しているように、メモリ動作は、LS1バッファ60から、クロックサイクルCLK2の最後に一時バッファ68に移動する。メモリ動作は、クロックサイクルCLK2の間は、LS1パイプラインのデータキャッシュ段へのアドレスにある。

#### 【0105】

クロックサイクルCLK3において、データアドレスはデータキャッシュ28にアクセスする。メモリ動作に対応するデータは（メモリ動作がロードの場合）、クロックサイクルCLK3の最後にフォワードされる。より具体的には、ロードアドレスのインデックス部がLS2バッファ62内のストアアドレスのインデックス部と一致し、かつ、ストアがデータキャッシュ28内でヒットしていれば、LS2バッファ62からのデータは、クロックサイクルCLK3においてキャッシュデータの代わりにフォワードされる。加えて、メモリ動作は、一時バッファ68からLS2バッファ62に送られる。メモリ動作は、クロックサイクルCLK3においてはキャッシュアクセス段にある。

#### 【0106】

クロックサイクルCLK4において、メモリ動作に従属する命令（メモリ動作がロードの場合）が実行される。したがって、図7に示したパイプラインでは、3クロックサイクルアドレス生成が、従属動作実行ロードレイテンシに対して与えられている。加えて、メモリ動作は、クロックサイクル4においては応答パイプライン段にある。データキャッシュ28は、この応答段においてヒット/ミス情報（ヒットのウェイ表示を含む）および物

理アドレスを与える。このように、LS2制御回路66は、ヒットノミス情報および物理アドレスをこの応答段においてメモリ動作と関連付ける。さらに、ロードに対するヒットノミス表示およびウェイ表示を用いて、クロックサイクルCLK3においてLS2バッファ62からフォワードされたデータを確認する（利用できる場合）。フォワードされたデータが、ロードがミスであるまたは異なるウェイでヒットしたために誤ってフォワードされたものであれば、フォワード取消信号がアサートされる。

#### 【0107】

クロックサイクルCLK5において、メモリ動作は応答2パイプライン段にある。この段の間、メモリ動作がアクセスしたキャッシュラインに割当てられたミスアドレスバッファエントリを識別するミスアドレスバッファタグ（メモリ動作がミスの場合）が、データキャッシュ28により与えられる。このように、LS2制御回路66は、データキャッシュ28から受けたMABタグを応答2段のメモリ動作に関連付ける。

#### 【0108】

次に図8を参照して、LS2バッファ62からデータキャッシュ28を再探索するメモリ動作のパイプラインの例を示すタイミング図が示されている。異なるパイプラインを用いたこれ以外の実施例が可能であり意図されている。図8において、クロックサイクルは垂直方向の実線で区切られている。水平方向の点線も示されている。プロセッサ10の他の部分に関連するパイプライン段を示して、他の構成要素のロードノストアユニット26へのインターフェイスを示している。

#### 【0109】

クロックサイクルCLK0において、メモリ動作が、LS2バッファエントリのスキャンに加わり、データキャッシュ28を再探索するために選択される。クロックサイクルCLK0の下の矢印によって示しているように、このメモリ動作が選択されるのは、メモリ動作についてMABタグに一致する充填タグを受けた場合、メモリ動作がLS2バッファ62内より古いストアにヒットしているロードである場合（データは過去の探索に利用可能でなかった）、または、メモリ動作がリオーダバッファ32がリタイアしたストアである場合、である。

#### 【0110】

クロックサイクルCLK1において、スキャン1段で選択されたメモリ動作はスキャン2段に進む。スキャン2段において、メモリ動作はマルチプレクサ76および72を通して選択されてデータキャッシュ28に送られる。したがって、LS2制御回路66は、マルチプレクサ76を通してスキャン2段のメモリ動作を選択する。クロックサイクルCLK2、CLK3、CLK4およびCLK5は、LS2バッファ再探索パイプラインのデータキャッシュへのアドレス、キャッシュアクセス、応答、および応答2段であり、先に述べた対応する段と同様である。したがって、この実施例では、バスインターフェイスユニット37は、対応するデータを与える4クロック前にMABタグをとて、対応する充填データにアクセスするロードの選択が、充填データがデータキャッシュ28に到達した（従って充填データはフォワードされた）クロックサイクルのキャッシュアクセス段において行なわれるようとする。

#### 【0111】

なお、図7および8の点線の上の命令パイプライン段と点線の下のメモリ動作パイプライン段との間のタイミングを、図7および8に示したものから延長してもよい。たとえば、図7では、アドレスは、厳密にデコード/ディスパッチサイクル直後のクロックサイクルで生成されない場合がある。その代わりに、オペランドが利用できないまたはアドレス生成のために古い命令が選択される場合がある。さらに、メモリ動作は、アドレスが与えられたクロックサイクル中にアクセスのためにスキャンされないかもしれません、他の古いメモリ動作がその代わりにスキャンされるかもしれません。

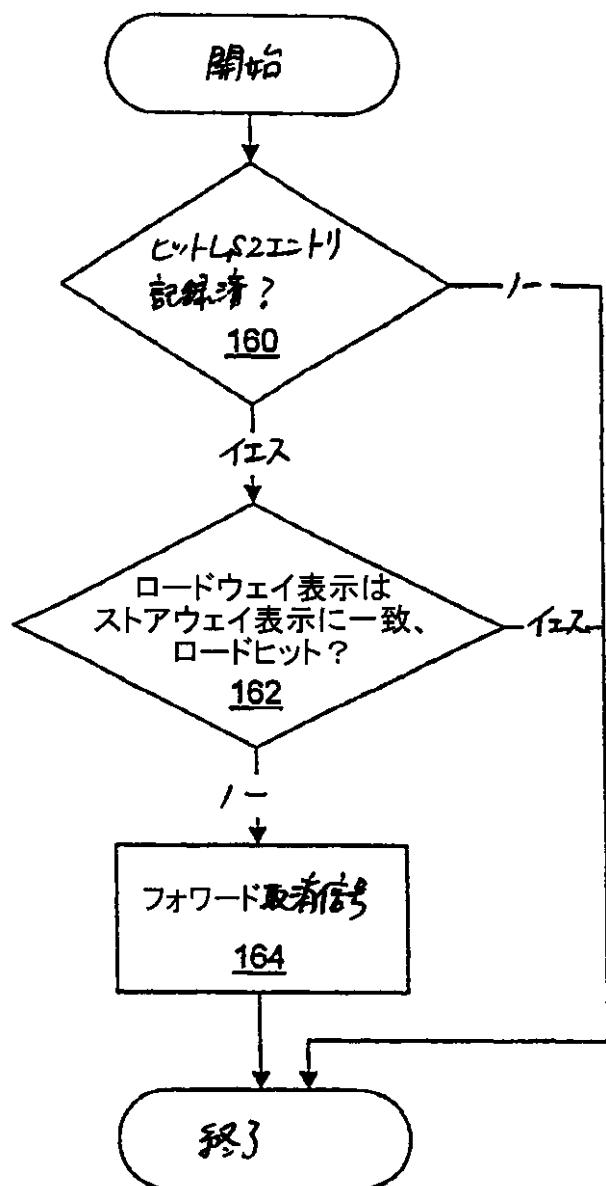

#### 【0112】

次に図9を参照して、ヒット制御回路132が、ロードの探索中にデータを選択してLS2バッファ62からフォワードする実施例の動作を示すフローチャートが示される（た

とえばロードの探索のキャッシュアクセスバイライン段）。他の実施例が可能であり意図されている。図9に示したステップは、理解しやすくするために特定の順序で示されているが、その他の適切な順序を用いてもよい。加えて、ステップを、ヒット制御回路132内で組合せ論理により並列に実行してもよい。

#### 【0113】

ヒット制御回路132は、ロードがストアにヒットしストアがキャッシュヒットであるかどうかを判断する（判断ブロック150）。より具体的には、ヒット制御回路132は、ロードインデックスがストアインデックスに一致している（かつオフセットおよびサイズ情報が一致している）場合にロードがストアにヒットしていると判断する。この判断は、ロードヒット情報およびウェイ表示を後続のクロックサイクルで利用できるときに、その正誤が検査される（図10に示す）。判断ブロック150の結果が「イエス」であれば、ヒット制御回路132は、データキャッシュ28に信号を送り、キャッシュデータの代わりに、LS2バッファ62から与えられるデータを選択し、ヒットであるエントリからのデータをマルチプレクスし（ステップ152）、ヒットであるLS2バッファエントリをヒットエントリレジスタ134に記録する（ステップ154）。判断ブロック150の結果が「ノー」であれば、ヒット制御回路132はロードに関してそれ以上の作業は行なわない。

#### 【0114】

図10は、ヒット制御回路132がロードの探索中にLS2バッファ62からのフォワードィングを検査する実施例の動作を示すフローチャートである（たとえばロードの探索の応答バイライン段）。これ以外の実施の形態が可能であり意図されている。図10に示したステップは理解しやすくするために特定の順序で示されているが、これ以外の適切な順序を用いてもよい。加えて、これらのステップをヒット制御回路132内で組合せ論理により並列に実行してもよい。

#### 【0115】

ヒット制御回路132は、エントリがヒットエントリレジスタ134に記録されているかどうか判断する（判断ブロック160）。たとえば、ヒットエントリレジスタ134は、データがインデックス比較およびストアがヒットであることに基づいてフォワードされたときにセットされ、ロードのヒットの検査およびウェイ表示の一致後にリセットされる、有効ビットを含み得る。エントリがヒットエントリレジスタ134に記録されていなければ、ヒット制御回路132はロードに関してさらなる作業は行なわない。エントリがヒットエントリレジスタ134に記録されていれば、ヒット制御回路134は、ロードウェイ表示がヒットエントリレジスタ134に記録されたエントリのストアウェイ表示に一致しているかどうか、および、ロードがヒットかどうか判断する（判断ブロック162）。ロードがミスであるまたはロードウェイ表示がストアウェイ表示に一致していなければ、ヒット制御回路132は、フォワード取消信号をアサートする（ステップ164）。ロードがヒットでありロードウェイ表示がヒットエントリレジスタ134に記録されたエントリのストアウェイ表示に一致していれば、ヒット制御回路132はロードに関してさらなる作業は行なわない。

#### 【0116】

なお、ここでは種々の信号のアサートについて述べている。本明細書では、ある信号は、この信号が特定の状態を示す値を伝える場合に「アサートされる」。逆に、ある信号は、その信号が特定の状態がないことを示す値を伝える場合に「デアサートされる」。ある信号は、論理ゼロ値を伝える場合または逆に論理1値を伝える場合にアサートされると定義してもよい。

#### 【0117】

##### コンピュータシステム

次に図11を参照して、バスブリッジ202を通して種々のシステム構成要素に結合されたプロセッサ10を含むコンピュータシステム200の一実施例のブロック図が示される。これ以外の実施例が可能であり意図されている。ここで示しているシステムでは、メ

インメモリ 204 はメモリバス 206 を通してバスブリッジ 202 に結合され、グラフィックスコントローラ 208 は AGP バス 210 を通してバスブリッジ 202 に結合される。最後に、複数の PCI 装置 212A - 212B が PCI バス 214 を通してバスブリッジ 202 に結合される。第 2 のバスブリッジ 216 をさらに設けて、ISA / ISA バス 220 を通して 1 以上の ISA または ISA 装置 218 への電気的インターフェイスに対応するようにしてもよい。プロセッサ 10 は、CPU バス 224 を通してバスブリッジ 202 に結合され、任意的選択の L2 キャッシュ 228 に結合される。CPU バス 224 および L2 キャッシュ 228 へのインターフェイスは、バスインターフェイスユニット 37 が結合されたインターフェイスを含むものでもよい。

#### 【 0118 】

バスブリッジ 202 は、プロセッサ 10、メインメモリ 204、グラフィックスコントローラ 208 および PCI バス 214 に取付けられた装置間のインターフェイスとなる。バスブリッジ 202 に接続されたこれら装置のうち 1 つから動作を受けると、バスブリッジ 202 はその動作のターゲットを識別する（たとえば特定の装置、または、PCI バス 214 の場合はターゲットが PCI バス 214 にあることを識別）。バスブリッジ 202 は、その動作をターゲットの装置に送る。一般的に、バスブリッジ 202 は、ある動作を、ソースである装置またはバスが用いるプロトコルから、ターゲットである装置またはバスが用いるプロトコルに変換する。

#### 【 0119 】

第 2 のバスブリッジ 216 は、PCI バス 214 に対して ISA / ISA バスへのインターフェイスを与えることに加え、所望に応じてさらなる機能を取り入れてもよい。入出力コントローラ（図示せず）は、第 2 のバスブリッジ 216 外のものでもバスブリッジ 216 と一体化されたものであっても、コンピュータシステム 200 内に設けられて、所望に応じて、キーボードおよびマウス 222 のためのならびに種々のシリアルおよびパラレルポートのための動作支援を行なってもよい。他の実施例において、外部キャッシュユニット（図示せず）をさらに、プロセッサ 10 およびバスブリッジ 202 間で CPU バス 224 に結合してもよい。その代わりに、外部キャッシュをバスブリッジ 202 に結合し、外部キャッシュのためのキャッシュ制御回路をバスブリッジ 202 と一体化させてもよい。L2 キャッシュ 228 が、プロセッサ 10 の裏側の構成として示されている。なお、L2 キャッシュ 228 はプロセッサ 10 から離れていてもよく、プロセッサ 10 とともにカートリッジに組込まれていてもよく（たとえばスロット 1 またはスロット A）、またはプロセッサ 10 とともに半導体基板上に集積されてもよい。

#### 【 0120 】

メインメモリ 204 は、アプリケーションプログラムがストアされているメモリであり、このメモリから、プロセッサ 10 は主として実行する。適切なメインメモリ 204 は、DRAM（ダイナミックランダムアクセスメモリ）を含む。たとえば、SDRAM（同期型（synchronous）DRAM）またはランバス（Rambus）DRAM（RDRAM）の複数のバンクが適切である。

#### 【 0121 】

PCI 装置 212A - 212B は、例えばネットワークインターフェイスカード、ビデオアクセラレータ、オーディオカード、ハードまたはフロッピー（R）ディスクドライブまたはドライブコントローラ、SCSI（スマートコンピュータシステムインターフェイス）アダプタおよびテレホンカードといった種々の周辺装置の例である。同様に、ISA 装置 218 は、モデム、サウンドカードおよび種々のデータ取得カード（たとえば GPIB またはフィールドバスインターフェイスカード）といった種々の周辺装置の例である。

#### 【 0122 】

グラフィックスコントローラ 208 は、テキストおよび画像のディスプレイ 226 へのレンダリングを制御するために設けられる。グラフィックスコントローラ 208 は、一般的に当該技術ではメインメモリ 204 およびメインメモリ 204 から効果的にシフト可能な 3 次元データ構造をレンダリングする典型的なグラフィックスアクセラレータを実現

している。グラフィックスコントローラ 208 はしたがって、バスブリッジ 202 内のターゲットインターフェイスにアクセスを要求しアクセスを受けることができ、従ってメインメモリ 204 へのアクセスを得るという点において、AGP バス 210 のマスタである。専用グラフィックスバスが、メインメモリ 204 からデータを迅速に取出すことができるようになる。いくつかの動作では、グラフィックスコントローラ 208 がさらに、AGP バス 210 上で PCI プロトコルトランザクションを生成するように構成されていてよい。バスブリッジ 202 の AGP インターフェイスはこのように、AGP プロトコルトランザクションならびに PCI プロトコルターゲットおよびイニシエータトランザクション双方を支援する機能を有する。ディスプレイ 226 は、画像またはテキストを表示できる電子表示装置である。適切なディスプレイ 226 は、陰極線管（「CRT」）、液晶ディスプレイ（「LCD」）などを含む。

#### 【0123】

上記の説明では AGP、PCI、および ISA または EISA バスを例として用いているが、所望に応じていかなるバスアーキテクチャに代えてもよい。さらに、コンピュータシステム 200 は、さらなるプロセッサ（たとえばコンピュータシステム 200 の任意的選択構成要素としてのプロセッサ 10a）を含む多重処理コンピュータシステムでもよい。プロセッサ 10a はプロセッサ 10 と同様のものである。より具体的には、プロセッサ 10a は、プロセッサ 10 をそのままコピーしたものである。プロセッサ 10a は独立したバス（図 11 に示したもの）を介してバスブリッジ 202 に接続されてもよく、プロセッサ 10 と CPU バス 224 を共有してもよい。さらに、プロセッサ 10a は L2 キャッシュ 228 と同様の任意的選択の L2 キャッシュ 228a に結合されてもよい。

#### 【0124】

次に図 12 を参照して、コンピュータシステム 300 のもう 1 つの実施例が示されている。これ以外の実施例が可能であり意図されている。図 12 に示した実施例では、コンピュータシステム 300 は、数個の処理ノード 312A、312B、312C および 312D を含む。各処理ノードは、それぞれ処理ノード 312A - 312D 内に含まれたメモリコントローラ 316A - 316D を介してメモリ 314A - 314D 各々に結合される。加えて、処理ノード 312A - 312D は、処理ノード 312A - 312D 間の連絡に用いられるインターフェイス論理を含む。たとえば、処理ノード 312A は、処理ノード 312B との通信のためのインターフェイス論理 318A、処理ノード 312C との通信のためのインターフェイス論理 318B、および、別のさらなる処理ノード（図示せず）との通信のための第 3 のインターフェイス論理 318C を含む。同様に、処理ノード 312B は、インターフェイス論理 318D、318E および 318F を含み、処理ノード 312C は、インターフェイス論理 318G、318H および 318I を含み、処理ノード 312D は、インターフェイス論理 318J、318K および 318L を含む。処理ノード 312D は、複数の入出力装置（たとえばデイジーチェーン構成の装置 320A - 320B）とインターフェイス論理 318L を介して通信するよう結合されている。同様にこれ以外の処理ノードが他の I/O 装置と通信してもよい。

#### 【0125】

処理ノード 312A - 312D は、処理ノード間通信のためのパケットに基づいたリンクを実現する。この実施例において、このリンクは、単方向ラインの組として実現される。（たとえばライン 324A は処理ノード 312A から処理ノード 312B にパケットを転送するために用いられ、ライン 324B は処理ノード 312B から処理ノード 312A にパケットを転送するために用いられる。）図 12 に示されているように、これ以外のライン 324C - 324H の組を用いて他の処理ノード間でのパケットの転送を行なう。一般的に、ライン 324 の組各々は、1 以上のデータライン、このデータラインに対応する 1 以上のクロックラインおよび送られているパケットの種類を示す 1 以上の制御ラインを含む。リンクは、処理ノード間の通信に対してはキャッシュコヒーレントの態様で動作し、または、処理ノードおよび I/O 装置間の（またはバスブリッジから PCI バスまたは

I S A バスといった従来の構成の I / O バスへの ) 通信については、非コヒーレントな態様で動作する。さらに、リンクは、図示のような I / O 装置間のデイジーチェーン構成を用いて非コヒーレントな態様で動作してもよい。なお、1 つの処理ノードから別の処理ノードに転送されるパケットは、1 以上の中間ノードを通過し得る。たとえば、処理ノード 3 1 2 A により処理ノード 3 1 2 D に転送されるパケットは、図 1 2 に示すように、処理ノード 3 1 2 B または処理ノード 3 1 2 C を通過する。任意の適切な経路指定アルゴリズムを用いることができる。コンピュータシステム 3 0 0 のこれ以外の実施例では、図 1 2 に示した実施例よりも多いまたは少ない処理ノードを含み得る。

#### 【 0 1 2 6 】

一般的に、パケットは、ノード間のライン 3 2 4 上で 1 以上のビットタイムとして転送される。ビットタイムとは、対応するクロックライン上のクロック信号の立上がりまたは立下がりエッジである。パケットは、トランザクション開始のためのコマンドパケット、キャッシュコヒーレント維持のための探索パケット、および探索およびコマンドへの応答のための応答パケットを含み得る。

#### 【 0 1 2 7 】

処理ノード 3 1 2 A - 3 1 2 D は、メモリコントローラおよびインターフェイス論理に加えて、1 以上のプロセッサを含む。一般的にいえば、処理ノードは少なくとも 1 つのプロセッサを含み、任意として、所望に応じてメモリおよび他の論理との通信のためのメモリコントローラを含む。具体的には、処理ノード 3 1 2 A - 3 2 1 D はプロセッサ 1 0 を含む。外部インターフェイスユニット 4 6 は、ノード内のインターフェイス論理 3 1 8 およびメモリコントローラ 3 1 6 を含む。

#### 【 0 1 2 8 】

メモリ 3 1 4 A - 3 1 4 D は、適切な記憶装置を含む。たとえば、メモリ 3 1 4 A - 3 1 4 D は、1 以上のランバス D R A M ( R D R A M ) 、同期型 D R A M ( S D R A M ) 、スタティック R A M などを含む。コンピュータシステム 3 0 0 のアドレス空間は、メモリ 3 1 4 A - 3 1 4 D 間で分割される。各処理ノード 3 1 2 A - 3 1 2 D は、どのアドレスがどのメモリ 3 1 4 A - 3 1 4 D にマッピングされているかを判断して、特定のアドレスに対するメモリ要求をどの処理ノード 3 1 2 A - 3 1 2 D に送るかを判断するために用いるメモリマップを含む。ある実施例では、コンピュータシステム 3 0 0 内のアドレスに対するコヒーレントなポイントは、アドレスに対応するバイトをストアするメモリに結合されたメモリコントローラ 3 1 6 A - 3 1 6 D である。言い換えれば、メモリコントローラ 3 1 6 A - 3 1 6 D は、対応するメモリ 3 1 4 A - 3 1 4 D への各メモリアクセスが確実にキャッシュコヒーレントな態様で生じるようにする。メモリコントローラ 3 1 6 A - 3 1 6 D は、メモリ 3 1 4 A - 3 1 4 D へのインターフェイスのための制御回路を含む。加えて、メモリコントローラ 3 1 6 A - 3 1 6 D は、メモリ要求を待ち行列に入れるための要求待ち行列を含む。

#### 【 0 1 2 9 】

一般的に、インターフェイス論理 3 1 8 A - 3 1 8 L は、リンクからパケットを受けるためかつそのリンク上で転送されるパケットをバッファするための種々のバッファを含む。コンピュータシステム 3 0 0 は、パケット転送のために適切なフロー制御メカニズムを用いる。たとえば、ある実施例では、各インターフェイス論理 3 1 8 は、そのインターフェイス論理が接続されたリンクの他端の受信装置内のバッファの各種類の数のカウントをストアする。インターフェイス論理は、受けたインターフェイス論理にパケットをストアする空きのバッファがないのであればパケットを転送しない。受けたバッファをパケットを送出することによって空にすれば、受けたインターフェイス論理は送ったインターフェイス論理にメッセージを送信してバッファが空になっていることを知らせる。こうしたメカニズムのことを「クーポンに基づいた」システムと呼ぶ。

#### 【 0 1 3 0 】

I / O 装置 3 2 0 A - 3 2 0 B は、任意の適切な I / O 装置である。たとえば、I / O 装置 3 2 0 A - 3 2 0 B は、ネットワークインターフェイスカード、ビデオアクセラレー

タ、オーディオカード、ハードまたはフロッピー（R）ディスクドライブまたはドライブコントローラ、SCSI（スマートコンピュータシステムインターフェイス）アダプタおよびテレホンカード、モデム、サウンドカード、ならびに種々のデータ取得カード（GPIBまたはフィールドバスインターフェイスカードなど）を含む。

【0131】

上記の開示を十分に理解すれば当業者には多数の変形例および修正例が明らかになるであろう。前掲の特許請求の範囲はこうした変形例および修正例すべてを含むと解釈すべきものである。

【図面の簡単な説明】

【図1】ストア待ち行列の一実施例のブロック図である。

【図2】プロセッサの一実施例のブロック図である。

【図3】図2に示したデコードユニット、リザベーションステーション、機能ユニット、リオーダバッファ、ロード／ストアユニット、データキャッシュおよびバスインターフェイスユニットの一実施例を示すブロック図であり、相互接続の一実施例を強調している。

【図4】図2および3に示したロード／ストアユニットの一実施例のブロック図である。

【図5】ロード／ストアユニットおよびデータキャッシュの一実施例の一部のブロック図である。

【図6】図5に示した制御回路の一部を示すブロック図である。

【図7】一実施例に従う図4に示したLS1バッファから選択されるメモリ動作に対応するタイミング図である。

【図8】一実施例に従う図4に示したLS2バッファから選択されるメモリ動作に対応するタイミング図である。

【図9】図6に示した制御回路の一実施例の、ストアアドレスにヒットするロードアドレスの検出中の動作を示すフローチャートである。

【図10】図6に示した制御回路の一実施例の、ロードアドレスがストアアドレスにヒットすることを検査する際の動作を示すフローチャートである。

【図11】コンピュータシステムの第1の実施例のブロック図である。

【図12】コンピュータシステムの第2の実施例のブロック図である。

【誤訳訂正2】

【訂正対象書類名】図面

【訂正対象項目名】図1

【訂正方法】変更

【訂正の内容】

【図1】

Fig. 1

【誤訛訂正3】

【訂正対象書類名】図面

【訂正対象項目名】図4

【訂正方法】変更

【訂正の内容】

【図4】

Fig. 4

## 【誤訳訂正4】

【訂正対象書類名】図面

### 【訂正対象項目名】図 5

## 【訂正方法】変更

## 【訂正の内容】

【図5】

Fig. 5

【誤訛訂正 5】

【訂正対象書類名】図面

【訂正対象項目名】図 6

【訂正方法】変更

【訂正の内容】

【図6】

Fig. 6

## 【誤訳訂正6】

【訂正対象書類名】 団面

### 【訂正対象項目名】図 7

## 【訂正方法】変更

## 【訂正の内容】

【 図 7 】

Fig. 7

## 【誤訳訂正 7】

### 【訂正対象書類名】 図面

### 【訂正対象項目名】図 8

## 【訂正方法】変更

## 【訂正の内容】

【図 8】

Fig. 8

【誤訛訂正 8】

【訂正対象書類名】図面

【訂正対象項目名】図 10

【訂正方法】変更

【訂正の内容】

【図 10】

Fig. 10