(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6474625号

(P6474625)

(45) 発行日 平成31年2月27日(2019.2.27)

(24) 登録日 平成31年2月8日(2019.2.8)

(51) Int.Cl.

F 1

|              |           |      |        |      |

|--------------|-----------|------|--------|------|

| HO1L 21/336  | (2006.01) | HO1L | 29/78  | 616K |

| HO1L 29/786  | (2006.01) | HO1L | 29/78  | 617J |

| HO1L 21/8238 | (2006.01) | HO1L | 27/092 | G    |

| HO1L 27/092  | (2006.01) | HO1L | 27/088 | 331E |

| HO1L 27/088  | (2006.01) | HO1L | 21/28  | 301B |

請求項の数 3 (全 56 頁) 最終頁に続く

(21) 出願番号

特願2015-15863 (P2015-15863)

(22) 出願日

平成27年1月29日(2015.1.29)

(65) 公開番号

特開2015-164185 (P2015-164185A)

(43) 公開日

平成27年9月10日(2015.9.10)

審査請求日

平成30年1月22日(2018.1.22)

(31) 優先権主張番号

特願2014-15551 (P2014-15551)

(32) 優先日

平成26年1月30日(2014.1.30)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 田中 哲弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の絶縁体上に、第1の領域と、第2の領域と、前記第1の領域と前記第2の領域との間の第3の領域と、を有する酸化物半導体を形成する工程と、

第2の絶縁体を介して前記第3の領域と重なる領域を有する第1の導電体を形成する工程と、

前記第1の導電体の側面及び前記第2の絶縁体の側面に接する第3の絶縁体と、前記酸化物半導体の側面に接する領域を有する第4の絶縁体と、を形成する工程と、

前記第1の領域上に第2の導電体を選択的に成長させる工程と、を有し、

前記第3の領域は、トランジスタのチャネル形成領域として機能し、

前記第1の絶縁体は、前記酸化物半導体と重ならない領域において、前記第3の領域と重なる領域よりも膜厚の小さい部分を有し、

前記第1の絶縁体の前記部分は、前記トランジスタのチャネル長方向において、前記第3の絶縁体と接する領域を有さず、且つ前記第4の絶縁体と接する領域を有さない、半導体装置の作製方法。

## 【請求項 2】

請求項1において、

前記第1の領域及び前記第2の領域は、シリコンを有し、

前記第2の導電体は、タンゲステンを有するガスを用いた化学気相成長法により形成する、半導体装置の作製方法。

10

20

**【請求項 3】**

請求項 1において、

前記第 1 の領域及び前記第 3 の領域は、チタンを有し、

前記第 2 の導電体は、アルミニウムを有するガスを用いた化学気相成長法により形成する、半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または組成物（コンポジション・オブ・マター）に関する。特に、10 本発明は、例えば、半導体、半導体装置、表示装置、発光装置、照明装置、蓄電装置、記憶装置またはプロセッサに関する。または、半導体、半導体装置、表示装置、発光装置、照明装置、蓄電装置、記憶装置またはプロセッサの製造方法に関する。または、半導体装置、表示装置、発光装置、照明装置、蓄電装置、記憶装置またはプロセッサの駆動方法に関する。

**【0002】**

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。表示装置、発光装置、照明装置、電気光学装置、半導体回路および電子機器は、半導体装置を有する場合がある。

**【背景技術】****【0003】**

絶縁表面を有する基板上の半導体を用いて、トランジスタを構成する技術が注目されている。当該トランジスタは集積回路や表示装置のような半導体装置に広く応用されている。トランジスタに適用可能な半導体としてシリコンが知られている。

**【0004】**

トランジスタの半導体に用いられるシリコンは、用途によって非晶質シリコン、多結晶シリコン、単結晶シリコンなどが使い分けられている。例えば、大型の表示装置を構成するトランジスタに適用する場合、大面積基板への成膜技術が確立されている非晶質シリコンを用いると好適である。一方、駆動回路と画素回路とを同一基板上に形成するような高機能の表示装置を構成するトランジスタに適用する場合、高い電界効果移動度を有するトランジスタを作製可能な多結晶シリコンを用いると好適である。また、集積回路などを構成するトランジスタに適用する場合、さらに高い電界効果移動度を有する単結晶シリコンを用いると好適である。多結晶シリコンは、非晶質シリコンに対し高温での熱処理、またはレーザ光処理を行うことで形成する方法が知られる。30

**【0005】**

また、近年は、酸化物半導体が注目されている。酸化物半導体は、スパッタリング法などを用いて成膜できるため、大型の表示装置を構成するトランジスタの半導体に用いることができる。また、酸化物半導体を用いたトランジスタは、高い電界効果移動度を有するため、駆動回路と画素回路とを同一基板上に形成するような高機能の表示装置を実現できる。また、非晶質シリコンを用いたトランジスタの生産設備の一部を改良して利用することが可能であるため、設備投資を抑えられるメリットもある。40

**【0006】**

ところで、酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流が小さいことが知られている。例えば、酸化物半導体を用いたトランジスタのリーク特性を応用した低消費電力の C P U などが開示されている（特許文献 1 参照。）。このように、C P U などの集積回路に酸化物半導体を用いたトランジスタを応用する場合、トランジスタを縮小し、高集積化することが好ましい。

**【0007】**

半導体装置は、高集積化を進めると、配線や電極などが重なり合うことに起因して形成される寄生容量の影響が無視できなくなる場合がある。特許文献 2 には、導体電極から半導

10

20

30

40

50

体中に電子を流入させることで、オフセット領域が設けられても優れた電気特性を有するトランジスタが得られることが開示されている。特許文献2に開示された技術を用いることで、配線や電極などが重なり合うことに起因して形成される寄生容量を低減することができる。

#### 【0008】

また、半導体からなる活性層で井戸型ポテンシャルを構成することにより、高い電界効果移動度を有するトランジスタが得られることが開示されている（特許文献3参照。）。

#### 【先行技術文献】

##### 【特許文献】

##### 【0009】

10

【特許文献1】特開2012-257187号公報

【特許文献2】特開2011-22507号公報

【特許文献3】特開2012-59860号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0010】

寄生容量の小さいトランジスタを提供することを課題の一とする。または、優れたスイッチング特性を有するトランジスタを提供することを課題の一とする。または、非導通時の電流の小さいトランジスタを提供することを課題の一とする。または、導通時の電流の大きいトランジスタを提供することを課題の一とする。または、当該トランジスタを有する半導体装置を提供することを課題の一とする。または、寄生容量の小さい半導体装置を提供することを課題の一とする。または、消費電力の小さい半導体装置を提供することを課題の一とする。または、優れた周波数特性を有する半導体装置を提供することを課題の一とする。または、集積度の高い半導体装置を提供することを課題の一とする。または、丈夫な半導体装置を提供することを課題の一とする。または、新規な半導体装置を提供することを課題の一とする。

20

##### 【0011】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

30

#### 【課題を解決するための手段】

##### 【0012】

##### (1)

本発明の一態様は、半導体と、第1の導電体と、第2の導電体と、第3の導電体と、絶縁体と、を有し、半導体が、第1の導電体と接する第1の領域と、第2の導電体と接する第2の領域と、絶縁体と接する第3の領域と、を有し、第3の導電体が、絶縁体を介して第3の導電体と半導体とが互いに重なる領域を有し、第1の領域と、第3の領域と、が互いに重ならず、第2の領域と、第3の領域と、が互いに重ならない半導体装置の作製方法であって、第1の導電体を第1の領域上に選択成長させ、第2の導電体を第2の領域上に選択成長させる。

40

##### 【0013】

##### (2)

本発明の一態様は、第1の絶縁体上に半導体を形成し、半導体上に第2の絶縁体を形成し、第2の絶縁体上に第1の導電体を形成し、第1の導電体の一部をエッティングすることで、第2の絶縁体を介して半導体と重なる領域を有する第2の導電体を形成し、第2の絶縁体の一部をエッティングすることで、第2の導電体と重なる領域に第3の絶縁体を形成し、第2の導電体をマスクとして、半導体に不純物を加え、半導体上および第2の導電体上に第4の絶縁体を形成し、第4の絶縁体を異方性エッティングすることで、第2の導電体の側面に接する領域を有する第5の絶縁体を形成し、異方性エッティングとともに第2の絶縁体

50

の露出した領域をエッティングし、異方性エッティングとともに第1の絶縁体の露出した領域をエッティングすることで、第1の絶縁体に厚さの小さい領域を形成し、半導体の不純物の加えられた領域のうち、露出された領域上に導電体を選択成長させる。

【0014】

(3)

本発明の一態様は、第1の絶縁体上に半導体を形成し、半導体上に第2の絶縁体を形成し、第2の絶縁体上に第1の導電体を形成し、第1の導電体の一部をエッティングすることで、第2の絶縁体を介して半導体と重なる領域を有する第2の導電体を形成し、第2の絶縁体上および第2の導電体上に第3の絶縁体を形成し、第2の導電体をマスクとして、半導体に不純物を加えた後、第3の絶縁体上に第4の絶縁体を形成し、第3の絶縁体および第4の絶縁体を異方性エッティングすることで、第2の導電体の側面に接する領域を有する第5の絶縁体を形成し、異方性エッティングとともに第2の絶縁体の露出した領域をエッティングし、異方性エッティングとともに第1の絶縁体の露出した領域をエッティングすることで、第1の絶縁体に厚さの小さい領域を形成し、半導体の不純物の加えられた領域のうち、露出された領域上に導電体を選択成長させる。

【0015】

(4)

本発明の一態様は、不純物は、イオン注入法により加えられる(2)または(3)に記載の半導体装置の作製方法である。

【0016】

(5)

本発明の一態様は、不純物は、クラスタイオンを用いたイオン注入法により加えられる(2)または(3)に記載の半導体装置の作製方法である。

【0017】

(6)

本発明の一態様は、不純物がシリコンを有し、導電体の選択成長は、タンゲステンを有するガスを用いた化学気相成長法により行う(2)乃至(5)のいずれか一に記載の半導体装置の作製方法である。

【0018】

(7)

本発明の一態様は、タンゲステンを有するガスは、六フッ化タンゲステンガスと、モノシリガスと、を有する(6)に記載の半導体装置の作製方法である。

【0019】

(8)

本発明の一態様は、不純物がチタンを有し、導電体の選択成長は、アルミニウムを有するガスを用いた化学気相成長法により行う(2)乃至(5)のいずれか一に記載の半導体装置の作製方法である。

【0020】

(9)

本発明の一態様は、アルミニウムを有するガスは、ジエチルアルミニウムハイドライドガスを有する(8)に記載の半導体装置の作製方法である。

【発明の効果】

【0021】

寄生容量の小さいトランジスタを提供することができる。または、優れたスイッチング特性を有するトランジスタを提供することができる。または、非導通時の電流の小さいトランジスタを提供することができる。または、導通時の電流が大きいトランジスタを提供することができる。または、当該トランジスタを有する半導体装置を提供することができる。または、寄生容量の小さい半導体装置を提供することができる。または、消費電力の小さい半導体装置を提供することができる。または、優れた周波数特性を有する半導体装置を提供することができる。または、集積度の高い半導体装置を提供することができる。ま

10

20

30

40

50

たは、丈夫な半導体装置を提供することができる。または、新規な半導体装置を提供することができる。

#### 【0022】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

#### 【図面の簡単な説明】

#### 【0023】

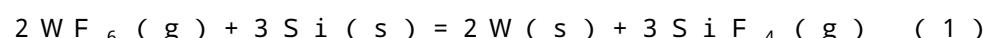

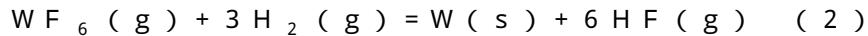

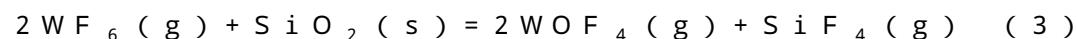

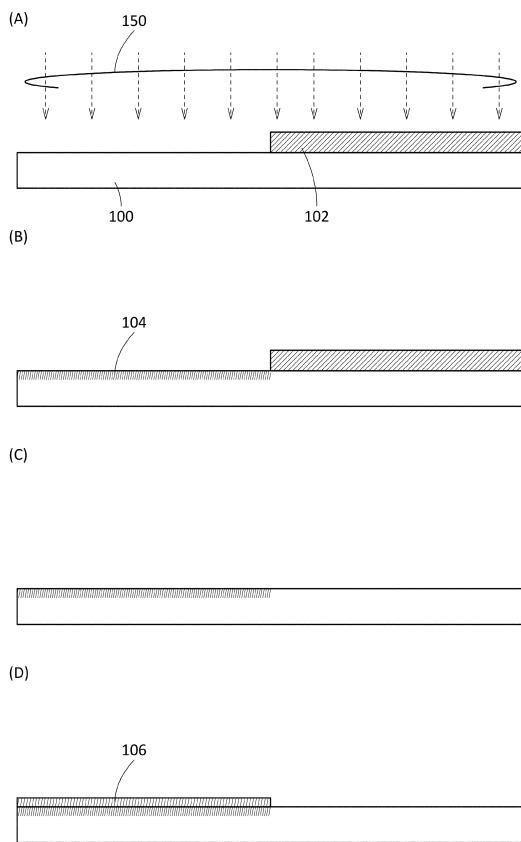

【図1】本発明の一態様に係る導電体の選択成長を示す断面図。

10

【図2】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図3】本発明の一態様に係るトランジスタの作製方法を示す断面図。

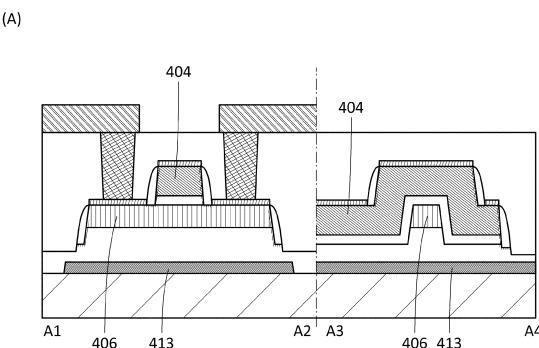

【図4】本発明の一態様に係るトランジスタの作製方法を示す断面図。

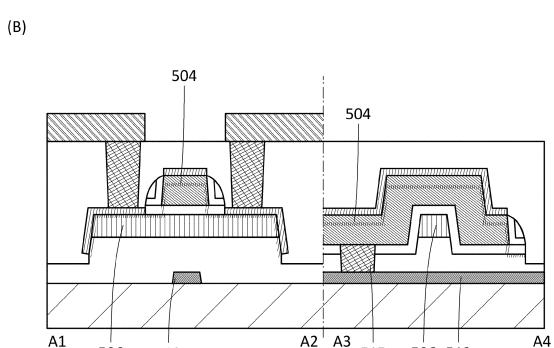

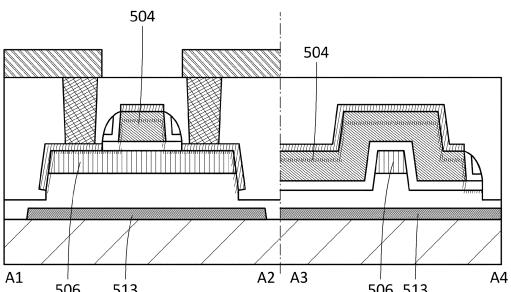

【図5】本発明の一態様に係るトランジスタの作製方法を示す断面図。

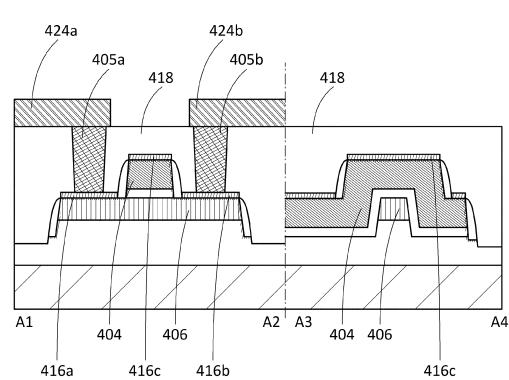

【図6】本発明の一態様に係るトランジスタを示す断面図および上面図。

【図7】本発明の一態様に係るトランジスタを示す断面図。

【図8】本発明の一態様に係るトランジスタを示す断面図。

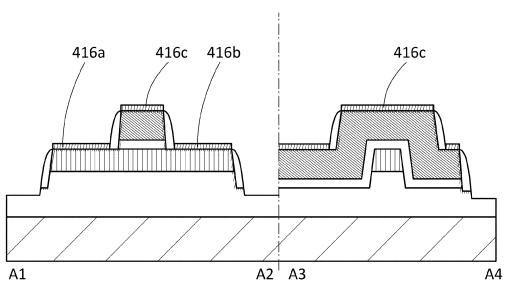

【図9】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図10】本発明の一態様に係るトランジスタの作製方法を示す断面図。

20

【図11】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図12】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図13】本発明の一態様に係るトランジスタを示す断面図および上面図。

【図14】本発明の一態様に係るトランジスタを示す断面図。

【図15】本発明の一態様に係るトランジスタを示す断面図。

【図16】本発明の一態様に係る半導体装置の断面図。

【図17】本発明の一態様に係る半導体装置の回路図。

【図18】本発明の一態様に係る記憶装置の回路図。

【図19】本発明の一態様に係るRFタグのブロック図。

【図20】本発明の一態様に係るRFタグの使用例を示す図。

【図21】本発明の一態様に係るCPUを示すブロック図。

30

【図22】本発明の一態様に係る記憶素子の回路図。

【図23】本発明の一態様に係る表示装置の上面図および回路図。

【図24】本発明の一態様に係る表示モジュールを説明する図。

【図25】本発明の一態様に係る電子機器を示す図。

【図26】本発明の一態様に係る電子機器を示す図。

【図27】C A A C - O S の断面におけるCs補正高分解能TEM像、およびC A A C - O S の断面模式図。

【図28】C A A C - O S の平面におけるCs補正高分解能TEM像。

【図29】C A A C - O S および単結晶酸化物半導体のXRDによる構造解析を説明する図。

40

【図30】C A A C - O S の電子回折パターンを示す図。

【図31】In - Ga - Zn酸化物の電子照射による結晶部の変化を示す図。

【図32】半導体の積層を示す断面図、およびバンド構造を示す図。

【図33】本発明の一態様に係るトランジスタを示す断面図。

【図34】本発明の一態様に係るトランジスタを示す断面図。

#### 【発明を実施するための形態】

#### 【0024】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるもの

50

ではない。なお、図面を用いて発明の構造を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

#### 【0025】

なお、図において、大きさ、膜（層）の厚さ、または領域は、明瞭化のために誇張されている場合がある。

#### 【0026】

また、電圧は、ある電位と、基準の電位（例えば接地電位（GND）またはソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。

10

#### 【0027】

なお、第1、第2として付される序数詞は便宜的に用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

#### 【0028】

なお、「半導体」と表記した場合でも、例えば、導電性が十分低い場合は「絶縁体」としての特性を有する場合がある。また、「半導体」と「絶縁体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「絶縁体」と言い換えることができる場合がある。同様に、本明細書に記載の「絶縁体」は、「半導体」と言い換えることができる場合がある。

20

#### 【0029】

また、「半導体」と表記した場合でも、例えば、導電性が十分高い場合は「導電体」としての特性を有する場合がある。また、「半導体」と「導電体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「導電体」と言い換えることができる場合がある。同様に、本明細書に記載の「導電体」は、「半導体」と言い換えることができる場合がある。

#### 【0030】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物である。不純物が含まれることにより、例えば、半導体にDOS(Density of State)が形成されることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第14族元素、第15族元素、主成分以外の遷移金属などがあり、特に、例えば、水素（水にも含まれる）、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

30

#### 【0031】

なお、以下に示す実施の形態では、半導体が酸化物半導体である場合について説明するが、これに限定されるものではない。例えば、半導体として、多結晶構造、単結晶構造などのシリコン、ゲルマニウム、などを用いてもよい。または、歪みシリコンなどの歪みを有する半導体を用いてもよい。または、半導体としてHEMTに適用可能なヒ化ガリウム、ヒ化アルミニウムガリウム、ヒ化インジウムガリウム、窒化ガリウム、リン化インジウム、シリコンゲルマニウムなどを用いてもよい。これらの半導体を用いることで、高速動作をすることに適したトランジスタとすることができます。

40

#### 【0032】

なお、本明細書において、Aが濃度Bの領域を有する、と記載する場合、例えば、Aのある領域における深さ方向全体の濃度がBである場合、Aのある領域における深さ方向の濃

50

度の平均値がBである場合、Aのある領域における深さ方向の濃度の中央値がBである場合、Aのある領域における深さ方向の濃度の最大値がBである場合、Aのある領域における深さ方向の濃度の最小値がBである場合、Aのある領域における深さ方向の濃度の収束値がBである場合、測定上Aそのものの確からしい値の得られる領域における濃度がBである場合などを含む。

#### 【0033】

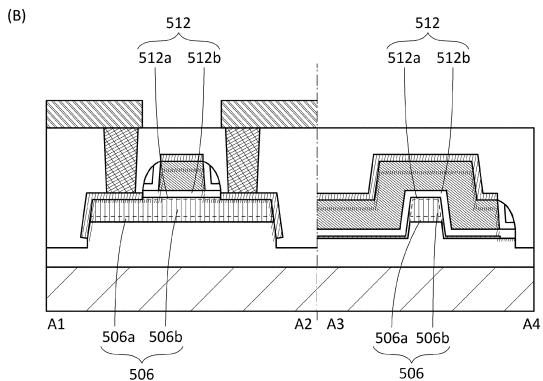

また、本明細書において、Aが大きさB、長さB、厚さB、幅Bまたは距離Bの領域を有する、と記載する場合、例えば、Aのある領域における全体の大きさ、長さ、厚さ、幅、または距離がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の平均値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の中央値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の最大値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の最小値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の収束値がBである場合、測定上Aそのものの確からしい値の得られる領域での大きさ、長さ、厚さ、幅、または距離がBである場合などを含む。10

#### 【0034】

なお、本明細書において、絶縁体、半導体、導電体などの形成は、特に断りがある場合を除き、スパッタリング法、化学気相成長(CVD: Chemical Vapor Deposition)法、分子線エピタキシー(MBE: Molecular Beam Epitaxy)法またはパルスレーザ堆積(PLD: Pulsed Laser Deposition)法、原子層堆積法(ALD: Atomic Layer Deposition)法などを用いて行うことができる。20

#### 【0035】

なお、CVD法は、プラズマを利用するプラズマCVD(PECVD: Plasma Enhanced CVD)法、熱を利用する熱CVD(TCVD: Thermal CVD)法などに分類できる。さらに用いる原料ガスによって金属CVD(MCVD: Metal CVD)法、有機金属CVD(MOCVD: Metal Organic CVD)法に分けることができる。

#### 【0036】

プラズマCVD法は、比較的低温で高品質の膜が得られる。熱CVD法は、プラズマを用いないため、プラズマダメージが生じず、欠陥の少ない膜が得られる。30

#### 【0037】

CVD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、MCVD法およびMOCVD法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、MCVD法およびMOCVD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間の分、成膜に掛かる時間を短くすることができる。したがって、トランジスタの生産性を高めることができる。

#### 【0038】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。40

#### 【0039】

チャネル幅とは、例えば、上面図において半導体（またはトランジスタがオン状態のとき50

に半導体の中で電流の流れる部分)とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

#### 【0040】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅(以下、実効的なチャネル幅と呼ぶ。)と、トランジスタの上面図において示されるチャネル幅(以下、見かけ上のチャネル幅と呼ぶ。)と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

10

#### 【0041】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

20

#### 【0042】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが互いに重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅(SCW: Surrounded Channel Width)」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを取得して、その画像を解析することなどによって、値を決定することができる。

30

#### 【0043】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

#### 【0044】

<導電体の選択成長>

以下では、本発明の一態様に係る導電体の選択成長について図1を用いて説明する。

#### 【0045】

まず、試料100上的一部分にマスク102を形成する。

40

#### 【0046】

次に、不純物150を添加する処理を行う(図1(A)参照。)。不純物150の添加は、イオンドーピング法またはイオン注入法などによって行えばよい。なお、本明細書において、イオンドーピング法とは、質量分離を行っていないイオンを添加することをいう。また、イオン注入法とは、質量分離を行ったイオンを添加することをいう。

#### 【0047】

不純物150は、後に選択成長させる導電体の種類によって適宜変更する。不純物150として、例えば、シリコンまたはチタンを有するイオンを添加すればよい。なお、不純物150としてクラスタ状のイオン(クラスタイオンともいう。)を用いてもよい。クラスタイオンを用いることで、不純物150を試料100の浅い領域(上面近傍)に添加する

50

ことができるため、都合がよい場合がある。なお、シリコンを有するクラスタイオンとしては、 $\text{Si}_n$  ( $n$  は 2 以上 60 以下の整数。好ましくは、 $n$  は 6 または 10。) イオンなどが挙げられる。また、チタンを含むクラスタイオンとしては、 $\text{Ti}_n$  ( $n$  は 2 以上 16 以下の整数) などが挙げられる。

#### 【0048】

なお、不純物 150 の添加は、イオンドーピング法またはイオン注入法に限定されるものではない。例えば、試料 100 上に不純物 150 を有する膜を成膜した後、試料 100 をプラズマ処理、イオンドーピング法またはイオン注入法を行うことでノックオン効果（ミキシング効果ともいう。）により不純物 150 を添加しても構わない。この場合、添加されなかった膜の残りを除去してもよい。除去の方法は、ウェットエッティング法またはドライエッティング法などによって行えばよい。10

#### 【0049】

不純物 150 は、マスク 102 の設けられていない領域のみに添加され、試料 100 の一部の上面に領域 104 を形成する（図 1 (B) 参照。）。領域 104 は、不純物 150 の濃度が高い領域である。例えば、領域 104 は、不純物 150 を構成する元素の一が  $1 \times 10^{19} \text{ atoms/cm}^3$  以上の濃度となる領域を有する。

#### 【0050】

次に、マスク 102 を除去する（図 1 (C) 参照。）。マスク 102 の除去は、ウェットエッティング法またはドライエッティング法などによって行えばよい。このとき、領域 104 の少なくとも一部が残存する条件を用いる。20

#### 【0051】

次に、領域 104 上に導電体 106 を選択成長させる。導電体 106 の選択成長の方法は特に限定されないが、例えば、CVD 法を用いると好ましい。ここでは、特に MCD 法または MOCVD 法によって導電体 106 を選択成長させる場合について説明する。

#### 【0052】

領域 104 上に導電体 106 を選択成長させるためには、適切に不純物 150 と導電体 106 の原料ガスとを組み合わせればよい。例えば、不純物 150 として、領域 104 がシリコンを有する場合、導電体 106 の原料ガスとして、六フッ化タンゲステン（WF<sub>6</sub>）ガス、または WF<sub>6</sub> ガスおよびモノシラン（SiH<sub>4</sub>）ガスを用いることでタンゲステンを選択成長させることができる。30

#### 【0053】

具体的には、下式 (1) に示すような Si 還元反応により、領域 104 上にタンゲステンを選択成長させることができる。

#### 【0054】

#### 【0055】

Si 還元反応では、タンゲステンの生成とともにシリコンのエッティングが起こるため、添加されたシリコンが失われると反応も終了する。

#### 【0056】

このような方法でタンゲステンを選択成長させると、領域 104 のシリコンは選択成長とともに失われるため、例えば、タンゲステンの厚さをシリコンの添加量や添加する深さによって制御することも可能となる。なお、同様の方法を用いることで、不純物 150 と原料ガスとの異なる組み合わせによっても、導電体 106 の厚さを制御することができる場合がある。40

#### 【0057】

一方、タンゲステンをより厚く形成するために、領域 104 のシリコンが失われた後に、タンゲステン上に新たな導電体を選択成長させることができる。例えば、原料ガスとして WF<sub>6</sub> ガスおよび水素 (H<sub>2</sub>) ガスを用いることで、タンゲステンをさらに厚く成長させることができる。

#### 【0058】

10

20

30

40

50

具体的には、下式(2)に示すようなH<sub>2</sub>還元反応により、タンゲステンを選択成長させることができる。

【0059】

【0060】

H<sub>2</sub>還元反応は、活性化エネルギーが0.71eVであり、タンゲステン表面で起きるH<sub>2</sub>の吸着・解離過程が全反応を律速することが知られている。H<sub>2</sub>還元反応は、比較的高い温度で成長速度が高くなる。タンゲステンの選択成長では、例えば、試料100の表面温度を300以上600以下、350以上550以下、または400以上500以下とすればよい。

10

【0061】

なお、式(1)に示したSi還元反応では、2nm以上の酸化シリコン表面および酸化窒化シリコン表面にタンゲステンが生成されにくいため、領域104にタンゲステンを選択成長させることができる。

【0062】

酸化シリコン表面におけるWF<sub>6</sub>ガスの反応を下式(3)に示す。

【0063】

【0064】

したがって、酸化シリコン表面では、WF<sub>6</sub>ガスとの反応により、酸化シリコンのエッチングが行われるので反応生成物は全てガスとして排気される。

20

【0065】

または、下式(4)に示すようなSiH<sub>4</sub>還元反応により、領域104にタンゲステンを選択成長させることができる。

【0066】

【0067】

WF<sub>6</sub>とSiH<sub>4</sub>がシリコン近傍に存在した場合、SiH<sub>4</sub>の吸着確率が低く、WF<sub>6</sub>とシリコンとの反応の起こる確率が高くなる。したがって、SiH<sub>4</sub>還元反応は、シリコン還元で析出したタンゲステン表面で起きる。SiH<sub>4</sub>還元反応は180以上450以下で起こるため、タンゲステンの選択成長では、例えば、試料100の表面温度を180以上450以下、190以上380以下、または200以上320以下とすればよい。

30

【0068】

なお、SiH<sub>4</sub>ガスに替えてジシラン(Si<sub>2</sub>H<sub>6</sub>)ガスなどを用いても同様の還元反応を起こすことができる。例えば、Si<sub>2</sub>H<sub>6</sub>還元反応は、80以上240以下で起こるため、タンゲステンの選択成長では、例えば、試料100の表面温度を80以上240以下、100以上210以下、または120以上180以下とすればよい。

または、SiH<sub>4</sub>ガスに替えてジボラン(B<sub>2</sub>H<sub>6</sub>)ガスを用いたB<sub>2</sub>H<sub>6</sub>還元反応によるタンゲステンの選択成長を行っても構わない。

40

【0069】

なお、SiH<sub>4</sub>還元反応などのシランを用いた還元反応では、シリコンがタンゲステン中に残存しやすい。そして、タンゲステン中のシリコン濃度は温度とともに高くなる。例えば、試料100の表面温度が400程度のときにはW<sub>5</sub>Si<sub>3</sub>が生成される場合がある。

【0070】

また、マスク102として、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニア、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、

50

単層で、または積層で用いればよい。また、マスク 102 が不純物を有することで、導電体 106 の選択性を高くすることができる。不純物としては、例えば、リンなどを用いればよい。

#### 【0071】

または、例えば、不純物 150 として、領域 104 がチタンを有する場合、導電体 106 の原料ガスとして、ジエチルアルミニウムハイドライド [ (CH<sub>3</sub>)<sub>2</sub>AlH ] ガスを用いることでアルミニウムを選択成長させることができる。

#### 【0072】

なお、上述した不純物 150 と導電体 106 の原料ガスとの組み合わせは一例である。したがって、本発明の一態様が、この組み合わせのみに限定されるものではない。

10

#### 【0073】

上述した導電体の選択成長方法を利用することで、寄生容量の低減された半導体装置などを作製することができる。

#### 【0074】

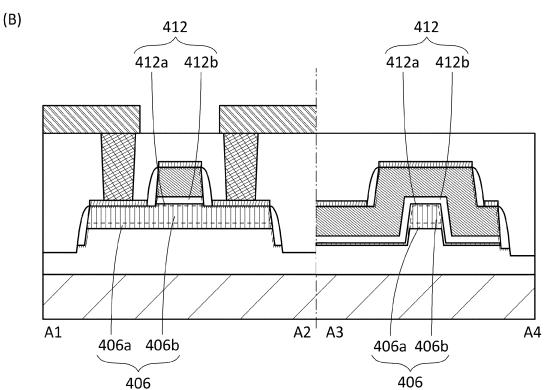

##### <トランジスタ構造 1 >

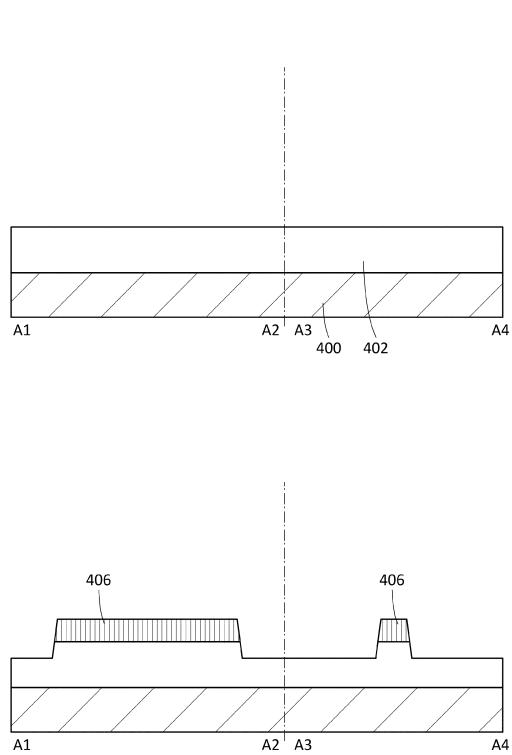

以下では、本発明の一態様に係るトランジスタおよびその作製方法について説明する。なお、トランジスタの作製方法は、チャネル長方向 (A1 - A2 断面) およびチャネル幅方向 (A3 - A4 断面) を用いて説明する。

#### 【0075】

まずは、基板 400 を準備する。

20

#### 【0076】

基板 400 としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板 (イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムなどの化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば SOI (Silicon On Insulator) 基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

30

#### 【0077】

また、基板 400 として、可とう性基板を用いてもよい。なお、基板 400 として、繊維を編みこんだシート、フィルムまたは箔などを用いてもよい。また、基板 400 が伸縮性を有してもよい。また、基板 400 は、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有してもよい。または、元の形状に戻らない性質を有してもよい。基板 400 の厚さは、例えば、5 μm 以上 700 μm 以下、好ましくは 10 μm 以上 500 μm 以下、さらに好ましくは 15 μm 以上 300 μm 以下とする。基板 400 を薄くすると、半導体装置を軽量化することができる。また、基板 400 を薄くすることで、ガラスなどを用いた場合にも伸縮性を有する場合や、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有する場合がある。そのため、落下などによって基板 400 上の半導体装置に加わる衝撃などを緩和することができる。即ち、丈夫な半導体装置を提供することができる。

40

#### 【0078】

可とう性基板である基板 400 としては、例えば、金属、合金、樹脂もしくはガラス、またはそれらの繊維などを用いることができる。可とう性基板である基板 400 は、線膨張率が低いほど環境による変形が抑制されて好ましい。可とう性基板である基板 400 としては、例えば、線膨張率が  $1 \times 10^{-3} / K$  以下、 $5 \times 10^{-5} / K$  以下、または  $1 \times 1$

50

$0 \sim 5 / K$  以下である材質を用いればよい。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネート、アクリルなどがある。特に、アラミドは、線膨張率が低いため、可とう性基板である基板 400 として好適である。

#### 【0079】

なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板に転置する方法もある。その場合には、非可とう性基板である基板 400 上に剥離層を設けるとよい。

#### 【0080】

次に、絶縁体 402 を形成する（図 2 (A) 参照。）。絶縁体 402 としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。なお、絶縁体 402 が、窒化酸化シリコン、窒化シリコンなどの窒素を有する絶縁体を有しても構わない。

#### 【0081】

また、絶縁体 402 は、基板 400 からの不純物の拡散を防止する役割を有してもよい。

#### 【0082】

また、絶縁体 402 は、過剰酸素を含む絶縁体であってもよい。

#### 【0083】

例えば、過剰酸素を含む絶縁体は、加熱処理によって酸素を放出する機能を有する絶縁体である。例えば、過剰酸素を含む酸化シリコンは、加熱処理などによって酸素を放出することができる酸化シリコンである。したがって、絶縁体 402 は膜中を酸素が移動可能な絶縁体である。

#### 【0084】

ここで、加熱処理によって酸素を放出する絶縁体は、TDS 分析にて、100 以上 700 以下または 100 以上 500 以下の表面温度の範囲で  $1 \times 10^{18} \text{ atoms/cm}^3$  以上、 $1 \times 10^{19} \text{ atoms/cm}^3$  以上または  $1 \times 10^{20} \text{ atoms/cm}^3$  以上の酸素（酸素原子数換算）を放出することもある。

#### 【0085】

ここで、TDS 分析を用いた酸素の放出量の測定方法について、以下に説明する。

#### 【0086】

測定試料を TDS 分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比例する。そして標準試料との比較により、気体の全放出量を計算することができる。

#### 【0087】

例えば、標準試料である所定の密度の水素を含むシリコン基板の TDS 分析結果、および測定試料の TDS 分析結果から、測定試料の酸素分子の放出量 ( $N_{O_2}$ ) は、下に示す式で求めることができる。ここで、TDS 分析で得られる質量電荷比 32 で検出されるガスの全てが酸素分子由来と仮定する。CH<sub>3</sub>O<sub>H</sub> の質量電荷比は 32 であるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数 17 の酸素原子および質量数 18 の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

#### 【0088】

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times$$

#### 【0089】

$N_{H_2}$  は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$  は、標準試料を TDS 分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$  とする。 $S_{O_2}$  は、測定試料を TDS 分析したときのイオン強度の積分値である。 は、TDS 分析におけるイオン強度に影響する係数である。上に示す式の詳細に関しては、特開平 6 - 275697 公報を参照する。なお、上記酸素の放出量は、電子科

10

20

30

40

50

学株式会社製の昇温脱離分析装置 E M D - W A 1 0 0 0 S / W を用い、標準試料として、例えば  $1 \times 10^{-6}$  atoms/cm<sup>2</sup> の水素原子を含むシリコン基板を用いて測定する。

#### 【 0 0 9 0 】

また、 T D S 分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

#### 【 0 0 9 1 】

なお、  $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の 2 倍となる。 10

#### 【 0 0 9 2 】

または、加熱処理によって酸素を放出する絶縁体は、過酸化ラジカルを含むこともある。具体的には、過酸化ラジカルに起因するスピニ密度が、  $5 \times 10^{17}$  spins/cm<sup>3</sup> 以上であることをいう。なお、過酸化ラジカルを含む絶縁体は、 E S R にて、 g 値が 2.01 近傍に非対称の信号を有することもある。

#### 【 0 0 9 3 】

または、過剰酸素を含む絶縁体は、酸素が過剰な酸化シリコン (  $SiO_x$  (  $X > 2$  ) ) であってもよい。酸素が過剰な酸化シリコン (  $SiO_x$  (  $X > 2$  ) ) は、シリコン原子数の 2 倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法 ( R B S : Rutherford Backscattering Spectrometry ) により測定した値である。 20

#### 【 0 0 9 4 】

次に、半導体 406 を形成する ( 図 2 ( B ) 参照。 ) 。半導体 406 は、半導体 406 となる半導体を形成した後で、該半導体の一部をエッチングすることで形成すればよい。

#### 【 0 0 9 5 】

半導体 406 は、例えば、インジウムを含む酸化物半導体である。半導体 406 は、例えば、インジウムを含むと、キャリア移動度 ( 電子移動度 ) が高くなる。また、半導体 406 は、元素 M を含むと好ましい。元素 M は、好ましくは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素 M に適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、イットリウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステンなどがある。ただし、元素 M として、前述の元素を複数組み合わせても構わない場合がある。元素 M は、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素 M は、例えば、酸化物半導体のエネルギーギャップを大きくする機能を有する元素である。また、半導体 406 は、亜鉛を含むと好ましい。酸化物半導体は、亜鉛を含むと結晶化しやすくなる場合がある。 30

#### 【 0 0 9 6 】

ただし、半導体 406 は、インジウムを含む酸化物半導体に限定されない。半導体 406 は、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物などの、インジウムを含まず、亜鉛を含む酸化物半導体、ガリウムを含む酸化物半導体、スズを含む酸化物半導体などであっても構わない。 40

#### 【 0 0 9 7 】

半導体 406 は、例えば、エネルギーギャップが大きい酸化物を用いる。半導体 406 のエネルギーギャップは、例えば、2.5 eV 以上 4.2 eV 以下、好ましくは 2.8 eV 以上 3.8 eV 以下、さらに好ましくは 3 eV 以上 3.5 eV 以下とする。

#### 【 0 0 9 8 】

トランジスタのオン電流は、電子の移動を阻害する要因を低減するほど、高くすることができる。例えば、電子の移動を阻害する要因のない場合、効率よく電子が移動すると推定される。電子の移動は、例えば、チャネル形成領域の物理的な凹凸が大きい場合にも阻害 50

される。

**【0099】**

トランジスタのオン電流を高くするためには、例えば、半導体406の上面または下面(被形成面、ここでは絶縁体402)の、 $1 \mu\text{m} \times 1 \mu\text{m}$ の範囲における二乗平均平方根(RMS: Root Mean Square)粗さが1nm未満、好ましくは0.6nm未満、さらに好ましくは0.5nm未満、より好ましくは0.4nm未満とすればよい。また、 $1 \mu\text{m} \times 1 \mu\text{m}$ の範囲における平均面粗さ(Raともいう。)が1nm未満、好ましくは0.6nm未満、さらに好ましくは0.5nm未満、より好ましくは0.4nm未満とすればよい。また、 $1 \mu\text{m} \times 1 \mu\text{m}$ の範囲における最大高低差(P-Vともいう。)が10nm未満、好ましくは9nm未満、さらに好ましくは8nm未満、より好ましくは7nm未満とすればよい。RMS粗さ、RaおよびP-Vは、エスアイアイ・ナノテクノロジー株式会社製走査型プローブ顕微鏡システムSPA-500などを用いて測定することができる。

10

**【0100】**

酸化物半導体において、酸素欠損はトランジスタの電気特性を劣化させる要因となる場合がある。よって、チャネル形成領域における酸素欠損を低減することがトランジスタに安定した電気特性を付与するためには重要となる。一方、トランジスタのソース領域およびドレイン領域に酸化物半導体を用いる場合、酸素欠損に起因して酸化物半導体を低抵抗化させることができる。よって、トランジスタのオン電流を大きくするために酸素欠損を有するほうがよい場合がある。

20

**【0101】**

例えば、酸化物半導体が酸素欠損(V<sub>o</sub>とも表記。)を有する場合、酸素欠損のサイトに水素が入り込むことでドナー準位を形成することがある。以下では酸素欠損のサイトに水素が入り込んだ状態をV<sub>oH</sub>と表記する場合がある。なお、酸素欠損のサイトは、水素に入るよりも酸素が入る方が安定する。したがって、酸化物半導体に酸素を供給することで、V<sub>oH</sub>を低減することができる。

**【0102】**

例えば、半導体406と絶縁体402との間に、例えば、二次イオン質量分析法(SIM-S: Secondary Ion Mass Spectrometry)において、 $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $2 \times 10^{18} \text{ atoms/cm}^3$ 未満のシリコン濃度となる領域を有する。

30

**【0103】**

なお、酸化物半導体に銅が混入すると、電子トラップを生成する場合がある。電子トラップは、トランジスタのしきい値電圧をプラス方向へ変動させる場合がある。したがって、半導体406の表面または内部における銅濃度は低いほど好ましい。例えば、半導体406は、銅濃度が $1 \times 10^{19} \text{ atoms/cm}^3$ 以下、 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下、または $1 \times 10^{18} \text{ atoms/cm}^3$ 以下となる領域を有すると好ましい。

**【0104】**

以下では、酸化物半導体の構造について説明する。

40

**【0105】**

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

**【0106】**

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

50

## 【0107】

<酸化物半導体の構造>

以下では、酸化物半導体の構造について説明する。

## 【0108】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、nc-OS (nanocrystalline Oxide Semiconductor)、擬似非晶質酸化物半導体 (a-like OS: amorphous like Oxide Semiconductor)、非晶質酸化物半導体などがある。 10

## 【0109】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC-OS、多結晶酸化物半導体、nc-OSなどがある。

## 【0110】

非晶質構造の定義としては、一般に、準安定状態で固定化していないこと、等方的であって不均質構造を持たないことなどが知られている。また、結合角度が柔軟であり、短距離秩序性は有するが、長距離秩序性を有さない構造と言い換えることもできる。

## 【0111】

逆の見方をすると、本質的に安定な酸化物半導体の場合、完全な非晶質 (completely amorphous) 酸化物半導体と呼ぶことはできない。また、等方的でない (例えば、微小な領域において周期構造を有する) 酸化物半導体を、完全な非晶質酸化物半導体と呼ぶことはできない。ただし、a-like OSは、微小な領域において周期構造を有するものの、鬆を有し、不安定な構造である。そのため、物性的には非晶質酸化物半導体に近いといえる。 20

## 【0112】

<CAAC-OS>

まずは、CAAC-OSについて説明する。

## 【0113】

CAAC-OSは、c軸配向した複数の結晶部 (ペレットともいう。) を有する酸化物半導体の一つである。 30

## 【0114】

透過型電子顕微鏡 (TEM: Transmission Electron Microscope) によって、CAAC-OSの明視野像と回折パターンとの複合解析像 (高分解能TEM像ともいう。) を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像ではペレット同士の境界、即ち結晶粒界 (グレインバウンダリーともいう。) を明確に確認することができない。そのため、CAAC-OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

## 【0115】

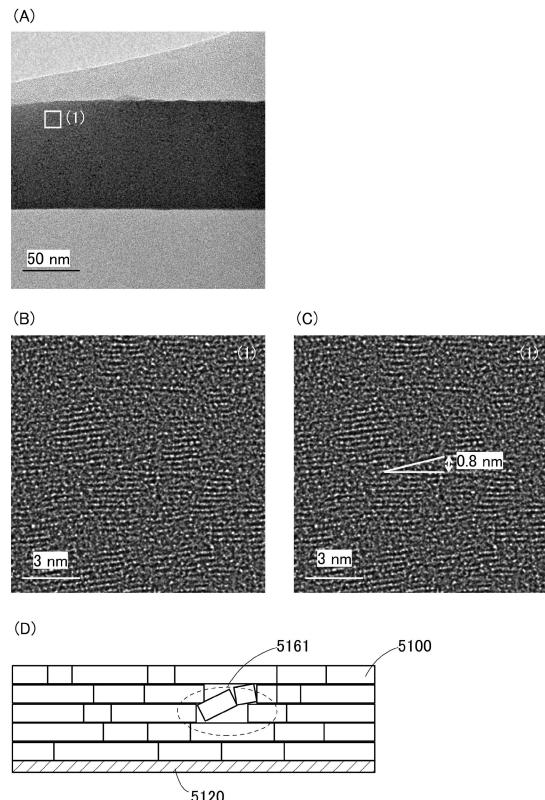

以下では、TEMによって観察したCAAC-OSについて説明する。図27(A)に、試料面と略平行な方向から観察したCAAC-OSの断面の高分解能TEM像を示す。高分解能TEM像の観察には、球面収差補正 (Spherical Aberration Corrector) 機能を用いた。球面収差補正機能を用いた高分解能TEM像を、特にCs補正高分解能TEM像と呼ぶ。Cs補正高分解能TEM像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM-ARM200Fなどによって行うことができる。 40

## 【0116】

図27(A)の領域(1)を拡大したCs補正高分解能TEM像を図27(B)に示す。図27(B)より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、CAAC-OSの膜を形成する面 (被形成面ともいう。) ま 50

たは上面の凹凸を反映しており、 C A A C - O S の被形成面または上面と平行となる。

#### 【 0 1 1 7 】

図 2 7 ( B ) に示すように、 C A A C - O S は特徴的な原子配列を有する。図 2 7 ( C ) は、特徴的な原子配列を、補助線で示したものである。図 2 7 ( B ) および図 2 7 ( C ) より、ペレット一つの大きさは 1 n m 以上 3 n m 以下程度であり、ペレットとペレットとの傾きにより生じる隙間の大きさは 0 . 8 n m 程度であることがわかる。したがって、ペレットを、ナノ結晶 ( n c : n a n o c r y s t a l ) と呼ぶこともできる。また、 C A A C - O S を、 C A N C ( C - A x i s A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体と呼ぶこともできる。

#### 【 0 1 1 8 】

ここで、 C s 補正高分解能 T E M 像をもとに、基板 5 1 2 0 上の C A A C - O S のペレット 5 1 0 0 の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる（図 2 7 ( D ) 参照。）。図 2 7 ( C ) で観察されたペレットとペレットとの間で傾きが生じている箇所は、図 2 7 ( D ) に示す領域 5 1 6 1 に相当する。

#### 【 0 1 1 9 】

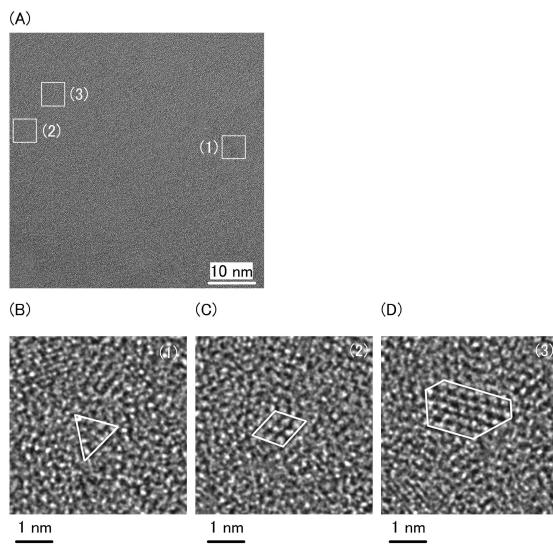

また、図 2 8 ( A ) に、試料面と略垂直な方向から観察した C A A C - O S の平面の C s 補正高分解能 T E M 像を示す。図 2 8 ( A ) の領域 ( 1 ) 、領域 ( 2 ) および領域 ( 3 ) を拡大した C s 補正高分解能 T E M 像を、それぞれ図 2 8 ( B ) 、図 2 8 ( C ) および図 2 8 ( D ) に示す。図 2 8 ( B ) 、図 2 8 ( C ) および図 2 8 ( D ) より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

#### 【 0 1 2 0 】

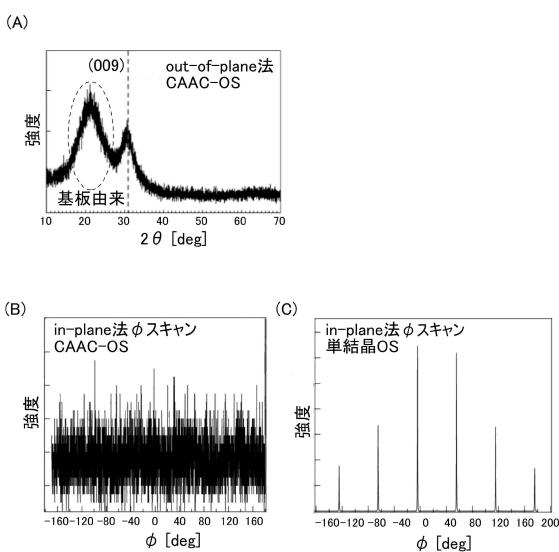

次に、 X 線回折 ( X R D : X - R a y D i f f r a c t i o n ) によって解析した C A A C - O S について説明する。例えば、 I n G a Z n O<sub>4</sub> の結晶を有する C A A C - O S に対し、 o u t - o f - p l a n e 法による構造解析を行うと、図 2 9 ( A ) に示すように回折角 ( 2 ) が 3 1 ° 近傍にピークが現れる場合がある。このピークは、 I n G a Z n O<sub>4</sub> の結晶の ( 0 0 9 ) 面に帰属されることから、 C A A C - O S の結晶が c 軸配向性を有し、 c 軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

#### 【 0 1 2 1 】

なお、 C A A C - O S の o u t - o f - p l a n e 法による構造解析では、 2 が 3 1 ° 近傍のピークの他に、 2 が 3 6 ° 近傍にもピークが現れる場合がある。 2 が 3 6 ° 近傍のピークは、 C A A C - O S 中の一部に、 c 軸配向性を有さない結晶が含まれることを示している。より好ましい C A A C - O S は、 o u t - o f - p l a n e 法による構造解析では、 2 が 3 1 ° 近傍にピークを示し、 2 が 3 6 ° 近傍にピークを示さない。

#### 【 0 1 2 2 】

一方、 C A A C - O S に対し、 c 軸に略垂直な方向から X 線を入射させる i n - p l a n e 法による構造解析を行うと、 2 が 5 6 ° 近傍にピークが現れる。このピークは、 I n G a Z n O<sub>4</sub> の結晶の ( 1 1 0 ) 面に帰属される。 C A A C - O S の場合は、 2 を 5 6 ° 近傍に固定し、試料面の法線ベクトルを軸 ( c 軸) として試料を回転させながら分析 ( スキャン) を行っても、図 2 9 ( B ) に示すように明瞭なピークは現れない。これに対し、 I n G a Z n O<sub>4</sub> の単結晶酸化物半導体であれば、 2 を 5 6 ° 近傍に固定してスキャンした場合、図 2 9 ( C ) に示すように ( 1 1 0 ) 面と等価な結晶面に帰属されるピークが 6 本観察される。したがって、 X R D を用いた構造解析から、 C A A C - O S は、 a 軸および b 軸の配向が不規則であることが確認できる。

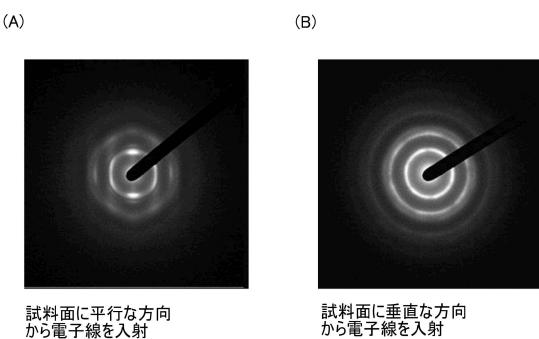

#### 【 0 1 2 3 】

次に、電子回折によって解析した C A A C - O S について説明する。例えば、 I n G a Z n O<sub>4</sub> の結晶を有する C A A C - O S に対し、試料面に平行にプローブ径が 3 0 0 n m の電子線を入射させると、図 3 0 ( A ) に示すような回折パターン ( 制限視野透過電子回折パターンともいう。) が現れる場合がある。この回折パターンには、 I n G a Z n O<sub>4</sub> の結晶の ( 0 0 9 ) 面に起因するスポットが含まれる。したがって、電子回折によっても、

10

20

30

40

50

C A A C - O S に含まれるペレットが c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が 300 nm の電子線を入射させたときの回折パターンを図 30 (B) に示す。図 30 (B) より、リング状の回折パターンが確認される。したがって、電子回折によっても、C A A C - O S に含まれるペレットの a 軸および b 軸は配向性を有さないことがわかる。なお、図 30 (B) における第 1 リングは、InGaZnO<sub>4</sub> の結晶の (010) 面および (100) 面などに起因すると考えられる。また、図 30 (B) における第 2 リングは (110) 面などに起因すると考えられる。

#### 【0124】

上述したように、C A A C - O S は結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、逆の見方をすると C A A C - O S は不純物や欠陥（酸素欠損など）の少ない酸化物半導体ともいえる。

#### 【0125】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

#### 【0126】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

#### 【0127】

不純物および酸素欠損の少ない C A A C - O S は、キャリア密度の低い酸化物半導体である。具体的には、キャリア密度を  $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。C A A C - O S は、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。

#### 【0128】

< n c - O S >

次に、n c - O S について説明する。

#### 【0129】

n c - O S は、高分解能 TEM 像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。n c - O S に含まれる結晶部は、1 nm 以上 10 nm 以下、または 1 nm 以上 3 nm 以下の大きさであることが多い。なお、結晶部の大きさが 10 nm より大きく 100 nm 以下である酸化物半導体を微結晶酸化物半導体と呼ぶことがある。n c - O S は、例えば、高分解能 TEM 像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、C A A C - O S におけるペレットと起源を同じくする可能性がある。そのため、以下では n c - O S の結晶部をペレットと呼ぶ場合がある。

#### 【0130】

n c - O S は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - O S に対し、ペレットよりも大きい径の X 線を用いた場合、o u t - o f - p l a n e 法による解析では、結晶面を示すピークは検

10

20

30

40

50

出されない。また、n c - O Sに対し、ペレットよりも大きいプローブ径（例えば50nm以上）の電子線を用いる電子回折を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O Sに対し、ペレットの大きさと近いかペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O Sに対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

#### 【0131】

このように、ペレット（ナノ結晶）間では結晶方位が規則性を有さないことから、n c - O Sを、RANC（Random Aligned nanocrystals）を有する酸化物半導体、またはNANC（Non-Aligned nanocrystals）を有する酸化物半導体と呼ぶこともできる。10

#### 【0132】

n c - O Sは、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - O Sは、a - like O Sや非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O Sは、異なるペレット間で結晶方位に規則性が見られない。そのため、n c - O Sは、CAAC - O Sと比べて欠陥準位密度が高くなる。

#### 【0133】

<a - like O S>

a - like O Sは、n c - O Sと非晶質酸化物半導体との間の構造を有する酸化物半導体である。20

#### 【0134】

a - like O Sは、高分解能TEM像において鬆（ボイドともいう。）が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

#### 【0135】

鬆を有するため、a - like O Sは、不安定な構造である。以下では、a - like O Sが、CAAC - O Sおよびn c - O Sと比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。

#### 【0136】

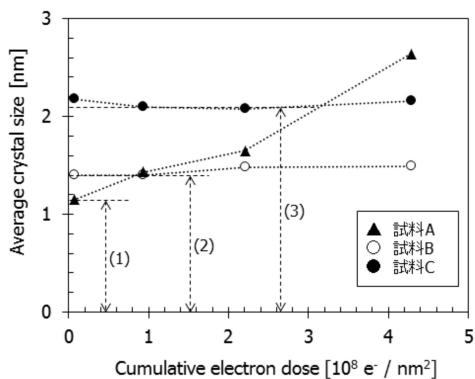

電子照射を行う試料として、a - like O S（試料Aと表記する。）、n c - O S（試料Bと表記する。）およびCAAC - O S（試料Cと表記する。）を準備する。いずれの試料もIn - Ga - Zn酸化物である。30

#### 【0137】

まず、各試料の高分解能断面TEM像を取得する。高分解能断面TEM像により、各試料は、いずれも結晶部を有することがわかる。

#### 【0138】

なお、どの部分を一つの結晶部と見なすかの判定は、以下のように行えばよい。例えば、 $InGaZnO_4$ の結晶の単位格子は、In - O層を3層有し、またGa - Zn - O層を6層有する、計9層がc軸方向に層状に重なった構造を有することが知られている。これらの近接する層同士の間隔は、(009)面の格子面間隔（d値ともいう。）と同程度であり、結晶構造解析からその値は0.29nmと求められている。したがって、格子縞の間隔が0.28nm以上0.30nm以下の箇所を、 $InGaZnO_4$ の結晶部と見なすことができる。なお、格子縞は、 $InGaZnO_4$ の結晶のa - b面に対応する。40

#### 【0139】

図31は、各試料の結晶部（22箇所から45箇所）の平均の大きさを調査した例である。ただし、上述した格子縞の長さを結晶部の大きさとしている。図31より、a - like O Sは、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図31中に（1）で示すように、TEMによる観察初期においては1.2nm程度の大きさだった結晶部（初期核ともいう。）が、累積照射量が $4.2 \times 10^8 e^- / nm$ 50

<sup>2</sup>においては2.6 nm程度の大きさまで成長していることがわかる。一方、n c - O SおよびC A A C - O Sは、電子照射開始時から電子の累積照射量が $4.2 \times 10^8 e^- / nm^2$ までの範囲で、結晶部の大きさに変化が見られないことがわかる。具体的には、図31中の(2)および(3)で示すように、電子の累積照射量によらず、n c - O SおよびC A A C - O Sの結晶部の大きさは、それぞれ1.4 nm程度および2.1 nm程度であることがわかる。

#### 【0140】

このように、a - l i k e O Sは、電子照射によって結晶部の成長が見られる場合がある。一方、n c - O SおよびC A A C - O Sは、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a - l i k e O Sは、n c - O SおよびC A A C - O Sと比べて、不安定な構造であることがわかる。

10

#### 【0141】

また、鬆を有するため、a - l i k e O Sは、n c - O SおよびC A A C - O Sと比べて密度の低い構造である。具体的には、a - l i k e O Sの密度は、同じ組成の単結晶の密度の78.6%以上92.3%未満となる。また、n c - O Sの密度およびC A A C - O Sの密度は、同じ組成の単結晶の密度の92.3%以上100%未満となる。単結晶の密度の78%未満となる酸化物半導体は、成膜すること自体が困難である。

#### 【0142】

例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において、菱面体晶構造を有する単結晶InGaZnO<sub>4</sub>の密度は6.357 g / cm<sup>3</sup>となる。よって、例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において、a - l i k e O Sの密度は5.0 g / cm<sup>3</sup>以上5.9 g / cm<sup>3</sup>未満となる。また、例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において、n c - O Sの密度およびC A A C - O Sの密度は5.9 g / cm<sup>3</sup>以上6.3 g / cm<sup>3</sup>未満となる。

20

#### 【0143】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

30

#### 【0144】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えば、非晶質酸化物半導体、a - l i k e O S、n c - O S、C A A C - O Sのうち、二種以上を有する積層膜であってもよい。

#### 【0145】

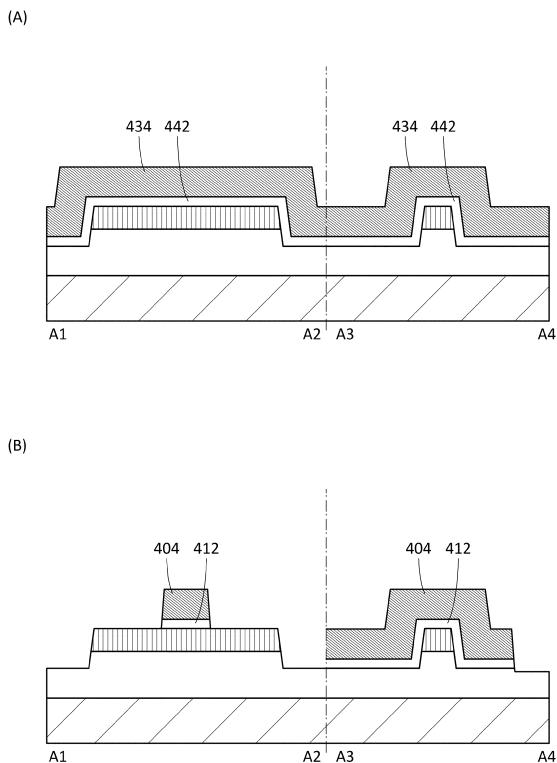

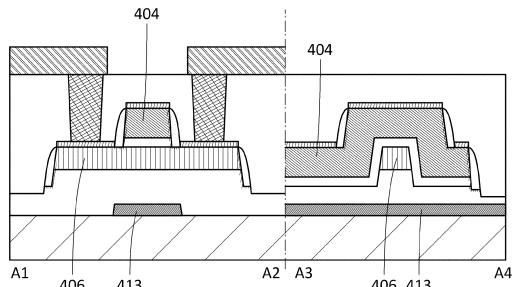

トランジスタの作製方法に戻り、次に絶縁体442および導電体434を、この順に形成する(図3(A)参照。)。絶縁体442としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。

40

#### 【0146】

導電体434としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0147】

次に、導電体 434 の一部をエッティングすることで導電体 404 を形成する。次に、絶縁体 442 の一部をエッティングすることで絶縁体 412 を形成する(図 3(B) 参照。)。

#### 【0148】

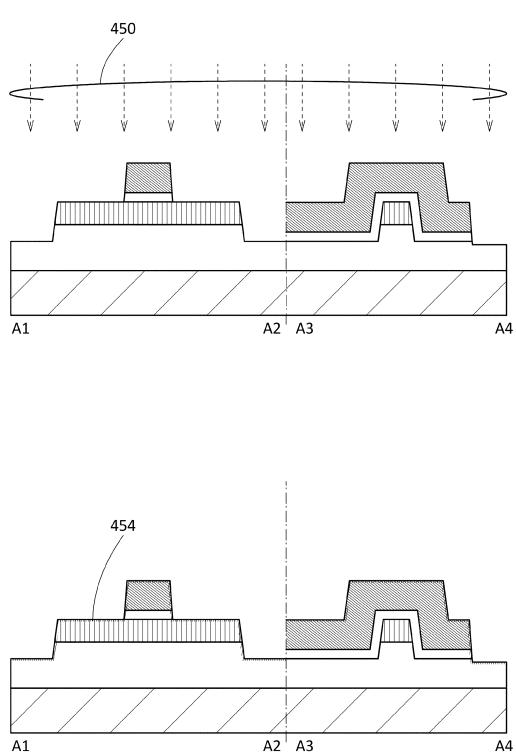

次に、不純物 450 を添加する処理を行う(図 4(A) 参照。)。不純物 450 については、不純物 150 の記載を参照する。

#### 【0149】

不純物 450 は、絶縁体 402、半導体 406、絶縁体 412 および導電体 404 の表面近傍の領域に添加される。該領域を、領域 454 と呼ぶ(図 4(B) 参照。)。領域 454 については、領域 104 の記載を参照する。

#### 【0150】

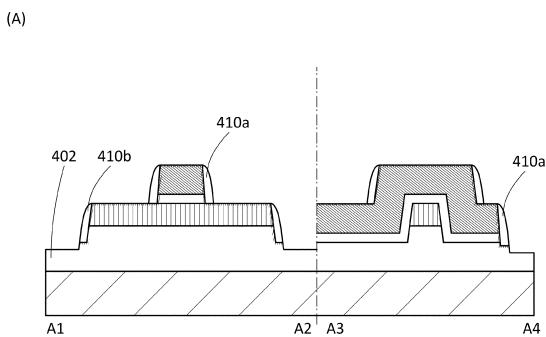

次に、絶縁体を形成する。該絶縁体を異方性エッティングすることで、導電体 404 の側面に接する絶縁体 410a と、半導体 406 の側面に接する絶縁体 410b と、を形成する。絶縁体 410a および絶縁体 410b としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。異方性エッティングは、ドライエッティング法などによって行えればよい。なお、異方性エッティングを行う際、絶縁体 402 がハーフエッティングされ、絶縁体 402 の一部の領域は除去される(図 5(A) 参照。)。

#### 【0151】

次に、領域 454 の露出された領域に対し、導電体を選択成長させる。その結果、半導体 406 上には、導電体 416a および導電体 416b が形成される。また、導電体 404 上には、導電体 416c が形成される(図 5(B) 参照。)。導電体 416a、導電体 416b および導電体 416c の選択成長については、導電体 106 の選択成長の記載を参照する。

#### 【0152】

次に、絶縁体 418 を形成する。絶縁体 418 としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。

#### 【0153】

次に、絶縁体 418 に導電体 416a および導電体 416b に達する開口部をそれぞれ形成し、それらの開口部をそれぞれ導電体 405a および導電体 405b を用いて埋める。なお、開口部が導電体 416a および導電体 416b を突き抜け、半導体 406 に達していても構わない。導電体 405a および導電体 405b としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタングステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0154】

次に、導電体 405a および導電体 405b と、それぞれ接する導電体 424a および導電体 424b を形成する(図 6(A) 参照。)。導電体 424a および導電体 424b としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタングステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む

10

20

30

40

50

導電体などを用いてもよい。

**【0155】**

なお、導電体405aおよび導電体424aを兼ねて一つの導電体を用いても構わない。また、導電体405bおよび導電体424bを兼ねて一つの導電体を用いても構わない。

**【0156】**

以上のようにして、本発明の一態様に係るトランジスタを作製することができる。なお、作製されたトランジスタが、上述した全ての絶縁体、半導体、導電体を有さなくてもよい。例えば、絶縁体410b、絶縁体418、導電体405a、導電体405b、導電体424a、導電体424bなどのいずれか一以上を有さなくても構わない場合がある。

**【0157】**

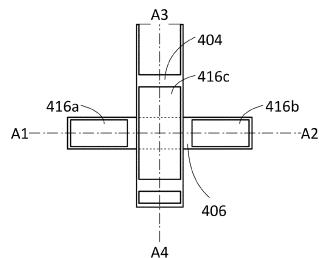

図6(B)は、トランジスタの上面図である。理解を容易にするため、各絶縁体、導電体405a、導電体405b、導電体424aおよび導電体424bを省略して示す。

**【0158】**

図6(B)にも示すように、トランジスタは導電体同士が絶縁体を介して重なる領域を有さない構造となっていることがわかる。したがって、該トランジスタは寄生容量の小さいトランジスタといえる。

**【0159】**

図6(A)および図6(B)に示すトランジスタは、導電体404の電界によって、半導体406を電気的に取り囲むことができるsurrounded channel(s-channel)構造である。そのため、半導体406の全体(バルク)にチャネルが形成される場合がある。s-channel構造では、トランジスタのソース-ドレイン間に大電流を流すことができ、導通時の電流(オン電流)を高くすることができる。

**【0160】**

高いオン電流が得られるため、s-channel構造は、微細化されたトランジスタに適した構造といえる。トランジスタを微細化できるため、該トランジスタを有する半導体装置は、集積度の高い、高密度化された半導体装置とすることが可能となる。例えば、トランジスタは、チャネル長が好ましくは40nm以下、さらに好ましくは30nm以下、より好ましくは20nm以下の領域を有し、かつ、トランジスタは、チャネル幅が好ましくは40nm以下、さらに好ましくは30nm以下、より好ましくは20nm以下の領域を有する。

**【0161】**

なお、トランジスタがs-channel構造を有する場合、半導体406の全体にチャネルが形成される。したがって、半導体406が厚いほどチャネル領域は大きくなる。即ち、半導体406が厚いほど、トランジスタのオン電流を高くすることができる。例えば、20nm以上、好ましくは40nm以上、さらに好ましくは60nm以上、より好ましくは100nm以上の厚さの領域を有する半導体406とすればよい。ただし、半導体装置の生産性が低下する場合があるため、例えば、300nm以下、好ましくは200nm以下、さらに好ましくは150nm以下の厚さの領域を有する半導体406とすればよい。なお、トランジスタがs-channel構造を有さなくても構わない。

**【0162】**

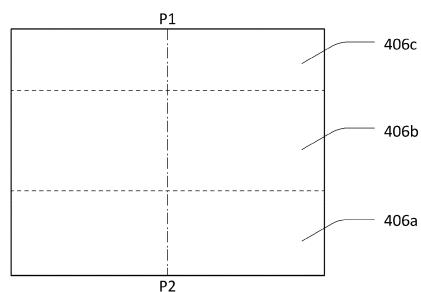

なお、図6(A)では、トランジスタが半導体を1層有する構造を示したが、本発明の一態様はその構造に限定されない。トランジスタが半導体を複数層有する構造であっても構わない。例えば、図7(A)に示すように、トランジスタの半導体406が、半導体406aと、半導体406a上の半導体406bと、半導体406b上の半導体406cと、を有してもよい。

**【0163】**

図7(A)に示す半導体406bは、例えば、酸化物半導体である。また、半導体406bは、例えば、図2(B)などに示した半導体406についての記載を参照する。

**【0164】**

また、例えば、半導体406aおよび半導体406cは、半導体406bを構成する酸素

10

20

30

40

50

以外の元素のうち一種以上、または二種以上から構成される酸化物半導体である。半導体406bを構成する酸素以外の元素のうち一種以上、または二種以上から半導体406aおよび半導体406cが構成されるため、半導体406aと半導体406bとの界面、および半導体406bと半導体406cとの界面において、界面準位が形成されにくい。

#### 【0165】

半導体406a、半導体406bおよび半導体406cは、少なくともインジウムを含むと好ましい。なお、半導体406aがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。また、半導体406bがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが25atomic%以上、Mが75atomic%未満、さらに好ましくはInが34atomic%以上、Mが66atomic%未満とする。また、半導体406cがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。なお、半導体406cは、半導体406aと同種の酸化物を用いても構わない。10

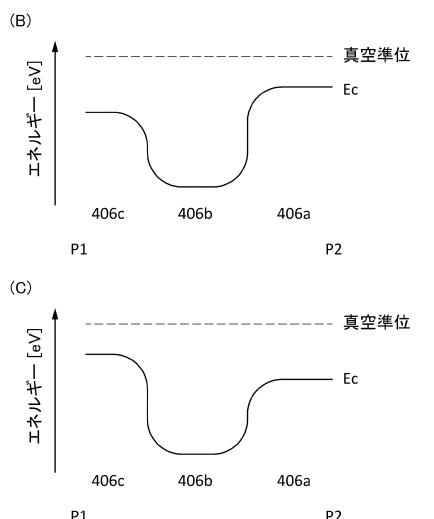

#### 【0166】

半導体406bは、半導体406aおよび半導体406cよりも電子親和力の大きい酸化物を用いる。例えば、半導体406bとして、半導体406aおよび半導体406cよりも電子親和力の0.07eV以上1.3eV以下、好ましくは0.1eV以上0.7eV以下、さらに好ましくは0.15eV以上0.4eV以下大きい酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。20

#### 【0167】

なお、インジウムガリウム酸化物は、小さい電子親和力と、高い酸素ブロック性を有する。そのため、半導体406cがインジウムガリウム酸化物を含むと好ましい。ガリウム原子割合[Ga / (In + Ga)]は、例えば、70%以上、好ましくは80%以上、さらに好ましくは90%以上とする。

#### 【0168】

このとき、ゲート電圧を印加すると、半導体406a、半導体406b、半導体406cのうち、電子親和力の大きい半導体406bにチャネルが形成される。30

#### 【0169】

ここで、半導体406aと半導体406bとの間には、半導体406aと半導体406bとの混合領域を有する場合がある。また、半導体406bと半導体406cとの間には、半導体406bと半導体406cとの混合領域を有する場合がある。混合領域は、界面準位密度が低くなる。そのため、半導体406a、半導体406bおよび半導体406cの積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する（連続接合ともいう。）バンド構造となる。なお、図32(A)は、半導体406a、半導体406bおよび半導体406cが、この順番に積層した断面図である。図32(B)は、図32(A)の一点鎖線P1-P2に対応する伝導帯下端のエネルギー(Ec)であり、半導体406aより半導体406cの電子親和力が大きい場合を示す。また、図32(C)は、半導体406aより半導体406cの電子親和力が小さい場合を示す。40

#### 【0170】

このとき、電子は、半導体406a中および半導体406c中ではなく、半導体406b中を主として移動する。半導体406aおよび半導体406bの界面における界面準位密度、半導体406bと半導体406cとの界面における界面準位密度を低くすることによって、半導体406b中で電子の移動が阻害されることが少なく、トランジスタのオン電流を高くすることができる。

#### 【0171】

また、トランジスタのオン電流を高くするためには、半導体406cの厚さは小さいほど50

好ましい。例えば、10 nm未満、好ましくは5 nm以下、さらに好ましくは3 nm以下の領域を有する半導体406cとすればよい。一方、半導体406cは、チャネルの形成される半導体406bへ、隣接する絶縁体を構成する酸素以外の元素（水素、シリコンなど）が入り込まないようロックする機能を有する。そのため、半導体406cは、ある程度の厚さを有することが好ましい。例えば、0.3 nm以上、好ましくは1 nm以上、さらに好ましくは2 nm以上の厚さの領域を有する半導体406cとすればよい。また、半導体406cは、絶縁体402などから放出される酸素の外方拡散を抑制するために、酸素をロックする性質を有すると好ましい。

#### 【0172】

また、信頼性を高くするためには、半導体406aは厚く、半導体406cは薄いことが好ましい。例えば、10 nm以上、好ましくは20 nm以上、さらに好ましくは40 nm以上、より好ましくは60 nm以上の厚さの領域を有する半導体406aとすればよい。10

半導体406aの厚さを、厚くすることで、隣接する絶縁体と半導体406aとの界面からチャネルの形成される半導体406bまでの距離を離すことができる。ただし、半導体装置の生産性が低下する場合があるため、例えば、200 nm以下、好ましくは120 nm以下、さらに好ましくは80 nm以下の厚さの領域を有する半導体406aとすればよい。

#### 【0173】

例えば、半導体406bと半導体406aとの間に、例えば、SIMSにおいて、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。20

また、半導体406bと半導体406cとの間に、SIMSにおいて、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。当該シリコン濃度となる領域は、例えば、導電体404と半導体406と、が互いに重なる領域であつてもよい。

#### 【0174】

また、半導体406bの水素濃度を低減するために、半導体406aおよび半導体406cの水素濃度を低減すると好ましい。半導体406aおよび半導体406cは、SIMSにおいて、 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下の水素濃度となる領域を有する。また、半導体406bの窒素濃度を低減するために、半導体406aおよび半導体406cの窒素濃度を低減すると好ましい。半導体406aおよび半導体406cは、SIMSにおいて、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下の窒素濃度となる領域を有する。30

#### 【0175】

また、半導体406aの表面または内部における銅濃度は低いほど好ましい。例えば、半導体406aは、銅濃度が $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、または $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下となる領域を有すると好ましい。また、半導体406cの表面または内部における銅濃度は低いほど好ましい。例えば、半導体406cは、銅濃度が $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、または $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下となる領域を有すると好ましい。40

#### 【0176】

上述の3層構造は一例である。例えば、半導体406が、半導体406aまたは半導体406cを有さない2層構造であっても構わない。または、半導体406が、半導体406aの上もしくは下、または半導体406c上もしくは下に、半導体406a、半導体406bおよび半導体406cとして例示した半導体のいずれか一を有する4層構造であって50

構わない。または、半導体 406 が、半導体 406a の上、半導体 406a の下、半導体 406c の上、半導体 406c の下のいずれか二箇所以上に、半導体 406a、半導体 406b および半導体 406c として例示した半導体のいずれか一を有する n 層構造 (n は 5 以上の整数) であっても構わない。

#### 【0177】

また、例えば、図 7 (B) に示すように、トランジスタの半導体 406 が、半導体 406a と、半導体 406a 上の半導体 406b と、を有してもよい。また、絶縁体 412 が、絶縁体 412a と、絶縁体 412a 上の絶縁体 412b と、を有してもよい。

#### 【0178】

なお、絶縁体 412b は、例えば、図 3 (B) などに示した絶縁体 412 についての記載を参照する。また、絶縁体 412a は、例えば、図 7 (A) に示した半導体 406c についての記載を参照する。即ち、絶縁体 412a は半導体であってもよい。

#### 【0179】

図 7 (B) は、図 7 (A) に類似しており、トランジスタのチャネル形成領域を有する半導体 406b が、半導体 406a と絶縁体 412a と、に挟まれる構造を有する。したがって、図 7 (B) に示すトランジスタは、高いオン電流を有するトランジスタとなる。また、図 7 (B) に示すトランジスタは、チャネル幅方向において、半導体 406b が、半導体 406a と絶縁体 412a と、に囲まれる構造を有する。したがって、半導体 406b の側面においても界面準位密度が低減された構造である。

#### 【0180】

また、例えば、図 8 (A) に示すように、トランジスタの下方に導電体 413 を有しても構わない。導電体 413 は、例えば、トランジスタを遮光する機能を有する。導電体 413 を、トランジスタの遮光を利用する場合、例えば、導電体 413 を、半導体 406 よりも大きくすると好ましい場合がある。または、導電体 413 は、例えば、トランジスタの第 2 のゲート電極としての機能を有する。導電体 413 を、トランジスタの第 2 のゲート電極として利用する場合、例えば、導電体 413 に印加する電位によってトランジスタのしきい値電圧を調整することができる。

#### 【0181】

例えば、導電体 413 に、ソース電極よりも低い電圧または高い電圧を印加し、トランジスタのしきい値電圧をプラス方向またはマイナス方向へ変動させてもよい。トランジスタのしきい値電圧をプラス方向に変動させることで、ゲート電圧が 0 V であってもトランジスタが非導通状態（オフ状態）となる、ノーマリーオフが実現できる場合がある。なお、導電体 413 に印加する電圧は、可変であってもよいし、固定であってもよい。導電体 413 に印加する電圧を可変にする場合、電圧を制御する回路を導電体 413 と電気的に接続してもよい。

#### 【0182】

導電体 413 としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニアム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

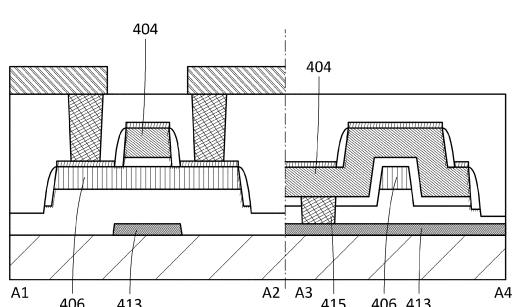

#### 【0183】

また、例えば、トランジスタは、図 8 (B) に示すように導電体 404 と導電体 413 と、が導電体 415 を介して電気的に接続する構造であっても構わない。このような構造とすることで、導電体 404 と導電体 413 とに同じ電位が供給されるため、トランジスタのスイッチング特性を向上させることができる。

#### 【0184】

導電体 415 としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム

10

20

30

40

50

ニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニアム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0185】

なお、導電体413は、図33(A)に示すように、チャネル長方向において導電体404よりも広い(横に迫り出す)形状を有してもよい。これにより、遮光する機能を高くすることができる。または、導電体413は、図33(B)に示すように、チャネル長方向において導電体404よりも狭い(内側に収まる)形状を有してもよい。これにより、寄生容量を小さくすることができる。なお、導電体415は、図33(A)のように設けないようにしてよいし、図33(B)に示すように、設けてよい。

#### 【0186】

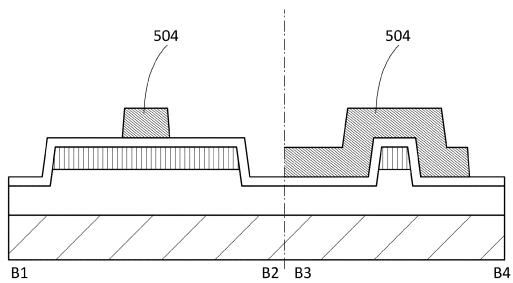

<トランジスタ構造2>

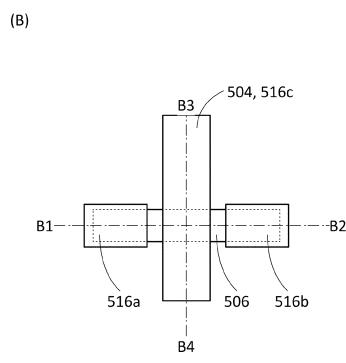

次に、上述したトランジスタとは、異なる構造を有するトランジスタおよびその作製方法について説明する。なお、トランジスタの作製方法は、チャネル長方向(B1-B2断面)およびチャネル幅方向(B3-B4断面)を用いて説明する。

#### 【0187】

まずは、基板500を準備する。

#### 【0188】

基板500としては、例えば、基板400についての記載を参照する。

#### 【0189】

次に、絶縁体502を形成する。絶縁体502としては、例えば、絶縁体402についての記載を参照する。

#### 【0190】

次に、半導体506を形成する。半導体506は、半導体506となる半導体を形成した後で、該半導体の一部をエッチングすることで形成すればよい。

#### 【0191】

半導体506は、例えば、半導体406についての記載を参照する。

#### 【0192】

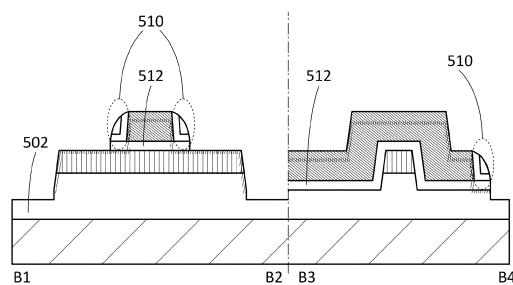

次に絶縁体542および導電体534を、この順に形成する(図9(A)参照。)。絶縁体542としては、例えば、絶縁体442についての記載を参照する。導電体534としては、例えば、導電体434についての記載を参照する。

#### 【0193】

次に、導電体534の一部をエッチングすることで導電体504を形成する(図9(B)参照。)。

#### 【0194】

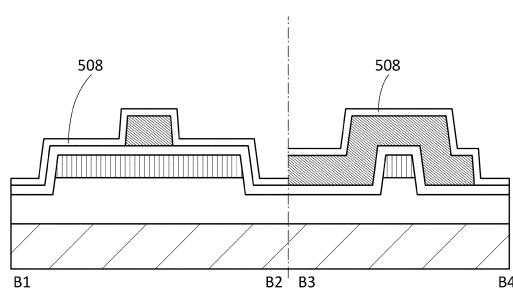

次に、絶縁体508を形成する(図10(A)参照。)。絶縁体508としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニアム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。なお、絶縁体508が、窒化酸化シリコン、窒化シリコンなどの窒素を有する絶縁体を有しても構わない。

#### 【0195】

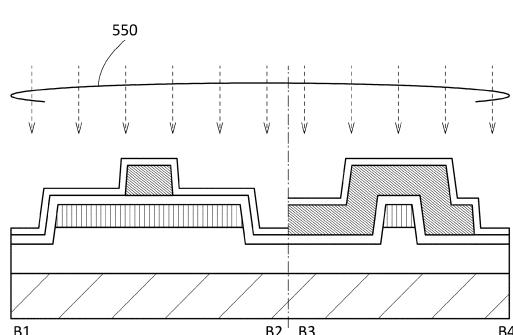

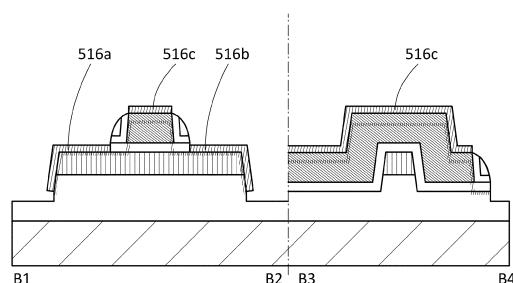

次に、不純物550を添加する処理を行う(図10(B)参照。)。不純物550の添加する処理は、不純物450を添加する処理についての記載を参照する。

#### 【0196】

不純物550は、絶縁体502および半導体506の表面近傍の領域などに添加される。該領域を、領域554と呼ぶ(図11(A)参照。)。領域554については、領域45

10

20

30

40

50

4の記載を参照する。

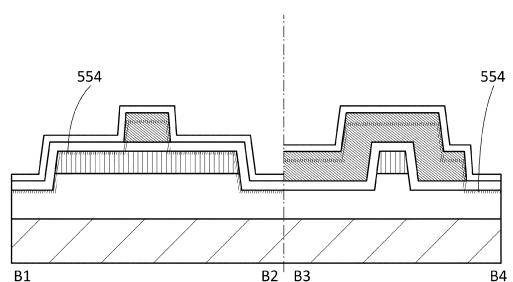

**【0197】**

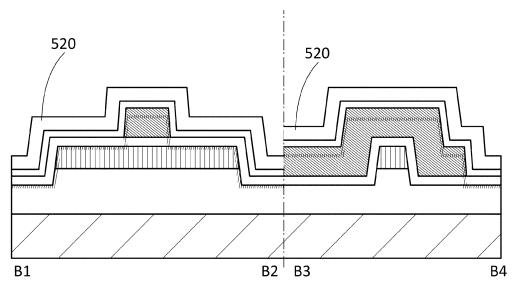

次に、絶縁体520を形成する(図11(B)参照。)。絶縁体520および絶縁体508を異方性エッチングすることで、導電体504の側面に接する絶縁体510を形成する。絶縁体510としては、例えば、絶縁体410aについての記載を参照する。なお、異方性エッチングを行う際、絶縁体542がエッチングされ、絶縁体512が形成される。また、同時に絶縁体502がハーフエッチングされ、絶縁体502の一部の領域は除去される(図12(A)参照。)。

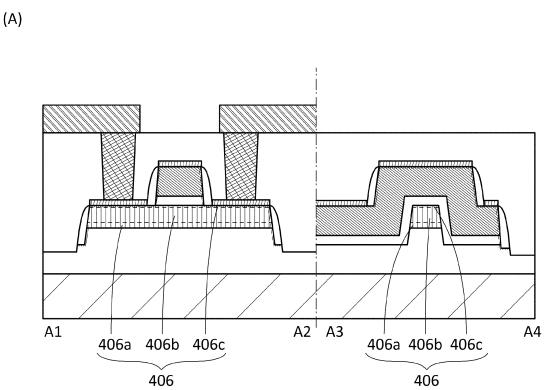

**【0198】**

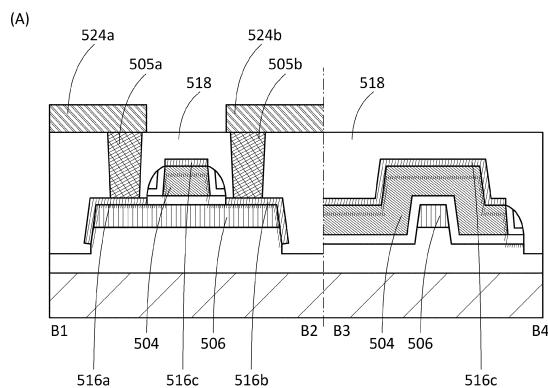

次に、領域554の露出された領域上に対し、導電体を選択成長させる。その結果、半導体506上には、導電体516aおよび導電体516bが形成される。また、導電体504上には、導電体516cが形成される(図12(B)参照。)。導電体516a、導電体516bおよび導電体516cの選択成長については、導電体106の選択成長の記載を参照する。10

**【0199】**

次に、絶縁体518を形成する。絶縁体518としては、例えば、絶縁体418についての記載を参照する。

**【0200】**

次に、絶縁体518に導電体516aおよび導電体516bを達する開口部をそれぞれ形成し、それらの開口部をそれぞれ導電体505aおよび導電体505bを用いて埋める。20 なお、開口部が導電体516aおよび導電体516bを突き抜け、半導体506に達していても構わない。導電体505aおよび導電体505bとしては、例えば、導電体405aおよび導電体405bについての記載を参照する。

**【0201】**

次に、導電体505aおよび導電体505bと、それぞれ接する導電体524aおよび導電体524bを形成する(図13(A)参照。)。導電体524aおよび導電体524bとしては、例えば、導電体424aおよび導電体424bについての記載を参照する。

**【0202】**

以上のようにして、本発明の一態様に係るトランジスタを作製することができる。なお、作製されたトランジスタが、上述した全ての絶縁体、半導体、導電体を有さなくてもよい。例えば、絶縁体518、導電体505a、導電体505b、導電体524a、導電体524bなどのいずれか一以上を有さなくても構わない場合がある。30

**【0203】**

図13(B)は、トランジスタの上面図である。理解を容易にするため、各絶縁体、導電体505a、導電体505b、導電体524aおよび導電体524bを省略して示す。

**【0204】**

図13(B)にも示すように、トランジスタは導電体同士が絶縁体を介して重なる領域を有さない構造となっていることがわかる。したがって、該トランジスタは寄生容量の小さいトランジスタといえる。

**【0205】**

図13(A)および図13(B)に示すトランジスタは、導電体504の電界によって、半導体506を電気的に取り囲むことができるs-channel構造である。そのため、導通時の電流(オン電流)を高くすることができる。トランジスタのソース-ドレイン間に大電流を流すことができ、導通時の電流(オン電流)を高くすることができる。なお、トランジスタがs-channel構造を有さなくても構わない。

**【0206】**

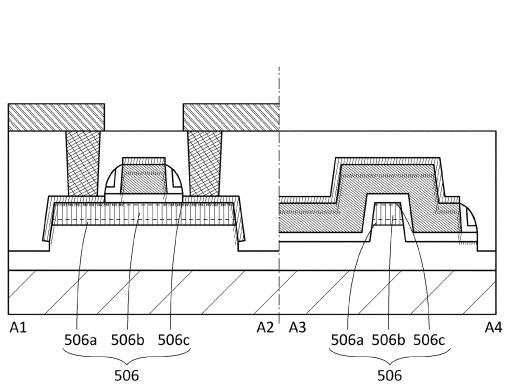

なお、図13(A)では、トランジスタが半導体を1層有する構造を示したが、本発明の一態様はその構造に限定されない。トランジスタが半導体を複数層有する構造であっても構わない。例えば、図14(A)に示すように、トランジスタの半導体506が、半導体506aと、半導体506a上の半導体506bと、半導体506b上の半導体506c4050

と、を有してもよい。

**【0207】**

図14(A)に示す半導体506bは、例えば、半導体406bについての記載を参照する。また、半導体506aは、例えば、半導体406aについての記載を参照する。また、半導体506cは、例えば、半導体406cについての記載を参照する。

**【0208】**

また、例えば、図14(B)に示すように、トランジスタの半導体506が、半導体506aと、半導体506a上の半導体506bと、を有してもよい。また、絶縁体512が、絶縁体512aと、絶縁体512a上の絶縁体512bと、を有してもよい。

**【0209】**

なお、絶縁体512bは、例えば、絶縁体412bについての記載を参照する。また、絶縁体512aは、例えば、絶縁体412aについての記載を参照する。

**【0210】**

図14(B)は、図14(A)に類似しており、トランジスタのチャネル形成領域を有する半導体506bが、半導体506aと絶縁体512aと、に挟まれる構造を有する。したがって、図14(B)に示すトランジスタは、高いオン電流を有するトランジスタとなる。また、図14(B)に示すトランジスタは、チャネル幅方向において、半導体506bが、半導体506aと絶縁体512aと、に囲まれる構造を有する。したがって、半導体506bの側面においても界面準位密度が低減された構造である。

**【0211】**

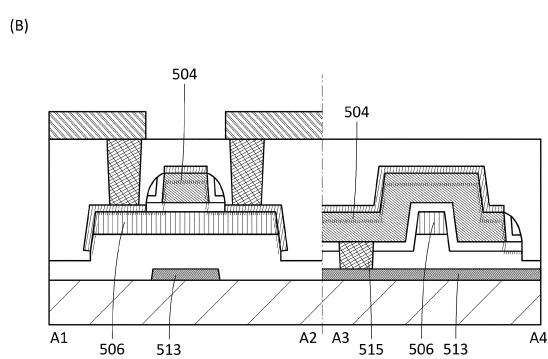

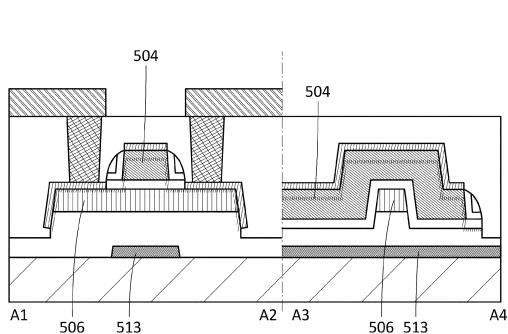

また、例えば、図15(A)に示すように、トランジスタの下方に導電体513を有しても構わない。導電体513は、例えば、導電体413についての記載を参照する。

**【0212】**

また、例えば、トランジスタは、図15(B)に示すように、導電体504と導電体513と、が導電体515を介して電気的に接続する構造であっても構わない。このような構造とすることで、導電体504と導電体513と同じ電位が供給されるため、トランジスタのスイッチング特性を向上させることができる。導電体515としては、例えば、導電体415についての記載を参照する。

**【0213】**

なお、導電体513は、図34(A)に示すように、チャネル長方向において導電体504よりも広い(横に迫り出す)形状を有してもよい。これにより、遮光する機能を高くすることができる。または、導電体513は、図34(B)に示すように、チャネル長方向において導電体504よりも狭い(内側に収まる)形状を有してもよい。これにより、寄生容量を小さくすることができる。なお、導電体515は、図34(A)のように設けないようにしてよいし、図34(B)に示すように、設けてよい。

**【0214】**

以上に示したトランジスタの構造は一例であり、これらを組み合わせたものも本発明の一態様の範疇に含まれる。

**【0215】**

<半導体装置>

以下では、本発明の一態様に係る半導体装置を例示する。

**【0216】**

以下では、本発明の一態様に係るトランジスタを利用した半導体装置の一例について説明する。

**【0217】**

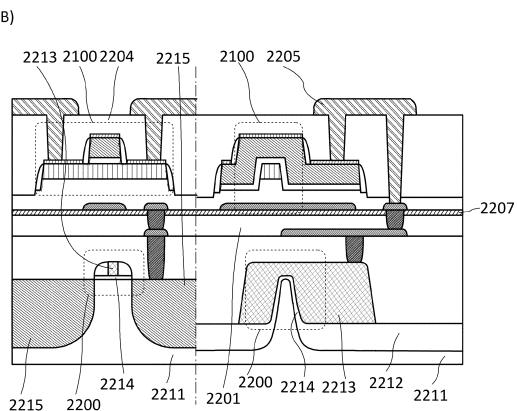

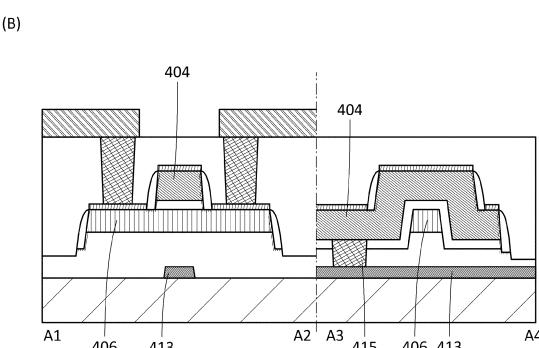

図16(A)に本発明の一態様の半導体装置の断面図を示す。図16(A)に示す半導体装置は、下部に第1の半導体を用いたトランジスタ2200を有し、上部に第2の半導体を用いたトランジスタ2100を有している。図16(A)では、第2の半導体を用いたトランジスタ2100として、図6で例示したトランジスタを適用した例を示している。

**【0218】**

10

20

30

40

50

第1の半導体は、第2の半導体と異なるエネルギーギャップを持つ半導体を用いてもよい。例えば、第1の半導体を酸化物半導体以外の半導体とし、第2の半導体を酸化物半導体とする。第1の半導体として多結晶構造、単結晶構造などのシリコン、ゲルマニウム、などを用いてもよい。または、歪みシリコンなどの歪みを有する半導体を用いてもよい。または、第1の半導体として高電子移動度トランジスタ(HEMT: High Electron Mobility Transistor)に適用可能なヒ化ガリウム、ヒ化アルミニウムガリウム、ヒ化インジウムガリウム、窒化ガリウム、リン化インジウム、シリコンゲルマニウムなどを用いてもよい。これらの半導体を第1の半導体に用いることで、高速動作をすることに適したトランジスタ2200とすることができます。また、酸化物半導体を第2の半導体に用いることで、オフ電流の小さいトランジスタ2100とすること 10 ができる。

#### 【0219】

なお、トランジスタ2200は、nチャネル型、pチャネル型のどちらでもよいが、回路によって適切なトランジスタを用いる。また、トランジスタ2100または/およびトランジスタ2200として、上述したトランジスタや図16(A)に示したトランジスタを用いなくても構わない場合がある。

#### 【0220】

図16(A)に示す半導体装置は、絶縁体2201および絶縁体2207を介して、トランジスタ2200の上部にトランジスタ2100を有する。また、トランジスタ2200とトランジスタ2100の間には、配線として機能する複数の導電体2202が配置されている。また各種絶縁体に埋め込まれた複数の導電体2203により、上層と下層にそれぞれ配置された配線や電極が電気的に接続されている。また、該半導体装置は、トランジスタ2100上の絶縁体2204と、絶縁体2204上の導電体2205と、を有する。 20

#### 【0221】

絶縁体2204は、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。なお、絶縁体2204が、窒化酸化シリコン、窒化シリコンなどの窒素を有する絶縁体を有しても構わない。

#### 【0222】

または、絶縁体2204は、樹脂を用いてもよい。例えば、ポリイミド、ポリアミド、アクリル、シリコーンなどを含む樹脂を用いればよい。樹脂を用いることで、絶縁体2204の上面を平坦化処理しなくてもよい場合がある。また、樹脂は短い時間で厚い膜を成膜することができるため、生産性を高めることができる。 30

#### 【0223】

複数のトランジスタを積層した構造とすることにより、高密度に複数の回路を配置することができる。

#### 【0224】

ここで、トランジスタ2200に用いる第1の半導体に半導体基板2211に含まれる単結晶シリコンを用いた場合、トランジスタ2200の第1の半導体の近傍の絶縁体の水素濃度が高いことが好ましい。該水素により、シリコンのダングリングボンドを終端させることで、トランジスタ2200の信頼性を向上させることができる。一方、トランジスタ2100に用いる第2の半導体に酸化物半導体を用いた場合、トランジスタ2100の第2の半導体の近傍の絶縁体の水素濃度が低いことが好ましい。該水素は、酸化物半導体中にキャリアを生成する要因の一つとなるため、トランジスタ2100の信頼性を低下させる要因となる場合がある。したがって、単結晶シリコンを用いたトランジスタ2200、および酸化物半導体を用いたトランジスタ2100を積層する場合、これらの間に水素をブロックする機能を有する絶縁体2207を配置することは両トランジスタの信頼性を高めるために有効である。 40

#### 【0225】

10

20

30

40

50

絶縁体 2207 としては、例えば酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、イットリア安定化ジルコニア(YSZ)などを含む絶縁体を、単層で、または積層で用いればよい。

#### 【0226】

また、酸化物半導体を用いたトランジスタ 2100 を覆うように、トランジスタ 2100 上に水素をブロックする機能を有する絶縁体を形成することが好ましい。絶縁体としては、絶縁体 2207 と同様の絶縁体を用いることができ、特に酸化アルミニウムを適用することが好ましい。酸化アルミニウム膜は、水素、水分などの不純物および酸素の双方に対して膜を透過させない遮断効果が高い。したがって、トランジスタ 2100 を覆う絶縁体として酸化アルミニウム膜を用いることで、トランジスタ 2100 に含まれる酸化物半導体からの酸素の脱離を防止するとともに、酸化物半導体への水および水素の混入を防止することができる。10

#### 【0227】

なお、トランジスタ 2200 は、プレーナ型のトランジスタだけでなく、様々なタイプのトランジスタとすることができる。例えば、FIN(フィン)型のトランジスタなどとすることができる。その場合の断面図の例を、図 16(B) に示す。半導体基板 2211 の上に、絶縁体 2212 が配置されている。半導体基板 2211 は、先端の細い凸部(フィンともいう。)を有する。なお、凸部は、先端が細くなくてもよく、例えば、略直方体の凸部であってもよいし、先端が太い凸部であってもよい。半導体基板 2211 の凸部の上には、ゲート絶縁体 2214 が配置され、その上には、ゲート電極 2213 が配置されている。半導体基板 2211 には、ソース領域およびドレイン領域 2215 が形成されている。なお、ここでは、半導体基板 2211 が、凸部を有する例を示したが、本発明の一態様に係る半導体装置は、これに限定されない。例えば、SOI 基板を加工して、凸型の半導体領域を形成しても構わない。20

#### 【0228】

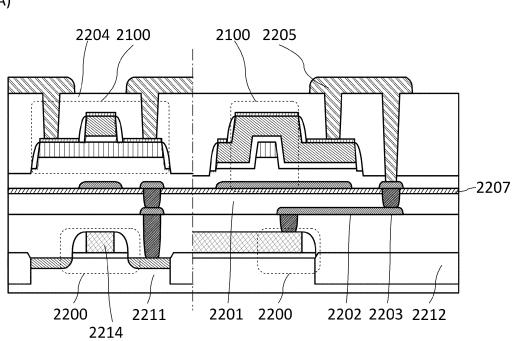

上記回路において、トランジスタ 2100 やトランジスタ 2200 の電極の接続を異ならすことにより、様々な回路を構成することができる。以下では、本発明の一態様の半導体装置を用いることにより実現できる回路構成の例を説明する。

#### 【0229】

図 17(A) に示す回路図は、p チャネル型のトランジスタ 2200 と n チャネル型のトランジスタ 2100 を直列に接続し、かつそれぞれのゲートを接続した、いわゆる CMOS インバータの構成を示している。30

#### 【0230】

また図 17(B) に示す回路図は、トランジスタ 2100 とトランジスタ 2200 のそれぞれのソースとドレインを接続した構成を示している。このような構成とすることで、いわゆる CMOS アナログスイッチとして機能させることができる。

#### 【0231】

本発明の一態様に係るトランジスタを用いた、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を図 18 に示す。40

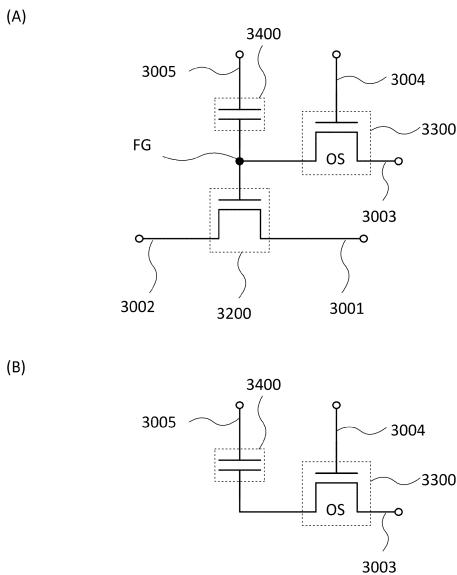

#### 【0232】

図 18(A) に示す半導体装置は、第 1 の半導体を用いたトランジスタ 3200 と第 2 の半導体を用いたトランジスタ 3300、および容量素子 3400 を有している。なお、トランジスタ 3300 としては、上述したトランジスタを用いることができる。

#### 【0233】

トランジスタ 3300 は、酸化物半導体を用いたトランジスタである。トランジスタ 3300 のオフ電流が小さいことにより、半導体装置の特定のノードに長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作を必要としない、またはリフレッシュ動作の頻度が極めて少なくすることが可能となるため、消費電力の低い半導体装置50

となる。

**【0234】**

図18(A)において、第1の配線3001はトランジスタ3200のソースと電気的に接続され、第2の配線3002はトランジスタ3200のドレインと電気的に接続される。また、第3の配線3003はトランジスタ3300のソース、ドレインの一方と電気的に接続され、第4の配線3004はトランジスタ3300のゲートと電気的に接続されている。そして、トランジスタ3200のゲート、およびトランジスタ3300のソース、ドレインの他方は、容量素子3400の電極の一方と電気的に接続され、第5の配線3005は容量素子3400の電極の他方と電気的に接続されている。

**【0235】**

図18(A)に示す半導体装置は、トランジスタ3200のゲートの電位が保持可能という特性を有することで、以下に示すように、情報の書き込み、保持、読み出しが可能である。

**【0236】**

情報の書き込みおよび保持について説明する。まず、第4の配線3004の電位を、トランジスタ3300が導通状態となる電位にして、トランジスタ3300を導通状態とする。これにより、第3の配線3003の電位が、トランジスタ3200のゲート、および容量素子3400の電極の一方と電気的に接続するノードFGに与えられる。すなわち、トランジスタ3200のゲートには、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という。)のどちらかが与えられるものとする。その後、第4の配線3004の電位を、トランジスタ3300が非導通状態となる電位にして、トランジスタ3300を非導通状態とすることにより、ノードFGに電荷が保持される(保持)。

**【0237】**

トランジスタ3300のオフ電流は極めて小さいため、ノードFGの電荷は長期間にわたって保持される。

**【0238】**

次に情報の読み出しについて説明する。第1の配線3001に所定の電位(定電位)を与えた状態で、第5の配線3005に適切な電位(読み出し電位)を与えると、第2の配線3002は、ノードFGに保持された電荷量に応じた電位をとる。これは、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲートにHighレベル電荷が与えられている場合の見かけ上のしきい値電圧 $V_{th\_H}$ は、トランジスタ3200のゲートにLowレベル電荷が与えられている場合の見かけ上のしきい値電圧 $V_{th\_L}$ より低くなるためである。ここで、見かけ上のしきい値電圧とは、トランジスタ3200を「導通状態」とするために必要な第5の配線3005の電位をいうものとする。したがって、第5の配線3005の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、ノードFGに与えられた電荷を判別できる。例えば、書き込みにおいて、ノードFGにHighレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0 (> V_{th\_H})$ となれば、トランジスタ3200は「導通状態」となる。一方、ノードFGにLowレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0 (< V_{th\_L})$ となっても、トランジスタ3200は「非導通状態」のままである。このため、第2の配線3002の電位を判別することで、ノードFGに保持されている情報を読み出すことができる。

**【0239】**

なお、メモリセルをアレイ状に配置する場合、読み出し時には、所望のメモリセルの情報を読み出さなくてはならない。ほかのメモリセルの情報を読み出さないためには、ノードFGに与えられた電荷によらずトランジスタ3200が「非導通状態」となるような電位、つまり、 $V_{th\_H}$ より低い電位を第5の配線3005に与えればよい。または、ノードFGに与えられた電荷によらずトランジスタ3200が「導通状態」となるような電位、つまり、 $V_{th\_L}$ より高い電位を第5の配線3005に与えればよい。

10

20

30

40

50

**【 0 2 4 0 】**

図18(B)に示す半導体装置は、トランジスタ3200を有さない点で図18(A)に示した半導体装置と異なる。この場合も図18(A)に示した半導体装置と同様の動作により情報の書き込みおよび保持動作が可能である。

**【 0 2 4 1 】**

図18(B)に示す半導体装置における、情報の読み出しについて説明する。トランジスタ3300が導通状態になると、浮遊状態である第3の配線3003と容量素子3400とが導通し、第3の配線3003と容量素子3400の間で電荷が再分配される。その結果、第3の配線3003の電位が変化する。第3の配線3003の電位の変化量は、容量素子3400の電極の一方の電位(または容量素子3400に蓄積された電荷)によって、異なる値をとる。10

**【 0 2 4 2 】**

例えば、容量素子3400の電極の一方の電位をV、容量素子3400の容量をC、第3の配線3003が有する容量成分をCB、電荷が再分配される前の第3の配線3003の電位をVB0とすると、電荷が再分配された後の第3の配線3003の電位は、 $(CB \times VB_0 + C \times V) / (CB + C)$ となる。したがって、メモリセルの状態として、容量素子3400の電極の一方の電位がV1とV0( $V1 > V0$ )の2つの状態をとるとする、電位V1を保持している場合の第3の配線3003の電位( $= (CB \times VB_0 + C \times V1) / (CB + C)$ )は、電位V0を保持している場合の第3の配線3003の電位( $= CB \times VB_0 + C \times V0) / (CB + C)$ )よりも高くなることがわかる。20

**【 0 2 4 3 】**

そして、第3の配線3003の電位を所定の電位と比較することで、情報を読み出すことができる。

**【 0 2 4 4 】**

この場合、メモリセルを駆動させるための駆動回路に上記第1の半導体が適用されたトランジスタを用い、トランジスタ3300として第2の半導体が適用されたトランジスタを駆動回路上に積層して配置する構成とすればよい。

**【 0 2 4 5 】**

以上に示した半導体装置は、酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、長期にわたって記憶内容を保持することが可能となる。つまり、リフレッシュ動作が不要となるか、またはリフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力の低い半導体装置を実現することができる。また、電力の供給がない場合(ただし、電位は固定されていることがほしい)であっても、長期にわたって記憶内容を保持することが可能である。30

**【 0 2 4 6 】**

また、該半導体装置は、情報の書き込みに高い電圧が不要であるため、素子の劣化が起りにくい。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行わないため、絶縁体の劣化といった問題が生じない。すなわち、本発明の一態様に係る半導体装置は、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上した半導体装置である。さらに、トランジスタの導通状態、非導通状態によって、情報の書き込みが行われるため、高速な動作が可能となる。40

**【 0 2 4 7 】**

<RFタグ>

以下では、上述したトランジスタ、または記憶装置を含むRFタグについて、図19を用いて説明する。

**【 0 2 4 8 】**

本発明の一態様に係るRFタグは、内部に記憶回路を有し、記憶回路に情報を記憶し、非接触手段、例えば無線通信を用いて外部と情報の授受を行うものである。このような特徴から、RFタグは、物品などの個体情報を読み取ることにより物品の識別を行う個体認証50

システムなどに用いることが可能である。なお、これらの用途に用いるためには高い信頼性が要求される。

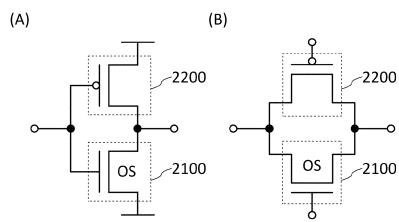

#### 【0249】

R F タグの構成について図19を用いて説明する。図19は、R F タグの構成例を示すブロック図である。

#### 【0250】

図19に示すようにR F タグ800は、通信器801（質問器、リーダ／ライタなどともいう）に接続されたアンテナ802から送信される無線信号803を受信するアンテナ804を有する。またR F タグ800は、整流回路805、定電圧回路806、復調回路807、変調回路808、論理回路809、記憶回路810、ROM811を有している。

なお、復調回路807に含まれる整流作用を示すトランジスタの半導体には、逆方向電流を十分に抑制することが可能な、例えば、酸化物半導体を用いてもよい。これにより、逆方向電流に起因する整流作用の低下を抑制し、復調回路の出力が飽和することを防止できる。つまり、復調回路の入力に対する復調回路の出力を線形に近づけることができる。なお、データの伝送形式は、一対のコイルを対向配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別される。R F タグ800は、そのいずれの方式に用いることも可能である。

10

#### 【0251】

次に各回路の構成について説明する。アンテナ804は、通信器801に接続されたアンテナ802との間で無線信号803の送受信を行うためのものである。また、整流回路805は、アンテナ804で無線信号を受信することにより生成される入力交流信号を整流、例えば、半波2倍圧整流し、後段の容量素子により、整流された信号を平滑化することで入力電位を生成するための回路である。なお、整流回路805の入力側または出力側には、リミッタ回路を有してもよい。リミッタ回路とは、入力交流信号の振幅が大きく、内部生成電圧が大きい場合に、ある電力以上の電力を後段の回路に入力しないように制御するための回路である。

20

#### 【0252】

定電圧回路806は、入力電位から安定した電源電圧を生成し、各回路に供給するための回路である。なお、定電圧回路806は、内部にリセット信号生成回路を有していてもよい。リセット信号生成回路は、安定した電源電圧の立ち上がりを利用して、論理回路809のリセット信号を生成するための回路である。

30

#### 【0253】

復調回路807は、入力交流信号を包絡線検出することにより復調し、復調信号を生成するための回路である。また、変調回路808は、アンテナ804より出力するデータに応じて変調をおこなうための回路である。

#### 【0254】

論理回路809は復調信号を解析し、処理を行うための回路である。記憶回路810は、入力された情報を保持する回路であり、ロウデコーダ、カラムデコーダ、記憶領域などを有する。また、ROM811は、固有番号(ID)などを格納し、処理に応じて出力を行うための回路である。

40

#### 【0255】

なお、上述の各回路は、適宜、取捨することができる。

#### 【0256】

ここで、上述した記憶装置を、記憶回路810に用いることができる。本発明の一態様に係る記憶装置は、電源が遮断された状態であっても情報を保持できるため、R F タグに好適である。さらに本発明の一態様に係る記憶装置は、データの書き込みに必要な電力(電圧)が従来の不揮発性メモリに比べて低いため、データの読み出し時と書き込み時の最大通信距離の差を生じさせないことも可能である。さらに、データの書き込み時に電力が不足し、誤動作または誤書き込みが生じることを抑制することができる。

#### 【0257】

50

また、本発明の一態様に係る記憶装置は、不揮発性メモリとして用いることが可能であるため、ROM 811に適用することもできる。その場合には、生産者がROM 811にデータを書き込むためのコマンドを別途用意し、ユーザが自由に書き換えできないようにしておくことが好ましい。生産者が出荷前に固有番号を書込んだのちに製品を出荷することで、作製したRFタグすべてについて固有番号を付与するのではなく、出荷する良品にのみ固有番号を割り当てることが可能となり、出荷後の製品の固有番号が不連続になることがなく出荷後の製品に対応した顧客管理が容易となる。

#### 【0258】

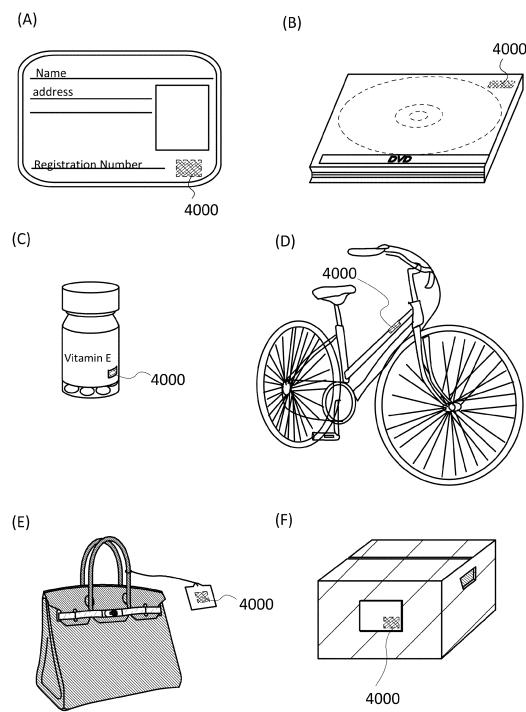

##### <RFタグの使用例>

以下では、本発明の一態様に係るRFタグの使用例について図20を用いて説明する。RFタグの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図20（A）参照。）、包装用容器類（包装紙やボトル等、図20（C）参照。）、記録媒体（DVDやビデオテープ等、図20（B）参照。）、乗り物類（自転車等、図20（D）参照。）、身の回り品（鞄や眼鏡等）、食品類、植物類、動物類、人体、衣類、生活用品類、薬品や薬剤を含む医療品、または電子機器（液晶表示装置、EL表示装置、テレビジョン装置、または携帯電話）等の物品、もしくは各物品に取り付ける荷札（図20（E）および図20（F）参照。）等に設けて使用することができる。

#### 【0259】

本発明の一態様に係るRFタグ4000は、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込み、有機樹脂からなるパッケージであれば当該有機樹脂の内部に埋め込み、各物品に固定される。本発明の一態様に係るRFタグ4000は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類等に本発明の一態様に係るRFタグ4000により、認証機能を付与することができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器等に本発明の一態様に係るRFタグ4000を取り付けることにより、検品システム等のシステムの効率化を図ることができる。また、乗り物類であっても、本発明の一態様に係るRFタグ4000を取り付けることにより、盗難などに対するセキュリティ性を高めることができる。

#### 【0260】

以上のように、本発明の一態様に係るRFタグは、上述したような各用途に用いることができる。

#### 【0261】

##### <CPU>

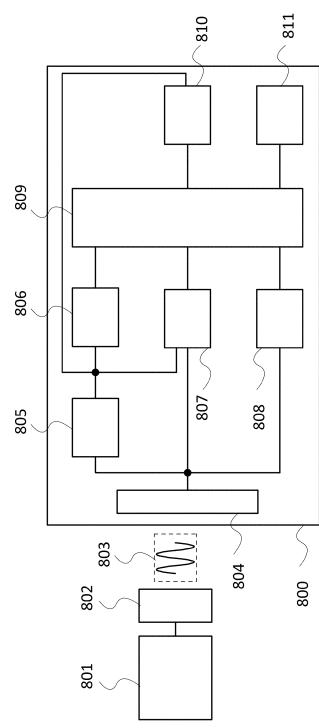

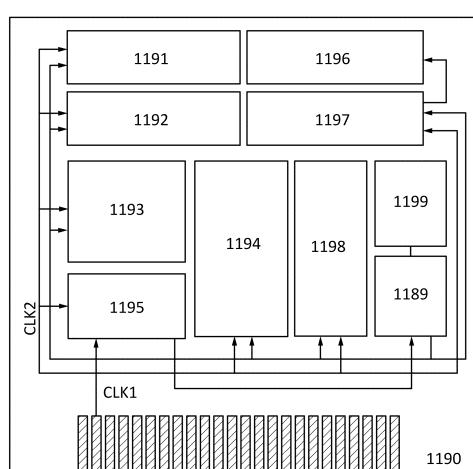

以下では、上述したトランジスタや上述した記憶装置などの半導体装置を含むCPUについて説明する。

#### 【0262】

図21は、上述したトランジスタを一部に用いたCPUの一例の構成を示すブロック図である。

#### 【0263】

図21に示すCPUは、基板1190上に、ALU1191（ALU：Arithmetic logic unit、演算回路）、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198（Bus I/F）、書き換え可能なROM1199、およびROMインターフェース1189（ROM I/F）を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてよい。もちろん、図21に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。例え

10

20

30

40

50

ば、図21に示すCPUまたは演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するような構成としてもよい。また、CPUが内部演算回路やデータバスで扱えるビット数は、例えば8ビット、16ビット、32ビット、64ビットなどとすることができます。

#### 【0264】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

#### 【0265】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

#### 【0266】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、内部クロック信号CLK2を上記各種回路に供給する。

#### 【0267】

図21に示すCPUでは、レジスタ1196に、メモリセルが設けられている。レジスタ1196のメモリセルとして、上述したトランジスタや記憶装置などを用いることができる。

#### 【0268】

図21に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。

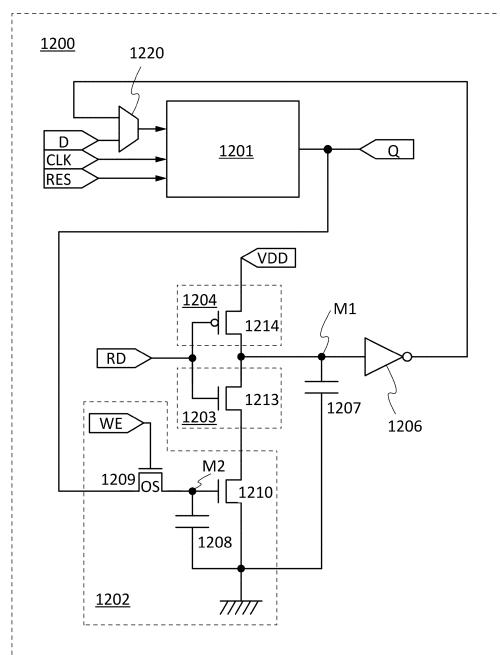

#### 【0269】

図22は、レジスタ1196として用いることのできる記憶素子1200の回路図の一例である。記憶素子1200は、電源遮断で記憶データが揮発する回路1201と、電源遮断で記憶データが揮発しない回路1202と、スイッチ1203と、スイッチ1204と、論理素子1206と、容量素子1207と、選択機能を有する回路1220と、を有する。回路1202は、容量素子1208と、トランジスタ1209と、トランジスタ1210と、を有する。なお、記憶素子1200は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の素子をさらに有していてもよい。

#### 【0270】

ここで、回路1202には、上述した記憶装置を用いることができる。記憶素子1200への電源電圧の供給が停止した際、回路1202のトランジスタ1209のゲートにはGND(0V)、またはトランジスタ1209がオフする電位が入力され続ける構成とする。例えば、トランジスタ1209のゲートが抵抗等の負荷を介して接地される構成とする

10

20

30

40

50

。

### 【0271】

スイッチ1203は、一導電型（例えば、nチャネル型）のトランジスタ1213を用いて構成され、スイッチ1204は、一導電型とは逆の導電型（例えば、pチャネル型）のトランジスタ1214を用いて構成した例を示す。ここで、スイッチ1203の第1の端子はトランジスタ1213のソースとドレインの一方に対応し、スイッチ1203の第2の端子はトランジスタ1213のソースとドレインの他方に対応し、スイッチ1203はトランジスタ1213のゲートに入力される制御信号RDによって、第1の端子と第2の端子の間の導通または非導通（つまり、トランジスタ1213の導通状態または非導通状態）が選択される。スイッチ1204の第1の端子はトランジスタ1214のソースとドレインの一方に対応し、スイッチ1204の第2の端子はトランジスタ1214のソースとドレインの他方に対応し、スイッチ1204はトランジスタ1214のゲートに入力される制御信号RDによって、第1の端子と第2の端子の間の導通または非導通（つまり、トランジスタ1214の導通状態または非導通状態）が選択される。10

### 【0272】

トランジスタ1209のソースとドレインの一方は、容量素子1208の一対の電極のうちの一方、およびトランジスタ1210のゲートと電気的に接続される。ここで、接続部分をノードM2とする。トランジスタ1210のソースとドレインの一方は、低電源電位を供給することのできる配線（例えばGND線）に電気的に接続され、他方は、スイッチ1203の第1の端子（トランジスタ1213のソースとドレインの一方）と電気的に接続される。スイッチ1203の第2の端子（トランジスタ1213のソースとドレインの他方）はスイッチ1204の第1の端子（トランジスタ1214のソースとドレインの一方）と電気的に接続される。スイッチ1204の第2の端子（トランジスタ1214のソースとドレインの他方）は電源電位VDDを供給することのできる配線と電気的に接続される。スイッチ1203の第2の端子（トランジスタ1213のソースとドレインの他方）と、スイッチ1204の第1の端子（トランジスタ1214のソースとドレインの一方）と、論理素子1206の入力端子と、容量素子1207の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノードM1とする。容量素子1207の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子1207の一対の電極のうちの他方は、低電源電位を供給することのできる配線（例えばGND線）と電気的に接続される。容量素子1208の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子1208の一対の電極のうちの他方は、低電源電位を供給することのできる配線（例えばGND線）と電気的に接続される。20

### 【0273】

なお、容量素子1207および容量素子1208は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。30

### 【0274】

トランジスタ1209のゲートには、制御信号WEが入力される。スイッチ1203およびスイッチ1204は、制御信号WEとは異なる制御信号RDによって第1の端子と第2の端子の間の導通状態または非導通状態を選択され、一方のスイッチの第1の端子と第2の端子の間が導通状態のとき他方のスイッチの第1の端子と第2の端子の間は非導通状態となる。40

### 【0275】

トランジスタ1209のソースとドレインの他方には、回路1201に保持されたデータに対応する信号が入力される。図22では、回路1201から出力された信号が、トランジスタ1209のソースとドレインの他方に入力される例を示した。スイッチ1203の第2の端子（トランジスタ1213のソースとドレインの他方）から出力される信号は、50

論理素子 1206 によってその論理値が反転された反転信号となり、回路 1220 を介して回路 1201 に入力される。

#### 【0276】

なお、図 22 では、スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）から出力される信号は、論理素子 1206 および回路 1220 を介して回路 1201 に入力する例を示したがこれに限定されない。スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）から出力される信号が、論理値を反転させられることなく、回路 1201 に入力されてもよい。例えば、回路 1201 内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）から出力される信号を当該ノードに入力することができる。10

#### 【0277】

また、図 22 において、記憶素子 1200 に用いられるトランジスタのうち、トランジスタ 1209 以外のトランジスタは、酸化物半導体以外の半導体でなる膜または基板 1190 にチャネルが形成されるトランジスタとすることができる。例えば、シリコンでなる膜またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子 1200 に用いられるトランジスタ全てを、チャネルが酸化物半導体で形成されるトランジスタとすることもできる。または、記憶素子 1200 は、トランジスタ 1209 以外にも、チャネルが酸化物半導体で形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板 1190 にチャネルが形成されるトランジスタとすることもできる。20

#### 【0278】

図 22 における回路 1201 には、例えばフリップフロップ回路を用いることができる。また、論理素子 1206 としては、例えばインバータやクロックドインバータ等を用いることができる。

#### 【0279】

本発明の一態様に係る半導体装置では、記憶素子 1200 に電源電圧が供給されない間は、回路 1201 に記憶されていたデータを、回路 1202 に設けられた容量素子 1208 によって保持することができる。

#### 【0280】

また、酸化物半導体にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく小さい。そのため、当該トランジスタをトランジスタ 1209 として用いることによって、記憶素子 1200 に電源電圧が供給されない間も容量素子 1208 に保持された信号は長期間にわたり保たれる。こうして、記憶素子 1200 は電源電圧の供給が停止した間も記憶内容（データ）を保持することが可能である。30

#### 【0281】

また、スイッチ 1203 およびスイッチ 1204 を設けることによって、プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路 1201 が元のデータを保持しなおすまでの時間を短くすることができる。40

#### 【0282】

また、回路 1202 において、容量素子 1208 によって保持された信号はトランジスタ 1210 のゲートに入力される。そのため、記憶素子 1200 への電源電圧の供給が再開された後、容量素子 1208 によって保持された信号を、トランジスタ 1210 の状態（導通状態、または非導通状態）に変換して、回路 1202 から読み出すことができる。それ故、容量素子 1208 に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

#### 【0283】

このような記憶素子 1200 を、プロセッサが有するレジスタやキャッシュメモリなどの50

記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、または複数の論理回路において、短い時間でも電源停止を行うことができるため、消費電力を抑えることができる。

#### 【0284】

記憶素子1200をCPUに用いる例として説明したが、記憶素子1200は、DSP (Digital Signal Processor)、カスタムLSI、PLD (Programmable Logic Device) 等のLSI、RF-ID (Radio Frequency Identification) にも応用可能である。 10

#### 【0285】

##### <表示装置>

以下では、本発明の一態様に係る表示装置の構成例について説明する。

#### 【0286】

##### [構成例]

図23(A)には、本発明の一態様に係る表示装置の上面図を示す。また、図23(B)には、本発明の一態様に係る表示装置の画素に液晶素子を用いた場合における画素回路を示す。また、図23(C)には、本発明の一態様に係る表示装置の画素に有機EL素子を用いた場合における画素回路を示す。 20

#### 【0287】

画素に用いるトランジスタは、上述したトランジスタを用いることができる。ここでは、nチャネル型のトランジスタを用いる例を示す。なお、画素に用いたトランジスタと、同一工程を経て作製したトランジスタを駆動回路として用いても構わない。このように、画素や駆動回路に上述したトランジスタを用いることにより、表示品位が高い、または/および信頼性の高い表示装置となる。 30

#### 【0288】

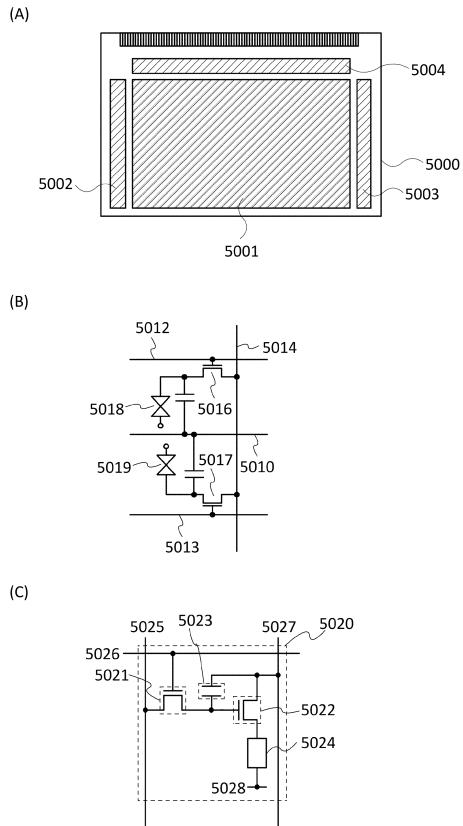

アクティブマトリクス型表示装置の上面図の一例を図23(A)に示す。表示装置の基板5000上には、画素部5001、第1の走査線駆動回路5002、第2の走査線駆動回路5003、信号線駆動回路5004が配置される。画素部5001は、複数の信号線によって信号線駆動回路5004と電気的に接続され、複数の走査線によって第1の走査線駆動回路5002、および第2の走査線駆動回路5003と電気的に接続される。なお、走査線と信号線とによって区切られる領域には、それぞれ表示素子を有する画素が配置されている。また、表示装置の基板5000は、FPC (Flexible Printed Circuit) 等の接続部を介して、タイミング制御回路(コントローラ、制御ICともいう)に電気的に接続されている。 30

#### 【0289】

第1の走査線駆動回路5002、第2の走査線駆動回路5003および信号線駆動回路5004は、画素部5001と同じ基板5000上に形成される。そのため、駆動回路を別途作製する場合と比べて、表示装置を作製するコストを低減することができる。また、駆動回路を別途作製した場合、配線間の接続数が増える。したがって、同じ基板5000上に駆動回路を設けることで、配線間の接続数を減らすことができ、信頼性の向上、または/および歩留まりの向上を図ることができる。 40

#### 【0290】

##### [液晶表示装置]

また、画素の回路構成の一例を図23(B)に示す。ここでは、VA型液晶表示装置の画素などに適用することができる画素回路を示す。

#### 【0291】

この画素回路は、一つの画素に複数の画素電極を有する構成に適用できる。それぞれの画素電極は異なるトランジスタに接続され、各トランジスタは異なるゲート信号で駆動できるように構成されている。これにより、マルチドメイン設計された画素の個々の画素電極 50

に印加する信号を、独立して制御できる。

**【0292】**

トランジスタ5016のゲート配線5012と、トランジスタ5017のゲート配線5013には、異なるゲート信号を与えることができるよう分離されている。一方、データ線として機能するソース電極またはドレイン電極5014は、トランジスタ5016とトランジスタ5017で共通に用いられている。トランジスタ5016とトランジスタ5017は上述したトランジスタを適宜用いることができる。これにより、表示品位が高い、または/および信頼性の高い液晶表示装置を提供することができる。

**【0293】**

トランジスタ5016と電気的に接続する第1の画素電極と、トランジスタ5017と電気的に接続する第2の画素電極の形状について説明する。第1の画素電極と第2の画素電極の形状は、スリットによって分離されている。第1の画素電極はV字型に広がる形状を有し、第2の画素電極は第1の画素電極の外側を囲むように形成される。

10

**【0294】**

トランジスタ5016のゲート電極はゲート配線5012と電気的に接続され、トランジスタ5017のゲート電極はゲート配線5013と電気的に接続されている。ゲート配線5012とゲート配線5013に異なるゲート信号を与えてトランジスタ5016とトランジスタ5017の動作タイミングを異ならせ、液晶の配向を制御することができる。

**【0295】**

また、容量配線5010と、誘電体として機能するゲート絶縁体と、第1の画素電極または第2の画素電極と電気的に接続する容量電極とで容量素子を形成してもよい。

20

**【0296】**

マルチドメイン構造は、一画素に第1の液晶素子5018と第2の液晶素子5019を備える。第1の液晶素子5018は第1の画素電極と対向電極とその間の液晶層とで構成され、第2の液晶素子5019は第2の画素電極と対向電極とその間の液晶層とで構成される。

**【0297】**

なお、本発明の一態様に係る表示装置は、図23(B)に示す画素回路に限定されない。例えば、図23(B)に示す画素回路に新たにスイッチ、抵抗素子、容量素子、トランジスタ、センサー、または論理回路などを追加してもよい。

30

**【0298】**

**[有機EL表示装置]**

画素の回路構成の他の一例を図23(C)に示す。ここでは、有機EL素子を用いた表示装置の画素構造を示す。

**【0299】**

有機EL素子は、発光素子に電圧を印加することにより、有機EL素子が有する一対の電極の一方から電子が、他方から正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、電子および正孔が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

40

**【0300】**

図23(C)は、画素回路の一例を示す図である。ここでは1つの画素にnチャネル型のトランジスタを2つ用いる例を示す。なお、nチャネル型のトランジスタには、上述したトランジスタを用いることができる。また、当該画素回路は、デジタル時間階調駆動を適用することができる。

**【0301】**

適用可能な画素回路の構成およびデジタル時間階調駆動を適用した場合の画素の動作について説明する。

**【0302】**

画素5020は、スイッチング用トランジスタ5021、駆動用トランジスタ5022、

50

発光素子 5024 および容量素子 5023 を有する。スイッチング用トランジスタ 5021 は、ゲート電極が走査線 5026 に接続され、第 1 電極（ソース電極、ドレイン電極の一方）が信号線 5025 に接続され、第 2 電極（ソース電極、ドレイン電極の他方）が駆動用トランジスタ 5022 のゲート電極に接続されている。駆動用トランジスタ 5022 は、ゲート電極が容量素子 5023 を介して電源線 5027 に接続され、第 1 電極が電源線 5027 に接続され、第 2 電極が発光素子 5024 の第 1 電極（画素電極）に接続されている。発光素子 5024 の第 2 電極は共通電極 5028 に相当する。共通電極 5028 は、同一基板上に形成される共通電位線と電気的に接続される。

#### 【0303】

スイッチング用トランジスタ 5021 および駆動用トランジスタ 5022 は上述したトランジスタを用いることができる。これにより、表示品位の高い、または／および信頼性の高い有機 E-L 表示装置となる。

#### 【0304】

発光素子 5024 の第 2 電極（共通電極 5028）の電位は低電源電位に設定する。なお、低電源電位とは、電源線 5027 に供給される高電源電位より低い電位であり、例えば GND、0Vなどを低電源電位として設定することができる。発光素子 5024 の順方向のしきい値電圧以上となるように高電源電位と低電源電位を設定し、その電位差を発光素子 5024 に印加することにより、発光素子 5024 に電流を流して発光させる。なお、発光素子 5024 の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。

#### 【0305】

なお、容量素子 5023 は駆動用トランジスタ 5022 のゲート容量を代用することにより省略できる場合がある。駆動用トランジスタ 5022 のゲート容量については、チャネル形成領域とゲート電極との間で容量が形成されていてもよい。

#### 【0306】

次に、駆動用トランジスタ 5022 に入力する信号について説明する。電圧入力電圧駆動方式の場合、駆動用トランジスタ 5022 がオンまたはオフの二つの状態となるようなビデオ信号を、駆動用トランジスタ 5022 に入力する。なお、駆動用トランジスタ 5022 を線形領域で動作させるために、電源線 5027 の電圧よりも高い電圧を駆動用トランジスタ 5022 のゲート電極に与える。また、信号線 5025 には、電源線電圧に駆動用トランジスタ 5022 のしきい値電圧 V<sub>th</sub> を加えた値以上の電圧をかける。

#### 【0307】

アナログ階調駆動を行う場合、駆動用トランジスタ 5022 のゲート電極に発光素子 5024 の順方向電圧に駆動用トランジスタ 5022 のしきい値電圧 V<sub>th</sub> を加えた値以上の電圧をかける。なお、駆動用トランジスタ 5022 が飽和領域で動作するようにビデオ信号を入力し、発光素子 5024 に電流を流す。また、駆動用トランジスタ 5022 を飽和領域で動作させるために、電源線 5027 の電位を、駆動用トランジスタ 5022 のゲート電位よりも高くする。ビデオ信号をアナログとすることで、発光素子 5024 にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

#### 【0308】

なお、本発明の一態様に係る表示装置は、図 23 (C) に示す画素構成に限定されない。例えば、図 23 (C) に示す画素回路にスイッチ、抵抗素子、容量素子、センサー、トランジスタまたは論理回路などを追加してもよい。

#### 【0309】

図 23 で例示した回路に上述したトランジスタを適用する場合、低電位側にソース電極（第 1 の電極）、高電位側にドレイン電極（第 2 の電極）がそれぞれ電気的に接続される構成とする。さらに、制御回路等により第 1 のゲート電極の電位を制御し、第 2 のゲート電極にはソース電極に与える電位よりも低い電位など、上記で例示した電位を入力可能な構成とすればよい。

#### 【0310】

10

20

30

40

50

例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、および発光素子を有する装置である発光装置は、様々な形態を用いること、または様々な素子を有することが出来る。表示素子、表示装置、発光素子または発光装置の一例としては、E L 素子（有機物および無機物を含むE L 素子、有機E L 素子、無機E L 素子）、L E D（白色L E D、赤色L E D、緑色L E D、青色L E Dなど）、トランジスタ（電流に応じて発光するトランジスタ）、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ（G L V）、プラズマディスプレイパネル（P D P）、M E M S（マイクロ・エレクトロ・メカニカル・システム）を用いた表示素子、デジタルマイクロミラーデバイス（D M D）、D M S（デジタル・マイクロ・シャッター）、I M O D（インターフェアレンス・モジュレーション）素子、シャッター方式のM E M S表示素子、光干渉方式のM E M S表示素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有するものがある。E L 素子を用いた表示装置の一例としては、E L ディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッショニングディスプレイ（F E D）またはS E D方式平面型ディスプレイ（S E D：Surface-conduction Electron-emitter Display）などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ（透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ）などがある。電子インク、または電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。なお、半透過型液晶ディスプレイや反射型液晶ディスプレイを実現する場合には、画素電極の一部または全部が、反射電極としての機能を有するようにすればよい。例えば、画素電極の一部または全部が、アルミニウム、銀などを有するようにすればよい。さらに、その場合、反射電極の下に、S R A Mなどの記憶回路を設けることも可能である。これにより、消費電力をさらに低減することができる。

10

### 【0311】

なお、バックライト（有機E L 素子、無機E L 素子、L E D、蛍光灯など）に白色光（W）を用いて表示装置をフルカラー表示させるために、着色層（カラーフィルターともいう。）を用いてもよい。着色層は、例えば、レッド（R）、グリーン（G）、ブルー（B）、イエロー（Y）などを適宜組み合わせて用いることができる。着色層を用いることで、着色層を用いない場合と比べて色の再現性を高くすることができる。このとき、着色層を有する領域と、着色層を有さない領域と、を配置することによって、着色層を有さない領域における白色光を直接表示に利用しても構わない。一部に着色層を有さない領域を配置することで、明るい表示の際に、着色層による輝度の低下を少なくでき、消費電力を2割から3割程度低減できる場合がある。ただし、有機E L 素子や無機E L 素子などの自発光素子を用いてフルカラー表示する場合、R、G、B、Y、Wを、それぞれの発光色を有する素子から発光させても構わない。自発光素子を用いることで、着色層を用いた場合よりも、さらに消費電力を低減できる場合がある。

20

### 【0312】

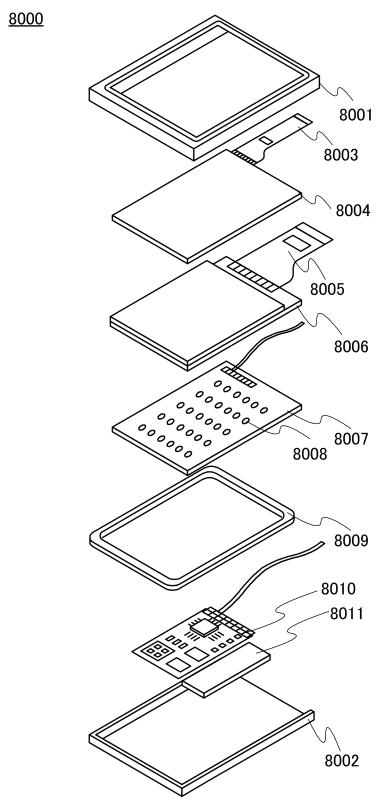

#### <モジュール>

以下では、本発明の一態様に係る半導体装置を適用した表示モジュールについて、図24を用いて説明を行う。

30

### 【0313】

図24に示す表示モジュール8000は、上部カバー8001と下部カバー8002との間に、F P C 8003に接続されたタッチパネル8004、F P C 8005に接続されたセル8006、バックライトユニット8007、フレーム8009、プリント基板8010、バッテリー8011を有する。なお、バックライトユニット8007、バッテリー8011、タッチパネル8004などを有さない場合もある。

### 【0314】

本発明の一態様に係る半導体装置は、例えば、セル8006に用いることができる。

40

**【 0 3 1 5 】**

上部カバー 8 0 0 1 および下部カバー 8 0 0 2 は、タッチパネル 8 0 0 4 およびセル 8 0 0 6 のサイズに合わせて、形状や寸法を適宜変更することができる。

**【 0 3 1 6 】**

タッチパネル 8 0 0 4 は、抵抗膜方式または静電容量方式のタッチパネルをセル 8 0 0 6 に重畠して用いることができる。また、セル 8 0 0 6 の対向基板（封止基板）に、タッチパネル機能を持たせるようにすることも可能である。または、セル 8 0 0 6 の各画素内に光センサーを設け、光学式のタッチパネルとすることも可能である。または、セル 8 0 0 6 の各画素内にタッチセンサー用電極を設け、静電容量方式のタッチパネルとすることも可能である。

10

**【 0 3 1 7 】**

バックライトユニット 8 0 0 7 は、光源 8 0 0 8 を有する。光源 8 0 0 8 をバックライトユニット 8 0 0 7 の端部に設け、光拡散板を用いる構成としてもよい。

**【 0 3 1 8 】**

フレーム 8 0 0 9 は、セル 8 0 0 6 の保護機能の他、プリント基板 8 0 1 0 の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有してもよい。またフレーム 8 0 0 9 は、放熱板としての機能を有していてもよい。

**【 0 3 1 9 】**

プリント基板 8 0 1 0 は、電源回路、ビデオ信号およびクロック信号を出力するための信号処理回路を有する。電源回路に電力を供給する電源としては、外部の商用電源であってもよいし、別途設けたバッテリー 8 0 1 1 による電源であってもよい。商用電源を用いる場合には、バッテリー 8 0 1 1 を有さなくてもよい。

20

**【 0 3 2 0 】**

また、表示モジュール 8 0 0 0 には、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。

**【 0 3 2 1 】**

<電子機器>

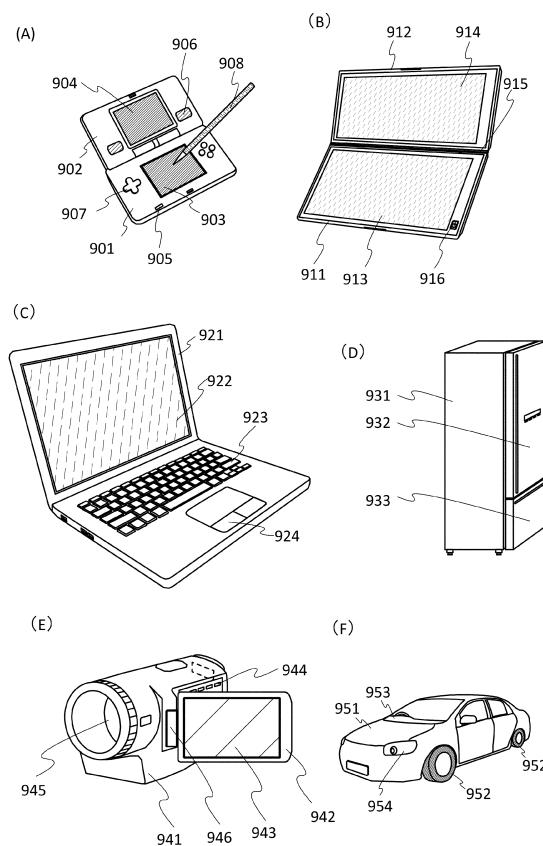

本発明の一態様に係る半導体装置は、表示機器、パソコンコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図25に示す。

30

**【 0 3 2 2 】**

図25（A）は携帯型ゲーム機であり、筐体 9 0 1 、筐体 9 0 2 、表示部 9 0 3 、表示部 9 0 4 、マイクロフォン 9 0 5 、スピーカー 9 0 6 、操作キー 9 0 7 、スタイルスティラス 9 0 8 等を有する。なお、図25（A）に示した携帯型ゲーム機は、2つの表示部 9 0 3 と表示部 9 0 4 とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

40

**【 0 3 2 3 】**

図25（B）は携帯データ端末であり、第1筐体 9 1 1 、第2筐体 9 1 2 、第1表示部 9 1 3 、第2表示部 9 1 4 、接続部 9 1 5 、操作キー 9 1 6 等を有する。第1表示部 9 1 3 は第1筐体 9 1 1 に設けられており、第2表示部 9 1 4 は第2筐体 9 1 2 に設けられている。そして、第1筐体 9 1 1 と第2筐体 9 1 2 とは、接続部 9 1 5 により接続されており、第1筐体 9 1 1 と第2筐体 9 1 2 の間の角度は、接続部 9 1 5 により変更が可能である。第1表示部 9 1 3 における映像を、接続部 9 1 5 における第1筐体 9 1 1 と第2筐体 9

50

12との間の角度にしたがって、切り替える構成としてもよい。また、第1表示部913および第2表示部914の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしてもよい。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。または、位置入力装置としての機能は、フォトセンサーとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。

## 【0324】

図25(C)はノート型パーソナルコンピュータであり、筐体921、表示部922、キーボード923、ポインティングデバイス924等を有する。

## 【0325】

図25(D)は電気冷凍冷蔵庫であり、筐体931、冷蔵室用扉932、冷凍室用扉933等を有する。

## 【0326】

図25(E)はビデオカメラであり、第1筐体941、第2筐体942、表示部943、操作キー944、レンズ945、接続部946等を有する。操作キー944およびレンズ945は第1筐体941に設けられており、表示部943は第2筐体942に設けられている。そして、第1筐体941と第2筐体942とは、接続部946により接続されており、第1筐体941と第2筐体942の間の角度は、接続部946により変更が可能である。表示部943における映像を、接続部946における第1筐体941と第2筐体942との間の角度にしたがって切り替える構成としてもよい。

## 【0327】

図25(F)は普通自動車であり、車体951、車輪952、ダッシュボード953、ライト954等を有する。

## 【0328】

<表示領域または発光領域に曲面を有する電子機器>

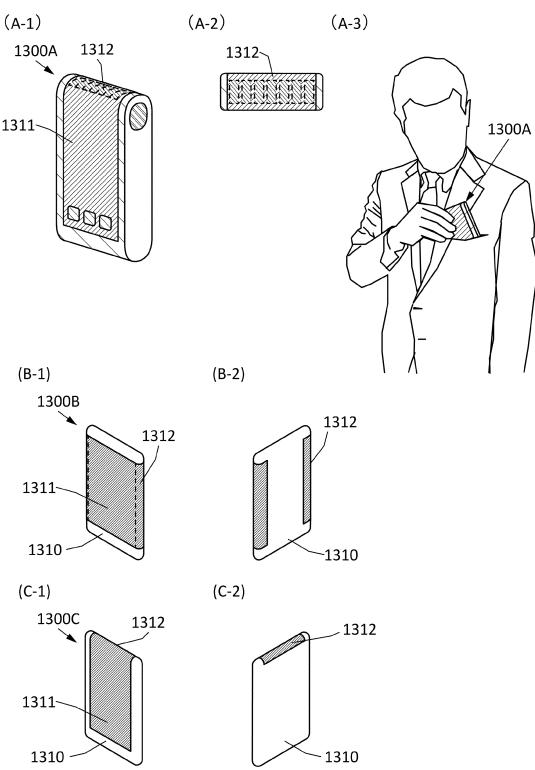

以下では、本発明の一態様に係る電子機器の一例である表示領域または発光領域に曲面を有する電子機器について、図26を参照しながら説明する。なお、ここでは、電子機器の一例として、情報機器、特に携帯性を有する情報機器(携帯機器)について説明する。携帯性を有する情報機器としては、例えば、携帯電話機(ファブレット、スマートフォン(スマホ))、タブレット端末(ストレートP C)なども含まれる。

## 【0329】

図26(A-1)は、携帯機器1300Aの外形を説明する斜視図である。図26(A-2)は、携帯機器1300Aの上面図である。図26(A-3)は、携帯機器1300Aの使用状態を説明する図である。

## 【0330】

図26(B-1)および図26(B-2)は、携帯機器1300Bの外形を説明する斜視図である。

## 【0331】

図26(C-1)および図26(C-2)は、携帯機器1300Cの外形を説明する斜視図である。

## 【0332】

<携帯機器>

携帯機器1300Aは、例えば電話、電子メール作成閲覧、手帳または情報閲覧などの機能から選ばれた一つまたは複数の機能を有する。

## 【0333】

携帯機器1300Aは、筐体の複数の面に沿って表示部が設けられている。例えば、可とう性を有する表示装置を、筐体の内側に沿うように配置することで表示部を設ければよい。これにより、文字情報や画像情報を第1の領域1311または/および第2の領域1312に表示することができる。

## 【0334】

10

20

30

40

50

例えば、3つの操作の用に供する画像を第1の領域1311に表示することができる（図26（A-1）参照。）。また、図中に破線の矩形で示すように文字情報などを第2の領域1312に表示することができる（図26（A-2）参照。）。

**【0335】**

携帯機器1300Aの上部に第2の領域1312を配置した場合、携帯機器1300Aを洋服の胸ポケットに収納したままの状態で、携帯機器1300Aの第2の領域1312に表示された文字や画像情報を、使用者は容易に確認することができる（図26（A-3）参照。）。例えば、着信した電話の発信者の電話番号または氏名などを、携帯機器1300Aの上方から観察できる。

**【0336】**

なお、携帯機器1300Aは、表示装置と筐体との間、表示装置内または筐体上に入力装置などを有してもよい。入力装置は、例えば、タッチセンサー、光センサー、超音波センサーなどを用いればよい。入力装置を表示装置と筐体との間または筐体上に配置する場合、マトリクススイッチ方式、抵抗膜方式、超音波表面弾性波方式、赤外線方式、電磁誘導方式、静電容量方式などのタッチパネルを用いればよい。また、入力装置を表示装置内に配置する場合、インセルタイプのセンサー、またはオンセルタイプのセンサーなどを用いればよい。

10

**【0337】**

なお、携帯機器1300Aは、振動センサーなどと、当該振動センサーなどに検知された振動に基づいて、着信を拒否するモードに移行するプログラムを記憶した記憶装置を備えることができる。これにより、使用者は携帯機器1300Aを洋服の上から軽く叩いて振動を与えることにより着信を拒否するモードに移行させることができる。

20

**【0338】**

携帯機器1300Bは、第1の領域1311および第2の領域1312を有する表示部と、表示部を支持する筐体1310を有する。

**【0339】**

筐体1310は複数の屈曲部を備え、筐体1310が備える最も長い屈曲部が、第1の領域1311と第2の領域1312に挟まれる。

**【0340】**

携帯機器1300Bは、最も長い屈曲部に沿って設けられた第2の領域1312を側面に向けて使用することができる。

30

**【0341】**

携帯機器1300Cは、第1の領域1311および第2の領域1312を有する表示部と、表示部を支持する筐体1310を有する。

**【0342】**

筐体1310は複数の屈曲部を備え、筐体1310が備える二番目に長い屈曲部が、第1の領域1311と第2の領域1312に挟まれる。

**【0343】**

携帯機器1300Cは、第2の領域1312を上部に向けて使用することができる。

**【符号の説明】**

40

**【0344】**

100 試料

102 マスク

104 領域

106 導電体

150 不純物

400 基板

402 絶縁体

404 導電体

405a 導電体

50

|         |        |    |

|---------|--------|----|

| 4 0 5 b | 導電体    |    |

| 4 0 6   | 半導体    |    |

| 4 0 6 a | 半導体    |    |

| 4 0 6 b | 半導体    |    |

| 4 0 6 c | 半導体    |    |

| 4 1 0 a | 絶縁体    |    |

| 4 1 0 b | 絶縁体    |    |

| 4 1 2   | 絶縁体    |    |

| 4 1 2 a | 絶縁体    |    |

| 4 1 2 b | 絶縁体    | 10 |

| 4 1 3   | 導電体    |    |

| 4 1 5   | 導電体    |    |

| 4 1 6 a | 導電体    |    |

| 4 1 6 b | 導電体    |    |

| 4 1 6 c | 導電体    |    |

| 4 1 8   | 絶縁体    |    |

| 4 2 4 a | 導電体    |    |

| 4 2 4 b | 導電体    |    |

| 4 3 4   | 導電体    |    |

| 4 4 2   | 絶縁体    | 20 |

| 4 5 0   | 不純物    |    |

| 4 5 4   | 領域     |    |

| 5 0 0   | 基板     |    |

| 5 0 2   | 絶縁体    |    |

| 5 0 4   | 導電体    |    |

| 5 0 5 a | 導電体    |    |

| 5 0 5 b | 導電体    |    |

| 5 0 6   | 半導体    |    |

| 5 0 6 a | 半導体    |    |

| 5 0 6 b | 半導体    | 30 |

| 5 0 6 c | 半導体    |    |

| 5 0 8   | 絶縁体    |    |

| 5 1 0   | 絶縁体    |    |

| 5 1 2   | 絶縁体    |    |

| 5 1 2 a | 絶縁体    |    |

| 5 1 2 b | 絶縁体    |    |

| 5 1 3   | 導電体    |    |

| 5 1 5   | 導電体    |    |

| 5 1 6 a | 導電体    |    |

| 5 1 6 b | 導電体    | 40 |

| 5 1 6 c | 導電体    |    |

| 5 1 8   | 絶縁体    |    |

| 5 2 0   | 絶縁体    |    |

| 5 2 4 a | 導電体    |    |

| 5 2 4 b | 導電体    |    |

| 5 3 4   | 導電体    |    |

| 5 4 2   | 絶縁体    |    |

| 5 5 0   | 不純物    |    |