(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2024-58185

(P2024-58185A)

(43)公開日 令和6年4月25日(2024.4.25)

## (51)国際特許分類

H 01 L 27/146 (2006.01)

H 04 N 25/70 (2023.01)

F I

H 01 L 27/146

H 04 N 5/369

H 01 L 27/146A

5/369

D

## テーマコード(参考)

4 M 1 1 8

5 C 0 2 4

審査請求 未請求 請求項の数 19 O L (全31頁)

(21)出願番号 特願2022-165393(P2022-165393)

(22)出願日 令和4年10月14日(2022.10.14)

(71)出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100126240

弁理士 阿部 琢磨

(74)代理人 100223941

弁理士 高橋 佳子

(74)代理人 100159695

弁理士 中辻 七郎

(74)代理人 100172476

弁理士 富田 一史

(74)代理人 100126974

弁理士 大朋 靖尚

(72)発明者 市野 真也

東京都大田区下丸子3丁目30番2号

最終頁に続く

(54)【発明の名称】 光電変換装置、光電変換装置の駆動方法、半導体基板、機器

## (57)【要約】

【課題】 単位画素が備える選択トランジスタのウェルの電位を適切に設定することが困難であった。

【解決手段】 出力線と複数の単位画素を有し、複数の単位画素の各々は、入射光に基づいて信号電荷を生成する光電変換素子と、前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、増幅トランジスタと出力線とを接続する選択トランジスタと、ゲートの電位をリセットするリセットトランジスタと、を有し、選択トランジスタが設けられた第1ウェルと、リセットトランジスタが設けられた第2ウェルとを有し、第1ウェルと前記第2ウェルが電気的に分離されていることを特徴とする光電変換装置である。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

出力線と複数の単位画素を有し、

前記複数の単位画素の各々は、

入射光に基づいて信号電荷を生成する光電変換素子と、

前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、

前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、

前記ゲートの電位をリセットするリセットトランジスタと、

を有し、

前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有し、

前記第1ウェルと前記第2ウェルが電気的に分離されていることを特徴とする光電変換装置。

**【請求項 2】**

前記第1ウェルと前記第2ウェルは、絶縁体分離部によって電気的に分離され、前記第1ウェルは前記絶縁体分離部に囲われていることを特徴とする請求項1に記載の光電変換装置。

**【請求項 3】**

前記選択トランジスタはN型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記選択トランジスタがオフ状態にある期間における前記第1ウェルの電位よりも高い電位であることを特徴とする請求項1に記載の光電変換装置。

**【請求項 4】**

前記オン状態にある期間における前記第1ウェルの電位が接地電位であることを特徴とする請求項3に記載の光電変換装置。

**【請求項 5】**

前記選択トランジスタはP型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記選択トランジスタがオフ状態にある期間における前記第1ウェルの電位よりも低い電位であることを特徴とする請求項1に記載の光電変換装置。

**【請求項 6】**

前記選択トランジスタはN型のトランジスタであって、前記選択トランジスタがオフ状態にある期間における前記第1ウェルの電位が、前記期間における前記第2ウェルの電位よりも低いことを特徴とする請求項1に記載の光電変換装置。

**【請求項 7】**

前記期間における前記第2ウェルの電位が接地電位であることを特徴とする請求項6に記載の光電変換装置。

**【請求項 8】**

前記選択トランジスタはN型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記期間における前記第2ウェルの電位よりも高いことを特徴とする請求項1に記載の光電変換装置。

**【請求項 9】**

前記選択トランジスタはP型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記期間における前記第2ウェルの電位よりも低いことを特徴とする請求項1に記載の光電変換装置。

**【請求項 10】**

前記ゲートへの容量の接続と非接続を変更するトランジスタが前記第2ウェルに設けられていることを特徴とする請求項1に記載の光電変換装置。

**【請求項 11】**

10

20

30

40

50

前記第2ウェルに前記増幅トランジスタが設けられていることを特徴とする請求項10に記載の光電変換装置。

【請求項12】

前記第2ウェルに前記光電変換素子が設けられていることを特徴とする請求項11に記載の光電変換装置。

【請求項13】

第1部品と第2部品とが貼り合わされた構造を備え、

前記光電変換素子は前記第1部品に配されており、

前記第1ウェルおよび前記第2ウェルが前記第2部品に配されていることを特徴とする請求項1に記載の光電変換装置。

10

【請求項14】

前記第2部品は半導体基板を備え、

前記第1部品と前記第2部品は、前記半導体基板の一方の面から、前記一方の面に対向する他方の面まで設けられた絶縁体を貫通する導電体によって電気的に接続されていることを特徴とする請求項13に記載の光電変換装置。

【請求項15】

前記第2部品に貼り合わされた第3部品をさらに有する構造を備え、

前記第3部品は、前記複数の単位画素の各々が出力する、前記信号電荷に基づく画素信号を処理するロジック回路を有することを特徴とする請求項13に記載の光電変換装置。

20

【請求項16】

前記第2部品に貼り合わされた第3部品をさらに有する構造を備え、

前記第3部品は、前記複数の単位画素の各々が出力する、前記信号電荷に基づく画素信号を処理するロジック回路を有することを特徴とする請求項14に記載の光電変換装置。

【請求項17】

請求項1乃至16のいずれか1項に記載の光電変換装置を備える機器であって、

前記光電変換装置に対応した光学装置、

前記光電変換装置を制御する制御装置、

前記光電変換装置から出力された信号を処理する処理装置、

前記光電変換装置で得られた情報を表示する表示装置、

前記光電変換装置で得られた情報を記憶する記憶装置、および、

前記光電変換装置で得られた情報に基づいて動作する機械装置、の少なくともいずれかを更に備えることを特徴とする機器。

30

【請求項18】

出力線と複数の単位画素を有し、

前記複数の単位画素の各々は、

入射光に基づいて信号電荷を生成する光電変換素子と、

前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、

前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、

前記ゲートの電位をリセットするリセットトランジスタと、

を有し、

前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有する光電変換装置の駆動方法であって、

前記選択トランジスタがオフ状態にある期間に、前記第2ウェルの電位を第1電位に設定し、

前記選択トランジスタがオン状態にある期間に、前記第2ウェルの電位を前記第1電位とは異なる第2電位に設定することを特徴とする光電変換装置の駆動方法。

40

【請求項19】

入射光に基づいて信号電荷を生成する光電変換素子が設けられた部品に積層するための半導体基板であって、

50

出力線と、

前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、

前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、

前記ゲートの電位をリセットするリセットトランジスタと、

を有し、

前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有し、

前記第1ウェルと前記第2ウェルが電気的に分離されていることを特徴とする半導体基板。

10

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、光電変換装置、光電変換装置の駆動方法、半導体基板、機器に関する。

#### 【背景技術】

#### 【0002】

複数の単位画素を備える光電変換装置が知られている。この複数の単位画素には、入射光の光電変換することで信号電荷を生成する光電変換部と、信号電荷が入力されるゲートを備える増幅トランジスタとが備わる。単位画素は、ゲートの電位をリセットするリセットトランジスタをさらに備える。増幅トランジスタのゲートとリセットトランジスタは電気的に接続されている。このように、単位画素の少なくとも一部のトランジスタは、信号電荷が入力される、電気的に接続された1つのノードを形成する。

20

#### 【0003】

特許文献1には、増幅トランジスタであるアンプ用トランジスタが設けられたウェルが、他のトランジスタが設けられたウェルとは電気的に分離された構成が開示されている。信号電荷が入力される、電気的に接続された1つのノードの一部であるリセット用トランジスタは、行選択用トランジスタと同じウェルに設けられた構成となっている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】特開2001-160619号公報

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

特許文献1の構成では、信号電荷が入力される、電気的に接続された1つのノードを形成するトランジスタの1つであるリセット用トランジスタと行選択用トランジスタがウェルを共有している。このため、選択トランジスタのウェルの電位を適切に設定することが困難であった。

#### 【課題を解決するための手段】

#### 【0006】

本開示の技術の一の側面は、出力線と複数の単位画素を有し、前記複数の単位画素の各々は、入射光に基づいて信号電荷を生成する光電変換素子と、前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、前記ゲートの電位をリセットするリセットトランジスタと、を有し、前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有し、前記第1ウェルと前記第2ウェルが電気的に分離していることを特徴とする光電変換装置である。

40

#### 【0007】

別の側面は、出力線と複数の単位画素を有し、前記複数の単位画素の各々は、入射光に基づいて信号電荷を生成する光電変換素子と、前記信号電荷が入力されるゲートを備え、

50

前記ゲートの電位に基づく信号を出力する増幅トランジスタと、前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、前記ゲートの電位をリセットするリセットトランジスタと、を有し、前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有する光電変換装置の駆動方法であって、前記選択トランジスタがオフ状態にある期間に、前記第2ウェルの電位を第1電位に設定し、前記選択トランジスタがオン状態にある期間に、前記第2ウェルの電位を前記第1電位とは異なる第2電位に設定することを特徴とする光電変換装置の駆動方法である。

#### 【0008】

別の側面は、入射光に基づいて信号電荷を生成する光電変換素子が設けられた部品に積層するための半導体基板であって、出力線と、前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、前記ゲートの電位をリセットするリセットトランジスタと、を有し、前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有し、前記第1ウェルと前記第2ウェルが電気的に分離されることを特徴とする半導体基板である。

#### 【発明の効果】

#### 【0009】

本開示の技術により、選択トランジスタのウェルの電位を適切に設定することができる。

#### 【図面の簡単な説明】

#### 【0010】

【図1】光電変換装置の全体構成を示す図

【図2】単位画素の等価回路を示す図

【図3】単位画素の平面視の構成を示す図

【図4】単位画素の断面視の構成を示す図

【図5】光電変換装置の駆動タイミングを示す図

【図6】選択トランジスタの各ノードの電位を示す図

【図7】単位画素の等価回路を示す図

【図8】単位画素の平面視の構成を示す図

【図9】単位画素の断面視の構成を示す図

【図10】光電変換装置の全体構成を示す図

【図11】単位画素の等価回路を示す図

【図12】光電変換装置の断面視の構成を示す図

【図13】単位画素の一部の構成の平面視の構成を示す図

【図14】単位画素の一部の構成の断面視の構成を示す図

【図15】光電変換装置の駆動タイミングを示す図

【図16】単位画素の等価回路を示す図

【図17】単位画素の一部の構成の平面視の構成を示す図

【図18】単位画素の一部の構成の断面視の構成を示す図

【図19】単位画素の一部の構成の平面視の構成を示す図

【図20】単位画素の一部の構成の平面視の構成を示す図

【図21】機器の構成を示す図

#### 【発明を実施するための形態】

#### 【0011】

以下、図面を参照しながら各実施例を説明する。

#### 【0012】

以下に述べる各実施形態では、光電変換装置の一例として、撮像装置を中心に説明する。ただし、各実施形態は、撮像装置に限られるものではなく、光電変換装置の他の例にも適用可能である。例えば、測距装置（焦点検出やTOF（Time Of Flight））を用いた距離測定等の装置）、測光装置（入射光量の測定等の装置）などがある。

10

20

30

40

50

## 【0013】

また、以下に述べる実施形態中に記載される半導体領域、ウェルの導電型や注入されるドーパントは一例であって、実施形態中に記載された導電型、ドーパントのみに限定されるものでは無い。実施形態中に記載された導電型、ドーパントに対して適宜変更できるし、この変更に伴って、半導体領域、ウェルの電位は適宜変更される。

## 【0014】

なお、以下に述べる実施形態に記載されるトランジスタの導電型は一例のものであって、実施例中に記載された導電型のみに限定されるものでは無い。実施形態中に記載された導電型に対し、導電型は適宜変更できるし、この変更に伴って、トランジスタのゲート、ソース、ドレインの電位は適宜変更される。

10

## 【0015】

例えば、スイッチとして動作させるトランジスタであれば、ゲートに供給する電位のローレベルとハイレベルとを、導電型の変更に伴って、実施例中の説明に対し逆転させるようすればよい。また、以下に述べる実施例中に記載される半導体領域の導電型についても一例のものであって、実施例中に記載された導電型のみに限定されるものでは無い。実施例中に記載された導電型に対し、導電型は適宜変更できるし、この変更に伴って、半導体領域の電位は適宜変更される。

## 【0016】

(第1実施形態)

本実施形態による光電変換装置およびその駆動方法について、図1～図9を用いて説明する。

20

## 【0017】

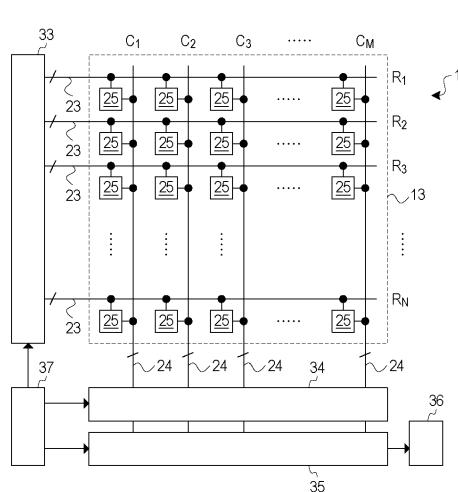

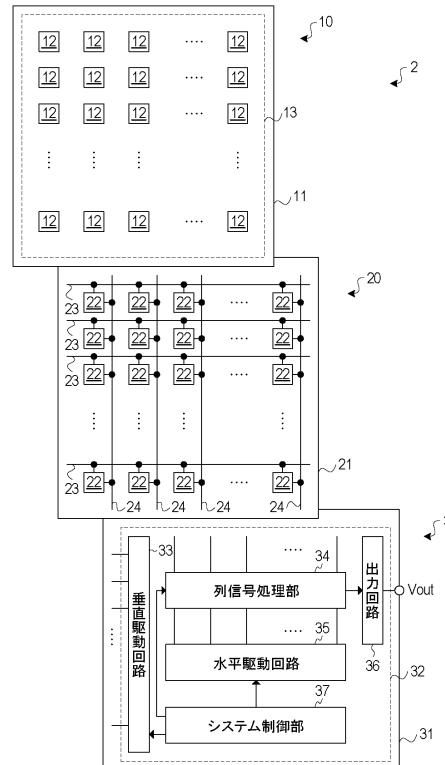

図1は、第1実施形態における光電変換装置のブロック図である。本実施形態による光電変換装置1は、画素領域13、垂直駆動回路33、列信号処理部34、水平駆動回路35、出力回路36、システム制御部37を有する。

## 【0018】

画素領域13は、複数行および複数列に配列され、受光量に応じた画素信号を出力する複数の単位画素25を備える。それぞれの単位画素25は入射光に基づき信号電荷を生成および蓄積する光電変換部を備える。図1には、第R1行～第RN行、第C1列～第CM列からなるN行M列の単位画素25が示されている。

30

## 【0019】

画素領域13の各行には、制御線群23が水平方向(画素行に沿った方向)に延在している。制御線群23の各々は、同じ行に並ぶ複数の単位画素25に接続され、複数の単位画素25に共通の信号線をなしている。制御線群23の各々は、複数の信号線を含み得る。制御線群23は、垂直駆動回路33に接続されている。

## 【0020】

画素領域13の各列には、出力線24が垂直方向(画素列に沿った方向)に延在している。出力線24の各々は、対応する列に並ぶ複数の単位画素25に接続され、複数の単位画素25に共通の信号線をなしている。出力線24の各々は、複数の出力線を含み得る。出力線24は、列信号処理部34に接続されている。

40

## 【0021】

垂直駆動回路33は、システム制御部37から供給される制御信号を受け、単位画素25を駆動するための制御信号を生成し、制御線群23を介して単位画素25に供給する機能を備える制御回路である。単位画素25から行単位で読み出された信号は、出力線24を介して列信号処理部34に入力される。

## 【0022】

列信号処理部34は、複数の出力線24の1つに各々が対応して設けられた複数の列回路(不図示)を備える。この複数の列回路の各々は、処理回路および信号保持回路を備える。処理回路は、対応する出力線24を介して出力される画素信号に対して所定の信号処理を行う機能を備える。処理回路が行う信号処理としては、例えば、増幅処理、相関二重

50

サンプリング ( C D S : Correlated Double Sampling ) による補正処理、アナログ・デジタル変換 ( A D 変換 ) 処理などが挙げられる。信号保持回路は、処理回路で処理された画素信号を保持するためのメモリを備える。

【 0 0 2 3 】

水平駆動回路 3 5 は、システム制御部 3 7 から供給される制御信号を受け、列信号処理部 3 4 から画素信号を読み出すための制御信号を生成し、列信号処理部 3 4 に供給する機能を備える制御回路である。水平駆動回路 3 5 は、列信号処理部 3 4 の各列の列回路を順次走査し、各々に保持されている画素信号を、出力回路 3 6 へと出力させる。

【 0 0 2 4 】

出力回路 3 6 は、外部インターフェース回路を有し、列信号処理部 3 4 で処理された信号を光電変換装置 1 の外部へ出力するための回路である。なお、出力回路 3 6 が備える外部インターフェース回路は、特に限定されるものではない。

【 0 0 2 5 】

システム制御部 3 7 は、垂直駆動回路 3 3 、列信号処理部 3 4 及び水平駆動回路 3 5 の動作を制御する制御信号を生成し、各機能ブロックに供給する制御回路である。

【 0 0 2 6 】

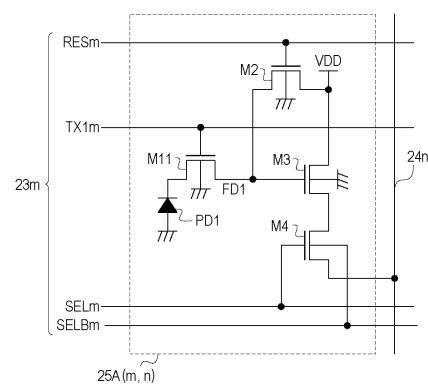

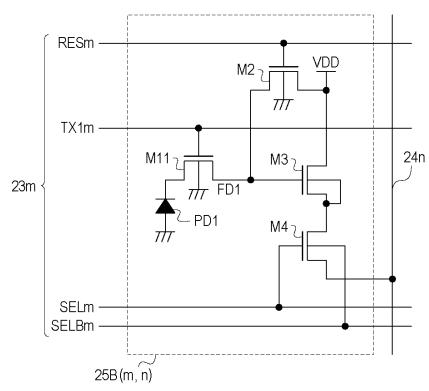

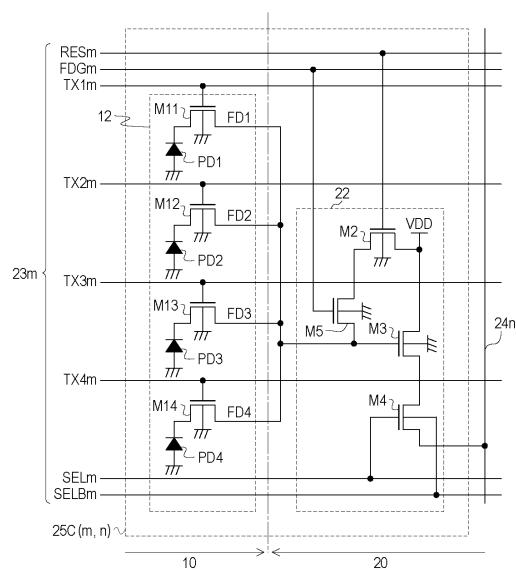

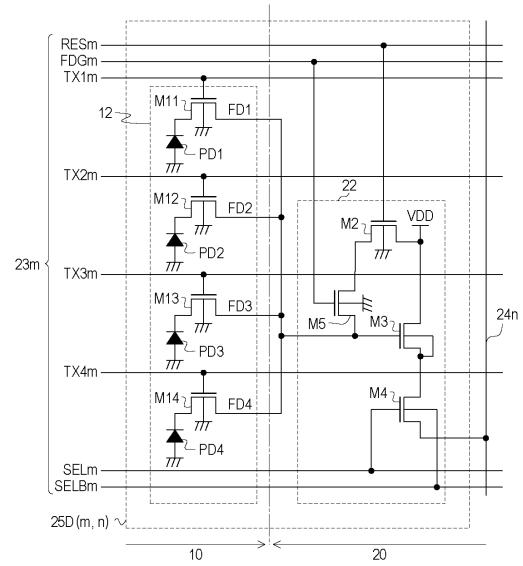

図 2 は、本実施形態における 1 例目の単位画素 2 5 の等価回路図である。図 2 には、第 m 行、第 n 列に配された単位画素 2 5 A ( m , n ) が示されている。ここで、 m は 1 ~ M の整数であり、 n は 1 ~ N の整数である。画素領域 1 3 を構成するその他の単位画素 2 5 は、単位画素 2 5 A ( m , n ) と同様の回路構成を含み得る。

【 0 0 2 7 】

単位画素 2 5 A ( m , n ) は、光電変換素子 P D 1 、転送トランジスタ M 1 1 、リセットトランジスタ M 2 、増幅トランジスタ M 3 、選択トランジスタ M 4 を含む。

【 0 0 2 8 】

光電変換素子 P D 1 は、例えばフォトダイオードであって、入射光を光電変換し、電荷の蓄積を行なう。単位画素 2 5 A あたりの光電変換素子の数は 1 つに限定されない。なお、光電変換素子 P D 1 は有機薄膜と無機薄膜の少なくとも一方を含んで構成される光電変換膜であっても良い。

【 0 0 2 9 】

転送トランジスタ M 1 1 は光電変換素子 P D 1 が生成する信号電荷（単に電荷と表記することもある）を、半導体基板に設けられた浮遊拡散領域に転送するために設けられる。浮遊拡散領域と、増幅トランジスタ M 3 のゲートと、リセットトランジスタ M 2 のソース、ドレインの一方とを含んで F D ノード（ F D は F l o a t i n g D i f f u s i o n の略）が構成される。さらに F D ノードは、浮遊拡散領域と増幅トランジスタ M 3 のゲートとを接続する金属配線とを含む。 F D ノードは、増幅トランジスタ M 3 とリセットトランジスタ M 2 を含んで形成される、電気的に共通なノードである。転送トランジスタ M 1 1 のゲートには垂直駆動回路 3 3 から第 m 行の制御線 2 3 m を介して制御信号 T X 1 m が与えられる。制御信号 T X 1 m がハイレベルとなると、光電変換素子 P D 1 に入射した光により発生および蓄積された電荷が、転送トランジスタ M 1 1 を介して F D ノードに転送される。 F D ノードは、転送トランジスタ M 1 1 のドレイン、リセットトランジスタ M 2 のソースおよび増幅トランジスタ M 3 のゲートのそれぞれの配線および電極から構成される。

【 0 0 3 0 】

光電変換素子 P D 1 から転送された電荷は、 F D ノードに保持される。 F D ノードに保持された電荷は、電圧に変換される。すなわち、 F D ノードにおける電圧は、光電変換素子 P D 1 から転送された電荷の量に応じた値となる。

【 0 0 3 1 】

リセットトランジスタ M 2 は F D ノードの電位を電源電圧 V D D に応じた電圧にリセットする。別の見方では、リセットトランジスタ M 2 は、増幅トランジスタ M 3 のゲートの電位を電源電圧 V D D に応じた電圧にリセットする。リセットトランジスタ M 2 のゲート

10

20

30

40

50

には、垂直駆動回路 33 から制御線 23 m を介して制御信号 RESm が供給される。制御信号 RESm がハイレベルになると、FD ノードの電位は電源電圧 VDD に応じた電圧へリセットされる。また、制御信号 RESm がハイレベルになるとともに制御信号 TX1m がハイレベルになることで、光電変換素子 PD1 の電圧は電源電圧 VDD に応じた電圧にリセットすることができる。ただし、制御信号 RESm と制御信号 TXm がともにハイレベルになる必要は無い。例えば、制御信号 TXm がハイレベルとなって光電変換素子 PD1 の信号電荷が FD に転送される。その後、制御信号 RESm がハイレベルとなって FD をリセットすることによっても、光電変換素子 PD1 の信号電荷はリセットされる。

#### 【 0 0 3 2 】

増幅トランジスタ M3 は、選択トランジスタ M4 を介して第 n 列の出力線 24n に信号を出力する。増幅トランジスタ M3 のドレインには電源電圧 VDD が印加される。増幅トランジスタ M3 のソースは、選択トランジスタ M4 のドレインに接続されている。増幅トランジスタ M3 は、列信号処理部 34 に含まれる電流源とともにソースフォロワを構成する。増幅トランジスタ M3 は、選択トランジスタ M4 が導通状態（オン状態）にある場合、FD ノードの電圧に対応する信号を出力する。これにより、出力線 24 の信号レベルは、増幅トランジスタ M3 が output する信号レベルとなる。

#### 【 0 0 3 3 】

選択トランジスタ M4 は、増幅トランジスタ M3 と出力線 24n との間に設けられる。選択トランジスタ M4 のゲートには、垂直駆動回路 33 から制御線 23m を介して制御信号 SELm が与えられる。制御信号 SELm がハイレベルに遷移すると、選択トランジスタ M4 は増幅トランジスタ M3 からの出力を出力線 24n に出力する。

#### 【 0 0 3 4 】

選択トランジスタ M4 は導通状態において、選択トランジスタ M4 のゲートおよびソース間の電圧 (VGS) に依存する抵抗成分（以下、オン抵抗と呼ぶ）を有している。詳細な説明は後述するが、各単位画素 25 の浮遊拡散領域、FD ノードの電位によってオン抵抗が変化し、信号の線形性（リニアリティ）が低下する。

#### 【 0 0 3 5 】

選択トランジスタ M4 が配されたウェル WSEL は、制御線 23m と電気的に接続されている。つまり、制御信号 SELBm によって定まる電位が、選択トランジスタ M4 が配されたウェル WSEL に与えられる。リセットトランジスタ M2 が配されたウェル（第 2 ウェル）は、それぞれ接地電位に接続されている。一方で、選択トランジスタ M4 のウェル WSEL（第 1 ウェル）の電位は、他の画素トランジスタのウェル電位とは独立に制御される。つまり、本実施形態の光電変換装置は、選択トランジスタ M4 のウェル WSEL の電位が、リセットトランジスタ M2 が配されたウェルの電位とは異なる期間を有する。なお、光電変換装置の動作時に、選択トランジスタ M4 のウェル WSEL の電位が常にリセットトランジスタ M2 が配されたウェルの電位とは異なるようにしても良い。また、一部の期間のみにおいて、選択トランジスタ M4 のウェル WSEL の電位が、リセットトランジスタ M2 が配されたウェルの電位とは異なるようにしても良い。なお、リセットトランジスタ M2 が配されたウェルにさらに別の素子が配されていても良く、例えば、光電変換素子 PD、転送トランジスタ M11、増幅トランジスタ M3 がさらに配されていても良い。

#### 【 0 0 3 6 】

以下、ウェル WSEL の構造を中心に単位画素 25 の構造を説明する。なお、以下の説明では、リセットトランジスタ M2 が配されたウェルに、光電変換素子 PD、転送トランジスタ M11、増幅トランジスタ M3 がさらに配された例を説明する。

#### 【 0 0 3 7 】

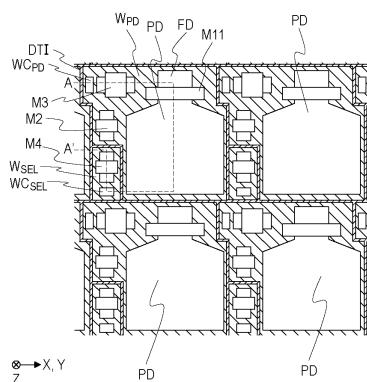

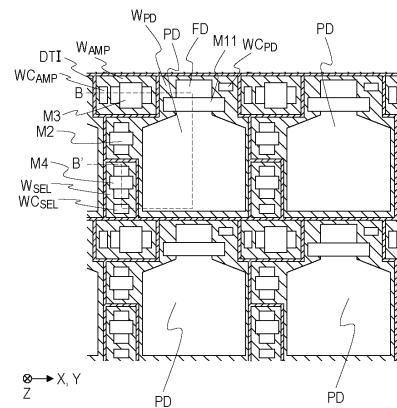

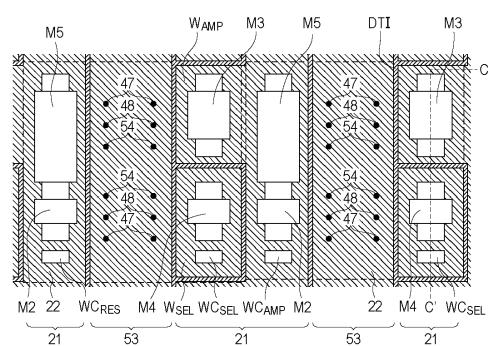

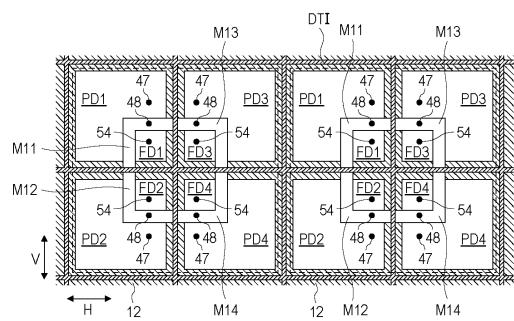

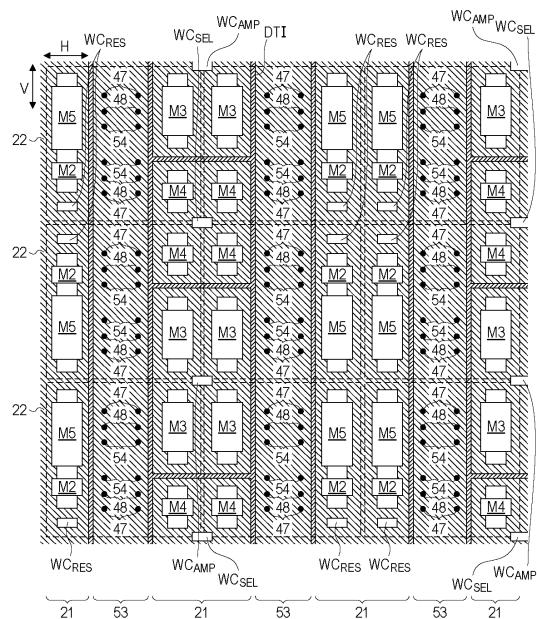

図 3 は、本実施形態の単位画素 25 の構造を示した図である。

#### 【 0 0 3 8 】

図 3 では、平面視で 2 行 × 2 列の計 4 つの単位画素 25A を示している。ここで示す 4 つの単位画素 25A は、それぞれが図 2 の等価回路に対応するもので、単位画素 25A を

10

20

30

40

50

構成する各要素は共通の構成を成している。図3の横方向がXまたはY方向であり、紙面に対して奥行に向かう方向がZ方向である。本明細書において「平面視」とは、半導体基板のトランジスタのゲートが配されている側の面と平行な面を該平行な面に対して垂直方向から視ることを指す。つまり、「平面視」とは、図3において、半導体基板の第1面に平行な面に対してZ方向又は-Z方向から視ることを指す。

#### 【0039】

単位画素25Aは、平面視で、絶縁体分離部DTIにより少なくとも2つの領域に分離されている。DTIはDeep Trench Isolationの略である。一方の領域に選択トランジスタM4が配され、他方の領域に光電変換素子PDが配される。平面視で、選択トランジスタM4と光電変換素子PDとの間には絶縁体分離部DTIが配されている。絶縁体分離部DTIは、選択トランジスタM4を取り囲むように配されている。絶縁体分離部DTIは、選択トランジスタM4のチャネルとなる領域を含むウェルWSELと、リセットトランジスタM2が配されたが配されたウェルWPDとを分離する機能をもつ。このウェルWPDには、さらに光電変換素子PDが配されている。図3では、絶縁体分離部DTIは、画素間のPDが配されたウェルWPD間も分離しているが、画素間におけるウェルWPD間は分離されていなくてもよい。

#### 【0040】

ウェルWSELは、ウェルWSELのウェルコンタクトWCSELを介して制御信号SELと電気的に接続されている。ウェルWPDは、ウェルWPDに配されたPDウェルコンタクトWCPDを介して接地電圧と電気的に接続されている。転送トランジスタM11、リセットトランジスタM2、増幅トランジスタM3はそれぞれウェルWPDに配されている。つまり、選択トランジスタM4と、リセットトランジスタM2および増幅トランジスタM3と、の間には、絶縁体分離部DTIが配されている。FDは、光電変換素子PDの信号電荷が転送される浮遊拡散領域であり、FDノードの一部である。

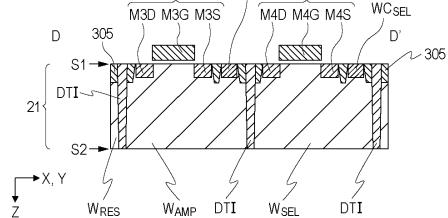

#### 【0041】

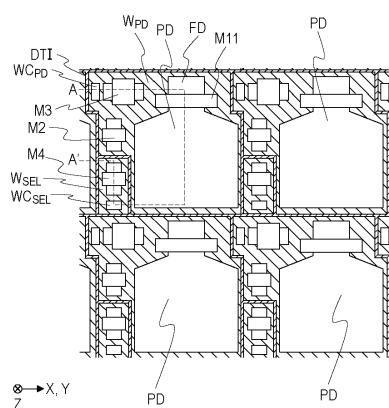

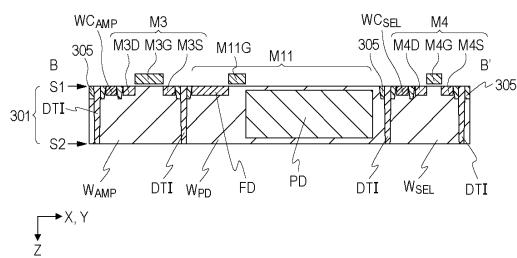

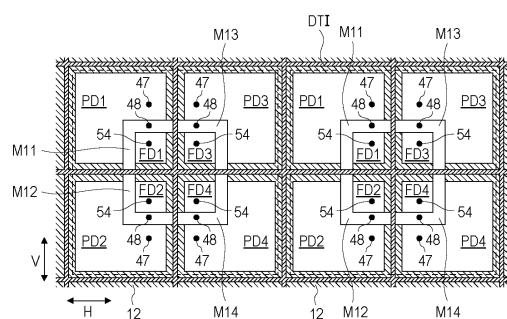

図4は、図3のA-A'の概略断面図である。半導体基板301において、増幅トランジスタM3のゲートとなる電極M3Gが配されている側の面を第1面S1といい、第1面S1に対向する面を第2面S2という。第1面S1から第2面S2に向かう方向がZ方向である。図4では、第2面S2から光が入射する。第2面S2を裏面と呼び、第1面S1を表面と呼ぶこともある。半導体基板としては、例えば、シリコン基板である。このシリコン基板は、典型的には、その基板が含む元素の中で最も多くを占めるのがSiである基板である。また、別の半導体基板の例として、SOI(Silicon on Insulator)基板を用いることができる。なお、光の入射方向は第1面S1からでもよい。

#### 【0042】

FD、および転送トランジスタM11、リセットトランジスタM2、増幅トランジスタM3、選択トランジスタM4等の画素トランジスタのソース、ドレインはN型の不純物が拡散されたN型半導体領域を含む。増幅トランジスタM3のゲートとなる電極M3G、転送トランジスタM11のゲートとなる電極M11G、選択トランジスタM4のゲートとなる電極M4Gは、第1面S1の上に配される。ウェルWSELのウェルコンタクトWCSELと、ウェルWPDのウェルコンタクトWCPDは、半導体基板301内に配される。ウェルコンタクトWCSEL、ウェルコンタクトWCPDのそれぞれはP型の不純物が拡散されたP型半導体領域を含む。ウェルコンタクトWCSELとウェルコンタクトWCPDとは、半導体基板301の第1面S1の一部を構成する。複数の画素の間の領域、および1画素の光電変換素子PDと画素トランジスタ領域との間の領域のそれぞれには、素子分離部305が配される。素子分離部305はSTI構造あるいはLOCOS構造により構成されている。図4に示すように、Z方向において、絶縁体分離部DTIは、半導体基板301を貫通している。つまり、半導体基板301の第1面S1から第2面S2に渡って、Z方向(深さ方向)にて絶縁体分離部DTIが延在している。半導体基板301内において、選択トランジスタM4のチャネルとなる領域を含むウェルWSELと光電変換素

10

20

30

40

40

50

子 P D を含むウェル W P D とが絶縁体分離部 D T I で電気的に分離されている。

【 0 0 4 3 】

本実施形態によれば、半導体基板 3 0 1 を貫通する絶縁体分離部 D T I によりウェル W S E L と光電変換素子 P D とは電気的に分離されている。この電気的な分離は、実質的に絶縁されている状態と見なせる。つまり、ウェル W S E L とウェル W P D とは絶縁体分離部 D T I により電気的に分離される。この電気的な分離は、実質的に絶縁されている状態と見なせる。なお、図 4 の構成では絶縁体分離部 D T I による電気的な分離を説明したが、別の例として、P N 接合による電気的な分離を用いて、ウェル W S E L とウェル W P D とを電気的に分離することもできる。よって、ウェルの電気的な分離方法については、本実施形態で示した分離方法に限定されるものではない。ただし、P N 接合による電気的な分離に比べて、絶縁体分離部 D T I による電気的な分離は、より強く電気的に分離することができる点で好適である。

10

【 0 0 4 4 】

以上述べたように、選択トランジスタ M 4 のウェル W S E L の電位を他の画素トランジスタのウェルと電気的に切り離すことによって、制御線 2 3 m の制御信号 S E L B m で定まる電位をウェル W S E L に与えることができる。

【 0 0 4 5 】

続いて、本実施形態における光電変換装置の駆動方法について、図 3 を用いて説明する。

20

【 0 0 4 6 】

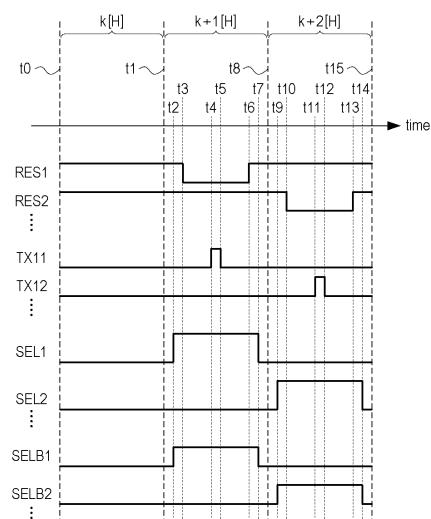

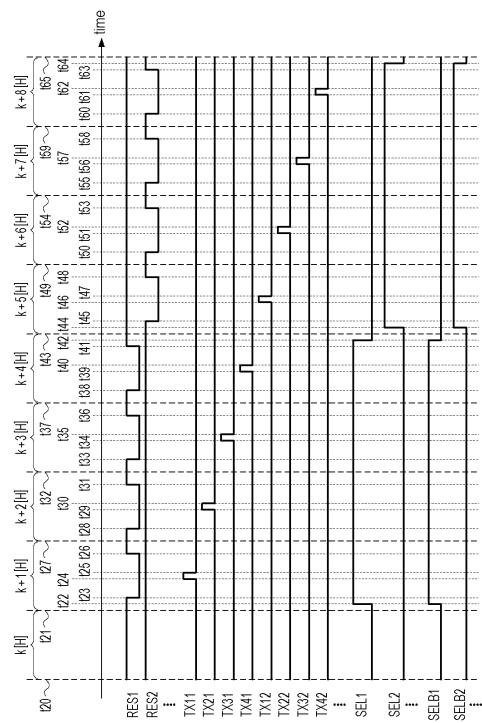

図 5 は、本実施形態における単位画素 2 5 の信号読み出しを説明する駆動タイミング図である。図 5 には、水平走査期間  $k \sim k + 2$  ( $k$  は整数) において垂直駆動回路 3 3 から単位画素 2 5 (1, n) ~ 2 5 (2, n) に供給される制御信号 R E S 1 ~ R E S 2、T X 1 1 ~ T X 1 2、S E L 1 ~ S E L 2 のタイミング図が示されている。なお、各制御信号は、ハイレベルにおいてアクティブ状態であり、ローレベルにおいて非アクティブ状態であるものとする。また、制御信号 S E L B 1 ~ S E L B 2 は、選択トランジスタ M 4 のウェル W S E L に与える電位を示したもので、ハイレベルまたはローレベルの電位がウェルコンタクト W C S E L を介してウェル W S E L に供給される。

【 0 0 4 7 】

時刻  $t_0 \sim t_1$  の期間において、画素信号の読み出しは行われない。この期間において、制御信号 R E S 1 ~ R E S 2 はハイレベルに維持される。よって、単位画素 2 5 (1, n) ~ 2 5 (2, n) の各リセットトランジスタ M 2 のオン状態が維持され、F D ノードのリセット動作が継続する。また、制御信号 T X 1 1 ~ T X 1 2、S E L 1 ~ S E L 2、S E L B 1 ~ S E L B 2 はローレベルに維持される。このとき、選択トランジスタ M 4 のウェル W S E L には、負電位などのローレベルに対応する電位（第 1 電位）が与えられる。

30

【 0 0 4 8 】

時刻  $t_1 \sim t_8$  の期間は、単位画素 2 5 (1, n) の読み出し期間に対応し、単位画素 2 5 (1, n) に対する光電変換素子 P D からの信号の読み出しが実行される。

40

【 0 0 4 9 】

時刻  $t_2$  において、制御信号 S E L 1 はローレベルからハイレベルに遷移し、単位画素 2 5 (1, n) の選択トランジスタ M 4 がオン状態になる。これにより、単位画素 2 5 (1, n) が出力線 2 4 n と電気的に接続される。

【 0 0 5 0 】

同じく時刻  $t_2$  において、制御信号 S E L B 1 はローレベルからハイレベルに遷移し、単位画素 2 5 (1, n) の選択トランジスタ M 4 のウェル W S E L には、接地電位などのハイレベルに対応する電位が与えられる。ここで、ハイレベルに対応する電位とは、時刻  $t_0 \sim t_1$  の期間にウェル W S E L に与えられる電位とは相対的に高いレベルの電位（第 2 電位）である。

【 0 0 5 1 】

50

時刻  $t_3$  において、制御信号  $R_E S_1$  はハイレベルからローレベルに遷移し、単位画素  $25(1, n)$  のリセットトランジスタ  $M_2$  がオフ状態になる。これにより、単位画素  $25(1, n)$  内の  $F D$  ノードのリセット状態が解除される。その後、 $F D$  ノードの電位はリセットトランジスタ  $M_2$  のゲートとの間のカップリングによって所定の電位まで下がる。リセットトランジスタ  $M_2$  がオフ状態になった後に静定する  $F D$  ノードの電圧が、単位画素  $25(1, n)$  内の  $F D$  ノードのリセット電圧となる。

#### 【0052】

単位画素  $25(1, n)$  の  $F D$  ノードのリセット電圧に応じた信号は、増幅トランジスタ  $M_3$  および選択トランジスタ  $M_4$  を介して出力線  $24n$  に出力される。その後、列信号処理部  $34$  で処理され、単位画素  $25(1, n)$  の  $N$  信号として読み出される。

10

#### 【0053】

時刻  $t_4$  において、制御信号  $T X_{11}$  はローレベルからハイレベルに遷移し、単位画素  $25(1, n)$  の転送トランジスタ  $M_{11}$  がオン状態になる。これにより、所定の露光期間の間に単位画素  $25(1, n)$  の光電変換素子  $P D$  に蓄積された電荷が単位画素  $25(1, n)$  の  $F D$  ノードに転送される。

20

#### 【0054】

単位画素  $25(1, n)$  の光電変換素子  $P D$  から  $F D$  ノードに転送された電荷の量に応じた信号は、増幅トランジスタ  $M_3$  および選択トランジスタ  $M_4$  を介して出力線  $24n$  に出力される。出力線  $24n$  の電圧は、光電変換素子  $P D$  で生じた電荷の量に応じて変化する。

20

#### 【0055】

時刻  $t_5$  において、制御信号  $T X_{11}$  はハイレベルからローレベルに遷移し、単位画素  $25(1, n)$  の転送トランジスタ  $M_{11}$  がオフ状態になる。これにより、単位画素  $25(1, n)$  における光電変換素子  $P D$  から  $F D$  ノードへの電荷の転送期間が終了する。単位画素  $25(1, n)$  から出力線  $24n$  に出力された信号は、静定後に列信号処理部  $34$  で処理され、単位画素  $25(1, n)$  内の光電変換素子  $P D$  の  $S$  信号として読み出される。

#### 【0056】

時刻  $t_6$  において、制御信号  $R_E S_1$  はローレベルからハイレベルに遷移し、単位画素  $25(1, n)$  のリセットトランジスタ  $M_2$  がオン状態になる。これにより、単位画素  $25(1, n)$  内の  $F D$  ノードのリセット動作が開始される。

30

#### 【0057】

時刻  $t_7$  において、制御信号  $S_E L_1$  はハイレベルからローレベルに遷移し、単位画素  $25(1, n)$  の選択トランジスタ  $M_4$  がオフ状態になる。これにより、単位画素  $25(1, n)$  は出力線  $24n$  と電気的に非接続となる。

#### 【0058】

同じく時刻  $t_7$  において、制御信号  $S_E L_B_1$  はハイレベルからローレベルに遷移し、単位画素  $25(1, n)$  の選択トランジスタ  $M_4$  のウェル  $W_{S E L}$  の電位がローレベルに対応する電位となる。

40

#### 【0059】

以上のように、時刻  $t_1 \sim t_8$  の水平走査期間で、単位画素  $25(1, n)$  の信号読み出しを行う。

#### 【0060】

続いて、時刻  $t_8 \sim t_{15}$  の水平走査期間は、単位画素  $25(2, n)$  の読み出し期間に対応し、単位画素  $25(2, n)$  に対する光電変換素子  $P D$  からの信号の読み出しが実行される。各制御信号については、前述した 1 水平期間前の駆動と同様であり、以下、順次走査して画素領域全体の読み出しを行う。

#### 【0061】

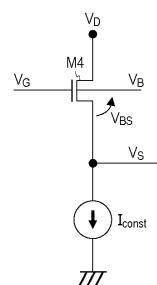

ここで、選択トランジスタ  $M_4$  のウェル  $W_{S E L}$  の電位が信号の線形性に与える影響について、図 6 を参照しながら詳細に説明する。ここでは、選択トランジスタ  $M_4$  の入力に

50

対応するドレインと、選択トランジスタM 4 の出力に対応するソースについて、入出力信号の線形性に着目して説明を行う。

【 0 0 6 2 】

選択トランジスタM 4 の出力信号は、概ね以下に示す（式1）から求めることができる。

【 0 0 6 3 】

【 数 1 】

$$V_S = V_D - R_{ON} \cdot I_{const} \quad (式 1)$$

10

【 0 0 6 4 】

ここで、 $V_S$  は選択トランジスタM 4 のソースの電位、 $V_D$  は選択トランジスタM 4 のドレインの電位、 $R_{ON}$  は選択トランジスタM 4 のオン抵抗、 $I_{const}$  は列信号処理部3 4 に含まれる電流源により決まる一定電流である。

【 0 0 6 5 】

また、選択トランジスタM 4 のオン抵抗 $R_{ON}$  は、概ね以下に示す（式2）から求めることができる。

【 0 0 6 6 】

【 数 2 】

$$R_{ON} = \frac{L}{W \cdot \mu \cdot C_{OX} \cdot (V_{GS} - V_{TH})} \quad (式 2)$$

20

【 0 0 6 7 】

ここで、 $L$  は選択トランジスタM 4 のゲート長、 $W$  は選択トランジスタM 4 のゲート幅、 $\mu$  は選択トランジスタM 4 のチャネル電子の移動度、 $C_{OX}$  は選択トランジスタM 4 の単位面積当たりの容量、 $V_{TH}$  は選択トランジスタM 4 の閾値電圧である。

30

【 0 0 6 8 】

式1に示すように、選択トランジスタM 4 の入出力に対する線形性を保つには、一定電流 $I_{const}$  とオン抵抗 $R_{ON}$  による電圧降下が一定であることが好適である。しかし、式2に示すように、オン抵抗 $R_{ON}$  は、選択トランジスタM 4 のゲート - ソース間電圧 $V_{GS}$  を変数にもつ。そのため、FDノードの電位変化に応ずる出力線2 4 n の電位変化によって、選択トランジスタM 4 のオン抵抗 $R_{ON}$  が変化する。すなわち、光電変換素子PDで発生する信号量に応じてオン抵抗 $R_{ON}$  が変化することで、線形性の低下が生じる。

【 0 0 6 9 】

ここで、信号読み出し時（オン状態）の線形性低下の抑制には、選択トランジスタM 4 のオン抵抗 $R_{ON}$  を小さくするために、選択トランジスタM 4 の閾値電圧 $V_{TH}$  を小さく設計することが好ましい。一方で、選択トランジスタM 4 は、制御線2 3 m からローレベルが供給されるオフ状態では、增幅トランジスタM 3 と出力線2 4 n を電気的に切り離す機能をもつ。つまり、オフ状態を考慮すると、リーク電流を抑制するために閾値電圧 $V_{TH}$  を大きく設計することが好ましい。したがって、オフ状態の閾値電圧 $V_{TH}$  を維持したまま、オン状態の閾値電圧 $V_{TH}$  を低減することが、線形性低下の抑制に効果的である。

40

【 0 0 7 0 】

ここで、選択トランジスタM 4 の閾値電圧 $V_{TH}$  は、概ね以下に示す（式3）から求めることができる。

【 0 0 7 1 】

50

## 【数3】

$$V_{TH} = V_{TH0} + \gamma \left( \sqrt{-V_{BS} + 2\phi_F} - \sqrt{2\phi_F} \right) \quad (\text{式3})$$

## 【0072】

$V_{BS}$  は選択トランジスタ M4 のウェル - ソース間電圧、 $V_{TH0}$  は  $V_{BS}$  が 0 V 時の選択トランジスタ M4 の閾値電圧、 $2\phi_F$  は表面ポテンシャル、 $\gamma$  は基板効果パラメータである。

10

## 【0073】

式3に示すように、選択トランジスタ M4 の閾値電圧  $V_{TH}$  はウェル - ソース間電圧  $V_{BS}$  を変数にもつ。これは、選択トランジスタ M4 のソースの電位が一定の場合、ウェル電位  $V_B$  が閾値電圧  $V_{TH}$  の変数になることと等価である。これをを利用して、本実施形態の単位画素 25 は、制御線 23m からの制御信号 SELBm によって、選択トランジスタ M4 のウェル電位  $V_B$  を制御し、オン状態とオフ状態で実効的な閾値電圧  $V_{TH}$  を変更させている。これにより、選択トランジスタ M4 がオフ状態にあるときには、選択トランジスタ M4 のリーク電流を抑制することができる。また、選択トランジスタ M4 がオン状態にあるときには、線形性の低下が抑制された画素信号の出力を得ることができる。

20

## 【0074】

より具体的には、選択トランジスタ M4 のオン状態で与えられるウェル  $W_{SEL}$  のウェル電位  $V_B$  を、オフ状態でウェル  $W_{SEL}$  に与えられるウェル電位  $V_B$  よりも、相対的に高く設定している。例えば、ハイレベルに接地電位、ローレベルに負電位を設定することができる。この条件では、ウェル  $W_{SEL}$  のウェル電位  $V_B$  が接地電位に接続される場合と同等なオフ状態の実効的な閾値電圧  $V_{TH}$  を維持するための、オン状態の閾値電圧  $V_{TH}$  を低減させることができると可能になる。また、選択トランジスタ M4 のオン状態で与えられるウェル  $W_{SEL}$  のウェル電位  $V_B$  が、ウェル  $W_{PD}$  の電位と同じ電位であっても良い。つまり、選択トランジスタ M4 がオフ状態である期間に、ウェル  $W_{SEL}$  のウェル電位  $V_B$  は、ウェル電位  $W_{PD}$  より小さい電位となる。また、選択トランジスタ M4 のオン状態で与えられるウェル  $W_{SEL}$  のウェル電位  $V_B$  が、ウェル  $W_{PD}$  の電位よりも高い電位であっても良い。

30

## 【0075】

また、本実施形態では、ウェル  $W_{SEL}$  のウェル電位  $V_B$  を変化させていた。他の例として、光電変換装置が動作している期間の全体に渡って、ウェル  $W_{SEL}$  のウェル電位  $V_B$  をウェル  $W_{PD}$  の電位よりも高い電位として、選択トランジスタ M4 が output する画素信号の線形性の低下を抑制した構成としても良い。

40

## 【0076】

つまり、本実施形態によって重要なのは、選択トランジスタ M4 が設けられたウェル  $W_{SEL}$  がウェル  $W_{PD}$  とは電気的に分離された構成である。これにより、ウェル  $W_{SEL}$  の電位をウェル  $W_{PD}$  とは独立して設定することができる。この構成によって、選択トランジスタ M4 のリーク電流の抑制と、線形性の低下が抑制された画素信号の取得の少なくとも一方を得ることができる。

40

## 【0077】

また、ここで着目する点は、選択トランジスタ M4 のオン状態のウェル電位  $V_B$  が、オフ状態のウェル電位  $V_B$  よりも相対的に高くなることである。ウェル電位  $V_B$  が高くなると、式3に示すように、実効的な閾値電圧  $V_{TH}$  が減少するため、オン抵抗  $R_{ON}$  が小さくなる。よって、式1に示すように、オン抵抗の減少は線形性低下を抑制し、高品質な画像を取得することができる。

## 【0078】

本実施形態では、制御信号 SELBm から供給される選択トランジスタ M4 のウェル電

50

位  $V_B$  のハイレベルを接地電位とし、ローレベルを負電位として、それぞれ設定した。しかし、ウェル電位  $V_B$  の電位はこれらの電位に限定されるものではない。他の例として、ウェル電位  $V_B$  を正電位で設定することも可能である。この場合、ウェル - ソース間およびウェル - ドレイン間の電圧が順方向にならない範囲で設定することが好みしい。

#### 【0079】

また、制御信号  $SELm$  のローレベルは、制御信号  $SELBm$  のローレベルと同等の電位に設定するとよい。より具体的には、制御信号  $SELBm$  のローレベルを負電位に設定した場合は、制御信号  $SELm$  のローレベルも同一の負電位に設定すると良い。

#### 【0080】

本実施形態の光電変換装置は、選択トランジスタ  $M4$  のオン抵抗を減少させることができ、高品質な画像を取得することができる。 10

#### 【0081】

なお、本実施形態では、選択トランジスタ  $M4$  が  $N$  型のトランジスタであるとして、電位の関係を説明した。前述したように、本明細書に記載の事項は、トランジスタの導電型の変更に伴って、電位は適宜変更される。つまり、選択トランジスタ  $M4$  を  $P$  型のトランジスタとした場合には、選択トランジスタ  $M4$  のオン状態で与えられるウェル  $W_{SEL}$  のウェル電位  $V_B$  を、オフ状態でウェル  $W_{SEL}$  に与えられるウェル電位  $V_B$  よりも、相対的に低く設定するようにすればよい。

#### 【0082】

また、本実施形態では、リセットトランジスタ  $M2$  が設けられたウェル  $W_{PD}$  と、選択トランジスタ  $M4$  が設けられたウェル  $W_{SEL}$  とが電気的に分離されている構成を例に説明した。この構成によって、選択トランジスタ  $M4$  のリーク電流の抑制と、線形性の低下が抑制された画素信号の取得の少なくとも一方を得ることができる。 20

#### 【0083】

また、単位画素  $24n$  の構成は適宜変更できる。たとえば、転送トランジスタ  $M11$  と浮遊拡散領域は省略することができる。つまり、光電変換素子  $PD$  の一部領域にコンタクトが設けられ、当該コンタクトと増幅トランジスタ  $M3$  のゲートとを接続するようにしても良い。この構成においても、ウェル  $W_{SEL}$  は、リセットトランジスタが設けられたウェルとは独立して電位を設定することができる。この場合の  $FD$  ノードを構成する複数のトランジスタは、リセットトランジスタ  $M2$  と増幅トランジスタ  $M3$  であるが、 $FD$  ノードの容量値を切り替えるトランジスタをさらに含んでも良い。 30

#### 【0084】

##### (第2実施形態)

本実施形態について、第1実施形態と異なる点を中心に説明する。

#### 【0085】

図7は、本実施形態における2例目の単位画素  $25$  の等価回路図である。図7には、第  $m$  行、第  $n$  列に配された単位画素  $25B$  ( $m, n$ ) が示されている。単位画素  $25B$  は、単位画素  $25A$  に対し、増幅トランジスタ  $M3$  が配されたウェル  $W_{AMP}$  が、ウェル  $W_{SEL}$  およびウェル  $W_{PD}$  と電気的に分離され、増幅トランジスタ  $M3$  のソースと電気的に接続されている。 40

#### 【0086】

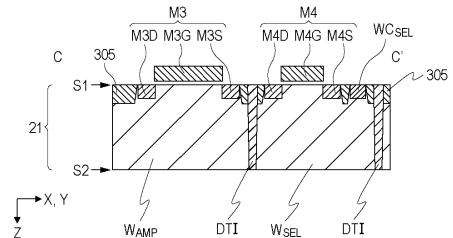

図8は、図7の等価回路図に対応した単位画素  $25B$  を含むレイアウトであり、平面視で2行×2列の計4つの単位画素  $25B$  を示している。

#### 【0087】

単位画素  $25B$  は、平面視で、絶縁体分離部  $DTI$  により少なくとも3つの領域に分離されている点が第1実施形態と異なる。第1の領域には選択トランジスタ  $M4$  が配され、第2の領域には光電変換素子  $PD$  が配され、第3の領域には増幅トランジスタ  $M3$  が配される。絶縁体分離部  $DTI$  は、選択トランジスタ  $M4$  と増幅トランジスタ  $M3$  をそれぞれ取り囲むように配されている。絶縁体分離部  $DTI$  は、選択トランジスタ  $M4$  のチャネルとなる領域を含むウェル  $W_{SEL}$  と、光電変換素子  $PD$  が配されたウェル  $W_{PD}$  と、増幅

トランジスタM3のチャネルとなる領域を含むウェルW<sub>A M P</sub>とを分離する機能をもつ。

【0088】

ウェルW<sub>A M P</sub>は、ウェルW<sub>A M P</sub>に配されたウェルコンタクトW<sub>C A M P</sub>を介して増幅トランジスタM3のソースと電気的に接続されている。転送トランジスタM11、リセットトランジスタM2はそれぞれウェルW<sub>P D</sub>に配されている。つまり、選択トランジスタM4と、リセットトランジスタM2と、増幅トランジスタM3との間には、それぞれ、絶縁体分離部D<sub>T I</sub>が配されている。

【0089】

図9は、図8のB-B'の概略断面図である。単位画素25Bは、単位画素25Aに対し、選択トランジスタM3のウェルW<sub>A M P</sub>とP<sub>D</sub>ウェルW<sub>P D</sub>を分離する絶縁体分離部D<sub>T I</sub>が追加されている。この絶縁体分離部D<sub>T I</sub>は、半導体基板301を貫通する構成になっている。ウェルW<sub>A M P</sub>のウェルコンタクトW<sub>C A M P</sub>は、半導体基板301内に配され、P型の不純物が拡散されたP型半導体領域により構成される。ウェルコンタクトW<sub>C A M P</sub>は、半導体基板301の第1面S1の一部を構成する。

10

【0090】

単位画素25Bでは、ウェルW<sub>A M P</sub>を、ウェルW<sub>S E L</sub>およびウェルW<sub>P D</sub>と電気的に分離する。また、増幅トランジスタM3のソースとウェルW<sub>A M P</sub>が電気的に接続されているため、増幅トランジスタのウェル-ソース間電圧V<sub>B S</sub>は0Vで実質的に固定される。そのため、基板バイアス効果による増幅トランジスタM3の閾値電圧V<sub>T H</sub>を実質的に一定にすることができる。これにより、増幅トランジスタM3のウェル電位V<sub>B</sub>が接地電位に接続されている場合と比較して、画素信号の線形線が非線形になりにくくなる。

20

【0091】

以上の説明の通り、単位画素25Bでは、選択トランジスタM4による線形性低下の抑制に加え、増幅トランジスタM3の基板バイアス効果による信号の線形性の低下をさらに抑制することができる。

30

【0092】

上述の通り、本実施形態によれば、選択トランジスタM4のウェルW<sub>S E L</sub>をP<sub>D</sub>が配されたウェルW<sub>P D</sub>と分離して、ウェルW<sub>S E L</sub>の電位を選択トランジスタのオン状態とオフ状態で制御することで、信号の線形性の低下をさらに抑制することができる。

【0093】

(第3実施形態)

本実施形態による光電変換装置およびその駆動方法について、図10～図20を用いて説明する。図10は、本実施形態における光電変換装置のブロック図である。

【0094】

図10に示すように、光電変換装置2は、第1部品10、第2部品20、及び第3部品30の3つの部品を備えている。光電変換装置2は、これら3つの部品を貼り合わせて構成された積層型の光電変換装置である。また、第1部品10、第2部品20、及び第3部品30は、この順に積層されている。

【0095】

第1部品10は、光電変換を行う複数のセンサ部12が設けられた第1半導体基板11を有する。複数のセンサ部12は、第1部品10における画素領域13内に複数行および複数列に設けられている。複数のセンサ部12の各々は、光電変換素子P<sub>D</sub>と転送トランジスタM11を含む。複数のセンサ部12は、入射光の光量に応じた信号電荷を出力する。また、第1部品10は、第1半導体基板11から見て第2半導体基板21の側に設けられた絶縁膜などの各種の膜を含む。

40

【0096】

第2部品20は、センサ部12から出力された電荷に基づく画素信号を出力する読み出し回路22が設けられた第2半導体基板21を有する。読み出し回路22は画素トランジスタを含む。また、第2部品20は水平方向に延在する複数の制御線23と、垂直方向に延在する複数の出力線24とを有している。制御線23は、垂直駆動回路33に接続され

50

ている。出力線 24 の各々は、垂直方向に並ぶ読み出し回路 22 に接続され、これら読み出し回路 22 に共通の信号線をなしている。出力線 24 は、列信号処理部 34 に接続されている。また、第 2 部品 20 は、第 2 半導体基板 21 から見て、第 1 半導体基板 11 の側と、第 3 半導体基板 31 の側の少なくとも一方に設けられた絶縁膜などの各種の膜を含む。

#### 【0097】

第 3 部品 30 は、画素信号を処理するロジック回路 32 が設けられた第 3 半導体基板 31 を有する。ロジック回路 32 は、例えば、垂直駆動回路 33、列信号処理部 34、水平駆動回路 35、出力回路 36、及びシステム制御部 37 を有している。また、第 3 部品 30 は、第 3 半導体基板 31 から見て、第 2 半導体基板 21 の側に設けられた絶縁膜などの各種の膜を含む。

10

#### 【0098】

第 1 部品 10 と第 2 部品 20 は、互いが備える絶縁膜同士を貼り合わせて積層される。また、第 2 部品 20 と第 3 部品 30 もまた、互いが備える絶縁膜同士を貼り合わせて積層される。

#### 【0099】

以上より、本実施形態では、図 10 で説明したような 3 つの部品が積層された構成を備える。また、本実施形態では、単位画素が含む構成のうち、光電変換素子 PD は第 1 半導体基板 11 に設けられ、転送トランジスタを除く画素トランジスタが第 2 半導体基板 21 に設けられる。これにより、画素トランジスタを配置するスペースを確保しやすくなり、画素ピッチをさらに縮小させることができる。よって、微細化に適した光電変換装置を実現できる。

20

#### 【0100】

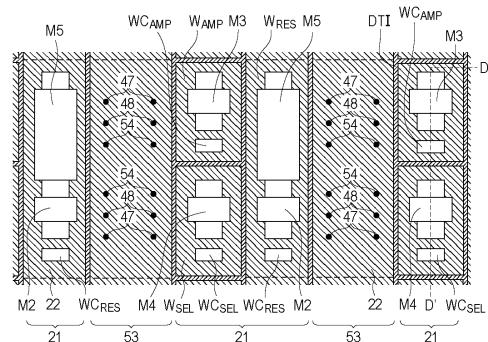

図 11 は、本実施形態における 1 例目の単位画素 25 の等価回路図である。図 11 には、第 m 行、第 n 列に配された単位画素 25C (m, n) が示されている。単位画素 25C は、等価回路図上では、単位画素 25A に対し、4 つのフォトダイオード PD1 ~ PD4 の信号を、それぞれの PD に対応する転送トランジスタ M11 ~ M14 を介して FD1 ~ FD4 に転送し、共通の読み出し回路 22 で読み出す構成となる。図 11 では、4 つの PD の信号を 1 つの読み出し回路 22 で読み出す構成を取っているが、1 つの読み出し回路 22 に接続される光電変換素子 PD の数は任意の数に変更可能である。

30

#### 【0101】

また、図 11 では、リセットトランジスタ M2 のソースと FD ノードとの間に、FD 容量切り替えトランジスタ M5 を配置している。FD 容量切り替えトランジスタ M5 のゲートには、垂直駆動回路 33 から制御信号 FDGM が供給される。FD 容量切り替えトランジスタ M5 をオン / オフ切り替えすることで、FD 容量の容量値を可変にし、変換効率を切り替えることができる。つまり、FD 容量切り替えトランジスタ M5 は、増幅トランジスタ M3 のゲートへの容量の接続、非接続を切り替えるトランジスタである。本実施形態では、この容量は、FD 容量切り替えトランジスタ M5 自身が備える容量としている。この例に限定されるものではなく、例えば、リセットトランジスタ M2 と FD 容量切り替えトランジスタ M5 との間の電気的経路に、容量素子を設けても良い。この容量素子は、MIM 容量、MOM 容量、MOS 容量、MIS 容量等、容量を備えるものであればよい。ここで、MIM は Metal Insulator Metal の略であり、絶縁層が複数の金属層（ポリシリコンの場合を含む）で挟まれた構造である。MOM は Metal Oxide Metal の略であり、シリコン酸化膜などの酸化膜（酸窒化膜の場合も含む）が複数の金属層（ポリシリコンの場合を含む）に挟まれた構造である。MOS は Metal Oxide Silicon の略であり、シリコン酸化膜などの酸化膜（酸窒化膜の場合も含む）がシリコン基板内の半導体層と金属層（ポリシリコンの場合を含む）に挟まれた構造である。MIS は Metal Insulator Silicon の略であり、絶縁膜がシリコン基板内の半導体層と金属層（ポリシリコンの場合を含む）に挟まれた構造である。

40

50

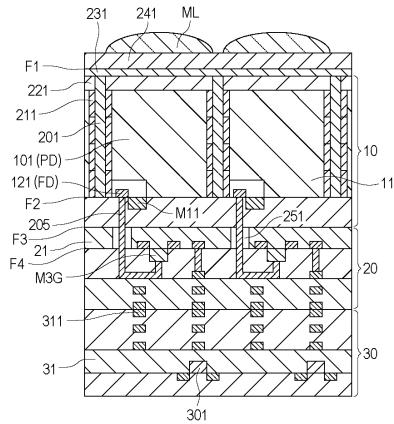

## 【0102】

図12は本実施形態の光電変換装置の断面図である。この断面図は、第1部品10、第2部品20、第3部品30において、光電変換素子PD、転送トランジスタM11のゲートを通る線の断面を示している。光電変換素子PDは、N型の半導体領域101を含んで構成されている。図12の断面図では、4つのセンサ部12のうち、1つの断面に現れる2つのセンサ部12を示している。

## 【0103】

転送トランジスタM11のゲートは、光電変換素子PDとFDの領域である半導体領域121との間の導通を制御する。半導体領域121はN型の半導体領域である。画素分離部201は、複数の半導体領域101の間に12の間に設けられており、複数の半導体領域101を電気的に分離している。画素分離部201は、シリコン酸化物等の絶縁部を含んで構成されていても良いし、ポテンシャル障壁を形成する半導体領域であっても良い。典型的には、光電変換素子PDが蓄積する信号電荷とは反対の極性の電荷を主たるキャリアとする半導体領域である。画素分離部201と半導体領域101との間には画素分離層211が設けられている。画素分離層211は、特に画素分離部201が絶縁部で設けられている場合、暗電流を低減する役割を持つ。FDである半導体領域121と増幅トランジスタM3のゲートM3Gは導電体205を介して接続される。導電体205はタンゲステン、銅などの金属を主に含んで構成される。導電体205は、半導体基板21を分離する絶縁体251を貫通して形成されている。絶縁体251は、複数の読み出し回路22を互いに電気的に分離する。また、絶縁体251は半導体基板21の一方の面である第3面F3から、第3面F3に対向する他方の面である第4面F4まで貫通して設けられている。導電体205は、この絶縁体251の内部を貫通する貫通電極である。

10

20

30

## 【0104】

半導体基板11は入射面側の第1面F1と、第1面に対向する第2面F2を備える。半導体領域221は半導体領域101の第1面F1の側(入射面側)の領域に設けられたP型の半導体領域である。固定電荷膜231は半導体基板14の第1面F1の上に設けられている。半導体領域221、固定電荷膜231により、半導体領域101に入る暗電流を低減している。

## 【0105】

マイクロレンズMLは、半導体領域101に光を導く。マイクロレンズMLと固定電荷膜231との間には平坦化層241が設けられている。なお、複数のセンサ部12の各々にさらにカラーフィルタを設けて色分離を行うようにしても良い。

30

## 【0106】

第1部品10、第2部品20、第3部品30は積層されている。第2部品20は、第1部品10と第3部品30との間に設けられている。第3部品30の半導体基板31には、トランジスタ301が設けられている。接続部311を介して、第2部品20と第3部品30は電気的に接続されている。接続部311は金属で形成される。典型的には接続部311は銅を主に含む。また、接続部311は銅の拡散を抑制するためのバリアメタル(チタン、ニッケルなど)をさらに含んで形成される。

40

## 【0107】

続いて、本実施形態における、各画素の浮遊拡散部の電位に応じて選択トランジスタM4のオン抵抗が変化することで生じ得る信号の線形性の低下を抑制し得る光電変換装置の駆動方法について、図16を用いて説明する。

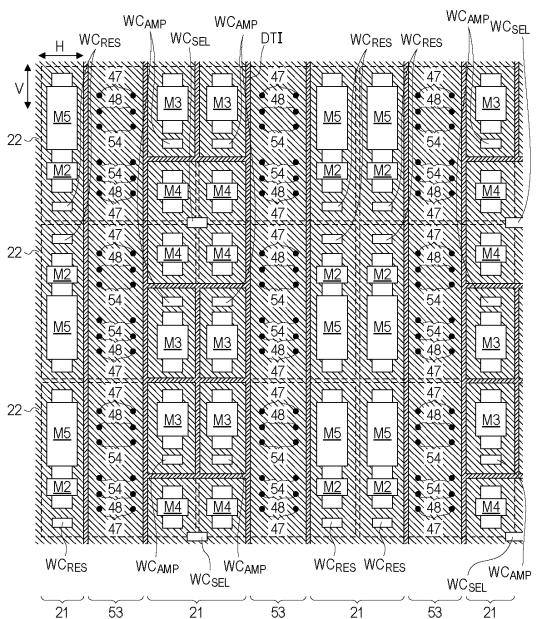

## 【0108】

図13は、図11の等価回路図に対応した単位画素25Cを含むレイアウトであり、平面視で1行×2列の計2つの単位画素25Cを示している。ここで示す2つの単位画素25Cは、それぞれが図11の等価回路に対応するもので、単位画素25Cを構成する各要素は共通の構成を成している。図13の上側の図は、図10の第1部品10の平面視によるレイアウトである。図13の下側の図は、図10の第2部品20の平面視によるレイアウトである。複数の貫通電極47、複数の貫通電極48および複数の貫通電極54を介し

50

て、第1部品10と第2部品20は電気的に接続されている。図13に示した貫通電極54は、図12に示した導電体205の一部である。

【0109】

図13に示すように、第2部品20は、平面視で、第2半導体基板21と、貫通電極54等を含む絶縁層53の領域で構成される。半導体基板21の領域には、読み出し回路22に含まれる画素トランジスタが配されている。

【0110】

増幅トランジスタM3は、平面視で右側に隣接する読み出し回路22に配されるリセットトランジスタM2およびFD切り替えトランジスタM5と共にウェル上に配される。また、絶縁体分離部DTIは、選択トランジスタM4を取り囲むように配されている。そのため、選択トランジスタM4のウェルWSELは、他の画素トランジスタが含まれるウェルWAMPとは電気的に分離されている。

10

【0111】

図14は、図13のC-C'の概略断面図である。絶縁体分離部DTIによって、選択トランジスタM4が配されるWSELと、増幅トランジスタM3等が配されるウェルWAMPが電気的に分離されている。

20

【0112】

図16は、本実施形態における2例目の単位画素25の等価回路図である。図16には、第m行、第n列に配された単位画素25D(m, n)が示されている。単位画素25Dは、単位画素25Cに対し、増幅トランジスタM3が配されたウェルWAMPが、ウェルWSELおよびウェルWRRESと電気的に分離され、増幅トランジスタM3のソースと電気的に接続されている。

20

【0113】

図16は、本実施形態における単位画素25の信号読み出しを説明する駆動タイミング図である。図16では、水平走査期間k~k+8(kは整数)において垂直駆動回路33から単位画素25(1, n)~25(2, n)に供給される制御信号RES1~RES2を示している。さらに、図16では、垂直駆動回路33から単位画素25(1, n)~25(2, n)に供給される制御信号TX11~TX42、SEL1~SEL2、制御信号SELB1~SELB2を示している。

30

【0114】

時刻t21~t43の期間は、単位画素25(1, n)の読み出し期間に対応し、単位画素25(1, n)に対する光電変換素子PD1~PD4からの信号の読み出しが実行される。各水平走査期間でそれぞれ1つのPDの信号を読み出し、4水平走査期間をかけて4つのPDの信号の読み出しを行う。時刻t22~t42の期間は、単位画素25(1, n)を含む行の単位画素25が選択される期間であり、SEL1およびSELB1がハイレベルに固定される。

30

【0115】

続いて、時刻t43~t65の期間は、単位画素25(2, n)の読み出し期間に対応し、単位画素25(2, n)に対する光電変換素子PD1~PD4からの信号の読み出しが実行される。時刻t44~t64の期間は、単位画素25(2, n)を含む行の単位画素25が選択される期間であり、SEL2およびSELB2がハイレベルに固定される。

40

【0116】

ここで、本実施形態においても、選択トランジスタM4のオン状態のタイミングで、制御信号SELBmによって、選択トランジスタM4のウェルWSELにハイレベルの電位が与えられる。これにより、選択トランジスタM4のオン状態のウェル電位VBが、オフ状態のウェル電位VBよりも相対的に高くなる。ウェル電位VBが高くなると、実効的な閾値電圧VTHが減少するため、選択トランジスタM4のオン抵抗RONが小さくなる。選択トランジスタM4のオン抵抗の減少は線形性低下を抑制し、高品質な画像を取得することが可能になる。

【0117】

50

図17は、図16の等価回路図に対応した単位画素25Dを含むレイアウトであり、平面視で1行×2列の計2つの単位画素25Dを示している。図17の上側の図は、図10の第1部品10の平面視によるレイアウトである。図17の下側の図は、図10の第2部品20の平面視によるレイアウトである。

【0118】

単位画素25Dは、単位画素25Cのレイアウトに対し、増幅トランジスタM3も絶縁体分離部DTIによって取り囲まれている。これにより、ウェルWSELと、ウェルWAMPと、ウェルWRESとがそれぞれ電気的に分離される。なお、ウェルWSELは選択トランジスタM4のチャネルとなる領域を含む領域である。また、ウェルWAMPは増幅トランジスタM3のチャネルとなる領域を含む領域である。また、ウェルWRESはリセットトランジスタM2およびFD容量切り替えトランジスタM5のチャネルとなる領域を含む領域である。

10

【0119】

図18は、図17のD-D'の概略断面図である。絶縁体分離部DTIによって、選択トランジスタM4が配されるWSELと、増幅トランジスタM3等が配されるウェルWAMPと、リセットトランジスタM2およびFD容量切り替えトランジスタM5が配されるウェルWRESが電気的に分離されている。

【0120】

単位画素25Dでは、ウェルWAMPを、ウェルWSELおよびウェルWRESと物理的に分離し、増幅トランジスタM3のソースとウェルWAMPを電気的に接続しているため、増幅トランジスタのウェル-ソース間電圧VBSは0Vで固定される。そのため、基板バイアス効果による増幅トランジスタM3の閾値電圧VTHを一定にすることができ、ウェル電位VBが接地電位に接続されている場合と比較して、信号の線形線が非線形とならない。

20

【0121】

以上の説明の通り、単位画素25Dでは、選択トランジスタM4による線形性の低下の抑制に加え、増幅トランジスタM3の基板バイアス効果による信号の線形性の低下を抑制することができる。

【0122】

上述の通り、本実施形態によれば、選択トランジスタM4のウェルWSELを他の画素トランジスタが配されるウェルと電気的に分離して、ウェルWSELの電位を選択トランジスタのオン状態とオフ状態で制御する。これにより、単位画素が出力する信号の線形性の低下を抑制することができる。また、選択トランジスタのリーク電流を低減することができる。

30

【0123】

図19は、図11の等価回路図に対応した単位画素25Cを含む、第2部品20のレイアウトであり、平面視で3行×3列の計9つの単位画素25Cを示している。

【0124】

図19に示すように、読み出し回路22に配される画素トランジスタは、水平方向および垂直方向で隣接する同一電位のウェルを共有するレイアウト構成を成している。より具体的には、選択トランジスタM4のウェルWSELと増幅トランジスタM3のウェルWAMPが、隣接する2行×2列でそれぞれ共有されている。また、リセットトランジスタM2とFD容量切り替えトランジスタM5は、垂直方向に隣接する読み出し回路22の間で、ウェルWRESを共有している。

40

【0125】

このように、水平方向および垂直方向で隣接する同電位のウェルを共有することで、ウェル上に配されるウェルコンタクトの数を減少させることができ、レイアウト効率を向上させることができる。より具体的には、共有する4つの増幅トランジスタM3のウェルWAMPおよび共有する4つの選択トランジスタM4のウェルWSELに対し、ウェルコンタクトWCAMPおよびWCSELをそれぞれ1つずつ配置している。また、ウェルを共

50

有することで、それぞれのウェル間の電位ばらつきを抑制することができ、レイアウト効率と電位ばらつきの抑制に効果的なレイアウトである。

【0126】

図20は、図16の等価回路図に対応した単位画素25Dを含む、第2部品20のレイアウトであり、平面視で3行×3列の計9つの単位画素25Dを示している。

【0127】

図20に示すレイアウト構成でも、図19で示したレイアウト構成と同様に、水平方向および垂直方向に隣接する同電位のウェルを共有することで、レイアウト効率と電位ばらつきの抑制に効果的なレイアウトを実現することができる。

【0128】

なお、上記実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

【0129】

(第4実施形態)

本実施形態は、第1～第3実施形態のいずれにも適用可能である。

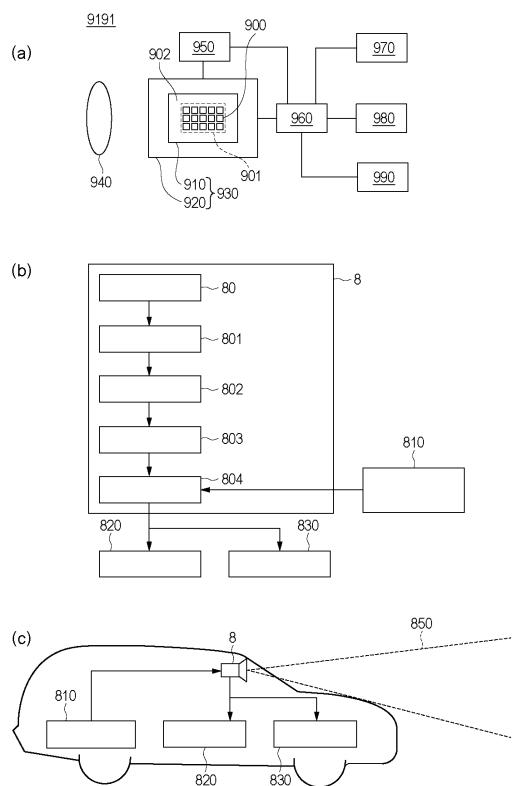

【0130】

図21(a)は本実施形態の光電変換装置930を備えた機器9191を説明する模式図である。光電変換装置930は、第1～第3実施形態で説明した光電変換装置のいずれか、あるいは複数の実施形態を組み合わせた光電変換装置とすることができます。光電変換装置930を備える機器9191について詳細に説明する。光電変換装置930は、上述のように、半導体層10を有する半導体デバイス910のほかに、半導体デバイス910を収容するパッケージ920を含むことができる。パッケージ920は、半導体デバイス910が固定された基体と、半導体デバイス910に対向するガラスなどの蓋体と、を含むことができる。パッケージ920は、さらに、基体に設けられた端子と半導体デバイス910に設けられた端子とを接続するボンディングワイヤやバンプなどの接合部材を含むことができる。

【0131】

機器9191は、光学装置940、制御装置950、処理装置960、表示装置970、記憶装置980、機械装置990の少なくともいずれかを備えることができる。光学装置940は、光電変換装置930に対応する。光学装置940は、例えばレンズやシャッター、ミラーである。制御装置950は、光電変換装置930を制御する。制御装置950は、例えばASICなどの光電変換装置である。

【0132】

処理装置960は、光電変換装置930から出力された信号を処理する。処理装置960は、AFE(アナログフロントエンド)あるいはDFE(デジタルフロントエンド)を構成するための、CPUやASICなどの半導体装置である。表示装置970は、光電変換装置930で得られた情報(画像)を表示する、EL表示装置や液晶表示装置である。記憶装置980は、光電変換装置930で得られた情報(画像)を記憶する、磁気デバイスや半導体デバイスである。記憶装置980は、SRAMやDRAMなどの揮発性メモリ、あるいは、フラッシュメモリやハードディスクドライブなどの不揮発性メモリである。

【0133】

機械装置990は、モーターやエンジンなどの可動部あるいは推進部を有する。機器9191では、光電変換装置930から出力された信号を表示装置970に表示したり、機器9191が備える通信装置(不図示)によって外部に送信したりする。そのために、機器9191は、光電変換装置930が有する記憶回路や演算回路とは別に、記憶装置980や処理装置960をさらに備えることが好ましい。機械装置990は、光電変換装置930から出力された信号に基づいて制御されてもよい。

【0134】

10

20

30

40

50

また、機器 9191 は、撮影機能を有する情報端末（例えばスマートフォンやウエアラブル端末）やカメラ（例えばレンズ交換式カメラ、コンパクトカメラ、ビデオカメラ、監視カメラ）などの電子機器に適する。カメラにおける機械装置 990 はズーミングや合焦、シャッター動作のために光学装置 940 の部品を駆動することができる。あるいは、カメラにおける機械装置 990 は防振動作のために光電変換装置 930 を移動することができる。

【0135】

また、機器 9191 は、車両や船舶、飛行体などの輸送機器であり得る。輸送機器における機械装置 990 は移動装置として用いられる。輸送機器としての機器 9191 は、光電変換装置 930 を輸送するものや、撮影機能により運転（操縦）の補助および／または自動化を行うものに好適である。運転（操縦）の補助および／または自動化のための処理装置 960 は、光電変換装置 930 で得られた情報に基づいて移動装置としての機械装置 990 を操作するための処理を行うことができる。あるいは、機器 9191 は内視鏡などの医療機器や、測距センサなどの計測機器、電子顕微鏡のような分析機器、複写機などの事務機器、ロボットなどの産業機器であってもよい。

10

【0136】

上述した実施形態によれば、良好な画素特性を得ることが可能となる。従って、光電変換装置の価値を高めることができる。ここでいう価値を高めることには、機能の追加、性能の向上、特性の向上、信頼性の向上、製造歩留まりの向上、環境負荷の低減、コストダウン、小型化、軽量化の少なくともいずれかが該当する。

20

【0137】

従って、本実施形態に係る光電変換装置 930 を機器 9191 に用いれば、機器の価値をも向上することができる。例えば、光電変換装置 930 を輸送機器に搭載して、輸送機器の外部の撮影や外部環境の測定を行う際に優れた性能を得ることができる。よって、輸送機器の製造、販売を行う上で、本実施形態に係る光電変換装置を輸送機器へ搭載することを決定することは、輸送機器自体の性能を高める上で有利である。特に、光電変換装置で得られた情報を用いて輸送機器の運転支援および／または自動運転を行う輸送機器に光電変換装置 930 は好適である。

【0138】

また、本実施形態の光電変換システム及び移動体について、図 21 (b)、(c) を用いて説明する。

30

【0139】

図 21 (a) は、車載カメラに関する光電変換システムの一例を示したものである。光電変換システム 8 は、光電変換装置 80 を有する。光電変換装置 80 は、上記のいずれかの実施形態に記載の光電変換装置（撮像装置）である。光電変換システム 8 は、光電変換装置 80 により取得された複数の画像データに対し、画像処理を行う画像処理部 801 と、光電変換システム 8 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差取得部 802 を有する。また、光電変換システム 8 は、算出された視差に基づいて対象物までの距離を算出する距離取得部 803 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 804 と、を有する。ここで、視差取得部 802 や距離取得部 803 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 804 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated Circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

40

【0140】

光電変換システム 8 は車両情報取得装置 810 と接続されており、車速、ヨーレート、

50

舵角などの車両情報を取得することができる。また、光電変換システム8は、衝突判定部804での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御E C U 8 2 0が接続されている。また、光電変換システム8は、衝突判定部804での判定結果に基づいて、ドライバーへ警報を発する警報装置830とも接続されている。例えば、衝突判定部804の判定結果として衝突可能性が高い場合、制御E C U 8 2 0はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置830は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0141】

10

本実施形態では、車両の周囲、例えば前方又は後方を光電変換システム8で撮像する。図21(c)に、車両前方(撮像範囲850)を撮像する場合の光電変換システムを示した。車両情報取得装置810が、光電変換システム8ないしは光電変換装置80に指示を送る。このような構成により、測距の精度をより向上させることができる。

#### 【0142】

20

上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、光電変換システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体(移動装置)に適用することができる。加えて、移動体に限らず、高度道路交通システム(ITS)等、広く物体認識を利用する機器に適用することができる。

#### 【0143】

30

以上、説明した実施形態は、技術思想を逸脱しない範囲において適宜変更が可能である。なお、本明細書の開示内容は、本明細書に記載したことのみならず、本明細書および本明細書に添付した図面から把握可能な全ての事項を含む。また本明細書の開示内容は、本明細書に記載した概念の補集合を含んでいる。すなわち、本明細書に例えば「AはBよりも大きい」旨の記載があれば、「AはBよりも大きくない」旨の記載を省略しても、本明細書は「AはBよりも大きくない」旨を開示していると云える。なぜなら、「AはBよりも大きい」旨を記載している場合には、「AはBよりも大きくない」場合を考慮していることが前提だからである。

#### 【0144】

本実施形態の開示は、以下の構成および方法を含む。

#### 【0145】

(構成1)

出力線と複数の単位画素を有し、

前記複数の単位画素の各々は、

入射光に基づいて信号電荷を生成する光電変換素子と、

前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、

前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、

前記ゲートの電位をリセットするリセットトランジスタと、

を有し、

前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有し、

前記第1ウェルと前記第2ウェルが電気的に分離されていることを特徴とする光電変換装置。

#### 【0146】

(構成2)

40

前記第1ウェルと前記第2ウェルは、絶縁体分離部によって電気的に分離され、前記第1ウェルは前記絶縁体分離部に囲われていることを特徴とする構成1に記載の光電変換装

50

置。

【 0 1 4 7 】

( 構成 3 )

前記選択トランジスタはN型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記選択トランジスタがオフ状態にある期間における前記第1ウェルの電位よりも高い電位であることを特徴とする構成1または2に記載の光電変換装置。

【 0 1 4 8 】

( 構成 4 )

前記オン状態にある期間における前記第1ウェルの電位が接地電位であることを特徴とする構成3に記載の光電変換装置。 10

【 0 1 4 9 】

( 構成 5 )

前記選択トランジスタはP型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記選択トランジスタがオフ状態にある期間における前記第1ウェルの電位よりも低い電位であることを特徴とする構成1または2に記載の光電変換装置。

【 0 1 5 0 】

( 構成 6 )

前記選択トランジスタはN型のトランジスタであって、前記選択トランジスタがオフ状態にある期間における前記第1ウェルの電位が、前記期間における前記第2ウェルの電位よりも低いことを特徴とする構成1または2に記載の光電変換装置。 20

【 0 1 5 1 】

( 構成 7 )

前記期間における前記第2ウェルの電位が接地電位であることを特徴とする構成6に記載の光電変換装置。

【 0 1 5 2 】

( 構成 8 )

前記選択トランジスタはN型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記期間における前記第2ウェルの電位よりも高いことを特徴とする構成1または2に記載の光電変換装置。 30

【 0 1 5 3 】

( 構成 9 )

前記選択トランジスタはP型のトランジスタであって、前記選択トランジスタがオン状態にある期間における前記第1ウェルの電位が、前記期間における前記第2ウェルの電位よりも低いことを特徴とする構成1または2に記載の光電変換装置。

【 0 1 5 4 】

( 構成 10 )

前記ゲートへの容量の接続と非接続を変更するトランジスタが前記第2ウェルに設けられていることを特徴とする構成1乃至9のいずれか1つに記載の光電変換装置。

【 0 1 5 5 】

( 構成 11 )

前記第2ウェルに前記増幅トランジスタが設けられていることを特徴とする構成10に記載の光電変換装置。

【 0 1 5 6 】

( 構成 12 )

前記第2ウェルに前記光電変換素子が設けられていることを特徴とする構成11に記載の光電変換装置。

【 0 1 5 7 】

( 構成 13 )

40

50

第1部品と第2部品とが貼り合わされた構造を備え、

前記光電変換素子は前記第1部品に配されており、

前記第1ウェルおよび前記第2ウェルが前記第2部品に配されていることを特徴とする構成1乃至11のいずれか1つに記載の光電変換装置。

## 【0158】

(構成14)

前記第2部品は半導体基板を備え、

前記第1部品と前記第2部品は、前記半導体基板を貫通する貫通電極によって電気的に接続されていることを特徴とする構成13に記載の光電変換装置。

## 【0159】

10

(構成15)

前記第2部品に貼り合わされた第3部品をさらに有する構造を備え、

前記第3部品は、前記複数の単位画素の各々が output する、前記信号電荷に基づく画素信号を処理するロジック回路を有することを特徴とする構成13に記載の光電変換装置。

## 【0160】

(構成16)

前記第2部品に貼り合わされた第3部品をさらに有する構造を備え、

前記第3部品は、前記複数の単位画素の各々が output する、前記信号電荷に基づく画素信号を処理するロジック回路を有することを特徴とする構成14に記載の光電変換装置。

## 【0161】

20

(構成17)

構成1乃至16のいずれか1項に記載の光電変換装置を備える機器であって、

前記光電変換装置に対応した光学装置、

前記光電変換装置を制御する制御装置、

前記光電変換装置から出力された信号を処理する処理装置、

前記光電変換装置で得られた情報を表示する表示装置、

前記光電変換装置で得られた情報を記憶する記憶装置、および、

前記光電変換装置で得られた情報に基づいて動作する機械装置、の少なくともいずれかを更に備えることを特徴とする機器。

## 【0162】

30

(構成18)

出力線と複数の単位画素を有し、

前記複数の単位画素の各々は、

入射光に基づいて信号電荷を生成する光電変換素子と、

前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、

前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、

前記ゲートの電位をリセットするリセットトランジスタと、

を有し、

前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有する光電変換装置の駆動方法であって、

前記選択トランジスタがオフ状態にある期間に、前記第2ウェルの電位を第1電位に設定し、

前記選択トランジスタがオン状態にある期間に、前記第2ウェルの電位を前記第1電位とは異なる第2電位に設定することを特徴とする光電変換装置の駆動方法。

## 【0163】

40

(構成19)

入射光に基づいて信号電荷を生成する光電変換素子が設けられた部品に積層するための半導体基板であって、

出力線と、

50

前記信号電荷が入力されるゲートを備え、前記ゲートの電位に基づく信号を出力する増幅トランジスタと、

前記増幅トランジスタと前記出力線とを接続する選択トランジスタと、

前記ゲートの電位をリセットするリセットトランジスタと、

を有し、

前記選択トランジスタが設けられた第1ウェルと、前記リセットトランジスタが設けられた第2ウェルとを有し、

前記第1ウェルと前記第2ウェルが電気的に分離されていることを特徴とする半導体基板。

#### 【符号の説明】

10

#### 【0 1 6 4】

1、2 光電変換装置

13 画素領域

25 単位画素

PD 光電変換素子

FD 浮遊拡散領域

DTI 絶縁体分離部

WCSEL 選択トランジスタが配されるウェルコンタクト

WCPD PDが配されるウェルコンタクト

WCAMP 増幅トランジスタが配されるウェルコンタクト

20

WCRES リセットトランジスタが配されるウェルコンタクト

WSEL 選択トランジスタが配されるウェル

WPD PDが配されるウェル

WAMP 増幅トランジスタが配されるウェル

WRES リセットトランジスタが配されるウェル

#### 【図面】

【図1】

【図2】

30

40

50

【図3】

【図4】

10

20

【図5】

【図6】

30

40

50

【図7】

【図8】

10

20

30

40

【図9】

【図10】

50

【図 1 1】

【図 1 2】

10

20

30

40

【図 1 3】

【図 1 4】

50

50

【図 1 5】

【図 1 6】

10

20

30

40

【図 1 7】

【図 1 8】

50

【図19】

【図20】

10

20

30

40

【図21】

50

---

フロントページの続き

ヤノン株式会社内

(72)発明者 池戸 秀樹

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

F ターム (参考) 4M118 AA10 AB01 AB03 CA02 DD04 DD12 FA06 FA27 FA28 FA33

GA02 GC07 GD04 GD07

5C024 GX02 HX17 HX40 HX50