(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-301095

(P2005-301095A)

(43) 公開日 平成17年10月27日(2005.10.27)

(51) Int.CI.<sup>7</sup>

**G09G 3/30**

**G02F 1/133**

**G09G 3/20**

**G09G 3/36**

**H05B 33/14**

F 1

G09G 3/30 J

G02F 1/133 5 7 5

G09G 3/20 6 1 1 A

G09G 3/36 6 1 2 T

H05B 33/14 G09G 3/20 6 1 2 U

テーマコード(参考)

2 H093

3 K007

5 C006

5 C080

審査請求 未請求 請求項の数 18 O L (全 25 頁) 最終頁に続く

(21) 出願番号

特願2004-119893 (P2004-119893)

(22) 出願日

平成16年4月15日 (2004.4.15)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100099173

弁理士 濵谷 孝

(72) 発明者 宮川 恵介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 2H093 NA51 NA52 NA58

3K007 AB05 AB17 BA06 DB03 GA00

GA04

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】 表示時間割合を制御することで表示パネルの消費電力を低減することができる表示装置を提供する。

【解決手段】 1フレームの映像信号を1フレーム平均階調計算部5で求めた平均階調が一定値を越えると画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブル6の出力に基づいて表示手段1の画素の表示時間割合を制御する階調制御回路2を備える。表示時間割合テーブル6の出力信号に基づいて表示手段の画素に書き込まれた映像信号を消去することによって画素の表示時間を制御する。

平均階調が高い画像を表示すると、画面全体が明るく消費電力が上昇するが、1フレームの映像信号の平均階調がある一定値を越えると表示時間割合を下げることで消費電力をある一定値に抑えることができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

1 フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とする表示装置。

**【請求項 2】**

1 フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備え、

前記表示時間割合テーブルの出力信号に基づいて前記表示手段の画素に書き込まれた映像信号を消去することによって階調を制御することを特徴とする表示装置。 10

**【請求項 3】**

1 フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調が一定値を越えると画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とする表示装置。 20

**【請求項 4】**

1 フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調が一定値を越えると画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備え、

前記表示時間割合テーブルの出力信号に基づいて前記表示手段の画素に書き込まれた映像信号を消去することによって階調を制御することを特徴とする表示装置。

**【請求項 5】**

前記表示時間割合テーブルは、前記平均階調が一定値を越えると表示時間割合を低減する倍率信号を発生することを特徴とする請求項 1、2、3 又は 4 の表示装置。 30

**【請求項 6】**

前記表示時間割合テーブルは、前記平均階調が一定値を越えると表示時間割合を低減する倍率信号を発生し、該倍率信号に応じて前記表示手段の画素に書き込まれた映像信号を消去することを特徴とする請求項 1、2、3 又は 4 の表示装置。

**【請求項 7】**

1 フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力する A / D 変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、表示手段に前記デジタル映像信号を出力するデータコントローラと、 40

前記 A / D 変換部からのデジタル映像信号の各画素の階調を 1 フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を備えることを特徴とする表示装置。

**【請求項 8】**

1 フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力 50

する A / D 変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、該デジタル映像信号をアナログ映像信号に変換して表示手段に前記アナログ映像信号を出力するデータコントローラと、

前記 A / D 変換部からのデジタル映像信号の各画素の階調を 1 フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を備えることを特徴とする表示装置。

10

#### 【請求項 9】

前記表示手段は、画素がマトリクス状に配列された E L 素子でなることを特徴とする請求項 1、2、3、4、5、6、7 又は 8 の表示装置。

#### 【請求項 10】

前記表示手段は、画素がマトリクス状に配列された液晶素子でなることを特徴とする請求項 1、2、3、4、5、6、7 又は 8 の表示装置。

#### 【請求項 11】

ソース信号線駆動回路と、第 1 のゲート信号線駆動回路と、第 2 のゲート信号線駆動回路と、画素部と、前記ソース信号線駆動回路に接続された複数のソース信号線と、前記第 1 のゲート信号線駆動回路に接続された複数の第 1 のゲート信号線と、前記第 2 のゲート信号線駆動回路に接続された複数の第 2 のゲート信号線と、電源供給線とを有し、

前記画素部は複数の画素を有しており、

前記複数の画素は、スイッチング用トランジスタ、E L 駆動用トランジスタ、消去用トランジスタ及び E L 素子をそれぞれ有しております、

前記スイッチング用トランジスタのゲート電極は前記第 1 のゲート信号線と接続されており、

前記スイッチング用トランジスタが有するソース領域とドレイン領域は、一方は前記複数のソース信号線と、他方は前記 E L 駆動用トランジスタが有するゲート電極と接続されており、

前記消去用トランジスタが有するゲート電極は前記第 2 のゲート信号線と接続されており、

前記消去用トランジスタが有するソース領域とドレイン領域は、一方は前記電源供給線と、他方は前記 E L 駆動用トランジスタが有するゲート電極と接続されており、

前記 E L 駆動用トランジスタが有するソース領域とドレイン領域は、一方は前記電源供給線に、他方は前記 E L 素子に接続されてなるアクティブマトリクス型表示手段と、

1 フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力する A / D 変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、表示手段に前記デジタル映像信号を出力するデータコントローラと、

前記 A / D 変換部からのデジタル映像信号の各画素の階調を 1 フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると映像信号の表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を有する階調制御回路と

を備え、

前記消去開始信号を前記第 2 のゲート信号線駆動回路に供給して前記画素に書き込まれた映像信号を消去することを特徴とする表示装置。

#### 【請求項 12】

20

30

40

50

ソース信号線駆動回路と、ゲート信号線駆動回路と、画素部と、前記ソース信号線駆動回路に接続された複数のソース信号線と、前記ゲート信号線駆動回路に接続された複数のゲート信号線と、電源供給線とを有し、

前記画素部は複数の画素を有しており、

前記複数の画素は、スイッチング用トランジスタ、EL駆動用トランジスタ及びEL素子をそれぞれ有しており、

前記スイッチング用トランジスタのゲート電極は前記ゲート信号線と接続されており、

前記スイッチング用トランジスタが有するソース領域とドレイン領域は、一方は前記複数のソース信号線と、他方は前記EL駆動用トランジスタが有するゲート電極と接続されており、

前記EL駆動用トランジスタが有するソース領域とドレイン領域は、一方は前記電源供給線に、他方は前記EL素子に接続されてなるアクティブマトリクス型表示手段と、

1フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力するA/D変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、表示手段にアナログ映像信号を出力するデータコントローラと、

前記A/D変換部からのデジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を有する階調制御回路と

を備え、

前記消去開始信号を前記ゲート信号線駆動回路に供給して前記画素に書き込まれた映像信号を消去することを特徴とする表示装置。

#### 【請求項13】

請求項1、2、3、4、5、6、7、8、9、10、11又は12に記載の表示装置において、1フレームの映像信号を複数のサブフレームに分割し、サブフレーム毎に前記表示時間割合を制御して時分割階調表示を行うことを特徴とする表示装置。

#### 【請求項14】

1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段とを備えることを特徴とするデジタルスチルカメラ。

#### 【請求項15】

1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段とを備えることを特徴とするコンピュータ。

#### 【請求項16】

1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段とを備えることを特徴とする画像再生装置。

#### 【請求項17】

1フレームの映像信号の平均階調を求める平均階調計算手段と、

10

20

30

40

50

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段とを備えることを特徴とするビデオカメラ。

【請求項 1 8】

1 フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段とを備えることを特徴とする携帯電話。 10

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、階調表示を容易にした E L 素子等を用いた表示装置、該表示装置を備えた電子機器に関する。 20

【背景技術】

【0 0 0 2】

近年、エレクトロルミネセンス素子（以下、E L 素子という。）等を始めとした発光素子を用いた表示装置の開発が進められている。ここで、E L 素子とは、一重項励起子からの発光を利用するものと三重項励起子からの発光を利用するものが知られている。 20

E L 素子は、一対の電極（陽極と陰極）間に発光層が挟まれる形で構成され、通常、積層構造を採用している。一例を挙げれば、「正孔輸送層・発光層・電子輸送層」という積層構造が挙げられる。また、これ以外にも、陽極上に「正孔注入層・正孔輸送層・発光層・電子輸送層」又は「正孔注入層・正孔輸送層・発光層・電子輸送層・電子注入層」の順に積層する構造のものも知られている（例えば、特許文献1参照）。 30

【0 0 0 3】

【特許文献1】特開2001-343933号公報

【0 0 0 4】

従来、発光素子、例えばL E Dの輝度を調整でき、階調表示ができるL E D駆動装置としてL E D表示アレーの1走査線期間中のL E D発光時間が変化し、つまりデューティが変化し、L E D表示アレーの表示輝度を変化させる表示装置が提案された（例えば、特許文献2）。 30

【0 0 0 5】

【特許文献2】特開平5-341728号公報

【0 0 0 6】

前記提案された表示装置は、L E Dのデューティが外部輝度データで変化するので外部輝度データを制御して階調表示を行い、発光データのパルスのデューティを変化させることで発光時間割合を調節している表示装置である。 40

このL E D表示装置の場合、階調表示は、発光データのパルス時間が全フィールドで等間隔であるため、階調数とフィールド数を等しくする必要があり、階調数を増やすためにはフィールド数を増やす必要があり、表示可能な階調数に限界があった。

【0 0 0 7】

一方、前記E L 素子を用いた多階調表示の可能な表示装置としてデジタル階調方法と時間階調方法を採用した表示装置が知られている（前記特許文献1）。 40

【0 0 0 8】

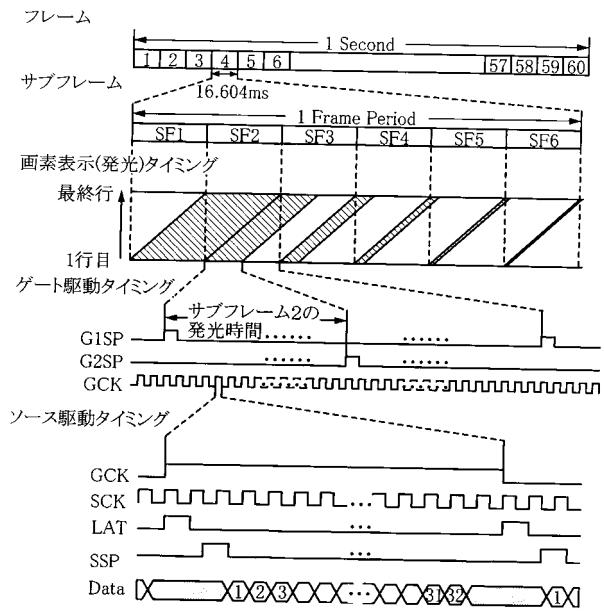

前記時間階調方法は、E L 素子が発光している時間を制御して階調表現を行うものである。時間階調方法について図23乃至図26を参照しながら説明する。

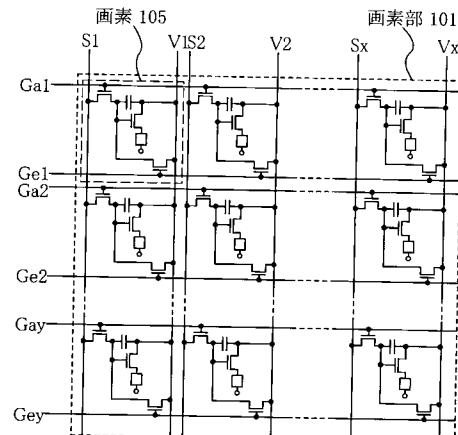

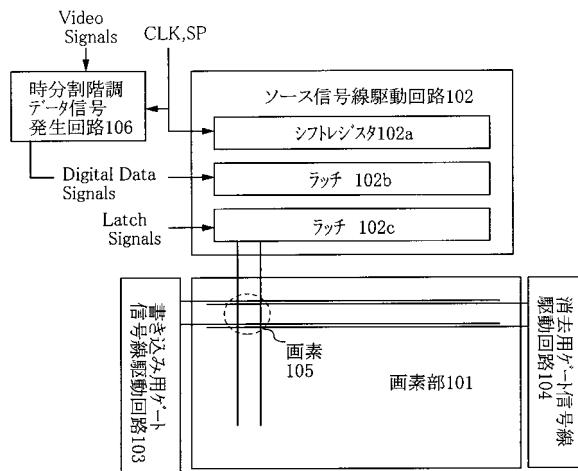

図23及び図24に示すように、E L 表示装置は、基板上に形成されたTFT（薄膜トランジスタ）によってマトリクス状に配列された画素105を有する画素部101、画素部の周辺に配置されたソース信号線駆動回路102、書き込み用ゲート信号線駆動回路1 50

03、消去用ゲート信号線駆動回路104を有している。前記ソース信号線駆動回路102はシフトレジスタ102a、ラッチ102b、ラッチ102cを備えている。

#### 【0009】

前記画素部101は、ソース信号線駆動回路102のラッチ102cに接続されたソース信号線(SI~SX)、電源供給線(V1~VX)、書き込み用ゲート信号線駆動回路103に接続された書き込み用ゲート信号線(Ga1~Gay)、消去用ゲート信号線駆動回路104に接続された消去用ゲート信号線(Ge1~GeY)を備えている。そして、前記各信号線はマトリクス状に配列された画素105にそれぞれ接続されている。

#### 【0010】

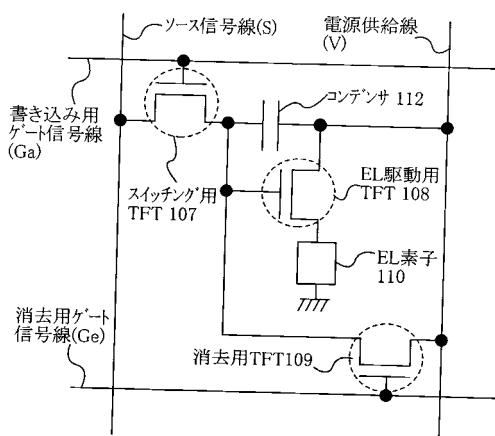

前記画素105は、図25に示すようにスイッチング用TFT107、EL素子110に接続されたEL駆動用TFT108、消去用TFT109、コンデンサ112を備えている。10

前記スイッチング用TFT107のゲート電極は書き込み用ゲート信号線Gaに、ソース領域とドレイン領域は、一方がソース信号線Sに、他方がEL駆動用TFT108のゲート電極に、各画素が有するコンデンサ112及び消去用TFT109のソース領域又はドレイン領域にそれぞれ接続されている。ここでコンデンサ112はスイッチング用TFT107がオフ状態(非選択状態)にある時、EL駆動用TFT108のゲート電圧を保持するために設けられている。

#### 【0011】

前記EL駆動用TFT108のソース領域とドレイン領域は、一方が電源供給線Vに接続され、他方はEL素子110に接続され、電源供給線Vはコンデンサ112に接続されている。また、消去用TFT109のソース領域とドレイン領域のうち、スイッチング用TFTに接続されていない方は電源供給線Vに接続され、ゲート電極は消去用ゲート信号線Geに接続されている。20

#### 【0012】

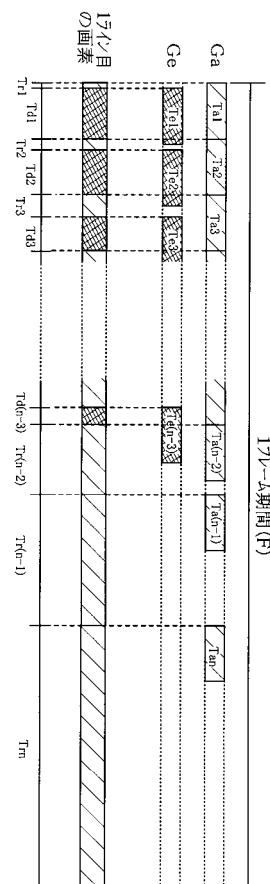

以下、前記EL表示装置の駆動及び階調表示を図26を参照しながら説明する。

前記書き込み用ゲート信号線駆動回路103から書き込み用選択信号が入力されると、1行目の書き込み用ゲート信号線Ga1に接続されている全ての画素のスイッチングTFT107がオン状態になる。同時にソース信号線S1~SXにラッチ102cからデジタル信号に変換された映像信号の1ビット目のデジタルデータ「0」又は「1」が入力される。30

このデジタルデータはスイッチング用TFTを介してEL駆動用TFT108のゲート電極に入力され、デジタルデータが「1」のときはEL駆動用TFT108はオンしてEL素子110は発光し、デジタルデータが「0」の時はEL駆動用TFT108はオフしてEL素子110は発光しないようになっている。

#### 【0013】

このように1行目に前記デジタルデータが入力されると、EL素子が発光または非発光を行い、1行目の画素は表示を行う。ここで、画素が表示を行っている期間を図示のように表示期間Trとし、1ビット目のデジタルデータが入力されて表示する表示期間をTr1とし、後続するデジタルデータのビットによる表示期間を順次Tr2、Tr3…とする。40

#### 【0014】

次に、前記書き込み用ゲート信号線Ga1への書き込み用選択信号の入力が終了すると同時に、書き込み用ゲート信号線Ga2に同様に書き込み用選択信号が入力される。

すると書き込み用ゲート信号線Ga2に接続されている全ての画素のスイッチング用TFT107がオン状態になり、2ライン目の画素にソース信号線S1~SXから1ビット目のデジタルデータが入力される。そして順次全ての書き込み用ゲート信号線(Ga1~Gay)に書き込み用選択信号が入力されて全ての書き込み用ゲート信号線が選択され、全てのラインの画素に1ビット目のデジタルデータが入力されるまでの期間が書き込み期間Ta1である。

#### 【0015】

一方、全ての行の画素に 1 ビット目のデジタルデータが入力される前、言い換えると書き込み期間  $T_{a1}$  が終了する前に、画素への 1 ビット目のデジタルデータの入力と並行して消去用ゲート信号線駆動回路 104 からの消去用ゲート信号線  $G_{e1}$  への消去用選択信号が入力される。すると消去用データ信号線  $G_{e1}$  に接続されている全ての画素（1 行目の画素）の消去用 TFT109 がオンし、電源供給線（ $V_1 \sim V_x$ ）の電源電位が EL 駆動用 TFT108 のゲート電極に与えられて EL 駆動用 TFT108 はオフする。これによって電源電位が EL 素子 110 の画素電極に与えられなくなり、1 行目の画素が有する EL 素子は全て非発光の状態となり、1 行目の画素が表示を行わなくなる。

ここで、前記消去されてから画素が表示を行わない期間を図示のように非表示期間  $T_d$  であり、1 行目の非表示期間は  $T_{d1}$  である。10

#### 【0016】

そして、後続する行を 1 行目と同様の書き込み動作と消去動作を行い、全ての行の画素が保持している 1 ビット目のデジタルデータが消去される。ここで全ての行の画素が保持している 1 ビット目のデジタルデータが消去されるまでの期間を図示のように消去期間  $T_{e1}$  として示されている。さらに 2 ビット目のデジタルデータの消去期間は  $T_{e2}$  として示されている。

#### 【0017】

以上のようにして書き込み、表示、消去、非表示の動作が  $n$  ビット目のデジタルデータが画素に入力されるまで繰り返され、表示期間  $T_r$  と非表示期間  $T_d$  が繰り返し出現し、全ての表示期間（ $T_{r1} \sim T_{rn}$ ）が終了すると一つの画像、つまり 1 フレームの画像を表示することができる。20

#### 【0018】

以上の動作を行う EL 表示装置の階調表示は、前記表示期間  $T_r$  の長さを、 $T_{r1} : T_{r2} : \dots : T_{rn} = 2^0 : 2^1 : \dots : 2^{(n-1)}$  となるように設定する。この表示期間の組み合わせで  $2^n$  階調のうち所望の階調表示を行うことができる。ここで 1 フレーム期間中に EL 素子が発光した表示期間の総和を求めることによって、当該フレーム期間における画素の表示した階調が決まる。例えば  $n = 8$ （256 階調）の時、全部の表示期間で画素が発光した場合の輝度を 100% とすると、 $T_{r1}$  と  $T_{r2}$  において画素が発光した場合は 1% の輝度が表現でき、 $T_{r3}$  と  $T_{r5}$  と  $T_{r8}$  を選択した場合は 60% の輝度を表現できる。30

#### 【0019】

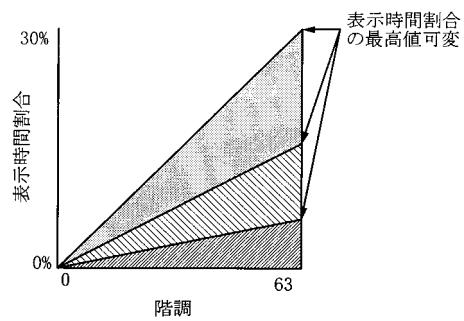

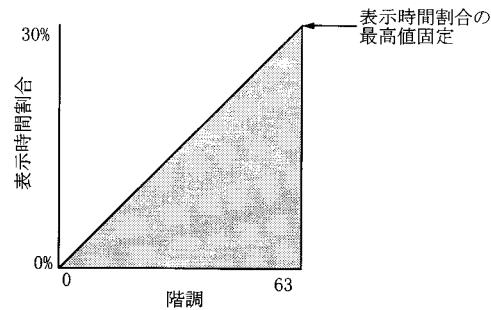

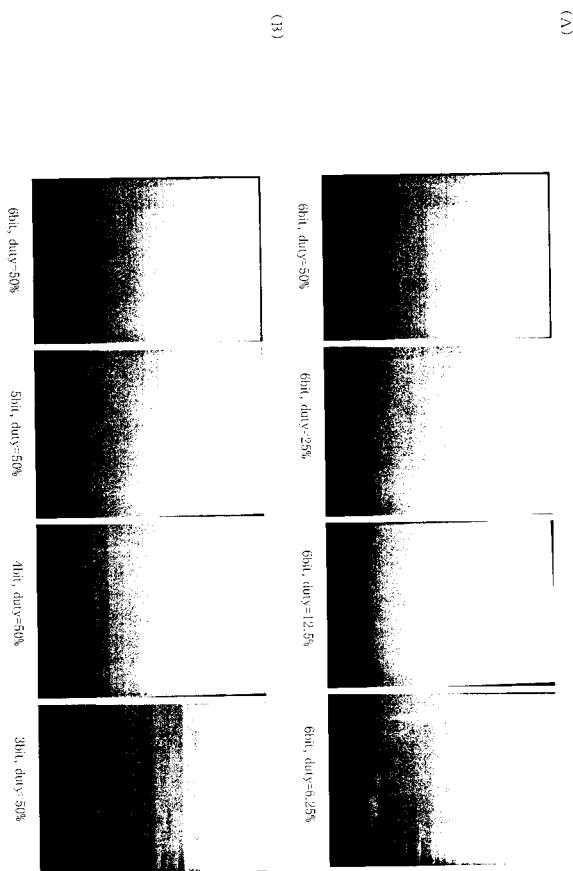

ここで前記階調表示について見方を変えると、1 フレーム期間において、表示時間 / (表示時間 + 非表示時間) = 表示時間割合とし、最高階調での表示時間割合を表示時間割合の最高値とすると、図 9 に示すように階調を表現する際、表示時間割合の最高値を固定して階調表現を行っていると見ることができる。表示時間割合の最高値を固定すると、後述するように階調が増すにつれて表示手段（EL 表示パネル）の消費電力の増大に繋がる。

また、図 14 (B) に示すように、階調を下げることで輝度を変えると表示階調数が減ることが実験的に分かった。図 14 (B) において  $b_{it}$  は階調レベル数に、 $duty$  は前記表示時間割合に対応している。40

ここで表示手段を構成する画素が EL の場合は、EL は発光素子であるので、前記表示時間及び非表示時間は発光時間及び非発光時間と等価であるので図 9 では表示時間割合は発光時間割合である。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0020】

本発明は、前記階調が増すにつれて前記表示時間割合が増加するという点に鑑み、階調を増しても EL 表示パネルや液晶表示パネル等の表示手段の消費電力が増大しない階調制御回路を備えた表示装置を提案するものである。

#### 【課題を解決するための手段】

**【0021】**

本発明の表示装置は、1フレームの映像信号の平均階調を求める平均階調計算手段と、前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段とを備える。

階調の制御を1フレームの映像信号の平均階調に応じて制御すると、表示時間割合を低減することができ、表示手段の消費電力が低減する。

**【発明の効果】****【0022】**

平均階調が高い画像を表示すると、画面全体が明るく消費電力が上昇するが、1フレームの映像信号の平均階調がある一定値を越えると表示時間割合を下げることで消費電力をある一定値に抑えることができる。消費電力を一定値に抑えることで表示手段の消費電力を低減することができる。

**【発明を実施するための最良の形態】****【0023】**

本発明は、EL表示パネルや液晶表示パネル等の表示手段に入力される映像信号としてデジタル映像信号又はアナログ映像信号のいずれの映像信号にも適用できるが、以下表示手段に入力される映像信号をデジタル化したデジタル映像信号の例で説明し、アナログ映像信号の例については後述する。

**【0024】**

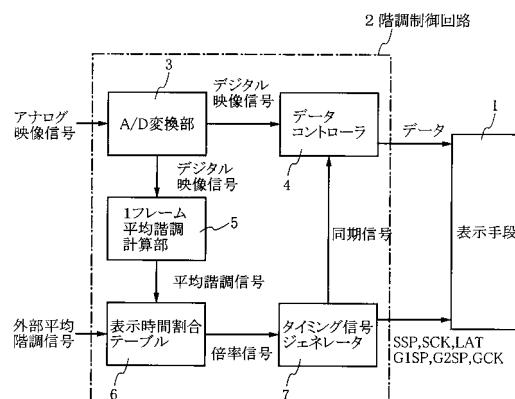

図1に示すように、本発明の表示装置は、EL表示パネルや液晶表示パネル等の表示手段1及び該表示手段1の階調を制御する階調制御回路2を備えている。

前記階調制御回路2は、アナログ映像信号をデジタル映像信号に変換するA/D変換部3、デジタル映像信号を取り込むデータコントローラ4、デジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調レベルを計算して平均階調信号を出力する1フレーム平均階調計算部5、平均階調信号を受けて後述する倍率信号を発生する表示時間割合テーブル6、該倍率信号が入力されるタイミング信号ジェネレータ7を備え、前記データコントローラ4の出力データ及びタイミング信号ジェネレータ7によって前記表示手段1の階調が制御される。

**【0025】**

前記階調制御回路2において、アナログ映像信号が前記A/D変換部3でデジタル映像信号に変換されると、該デジタル映像信号はデータコントローラ4に入力され、該データコントローラ4において前記表示手段1に対応した形式のデータに変換され、前記タイミング信号ジェネレータ7からの同期信号に同期して前記表示手段1に出力する。

**【0026】**

前記データコントローラ4は、フレームメモリを内部に備えており、1フレーム分のデジタル映像信号を該フレームメモリに保持し、後述する各サブフレームに対応する階調ビットをデータとして前記表示手段1に出力する。

前記1フレーム平均階調計算部5は、デジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調を計算する。そして、後述するように全画素の階調の総和を加算器とメモリによって演算し、上位の数ビット、例えば上位4ビットを平均階調信号として出力する。前記1フレーム平均階調計算部5の回路例は後述する。

**【0027】**

前記表示時間割合テーブル6（以下、テーブル6という。）は、前記1フレーム平均階調計算部5又は外部機器からの平均階調の信号の入力に対して決められた入出力関係を有する一種のルックアップテーブルであって、ハードウェア的にはROMやRAM等のメモリで構成され、例えば、表1に示すようなデータが記憶されている。もちろんテーブルのデータは表1に限らず、消費電力や求める画質に応じて任意に設けることができる。

表1に示すテーブルに基づき前記1フレーム平均階調計算部5で計算した結果の上位の4ビットの入力に対して3ビットに変換して出力する。このテーブルの各欄において、階

10

20

30

40

50

調は対象となる映像信号の1フレームの平均階調を示し、倍率は前記フレームメモリの保持時間の減衰率をそれぞれ示す。

## 【0028】

【表1】

| 階調 | 倍率   | 入力      | 出力    | 階調 | 倍率   | 入力      | 出力    |

|----|------|---------|-------|----|------|---------|-------|

| 0  | 1.00 | 0 0 0 0 | 1 1 1 | 32 | 1.00 | 1 0 0 0 | 1 1 1 |

| 1  | 1.00 | 0 0 0 0 | 1 1 1 | 33 | 0.97 | 1 0 0 0 | 1 1 0 |

| 2  | 1.00 | 0 0 0 0 | 1 1 1 | 34 | 0.94 | 1 0 0 0 | 1 1 0 |

| 3  | 1.00 | 0 0 0 0 | 1 1 1 | 35 | 0.91 | 1 0 0 0 | 1 1 0 |

| 4  | 1.00 | 0 0 0 1 | 1 1 1 | 36 | 0.89 | 1 0 0 1 | 1 1 0 |

| 5  | 1.00 | 0 0 0 1 | 1 1 1 | 37 | 0.86 | 1 0 0 1 | 1 1 0 |

| 6  | 1.00 | 0 0 0 1 | 1 1 1 | 38 | 0.84 | 1 0 0 1 | 1 0 1 |

| 7  | 1.00 | 0 0 0 1 | 1 1 1 | 39 | 0.82 | 1 0 0 1 | 1 0 1 |

| 8  | 1.00 | 0 0 1 0 | 1 1 1 | 40 | 0.80 | 1 0 1 0 | 1 0 1 |

| 9  | 1.00 | 0 0 1 0 | 1 1 1 | 41 | 0.78 | 1 0 1 0 | 1 0 1 |

| 10 | 1.00 | 0 0 1 0 | 1 1 1 | 42 | 0.76 | 1 0 1 0 | 1 0 1 |

| 11 | 1.00 | 0 0 1 0 | 1 1 1 | 43 | 0.74 | 1 0 1 0 | 1 0 1 |

| 12 | 1.00 | 0 0 1 1 | 1 1 1 | 44 | 0.73 | 1 0 1 1 | 1 0 1 |

| 13 | 1.00 | 0 0 1 1 | 1 1 1 | 45 | 0.71 | 1 0 1 1 | 1 0 1 |

| 14 | 1.00 | 0 0 1 1 | 1 1 1 | 46 | 0.70 | 1 0 1 1 | 1 0 0 |

| 15 | 1.00 | 0 0 1 1 | 1 1 1 | 47 | 0.68 | 1 0 1 1 | 1 0 0 |

| 16 | 1.00 | 0 1 0 0 | 1 1 1 | 48 | 0.67 | 1 1 0 0 | 1 0 0 |

| 17 | 1.00 | 0 1 0 0 | 1 1 1 | 49 | 0.65 | 1 1 0 0 | 1 0 0 |

| 18 | 1.00 | 0 1 0 0 | 1 1 1 | 50 | 0.64 | 1 1 0 0 | 1 0 0 |

| 19 | 1.00 | 0 1 0 0 | 1 1 1 | 51 | 0.63 | 1 1 0 0 | 1 0 0 |

| 20 | 1.00 | 0 1 0 1 | 1 1 1 | 52 | 0.62 | 1 1 0 1 | 1 0 0 |

| 21 | 1.00 | 0 1 0 1 | 1 1 1 | 53 | 0.60 | 1 1 0 1 | 1 0 0 |

| 22 | 1.00 | 0 1 0 1 | 1 1 1 | 54 | 0.59 | 1 1 0 1 | 1 0 0 |

| 23 | 1.00 | 0 1 0 1 | 1 1 1 | 55 | 0.58 | 1 1 0 1 | 1 0 0 |

| 24 | 1.00 | 0 1 1 0 | 1 1 1 | 56 | 0.57 | 1 1 1 0 | 1 0 0 |

| 25 | 1.00 | 0 1 1 0 | 1 1 1 | 57 | 0.56 | 1 1 1 0 | 0 1 1 |

| 26 | 1.00 | 0 1 1 0 | 1 1 1 | 58 | 0.55 | 1 1 1 0 | 0 1 1 |

| 27 | 1.00 | 0 1 1 0 | 1 1 1 | 59 | 0.54 | 1 1 1 0 | 0 1 1 |

| 28 | 1.00 | 0 1 1 1 | 1 1 1 | 60 | 0.53 | 1 1 1 1 | 0 1 1 |

| 29 | 1.00 | 0 1 1 1 | 1 1 1 | 61 | 0.52 | 1 1 1 1 | 0 1 1 |

| 30 | 1.00 | 0 1 1 1 | 1 1 1 | 62 | 0.52 | 1 1 1 1 | 0 1 1 |

| 31 | 1.00 | 0 1 1 1 | 1 1 1 | 63 | 0.51 | 1 1 1 1 | 0 1 1 |

## 【0029】

後述するように、前記テーブル6を用いて表示手段1の階調を制御することで、明るい画面(画像)ほど保持時間を小さくすることで最高消費電力を制限し、かつ暗い画面(画像)では保持時間を大きくすることでコントラストの強いメリハリのある高品位の映像を表示することができる。

## 【0030】

前記タイミング信号ジェネレータ7は、後述する表示手段のソース信号線駆動回路と書き込み用のゲート信号線駆動回路と前記データコントローラ4の同期信号の他、表示手段に供給するシフトレジスタ走査開始信号S S P、クロックS C K、ラッチ信号L A T、書き込み開始信号G 1 S P、消去用ゲート信号線駆動回路の消去開始信号G 2 S Pなどのパルス信号を生成する。該タイミング信号ジェネレータ7の回路例については後述する。

また、前記表示手段は画素がE L素子や液晶で構成されデジタル映像信号又はアナログ映像信号が取り込まれて画像を表示する。

## 【0031】

まず、前記構成を備えた表示手段1の階調制御回路2の原理について説明する。

1フレーム期間において、表示時間 / (表示時間 + 非表示時間) = 表示時間割合とし、図8に示すように、階調と表示時間割合の関係を可変とし、最高階調での表示時間割合を低

10

20

30

40

50

減させるものである。

#### 【0032】

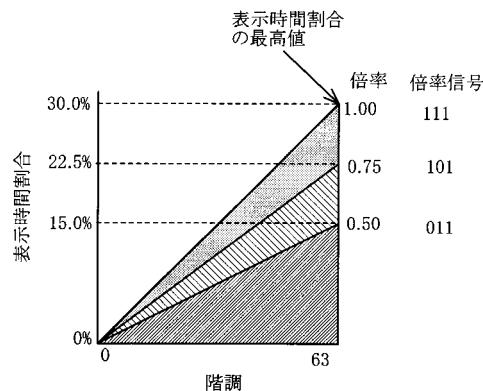

ここで前記原理による本発明による表示手段の階調制御を実現するための前記テーブルの目的について図5を参照しながら説明する。

前記テーブルは、表1に示す平均階調信号に応じて倍率を決め、その倍率によって階調と表示時間割合の関係を決定する。

ここで表示時間割合は前述したように、1フレーム期間において、表示時間 / (表示時間 + 非表示時間) とする。

図5に示すように前記倍率は設計上の表示時間割合の最高値(図5では30.0%)を基準(倍率1.00倍)としている。この倍率信号は任意のビット数(テーブルでは3ビット)で表現する。10

#### 【0033】

一例として1倍で最大の(111)とし、0.75倍では(101)、0.5倍では(011)と表現する。ここでは倍率を倍率信号に変換するときの端数の処理は任意とする。例えば、(111)の0.5倍は(100)と(011)の中間付近だが、テーブルでは切り捨てとしている。最終的には平均階調(テーブルの入力)と倍率(テーブルの出力)の関係のみを表示時間割合テーブルとして設定する。

この倍率を使うことで、後述する消去開始信号発生回路(図3、図4)を用いて階調と倍率の関係から階調と表示時間割合の関係を調節する。

#### 【0034】

ここで、前記表1に示すテーブルを用いて表示手段の階調を制御する技術的意義について説明する。

平均階調が高い画像を表示すると、画面全体が明るく消費電力が上昇する。この最高消費電力は平均階調が最高階調と同じ階調レベル(図7に示す例では0~63階調の63階調)のときに発生する。ここで表示手段の製品の仕様の一つである消費電力や発熱量などは最高消費電力を基準として規定し、かつその条件での製品保証をしなければならない。

ところが実際の仕様条件では写真などの中間調の表示が多く、平均階調はそれほど高くならない。

#### 【0035】

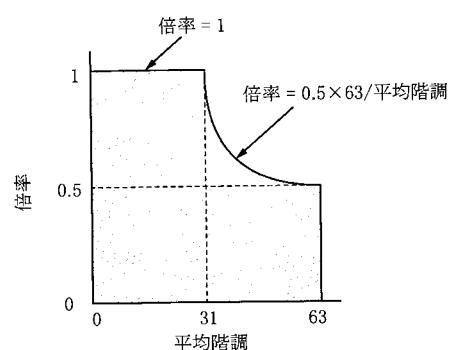

そこで平均階調がある一定値を越えると表示時間割合を下げるようなテーブルを作成することで最高消費電力を抑えることができ、表示手段の消費電力を低減することが可能となる。30

例えば、図6に示すように、平均階調が0から31階調までは一定の表示時間割合(倍率1倍)とし、平均階調が31を越えて63階調では平均階調に応じて表示時間割合を減らす(倍率1倍から0.5倍まで、倍率 = (0.5 × 63) / 平均階調)ようにする。すると表示時間割合が低減されて表示手段は暗くなるため消費電力を一定値(従来例の0.5倍の消費電力)に抑えることができる。

#### 【0036】

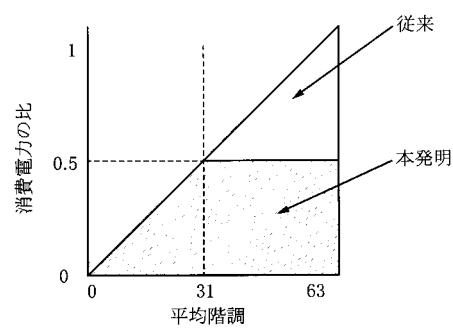

ここで、前記表示時間割合の最高値を固定した場合と表示時間割合の最高値を固定せずに可変とした場合の消費電力について比較してみる。40

図7には前記図6に示す平均階調と倍率との関係を使った場合の平均階調と表示手段の消費電力の関係を示している。

従来のように最高階調と表示時間割合(表示時間割合の最高値)の関係を固定すると、平均階調に比例して消費電力も増加する。もし最高消費電力が大きすぎるなら設計を変えてもっと暗い表示にする必要があるが、これでは平均階調が低く且つ一部に明るい発光の映像(例えば花火のような映像)も暗くなってしまう。

これに対し、本発明では平均階調が大きくなても消費電力はある一定値に抑えることができる。そして、最高消費電力を抑えつつ、平均階調が低い映像での輝度を抑えることのない映像表現が可能となる。

図7では最高消費電力を従来の半分(0.5倍)に制限した場合を示したが、前記テー50

ブルのデータを変えることで最高消費電力をさらに抑えることも可能である。

前記最高消費電力を従来の 倍 ( 1 ) とするには、平均階調が 0 から ( × 最高階調 ) までは一定の表示割合 ( 倍率 1 倍 ) とし、平均階調が ( × 最高階調 ) を越えて最高階調までは、倍率 = ( × 最高階調 ) / 平均階調となるようにすればよい。

なお、平均階調と倍率との関係は図 6 に示すものに限られるものではなく、例えば、平均階調が 0 から ( × 最高階調 ) までは一定の表示割合 ( 倍率 1 倍 ) とし、平均階調が ( × 最高階調 ) を越えて最高階調までは、倍率 = 1 + - ( 平均階調 / 最高階調 ) としてもよい。

#### 【 0 0 3 7 】

表示手段の一種であるブラウン管には平均階調が高いときにはピーク輝度が低く、平均階調が低いときにはピーク輝度を高くする特性があり、この特性がメリハリのある映像表現を実現している。 10

また、従来、液晶表示パネルでは、前記ブラウン管と同じ特性を得るためにバックライトの輝度を調節することで実現していた（例えば、特開 2001-147667 号公報参照）。しかしバックライトを高速に正確に制御することは困難であった。

#### 【 0 0 3 8 】

本発明は、前記テーブルを設定するだけで平均階調とピーク輝度の関係を規定することができる。さらに 1 フレーム毎の設定が可能なため、階調の高速制御が可能となる。 20

#### 【 0 0 3 9 】

人間の視覚特性は、明環境では明るいものが見やすくなり（明順応）、暗環境では暗いものが見分けられるようになる（暗順応）。また同時に見える輝度範囲は狭いが、順応すれば非常に広域の輝度範囲が見える。 20

従来の表示装置では最高階調と輝度の関係が固定であったため、明るい表示をしようとするとハイライト部分が白飛びを生じ、暗い表示をしようとすると影部分が潰れてしまう（黒潰れ）という問題があったが、前記テーブルを用いれば、階調と輝度の関係を平均階調によって動的に変化させることができたため、より人間の視覚特性に近いダイナミックレンジの広い表現が可能となる。例えば、ハイライト部分の表現力を高めたいなら前記倍率を 1 に近く設定し、影部分の表現力を高めたいなら前記倍率を低くすればよい。

#### 【 0 0 4 0 】

表示装置は輝度調節機能を有するのが一般的となっている。輝度調節を電源電圧を変えることで行うことも可能であるが、EL 素子を表示手段に用いた場合は該 EL 素子は電圧と輝度の関係が非線形の素子であるので発光を直線的に調節することは困難である。 30

前記テーブルを用いれば平均階調と表示時間割合の関係を変えることで輝度調節ができるので、デジタル処理を採用すると高速、正確且つ簡単に輝度調節が可能となる。

従来は図 14 ( B ) に示すように輝度を調節するために階調を下げるとき表示階調数が減ったが、本発明では図 14 ( A ) の本発明の実験データが示すように、前記テーブルに基づいて平均階調と表示時間割合の関係を変えることで輝度を調節すると表示階調数を維持したまま暗くすることが可能となる。

#### 【 0 0 4 1 】

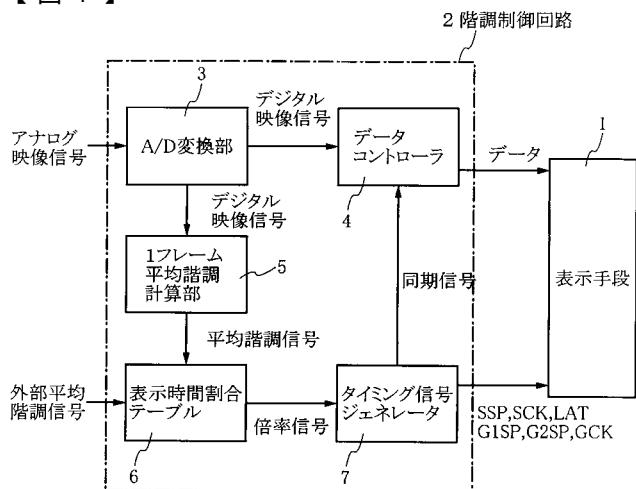

ここで、前記図 1 に示す前記 1 フレーム平均階調計算部 5 について図 2 を参照しながら説明する。 40

平均階調はデジタル映像信号の 1 フレーム全画素の累積階調から求められる。図 2 に示すように、1 フレーム平均階調計算部 5 は加算器 5 a と累算器 5 b とから構成されている。

前記加算器 5 a にはデジタル映像信号と前記累算器 5 b の出力とが入力され、これら入力の和が前記累算器 5 b に入力される。

前記累算器 5 b はデジタル映像信号と同期したクロックのタイミングで前記加算器 5 a の出力を記録し、1 フレームと同期したリセット信号によって初期化される。

前記累算器 5 b の記録するビット数は、デジタル映像信号のビット数と表示手段の画素数によって決定する。例えば、デジタル映像信号を 6 ビット、表示手段の画素数が  $320 \times 240 \times 3 = 230400$  画素  $< 2^{18}$  のとき、 $6 + 18 = 24$  ビット記録できる累算器 50

を利用する。

【0042】

この1フレーム平均階調計算部5に1フレーム全画素のデジタル映像信号が入力されると、前記累算器5bには1フレーム全画素の累積階調が記録される。累積階調は平均階調に比例するため、前記累算器5bの上位数ビットを平均階調信号とすることができる。前記テーブルでは上位4ビットが入力され、平均階調信号としている。ここで、前記回路を内蔵しても外部機器で求めた平均階調信号を利用してもよい。

【0043】

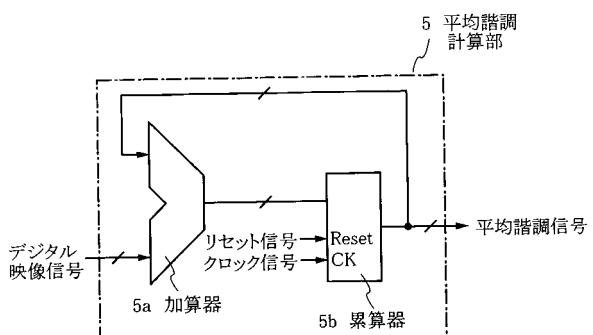

次に、図1に示す表示手段1の階調を制御する階調制御回路2を図12に示すタイミングチャートで説明する際、表示手段1の画素に書き込まれたデジタル映像信号を消去するためのタイミング信号(消去開始信号G2SP)の生成に前記テーブルの倍率信号を必要とするので該タイミング信号の生成について予め説明する。

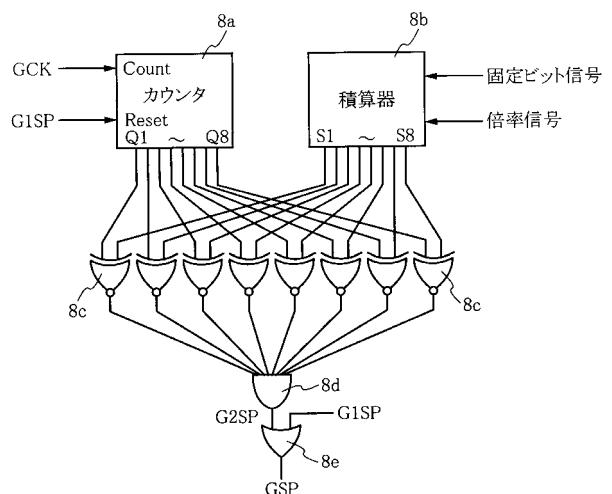

図3に示すように消去開始信号生成回路8は、カウンタ8aと積算器8bとEXNOR回路8cとAND回路8dで構成される。

前記カウンタ8aは、画素への書き込み走査開始信号G1SPをリセット信号として書き込みクロックGCKをカウントする。前記カウンタ8aの出力は前記G1SPが入力されてからの経過時間に比例する。

【0044】

前記積算器8bには前記テーブルからの平均階調に対応したビット信号と倍率信号が入力される。このビット信号は、例えば図12のタイミングチャートに示すように、1フレームを6個のサブフレームSF1～SF6に分割して階調ビット数6に等しくし、第1のサブフレームSF1での重み32( $2^5$ )、第2のサブフレームSF2での重み16( $2^4$ )、第3のサブフレームSF3での重み8( $2^3$ )、第4のサブフレームSF4での重み4( $2^2$ )、第5のサブフレームSF5での重み2( $2^1$ )、第6のサブフレームSF6での重み1( $2^0$ )と各ビットの重み(画素の発光時間)に対応した信号とする。

そして、前記積算器8bの出力は前記サブフレームSF1～SF6の各サブフレームでの重みと倍率信号の積となる。

【0045】

ここで、前記EXNOR回路8cと前記AND回路8dで構成された一致回路は、前記カウンタ8aの出力Q1～Q8と前記積算器8bの出力S1～S8の出力が一致したときに前記消去開始信号G2SPを出力する。

このように、前記各サブフレームでの重みと倍率信号の積により前記消去開始信号G2SPが生成されるタイミングを制御して画素の表示時間割合を制御する。

【0046】

以上、前記テーブルの技術的意義について説明したが、以下前記階調制御の実際を図1に示す階調制御回路2のブロック図及び図12に示すタイミングチャートを参照しながら説明する。

図12のタイミングチャートに示すように、1秒間の映像信号60フレーム中のそれぞれのフレームを、図示の例では第4フレームを複数のサブフレーム、例えば前記消去開始信号生成回路で説明したように6個のサブフレームSF1～SF6に分割されている。

そして、前記各サブフレームSF1～SF6において、書き込み開始信号G1SPと消去開始信号G2SPとの間隔(図12ではサブフレームSF2のみ例として示している)の比が2の階乗となるとき、階調ビット数はサブフレームの数と同じ6ビットとなり、表示階調レベル数が $2^6=64$ となる。ここでサブフレームを増やすとそれだけ表示階調数が大きくなり、サブフレームの数をnとすれば、表示階調数は $2^n$ 階調となり、前記テーブルの表示階調数は前記サブフレームの数を増やすことで変更することができる。

【0047】

そして画素表示のタイミングは、縦軸が画素アレイの行を示し、網掛部は前記各サブフレームSF1～SF6での表示時間を示す。ここから明らかなようにサブフレームによって表示時間が異なることを示している。

実施例の欄で説明するように、図1に示す表示手段はゲート信号線を選択するゲート信号線駆動回路及び選択されたゲート信号線に接続された画素に映像信号を供給するソース信号線駆動回路を有している。

ゲート信号線駆動回路のタイミング信号は、例えばタイミングチャートに一例として示す第2のサブフレームS F 2について見ると、G 1 S Pを書き込み走査開始信号としてクロックG C Kに同期して画素アレイを行目から最終行まで順次走査する。その後、クロックG C Kに同期して前記G 2 S Pを消去開始信号として画素アレイを行目から最終行まで順次走査して非表示状態とする。

#### 【0048】

このようにして前記G 1 S Pから前記G 2 S Pまでの時間が各サブフレームでの発光時間を決定する。本発明は各サブフレームにおいてG 2 S Pのタイミングを前記テーブルの出力に基づいて変えることで表示時間割合を制御する点に特徴を有している。

先に、消去開始信号G 2 S Pの生成回路(図3)で説明したように、前記各サブフレームS F 1～S F 6での重みと前記テーブルの倍率の積により消去開始信号G 2 S Pが生成されるようにしたから、該消去開始信号G 2 S Pが発生するタイミングを前記テーブルに基づいて制御することで、平均階調がある一定値を越えて表示時間割合の最高値を下げるこ(図6、図8)が可能となり、図7に示すように最高消費電力をある一定値に抑えることができ、表示手段の消費電力を低減することができる。

#### 【0049】

以下、E L表示パネルを表示手段に用いた表示装置の階調制御の実施例を説明する。

10

#### 【実施例1】

#### 【0050】

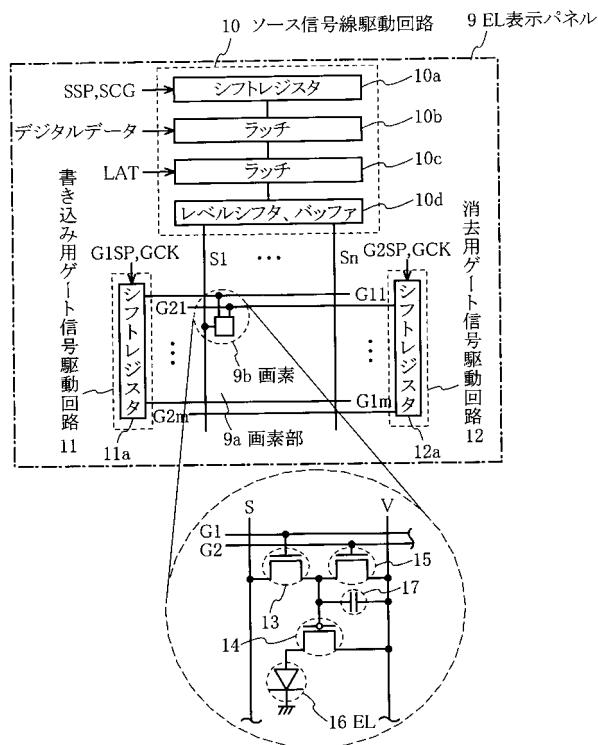

図10に示すように、画素にE L素子を利用したデジタル信号入力アクティブマトリクス型のE L表示パネル9は、マトリクス状に配列された画素9 bを有する画素部9 a、該画素部9 aの周辺に配置されたソース信号線駆動回路10、書き込み用ゲート信号線駆動回路11、消去用ゲート信号線駆動回路12を有している。

前記ソース信号線駆動回路10は、シフトレジスタ10 a、ラッチ10 b、ラッチ10 c、レベルシフタ・バッファ10 dを備え、ゲート信号線駆動回路11及び12はそれぞれシフトレジスタ11 a、12 aを備えている。

#### 【0051】

さらに前記画素部9 aは、前記ソース信号線駆動回路10のレベルシフタ・バッファ10 dに接続されたソース信号線(S 1～S n)、前記書き込み用ゲート信号線駆動回路1のシフトレジスタ11 aに接続された書き込み用ゲート信号線(G 11～G 1 m)、前記消去用ゲート信号線駆動回路12のシフトレジスタ12 aに接続された消去用ゲート信号線(G 21～G 2 m)を備えている。そして、前記各信号線はマトリクス状に配列されたE Lでなる画素9 bにそれぞれ接続されている。

30

#### 【0052】

前記画素9 bは、書き込みスイッチング用T F T 13、E L 16に接続されたE L駆動用T F T 14、消去用T F T 15、コンデンサ17で構成されている。ここでT F Tは薄膜トランジスタを意味するが、同じ機能を有するものであれば他のトランジスタを用いても実施することが可能である。

40

前記書き込みスイッチング用T F T 13のゲート電極は書き込み用ゲート信号線G 1に、ソース領域とドレイン領域は、一方がソース信号線Sに、他方が前記E L駆動用T F T 14のゲート電極に接続されている。

さらに、前記書き込みスイッチング用T F T 13は各画素が有するコンデンサ17及び前記消去用T F T 15のソース領域又はドレイン領域にそれぞれ接続されている。

ここで前記コンデンサ17は前記書き込みスイッチング用T F T 13がオフ状態(非選択状態)にある時、前記E L駆動用T F T 14のゲート電圧を保持するために設けられている。

#### 【0053】

50

前記 E L 駆動用 TFT14 のソース領域とドレイン領域は、一方が電源供給線 V に接続され、他方は E L 16 のアノードに接続され、電源供給線 V は前記コンデンサ 17 に接続されている。また前記消去用 TFT15 のソース領域とドレイン領域のうち、前記書き込みスイッチング用 TFT13 に接続されていない領域は前記電源供給線 V に接続され、さらに前記消去用 TFT15 のゲートは消去用ゲート信号線 G 2 に接続されている。

#### 【 0 0 5 4 】

以下、前記階調制御回路 2 を用いた前記 E L 表示パネルの階調制御について図 12 のタイミングチャート及び図 10 を参照しながら説明する。

前記ソース信号線駆動回路 10 のシフトレジスタ 10a は同期信号 SCK に同期する走査開始信号 SSP によって走査を開始するとソース信号線 S1 ~ Sn に対応するラッチ 10b に前記データコントローラ 4 ( 図 1 ) のフレームメモリに保持されているデジタル映像信号の一桁分が取り込まれる。前記ラッチ 10b に取り込まれたデジタル映像信号はラッチ信号 LAT が前記ラッチ 10c に入力されて該ラッチ 10c にラッチされるとともに前記レベルシフタ・バッファ 10d で増幅されて前記ソース信号線 S1 ~ Sn に順次出力される。

#### 【 0 0 5 5 】

一方、前記書き込み用ゲート信号線駆動回路 11 のシフトレジスタ 11a は同期信号 GCK に同期した走査開始信号 G1SP によって走査を開始し、前記書き込み用ゲート信号線 G11 ~ G1m を順次選択する。

前記書き込み用ゲート信号線が順次選択されると、選択された各書き込み用ゲート信号線の選択期間内にソース信号線 S1 ~ Sn から選択された前記書き込み用ゲート信号線に接続された画素に 1 行分ずつのデジタルデータが入力される。

#### 【 0 0 5 6 】

以下、前記 E L 表示パネル 9 への 6 ビットのデジタル映像信号の書き込み及び消去の一例を説明する。

前記書き込み用ゲート線駆動回路 11 に走査開始信号 G1SP が入力されると、1 行目の書き込み用ゲート信号線 G11 に接続されている全ての画素の書き込みスイッチング TFT13 がオン状態になる。同時にソース信号線 S1 ~ Sn に前記ラッチ 10c からデジタル映像信号の 2 ビット目のデジタルデータ「0」又は「1」が入力される。このデジタルデータは前記書き込みスイッチング用 TFT13 を介して前記 E L 駆動用 TFT14 のゲート電極に入力され、デジタルデータが「1」のときは前記 E L 駆動用 TFT14 はオンして E L は発光し、デジタルデータが「0」のときは前記 E L 駆動用 TFT14 はオフして E L は非発光になっている。

このように 1 行目に前記デジタルデータが入力されると、E L が発光または非発光を行い、1 行目の画素は表示を行う。

#### 【 0 0 5 7 】

次に、2 行目の書き込み用ゲート信号線 G12 が選択されると書き込み用ゲート信号線 G12 に接続されている全ての画素の前記書き込みスイッチング用 TFT13 がオン状態になり、2 行目の画素にソース信号線 S1 ~ Sn から 2 ビット目のデジタルデータが入力される。そして順次全ての書き込み用ゲート信号線 ( G11 ~ G1m ) が順次選択されて、サブフレーム SF2 において全ての行の画素に 2 ビット目のデジタルデータが入力される。

#### 【 0 0 5 8 】

そして、前記信号 G1SP が入力されて後、前記倍率信号に応じた時間が経過するとクロック GCK に同期した消去開始信号 G2SP が消去用信号線駆動回路 12 のシフトレジスタ 12a に入力される。すると、前記シフトレジスタ 12a から消去用ゲート信号線 G21 に接続されている全ての画素の消去用 TFT15 がオンして、E L 駆動用 TFT14 のソース領域とゲート電極が同電位となって前記 E L 駆動用 TFT14 はオフする。これによって電源供給線 V からの電源電位が E L に与えられなくなり、1 行目の画素が有する E L は全て非発光の状態となり、1 行目の画素が表示を行わなくなる。

10

20

30

40

50

次に、2行目の消去用ゲート信号線G22が選択されると、該消去用ゲート信号線G22に接続されている全ての画素の消去用TFT15がオンして、EL駆動用TFT14のソース領域とゲート電極が同電位となって前記EL駆動用TFT14はオフする。そして、順次全ての消去用ゲート信号線(G21～G2m)が順次選択されて、サブフレームSF2において全ての行のELが順次非発光状態となる。

#### 【0059】

このように前記テーブルの倍率信号に基づくタイミングで生成された消去開始信号G2SPを消去用ゲート信号線駆動回路の走査開始信号として消去用ゲート信号線に接続された画素に供給されたデジタル映像信号を消去することで表示(発光)時間割合を制御することができる。

10

#### 【0060】

以上のようにして表示、消去の動作が1ビット目から6ビット目のデジタルデータが画素に入力するまで繰り返され、全てのサブフレームにおいて発光時間が前記G2SPによって制御され、全てのサブフレームにおける発光時間が終了すると前記テーブルの出力によって階調が制御された1フレームの画像が表示される。

このように、各サブフレームにおける発光時間を前記テーブルが出力する倍率信号に基づいて制御すると、発光時間割合の最高値を低減することができるため、前記EL表示パネル9で消費される電力を低減することができる。

20

#### 【0061】

さらに、前記各サブフレームSF1～SF6での発光時間を前記テーブルから出力される倍率信号に基づいて制御すると、各サブフレームで発光時間を前記消去開始信号G2SPのタイミングで可変にできることから異なる任意の発光時間を選択でき、サブフレーム数より多くの階調数を表示することができる。

20

例えば、1フレームがn個のサブフレームで成るとき、前記選択された異なる任意の発光時間をそれぞれ $2^0 \sim 2^{n-1}$ とすることで任意の $2^n$ 階調の表示を行うことができる。

#### 【実施例2】

#### 【0062】

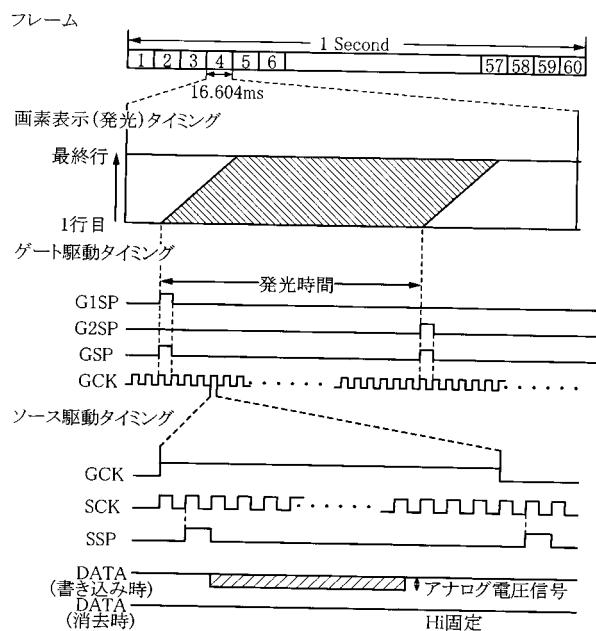

次に、映像信号をアナログ信号として表示手段に取り込んだ場合の前記テーブルを利用した階調制御の実施例について説明する。

30

映像信号がアナログ信号の場合は、図1に示すブロック図において、データコントローラ4の内部に、前記A/D変換部3でデジタル信号に変換された映像信号をアナログ信号に変換するD/A変換部を設け、その他の構成要素はそのまま利用することができる。

30

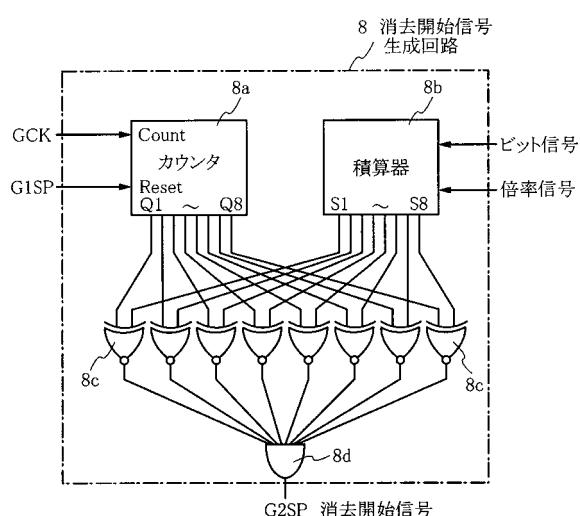

そこで、前記表1に示すテーブルの倍率信号を利用するため、予め消去開始信号GSPを生成する消去開始信号発生回路を図4を参照しながら説明する。

図4に示すように消去開始信号生成回路は、カウンタ8aと積算器8bとEXNOR回路8cとAND回路8dとOR回路8eで構成されている。

40

前記カウンタ8aは画素への書き込み走査開始信号G1SPをリセット信号として書き込みクロックGCK(後述する図13に示すタイミングチャート)をカウントする。前記カウンタ8aの出力は前記書き込み走査開始信号G1SPが入力されてからの経過時間に比例する。

40

#### 【0063】

前記積算器8bには前記テーブルからの階調に対応した倍率信号と固定ビット信号が入力される。表示装置に入力される映像信号はアナログ信号で且つデジタル映像信号のように前記フレームの分割は行わないため、ビット信号は一定のデジタルデータに固定する。

例えば、固定ビット信号「111111」に固定する。そして、前記積算器8bの出力は該固定ビット信号と前記倍率信号の積となる。

#### 【0064】

ここで、前記EXNOR回路8cと前記AND回路8dで構成された一致ゲートは、前記カウンタ8aの出力Q1～Q8と前記積算器8bの出力S1～S8の出力が一致したときに前記消去開始信号G2SPを出力する。

50

そして、前記 G 2 S P 及び G 1 S P を O R 回路 8 e に入力して該 O R 回路 8 e の出力 G S P を書き込み走査開始信号 G 1 S P 及び消去開始信号 G 2 S P として利用する。

#### 【 0 0 6 5 】

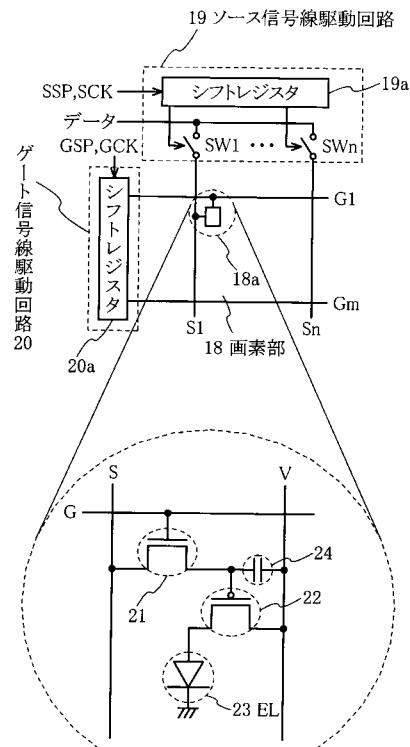

図 1 1 には E L 表示パネルを利用したアナログ信号入力アクティブマトリクス型の表示装置を示している。

図 1 1 に示すように、アナログ信号入力アクティブマトリクス型の E L 表示パネルは、マトリクス状に配列された画素 1 8 a を有する画素部 1 8 、該画素部 1 8 の周辺に配置されたソース信号線駆動回路 1 9 、ゲート信号線駆動回路 2 0 を有している。前記ソース信号線駆動回路 1 9 はシフトレジスタ 1 9 a 、該シフトレジスタ 1 9 a の出力に基づいてアナログ映像信号をサンプリングするサンプリングスイッチ SW 1 ~ SW n を備え、前記ゲート信号線駆動回路 2 0 はシフトレジスタ 2 0 a を有している。10

#### 【 0 0 6 6 】

さらに前記画素部 1 8 は、前記各サンプリングスイッチ SW 1 ~ SW n に接続されたソース信号線 ( S 1 ~ S n ) 、ゲート信号線駆動回路 2 0 のシフトレジスタ 2 0 a に接続されたゲート信号線 ( G 1 ~ G m ) を有し、前記各信号線はマトリクス状に配列された画素 1 8 a にそれぞれ接続されている。

#### 【 0 0 6 7 】

前記画素 1 8 a は、スイッチング用 T F T 2 1 、 E L 2 3 に接続された E L 駆動用 T F T 2 2 、コンデンサ 2 4 で構成されている。

前記スイッチング用 T F T 2 1 のゲート電極はゲート信号線 G に、ソース領域とドレイン領域は、一方がソース信号線 S に、他方が E L 駆動用 T F T 2 2 のゲート電極及びコンデンサ 2 4 にそれぞれ接続されている。20

ここで前記コンデンサ 2 4 はスイッチング用 T F T 2 1 がオフ状態（非選択状態）にある時、 E L 駆動用 T F T 2 2 のゲート電圧を保持するために設けられている。

前記 E L 駆動用 T F T 2 2 のソース領域とドレイン領域は、一方が電源供給線 V に接続され、他方は E L 2 3 のアノードに接続され、さらに電源供給線 V は前記コンデンサ 2 4 に接続されている。

#### 【 0 0 6 8 】

以下、前記実施例 2 の階調制御について図 1 1 及び図 1 3 のタイミングチャートを参照しながら説明する。30

前記ソース信号線駆動回路 1 9 のシフトレジスタ 1 9 a は同期信号 S C K に同期した走査開始信号 S S P が入力されると、ソース信号線 S 1 ~ S n に対応するサンプリングスイッチ SW 1 ~ SW n を順次選択する。前記シフトレジスタ 1 9 a によって選択されたサンプリングスイッチに対応するソース信号線 S 1 ~ S n に映像データが取り込まれる。

#### 【 0 0 6 9 】

一方、前記ゲート信号線駆動回路 2 0 のシフトレジスタ 2 0 a は、同期信号 G C K に同期した書き込み走査開始信号 G S P ( G 1 S P ) が入力されるとゲート信号線 G 1 ~ G m を順次選択する。

前記ゲート信号線駆動回路 2 0 に書き込み走査開始信号 G 1 S P が入力されると、1 行目のゲート信号線 G 1 に接続されている全ての画素のスイッチング T F T 2 1 がオン状態になると同時にソース信号線 S 1 ~ S n からの映像信号が E L 駆動用 T F T 2 2 のゲート電極に入力され、映像信号に応じて一行目の各 E L 2 3 は発光又は非発光を行い、1 行目の画素は表示を行う。そして、全てのゲート信号線 ( G 1 ~ G m ) が順次選択されて、全ての行の画素に映像信号のデータが入力される。40

#### 【 0 0 7 0 】

1 フレーム分のアナログ映像信号が全ての画素に取り込まれて表示が行われるが、その後垂直帰線期間において前記テーブルの倍率信号に基づく消去開始信号 G S P ( G 2 S P ) が前記ゲート信号線駆動回路 2 0 に入力される。この垂直帰線期間において、ソース信号線 S 1 ~ S n の電位を画素を消去する電位に予め固定する。具体的には垂直帰線期間の開始前に取り込まれたアナログ映像信号を消去電位にした状態でシフトレジスタ 1 9 a を50

動作させソース信号線 S<sub>1</sub> ~ S<sub>n</sub> に消去電位を取り込む。

そして、前記倍率信号によって発生するタイミングが制御された消去開始信号 G<sub>2</sub>SP を消去走査開始信号としてゲート信号線 G<sub>1</sub> ~ G<sub>m</sub> を順次選択し、各ゲート信号線の選択期間内にソース信号線 S<sub>1</sub> ~ S<sub>n</sub> を順次選択し、且つ前記消去電位が入力され、ゲート信号線とソース信号線に選択された画素の映像信号が消去される。

#### 【0071】

つまり、前記書き込み走査開始信号 G<sub>1</sub>SP が入力されて後、前記倍率信号に応じた時間が経過すると消去開始信号 G<sub>2</sub>SP がゲート信号線駆動回路 20 のシフトレジスタ 20a に入力されて前記シフトレジスタ 20a からゲート信号線 G<sub>1</sub> ~ G<sub>m</sub> に接続されている全ての E<sub>L</sub>23 の E<sub>L</sub> 駆動用 TFT22 がオフして電源供給線 V から電源電位が E<sub>L</sub>23 に与えられなくなり、E<sub>L</sub>23 は全て非発光の状態となり、表示を行わなくなる。10

このように前記テーブルの倍率信号に基づくタイミングで生成された消去開始信号 G<sub>2</sub>SP を走査開始信号として画素に入力し、当該画素の有する E<sub>L</sub>23 に供給されたアナログ映像信号を消去することで前記発光時間割合を制御することができる。

#### 【0072】

書き込まれる映像信号がアナログの場合も、1 フレームにおける発光時間を前記テーブルが出力する倍率信号に基づいて制御すると、発光時間割合の最高値を低減することができるため、アナログ信号入力アクティブマトリクス型の表示手段の画素において消費される電力を低減することができる。

#### 【実施例 3】

#### 【0073】

前記アナログ映像信号を画像データとして取り込んで表示する実施例で、画素として E<sub>L</sub> 素子を利用した表示パネルを採用したが、画素として液晶を用いた液晶表示パネルにも適用することができる。

液晶を画素とする表示パネルは電圧駆動であるため、表示パネルに対応した電圧値に D/A 変換して前記ソース信号線駆動回路 19 に取り込むことで、前記 E<sub>L</sub> 素子を液晶素子に代えて前記階調制御回路を用いることで同様に実施することができる。20

#### 【0074】

表示手段の階調が前記階調制御回路で制御される本発明の表示装置を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポーネント等）、ノート型コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機、電子書籍、記録媒体（具体的には Digital Video Disc 等）を再生してその画像を表示しうる表示手段を備えた画像再生装置等が挙げられる。以下、これらの電子機器の具体例を説明する。30

#### 【実施例 4】

#### 【0075】

図 15 は表示装置であり、筐体 2001、支持台 2002、表示部 2003、スピーカー部 2004、ビデオ入力端子 2005 等を備えている。表示部 2003 に本発明による表示装置を利用すると、消費電力を低減することができる。

本発明の表示装置を用いると、E<sub>L</sub> 表示装置ではバックライトの必要がなく、また、液晶表示装置では、階調の制御にバックライトの輝度調整を必要としなくなる。この表示装置は、コンピュータ用、TV 放送受信用、広告表示用等の全ての情報表示用表示装置に利用することができる。40

#### 【実施例 5】

#### 【0076】

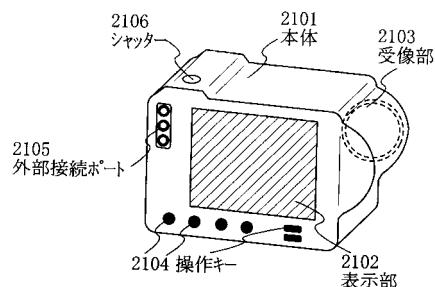

図 16 にはデジタルスチルカメラに利用した例を示しており、該デジタルスチルカメラは本体 2101、本発明の表示装置を用いた表示部 2102、受像部 2103、操作キー 2104、外部接続ポート 2105、シャッター 2106 等を備えている。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が50

可能となる。

【実施例 6】

【0077】

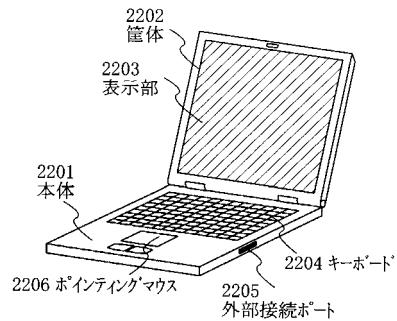

図17にはノート型コンピュータに利用した例を示しており、本体2201、筐体2202、本発明の表示装置を利用した表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を備えている。充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

【実施例 7】

【0078】

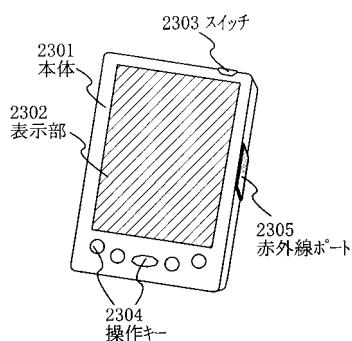

図18にはモバイルコンピュータに利用した例を示しており、該モバイルコンピュータは本体2301、本発明の表示装置を用いた表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を備えている。10

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

【実施例 8】

【0079】

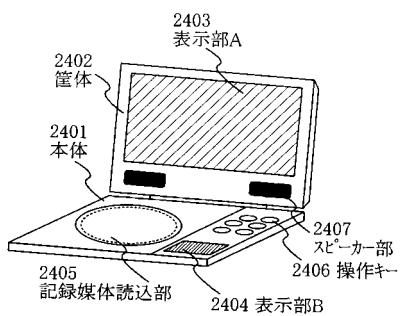

図19には記録媒体を備えた携帯型の画像再生装置（具体的にはDVD再生装置）に利用した例を示しており、本体2401、筐体2402、本発明の表示装置を利用した表示部A2403及び表示部B2404、記録媒体（DVD等）読み込み部2405、操作キー2406、スピーカー部2407等を備えている。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する。該記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。これら表示部に本発明の表示装置を利用することで消費電力を低減することが可能となり、節電に繋がる。20

【実施例 9】

【0080】

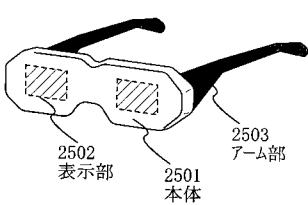

図20にはゴーグル型ディスプレイ（ヘッドマウントディスプレイ）に利用した例を示しており、本体2501、本発明の表示装置を利用した表示部2502、アーム部2503等を備えている。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。30

【実施例 10】

【0081】

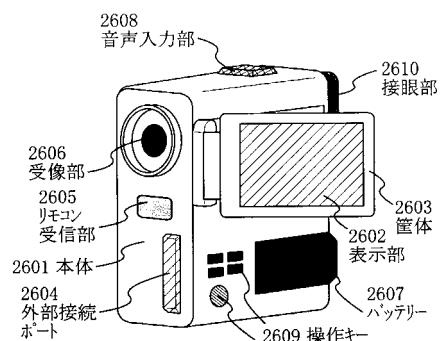

図21にはビデオカメラに利用した例を示しており、本体2601、本発明の表示装置を利用した表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、接眼部2610等を備えている。また、前記接眼部2610に本発明の表示装置を利用することもできる。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

【実施例 11】

【0082】

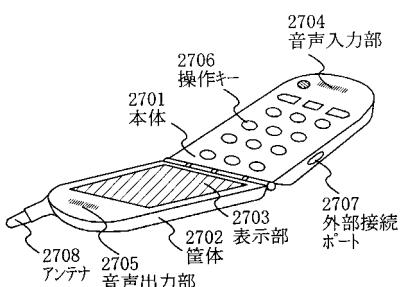

図22には携帯電話に利用した例を示しており、本体2701、筐体2702、本発明の表示装置を利用した表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を備えている。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

【0083】

以上、前記各電子機器に本発明の表示装置を利用すると、電子機器の消費電力を低減することができ、特に携帯用の電子機器の表示部に利用すると充電型電源の長時間維持が可能となる。

10

20

30

40

50

**【図面の簡単な説明】****【0084】**

【図1】本発明表示装置の階調制御回路のブロック図である。

【図2】本発明の階調制御回路の平均階調計算部の一例である。

【図3】本発明に用いる消去開始信号生成回路の一例である。

【図4】本発明に用いる消去開始信号生成回路の他の一例である。

【図5】本発明の表示時間割合テーブルの説明図である。

【図6】本発明の表示時間割合テーブルの説明図である。

【図7】平均階調と消費電力の関係の説明図である。

【図8】本発明の階調と表示時間割合の関係の説明図である。

10

【図9】従来の表示装置の階調と表示時間割合の関係の説明図である。

【図10】本発明の表示装置の回路構成を示す回路図の一例である。

【図11】本発明の表示装置の回路構成を示す他の回路図である。

【図12】本発明の表示装置を駆動する際のデジタル信号によるタイミングチャートである。

【図13】本発明の表示装置を駆動する際のアナログ信号によるタイミングチャートである。

【図14】(A)は本発明の表示装置の表示例、(B)は従来の表示装置の表示例である。

【図15】本発明を表示装置に利用した例である。

【図16】本発明をビデオカメラの表示部に利用した例である。

20

【図17】本発明をノート型コンピュータの表示部に利用した例である。

【図18】本発明をモバイルコンピュータの表示部に利用した例である。

【図19】本発明を携帯型画像再生装置の表示部に利用した例である。

【図20】本発明をゴーグル型ディスプレイの表示部に利用した例である。

【図21】本発明をデジタルビデオカメラの表示部に利用した例である。

【図22】本発明を携帯電話の表示部に利用した例である。

【図23】従来の表示装置の画素部の回路図である。

【図24】従来の表示装置の回路構成図である。

【図25】従来の表示装置の画素の回路図である。

【図26】従来の表示装置の駆動方法の説明図である。

30

**【符号の説明】****【0085】**

1・・・表示手段 2・・・階調制御回路 5・・・1フレーム平均階調計算部 6・・・表示時間割合テーブル 8・・・消去開始信号生成回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図21】

【図20】

【図22】

【図23】

【図24】

【図25】

【図26】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

| F I           | テーマコード(参考) |

|---------------|------------|

| G 0 9 G 3/20  | 6 2 2 D    |

| G 0 9 G 3/20  | 6 2 3 F    |

| G 0 9 G 3/20  | 6 2 3 N    |

| G 0 9 G 3/20  | 6 2 4 B    |

| G 0 9 G 3/20  | 6 3 1 U    |

| G 0 9 G 3/20  | 6 4 1 C    |

| G 0 9 G 3/20  | 6 4 1 E    |

| G 0 9 G 3/20  | 6 4 1 K    |

| G 0 9 G 3/20  | 6 4 2 E    |

| G 0 9 G 3/20  | 6 8 0 S    |

| G 0 9 G 3/20  | 6 8 0 V    |

| G 0 9 G 3/36  |            |

| H 0 5 B 33/14 | A          |

F ターム(参考) 5C006 AA15 AA16 AA17 AC11 AF11 AF33 AF42 AF44 AF45 AF51

AF53 AF69 AF71 AF73 AF81 AF82 BB16 BC02 BC03 BC06

BC12 BC13 BC22 BF03 BF04 BF11 BF14 BF22 BF25 BF28

BF42 FA47 FA54 FA56 GA02 GA03

5C080 AA06 AA10 BB05 DD03 DD26 EE29 FF11 HH09 JJ01 JJ02

JJ03 JJ04 JJ06 KK02 KK04 KK07 KK43