(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4440473号

(P4440473)

(45) 発行日 平成22年3月24日(2010.3.24)

(24) 登録日 平成22年1月15日(2010.1.15)

|                      |                 |

|----------------------|-----------------|

| (51) Int.Cl.         | F 1             |

| HO4B 14/04 (2006.01) | HO4B 14/04 B    |

| HO3H 17/00 (2006.01) | HO3H 17/00 621Z |

| HO3H 17/02 (2006.01) | HO3H 17/02 661E |

| HO4L 27/00 (2006.01) | HO4L 27/00 Z    |

請求項の数 10 (全 17 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-577767 (P2000-577767)  |

| (86) (22) 出願日 | 平成11年9月15日(1999.9.15)         |

| (65) 公表番号     | 特表2002-528945 (P2002-528945A) |

| (43) 公表日      | 平成14年9月3日(2002.9.3)           |

| (86) 国際出願番号   | PCT/US1999/021274             |

| (87) 国際公開番号   | W02000/024122                 |

| (87) 国際公開日    | 平成12年4月27日(2000.4.27)         |

| 審査請求日         | 平成18年9月15日(2006.9.15)         |

| (31) 優先権主張番号  | 09/174,861                    |

| (32) 優先日      | 平成10年10月19日(1998.10.19)       |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 09/176,781                    |

| (32) 優先日      | 平成10年10月22日(1998.10.22)       |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390009597<br>モトローラ・インコーポレイテッド<br>MOTOROLA INCORPORATED<br>ED<br>アメリカ合衆国イリノイ州シャンバード、<br>イースト・アルゴンクイン・ロード130<br>3 |

| (74) 代理人  | 100116322<br>弁理士 桑垣 衛                                                                                           |

| (74) 代理人  | 100112759<br>弁理士 藤村 直樹                                                                                          |

| (72) 発明者  | ジェームズ・ウェスレイ・マッコイ<br>アメリカ合衆国テキサス州イルビング、ナ<br>ンバー2024、レッド・リバー・トレイ<br>ル408                                          |

最終頁に続く

(54) 【発明の名称】多重チャネル多相フィルタにおいて非整数サンプリング・レート変更を行う装置

## (57) 【特許請求の範囲】

## 【請求項 1】

M サブサブチャネルの変調を並列に促進する変調エンジンで、M は 1 よりも大きい正の整数である、変調エンジンであって：

第 1 処理手段であって：

前記 M サブサブチャネルに対応し、かつベースバンド・サンプリング・レートにてサンプリングされた M ベースバンド信号を受け取り；および

前記 M ベースバンド信号を、それぞれが前記ベースバンド・サンプリング・レートにてサンプリングされた M 時間領域信号に変換する；

よう構成された第 1 処理手段と；

前記第 1 処理手段に結合され、前記 M 時間領域信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタであって、前記多重チャネル多相フィルタは：

前記 M 時間領域信号を受け取り、処理する第 2 処理手段からなり、前記第 2 処理手段は：

前記多重チャネル多相フィルタの交換子を与え、ここで前記交換子の位置は、前記位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより前記多重チャネル多相フィルタは、前記 M 時間領域信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作でき；および

前記非整数サンプリング・レート変更を得るために、前記 M 時間領域信号のサンプリング・レートの非整数倍にて前記多重チャネル多相フィルタを動作する；

10

20

ように構成される、第2処理手段からなる多重チャネル多相フィルタと；

によって構成されることを特徴とする変調エンジン。

【請求項2】

前記第2処理手段は：

前記Mベースバンド信号を表し、かつ前記ベースバンド・サンプリング・レートの非整数倍である周波数間隔を有する周波数多重化合成信号を生成する；

ようにさらに構成されることを特徴とする請求項1に記載の変調エンジン。

【請求項3】

前記第1および第2処理手段は、1つのデジタル信号プロセッサによって実現されることを特徴とする請求項1に記載の変調エンジン。

10

【請求項4】

Mサブチャネルのうち少なくとも2つの復調を並列に促進する復調エンジンで、Mは1よりも大きい正の整数である、復調エンジンであって：

前記Mサブチャネルのうち前記少なくとも2つから導出された合成信号を受信機から受け取り、かつ前記合成信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタであって、前記多重チャネル多相フィルタは：

前記合成信号を受け取り、処理する第1処理手段からなり、前記第1処理手段は：

前記多重チャネル多相フィルタの交換子を与え、ここで前記交換子の位置は、前記位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより前記多重チャネル多相フィルタは、前記合成信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作でき；および

20

前記非整数サンプリング・レート変更を得るために、前記合成信号のサンプリング・レートの非整数倍にて前記多重チャネル多相フィルタを動作して、それにより少なくとも2つのレート変更済み信号を生成する；

ように構成された第1処理手段、によって構成される多重チャネル多相フィルタと；

前記多重チャネル多相フィルタに結合され、かつ前記少なくとも2つのレート変更済み信号を少なくとも2つの周波数領域信号に変換し、それにより少なくとも2つのベースバンド信号を生成するように構成された第2処理手段と；

によって構成されることを特徴とする復調エンジン。

【請求項5】

30

前記第1および第2処理手段は、1つのデジタル信号プロセッサによって実現されることを特徴とする請求項4に記載の復調エンジン。

【請求項6】

Mサブチャネル信号を並列に変調する送信機で、Mは1よりも大きい正の整数である、送信機であって：

第1処理手段であって：

前記Mサブチャネルに対応し、かつベースバンド・サンプリング・レートにてサンプリングされたMベースバンド信号を受け取り；および

前記Mベースバンド信号を、それぞれが前記ベースバンド・サンプリング・レートにてサンプリングされたM時間領域信号に変換する；

40

ように構成された第1処理手段と；

前記第1処理手段に結合され、前記M時間領域信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタであって、前記多重チャネル多相フィルタは：

前記M時間領域信号を受け取り、処理する第2処理手段からなり、前記第2処理手段は：

前記多重チャネル多相フィルタの交換子を与え、ここで前記交換子の位置は、前記位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより前記多重チャネル多相フィルタは、前記ベースバンド・サンプリング・レートの非整数倍であるサンプリング・レートにて動作でき；および

前記非整数サンプリング・レート変更を得て、周波数多重化合成信号を生成するた

50

めに、前記ベースバンド・サンプリング・レートの前記非整数倍にて前記多重チャネル多相フィルタを動作する；

ように構成された第2手段からなる多重チャネル多相フィルタと；

ワイヤレス搬送波を前記周波数多重化合成信号で変調して、Mサブチャネルを有するワイヤレス信号を生成するワイヤレス変調器と；

によって構成されることを特徴とする送信機。

【請求項7】

前記第2処理手段は：

前記Mベースバンド信号を表し、かつ前記ベースバンド・サンプリング・レートの非整数倍である周波数間隔を有する周波数多重化合成信号を生成する；

10

ようにさらに構成されることを特徴とする請求項6に記載の送信機。

【請求項8】

前記第1および第2処理手段は、1つのデジタル信号プロセッサによって実現されることを特徴とする請求項6に記載の送信機。

【請求項9】

Mサブチャネルのうち少なくとも2つを並列に復調する受信機で、Mは1よりも大きい正の整数である、受信機であって：

前記Mサブチャネルを有するワイヤレス信号を、サンプリング・レートを有し、かつ前記Mサブチャネルのうち前記少なくとも2つから導出された合成信号に変換する受信機フロントエンドと；

20

前記受信機フロントエンドに結合され、前記受信機から前記合成信号を受け取り、前記合成信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタであって、前記多重チャネル多相フィルタは：

前記合成信号を受け取り、処理する第1処理手段からなり、前記第1処理手段は：

前記多重チャネル多相フィルタの交換子を与え、ここで前記交換子の位置は、前記位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより前記多重チャネル多相フィルタは、前記合成信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作でき；および

前記非整数サンプリング・レート変更を得るために、前記合成信号のサンプリング・レートの前記非整数倍にて前記多重チャネル多相フィルタを動作し、それにより少なくとも2つのレート変更済み信号を生成する；

30

ように構成された第1処理手段からなる多重チャネル多相フィルタと；

前記多重チャネル多相フィルタに結合され、かつ前記少なくとも2つのレート変更済み信号を少なくとも2つの周波数領域信号に変換し、それにより少なくとも2つのベースバンド信号を生成するように構成された第2処理手段と；

によって構成されることを特徴とする受信機。

【請求項10】

前記第1および第2処理手段は、1つのデジタル信号プロセッサによって実現されることを特徴とする請求項9に記載の受信機。

【発明の詳細な説明】

(産業上の利用分野)

本発明は、一般に、デジタル信号処理方法に関し、さらに詳しくは、多重チャネル多相フィルタにおいて非整数サンプリング・レート変更を行う方法および装置に関する。

40

【0001】

(関連出願)

本出願は、1998年10月19日にMcCoyによって出願された出願文書番号P F 1687 N Aの"APPARATUS FOR PERFORMING A NON-INTEGER SAMPLING RATE CHANGE IN A MULTIC CHANNEL POLYPHASE FILTER"の一部継続出願である。該出願は、本明細書に参考として含まれる。

【0002】

50

## (従来の技術)

多相フィルタ(polyphase filter)は周知である。このようなフィルタは、フィルタ・インパルス応答の選択された位相またはサンプルを入力信号のサンプルで乗算することによって動作する。従来の多重チャネル多相フィルタは、フィルタ・インパルス応答の選択された位相をフィルタの交換子(commutator)の位置と同期させる。従来の多重チャネル多相フィルタでは、交換子の位置はフィルタ・インパルス応答の所定の位相と固有に対応する。実際、多相フィルタ設計の分野の当業者であれば、多重サブチャネル多相変調器において、サブチャネル・サンプリング・レートは入力サンプル・レートの整数倍であり、このことはチャネル帯域幅が入力サンプル・レートの整数倍でなければならないことを意味することを単純に認めている。従って、多相フィルタを利用する従来の多重サブチャネル変調器および復調器では、サブチャネル帯域幅は入力サンプル・レートと同じで、受信機が適切に隣接サブチャネルをフィルタ除去するには密接すぎる間隔のサブチャネルとなるか、あるいはサブチャネル帯域幅は入力サンプル・レートの二倍で、そのため過剰に分離したサブチャネルでスペクトルを無駄にするかのいずれかである。

10

## 【0003】

上記の理由により、スペクトルを無駄にせずに隣接サブチャネル干渉を防ぐために、入力サンプル・レートよりもわずかに大きい、例えば、12パーセント大きいサブチャネル帯域幅が望ましいところの、多重サブチャネル変調器および復調器では、多重チャネル多相フィルタはよい選択とはみなされていない。一方、多相フィルタはサンプリング・レート変更を得るための最も効率的な方法の一つであることが知られている。

20

## 【0004】

従って、必要なのは、多重チャネル多相フィルタにおいて非整数サンプリング・レート変更を行うための装置である。この装置は、好ましくは、サブチャネル間隔の優れた柔軟性を有する、効率的な多重サブチャネル多相変調器／復調器を可能にする。

## 【0005】

## (発明の概要)

本発明の一態様は、非整数サンプリング・レート変更を行う多重チャネル多相フィルタである。多重チャネル多相フィルタは、それが入力サンプリング・レートにてサンプリングされたM入力チャネルのデータを受け取って処理する処理システムによって構成され、ここでMは一(unity)よりも大きい正の整数である。処理システムは、多重チャネル多相フィルタの交換子を与えるようにプログラミングされ、ここで交換子の位置は、この位置について選択されたフィルタ・インパルス応答の位相から分離(decouple)され、それにより多重チャネル多相フィルタは、入力サンプリング・レートの非整数倍であるサンプリング・レートにて動作できる；また非整数サンプリング・レート変更を得るために、入力サンプリング・レートの非整数倍にて多重チャネル多相フィルタを動作すべくプログラミングされる。

30

## 【0006】

本発明の別の態様は、Mサブチャネルの変調を並列に促進するための変調エンジンであり、ここでMは一よりも大きい正の整数である。変調エンジンは、Mサブチャネルに対応し、かつベースバンド・サンプリング・レートにてサンプリングされたMベースバンド信号を受け取り；またMベースバンド信号を、それがベースバンド・サンプリング・レートにてサンプリングされたM時間領域信号(time-domain signals)に変換すべく構成された第1処理要素によって構成される。さらに、変調エンジンは、第1処理要素に結合され、M時間領域信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタによって構成される。多重チャネル多相フィルタは、M時間領域信号を受け取り、処理する第2処理要素によって構成される。第2処理要素は、多重チャネル多相フィルタの交換子を与えるべく構成され、ここで交換子の位置は、この位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより多重チャネル多相フィルタはM時間領域信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作できる；また非整数サンプリング・レート変更を得るために、M時間領域信号のサンプリング

40

50

・レートの非整数倍にて多重チャネル多相フィルタを動作すべく構成される。

【0007】

本発明の第3の態様は、Mサブチャネルのうち少なくとも2つの復調を並列に促進するための復調エンジンであり、ここでMは一よりも大きい正の整数である。復調エンジンは、Mサブチャネルのうち少なくとも2つから導出された合成信号を受信機から受け取り、この合成信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタによって構成される。多重チャネル多相フィルタは、合成信号を受け取り、処理する第1処理要素によって構成される。第1処理要素は、多重チャネル多相フィルタの交換子を与えるべく構成され、ここで交換子の位置は、この位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより多重チャネル多相フィルタは合成信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作できる；また非整数サンプリング・レート変更を得るために、合成信号のサンプリング・レートの非整数倍にて多重チャネル多相フィルタを動作すべく構成され、それにより少なくとも2つのレート変更済み信号(rate-changed signals)を生成する。さらに、多重チャネル多相フィルタは、多重チャネル多相フィルタに結合され、少なくとも2つのレート変更済み信号を少なくとも2つの周波数領域信号に変換し、それにより少なくとも2つのベースバンド信号を生成すべく構成された第2処理要素によって構成される。

【0008】

本発明の第4の態様は、Mサブチャネルを並列に変調する送信機であり、ここでMは一よりも大きい正の整数である。送信機は、Mサブチャネルに対応し、かつベースバンド・サンプリング・レートにてサンプリングされたMベースバンド信号を受け取り；またMベースバンド信号を、それぞれがベースバンド・サンプリング・レートにてサンプリングされたM時間領域信号に変換すべく構成された第1処理要素によって構成される。さらに、送信機は、第1処理要素に結合され、M時間領域信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタによって構成される。多重チャネル多相フィルタは、M時間領域信号を受け取り、処理する第2処理要素によって構成される。第2処理要素は、多重チャネル多相フィルタの交換子を与えるべく構成され、ここで交換子の位置は、この位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより多重チャネル多相フィルタはベースバンド・サンプリング・レートの非整数倍であるサンプリング・レートにて動作できる；また非整数サンプリング・レート変更を得て、周波数多重化合成信号を生成するために、ベースバンド・サンプリング・レートの非整数倍にて多重チャネル多相フィルタを動作すべく構成される。さらに、送信機は、ワイヤレス搬送波を周波数多重化合成信号で変調して、Mサブチャネルを有するワイヤレス信号を生成するワイヤレス変調器によって構成される。

【0009】

本発明の第5の態様は、Mサブチャネルのうち少なくとも2つを並列に復調する受信機であり、ここでMは一よりも大きい正の整数である。受信機は、Mサブチャネルを有するワイヤレス信号を、サンプリング・レートを有しつつMサブチャネルのうち少なくとも2つから導出された合成信号に変換する受信機フロントエンドと、受信機フロントエンドに結合され、受信機から合成信号を受け取り、かつ合成信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタとによって構成される。多重チャネル多相フィルタは、合成信号を受け取り、処理する第1処理要素によって構成される。第1処理要素は、多重チャネル多相フィルタの交換子を与えるべく構成され、ここで交換子の位置は、この位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより多重チャネル多相フィルタは合成信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作できる；また非整数サンプリング・レート変更を得るために、合成信号のサンプリング・レートの非整数倍にて多重チャネル多相フィルタを動作すべく構成され、それにより少なくとも2つのレート変更済み信号を生成する。さらに受信機は、多重チャネル多相フィルタに結合され、かつ少なくとも2つのレート変更済み信号を少なくとも2つの周波数領域信号に変換して、それにより少なくとも2つのベースバンド信号を

生成すべく構成された第2処理要素によって構成される。

【0010】

(好適な実施例の説明)

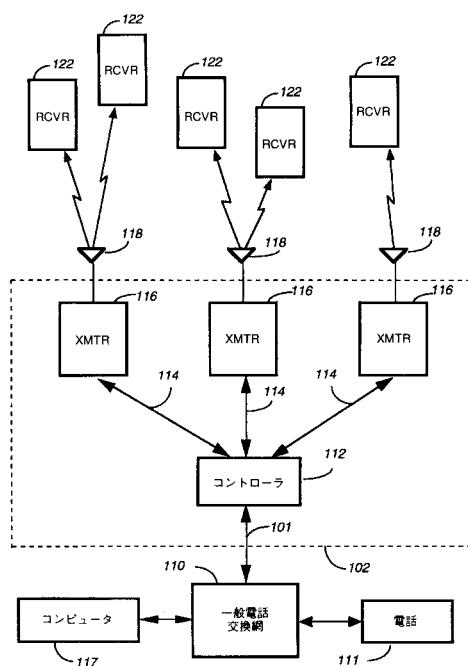

図1は、コントローラ112および複数の送信機116を含む固定部分102によって構成される、本発明による一例としてのワイヤレス通信システムの電気ブロック図を示し、このワイヤレス通信システムは、複数の受信機122も含む。送信機116は、従来のワイヤレス通信方法であって、例えば無線、赤外線、超音波チャネルを利用して受信機122と好ましくは通信し、送信機116を制御するコントローラ112に通信リンク114によって結合される。

【0011】

10

好ましくは、コントローラ112は、モトローラ・インク社製のWireless Messaging Gateway (WMG (商標)) Administrator!ページング端末と、RF-Conductor! (商標) メッセージ配信装置の組合せである。好ましくは、送信機116は、本発明に従って修正されたRF-Orchestra!送信機と同様である。好ましくは、受信機122は、モトローラ・インク社製のPageWriter (商標) ワイヤレス通信ユニットと同様であり、以下でさらに説明するように、本発明に従って修正されたハードウェアおよびソフトウェアを有する。なお、コントローラ112、送信機116および受信機122について他の同様な機器も利用できることが理解される。

【0012】

20

各送信機116は、アンテナ118を介してRF信号を受信機122に送信する。送信機116によって受信機122に送信されるRF信号(アウトバウンド・メッセージ(outbound message))は、受信機122を識別する選択呼出アドレスと、発呼者によって発信されたデータ・メッセージと、ワイヤレス通信システムの動作パラメータを調整するためにコントローラ112によって発信されたコマンドとによって構成される。

【0013】

30

好ましくは、コントローラ112は、選択呼出メッセージ発信を受信するために、電話リンク101によって一般電話交換網(PSTN)110に結合される。PSTN110からの音声およびデータ・メッセージからなる選択呼出発信は、例えば、従来の電話111もしくはPSTN110に結合された従来のコンピュータ117から生成できる。あるいは、パケット交換網、インターネット、ローカル・エリア・ネットワークなど、他の種類の通信網も発信メッセージをコントローラ112に伝送するために利用できることが理解される。

【0014】

40

送信のために利用される空中プロトコル(over-the-air protocol)は、モトローラ社の周知のFLEX (商標) ファミリーのデジタル選択呼出シグナリング・プロトコルから好ましくは選択される。これらのプロトコルは、周知の誤り検出および誤り訂正手法を利用し、そのためビット誤りが多すぎなければ、送信中に生じるビット誤りに対して耐性がある。なお、他の適切なプロトコルも利用できることが理解される。さらに、本発明を実施するための一実施例は単方向ワイヤレス通信システムであるが、本発明は双方向ワイヤレス通信システムにも適用可能であることが理解される。

【0015】

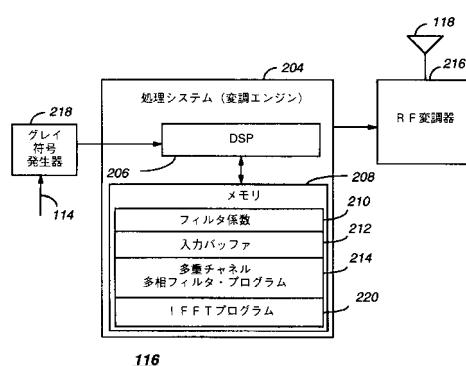

図2は、本発明による一例としての送信機116の電気ブロック図である。好ましくは、送信機116は、コントローラ112に応答して、Mサブチャネルに対応し、かつ第1ベースバンド・サンプリング・レートにてサンプリングされたMベースバンド信号を生成するグレイ符号発生器(gray code generator)218によって構成され、ここでMは1(unit)よりも大きい正の整数で、例えば、16である。グレイ符号発生器218は、Mベースバンド信号を受け取り、処理するための処理システム204または変調エンジンに結合される。好ましくは、処理システム204は、従来のデジタル信号プロセッサ(DSP)206と、入力バッファ212を与えるためのRAMおよびフィルタ係数210、多重チャネル多相フィルタ・プログラム214ならびに逆高速フーリエ変換(IFT: inverse

50

fast Fourier transform) プログラム 220 などのあらかじめプログラミングされたパラメータおよびソフトウェアを格納するための ROM を含む、従来のメモリとによって構成される。さらに、送信機 116 は、ワイヤレス搬送波を周波数多重化合成信号(処理システム 204 によって生成される)で変調して、M サブチャネルを有するワイヤレス信号で、例えは RF 信号を生成するための、従来の RF 变調器 216 などのワイヤレス变調器によって構成される。好適な実施例では、DSP 206 は、イリノイ州ショーンブルグのモトローラ・インク社製のモデル DSP56800 であり、本開示の教示があれば、当業者によって容易に書けるソフトウェアを実行する。あるいは、DSP56800 の代わりに他の同様な DSP を代用してもよいことが理解される。さらに、処理システム 204 の一部または全ては、DSP 206 のソフトウェア・プログラミングによるのではなく、ハードウェア内で実現でき、さらに、メモリ 208 は DSP 206 に一体化できることが理解される。本発明による処理システム 204 の動作については、以下でさらに詳しく説明する。

【0016】

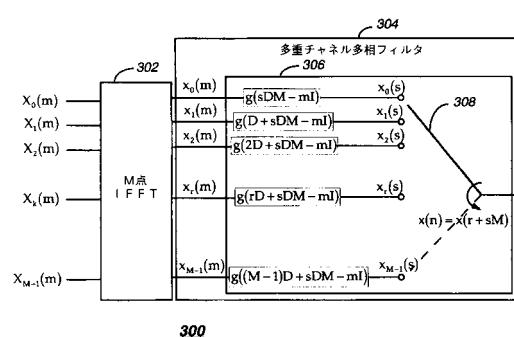

図 3 は、本発明による一例としての多重チャネル変調エンジン 300 のアーキテクチャ図である。好ましくは、変調エンジン 300 は、M サブチャネルに対応し、かつベースバンド・サンプリング・レートにてサンプリングされた M ベースバンド信号をグレイ符号発生器から受け取り、それぞれがベースバンド・サンプリング・レートにてサンプリングされた M 時間領域信号に、周知の手法によって M ベースバンド信号を変換する、M 点逆高速フーリエ変換(IFT) プロセッサ 302 によって構成される。

【0017】

さらに、変調エンジン 300 は、IFT に結合され、M 時間領域信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタ 304 によって構成される。多重チャネル多相フィルタ 304 は、M 時間領域信号を受け取り、処理するフィルタ・プロセッサ 306 によって構成される。本発明に従って、フィルタ・プロセッサ 306 は、多重チャネル多相フィルタ 304 の交換子(commutator)を与えるべく構成され、ここで交換子 308 の位置は、この位置について選択されたフィルタ・インパルス応答  $g(u)$  の位相から分離(decouple)され、それにより多重チャネル多相フィルタ 304 は、M 時間領域信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作できる。さらに、フィルタ・プロセッサ 306 は、非整数サンプリング・レート変更を得るために、M 時間領域信号のサンプリング・レートの非整数倍にて多重チャネル多相フィルタを動作すべく構成される。好ましくは、IFT プロセッサ 302 およびフィルタ・プロセッサ 306 の両方は、処理システム 204 ナインで実装される。

【0018】

さらに詳しくは、 $x_k(m)$  は k 番目のサブチャネルのグレイ符号化シンボルまたはベースバンド信号であり、 $x_r(m)$  は r 番目の IFT 出力であり、 $x_r(s)$  は r 番目のフィルタ出力である。フィルタ・インパルス応答  $g(u)$  は、周知の手法により、ベースバンド・シンボル・レートの I 倍の処理レートにて設計された低域通過フィルタについて得られる。M フィルタのそれぞれは、I / (DM) のサンプリング・レート変更を行い、ここで M は IFT における点の数で、例えば 16 であり、I は補間レート(interpolation rate)で、例えば 125 であり、D は間引きレート(decimation rate)で、例えば 7 である。従って、例示の値のサンプリング・レート変更は 125 / 112 であり、分数レート変更(fractional rate change)である。合成周波数間隔(synthesized frequency spacing)は次式によって与えられる：

【0019】

【数 1】

10

20

30

40

$$f_{\Delta} = \frac{I}{DM} f_b$$

ここで  $f_b$  はベースバンド・シンボルまたはサンプル・レートである。フィルタ・インパルス応答  $g(u)$  は、 $f_s = I f_b$  のサンプリング・レートにて設計される。フィルタ・バンク・アーキテクチャは次のように導出される。

【0020】

M サブチャネルのデータをパルス整形または濾波し、変調することが望ましい。k 番目のサブチャネルの濾波および変調は、フェーザ(phasor)と畳込み和(convolution sum)の積として表すことができる。

【0021】

【数2】

$$x_k(n) = e^{j\frac{2\pi}{M}kn} \sum_{m=-\infty}^{\infty} X_k(m)g(nD - mI)$$

10

20

次に、合成波形(composite waveform)は、全  $x_k(n)$  の和として表される。

【0022】

【数3】

$$x(n) = \frac{1}{M} \sum_{k=0}^{M-1} e^{j\frac{2\pi}{M}kn} \sum_{m=-\infty}^{\infty} X_k(m)g(nD - mI)$$

30

総和(summation)の次数を切り換えることにより、これは次式のように表すことができる

:

【0023】

【数4】

$$x(n) = \sum_{m=-\infty}^{\infty} g(nD - mI) \frac{1}{M} \sum_{k=0}^{M-1} X_k(m) e^{j\frac{2\pi}{M}kn}$$

40

$n = r + sM$  を代入すると、次式が得られる：

【0024】

【数5】

$$x(r + sM) = \sum_{m=-\infty}^{\infty} g(rD + sMD - mI) \frac{1}{M} \sum_{k=0}^{M-1} X_k(m) e^{j\frac{2\pi}{M}k(r+sM)}$$

$e^{j2\pi Z}$  は、Z が任意の整数の場合に、1 に等しいので、内側の総和はIFFT の形式で表すことができる。

50

【0025】

【数6】

$$x(r+sM) = \sum_{m=-\infty}^{\infty} g(rD+sMD-mI) \frac{1}{M} \sum_{k=0}^{M-1} X_k(m) e^{j\frac{2\pi}{M}kr}$$

あるいは、等価的に次式のようになる：

【0026】

【数7】

$$x_r(s) = \sum_{m=-\infty}^{\infty} g(rD+sMD-mI) x_r(m)$$

10

ここで  $x_r(m)$  は IFFT 出力の  $r$  番目の点である。これは、フィルタリンク関数  $g(u)$  による、信号のアップ・ダウン・リサンプリング(up-down resampling)の一般式である。

【0027】

従来、このようなフィルタ・バンク構造は、上で説明したように、バー・レートまたは基底サンプリング・レートと、効率的なスペクトル利用に必要な所望の周波数間隔との間の非整数関係のために、多重サブチャネルを生成するには望ましくないと考えられてきた。しかし、この構造は単一チャネル多相補間 / 間引き構造との多くの類似性がある。

20

【0028】

以下の単一チャネル・インタポレータ / デシメータ(single channel interpolator/decimator)について検討する。

【0029】

【数8】

$$x(n) = \sum_{m=-\infty}^{\infty} g(nD-mI) x(m)$$

30

これは、多重チャネル・インタポレータ / デシメータと同じように分解・実行できる。

【0030】

【数9】

$$x_r(s) = \sum_{m=-\infty}^{\infty} g(rD+sMD-mI) x_r(m)$$

40

実行における唯一の相違点は、多重チャネルの場合におけるフィルタ履歴(filter history)は、交換子位置インデクス(commutator position index)の変化毎に変化することである。同期バッファがあれば、これは最小限のアドレス指定オーバヘッドで達成できる。

【0031】

従来の多相フィルタは、交換子の位置をフィルタ・インパルス応答の位相と同期させる。本発明は、各交換子位置について用いられるフィルタ・インパルス応答の位相を、多相フィルタの動作を妨げずに、交換子の位置から分離できることを実証するが、これは予想外

50

の結果である。交換子の位置からフィルタ・インパルス応答の位相を分離することにより、多相フィルタは、以下で説明するように、非整数サンプリング・レート変更を行うことができ、有利である。

【0032】

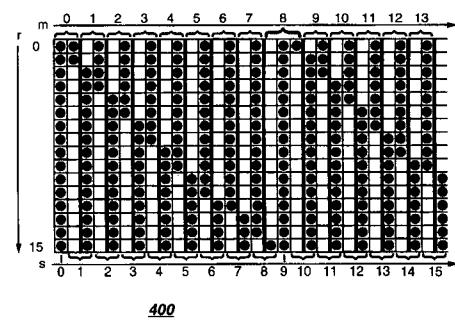

入力バッファは、本発明による多重サブチャネル変調エンジン300の一例としての入力バッファ・インクリメンテーション図400を示す図4に図示するように、全チャネルにおいて同期的にインクリメントされる。各行(row)は、交換子位置インデクス<sub>r</sub>によって決定される交換子308の位置を表す。入力サンプル・インデクス<sub>m</sub>は、フィルタ304によって処理される入力サンプルを表す。交換子サイクル・インデクス<sub>s</sub>は、交換子308が例えれば16であるM計算のフル・サイクルを完了する毎に進む。黒点は、<sub>r</sub>, <sub>s</sub>, <sub>m</sub>に対応するフィルタ・インパルス応答の選択された所定の位相を介したステップを表す。例えば、列(column)1および2において、入力と出力との間の非整数レート変更のため、多相フィルタ304は、最初の入力サンプルについてフィルタ・インパルス応答の18個の位相を利用する。（従来の多相フィルタであれば、16, 32, 48, . . . 個の位相を利用し、ここでMは、この例と同様にM=16である。）従来のフィルタにおいて、16個の入力サンプルのそれぞれが各交換子フル・サイクルについて一回触れられると、これはクリティカル・サンプリング（サブチャネル間の分離なし）の例となり、16個の入力サンプルのそれぞれが各ブロック（太い線によって区切られる）において整数回触れられると、これは従来のFFT/多相多重サブチャネル変調の典型的な用途（サブチャネルの分離が広すぎ）となる。

10

20

【0033】

なお、上記の例におけるフィルタ・インパルス応答の18個の位相は、格納されたフィルタ・インパルス応答全体の選択された位相における一つの通過(single pass)を表すことに留意されたい。すなわち、選択された列の最初の2つの行について用いられる位相は、従来の多相フィルタの場合と同様に、最初の列の最初の2つの行について用いられる位相と同じ位相ではない。交換子位置に固定されるのではなく、フィルタ・インパルス応答の現位相インデクス<sub>n</sub>は、多重チャネル多相フィルタの間引きレートD, 補間レートI, 開始位相インデクス<sub>s</sub>および出力サンプル・インデクス<sub>n</sub>の関数として計算される。

【0034】

【数10】

30

$$\phi_n = (Dn + \phi_s) \bmod (I)$$

また、従来技術とは異なり、入力サンプル・インデクス<sub>m</sub>は交換子サイクル・インデクス<sub>s</sub>と同期して進まずに、現位相インデクス<sub>n</sub>、間引きレートDおよび補間レートIから求められる。

【0035】

【数11】

40

$$\text{If } (\phi_n + D) > I$$

それから、現計算の後に、入力サンプル・インデクスを進める。

【0036】

なお、図400において、 $m = 6$ および $m = 13$ に相当する列には、 $m$ の他の値に相当する18個の位相ではなく、フィルタ・インパルス応答の17個の位相しかないことに留意されたい。これは、この例において、 $I = 125$ および $D = 7$ であるためである。従って

50

、7個の位相だけ離れたホップでステッピングする125個の可能な位相インデクス値が存在する。このとき、 $I / D = 125 / 7 = 17 \quad 6 / 7$  が成立する。従って、フィルタ・インパルス応答の位相における7番目の通過ごとに、17回のホップでフィルタの最後に達し、次の入力サンプルに移動する時間となる。

【0037】

有利な点は、この方法では極めてわずかなRAMしか必要としないことである。IFFTは同相アルゴリズム(in-phase algorithm)で実行でき、濾波のために中間的な信号格納は不要ない。複雑なシンボルまたはサンプルでは、濾波プロセス全体に必要なメモリは、フィルタ係数(filter coefficients)について、(バッチ期間(batch duration)と出力レートの積の4倍の)RAM番地と、(フィルタ応答におけるシンボル数のI倍の)ROM番地にほぼ等しい。

【0038】

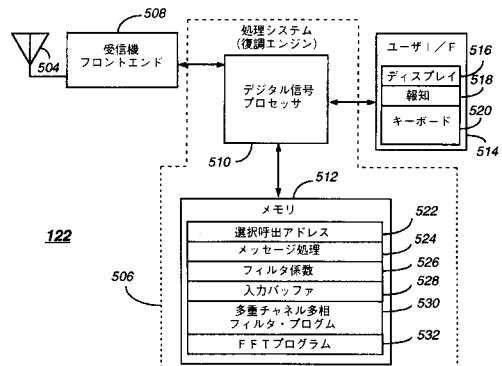

図5は、本発明によるMサブチャネルのうち少なくとも2つを並列に復調する一例としての受信機122の電気ブロック図であり、ここでMは一よりも大きい正の整数である。受信機122は、メッセージを傍受するアンテナ504によって構成される。アンテナ504は、メッセージを受信する従来の受信機フロントエンド508に結合される。受信機フロントエンド508は、Mサブチャネルを有するワイヤレス信号を、サンプリング・レートを有し、かつMサブチャネルのうち少なくとも2つから導出される合成信号(composite signal)に変換する。受信機フロントエンド508は、メッセージを処理し、受信機122を制御する処理システム506に結合される。また、好ましくは、ユーザ・インターフェース514も、ユーザとのインターフェースを与えるために処理システム506に結合される。好ましくは、ユーザ・インターフェース514は、メッセージを表示する従来のディスプレイ516と、メッセージが着信したことをユーザに報知する従来の報知要素518と、受信機122を制御する従来のキーボード520とによって構成される。なお、受信機122のいくつかのモデル、例えば、デバイスを制御するための受信機は、ユーザ・インターフェース514を従来のデバイス・インターフェース(図示せず)と置換できることが理解される。好ましくは、処理システム506は、従来のデジタル信号プロセッサ(DSP)510および従来のメモリ512によって構成される。好適な実施例では、DSPはイリノイ州ショーンブルグのモトローラ・インク社製のモデルDSP56800であり、本開示の教示があれば、当業者によって容易に書けるソフトウェアを実行する。あるいは、DSP56800の代わりに他の同様なDSPを代用してもよいことが理解される。さらに、処理システム506の一部または全ては、DSPのソフトウェア・プログラミングによるのではなく、ハードウェア内で実現でき、さらに、メモリ512はDSP510に一体化できることが理解される。

【0039】

メモリ512は、本発明に従って処理システム506をプログラミングするためのソフトウェア要素および変数によって構成される。好ましくは、メモリ512は、受信機122が応答するところの選択呼出アドレス522を含む。さらに、メモリ512は、周知の手法を介してメッセージを処理するように処理システム506をプログラミングするためのメッセージ処理要素524を含む。また、メモリ512は、本発明に従ってフィルタ・インパルス応答を記述するフィルタ係数526を含む。さらに、メモリ512は、入力バッファを格納するために用いられる入力バッファ528を含む。さらに、メモリ512は、本発明による多重チャネル多相フィルタ・プログラム530および高速フーリエ変換(FFT)プログラム532によって構成される。本発明による処理システム506の動作については、以下でさらに詳しく説明する。

【0040】

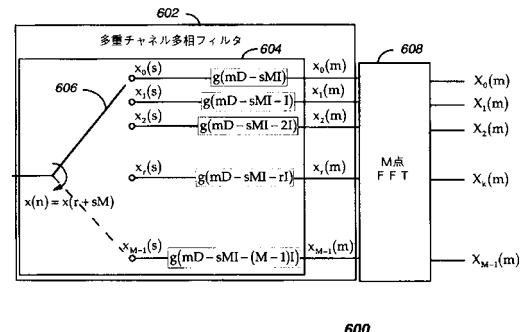

図6は、本発明による一例としての多重サブチャネル復調エンジンのアーキテクチャ図である。復調エンジン600は、受信機フロントエンド508から合成信号を受け取り、この合成信号に対して非整数サンプリング・レート変更を行う多重チャネル多相フィルタ602によって構成される。多重チャネル多相フィルタ602は、合成信号を受け取り、処

10

20

30

40

50

理するフィルタ・プロセッサ 604 によって構成される。フィルタ・プロセッサ 604 は、多重チャネル多相フィルタ 602 の交換子 606 を与えるべく構成され、ここで交換子 606 の位置は、この位置について選択されたフィルタ・インパルス応答の位相から分離され、それにより多重チャネル多相フィルタ 602 は、合成信号のサンプリング・レートの非整数倍であるサンプリング・レートにて動作できる。さらに、フィルタ・プロセッサ 604 は、非整数サンプリング・レート変更を得るために、合成信号のサンプリング・レートの非整数倍にて多重チャネル多相フィルタ 602 を動作すべく構成され、それにより少なくとも 2 つのレート変更済み信号(rate-changed signal)を生成する。また、復調エンジン 600 は、多重チャネル多相フィルタ 602 に結合され、かつ少なくとも 2 つのレート変更済み信号を少なくとも 2 つの周波数領域信号に変換して、それにより少なくとも 2 つのベースバンド信号を生成すべく構成された高速フーリエ変換(FFT)プロセッサ 608 を含む。好ましくは、フィルタ・プロセッサ 604 および FFT プロセッサ 608 は、処理システム 506 内で実装される。

## 【0041】

さらに詳しくは、 $x_k(m)$  は  $k$  番目のサブチャネルの低サンプリング・レート非同期波形であり、 $x_r(s)$  は  $r$  番目のフィルタ・バンク入力であり、 $x_r(m)$  は  $r$  番目のフィルタ出力である。フィルタ・インパルス応答  $g(u)$  は、周知の手法により、 $x(n)$  のサンプリング・レートの  $I$  倍の処理レートにて設計された低域通過フィルタについて得られる。M フィルタのそれぞれは、IM/D のレート変更を行い、ここで  $M$  は FFT における点の数である。交換(commutation)後、合成周波数間隔は次式によって与えられる：

## 【0042】

## 【数12】

$$f_\Delta = \frac{1}{M} f_s$$

ここで、 $f_s$  は  $x(n)$  のサンプル・レートである。フィルタ・バンク・アーキテクチャは次のように導出される。

## 【0043】

M サブチャネルのデータを復調し、パルス整形または濾波することが望ましい。 $k$  番目のサブチャネルの濾波およびダウンサンプリングは、次式のように表すことができる。

## 【0044】

## 【数13】

$$X_k(m) = \sum_{n=-\infty}^{\infty} x(n) e^{-j \frac{2\pi}{M} kn} g(mD - nI)$$

交換は、 $n = r + sM$  を代入して表すことができる。

## 【0045】

## 【数14】

$$X_k(m) = \sum_{r=0}^{M-1} \sum_{s=-\infty}^{\infty} x(r + sM) e^{-j \frac{2\pi}{M} k(r+sM)} g(mD - sMI - rI)$$

$e^{j2\pi Z}$  は、 $Z$  が任意の整数の場合に、1 に等しいので、指數関数項は総和から抜き出すことができる。

10

20

30

40

50

【 0 0 4 6 】

【 数 1 5 】

$$X_k(m) = \sum_{r=0}^{M-1} e^{-j\frac{2\pi}{M}kr} \sum_{s=-\infty}^{\infty} x(r+sM)g(mD-sMI-rI)$$

または

【 0 0 4 7 】

【 数 1 6 】

10

$$X_k(m) = \sum_{r=0}^{M-1} x_r(m) e^{-j\frac{2\pi}{M}kr}$$

ここで、 $x_r(m)$  は  $r$  番目のフィルタ出力である。

【 0 0 4 8 】

前で説明したように、従来において、このようなフィルタ・バンク構造は、ボーレートまたは基底サンプリング・レートと、所望の周波数間隔との間の非整数関係のために、多重サブチャネルでは望ましくないと考えられてきた。しかし、この構造は単一チャネル多相補間 / 間引き構造との多くの類似性がある。以下の単一チャネル・インタポレータ / デシメータについて検討する。

20

【 0 0 4 9 】

【 数 1 7 】

$$y(m) = \sum_{n=-\infty}^{\infty} g(mD-nI)x(n)$$

30

これは、多重チャネル・インタポレータ / デシメータと同じように分解・実行できる。

【 0 0 5 0 】

【 数 1 8 】

$$y(m) = \sum_{r=0}^{M-1} \sum_{s=-\infty}^{\infty} g(mD-sMI-rI)x(r+sM)$$

40

実行における唯一の相違点は、多重チャネルの場合における各フィルタ・バンクの出力は、異なる FFT 入力に送られることである。

【 0 0 5 1 】

前述の場合と同様に、重要な点は、フィルタ・インパルス応答の位相を交換子 606 の位置から分離することにより、多重チャネル多相フィルタ 602 において非整数レート変更が有利に可能になることである。交換子位置に固定されるのではなく、フィルタ・インパルス応答の現位相インデクス  $r_m$  は、多重チャネル多相フィルタの間引きレート  $D$ 、補間レート  $I$ 、出力サンプル・インデクス  $m$ 、交換子位置インデクス  $r$ 、FFT における点

50

の数 M および開始位相インデクス  $s$  の関数として計算される。

【0052】

【数19】

$$\phi_{r,m} = (\phi_s + Dm - Ir) \bmod (MI)$$

なお、開始時に、開始位相インデクス  $s$  は、周知の同期手法により、フィルタ・インパルス応答を入力サンプル  $\times (n)$  のシンボル中心に時間整合させる値に好ましくは設定されることを理解されたい。

【0053】

また、従来技術とは異なり、出力サンプル・インデクス  $m$  および交換子サイクル・インデクス  $s$  は同期して進まずに、交換子サイクル・インデクス  $s$  の前進は、現位相インデクス  $r,m$  , FFT における点の数  $M$  , 補間レートおよび間引きレート  $D$  から求められる。

【0054】

【数20】

$$If (\phi_{r,m} + D) > MI$$

10

20

それから、現計算の後に、交換子サイクル・インデクス  $s$  を進める。なお、  $s$  は着信データ・ストリームと同期して変化しなければならず、そのため処理システム 506 の計算のタイミングはそういうことを保証するように手配される。

【0055】

変調エンジン 300 の場合と同様に、この方法では極めてわずかな RAM しか必要としない。FFT は同相アルゴリズムで実行でき、濾波のために中間的な信号格納は必要ない。複雑なシンボルまたはサンプルでは、濾波プロセス全体に必要なメモリは、フィルタ係数について、(バッチ期間と出力レートの積の 4 倍の) RAM 番地と、(フィルタ応答における基底サンプリング・レート・サンプル数の I 倍の) ROM 番地にほぼ等しい。一つの評価した用途では、本発明により、従来の方法に比べて、処理能力条件、すなわち MIPS は約 3 分の 1 に軽減し、また RAM 条件の著しい改善が得られた。

【0056】

以上、本発明は多重チャネル多相フィルタにおいて非整数サンプリング・レート変更を行うための装置を提供したことが、上記の開示から明らかであろう。有利な点は、本装置は、サブチャネル間隔の優れた柔軟性を有する効率的な多重サブチャネル多相変調および復調エンジンを可能にする。

【0057】

本発明の多くの修正および変形は、上記の教示に鑑みて可能である。従って、特許請求の範囲内で、本発明は本明細書で具体的に説明した以外でも実施できるものとする。

【図面の簡単な説明】

【図1】 本発明による一例としてのワイヤレス通信システムの電気ブロック図である。

【図2】 本発明による一例としての送信機の電気ブロック図である。

【図3】 本発明による一例としての多重サブチャネル変調エンジンのアーキテクチャ図である。

【図4】 本発明による多重サブチャネル変調エンジンの一例としての入力バッファ・インクリメンテーション図である。

【図5】 本発明による一例としての受信機の電気ブロック図である。

【図6】 本発明による一例としての多重サブチャネル復調エンジンのアーキテクチャ図

30

40

50

である。

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

---

フロントページの続き

審査官 田中 庸介

(56)参考文献 特表平09-501279(JP, A)

特開平09-135149(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04B 14/00-14/08

H03H 17/00-17/08

H04L 27/00-27/30