(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3818433号

(P3818433)

(45) 発行日 平成18年9月6日(2006.9.6)

(24) 登録日 平成18年6月23日(2006.6.23)

(51) Int.CI.

F 1

HO3K 19/0175 (2006.01)

HO3K 19/00 101J

請求項の数 10 (全 9 頁)

(21) 出願番号 特願2001-247518 (P2001-247518)

(22) 出願日 平成13年8月17日 (2001.8.17)

(65) 公開番号 特開2002-111472 (P2002-111472A)

(43) 公開日 平成14年4月12日 (2002.4.12)

審査請求日 平成15年8月26日 (2003.8.26)

(31) 優先権主張番号 09/641085

(32) 優先日 平成12年8月17日 (2000.8.17)

(33) 優先権主張国 米国(US)

(73) 特許権者 500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン パークウェイ エヌイー 1110

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100101498

弁理士 越智 隆夫

最終頁に続く

(54) 【発明の名称】外部プルアップ抵抗器検出および出力バッファの補償

## (57) 【特許請求の範囲】

## 【請求項 1】

電子回路であって、

バッファ入力において入力信号を受信しバッファ出力においてバッファ信号を生成するバッファであって、該入力信号と、該バッファの駆動力を可変し得るバッファ制御信号とに応答するバッファと、

該バッファが高インピーダンス出力状態にあるときに該バッファ出力においてプルアップ抵抗器の値を含むパラメータを測定し、該測定したパラメータに基づいて該バッファ制御信号を生成するパラメータ検出器とからなることを特徴とする電子回路。

## 【請求項 2】

請求項 1 に記載の電子回路において、該バッファは、該バッファ制御信号に基づく電圧レベルと該入力信号の電圧レベルとを有するバッファ信号を生成することを特徴とする電子回路。

## 【請求項 3】

請求項 1 に記載の電子回路において、該バッファは、3 状態可能な CMOS バッファ回路であることを特徴とする電子回路。

## 【請求項 4】

請求項 1 に記載の電子回路において、該バッファは、較正信号に応答して高インピーダンス出力状態になることを特徴とする電子回路。

## 【請求項 5】

10

20

請求項 1 に記載の電子回路において、該パラメータ検出器はさらに、較正信号に応答して、該バッファ出力を該パラメータ検出器の回路経路に選択的に連結するスイッチを含むことを特徴とする電子回路。

【請求項 6】

請求項 1 に記載の電子回路において、該バッファ制御信号は複数の制御ビットを含むことを特徴とする電子回路。

【請求項 7】

バッファ入力において入力信号を受信しバッファ出力においてバッファ信号を生成するバッファ手段であって、該入力信号と、該バッファの駆動力を可変し得るバッファ制御信号とに応答するバッファ手段と、

該バッファ手段が高インピーダンス出力状態にあるときに該バッファ出力においてプルアップ抵抗器の値を含むパラメータを測定し、該測定したパラメータに基づいて該バッファ制御信号を生成する検出器手段とからなることを特徴とする電子回路。

【請求項 8】

該バッファを高インピーダンス出力状態に置く段階と、

該バッファが該高インピーダンス出力状態にある間に該バッファ出力においてプルアップ抵抗器の値を含むパラメータを測定する段階と、

該測定したパラメータに基づいて該バッファの駆動力を調整する段階からなることを特徴とするバッファを較正する方法

【請求項 9】

請求項 8 に記載の方法において、該方法はさらに、

該測定したパラメータに基づいてバッファ制御信号を生成する段階と、

該バッファが入力信号と該バッファ制御信号とにに基づいてバッファ信号を生成するように、該バッファ制御信号に基づいて該バッファの駆動力を調整する段階とからなることを特徴とする方法。

【請求項 10】

請求項 9 に記載の方法において、該生成する段階はさらに、複数の制御ビットを有するバッファ制御信号を生成する段階を含むことを特徴とする方法。

【発明の詳細な説明】

【0001】

【発明の背景】

本発明は、バッファに連結されたプルアップ抵抗器を補償するシステムおよび方法に関するもので、特にプルアップ抵抗器が未知の抵抗値を有する場合にそれを補償するシステムおよび方法に関するものである。

【0002】

集積回路出力バッファは、しばしばオフチッププルアップ抵抗器(off-chip pull-up resistor)に連結されている。このプルアップ抵抗器は、出力バッファの性能に影響を与える。それは、バッファによって出力される信号の低から高の遷移の速度を上昇させ、高から低の遷移の速度を低下させるためである。立上りおよび立下り時間またはデューティサイクルひずみ(duty cycle distortion)に対し非常に厳密な仕様を有するバッファに対し、プルアップ抵抗器によってもたらされる性能の変化は問題がある。通常の解決法は、定義された抵抗値を有する既知のプルアップ抵抗器を補償するバッファを設計することにより、その既知のプルアップ抵抗器によってもたらされる性能ひずみが低減されるようにする、というものである。

【0003】

しかしながら、大容量記憶装置のアプリケーションで広く使用されるATAバスなど、プルアップ抵抗器の値が未知であり非常に広く変動する可能性のあるシステムがある。このプルアップ抵抗器の値の変動は、出力バッファの性能に悪影響を及ぼす。出力バッファは、未知または可変の抵抗を有するプルアップ抵抗器によってもたらされるひずみを正確に補償するようには設計されていないためである。既知の出力バッファが未知の値を有する

10

20

30

40

50

プルアップ抵抗器を補償することができないということは、データ伝送の速度が上昇することによってより悪化するのみである。それは、パルス幅が狭くなるほどひずみの割合が増大することによる。

#### 【0004】

したがって、未知または可変の抵抗を有するプルアップ抵抗器を補償する改良された出力バッファが必要とされる。

#### 【0005】

##### 【発明の概要】

本発明は、バッファ出力において、プルアップ抵抗器の値などのパラメータを測定しそれに応答することができるバッファ回路を提供することにより、従来のシステムにおける問題を解決する。本発明は、1つの実施例によれば、バッファとパラメータ検出器とを含む電子回路を含む。バッファは、バッファ入力において入力信号を受信し、バッファ出力においてバッファ信号を生成する。パラメータ検出器は、バッファが高インピーダンス出力状態にあるときにバッファ出力においてパラメータを測定し、測定したパラメータに基づいてバッファ制御信号を生成する。バッファは、パラメータ検出器によって生成されるバッファ制御信号に応答する。10

#### 【0006】

本発明の他の実施例は、バッファを較正する方法を提供する。本方法は、バッファを高インピーダンス出力状態にするステップと、バッファ出力においてパラメータを測定するステップと、測定されたパラメータに基づいてバッファを調整するステップと、を含む。本発明のこの実施例によれば、バッファ出力におけるパラメータは、バッファが高インピーダンス出力状態にある間に測定される。20

#### 【0007】

本発明の特徴および利点は、添付図面において示されているように、以下の説明から明らかとなろう。なお、図面において同じ参照符号は異なる図面を通して同じ要素を参照する。。

#### 【0008】

##### 【発明の詳細な記述】

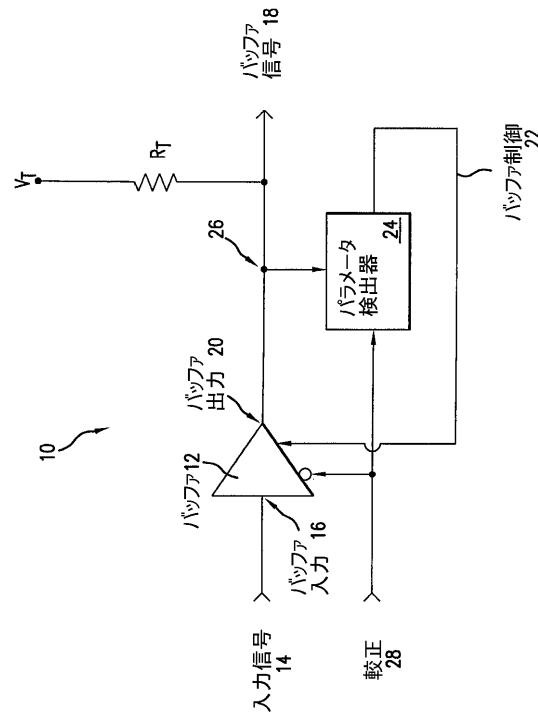

図1は、本発明による電子回路10のブロック図を示す。電子回路10は、バッファ12とパラメータ検出器24とを含む。バッファ12は、バッファ入力16において入力信号14を受信し、バッファ出力20においてバッファ信号18を生成する。パラメータ検出器24は、バッファ12が高インピーダンス出力状態にあるときにバッファ出力20においてパラメータを測定し、測定したパラメータに基づいてバッファ制御信号22を生成する。バッファ12は、入力信号14とパラメータ検出器24によって生成されるバッファ制御信号22とに応答する。30

#### 【0009】

本明細書で使用される「バッファ」という用語は、被駆動回路が駆動回路に影響を及ぼすのを防止するために使用される分離回路を言う。バッファは、大きさが入力信号と等しい出力信号を生成する単位利得バッファを含む。

#### 【0010】

動作時、バッファ12は、バッファ12を高インピーダンス出力状態にし、バッファ出力20においてパラメータを測定し、測定したパラメータに基づいてバッファ12を調整することによって、較正される。更に、パラメータを測定するステップは、バッファ12が高インピーダンス出力状態にある間に行わなければならない。バッファ12に対し高インピーダンス状態をトリガすることと、パラメータ検出器24によってパラメータの測定をトリガすることと、の両方のために、較正信号28を使用することができる。パラメータ検出器24は、プルアップ抵抗器 $R_T$ の強度を決定するために、バッファ出力において電圧、電流または抵抗等の指定された電気特性を測定する。バッファ12とパラメータ検出器24とを使用することにより、電子回路10は、電圧 $V_T$ に終端される未知の抵抗を有するプルアップ抵抗器 $R_T$ に対しバッファ12を較正する能力を提供する。バッファ140

2が適当に較正された後、プルアップ抵抗器の未知の抵抗の悪影響は実質的に低減される。

#### 【0011】

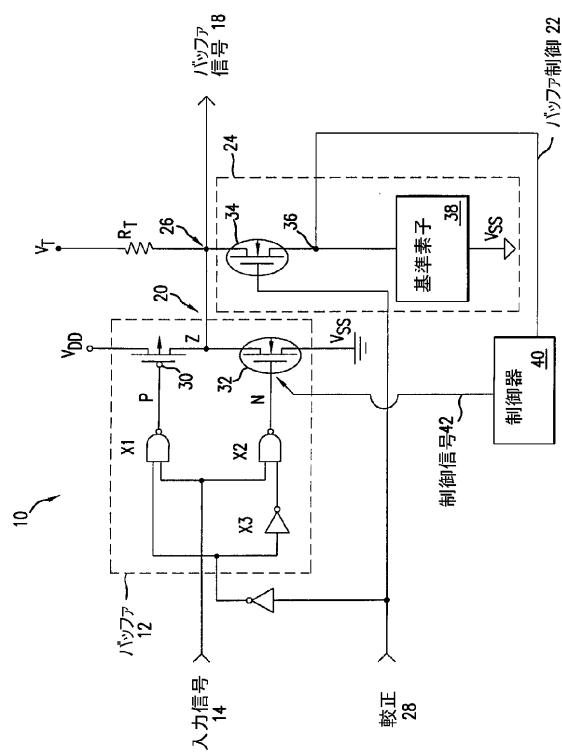

図2は、図1の電子回路10の更なる詳細を示す混合ブロックおよび略図である。バッファ12は、図2に示すように、3状態可能CMOS出力バッファ(tri-statable CMOS output buffer)とすることができます。図2に示す例示的なバッファ12は、NANDゲートX1と、NORゲートX2と、インバータX3と、電圧レベル $V_{dd}$ および別の電圧レベル $V_{ss}$ 間に直列に接続されたトランジスタ30およびトランジスタ32から形成された出力段とを含むことができる。また、バッファは、較正信号28に対する特別な入力を含むことができる。そして、較正信号28は、Nチャネルトランジスタ34のゲートに動作可能に結合することができる。10

#### 【0012】

動作時、較正信号28がローであるとき、入力信号14は、入力信号14がハイである時にノードNおよびPがローであるように、NANDゲートX1およびNORゲートX2を駆動する。これにより、Nチャネルトランジスタ32がオフとなり、Pチャネルトランジスタ30がオンとなって、出力ノード26が $V_{dd}$ まで引上げられる。オフチップ抵抗器RTは、出力ノード26のプルアップを助ける。入力信号14がローであるとき、ノードNおよびPはハイである。これにより、トランジスタ32がオンとなりトランジスタ30がオフとなって、出力ノード26が $V_{ss}$ まで引下げられる。この場合、抵抗器RTはこのプルダウンに抵抗する。20

#### 【0013】

抵抗器は、電圧VTで終端する。この電圧は、 $V_{dd}$ に等しくあってよく、あるいはそれより相当に高くてよい。較正入力28がハイであるとき、入力信号14の状態に関わらずノードNはローでありノードPはハイである。これにより、両トランジスタ30および32はオフとなり、これはバッファ12の高インピーダンス出力状態と呼ばれる。高インピーダンス出力状態では、プルアップ抵抗器RTは出力ノード26を終端電圧VTまで自由に引上げることができる。

#### 【0014】

更に、図2は、パラメータ検出器24がスイッチ34を含むことができることを示している。スイッチ34は、トランジスタとすることができる。スイッチ34は、バッファ出力20のパラメータを測定することができるよう、バッファ出力20をパラメータ検出器24の回路経路36に選択的に結合する。好ましくは、スイッチ34は、較正信号28に応じてバッファ出力20と回路経路36とを選択的に結合する。また、スイッチ34は、バッファ出力20に高インピーダンスカップリングを含むことができる。高インピーダンスカップリングにより、較正信号28が無効(disable)である間にパラメータ検出器24がバッファ信号18を実質的にひずませることが防止される。30

#### 【0015】

また、パラメータ検出器24は、スイッチ34に動作可能に連結されている基準素子38を含むことができる。基準素子38は、測定されたパラメータを比較し、それによってプルアップ抵抗器RTの値および強度を決定するための、既知のベースラインを提供する。基準素子38は、既知の抵抗値、既知の電流源、既知の電圧源、またはそれらの組合せとすることができる。基準素子38が抵抗値RCTを有する既知の抵抗器である場合、出力ノード26の電圧は、 $V_Z (V_Z = VT \times (RT / (RT + R_{C O N T})) )$ となる。代替的に、基準素子38を、既知の電流ICSを有する電流源とすることができる。この場合、 $V_Z = VT - (I_{C S} \times RT)$ である。いずれの場合も、ノード26またはノード36における電圧VZなど、バッファ出力におけるパラメータを測定することにより、プルアップ抵抗器の強度が直接決定される。40

#### 【0016】

たとえば、基準素子38が既知の抵抗RCTを有する場合、抵抗器RTおよびRCNTは、既知の電圧VTと $V_{ss}$ との間に分圧器を形成する。バッファ12が高インピーダ50

ンス状態にされると、パラメータ検出器 24 はノード 26 またはノード 36 で電圧を測定し、バッファ信号 18 におけるプルアップ抵抗器  $R_T$  の効果を示す適当なバッファ制御信号 22 を生成することができる。

#### 【0017】

プルアップ抵抗器  $R_T$  の効果が識別されると、バッファ 12 は、出力バッファの要素のいずれかの相対強度を変更することにより、測定された電圧に応答することができる。与えられた信号に応答して出力バッファの強度を変更する回路は、当業者には周知である。

#### 【0018】

また、電子回路 10 は、図 2 に示すように、バッファ 12 とパラメータ検出器 24 との間に動作可能に連結された制御器 40 も含むことができる。制御器 40 は、パラメータ検出器 24 の内部または外部に配置することができる。制御器 40 は、測定されたパラメータに基づいてバッファに対し制御信号 42 を生成する。制御器 40 は、プルアップ抵抗器  $R_T$  の効果に応じてバッファがその相対強度を変更するのを支援する回路を表す。たとえば、制御器 40 は、電圧デジタル変換器かまたは電流デジタル変換器とすることができる。

10

#### 【0019】

本発明の 1 つの実施例では、制御器 40 は、電圧デジタル（たとえば、アナログデジタル）変換器である。制御器 40 は、バッファ制御信号 22 のアナログ電圧をデジタル制御信号 42 に変換する。デジタル制御信号 42 は、N ビット制御信号  $F_n$ （すなわち、個々の制御ビット  $F_0, F_1, \dots, F_n$  を有する）とすることができる。デジタル制御信号 42 は、プルアップ抵抗器が無い場合は制御信号  $F_n$  の値がすべてローであるが、抵抗器のプルアップ強度が増大するに従って制御信号  $F_n$  のビットがより多くハイになるよう、調整することができる。そして、デジタル制御信号 42 は、各々がバッファ 12 の駆動強度を変更することができるバッファ 12 の「N」個の要素を、オンにするかまたはオフにするために使用することができる。

20

#### 【0020】

更に本発明のこの実施例によれば、バッファ 12 のトランジスタ 32 は、複数の並列トランジスタ（図示せず）を含むことができる。複数の並列トランジスタは、共通のソースおよびドレンを有することができるが、入力が信号 N（すなわち、NOR ゲート X2 の出力）および  $F_n$  である AND ゲートによって駆動されるゲートを有することも可能である。このため、動作時、 $R_T$  のプルアップ強度が増大するに従い、制御信号 42 の制御ビットがより多くハイとなり、それによってトランジスタ 32 の有効サイズが増大するように、複数のトランジスタのうちの少なくとも 1 つが選択的に使用される。このようにトランジスタ 32 のサイズが増大することにより、プルアップ抵抗器  $R_T$  が補償される。同様に、制御信号 42 は、トランジスタ 30 とゲート X1 および X2 など、バッファ 12 の他の要素の相対強度を調整するために使用することができる。

30

#### 【0021】

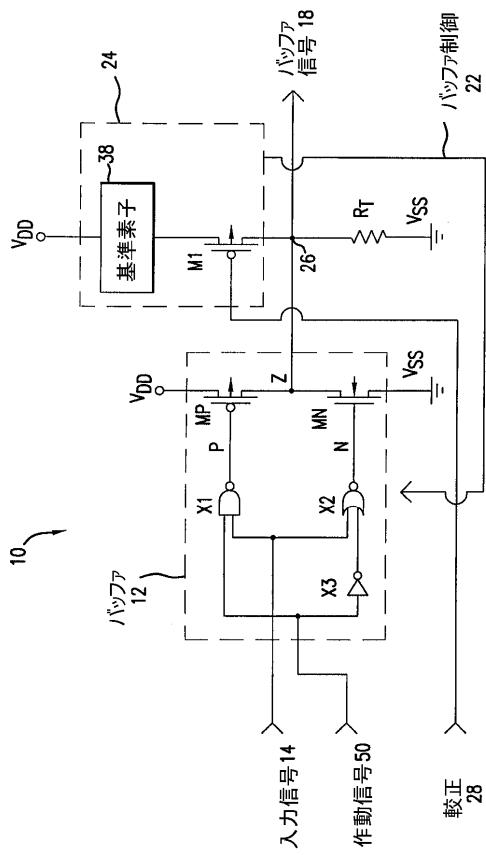

図 3 は、電子回路 10 の代替的な特徴を示す混合ブロックおよび略図である。図 3 では、基準素子 38 がノード 26 と高電圧信号  $V_{dd}$  との間に動作可能に連結されており、未知の抵抗値を有する抵抗器  $R_T$  がノード 26 と低電圧信号  $V_{ss}$  との間に動作可能に連結されている。 $R_T$  は、バッファが高インピーダンス状態にあるときに、ノード 26 を  $V_{ss}$  まで引下げる外部抵抗器である。このように、図 3 は、プルダウン抵抗器の効果が電子回路 10 によっても測定し補償することができることを示す。

40

#### 【0022】

図 3 に示すように、本発明の追加の実施例において、バッファ 12 における高インピーダンス状態をトリガするために作動信号 (enable signal) 50 を使用することができる。図 3 に示すように、パラメータ検出器 24 を制御するためにのみ較正信号 28 が使用される。一般に、バッファ 12 が高インピーダンス状態にある間にパラメータ検出器 24 が出力バッファにおいてパラメータを測定することを保証するために、作動信号 50 と較正信号 28 との同期がとられる。

#### 【0023】

50

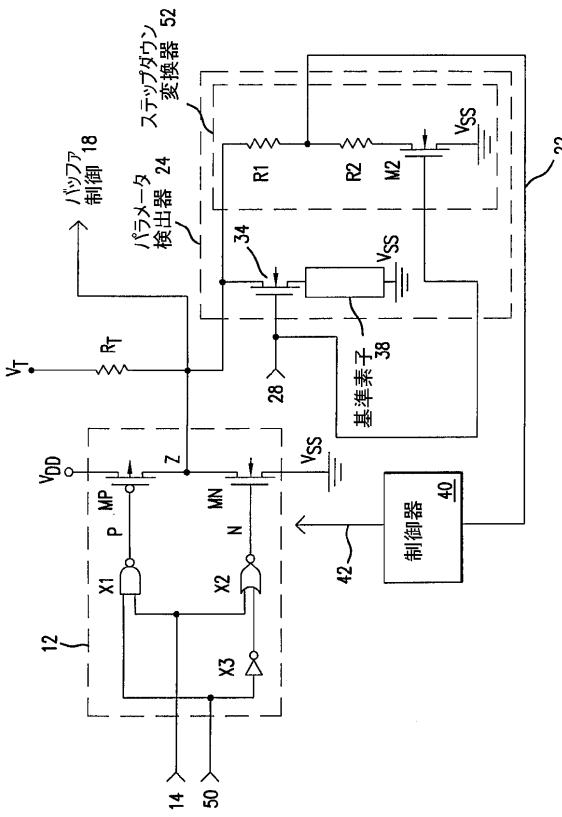

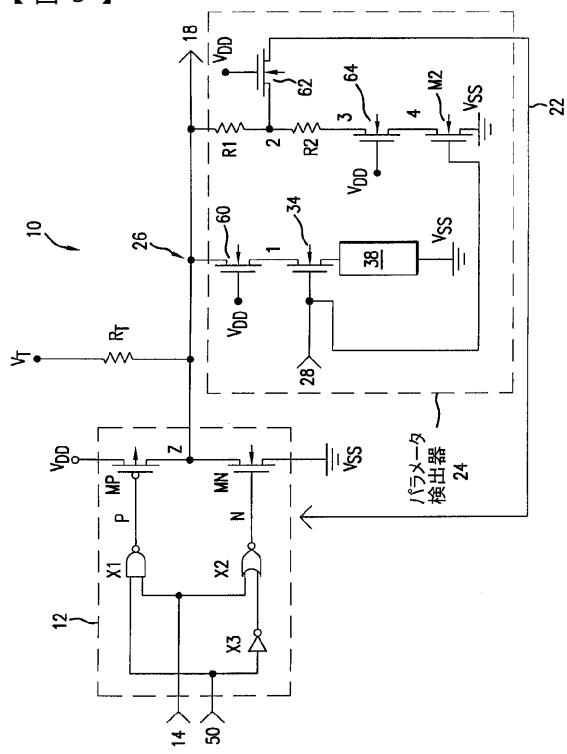

図4は、パラメータ検出器24がステップダウン変換器52を含む場合の電子回路10を示す。ステップダウン変換器52は、パラメータ検出器24によって出力される電圧レベルを低減する回路を含む。図4に示すように、ステップダウン変換器52は、抵抗器R1、抵抗器R2およびスイッチM2を含むことができる。抵抗器R1およびR2は、分圧器として作用し、スイッチM2は、較正信号28に応じてステップダウン変換器52を駆動するために使用される。

#### 【0024】

ステップダウン変換器52は、好ましくは、電圧VTが電圧V<sub>dd</sub>より相当に大きい場合に利用される。ステップダウン変換器52は、電子回路10の他の回路に対する損害を防止するためにパラメータ検出器24によって出力される電圧レベルを低減する。たとえば、ステップダウン変換器52は、信号22の電圧レベルを低減することにより、制御器40に対する損害または範囲外電圧入力を防止することができる。10

#### 【0025】

図5は、パラメータ検出器24が少なくとも1つのソースフォロワを含む電子回路10を示す。特に、例示されている電子回路10は、パラメータ検出器24にソースフォロワ60、62および64を含む。

#### 【0026】

各ソースフォロワは、関連するMOSトランジスタのゲートの前後の電圧かまたはソースからドレインへの電圧が、3.3ボルトなどの指定された電圧限界値を越えないことを保証する。図5に示すソースフォロワ60、62、64の各々は、この例では3.3ボルトであると仮定される電源V<sub>DD</sub>にゲートが連結されているトランジスタを含む。トランジスタの各々により、それらの下の電圧がV<sub>DD</sub> - V<sub>tn</sub> (V<sub>tn</sub>は約0.7ボルトのNチャネル閾値電圧)より上に上昇するのが防止される。20

#### 【0027】

ソースフォロワは、好ましくは、終端電圧VTが、使用されている回路テクノロジの安全動作範囲を越える場合に使用される。たとえば、5ボルトVTは、3.3ボルト電源V<sub>dd</sub>で動作しているCMOS回路テクノロジの安全動作範囲を越える可能性がある。このため、VTがノード26を5ボルトまで引上げると、トランジスタ34およびトランジスタM2のゲートは、損害を与える5ボルト信号に晒される可能性がある。ソースフォロワ60および64は、5ボルト信号をV<sub>dd</sub>にクランプすることによって、それらの関連するトランジスタ34およびM2がそれぞれ、損害を与える5ボルト信号に晒されないようにする。更に、ソースフォロワ62は、バッファ12または制御器40の回路に、潜在的に損害を与える5ボルト信号が与えられないようとする。30

#### 【0028】

本発明のいくつかの特定の実施の形態を説明したが、当業者には、種々の改変、変更および改良が容易に思いつくであろう。かかる改変、変更および改良は、この開示によって明らかとなるように、本明細書では明白に述べられていないがこの説明の一部であると解釈され、本発明の精神および範囲内にあるよう解釈される。したがって、上述した説明は單なる例示にすぎず、限定するものではない。

#### 【図面の簡単な説明】

【図1】本発明による電子回路のプロック図である。

【図2】図1の発明の更なる詳細を示す混合ブロックおよび略図である。

【図3】図1の発明の代替的な特徴を示す混合ブロックおよび略図である。

【図4】図1の発明のステップダウン変換器の特徴を示す略図である。

【図5】ソースフォロワを備えた図4の本発明を示す略図である。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【 四 5 】

---

フロントページの続き

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100106703

弁理士 産形 和央

(74)代理人 100091889

弁理士 藤野 育男

(74)代理人 100102808

弁理士 高梨 憲通

(74)代理人 100107401

弁理士 高橋 誠一郎

(74)代理人 100106183

弁理士 吉澤 弘司

(72)発明者 バーナード リー モ里斯

アメリカ合衆国 18049 ペンシルヴァニア, エマウス, グレンウッド ドライヴ 4324

審査官 石田 勝

(56)参考文献 特開平08-335830(JP,A)

特開平07-202671(JP,A)

特開平10-261948(JP,A)

特開平08-079051(JP,A)

特開平06-125265(JP,A)

特開平05-064346(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/00-19/00、103;19/01-19/082;19/092-19/096@Z