# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2007/0086266 A1

Freebern et al.

Apr. 19, 2007 (43) Pub. Date:

### (54) DIRECTED AUTO-REFRESH FOR A DYNAMIC RANDOM ACCESS MEMORY

(76) Inventors: Margaret Clark Freebern, Richmond, VT (US); Kazimierz Szczypinski, Munchen (DE)

Correspondence Address:

DICKÉ, BILLIG & CZAJA, P.L.L.C. FIFTH STREET TOWERS 100 SOUTH FIFTH STREET, SUITE 2250 MINNEAPOLIS, MN 55402 (US)

(21) Appl. No.: 11/251,683

(22) Filed: Oct. 17, 2005

#### **Publication Classification**

(51) Int. Cl.

(52)

(2006.01)

G11C 8/00

#### **ABSTRACT** (57)

A memory includes a row address latch. The row address latch includes a first stage configured to latch a row address for a memory read or write operation, and a second stage configured to latch a row address for a memory bank auto-refresh. The row address latch provides the row address from the first stage in response to an activate command and provides the row address from the second stage in response to a directed auto-refresh command.

Fig. 1

Fig. 4

# DIRECTED AUTO-REFRESH FOR A DYNAMIC RANDOM ACCESS MEMORY

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is related to U.S. patent application Ser. No. \_\_\_\_\_\_, Attorney Docket Number 1331.260.101, entitled "DIRECTED AUTO-REFRESH FOR A DYNAMIC RANDOM ACCESS MEMORY," filed Oct. 17, 2005, and U.S. patent application Ser. No. \_\_\_\_\_\_, Attorney Docket Number 1331.261.101, entitled "DIRECTED AUTO-REFRESH FOR A DYNAMIC RANDOM ACCESS MEMORY," filed Oct. 17, 2005, which are incorporated herein by reference.

#### **BACKGROUND**

[0002] One type of memory is a dynamic random access memory (DRAM). DRAMs are a volatile memory in which the contents of the memory cells leak away over time. The memory cells are periodically refreshed to maintain their values. One mode for periodically refreshing the memory cells includes an auto-refresh or constant bit rate (CBR) refresh. Auto-refresh or CBR refresh is one method of refreshing DRAM memory cells. This method involves stopping normal read and write operations, precharging all memory banks, refreshing a group of memory cells in each bank, reactivating the memory banks, and then continuing with normal read and write operations. The memory cells are refreshed at a frequency such that every memory cell is refreshed within its retention time. The precharge and reactivation of the memory banks reduces the bandwidth of the DRAM because the precharge and reactivation of the memory banks inserts cycles where data is being neither read nor written and no memory cells are being refreshed.

[0003] Typical auto-refresh implementations use a DRAM controller to issue auto-refresh commands frequently enough that the entire memory is refreshed within the specified retention time. Because each command is issued separately, a user may schedule the auto-refreshes to occur when the DRAM is not being actively read or written, or whenever it is most bandwidth efficient to do so. These scheduling strategies may reduce the bandwidth penalty; however, they are still insufficient for some applications.

### SUMMARY

[0004] One embodiment of the present invention provides a memory. The memory includes a row address latch. The row address latch includes a first stage configured to latch a row address for a memory read or write operation, and a second stage configured to latch a row address for a memory bank auto-refresh. The row address latch provides the row address from the first stage in response to an activate command and provides the row address from the second stage in response to a directed auto-refresh command.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0005] The accompanying drawings are included to provide a further understanding of the present invention and are incorporated in and constitute a part of this specification. The drawings illustrate the embodiments of the present invention and together with the description serve to explain the principles of the invention. Other embodiments of the

present invention and many of the intended advantages of the present invention will be readily appreciated as they become better understood by reference to the following detailed description. The elements of the drawings are not necessarily to scale relative to each other. Like reference numerals designate corresponding similar parts.

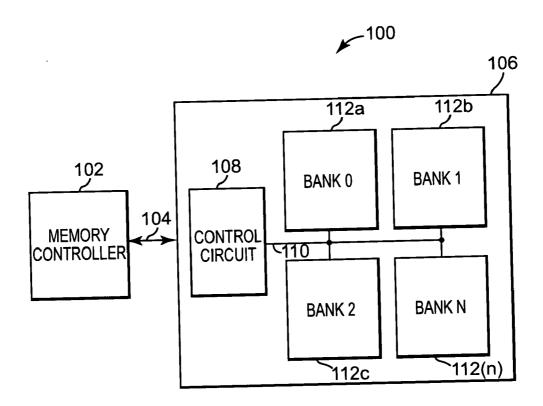

[0006] FIG. 1 is a block diagram illustrating one embodiment of a memory device.

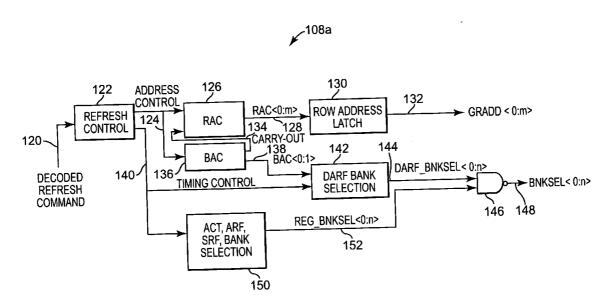

[0007] FIG. 2 is a block diagram illustrating one embodiment of a refresh control circuit.

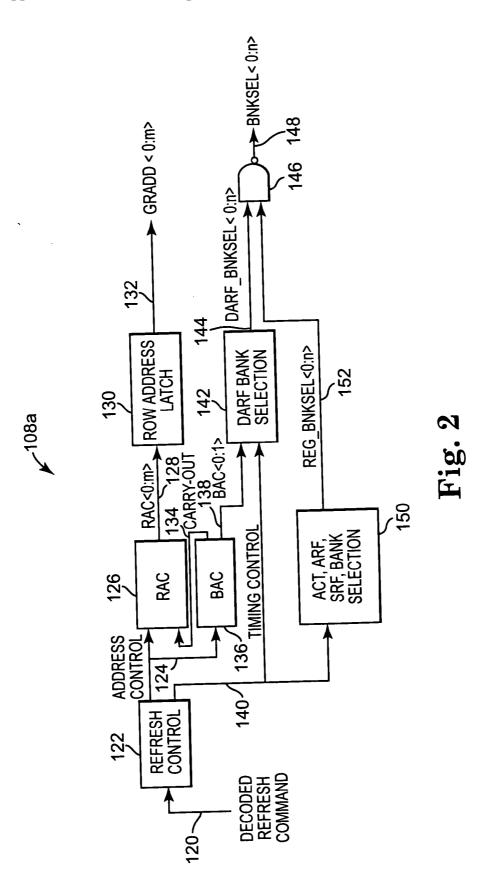

[0008] FIG. 3 is block diagram illustrating another embodiment of a refresh control circuit.

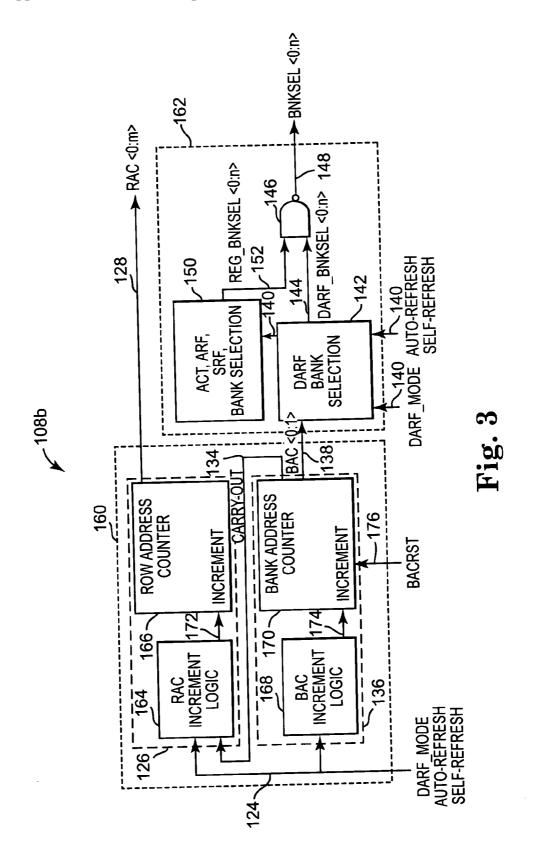

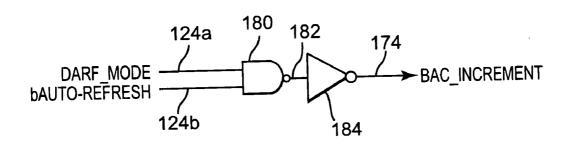

[0009] FIG. 4 is a diagram illustrating one embodiment of bank address counter increment logic.

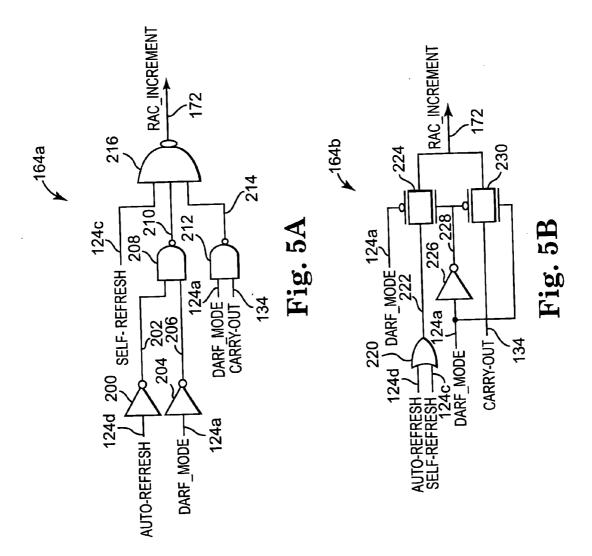

[0010] FIG. 5A is a diagram illustrating one embodiment of row address counter increment logic.

[0011] FIG. 5B is a diagram illustrating another embodiment of row address counter increment logic.

[0012] FIG. 5C is a diagram illustrating another embodiment of row address counter increment logic and bank address counter logic.

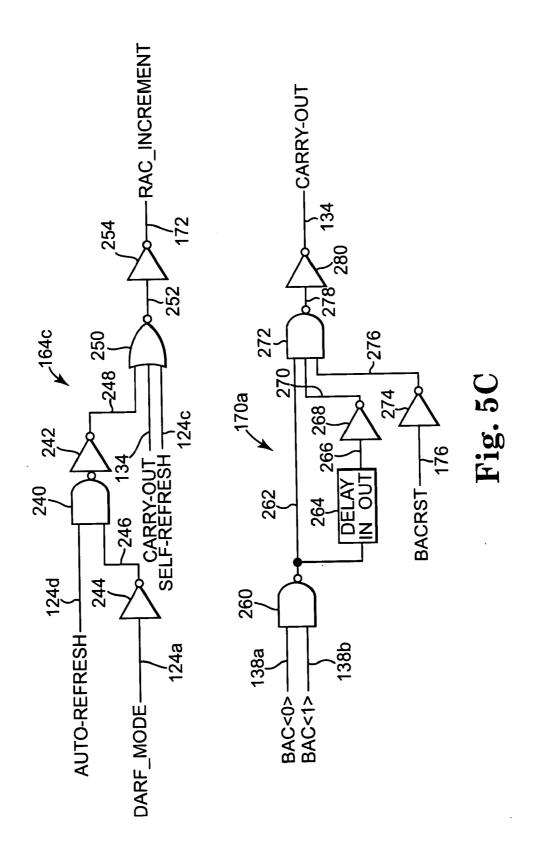

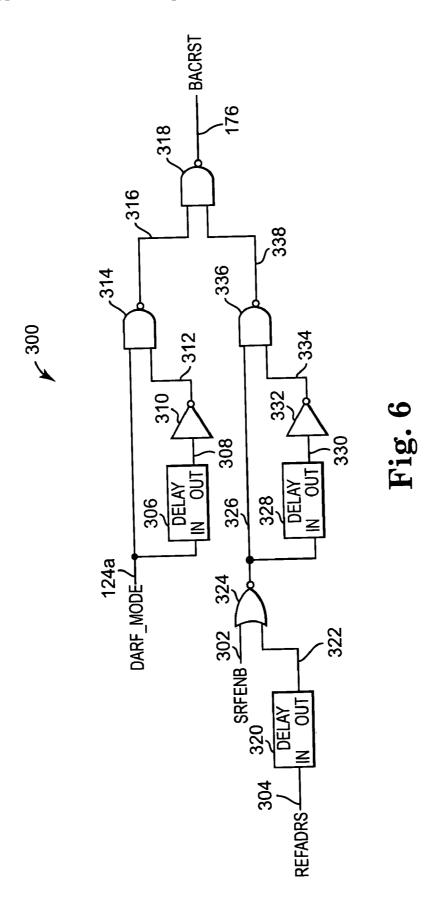

[0013] FIG. 6 is a diagram illustrating one embodiment of a circuit for resetting a bank address counter.

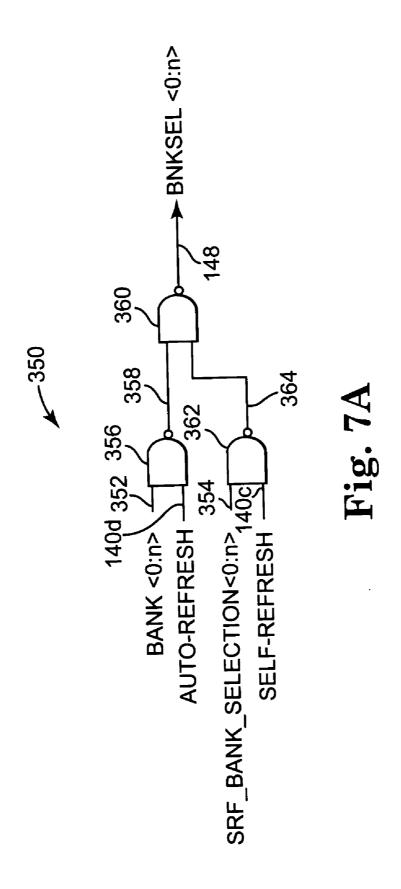

[0014] FIG. 7A is a diagram illustrating one embodiment of a circuit for selecting memory banks.

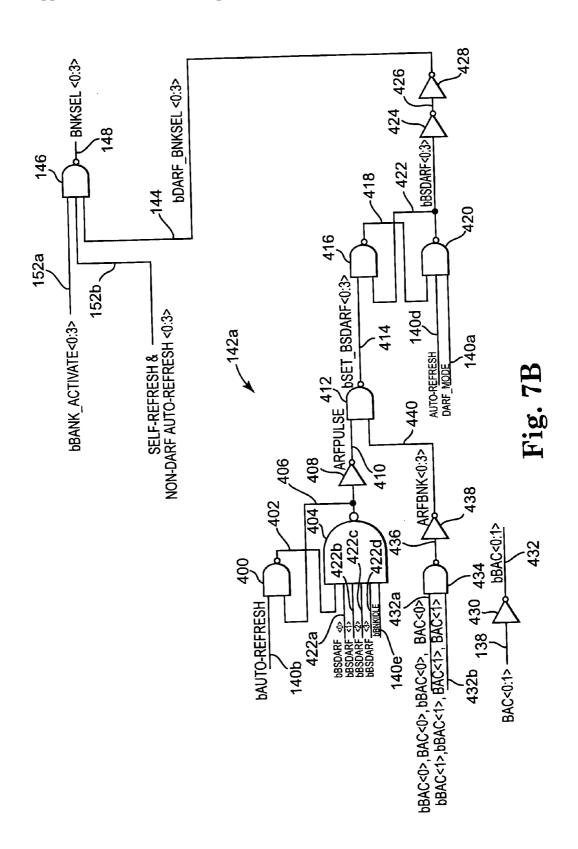

[0015] FIG. 7b is a diagram illustrating another embodiment of a circuit for selecting memory banks.

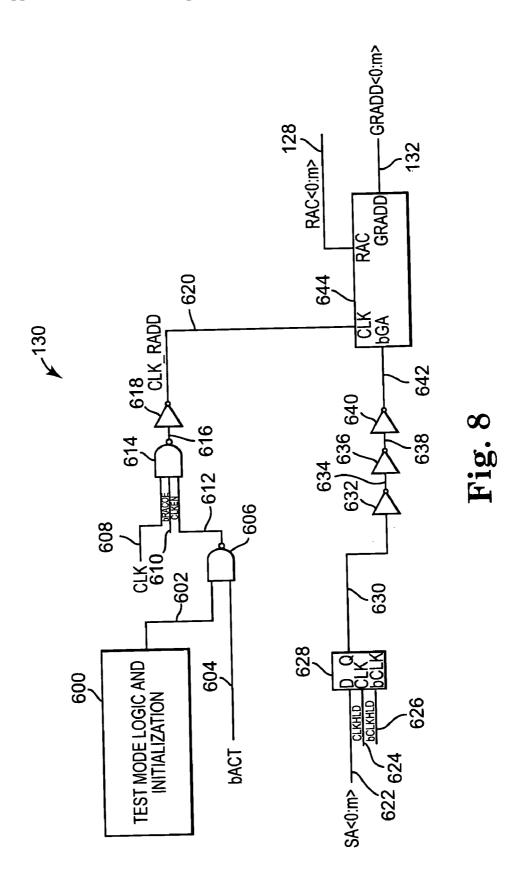

[0016] FIG. 8 is a diagram illustrating one embodiment of a two stage row address latch.

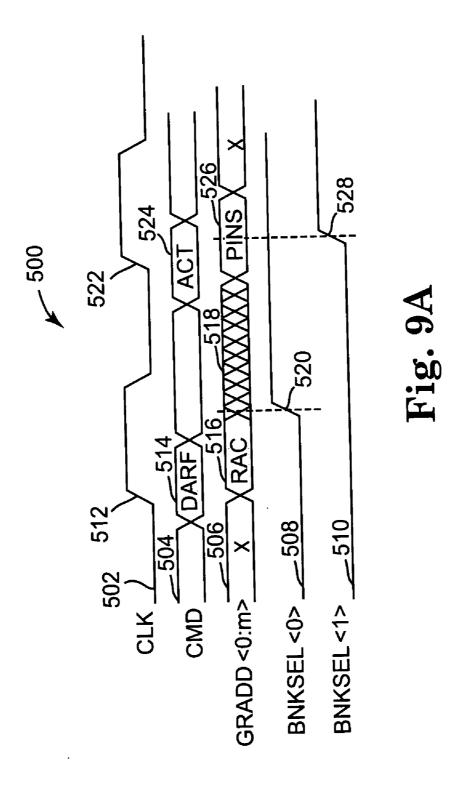

[0017] FIG. 9A is a timing diagram illustrating one embodiment of the timing of signals for back-to-back directed auto-refresh and activate commands.

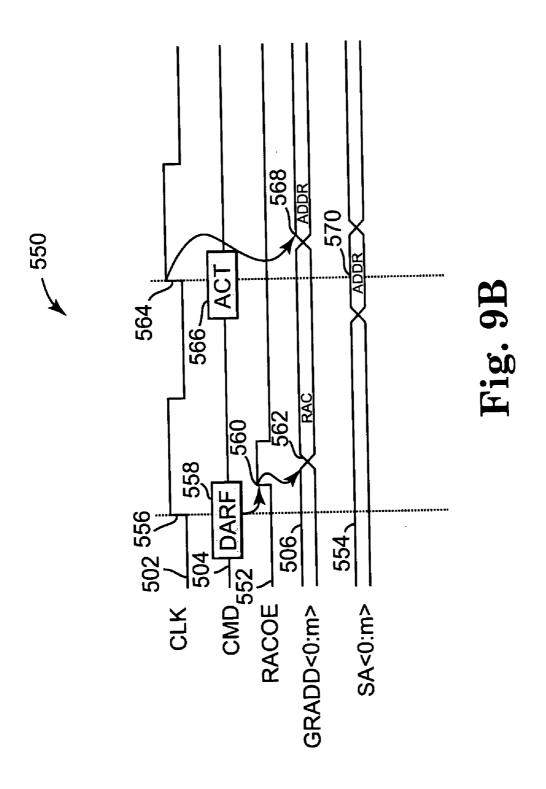

[0018] FIG. 9B is a timing diagram illustrating another embodiment of the timing of signals for back-to-back directed auto-refresh and activate commands.

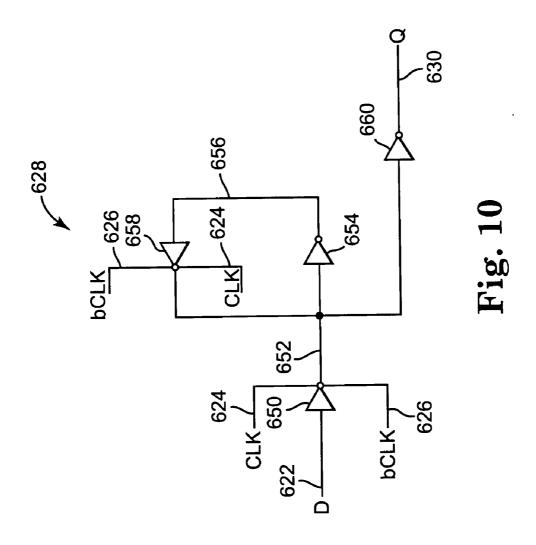

[0019] FIG. 10 is a diagram illustrating one embodiment of the first latch stage of the row address latch.

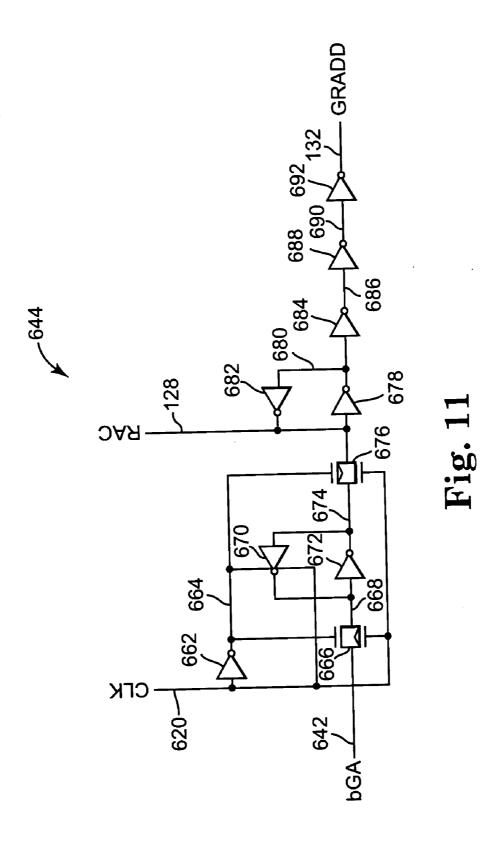

[0020] FIG. 11 is a diagram illustrating one embodiment of the second latch stage of the row address latch.

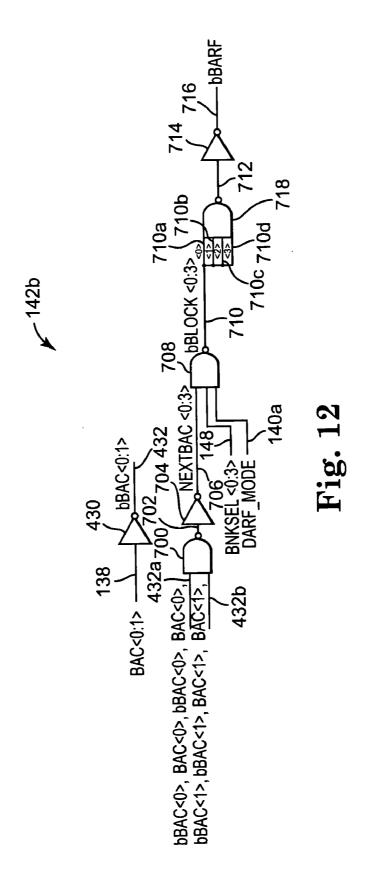

[0021] FIG. 12 is a diagram illustrating one embodiment of a circuit for bypassing a memory bank.

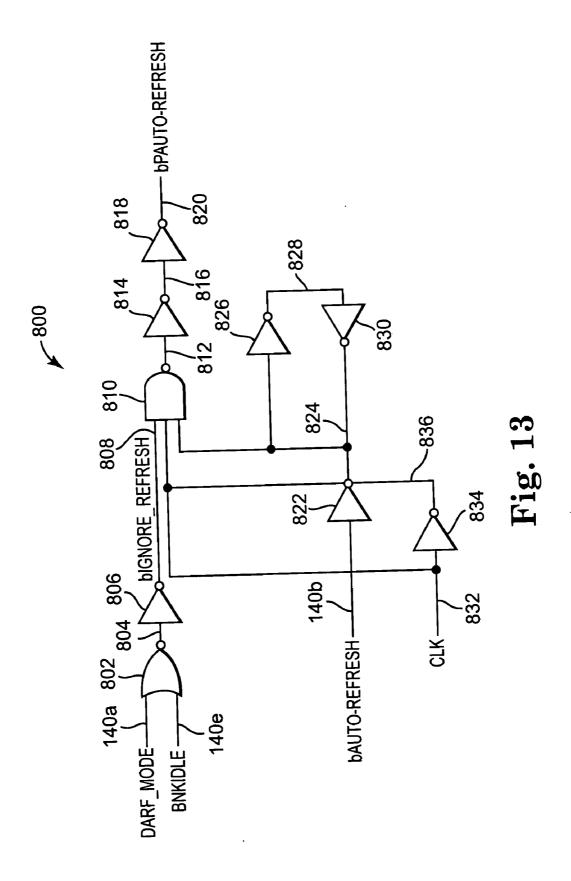

[0022] FIG. 13 is a diagram illustrating one embodiment of a circuit for allowing a directed auto-refresh while another memory bank is active.

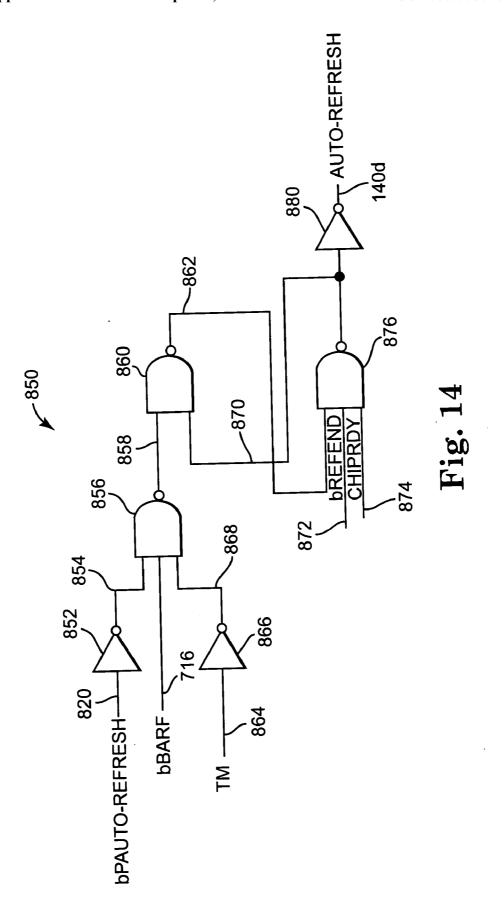

[0023] FIG. 14 is a diagram illustrating one embodiment of a circuit for providing an auto-refresh signal.

## DETAILED DESCRIPTION

[0024] FIG. 1 is a block diagram illustrating one embodiment of a memory device 100. In one embodiment, memory device 100 includes a dynamic random access memory (DRAM). Memory device 100 includes a memory controller 102 and a memory 106. Memory controller 102 is electrically coupled to memory 106 through communication path 104. Memory controller 102 controls the operation of

memory 106. Memory 106 includes a control circuit 108 and a plurality of memory banks 112a-112(n), where "n" equals any suitable number of memory banks. In one embodiment "n" equals 3. Control circuit 108 is electrically coupled to memory banks 112a-112(n) through communication path 110.

[0025] Control circuit 108 is configured to implement a directed auto-refresh (DARF) mode for memory 106. The DARF mode implementation provides auto-refresh scheduling flexibility that reduces the bandwidth penalty of refreshing memory cells within memory banks 112a-112(n). A DARF command is an auto-refresh command that is issued when memory 106 is in DARF mode. One DARF command refreshes one memory bank 112a-112(n) at a time, and rotation through memory banks 112a-112(n) proceeds in a directed order.

[0026] For example, a first DARF command refreshes memory cells at a selected row address in memory bank zero 112a. A second DARF command refreshes memory cells at the selected row address in memory bank one 112b. A third DARF command refreshes memory cells at the selected row address in memory bank two 112c. The DARF commands continue to be issued to the memory banks until the memory cells at the selected row address in memory bank N 112(n) have been refreshed. After the memory cells at the selected row address in each memory bank 112a-112(n) have been refreshed, the following DARF command refreshes the memory cells at the next row address in memory bank zero 112a. The DARF commands continue to be issued to refresh all memory cells at all row addresses in each memory bank 112a-112(n).

[0027] DARF scheduling improves the bandwidth of memory 106. In the typical auto-refresh with DARF mode disabled, all memory banks 112a-112(n) are precharged, and then an auto-refresh command is issued to refresh the memory cells at the selected row address in all the memory banks simultaneously. No operation (NOP) commands are issued during the auto-refresh to activate delay (tRFC) time. Once the tRFC time has expired, a memory bank 112a-112(n) can be activated and read and write operations can resume. With DARF mode enabled, a user can access a first memory bank 112a-112(n) continuously, issue a DARF command to a second memory bank 112a-112(n), and then continue on the next clock cycle to access the first memory bank 112a-112(n). With DARF mode enabled, DARF commands are issued at a rate four times that of typical autorefresh commands for a memory having four memory banks, however, the tRFC time is not wasted on NOP commands.

[0028] In one embodiment, enabling and disabling DARF mode functionality for memory 106 is determined by setting or resetting a mode register set command. In another embodiment, a fuse within memory 106 is used to enable or disable DARF mode functionality. In one embodiment, a bank address counter (BAC) is used for incrementing through memory banks 112a-112(n) for DARF operations, and a row address counter (RAC) is used for incrementing through row addresses of memory banks 112a-112(n) for DARF operations. In one embodiment, a two-bit BAC is implemented as the two least significant bits of the RAC for DARF operations. The BAC is reset when DARF mode is entered and when self-refresh (SRF) mode exits to remain in sync with memory controller 102.

[0029] In one embodiment, control circuit 108 includes DARF mode command controls that use typical auto-refresh detection, timing, set, and reset circuitry. Transitions into and out of self-refresh mode are managed to avoid skipping memory banks or rows of memory cells. This management and control includes resetting the BAC to ensure no memory banks or rows of memory cells are skipped. In one embodiment, a dedicated BAC bus is used to select the memory bank 112a-112(n) on which to perform the DARF, thereby eliminating all timing constraints imposed by high-frequency back-to-back DARF and activate (ACT) commands. In one embodiment, a two-stage row address latch is used to allow high-frequency back-to-back DARF and ACT commands. A DARF command can be issued to one memory bank 112a-112(n) while another memory bank 112a-112(n)is active for read or write access. A directed auto-refresh command is blocked if the command is issued to an active memory bank 112a-112(n). The directed auto-refresh command, however, is reissued to the memory bank 112a-112(n)once read or write access to the memory bank 112a-112(n)is complete so as not to skip the auto-refresh of the memory bank 112a-112(n).

[0030] FIG. 2 is a block diagram illustrating one embodiment of a refresh control circuit 108a. In one embodiment, refresh control circuit 108a is a portion of control circuit 108. Refresh control circuit 108a includes refresh control circuit 122, row address counter (RAC) 126, bank address counter (BAC) 136, row address latch 130, DARF bank selection circuit 142, activate (ACT), auto-refresh (ARF), self-refresh (SRF), and bank selection circuit 150, and NAND gate 146.

[0031] An input of refresh control circuit 122 receives a decoded refresh command on decoded refresh command communication path 120. An output of refresh control circuit 122 is electrically coupled to an input of RAC 126 and an input of BAC 136 through address control communication path 124. Another output of refresh control circuit 122 is electrically coupled to an input of DARF bank selection circuit 142 and an input of ACT, ARF, SRF, and bank selection circuit 150 through timing control communication path 140. An output of RAC 126 is electrically coupled to an input of row address latch 130 through row address counter address (RAC<0:m>) communication path 128. An output of BAC 136 is electrically coupled to an input of RAC 126 through carry-out (CARRY-OUT) signal path 134. Another output of BAC 136 is electrically coupled to DARF bank selection circuit 142 through bank address counter address (BAC<0:1>) communication path 138.

[0032] The output of row address latch 130 provides the global row address (GRADD<0:m>) on GRADD<0m> communication path 132. The output of DARF bank selection circuit 142 is electrically coupled to a first input of NAND gate 146 through DARF bank selection (DARF\_BNKSEL<0:n>) communication path 144. The output of ACT, ARF, SRF, and bank selection circuit 150 is electrically coupled to a second input of NAND gate 146 through regular bank select (REG\_BNKSEL<0:n>) communication path 152. The output of NAND gate 146 provides the bank select (BANKSEL<0:n>) signals on BNKSEL<0:n> communication path 148.

[0033] Refresh control circuit 122 receives a decoded refresh command signal on decoded refresh command com-

munication path 120 to provide address control signals on address control communication path 124 and timing control signals on timing control communication path 140. RAC 126 receives the address control signals on address control communication path 124 and the CARRY-OUT signal on CARRY-OUT signal path 134 to provide the RAC<0:m> signals on RAC<0:m> communication path 128. Based on the address control signals and the CARRY-OUT signal, RAC 126 increments through the row addresses of memory banks 112a-122(n) in self-refresh mode, in auto-refresh mode, or in directed auto-refresh mode for refreshing the memory cells at the row addresses.

[0034] BAC 136 receives the address control signals on address control communication path 124 to provide the BAC<0:1> signals on BAC<0:1> communication path 138 and the CARRY-OUT signal on CARRY-OUT signal path 134. Based on the address control signals, BAC 136 increments through the bank addresses of memory banks 112a-112(n) in DARF mode for refreshing the memory cells within each memory bank 112a-112(n). Each time the count of BAC 136 reaches the total number of memory banks "n" plus one, BAC 136 provides a logic high CARRY-OUT signal to increment RAC 126. BAC 136 is not used if DARF mode is disabled.

[0035] Row address latch 130 receives the RAC<0:m> signals on RAC<0:m> communication path 128 to provide the GRADD<0:m> signals on GRADD<0:m> communication path 132. Row address latch 130 latches the RAC<0:m> signals from RAC 126 in self-refresh, auto-refresh, or directed auto-refresh mode. Row address latch 130 latches the row addresses for a read or write operation from memory controller 102 during a memory bank activate command. Row address latch 130 provides the row addresses from memory controller 102 on GRADD<0:m> communication path 132 for an active memory bank read or write operation. Row address latch 130 provides the RAC<0:m> signals on GRADD<0:m> communication path 132 for an inactive memory bank self-refresh, auto-refresh, or directed auto-refresh operation.

[0036] DARF bank selection circuit 142 receives the BAC<0:1> signals on BAC<0:1> communication path 138 and the timing control signals on timing control communication path 140 to provide the DARF\_BNKSEL<0:n> signals on DARF\_BNKSEL<0:n> communication path 144. DARF bank selection circuit 142 selects the memory bank 112a-112(n) for a directed auto-refresh based on the BAC<0:1> signals and the timing control signals.

[0037] ACT, ARF, SRF, and bank selection circuit 150 receives the timing control signals on timing control communication path 140 to provide the REG\_BNKSEL<0:n> signals on REG\_BNKSEL<0:n> communication path 152. With DARF mode enabled or disabled, ACT, ARF, SRF, and bank selection circuit 150 selects the memory banks 112*a*-112(*n*) for activation and self-refresh based on the timing control signals. With DARF mode disabled, ACT, ARF, SRF, and bank selection circuit 150 also selects the memory banks 112*a*-112(*n*) for auto-refresh based on the timing control signals.

[0038] NAND gate 146 receives the DARF\_BNKSEL<0:n> signals on DARF\_BNKSEL<0:n> communication path 144 and the REG\_BNKSEL<0:n> signals on REG\_BNKSEL<0:n> communication path 152 to

provide the BNKSEL<0:n> signals on BNKSEL<0:n> communication path 148. In response to a logic high DARF\_BNKSEL<0:n> signal and a corresponding logic high REG\_BNKSEL<0:n> signal, NAND gate 146 outputs a corresponding logic low BNKSEL<0:n> signal. In response to a logic low DARF\_BNKSEL<0:n> signal or a corresponding logic low REG\_BNKSEL<0:n> signal, NAND gate 146 outputs a corresponding logic high BNKSEL<0:n> signal.

[0039] In operation, with DARF mode disabled, BAC 136 and DARF bank selection circuit 142 are inactive and auto-refresh occurs in the typical manner with all memory banks 112a-112(n) refreshed simultaneously. With DARF mode enabled, BAC 136 and DARF bank selection circuit 142 are active and one memory bank 112a-112(n) is refreshed at a time based on the count of BAC 136 provided on BAC<0:1> communication path 138. Therefore, while one memory bank 112a-112(n) is being refreshed, another memory bank 112a-112(n) can be active for read or write operations. In one embodiment, a logic low DARF\_BNKSEL<0:n> signal or a corresponding logic low REG\_BNKSEL<0:n> signal selects the corresponding memory bank 112a-112(n) by providing a corresponding logic high BNKSEL<0:n> signal for activating or refreshing the selected memory bank 112a-112(n).

[0040] FIG. 3 is a block diagram illustrating another embodiment of a refresh control circuit 108b. In one embodiment, refresh control circuit 108b is a portion of control circuit 108. Refresh control circuit 108b includes an address counter block 160 and a row control block 162. Address counter block 160 includes RAC 126, which includes RAC increment logic 164 and row address counter 166. Address counter block 160 also includes BAC 136, which includes BAC increment logic 168 and bank address counter 170. Row control block 162 includes ACT, ARF, SRF, and bank selection circuit 150, DARF bank selection circuit 142, and NAND gate 146.

[0041] An input of RAC increment logic 164 and an input of BAC increment logic 168 receive the DARF\_MODE, AUTO-REFRESH, and SELF-REFRESH signals on address control communication path 124. An output of RAC increment logic 164 is electrically coupled to the INCRE-MENT input of row address counter 166 through signal path 172. The output of row address counter 166 provides the RAC<0:m> signals on RAC<0:m> communication path 128. The output of BAC increment logic 168 is electrically coupled to the INCREMENT input of bank address counter 170 through signal path 174. An input of bank address counter 170 receives the BAC reset (BACRST) signal on BACRST signal path 176. An output of bank address counter 170 is electrically coupled to an input of RAC increment logic 164 through CARRY-OUT signal path 134. Another output of bank address counter 170 is electrically coupled to an input of DARF bank selection circuit 142 through BAC<0:1> communication path 138.

[0042] Inputs of DARF bank selection circuit 142 receive the DARF\_MODE, AUTO-REFRESH, and SELF-RE-FRESH signals on timing control communication path 140. The output of DARF bank selection circuit 142 is electrically coupled to a first input of NAND gate 146 through DARF\_BNKSEL<0:n> communication path 144. An input of ACT, ARF, SRF, and bank selection circuit 150 receives

the AUTO-REFRESH and SELF-REFRESH signals on timing control communication path 140. The output of ACT, ARF, SRF, and bank selection circuit 150 is electrically coupled to a second input of NAND gate 146 through REG\_BNKSEL<0:n> communication path 152. The output of NAND gate 146 provides the BNKSEL<0:n> signals on BNKSEL<0:n> communication path 148.

[0043] RAC increment logic 164 receives the DARF\_MODE, AUTO-REFRESH, and SELF-REFRESH signals on address control communication path 124 and the CARRY-OUT signal on CARRY-OUT signal path 134 to provide the RAC increment signal on signal path 172. RAC increment logic 164 determines when to increment row address counter 166 based on the DARF\_MODE, AUTO-REFRESH, SELF-REFRESH, and CARRY-OUT signals.

[0044] Row address counter 166 receives the RAC increment signal on signal path 172 to provide the RAC<0:m> signals on RAC<0:m> communication path 128. The count of row address counter 166 increments in response to each logic high RAC increment signal. The count of row address counter 166 is output on the RAC<0:m> signals.

[0045] BAC increment logic 168 receives the DARF\_MODE, AUTO-REFRESH, and SELF-REFRESH signals on address control communication path 124 to provide the BAC increment signal on signal path 174. BAC increment logic 168 determines when to increment bank address counter 170 based on the DARF\_MODE, AUTO-RE-FRESH, and SELF-REFRESH signals.

[0046] Bank address counter 170 receives the BAC increment signal on signal path 174 and the BACRST signal on BACRST signal path 176 to provide the CARRY-OUT signal on CARRY-OUT signal path 134 and the BAC<0:1> signals on BAC<0:1> communication path 138. The count of bank address counter 170 increments in response to each logic high BAC increment signal. The count of bank address counter 170 is reset in response to each logic high BACRST signal. In one embodiment, bank address counter 170 is implemented as the two least significant bits of row address counter 166. The count of bank address counter 170 is output on the BAC<0:1> signals.

[0047] ACT, ARF, SRF, and bank selection circuit 150 functions similarly to the ACT, ARF, SRF, and bank selection circuit 150 previously described with reference to FIG. 2. DARF bank selection circuit 142 functions similarly to the DARF bank selection circuit 142 previously described with reference to FIG. 2. NAND gate 146 functions similarly to the NAND gate 146 previously described with reference to FIG. 2. The overall operation of refresh control circuit 108b is similar to the operation of refresh control circuit 108a previously described with reference to FIG. 2.

[0048] FIG. 4 is a diagram illustrating one embodiment of BAC increment logic 168. BAC increment logic 168 includes NAND gate 180 and inverter 184. A first input of NAND gate 180 receives the DARF\_MODE signal on DARF\_MODE signal path 124a. A second input of NAND gate 180 receives the inverted auto refresh (bAUTO-RE-FRESH) signal on bAUTO-REFRESH signal path 124b. The output of NAND gate 180 is electrically coupled to the input of inverter 184 through signal path 182. The output of inverter 184 provides the BAC\_INCREMENT signal on BAC\_INCREMENT signal path 174.

[0049] The DARF\_MODE signal on DARF\_MODE signal path 124a is logic high if DARF mode is enabled and logic low if DARF mode is disabled. The bAUTO-REFRESH signal on bAUTO-REFRESH signal path 124b is logic low if an auto-refresh is in progress and logic high if an auto-refresh is not in progress. At the conclusion of an auto-refresh, the bAUTO-REFRESH signal transitions from logic low to logic high. In response to a logic high DARF\_MODE signal and a logic high bAUTO-REFRESH signal, NAND gate 180 outputs a logic low signal on signal path 182. In response to a logic low DARF\_MODE signal or a logic low bAUTO-REFRESH signal, NAND gate 180 outputs a logic high signal on signal path 182. Inverter 184 inverts the signal on signal path 182 to provide the BAC\_IN-CREMENT signal on BAC\_INCREMENT signal path 174.

[0050] In operation with DARF mode enabled, the DARF\_MODE signal is logic high and the bAUTO-REFRESH signal transitions to logic high at the conclusion of each auto-refresh. In response to the logic high DARF\_MODE signal and a logic high bAUTO-REFRESH signal, the BAC\_INCREMENT signal transitions to logic high to increment the count of bank address counter 170. With DARF mode disabled, the DARF\_MODE signal is logic low. In response to the logic low DARF\_MODE signal, the BAC\_INCREMENT signal is logic low and the count of bank address counter 170 does not increment.

[0051] FIG. 5A is a diagram illustrating one embodiment of RAC increment logic 164a. RAC increment logic 164a includes inverters 200 and 204 and NAND gates 208, 212, and 216. The input of inverter 200 receives the AUTO-REFRESH signal on AUTO-REFRESH signal path 124d. The output of inverter 200 is electrically coupled to a first input of NAND gate 208 through signal path 202. Inverter 202 receives the DARF\_MODE signal on DARF\_MODE signal path 124a. The output of inverter 204 is electrically coupled to a second input of NAND gate 208 through signal path 206. A first input of NAND gate 212 receives the DARF\_MODE signal on DARF\_MODE signal path 124a. A second input of NAND gate 212 receives the CARRY-OUT signal on CARRY-OUT signal path 134. The output of NAND gate 208 is electrically coupled to a first input of NAND gate 216 through signal path 210. The output of NAND gate 212 is electrically coupled to a second input of NAND gate 216 through signal path 214. A third input of NAND gate 216 receives the SELF-REFRESH signal on SELF-REFRESH signal path 124c. The output of NAND gate 216 provides the RAC\_INCREMENT signal on RAC\_INCREMENT signal path 172.

[0052] The SELF-REFRESH signal on SELF-REFRESH signal path 124c is logic high when a self-refresh is in progress and logic low when a self refresh is not in progress. The AUTO-REFRESH signal on AUTO-REFRESH signal path 124d is logic high when an auto-refresh is in progress and logic low when an auto-refresh is not in progress Inverter 200 inverts the AUTO-REFRESH signal on AUTO-REFRESH signal path 124d to provide the signal on signal path 202. Inverter 204 inverts the DARF\_MODE signal on DARF\_MODE signal path 124a to provide the signal on signal path 206. In response to a logic high signal on signal path 206 and a logic high signal on signal path 206 named a logic low signal on signal path 210. In response to a logic low signal path 210 or a logic

low signal on signal path 206, NAND gate 208 outputs a logic high signal on signal path 210.

[0053] In response to a logic high DARF\_MODE signal on DARF\_MODE signal path 124a and a logic high CARRY-OUT signal on CARRY-OUT signal path 134, NAND gate 212 outputs a logic low signal on signal path 214. In response to a logic low DARF\_MODE signal on DARF\_MODE signal path 124 or a logic low CARRY-OUT signal on CARRY-OUT signal path 134, NAND gate 212 outputs a logic high signal on signal path 214.

[0054] In response to a logic high SELF-REFRESH signal on SELF-REFRESH signal path 124c, a logic high signal on signal path 210, and a logic high signal on signal path 214, NAND gate 216 outputs a logic low RAC\_INCREMENT signal on RAC\_INCREMENT signal path 172. In response to a logic low SELF-REFRESH signal on SELF-REFRESH signal path 124c, a logic low signal on signal path 210, or a logic low signal on signal path 214, NAND gate 216 outputs a logic high RAC\_INCREMENT signal on RAC\_INCREMENT signal path 172.

[0055] In operation with DARF mode enabled or disabled, a logic high RAC\_INCREMENT signal is provided in response to a self-refresh exit. With DARF mode disabled, a logic high RAC\_INCREMENT signal is provided in response to a completed auto-refresh. With DARF mode enabled, a logic high RAC\_INCREMENT signal is provided in response to a logic high CARRY-OUT signal. In response to a logic high RAC\_INCREMENT signal, the count of row address counter 166 increments. In response to a logic low RAC\_INCREMENT signal, the count of row address counter 166 does not increment.

[0056] FIG. 5B is a diagram illustrating another embodiment of RAC increment logic 164b. RAC increment logic 164b includes OR gate 220, inverter 226, and transmission gates 224 and 230. A first input of OR gate 220 receives the AUTO-REFRESH signal on AUTO-REFRESH signal path 124d. A second input of OR gate 220 receives the SELF-REFRESH signal on SELF-REFRESH signal path 124c. The output of OR gate 220 is electrically coupled to the data input of transmission gate 224 through signal path 222. The input of inverter 226, the logic high enable input of transmission gate 230, and the logic low enable input of transmission gate 224 receive the DARF\_MODE signal on DARF\_MODE signal path 124a. The output of inverter 226 is electrically coupled to the logic high enable input of transmission gate 224 and the logic low enable input of transmission gate 230 through signal path 228. The data input of transmission gate 230 receives the CARRY-OUT signal on CARRY-OUT signal path 134. The data output of transmission gate 224 and the data output of transmission gate 230 provide the RAC\_INCREMENT signal on RAC\_INCREMENT signal path 172.

[0057] In response to a logic high AUTO-REFRESH signal on AUTO-REFRESH signal path 124d or a logic high SELF-REFRESH signal on SELF-REFRESH signal path 124c, OR gate 220 outputs a logic high signal on signal path 222. In response to a logic low AUTO-REFRESH signal on AUTO-REFRESH signal path 124d and a logic low SELF-REFRESH signal on SELF-REFRESH signal path 124c, OR gate 220 outputs a logic low signal on signal path 222. Inverter 226 inverts the DARF\_MODE signal on DARF\_MODE signal path 124a to provide the signal on signal path 228.

[0058] In response to a logic low DARF\_MODE signal on DARF\_MODE signal path 124a and a logic high signal on signal path 228, transmission gate 224 turns on to pass the signal on signal path 222 to RAC\_INCREMENT signal path 172. In response to a logic high DARF\_MODE signal on DARF\_MODE signal path 124a and a logic low signal on signal path 228, transmission gate 224 turns off to block the signal on signal path 222 from passing to RAC\_INCREMENT signal path 172.

[0059] In response to a logic low signal on signal path 228 and a logic high DARF\_MODE signal on DARF\_MODE signal path 124a, transmission gate 230 turns on to pass the CARRY-OUT signal on CARRY-OUT signal path 134 to RAC\_INCREMENT signal path 172. In response to a logic high signal on signal path 228 and a logic low DARF\_MODE signal on DARF\_MODE signal 30 path 124a, transmission gate 230 turns off to block the CARRY-OUT signal on CARRY-OUT signal path 134 from passing to RAC\_INCREMENT signal path 172.

[0060] In operation with DARF mode disabled, a logic high RAC\_INCREMENT signal is provided in response to a logic high SELF-REFRESH signal or a logic high AUTO-REFRESH signal. With DARF mode enabled, a logic high RAC\_INCREMENT signal is provided in response to a logic high CARRY-OUT signal. In response to a logic high RAC\_INCREMENT signal, the count of row address counter 166 increments. In response to a logic low RAC\_INCREMENT signal, the count of row address counter 166 does not increment.

[0061] FIG. 5C is a diagram illustrating another embodiment of RAC increment logic 164c and a portion 170a of bank address counter 170. RAC increment logic 164c includes NAND gate 240, inverters 242, 244, and 254, and NOR gate 250. Portion 170a of bank address counter 170 includes NAND gates 260 and 272, delay 264, and inverters 268, 274, and 280.

[0062] The input of inverter 244 receives the DARF-\_MODE signal on DARF\_MODE signal path 124a. The output of inverter 244 is electrically coupled to a first input of NAND gate 240 through signal path 246. A second input of NAND gate 240 receives the AUTO-REFRESH signal on AUTO-REFRESH signal path 124d. The output of NAND gate 240 is electrically coupled to the input of inverter 242. The output of inverter 242 is electrically coupled to a first input of NOR gate 250. A second input of NOR gate 250 receives the CARRY-OUT signal on CARRY-OUT signal path 134. A third input of NOR gate 250 receives the SELF-REFRESH signal on SELF-REFRESH signal path 124c. The output of NOR gate 250 is electrically coupled to the input of inverter 254. The output of inverter 254 provides the RAC\_INCREMENT signal on RAC\_INCREMENT signal path 172.

[0063] A first input of NAND gate 260 receives the BAC<0> signal on BAC<0> signal path 138a. A second input of NAND gate 260 receives the BAC<1> signal on BAC<1> signal path 138b. The output of NAND gate 260 is electrically coupled to a first input of NAND gate 272 and the input (IN) of delay 264 through signal path 262. The output (OUT) of delay 266 is electrically coupled to the input of inverter 268 through signal path 266. The output of inverter 268 is electrically coupled to a second input of NAND gate 272 through signal path 270. The input of

inverter **274** receives the BACRST signal on BACRST signal path **176**. The output of inverter **274** is electrically coupled to a third input of NAND gate **272** through signal path **276**. The output of NAND gate **272** is electrically coupled to the input of inverter **280** through signal path **278**. The output of inverter **280** provides the CARRY-OUT signal on CARRY-OUT signal path **134**.

[0064] Inverter 244 inverts the DARF\_MODE signal on DARF\_MODE signal path 124a to provide the signal on signal path 246. In response to a logic high AUTO-REFRESH signal on AUTO-REFRESH signal path 124d and a logic high signal on signal path 246, NAND gate 240 outputs a logic low signal. In response to a logic low AUTO-REFRESH signal on AUTO-REFRESH signal path 124d or a logic low signal on signal path 246, NAND gate 240 outputs a logic high signal. Inverter 242 inverts the output signal from NAND gate 240 to provide the signal on signal path 248.

[0065] In response to a logic low signal on signal path 248, a logic low CARRY-OUT signal on CARRY-OUT signal path 134, and a logic low SELF-REFRESH signal on SELF-REFRESH signal path 124c, NOR gate 250 outputs a logic high signal on signal path 252. In response to a logic high signal on signal path 248, a logic high CARRY-OUT signal on CARRY-OUT signal path 134, or a logic high SELF-REFRESH signal on SELF-REFRESH signal path 124c, NOR gate 250 outputs a logic low signal on signal path 252. Inverter 254 inverts the signal on signal path 252 to provide the RAC\_INCREMENT signal on RAC\_INCREMENT signal path 172.

[0066] In response to a logic high BAC<0> signal on BAC<0> signal path 138a and a logic high BAC<1> signal on BAC<1> signal path 138b, NAND gate 260 outputs a logic low signal on signal path 262. In response to a logic low BAC<0> signal on BAC<0> signal path 138a or a logic low BAC<1> signal on BAC<1> signal path 138b, NAND gate 260 outputs a logic high signal on signal path 262. Delay 264 delays the signal on signal path 262 to provide the signal on signal path 266. Inverter 268 inverts the signal on signal path 270. Inverter 272 inverts the BACRST signal on BACRST signal path 176 to provide the signal on signal path 276.

[0067] In response to a logic high signal on signal path 262, a logic high signal on signal path 270, and a logic high signal on signal path 276, NAND gate 272 outputs a logic low signal on signal path 278. In response to a logic low signal on signal path 262, a logic low signal on signal path 270, or a logic low signal on signal path 276, NAND gate 272 outputs a logic high signal on signal path 278. Inverter 280 inverts the signal on signal path 278 to provide the CARRY-OUT signal on CARRY-OUT signal path 134.

[0068] In operation, portion 170a of bank address counter 170 provides a logic high CARRY-OUT pulse in response to a logic low BACRST signal and the BAC<0> signal and the BAC<1> signal both transitioning from logic high to logic low (i.e. the count of bank address counter 170 resets from "11" to "00"). In response to a logic high BACRST signal, the CARRY-OUT signal remains logic low while the count of bank address counter 170 is reset.

[0069] In operation with DARF mode enabled, a logic high RAC\_INCREMENT signal is provided in response to

a logic high SELF-REFRESH signal or a logic high CARRY-OUT signal. With DARF mode disabled, a logic high RAC\_INCREMENT signal is provided in response to a logic high AUTO-REFRESH signal or a logic high SELF-REFRESH signal. In response to a logic high RAC\_INCREMENT signal, the count of row address counter 166 increments. In response to a logic low RAC\_-INCREMENT signal, the count of row address counter 166 does not increment.

[0070] FIG. 6 is a diagram illustrating one embodiment of a circuit 300 for resetting bank address counter 170. Circuit 300 includes delays 306, 320, and 328, NOR gate 324, inverters 310 and 332, and NAND gates 314, 318, and 336. A first input of NAND gate 314 and the input (IN) of delay 306 receive the DARF\_MODE signal on DARF\_MODE signal path 124a. The output (OUT) of delay 306 is electrically coupled to the input of inverter 310 through signal path 308. The output of inverter 310 is electrically coupled to a second input of NAND gate 314 through signal path 312. The output of NAND gate 314 is electrically coupled to a first input of NAND gate 318 through signal path 316.

[0071] The input (IN) of delay 320 receives the refresh address (REFADRS) signal on REFADRS signal path 304. The output (OUT) of delay 320 is electrically coupled to a first input of NOR gate 324 through signal path 322. A second input of NOR gate 324 receives the self-refresh enable (SRFENB) signal on SRFENB signal path 302. The output of NOR gate 324 is electrically coupled to a first input of NAND gate 336 and the input (IN) of delay 328 through signal path 326. The output (OUT) of delay 328 is electrically coupled to the input of inverter 332 through signal path 330. The output of inverter 332 is electrically coupled to a second input of NAND gate 336 through signal path 334. The output of NAND gate 336 is electrically coupled to a second input of NAND gate 318 through signal path 338. The output of NAND gate 318 provides the BACRST signal on BACRST signal path 176.

[0072] The SRFENB signal is logic high if a self-refresh or auto-refresh is in progress and logic low if a self-refresh or auto-refresh is not in progress. The REFADRS signal is used to select between the row addresses for a memory bank read or write operation and the row addresses from row address counter 166 for a memory bank refresh. The REFADRS signal is logic high for at least the start of a memory bank refresh. After a memory bank refresh has started or for a memory bank read or write operation, the REFADRS signal is logic low.

[0073] Delay 306 delays the DARF\_MODE signal on DARF\_MODE signal path 124a to provide the signal on signal path 308. Inverter 310 inverts the signal on signal path 308 to provide the signal on signal path 312. In response to a logic high DARF\_MODE signal on DARF\_MODE signal path 124a and a logic high signal on signal path 312, NAND gate 314 outputs a logic low signal on signal path 316. In response to a logic low DARF\_MODE signal on DARF\_MODE signal path 124a or a logic low signal on signal path 312, NAND gate 314 outputs a logic high signal on signal path 312, NAND gate 314 outputs a logic high signal on signal path 316.

[0074] Delay 320 delays the REFADRS signal on REFADRS signal path 304 to provide the signal on signal path 322. In response to a logic low SRFENB signal on SRFENB signal path 302 and a logic low signal on signal

path 322, NOR gate 324 outputs a logic high signal on signal path 326. In response to a logic high SRFENB signal on SRFENB signal path 302 or a logic high signal on signal path 322, NOR gate 324 outputs a logic low signal on signal path 326.

[0075] Delay 328 delays the signal on signal path 326 to provide the signal on signal path 330. Inverter 332 inverts the signal on signal path 330 to provide the signal on signal path 334. In response to a logic high signal on signal path 326 and a logic high signal on signal path 334, NAND gate 336 outputs a logic low signal on signal path 338. In response to a logic low signal on signal path 326 or a logic low signal on signal path 336 outputs a logic high signal on signal path 338.

[0076] In response to a logic high signal on signal path 316 and a logic high signal on signal path 338, NAND gate 318 outputs a logic low BACRST signal on BACRST signal path 176. In response to a logic low signal on signal path 316 or a logic low signal on signal path 338, NAND gate 318 outputs a logic high signal on BACRST signal path 176.

[0077] In operation, when DARF mode is enabled the DARF\_MODE signal transitions from logic low to logic high. In response to the DARF\_MODE signal transitioning to logic high, a pulse is provided on BACRST signal path 176. When self-refresh exits, the SRFENB signal transitions from logic high to logic low. In response to the SRFENB signal transitioning to logic low, a pulse is provided on BACRST signal path 176.

[0078] After an auto-refresh has started, the REFADRS signal transitions from logic high to logic low. In response to the REFADRS signal transitioning to logic low and after a delay defined by delay 320, a pulse is provided on BACRST signal path 176. Row address counter 166 is incremented when self-refresh exits. Bank address counter 170 is reset after row address counter 166 is incremented to prevent skipping bank zero 112a for the following row address. In response to a logic high BACRST signal, the count of bank address counter 170 is reset. In response to a logic low BACRST signal, the count of bank address counter 170 is not reset.

[0079] FIG. 7A is a diagram illustrating one embodiment of a circuit 350 for selecting memory banks 112a-112(n). Circuit 350 includes NAND gates 356, 362, and 360. A first input of NAND gate 356 receives the BANK<0:n> signals on BANK<0:n> communication path 352. A second input of NAND gate 356 receives the AUTO-REFRESH signal on AUTO-REFRESH signal path 140d. The output of NAND gate 356 is electrically coupled to a first input of NAND gate 360 through communication path 358. A first input of gate 362 receives SRF\_BANK\_SELECTION<0:n> signals SRF\_BANK\_SELECTION<0:n> communication path 354. A second input of NAND gate 362 receives the SELF-REFRESH signal on SELF-REFRESH signal path 140c. The output of NAND gate 362 is electrically coupled to a second input of NAND gate 360 through communication path 364. The output of NAND gate 360 provides the BNKSEL<0:n> signals on BNKSEL<0:n> communication path 148.

[0080] The BANK<0:n:> signals are logic high for all memory banks 112a-112(n) with DARF mode disabled.

With DARF mode enabled, the BANK<0:n> signals are logic high for the memory bank 112a-112(n) to be autorefreshed and logic low for the memory banks 112a-112(n) not being auto-refreshed. The SRF\_BANK\_SELECTION<0:n> signals are logic high for the memory banks 112a-112(n) being refreshed in self-refresh mode and logic low for the memory banks 112a-112(n) not being refreshed in self-refresh mode.

[0081] In response to a logic high BANK<0:n> signal on BANK<0:n> communication path 352 and a logic high AUTO-REFRESH signal on AUTO-REFRESH signal path 140d, NAND gate 356 outputs a corresponding logic low signal on communication path 358. In response to a logic low BANK<0:n> signal on BANK<0:n> communication path 352 or a logic low AUTO-REFRESH signal on AUTO-REFRESH signal path 140d, NAND gate 356 outputs a corresponding logic high signal on communication path 358.

[0082] In response logic high SRF\_BANK\_SELECTION<0:n> signal on SRF\_BANK\_SELECTION<0:n> communication path 354 and a logic high SELF-REFRESH signal on SELF-RE-FRESH signal path 140c, NAND gate 362 outputs a corresponding logic low signal on communication path 364. In response to a logic low SRF BANK SELECTION<0:n> signal on SRF\_BANK\_SELECTION<0:n> communication path 354 or a logic low SELF-REFRESH signal on SELF-REFRESH signal path 140c, NAND gate 362 outputs a corresponding logic high signal on communication path 364.

[0083] In response to a logic high signal on communication path 358 and a corresponding logic high signal on communication path 364, NAND gate 360 outputs a corresponding logic low BNKSEL<0:n> signal on BNKSEL<0:n> communication path 148. In response to a logic low signal on communication path 358 or a corresponding logic low signal on communication path 364, NAND gate 360 outputs a corresponding logic high BNKSEL<0:n> signal on BNKSEL<0:n> communication path 148.

[0084] In operation, the AUTO-REFRESH signal is combined with the BANK<0:n> signals and the SRF\_BANK\_SELECTION<0:n> signals are combined with the SELF-REFRESH signal to select the designated memory banks 112a-112(n). A logic high BNKSEL<0:n> signal for a memory bank 112a-112(n) indicates the memory bank 112a-112(n) is selected.

[0085] FIG. 7B is a diagram illustrating another embodiment of a circuit for selecting memory banks 112a-112(n)including DARF bank selection circuit 142a and NAND gate 146. In this embodiment, n equals 3. DARF bank selection circuit 142a includes NAND gates 400, 404, 412, 416, 420, and 434 and inverters 408, 424, 428, 430, and 438. A first input of NAND gate 400 receives the bAUTO-REFRESH signal on bAUTO-REFRESH signal path 140b. The output of NAND gate 400 is electrically coupled to a first input of NAND gate 404 through signal path 402. The output of NAND gate 404 is electrically coupled to a second input of NAND gate 400 and the input of inverter 408 through signal path 406. A second input of NAND gate 404 receives the inverted bank idle (bBNKIDLE) signal on bBNKIDLE signal path 140e. The output of inverter 408 is electrically coupled to a first input of NAND gate 412 through auto-refresh pulse (ARFPULSE) signal path 410.

[0086] The input of inverter 430 receives the BAC<0:1> signals on BAC<0:1> communication path 138. The output of inverter 430 provides the bBAC<0:1> signals on bBAC<0:1> communication path 432. A first input of NAND gate 434 receives the bBAC<0>, BAC<0>, bBAC<0>, and BAC<0> signals through communication path 432a. A second input of NAND gate 434 receives the bBAC<1>, bBAC<1>, and BAC<1> signals through communication path 432b. The output of NAND gate 434 is electrically coupled to the input of inverter 438 through communication path 436. The output of inverter 438 is electrically coupled to a second input of NAND gate 412 through auto-refresh bank (ARFBNK<0:3>) communication path 440. The output of NAND gate 412 is electrically coupled to a first input of NAND gate 416 through inverted set bank select for DARF (bSET\_BSDARF<0:3>) communication path 414.

[0087] The output of NAND gate 416 is electrically coupled to a first input of NAND gate 420 through communication path 418. The output of NAND gate 420 is electrically coupled to a second input of NAND gate 416, the input of inverter 424, and the inputs of NAND gate 404 through bBSDARF<0:3> communication path 422. A third input of NAND gate 404 receives the bBSBARF<0> signal on bBSBARF<0> signal path 422a. A fourth input of NAND gate 404 receives the bBSBARF<1> signal on bBSBARF<1> signal path 422b. A fifth input of NAND gate 404 receives the bBSBARF<2> signal on bBSBARF<2> signal path 422c. A sixth input of NAND gate 404 receives the bBSBARF<3> signal on bBSBARF<3> signal path 422d. A second input of NAND gate 420 receives the AUTO-REFRESH signal on AUTO-REFRESH signal path 140d. A third input of NAND gate 420 receives the DARF-\_MODE signal on DARF\_MODE signal path 140a. The output of inverter 424 is electrically coupled to the input of inverter 428 through communication path 426. The output of inverter 428 is electrically coupled to a first input of NAND gate 146 through bDARF\_BNKSEL<0:3> communication path 144.

[0088] A second input of NAND gate 146 receives the inverted bank activate (bBANK\_ACTIVATE<0:3>) signals on bBANK\_ACTIVATE<0:3>communication path 152a. A third input of NAND gate 146 receives the SELF-REFRESH and NON-DARF AUTO-REFRESH<0:3> signals on SELF-REFRESH and NON-DARF AUTO-REFRESH<0:3> communication path 152b. The output of NAND gate 146 provides the BNKSEL<0:3> signals on BNKSEL<0:3> communication path 148.

[0089] The bBANK\_ACTIVATE<0:3> signals are logic low for each memory bank 112a-112(n) selected to be activated and logic high for each memory bank 112a-112(n) not selected to be activated. The SELF-REFRESH and NON-DARF AUTO-REFRESH<0:3> signals are logic low for each memory bank 112a-112(n) selected to be self-refreshed. The SELF-REFRESH and NON-DARF AUTO-REFRESH<0:3> signals are also logic low for each memory bank 112a-112(n) selected to be auto-refreshed with DARF mode disabled. The SELF-REFRESH and NON-DARF AUTO-REFRESH<0:3> signals are logic high for each memory bank 112a-112(n) not being self-refreshed or not being auto-refreshed with DARF mode disabled. The bBNKIDLE signal is logic low if all memory banks 112a-

112(n) are idle and logic high if a memory bank 112a-112(n) is being precharged or is active.

[0090] In response to a logic high bAUTO-REFRESH signal on bAUTO-REFRESH signal path 140b and a logic high signal on signal path 406, NAND gate 400 outputs a logic low signal on signal path 402. In response to a logic low bAUTO-REFRESH signal on bAUTO-REFRESH signal path 140b or a logic low signal on signal path 406, NAND gate 400 outputs a logic high signal on signal path 402

[0091] In response to a logic high signal on signal path 402, a logic high bBSDARF<0> signal on BSDARF<0> signal path 422a, a logic high bBSDARF<1> signal on BSDARF<1> signal path 422b, a logic high bBSDARF<2> signal on BSDARF<2> signal path 422c, a logic high bBSDARF<3> signal on BSDARF<3> signal path 422d, and a logic high bBNKIDLE signal on bBNKIDLE signal path 140e, NAND gate 404 outputs a logic low signal on signal path 406. In response to a logic low signal on signal path 402, a logic low bBSDARF<0> signal on BSDARF<0> signal path 422a, a logic low bBSDARF<1> signal on BSDARF<1> signal path 422b, a logic low bBSDARF<2> signal on BSDARF<2> signal path 422c, a logic low bBS-DARF<3> signal on BSDARF<3> signal path 422d, or a logic low bBNKIDLE signal on bBNKIDLE signal path 140e, NAND gate 404 outputs a logic high signal on signal path 406. NAND gate 400 and NAND gate 404 provide a

[0092] Inverter 408 inverts the signal on signal path 406 to provide the ARFPULSE signal on ARFPULSE signal path 410. Inverter 430 inverts the BAC<0:1> signals on BAC<0:1> communication path 138 to provide the bBAC<0:1> signals on bBAC<0:1> communication path 432. In response to a logic high signal on communication path 432a and a corresponding logic high signal on communication path 432b, NAND gate 434 outputs a corresponding logic low signal on communication path 436. In response to a logic low signal on communication path 432a or a corresponding logic low signal on communication path 432b, NAND gate 434 outputs a corresponding logic high signal on communication path 432b, NAND gate 434 outputs a corresponding logic high signal on communication path 436.

[0093] Inverter 438 inverts the signals on communication path 436 to provide the ARFBNK<0:3> signals on ARFBNK<0:3> communication path 440. In response to a logic high ARFPULSE signal on ARFPULSE signal path 410 and a logic high ARFBNK<0:3> signal on ARFBNK<0:3> communication path 440, NAND gate 412 outputs a corresponding logic low bSET\_BSDARF<0:3> signal on bSET\_BSDARF<0:3> communication path 414. In response to a logic low ARFPULSE signal on ARFPULSE signal path 410 or a logic low ARFBNK<0:3> signal on ARFBANK<0:3> communication path 412 outputs a corresponding logic high bSET-BSDARF<0:3> signal on bSET\_BSDARF<0:3> signal on bSET\_BSDARF<0:3> signal on bSET\_BSDARF<0:3> signal on bSET\_BSDARF<0:3> communication path 414.

[0094] In response to a logic high bSET\_BSDARF<0:3> signal on bSET\_BSDARF<0:3> communication path 414 and a corresponding logic high bBSDARF<0:3> signal on bBSDARF<0:3> communication path 422, NAND gate 416 outputs a corresponding logic low signal on communication path 418. In response to a logic low bSET\_BSDARF<0:3> signal on bSET\_BSDARF<0:3> communication path 414 or a corresponding logic low bBSDARF<0:3> signal on bBS-

DARF<0:3> communication path 422, NAND gate 416 outputs a corresponding logic high signal on communication path 418.

[0095] In response to a logic high signal on communication path 418, a logic high AUTO-REFRESH signal on AUTO-REFRESH signal path 140d, and a logic high DARF\_MODE signal on DARF\_MODE signal path 140a, NAND gate 420 outputs a corresponding logic low bBS-DARF<0:3> signal on bBSDARF<0:3> communication path 422. In response to a logic low signal on communication path 418, a logic low AUTO-REFRESH signal on AUTO-REFRESH signal path 140d, or a logic low DARF\_MODE signal on DARF\_MODE signal path 140a, NAND gate 420 outputs a corresponding logic high bBS-DARF<0:3> signal on bBSDARF<0:3> communication path 422. NAND gate 416 and NAND gate 420 provide a latch.

[0096] Inverter 424 inverts the bBSDARF<0:3> signals on bBSDARF<0:3> communication path 422 to provide the signals on communication path 426. Inverter 428 inverts a signals on communication path 426 to provide the bDARF\_BNKSEL<0:3> signals on bDARF\_BNKSEL<0:3> communication path 144.

[0097] In response to a logic high bBANK\_ACTI-VATE<0:3> signal on bBANK\_ACTIVATE<0:3> communication path 152a, a corresponding logic high SELF-RE-FRESH and NON-DARF AUTO-REFRESH<0:3> signal on SELF-REFRESH and NON-DARF **AUTO-RE-**FRESH<0:3> communication path 152b, and a corresponding logic high bDARF\_BNKSEL<0:3> signal on bDARF-\_BNKSEL<0:3> communication path 144, NAND gate 146 outputs a corresponding logic low BNKSEL<0:3> signal on BNKSEL<0:3> communication path 148. In response to a low bBANK\_ACTIVATE<0:3> signal bBANK\_ACTIVATE<0:3> communication path 152a, a corresponding logic low SELF-REFRESH and NON-DARF AUTO-REFRESH<0:3> signal on SELF-REFRESH and NON-DARF AUTO-REFRESH<0:3> communication path 152b, or a corresponding logic low bDARF\_BNKSEL<0:3> signal on bDARF\_BNKSEL<0:3> communication path 144, NAND gate 146 outputs a corresponding logic high BNKSEL<0:3> signal on BNKSEL<0:3> communication path 148.

[0098] In operation, the BAC<0:1> signals provide the memory bank address for the next memory bank 112a-112(n) to be refreshed in DARF mode. The memory bank addresses are decoded into a single value for each memory bank to provide the ARFBNK<0:3> signals. When the auto-refresh command is decoded, it produces the bAUTO-REFRESH signal, which sets the first set/reset latch provided by NAND gate 400 and NAND gate 404. This generates the ARFPULSE signal, which combines with the ARFBANK<0:3> signals to provide the bSET\_BS-DARF<0:3> signals, which pulse logic low for the memory bank 112a-112(n) on which the DARF is to be performed. This sets the memory bank selection set/reset latch (NAND gate 416 and NAND gate 420) for that memory bank. The bBSDARF<0:3> signals then return to reset the first set/reset latch of NAND gate 400 and NAND gate 404, which releases the set for the second set/reset latch of NAND gate 416 and NAND gate 420. The memory bank selection is released when the auto-refresh is over.

[0099] The DARF\_MODE signal is an input to the second set/reset latch provided by NAND gates 416 and 420 so that the latch is held in the reset state when DARF mode is disabled. The BNKIDLE signal transitions to logic low when the refresh operation is complete. The BNKIDLE signal is an input to NAND gate 404 to reset the latch of NAND gate 400 and 404 when the refresh is complete.

[0100] FIG. 8 is a diagram illustrating one embodiment of two stage row address latch 130. Two stage row address latch 130 includes test mode logic and initialization circuit 600, latches 628 and 644, NAND gates 606 and 614, and inverters 618, 632, 636, and 640. The output of test mode logic and initialization circuit 600 is electrically coupled to a first input of NAND gate 606 through signal path 602. A second input of NAND gate 606 receives the inverted activate (bACT) signal on bACT signal path 604. The output of NAND gate 606 is electrically coupled to a first input of NAND gate 614 through clock enable (CLKEN) signal path 612. A second input of NAND gate 614 receives a clock (CLK) signal on CLK signal path 608. A third input of NAND gate 614 receives the inverted row address counter output enable (bRACOE) signal on bRACOE signal path 610. The output of NAND gate 614 is electrically coupled to the input of inverter 618 through signal path 616. The output of inverter 618 is electrically coupled to the clock (CLK) input of latch 644 through clock row address (CLK\_RADD) signal path 620.

[0101] The D input of latch 628 receives the row address for a read or write operation (SA<0:m>) signals on SA<0:m> communication path 622. The clock (CLK) input of latch 628 receives the clock hold (CLKHLD) signal on CLKHLD signal path 624. The inverted clock (bCLK) input of latch 628 receives the inverted clock hold (bCLKHLD) signal on bCLKHLD signal path 626. The Q output of latch 628 is electrically coupled to the input of inverter 632 through communication path 630. The output of inverter 632 is electrically coupled to the input of inverter 636 through communication path 634. The output of inverter 636 is electrically coupled to the input of inverter 640 through communication path 638. The output of inverter 640 is electrically coupled to the inverted row address for a read or write operation (bGA) input of latch 644 through communication path 642. The RAC input of latch 644 receives the RAC<0:m> signals on RAC<0:m> communication path 128. The GRADD output of latch 644 provides the GRADD<0:m> signals on GRADD<0:m> communication path 132.

[0102] Test mode logic and initialization circuit 600 outputs a logic low signal on signal path 602 with memory 106 not ready for operation. Test mode logic and initialization circuit 600 outputs a logic high signal on signal path 602 with memory 106 ready for operation. The bACT signal is logic low if a memory bank 112a-112(n) is being activated for read or write access and logic high if a memory bank 112a-112(n) is not being activated for read or write access. The bRACOE signal is logic low with the output of row address counter 166 enabled and logic high with the output of row address counter 166 disabled. The CLKHLD signal and the bCLKHLD signal are signals used to latch commands.

[0103] In response to a logic high signal on signal path 602 and a logic high bACT signal on bACT signal path 604,

NAND gate **606** outputs a logic low CLKEN signal on CLKEN signal path **612**. In response to a logic low signal on signal path **602** or a logic low bACT signal on bACT signal path **604**, NAND gate **606** outputs a logic high CLKEN signal on CLKEN signal path **612**.

[0104] In response to a logic high CLK signal on CLK signal path 608, a logic high bRACOE signal on bRACOE signal path 610, and a logic high CLKEN signal on CLKEN signal path 612, NAND gate 614 outputs a logic low signal on signal path 616. In response to a logic low CLK signal on CLK signal path 608, a logic low bRACOE signal on bRACOE signal path 610, or a logic low CLKEN signal on CLKEN signal path 612, NAND gate 614 outputs a logic high signal on signal path 616. Inverter 618 inverts the signal on signal path 616 to provide the CLK\_RADD signal on CLK\_RADD signal path 620.

[0105] Latch 628 receives the SA<0:m> signals on SA<0:m> communication path 622, the CLKHLD signal on CLKHLD signal path 624, and the bCLKHLD signal on bCLKHLD signal path 626 to provide the signals on communication path 630. In response to a logic low CLKHLD signal and a logic high bCLKHLD signal, latch 628 receives the SA<0:m> signals into the latch. In response to a logic high CLKHLD signal and a logic low bCLKHLD signal, latch 628 latches the SA<0:m> signals and passes the SA<0:m> signals to communication path 630.

[0106] Inverter 632 inverts the signals on communication path 630 to provide the signals on communication path 634. Inverter 636 inverts the signals on communication path 634 to provide the signals on communication path 638. Inverter 640 inverts the signals on communication path 638 to provide the signals on communication path 642.

[0107] Latch 644 receives the signals on communication path 642, the CLK\_RADD signal on CLK\_RADD signal path 620, and the RAC<0:m> signals on RAC<0:m> communication path 128 to provide the GRADD<0:m> signals on GRADD<0:m> communication path 132. In response to a logic low CLK\_RADD signal, latch 644 receives the signals on communication path 642 into the latch and passes the RAC<0:m> signals to GRADD<0:m> communication path 132. In response to a logic high CLK\_RADD signal, latch 644 latches the signals on communication path 642 and passes the passes the signals to GRADD<0:m> communication path 132.

[0108] In operation, the two-stage latching scheme is used to enable back-to-back directed auto-refresh and activate commands. The decoded DARF command enters refresh control circuit 122 and triggers a RACOE signal that is input to row address latch 130. The RACOE signal closes a gate to stop the row addresses for a read or write operation from driving onto the row address bus (GRADD<0:m>) and opens a gate from row address counter 166 to allow the refresh row address to drive onto the row address bus. The RACOE signal is long enough to flip latch 644. On the next activate command, the bRACOE signal is logic high. With a logic high CLKHOLD signal, the row addresses for a read or write operation are passed to the row address bus (GRADD<0:m>).

[0109] FIG. 9A is a timing diagram 500 illustrating one embodiment of the timing of signals for back-to-back directed auto-refresh and activate commands. Timing dia-

gram 500 includes clock (CLK) signal 502 on CLK signal path 608, command (CMD) signal 504, GRADD<0:m> signals 506 on GRADD<0:m> communication path 132, BNKSEL<0> signal 508 on BNKSEL<0:3> communication path 148, and BNKSEL<1> signal 510 on BNKSEL<0:3> communication path 148. To achieve a bandwidth improvement with DARF mode enabled, a DARF is performed on a first memory bank 112a-112(n) in response to a clock cycle and an activate command is performed on a second memory bank 112a-112(n) in response to the following clock cycle. This places a new timing constraint on the bank and row address busses. The data is valid for one cycle of the DARF and then is used in the next clock cycle for the activate command.

[0110] In response to rising edge 512 of CLK signal 502, a DARF mode command at 514 on CMD signal 504 is received. In response to the DARF mode command at 514, the row address counter addresses are provided on GRADD<0:m> signals 506 at 516. At 520, bank zero is selected. In response to rising edge 522 of CLK signal 502, an activate command is received at 524. In response to the activate command, the row addresses from the pins for the read or write operation are provided on GRADD<0:m> signals 506 at 526. The global row address is complete before BNKSEL<1> signal 510 transitions to logic high at 528. GRADD<0:m> signals 506 are valid long enough to be latched by row address latch 130 with BNKSEL<0> signal 508, but short enough that the next command is not affected.

[0111] FIG. 9B is a timing diagram 550 illustrating another embodiment of the timing of signals for back-toback directed auto-refresh and activate commands. Timing diagram 550 includes CLK signal 502 on CLK signal path 608, CMD signal 504, row address counter output enable (RACOE) signal 552, GRADD<0:m> signals 506 on GRADD<0:m> communication path 132, and SA<0:m> signals 554 on SA<0:m> communication path 622. In response to rising edge 556 of CLK signal 502, a DARF command is received at 558 on CMD signal 504. In response to the DARF command, RACOE signal 552 transitions to logic high at 560. In response to the rising edge 560 of RACOE signal 552, the row address counter address is provided on GRADD<0:m> signals 506 at 562. In response to rising edge 564 of CLK signal 502, an activate command is received at 566 on CMD signal 504. In response to the activate command, the address on SA<0:m> signals 554 at 570 are provided on GRADD<0:m> signals 506 at 568.

[0112] FIG. 10 is a diagram illustrating one embodiment of first latch stage 628 of row address latch 130. First latch stage 628 includes tri-state inverters 650 and 658 and inverters 654 and 660. The data input of tri-state inverter 650 receives the SA<0:m> signals on input D communication path 622. The logic low enable input of tri-state inverter 650 receives the CLKHLD signal on CLK input signal path 624. The logic high enable input of tri-state inverter 650 receives the bCLKHLD signal on bCLK input signal path 626. The data output of tri-state inverter 650 is electrically coupled to the data output of tri-state inverter 658, the input of inverter 654, and the input of inverter 660 through communication path 652.

[0113] The output of inverter 654 is electrically coupled to the data input of tri-state inverter 658 through communication path 656. The logic low enable input of tri-state inverter

658 receives the bCLKHLD signal on bCLK input signal path 626. The logic high enable input of tri-state inverter 658 receives the CLKHLD signal on CLK input signal path 624. The output of inverter 660 provides the signals on output Q communication path 630.

[0114] In response to a logic low CLKHLD signal on CLK input signal path 624 and a logic high bCLKHLD signal on bCLK input signal path 626, tri-state inverter 650 is turned on to pass and invert the SA<0:m> signals on input D communication path 622 to provide the signals on communication path 652. In response to a logic high CLKHLD signal on CLK input signal path 624 and a logic low bCLKHLD signal on bCLK input signal path 626, tri-state inverter 650 is turned off to block the SA<0:m> signals on input D communication path 622 from being inverted and passed to communication path 652. With tri-state inverter 650 turned off, the output of tri-state inverter 650 is high impedance. Inverter 654 inverts the signals on communication path 652 to provide the signals on communication path 656. Inverter 660 inverts the signals on communication path 652 to provide the signals on output Q communication path

[0115] In response to a logic high CLKHLD signal on CLK input signal path 624 and a logic low bCLKHLD signal on bCLK input signal path 626, tri-state inverter 658 is turned on to pass and invert the signals on communication path 656 to provide the signals on communication path 652. In response to a logic low CLKHLD signal on CLK input signal path 624 and a logic high bCLKHLD signal on bCLK input signal path 626, tri-state inverter 658 is turned off to block the signals on communication path 656 from being inverted and passed to communication path 652. With tri-state inverter 658 turned off, the output of tri-state inverter 658 is high impedance. Tri-state inverter 658 and inverter 654 provide a latch for latching the SA<0:m> signals on input D communication path 622.

[0116] In operation, in response to a logic low CLKHLD signal and a logic high bCLKHLD signal, the SA<0:m> signals pass to the latch provided by inverter 654 and tri-state inverter 658. In response to a logic high CLKHLD signal and a logic low bCLKHLD signal, the SA<0:m> signals are latched by inverter 654 and tri-state inverter 658 to provide the SA<0:m> signals on output Q communication path 630.

[0117] FIG. 11 is a diagram illustrating one embodiment of second latch stage 644 of row address latch 130. Second latch stage 644 includes inverters 662, 672, 678, 682, 684, 688, and 692, tri-state inverter 670, and transmission gates 666 and 676. The input of inverter 662, the logic high enable input of tri-state inverter 670, the logic low enable input of transmission gate 666, and the logic high enable input of transmission gate 676 receive the CLK\_RADD signal on CLK input signal path 620. The output of inverter 662 is electrically coupled to the logic high enable input of transmission gate 666, the logic low enable input of tri-state inverter 670, and the logic low enable input of transmission gate 676.

[0118] The data input of transmission gate 666 receives the signal on bGA input communication path 642. The data output of transmission gate 666 is electrically coupled to the input of inverter 672 and the output of tri-state inverter 670 through communication path 668. The output of inverter 672

is electrically coupled to the data input of transmission gate 676 and the data input of tri-state inverter 670 through communication path 674. The data output of transmission gate 676 is electrically coupled to the output of inverter 682 and the input of inverter 678 through RAC input communication path 128. The output of inverter 678 is electrically coupled to the input of inverter 682 and the input of inverter 684 through communication path 680. The output of inverter 684 through communication path 686. The output of inverter 688 is electrically coupled to the input of inverter 688 is electrically coupled to the input of inverter 692 through communication path 690. The output of inverter 692 provides the GRADD<0:m> signals on GRADD output communication path 132.

[0119] Inverter 662 inverts the CLK\_RADD signal on CLK input signal path 620 to provide the signal on signal path 664. In response to a logic low CLK\_RADD signal on CLK input signal path 620 and a logic high signal on signal path 664, transmission gate 666 is turned on to pass the signals on bGA input communication path 642 to communication path 668. In response to a logic high CLK\_RADD signal on CLK input signal path 620 and a logic low signal on signal path 664, transmission gate 666 is turned off to block the signals on bGA input communication path 642 from passing to communication path 668.

[0120] Inverter 672 inverts the signals on communication path 668 to provide the signals on communication path 674. In response to a logic high CLK\_RADD signal on CLK input signal path 620 and a logic low signal on signal path 664, tri-state inverter 670 is turned on to pass and invert the signals on communication path 674 to provide the signals on communication path 668. In response to a logic low CLK\_RADD signal on CLK input signal path 620 and a logic high signal on signal path 664, tri-state inverter 670 is turned off to block the signals on communication path 674 from being inverted and passed to communication path 668. With tri-state inverter 670 turned off, the output of tri-state inverter 670 is high impedance. Tri-state inverter 670 and inverter 672 provide a latch.

[0121] In response to a logic high CLK\_RADD signal on CLK input signal path 620 and a logic low signal on signal path 664, transmission gate 676 is turned on to pass the signals on communication path 674 to RAC input communication path 128. In response to a logic low CLK\_RADD signal on CLK input signal path 620 and a logic high signal on signal path 664, transmission gate 676 is turned off to block the signals on communication path 674 from passing to RAC input communication path 128.

[0122] Inverter 678 inverts the signals on RAC input communication path 128 to provide the signals on communication path 680. Inverter 682 inverts the signals on RAC input communication path 680 to provide the signals on RAC input communication path 128. Inverters 678 and 682 provide a latch. Inverter 184 inverts the signals on communication path 680 to provide the signals on communication path 686. Inverter 688 inverts the signals on communication path 686 to provide the signals on communication path 690. Inverter 692 inverts the signals on communication path 690 to provide the GRADD<0:m> signals on GRADD output communication path 132.

[0123] In operation, in response to a logic low CLK\_RADD signal, the signals on bGA input communica-

tion path 642 are passed to the latch provided by inverter 672 and tri-state inverter 670. In response to a logic high CLK\_RADD signal, the signals on bGA input communication path 642 are latched by inverter 672 and tri-state inverter 670 and passed to the latch provided by inverters 678 and 682 with the RACOE signal logic low. The latch provided by inverters 678 and 682 latches the RAC<0:m> signals on RAC input communication path 128 with the RACOE signal logic high. The output GRADD<0:m> signals are the RAC<0:m> signals if the CLK\_RADD signal is logic low and the SA<0:m> signals if the CLK\_RADD signal is logic high.

[0124] FIG. 12 is a diagram illustrating one embodiment of a circuit 142b for bypassing a memory bank 112a-112(n). In this embodiment, n equals 3. In one embodiment, circuit 142b is part of DARF bank selection circuit 142. Circuit 142b includes inverters 430, 704, and 714 and NAND gates 700, 708, and 718. Inverter 430 receives the BAC<0:1> signals on BAC<0:1> communication path 138 to provide the bBAC<0:1> signals on bBAC<0:1> communication path 432. A first input of NAND gate 700 receives the bBAC<0>, BAC<0>, bBAC<0>, and BAC<0> signals through communication path 432a. A second input of NAND gate 700 receives the bBAC<1>, bBAC<1>, and BAC<1> signals through communication path 432b. The output of NAND gate 700 is electrically coupled to the input of inverter 704 through communication path 702.

[0125] The output of inverter 704 is electrically coupled to a first input of NAND gate 708 through next bank address counter (NEXTBAC<0:3>) communication path 706. A second input of NAND gate 708 receives the BNK-SEL<0:3> signals on BANKSEL<0:3> communication path 148. A third input of NAND gate 708 receives the DARF-\_MODE signal on DARF\_MODE signal path 140a. The output of NAND gate 708 is electrically coupled to the inputs of NAND gate 718 through inverted block (bBLOCK<0:3>) communication path 710. A first input of NAND gate 718 is electrically coupled to bBLOCK<0> communication path 710a, a second input of NAND gate 718 is electrically coupled to bBLOCK<1> signal path 710b, a third input of NAND gate 718 is electrically coupled to bBLOCK<2> signal path 710c, and a fourth input of NAND gate 718 is electrically coupled to bBLOCK<3> signal path 710d. The output of NAND gate 718 is electrically coupled to the input of inverter 714 through signal path 712. The output of inverter 714 provides the inverted bypass autorefresh (bBARF) signal on bBARF signal path 716.

[0126] Inverter 430 inverts the BAC<0:1> signals on BAC<0:1> communication path 138 to provide the bBAC<0:1> signals on bBAC<0:1> communication path 432. In response to a logic high signal on communication path 432a and a corresponding logic high signal on communication path 432b, NAND gate 700 outputs a corresponding logic low signal on communication path 702. In response to a logic low signal on communication path 432a or a corresponding logic low signal on communication path 432b, NAND gate 700 outputs a corresponding logic high signal on communication path 702. Inverter 704 inverts the signals on communication path 702 to provide the NEXT-BAC<0:3> signals on NEXTBAC<0:3> communication path 706.

[0127] In response to a logic high NEXTBAC<0:3> signal on NEXTBAC<0:3> communication path 706, a corresponding logic high BNKSEL<0:3> signal on BNK-SEL<0:3> communication path 148, and a logic high DARF\_MODE signal on DARF\_MODE signal path 140a, NAND gate 708 outputs a corresponding logic low bBLOCK<0:3> signal on bBLOCK<0:3> communication path 710. In response to a logic low NEXTBAC<0:3> signal on NEXTBAC<0:3> communication path 706, a corresponding logic low BNKSEL<0:3> signal on BNK-SEL<0:3> communication path 148, or a logic low DARF\_MODE signal on DARF\_MODE signal path 140a, NAND gate 708 outputs a corresponding logic high signal on bBLOCK<0:3> communication path 710.

[0128] In response to a logic high bBLOCK<0> signal on bBLOCK<0> signal path 710a, a logic high bBLOCK<1> signal on bBLOCK<1> signal path 710b, a logic high bBLOCK<2> signal on bBLOCK<2> signal path 710c, and a logic high bBLOCK<3> signal path 710c, and a logic high bBLOCK<3> signal on bBLOCK<3> signal path 710d, NAND gate 718 outputs a logic low signal on signal path 712. In response to a logic low bBLOCK<0> signal on bBLOCK<0> signal 710a, a logic low bBLOCK<1> signal path 710b, a logic low bBLOCK<1> signal on bBLOCK<1> signal path 710b, a logic low bBLOCK<2> signal on bBLOCK<2> signal on bBLOCK<3> signal path 710c, or a logic low bBLOCK<3> signal on bBLOCK<3> signal path 710d, NAND gate 718 outputs a logic high signal on signal path 710d. Inverter 714 inverts the signal on signal path 712 to provide the bBARF signal on bBARF signal path 716.

[0129] In operation, when a memory bank 112a-112(n) is active and BAC 136 is set to increment to that active memory bank 112a-112(n) on the next auto-refresh command, the bBARF signal is logic low to block the auto-refresh command. When a memory bank 112a-112(n) is not active and the BAC 136 is set to increment to that non-active memory bank 112a-112(n) on the next auto-refresh command, the bBARF signal is logic high to allow the auto-refresh command.

[0130] FIG. 13 is a diagram illustrating one embodiment of a circuit 800 for allowing a directed auto-refresh while another memory bank 112*a*-112(*n*) is active. Circuit 800 includes NOR gate 802, inverters 806, 814, 818, 826, 830, and 834, NAND gate 810, and tri-state inverter 822. A first input of NOR gate 802 receives the DARF\_MODE signal on DARF\_MODE signal path 140*a*. A second input of NOR gate 802 receives the BNKIDLE signal path 140*e*. The output of NOR gate 802 is electrically coupled to the input of inverter 806 through signal path 804.

[0131] The output of inverter 806 is electrically coupled to a first input of NAND gate 810 through inverted ignore refresh (bIGNORE\_REFRESH) signal path 808. A second input of NAND gate 810, the input of inverter 834, and the logic low enable input of tri-state inverter 822 receive the CLK signal on CLK signal path 832. The output of inverter 834 is electrically coupled to the logic high enable input of tri-state inverter 822 through signal path 836. The data input of tri-state inverter 822 receives the bAUTO-REFRESH signal on bAUTO\_REFRESH signal path 140b. The data output of tri-state inverter 822 is electrically coupled to a third input of NAND gate 810, the input of inverter 826, and the output of inverter 830 through signal path 824. The output of inverter 826 is electrically coupled to the input of

inverter 830 through signal path 828. The output of NAND gate 810 is electrically coupled to the input of inverter 814 through signal path 812. The output of inverter 814 is electrically coupled to the input of inverter 818 through signal path 816. The output of inverter 818 provides the bPAUTO-REFRESH signal on bPAUTO-REFRESH signal path 820.