(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-217618

(P2006-217618A)

(43) 公開日 平成18年8月17日(2006.8.17)

(51) Int.C1.

HO3K 19/0175 (2006.01)

F 1

HO3K 19/00

HO3K 19/00

101F

101Q

テーマコード(参考)

5J056

審査請求 未請求 請求項の数 36 O L (全 15 頁)

(21) 出願番号 特願2006-24716 (P2006-24716)

(22) 出願日 平成18年2月1日 (2006.2.1)

(31) 優先権主張番号 10-2005-0009103

(32) 優先日 平成17年2月1日 (2005.2.1)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国 443-742 京畿道水原市靈通

区梅灘洞 416

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

最終頁に続く

(54) 【発明の名称】出力インピーダンス回路及びこれを適用した出力バッファ回路

## (57) 【要約】

【課題】 出力インピーダンス回路及びこれを適用した出力バッファ回路を提供すること。

【解決手段】 出力インピーダンス回路は、出力ステージ及びインピーダンス制御ステージを備える。出力ステージは、DCバイアス電圧に対応する出力信号を出力端子を通じて出力し、インピーダンス制御ステージは、出力信号に応答して前記出力ステージに流れる電流を制御する。出力ステージは、抵抗素子及び第1MOSトランジスタを備える。抵抗素子は、一端が出力端子に接続される。第1MOSトランジスタは、一端が抵抗素子の他端に接続され、他端が電源電圧に接続され、ゲートに入力信号が印加される。

【選択図】 図3

## 【図3】

## 【特許請求の範囲】

## 【請求項 1】

出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定である出力インピーダンス回路において、

D C バイアス電圧に対応する電流を前記出力端子に供給する出力ステージと、

前記出力信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力インピーダンス回路。

## 【請求項 2】

前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が第 1 電源電圧に接続され、ゲートに前記 D C バイアス電圧が印加される第 1 M O S トランジスタとを備えることを特徴とする請求項 1 に記載の出力インピーダンス回路。

10

## 【請求項 3】

前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第 1 M O S トランジスタの共通端子に接続され、他端が前記第 1 電源電圧に接続され、ゲートに前記出力信号が印加される第 2 M O S トランジスタを備えることを特徴とする請求項 2 に記載の出力インピーダンス回路。

20

## 【請求項 4】

前記第 1 電源電圧は、

前記出力インピーダンス回路を含むシステムで用いられる電源電圧よりも低い電圧レベルを有する電圧であることを特徴とする請求項 3 に記載の出力インピーダンス回路。

## 【請求項 5】

前記第 1 M O S トランジスタ及び前記第 2 M O S トランジスタは、

N 型 M O S トランジスタであることを特徴とする請求項 4 に記載の出力インピーダンス回路。

30

## 【請求項 6】

前記出力端子は、

半導体装置のパッドであることを特徴とする請求項 5 に記載の出力インピーダンス回路。

40

## 【請求項 7】

前記抵抗素子は、

多結晶シリコン、 P S G 、及び拡散された活性層のうち一つを利用して形成された抵抗であることを特徴とする請求項 2 に記載の出力インピーダンス回路。

## 【請求項 8】

前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が第 2 電源電圧に接続され、ゲートに前記 D C バイアス電圧が印加される第 3 M O S トランジスタとを備えることを特徴とする請求項 1 に記載の出力インピーダンス回路。

## 【請求項 9】

前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第 3 M O S トランジスタの共通端子に接続され、他端が前記第 2 電源電圧に接続され、ゲートに前記出力信号が印加される第 4 M O S トランジスタを備えることを特徴とする請求項 8 に記載の出力インピーダンス回路。

## 【請求項 10】

前記第 2 電源電圧は、

前記出力インピーダンス回路を含むシステムで用いられる電源電圧よりも高い電圧レベルを有する電圧であることを特徴とする請求項 9 に記載の出力インピーダンス回路。

50

## 【請求項 11】

前記第3MOSトランジスタ及び前記第4MOSトランジスタは、

P型MOSトランジスタであることを特徴とする請求項10に記載の出力インピーダンス回路。

【請求項12】

前記出力端子は、

半導体装置のパッドであることを特徴とする請求項11に記載の出力インピーダンス回路。

【請求項13】

前記抵抗素子は、

多結晶シリコン、PSG、及び拡散された活性層のうち一つを利用して形成された抵抗 10 であることを特徴とする請求項8に記載の出力インピーダンス回路。

【請求項14】

入力信号に応答して出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であるインピーダンス回路を備える出力バッファ回路において、

一端が前記出力端子に接続され、他端が高電源電圧に接続され、ゲートに前記入力信号が印加される駆動トランジスタと、

DC電圧を受信して動作し、一端が低電源電圧に接続され、他端が前記出力端子に接続されたインピーダンス回路とを備え、

前記インピーダンス回路は、

前記DCバイアス電圧に対応する電流を前記出力端子に供給する出力ステージと、

前記出力信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力バッファ回路。

【請求項15】

前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が前記低電源電圧に接続され、ゲートに前記DCバイアス電圧が印加される第1MOSトランジスタとを備えることを特徴とする請求項14に記載の出力バッファ回路。

【請求項16】

前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第1MOSトランジスタの共通端子に接続され、他端が前記低電源電圧に接続され、ゲートに前記出力信号が印加される第2MOSトランジスタを備えることを特徴とする請求項15に記載の出力バッファ回路。

【請求項17】

前記第1MOSトランジスタ及び前記第2MOSトランジスタは、

N型MOSトランジスタであることを特徴とする請求項16に記載の出力バッファ回路。

。

【請求項18】

前記駆動トランジスタは、

P型MOSトランジスタであることを特徴とする請求項17に記載の出力バッファ回路。

。

【請求項19】

前記出力端子は、

半導体装置のパッドであることを特徴とする請求項18に記載の出力バッファ回路。

【請求項20】

前記抵抗素子は、

多結晶シリコン、PSG、及び拡散された活性層のうち一つを利用して形成された抵抗であることを特徴とする請求項15に記載の出力バッファ回路。

【請求項21】

10

20

30

40

50

入力信号に応答して出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であるインピーダンス回路を備える出力バッファ回路において、

D C 電圧を受信して動作し、一端が高電源電圧に接続され、他端が前記出力端子に接続されたインピーダンス回路と、

一端が前記出力端子に接続され、他端が低電源電圧に接続され、ゲートに前記入力信号が印加される駆動トランジスタとを備え、

前記インピーダンス回路は、

前記 D C バイアス電圧に対応する電流を前記出力端子に供給する出力ステージと、

前記出力信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力バッファ回路。 10

【請求項 2 2】

前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が前記低電源電圧に接続され、ゲートに前記 D C バイアス電圧が印加される第 1 M O S トランジスタとを備えることを特徴とする請求項 2 1 に記載の出力バッファ回路。 20

【請求項 2 3】

前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第 1 M O S トランジスタの共通端子に接続され、他端が前記低電源電圧に接続され、ゲートに前記出力信号が印加される第 2 M O S トランジスタを備えることを特徴とする請求項 2 2 に記載の出力バッファ回路。 20

【請求項 2 4】

前記第 1 M O S トランジスタ及び前記第 2 M O S トランジスタは、

N 型 M O S トランジスタであることを特徴とする請求項 2 3 に記載の出力バッファ回路。

。

【請求項 2 5】

前記駆動トランジスタは、

P 型 M O S トランジスタであることを特徴とする請求項 2 4 に記載の出力バッファ回路。

。

【請求項 2 6】

前記出力端子は、

半導体装置のパッドであることを特徴とする請求項 2 5 に記載の出力バッファ回路。 30

【請求項 2 7】

前記抵抗素子は、

多結晶シリコン、 P S G 、及び拡散された活性層のうち一つを利用して形成された抵抗であることを特徴とする請求項 2 2 に記載の出力バッファ回路。 40

【請求項 2 8】

出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であり、正常動作状態及びハイインピーダンス状態を選択できる出力インピーダンス回路において、

制御信号及び逆制御信号に応答して動作し、前記出力信号を利用して前記出力インピーダンス回路の動作状態を選択するオンオフ信号を出力するオンオフ選択器と、

前記逆制御信号に対応する電流を前記出力端子に供給する出力ステージと、

前記オンオフ信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力インピーダンス回路。 40

【請求項 2 9】

前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が電源電圧に接続され、ゲートに前記逆制

50

御信号が印加される第1MOSトランジスタとを備えることを特徴とする請求項28に記載の出力インピーダンス回路。

【請求項30】

前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第1MOSトランジスタの共通端子に接続され、他端が前記電源電圧に接続され、ゲートに前記オンオフ信号が印加される第2MOSトランジスタを備えることを特徴とする請求項29に記載の出力インピーダンス回路。

【請求項31】

前記オンオフ選択器は、

一端に接続された前記出力信号を前記制御信号及び逆制御信号に応答してスイッチングするスイッチと、

一端が前記スイッチの他端に接続され、他端が前記電源電圧に接続され、ゲートに前記逆制御信号が印加される第3MOSトランジスタとを備えることを特徴とする請求項30に記載の出力インピーダンス回路。

【請求項32】

前記スイッチは、

一端が前記出力端子に接続され、他端が前記第3MOSトランジスタの一端に接続され、前記制御信号及び前記逆制御信号によって動作し、前記制御信号が論理的にハイレベルである時にスイッチがオンになることを特徴とする請求項31に記載の出力インピーダンス回路。

10

20

【請求項33】

前記制御信号及び前記逆制御信号は、

位相が互いに逆相であることを特徴とする請求項28に記載の出力インピーダンス回路。

【請求項34】

前記出力インピーダンス回路は、

前記逆制御信号の位相を反転させて前記制御信号を出力するインバータをさらに備えることを特徴とする請求項28に記載の出力インピーダンス回路。

【請求項35】

出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であり、正常動作状態及びハイインピーダンス状態を選択できる出力バッファ回路において、

制御信号及び逆制御信号に応答して動作し、前記出力信号を利用して前記出力インピーダンス回路の動作状態を選択するオンオフ信号を出力するオンオフ選択器と、

前記オンオフ信号に応答して前記逆制御信号に対応する電流を一端に接続された第1電源電圧を通じて他端に接続された前記出力端子に供給する出力インピーダンス回路と、

入力信号に対応する電流を一端に接続された第2電源電圧を通じて他端に接続された出力端子に供給する駆動装置とを備えることを特徴とする出力バッファ回路。

30

【請求項36】

前記第1電源電圧は、

40

前記出力バッファ回路で用いられる電源電圧よりも低い電源電圧であり、

前記第2電源電圧は、

前記出力バッファ回路で用いられる電源電圧よりも高い電源電圧であることを特徴とする請求項35に記載の出力バッファ回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の出力インピーダンス回路に係り、特に、接続されるシステムにかかわらず、一定の線形的な特性を有する出力インピーダンス(Out put ImpedanceまたはTerminator Impedance)を有する負荷として用

50

いられる出力インピーダンス回路に関する。

【背景技術】

【0002】

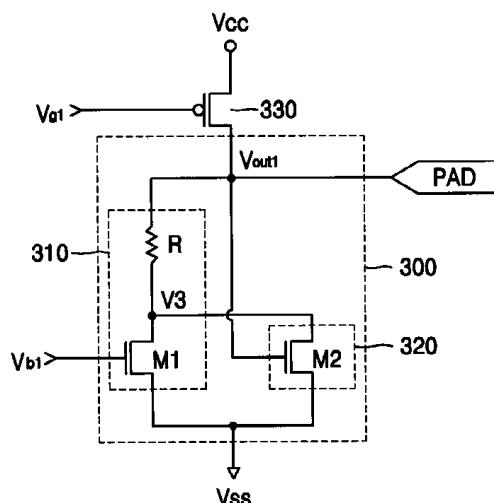

図1は、従来の出力インピーダンス回路を示す回路図である。図1を参照すれば、出力インピーダンス回路100は、3個のP型MOSトランジスタP1～P3及び抵抗Rを備える。MOSトランジスタP4は、出力インピーダンス回路100を負荷として使用するインバータを構成するMOSトランジスタであって、ゲートに印加される入力電圧Vgを反転させる。

【0003】

前記出力インピーダンス回路の構成上の特徴は、次の通りである。第1P型MOSトランジスタP1の一端は、高電源電圧Vccに接続され、ゲートにはDCバイアス電圧Vbが印加される。第2P型MOSトランジスタP2の一端は、高電源電圧Vccに接続され、ゲートにはDCバイアス電圧Vbが印加される。第3P型MOSトランジスタP3の一端は、第2P型MOSトランジスタP2の他端に接続され、他端及びゲート電極はパッド(PAD)に接続される。抵抗Rは、一端が第1P型MOSトランジスタの他端に接続され、他端はパッドに接続される。

【0004】

第1P型MOSトランジスタP1の他端と抵抗Rの一端とが接続されるノード電圧はV1であり、第2P型MOSトランジスタP2の他端と第3P型MOSトランジスタP3の一端が接続されるノード電圧はV2であると仮定し、図1に示された従来の出力インピーダンス回路の動作を説明する。

【0005】

式1は、高電源電圧Vcc及びパッド間の電圧Vo、インピーダンスZo、及び高電源電圧Vccとパッドとの間を流れる電流Ioに対するオームの法則を表す。

【0006】

$$Zo = Vo / Io \quad \dots \text{ (式1)}$$

【0007】

最も理想的な場合は、Vo及びIoが変わってもZoが変わらず、パッドにいかなるシステムが接続されても前記出力インピーダンス回路及びシステムのインピーダンス差に誤動作が発生しない。ここで、インピーダンス差による誤動作は、例えば、伝送されずに反射される信号による誤動作を含む。

【0008】

まず、第1P型MOSトランジスタP1及び抵抗Rのみを備える抵抗回路について説明する。

【0009】

第4MOSトランジスタP4のゲートに印加される入力電圧Vgの値に応答してパッド電圧が低くなると、高電源電圧Vccとパッド間の電圧Voが増加する。高電源電圧Vccとパッド間のインピーダンス成分Zoが一定であると、高電源電圧Vccとパッドとの間に流れる電流Ioは増加する。ここで、インピーダンス成分Zoは、抵抗R及び第1MOSトランジスタP1のオン抵抗Zonの和となる。MOSトランジスタのオン抵抗を式2で示す。

【0010】

$$Zon = Vds / Ids \quad \dots \text{ (式2)}$$

【0011】

ここで、Vdsは、MOSトランジスタのドレイン及びソース間の電圧を示し、Idsは、MOSトランジスタのドレインとソースとの間を流れる電流を意味する。

【0012】

電圧Voが増加するが、まだ電流Ioが増加していないと仮定すると、抵抗Rで降下する電圧が一定になるので、結果として、第1ノード電圧V1がパッドの電圧が低くなる場合と同じ電圧に低くなる。すなわち、第1MOSトランジスタP1のドレインとソース間

10

20

30

40

50

の電圧  $V_{ds}$  が増加し、第 1 MOS ランジスタ P1 のゲート及びソース間の電圧  $V_{gs}$  は変わらないが、ドレイン及びソース間の電圧  $V_{ds}$  が増加するので、ドレイン及びソース間の電流  $I_{ds}$  も増加する。

#### 【0013】

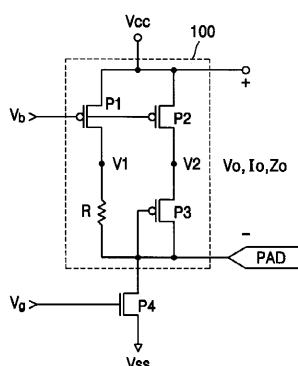

図 2 は、MOS ランジスタの電圧 - 電圧特性曲線である。図 2 を参照すれば、ゲートとソースとの間の電圧  $V_{gs} - V_t$  が一定の場合、ドレインとソースとの間の電圧  $V_{ds}$  が増加するときに、ドレインとソースとの間に流れる電流  $I_{ds}$  が急増する領域(線形領域)と緩やかに増加する領域(飽和領域)に区分される。点線が前記 2 領域を区分するが、前記点線の左側にある領域が線形領域であり、右側にある領域が飽和領域である。

#### 【0014】

第 1 MOS ランジスタ P1 は、飽和領域で動作するが、上述のように飽和領域では、ドレインとソースとの間の電圧  $V_{ds}$  の増加と同じ割合でドレインとソースとの間の電流  $I_{ds}$  が増加しないので、オン抵抗  $Z_{on}$  が増加し、パッドに適当な電流を供給できなくなるという問題がある。これは、パッドから見たインピーダンス成分 ( $Z_{o1} = R + Z_{on}$ ) が増加するということと同じ意味である。

#### 【0015】

このような問題を解決するために、直列接続された第 2 MOS ランジスタ P2 及び第 3 MOS ランジスタ P3 を、直列接続された第 1 MOS ランジスタ P1 及び抵抗 R に並列に接続することが提案された。

#### 【0016】

この場合、第 1 MOS ランジスタ P1 のドレイン及びソース間の電圧  $V_{ds}$  の変化に追いつかない電流を、第 2 MOS ランジスタ P2 及び第 3 MOS ランジスタ P3 を通じてパッドに供給する。また、第 2 MOS ランジスタ P2 及び第 3 MOS ランジスタ P3 のインピーダンス成分  $Z_{o2}$  が、第 1 MOS ランジスタ P1 及び抵抗 R によるインピーダンス成分  $Z_{o1}$  と並列に接続されるので、パッドから見たインピーダンス成分 ( $Z_o = Z_{o1} // Z_{o2}$ ) は減少する。ここで、//は  $Z_{o1}$  と  $Z_{o2}$  とが相互に並列に接続されていることを意味する。

#### 【0017】

上述のように、従来の出力インピーダンス回路は、パッド電圧が低くなっても、インピーダンス成分を安定させうるという利点がある。

#### 【0018】

しかしながら、パッドに接続された出力インピーダンス回路のインピーダンス成分の値を一定に維持させるために使用する第 2 MOS ランジスタ P2 及び第 3 MOS ランジスタ P3 は、工程によってそのサイズ及び抵抗が敏感に変わるという問題がある。また、第 2 MOS ランジスタ P2 及び第 3 MOS ランジスタ P3 が飽和領域で動作するので、パッド電圧によって電流量が急増し、低いパッド電圧ではインピーダンス成分を必要以上に減少させてしまうという問題がある。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0019】

本発明が達成しようとする技術的課題は、工程の変化に対し安定的であり、パッド電圧に関係なく一定の出力インピーダンスを有する出力インピーダンス回路を提供することである。

#### 【0020】

本発明が達成しようとする他の技術的課題は、工程の変化に対し安定的であり、パッド電圧に関係なく一定の出力インピーダンスを有する出力バッファ回路を提供することである。

#### 【課題を解決するための手段】

#### 【0021】

前記技術的課題を達成するための本発明による出力インピーダンス回路は、出力ステー

10

20

30

40

50

ジ及びインピーダンス制御ステージを備える。

【0022】

前記出力ステージは、DCバイアス電圧に対応する前記出力信号を出力端子を通じて出力し、前記インピーダンス制御ステージは、前記出力信号に応答して前記出力ステージに流れる電流を制御する。

【0023】

前記出力ステージは、抵抗素子及び第1MOSトランジスタを備える。前記抵抗素子は、一端が前記出力端子に接続される。前記第1MOSトランジスタは、一端が前記抵抗素子の他端に接続され、他端が電源電圧に接続され、ゲートに前記入力信号が印加される。

【0024】

前記インピーダンス制御ステージは、一端が前記抵抗素子及び前記第1MOSトランジスタの共通端子に接続され、他端が前記電源電圧に接続され、ゲートに前記出力信号が印加される第2MOSトランジスタを備える。

【0025】

前記他の技術的課題を達成するための本発明による出力バッファ回路は、入力信号に応答して出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であり、駆動トランジスタ及びインピーダンス回路を備える。

【0026】

前記駆動トランジスタは、一端が前記出力端子に接続され、他端が高電源電圧に接続され、ゲートに前記入力信号が印加される。

【0027】

前記インピーダンス回路は、DC電圧を受信して動作し、一端が低電源電圧に接続され、他端が前記出力端子に接続される。前記インピーダンス回路は、出力ステージ及びインピーダンス制御ステージを備える。前記出力ステージは、前記DCバイアス電圧に対応する電流を前記出力端子に供給する。前記インピーダンス制御ステージは、前記出力信号に応答して前記出力ステージに流れる電流を制御する。

【発明の効果】

【0028】

本発明による出力インピーダンス回路は、工程の変化に対し安定的であり、パッド電圧に関係なく一定の出力インピーダンスを有するという利点がある。

【発明を実施するための最良の形態】

【0029】

本発明と本発明の動作上の利点及び本発明の実施によって達成される目的を十分に理解するためには、本発明の望ましい実施形態を例示する添付図面及び図面に記載された内容を参照しなければならない。

【0030】

以下、添付した図面を参照して本発明の望ましい実施形態を説明することによって、本発明を詳細に説明する。各図面に付された同一の参照符号は、同様の構成要素を示す。

【0031】

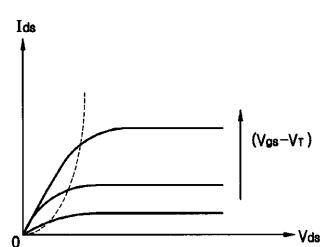

図3は、本発明の好適な一実施形態の一側面による出力インピーダンス回路300を備える出力バッファ回路の回路図である。

【0032】

図3を参照すれば、前記出力バッファ回路は、駆動トランジスタ330及び出力インピーダンス回路300を備える。

【0033】

駆動トランジスタ330は、入力信号V<sub>g1</sub>に応答して出力端子の出力電圧V<sub>out1</sub>を決定する機能を持ち、そのために前記出力インピーダンス回路を負荷として使用する。駆動トランジスタ330の一端は、高電源電圧V<sub>cc</sub>に接続され、他端が出力端子に接続され、ゲートに入力信号V<sub>g1</sub>が印加される。

【0034】

10

20

30

40

50

出力インピーダンス回路300は、出力ステージ310及びインピーダンス制御ステージ320を備え、入力信号 $V_{g1}$ の電圧レベルに対応して出力信号 $V_{out1}$ の電圧レベルが変わっても、出力端子でのインピーダンス成分が一定である。

【0035】

出力ステージ310は、抵抗R及び第1MOSトランジスタM1を備える。抵抗または抵抗素子Rは、一端が前記出力端子に接続される。第1MOSトランジスタM1は、一端が抵抗Rの他端 $V_3$ に接続され、他端が低電源電圧 $V_{ss}$ に接続され、ゲートにDCバイアス電圧 $V_{b1}$ が印加される。ここで、DCバイアス電圧 $V_{b1}$ は、第1MOSトランジスタM1をターンオンさせうる電圧であって、高電源電圧 $V_{cc}$ に接続させても良い。

【0036】

インピーダンス制御ステージ320は、一端が抵抗R及び第1MOSトランジスタM1の共通端子 $V_3$ に接続され、他端が電源電圧 $V_{ss}$ に接続され、ゲートに出力信号が印加される第2MOSトランジスタを備える。

【0037】

第1電源電圧 $V_{cc}$ は、前記出力インピーダンス回路を備える出力バッファ回路で用いられる電源電圧よりも高い電源電圧であり、第2電源電圧 $V_{ss}$ は、前記出力インピーダンス回路を備える出力バッファ回路で用いられる電源電圧よりも低い電源電圧である。第1MOSトランジスタM1及び第2MOSトランジスタM2は、N型MOSトランジスタであることが望ましい。

【0038】

出力端子は、半導体装置のパッドであり、抵抗Rは、多結晶シリコン(Poly-Silicon)、PSG(Phospho Silicate Glass)、及び拡散された活性層(Diffused Active layer)のうち一つを利用して形成される。

【0039】

以下、図3に示された本発明の好適な一実施形態の一側面による出力インピーダンス回路の動作について説明する。

【0040】

図3に示された本発明の好適な一実施形態による出力インピーダンス回路がパッド電圧に関係なく一定のインピーダンスを提供するためには、ノード $V_3$ の電圧がパッドの電圧に関係なく一定であるべきである。

【0041】

入力信号 $V_{g1}$ の電圧によってパッドの電圧が上昇すれば、出力インピーダンスの両端子で降下する電圧が増加する。この時、抵抗Rを通じて流れる電流量が増加しなければならず、このためにはノード $V_3$ の電圧が上昇しなければならない。しかしながら、ノード $V_3$ の電圧が上昇すれば、抵抗Rの両端の電圧が減少するので、結果として、パッドから見たインピーダンスは増加する。

【0042】

本発明は、このような問題を解決するために、インピーダンス制御ステージ320として第2MOSトランジスタM2を用いる。パッドの電圧が上昇すれば、第2MOSトランジスタM2のゲートに印加される電圧が増加するので、結果として、第2MOSトランジスタM2を通じて流れる電流も増加する。しかしながら、第2MOSトランジスタM2のゲート電圧が増加してもノード $V_3$ の電圧は増加しない。この点が従来の出力インピーダンス回路と相異する。

【0043】

図2に示された電流-電圧曲線を参照すれば、ゲート及びソース間の電圧 $V_{gs}$ が固定されている場合、ドレインとソースとの間の電流 $I_{ds}$ を増加させるためには、ドレインとソースとの間の電圧 $V_{ds}$ が増加しなければならない。しかしながら、ゲート及びソース間の電圧 $V_{gs}$ が増加すれば、電流 $I_{ds}$ を増加させるためにドレインとソースとの間の電圧 $V_{ds}$ が増加する必要がない。したがって、本発明の好適な一実施形態による出力

10

20

30

40

50

インピーダンス回路は、出力信号の値によって供給すべき電流が変わっても、これに対応して動作するインピーダンス制御用のトランジスタM2の役割によって、出力インピーダンスはほとんど変わらない。

【0044】

したがって、パッドの電圧が増加して第2MOSトランジスタM2のゲート及びソース間の電圧V<sub>gs</sub>が増加しても、図1に示された従来の出力インピーダンス回路でのノード電圧V<sub>1</sub>が増加する程度の電圧上昇が起こらない。

【0045】

このような構造を有することによって、パッドから見たインピーダンス値をあらゆる領域に対して一定に維持させうる。

【0046】

以下、前述した本発明の技術的思想を、実際の設計でどのように具現できるかを説明する。

【0047】

パッドの電圧の変化によって、第1MOSトランジスタM1及び第2MOSトランジスタM2の動作は、3つの領域に大別される。

【0048】

第1に、出力電圧V<sub>out1</sub>がMOSトランジスタのしきい電圧V<sub>th</sub>に比べて小さい場合であり、第1MOSトランジスタM1のみ線形領域で動作し、第2MOSトランジスタM2は動作しない場合に抵抗Rを通じて流れる電流を数式3で示した。第1MOSトランジスタM1及び第2MOSトランジスタM2のしきい電圧は、いずれもV<sub>th</sub>とする。ここで、V<sub>b1</sub>が電源電圧V<sub>cc</sub>に接続され、電源電圧V<sub>ss</sub>は接地電圧と同じ0Vと仮定する。

【0049】

$$\begin{aligned} I_{r1} &= K_1 \{ (V_{cc} - V_{th}) V_{ds1} - 1/2 V_{ds1}^2 \} \\ &= K_1 \{ (V_{cc} - V_{th}) a V_{out1} - 1/2 a^2 V_{out1}^2 \} \quad \dots \text{ (数式3) } \end{aligned}$$

【0050】

ここで、V<sub>ds1</sub>はV<sub>3</sub>で、V<sub>3</sub>は比例定数aを含むaV<sub>out1</sub>であると仮定する。また、K1は、工程パラメータによって決定される値を有する。V<sub>cc</sub> > > V<sub>out1</sub>であるので、(V<sub>cc</sub> - V<sub>th</sub>)aV<sub>out1</sub> > > 1/2 a<sup>2</sup> V<sub>out1</sub><sup>2</sup>となってI<sub>r1</sub>は数式4のように表される。

【0051】

$$I_{r1} = K_1 * (V_{cc} - V_{th}) * a V_{out1} \quad \dots \text{ (数式4) }$$

【0052】

第2に、第1MOSトランジスタM1は線形領域で動作し、第2MOSトランジスタM2は飽和領域で動作する場合であって、出力電圧V<sub>out1</sub>がしきい電圧V<sub>th</sub>よりは高いが、2倍のしきい電圧(2V<sub>th</sub>)に比べて低い電圧(V<sub>th</sub> < V<sub>out1</sub> < 2V<sub>th</sub>)を有する時の電流I<sub>r2</sub>は、数式5で示される。

【0053】

$$\begin{aligned} I_{r2} &= K_1 \{ (V_{cc} - V_{th}) V_{ds1} - 1/2 V_{ds1}^2 \} + 1/2 K_2 (V_{out1} - V_{th})^2 \\ &= K_1 \{ (V_{cc} - V_{th}) a V_{out1} - 1/2 a^2 V_{out1}^2 \} + 1/2 K_2 (V_{out1} - V_{th})^2 \\ &= V_{out1} \{ a K_1 (V_{cc} - V_{th}) - K_2 V_{th} \} - 1/2 V_{out1}^2 (a^2 K_1 - K_2) + 1/2 K_2 V_{th}^2 \quad \dots \text{ (数式5) } \end{aligned}$$

【0054】

ここで、(a<sup>2</sup> K<sub>1</sub> - K<sub>2</sub>)を0に収束するように設計すれば、電流I<sub>r2</sub>は数式6のように示される。ここで、K<sub>2</sub>も工程パラメータによって決定される値である。

【0055】

$$I_{r2} = V_{out1} \{ a K_1 (V_{cc} - V_{th}) - K_2 V_{th} \} + 1/2 K_2 V_{th}^2 \quad \dots \text{ (数式6) }$$

【0056】

最後に、出力電圧V<sub>out1</sub>が2倍のしきい電圧2V<sub>th</sub>より高い電圧(V<sub>out1</sub> >

$2V_{th}$ )を示す場合の電流  $I_{r3}$  を数式7で示す。

【0057】

$$\begin{aligned} I_{r3} &= K1\{(V_{cc}-V_{th})V_{ds1}-1/2V_{ds1}^2\} + K2\{(V_{out1}-V_{th})V_{ds2}-1/2V_{ds2}^2\} \\ &= K1\{(V_{cc}-V_{th})aV_{out1}-1/2a^2V_{out1}^2\} + K2\{(V_{out1}-V_{th})aV_{out1}-1/2a^2V_{out1}^2\} \\ &= V_{out1}\{aK1(V_{cc}-V_{th}) - K2V_{th}\} - V_{out1}^2(a^2K1/K2-aK2+1/2a^2) \quad \dots \text{ (数式7) } \end{aligned}$$

【0058】

設計時には、第1MOSトランジスタM1及び第2MOSトランジスタM2のサイズを調節してK1及びK2を適切に制御すれば、数式7で示された電流  $I_{r3}$  は、数式8のように表わされる。

【0059】

$$I_{r3} = V_{out1}\{aK1(V_{cc}-V_{th}) - K2V_{th}\} \quad \dots \text{ (数式8) }$$

【0060】

数式4、6及び8を満足する適切なK1及びK2を考慮して設計すれば、理想的なインピーダンスを有する出力インピーダンス回路を作製することができる。

【0061】

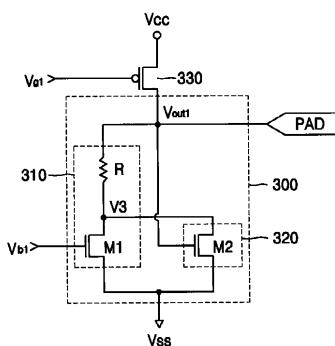

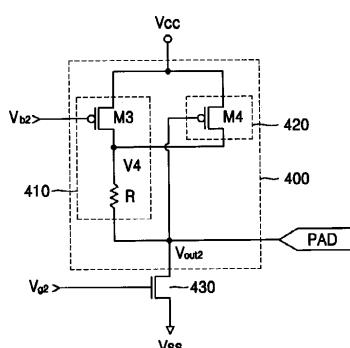

図4は、本発明の好適な一実施形態の他の一側面による出力インピーダンス回路400を備える出力バッファ回路の回路図である。

【0062】

図4を参照すれば、前記出力バッファ回路は、駆動トランジスタ430及び出力インピーダンス回路400を備える。

【0063】

駆動トランジスタ430は、入力信号  $V_{g2}$  に応答して出力端子の出力電圧  $V_{out2}$  を決定する機能を持ち、そのために前記出力インピーダンス回路を負荷として使用する。駆動トランジスタ430の一端は、低電源電圧  $V_{ss}$  に接続され、他端が出力端子に接続され、ゲートに入力信号  $V_{g2}$  が印加される。

【0064】

出力インピーダンス回路400は、出力ステージ410及びインピーダンス制御ステージ420を備える。

【0065】

出力ステージ420は、抵抗R及び第3MOSトランジスタM3を備える。抵抗または抵抗素子Rは、一端が前記出力端子に接続される。第3MOSトランジスタM3は、一端が抵抗Rの他端  $V_4$  に接続され、他端が電源電圧  $V_{cc}$  に接続され、ゲートにDCバイアス電圧  $V_{b2}$  が印加される。ここで、DCバイアス電圧  $V_{b2}$  は、第3MOSトランジスタM3がターンオンできる電圧であって、低電源電圧  $V_{ss}$  を使用しても良い。

【0066】

インピーダンス制御ステージ420は、一端が抵抗R及び第3MOSトランジスタM3の共通端子  $V_4$  に接続され、他端が電源電圧  $V_{cc}$  に接続され、ゲートに出力信号  $V_{out2}$  が印加される第4MOSトランジスタM4を備える。

【0067】

ここで、電源電圧  $V_{cc}$  は、出力インピーダンス回路を含むシステムで用いられる電源電圧よりも高い電圧レベルを有する電圧であり、電源電圧  $V_{ss}$  は、出力インピーダンス回路を含むシステムで用いられる電源電圧よりも低い電源電圧である。第3MOSトランジスタM3及び第4MOSトランジスタM4は、P型MOSトランジスタであることが望ましい。

【0068】

出力端子は、半導体装置のパッドであり、抵抗Rは、多結晶シリコン、PSG、及び拡散された活性層のうち一つを利用して形成された抵抗である。

【0069】

図4に示された本発明の好適な一実施形態の他の一側面による出力インピーダンス回路の動作は、図3の説明と同様なので、ここでは省略する。

10

20

30

40

50

## 【0070】

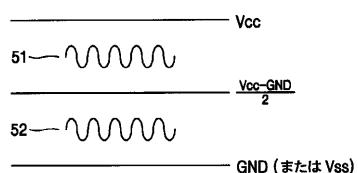

図5は、図3及び図4に示された本発明による出力インピーダンス回路を備える出力バッファ回路が最適に用いられる領域を示す図面である。

## 【0071】

図5を参照すれば、出力バッファ回路の出力電圧の範囲が51である場合には、図3に示された出力バッファ回路が用いられることが好ましく、出力バッファ回路の出力電圧の範囲が52である場合には、図4に示された出力バッファ回路を使用することが好ましい。

## 【0072】

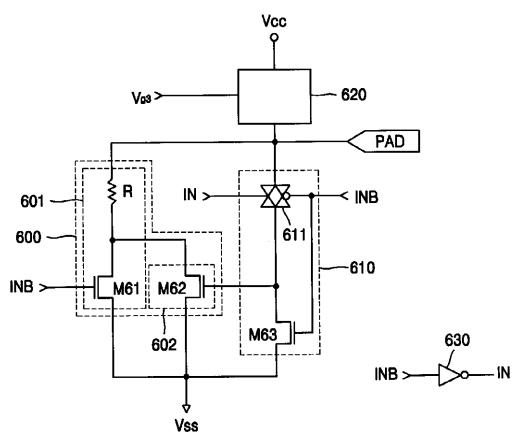

図6は、本発明の好適な他の一実施形態による出力インピーダンス回路の回路図である。

## 【0073】

図6を参照すれば、前記出力バッファ回路は、出力インピーダンス回路600、オンオフ選択器610、及び駆動装置620を備える。

## 【0074】

駆動装置620は、図3及び図4に示された駆動トランジスタ330及び430と同じ機能を持つので、その説明を省略する。

## 【0075】

出力インピーダンス回路600は、出力ステージ601及びインピーダンス制御ステージ602を備える。出力ステージ601及びインピーダンス制御ステージ602は、図3及び図4に示された出力ステージ310及び410及びインピーダンス制御ステージ320及び420と同様なので、その説明を省略する。

## 【0076】

オンオフ選択器610は、スイッチとして用いられるトランスマッチングゲート611及びMOSトランジスタM63を備える。

## 【0077】

トランスマッチングゲート611は、制御信号IN及び逆制御信号INBによって動作する。制御信号IN及び逆制御信号INBは、位相が互いに逆相であることが好ましい。MOSトランジスタM63のゲートには、逆制御信号INBが印加されるが、逆制御信号INBがMOSトランジスタM61及びMOSトランジスタM63をターンオンさせる程度に高電圧（論理的にハイレベル）である場合には、出力インピーダンス回路600が正常に動作してインピーダンス成分として動作する。しかしながら、逆制御信号INBが前記2つのトランジスタのしきい電圧より低い電圧である場合には、出力インピーダンス回路600は、正常に動作せずにハイインピーダンス状態となる。

## 【0078】

制御信号IN及び逆制御信号INBは、インバータ630を利用して容易に生成することができる。

## 【0079】

以上のように、図面と明細書とにより最適の実施形態が開示された。ここで、特定の用語が使われたが、これは、単に本発明を説明するための目的として使われただけであり、意味の限定や特許請求の範囲に記載された本発明の範囲を制限するために使われたものではない。したがって、当業者ならば、これから多様な変形及び均等な他の実施形態が可能であるという点が理解できるであろう。したがって、本発明の技術的範囲は、特許請求の範囲の記載に基づいて定められなければならない。

## 【産業上の利用可能性】

## 【0080】

本発明による出力インピーダンス回路及び出力バッファ回路は、内部で生成した信号を出力するあらゆる電子システムに適用可能である。前記回路は、少ない消費電力を基本とする半導体装置で用いられるだけでなく、高い電源で動作するので、消費電力が非常に大きい電気システムにも使用可能である。

### 【図面の簡単な説明】

〔 0 0 8 1 〕

【図1】従来の出力インピーダンス回路を示す回路図である。

【図2】MOSトランジスタの電圧-電圧特性曲線を示すグラフである。

【図3】本発明の好適な一実施形態の一側面による出力インピーダンス回路を備える出力バッファ回路の回路図である。

【図4】本発明の好適な一実施形態の他の一側面による出力インピーダンス回路を備える出力バッファ回路の回路図である。

【図5】図3及び図4に示された本発明の好適な実施の形態による出力インピーダンス回路を備える出力バッファ回路が最適に用いられる領域を示す図面である。

〔図6〕本発明の好適な他の一実施形態による出力インピーダンス回路の回路図である。

## 【 符号の説明 】

【 0 0 8 2 】

### 3.0.0 出力インピーダンス回路

### 3.1.0 出力ステージ

### 3.2.0 インピーダンス制御ステージ

330 駆動トランジスタ

M 1 第 1 MOS トランジスタ

M 2 第 2 M O S トランジスタ

〔図1〕

【図 1】(従来の技術)

【圖 2】

【図 2】(従来の技術)

【図3】

〔四三〕

【図4】

【图 4】

【図5】

【図 5】

【図6】

〔四 6〕

---

フロントページの続き

(72)発明者 金泰亨

大韓民国京畿道城南市盆唐区書 ヒエオン 洞337-5番地201号

(72)発明者 趙郁來

大韓民国京畿道水原市靈通区望浦洞683番地現代アイパークアパート205棟105号

F ターム(参考) 5J056 AA04 BB21 BB59 CC00 DD13 DD28 EE11 FF07 FF08 KK01