(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년10월05일

(11) 등록번호 10-1904409

(24) 등록일자 2018년09월27일

- (51) 국제특허분류(Int. Cl.)

*H01L 25/10* (2006.01) *H01L 21/56* (2006.01)

*H01L 21/60* (2006.01)

- (21) 출원번호 10-2014-7013310

- (22) 출원일자(국제) 2012년10월17일

심사청구일자 2017년10월17일

- (85) 번역문제출일자 2014년05월19일

- (65) 공개번호 10-2014-0085520

- (43) 공개일자 2014년07월07일

- (86) 국제출원번호 PCT/US2012/060585

- (87) 국제공개번호 WO 2013/059297

국제공개일자 2013년04월25일

- (30) 우선권주장

13/277,330 2011년10월20일 미국(US)

- (56) 선행기술조사문현

JP11135713 A

JP2005353837 A

KR1020060120365 A

US20070252256 A1

전체 청구항 수 : 총 72 항

심사관 : 안경민

- (54) 발명의 명칭 적층된 마이크로전자 유닛이 있는 마이크로전자 패키지 및 그의 제조 방법

**(57) 요 약**

마이크로전자 패키지(10)는 제1 칩 콘택(28)을 갖는 반도체 칩(16A), 반도체 칩의 에지에 접촉하는 인캡슐런트(30), 그리고 인캡슐런트(30)의 표면에 노출되고 제1 칩 콘택(28)과 전기적으로 연결되는 제1 유닛 콘택(42)을 포함하는 제1 마이크로전자 유닛(12)을 포함할 수 있다. 패키지(10)는 표면에 제2 칩 콘택(28C)을 갖는 반도체

(뒷면에 계속)

**대 표 도** - 도10

칩(16C), 그리고 제2 마이크로전자 유닛(14)의 칩의 에지에 접촉하며 에지로부터 멀어지도록 연장하는 표면을 갖는 인캡슐런트(54)를 포함하는 제2 마이크로전자 유닛(14)을 포함할 수 있다. 반도체 칩(16C)의 표면 및 제2 마이크로전자 유닛(14)의 인캡슐런트(54)는 제2 마이크로전자 유닛의 표면을 형성한다. 이러한 표면에서의 패키지 단자(76)는 제1 유닛 콘택(42)과 전기적으로 연결된 본드 와이어(100)를 통해 제1 유닛 콘택(42)과 전기적으로 연결될 수 있고, 제2 칩 콘택(28C)과 접촉하여 형성되는 트레이스(74) 및 금속화된 비아(72)를 통해 제2 칩 콘택(28C)과 전기적으로 연결될 수 있다.

---

## 명세서

### 청구범위

#### 청구항 1

마이크로전자 패키지에 있어서,

제1 칩 콘택을 갖는 반도체 칩, 상기 반도체 칩의 에지에 접촉하는 인캡슐런트(encapsulant), 그리고 상기 인캡슐런트의 표면에 노출되며 상기 제1 칩 콘택과 전기적으로 연결되는 제1 유닛 콘택을 포함하는 제1 마이크로전자 유닛;

표면에 제2 칩 콘택을 갖는 반도체 칩, 그리고 제2 마이크로전자 유닛의 상기 반도체 칩의 에지에 접촉하며 상기 제2 마이크로전자 유닛의 반도체 칩의 에지로부터 멀어지도록 연장하는 표면을 갖는 인캡슐런트를 포함하는 상기 제2 마이크로전자 유닛으로서, 상기 제2 마이크로전자 유닛의 반도체 칩의 표면 및 상기 제2 마이크로전자 유닛의 상기 인캡슐런트는 상기 제2 마이크로전자 유닛의 표면을 형성하는, 상기 제2 마이크로전자 유닛;

상기 제1 유닛 콘택과 전기적으로 연결되는 본드 와이어(bond wire); 및

(i) 상기 본드 와이어를 통해 상기 제1 유닛 콘택과 전기적으로 연결되고 (ii) 상기 제2 칩 콘택에 접촉하여 형성되는 트레이스(trace) 및 금속화된 비아를 통해 상기 제2 칩 콘택과 전기적으로 연결되는, 상기 제2 마이크로전자 유닛의 표면에서의 패키지 단자를 포함하는,

마이크로전자 패키지.

#### 청구항 2

제1항에 있어서,

상기 제1 마이크로전자 유닛은, 메모리 저장 어레이 기능(memory storage array function)을 제공하도록 구성되는, 마이크로전자 패키지.

#### 청구항 3

제2항에 있어서,

상기 제2 마이크로전자 유닛은 로직 기능을 제공하도록 구성되는, 마이크로전자 패키지.

#### 청구항 4

제1항에 있어서,

상기 제1 마이크로전자 유닛은, 제1 반도체 칩 및 제2 반도체 칩을 포함하고,

상기 제1 반도체 칩은 상기 제1 마이크로전자 유닛의 표면에 노출된 제1 칩 콘택을 가지며, 상기 제2 반도체 칩의 제1 칩 콘택은 상기 제1 마이크로전자 유닛의 인캡슐런트를 통해 연장하는 전기 전도성 비아를 통하여 상기 제1 유닛 콘택과 연결되는, 마이크로전자 패키지.

#### 청구항 5

제4항에 있어서,

상기 제2 반도체 칩의 제1 칩 콘택 중 적어도 하나는 상기 제1 마이크로전자 유닛의 인캡슐런트의 관통 개구(through opening)에 노출되는, 마이크로전자 패키지.

#### 청구항 6

제4항에 있어서,

상기 제1 반도체 칩 및 상기 제2 반도체 칩은, 메모리 저장 어레이 기능을 제공하도록 구성되는, 마이크로전자

패키지.

### 청구항 7

제6항에 있어서,

상기 제2 반도체 칩은 상기 제1 반도체 칩 위에 부분적으로 놓임으로써 상기 제2 반도체 칩의 제1 칩 콘택이 상기 제1 반도체 칩의 에지를 넘어 배치되는, 마이크로전자 패키지.

### 청구항 8

제6항에 있어서,

상기 제1 반도체 칩의 제1 칩 콘택과 상기 제2 반도체 칩의 제1 칩 콘택은 각각 상기 제1 반도체 칩의 에지와 상기 제2 반도체 칩의 에지에 인접하게 배치되는, 마이크로전자 패키지.

### 청구항 9

제1항에 있어서,

상기 패키지 단자에 결합되는 전기 전도성 결합 유닛을 더 포함하는, 마이크로전자 패키지.

### 청구항 10

제1항에 있어서,

상기 본드 와이어 중 적어도 일부는 상기 제2 마이크로전자 유닛의 에지 주위로 연장하는, 마이크로전자 패키지.

### 청구항 11

제1항에 있어서,

상기 본드 와이어 중 적어도 일부는, 상기 제2 마이크로전자 유닛의 인캡슐런트의 관통 개구를 통해 연장하는, 마이크로전자 패키지.

### 청구항 12

제11항에 있어서,

상기 패키지 단자 중 적어도 일부는, 상기 관통 개구와 상기 제2 마이크로전자 유닛의 에지 사이에 배치되는, 마이크로전자 패키지.

### 청구항 13

제12항에 있어서,

상기 패키지 단자 중 적어도 일부는, 전원 단자 또는 접지 단자 중 하나 이상을 포함하는, 마이크로전자 패키지.

### 청구항 14

제11항에 있어서,

상기 패키지 단자 중 적어도 일부는, 상기 관통 개구와 상기 제2 마이크로전자 유닛의 반도체 칩의 에지 사이에 배치되는, 마이크로전자 패키지.

### 청구항 15

제1항에 있어서,

상기 제1 마이크로전자 유닛의 인캡슐런트는, 상기 제1 칩 콘택이 배치되는 표면에 대향하는, 내부의 상기 제1 마이크로전자 유닛의 반도체 칩의 표면 위에 놓이는, 마이크로전자 패키지.

### 청구항 16

제1항에 있어서,

상기 제2 마이크로전자 유닛의 인캡슐런트는, 상기 제2 칩 콘택이 배치되는 표면에 대향하는, 내부의 상기 제2 마이크로전자 유닛의 반도체 칩의 표면 위에 놓이는, 마이크로전자 패키지.

### 청구항 17

제1항에 있어서,

상기 제1 마이크로전자 유닛 및 상기 제2 마이크로전자 유닛 중 하나 이상은, 상기 제1 마이크로전자 유닛 및 상기 제2 마이크로전자 유닛이 있는 상기 마이크로전자 패키지의 형성 전에 기능적으로 테스트되는, 마이크로전자 패키지.

### 청구항 18

제1항에 있어서,

상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 각각은, 상기 제1 마이크로전자 유닛 및 상기 제2 마이크로전자 유닛이 있는 상기 마이크로전자 패키지의 형성 전에 기능적으로 테스트되는, 마이크로전자 패키지.

### 청구항 19

마이크로전자 패키지의 제조 방법에 있어서,

제1 마이크로전자 유닛을 제2 마이크로전자 유닛 위에 적층하는 단계로서, 상기 제1 마이크로전자 유닛은 제1 칩 콘택을 갖는 반도체 칩, 상기 반도체 칩의 에지에 접촉하는 인캡슐런트, 그리고 상기 인캡슐런트의 표면에 노출되며 상기 제1 칩 콘택과 전기적으로 연결되는 제1 유닛 콘택을 포함하고, 상기 제2 마이크로전자 유닛은 표면에 제2 칩 콘택을 갖는 반도체 칩, 그리고 제2 마이크로전자 유닛의 상기 반도체 칩의 에지에 접촉하며 상기 제2 마이크로전자 유닛의 반도체 칩의 에지로부터 멀어지도록 연장하는 표면을 갖는 인캡슐런트를 포함하며 상기 제2 마이크로전자 유닛의 반도체 칩의 표면 및 상기 제2 마이크로전자 유닛의 인캡슐런트는 상기 제2 마이크로전자 유닛의 표면을 형성하는, 적층 단계; 및

상기 제1 유닛 콘택을 상기 제2 마이크로전자 유닛의 표면에서의 패키지 단자와 전기적으로 연결하는 본드 와이어를 형성하는 단계로서, 상기 패키지 단자는 상기 제2 칩 콘택에 접촉하여 형성되는 트레이스 및 금속화된 비아를 통해 상기 제2 칩 콘택과 전기적으로 연결되는, 본드 와이어 형성 단계를 포함하는,

마이크로전자 패키지의 제조 방법.

### 청구항 20

제19항에 있어서,

상기 비아 및 트레이스는, 증착되는, 마이크로전자 패키지의 제조 방법.

### 청구항 21

제19항에 있어서,

상기 제1 마이크로전자 유닛은, 메모리 저장 어레이 기능을 제공하도록 구성되는, 마이크로전자 패키지의 제조 방법.

### 청구항 22

제19항에 있어서,

상기 제2 마이크로전자 유닛은, 로직 기능을 제공하도록 구성되는, 마이크로전자 패키지의 제조 방법.

### 청구항 23

제19항에 있어서,

상기 제1 마이크로전자 유닛은, 제1 반도체 칩 및 제2 반도체 칩을 포함하고,

상기 제1 반도체 칩은 상기 제1 마이크로전자 유닛의 표면에 노출된 제1 칩 콘택을 가지며, 상기 제2 반도체 칩의 제1 칩 콘택은 상기 제1 마이크로전자 유닛의 인캡슐런트를 통해 연장하는 전기 전도성 비아를 통해 상기 제1 유닛 콘택과 연결되는, 마이크로전자 패키지의 제조 방법.

#### 청구항 24

제23항에 있어서,

상기 제1 반도체 칩 및 상기 제2 반도체 칩은, 메모리 저장 어레이 기능을 제공하도록 구성되는, 마이크로전자 패키지의 제조 방법.

#### 청구항 25

제23항에 있어서,

상기 제2 반도체 칩은 상기 제1 반도체 칩 위에 부분적으로 놓임으로써 상기 제2 반도체 칩의 제1 칩 콘택이 상기 제1 반도체 칩의 에지를 넘어 배치되는, 마이크로전자 패키지의 제조 방법.

#### 청구항 26

제19항에 있어서,

상기 본드 와이어 형성 단계는, 상기 본드 와이어 중 적어도 일부를 상기 제2 마이크로전자 유닛의 에지 주위로 연장하도록 형성하는, 마이크로전자 패키지의 제조 방법.

#### 청구항 27

제19항에 있어서,

상기 본드 와이어 형성 단계는, 상기 본드 와이어 중 적어도 일부를 상기 제2 마이크로전자 유닛의 인캡슐런트의 관통 개구를 통해 연장하도록 형성하는, 마이크로전자 패키지의 제조 방법.

#### 청구항 28

제27항에 있어서,

상기 제2 마이크로전자 유닛의 인캡슐런트의 상기 관통 개구는, 상기 제2 마이크로전자 유닛의 제2 반도체 칩 주위에 상기 제2 마이크로전자 유닛의 인캡슐런트를 몰딩(molding)하는 과정 동안 형성되는, 마이크로전자 패키지의 제조 방법.

#### 청구항 29

제28항에 있어서,

상기 관통 개구와 동일한 구성을 갖는 요소가 상기 몰딩하는 과정 동안 상기 관통 개구를 형성하는, 마이크로전자 패키지의 제조 방법.

#### 청구항 30

제19항에 있어서,

상기 적층 단계 이전에 상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 중 하나 이상을 기능적으로 테스트하는 단계를 더 포함하는, 마이크로전자 패키지의 제조 방법.

#### 청구항 31

제19항에 있어서,

상기 적층 단계 이전에 상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 각각을 기능적으로 테스

트하는 단계를 더 포함하는, 마이크로전자 패키지의 제조 방법.

### 청구항 32

제19항에 있어서,

상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 중 하나 이상은, 재구성된 웨이퍼 또는 회로 패널인, 마이크로전자 패키지의 제조 방법.

### 청구항 33

마이크로전자 패키지에 있어서,

제1 칩 콘택을 갖는 제1 반도체 칩, 상기 제1 반도체 칩의 에지에 접촉하는 인캡슐런트(encapsulant), 그리고 상기 인캡슐런트의 표면에 노출되며 상기 제1 칩 콘택과 전기적으로 결합되는 제1 유닛 콘택을 포함하는 제1 마이크로전자 유닛;

전면 표면과 상기 전면 표면으로부터 멀어지게 연장되는 에지, 및 상기 전면 표면에 있는 제2 칩 콘택을 갖는 제2 반도체 칩, 그리고 상기 제2 반도체 칩의 에지에 접촉하며 상기 제2 반도체 칩의 에지로부터 멀어지도록 연장하는 평면 표면을 갖는 인캡슐런트를 포함하는 제2 마이크로전자 유닛으로서, 상기 제2 반도체 칩의 전면 표면 및 상기 제2 마이크로전자 유닛의 인캡슐런트의 평면 표면은 상기 제2 마이크로전자 유닛의 표면을 형성하고, 상기 제2 마이크로전자 유닛의 표면이 상기 제1 마이크로전자 유닛으로부터 이격되어 마주보도록 상기 제 1 및 제 2 마이크로전자 유닛이 적층되는, 제2 마이크로전자 유닛; 및

상기 제2 마이크로전자 유닛의 평면 표면에 있는 패키지 단자로서, (i) 상기 패키지 단자에 대하여 측면으로 상기 제2 마이크로전자 유닛의 평면 표면의 위에 연장되는 제1 전기 전도성 구조체를 통해 상기 제1 유닛 콘택과 전기적으로 결합되고 (ii) 상기 제2 칩 콘택에 결합된 제2 전기 전도성 구조체를 통해 상기 제2 칩 콘택과 전기적으로 결합되는, 패키지 단자를 포함하는,

마이크로전자 패키지.

### 청구항 34

제33항에 있어서,

상기 제1 전기 전도성 구조체는 본드 와이어를 포함하는, 마이크로전자 패키지.

### 청구항 35

제33항에 있어서,

상기 제1 마이크로전자 유닛은, 메모리 저장 어레이 기능을 제공하도록 구성되는, 마이크로전자 패키지.

### 청구항 36

제35항에 있어서,

상기 제2 마이크로전자 유닛은 로직 기능을 제공하도록 구성되는, 마이크로전자 패키지.

### 청구항 37

제33항에 있어서,

상기 제1 마이크로전자 유닛은, 상기 제1 반도체 칩 위에 적어도 부분적으로 놓이는 제3 반도체 칩을 더 포함하고,

상기 제3 반도체 칩은 상기 제1 마이크로전자 유닛의 표면에 노출된 제3 칩 콘택을 가지는, 마이크로전자 패키지.

### 청구항 38

제37항에 있어서,

상기 제3 반도체 칩의 제3 칩 콘택 중 적어도 하나는 상기 제1 마이크로전자 유닛의 인캡슐런트의 관통 개구에 노출되는, 마이크로전자 패키지.

#### 청구항 39

제37항에 있어서,

상기 제3 반도체 칩의 제3 칩 콘택 중 적어도 일부가 상기 제1 반도체 칩의 에지를 넘어 배치되는, 마이크로전자 패키지.

#### 청구항 40

제37항에 있어서,

상기 제1 칩 콘택과 상기 제3 칩 콘택은 각각 상기 제1 반도체 칩의 에지와 상기 제3 반도체 칩의 에지에 인접하게 배치되는, 마이크로전자 패키지.

#### 청구항 41

제34항에 있어서,

상기 본드 와이어 중 적어도 일부는 상기 제2 마이크로전자 유닛의 에지 주위로 연장하는, 마이크로전자 패키지.

#### 청구항 42

제34항에 있어서,

상기 본드 와이어 중 적어도 일부는, 상기 제2 마이크로전자 유닛의 인캡슐런트의 관통 개구를 통해 연장하는, 마이크로전자 패키지.

#### 청구항 43

제42항에 있어서,

상기 패키지 단자 중 적어도 일부는, 상기 관통 개구와 상기 제2 마이크로전자 유닛의 에지 사이에 배치되는, 마이크로전자 패키지.

#### 청구항 44

제43항에 있어서,

상기 패키지 단자 중 적어도 일부는, 전원 단자 또는 접지 단자 중 하나 이상을 포함하는, 마이크로전자 패키지.

#### 청구항 45

제33항에 있어서,

상기 제1 마이크로전자 유닛의 인캡슐런트는, 상기 제1 칩 콘택이 배치되는 표면에 대향하는, 내부의 상기 제1 반도체 칩의 표면 위에 놓이는, 마이크로전자 패키지.

#### 청구항 46

제33항에 있어서,

상기 제2 마이크로전자 유닛의 인캡슐런트는, 상기 제2 반도체 칩의 전면 표면에 대향하는, 상기 제2 반도체 칩의 표면 위에 놓이는, 마이크로전자 패키지.

#### 청구항 47

제33항에 있어서,

상기 제1 마이크로전자 유닛 및 상기 제2 마이크로전자 유닛 중 적어도 하나가, 상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 중 다른 것과 결합되지 않은 상태에서 기능적으로 테스트되는, 마이크로전자 패키지.

#### 청구항 48

제33항에 있어서,

상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 각각은, 상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 중 다른 것과 결합되지 않은 상태에서 기능적으로 테스트되는, 마이크로전자 패키지.

#### 청구항 49

마이크로전자 패키지로서,

제1 칩 콘택을 갖는 제1 반도체 칩, 상기 제1 반도체 칩의 에지에 접촉하는 인캡슐런트, 그리고 상기 인캡슐런트의 표면에 노출되며 상기 제1 칩 콘택과 전기적으로 연결되는 제1 유닛 콘택을 포함하는 제1 마이크로전자 유닛;

제2 칩 콘택을 갖는 제2 반도체 칩, 상기 제2 반도체 칩의 에지에 접촉하고 상기 제2 반도체 칩의 에지로부터 멀어지도록 연장하는 표면을 갖는 인캡슐런트를 포함하는 제2 마이크로전자 유닛으로서, 상기 제2 반도체 칩의 표면 및 상기 제2 마이크로전자 유닛의 인캡슐런트는 상기 제2 마이크로전자 유닛의 표면을 형성하고, 상기 제2 마이크로전자 유닛의 표면이 상기 제1 마이크로전자 유닛으로부터 이격되어 마주보도록 상기 제1 및 제2 마이크로전자 유닛이 적층되는, 상기 제2 마이크로전자 유닛; 및

상기 제2 마이크로전자 유닛의 표면에 있는 패키지 단자로서, (i) 상기 패키지 단자에 대하여 측면으로 상기 제2 마이크로전자 유닛의 표면의 위에 연장되는 본드 와이어를 포함하는 제1 전기 전도성 구조체를 통해 상기 제1 유닛 콘택과 전기적으로 연결되고 (ii) 상기 제2 칩 콘택에 결합되는 제2 전기 전도성 구조체를 통해 상기 제2 칩 콘택과 전기적으로 연결되는, 패키지 단자를 포함하고,

상기 본드 와이어 중 적어도 일부는 상기 제2 마이크로전자 유닛의 인캡슐런트 내의 관통 개구를 통해 연장되는, 마이크로전자 패키지.

#### 청구항 50

제49항에 있어서,

상기 제1 마이크로전자 유닛 또는 상기 제2 마이크로전자 유닛 중 적어도 하나가, 상기 제1 마이크로전자 유닛과 상기 제2 마이크로전자 유닛 중 임의의 다른 것과 결합되지 않은 적어도 하나의 마이크로전자 유닛의 상태에서 기능적으로 테스트되는, 마이크로전자 패키지.

#### 청구항 51

제50항에 있어서,

상기 패키지 단자 중 적어도 일부는, 상기 관통 개구와 상기 제2 마이크로전자 유닛의 제2 반도체 칩의 에지 사이에 배치되는, 마이크로전자 패키지.

#### 청구항 52

제51항에 있어서,

상기 패키지 단자 중 적어도 일부는, 전원 단자 또는 접지 단자 중 하나 이상을 포함하는, 마이크로전자 패키지.

#### 청구항 53

마이크로전자 패키지에 있어서,

제1 마이크로전자 유닛으로서, 제1 칩 콘택을 갖는 제1 반도체 칩, 및 상기 제1 마이크로전자 유닛의 표면에 위

치되며 상기 제1 칩 콘택과 전기적으로 결합되는 제1 유닛 콘택을 포함하는, 제1 마이크로전자 유닛;

전면 표면과 상기 전면 표면으로부터 멀어지도록 연장하는 에지를 갖는 제2 반도체 칩, 및 상기 전면 표면에 있는 제2 칩 콘택을 포함하는 제2 마이크로전자 유닛으로서, 상기 제1 및 제2 마이크로전자 유닛이 기판 없이 적층되어, 상기 제1 유닛 콘택 중 하나 이상이 상기 제2 마이크로전자 유닛의 에지를 넘어 연장되는 제1 마이크로전자 유닛의 일부에 위치되는, 제2 마이크로전자 유닛;

(i) 제1 전기 전도성 구조체를 통해 상기 제1 유닛 콘택 중 하나 이상과 전기적으로 연결되고 (ii) 상기 제2 칩 콘택과 결합된 제2 전기 전도성 구조체를 통해 상기 제2 칩 콘택과 전기적으로 연결되는, 상기 제2 마이크로전자 유닛의 표면에서의 패키지 단자를 포함하는,

마이크로전자 패키지.

#### 청구항 54

제53항에 있어서,

상기 전기 전도성 구조체는 본드 와이어를 포함하는, 마이크로전자 패키지.

#### 청구항 55

제53항에 있어서,

상기 제1 마이크로전자 유닛은, 메모리 저장 어레이 기능을 제공하도록 구성되는, 마이크로전자 패키지.

#### 청구항 56

제55항에 있어서,

상기 제2 마이크로전자 유닛은 로직 기능을 제공하도록 구성되는, 마이크로전자 패키지.

#### 청구항 57

제53항에 있어서,

상기 제1 마이크로전자 유닛은, 상기 제1 반도체 칩 위에 적어도 부분적으로 놓여있는 제3 반도체 칩을 더 포함하고, 상기 제3 반도체 칩은 상기 제3 반도체 칩의 표면에 위치된 제3 칩 콘택을 갖는, 마이크로전자 패키지.

#### 청구항 58

제57항에 있어서,

상기 제3 반도체 칩의 제3 칩 콘택 중 적어도 하나는 상기 제3 반도체 칩의 표면에 있는 제2 유닛 콘택과 결합되는, 마이크로전자 패키지.

#### 청구항 59

제57항에 있어서,

상기 제3 반도체 칩의 제3 칩 콘택 중 적어도 일부는 상기 제1 반도체 칩의 에지를 넘어 배치되는, 마이크로전자 패키지.

#### 청구항 60

제57항에 있어서,

상기 제1 칩 콘택 및 상기 제3 칩 콘택은 상기 제1 반도체 칩 및 상기 제3 반도체 칩의 에지에 각각 인접하게 배치되는, 마이크로전자 패키지.

#### 청구항 61

제54항에 있어서,

상기 본드 와이어 중 적어도 일부는 상기 제2 마이크로전자 유닛의 에지 주위로 연장되는, 마이크로전자

패키지.

### 청구항 62

제54항에 있어서,

상기 본드 와이어 중 적어도 일부는 상기 제2 마이크로전자 유닛의 제2 반도체 칩의 에지에 접촉되는 인캡슐런트 내의 관통 개구를 통해 연장되는, 마이크로전자 패키지.

### 청구항 63

제62항에 있어서,

상기 패키지 단자 중 적어도 일부는 상기 제2 마이크로전자 유닛의 에지와 상기 관통 개구 사이에 배치되는, 마이크로전자 패키지.

### 청구항 64

제63항에 있어서,

상기 패키지 단자 중 적어도 일부는 전원 단자 또는 접지 단자 중 적어도 하나를 포함하는, 마이크로전자 패키지.

### 청구항 65

제53항에 있어서,

상기 제1 마이크로전자 유닛은 상기 제2 마이크로전자 유닛으로부터 측면으로 오프셋되는, 마이크로전자 패키지.

### 청구항 66

제53항에 있어서,

상기 제1 마이크로전자 유닛은 상기 제2 마이크로전자 유닛보다 넓은, 마이크로전자 패키지.

### 청구항 67

제53항에 있어서,

상기 제1 또는 제2 마이크로전자 유닛 중 적어도 하나는 상기 제1 또는 제2 마이크로전자 유닛 중 다른 것과 결합되지 않은 상태로 기능적으로 테스트되는, 마이크로전자 패키지.

### 청구항 68

제53항에 있어서,

상기 제1 또는 제2 마이크로전자 유닛의 각각이 상기 제1 또는 제2 마이크로전자 유닛 중 다른 것과 결합되지 않은 상태로 기능적으로 테스트되는, 마이크로전자 패키지.

### 청구항 69

마이크로전자 패키지로서,

제1 칩 콘택을 갖는 제1 반도체 칩을 포함하는 제1 마이크로전자 유닛으로서, 상기 제1 마이크로전자 유닛의 표면에 위치되고 상기 제1 칩 콘택과 전기적으로 결합되는 제1 유닛 콘택을 가지는, 제1 마이크로전자 유닛;

제2 칩 콘택을 갖는 제2 반도체 칩을 포함하는 제2 마이크로전자 유닛으로서, 상기 제2 반도체 칩의 표면은 상기 제2 마이크로전자 유닛의 표면을 적어도 부분적으로 형성하고, 상기 제1 및 제2 마이크로전자 유닛이 기판 없이 적층되어 상기 제1 유닛 콘택 중 하나 이상이 상기 제2 마이크로전자 유닛의 에지를 넘어 연장되는 제1 마이크로전자 유닛의 일부에 위치되는, 제2 마이크로전자 유닛; 및

상기 제2 마이크로전자 유닛의 표면에 있는 패키지 단자로서, (i) 상기 패키지 단자에 대해 측면으로 상기 제2 마이크로전자 유닛의 표면 위에 연장되는 본드 와이어를 포함하는 제1 전기 전도성 구조체를 통해 상기 제1 유

닛 콘택과 전기적으로 연결되고 (ii) 상기 제2 칩 콘택과 결합된 제2 전기 전도성 구조체를 통해 상기 제2 칩 콘택과 전기적으로 연결되는, 패키지 단자를 포함하고,

상기 본드 와이어 중 적어도 일부는 상기 제2 마이크로전자 유닛의 표면의 관통 개구를 통해 연장되는, 마이크로전자 패키지.

### 청구항 70

제69항에 있어서,

상기 제1 또는 제2 마이크로전자 유닛 중 적어도 하나는 상기 제1 및 제2 마이크로전자 유닛 중 임의의 다른 것과 결합되지 않은 적어도 하나의 마이크로전자 유닛의 상태로 기능적으로 테스트되는, 마이크로전자 패키지.

### 청구항 71

제70항에 있어서,

상기 제1 마이크로전자 유닛이 상기 제2 마이크로전자 유닛으로부터 측면으로 오프셋되는, 마이크로전자 패키지.

### 청구항 72

제71항에 있어서,

상기 제1 마이크로전자 유닛은 상기 제2 마이크로전자 유닛보다 넓은, 마이크로전자 패키지.

## 발명의 설명

### 기술 분야

[0001]

관련 출원에 대한 상호 참조

[0002]

본 출원은 2011년 10월 20일에 출원된 미국 특허 출원 제13/277,330호의 계속 출원이며, 상기 미국 특허 출원은 그 내용 전체가 원용에 의해 본 명세서에 포함된다.

[0003]

본 발명은 적층된 마이크로전자 유닛을 포함하는 마이크로전자 패키지와, 이러한 패키지를 제조하는 방법에 관한 것이다.

### 배경 기술

[0004]

반도체 칩은 칩 자체의 내부 전기 회로에 연결된, 전면에 배치된 콘택이 있는 평평한 바디(body)이다. 칩은 일반적으로 패키지되어 패키지의 콘택에 전기적으로 연결되는 단자를 갖는 마이크로전자 패키지를 형성한다. 패키지의 단자는 외부 마이크로전자 컴포넌트, 예컨대, 회로 패널에 연결될 수 있다.

[0005]

공간을 절약하기 위하여, 보통 마이크로전자 패키지를 적어도 하나의 반도체 칩을 각각 포함하는 복수의 마이크로전자 패키지가 다른 패키지의 위에 배치되는 "적층" 구성으로 패키지하는 것이 바람직하다. 적층된 칩 패키지 구조 또는 패키지 온 패키지(Package-on-Package: PoP)에서, 각각의 패키지의 칩은 모든 칩의 전체 표면 면적보다 작은 표면 면적을 차지하도록 장착된다. PoP의 칩의 감소된 면적은, PoP의 칩이 결국 부착될 수 있는 인쇄 회로 보드(printed circuit board: PCB) 상의 면적을 매우 효율적으로 이용할 수 있도록 한다.

[0006]

일반적으로, PoP에 포함된 마이크로전자 패키지는, 그 패키지가 PoP를 형성하기 위해 적층 구조에 결합되기 전에, 그 칩 콘택에서 개별 패키지의 칩의 테스트를 허용할 수 있을 만큼 충분히 큰 사이즈를 갖는다. 또한, 일부 PoP에서는, 전도성 구조가 각각의 패키지의 칩의 칩 콘택을 서로 전기적으로 연결하고, 이러한 전도성 구조는 패키지 간의 바람직하지 않은 높은 기생 성분(parasitics)을 야기하는 길이를 가질 수 있다.

[0007]

따라서, 외부의 마이크로전자 컴포넌트에 연결될 수 있고, 각각이 반도체 칩과 같은 마이크로전자 요소를 포함하는 적층된 마이크로전자 유닛을 포함하는 마이크로전자 패키지를 생산하는 분야에서 추가의 개선이 바람직하다.

## 발명의 내용

[0008]

본 발명의 일 실시예에 따르면, 마이크로전자 패키지는 제1 칩 콘택을 갖는 반도체 칩, 반도체 칩의 에지에 접촉하는 인캡슐런트, 그리고 인캡슐런트의 표면에 노출되며 제1 칩 콘택과 전기적으로 연결되는 제1 유닛 콘택을 포함하는 제1 마이크로전자 유닛을 포함할 수 있다. 이러한 패키지는 표면에 제2 칩 콘택을 갖는 반도체 칩, 그리고 제2 마이크로전자 유닛의 반도체 칩의 에지에 접촉하며 그 에지로부터 멀어지도록 연장하는 표면을 갖는 인캡슐런트를 포함하는 제2 마이크로전자 유닛을 포함할 수 있고, 반도체 칩의 표면 및 제2 마이크로전자 유닛의 인캡슐런트는 제2 마이크로전자 유닛의 표면을 형성한다. 이러한 패키지는 또한 제1 유닛 콘택과 전기적으로 연결되는 본드 와이어를 포함할 수 있다. 이러한 패키지는 (i) 본드 와이어를 통해 제1 유닛 콘택과 전기적으로 연결되고 (ii) 제2 칩 콘택에 접촉하여 형성되는 트레이스 및 금속화된 비아를 통해 제2 칩 콘택과 전기적으로 연결되는, 제2 마이크로전자 유닛의 면에서의 패키지 단자를 더 포함할 수 있다.

[0009]

본 발명의 다른 실시예에서, 마이크로전자 패키지 제조 방법은 제1 마이크로전자 유닛을 제2 마이크로전자 유닛 위에 적층하는 단계를 포함할 수 있다. 제1 마이크로전자 유닛은 제1 칩 콘택을 갖는 반도체 칩, 반도체 칩의 에지에 접촉하는 인캡슐런트, 그리고 인캡슐런트의 표면에 노출되며 제1 칩 콘택과 전기적으로 연결되는 제1 유닛 콘택을 포함할 수 있다. 제2 마이크로전자 유닛은 표면에 제2 칩 콘택을 갖는 반도체 칩, 그리고 제2 마이크로전자 유닛의 반도체 칩의 에지에 접촉하며 그러한 에지로부터 멀어지도록 연장하는 표면을 갖는 인캡슐런트를 포함할 수 있고, 반도체 칩의 표면 및 제2 마이크로전자 유닛의 인캡슐런트는 제2 마이크로전자 유닛의 표면을 형성한다. 이러한 방법은 제1 유닛 콘택을 제2 마이크로전자 유닛의 표면에서의 패키지 단자와 전기적으로 연결하는 본드 와이어를 형성하는 단계를 포함할 수 있으며, 여기서 패키지 단자는 제2 칩 콘택에 접촉하여 형성되는 트레이스 및 금속화된 비아를 통해 제2 칩 콘택과 전기적으로 연결된다.

## 도면의 간단한 설명

[0010]

도 1-2는 본 발명의 일 실시예에 따른, 수직으로 적층된 마이크로전자 요소를 포함하는 마이크로전자 유닛 제조 방법의 단계를 나타내는 개략적인 단면도이다.

도 3a는 본 발명의 일 실시예에 따른, 수직으로 적층된 마이크로전자 요소를 포함하는 마이크로전자 유닛의 일부분의 개략적인 단면도이다.

도 3b는 본 발명의 다른 실시예에 따른, 수직으로 적층된 마이크로전자 요소를 포함하는 마이크로전자 유닛의 일부분의 개략적인 단면도이다.

도 4-8은 본 발명의 일 실시예에 따른, 패키지 단자가 있는 마이크로전자 유닛의 제조 방법의 단계를 나타내는 개략적인 단면도이다.

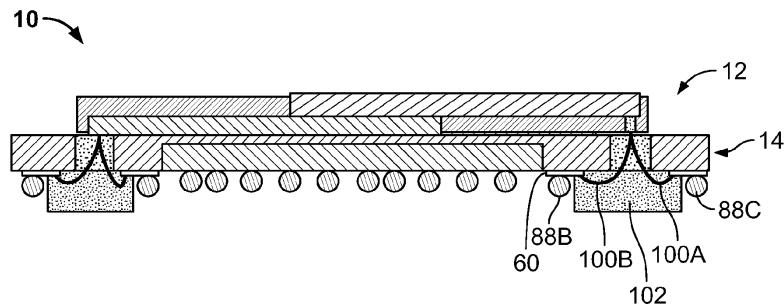

도 9-11은 본 발명의 일 실시예에 따른, 도 1-3 및 도 4-8의 방법을 이용하여 형성되는 적층된 마이크로전자 유닛을 갖는 마이크로전자 패키지의 제조 방법의 단계를 나타내는 개략적인 단면도이다.

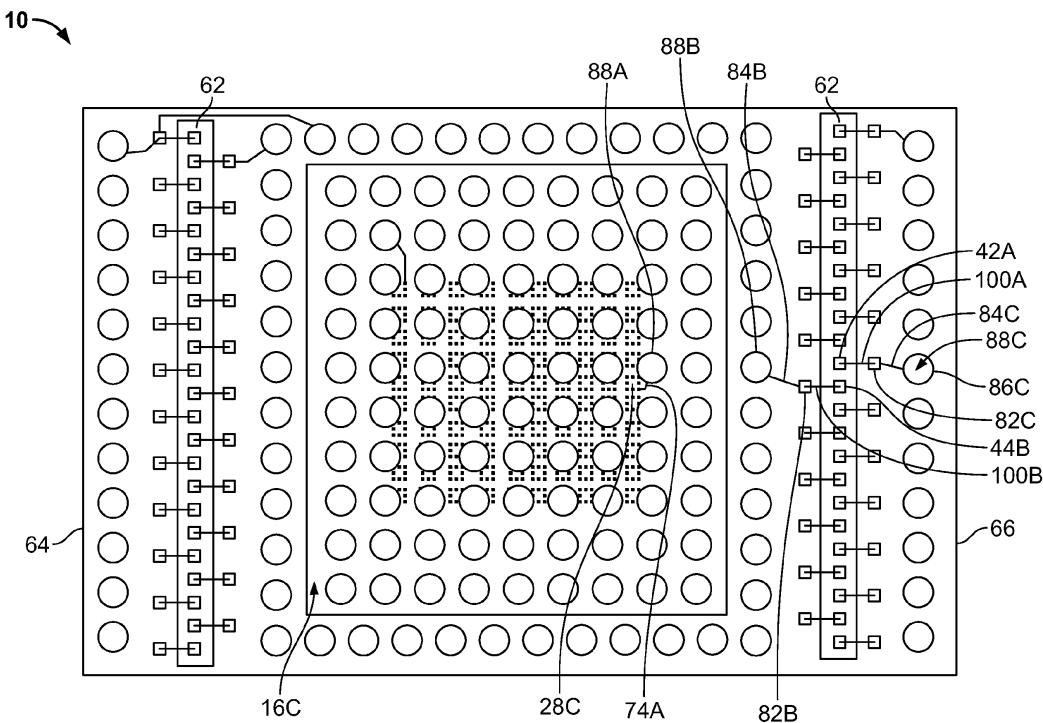

도 12는 도 11의 패키지의 하부, 평면도이다.

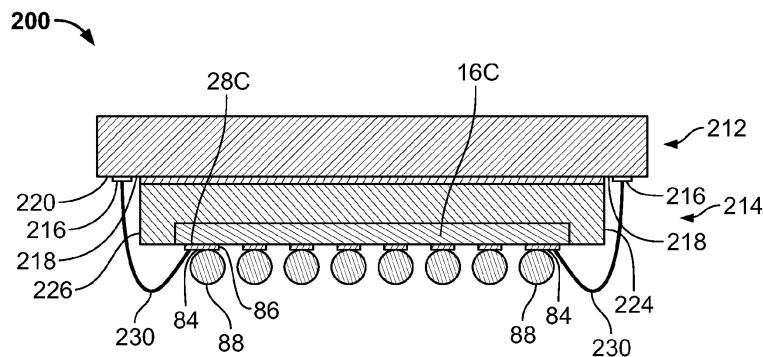

도 13은 본 발명의 다른 실시예에 따른, 마이크로전자 패키지의 개략적인 단면도이다.

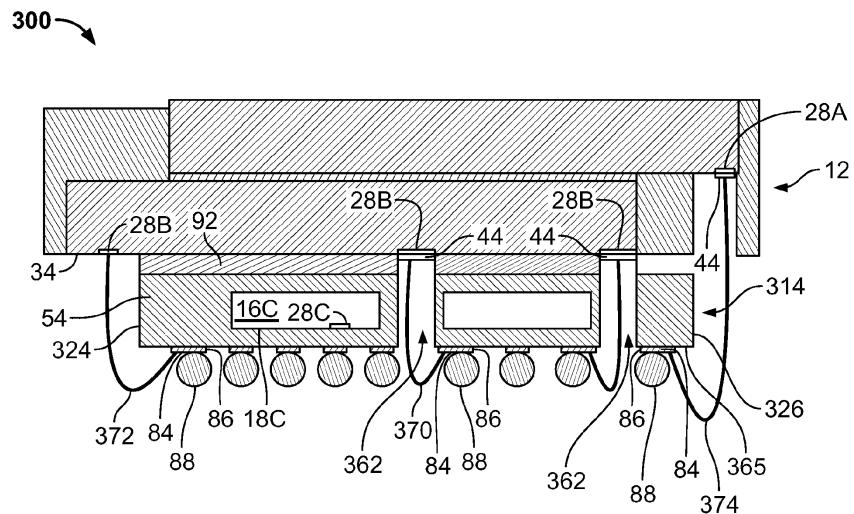

도 14는 본 발명의 다른 실시예에 따른, 마이크로전자 패키지의 개략적인 단면도이다.

도 15는 본 발명의 일 실시예에 따른 시스템의 개략도이다.

## 발명을 실시하기 위한 구체적인 내용

[0011]

도 1-11에 도시된 바와 같이, 각각 마이크로전자 요소를 포함하는, 적층된 마이크로전자 유닛(12 및 14)을 포함하는 마이크로전자 패키지(10)가 본 발명의 일 실시예에 따라 제조될 수 있다. 각각의 마이크로전자 요소는 반도체 칩, 웨이퍼 등일 수 있다. 칩은 복수의 능동 디바이스(예컨대, 트랜지스터, 다이오드 등), 복수의 수동 디바이스(예컨대, 저항, 커패시터, 인덕터 등), 또는 능동 디바이스 및 수동 디바이스 양자 모두를 포함할 수 있다. 일반적으로, 적어도 하나의 칩은 능동 디바이스 또는 능동 디바이스 및 수동 디바이스 양자 모두를 포함할 수 있다. 각각의 칩은 마이크로전자 유닛 내의 다른 칩들과 동일한 타입일 수 있고 또는 칩들은 상이한 타입일 수 있다.

[0012]

특정 실시예에서, 패키지(10) 내의, 예컨대, 마이크로전자 유닛(14)과 같은 마이크로전자 유닛 중 하나 이상은,

예컨대, 특히 프로그램가능한 범용의 또는 특정 용도의 프로세서, 마이크로컨트롤러, FPGA(field programmable gate array) 디바이스, ASIC(application specific integrated circuit), 디지털 신호 프로세서와 같은 로직 칩으로서 주된 기능을 갖도록 구성되는 칩들을 포함할 수 있다. 이러한 실시예에서, 패키지(10) 내의 마이크로전자 유닛 중 하나 이상, 예컨대, 마이크로전자 유닛(12)은 로직 칩으로서가 아닌 다른 주된 기능을 갖는 칩들을 포함할 수 있다. 예를 들어, 하나 이상의 로직 칩이 있는 마이크로전자 유닛(14)은 각각 주된 메모리 기능을 갖는 하나 이상의 저장 어레이(storage array) 칩을 포함하는 하나 이상의 마이크로전자 유닛(12)과 결합될 수 있다. 이러한 메모리 저장 어레이 칩은 예컨대 DRAM(dynamic random access memory), SRAM(static random access memory)과 같은 휘발성 메모리 저장 영역, 예컨대 플래시 메모리 또는 MRAM(magnetic random access memory)과 같은 비휘발성 메모리 저장 어레이, 또는 휘발성 및 비휘발성 저장 어레이의 결합을 포함할 수 있다. 특정 실시예에서, 패키지(10)의 마이크로전자 유닛 중 하나 이상은 동일한 칩에서 로직 기능 및 실질적인 다른 기능, 예컨대, 실질적인 메모리 기능을 결합하는 칩을 포함할 수 있다.

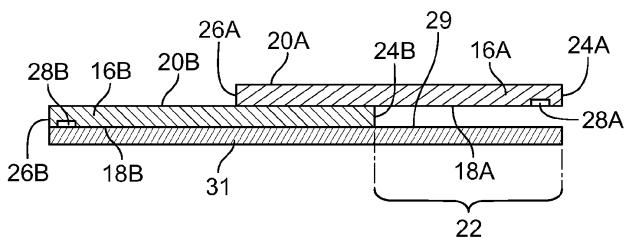

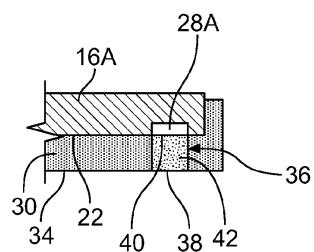

[0013] 도 1-2를 참조하면, 마이크로전자 유닛(12)은 수직으로 적층된 칩(16A 및 16B)을 포함할 수 있다. 칩(16)은 각각 전면(front surface)(18) 및 전면(18)에 대향하는 배면(rear surface)(20)을 가질 수 있다. 마이크로전자 유닛(12)은 하나의 칩의 전면이 다른 칩의 배면을 향하도록 형성될 수 있으며, 마이크로전자 유닛(12)은 수직 적층으로 배열된 둘 이상의 칩(16)을 포함할 수 있다. 칩(16)은 접착층(도시되지 않음)에 의해 그들의 마주보는 표면에 부착될 수 있고, 예컨대, 칩(16A)과 칩(16B)을 포함하는 적층체(stack) 내의 칩(16B)과 같은 칩의 적층체 내의 맨 아래 칩(bottom chip)은 또한 접착층(도시되지 않음)에 의해 캐리어 플레이트(carrier plate)(31)의 표면(29)에 부착될 수 있다. 캐리어 플레이트(31)는 유전체 재료 또는 유리로부터 형성될 수 있다. 접착층은 다이 부착 접착제(die attach adhesive)를 포함할 수 있고, 컴플라이언시(compliancy), 열 전도성(thermally conductivity), 습기 또는 다른 오염물에 대한 불투과성(impermeability)의 속성, 또는 이러한 속성의 조합을 위하여 선택될 수 있다. 접착층은, 예를 들어, 칩(16)의 전면 또는 배면 위에 놓이도록 도포된 유동성 접착제 또는 접착성(tacky)(부분적으로 경화됨) 접착제일 수 있으며, 그 후에 예컨대, 퍽 앤드 플레이스툴(pick-and-place tool)을 이용하여 칩이 접착층에 부착될 수 있다. 대안적으로, 접착층은 액체로서 박리성 백킹(peelable backing)에 증착될 수 있고, 또는 부분적으로 경화된 접착층으로서 박리성 백킹에 접착될 수 있으며, 그 후에 칩(16)이 접착층에 부착될 수 있다. 박리성 백킹을 제거한 후에, 접착층은 다른 칩 또는 캐리어 플레이트(31)와 정렬 및 결합될 수 있다.

[0014] 본 명세서에서 사용되는, 예컨대, "위로", "아래로", "수직으로", 그리고 "수평으로"와 같은 용어는 지정된 요소의 좌표계를 지칭하는 것으로서 이해되어야 하며, 보통의 중력 좌표계를 따를 필요는 없다. 또한, 편의상, 본 명세서에서 방향은 마이크로전자 패키지(10) 내의 마이크로전자 유닛(14) 위에 적층된 마이크로전자 유닛(12)의 "전면", 예컨대, 도 1에 도시된 바와 같이 칩(16B)의 표면(18B)을 참조하여 언급된다. 일반적으로, "위쪽" 또는 "로부터 상승하는"으로 지칭되는 방향은 마이크로전자 유닛(12)의 전면으로부터 직각으로 멀어지는 방향을 지칭할 것이다. "아래쪽"으로 지칭되는 방향은 마이크로전자 유닛(12)의 전면에 직각인 방향과 대향하는 위쪽 방향을 지칭할 것이다. "수직" 방향은 마이크로전자 유닛(12)의 전면에 직각인 방향을 지칭할 것이다. 기준점 "위에"라는 용어는 기준점의 위쪽 지점(point)을 지칭하며, 기준점 "아래에"라는 용어는 기준점의 아래쪽 지점을 지칭할 것이다. 임의의 개개의 요소의 "맨 위(top)"는 위쪽 방향으로 가장 멀리 연장하는 그 요소의 지점 또는 지점들을 지칭하며, 임의의 요소의 "맨 아래(bottom)"라는 용어는 아래쪽 방향으로 가장 멀리 연장하는 그 요소의 지점 또는 지점들을 지칭할 것이다.

[0015] 마이크로전자 유닛(12)에서, 칩(16B)의 에지(24B)를 지나서 칩(16A)의 에지(24A)까지 연장하는 전면(18A)의 표면 부분(22)을 제외하고, 칩(16B)은 칩(16A)의 전면(18A) 위에 놓일 수 있다. 에지(24)에 대향하는 각각의 칩(16)의 에지(26)는 수직으로 정렬되거나 정렬되지 않을 수 있다. 일 실시예에서, 칩(16A, 16B)은, 칩(16A)의 전면(18A)의 부분(22)이 각각 칩(16B)의 에지(24B 및 26B)를 지나서 연장하도록 적층 및 구성될 수 있다.

[0016] 회로 또는 칩(16) 내의 다른 전도성 요소(도시되지 않음)에 전기적으로 연결된 칩 콘택(28) 또는 요소는 칩(16A)의 전면(18A)의 부분(22)에, 그리고 적층된 칩의 칩(16B)의 전면(18B)에 노출될 수 있다.

[0017] 본 명세서에서 사용되는 것처럼, 금속 특징부가 반도체 칩의 윗면을 형성하는 유전체층의 표면과 같은 표면에 도포된 본딩(bonding) 재료 또는 콘택에 액세스 가능하면, 전기 전도성 특징부가 이러한 표면에 "노출"되는 것으로 생각될 수 있다. 따라서, 유전체의 표면으로부터 돌출되거나 유전체의 표면과 동일 평면을 이루는 금속 특징부는 이러한 표면에 노출되고; 반면 유전체 내의 홀(hole)에 배치되거나 홀과 정렬되는 함몰된 전도성 특징부 또한 이러한 표면에 노출된다.

- [0018] 예컨대, 반도체 칩 상의 콘택(28)은 알루미늄 또는 구리를 포함할 수 있고, 서브미크론 크기의 노출된 전면을 가질 수 있다. 콘택(28)의 전면은, 콘택이 그 콘택을 덮는 전도성 재료를 통하여 패키지의 요소 또는 다른 전기 전도성 재료에 전기적으로 연결되는 것을 제공하면서, 이후의 공정, 예컨대, 이하에 설명되는 바와 같이 칩의 전면 위에 놓이는 유전체 재료의 레이징 동안 콘택(28)이 손상되지 않도록 보호하는 다른 전기 전도성 재료 또는 금속으로 덮일 수 있다. 원용에 의해 본 명세서에 포함되는 2011년 8월 1일에 출원된 미국 특허 출원 제 13/195,187호를 참조.

- [0019] 도 2를 참조하면, 마이크로전자 유닛(12)의 제조의 한 단계에서, 인캡슐런트층(layer of encapsulant)(30)은 기판(18A)의 덮이지 않은 부분(22) 위에 형성되어 칩(16B)의 에지(26A), 칩(16A 및 16B)의 에지(24 및 26) 그리고 칩(16B)의 배면(20B)의 덮이지 않은 부분으로부터 멀어지도록 연장할 수 있다. 외부 환경으로부터 캡슐화된 구성요소를 보호하는 인캡슐런트는 유전체 재료 또는 레진(resin)을 포함할 수 있다. 일 실시예에서, 인캡슐런트는 칩(16A)의 배면(20A)과 동일 평면 상에 있으며 그로부터 연장하는 인캡슐런트(30)의 평탄한 상면(32)을 형성하는 몰딩 공정에 의해 형성될 수 있다. 또한, 인캡슐런트는 칩(16B)의 전면(18B)과 동일 평면 상에 있으며 그로부터 연장하는 평탄한 배면(34)을 형성할 수 있다. 인캡슐런트의 형성에 이어, 캐리어 플레이트(31)가 예컨대, 샌딩(sanding), 에칭, 또는 유사한 기술에 의해 제거됨으로써, 인캡슐런트에 의해 덮인 노출된 표면을 갖는 적층된 칩(16)이 있는 마이크로전자 유닛(12)을 얻을 수 있다.

- [0020] 인캡슐런트(30)가 칩(16A)의 콘택(28A)을 덮도록 형성되는 일 실시예에서, 제조의 추가 단계는 배면(34)으로부터 인캡슐런트(30)를 통해 칩(16A)의 전면의 표면 부분(22)을 향하여 연장하는 홀(hole)(36)을 형성하는 단계를 포함할 수 있다. 칩(16A)의 전면(18A)의 부분(22)에서 콘택(28A)을 덮는 전도성 재료는 홀(36) 내에서 노출된다.

- [0021] 홀(36)은 칩으로부터 이격되어 있는 수직인 또는 대략 수직인 축을 따라 연장할 수 있다. 도 3a를 참조하면, 홀(36)은 실질적으로 원추형이거나 또는 칩(16A)의 콘택(28A)에 인접한 실질적으로 원형인 하단부(40)와 배면(34)에서 실질적으로 원형인 상단부(38)를 갖는 원통형일 수 있다. 다른 실시예에서, 홀(36)은 약 25미크론의 평균 직경 또는 폭을 가질 수 있다. 홀의 상단부의 직경 또는 폭과 하단부의 직경 또는 폭 간의 차이는 약 5-10미크론일 수 있다. 일부 예에서, 홀의 하단부의 폭은 상단부의 폭보다 작을 수 있고; 다른 예에서, 홀의 하단부 폭이 상단부 폭과 동일할 수 있다.

- [0022] 추가 실시예에서, 홀(36)은 마이크로전자 유닛(12)의 칩의 전면에 대략 평행하게 연장하는 슬롯(slot) 형태일 수 있다.

- [0023] 일 실시예에서, 홀(36)은 인캡슐런트의 에칭, 편칭(punching), 또는 레이저를 이용한 삭마(ablating)에 의해 인캡슐런트에 형성될 수 있다.

- [0024] 다른 실시예에서, 인캡슐런트(30)는 칩(16A, 16B)의 에지의 형상, 그리고 칩(16A)의 전면 및 칩(16B)의 배면의 덮이지 않은 부분을 가지도록 미리 제조될 수 있고, 또한 칩(16A)의 노출된 요소 콘택(28A)과 일치하도록 패턴된 미리 형성된 홀을 포함하도록 미리 제조될 수 있다. 인캡슐런트(30)는 그 다음, 홀이 콘택(28A)과 수직으로 정렬되도록, 연화된 상태로 적층된 칩 위의 위치에 부착, 예컨대, 압입될 수 있다. 일 실시예에서, 이러한 경우에 인캡슐런트는 적층된 칩에 부착될 때 부분적으로 경화된, 예컨대, "B-스테이지" 재료일 수 있다.

- [0025] 제조의 추가 단계에서, 도 3a를 참조하면, 마이크로전자 유닛 콘택은 배면(34)으로부터 홀(36)을 통해 콘택(28A)을 향하여 연장하는 금속화된 비아(42)로서 형성될 수 있다. 예를 들어, 비아(42)는 배면(34)으로부터 콘택(28A)을 덮는 범프(bump) 또는 포스트(post)(도시되지 않음)까지 연장할 수 있다. 비아(42)는 예칭 가능한 전도성 재료를 포함할 수 있는데, 이러한 전도성 재료는 바람직하게는 구리, 구리계 합금, 알루미늄, 니켈 및 금과 같은 금속이다.

- [0026] 일 실시예에서, 비아(42)는 증착, 예를 들어, 전해 또는 무전해 금속 도금, 전도성 재료 또는 전도성 매트릭스 재료의 증착에 의해 형성될 수 있고, 또는 전도성 비아를 형성하도록 스텐실을 이용하여 홀 내에 전도성 페이스트를 선택적으로 프린팅함으로써 형성될 수 있다. 추가 실시예에서, 전도성 비아(42)가 형성되기 전에, 전도성 시드층(conductive seed layer)(도시되지 않음)이 홀(36)에 형성될 수 있다.

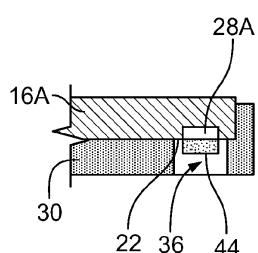

- [0027] 대안적인 실시예에서, 인캡슐런트(30)는 몰딩 공정에 의해 칩(16A 및 16B)의 전면 및 배면의 덮이지 않은 부분 및 칩(16)의 에지 위에 각각 몰딩될 수 있고, 몰딩 공정 동안 몰드의 구조 요소(structural element) 또는 다른 요소, 예컨대, 편은 콘택(28A)과 수직으로 정렬되고 홀(36)을 형성한다. 인캡슐런트의 형성에 이어, 도 3b를 참조하면, 전도성 재료가 홀(36)에 증착되어 표면 부분(22)에 전도성 패드(44)를 형성할 수 있는데, 이러한 전

도성 패드는 칩 콘택(28A)과 전기적으로 연결되는 마이크로전자 유닛(12)의 유닛 콘택의 역할을 할 수 있다.

[0028] 앞서 설명된 다양한 제조 단계는 바람직하게는 마이크로전자 유닛(12)을 형성하도록 예컨대, 캐리어 플레이트에 배열된 칩의 복수의 적층에 대해 행해질 수 있고, 캐리어 플레이트의 제거 전에 또는 제거 후에, 적절하게, 인캡슐런트의 다이싱 레인(dicing lane)에서 유닛들 사이의 인캡슐런트를 절단함으로써 마이크로전자 유닛(12)의 개별 유닛이 얻어질 수 있다는 것을 제공한다. 마이크로전자 유닛(12)은 바람직하게는 적어도 하나의 칩을 지지하기 위하여 완성된 마이크로전자 유닛에 패키지 기판을 필요로 하지 않으면서 구성될 수 있다.

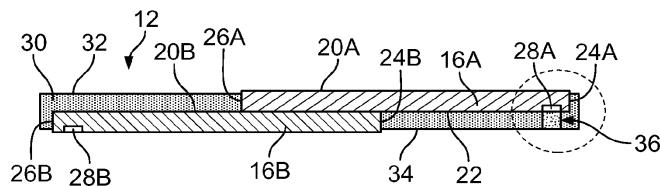

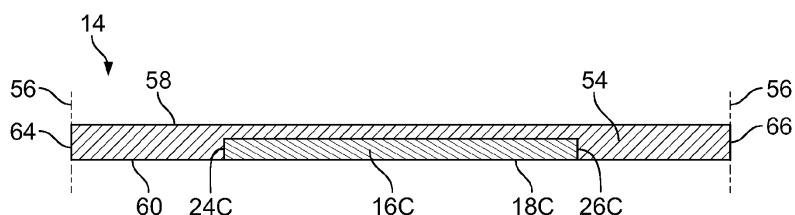

[0029] 도 4-8을 참조하면, 마이크로전자 유닛(14)을 형성하기 위하여, 반도체 칩(16C)이 그들의 전면(18C)에서 접착층(도시되지 않음)에 의해 캐리어 플레이트(52)의 표면(50)에 접착될 수 있다. 캐리어 플레이트(52) 및 접착층은 마이크로전자 유닛(12)의 형성에 대해 앞서 설명된 것과 유사한 재료로부터 형성될 수 있다.

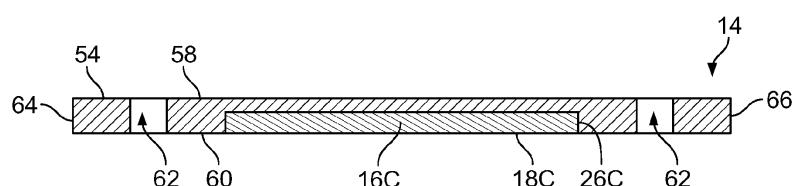

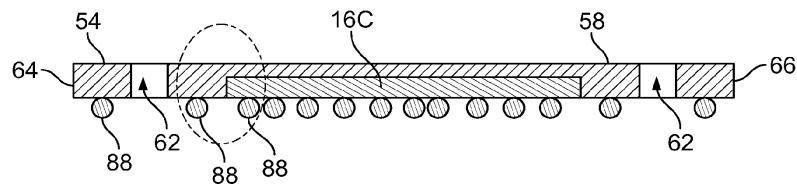

[0030] 도 5를 참조하면, 인캡슐런트층(54)은 칩(16C)의 배면(20C) 및 에지(24C, 26C) 위에 형성될 수 있다. 인캡슐런트(54)는 마이크로전자 유닛(12)에 대해 앞서 설명한 바와 유사한 재료를 포함할 수 있고 그와 유사하게 몰딩에 의해 형성될 수 있고, 그 다음 캐리어 플레이트(52)가 제거될 수 있다. 다음으로, 각각 칩(16C)을 포함하고 대향하는 에지(64, 66)를 갖는 개별 마이크로전자 유닛(14)은 다이싱 레인(56)을 따라 인캡슐런트를 절단, 예컨대, 인캡슐런트의 소잉(sawing) 또는 스크라이빙(scribing)에 의해 형성될 수 있다. 대안적인 실시예에서, 캐리어 플레이트(52)가 제거되기 전에 개별 패키지를 얻기 위하여 절단이 수행될 수 있다.

[0031] 일 실시예에서, 인캡슐런트(54)는, 에지(64)와 에지(66) 사이에서 연장하는 인캡슐런트(54)의 평탄한 상면(58)과, 칩(16C)의 전면(18C)과 동일 평면상에 있으며 칩(16C)의 에지(26C)와 에지(66) 사이에서 그리고 칩(16C)의 에지(24C)와 에지(64) 사이에서 연장하는 평탄한 배면(60)을 형성하는 몰딩 공정에 의해 형성될 수 있다.

[0032] 도 6을 참조하면, 홀(62)은 인캡슐런트(54)의 전체 두께를 관통하여 배면(60)으로부터 상면(58)까지 연장하도록 인캡슐런트(54)를 통하여 형성될 수 있다. 홀(62)은 표면(58 및 60)을 따라 미리 결정된 위치에 위치함으로써, 이하에서 상세하게 설명되는 바와 같이, 전도성 요소가 그를 통해 통과하는 것을 가능하게 하고 마이크로전자 유닛(14)의 콘택을 마이크로전자 유닛(14)에 적층되어 패키지(10)를 형성하는 다른 마이크로전자 유닛, 예컨대 마이크로전자 유닛(12)의 마이크로전자 유닛 콘택과 전기적으로 연결하는 것을 가능하게 한다. 홀(62)은 약 400미크론-1밀리미터(mm)의 직경의 원통형 슬롯의 형태일 수 있다. 일 실시예에서, 홀(62)은 에지(26C)와 에지(66) 사이의 홀과, 에지(24C)와 에지(64) 사이의 홀을 포함할 수 있다. 다른 실시예에서, 홀(62)은 마이크로전자 유닛(14)에 대략 수평으로 연장하는 슬롯으로서 구성될 수 있다. 홀(62)은 홀(36)의 형성에 대해 앞서 설명된 바와 유사한 공정을 이용하여 형성될 수 있다.

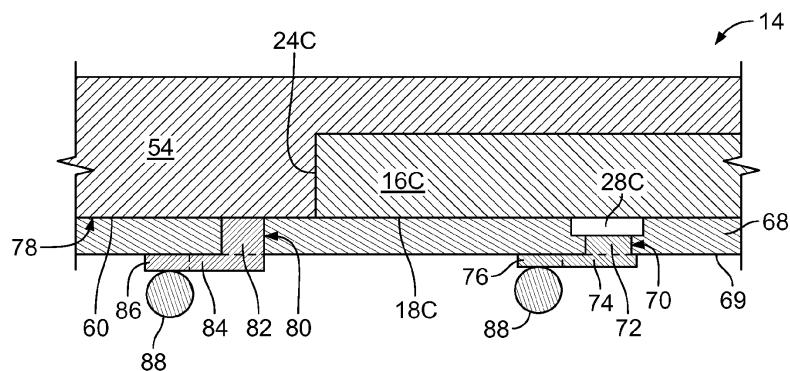

[0033] 도 7, 그리고 전면(18C)에 노출된 칩(16C)의 콘택(28C)을 포함하는 마이크로전자 유닛(14)의 일부분의 확대도를 나타내는 도 8을 참조하면, 유전체 재료층(68)이 칩(16C)의 전면(18C) 위에, 전면(18C)으로부터 멀어져서 홀(62)까지 연장하는 인캡슐런트(54)의 배면(60) 위에, 그리고 또한 홀(62)로부터 에지(64 및 66)까지 연장하는 배면(60) 위에 형성될 수 있다. 다음으로 홀(70)은 유전체층(68)을 통해 콘택(28C)을 향하여 연장하도록 형성되어, 콘택(28C)을 덮는 전도성 재료(도시되지 않음)를 노출시킬 수 있다. 그 다음 유전체층(68)의 배면(69)으로부터 홀(70)을 통하여 콘택(28C)을 덮는 전도성 재료까지 연장하는 전기 전도성 비아(72), 표면(69)을 따라 비아(72)로부터 멀어지도록 연장하는 전도성 트레이스(74), 그리고 바람직하게는 트레이스(74)로부터 연장하고 전기적으로 연결되는 표면(69)에서의 단자(76)를 포함하는 전기 전도성 부분들이 전면(18C)에 형성될 수 있다. 단자(76)는 마이크로전자 유닛(14)의 배면(78)에 있거나 배면(78)에 노출되고, 트레이스(74)와 비아(70)를 통해 콘택(28C)에 전기적으로 연결된다.

[0034] 다른 실시예에서, 일련의 중첩이 금속화된 비아 및 하나 또는 둘 이상의 전기 전도성 트레이스층 및 유전체 재료층을 포함하는 전도성 구조체를 구축하기 위하여 캡슐화된 어셈블리(encapsulated assembly)에서 수행될 수 있다.

[0035] 또한, 홀(80)은 유전체층(68)을 통해 마이크로전자 유닛(14)의 인캡슐런트(54)의 배면(60)까지 연장하도록 형성될 수 있다. 도면에 도시되지는 않았으나, 홀(80)은 표면(60)의 길이를 따라 그와 평행하게 마이크로전자 유닛(14)의 다른 전기적 요소, 예컨대, 전원 공급장치의 양의 또는 음의 접지 단자(도시되지 않음)까지 연장할 수 있다. 유전체층(68)의 배면(69)으로부터 홀(80)을 통하여 인캡슐런트(54)의 배면(60)까지 연장하는 전기 전도성 비아(82), 표면(69)을 따라 비아(82)로부터 연장하는 전도성 트레이스(84), 그리고 바람직하게는 트레이스(84)로부터 연장하고 전기적으로 연결된 표면(69)에서의 단자(86)를 포함하는 전기 전도성 부분이 그 다음 마이크로전자 유닛(14)의 표면(78)에 형성될 수 있다. 일 실시예에서, 비아(82)의 전도성 재료는 배면(60)을 따라

연장하여 전원 공급장치(도시되지 않음)의 양의 단자 및 음의 단자를 구성하는 외부 커넥터에 연결될 수 있다.

[0036] 마이크로전자 유닛(14)의 인캡슐런트의 배면(60)에서의 단자, 트레이스, 그리고 비아를 형성하는 전도성 부분은 앞서 설명된 마이크로전자 유닛(12)의 유닛 콘택을 형성하는데 사용된 재료와 동일한 재료를 포함할 수 있고, 포토리소그래피 패터닝 또는 유사한 공정에 의해 형성될 수 있다. 트레이스는 예를 들어, 스퍼터링, 무전해 또는 전해 도금, 또는 전기 전도성 페이스트 또는 전도성 매트릭스 재료의 스텐실 또는 프린팅을 포함하는 임의의 적절한 금속 중착 기술에 의해 형성될 수 있다.

[0037] 솔더 레지스트층(solder resist layer)(도시되지 않음)이 유전체층(68)의 배면(69)의 덮이지 않은 부분 위에 놓일 수 있고, 트레이스(74 및 84)를 덮도록 패턴화될 수 있으며, 이에 따라 단자(76 및 86)가 표면(69)에 노출되도록 할 수 있다.

[0038] 또한, 솔더 레지스트층의 형성에 이어, 예컨대 본드 금속(bond metal), 솔더, 전도성 페이스트, 전도성 매트릭스 재료 등과 같은 전기 전도성 재료의 매스(mass)(88)를 포함할 수 있는 결합 유닛(joining unit)이 단자(74 및 84)로서 역할하는 전도성 부분의 외부 표면의 노출된 부분에 형성될 수 있다. 따라서, 매스(88) 중 일부는 단자(76), 전도성 트레이스(74) 및 비아(72)를 통해 칩(16C)의 콘택(28C)에 전기적으로 상호연결될 수 있다. 또한, 매스(88) 중 일부는 단자(86), 전도성 트레이스(84) 및 비아(82)를 통해 예를 들어, 마이크로전자 유닛(14)과 연관된 또는 그에 포함된 다른 전자 회로와 전기적으로 상호연결될 수 있다. 매스(88)는 솔더, 금, 주석 또는 인듐과 같은 본드 금속을 포함할 수 있다. 매스의 형성 후에, 솔더 레지스트층이 제거될 수 있다.

[0039] 마이크로전자 유닛(14)은, 마이크로전자 유닛(12)과 유사하게, 내부에 적어도 하나의 칩을 지지하기 위하여 완성된 마이크로전자 유닛에 패키지 기관을 필요로 하지 않고 구성될 수 있다.

[0040] 앞서 설명된 바와 같이 형성된 마이크로전자 유닛(12) 및 마이크로전자 유닛(14)은, 따라서, 테스트 가능한 유닛을 구성할 수 있는데, 이러한 유닛은 각각 그 내부에 포함된 칩들의 원하는 전기적 기능성 및 운전성을 확인하는 테스트를 받을 수 있다. 예를 들어, 마이크로전자 유닛(12)의 칩(16A)은 유닛 콘택과 상호연결함으로써 기능 테스트를 받을 수 있고, 칩(16B)은 노출된 콘택(28B)과 상호연결함으로써 기능 테스트를 받을 수 있다. 또한, 마이크로전자 유닛(14)의 단자들은 칩(16C)의 기능 테스트에 적합하다. 따라서, 각각의 마이크로전자 유닛(12 및 14) 내의 칩들은 그 유닛을 적층된 배열로 조립하기 전에 선택적으로 다른 마이크로전자 유닛과 함께 기능적으로 테스트됨으로써, 이하에서 설명하는 바와 같은 패키지(10)와 같은 공통 패키지를 형성할 수 있다.

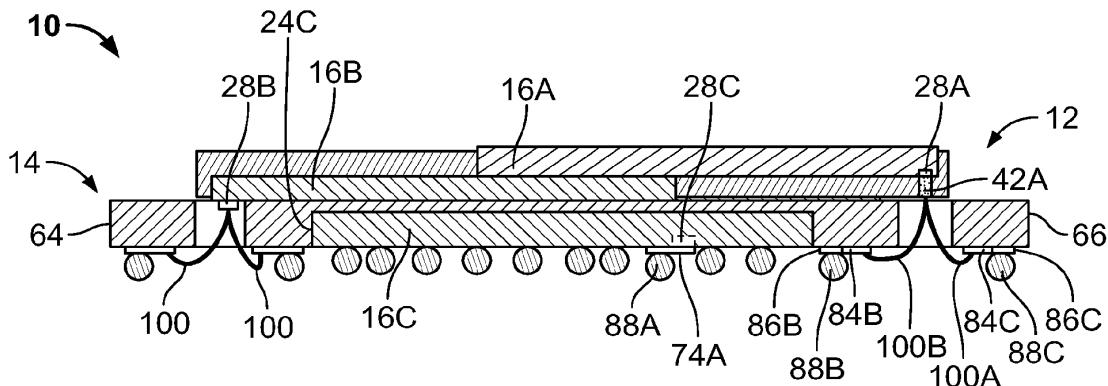

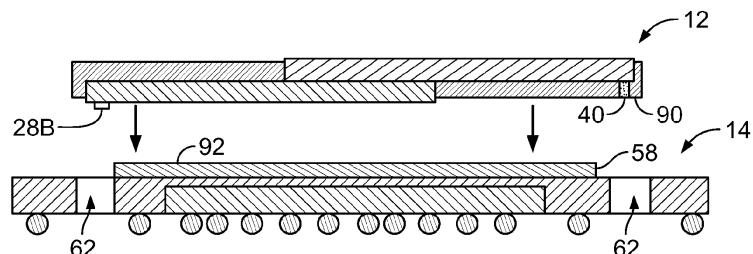

[0041] 도 9-11을 참조하면, 마이크로전자 유닛(12)은, 바람직하게는 그 유닛의 테스트 후에, 마이크로전자 유닛(14)에, 또한 바람직하게는 그 유닛의 테스트 후에, 수직으로 적층된 배열로 부착되어 패키지(10)를 형성할 수 있다. 마이크로전자 유닛(12)은, 배면(34 및 18B)으로부터 형성된, 그 배면(90)에서 접착층(92)에 의해 마이크로전자 유닛(14)의 인캡슐런트(54)의 상면(58)의 일부분에 부착될 수 있다. 접착층(92)은 앞서 설명된, 마이크로전자 유닛(12)의 칩들을 서로 부착하는데 사용된 접착제와 유사할 수 있다. 마이크로전자 유닛(12) 및 마이크로전자 유닛(14)은, 마이크로전자 유닛(14)의 홀(62)이 마이크로전자 유닛(12)의 유닛 콘택, 예컨대, 비아(42)와 노출된 칩 콘택(28B)과 수직으로 정렬된 상태로 서로 부착될 수 있다.

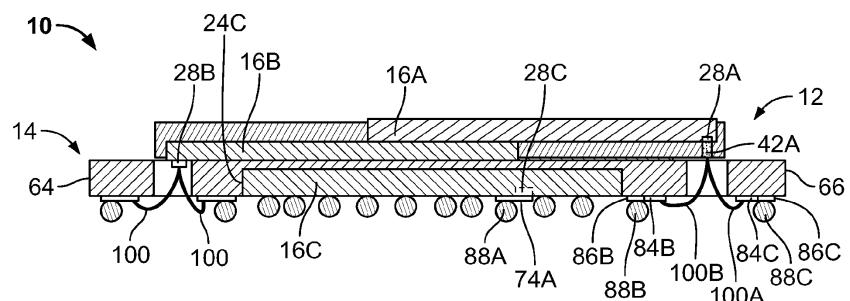

[0042] 도 10을 참조하면, 적층된 마이크로전자 유닛(12) 및 마이크로전자 유닛(14)으로부터 형성된 패키지(10)는 본드 와이어(bond wire)(100)를 가질 수 있는데, 이러한 본드 와이어는 일 단부에서 트레이스(84)의 노출된 부분에 연결되고 다른 단부에서 유닛 콘택 또는 마이크로전자 유닛(12)의 칩들의 칩 콘택에 연결되도록 형성될 수 있다. 예를 들어, 개략적으로 도시된 전도성 요소 간에 전기적 연결이 있는 패키지(10)의 하부 평면도인 도 12를 또한 참조하면, 본드 와이어(100A)는, 단자(86C) 및 매스(88C)에 전기적으로 연결된 트레이스(84C)를, 마이크로전자 유닛(12)의 칩(16A)의 콘택(28A)과 전기적으로 연결된 비아(42A)와 연결할 수 있다. 또한, 본드 와이어(100B)는 단자(86B) 및 매스(88B)에 전기적으로 연결된 트레이스(84B)를, 마이크로전자 유닛(12)의 칩(16A)의 상이한 콘택(28A)과 전기적으로 연결된 패드(도시되지 않음)와 같은 마이크로전자 유닛 콘택과 연결할 수 있다. 더욱이, 마이크로전자 유닛(14)의 형성과 관련하여 앞서 논의된 바와 같이, 칩(16C)의 콘택(28C)은 전도성 비아(72A)(도 12에 도시되지 않음), 트레이스(74A) 및 단자(76A)(도 12에 도시되지 않음)를 통해 매스(88A)와 전기적으로 연결될 수 있다. 일 실시예에서, 마이크로전자 유닛(14)의 홀(62)과 에지(64 또는 66) 사이에 위치하며, 서로 전기적으로 연결되는 관련된 트레이스, 비아 및 매스(88)가 있는 단자(86)는, 본드 와이어(100)가 전기적으로 연결된 전원 단자 및 접지 단자를 구성할 수 있는 반면, 마이크로전자 유닛(14)의 홀(62)과 인접한 에지(24 또는 26) 사이에 있으며, 서로 전기적으로 연결되는 관련된 트레이스, 비아 및 매스(88)가 있는 단자(86)는 그에 전기적으로 연결된 본드 와이어(100)를 통해 마이크로전자 유닛(12)의 칩들과 데이터 교환을 제공한다.

- [0043] 일 실시예에서, 일반적으로 금, 구리, 또는 구리 합금인 본드 와이어(100)는 캐필러리(capillary)의 단부에 노출된 와이어의 단부를 연화하기 위해 그 단부를 가열함으로써 사용될 수 있고 이에 따라 그 단부는 유닛 콘택, 예컨대 비아(42) 및 트레이스(84)에 놀려지는 경우 유닛 콘택 및 트레이스(84)에 베이스(base)(도시되지 않으)를 형성하는 볼 본드(ball bond)를 형성한다.

- [0044] 대안적으로, 본드 와이어는 웨지 본딩(wedge bonding)에 의해 형성될 수 있다. 웨지 본딩은 와이어의 단부에 인접한 부분을 가열하고 그에 인가된 압력으로 마이크로전자 유닛(14)의 배면에서 유닛 콘택 및 트레이스를 따라 드래그(drag)함으로써 형성될 수 있다. 알루미늄 본드 와이어는 이런 방식으로 형성될 수 있다. 이러한 공정은, 원용에 의해 그 내용 전체가 본 명세서에 포함된 미국 등록 특허 제7,391,121호에 더욱 상세하게 설명된다.

- [0045] 도 11을 참조하면, 홀(62)에 인접한 그리고 홀(62)에 있는, 인캡슐런트(54)의 배면(60)의 덮이지 않은 부분 위에 인캡슐런트(102)가 형성되어 본드 와이어(100)를 캡슐화할 수 있다. 인캡슐런트(102)는 에폭시 재료를 포함할 수 있다.

- [0046] 다른 실시예에서, 도 13을 참조하면, 마이크로전자 패키지(200)는 마이크로전자 유닛(14)과 유사한 구조를 갖는 마이크로전자 유닛(214)과 마이크로전자 유닛(12)과 유사한 구조를 갖는 마이크로전자 유닛(212)을 포함할 수 있는데, 마이크로전자 유닛(212)은 마이크로전자 유닛(214)의 상부에 수직으로 적층된다. 패키지(200)에서, 마이크로전자 유닛(212)은 그것의 배면(220)의 부분(218)에 노출된, 마이크로전자 유닛(214)의 대향하는 에지(224 및 226)로부터 멀어지도록 연장하는 칩 콘택(216)을 가지며, 이에 따라 마이크로전자 유닛(214)은 그를 통해 연장하는, 그리고 본드 와이어가 통하여 연장하는 홀을 포함하지 않는다. 본드 와이어(230)는 마이크로전자 유닛(212)의 콘택(216)을 덮는 전도성 재료(도시하지 않음)로부터, 에지(226 및 224) 주위를 돌아서, 트레이스(84)까지 연장하며, 트레이스(84)는, 앞서 논의된 패키지(10)에서와 유사하게, 단자(86)를 마이크로전자 유닛(214)내의 반도체 칩(16C)의 칩 콘택(28C)에 전기적으로 연결한다.

- [0047] 다른 실시예에서, 도 14를 참조하면, 마이크로전자 패키지(300)는 마이크로전자 유닛(314)에 수직으로 적층된, 앞서 설명된 바와 같은 마이크로전자 유닛(12)을 포함할 수 있다. 마이크로전자 유닛(314)은, 인캡슐런트(54)의 배면이 마이크로전자 유닛(314)의 배면(365)을 형성하고 인캡슐런트 재료가 칩 콘택(28C)이 배치되는 칩(16)의 전면(18C)으로부터 마이크로전자 유닛(314)의 배면(365)까지 연장한다는 점을 제외하고는, 앞서 설명된 마이크로전자 유닛(14)과 유사한 구조를 갖는다. 또한 이 실시예에서, 홀(362)은 배면(365)으로부터 마이크로전자 유닛(314)의 두께를 통하여 마이크로전자 유닛(12)의 표면(34)까지 연장하고, 위에 놓이는 마이크로전자 유닛(12)의 칩(16B)의 콘택(28B)과 수직으로 정렬된다. 본드 와이어(370)는 마이크로전자 유닛(12)의 유닛 콘택(44)으로부터 홀(362)을 통하여 마이크로전자 유닛(314)의 배면(365)에 있는 트레이스(84)까지 연장한다. 또한, 본드 와이어(372)는 콘택(28B)으로부터 마이크로전자 유닛(314)의 에지(324) 주위를 돌아서 마이크로전자 유닛(314)의 배면 상의 트레이스(84)까지 연장하여 단자(86)를 칩 콘택(28B)과 전기적으로 연결한다. 또한, 본드 와이어(374)는 콘택(28A)에 전기적으로 연결된 유닛 콘택(44)으로부터 마이크로전자 유닛(314)의 에지(326) 주위를 돌아서 마이크로전자 유닛(314)의 배면 상의 트레이스(84)까지 연장하며, 따라서 단자(86)를 콘택(28A)에 전기적으로 연결한다.

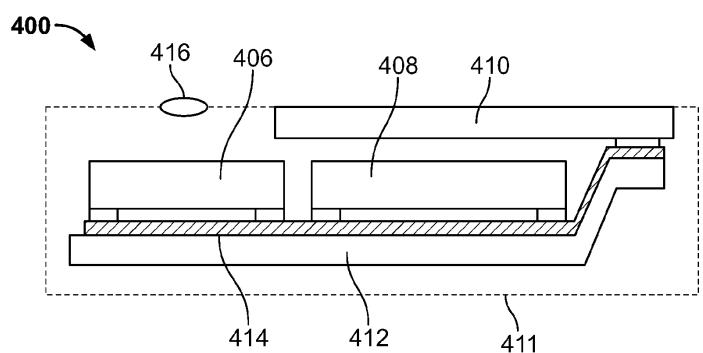

- [0048] 앞서 설명된 마이크로전자 패키지는, 도 15에 도시된 바와 같이, 다양한 전자 시스템의 구성에 이용될 수 있다. 예를 들어, 본 발명의 추가 실시예에 따른 시스템(400)은 다른 전자 컴포넌트(408 및 410)와 함께 앞서 설명된 마이크로전자 패키지(406)를 포함한다. 도시된 예에서, 컴포넌트(408)는 반도체 칩이고, 반면 컴포넌트(410)는 디스플레이 스크린이지만, 임의의 다른 컴포넌트가 사용될 수 있다. 물론, 명확성을 위하여 두 개의 추가 컴포넌트만이 도 15에 도시되어 있으나, 시스템은 임의의 개수의 이러한 컴포넌트를 포함할 수 있다. 마이크로전자 패키지 또는 어셈블리(406)는 앞서 설명된 패키지 또는 어셈블리 중 임의의 것일 수 있다. 추가의 변형예에서, 임의의 개수의 이러한 마이크로전자 패키지 또는 어셈블리가 사용될 수 있다. 마이크로전자 패키지 또는 어셈블리(406) 및 컴포넌트(408 및 410)는 파선으로 도시된 공통의 하우징(411)에 장착되고, 원하는 회로를 형성하기 위하여 필요한 대로 서로 전기적으로 상호연결된다. 도시된 예시적인 시스템에서, 시스템은 연성 인쇄 회로 보드(flexible printed circuit board)와 같은 회로 패널(412)을 포함하고, 이러한 회로 패널은 컴포넌트들을 상호연결하는 전도체(414)를 포함하는데, 도 15에는 하나의 전도체만이 도시되어 있으나, 다수의 전도체를 포함할 수 있다. 다만, 이것은 단지 예시에 불과하며; 전기적 연결을 만들기 위한 임의의 적절한 구조가 사용될 수 있다. 하우징(411)은 예를 들어, 셀룰러 폰 또는 PDA(personal digital assistant)에서 사용 가능한 태입의 휴대용 하우징으로서 도시되어 있고, 스크린(410)은 하우징의 표면에 노출된다. 구조체(406)가 이미징 칩과 같은 감광성 요소를 포함하는 경우, 렌즈(416) 또는 다른 광학 디바이스 또한 이러한 구조체에 광을 라우팅하기

위해 제공될 수 있다. 다시, 도 15에 도시된 단순화된 시스템은 단지 예시에 불과하며; 고정 구조로서 통상 간주되는 시스템을 포함하는 다른 시스템, 예컨대, 데스크톱 컴퓨터, 라우터 등이 앞서 설명되는 구조를 이용하여 만들어질 수 있다.

따라서, 본 발명의 실시예들은 테스트 가능한 마이크로전자 유닛들을 공통의 패키지에 조립하는 방법을 제공하며, 이러한 패키지는 외부 컴포넌트, 예컨대, 회로 보드 또는 연성 회로 패널과 같은 회로 패널과의 상호연결을 위한 공통 패키지 단자 세트를 갖는다. 각각의 마이크로전자 유닛은 적어도 하나의 반도체 칩을 포함하고, 마이크로전자 유닛 중 제1 마이크로전자 유닛의 표면에 노출된 유닛 콘택은 제1 마이크로전자 유닛의 적어도 하나의 칩의 칩 콘택 및 적층된 제1 마이크로전자 유닛 및 제2 마이크로전자 유닛 중 제2 마이크로전자 유닛의 표면에 있는 패키지 단자와 전기적으로 연결된다. 각각의 마이크로전자 유닛은 적어도 하나의 칩을 지지하기 위하여 완성된 마이크로전자 유닛에 패키지 기판을 필요로 하지 않고 구성될 수 있다. 유닛 콘택은 제1 마이크로전자 유닛의 반도체 칩의 칩 콘택으로부터 제1 마이크로전자 유닛의 노출된 표면을 따르는 적어도 하나의 방향으로 변위될(displace) 수 있다. 패키지의 마이크로전자 유닛은 웨이퍼-레벨 칩-스케일 패키지(wafer-level chip-scale package: WLCSP) 또는 팬-아웃 웨이퍼-레벨 패키지(fan-out wafer-level package: FO-WLP)의 마이크로전자 유닛과 유사한 특징, 즉, 내부에 적어도 하나의 반도체 칩을 갖는 캡슐화된 어셈블리 위에 전기 전도성 재료를 증착함으로써 와이어-본딩 패드(wire-bondable pad)와 같은 유닛 콘택이 형성되는 특징을 가질 수 있다. 예를 들어, 마이크로전자 유닛은 재구성된 웨이퍼(reconstituted wafer) 또는 회로 패널의 일부분일 수 있다.

공통 패키지에 하나 이상의 제1 마이크로전자 유닛을 하나 이상의 제2 마이크로전자 유닛과 함께 조립하기 전에 제1 마이크로전자 유닛 및 제2 마이크로전자 유닛 각각의 칩이 기능적으로 테스트될 수 있도록, 유닛 콘택은 각각의 제1 마이크로전자 유닛의 적어도 하나의 반도체 칩의 기능 테스트에 적합하고, 단자는 각각의 제2 마이크로전자 유닛의 적어도 하나의 반도체 칩의 기능 테스트에 적합하다.

본 발명이 본 명세서에서 특정 실시예와 관련하여 설명되었지만, 이를 실시예는 단지 본 발명의 원리 및 응용의 예시임이 이해되어야 한다. 따라서 도시된 실시예에 대해 다수의 수정이 이루어질 수 있으며 첨부된 청구항에 의해 정해지는 본 발명의 사상 및 범위를 벗어남이 없이 다른 구성이 고안될 수 있음이 이해되어야 한다.

## 도면

## 도면1

## 도면2

도면3a

도면3b

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

## 도면14

## 도면15