(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-22642

(P2004-22642A)

(43) 公開日 平成16年1月22日(2004.1.22)

(51) Int.Cl.<sup>7</sup>H01L 21/8242

H01L 27/108

F 1

H01L 27/10 625A

テーマコード(参考)

5FO83

審査請求 未請求 請求項の数 15 O L (全 13 頁)

(21) 出願番号

特願2002-172629 (P2002-172629)

(22) 出願日

平成14年6月13日 (2002. 6. 13)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100068814

弁理士 坪井 淳

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

(57) 【要約】 (修正有)

【課題】トレンチキャバシタのストレージノード電極とMOSトランジスタのn型ソース／ドレイン拡散層とを接続するn型多結晶シリコン膜のエピタキシャル成長を防止すること。

【解決手段】n型多結晶シリコン膜(ストレージノード電極)12をn型多結晶シリコン膜15を介してMOSトランジスタのn型ソース／ドレイン拡散層23に接続させる際に、n型多結晶シリコン膜15とn型ソース／ドレイン拡散層23との間にWSiN層14を介在させる。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

表面に溝を有する半導体基板と、

前記溝の内部に設けられた多結晶半導体膜と、

前記半導体基板の表面に設けられた拡散層と

前記拡散層と前記多結晶半導体膜との間に設けられ、金属、窒素および前記半導体基板を構成する半導体を含み、前記拡散層と前記多結晶半導体膜とを電気的に接続するための金属半導体窒化物層と

を具備してなることを特徴とする半導体装置。

**【請求項 2】**

表面に溝を有する半導体基板と、

前記溝の開口面に達しないように、前記溝の内部に埋め込まれた第1の多結晶半導体膜と

、

前記第1の多結晶半導体膜上に設けられた、前記溝内の第2の多結晶半導体膜と、

前記半導体基板の表面に設けられた第1の拡散層と、

前記第1の拡散層と前記第2の多結晶半導体膜との間に設けられ、金属、窒素および前記半導体基板を構成する半導体を含み、前記第1の拡散層と前記第2の多結晶半導体膜とを電気的に接続するための金属半導体窒化物層と

を具備してなることを特徴とする半導体装置。

**【請求項 3】**

前記溝の周囲の前記半導体基板内に設けられた第2の拡散層と、前記溝の内側面と前記第1の多結晶半導体膜との間に設けられた絶縁膜とをさらに備え、前記第2の拡散層、前記絶縁膜および前記第1の多結晶半導体膜はトレンチキャパシタを構成し、前記第1の拡散層はMOSトランジスタのソース／ドレイン拡散層であることを特徴とする請求項2に記載の半導体装置。

**【請求項 4】**

前記金属半導体窒化物層を構成する金属は、該金属が窒化物を形成する際のGibbsの自由エネルギーの低下と前記半導体基板を構成する半導体が窒化物を形成する際のGibbsの自由エネルギーの低下とを比較したときに、後者の低下分の方が大きくなるものであることを特徴とする請求項1または2に記載の半導体装置の形成方法。

**【請求項 5】**

前記半導体基板を構成する半導体はシリコン、前記金属半導体窒化物層を構成する金属は、タンゲステン、モリブデンまたはクロムであることを特徴とする請求項1または2に記載の半導体装置

**【請求項 6】**

前記金属半導体窒化物層は、アモルファス状態のものであることを特徴とする請求項1または2に記載の半導体装置。

**【請求項 7】**

前記半導体基板は、単結晶のものであることを特徴とする請求項1ないし6のいずれか1項に記載の半導体装置。

**【請求項 8】**

半導体基板の表面に溝を形成する工程と、

前記溝の開口面よりも下の部分を第1の多結晶半導体膜で埋め込む工程と、

前記第1の多結晶半導体膜で埋め込まれていない前記溝の側面を金属窒化物膜で覆う工程と、

热処理により、前記溝の側面とそれに接した前記金属窒化物膜とを反応させ、前記溝の側面に接した前記金属窒化物膜を、前記金属窒化物膜を構成する金属および窒素と、前記半導体基板を構成する半導体とを含む、金属半導体窒化物層に変える工程と、

前記金属半導体窒化物層を残して前記金属窒化物膜を除去する工程と、

前記溝の内部に第2の多結晶半導体膜を形成する工程と、

10

20

30

40

50

前記半導体基板の表面上に、前記金属半導体窒化物層を介して前記第2の多結晶半導体膜と電気的に接続するための拡散層を形成する工程と

を有することを特徴とする半導体装置の製造方法。

**【請求項9】**

半導体基板の表面上に溝を形成する工程と、

前記溝の側面および底面を絶縁膜で覆う工程と、

前記溝の開口面よりも下の部分を第1の多結晶半導体膜で埋め込む工程と、

前記第1の多結晶半導体膜が埋め込まれていない前記溝の側面を覆う前記絶縁膜を除去する工程と、

前記絶縁膜を除去して露出した前記溝の側面を金属窒化物膜で覆う工程と、

熱処理により、前記溝の側面とそれに接した前記金属窒化物膜とを反応させ、前記溝の側面に接した前記金属窒化物膜を、前記金属窒化物膜を構成する金属および窒素と、前記半導体基板を構成する半導体とを含む、金属半導体窒化物層に変える工程と、

前記金属半導体窒化物層を残して前記金属窒化物膜を除去する工程と、

前記溝の内部に第2の多結晶半導体膜を形成する工程と、

前記半導体基板の表面上に、前記金属半導体窒化物層を介して前記第2の多結晶半導体膜と電気的に接続するための第1の拡散層を形成する工程と

を有することを特徴とする半導体装置の製造方法。

10

**【請求項10】**

前記溝の側面および底面を前記絶縁膜で覆う工程の前に、前記溝の周囲の前記半導体基板内に第2の拡散層を形成する工程をさらに有することを特徴とする請求項9に記載の半導体装置の製造方法。

20

**【請求項11】**

前記金属窒化物膜を構成する金属は、該金属が窒化物を形成する際の Gibbsの自由エネルギーの低下と前記半導体基板を構成する半導体が窒化物を形成する際の Gibbsの自由エネルギーの低下を比較したときに、後者の低下分の方が大きくなるものであることを特徴とする請求項8または9に記載の半導体装置の形成方法。

**【請求項12】**

前記金属半導体窒化物層は、アモルファス状態のものであることを特徴とする請求項8または9に記載の半導体装置の形成方法。

30

**【請求項13】**

前記半導体基板を構成する半導体はシリコン、前記金属窒化物膜を構成する金属は、タンゲステン、モリブデンまたはクロムであることを特徴とする請求項8または9に記載の半導体装置の製造方法。

**【請求項14】**

前記熱処理を非酸化性雰囲気中で行うことを行なうことを特徴とする請求項8または9に記載の半導体装置の製造方法。

**【請求項15】**

前記半導体基板は、単結晶のものであることを特徴とする請求項8ないし14のいずれか1項に記載の半導体装置。

40

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、半導体装置およびその製造方法に係わり、特にトレンチキャパシタとそれに接続したソース／ドレイン拡散層を含む半導体装置およびその製造方法に関する。

**【0002】**

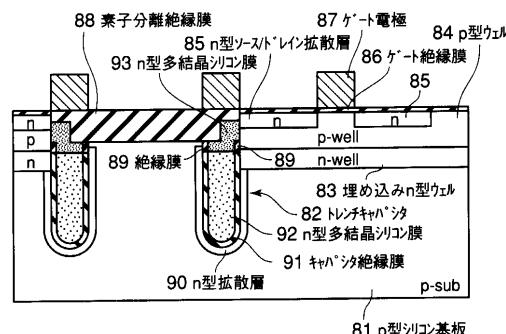

**【従来の技術】**

図6に、従来のトレンチキャパシタを有するDRAMセルの断面図を示す。図6において、81は単結晶のp型シリコン基板、82はトレンチキャパシタ、83は埋め込みn型ウェル、84はp型ウェル、85はn型ソース／ドレイン拡散層、86はゲート絶縁膜、8

50

7はゲート電極、8 8は素子分離絶縁膜、8 9は絶縁膜をそれぞれ示している。

【0003】

トレンチキャパシタ8 2は、n型拡散層9 0（プレート電極）とキャパシタ絶縁膜9 1とn型多結晶シリコン膜9 2（ストレージノード電極）とで構成されている。

【0004】

n型多結晶シリコン膜9 2上にはn型多結晶シリコン膜9 3が設けられ、n型多結晶シリコン膜9 3はn型ソース／ドレイン拡散層8 5に直接接続されている。すなわち、トレンチキャパシタ8 2は接続部としてのn型多結晶シリコン膜9 3を介してn型ソース／ドレイン拡散層8 5に接続されている。

【0005】

ここで、n型ソース／ドレイン拡散層8 5は単結晶であるため、DRAMプロセスの熱工程において、n型多結晶シリコン膜9 3は、ソース／ドレイン拡散層8 5をシードにしてエピタキシャル成長する恐れがある。上記熱工程は、例えばトレンチキャパシタ8 2およびMOSトランジスタを形成した後のパッシベーション膜の形成工程である。

【0006】

n型多結晶シリコン膜9 3がエピタキシャル成長すると、素子内に応力が発生して基板内に結晶欠陥が生じる。この種の結晶欠陥はリーク電流の原因となる。キャパシタに蓄えられる電荷の量は、一般に、DRAMの高集積化に伴って減少する。そのため、今後開発される高集積度のDRAMにおいては、上記リーク電流は無視できなくなる。

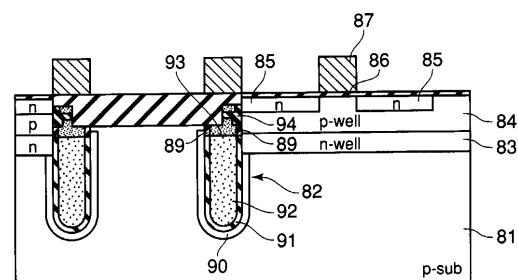

【0007】

上記リーク電流の発生を防止する手法の一つとして、図7に示すようなDRAMセルの採用が考えられる。図7のDRAMセルにおいては、n型多結晶シリコン膜9 3は、シリコン窒化膜9 4を介して、ソース／ドレイン拡散層8 5に間接接続されている。これにより、シリコン窒化膜9 4がバリアとなって、ソース／ドレイン拡散層8 5はシードとして働くくなり、n型多結晶シリコン膜9 3のエピタキシャル成長を防止できるようになる。

【0008】

ここで、シリコン窒化膜9 4は絶縁膜の一種であるため、n型多結晶シリコン膜9 3とソース／ドレイン拡散層8 5との間の電気的接続を確保するためには、シリコン窒化膜9 4を非常に薄く形成する必要がある。

【0009】

しかしながら、非常に薄いシリコン窒化膜9 4を形成したとしても、シリコン窒化膜9 4が絶縁膜であることには変わりはないので、トレンチキャパシタ8 2とソース／ドレイン拡散層8 5との間のコンタクト抵抗の増加は避けられない。

【0010】

【発明が解決しようとする課題】

上述の如く、従来のトレンチキャパシタを有するDRAMセルにおいては、トレンチキャパシタは、n型多結晶シリコン膜、またはn型多結晶シリコン膜／シリコン窒化膜を介して、ソース／ドレイン拡散層に接続されている。

【0011】

しかしながら、前者の場合には、トレンチキャパシタを構成するn型多結晶シリコン膜（ストレージノード電極）のエピタキシャル成長によって、素子内にリーク電流の原因となる応力が発生し、後者の場合には、上記n型多結晶シリコン膜とソース／ドレイン拡散層との間のコンタクト抵抗の増加は避けられない。

【0012】

本発明は、上記事情を考慮してなされたもので、その目的とするところは、溝内に埋め込まれ、半導体基板の表面の拡散層と電気的に接続するための多結晶半導体膜のエピタキシャル成長の発生防止、および上記多結晶半導体膜と上記拡散層との間のコンタクト抵抗の増加防止を図れる半導体装置およびその製造方法を提供することにある。

【0013】

【課題を解決するための手段】

10

20

30

40

50

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば下記の通りである。すなわち、上記目的を達成するために、本発明に係る半導体装置は、表面に溝を有する半導体基板と、前記溝の内部に設けられた多結晶半導体膜と、前記拡散層と前記多結晶半導体膜との間に設けられ、金属、窒素および前記半導体基板を構成する半導体を含み、前記拡散層と前記多結晶半導体膜とを電気的に接続するための金属半導体窒化物層とを備えていることを特徴とする。

#### 【0014】

また、本発明に係る他の半導体装置は、表面に溝を有する半導体基板と、前記溝の開口面に達しないように、前記溝の内部に埋め込まれた第1の多結晶半導体膜と、前記第1の多結晶半導体膜上に設けられた、前記溝内の第2の多結晶半導体膜と、前記半導体基板の表面に設けられた第1の拡散層と、金属、窒素および前記半導体基板を構成する半導体を含み、前記第1の拡散層と前記第2の多結晶半導体膜とを電気的に接続するための金属半導体窒化物層とを備えていることを特徴とする。

#### 【0015】

また、本発明に係る半導体装置の製造方法は、半導体基板の表面に溝を形成する工程と、前記溝の開口面よりも下の部分を第1の多結晶半導体膜で埋め込む工程と、前記第1の多結晶半導体膜で埋め込まれていない前記溝の側面を金属窒化物膜で覆う工程と、熱処理により、前記溝の側面とそれに接した前記金属窒化物膜とを反応させ、前記溝の側面に接した前記金属窒化物膜を、前記金属窒化物膜を構成する金属および窒素と、前記半導体基板を構成する半導体とを含む、金属半導体窒化物層に変える工程と、前記金属半導体窒化物層を残して前記金属窒化物膜を除去する工程と、前記溝の内部に第2の多結晶半導体膜を形成する工程と、前記半導体基板の表面に、前記金属半導体窒化物層を介して前記第2の多結晶半導体膜と電気的に接続するための拡散層を形成する工程とを有することを特徴とする。

#### 【0016】

また、本発明に係る他の半導体装置の製造方法は、半導体基板の表面に溝を形成する工程と、前記溝の側面および底面を絶縁膜で覆う工程と、前記溝の開口面よりも下の部分を第1の多結晶半導体膜で埋め込む工程と、前記第1の多結晶半導体膜が埋め込まれていない前記溝の側面を覆う前記絶縁膜を除去する工程と、前記絶縁膜を除去して露出した前記溝の側面を金属窒化物膜で覆う工程と、熱処理により、前記溝の側面とそれに接した前記金属窒化物膜とを反応させ、前記溝の側面に接した前記金属窒化物膜を、前記金属窒化物膜を構成する金属および窒素と、前記半導体基板を構成する半導体とを含む、金属半導体窒化物層に変える工程と、前記金属半導体窒化物層を残して前記金属窒化物膜を除去する工程と、前記溝の内部に第2の多結晶半導体膜を形成する工程と、前記半導体基板の表面に、前記金属半導体窒化物層を介して前記第2の多結晶半導体膜と電気的に接続するための第1の拡散層を形成する工程とを有することを特徴とする。

#### 【0017】

本発明によれば、溝内の多結晶半導体膜が金属半導体窒化物層を介して半導体基板の表面に形成された拡散層に接続されるので、上記金属半導体窒化物層がバリアとなって、熱工程における上記拡散層をシードする上記多結晶多結晶膜のエピタキシャル成長は防止される。また、上記金属半導体窒化物層が金属を含んでいるので、上記多結晶半導体膜と上記拡散層との間のコンタクト抵抗の増加は防止される。

#### 【0018】

本発明の上記ならびにその他の目的と新規な特徴は、本明細書の記載および添付図面によって明らかになるであろう。

#### 【0019】

##### 【発明の実施の形態】

以下、図面を参照しながら本発明の実施の形態を説明する。

#### 【0020】

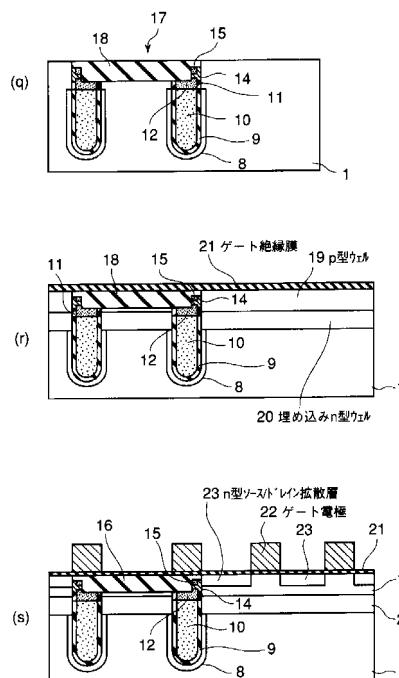

図1～図3は、本発明の一実施形態に係るDRAMセルの製造工程を示す断面図である。

10

20

30

40

50

## 【0021】

まず、図1(a)に示すように、単結晶のp型シリコン基板1の表面に薄いシリコン酸化膜2を熱酸化により形成し、続いてシリコン酸化膜2上に厚さ20nm程度のシリコン窒化膜(Si<sub>3</sub>N<sub>4</sub>膜)3を堆積し、続いてフォトリソグラフィとRIE等のエッチングとを用いて、トレンチキャパシタのトレンチが形成される領域上のシリコン酸化膜2およびシリコン窒化膜3に開口部4を形成する。

## 【0022】

次に、図1(b)に示すように、シリコン窒化膜3をマスクにしてp型シリコン基板1をRIE等の異方性エッチングにより加工してトレンチ5を形成し、続いてLP-CVDプロセスにより、トレンチ5の内壁を被覆するように、AssG膜(As添加シリゲートガラス膜)6を全面に堆積する。

## 【0023】

次に、図1(c)に示すように、トレンチ5内をその途中の深さまでレジスト7で埋め込み、続いてレジスト7をマスクにしてHFを含む液でAssG膜6のエッチングを行い、レジスト7で被覆されていないAssG膜6を除去する。その後、レジスト7を除去する。

## 【0024】

次に、図1(d)に示すように、熱処理により、AssG膜6中のAsをトレンチ5の内壁(側面および底面)のp型シリコン基板1中に拡散させ、トレンチキャパシタのプレート電極を構成するn型拡散層8を形成する。その後、AssG膜6を除去する。

## 【0025】

次に、図1(e)に示すように、トレンチ5の内壁を被覆するように、窒化シリコンを主成分とするキャパシタ絶縁膜9を形成し、続いてトレンチ5の内部を埋め込むように、トレンチキャパシタのストレージ電極の一部を構成する、リン等のn型不純物を含むn型多結晶シリコン膜10を堆積し、続いてトレンチ5の外部に堆積したn型多結晶シリコン膜10を例えばCMP(Chemical Mechanical Polishing)プロセスにより除去する。

## 【0026】

次に、図1(f)に示すように、開口部4内およびトレンチ5内のn型多結晶シリコン膜10をエッチングにより除去し、さらにn型多結晶シリコン膜10を除去して露出したキャパシタ絶縁膜9をエッチングにより除去し、続いてn型多結晶シリコン膜10およびキャパシタ絶縁膜9を除去して露出した開口部4およびトレンチ5の側面をシリコン酸化膜(側壁絶縁膜)11で覆う。

## 【0027】

シリコン酸化膜11は、例えばいわゆる側壁残しプロセスにより形成する。すなわち、開口部4およびトレンチ5の側面を被覆するように、側壁絶縁膜となるシリコン酸化膜(SiO<sub>2</sub>膜)をLP-CVDプロセスにより全面に堆積し、続いて上記シリコン酸化膜をRIE等の異方性エッチングにより全面エッチングすることにより、n型多結晶シリコン膜10およびキャパシタ絶縁膜9を除去して露出した開口部4およびトレンチ5の側面を覆うシリコン酸化膜11が得られる。また、側壁絶縁膜としてシリコン酸化膜を使用したが、他の絶縁膜を使用することも可能である。

## 【0028】

次に、図1(g)に示すように、トレンチ5内をその途中の深さまでストレージノード電極の一部を構成するn型多結晶シリコン膜12で埋め込み、続いてn型多結晶シリコン膜12をマスクにしてHFを含む液でシリコン酸化膜11をエッチングし、n型多結晶シリコン膜12で被覆されていないトレンチ5および開口部4の側面上のシリコン酸化膜11を除去する。図には、n型多結晶シリコン膜12で被覆された部分のシリコン酸化膜11の上部が多少エッチングされた様子が示されている。

## 【0029】

n型多結晶シリコン膜12は、例えば以下のプロセスにより形成する。すなわち、トレン

10

20

30

40

50

チ5の内部を埋め込むようにn型多結晶シリコン膜12となるn型多結晶シリコン膜を全面に堆積し、続いて該n型多結晶シリコン膜を所望の高さまでリセスすることにより、n型多結晶シリコン膜12が得られる。

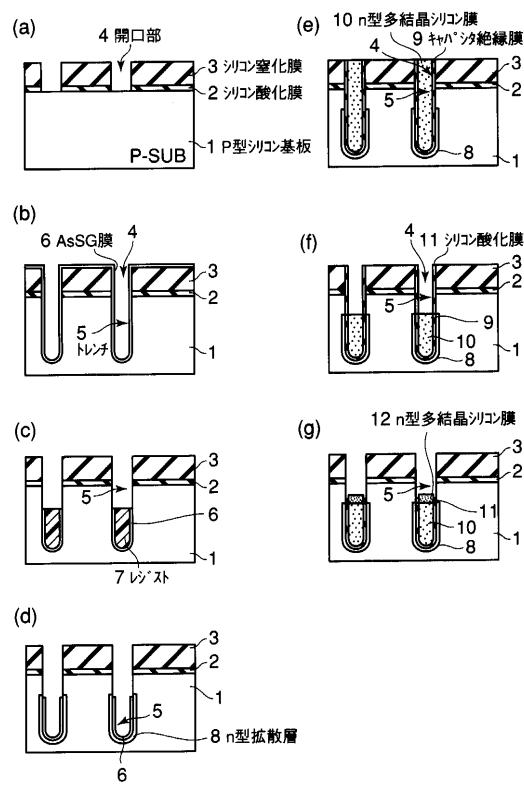

#### 【0030】

次に、図2(h)に示すように、n型多結晶シリコン膜10, 12で埋め込まれていないトレンチ5の側面および多結晶シリコン膜12の上面を被覆するように、薄いタンゲステン窒化膜(WNx膜)13を全面に堆積する。ここでは、タンゲステン窒化膜13を全面に堆積したが、少なくともトレンチ5のSiが露出した側面を完全に被覆するように堆積すれば良い。

#### 【0031】

タンゲステン窒化膜13の堆積方法としては、PVD法およびCVD法のいずれの方法でも良く、タンゲステン窒化膜13の膜厚は最も薄い部分で5nm程度あれば良い。また、タンゲステン窒化膜13の窒素濃度は10~30atm.%程度が好適である。

#### 【0032】

次に、非酸化雰囲気、例えば窒素雰囲気中で450~1100の熱処理を行う。上記非酸化雰囲気は、窒素雰囲気に限定されるものではなく、例えば水素雰囲気つまり還元性雰囲気でも構わない。また、上記熱処理の雰囲気は、アルゴン等の不活性雰囲気でも構わないし、さらに窒素、アルゴン、水素の混合ガス雰囲気でも構わない。

#### 【0033】

このような熱処理を行うことにより、タンゲステン窒化膜13とそれに接した部分のトレンチ5の側面のSiとがごく僅か反応し、図2(i)に示すように、トレンチ5の側面の表面に接したタンゲステン窒化膜13はW、SiおよびNを含むアモルファスの層(WSi<sub>x</sub>N層)14に変化する。

#### 【0034】

同様な反応により、n型多結晶シリコン膜12の上面のタンゲステン窒化膜13もアモルファスのWSi<sub>x</sub>N層14に変わる。このn型多結晶シリコン膜12の上面のアモルファスのWSi<sub>x</sub>N層14は、プロセス上形成されるものであって、無くても構わない。

#### 【0035】

このような方法によれば、厚さ1nm程度のWSi<sub>x</sub>N層14を非常に再現性良く形成することができる。WSi<sub>x</sub>N層14は、タンゲステン窒化膜13からトレンチ5の側面およびn型多結晶シリコン膜12に窒素が再分布することにより形成される。

#### 【0036】

また、WSi<sub>x</sub>N層14は、Si-N結合を含み、さらにWも含むため単純なシリコン窒化膜よりも抵抗は低いものとなる。

#### 【0037】

さらに、WSi<sub>x</sub>N層14の膜構造はアモルファスであるため、後工程で行われる熱工程におけるn型多結晶シリコン膜12のエピタキシャル成長を防止するバリアとして働く。また、WSi<sub>x</sub>N層14は950以上的高温の熱処理工程に対しても非常に安定である。そのため、WSi<sub>x</sub>N層14によるエピタキシャル成長防止の効果は、高温の熱処理工程においても失われない。

#### 【0038】

ここで、金属、シリコンおよび窒素を含む金属半導体窒化物膜として、WSi<sub>x</sub>N層14を例としてあげたが、上記金属はタンゲステン(W)に限定されるものではない。

#### 【0039】

すなわち、金属が窒化物を形成する際の Gibbs自由エネルギーの低下とSiが窒化物を形成する際の Gibbs自由エネルギーの低下を比較したときに後者の低下分が大きくなるような金属ならば何でも良く、Wの他に例えばモリブデン(Mo)、クロム(Cr)なども好適である。

#### 【0040】

このような条件を満たす金属は、窒素との化合物の形で存在するよりもシリコンとの化合

10

20

30

40

50

物の形で存在する方がエネルギー的に安定である。そのため、図2(i)の工程で、タンゲステン窒化膜13からトレンチ5の側面およびn型多結晶シリコン膜12に窒素を容易に再分布させることができ、WSiN層14を確実に形成することが可能となる。

#### 【0041】

次に、図2(j)に示すように、H<sub>2</sub>O<sub>2</sub>、H<sub>2</sub>O<sub>2</sub>とH<sub>2</sub>SO<sub>4</sub>の混合液、H<sub>2</sub>O<sub>2</sub>とHClの混合液、あるいはH<sub>2</sub>O<sub>2</sub>とNH<sub>3</sub>の混合液などを用いてウェットエッチングを行うことにより、WSiN層14を残存させ、タンゲステン窒化膜13を除去する。

#### 【0042】

WSiN層14に対してタンゲステン窒化膜13を選択的に除去できるようなエッ칭<sup>10</sup>であれば、薬液の組み合わせは上記の組み合わせに限ったものでは無く、またドライエッ칭を用いても構わない。

#### 【0043】

次に、図2(k)に示すように、WSiN層14を介して、トレンチ5内をその途中の深さまでキャパシタのストレージノード電極の一部を構成するn型多結晶シリコン膜15でさらに埋め込む。n型多結晶シリコン膜15の形成方法は、第2のn型多結晶シリコン膜12のそれと同様である。

#### 【0044】

次に、図2(l)に示すように、開口部4およびトレンチ5内を埋め込むように、シリコン酸化膜16を全面に堆積する。<sup>20</sup>

#### 【0045】

次に、図2(m)に示すように、フォトリソグラフィとエッ칭を用いて、隣接するトレンチ5を跨ぐ領域のシリコン酸化膜16を除去する。すなわち、素子分離領域上のシリコン酸化膜16を除去する。

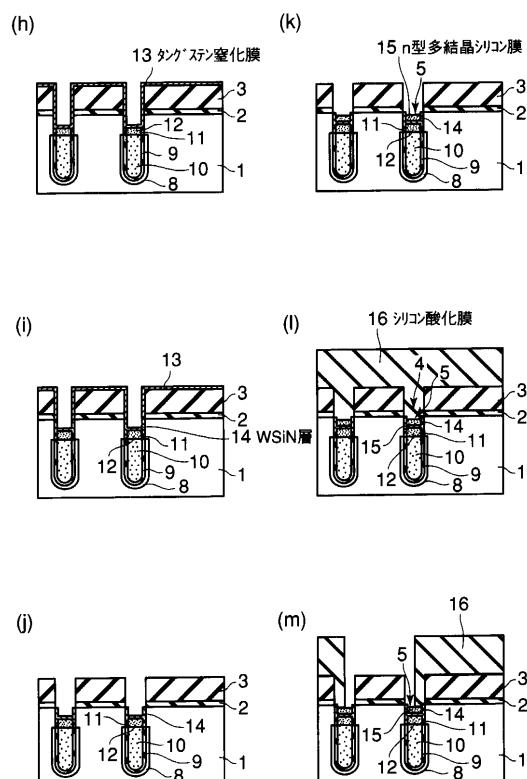

#### 【0046】

次に、図3(n)に示すように、シリコン酸化膜16をマスクにして、シリコン窒化膜3、薄いシリコン酸化膜2、p型シリコン基板1、多結晶シリコン膜15、WSiN層14、多結晶シリコン膜12およびシリコン酸化膜11をエッ칭し、素子分離用の深い溝(素子分離溝)17を形成する。このとき、素子分離溝17の底が第1のn型多結晶シリコン膜10に達しないように、素子分離溝17の深さを設定する。<sup>30</sup>

#### 【0047】

次に、図3(o)に示すように、シリコン酸化膜16を除去し、続いて溝17を埋め込むようにシリコン酸化膜18を全面に堆積する。

#### 【0048】

次に、図3(p)に示すように、素子分離溝17の外部のシリコン酸化膜18が除去され、かつシリコン酸化膜18およびシリコン窒化膜3の表面が平坦になるまで、CMPプロセスによりシリコン酸化膜18およびシリコン窒化膜3を研磨する。

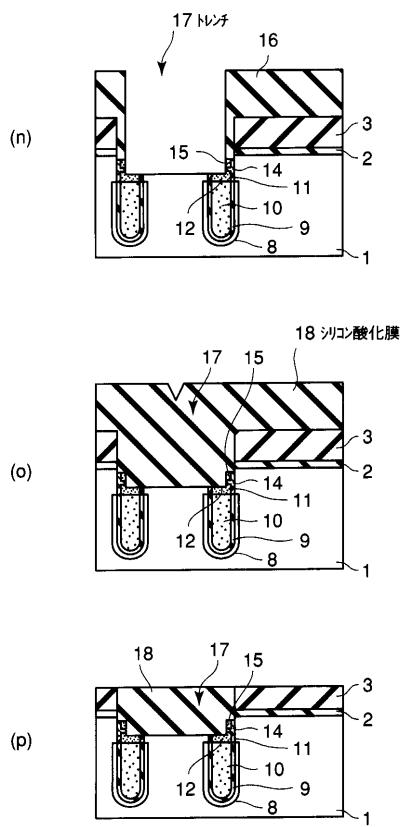

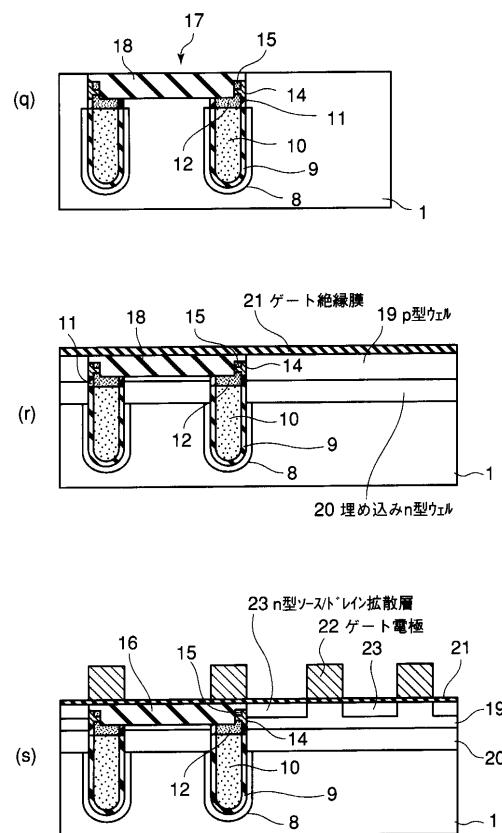

#### 【0049】

次に、図4(q)に示すように、シリコン窒化膜3を例えば熱磷酸を用いて除去し、続いてシリコン酸化膜2,18を例えば希HFを用いて除去することにより、素子分離溝17をシリコン酸化膜(素子分離絶縁膜)18で埋め込んでなる素子分離(STI:Shallow Trench Isolation)が得られる。<sup>40</sup>

#### 【0050】

シリコン酸化膜18は、工程中で繰り返し行われる希HFを含む洗浄処理などでエッティングされて徐々に薄くなる。このことをあらかじめ考慮し、MOSトランジスタを形成する段階でシリコン酸化膜18の表面がp型シリコン基板1の表面に対して所望の高さになるように、図3(p)の工程でのCMP量を加減し、図4(q)の工程時におけるシリコン酸化膜18の高さを決定する。

#### 【0051】

次に、図4(r)に示すように、p型シリコン基板1の表面にp型ウェル19および埋め<sup>50</sup>

込み $n$ 型ウェル20を形成し、続いて埋め込み $n$ 型ウェル20および素子分離絶縁膜18上にゲート絶縁膜21を形成する。

【0052】

$p$ 型ウェル19および埋め込み $n$ 型ウェル20は、その接合部分が、シリコン酸化膜11の中間に位置するように形成する。さらに、埋め込み $n$ 型ウェル20は $n$ 型拡散層（キャパシタ電極）8と接続するように形成する。

【0053】

次に、図4(s)に示すように、ゲート電極22を形成し、続いてゲート電極22をマスクにして $n$ 型不純物を $p$ 型ウェル19の表面にイオン注入し、 $n$ 型不純物の活性化アニールを行って $n$ 型ソース／ドレイン拡散層22を形成し、メモリセルの $n$ チャネルMOSトランジスタが完成する。 $n$ チャネルMOSトランジスタの二つの $n$ 型ソース／ドレイン拡散層23のうちWSiN層14に隣接する側のものは、WSiN層14を介して $n$ 型多結晶シリコン膜12にコンタクトする。

【0054】

この後、通常のDRAMプロセスにより配線層等が形成され、DRAMセルが完成する。

【0055】

以上述べたように、本実施形態のDRAMセルにおいては、トレンチキャパシタの $n$ 型多結晶シリコン膜12とMOSトランジスタのソース／ドレイン拡散層23とが、 $n$ 型多結晶シリコン膜12とWSiN層14とで構成された接続部により電気的に接続されている。

【0056】

このような構成であれば、 $n$ 型多結晶シリコン膜12の形成後の高温を伴う熱工程（パッシベーション膜の形成工程）における、トレンチ5の側面（単結晶シリコン）からの $n$ 型多結晶シリコン膜12のエピタキシャル成長をWSiN層14により抑制でき、 $p$ 型シリコン基板1中に結晶欠陥が発生することを防止できる。したがって、結晶欠陥の発生によるリーク電流の発生を防止できる。

【0057】

また、WSiN層14は金属であるWを含むため、従来の接続部に使用されているシリコン窒化膜に比べて抵抗が低い。そのため、WSiN層14とソース／ドレイン拡散層22との間のコンタクト抵抗の増加を抑制でき、これによりメモリの動作速度の低下を防止できる。

【0058】

さらに、WSiN層14の抵抗が低いことから、WSiN層14を非常に薄く形成する必要はない。そのため、WSiN層14の膜厚のばらつきによって、コンタクト抵抗が大きくなったり、あるいはメモリセル間のコンタクト抵抗のばらつきが大きくなるという問題もない。

【0059】

なお、本発明は、上記実施形態に限定されるものではない。例えば、上記実施形態では、接続部の多結晶半導体膜として多結晶シリコン膜を用いたが、その代わりに、多結晶ゲルマニウム膜や多結晶ゲルマニウムシリコン膜等の多結晶半導体膜を用いても構わない。

【0060】

また、上記実施形態では、トレンチキャパシタが $n$ チャネルMOSトランジスタに接続する場合について説明したが、トレンチキャパシタが $p$ チャネルMOSトランジスタに接続する場合にも本発明は有効であり、さらにCMOS（デュアルゲート）に対しても本発明は有効である。

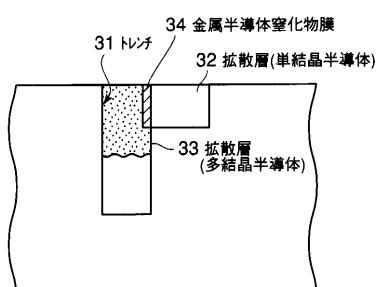

【0061】

また、上記実施形態では、トレンチキャパシタのトレンチ側面からの多結晶半導体膜のエピタキシャル成長を抑制する場合について説明したが、本発明は図5に示すように、トレンチ31の側面の拡散層（単結晶半導体）32と多結晶半導体膜33とが接続する構造であれば、それらの間に金属半導体窒化物層34を挿設することにより、素子の種類に關係

10

20

30

40

50

なく、後工程での高温熱処理時における多結晶半導体膜33の単結晶化を防止できる。また、多結晶半導体膜33の下の構造は特に限定されない。

#### 【0062】

また、上記実施形態では、トレンチ内に合計三つの多結晶シリコン膜10, 12, 15を形成したが、一つもしくは二つの多結晶シリコン膜、または四つ以上の多結晶シリコン膜を形成して、そのトレンチ内の多結晶シリコン膜と基板表面の拡散層とを金属半導体窒化物層を用いて電気的に接続する構造とすることも可能である。

#### 【0063】

さらに、上記実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の発明が抽出され得る。例えば、実施形態に示される全構成要件から幾つかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題を解決できる場合には、この構成要件が削除された構成が発明として抽出され得る。10

#### 【0064】

その他、本発明の要旨を逸脱しない範囲で、種々変形して実施できる。

#### 【0065】

#### 【発明の効果】

以上詳説したように本発明によれば、溝内に埋め込まれ、半導体基板の表面の拡散層と電気的に接続するための多結晶半導体膜のエピタキシャル成長の発生防止、および上記多結晶半導体膜と上記拡散層との間のコンタクト抵抗の増加防止を図れる半導体装置およびその製造方法を実現できるようになる。20

#### 【図面の簡単な説明】

【図1】本発明の一実施形態に係るトレンチキャパシタを有するDRAMセルの製造工程を示す断面図

【図2】図1に続く同DRAMセルの製造工程を示す断面図

【図3】図2に続く同DRAMセルの製造工程を示す断面図

【図4】図3に続く同DRAMセルの製造工程を示す断面図

【図5】本発明の他の実施形態を説明するための断面図

【図6】従来のトレンチキャパシタを有するDRAMセルを示す断面図

【図7】従来の他のトレンチキャパシタを有するDRAMセルを示す断面図30

#### 【符号の説明】

1 ... p型シリコン基板

2 ... シリコン酸化膜

3 ... シリコン窒化膜

4 ... 開口部

5 ... トレンチ

6 ... ASG膜

7 ... レジスト

8 ... n型拡散層(プレート電極)

9 ... キャパシタ絶縁膜

10 ... n型多結晶シリコン膜(ストレージノード電極:第1の多結晶半導体膜)40

11 ... シリコン酸化膜(側壁絶縁膜)

12 ... n型多結晶シリコン膜(ストレージノード電極:第1の多結晶半導体膜)

13 ... タングステン窒化膜

14 ... WSiN層(金属半導体窒化物層)

15 ... n型多結晶シリコン膜(第2の多結晶半導体膜)

16 ... シリコン酸化膜

17 ... トレンチ

18 ... シリコン酸化膜(素子分離絶縁膜)

19 ... p型ウェル

40

50

2 0 ... 埋め込み n 型ウェル

2 1 ... ゲート電極

2 2 ... n 型ソース / ドレイン拡散層

3 1 ... トレンチ

3 2 ... 拡散層 ( 単結晶半導体 )

3 3 ... 多結晶半導体膜

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

フロントページの続き

(74)代理人 100070437

弁理士 河井 将次

(72)発明者 赤坂 泰志

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

F ターム(参考) 5F083 AD17 GA02 GA06 JA39 JA40 JA60 PR09 PR40