(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5235287号

(P5235287)

(45) 発行日 平成25年7月10日(2013.7.10)

(24) 登録日 平成25年4月5日(2013.4.5)

(51) Int.Cl.

F 1

**H01L 21/318 (2006.01)**

**H01L 21/336 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 29/792 (2006.01)**

**H01L 21/8247 (2006.01)**

H01L 21/318 M

H01L 29/78 371

H01L 27/10 434

請求項の数 6 (全 17 頁) 最終頁に続く

(21) 出願番号 特願2006-233367 (P2006-233367)

(22) 出願日 平成18年8月30日 (2006.8.30)

(65) 公開番号 特開2007-67412 (P2007-67412A)

(43) 公開日 平成19年3月15日 (2007.3.15)

審査請求日 平成21年8月31日 (2009.8.31)

(31) 優先権主張番号 10-2005-0080525

(32) 優先日 平成17年8月31日 (2005.8.31)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100093779

弁理士 服部 雅紀

(72) 発明者 季 聖海

大韓民国京畿道水原市靈通洞シンナムシルシンスンアパート521棟1706

号

最終頁に続く

(54) 【発明の名称】SONOS型の不揮発性半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上にシリコン酸化物からなる第1酸化膜を形成する段階と、

シリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施して前記第1酸化膜上にシリコン窒化物( $\text{Si}_x\text{Ny}$ )を含むシリコン窒化膜を形成する段階と、

前記シリコン窒化膜上に第2酸化膜を形成する段階と、

前記第2酸化膜上に導電膜を形成する段階と、

前記導電膜、前記第2酸化膜、前記シリコン窒化膜及び前記第1酸化膜を順にエッチングし、前記半導体基板の上部に第1酸化膜パターン、シリコン窒化膜パターン及び第2酸化膜パターンの多層構造を有する電荷トラップ絶縁体、ならびに導電性パターンを含むゲート構造物を形成する段階と、

前記ゲート構造物と隣接する前記半導体基板の表面部に不純物をドーピングしてソース/ドレイン領域を形成する段階と、を含み、

前記シリコン窒化物は、 $x/y$ の値が0.85~1.5であることを特徴とするSONOS型の不揮発性半導体装置の製造方法。

## 【請求項 2】

前記シリコンソース物質は、 $\text{Si}_2\text{C}_{1.6}$ または $\text{Si}_3\text{C}_{1.8}$ を含み、前記窒素ソースガスは $\text{NH}_3$ ガス、 $4\text{NH}_2$ ガスまたはこれらの混合ガスを含むことを特徴とする請求項1記載のSONOS型の不揮発性半導体装置の製造方法。

**【請求項 3】**

前記サイクリック化学気相蒸着工程は、400～700で実施することを特徴とする請求項1記載のSONOS型の不揮発性半導体装置の製造方法。

**【請求項 4】**

半導体基板上にシリコン酸化物からなる第1酸化膜を形成する段階と、

前記第1酸化膜上にシリコン窒化物(Si<sub>a</sub>N<sub>b</sub>、a/bの比が0.7～0.85である)からなる第1シリコン窒化薄膜を形成する段階と、

前記第1シリコン窒化薄膜上にシリコンソース物質と窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施してシリコン窒化物(Si<sub>c</sub>N<sub>d</sub>、c/dの比が0.85～1.5である)からなる第2シリコン窒化薄膜を形成する段階と、

前記第2シリコン窒化膜上に第2酸化膜を形成する段階と、

前記第2酸化膜上に導電膜を形成する段階と、

前記導電膜、前記第2酸化膜、前記第1シリコン窒化薄膜及び前記第2シリコン窒化薄膜を含むシリコン窒化膜、ならびに前記第1酸化膜を順にエッティングして前記半導体基板の上部に第1酸化膜パターン、シリコン窒化膜パターン及び第2酸化膜パターンの多層構造を有する電荷トラップ絶縁体、ならびに導電性パターンを含むゲート構造物を形成する段階と、

前記ゲート構造物と隣接する前記半導体基板の表面部に不純物をドーピングしてソース/ドレイン領域を形成する段階と、

を含むことを特徴とするSONOS型の不揮発性半導体装置の製造方法。

**【請求項 5】**

前記第1シリコン窒化薄膜は前記シリコン窒化膜のうちその5～60%の厚さを有し、前記第2シリコン窒化薄膜は前記シリコン窒化膜のうちその40～95%の厚さを有することを特徴とする請求項4記載のSONOS型の不揮発性半導体装置の製造方法

**【請求項 6】**

前記第2シリコン窒化薄膜上にシリコン窒化物(Si<sub>x</sub>N<sub>y</sub>、x/yの値が0.7～0.85である)からなる第3シリコン窒化薄膜をさらに形成することを特徴とする請求項4記載のSONOS型の不揮発性半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明はSONOS型の不揮発性半導体装置の製造方法に関し、より詳細にはシリコンリッチ(silicon-rich)窒化薄膜を含む電荷トラップ絶縁膜を用いたSONOS型の不揮発性半導体装置の製造方法に関する。

**【背景技術】****【0002】**

一般的に、不揮発性半導体装置は単位セルの構造によりフローティングゲート型の不揮発性半導体装置と、フローティングトラップ型の半導体装置と、に区分することができる。特に、前記フローティングトラップ型の不揮発性半導体装置は主にSONOS(Silicon Oxide Nitride Oxide Semiconductor)型の不揮発性半導体装置で示す。

**【0003】**

前記フローティングゲート型の不揮発性半導体装置は、単位セルとして半導体基板上に形成するトンネル酸化膜、フローティングゲート、誘電膜及びコントロールゲートを含む。そして、前記フローティングゲート内に自由電荷(free carriers)の形態で電荷を貯蔵する方法でプログラミングを実施する。特に、前記フローティングゲート型の不揮発性半導体装置は前記フローティングゲートと半導体基板との間に介在する前記トンネル酸化膜に欠陥が発生すると、前記フローティングゲートに貯蔵された電荷をすべてなくしてしまうので、前記トンネル酸化膜を相対的に厚く形成しなければならない。しかし、前記トンネル酸化膜を多少厚く形成する場合には高い動作電圧を必要とし、その結果、周辺回路の構造が複雑となる。従って、前記フローティングゲート型の不揮発性半導体装置は高集積

10

20

30

40

50

化に限界を示す。

#### 【0004】

前記SONOS型の不揮発性半導体装置は、単位セルとして半導体基板上に形成する第1シリコン酸化膜、シリコン窒化膜及び第2シリコン酸化膜の多層構造を有する電荷トラップ絶縁体と、前記電荷トラップ絶縁体上に形成する単一電極と、を含む。そして、前記SONOS型の不揮発性半導体装置は、前記単一電極と半導体基板との間に介在された前記電荷トラップ絶縁体で形成されるトラップに電子(e)を貯蔵する方法でプログラミングを実施する。特に、前記電子は前記シリコン窒化膜の深い順位トラップ(deep level trap)に貯蔵されるので、前記第1シリコン酸化膜を相対的に薄く形成することができる。10

#### 【0005】

このように、前記第1シリコン酸化膜を多少薄く形成する場合には低動作電圧でも駆動が可能であり、その結果、周辺回路の構造が簡単となる。従って、SONOS型の不揮発性半導体装置は高集積化の実現が容易である。

#### 【0006】

前記SONOS型の不揮発性半導体装置に対する例は、特許文献1に開示されている。しかし、前記SONOS型の不揮発性半導体装置は、前記シリコン窒化膜に貯蔵された電荷である電子を消去するとき、前記電子を完全に消去することができないという状況が頻繁に発生する。その理由は、前記消去を実施するとき、前記シリコン窒化膜に貯蔵された電子がファウラーノルドハイム(Fowler-Nordheim)トンネリングによって、前記シリコン窒化膜から前記第1シリコン酸化膜をトンネルし前記半導体基板に完全に移動しなければならないが、前記シリコン窒化膜に電子が継続的に残っている状況が発生するからである。具体的に、前記シリコン窒化膜に貯蔵された電子を消去するとき、前記単一電極から生成された電子が前記第2シリコン酸化膜を通じて前記シリコン窒化膜に移動する。20

#### 【0007】

また、前記SONOS型の不揮発性半導体装置の製造方法は、特許文献2に開示されている。このようなSONOS型の不揮発性半導体装置を製造するためには、基板上に下部誘電体膜(BTM)でシリコン酸化膜(SiO<sub>2</sub>)膜を形成する。続いて、シリコン酸化膜上にSiCl<sub>4</sub>またはSi<sub>2</sub>Cl<sub>6</sub>ガス及びアンモニア(NH<sub>3</sub>)ガスを用いた原子層蒸着(ALD)工程を実施し、電荷蓄積膜であるシリコン窒化膜を形成する。以後、前記シリコン窒化膜上に上部誘電膜及びゲート電極を形成することでSONOS型の不揮発性半導体装置が完成される。30

#### 【0008】

しかし、特許文献2に開示されているSONOS型の不揮発性半導体装置の製造方法は、ただ、前記シリコン窒化膜のインキュベーション時間を減少し、前記シリコン窒化膜の界面特性を向上させるために原子層蒸着工程を実施するシリコン窒化膜(SixNy)を形成することにある。従って、トラップ密度の高い前記シリコン窒化膜を形成することは困難であるという問題を有する。また、アンモニウムガスの流量を増加させ前記シリコン窒化膜を形成するので、前記シリコン窒化膜にトラップされた電子を除去するプログラム消去速度の向上には限界がある。これは、前記シリコン窒化膜がシリコンリッチ窒化物を含んでいないからである。40

#### 【0009】

【特許文献1】米国特許第6,501,681号明細書

【特許文献2】特開2002-217317号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

本発明の第1目的は、電子トラップ密度が高く電子の円滑な消去が可能となるシリコンリッチ窒化物を含む電荷トラップ絶縁体の製造方法を提供することにある。

#### 【0011】

本発明の第2目的は、電荷トラップ絶縁膜を含むSONOS型の不揮発性半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0012】

前記第1目的を達成するための本発明による電荷トラップ絶縁体の製造方法は、シリコン酸化物からなる第1酸化膜を形成する。シリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施して前記第1酸化膜上にシリコンリッチ窒化物( $\text{Si}_x\text{Ny}$ 、 $x/y$ の値が0.7~1.5である)を含むシリコン窒化膜を形成する。前記シリコン窒化膜上に第2酸化膜を形成する。その結果、半導体基板上には電荷の消去特性が高い電荷トラップ絶縁体が形成される。

10

【0013】

特に、シリコンリッチ窒化物は化学式 $\text{Si}_x\text{Ny}$ で $x/y$ の値が0.85~1.5であることが望ましい。前記シリコンソース物質として $\text{Si}_2\text{Cl}_6$ または $\text{Si}_3\text{Cl}_8$ を用い、窒素ソースガスとして $\text{NH}_3$ ガス、 $4\text{NH}_2$ ガス、またはこれらの混合ガスを用いることが望ましい。また、前記シリコンリッチ窒化物 $\text{Si}_x\text{Ny}$ で前記 $y$ が4の場合 $x$ が3以上であることが望ましい。

【0014】

前記第1目的を達成するための本発明による電荷トラップ絶縁体の製造方法は、シリコン酸化物からなる第1酸化膜を形成する。前記第1酸化膜上にシリコン窒化物( $\text{Si}_{a/b}$ 、 $a/b$ の値が0.7~0.85である)からなる第1シリコン窒化薄膜を形成する。前記第1シリコン窒化薄膜上にシリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施してシリコンリッチ窒化物( $\text{Si}_{c/d}$ 、 $c/d$ の値が0.85~1.5である)からなる第2シリコン窒化薄膜を形成する。前記第2シリコン窒化薄膜上に第2酸化膜を形成する。その結果、半導体基板上には電荷の消去特性が高い電荷トラップ絶縁体が形成される。

20

【0015】

特に、前記電荷トラップ絶縁体の製造方法において、前記第1シリコン窒化薄膜及び前記第2シリコン窒化薄膜はインサイチュで形成することが望ましい。また、前記第1シリコン窒化薄膜はシリコン窒化膜全体の厚さのうち5~60%の厚さを有し、前記第2シリコン窒化薄膜は前記シリコン窒化膜厚さのうち40~95%の厚さを有することが望ましい。

30

【0016】

前記第2目的を達成するための本発明によるSONOS型の不揮発性半導体装置の製造方法は、半導体基板上にシリコン酸化物からなる第1酸化膜を形成する。シリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施して前記第1酸化膜上にシリコンリッチ窒化物( $\text{Si}_x\text{Ny}$ 、 $x/y$ の値が0.7~1.5である)を含むシリコン窒化膜を形成する。前記シリコン窒化膜上に第2酸化膜を形成する。前記第2酸化膜上に導電膜を形成する。前記導電膜、第2酸化膜、シリコン窒化膜及び第1酸化膜を順にエッティングし、前記半導体基板の上部に第1酸化膜パターン、シリコン窒化膜パターン及び第2酸化膜パターンからなる電荷トラップ絶縁体、ならびに導電性パターンを含むゲート構造物を形成する。前記ゲート構造物と隣接する前記半導体基板の表面部に不純物をドーピングしてソース/ドレイン領域を形成する。その結果、前記絶縁体にトラップされた電荷の消去が容易なSONOS型の不揮発性半導体装置が形成される。

40

【0017】

前記第2目的を達成するための本発明によるSONOS型の不揮発性半導体装置の製造方法は、半導体基板上にシリコン酸化物からなる第1酸化膜を形成する。前記第1酸化膜上にシリコン窒化物( $\text{Si}_{a/b}$ 、 $a/b$ の比が0.7~0.85である)からなる第1シリコン窒化薄膜を形成する。前記第1シリコン窒化薄膜上にシリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施してシリコンリッチ窒化物( $\text{Si}_{c/d}$ 、 $c/d$ の比が0.85~1.5である)からなる第2シリコン窒化薄膜を形

50

成する。前記シリコン窒化膜上に第2酸化膜を形成する。前記第2酸化膜上に導電膜を形成する。前記導電膜、第2酸化膜、前記第1シリコン窒化薄膜、及び第2シリコン窒化薄膜を含むシリコン窒化膜、及び第1酸化膜を順にエッティングして前記半導体基板の上部に第1酸化膜パターン、シリコン窒化膜パターン及び第2酸化膜パターンの多層構造を有する電荷トラップ絶縁体、ならびに導電性パターンを含むゲート構造物を形成する。前記ゲート構造物と隣接する前記半導体基板の表面部に不純物をドーピングしてソース／ドレイン領域を形成する。その結果、前記絶縁体にトラップされた電荷の消去が容易なSONOS型の不揮発性半導体装置が形成される。

## 【0018】

言及したように、本発明によると、SONOS型の不揮発性半導体装置に適用するシリコンリッチ窒化物を含む電荷トラップ絶縁体は電荷の貯蔵能力は向上し、一定の電圧下で前記電荷トラップ絶縁体に貯蔵された電子の消去が容易な特性を有する。そのため、本発明のSONOS型の不揮発性半導体装置でプログラム入力速度及びプログラム消去速度を顕著に増加させることができる。10

## 【発明を実施するための最良の形態】

## 【0019】

以下、添付図面を参照して、本発明の好ましい実施形態をより詳細に説明する。

## (電荷トラップ絶縁体)

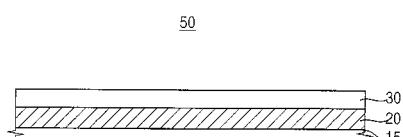

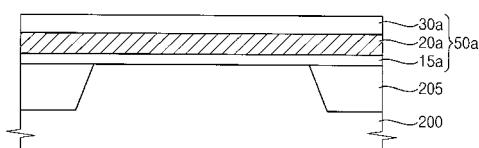

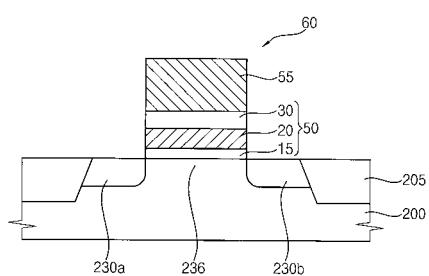

図1は本発明の一実施例による電荷トラップ絶縁体を示す概略的な断面図である。

図1を参照すると、前記電荷トラップ絶縁体50は、SONOS型の不揮発性半導体装置に適用され、第1酸化膜15、シリコン窒化膜20及び第2酸化膜30の多層構造を有する。20

## 【0020】

具体的に、前記第1酸化膜15は、電子トンネリングでエネルギー障壁を提供するトンネル膜に該当する。本実施例の第1酸化膜15はシリコン酸化膜である。また、前記第1酸化膜15は約20～50の厚さを有し、望ましくは、約20～40の厚さを有する。より望ましくは、約25～35の厚さを有する。最も、望ましくは約30の厚さを有する。ここで、前記第1酸化膜15を相対的に薄く形成することができるのを言及したようにSONOS型の不揮発性半導体装置が電荷トラップ絶縁体50で形成されるトラップに電子を貯蔵する方法でプログラミングを実施するからである。30

## 【0021】

前記シリコン窒化膜20は、電子(電荷)を貯蔵する貯蔵膜に該当する。本実施例のシリコン窒化膜20はシリコンリッチ窒化物を含む。前記シリコンリッチ窒化物を含むシリコン窒化膜20はシリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程で形成される。

## 【0022】

特に、前記シリコン窒化膜に含まれたシリコンリッチ窒化物(Si<sub>x</sub>N<sub>y</sub>)におけるx/yの値は、0.7～1.5を満足し、望ましくはx/yの値は0.85～1.3を満足する。より望ましくは、x/yの値は、0.9～1.2を満足する。また、前記シリコンリッチ窒化物Si<sub>x</sub>N<sub>y</sub>でyが4の場合望ましくはxは3～6であり、より望ましくは、xは3.5～5.5である。40

## 【0023】

また、本実施例においては前記シリコン窒化膜20は約50～100の厚さを有する。望ましくは、約60～90の厚さを有し、より望ましくは約65～80の厚さを有する。最も望ましくは、約70の厚さを有する。

前記第2酸化膜30は、前記SONOS型の不揮発性半導体装置の電極(図示せず)から印加される電圧を遮断する遮断膜に該当する。前記第2酸化膜30は、シリコン酸化物または金属酸化物を含む。本実施例においては前記第2酸化膜30の例としては金属酸化膜を挙げることができる。

## 【0024】

10

20

30

40

50

(電荷トラップ絶縁体の製造方法)

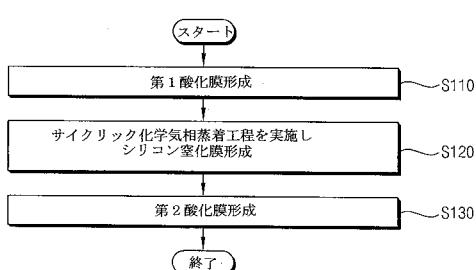

図2は図1に示された電荷トラップ絶縁体の製造方法を示す工程流れ図である。

図1及び図2を参照すると、まず、半導体基板上にシリコン酸化物からなる第1酸化膜15を形成する(段階S110)。

具体的に、前記第1酸化膜15は化学気相蒸着工程、サブ・大気化学気相蒸着(Sub-Atmospheric CVD)工程、低圧・化学気相蒸着工程(Low Pressure CVD)工程または強化プラズマ化学気相蒸着(Plasma Enhanced CVD)工程、熱酸化工程で形成することができる。特に、本実施例の前記第1酸化膜15は熱酸化工程を実施することが望ましい。

【0025】

前記第1酸化膜15を形成するための熱酸化は約900～1200の温度で実施する。特に、熱酸化の実施においては前記半導体基板15が急激な温度変化がないように低い温度から言及した約900～1200の酸化温度まで徐々に上昇させる。そして、±1範囲で前記酸化温度を保持し前記酸化を実施して第1酸化膜15を形成した後、前記温度を徐々に下降させる。さらに、前記熱酸化では前記酸化のための反応物質として酸素(O<sub>2</sub>)または水蒸気(H<sub>2</sub>O)を提供する。

【0026】

また、本実施例においては、前記第1酸化膜15を約20～50の厚さを有するように形成する。望ましくは、約20～40の厚さを有するように形成し、より望ましくは、約25～35の厚さを有するように形成する。最も望ましくは、約30の厚さを有するように形成する。ここで、前記第1酸化膜15を相対的に薄く形成することができるのは、言及したようにSONOS型の不揮発性半導体装置が電荷トラップ絶縁体で形成されるトラップに電子を貯蔵する方法でプログラミングを実施するからである。

【0027】

続いて、前記第1酸化膜15上にシリコンリッチ窒化物を含むシリコン窒化膜20を形成する(段階S120)。

具体的に、気体状態のシリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施して前記第1酸化膜上にシリコンリッチ窒化物(Si<sub>x</sub>N<sub>y</sub> x/yの値が0.7～1.5である)を含むシリコン窒化膜20を形成する。

【0028】

一般的に、前記シリコンリッチ窒化物を含むシリコン窒化膜20はジクロロシラン(SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>)ガス及びアンモニウムガスを用いた化学気相蒸着工程で形成することができる。しかし、前記化学気相蒸着方式で前記シリコン窒化膜20を形成するためには前記ジクロロシランガスの使用量を増加させることが必須的である。前記ジクロロシランの使用量の増加は反応副産物であるNH<sub>4</sub>C<sub>1</sub>塩の生成を増加させるという問題点を招く。ここで、前記NH<sub>4</sub>C<sub>1</sub>塩は前記半導体基板上でパーティクルとして作用する。

【0029】

従って、本実施例においては前記シリコンリッチ窒化物を含むシリコン窒化膜20はサイクリック化学気相蒸着工程で形成することが望ましい。以下、一例で、前記サイクリック化学気相蒸着工程を実施しシリコン窒化膜を形成する方法を具体的に説明する。

【0030】

まず、化学気相蒸着チャンバ内にローディングされた半導体基板の上部にシリコンソース物質を約0.5秒～5秒の間提供する。特に、本実施例においては前記反応物質を約1秒の間提供する。前記シリコンソース物質の提供ではLDS(liquid delivery system)を使用する。前記半導体基板上には第1酸化膜が形成されている。

【0031】

前記シリコンリッチ窒化物を含むシリコン窒化膜を形成するために適用される前記シリコンソース物質の例としては、Si<sub>2</sub>C<sub>1</sub><sub>6</sub>またはSi<sub>3</sub>C<sub>1</sub><sub>8</sub>を挙げることができる。本実施例においては、シリコンソース物質として、液体状態のSi<sub>2</sub>C<sub>1</sub><sub>6</sub>を気化させ気体状態のSi<sub>2</sub>C<sub>1</sub><sub>6</sub>ガスを使用することが望ましい。

その結果、前記シリコンソース物質の一部は前記第1酸化膜上に化学吸着され、残りの

10

20

30

40

50

シリコンソース物質は前記第1酸化膜上部で物理的に吸着又は前記チャンバ内に残留する。

#### 【0032】

続いて、前記チャンバ内部にバージガスを提供する。前記バージガスの例としては、アルゴンガス、窒素ガスなどのような不活性ガスを挙げることができる。この際、前記バージガスは約1秒～30秒の間提供する。前記チャンバ内部にバージガスを提供することにより、前記チャンバ内に残留又は前記第1酸化膜15上部で物理的吸着されたシリコンソース物質は除去される。その結果、前記第1酸化膜に化学吸着されていない残存する余剰のシリコンソース物質は除去される。

#### 【0033】

10

続いて、前記チャンバ内部に前記窒素ソースガスを提供する。前記窒素ソースガスの例としては、 $\text{NH}_3$ ガス及び $4\text{NH}_2$ ガスを挙げることができる。これらは単独で使用することが望ましく、場合によって2つ以上を混合して使用することもできる。このとき、窒素ソースガスは約0.5秒～5秒の間提供する。このように、窒素ソースガスを提供することによって前記第1酸化膜上に吸着されたシリコンソース物質と窒素ソースガスとは化学的に反応し、シリコンリッチ窒化物が形成される。

#### 【0034】

続いて、前記チャンバ内部にバージガスを提供する。前記バージガスの種類及び提供時間は上述したのと同一である。このように、前記チャンバ内部にバージガスを提供することで、前記シリコンソース物質と化学的に反応していない余剰の窒素ソースガスが前記チャンバから除去される。その結果、前記第1酸化膜15上には所定の厚さを有するシリコンリッチ窒化物 $\text{Si}_x\text{Ny}$ が形成される。即ち、予備シリコン窒化膜が形成される。

20

#### 【0035】

特に、前記シリコンリッチ窒化物 $\text{Si}_x\text{Ny}$ において、 $x/y$ 値は0.7～1.5を満足し、望ましくは、 $x/y$ の値は0.85～1.3を満足する。より望ましくは、 $x/y$ の値は0.9～1.2を満足する。また、シリコンリッチ窒化物 $\text{Si}_x\text{Ny}$ において、 $y$ が4の場合、望ましくは $x$ は3～6であり、より望ましくは $x$ は3.5～5.5である。

#### 【0036】

続いて、前記予備シリコン窒化膜を形成する段階を少なくとも5～10回反復して実施する。その結果、前記第1酸化膜15上には予備シリコン窒化膜を積層したシリコン窒化膜20が形成される。この際、前記シリコン窒化膜20はシリコンリッチ窒化物( $\text{Si}_x\text{Ny}$ : $x/y$ の値が0.7～1.5である)を含有する。そして、前記シリコン窒化膜20の厚さは、前記予備シリコン窒化膜を形成するための工程の反復回数によって調節することができる。

30

#### 【0037】

また、本実施例のシリコン窒化膜を形成するためのサイクリック化学気相蒸着工程は、望ましくは約400～700で実施する。より望ましくは約450～650で実施する。他の例で、前記予備シリコン窒化膜を形成する工程の際シランガスを追加導入しシリコン含量がより高いシリコンリッチ窒化物を形成することができる。

#### 【0038】

40

また、本実施例においては、前記シリコン窒化膜20を約50～100の厚さを有するように形成する。望ましくは、約60～90の厚さを有するように形成し、より望ましくは約65～80の厚さを有するように形成する。最も望ましくは、約70の厚さを有するように形成する。

#### 【0039】

続いて、前記シリコンリッチ窒化物を含むシリコン窒化膜上に第2酸化膜を形成する(段階S130)。

具体的に、前記第2酸化膜30は図1で言及した電荷トラップ絶縁体50の金属酸化膜またはシリコン酸化膜30で形成される。前記第2酸化膜30が金属酸化膜の場合、前記第2酸化膜30は化学気相蒸着工程で形成することが望ましい。反面、前記第2酸化膜が

50

シリコン酸化膜の場合、前記第2酸化膜はラジカル酸化工程で形成することが望ましい。

**【0040】**

本実施例においては、前記第2酸化膜30を約100～200の厚さを有するように形成する。望ましくは、約120～180の厚さを有するように形成し、より望ましくは約130～170の厚さを有するように形成する。最も望ましくは約150の厚さを有するように形成する。

**【0041】**

(SONOS型の不揮発性半導体装置)

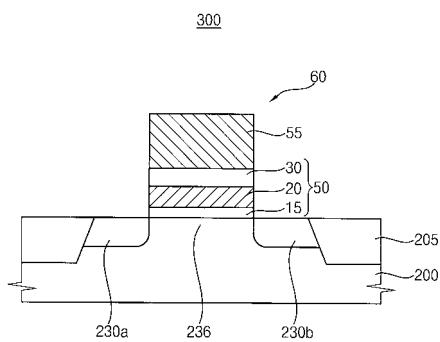

図3は図1に示された電荷トラップ絶縁体を適用した本発明の実施例によるSONOS型の不揮発性半導体装置を示す断面図である。

10

図3を参照すると、SONOS型の不揮発性半導体装置300は、単位セルとして電荷トラップ絶縁体50及び電極55を含むゲート構造物60が形成されている半導体基板200を含む。前記半導体基板200の例としてはシリコン基板、シリコン-オン-インシユレータ(SOI)基板、ゲルマニウム基板、ゲルマニウム-オン-インシユレータ基板(GOI)、シリコン-ゲルマニウム基板、選択的エピタキシャル成長(SEG)を実施し獲得したエピタキシャル薄膜の基板などを挙げることができる。

**【0042】**

そして、前記半導体基板200にはアクティブ領域とフィールド領域とを限定するための素子分離膜205が形成される。前記素子分離膜250の例としてはフィールド酸化膜、トレンチ素子分離膜などを挙げることができる。

20

また、前記半導体基板200の表面部には不純物がドーピングされた領域であるソース/ドレイン230a、230bが形成される。具体的に、前記ソース/ドレイン230a、230bは、前記半導体基板200上部に位置するゲート構造物60と隣接する半導体基板200の表面部に形成される。また、前記ソース/ドレイン230a、230bの形成のための不純物の例としては、周期率表の5族元素であるN型不純物としてリン、ヒ素などを挙げができる。これらは単独で使用することが望ましく、場合によってこれらを混合して使用することもできる。また、前記ソース/ドレイン230a、230bを形成のための不純物は主にイオン注入を実施して前記半導体基板200にドーピングさせることが望ましい。

**【0043】**

30

このように、前記半導体基板200の表面の下にソース/ドレイン230a、230bを形成することで前記ソース/ドレイン230a、230bの間にはチャンネル領域236が位置する。

従って、前記ゲート構造物60は、前記半導体基板200のチャンネル領域236上部に位置する。そして、前記ゲート構造物60は、第1酸化膜パターン15及びシリコンリッチ窒化物を含むシリコン窒化膜パターン20と、第2酸化膜パターン30を含む電荷トラップ絶縁体50と、電極55とからなる。特に、前記シリコンリッチ窒化膜パネル20は、化学式 $\text{Si}_x\text{N}_y$ で示される組成を有し、前記化学式において $x/y$ の値が0.7～1.5であり、望ましくは $x/y$ の値が0.85～1.3である。

**【0044】**

40

以下、前記電荷トラップ絶縁体50と電極55のゲート構造物60を単位セルで含むSONOS型の不揮発性半導体装置を使用した情報の記録と消去について説明する。

前記SONOS型の不揮発性半導体装置300を使用して情報を記録する場合には、前記半導体基板200をアースさせ、前記ゲート構造物60の電極55に正電圧( $V_g > 0$ )を印加する。そうすると、前記半導体基板200と前記ゲート構造物60の単一電極との間に電場が形成されることで前記電荷トラップ絶縁体50の第1酸化膜パターン15を横切るファウラーノルドハイム電流が発生する。それにより、前記ソース/ドレイン230a、230bの間のチャンネル領域236を進行していた電子は、前記ファウラーノルドハイム電流によって前記第1酸化膜パターン15のエネルギー障壁をトンネリングし、前記シリコンリッチ窒化物を含むシリコン窒化膜パターン20に移動する。そして、前記シ

50

リコン窒化膜パターン20に貯蔵された電子は、前記電荷トラップ絶縁体の第2酸化膜パターン30のエネルギー障壁によって前記電極55への移動が遮断され、その結果、前記シリコンリッチ窒化膜パターン20にトラップされることで情報が記録される。

#### 【0045】

前記SONOS型の不揮発性半導体装置300を使用して情報を消去する場合には、前記半導体基板200をアースさせ、前記ゲート構造物60の電極55に負電圧( $V_g < 0$ )を印加する。そうすると、前記情報を記録するときとは反対方向に電場が形成され、その結果、前記電荷トラップ絶縁体50の第1酸化膜パターン15を横切るファウラーノルドハイム電流も前記情報を記録するときには反対方向に発生する。それにより、前記電荷トラップ絶縁体50のシリコン窒化膜パターン20に貯蔵された電子は、前記ファウラーノルドハイム電流によって前記第1酸化膜パターン15のエネルギー障壁をトンネリングし、前記半導体基板200に移動することで情報が削除される。10

#### 【0046】

##### (SONOS型の不揮発性半導体装置の製造)

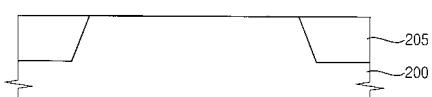

図4～図8は図3のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

図4を参照すると、前記半導体基板200にトレンチ素子分離膜205を形成してアクティブ領域とフィールド領域とを区画する。前記トレンチ素子分離膜205を形成することは言及したように集積度的な側面を考慮するからである。

#### 【0047】

図5を参照すると、前記素子分離膜205が形成された半導体基板200上にシリコン酸化物の第1酸化膜15aを形成する。ここで、前記第1酸化膜15aは、図3で言及した電荷トラップ絶縁体50の第1酸化膜15に形成するため適用される。前記第1酸化膜15aは主に熱酸化を実施して形成することが望ましい。20

#### 【0048】

また、本実施例においては、前記第1酸化膜15aを約20～50の厚さを有するように形成し、望ましくは、約20～40の厚さを有するように形成し、最も望ましくは約30の厚さを有するように形成する。ここで、前記第1酸化膜15aを相対的に薄く形成することができるのは、言及したようにSONOS型の不揮発性半導体装置が電荷トラップ絶縁体50で形成されるトラップに電子eを貯蔵する方法でプログラミングを実施するからである。30

#### 【0049】

図6を参照すると、前記シリコン酸化物の第1酸化膜15a上にシリコンリッチ窒化物からなるシリコン窒化膜20aを形成する。ここで、前記シリコン窒化膜20aは、図3で言及した電荷トラップ絶縁体50のシリコン窒化膜パターン20を形成するためのものである。前記シリコン窒化膜20は、シリコンソース物質と窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施して形成することが望ましい。

#### 【0050】

具体的に、前記サイクリック化学気相蒸着工程は、シリコンソース物質で $\text{Si}_2\text{Cl}_6$ または $\text{Si}_3\text{Cl}_8$ を用い、前記窒素ソースガスとして $\text{NH}_3$ ガスまたは $4\text{NH}_2$ を用いて約400～700の温度で実施することが望ましい。40

#### 【0051】

シリコン窒化膜 $\text{Si}_x\text{N}_y$ において、 $x/y$ の値は0.7～1.5を満足し、望ましくは $x/y$ の値は0.85～1.3を満足する。より望ましくは $x/y$ の値は0.9～1.2を満足する。また、シリコン窒化膜 $\text{Si}_x\text{N}_y$ で $y$ が4の場合、望ましくは $x$ は3～6であり、より望ましくは $x$ は3.5～5.5である。

#### 【0052】

図6に示されたように、前記シリコン窒化膜20a上に金属酸化物の第2酸化膜30aを形成する。ここで、前記第2酸化膜30aは図3で言及した電荷トラップ絶縁体50の第2酸化膜パターン30を形成するために使用される。そして、前記金属酸化物の第3酸50

化膜 30a は化学気相蒸着工程を実施し形成することが望ましい。

図 7 を参照すると、前記第 2 酸化膜 30a 上に電荷キャリアとして正孔の生成が可能な不純物がドーピングされた導電膜 55a を形成する。前記導電膜 55a は図 3 に示されたゲート構造物 60 の電極 55 を形成するために適用される。

#### 【 0053】

図 8 を参照すると、前記半導体基板 200 上に形成された導電膜 55a、第 2 酸化膜 30a、シリコンリッチ窒化物を含むシリコン窒化膜 20a、第 1 酸化膜 10a をエッティングマスクとして用いて順にパターニングする。その結果、前記半導体基板 200 上部には第 1 酸化膜パターン 15、シリコン窒化膜パターン 20、第 2 酸化膜パターン 30 を含む電荷トラップ絶縁体 50 と電極 55 からなるゲート構造物 60 が形成される。

10

#### 【 0054】

続いて、前記ゲート構造物をマスクとして使用して前記ゲート構造物に露出された半導体基板の表面の下に不純物をイオン注入する。それにより、前記ゲート構造物 100 と隣接する半導体基板 200 の表面部にはソース / ドレイン 230a、230b が形成される。このように、前記ソース / ドレイン 230a、230b を形成することにより、前記ソース / ドレイン 230a、230b の間にはチャンネル領域 236 が形成される。

#### 【 0055】

その結果、シリコンリッチ窒化物からなるシリコン窒化膜パターン 20 を含む電荷トラップ絶縁体 50 と電極 55 からなるゲート構造物 60 を単位セルとして有する SONOS 型の不揮発性半導体装置 300 が完成される。

20

言及した本実施例においては前記 SONOS 型の不揮発性半導体装置 300 のゲート構造物としてプレナー型に限定して説明しているが、他の実施例として前記ゲート構造物をパーティカル型、ピン型などからも形成することができる。

#### 【 0056】

##### (電荷トラップ絶縁体)

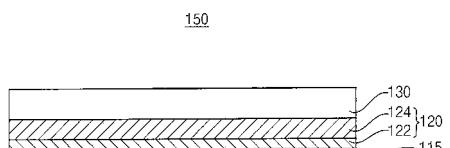

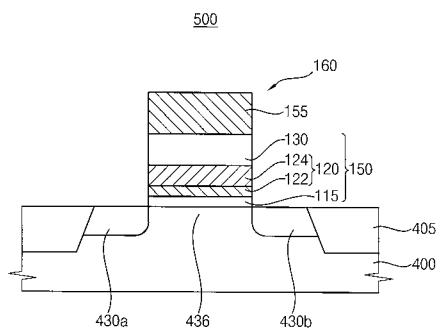

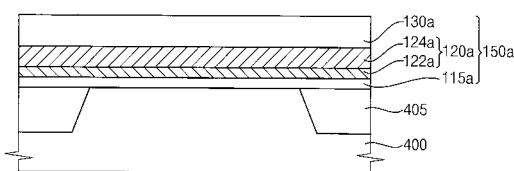

図 9 は本発明の他の実施例による電荷トラップ絶縁体を示す概略的な断面図である。

図 9 を参照すると、前記電荷トラップ絶縁体 150 は、SONOS 型の不揮発性半導体装置に適用するためのものであり、第 1 酸化膜 115、第 1 シリコン窒化薄膜 122、及びシリコンリッチ窒化物からなる第 2 シリコン窒化薄膜 124 を含むシリコン窒化膜 120 及び第 2 酸化膜 130 の多層構造を有する。

30

#### 【 0057】

具体的に、前記第 1 酸化膜 115 は、電子のトンネリングによるエネルギー障壁を提供するトンネル膜に該当する。本実施例の第 1 酸化膜 115 は、シリコン酸化膜であり、約 20 ~ 50 の厚さを有する。前記第 1 酸化膜 115 は、前記 SONOS 型の不揮発性半導体装置のプログラミングまたは消去効率によってその厚さを変更することができる。

#### 【 0058】

前記シリコン窒化膜 120 は、電子（電荷）を貯蔵する貯蔵膜として第 1 シリコン窒化薄膜 122、シリコンリッチ窒化物からなる第 2 シリコン窒化薄膜 124 が積層された構造を有する。前記第 1 シリコン窒化薄膜 122 は一般的なシリコン窒化物からなり、前記第 1 シリコン窒化薄膜 124 はシリコン含量の高いシリコンリッチ窒化物からなる。

40

#### 【 0059】

特に、第 1 シリコン窒化薄膜を構成するシリコン窒化物（Si<sub>a</sub>N<sub>b</sub>）において望ましい a / b の値は 0.7 ~ 0.85 であり、より望ましい a / b の値は 0.7 ~ 0.8 である。最も望ましい、a / b の値は 0.75 である。反面、前記第 2 シリコン窒化薄膜 124 に含まれたシリコンリッチ窒化物 Si<sub>c</sub>N<sub>d</sub> において、望ましい c / d の値は、0.85 ~ 1.5 であり、より望ましい c / d の値は 0.9 ~ 1.3 である。最も望ましい c / d の値は 1.0 である。また、前記シリコンリッチ窒化物 Si<sub>c</sub>N<sub>d</sub> において、d が 4 の場合、望ましくは c は 3 ~ 6 であり、より望ましくは c は 3.5 ~ 5.5 である。本実施例において適用される第 1 シリコン窒化薄膜 120 は、SONOS 型の不揮発性半導体装置のプログラムの際、前記シリコンリッチ窒化膜 124 にトラップされる電子の保持特

50

性を向上させるために適用される。

**【0060】**

他の例として、前記シリコン窒化膜120は第1シリコン窒化薄膜122、第2シリコン窒化薄膜124及び第3シリコン窒化薄膜(図示せず)が積層された構造を有していてもよい。前記第1シリコン窒化薄膜122は、前記第1シリコン窒化薄膜と同一の特性及び組成を有する。

**【0061】**

前記第2酸化膜130は前記SONOS型の不揮発性半導体装置の電極(図示せず)から印加される電圧を遮断する遮断膜に該当する。前記第2酸化膜130はシリコン酸化物または金属酸化物を含む。本実施例においては前記第2酸化膜130の例としては金属酸化膜を挙げることができる。10

**【0062】**

(電荷トラップ絶縁体の製造)

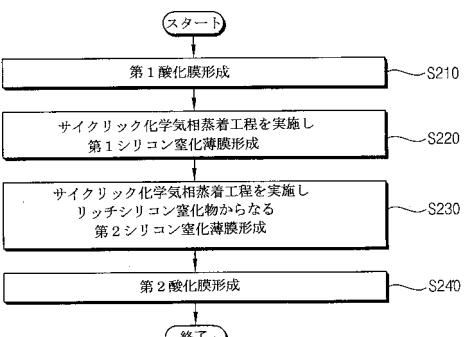

図10は図9に示された電荷トラップ絶縁体の製造方法を示す工程流れ図である。

図9及び図10を参照すると、まず、半導体基板110上にシリコン酸化物からなる第1酸化膜115を形成する(段階S210)。前記第1酸化膜の形成方法及びその特性は図2及び図9に示された第1酸化膜についての詳細な説明と同一である。

**【0063】**

続いて、前記気体状態のシリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施し前記第1酸化膜上にシリコン窒化物(Si<sub>a</sub>N<sub>b</sub>、a/bの値が0.7~0.85である)を含む第1シリコン窒化薄膜122を形成する(段階S220)。20

**【0064】**

特に、前記第1シリコン窒化薄膜122はSONOS型の不揮発性半導体装置のプログラムの際前記シリコンリッチ窒化物からなる第2シリコン窒化膜124にトラップされる電子の保持特性を向上させるために適用される。前記第1シリコン窒化薄膜122の形成方法及びその特性は図9に示された第1シリコン窒化膜の詳細と同一である。

**【0065】**

続いて、気体状態のシリコンソース物質及び窒素ソースガスを用いたサイクリック化学気相蒸着工程を実施し前記第1シリコン窒化薄膜上にシリコンリッチ窒化物(Si<sub>c</sub>N<sub>d</sub>、c/dの値が0.85~1.5である)からなる第2シリコン窒化薄膜124を形成する(段階S230)。前記第2シリコン窒化薄膜124の形成方法及びその特性は、図1及び図2に示されたシリコン窒化膜の詳細な説明と同一である。特に、サイクリック化学気相蒸着工程を実施し前記第2シリコン窒化薄膜124を形成する場合シランガスを追加的に導入することが望ましい。30

**【0066】**

その結果、第1シリコン窒化薄膜122及びシリコンリッチ窒化物からなる第2シリコン窒化薄膜124が積層された構造を有するトラップ用シリコン窒化膜120が形成される。

具体的に、本実施例の第1シリコン窒化薄膜122は、前記シリコン窒化膜120全体の厚さのうち5%~60%に該当する厚さを有し、望ましくは25%~45%に該当する厚さを有する。より望ましくは、30%~40%の厚さを有する。これに反して、前記第2シリコン窒化薄膜124は、前記シリコン窒化膜120全体厚さのうち40%~95%に該当する厚さを有し、望ましくは60%~75%に該当する厚さを有する。より望ましくは65%~70%の厚さを有する。40

**【0067】**

本実施例においては、前記第1シリコン窒化薄膜122、及び前記第2シリコン窒化薄膜124は、インサイチュで形成することが望ましい。

他の例として、前記第1シリコン窒化薄膜122及び前記第2シリコン窒化薄膜を含むシリコン窒化膜120は、第3シリコン窒化薄膜(図示せず)をさらに形成することがで50

きる。前記第3シリコン窒化薄膜(図示せず)は前記第1シリコン窒化薄膜と同一の特性を有し、同一の方法で形成される。

#### 【0068】

続いて、前記シリコン窒化膜120上に第2酸化膜130を形成する(段階S230)。本実施例の前記第2酸化膜は金属酸化膜である。前記第2酸化膜130についての説明は図1に示された第2酸化膜について詳細な説明と同一である。

#### 【0069】

##### (SONOS型の不揮発性半導体装置)

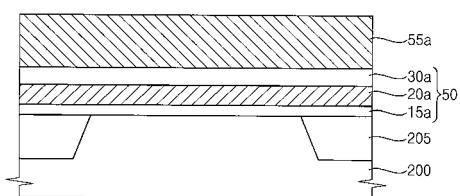

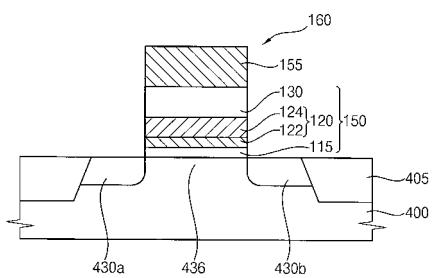

図11は図9に示された本発明の実施形態によるSONOS型の不揮発性半導体装置を示す断面図である。

10

図11を参照すると、SONOS型の不揮発性半導体装置500は、アクティブ領域とフィールド領域とを区画するための素子分離膜405が形成された半導体基板400、ならびに電荷トラップ絶縁体150及び電極155からなるゲート構造物160を含む。具体的に、電荷トラップ絶縁体150は、第1酸化膜パターン115、第1シリコン窒化薄膜パターン122、シリコンリッチ窒化物からなる第2シリコン窒化薄膜パターン124、及び第2酸化膜パターン130を含む。

#### 【0070】

特に、前記第1シリコン窒化薄膜パターン122は、化学式 $\text{Si}_a\text{N}_b$ の組成で示されており、 $a/b$ の値が0.7~0.85を有するシリコン窒化物からなる。このシリコン窒化物の組成は、望ましくは、 $a/b$ の値が0.7~0.8を有することが望ましい。この際、前記第1シリコン窒化薄膜パターンは、前記シリコン窒化膜パターン120が全体の厚さの5%~60%に該当する厚さを有し、望ましくは25%~45%に該当する厚さを有する。より望ましくは30%~40%の厚さを有する。

20

#### 【0071】

これに反して、前記第2シリコン窒化薄膜パターンは、化学式 $\text{Si}_c\text{N}_d$ の組成で示されており、 $c/d$ の値が0.85~0.15を有するシリコン窒化物からなる。このシリコン窒化物の組成は、望ましくは、 $c/d$ の値が0.9~1.3を有することが望ましい。この際、前記第2シリコン窒化薄膜パターン124は、前記シリコン窒化膜パターン120が全体の厚さの40%~95%に該当する厚さを有し、望ましくは60%~75%に該当する厚さを有する。より望ましくは65%~70%の厚さを有する。

30

#### 【0072】

他の例として、前記電荷トラップ絶縁体150は第3シリコン窒化薄膜パターンをさらに含むことができる。

また、前記半導体基板400の表面部には不純物がドーピングされた領域であるソース/ドレイン430a、430bが形成される。このように、前記半導体基板400の表面部にソース/ドレイン430a、430bを形成することで、前記ソース/ドレイン430a、430bの間にはチャンネル領域436が位置するようになる。前記素子分離膜及びソース/ドレイン230a、230bは図3の説明と同一であるので省略する。

#### 【0073】

##### (SONOS型の不揮発性半導体装置製造)

40

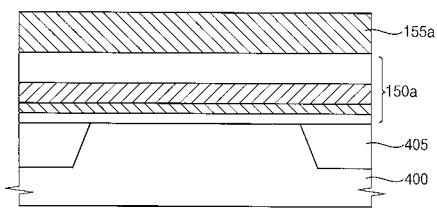

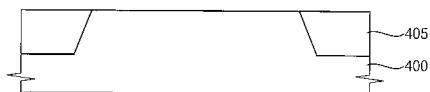

図12~図15は図11のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

図12を参照すると、前記半導体基板400にトレンチ素子分離膜405を形成しアクティブ領域とフィールド領域とを区画する。

図13を参照すると、前記素子分離膜405が形成された半導体基板400上には、シリコン窒化物の第1酸化膜115aが形成される。ここで、前記第1酸化膜115aは、図11で言及した電荷トラップ絶縁体150の第1酸化膜パターン115で形成する。

#### 【0074】

続いて、シリコン酸化物の第1酸化膜115a上にシリコン窒化物( $\text{Si}_a\text{N}_b$ の化学式で $a/b$ の値が0.7~0.85である)からなる第1シリコン窒化薄膜122aを形

50

成する。ここで、前記第1シリコン窒化薄膜122aの形成方法及びその特性は図9及び図10の詳細な説明と同一である。

#### 【0075】

続いて、前記第1シリコン窒化薄膜122a上にサイクリック化学気相蒸着工程を実施しシリコンリッチ窒化物(Si<sub>x</sub>C<sub>y</sub>N<sub>d</sub>の化学式で示され、x/yの値が0.85~1.85である)からなる第2シリコン窒化薄膜124aを形成する。ここで、前記第2シリコン窒化薄膜124aの形成の方法及びその特性は図9及び図10の詳細な説明と同一である。

#### 【0076】

その結果、第1シリコン窒化薄膜122a及び第2シリコン窒化薄膜124aが積層された構造を有する電荷トラップシリコン窒化膜120aが形成される。10

シリコン窒化膜120a上に金属酸化物の第2酸化膜130aを形成する。ここで、前記第2酸化膜130aは、図11で言及した電荷トラップ絶縁体150の第2酸化膜パターン130を形成するために使用される。そして、前記金属酸化物の第3酸化膜130aは化学気相蒸着工程を実施し形成することが望ましい。

#### 【0077】

図14を参照すると、前記第2酸化膜130a上に導電膜155aを形成する。前記導電膜155aは、図11に示されたゲート構造物160の電極155を形成するために適用される。

図15を参照すると、前記半導体基板400上に形成された導電膜155a、第2酸化膜130a、第1シリコン窒化薄膜122a及び第2シリコン窒化薄膜124aを含むシリコン窒化膜120a、ならびに第1酸化膜110aをエッチングマスクとして用いて順にパターニングする。その結果、前記半導体基板400上部には図11で言及した第1酸化膜パターン110、シリコン窒化膜パターン120、第2酸化膜パターン130を含む電荷レベル絶縁体150と電極155を含むゲート構造物160とが形成される。20

#### 【0078】

続いて、前記ゲート構造物160から露出した半導体基板の表面部に不純物をイオン注入して前記ゲート構造物160と隣接する半導体基板400の表面部にはソース/ドレイン430a、430bを形成する。このように、前記ソース/ドレイン430a、430bを形成することにより、前記ソース/ドレイン430a、430bの間にはチャンネル領域436が形成される。30

その結果、シリコンリッチ窒化薄膜パターン124を含む電荷トラップ絶縁体150と、電極155からなるゲート構造物160と、を単位セルとして有するSONOS型の不揮発性半導体装置500が完成される。

#### 【0079】

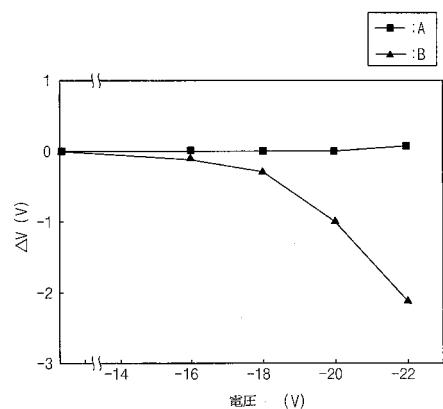

##### (SONOS型の不揮発性半導体装置のプログラム消去評価)

一般的に、化学気相蒸着工程で形成されたシリコン窒化膜を有する電荷トラップ絶縁体を含むSONOS型の不揮発性半導体装置(サンプルA)の消去特性と、図9に示されたシリコンリッチ窒化薄膜を有する電荷トラップ絶縁体を含むSONOS型の不揮発性半導体装置(サンプルB)の消去特性と、を比較した。その結果を図16のグラフに示した。40

#### 【0080】

図16は、図9に示されたSONOS型の不揮発性半導体装置の印加電圧による電圧の変化を示すグラフである。

図16を参照すると、前記サンプルAのSONOS型の不揮発性半導体装置の消去特性は、印加電圧が増加しても、前記電荷トラップ絶縁体のシリコン窒化膜に貯蔵された電子の変化が殆どないことがわかる。即ち、電圧が増加しても、電子が消去できず、かえって増加することが確認できた。

#### 【0081】

反面、サンプルBのSONOS型の不揮発性半導体装置の消去特性は、電圧の増加にともない、前記電荷トラップ絶縁体のシリコンリッチ窒化薄膜に貯蔵された電子の変化が顕50

著であることがわかる。即ち、電圧が増加すると、電子の消去量が顕著に増加することがわかる。

#### 【0082】

##### (産業上の利用可能性)

本発明を適用した実施例によるSONOS型の不揮発性半導体装置を使用して消去を実施するとき、電荷トラップ絶縁体にトラップされた電子は充分に減少する。従って、前記SONOS型の不揮発性半導体装置を使用した消去を安定的に実施することができる。

以上のように、本発明を適用したSONOS型の不揮発性半導体装置を、より積極的に活用することができる。

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離脱することなく、本発明を修正または変更できる。10

#### 【図面の簡単な説明】

#### 【0083】

【図1】本発明は一実施例による電荷トラップ絶縁体を示す概略的な断面図である。

【図2】図1に示された電荷トラップ絶縁体の製造方法を示す工程流れ図である。

【図3】図1に示された電荷トラップ絶縁体を適用した本発明の一実施例によるSONOS型の不揮発性半導体装置を示す断面図である。

【図4】図3のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。20

【図5】図3のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

【図6】図3のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

【図7】図3のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

【図8】図3のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

【図9】本発明の他の実施例による電荷トラップ絶縁体を示す概略的な断面図である。

【図10】図9に示された電荷トラップ絶縁体の製造方法を示す工程流れ図である。30

【図11】図9に示された電荷とラップ絶縁体を適用した本発明の他の実施例によるSONOS型の不揮発性半導体装置を示す断面図である。

【図12】図11のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

【図13】図11のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

【図14】図11のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。

【図15】図11のSONOS型の不揮発性半導体装置を製造する方法を概略的に示す断面図である。40

【図16】図9に示されたSONOS型の不揮発性半導体装置の印加電圧による電圧の変化を示すグラフである。

#### 【符号の説明】

#### 【0084】

15、115：第1酸化膜、120、20：シリコン窒化膜、122：第1シリコン窒化薄膜、124：第2シリコン窒化薄膜、30、130：第2酸化膜、50、150：電荷トラップ絶縁体

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図7】

【図10】

【図8】

【図11】

【図14】

【図12】

【図13】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/115 (2006.01)

(72)発明者 林 柱完

大韓民国ソウル特別市冠岳区奉天11洞196-90番地401戸

(72)発明者 安 宰永

大韓民国京畿道城南市盆唐区盆唐洞チャンアンタウン建栄アパート104棟401号

(72)発明者 楊 尚烈

大韓民国京畿道華城市台安邑ビョンチョム里住公アパート803棟1806号

(72)発明者 黄 棋鉉

大韓民国京畿道城南市盆唐区亭子洞ハンソルマウルエルジーアパート202棟604号

審査官 宮本 靖史

(56)参考文献 特開2007-329343 (JP, A)

特開2007-250582 (JP, A)

特開平01-086562 (JP, A)

特開平05-145078 (JP, A)

特開平08-293563 (JP, A)

特開2002-217317 (JP, A)

米国特許第06501681 (US, B1)

特開2007-043147 (JP, A)

特開2005-232591 (JP, A)

特開2005-184029 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 318

H 01 L 21 / 336

H 01 L 21 / 205

H 01 L 21 / 31

H 01 L 21 / 8247

H 01 L 27 / 115

H 01 L 29 / 788

H 01 L 29 / 792