(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6122533号

(P6122533)

(45) 発行日 平成29年4月26日(2017.4.26)

(24) 登録日 平成29年4月7日(2017.4.7)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

G09G 3/36

**G09G 3/20 (2006.01)**

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

6 1 1 H

6 2 2 D

6 2 2 C

6 7 0 K

請求項の数 1 (全 24 頁)

(21) 出願番号

特願2016-113721 (P2016-113721)

(22) 出願日

平成28年6月7日(2016.6.7)

(62) 分割の表示

特願2011-238196 (P2011-238196)

の分割

原出願日 平成23年10月31日(2011.10.31)

(65) 公開番号

特開2016-167096 (P2016-167096A)

(43) 公開日

平成28年9月15日(2016.9.15)

審査請求日 平成28年6月8日(2016.6.8)

(31) 優先権主張番号

特願2010-248017 (P2010-248017)

(32) 優先日

平成22年11月5日(2010.11.5)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 森口 忠紀

最終頁に続く

(54) 【発明の名称】表示装置の駆動方法

(57) 【特許請求の範囲】

## 【請求項 1】

複数のフレーム期間において複数の走査線及び信号線により、複数の画素に供給する画像信号を制御して画像表示を行う表示装置の駆動方法において、

前記表示装置は、素子基板および表示制御回路を有し、

前記素子基板は、表示部と、走査線駆動回路と、信号線駆動回路と、を有し、

前記表示制御回路は、クロック生成回路と、パルス幅制御回路と、を有し、

前記表示部は、前記複数の走査線と、前記複数の信号線と、前記複数の画素と、を有し、

前記複数の走査線の各々は、酸化物半導体を有するトランジスタのゲートに電気的に接続されており、

前記表示装置において、第1のフレーム期間では、第1の走査線を第1の選択期間で選択し、前記第1の走査線以外の第2の走査線を第2の選択期間で選択し、

前記表示装置において、第2のフレーム期間では、前記第2の走査線を前記第1の選択期間で選択し、前記第2の走査線以外の前記第1の走査線を前記第2の選択期間で選択し、

前記第1のフレーム期間における前記第1の選択期間は、前記第1の走査線にハイレベルの20V以上の電圧を印加する期間であり、

前記第1のフレーム期間における前記第2の選択期間は、前記第2の走査線にハイレベルの電位を印加する期間であり、

10

20

前記第1の選択期間は、1ms以上の期間であり、

前記第1の選択期間は、前記第2の選択期間より長い期間であり、

前記第1の選択期間及び前記第2の選択期間の長さは、前記パルス幅制御回路により制御されることを特徴とする表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置の駆動方法に関する。または、複数の画素を有する表示装置において、各画素に設けられるトランジスタの半導体層に酸化物半導体を用いる構成における、表示装置の駆動方法に関する。

10

【背景技術】

【0002】

アモルファスシリコンを用いたトランジスタを、液晶等の表示素子を駆動するための駆動用素子として用いる表示装置は、コンピュータのモニタやテレビジョン装置などの市販製品で広く用いられている。アモルファスシリコンを用いたトランジスタの製造技術はすでに確立され、60インチを超える液晶パネルも生産されている。

10

【0003】

しかし、アモルファスシリコンを用いたトランジスタは動作速度が遅く、これ以上の高性能化が望めないことから、ポリシリコンを用いた薄膜トランジスタの開発も進められてきている。しかし、ポリシリコンを作製するには結晶化工程が必要となり、これがトランジスタの特性バラツキの要因や、パネルサイズの大面積化に対する阻害要因となっていた。

20

【0004】

これに対し、シリコン系以外のトランジスタ材料として酸化物半導体材料への注目が高まっている。酸化物半導体の材料としては、酸化亜鉛を成分とするものが知られている。例えば特許文献1には、電子キャリア濃度が $10^{18} / \text{cm}^3$ 未満である非晶質酸化物(酸化物半導体)なるもので形成されたトランジスタを表示装置の駆動用素子として用いる構成について開示している。

【先行技術文献】

【特許文献】

【0005】

30

【特許文献1】特開2006-165528号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら酸化物半導体を用いて作製されるトランジスタは、電気的特性が安定せずに、外部環境に応じて諸特性が変化してしまう問題がある。具体的には、酸化物半導体を用いて作製されるトランジスタに400nm以下の波長の光を照射しつつ、ゲートに負バイアスを印加すると、しきい値電圧が変動するといった特性の劣化を生じてしまう。

【0007】

本発明の一態様は、表示装置の駆動用素子に用いる、酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することの出来る表示装置の駆動方法を提供することを課題の一とする。

40

【課題を解決するための手段】

【0008】

本発明の一態様は、400nm以下の波長の光が照射されつつ、ゲートに負バイアスを印加されることでしきい値電圧が変動したトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加することで、当該トランジスタのしきい値電圧の変動を変動前と同程度の状態まで回復させる表示装置の駆動方法を提供するものである。具体的には、複数のフレーム期間により画像表示を行う表示装置の駆動方法において、各フレーム期間における複数の走査線のうち、いずれか一の走査線を選択する期間で駆動用素子であるトランジス

50

タに対し、ゲートに20V以上の電圧を1m秒以上印加できるよう駆動する。そして複数のフレーム期間にわたって、各行を選択していくことで全ての駆動用素子であるトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加できるようにし、トランジスタの特性劣化を回復するものである。

#### 【0009】

本発明の一態様は、複数のフレーム期間において複数の走査線及び信号線により、複数の画素に供給する画像信号を制御して画像表示を行う表示装置の駆動方法において、第1のフレーム期間では、第1の走査線を第1の選択期間で選択し、第1の走査線以外の第2の走査線を含む走査線を第2の選択期間で選択し、第2のフレーム期間では、第2の走査線を第1の選択期間で選択し、第2の走査線以外の第1の走査線を含む走査線を第2の選択期間で選択し、第1の選択期間及び第2の選択期間は、画素に設けられる酸化物半導体を有するトランジスタのゲートにハイレベルの電位を印加する期間であり、第1の選択期間は、第2の選択期間より長い期間である表示装置の駆動方法である。10

#### 【0010】

本発明の一態様は、複数のフレーム期間において複数の走査線及び信号線により、複数の画素に供給する画像信号を制御して画像表示を行う表示装置の駆動方法において、第1のフレーム期間では、第1の走査線を第1の選択期間で選択し、第1の走査線以外の第2の走査線を含む走査線を第2の選択期間で選択し、第2のフレーム期間では、第2の走査線を第1の選択期間で選択し、第2の走査線以外の第1の走査線を含む走査線を第2の選択期間で選択し、第1の選択期間及び第2の選択期間は、画素に設けられる酸化物半導体を有するトランジスタのゲートにハイレベルの電位を印加する期間であり、第1の選択期間において、トランジスタに電気的に接続される信号線には、ローレベルの電位の画像信号が供給され、第1の選択期間は、第2の選択期間より長い期間である表示装置の駆動方法である。20

#### 【0011】

本発明の一態様において、トランジスタに電気的に接続される表示素子は、液晶素子である表示装置の駆動方法でもよい。

#### 【0012】

本発明の一態様において、第1の選択期間で選択する走査線は、複数である表示装置の駆動方法でもよい。30

#### 【発明の効果】

#### 【0013】

本発明の一態様により、表示装置の駆動用素子に用いる、酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することの出来る表示装置の駆動方法を提供することができる。

#### 【図面の簡単な説明】

#### 【0014】

【図1】実施の形態1を説明するための図。

【図2】実施の形態1を説明するための図。

【図3】実施の形態1を説明するための図。

【図4】実施の形態1を説明するための図。

【図5】実施の形態2を説明するための図。

【図6】実施の形態2を説明するための図。

【図7】実施の形態2を説明するための図。

【図8】実施の形態3を説明するための図。

【図9】実施の形態4を説明するための図。

【図10】実施の形態6を説明するための図。

【図11】実施の形態7を説明するための図。

【図12】実施例1を説明するための図。

【図13】実施例1を説明するための図。

40

50

【図14】実施例1を説明するための図。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態及び実施例について図面を参照しながら説明する。但し、実施の形態は多くの異なる様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同様のものを指す符号は異なる図面間で共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

【0016】

10

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、信号波形のなまり、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

【0017】

なお、本明細書にて用いる「第1」、「第2」、「第3」等などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0018】

(実施の形態1)

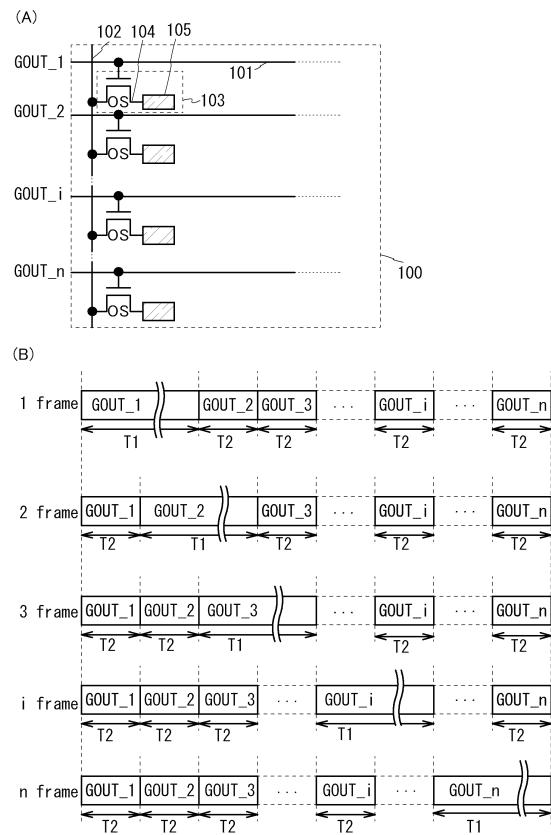

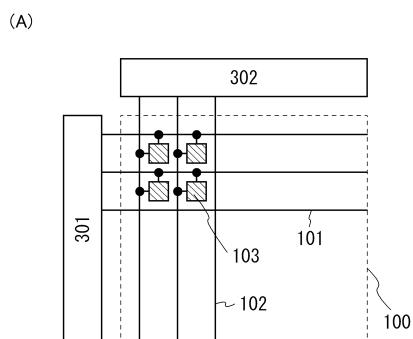

まず、表示装置における表示部(または画素部ともいう)の簡単な回路構成について図1(A)に示す。

20

【0019】

図1(A)は、画像信号が供給される画素の回路図について示している。図1(A)では、表示部100における、走査線101(ゲート線)、信号線102(データ線)、画素103、トランジスタ104、表示素子105を示している。なお表示部100には、n本(nは2以上の自然数)の走査線、m本(mは2以上の自然数)の信号線が設けられ、複数の画素103におけるトランジスタ104の導通状態を制御するものとして、以下説明する。

【0020】

30

走査線101は、表示部100にマトリクス状に設けられる画素103を行方向に一斉に選択するための配線である。具体的には、走査線101は、トランジスタ104のゲートに接続されており、ゲートに印加する電位に応じて、トランジスタのソースとドレインとの間の導通状態を制御する。なお図1(A)において、1行目の走査線はGOUT\_1、2行目の走査線はGOUT\_2、i行目(iはn以下の自然数)の走査線はGOUT\_i、n行目の走査線はGOUT\_nとして示している。

【0021】

信号線102は、表示部100にマトリクス状に設けられる画素103の表示素子105に画像信号を供給するための配線である。具体的には、信号線102は、トランジスタ104のソースまたはドレインの一方にあたる第1端子に接続されており、トランジスタの導通状態に応じて画像信号をソースまたはドレインの他方にあたる第2端子に供給する。そして表示素子105では、階調の制御が行われる。

40

【0022】

表示部100においてマトリクス状に設けられる画素103は、走査線101及び信号線102に接続されている。一例としては、画素103は、走査線101及び信号線102の交差部に応じて設けられる構成となる。なお画素103は表示部100において、必ずしも縦横に並べて配置する構成でなくてもよい。例えば画素103は、走査線101及び/または信号線102を蛇行させた上で画素103をジグザグに配置する構成としてもよい。

【0023】

なお、画素とは、一つの色要素(例えばR(赤)G(緑)B(青)のいずれか1つ)の明るさを制御できる表示単位に相当するものとする。従って、カラー表示装置の場合には、

50

カラー画像の最小表示単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。ただし、カラー画像を表示するための色要素は、三色に限定されず、三色以上を用いても良いし、RGB以外の色を用いても良い。

#### 【0024】

トランジスタ104は、酸化物半導体を半導体層に用いて作成されたトランジスタである。トランジスタ104のゲートは走査線101に接続され、第1端子は信号線102に接続され、第2端子は表示素子105に接続される。

#### 【0025】

なお図面においてトランジスタの記号に付す「OS」は、半導体層に酸化物半導体(Oxide Semiconductor)を用いたトランジスタであることを示している。

10

#### 【0026】

なお、酸化物半導体は、四元系金属酸化物であるIn-Sn-Ga-Zn-O系酸化物半導体や、三元系金属酸化物であるIn-Ga-Zn-O系酸化物半導体、In-Sn-Zn-O系酸化物半導体、In-Al-Zn-O系酸化物半導体、Sn-Ga-Zn-O系酸化物半導体や、Al-Ga-Zn-O系酸化物半導体、Sn-Al-Zn-O系酸化物半導体や、二元系金属酸化物であるIn-Zn-O系酸化物半導体、Sn-Zn-O系酸化物半導体、Al-Zn-O系酸化物半導体、Zn-Mg-O系酸化物半導体、Sn-Mg-O系酸化物半導体、In-Mg-O系酸化物半導体、In-Ga-O系酸化物半導体や、In-O系酸化物半導体、Sn-O系酸化物半導体、Zn-O系酸化物半導体などを用いることができる。なお、本明細書においては、例えば、In-Sn-Ga-Zn-O系酸化物半導体とは、インジウム(In)、錫(Sn)、ガリウム(Ga)、亜鉛(Zn)を有する金属酸化物、という意味であり、その化学量論的組成比は特に問わない。また、上記酸化物半導体は、珪素を含んでいてもよい。

20

#### 【0027】

あるいは、酸化物半導体は、化学式 $InMO_3 (ZnO)_m (m > 0)$ で表記することができる。ここで、Mは、Ga、Al、Mn及びCoから選ばれた一又は複数の金属元素を示す。

30

#### 【0028】

酸化物半導体膜は、水素、水、水酸基又は水素化物などの不純物が混入しにくい方法で作製するのが望ましい。酸化物半導体膜は、例えば、スパッタリング法などを用いて作製することができる。

#### 【0029】

なお、トランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本明細書においては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それを一方の端子、他方の端子と表記する場合がある。

40

#### 【0030】

なお画素に設けるトランジスタの構造については逆スタガ型の構造でもよいし、順スタガ型の構造でもよい。または、チャネル領域が複数の領域に分かれて直列に接続された、ダブルゲート型の構造でもよい。または、ゲート電極がチャネル領域の上下に設けられたデュアルゲート型の構造でもよい。また、トランジスタを構成する半導体層を複数の島状の半導体層にわけて形成し、スイッチング動作を実現しうるトランジスタ素子としてもよい。

#### 【0031】

表示素子105は、一例として光の透過または非透過を制御する素子であればよく、例えば液晶素子を用いればよい。なお表示素子105としては、液晶素子の他にも例えばMEMS(Micro Electro Mechanical System)素子を用い

50

てもよい。なお表示素子 105 には液晶素子の他に保持容量を併設する構成もある。また表示素子 105 として EL 素子等の自発光素子を用いる構成でもよい。

#### 【0032】

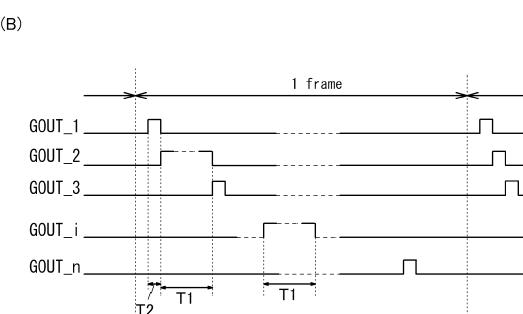

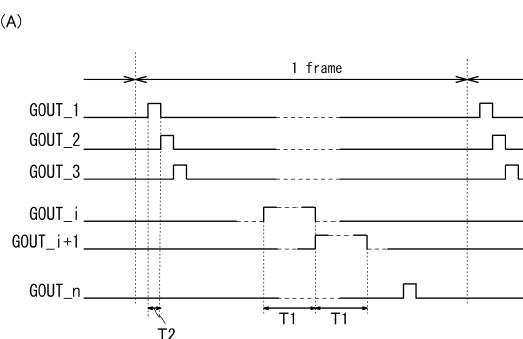

次いで図 1 (B) では、図 1 (A) で示した走査線 101 の GOUT\_1 乃至 GOUT\_n による画素の選択期間について模式的に示したものである。また図 1 (B) では、画像表示を行うための複数のフレーム期間の一部について示している。そして図 1 (B) では第 1 のフレーム期間乃至第 n のフレーム期間にわたって順に示している。例えば第 1 のフレーム期間における GOUT\_1 が第 1 の選択期間 T1 で画素を選択し、次いで GOUT\_2 が第 2 の選択期間 T2 で画素を選択していき、そして最終行である GOUT\_n が第 2 の選択期間 T2 で画素を選択するものである。第 1 のフレーム期間乃至第 n のフレーム期間では、1 行目から n 行目までの走査線 101 の選択期間の累計によって、およそその 1 フレーム期間の長さが決まってくる。

10

#### 【0033】

なお走査線 101 の GOUT\_1 乃至 GOUT\_n による画素の選択期間とは、ハイレベルの電位を走査線 101 に供給することで、トランジスタ 104 のソースとドレインとの間を導通状態とする期間のことをいう。逆に、選択期間以外の期間となる非選択期間では、ローレベルの電位を走査線 101 に供給し、トランジスタ 104 のソースとドレインとの間が非導通状態となる。

#### 【0034】

図 1 (B) では、前述したように第 1 のフレーム期間において 1 行目の走査線 GOUT\_1 (第 1 の走査線ともいう) に接続された画素を第 1 の選択期間 T1 で選択し、1 行目以外の走査線に接続された画素を第 2 の選択期間 T2 で選択する。同様に第 2 のフレーム期間において 2 行目の走査線 GOUT\_2 (第 2 の走査線ともいう) に接続された画素を第 1 の選択期間 T1 で選択し、2 行目以外の走査線に接続された画素を第 2 の選択期間 T2 で画素を選択する。同様に第 i のフレーム期間において i 行目の走査線 GOUT\_i を接続された画素第 1 の選択期間 T1 で選択し、i 行目以外の走査線に接続された画素を第 2 の選択期間 T2 で選択する。同様に第 n のフレーム期間において n 行目の走査線 GOUT\_n に接続された画素を第 1 の選択期間 T1 で選択し、n 行目以外の走査線に接続された画素を第 2 の選択期間 T2 で画素を選択する。

20

#### 【0035】

すなわち 1 フレーム期間に 1 行の走査線による選択期間を第 1 の選択期間 T1 とし、残りの行での走査線による選択期間を第 2 の選択期間 T2 としている。従って 1 行目から n 行目までの走査線 101 の選択期間の累計による 1 フレーム期間の長さは、第 1 のフレーム期間乃至第 n のフレーム期間で同じ長さとなる。

30

#### 【0036】

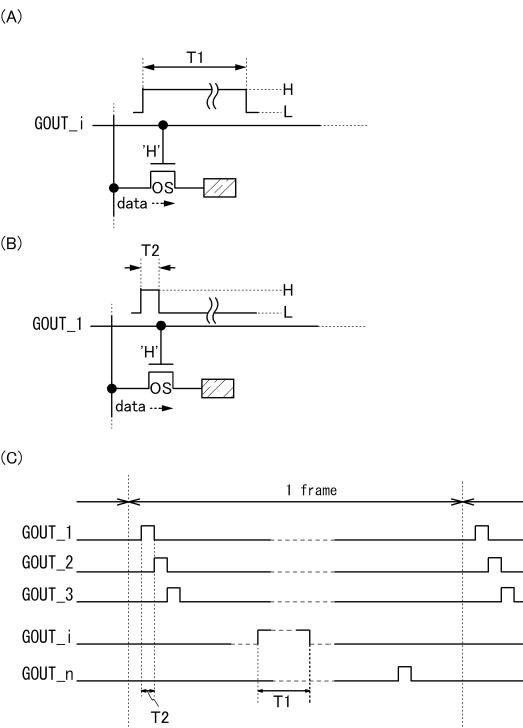

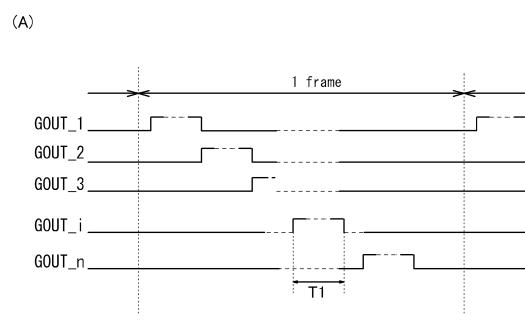

具体的な一例としては図 2 (A) に示すように、第 1 の選択期間 T1 はトランジスタのゲートにハイレベルの電位を印加する期間であり、当該期間の長さを 1 m 秒以上とするものである。そして第 1 の選択期間 T1 では、信号線より画像信号 data が表示素子側に供給されることとなる。また図 2 (B) に示すように、第 2 の選択期間 T2 はトランジスタのゲートにハイレベルの電位を印加する期間であり、当該期間の長さを数 μ 秒程度とするものである。そして第 2 の選択期間 T2 では、信号線より画像信号 data が表示素子側に供給されることとなる。また図 2 (C) に示すように 1 フレーム期間は、走査線 101 の GOUT\_1 乃至 GOUT\_n による第 1 の選択期間 T1 及び第 2 の選択期間 T2 の累積期間により、1 フレーム期間の長さが定まることとなる。

40

#### 【0037】

本実施の形態の構成では、図 1 (B) のように走査線は複数のフレーム期間のそれぞれに第 1 の選択期間 T1 を挿入するよう走査する。そして、ゲートに負バイアスを印加されることでしきい値電圧が変動した各行のトランジスタに対し、ゲートに 20V 以上の電圧を 1 m 秒以上印加することで、前述のしきい値電圧の変動を回復させることができるものである。その結果、酸化物半導体を半導体層として具備するトランジスタにおいて、当該ト

50

ランジスタの特性劣化を回復することが出来る。

**【0038】**

図2(C)に示す図と比較するために図3(A)、図3(B)には、走査線101のGOUT\_1乃至GOUT\_nによる第1の選択期間T1のみによる走査、及び第2の選択期間T2のみによる走査について示している。

**【0039】**

図3(A)に示す構成で1フレーム期間の長さは、走査線101のGOUT\_1乃至GOUT\_nによる第1の選択期間T1の累積期間により、1フレーム期間の長さが定まることとなる。そのため、1m秒以上の期間を要する第1の選択期間T1が累積すると、1フレーム期間の長さが長くなり、複数のフレーム期間による動画表示等が困難になってしまう。

10

**【0040】**

また図3(B)に示す構成で1フレーム期間の長さは、走査線101のGOUT\_1乃至GOUT\_nによる第2の選択期間T2の累積期間により、1フレーム期間の長さが定まることとなる。そのため、1秒間を60フレームで表示を行う場合1フレーム期間は16.6m秒となり、数μ秒程度の期間を要する第2の選択期間T2が累積しても1フレーム期間内に収めることができる。しかしながら当該駆動ではゲートに20V以上の電圧を1m秒以上印加するといった駆動が困難となる。

**【0041】**

本実施の形態の構成においては、図1(B)及び図2(C)で説明したように、走査線の駆動を複数のフレーム期間にわたって第1の選択期間T1を挿入するよう走査することで、動画表示等が困難になることなく、ゲートに負バイアスを印加されることでしきい値電圧が変動した各行のトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加することで、前述のしきい値電圧の変動を回復させることができるものである。その結果、酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することが出来る。

20

**【0042】**

なお図1(B)及び図2(C)で説明したように、走査線の駆動を複数のフレーム期間にわたって第1の選択期間T1を挿入する走査は、走査線101のGOUT\_1乃至GOUT\_nのいずれか一に限らず、2行以上の走査線で行う構成としてもよい。具体的には、図4(A)に示すように1フレーム期間において、走査線101のGOUT\_i及びGOUT\_i+1を第1の選択期間T1とする構成であってもよい。また図4(A)に示したように連続する走査線に限らず、図4(B)に示すように離間した走査線である走査線101のGOUT\_2及びGOUT\_iを第1の選択期間T1とする構成であってもよい。図4(B)は図4(A)に比べ、第1の選択期間T1で選択することによるちらつきを小さくすることができる。

30

**【0043】**

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

**【0044】**

40

(実施の形態2)

本実施の形態では上記実施の形態1で説明した表示素子として液晶素子を具備する液晶表示装置の構成例を示し、液晶表示装置における反転駆動を行う際の駆動方法について説明する。

**【0045】**

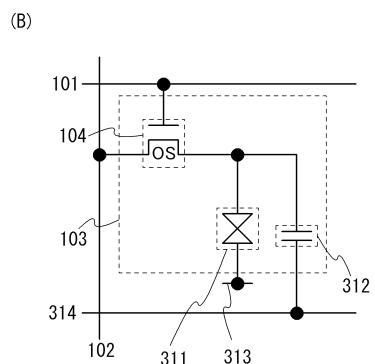

まず液晶表示装置の構成について図5(A)に示す。図5(A)に示す液晶表示装置は、複数の画素103を有する表示部100と、走査線駆動回路301と、信号線駆動回路302と、走査線駆動回路301によって電位が制御されるn本の走査線101と、信号線駆動回路302によって電位が制御されるm本の信号線102と、を有する。

**【0046】**

50

図5( B )は、図5( A )に示す液晶表示装置が有する画素103の回路図の一例を示す図である。図5( B )に示す画素103は、ゲートが走査線101に接続され、ソース及びドレインの一方が信号線102に接続されたトランジスタ104と、一方の電極がトランジスタ104のソース及びドレインの他方に接続され、他方の電極が容量電位を供給する配線314(容量配線ともいう)に接続された容量素子312と、一方の電極(画素電極ともいう)がトランジスタ104のソース及びドレインの他方及び容量素子312の一方の電極に接続され、他方の電極(対向電極ともいう)が対向電位を供給する配線313に接続された液晶素子311と、を有する。

#### 【0047】

なお、トランジスタ104は、nチャネル型のトランジスタである。また、容量電位と対向電位を同一の電位とすることが可能である。10

#### 【0048】

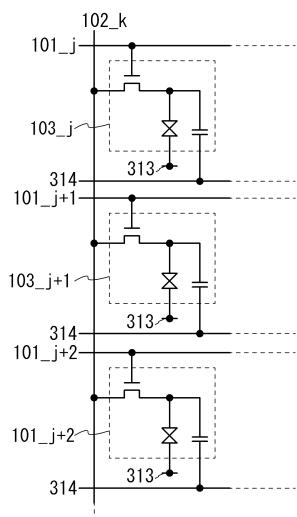

次いで、図6には図5( B )で示した画素103の回路図を信号線が延在する方向に並べて表したものである。図6においては、走査線101\_j( jはn以下の自然数)、走査線101\_{j+1}、及び走査線101\_{j+2}、並びに信号線102\_k( kはm以下の自然数)を示している。また図6では走査線101\_j( jはn以下の自然数)及び信号線102\_kに接続される画素として画素103\_j、走査線101\_{j+1}( jはn以下の自然数)及び信号線102\_kに接続される画素として画素103\_{j+1}、走査線101\_{j+2}( jはn以下の自然数)及び信号線102\_kに接続される画素として画素103\_{j+2}を示している。なお各画素における表示素子としては、液晶素子を示している。20

#### 【0049】

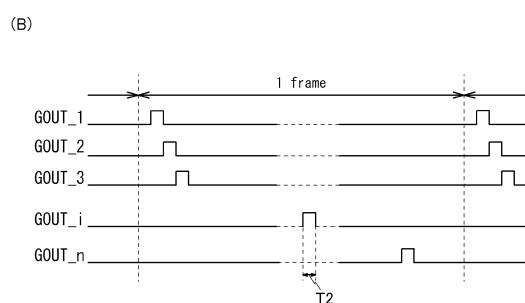

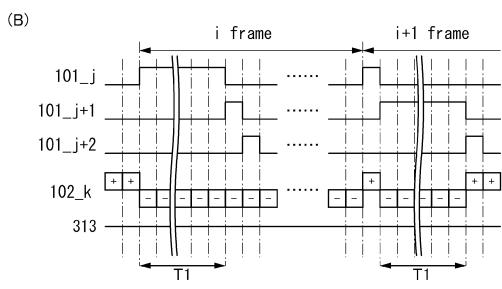

図7( A )には、図6に示す回路図を上記実施の形態1で説明した構成で駆動する際のタイミングチャートについて示したものである。図7( A )ではiフレーム目において走査線101\_jにおける選択信号を第1の選択信号T1とし、i+1フレーム目において走査線101\_{j+1}における選択信号を第1の選択信号T1としている。なおiフレーム目およびi+1フレーム目では、第1の選択期間T1以外の期間を第2の選択期間T2として走査線を走査している。

#### 【0050】

また図7( A )では液晶素子に印加する電圧をフレーム毎に反転させて行う所謂フレーム反転駆動のために、iフレーム目とi+1フレーム目において信号線102\_kに供給する画像信号を反転する極性(図中、+記号、-記号で表記)となるよう、交互に切り替わる様子を示している。なお図7( A )では対向電位が供給される配線の電位を併せて示しており、ここでは一定の電位が供給される様子を表しているが、反転駆動の方式に応じて適宜変動するよう動作させることも可能である。30

#### 【0051】

本実施の形態の構成においては、図7( A )に示すように、走査線の駆動を複数のフレーム期間にわたって第1の選択期間T1を挿入するよう走査することで、動画表示等が困難になることなく、ゲートに負バイアスを印加されることでしきい値電圧が変動した各行のトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加することで、前述のしきい値電圧の変動を回復させることができるものである。その結果、酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することが出来る。40

#### 【0052】

なお第1の選択期間T1では、信号線102\_kに供給する画像信号の極性を、反転駆動を行う際の画像信号の極性に関わらず、ローレベルの電位となるようにすることも可能である。具体的なタイミングチャートについて図7( B )に示す。図7( B )に示すようにi+1フレーム目でハイレベルの電位となる画像信号の極性の場合に走査線101\_{j+1}が第1の選択信号T1によるハイレベルの電位の際に、ローレベルの電位となる画像信号の極性とするものである。当該構成とすることにより、ゲートに負バイアスを印加する50

際の負バイアスの大きさを大きくすることが出来るため、しきい値電圧が変動した各行のトランジスタに対し、前述のしきい値電圧の変動を回復させる効果を高めることができる。

#### 【 0 0 5 3 】

なお図7( A )、( B )では、フレーム反転駆動の例を説明したが、ゲートライン反転駆動や、ソースライン反転駆動とすることもできる。またドット反転駆動とすることもできる。

#### 【 0 0 5 4 】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

10

#### 【 0 0 5 5 】

##### ( 実施の形態 3 )

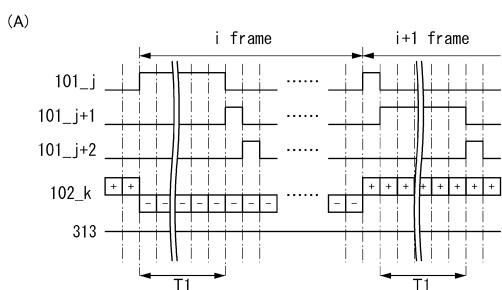

本実施の形態では、上記実施の形態で説明した駆動方法を実現しうる表示装置のブロック図について説明する。

#### 【 0 0 5 6 】

図8に示すブロック図は、素子基板500及び表示制御回路501を示している。

#### 【 0 0 5 7 】

図8に示すブロック図の素子基板500は、走査線駆動回路301と、信号線駆動回路302と、表示部100と、を有する。

#### 【 0 0 5 8 】

図8に示すブロック図の表示制御回路501は、画像信号(図8中、data)が外部より入力される。また表示制御回路501は、走査線駆動回路301及び信号線駆動回路302を駆動するためのクロック信号を生成するクロック生成回路502と、走査線駆動回路301に出力するクロック信号のパルス幅を制御するためのパルス幅制御回路503と、を有する。

20

#### 【 0 0 5 9 】

なお走査線駆動回路301及び信号線駆動回路302は、必ずしも表示部100と同じ素子基板500上に設けられる構成でなくてもよい。

#### 【 0 0 6 0 】

クロック生成回路502は、所定の周波数のクロック信号を出力して走査線駆動回路301及び信号線駆動回路302を駆動するための回路である。またパルス幅制御回路503は、走査線駆動回路301でのフレーム毎に第1の選択信号が各行に出力されるようクロック信号のパルス幅を制御するための回路である。具体的には、第1の選択信号T1を出力する期間ではクロック信号がハイレベルの電位を保持するように走査線駆動回路301に出力するクロック信号のパルス幅を制御する。

30

#### 【 0 0 6 1 】

なお上記実施の形態で説明したように第1の選択信号T1及び第2の選択信号T2をフレーム期間毎に切り替えて出力できる回路であれば、本実施の形態以外の構成であってもよい。

#### 【 0 0 6 2 】

40

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【 0 0 6 3 】

##### ( 実施の形態 4 )

本実施の形態では、液晶素子を有する素子基板について説明する。なお本実施の形態で説明する液晶素子を有する素子基板を液晶表示装置という。

#### 【 0 0 6 4 】

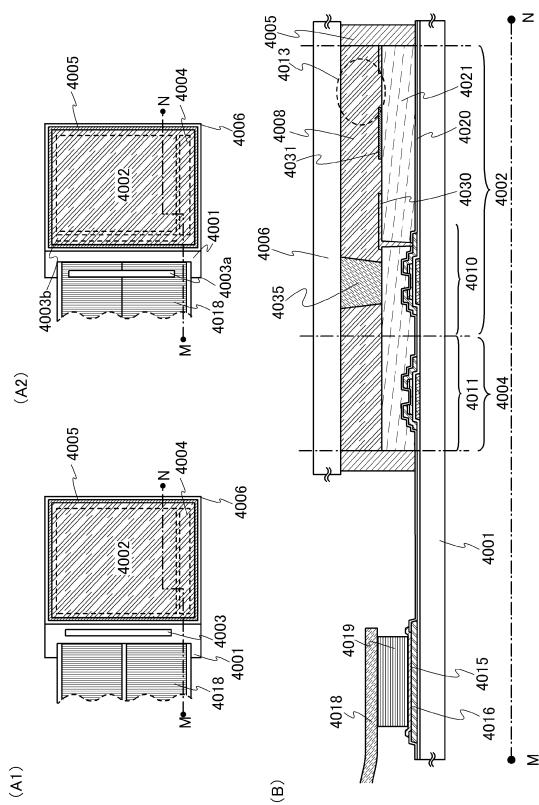

液晶表示装置の素子基板の外観及び断面について、図9を用いて説明する。図9( A 1 )( A 2 )は、第1の基板4001上に形成されたトランジスタ4010、4011及び液晶素子4013を、第2の基板4006との間にシール材4005によって封止したパネ

50

ルの上面図であり、図9( B )は、図9( A 1 )( A 2 )のM - Nにおける断面図に相当する。

#### 【 0 0 6 5 】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また、画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。

#### 【 0 0 6 6 】

また、図9( A 1 )は第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路4003が実装されている。なお、図9( A 2 )は信号線駆動回路の一部を第1の基板4001上に酸化物半導体を用いたトランジスタで形成する例であり、第1の基板4001上に信号線駆動回路4003bが形成され、かつ別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路4003aが実装されている。10

#### 【 0 0 6 7 】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG方法、ワイヤボンディング方法、またはTAB方法などを用いることができる。図9( A 1 )は、COG方法により信号線駆動回路4003を実装する例であり、図9( A 2 )は、TAB方法により信号線駆動回路4003を実装する例である。20

#### 【 0 0 6 8 】

また、第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、トランジスタを複数有しており、図9( B )では、画素部4002に含まれるトランジスタ4010と、走査線駆動回路4004に含まれるトランジスタ4011とを例示している。トランジスタ4010、4011上には絶縁層4020、4021が設けられている。

#### 【 0 0 6 9 】

トランジスタ4010、4011は、上記実施の形態1でも説明したように酸化物半導体膜を用いて半導体層を作製するものである。30

#### 【 0 0 7 0 】

また、第1の基板4001上に画素電極層4030及び共通電極層4031が設けられ、画素電極層4030は、トランジスタ4010と電気的に接続されている。液晶素子4013は、画素電極層4030、共通電極層4031、及び液晶層4008を含む。

#### 【 0 0 7 1 】

また、ブルー相を示す液晶層4008を有する液晶表示装置において、基板に概略平行（すなわち水平な方向）な電界を生じさせて、基板と平行な面内で液晶分子を動かして、階調を制御する方式を用いることができる。このような方式として、本実施の形態では、図9に示すようなIPS(In Plane Switching)モードで用いる電極構成を適用する場合を示している。なお、IPSモードに限らず、FFS(Fringing Field Switching)モードで用いる電極構成を適用することも可能である。40

なお特にブルー相を示す液晶層を用いる構成は、高い印加電圧により配向を制御する必要があり、上記実施の形態1で説明した、ゲートに負バイアスを印加されることでしきい値電圧が変動したトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加することで、当該トランジスタのしきい値電圧の変動を変動前と同程度の状態まで回復させる表示装置の駆動方法を行うのに好適である。

#### 【 0 0 7 2 】

なお、第1の基板4001、第2の基板4006としては、透光性を有するガラス、プラスチックなどを用いることができる。プラスチックとしては、ポリエーテルサルファン(PES)、ポリイミド、FRP(Fiberglass-Reinforced Pla50

s t i c s ) 板、P V F (ポリビニルフルオライド) フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルを P V F フィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

**【 0 0 7 3 】**

また、液晶層 4 0 0 8 の膜厚 (セルギャップ) を制御するために設けられている柱状のスペーサ 4 0 3 5 は、絶縁膜を選択的にエッチングすることにより設けることができる。なお、柱状のスペーサ 4 0 3 5 の代わりに、球状のスペーサを用いていてもよい。

**【 0 0 7 4 】**

保護膜として機能する絶縁層 4 0 2 0 でトランジスタ 4 0 1 0 、 4 0 1 1 を覆う構成としてもよいが、特に限定されない。

10

**【 0 0 7 5 】**

なお、保護膜は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。保護膜は、スパッタ法を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜の単層、又は積層で形成すればよい。

**【 0 0 7 6 】**

また、保護膜を形成した後に、半導体層のアニール (3 0 0 ~ 4 0 0 ) を行ってもよい。

**【 0 0 7 7 】**

画素電極層 4 0 3 0 、共通電極層 4 0 3 1 は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物 (ITO) 、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

20

**【 0 0 7 8 】**

また、画素電極層 4 0 3 0 、共通電極層 4 0 3 1 として、導電性高分子 (導電性ポリマーともいう) を含む導電性組成物を用いて形成することができる。

**【 0 0 7 9 】**

また、別途形成された信号線駆動回路 4 0 0 3 と、走査線駆動回路 4 0 0 4 または画素部 4 0 0 2 に与えられる各種信号及び電位は、F P C 4 0 1 8 から供給されている。

30

**【 0 0 8 0 】**

また、トランジスタは静電気などにより破壊されやすいため、ゲート線またはソース線に対して、駆動回路保護用の保護回路を同一基板上に設けることが好ましい。保護回路は、酸化物半導体を用いた非線形素子を用いて構成することが好ましい。

**【 0 0 8 1 】**

図 9 では、接続端子電極 4 0 1 5 が、画素電極層 4 0 3 0 と同じ導電膜から形成され、端子電極 4 0 1 6 は、トランジスタ 4 0 1 0 、 4 0 1 1 のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

**【 0 0 8 2 】**

接続端子電極 4 0 1 5 は、F P C 4 0 1 8 が有する端子と、異方性導電膜 4 0 1 9 を介して電気的に接続されている。

40

**【 0 0 8 3 】**

また、図 9 においては、信号線駆動回路 4 0 0 3 を別途形成し、第 1 の基板 4 0 0 1 に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装してもよいし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装してもよい。

**【 0 0 8 4 】**

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

50

**【0085】**

(実施の形態5)

本実施の形態では実施の形態4でも説明したトランジスタの半導体層に用いる酸化物半導体膜の作製方法の具体例について説明する。

**【0086】**

まず、減圧状態に保持された成膜室内に基板を保持し、基板温度が、200以上500以下、好ましくは300以上500以下となるように加熱する。

**【0087】**

次に、成膜室内の残留水分を除去しつつ、水素、水、水酸基、水素化物などの不純物が十分に除去された高純度ガスを導入し、上記ターゲットを用いて基板上に酸化物半導体膜を成膜する。10 成膜室内の残留水分を除去するためには、排気手段として、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどの吸着型の真空ポンプを用いることが望ましい。また、排気手段は、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素、水、水酸基または水素化物などの不純物（より好ましくは炭素原子を含む化合物も）などが除去されているため、当該成膜室で成膜した酸化物半導体膜に含まれる水素、水、水酸基または水素化物などの不純物の濃度を低減することができる。

**【0088】**

成膜中の基板温度が低温（例えば、100以下）の場合、酸化物半導体に水素原子を含む物質が混入するおそれがあるため、基板を上述の温度で加熱することが好ましい。20 基板を上述の温度で加熱して、酸化物半導体膜の成膜を行うことにより、基板温度は高温となるため、水素結合は熱により切断され、水素原子を含む物質が酸化物半導体膜に取り込まれにくい。したがって、基板が上述の温度で加熱された状態で、酸化物半導体膜の成膜を行うことにより、酸化物半導体膜に含まれる水素、水、水酸基または水素化物などの不純物の濃度を十分に低減することができる。また、スパッタリングによる損傷を軽減することができる。

**【0089】**

成膜条件の一例として、基板とターゲットとの間との距離を60mm、圧力を0.4Pa、直流(DC)電源を0.5kW、基板温度を400、成膜雰囲気を酸素（酸素流量比率100%）雰囲気とする。30 なお、パルス直流電源を用いると、成膜時に発生する粉状物質（パーティクル、ごみともいう）が軽減でき、膜厚分布も均一となるため好ましい。

**【0090】**

なお、酸化物半導体膜をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、酸化物半導体膜の被形成表面に付着している粉状物質（パーティクル、ごみともいう）を除去することが好ましい。逆スパッタとは、基板に電圧を印加し、基板近傍にプラズマを形成して、基板側の表面を改質する方法である。なお、アルゴンに代えて、窒素、ヘリウム、酸素などのガスを用いてもよい。

**【0091】**

また、酸化物半導体膜を加工することによって、島状の酸化物半導体膜を形成する。40 酸化物半導体膜の加工は、所望の形状のマスクを酸化物半導体膜上に形成した後、当該酸化物半導体膜をエッチングすることによって行うことができる。

**【0092】**

その後、酸化物半導体膜に対して、熱処理（第1の熱処理）を行ってもよい。熱処理を行うことによって、酸化物半導体膜中に含まれる水素原子を含む物質をさらに除去し、酸化物半導体膜の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。熱処理の温度は、不活性ガス雰囲気下、250以上700以下、好ましくは450以上600以下、または基板の歪み点未満とする。不活性ガス雰囲気としては、窒素、または希ガス（ヘリウム、ネオン、アルゴン等）を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好50

ましくは 7 N ( 9 9 . 9 9 9 9 9 % ) 以上 ( すなわち、不純物濃度が 1 p p m 以下、好ましくは 0 . 1 p p m 以下 ) とする。

#### 【 0 0 9 3 】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450 、1時間の条件で行うことができる。この間、酸化物半導体膜は大気に触れさせず、水や水素の混入が生じないようにする。

#### 【 0 0 9 4 】

熱処理を行うことによって不純物を低減し、i型 ( 真性半導体 ) または i 型に限りなく近い酸化物半導体膜を形成することで、極めて優れた特性のトランジスタを実現することができる。

10

#### 【 0 0 9 5 】

ところで、上述の熱処理には水素や水などを除去する効果があるため、当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該熱処理は、例えば、酸化物半導体膜を島状に加工する前、ゲート絶縁膜の形成後などのタイミングにおいて行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

#### 【 0 0 9 6 】

なお、酸化物半導体は不純物に対して鈍感であり、膜中にはかなりの金属不純物が含まれていても問題がなく、ナトリウムのようなアルカリ金属が多量に含まれる廉価なソーダ石灰ガラスも使えると指摘されている ( 神谷、野村、細野、「アモルファス酸化物半導体の物性とデバイス開発の現状」、固体物理、2009年9月号、Vol. 44、p. 621 - 633 ) 。しかし、このような指摘は適切でない。アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうち Na は、酸化物半導体膜に接する絶縁膜が酸化物である場合、当該絶縁膜中に拡散して  $\text{Na}^+$  となる。また、Na は、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、或いは、その結合中に割り込む。その結果、例えば、閾値電圧がマイナス方向にシフトすることによるノーマリオン化、移動度の低下等の、トランジスタの特性の劣化が起こり、加えて、特性のばらつきも生じる。この不純物によりもたらされるトランジスタの特性の劣化と、特性のばらつきは、酸化物半導体膜中の水素の濃度が十分に低い場合において顕著に現れる。従って、酸化物半導体膜中の水素の濃度が  $5 \times 10^{19} / \text{cm}^3$  以下、特に  $5 \times 10^{18} / \text{cm}^3$  以下である場合には、上記不純物の濃度を低減することが望ましい。具体的に、二次イオン質量分析法による Na 濃度の測定値は、 $5 \times 10^{16} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{16} / \text{cm}^3$  以下、更に好ましくは  $1 \times 10^{15} / \text{cm}^3$  以下とするとよい。同様に、Li 濃度の測定値は、 $5 \times 10^{15} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{15} / \text{cm}^3$  以下とするとよい。同様に、K 濃度の測定値は、 $5 \times 10^{15} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{15} / \text{cm}^3$  以下とするとよい。

20

#### 【 0 0 9 7 】

なお、酸化物半導体膜は非晶質であっても良いが、トランジスタのチャネル形成領域として結晶性を有する酸化物半導体膜を用いることが好ましい。結晶性を有する酸化物半導体膜を用いることで、トランジスタの信頼性 ( ゲート・バイアス・ストレス耐性 ) を高めることができるからである。

30

#### 【 0 0 9 8 】

結晶性を有する酸化物半導体膜としては、理想的には単結晶であることが望ましいが、c 軸配向を有した結晶 ( C A x i s A l i g n e d C r y s t a l l i n e : C A A C とも呼ぶ ) を含む酸化物を用いることが好ましい。

40

#### 【 0 0 9 9 】

C A A C 膜は、スパッタリング法によつても作製することができる。スパッタリング法によつて C A A C 膜を得るには酸化物半導体膜の堆積初期段階において六方晶の結晶が形成されるようにすることと、当該結晶を種として結晶が成長されるようにすることが肝要で

50

ある。そのためには、ターゲットと基板の距離を広くとり（例えば、150mm～200mm程度）、基板加熱温度を100～500、好適には200～400、さらに好適には250～300にすると好ましい。また、これに加えて、成膜時の基板加熱温度よりも高い温度で、堆積された酸化物半導体膜を熱処理することで膜中に含まれるミクロな欠陥や、積層界面の欠陥を修復することができる。

#### 【0100】

以上のようにして酸化物半導体膜を成膜することができる。

#### 【0101】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

10

#### 【0102】

##### (実施の形態6)

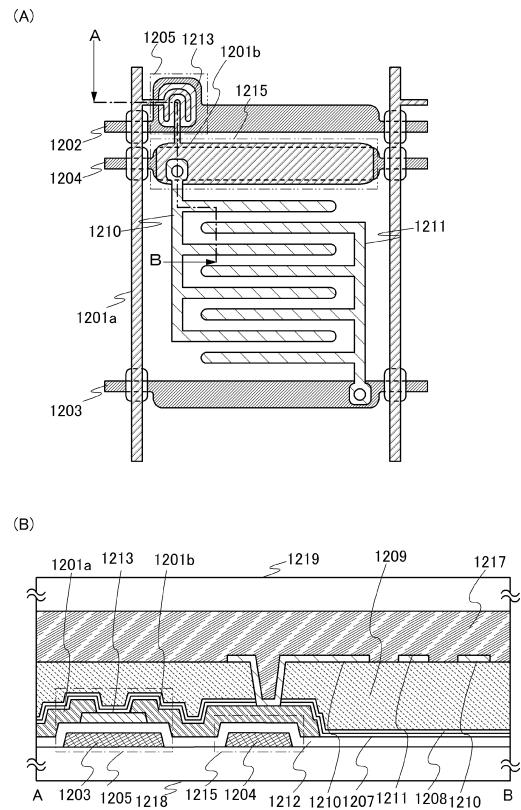

本実施の形態では、液晶表示装置の画素の平面図及び断面図の一例について図面を用いて説明する。

#### 【0103】

図10(A)は表示パネルが有する複数の画素の1つの平面図を示している。図10(B)は図10(A)の一点鎖線A-Bにおける断面図である。

#### 【0104】

図10(A)において、信号線となる配線層(ソース電極層1201a及びドレイン電極層1201を含む)は、図中上下方向(列方向)に延伸するように配置されている。走査線となる配線層(ゲート電極層1202を含む)は、図中左右方向(行方向)に延伸するように配置されている。コモン線となる配線層(ゲート電極層1203を含む)は、ソース電極層1201aに概略直交する方向(図中左右方向(行方向))に延伸するように配置されている。容量配線層1204は、ゲート電極層1202及びゲート電極層1203に概略平行な方向であって、且つ、ソース電極層1201aに概略直交する方向(図中左右方向(行方向))に延伸するように配置されている。

20

#### 【0105】

図10(A)において、表示パネルの画素には、ゲート電極層1202を有するトランジスタ1205が設けられている。トランジスタ1205上には、絶縁膜1207、絶縁膜1208、及び層間膜1209が設けられている。

30

#### 【0106】

図10(A)、図10(B)に示す表示パネルの画素は、トランジスタ1205に接続される第1の電極層として透明電極層1210、ゲート電極層1203に接続される第2の電極層として透明電極層1211を有する。透明電極層1210及び透明電極層1211は、互いの櫛歯状の形状が噛み合うように、且つ離間して設けられている。トランジスタ1205上の絶縁膜1207、絶縁膜1208、及び層間膜1209には、開口(コンタクトホール)が形成されている。開口(コンタクトホール)において、透明電極層1210とトランジスタ1205とが接続されている。

#### 【0107】

図10(A)、図10(B)に示すトランジスタ1205は、ゲート絶縁層1212を介してゲート電極層1202上に配置された半導体層1213を有し、半導体層1213に接してソース電極層1201a及びドレイン電極層1201bを有する。また、容量配線層1204、ゲート絶縁層1212、及びドレイン電極層1201bが積層して、容量素子1215を形成している。

40

#### 【0108】

また、トランジスタ1205及び液晶層1217を間に挟んで、第1の基板1218と第2の基板1219とが重畠ように配置されている。

#### 【0109】

なお図10(B)では、トランジスタ1205としてボトムゲート構造の逆スタガ型トランジスタを用いる例を示したが、本明細書に開示する表示装置に適用できるトランジスタ

50

の構造は特に限定されない。例えば、ゲート絶縁層を介してゲート電極層が半導体層の上側に配置されるトップゲート構造のトランジスタ、及び、ゲート絶縁層を介してゲート電極層が半導体層の下側に配置されるボトムゲート構造のスタガ型トランジスタ及びプレーナ型トランジスタなどを用いることができる。

#### 【0110】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0111】

##### (実施の形態7)

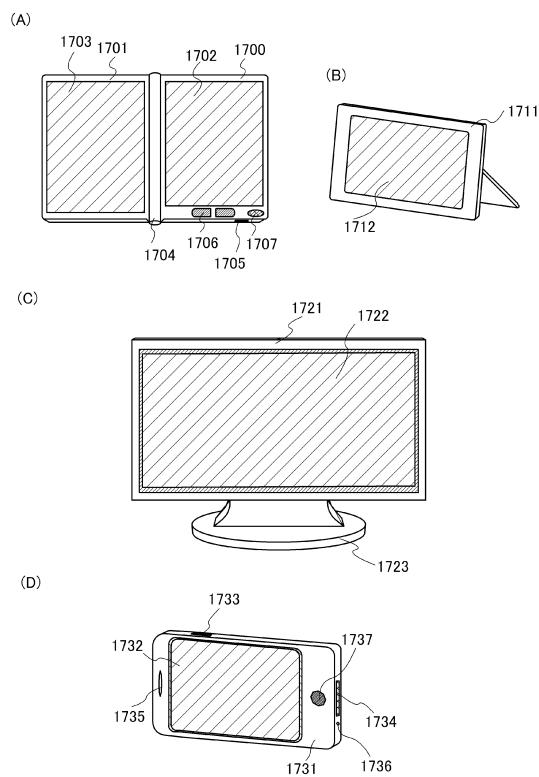

本実施の形態においては、電子機器の例について説明する。

10

#### 【0112】

上記実施の形態に係る表示装置は、さまざまな電子機器（遊技機も含む）に適用することができます。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用のモニタ、電子ペーパー、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機等の大型ゲーム機等が挙げられる。

#### 【0113】

上記実施の形態に係る表示装置は、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍（電子ブック）、ポスター、電車等の乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図11に示す。

20

#### 【0114】

図11(A)は、電子書籍の一例を示している。図11(A)に示す電子書籍は、筐体1700及び筐体1701の2つの筐体で構成されている。筐体1700及び筐体1701は、蝶番1704により一体になっており、開閉動作を行うことができる。このような構成により、書籍のような動作を行うことが可能となる。

#### 【0115】

筐体1700には表示部1702が組み込まれ、筐体1701には表示部1703が組み込まれている。表示部1702及び表示部1703は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部（図11(A)では表示部1702）に文章を表示し、左側の表示部（図11(A)では表示部1703）に画像を表示することができる。

30

#### 【0116】

図11(B)は、表示装置を用いたデジタルフォトフレームの一例を示している。例えば、図11(B)に示すデジタルフォトフレームは、筐体1711に表示部1712が組み込まれている。表示部1712は、各種画像を表示することが可能であり、例えば、デジタルカメラ等で撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

#### 【0117】

40

図11(C)は、表示装置を用いたテレビジョン装置の一例を示している。図11(C)に示すテレビジョン装置は、筐体1721に表示部1722が組み込まれている。表示部1722により、映像を表示することが可能である。また、ここでは、スタンド1723により筐体1721を支持した構成を示している。表示部1722は、上記実施の形態に示した表示装置を適用することができる。

#### 【0118】

図11(D)は、表示装置を用いた携帯電話機の一例を示している。図11(D)に示す携帯電話機は、筐体1731に組み込まれた表示部1732の他、操作ボタン1733、操作ボタン1737、外部接続ポート1734、スピーカ1735、及びマイク1736等を備えている。

50

## 【0119】

図11(D)に示す携帯電話機は、表示部1732がタッチパネルになっており、指等の接触により、表示部1732の表示内容を操作することができる。また、電話の発信、或いはメールの作成等は、表示部1732を指等で接触することにより行うことができる。

## 【0120】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

## 【実施例1】

## 【0121】

本実施例では、実施の形態1で述べた、ゲートに20V以上の電圧を1m秒以上印加することでトランジスタのしきい値電圧の変動を回復させることに関して、トランジスタのゲートに対して印加する正の電圧の印加条件を変化させる実験に基づいた測定結果の説明を行う。

10

## 【0122】

トランジスタのゲートに印加する正の電圧の印加時間を変化させ、光照射前後の光応答特性を測定した。具体的には、正の電圧の印加時間を変化させることで、光照射前後の光応答特性の測定結果はどのように変化するのか、について測定した。

## 【0123】

なお測定に用いたトランジスタの作製条件は以下の通りである。

20

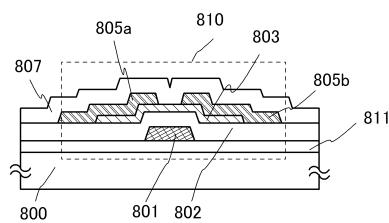

## 【0124】

測定に用いたトランジスタは、図12に示すように、ボトムゲート構造の一つであるチャネルエッチ型と呼ばれる逆スタガ型薄膜トランジスタである。トランジスタ810は、ガラス基板800上に、下地膜811、ゲート電極層801、ゲート絶縁層802、酸化物半導体層803、ソース電極層805a、ドレイン電極層805b、絶縁層807を含んで構成されている。

## 【0125】

チャネル長(L)は30μm、チャネル幅(W)は10000μmであり、ソース電極層805a及びドレイン電極層805bはヘビのように曲がりくねった形状を有する。またソース電極層805aとゲート電極層801とが重畠する長さ、及びドレイン電極層805bとゲート電極層801とが重畠する長さは、特に限定していない。

30

## 【0126】

まず、絶縁表面を有するガラス基板800上に、下地膜811となる絶縁膜を形成した。下地膜811は、膜厚100nmの窒化シリコン膜、膜厚150nmの酸化窒化シリコン膜を、順に積層して形成した。

## 【0127】

次いで、下地膜811上に、ゲート電極層801を形成した。ゲート電極層801は、膜厚100nmのタンクステン膜を単層で形成した。なお、ゲート電極層801の端部はテーパー形状とした。ここで、テーパー角は、例えば、30°以上60°以下とした。テーパー角とは、テーパー形状を有する層(例えば、ゲート電極層801)を、その断面(基板の表面と直交する面)に垂直な方向から観察した際に、当該層の側面と底面がなす傾斜角を示す。更に、ゲート電極層801を覆うように、ゲート絶縁層802を形成した。ゲート絶縁層802は、膜厚100nmの酸化窒化シリコン膜を、単層で形成した。

40

## 【0128】

次いで、組成比としてIn<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:2[mol数比]を有する酸化物ターゲットを用いたスパッタ法により、ガラス基板(126.6mm×126.6mm)上に膜厚35nmのIn-Ga-Zn-O膜を成膜した。なお、In-Ga-Zn-O膜の成膜条件は、成膜温度200°C、圧力0.6Pa、電力5kWとした。

## 【0129】

その後、窒素雰囲気下で450°C、1時間の加熱処理を行った。この加熱処理は、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれない雰囲気、例

50

えは雰囲気の露点が -40 以下、好ましくは -60 以下であることが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6 N (99.9999%) 以上好ましくは 7 N (99.9999%) 以上（即ち不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下）とすることが好ましい。

#### 【0130】

加熱処理後にスパッタ法により膜厚 100 nm のチタン膜、膜厚 400 nm のアルミニウム膜、膜厚 100 nm のチタン膜の順に積層して導電膜の積層を形成した。フォトリソグラフィ工程により導電膜の積層上にレジストマスクを形成し、選択的にエッチングを行つてソース電極層 805 a 及びドレイン電極層 805 b を形成した後、レジストマスクを除去した。その後、窒素雰囲気下で 300 、1 時間の加熱処理を行つた。

10

#### 【0131】

次いで、酸化シリコンターゲットを用いるスパッタ法により、ソース電極層 805 a 及びドレイン電極層 805 b 上に膜厚 400 nm の酸化シリコン膜を成膜した。なお、酸化シリコン膜の成膜条件は、成膜温度 200 、時間 2 分、電力 6 kW とした。その後、窒素雰囲気で 300 、1 時間の加熱処理を行つた。上述のように作製されたトランジスタ 810 を図 12 に示す。

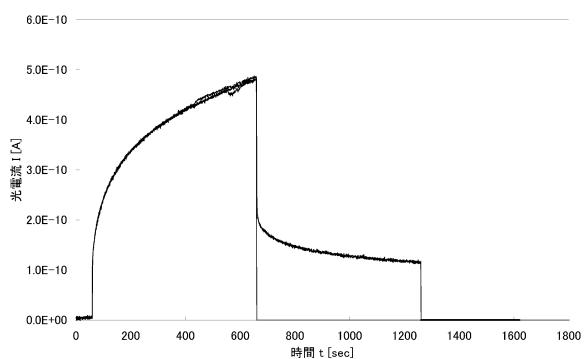

#### 【0132】

上述のように作製されたトランジスタ 810 を用いて、光応答特性の測定を行つた。図 13 に、光照射前後の光応答特性（光電流 - 時間特性）の測定結果を示す。図 13 に示す各図において、縦軸を光電流値、横軸を時刻としている。なお、図 13 に示すように光応答特性を、第 1 の期間 51 、第 2 の期間 52 、第 3 の期間 53 、第 4 の期間 54 に分割して説明する。第 1 の期間 51 は、光照射期間でありゲートに電圧を印加していない期間である。第 2 の期間 52 は、光消灯期間でありゲートに電圧を印加していない期間である。第 3 の期間 53 は、光消灯期間でありゲートに正の電圧を印加している期間である。第 4 の期間 54 は、光消灯期間でありゲートに電圧を印加していない期間である。

20

#### 【0133】

図 13 における a は光照射開始時間、 b は光消灯開始時間、 c は正の電圧印加開始時間（光消灯中）、 d は正の電圧印加終了時間（光消灯中）、 e は測定終了時間をそれぞれ示すものとする。

#### 【0134】

第 1 の期間 51 は 600 秒、第 2 の期間 52 は 600 秒、第 4 の期間 54 は 300 秒、すなわち光照射開始時間 a から、測定終了時間 e までの時間は 1620 秒であった。第 1 の期間 51 では、測定対象のトランジスタ 810 の遮光されていない側から、すなわち当該トランジスタ 810 の基板表面に対して垂直な方向から光照射を行つた。なお、照射強度は、3.5 mW / cm<sup>2</sup> であり、光源は波長 400 nm 以下の光として、分光した光を照射することのできる波長 400 nm のキセノン光源を利用した。また第 3 の期間 53 では、正の電圧を印加した。本実施例において正の電圧を印加するとは、測定対象のトランジスタ 810 のゲートに 20 V 以上の電圧として、ここでは 20 V の電圧をそれぞれ印加することを意味する。なお測定対象のトランジスタ 810 のゲートに正の電圧を印加する際、トランジスタのソースを 0 V 、ドレインを 0 V としている。

30

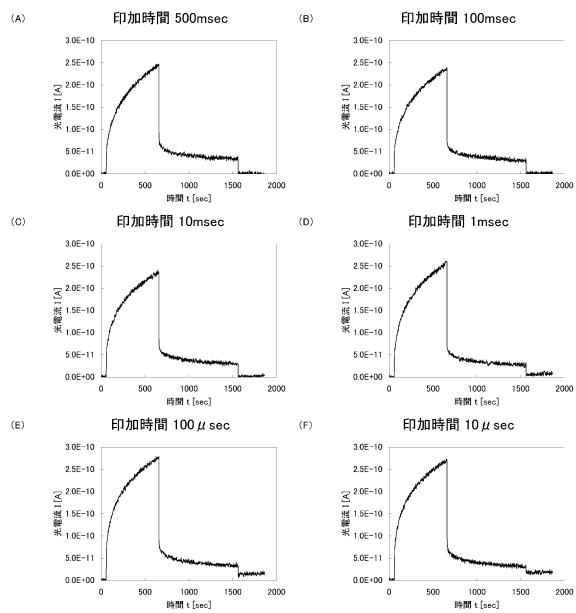

#### 【0135】

上述したトランジスタ 810 を用いて、光応答特性の測定を行つた。図 13 の第 3 の期間 53 である正の電圧の印加時間を、500 m 秒、100 m 秒、10 m 秒、1 m 秒、100 μ 秒、10 μ 秒、の 6 段階で変化させて測定を行つた。図 14 (A) は、印加時間 500 m 秒、図 14 (B) は、印加時間 100 m 秒、図 14 (C) は、印加時間 10 m 秒、図 14 (D) は、印加時間 1 m 秒、図 14 (E) は、印加時間 100 μ 秒、図 14 (F) は、印加時間 10 μ 秒における、光照射前後の光応答特性の測定結果をそれぞれ示している。

40

#### 【0136】

図 14 (A) 乃至 (F) に示すように印加時間が 500 m 秒乃至 10 μ 秒の範囲において、正の電圧印加後の光電流の値が低減できることがわかった。すなわち、トランジスタの

50

ゲートに正の電圧を印加することで光照射による光電流が上昇してしまう特性劣化の回復を確認できた。特にゲートに負バイアスを印加されることでしきい値電圧が変動したトランジスタに対してゲートに20V以上の電圧を1m秒以上印加する場合には、光照射による光電流が上昇してしまう特性劣化の回復を顕著に確認できた。

## 【符号の説明】

## 【0137】

|           |          |    |

|-----------|----------|----|

| T 1       | 期間       |    |

| T 2       | 期間       |    |

| 5 1       | 期間       |    |

| 5 2       | 期間       | 10 |

| 5 3       | 期間       |    |

| 5 4       | 期間       |    |

| 1 0 0     | 表示部      |    |

| 1 0 1     | 走査線      |    |

| 1 0 1 _ j | 走査線      |    |

| 1 0 2     | 信号線      |    |

| 1 0 2 _ k | 信号線      |    |

| 1 0 3     | 画素       |    |

| 1 0 3 _ j | 画素       |    |

| 1 0 4     | トランジスタ   | 20 |

| 1 0 5     | 表示素子     |    |

| 3 0 1     | 走査線駆動回路  |    |

| 3 0 2     | 信号線駆動回路  |    |

| 3 1 1     | 液晶素子     |    |

| 3 1 2     | 容量素子     |    |

| 3 1 3     | 配線       |    |

| 3 1 4     | 配線       |    |

| 5 0 0     | 素子基板     |    |

| 5 0 1     | 表示制御回路   |    |

| 5 0 2     | クロック生成回路 | 30 |

| 5 0 3     | パルス幅制御回路 |    |

| 8 0 0     | ガラス基板    |    |

| 8 0 1     | ゲート電極層   |    |

| 8 0 2     | ゲート絶縁層   |    |

| 8 0 3     | 酸化物半導体層  |    |

| 8 0 5 a   | ソース電極層   |    |

| 8 0 5 b   | ドレイン電極層  |    |

| 8 0 7     | 絶縁層      |    |

| 8 1 0     | トランジスタ   |    |

| 8 1 1     | 下地膜      | 40 |

| 1 2 0 1 a | ソース電極層   |    |

| 1 2 0 1 b | ドレイン電極層  |    |

| 1 2 0 2   | ゲート電極層   |    |

| 1 2 0 3   | ゲート電極層   |    |

| 1 2 0 4   | 容量配線層    |    |

| 1 2 0 6   | トランジスタ   |    |

| 1 2 0 7   | 絶縁膜      |    |

| 1 2 0 8   | 絶縁膜      |    |

| 1 2 0 9   | 層間膜      |    |

| 1 2 1 0   | 透明電極層    | 50 |

|           |         |    |

|-----------|---------|----|

| 1 2 1 1   | 透明電極層   |    |

| 1 2 1 2   | ゲート絶縁層  |    |

| 1 2 1 3   | 半導体層    |    |

| 1 2 1 5   | 容量素子    |    |

| 1 2 1 7   | 液晶層     |    |

| 1 2 1 8   | 基板      |    |

| 1 2 1 9   | 基板      |    |

| 1 7 0 0   | 筐体      |    |

| 1 7 0 1   | 筐体      |    |

| 1 7 0 2   | 表示部     | 10 |

| 1 7 0 3   | 表示部     |    |

| 1 7 0 4   | 蝶番      |    |

| 1 7 1 1   | 筐体      |    |

| 1 7 1 2   | 表示部     |    |

| 1 7 2 1   | 筐体      |    |

| 1 7 2 2   | 表示部     |    |

| 1 7 2 3   | スタンド    |    |

| 1 7 3 1   | 筐体      |    |

| 1 7 3 2   | 表示部     |    |

| 1 7 3 3   | 操作ボタン   | 20 |

| 1 7 3 4   | 外部接続ポート |    |

| 1 7 3 5   | スピーカ    |    |

| 1 7 3 6   | マイク     |    |

| 1 7 3 7   | 操作ボタン   |    |

| 4 0 0 1   | 基板      |    |

| 4 0 0 2   | 画素部     |    |

| 4 0 0 3   | 信号線駆動回路 |    |

| 4 0 0 3 a | 信号線駆動回路 |    |

| 4 0 0 3 b | 信号線駆動回路 |    |

| 4 0 0 4   | 走査線駆動回路 | 30 |

| 4 0 0 5   | シール材    |    |

| 4 0 0 6   | 基板      |    |

| 4 0 0 8   | 液晶層     |    |

| 4 0 1 0   | トランジスタ  |    |

| 4 0 1 1   | トランジスタ  |    |

| 4 0 1 3   | 液晶素子    |    |

| 4 0 1 5   | 接続端子電極  |    |

| 4 0 1 6   | 端子電極    |    |

| 4 0 1 8   | F P C   |    |

| 4 0 1 9   | 異方性導電膜  | 40 |

| 4 0 2 0   | 絶縁層     |    |

| 4 0 3 0   | 画素電極層   |    |

| 4 0 3 1   | 共通電極層   |    |

| 4 0 3 5   | スペーサ    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開平10-133176(JP,A)

特開平6-067154(JP,A)

特開2006-208966(JP,A)

特開2008-242388(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38