(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3724954号

(P3724954)

(45) 発行日 平成17年12月7日(2005.12.7)

(24) 登録日 平成17年9月30日(2005.9.30)

(51) Int.C1.<sup>7</sup>

F 1

H01L 23/12

H01L 23/12 501S

H01L 21/60

H01L 21/60 311Q

H05K 1/18

H05K 1/18 J

H01L 23/12 J

請求項の数 6 (全 11 頁)

(21) 出願番号

特願平10-204002

(22) 出願日

平成10年7月17日(1998.7.17)

(65) 公開番号

特開平11-135679

(43) 公開日

平成11年5月21日(1999.5.21)

審査請求日

平成16年5月6日(2004.5.6)

(31) 優先権主張番号

特願平9-233695

(32) 優先日

平成9年8月29日(1997.8.29)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100077849

弁理士 須山 佐一

(72) 発明者 池水 守彦

神奈川県川崎市幸区小向東芝町1 株式会

社東芝 多摩川工場内

(72) 発明者 大家 宣昭

神奈川県川崎市幸区小向東芝町1 株式会

社東芝 多摩川工場内

(72) 発明者 岩崎 建

神奈川県横浜市磯子区新磯子町33 株式

会社東芝 生産技術研究所内

最終頁に続く

(54) 【発明の名称】電子装置および半導体パッケージ

## (57) 【特許請求の範囲】

## 【請求項1】

一主面に接続端子が配設された配線基板と、

デバイスホールを有し、一主面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、前記配線基板の熱膨脹率とほぼ等しい熱膨脹率を有する金属により構成されており、前記配線フィルムの他主面の前記デバイスホールを囲む領域に配設された枠形の形状保持板とを有する半導体パッケージと、

前記半導体パッケージの外部接続端子と前記配線基板の接続端子とを電気的・機械的に接続するバンプとを備えた電子装置であって、

前記形状保持板が、25Cr-20Niステンレス鋼、または0.01~0.03重量%のZrを含む銅合金により構成されていることを特徴とする電子装置。

## 【請求項2】

一主面に接続端子が配設された配線基板と、

デバイスホールを有し、一主面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、前記配線基板の熱膨脹率とほぼ等しい熱膨脹率を有する金属により構成されており、前記半導体素子の外側を覆って配置されかつ前記配線フィルムの他主面に接着された形状保持性を有する

10

20

被覆部材とを有する半導体パッケージと、

前記半導体パッケージの外部接続端子と前記配線基板の接続端子とを電気的・機械的に接続するバンプとを備えた電子装置であって、

前記した形状保持性を有する被覆部材が、 $25\text{Cr}-20\text{Ni}$ ステンレス鋼、または $0.01\sim0.03$ 重量%の $Zr$ を含む銅合金により構成されていることを特徴とする電子装置。

【請求項3】

前記バンプが、 $\text{Pb}-\text{Sn}$ 系のはんだバンプであることを特徴とする請求項1または2記載の電子装置。

【請求項4】

デバイスホールを有し、一主面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、 $13\times10^{-6}\sim17\times10^{-6}$ （/K）の熱膨脹率を有する金属により構成され、前記配線フィルムの他主面の前記デバイスホールを囲む領域に配設された枠形の形状保持板とを備えた半導体パッケージであり、

前記形状保持板が、 $25\text{Cr}-20\text{Ni}$ ステンレス鋼、または $0.01\sim0.03$ 重量%の $Zr$ を含む銅合金により構成されていることを特徴とする半導体パッケージ。

【請求項5】

デバイスホールを有し、一主面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、 $13\times10^{-6}\sim17\times10^{-6}$ （/K）の熱膨脹率を有する金属により構成されており、前記半導体素子の外側を覆って配置されかつ前記配線フィルムの他主面に接着された形状保持性を有する被覆部材とを備えた半導体パッケージであり、

前記した形状保持性を有する被覆部材が、 $25\text{Cr}-20\text{Ni}$ ステンレス鋼、または $0.01\sim0.03$ 重量%の $Zr$ を含む銅合金により構成されていることを特徴とする半導体パッケージ。

【請求項6】

前記外部接続端子上に、 $\text{Pb}-\text{Sn}$ 系のはんだバンプが配設されていることを特徴とする請求項4または5記載の半導体パッケージ。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、電子装置および半導体パッケージに係わり、さらに詳しくは、半導体パッケージをマザーボードである配線基板に搭載した信頼性の高い電子装置、およびマザーボードである配線基板に搭載したときに、信頼性の高い構造を有する半導体パッケージに関する。

【0002】

【従来の技術】

電子機器の小型化や回路機構のコンパクト化を目的とし、セラミック等の多層配線基板上に半導体素子（例えばICチップ）を搭載・実装し、さらにその実装領域を、金属製等のキャップで封止するか、あるいはモールド樹脂で被覆・封止した半導体装置が広く実用化されている。

【0003】

特にCPU等の高パワーの消費を伴う半導体装置では、放熱体（ヒートシンク）を付設し、動作時に発生する熱を放熱体から放出させる構成を採っている。

【0004】

さらに、コストの低減および構成の簡略化等を目的とし、インナーリード等の配線を有するキャリアテープに半導体素子を搭載し実装する一方、スティフナーと呼ばれる形状保持板を付設し、さらに放熱性を有するカバーを備えたTCP（テープキャリアパッケージ）

10

20

30

40

50

も知られている。そしてこのようなT C Pでは、入出力端子数の増加、外形の小型化、実装の容易性等の観点から、外部回路との接続用端子（外部接続端子）である接続パッド上に、はんだボール等のバンプを配設し、これらのバンプを格子状に配列した、ボールグリッドアレイ（以下、B G Aと示す。）と呼ばれる構造が採られている。

#### 【0005】

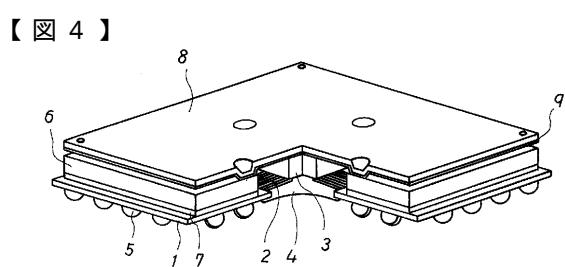

図4は、このようなTape-B G A型半導体パッケージの構造の一例を示す斜視図である。図において、符号1は、デバイスホールを有する絶縁樹脂フィルム（例えば、ポリイミド樹脂フィルム）、2は、この絶縁樹脂フィルム1の一主面（図では下面）に配設され先端がデバイスホールに突出したインナーリードをそれぞれ示す。ここで、インナーリード2は、搭載される半導体素子の電極端子群に対応して配設され、その後端側には、信号線等の配線（図示を省略。）が延設されている。そして、各配線の端部には、外部接続端子である接続パッド（図示を省略。）が配設されている。また符号3は、デバイスホール内にフェースダウンに配置された半導体素子を示し、この半導体素子3の各電極端子は、対応するインナーリード2の先端部に電気的に接続（インナーリードボンディング）されている。さらに、符号4は、半導体素子3の接続領域を被覆し封止する樹脂封止層、5は、接続パッド上に設けられるはんだボール等のバンプをそれぞれ示す。またさらに、符号6は、絶縁樹脂フィルム1の他主面（図では上面）に、接着剤層7を介して接着された枠形の形状保持板（スティフナー）を示し、8は、スティフナー6と半導体素子3の他主面（図では上面）側に配設され、接着剤層9を介して接着された放熱性を有するカバープレートを示す。

10

20

#### 【0006】

このような半導体パッケージは、ホスト側の配線基板（マザーボード）に搭載・実装されて電子装置を構成する。すなわち、マザーボードの一主面には、半導体パッケージの外部接続端子（接続パッド）と対応して接続パッドが配設されており、このマザーボードの接続パッドと半導体パッケージの外部接続端子とが、はんだボール5等のバンプにより接続される。

#### 【0007】

##### 【発明が解決しようとする課題】

しかしながら、このように半導体パッケージが搭載された電子装置においては、搭載時や実際の使用環境下で印加される熱負荷等に起因する応力が、半導体パッケージの外部接続端子とマザーボードの接続パッドとを接合するはんだボール5に集中し、歪みが発生するという問題があった。

30

#### 【0008】

すなわち、マザーボードとしては、通常、ガラスクロス-エポキシ樹脂含浸層と銅配線層とを積層したガラスエポキシ配線基板が使用されており、この配線基板の熱膨張率（線膨張率）は、配線密度や配線方向によっても異なるが、平均して $13 \times 10^{-6} \sim 18 \times 10^{-6}$  / ( / K ) の範囲にある。

#### 【0009】

これに対して、図4に示した半導体パッケージでは、厚さの点で最も大きな割合を占め、したがってパッケージ全体の熱膨張率を決定しているスティフナー6が、 $17 \times 10^{-6}$  ( / K ) を越える大きな熱膨張率を有するステンレス鋼（例えばSUS304；熱膨張率 $17.3 \times 10^{-6}$ ）により構成されているため、半導体パッケージとマザーボードとの間に熱的な物性の不整合が生じている。

40

#### 【0010】

そして、このように物性が大きく異なる場合、Q F P (Quad Flat Package)では、ガルウイング形状に成形されたアウターリード部が弾性変形することにより、応力集中による歪みを吸収し緩和するようになっているが、B G A型の半導体パッケージでは、そのような歪みを吸収緩和する部分がないため、周期的な温度変化により、半導体パッケージとマザーボードとの接続部であるはんだボール5等のバンプに、繰り返し応力が働き、ついにはバンプが疲労して破壊に至るという問題があった。

50

## 【0011】

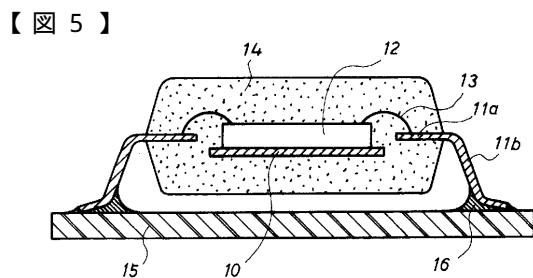

なお、QFPをガラスエポキシ配線基板に搭載し実装した電子装置を、図5に示す。この図において、符号10はリードフレームのベッド部、11aはインナーリード部、11bはアウターリード部、12は半導体素子、13は半導体素子12の電極端子（図示を省略。）とインナーリード部11aとを結線するボンディングワイヤ、14はエポキシ樹脂等のモールド樹脂層、15はマザーボードであるガラスエポキシ配線基板、16は、QFPのアウターリード部11bをガラスエポキシ配線基板15の所定の配線部（図示を省略。）に接合するはんだフィレットをそれぞれ示している。

## 【0012】

本発明は、このような問題を解決するためになされたもので、半導体パッケージとマザーボードとの接続部の信頼性の高い電子装置を提供することを目的とする。また、マザーボードへの搭載により、信頼性の高い電子装置を得ることができる半導体パッケージを提供することを目的とする。

## 【0013】

## 【課題を解決するための手段】

本発明の第1の発明の電子装置は、一正面に接続端子が配設された配線基板と、デバイスホールを有し、一正面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、前記配線基板の熱膨脹率とほぼ等しい熱膨脹率を有する金属により構成されており、前記配線フィルムの他正面の前記デバイスホールを囲む領域に配設された枠形の形状保持板とを有する半導体パッケージと、前記半導体パッケージの外部接続端子と前記配線基板の接続端子とを電気的・機械的に接続するバンプとを備えた電子装置であって、前記形状保持板が、25Cr-20Niステンレス鋼、または0.01~0.03重量%のZrを含む銅合金により構成されていることを特徴とする。

## 【0014】

ここで、半導体パッケージの外部接続端子とマザーボードである配線基板の接続端子とを電気的・機械的に接続するバンプは、Pb-Sn系などのはんだから成るボール状のバンプとすることができます。はんだバンプの形成は、例えば、予め整形されたはんだボールを、配線フィルムの外部接続端子である接続パッド上に配置し、加熱してはんだを溶融させる（リフローする）ことにより行なわれる。

## 【0015】

また、半導体パッケージの半導体素子の外側に、放熱性を有する被覆部材を配設することができる。放熱性を有する被覆部材としては、例えば、銅やアルミニウムのような熱伝導率の高い金属から成る板や、アルミナ（酸化アルミニウム）や窒化アルミニウムのようなセラミックから成る板、またはこれらの板材の複数枚を積層的に配置した構成のものが使用される。被覆部材の厚さや形状などは、半導体素子の容量や熱放出性などを考慮して適宜選択される。

## 【0016】

さらに、配線基板として、ガラスクロス-エポキシ樹脂含浸層と銅配線層とを積層一体化した構造のガラスエポキシ配線基板を用いるとともに、形状保持板を、このガラスエポキシ配線基板の熱膨脹率（ $13 \times 10^{-6} \sim 18 \times 10^{-6} / K$ ）とほぼ等しい、 $13 \times 10^{-6} \sim 17 \times 10^{-6} / K$ の熱膨脹率を有する金属により構成することができる。そして、 $13 \times 10^{-6} \sim 17 \times 10^{-6} / K$ の熱膨脹率を有する金属としては、25Cr-20Niステンレス鋼（例えばSUS310S；熱膨脹率 $15.9 \times 10^{-6} / K$ ）、または0.01~0.03重量%のZrを含む銅合金（例えばCDA Alloy C15150；熱膨脹率 $16.7 \times 10^{-6} / K$ ）を使用することができる。特にCDA Alloy C15150は、熱伝導率が $15 \sim 20 W \cdot m / K$ と極めて高く、放熱性に優れているので、形状保持板の構成材料として好適している。またSUS310Sは、入手が容易で比較的低価格であるうえ、耐食性が良好である。

## 【0017】

10

20

30

40

50

また、本発明の第2の発明の電子装置は、一主面に接続端子が配設された配線基板と、デバイスホールを有し、一主面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、前記配線基板の熱膨脹率とほぼ等しい熱膨脹率を有する金属により構成されており、前記半導体素子の外側を覆って配置されかつ前記配線フィルムの他主面に接着された形状保持性を有する被覆部材とを有する半導体パッケージと、前記半導体パッケージの外部接続端子と前記配線基板の接続端子とを電気的・機械的に接続するバンプとを備えた電子装置であって、前記した形状保持性を有する被覆部材が、 $25\text{Cr}-20\text{Ni}$ ステンレス鋼、または0.01~0.03重量%のZrを含む銅合金により構成されていることを特徴とする。

10

## 【0018】

ここで、半導体パッケージの外部接続端子とマザーボードである配線基板の接続端子とを電気的・機械的に接続するバンプは、 $\text{Pb}-\text{Sn}$ 系などのはんだから成るボール状のバンプとすることができます。

## 【0019】

また、配線基板として、前記したガラスエポキシ配線基板を用いるとともに、形状保持性を有する被覆部材を、このガラスエポキシ配線基板の熱膨脹率とほぼ等しい、 $13 \times 10^{-6}$ ~ $17 \times 10^{-6}$  / Kの熱膨脹率を有する金属により構成することができる。このような範囲の熱膨脹率を有する金属としては、例えばSUS310 Sのような $25\text{Cr}-20\text{Ni}$ ステンレス鋼や、CDA Alloy C15150のような銅合金を使用することができます。

20

## 【0020】

さらに、本発明の第3の発明の半導体パッケージは、デバイスホールを有し、一主面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、 $13 \times 10^{-6}$ ~ $17 \times 10^{-6}$  ( / K )の熱膨脹率を有する金属により構成され、前記配線フィルムの他主面の前記デバイスホールを囲む領域に配設された枠形の形状保持板とを備えた半導体パッケージであり、前記形状保持板が、 $25\text{Cr}-20\text{Ni}$ ステンレス鋼、または0.01~0.03重量%のZrを含む銅合金により構成されていることを特徴とする。

## 【0021】

30

また、本発明の第4の発明の半導体パッケージは、デバイスホールを有し、一主面に外部接続端子および前記デバイスホールに突出したインナーリードがそれぞれ配設された配線フィルムと、この配線フィルムの前記デバイスホール内に配置され、前記インナーリードに電気的に接続された半導体素子と、 $13 \times 10^{-6}$ ~ $17 \times 10^{-6}$  ( / K )の熱膨脹率を有する金属により構成されており、前記半導体素子の外側を覆って配置されかつ前記配線フィルムの他主面に接着された形状保持性を有する被覆部材とを備えた半導体パッケージであり、前記した形状保持性を有する被覆部材が、 $25\text{Cr}-20\text{Ni}$ ステンレス鋼、または0.01~0.03重量%のZrを含む銅合金により構成されていることを特徴とする。

## 【0022】

40

ここで、形状保持板または形状保持性を有する被覆部材を構成する $13 \times 10^{-6}$ ~ $17 \times 10^{-6}$  ( / K )の熱膨脹率を有する金属としては、例えばSUS310 Sのような $25\text{Cr}-20\text{Ni}$ ステンレス鋼や、CDA Alloy C15150のような銅合金を使用することができます。

## 【0023】

また、外部接続端子上に、 $\text{Pb}-\text{Sn}$ 系などのはんだから成るボール状のバンプを配設し、このはんだバンプを介して、マザーボードの接続端子との電気的・機械的接続を行なうように構成することができる。

## 【0024】

本発明の半導体パッケージおよび電子装置において、デバイスホールを有する配線フィルムの基材としては、例えばポリイミド樹脂フィルムなどの絶縁樹脂フィルムを使用することができます。絶縁樹脂フィルムの厚さは、半導体パッケージの品種、形状、大きさ等にも

50

よるが、50～125μm程度とすることが好ましい。デバイスホールの大きさと平面形状は、搭載・実装する半導体素子の平面的なサイズや形状等に対応して設定される。

【0025】

そして、このような絶縁樹脂フィルムの一方の主面に、信号線等の配線と、一端がデバイスホールに突出し他端が信号線等に接続されたインナーリードが、それぞれ配設されている。また、配線の端部には、外部接続端子である接続パッドが配設されている。インナーリードを含むこのような配線は、いずれも、Cu、Cu系合金、42アロイのようなNi系合金等から構成され、絶縁樹脂フィルムへの蒸着パターニング、または絶縁樹脂フィルムの片面に設けられたCu箔または前記合金層をフォトパターニングすることにより形成される。なお、インナーリードのピッチや配列は、搭載・実装される半導体素子の電極端子のピッチや配列に対応して設定される。

【0026】

このような配線フィルムに搭載・実装される半導体素子は、例えばCPU、DSP、各種メモリ等の素子であり、特にチップ型のものに限定されない。このような半導体素子は、フェースダウンでデバイスホール内に配置され、A1等から成る電極端子が対応するインナーリードの先端部に、金パンプ等を介して接合されることにより、電気的に接続される。また、半導体素子を外界の水分や不純物などに対してあるいは機械的に保護するために、このような半導体素子の接続領域を、樹脂層により被覆し封止することができる。ここで樹脂としては、エポキシ樹脂やスルフオン酸樹脂のような、通常半導体素子の封止に使用されている樹脂を使用することができる。

【0027】

本発明の電子装置においては、半導体パッケージに設けられた形状保持板または形状保持性を有する被覆部材が、マザーボードと近似した熱膨脹率を有する金属により構成されており、パッケージ全体の熱膨脹率がマザーボードの熱膨脹率とほぼ等しくなっているので、搭載時や使用環境下で周期的な温度変化が印加されたとき、半導体パッケージとマザーボードとの接合部であるはんだボール等のパンプに、応力が集中することができない。したがって、熱負荷に起因する歪みおよび疲労破壊の発生が抑制され、半導体パッケージとマザーボードとの接続の信頼性が向上する。

【0028】

また、形状保持板または形状保持性を有する被覆部材を構成する金属は、他の剛性材料であるセラミック等に比べて、高い熱伝導率を有し、放熱性が良好であるうえに、成形・加工性が良好であり、さらに平坦性が良く、反り等が生じても元の平坦面に戻しやすいという多くの利点を有している。さらに、材料の選択性が良好で、各種の金属材料の中から、マザーボードの熱膨脹率にできるだけ近い熱膨脹率を有する材料を選択して使用することができるので、形状保持板等の構成材料として好適しており、特性に優れた電子装置を生産性良く得ることができる。

【0029】

さらに、形状保持性を有する被覆部材を備えた半導体パッケージ、およびこの半導体パッケージを搭載した電子装置においては、パッケージおよび装置全体を薄くすることが可能であるうえに、部品点数をより少なくすることができる。また、キャップ形状等を有する被覆部材の成形は、金属を使用してはじめて可能であり、簡略化された工程で容易に成形を行なうことができる。

【0030】

【発明の実施の形態】

以下、本発明の実施例を図面に基づいて説明する。

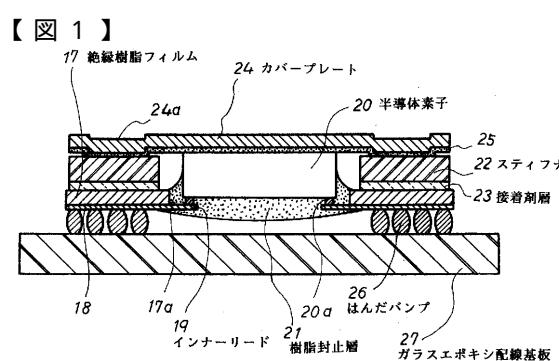

【0031】

図1は、本発明の電子装置の第1の実施例の要部を断面的に示したものであり、Tape-BGA型の半導体パッケージをマザーボードに搭載したものである。

【0032】

図において、符号17は、デバイスホール17aを有するポリイミド樹脂フィルムのよう

10

20

30

40

50

な絶縁樹脂フィルムを示し、この絶縁樹脂フィルム 17 の一方の正面（図では下面）には、信号線等の配線 18 と、後端部が信号線等の配線 18 に接続され先端部がデバイスホール 17a に突出したインナーリード 19 が、それぞれ配設されている。また、信号線等の配線 18 の他端部には、外部接続端子である接続パッド（図示を省略。）が、格子状のパターンで配設されている。また、このような配線フィルムのデバイスホール 17a 内には、半導体素子 20 がフェースダウンに配置されており、この半導体素子 20 の各電極端子（図示を省略。）は、対応するインナーリード 19 の先端部に、金パンプ 20a 等を介して電気的に接続されている。さらに、このような半導体素子 20 の電極端子とインナーリード 19 との接合部の外側には、半導体素子の保護および補強のために、エポキシ樹脂等の樹脂封止層 21 が被覆されている。

10

### 【0033】

また、絶縁樹脂フィルム 17 の配線形成面と反対側の面（図では上面）のデバイスホール 17a を囲む領域には、SUS310S（熱膨脹率  $15.9 \times 10^{-6} / K$ ）や CDA Alloy C15150（熱膨脹率  $16.7 \times 10^{-6} / K$ ）のような、 $13 \times 10^{-6} \sim 17 \times 10^{-6} / K$  の熱膨脹率を有する金属から構成された枠形の形状保持板（スティフナー） 22 が、熱可塑性のポリエステル系樹脂のような熱可塑性樹脂から成る接着剤層 23 を介して接着されており、さらにこのスティフナー 22 の上面および半導体素子 20 の上面（電極端子形成面と反対側の面）には、銅、アルミニウム等の放熱性を有する金属からなる板状のカバー（カバープレート） 24 が配設され、熱可塑性ポリエステル系樹脂等から成る接着剤層 25 を介して接着されている。なお、カバープレート 24 は、半導体素子 20 の上面には全面的に接着されているが、スティフナー 22 の上面には、下側に突出形成された凹部 24a のみが接着されている。

20

### 【0034】

さらに、配線フィルムの外部接続端子（接続パッド）上には、それぞれボール状のはんだパンプ 26 が設けられ、半導体パッケージが構成されている。

### 【0035】

一方、符号 27 は、マザーボードであるガラスエポキシ配線基板を示し、その一方の正面（図では上面）には、配線の一部として接続パッド（図示を省略。）が配設されている。そして、このガラスエポキシ配線基板 27 上に前記した半導体パッケージが搭載され、半導体パッケージの外部接続端子（接続パッド）とガラスエポキシ配線基板 27 の接続パッドとが、はんだパンプ 26 により電気的・機械的に接続されている。

30

### 【0036】

このように構成される第 1 の実施例の電子装置においては、スティフナー 22 が、SUS310S や CDA Alloy C15150 のような  $13 \times 10^{-6} \sim 17 \times 10^{-6} / K$  の熱膨脹率を有する金属から構成されており、半導体パッケージ全体の熱膨脹率が、マザーボードであるガラスエポキシ配線基板 27 の熱膨脹率と近似した値となっているので、周期的な熱負荷が加えられたときに、半導体パッケージとマザーボードとを接続するはんだパンプ 26 の歪みが 3% 以下と小さく、接続部が高い信頼性を有する。

### 【0037】

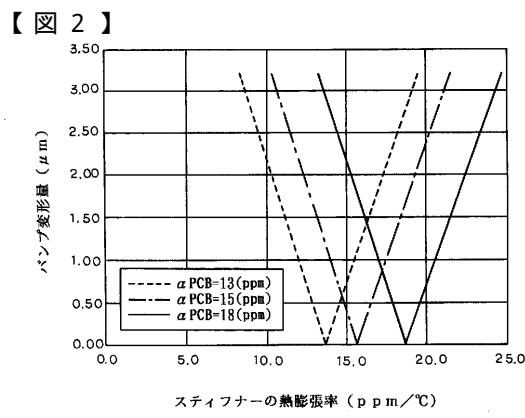

次に、具体的な効果をより明らかにするために、図 1 に示す構造の電子装置において、スティフナーを熱膨脹率の異なる種々の金属により構成した構造をシミュレーションし、温度サイクル試験（-65 ~ 120）を行なった。すなわち、スティフナーの厚さを 250  $\mu m$ 、接着剤層の厚さを 100  $\mu m$  とし、スティフナーを構成する金属材料の熱膨脹率を変えた半導体パッケージ（パッケージサイズ 35mm × 35mm）を、 $13 \times 10^{-6} / K$  (13ppm/K)、15ppm/K および 18ppm/K の熱膨脹率を有するガラスエポキシ配線基板上にそれぞれ搭載・実装した電子装置において、-65 × 30 分次いで 120 × 30 分の温度サイクルを繰り返した後のはんだパンプの変形量を、シミュレーションにより求めた。結果を図 2 に示す。

40

### 【0038】

この結果から、スティフナーを SUS310S や CDA Alloy C15150 のような熱膨脹率が 13 ~ 17ppm/K の金属により構成した実施例の電子装置では、マザーボードであるガラスエポキシ配線基板の熱膨脹率が、13ppm/K、15ppm/K あるいは 18ppm/K のいずれであっても、17ppm/K

50

K以上熱膨脹率を有する金属(SUS304)によりスティフナーが構成された従来の電子装置に比べて、はんだバンプの変形量が著しく小さくなっていることがわかる。したがって、実施例の電子装置は、従来の電子装置に比べて、数倍から10数倍の回数の温度サイクルに耐え得ることがわかる。

【0039】

実際に、スティフナーの構成材料としてCDA Alloy C15150を使用し、図1に示す電子装置を作製して温度サイクル試験(-65 ~ 120)を行なったところ、1000サイクルを越えた時点でも、はんだバンプに疲労破壊の発生が認められず、信頼性の高い接続が保持されていることが確認された。

【0040】

また、第1の実施例に使用した半導体パッケージにおいては、スティフナーを構成する剛性材料として金属が使用されているが、金属は、他の剛性材料(例えばセラミック)に比べて、高い熱伝導率を有し、放熱性が良好であるうえに、成形・加工性が良好で曲げ加工や切断加工が容易であり、さらに平坦性が良く、反り等が生じても元の平坦面に戻しやすいという種々の利点を有している。したがって、平坦性が良好なスティフナーを容易に成形することができ、放熱性の良好な半導体パッケージを得ることができる。

【0041】

スティフナーを構成する剛性材料として、金属(例えば、CDA Alloy C15150)とセラミック(例えば、アルミナ)とをそれぞれ選択し、それらの特性を比較したものを、以下の表1に示す。

【0042】

【表1】

|                 | 実施例              | 比較例                           |

|-----------------|------------------|-------------------------------|

| スティフナーの構成材料     | CDA Alloy C15150 | アルミナ                          |

| 熱膨脹率(ppm/°C)    | 16.7             | 7.0                           |

| 放熱性-熱伝導率(W・m/K) | 373              | 15~20                         |

| 成形・加工性          | 良好<br>曲げ加工しやすい   | 切断端面に亀裂が生じやすい<br>キャップ形状の成形不可能 |

| 平坦性             | 良好<br>平坦面に戻しやすい  | 不良<br>反りやすく、平坦面に戻しにくい         |

次に、本発明の第2の実施例について説明する。

【0043】

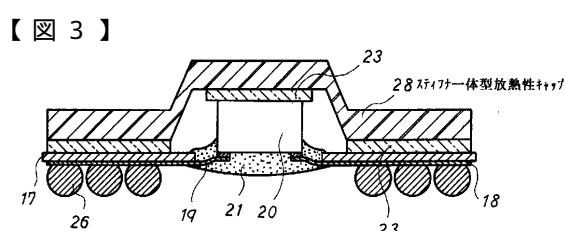

図3は、本発明の第2の実施例に係る半導体パッケージの要部を断面的に示したものである。なお、図3において、図1と同一の部分には同一の符号を付して、説明を省略する。

【0044】

この実施例の半導体パッケージでは、半導体素子20および絶縁フィルム17の上側に、形状保持性を有する放熱キャップ(スティフナータイプ放熱キャップ)28が配置され、この放熱キャップ28が、熱可塑性ポリエステル系樹脂等から成る接着剤層23を介して、半導体素子20の上面および絶縁フィルム17の上面に接着されている。そして、このスティフナータイプ放熱キャップ28が、SUS310SやCDA Alloy C15150のような、 $13 \times 10^{-6}$  ~  $17 \times 10^{-6}$  / Kの熱膨脹率を有する金属により構成されている。

【0045】

この実施例の半導体パッケージにおいても、これをガラスエポキシ配線基板27上に搭載し、はんだバンプ26を介して所要の接続を行なうことで、信頼性の高い接続が得られる。すなわち、第2の実施例の半導体パッケージの外部接続端子(接続パッド)と、マザー

10

20

30

40

50

ボードであるガラスエポキシ配線基板27の接続パッドとを、はんだバンプ26により電気的・機械的に接続した電子装置では、熱サイクル時にはんだバンプ26に応力集中による歪みが生じにくく、信頼性の高い接続が保持される。

【0046】

また、第2の実施例の半導体パッケージでは、スティフナーと放熱性のカバープレートとが重ねて配置される代わりに、これらの機能を併せ持ったスティフナータイプ放熱キャップ28が配設され、かつこれがSUS310SやCDA Alloy C15150のような金属から構成されているので、半導体パッケージおよびパッケージが搭載された電子装置全体を薄くすることが可能であるうえに、放熱キャップの成形が容易であり、製造工程が簡略化される。また、部品点数が少なくて済む。さらに、スティフナータイプ放熱キャップ28と絶縁フィルム17との接着面積が大きく、放熱経路の断面積が大きくなっているので、放熱性が良好である。

【0047】

なお、本発明は、前記した第1および第2の実施例の半導体パッケージおよび電子装置に限定されるものではなく、発明の趣旨を逸脱しない範囲でいろいろに変形させることができる。例えばマザーボードとして、ガラスエポキシ配線基板以外に、ガラスポリイミド配線基板やガラスBT樹脂配線基板のようなガラス樹脂配線基板、あるいはアルミナや窒化アルミニウムのようなセラミックを絶縁基材とするセラミック配線基板を使用することができる。

【0048】

【発明の効果】

以上の説明から明らかなように、本発明の電子装置によれば、形状保持板または形状保持性を有する被覆部材の構成材料として、マザーボードと近似した熱膨脹率を有する金属が使用されており、半導体パッケージ全体の熱膨脹率がマザーボードの熱膨脹率とほぼ等しくなっているので、実際の使用環境等において、周期的に印加される熱的な負荷に起因して接続部に生じる応力を緩和することができる。したがって、半導体パッケージとマザーボードとの接続の信頼性が向上される。

【0049】

また、本発明の半導体パッケージによれば、これをマザーボードに搭載した場合に、形状保持板または形状保持性を有する被覆部材の熱膨脹率とマザーボードの熱膨脹率との差に起因して生じる応力を緩和することができるので、接続部であるはんだボール等のバンプの歪み等が抑制され、疲労破壊が生じにくくなる。したがって、電子装置の接続信頼性を大きく向上させることができる。

【図面の簡単な説明】

【図1】本発明の第1の実施例に係る電子装置の要部の構成を示す断面図。

【図2】図1に示す電子装置において、スティフナーを熱膨脹率の異なる金属により構成して、シミュレーションにより温度サイクル試験を行なった結果を示すグラフ。

【図3】本発明の第2の実施例に係る半導体パッケージの要部の構成を示す断面図。

【図4】従来からのTape-BGA型半導体パッケージの構成を示す斜視図。

【図5】QFPをマザーボードに実装した電子装置の断面図。

【符号の説明】

- 17 ..... 絶縁樹脂フィルム

- 17a ..... デバイスホール

- 19 ..... インナーリード

- 20 ..... 半導体素子

- 21 ..... 樹脂封止層

- 22 ..... スティフナー

- 23 ..... 接着剤層

- 24 ..... カバープレート

- 26 ..... はんだバンプ

10

20

30

40

50

- 27 ガラスエポキシ配線基板

28 スティフナ一体型放熱キャップ

---

フロントページの続き

審査官 藤原 敬士

(56)参考文献 特開平09-181209 (JP, A)

特開平10-303339 (JP, A)

特開平08-037204 (JP, A)

特開平10-065040 (JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 23/12 501

H01L 23/12

H01L 21/60 311

H05K 1/18