(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4536718号

(P4536718)

(45) 発行日 平成22年9月1日(2010.9.1)

(24) 登録日 平成22年6月25日(2010.6.25)

(51) Int.Cl.

G06F 9/455 (2006.01)

G06F 9/30 (2006.01)

F 1

G06F 9/44 310A

G06F 9/30 310E

請求項の数 20 (全 26 頁)

(21) 出願番号 特願2006-506194 (P2006-506194)

(86) (22) 出願日 平成16年4月28日 (2004.4.28)

(65) 公表番号 特表2006-525572 (P2006-525572A)

(43) 公表日 平成18年11月9日 (2006.11.9)

(86) 國際出願番号 PCT/GB2004/001824

(87) 國際公開番号 WO2004/097631

(87) 國際公開日 平成16年11月11日 (2004.11.11)

審査請求日 平成19年4月19日 (2007.4.19)

(31) 優先権主張番号 0310180.5

(32) 優先日 平成15年5月2日 (2003.5.2)

(33) 優先権主張国 英国(GB)

(31) 優先権主張番号 0326437.1

(32) 優先日 平成15年11月13日 (2003.11.13)

(33) 優先権主張国 英国(GB)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】 プログラム・コード変換用の中間表現を生成するための改善されたアーキテクチャ

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサと該プロセッサに結合されたメモリとを有するとともに、目的コンピューティング環境において使用され、対象コンピューティング環境において適切な対象プログラム・コードをトランスレートして、前記目的コンピューティング環境に適切な目的プログラム・コードを生成するためのトランスレータ装置であって、

前記対象プログラム・コードにおける命令をデコードするように構成されたデコーディング機構と、

前記デコードされた命令の中間表現を生成するように構成された中間表現生成機構であって、該生成機構は、前記中間表現における複数のIRノードを、少なくともベース・ノードおよび複合ノードを含む複数の可能なタイプのIRノードから選択された対象プログラム・コードの命令によって行われる式、計算、および処理の抽象表現として設けることを含み、前記ベース・ノードのセマンティクスを、より単純なセマンティクスを表わす他のノードに分解することができないように、前記ベース・ノードは、対象プログラム・コードの最も基本的なセマンティクスを表わし、前記複合ノードによって、対象プログラム・コードにおける複合命令のセマンティクスは、ベース・ノード表現の場合よりもコンパクトに表現される、中間表現生成機構と、

前記デコードされた対象プログラム・コードにおける個々の命令に対する中間表現においてどのタイプのIRノードを生成するのかを決定するように構成された中間表現タイプ決定機構と、

10

20

を備えるトランスレータ装置。

**【請求項 2】**

前記ベース・ノードは、複数の可能な対象アーキテクチャに渡って汎用的である、請求項 1 に記載のトランスレータ装置。

**【請求項 3】**

前記複合ノードは、直接タイプ命令を表わし、該直接タイプ命令では、定数オペランド値が直接フィールドにおいて直接タイプ命令自身にエンコードされている、請求項 1 に記載のトランスレータ装置。

**【請求項 4】**

前記複合ノードを、複数のベース・ノードに分解して、前記デコードされたプログラム・コードにおける命令の同じセマンティクスを表わすようにすることができる、請求項 1 に記載のトランスレータ装置。 10

**【請求項 5】**

前記プログラム・コードは、対象アーキテクチャによって実行されるように構成され、前記中間表現生成機構は、さらに、対象アーキテクチャ上で対応して構成可能な特性に対してのみ複合ノードを生成するための複合ノード生成機構を含む、請求項 1 に記載のトランスレータ装置。

**【請求項 6】**

前記複数の可能なタイプの I R ノードは、さらに、ポリモーフィック・ノードを含む、請求項 1 に記載のトランスレータ装置。 20

**【請求項 7】**

前記対象プログラム・コードは、対象アーキテクチャ上での実行のために構成されるとともに、目的アーキテクチャ上での実行のために目的コードに動的にトランスレートされ、前記中間表現生成機構は、さらに、

ポリモーフィック・ノードを含むように中間表現を生成するためのポリモーフィック・ノード生成機構であって、前記ポリモーフィック・ノードは、前記対象コードにおける特定の命令に特有の目的アーキテクチャの関数に対する関数ポインタを含む、ポリモーフィック・ノード生成機構、

を含む、請求項 6 に記載のトランスレータ装置。

**【請求項 8】**

前記ポリモーフィック・ノード生成機構は、目的アーキテクチャの特性によって、特定の対象命令のセマンティクスが、ベース・ノードとして実現されたときに失われる場合に、ポリモーフィック・ノードを生成する、請求項 7 に記載のトランスレータ装置。 30

**【請求項 9】**

各ポリモーフィック・ノードは、前記対象コードにおける特定の命令と目的アーキテクチャの関数との組み合わせに特有である、請求項 7 に記載のトランスレータ装置。

**【請求項 10】**

前記中間表現タイプ決定機構は、さらに、ポリモーフィック・ノードとして実現すべきポリモーフィック命令のリスト上の命令に対応する対象コードにおける命令を識別するためのポリモーフィック識別機構を含み、 40

対象命令が、前記ポリモーフィック命令のリスト上の命令に対応する場合、前記中間表現生成機構は、前記ポリモーフィック命令のリスト上の命令に対応する対象命令に対してのみポリモーフィック・ノードを生成する、請求項 7 に記載のトランスレータ装置。

**【請求項 11】**

前記複数の可能なタイプの I R ノードは、さらに、アーキテクチャ特定ノードを含む、請求項 1 に記載のトランスレータ装置。

**【請求項 12】**

前記対象プログラム・コードは、対象アーキテクチャ上での実行のために構成されるとともに、目的アーキテクチャ上での実行のために目的コードに動的にトランスレートされ、 50

前記中間表現生成機構は、さらに、

対象アーキテクチャと目的アーキテクチャとの特定の組み合わせに特有のアーキテクチャ特定ノードを含むように中間表現を生成するためのアーキテクチャ特定ノード生成機構を含む、請求項11に記載のトランスレータ装置。

**【請求項13】**

前記中間表現生成機構は、

最初に、前記対象プログラム・コードにおけるすべての命令を、複数の対象アーキテクチャ特定ノードとして表わすことであって、各対象アーキテクチャ特定ノードは、前記対象プログラム・コードにおける個々の命令に対応する、表わすこと、

前記対象プログラム・コードにおける命令が、目的アーキテクチャに特化された変換関数を与える命令であるか否かを判断すること、

10

目的アーキテクチャに特化された変換関数を与えると判断された命令に対しては、対象アーキテクチャ特定ノードを目的アーキテクチャ特定ノードに変換すること、

目的アーキテクチャに特化されたコード生成関数を与えるとは識別されない残りの対象アーキテクチャ特定ノードから、ベース・ノードを生成すること、

を実行するように構成されている、請求項12に記載のトランスレータ装置。

**【請求項14】**

前記目的アーキテクチャ特定ノードから、目的アーキテクチャに対して特化されている対応する目的コードを生成するための特化目的コード生成機構、

をさらに備える、請求項12に記載のトランスレータ装置。

20

**【請求項15】**

前記ベース・ノードから、目的アーキテクチャに対して特化されていない対応する目的コードを生成するための非特化目的コード生成機構、

をさらに備える、請求項12に記載のトランスレータ装置。

**【請求項16】**

前記生成されたポリモーフィック・ノードによって、目的コードを生成する間に割り当てられるべきレジスタが特定される、請求項7に記載のトランスレータ装置。

**【請求項17】**

前記生成されたポリモーフィック・ノードを汎用的なカーネル最適化において利用することは、前記ポリモーフィック・ノードにおける関数ポインタからの情報を推測することによって行なわれ、該情報は、推測されない場合には、前記ポリモーフィック・ノードからは決定不可能な場合もある、請求項7に記載のトランスレータ装置。

30

**【請求項18】**

対象命令が、前記ポリモーフィック命令のリスト上の命令に対応する場合、前記中間表現生成機構は、前記ポリモーフィック命令のリスト上の命令に対応する対象命令に対してポリモーフィック・ノードまたはベース・ノードのいずれかを生成する、請求項10に記載のトランスレータ装置。

**【請求項19】**

対象コードの目的コードへのトランスレーションの間にコンピュータが中間表現を生成する方法であって、

40

前記コンピュータのデコーディング機構が、対象コードにおける複数の命令をデコードするステップと、

前記コンピュータの中間表現生成機構が、前記デコードされた命令の中間表現をメモリ内に生成するステップであって、該生成するステップは、前記中間表現における複数のIRノードを、少なくともベース・ノードおよび複合ノードを含む複数の可能なタイプのIRノードから選択された対象コードの命令によって行われる式、計算、および処理の抽象表現として設けることを含み、前記ベース・ノードのセマンティクスを、より単純なセマンティクスを表わす他のノードに分解することができないように、前記ベース・ノードは、対象コードの最も基本的なセマンティクスを表わし、前記複合ノードによって、プログラム・コードにおける複合命令のセマンティクスは、ベース・ノード表現の場合よりもコ

50

ンパクトに表現される、前記生成するステップと、

前記コンピュータの中間表現タイプ決定機構が、前記複数の可能なタイプのIRノードから少なくとも一つのタイプのIRノードを決定するステップであって、前記デコードされた対象コードにおける個々の命令に対する中間表現において生成するように決定する、前記決定するステップと

を含む、前記方法。

#### 【請求項 20】

対象コードの目的コードへのトランスレーションの間に中間表現を生成するコンピュータに、請求項19に記載の方法の各ステップを実行させるためのコンピュータ・プログラム。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、コンピュータおよびコンピュータ・ソフトウェアの分野に関する。より詳細には、たとえばコード・トランスレータ、エミュレータ、アクセラレータにおいて有用なプログラム・コード変換方法および装置に関する。

##### 【背景技術】

##### 【0002】

組込型および非組込型CPUの市場では、主流的な命令セット・アーキテクチャ(ISA : Instruction Set Architecture)に対する大量のソフトウェアが存在する。これらのソフトウェアを、性能を上げるために「アクセラレート」することもできるし、より優れたコスト/性能の利点を示す無数の高性能なプロセッサに「トランスレート」することもできる。ただし、このようなプロセッサは、関連するソフトウェアに透過的にアクセスできなければならない。主流的なCPUアーキテクチャもまた、そのISAに歩調を合わせられるため、性能または市場の範囲を発展させることができず、「複合CPU(Synthetic CPU)」共通アーキテクチャの利点を受ける。

20

##### 【0003】

第1のタイプのコンピュータ・プロセッサ(「対象(subject)」プロセッサ)用に書かれたプログラム・コードを、第2のタイプのプロセッサ(「目的(target)」プロセッサ)上で実行することが望まれることは珍しいことではない。この場合、対象プログラムを目的プロセッサ上で実行できるように、エミュレータまたはトランスレータを用いて、プログラム・コードのトランスレーションを行なう。エミュレータを用いて対象プロセッサをエミュレートすることによって、対象プログラムを対象プロセッサ上でネイティブに実行しているかのような仮想環境が実現される。

30

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0004】

従来では、いわゆるベース・ノードを用いた実行時トランスレーションの間に、対象コードをコンピュータ・プログラムの中間表現に変換している。このことは、「プログラム・コード変換」と題された出願公開WO00/22521に、その出願の図1~5に関連して記載されている。中間表現「IR(Intermediate Representation)」は、コンピュータ業界で広く使用されている用語であり、プログラムを表現することができる抽象的なコンピュータ言語の形態を指すものである。しかし、中間表現「IR」は、何らかの特定のプロセッサに特有でもなければ、何らかの特定のプロセッサ上で直接実行されることが意図されたものでもない。中間表現を用いて前述のアクセラレーション、トランスレーション、および共通アーキテクチャ能力を促進するプログラム・コード変換方法および装置が、たとえば、前述の出願公開WO00/22521において取り扱われている。

40

##### 【課題を解決するための手段】

##### 【0005】

本発明によれば、添付の特許請求の範囲で述べるような装置および方法が提供される。

50

本発明の好ましい特徴は、従属請求項、および以下に述べる説明から明らかとなる。

以下、本発明によるプログラム・コード変換用の改善されたアーキテクチャの種々の実施形態による実現可能な種々の態様および優位性の概要を示す。この概要是、当業者が、後に続く本発明の詳細な説明を迅速に理解するための助けとなる導入部として設けられている。この概要是、添付の特許請求の範囲を限定するものでもなければ、限定することを意図したものでもない。

#### 【0006】

後述する種々の実施形態は、プログラム・コード変換装置用の改善されたアーキテクチャに関するとともに、対象コンピューティング環境において実行可能な対象コードを、目的コンピューティング環境において実行可能な目的コードに変換するための関連方法に関する。プログラム・コード変換装置によって、対象コードの中間表現（「IR」）が形成される。次に、中間表現（「IR」）を、目的コンピューティング環境に対して最適化して、目的コードをより効率的に生成できるようにする。変換に関する対象および目的コンピューティング環境の特定のアーキテクチャに依存して、一実施形態のプログラム・コード変換装置は、中間表現において、以下のタイプのIRノードのうちのどれを生成するかを、決定する。ベース・ノード、複合ノード、ポリモーフィック・ノード、およびアーキテクチャ特定ノードである。初期設定では、プログラム・コード変換アーキテクチャは、中間表現を形成するときにベース・ノードを生成する。これは、別のタイプのノードの方が、実行されている特定の変換に対してより適切であると判断される場合を除いて、行なわれる。

10

#### 【0007】

ベース・ノードは、対象コードを実行する任意の対象アーキテクチャのセマンティクスを表わすのに必要最小限のノードの組（すなわち抽象式）を与えることにより、RISCと同様の機能を提供する。複合ノードは、対象コードを実行する対象アーキテクチャのCISCと同様のセマンティクスを、ベース・ノードよりもコンパクトな表現で表わす汎用ノードである。すべての複合ノードは、同じセマンティクスを有するベース・ノード表現に分解することができるが、複合ノードは、トランスレータの性能を向上させるために、複合命令のセマンティクスを单一のIRノード内に保持する。複合ノードによって、基本的に、対象コード内のCISCと同様の命令に対するベース・ノードの組が増える。ベース・ノードおよび複合ノードは両方とも、可能な対象および目的アーキテクチャの広い範囲に渡って汎用的に用いられる。そのため、ベース・ノードおよび複合ノードから構成される対応するIRツリー上で、汎用的な最適化を行なうことができる。

20

#### 【0008】

プログラム・コード変換装置が、中間表現においてポリモーフィック・ノードを用いるのは、目的コンピューティング環境の特性が原因で、特定の対象命令のセマンティクスが、汎用的なIRノードとして実現されたときに失われる場合である。ポリモーフィック・ノードには、ソース・コード内の特定の対象命令に特有の目的コンピューティング環境の関数に対する関数ポインタが含まれる。プログラム・コード変換装置がさらに、アーキテクチャ特定ノードを用いるのは、特定の目的コンピューティング環境に対する特化されたコード生成関数を実行するために、目的に特化された変換コンポーネントを与えるためである。

30

#### 【0009】

以下で説明する改善されたIR生成方法によって、プログラム・コード変換装置を、最適なレベルの性能を維持しトランスレーションの速度を最大にする一方で、任意の対象および目的プロセッサ・アーキテクチャの組み合わせに対して構成することができる。

#### 【発明を実施するための最良の形態】

#### 【0010】

本発明をより良好に理解するために、かつ本発明の実施形態をどのように実行に移すかを示すために、次に、添付図面を一例として参照する。

以下の説明は、いかなる当業者であっても本発明を製造し、かつ用いることができるよ

40

50

うに設けられており、また発明を行なう発明者が意図する最良のモードが述べられている。しかし、種々の変更が、当業者には容易に分かるであろう。何故なら、プログラム・コード変換装置に対する改善されたアーキテクチャを提供するために、本明細書では本発明の一般的原理を具体的に規定しているからである。

#### 【0011】

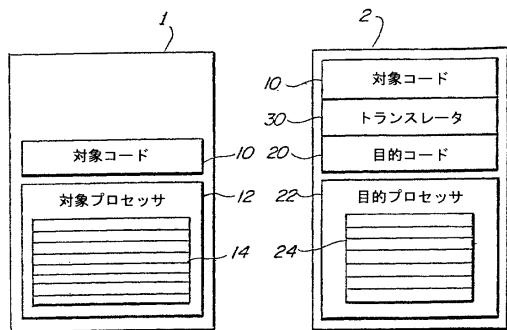

図1を参照すると、コンピューティング環境の例として、対象コンピューティング環境1および目的コンピューティング環境2を含むものが示されている。対象環境1では、対象コード10は、対象プロセッサ12上でネイティブに実行可能である。対象プロセッサ12には、対象レジスタ14の組が含まれている。ここで、対象コード10は、対象コード10と対象プロセッサ12との間に中間層（たとえば、コンパイラ）を有するような任意の好適な言語で表わされても良い。これは、当業者には良く知られていることである。10

#### 【0012】

対象コード10を、目的コンピューティング環境2において実行することが望ましい。目的コンピューティング環境2には、目的レジスタ24の組を用いる目的プロセッサ22が設けられている。これら2つのプロセッサ12, 22は、本質的に非互換性であり、異なる命令セットを用いても良い。したがって、目的コンピューティング環境2には、その非互換性の環境において対象コード10を実行できるように、プログラム・コード変換アーキテクチャ30が設けられている。プログラム・コード変換アーキテクチャ30には、トランスレータ、エミュレータ、アクセラレータ、または一つのプロセッサ・タイプ用に構成されたプログラム・コードを他のタイプのプロセッサ上で実行可能なプログラム・コードに変換するのに好適な任意の他のアーキテクチャが含まれていても良い。以下、本発明を説明する上で、プログラム・コード変換アーキテクチャ30を「トランスレータ30」と呼ぶ。2つのプロセッサ12, 22は、たとえばアクセラレータの場合には、同じアーキテクチャ・タイプになり得るに注意されたい。20

#### 【0013】

トランスレータ30は、対象コード10に対してトランスレーション・プロセスを行なって、トランスレート済み目的コード20を与え、目的プロセッサ22が実行できるようになる。好適には、トランスレータ30はバイナリ・トランスレーションを行なう。バイナリ・トランスレーションでは、対象プロセッサ12に適した実行可能なバイナリ・コードの形態の対象コード10が、目的プロセッサ22に適した実行可能なバイナリ・コードにトランスレートされる。トランスレーションは、静的に行なわれても良いし、動的に行なわれても良い。静的なトランスレーションの場合には、プログラム全体をトランスレートすることが、トランスレート済みプログラムを目的プロセッサ上で実行する前に行なわれる。これには、著しい遅延が伴う。したがって、トランスレータ30は好ましくは、対象コード10の小さいセクションを動的にトランスレートして、目的プロセッサ22上で即座に実行できるようにする。これは、はるかに効率的である。何故なら、対象コード10の大きなセクションは、実際には用いられないか、あるいはめったに用いられないからである。30

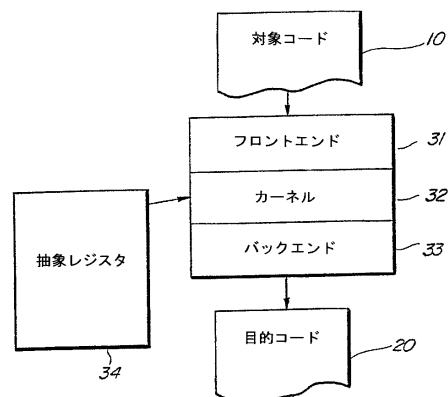

#### 【0014】

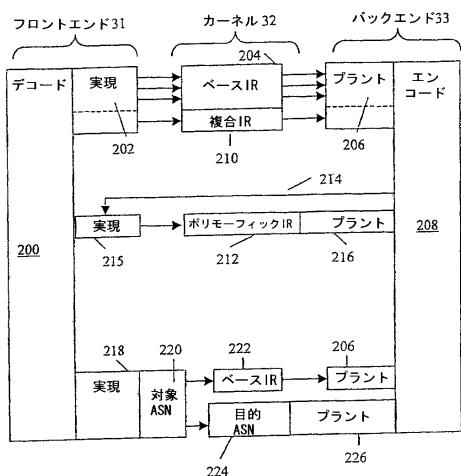

次に、図2を参照すると、トランスレータ30の好ましい実施形態が詳細に示されている。トランスレータ30には、フロントエンド31、カーネル32、およびバックエンド33が含まれている。フロントエンド31は、対象コードに関連する対象プロセッサ12に特有に構成される。フロントエンド31は、対象コード10の所定のセクションを選択して、汎用的な中間表現のブロック（「IRブロック」）を与える。カーネル32は、フロントエンド31が生成する各IRブロックを、最適化技法を用いることによって最適化する。これは、当業者であれば容易に分かることである。バックエンド33は、最適化されたIRブロックをカーネル32から取得して、目的プロセッサ22が実行可能な目的コード20を生成する。40

#### 【0015】

好適には、フロントエンド31は、対象コード10を基本ブロックに分割する。各基本50

ブロックは、一意的なエントリ・ポイントにおける第1の命令と一意的なエグジット・ポイントにおける最後の命令との間の、連續的な命令（たとえばジャンプ、コール、またはブランチ命令）の組である。カーネル32は、単一ユニットとして共に処理されるべき2つ以上の基本ブロックを含むグループ・ブロックを選択しても良い。さらにフロントエンド31は、異なるエントリ条件の下での対象コードの同じ基本ブロックを表わす等ブロック（iso-block）を形成しても良い。使用時には、対象コード10の第1の所定のセクションが、たとえば基本ブロックとして識別され、トランスレーション・モードにおいて、目的プロセッサ22上で実行されるトランスレータ30によって、トランスレートされる。次いで、目的コード20の最適化され、かつトランスレート済みの対応するブロックが、目的プロセッサ22によって実行される。

10

#### 【0016】

トランスレータ30には、複数の抽象レジスタ34が含まれており、カーネル32において適切に設けられている。抽象レジスタ34は、対象コード10を実行するための対象プロセッサ12内で使用される物理的な対象レジスタ14に相当する。抽象レジスタ34によって、エミュレートされている対象プロセッサ12の状態が規定される。その規定は、対象プロセッサ・レジスタ上での対象コード命令の予想される効果を表わすことによって行なわれる。

#### 【0017】

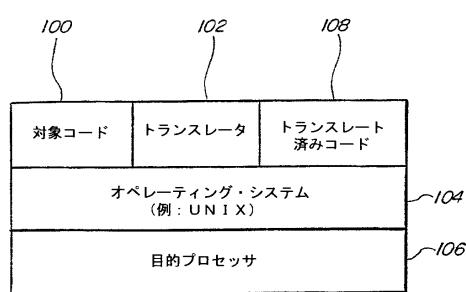

図3に、以上のような実装を採用した構造を示す。図示したように、コンパイルされたネイティブの対象コードが、適切なコンピュータ・メモリ記憶媒体100内に存在することが示されている。特定のかつ代替的なメモリ記憶機構は、当業者には良く知られている。ソフトウェア・コンポーネントには、トランスレートされるべきネイティブの対象コード、トランスレータ・コード、トランスレート済みコード、およびオペレーティング・システムが含まれる。トランスレータ・コード、すなわちトランスレータを実施するコンパイルされたバージョンのソース・コードは、適切なコンピュータ・メモリ記憶媒体102上に、同様に存在している。トランスレータは、メモリに記憶されたオペレーティング・システム104、たとえ目的プロセッサ106（通常はマイクロプロセッサまたは他の好適なコンピュータ）上で実行されるUNIX（登録商標）とともに、実行される。図3に示した構造は典型例に過ぎず、たとえば本発明による方法およびプロセスを、オペレーティング・システムとともに存在するか、あるいはその下に存在するコードにおいて実施しても良いことは理解されよう。トランスレート済みコードは、適切なコンピュータ・メモリ記憶媒体108内に存在することが示されている。対象コード、トランスレータ・コード、オペレーティング・システム、トランスレート済みコード、および記憶機構は、多種多様のタイプのいかなるものであっても良い。これは当業者には知られている。

20

#### 【0018】

本発明の好ましい実施形態においては、実行時にプログラム・コード変換が動的に行なわれる間に、トランスレート済みプログラムが、目的コンピューティング環境において実行されている。トランスレータ30は、トランスレート済みプログラムに従って実行される。トランスレート済みプログラムの実行バスは、以下のステップを含む制御ループである。トランスレータ・コードを実行して、対象コードのブロックをトランスレート済みコードにトランスレートするステップと、その後に、そのトランスレート済みコードのブロックを実行するステップである。トランスレート済みコードの各ブロックの最後には、トランスレータ・コードに制御を戻す命令が含まれている。言い換えれば、トランスレートするステップと、その後に対象コードを実行するステップとが組み合わせられて、対象プログラムの一部のみが一度にトランスレートされるようになっている。

30

#### 【0019】

トランスレータ30のトランスレーションの基本単位は、基本ブロックである。すなわち、トランスレータ30が行なう対象コードのトランスレーションは、一度に1つの基本ブロックである。基本ブロックは正式には、厳密に1つのエントリ・ポイントと厳密に1つのエグジット・ポイントとを有するコードのセクションとして定義される。これによっ

40

50

て、そのブロック・コードが単一の制御バスに制限される。この理由により、基本ブロックは、制御フローの基本単位である。

#### 【0020】

##### 中間表現（IR）ツリー

トランスレート済みコードを生成するプロセスでは、対象命令シーケンスに基づいて、中間表現（「IR」）ツリーが生成される。IRツリーには、対象プログラムによって計算された式と対象プログラムによって実行された処理との抽象表現であるノードが含まれる。次に、トランスレート済みコードが、IRツリーに基づいて生成される。本明細書で説明するIRノードを集合は、俗稱的には「ツリー」と呼ばれる。なお正式には、このような構造は実際には、有向非巡回グラフ（DAG：Directed Acyclic Graph）であり、ツリーではないことに注意されたい。ツリーの正式な定義では、各ノードのペアレントは高々1つである必要がある。説明する実施形態では、IRが生成される間に共通部分式の除去が用いられるため、ノードは複数のペアレントを有することが多い。たとえば、フラグに影響を与える命令結果のIRは、2つの抽象レジスタ（デスティネーション・対象レジスタおよびフラグ結果パラメータに対応するもの）によって参照されても良い。

10

#### 【0021】

たとえば、対象命令（add %r1, %r2, %r3）によって、対象レジスタ%r2および%r3の内容の加算が行なわれて、結果が対象レジスタ%r1内に記憶される。すなわち、この命令は、抽象式「%r1 = %r2 + %r3」に対応する。この例には、抽象レジスタ%r1の定義が含まれる。その定義には、命令オペランド%r1および%r2を表わす2つの部分式が含まれる加算式が含まれている。対象プログラムに関連して言えば、これらの部分式は、それより前の他の対象命令に対応していても良いし、あるいはそれらの部分式は、現在の命令の詳細、たとえば直接定数値を表していても良い。

20

#### 【0022】

「加算」命令が構文解析されると、加算に対する抽象的な数学的オペレータに対応して、新たな「Y」IRノードが生成される。「Y」IRノードには、オペランド（対象レジスタに保持され、部分式ツリーとして表わされる）を表わす他のIRノードに対する参照が記憶される。「Y」ノード自体は、適切な対象レジスタ定義（%r1に対する抽象レジスタ、命令のデスティネーション・レジスタ）によって参照される。当業者であれば理解できるように、一実施形態においては、トランスレータは、オブジェクト指向のプログラミング言語、たとえばC++を用いて具体化される。たとえば、IRノードは、C++オブジェクトとして具体化され、他のノードに対する参照は、これら他のノードに対応するC++オブジェクトに対するC++参照として具体化される。したがって、IRツリーは、互いに様々に参照し合うIRノード・オブジェクトの集合として具体化される。

30

#### 【0023】

##### 抽象レジスタ

さらに、説明している実施形態においては、IR生成は、抽象レジスタ34の組を用いる。これらの抽象レジスタ34は、対象アーキテクチャの特定の特性に対応する。たとえば、対象アーキテクチャ12上の各物理レジスタ14に対して、一意的な抽象レジスタ34が存在する。抽象レジスタ34は、IR生成の間にIRツリーに対するプレースホルダとして機能する。たとえば、対象命令シーケンスにおける所定の点における対象レジスタ%r2の値は、対象レジスタ%r2に対する抽象レジスタ34に関連する特定のIR式ツリーによって表わされる。一実施形態においては、抽象レジスタ34は、C++オブジェクトとして具体化される。C++オブジェクトは、特定のIRツリーに、そのツリーのルート・ノード・オブジェクトに対するC++参照を介して関連する。

40

#### 【0024】

前述した命令シーケンスの例では、「加算」命令に先行する対象命令を構文解析する間に、トランスレータ30によって、%r2および%r3の値に対応するIRツリーがすでに生成されている。言い換えれば、%r2および%r3の値を計算する部分式は、IRツリーとしてすでに表わされている。「add %r1, %r2, %r3」命令に対するIR

50

ツリーを生成するときには、新たな「Y」ノードには、%r<sub>2</sub>および%r<sub>3</sub>に対するIRサブツリーへの参照が含まれる。

#### 【0025】

抽象レジスタ34の実施は、トランスレータ30およびトランスレート済みコードの両方におけるコンポーネント間に分割される。トランスレータに関連して言えば、抽象レジスタは、IR生成の過程で用いられるプレースホルダである。これは、抽象レジスタ34が、特定の抽象レジスタ34が対応する対象レジスタ14の値を計算するIRツリーに関連するように、なされている。したがって、トランスレータにおける抽象レジスタ34は、IRノード・オブジェクトへの参照（すなわちIRツリー）を含むC++オブジェクトとして具体化されても良い。トランスレート済みコードに関連して言えば、抽象レジスタ34は、抽象レジスタ記憶装置内の特定の箇所であり、その箇所まで、かつその箇所から、対象レジスタ14の値は実際の目的レジスタ24と同期する。あるいは、抽象レジスタ記憶装置からロードされた値が存在する場合には、トランスレート済みコードにおける抽象レジスタ34は、トランスレート済みコードがレジスタ記憶装置に戻されて保存される前に実行されている間に、対象レジスタの値を一時的に保持する目的レジスタ26であると理解することができる。10

#### 【0026】

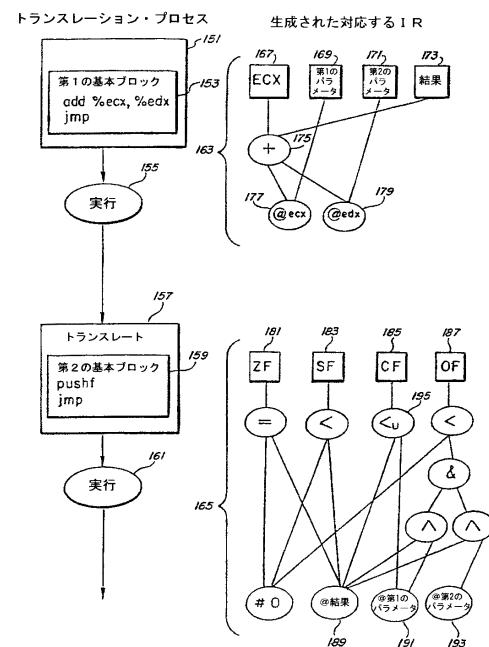

図4に、説明したプログラム・トランスレーションの例を示す。図4に示すのは、x86命令の2つの基本ブロックのトランスレーション、およびそのトランスレーションのプロセスにおいて生成される対応するIRツリーである。図4の左側に示すのは、トランスレーションを行なう間のエミュレータの実行パスである。トランスレータ30は、対象コードの第1の基本ブロック153を目的コードにトランスレートして(151)、次に、その目的コードを実行する(155)。目的コードの実行が終了すると、エミュレータに制御が戻される(157)。次に、トランスレータ30は、対象コードの次の基本ブロック159を目的コードにトランスレートして(157)、その目的コードを実行する(161)、等々。20

#### 【0027】

対象コードの第1の基本ブロック153を目的コードにトランスレートする過程151で、トランスレータ30は、その基本ブロックに基づいてIRツリー163を生成する。この場合に、IRツリー163は、フラグに影響を与える命令であるソース命令「add %eax, %edx」から生成される。IRツリー163を生成する過程で、この命令によって4つの抽象レジスタが定義される。すなわち、デスティネーション・レジスタ%ecx167、フラグに影響を与える第1の命令パラメータ169、フラグに影響を与える第2の命令パラメータ171、およびフラグに影響を与える命令の結果173である。「加算」命令に対応するIRツリーは、単純な「Y」（算術加算）オペレータ175であり、そのオペランドは、対象レジスタ%ecx177, %edx179である。30

#### 【0028】

第1の基本ブロックをエミュレートすると、フラグに影響を与える命令のパラメータおよび結果を記憶することによって、フラグが待ち状態に置かれる。フラグに影響を与える命令は、「add %ecx, %edx」である。命令のパラメータは、エミュレートされた対象レジスタ%ecx177, %edx179の現在の値である。使用される対象レジスタ177, 179の前にある「@」記号は、対象レジスタの値が、グローバル・レジスタ記憶装置の%ecx, %edxに対応する箇所から、それぞれ取り出されることを示す。この理由は、これらの特定の対象レジスタは、現在の基本ブロックによって事前にロードされてはいなかったからである。これらのパラメータの値は、第1のフラグ・パラメタ抽象レジスタ169と第2のフラグ・パラメタ抽象レジスタ171とに記憶される。加算操作175の結果は、フラグ結果抽象レジスタ173に記憶される。40

#### 【0029】

IRツリーが生成された後、対応する目的コードが、そのIRに基づいて生成される。汎用的なIRから目的コードを生成するプロセスは、当該技術分野において良く理解され50

ている。トランスレート済みブロックの最後に目的コードが挿入されている。これは、抽象レジスタ（フラグ結果 173、およびフラグ・パラメータ 169, 171に対するものを含む）を、グローバル・レジスタ記憶装置に保存するためである。目的コードが生成された後、トランスレート済みブロックは実行される（155）。

#### 【0030】

対象コードの第2の基本ブロック 159 をトランスレートする過程 157 で、トランスレータ 30 は、その基本ブロックに基づいて IR ツリー 165 を生成する。IR ツリー 165 は、ソース命令「pushf」から生成される。ソース命令「pushf」は、フラグを用いた命令である。「pushf」命令のセマンティクスは、すべての状態フラグの値をスタック上に記憶することである。こうするためには、各フラグを明確に計算する必要がある。そのため 4 つの状態フラグの値に対応した抽象レジスタが、IR を生成する間に定義される。すなわち、ゼロ・フラグ（「ZF : Zero Flag」）181、符号フラグ（「SF : Sign Flag」）183、キャリー・フラグ（「CF : Carry Flag」）185、およびオーバーフロー・フラグ（「OF : Overflow flag」）187 である。ノード 195 は、算術比較オペレータ「無符号未満」である。状態フラグの計算は、フラグに影響を与える事前の命令からの情報に基づいている。この場合、この命令は、第1の基本ブロック 153 からの「add %ecx, %edx」命令である。状態フラグの値を計算する IR 165 は、フラグに影響を与える命令の結果 189 およびパラメータ 191, 193 に基づいている。前述したように、フラグ・パラメータ・ラベルの前にある「@」記号は、これらの値を、使用前にグローバル・レジスタ記憶装置からロードするために、目的コードをエミュレータが挿入することを示す。10

#### 【0031】

したがって、第2の基本ブロックによって、フラグの値は強制的に規格化される。フラグの値は、（「pushf」命令をエミュレートする目的コードにより）計算および使用された後、グローバル・レジスタ記憶装置に記憶される。同時に、待ち状態のフラグ抽象レジスタ（パラメータおよび結果）は、フラグの値が明確に記憶されている（すなわち、フラグが規格化されている）という事実を反映するために、未定義の状態におかれる。20

#### 【0032】

図 5 に、トランスレーションにおいて使用され得る複数の異なるタイプの IR ノードを生成できるような、本発明の好ましい実施形態により形成されるトランスレータ 30 を示す。また、これらの異なるタイプの IR ノードの実施が、トランスレータ 30 のフロントエンド 31、カーネル 32、およびバックエンド 33 コンポーネントの間でどのように分散されるのかを示す。用語「実現する」は、対象コードの対象命令 10 がデコードされる（すなわち、構文解析される）ときに、フロントエンド 31 において行なわれる IR 生成を意味する。用語「プラントする」は、バックエンド 33 において行なわれる目的コード生成を意味する。30

#### 【0033】

なお、以下ではトランスレーション・プロセスを単一の対象命令に関して述べるが、これらの処理は実際には、前述したように、対象命令の基本ブロック全体に対して一度に行なわれる。言い換えれば、基本ブロック全体が最初にデコードされて IR フォレストが生成され、次にカーネル 32 によって、IR フォレスト全体に最適化が適用される。最後に、最適化された IR フォレストの 1 ノードに対する目的コード生成が、バックエンド 33 によって、一度に行なわれる。40

#### 【0034】

基本ブロックに対して IR フォレストを生成するとき、トランスレータ 30 は、所望のトランスレータ性能と、ソース・プロセッサおよび目的プロセッサの組み合わせの特定のアーキテクチャとに依存して、ベース・ノード、複合ノード、ポリモーフィック・ノード、もしくはアーキテクチャ特定ノード（ASN : Architecture Specific Node）、またはこれらの任意の組み合わせを生成しても良い。

#### 【0035】

10

20

30

40

50

ベース・ノード

ベース・ノードは、任意の対象アーキテクチャのセマンティクス（すなわち、式、計算、および処理）の抽象表現であり、対象アーキテクチャのセマンティクスを表わすのに必要な標準的または基本的なノードの最小の組を与えるものである。したがって、ベース・ノードによって、単純な縮小命令セット・コンピュータ（RISC : Reduced Instruction Set Computer）と同様の機能、たとえば「加算」処理が得られる。他のタイプのノードとは異なり、各ベース・ノードは縮小することができない。すなわち、これ以上分解して他のIRノードにすることはできない。またベース・ノードは、単純するために、すべてのバックエンド33上で、トランスレータ30によって容易に目的命令にトランスレートされる（すなわち、目的アーキテクチャ）。

10

## 【0036】

ベースIRノードのみを利用するときには、トランスレーション・プロセスは全体に、図5の上部（すなわち、「ベースIR」ブロック204を通過するパス）において行なわれる。フロントエンド31は、対象プログラム・コード10からの対象命令を、デコード・ブロック200においてデコードし、ベース・ノードからなる対応するIRツリーを、実現ブロック202において実現する（生成する）。次に、IRツリーは、フロントエンド31から、カーネル32におけるベースIRブロック204へ送られて、そこでIRフォレスト全体に最適化が適用される。ベースIRブロック204によって最適化されたIRフォレストは、ベース・ノードのみから構成されるため、任意のプロセッサ・アーキテクチャに対して完全に汎用的である。次に、最適化されたIRフォレストは、カーネル32におけるベースIRブロック204からバックエンド33へ送られる。そこでは、プラント・ブロック206において、各IRノードに対する対応する目的コード命令がプラント（生成）される。次に、目的コード命令は、エンコード・ブロック208によってエンコードされて、目的プロセッサが実行できるようにされる。

20

## 【0037】

前述したように、ベース・ノードはすべてのバックエンド33上において、目的命令に容易にトランスレートされる。またトランスレート済みコードは通常、ベース・ノードのみを利用することによって完全に生成される。ベース・ノードのみを用いることにより、トランスレータ30の実行は非常に迅速になるが、トランスレート済みコードにおける性能は最適なものとはならない。トランスレート済みコードの性能を高めるために、トランスレータ30を特化して、目的プロセッサ・アーキテクチャの特性を利用できるようにすることができる。特性の利用は、代替タイプのIRノード、たとえば複合ノード、ポリモーフィック・ノード、およびアーキテクチャ特定ノード（ASN）を用いることによってなされる。

30

## 【0038】

複合ノード

複合ノードは、対象アーキテクチャのセマンティクスを、ベース・ノードよりもコンパクトな表現で表わす汎用ノードである。複合ノードによって、「複合命令セット・コンピュータ（CISC : Complex Instruction Set Computer）と同様の機能、たとえば「ad d \_ imm」（レジスタおよび直接定数を加算する）が得られる。具体的には、複合ノードは通常、直接定数フィールドを有する命令を表わす。直接タイプの命令は、定数オペランドの値が、「直接」フィールドにおける命令自身にエンコードされる命令である。定数値が、直接フィールドに組み込まれるほどに十分に小さい場合には、このような命令によって、定数を保持するためにレジスタを1つ用いることが回避される。複合命令の場合には、複合ノードは、同じセマンティクスを特徴付ける同等なベース・ノード表現よりもはるかに少ないノードを用いて、複合命令のセマンティクスを表わすことができる。複合ノードは基本的に、同じセマンティクスを有するベース・ノード表現に分解することができるが、複合ノードは、直接タイプの命令のセマンティクスを単一のIRノードに保持するのに有用であるため、トランスレータ30の性能を向上させることができる。さらに、状況によっては、複合命令のセマンティクスは、複合命令をベース・ノードにより表わすこ

40

50

とによって失われる。そのため複合ノードは基本的に、このような「CISCと同様の」命令に対するIRノードを含むように、ベース・ノードの組を増やす。

#### 【0039】

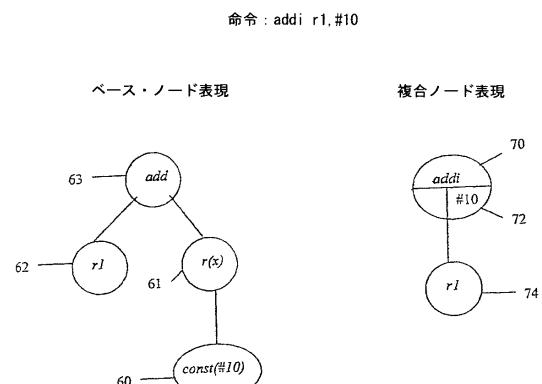

次に、図6を参照して、複合ノードを用いることによって達成される効率の例を、ベース・ノードの場合の効率と比較して説明する。たとえば、MIPS直接加算命令「add ir1, #10」のセマンティクスは、レジスタr1に保持される値に、10を加える。定数値(10)をレジスタにロードした後に2つのレジスタを加算するのではなくて、add命令では、定数値10を直接、命令フィールド自体に単純にエンコードするため、第2のレジスタを用いる必要がない。厳密にベース・ノードを用いてこれらのセマンティクスの中間表現の生成を行なってみると、この命令に対するベース・ノード表現では、最初に、const(#10)ノード60からレジスタ・ノードr(x)61へ定数値10をロードし、次に、addノード63を用いて、レジスタ・ノードr1 62とレジスタ・ノードr(x)61との加算を行なう。複合ノード表現は、単一の「直接に加算」IRノード70からなる。IRノード70は、ノード70の部分72に定数値10を含み、またレジスタr1 74への参照を含む。ベース・ノードの場合では、バックエンド33は、「直接に加算」目的命令を認識し、かつ生成するために、図6に示す4つのノード・パターンを認識することができるイディオム認識を行なう必要がある。イディオム認識がないときには、バックエンド33は、レジスタへの定数値10のロードをレジスタ・レジスタ加算の実行の前に行なうための余分な命令を出す。

#### 【0040】

複合ノードの場合には、バックエンド33においてイディオム認識を行なう必要が減る。何故なら、複合ノードに含まれるセマンティック情報は、それらのベース・ノード同等物の場合よりも多いからである。具体的には、複合ノードの場合には、バックエンド33が定数オペランドのイディオム認識を行なう必要がなくなる。比較すると、直接タイプの対象命令がベース・ノードに分解された（かつ、目的アーキテクチャに直接タイプ命令が含まれた）場合には、トランスレータ30は、高価なバックエンド33イディオム認識を行なって、複数のノード・クラスタを直接命令候補として識別する必要があるか、あるいは非効率的な目的コードを生成する（すなわち、必要数よりも多い目的レジスタを用いて、必要数よりも多い命令を生成する）。言い換えれば、ベース・ノードのみを利用するとき、性能が、トランスレータ30内で失われるか（イディオム認識を通して）、あるいはトランスレート済みコード内で失われる（イディオム認識を行なわずに、余分に生成されたコードを通して）。より一般的には、複合ノードは、セマンティック情報のよりコンパクトな表現であるために、複合ノードを用いると、トランスレータ30が形成し、横断し、および削除しなければならないIRノードの数が減る。

#### 【0041】

直接タイプの命令は、多くのアーキテクチャに共通である。したがって、複合ノードは、アーキテクチャの範囲全体において再利用可能であるという点で、汎用的である。しかし、すべてのトランスレータのIRノードの組において、すべての複合ノードが存在するわけではない。トランスレータの特定の汎用的な特性が構成可能である。すなわち、特定のソースおよび目的アーキテクチャの組み合わせに対してトランスレータがコンパイルされているときに、そのトランスレータ構成に適用されない特性をコンパイルから除くことができる。たとえば、MIPS MIPS(MIPS対MIPS)トランスレータでは、いずれかのMIPS命令のセマンティクスにマッチングしない複合ノードは、IRノードの組から除かれる。何故なら、このような複合ノードは、利用されることがないからである。

#### 【0042】

複合ノードの場合、生成される目的コードの性能を、間順走査を行なうことによりさらに向上させることができる。間順走査は、IRツリー内のIRノードを目的コードに生成する順番を決定する複数の代替的IR走査アルゴリズムのうちの1つである。具体的には、間順走査を行なうと、各IRノードが、そのノードが最初に走査されるときに生成され

る。この結果、IRツリー全体に渡って別個の最適化パスが存在しないために起こるバックエンド33イディオム認識が防がれる。複合ノードの場合、ノード当たりのセマンティック情報はベース・ノードの場合よりも多いため、イディオム認識の作業の一部は、複合ノード自体内において暗黙的である。この結果、トランスレータ30は、ベース・ノードのみの場合と同様に、目的コード性能におけるペナルティをそれほど被ることなく、間順走査を用いることができる。

#### 【0043】

トランスレータ30が複合ノード（すなわち、図5の複合IRブロック210を通るパス）を生成する場合、トランスレーション・プロセスは、ベース・ノードに対して前述したトランスレーション・プロセスと同様である。唯一の相違点は、複合ノードのセマンティクスにマッチングする対象命令は、実現ブロック202内の複合ノードとして実現され、ベース・ノードとして実現されるわけではないことである（実現ブロック202を分離する破線によって示す）。複合ノードの場合でもやはり、広範囲のアーキテクチャに渡って汎用であり、カーネル32の最適化をやはり、IRフォレスト全体に適用することができる。さらに、CISCタイプの目的アーキテクチャ上の複合ノードに対する目的コード生成は、ベース・ノード同等物の場合よりも効率的であり得る。

#### 【0044】

##### ポリモーフィック・ノード

図5に示すトランスレータ30の好ましい実施形態ではさらに、ポリモーフィック中間表現を利用してても良い。ポリモーフィック中間表現は、バックエンド33が、特定の性能重要な対象命令に対して目的アーキテクチャの特性を効率的に利用するために特化されたコード生成を与えることができる機構である。ポリモーフィック機構は、バックエンド33のコード生成関数に対する関数ポインタを含む汎用的なポリモーフィック・ノードとして具体化される。各関数ポインタは、特定の対象命令に特化される。このポリモーフィック機構は、標準的なフロントエンド31のIR生成機構の代わりに行なわれる。フロントエンド31のIR生成機構は、さもなければ、対象命令をベース・ノードまたは複合ノードにデコードする。ポリモーフィック機構がない場合には、これらのベース・ノードの生成によって、バックエンド33において、最適ではない目的コードが生成されるか、あるいは高価なイディオム認識を行なって対象命令のセマンティクスを再構成する必要が生じる。

#### 【0045】

各ポリモーフィック関数は、特定の対象命令および目的アーキテクチャ関数の組み合わせに特有である。それらの関数についての最小限の情報が、ポリモーフィック・ノードによってカーネル32に公開される。ポリモーフィック・ノードは、通常のカーネル32の最適化、たとえば式シェアリングおよび式フォールディングに関与することができる。カーネル32は、関数ポインタを用いて、2つのポリモーフィック・ノードが同じか否かを判断することができる。ポリモーフィック・ノードには、対象命令のいかなるセマンティク情報も保持しないが、このようなセマンティック情報は、関数ポインタから推測することができる。

#### 【0046】

ポリモーフィック・ノードは、対象命令に対して使用され、慎重に選択された一連の目的命令によって表現することができるため、最良の目的命令は実行時であることをカーネル32が判断する必要がない。ポリモーフィック・ノードの実現が、ベース・ノードを用いるフロントエンド31によってなされていない場合、カーネル32は、これらのノードをポリモーフィック・ノードとして実現することを選択しても良い。

#### 【0047】

さらに、ポリモーフィック・ノードは、レジスタ割り当てヒントを含むことができる。目的命令が既知であるため、CISCアーキテクチャ上で必要とされ得る個々のレジスタも既知である。ポリモーフィック・ノードを用いた場合、それらのオペランドおよび結果は、IR構成時に選択されるレジスタ内に現れることができる。

10

20

30

40

50

## 【0048】

トランスレータ30がポリモーフィック・ノード（すなわち、図5のポリモーフィックIRブロック212を通るパス）を利用することになるように、バックエンド33は、対象命令・目的関数ポインタの組み合わせのリストを、フロントエンド31に与える。与えられたリスト上にある対象命令は、対応するバックエンド33の関数ポインタを含むポリモーフィック・ノードとして実現される。リスト上にない対象命令は、前述したように、複合またはベースIRツリーとして実現される。図5において、バックエンド33からフロントエンド31へ向かう矢印214によって反映されるパスは、フロントエンド31でブロック215を実現するために与えられる対象命令・目的関数ポインタの組み合わせのリストを示す。フロントエンド31は、実現ブロック215において実現（すなわち、IRノードへの対象命令のマッピング）を行なうが、このプロセスは、パス214を通してバックエンド33から受け取る情報によって変更される。10

## 【0049】

カーネル32のポリモーフィックIRブロック212においては、ポリモーフィック・ノードの場合でもやはり、汎用的な最適化に関与することができる。何故なら、カーネル32は、ポリモーフィック・ノードのセマンティクスを、各ノード内の関数ポインタから推測することができるからである。バックエンド33では、目的コード生成関数を指し示す目的関数ポインタが、単純に逆参照されて実行される。この状況は、バックエンド33が特定のIRノードを特定のコード生成関数に対してマッピングするベース・ノードおよび複合ノードの場合とは異なる。ポリモーフィック・ノードを用いた場合、ポリモーフィック関数は、ノード自体において直接エンコードされるため、バックエンド33が行なう計算は少なくなる。図5において、この相違点は、ポリモーフィック・プラント・ブロック216が、ポリモーフィックIRブロック212およびバックエンド33の両方と隣接する（すなわち、ポリモーフィックIRブロック212とポリモーフィック・プラント・ブロック216との間に、重要な計算を表す矢印が示されていない）という事実によって表されている。20

## 【0050】

例1：ポリモーフィックIRの例

IRにおいてポリモーフィック・ノードを利用するためトランスレータ30を最適化するプロセスを示すことを目的として、以下の例では、PPC (PowerPC (登録商標)) 「SHL64」命令（左シフト、64ビット）のトランスレーションを説明する。これは、最初にベース・ノードを使用して、次にポリモーフィック・ノードを使用するPPC P4 (PowerPC to Pentium4 (登録商標))トランスレータにおいて必要とされるものである。30

## 【0051】

ポリモーフィック・ノードの実施に対してトランスレータを最適化することなく、PPC SHL64命令のトランスレーションにおいてベース・ノードのみを用いる。

PPC SHL64 => ベースIRの複数ノード => P4の複数命令

最適化されていないトランスレータのフロントエンド・デコーダ200は、現在のブロックをデコードして、PPC SHL64命令を生成する。次に、フロントエンド実現ブロック202は、カーネル32に、複数のベース・ノードからなるIRを構成するよう命令を出す。次に、カーネル32は、（命令の現在のブロックから生成された）IRフォレストを最適化して、順序付け走査を行なってベースIRブロック204におけるコード生成の順番を決定する。次に、カーネル32は、各IRノードに対して順番にコード生成を行ない、バックエンド33に、適切なRISCタイプ命令をプラントするように命令を出す。最後に、バックエンド33は、プラント・ブロック206においてコードをプラントして、エンコード・ブロック208において、1つまたは複数の目的アーキテクチャ命令を用いて各RISCタイプ命令をエンコードする。40

## 【0052】

性能重要な命令に対してフロントエンド31およびバックエンド33を特化することに

50

よって、特定の目的アーキテクチャに対して最適化する場合は、以下の通り。

**P P C S H L 6 4 > ポリ I R の単一ノード > P 4 の单一 / 少数の命令**

最適化されたトランスレータ 3 0 のフロントエンド・デコーダ 2 0 0 は、現在のブロックをデコードして、P P C S H L 6 4 命令を生成する。次に、フロントエンド実現ブロック 2 0 2 は、カーネル 3 2 に、単一のポリモーフィック I R ノードからなる I R を構成するように命令を出す。単一のポリモーフィック・ノードが形成されたとき、バックエンド 3 3 には、S H L 6 4 のシフト・オペランドが特定のレジスタ (P 4 上の % e c x ) 内に存在しなければならないということが知らされる。この要求は、ポリモーフィック・ノードにおいてエンコードされる。次に、カーネル 3 2 は、現在のブロックに対して I R フォレストを最適化するとともに、ポリモーフィック I R ブロック 2 1 2 におけるコード生成の順番を固定するために順序付け走査を行なう。次に、カーネル 3 2 は、各ノードに対してコード生成を行ない、バックエンド 3 3 に、適切な R I S C タイプ命令をプラントするように命令を出す。しかし、コードを生成する間、ポリモーフィック・ノードを処理する仕方は、ベース・ノードの場合とは異なる。各ポリモーフィック・ノードによって、バックエンド 3 3 に存在する特化されたコード・ジェネレータ関数が呼び出される。バックエンド 3 3 の特化されたコード・ジェネレータ関数は、プラント・ブロック 2 1 6 においてコードをプラントし、エンコード・ブロック 2 0 8 において、1つまたは複数の目的アーキテクチャ命令を用いて各対象アーキテクチャ命令をエンコードする。生成段階におけるレジスタ割り当ての間に、特定のレジスタ情報を用いて、正確なレジスタが割り当てられる。この結果、不適切なレジスタが割り当てられていたならば必要とされたであろうバックエンド 3 3 によって行なわれる計算が減る。このコード生成には、一時的なレジスタに対するレジスタ割り当てが伴っても良い。10

20

#### 【 0 0 5 3 】

##### 例 2：困難な命令

以下の例では、本発明のトランスレータ 3 0 が行なう P P C M F F S 命令 (3 2 ビット F P U 制御レジスタを 6 4 ビットの一般的な F P U レジスタへ移動させる) のトランスレーションおよび最適化を示す。この対象命令は、ベース・ノードにより表わすには非常に複雑である。

#### 【 0 0 5 4 】

最適化されていない場合には、この命令は、置換関数を用いてトランスレートされる。置換関数は、標準的なトランスレーション方式を用いてトランスレートすることが特に困難な対象命令の特別な場合に対する明示的なトランスレーションである。置換関数のトランスレーションは、対象命令のセマンティクスを行なう目的コード関数として具体化される。置換関数のトランスレーションは、標準的な I R 命令に基づくトランスレーション方式よりもはるかに高い実行コストがかかる。この命令に対する最適化されていないトランスレーション方式は、以下のようになる。30

#### 【 0 0 5 5 】

**P P C M F F S の命令 = > ベース I R の置換関数 = > P 4 の置換関数**

ポリモーフィック I R を用いるトランスレータ 3 0 においては、このような特別な場合の命令は、ポリモーフィック・ノードを用いてトランスレートされる。ポリモーフィック・ノードの関数ポインタによって、困難な対象命令のカスタムなトランスレーションをバックエンド 3 3 が提供するためのより効率的な機構が得られる。したがって、同じ命令に対する最適化されたトランスレーション方式は、以下のようになる。40

#### 【 0 0 5 6 】

**P P C M F F S の命令 = > 単一のポリモーフィックの I R ノード = > P 4 S S E 2 の命令**

##### アーキテクチャ特定ノード

本発明のトランスレータ 3 0 の他の好ましい実施形態においては、トランスレータ 3 0 は、図 5 に示すように、アーキテクチャ特定ノード (A S N : Architecture Specific Node) を用いても良い。アーキテクチャ特定ノードは、特定のアーキテクチャ (すなわち、50

特定のソース・アーキテクチャおよび目的アーキテクチャの組み合わせ)に特有である。各アーキテクチャ特定ノード(ASN)は、特定の命令に対して特定的に仕立てられるため、ASNは、特定のアーキテクチャに特有のものとなる。ASN機構を用いている場合、アーキテクチャ特定の最適化として、ASNのセマンティクスを包含し、したがってASN上で動作可能なものを実施することができる。

#### 【0057】

IRノードには、最大3つのコンポーネントが含まれていても良い。すなわち、データ・コンポーネント、実施コンポーネント、および変換コンポーネントである。データ・コンポーネントは、ノード自体においては固有ではない何らかのセマンティック情報(たとえば定数直接命令フィールドの値)を保持する。実施コンポーネントは、コード生成を実行し、したがって、特定のアーキテクチャに特定的に関係する。変換コンポーネントは、ノードを、異なるタイプのIRノード、ASNノードまたはベース・ノードに変換する。トランスレータにおける本発明の所定の実施形態においては、生成されたIRにおけるベース・ノードおよびASNのそれぞれに、変換コンポーネントまたは実施コンポーネントのいずれかが含まれるが、両方ではない。

10

#### 【0058】

各ベース・ノードは、目的アーキテクチャに特有の実施コンポーネントを有する。ベース・ノードは、変換コンポーネントは有さない。何故なら、ベース・ノードがIRノード階層内でエンコードするセマンティック情報の量は可能な限り少ないものであるため、ベース・ノードを他のタイプのIRノードに変換しても、何ら利点がないからである。ベース・ノードを他のタイプのIRノードにする前述のような変換はいかなるものであっても、イディオム認識を通してセマンティック情報を再収集する必要がある。

20

#### 【0059】

ASNの実施コンポーネントは、ノードのアーキテクチャに、そのASKに対応するアーキテクチャ特定の命令をコンポーネントが生成するように、特有である。たとえば、MIPSロードASNの実施コンポーネントによって、MIPS「1d」(ロード)命令が生成される。本発明のトランスレータを、対象および目的のアーキテクチャが同じ状態で(すなわちアクセラレータとして)用いる場合、対象ASNは実施コンポーネントを有する。トランスレータを、対象および目的のアーキテクチャが異なる状態で用いる場合、対象ASNは変換コンポーネントを有する。

30

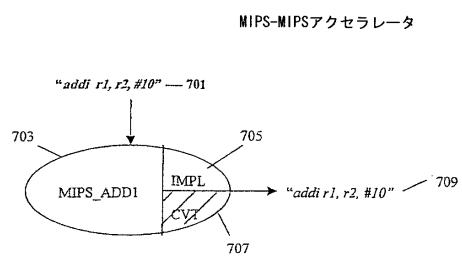

#### 【0060】

たとえば、図7に示すのは、本発明の実施形態をMIPS-MIPSアクセラレータで用いた場合の、MIPS命令に対するASNである。フロントエンド31は、MIPS「addi」(直接加算)命令701をデコードして、対応するASN、MIPS\_ADD\_I703を含むようにIRを生成する。対象および目的アーキテクチャは、アクセラレータに対して同じであるため、変換コンポーネント「CVT」707は定義されていない。実施コンポーネント「IMPL」705は、同じMIPS「加算」命令709を生成するように定義され、コード生成パスにおいてレジスタ割り当ての差を受ける。

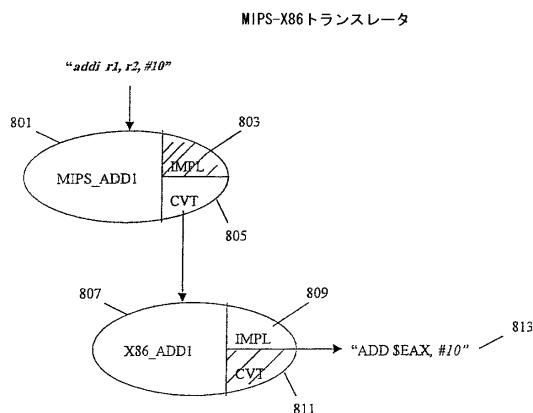

#### 【0061】

図8に示すのは、本発明の実施形態をMIPS\_X86トランスレータで用いた場合の、同じMIPS命令に対するIR内のASNである。フロントエンド31は、MIPS「addi」対象命令をデコードして、対応する対象ASN、MIPS\_ADDI801を生成する。ソースおよび目的アーキテクチャは、このトランスレータに対して異なっているため、対象ASN801の実施コンポーネント803は定義されていない。MIPS\_ADDIの変換コンポーネント805は、特化された変換コンポーネントであり、対象ASN801を目的ASN807に変換するものである。汎用的な変換コンポーネントの場合には、比較により、対象ASN801をベース・ノード表現に変換する。MIPS\_ADDIノード801の目的ASN表現は、単一のX86\_ADDIノード807である。目的ASN807の変換コンポーネント811は、定義されていない。目的ASN807の実施コンポーネント809は、目的命令813(この場合にはX86命令「ADD\$E

40

50

A X , # 1 0 」)を、生成する。

#### 【 0 0 6 2 】

トランスレータ 3 0 が A S N を用いている場合、すべての対象命令は、対象特定の A S N として実現される。図 5において、フロントエンド・デコード・ブロック 2 0 0 、 A S N 実現ブロック 2 1 8 、および対象 A S N ブロック 2 2 0 が互いに隣接しているという事実は、 A S N がフロントエンド 3 1 によって規定されるという事実、かつ実現することは自明であるという事実を示している。何故なら、対象命令タイプと対象 A S N タイプとの間には、1 対 1 の関係が存在するからである。フロントエンド 3 1 には、対象 A S N のセマンティクスを理解し、対象 A S N 上で動作可能な対象特定の最適化が含まれている。言い換えれば、対象コードは最初に、全体として対象 A S N からなる I R フォレストとして実現され、次に、これに対して、対象特定の最適化が適用される。10

#### 【 0 0 6 3 】

初期設定により、対象 A S N は、ベース・ノードの I R ツリーを生成する汎用的な変換コンポーネントを有する。この結果、新しい対象アーキテクチャに対するサポートを、汎用的な I R ノードを用いて迅速に実施することができる。対象 A S N は、図 5 の A S N ベース I R ブロック 2 2 2 およびプラント・ブロック 2 0 6 を通じて延びるパスを通して、ベース・ノードとして実現される。このベース・ノードは、すでに詳細に述べた他のベース・ノードの場合と同様の仕方で、目的コードにトランスレートされる。

#### 【 0 0 6 4 】

性能に対して重要である対象命令の場合には、対応する対象 A S N ノードによって、特化された変換コンポーネントが得られる。特化された変換コンポーネントによって、目的 A S N ノードの I R ツリーが生成される。特化された変換コンポーネントを実施するか否かを検討する際の要因には、以下のものが含まれる。(1) 目的アーキテクチャの特性によって、ベース・ノード・トランスレーションの場合には失われる特に効率的なトランスレーションが得られるか否か、(2) 対象命令が、性能に著しい影響を与えるような頻度で行なわれるか否か。これらの特化された変換コンポーネントは、対象及び目的アーキテクチャの組み合わせに特有である。目的 A S N (定義により、目的と同じアーキテクチャである)には、実施コンポーネントが含まれる。20

#### 【 0 0 6 5 】

特化された変換コンポーネントを実施すると、対応する対象 A S N ノードによって、目的に特化された変換コンポーネントが与えられ、このコンポーネントにより、対象 A S N が目的 A S N に、目的 A S N ブロック 2 2 4 を通じて変換される。次に、目的 A S N の実施コンポーネントが呼び出されて、目的 A S N プラント・ブロック 2 2 6 においてコード生成が行なわれる。各目的 A S N は、1 つの特定の目的命令に対応しており、目的 A S N から生成されるコードは単純に、 A S N がエンコードする対応する目的命令となるようになっている。したがって、目的 A S N を用いるコード生成は、計算量が最小である(このことは図 5において、目的 A S N プラント・ブロック 2 2 6 を、目的 A S N ブロック 2 2 4 とバックエンド 3 3 内のエンコード・ブロック 2 0 8 との両方に隣接するように図示することによって反映されるよう表わされており、これらのコンポーネント間には重要な計算を示す矢印は示されていない)。さらに、 I R 走査、変換、およびコード生成プロセスはすべて、カーネル 3 2 によって制御される。3040

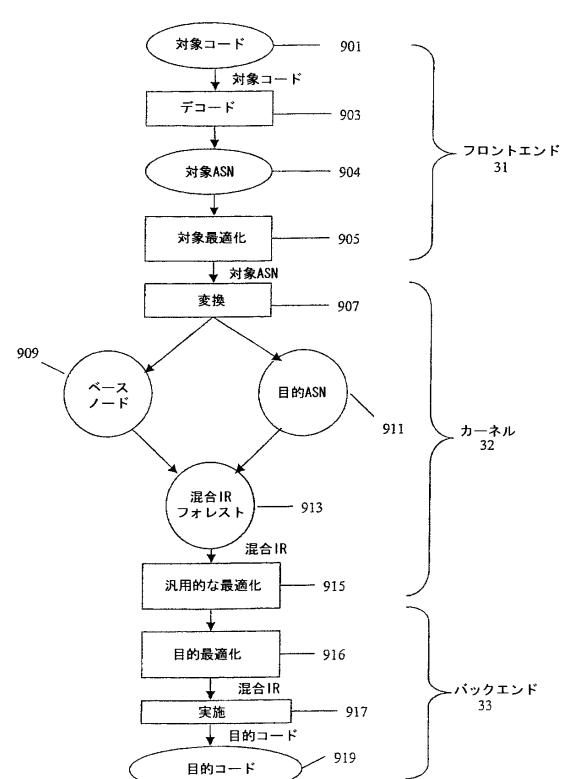

#### 【 0 0 6 6 】

図 9 に、 A S N 機構を利用する本発明のトランスレータの好ましい実施形態により行なわれるトランスレーション・プロセスを示す。フロントエンド 3 1 では、ステップ 9 0 3 において、トランスレータが、対象コード 9 0 1 を対象 A S N 9 0 4 にデコードする。ステップ 9 0 5 において、トランスレータは、対象 A S N から構成される I R ツリー上で、対象特定の最適化を行なう。次にステップ 9 0 7 において、対象 A S N の変換コンポーネントを呼び出すことによって、各対象 A S N 9 0 4 が、目的互換性 I R ノード(目的 A S N 9 1 1 )に変換される。初期設定により汎用的な変換コンポーネントを有する対象 A S N ノードは、ベース・ノード 9 0 9 に変換される。特化された変換コンポーネントを有す50

る対象 A S N ノードは、バックエンド 9 2 5 によって与えられるときに、目的 A S N 9 1 1 に変換される。したがって、この変換により、ベース・ノード 9 0 9 および目的 A S N 9 1 1 の両方を含む混合された I R フォレスト 9 1 3 が生成される。カーネル 3 2 では、ステップ 9 1 5 において、トランスレータが、混合された I R フォレスト 9 1 3 におけるベース・ノード上で、汎用的な最適化を行なう。次に、ステップ 9 1 6 において、トランスレータが、混合された I R フォレスト 9 1 3 における目的 A S N 上で、目的特定の最適化を行なう。最後に、ステップ 9 1 7 において、コード生成によって、混合ツリーにおける各ノードの実施コンポーネントが呼び出され（ベース・ノードおよび目的 A S N ノードの両方とも実施コンポーネントを有する）、目的コード 9 1 9 が生成される。

## 【 0 0 6 7 】

10

コード・アクセラレータを用いる特別な場合には、対象および目的アーキテクチャは、両方とも同じである。この状況では、対象 A S N は、トランスレーションの間中、存続する。フロントエンド 3 1 では、デコーディングによって、対象命令から対象 A S N が生成される。カーネル 3 2 では、対象 A S N は、アーキテクチャ特定の最適化を経る。コード生成によって、対象 A S N の実施コンポーネントが呼び出されて、対応する命令が生成される。したがって、コード・アクセラレータでは、A S N を用いることによってコード爆発が防止される。その防止は、最小の対象対目的命令変換比率 1 : 1 を保証することによってなされる。この比率は、最適化によって増やすことができる。

## 【 0 0 6 8 】

20

本発明のトランスレータの種々の実施形態を、特定のトランスレータの応用例（すなわち、特定の対象アーキテクチャおよび目的アーキテクチャの組み合わせ）に対して構成することができる。したがって、本発明のトランスレータは、任意の対象アーキテクチャ上で実行するように構成された対象コードを、任意の目的アーキテクチャ上で実行可能な目的コードに変換するように、構成可能である。各ベース・ノードは、複数のトランスレータの応用例において複数の実施コンポーネントを有する。実施コンポーネントは、サポートされる各目的アーキテクチャに対して 1 つである。開始されている特定の構成（すなわち、条件付きコンパイル）によって、どの I R ノードおよびそれらのノードのうちのどのコンポーネントが、特定のトランスレータの応用例に含められるかが決定される。

## 【 0 0 6 9 】

30

本発明の好ましい実施形態における A S N を用いることによって、複数の優位な利点が得られる。第 1 に、対象命令の汎用的な I R の実施形態を用いることで、スクラッチから構成されるトランスレータ製品を迅速に開発することができる。第 2 に、性能に対して重要な対象命令（予め分かっているかまたは経験的に決定される）に対して目的特定の変換コンポーネントを実施することで、既存のトランスレータ製品を徐々に増加させることができる。第 3 に、開発されるトランスレータ製品の数が増加するにつれて、A S N ノード（および実施される機能）のライブラリも時間とともに増加するため、将来のトランスレータ製品の実施または最適化を迅速に行なうことができる。

## 【 0 0 7 0 】

30

本発明のこの実施形態では、バックエンド実施により、どの対象命令が（目的に特化された変換コンポーネントを規定することによる）最適化に値するかを、慎重に選ぶ。汎用的な変換コンポーネントによって、A S N ベースのトランスレータを迅速に開発することができる一方で、特化された変換コンポーネントによって、性能重要な命令を、選択的かつ徐々に最適化することができる。

## 【 0 0 7 1 】

40

例 3 : A S N を用いた困難な命令

前述した例 2 の P o w e r P C S H L 6 4 命令に戻って、A S N を用いるトランスレータ 3 0 では、以下のステップが行なわれる。フロントエンド・デコーダ 2 0 0 は、現在のブロックをデコードして、P o w e r P C S H L 6 4 命令を生成する。次に、フロントエンド 3 1 が、その命令に対する単一の A S N 、 S H L 6 4 P P C P 4 を実現する。次に、カーネル 3 2 が、命令の現在のブロックに対する I R を最適化して、コード生成

50

に備えて I R の順序付け走査を行なう。次に、カーネル 3 2 が、各特定の A S N ノードのコード・ジェネレータ関数を呼び出すことによって、A S N ノードに対してコード生成を行なう。コード・ジェネレータ関数は、実施コンポーネントの要素である。次に、バックエンド 3 3 が、対象アーキテクチャ ( P P C ) 命令を、1つまたは複数の目的アーキテクチャ ( P 4 ) 命令にエンコードする。

#### 【 0 0 7 2 】

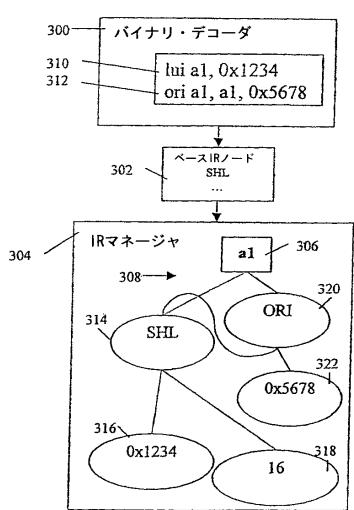

##### M I P S の例

次に、図 1 0 , 1 1 , 1 2 を参照して、ベース I R ノード、M I P S - M I P S A S N I R ノード、および M I P S - X 8 6 A S N I R ノードをそれぞれ用いて、同じ M I P S 命令シーケンスから生成され異なる I R ツリーを表わす例を示す。M I P S 対象命令シーケンスの例（上位の即値をロード、次に即値をビット単位 O R ）のセマンティクスは、3 2 ビット定数値  $0 \times 1 2 3 4 5 6 7 8$  を対象レジスタ「 a 1 」にロードすることである。

10

#### 【 0 0 7 3 】

図 1 0 において、バイナリ・デコーダ 3 0 0 は、対象コードを別個の対象命令にデコード（構文解析）するトランスレータ 3 0 のフロントエンド 3 1 のコンポーネントである。対象命令は、デコードされた後、ベース・ノード 3 0 2 として実現され、命令の現在のブロックに対する作業用 I R フォレストに追加される。I R マネージャ 3 0 4 は、I R を生成する間に作業用 I R フォレストを保持するトランスレータ 3 0 の部分である。I R マネージャ 3 0 4 は、抽象レジスタおよびそれらに関連する I R ツリーからなる（I R フォレストのルートは抽象レジスタである）。たとえば、図 1 0 において、抽象レジスタ " a V 3 0 6 " は、5 つのノードからなる I R ツリー 3 0 8 のルートであり、現在のブロックの作業用 I R フォレストの一部である。C + + により具体化されるトランスレータ 3 0 の場合には、I R マネージャ 3 0 4 を、抽象レジスタ・オブジェクト（または I R ノード・オブジェクトに対する参照）の組を含む C + + オブジェクトとして具体化しても良い。

20

#### 【 0 0 7 4 】

図 1 0 に示すのは、ベース・ノードのみを用いた M I P S 对 X 8 6 トランスレータによって生成される I R ツリー 3 0 8 である。M I P S \_ L U I 命令 3 1 0 によって、2 つのオペランド・ノード 3 1 6 , 3 1 8 を有する「 S H L 」（左ヘシフト）ベース・ノード 3 1 4 が実現される。2 つのオペランド・ノード 3 1 6 , 3 1 8 は、この場合には、両方とも定数である。M I P S \_ L U I 命令 3 1 0 のセマンティクスは、定数値（ $0 \times 1 2 3 4$ ）を、一定数のビット（1 6）だけ左ヘシフトさせることである。M I P S \_ O R I 命令 3 1 2 によって、2 つのオペランド・ノード 3 1 4 , 3 2 2 、すなわち S H L ノード 3 1 4 の結果および定数値を有する「 O R I 」（即値をビット単位 O R ）ベース・ノード 3 2 0 が実現される。M I P S \_ O R I 命令 3 1 2 のセマンティクスは、定数値（ $0 \times 5 6 7 8$ ）を有する既存のレジスタ内容のビット単位 O R を行なうことである。

30

#### 【 0 0 7 5 】

最適化されていないコード・ジェネレータの場合には、ベース・ノードには、即値ロード以外の直接タイプのオペレータは含まれていない。そのため、各定数ノードによって、即値ロード命令が生成される。したがって、最適化されていないベース・ノード・トランスレータの場合には、この対象命令シーケンスに対して5つのR I S C タイプの処理（ロード、ロード、シフト、ロード、O R ）が必要となる。バックエンド 3 3 イディオム認識によって、この数を5から2へ、定数ノードをそれらのペアレント・ノードと合体されることにより減らして、直接タイプの目的命令（すなわち、即値シフトおよび即値 O R ）を生成することができる。この結果、目的命令の数が減って2になるが、これは、コード・ジェネレータでイディオム認識を行なう際のトランスレーション・コストが増加する場合である。

40

#### 【 0 0 7 6 】

I R において複合ノードを用いることで、直接タイプ I R ノードを実現することができる。その結果、バックエンド 3 3 でイディオム認識を行なう必要がなくなり、コード・ジ

50

エネレータのトランスレーション・コストが減る。本来の対象命令よりも、複合ノードが保持するセマンティクスは多く、実現するIRノードは少ない。ノード生成のトランスレーション・コストも、複合ノードを用いると下がる。

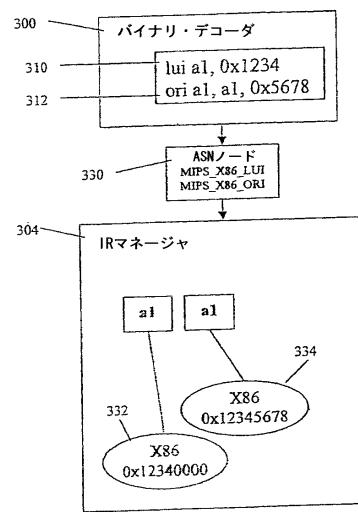

#### 【0077】

図11に、ASNを用いたMIPS\_X86(MIPS対X86)トランスレータによって生成されるIRツリーを示す。対象命令は、バイナリ・デコーダ300によってデコードされた後、MIPS\_X86 ASNノード330として実現される。次に、MIPS\_X86 ASNノード330は、現在のブロックに対する作業用IRフォレストに追加される。第1に、MIPS\_X86\_LUI ASNノードは、ASNの変換コンポーネントによって、X86\_32ビット定数ノード332に変換される。第2に、MIPS\_X86\_ORI ASNノードによって、X86\_ORIノードが生成され、このX86\_ORIノードは即座に、以前のX86定数ノードによってフォールディングされる(定数フォールディング)。その結果、単一のX86\_32ビット定数ノード334となる。このノード334は、単一のX86のロード定数命令「mov %eax, \$0x12345678」に、エンコードされる。図に示すように、ASNノードの結果、ノードの数はベース・ノードの例よりも少なくなる。そのため、トランスレーション・コストが下がり、より良好な目的コードが得られる。

10

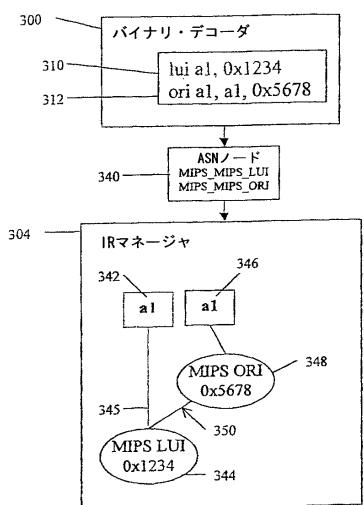

#### 【0078】

図12に、ASNを用いたMIPS-MIPSトランスレータ(すなわち、MIPSアクセラレータ)によって生成されるIRツリーを示す。対象命令310, 312は、バイナリ・デコーダ300によってデコードされた後、MIPS\_MIPS ASNノード340として実現される。次いで、このMIPS\_MIPS ASNノード340は、現在のブロックに対する作業用IRフォレストに追加される。ソースおよび目的アーキテクチャは、MIPS-MIPSトランスレータに対して同じであるため、MIPS\_MIPS-LUIおよびMIPS\_MIPS\_ORI ASNノード340では、変換コンポーネントがヌル(未定義)である。したがって、対象命令と、コードを生成するために使用される最終的なIRノードとの間には、直接的な対応関係がある。これによって、何らかの最適化が適用される前であっても、1:1の対象対目的の命令トランスレーション比率が保証される。言い換えれば、ASNノードによって、同一-同一トランスレータ(アクセラレータ)に対するコード爆発がなくなる。またASNノードによって、16ビット定数ノードを共有することができる。これは、MIPSプラットフォーム上で、連続するメモリ・アクセスを効率的にトランスレートする上で有用である。

20

30

#### 【0079】

命令の基本ブロックは、一度に1つの対象命令がトランスレートされる。各対象命令によって、IRツリーが形成(実現)される。IRツリーは、所定の命令に対して形成された後、現在のブロックに対する作業用IRフォレストに統合される。作業用IRフォレストのルートは、抽象レジスタである。抽象レジスタは、対象レジスタと対象アーキテクチャの他の特性とに対応する。最後の対象命令がデコードされ、実現され、そのIRツリーが作業用IRフォレストに統合されたときに、そのブロックに対するIRフォレストは完成する。

40

#### 【0080】

図12では、第1の対象命令310は、「lui a1, 0x1234」である。この命令310のセマンティクスは、定数値0x1234を、対象レジスタ「a1」342の上位16ビットにロードすることである。この命令310によって、MIPS\_MIPS-LUIノード344が、0x1234の直接フィールド定数値を用いて実現される。トランスレータによって、このノードは作業用IRフォレストに追加される。この追加は、抽象レジスタ「a1」342(対象命令のデスティネーション・レジスタ)を、MIPS\_MIPS-LUI IRノード344を指し示すように設定することによって行なわれる。

#### 【0081】

図12の同じ例において、第2の対象命令312は、「ori a1, a1, 0x5678」である。この命令312のセマンティクスは、対象レジスタ「a1」342の現在の内容を用いて定数値 $0 \times 5678$ のビット単位ORを行ない、対象レジスタ「a1」346内の結果を記憶することである。この命令312によって、MIPS\_MIPS\_ORIノード348が、 $0 \times 5678$ の直接フィールド定数値を用いて実現される。トランスレータによって、このノードは作業用IRフォレストに追加される。この追加は、最初にORIノードを、抽象レジスタ「a1」342（対象命令のソース・レジスタ）が現在指示しているIRツリーを指示するように設定し、次に、抽象レジスタ「a1」346（対象命令のデスティネーション・レジスタ）を、ORIノード348を指示するように設定することによって行なわれる。言い換えれば、抽象レジスタ342をルートとする既存の「a1」ツリー（すなわち、LUIノード）は、ORIノード348のサブツリー350になり、次に、ORIノード348は新たなa1ツリーになる。古い「a1」ツリー（LUIより後だがORIより前）は、抽象レジスタ342をルートとしており、ライン345によってリンクされるように示されている。一方で、現在の「a1」ツリー（ORIより後）は、抽象レジスタ346をルートとする。

#### 【0082】

前述したことから分かるように、本発明により形成される改善されたプログラム・コード変換装置は、最適なレベルの性能を維持し、かつトランスレーションの速度とトランスレート済み目的コードの効率とをバランスさせる一方で、任意の対象および目的プロセッサ・アーキテクチャの組み合わせに対して構成可能である。さらに、変換に関する対象および目的コンピューティング環境の特定のアーキテクチャに依存して、本発明のプログラム・コード変換装置を、汎用的および特定の変換特性のハイブリッド設計を用いて構成することが、ベース・ノード、複合ノード、ポリモーフィック・ノード、およびアーキテクチャ特定ノードの組み合わせを、その中間表現において用いることによって可能である。

#### 【0083】

本発明の改善されたプログラム・コード変換装置の種々の構造が、前述の実施形態のそれぞれにおいて別個に説明されている。しかし、本明細書で説明した各実施形態の別個の様子を、本明細書で説明した他の実施形態と組み合わせても良いことは、本発明の発明者によって完全に意図されている。たとえば、本発明により形成されるトランスレータには、種々のIRタイプのハイブリッド最適化が含まれていても良い。当業者ならば理解するように、説明した好ましい実施形態の種々の適合および変更を、本発明の範囲および技術思想から逸脱することなく構成することができる。したがって、本発明を、添付の特許請求の範囲内で、本明細書で具体的に説明したこと以外で、実行しても良いことが理解される。

#### 【0084】

いくつかの好ましい実施形態を示し説明してきたが、当業者ならば理解するように、添付の特許請求の範囲において規定される本発明の範囲から逸脱することなく、種々の変形および変更を施しても良い。

#### 【0085】

本出願に関連し、本明細書と同時にまたは以前に提出され、かつ本明細書を用いて公衆の便覧に公開されたすべての論文および文献に対して注意を払うものであり、このような論文および文献はすべて、その内容が本明細書において参照されることにより取り入れられるものとする。

#### 【0086】

本明細書（すべての添付の特許請求の範囲、要約書、および図面を含む）で開示されたすべての特徴、および／または同様に開示されたいずれかの方法またはプロセスのすべてのステップは、このような特徴および／またはステップの少なくとも一部が互いに相容れない組み合わせを除いて、任意の組み合わせで組み合わされても良い。

#### 【0087】

10

20

30

30

40

40

50

本明細書（すべての添付の特許請求の範囲、要約書、および図面を含む）で開示された各特徴は、特にことわらない限り、同じ、同等、または類似の目的を満たす代替的な特徴と取り替えてても良い。したがって、特にことわらない限り、開示された各特徴は、同等または類似の特徴の包括的な組の1つの例に過ぎない。

#### 【0088】

本発明は、前述した実施形態の詳細に限定されない。本発明は、本明細書（すべての添付の特許請求の範囲、要約書、および図面を含む）で開示された特徴の任意の新しい1つまたは任意の新しい組み合わせに及ぶか、または同様に開示された任意の方法またはプロセスのステップの任意の新しい1つまたは任意の新しい組み合わせに及ぶ。

#### 【図面の簡単な説明】

10

#### 【0089】

【図1】対象および目的コンピューティング環境を含むコンピューティング環境の例。

【図2】好ましいプログラム・コード変換装置。

【図3】対象コードの目的コードへのトランスレーションを示す例示的なコンピューティング環境を示す説明図。

【図4】本発明の好ましい実施形態によるプログラム・コード変換装置によって実現される種々の中間表現を示す説明図。

【図5】好ましいプログラム・コード変換装置の詳細な説明図。

【図6】ベース・ノードおよび複合ノードを用いて生成されるIRツリーの例。

【図7】アクセラレータにおいて本発明を実施した場合のASN生成の例を示す説明図。

20

【図8】トランスレータにおいて本発明を実施した場合のASN生成の例を示す説明図。

【図9】本発明の好ましい実施形態による、ASNを利用する際のトランスレーション・プロセスの処理フロー図。

【図10】トランスレーション・プロセス、およびそのプロセスの間に生成される対応するIRの例を示す説明図。

【図11】トランスレーション・プロセス、およびそのプロセスの間に生成される対応するIRの別の例を示す説明図。

【図12】トランスレーション・プロセス、およびそのプロセスの間に生成される対応するIRのさらに別の例を示す説明図。

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

〔 図 7 〕

【 図 8 】

( 9 )

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 オーウェン、ダニエル

イギリス国 M3 2EG マンチェスター ブラックフライアーズ ストリート メイブルック

ハウス トランジティブ リミテッド 内

(72)発明者 アンドリューズ、ジョナサン ジェイ

イギリス国 M3 2EG マンチェスター ブラックフライアーズ ストリート メイブルック

ハウス トランジティブ リミテッド 内

(72)発明者 ホーソン、マイルズ フィリップ

イギリス国 M3 2EG マンチェスター ブラックフライアーズ ストリート メイブルック

ハウス トランジティブ リミテッド 内

(72)発明者 ハイケン、デイビッド

イギリス国 M3 2EG マンチェスター ブラックフライアーズ ストリート メイブルック

ハウス トランジティブ リミテッド 内

審査官 坂庭 剛史

(56)参考文献 特表2002-543490(JP,A)

特表2002-527815(JP,A)

特開2002-312180(JP,A)

特開2000-347873(JP,A)

特開平11-194948(JP,A)

特開平07-105015(JP,A)

特開平06-250846(JP,A)

特開平04-014144(JP,A)

実開平04-036646(JP,U)

(58)調査した分野(Int.Cl., DB名)

G06F 9/455

G06F 9/30