(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0135648

(43) 공개일자 2014년11월26일

(51) 국제특허분류(Int. Cl.)

**H01L 29/786** (2006.01)

(21) 출원번호 10-2014-0058414

(22) 출원일자 2014년05월15일

심사청구일자 **없음**

(30) 우선권주장

JP-P-2013-104320 2013년05월16일 일본(JP)

(뒷면에 계속)

(71) 출원인

가부시키가이샤 **한도오따이 에네루기 켄큐쇼**

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자

**가토 기요시**

일본 243-0036 가나가와Ken 아쓰기시 하세 398 가

부시키가이샤 **한도오따이 에네루기 켄큐쇼** 내

**오누키 다츠야**

일본 243-0036 가나가와Ken 아쓰기시 하세 398 가

부시키가이샤 **한도오따이 에네루기 켄큐쇼** 내

(74) 대리인

**양영준, 박충범**

전체 청구항 수 : 총 14 항

(54) 발명의 명칭 **반도체 장치**

### (57) 요 약

소자의 미세화를 진행시켜도 데이터의 유지에 필요한 유지 용량을 확보할 수 있는, 신규 구성의 반도체 장치를 제공한다.

용량 소자를 구성하는 전극을 트랜지스터의 게이트로 되는 전극과, 소스 및 드레인으로 되는 전극과, 동일층에 설치된 전극으로 구성한다. 그리고, 트랜지스터의 게이트로 되는 전극을 설치하는 층과, 복수의 메모리간의 트랜지스터의 게이트를 접속하는 배선층을 다른 층에 설치하는 구성으로 한다. 상기 구성에 의해, 트랜지스터의 게이트에 형성되는 기생 용량을 억제하는 구성으로 할 수 있다. 또한 트랜지스터의 게이트로 되는 전극을 설치하는 층을, 복수의 메모리간의 트랜지스터의 게이트를 접속하는 배선층과, 다른 층에 설치할 수 있기 때문에, 그만큼 용량 소자를 형성하는 면적을 증가시킬 수 있다.

### 대 표 도 - 도1

(30) 우선권주장

JP-P-2013-227346 2013년10월31일 일본(JP)

JP-P-2014-025003 2014년02월13일 일본(JP)

---

## 특허청구의 범위

### 청구항 1

반도체 장치로서,

복수의 메모리; 및

상기 복수의 메모리 사이의 제1 배선

을 포함하고,

상기 복수의 메모리 각각은,

제1 데이터 유지부를 포함하는 휘발성 메모리; 및

제2 데이터 유지부를 포함하는 불휘발성 메모리를 포함하고,

상기 제2 데이터 유지부는 제1 트랜지스터 및 제1 용량 소자를 포함하고,

상기 제1 트랜지스터의 제1 전극은 상기 제1 데이터 유지부에 전기적으로 접속되고,

상기 제1 트랜지스터의 제2 전극은 상기 제1 용량 소자의 제1 전극에 전기적으로 접속되고,

상기 제1 용량 소자의 상기 제1 전극과 상기 제1 트랜지스터의 상기 제1 전극은 동일한 층에 있고,

상기 제1 용량 소자의 제2 전극과 상기 제1 트랜지스터의 게이트는 동일한 층에 있고,

상기 제1 배선은 상기 복수의 메모리의 제1 트랜지스터의 게이트를 전기적으로 접속하고,

상기 제1 배선이 설치되는 층과, 상기 제1 트랜지스터의 상기 게이트가 설치되는 층은 상이한, 반도체 장치.

### 청구항 2

제1항에 있어서,

상기 제2 데이터 유지부에서, 상기 제1 트랜지스터를 비도통 상태로 하고, 상기 제1 트랜지스터의 상기 제2 전극과 상기 제1 용량 소자의 상기 제1 전극 사이에 전하를 유지함으로써, 상기 제1 데이터 유지부에 기억된 데이터를 유지하는, 반도체 장치.

### 청구항 3

제1항에 있어서,

상기 제1 트랜지스터는, 산화물 반도체를 포함하는 반도체층을 구비하는, 반도체 장치.

### 청구항 4

제1항에 있어서,

상기 제1 트랜지스터는 톱 게이트 구조의 트랜지스터인, 반도체 장치.

### 청구항 5

제1항에 있어서,

상기 제1 데이터 유지부는, 실리콘을 포함하는 반도체층을 구비하는 제2 트랜지스터를 포함하는 회로인, 반도체 장치.

### 청구항 6

제5항에 있어서,

상기 제1 트랜지스터는 상기 제2 트랜지스터 위에 설치되는, 반도체 장치.

**청구항 7**

제6항에 있어서,

상기 복수의 메모리 각각은, 상기 제1 트랜지스터가 설치되는 층과, 상기 제2 트랜지스터가 설치되는 층 사이의 제2 배선을 더 포함하고,

상기 제2 배선은 상기 제1 트랜지스터 및 상기 제2 트랜지스터를 전기적으로 접속하는, 반도체 장치.

**청구항 8**

반도체 장치로서,

복수의 메모리; 및

상기 복수의 메모리 사이의 제1 배선

을 포함하고,

상기 복수의 메모리 각각은,

제1 데이터 유지부 및 제2 데이터 유지부를 포함하는 휘발성 메모리; 및

제3 데이터 유지부 및 제4 데이터 유지부를 포함하는 불휘발성 메모리를 포함하고,

상기 제3 데이터 유지부는 제1 트랜지스터 및 제1 용량 소자를 포함하고,

상기 제4 데이터 유지부는 제2 트랜지스터 및 제2 용량 소자를 포함하고,

상기 제1 트랜지스터의 제1 전극은 상기 제1 데이터 유지부에 전기적으로 접속되고,

상기 제1 트랜지스터의 제2 전극은 상기 제1 용량 소자의 제1 전극에 전기적으로 접속되고,

상기 제2 트랜지스터의 제1 전극은 상기 제2 데이터 유지부에 전기적으로 접속되고,

상기 제2 트랜지스터의 제2 전극은 상기 제2 용량 소자의 제1 전극에 전기적으로 접속되고,

상기 제1 용량 소자의 상기 제1 전극과 상기 제1 트랜지스터의 상기 제1 전극은 동일한 층에 있고,

상기 제1 용량 소자의 제2 전극, 상기 제2 용량 소자의 제2 전극, 상기 제1 트랜지스터의 게이트, 및 상기 제2 트랜지스터의 게이트는 동일한 층에 있고,

상기 제1 배선은 상기 제1 트랜지스터의 상기 게이트와 상기 제2 트랜지스터의 상기 게이트를 전기적으로 접속하고,

상기 제1 배선이 설치되는 층과, 상기 제1 트랜지스터의 상기 게이트 및 상기 제2 트랜지스터의 상기 게이트가 설치되는 층은 상이한, 반도체 장치.

**청구항 9**

제8항에 있어서,

상기 제3 데이터 유지부에서, 상기 제1 트랜지스터를 비도통 상태로 하고, 상기 제1 트랜지스터의 상기 제2 전극과 상기 제1 용량 소자의 상기 제1 전극 사이에 전하를 유지함으로써, 상기 제1 데이터 유지부에 기억된 데이터를 유지하고,

상기 제4 데이터 유지부에서, 상기 제2 트랜지스터를 비도통 상태로 하고, 상기 제2 트랜지스터의 상기 제2 전극과 상기 제2 용량 소자의 상기 제1 전극 사이에 전하를 유지함으로써, 상기 제2 데이터 유지부에 기억된 데이터를 유지하는, 반도체 장치.

**청구항 10**

제8항에 있어서,

상기 제1 트랜지스터 및 상기 제2 트랜지스터 각각은, 산화물 반도체를 포함하는 반도체층을 구비하는, 반도체

장치.

### 청구항 11

제8항에 있어서,

상기 제1 트랜지스터 및 상기 제2 트랜지스터 각각은 톱 게이트 구조의 트랜지스터인, 반도체 장치.

### 청구항 12

제8항에 있어서,

상기 제1 데이터 유지부는 제3 트랜지스터를 포함하는 회로이고, 상기 제2 데이터 유지부는 제4 트랜지스터를 포함하는 회로이고,

상기 제3 트랜지스터 및 상기 제4 트랜지스터 각각은, 실리콘을 포함하는 반도체층을 구비하는, 반도체 장치.

### 청구항 13

제12항에 있어서,

상기 제1 트랜지스터 및 상기 제2 트랜지스터는 상기 제3 트랜지스터 위에 설치되는, 반도체 장치.

### 청구항 14

제13항에 있어서,

상기 복수의 메모리 각각은, 상기 제1 트랜지스터 및 상기 제2 트랜지스터가 설치되는 층과, 상기 제3 트랜지스터 및 상기 제4 트랜지스터가 설치되는 층 사이의 제2 배선을 더 포함하고,

상기 제2 배선은 상기 제1 트랜지스터, 상기 제2 트랜지스터, 상기 제3 트랜지스터 및 상기 제4 트랜지스터를 전기적으로 접속하는, 반도체 장치.

## 명세서

### 기술분야

[0001]

본 발명은 물, 방법 또는 제조 방법에 관한 것이다. 또는, 본 발명은 프로세스, 머신, 매뉴팩처 또는 조성물(콤파지션·오브·메터)에 관한 것이다. 특히, 본 발명은 예를 들어 반도체 장치, 표시 장치, 발광 장치, 축전 장치, 기억 장치, 그들의 구동 방법, 또는 그들의 제조 방법에 관한 것이다. 특히, 본 발명은 반도체 장치에 관한 것이다.

### 배경기술

[0002]

실리콘(Si)을 반도체층에 사용한 트랜지스터와, 산화물 반도체(Oxide Semiconductor:OS)를 반도체층에 사용한 트랜지스터를 조합하여 데이터의 유지를 가능하게 한 반도체 장치가 주목받고 있다(특허문헌 1 및 특허문헌 2를 참조).

[0003]

최근, 취급되는 데이터량의 증대에 수반하여, 보다 큰 기억 용량을 갖는 반도체 장치가 요구되고 있다. 단위 면적당 기억 용량을 증가시키기 위해서는, 반도체 장치를 구성하는 트랜지스터나 용량 소자의 미세화를 도모하는 것이 유효하다.

### 선행기술문헌

#### 특허문헌

[0004]

(특허문헌 0001) 일본 특허 공개 제2013-8437호 공보

(특허문헌 0002) 일본 특허 공개 제2013-8436호 공보

## 발명의 내용

### 해결하려는 과제

[0005] 그러나, 반도체 장치를 구성하는 소자를 미세화하면, 아울러 용량 소자의 면적도 감소되기 때문에, 데이터를 유지하기 위한 유지 용량이 작아진다. 이 유지 용량의 저하에 의해, 용량 소자에 접속되는 트랜지스터의 기생 용량을 무시할 수 없게 되고, 데이터의 유지 및/또는 퇴피(退避) · 복귀가 어려워진다.

[0006] 따라서, 본 발명의 일 형태에서는, 트랜지스터의 오프 전류가 매우 작은 것을 이용하여 용량 소자에서의 전하의 유지를 행하여, 데이터를 유지하는 반도체 장치의 구성에 있어서, 소자의 미세화를 진행시켜도 데이터의 유지에 필요한 유지 용량을 확보할 수 있는, 신규 구성의 반도체 장치를 제공하는 것을 과제의 하나로 한다. 또는, 본 발명의 일 형태에서는, 반도체 장치의 제조 프로세스나 회로를 구성하는 배선이나 동작을 복잡하게 하지 않고, 트랜지스터의 온 전류를 크게 할 수 있는, 신규 구성의 반도체 장치를 제공하는 것을 과제의 하나로 한다. 또는, 본 발명의 일 형태에서는, 신규 반도체 장치 등을 제공하는 것을 과제의 하나로 한다.

[0007] 또한, 이들 과제의 기재는, 다른 과제의 존재를 방해하는 것은 아니다. 또한, 본 발명의 일 형태는, 이들 과제 모두를 해결할 필요는 없는 것으로 한다. 또한, 상기 이외의 과제는, 명세서, 도면, 청구항 등의 기재로부터, 저절로 명확해지는 것으로, 명세서, 도면, 청구항 등의 기재로부터, 상기 이외의 과제를 추출하는 것이 가능하다.

### 과제의 해결 수단

[0008] 본 발명의 일 형태는, 복수의 메모리를 갖는 반도체 장치로서, 메모리는, 제1 데이터 유지부를 갖는 휘발성 메모리와, 제2 데이터 유지부를 갖는 불휘발성 메모리를 갖고, 제2 데이터 유지부는, 제1 트랜지스터 및 제1 용량 소자를 갖고, 제1 트랜지스터의 소스 및 드레인 중 한쪽은, 제1 데이터 유지부에 전기적으로 접속되고, 제1 트랜지스터의 소스 및 드레인 중 다른 쪽은, 제1 용량 소자의 한쪽 전극에 전기적으로 접속되고, 제1 용량 소자의 한쪽 전극은, 제1 트랜지스터의 소스 및 드레인으로 되는 전극과 동일한 층에 설치된 전극이며, 제1 용량 소자의 다른 쪽 전극은, 제1 트랜지스터의 게이트로 되는 전극과 동일한 층에 설치된 전극이며, 복수의 메모리간에 설치되는, 제1 트랜지스터의 게이트를 전기적으로 접속하기 위한 배선은, 제1 용량 소자의 다른 쪽 전극과는 다른 층에 설치된 배선인 반도체 장치이다.

[0009] 본 발명의 일 형태에 있어서, 제2 데이터 유지부는, 제1 트랜지스터를 비도통 상태로 하고, 제1 트랜지스터의 소스 및 드레인 중 다른 쪽과, 제1 용량 소자의 한쪽 전극 사이에 전하를 유지함으로써, 제1 데이터 유지부에 기억된 데이터의 유지를 행하는 데이터 유지부인 반도체 장치가 바람직하다.

[0010] 본 발명의 일 형태에 있어서, 제1 트랜지스터는, 반도체층이 산화물 반도체인 반도체 장치가 바람직하다.

[0011] 본 발명의 일 형태에 있어서, 제1 트랜지스터는, 텁 게이트 구조의 트랜지스터인 반도체 장치가 바람직하다.

[0012] 본 발명의 일 형태에 있어서, 제1 데이터 유지부는, 반도체층이 실리콘인 제2 트랜지스터를 사용하여 구성된 회로인 반도체 장치가 바람직하다.

[0013] 본 발명의 일 형태에 있어서, 제2 트랜지스터 위에는, 제1 트랜지스터가 적층하여 설치되는 반도체 장치가 바람직하다.

[0014] 본 발명의 일 형태에 있어서, 제1 트랜지스터가 설치된 층과, 제2 트랜지스터가 설치된 층 사이에는, 제1 트랜지스터 및 제2 트랜지스터를 전기적으로 접속하기 위한 배선층이 설치되는 반도체 장치가 바람직하다.

[0015] 본 발명의 일 형태는, 복수의 메모리를 갖는 반도체 장치로서, 메모리는, 제1 데이터 유지부 및 제2 데이터 유지부를 갖는 휘발성 메모리와, 제3 데이터 유지부 및 제4 데이터 유지부를 갖는 불휘발성 메모리를 갖고, 제3 데이터 유지부는, 제1 트랜지스터 및 제1 용량 소자를 갖고, 제4 데이터 유지부는, 제2 트랜지스터 및 제2 용량 소자를 갖고, 제1 트랜지스터의 소스 및 드레인 중 한쪽은, 제1 데이터 유지부에 전기적으로 접속되고, 제1 트랜지스터의 소스 및 드레인 중 다른 쪽은, 제1 용량 소자의 한쪽 전극에 전기적으로 접속되고, 제2 트랜지스터의 소스 및 드레인 중 한쪽은, 제2 데이터 유지부에 전기적으로 접속되고, 제2 트랜지스터의 소스 및 드레인 중 다른 쪽은, 제2 용량 소자의 한쪽 전극에 전기적으로 접속되고, 제1 용량 소자의 한쪽 전극은, 제1 트랜지스터의 소스 및 드레인으로 되는 전극과 동일한 층에 설치된 전극이며, 제1 용량 소자의 다른 쪽 전극 및 제2 용량 소자의 다른 쪽 전극은, 제1 트랜지스터의 게이트로 되는 전극 및 제2 트랜지스터의 게이트로 되는 전극과 동일

한 층에 설치된 전극이며, 제1 트랜지스터의 게이트와 제2 트랜지스터의 게이트를 전기적으로 접속하기 위한 배선은, 제1 용량 소자의 다른 쪽 전극 및 제2 용량 소자의 다른 쪽 전극과는 다른 층에 설치된 배선인 반도체 장치이다.

[0016] 본 발명의 일 형태는 복수의 메모리를 갖는 반도체 장치로서, 메모리는, 제1 데이터 유지부 및 제2 데이터 유지부를 갖는 휘발성 메모리와, 제3 데이터 유지부 및 제4 데이터 유지부를 갖는 불휘발성 메모리를 갖고, 제3 데이터 유지부는, 제1 트랜지스터 및 제1 용량 소자를 갖고, 제4 데이터 유지부는, 제2 트랜지스터 및 제2 용량 소자를 갖고, 제1 트랜지스터의 소스 및 드레인 중 한쪽은, 제1 데이터 유지부에 전기적으로 접속되고, 제1 트랜지스터의 소스 및 드레인 중 다른 쪽은, 제1 용량 소자의 한쪽 전극에 전기적으로 접속되고, 제2 트랜지스터의 소스 및 드레인 중 다른 쪽은, 제2 데이터 유지부에 전기적으로 접속되고, 제2 트랜지스터의 소스 및 드레인 중 다른 쪽은, 제2 용량 소자의 한쪽 전극에 전기적으로 접속되고, 제1 용량 소자의 한쪽 전극은, 제1 트랜지스터의 소스 및 드레인으로 되는 전극과 동일한 층에 설치된 전극이며, 제1 용량 소자의 다른 쪽 전극 및 제2 용량 소자의 다른 쪽 전극은, 제1 트랜지스터의 게이트로 되는 전극 및 제2 트랜지스터의 게이트로 되는 전극과 동일한 층에 설치된 전극이며, 제1 트랜지스터의 게이트와 제2 트랜지스터의 게이트를 전기적으로 접속하기 위한 배선은, 제1 용량 소자의 다른 쪽 전극 및 제2 용량 소자의 다른 쪽 전극과는 다른 층에 설치된 배선이며, 제1 트랜지스터 및 제2 트랜지스터 반도체층에 있어서의 채널 형성 영역은, 고전원 전위를 부여하는 배선에 중첩하여 설치되는 것을 특징으로 하는 반도체 장치이다.

[0017] 본 발명의 일 형태에 있어서, 제3 데이터 유지부는, 제1 트랜지스터를 비도통 상태로 하고, 제1 트랜지스터의 소스 및 드레인 중 다른 쪽과, 제1 용량 소자의 한쪽 전극 사이에 전하를 유지함으로써, 제1 데이터 유지부에 기억된 데이터의 유지를 행하는 데이터 유지부이며, 제4 데이터 유지부는, 제2 트랜지스터를 비도통 상태로 하고, 제2 트랜지스터의 소스 및 드레인 중 다른 쪽과, 제2 용량 소자의 한쪽 전극 사이에 전하를 유지함으로써, 제2 데이터 유지부에 기억된 데이터의 유지를 행하는 데이터 유지부인 반도체 장치가 바람직하다.

[0018] 본 발명의 일 형태에 있어서, 제1 트랜지스터 및 제2 트랜지스터는, 반도체층이 산화물 반도체인 반도체 장치가 바람직하다.

[0019] 본 발명의 일 형태에 있어서, 제1 트랜지스터 및 제2 트랜지스터는, 톱 게이트 구조의 트랜지스터인 반도체 장치가 바람직하다.

[0020] 본 발명의 일 형태에 있어서, 제1 데이터 유지부 및 제2 데이터 유지부는, 반도체층이 실리콘인 제3 트랜지스터를 사용하여 구성된 회로인 반도체 장치가 바람직하다.

[0021] 본 발명의 일 형태에 있어서, 제3 트랜지스터 위에는, 제1 트랜지스터 및 제2 트랜지스터가 적층하여 설치되는 반도체 장치가 바람직하다.

[0022] 본 발명의 일 형태에 있어서, 제1 트랜지스터 및 제2 트랜지스터가 설치된 층과, 제3 트랜지스터가 설치된 층 사이에는, 제1 트랜지스터, 제2 트랜지스터 및 제3 트랜지스터를 전기적으로 접속하기 위한 배선층이 설치되는 것을 특징으로 하는 반도체 장치가 바람직하다.

### 발명의 효과

[0023] 본 발명의 일 형태에 의해, 트랜지스터의 오프 전류가 매우 작은 것을 이용하여 용량 소자에서의 전하의 유지를 행하고, 데이터를 유지하는 반도체 장치의 구성에 있어서, 소자의 미세화를 진행시켜도 데이터의 유지에 필요한 유지 용량을 확보할 수 있는, 신규 구성의 반도체 장치를 제공할 수 있다. 또는 본 발명의 일 형태에 의해, 반도체 장치의 제조 프로세스나 회로를 구성하는 배선이나 동작을 복잡하게 하지 않고, 트랜지스터의 온 전류를 크게 할 수 있는, 신규 구성의 반도체 장치를 제공할 수 있다. 또는, 본 발명의 일 형태에 의해, 신규 반도체 장치 등을 제공할 수 있다.

[0024] 또한, 본 발명의 일 형태는 이들 효과에 한정되는 것은 아니다. 예를 들어, 본 발명의 일 형태는, 경우에 따라서는 또는 상황에 따라서, 이들 효과 이외의 효과를 갖는 경우도 있다. 또는, 예를 들어 본 발명의 일 형태는, 경우에 따라서는 또는 상황에 따라서, 이들 효과를 갖지 않는 경우도 있다.

### 도면의 간단한 설명

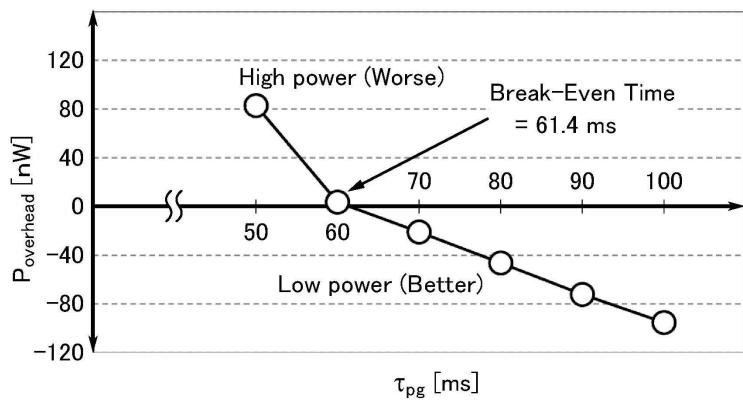

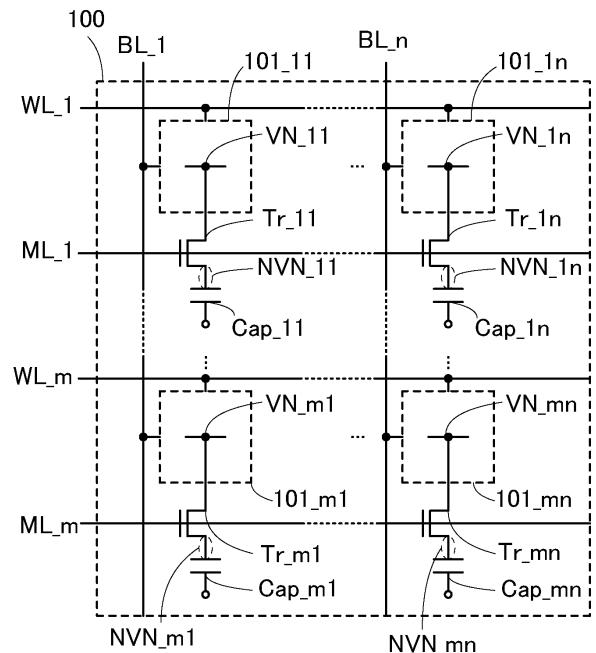

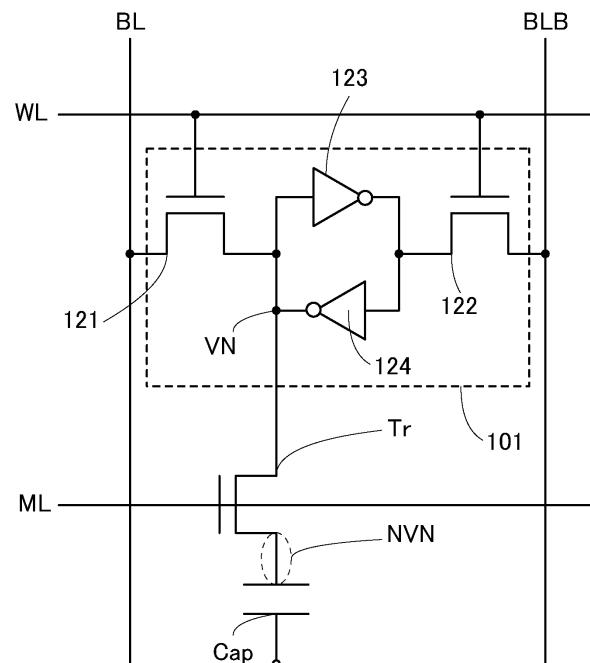

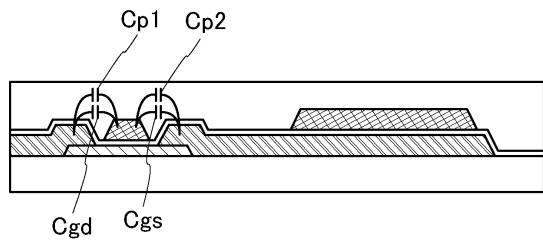

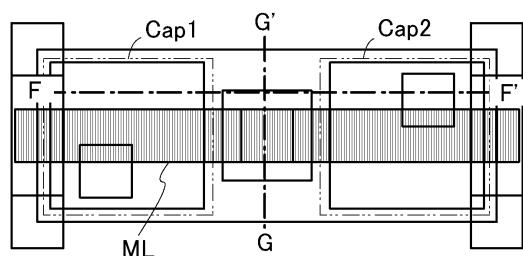

[0025] 도 1은 메모리 셀의 회로도 및 단면의 모식도.

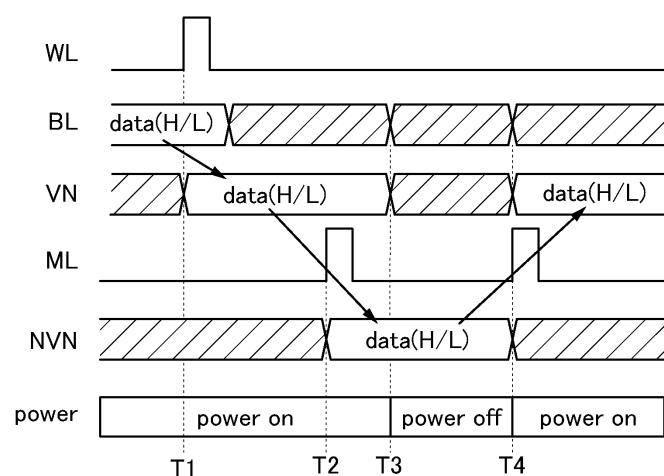

- 도 2는 메모리 셀의 회로도 및 타이밍차트.

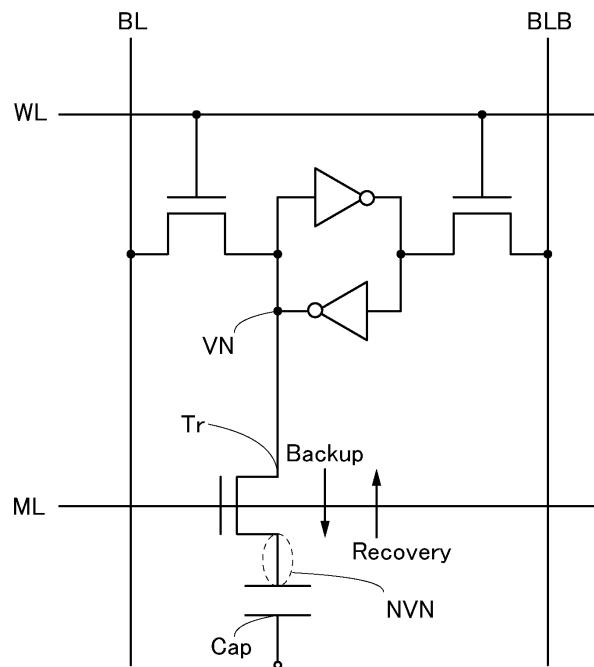

- 도 3은 메모리 셀의 회로도.

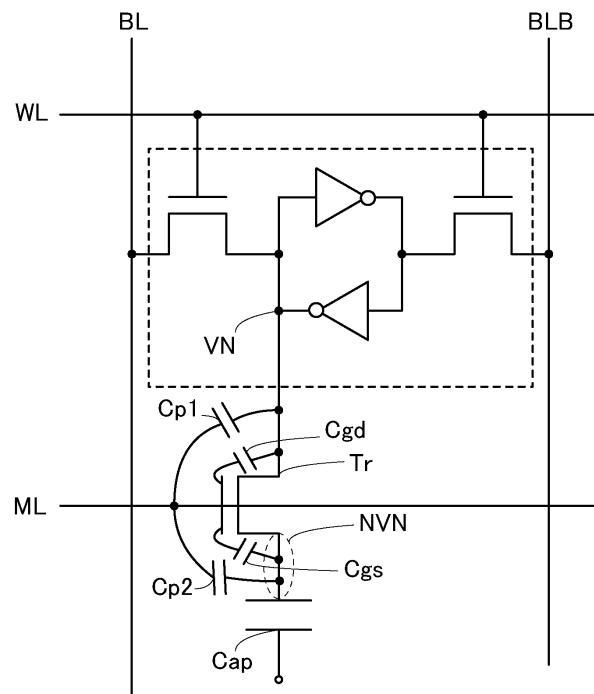

- 도 4는 메모리 셀의 회로도.

- 도 5는 메모리 셀의 단면 모식도.

- 도 6은 메모리 셀의 회로도.

- 도 7은 메모리 셀의 상면도 및 단면의 모식도.

- 도 8은 메모리 셀의 상면도.

- 도 9는 메모리 셀의 단면도.

- 도 10은 메모리 셀의 상면도 및 단면의 모식도.

- 도 11은 메모리 셀의 상면도.

- 도 12는 메모리 셀의 단면도.

- 도 13은 반도체 장치의 제작 공정을 나타내는 플로우차트도 및 사시 모식도.

- 도 14는 반도체 장치를 사용한 전자 기기.

- 도 15는 메모리 셀의 상면도 및 단면의 모식도.

- 도 16은 메모리 셀의 상면도.

- 도 17은 메모리 셀의 단면도.

- 도 18은 메모리 셀의 단면도.

- 도 19는 메모리 셀의 회로도 및 타이밍차트.

- 도 20은 OS-SRAM의 회로도.

- 도 21은 OS-SRAM의 Power-Gating sequence.

- 도 22는 OS-SRAM 마스크 레이아웃과 층 구조를 도시하는 도면.

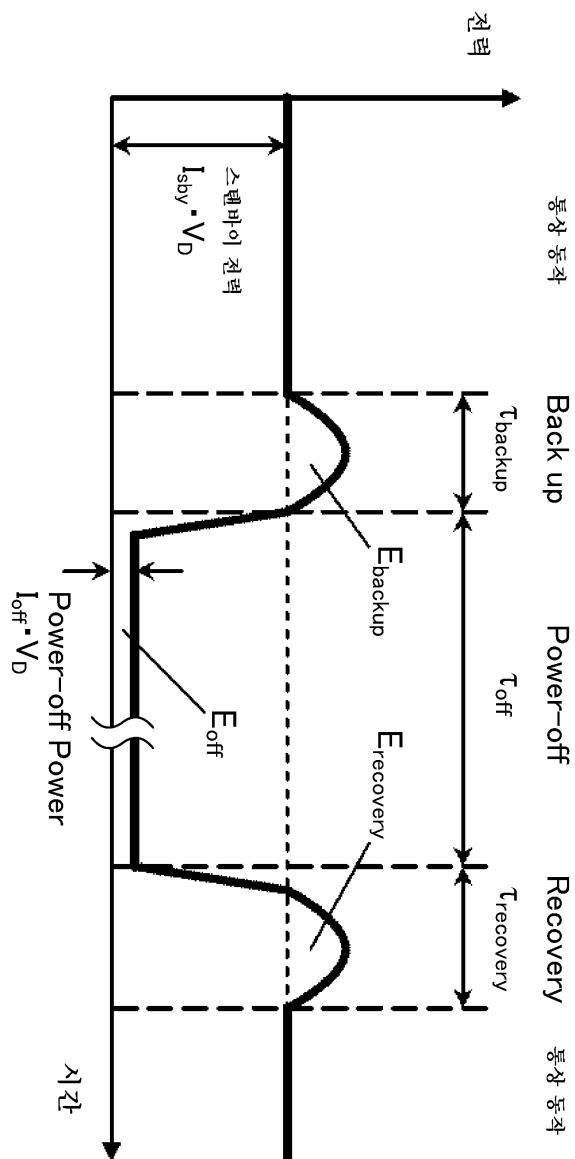

- 도 23은 OS-SRAM의 소비 전력 시간 변화 개략도.

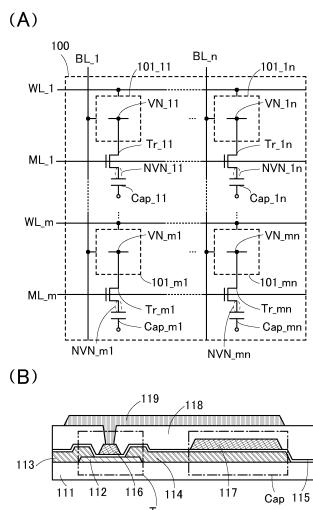

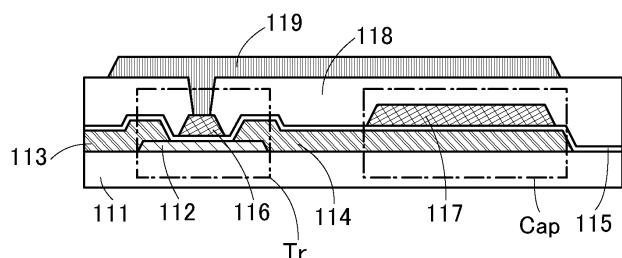

- 도 24는 Break-even time 견적을 도시하는 도면.

- 도 25는 OS-SRAM/standard-SRAM의 static noise margin 비교를 위한 도면.

- 도 26은 시험 제작한 32-bit microprocessor의 칩 사진.

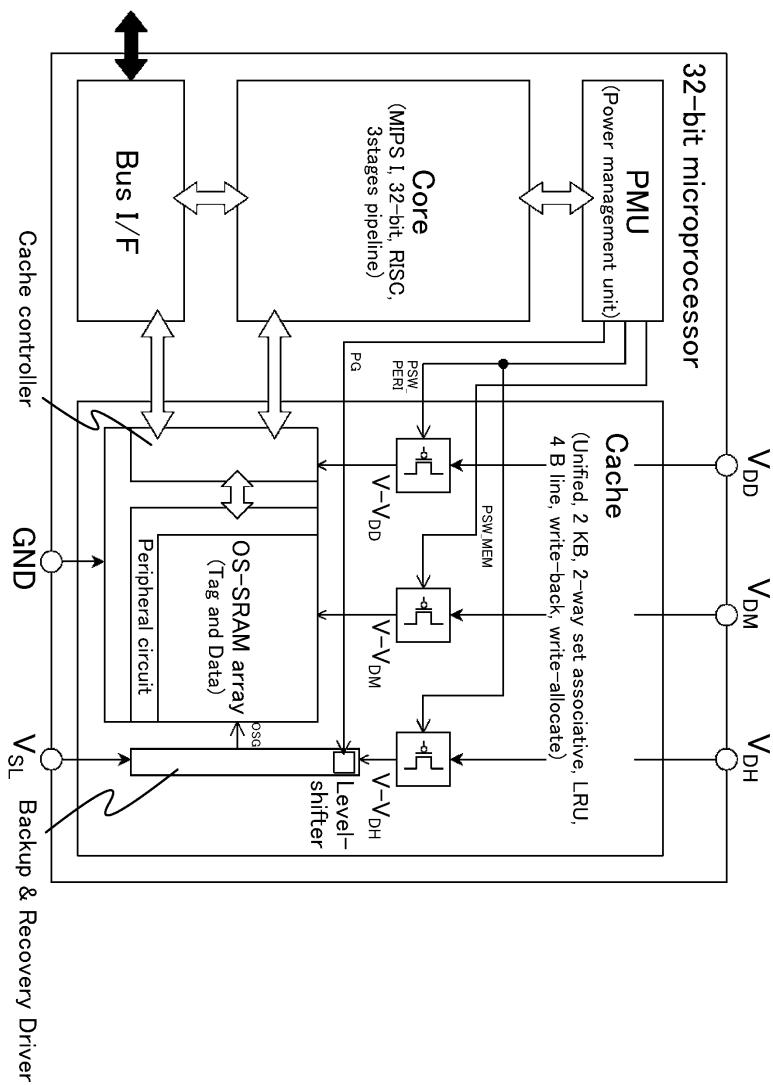

- 도 27은 32-bit microprocessor 블록도.

- 도 28은 Cache memory Power-Gating 시의 오실로스코프 파형.

- 도 29는 Power-Gating overhead 전력의 측정 개념도.

- 도 30은 Power-Gating overhead 전력의 측정 결과를 도시하는 도면.

### 발명을 실시하기 위한 구체적인 내용

[0026]

이하, 실시 형태에 대하여 도면을 참조하면서 설명한다. 단, 실시 형태는 많은 다른 형태로 실시하는 것이 가능하고, 취지 및 그 범위로부터 일탈하지 않고 그 형태 및 상세를 다양하게 변경할 수 있는 것은 당업자라면 용이하게 이해된다. 따라서, 본 발명은 이하의 실시 형태의 기재 내용에 한정하여 해석되는 것은 아니다. 또한, 이하에 설명하는 발명의 구성에 있어서, 동일한 물을 지시하는 부호는 다른 도면간에 있어서 공통으로 한다.

[0027]

또한, 도면에 있어서, 크기, 층의 두께, 또는 영역은, 명료화를 위하여 과장 되어 있는 경우가 있다. 따라서, 반드시 그 스케일에 한정되지 않는다. 또한 도면은, 이상적인 예를 모식적으로 나타낸 것이며, 도면에 나타내는 형상 또는 값 등에 한정되지 않는다. 예를 들어, 노이즈에 의한 신호, 전압, 또는 전류의 변동, 또는, 타이

밍의 어긋남에 의한 신호, 전압, 또는 전류의 변동 등을 포함하는 것이 가능하다.

[0028] 또한 본 명세서 등에 있어서, 트랜지스터란, 게이트와, 드레인과, 소스를 포함하는 적어도 3개의 단자를 갖는 소자이다. 그리고, 드레인(드레인 단자, 드레인 영역 또는 드레인 전극)과 소스(소스 단자, 소스 영역 또는 소스 전극) 사이에 채널 영역을 갖고 있으며, 드레인과 채널 영역과 소스를 통해서 전류를 흘릴 수 있는 것이다.

[0029] 여기서, 소스와 드레인이란, 트랜지스터의 구조 또는 동작 조건 등에 따라 바뀌기 위해, 어느 하나가 소스 또는 드레인인지를 한정하는 것이 곤란하다. 따라서, 소스로서 기능하는 부분 및 드레인으로서 기능하는 부분을, 소스 또는 드레인이라 칭하지 않고, 소스와 드레인 중 한쪽을 제1 전극이라 표기하고, 소스와 드레인 중 다른 쪽을 제2 전극이라 표기하는 경우가 있다.

[0030] 또한 본 명세서에서 사용하는 「제1」, 「제2」, 「제3」이라고 하는 서수사는, 구성 요소의 혼동을 피하기 위하여 부여한 것이며, 수적으로 한정하는 것은 아닌 것을 부기한다.

[0031] 또한 본 명세서에 있어서, A와 B가 접속되어 있다란, A와 B가 직접 접속되어 있는 것 외에, 전기적으로 접속되어 있는 것을 포함하는 것으로 한다. 여기서, A와 B가 전기적으로 접속되고 있다란, A와 B 사이에서, 어떠한 전기적 작용을 갖는 대상물이 존재할 때, A와 B의 전기 신호의 수수를 가능하게 하는 것을 말한다.

[0032] 또한 본 명세서에 있어서, 「위에」, 「아래에」 등의 배치를 나타내는 어구는, 구성끼리의 위치 관계를, 도면을 참조하여 설명하기 위해서, 편의 상 사용하고 있다. 또한, 구성끼리의 위치 관계는, 각 구성의 위치를, 방향에 따라서 적절히 변화하는 것이다. 따라서, 명세서에서 설명한 어구에 한정되지 않고, 상황에 따라서 적절하게 바꿔서 말할 수 있다.

[0033] 또한 도면에 있어서의 각 회로 블록의 배치는, 설명을 위해 위치 관계를 특정하는 것이며, 다른 회로 블록에서 별도의 기능을 실현하도록 도면에서 나타내고 있어도, 실제 회로 블록에서는, 동일한 회로 블록 내에서 별도의 기능을 실현할 수 있도록 되어 있는 경우도 있다. 또한 도면에서의 각 회로 블록의 기능은, 설명을 위해 기능을 특정하는 것이며, 하나의 회로 블록으로서 나타내고 있어도, 실제 회로 블록에서는, 하나의 회로 블록에서 행하는 처리를 복수의 회로 블록에서 행하도록 되어 있는 경우도 있다.

[0034] 또 전압이란, 어떤 전위와, 기준 전위(예를 들어 접지 전위)와의 전위차를 나타내는 경우가 많다. 따라서, 전압, 전위, 전위차를, 각각, 전위, 전압, 전압 차로 바꿔 말하는 것이 가능하다. 또 전압이란, 2점간에서의 전위차를 말하며, 전위란 어느 1점에 있어서의 정전기장 중에 있는 단위 전하가 갖는 정전 에너지(전기적인 위치 에너지)를 말한다.

[0035] 또한, 일반적으로, 전위나 전압은, 상대적인 것이다. 따라서, 접지 전위는, 반드시 0볼트라고 한정되지는 않는다.

[0036] 또한 본 명세서 등에 있어서, 「평행」이란, 2개의 직선이  $-10^\circ$  이상  $10^\circ$  이하인 각도로 배치되어 있는 상태를 말한다. 따라서,  $-5^\circ$  이상  $5^\circ$  이하인 경우도 포함된다. 또한, 「수직」이란, 2개의 직선이  $80^\circ$  이상  $100^\circ$  이하인 각도로 배치되어 있는 상태를 말한다. 따라서,  $85^\circ$  이상  $95^\circ$  이하인 경우도 포함된다.

[0037] 또한 본 명세서 등에 있어서, 결정이 삼방정 또는 능면체정인 경우, 육방정계로서 나타낸다.

[0038] (실시 형태 1)

[0039] 본 실시 형태에서는, 개시하는 발명의 일 형태에 따른 반도체 장치가 갖는, 메모리 셀의 회로 구성 및 그 단면의 모식도에 대해서, 도 1을 참조하여 설명한다.

[0040] 또한, 반도체 장치란, 반도체 소자를 갖는 장치를 말한다. 또한, 반도체 장치는, 반도체 소자를 포함하는 회로를 구동시키는 구동 회로 등을 포함한다. 또한, 반도체 장치는, 메모리 셀 외에, 다른 기판 위에 배치된 구동 회로, 전원 회로 등을 포함하는 경우가 있다.

[0041] 도 1의 (A)는 메모리 셀(100)의 일례를 나타내는 회로도이다.

[0042] 도 1의 (A)에 나타내는 메모리 셀(100)에서는, 기억 회로(101\_11 내지 101\_mn)(m, n은 자연수), 트랜지스터 Tr\_11 내지 Tr\_mn 및 용량 소자 Cap\_11 내지 Cap\_mn을 갖는다. 또한 기억 회로(101\_mn), 트랜지스터 Tr\_mn 및 용량 소자 Cap\_mn은, m행 n열에 있는 메모리를 구성하는 회로 및 소자이다. 또한 기억 회로(101\_11 내지 101\_mn), 트랜지스터 Tr\_11 내지 Tr\_mn 및 용량 소자 Cap\_11 내지 Cap\_mn으로 구성되는 메모리는, 매트릭스 형상으로 복수 설치되어 있다.

- [0043] 또한 도 1의 (A)에서는, 워드선 WL\_1 내지 WL\_m, 비트선 BL\_1 내지 BL\_n 및 데이터 제어선 ML\_1 내지 ML\_m을 나타내고 있다.

- [0044] 또한 도 1의 (A)에서는, 기억 회로(101\_11 내지 101\_mn) 내에, 데이터에 따른 전위를 유지하는 노드에 상당하는, 휘발성 메모리부 VN\_11 내지 VN\_mn을 나타내고 있다. 또한, 도 1의 (A)에서는, 트랜지스터 Tr\_11 내지 Tr\_mn과 용량 소자 Cap\_11 내지 Cap\_mn 사이의 노드에서, 데이터에 따른 전위를 유지하는, 불휘발성 메모리부 NVN\_11 내지 NVN\_mn을 나타내고 있다.

- [0045] 또한 본 명세서에 있어서, 노드란, 소자간을 전기적으로 접속하기 위해서 설치되는 배선 위의 어느 하나의 개소이다.

- [0046] 본 실시 형태에서 설명하는 반도체 장치에서는, 용량 소자 Cap\_11 내지 Cap\_mn을 구성하는 2개의 전극을, 트랜지스터 Tr\_11 내지 Tr\_mn의 게이트로 되는 전극과 동일층에 설치된 전극, 소스 및 드레인으로 되는 전극과 동일층에 설치된 전극으로 구성한다. 그리고, 트랜지스터 Tr\_11 내지 Tr\_mn의 게이트로 되는 전극을 설치하는 층(게이트 전극층)과, 복수의 메모리간의 트랜지스터 Tr\_11 내지 Tr\_mn의 게이트를 접속하는 배선층(메모리 셀 배선층)을 다른 층에 설치하는 구성으로 한다.

- [0047] 본 실시 형태에서 설명하는 구성은, 게이트 전극층과 메모리 셀 배선층을 다른 층에 설치함으로써, 트랜지스터 Tr\_11 내지 Tr\_mn의 게이트에 형성되는 기생 용량을 억제하는 구성으로 할 수 있다. 또한 게이트 전극층을, 메모리 셀 배선층을 다른 층에 설치함으로써, 게이트 전극층과 동일층에 한쪽 전극이 설치되는 용량 소자 Cap\_11 내지 Cap\_mn을 형성하는 면적을 증가시킬 수 있다.

- [0048] 계속해서, 메모리 셀(100)이 갖는 각 회로에 대하여 설명한다.

- [0049] 기억 회로(101\_11 내지 101\_mn)는, 비트선 BL\_1 내지 BL\_n에 부여되는 데이터에 따른 전위가, 워드선 WL\_1 내지 WL\_m에 부여되는 워드 신호에 따라서 기입되는 회로이다. 일례로서 기억 회로(101\_11 내지 101\_mn)는, 트랜지스터 Tr\_11 내지 Tr\_mn이 비도통 상태일 때, SRAM(Static Random Access Memory)으로서 기능하는 회로이다. 구체적으로, 기억 회로(101\_11 내지 101\_mn)는, 2개의 트랜지스터와 2개의 인버터 회로로 구성할 수 있다.

- [0050] 휘발성 메모리부 VN\_11 내지 VN\_mn은, 기억 회로(101\_11 내지 101\_mn)에 전원 공급이 되어 있는 경우에 데이터에 따른 전위를 유지하는 노드를 말한다. 기억 회로(101\_11 내지 101\_mn)가 SRAM인 경우, 2개의 인버터 회로의 출력 신호가 출력되는, 적어도 한쪽 노드가 휘발성 메모리부 VN\_11 내지 VN\_mn에 상당한다.

- [0051] 또한 본 명세서에 있어서, 데이터를 기입한다란, 신호를 제어함으로써 배선의 전위가, 별도의 배선의 전위에 따라서 변화하는 것을 말한다. 예를 들어, 워드선 WL\_1에 부여되는 워드 신호를 제어함으로써, 휘발성 메모리부 VN\_11 내지 VN\_1n의 전위가, 비트선 BL\_1 내지 BL\_n의 전위로 되는 것을, 기억 회로(101\_11 내지 101\_1n)에 데이터를 기입한다고 한다.

- [0052] 트랜지스터 Tr\_11 내지 Tr\_mn은, 불휘발성 메모리부 NVN\_11 내지 NVN\_mn에의 데이터의 기입을 제어하는 스위치로서의 기능을 갖는다. 그 때문에 트랜지스터 Tr\_11 내지 Tr\_mn은, 게이트에 부여되는 신호에 의해, 도통 상태와 비도통 상태를 전환할 수 있다. 또한 트랜지스터 Tr\_11 내지 Tr\_mn은, 비도통 상태를 유지함으로써, 기입한 데이터를 유지하는 기능을 갖는다. 또한 트랜지스터 Tr\_11 내지 Tr\_mn은, 제1 트랜지스터라고도 한다. 또한, 트랜지스터 Tr\_11 내지 Tr\_mn은, n 채널형의 트랜지스터로서, 설명을 행하기로 한다.

- [0053] 또한 트랜지스터 Tr\_11 내지 Tr\_mn은, 비도통 상태에 있어서 소스와 드레인 사이를 흐르는 전류(오프 전류)가 낮은 트랜지스터가 사용되는 것이 적합하다. 여기에서는, 오프 전류가 낮다란, 실온에서, 소스와 드레인 사이의 전압을 10V로 하고, 채널폭  $1\mu m$ 당 규격화된 오프 전류가  $10ZA$  이하인 것을 말한다. 이와 같이 오프 전류가 적은 트랜지스터로서는, 반도체층에 산화물 반도체를 갖는 트랜지스터를 들 수 있다.

- [0054] 용량 소자 Cap\_11 내지 Cap\_mn은, 트랜지스터 Tr\_11 내지 Tr\_mn을 도통 상태로 함으로써 휘발성 메모리부 VN\_11 내지 VN\_mn의 데이터가 기입되는 용량 소자이다. 또한, 용량 소자 Cap\_11 내지 Cap\_mn은, 트랜지스터 Tr\_11 내지 Tr\_mn을 비도통 상태로 함으로써, 외부로부터의 전원 공급이 없어도 전하를 유지하는 용량 소자이다. 또한, 트랜지스터 Tr\_11 내지 Tr\_mn을 도통 상태로 함으로써, 용량 소자 Cap\_11 내지 Cap\_mn으로 유지된 데이터를 휘발성 메모리부 VN\_11 내지 VN\_mn에 기입한다.

- [0055] 데이터 제어선 ML\_1 내지 ML\_m은, 트랜지스터 Tr\_11 내지 Tr\_mn의 도통 상태와 비도통 상태를 전환하기 위한 신호가 부여되는 배선이다. 데이터 제어선 ML\_1 내지 ML\_m 중 어느 하나(예를 들어 데이터 제어선 ML\_1)에 대하여 H 레벨의 신호를 부여하면, 선택한 데이터 제어선에 접속된 트랜지스터 Tr\_11 내지 Tr\_1n은 도통 상태로 되

고, L 레벨의 신호를 부여하면, 선택한 데이터 제어선에 접속된 트랜지스터 Tr\_11 내지 Tr\_1n은 비도통 상태로 된다.

[0056] 불휘발성 메모리부 NVN\_11 내지 NVN\_mn은, 트랜지스터 Tr\_11 내지 Tr\_mn과 용량 소자 Cap\_11 내지 Cap\_mn 사이의 노드를 말한다. 트랜지스터 Tr\_11 내지 Tr\_mn이 비도통 상태인 경우, 불휘발성 메모리부 NVN\_11 내지 NVN\_mn에서는, 용량 소자 Cap\_11 내지 Cap\_mn에 유지된 전하가 트랜지스터 Tr\_11 내지 Tr\_mn을 통해서 거의 누설되지 않은 것을 이용하여, 전원 공급이 정지해도 휘발성 메모리부 VN\_11 내지 VN\_mn의 데이터를 계속 기억할 수 있다.

[0057] 도 1의 (A)에 나타내는 불휘발성 메모리부 NVN\_11 내지 NVN\_mn의 구성에서는, 트랜지스터 Tr\_11 내지 Tr\_mn의 비도통 상태를 유지함으로써, 기입한 데이터를 유지하고 있다. 그로 인해, 불휘발성 메모리부 NVN\_11 내지 NVN\_mn에서의 전하의 이동을 수반한 전위의 변동을 억제하는 스위치로서, 상술한 바와 같이, 오프 전류가 적은 트랜지스터가 사용되는 것이 특히 바람직하다.

[0058] 트랜지스터 Tr\_11 내지 Tr\_mn은, 오프 전류가 적은 트랜지스터로서 비도통 상태를 유지함으로써, 불휘발성 메모리부 NVN\_11 내지 NVN\_mn을 불휘발성의 메모리로 할 수 있다. 따라서, 일단, 불휘발성 메모리부 NVN\_11 내지 NVN\_mn에 기입된 데이터는, 다시 트랜지스터 Tr\_11 내지 Tr\_mn을 도통 상태로 할 때까지, 불휘발성 메모리부 NVN\_11 내지 NVN\_mn에 계속 유지할 수 있다.

[0059] 계속해서, 도 1의 (A)에 나타내는 메모리 셀(100)에 있어서의 트랜지스터 Tr\_11 내지 Tr\_mn, 용량 소자 Cap\_11 내지 Cap\_mn의 단면의 모식도를 도 1의 (B)에서 설명하고, 본 실시 형태의 구성으로 하는 것에 의한 작용 및 효과에 대하여 설명한다. 또한 도 1의 (B)에서는, 트랜지스터 Tr\_11 내지 Tr\_mn 중 어느 하나로서 트랜지스터 Tr, 용량 소자 Cap\_11 내지 Cap\_mn 중 어느 하나로서 용량 소자 Cap를 나타내고 있다.

[0060] 도 1의 (B)에 나타내는 단면의 모식도는, 트랜지스터 Tr 및 용량 소자 Cap의 단면의 구조를 나타내는 것이다. 또한 도 1의 (B)에 나타내는 트랜지스터 Tr 및 용량 소자 Cap는, 도 1의 (A)에서 설명한 기억 회로(101\_11 내지 101\_mn)를 구성하는 트랜지스터 및 그 트랜지스터끼리를 접속하기 위한 배선 위에 설치되는 구성으로 된다.

[0061] 도 1의 (B)에서는, 트랜지스터 Tr 및 용량 소자 Cap를 설명하기 위한 구성으로서, 절연층(111), 반도체층(112), 소스 및 드레인 중 한쪽으로 되는 제1 전극(113), 소스 및 드레인 중 다른 쪽으로 되는 제2 전극(114), 게이트 절연층(115), 게이트 전극(116), 게이트 전극(116)과 동일한 층에 설치되는 전극(117), 중간 절연층(118) 및 배선층(119)을 나타내고 있다.

[0062] 도 1의 (B)에 나타낸 바와 같이 본 실시 형태에서 설명하는 반도체 장치에서는, 용량 소자 Cap를 구성하는 전극을 트랜지스터 Tr의 게이트 전극(116)과, 소스 및 드레인 중 다른 쪽으로 되는 제2 전극(114)과, 동일층에 설치된 전극으로 구성한다. 그리고 게이트 전극(116)을 설치하는 층과, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극(116)을 접속하는 배선층(119)을 다른 층에 설치하는 구성으로 한다.

[0063] 본 실시 형태에서 설명하는 구성은, 게이트 전극(116)과 배선층(119)을 다른 층에 설치함으로써, 트랜지스터 Tr의 게이트 전극(116)에서의 기생 용량을 억제하는 구성으로 할 수 있다. 또한 트랜지스터 Tr의 게이트 전극(116)을 설치하는 층을 배선층(119)과 다른 층에 설치할 수 있기 때문에, 게이트 전극(116)과 동일층에 한쪽 전극이 설치되는 용량 소자 Cap를 형성하는 면적을 증가시킬 수 있다.

[0064] 계속해서, 도 1의 (B)의 단면의 모식도로 나타낸 각 구성에 대하여 설명한다.

[0065] 절연층(111)은 일례로서는, 무기 절연층을 사용하면 된다. 무기 절연층으로서는, 질화실리콘막, 산화질화실리콘막, 또는 질화산화실리콘막 등을, 단층 또는 다층으로 형성하는 것이 바람직하다. 또한 절연층(111)보다 하층에는, 도 1의 (B)에서는 생략했지만, 트랜지스터, 및 도전층으로 구성되는 배선층이 설치된다. 또한 절연층(111)은 절연층(111)보다 하층에 설치된 소자와, 절연층(111)보다 상층에 설치된 소자를 전기적으로 접속하기 위한, 도전층을 갖는 구성이어야 된다.

[0066] 반도체층(112)은 트랜지스터 Tr을 비도통 상태에 있어서 소스와 드레인 사이를 흐르는 전류(오프 전류)가 낮은 트랜지스터로 하기 위해서, 산화물 반도체를 사용하는 것이 적합하다.

[0067] 소스 및 드레인 중 한쪽으로 되는 제1 전극(113), 및 소스 및 드레인 중 다른 쪽으로 되는 제2 전극(114)은 일례로서는, 알루미늄, 구리, 티타늄, 탄탈륨, 텅스텐 등의 금속 재료를 단층 또는 적층시켜서 사용할 수 있다.

[0068] 게이트 절연층(115)은 절연층(111)과 마찬가지로, 무기 절연층을 사용하면 된다.

- [0069] 게이트 전극(116) 및 게이트 전극(116)과 동일한 층에 설치되는 전극(117)은 제1 전극(113) 및 제2 전극(114)과 마찬가지로, 알루미늄, 구리, 티타늄, 탄탈륨, 텡스텐 등의 금속 재료를 단층 또는 적층시켜서 사용할 수 있다.

- [0070] 층간 절연층(118)은 무기 절연층 또는 유기 절연층을, 단층 또는 다층으로 형성하는 것이 바람직하다. 유기 절연층으로서는, 폴리이미드 또는 아크릴 등을, 단층 또는 다층으로 형성하는 것이 바람직하다.

- [0071] 배선층(119)은 게이트 전극(116) 및 전극(117), 및 제1 전극(113) 및 제2 전극(114)과 마찬가지로, 알루미늄, 구리, 티타늄, 탄탈륨, 텡스텐 등의 금속 재료를 단층 또는 적층시켜서 사용할 수 있다.

- [0072] 도 1의 (B)의 단면의 모식도의 구성에서는, 제2 전극(114)과 전극(117) 사이에 게이트 절연층(115)을 사이에 두고 형성한 용량 소자를 용량 소자 Cap로 하고 있다. 게이트 절연층(115)은 층간 절연층(118)과 비교하여, 막 두께가 작다. 그로 인해, 동일한 면적으로 했을 때, 보다 많은 정전 용량을 확보할 수 있는 용량 소자로 할 수 있다.

- [0073] 또한 도 1의 (B)의 단면의 모식도의 구성에서는, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극(116)을 접속하는 배선층(119)을 게이트 전극(116)과는 다른 층에 설치하는 구성으로 한다. 그로 인해, 배선층(119)은 다른 도전층과 이격하여 설치하는 구성으로 할 수 있다. 그로 인해, 배선층(119)에 형성되는 기생 용량을 저감할 수 있어, 게이트 전극(116)과 동일한 층에서 복수의 메모리간의 트랜지스터 Tr의 게이트 전극(116)을 접속하는 경우와 비교하여, 트랜지스터 Tr의 게이트에 형성되는 기생 용량을 억제하는 구성으로 할 수 있다.

- [0074] 또한 도 1의 (B)의 단면의 모식도의 구성에서는, 게이트 전극(116)과는 다른 층에서 복수의 메모리간의 트랜지스터 Tr의 게이트 전극(116)을 접속하는 구성으로 하고 있다. 이 구성의 경우, 게이트 전극(116)과 동일한 층에서 복수의 메모리간의 트랜지스터 Tr의 게이트 전극(116)을 접속할 필요가 없기 때문에, 그만큼, 용량 소자 Cap가 차지하는 면적을 확보할 수 있다.

- [0075] 도 1의 (B)의 단면의 모식도의 구성과는 반대로, 게이트 전극(116)과 동일한 층에서 복수의 메모리간의 트랜지스터 Tr의 게이트 전극(116)을 접속하는 경우, 게이트 전극(116)과 전극(117)이 단락하지 않도록, 동일한 층에서 이격하여 설치할 필요가 있고, 그만큼, 용량 소자 Cap가 차지하는 면적이 축소되어 버린다. 그로 인해, 용량 소자 Cap의 정전 용량이 저하되고, 트랜지스터 Tr의 기생 용량을 무시할 수 없게 됨으로써, 데이터의 유지, 및/또는 퇴피·복귀가 어려워지게 된다.

- [0076] 계속해서 메모리 셀(100)의 구체적인 회로 구성 및 그 동작에 대해서, 도 2 내지 도 5를 참조하여 설명한다.

- [0077] 도 2의 (A)는 도 1의 (A)에서 나타낸 메모리 셀(100)이 갖는 단위 메모리 셀의 구체적인 회로 구성을 도시하는 도면이다.

- [0078] 도 2의 (A)에서는, 도 1의 (A)와 마찬가지로, 기억 회로(101), 트랜지스터 Tr 및 용량 소자 Cap를 나타내고 있다.

- [0079] 또한 도 2의 (A)에서는, 워드선 WL, 비트선 BL, 반전 비트선 BLB 및 데이터 제어선 ML을 나타내고 있다.

- [0080] 또한 도 2의 (A)에서는, 기억 회로(101) 내에 SRAM을 구성하는, 트랜지스터(121), 트랜지스터(122), 인버터 회로(123) 및 인버터 회로(124)를 나타내고 있다. 또한 기억 회로(101) 내에는, 인버터 회로(124)의 출력 신호가 출력되는 노드를 휘발성 메모리부 VN으로서 나타내고 있다.

- [0081] 또한 트랜지스터(121) 및 트랜지스터(122), 및 인버터 회로(123) 및 인버터 회로(124)를 구성하는 트랜지스터는, 채널이 실리콘으로 형성되어 있는 트랜지스터로 하는 것이 바람직하다. 채널이 실리콘으로 형성되어 있는 트랜지스터는, 반도체층에 산화물 반도체를 사용한 트랜지스터인 트랜지스터 Tr이나 용량 소자 Cap와 적층하여 설치할 때, 특히 바람직하다.

- [0082] 또한, 도 2의 (A)에서는, 도 1의 (A)와 마찬가지로, 트랜지스터 Tr과 용량 소자 Cap 사이의 노드에서, 데이터에 따른 전위를 유지하는, 불휘발성 메모리부 NVN을 나타내고 있다.

- [0083] 도 2의 (A)에 나타내는 단위 메모리 셀의 구성은, 도 1의 (A) 및 도 1의 (B)와 마찬가지이다.

- [0084] 계속해서, 단위 메모리 셀의 동작에 대하여 설명한다.

- [0085] 도 2의 (B)에 나타내는 타이밍차트에서는, 도 2의 (A)에서 나타낸 워드선 WL, 비트선 BL, 휘발성 메모리부 VN, 데이터 제어선 ML, 불휘발성 메모리부 NVN의 전위 및 전원 공급의 유무(도면 중, power로서 표기)를 나타내고 있다. 또한 도 2의 (B) 중, 붙여진 평행 사선은, 실제로는 신호가 부여되고 있지만, 여기에서는 동작의 설명은

불필요하며, 특히 설명을 생략하기 위해 붙인 것이다.

- [0086] 우선 시각 T1에서 워드선 WL에 부여되는 워드 신호를 H 레벨로 하고, 비트선 BL에 부여된 H 레벨 또는 L 레벨의 전위에 상당하는 데이터(도면 중, data(H/L)라 표기)가 휘발성 메모리부 VN에 기입된다. 또한 반전 비트선 BLB에 있어서도, 비트선 BL과는 역의 전위에 상당하는 데이터가 부여된다.

- [0087] 이어서 시각 T2에서 데이터 제어선 ML에 부여되는 신호를 H 레벨로 하고, 휘발성 메모리부 VN에 기입된 데이터가, 불휘발성 메모리부 NVN에 기입된다. 또한, 시각 T2에서 행해지는, 불휘발성 메모리부 NVN에의 데이터의 기입을, 데이터의 퇴피(또는 backup이라고도 함)라고도 한다.

- [0088] 이어서 시각 T3에서 전원 공급을 정지한다. 이때, 휘발성 메모리부 VN에 기입된 데이터는 잃게 되지만, 불휘발성 메모리부 NVN에 기입된 데이터는, 오프 전류가 매우 작은 트랜지스터 Tr을 비도통 상태로 함으로써, 계속 유지할 수 있다.

- [0089] 이어서 시각 T4에서 전원 공급을 재개한다. 그리고 불휘발성 메모리부 NVN에 유지된 데이터를, 휘발성 메모리부 VN에 다시 기입하는 처리를 행한다. 이 휘발성 메모리부 VN에의 데이터의 기입은, 데이터 제어선 ML에 부여되는 신호를 H 레벨로 하여 행해진다. 또한, 시각 T4에서 행해지는, 휘발성 메모리부 VN에의 데이터의 기입을, 데이터의 복귀(또는 recovery라고도 함)라고도 한다.

- [0090] 또한 도 2의 (B)에서 설명한, 데이터의 퇴피·복귀는, 회로도 상에서 모식적으로 나타내면, 도 3과 같이 나타낼 수 있다. 도 2의 (B), 도 3에서 설명한, 데이터의 퇴피·복귀의 동작에서는, 모두, 데이터 제어선 ML에 H 레벨을 부여하여 트랜지스터 Tr을 도통 상태로 하고 있다.

- [0091] 트랜지스터 Tr에서의, 게이트와 소스 사이의 기생 용량 및 게이트와 드레인 사이의 기생 용량이, 용량 소자 Cap의 정전 용량과 비교하여 무시할 수 없는 크기가 되면, 데이터 제어선 ML의 전위의 변동에 수반하여, 휘발성 메모리부 VN 및 불휘발성 메모리부 NVN의 전위도 변동한다. 휘발성 메모리부 VN 및 불휘발성 메모리부 NVN에 있어서의 전위의 변화가 데이터의 퇴피·복귀의 동작 시에 발생하면, 정상적인 동작을 하는 것이 어려워진다.

- [0092] 반대로 말하면, 트랜지스터 Tr에서의, 게이트와 소스 사이의 기생 용량 및 게이트와 드레인 사이의 기생 용량이, 용량 소자 Cap의 정전 용량과 비교하여 무시할 수 있을 만큼 작아지면, 데이터 제어선 ML의 전위가 변동해도, 휘발성 메모리부 VN 및 불휘발성 메모리부 NVN의 전위가 변동하지 않도록 할 수 있다.

- [0093] 본 실시 형태의 구성에서는, 상술한 바와 같이, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층을, 게이트 전극과는 다른 층에 설치하는 구성으로 한다. 그로 인해, 배선층은, 그 외의 도전층과 이격하여 설치하는 구성으로 할 수 있고, 트랜지스터 Tr의 게이트에 형성되는 기생 용량을 억제하는 구성으로 할 수 있다. 기생 용량을 억제함으로써, 데이터의 퇴피·복귀의 동작 시에 있어서의, 휘발성 메모리부 VN 및 불휘발성 메모리부 NVN에 있어서의 전위의 변화를 작게 하여, 정상적인 동작을 행할 수 있다.

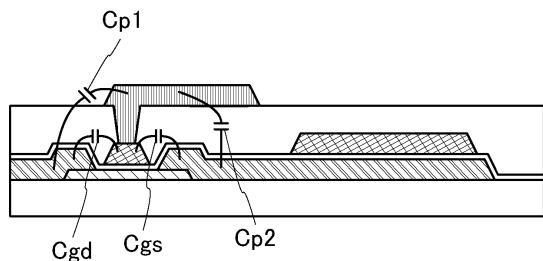

- [0094] 도 4에서는, 회로도에 있어서, 트랜지스터 Tr의 게이트와 소스 사이의 기생 용량 Cgs 및 게이트와 드레인 사이의 기생 용량 Cgd, 및 배선층과 트랜지스터 Tr의 소스 사이의 기생 용량 Cp1 및 배선층과 트랜지스터 Tr의 드레인 사이의 기생 용량 Cp2를 모식적으로 나타낸 도면이다. 또한 도 4에서는, 소스 및 드레인 중 한쪽을 소스라 하고, 소스 및 드레인 중 다른 쪽을 드레인이라 하여 설명하고 있다.

- [0095] 데이터 제어선 ML이 연장 설치되는 방향으로 설치되는 배선층을, 다른 도전층과 이격하여 설치함으로써, 도 4에 나타내는 회로도에 있어서의, 기생 용량 Cp1 및 기생 용량 Cp2를 작게 할 수 있다.

- [0096] 예를 들어, 도 5의 (A)에 나타내는 단면의 모식도에 있는 바와 같이, 배선층이, 트랜지스터의 게이트 전극과 동일한 층에 있는 경우, 게이트 절연층이라고 하는 다른 층보다 얇은 절연층을 통해서 다른 층과 기생 용량 Cp1 및 기생 용량 Cp2를 형성하는 구성으로 된다. 한편, 도 5의 (B)에 나타내는 단면의 모식도에 있는 바와 같이, 배선층이, 트랜지스터의 게이트 전극과 다른 층에 있는 경우, 층간 절연층과 같은 다른 층보다 두꺼운 절연층을 통해서 다른 층과 기생 용량 Cp1 및 기생 용량 Cp2를 형성하는 구성으로 된다. 그로 인해, 도 5의 (B)의 구성에서는, 도 5의 (A)의 구성에 비해, 기생 용량을 작게 할 수 있다.

- [0097] 또한, 데이터 제어선 ML이 연장 설치되는 방향으로 설치되는 배선층을, 트랜지스터 Tr의 게이트 전극과 동일층에 있는 용량 소자의 전극은 다른 층에 설치하는 구성으로 함으로써, 도 4에 나타내는 회로도에 있어서의, 용량 소자 Cap가 차지하는 면적을 확보할 수 있다. 그로 인해, 본 실시 형태의 구성에서는, 트랜지스터의 기생 용량을 저감하는 점, 용량 소자의 정전 용량을 증가하는 점의, 두가지 점에서 데이터의 퇴피·복귀의 동작 시에 있어서의, 휘발성 메모리부 VN 및 불휘발성 메모리부 NVN에 있어서의 전위의 변화를 작게 하여, 정상적인 동작을

행하는 구성으로 할 수 있다.

[0098] 이상 설명한, 본 실시 형태의 구성에서는, 트랜지스터 Tr의 게이트에 형성되는 기생 용량을 억제하는 구성에 더하여, 게이트 전극과 동일층에서 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하지 않음으로써, 용량 소자가 차지하는 면적을 확보할 수 있다. 그로 인해, 트랜지스터 및 용량 소자의 미세화를 진행시켜도, 기생 용량의 저감 및 용량 소자를 형성하기 위한 면적 확보를 도모할 수 있고, 휘발성 메모리부 VN 및 불휘발성 메모리부 NVN의 전위의 변동을 작게 할 수 있다.

[0099] 이상, 본 실시 형태에 나타내는 구성은, 다른 실시 형태에 나타내는 구성과 적절히 조합하여 사용할 수 있다.

[0100] (실시 형태 2)

[0101] 본 실시 형태에서는, 개시하는 발명의 일 형태에 따른 반도체 장치의 메모리 셀이 갖는 트랜지스터의 단면 구조에 대해서, 회로도, 상면도 등을 참조하여 설명한다. 또한 본 실시 형태에서는, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층을, 게이트 전극과는 다른 층에 설치하는 구성으로 하는 것의 이점을 설명하기 위해, 상면도 및 단면도에 있어서, 배선층과 게이트 전극을 동일한 층으로 한 구성과, 배선층과 게이트 전극을 다른 층으로 한 구성에 대하여 함께 설명한다.

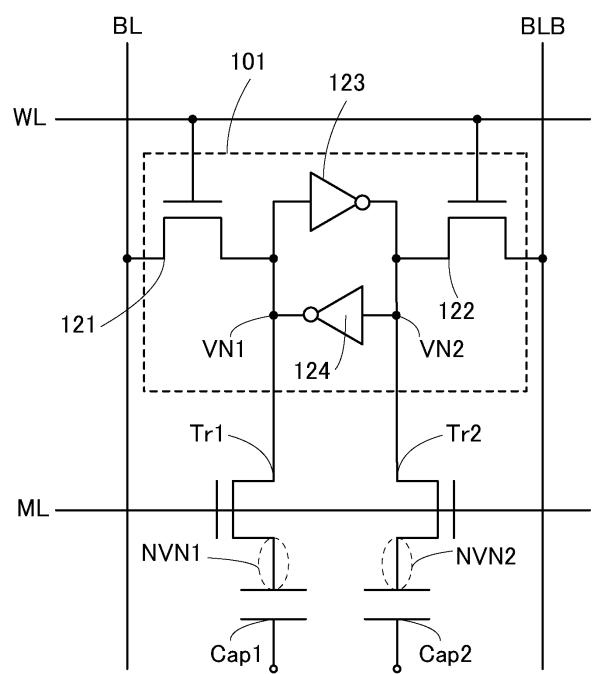

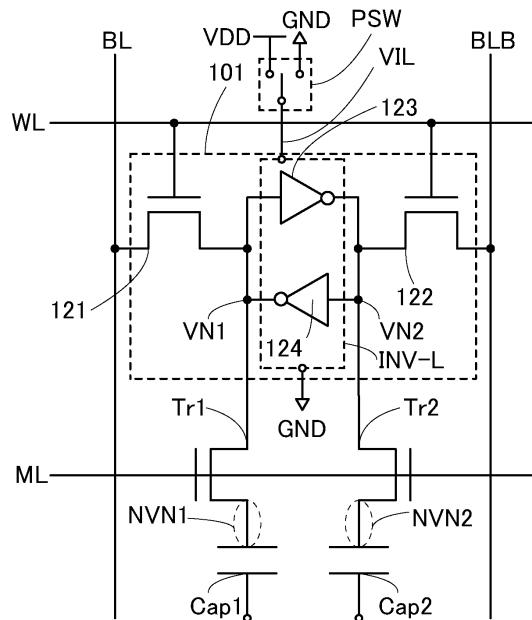

[0102] 먼저 본 실시 형태에서 일례로서 설명하는, 메모리 셀의 회로로 구성에 대하여 도 6에 나타내었다. 도 6에 나타내는 회로 구성은, 배선층과 게이트 전극을 동일한 층으로 한 구성과, 배선층과 게이트 전극을 다른 층으로 한 구성에 공통된다.

[0103] 도 6에서는, 기억 회로(101), 트랜지스터 Tr1, 트랜지스터 Tr2, 용량 소자 Cap1 및 용량 소자 Cap2를 나타내고 있다.

[0104] 또한 도 6에서는, 워드선 WL, 비트선 BL, 반전 비트선 BLB 및 데이터 제어선 ML을 나타내고 있다.

[0105] 또한 도 6에서는, 도 2의 (A)와 마찬가지로, 기억 회로(101) 내에 SRAM을 구성하는, 트랜지스터(121), 트랜지스터(122), 인버터 회로(123) 및 인버터 회로(124)를 나타내고 있다. 또한 기억 회로(101) 내에는, 인버터 회로(124)의 출력 신호가 출력되는 노드를 휘발성 메모리부 VN1로서 나타내고 있다. 또한 기억 회로(101) 내에는, 인버터 회로(123)의 출력 신호가 출력되는 노드를 휘발성 메모리부 VN2로서 나타내고 있다.

[0106] 또한, 도 6에서는, 트랜지스터 Tr1과 용량 소자 Cap1 사이의 노드에서, 데이터에 따른 전위를 유지하는, 불휘발성 메모리부 NVN1을 나타내고 있다. 또한, 도 6에서는, 트랜지스터 Tr2와 용량 소자 Cap2 사이의 노드에서, 데이터에 따른 전위를 유지하는, 불휘발성 메모리부 NVN2를 나타내고 있다.

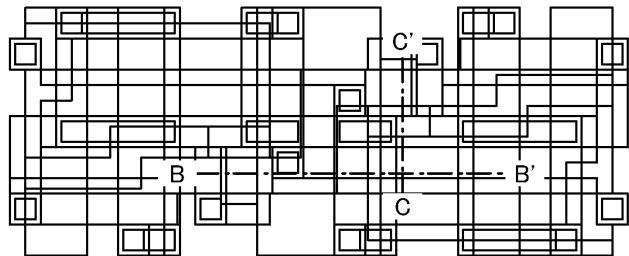

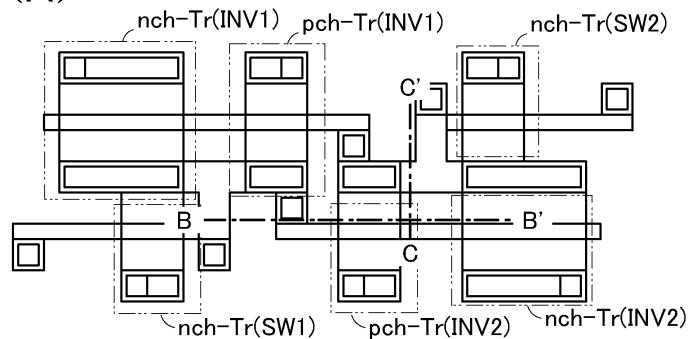

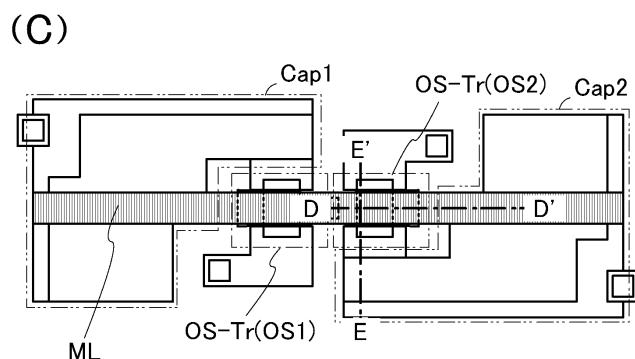

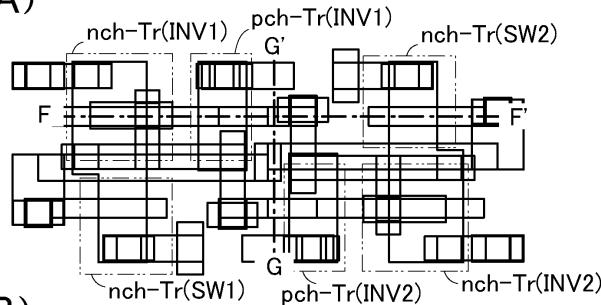

[0107] 계속해서, 도 7의 (A) 및 도 8에서는, 배선층과 게이트 전극을 동일한 층으로 한 구성에 대해서, 도 6에 나타낸 회로 구성에 대응하는 상면도를 나타낸다. 또한 도 9에서는, 도 7의 (A) 및 도 8에 나타내는 일점쇄선 B-B' 및 일점쇄선 C-C'에 있어서의 단면도를 도시한다.

[0108] 먼저, 도 7의 (A)에 나타내는 상면도는, 도 6에 나타낸 회로도에 있어서의, 트랜지스터(121), 트랜지스터(122), 인버터 회로(123), 인버터 회로(124), 트랜지스터 Tr1, 트랜지스터 Tr2, 용량 소자 Cap1 및 욹량 소자 Cap2의 배치를 나타내는 것이다.

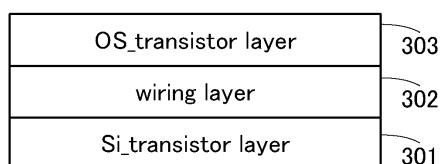

[0109] 도 7의 (A)에 있어서의 트랜지스터의 배치를 이해하기 쉽게 하기 위해서, 도 7의 (B)에서는 도 7의 (A)에 있어서의 각 소자의 층 구조에 관한 모식도를 나타내고 있다. 도 7의 (B)에 나타내는 제1 층(301)은 반도체층에 실리콘을 사용한 트랜지스터가 설치된 층(도면 중, Si\_transistor layer라 표기)이다. 도 7의 (B)에 나타내는 제2 층(302)은 전원 공급을 행하기 위한 배선층이 설치된 층(도면 중, wiring layer라 표기)이다. 도 7의 (B)에 나타내는 제3 층(303)은 반도체층에 산화물 반도체를 사용한 트랜지스터가 설치된 층(도면 중, OS\_transistor layer라 표기)이다.

[0110] 도 7의 (B)에 나타내는 제1 층(301)은 반도체층에 실리콘을 사용한 트랜지스터, 즉 트랜지스터(121)(SW1) 및 트랜지스터(122)(SW2), 및 인버터 회로(123)(INV1) 및 인버터 회로(124)(INV2)를 갖는다. 도 7의 (B)에 나타내는 제2 층(302)은 접지 전위를 부여하는 배선 GND, 비트선 BL, 고전원 전위를 부여하는 배선 VIL, 반전 비트선 BLB로 되는 배선층을 갖는다. 도 7의 (B)에 나타내는 제3 층(303)은 반도체층에 산화물 반도체를 사용한 트랜지스터, 즉 트랜지스터 Tr1(OS1) 및 트랜지스터 Tr2(OS2), 및 용량 소자 Cap1 및 용량 소자 Cap2를 갖는다.

[0111] 도 8의 (A)에서는, 도 7의 (B)에 나타내는 제1 층(301)의 상면도를 나타내고 있다. 도 8의 (A)의 상면도에서는, 반도체층에 실리콘을 사용한 트랜지스터를 구성하는, 반도체층, 게이트 전극과 동일한 층에 설치

되는 배선층, 소스 전극 및 드레인 전극과 동일한 층에 설치되는 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

[0112] 도 8의 (A)에 나타내는 상면도에서는, 트랜지스터(121)로 되는 n 채널형 트랜지스터(nch-Tr(SW1)), 트랜지스터(122)로 되는 n 채널형 트랜지스터(nch-Tr(SW2)), 인버터 회로(123)를 구성하는 p 채널형 트랜지스터(pch-Tr(INV1)) 및 n 채널형 트랜지스터(nch-Tr(INV1)) 및 인버터 회로(124)를 구성하는 p 채널형 트랜지스터(pch-Tr(INV2)) 및 n 채널형 트랜지스터(nch-Tr(INV2))의 배치를 나타내고 있다.

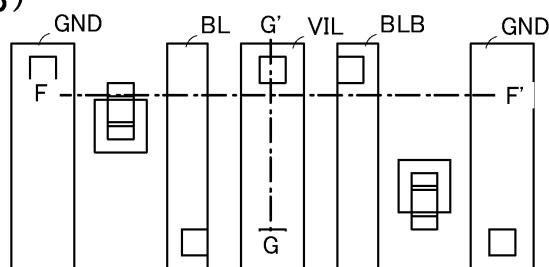

[0113] 도 8의 (B)에서는, 도 7의 (B)에 나타내는 제2 층(302)의 상면도를 나타내고 있다. 도 8의 (B)의 상면도에서는, 복수의 층에 설치된 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

[0114] 도 8의 (B)에 나타내는 상면도에서는, 접지 전위를 부여하는 배선 GND, 비트선 BL, 고전원 전위를 부여하는 배선 VIL, 반전 비트선 BLB의 배치를 나타내고 있다.

[0115] 도 8의 (C)에서는, 도 7의 (B)에 나타내는 제3 층(303)의 상면도를 나타내고 있다. 도 8의 (C)의 상면도에서는, 반도체층에 산화물 반도체를 사용한 트랜지스터를 구성하는, 반도체층, 게이트 전극과 동일한 층에 설치되는 배선층, 소스 전극 및 드레인 전극과 동일한 층에 설치되는 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

[0116] 도 8의 (C)에 나타내는 상면도에서는, 트랜지스터 Tr1로 되는 n 채널형 트랜지스터(OS-Tr(OS1)), 트랜지스터 Tr2로 되는 n 채널형 트랜지스터(OS-Tr(OS2)), 용량 소자 Cap1 및 용량 소자 Cap2 및 각 층을 접속하기 위한 개구부 배치를 나타내고 있다.

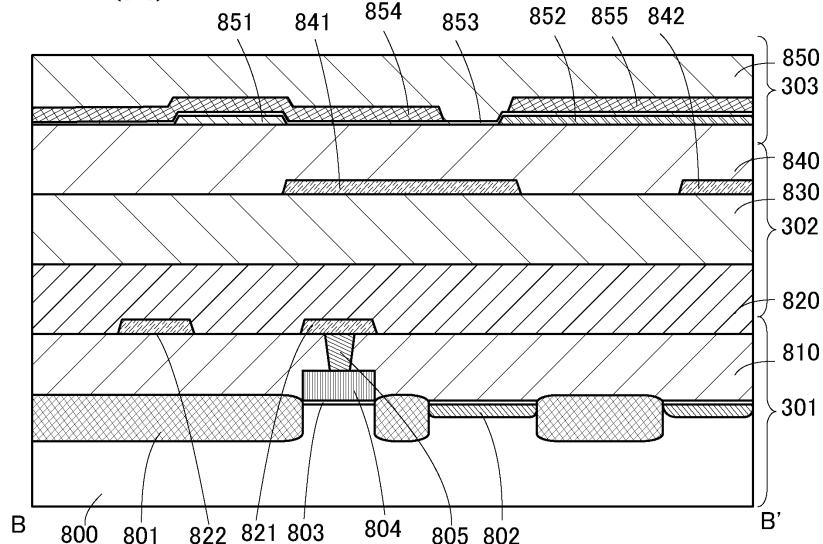

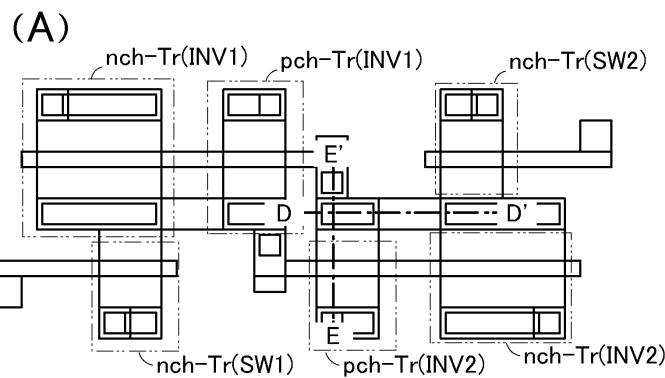

[0117] 이어서 도 9의 (A)에서는, 도 7의 (A) 및 도 8의 일점쇄선 B-B'에 있어서의 단면도, 도 9의 (B)에서는, 도 7의 (A) 및 도 8의 일점쇄선 C-C'에 있어서의 단면도를, 예시하고 있다.

[0118] 또한, 본 실시 형태에서는, 제1 층(301)의 트랜지스터가 단결정의 실리콘 기판에 형성되고, 제2 층(302)의 배선 층이 제1 층(301) 위에 형성되고, 제3 층(303)의 트랜지스터가 제2 층(302) 위에 형성되어 있는 경우를 예시하고 있다. 제1 층(301)의 트랜지스터는, 비정질, 미결정, 다결정 또는 단결정인, 실리콘 또는 게르마늄 등의 박막의 반도체를 반도체층에 사용하고 있어도 된다.

[0119] 도 9의 (A)에서는, 반도체 기판(800), 소자 분리용 절연막(801), 불순물 영역(802), 게이트 절연층(803), 게이트 전극(804), 배선층(805), 층간 절연층(810), 배선층(821), 배선층(822), 층간 절연층(820), 층간 절연층(830), 층간 절연층(840), 배선층(841), 배선층(842), 층간 절연층(850), 반도체층(851), 도전층(852), 게이트 절연층(853), 도전층(854) 및 도전층(855)을 나타내고 있다.

[0120] 도 9의 (B)에서는, 반도체 기판(800), 소자 분리용 절연막(801), 게이트 절연층(803), 게이트 전극(804), 배선 층(823), 층간 절연층(810), 층간 절연층(820), 층간 절연층(830), 배선층(831), 층간 절연층(840), 층간 절연층(850), 반도체층(851), 도전층(852), 게이트 절연층(853), 도전층(854), 도전층(855) 및 도전층(856)을 나타내고 있다.

[0121] 반도체 기판(800)은, 예를 들어 n형 또는 p형 도전형을 갖는 실리콘 기판, 게르마늄 기판, 실리콘 게르마늄 기판, 화합물 반도체 기판(GaAs 기판, InP 기판, GaN 기판, SiC 기판, GaInAsP 기판, ZnSe 기판 등) 등을 사용할 수 있다.

[0122] 제1 층(301)의 트랜지스터는, 소자 분리용 절연막(801)에 의해, 다른 트랜지스터와 전기적으로 분리되어 있다. 소자 분리용 절연막(801)의 형성에는, 선택 산화법(LOCOS(Local Oxidation of Silicon)법) 또는 트렌치 분리법 등을 사용할 수 있다.

[0123] 불순물 영역(802)은 p형을 부여하는 불순물 원소 또는 n형을 부여하는 불순물 원소를, 이온 도핑법 또는 이온 주입법 등을 적절히 사용하여, 반도체 기판(800) 내에 첨가하여 형성한다.

[0124] 게이트 절연층(803)은 열처리를 행하고, 반도체 기판(800)의 표면을 산화하여 산화실리콘막을 형성한 후, 선택적으로 예칭하여, 형성한다. 또는, 산화실리콘, 산화질화실리콘, 고유전율 물질(high-k 재료라고도 함)인 산화하프늄 등의 금속 산화물 등을, CVD법, 스퍼터링법 등을 사용하여 형성한 후, 선택적으로 예칭하여, 형성한다.

[0125] 게이트 전극(804), 배선층(805), 배선층(821), 배선층(822), 배선층(823), 배선층(831), 배선층(841), 배선층(842), 도전층(852), 도전층(854), 도전층(855) 및 도전층(856)은 알루미늄, 구리, 티타늄, 탄탈륨, 텉스텐 등의 금속 재료를 사용하는 것이 바람직하다. 또한, 인 등의 불순물을 첨가한 다결정 실리콘을 사용할 수 있다.

형성 방법은, 증착법, PE-CVD법, 스퍼터링법, 스판 코트법 등의 각종 성막 방법을 사용할 수 있다.

- [0126] 층간 절연층(810), 층간 절연층(820), 층간 절연층(830), 층간 절연층(840) 및 층간 절연층(850)은 무기 절연층 또는 유기 절연층을, 단층 또는 다층으로 형성하는 것이 바람직하다. 무기 절연층으로서는, 질화실리콘막, 산화질화실리콘막, 또는 질화산화실리콘막 등을, 단층 또는 다층으로 형성하는 것이 바람직하다. 유기 절연층으로서는, 폴리이미드 또는 아크릴 등을, 단층 또는 다층으로 형성하는 것이 바람직하다. 또한, 층간 절연층(810), 층간 절연층(820), 층간 절연층(830), 층간 절연층(840) 및 층간 절연층(850)의 제작 방법에 특별히 한정은 없지만, 예를 들어 스퍼터링법, MBE법, PE-CVD법, 필스 레이저 퇴적법, ALD(Atomic Layer Deposition)법 등을 적절히 사용할 수 있다.

- [0127] 반도체층(851)은 산화물 반도체를 단층 또는 적층하여 설치하면 된다. 산화물 반도체는, 일례로서, 인듐, 갈륨 및 아연을 포함하는 산화물이며, In-Ga-Zn계 산화물(IGZO라고도 표기함)을 사용할 수 있다. 또한, In-Ga-Zn계 산화물이란, In과 Ga와 Zn을 포함하는 산화물이라고 하는 의미이며, In과 Ga와 Zn 이외의 금속 원소가 들어 있어도 된다. 예를 들어, In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물을 사용할 수 있다. 산화물 반도체의 형성 방법으로서는, 스퍼터링법, ALD법, 증착법, 도포법 등을 사용할 수 있다.

- [0128] 게이트 절연층(853)은 무기 절연층을, 단층 또는 다층으로 형성하는 것이 바람직하다. 또한, 게이트 절연층(853)은 반도체층(851)에 산소를 공급하는 효과가 있으면 보다 바람직하다.

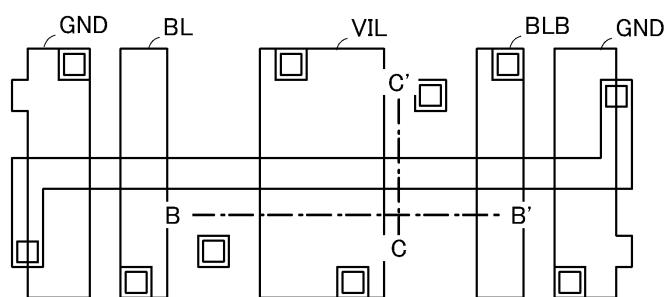

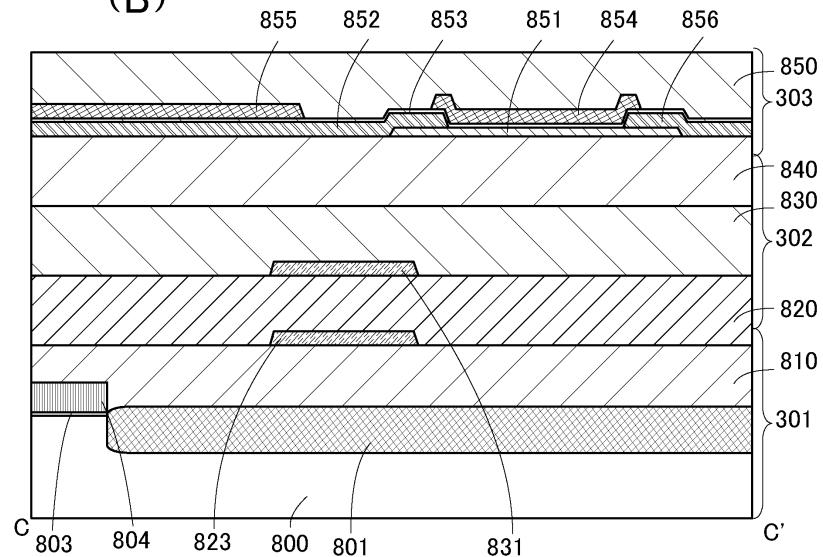

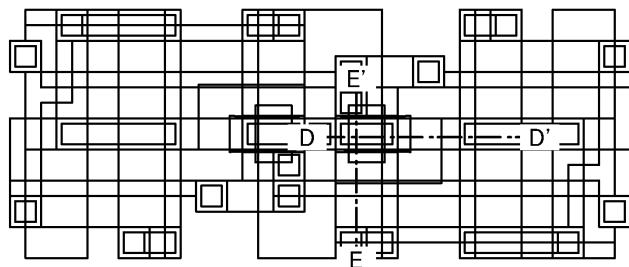

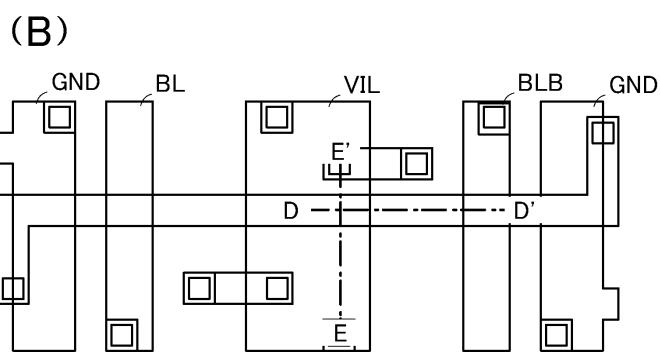

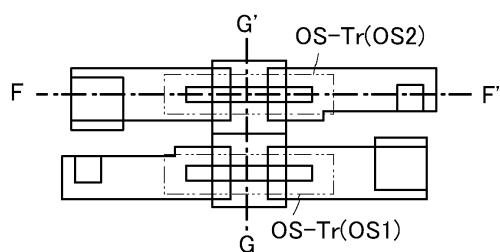

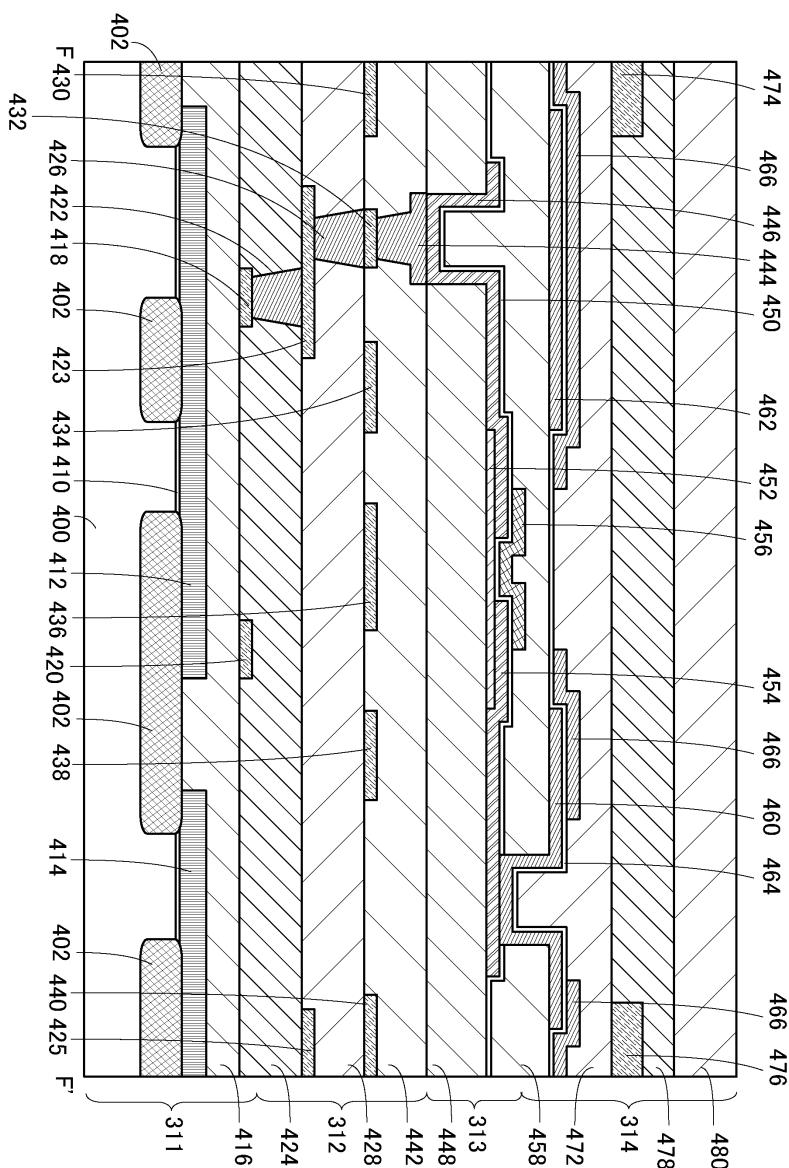

- [0129] 계속해서, 도 10의 (A) 및 도 11에서는, 배선층과 게이트 전극을 다른 층으로 한 구성에 대해서, 도 6에 나타낸 회로 구성에 대응하는 상면도를 나타낸다. 또한 도 12에서는, 도 10의 (A) 및 도 11에 나타내는 일점쇄선 D-D' 및 일점쇄선 E-E'에 있어서의 단면도를 도시한다.

- [0130] 먼저, 도 10의 (A)에 나타내는 상면도는, 도 7의 (A)와 마찬가지로 하여, 도 6에 나타낸 회로도에 있어서의, 트랜지스터(121), 트랜지스터(122), 인버터 회로(123), 인버터 회로(124), 트랜지스터 Tr1, 트랜지스터 Tr2, 용량 소자 Cap1 및 용량 소자 Cap2의 배치를 나타내는 것이다.

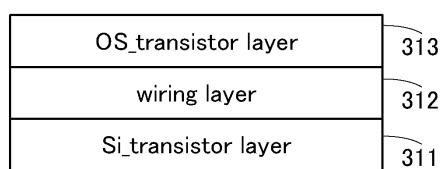

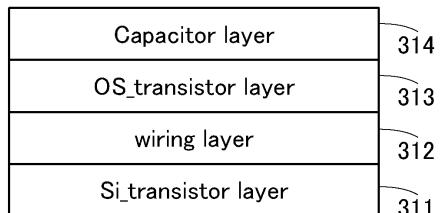

- [0131] 도 10의 (A)에 있어서의 트랜지스터의 배치를 이해하기 쉽게 하기 위해서, 도 10의 (B)에서는 도 10의 (A)에 있어서의 각 소자의 층 구조에 관한 모식도를 나타내고 있다. 도 10의 (B)에 나타내는 제1 층(311)은 반도체층에 실리콘을 사용한 트랜지스터가 설치된 층(도면 중, Si\_transistor layer라 표기)이다. 도 10의 (B)에 나타내는 제2 층(312)은 전원 공급을 행하기 위한 배선층이 설치된 층(도면 중, wiring layer라 표기)이다. 도 10의 (B)에 나타내는 제3 층(313)은 반도체층에 산화물 반도체를 사용한 트랜지스터가 설치된 층(도면 중, OS\_transistor layer라 표기)이다.

- [0132] 도 10의 (B)에 나타내는 제1 층(311), 제2 층(312) 및 제3 층(313)은 도 7의 (B)에서 설명한 제1 층(301), 제2 층(302) 및 제3 층(303)에서의 설명과 마찬가지이며, 여기서의 설명을 생략한다.

- [0133] 도 11의 (A) 및 도 11의 (B)에 나타내는 상면도의 설명도 또한, 도 8의 (A) 및 도 8의 (B)에 함께 나타내고 있다. 도 11의 (A) 및 도 11의 (B)에 나타내는 제1 층(311) 및 제2 층(312)에서의 설명은, 도 8의 (A) 및 도 8의 (B)에 나타내는 제1 층(301) 및 제2 층(302)에서의 설명과 마찬가지이다.

- [0134] 도 11의 (C)에서는, 도 10의 (B)에 나타내는 제3 층(313)의 상면도를 나타내고 있다. 도 11의 (C)의 상면도에서는, 반도체층에 산화물 반도체를 사용한 트랜지스터를 구성하는, 반도체층, 게이트 전극과 동일한 층에 설치되는 배선층, 소스 전극 및 드레인 전극과 동일한 층에 설치되는 배선층, 메모리 셀간의 게이트 전극을 접속하기 위한 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

- [0135] 도 11의 (C)에 나타내는 상면도에서는, 트랜지스터 Tr1로 되는 n 채널형 트랜지스터(OS-Tr(OS1)), 트랜지스터 Tr2로 되는 n 채널형 트랜지스터(OS-Tr(OS2)), 용량 소자 Cap1 및 용량 소자 Cap2, 메모리 셀간의 게이트 전극을 접속하기 위한 배선층(도 11의 (C) 중, 평행 사선을 붙인 영역 ML) 및 각 층을 접속하기 위한 개구부 배치를 나타내고 있다.

- [0136] 또한, 도 11의 (A) 내지 도 11의 (C)에 나타내는 상면도의 레이아웃이, 도 8의 (A) 내지 도 8의 (C)에 나타내는 상면도의 레이아웃과 다른 점은, 제3 층에 있어서의 영역 ML에 관련된 레이아웃에 관한 점이다. 구체적으로는, 도 11의 (C)의 최상층에, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층(도 11의 (C) 중, 영역 ML)을 설치하고, 용량 소자 Cap1 및 용량 소자 Cap2를 설치할 수 있는 면적을 확보하는 점에서 다르다.

- [0137] 이어서 도 12의 (A)에서는, 도 10의 (A) 및 도 11의 일점쇄선 D-D'에 있어서의 단면도, 도 12의 (B)에서는, 도

10의 (A) 및 도 11의 일점쇄선 E-E'에 있어서의 단면도를, 예시하고 있다.

[0138] 또한, 본 실시 형태에서는, 제1 층(311)의 트랜지스터가, 단결정의 실리콘 기판에 형성되고, 제2 층(312)의 배선층이, 제1 층(311) 위에 형성되고, 제3 층(313)의 트랜지스터가, 제2 층(312) 위로 형성되어 있는 경우를 예시하고 있다. 제1 층(311)의 트랜지스터는, 비정질, 미결정, 다결정 또는 단결정인, 실리콘 또는 게르마늄 등의 박막의 반도체를 반도체층에 사용하고 있어도 된다.

[0139] 도 12의 (A)에서는, 반도체 기판(600), 소자 분리용 절연막(601), 불순물 영역(602), 불순물 영역(603), 게이트 절연층(604), 배선층(605), 배선층(606), 층간 절연층(610), 층간 절연층(620), 배선층(621), 층간 절연층(630), 배선층(631), 층간 절연층(640), 배선층(641), 배선층(642), 층간 절연층(650), 반도체층(651), 도전층(652), 게이트 절연층(653), 도전층(654), 도전층(655), 도전층(656), 도전층(657)을 나타내고 있다.

[0140] 도 12의 (B)에서는, 반도체 기판(600), 소자 분리용 절연막(601), 게이트 절연층(604), 불순물 영역(607), 불순물 영역(608), 게이트 전극(609), 층간 절연층(610), 배선층(611), 배선층(612), 배선층(613), 배선층(614), 배선층(622), 배선층(623), 배선층(624), 층간 절연층(620), 층간 절연층(630), 배선층(632), 배선층(633), 배선층(634), 층간 절연층(640), 배선층(643), 층간 절연층(650), 반도체층(651), 도전층(659), 도전층(660), 게이트 절연층(653), 게이트 전극(661), 도전층(662) 및 배선층(663)을 나타내고 있다.

[0141] 반도체 기판(600)은, 예를 들어 n형 또는 p형 도전형을 갖는 실리콘 기판, 실리콘 게르마늄 기판, 화합물 반도체 기판(GaAs 기판, InP 기판, GaN 기판, SiC 기판, GaP 기판, GaInAsP 기판, ZnSe 기판 등) 등을 사용할 수 있다.

[0142] 제1 층(311)의 트랜지스터는, 소자 분리용 절연막(601)에 의해, 다른 트랜지스터와, 전기적으로 분리되고 있다. 소자 분리용 절연막(601)의 형성에는, 선택 산화법(LOCOS(Local Oxidation of Silicon)법) 또는 트렌치 분리법 등을 사용할 수 있다.

[0143] 불순물 영역(602), 불순물 영역(603), 불순물 영역(607) 및 불순물 영역(608)은 p형을 부여하는 불순물 원소 또는 n형을 부여하는 불순물 원소를, 이온 도핑법 또는 이온 주입법 등을 적절히 사용하여, 반도체 기판(600) 내에 첨가하여 형성한다.

[0144] 게이트 절연층(604)은 열처리를 행하고, 반도체 기판(600)의 표면을 산화하여 산화실리콘막을 형성한 후, 선택적으로 에칭하여, 형성한다. 또는, 산화실리콘, 산화질화실리콘, 고유전율 물질(high-k 재료라고도 함)인 산화하프늄 등의 금속 산화물을 등을, CVD법, 스퍼터링법 등을 사용하여 형성한 후, 선택적으로 에칭하여, 형성한다.

[0145] 배선층(605), 배선층(606), 배선층(621), 배선층(631), 배선층(641), 배선층(642), 도전층(652), 도전층(654), 도전층(655), 도전층(656), 도전층(657), 게이트 전극(609), 배선층(611), 배선층(612), 배선층(613), 배선층(614), 배선층(622), 배선층(623), 배선층(624), 배선층(632), 배선층(633), 배선층(634), 배선층(643), 도전층(660), 게이트 전극(661), 도전층(662) 및 배선층(663)은 알루미늄, 구리, 티타늄, 탄탈륨, 텉스텐 등의 금속 재료를 사용하는 것이 바람직하다. 또한, 인 등의 불순물을 첨가한 다결정 실리콘을 사용할 수 있다. 형성 방법은, 증착법, PE-CVD법, 스퍼터링법, 스판 코트법 등의 각종 성막 방법을 사용할 수 있다.

[0146] 층간 절연층(610), 층간 절연층(620), 층간 절연층(630), 층간 절연층(640) 및 층간 절연층(650)은 무기 절연층 또는 유기 절연층을, 단층 또는 다층으로 형성하는 것이 바람직하다. 무기 절연층으로서는, 질화실리콘막, 산화질화실리콘막, 또는 질화산화실리콘막 등을, 단층 또는 다층으로 형성하는 것이 바람직하다. 유기 절연층으로서는, 폴리이미드 또는 아크릴 등을, 단층 또는 다층으로 형성하는 것이 바람직하다. 또한, 층간 절연층(610), 층간 절연층(620), 층간 절연층(630), 층간 절연층(640) 및 층간 절연층(650)의 제작 방법에 특별히 한정은 없지만, 예를 들어 스퍼터링법, MBE법, PE-CVD법, 펄스 레이저 퇴적법, ALD법 등을 적절히 사용할 수 있다.

[0147] 반도체층(651)은 산화물 반도체를 단층 또는 적층하여 설치하면 된다.

[0148] 게이트 절연층(653)은 무기 절연층을, 단층 또는 다층으로 형성하는 것이 바람직하다. 또한, 게이트 절연층(653)은 반도체층(651)에 산소를 공급하는 효과가 있으면 바람직하다.

[0149] 본 실시 형태의 구성인 도 10 내지 도 12의 상면도 및 단면도의 구성에서는, 상기 실시 형태 1에서도 설명한 바와 같이, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층을, 게이트 전극과는 다른 층에 설치하는 구성으로 한다. 그로 인해, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층은, 그 외의 도전층과 이격하여 설치하는 구성으로 할 수 있다. 그로 인해, 트랜지스터 Tr의 게이트에 형성되는 기생

용량을 억제하는 구성으로 할 수 있다.

[0150] 대조적으로 도 7 내지 도 9의 상면도 및 단면도의 구성에서는, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층이, 트랜지스터의 게이트 전극과 동일한 층에 있기 때문에, 게이트 절연층이라고 하는 다른 층보다 얇은 절연층을 통해서 다른 층과 기생 용량을 형성하는 구성으로 된다.

[0151] 또한 본 실시 형태의 구성인 도 10 내지 도 12의 상면도 및 단면도의 구성에서는, 상기 실시 형태 1에서도 설명한 바와 같이, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층을, 게이트 전극과는 다른 층에 설치하는 구성으로 한다. 그 때문에 트랜지스터 Tr의 게이트 전극과 동일한 층에 형성되는, 용량 소자 Cap1 및 용량 소자 Cap2의 전극 면적을, 크게 줄일 수 있다. 그로 인해, 용량 소자 Cap1 및 용량 소자 Cap2의 정전 용량을 크게 할 수 있다.

[0152] 대조적으로 도 7 내지 도 9의 상면도 및 단면도의 구성에서는, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층이, 트랜지스터의 게이트 전극과 동일한 층에 있다. 그로 인해, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층은, 그 외의 도전층과 이격하여 설치하는 구성이 필요해지고, 이 배선층과 동일층에 설치되는 용량 소자 Cap1 및 용량 소자 Cap2가 차지하는 면적도 축소되어 버린다. 그로 인해, 용량 소자 Cap1 및 용량 소자 Cap2의 정전 용량을 크게 할 수 없다.

[0153] 또한 본 실시 형태의 구성인 도 10 내지 도 12의 상면도 및 단면도의 구성에서는, 전원 공급을 행하기 위한 배선층이 설치된 층을, 반도체층에 실리콘을 사용한 트랜지스터가 설치된 층과, 반도체층에 산화물 반도체를 사용한 트랜지스터가 설치된 층 사이에 설치하는 구성으로 하고 있다. 그로 인해, 반도체층에 산화물 반도체를 사용한 트랜지스터가 설치된 층보다도 상층에, 전원 공급을 행하기 위한 배선층이 설치된 층을 형성하는 경우와 비교하여, 용량 소자 Cap1 및 용량 소자 Cap2에 설치하는 개구부의 수를 최소한으로 할 수 있다.

[0154] 이상 설명한 본 실시 형태의 구성에서는, 트랜지스터 Tr의 게이트에 형성되는 기생 용량을 억제하는 구성에 더하여, 게이트 전극과 동일층에서 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하지 않음으로써, 용량 소자가 차지하는 면적을 확보할 수 있다. 그로 인해, 트랜지스터 및 용량 소자의 미세화를 진행시켜도, 기생 용량의 저감 및 용량 소자를 형성하기 위한 면적 확보를 도모할 수 있고, 휘발성 메모리부 VN 및 불휘발성 메모리부 NVN의 전위의 변동을 작게 할 수 있다.

[0155] 본 실시 형태는, 다른 실시 형태와 적절히 조합하여 실시할 수 있다.

[0156] (실시 형태 3)

[0157] 본 실시 형태에서는, 상기 실시 형태 2의 도 10 내지 도 12에서 설명한 상면도 및 단면도의 구성과는 다른 구성에 대해서, 도 15 내지 도 18을 참조하여 설명한다. 또한 도 15 내지 도 17에서 나타내는 상면도 및 단면도에 대응하는 회로도는, 도 6에 나타내는 회로도이다.

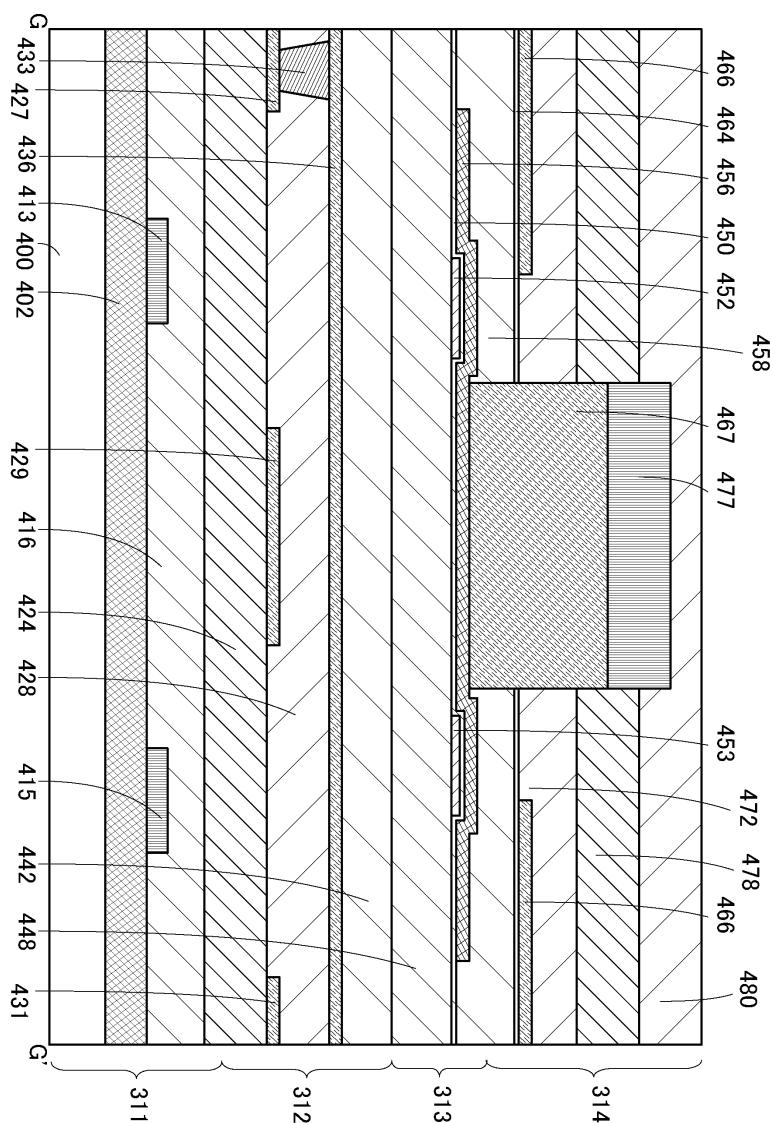

[0158] 계속해서, 도 15의 (A) 및 도 16에서는, 배선층과 게이트 전극을 다른 층으로 하고, 트랜지스터 Tr1 및 트랜지스터 Tr2를, 고전원 전위를 부여하는 배선 VIL에 중첩하는 구성에 대해서, 도 6에 나타낸 회로로 구성에 대응하는 상면도를 나타낸다. 또한 도 17에서는, 도 15의 (A) 및 도 16에 나타내는 일점쇄선 F-F'에 있어서의 단면도, 도 18에서는 일점쇄선 G-G'에 있어서의 단면도를 도시한다.

[0159] 먼저, 도 15의 (A)에 나타내는 상면도는, 도 6에 나타낸 회로도에 있어서의, 트랜지스터(121), 트랜지스터(122), 인버터 회로(123), 인버터 회로(124), 트랜지스터 Tr1, 트랜지스터 Tr2, 용량 소자 Cap1 및 욹량 소자 Cap2의 배치를 나타내는 것이다.

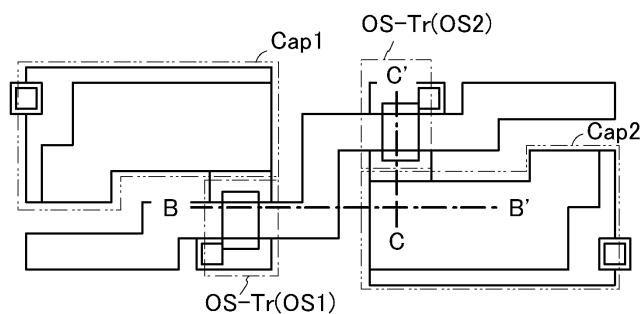

[0160] 도 15의 (A)에 있어서의 트랜지스터의 배치를 이해하기 쉽게 하기 위해서, 도 15의 (B)에서는 도 15의 (A)에 있어서의 각 소자의 층 구조에 관한 모식도를 나타내고 있다. 도 15의 (B)에 나타내는 제1 층(311)은 반도체층에 실리콘을 사용한 트랜지스터가 설치된 층(도면 중, Si\_transistor layer라 표기)이다. 도 15의 (B)에 나타내는 제2 층(312)은 전원 공급을 행하기 위한 배선층이 설치된 층(도면 중, wiring layer라 표기)이다. 도 15의 (B)에 나타내는 제3 층(313)은 반도체층에 산화물 반도체를 사용한 트랜지스터가 설치된 층(도면 중, OS\_transistor layer라 표기)이다. 도 15의 (B)에 나타내는 제4 층(314)은 용량 소자 및 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층이 설치된 층(도면 중, Capacitor layer라 표기)이다.

[0161] 도 15의 (B)에 나타내는 제1 층(311)은 반도체층에 실리콘을 사용한 트랜지스터, 즉 트랜지스터(121)(SW1) 및 트랜지스터(122)(SW2), 및 인버터 회로(123)(INV1) 및 인버터 회로(124)(INV2)를 갖는다. 도 15의 (B)에 나타내는 제2 층(312)은 접지 전위를 부여하는 배선 GND, 비트선 BL, 고전원 전위를 부여하는 배선 VIL, 반전 비트

선 BLB로 되는 배선층을 갖는다. 도 15의 (B)에 나타내는 제3 층(313)은 반도체층에 산화물 반도체를 사용한 트랜지스터, 즉 트랜지스터 Tr1(OS1) 및 트랜지스터 Tr2(OS2)를 갖는다. 도 15의 (B)에 나타내는 제4 층(314)은 용량 소자 Cap1, 용량 소자 Cap2 및 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층을 갖는다.

[0162] 도 16의 (A)에서는, 도 15의 (B)에 나타내는 제1 층(311)의 상면도를 나타내고 있다. 도 16의 (A)의 상면도에서는, 반도체층에 실리콘을 사용한 트랜지스터를 구성하는, 반도체층, 게이트 전극과 동일한 층에 설치되는 배선층, 소스 전극 및 드레인 전극과 동일한 층에 설치되는 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

[0163] 도 16의 (A)에 나타내는 상면도에서는, 트랜지스터(121)로 되는 n 채널형 트랜지스터(nch-Tr(SW1)), 트랜지스터(122)로 되는 n 채널형 트랜지스터(nch-Tr(SW2)), 인버터 회로(123)를 구성하는 p 채널형 트랜지스터(pch-Tr(INV1)) 및 n 채널형 트랜지스터(nch-Tr(INV1)) 및 인버터 회로(124)를 구성하는 p 채널형 트랜지스터(pch-Tr(INV2)) 및 n 채널형 트랜지스터(nch-Tr(INV2))의 배치를 나타내고 있다.

[0164] 도 16의 (B)에서는, 도 15의 (B)에 나타내는 제2 층(312)의 상면도를 나타내고 있다. 도 16의 (B)의 상면도에서는, 복수의 층에 설치된 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

[0165] 도 16의 (B)에 나타내는 상면도에서는, 접지 전위를 부여하는 배선 GND, 비트선 BL, 고전원 전위를 부여하는 배선 VIL, 반전 비트선 BLB의 배치를 나타내고 있다.

[0166] 도 16의 (C)에서는, 도 15의 (B)에 나타내는 제3 층(313)의 상면도를 나타내고 있다. 도 16의 (C)의 상면도에서는, 반도체층에 산화물 반도체를 사용한 트랜지스터를 구성하는, 반도체층, 게이트 전극, 소스 전극 및 드레인 전극과 동일한 층에 설치되는 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

[0167] 도 16의 (C)에 나타내는 상면도에서는, 트랜지스터 Tr1로 되는 n 채널형 트랜지스터(OS-Tr(OS1)), 트랜지스터 Tr2로 되는 n 채널형 트랜지스터(OS-Tr(OS2)) 및 각 층을 접속하기 위한 개구부 배치를 나타내고 있다.

[0168] 도 16의 (D)에서는, 도 15의 (B)에 나타내는 제4 층(314)의 상면도를 나타내고 있다. 도 16의 (D)의 상면도에서는, 용량 소자를 구성하는 도전층, 메모리 셀간의 게이트 전극을 접속하기 위한 배선층 및 각 층을 접속하기 위한 개구부에 관한 배치를 나타내고 있다.

[0169] 도 16의 (D)에 나타내는 상면도에서는, 용량 소자 Cap1 및 용량 소자 Cap2 및 메모리 셀간의 게이트 전극을 접속하기 위한 배선층(도 16의 (D) 중, 평행 사선을 붙인 영역 ML)의 배치를 나타내고 있다.

[0170] 또한, 도 16의 (A) 내지 도 16의 (D)에 나타내는 상면도의 레이아웃이, 도 11의 (A) 내지 도 11의 (C)에 나타내는 상면도의 레이아웃과 다른 점은, 트랜지스터 Tr1 및 트랜지스터 Tr2를, 고전원 전위를 부여하는 배선 VIL에 중첩하여 설치하는 점에 있다. 또한, 도 16의 (A) 내지 도 16의 (D)에 나타내는 상면도의 레이아웃이, 도 11의 (A) 내지 도 11의 (C)에 나타내는 상면도의 레이아웃과 다른 점은, 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층과 동일한 제4 층(314)에, 용량 소자 Cap1 및 용량 소자 Cap2를 설치하는 점에 있다.

[0171] 도 6에 나타내는 회로 구성에 있어서, 데이터의 퇴피 · 복귀를 행하기 위한 속도는, OS-Tr(OS1) 및 OS-Tr(OS2)의 각 트랜지스터의 온 전류에 크게 의존하여, 온 전류를 가능한 한 크게 하는 것이 바람직하다. 그러나, 미세화에 수반하여 구동 전압을 저하시킬 필요가 있으며, 상기 트랜지스터의 온 전류의 크기를 유지하는 것이 곤란해진다. 또한 트랜지스터 사이즈를 변경하지 않고, 온 전류를 크게 하는 구성으로서는, 백 게이트로 되는 전극을 새롭게 추가하여, 백 게이트에 전압을 인가하여 온 전류를 크게 하는 구성으로도 실현할 수 있지만, 반도체 장치의 제조 프로세스나 회로를 구성하는 배선이나 동작이 복잡해져 버린다.

[0172] 본 실시 형태에서 나타내는 구성과 같이 트랜지스터 Tr1 및 트랜지스터 Tr2를, 고전원 전위를 부여하는 배선 VIL에 중첩하여 설치함으로써, 전술한 온 전류를 크게 할 수 있다.

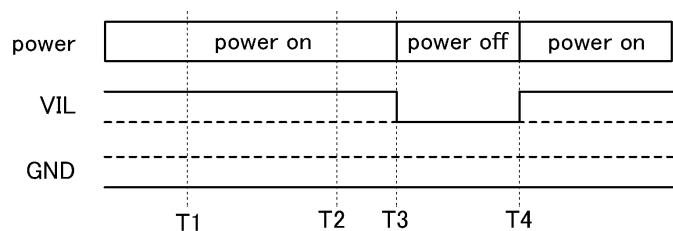

[0173] 또한 본 실시 형태의 구성에 있어서, 전원 공급의 유무를 전환하기 위해 제어되는 배선 VIL의 전위는, 반도체 장치에 전원 공급을 행하는 경우에는 고전원 전위(VDD)로 하고, 전원 공급을 행하지 않는 경우에는 접지 전위(배선 GND와 등전위)로 한다. 이 경우, 일례로서는, 도 19의 (A)의 회로 구성으로 하면 된다.

[0174] 도 19의 (A)의 회로 구성에서는, 고전원 전위를 부여하는 배선에, 스위치 PSW를 접속하고, 그 스위치 PSW의 제어에 의해, 배선 VIL을 VDD나 GND로 전환하는 구성으로 한다. 상기 구성에서는, 스위치 PSW를 VDD로 전환한 경우에는, 메모리 셀에 전원 공급하고, 스위치 PSW를 GND로 전환한 경우에는, 메모리 셀로의 전원 공급을 정지한

다.

[0175] 이 배선 VIL의 전위의 전환을, 도 2의 (B)에 나타내는 타이밍차트에 맞춰서 나타내면, 도 19의 (B)와 같이 나타낼 수 있다. 도 19의 (B)에서는, 전원 공급의 유무에 대하여 나타낸 power와, 배선 VIL 및 배선 GND의 전위의 변화에 대하여 나타내고 있다. 도 19의 (B)에서 나타낸 바와 같이 전원 전위를 부여하는 배선 VIL의 전위를, 반도체 장치에 전원 공급을 행하는 경우에는 고전원 전위으로 하고, 트랜지스터 Tr1 및 트랜지스터 Tr2의 백 게이트로서의 기능을 배선 VIL에 부여함으로써, 트랜지스터 Tr1 및 트랜지스터 Tr2의 온 전류를 크게 할 수 있다. 한편, 도 19의 (B)에서 나타낸 바와 같이 전원 전위를 부여하는 배선 VIL의 전위를, 반도체 장치에 전원 공급을 행하지 않는 경우에는 접지 전위로 하고, 트랜지스터 Tr1 및 트랜지스터 Tr2의 백 게이트로서의 기능을 배선 VIL에 부여함으로써, 트랜지스터 Tr1 및 트랜지스터 Tr2의 오프 전류가 낮다고 하는 특성을 저해하는 일은 없다. 그로 인해, 반도체 장치의 제조 프로세스나 회로를 구성하는 배선이나 동작을 복잡하게 하지 않고, 미세화가 진행된 트랜지스터 Tr1 및 트랜지스터 Tr2의 온 전류의 크기를 유지할 수 있다.

[0176] 이어서 도 17에서는, 도 15의 (A) 및 도 16의 일점쇄선 F-F'에 있어서의 단면도, 도 18에서는, 도 15의 (A) 및 도 16의 일점쇄선 G-G'에 있어서의 단면도를, 예시하고 있다.

[0177] 또한, 본 실시 형태에서는, 제1 층(311)의 트랜지스터가, 단결정의 실리콘 기판에 형성되고, 제2 층(312)의 배선층이, 제1 층(311) 위에 형성되고, 제3 층(313)의 트랜지스터가, 제2 층(312) 위에 형성되고, 제4 층(314)의 용량 소자 및 복수의 메모리간의 트랜지스터 Tr의 게이트 전극을 접속하는 배선층이, 제3 층(313) 위에 형성되어 있는 경우를 예시하고 있다. 제1 층(311)의 트랜지스터는, 비정질, 미결정, 다결정 또는 단결정인, 실리콘 또는 게르마늄 등의 박막의 반도체를 반도체층에 사용하고 있어도 된다.

[0178] 도 17에서는 반도체 기판(400), 소자 분리용 절연막(402), 게이트 절연층(410), 게이트 전극(412), 게이트 전극(414), 층간 절연층(416), 배선층(418), 배선층(420), 도전층(422), 층간 절연층(424), 배선층(423), 도전층(426), 층간 절연층(428), 배선층(430), 배선층(432), 배선층(434), 배선층(436), 배선층(438), 배선층(440), 도전층(444), 층간 절연층(442), 배선층(446), 층간 절연층(448), 반도체층(452), 게이트 절연층(450), 배선층(454), 게이트 전극(456), 층간 절연층(458), 도전층(460), 도전층(462), 절연층(464), 도전층(466), 도전층(468), 층간 절연층(472), 배선층(474), 배선층(476), 층간 절연층(478) 및 층간 절연층(480)을 나타내고 있다.

[0179] 도 18에서는, 반도체 기판(400), 소자 분리용 절연막(402), 게이트 전극(413), 게이트 전극(415), 층간 절연층(416), 층간 절연층(424), 배선층(427), 배선층(429), 배선층(431), 도전층(433), 층간 절연층(428), 배선층(436), 층간 절연층(442), 층간 절연층(448), 반도체층(452), 반도체층(453), 게이트 절연층(450), 게이트 전극(456), 층간 절연층(458), 절연층(464), 도전층(466), 층간 절연층(472), 층간 절연층(478), 도전층(467), 배선층(477) 및 층간 절연층(480)을 나타내고 있다.

[0180] 반도체 기판(400)은, 예를 들어 n형 또는 p형 도전형을 갖는 실리콘 기판, 실리콘 게르마늄 기판, 화합물 반도체 기판(GaAs 기판, InP 기판, GaN 기판, SiC 기판, GaP 기판, GaInAsP 기판, ZnSe 기판 등) 등을 사용할 수 있다.

[0181] 제1 층(311)의 트랜지스터는, 소자 분리용 절연막(402)에 의해, 다른 트랜지스터와, 전기적으로 분리되어 있다. 소자 분리용 절연막(402)의 형성에는, 선택 산화법(LOCOS(Local Oxidation of Silicon)법) 또는 트렌치 분리법 등을 사용할 수 있다.

[0182] 게이트 절연층(410)은 열처리를 행하고, 반도체 기판(400)의 표면을 산화하여 산화실리콘막을 형성한 후, 선택적으로 에칭하여, 형성한다. 또는, 산화실리콘, 산화질화실리콘, 고유전율 물질(high-k 재료라고도 함)인 산화하프늄 등의 금속 산화물 등을, CVD법, 스퍼터링법 등을 사용하여 형성한 후, 선택적으로 에칭하여, 형성한다.

[0183] 게이트 전극(412), 게이트 전극(413), 게이트 전극(414), 게이트 전극(415), 배선층(418), 배선층(420), 도전층(422), 배선층(423), 도전층(426), 배선층(430), 배선층(427), 배선층(429), 배선층(431), 도전층(433), 배선층(432), 배선층(434), 배선층(436), 배선층(438), 배선층(440), 도전층(444), 배선층(446), 배선층(454), 게이트 전극(456), 도전층(460), 도전층(462), 도전층(466), 도전층(468), 배선층(474), 배선층(476), 도전층(467) 및 배선층(477)은 알루미늄, 구리, 티타늄, 탄탈륨, 텡스텐 등의 금속 재료를 사용하는 것이 바람직하다. 또한, 인 등의 불순물을 첨가한 다결정 실리콘을 사용할 수 있다. 형성 방법은, 증착법, PE-CVD법, 스퍼터링법, 스펀 코트법 등의 각종 성막 방법을 사용할 수 있다.

[0184] 층간 절연층(416), 층간 절연층(424), 층간 절연층(428), 층간 절연층(442), 층간 절연층(448), 층간 절연층

(458), 절연층(464), 층간 절연층(472), 층간 절연층(478) 및 층간 절연층(480)은 무기 절연층 또는 유기 절연층을, 단층 또는 다층으로 형성하는 것이 바람직하다. 무기 절연층으로서는, 질화실리콘막, 산화질화실리콘막, 또는 질화산화실리콘막 등을, 단층 또는 다층으로 형성하는 것이 바람직하다. 유기 절연층으로서는, 폴리이미드 또는 아크릴 등을, 단층 또는 다층으로 형성하는 것이 바람직하다. 또한, 각 절연층의 제작 방법에 특별히 한정은 없지만, 예를 들어 스퍼터링법, MBE법, PE-CVD법, 펠스 레이저 퇴적법, ALD법 등을 적절히 사용할 수 있다.

[0185] 반도체층(452) 및 반도체층(453)은 산화물 반도체를 단층 또는 적층하여 설치하면 된다. 산화물 반도체는, 일례로서, 인듐, 갈륨 및 아연을 포함하는 산화물이며, In-Ga-Zn계 산화물(IGZO라고도 표기함)을 사용할 수 있다. 또한, In-Ga-Zn계 산화물이란, In과 Ga와 Zn을 포함하는 산화물이라고 하는 의미이며, In과 Ga와 Zn 이외의 금속 원소가 들어 있어도 된다. 예를 들어, In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물을 사용할 수 있다. 산화물 반도체의 형성 방법으로서는, 스퍼터링법, ALD법, 증착법, 도포법 등을 사용할 수 있다.

[0186] 게이트 절연층(450)은 무기 절연층을, 단층 또는 다층으로 형성하는 것이 바람직하다. 또한, 게이트 절연층(450)은 반도체층(452) 및 반도체층(453)에 산소를 공급하는 효과가 있으면 보다 바람직하다.

[0187] 이상 설명한 본 실시 형태의 구성에서는, 반도체 장치에 전원 공급을 행하는 경우에 트랜지스터 Tr1 및 트랜지스터 Tr2의 온 전류를 크게 할 수 있다. 한편, 반도체 장치에 전원 공급을 행하지 않은 경우에는, 배선 VIL의 전위가 접지 전위를 위해, 트랜지스터 Tr1 및 트랜지스터 Tr2의 오프 전류가 낮다는 특성을 저해하는 일은 없다. 그로 인해, 반도체 장치의 제조 프로세스나 회로를 구성하는 배선이나 동작을 복잡하게 하지 않고, 미세화가 진행된 트랜지스터 Tr1 및 트랜지스터 Tr2의 온 전류의 크기를 유지할 수 있다.

[0188] 본 실시 형태는, 다른 실시 형태와 적절히 조합하여 실시할 수 있다.

[0189] (실시 형태 4)

[0190] 본 실시 형태에서는, 상기 실시 형태에서 설명한 오프 전류가 낮은 트랜지스터의 반도체층에 사용할 수 있는 산화물 반도체에 대하여 설명한다.

[0191] 트랜지스터의 반도체층 중 채널 형성 영역에 사용하는 산화물 반도체로서는, 적어도 인듐(In) 또는 아연(Zn)을 포함하는 것이 바람직하다. 특히 In 및 Zn을 포함하는 것이 바람직하다. 또한, 그들에 더하여, 산소를 강하게 결부시키는 스테빌라이저를 갖는 것이 바람직하다. 스테빌라이저로서는, 갈륨(Ga), 주석(Sn), 지르코늄(Zr), 하프늄(Hf) 및 알루미늄(Al) 중 적어도 어느 하나를 가지면 된다.

[0192] 또한, 다른 스테빌라이저로서, 란타노이드인, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 에르븀(Er), 틸뮴(Tm), 이테르븀(Yb), 루테튬(Lu) 중 어느 한종 또는 복수종을 가져도 된다.

[0193] 트랜지스터의 반도체층으로서 사용되는 산화물 반도체로서는, 예를 들어 산화인듐, 산화주석, 산화아연, In-Zn계 산화물, Sn-Zn계 산화물, Al-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물, In-Ga-Zn계 산화물(IGZO라고도 표기함), In-Al-Zn계 산화물, In-Sn-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-Zr-Zn계 산화물, In-Ti-Zn계 산화물, In-Sc-Zn계 산화물, In-Y-Zn계 산화물, In-La-Zn계 산화물, In-Ce-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물, In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Hf-Zn계 산화물, In-Hf-Al-Zn계 산화물 등이 있다.

[0194] 예를 들어, In:Ga:Zn=1:1:1, In:Ga:Zn=3:1:2, 또는 In:Ga:Zn=2:1:3의 원자수비의 In-Ga-Zn계 산화물이나 그 조성의 근방 산화물을 사용하면 된다.

[0195] 반도체층을 구성하는 산화물 반도체막에 수소가 다량으로 포함되면, 산화물 반도체와 결합함으로써, 수소의 일부가 도너로 되어, 캐리어인 전자를 발생해 버린다. 이에 의해, 트랜지스터의 임계값 전압이 마이너스 방향으로 시프트되어 버린다. 그로 인해, 산화물 반도체막의 형성 후에 있어서, 탈수화 처리(탈수소화 처리)를 행하여 산화물 반도체막으로부터, 수소 또는 수분을 제거하여 불순물이 최대한 포함되지 않도록 고순도화하는 것이 바람직하다.

- [0196] 또한, 산화물 반도체막으로의 탈수화 처리(탈수소화 처리)에 의해, 산화물 반도체막으로부터 산소가 감소되어 버리는 경우가 있다. 따라서, 산화물 반도체막으로의 탈수화 처리(탈수소화 처리)에 의해 증가한 산소 결손을 보충하기 위하여 산소를 산화물 반도체막에 첨가하는 처리를 행하는 것이 바람직하다. 본 명세서 등에 있어서, 산화물 반도체막에 산소를 공급하는 경우를 가산소화 처리라고 기재하는 경우가 있고, 또는 산화물 반도체막에 포함되는 산소를 화학양론적 조성보다도 많게 하는 경우를 과산소화 처리라고 기재하는 경우가 있다.

- [0197] 이와 같이, 산화물 반도체막은, 탈수화 처리(탈수소화 처리)에 의해, 수소 또는 수분이 제거되고, 가산소화 처리에 의해 산소 결손을 보충함으로써, i형(진성)화 또는 i형에 더없이 가까워 실질적으로 i형(진성)인 산화물 반도체막으로 할 수 있다. 또한, 실질적으로 진성이란, 산화물 반도체막 중에 도너에서 유래되는 캐리어가 매우 적어(제로에 가까워), 캐리어 밀도가  $1 \times 10^{17}/\text{cm}^3$  이하,  $1 \times 10^{16}/\text{cm}^3$  이하,  $1 \times 10^{15}/\text{cm}^3$  이하,  $1 \times 10^{14}/\text{cm}^3$  이하,  $1 \times 10^{13}/\text{cm}^3$  이하인 것을 말한다.

- [0198] 또한, 이와 같이, i형 또는 실질적으로 i형인 산화물 반도체막을 구비하는 트랜지스터는, 매우 우수한 오프 전류 특성을 실현할 수 있다. 예를 들어, 산화물 반도체막을 사용한 트랜지스터가 오프 상태일 때의 드레인 전류를, 실온(25°C 정도)에서  $1 \times 10^{-18}\text{ A}$  이하, 바람직하게는  $1 \times 10^{-21}\text{ A}$  이하, 더욱 바람직하게는  $1 \times 10^{-24}\text{ A}$  이하, 또는 85°C에서  $1 \times 10^{-15}\text{ A}$  이하, 바람직하게는  $1 \times 10^{-18}\text{ A}$  이하, 더욱 바람직하게는  $1 \times 10^{-21}\text{ A}$  이하로 할 수 있다. 또한, 트랜지스터가 오프 상태란, n 채널형 트랜지스터의 경우, 게이트 전압이 임계값 전압보다도 충분히 작은 상태를 말한다. 구체적으로는, 게이트 전압이 임계값 전압보다도 1V 이상, 2V 이상 또는 3V 이상 작으면, 트랜지스터는 오프 상태로 된다.

- [0199] 또한, 성막되는 산화물 반도체는, 예를 들어 비단결정을 가져도 된다. 비단결정은, 예를 들어 CAAC(C Axis Aligned Crystal), 다결정, 미결정, 비정질부를 갖는다.

- [0200] 산화물 반도체는, 예를 들어 CAAC를 가져도 된다. 또한, CAAC를 갖는 산화물 반도체를, CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)라고 칭한다.

- [0201] CAAC-OS는, 예를 들어 투과형 전자 현미경(TEM: Transmission Electron Microscope)에 의한 관찰상에서, 결정부를 확인할 수 있는 경우가 있다. CAAC-OS에 포함되는 결정부는, 예를 들어 TEM에 의한 관찰상에서, 1변 100 nm의 입방체 내에 수용되는 크기인 경우가 많다. 또한, CAAC-OS는, TEM에 의한 관찰상에서, 결정부와 결정부의 경계를 명확하게 확인할 수 없는 경우가 있다. 또한, CAAC-OS는, TEM에 의한 관찰상에서, 입계(그레인바운더리라고도 함)를 명확하게 확인할 수 없는 경우가 있다. CAAC-OS는, 예를 들어 명확한 입계를 갖지 않기 때문에, 불순물이 편석하는 경우가 적다. 또한, CAAC-OS는, 예를 들어 명확한 입계를 갖지 않기 때문에, 결함 준위 밀도가 높아지는 경우가 적다. 또한, CAAC-OS는, 예를 들어 명확한 입계를 갖지 않기 때문에, 전자 이동도의 저하가 작다.

- [0202] CAAC-OS는, 예를 들어 복수의 결정부를 갖고, 그 복수의 결정부에 있어서 c축이 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향으로 정렬되어 있는 경우가 있다. 또한, CAAC-OS는, 예를 들어 X선 회절(XRD: X-Ray Diffraction) 장치를 사용하여, out-of-plane법에 의한 분석을 하면, 배향을 나타내는  $2\theta$ 가  $31^\circ$  근방의 피크가 나타나는 경우가 있다. 또한, CAAC-OS는, 예를 들어 전자선 회절 패턴으로, 스포(회점)이 관측되는 경우가 있다. 또한, 특히, 범 직경이  $10\text{nm}\phi$  이하, 또는  $5\text{nm}\phi$  이하의 전자선을 사용하여 얻어지는 전자선 회절 패턴을, 극히 전자선 회절 패턴이라 칭한다. 또한, CAAC-OS는, 예를 들어 다른 결정부 사이에서, 각각 a축 및 b축의 방향이 정렬되어 있지 않은 경우가 있다. CAAC-OS는, 예를 들어 c축 배향하고, a축 또는/및 b축은 매크로로 정렬되어 있지 않은 경우가 있다.

- [0203] CAAC-OS에 포함되는 결정부는, 예를 들어 c축이 CAAC-OS의 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향이 되도록 정렬되고, 또한 ab면에 수직인 방향에서 볼 때 금속 원자가 삼각형상 또는 육각형상으로 배열하고, c축으로 수직인 방향에서 볼 때 금속 원자가 층형상 또는 금속 원자와 산소 원자가 층형상으로 배열되어 있다. 또한, 다른 결정부 사이에서, 각각 a축 및 b축의 방향이 달라도 된다. 본 명세서에 있어서, 단순히 수직이라 기재하는 경우,  $80^\circ$  이상  $100^\circ$  이하, 바람직하게는  $85^\circ$  이상  $95^\circ$  이하의 범위도 포함되는 것으로 한다. 또한, 단순히 평행이라 기재하는 경우,  $-10^\circ$  이상  $10^\circ$  이하, 바람직하게는  $-5^\circ$  이상  $5^\circ$  이하의 범위도 포함되는 것으로 한다.

- [0204] 또한, CAAC-OS는, 예를 들어 결함 준위 밀도를 저감함으로써 형성할 수 있다. 산화물 반도체에 있어서, 예를 들어 산소 결손은 결함 준위이다. 산소 결손은, 트랩 준위가 되는 것이나, 수소를 포함함으로써 캐리어 발생원

으로 되는 것이다. CAAC-OS를 형성하기 위해서는, 예를 들어 산화물 반도체에 산소 결손을 발생시키지 않는 것이 중요해진다. 따라서, CAAC-OS는, 결함 준위 밀도가 낮은 산화물 반도체이다. 또는, CAAC-OS는 산소 결손이 적은 산화물 반도체이다.

[0205] 불순물 농도가 낮고, 결함 준위 밀도가 낮은(산소 결손이 적은) 것을 고순도 진성 또는 실질적으로 고순도 진성이라고 칭한다. 고순도 진성 또는 실질적으로 고순도 진성인 산화물 반도체는, 캐리어 발생원이 적기 때문에, 캐리어 밀도를 낮게 할 수 있는 경우가 있다. 따라서, 상기 산화물 반도체를 채널 형성 영역에 사용한 트랜지스터는, 임계값 전압이 마이너스로 되는 전기 특성(노멀리 온이라고도 함)이 되는 것이 적은 경우가 있다. 또한, 고순도 진성 또는 실질적으로 고순도 진성인 산화물 반도체는, 결함 준위 밀도가 낮기 때문에, 트랩 준위 밀도도 낮아지는 경우가 있다. 따라서, 당해 산화물 반도체를 채널 형성 영역에 사용한 트랜지스터는, 전기 특성의 변동이 작고, 신뢰성이 높은 트랜지스터로 되는 경우가 있다. 또한, 산화물 반도체의 트랩 준위에 포함된 전하는, 소실할 때까지 필요로 하는 시간이 길어, 마치 고정 전하처럼 행동하는 경우가 있다. 그로 인해, 트랩 준위 밀도가 높은 산화물 반도체를 채널 형성 영역에 사용한 트랜지스터는, 전기 특성이 불안정해지는 경우가 있다.

[0206] 또한, 고순도 진성 또는 실질적으로 고순도 진성인 CAAC-OS를 사용한 트랜지스터는, 가시광이나 자외광의 조사에 의한 전기 특성의 변동이 작다.

[0207] 산화물 반도체는, 예를 들어 다결정을 가져도 된다. 또한, 다결정을 갖는 산화물 반도체를, 다결정 산화물 반도체라 칭한다. 다결정 산화물 반도체는 복수의 결정립을 포함한다.

[0208] 산화물 반도체는, 예를 들어 미결정을 가져도 된다. 또한, 미결정을 갖는 산화물 반도체를, 미결정 산화물 반도체라 칭한다.

[0209] 미결정 산화물 반도체는, 예를 들어 TEM에 의한 관찰상에서는, 명확하게 결정부를 확인할 수 없는 경우가 있다. 미결정 산화물 반도체에 포함되는 결정부는, 예를 들어 1nm 이상 100nm 이하, 또는 1nm 이상 10nm 이하의 크기인 경우가 많다. 특히, 예를 들어 1nm 이상 10nm 이하의 미결정을 나노 결정(nc:nanocrystal)이라고 칭한다. 나노 결정을 갖는 산화물 반도체를, nc-OS(nanocrystalline Oxide Semiconductor)라고 칭한다. 또한, nc-OS는, 예를 들어 TEM에 의한 관찰상에서는, 결정부와 결정부의 경계를 명확하게 확인할 수 없는 경우가 있다. 또한, nc-OS는, 예를 들어 TEM에 의한 관찰상에서는, 명확한 입계를 갖지 않기 때문에, 불순물이 편석하는 경우가 적다. 또한, nc-OS는, 예를 들어 명확한 입계를 갖지 않기 때문에, 결함 준위 밀도가 높아지는 경우가 적다. 또한, nc-OS는, 예를 들어 명확한 입계를 갖지 않기 때문에, 전자 이동도의 저하가 작다.

[0210] nc-OS는, 예를 들어 미소한 영역(예를 들어, 1nm 이상 10nm 이하의 영역)에 있어서 원자 배열에 주기성을 갖는 경우가 있다. 또한, nc-OS는, 예를 들어 결정부와 결정부 사이에서 규칙성이 없기 때문에, 거시적으로는 원자 배열에 주기성이 보이지 않는 경우, 또는 장거리 질서가 보이지 않는 경우가 있다. 따라서, nc-OS는, 예를 들어 분석 방법에 따라서는, 비정질 산화물 반도체와 구별이 되지 않는 경우가 있다. nc-OS는, 예를 들어 XRD 장치를 사용하여, 결정부보다도 큰 빔 직경의 X선으로 out-of-plane법에 의한 분석을 행하면, 배향을 나타내는 피크가 검출되지 않는 경우가 있다. 또한, nc-OS는, 예를 들어 결정부보다도 큰 빔 직경(예를 들어, 20nmΦ 이상, 또는 50nmΦ 이상)의 전자선을 사용하는 전자선 회절 패턴으로는, 할로 패턴이 관측되는 경우가 있다. 또한, nc-OS는, 예를 들어 결정부와 같거나 결정부보다 작은 빔 직경(예를 들어, 10nmΦ 이하, 또는 5nmΦ 이하)의 전자선을 사용하는 극미 전자선 회절 패턴으로는 스포트이 관측되는 경우가 있다. 또한, nc-OS의 극미 전자선 회절 패턴은, 예를 들어 원을 그리도록 휘도가 높은 영역이 관측되는 경우가 있다. 또한, nc-OS의 극미 전자선 회절 패턴은, 예를 들어 상기 영역 내에 복수의 스포트이 관측되는 경우가 있다.

[0211] nc-OS는, 미소한 영역에서 원자 배열에 주기성을 갖는 경우가 있기 때문에, 비정질 산화물 반도체보다도 결함 준위 밀도가 낮아진다. 단, nc-OS는 결정부와 결정부 사이에서 규칙성이 없기 때문에, CAAC-OS와 비교하여 결함 준위 밀도가 높아진다.

[0212] 또한, 산화물 반도체가, CAAC-OS, 다결정 산화물 반도체, 미결정 산화물 반도체, 비정질 산화물 반도체의 2종 이상을 갖는 혼합막이어야 된다. 혼합막은, 예를 들어 비정질 산화물 반도체의 영역, 미결정 산화물 반도체의 영역, 다결정 산화물 반도체의 영역, CAAC-OS의 영역, 중 어느 2종 이상의 영역을 갖는 경우가 있다. 또한, 혼합막은, 예를 들어 비정질 산화물 반도체의 영역, 미결정 산화물 반도체의 영역, 다결정 산화물 반도체의 영역, CAAC-OS의 영역 중 어느 2종 이상의 영역 적층 구조를 갖는 경우가 있다.

[0213] 본 실시 형태는, 다른 실시 형태와 적절히 조합하여 실시할 수 있다.

- [0214] (실시 형태 5)

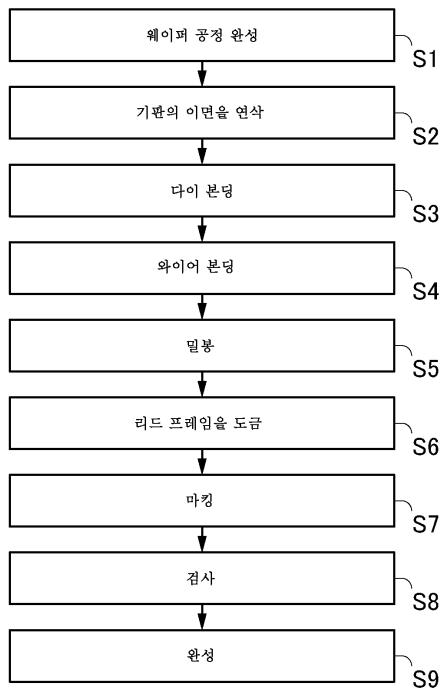

- [0215] 본 실시 형태에서는, 상술한 실시 형태에서 설명한 반도체 장치를 전자 부품에 적용하는 예 및 그 전자 부품을 구비하는 전자 기기에 적용하는 예에 대해서, 도 13, 도 14를 사용하여 설명한다.

- [0216] 도 13의 (A)에서는 상술한 실시 형태에서 설명한 반도체 장치를 전자 부품에 적용하는 예에 대하여 설명한다. 또한 전자 부품은, 반도체 패키지, 또는 IC용 패키지라고도 한다. 이 전자 부품은, 단자 취출 방향이나, 단자의 형상에 따라서, 복수의 규격이나 명칭이 존재한다. 따라서, 본 실시 형태에서는, 그 일례에 대하여 설명하기로 한다.

- [0217] 상기 실시 형태 2의 도 10 내지 도 12, 실시 형태 3의 도 15 내지 도 19에 나타낸 바와 같은 트랜지스터로 구성되는 반도체 장치는, 조립 공정(후속 공정)을 거쳐, 프린트 기판에 탈착 가능한 부품이 복수 합쳐짐으로써 완성된다.

- [0218] 후속 공정에 대해서는, 도 13의 (A)에 나타내는 각 공정을 거침으로써 완성 시킬 수 있다. 구체적으로는, 전(前)공정에서 얻어지는 소자 기판이 완성(스텝 S1)된 후, 기판의 이면을 연삭한다(스텝 S2). 이 단계에서 기판을 박막화함으로써, 전공정에서의 기판의 휨 등을 저감하고, 부품으로서의 소형화를 도모하기 위해서이다.

- [0219] 기판의 이면을 연삭하여, 기판을 복수의 칩으로 분리하는 다이싱 공정을 행한다. 그리고, 분리한 칩을 개별로 핀업하여 리드 프레임 위에 탑재하여 접합하는, 다이 본딩 공정을 행한다(스텝 S3). 이 다이 본딩 공정에서의 칩과 리드 프레임의 접착은, 수지에 의한 접착이나, 테이프에 의한 접착 등, 적절히 제품에 따라서 적합한 방법을 선택한다. 또한, 다이 본딩 공정은, 인터포저 위에 탑재하여 접합해도 된다.

- [0220] 이어서 리드 프레임의 리드와 칩 위의 전극을, 금속의 세선(와이어)으로 전기적으로 접속하는, 와이어 본딩을 행한다(스텝 S4). 금속의 세선에는, 은선이나 금선을 사용할 수 있다. 또한, 와이어 본딩은, 볼 본딩이나, 웨지 본딩을 사용할 수 있다.

- [0221] 와이어 본딩된 칩은, 애폭시 수지 등으로 밀봉되는, 몰드 공정이 실시된다(스텝 S5). 몰드 공정을 행함으로써 전자 부품의 내부가 수지로 충전되어, 기계적인 외력에 의해, 내장되는 회로부나 와이어를 보호할 수 있고, 또한 수분이나 먼지에 의한 특성의 열화를 저감할 수 있다.

- [0222] 이어서 리드 프레임의 리드를 도금 처리한다. 그리고 리드를 절단 및 성형 가공한다(스텝 S6). 이 도금 처리에 의해 리드의 녹을 방지하고, 후에 프린트 기판에 실장할 때의 납땜을 보다 확실하게 행할 수 있다.

- [0223] 이어서 패키지의 표면에 인자 처리(마킹)를 실시한다(스텝 S7). 그리고 최종적인 검사 공정(스텝 S8)을 거쳐서 전자 부품이 완성된다(스텝 S9).

- [0224] 이상 설명한 전자 부품은, 상술한 실시 형태에서 설명한 반도체 장치를 포함하는 구성으로 할 수 있다. 그로 인해, 소자의 미세화를 진행시켜도 데이터의 유지에 필요한 유지 용량을 확보할 수 있고, 또한 트랜지스터의 기생 용량을 저감하는 것에 의한 정상적인 동작에 필요한 유지 용량의 삭감을 도모할 수 있는 반도체 장치를 갖는 전자 부품을 실현할 수 있다. 상기 전자 부품은, 데이터의 퇴피·복귀를 행하는 트랜지스터의 기생 용량의 저감이 도모됨으로써, 데이터의 유지에 필요한 유지 용량을 확보하는 것을 용이하게 할 수 있는 메모리 셀을 갖는 반도체 장치를 포함한다. 그로 인해, 데이터의 퇴피·복귀를 보다 확실하게 행할 수 있는 전자 부품이다.

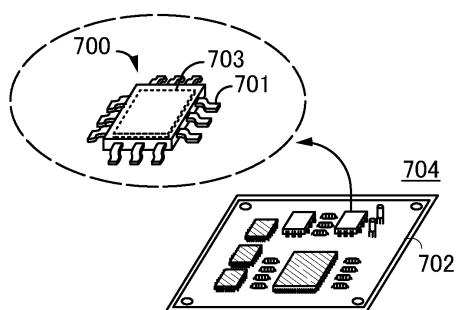

- [0225] 또한, 완성된 전자 부품의 사시 모식도를 도 13의 (B)에 나타내었다. 도 13의 (B)에서는, 전자 부품의 일례로서, QFP(Quad Flat Package)의 사시 모식도를 나타내고 있다. 도 13의 (B)에 나타내는 전자 부품(700)은 리드(701) 및 반도체 장치(703)를 나타내고 있다. 도 13의 (B)에 나타내는 전자 부품(700)은 예를 들어 프린트 기판(702)에 실장된다. 이러한 전자 부품(700)이 복수 조합되어, 각각이 프린트 기판(702) 위에서 전기적으로 접속됨으로써 전자 부품이 실장된 기판(실장 기판(704))이 완성된다. 완성된 실장 기판(704)은 전자 기기 등의 내부에 설치된다.

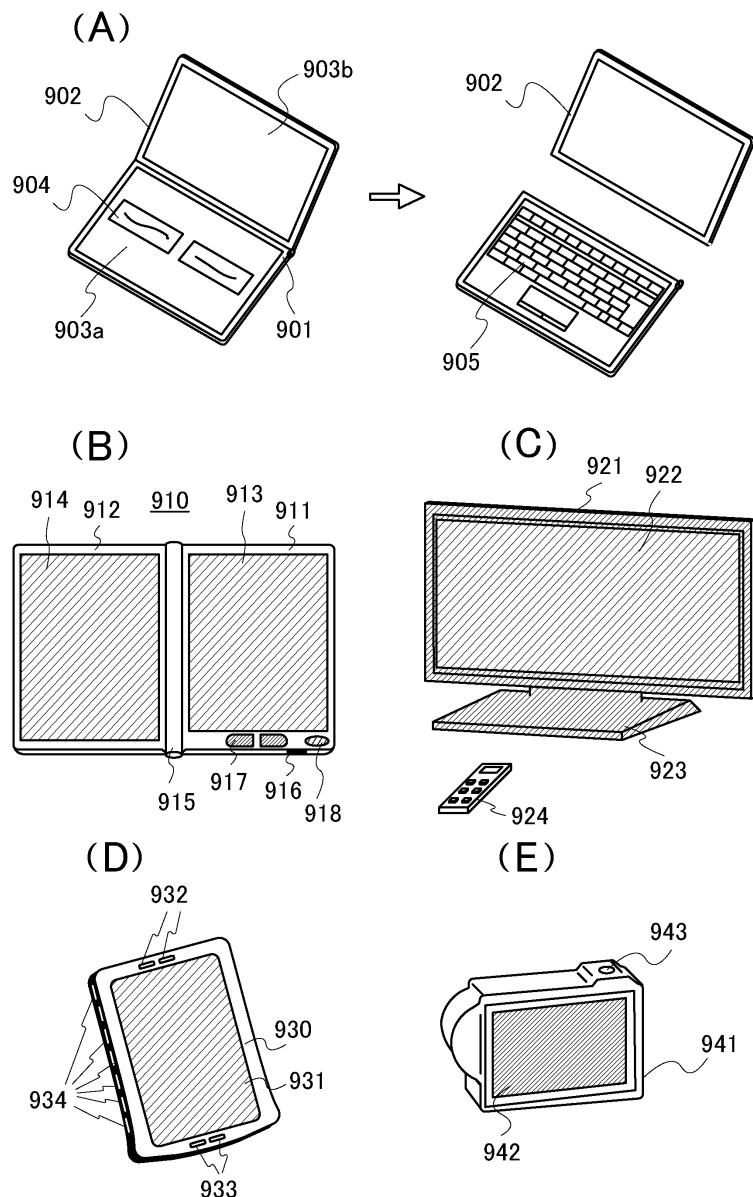

- [0226] 계속해서, 컴퓨터, 휴대 정보 단말기(휴대 전화, 휴대형 게임기, 음향 재생 장치 등도 포함), 전자 페이퍼, 텔레비전 장치(텔레비전, 또는 텔레비전 수신기라고도 함), 디지털비디오카메라 등의 전자 기기에, 상술한 전자 부품을 적용하는 경우에 대하여 설명한다.

- [0227] 도 14의 (A)는 휴대형 정보 단말기이며, 하우징(901), 하우징(902), 제1 표시부(903a), 제2 표시부(903b) 등에 의해 구성되어 있다. 하우징(901)과 하우징(902) 중 적어도 일부에는, 상술한 실시 형태에 나타내는 반도체 장치를 갖는 실장 기판이 설치되어 있다. 그로 인해, 데이터의 퇴피·복귀를 보다 확실하게 행할 수 있는 휴대형

정보 단말기가 실현된다.

[0228] 또한, 제1 표시부(903a)는 터치 입력 기능을 갖는 패널로 되어 있고, 예를 들어 도 14의 (A)의 좌측 도면과 같이, 제1 표시부(903a)에 표시되는 선택 버튼(904)에 의해 「터치 입력」을 행할지, 「키보드 입력」을 행할지를 선택할 수 있다. 선택 버튼은 다양한 크기로 표시할 수 있기 때문에, 폭넓은 세대의 사람이 편리한 사용을 실감할 수 있다. 여기서, 예를 들어 「터치 입력」을 선택한 경우, 도 14의 (A)의 우측 도면과 같이 제1 표시부(903a)에는 키보드(905)가 표시된다. 이에 의해, 종래의 정보 단말기와 마찬가지로, 키 입력에 의한 신속한 문자 입력 등이 가능하게 된다.

[0229] 또한, 도 14의 (A)에 나타내는 휴대형 정보 단말기는, 도 14의 (A)의 우측 도면과 같이, 제1 표시부(903a) 및 제2 표시부(903b) 중, 한쪽을 제거할 수 있다. 제1 표시부(903a)도 터치 입력 기능을 갖는 패널로 하고, 운반시, 한쪽 경량화를 도모할 수 있어, 한쪽 손으로 하우징(902)을 갖고, 다른 쪽 손으로 조작할 수 있기 때문에 편리하다.

[0230] 도 14의 (A)에 나타내는 휴대형 정보 단말기는, 여러가지 정보(정지 화상, 동화상, 텍스트 화상 등)를 표시하는 기능, 캘린더, 날짜 또는 시각 등을 표시부에 표시하는 기능, 표시부에 표시한 정보를 조작 또는 편집하는 기능, 여러가지 소프트웨어(프로그램)에 의해 처리를 제어하는 기능, 등을 가질 수 있다. 또한, 하우징의 이면이나 측면에, 외부 접속용 단자(이어폰 단자, USB 단자 등), 기록 매체 삽입부 등을 구비하는 구성으로 해도 된다.

[0231] 또한, 도 14의 (A)에 나타내는 휴대형 정보 단말기는, 무선으로 정보를 송수신할 수 있는 구성으로 해도 된다. 무선에 의해, 전자 서적 서버로부터, 원하는 서적 데이터 등을 구입하고, 다운로드하는 구성으로 하는 것도 가능하다.

[0232] 또한, 도 14의 (A)에 나타내는 하우징(902)에 안테나나 마이크 기능이나 무선 기능을 갖게 하여, 휴대 전화로서 사용해도 된다.

[0233] 도 14의 (B)는 전자 페이퍼를 실장한 전자 서적(910)이며, 하우징(911)과 하우징(912)에 2개의 하우징으로 구성되어 있다. 하우징(911) 및 하우징(912)에는, 각각 표시부(913) 및 표시부(914)가 설치되어 있다. 하우징(911)과 하우징(912)은 축부(915)에 의해 접속되어 있고, 그 축부(915)를 축으로 해서 개폐 동작을 행할 수 있다. 또한, 하우징(911)은 전원(916), 조작 키(917), 스피커(918) 등을 구비하고 있다. 하우징(911), 하우징(912) 중 적어도 1개에는, 상술한 실시 형태에 나타내는 반도체 장치를 갖는 실장 기판이 설치되어 있다. 그로 인해, 데이터의 퇴피·복귀를 보다 확실하게 행할 수 있는 전자 서적이 실현된다.

[0234] 도 14의 (C)는 텔레비전 장치이며, 하우징(921), 표시부(922), 스탠드(923) 등으로 구성되어 있다. 텔레비전 장치(920)의 조작은, 하우징(921)이 구비하는 스위치나, 리모콘 조작기(924)에 의해 행할 수 있다. 하우징(921) 및 리모콘 조작기(924)에는, 상술한 실시 형태에 나타내는 반도체 장치를 갖는 실장 기판이 탑재되어 있다. 그로 인해, 데이터의 퇴피·복귀를 보다 확실하게 행할 수 있는 텔레비전 장치가 실현된다.

[0235] 도 14의 (D)는 스마트폰이며, 본체(930)에는, 표시부(931)와, 스피커(932)와, 마이크(933)와, 조작 버튼(934) 등이 설치되어 있다. 본체(930) 내에는, 상술한 실시 형태에 나타내는 반도체 장치를 갖는 실장 기판이 설치되어 있다. 그 때문에 데이터의 퇴피·복귀를 보다 확실하게 행할 수 있는 스마트폰이 실현된다.

[0236] 도 14의 (E)는 디지털 카메라이며, 본체(941), 표시부(942), 조작 스위치(943) 등에 의해 구성되어 있다. 본체(941) 내에는, 상술한 실시 형태에 나타내는 반도체 장치를 갖는 실장 기판이 설치되어 있다. 그로 인해, 데이터의 퇴피·복귀를 보다 확실하게 행할 수 있는 디지털 카메라가 실현된다.

[0237] 이상과 같이, 본 실시 형태에 나타내는 전자 기기에는, 상술한 실시 형태에 따른 반도체 장치를 갖는 실장 기판이 탑재되어 있다. 이로 인해, 데이터의 퇴피·복귀를 보다 확실하게 행할 수 있는 전자 기기가 실현된다.

[0238] [실시예 1]

[0239] 본 실시예에서는, 상기 실시 형태 3에서 설명한 반도체 장치(이하, OS-SRAM이라고 함)의 구성의 캐시 메모리를 내장한 32bit 마이크로프로세서에 대하여 시험 제작했으므로, 평가 결과에 대하여 설명한다.

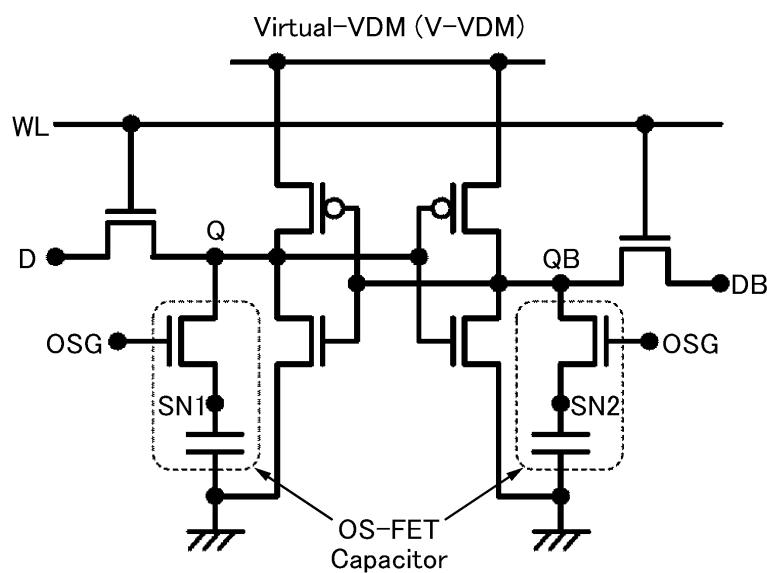

[0240] OS-SRAM의 회로도와 Power-Gating(PG) 시퀀스를 도 20, 도 21에 각각 나타낸다.

[0241] 도 20에 나타낸 바와 같이 OS-SRAM은 표준적인 SRAM(6T형)에, 2개의 반도체층에 산화물 반도체를 사용한 트랜지스터(이하, OS-FET라고 함)와 2개의 용량 소자(이하, Capacitor라고 함)를 추가함으로써 구성된다.

[0242]

또한 도 20에 나타내는 OS-SRAM이 갖는 트랜지스터의 파라미터는, 표 1과 같다.

표 1

|                  |                     |        |

|------------------|---------------------|--------|

| 트랜지스터의 폭/길이 [nm] | Drive               | 200/45 |

|                  | Access              | 130/45 |

|                  | Load                | 130/45 |

| OS-FET           | 40/100              |        |

| 용량 소자의 용량 [fF]   |                     | 0.94   |

| 전원 전압 [V]        | VDM<br>(for Si-FET) | 1.1    |

|                  | VDH<br>(for OS-FET) | 2.5    |

[0243]

도 21에 나타내는 PG 시퀀스에 의하면, 쌍안정부 Q, QB에 보유 지지되어 있는 데이터를 노드 SN1, SN2에 퇴피하고, 그 후 Virtual- $V_{DM}$ ( $V-V_{DM}$ )을 차단함으로써 전원 공급을 정지한다. 복귀 시에는 노드 SN1, SN2에 보유 지지되어 있는 데이터를 쌍안정부 Q, QB로 되돌림으로써 PG 전의 상태로부터 통상 동작을 재개할 수 있다.

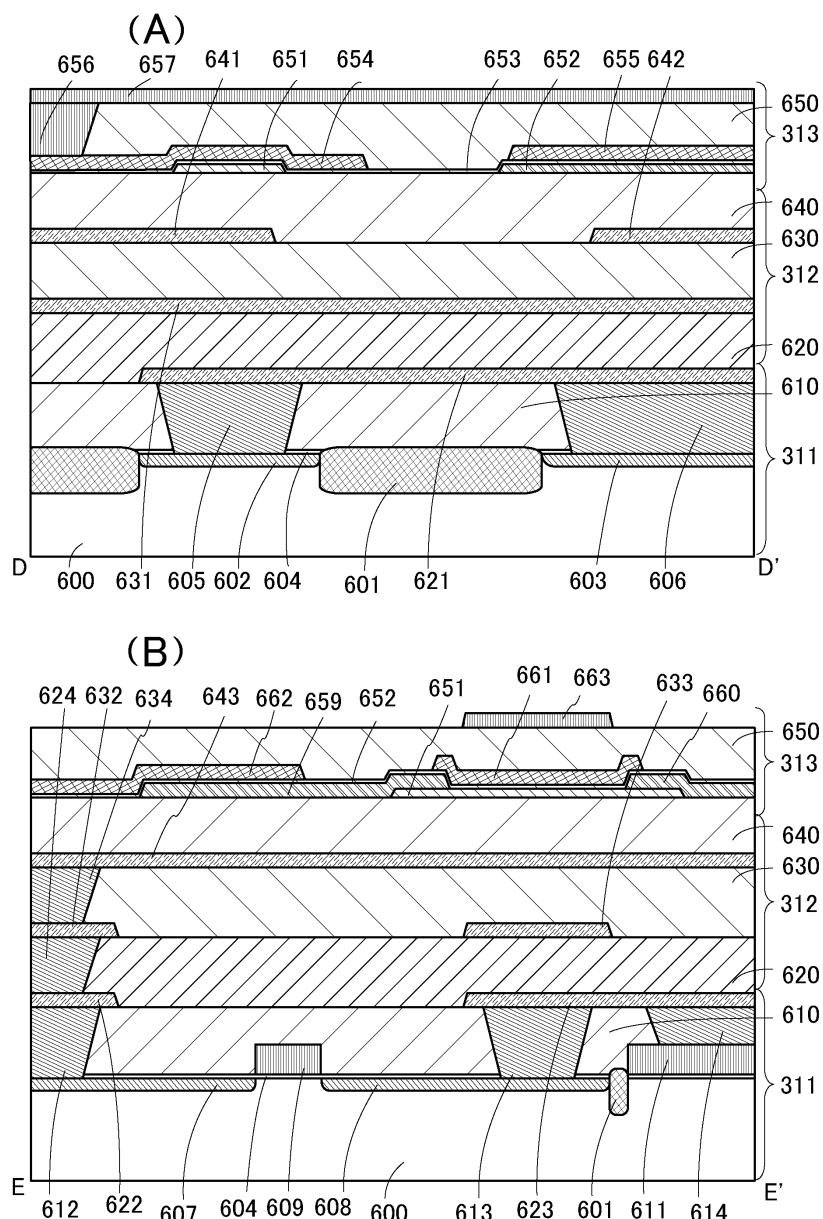

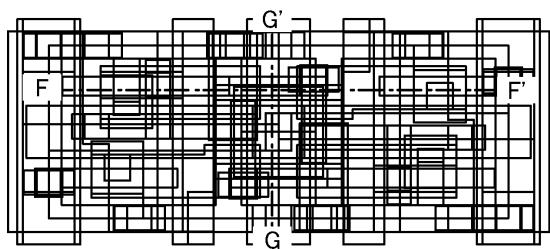

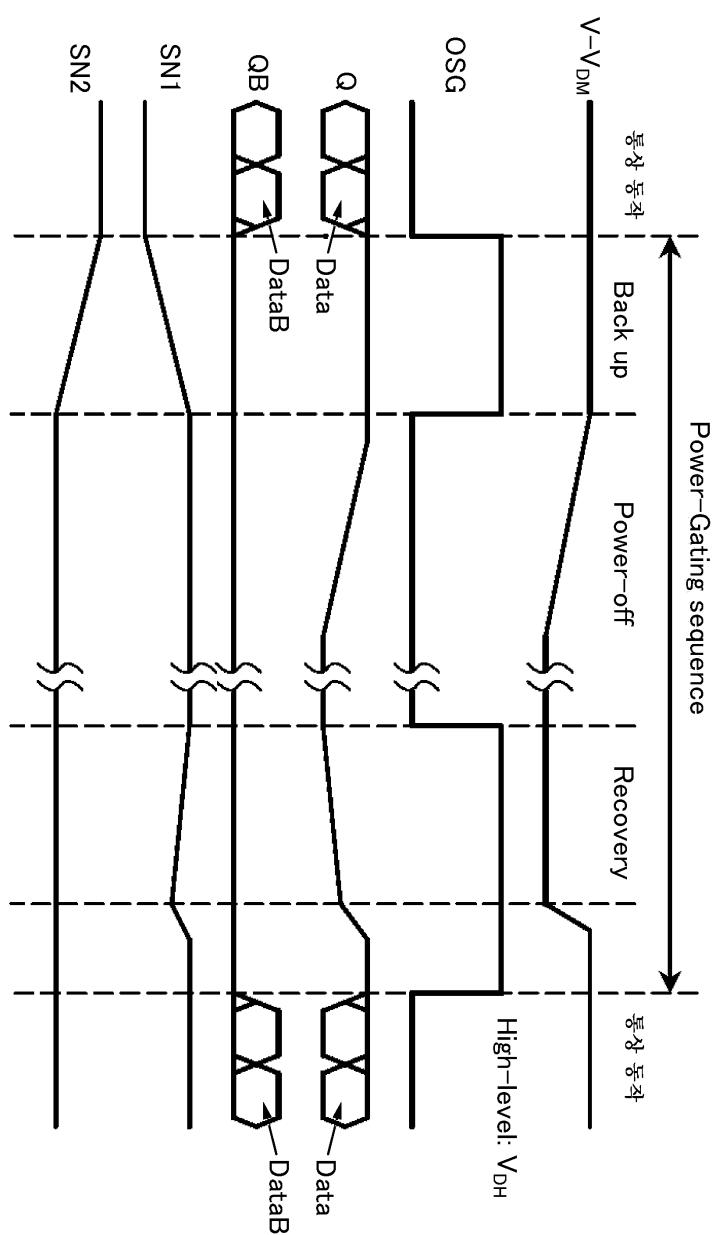

[0245]

도 22에 OS-SRAM의 레이아웃을 나타낸다. 데이터를 퇴피하기 위하여 추가하는 부분(2개의 OS-FET와 2개의 Capacitor)은 표준적인 SRAM이 형성되어 있는 층 위에 적층할 수 있다. 따라서, 표준적인 SRAM으로부터 OS-SRAM으로의 변경에 의해 수반하는 면적 증가는 0%로 할 수 있다. OS-SRAM 셀의 면적은  $0.46\mu\text{m} \times 1.24\mu\text{m} = 0.5704\mu\text{m}^2$  ( $135\text{F}^2$ )로 되어 있다.

[0246]

데이터를 퇴피할 수 있는 SRAM은, OS-SRAM 외에 MRAM(Magnetoresistive RAM), FeRAM(Ferroelectric Random Access Memory) 등을 사용하는 방법도 제안되어 있다. 그러나, 모두 표준적인 SRAM으로부터의 면적 증가가 있고, 면적 증가가 없이 데이터를 퇴피할 수 있는 SRAM은 OS-SRAM만이다.

[0247]

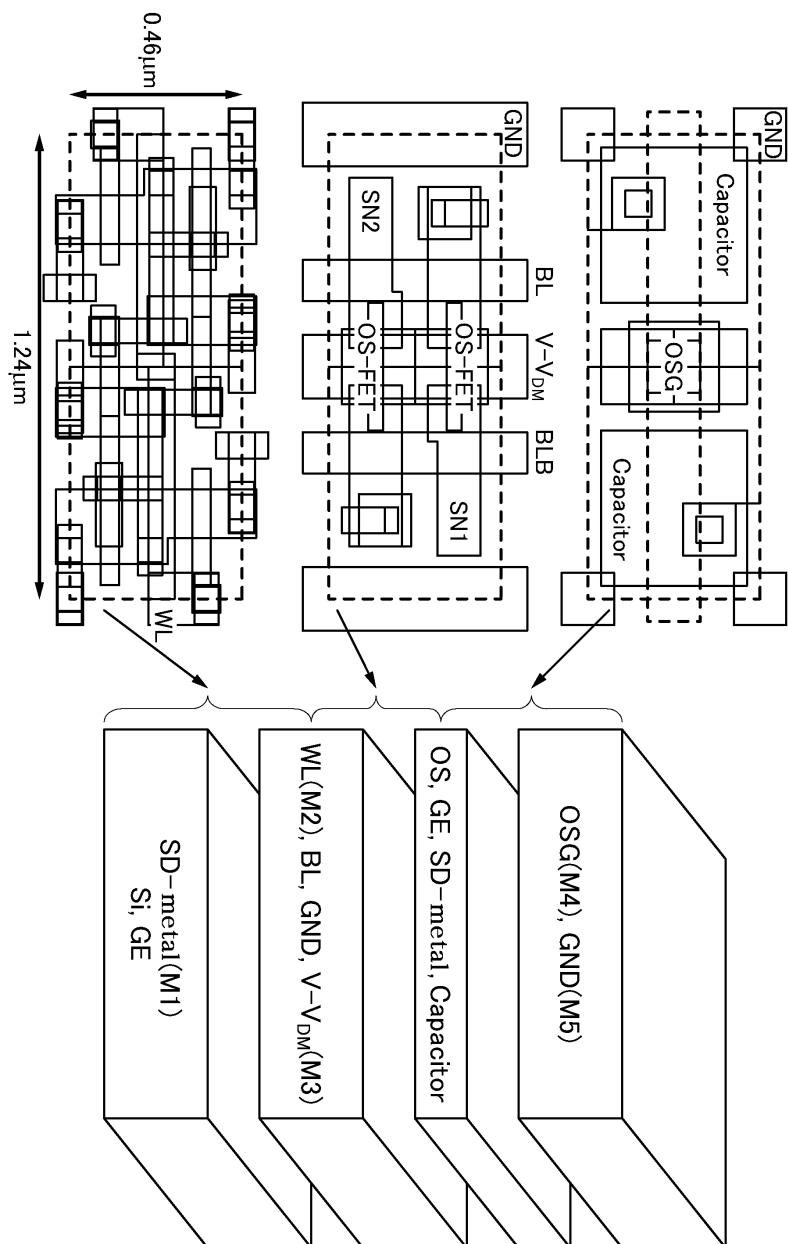

OS-SRAM의 PG 시퀀스에 있어서의, 퇴피(Backup) 시간, 복귀(Recovery) 시간은 각각 3.9ns, 2.0ns로 가능한 것을 시뮬레이션에서 확인하였다. 여기서, 각 구간에서의 소비 에너지에 대하여 도 23에 정리하여 나타낸다.

[0248]

Backup 구간: 쌍안정부 Q, QB에 보유 지지되어 있는 데이터를 퇴피할 때, OS-FET의 게이트 용량이나 Capacitor로의 충방전에 의해 에너지가 소비된다( $E_{\text{backup}}$ ).

[0249]

Power-off 구간: 전원 차단을 행함으로써 스텐바이 전력을 삭감한다. 이상적으로는 차단 중 누설 전류  $I_{\text{off}}=0$ 이지만, 현실적으로는 전원 차단을 행하는 파워 스위치로 누설 전류가 발생하고, 이 값은 파워 스위치용 트랜지스터의 설계 사이즈로 좌우된다. 본 시뮬레이션에서는 설계 사양에 좌우되지 않는 본질적인 PG 효과를 조사하기 위해 파워 스위치의 누설 전류를 제로( $I_{\text{off}}=0$ )로 하였다.

[0250]

Recovery 구간: backup부(노드 SN1, SN2)로부터 쌍안정부 Q, QB에 데이터를 복귀시키기 위하여  $E_{\text{recovery}}$ 가 소비된다.  $E_{\text{recovery}}$ 에는 OS-FET의 게이트 용량이나  $V-V_{DM}$  배선에의 충전, 쌍안정부 Q, QB에서의 동작 개시 시에 있어서의 관통 전류가 있다.

[0251]

스텐바이 상태 시에는 스템바이 전력( $I_{\text{sb}} \times V_{\text{D}}$ )이 항상 소비되지만, PG를 행함으로써 이 스템바이 전력을 제로로 할 수 있다. 어떤 일정 구간  $\tau_{\text{total}}$ 의 스템바이 전력을 PG에 의해 삭감하는 경우, PG 적용 시의 전체 구간 에너지( $E_{\text{backup}}+E_{\text{off}}+E_{\text{recovery}}$ )와, 스템바이 전력( $I_{\text{sb}} \times V_{\text{D}} \times \tau_{\text{total}}$ )의 차분  $E_{\text{overhead}}$ 는 수학식 1로 표현된다.

## 수학식 1

$$E_{\text{overhead}} = (E_{\text{backup}} + E_{\text{off}} + E_{\text{recovery}}) - (I_{\text{sby}} \times V_D \times \tau_{\text{total}}) \quad (1)$$

[0252]

[0253] 여기에서 주의해야 할 점은, 「스탠바이 전력 제로≠저소비 전력」이라는 것이다.  $E_{\text{overhead}}=0$ 이 되는 시간 (BET:Break-Even Time)보다도 짧은 시간의 PG를 행한 경우, PG를 행함으로써 반대로 소비 전력이 증가하는 것을 수학식 1에서 알 수 있다. BET는 수학식 2로 표현된다.

## 수학식 2

$$BET = (E_{\text{backup}} + E_{\text{off}} + E_{\text{recovery}}) / (I_{\text{sby}} \times V_D) \quad (2)$$

[0254]

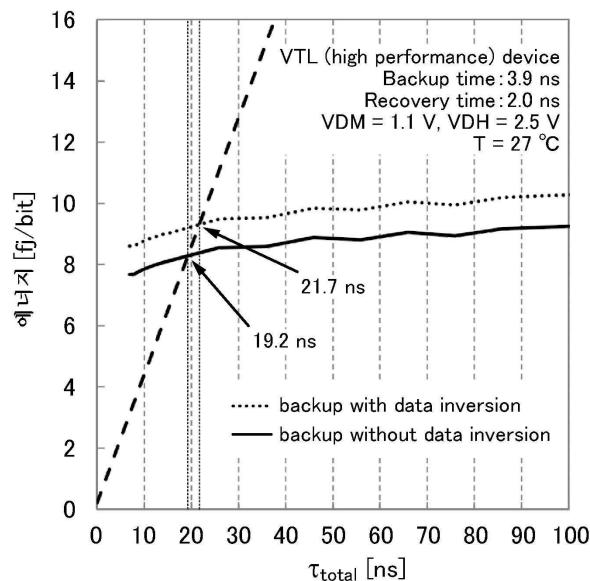

[0255] 이와 같이, BET보다도 짧은 시간의 PG를 행하는 테에는 저소비 전력의 효과는 없고, 어떻게 BET를 짧게 할지가 중요하다. OS-SRAM에 있어서 PG를 행한 경우의 에너지를 도 24에 나타내었다. 전원 차단을 행하는 시간( $\tau_{\text{off}}$ )을 할당함으로써 PG와 스탠바이 시의 에너지가 같아지는 시간을 구하고 있다. 시뮬레이션의 초기 조건에는, 쌍안정부 Q, QB와 backup부의 데이터가 다른 경우와 동일한 경우의 두 가지를 가정하고 있다. 이 두 조건(backup with data inversion, backup without data inversion)에서의 BET는 각각 21.7ns, 19.2ns로 예측되었다.

[0256]

표준적인 SRAM으로부터 OS-SRAM으로 변경한 것에 의한 통상 동작에의 영향에 대하여 조사하였다.

[0257]

대기 전력 : OS-SRAM, 표준적인 SRAM 모두 419nW이다.

[0258]

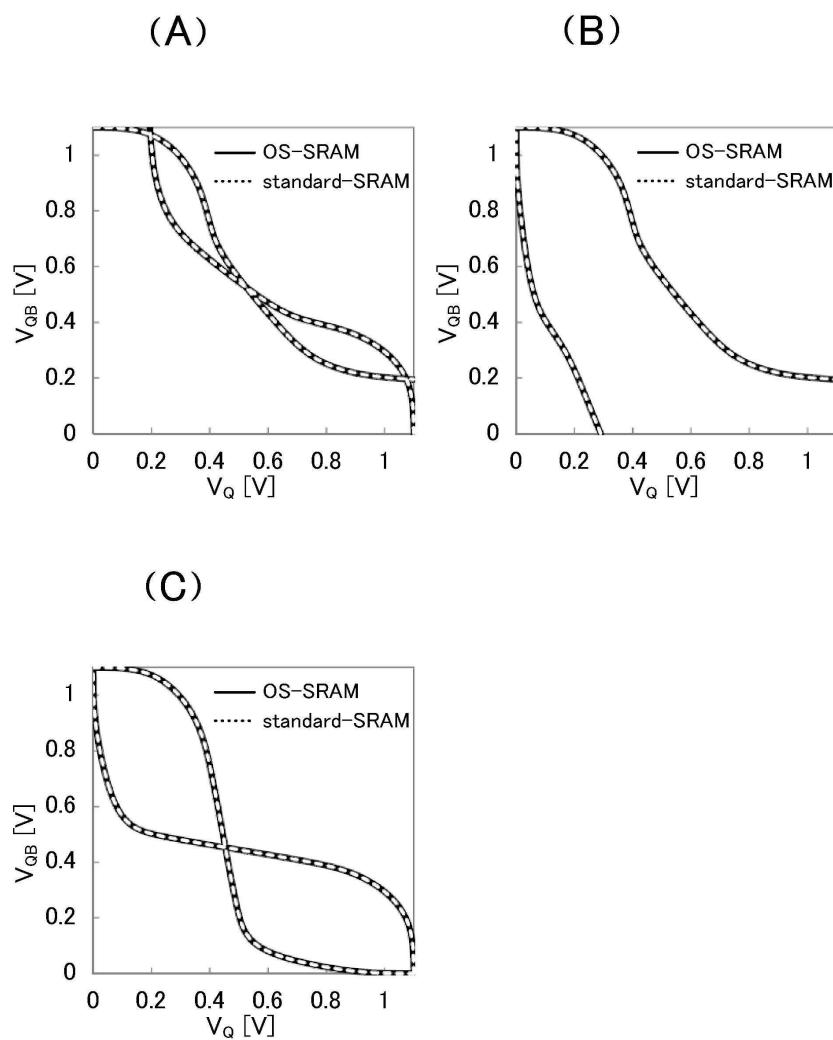

스태틱 노이즈 마진(SNM): 도 25의 (A) 내지 (C)에 Read, Write, Hold 동작 시의 SNM을 나타낸다. 도면에서 알 수 있듯이, SNM이 중첩되어 있고, SNM의 열화는 전혀 없다.

[0259]

지연 시간: 쌍안정부 Q, QB의 반전 지연은 OS-SRAM에서 17.7ps, 표준적인 SRAM에서 15.2ps였다. 워드선의 지연, 비트선의 지연을 시뮬레이션하기 위해서, 256행×128열의 OS-SRAM array 및 표준적인 SRAM array를 가정하였다. 워드선의 승압 시간은 OS-SRAM에서 39.4ps, 표준적인 SRAM에서 36.9ps였다. 판독 동작 시에, 워드선이 상승되고나서 비트선의 전위가 ( $V_D - V_{BLSENSE}$ )로 방전될 때까지의 시간은, OS-SRAM에서 131ps, 표준적인 SRAM에서 126ps였다( $V_{BLSENSE}=0.3V$ ).

[0260]

동적 소비 전력:지연의 시뮬레이션과 동일한 테스트 벤치를 사용하였다. OS-SRAM과 표준적인 SRAM에 있어서, 쌍안정부 Q, QB의 반전에 의한 소비 전력:3.73fJ, 3.24fJ, 워드선에 의한 소비 전력:79.9fJ, 76.6fJ, 비트선에 의한 소비 전력:3.81pJ, 3.77pJ였다.

[0261]

이상과 같이, 표준적인 SRAM으로부터 OS-SRAM으로 변경한 것에 의한 통상 동작에의 영향은 거의 무시할 수 있다. 이것은, 통상 동작 시에 사용하는 쌍안정부 Q, QB와 backup부를 OS-FET에 의해 전기적으로 분리하였기 때문이다.

[0262]

OS-SRAM의 특성에 대하여 표 2에 정리하였다.

표 2

|                                | OS-SRAM       | Standard-SRAM |

|--------------------------------|---------------|---------------|

| Area [ $\mu\text{m}^2$ ]       | 0.5704 (+0%)  | 0.5704        |

| 스탠바이 전력 [nW/bit]               | 419 (+0%)     | 419           |

| 스태틱 노이즈 마진                     | 열화 없음         | -             |

| 쌍안정부 반전 지연 [ps]                | 17.7 (+16.1%) | 15.2          |

| 워드선 지연 [ps]                    | 39.4 (+6.7%)  | 36.9          |

| 비트선 지연 [ps]                    | 131 (+3.9%)   | 126           |

| VTL 쌍안정부 반전 에너지 [fJ/bit]       | 3.73 (+15.2%) | 3.24          |

| (HP) 워드선 다이내믹 에너지 [fJ]         | 79.9 (+4.3%)  | 76.6          |

| 비트선 다이내믹 에너지 [pJ]              | 3.81 (+1.1%)  | 3.77          |

| 퇴피 시간 [ns]                     | 3.9           | -             |

| 복귀 시간 [ns]                     | 2.0           | -             |

| PG에 대한 에너지 [fJ/bit]            | 9.09          | -             |

| BET [ns]                       | 21.7          | -             |

| 스탠바이 전력 [nW/bit]               | 45.7(+0%)     | 45.7          |

| VTG (LP) PG에 대한 에너지 [fJ/bit]   | 7.09          | -             |

| BET [ns]                       | 155           | -             |

| 스탠바이 전력 [nW/bit]               | 0.589(+0%)    | 0.589         |

| VTH (LSTP) PG에 대한 에너지 [fJ/bit] | 6.89          | -             |

| BET [ns]                       | 11700         | -             |

[0263]

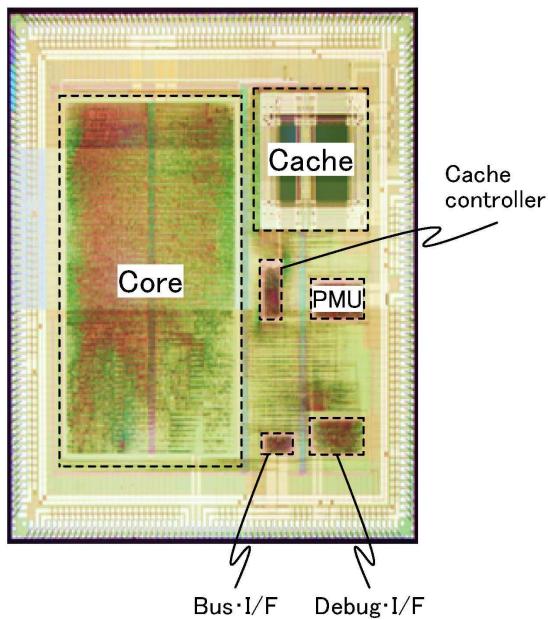

[0264] OS-SRAM을 32-bit 마이크로프로세서의 캐시 메모리에 적용하였다. 시험 제작한 2KB의 캐시는, CMOS:350nm, OS:180nm process technology를 사용하여, OS-SRAM의 backup부는 W/L=800nm/180nm의 OS-FET와 C=27.1fF의 Capacitor로 구성하였다. 도 26에 칩 사진을 나타낸다. 또한, 마이크로프로세서의 사양을 표 3에 나타내었다.

## 표 3

| Technology           |               | CMOS: 350 nm               | OS: 180 nm       |

|----------------------|---------------|----------------------------|------------------|

| Cache                | Configuration | Unified                    |                  |

|                      | Capacity      | 2 KB                       |                  |

|                      | Associativity | 2 way set associative      |                  |

|                      | Displacement  | LRU method                 |                  |

|                      | Block size    | 4 B                        |                  |

|                      | Write method  | write-back, write-allocate |                  |

|                      | Hit latency   | 2 clock cycle              |                  |

| ISA                  |               | MIPS I (32-bit, RISC)      |                  |

| Power-supply voltage |               | Si: 2.5 V                  | OS: 2.5 V / -1 V |

| Clock frequency      |               | 15 MHz                     |                  |

[0265]

[0266] 또한 도 27에 마이크로프로세서의 블록도를 나타낸다. 캐쉬의 파워 도메인은 OS-SRAM array부, 구동 회로부(cache controller 포함함), Backup & Recovery Driver부(2.5V/-1V 사양)의 3개가 있고, 각각의 high-level(V- $V_{DD}$ , V- $V_{DM}$ , V- $V_{DH}$ )측에 파워 스위치를 설치하였다. PMU(Power Management Unit)로부터 OS-FET를 제어하는 PG 신호와 파워 스위치를 제어하는 PSW\_PERI 신호, PSW\_MEM 신호가 캐쉬에 입력됨으로써 PG 시퀀스가 실행된다.

[0267]

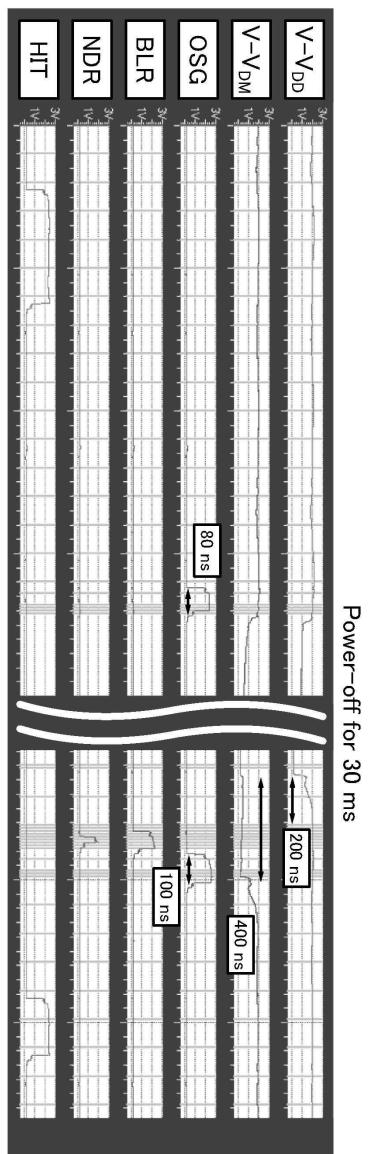

도 28에 나타내는 PG 시의 오실로스코프 파형으로부터 정상적인 PG 동작을 확인할 수 있다. 도면 중 BLR 신호와 NDR 신호는, 복귀 동작 개시 시에서 SRAM 셀중 쌍안정부 Q, QB를 GND 전위에 프리차지하기 위하여 사용하고 있다. 측정으로부터 80ns의 퇴피 동작, 400ns의 복귀 동작(전원 안정화를 위한 200ns를 포함함)을 확인하였다. 스탠바이 전력은 통상 시 922nW, 전원 차단 시 22.5nW가 얻어지고, PG에 의해 97.6%의 Standby 전력을 삭감할 수 있는 것을 확인할 수 있었다.

[0268]

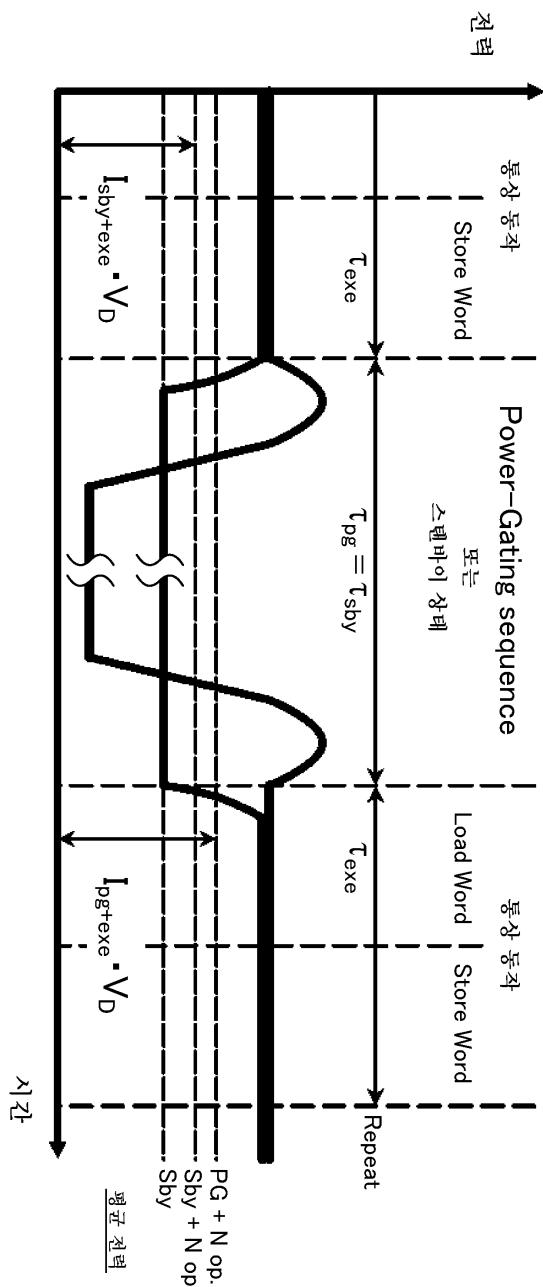

도 29에 나타내는 BET 평가는, 통상 동작(Store Word, Load Word) 간에 PG 상태를  $\tau_{pg}$  삽입했을 때의 평균 전력  $P_{pg+exe}$ 와, 통상 동작간에 Standby 상태를  $\tau_{sby} (= \tau_{pg})$  삽입했을 때의 평균 전력  $P_{sby+exe}$ 의 차분을 취함으로써 오버헤드 전력을 측정하여(수학식 3을 참조), 수학식 3에 있어서의 오버헤드 전력이 0이 되는 시간을 BET로 하였다.

## 수학식 3

$$P_{overhead} = P_{pg+exe} - P_{sby+exe} \quad (3)$$

[0269]

[0270] 도 30으로부터 BET=61.4ms가 얻어졌다. 또한, 85°C에서 1일 이상의 데이터 유지 특성을 확인하였다.

[0271] 금회의 시험 제작에서는 CMOS:350nm/OS:180nm의 적층 프로세스가 실증되었고, 최첨단 프로세스에 있어서의 회로 면적을 크게 하지 않고 OS-SRAM을 적용할 수 있는 것이 실증되었다. 350nm CMOS process에서는, 원래 누설 전력이 크지 않기 때문에 2KB cache의 BET는 ms order에 머물지만, 미세화가 진행되어 Si-FET의 누설 전류가 커지면 과연 OS-SRAM에 의한 PG 기술은 효과를 발휘한다.

## 부호의 설명

[0272] 100 : 메모리 셀

101 : 기억 회로

101\_mn : 기억 회로

101\_11 : 기억 회로

111 : 절연층

112 : 반도체층

113 : 전극

114 : 전극

115 : 게이트 절연층

116 : 게이트 전극

117 : 전극

118 : 층간 절연층

119 : 배선층

121 : 트랜지스터

122 : 트랜지스터

123 : 인버터 회로

124 : 인버터 회로

400 : 반도체 기판

402 : 소자 분리용 절연막

410 : 게이트 절연층

412 : 게이트 전극

413 : 게이트 전극

414 : 게이트 전극

415 : 게이트 전극

416 : 층간 절연층

418 : 배선층

420 : 배선층

422 : 도전층

423 : 배선층

424 : 층간 절연층

426 : 도전층

427 : 배선층

428 : 층간 절연층

429 : 배선층

430 : 배선층

431 : 배선층

432 : 배선층

- 433 : 도전총

434 : 배선총

436 : 배선총

438 : 배선총

440 : 배선총

442 : 층간 절연총

444 : 도전총

446 : 배선총

448 : 층간 절연총

450 : 게이트 절연총

452 : 반도체총

453 : 반도체총

454 : 배선총

456 : 게이트 전극

458 : 층간 절연총

460 : 도전총

462 : 도전총

464 : 절연총

466 : 도전총

467 : 도전총

468 : 도전총

472 : 층간 절연총

474 : 배선총

476 : 배선총

477 : 배선총

478 : 층간 절연총

480 : 층간 절연총

600 : 반도체 기판

601 : 소자 분리용 절연막

602 : 불순물 영역

603 : 불순물 영역

604 : 게이트 절연총

605 : 배선총

606 : 배선총

607 : 불순물 영역

608 : 불순물 영역

609 : 게이트 전극

610 : 층간 절연층

611 : 배선층

612 : 배선층

613 : 배선층

614 : 배선층

620 : 층간 절연층

621 : 배선층

622 : 배선층

623 : 배선층

624 : 배선층

630 : 층간 절연층

631 : 배선층

632 : 배선층

633 : 배선층

634 : 배선층

640 : 층간 절연층

641 : 배선층

642 : 배선층

643 : 배선층

650 : 층간 절연층

651 : 반도체층

652 : 도전층

653 : 게이트 절연층

654 : 도전층

655 : 도전층

656 : 도전층

657 : 도전층

659 : 도전층

660 : 도전층

661 : 게이트 전극

662 : 도전층

663 : 배선층

700 : 전자 부품

701 : 리드

702 : 프린트 기판

703 : 반도체 장치

704 : 실장 기판

800 : 반도체 기판

801 : 소자 분리용 절연막

802 : 불순물 영역

803 : 게이트 절연층

804 : 게이트 전극

805 : 배선층

810 : 층간 절연층

820 : 층간 절연층

821 : 배선층

822 : 배선층

823 : 배선층

830 : 층간 절연층

831 : 배선층

840 : 층간 절연층

841 : 배선층

842 : 배선층

850 : 층간 절연층

851 : 반도체층

852 : 도전층

853 : 게이트 절연층

854 : 도전층

855 : 도전층

856 : 도전층

901 : 하우징

902 : 하우징

903a : 표시부

903b : 표시부

904 : 선택 버튼

905 : 키보드

910 : 전자 서적

911 : 하우징

912 : 하우징

913 : 표시부

914 : 표시부

- 915 : 축부

916 : 전원

917 : 조작 키

918 : 스피커

920 : 텔레비전 장치

921 : 하우징

922 : 표시부

923 : 스탠드

924 : 리모콘 조작기

930 : 본체

931 : 표시부

932 : 스피커

933 : 마이크

934 : 조작 버튼

941 : 본체

942 : 표시부

## 도면

## 도면1

(A)

(B)

## 도면2

(A)

(B)

도면3

도면4

## 도면5

(A)

(B)

## 도면6

도면7

(A)

(B)

## 도면8

(A)

(B)

(C)

도면9

(A)

(B)

도면10

(A)

(B)

## 도면11

## 도면12

## 도면13

(A)

(B)

## 도면14

도면15

(A)

(B)

## 도면16

(A)

(B)

(C)

(D)

도면17

도면18

## 도면19

(A)

(B)

## 도면20

도면21

도면22

### 도면23

## 도면24

## 도면25

도면26

도면27

도면28

도면29

도면30