(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6084027号

(P6084027)

(45) 発行日 平成29年2月22日(2017.2.22)

(24) 登録日 平成29年2月3日(2017.2.3)

|                        |               |

|------------------------|---------------|

| (51) Int.Cl.           | F 1           |

| G02B 6/12 (2006.01)    | GO2B 6/12 301 |

| G02B 6/13 (2006.01)    | GO2B 6/13     |

| G02B 6/42 (2006.01)    | GO2B 6/42     |

| H01L 31/0232 (2014.01) | H01L 31/02 D  |

請求項の数 7 (全 16 頁)

(21) 出願番号 特願2012-277550 (P2012-277550)

(22) 出願日 平成24年12月20日 (2012.12.20)

(65) 公開番号 特開2014-122929 (P2014-122929A)

(43) 公開日 平成26年7月3日 (2014.7.3)

審査請求日 平成27年11月6日 (2015.11.6)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 柳沢 賢司

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 奥村 政人

最終頁に続く

(54) 【発明の名称】光導波路装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板の上面に形成された上側配線層と、

前記基板の下面に形成された下側配線層と、

前記基板に形成された開口部と

を備えた配線基板と、

前記配線基板の下側配線層側に形成された光導波路と、

前記配線基板の上側配線層に接続された第1光素子と、

前記上側配線層を介して前記第1光素子に電気的に接続された第1回路素子と、

第2光素子のバンプ電極が前記配線基板の開口部に挿通されて前記下側配線層に電気的に接続された前記第2光素子と、

第2回路素子のバンプ電極が前記配線基板の開口部に挿通されて前記下側配線層に接続され、前記下側配線層を介して前記第2光素子に電気的に接続された前記第2回路素子とを有することを特徴とする光導波路装置。

## 【請求項 2】

前記光導波路は、第1光路用コア層と第2光路用コア層とが水平方向に交互に並んで配置されており、前記第1光素子が前記第1光路用コア層に光結合され、前記第2光素子が前記第2光路用コア層に光結合されていることを特徴とする請求項1に記載の光導波路装置。

10

20

**【請求項 3】**

前記配線基板に光透過用開口部が設けられており、前記第1光素子及び第2光素子は前記光透過用開口部を介して前記光導波路に光結合されることを特徴とする請求項1又は2に記載の光導波路装置。

**【請求項 4】**

前記配線基板の上側配線層及び下側配線層は、コネクタを介して別の電子基板に接続されることを特徴とする請求項1乃至3のいずれか一項に記載の光導波路装置。

**【請求項 5】**

前記第1光素子及び第2光素子は発光素子又は受光素子であり、前記第1回路素子及び第2回路素子はドライバ素子又はアンプ素子であることを特徴とする請求項1乃至4のいずれか一項に記載の光導波路装置。 10

**【請求項 6】**

両面に金属層が形成された基板を用意する工程と、

前記両面の各金属層をパターニングすることにより、上側配線層と下側配線層とを形成する工程と、

前記基板に開口部を形成する工程と、

前記基板の前記下側配線層側に光導波路を形成する工程と、

第1光素子と第1回路素子とが前記上側配線層を介して電気的に接続され、かつ、第2光素子が前記基板の開口部を介して前記下側配線層に接続され、前記第2光素子と第2回路素子とが前記下側配線層を介して電気的に接続される構造を得る工程とを有し、 20

前記第2光素子のバンプ電極を前記配線基板の開口部に挿通させて前記下側配線層に電気的に接続すると共に、

前記第2回路素子のバンプ電極を前記配線基板の開口部に挿通させて前記下側配線層に接続することを特徴とする光導波路装置の製造方法。

**【請求項 7】**

前記光導波路を形成する工程において、

前記光導波路は、第1光路用コア層と第2光路用コア層とが水平方向に交互に並んで配置され、

前記構造を得る工程において、

前記第1光素子が前記第1光路用コア層に光結合され、前記第2光素子が前記第2光路用コア層に光結合されることを特徴とする請求項6に記載の光導波路装置の製造方法。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、光導波路装置及びその製造方法に関する。

**【背景技術】****【0002】**

近年、光ファイバ通信技術を中心に基幹系の通信回線の整備が着々と進行する中でボトルネックとなりつつあるのが電気機器や情報端末内の電気信号の伝送速度である。このような背景から、すべての信号伝送を電気信号によって行う従来の電気回路基板に代わって、電気信号の伝送速度の限界を補うために、高速部分を光信号で伝送するタイプの光電気複合基板が提案されている。 40

**【0003】**

光電気複合基板では、光信号はコア層がクラッド層で囲まれた構造の光導波路によって伝送される。そして、光導波路の端部に設けられた光路変換ミラーによってコア層を伝播する光を垂直方向に反射させて光路を変換させる。

**【0004】**

光電気複合基板として、光導波路の上に電気配線基板が配置され、光素子が電気配線基板の開口部を介して光導波路に光結合された構造が開示されている。

**【先行技術文献】**

10

20

30

40

50

**【特許文献】****【0005】**

【特許文献1】特開2004-235418号公報

【特許文献2】特開2008-152064号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

後述する予備的事項の欄で説明するように、2つの第1、第2発光素子を光導波路の一端側に配置する場合は、それらを第1、第2ドライバ素子にそれぞれ接続する必要がある。このとき、第1発光素子は配線基板の上側配線層を介して第1ドライバ素子に接続される。また、第2発光素子は配線基板のビア導体及び下側配線層を介して第2ドライバ素子に接続される。

**【0007】**

このため、高速な電気伝送時にビア導体での反射などによって伝送損失が発生し、高速な信号伝送が阻害される。

**【0008】**

また、ビア導体を有する配線基板では、無電解めっきの影響によって配線層の幅や厚みの寸法精度が低下することから、伝送経路でのインピーダンスの不整合が生じ、信号伝送特性が劣化する。

**【0009】**

2つの光素子が光導波路の一端側に配置され、各光素子が配線基板を介して回路素子に接続される光導波路装置において、良好な信号伝送特性を得ることを目的とする。

**【課題を解決するための手段】****【0010】**

以下の開示の一観点によれば、基板と、前記基板の上面に形成された上側配線層と、前記基板の下面に形成された下側配線層と、前記基板に形成された開口部とを備えた配線基板と、前記配線基板の下側配線層側に形成された光導波路と、前記配線基板の上側配線層に接続された第1光素子と、前記上側配線層を介して前記第1光素子に電気的に接続された第1回路素子と、第2光素子のバンプ電極が前記配線基板の開口部に挿通されて前記下側配線層に電気的に接続された前記第2光素子と、第2回路素子のバンプ電極が前記配線基板の開口部に挿通されて前記下側配線層に接続され、前記下側配線層を介して前記第2光素子に電気的に接続された前記第2回路素子とを有する光導波路装置が提供される。

**【0011】**

また、その開示の他の観点によれば、両面に金属層が形成された基板を用意する工程と、前記両面の各金属層をパターニングすることにより、上側配線層と下側配線層とを形成する工程と、前記基板に開口部を形成する工程と、前記基板の前記下側配線層側に光導波路を形成する工程と、第1光素子と第1回路素子とが前記上側配線層を介して電気的に接続され、かつ、第2光素子が前記基板の開口部を介して前記下側配線層に接続され、前記第2光素子と第2回路素子とが前記下側配線層を介して電気的に接続される構造を得る工程とを有し、前記第2光素子のバンプ電極を前記配線基板の開口部に挿通させて前記下側配線層に電気的に接続すると共に、前記第2回路素子のバンプ電極を前記配線基板の開口部に挿通させて前記下側配線層に接続する光導波路装置の製造方法が提供される。

**【発明の効果】****【0012】**

以下の開示によれば、光導波路装置では、上側配線層と下側配線層とを備えた配線基板の下側に光導波路が配置されている。そして、第1、第2光素子が光導波路に光結合され、それらに第1、第2回路素子が電気的に接続されている。

**【0013】**

第1光素子と第1回路素子とは上側配線層を介して接続されている。また、配線基板はビア導体を備えておらず、第2光素子は配線基板の開口部を介して下側配線層に接続され

10

20

30

40

50

、下側配線層を介して第2回路素子に接続されている。

**【0014】**

このため、高速電気伝送時にビア導体での反射などによる伝送損失の発生が抑制され、高速で高品質な信号伝送を実現することができる。

**【0015】**

また、配線基板の下側、上側配線層は、基板の両面に形成された厚み精度の高い金属層をフォトリソグラフィによってパターニングすることにより得られる。このため、配線層の幅や厚みの寸法精度を向上させることができるので、伝送経路でのインピーダンス整合を得ることができる。

**【図面の簡単な説明】**

10

**【0016】**

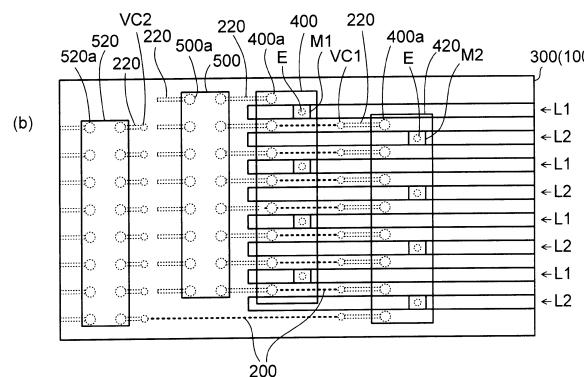

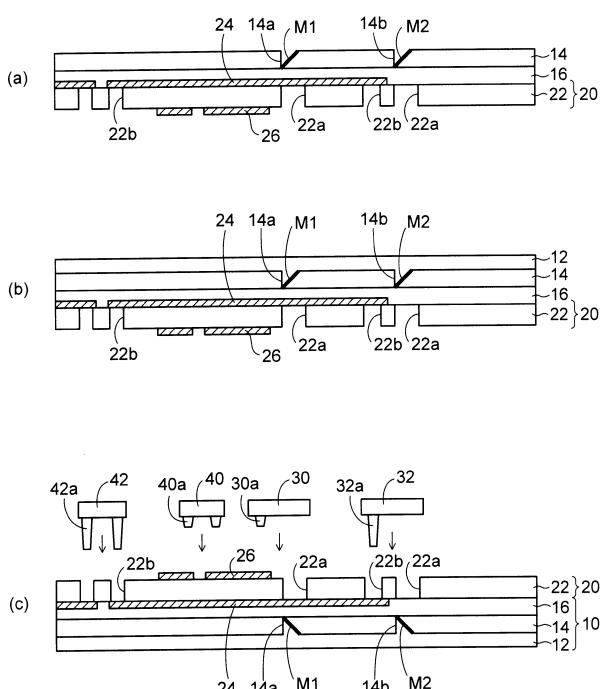

**【図1】**図1(a)及び(b)は予備的事項に係る光導波路装置を示す断面図及び平面図である。

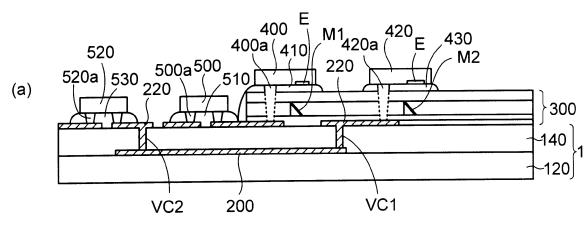

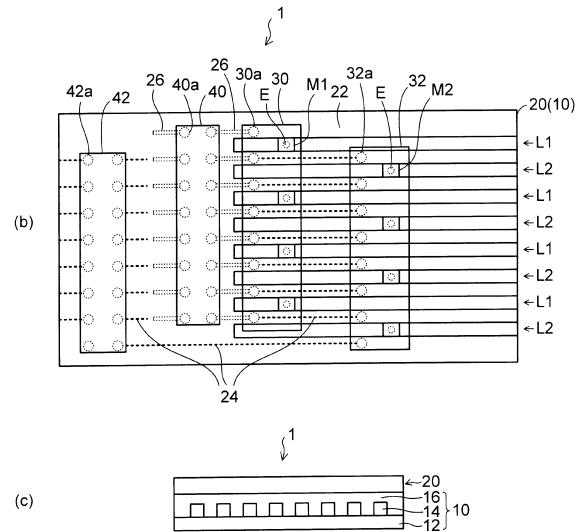

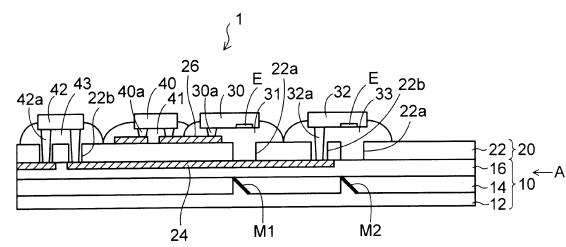

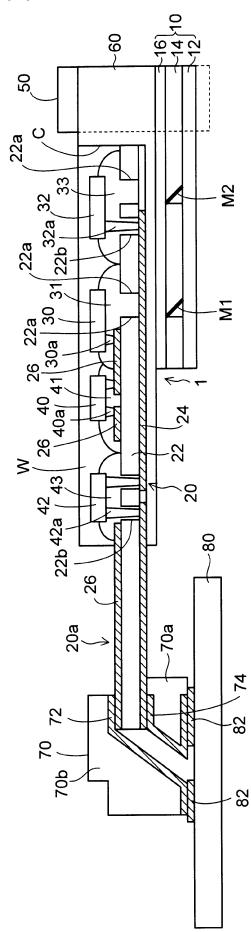

**【図2】**図2(a)～(c)は実施形態の光導波路装置を示す断面図、平面図及び側面図である。

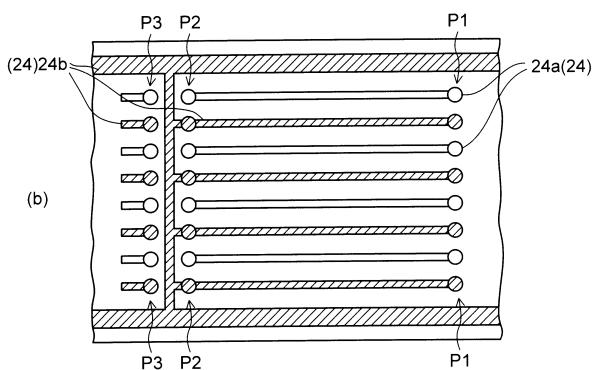

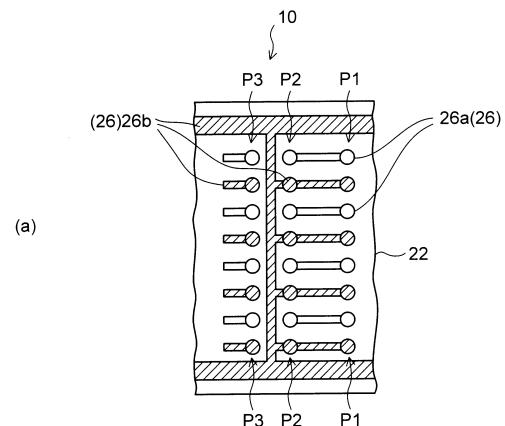

**【図3】**図3(a)は図2(a)の配線基板の上側配線層のレイアウトの一例を示す平面図、図3(b)は図2(a)の配線基板の下側配線層のレイアウトの一例を示す平面図である。

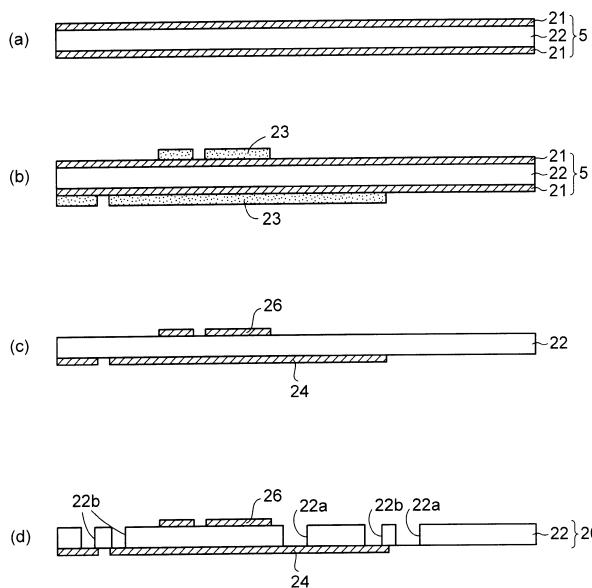

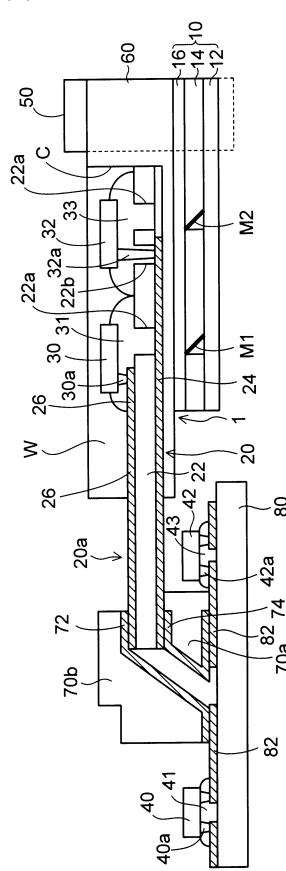

**【図4】**図4(a)～(d)は実施形態の光導波路装置の製造方法を示す断面図(その1)である。

20

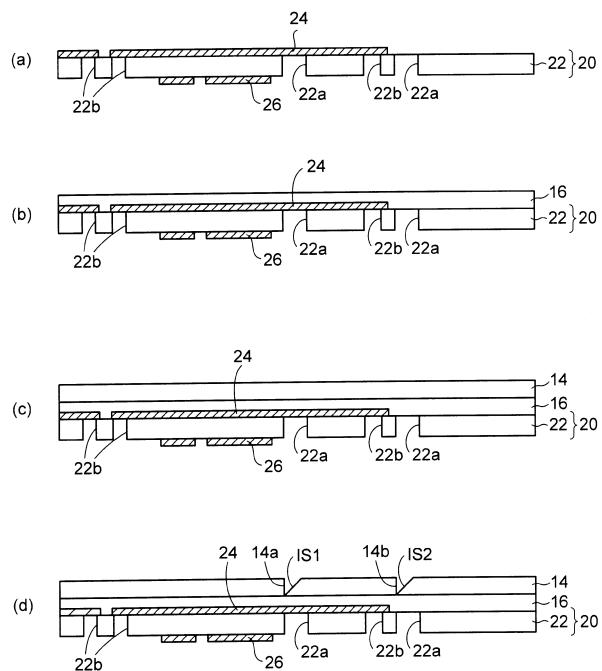

**【図5】**図5(a)～(d)は実施形態の光導波路装置の製造方法を示す断面図(その2)である。

**【図6】**図6(a)～(c)は実施形態の光導波路装置の製造方法を示す断面図(その3)である。

**【図7】**図7は実施形態の光導波路装置が電子基板に接続された例を示す断面図である。

**【図8】**図8は実施形態の光導波路装置が電子基板に接続された別の例を示す断面図である。

**【発明を実施するための形態】**

**【0017】**

以下、実施の形態について、添付の図面を参照して説明する。

30

**【0018】**

実施形態を説明する前に、基礎となる予備的事項について説明する。図1(a)に示すように、予備的事項の光導波路装置では、配線基板100の上に光導波路300が配置されている。配線基板100では、基板120の上に下側配線層200が形成されている。

**【0019】**

基板120及び下側配線層200の上には、絶縁樹脂からなる層間絶縁層140が形成されている。層間絶縁層140の上には上側配線層220が形成されている。層間絶縁層140には厚み方向に貫通する第1ビア導体VC1及び第2ビア導体VC2が形成されている。下側配線層200と上側配線層220とが第1、第2ビア導体VC1, VC2を介して相互接続されている。

40

**【0020】**

図1(b)は図1(a)を平面視した様子を模式的に描いた平面図である。図1(b)の平面図に示すように、光導波路300は複数の第1光路L1と複数の第2光路L2を備えている。第1光路L1と第2光路L2とは交互に並んで配置されている。

**【0021】**

各第1光路L1の所定部に第1光路変換ミラーM1が設けられ、各第2光路用コア層L2の所定部に第2光路変換ミラーM2が設けられている。

**【0022】**

そして、配線基板100の上に、光導波路300の第1光路L1に光結合された第1発光素子400が配置されている。また、配線基板100の上に、第2光路L2に光結合さ

50

れた第2発光素子420が配置されている。

【0023】

第1発光素子400のバンプ電極400aが光導波路300の開口部を介して配線基板100の上側配線層220に接続されている。第1発光素子400の下側にはアンダーフィル樹脂410が充填されている。

【0024】

また同様に、第2発光素子420のバンプ電極420aが光導波路300の開口部を介して配線基板100の上側配線層220に接続されている。第2発光素子420の下側にはアンダーフィル樹脂430が充填されている。

【0025】

第1、第2発光素子400, 420は複数の発光部Eをそれぞれ備えている。第1発光素子400の各発光部Eは第1光路L1の第1光路変換ミラーM1に光結合されている。また、第2発光素子420の各発光部Eは第2光路L2の第2光路変換ミラーM2に光結合されている。

10

【0026】

このように、第1発光素子400の発光部Eと第2発光素子420の発光部Eとが第1、第2光路L1, L2に交互に光結合されている。

【0027】

ここで、第1発光素子400の発光部Eの配置ピッチは250μm程度である。このため、一つの第1発光素子400を配置する場合は、光導波路300の光路の配置ピッチも250μmとなり、光路の配置ピッチをこれ以上狭くすることは困難である。

20

【0028】

そこで、第1光素子400が光結合される複数の第1光路L1の間の領域に第2光路L2を配置し、その第2光路L2に第2発光素子420を光結合させている。

【0029】

これにより、複数の第1光路L1と複数の第2光路L2とを組み合わせた光路の配置ピッチは、第1発光素子400の発光部Eの半分の配置ピッチ(125μm)になる。これにより、光導波路300の光路の狭ピッチ化を図ることができる。

【0030】

また、配線基板100の上側配線層220に第1ドライバ素子500のバンプ電極500aが接続されている。第1ドライバ素子500の下側にはアンダーフィル樹脂510が充填されている。第1発光素子400は上側配線層220を介して第1ドライバ素子500に電気的に接続されている。

30

【0031】

また同様に、配線基板100の上側配線層220に第2ドライバ素子520のバンプ電極520aが接続されている。第2ドライバ素子520の下側にはアンダーフィル樹脂530が充填されている。第2発光素子420は、上側配線層220、第1ビア導体VC1、下側配線層200、第2ビア導体VC2、及び上側配線層220を介して第2ドライバ素子520に電気的に接続されている。

40

【0032】

予備的事項の光導波路装置では、第1、第2発光素子400, 420と第1、第2ドライバ素子500, 520とをそれぞれ電気的に接続するために、第1、第2ビア導体VC1, VC2を備えた多層配線構造の配線基板100を使用している。

【0033】

このため、高速な電気伝送時に、第1、第2ビア導体VC1, VC2での反射などによって伝送損失が発生し、高速な信号伝送が阻害される。

【0034】

また、配線基板100の第1、第2ビア導体VC1, VC2を形成する際には、まず、パターン化された上側配線層220に繋がるように基板にビアホールを形成する。さらに、無電解めっきによってビアホール内にビア導体VCを形成して下側配線層200と上側

50

配線層 220 とを接続する手法が採用される。

**【0035】**

このとき、上側配線層 220 の表面にも無電解めっきが施される。このため、無電解めっきによって上側配線層 220 の幅や厚みがばらついて寸法精度が低下することからインピーダンスの不整合が生じ、信号伝送特性が劣化する。

**【0036】**

発光素子とドライバ素子を接続する形態を説明したが、受光素子とアンプ素子を接続する場合も同様な問題が発生する。

**【0037】**

以下に説明する実施形態では、前述した不具合を解消することができる。

10

**【0038】**

(実施形態)

図 2 (a) は実施形態の光導波路装置を示す断面図、図 2 (b) は同じく光導波路装置を示す平面図、図 2 (c) は図 2 (a) を A 方向からみた側面図である。また、図 4 ~ 図 6 は実施形態の光導波路装置の製造方法を示す断面図である。

**【0039】**

図 2 (a) 及び (c) に示すように、実施形態の光導波路装置 1 では、配線基板 20 の下に光導波路 10 が配置されている。光導波路 10 は、第 1 クラッド層 12 と、その上に形成されたコア層 14 と、それを被覆して第 1 クラット層 12 の上に形成された第 2 クラッド層 16 とを備え、コア層 14 が第 1、第 2 クラッド層 12, 16 で囲まれた構造を有する。

20

**【0040】**

コア層 14 の屈折率は、第 1 クラッド層 12 及び第 2 クラッド層 16 の屈折率よりも高くなるように設定されている。

**【0041】**

図 2 (b) は図 2 (a) を平面視した様子を模式的に描いた平面図である。図 2 (b) の例では、コア層 14 は、4 本の第 1 光路用コア層 L1 と、それらの間の領域にそれぞれ配置された 4 本の第 2 光路用コア層 L2 を備えて配置されている。

**【0042】**

このように、第 1 光路コア層 L1 と第 2 光路用コア層 L2 とが互い違いになるように水平方向に交互に並んで配置されている。

30

**【0043】**

後述するように、複数の第 1 光路用コア層 L1 に第 1 光素子が光結合され、複数の第 2 光路用コア層 L2 に第 2 光素子が光結合される。

**【0044】**

図 2 (a) 及び (b) に示すように、第 1 光路用コア層 L1 には第 1 光素子に光結合される第 1 光路変換ミラー M1 がそれぞれ設けられている。また、第 2 光路用コア層 L2 には、第 2 光素子に光結合される第 2 光路変換ミラー M2 がそれぞれ設けられている。

**【0045】**

光導波路 10 の上に配置された配線基板 20 は、基板 22 と、その下面に形成された下側配線層 24 と、その上面に形成された上側配線層 26 とを備えている。また、基板 22 は、光素子と光導波路 10 とを光結合させるための光透過用開口部 22a を第 1、第 2 光路変換ミラー M1, M2 の上に備えている。さらに、基板 22 は、光素子などを配線基板 20 の下側配線層 24 に接続するための接続用開口部 22b を下側配線層 24 の上に備えている。

40

**【0046】**

基板 22 としては、ポリイミドフィルムなどのフレキシブルな薄膜材料を使用することが好ましい。あるいは、ガラスエポキシ樹脂などのリジット基板を使用しても差し支えない。

**【0047】**

50

そして、配線基板 20 の上側配線層 26 に第 1 光素子 30 のバンプ電極 30a が接続されている。第 1 光素子 30 と配線基板 20 との隙間及び光透過用開口部 22a に透明なアンダーフィル樹脂 31 が充填されている。第 1 光素子 30 は光透過用開口部 22a を介して第 1 光路用コア層 L1 に光結合されている。

#### 【0048】

また、第 2 光素子 32 のバンプ電極 32a が配線基板 20 の接続用開口部 22b を介して、その底に配置された下側配線層 24 に接続されている。第 2 光素子 32 と配線基板 20 との隙間及び光透過用開口部 22a に透明なアンダーフィル樹脂 33 が充填されている。第 2 光素子 32 は光透過用開口部 22a を介して第 2 光路用コア層 L2 に光結合されている。

10

#### 【0049】

図 2 (b) の平面図では、下側配線層 24 は太破線で描かれており、第 1 回路素子 40 の周りで省略されている。また、図 2 (a) の配線基板 20 の光透過用開口部 22a、接続用開口部 22b、及び第 1、第 2 光素子 30, 32 の下側のアンダーフィル樹脂 31, 33 が省略されている。

#### 【0050】

第 1、第 2 光素子 30, 32 は、発光素子又は受光素子のいずれかの同一素子である。発光素子としては、面発光レーザ (VCSEL : Vertical Cavity Surface Emitting Laser) が好適に使用される。また、受光素子としては、フォトダイオードが好適に使用される。

20

#### 【0051】

以下では、第 1、第 2 光素子 30, 32 が発光素子からなる形態を例に挙げて説明する。図 2 (a) 及び (b) に示すように、第 1、第 2 光素子 30, 32 が発光素子からなる場合は、第 1、第 2 光素子 30, 32 は下面に複数の発光部 E を備えている。第 1 光素子 30 の発光部 E が第 1 光路用コア層 L1 に設けられた第 1 光路変換ミラー M1 にそれぞれ光結合される。

#### 【0052】

このとき、予備的事項でも説明したように、第 1 光素子 30 の発光部 E の配置ピッチは 250 μm 程度である。このため、一つの第 1 光素子 30 のみを配置する場合は、光導波路 10 のコア層 14 の配置ピッチも 250 μm となり、それよりも狭ピッチにすることは困難である。

30

#### 【0053】

そこで、本実施形態では、第 1 光路用コア層 L1 の間の領域に第 2 光路用コア層 L2 をそれぞれ配置している。そして、第 2 光路用コア層 L2 に設けられた第 2 光路変換ミラー M2 に第 2 光素子 32 の発光部 E が光結合するように第 2 光素子 32 を配置している。

#### 【0054】

このように、第 1 光素子 30 に光結合される第 1 光路用コア層 L1 と、第 2 光素子 32 に光結合される第 2 光路用コア層 L2 とを水平方向に交互に配置している。これにより、得られる光路の配置ピッチを第 1 光素子 30 の発光部 E の配置ピッチの半分に狭小化することができ、光導波路装置の高密度化及び小型化を図ることができる。

40

#### 【0055】

第 1、第 2 光素子 30, 32 が受光素子の場合も、同様に、第 1 光素子 30 の複数の受光部が各第 1 光路用コア層 L1 に光結合されるように、第 1 光素子 30 が配置される。さらに、第 1 光路用コア層 L1 の間の領域に配置された各第 2 光路用コア層 L2 に第 2 光素子 32 の複数の受光部がそれぞれ光結合するように、第 2 光素子 32 が配置される。

#### 【0056】

また、配線基板 20 の上側配線層 26 には第 1 回路素子 40 のバンプ電極 40a が接続されている。第 1 回路素子 40 と配線基板 20 との隙間にアンダーフィル樹脂 41 が充填されている。このようにして、第 1 光素子 30 は配線基板 20 の上側配線層 26 を介して第 1 回路素子 40 に電気的に接続されている。

50

**【0057】**

また、第2回路素子42のバンプ電極42aが配線基板20の接続用開口部22bを介して、その底に配置された下側配線層24に接続されている。第2回路素子42と配線基板20との隙間及び接続用開口部22bにアンダーフィル樹脂43が充填されている。このようにして、第2光素子32は配線基板20の下側配線層24を介して第2回路素子42に電気的に接続されている。

**【0058】**

図2(a)の平面図では、第1、第2回路素子40, 42の下側のアンダーフィル樹脂41, 43、及び基板22の接続用開口部22bが省略されている。

**【0059】**

第1、第2光素子30, 32が発光素子の場合は、第1、第2回路素子40, 42としてドライバ素子が使用される。あるいは、第1、第2光素子30, 32が受光素子の場合は、第1、第2回路素子40, 42としてアンプ素子(TIA: Transimpedance Amplifierなど)が使用される。

**【0060】**

このように、本実施形態の光導波路装置1では、配線基板20はビア導体を備えておらず、第2光素子32と第2回路素子42とは、配線基板20の接続用開口部22bを介して下側配線層24に直接接続されている。

**【0061】**

このため、高速電気伝送時にビア導体での反射などによる伝送損失の発生が抑制され、高速で高品質な信号伝送を実現することができる。

**【0062】**

また、配線基板20の下側、上側配線層24, 26は、めっき法を使用することなく、基板22の両面に形成された厚み精度の高い銅箔などをフォトリソグラフィでパターニングすることにより得られる。このため、下側、上側配線層24, 26の幅や厚みのばらつきが抑えられて寸法精度を向上させることができるので、伝送経路でのインピーダンス整合を得ることができる。

**【0063】**

また、第1、第2光素子30, 32は、第1光路用コア層L1及び第2光路用コア層L2にそれぞれ交互に光結合するように横方向に並んで配置されている。このため、第1、第2光素子30, 32の発光部Eの配置ピッチの半分のピッチの光路を配置することができるので、高密度な光導波路を実現することができる。

**【0064】**

図3(a)には、配線基板20の上側配線層26のレイアウトの一例が平面図で示されている。図3(a)に示すように、上側配線層26は、白パターンで描かれた信号用配線層26aと斜線ハッチングされて描かれたグランド用配線層26bとを備えている。

**【0065】**

図2(a)を加えて参照すると、信号用配線層26a及びグランド用配線層26bの第1接続パッドP1の群に第1光素子30のバンプ電極30aが接続される。また、信号用配線層24a及びグランド用配線層24bの第2接続パッドP2及び第3接続パッドP3の群に第1回路素子40のバンプ電極40aが接続される。

**【0066】**

このようにして、第1光素子30が上側配線層26を介して第1回路素子40に電気的に接続される。

**【0067】**

また、図3(b)には、配線基板20の下側配線層24のレイアウトの一例が平面図で示されている。図3(b)に示すように、下側配線層24は、白パターンで描かれた信号用配線層24aと斜線ハッチングされて描かれたグランド用配線層24bとを備えている。

**【0068】**

10

20

30

40

50

図2(a)を加えて参照すると、信号用配線層24a及びグランド用配線層24bの第1接続パッドPの群に第2光素子32のバンプ電極32aが接続される。また、信号用配線層24a及びグランド用配線層24bの第2接続パッドP2及び第3接続パッドP3の群に第2回路素子42のバンプ電極42aが接続される。

#### 【0069】

このようにして、第2光素子32が下側側配線層24を介して第2回路素子42に電気的に接続される。

#### 【0070】

次に、本実施形態の光導波路装置1の光伝搬について図2(a)を参考しながら説明する。第1、第2光素子30, 32が発光素子の場合は、第1、第2回路素子40, 42がドライバ素子として配置される。そして、第1、第2回路素子40, 42から出力される電気信号が第1、第2光素子30, 32にそれぞれ供給され、それらの発光部Eから下側に光が同時に射出される。10

#### 【0071】

第1、第2光素子30, 32からそれぞれ射出される光は、アンダーフィル樹脂31, 33、第2クラッド層16及びコア層14を透過して第1、第2光路変換ミラーM1, M2にそれぞれ到達する。さらに、第1、第2光路変換ミラーM1, M2で光が反射され、光路が90°変換されてコア層14に入射する。

#### 【0072】

次いで、コア層14に入射した光は、コア層14内で全反射を繰り返して伝播し、別の光路変換ミラーによって他端側の受光素子に入力される。あるいは、コネクタ部が接続される場合は、コア層14を伝搬する光がコネクタ部に連結される外部の光ファイバなどに入射される。20

#### 【0073】

第1、第2光素子30, 32が受光素子の場合は、第1、第2回路素子40, 42がアンプ素子として配置される。この場合は、上記した光経路と逆方向に光伝搬され、受光素子の受光部に光が入射される。さらに、受光素子は光信号を電気信号に変換し、アンプ素子に電気信号が供給される。

#### 【0074】

次に、実施形態の光導波路装置の製造方法について説明する。図4(a)に示すように、まず、基板22の両面に銅箔21が貼付された積層体5を用意する。基板22はポリイミドフィルムなどのフレキシブル材から形成され、その厚みは好適には10~30μmであり、例えば20μm程度である。また、銅箔21の厚みは好適には5μm~20μmであり、例えば9μm程度である。30

#### 【0075】

銅箔21は、その厚みの面内のばらつきが±10%以下に抑えられており、めっき法で形成される銅層よりも厚みの寸法精度が高い。

#### 【0076】

なお、金属層として銅箔21を例示するが、配線層として機能する金属層が両面に均一に形成された基板を用意すればよい。40

#### 【0077】

次いで、図4(b)に示すように、積層体5の両面側に、下側、上側配線層24, 26を得るためのレジストパターン23をフォトリソグラフィに基づいてそれぞれ形成する。

#### 【0078】

さらに、図4(c)に示すように、積層体5の両面側において、レジストパターン23をマスクにして銅箔21をウェットエッチングする。銅箔21のエッチャントとしては、塩化第二銅水溶液、又は塩化第二鉄水溶液などがある。その後に、レジストパターン23が除去される。

#### 【0079】

これにより、基板22の下面に下側配線層24が形成され、上面に上側配線層26が形50

成される。

**【0080】**

続いて、基板22をレーザなどで貫通加工することにより、基板22に第1、第2光素子30,32を光導波路10に光結合させるための光透過用開口部22aを形成する。また同時に、基板22に第2光素子32及び第2回路素子42を接続するための接続用開口部22bを形成する。これにより、配線基板20が得られる。

**【0081】**

次いで、図5(a)に示すように、図4(d)の配線基板20を上下反転させる。さらに、図5(b)に示すように、配線基板20の上に第2クラッド層16を得るための感光性樹脂層(不図示)を形成し、フォトリソグラフィに基づいて露光/現像を行う。その後に、感光性樹脂層を100~140程度の加熱処理によって硬化させる。

10

**【0082】**

これより、配線基板20の下側配線層24側(図5(a)では上側)に第2クラッド層16が形成される。第2クラッド層16の厚みは、例えば10μm~30μm程度である。

。

**【0083】**

感光性樹脂層としては、UV硬化型エポキシ樹脂などが好適に使用される。感光性樹脂層の形成方法としては、半硬化状態(B-ステージ)の感光性樹脂シートを貼付してもよいし、あるいは、液状の感光性樹脂を塗布してもよい。

**【0084】**

後述するコア層14及び第1クラッド層12を形成する工程においても同様な樹脂が好適に使用される。

20

**【0085】**

続いて、図5(c)に示すように、第2クラッド層16の上にコア層を得るための感光性樹脂層(不図示)を形成する。さらに、フォトリソグラフィに基づいて露光/現像を行った後に、感光性樹脂層を100~140程度の加熱処理によって硬化させる。

**【0086】**

これにより、第1クラッド層12の上にコア層14が複数の帯状パターンとして並んで形成される。前述したように、コア層14は、第1光路用コア層L1と、それらの間の領域にそれぞれ配置された第2光路用コア層L2とを備えて形成される。

30

**【0087】**

次いで、図5(d)に示すように、コア層14をレーザで局所的に加工することにより、コア層14の第1光路用コア層L1(図2(b))にV字状の第1溝部14aを形成する。第1溝部14aは光路変換するための第1傾斜面IS1を備えて形成される。

**【0088】**

また同時に、コア層14の第2光路用コア層L2(図2(b))にV字状の第2溝部14bが形成される。第2溝部14bは光路変換するための第2傾斜面IS2を備えて形成される。第1、第2傾斜面IS1, IS2は、配線基板20の表面に対して好適には45°で傾斜して形成される。

**【0089】**

次いで、図6(a)に示すように、マスク蒸着などにより、コア層14の第1、第2傾斜面IS1, IS2(図5(d))に光反射性の金属層を部分的に形成して第1、第2光路変換ミラーM1, M2を得る。光反射性の金属として、金又はアルミニウムなどがある。

40

**【0090】**

第1、第2光路変換ミラーM1, M2の別の形成方法としては、傾斜面に光反射性の金属層が形成された透明な三角柱状の光学部品を未硬化状態のコア層に埋め込んだ後に、コア層を硬化させてもよい。これにより、光学部品の傾斜面の金属層が光路変換ミラーとして機能する。

**【0091】**

10

20

30

40

50

続いて、図6(b)に示すように、第2クラッド層16及びコア層14の上に第1クラッド層12を得るための感光性樹脂層(不図示)を形成し、フォトリソグラフィに基づいて露光／現像を行う。その後に、感光性樹脂層を100～140程度の加熱処理によって硬化させる。

#### 【0092】

これより、コア層14を被覆する第1クラッド層12が第2クラッド層16の上に形成される。第1クラッド層12はコア層14に形成された第1、第2光路変換ミラーM1、M2の段差を埋め込み、その上面が平坦になって形成される。第1クラッド層12の厚みは、コア層14上で例えば10μm～30μm程度になるよう設定される。

#### 【0093】

その後に、図6(c)に示すように、図6(b)の構造体を上下反転させる。そして、第1光素子30のバンプ電極30aを配線基板20の上側配線層26にはんだなどで接続する。また、第2光素子32のバンプ電極32aを配線基板20の接続用開口部22bを介して下側配線層24にはんだなどで接続する。

#### 【0094】

さらに、第1回路素子40のバンプ電極40aを配線基板20の上側配線層26にはんだなどで接続する。また、第2回路素子42のバンプ電極42aを配線基板20の接続用開口部22bを介して下側配線層24にはんだなどで接続する。

#### 【0095】

このようにして、第1光素子30と第1回路素子40とが上側配線層26を介して電気的に接続された構造を得る。また、第2光素子32が接続用開口部22bを介して下側配線層24に接続され、第2光素子32と第2回路素子42とが下側配線層24を介して電気的に接続される構造を得る。

#### 【0096】

第1、第2光素子30、32、及び第1、第2回路素子40、42の下側に充填されるアンダーフィル樹脂31、33、41、43(図2(a))は、各素子を実装するごとに形成してもよいし、一括して形成してもよい。

#### 【0097】

以上により、図2(a)及び(b)の本実施形態の光導波路装置1を製造することができる。

#### 【0098】

なお、前述した製造方法の他に、仮基板上で光導波路を作成した後に、光導波路を仮基板から剥離し、図5(a)の配線基板20の上に接着層で光導波路10を接着してもよい。つまり、配線基板20の上に光導波路10を作り込んで形成してもよいし、配線基板20の上に光導波路10の部品を接着して形成してもよい。

#### 【0099】

本実施形態の光導波路装置の製造方法では、配線基板20の下側、上側配線層24、26は、厚み精度の高い銅箔21がフォトリソグラフィ及びウェットエッティングによってパターニングされて形成される。

#### 【0100】

従って、下側、上側配線層24、26をめっき法に基づいて形成する場合よりも幅や厚みのばらつきを抑えることができるため、伝送経路でのインピーダンス整合を得やすくすることができる。その結果、信号の伝送損失が抑制され、良好な信号伝送特性を得ることができる。

#### 【0101】

次に、図7を参照しながら、本実施形態の光導波路装置1をマザーボードなどの電子基板に接続する例について説明する。図7に示すように、両側に壁部Wを備えて、一端側及び上側が開口されたキャビティCを備えたガラスなどからなる透明ケース60を用意する。そして、透明ケース60のキャビティCに図2(a)の光導波路装置1が配置されている。

10

20

30

40

50

**【0102】**

さらに、透明ケース60の他端側に光接続用のコネクタ部50が設けられている。コネクタ部50に、外部の光ファイバなどが光導波路10に位置合わせされて接続され、光導波路10に光結合するようになっている。

**【0103】**

光導波路装置1の配線基板20は透明ケース60の先端から外部に延びた延在部20aを備えている。配線基板20の延在部20aがフレキシブルコネクタ70に接続されている。フレキシブルコネクタ70は、支持部70aと、可動する蓋部70bとを有する。フレキシブルコネクタ70の支持部70aの上に配線基板20の延在部20aを配置し、蓋部70bを支持部70aに固定することで配線基板20とフレキシブルコネクタ70とが接続される。10

**【0104】**

配線基板20の延在部20aの上側配線層26及び下側配線層24にフレキシブルコネクタ70の第1配線層72及び第2配線層74が接続されている。

**【0105】**

さらに、フレキシブルコネクタ70の第1配線層72及び第2配線層74が電子基板80の配線層82に接続されている。

**【0106】**

このように、本実施形態の光導波路装置1は、透明ケース60に収容された状態で、配線基板20がフレキシブルコネクタ70を介してマザーボードなどの電子基板80に電気的に接続される。20

**【0107】**

ここで、比較例として、前述した図1(a)で説明した予備的事項の光導波路装置をマザーボードなどの電子基板に接続する場合に言及する。図1(a)の光導波路装置では、図示されていないが、基板120にも下側配線層200に接続されるピア導体が接続され、基板120の下面に外部端子としてはんだボールが搭載される。

**【0108】**

そして、図1(a)の光導波路装置のはんだボールが電子基板に電気的に接続される。この比較例では、伝送経路にはんだボールが存在するため、インピーダンス整合をとりづらい構造となり、効率よく信号を伝送することが困難になる。30

**【0109】**

しかしながら、本実施形態の図7の形態の例では、はんだボールを使用することなく銅などからなる配線層同士を接続するため、伝送経路でのインピーダンス整合をとりやすい構造となり、効率よく信号を伝送することができる。

**【0110】**

次に、図8を参照しながら、本実施形態の光導波路装置1をマザーボードなどの電子基板に接続する別の例について説明する。

**【0111】**

図8において図7と異なる点は、図7で光導波路装置1内に配置された第1回路素子40及び第2回路素子42が外部の電子基板80に配置されている。図8においてその他の要素は図7と同一であるので、同一符号を付してその詳しい説明を省略する。40

**【0112】**

第1光素子30は、配線基板20の上側配線層26、フレキシブルコネクタ70の第1配線層72、及び電子基板80の配線層82を介して第1回路素子40のバンプ電極40aに電気的に接続されている。

**【0113】**

また、第2光素子32は、配線基板20の下側配線層24、フレキシブルコネクタ70の第2配線層74、及び電子基板80の配線層82を介して第2回路素子42のバンプ電極40bに電気的に接続される。

**【0114】**

10

20

30

40

50

このように、第1回路素子40及び第2回路素子42がマザーボードなどの外部の電子基板80に配置された形態としてもよい。そして、電子基板80上に配置された第1回路素子40が上側配線層26などを介して配線基板20上の第1光素子30に電気的に接続される。また、電子基板80上に配置された第2回路素子42が下側配線層24などを介して配線基板20上の第2光素子32に電気的に接続される。

#### 【0115】

この形態では、光導波路装置は、第1回路素子40及び第2回路素子42が配置された電子基板80及びフレキシブルコネクタ70を備えて構築される。

#### 【0116】

図8の形態の例においても、はんだボールを使用しないため、伝送経路でのインピーダンス整合をとりやすい構造となり、効率よく信号を伝送することができる。

10

#### 【符号の説明】

#### 【0117】

1...光導波路装置、10...光導波路、12...第1クラッド層、14...コア層、14a, 14b...溝部、16...第2クラッド層、20...配線基板、20a...延在部、22...基板、22a...光透過用開口部、22b...接続用開口部、23...レジストパターン、24...下側配線層、24a, 26a...信号用配線層、24b, 26b...グランド用配線層、26...上側配線層、30...第1光素子、30a, 32a, 40a, 42a...バンプ電極、31, 33, 41, 43...アンダーフィル樹脂、32...第2光素子、40...第1回路素子、42...第2回路素子、50...コネクタ部、60...透明ケース、70...フレキシブルコネクタ、70a...支持部、70b...蓋部、72...第1配線層、74...第2配線層、80...電子基板、82...配線層、C...キャビティ、E...発光部、L1...第1光路用コア層、L2...第2光路用コア層、M1...第1光路変換ミラー、M2...第2光路変換ミラー、P1, P2, P3...接続パッド、IS1, IS2...傾斜面、W...壁部。

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2011-099921(JP,A)

特開2012-128153(JP,A)

米国特許出願公開第2010/0142881(US,A1)

特開平11-135891(JP,A)

特開2009-175418(JP,A)

特開2004-235418(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |                     |

|--------|---------------------|

| G 02 B | 6 / 12 - 6 / 14     |

| G 02 B | 6 / 26 - 6 / 27     |

| G 02 B | 6 / 30 - 6 / 34     |

| G 02 B | 6 / 42 - 6 / 43     |

| H 01 L | 23 / 12 - 23 / 15   |

| H 01 L | 31 / 00 - 31 / 0264 |

| H 01 L | 31 / 08 - 31 / 10   |

| H 01 L | 31 / 18             |

| H 01 L | 33 / 00             |

| H 01 L | 33 / 48 - 33 / 64   |

| H 01 L | 51 / 42             |

| H 01 S | 5 / 00 - 5 / 50     |

| H 01 P | 3 / 00 - 3 / 20     |

| H 05 K | 3 / 46              |