(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5932261号

(P5932261)

(45) 発行日 平成28年6月8日(2016.6.8)

(24) 登録日 平成28年5月13日(2016.5.13)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G06F 12/00 571B

G06F 12/00 550E

請求項の数 7 (全 8 頁)

(21) 出願番号 特願2011-161055 (P2011-161055)

(22) 出願日 平成23年7月22日 (2011.7.22)

(65) 公開番号 特開2012-84123 (P2012-84123A)

(43) 公開日 平成24年4月26日 (2012.4.26)

審査請求日 平成26年7月18日 (2014.7.18)

(31) 優先権主張番号 特願2010-209418 (P2010-209418)

(32) 優先日 平成22年9月17日 (2010.9.17)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 藤原 誠

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 落合 渉

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 滝谷 亮一

最終頁に続く

(54) 【発明の名称】メモリ制御装置、メモリ制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のマスタと省電力状態に遷移可能な複数のメモリとの間に接続されたメモリ制御装置であって、

前記複数のマスタからのメモリアクセス要求を調停し、前記複数のマスタの1つにメモリアクセス要求を許可する調停手段と、

前記複数のメモリのそれぞれが省電力状態にあるか否かを監視する監視手段とを有し、

前記調停手段は、前記監視手段の検出結果に応じて、省電力状態にあるメモリに対するメモリアクセス要求と省電力状態にないメモリに対するメモリアクセス要求が競合する場合、省電力状態にないメモリに対するメモリアクセス要求を優先的に選択している間に、省電力状態にあるメモリに対するメモリアクセス要求が所定回数以上、受け付けられなかった場合に、省電力状態にあるメモリへのメモリアクセス要求を選択対象に含めることを特徴とするメモリ制御装置。

## 【請求項 2】

前記調停手段は、前記監視手段の検出結果に応じて省電力状態にないメモリに対するメモリアクセス要求を候補として、当該候補の中から許可するメモリアクセス要求を選択する請求項1に記載のメモリ制御装置。

## 【請求項 3】

前記調停手段は、前記候補の中に選択すべきメモリアクセス要求がない場合に、省電力状態にあるメモリに対するメモリアクセス要求を候補として、当該候補の中から許可する

10

20

メモリアクセス要求を選択する請求項 2 に記載のメモリ制御装置。

【請求項 4】

前記調停手段は、マスタからのメモリアクセス要求が、省電力状態に投入されているメモリに対するアクセスであった場合に、メモリアクセス要求の優先順位を低くすることを特徴とする請求項 1 に記載のメモリ制御装置。

【請求項 5】

前記調停手段は、省電力状態に投入されているメモリに対するメモリアクセス要求が所定時間以上、受け付けられなかった場合に、省電力状態にあるメモリへのメモリアクセス要求を選択対象に含めることを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載のメモリ制御装置。

10

【請求項 6】

前記複数のマスタからの前記メモリアクセス要求が共通のバスを介して前記調停手段に送信されることを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載のメモリ制御装置

【請求項 7】

複数のマスタと省電力状態に遷移可能な複数のメモリとの間に接続されたメモリ制御装置におけるメモリ制御方法であって、

前記複数のマスタからのメモリアクセスを調停し、前記複数のマスタの 1 つにメモリアクセス要求を許可する調停工程と、

前記複数のメモリのそれぞれが省電力状態にあるか否かを監視する監視工程とを有し、前記調停工程では、前記監視工程の検出結果に応じて、省電力状態にあるメモリに対するメモリアクセス要求と省電力状態にないメモリに対するメモリアクセス要求が競合する場合、省電力状態にないメモリに対するメモリアクセス要求を優先的に選択している間に、省電力状態にあるメモリに対するメモリアクセス要求が所定回数以上、受け付けられなかった場合に、省電力状態にあるメモリへのメモリアクセス要求を選択対象に含めることを特徴とするメモリ制御方法。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は複数のマスタと複数のメモリに接続されたメモリ制御装置に関し、特にメモリアクセスが競合した場合にメモリアクセスの優先順位を制御するメモリ制御装置、メモリ制御方法に関する。

30

【背景技術】

【0002】

近年の L S I はチップ上に C P U 以外にも多数の I P ( i n f o r m a t i o n p r o c e s s o r ) を搭載し高機能化が進んでいる。このようなシステムにおいては、個々の I P が同時にデータ処理を行うため、大容量で高速なメモリを、 L S I と同時にシステム基板上に搭載するシステムも増えている。

【0003】

例えば、 S D R A M デバイスがメモリデバイスとして用いられていたが、昨今ではさらに高速アクセスのために D D R - S D R A M あるいは D D R 2 - S D R A M 、 D D R 3 - S D R A M といった高速なメモリデバイスが複数個用いられることがある。

40

【0004】

一方で、バッテリー駆動を前提とするシステムを中心に、システム全体の消費電力を下げる様々な取り組みが行われている。例えば、メモリデバイスにおいては、低消費電力モードが設けられ、メモリアクセスを行わない場合に、メモリを低消費電力モードに移行させることで、メモリデバイスの消費電力を下げることが可能となっている。

【0005】

メモリ制御装置としては、メモリを低消費電力モードにさせる期間を長くさせるようにメモリアクセスを制御することが省電力のために必要となる。

【0006】

50

例えば特許文献1は、メモリ(スレーブ)の状態を監視してメモリアクセスの優先順位を切替える必要があるが、メモリ(スレーブ)の状態を監視して複数バスマスタの転送要求の優先順位を切替える方法を開示している。特許文献1では、スレーブがバスマスタの転送要求を直ちに処理できる状態にあるかを判断し、直ちに処理できない状態にあると判断されたスレーブに対する転送要求をマスクして、直ちに処理できる状態にあると判断されたスレーブに対する転送要求のなかから転送を受け付ける処理を行っている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平8-153065

10

【発明の概要】

【発明が解決しようとする課題】

【0008】

システム内のスレーブモジュールの一つとしてチップ外部に接続されるDRAM等のメモリ制御装置が存在する。DRAMのメモリ制御装置はバスマスタからのメモリアクセスを接続されるDRAMのプロトコルに変換しメモリアクセスを発行する機能を有する。またメモリ制御装置は外部のDRAMの電力モードを制御する機能を有するものも存在する。外部DRAMの電力モードを制御する機能を有したメモリ制御回路の実装の形態として、システムから明示的に電力モードの指定を受け、パワーダウンやセルフリフレッシュの投入・復帰といった電力モード制御用のコマンドを発行するものがある。

20

【0009】

この場合、システムからの明示的な指定があるため、極め細やかな制御が困難であった。一方で、バスマスタからのメモリアクセスの受け付け状態により、自動的に電力モードの制御を行う機能を有するものもある。すなわち、バスマスタからの転送要求がない場合、メモリを省電力モードに投入し、省電力モードに投入されたメモリに転送要求があると、メモリを省電力モードから通常のメモリアクセスが可能な状態へ復帰させるような機能を有する。

【0010】

従来の調停方法は、スレーブの状態が、直ちに使用できない状態から直ちに使用できる状態へと自動的に切り替わることを前提に行われている。

30

【0011】

このようなメモリ制御装置において、「スレーブがバスマスタの転送要求を直ちに処理できない状態」を「メモリが省電力モードに投入された状態」と置き換えた場合、省電力モードに投入されたメモリへのアクセスがマスクされる。すなわち、省電力モードからの復帰することでメモリアクセス発行可能であるにも関わらず、メモリアクセスがマスクされることとなる。

【0012】

なお、省電力モードに投入されたメモリデバイスへのアクセスがマスクされると、省電力モードにあるメモリは、省電力モード状態にとどまり続けるためメモリ転送が行われない。

40

【0013】

一方、メモリが省電力モードに投入された状態を、スレーブがバスマスタ要求を直ちに処理できる状態とした場合、省電力モードに投入されたメモリデバイスへのメモリアクセスはマスクされない。しかしながら、メモリアクセスの発行順序に依存し、省電力モードに投入される期間が短くなり、省電力効果が少なくなる。

【0014】

以上の問題を鑑みて、本発明は省電力モードを有するメモリ制御回路におけるメモリアクセスと省電力の効率を向上させるメモリ制御装置、メモリ制御方法を提供することを目的とする。

【課題を解決するための手段】

50

## 【0015】

上記課題を解決するために本発明に係るメモリ制御装置は、複数のマスタと省電力状態に遷移可能な複数のメモリとの間に接続されたメモリ制御装置であって、前記複数のマスタからのメモリアクセス要求を調停し、前記複数のマスタの1つにメモリアクセス要求を許可する調停手段と、前記複数のメモリのそれぞれが省電力状態にあるか否かを監視する監視手段とを有し、前記調停手段は、前記監視手段の検出結果に応じて、省電力状態にあるメモリに対するメモリアクセス要求と省電力状態にないメモリに対するメモリアクセス要求が競合する場合、省電力状態にないメモリに対するメモリアクセス要求から優先的に選択している間に、省電力状態にあるメモリに対するメモリアクセス要求が所定回数以上受け付けられなかった場合に、省電力状態にあるメモリへのメモリアクセス要求を選択対象に含めることを特徴とする。

10

## 【発明の効果】

## 【0016】

本発明によれば、省電力モードに投入されたメモリに対するアクセスの処理優先度を下げる、省電力モードの時間を長くすることでシステム全体における消費電力の低減が可能となる。

## 【図面の簡単な説明】

## 【0017】

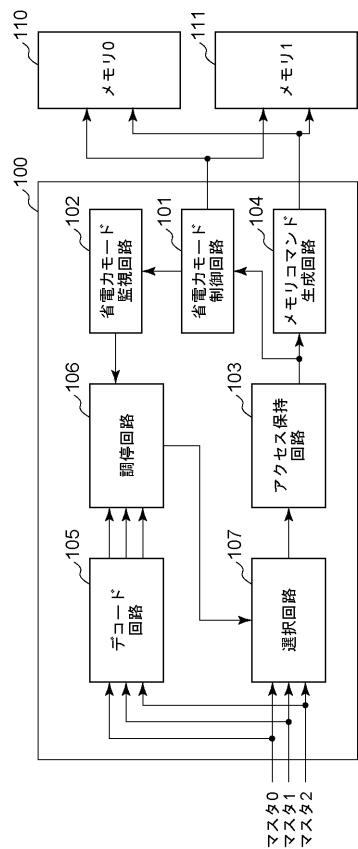

【図1】メモリ制御回路の概略ブロック図である。

20

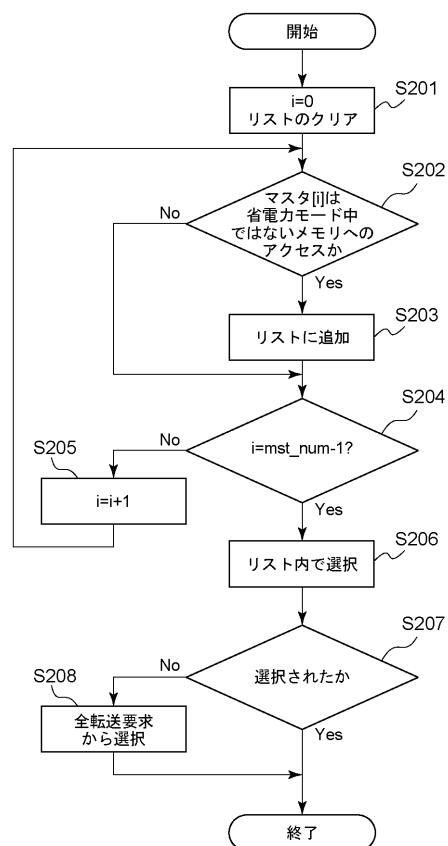

【図2】第1の実施形態における調停回路の制御フロー図である。

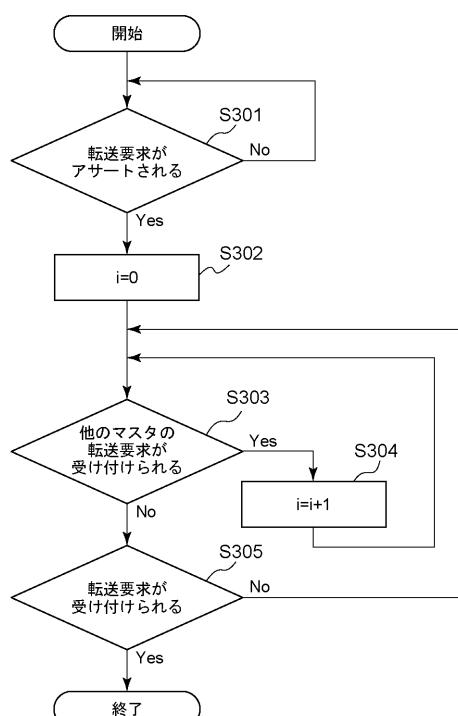

【図3】第2、第3の実施形態におけるカウンタ回路の制御フロー図である。

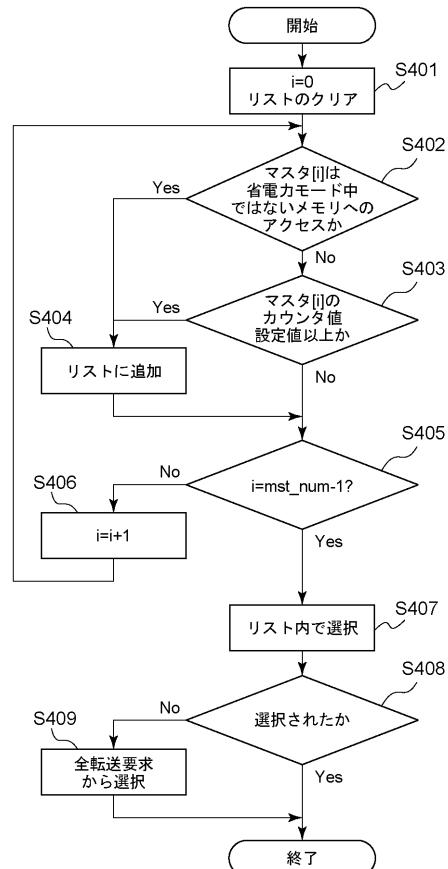

【図4】第2、第3の実施形態における調停回路の制御フロー図である。

## 【発明を実施するための形態】

## 【0018】

(第1の実施形態)

以下、図1、図2に基づき、本発明の一実施形態である第1の実施形態のメモリ制御装置(以下、メモリ制御回路と称す)について説明する。図1は実施形態1のメモリ制御回路の概略構成を示すブロック図である。

## 【0019】

図1において省電力モード(省電力状態)に遷移可能な複数のメモリ110、111がメモリ制御回路100によってアクセスされる構成になっている。省電力モード制御回路101はメモリ110、111に接続されこれらのメモリを省電力モード(省電力状態)へ投入、または解除をする。省電力モード監視回路102は省電力モード制御回路101によりメモリ110、111が省電力モードに投入されているか監視する。アクセス保持回路103はメモリアクセスコマンド(以下、単にアクセス)を複数保持する。

30

## 【0020】

メモリコマンド生成回路104はメモリ110と111に接続されアクセス保持回路103の先頭に登録されているアクセスを取り出し、メモリ110、111(例えば、SDRAM、DDR-SDRAM、DDR2~4-SDRAM)へアクセスするためのコマンドに変換し発行する。デコード回路105は外部からのアクセスがメモリ110、111のどちらに対するものかアドレスをデコードする。調停回路106はデコード回路105のデコード結果と省電力モード監視回路102の情報(検出結果)から複数のメモリアクセス要求のうちアクセスを許可するバスマスター(以下、バスマスターと称す)を決定する。選択回路107は、調停回路106で決定されたアクセスを選択してアクセス保持回路103に登録する。

40

## 【0021】

図2は図1に示す調停回路106がバスマスターからのアクセス要求のどれを選択するかを決定する処理のフローチャートである。調停回路106はバスマスターからの転送要求が発生すると、調停動作を開始する。まず、内部変数iと省電力モードではないメモリに対するアクセス要求を集計するためのリストをクリアする(S201)。

50

## 【0022】

次に、アクセス要求があり、かつ、アクセス要求されているメモリが省電力モードに投入中ではないメモリに対するアクセス要求を発行しているバスマスタについてバスマスタ0から順にバスマスタ番号をリストに登録する(S202)。

## 【0023】

全てのバスマスタのアクセス要求に対するリスト集計作業が終了したら、リストに登録されているバスマスタの中から、アクセスを許可するバスマスタを選択する。バスマスタの選択方法としては、固定優先順位方式や、ラウンドロビン方式など、既存の調停アルゴリズムによる選択を行うことが可能である。

## 【0024】

リストに登録されたバスマスタが選択された場合は、そのまま終了するが、リストにどのバスマスタも登録されない場合は、リスト以外のバスマスタも含めて、再度アクセスを許可するバスマスタを選択する。

## 【0025】

上記動作により、省電力モードに投入されているメモリに対するアクセス要求と、省電力モードに投入されていないメモリに対するアクセス要求が競合した場合に、省電力モードに投入されていないメモリに対するアクセス要求が優先的に選択される。そのため、省電力モードに投入されているメモリに対するアクセス要求が待たされることで、省電力モードに投入されているメモリは、長時間、省電力モードに投入された状態を保持することが可能となる。さらに、省電力モードから復帰したメモリに対してアクセス要求がまとまって実行されるように制御できるので、省電力モードと通常モードとの間を遷移する回数を低減させ、メモリの状態遷移に要する時間と状態遷移によって消費される消費電力を低減することができる。

## 【0026】

また、省電力モードに投入されていないメモリに対するアクセスが終了すると、自動的に省電力モードに投入されているメモリに対するアクセス要求が許可される。この時に、省電力モードから復帰したメモリに対するアクセス要求がまとまって実行されるので、少ししか省電力モードを継続できないような省電力モードへの遷移を抑制し、電力効率の悪化を抑制できる。本実施形態では、バスマスタが3個で、メモリが2個のメモリ制御回路に関して説明したが、メモリが2個以上であれば本発明を適用して省電力効果を向上できる。なお、調停回路106のリストは調停回路106内の不図示の記憶部にて保持される。

## 【0027】

(第2の実施形態)

第1の実施形態では省電力モードではないメモリに対するアクセス要求は必ず省電力モードのメモリに対するアクセス要求よりも優先して選択されるものである。ここで、省電力モードではないメモリに対するアクセス要求が連続であります。省電力モードであるメモリに対するアクセスが長時間待たされることで省電力モードのメモリにアクセス要求を行ったバスマスタの性能が低下することが考えられる。

## 【0028】

上記を考慮し、省電力モードのメモリに対するアクセスが優先されない回数の上限を設けてもよい。本実施形態では、調停回路106はバスマスタごとのカウンタ(不図示)を持ち、転送要求がありながら他のバスマスタが選択された回数をカウントする。カウント値が所定回数に達すると、省電力モードであるバスマスタへのアクセス要求であっても、前記リストに追加する。

## 【0029】

図3に転送要求が発行されてから他のバスマスタが選択された回数をカウントするカウンタの動作を示す。カウンタはバスマスタからのメモリアクセス(転送要求)がアサートされるまでウェイトし(S301)、転送要求のアサートに応じてカウント値iをクリアする、そして、他のバスマスタからの転送要求が受け付けられる毎にカウントし(S30

10

20

30

40

50

3、S304)、当初の転送要求が受け付けられると、カウントを終了する(S305)。このカウンタをバスマスターごとに設ける。

【0030】

図4は図1に示す調停回路106が、図3で示したカウンタの値を用いて、図2のフローチャートにバスマスターからのアクセス要求のどれを選択するかを決定する処理(S403)を追加したフローチャートである。図4のフローにより所定回数以上許可されなかつた省電力モードのメモリに対するアクセス要求は、省電力モードではないメモリに対するアクセスと同様に扱う。

【0031】

(第3の実施形態)

10

第2の実施形態では許可されなかつた回数を考慮したが、本実施形態では省電力モードのメモリに対するアクセスが優先されない時間の上限を用いる。例えば、調停回路106はバスマスターごとのカウンタを持ち、転送要求が開始されてからの時間をカウントする。カウント値が一定時間に達すると、省電力モードであるバスマスターへのアクセス要求であつても、前記リストに追加する。

【0032】

転送要求が発行されてからの時間をカウントするカウンタの動作を示すフローチャートは図3と同様である。この転送要求が発行されてからの時間をカウントするカウンタをバスマスターごとに設ける。図4は図1に示す調停回路106が、図3で示したカウンタの値を用いて、バスマスターからのアクセス要求のどれを選択するかを決定する処理を示すフローチャートである。図4のフローにより転送要求発行後、所定時間以上経過した省電力モードのメモリに対するアクセス要求は、省電力モードではないメモリに対するアクセスと同様に扱われる。

20

【0033】

以上、上述の実施形態によって省電力モードではないメモリに対するメモリアクセスを優先的にアクセス保持回路103に保持される。

【0034】

なお、上述の実施形態の説明では調停回路106が選択するバスマスターの候補をリストとして調停回路106が保持していたが、リスト形式で保持しなくても、単にバスマスターのID(識別情報)を保持するだけでもよい。なお、上述した複数の実施形態の方法を併用して用いることで、更に細かく複数のメモリアクセスを優先度順に並べることができる。

30

【符号の説明】

【0035】

- 100 メモリ制御回路

- 101 省電力モード制御回路

- 102 省電力モード監視回路

- 103 アクセス保持回路

- 104 メモリコマンド生成回路

- 105 デコード回路

- 106 調停回路

- 106 選択回路

- 110 メモリ0

- 111 メモリ1

40

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(56)参考文献 国際公開第2011/130548(WO, A1)

米国特許出願公開第2008/0040562(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12/00