## (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

23 May 2019 (23.05.2019)

(10) International Publication Number

WO 2019/097346 A1

(51) International Patent Classification:

G06F 15/82 (2006.01)

Road, MS P386, Poughkeepsie, NY 12601 (US). **SALAPURA, Valentina**; IBM Corporation, PO Box 218, 1101 Kitchawan Road, Yorktown Heights, New York 10598 (US).

(21) International Application Number:

PCT/IB2018/058618

(74) Agent: **GASCOYNE, Belinda**; IBM United Kingdom Limited, Intellectual Property Law, Hursley Park, Winchester Hampshire SO21 2JN (GB).

(22) International Filing Date:

02 November 2018 (02.11.2018)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

15/811,982 14 November 2017 (14.11.2017) US

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(71) Applicant: **INTERNATIONAL BUSINESS MACHINES CORPORATION** [US/US]; New Orchard Road, Armonk, New York 10504 (US).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV,

(71) Applicants (for MG only): **IBM UNITED KINGDOM LIMITED** [GB/GB]; PO Box 41, North Harbour, Portsmouth Hampshire PO6 3AU (GB). **IBM (CHINA) INVESTMENT COMPANY LIMITED** [CN/CN]; 25/F, Pangu Plaza, No.27, Central North 4th Ring Road, Chaoyang District, Beijing 100101 (CN).(72) Inventors: **GSCHWIND, Michael, Karl**; IBM Corporation, Intellectual Property Law Department, 2455 South

(54) Title: BULK STORE AND LOAD OPERATIONS OF CONFIGURATION STATE REGISTERS

FIG. 2

(57) Abstract: Bulk store and load operations of configuration state registers. An instruction to perform a bulk operation for a group of configuration state registers having a common characteristic is executed. To perform the bulk operation for the group of configuration state registers, a plurality of operations is performed, and based on performing the plurality of operations, the instruction is completed.

---

MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM,

TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW,

KM, ML, MR, NE, SN, TD, TG).

**Published:**

— *with international search report (Art. 21(3))*

## BULK STORE AND LOAD OPERATIONS OF CONFIGURATION STATE REGISTERS

### BACKGROUND

**[0001]** One or more aspects relate, in general, to processing within a computing environment, and in particular, to facilitating such processing.

**[0002]** Computers of a computing environment include central processing units (CPUs) or processors that control processing within the computers. Behavior of a central processing unit is controlled by control registers. Control registers are processor registers that perform particular tasks, such as interrupt control, switching the addressing mode, paging control and/or coprocessor control, as examples.

**[0003]** Control registers are typically implemented as latches, such as solid state elements directly on a processor chip. Some computers use a large number of control registers, as defined by the architectural implementation of the computers. Thus, control registers represent a growing area of the chip.

**[0004]** Moreover, some computers support multi-threading in which a central processing unit can execute multiple processes or threads concurrently. Each thread uses a separate set of control registers; thereby, increasing the number of control registers on a chip.

**[0005]** An increasing number of latch-based control registers may affect performance, chip area and/or power consumption. For instance, control registers are switched during context switches, and thus, an increase in the number of control registers, increases the cost of context switching. Further, with latch-based control registers, updates to controls occur in program order, which may also affect performance.

**[0006]** Different architectures may have different names for control registers. For instance, in the Power Architecture offered by International Business Machines Corporation, Armonk, New York, the control registers are referred to as special purpose register (SPRs). Other architectures may use other names. The use of control registers herein includes control registers of other names, including, for instance, SPRs, as well as others.

### SUMMARY

**[0007]** Shortcomings of the prior art are overcome and additional advantages are provided through the provision of a computer program product for facilitating processing within a computing environment. The computer program product includes a computer readable storage medium readable by a processing circuit and storing instructions for performing a method. The method includes, for instance, executing an instruction to perform a bulk operation for a group of configuration state registers having a common characteristic. Based on executing the instruction, a plurality of operations is performed to perform the bulk operation. Based on performing the plurality of operations, the instruction is completed. By performing particular operations in bulk for a group of configuration state registers processing is facilitated and performance is improved.

**[0008]** As one example, the instruction includes a store configuration state register instruction, and the plurality of operations includes a load operation to load contents of a configuration state register of the plurality of configuration state registers into a register, and a store operation to store the contents of the register to memory. In one embodiment, the plurality of operations includes the load operation and the store operation for each configuration state register of the group of configuration state registers of the bulk operation.

**[0009]** Further, in one embodiment, the group of configuration state registers are in-processor registers, and based on execution of the instruction, contents of the in-processor registers are stored in memory via a bulk store operation. The use of such a bulk store operation provides efficiencies in storing, thereby improving performance.

**[0010]** As a further example, the instruction includes a load configuration state register instruction, and the plurality of operations includes a load operation to load contents of a configuration state register of the group of configuration state registers from memory into a register, and a store register operation to store the contents of the register to an in-processor register. In one example, the plurality of operations includes the load operation and the store operation for each configuration state register of the group of configuration state registers of the bulk operation.

**[0011]** Further, in one embodiment, the group of configuration state registers are in-memory registers, and based on execution of the instruction, contents of the in-memory registers are stored in processor via a bulk load operation.

**[0012]** In one example, the completing includes completing the instruction in-order.

**[0013]** Further, in one embodiment, based on executing the instruction, an in-order point of processing is reached, and based on reaching the in-order point of processing, the performing is performed. In one example, the reaching the in-order point of processing and the completing the instruction are performed a single time for the bulk operation.

**[0014]** In a one aspect, the plurality of operations are performed absent a page fault. Further, in one example, the common characteristic is selected from a group of common characteristics consisting of: a numeric range of registers; having a same access permission; having a same functional purpose; and having a particular implementation property.

**[0015]** Computer-implemented methods and systems relating to one or more aspects are also described and claimed herein. Further, services relating to one or more aspects are also described and may be claimed herein.

**[0016]** Additional features and advantages are realized through the techniques described herein. Other embodiments and aspects are described in detail herein and are considered a part of the claimed aspects.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0017] One or more aspects are particularly pointed out and distinctly claimed as examples in the claims at the conclusion of the specification. The foregoing and objects, features, and advantages of one or more aspects are apparent from the following detailed description taken in conjunction with the accompanying drawings in which:

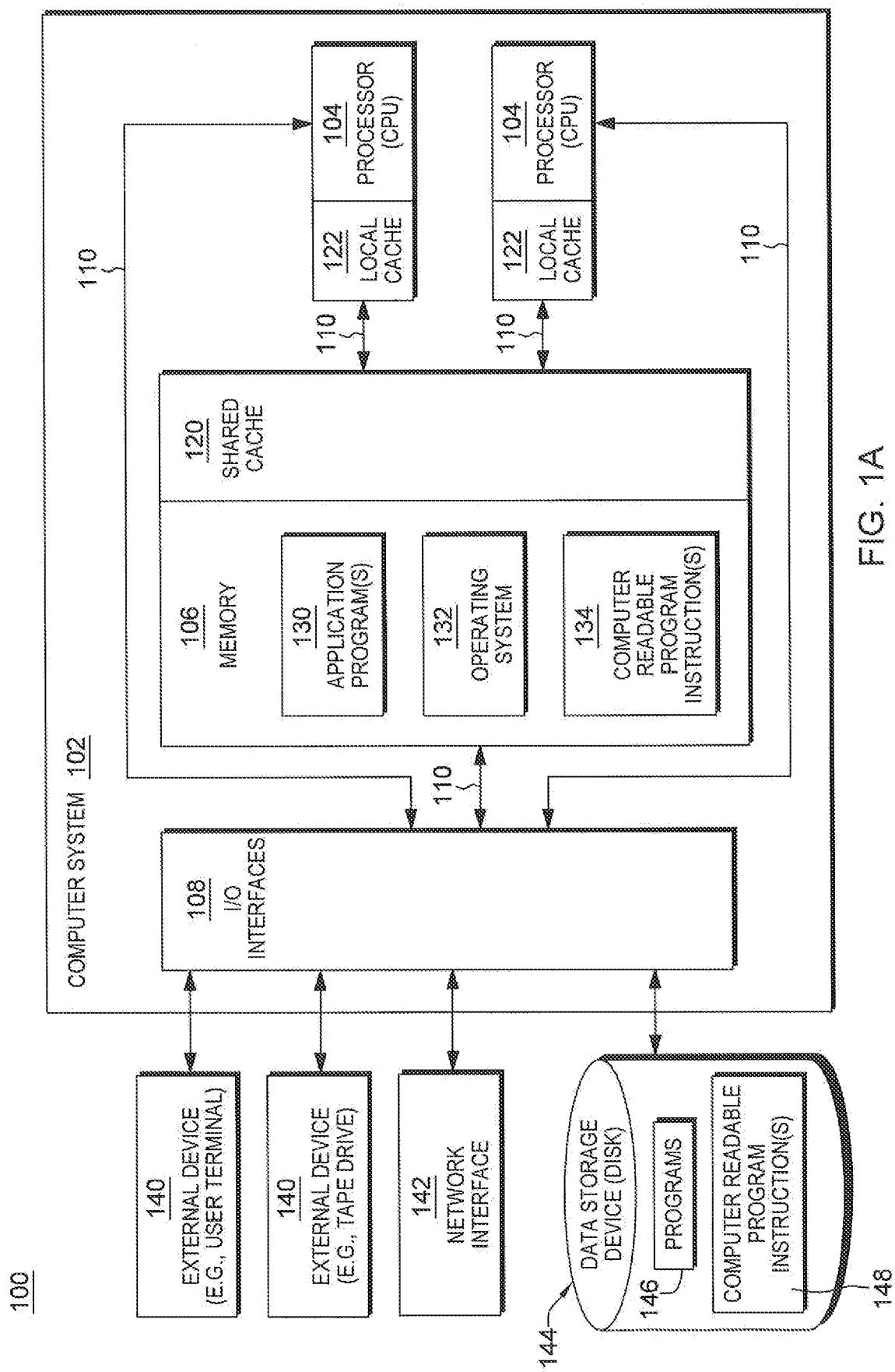

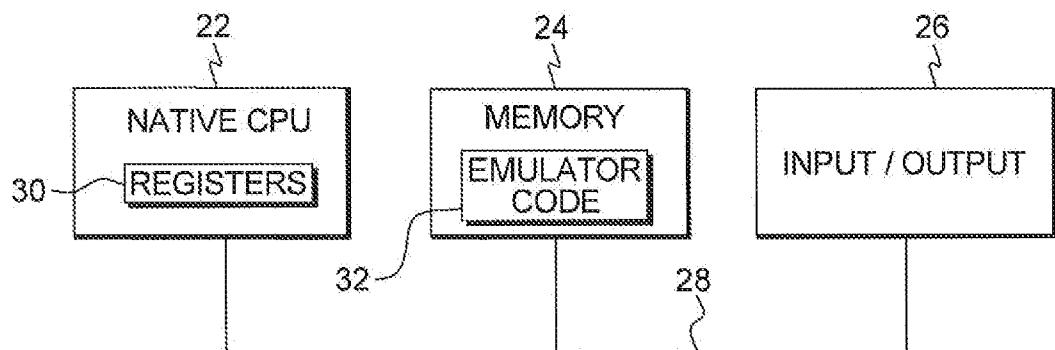

FIG. 1A depicts one example of a computing environment to incorporate and use one or more aspects of the present invention;

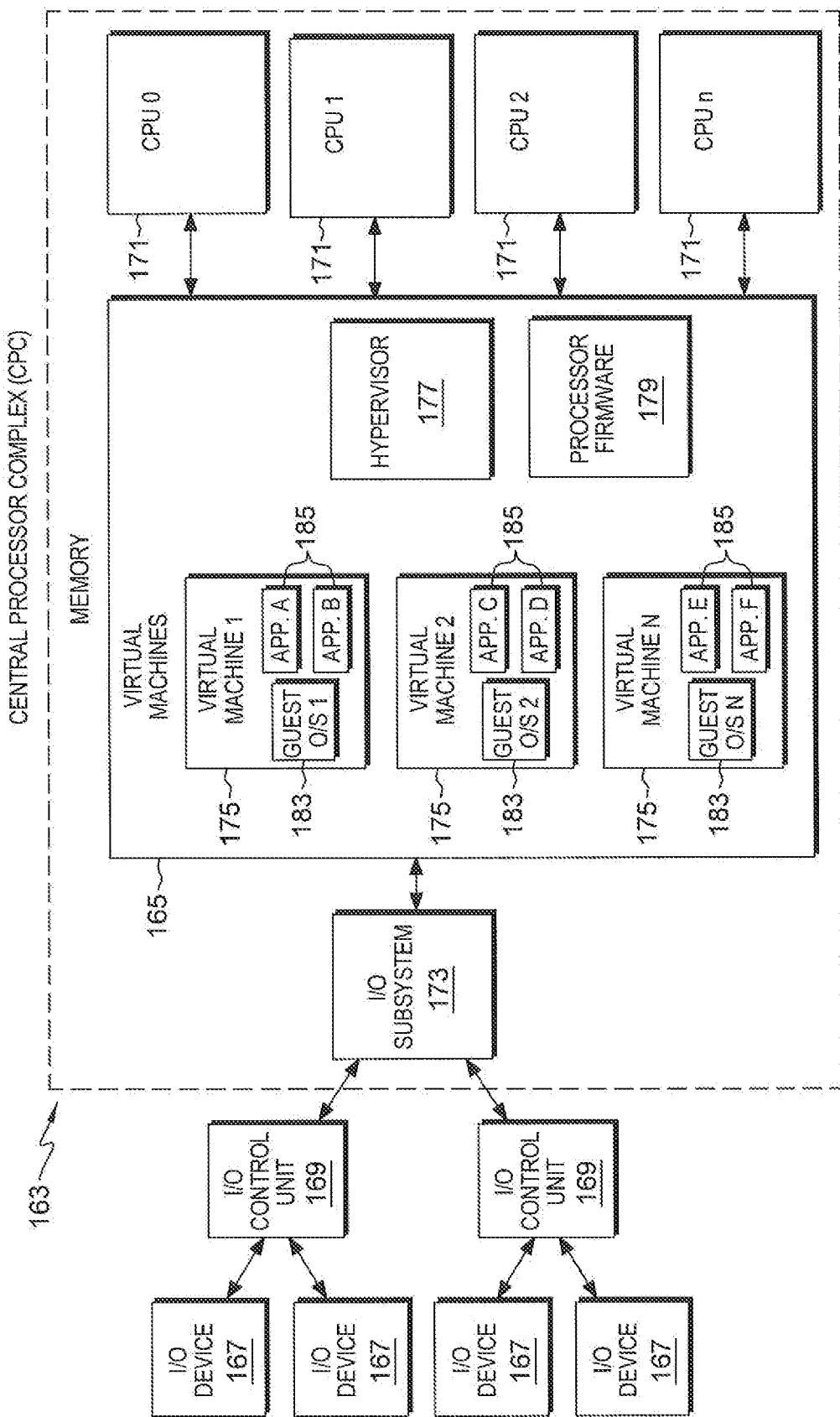

FIG. 1B depicts another example of a computing environment to incorporate and use one or more aspects of the present invention;

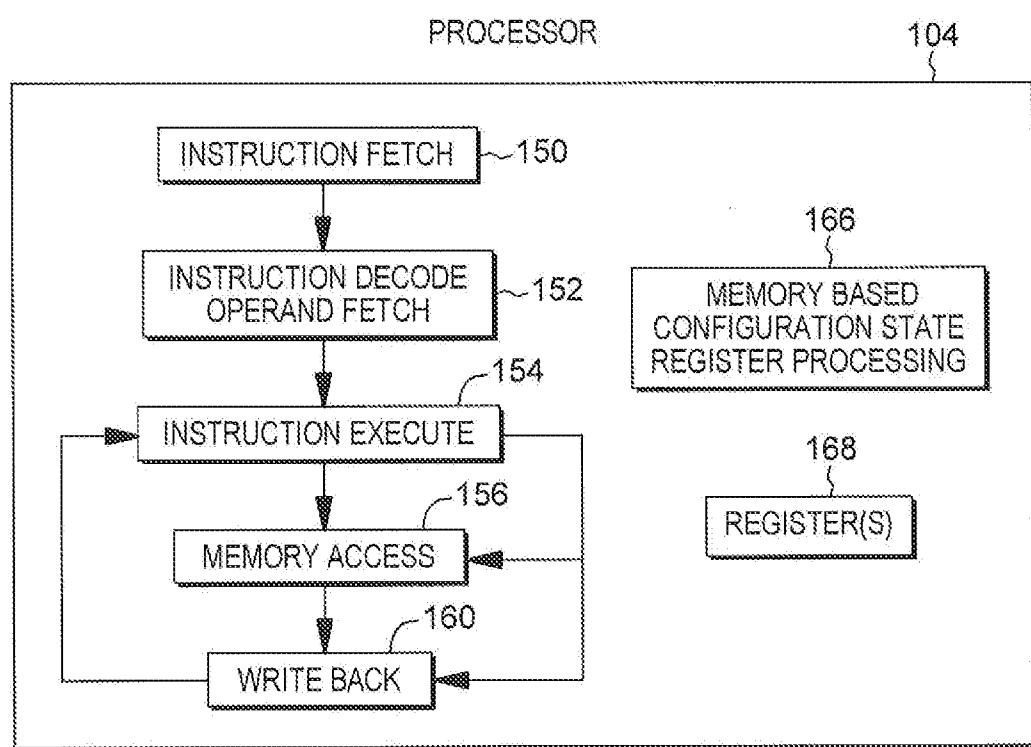

FIG. 1C depicts further details of a processor of FIG. 1A or FIG. 1B, in accordance with one or more aspects of the present invention;

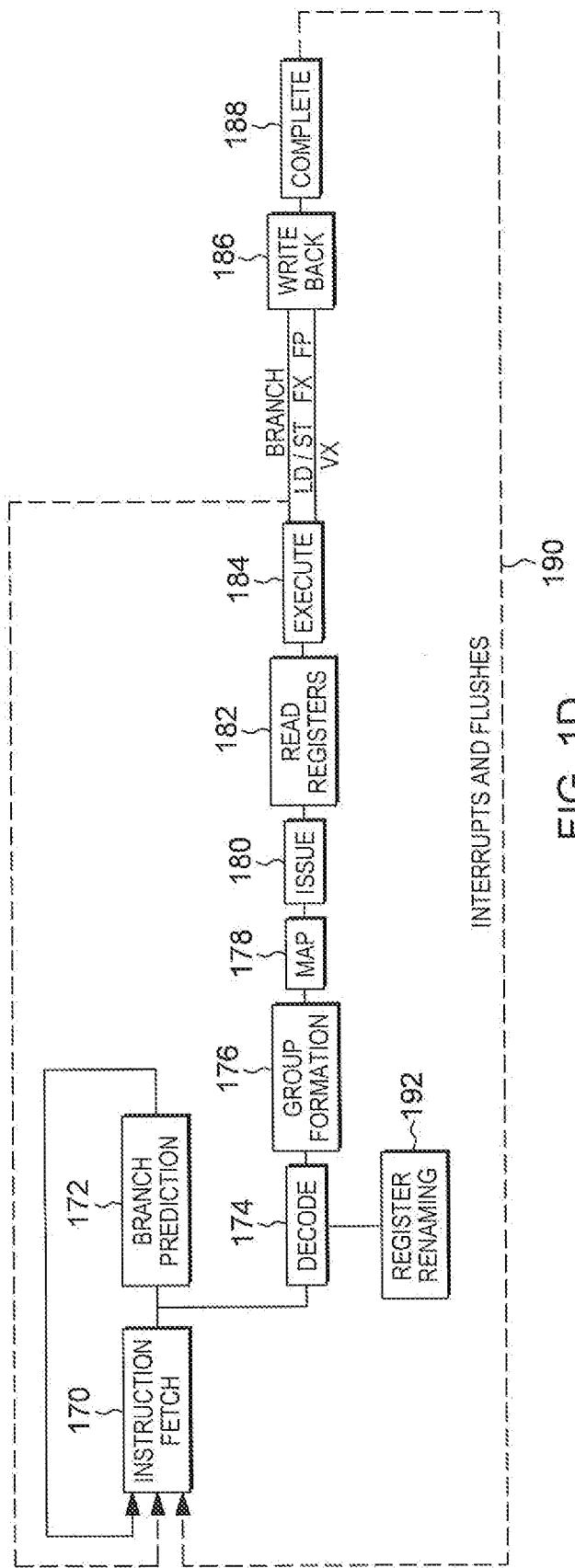

FIG. 1D depicts further details of one example of an instruction execution pipeline used in accordance with one or more aspects of the present invention;

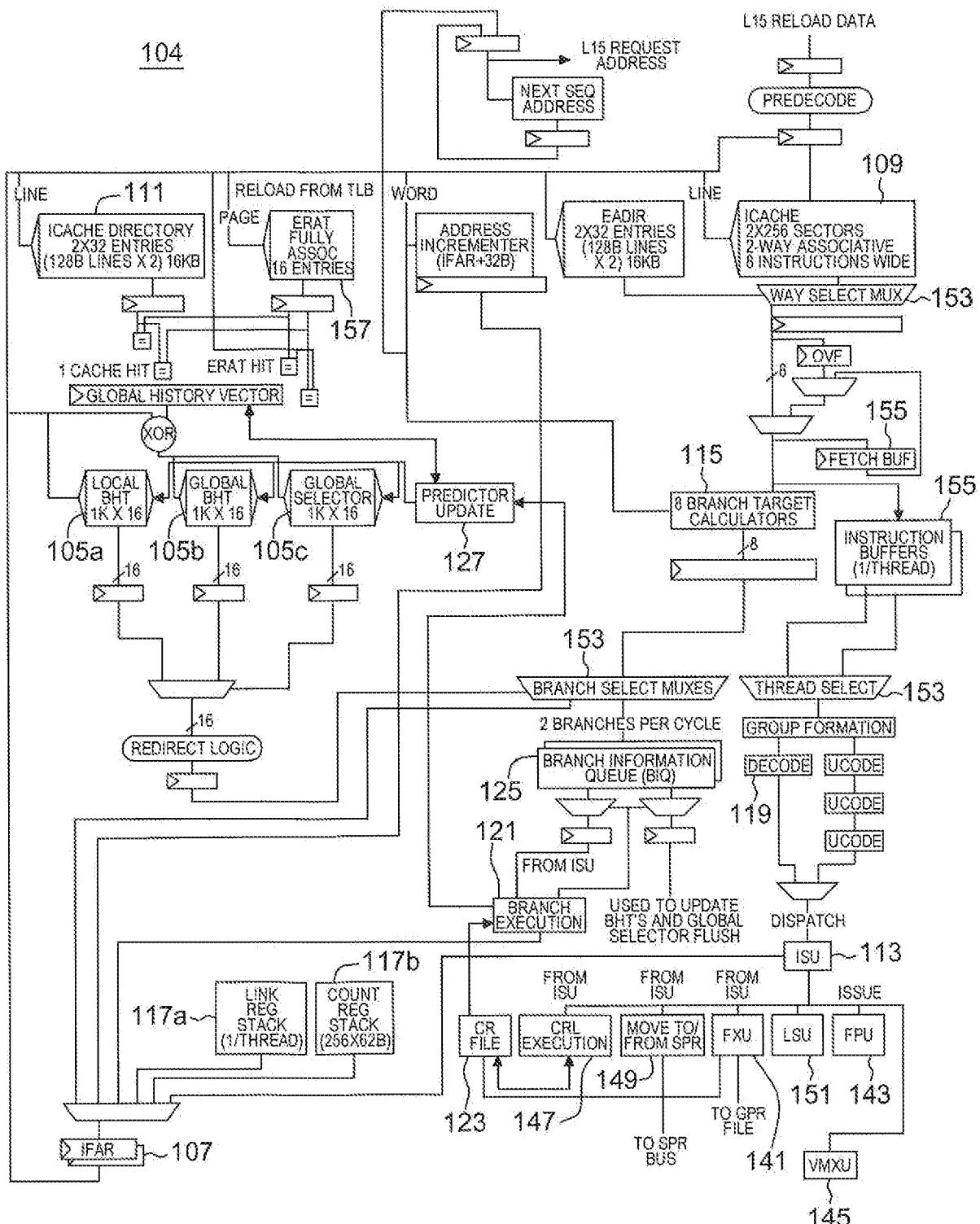

FIG. 1E depicts further details of one example of a processor, in accordance with an aspect of the present invention;

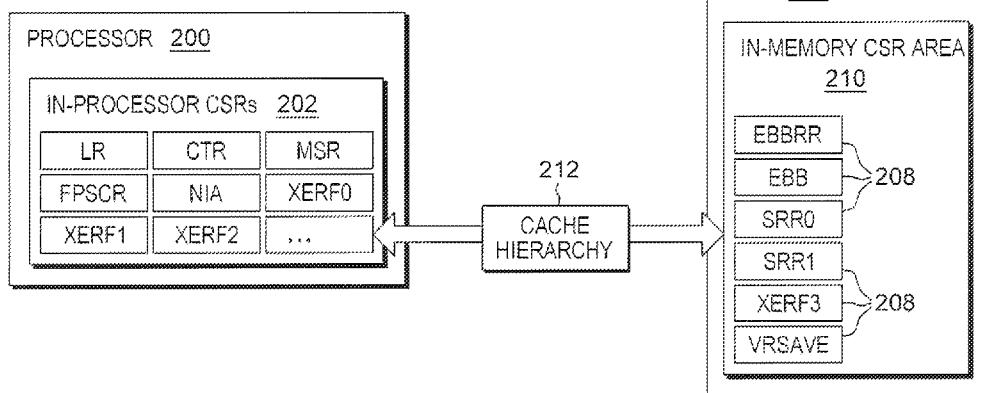

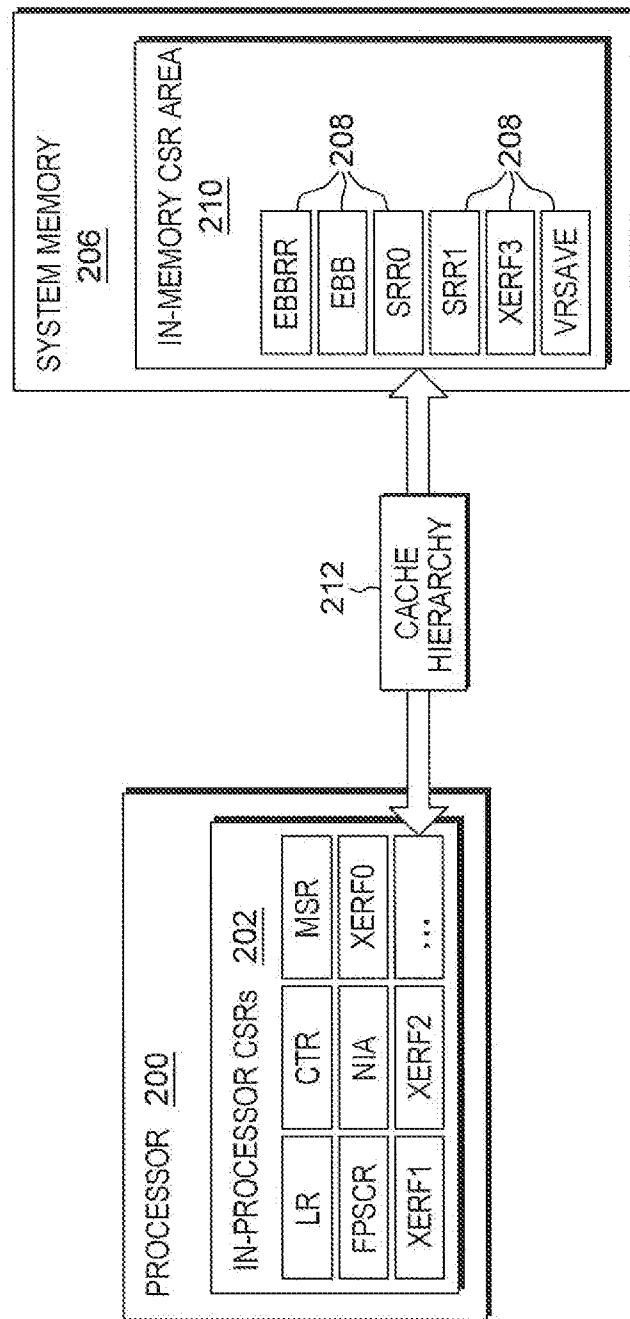

FIG. 2 depicts one example of in-processor configuration state registers and in-memory configuration state registers, in accordance with an aspect of the present invention;

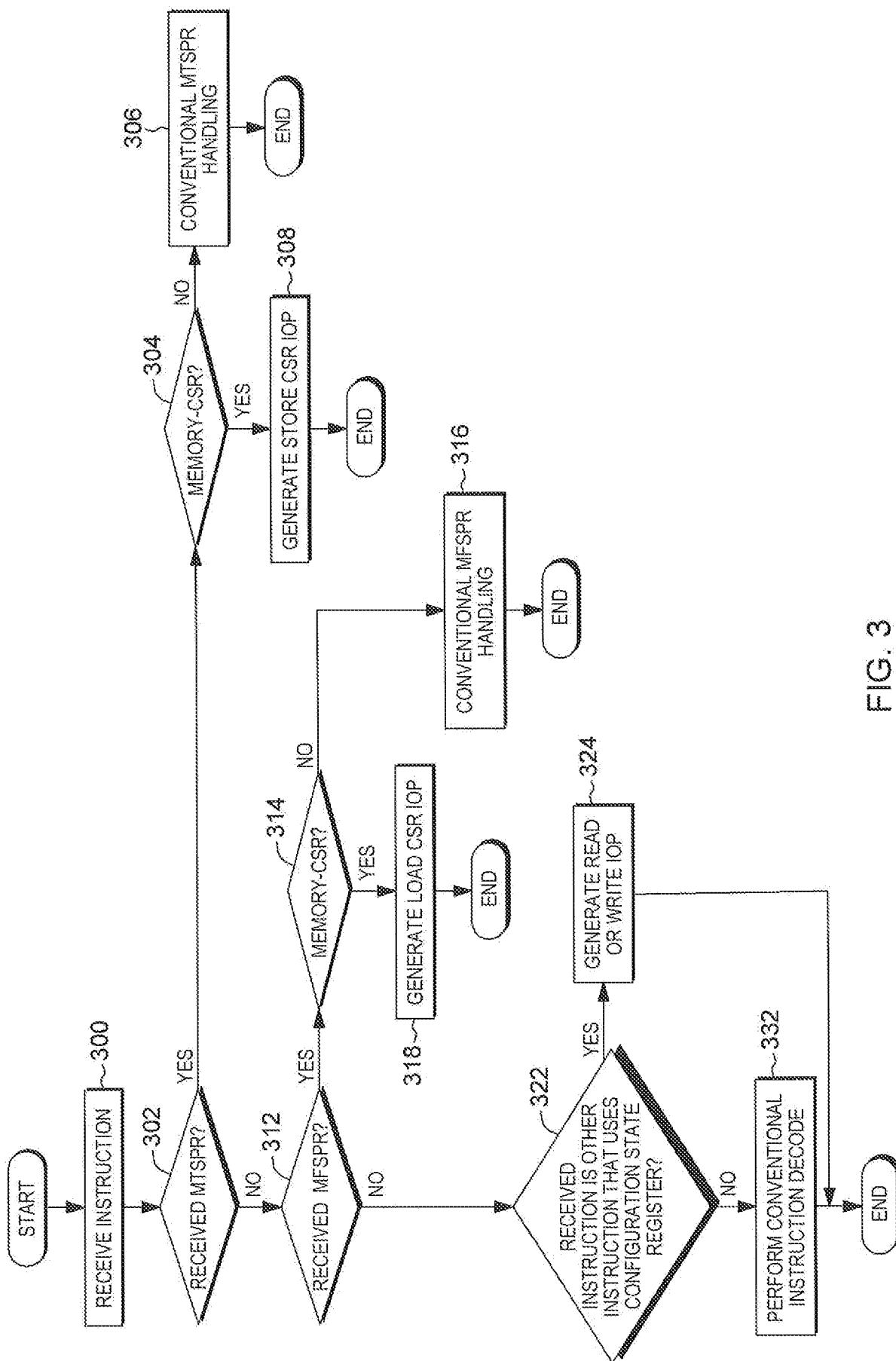

FIG. 3 depicts one example of decode logic associated with using in-memory configuration state registers, in accordance with an aspect of the present invention;

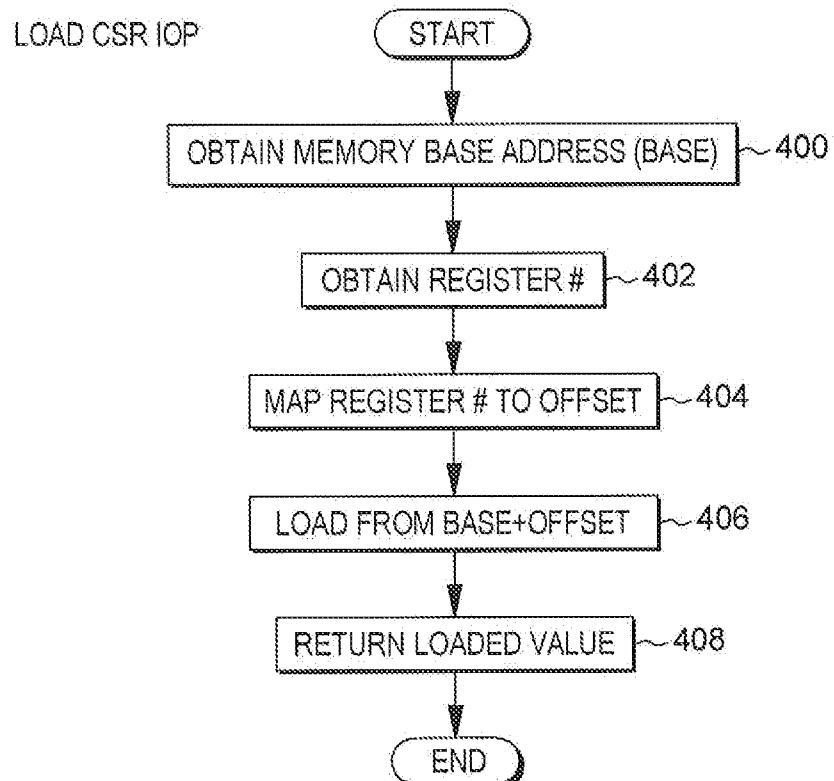

FIG. 4 depicts one example of a load configuration state register internal operation, in accordance with an aspect of the present invention;

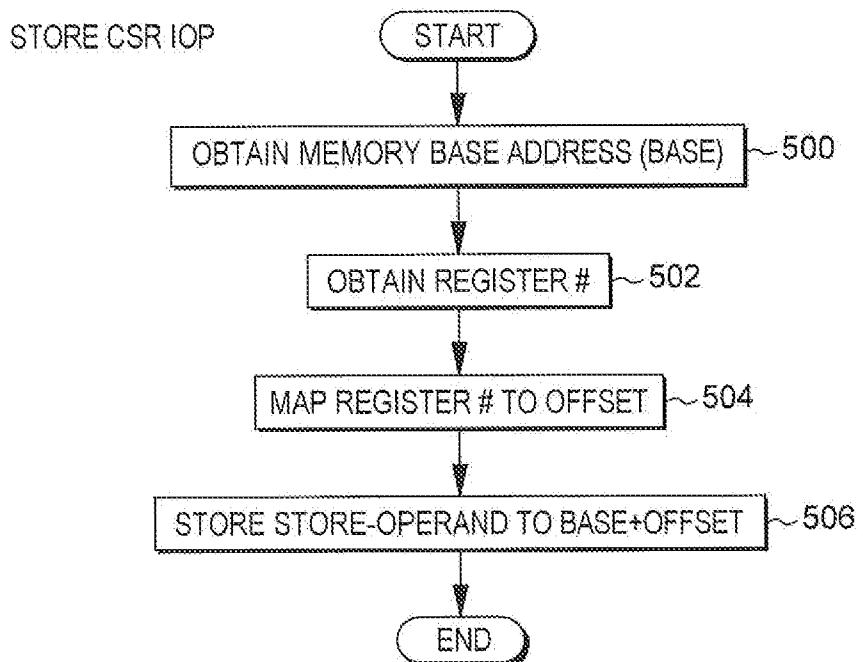

FIG. 5 depicts one example of a store configuration state register internal operation, in accordance with an aspect of the present invention;

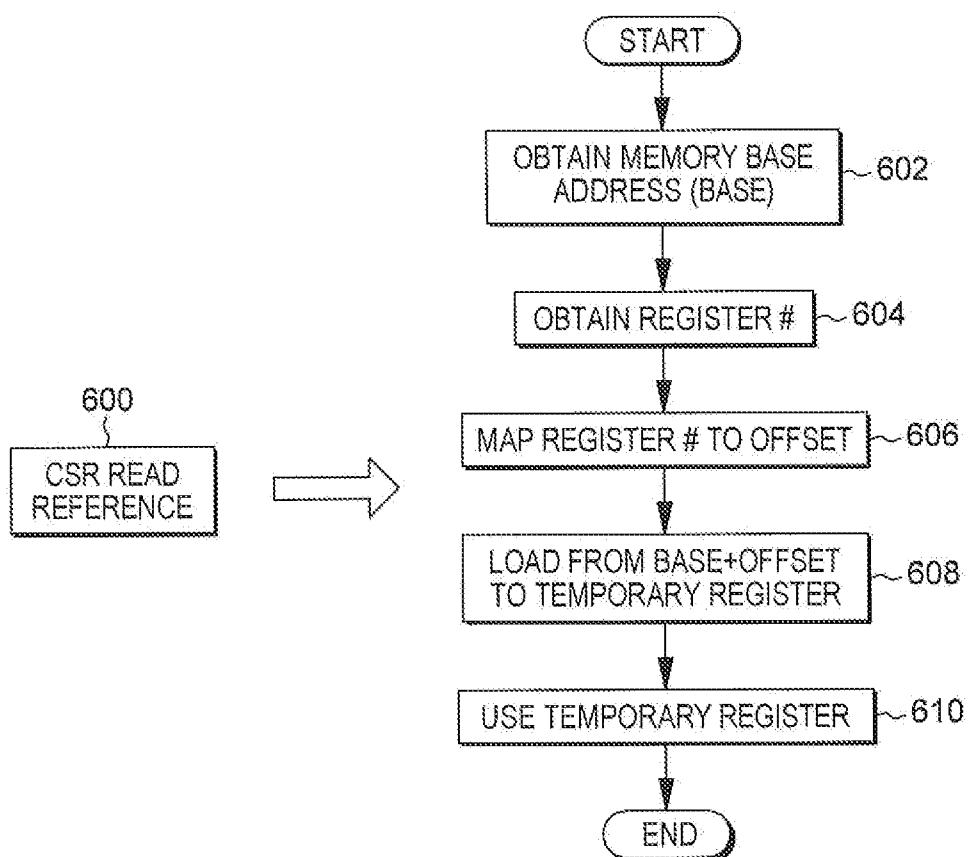

FIG. 6 depicts one example of using an in-memory configuration state register, in accordance with an aspect of the present invention;

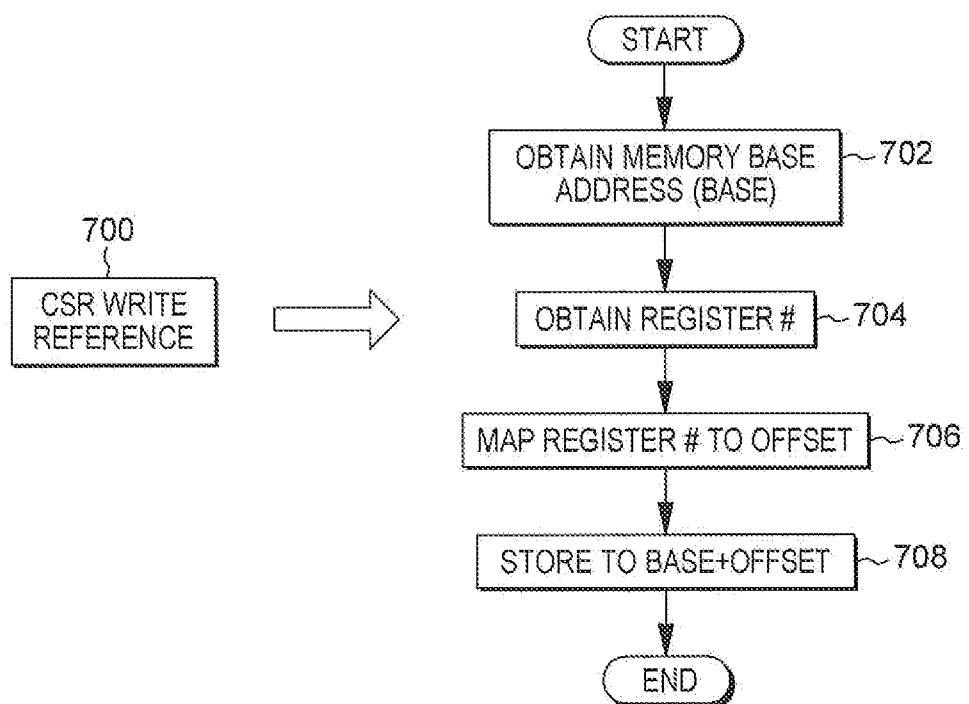

FIG. 7 depicts another example of using an in-memory configuration state register, in accordance with an aspect of the present invention;

FIG. 8 depicts one example of a configuration state register write operation, in accordance with an aspect of the present invention;

FIG. 9 depicts one example of a configuration state register read operation, in accordance with an aspect of the present invention;

FIG. 10 depicts one embodiment of decode logic associated with a move to or a move from configuration state register, in accordance with an aspect of the present invention;

FIG. 11 depicts further details associated with a move to configuration state register instruction, in accordance with an aspect of the present invention;

FIG. 12 depicts further details of a move from configuration state register instruction, in accordance with an aspect of the present invention;

FIG. 13A depicts one embodiment of logic associated with a composite configuration state register read reference, in accordance with an aspect of the present invention;

FIG. 13B depicts one embodiment of logic associated with a composite configuration state register write reference, in accordance with an aspect of the present invention;

FIG. 14 depicts one example of a composite configuration state register, in accordance with an aspect of the present invention;

FIGS. 15A-15B depict one example of linear mapping of configuration state registers, in accordance with an aspect of the present invention;

FIG. 16 depicts one example of remap flow logic for configuration state registers, in accordance with an aspect of the present invention;

FIG. 17A depicts one example of multiple configuration state register store operations;

FIG. 17B depicts one example of a bulk store configuration state register operation, in accordance with an aspect of the present invention;

FIG. 17C depicts one example of a bulk load configuration state register operation, in accordance with an aspect of the present invention;

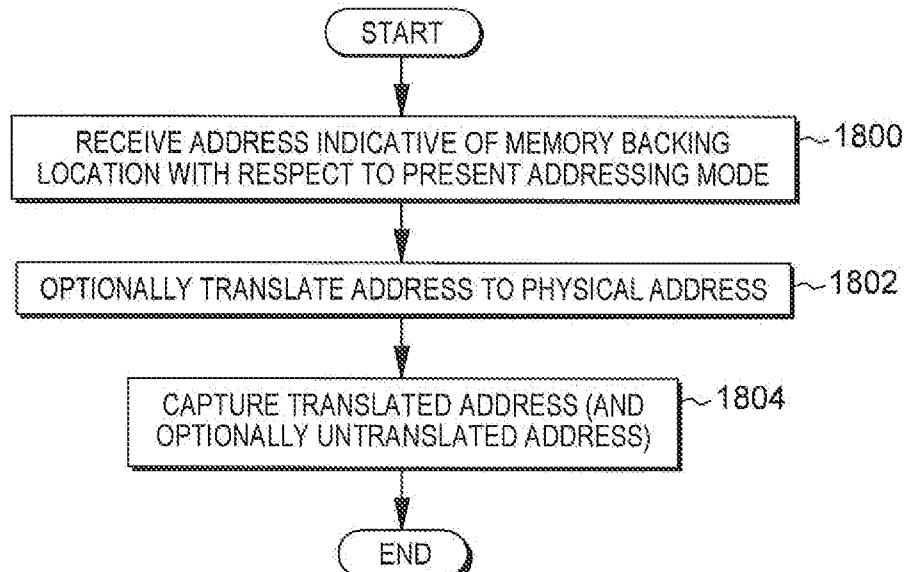

FIG. 18A depicts one example of specifying an architectural configuration control, in accordance with an aspect of the present invention;

FIG. 18B depicts another example of specifying an architectural configuration control, in accordance with an aspect of the present invention;

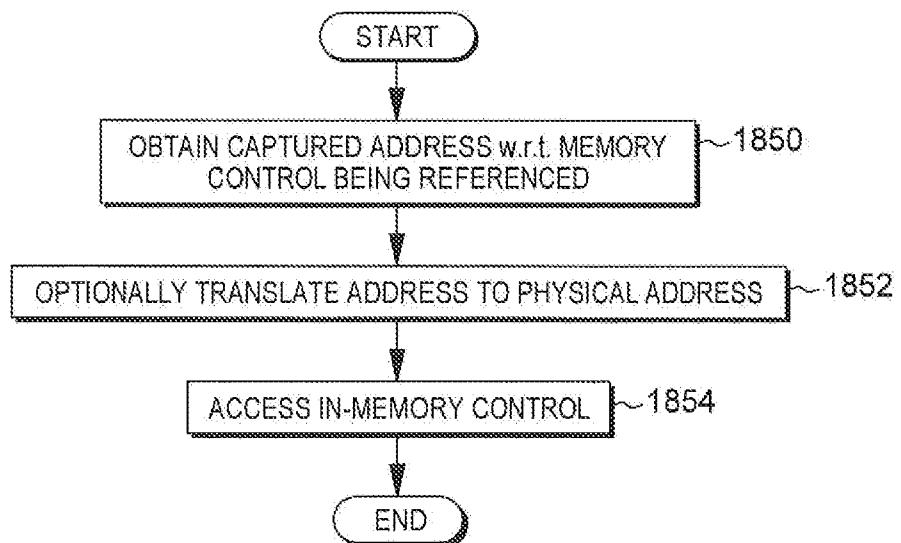

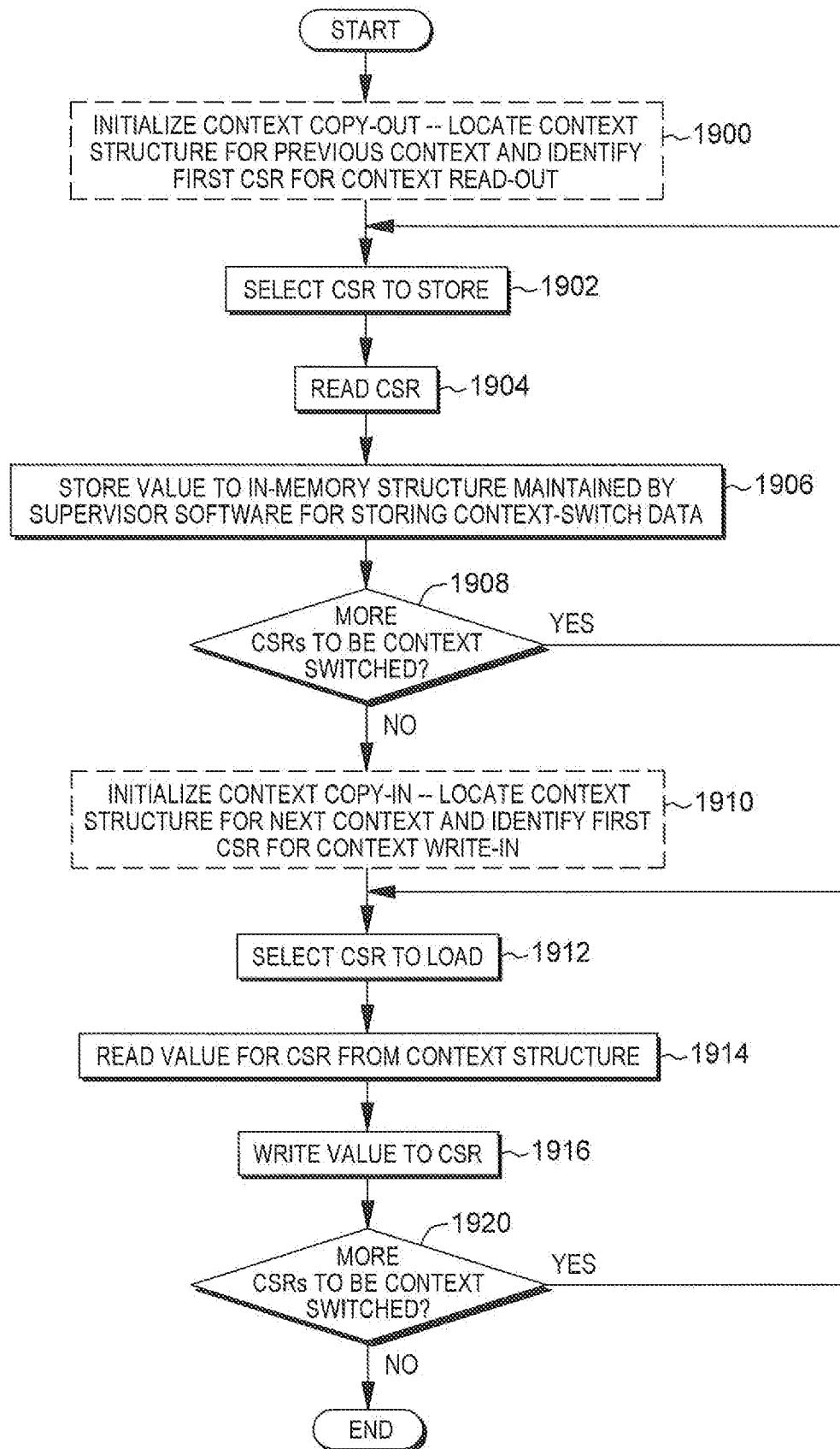

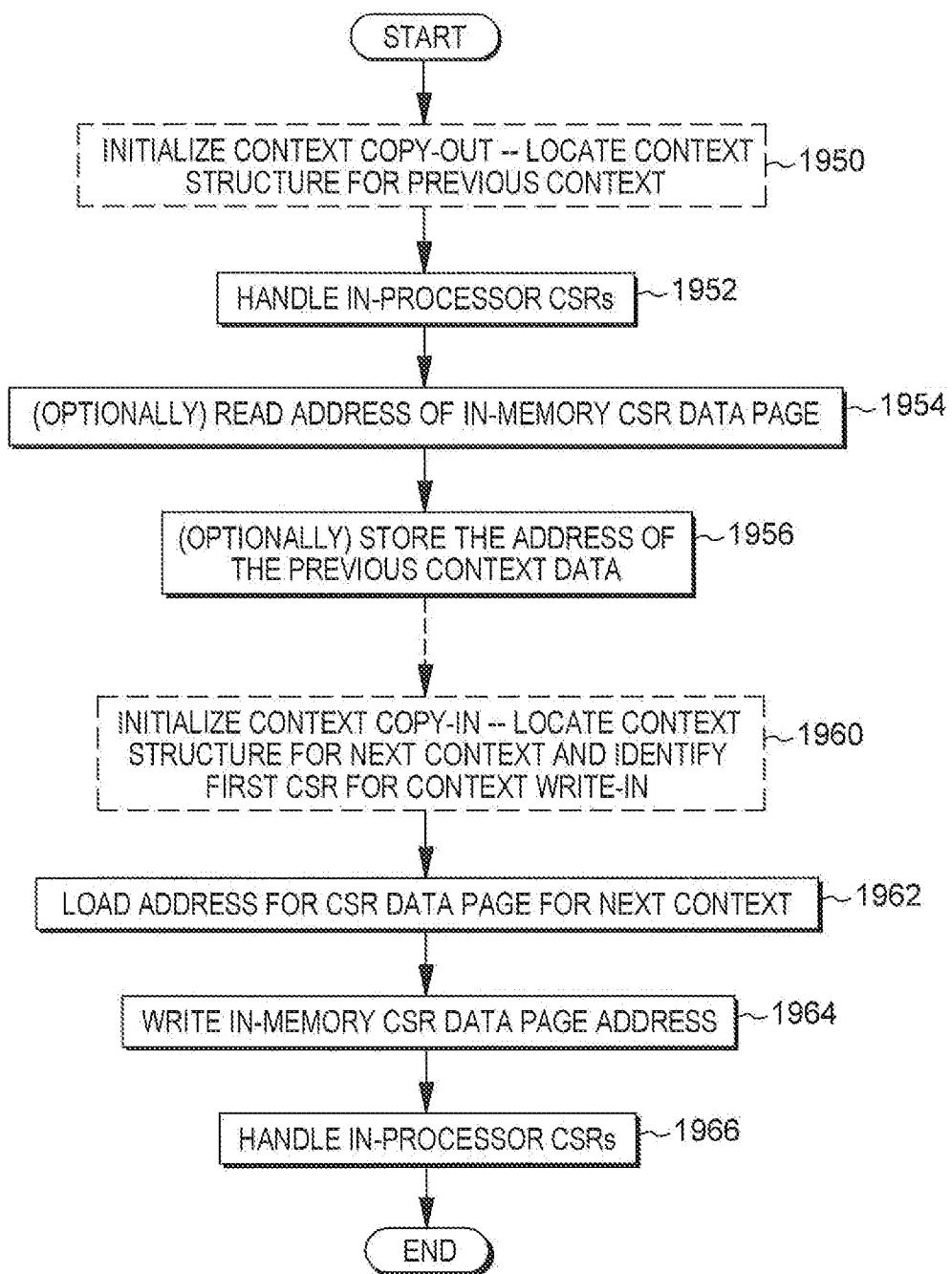

FIG. 19A depicts one example of performing a context switch, in accordance with an aspect of the present invention;

FIG. 19B depicts another example of performing a context switch, in accordance with an aspect of the present invention;

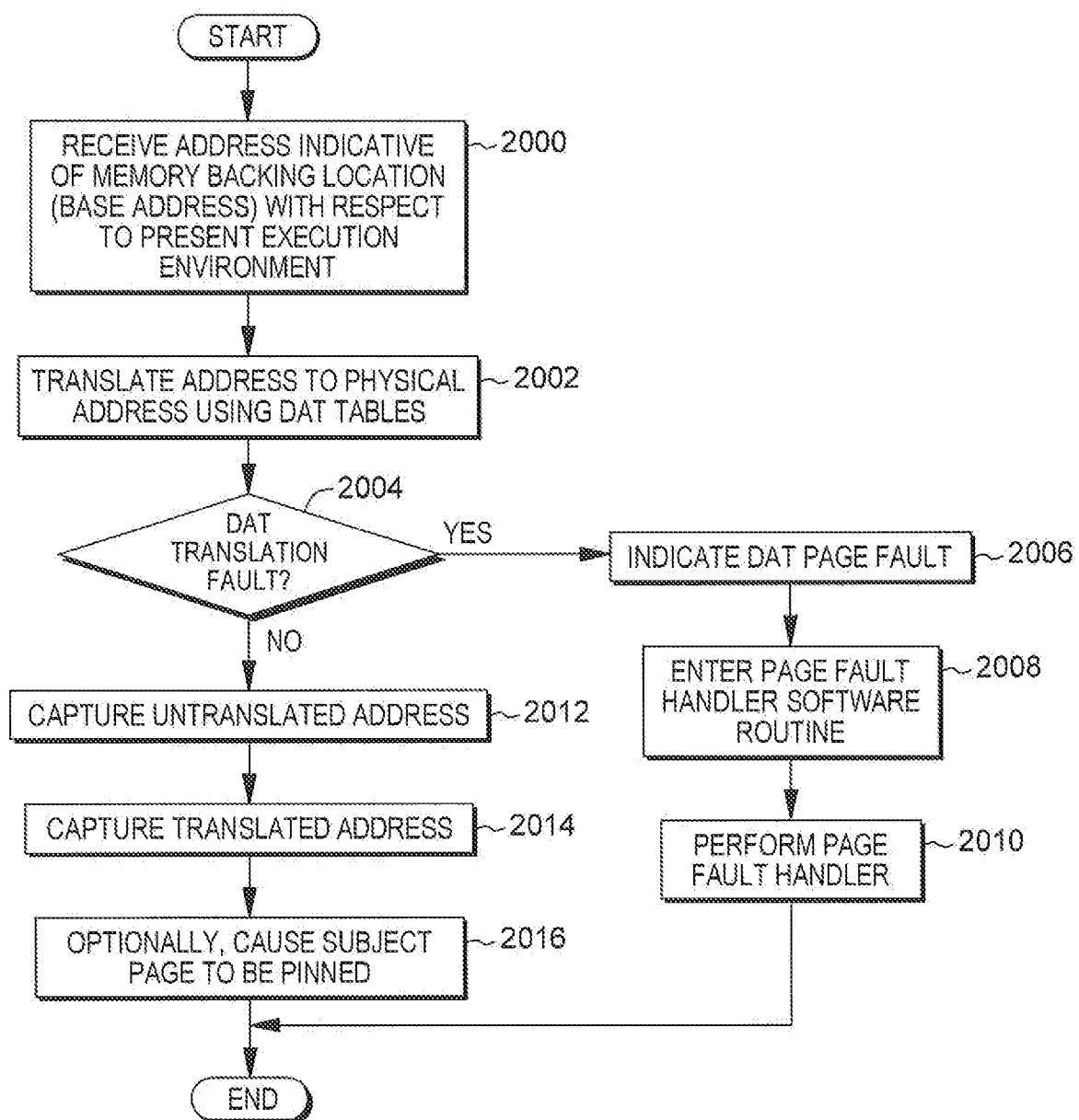

FIG. 20 depicts one embodiment of address translation associated with a move to configuration state register operation, in accordance with an aspect of the present invention;

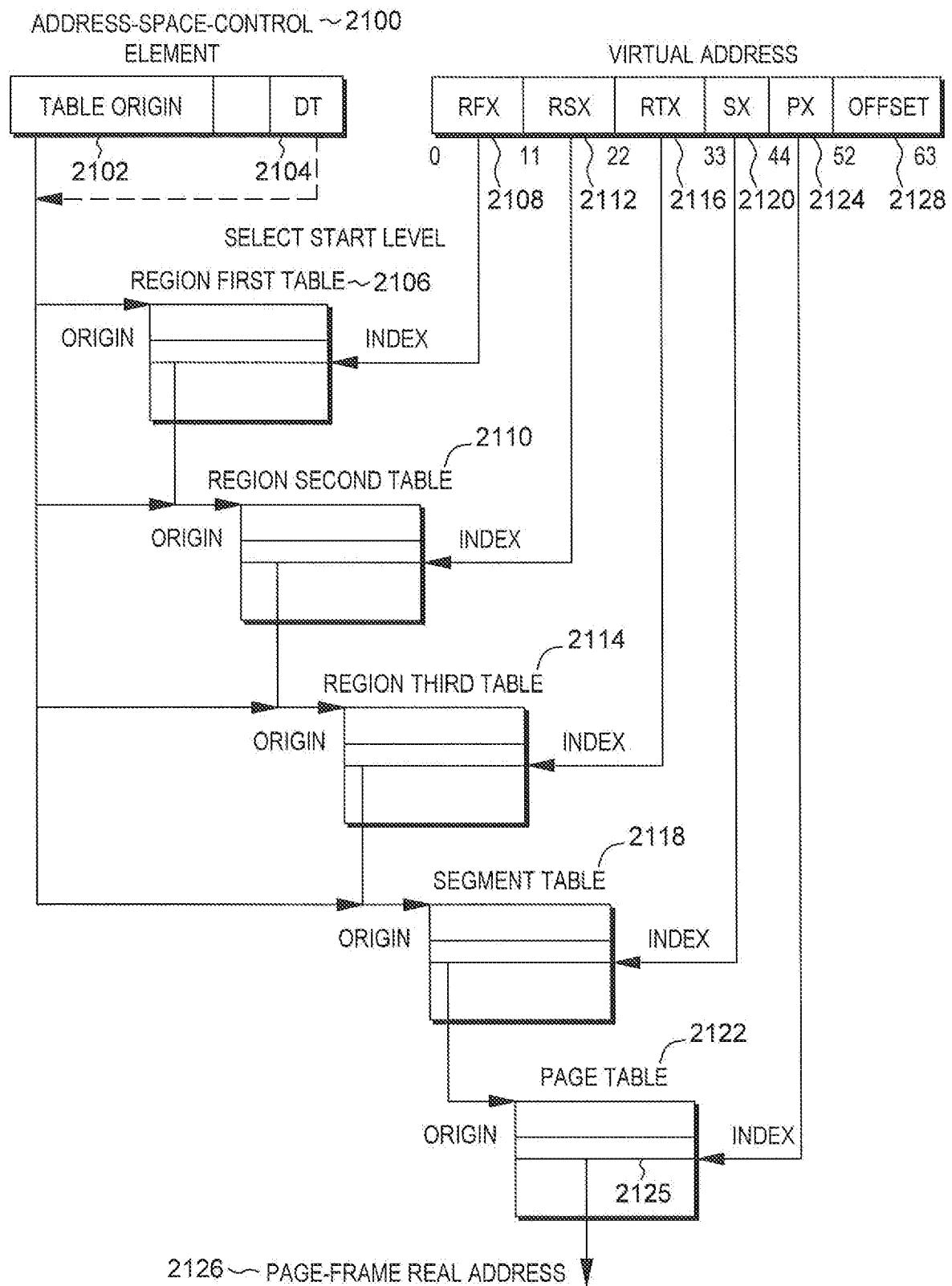

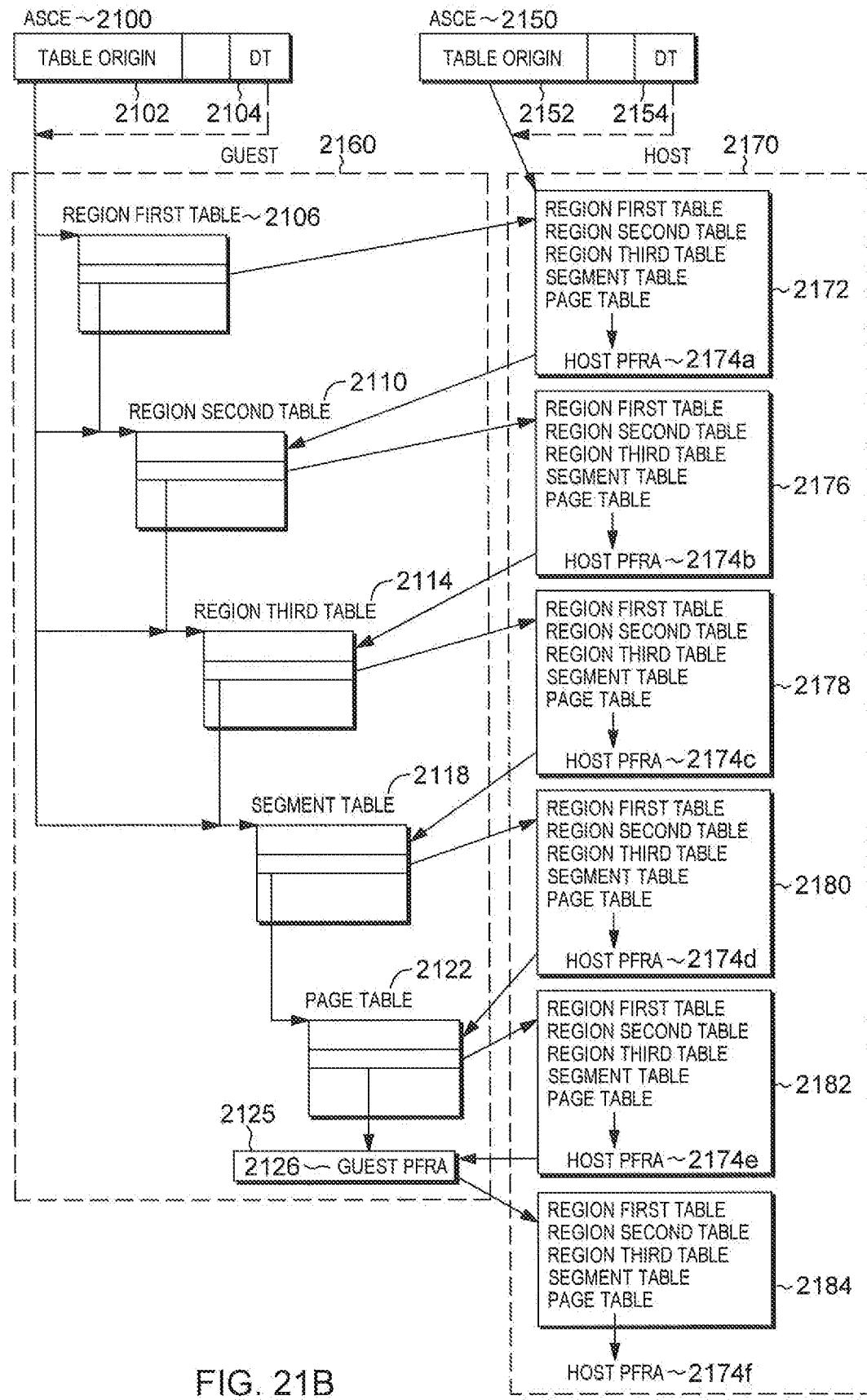

FIGS. 21A-21B depict examples of performing dynamic address translation, in accordance with aspects of the present invention;

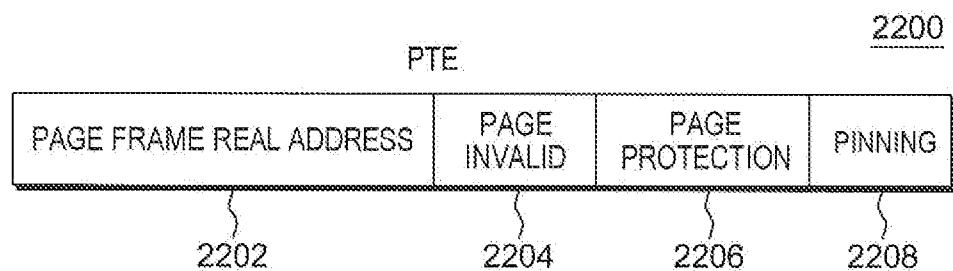

FIG. 22 depicts one example of a page table entry, in accordance with an aspect of the present invention;

FIG. 23 depicts one example of particular configuration state registers being associated with particular contexts, in accordance with an aspect of the present invention;

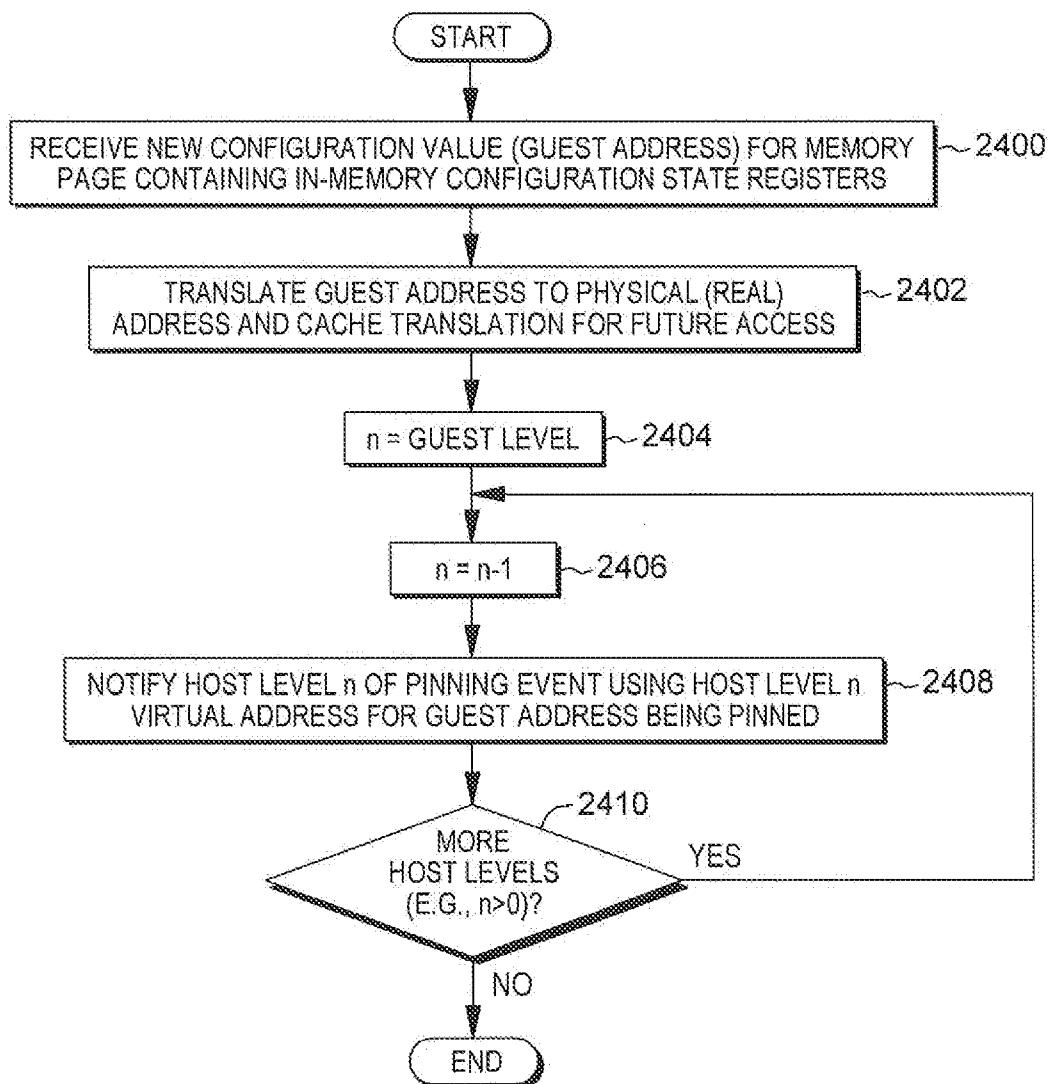

FIG. 24 depicts one embodiment of providing a pinning notification to a host system, in accordance with an aspect of the present invention;

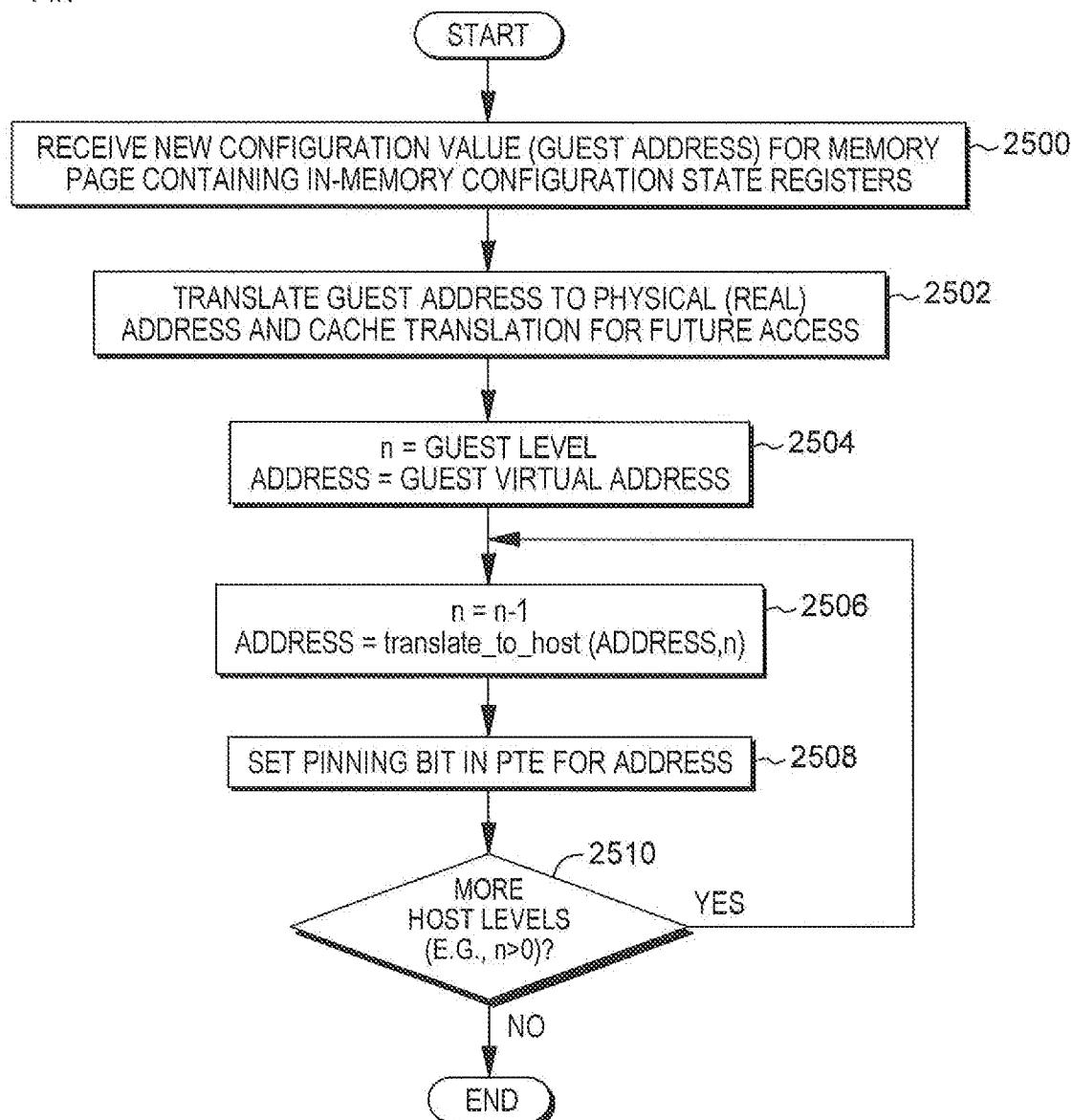

FIG. 25 depicts one embodiment of specifying a pin operation in a page table entry, in accordance with an aspect of the present invention;

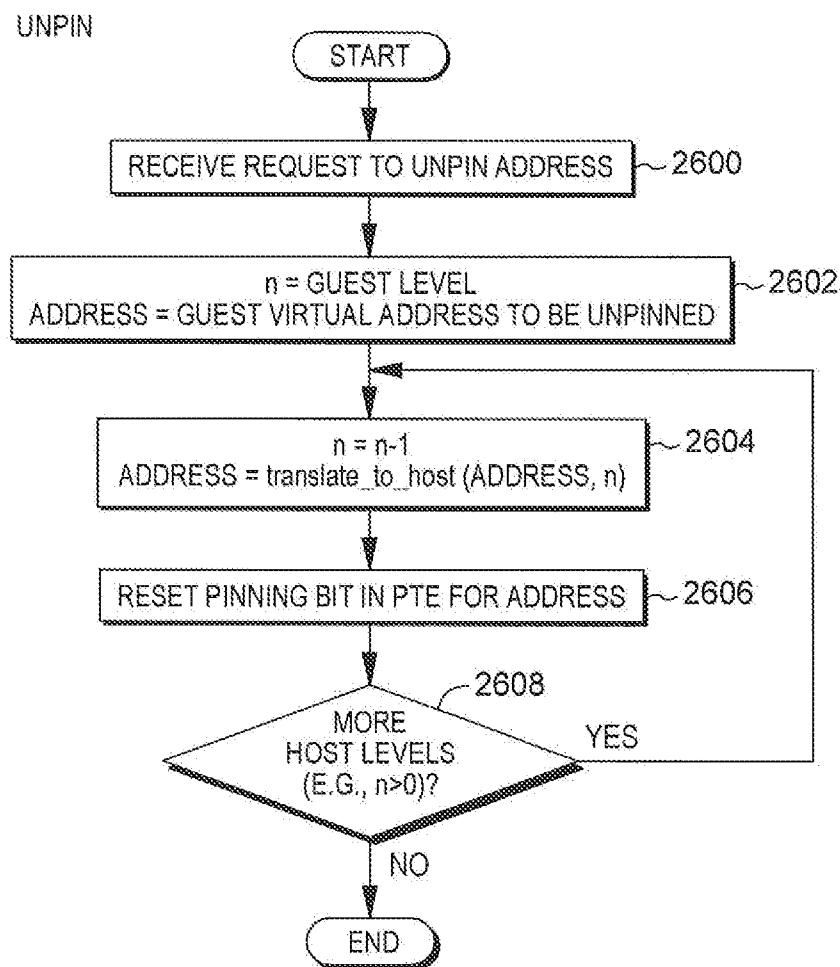

FIG. 26 depicts one embodiment of specifying an unpin operation in a page table entry, in accordance with an aspect of the present invention;

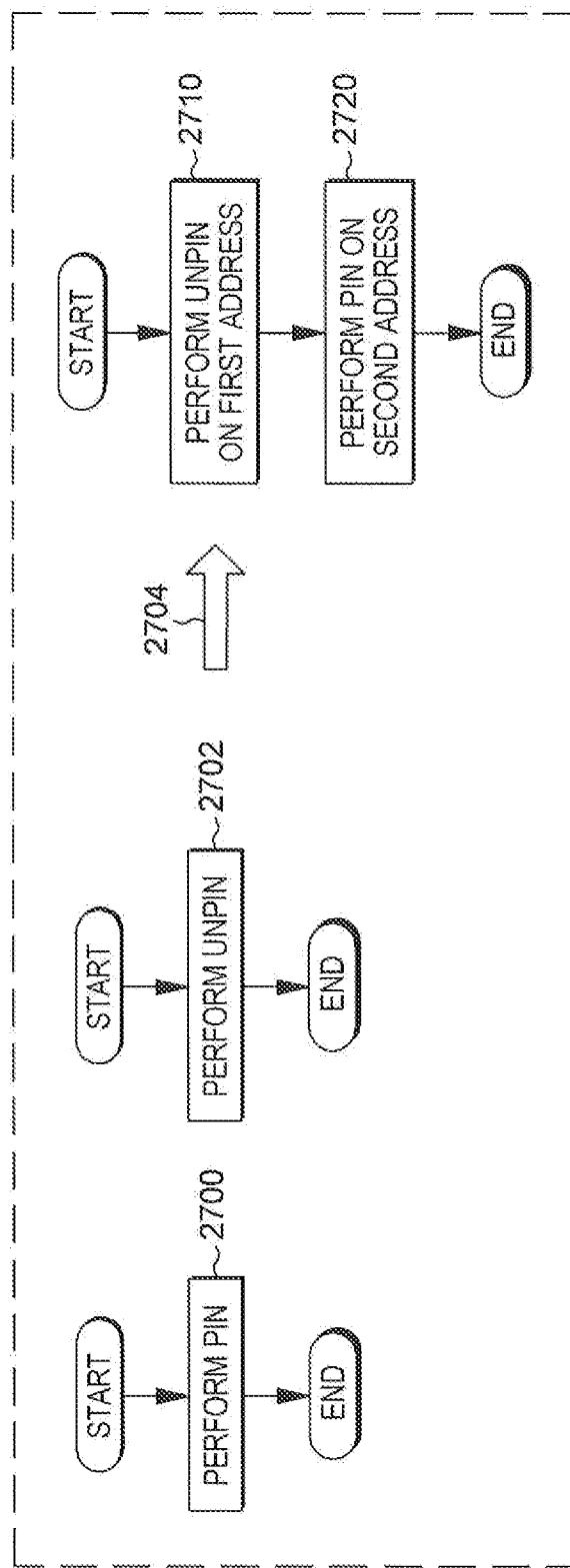

FIG. 27 depicts one example of combining a pin and an unpin operation in one hypervisor call, in accordance with an aspect of the present invention;

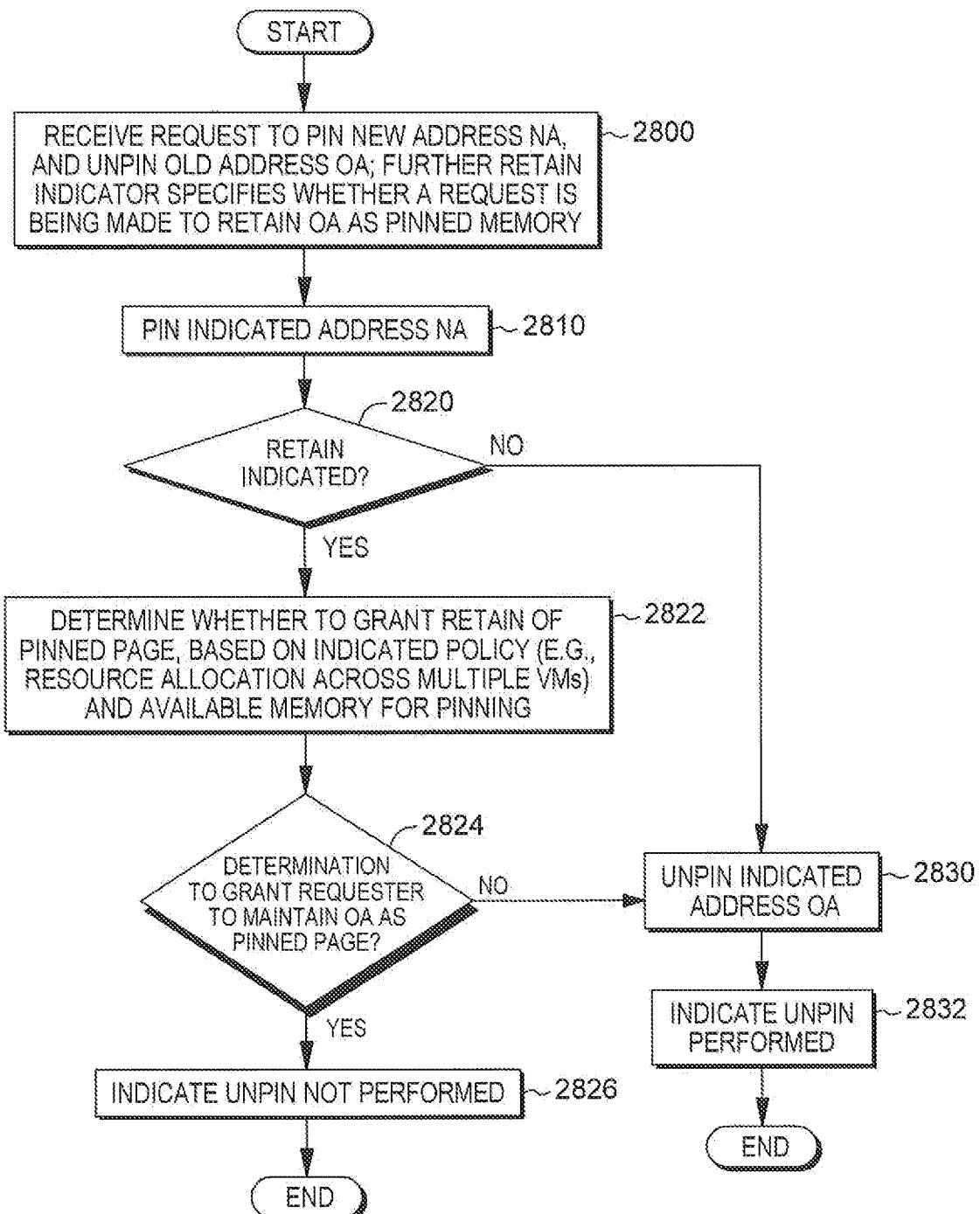

FIG. 28 depicts further details associated with performing a pin and an unpin operation based on a single call, in accordance with an aspect of the present invention;

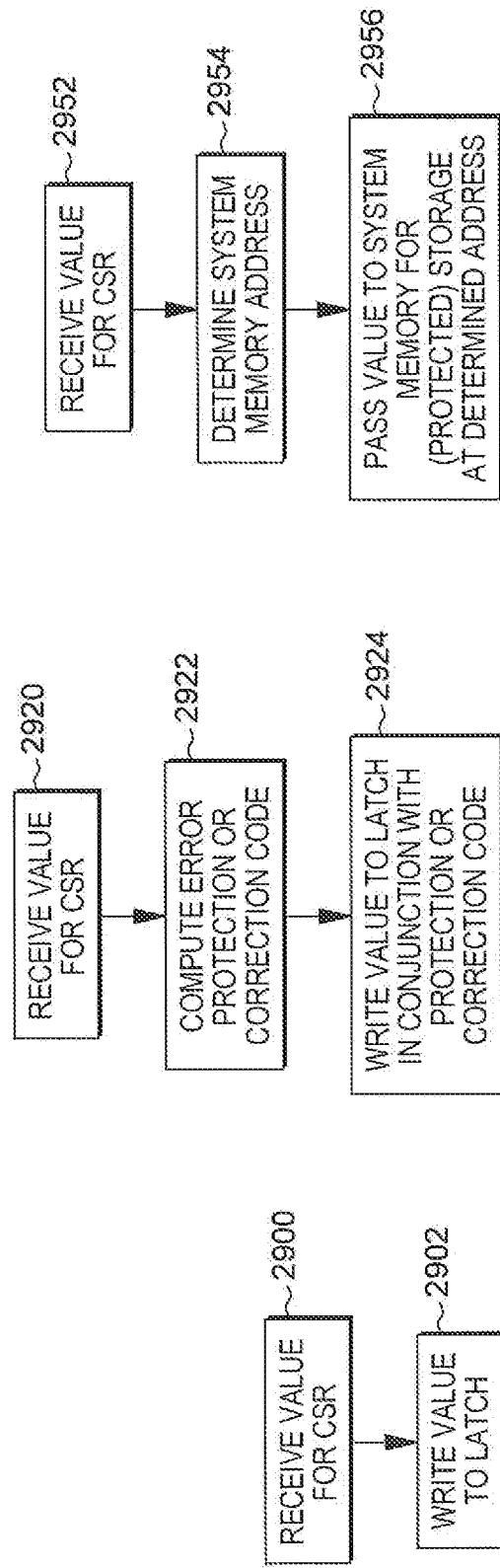

FIGS. 29A-29C provide various examples of a data write, in accordance with one or more aspects of the present invention;

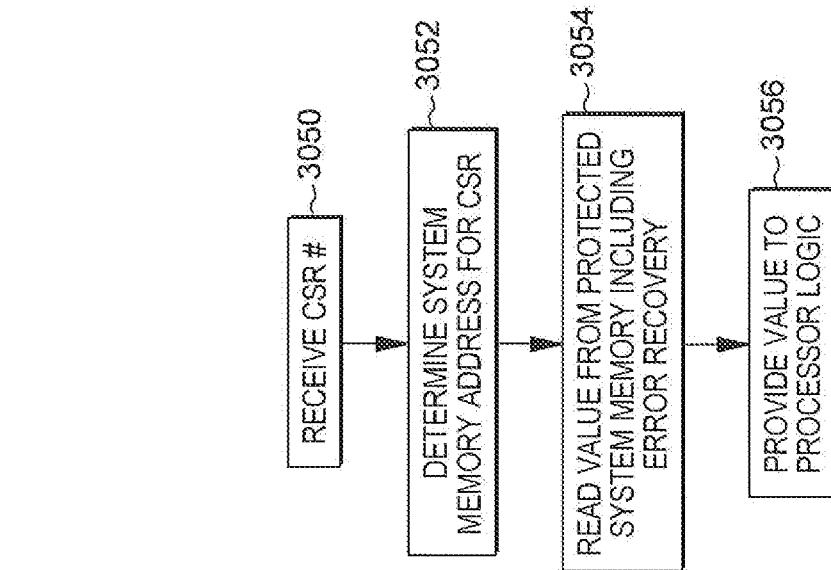

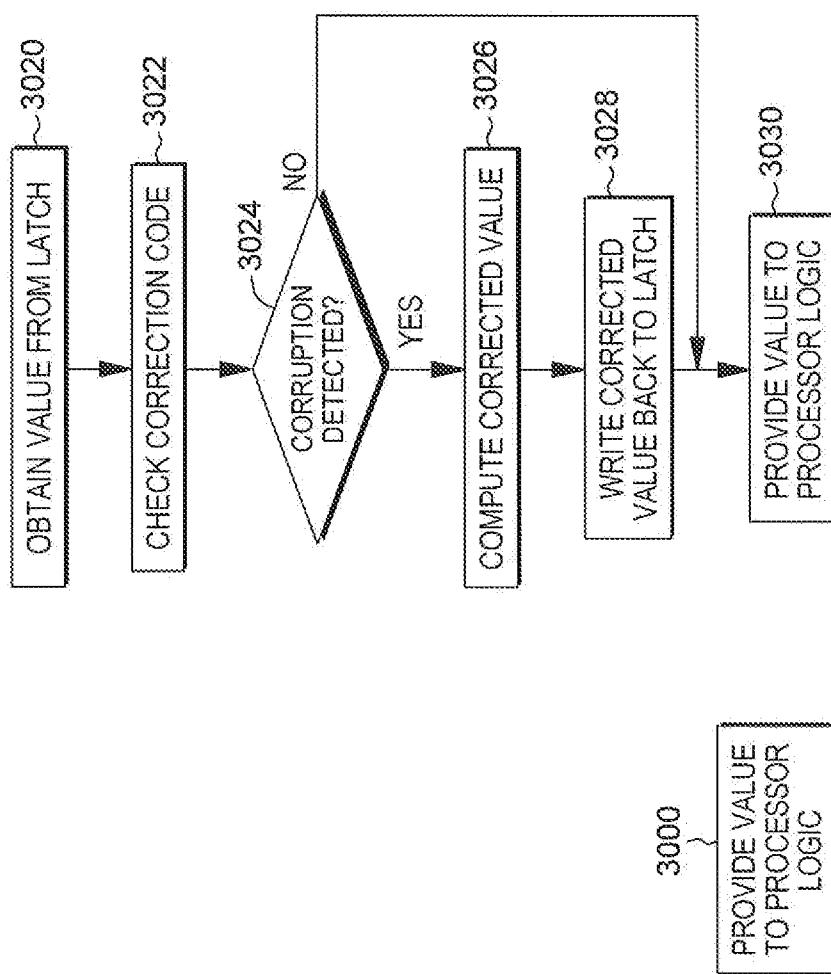

FIGS. 30A-30C provide various examples of a data read, in accordance with one or more aspects of the present invention;

FIGS. 31A-31B depict one embodiment of facilitating processing within a computing environment, in accordance with an aspect of the present invention;

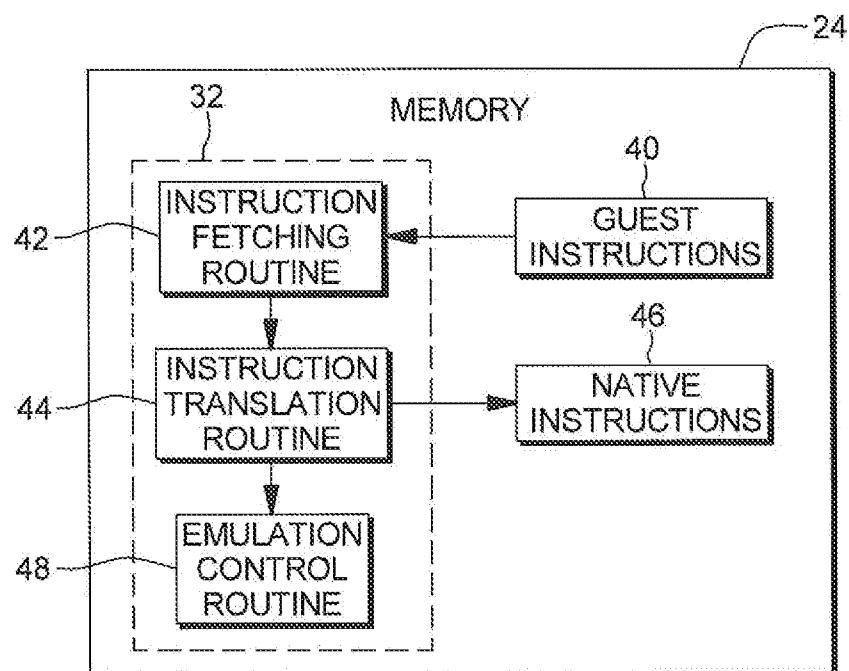

FIG. 32A depicts another example of a computing environment to incorporate and use one or more aspects of the present invention;

FIG. 32B depicts further details of the memory of FIG. 32A;

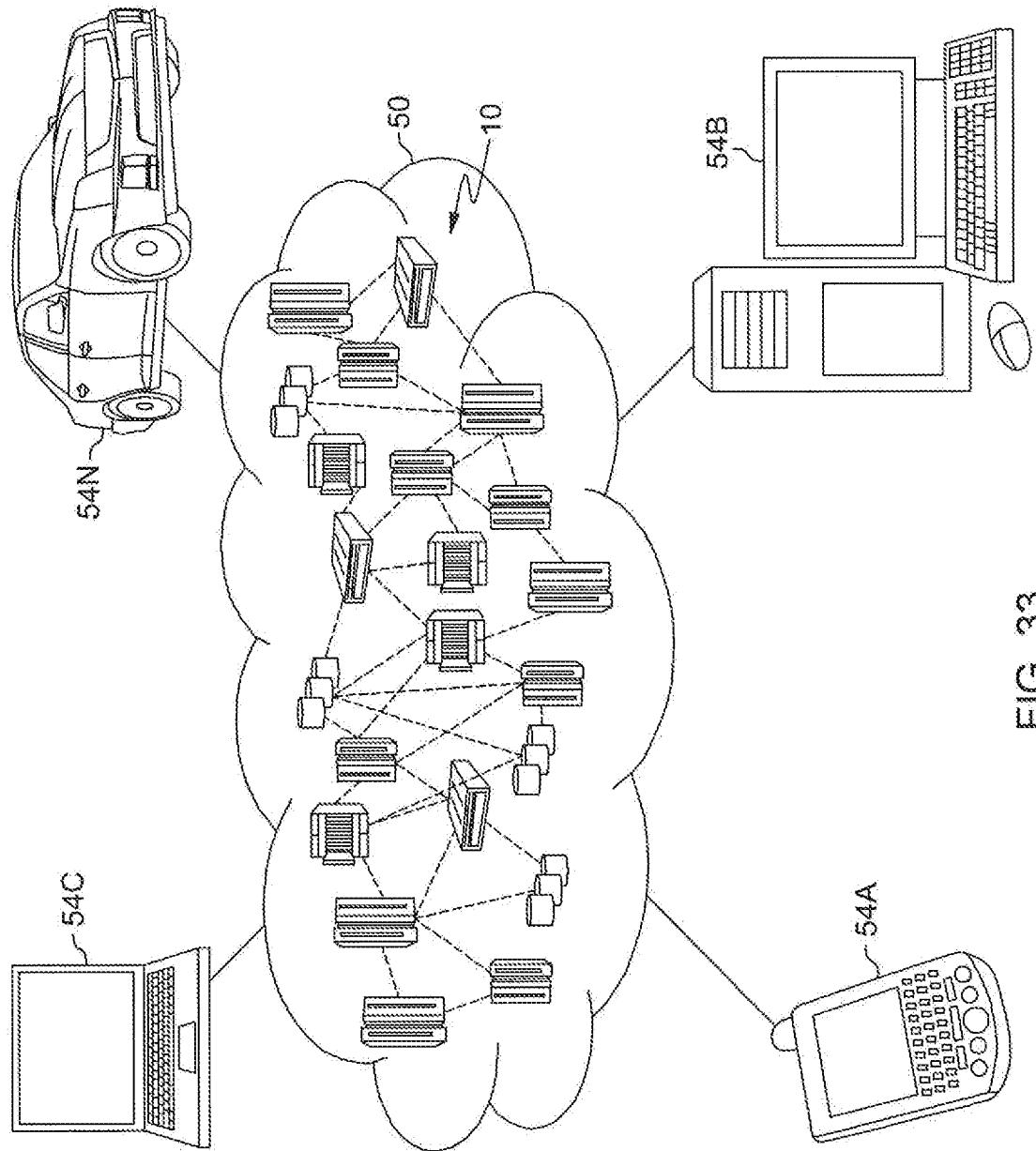

FIG. 33 depicts one embodiment of a cloud computing environment; and

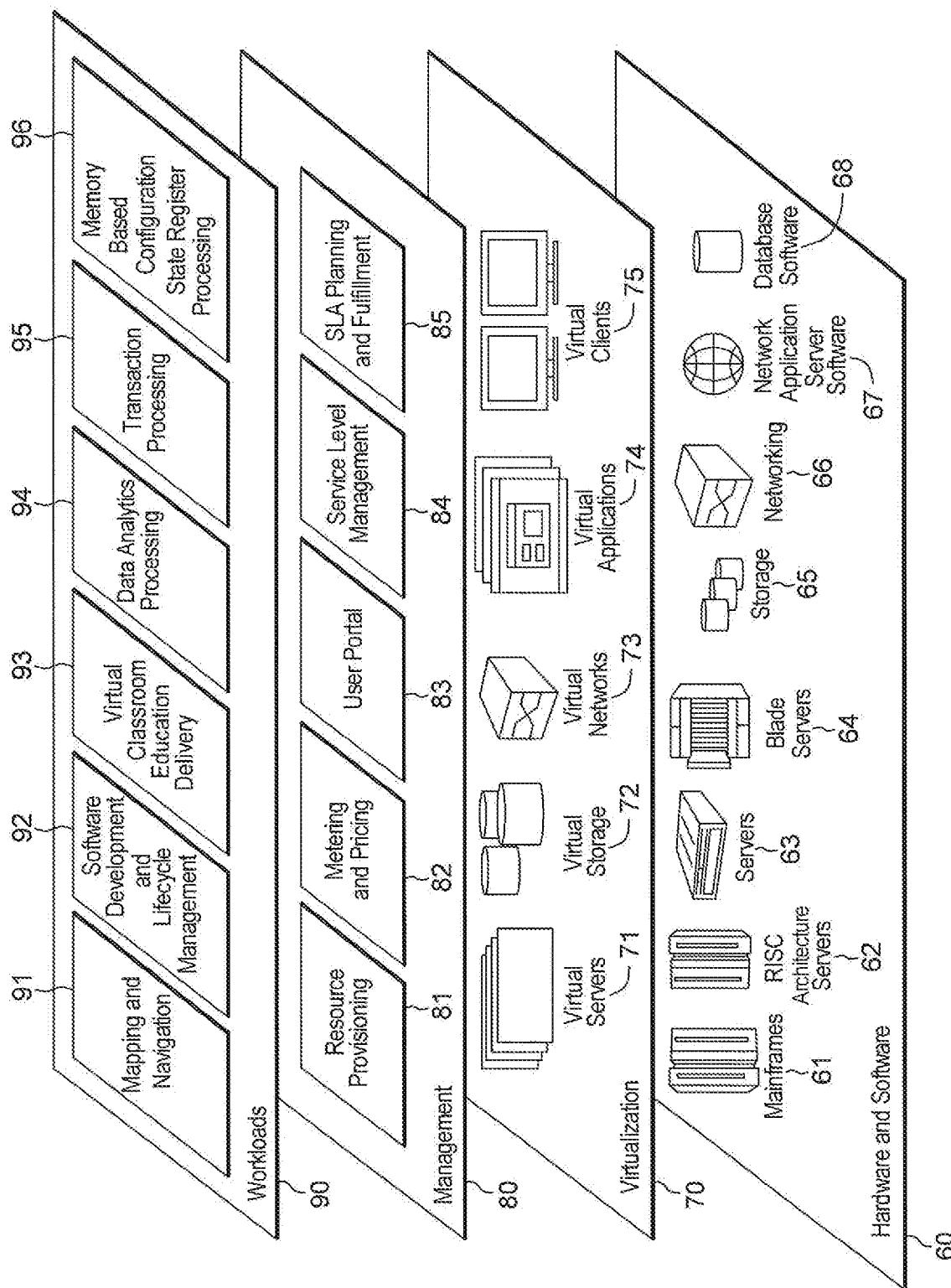

FIG. 34 depicts one example of abstraction model layers.

#### DETAILED DESCRIPTION

**[0018]** In accordance with an aspect of the present invention, various configuration state registers are provided in-memory rather than in-processor. As used herein, the term "configuration state register" includes control registers; machine state registers (MSRs), such as a program status word (PSW) or other machine state registers; status registers (e.g., floating point status control register); special purpose register (SPRs); configuration registers; and/or other registers that configure operations, e.g., of instructions.

**[0019]** Selected configuration state registers (or portions thereof in a further aspect) are provided in-memory, in which those registers are mapped to system memory and are included in the memory hierarchy which is coupled to, but separate from, the processor. The memory hierarchy includes, for instance, load/store queues, one or more memory caches, and system memory (also referred to herein as main memory, central storage, storage, main storage, memory). By being in-memory, instead of in-processor, the registers are accessed by using a memory address, and access requests may be re-ordered or speculatively processed. In contrast, access requests for configuration state registers that are in-processor are not processed out-of-order or speculatively. In-processor configuration state registers are implemented as, for instance, solid state elements (such as latches), e.g., directly on-chip. On-chip denotes or relates to circuitry included in a single integrated circuit or in the same integrated circuit as a given device.

**[0020]** Based on the configuration state registers being stored in system memory, certain instructions, such as a move to configuration state register instruction (e.g., move to SPR (mtspr) instruction) and a move from configuration state register instruction (e.g., move from SPR (mfspr) instruction), are replaced by load and store

instructions or operations by instruction decode logic. The load and store instructions/operations that are generated are committed to store queues, and typical load and store processing are performed.

**[0021]** As one example, a storage area to include the configuration state registers is defined by the operating system and/or a hypervisor and set aside for storing memory-based registers. In one embodiment, a physical memory region is architecturally specified (e.g., the first or last n pages of physical memory).

**[0022]** In a further aspect, one or more portions of a configuration state register are provided in-memory, while one or more other portions of the configuration state register are provided in-processor. In one example, the portions provided in-memory are those used less frequently.

**[0023]** In yet a further aspect, a remapping of configuration state registers is provided such that configuration state registers (or at least portions thereof) that are typically used together, are placed in memory together (e.g., in a single cache line or adjacent cache lines) to improve processing performance.

**[0024]** Further, in another aspect, instructions or operations are provided to perform a bulk store or load of multiple configuration state registers. This is to facilitate, for instance, context switching, improving performance thereof.

**[0025]** Yet further, in one aspect, processing is facilitated and performance is improved by defining a set of controls to identify where in memory the configuration state registers are stored.

**[0026]** In a further aspect, efficiencies are achieved during context switching by manipulating memory pointers of in-memory configuration state registers. The pointers are manipulated, rather than copying the old configuration data. This improves processing within the computing environment by increasing the speed and reducing complexity during context switches.

**[0027]** Moreover, in another aspect, based on executing an instruction that loads an address to be used as a base address, address translation is automatically performed in order to avoid a potential page fault later on in processing of the instruction.

**[0028]** In yet a further aspect, configuration state registers are segregated by context or group (e.g., hypervisor, operating system, process, thread) to facilitate processing by increasing management flexibility.

**[0029]** As a further aspect, an indication of automatic pinning for an initialized memory backing state is provided.

**[0030]** Yet further, in another aspect, pinning of memory pages is efficiently managed using paravirtualized pinning calls.

**[0031]** Even further, in one aspect, system memory is protected against single event upsets.

**[0032]** Various aspects are described herein. Further, many variations are possible without departing from a spirit of aspects of the present invention. It should be noted that, unless otherwise inconsistent, each aspect or feature described herein and variants thereof may be combinable with any other aspect or feature.

**[0033]** One embodiment of a computing environment to incorporate and use one or more aspects of the present invention is described with reference to FIG. 1A. In one example, the computing environment is based on the z/Architecture, offered by International Business Machines Corporation, Armonk, New York. One embodiment of the z/Architecture is described in "z/Architecture Principles of Operation," IBM Publication No. SA22-7832-10, March 2015, which is hereby incorporated herein by reference in its entirety. Z/ARCHITECTURE is a registered trademark of International Business Machines Corporation, Armonk, New York, USA.

**[0034]** In another example, the computing environment is based on the Power Architecture, offered by International Business Machines Corporation, Armonk, New York. One embodiment of the Power Architecture is described in "Power ISA™ Version 2.07B," International Business Machines Corporation, April 9, 2015, which is hereby incorporated herein by reference in its entirety. POWER ARCHITECTURE is a registered trademark of International Business Machines Corporation, Armonk, New York, USA.

**[0035]** The computing environment may also be based on other architectures, including, but not limited to, the Intel x86 architectures. Other examples also exist.

**[0036]** As shown in FIG. 1A, a computing environment 100 includes, for instance, a computer system 102 shown, e.g., in the form of a general-purpose computing device. Computer system 102 may include, but is not limited to, one or more processors or processing units 104 (e.g., central processing units (CPUs)), a memory 106 (a.k.a., system memory, main memory, main storage, central storage or storage, as examples), and one or more input/output (I/O) interfaces 108, coupled to one another via one or more buses and/or other connections 110.

**[0037]** Bus 110 represents one or more of any of several types of bus structures, including a memory bus or memory controller, a peripheral bus, an accelerated graphics port, and a processor or local bus using any of a variety of bus architectures. By way of example, and not limitation, such architectures include the Industry Standard Architecture (ISA), the Micro Channel Architecture (MCA), the Enhanced ISA (EISA), the Video Electronics Standards Association (VESA) local bus, and the Peripheral Component Interconnect (PCI).

**[0038]** Memory 106 may include, for instance, a cache 120, such as a shared cache, which may be coupled to local caches 122 of processors 104. Further, memory 106 may include one or more programs or applications 130, an operating system 132, and one or more computer readable program instructions 134. Computer readable program instructions 134 may be configured to carry out functions of embodiments of aspects of the invention.

**[0039]** Computer system 102 may also communicate via, e.g., I/O interfaces 108 with one or more external devices 140, one or more network interfaces 142, and/or one or more data storage devices 144. Example external devices include a user terminal, a tape drive, a pointing device, a display, etc. Network interface 142 enables

computer system 102 to communicate with one or more networks, such as a local area network (LAN), a general wide area network (WAN), and/or a public network (e.g., the Internet), providing communication with other computing devices or systems.

**[0040]** Data storage device 144 may store one or more programs 146, one or more computer readable program instructions 148, and/or data, etc. The computer readable program instructions may be configured to carry out functions of embodiments of aspects of the invention.

**[0041]** Computer system 102 may include and/or be coupled to removable/non-removable, volatile/non-volatile computer system storage media. For example, it may include and/or be coupled to a non-removable, non-volatile magnetic media (typically called a "hard drive"), a magnetic disk drive for reading from and writing to a removable, non-volatile magnetic disk (e.g., a "floppy disk"), and/or an optical disk drive for reading from or writing to a removable, non-volatile optical disk, such as a CD-ROM, DVD-ROM or other optical media. It should be understood that other hardware and/or software components could be used in conjunction with computer system 102. Examples, include, but are not limited to: microcode, device drivers, redundant processing units, external disk drive arrays, RAID systems, tape drives, and data archival storage systems, etc.

**[0042]** Computer system 102 may be operational with numerous other general purpose or special purpose computing system environments or configurations. Examples of well-known computing systems, environments, and/or configurations that may be suitable for use with computer system 102 include, but are not limited to, personal computer (PC) systems, server computer systems, thin clients, thick clients, handheld or laptop devices, multiprocessor systems, microprocessor-based systems, set top boxes, programmable consumer electronics, network PCs, minicomputer systems, mainframe computer systems, and distributed cloud computing environments that include any of the above systems or devices, and the like.

**[0043]** In another embodiment, the computing environment supports virtual machines. One example of such an environment is described with reference to FIG. 1B. In one example, a computing environment 161 includes a central processor complex (CPC) 163 providing virtual machine support. CPC 163 is coupled to one or more input/output (I/O) devices 167 via one or more control units 169. Central processor complex 163 includes, for instance, a memory 165 (a.k.a., system memory, main memory, main storage, central storage, storage) coupled to one or more processors (a.k.a., central processing units (CPUs)) 171, and an input/output subsystem 173, each of which is described below.

**[0044]** Memory 165 includes, for example, one or more virtual machines 175, a virtual machine manager, such as a hypervisor 177, that manages the virtual machines, and processor firmware 179. One example of hypervisor 177 is z/VM, offered by International Business Machines Corporation, Armonk, New York. The hypervisor is sometimes referred to as a host. Further, as used herein, firmware includes, e.g., the microcode of the processor. It includes, for instance, the hardware-level instructions and/or data structures used in implementation of higher level machine code. In one embodiment, it includes, for instance, proprietary code that is

typically delivered as microcode that includes trusted software or microcode specific to the underlying hardware and controls operating system access to the system hardware.

**[0045]** The virtual machine support of the CPC provides the ability to operate large numbers of virtual machines 175, each capable of operating with different programs 185 and running a guest operating system 183, such as Linux. Each virtual machine 175 is capable of functioning as a separate system. That is, each virtual machine can be independently reset, run a guest operating system, and operate with different programs. An operating system or application program running in a virtual machine appears to have access to a full and complete system, but in reality, only a portion of it is available.

**[0046]** Memory 165 is coupled to processors (e.g., CPUs) 171, which are physical processor resources assignable to virtual machines. For instance, virtual machine 175 includes one or more logical processors, each of which represents all or a share of a physical processor resource 171 that may be dynamically allocated to the virtual machine.

**[0047]** Further, memory 165 is coupled to an I/O subsystem 173. Input/output subsystem 173 directs the flow of information between input/output control units 169 and devices 167 and main storage 165. It is coupled to the central processing complex, in that it can be a part of the central processing complex or separate therefrom.

**[0048]** Further details regarding one example of a processor, such as processor 104 (or processor 171), are described with reference to FIG. 1C. A processor, such as processor 104 (or processor 171), includes a plurality of functional components used to execute instructions. These functional components include, for instance, an instruction fetch component 150 to fetch instructions to be executed; an instruction decode unit 152 to decode the fetched instructions and to obtain operands of the decoded instructions; instruction execution components 154 to execute the decoded instructions; a memory access component 156 to access memory for instruction execution, if necessary; and a write back component 160 to provide the results of the executed instructions. One or more of these components may, in accordance with an aspect of the present invention, be used to execute one or more instructions and/or operations associated with memory-based configuration state register processing 166.

**[0049]** Processor 104 (or processor 171) also includes, in one embodiment, one or more registers 168 to be used by one or more of the functional components. Processor 104 (or processor 171) may include additional, fewer and/or other components than the examples provided herein.

**[0050]** Further details regarding an execution pipeline of a processor, such as processor 104 or processor 171, are described with reference to FIG. 1D. Although various processing stages of the pipeline are depicted and described herein, it will be understood that additional, fewer and/or other stages may be used without departing from the spirit of aspects of the invention.

**[0051]** Referring to FIG. 1D, in one embodiment, an instruction is fetched 170 from an instruction queue, and branch prediction 172 and/or decoding 174 of the instruction may be performed. The decoded instruction may be

added to a group of instructions 176 to be processed together. The grouped instructions are provided to a mapper 178 that determines any dependencies, assigns resources and dispatches the group of instructions/operations to the appropriate issue queues. There are one or more issue queues for the different types of execution units, including, as examples, branch, load/store, floating point, fixed point, vector, etc. During an issue stage 180, an instruction/operation is issued to the appropriate execution unit. Any registers are read 182 to retrieve its sources, and the instruction/operation executes during an execute stage 184. As indicated, the execution may be for a branch, a load (LD) or a store (ST), a fixed point operation (FX), a floating point operation (FP), or a vector operation (VX), as examples. Any results are written to the appropriate register(s) during a write back stage 186. Subsequently, the instruction completes 188. If there is an interruption or flush 190, processing may return to instruction fetch 170.

**[0052]** Further, in one example, coupled to the decode unit is a register renaming unit 192, which may be used in the saving/restoring of registers.

**[0053]** Additional details regarding a processor are described with reference to FIG. 1E. In one example, a processor, such as processor 104 (or processor 171), is a pipelined processor that may include prediction hardware, registers, caches, decoders, an instruction sequencing unit, and instruction execution units, as examples. The prediction hardware includes, for instance, a local branch history table (BHT) 105a, a global branch history table (BHT) 105b, and a global selector 105c. The prediction hardware is accessed through an instruction fetch address register (IFAR) 107, which has the address for the next instruction fetch.

**[0054]** The same address is also provided to an instruction cache 109, which may fetch a plurality of instructions referred to as a "fetch group". Associated with instruction cache 109 is a directory 111.

**[0055]** The cache and prediction hardware are accessed at approximately the same time with the same address. If the prediction hardware has prediction information available for an instruction in the fetch group, that prediction is forwarded to an instruction sequencing unit (ISU) 113, which, in turn, issues instructions to execution units for execution. The prediction may be used to update IFAR 107 in conjunction with branch target calculation 115 and branch target prediction hardware (such as a link register prediction stack 117a and a count register stack 117b). If no prediction information is available, but one or more instruction decoders 119 find a branch instruction in the fetch group, a prediction is created for that fetch group. Predicted branches are stored in the prediction hardware, such as in a branch information queue (BIQ) 125, and forwarded to ISU 113.

**[0056]** A branch execution unit (BRU) 121 operates in response to instructions issued to it by ISU 113. BRU 121 has read access to a condition register (CR) file 123. Branch execution unit 121 further has access to information stored by the branch scan logic in branch information queue 125 to determine the success of a branch prediction, and is operatively coupled to instruction fetch address register(s) (IFAR) 107 corresponding to the one or more threads supported by the microprocessor. In accordance with at least one embodiment, BIQ entries are associated with, and identified by an identifier, e.g., by a branch tag, BTAG. When a branch associated with a BIQ

entry is completed, it is so marked. BIQ entries are maintained in a queue, and the oldest queue entries are deallocated sequentially when they are marked as containing information associated with a completed branch. BRU 121 is further operatively coupled to cause a predictor update when BRU 121 discovers a branch misprediction.

**[0057]** When the instruction is executed, BRU 121 detects if the prediction is wrong. If so, the prediction is to be updated. For this purpose, the processor also includes predictor update logic 127. Predictor update logic 127 is responsive to an update indication from branch execution unit 121 and configured to update array entries in one or more of the local BHT 105a, global BHT 105b, and global selector 105c. The predictor hardware 105a, 105b, and 105c may have write ports distinct from the read ports used by the instruction fetch and prediction operation, or a single read/write port may be shared. Predictor update logic 127 may further be operatively coupled to link stack 117a and count register stack 117b.

**[0058]** Referring now to condition register file (CRF) 123, CRF 123 is read-accessible by BRU 121 and can be written to by the execution units, including but not limited to, a fixed point unit (FXU) 141, a floating point unit (FPU) 143, and a vector multimedia extension unit (VMXU) 145. A condition register logic execution unit (CRL execution) 147 (also referred to as the CRU), and special purpose register (SPR) handling logic 149 have read and write access to condition register file (CRF) 123. CRU 147 performs logical operations on the condition registers stored in CRF file 123. FXU 141 is able to perform write updates to CRF 123.

**[0059]** Processor 104 (or processor 171) further includes, a load/store unit 151, and various multiplexors 153 and buffers 155, as well as address translation tables 157, and other circuitry.

**[0060]** Further details regarding various registers used by a processor 200, such as processor 104 or processor 171, are described with reference to FIG. 2. As shown, processor 200 includes a plurality of in-processor configuration state registers (CSRs) 202. As examples, the in-processor configuration state registers include a link register (LR), a counter register (CTR), a machine state register (MSR), a floating point status control register (FPSCR), a next instruction address (NIA) register, and one or more integer exception registers (XER) registers. Further, in accordance with an aspect of the present invention, system memory 206 coupled to processor 200 includes one or more in-memory configuration state registers 208. As examples, the in-memory configuration state registers include event based branch return registers (EBBRR), event based branch registers (EBB), state restoration registers (SRRs); an integer exception register (XER); and a vector register save register (VRSAVE). In one example, the in-memory configuration state registers 208 are stored in an in-memory configuration state register area 210 of system memory 206.

**[0061]** A configuration state register that is accessed frequently (e.g., several accesses in a row) may be moved to a cache hierarchy 212 coupled to processor 200 and system memory 206.

**[0062]** In accordance with one aspect, based on one or more configuration state registers being moved or placed in-memory, in-processor accesses to those configuration state registers are replaced with accesses to

memory. One example of decode logic that determines the type of access is described with reference to FIG. 3. This processing is performed by, e.g., the decode unit and/or another unit of the processor.

**[0063]** Referring to FIG. 3, initially, an instruction is received, STEP 300. A determination is made as to whether the instruction is a move to configuration state register instruction, such as a Move to SPR (mtspr) instruction, INQUIRY 302. If the instruction is a move to configuration state register instruction, then a further determination is made as to whether the configuration state register indicated in the instruction is an in-memory configuration state register, INQUIRY 304. If not, then conventional handling of the move to configuration state register instruction is performed, STEP 306. However, if the configuration state register is an in-memory configuration state register, then a store configuration state register internal operation is generated to store the configuration state register in memory (e.g., store the new contents of the configuration state register in memory), STEP 308.

**[0064]** Returning to INQUIRY 302, if the received instruction is not a move to configuration state register instruction, then a further determination is made as to whether the instruction is a move from configuration state register instruction, such as a Move from SPR (mfspr) instruction, INQUIRY 312. If the instruction is a move from configuration state register instruction, then a determination is made as to whether the configuration state register indicated in the instruction is in-memory, INQUIRY 314. If not, then conventional move from configuration state register handling is performed, STEP 316. Otherwise, a load configuration state register internal operation is generated to obtain the contents of the register from memory, STEP 318.

**[0065]** Returning to INQUIRY 312, if the received instruction is not a move to or move from configuration state register instruction, then yet a further determination may be performed to determine whether the received instruction is another instruction that uses a configuration state register, INQUIRY 322. If so, then a read and/or write internal operation may be generated depending on the function being performed by the instruction, STEP 324. Otherwise, processing continues to STEP 332, in which conventional instruction decode processing is performed.

**[0066]** In other aspects of the present invention, internal operations to load configuration state register and store configuration state register values are performed in conjunction with the performing of processor operations not corresponding to instructions, e.g., in response to entering an exception handler responsive to receiving an interrupt request.

**[0067]** Further details regarding a load configuration state register internal operation are described with reference to FIG. 4. This processing is performed by a processor. Referring to FIG. 4, initially, a memory base address (base) is obtained from a register or location (e.g., a base register, such as a thread control base register (TCBR)) that contains an address of a memory unit (e.g., memory page) that is the base address of the memory that includes the configuration state registers, STEP 400. Additionally, a register number indicated in the operation is obtained, STEP 402. That register number is mapped to an offset in memory, STEP 404. For instance, each configuration state register number (or other identification in another embodiment) is mapped to a particular location

in memory. That location, is a certain amount (e.g., offset) from the base address. Then, a load from an address (base address plus offset) is performed, STEP 406, and the loaded value is returned, STEP 408.

**[0068]** As used herein, base refers to a base address of the memory that includes the in-memory configuration state registers, and base register refers to a register that includes the base. One example of a base register is a thread control base register (TCBR), but other contexts (e.g., operating system, etc.) may use other base registers.

**[0069]** Further details regarding a store configuration state register internal operation are described with reference to FIG. 5. This processing is performed by a processor. Referring to FIG. 5, initially, a memory base address (base) is obtained, e.g., from a base register (e.g., from TCBR), STEP 500, as well as, the register number indicated in the operation, STEP 502. The register number is mapped to an offset in memory, STEP 504, and a store operand (e.g., the contents of the register) is stored at an address specified by the base address plus offset, STEP 506.

**[0070]** As indicated above, instructions other than a move from or a move to configuration state register instruction may use a configuration state register. Thus, processing associated with one of these instructions is described with reference to FIG. 6. This processing is performed by a processor. Referring to FIG. 6, in this embodiment, an instruction/operation is obtained that includes a configuration state register read reference, STEP 600. Based thereon, a memory base address (base) for the configuration state register indicated in the instruction/operation is obtained, e.g., from a base register (e.g., from TCBR), STEP 602, as well as the register number indicated in the instruction/operation, STEP 604. The register number is mapped to an offset in memory, STEP 606, and the contents from the address specified by base plus offset are loaded into a temporary register, STEP 608. The temporary register is then used, STEP 610.

**[0071]** Similar processing is performed for a configuration state register write reference, as described with reference to FIG. 7. This processing is performed by a processor. Referring to FIG. 7, in one example, a configuration state register write reference is obtained, STEP 700. Based thereon, a memory base address (base) is obtained, e.g., from a base register (e.g., from TCBR) for the configuration state register indicated in the instruction/operation, STEP 702, in addition to the register number specified in the instruction/operation, STEP 704. The register number is mapped to an offset, STEP 706, and the contents included in the write reference (e.g., in a temporary register) are stored at the address specified at base plus offset, STEP 708.

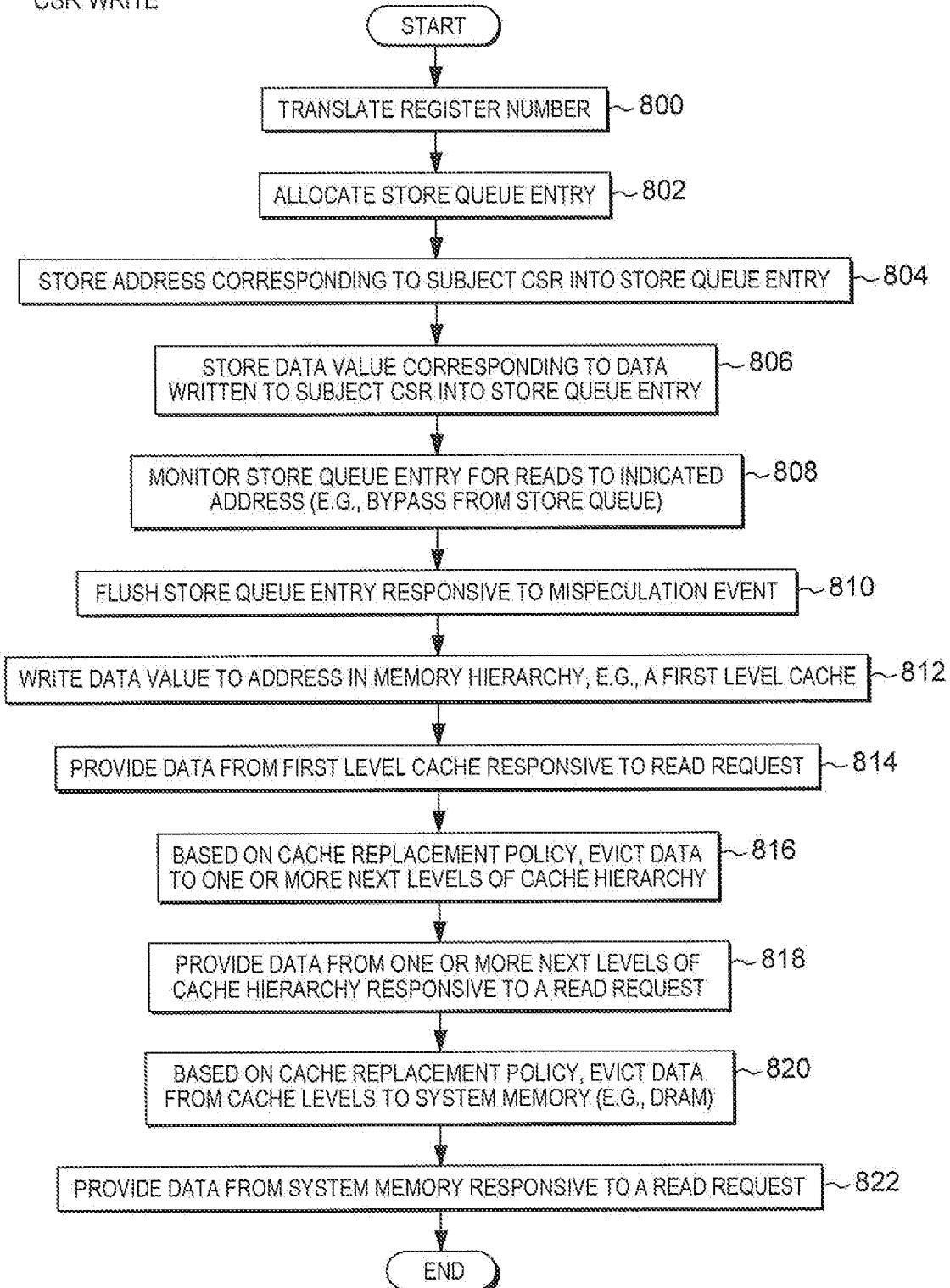

**[0072]** Further details regarding an operational implementation view of a configuration state register write operation (such as a move to configuration state register (e.g., mtspr)) are described with reference to FIG. 8. This processing is performed by a processor. Referring to FIG. 8, in one example, the register number specified in the operation is translated, STEP 800. For instance, the memory address corresponding to or mapped to the register number (or other indication) is determined (e.g., by using a look-up table or calculated). Further, a store queue entry is allocated, STEP 802, and the address corresponding to the subject configuration state register is stored into

the store queue entry, STEP 804. Moreover, the contents (e.g., data value(s)) corresponding to the data written to the subject configuration state register is written into the store queue entry, STEP 806. In one example, STEPS 804 and 806 may be performed out-of-order.

**[0073]** The store queue entry is monitored for reads to the indicated address (e.g., bypass from store queue), STEP 808. Further, the store queue entry may be flushed based on a mispeculation event, which, in one example, can occur up to an architectural in-order point, STEP 810.

**[0074]** The contents (e.g., data values) are written to an address in the memory hierarchy, e.g., a first level cache, STEP 812. The data from the first level cache is provided based on a read request, STEP 814. Further, based on a cache replacement policy, data is evicted from the first level cache to one or more next levels of the cache hierarchy, STEP 816. Data from one or more next levels of the cache hierarchy are provided based on a read request, STEP 818. Based on the cache replacement policy, data from the cache levels is evicted to system memory, e.g., DRAM, STEP 820. The data from the system memory is provided based on a read request, STEP 822.

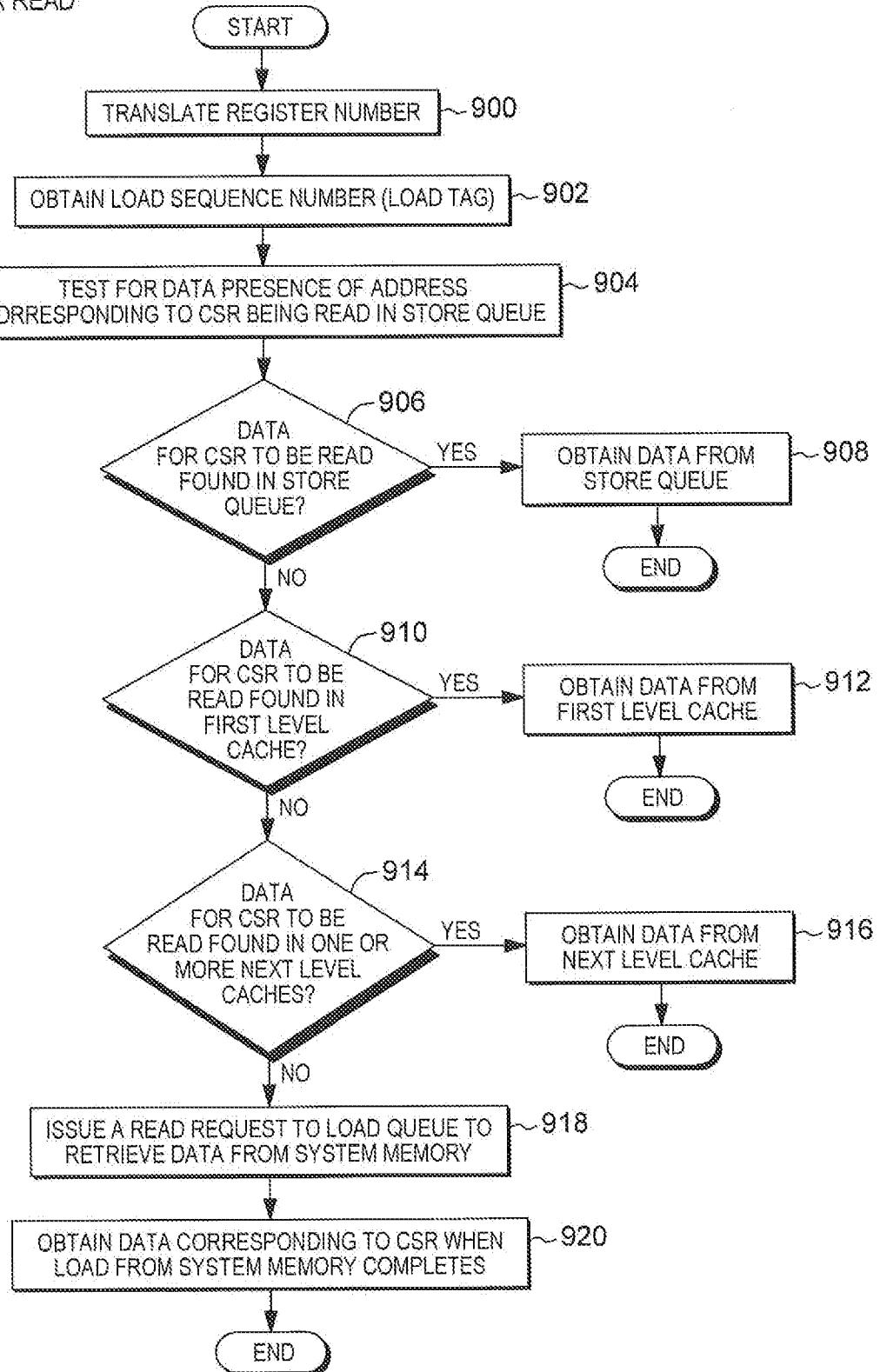

**[0075]** Further details regarding an operational implementation view of a configuration state register read operation are described with reference to FIG. 9. This processing is performed by a processor. Referring to FIG. 9, in one example, the register number specified by the read operation is translated to a corresponding memory address, STEP 900. A load sequence number used to indicate a position in a load queue used to track load requests and a load tag that tracks dependencies are obtained, STEP 902. A test for the presence of data at the address corresponding to the configuration state register being read in the store queue is performed, STEP 904 (i.e., is the data to be read from memory in the store queue). If the data for the configuration state register to be read is found in the store queue, INQUIRY 906, then the value is obtained from the store queue, STEP 908, and processing is complete.

**[0076]** Returning to INQUIRY 906, if the data for the configuration state register to be read is not found in the store queue, then a further determination is made as to whether the data for the configuration state register to be read is found in the first level cache, INQUIRY 910. If so, then the value is obtained from the first level cache, STEP 912, and processing is complete.

**[0077]** Returning to INQUIRY 910, however, if the data is not found in the first level cache, then a further determination is made as to whether the data for the configuration state register to be read is found in one or more next level caches, INQUIRY 914. If the data is found in one or more next level caches, then the data is obtained from a next level cache, STEP 916, and processing is complete.

**[0078]** Returning to INQUIRY 914, if the data is not in one or more next level caches, then a read request is issued to the load queue to retrieve the data from system memory, STEP 918. The data corresponding to the configuration state register is obtained when the load from system memory completes, STEP 920.

**[0079]** In accordance with an aspect of the present invention, the allocation of in-memory memory units (e.g., pages) is performed in order to provide software compatibility. For instance, the allocation is performed by firmware for a processor to be able to execute legacy hypervisors, and hypervisors to be able to execute legacy operating systems, and so forth.

**[0080]** In one example, upon initial boot of the system, firmware allocates in-memory pages for the in-memory configuration state registers, in firmware-owned memory. In one example, if a hypervisor is unaware of the in-memory configuration state registers, then the firmware-owned pages are used throughout the entire execution of the system without any further software reference to a base register, e.g., TCBR, etc.

**[0081]** As such, the hypervisor will simply perform context switches by reading the context using, e.g., a move from configuration state register, e.g., mfspr, and reloading the context with, e.g., a move to configuration state register, e.g., mtspr. This offers significant design simplicity and performance advantages within the computer system.

**[0082]** Further, in one example, when a hypervisor is aware of memory-backed pages, it may configure each new partition to have a set of backing pages. Further, if an operating system is unaware of in-memory configuration state registers, then the hypervisor owned page(s) is used throughout the entire execution of the system without any further software reference to, e.g., a base register, e.g., TCBR, etc. If the hypervisor is unaware as well, then the operating system will use firmware-owned pages.

**[0083]** As such, the operating system will simply perform context switches by reading the context using, e.g., a move from configuration state register, such as, e.g., mfspr, and reloading the context with, e.g., a move to configuration state register, such as, e.g., mtspr. This offers significant design simplicity and performance advantages, facilitating processing within the computer system.

**[0084]** As described herein, in accordance with one or more aspects, selected configuration state registers are stored in system memory. Thus, move to and from configuration state registers are replaced by load and store instructions by instruction decode logic. Loads and stores that are so generated are committed to store queues, and normal load and store processing are performed. In one example, the configuration state registers that are not constantly needed (e.g., those other than registers, such as the program counter (PC), data and address break point registers, PSW, floating point control, etc.) are those stored in memory.

**[0085]** As an example, the storage area is defined by the operating system and hypervisor and set aside for storing memory-based registers. In one embodiment, a physical memory region is architecturally specified (e.g., the first or last n pages of physical memory).

**[0086]** In at least one embodiment, in-memory configuration state registers are mapped to normal cacheable memory. When a configuration state register is to be updated, it is stored into a store queue. The store queue is not only a queuing mechanism, but effectively provides a way to rename locations for storage in order to enable

speculative execution of memory accesses. Multiple versions of speculative values for an address can be in the store queue (in addition to an authoritative, architected value at an architectural in-order point, which is in cache or system memory). The cache entries may be updated out-of-order, once they have been allocated. Also stores may be undone by flushing entries from the store queue.

**[0087]** Consequently, an in-memory configuration state register can be updated by using the store queue and read back out-of-order with no performance cost, where an in-core latch based configuration state register forces two serialization and in-order access cost penalties because implementing means for speculative execution of in-processor configuration state registers are most often prohibitively expensive.

**[0088]** Further, when a value is not in the store queue, a read of the value can be done more efficiently than from a latch because frequently used memory controls (e.g., in-memory configuration state registers) will be found in the cache and may be available in as little as 2-3 cycles (time to access a first level cache), much faster than the special purpose logic needed to access a latch based configuration state register in a processor.

**[0089]** In one embodiment, when a page is allocated to hold configuration state registers, the architecture disallows access to the page using memory operands. This avoids an interlock between a memory operation and move from/move to configuration state register instructions.

**[0090]** In accordance with a further aspect of the present invention, one or more portions of a configuration state register are provided in-memory, while one or more other portions of the configuration state register are provided in-processor. For instance, a configuration state register may have a plurality of portions (e.g., fields) and one or more of those portions that are, for instance, frequently accessed, may remain in-processor and the remaining portions that are, for instance, infrequently used, may be moved to memory. This is described in further detail with reference to FIGS. 10-14.

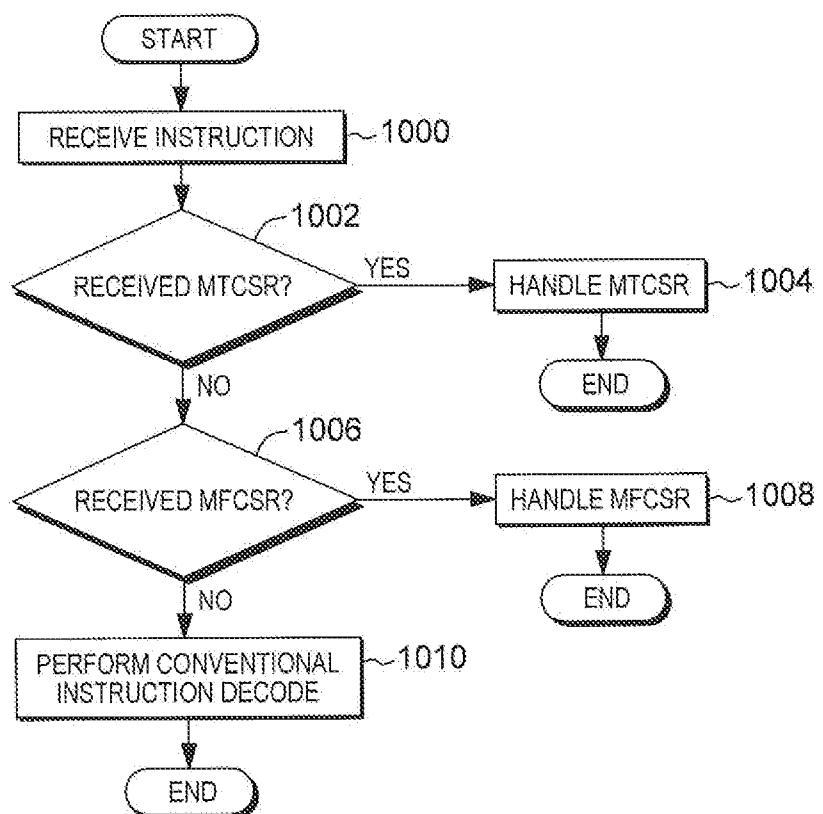

**[0091]** Initially, referring to FIG. 10, the decode unit of a processor (or another component) receives an instruction, STEP 1000. A determination is made by the decode unit (or another component) as to whether that instruction is a move to configuration state register instruction (mtcsr), such as to a Move to SPR (mtspr) instruction, INQUIRY 1002. If it is a move to configuration state register instruction, then that instruction is handled, STEP 1004, as described below.

**[0092]** Returning to INQUIRY 1002, if the instruction is not a move to configuration state register instruction, then a further determination is made as to whether the instruction is a move from configuration state register instruction (mfcsr), such as a Move from SPR (mfspr) instruction, INQUIRY 1006. If it is a move from configuration state register instruction, then that instruction is handled, as described below, STEP 1008. Returning to INQUIRY 1006, if the instruction is neither a move to or a move from configuration state register instruction, then conventional instruction decode is performed, STEP 1010.

**[0093]** In a further embodiment, other inquiries may be made as to whether it is another instruction that uses a configuration state register, and if so, those instructions may be handled, as appropriate, examples of which are described herein. In yet a further embodiment, processor operations not corresponding to instructions (e.g., initiating an exception handling sequence) may be similarly performed.

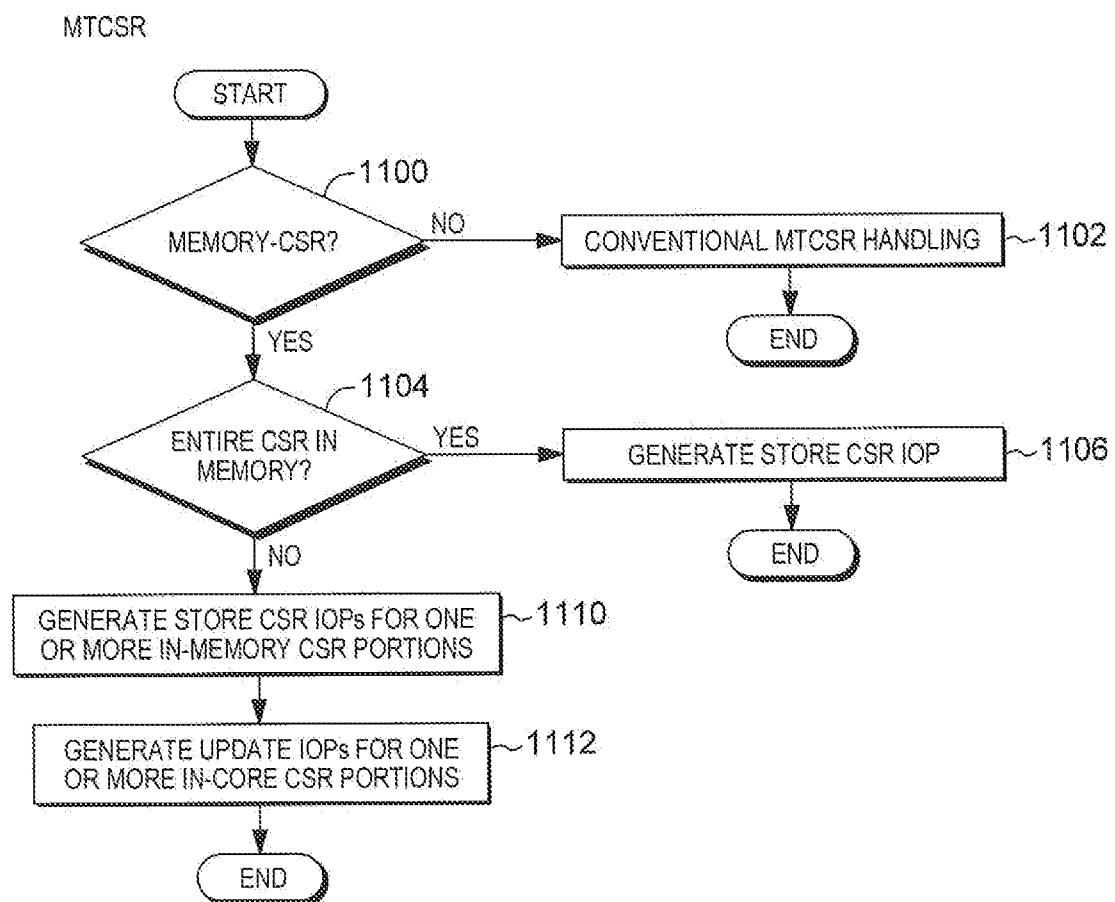

**[0094]** Further details regarding handling a move to configuration state register instruction are described with reference to FIG. 11. In one example, the configuration state register may be a special purpose register (SPR), and the instruction is a Move to SPR (mtspr) instruction. However, this is only one example. Other configuration state registers may be processed similarly. This logic is performed by a processor, such as, for instance, the decode unit of the processor. In other examples, one or more other components perform this logic.

**[0095]** Referring to FIG. 11, based on obtaining (e.g., receiving, provided, selecting, etc.) a move to configuration state register instruction, such as an mtspr instruction, a determination is made as to whether a least a portion of the configuration state register (CSR) specified by the instruction is in-memory, INQUIRY 1100. If not, then conventional processing of the move to configuration state register instruction (e.g., mtspr) is performed, STEP 1102.

**[0096]** Returning to INQUIRY 1100, if at least a portion of the configuration state register is in-memory, then a further determination is made as to whether the entire configuration state register is in-memory, INQUIRY 1104. If the entire configuration state register is in-memory, then a store configuration state register internal operation is generated, STEP 1106. An example of processing associated with this internal operation is described with reference to FIG. 5.

**[0097]** Returning to INQUIRY 1104, if only one or more portions of the configuration state register are in-memory, then one or more store configuration state register operations are generated for the one or more in-memory configuration state register portions, STEP 1110. Further, updated internal operations are generated for the one or more in-core configuration state register portions, STEP 1112. The updated internal operations may be one or more instructions, a state machine or other that performs the operation of copying the contents of one or more general purpose registers including data for the specified in-core portions to the appropriate portion(s) of the in-core configuration state register. Processing is complete.

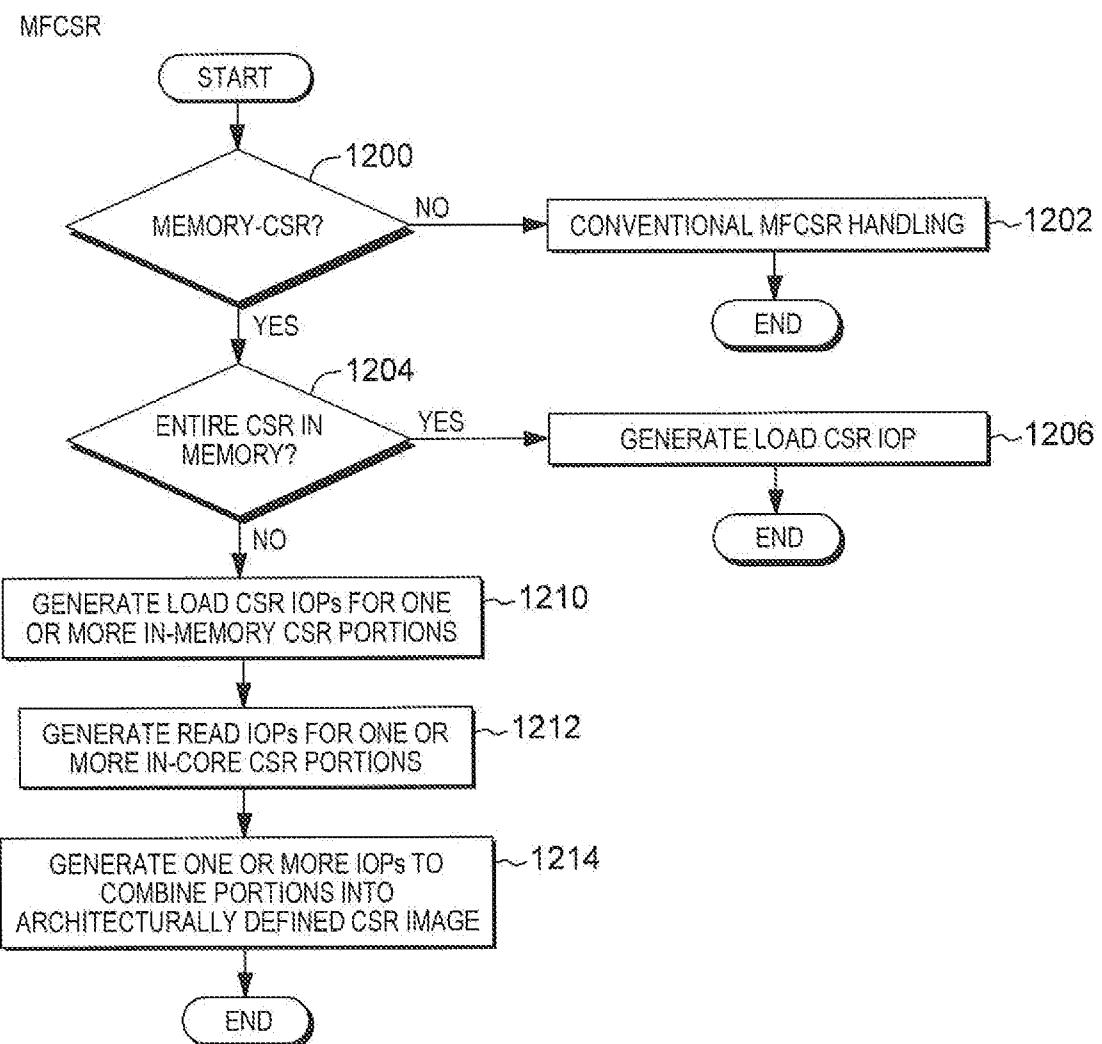

**[0098]** Further details regarding processing associated with handling a move from configuration state register instruction are described with reference to FIG. 12. In one example, the configuration state register may be a special purpose register (SPR), and the instruction is a Move from SPR (mfspr) instruction. However, this is only one example. Other configuration state registers may be processed similarly. This logic is performed by a processor, such as, for instance, the decode unit of the processor. In other examples, one or more other components perform this logic.

**[0099]** Referring to FIG. 12, based on obtaining (e.g., receiving, providing, selecting, etc.) a move from configuration state register instruction, such as an mfspr instruction, a determination is made as to whether at least a portion of the configuration state register is in-memory. If not, then conventional processing is performed for the move from configuration state register instruction, STEP 1202.

**[00100]** Returning to INQUIRY 1200, if at least a portion of the configuration state register is in-memory, then a further determination is made as to whether the entire configuration state register is in-memory, INQUIRY 1204. If the entire configuration state register is in-memory, then a load configuration state register internal operation is generated, STEP 1206. An example of processing associated with this operation is described with reference to FIG. 4.

**[00101]** Returning to INQUIRY 1204, if only one or more portions of the configuration state register are in-memory, then one or more load configuration state register internal operations are generated for one or more of the in-memory configuration state register portions, STEP 1210. Further, one or more read internal operations are generated for the one or more in-core configuration state register portions, STEP 1212.

**[00102]** Additionally, in one embodiment, one or more internal operations are generated to combine the in-memory and in-core portions into an architecturally defined configuration state register image, STEP 1214. This may include using, for instance, an Insert Under Mask instruction, or OR, AND, and/or NOT logic circuits, as described further below.

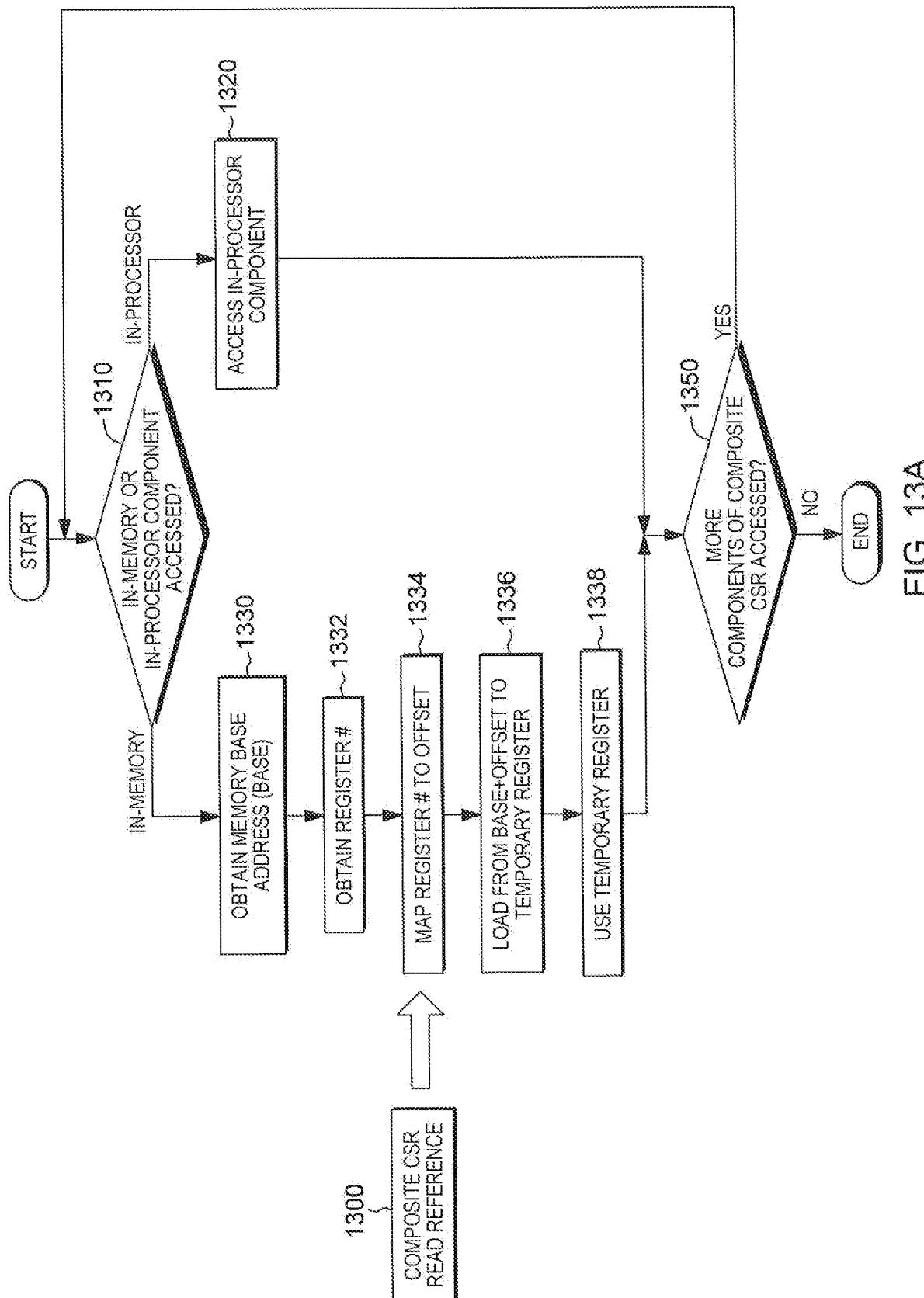

**[00103]** Further details regarding the use of a composite configuration state register in which one or more portions are in-processor and one or more portions are in-memory are described with reference to FIG. 13A, in which a read reference is described. This logic is performed by a processor, such as, for instance, the decode unit of the processor. In other examples, one or more other components perform this logic.

**[00104]** Referring to FIG. 13A, based on a composite configuration state register read reference 1300, a determination is made as to whether a particular portion (also referred to as a component; e.g., a field) being accessed is in-memory or in-processor, INQUIRY 1310. If it is in-processor, then the in-processor component is accessed, STEP 1320, and processing continues to INQUIRY 1350, described below. However, if the particular component is in-memory, INQUIRY 1310, then processing is performed, as described with reference to FIG. 6. For instance, the memory base address (base) is obtained, STEP 1330, as well as a register number indicated in the instruction referencing the composite configuration state register, STEP 1332. The register number is mapped to an offset, STEP 1334, and a load is performed from the address (base + offset) to a temporary register, STEP 1336. The temporary register is then used, STEP 1338. Thereafter, or after STEP 1320, a determination is made as to whether another component of the composite configuration register is to be accessed, INQUIRY 1350. If so, then processing continues with INQUIRY 1310. Otherwise, processing is complete.

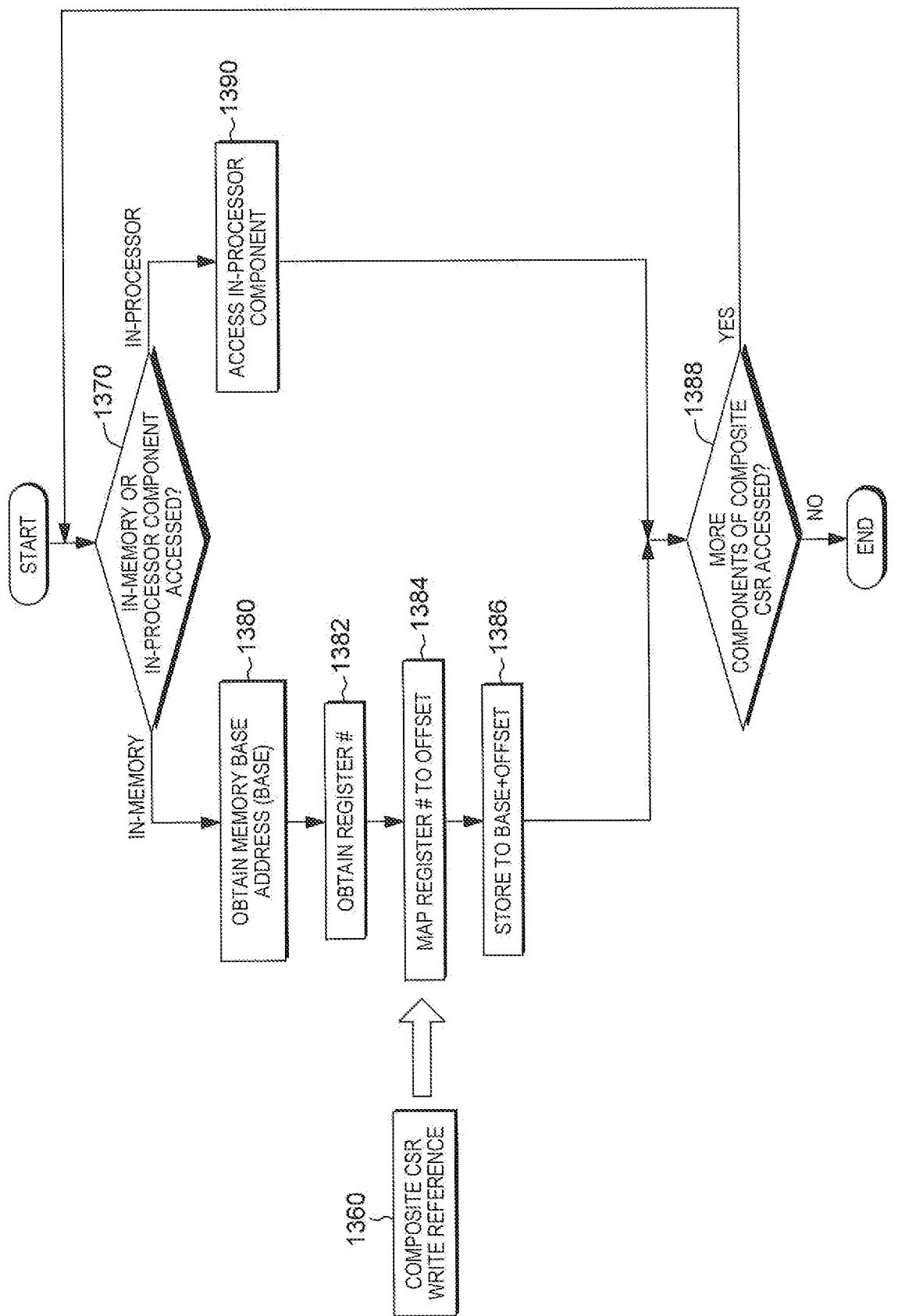

**[00105]** Further details regarding the use of a composite configuration state register in which one or more portions are in-processor and one or more portions are in-memory are described with reference to FIG. 13B, in which a write reference is described. This logic is performed by a processor, such as, for instance, the decode unit of the processor. In other examples, one or more other components perform this logic.

**[00106]** Referring to FIG. 13B, based on a composite configuration state register write reference 1360, a determination is made as to whether a particular portion (also referred to as a component; e.g., a field) being accessed is in-memory or in-processor, INQUIRY 1370. If it is in-processor, then the in-processor component is accessed, STEP 1390, and processing continues to INQUIRY 1388, described below. However, if the particular component is in-memory, INQUIRY 1370, then processing is performed, as described with reference to FIG. 7. For instance, the memory base address (base) is obtained, STEP 1380, as well as a register number indicated in the instruction referencing the composite configuration state register, STEP 1382. The register number is mapped to an offset, STEP 1384, and a store is performed to an address defined by base + offset, STEP 1386. Thereafter, or after STEP 1390, a determination is made as to whether another component of the composite configuration register is to be accessed, INQUIRY 1388. If so, then processing continues with INQUIRY 1370. Otherwise, processing is complete.

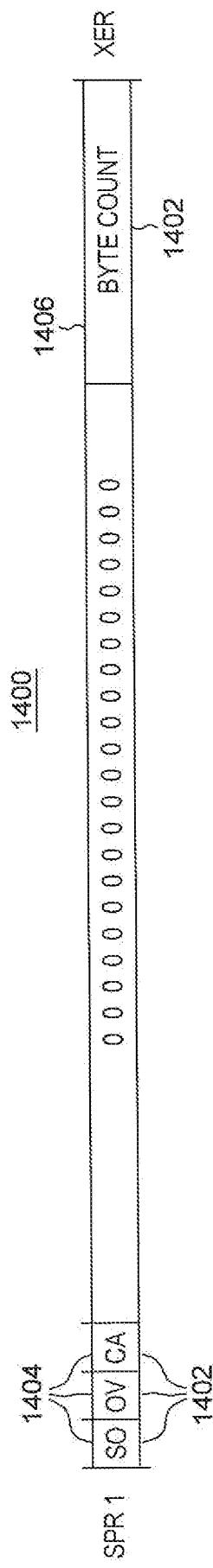

**[00107]** One example of a composite configuration state register is depicted in FIG. 14. As shown, in this example, a composite configuration state register 1400 is special purpose register (SPR) 1, which corresponds to an integer exception register (XER). This register includes a plurality of fields 1402. In one example, one or more of the fields are in-processor fields 1404, and another field 1406 is an in-memory field. In this particular example, Xerf0, 1, 2 (i.e., fields 0, 1, and 2 of XER) are renamed in-processor to SO (summary overflow), OV (overflow) and CA (carry); and Xerf3 (field 3 of XER), which is not renamed in this example, is a byte count field in-memory. With this configuration, the following IOP sequences may be generated and used to perform a mtspr and a mfspr, respectively, for a composite configuration state register:

**[00108]** mtspr\_xer mtxerf2

**[00109]** mtxerf0

**[00110]** mtxerf1

**[00111]** stxerf3

**[00112]** With the above, the mtspr for the XER register includes: a move to field 2 of XER (mtxerf2), in which contents of a general purpose register are copied to XER field 2; a move to field 0 of XER (mtxerf0), in which contents of a general purpose register are copied to XER field 0; and a move to field 1 of XER (mtxerf1), in which contents of a general purpose register are copied to XER field 1. It also includes a store to field 3 of XER (stxerf3), which is performed by a store operation, since field 3 is in memory.

[00113] mfspr\_xer mfxerf2

[00114] mfxerf0

[00115] or

[00116] ldxerf3

[00117] or

[00118] mfxerf1

[00119] or

[00120] For the move from XER, each of the fields is read, either from in-processor or in-memory and those fields are combined by, e.g., an OR operation. For example, the contents of field 2 and field 0 are read and an OR operation is performed to provide a result 1; then, the contents of field 3 are read (e.g., using a load, such as, for example, a load xerf3 internal operation, ldxerf3, since field 3 is in-memory) and OR'd with result 1 to produce result 2. Further, the contents of field 1 are read and OR'd with result 2 to provide a final result, which is an image of XER with its fields, regardless of whether in-processor or in-memory.

[00121] As described herein, in accordance with an aspect of the present invention, a move from configuration state register instruction generates a sequence of moves from the in-processor portions, and a read for the portion stored in-memory. The contents of the read in-memory and in-processor portions are collated, e.g., using a sequence of, e.g., OR instructions. Further, a move to configuration state register instruction generates a sequence of moves to the in-processor portions, and a store for the portion stored in-memory.

[00122] In one aspect, when memory is assigned to configuration state registers, the offsets are architecturally (e.g., defined and externally visible) or micro-architecturally (defined but not externally visible) specified. For instance, an offset may be derived directly from the configuration state register number (or other indication).

[00123] As one example mapping, each configuration state register is mapped to the corresponding offset (in doublewords), i.e., base \* configuration state register #, in which configuration state register 1 is at a first location; configuration state register 2 is at the first location plus a defined number of bytes (e.g., 8), and so forth.

[00124] However, configuration state register numbers are non-contiguous, wasting memory, and cache efficiency. Thus, in another embodiment in accordance with an aspect of the present invention, the configuration state register number is not used to directly derive an offset into a memory page, rather configuration state registers are allocated offsets based on functional affinity. Thus, configuration state registers that are used together in common operations are allocated to the same or adjacent cache lines, to enhance cache locality. For example, EBB handling uses the following registers: e.g., EBBHR, EBBRR, BESCR, and TAR. TAR is not contiguous with

the others. However, they all are to be allocated to memory, so that they end up in the same cache line or an adjacent cache line.

**[00125]** One example of a linear mapping is depicted in FIGS. 15A-15B. As shown, in one example, a linear mapping 1500 is sparse. For instance, in one example, 8 KB (2 pages) is used, even though fewer than 1K of configuration state registers is mapped. Further, jointly used configuration state registers, such as EBBHR, EBBRR, BESCR, and TAR, are not contiguous. Additionally, groups of configuration state registers are not on an alignment boundary to ensure they are in the same cache line (e.g., 779 MMCR0; 780 SIAR; 781 SDAR; 782 MMCR1). Yet further, some configuration state registers may refer to the same register; e.g., different access permissions, subfields, etc. This is an inefficient use of cache. There is a lack of prefetch (to ensure each activity only suffers one cache miss); and an overly large cache foot print (resulting in an increased working set which reduces hit rate). Thus, in accordance with an aspect of the present invention, configuration state registers are not stored at, e.g.,  $\text{base} + (\text{idx} * 8)$ . Rather, they are stored at, for instance,  $\text{base} + \text{remap}[\text{idx}]$ .

**[00126]** This remap ensures groups are adjacent in order to share a cache line; it eliminates/reduces sparsity, providing a more efficient cache use; and handles multiple names. As one example, the remapping is static and is performed at processor design and provided in a data structure, such as a table, or by computation of a defined equation. As another example, the remapping is dynamic and determined by use. For instance, if tracking of registers shows that registers of a set of registers are used together, then those registers are grouped and placed adjacent to one another. Other possibilities exist.

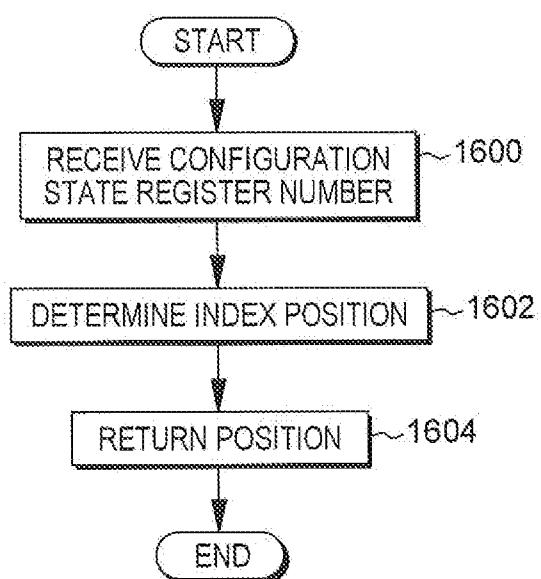

**[00127]** Further details of remapping are described with reference to FIG. 16. This processing is performed by a processor. In one example, a configuration state register number is obtained by the processor, STEP 1600. Based on the configuration state register number, an index position (a.k.a., an offset) into the memory unit (e.g., page) is determined, STEP 1602. This may be determined by a table look-up or by computation. The index position is returned to the requester (e.g., an internal operation), STEP 1604.

**[00128]** In a further example, a circuit that includes mapping logic is used. A configuration state register number is input to the mapping logic, and the output is a page index.

**[00129]** As described above, in one embodiment, the configuration state register numbers, as defined in the architecture, are remapped such that those configuration state registers that are used together are placed close to one another in order to provide a more efficient cache. This reduces the number of cache lines used for the configuration state registers and competes less with other programs for use of the cache. Further, it ensures that once a cache line is loaded with a particular configuration state register and the penalty is paid for a cache miss for that value, other configuration state registers that may also be used in conjunction with that configuration state register will hit in the cache and consequently not involve other cache miss penalties.

**[00130]** In a further embodiment, a sync\_o\_csr instruction writes a version stamp into a page when different offset assignments are possible. A version stamp may be used to adjust offsets when migrating a partition between different hosts; and/or to adjust offsets either directly in hardware (e.g., when a sync\_i\_csr may read an offset version number for a partition) or in software.

**[00131]** In accordance with another aspect of the present invention, a capability is provided to perform a bulk operation to store or load multiple configuration state registers. An individual load or store of a configuration state register is expensive, since each read or write is to be performed in-order, and is to complete before the next instruction is started. Further, correct exception/error sequencing is to be ensured, since a lack of renaming for in-processor configuration state registers disallows rollback. However, in accordance with one or more aspects of the present invention, bulk configuration state register load to and store from memory units, such as pages, are provided.

**[00132]** For instance, a store configuration state register instruction or operation (e.g., ST\_CSR) is used to store multiple in-processor configuration state registers in-memory (i.e., store the contents of the configuration state registers associated with the current context (e.g., application, thread, etc.) in select memory locations defined for the particular configuration state registers); and a load configuration state register instruction or operation (e.g., LD\_CSR) is used to load configuration state registers stored in-memory back to in-processor (i.e., load the contents of the configuration state registers associated with the current context from memory back into the processor).

**[00133]** In-processor (also referred to as non-memory backed) configuration state registers that may be stored in memory are assigned locations in memory, e.g., in backing memory units (e.g., pages). In one example, the memory locations and/or units are well-defined, pre-defined locations/units, and therefore, the instructions need not have an operand to specify the locations/units. In another embodiment, the specific locations/units may be specified as an operand of the instruction. Further in another embodiment, each instruction may include an operand to indicate specific registers to be stored/loaded. Other variations are also possible.

**[00134]** Further, pages are just one example of memory units. Other units are possible. Also, although a page is typically 4 KB, in other embodiments, it may be other sizes. Many possibilities exist.

**[00135]** In addition to the ST\_CSR and LD\_CSR instructions described above, another instruction that may be used, in accordance with an aspect of the present invention, is mtspr TCBR, next\_u->csr\_page. This instruction is used to load the base address of the memory region used to store the in-memory configuration state registers for a particular context (e.g., processor, thread, etc.) in a register, such as TCBR. This address is then used in processing that employs a base address, as described herein. In this instruction, next\_u->csr\_page refers to the user data structure that stores data for the context issuing the instruction. This data includes the base address of the memory unit (e.g., page) storing the in-memory configuration state registers. Although mtspr is specified, other move to configuration state register (mtcsr) instructions may be used. Also, TCBR is just one example of a base register. Other base registers may be specified. Many variations are possible.

**[00136]** In addition to the above instructions, two synchronization instructions may be provided to synchronize the cache with memory or in-processor registers. For example, sync\_o\_csr is used to synchronize the cache and one or more in-memory configuration state registers; and sync\_i\_csr is used to synchronize the cache and one or more in-processor configuration state registers.

**[00137]** As described herein, in one aspect, multiple configuration state registers are loaded or stored. There are no intervening exceptions; i.e., exceptions are avoided; the operation is either completed on all the configuration state registers of the operation or none. Further, there are no page faults (e.g., pages are pinned; also once a page has been loaded, references are guaranteed to the same page). If desired, hardware can make a process restartable; e.g., a load or store sequence in microcode or a state machine.

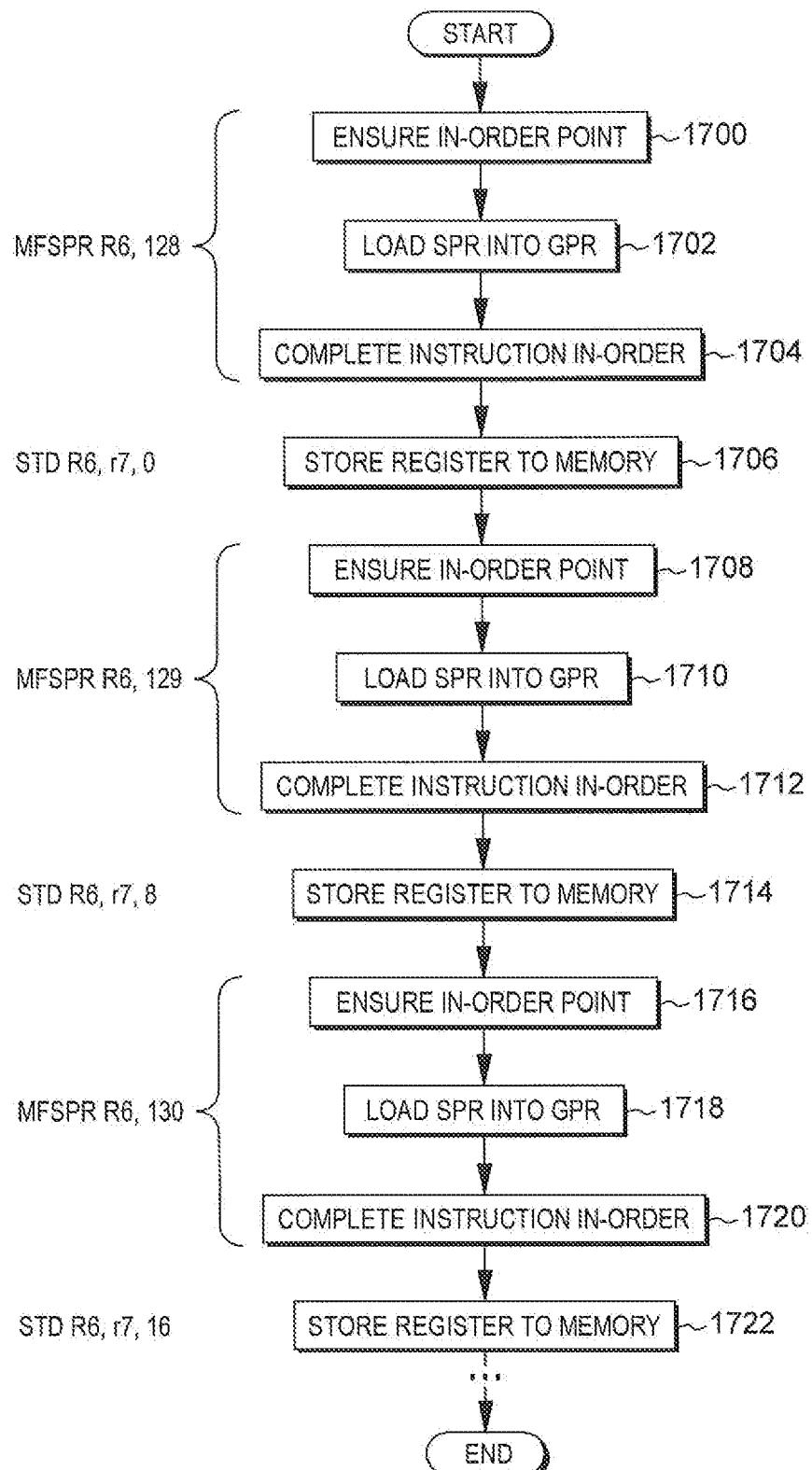

**[00138]** By using instructions to store/load multiple configuration state registers, certain expensive operations, such as ensure in-order point and complete instruction in-order, are used less frequently, as described with reference to FIGS. 17A-17C. The processing of FIGS. 17A-17C is performed by a processor.

**[00139]** Referring to FIG. 17A, one example of using individual instructions (i.e., not a bulk operation) to store a plurality of configuration state registers to memory is described with reference to FIG. 17A. In one example, to move a configuration state register to memory, a move from configuration state register instruction and a store instruction are used. For instance, in one example, the configuration state register is an SPR and the move from configuration state register instruction is an mfspr. Other configuration state registers and corresponding instructions may be used.

**[00140]** In this example, based on execution of a mfspr instruction, such as a Move from SPR (mfspr) instruction, an in-order point is ensured, STEP 1700. Then, contents of the configuration state register (e.g., SPR) specified by the instruction are copied from the configuration state register into, e.g., a general purpose register (GPR), STEP 1702. The instruction is completed in-order, STEP 1704. Thereafter, via a store instruction (STD), contents of the general purpose register are stored to memory, STEP 1706. This same process is repeated for each configuration state register to be stored in memory (e.g., STEPS 1708-1722), which may be many configuration state registers. Thus, requiring an ensure in-order point and complete instruction in-order operation for each configuration state register to be stored to memory.

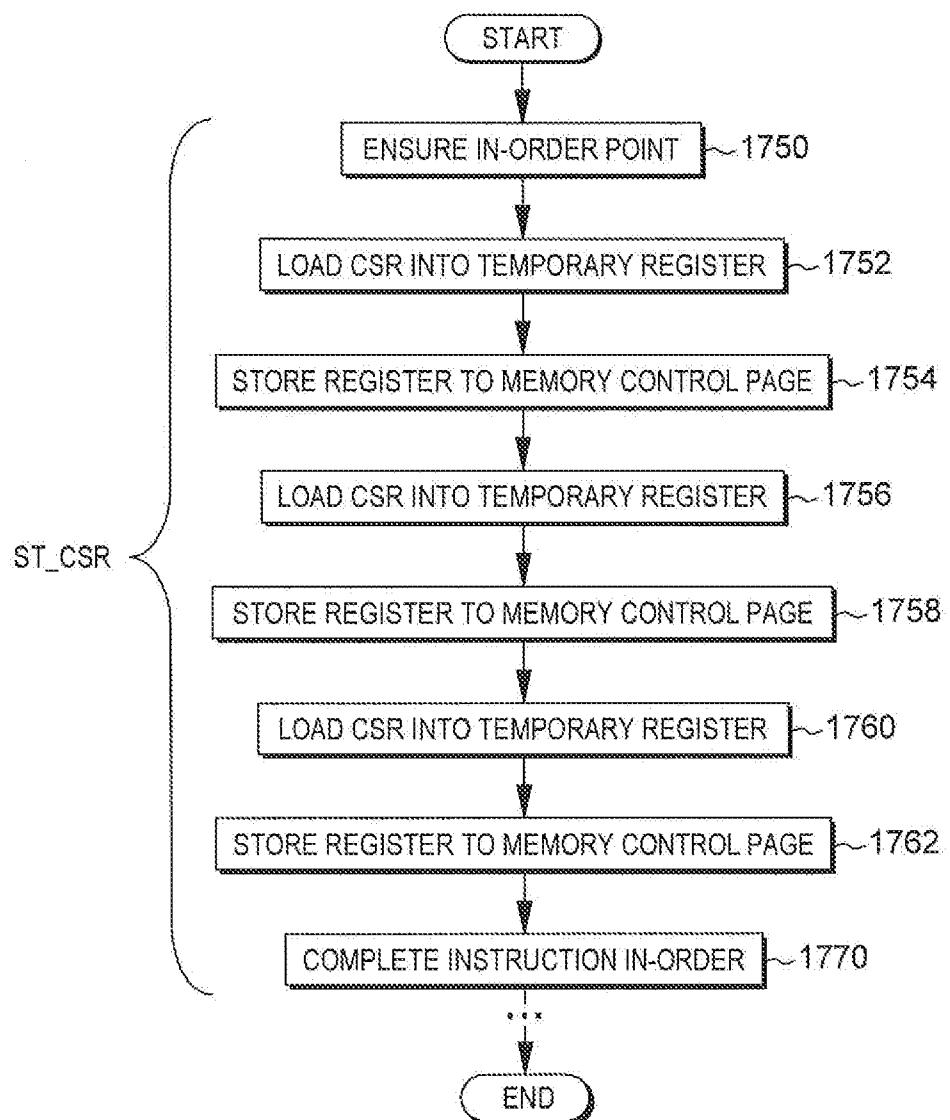

**[00141]** However, in accordance with an aspect of the present invention, a store configuration state register (ST\_CSR) instruction is provided that stores multiple configuration state registers in memory using a single ensure in-order point and a single complete instruction in-order operation, as described with reference to FIG. 17B.

**[00142]** Referring to FIG. 17B, based on execution of a store configuration state register instruction (ST\_CSR), an in-order point is reached, STEP 1750. Then, contents of a selected configuration state register are loaded into a temporary register, STEP 1752. Further, the contents of the temporary register are then stored to memory (e.g., a memory control page), STEP 1754. The load/store operations are repeated one or more times

1756-1762 for one or more additional configuration state registers. Subsequent to copying the chosen configuration state registers to memory (which may be many such registers), the instruction is completed in-order, STEP 1770.

**[00143]** In one example, the ST\_CSR instruction does not have an operand to specify the registers to be copied; instead, all of the in-processor configuration state registers of the current context (e.g., process, thread, etc.) are copied. In another example, an operand may be included and used to specify one or more configuration state registers to be copied to memory. Other variations are also possible.

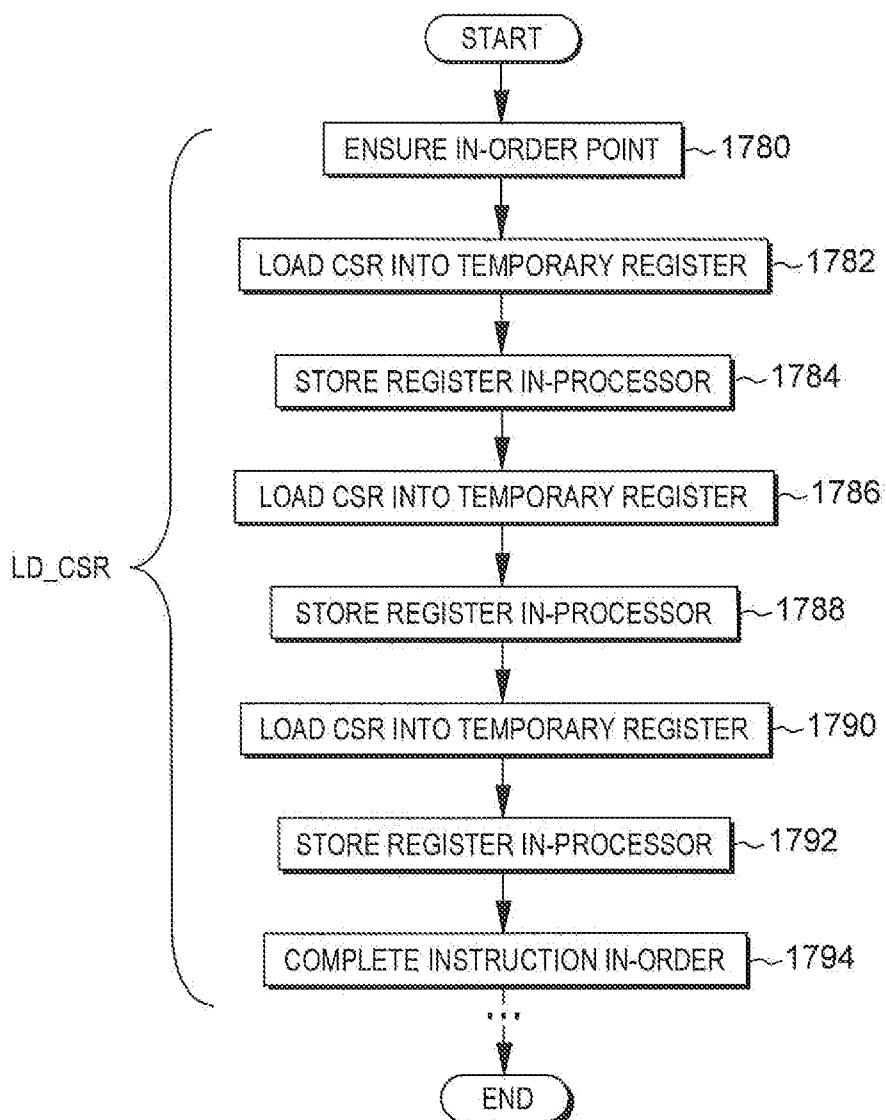

**[00144]** In a further example, multiple configuration state registers may be copied from memory to in-processor using a bulk load operation (e.g., LD\_CSR).

**[00145]** Referring to FIG. 17C, based on execution of a load configuration state register (LD\_CSR) instruction, an in-order point is ensured, STEP 1780. Then, contents of a selected configuration state register are obtained from memory and loaded into a temporary register, STEP 1782. Then, the contents of the temporary register are stored in a corresponding in-processor configuration state register, STEP 1784. The load/store operations are repeated one or more times 1786-1792 for one or more (and possibly many) additional configuration state registers. Thereafter, the instruction is completed in-order, STEP 1794.

**[00146]** In one example, the LD\_CSR instruction does not have an operand to specify the registers to be copied; instead, all of the configuration state registers of the current context (e.g., process, thread, etc.) are copied. In another example, an operand may be included and used to specify one or more configuration state registers to be copied from memory.