## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2007/0170529 A1 Partridge et al.

Jul. 26, 2007 (43) Pub. Date:

(54) WAFER ENCAPSULATED

MICROELECTROMECHANICAL STRUCTURE AND METHOD OF MANUFACTURING SAME

(76) Inventors:

Aaron Partridge, Cupertino, CA (US); Markus Lutz, Los Altos, CA (US); Pavan Gupta, Belmont, CA (US)

Correspondence Address: **NEIL A. STEINBERG** 2665 MARINE WAY, SUITE 1150 **MOUNTAIN VIEW, CA 94043**

(21) Appl. No.: 11/545,052

(22) Filed: Oct. 6, 2006

## Related U.S. Application Data

Division of application No. 11/336,521, filed on Jan. 20, 2006.

## **Publication Classification**

(51) Int. Cl. H01L 29/84 (2006.01)

(57)ABSTRACT

There are many inventions described and illustrated herein. In one aspect, the present inventions relate to devices, systems and/or methods of encapsulating and fabricating electromechanical structures or elements, for example, accelerometer, gyroscope or other transducer (for example, pressure sensor, strain sensor, tactile sensor, magnetic sensor and/or temperature sensor), filter or resonator. The fabricating or manufacturing microelectromechanical systems of the present invention, and the systems manufactured thereby, employ wafer bonding encapsulation techniques.

의

의

FIGURE 14

FIGURE 15A

FIGURE 15B

읻

임

FIGURE 24B

읻

FIGURE 28B

임

FIGURE 30B

FIGURE 30G

FIGURE 30H

FIGURE 33B

의

FIGURE 35B

**FIGURE 37A**

FIGURE 37B

## FIGURE 37C

FIGURE 39C

위

임

FIGURE 41B

의

FIGURE 43A

FIGURE 43B

FIGURE 43G

FIGURE 43H

임

FIGURE 45B

임

의

9

임

임

위

FIGURE 51F

FIGURE 53G

FIGURE 57B

## WAFER ENCAPSULATED MICROELECTROMECHANICAL STRUCTURE AND METHOD OF MANUFACTURING SAME

## **BACKGROUND**

[0001] There are many inventions described and illustrated herein. The inventions relate to encapsulation electromechanical structures, for example, microelectromechanical and/or nanoelectromechanical structure (collectively hereinafter "microelectromechanical structures") and devices/systems including same; and more particularly, in one aspect, for fabricating or manufacturing microelectromechanical systems having mechanical structures that are encapsulated using wafer level encapsulation techniques, and devices/systems incorporated same.

[0002] Microelectromechanical systems, for example, gyroscopes, resonators and accelerometers, utilize micromachining techniques (i.e., lithographic and other precision fabrication techniques) to reduce mechanical components to a scale that is generally comparable to microelectronics. Microelectromechanical systems typically include a mechanical structure fabricated from or on, for example, a silicon substrate using micromachining techniques.

[0003] The mechanical structures are typically sealed in a chamber. The delicate mechanical structure may be sealed in, for example, a hermetically sealed metal or ceramic container or bonded to a semiconductor or glass-like substrate having a chamber to house, accommodate or cover the mechanical structure. In the context of the hermetically sealed metal or ceramic container, the substrate on, or in which, the mechanical structure resides may be disposed in and affixed to the metal or ceramic container. The hermetically sealed metal or ceramic container often also serves as a primary package as well.

[0004] In the context of the semiconductor or glass-like substrate packaging technique, the substrate of the mechanical structure may be bonded to another substrate (i.e., a "cover" wafer) whereby the bonded substrates form a chamber within which the mechanical structure resides. In this way, the operating environment of the mechanical structure may be controlled and the structure itself protected from, for example, inadvertent contact.

# SUMMARY OF THE INVENTIONS

[0005] There are many inventions described and illustrated herein. The present inventions are neither limited to any single aspect nor embodiment thereof, nor to any combinations and/or permutations of such aspects and/or embodiments. Moreover, each of the aspects of the present inventions, and/or embodiments thereof, may be employed alone or in combination with one or more of the other aspects of the present inventions and/or embodiments thereof. For the sake of brevity, many of those permutations and combinations will not be discussed separately herein.

[0006] In one aspect, the present inventions are directed to a microelectromechanical device comprising a first substrate, a chamber, and a microelectromechanical structure, wherein the microelectromechanical structure is (i) formed from a portion of the first substrate and (ii) at least partially disposed in the chamber. In addition, in this aspect, the microelectromechanical device further includes a second substrate, bonded to the first substrate, wherein a surface of

the second substrate forms a wall of the chamber, as well as a contact. The contact includes (1) a first portion of the contact is (i) formed from a portion of the first substrate and (ii) at least a portion thereof is disposed outside the chamber, and (2) a second portion of the contact is formed from a portion of the second substrate.

[0007] In one embodiment, the second substrate includes polycrystalline silicon, porous polycrystalline silicon, amorphous silicon, silicon carbide, silicon/germanium, germanium, or gallium arsenide. The first substrate may include polycrystalline silicon, porous polycrystalline silicon, amorphous silicon, silicon carbide, silicon/germanium, germanium, or gallium arsenide.

[0008] In addition, in one embodiment, the first portion of the contact is a semiconductor material having a first conductivity, the second substrate is a semiconductor material having a second conductivity, and the second portion of the contact is a semiconductor material having the first conductivity. Notably, the second portion of the contact may be a polycrystalline or monocrystalline silicon that is counterdoped to include the first conductivity.

[0009] The microelectromechanical device may further include a trench, disposed in the second substrate and around at least a portion of the second portion of the contact. The trench may include a first material (for example, an insulation material) disposed therein to electrically isolate the second portion of the contact from the second substrate.

[0010] Notably, the first substrate is a semiconductor on insulator substrate.

[0011] In another principle aspect, the present inventions are directed to a microelectromechanical device comprising a first substrate, a second substrate, wherein the second substrate is bonded to the first substrate, a chamber, and a microelectromechanical structure, wherein the microelectromechanical structure is (i) formed from a portion of the second substrate and (ii) at least partially disposed in the chamber. The microelectromechanical device may further include a third substrate, bonded to the second substrate, wherein a surface of the third substrate forms a wall of the chamber. The microelectromechanical device may also include a contact having (1) a first portion of the contact is (i) formed from a portion of the second substrate and (ii) at least a portion thereof is disposed outside the chamber, and (2) a second portion of the contact is formed from a portion of the third substrate.

[0012] The second substrate may include polycrystalline silicon, porous polycrystalline silicon, amorphous silicon, silicon carbide, silicon/germanium, germanium, or gallium arsenide. The third substrate may include polycrystalline silicon, porous polycrystalline silicon, amorphous silicon, silicon carbide, silicon/germanium, germanium, or gallium arsenide.

[0013] In one embodiment, the first portion of the contact is a semiconductor material having a first conductivity, the third substrate is a semiconductor material having a second conductivity, and the second portion of the contact is a semiconductor material having the first conductivity. Notably, in one embodiment, the second portion of the contact may be a polycrystalline or monocrystalline silicon that is counterdoped to include the first conductivity.

[0014] The microelectromechanical device may further include a trench, disposed in the third substrate and around at least a portion of the second portion of the contact. The trench may include a first material (for example, an insula-

tion material) disposed therein to electrically isolate the second portion of the contact from the third substrate.

[0015] The microelectromechanical device may also include an isolation region disposed in the second substrate such that the trench is aligned with and juxtaposed to the isolation region. In this embodiment, the first portion of the contact may be a semiconductor material having a first conductivity, the isolation region may be a semiconductor material having a second conductivity, and the second portion of the contact may be a semiconductor material having the first conductivity. A trench may be included to electrically isolate the second portion of the contact from the second substrate. The trench may include a semiconductor material, disposed therein, having the second conductivity. [0016] In another embodiment, the microelectromechanical device may include an isolation region disposed in the first substrate such that the first portion of the contact is aligned with and juxtaposed to the isolation region.

[0017] In yet another embodiment, the microelectromechanical device may include a first isolation region and a second isolation region. The first isolation region may be disposed in the first substrate such that the first portion of the contact is aligned with and juxtaposed to the first isolation region. The second isolation region may be disposed in the second substrate such that the second portion of the contact is aligned with and juxtaposed to the second isolation region. In this embodiment, the first and second portions of the contact may be semiconductor materials having a first conductivity, and the first and second isolation regions may be semiconductor materials having the second conductivity. [0018] The microelectromechanical device of this embodiment may also include a trench, disposed in the third substrate and around at least a portion of the second portion of the contact. The trench may include a first material (for example, an insulator material) disposed therein to electrically isolate the second portion of the contact from the third substrate. The trench may be aligned with and juxtaposed to the second isolation region.

[0019] Notably, all forms of bonding, whether now known or later developed, are intended to fall within the scope of the present invention. For example, bonding techniques such as fusion bonding, anodic-like bonding, silicon direct bonding, soldering (for example, eutectic soldering), thermo compression, thermo-sonic bonding, laser bonding and/or glass reflow bonding, and/or combinations thereof.

[0020] Moreover, any of the embodiments described and illustrated herein may employ a bonding material and/or a bonding facilitator material (disposed between substrates, for example, the second and third substrates) to, for example, enhance the attachment of or the "seal" between the substrates (for example, the first and second, and/or the second and third), address/compensate for planarity considerations between substrates to be bonded (for example, compensate for differences in planarity between bonded substrates), and/or to reduce and/or minimize differences in thermal expansion (that is materials having different coefficients of thermal expansion) of the substrates and materials therebetween (if any). Such materials may be, for example, solder, metals, frit, adhesives, BPSG, PSG, or SOG, or combinations thereof.

[0021] Again, there are many inventions, and aspects of the inventions, described and illustrated herein. This Summary of the Inventions is not exhaustive of the scope of the present inventions. Moreover, this Summary of the Inventions is not intended to be limiting of the inventions and should not be interpreted in that manner. While certain embodiments have been described and/or outlined in this Summary of the Inventions, it should be understood that the present inventions are not limited to such embodiments, description and/or outline, nor are the claims limited in such a manner. Indeed, many others embodiments, which may be different from and/or similar to, the embodiments presented in this Summary, will be apparent from the description, illustrations and claims, which follow. In addition, although various features, attributes and advantages have been described in this Summary of the Inventions and/or are apparent in light thereof, it should be understood that such features, attributes and advantages are not required whether in one, some or all of the embodiments of the present inventions and, indeed, need not be present in any of the embodiments of the present inventions.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0022] In the course of the detailed description to follow, reference will be made to the attached drawings. These drawings show different aspects of the present inventions and, where appropriate, reference numerals illustrating like structures, components, materials and/or elements in different figures are labeled similarly. It is understood that various combinations of the structures, components, materials and/or elements, other than those specifically shown, are contemplated and are within the scope of the present inventions. [0023] FIG. 1A is a block diagram representation of a mechanical structure disposed on a substrate and encapsulated via at least a second substrate;

[0024] FIG. 1B is a block diagram representation of a mechanical structure and circuitry, each disposed on one or more substrates and encapsulated via a substrate;

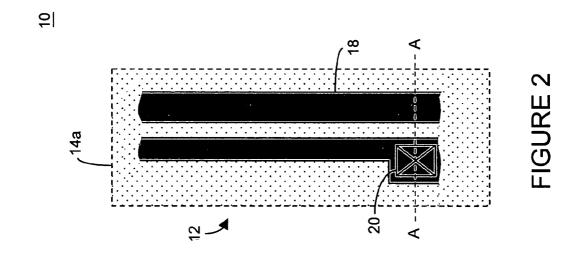

[0025] FIG. 2 illustrates a top view of a portion of a mechanical structure of a conventional resonator, including moveable electrode, fixed electrode, and a contact;

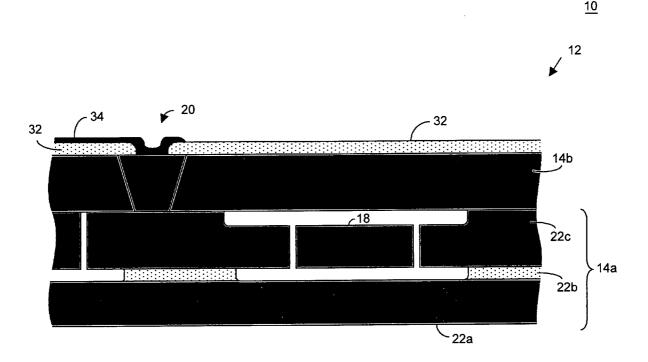

[0026] FIG. 3 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the first substrate employs an SOI wafer;

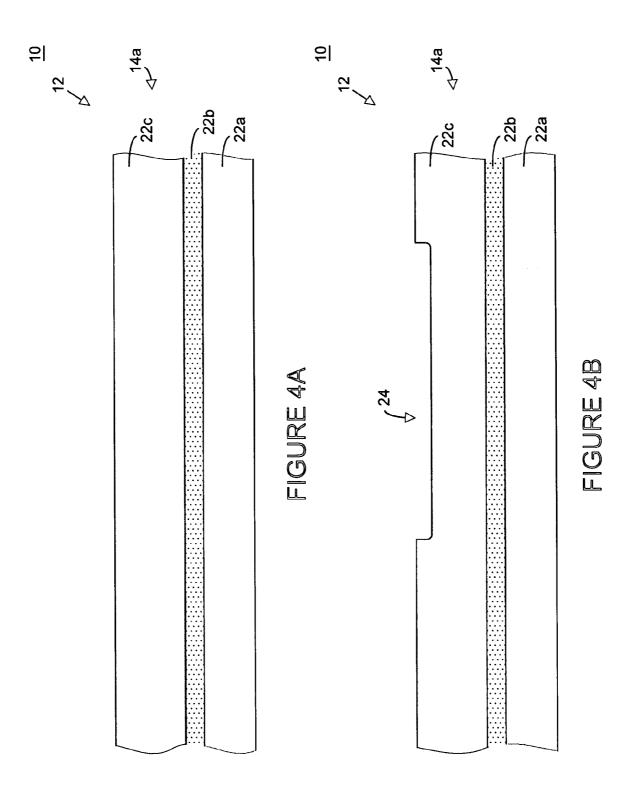

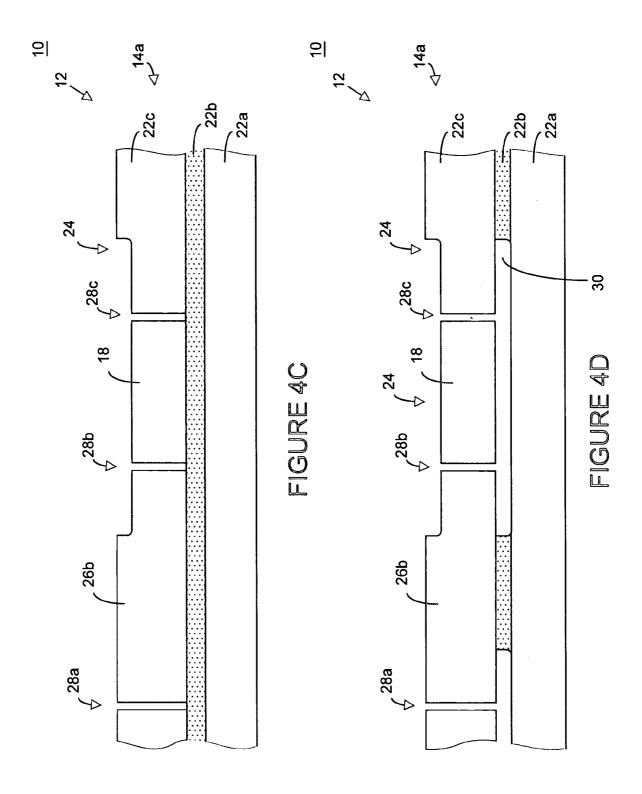

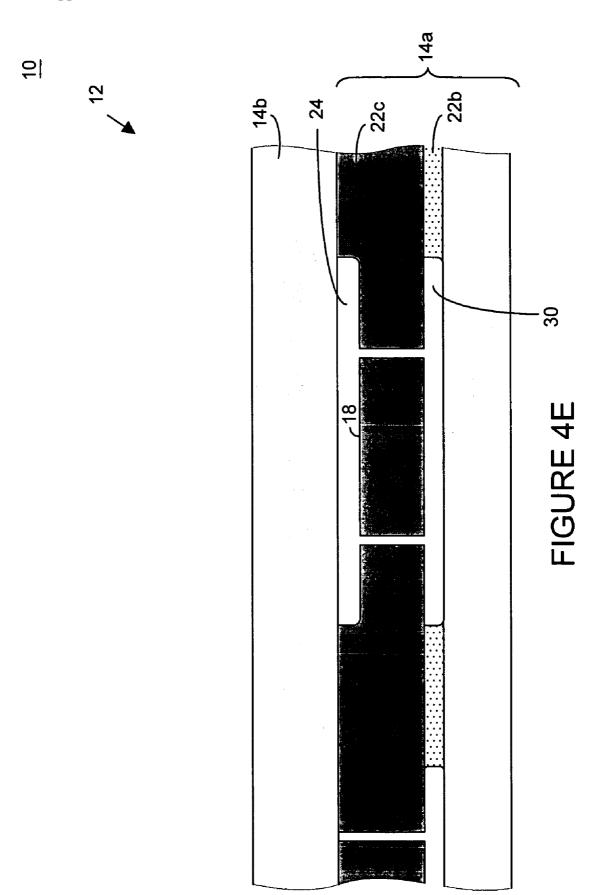

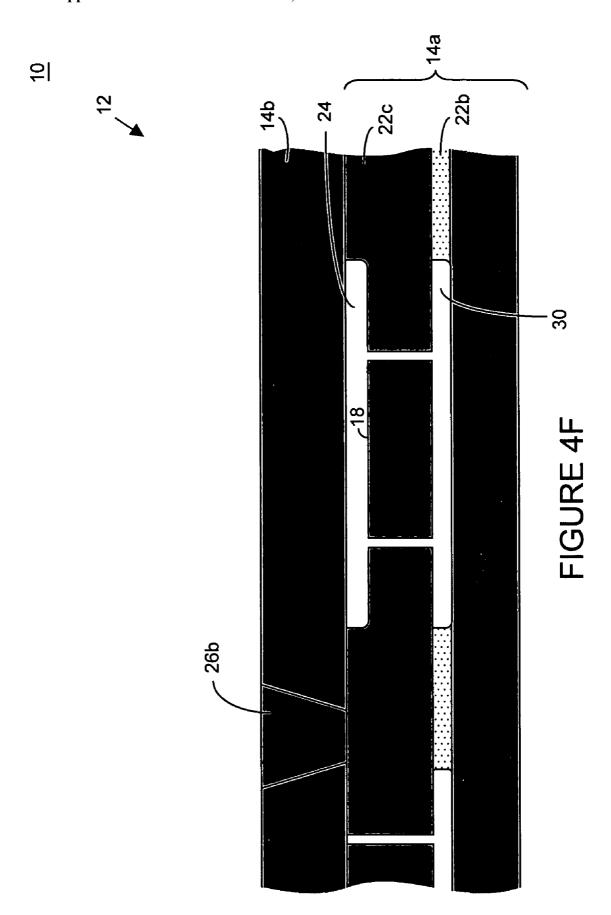

[0027] FIGS. 4A-4H illustrate cross-sectional views (sectioned along dotted line A-A' of FIG. 2) of the fabrication of the mechanical structure of FIGS. 2 and 3 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions:

[0028] FIG. 5 illustrates a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2, wherein microelectromechanical system includes electronic or electrical circuitry in conjunction with micromachined mechanical structure of FIG. 2, in accordance with an exemplary embodiment of the present inventions;

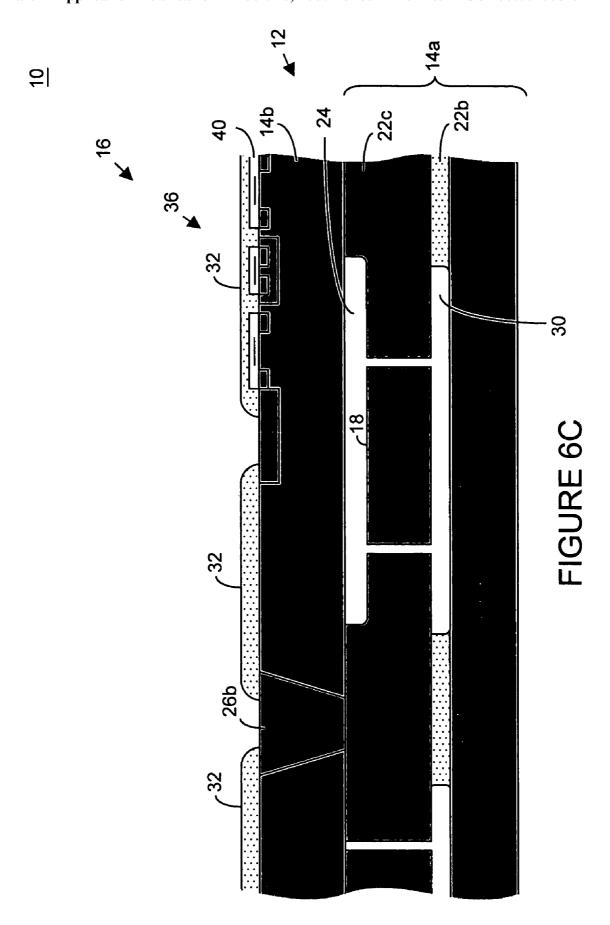

[0029] FIGS. 6A-6D illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 5 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

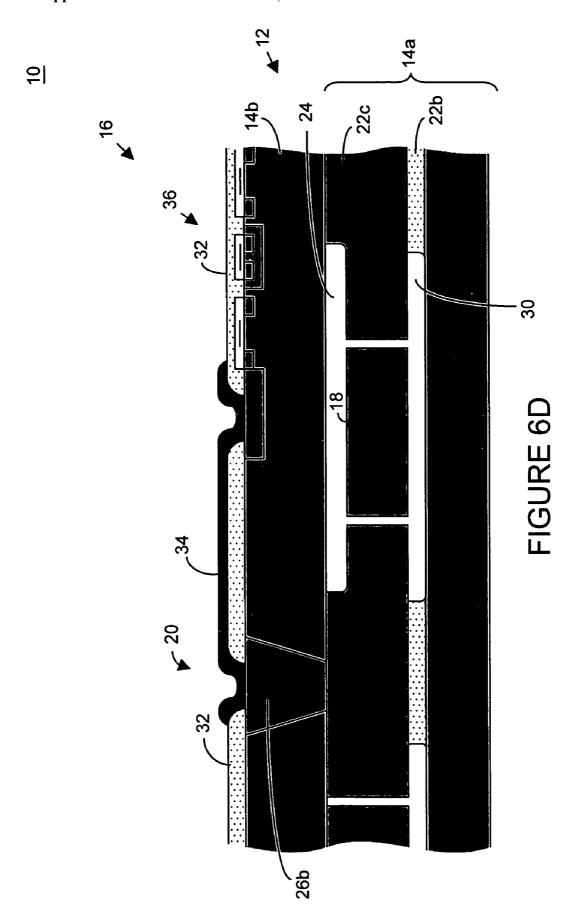

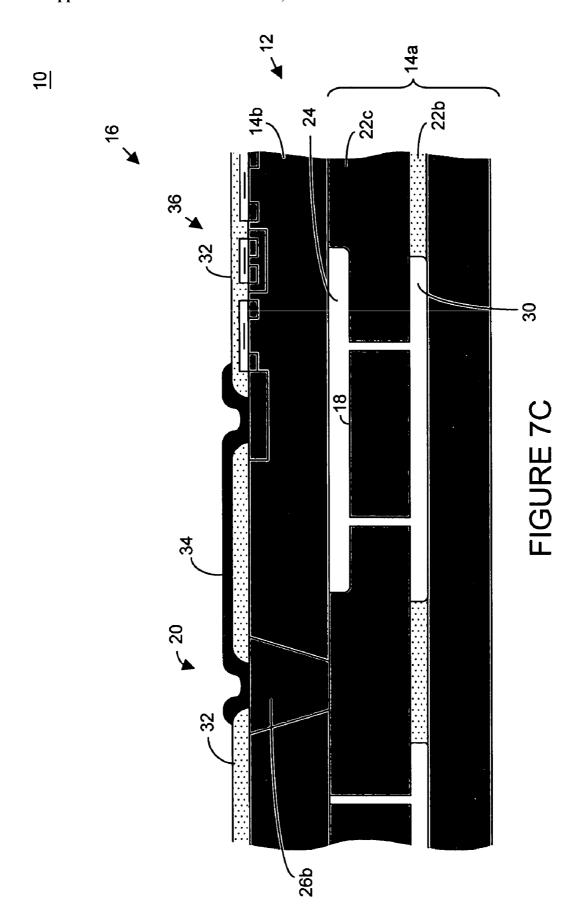

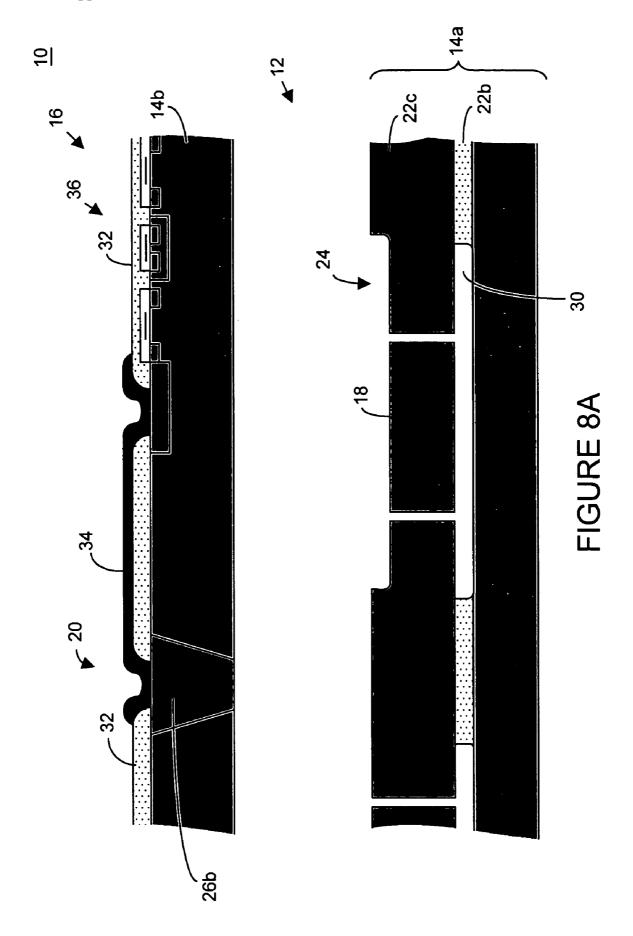

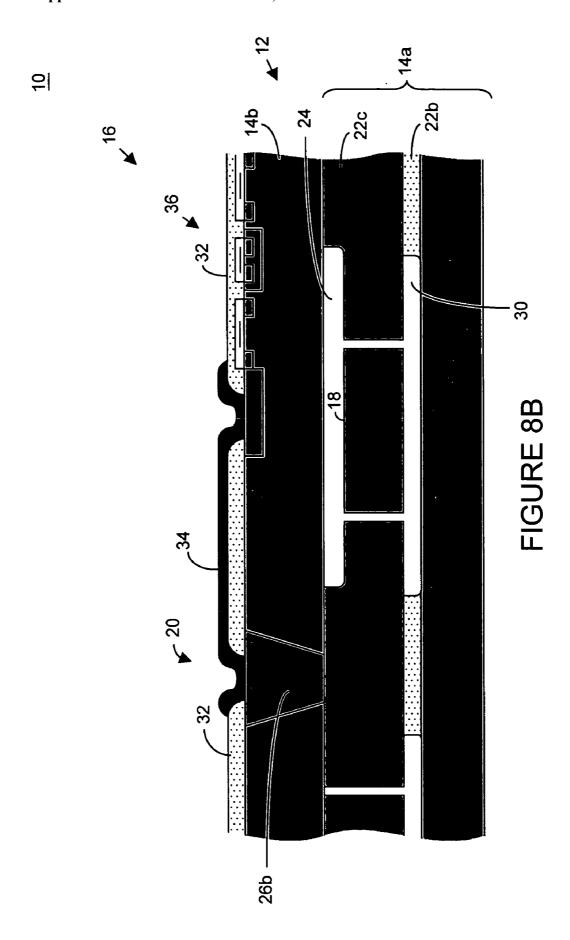

[0030] FIGS. 7A-7C, and 8A and 8B illustrate crosssectional views of two exemplary embodiments of the fabrication of the portion of the microelectromechanical system of FIG. 5 using processing techniques wherein electronic or electrical circuitry (at various stages of completeness) is formed in the second substrate prior to encapsulating the mechanical structure via securing the second substrate to the first substrate;

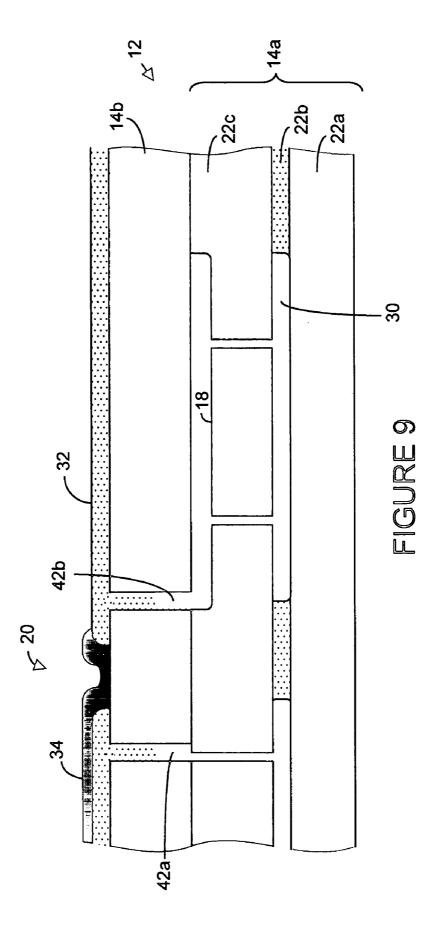

[0031] FIG. 9 illustrates a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2, wherein micromachined mechanical structure of FIG. 2 includes an isolation trench to electrically isolate the contact, in accordance with an exemplary embodiment of the present inventions;

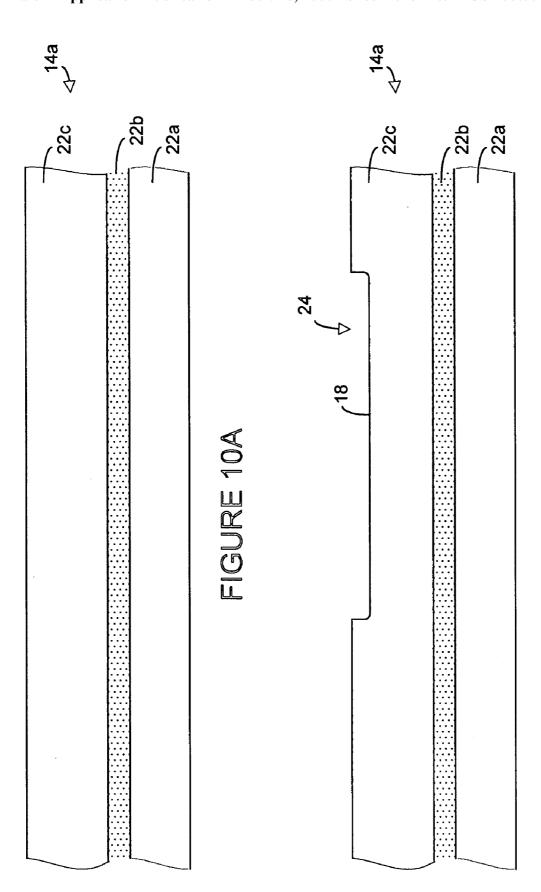

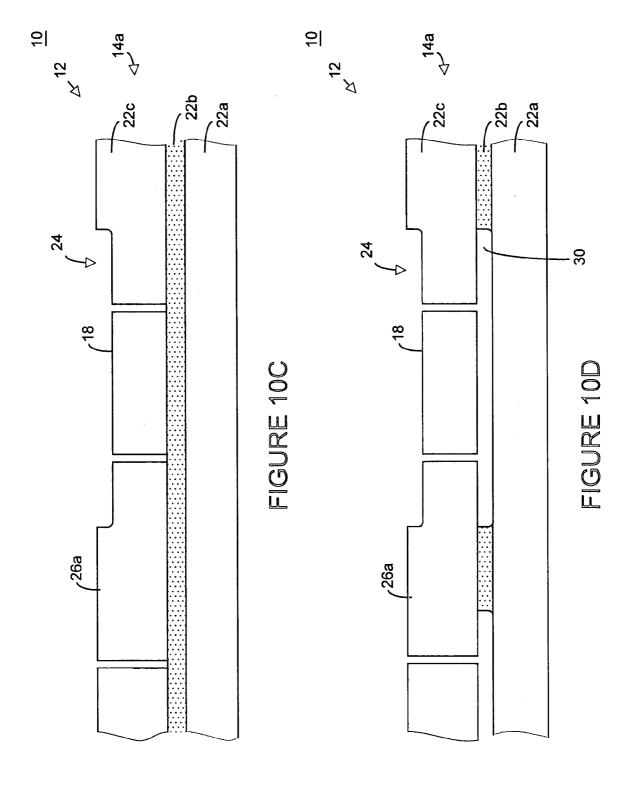

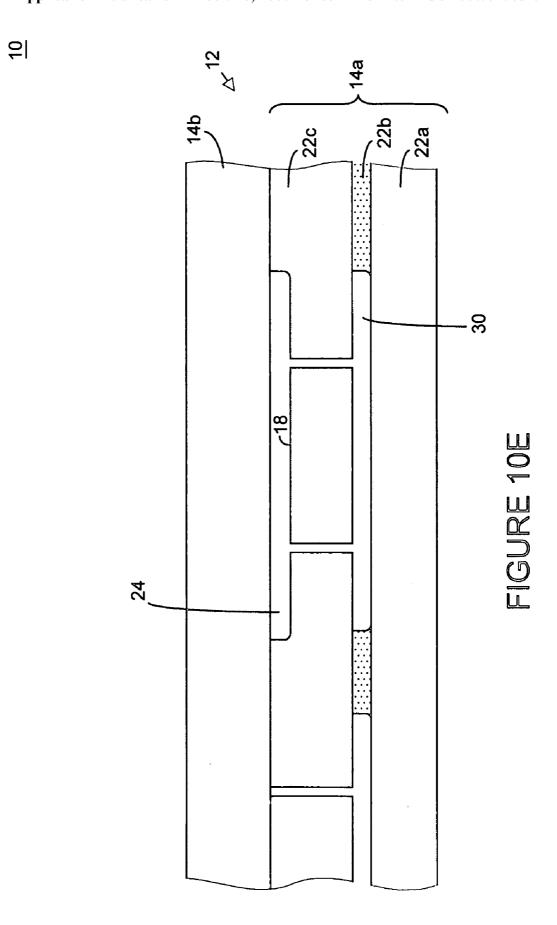

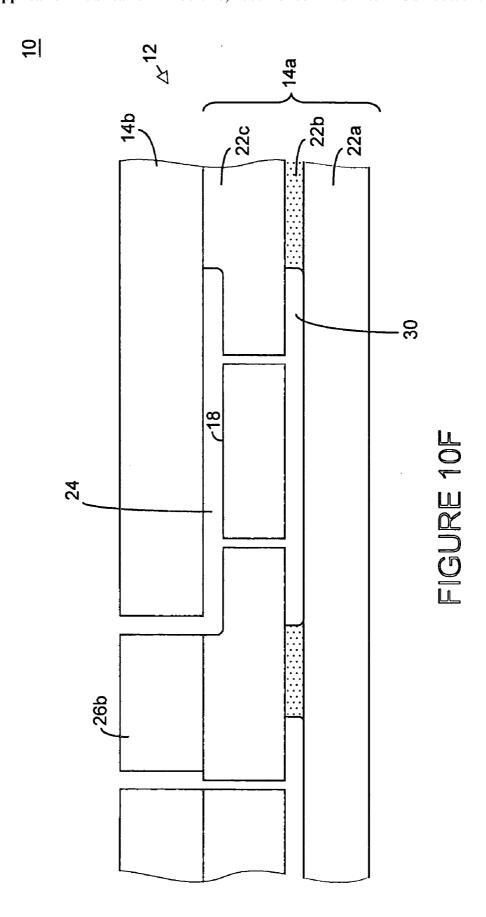

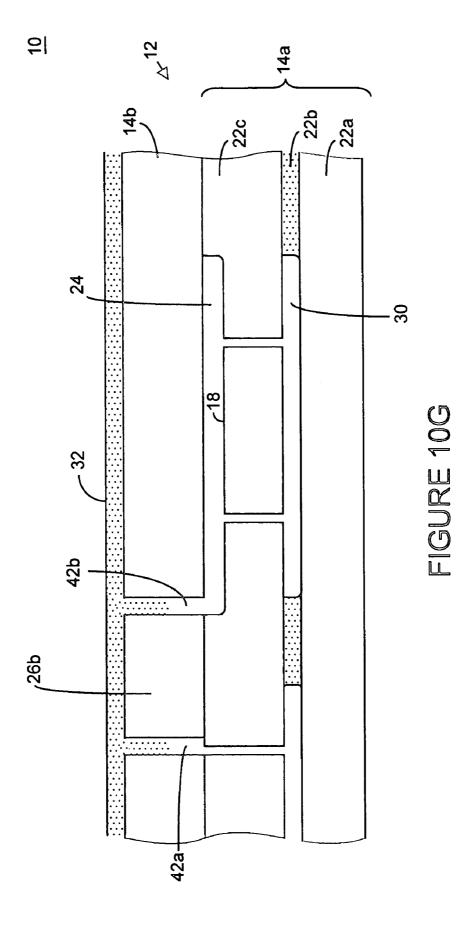

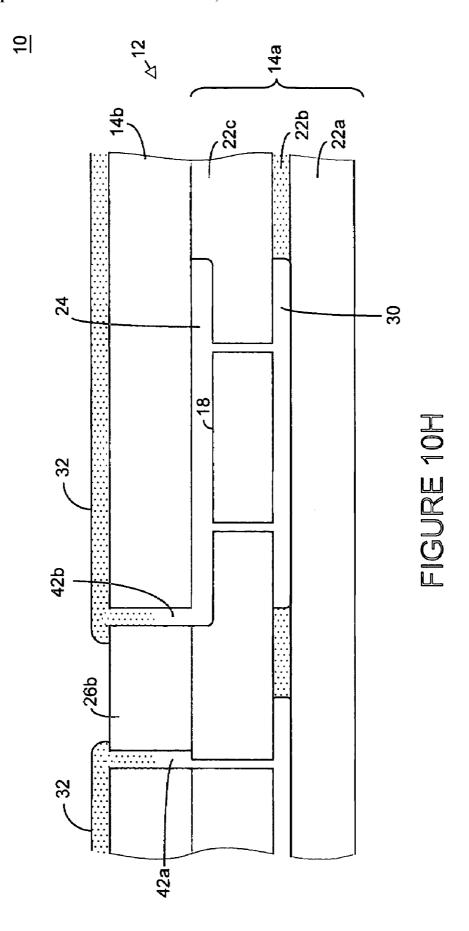

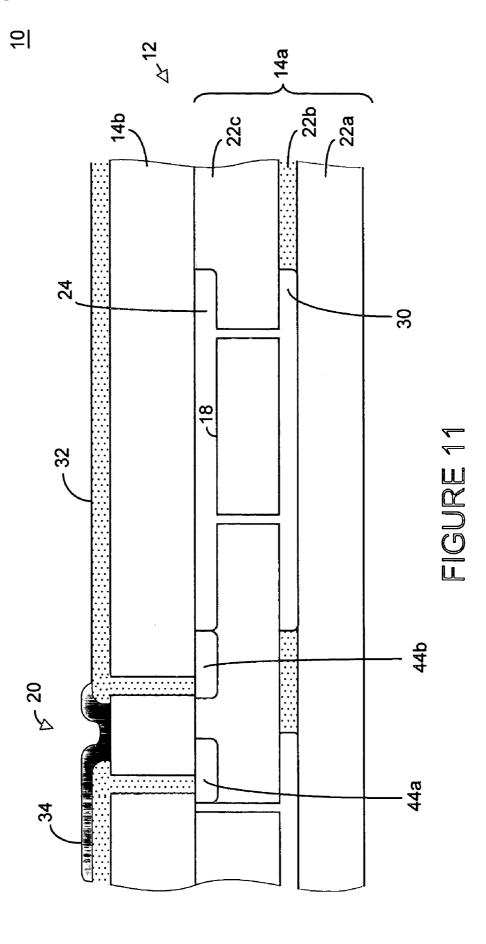

[0032] FIGS. 10A-10I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 9 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

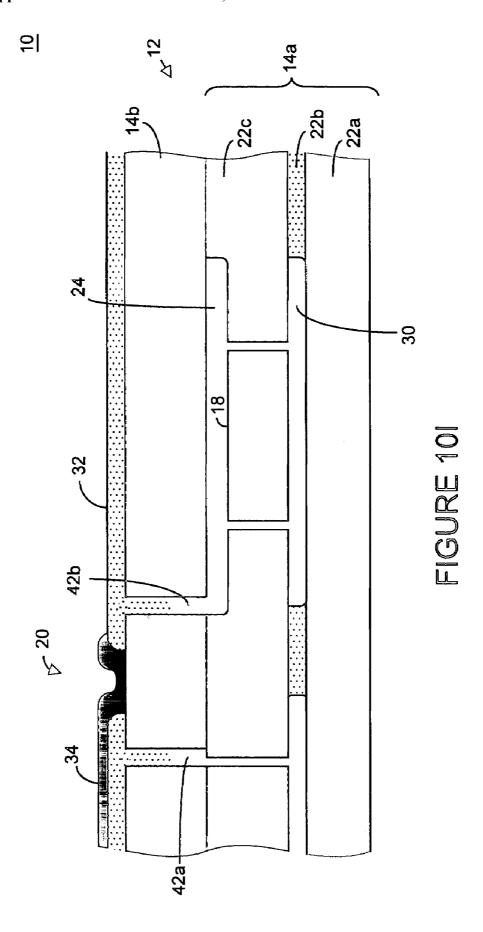

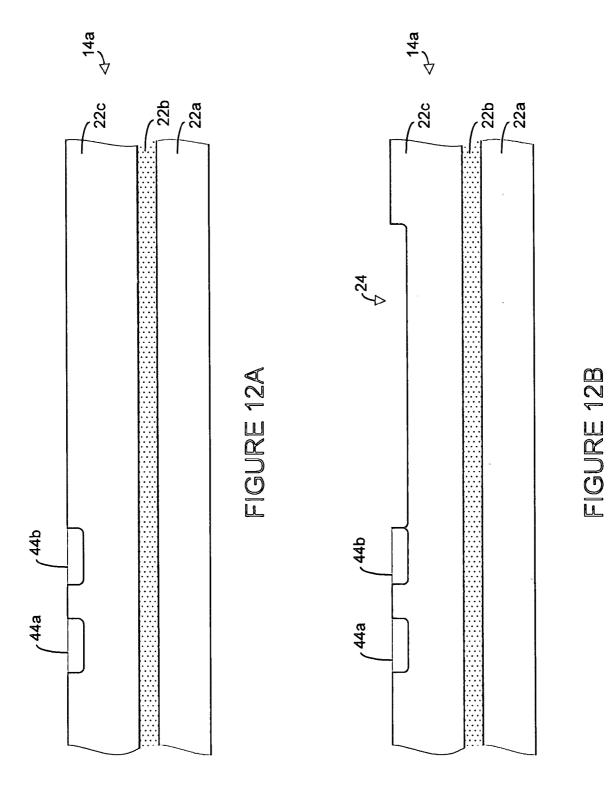

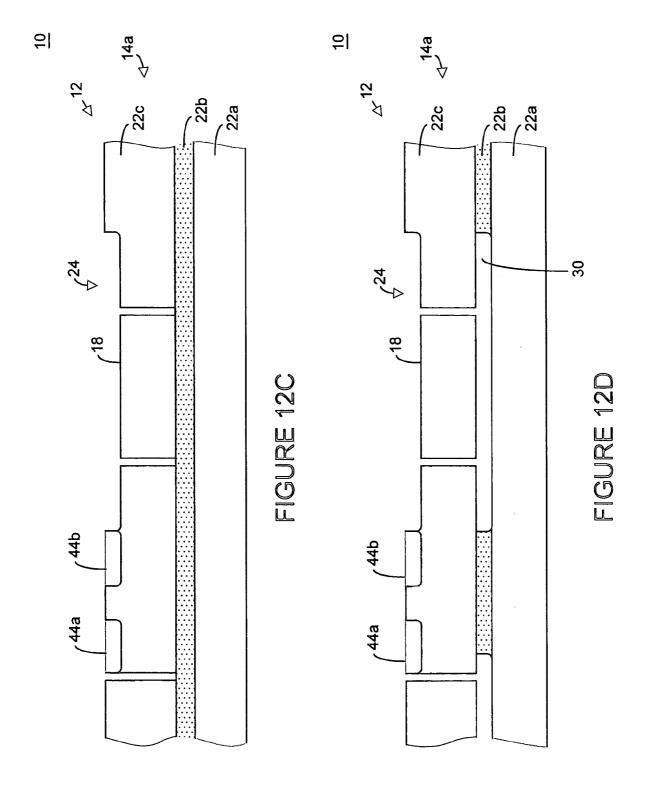

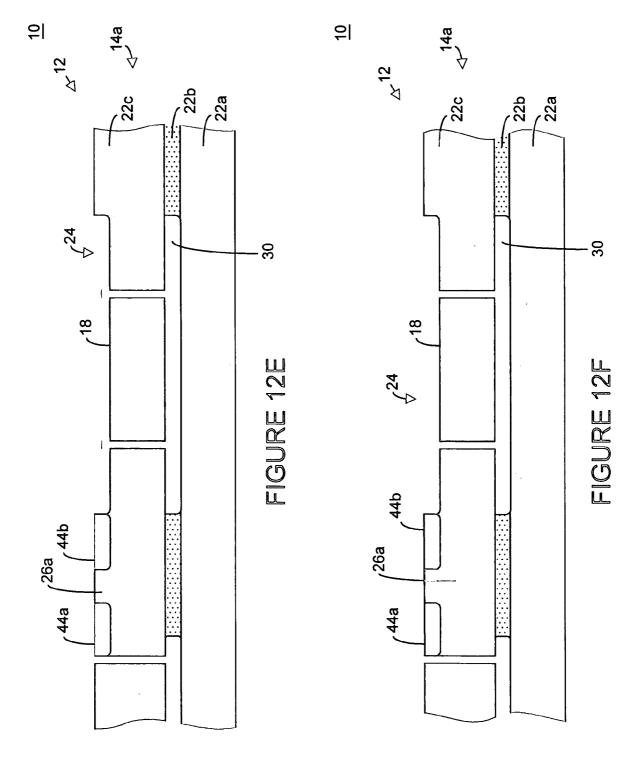

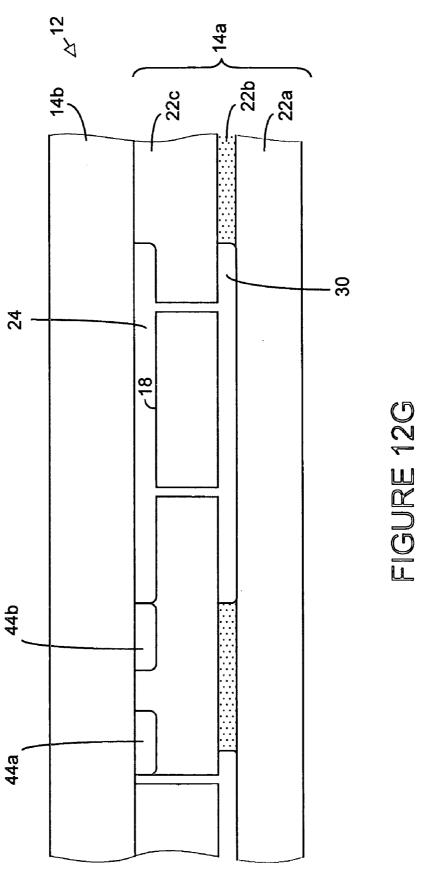

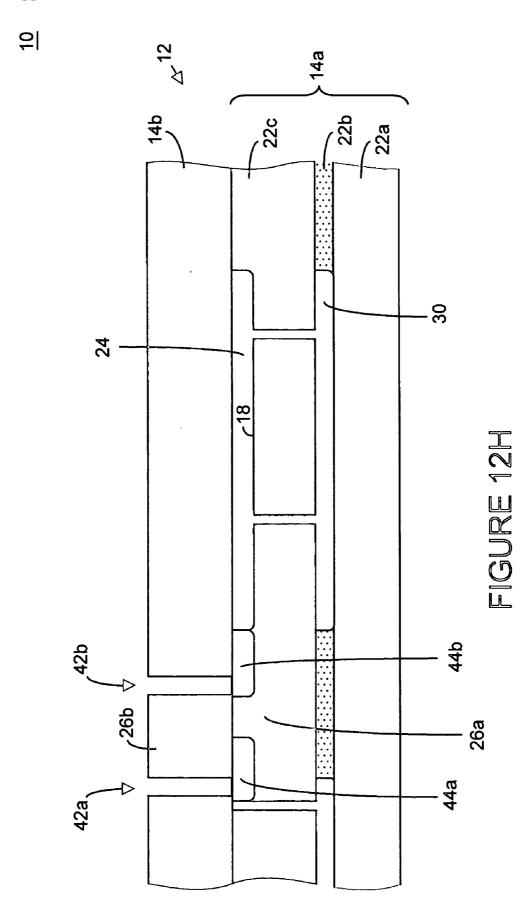

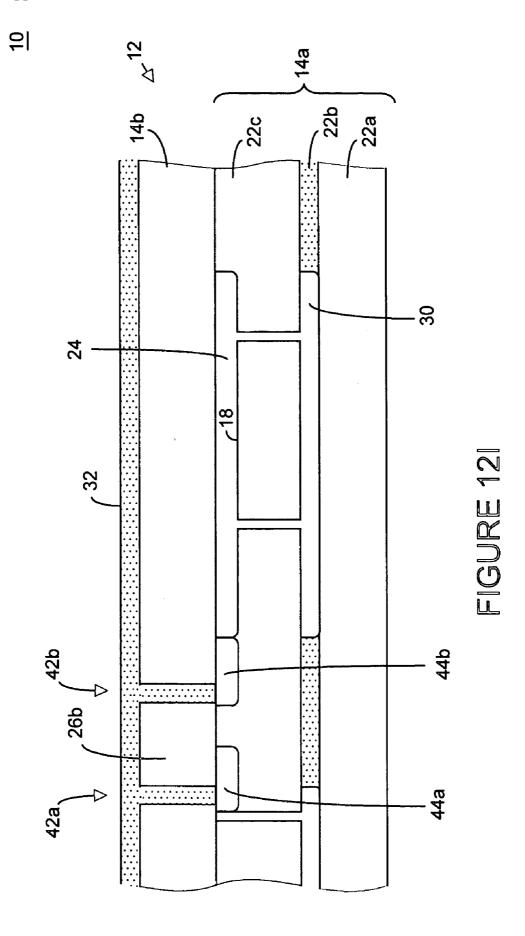

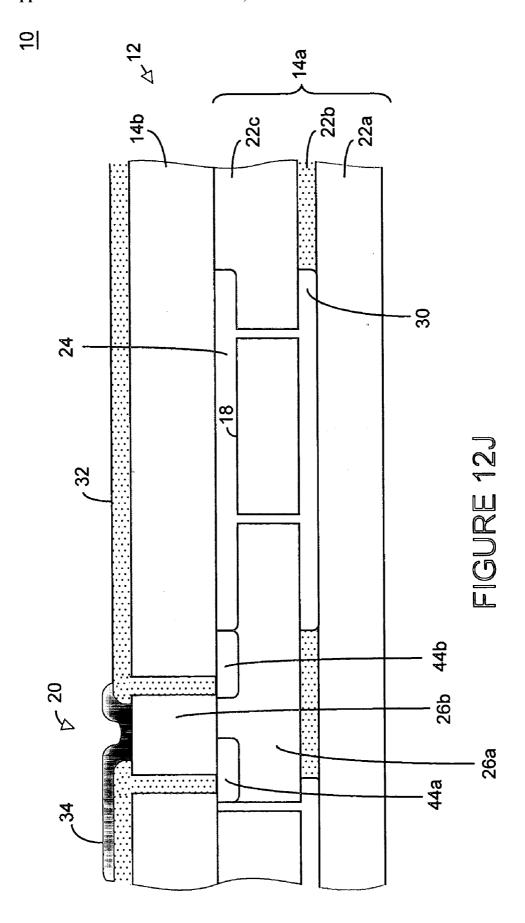

[0033] FIG. 11 illustrates a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2, wherein micromachined mechanical structure of FIG. 2 includes isolation regions and an isolation trench (aligned therewith) to electrically isolate the contact, in accordance with an exemplary embodiment of the present inventions; [0034] FIGS. 12A-12J illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 11 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

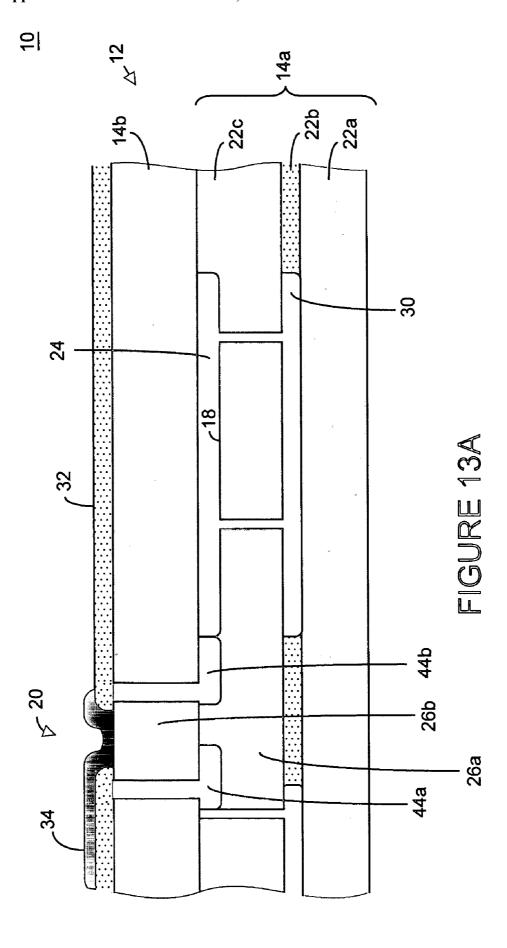

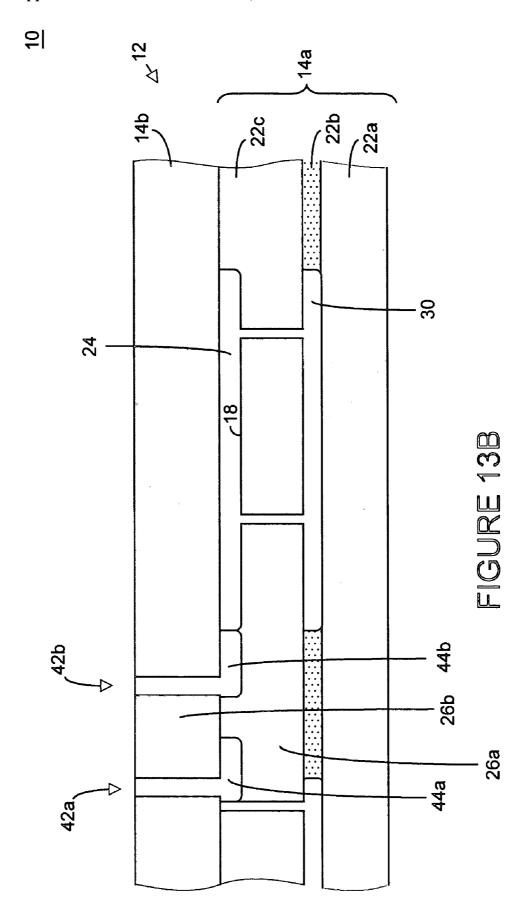

[0035] FIG. 13A illustrates a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2, wherein micromachined mechanical structure of FIG. 2 includes isolation regions and an isolation trench (aligned therewith), including an oppositely doped semiconductor (relative to the conductivity of second substrate 14b), to electrically isolate the contact, in accordance with an exemplary embodiment of the present inventions;

[0036] FIGS. 13B and 13C illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 13A at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

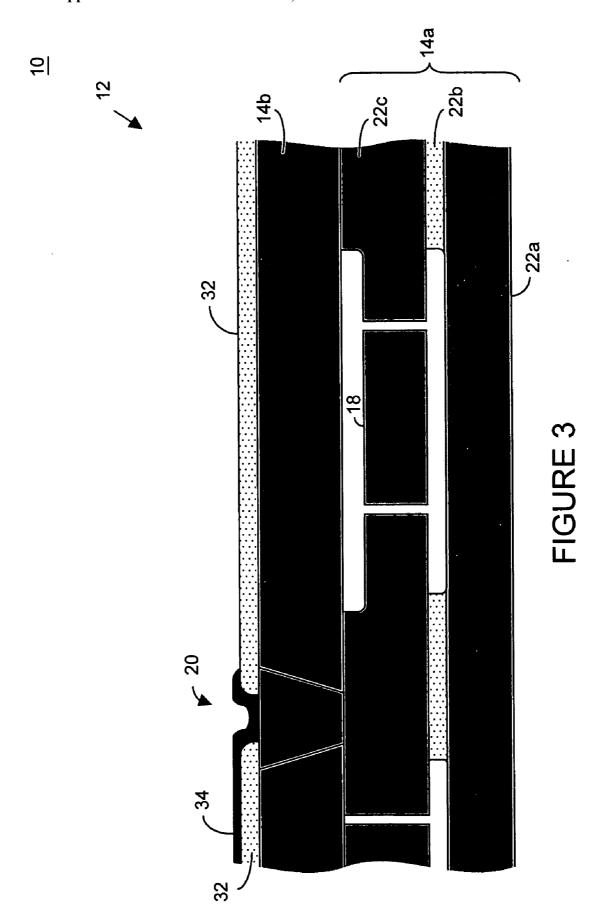

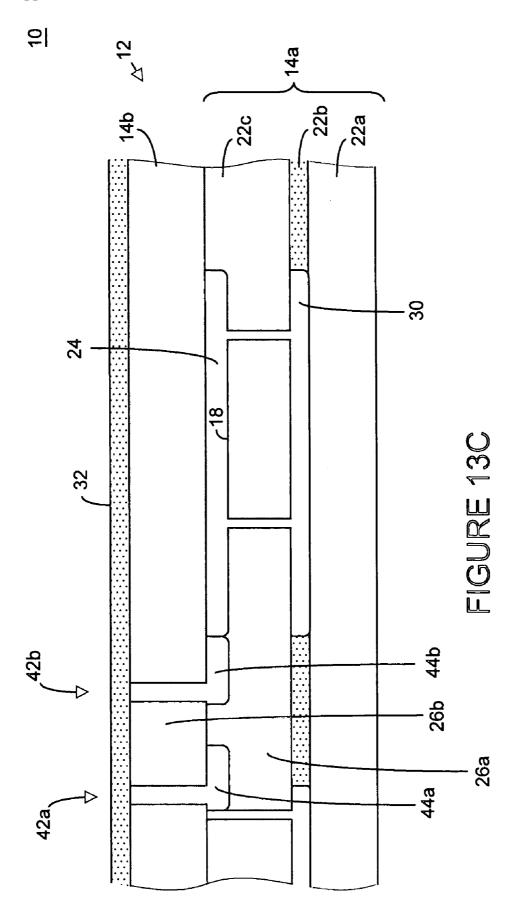

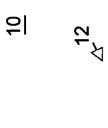

[0037] FIG. 14 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an embodiment of the present inventions wherein the microelectromechanical system employs three substrates;

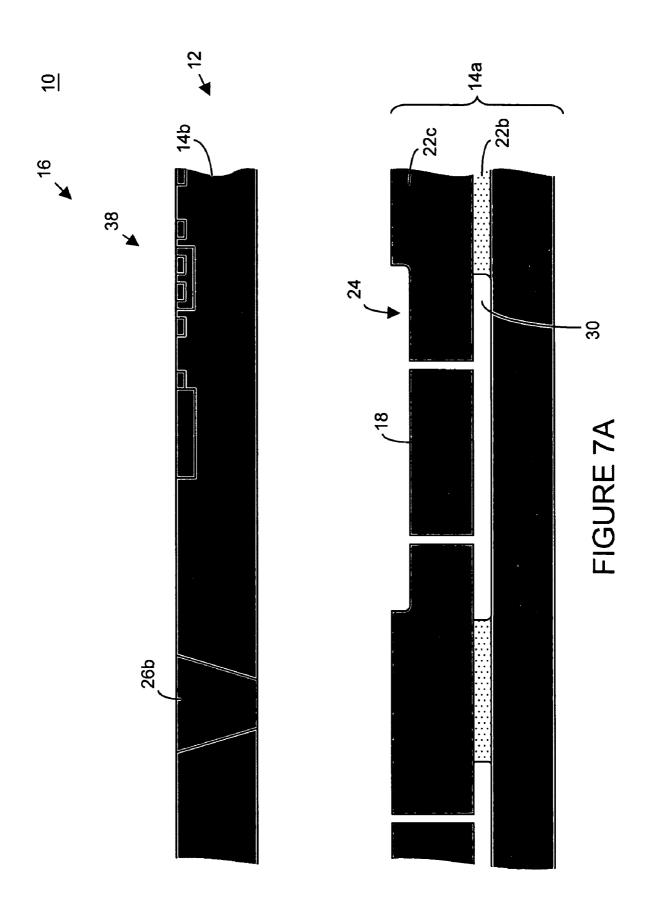

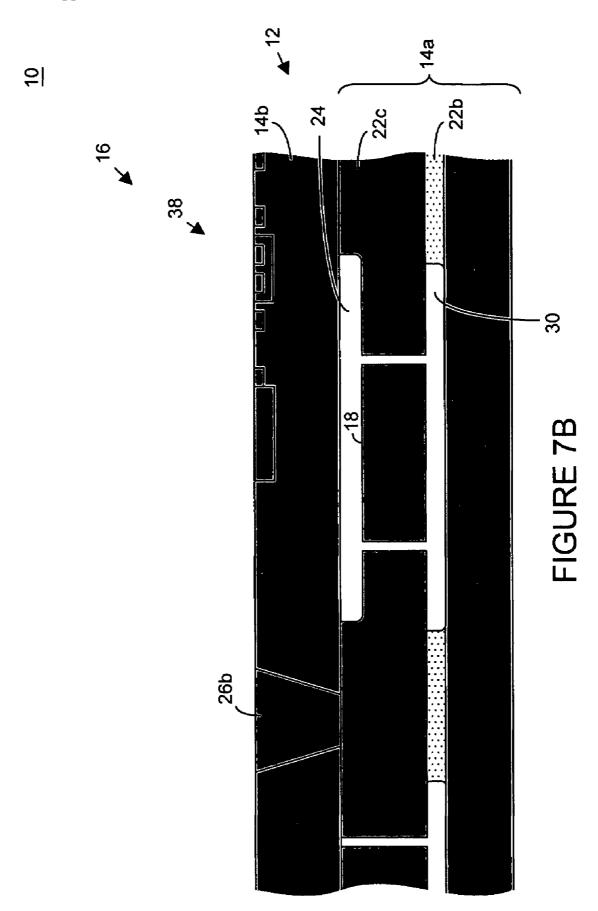

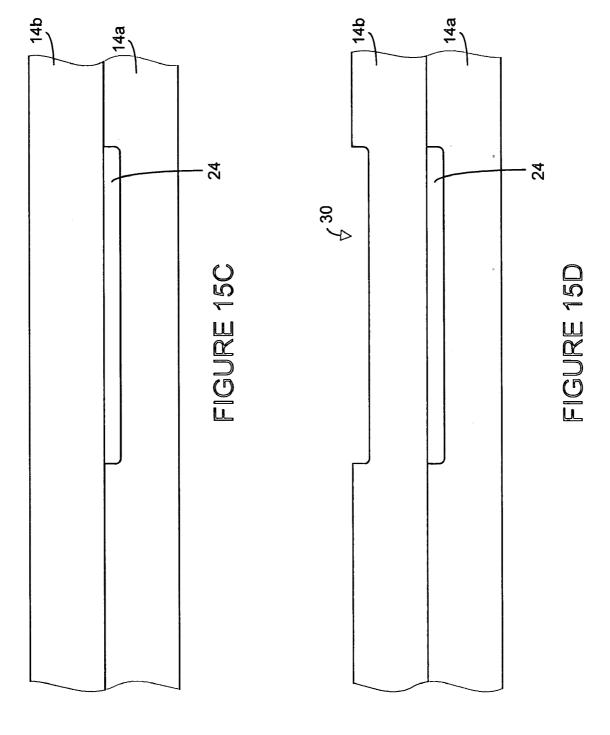

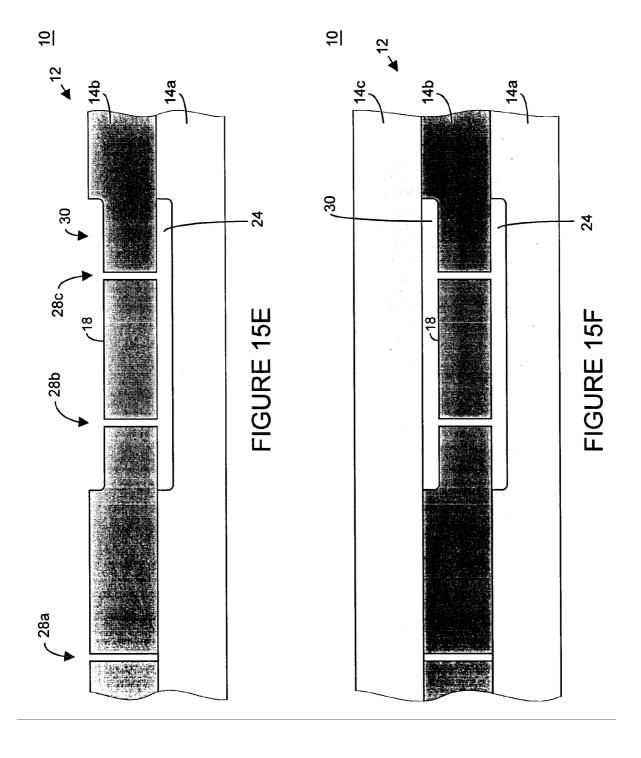

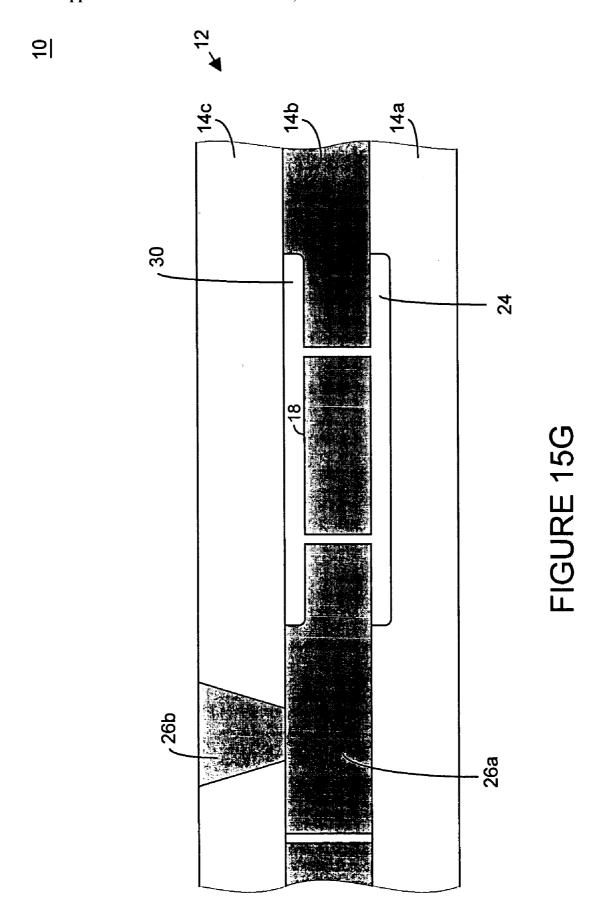

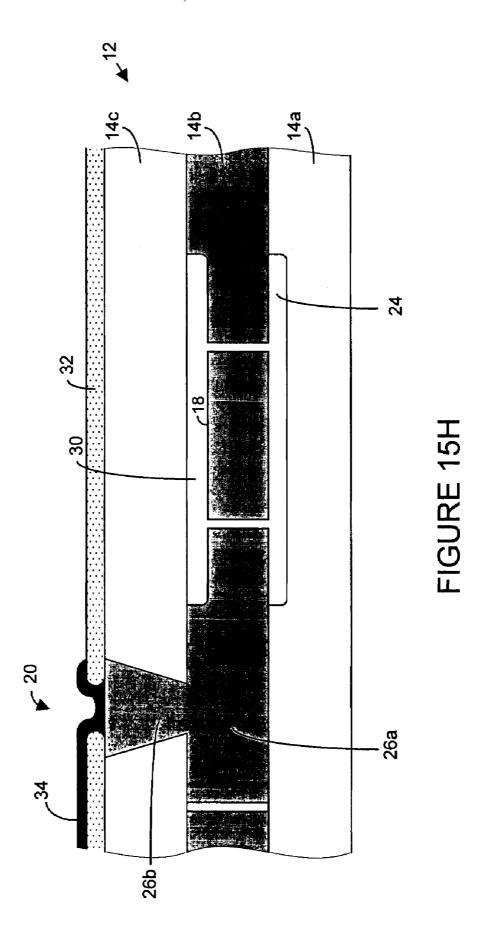

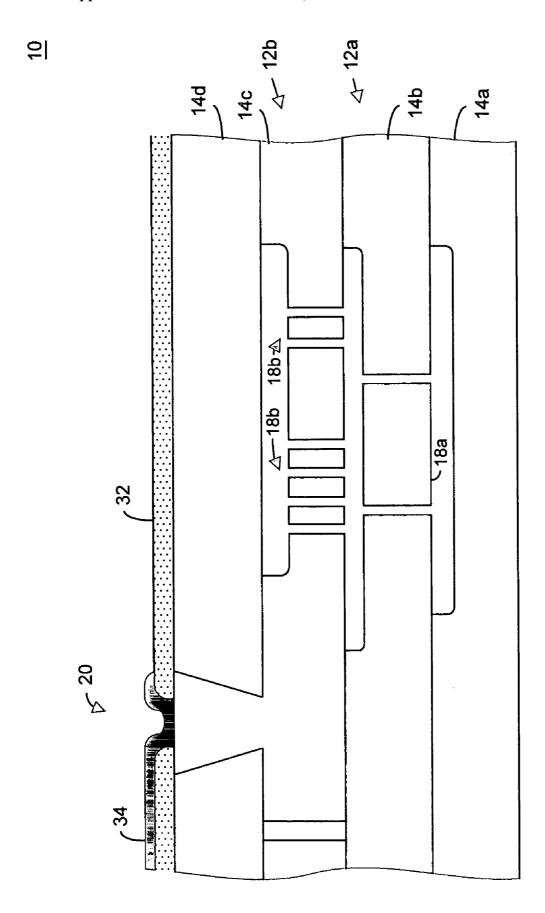

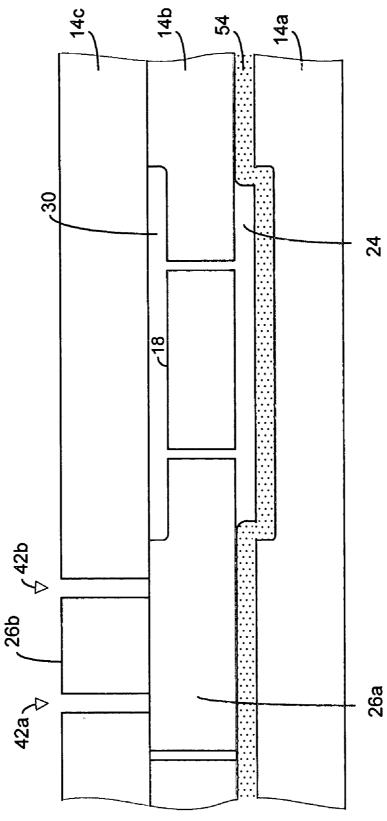

[0038] FIGS. 15A-15H illustrate cross-sectional views (sectioned along dotted line A-A' of FIG. 2) of the fabrication of the mechanical structure of FIGS. 2 and 14 at various stages of a process that employs an encapsulation technique according to certain aspects of the present inventions;

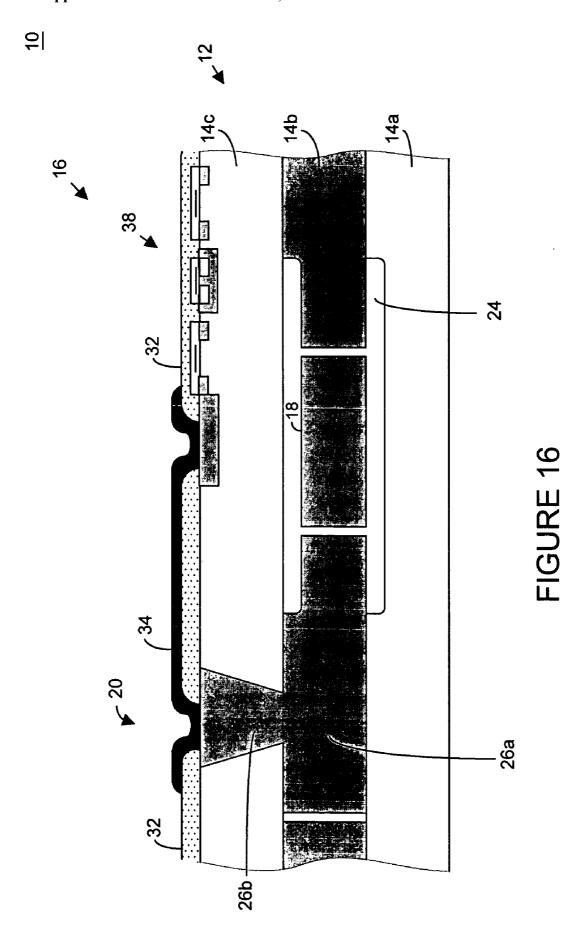

[0039] FIG. 16 illustrates a cross-sectional view of an embodiment of the fabrication of the microelectromechanical system of FIG. 14 wherein electronic or electrical circuitry (after fabrication) is formed in the third substrate according to certain aspects of the present inventions;

[0040] FIG. 17 illustrates a cross-sectional view of an exemplary embodiment of the present inventions of the microelectromechanical system including a plurality of micromachined mechanical structures wherein a first micromachined mechanical structure is formed in the second substrate and a second micromachined mechanical structure is formed in the third substrate wherein a fourth substrate

encapsulates one or more of the micromachined mechanical structures according to certain aspects of the present inventions;

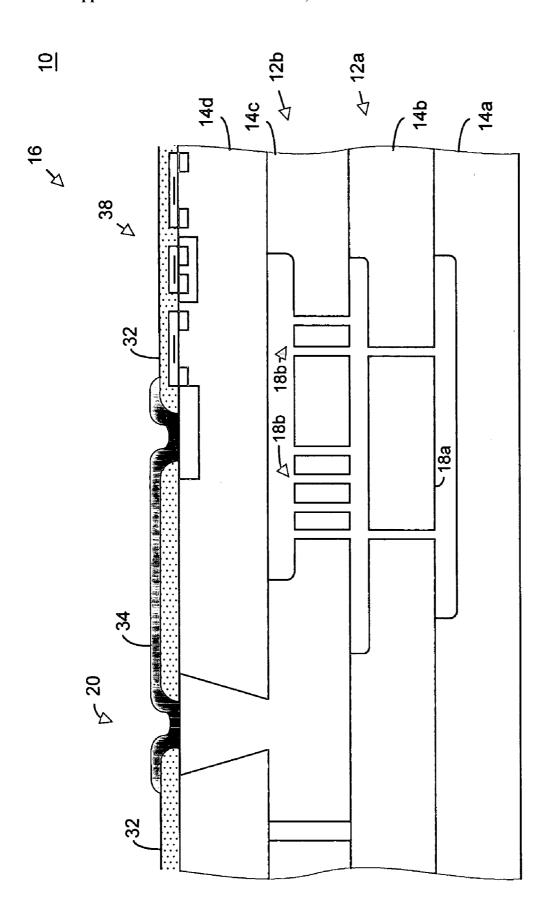

[0041] FIG. 18 illustrates a cross-sectional view of an exemplary embodiment of the present inventions of the microelectromechanical system including a plurality of micromachined mechanical structures wherein a first micromachined mechanical structure is formed in the second substrate and a second micromachined mechanical structure is formed in the third substrate wherein a fourth substrate encapsulates one or more of the micromachined mechanical structures and includes electronic or electrical circuitry according to certain aspects of the present inventions;

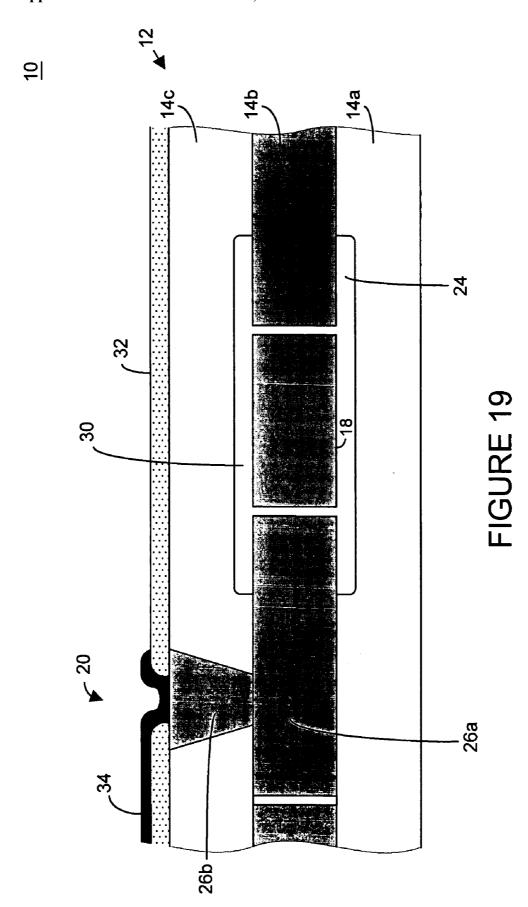

[0042] FIG. 19 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates and cavities are formed in the first and third substrates;

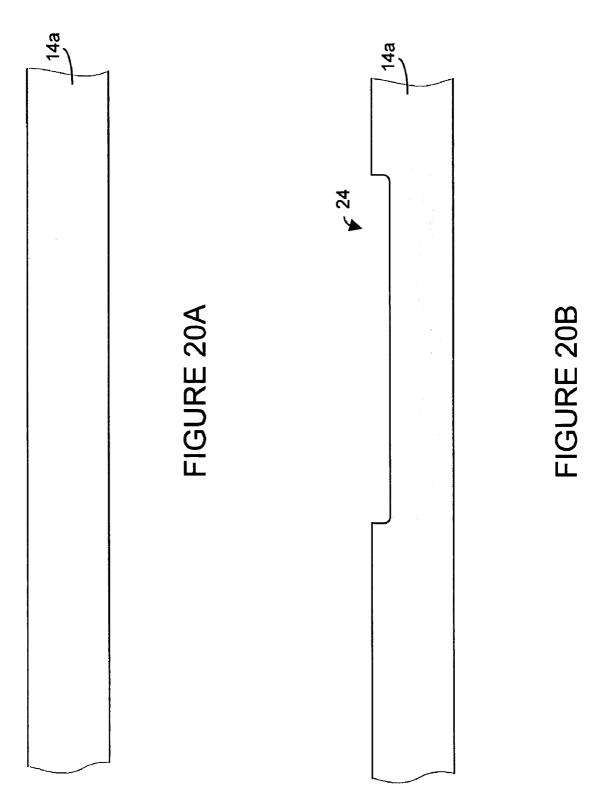

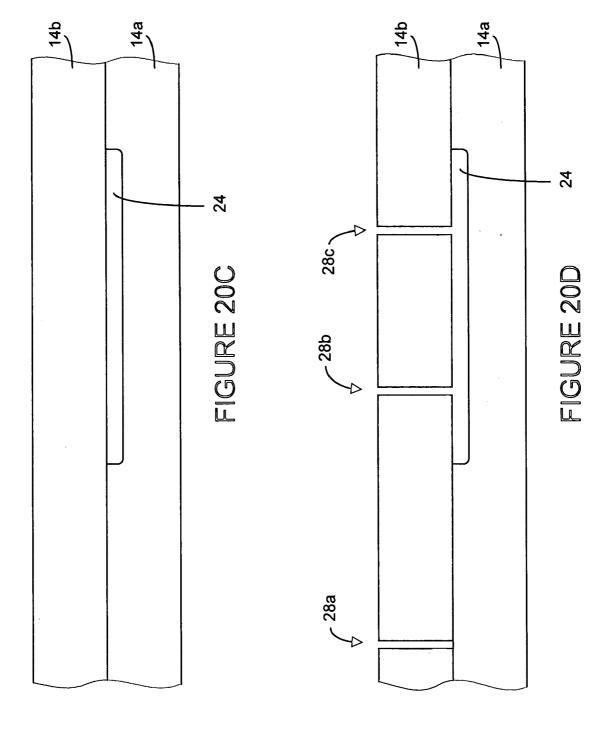

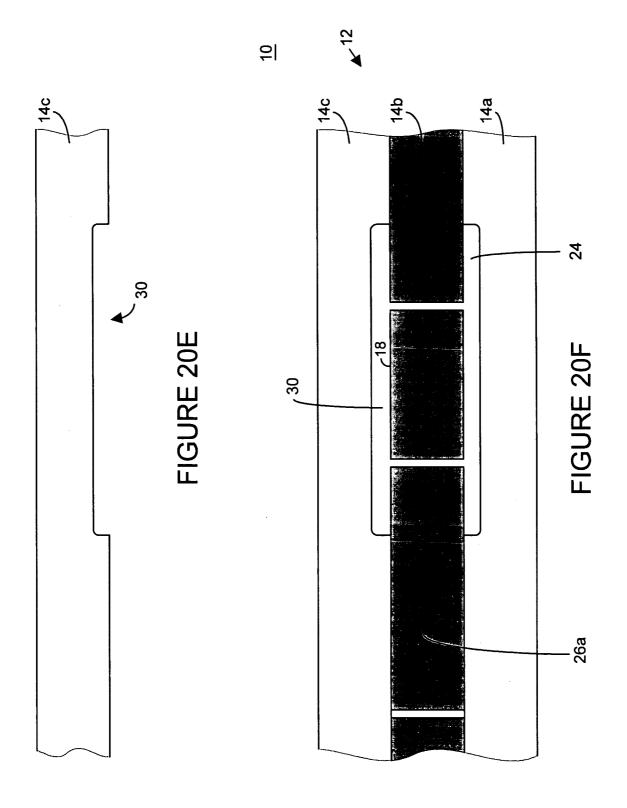

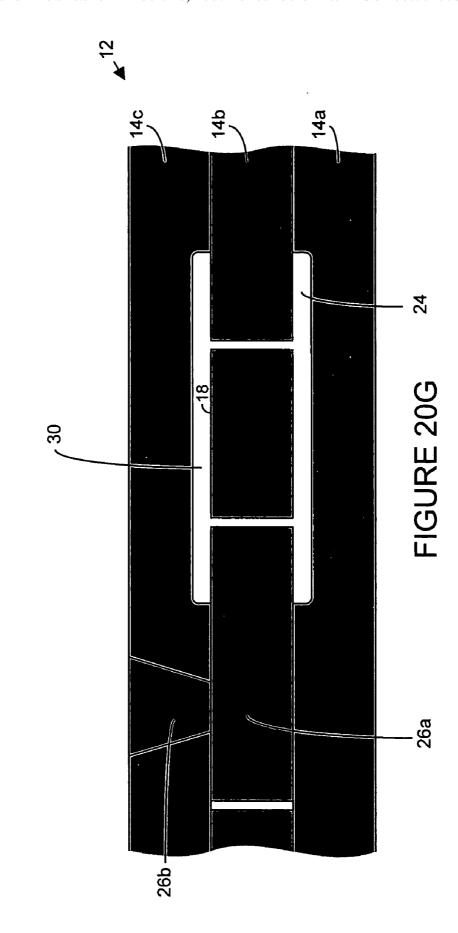

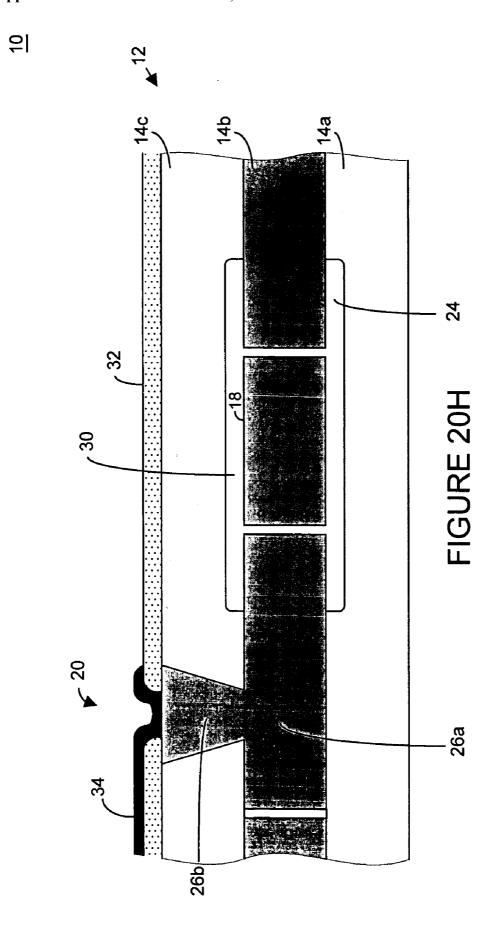

[0043] FIGS. 20A-20H illustrate cross-sectional views (sectioned along dotted line A-A' of FIG. 2) of the fabrication of the mechanical structure of FIGS. 2 and 19 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions:

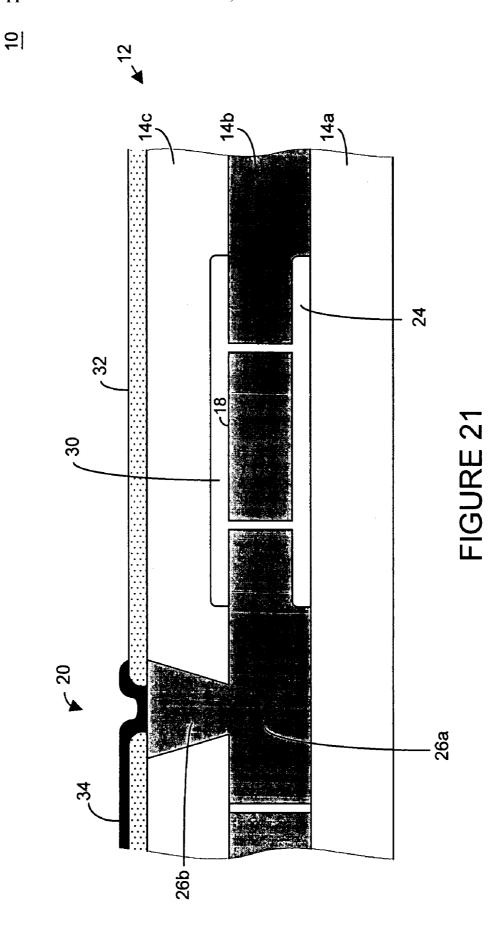

[0044] FIG. 21 illustrates a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2, wherein the first cavity is formed in the second substrate and a second cavity is formed in a third substrate according to certain aspects of the present inventions;

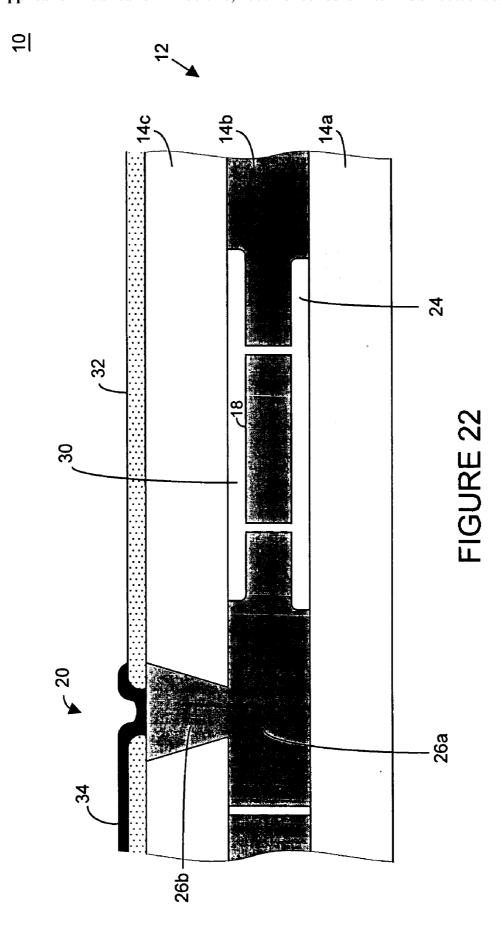

[0045] FIG. 22 illustrates a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2, wherein the first and second cavities are formed in the second substrate, according to certain aspects of the present inventions;

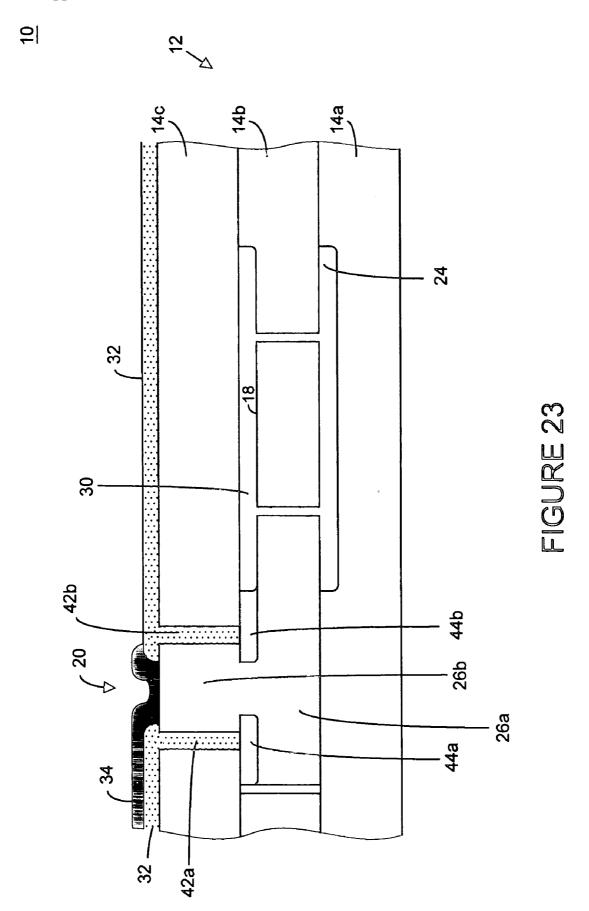

[0046] FIG. 23 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates and the second and third substrates include the same conductivity types;

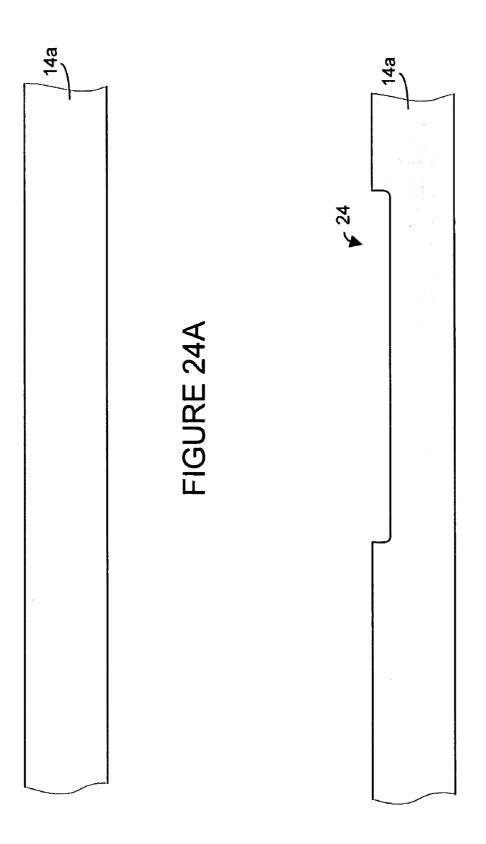

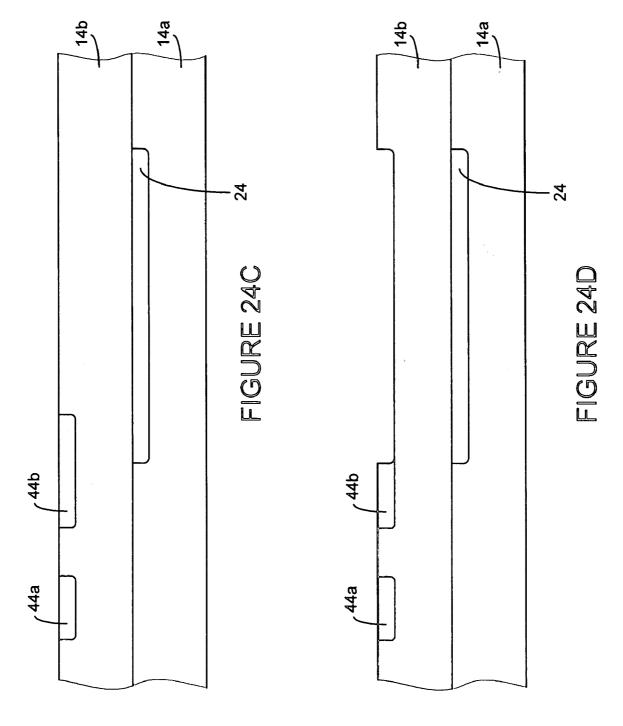

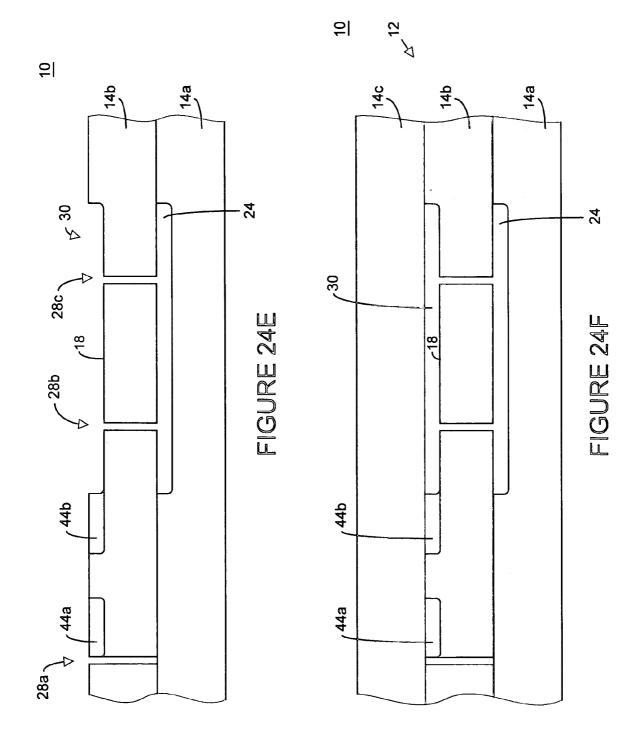

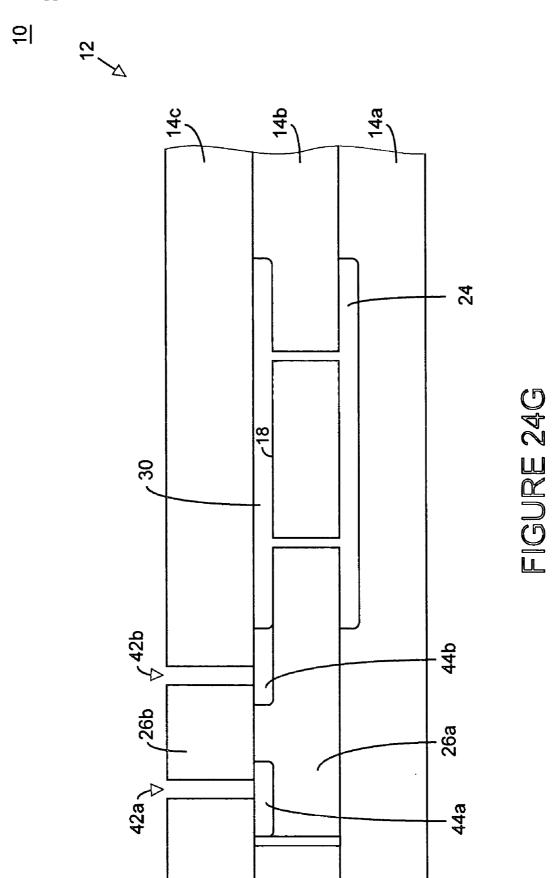

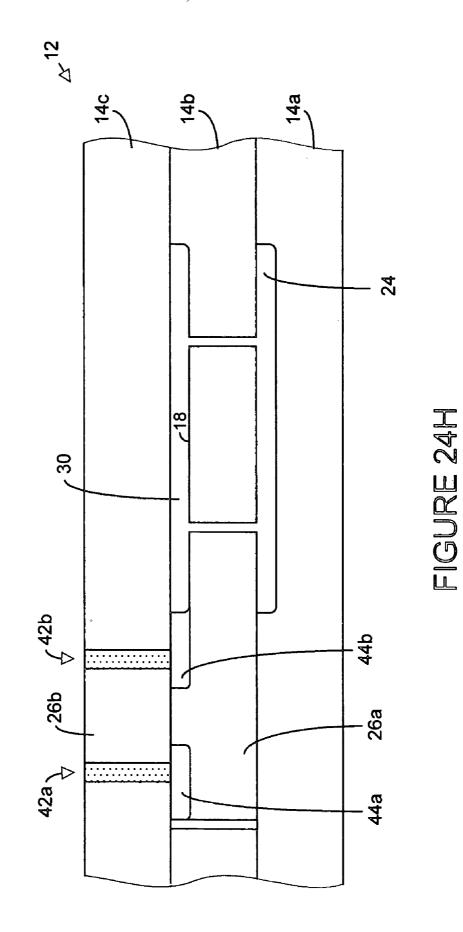

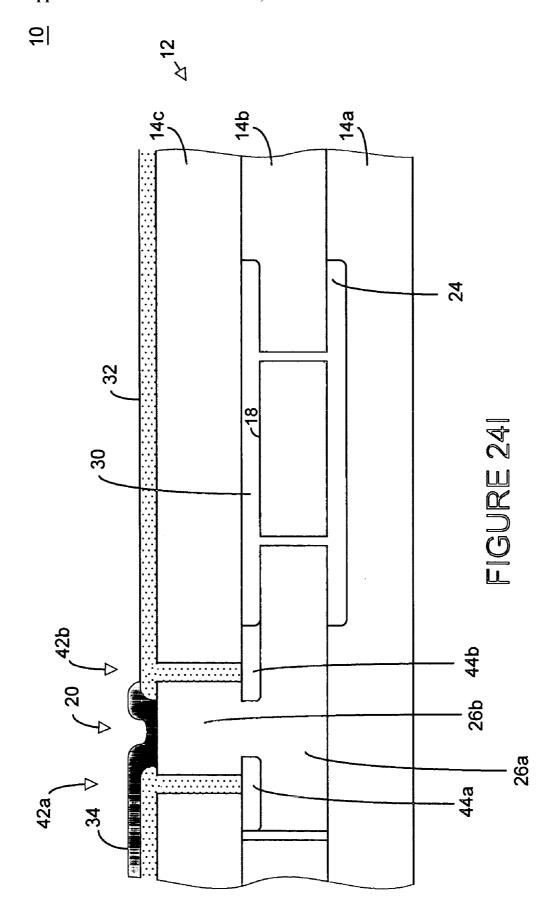

[0047] FIGS. 24A-24I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 23 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

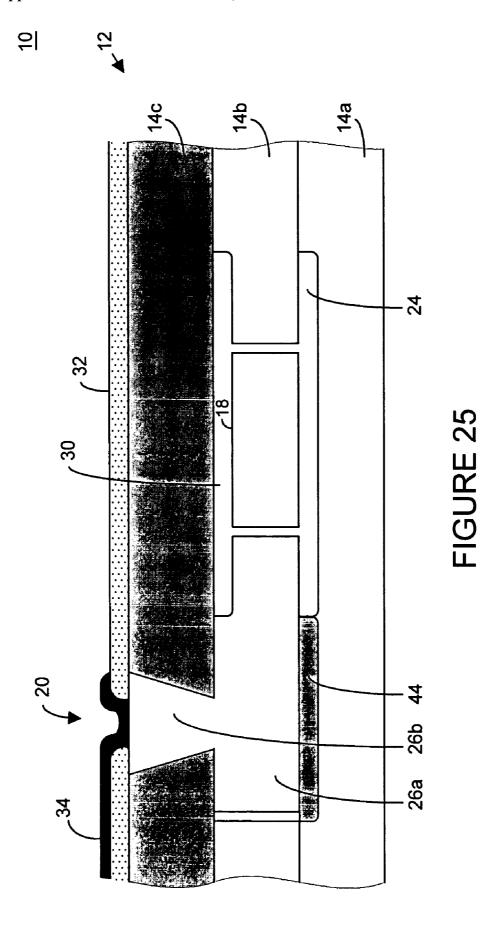

[0048] FIG. 25 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates and the first and second substrates include the same conductivity types;

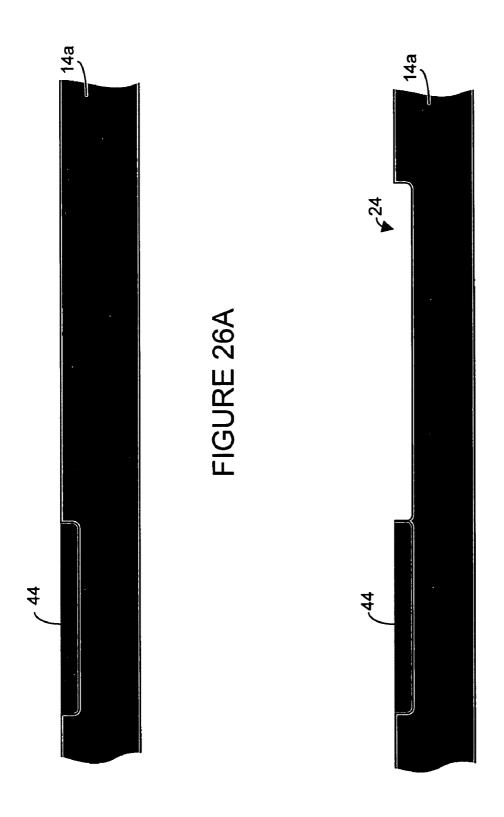

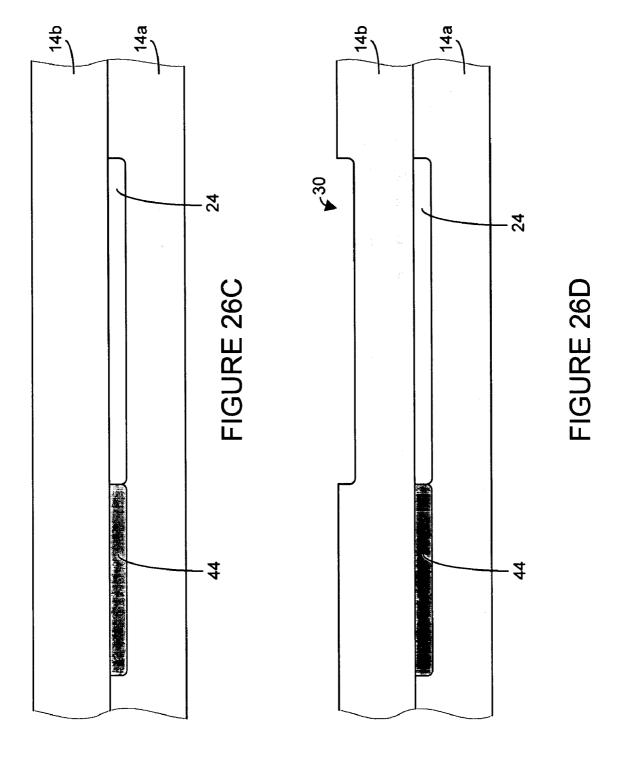

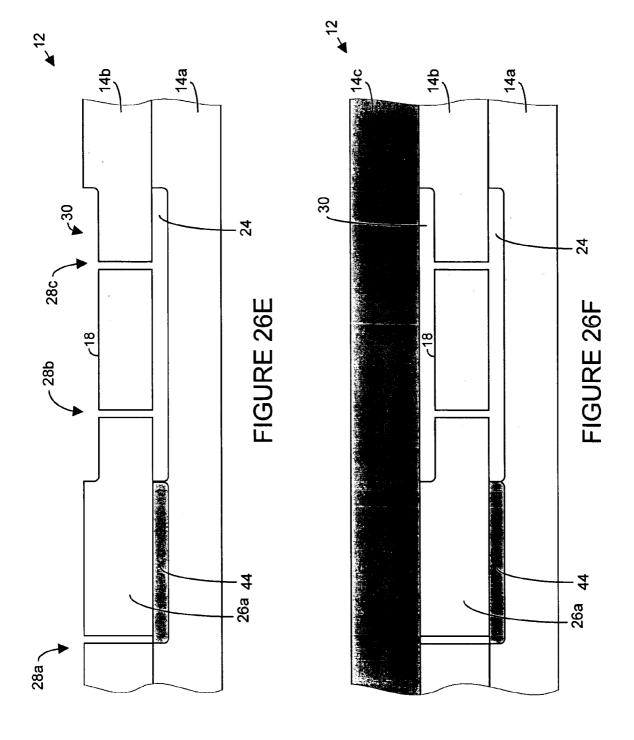

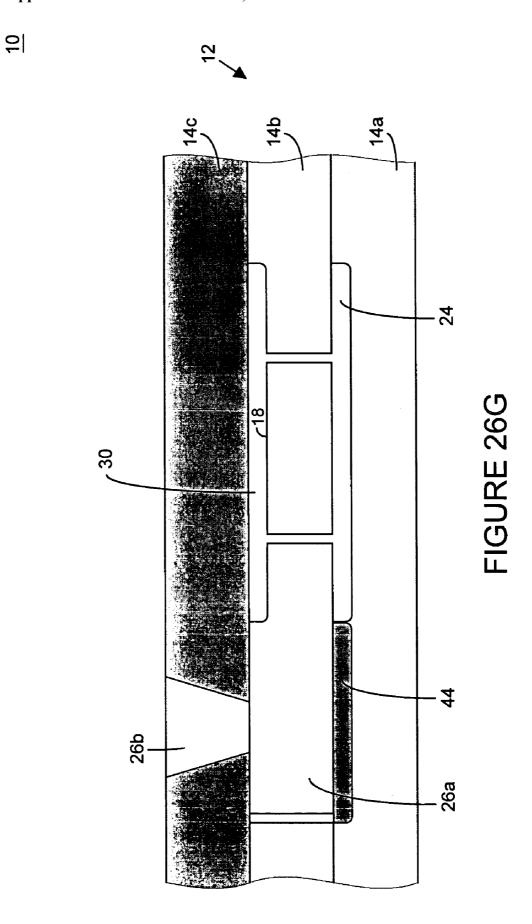

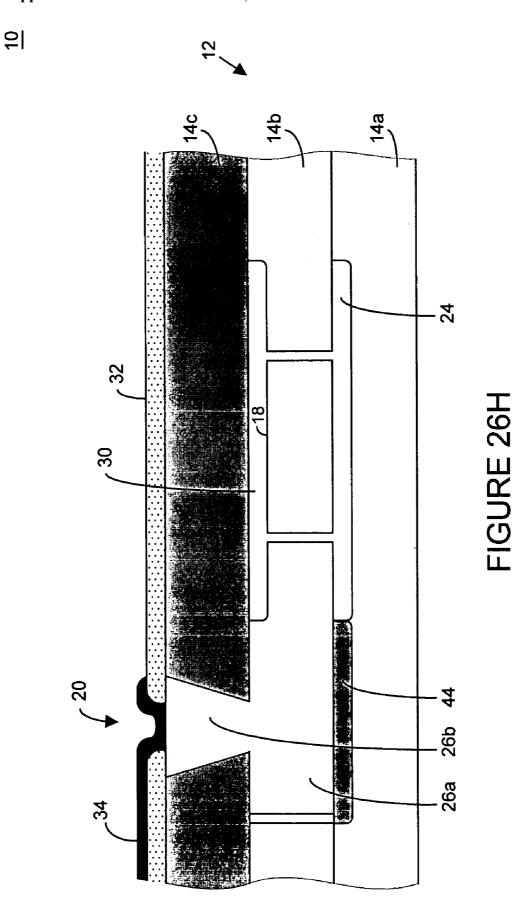

[0049] FIGS. 26A-26I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 25 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

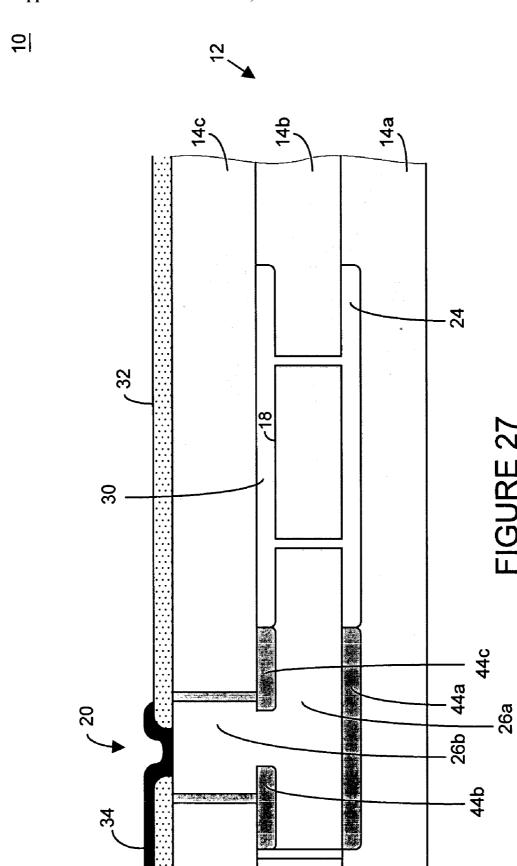

[0050] FIG. 27 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an

exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates which include the same conductivity types;

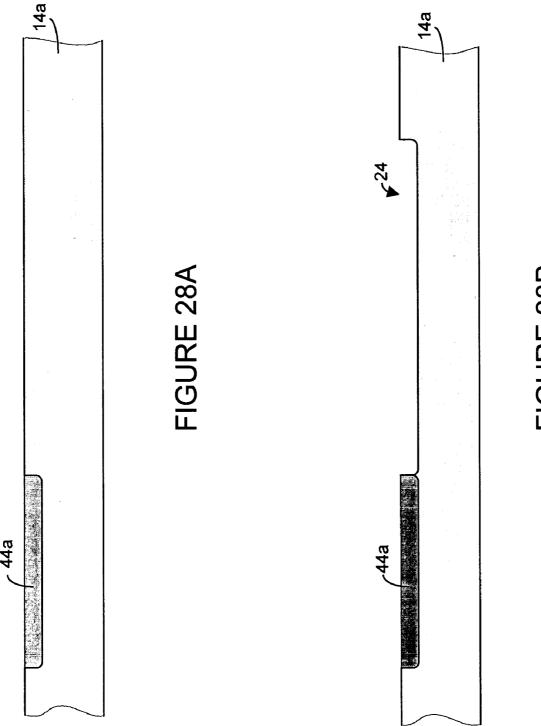

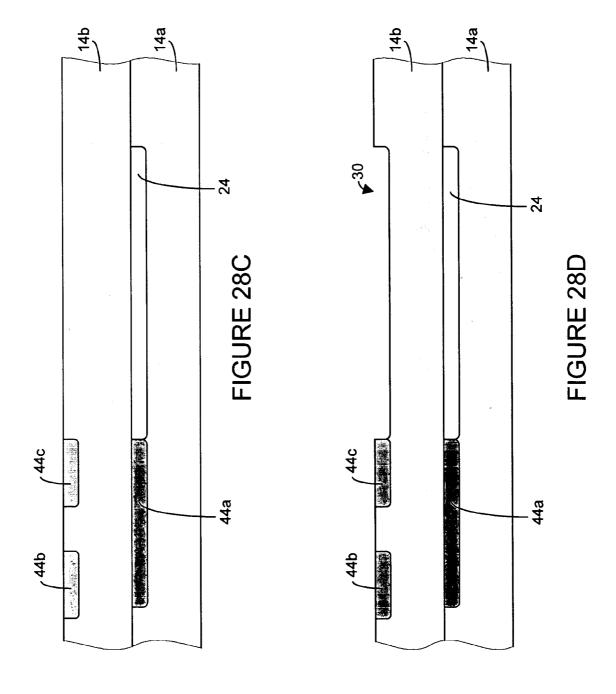

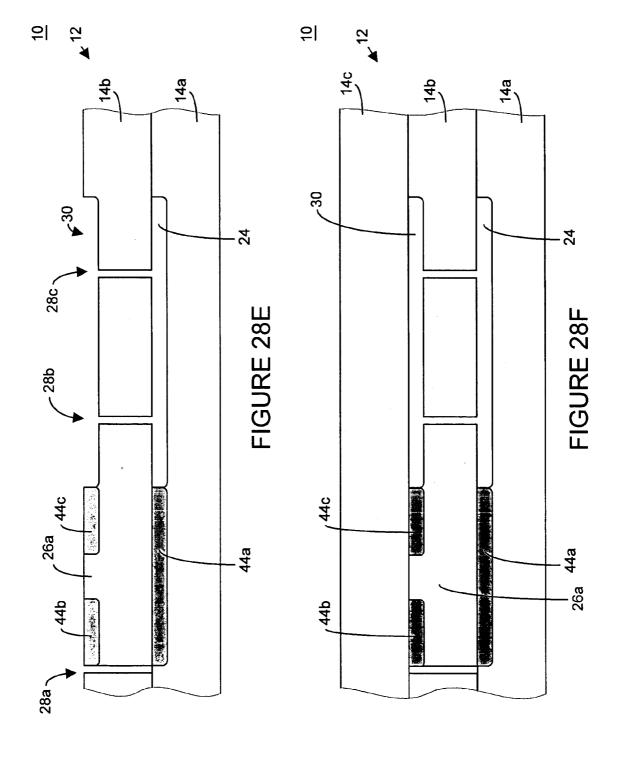

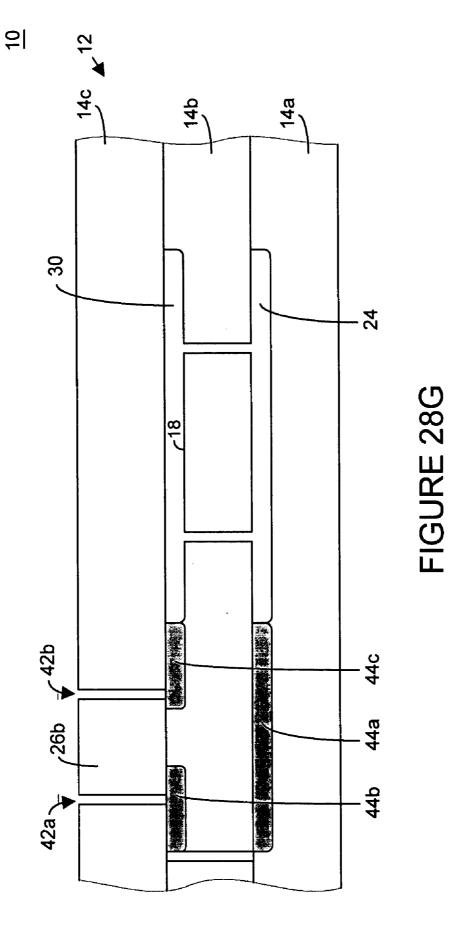

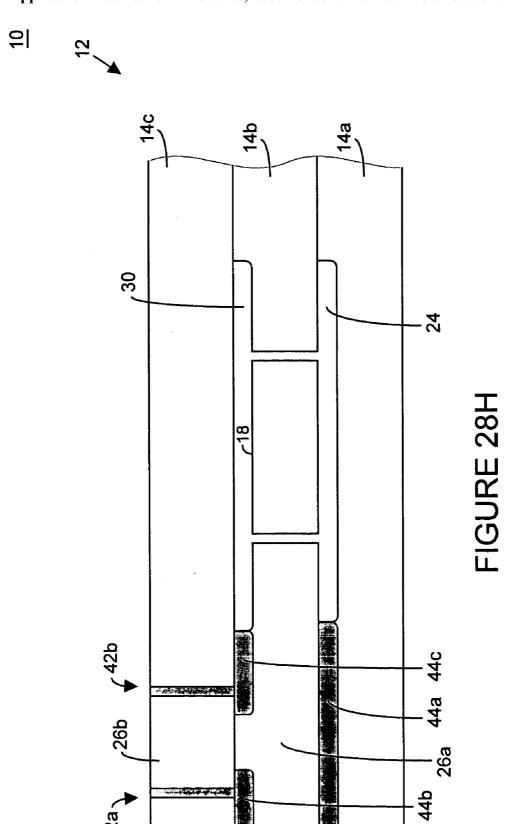

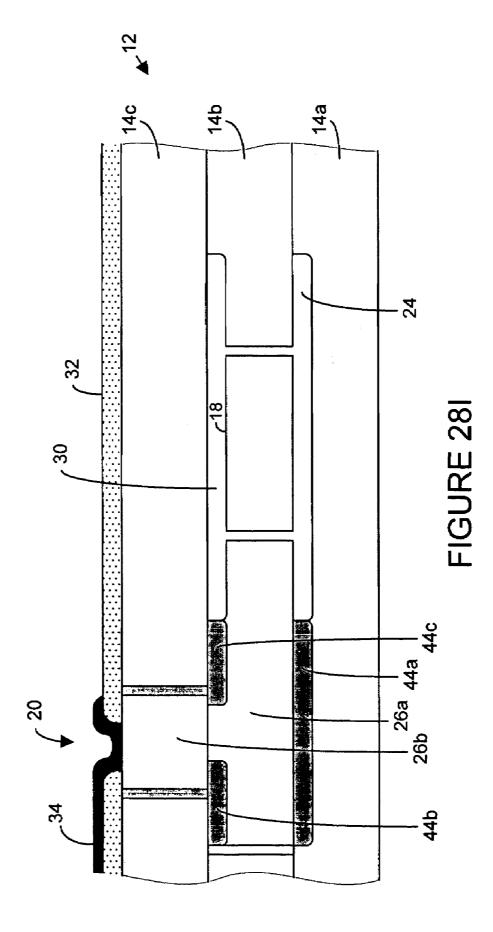

[0051] FIGS. 28A-28I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 27 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

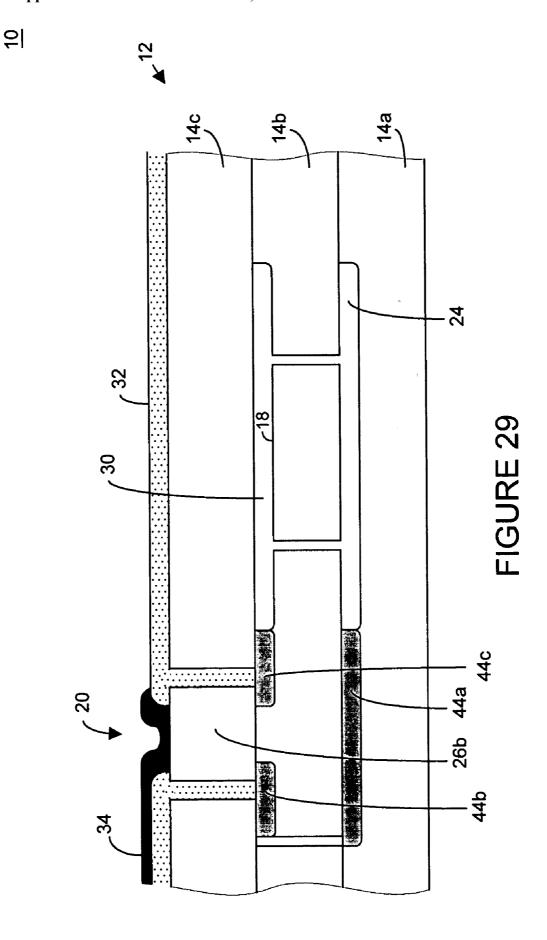

[0052] FIG. 29 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates which include the same conductivity types;

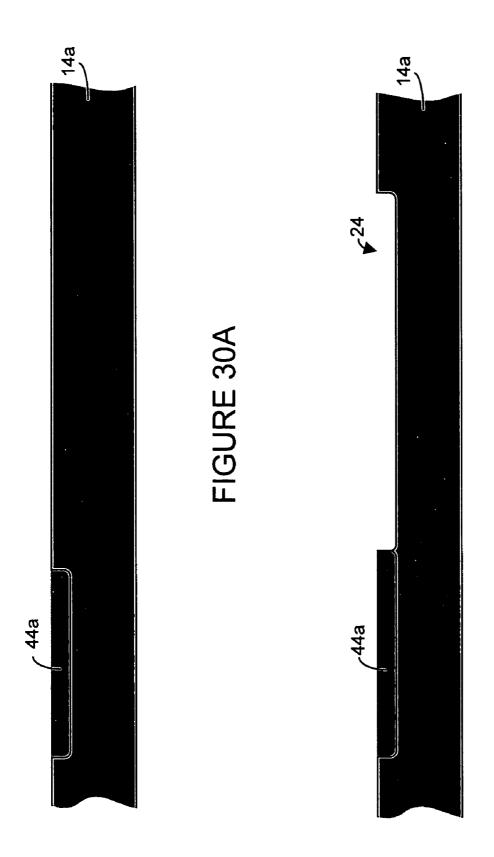

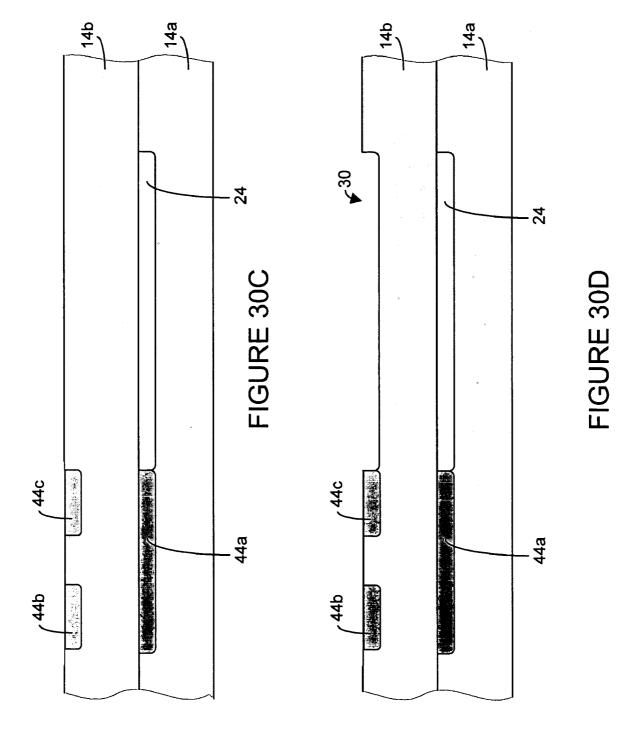

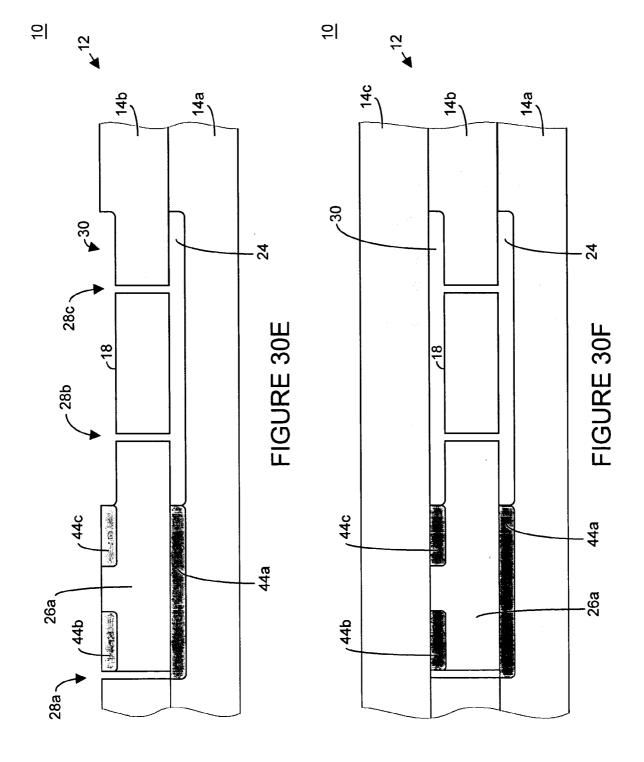

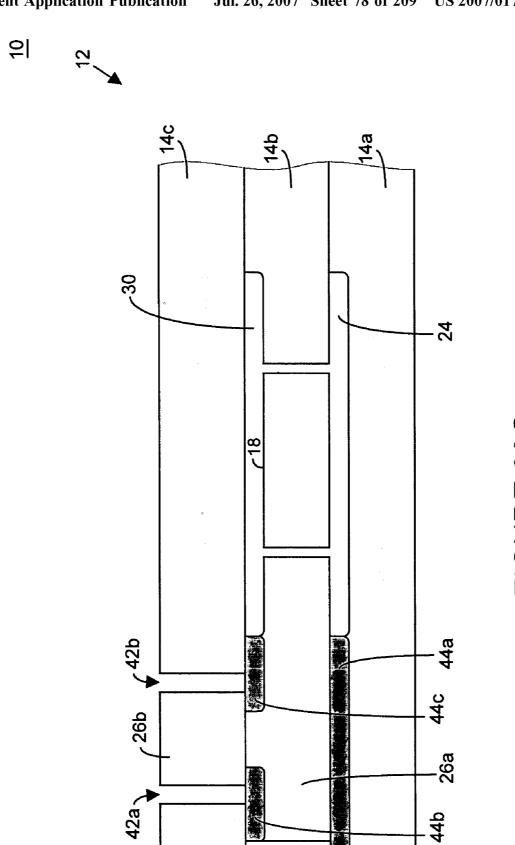

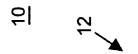

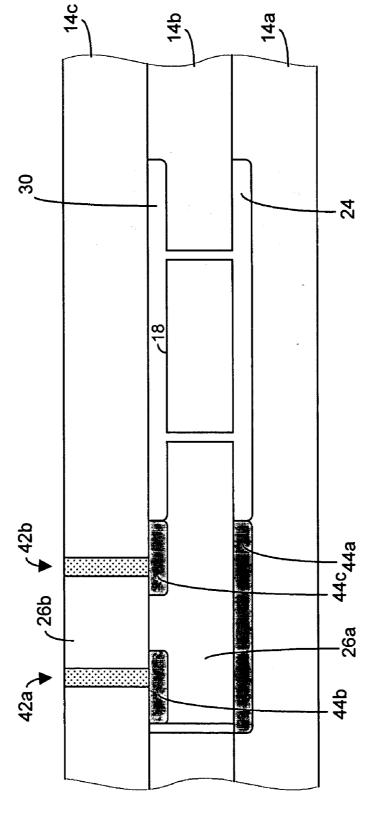

[0053] FIGS. 30A-30I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 29 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

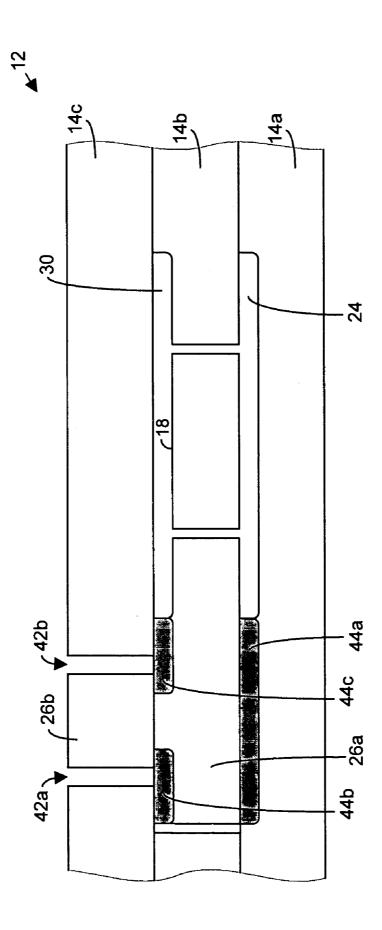

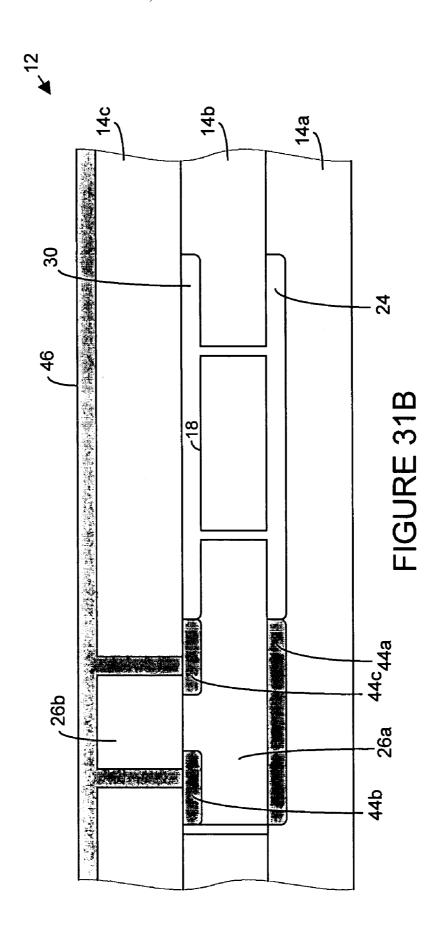

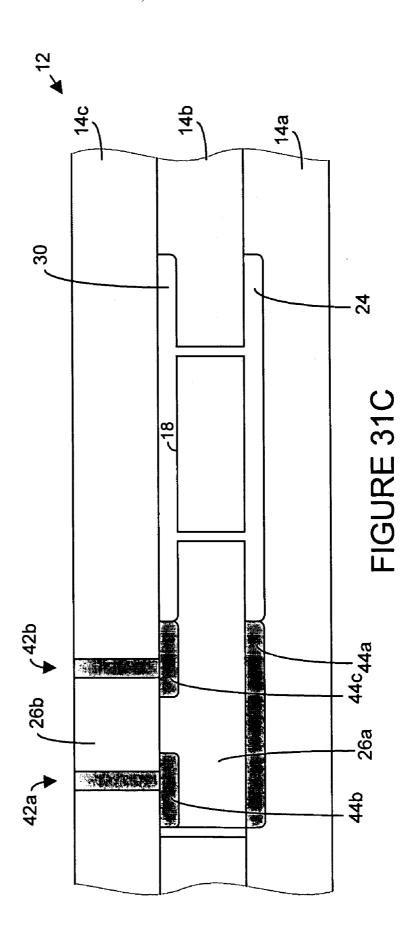

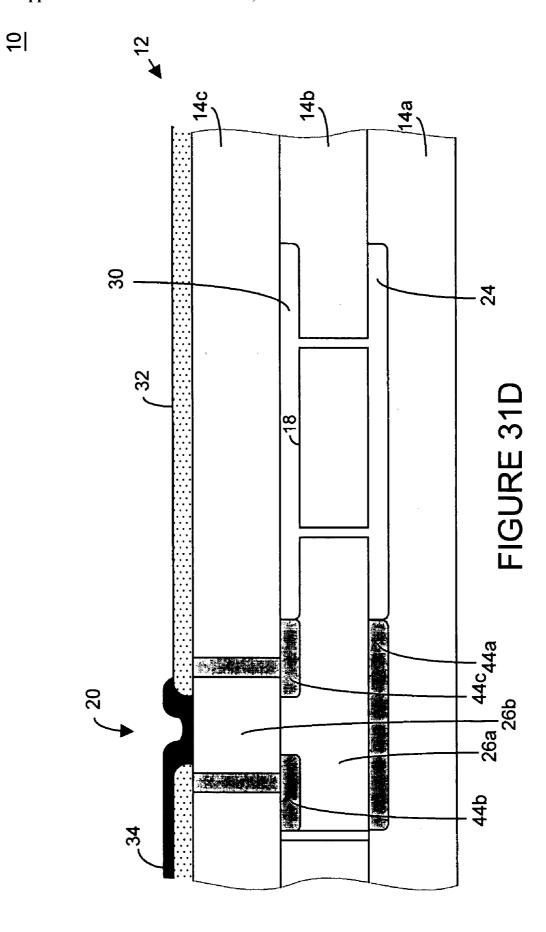

[0054] FIGS. 31A-31D illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 27 at various stages of an exemplary process that employs grinding and/or polishing to provide a desired surface, according to certain aspects of the present inventions:

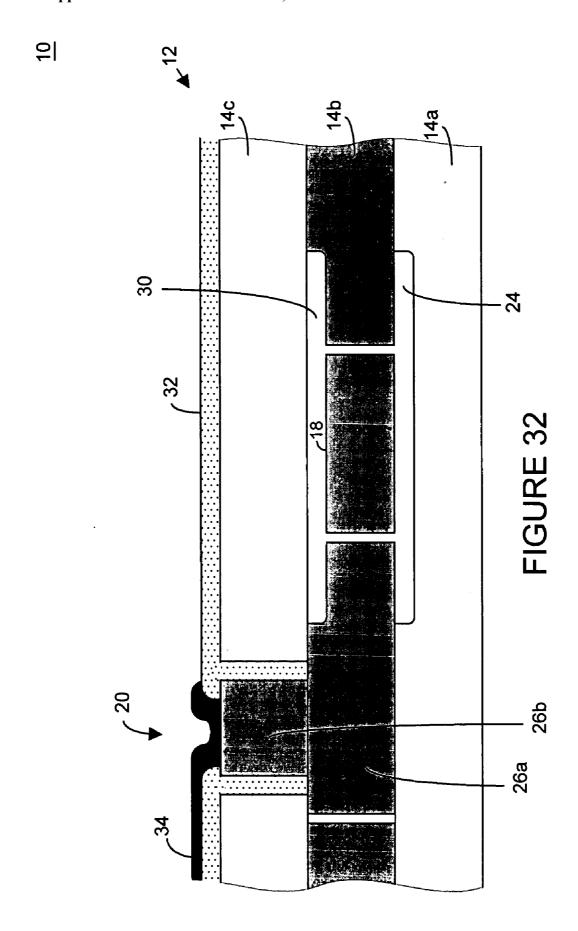

[0055] FIG. 32 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates:

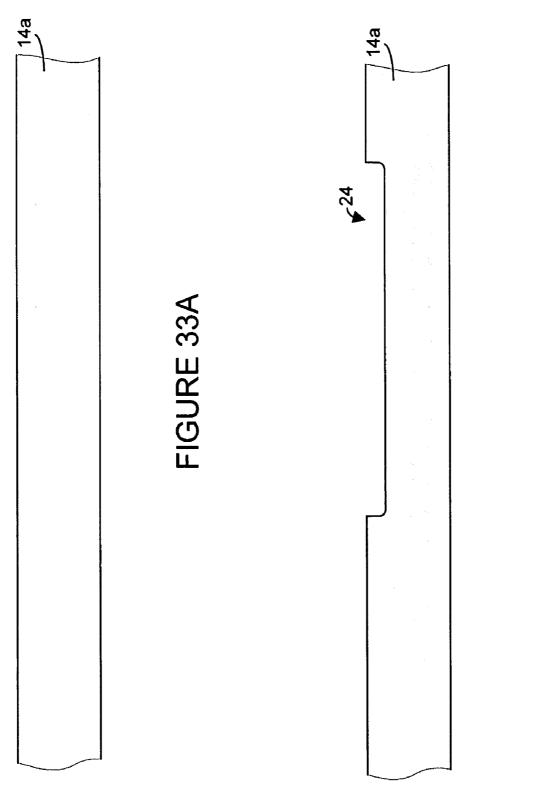

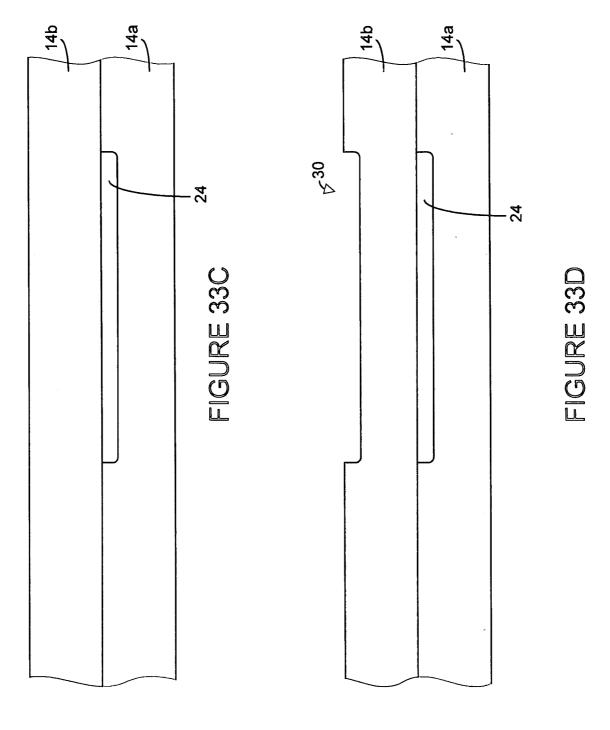

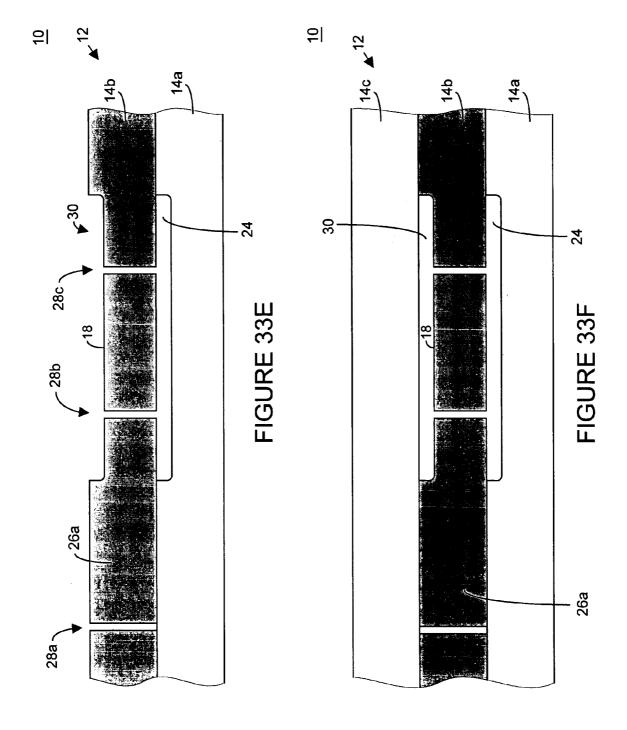

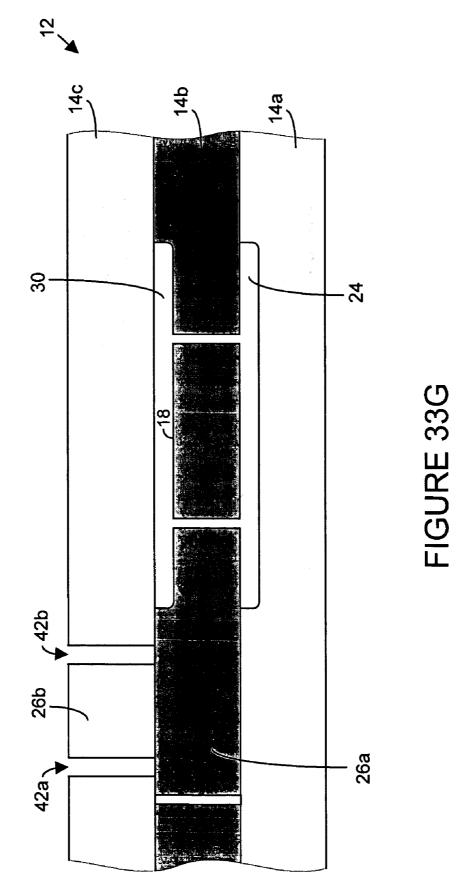

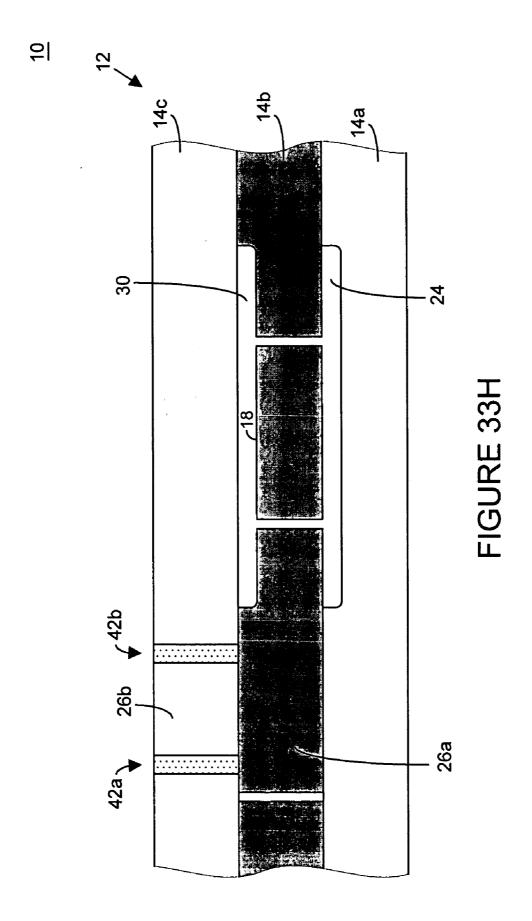

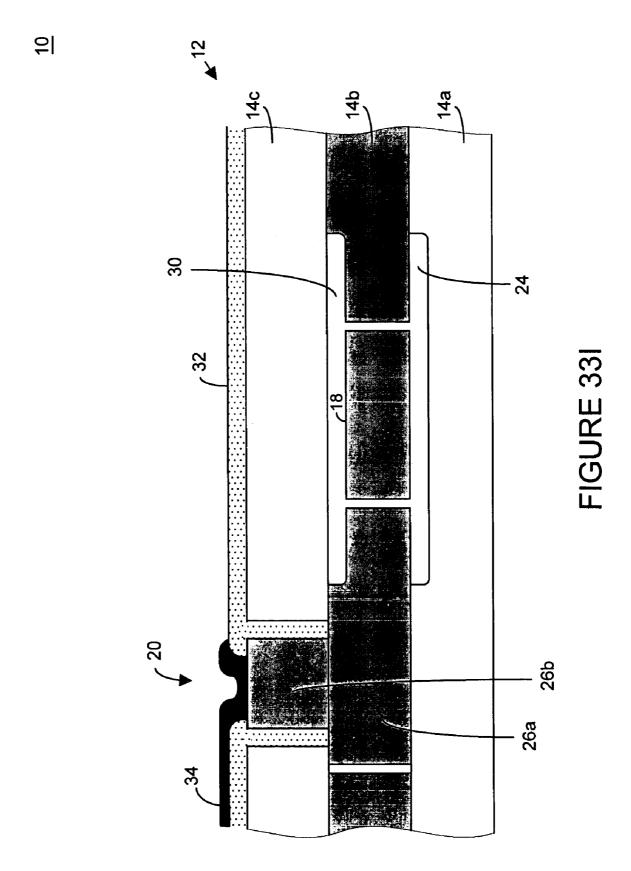

[0056] FIGS. 33A-33I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 32 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

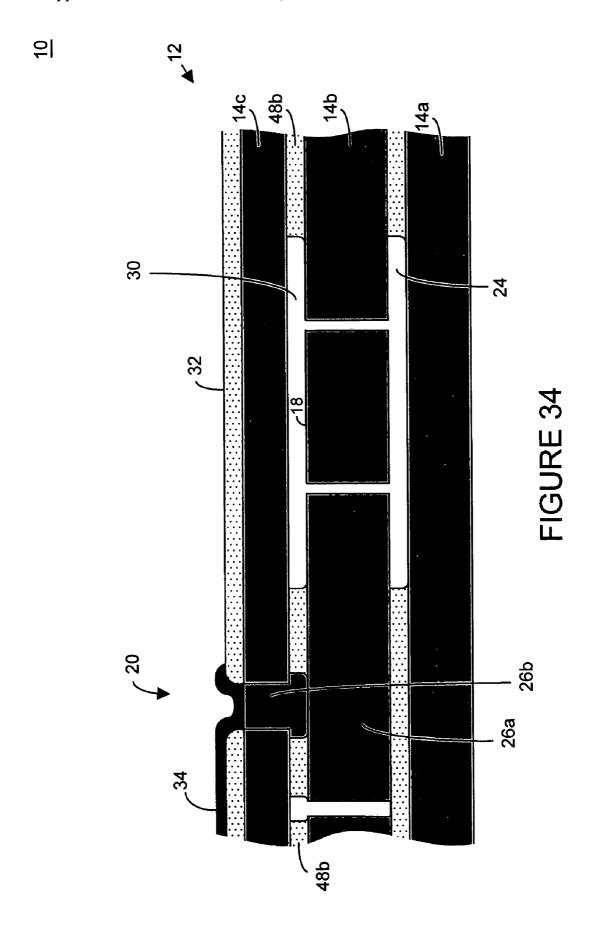

[0057] FIG. 34 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates wherein an insulative layer is disposed between each of the substrates;

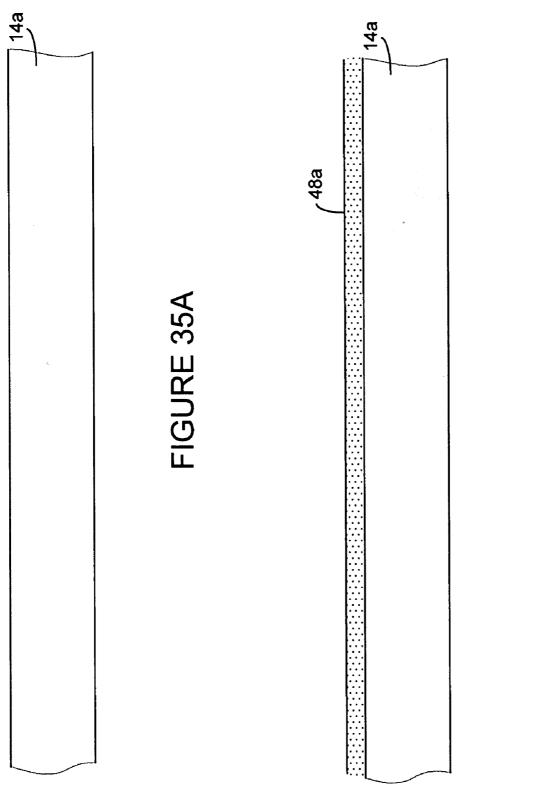

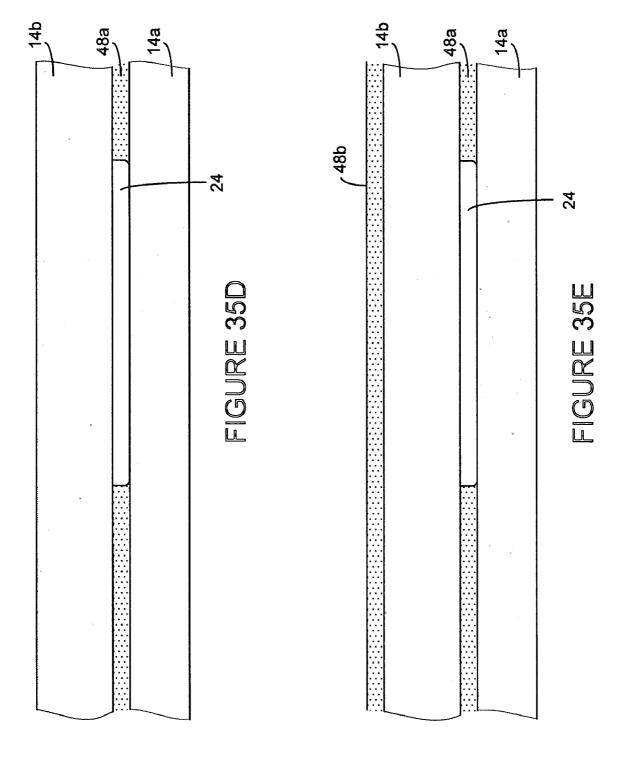

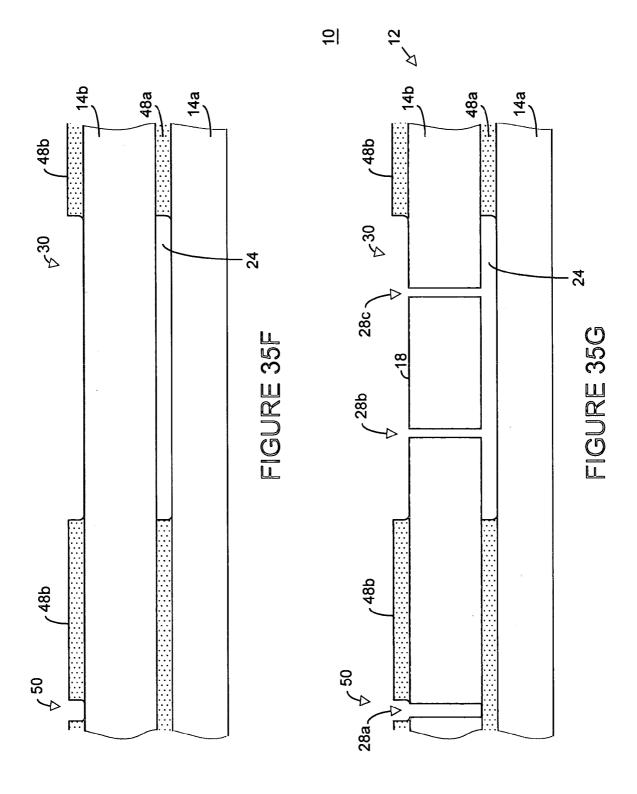

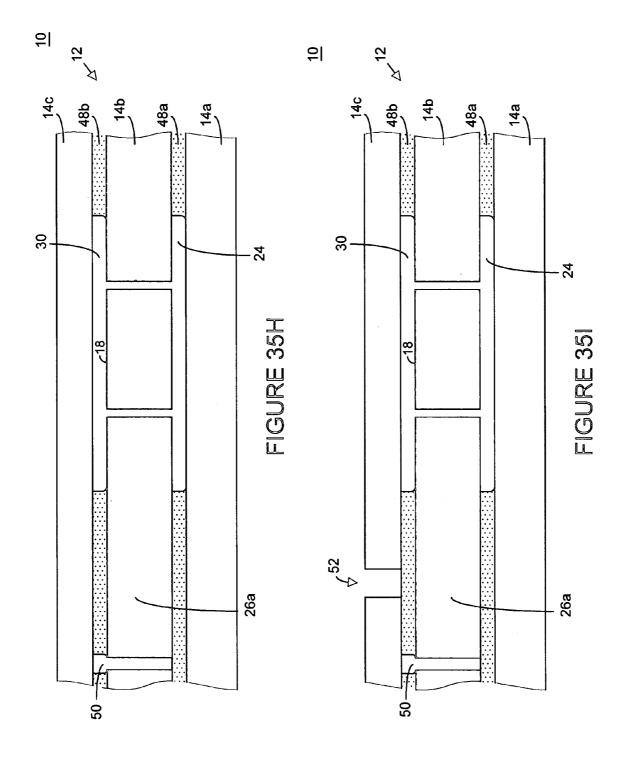

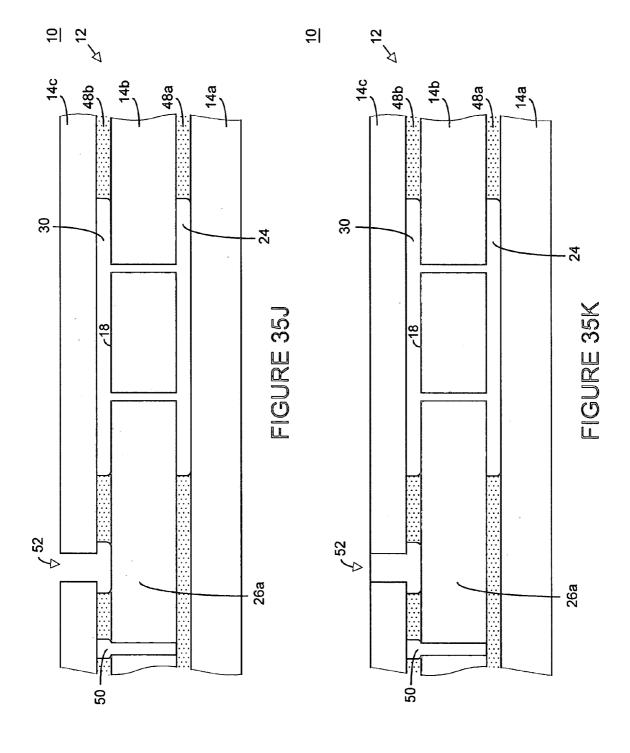

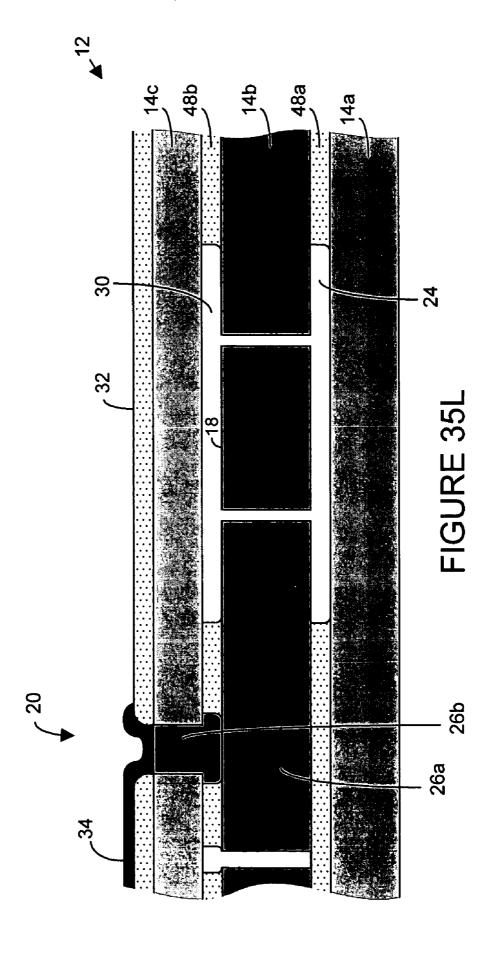

[0058] FIGS. 35A-35L illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 34 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

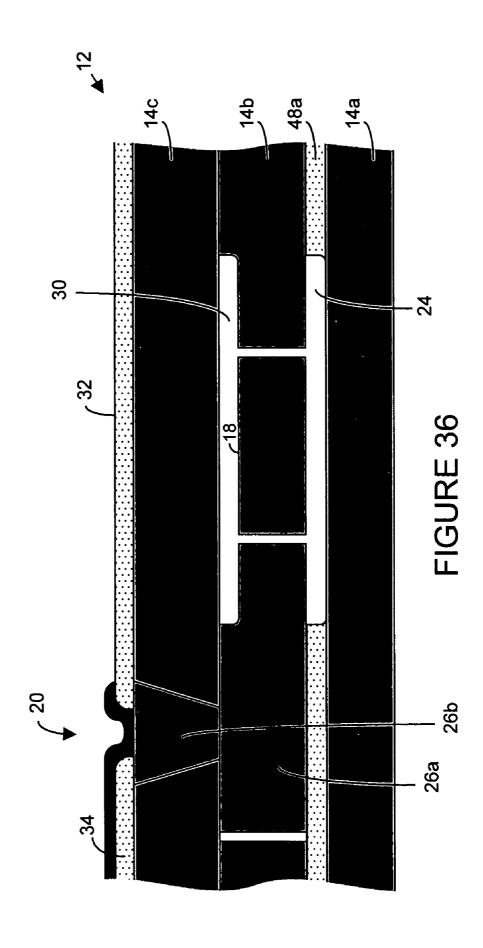

[0059] FIG. 36 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates wherein an insulative layer is disposed between two of the substrates;

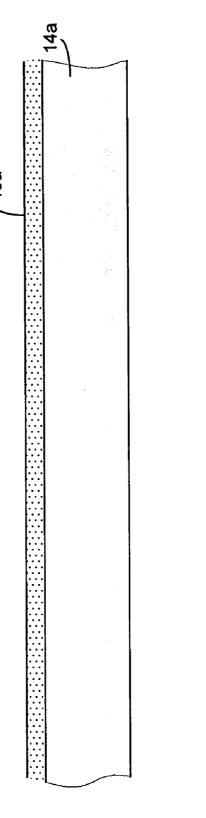

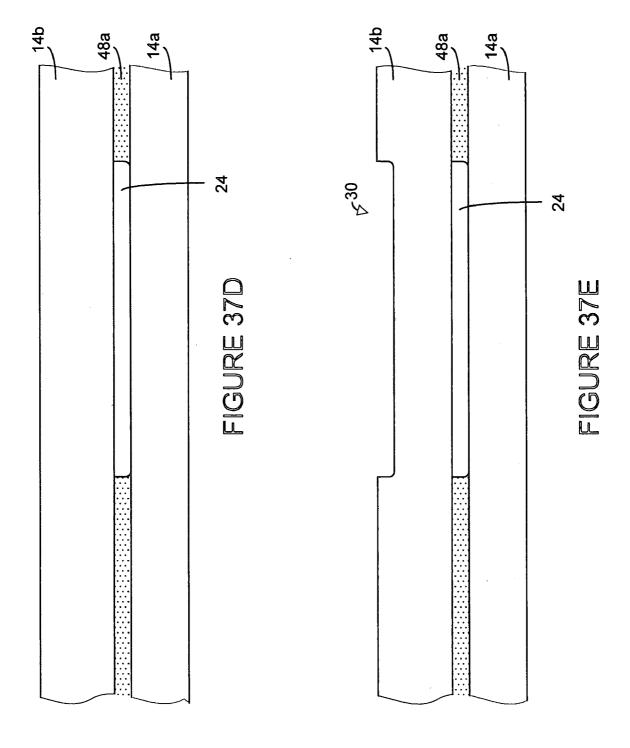

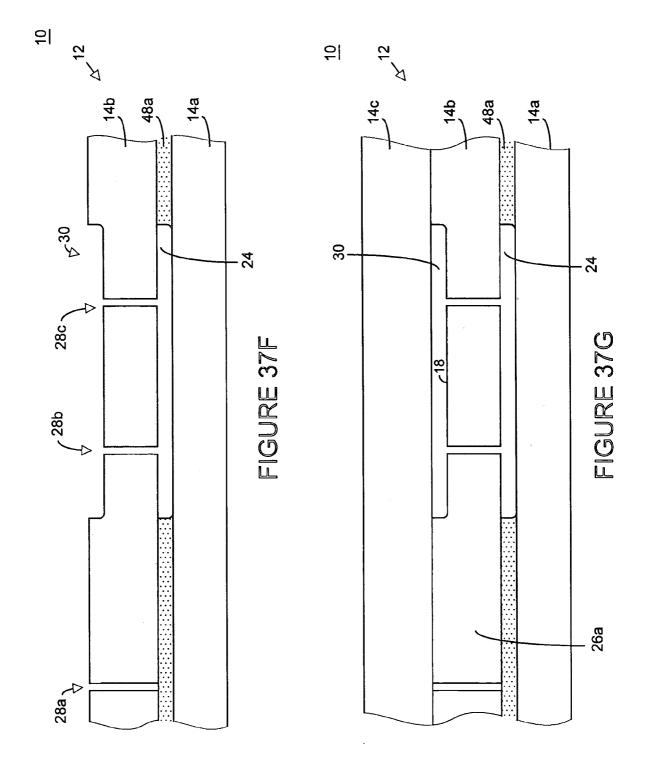

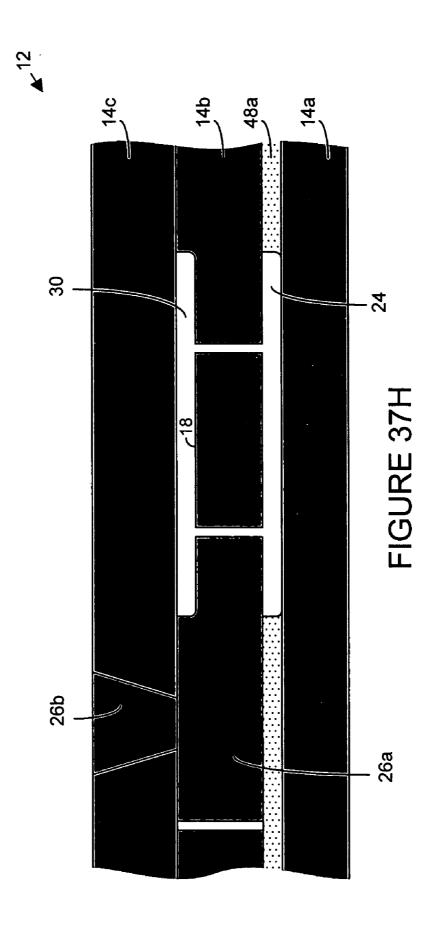

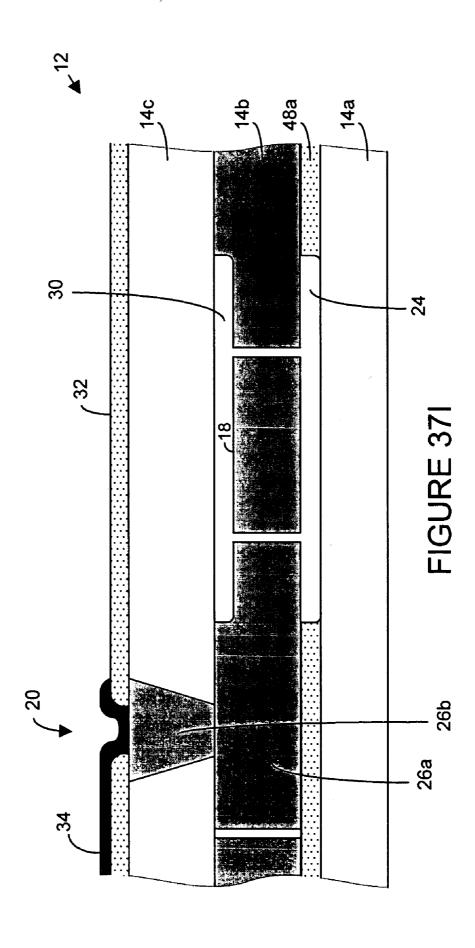

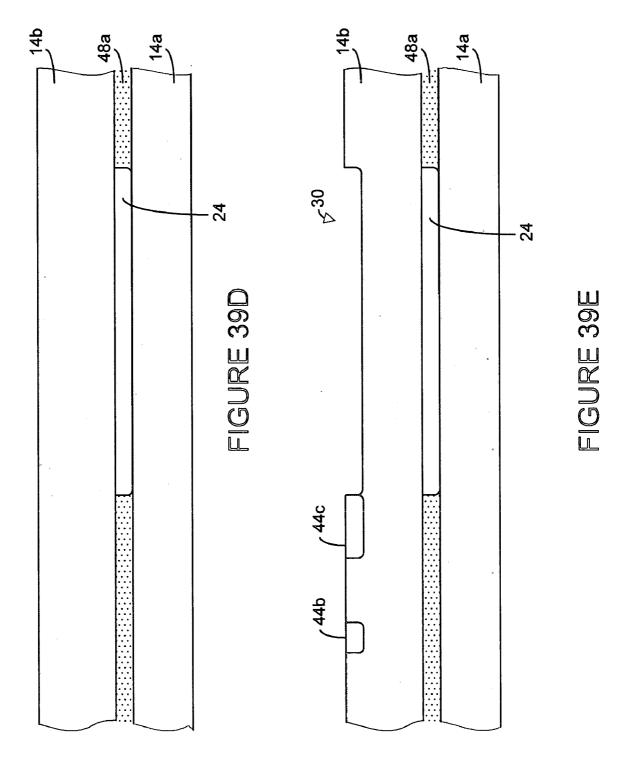

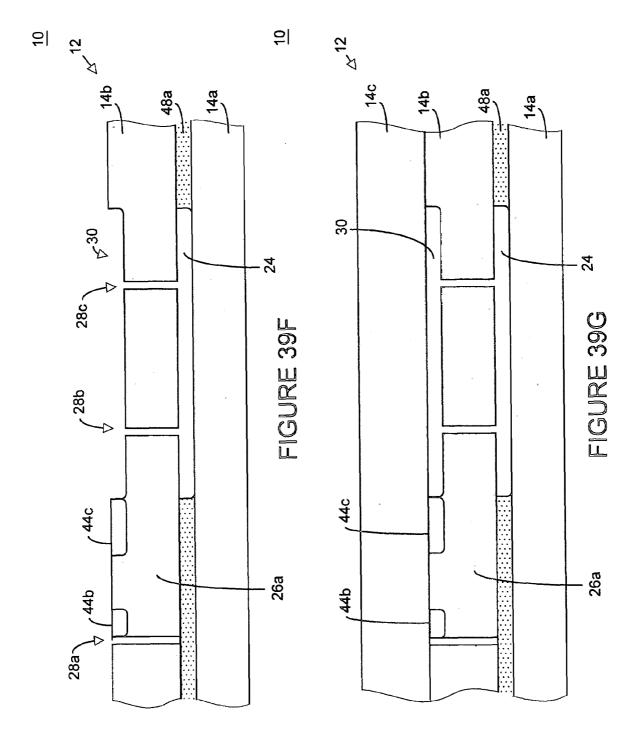

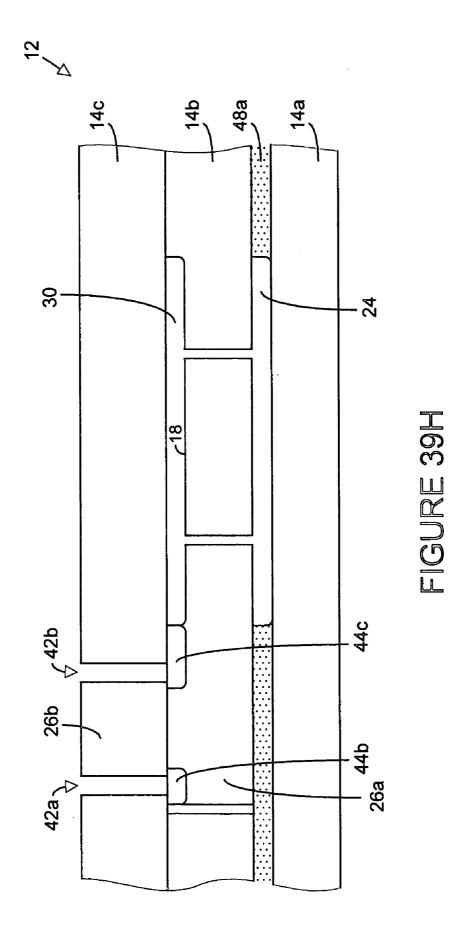

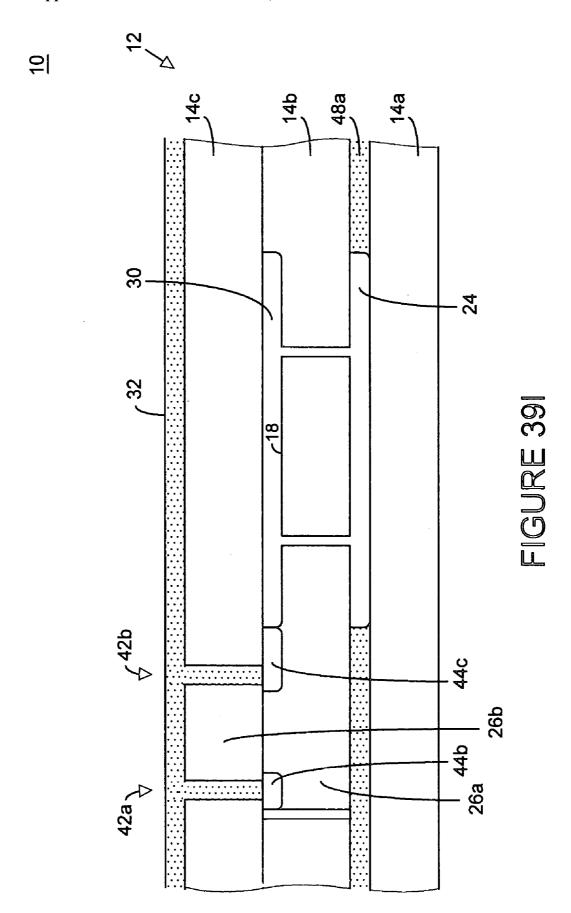

[0060] FIGS. 37A-37I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 36 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

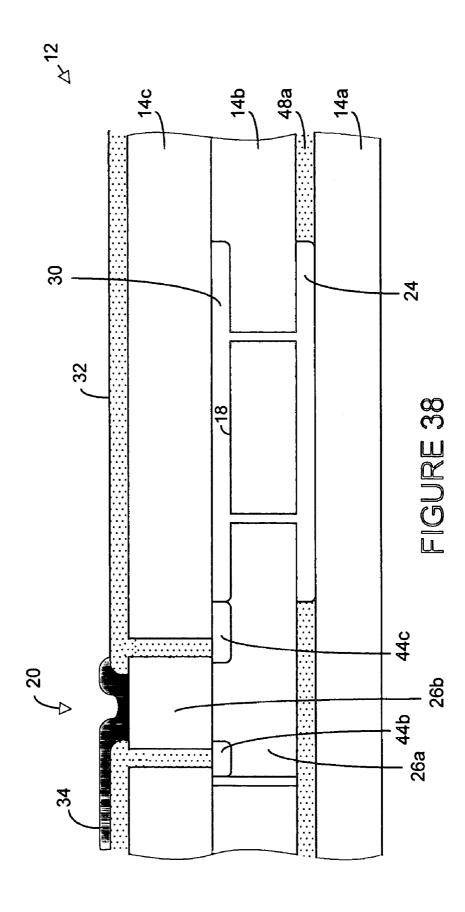

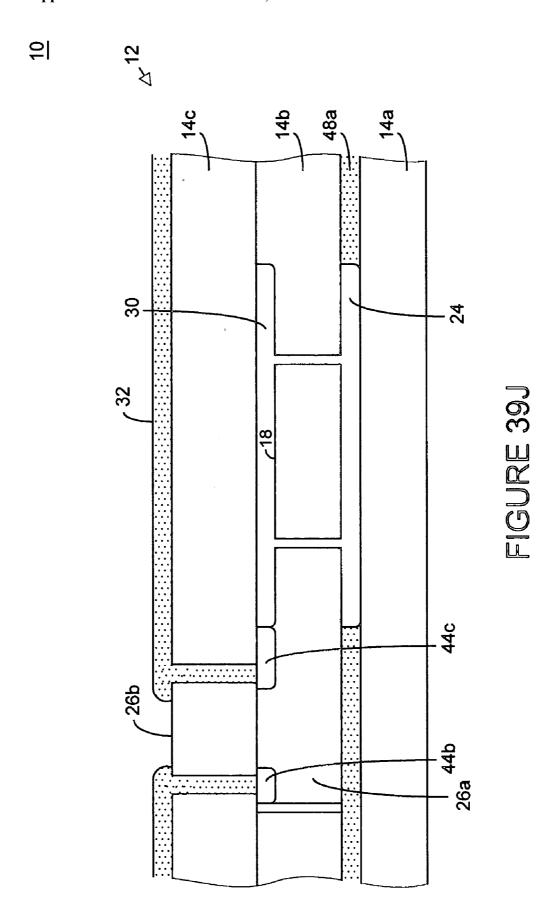

[0061] FIG. 38 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein

the microelectromechanical system employs three substrates wherein an insulative layer is disposed between two of the substrates and isolation trenches and regions electrically isolate the contact;

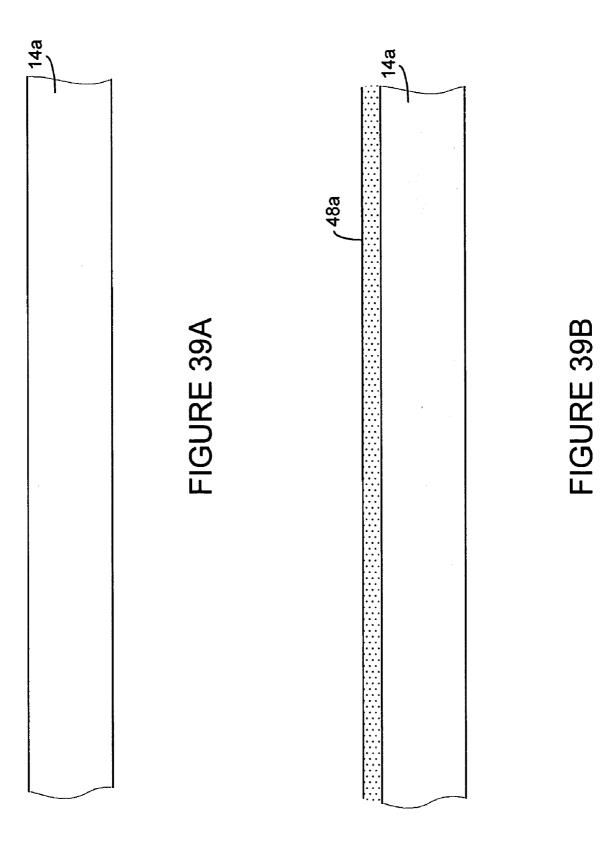

[0062] FIGS. 39A-39K illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 38 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

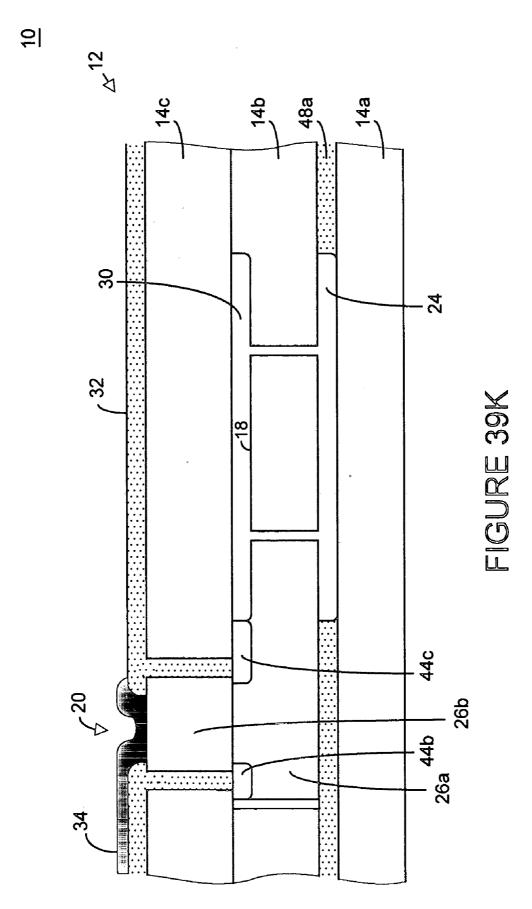

[0063] FIG. 40 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates wherein an intermediate layer (for example, a native oxide layer) is disposed between two of the substrates;

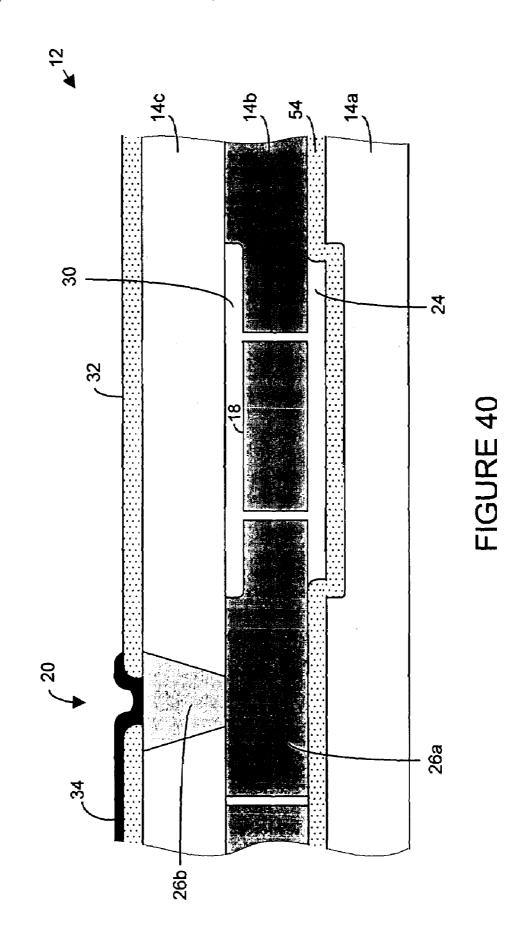

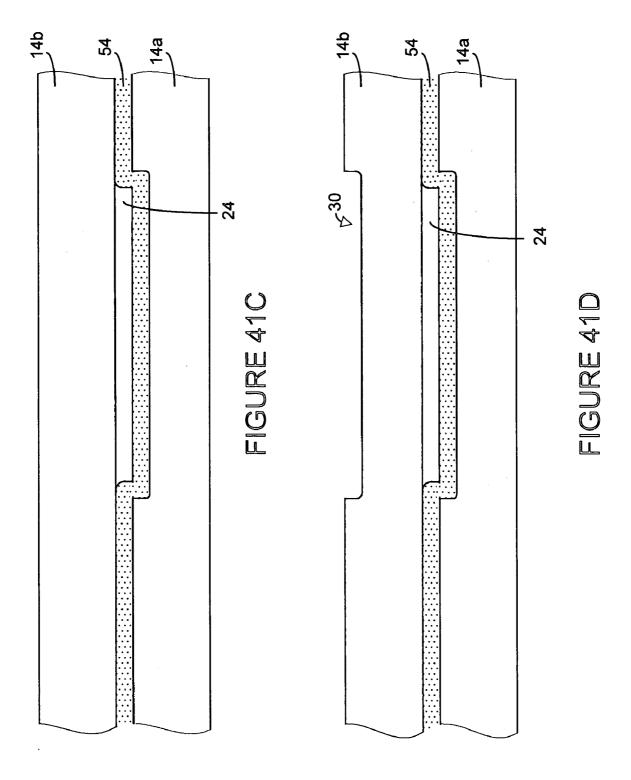

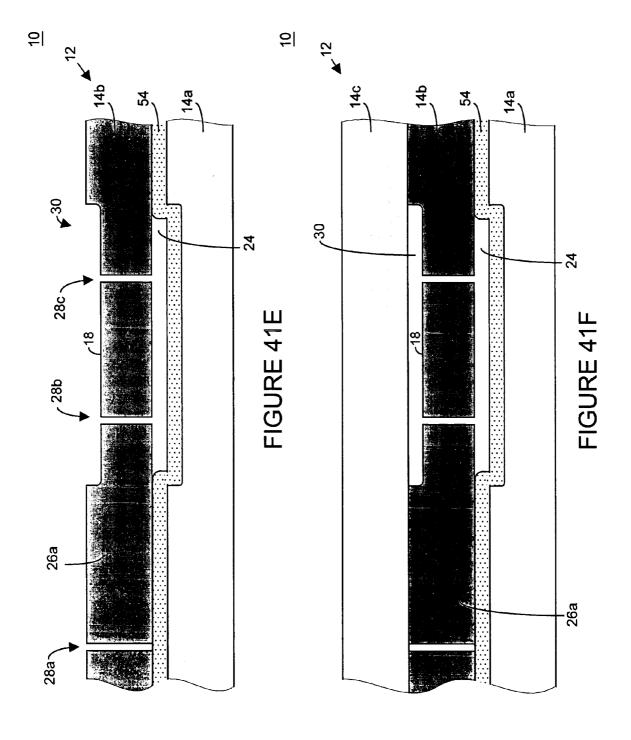

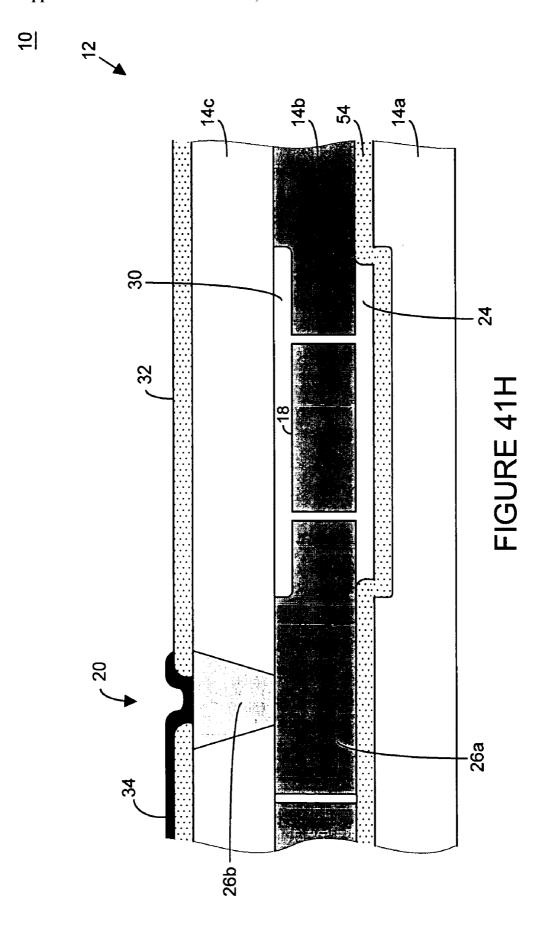

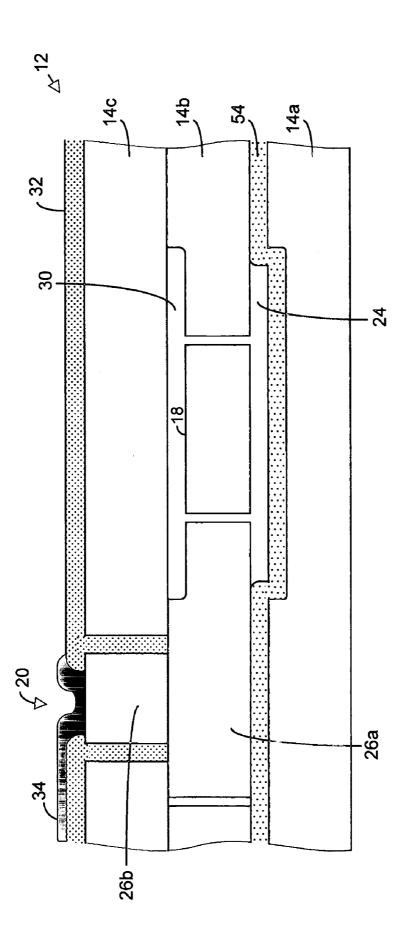

[0064] FIGS. 41A-41H illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 40 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

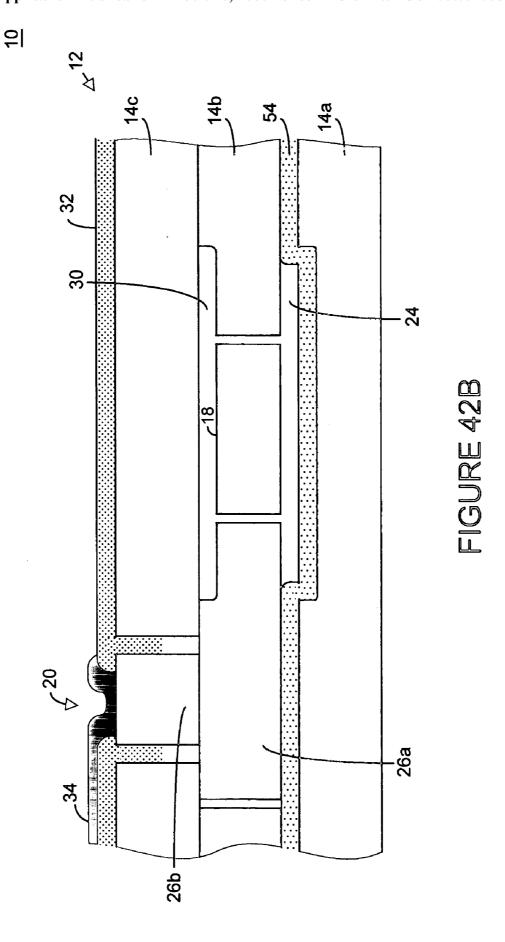

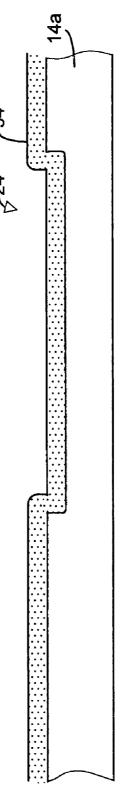

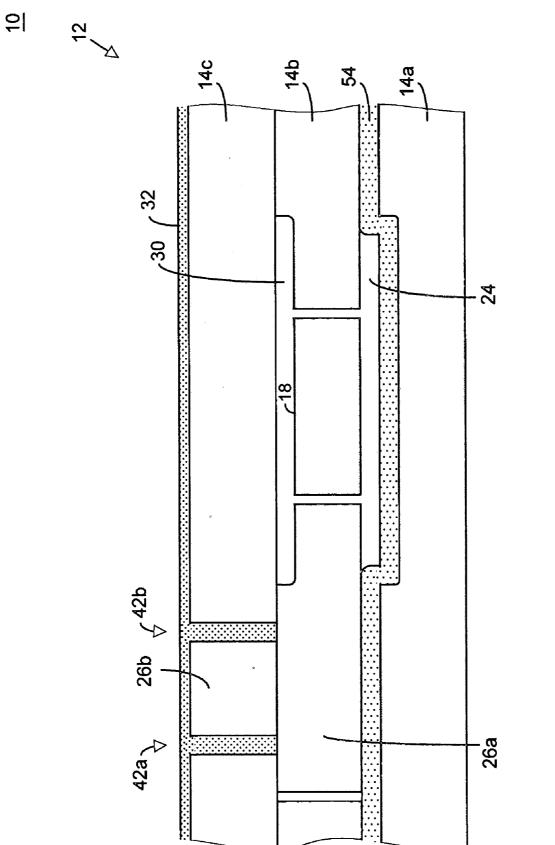

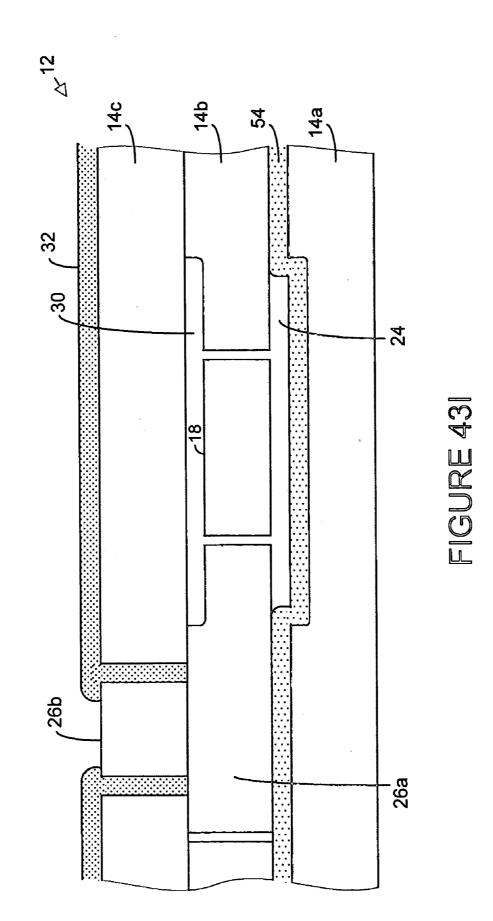

[0065] FIGS. 42A and 42B are cross-sectional views (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of exemplary embodiments of the present inventions wherein the microelectromechanical system employs three substrates wherein an intermediate layer (for example, a native oxide layer) is disposed (for example, deposited or grown) between two of the substrates;

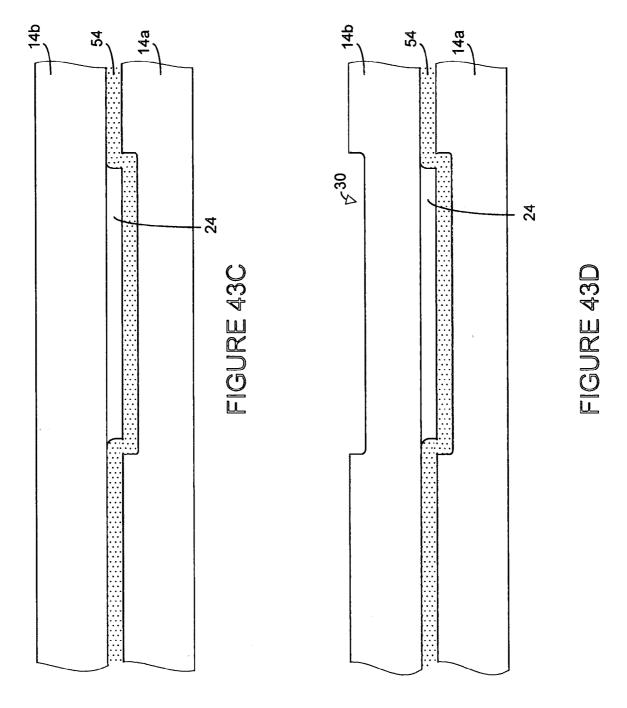

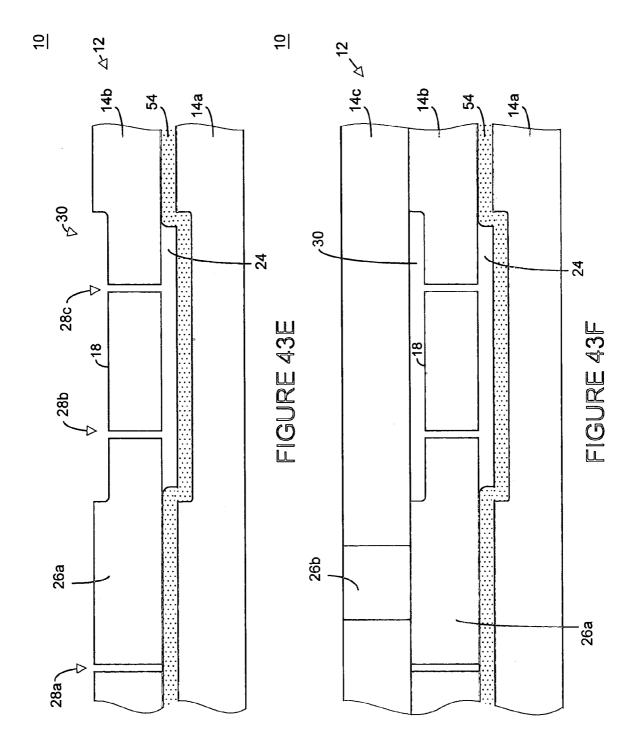

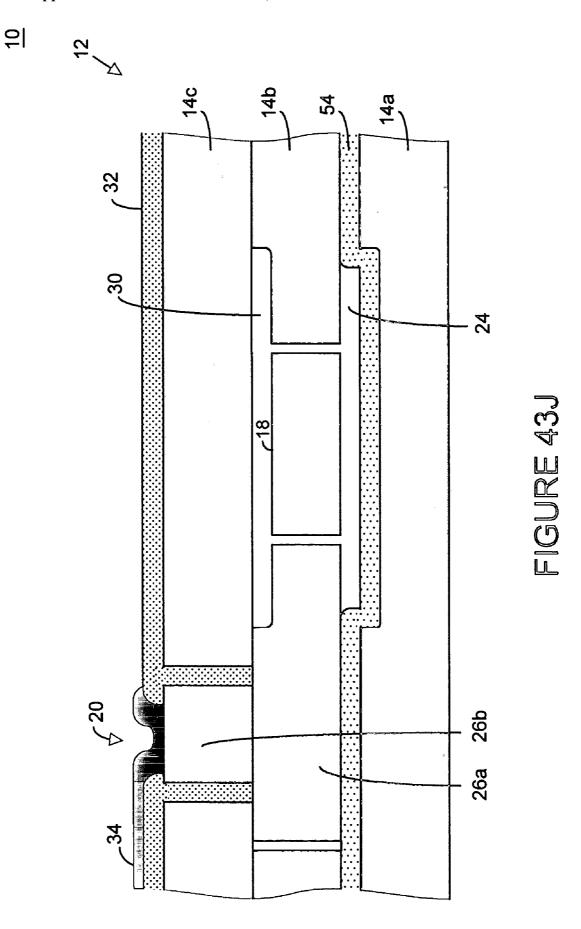

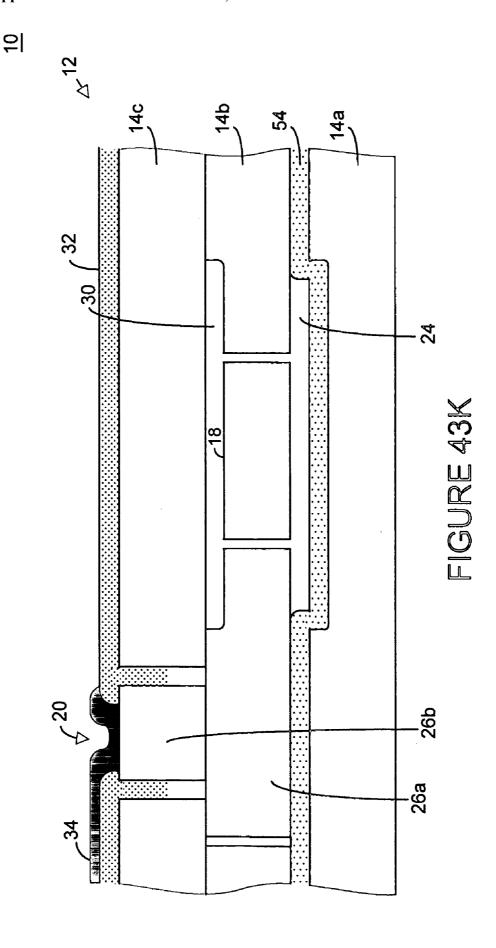

[0066] FIGS. 43A-43K illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical systems of FIGS. 42A and 42B at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

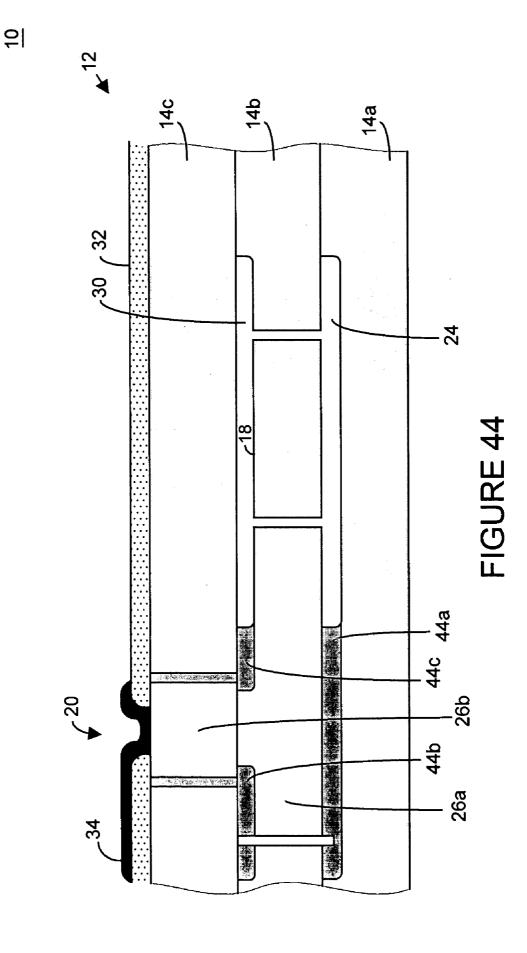

[0067] FIG. 44 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates and the processing techniques include alternative processing margins:

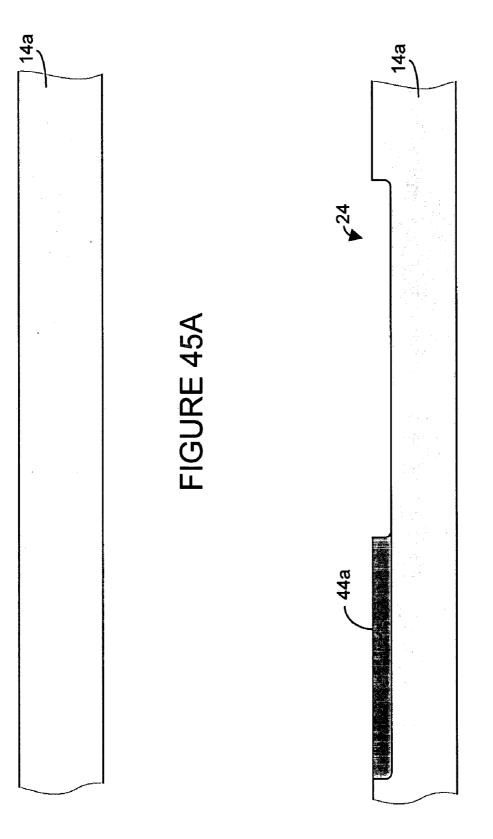

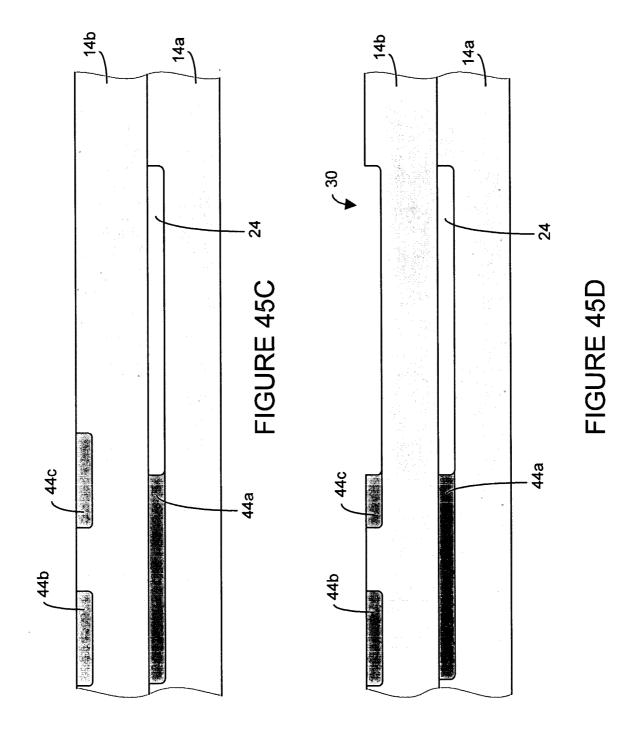

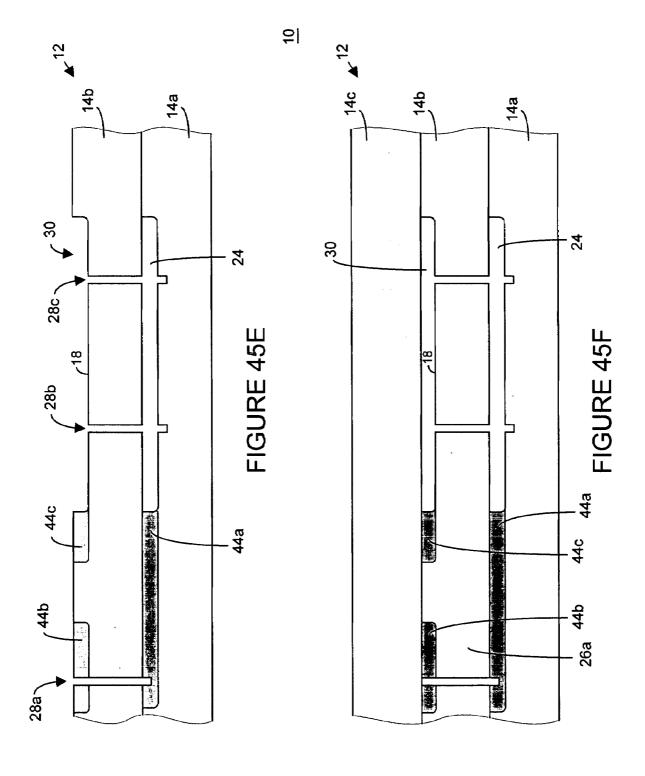

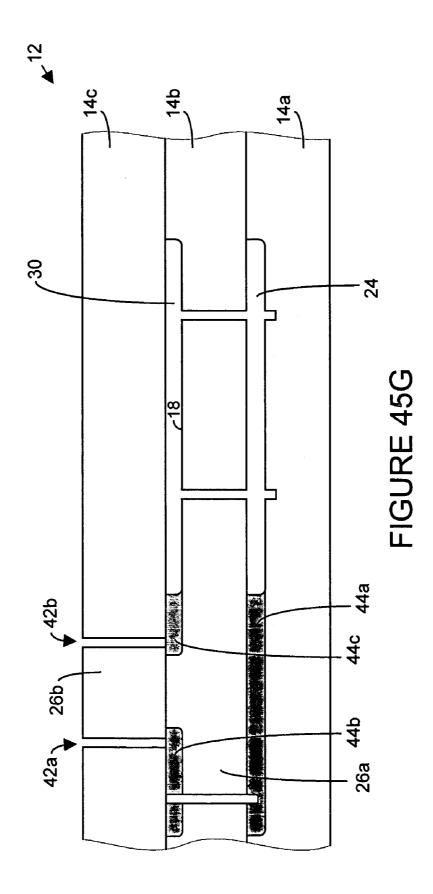

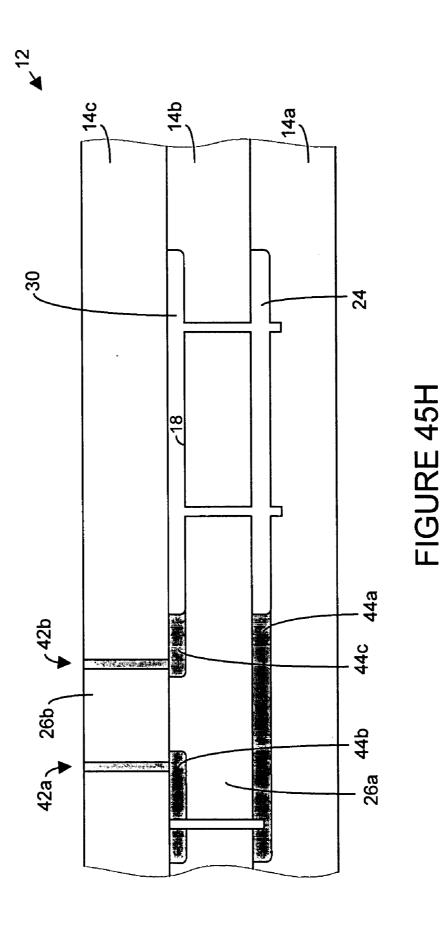

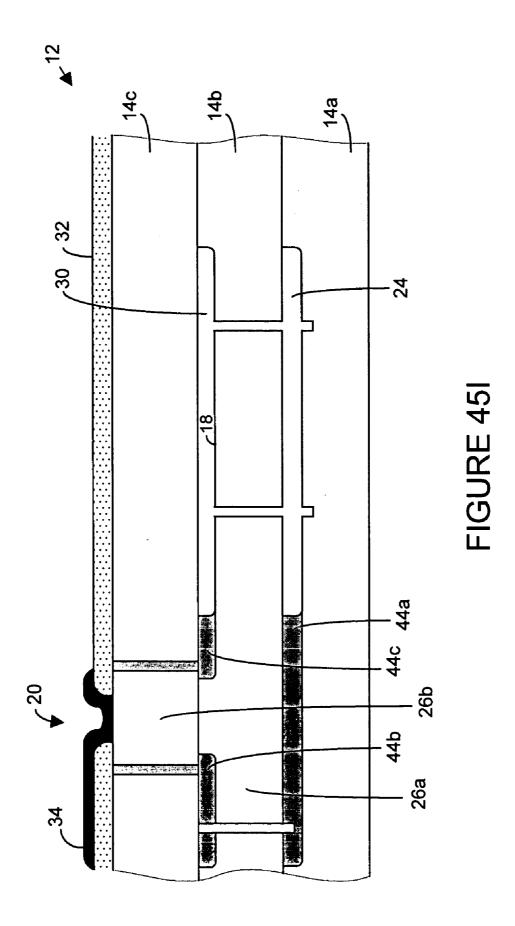

[0068] FIGS. 45A-45I illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 44 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

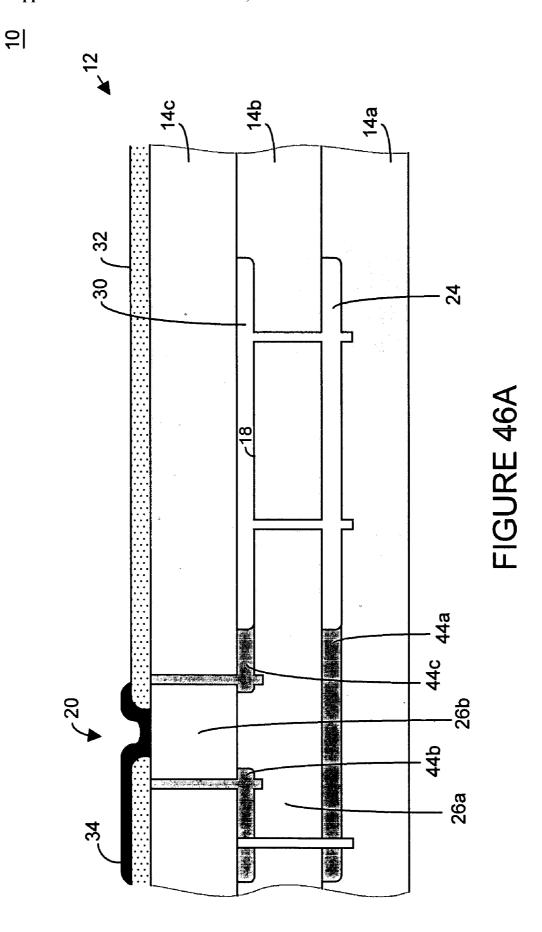

[0069] FIG. 46A is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates and the processing techniques include alternative processing margins wherein the isolation trenches include an over etch;

[0070] FIG. 46B is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates and a selected trench includes alternative processing margins:

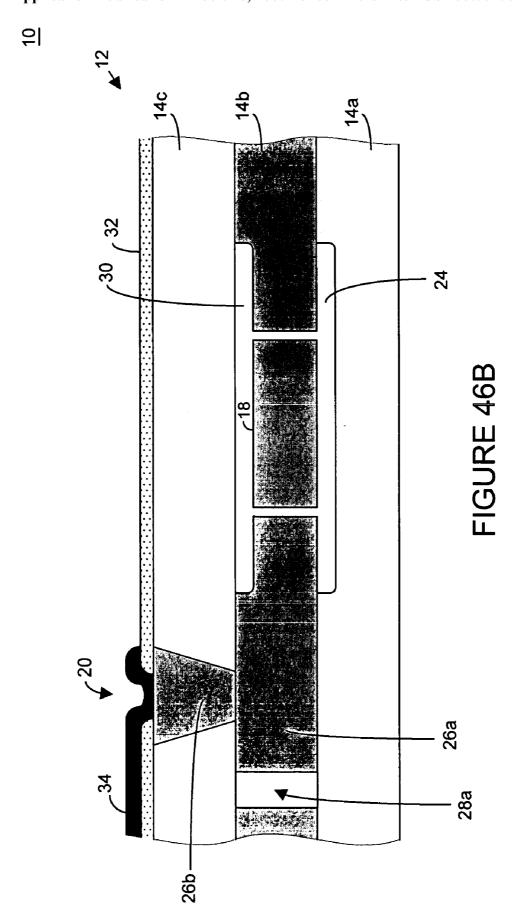

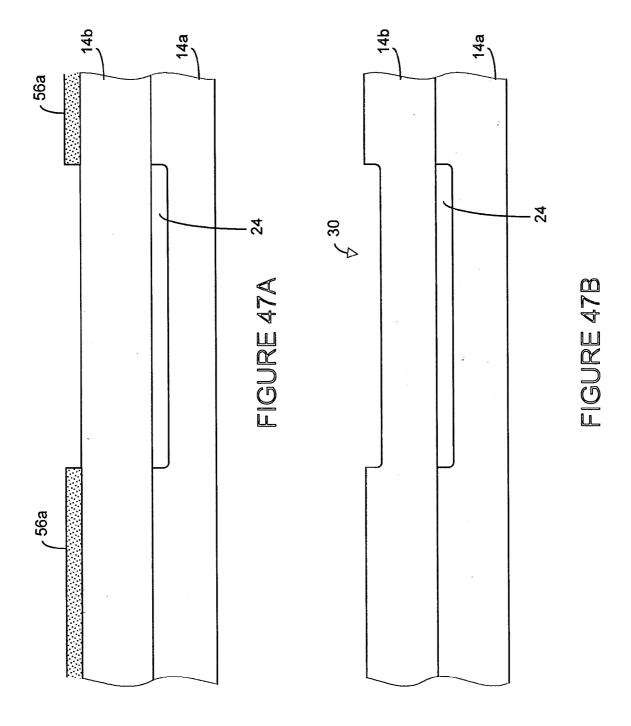

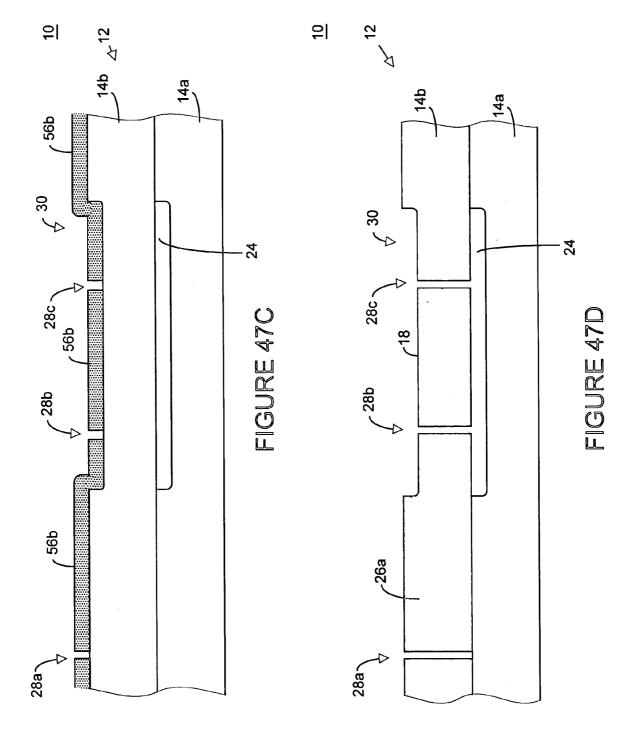

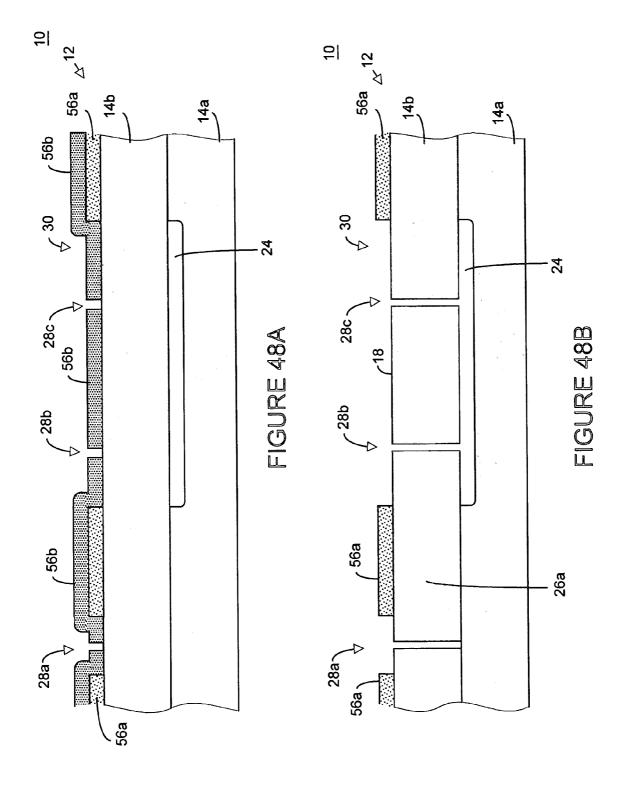

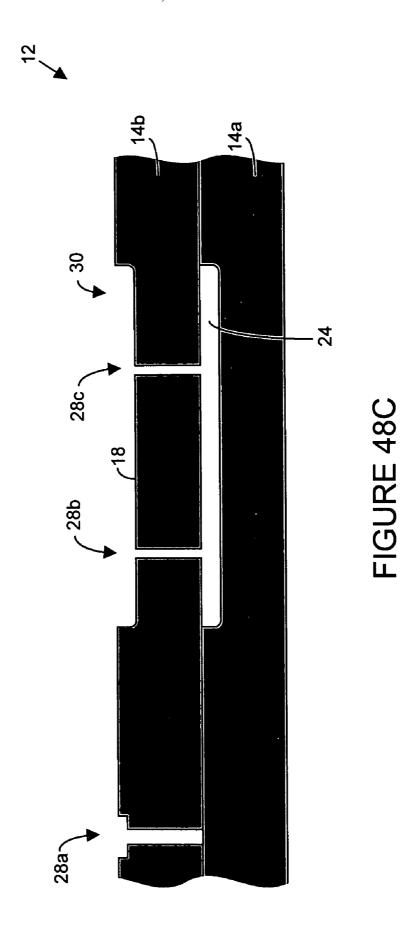

[0071] FIGS. 47A-47D and 48A-48C are cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the

contact of FIG. 2 of an embodiment of the present inventions having alternative exemplary processing techniques, flows and orders thereof;

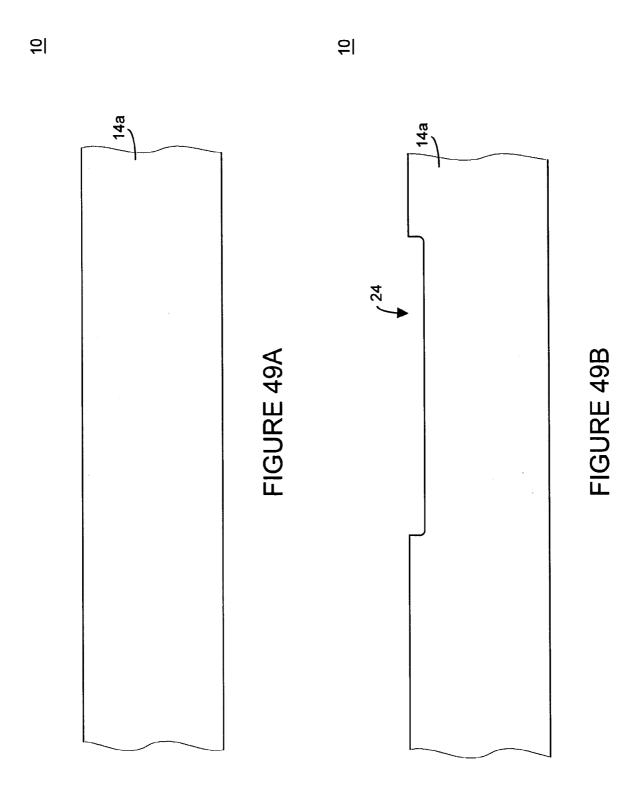

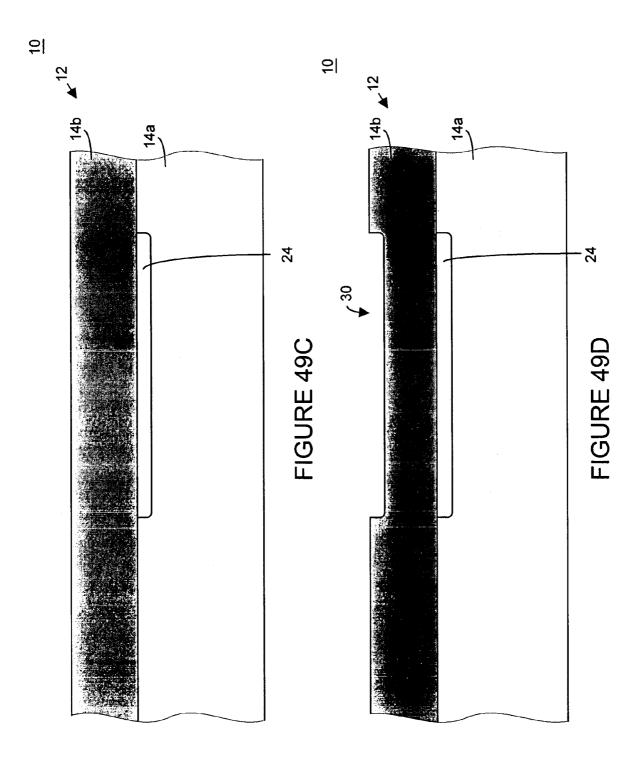

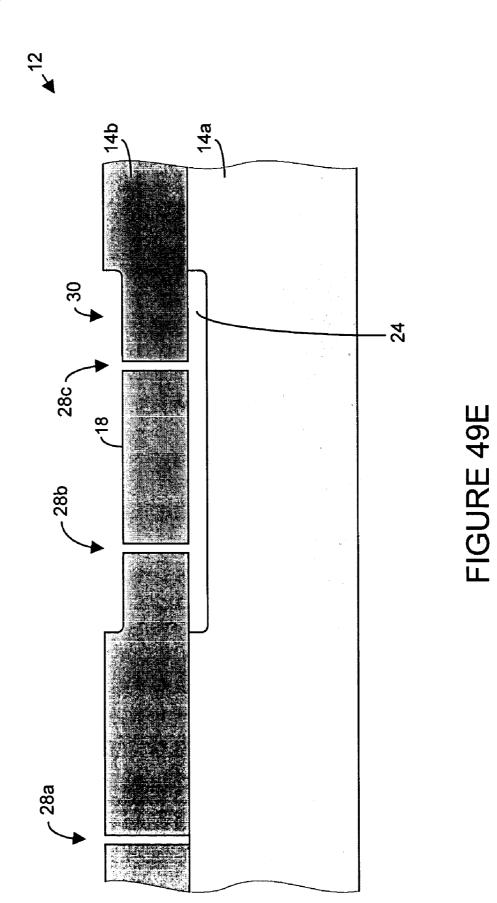

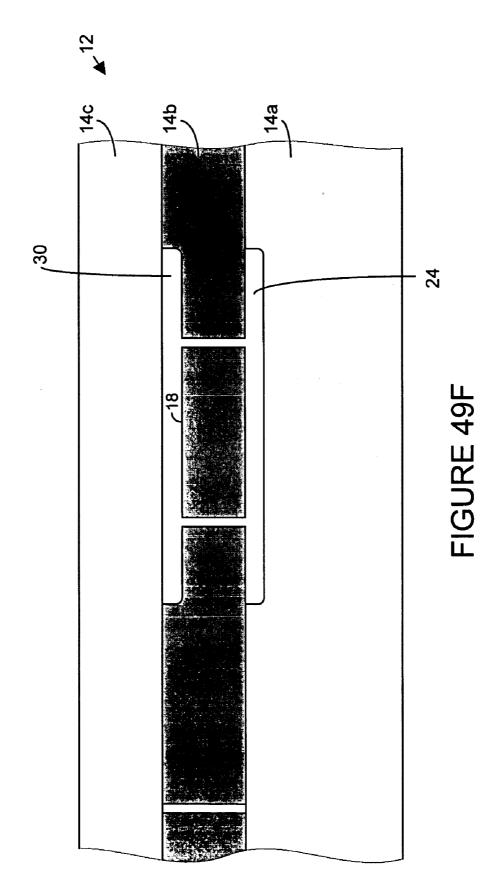

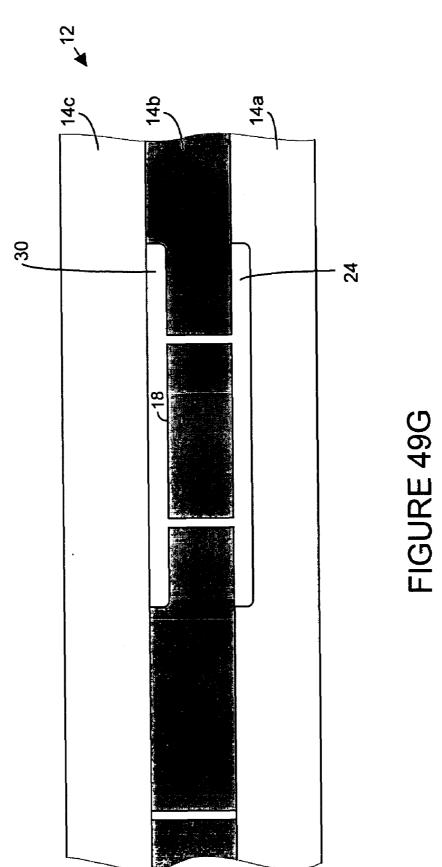

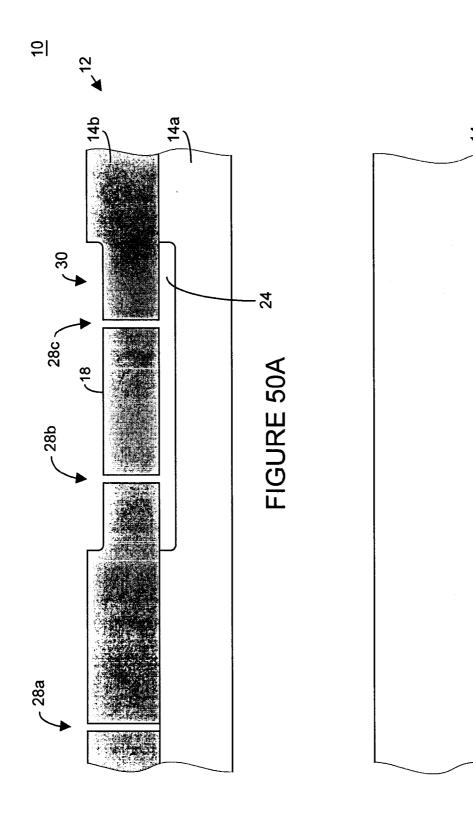

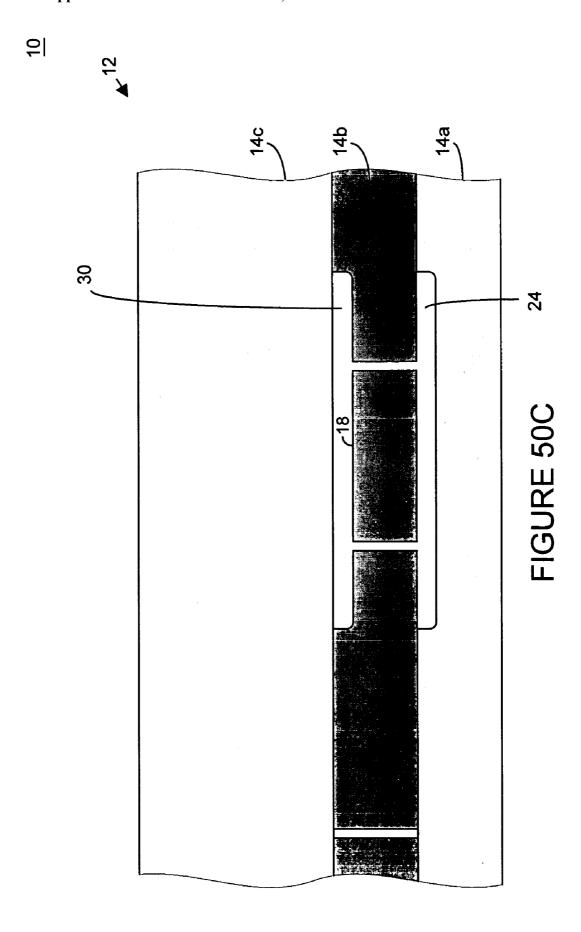

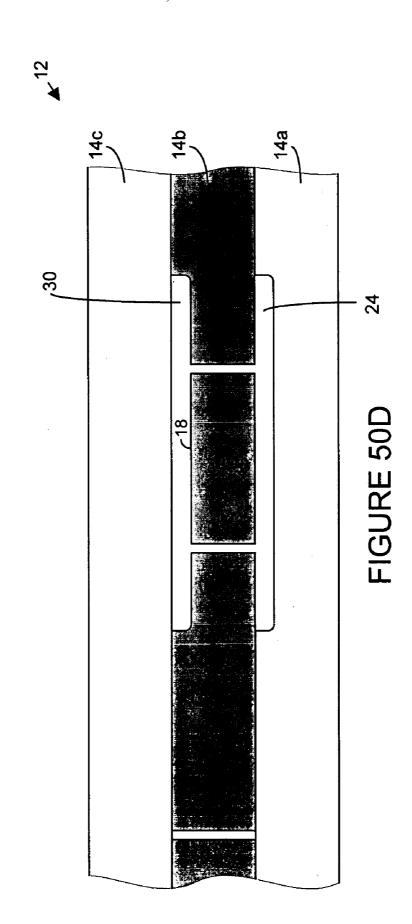

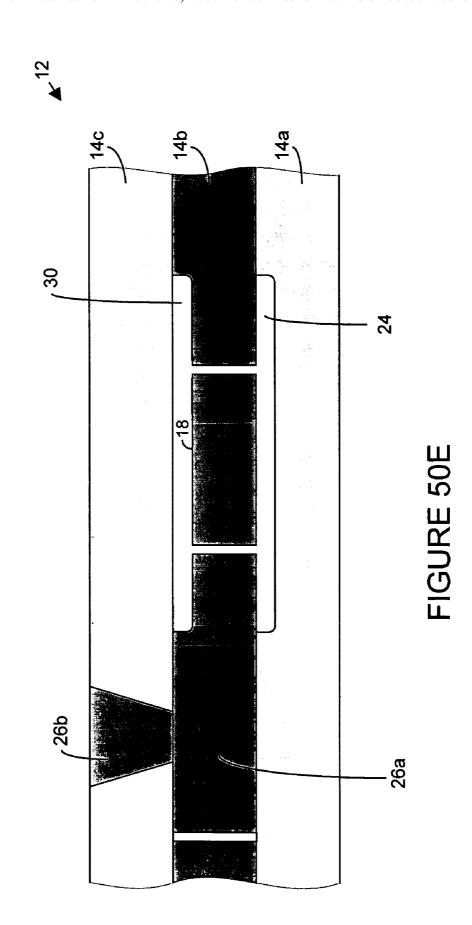

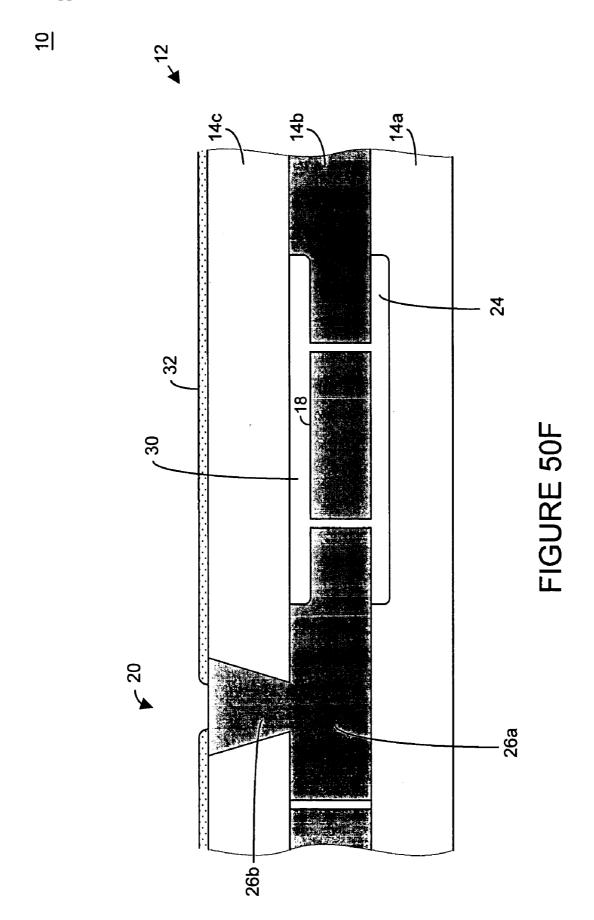

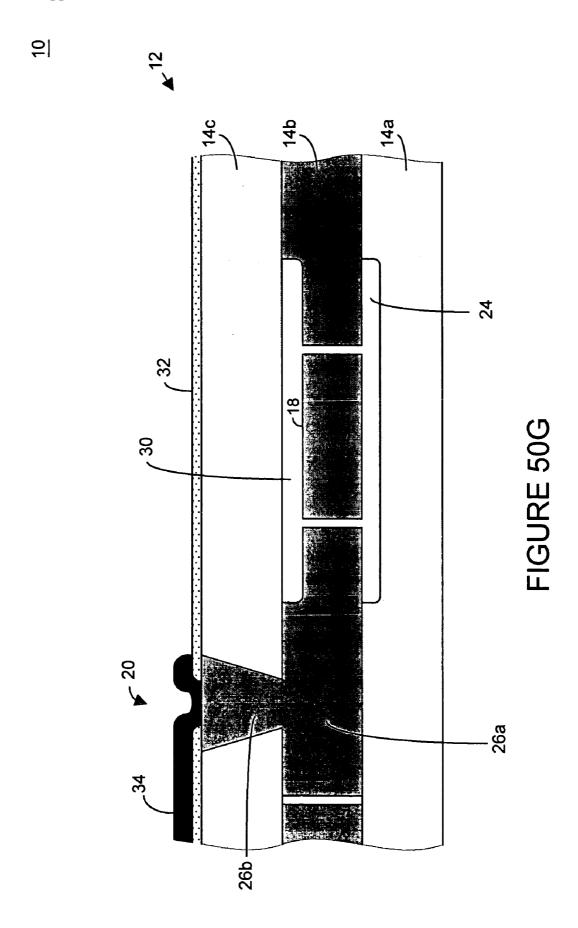

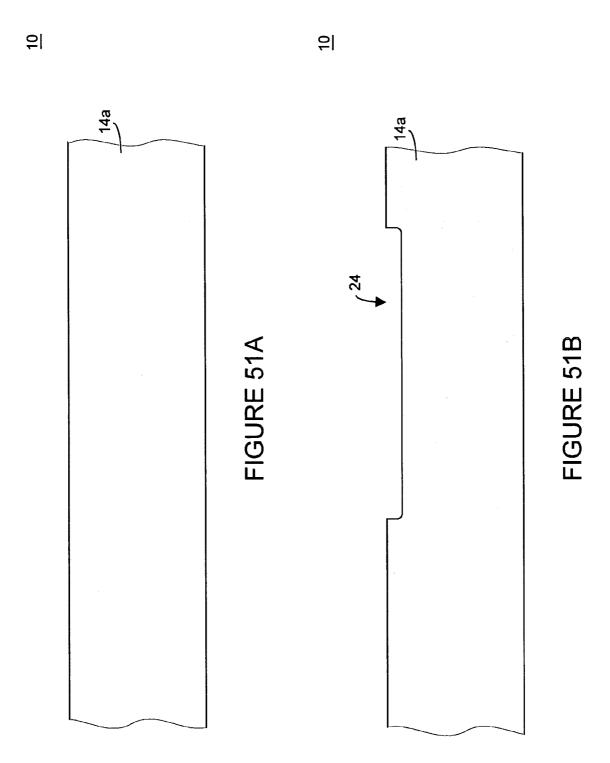

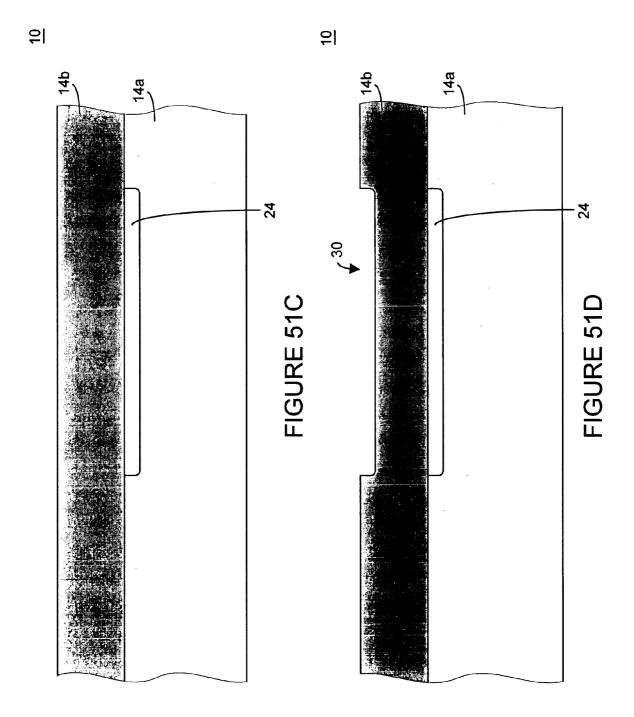

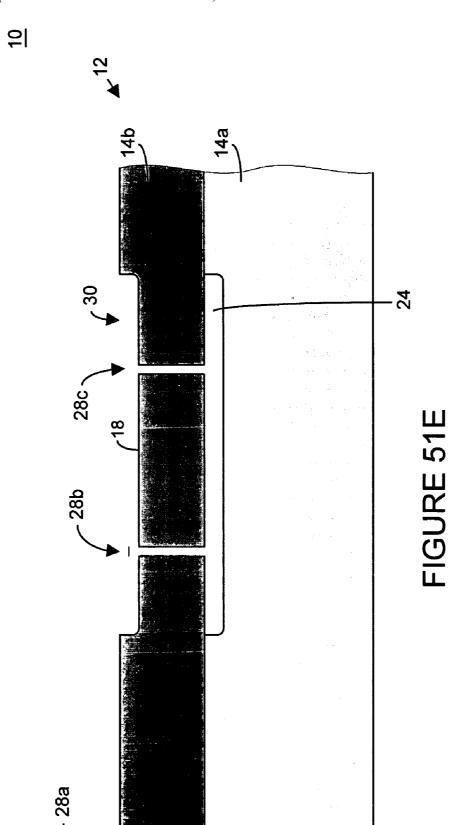

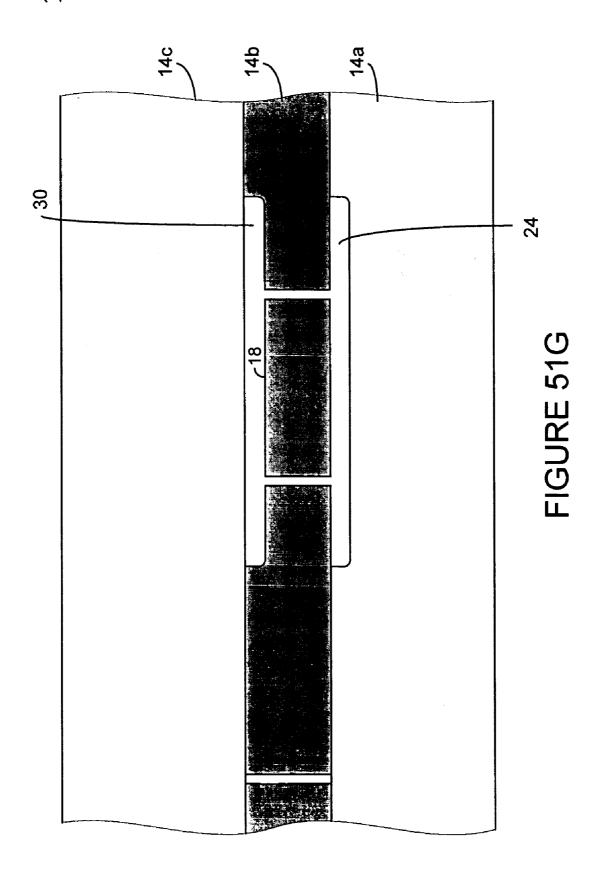

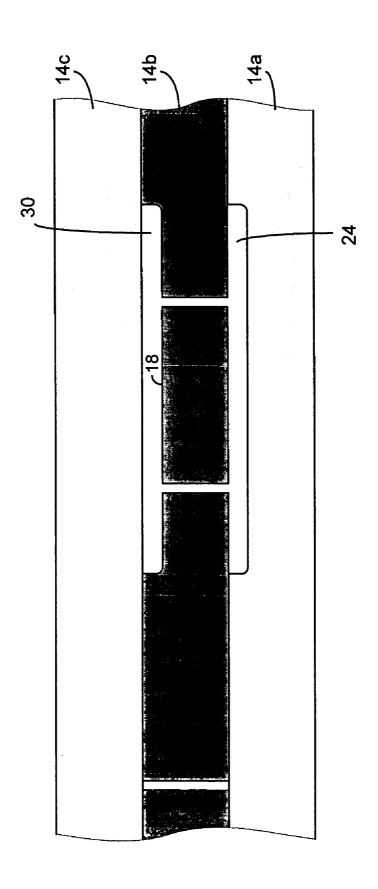

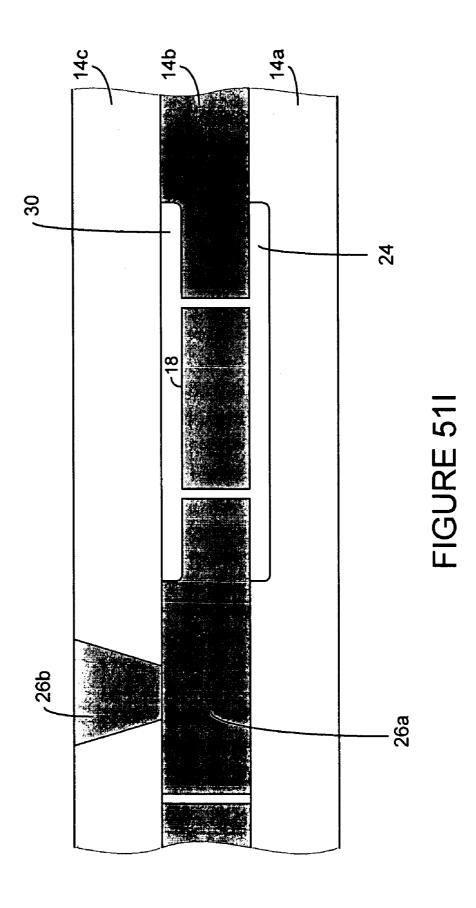

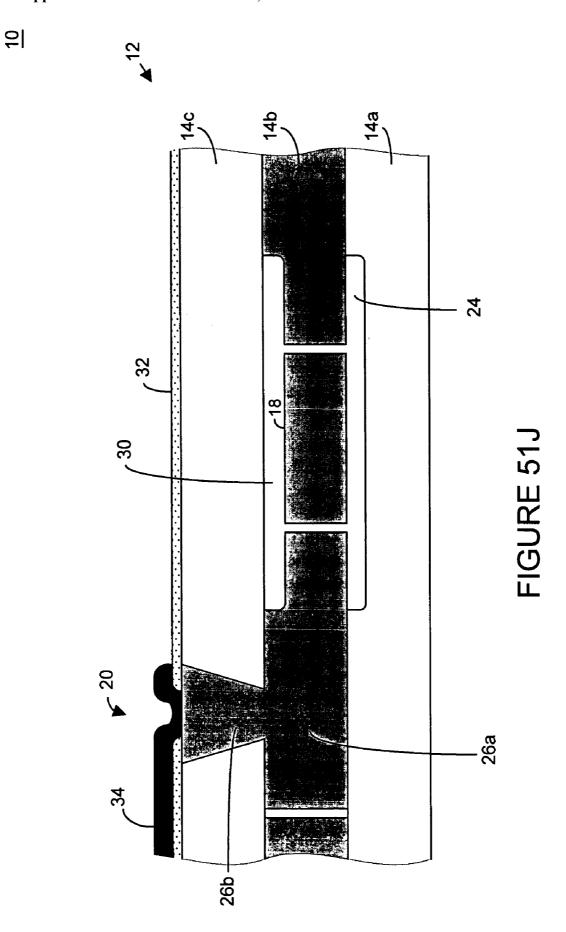

[0072] FIGS. 49A-49G, 50A-50G and 51A-51J are crosssectional views (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of exemplary embodiments of the present inventions having alternative processing techniques, flows and orders thereof relative to one or more of substrates:

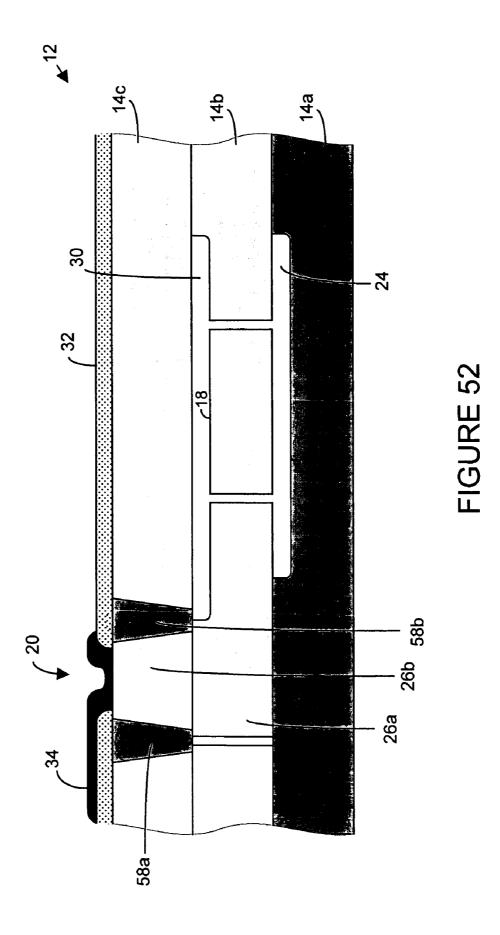

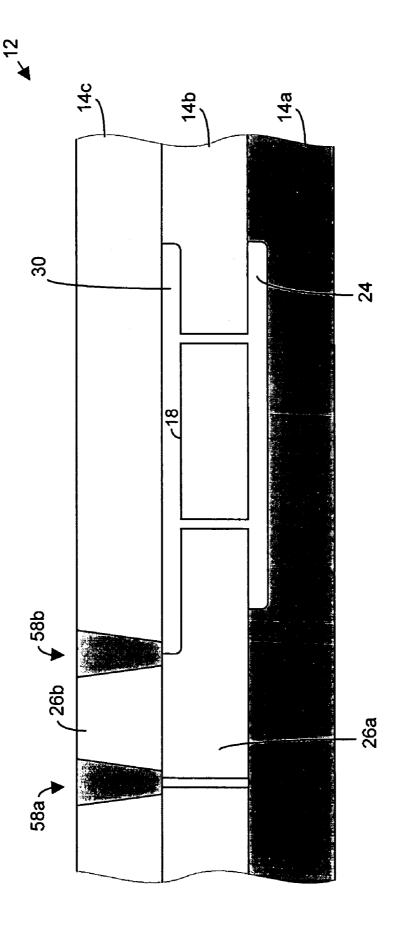

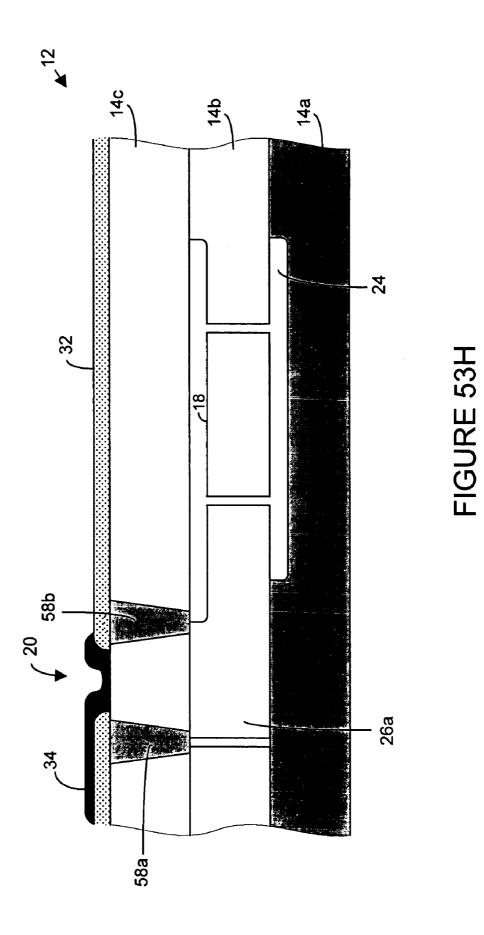

[0073] FIG. 52 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates wherein isolation regions are implanted in a cover substrate to electrically isolate the contact;

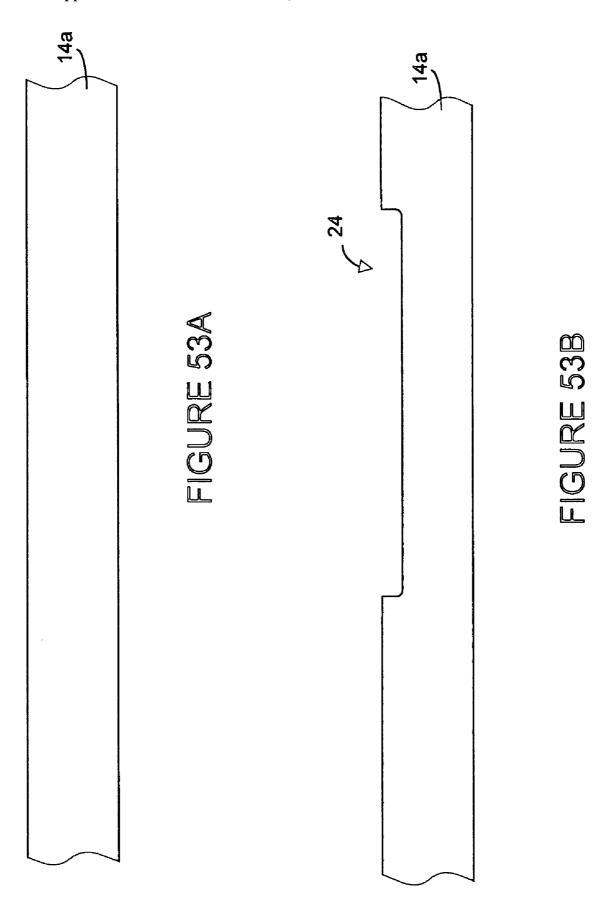

[0074] FIGS. 53A-53H illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 52 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

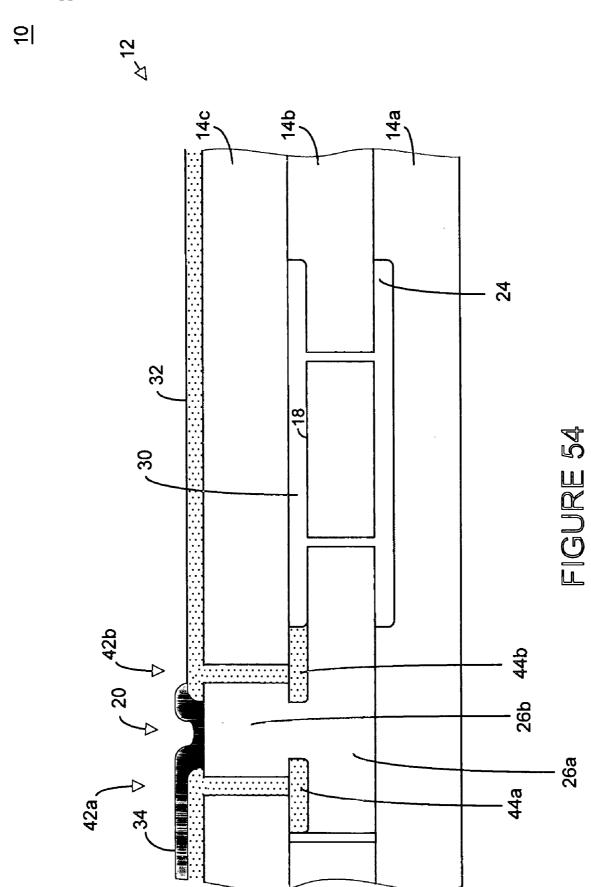

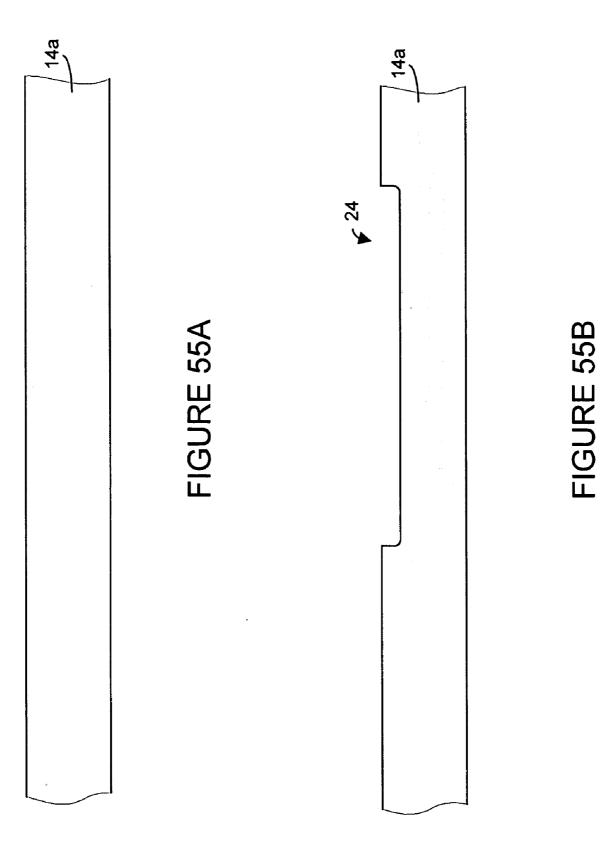

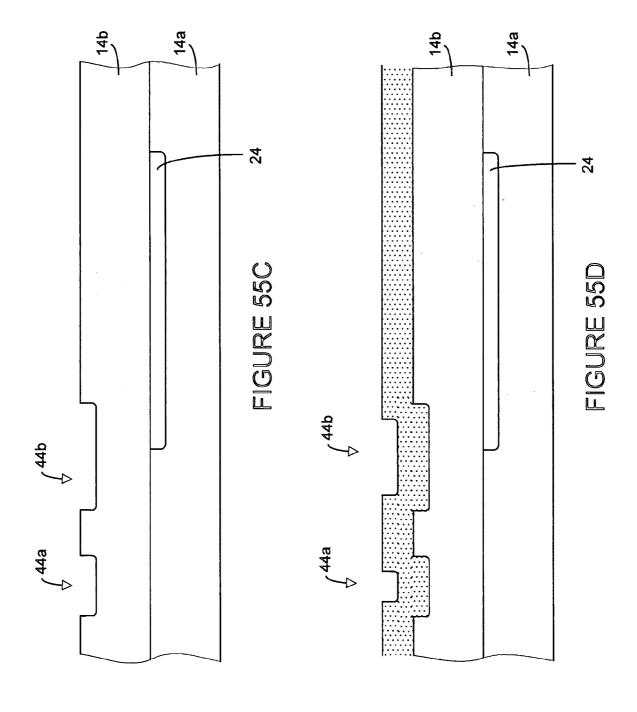

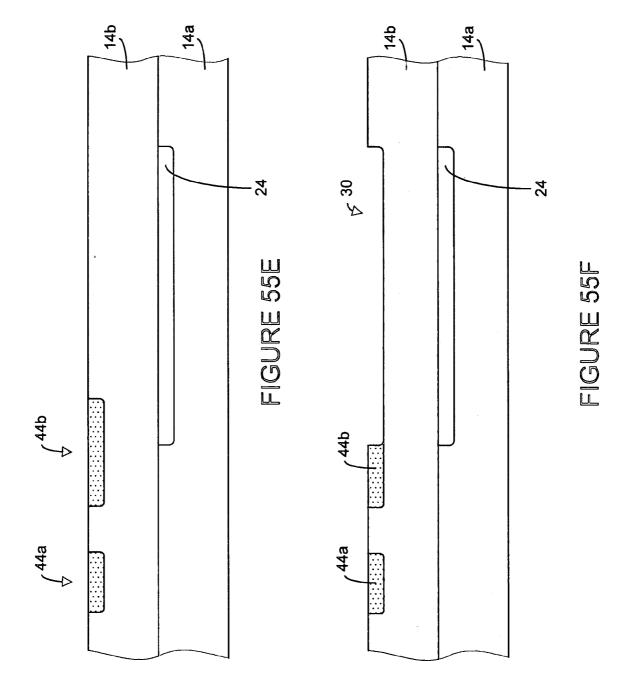

[0075] FIG. 54 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein the microelectromechanical system employs three substrates wherein isolation regions include an insulation material (for example, a silicon nitride or silicon dioxide);

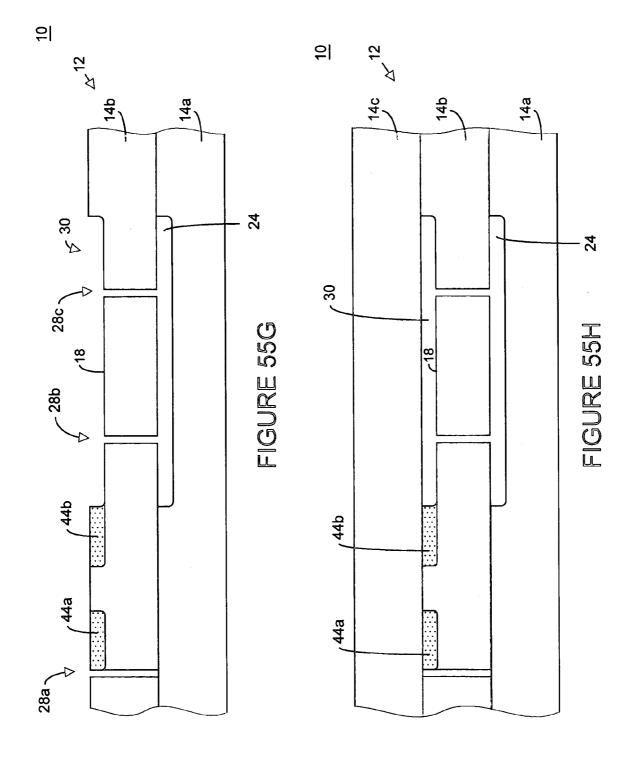

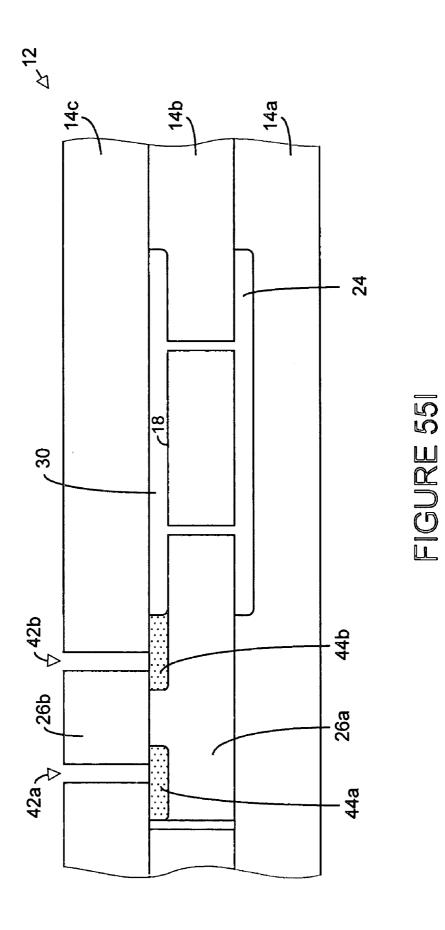

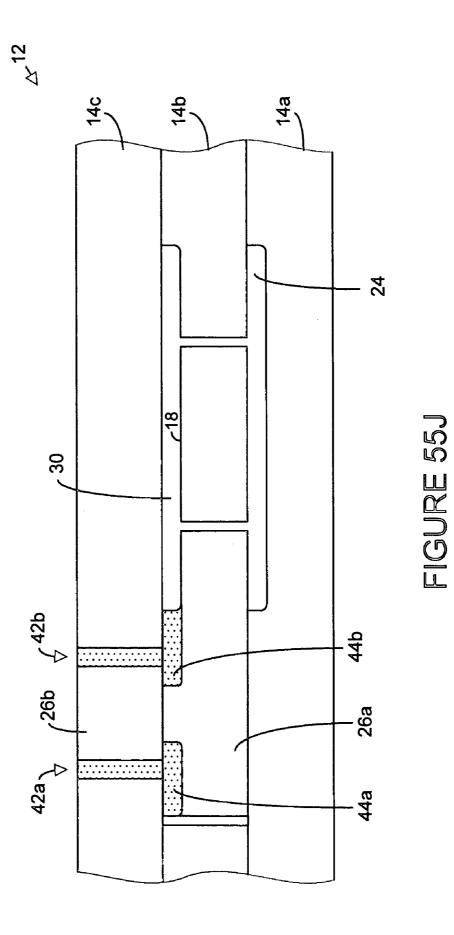

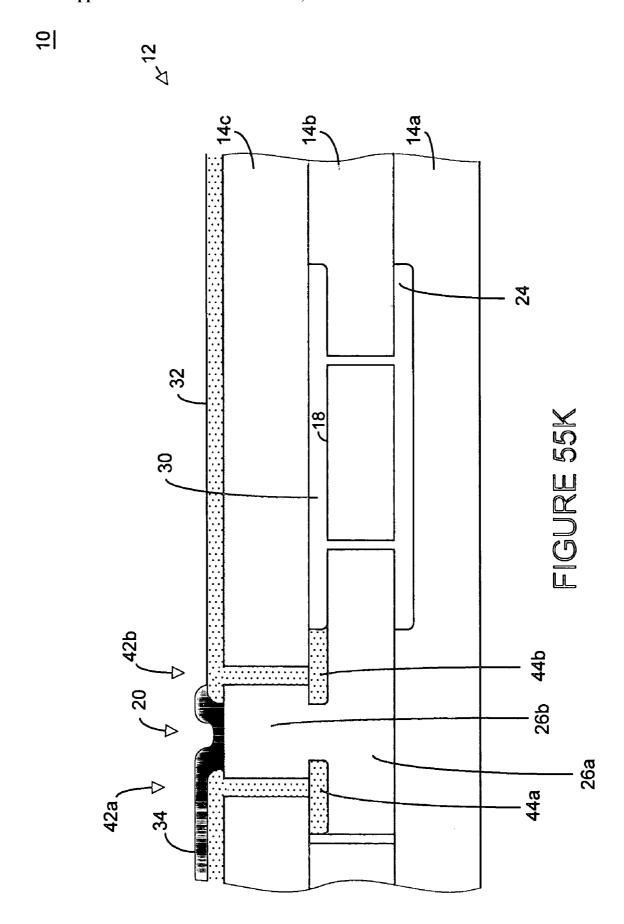

[0076] FIGS. 55A-55K illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 54 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

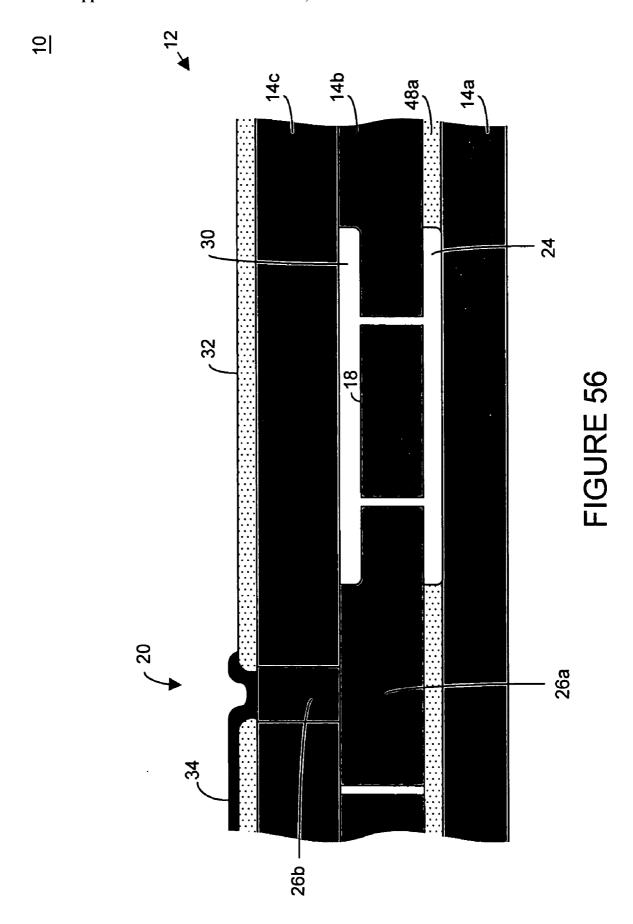

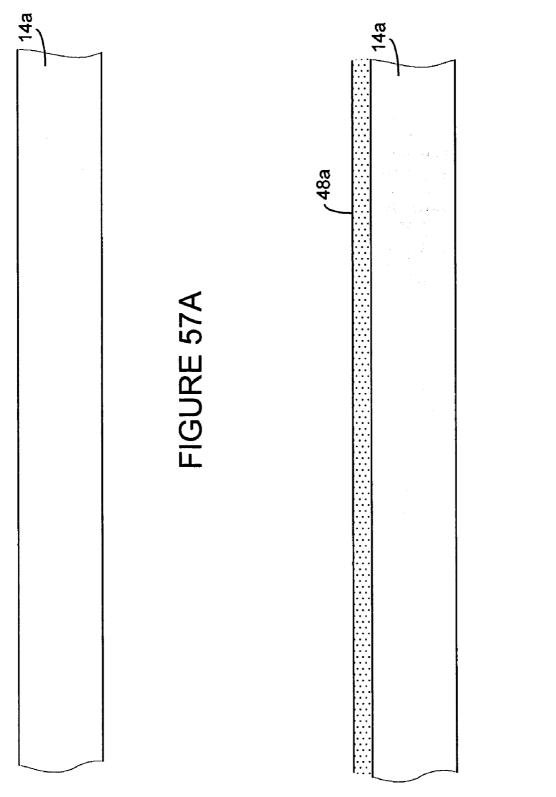

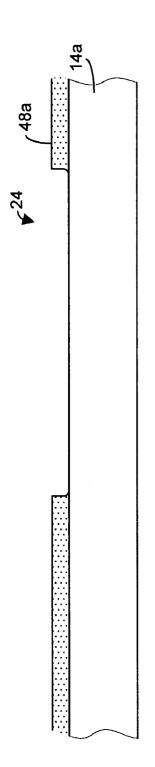

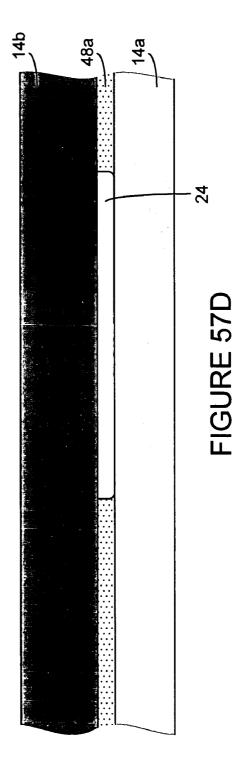

[0077] FIG. 56 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein a contact area is etched and formed in one of the "cover" substrate to provide for electrical conductivity with the an underlying contact area;

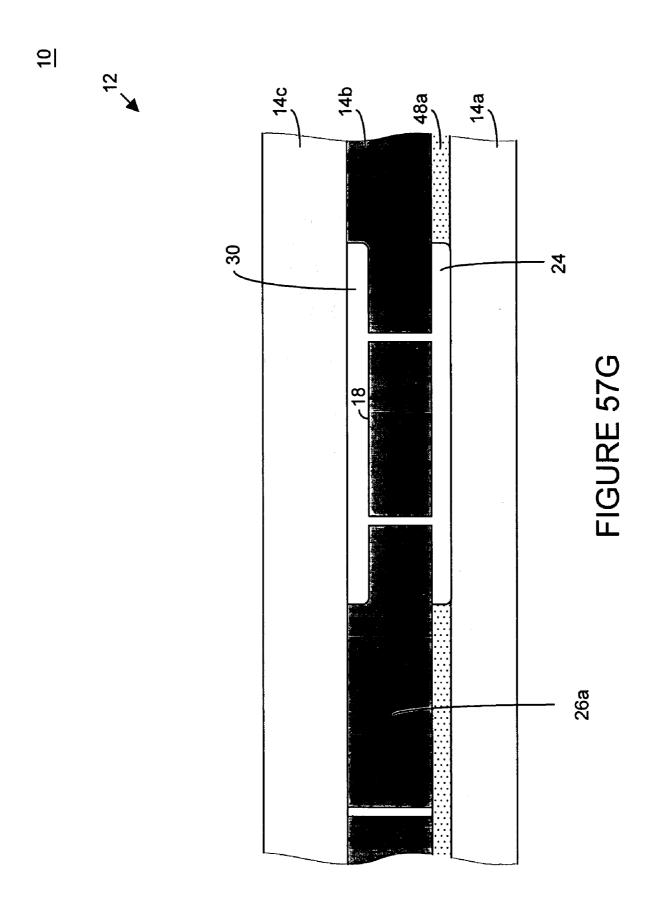

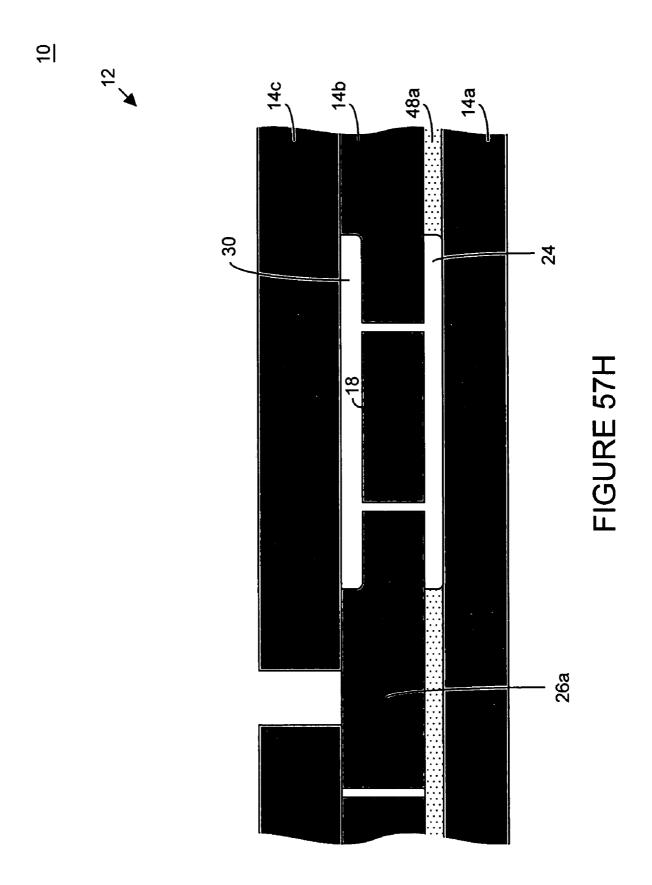

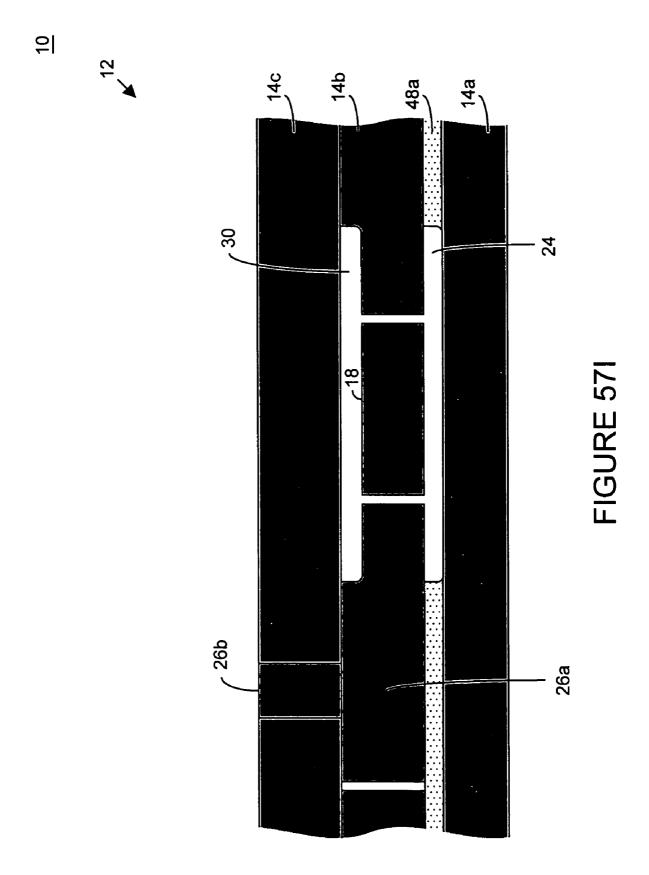

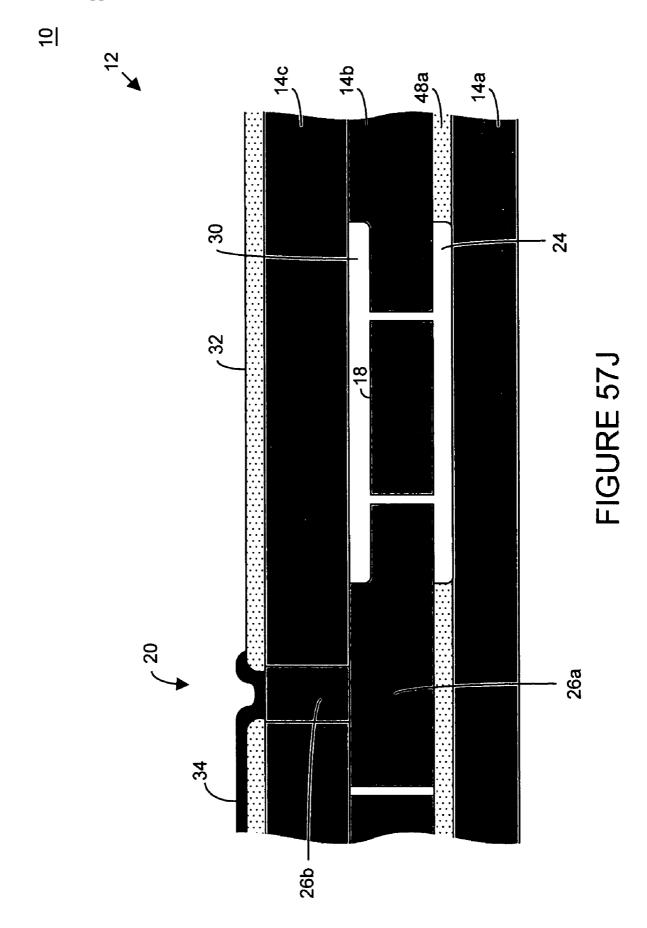

[0078] FIGS. 57A-57J illustrate cross-sectional views of an exemplary flow of the fabrication of the portion of the microelectromechanical system of FIG. 56 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions:

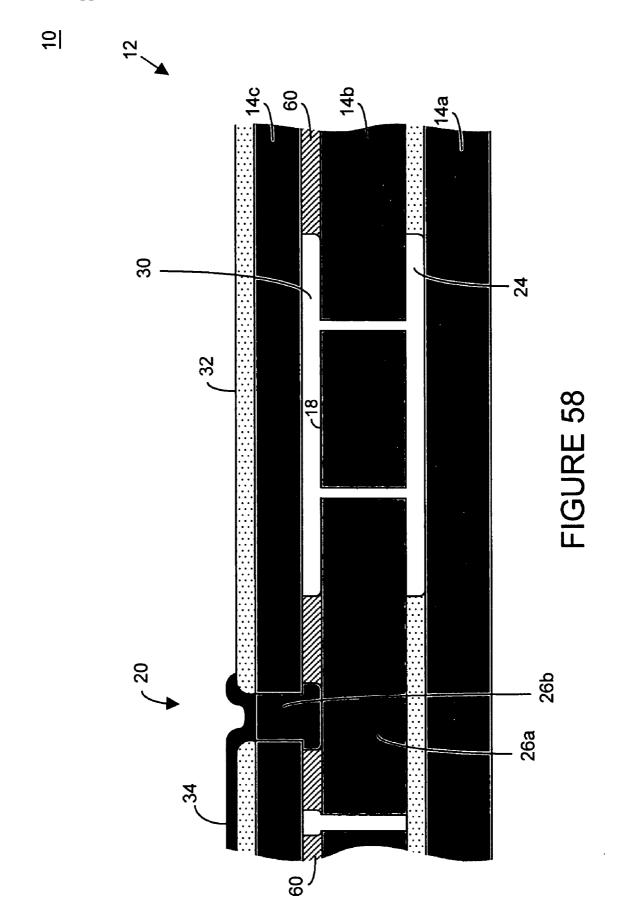

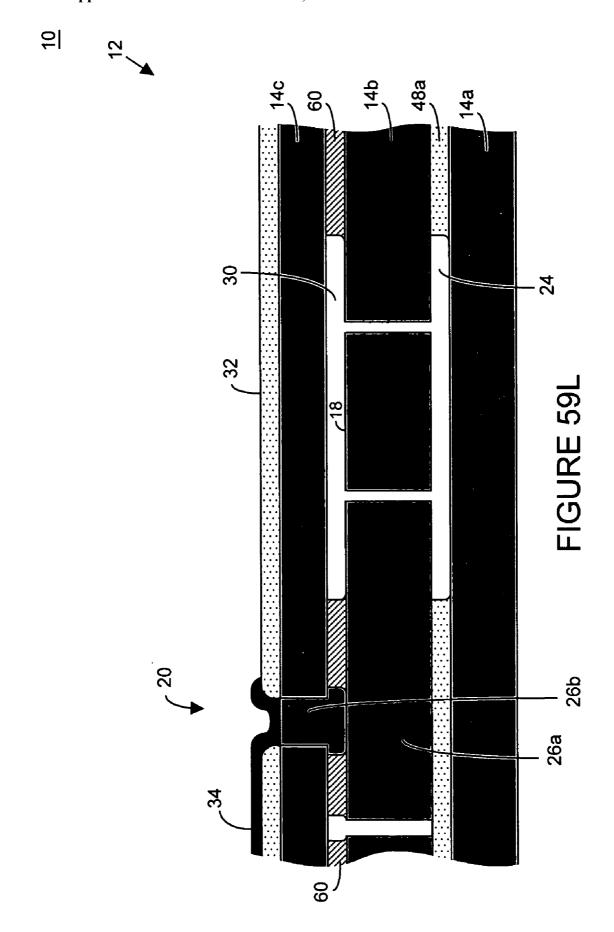

[0079] FIG. 58 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of an exemplary embodiment of the present inventions wherein bonding material and/or a bonding facilitator material is employed between substrates;

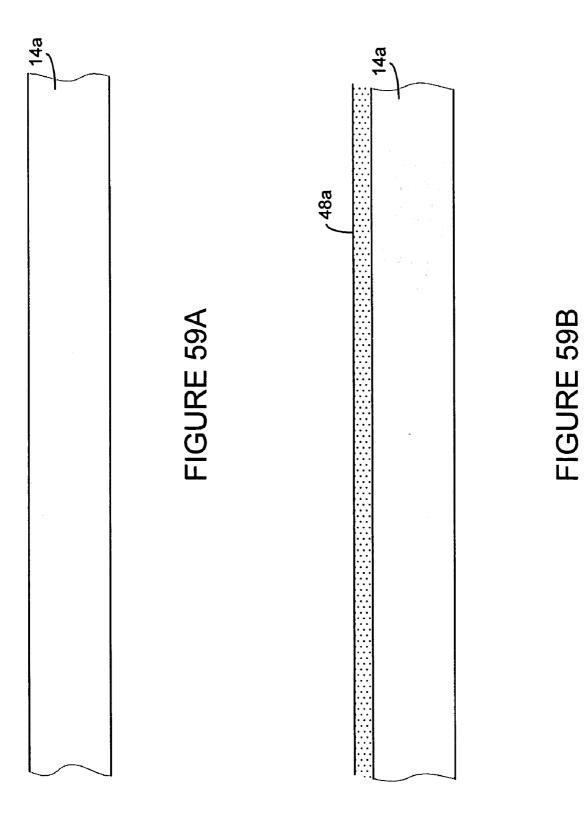

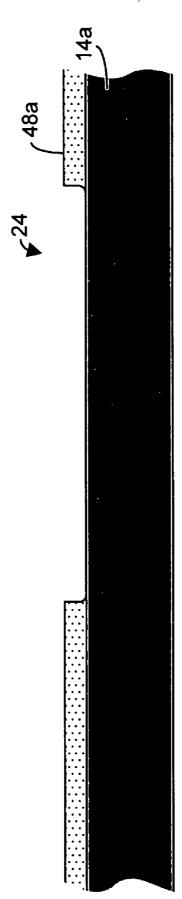

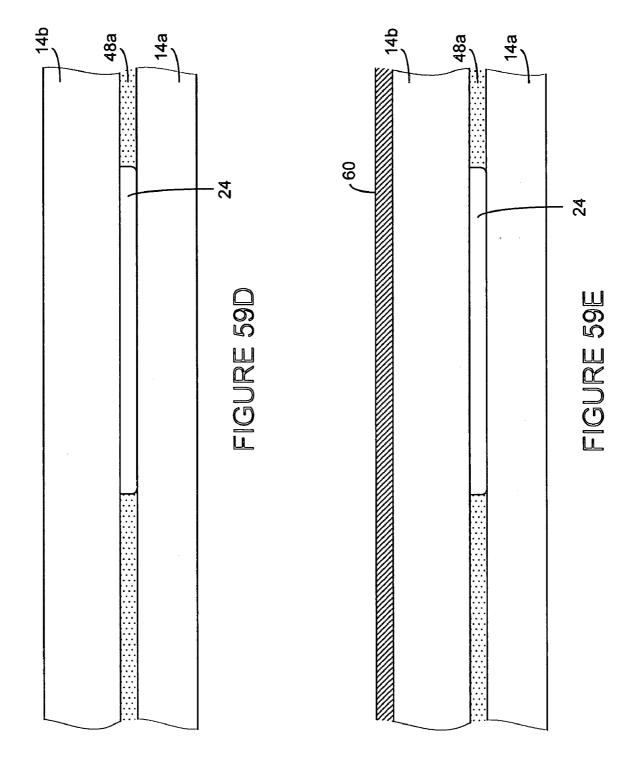

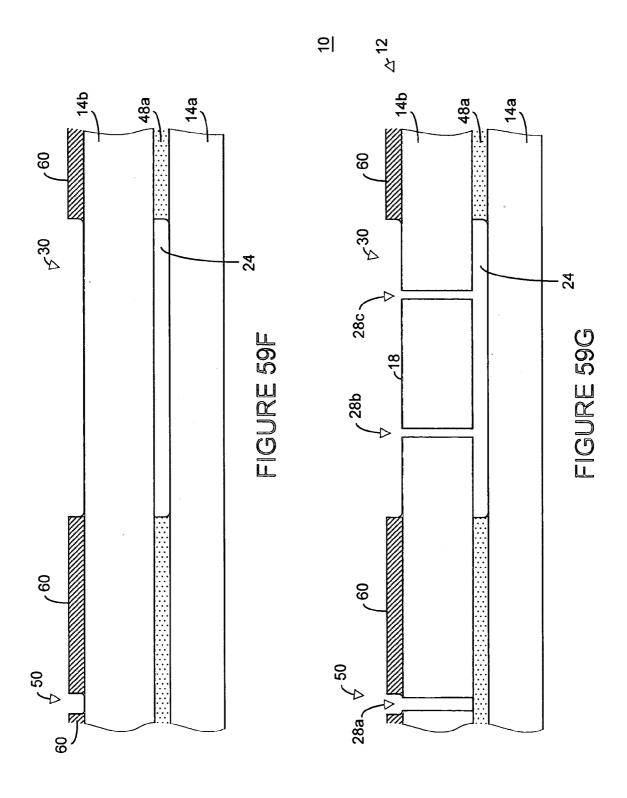

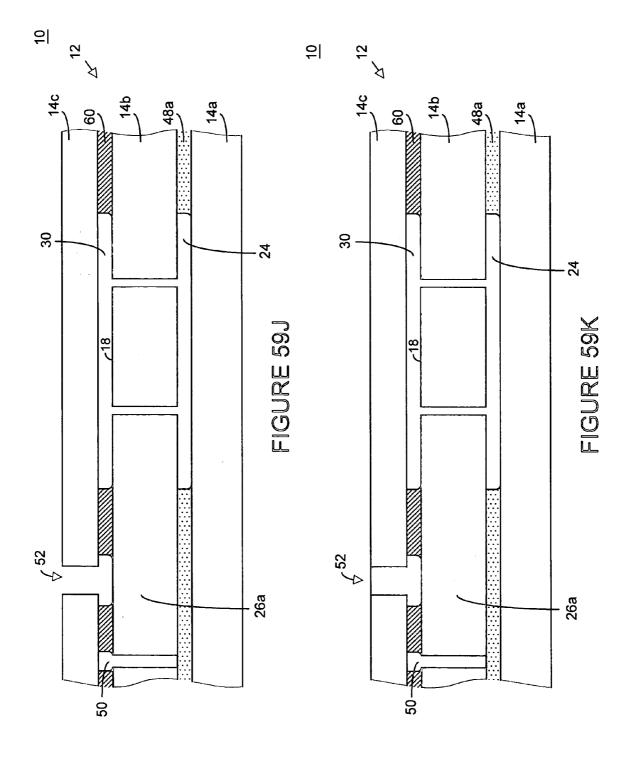

[0080] FIGS. 59A-59L illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 58 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

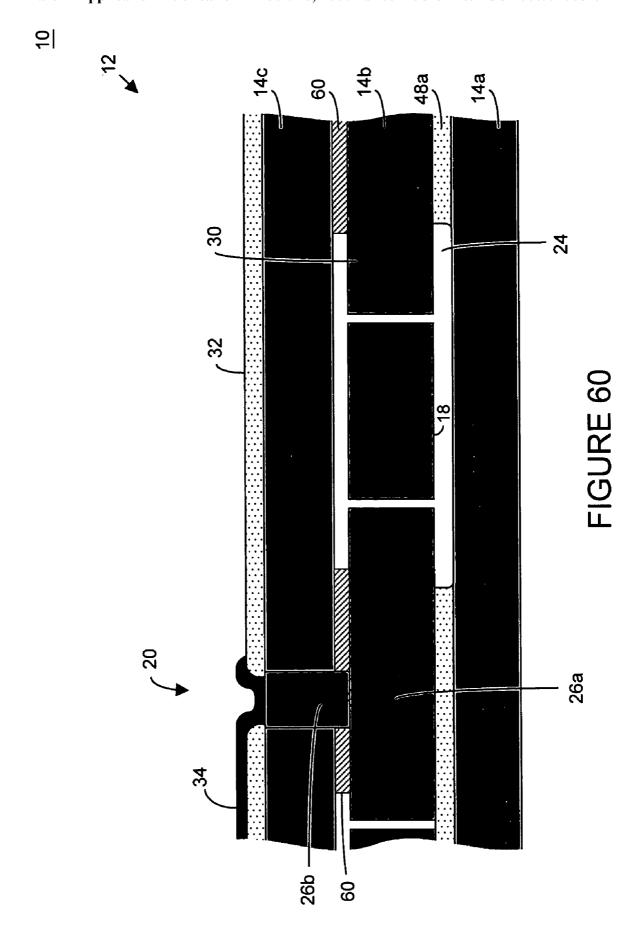

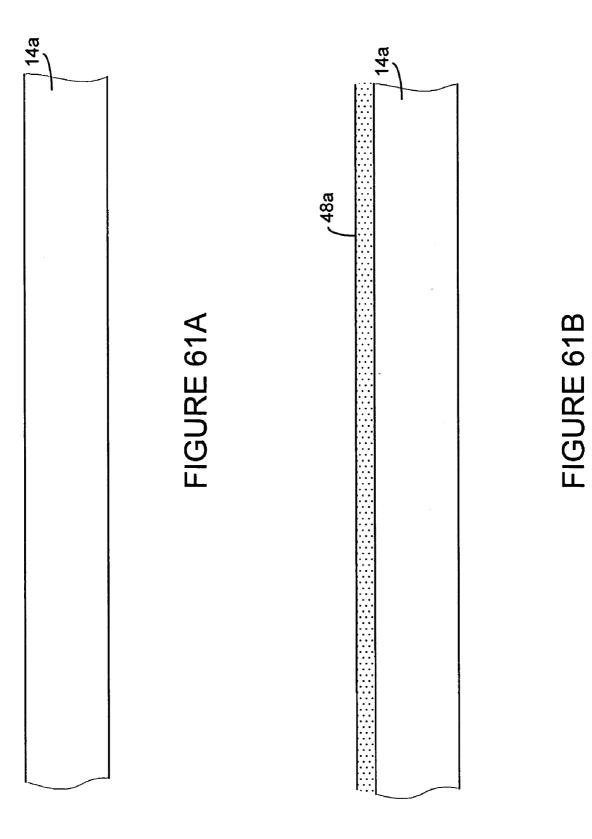

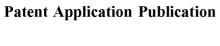

[0081] FIG. 60 is a cross-sectional view (sectioned along dotted line A-A' of FIG. 2) of a portion of the moveable electrode, fixed electrode, and the contact of FIG. 2 of another exemplary embodiment of the present inventions wherein bonding material and/or a bonding facilitator material is employed between substrates;

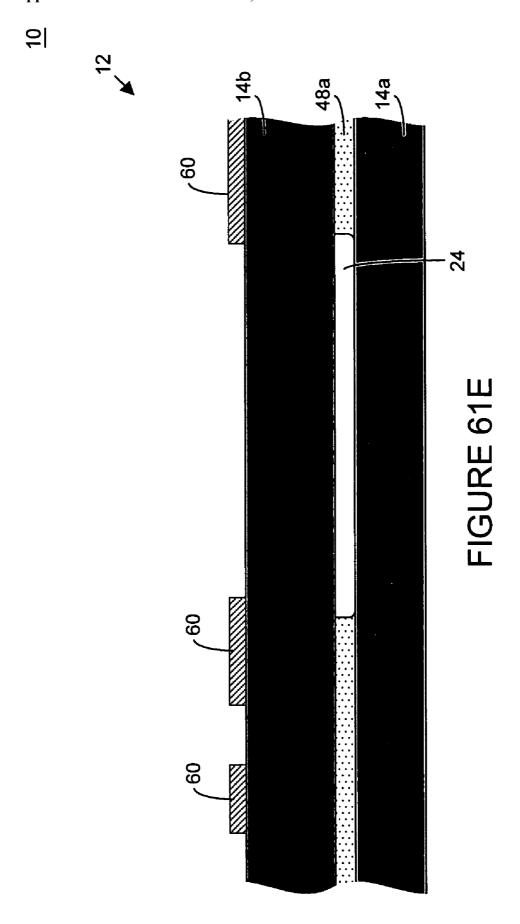

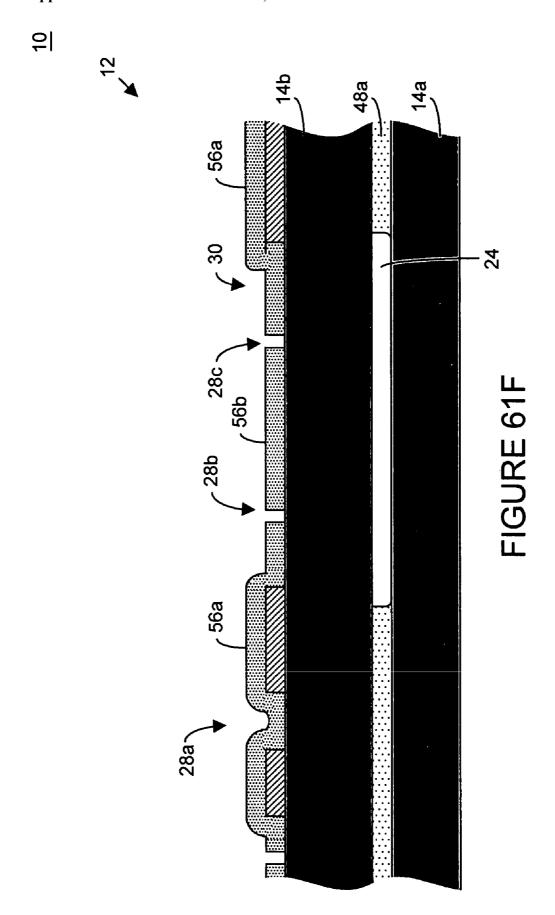

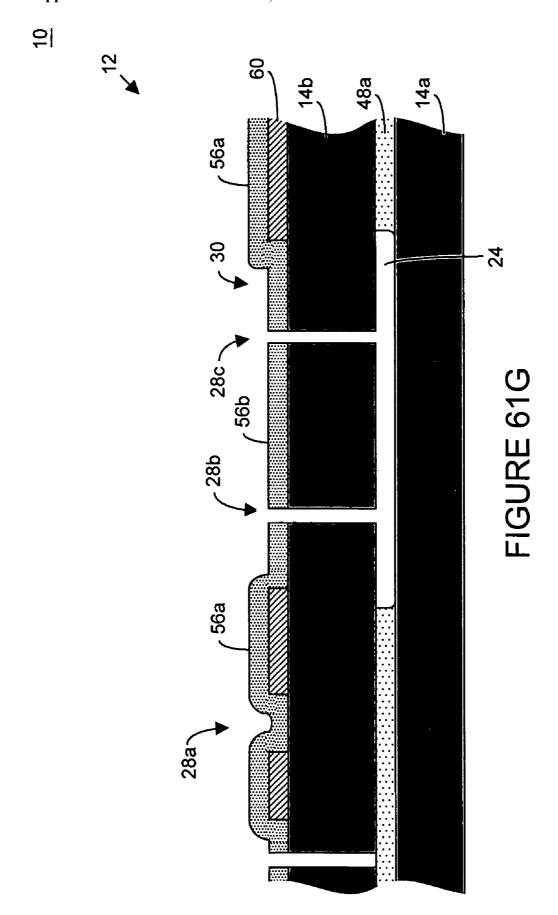

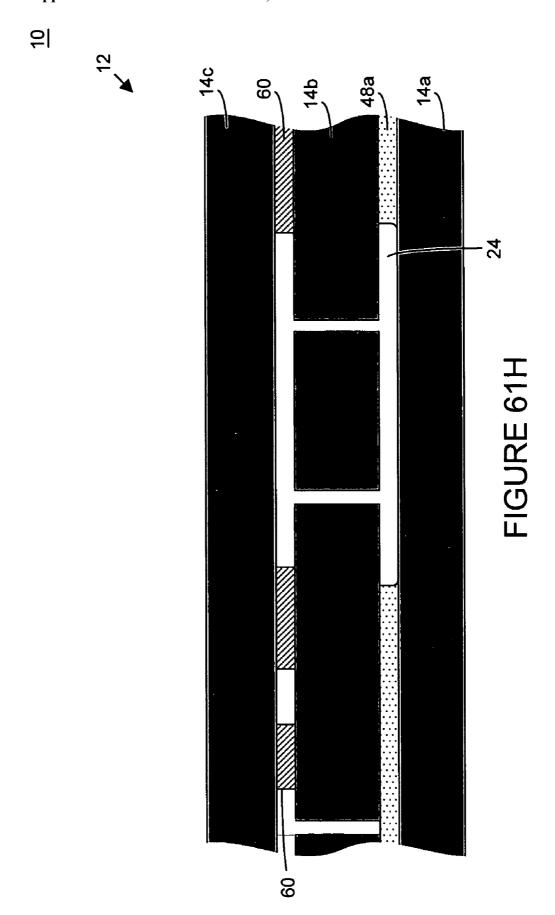

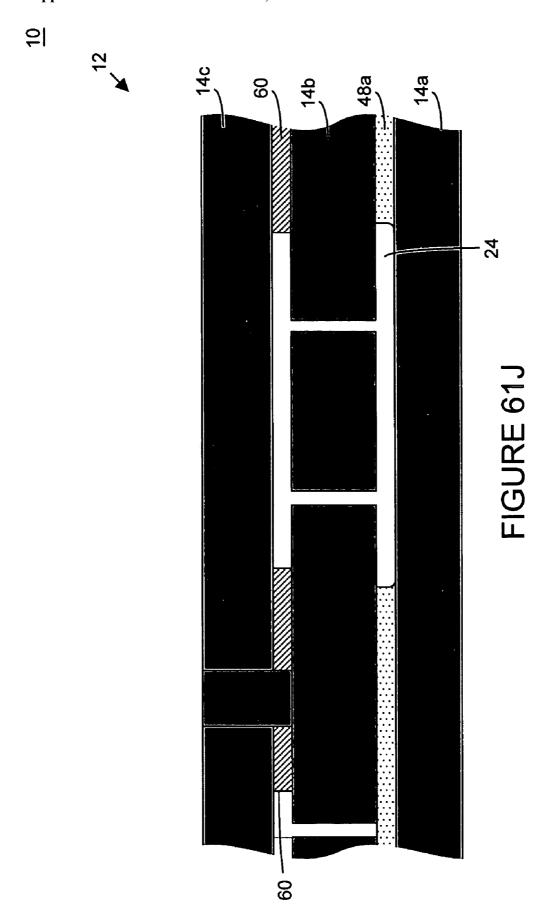

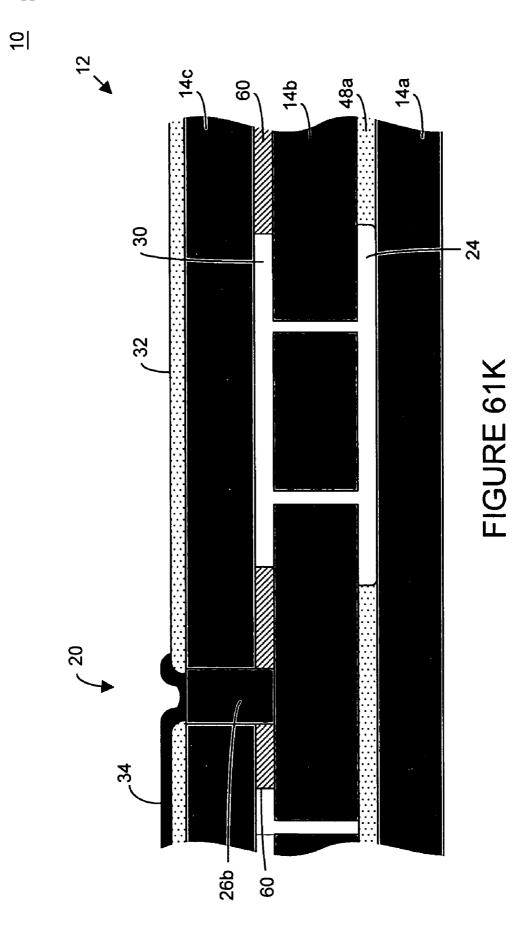

[0082] FIGS. 61A-61K illustrate cross-sectional views of the fabrication of the portion of the microelectromechanical system of FIG. 58 at various stages of an exemplary process that employs an encapsulation technique according to certain aspects of the present inventions;

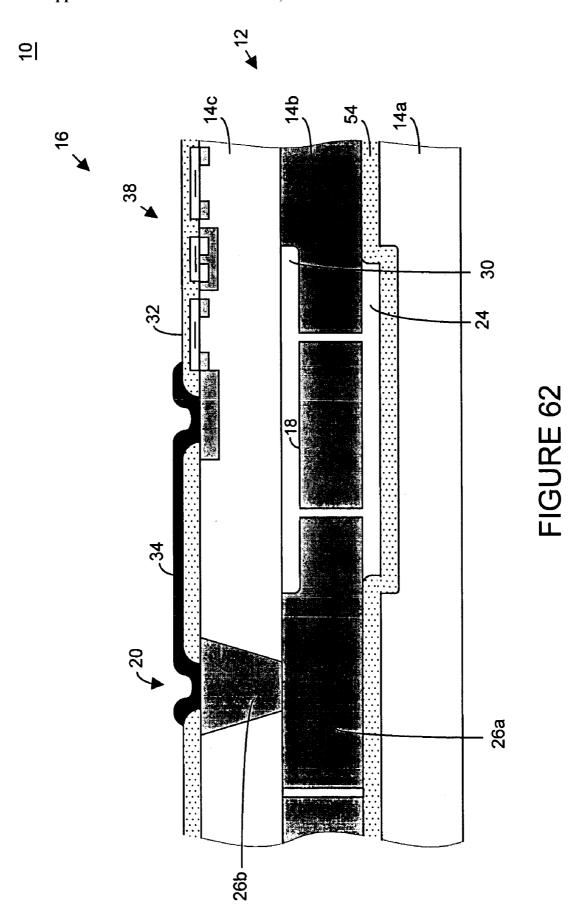

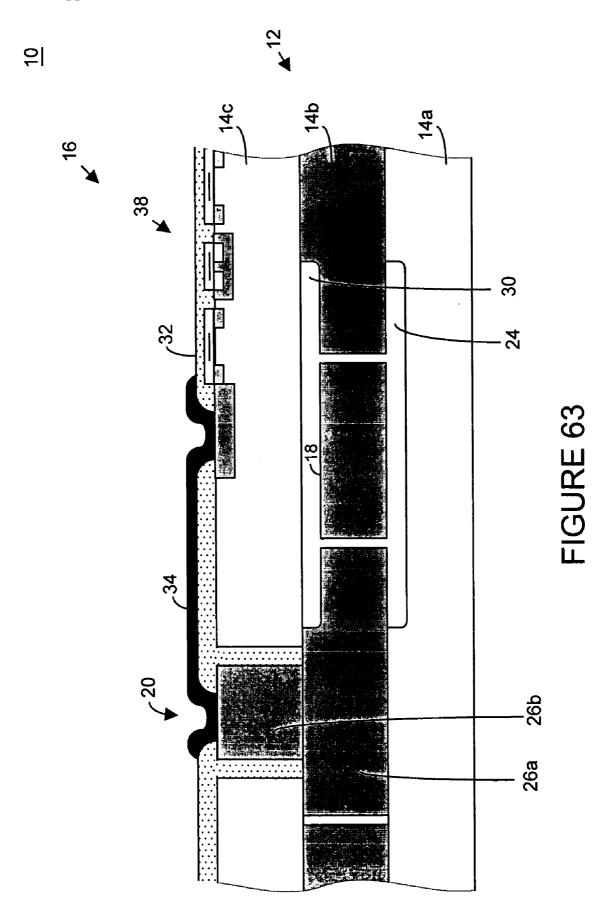

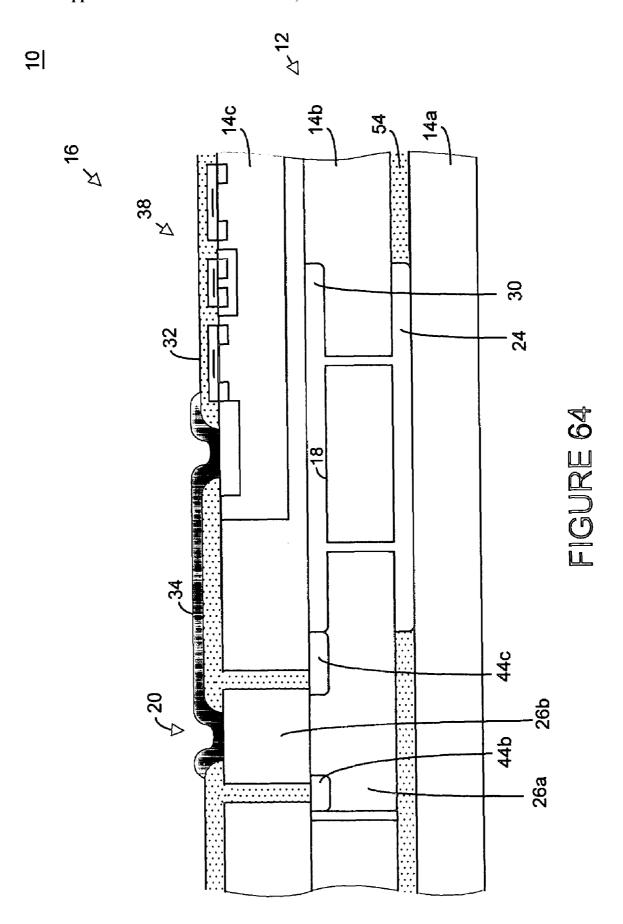

[0083] FIGS. 62-64 illustrates cross-sectional views of several embodiments of the fabrication of microelectromechanical systems of the present inventions wherein the microelectromechanical systems include electronic or electrical circuitry formed in a substrate, according to certain aspects of the present inventions; and

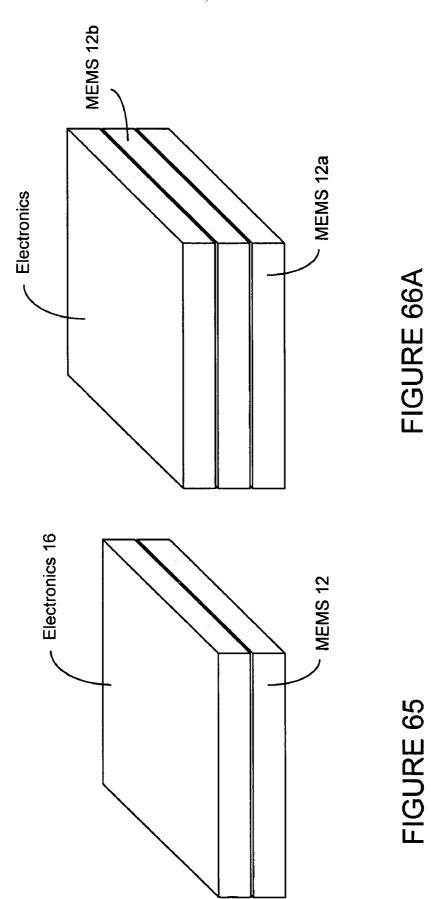

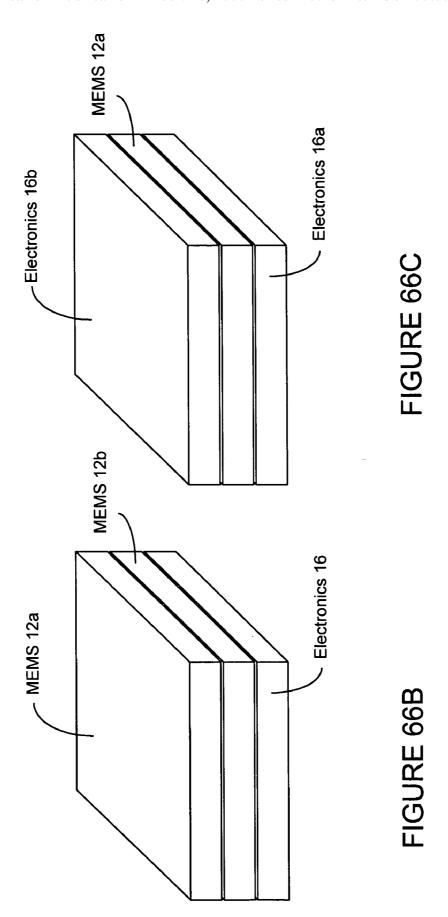

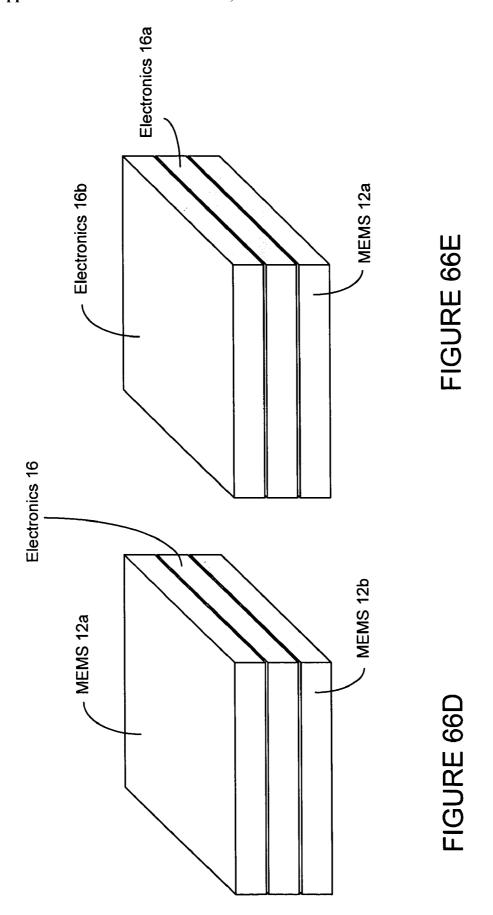

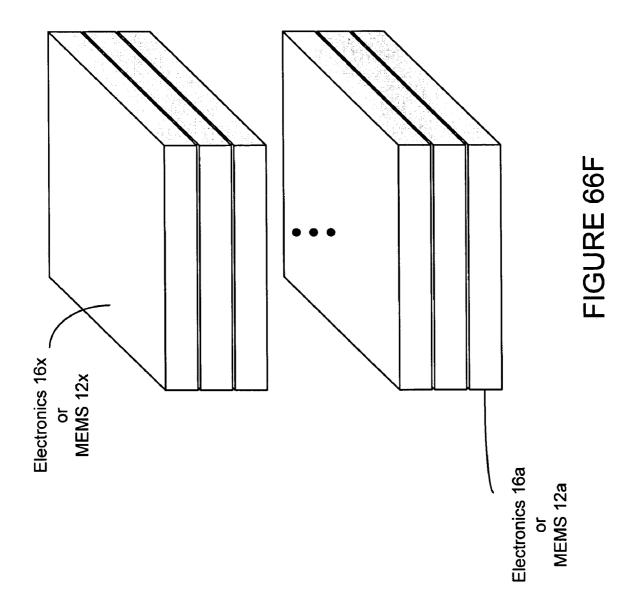

[0084] FIGS. 65 and 66A-66F are block diagram illustrations of various embodiments of the microelectromechanical systems of the present inventions wherein the microelectromechanical systems includes at least three substrates wherein one or more substrates include one or more micromachined mechanical structures and/or electronic or electrical circuitry, according to certain aspects of the present inventions.

## DESCRIPTION OF THE INVENTIONS

[0085] There are many inventions described and illustrated herein. In one aspect, the present inventions relate to devices, systems and/or methods of encapsulating and fabricating electromechanical structures or elements, for example, accelerometer, gyroscope or other transducer (for example, pressure sensor, strain sensor, tactile sensor, magnetic sensor and/or temperature sensor), filter or resonator The fabricating or manufacturing microelectromechanical systems of the present invention, and the systems manufactured thereby, employ wafer bonding encapsulation techniques.

[0086] With reference to FIGS. 1A, 1B and 2, in one exemplary embodiment, microelectromechanical device 10 includes micromachined mechanical structure 12 that is disposed on substrate 14, for example, a semiconductor, a glass, or an insulator material. The microelectromechanical device 10 may include electronics or electrical circuitry 16 (hereinafter collectively "circuitry 16") to, for example, drive mechanical structure 12, sense information from mechanical structure 12, process or analyze information generated by, and/or control or monitor the operation of micromachined mechanical structure 12. In addition, circuitry 16 (for example, CMOS circuitry) may generate clock signals using, for example, an output signal of micromachined mechanical structure 12, which may be a resonator type electromechanical structure. Under these circumstances, circuitry 16 may include frequency and/or phase compensation circuitry (hereinafter "compensation circuitry 18"), which receives the output of the resonator and adjusts, compensates, corrects and/or controls the frequency and/or phase of the output of resonator. In this regard, compensation circuitry uses the output of resonator to provide an adjusted, corrected, compensated and/or controlled output having, for example, a desired, selected and/or predetermined frequency and/or phase.

[0087] Notably, circuitry 16 may include interface circuitry to provide information (from, for example, micromachined mechanical structure 12) to an external device (not illustrated), for example, a computer, indicator/display and/or sensor.

[0088] With continued reference to FIGS. 1A, 1B and 2, micromachined mechanical structure 12 may include and/or be fabricated from, for example, materials in column IV of

the periodic table, for example silicon, germanium, carbon; also combinations of these, for example silicon germanium, or silicon carbide; also of III-V compounds for example gallium phosphide, aluminum gallium phosphide, or other III-V combinations; also combinations of III, IV, V, or VI materials, for example silicon nitride, silicon oxide, aluminum carbide, or aluminum oxide; also metallic silicides, germanides, and carbides, for example nickel silicide, cobalt silicide, tungsten carbide, or platinum germanium silicide; also doped variations including phosphorus, arsenic, antimony, boron, or aluminum doped silicon or germanium, carbon, or combinations like silicon germanium; also these materials with various crystal structures, including single crystalline, polycrystalline, nanocrystalline, or amorphous; also with combinations of crystal structures, for instance with regions of single crystalline and polycrystalline structure (whether doped or undoped).

[0089] As mentioned above, micromachined mechanical structure 12 illustrated in FIG. 2 may be a portion of an accelerometer, gyroscope or other transducer (for example, pressure sensor, strain sensor, tactile sensor, magnetic sensor and/or temperature sensor), filter or resonator. The micromachined mechanical structure 12 may also include mechanical structures of a plurality of transducers or sensors including one or more accelerometers, gyroscopes, pressure sensors, tactile sensors and temperature sensors. In the illustrated embodiment, micromachined mechanical structure 12 include moveable electrode 18.

[0090] With continued reference to FIG. 2, micromachined mechanical structure 12 may also include contact 20 disposed on or in substrate 14a. The contact 20 may provide an electrical path between micromachined mechanical structure 12 and circuitry 16 and/or an external device (not illustrated). The contact 20 may include and/or be fabricated from, for example, a semiconductor or conductive material, including, for example, silicon, (whether doped or undoped), germanium, silicon/germanium, silicon carbide, and gallium arsenide, and combinations and/or permutations thereof. Notably, micromachined mechanical structure 12 and circuitry 16 may include multiple contacts 20.

[0091] In one embodiment, the present inventions employ two or more substrates to form and encapsulate micromachined mechanical structure 12. For example, with reference to FIG. 3, in one embodiment, microelectromechanical system 10 includes semiconductor on insulator ("SOI") substrate 14a and cover substrate 14b. Briefly, by way of overview, in this embodiment, micromachined mechanical structure 12 (including moveable electrode 18 and contact 20) is formed in or on SOI substrate 14a and encapsulated via cover substrate 14b. In this regard, micromachined mechanical structure 12 is formed in the semiconductor portion of SOI substrate 14a that resides on the insulator portion of SOI substrate 14a. Thereafter, substrate 14b is secured (for example, bonded) to the exposed surface of the semiconductor portion of SOI substrate 14a to encapsulate micromachined mechanical structure 12.

[0092] In particular, with reference to FIG. 4A, microelectromechanical system 10 is formed in or on SOI substrate 14a. The SOI substrate 14a may include first substrate layer 22a (for example, a semiconductor (such as silicon), glass or sapphire), insulation layer 22b (for example, a silicon dioxide or silicon nitride layer) and first semiconductor layer 22c (for example, a materials in column IV of the periodic table, for example silicon, germanium, carbon, as well as combi-

nations of such materials, for example silicon germanium, or silicon carbide). In one embodiment, SOI substrate **14***a* is a SIMOX wafer. Where SOI substrate **36** is a SIMOX wafer, such wafer may be fabricated using well-known techniques including those disclosed, mentioned or referenced in U.S. Pat. Nos. 5,053,627; 5,080,730; 5,196,355; 5,288,650; 6,248,642; 6,417,078; 6,423,975; and 6,433,342 and U.S. Published Patent Applications 2002/0081824 and 2002/0123211, the contents of which are hereby incorporated by reference.

[0093] In another embodiment, SOI substrate 14a may be a conventional SOI wafer having a relatively thin semiconductor layer 22c. In this regard, SOI substrate 36 having a relatively thin semiconductor layer 22c may be fabricated using a bulk silicon wafer which is implanted and oxidized by oxygen to thereby form a relatively thin silicon dioxide layer 22b on a monocrystalline wafer surface 22a. Thereafter, another wafer (illustrated as layer 22c) is bonded to layer 22b. In this exemplary embodiment, semiconductor layer 22c (i.e., monocrystalline silicon) is disposed on insulation layer 22b (i.e. silicon dioxide), having a thickness of approximately 350 nm, which is disposed on a first substrate layer 22a (for example, monocrystalline silicon), having a thickness of approximately 190 nm.

[0094] Notably, all techniques for providing or fabricating SOI substrate 14a, whether now known or later developed, are intended to be within the scope of the present inventions. [0095] With reference to FIGS. 4A and 4B, an exemplary method of fabricating or forming micromachined mechanical structure 12 according to this embodiment of the present inventions may begin with forming first cavity 24 in semiconductor layer 22c using well-known lithographic and etching techniques. In this way, a selected portion of semiconductor layer 22c (for example, 1 µm) is removed to form first cavity 24 (which forms a portion of the chamber in which the mechanical structure, for example, moveable electrode 18, resides).

[0096] With reference to FIGS. 4C and 4D, thereafter, moveable electrode 18 and contact area 26 are formed in semiconductor layer 22c and moveable electrode 18 is "released" from insulation layer 22b. In this regard, trenches 28a-c are formed in semiconductor layer 22c to define moveable electrode 18 and contact area 26 therefrom. (See, FIG. 4C). The trenches 28a-c may be formed using well-known deposition and lithographic techniques. Notably, all techniques for forming or fabricating trenches 28a-c, whether now known or later developed, are intended to be within the scope of the present inventions.

[0097] After moveable electrode 18 is defined via trenches 28b and 28c, moveable electrode 18 may be "released" by etching portions of insulation layer 22b that are disposed under moveable electrode 18. For example, in one embodiment, where insulation layer 22b is comprised of silicon dioxide, selected portions may be removed/etched using well-known wet etching techniques and buffered HF mixtures (i.e., a buffered oxide etch) or well-known vapor etching techniques using vapor HF. The trenches 28b and 28c, in addition to defining the features of moveable electrode 18, may also permit etching and/or removal of at least selected portions of insulation layer 22b thereby providing a void or cavity 30 beneath moveable electrode 18. (See, FIG. 4D). Proper design of mechanical structures 12 (and in particular moveable electrode 18) and control of the HF etching process parameters may permit insulation layer 22b

to be sufficiently removed or etched to release moveable electrode 18 and permit proper operation of micromachined mechanical structure 12 and microelectromechanical system 10. Notably, cavities 24 and 30 form the chamber in which the mechanical structure, for example, moveable electrode 18, resides.

[0098] With reference to FIG. 4E, second substrate 14b may be fixed to the exposed portion(s) of semiconductor layer 22c. The second substrate 14b may be secured to the exposed portion(s) of semiconductor layer 22c using, for example, well-known bonding techniques such as fusion bonding, anodic-like bonding and/or silicon direct bonding. Other bonding technologies are suitable including soldering (for example, eutectic soldering), thermo compression bonding, thermo-sonic bonding, laser bonding and/or glass reflow, and/or combinations thereof. Indeed, all forms of bonding, whether now known or later developed, are intended to fall within the scope of the present invention.

[0099] In conjunction with securing second substrate 14b to the exposed portion(s) of semiconductor layer 22c, the atmosphere (including its characteristics) in which moveable electrode 18 operates may also be defined. In this regard, the chamber in which the moveable electrode 18 reside may be defined when second substrate 14b is secured and/or fixed to the exposed portion(s) of semiconductor layer 22c or after further processing (for example, an annealing step may be employed to adjust the pressure). Notably, all techniques of defining the atmosphere, including the pressure thereof, during the process of securing second substrate 14b to semiconductor layer 22c, whether now known or later developed, are intended to be within the scope of the present inventions.

[0100] For example, second substrate 14b may be secured to the exposed portion(s) of semiconductor layer 22c in a nitrogen, oxygen and/or inert gas environment (for example, helium). The pressure of the fluid (gas or vapor) may be selected, defined and/or controlled to provide a suitable and/or predetermined pressure of the fluid in the chamber immediately after fixing substrate 14b to the exposed portion (s) of semiconductor layer 22c (in order to avoid damaging portions of micromachined mechanical structure 12), after one or more subsequent processing steps (for example, an annealing step) and/or after completion of micromachined mechanical structure 12 and/or microelectromechanical system 10.

[0101] Notably, the gas(es) employed during these processes may provide predetermined reactions (for example, oxygen molecules may react with silicon to provide a silicon oxide). All such techniques are intended to fall within the scope of the present inventions.

[0102] The second substrate 14b may be formed from any material now known or later developed. In a preferred embodiment, second substrate 14b includes or is formed from, for example, materials in column IV of the periodic table, for example silicon, germanium, carbon; also combinations of these, for example silicon germanium, or silicon carbide; also of III-V compounds for example gallium phosphide, aluminum gallium phosphide, or other III-V combinations; also combinations of III, IV, V, or VI materials, for example silicon nitride, silicon oxide, aluminum carbide, or aluminum oxide; also metallic silicides, germanides, and carbides, for example nickel silicide, cobalt silicide, tungsten carbide, or platinum germanium silicide; also doped variations including phosphorus, arsenic, anti-

mony, boron, or aluminum doped silicon or germanium, carbon, or combinations like silicon germanium; also these materials with various crystal structures, including single crystalline, polycrystalline, nanocrystalline, or amorphous; also with combinations of crystal structures, for instance with regions of single crystalline and polycrystalline structure (whether doped or undoped).

[0103] Before or after second substrate 14b is secured to the exposed portion(s) of semiconductor layer 22c, contact area 26b may be formed in a portion of second substrate 14b to be aligned with, connect to or overlie contact area 26a in order to provide suitable, desired and/or predetermined electrical conductivity (for example, N-type or P-type) with contact area 26a when second substrate 14b is secured to first substrate 14a. (See, FIG. 4F). The contact area 26b may be formed in second substrate 14b using well-known lithographic and doping techniques. In this way, contact area 26b may be a highly doped region of second substrate 14b which provides enhanced electrical conductivity with contact area 26a

[0104] Notably, contact area 26b may be a counter-doped region or heavily counter-doped region of second substrate 14b which includes a conductivity that is different from the conductivity of the other portions of second substrate 14b. In this way, contact areas 26a and 26b are electrically isolated from the other portions of second substrate 14b. Thus, in this embodiment, semiconductor layer 22c may be a first conductivity type (for example, an N-type conductivity which may be provided, for example, via introduction of phosphorous and/or arsenic dopant(s), among others) and second substrate 14b may be a second conductivity type (for example, a P-type conductivity which may be provided, for example, via introduction of boron dopant(s), among others). As such, contact area 26b may be a counter-doped region or heavily counter-doped N-type region which provides suitable, desired and/or predetermined electrical conductivity characteristics when second substrate 14b is secured to first substrate 14a and contact areas 26a and 26b are in physical and electrical contact.

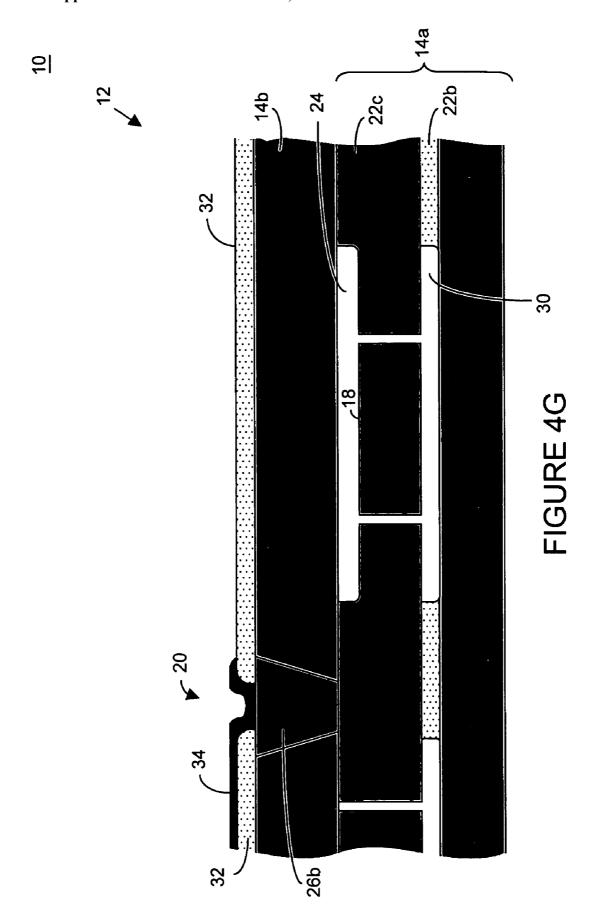

[0105] With reference to FIG. 4G, microelectromechanical system 10 may be completed by depositing, forming and/or growing insulation layer 32 and a contact opening may be etched to facilitate electrical contact/connection to contact area 26b, via conductive layer 34 (for example, a heavily doped polysilicon, metal (such as aluminum, chromium, gold, silver, molybdenum, platinum, palladium, tungsten, titanium, and/or copper), metal stacks, complex metals and/or complex metal stacks) may then be deposited (and/or formed) to provide the appropriate electrical connection to contact areas 26 (which includes, in this example, contacts areas 26a and 26b).

[0106] Notably, insulation layer 32 and/or conductive layer 34 may be formed, grown and/or deposited before or after second substrate 14b is secured to the exposed portion (s) of semiconductor layer 22c. Under these circumstances, when second substrate 14b is secured to first substrate 14a, the microelectromechanical system 10 may be completed. [0107] The insulating layer 32 may be, for example,

[0107] The insulating layer 32 may be, for example, silicon dioxide, silicon nitride, BPSG, PSG, or SOG, or combinations thereof. It may be advantageous to employ silicon nitride because silicon nitride may be deposited in a more conformal manner than silicon oxide. Moreover, sili-

con nitride is compatible with CMOS processing, in the event that microelectromechanical system 10 includes CMOS integrated circuits.

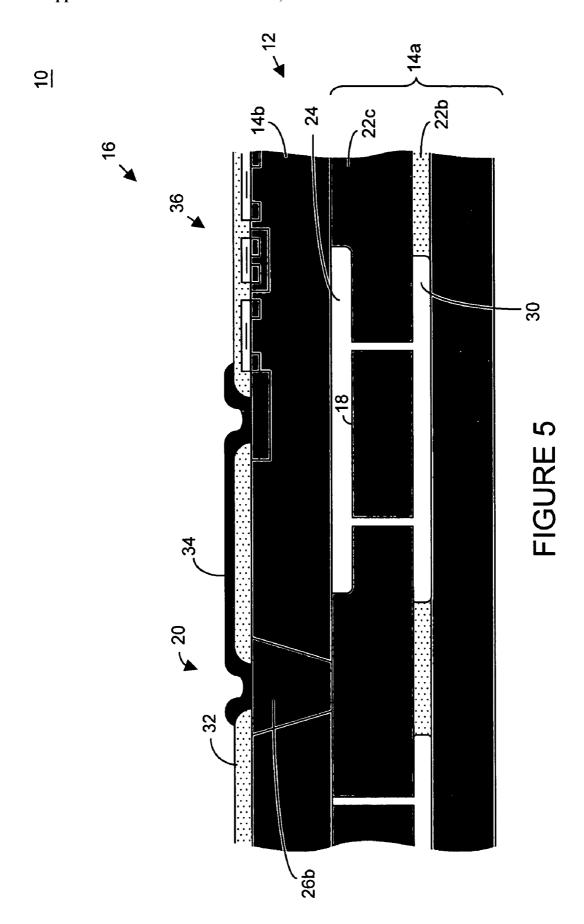

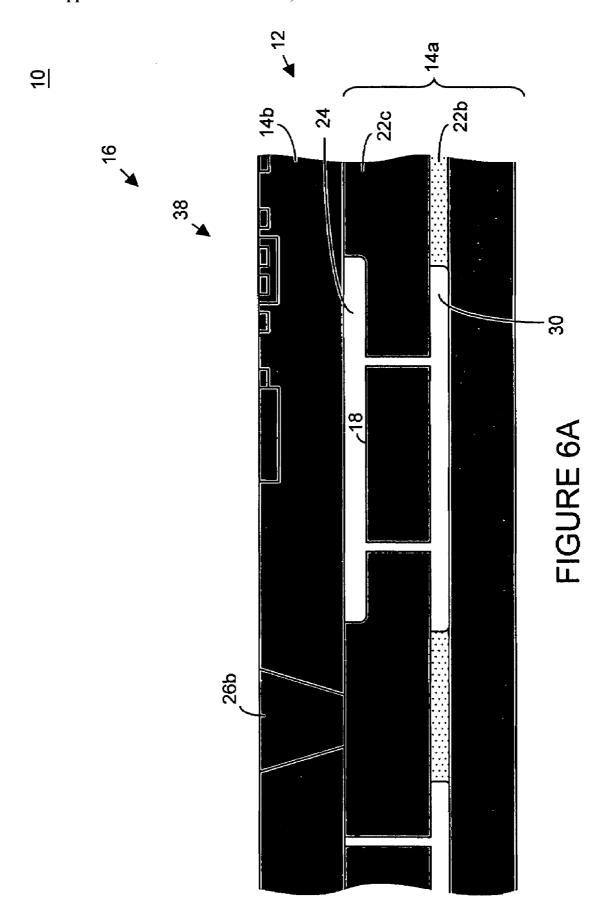

[0108] Notably, prior to formation, deposition and/or growth of insulation layer 32 and/or conductive layer 34, additional micromachined mechanical structures 12 and/or transistors of circuitry 16 may be formed and/or provided in second substrate 14b or in other substrates that may be fixed to first substrate 14a and/or second substrate 14b. In this regard, the exposed surface of second substrate 14b may be a suitable base upon which integrated circuits (for example, CMOS transistors) and/or micromachined mechanical structures 12 may be fabricated on or in. Such integrated circuits may be fabricated using well-known techniques and equipment. For example, with reference to FIG. 5, in one embodiment, transistor regions 36, which may be integrated circuits (for example, CMOS transistors) of circuitry 16, may be provided in second substrate 14b. The transistor regions 36 may be formed before or after second substrate 14b is secured (for example, bonded) to first substrate 14a. In this regard, with reference to FIG. 6A, transistor implants 38 may be formed using well-known lithographic and implant processes, after second substrate 14b is secured to first substrate 14a and concurrently with the formation of contact

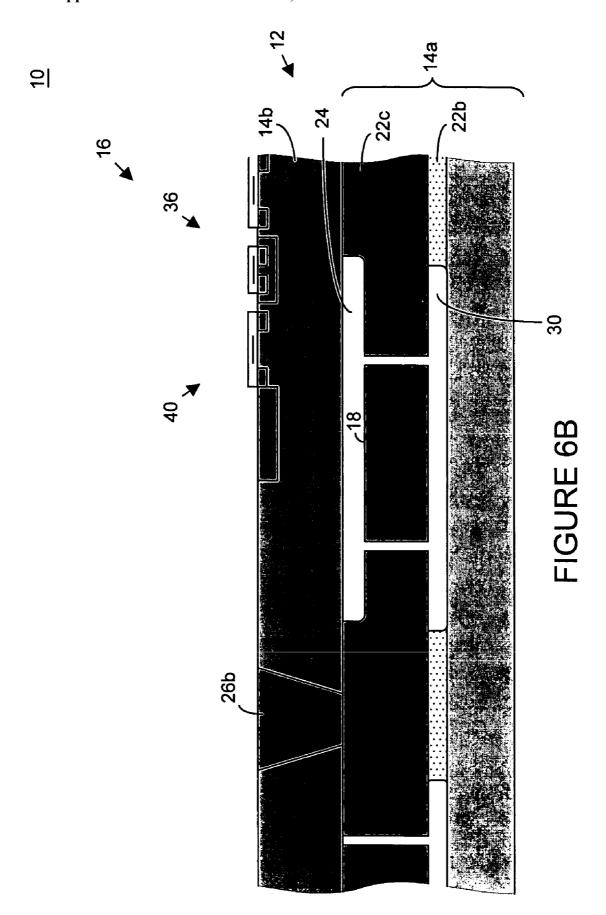

[0109] Thereafter, conventional transistor processing (for example, formation of gate and gate insulator 40) may be employed to complete the transistors of circuitry 16. (See, FIG. 6B). The "back-end" processing of microelectromechanical system 10 (for example, formation, growth and/or deposition of insulation layer 32 and conductive layer 34) may be performed using the same processing techniques as described above. (See, for example, FIGS. 6C and 6D). In this regard, insulation layer 32 may be deposited, formed and/or grown and patterned and, thereafter, conductive layer 34 (for example, a heavily doped polysilicon, metal (such as aluminum, chromium, gold, silver, molybdenum, platinum, palladium, tungsten, titanium, and/or copper), metal stacks, complex metals and/or complex metal stacks) is deposited and/or formed. In the illustrative embodiments, contact 20 is accessed directly by the transistors of circuitry 16 via conductive layer 34. Here, conductive layer 34 may be a low resistance electrical path that is deposited and patterned to facilitate connection of micromachined mechanical structure 12 and circuitry 16.

[0110] As noted above, the transistors of transistor region 36 may be formed prior to securing second substrate 14b to first substrate 14a. (See, for example, FIGS. 7A and 7B). Indeed, all of the "back-end" processing, in addition to formation of the transistors of transistor region 36, may be completed prior to securing second substrate 14b to first substrate 14a. (See, for example, FIGS. 8A and 8B).

[0111] With reference to FIGS. 9, 10A-10I, 11 and 12A-12J, in another embodiment of the present inventions, semi-conductor layer 22c of SOI substrate 14a is the same conductivity as second substrate 14b. In these embodiments, micromachined mechanical structure 12 may include additional features to electrically isolate contact 20. For example, with reference to FIG. 9, in one embodiment, micromachined mechanical structure 12 includes isolation trenches 42a and 42b that isolates contact 20 (and contact areas 26a and 26b) from portions of second substrate 14b. The isolation trenches 42a and 42b may include an insulator material, for example, silicon dioxide or silicon nitride.

Indeed, as illustrated, material that forms insulation layer 32 may also be deposited in isolation trenches 42a and 42b. Notably, FIGS. 10A-10I illustrate an exemplary process flow for fabricating microelectromechanical system 10 of FIG. 9.

[0112] With reference to FIG. 11, in another exemplary embodiment, isolation regions 44a and 44b are deposited and/or implanted into portions of semiconductor layer 22c of SOI substrate 14a in order to facilitate electrical isolation of contact 20 after second substrate 14b is secured or fixed (via, for example, bonding). The isolation regions 44a and 44b may be any material or structure that insulates contact 20, for example, an insulator material and/or an oppositely doped semiconductor region. FIGS. 12A-12J illustrate an exemplary process flow for fabricating microelectromechanical system 10 of FIG. 11 wherein isolation regions 44a and 44b are oppositely doped semiconductor regions and an insulation material is disposed in isolation trenches 42a and 42b

[0113] FIG. 13A illustrates an exemplary microelectromechanical system 10 wherein the isolation regions 44a and 44b are oppositely doped semiconductor regions (relative to the conductivity of second substrate 14b) and a semiconductor, having a conductivity different from the conductivity of the semiconductor of second substrate 14b, is disposed (for example using epitaxial deposition techniques) in isolation trenches 42a and 42b. FIGS. 13B and 13C illustrate selected portions of an exemplary process flow for fabricating microelectromechanical system 10 of FIG. 13A.

[0114] Notably, the embodiments of FIGS. 9, 11 and 13A may also include circuitry 16 disposed in second substrate 14b. The fabrication techniques described above and illustrated in FIGS. 5-8B may be employed in the embodiments of FIGS. 9 and 11. Indeed, prior to or after formation, deposition and/or growth of insulation layer 32 and/or conductive layer 34, additional micromachined mechanical structures 12 and/or transistors of circuitry 16 may be formed and/or provided in second substrate 14b or in other substrates that may be fixed to first substrate 14a and/or second substrate 14b. For the sake of brevity, those discussions, in connection with the embodiments of FIGS. 9, 11 and 13A, will not be repeated.

[0115] The present inventions may also employ more than two substrates to form and encapsulate micromachined mechanical structure 12. For example, with reference to FIG. 14, in one embodiment, microelectromechanical system 10 includes first substrate 14a, second substrate 14b and third substrate 14c. Briefly, by way of overview, in this embodiment, micromachined mechanical structure 12 (including moveable electrode 18 and contact 20) is formed in second substrate 14b and encapsulated via third substrate 14c. In this regard, micromachined mechanical structure 12 is formed in a portion of substrate 14b. Thereafter, substrate 14c is secured (for example, bonded) to exposed surface of substrate 14b to encapsulate micromachined mechanical structure 12. In this embodiment, the portion of substrate 14b in which micromachined mechanical structure 12 is formed includes a conductivity that is different from the conductivity of the semiconductor of first substrate 14a and third substrate 14c.

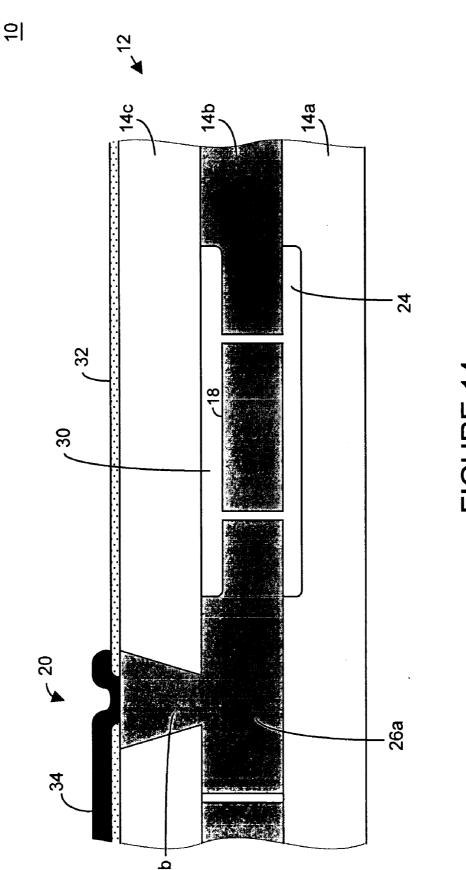

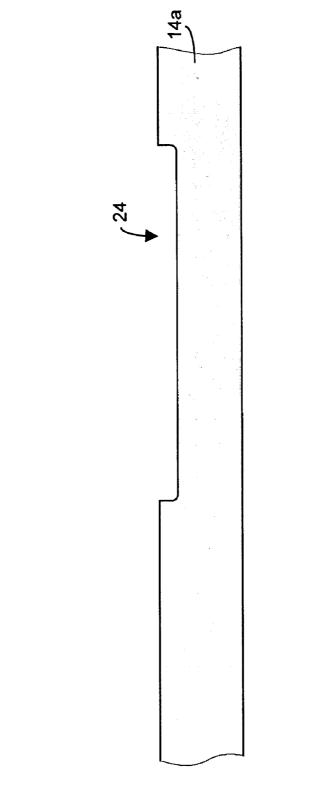

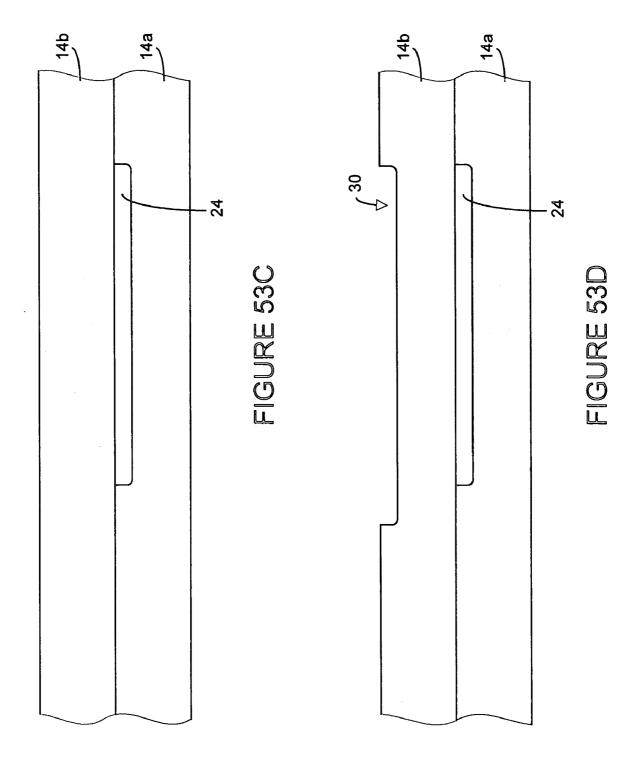

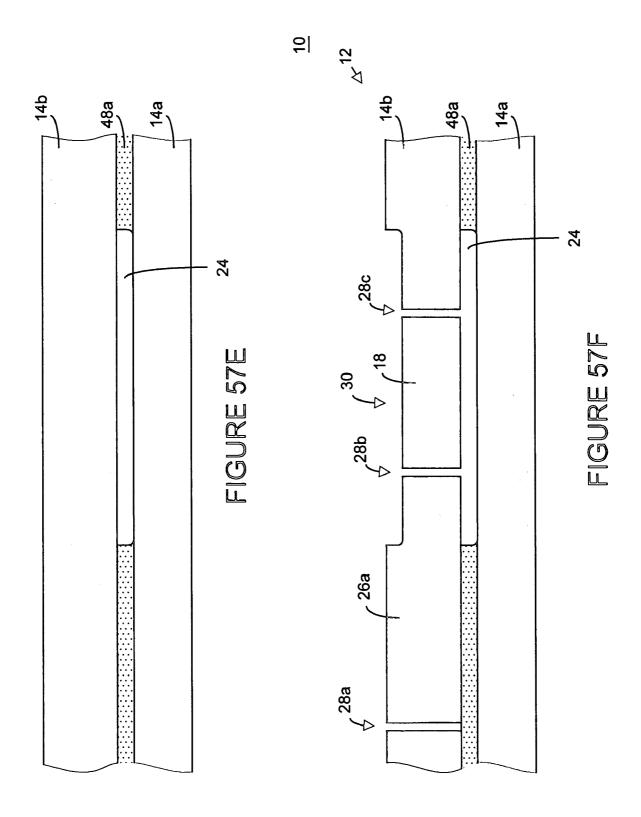

[0116] With reference to FIGS. 15A and 15B, an exemplary method of fabricating or forming micromachined mechanical structure 12 according to this embodiment of the present inventions may begin with forming first cavity 24 in

first substrate 14a using well-known lithographic and etching techniques. In one exemplary embodiment, first cavity 24 includes a depth of about 1  $\mu$ m.

[0117] With reference to FIGS. 15C and 15D, second substrate 14b may be fixed to first substrate 14a. The second substrate 14b may be secured to the exposed portion(s) of first substrate 14a using, for example, well-known bonding techniques such as fusion bonding, anodic-like bonding and/or silicon direct bonding. As mentioned above, other bonding technologies are suitable including soldering (for example, eutectic soldering), thermo compression bonding, thermo-sonic bonding, laser bonding and/or glass reflow, and/or combinations thereof. Indeed, all forms of bonding, whether now known or later developed, are intended to fall within the scope of the present invention.

[0118] Before or after securing second substrate 14b to first substrate 14a, second cavity 30 may be formed in second substrate 14b—again using well-known lithographic and etching techniques. In one exemplary embodiment, second cavity 30 also includes a depth of about 1  $\mu$ m. Thereafter, the thickness of second substrate 14b may be adjusted to accommodate further processing. For example, second substrate 14b may be grinded and polished (using, for example, well known chemical mechanical polishing ("CMP") techniques) to a thickness of between  $10 \mu$ m- $30 \mu$ m. Notably, cavities 24 and 30 form the chamber in which the mechanical structure, for example, moveable electrode 18, resides.

[0119] The second substrate 14b may be formed from any material now known or later developed. In a preferred embodiment, second substrate 14b includes or is formed from, for example, materials in column IV of the periodic table, for example silicon, germanium, carbon; also combinations of these, for example silicon germanium, or silicon carbide; also of III-V compounds for example gallium phosphide, aluminum gallium phosphide, or other III-V combinations; also combinations of III, IV, V, or VI materials, for example silicon nitride, silicon oxide, aluminum carbide, or aluminum oxide; also metallic silicides, germanides, and carbides, for example nickel silicide, cobalt silicide, tungsten carbide, or platinum germanium silicide; also doped variations including phosphorus, arsenic, antimony, boron, or aluminum doped silicon or germanium, carbon, or combinations like silicon germanium; also these materials with various crystal structures, including single crystalline, polycrystalline, nanocrystalline, or amorphous; also with combinations of crystal structures, for instance with regions of single crystalline and polycrystalline structure (whether doped or undoped).

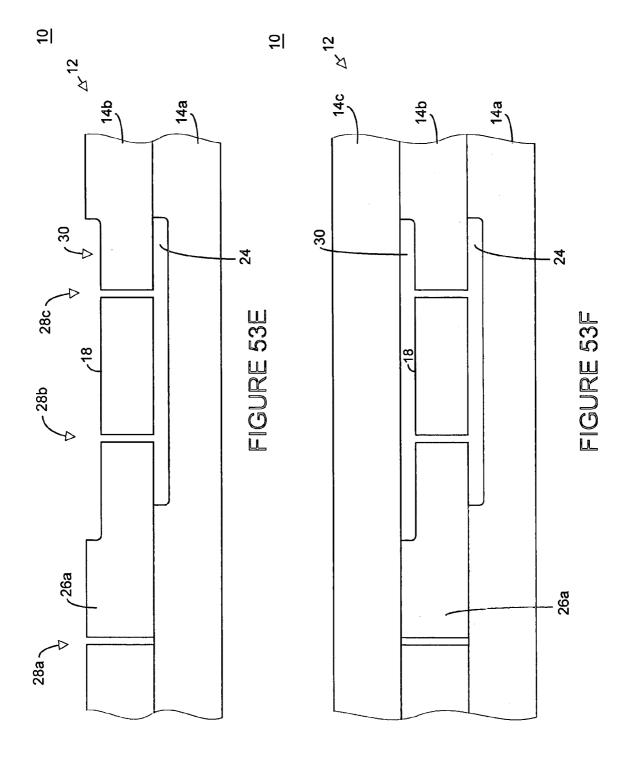

[0120] With reference to FIG. 15E, moveable electrode 18 and contact area 26 are defined and formed in second substrate 14b. In this regard, trenches 28a-c are formed in second substrate 14b to define moveable electrode 18 and contact area 26 therefrom. (See, FIG. 15E). The trenches 28a-c may be formed using well-known deposition and lithographic techniques. Notably, all techniques for forming or fabricating trenches 28a-c, whether now known or later developed, are intended to be within the scope of the present inventions.

[0121] Thereafter, third substrate 14c may be fixed to the exposed portion(s) of second substrate 14b. (See, FIG. 15F). The third substrate 14c may also be secured to the exposed portion(s) of second substrate 14b using, for example, well-known bonding techniques such as fusion bonding,

anodic-like bonding and/or silicon direct bonding. In conjunction with securing third substrate 14c to second substrate 14b, the atmosphere (including its characteristics) in which moveable electrode 18 operates may also be defined—for example, as described above. Notably, all techniques of defining the atmosphere, including the pressure thereof, during the process of securing third substrate 14c to second substrate 14b, whether now known or later developed, are intended to be within the scope of the present inventions.

**[0122]** The third substrate 14c may be formed from any material discussed above relative to second substrate 14b. For the sake of brevity, such discussions will not be repeated.

[0123] Before or after third substrate 14c is secured to second substrate 14b, contact area 26b may be formed in a portion of third substrate 14c to be aligned with, connect to or overlie contact area 26a. The contact area 26b may be a semiconductor region that includes a doping that provides the same conductivity as contact area 26a. In this way, a suitable, desired and/or predetermined electrical conductivity is provided with contact area 26a when third substrate 14c is secured to second substrate 14b. (See, FIG. 15G). Thus, contact area 26b may be a highly doped region of third substrate 14c which provides enhanced electrical conductivity with contact area 26a. The contact area 26b may be formed in third substrate 14c using well-known lithographic and doping techniques.

[0124] Notably, contact area 26b may be a counter-doped region or heavily counter-doped region of third substrate 14c which includes a conductivity that is different from the conductivity of the other portions of third substrate 14c. In this way, contact areas 26a and 26b are electrically isolated from the other portions of third substrate 14c. Thus, in this embodiment, second substrate 14b may be a first conductivity type (for example, an N-type conductivity) and third substrate 14c may be a second conductivity type (for example, a P-type conductivity). As such, contact area 26b may be a counter-doped region or heavily counter-doped N-type region which provides suitable, desired and/or predetermined electrical conductivity characteristics when third substrate 14c is secured to second substrate 14b and contact areas 26a and 26b are in physical contact.

[0125] With reference to FIG. 15H, microelectromechanical system 10 may be completed by depositing, forming and/or growing insulation layer 32 and a contact opening may be etched to facilitate electrical contact/connection to contact area 26b. The conductive layer 34 (for example, a heavily doped polysilicon, metal (such as aluminum, chromium, gold, silver, molybdenum, platinum, palladium, tungsten, titanium, and/or copper), metal stacks, complex metals and/or complex metal stacks) may then be deposited to provide the appropriate electrical connection to contact 26a and 26b.

[0126] Notably, insulation layer 32 and/or conductive layer 34 may be formed, grown and/or deposited before or after third substrate 14c is secured to second substrate 14b. Under these circumstances, when third substrate 14c is secured to second substrate 14c in the microelectromechanical system 10 may be completed.

[0127] The insulating layer 32 may be, for example, silicon dioxide, silicon nitride, BPSG, PSG, or SOG, or combinations thereof. It may be advantageous to employ silicon nitride because silicon nitride may be deposited in a

more conformal manner than silicon oxide. Moreover, silicon nitride is compatible with CMOS processing, in the event that microelectromechanical system 10 includes CMOS integrated circuits.

[0128] As mentioned above with respect to other embodiments of the present inventions, prior to formation, deposition and/or growth of insulation layer 32 and/or conductive layer 34, additional micromachined mechanical structures 12 and/or transistors of circuitry 16 may be formed and/or provided in third substrate 14c or in other substrates that may be fixed to first substrate 14a and/or second substrate 14b. (See, for example, FIGS. 16, 17 and 18). In this regard, the exposed surface of third substrate 14c or another substrate disposed thereon may be a suitable base upon which integrated circuits (for example, CMOS transistors) (see, FIG. 16) and/or micromachined mechanical structures 12 (see, FIGS. 17 and 18). Such integrated circuits and micromachined mechanical structures 12 may be fabricated using the inventive techniques described herein and/or wellknown fabrication techniques and equipment.

[0129] For example, with reference to FIG. 16, in one embodiment, transistor regions 36 (which may be integrated circuits (for example, CMOS transistors) of circuitry 16) may be provided in second substrate 14b. The transistor regions 36 may be formed before or after third substrate 14c is secured (for example, bonded) to second substrate 14b. The fabrication techniques described above and illustrated in FIGS. 5-8B may be employed in the embodiments of FIG. 14. Indeed, prior to or after formation, deposition and/or growth of insulation layer 32 and/or conductive layer 34, additional micromachined mechanical structures 12 and/or transistors of circuitry 16 may be formed and/or provided in second substrate 14b or in other substrates that may be fixed to first substrate 14a and/or second substrate 14b. For the sake of brevity, those discussions, in connection with the embodiments of FIG. 15, will not be repeated.

[0130] Notably, although second cavity 30 is described and illustrated in the previous embodiment as being formed in second substrate 14b, second cavity 30 may be formed in third substrate 14c, as illustrated in FIGS. 19 and 20A-20H. Indeed, a portion of second cavity 30 may be formed in second substrate 14b and a portion of second cavity 30 may be formed in third substrate 14c.

[0131] Similarly, first cavity 24 may be formed in second substrate 14b, as illustrated in FIG. 21. Indeed, first cavity 24 and second cavity 30 may both be formed in second substrate 14b. (See, for example, FIG. 22). Moreover, a portion of first cavity 24 may be formed in first substrate 14a and a portion of first cavity 24 may be formed in second substrate 14b. Indeed, all permutations of formation of first cavity 24 and second cavity 30 are intended to fall within the scope of the present inventions.

[0132] With reference to FIGS. 23-30I, in another embodiment of the present inventions, first substrate 14a and/or third substrate 14c are/is the same conductivity as second substrate 14b. In these embodiments, micromachined mechanical structure 12 may include additional features to electrically isolate contact 20. For example, with reference to FIG. 23, in one embodiment, second substrate 14b is a semiconductor having the same conductivity as the conductivity of third substrate 14c. In this embodiment, micromachined mechanical structure 12 includes isolation trenches 42a and 42b that isolates contact 20 (and contact areas 26a and 26b) from portions of third substrate 14c. In this

exemplary embodiment, the isolation trenches are aligned with isolation regions **44***a* and **44***b* which are disposed in or on second substrate **14***b*.

[0133] The isolation trenches 42a and 42b may include a material that insulates contact 20 (and contact areas 26a and 26b) from portions of third substrate 14c. In the exemplary embodiment of FIG. 23, an insulating material, for example, silicon dioxide or silicon nitride, is deposited and/or grown in isolation trenches 42a and 42b. Indeed, as illustrated, material that forms insulation layer 32 may also be deposited in isolation trenches 42a and 42b. Notably, FIGS. 24A-24I illustrate an exemplary process flow for fabricating microelectromechanical system 10 of FIG. 23.

[0134] As mentioned above, isolation regions 44a and 44b which are disposed in or on second substrate 14b. The isolation regions 44a and 44b may be any material or structure that insulates contact 20, for example, an insulator material and/or an oppositely doped semiconductor region. In the exemplary embodiment of FIG. 23, isolation regions 44a and 44b includes oppositely doped semiconductor material.

[0135] With reference to FIG. 25, in another exemplary embodiment, first substrate 14a is a semiconductor having the same conductivity as the conductivity of second substrate 14b. In this embodiment, micromachined mechanical structure 12 includes an isolation region 44 that isolates contact 20 (and, in particular, contact area 26a) from portions of first substrate 14a. In this exemplary embodiment, the isolation region 44 is aligned with cavity 24 and trench 28a in order to provide suitable contact isolation. The isolation region 44 may include any material or structure that insulates contact 20, for example, an insulator material and/or an oppositely doped semiconductor region. In the exemplary embodiment of FIG. 25, isolation regions 44a and 44b includes oppositely doped semiconductor material. Notably, FIGS. 26A-26H illustrate an exemplary process flow for fabricating microelectromechanical system 10 of FIG. 25.

[0136] In another exemplary embodiment, first, second and third substrates 14a, 14b and 14c include semiconductor regions having the same conductivity. With reference to FIG. 27, in this embodiment, micromachined mechanical structure 12 includes an isolation trenches 42a and 42b as well as isolation regions 44a, 44b, and 44c. The isolation trenches 42a and 42b, and isolation regions 44a, 44b, and 44c, in combination, electrically isolate contact 20 (and, in particular, contact areas 26a and 26b) from contiguous portions of first substrate 14a and third substrates 14c. In this exemplary embodiment, the isolation region 44a is aligned with cavity 24 and trench 28a, and isolation trenches 42a and 42b are aligned with isolation regions 44b and 44c. In this way, contact 20 includes suitable contact isolation.

[0137] The isolation trenches 42a and 42b may include any material that insulates contact 20 (and contact areas 26a and 26b) from portions of third substrate 14c. In the exemplary embodiment of FIG. 27, an oppositely doped semi-conductor is deposited and/or grown in isolation trenches 42a and 42b.

[0138] The isolation regions 44a, 44b and 44c may be disposed in or on first substrate 14a and/or second substrate 14b. In the exemplary embodiment of FIG. 27, isolation regions 44a and 44b includes oppositely doped semicon-

ductor material. Notably, FIGS. **28**A-**28**I illustrate an exemplary process flow for fabricating microelectromechanical system **10** of FIG. **23**.

[0139] As mentioned above, isolation trenches 42a and 42b may include any material or structure that insulates contact 20, for example, an insulator material and/or an oppositely doped semiconductor region. With reference to FIGS. 29 and 30A-30I, isolation trenches 42a and 42b may include an insulating material (for example, silicon dioxide or silicon nitride) which is deposited and/or grown in isolation trenches 42a and 42b. As illustrated, material that forms insulation layer 32 may also be deposited in isolation trenches 42a and 42b. In this regard, FIGS. 30A-30I illustrate an exemplary process flow for fabricating microelectromechanical system 10 of FIG. 29.

[0140] Although not previously illustrated, the present inventions may employ grinding and polishing (using, for example, well known chemical mechanical polishing ("CMP") techniques at various stages in order to, for example, provide a desired surface and/or thickness. For example, with reference to FIGS. 31A-31D, where material 46 is deposited and/or grown in isolation trenches 42a and 42b, the exposed surface may be subjected to grinding and polishing in order to remove a portion of the deposited and/or grown material from the upper surface of substrate 14c. With reference to FIG. 31C, after grinding and polishing, the surface is prepared for further processing, for example, "back-end" processing (see, for example, FIG. 31D) or incorporation of additional micromachined mechanical structures 12 and/or transistors of circuitry 16. [0141] Notably, it may be advantageous to employ isolation trenches 42 and isolation regions 44 in the embodiments where substrates 14a and 14c include a conductivity that is different from the conductivity of substrate 14b. (See, for example, FIG. 32 and FIGS. 33A-33I). In this embodiment, isolation trenches 42 and isolation regions 44 provide additional electrical isolation for contact 20. All permutations and/or combinations of such features are intended to fall within the scope of the present inventions.

[0142] The embodiments of FIGS. 23, 25, 27, 29 and 32 may also include circuitry 16 disposed in third substrate 14c. The fabrication techniques described above and illustrated in FIGS. 5-8B may be employed in the embodiments of FIGS. 23, 25, 27, 29 and 32. Indeed, prior to or after formation, deposition and/or growth of insulation layer 32 and/or conductive layer 34, additional micromachined mechanical structures 12 and/or transistors of circuitry 16 may be formed and/or provided in third substrate 14c or in other substrates that may be fixed to first substrate 14a and/or second substrate 14b. For the sake of brevity, those discussions, in connection with the embodiments of FIGS. 23, 25, 27, 29 and 32, will not be repeated.

[0143] In another aspect, the present inventions may employ an insulative layer between the substrate in which the micromachined mechanical structures 12 resides and one or more opposing or juxtaposed substrates. Such a configuration may provide certain processing advantages as well as enhance the electrical isolation of the micromachined mechanical structures 12 from one or more opposing or juxtaposed substrates. For example, with reference to FIG. 34, in this exemplary embodiment, micromachined mechanical structure 12 (including moveable electrode 18 and contact 20) is formed in second substrate 14b and encapsulated via third substrate 14c. In this regard, micro-

machined mechanical structure 12 is formed in a portion of substrate 14b. Thereafter, substrate 14c is secured (for example, bonded) to exposed surface of substrate 14b to encapsulate micromachined mechanical structure 12. In this embodiment, insulative layers 48a (having a thickness of about 1  $\mu$ m) is disposed and patterned on first substrate 14a to provide cavity 24 when second substrate 14b is disposed thereon. Similarly, insulative layer 48b (having a thickness of about 1  $\mu$ m) is disposed and patterned on second substrate 14b to provide cavity 30 when third substrate 14c is disposed thereon. Notably, substrate 14a, 14b and 14c may include the same or different conductivities.

[0144] The insulative layers 48a and 48b may include, for example, an insulation material (for example, a silicon dioxide, nitride, BPSG, PSG, or SOG, or combinations thereof). It may be advantageous to employ silicon nitride because silicon nitride may be deposited, formed and/or grown in a more conformal manner than silicon oxide. Moreover, silicon nitride is compatible with CMOS processing, in the event that microelectromechanical system 10 includes CMOS integrated circuits in one or more of substrates 14 thereof.

[0145] With reference to FIGS. 35A-35C, an exemplary method of fabricating or forming micromachined mechanical structure 12 according to this embodiment of the present inventions may begin with depositing, forming and/or growing insulative layer 48a on first substrate 14a. Thereafter, first cavity 24 is formed in insulative layer 48a using well-known lithographic and etching techniques. The thickness and characteristics of insulative layer 48a may be adjusted to accommodate further processing. For example, insulative layer 48a may be polished (using, for example, well known CMP techniques) to provide a smooth planar surface for receipt of second substrate 14b and provide a desired depth of first cavity 24. In one exemplary embodiment, first cavity 24 includes a depth of about 1 μm.

[0146] With reference to FIGS. 35D-35G, second substrate 14b may be fixed to insulative layer 48a using, for example, well-known bonding techniques such as fusion bonding and/or anodic-like bonding. The insulative layer 48b may then be deposited, formed and/or grown on first substrate 14b. The second cavity 30 may then be formed in insulative layer 48b—again using well-known lithographic and etching techniques. Thereafter, the thickness and characteristics of insulative layer 48b may be adjusted to accommodate further processing. For example, insulative layer 48b may be polished (using, for example, well known CMP techniques) to provide a smooth planar surface for receipt of second substrate 14c and provide a desired depth of second cavity 30. In one exemplary embodiment, second cavity 24 includes a depth of about 1  $\mu$ m.

[0147] In addition to forming second cavity 24 in insulative layer 48b, contact trench window 50 is also formed therein. (See, FIG. 35G). In this way, trench 28a may be formed concurrently with providing trenches 28b and 28c which permits definition of contact are 26a and moveable electrode 18 simultaneously. The trenches 28a-c may be formed using well-known deposition and lithographic techniques. Notably, all techniques for forming or fabricating trenches 28a-c, whether now known or later developed, are intended to be within the scope of the present inventions.

[0148] Notably, the first and second substrates 14b may be formed from any material now known or later developed. In a preferred embodiment, second substrate 14b includes or is