(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3941149号

(P3941149)

(45) 発行日 平成19年7月4日(2007.7.4)

(24) 登録日 平成19年4月13日(2007.4.13)

(51) Int.C1.

F 1

|              |           |              |      |

|--------------|-----------|--------------|------|

| G 11 C 16/06 | (2006.01) | G 11 C 17/00 | 639C |

| G 11 C 16/04 | (2006.01) | G 11 C 17/00 | 622E |

| G 11 C 29/42 | (2006.01) | G 11 C 29/00 | 631Q |

請求項の数 15 (全 21 頁)

(21) 出願番号 特願平9-55769

(22) 出願日 平成9年3月11日(1997.3.11)

(65) 公開番号 特開平10-222995

(43) 公開日 平成10年8月21日(1998.8.21)

審査請求日 平成15年9月26日(2003.9.26)

(31) 優先権主張番号 特願平8-323011

(32) 優先日 平成8年12月3日(1996.12.3)

(33) 優先権主張国 日本国(JP)

(31) 優先権主張番号 特願平8-324293

(32) 優先日 平成8年12月4日(1996.12.4)

(33) 優先権主張国 日本国(JP)

前置審査

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 荒瀬 謙士朗

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 野田 昌敬

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 杉山 寿伸

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】半導体不揮発性記憶装置

## (57) 【特許請求の範囲】

## 【請求項1】

電気的にデータの処理が行われるメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、

複数ビットデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、

前記複数ビットデータを単位としたデータの処理を当該複数単位のメモリセルに対して行い、チェック信号を受けると当該データ処理未終了メモリセルの個数を計数する手段と、

所定回数のデータ処理を繰り返し行った後に一括終点検出を行い、当該検出の結果、データ処理未終了メモリセルがあると前記チェック信号を出力してデータ処理未終了メモリセルの個数を計数させ、前記データ処理未終了メモリセルの個数が前記所定個数以内である場合に、当該データ処理未終了メモリセルを残したままデータの処理を終了し、当該データ処理未終了メモリセルを前記エラー訂正手段に救済させる手段と

を備えた半導体不揮発性記憶装置。

## 【請求項2】

電気的にデータのプログラムが行われるメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、

複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段

10

20

と、

前記複数ビットデータを単位としたデータプログラムを当該複数単位のメモリセルに対して行い、チェック信号を受けるとプログラム未終了メモリセルの個数を計数する手段と、

所定回数のプログラム動作を繰り返し行つた後に一括終点検出を行い、当該検出の結果、プログラム未終了メモリセルがあると前記チェック信号を出力してプログラム未終了メモリセルの個数を計数させ、前記プログラム未終了メモリセルの個数が前記所定個数以内である場合に、当該プログラム未終了メモリセルを残したままデータプログラムを終了し、当該プログラム未終了メモリセルを前記エラー訂正手段に救済させる手段と

を備えた半導体不揮発性記憶装置。

10

【請求項3】

セクタ単位のページデータが各ビット線毎に設けられたデータラッチ回路に転送されると共に、当該選択されたセクタを単位として一括して電気的にデータプログラムが行われるメモリセルがマトリクス配置された半導体不揮発性記憶装置であつて、

選択されたセクタのメモリセル毎にページデータの読み出しを行い、読み出した当該ページデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、

前記ページプログラムデータに従つたデータプログラムがベリファイ読み出し動作を介して複数回のプログラム動作を繰り返し行うことによりなされ、各プログラム動作毎に一括終点検出によりプログラム未終了メモリセルが存在するか否かを検知し、プログラム未終了メモリセルが存在する場合にチェック信号を出力する検知手段と、

20

プログラム未終了メモリセルが存在し、前記チェック信号を受けると、当該プログラム未終了メモリセルの個数を計数する計数手段と、

前記計数手段が前記チェック信号に応答して計数した結果、前記プログラム未終了メモリセルの個数が前記所定個数以内である場合に、当該プログラム未終了メモリセルを残したままデータプログラムを終了し、当該プログラム未終了メモリセルを前記エラー訂正手段に救済させる手段と

を備えた半導体不揮発性記憶装置。

【請求項4】

上記セクタ単位はワード線単位である

30

請求項3記載の半導体不揮発性記憶装置。

【請求項5】

前記エラー訂正手段は、プログラムすべき正規データよりエラー検査コードを発生する手段と、

前記正規データを記録するための正規メモリアレイ部と前記エラー検査コードを記録するためのパリティメモリアレイ部とから構成されたメモリアレイと、

前記正規データとエラー検査コードにより合成されたページデータを前記メモリアレイにページプログラムする手段と、

前記ページデータのデータ読み出し時に、読み出した正規データとエラー検査コードによりデータプログラム時のエラービットを訂正する手段と

40

を備えた請求項3記載の半導体不揮発性記憶装置。

【請求項6】

前記検知手段は、各プログラム動作後のベリファイ読み出し動作毎に、プログラムが終了したメモリセルの接続されたデータラッチ回路にラッチされているデータを順次反転させて再プログラムデータを自動設定する手段と、

前記再プログラムデータの自動設定後に、プログラム未終了のデータがラッチされているデータラッチ回路が存在するか否かを検出する終点検出手段と

を備えた請求項3記載の半導体不揮発性記憶装置。

【請求項7】

前記計数手段は、一定のクロックパルスに同期したカラムデコーダの動作によりページ

50

読み出しし、当該ページ読み出しデータを順次計数回路にシフト転送してプログラム未終了のデータの個数をカウントする

請求項 3 記載の半導体不揮発性記憶装置。

【請求項 8】

前記メモリセルがマトリクス配置されたメモリアレイは、複数のメモリセルが直列接続された N A N D 型構造をなす

請求項 3 記載の半導体不揮発性記憶装置。

【請求項 9】

前記メモリセルがマトリクス配置されたメモリアレイは、N O R 型構造をなし、かつ主ビット線がスイッチング手段を介して複数の副ビット線に階層化されている

請求項 3 記載の半導体不揮発性記憶装置。

10

【請求項 10】

電気的にデータの消去およびプログラムを行うことによりデータの書き換えが可能なメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、

複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ単位内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、

少なくとも 1 単位以上の前記複数ビットデータ単位のメモリセルに対してデータ消去を行い、チェック信号を受けると消去後に当該各複数ビットデータ単位内の消去未終了メモリセルの個数を計数する手段と、

20

所定回数の消去動作を繰り返し行った後に一括終点検出を行い、当該検出の結果、消去未終了メモリセルがあると前記チェック信号を出力して消去未終了メモリセルの個数を計数させ、前記消去未終了メモリセルの個数が前記所定個数以内である場合に、当該消去未終了メモリセルを残したままデータプログラムを行い、当該消去未終了メモリセルをデータ読み出し時に前記エラー訂正手段に救済させる手段と

を備えた半導体不揮発性記憶装置。

【請求項 11】

電気的にデータの消去およびプログラムを行うことによりデータの書き換えが可能なメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、

複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ単位内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、

30

少なくとも 1 単位以上の前記複数ビットデータ単位のメモリセルに対するデータ消去を、ベリファイ読み出し動作を介して複数回の消去電圧パルスを繰り返し印加して行い、各消去動作毎に一括終点検出により消去未終了メモリセルが存在するか否かを検知し、消去未終了メモリセルが存在する場合にチェック信号を出力する検知手段と、

プログラム未終了メモリセルが存在し、前記チェック信号を受けると、各複数ビットデータ単位内の消去未終了メモリセルの個数を計数する計数手段と、

前記計数手段が前記チェック信号に応答して計数した結果、前記消去未終了メモリセルの個数が前記所定個数以内である場合に、当該消去未終了メモリセルを残したままデータプログラムを行い、当該消去未終了メモリセルをデータ読み出し時に前記エラー訂正手段に救済させる手段と

40

を備えた半導体不揮発性記憶装置。

【請求項 12】

前記エラー訂正手段は、プログラムすべき正規データよりエラー検査コードを発生する手段と、

前記正規データを記録するための正規メモリアレイ部と前記エラー検査コードを記録するためのパリティメモリアレイ部とから構成されたメモリアレイと、

前記正規データとエラー検査コードにより合成された前記複数ビットデータ単位のプログラムデータをデータ消去後の前記メモリアレイにプログラムする手段と、

50

前記複数ビットデータ単位のデータ読み出し時に、読み出した正規データとエラー検査コードによりデータプログラム時のエラービットを訂正する手段と

を備えた請求項11記載の半導体不揮発性記憶装置。

【請求項13】

前記複数ビットデータ単位のメモリセルは、ワード線毎のページ単位のメモリセルである

請求項11記載の半導体不揮発性記憶装置。

【請求項14】

前記計数手段は、一定のクロックパルスに同期したカラムデコーダの動作によりページ読み出しし、読み出した当該ページデータを順次計数回路にシフト転送してプログラム未終了のデータの個数をカウントする

請求項11記載の半導体不揮発性記憶装置。

【請求項15】

複数ビットデータを単位とした電気的なデータプログラムを当該複数単位のメモリセルに対して行われるメモリセルがマトリクス配置されたメモリ本体と、

複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、

所定回数のプログラム動作を繰り返し行った後の一括終点検出でプログラム未終了メモリセルがあると判定された後に計数されたプログラム未終了メモリセルの個数が前記所定個数以内である場合に、当該プログラム未終了メモリセルを残したままデータプログラムを終了し、当該プログラム未終了メモリセルを前記エラー訂正手段に救済させる手段と

を備えたメモリシステム。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、電気的にデータのプログラムが可能な半導体不揮発性記憶装置に係り、特にデータプログラムおよび消去の高速化に関するものである。

【0002】

【従来の技術】

NAND型フラッシュメモリ、DINOR型フラッシュメモリ等の半導体不揮発性記憶装置においては、選択するワード線に接続されたすべてのメモリセル一括にデータプログラムが行われる。

すなわち、ワード線単位でページプログラムが行われる。

【0003】

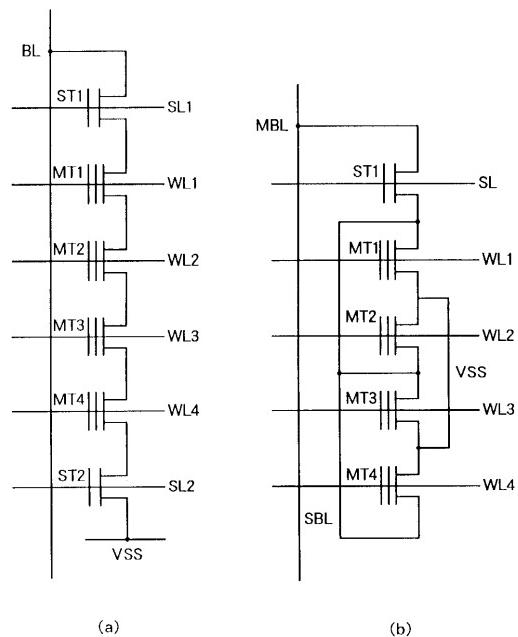

図7(a)、図7(b)は、それぞれNAND型、DINOR型フラッシュメモリにおける、メモリアレイ構造を示す図である。

【0004】

図7(a)は、便宜上、1本のビット線に接続されたNAND列1本に4個のメモリセルが接続された場合のNAND型フラッシュメモリアレイを示す図である。

図7(a)において、BLはビット線を示し、ビット線BLに2個の選択トランジスタタST1～ST2、および4個のメモリセルMT1～MT4が直列接続されたNAND列が接続されている。

選択トランジスタタST1～ST2はそれぞれ選択ゲート線SL1, SL2により制御され、またメモリセルMT1～MT4はそれぞれワード線WL1～WL4により制御される。

【0005】

図7(b)は、便宜上、1本の主ビット線に接続された副ビット線1本に4個のメモリトランジスタが接続された場合のDINOR型フラッシュメモリアレイを示す図である。

図7(b)において、MBLは主ビット線、SBLは副ビット線をそれぞれ示し、主ビッ

10

20

30

40

50

ト線 M B L および副ビット線 S B L は、選択ゲート線 S L により制御される選択トランジスタ S T 1 を介して作動的に接続される。

副ビット線 S B L は、4 本のワード線 W L 1 ~ W L 4 と交差し、各交差位置には 4 個のメモリセル M T 1 ~ M T 4 が配置されている。

【 0 0 0 6 】

また、N O R 型フラッシュメモリ等の半導体不揮発性記憶装置においては、データの書き換えは、所定のブロック単位（たとえば 64 K バイト程度）でデータの消去を行った後、当該消去ブロックのメモリセルに対してデータプログラムが行われる。

【 0 0 0 7 】

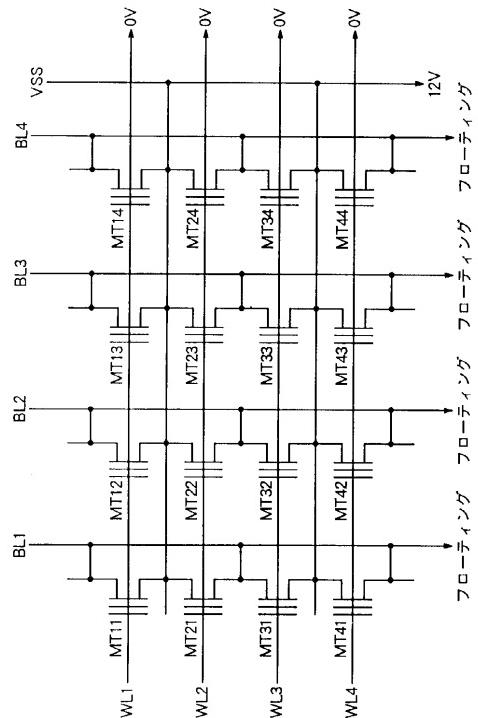

図 8 は、一般的な N O R 型フラッシュメモリにおける、メモリアレイ構造およびデータ消去時のバイアス条件を示す図である。 10

【 0 0 0 8 】

図 8 の N O R 型フラッシュメモリにおいては、便宜上、4 本のワード線 W L 1 ~ W L 4 と 4 本のビット線 B L 1 ~ B L 4 との格子位置にメモリセル M T 1 1 ~ M T 4 4 がマトリクス配置されている。 20

【 0 0 0 9 】

次に、図 8 の N O R 型フラッシュメモリにおいて、データ消去動作について説明する。

データ消去は、図 8 に示すように、消去ブロックメモリアレイ内のすべてのワード線 W L 1 ~ W L 4 を接地レベル (0 V) に、すべてのビット線 B L 1 ~ B L 4 をフローティング状態とし、共通ソース線 V S S に高電圧（たとえば 12 V）の消去電圧パルスを印加する。

その結果、データプログラム時に各メモリセルに蓄積されていた電子がソース側からトンネル電流により引き抜かれて、各メモリセルのしきい値電圧 V t h は、データプログラム状態の 6 V ~ 7 V から消去状態の 2 V ~ 3 V に遷移する。 20

【 0 0 1 0 】

【発明が解決しようとする課題】

ところで、上述した N A N D 型、D I N O R 型フラッシュメモリ等のようなワード線セクタを単位としたページプログラムを行う半導体不揮発性記憶装置においては、データのプログラムは選択ワード線に接続されたすべてのメモリセル一括にデータプログラムを行う。 30

しかし、選択ワード線に接続された各メモリセルは、製造プロセスに起因するサイズ等のバラツキのため、それぞれプログラム速度に差が生じる。

【 0 0 1 1 】

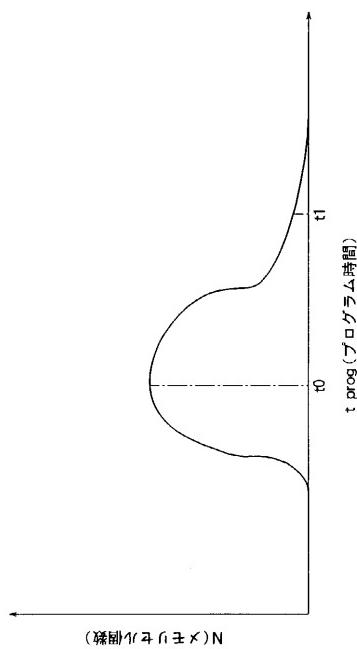

図 9 は上述した各選択ワード線に接続されたメモリセル間のプログラム速度の差を示す図である。

図 9 において、横軸は t P R O G ( プログラム時間 ) 、すなわち各メモリセルのプログラム必要時間を表わしている。

また、縦軸は N ( メモリセル個数 ) 、すなわち横軸 t P R O G ( プログラム時間 ) に対応したメモリセル個数の分布頻度を表わしている。 40

【 0 0 1 2 】

図 9 に示すように、N A N D 型フラッシュメモリ等のようなワード線セクタを単位としたページプログラムを行う半導体不揮発性記憶装置においては、メモリセル間でプログラム必要時間 t P R O G に分布が生じる。

このようなプログラム速度のバラツキを考慮して、一般的な N A N D 型フラッシュメモリ等においては、プログラム時のしきい値電圧 V t h の分布を狭く抑える観点から、プログラム動作がベリファイ動作を介して行われ、かつ当該プログラム / ベリファイ動作をプログラム終了メモリセルから順次プログラム禁止にしてすべてのメモリセルのプログラムが終了するまで繰り返し行う、いわゆるビット毎ベリファイ動作が行われる。

【 0 0 1 3 】

ところが図 9 に示すように、一般的なメモリセルの場合、プログラム必要時間 t P R O G 50

は図中  $t_0$  であるが、プロセス等のバラツキ要因から非常に長いプログラム必要時間  $t_{PRORG}$ 、たとえば図中  $t_1$  以上を要するメモリセルがごくまれに存在する場合がある。このような場合、ごくまれに存在するプログラムの遅いメモリセルのために、上述したプログラム／ベリファイ動作の回数も、たとえば 100 回以上と非常に多くなり、その結果、ページプログラムを終了するのに要する時間も非常に長くなる。

#### 【0014】

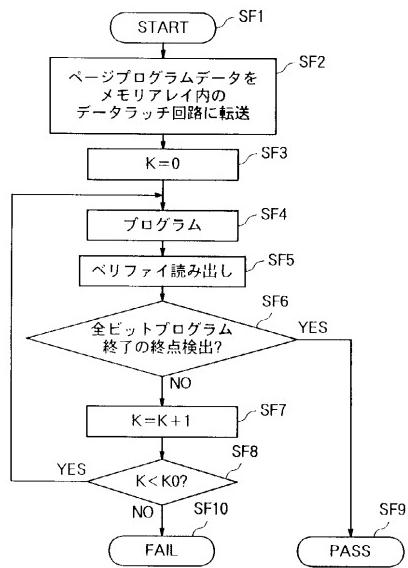

図 10 は、かかる従来の NAND 型フラッシュメモリ等のようなワード線セクタを単位としたページプログラムを行う半導体不揮発性記憶装置における、データプログラム時のシーケンスフローを示す図である。

以下、図 6 のシーケンスフローについて、順を追って説明する。

10

#### 【0015】

ステップステップ SF1 でデータプログラムが開始され、最初にステップ SF2 でページプログラムデータがメモリアレイ内の各ビット線毎に設けられたデータラッチ回路に転送される。

次に、ステップ SF3 でプログラムベリファイ回数  $K$  が 0 にリセットされ、プログラムパルスを印加するプログラム動作（ステップ SF4）、およびベリファイ読み出し後に再プログラムデータを自動設定するベリファイ読み出し動作（ステップ SF5）が連続して行われる。

次に、ステップ SF6 ですべてのメモリセルのプログラムが終了したかどうかの終点検出が、再プログラムデータ内に少なくとも 1 個以上のプログラム未終了メモリセルが残っているか否かを調べることにより行われる。

20

#### 【0016】

その結果、全ビットプログラム終了の終点検出ができた場合には、データプログラムを完了する（ステップ SF9）。

一方、全ビットプログラム終了の終点検出ができなかった場合には、さらにプログラムベリファイ回数  $K$  がインクリメントされ（ステップ SF7）、 $K$  が予め設定された所定回数  $k_0$ （たとえば 100 回程度）未満であるかどうかが調べられる（ステップ SF8）。

そして  $K$  が  $k_0$  未満である場合には、上述したステップ SF4 ~ SF8 のシーケンスフローが繰り返し行われ、 $K$  が  $k_0$  に到達した時点でデータプログラム失敗と判断される（ステップ SF10）。

30

#### 【0017】

この所定のプログラムベリファイ回数  $K_0$  は、ごくまれに存在するプログラムの遅いメモリセルのために、従来の NAND 型フラッシュメモリ等の場合たとえば 100 回以上と非常に多くなり、その結果、ページプログラムを終了するのに要する時間も非常に長くなっていた。

#### 【0018】

また、上述した NOR 型フラッシュメモリ等のような半導体不揮発性記憶装置においては、データの書き換えは、所定のブロック単位（たとえば 64K バイト程度）でデータ消去を行った後、当該ブロック単位でデータプログラムを行う。しかし、消去ブロック単位内の各メモリセルは、製造プロセスに起因するサイズ等のバラツキのため、それぞれ消去速度に差が生じる。

40

#### 【0019】

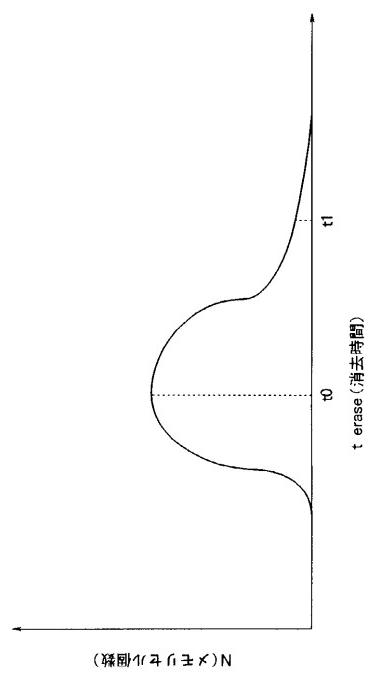

図 11 は上述した消去ブロック内のメモリセル間の消去速度の差を示す図である。

図 11 において、横軸は  $terase$ （消去時間）、すなわち各メモリセルの消去必要時間を表わしている。

また、縦軸は  $N$ （メモリセル個数）、すなわち横軸  $terase$ （消去時間）に対応したメモリセル個数の分布頻度を表わしている。

#### 【0020】

図 11 に示すように、NOR 型フラッシュメモリ等のような所定のブロック単位でデータ消去を行う半導体不揮発性記憶装置においては、メモリセル間で消去必要時間  $teras$

50

e に分布が生じる。

このような消去速度のバラツキを考慮して、一般的なN O R型フラッシュメモリにおいては、消去動作がベリファイ動作を介して行われ、かつ当該消去 / ベリファイ動作を消去ブロック内のすべてのメモリセルのデータ消去が終了するまで繰り返し行われる。

【0021】

ところが図11に示すように、一般的なメモリセルの場合、消去必要時間  $t_{erase}$  は図中  $t_0$  であるが、プロセス等のバラツキ要因から非常に長い消去必要時間  $t_{erase}$  、たとえば図中  $t_1$  以上を要するメモリセルがごくまれに存在する場合がある。

このような場合、ごくまれに存在する消去の遅いメモリセルのために、上述した消去 / ベリファイ動作の回数も、たとえば 100 回 ~ 1000 回以上と非常に多くなり、その結果、消去動作を終了するのに要する時間も非常に長くなり、ひいてはデータの書き換えに要する時間も長くなる。

さらに、ごくまれに存在する消去の遅いメモリセルのために消去 / ベリファイ動作の回数が非常に多くなると、消去の速いメモリセルが過剰消去されて当該メモリセルのしきい値電圧  $V_{th}$  がデプレーション状態 ( $V_{th} < 0$ ) となって、誤動作の原因となる。

【0022】

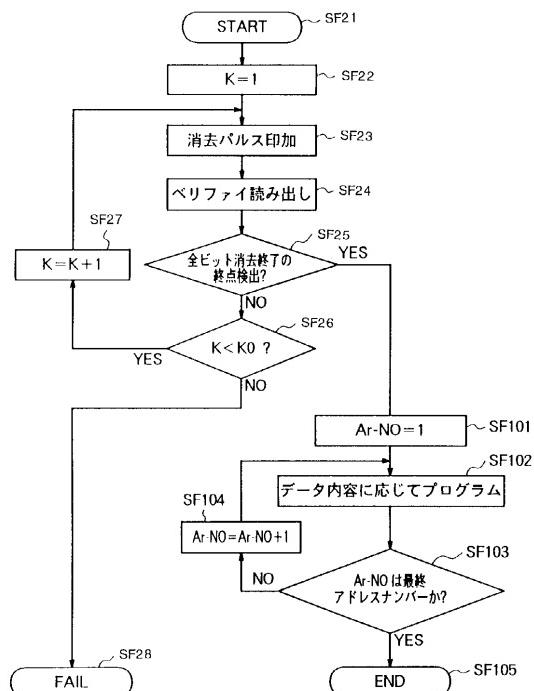

図12は、かかる従来のN O R型フラッシュメモリ等のような所定のブロック単位でデータの書き換えを行う半導体不揮発性記憶装置における、データ消去およびその後のデータプログラム時のシーケンスフローを示す図である。

以下、図12のシーケンスフローについて、順を追って説明する。

【0023】

ステップSF21でデータ消去が開始され、ステップSF22で消去ベリファイ回数  $K$  を最初の1に設定して消去パルスを印加する消去動作（ステップSF23）、およびベリファイ読み出し動作（ステップSF24）が連続して行われる。

ステップSF24のベリファイ読み出し動作の結果、ブロック内のすべてのメモリセルの消去終了の終点検出ができた場合には（ステップSF25）、データ消去を完了して、ステップSF101のデータプログラム動作が開始される。

【0024】

一方、ステップSF24のベリファイ読み出し動作の結果、ブロック内のすべてのメモリセルの消去終了の終点検出ができなかった場合には（ステップSF25）、ステップSF26において、消去ベリファイ回数  $K$  があらかじめ設定された所定回数  $K_0$ （たとえば 100 ~ 1000 回程度）未満であるか否かが調べられる。

その結果、消去ベリファイ回数  $K$  が設定回数  $K_0$  未満である場合には、さらに消去ベリファイ回数  $K$  がインクリメントされて（ステップSF27）、上述したステップSF23 ~ SF27のシーケンスフローが繰り返し行われる。そして、消去ベリファイ回数  $K$  が設定回数  $K_0$  に到達した時点でデータ消去失敗と判断される（ステップSF28）。

【0025】

次に、ブロック内のすべてのメモリセルの消去終了の終点検出ができた場合には、引き続いてデータプログラムが開始される。

まず、ステップSF101でメモリセルのアドレス番地  $A_r - N_O$  を最初の1に設定して、当該メモリセルに対してデータ内容に応じてデータプログラムが行われ（ステップSF102）、アドレス番地  $A_r - N_O$  が最終アドレス番地があるか否かが調べられる（ステップSF103）。

その結果、アドレス番地  $A_r - N_O$  が最終アドレス番地でない場合には、さらにアドレス番地  $A_r - N_O$  がインクリメントされて（ステップSF104）、上述したステップSF102 ~ SF104のシーケンスフローが繰り返し行われる。そして、アドレス番地  $A_r - N_O$  が最終アドレス番地に到達した時点でデータプログラムが完了する（ステップSF105）。

【0026】

上述したシーケンスフローにおいて、所定の消去ベリファイ回数  $K_0$  は、ごくまれに存在

10

20

30

40

50

する消去の遅いメモリセルのために、従来のNOR型フラッシュメモリ等の場合たとえば100回～1000回程度と非常に多くなり、その結果、消去動作を終了するのに要する時間も非常に長くなり、ひいてはデータの書き換えに要する時間も長くなっていた。さらには、上記消去の遅いメモリセルのために消去の速いメモリセルが過剰消去されて、誤動作の原因となっていた。

【0027】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、データプログラムおよびデータ消去を高速に行うことができ、データの書き換えを高速に行うことが可能で、さらには過剰消去メモリセルの発生を防止でき、信頼性の向上を図れる半導体不揮発性記憶装置を提供することにある。

10

【0028】

【課題を解決するための手段】

上記目的を達成するため、本発明は、電気的にデータの処理が行われるメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、複数ビットデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、前記複数ビットデータを単位としたデータの処理を当該複数単位のメモリセルに対して行い、チェック信号を受けると当該データ処理未終了メモリセルの個数を計数する手段と、所定回数のデータ処理を繰り返し行った後に一括終点検出を行い、当該検出の結果、データ処理未終了メモリセルがあると前記チェック信号を出力してデータ処理未終了メモリセルの個数を計数させ、前記データ処理未終了メモリセルの個数が前記所定個数以内である場合に、当該データ処理未終了メモリセルを残したままデータの処理を終了し、当該データ処理未終了メモリセルを前記エラー訂正手段に救済させる手段とを備えている。

20

【0029】

また、本発明は、電気的にデータのプログラムが行われるメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、前記複数ビットデータを単位としたデータプログラムを当該複数単位のメモリセルに対して行い、チェック信号を受けるとプログラム未終了メモリセルの個数を計数する手段と、所定回数のプログラム動作を繰り返し行った後に一括終点検出を行い、当該検出の結果、プログラム未終了メモリセルがあると前記チェック信号を出力してプログラム未終了メモリセルの個数を計数させ、前記プログラム未終了メモリセルの個数が前記所定個数以内である場合に、当該プログラム未終了メモリセルを残したままデータプログラムを終了し、当該プログラム未終了メモリセルを前記エラー訂正手段に救済させる手段とを備えている。

30

また、本発明は、複数ビットデータを単位とした電気的なデータプログラムを当該複数単位のメモリセルに対して行われるメモリセルがマトリクス配置されたメモリ本体と、複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、所定回数のプログラム動作を繰り返し行った後の一括終点検出でプログラム未終了メモリセルがあると判定された後に計数されたプログラム未終了メモリセルの個数が前記所定個数以内である場合に、当該プログラム未終了メモリセルを残したままデータプログラムを終了し、当該プログラム未終了メモリセルを前記エラー訂正手段に救済させる手段とを備えたメモリシステムである。

40

【0030】

また、本発明は、セクタ単位のページデータが各ビット線毎に設けられたデータラッチ回路に転送されると共に、当該選択されたセクタを単位として一括して電気的にデータプログラムが行われるメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、選択されたセクタのメモリセル毎にページデータの読み出しを行い、読み出した当該ページデータ内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、前記ページプログラムデータに従ったデータプログラムがベリファ

50

イ読み出し動作を介して複数回のプログラム動作を繰り返し行うことによりなされ、各プログラム動作毎に一括終点検出によりプログラム未終了メモリセルが存在するか否かを検知し、プログラム未終了メモリセルが存在する場合にチェック信号を出力する検知手段と、プログラム未終了メモリセルが存在し、前記チェック信号を受けると、当該プログラム未終了メモリセルの個数を計数する計数手段と、前記計数手段が前記チェック信号に応答して計数した結果、前記プログラム未終了メモリセルの個数が前記所定個数以内である場合に、当該プログラム未終了メモリセルを残したままデータプログラムを終了し、当該プログラム未終了メモリセルを前記エラー訂正手段に救済させる手段とを備えている。

#### 【0031】

また、好適には、前記エラー訂正手段は、プログラムすべき正規データよりエラー検査コードを発生する手段と、前記正規データを記録するための正規メモリアレイ部と前記エラー検査コードを記録するためのパリティメモリアレイ部とから構成されたメモリアレイと、前記正規データとエラー検査コードにより合成されたページデータを前記メモリアレイにページプログラムする手段と、前記ページデータのデータ読み出し時に、読み出した正規データとエラー検査コードによりデータプログラム時のエラービットを訂正する手段とを備えている。

#### 【0032】

また、好適には、前記検知手段は、各プログラム動作後のベリファイ読み出し動作毎に、プログラムが終了したメモリセルの接続されたデータラッチ回路にラッチされているデータを順次反転させて再プログラムデータを自動設定する手段と、前記再プログラムデータの自動設定後に、プログラム未終了のデータがラッチされているデータラッチ回路が存在するか否かを検出する終点検出手段とを備えている。

#### 【0033】

本発明の半導体不揮発性記憶装置によれば、所定回数のデータ処理、たとえばプログラム動作を繰り返し行った後にプログラム未終了メモリセルが存在しても、当該プログラム未終了メモリセルの個数がエラー訂正手段により訂正可能な所定個数以内のエラービットである場合には、プログラム未終了メモリセルを残したままデータプログラムを終了する。したがって、ごくまれに存在する非常にプログラムの遅いメモリセルに律速されことなく、高速にデータプログラムが可能となる。

#### 【0034】

また、本発明は、電気的にデータの消去およびプログラムを行うことによりデータの書き換えが可能なメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ単位内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、少なくとも1単位以上の前記複数ビットデータ単位のメモリセルに対してデータ消去を行い、チェック信号を受けると消去後に当該各複数ビットデータ単位内の消去未終了メモリセルの個数を計数する手段と、所定回数の消去動作を繰り返し行った後に一括終点検出を行い、当該検出の結果、消去未終了メモリセルがあると前記チェック信号を出力して消去未終了メモリセルの個数を計数させ、前記消去未終了メモリセルの個数が前記所定個数以内である場合に、当該消去未終了メモリセルを残したままデータプログラムを行い、当該消去未終了メモリセルをデータ読み出し時に前記エラー訂正手段に救済させる手段とを備えている。

#### 【0035】

また、本発明は、電気的にデータの消去およびプログラムを行うことによりデータの書き換えが可能なメモリセルがマトリクス配置された半導体不揮発性記憶装置であって、複数ビットデータを単位としてデータの読み出しを行い、当該複数ビットデータ単位内に所定個数以内のエラービットが存在する場合に当該エラービットを訂正するエラー訂正手段と、少なくとも1単位以上の前記複数ビットデータ単位のメモリセルに対するデータ消去を、ベリファイ読み出し動作を介して複数回の消去電圧パルスを繰り返し印加して行い、各消去動作毎に一括終点検出により消去未終了メモリセルが存在するか否かを検知し、消

10

20

30

40

50

去未終了メモリセルが存在する場合にチェック信号を出力する検知手段と、プログラム未終了メモリセルが存在し、前記チェック信号を受けると、各複数ビットデータ単位内の消去未終了メモリセルの個数を計数する計数手段と、前記計数手段が前記チェック信号に応答して計数した結果、前記消去未終了メモリセルの個数が前記所定個数以内である場合に、当該消去未終了メモリセルを残したままデータプログラムを行い、当該消去未終了メモリセルをデータ読み出し時に前記エラー訂正手段に救済させる手段とを備えている。

【0036】

また、好適には、前記エラー訂正手段は、プログラムすべき正規データよりエラー検査コードを発生する手段と、前記正規データを記録するための正規メモリアレイ部と前記エラー検査コードを記録するためのパリティメモリアレイ部とから構成されたメモリアレイと、前記正規データとエラー検査コードにより合成された前記複数ビットデータ単位のプログラムデータをデータ消去後の前記メモリアレイにプログラムする手段と、前記複数ビットデータ単位のデータ読み出し時に、読み出した正規データとエラー検査コードによりデータプログラム時のエラービットを訂正する手段とを備えている。

10

【0037】

また、好適には、前記計数手段は、一定のクロックパルスに同期したカラムデコーダの動作によりページ読み出しし、読み出した当該ページデータを順次計数回路にシフト転送してプログラム未終了のデータの個数をカウントする。

【0038】

本発明の半導体不揮発性記憶装置によれば、所定回数の消去動作を繰り返し行った後に消去未終了メモリセルが存在しても、当該消去未終了メモリセルの個数がエラー訂正手段により訂正可能な所定個数以内のエラービットである場合には、消去未終了メモリセルを残したままデータプログラムが行われる。

20

したがって、ごくまれに存在する非常に消去の遅いメモリセルに律速されることなく、高速にデータプログラムが可能となり、ひいてはデータの書き換えを高速に行うことができる。

さらには、消去の速いメモリセルが過剰消去されることを防止でき、信頼性の高い半導体不揮発性記憶装置を実現することができる。

【0039】

【発明の実施の形態】

30

第1実施例

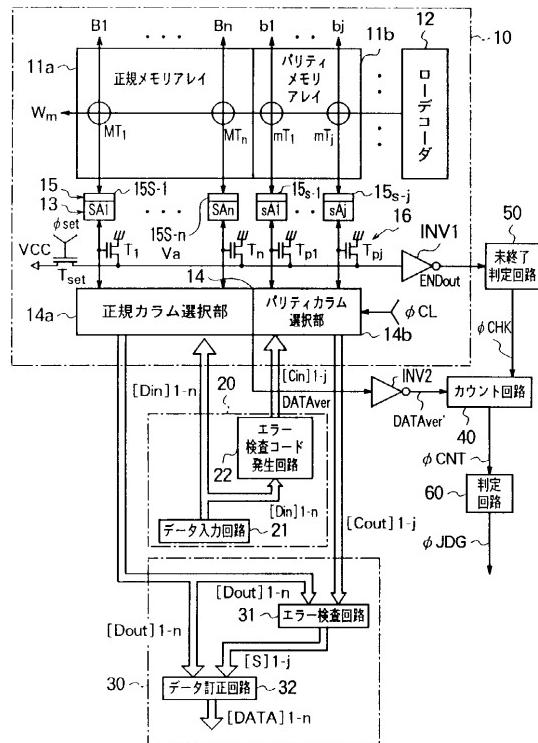

図1は、本発明に係る半導体不揮発性記憶装置、たとえばNAND型フラッシュメモリの具体的な構成例を示す図である。

【0040】

図1において、10はメモリ本体を示し、メモリ本体10は、メモリアレイ部11、ローデコーダ12、各ビット線毎に設けられたデータラッチ回路群13、カラム選択部14、再プログラムデータ自動設定回路群15および終点検出回路16等から構成されている。

【0041】

メモリアレイ11は、正規メモリアレイ11aとパリティメモリアレイ11bから構成されている。

40

正規メモリアレイ11aにはn本（通常は512バイト程度）の正規ビット線B1～Bnが配線され、パリティメモリアレイ11bにはj本（通常は10バイト程度）のパリティビット線b1～bjが配線されている。

なお、図中はワード線Wmを選択して、正規メモリセルMT1～MTnおよびパリティメモリセルmT1～mTjに対してページプログラムを行う場合を図示している。

【0042】

データラッチ回路群13は、正規データラッチ回路SA1～SA nおよびパリティデータラッチ回路sA1～sAjから構成され、カラム選択部14は正規カラム選択部14aおよびパリティカラム選択部14bから構成されている。

カラム選択部14はデータ転送クロック信号CLに同期して作動し、正規データラッチ

50

回路 S A 1 ~ S A n およびパリティデータラッチ回路 s A 1 ~ s A j にページプログラムデータをシフト転送し、またデータラッチ回路からページデータの読み出しを行う。

【 0 0 4 3 】

再プログラムデータ自動設定回路群 1 5 は、各正規データラッチ回路 S A 1 ~ S A n およびパリティデータラッチ回路 s A 1 ~ s A j 每に対応して設けられた自動設定回路 1 5 S - 1 ~ 1 5 S - n 、 1 5 s - 1 ~ 1 5 s - j により構成されている。

自動設定回路 1 5 S - 1 ~ 1 5 S - n 、 1 5 s - 1 ~ 1 5 s - j は、各プログラム動作後のベリファイ読み出し動作毎に、プログラムが終了したメモリセルの接続されたデータラッチ回路にラッチされているデータを順次反転させて再プログラムデータを自動設定する。

10

【 0 0 4 4 】

終点検出回路 1 6 は、各正規データラッチ回路 S A 1 ~ S A n およびパリティデータラッチ回路 s A 1 ~ s A j 每に設けられたトランジスタ T 1 ~ T n および T p 1 ~ T p j 、並びにトランジスタ T s e t 、および反転回路 I N V 1 により構成されている。

各トランジスタ T 1 ~ T n および T 1 ~ T j のゲート電極がそれぞれの正規データラッチ回路 S A 1 ~ S A n およびパリティデータラッチ回路 s A 1 ~ s A j の反転出力に、ソース電極が接地電位に、ドレン電極が共通接続されており、プログラム未終了セルが存在して少なくとも 1 個以上のデータラッチ回路の反転出力がハイレベルである場合に、共通接続された終点検出電位 V a が接地電位となり、反転回路 I N V 1 により終点検出信号 E N D o u t がハイレベルとして出力される。

20

またトランジスタ T s e t は、終点検出電位 V a を予め V C C レベルにプリチャージするために設けられ、終点検出に先だってプリチャージ信号 s e t により駆動される。

【 0 0 4 5 】

2 0 はデータ入力部を示し、データ入力部 2 0 は、データ入力回路 2 1 とエラー検査コード発生回路 2 2 により構成される。

データ入力回路 2 1 は正規入力データ [ D i n ] 1 ~ n をエラー検査コード発生回路 2 2 に入力し、エラー検査コード（パリティ入力データ） [ C i n ] 1 ~ j を発生する。正規入力データ [ D i n ] 1 ~ n およびエラー検査コード [ C i n ] 1 ~ j により合成されるページプログラムデータは、データ転送クロック信号 C L に同期して、それぞれ正規データラッチ回路 S A 1 ~ S A n およびパリティデータラッチ回路 s A 1 ~ s A j にシフト転送され、対応する正規メモリセルおよびパリティメモリセルにページプログラムされる。

30

【 0 0 4 6 】

3 0 はデータ出力部を示し、データ出力部 3 0 は、エラー検査回路 3 1 とデータ訂正回路 3 2 により構成される。

エラー検査回路 3 1 は、ページ読み出した正規出力データ [ D o u t ] 1 ~ n およびエラー検査コード（パリティ出力データ） [ C o u t ] 1 ~ j により、データ復調コード [ S ] 1 ~ j を発生する。

データ訂正回路 3 2 は、正規出力データ [ D o u t ] 1 ~ n およびデータ復調コード [ S ] 1 ~ j により、ページ読み出しデータ内に所定個数（たとえば 1 ビット）以内のエラービットが存在する場合にこれを訂正し、訂正後の正しい正規出力データ [ D A T A ] 1 ~ n を出力する。

40

【 0 0 4 7 】

4 0 はカウント回路（計数回路）を示し、カウント回路 4 0 は、所定回数のプログラムベリファイ回数（たとえば 10 回程度）を繰り返した後にプログラム未終了メモリセルが存在して終点検出できなかった場合、つまり少なくとも 1 個以上のデータラッチ回路の出力がローレベルである場合に、以下のようにプログラム未終了メモリセルの個数を計数する。

すなわち、基本データ転送クロック信号 C L に同期したベリファイページ読み出しデータ D A T A v e r の反転回路 I N V 2 の出力 D A T A v e r ' をシフト入力し、最後にチ

50

エック信号 C H K の入力に応じてプログラム未終了メモリセルの個数を計数する。

【0048】

未終了判定回路 50 は、メモリ本体 10 の反転回路 I N V 1 の出力信号 C H K をハイレベルで入力すると、プログラム未終了メモリセルがあるものとして、プログラム未終了メモリセルの個数の計数を開始するようにチェック信号 C H K をカウント回路 40 に出力する。

【0049】

判定回路 60 は、カウント回路 40 の出力チェック信号 C N T がハイレベルに切り換わったならば、プログラム未終了のセルが 1 つ以上あるものとして、図示しない制御系に出力する。

本実施形態の場合、判定回路 60 は、たとえばフリップフロップにより構成される。

10

【0050】

図 2 は、図 1 の半導体不揮発性記憶装置におけるエラー訂正手段において、1 ビットエラーに対処できる正規データビット数 n とパリティデータビット数（エラー検査ビット数）j との関係を示す図である。

【0051】

エラー訂正の原理、エラー検査コード発生回路 22、エラー検査回路 31、およびデータ訂正回路 32 については、本発明の骨子と直接関係しないため、ここでは詳述しない。

しかし図 2 によれば、512 ビットの正規データビット数には 10 ビットのエラー検査ビット数が必要であり、したがって一般的な 512 ビットの正規入力データ [ D i n ] 1 ~ n には 10 ビットのエラー検査コード [ C i n ] 1 ~ j を発生させる必要がある。

20

【0052】

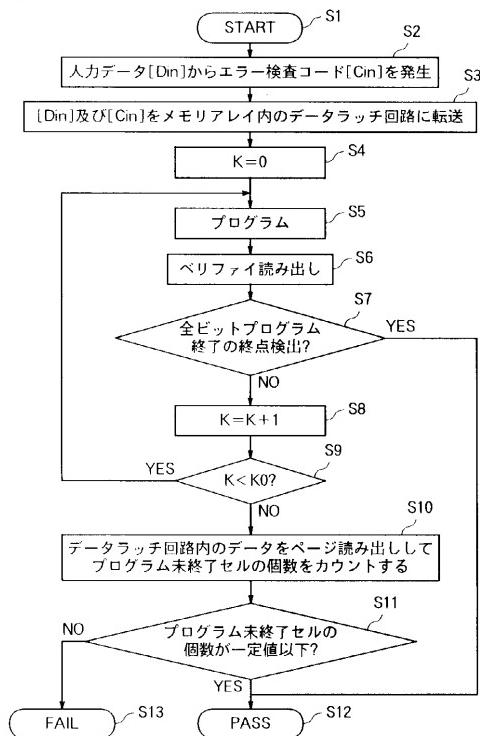

図 3 は、図 1 の半導体不揮発性記憶装置における、データプログラム時のシーケンスフローを示す図である。

以下、図 3 のシーケンスフローについて、図 1 の構成例等を参照しながら順を追って説明する。

【0053】

ステップ S 1 でデータプログラムが開始され、最初にデータ入力回路 21 を介して入力された正規入力データ [ D i n ] 1 ~ n に基づき、エラー検査コード発生回路 22 によりエラー検査コード [ C i n ] 1 ~ j が発生される（ステップ S 2）。

30

そして、正規入力データ [ D i n ] 1 ~ n およびエラー検査コード [ C i n ] 1 ~ j は正規カラム選択 14 a およびパリティカラム選択 14 b に入力され、合成したページプログラムデータがメモリアレイ内の各ビット線毎に設けられた正規データラッチ回路 S A 1 ~ S A n およびパリティデータラッチ回路 s A 1 ~ s A j に転送される（ステップ S 3）。

【0054】

次に、図示しないプログラム制御系によりステップ S 4 でプログラムベリファイ回数 K が 0 にリセットされ、プログラムパルスを印加するプログラム動作が行われ（ステップ S 5）、ベリファイ読み出し後に、自動設定回路 15 S - 1 ~ 15 S - n、15 s - 1 ~ 15 s - j においてプログラム終了メモリセルの正規データラッチ回路 S A 1 ~ S A n およびパリティデータラッチ回路 s A 1 ~ s A j 内のデータを順次反転させて再プログラムデータを自動設定するベリファイ読み出し動作（ステップ S 6）が連続して行われる。

40

【0055】

次に、ステップ S 7 で終了検出回路 16 および未終了判定回路 50 において、すべてのメモリセルのプログラムが終了したかどうかの終点検出が、再プログラムデータ内に少なくとも 1 個以上のプログラム未終了メモリセルに対応するデータが残っているか否かを調べることにより行われる。

【0056】

その結果、全ビットプログラム終了の終点検出ができた場合には、データプログラムを完了する（ステップ S 12）。

しかし、全ビットプログラム終了の終点検出ができなかった場合には、さらにプログラム

50

ベリファイ回数 K がインクリメントされて（ステップ S 8）、K が予め設定された所定回数 k 0（たとえば 10 回程度）未満であるかどうかが調べられる（ステップ S 9）。

そして K が k 0 未満である場合には、上述したステップ S 5～S 9 のシーケンスフローが繰り返し行われ、K が k 0 に到達した時点でステップ S 10 に進む。

#### 【0057】

次にステップ S 10 では、データラッチ回路内のデータがページ読み出しされて、プログラム未終了メモリセルの個数がカウント回路 40 でカウントされる。

次に、ステップ S 11 において、計数したプログラム未終了メモリセルの個数がエラー訂正可能な所定個数（たとえば 1 個）以内であるかどうかが調べられる。

その結果、プログラム未終了メモリセルの個数がエラー訂正可能な所定個数以内である場合にはデータプログラムを完了し（ステップ S 12）、所定個数を超えている場合にはデータプログラム失敗と判断される（ステップ S 13）。

#### 【0058】

以上のシーケンスフローによりデータプログラムが行われた本発明の半導体不揮発性記憶装置においては、データ読み出し時に、エラー検査回路 31 およびデータ訂正回路 32 によりプログラム未終了メモリセルのエラー訂正がなされ、正しい正規データ [DATA] 1～n が読み出される。

#### 【0059】

以上説明したように、本第 1 の実施例に係る半導体不揮発性記憶装置によれば、所定回数のプログラム動作を繰り返し行った後にプログラム未終了メモリセルが存在しても、当該プログラム未終了メモリセルの個数がエラー訂正手段により訂正可能な所定個数以内のエラービットである場合には、プログラム未終了メモリセルを残したままデータプログラムを終了する。

したがって、ごくまれに存在する非常にプログラムの遅いメモリセルに律速されることなく、高速にデータプログラムが可能となる。

#### 【0060】

### 第 2 実施例

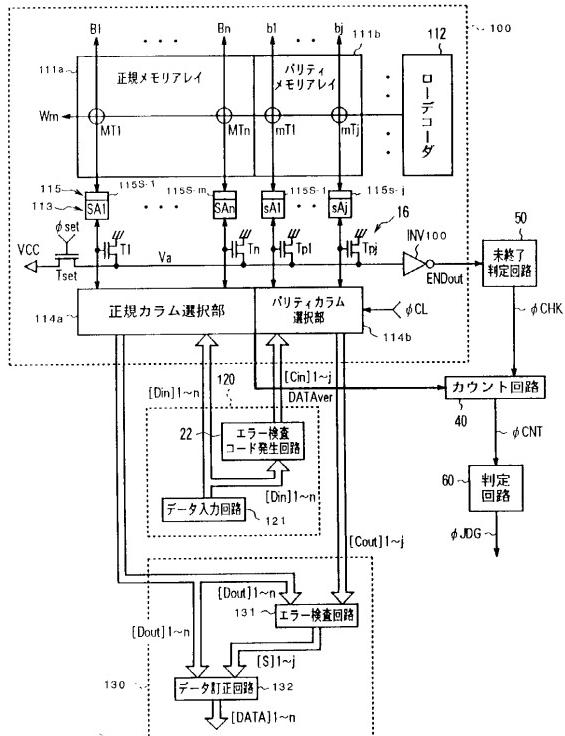

図 4 は、本発明に係る半導体不揮発性記憶装置、たとえば NOR 型フラッシュメモリの具体的な構成例を示す図である。

#### 【0061】

すなわち、図 4 において、100 はメモリ本体を示し、メモリ本体 100 は、メモリアレイ部 111、ローデコーダ 112、各ビット線毎に設けられたデータラッチ回路群 113、カラム選択部 114、再プログラムデータ自動設定回路群 115 および終点検出回路 116 等から構成されている。

#### 【0062】

メモリアレイ 111 は、正規メモリアレイ 111a とパリティメモリアレイ 111b とから構成されている。

正規メモリアレイ 111a には n 本（通常は 512 バイト程度）の正規ビット線 B1～Bn が配線され、パリティメモリアレイ 111b には j 本（通常は 10 バイト程度）のパリティビット線 b1～bj が配線されている。

なお、図中はワード線 Wm を選択して、正規メモリセル MT1～MTn およびパリティメモリセル mT1～mTj に対してページ読み出しを行う場合を図示している。

#### 【0063】

データラッチ回路群 113 は、正規データラッチ回路 SA1～SA n およびパリティデータラッチ回路 sA1～sA j から構成され、カラム選択部 114 は正規カラム選択部 114a およびパリティカラム選択部 114b から構成されている。

カラム選択部 114 はデータ転送クロック信号 CL に同期して作動し、正規データラッチ回路 SA1～SA n およびパリティデータラッチ回路 sA1～sA j にページプログラムデータをシフト転送し、またデータラッチ回路からワード線単位のページデータの読み出しを行う。

10

20

30

40

50

## 【0064】

再プログラムデータ自動設定回路群115は、各正規データラッチ回路S A 1 ~ S A n およびパリティデータラッチ回路s A 1 ~ s A j 每に対応して設けられた自動設定回路115 S - 1 ~ 115 S - n、115 s - 1 ~ 115 s - j により構成されている。

自動設定回路115 S - 1 ~ 115 S - n、115 s - 1 ~ 115 s - j は、各プログラム動作後のベリファイ読み出し動作毎に、プログラムが終了したメモリセルの接続されたデータラッチ回路にラッチされているデータを順次反転させて再プログラムデータを自動設定する。

## 【0065】

終点検出回路116は、各正規データラッチ回路S A 1 ~ S A n およびパリティデータラ 10 ッチ回路s A 1 ~ s A j 每に設けられたトランジスタT 1 ~ T n およびT p 1 ~ T p j 、並びにトランジスタT s e t 、および反転回路I N V 1 0 0 により構成されている。

各トランジスタT 1 ~ T n およびT p 1 ~ T p j のゲート電極がそれぞれの正規データラッ ッチ回路S A 1 ~ S A n およびパリティデータラッチ回路s A 1 ~ s A j の反転出力に、ソース電極が接地電位に、ドレイン電極が共通接続されており、消去未終了セルが存在して少なくとも1個以上のデータラッチ回路の反転出力がハイレベルである場合に、共通接続された終点検出電位V a が接地電位となり、反転回路I N V 1 により終点検出信号E N D o u t がハイレベルとして出力される。

またトランジスタT s e t は、終点検出電位V a を予めV C C レベルにプリチャージするためには設けられ、終点検出に先だってプリチャージ信号 s e t により駆動される。 20

## 【0066】

120はデータ入力部を示し、データ入力部120は、データ入力回路121とエラー検査コード発生回路122とにより構成される。

データ入力回路121は正規入力データ[D i n ] 1 ~ n をエラー検査コード発生回路122に入力し、エラー検査コード(パリティ入力データ)[C i n ] 1 ~ j を発生する。正規入力データ[D i n ] 1 ~ n およびエラー検査コード[C i n ] 1 ~ j により合成されるワード線単位のページプログラムデータは、データ転送クロック信号C L に同期して、それぞれ正規データラッチ回路S A 1 ~ S A n およびパリティデータラッチ回路s A 1 ~ s A j にシフト転送され、対応する正規メモリセルおよびパリティメモリセルに順次データプログラムされる。 30

## 【0067】

130はデータ出力部を示し、データ出力部130は、エラー検査回路131とデータ訂正回路132とにより構成される。

エラー検査回路131は、ページ読み出した正規出力データ[D o u t ] 1 ~ n およびエラー検査コード(パリティ出力データ)[C o u t ] 1 ~ j により、データ復調コード[S ] 1 ~ j を発生する。

データ訂正回路132は、正規出力データ[D o u t ] 1 ~ n およびデータ復調コード[S ] 1 ~ j により、ページ読み出しデータ内に所定個数(たとえば1ビット)以内のエラービットが存在する場合にこれを訂正し、訂正後の正しい正規出力データ[D A T A ] 1 ~ n を出力する。 40

## 【0068】

140はカウント回路(計数回路)を示し、カウント回路140は、所定回数の消去ベリファイ回数(たとえば10回~数10回程度)を繰り返した後に消去ブロック内の各ページ内に消去未終了メモリセルが存在して終点検出できなかった場合、つまり各ページ毎のベリファイ読み出し時に1個以上のデータラッチ回路の出力がハイレベルである場合に、以下のように消去未終了メモリセルの個数を計数する。

すなわち、基本データ転送クロック信号C L に同期したベリファイページ読み出しデータD A T A v e r をシフト入力し、最後にチェック信号C H K の入力に応じて消去未終了メモリセルの個数を計数する。

## 【0069】

未終了判定回路 150 は、メモリ本体 100 の反転回路 INV100 の出力信号 CHK をハイレベルで入力すると、消去未終了メモリセルがあるものとして、消去未終了メモリセルの個数の計数を開始するようにチェック信号 CHK をカウント回路 140 に出力する。

【0070】

判定回路 160 は、カウント回路 140 の出力チェック信号 CNT がハイレベルに切り換わったならば、消去未終了のセルが 1 つ以上あるものとして、図示しない制御系に出力する。

本実施例の場合も、判定回路 160 は、たとえばフリップフロップにより構成される。

【0071】

図 4 の半導体不揮発性記憶装置におけるエラー訂正手段において、1 ビットエラーに対処できる正規データビット数  $n$  とパリティデータビット数（エラー検査ビット数） $j$  との関係は、第 1 実施例の場合と同様に、図 2 に示すような関係である。

【0072】

エラー訂正の原理、エラー検査コード発生回路 122、エラー検査回路 131、およびデータ訂正回路 132 については、本発明の骨子と直接関係しないため、ここでは詳述しない。

しかし図 2 によれば、512 ビットの正規データビット数には 10 ビットのエラー検査ビット数が必要である。

したがって、ワード線を 512 バイトページサイズとして 128 ページの 64K バイトデータ消去ブロック単位が構成されている場合、各ページ毎で、512 バイトの正規入力データ [Din]1 ~ n には 10 ビットのエラー検査コード [Cin]1 ~ j を発生させる必要がある。

【0073】

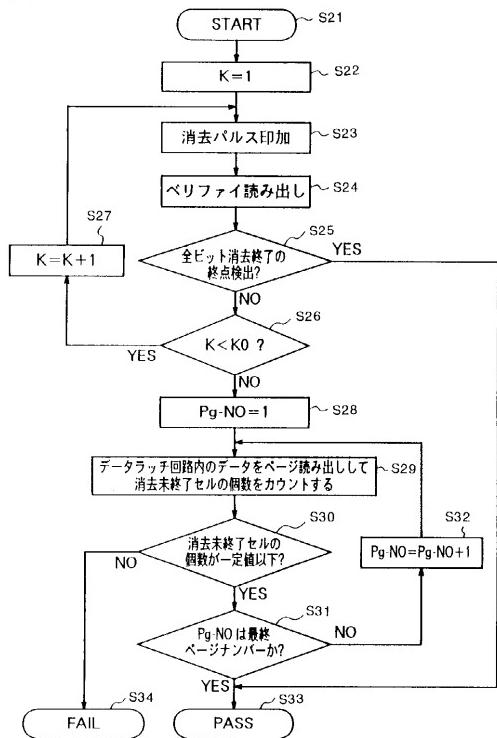

図 5 は、図 4 の半導体不揮発性記憶装置においてデータの書き換えを行う場合データ消去時のシーケンスフローを示す図である。

また、図 6 は、その後のデータプログラム時のシーケンスフローを示す図である。

以下、図 5 および図 6 のシーケンスフローについて、図 4 の構成例等を参照しながら順を追って説明する。

【0074】

まず、図 5 のデータ消去時のシーケンスフローについて説明する。

ステップ S21 でデータ消去が開始され、ステップ S22 で消去ベリファイ回数  $K$  を最初の 1 に設定して消去パルスを印加する消去動作（ステップ S23）、およびベリファイ読み出し動作（ステップ S24）が連続して行われる。

ステップ S24 のベリファイ読み出し動作の結果、ブロック内のすべてのメモリセルの消去終了の終点検出ができた場合には（ステップ S25）、データ消去を完了する。

【0075】

一方、ステップ S24 のベリファイ読み出し動作の結果、ブロック内のすべてのメモリセルの消去終了の終点検出ができなかった場合には（ステップ S25）、ステップ S26 において、消去ベリファイ回数  $K$  があらかじめ設定された所定回数  $K0$ （たとえば 100 ~ 1000 回程度）未満であるか否かが調べられる。その結果、消去ベリファイ回数  $K$  が設定回数  $K0$  未満である場合には、さらに消去ベリファイ回数  $K$  がインクリメントされて（ステップ S27）、上述したステップ S23 ~ S27 のシーケンスフローが繰り返し行われる。そして、消去ベリファイ回数  $K$  が設定回数  $K0$  に到達した時点で消去未終了メモリセルが存在するものとしてステップ S28 の処理に移行する。

【0076】

ステップ S28 において、消去ブロック内のページ番地 Pg - NO をまず最初の 1 に設定して、データラッチ回路の消去データをページ読み出しして、消去未終了メモリセルの個数がカウントされる（ステップ S29）。

【0077】

10

20

30

40

50

次に、ステップ S 3 0 で、計数した消去未終了メモリセルの個数がエラー訂正可能ま所定個数（たとえば 1 個）以内であるか否かが調べられる。

その結果、消去未終了メモリセルの個数がエラー訂正可能な所定個数を超える場合にはデータ消去失敗と判断される（ステップ S 3 4）。

一方、消去未終了メモリセルの個数がエラー訂正可能な所定個数以内である場合には、ページ番地 Pg - NO が最終アドレス番地であるか否かが調べられる（ステップ S 3 1）。そして、ページ番地 Pg - NO が最終アドレス番地でない場合には、さらにページ番地 Pg - NO がインクリメントされて（ステップ S 3 2）、上述したステップ S 2 9 ~ S 3 2 のシーケンスフローが繰り返し行われる。そして、ページ番地 Pg - NO が最終ページ番地に到達した時点で、データ消去完了と判断される（ステップ S 3 3）。 10

#### 【0078】

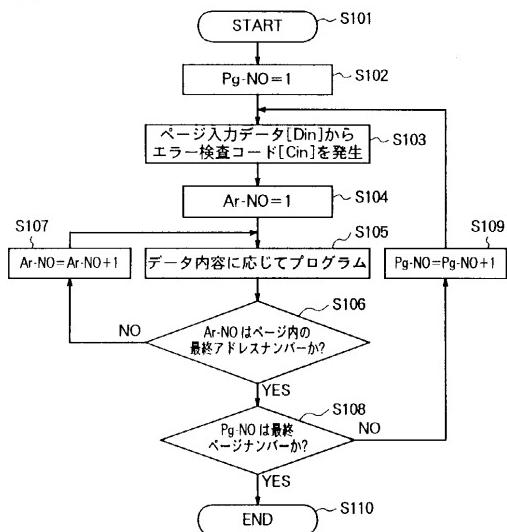

次に、図 6 のデータプログラム時のシーケンスフローについて説明する。

データの消去が完了した場合、（図 3 のステップ S 3 3）には、引き続いてデータプログラムが開始される（ステップ S 1 0 1）。

まず、ステップ S 1 0 2 でブロック内のページ番地 Pg - NO をまず最初の 1 に設定して、当該ページの正規入力データ [ D i n ] 1 ~ n に基づき、エラー検査コード発生回路 2 2 によりエラー検査コード [ C i n ] 1 ~ j が発生される（ステップ S 1 0 3）。

次に、当該ページ内でメモリセルのアドレス番地 Pg - NO を最初の 1 に設定して（ステップ S 1 0 4）、当該メモリセルに対してデータ内容に応じてデータプログラムが行われ（ステップ S 1 0 5）、アドレス番地 Ar - NO が最終アドレス番地であるか否かが調べられる（ステップ S 1 0 6）。 20

その結果、アドレス番地 Ar - NO が最終アドレス番地でない場合には、さらにアドレス番地 Ar - NO がインクリメントされて（ステップ S 1 0 7）、上述したステップ S 1 0 3 ~ S 1 0 7 のシーケンスフローが繰り返し行われる。そして、アドレス番地 Ar - NO が最終アドレス番地に到達した時点で当該ページのデータプログラムが完了する。

#### 【0079】

次に、ステップ S 1 0 8 でページ番地 Pg - NO が最終番地であるか否かが調べられる。

その結果、アドレス番地 Pg - NO が最終番地でない場合には、さらにページ番地 Pg - NO がインクリメントされて（ステップ S 1 0 9）、上述したステップ S 1 0 3 ~ S 1 0 9 のシーケンスフローが繰り返し行われる。そして、アドレス番地 Ar - NO が最終アドレス番地に到達した時点で当該ページのデータプログラムが完了する（S 1 1 0）。 30

#### 【0080】

以上のシーケンスフローによりデータの書き換えが行われた本発明の半導体不揮発性記憶装置においては、データ読み出し時に、エラー検査回路 3 1 およびデータ訂正回路 3 2 により消去未終了メモリセルのエラー訂正がなされ、正しい正規データ [ D A T A ] 1 ~ n が読み出される。

#### 【0081】

以上説明したように、本第 2 の実施例に係る半導体不揮発性記憶装置によれば、所定回数の消去動作を繰り返し行った後に消去未終了メモリセルが存在しても、当該消去未終了メモリセルの個数がエラー訂正手段により訂正可能な所定個数以内のエラービットである場合には、消去未終了メモリセルを残したままデータプログラムを行う。 40

したがって、ごくまれに存在する非常に消去の遅いメモリセルに律速されることなく、高速にデータプログラムが可能となり、ひいては、データの書き換えを高速に行うことができる。

さらには、消去の速いメモリセルが過剰消去されることを防止でき、信頼性の高い半導体不揮発性記憶装置を実現することができる。

#### 【0082】

#### 【発明の効果】

以上説明したように、本発明によれば、高速にデータプログラムを行うことができる半導体不揮発性記憶装置を実現することができる。 50

## 【0083】

また、本発明によれば、データ消去を高速に行うことができ、データの書き換えを高速に行うことが可能で、さらには過剰消去メモリセルの発生を防止でき、信頼性の向上を図れる半導体不揮発性記憶装置を実現することができる。

## 【図面の簡単な説明】

【図1】本発明に係る半導体不揮発性記憶装置の第1の実施例の構成例を示す図である。

【図2】図1の半導体不揮発性記憶装置におけるエラー訂正手段において、1ビットエラーに対処できる正規データビット数nとパリティデータビット数（エラー検査ビット数）jとの関係を示す図である。

【図3】図1の半導体不揮発性記憶装置における、データプログラム時のシーケンスフローを示す図である。 10

【図4】本発明に係る半導体不揮発性記憶装置の第2の実施例の構成例を示す図である。

【図5】図1の半導体不揮発性記憶装置における、データ消去時のシーケンスフローを示す図である。

【図6】図1の半導体不揮発性記憶装置における、データプログラム時のシーケンスフローを示す図である。

【図7】NAND型およびDINOR型フラッシュメモリにおける、メモリアレイ構造を示す図である。

【図8】一般的なNOR型フラッシュメモリにおける、メモリアレイ構造およびデータ消去時のバイアス条件を示す図である。 20

【図9】従来のワード線セクタを単位としたページプログラムを行う半導体不揮発性記憶装置のメモリセル間のプログラム速度の差を示す図である。

【図10】従来のワード線セクタを単位としたページプログラムを行う半導体不揮発性記憶装置における、データプログラム時のシーケンスフローを示す図である。

## 【図11】消去ブロック内のメモリセル間の消去速度の差を示す図である。

【図12】従来のNOR型フラッシュメモリにおけるデータ書き換え時のシーケンスフローを示す図である。

## 【符号の説明】

B<sub>1</sub> ~ B<sub>n</sub> ... 正規ビット線、b<sub>1</sub> ~ b<sub>j</sub> ... パリティビット線、W<sub>m</sub> ... 選択ワード線、M<sub>T</sub>

1 ~ M<sub>Tn</sub> ... 正規メモリセル、m<sub>T1</sub> ~ m<sub>Tj</sub> ... パリティメモリセル、S<sub>A1</sub> ~ S<sub>An</sub> ... 30

正規データラッチ回路、s<sub>A1</sub> ~ s<sub>Aj</sub> ... パリティデータラッチ回路、[D<sub>in</sub>]<sub>1</sub> ~ <sub>n</sub> ...

正規入力データ、[D<sub>out</sub>]<sub>1</sub> ~ <sub>n</sub> ... 正規出力データ、[DATA]<sub>1</sub> ~ <sub>n</sub> ... エラー

訂正後の正規出力データ、[C<sub>in</sub>]<sub>1</sub> ~ <sub>j</sub> ... 入力エラー検査コード、[C<sub>out</sub>]<sub>1</sub> ~ <sub>j</sub> ...

出力エラー検査コード、[S]<sub>1</sub> ~ <sub>j</sub> ... データ復調コード、DATAver ... ベリフ

アイページ読み出しデータ、C<sub>L</sub> ... データ転送クロック信号、check ... チェック

信号、set ... プリチャージ信号、ENDout ... 終点検出信号、Va ... 終点検出電位

、INV1 ~ INV2, INV100 ... 反転回路、10, 100 ... メモリ本体、11, 1

11 ... メモリアレイ部、11a, 111a ... 正規メモリアレイ、11b, 111b ... パリ

ティメモリアレイ、12, 112 ... ローデコーダ、13, 113 ... データラッチ回路、1

4, 114 ... カラム選択部、14a, 114a ... 正規カラム選択部、14b, 114b ... 40

パリティカラム選択部、15, 115 ... 再プログラムデータ自動設定回路、16, 116

... 終点検出回路、20, 120 ... データ入力部、21, 121 ... データ入力回路、22,

122 ... エラー検査コード発生回路、30, 130 ... データ出力部、31, 131 ... エラ

リ検査回路、32, 132 ... データ訂正回路、40, 140 ... カウント回路、50, 15

0 ... 未終了判定回路、60, 160 ... 判定回路。

【図1】

【図2】

| 正規データビット数n | 8 | 16 | 32 | 64 | 128 | 256 | 512 | 1024 |

|------------|---|----|----|----|-----|-----|-----|------|

| エラー検査ビット数j | 4 | 5  | 6  | 7  | 8   | 9   | 10  | 11   |

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 内貴 唯八

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 石川 正二

(56)参考文献 特開平06-131884 (JP, A)

特開平07-302175 (JP, A)

特開平07-226097 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/06

G11C 16/04

G11C 29/42