(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(à n'utiliser que pour les

commandes de reproduction)

2 647 582

(21) N° d'enregistrement national :

90 06531

(51) Int Cl<sup>s</sup> : G 11 C 16/06.

(12) **DEMANDE DE BREVET D'INVENTION** A1

(22) Date de dépôt : 25 mai 1990.

(71) Demandeur(s) : Société dite : KABUSHIKI KAISHA TOSHIBA. — JP.

(30) Priorité : JP, 25 mai 1989, n° 1-131854.

(72) Inventeur(s) : Yasuo Iijima.

(43) Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 48 du 30 novembre 1990.

(73) Titulaire(s) :

(60) Références à d'autres documents nationaux appartenants :

(74) Mandataire(s) : Cabinet Beau de Loménie.

(54) Procédé d'écriture de données dans une mémoire semi-conductrice, et dispositif permettant de mettre en œuvre ce procédé.

(57) Selon l'invention, non seulement l'arrivée à son terme d'une opération d'écriture de données est contrôlée par la délivrance d'un signal d'état par une mémoire, par exemple un signal d'état de fin d'écriture, mais le temps nécessaire pour l'opération d'écriture de données est contrôlé également S10, S11. Si une défaillance de la mémoire apparaît, on peut mettre fin à l'opération d'écriture de données S11 même lorsque le signal d'état de fin d'écriture n'a pas atteint un niveau représentant la fin de l'opération d'écriture de données S9. Il est donc possible d'empêcher parfaitement l'arrêt inopiné du système utilisant la mémoire.

D 40 27 14 04 12 10 08 06 04 02

La présente invention concerne un procédé d'écriture de données dans une mémoire semiconductrice telle que la mémoire de données d'une carte à circuit intégré et un dispositif permettant de mettre en oeuvre le procédé ; plus particulièrement, elle concerne un procédé d'écriture de données dans une mémoire utilisant un signal du type état prêt/état occupé, et autres, ainsi qu'un dispositif permettant de mettre en oeuvre le procédé.

Récemment, pour remplacer les mémoires mortes électriquement programmables (EPROM), les mémoires mortes programmables électriquement effaçables (EEPROM), que l'on peut électriquement effacer et où l'on peut réécrire des données, ont attiré l'attention comme mémoires semiconductrices. Puisque le temps d'écriture de données dans la EEPROM est plus long que celui relatif à la EPROM, diverses améliorations ont été apportées à la EEPROM.

Selon l'une des améliorations apportées à la EEPROM, il a été mis au point, pour réduire la charge d'un dispositif externe dans le traitement d'une opération d'écriture, une EEPROM qui délivre en sortie un signal d'état pour informer le dispositif externe que l'écriture de données dans la EPROM a été complètement réalisée. Plus spécialement, le dispositif externe peut facilement déterminer si l'opération d'écriture s'est ou non terminée par simple contrôle du signal d'état délivré par la EEPROM, après avoir envoyé les données d'écriture à la EEPROM.

Toutefois, dans cette EEPROM perfectionnée, lorsque la EEPROM connaît une défaillance, le signal d'état ne réussit parfois pas à atteindre un niveau indiquant la fin d'une opération d'écriture de données dans la EEPROM, même si les données d'écriture ont été envoyées par le dispositif externe et que l'opération d'écriture des données s'est achevée. Dans ce cas, l'inconvénient est que, non seulement, le dispositif externe ne peut pas déterminer si l'écriture de données dans la EEPROM s'est ou non achevée, mais, de plus, il s'arrête pour l'opération d'écriture de données.

C'est donc un but de l'invention de produire un procédé d'écriture de données, qui peut arriver au terme de l'opération

d'écriture de données et qui peut empêcher entièrement l'arrêt inopiné d'un système utilisant une mémoire même lorsqu'il se produit une défaillance de la mémoire, ainsi qu'un dispositif permettant de mettre en oeuvre le procédé.

05 Selon un premier aspect de l'invention, il est proposé un procédé d'écriture de données provenant d'un premier moyen qui sert à fournir les données dans un moyen de mémorisation qui sert à emmagasiner les données, comprenant les opérations suivantes :

recevoir les données de la part du premier moyen ;

10 écrire les données dans le moyen de mémorisation en réponse à l'opération de réception ;

compter le temps en réponse à l'opération d'écriture ;

comparer le temps compté de l'opération de comptage avec un temps prédéterminé ; et

15 donner, en réponse au résultat comparé de l'opération de comparaison, l'information selon laquelle l'opération d'écriture est arrivée à son terme.

Selon un autre aspect de l'invention, il est proposé un dispositif permettant d'écrire des données dans un moyen de mémorisation servant à mémoriser les données, ledit dispositif comprenant :

un moyen servant à fournir les données au moyen de mémorisation ;

25 un moyen servant à écrire dans le moyen de mémorisation les données fournies par le moyen de fourniture ;

un moyen servant à indiquer un temps de début lorsque le moyen d'écriture commence à écrire les données dans le moyen de mémorisation ;

30 un moyen servant à compter le temps en réponse au temps de début indiqué par le moyen d'indication ;

un moyen servant à comparer le temps compté par le moyen de comptage avec un temps prédéterminé ; et

35 un moyen servant à délivrer une information de fin d'écriture indiquant la fin d'une opération d'écriture du moyen d'écriture en réponse à un résultat comparé par le moyen de comparaison.

En plus de contrôler la fin de l'écriture à l'aide du signal d'état tel qu'un signal d'état de fin d'écriture délivré par la mémoire, on contrôle la durée d'écriture des données. Par conséquent, même si une défaillance de la mémoire se produit et que, par conséquent, le signal d'état de fin d'écriture n'atteint pas un niveau représentant la fin d'une opération d'écriture de données, il est possible d'arrêter l'opération d'écriture et, par conséquent, on peut empêcher entièrement l'arrêt inopiné du système utilisant la mémoire.

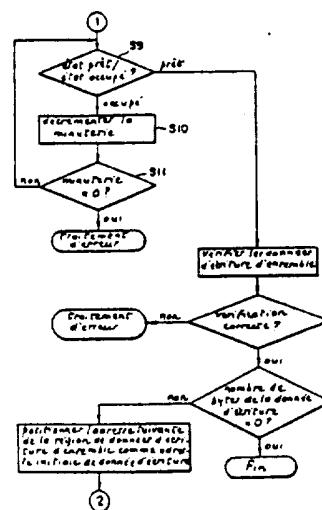

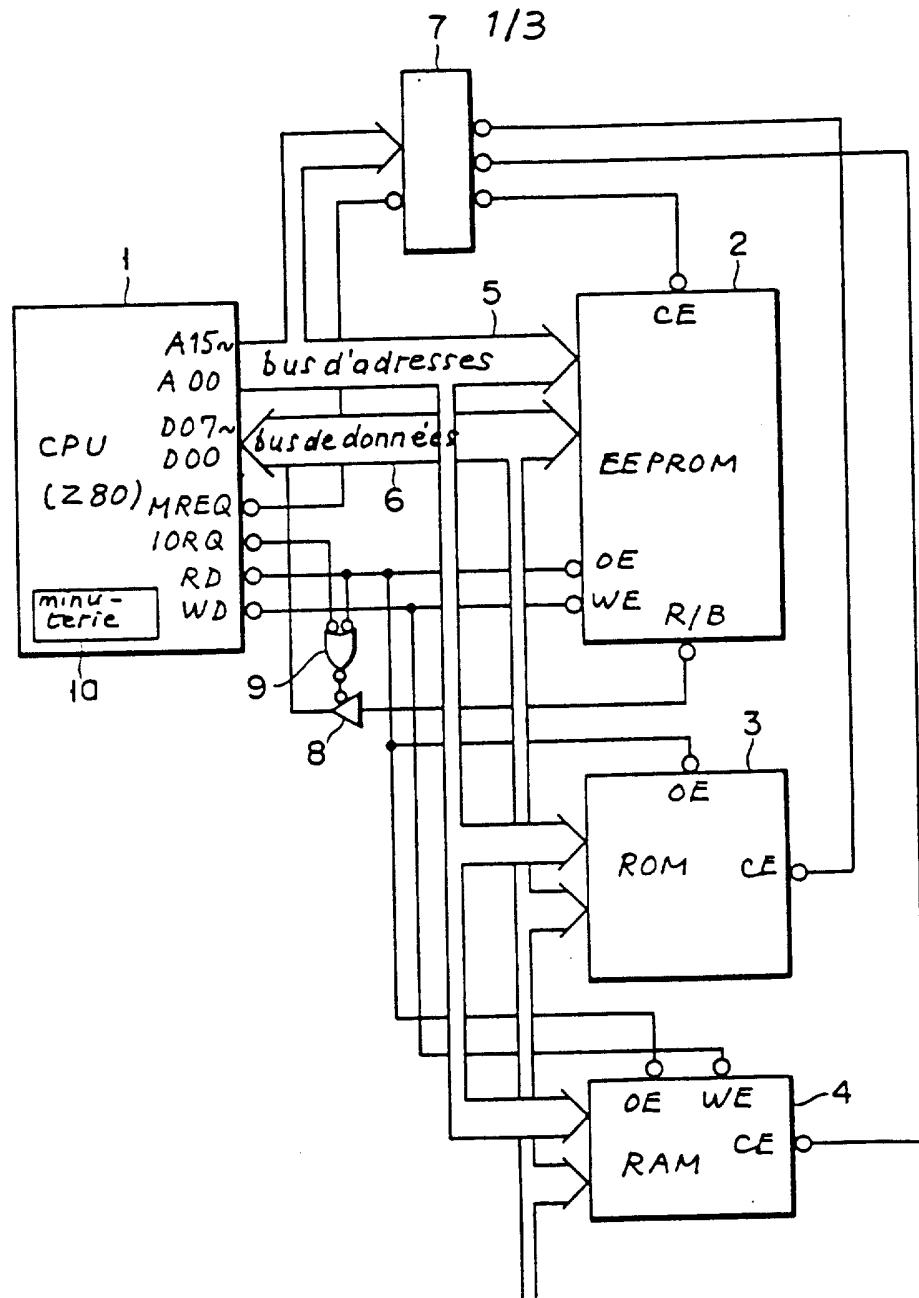

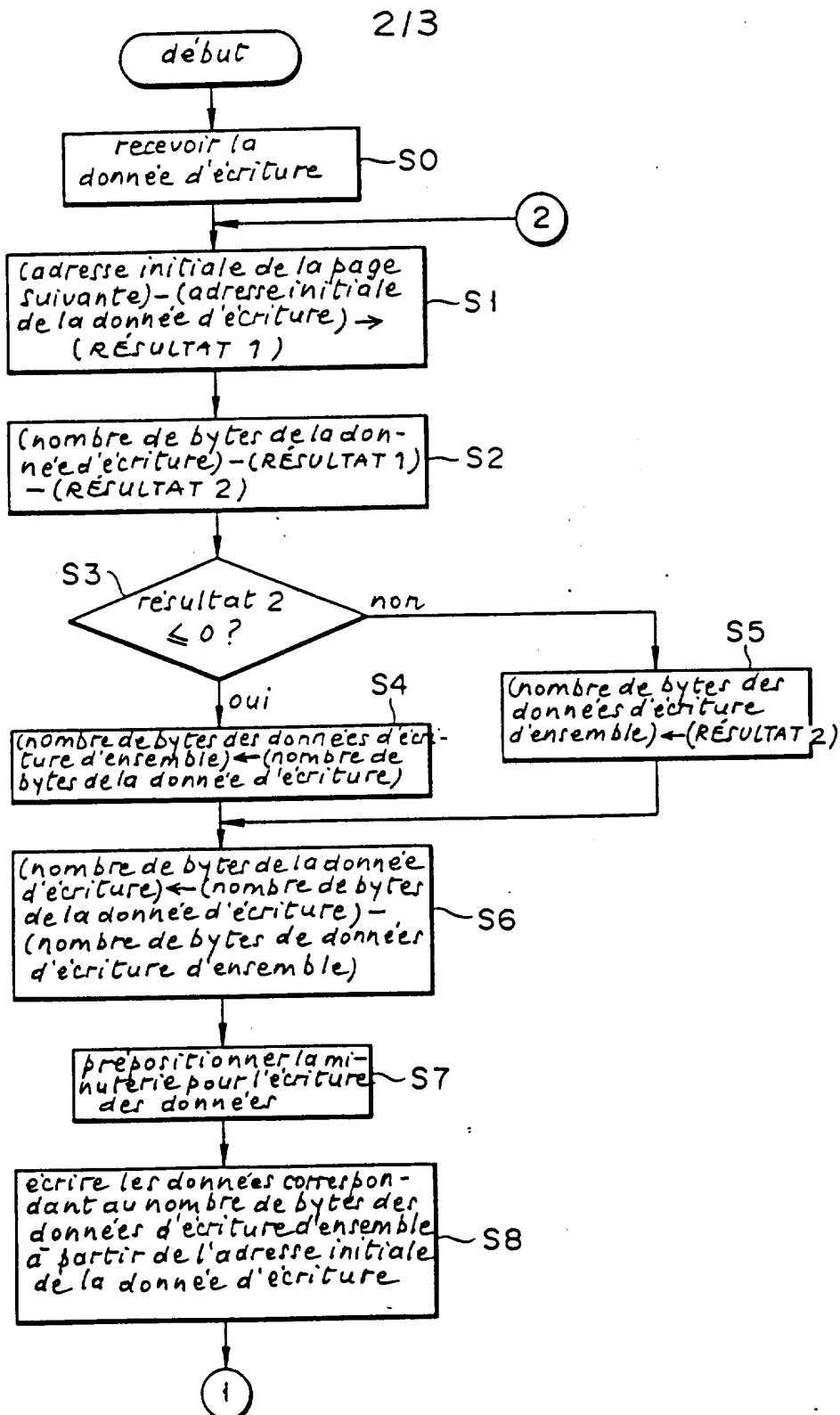

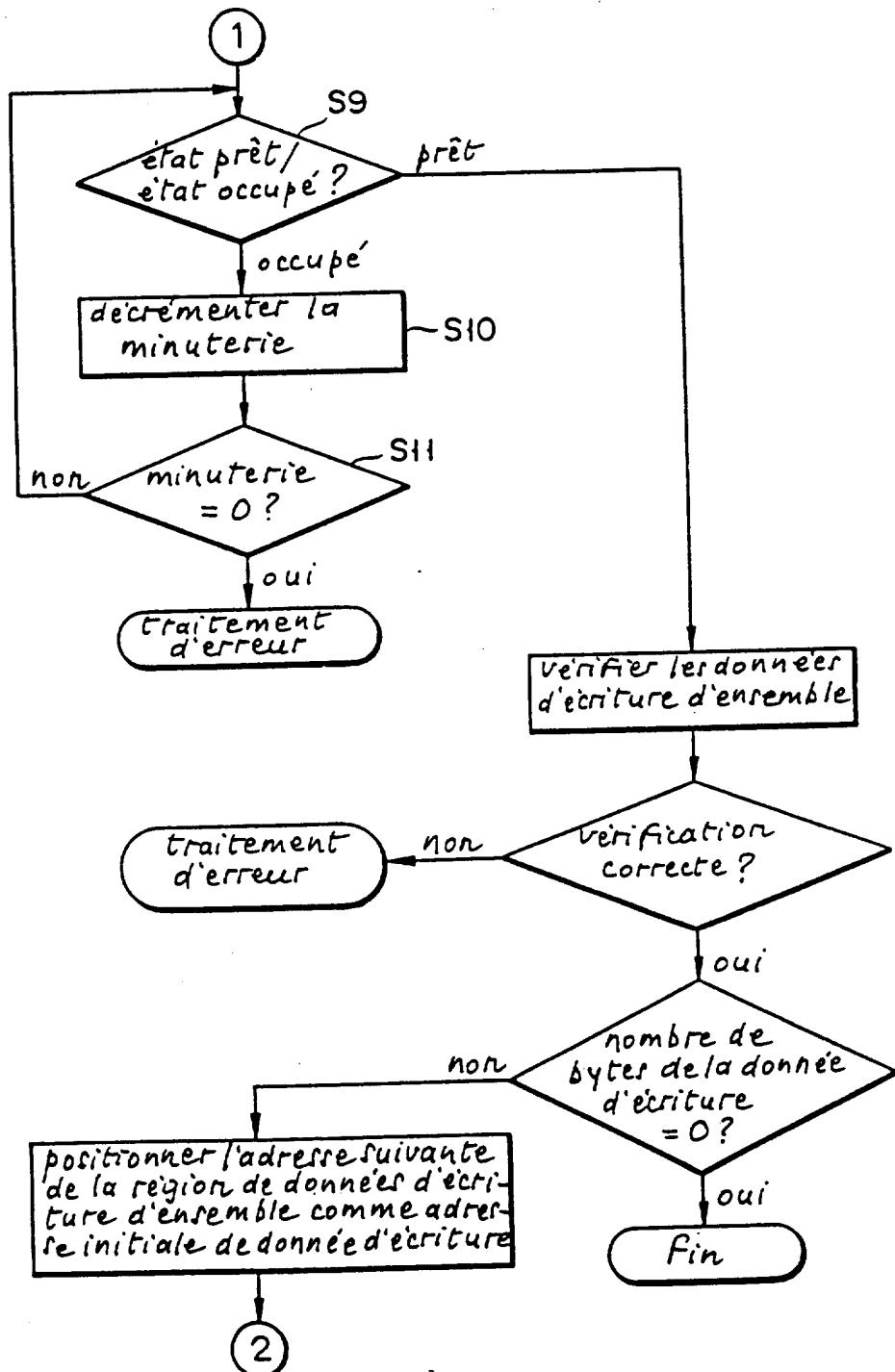

La description suivante, conçue à titre d'illustration de l'invention, vise à donner une meilleure compréhension de ses caractéristiques et avantages ; elle s'appuie sur les dessins annexés, parmi lesquels :

la figure 1 est un schéma de principe montrant une configuration d'un dispositif permettant d'écrire des données dans une mémoire semiconductrice selon un mode de réalisation de la présente invention ; et

les figures 2A et 2B sont des organigrammes illustrant l'opération d'écriture de données effectuée par le dispositif de l'invention.

Sur la figure 1, est représenté un schéma de principe qui montre une configuration d'un dispositif permettant d'écrire des données selon un mode de réalisation de l'invention. Ce mode de réalisation présente la configuration d'un système à micro-ordinateur, par exemple une carte à circuit intégré utilisant une unité centrale de traitement (CPU) du type Z80, que produit la société ZILOG. Sur cette figure, le numéro de référence 1 désigne une CPU, 2 une EEPROM servant à emmagasiner diverses données, 3 une mémoire morte ROM, (par exemple une ROM à masque) dans laquelle un programme d'exploitation de la CPU 1 est emmagasiné, et 4 une mémoire vive (RAM) servant de mémoire de travail pendant le fonctionnement de la CPU 1. Les mémoires 2, 3 et 4 sont disposées sur une carte mémoire de la CPU 1. Comme on peut le voir sur la figure 1, la CPU 1, la EEPROM 2, la ROM 3 et la RAM 4 sont connectées entre elles par un bus d'adresses de 16 bits 5 et un bus de données de 8 bits 6. La CPU 1 est connectée à un décodeur 7 par

l'intermédiaire du bus d'adresses 5. Le décodeur 7 reçoit les données d'adresses A00 à A15 et un signal de demande de mémoire MREQ de la part de la CPU 1 afin de produire un signal de validation de puce CE. Le signal de validation de puce CE est fourni aux mémoires 2, 3 et 4.

05 La EEPROM 2 délivre, sur sa borne R/B, un signal d'opération d'écriture interne, c'est-à-dire un signal d'état prêt/état occupé (R/B), comme signal d'état. Le signal R/B est fourni à une borne d'entrée d'une porte à trois états 8. La porte à trois états 8 est commandée par le signal de sortie d'un circuit OU 9, qui reçoit un signal de demande d'entrée/sortie IORQ et un signal d'impulsion de lecture RD de la part de la CPU 1. Le signal d'impulsion de lecture RD est également fourni à la EEPROM 2, la ROM 3 et la RAM 4, sur leurs entrées OE. La porte à trois états 8 passe de l'état non conducteur à l'état conducteur dans le seul cas où les deux signaux IORQ et RD venant de la CPU 1 prennent un niveau bas et la porte 8 transmet le signal R/B fourni à sa borne d'entrée au bit zéro du bus de données 6. La CPU 1 fournit un signal d'écriture WR aux bornes de validation d'écriture WE de la EEPROM 2 et de la RAM 4.

10 On va maintenant décrire, en relation avec les organigrammes des figures 2A et 2B le processus au cours duquel la CPU 1 lit une rangée de données de la RAM 4 et l'écrit dans la EEPROM 2. Une technique de pagination est utilisée comme système de gestion 15 de mémoire pour la EEPROM 2. Sur la figure 2A, des données d'écriture sont fournies par la RAM 4 à la EEPROM 2 via le bus de données 6 (étape S0). L'adresse initiale (adresse initiale d'écriture) d'une région de mémorisation de la EEPROM 2 pour laquelle a été faite une demande d'écriture est soustraite de 20 l'adresse initiale de la page faisant suite à la page à laquelle la première adresse initiale appartient, et le résultat de la soustraction est conservé sous la forme "RESULTAT 1" (état S1). Si l'on suppose que la EEPROM 2 utilisée dans le présent mode de réalisation est du type à 32 bytes/page, "RESULTAT 1" est calculé 25 de la manière suivante. Si l'adresse initiale d'écriture de la page est \$A000, l'adresse initiale de la page suivante est \$A020 et, par

conséquent, "RESULTAT 1" est 32 bytes. En outre, si l'adresse initiale de la page est \$AO82, l'adresse initiale de la page suivante est \$AOA0 et, par conséquent, "RESULTAT 1" est 30 bytes.

05 Du "nombre de bytes" des données d'écriture situées dans une rangée de données de la RAM 4 qui doivent être écrites dans la EEPROM 2, on soustrait le nombre de bytes de "RESULTAT 1" et, alors, on emmagasine le résultat de la soustraction sous la forme "RESULTAT 2" (étape S2). Si "RESULTAT 2" est nul ou négatif (étape S3), on utilise le "nombre de bytes" des données d'écriture comme 10 nombre de bytes des données d'écriture d'ensemble (étape S4). Si "RESULTAT 2" n'est ni nul, ni négatif, on utilise le "RESULTAT 2" lui-même comme nombre de bytes des données d'écriture d'ensemble (étape S5).

15 A l'étape S6, on soustrait du nombre de bytes des données d'écriture le nombre de bytes des données d'écriture d'ensemble utilisé à l'étape S4 ou S5, et le résultat de la soustraction est conservé comme nouveau nombre de bytes des données d'écriture. A l'étape S7, une minuterie est prépositionnée sur une durée prédéterminée en fonction du nombre de bytes des 20 données d'écriture. A l'étape S8, les données correspondant au nombre de bytes des données d'écriture d'ensemble sont écrites en séquence à partir de l'adresse initiale des données d'écriture dans la EEPROM 2 par une procédure d'écriture de pages.

25 A l'étape S9 de la figure 2B, si le bit le moins significatif (LSB) des données obtenues par une instruction d'entrée d'espace d'entrée/sortie (I/O) est dans l'état prêt "1", l'opération d'écriture de données est arrivée à son terme et, par conséquent, l'organigramme passe à l'étape S12. Si le bit le moins significatif est dans un état occupé "0", l'opération d'écriture de données n'est pas arrivée à son terme, si bien que la minuterie est décrémentée (étape S10), et il est ensuite confirmé si la minuterie est positionnée ou non à "0" (étape S11). Si la minuterie n'est pas positionnée à "0", l'organigramme revient à l'étape S9. Si la minuterie est positionnée à "0", l'opération d'écriture ne s'est 30 pas terminée dans les limites d'une durée prédéterminée, et le signal (R/B) d'opération d'écriture interne de la EEPROM 2 n'est 35

pas passé de l'état occupé à l'état prêt. On effectue donc le traitement d'erreur.

A l'étape S12, on vérifie les données à l'aide de l'adresse initiale des données d'écriture, du nombre de bytes des données d'écriture d'ensemble, et de la rangée des données d'écriture, qui ont été traités à l'étape S8 antérieure. Si le résultat de la vérification est négatif (étape S13), alors on effectue le traitement d'erreur. Si le résultat de la vérification est positif (étape S13), il est déterminé si le nombre de bytes qui ont été remis à jour à l'étape précédente S6 est ou non "0" (étape S14). Si le nombre de bytes est "0", l'opération d'écriture est arrivée à son terme. Si ce n'est pas "0", l'adresse suivante de la région courante des données d'écriture d'ensemble est alors positionnée comme adresse initiale des données d'écriture (étape S15), puis l'organigramme revient à l'étape S1 de la figure 2A.

Selon l'invention, non seulement on contrôle l'arrivée à son terme de l'opération d'écriture de données à l'aide du signal R/B, c'est-à-dire un signal d'état qui est délivré par la EEPROM 2 et représente la fin de l'opération d'écriture de données, mais on contrôle également, à l'aide de la minuterie, la durée nécessaire pourachever l'opération d'écriture de données. Même lorsqu'une défaillance de la EEPROM 2 se produit et que, par conséquent, le signal R/B continue de rester dans un état occupé, on peut mettre fin à l'opération d'écriture et on peut parfaitement empêcher l'arrêt inopiné du système utilisant la EEPROM 2.

Dans le mode de réalisation ci-dessus, on utilise la EEPROM 2, où le signal R/B est délivré par la borne R/B. Toutefois, par exemple, on peut utiliser une EEPROM employant un système d'appel de données. Alors qu'une minuterie d'un type logiciel est réalisée à l'étape S10 de l'organigramme ci-dessus, cette même fonction pourrait être exécutée par une minuterie 1a de type réel représentée sur la figure 1. Dans ce cas, la minuterie concrète 1a démarre à l'instant où l'opération d'écriture de données commence, à l'étape S8. En ce qui concerne le traitement d'erreurs intervenant après que la minuterie a été positionnée par "0" à l'étape

S11, il est souhaitable de passer de l'état occupé à l'état prêt par un procédé propre au type particulier de la EEPROM 2.

05 Comme décrit en détail, selon l'invention, on peut produire un procédé d'écriture de données dans une mémoire semi-conductrice où l'opération d'écriture de données peut prendre fin même lorsqu'une défaillance de la mémoire se produit, et, par conséquent, on peut parfaitement empêcher l'arrêt inopiné du système utilisant la mémoire.

10 Bien entendu, l'homme de l'art sera en mesure d'imaginer, à partir du procédé et du dispositif dont la description vient d'être donnée à titre simplement illustratif et nullement limitatif, diverses variantes et modifications ne sortant pas du cadre de l'invention.

REVENDICATIONS

1. Procédé d'écriture de données, à partir d'un premier moyen (4) servant à fournir les données, dans un moyen de mémorisation (2) servant à emmagasiner les données, caractérisé en ce qu'il comprend les opérations suivantes :

- recevoir (S0) les données en provenance du premier moyen (4) ;

- écrire (S8) les données dans le moyen de mémorisation (2) en réponse à l'opération de réception (S0) ;

- compter (S10) le temps en réponse à l'opération d'écriture (S8) ;

- comparer (S11) le temps compté dans l'opération de comptage (S10) avec un temps prédéterminé ; et

- donner, en réponse au résultat comparé par l'opération de comparaison (S11), l'information (S9) selon laquelle l'opération d'écriture (S8) est arrivée à son terme.

2. Procédé selon la revendication 1, caractérisé en ce qu'il comprend en outre l'opération consistant à déterminer (S6) la quantité de données devant être écrites dans le moyen de mémorisation (2).

3. Procédé selon la revendication 2, caractérisé en ce qu'il comprend en outre l'opération consistant à fixer (S7) le temps prédéterminé en réponse à la quantité de données prédéterminées dans l'opération de détermination (S6).

4. Procédé selon la revendication 1, caractérisé en ce que l'opération d'information comprend l'opération consistant à délivrer un signal d'erreur lorsque le temps compté dans l'opération de comptage (S10) est plus long que le temps prédéterminé de l'opération de comparaison (S11).

5. Dispositif d'écriture de données dans un moyen de mémorisation (2) servant à emmagasiner les données, ledit dispositif étant caractérisé en ce qu'il comprend :

- un moyen (S0) servant à fournir les données au moyen de mémorisation (2) ;

un moyen (S8) servant à écrire dans le moyen de mémorisation (2) les données fournies par le moyen de fourniture (S0) ;

un moyen (S7) servant à indiquer un temps de début lorsque le moyen d'écriture (S8) commence à écrire les données dans

05 le moyen de mémorisation (2) ;

un moyen (1a ; S10 ; S11) servant à compter le temps en réponse au temps de début indiqué par le moyen d'indication (S7) ;

un moyen (S11) servant à comparer le temps compté par le moyen de comptage (1a ; S10 ; S11) avec un temps prédéterminé ; et

10 un moyen (S9) servant à délivrer une information de fin d'écriture indiquant la fin d'une opération d'écriture du moyen d'écriture (S8) en réponse au résultat comparé par le moyen de comparaison (S11).

2647582

FIG. 1

FIG. 2A

3/3

FIG. 2B