(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4008776号

(P4008776)

(45) 発行日 平成19年11月14日(2007.11.14)

(24) 登録日 平成19年9月7日(2007.9.7)

(51) Int.C1.

F 1

|                        |             |      |

|------------------------|-------------|------|

| HO3K 19/0175 (2006.01) | HO3K 19/00  | 101Q |

| HO3K 17/687 (2006.01)  | HO3K 19/00  | 101F |

| HO3K 17/693 (2006.01)  | HO3K 17/687 | F    |

|                        | HO3K 17/693 | A    |

請求項の数 10 (全 22 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2002-218315 (P2002-218315) |

| (22) 出願日     | 平成14年7月26日 (2002.7.26)       |

| (65) 公開番号    | 特開2003-69416 (P2003-69416A)  |

| (43) 公開日     | 平成15年3月7日 (2003.3.7)         |

| 審査請求日        | 平成17年7月19日 (2005.7.19)       |

| (31) 優先権主張番号 | 09/921,025                   |

| (32) 優先日     | 平成13年8月2日 (2001.8.2)         |

| (33) 優先権主張国  | 米国(US)                       |

|           |                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 506076606<br>アバゴ・テクノロジーズ・ジェネラル・ア<br>イピー(シンガポール)プライベート・リ<br>ミテッド<br>シンガポール国シンガポール768923<br>,イーション・アベニュー・7・ナンバー<br>1 |

| (74) 代理人  | 110000246<br>特許業務法人才カダ・フシミ・ヒラノ                                                                                     |

| (74) 代理人  | 100087642<br>弁理士 古谷 聰                                                                                              |

| (74) 代理人  | 100076680<br>弁理士 溝部 孝彦                                                                                             |

| (74) 代理人  | 100121061<br>弁理士 西山 清春                                                                                             |

最終頁に続く

(54) 【発明の名称】出力ドライバ回路の出力インピーダンスを可変に調整する方法

## (57) 【特許請求の範囲】

## 【請求項1】

ノード上へ信号を駆動するよう構成された出力ドライバ回路の出力インピーダンスを、出力ドライバ制御回路を用いて可変に調整する方法であって、該出力ドライバ制御回路は、複数の抵抗性デバイスを備えており、該抵抗性デバイスのそれぞれは、第1の電源(VDD)および前記ノード(104)の間にプログラム可能なように電気的に並列接続可能であり、該方法は、

前記第1の電源と前記ノードとの間の第1の組の抵抗性デバイス(121)の電気的接続を、2進増分的な方法でプログラムするステップと、

前記第1の組における前記抵抗性デバイスのすべてがイネーブルされた時だけ、前記第1の電源と前記ノードとの間の第2の組の抵抗性デバイス(122)の電気的接続を、2進増分的な方法でプログラムするステップと、

を含む方法。

## 【請求項2】

先にプログラムされた前記第1および第2の組(121, 122)における抵抗性デバイスのすべてがイネーブルされたときだけ、前記第1の電源と前記ノードとの間に、抵抗性デバイスの1以上の追加の組(123)の電気的な接続を、2進増分的な方法でプログラムするステップを含む、

請求項1に記載の方法。

## 【請求項3】

10

20

前記第1の電源と前記ノードとの間に、前記複数の抵抗性デバイスのうちの少なくとも1つ(120, 236, 238)を、常時電気的に接続するステップをさらに含む、

請求項1または2に記載の方法。

【請求項4】

信号をノード上へ駆動するよう構成された可変インピーダンス出力ドライバ回路のための制御回路であって、

第1の電源(VDD)と前記ノードとの間に、プログラム可能なように電気的に接続可能な第1の組の抵抗性デバイスと、

前記第1の電源と前記ノードとの間に、プログラム可能なように電気的に接続可能な第2の組の抵抗性デバイスと、

前記第1の電源と前記ノードとの間の前記第1の組の抵抗性デバイスの電気的接続を、2進増分的な方法でプログラムし、前記第1組の前記抵抗性デバイスのすべてが前記第1の電源と前記ノードとの間に電気的に接続された時だけ、前記第1の電源と前記ノードとの間の前記第2の組の抵抗性デバイスの電気的接続を、2進増分的な方法でプログラムするコントローラと、

を備える、制御回路。

【請求項5】

前記第1の電源と前記ノードとの間に、プログラム可能なように電気的に接続可能な抵抗性デバイスの1以上の追加の組をさらに備え、

先にプログラムされた前記第1および第2の組の前記抵抗性デバイスのすべてが、前記第1の電源と前記ノードとの間に電気的に接続された時だけ、前記コントローラは、前記第1の電源と前記ノードとの間の前記抵抗性デバイスの1以上の追加の組のうちの少なくとも1つの電気的な接続を、2進増分的な方法でプログラムする、

請求項4に記載の制御回路。

【請求項6】

少なくとも1つの抵抗性デバイスは、前記第1の電源と前記ノードとの間に常時電気的に接続される、

請求項4または5に記載の制御回路。

【請求項7】

前記第1の組における抵抗性デバイスは、抵抗のバイナリ加重された符号を実現する、

請求項4から6のいずれかに記載された制御回路。

【請求項8】

前記第2の組における抵抗性デバイスは、抵抗のバイナリ加重された符号を実現する、

請求項4から7のいずれかに記載された制御回路。

【請求項9】

前記1以上の追加の組の少なくとも1つにおける抵抗性デバイスは、抵抗のバイナリ加重された符号を実現する、

請求項5から8のいずれかに記載された制御回路。

【請求項10】

前記第1の組、前記第2の組、前記1以上の追加の組のそれぞれにおける前記抵抗性デバイスは、電界効果トランジスタを含む、

請求項5から9のいずれかに記載された制御回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、一般に、集積回路の可変インピーダンス出力ドライバに関し、より具体的には、製造のプロセス、電圧および温度における変動に起因する集積回路出力ドライバの出力インピーダンスを制御するバイナリ加重温度符号に関する。

【0002】

【従来の技術】

集積回路は、一般にチップとしてパッケージ化される。チップ内の集積回路は、信号パッドとして知られているチップの外側にあるメタライゼーション層を介してチップの外界と通信する。チップパッケージ内の集積回路がチップ外に信号を送るため、「ドライバ回路」は、チップの外側にある信号パッド上に信号を駆動する。様々なチップの信号パッドが、信号線として知られる伝送線によって一緒に接続され、これにより、異なるチップ間の通信が可能になる。

#### 【0003】

チップ上の信号パッドは、チップのパッケージ（例えば、ピン）に接続されており、該チップのパッケージは、別の集積回路または電子デバイスに通ずる印刷回路基板上の信号トレースに接続される。チップパッケージを介した信号トレースへの信号パッドの電気的な接続は、信号パッドからの信号伝送を妨げる寄生抵抗、寄生インダクタンス、および寄生容量により特徴付けられる。寄生抵抗、寄生インダクタンス、および寄生容量を含む印刷回路基板の信号トレース自体の伝送線路特性もまた、信号パッドからの信号伝送品質を妨げる。前述のすべてが、出力ドライバ回路によって駆動されなければならない負荷インピーダンスに加わる。

#### 【0004】

チップ間の信号相互接続に現れる寄生抵抗、寄生容量、および寄生インダクタンスに起因して、これらの信号相互接続を駆動するドライバ回路は、（特に高速、または低消費電力I/Oのために）切り換えを行なったとき、過大な電圧振幅（voltage swing）を避けるよう設計されるのが望ましい。過大な電圧振幅は、リング（ringing）として知られている。現代の集積回路の高速な性能要件を満たすため、できる限り高速に切り換えつつ、リングを避けなければならない。

#### 【0005】

当業者には知られていることであるが、パッド上の電圧レベル切り換えに起因する信号反射、およびそれによる不所望な信号劣化を回避するため、所与の信号ドライバの出力インピーダンスを、それが駆動する伝送線路の特性インピーダンスに整合させることが重要である。

#### 【0006】

出力ドライバのインピーダンスを信号伝送線路の特性インピーダンスに整合させることは、いくつかの理由で問題がある。先ず、トランジスタの注入ドーピングレベル、電界効果トランジスタ（FET）のチャネルの実効長、トランジスタのゲート酸化物の厚み、および拡散抵抗のような、製造プロセスに固有のプロセス変量が、2つの同一であるべき回路の出力インピーダンスを異なるものとさせることができる。特に、上記のプロセスパラメータのいくつか、またはすべてにおける変動により、同一機能を実行するよう意図された異なる集積回路を、「低速」、「公称」、または「高速」に分類することができる。換言すれば、2つの同一であるべき集積回路は、プロセスパラメータのいくつか、またはすべてにおいて変動するおそれがある。これらのパラメータが上記の高速ケースに近づくと、チップ内の多数のコンポーネントの抵抗が低下する。それとは反対に、プロセスパラメータが理想的なケースから逸脱すればするほど、チップ性能は劣化し、特にチップ内の多数のコンポーネントの抵抗は増大する。この状況は、「低速」ケースと呼ばれる。

#### 【0007】

さらに、電圧および温度の変動により、所与のチップの出力インピーダンスに変動が生じることがある。具体的には、ドライバの出力インピーダンスは、小さい動作電圧の許容範囲内でさえ、動作電圧における変動間で著しく変化することがある。他の例では、集積回路の温度がその最大動作温度に近づくと、該集積回路のコンポーネントの抵抗が増加する。

#### 【0008】

上記を考慮して、可変インピーダンス出力ドライバが開発され、製造プロセス、電圧、および温度における変動に起因するドライバ出力インピーダンスの調整が可能となった。

#### 【0009】

10

20

20

30

40

50

集積回路のための出力パッドのインピーダンス整合を達成する一つの従来技術が、E s c h, J r. に対するもので、本譲受人に譲渡された「デジタル的に制御された出力ドライバとインピーダンス整合方法 (Digitally Controlled Output Driver and Method for Impedance Matching)」と題する米国特許第6,118,310号に記載されており、これを、ここで参照のために取り入れる。ここに記載された技術では、出力ドライバのインピーダンス整合は、その合成インピーダンスが伝送線路の特性インピーダンスに密接に整合するよう並列に配置されたF E Tの組み合わせを、プログラム可能なようにイネーブルすることによって達成される。

#### 【0010】

このような従来技術の可変インピーダンス出力ドライバは、P V T制御符号が更新される時に出力インピーダンスの変化を制限するため、P V Tインピーダンス整合制御のための純温度符号 (pure thermometer code) を一般に使用する。特に、インピーダンス回路は「温度 (thermometer)」符号を実現し、これにより、第n位の信号W<sub>n</sub>が起動された(「1」にセットされた)時に、すべての低位の信号W<sub>1</sub> ~ W<sub>n-1</sub>もまた起動される。純温度符号インピーダンス整合回路では、第1のF E Tの脚 (leg) が起動され、所望の出力インピーダンスが達成されるまで、後続のそれぞれのF E Tの脚が起動される。従って、少なくとも1つの脚が常時起動され、F E Tの脚のオンオフの切り換え期間中、出力インピーダンスにスパイクをもたらすようなF E Tの脚の全導通状態から全非導通状態への切り換え、またはその逆を招かぬよう保証している。表1は、11ビットの純温度符号を例示しており、ここで、符号語Wの各ビット0 : : 10は、10%のインクリメンタルなアドミタンス・ステップを表わしている。

#### 【0011】

##### 【表1】

| W <sub>0</sub> | W <sub>1</sub> | W <sub>2</sub> | W <sub>3</sub> | W <sub>4</sub> | W <sub>5</sub> | W <sub>6</sub> | W <sub>7</sub> | W <sub>8</sub> | W <sub>9</sub> | W <sub>10</sub> | アドミタンス (Y=1/Z) | インピーダンス (Z) |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|-------------|

| 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0               | 1              | 1           |

| 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0               | 1 + .1         | .909        |

| 1              | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0               | 1 + .2         | .833        |

| 1              | 1              | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0               | 1 + .3         | .769        |

| 1              | 1              | 1              | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0               | 1 + .4         | .714        |

| 1              | 1              | 1              | 1              | 1              | 1              | 0              | 0              | 0              | 0              | 0               | 1 + .5         | .667        |

| 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 0              | 0              | 0               | 1 + .6         | .625        |

| 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 0              | 0               | 1 + .7         | .588        |

| 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 0               | 1 + .8         | .555        |

| 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1               | 1 + .9         | .526        |

#### 【0012】

表1の温度符号の例に示したように、出力インピーダンスの感度の制御可能範囲は、インピーダンスが1から0.526の間に制限されている。ここで、各ステップごとにアドミタンスが0.1すなわち10%だけ変化する。また、表1に例示したように、純温度符号は、各ステップごとに1ビットを必要とする。従って、純温度符号の一つの欠点は、出力インピーダンスの大きい範囲を可能とするのに多数のビット(よって、制御線)が必要とされることである。必要なステップ感度の程度の増加に伴い、制御線の数は指数的に増加する。例えば、各ステップの感度を増やすために、アドミタンスを1%ずつステップさせるのが望ましい場合、P V T制御回路は、101本の制御線、すなわちそれを10%に調整するのに必要なライン数の10倍を必要とするであろう。代替的に、調整可能な出力インピーダンスの範囲を、1から0.25に増大させることが望まれる場合、各ステップが10%だけアドミタンスを変更する表1の例では、20ビット(制御線)を追加する必要

10

20

30

40

50

があるであろう。

【0013】

従って、PVT出力インピーダンスを調整するためには感度範囲を増やすのが望ましいが、純温度符号を用いて何らかの大きな感度範囲を実現するのに必要なビット数は、それを実現するのに必要な追加される複雑な設計およびチップ実面積によってさらに問題となる。

【0014】

純温度符号に固有の課題に対する代替的な解決策は、純バイナリ加重符号 (pure binary weighted code) の使用であり、これにより、PVT制御回路のそれぞれの脚は、そのバイナリ加重ビット位置の組合せに対応するアドミタンスを有する抵抗性デバイス (resistive device) を備える。換言すれば、それぞれの脚は  $2^{(\text{ビット位置})} Y$  のアドミタンスを有し、ここで  $Y$  は、設計に適した予め定義された最小アドミタンスを表わす。バイナリ加重符号によれば、ビット 0 の較正ワードがアドミタンス  $Y$  を有する FET を制御するならば、ビット 1 の較正ワードはアドミタンス  $2^1 Y$  を有する FET を制御し、ビット 2 の較正ワードはアドミタンス  $2^2 Y$  を有する FET を制御し、等々となる。実際、較正ワードのバイナリカウントがインクリメントするにつれ、より多くの抵抗がドライバ FET アレイ内に並列に加えられ、出力インピーダンス  $Z_{out}$  は低下する。表 2 は、バイナリ加重符号の一例を例示する。

【0015】

【表 2】

| $W_0$ | $W_1$ | $W_2$ | $W_3$ | アドミタンス ( $Y=1/Z$ ) | インピーダンス ( $Z$ ) |

|-------|-------|-------|-------|--------------------|-----------------|

| 0     | 0     | 0     | 0     | 0                  | 無限              |

| 1     | 0     | 0     | 0     | 0. 1               | 10              |

| 0     | 1     | 0     | 0     | 0. 2               | 5               |

| 1     | 1     | 0     | 0     | 0. 3               | 3. 333          |

| 0     | 0     | 1     | 0     | 0. 4               | 2. 5            |

| 1     | 0     | 1     | 0     | 0. 5               | 2               |

| 0     | 1     | 1     | 0     | 0. 6               | 1. 667          |

| 1     | 1     | 1     | 0     | 0. 7               | 1. 429          |

| 0     | 0     | 0     | 1     | 0. 8               | 1. 25           |

| 1     | 0     | 0     | 1     | 0. 9               | 1. 111          |

| 0     | 1     | 0     | 1     | 1. 0               | 1               |

| 1     | 1     | 0     | 1     | 1. 1               | 0. 909          |

| 0     | 0     | 1     | 1     | 1. 2               | 0. 833          |

| 1     | 0     | 1     | 1     | 1. 3               | 0. 769          |

| 0     | 1     | 1     | 1     | 1. 4               | 0. 714          |

| 1     | 1     | 1     | 1     | 1. 5               | 0. 667          |

10

20

30

40

【0016】

表 2 に示されるように、バイナリ加重符号を使用する利点は、より少ないビット (すなわち PVT 制御線) を用いてより大きな出力インピーダンス範囲を獲得するその能力である。しかしながら、純バイナリ加重符号において、ステップ状のインクリメントは、現在起動されているすべての脚が次のステップで起動されたままであることを保証しない。例えば、現在のバイナリ加重較正符号が二進 1110 (0.7 のアドミタンスに対応) であり、該符号が、二進 0001 (0.8 のアドミタンス値に対応) にインクリメントされることになっていると仮定する。電気的接続を 1110 から 0001 に切り替えたとき、非常に短い時間間隔にわたり、(PVT 符号の 1111 または 0000 にそれぞれ対応して)

50

すべての F E T が非導通であるか、またはすべての F E T が導通するような状態にスイッチが陥ることがある。これにより、信号パッド上に見られる出力インピーダンスに、不所望なスパイクを招くことがある。(本例では、表 2 によれば、出力インピーダンスが一時的に  $Z_{o_{UT}} = 1.429$  (アドミタンス 0.7 に対応) から  $Z_{o_{UT}} = 0.667$  (アドミタンス 1.5 (すべて「1」) に対応) へ、または  $Z_{o_{UT}} = 1.429$  (アドミタンス 0.7 に対応) から  $Z_{o_{UT}} = \infty$  (アドミタンス 1.5 (すべて「0」) に対応) へ変化することが起こり得る。

#### 【0017】

##### 【発明が解決しようとする課題】

従って、信号パッド上の出力インピーダンスにおけるスパイクを防止しつつ、より少ない制御線でより高い出力インピーダンス範囲を可能にする P V T 制御符号化技術の必要性が存在する。

#### 【0018】

##### 【課題を解決するための手段】

本発明は、出力ドライバの出力インピーダンスを調整する時に、バイナリ加重温度符号を使用して、機能的に同一の複数のチップにわたり、プロセス、電圧、および温度を考慮する新規な可変インピーダンス出力ドライバ制御回路および該回路のプログラミングする方法である。本発明の符号化体系は、信号パッド上の出力インピーダンスにおけるスパイクを防止しつつ、最小数の P V T 制御線で広範囲の感度を達成する。

#### 【0019】

本発明の一実施形態によれば、バイナリ加重温度符号は、出力ドライバ回路の出力インピーダンスを可変に調整するために、可変インピーダンス出力ドライバ制御回路において使用される。可変インピーダンス出力ドライバ制御回路は、複数の抵抗性デバイスで構成され、それぞれのデバイスは、第 1 の電源と信号パッドとの間に、プログラム可能なように電気的に並列接続ができる。複数の抵抗性デバイスは、複数の組に区分され、それにより、第 1 の電源と信号パッドとの間に第 1 の組における 1 つ以上の抵抗性デバイスを電気的に接続するように、該第 1 の組の抵抗性デバイスを 2 進増分的なやり方 (binary incremental manner) でプログラムすることができる。第 1 の組における抵抗性デバイスのすべてが、第 1 の電源と信号パッドとの間に電気的に接続された後でのみ、第 1 の電源と信号パッドとの間に第 2 の組における 1 つ以上の抵抗性デバイスを電気的に接続するよう、該第 2 の組の抵抗性デバイスを 2 進増分的なやり方でプログラムすることができる。抵抗性デバイスの追加の組を同様にプログラムすることができ、これにより、先にプログラムされた組における抵抗性デバイスのすべてが、第 1 の電源と信号パッドとの間に電気的に接続された後でのみ、第 1 の電源および信号パッドの間に追加の組における 1 以上の抵抗性デバイスが電気的に接続されるよう、該追加の組の抵抗性デバイスを 2 進増分的なやり方でプログラムすることができる。抵抗性デバイスのうちの少なくとも 1 つを、第 1 の電源と信号パッドとの間に常時電気的に接続し、信号パッド上の出力インピーダンスのスパイクを防ぐことが好ましい。さらに、抵抗性デバイスのそれぞれの組が純バイナリ加重符号を実現し、それぞれの組内において出力インピーダンス範囲を増大させるのが好ましい。

#### 【0020】

本発明の他の実施形態によれば、可変インピーダンス出力ドライバ回路のための制御回路は、第 1 の電源と信号パッドとの間でプログラム可能なように電気的に接続可能な第 1 の組の抵抗性デバイスと、第 1 の電源と信号パッドとの間でプログラム可能なように電気的に接続可能な第 2 の組の抵抗性デバイスと、コントローラとを含む。該コントローラは、第 1 の電源と信号パッドとの間ににおける第 1 の組の抵抗性デバイスの電気的接続を、2 進増分的なやり方でプログラムし、該第 1 の組における抵抗性デバイスのすべてが、第 1 の電源と信号パッドとの間に電気的に接続された時にのみ、第 1 の電源と信号パッドとの間ににおける第 2 の組の抵抗性デバイスの電気的接続を、2 進増分的なやり方でプログラムする。制御回路は、第 1 の電源と信号パッドとの間でプログラム可能なように電気的に接続

10

20

30

40

50

可能な抵抗性デバイスの1つ以上の追加の組を含むことができる。それにより、先にプログラムされた組のすべてにおける抵抗性デバイスのすべてが、第1の電源と信号パッドとの間で電気的に接続された場合にだけ、コントローラは、第1の電源と信号パッドとの間の抵抗性デバイスの追加の組のそれぞれを、2進増分的なやり方でプログラムすることができる。制御回路は、第1の電源と信号パッドとの間に電気的に常時接続される少なくとも1つの抵抗性デバイスを含むのが好ましい。好ましい実施形態では、抵抗性デバイスは、電界効果トランジスタ(FET)によって実現され、抵抗性デバイスのそれぞれの組は、抵抗のバイナリ加重された符号を実現する。

【0021】

【発明の実施の形態】

本発明は、図面と併せ以下の詳細な説明を通読することで、より良く理解されよう。図面中、同一の参照符号は同一要素を表わすのに用いられる。

【0022】

可変インピーダンス出力ドライバ制御回路の感度範囲を増やす新規な方法およびシステムを、以下に詳述する。本発明は特定の例示実施形態について説明するが、例示の実施形態は例として示しただけであり、本発明の範囲がそれにより制限されることを目的としないことは理解されたい。

【0023】

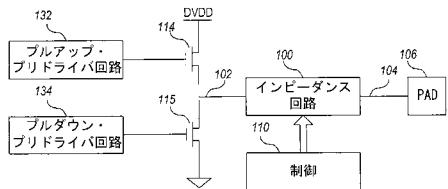

図1を参照すると、制御可能な可変出力インピーダンスを有するドライバ回路を例示するブロック図が示されている。より具体的には、ドライバ回路は、プルアップ・プリドライバ回路132およびプルダウン・プリドライバ回路134を含む。知られているように、プルアップ・プリドライバ回路132は、出力値をロー状態からハイ状態に(例えば論理ゼロから論理1に)駆動するよう動作し、プルダウン・プリドライバ回路134は、出力値をハイ状態からロー状態まで駆動するよう動作する。NFE114, 115は、プルアップ・プリドライバ回路132およびプルダウン・プリドライバ回路134の出力によってそれぞれ駆動される。ドライバ回路の出力は、NEET114のドレインおよびNFE115のソースの間の電気的接点である線102上に現われる値である。図2と関連してさらに説明されるように、インピーダンス回路100は、信号線102およびドライバパッド106の間に介在する。インピーダンス回路100は、制御可能な可変インピーダンスを提供し、これが、基板トレースのインピーダンスを整合させるよう、ドライバ回路の出力インピーダンスを変更する役割を果たす。インピーダンス回路100によって提供されるインピーダンスは、制御回路110によって制御される。インピーダンス回路100の出力は、導線104を介してドライバパッド106へ転送される。

【0024】

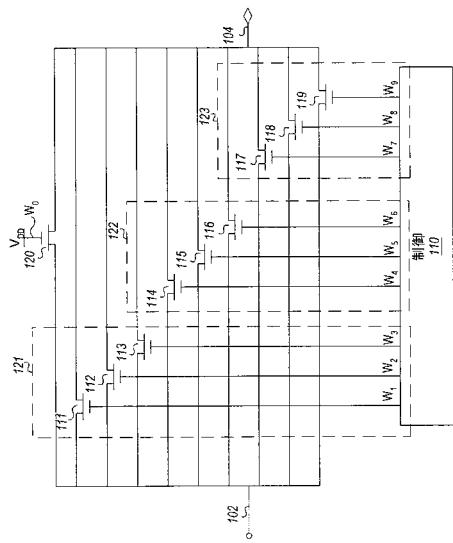

ここで、インピーダンス回路100の構造および動作をより詳しく説明するため、図2を参照すると、この回路がより詳細に示されている。具体的には、インピーダンス回路100は、信号線102, 104および制御回路110に関して示されている。インピーダンス回路は、線102と線104との間に電気的に並列に接続される複数の抵抗性デバイス111～120を含む。好ましい実施形態において、抵抗性デバイス111～120は、電界効果トランジスタ(FET)で実現されるが、スイッチと直列の抵抗器のような他のコンポーネントを用いて実現されることもできる。好ましい実施形態において、FET111～120のそれぞれは、そのFETデバイスのアドミタンスを規定するチャネル幅によって規定される。起動された時(すなわち、導通されて通電した時)、それぞれのFETは、線102と線104との間に電気的接続を提供し、それによって電流が流れることを可能にし、インピーダンス回路の合成並列抵抗の一因となるようになる。FETデバイス111～120のうちの一つ以上が導通すると、それらは抵抗器のように動作し、並列に組み合わさせて、より低い抵抗をもたらす。このようにして、ドライバ回路の出力インピーダンスを変化させることができる。

【0025】

本発明によれば、抵抗性デバイス111～119は、複数の組121, 122, 123に

10

20

30

40

50

区分される。図 2 の実施形態において、組 121 は、抵抗性デバイス 111, 112, 113 を含み、組 122 は、抵抗性デバイス 114, 115, 116 を含み、組 123 は、抵抗性デバイス 117, 118, 119 を含む。好ましくは、それぞれの組 121, 122, 123 内の第 1 の抵抗性デバイス 111, 114, 117 は、それぞれ、先の脚 (leg) のすべての合成アドミタンスの 10 % のアドミタンスにより特徴付けられており、それぞれの組内の抵抗性デバイスは、2 倍に増加したアドミタンス値を有するようにバイナリ加重される。したがって、制御ブロック 110 の総体的な出力は、デジタル較正ワード  $W_{1:\cdot:9}$  として動作し、抵抗性デバイス 111 ~ 119 のうちの選択されたものを起動し、後で図 3 にて説明する方法に従って、ドライバ回路の出力インピーダンスを正確に制御する。好ましい実施形態では、較正ワード  $W$  のビット 1 : : 9 が、対応する FET デバイス 111 ~ 119 のゲート上に駆動される値に対応する。回路すなわち制御ブロック 110 の論理は、プロセス、電圧、および温度 (PVT) に依存するが、ここでは記述する必要はない。インピーダンス回路 100 は、FET デバイスの切り換えの結果として一時に発生することのある信号パッド 106 上に見られる出力インピーダンスのスパイクを防止するため、信号線 102 から信号線 104 に信号が通過することができるよう少なくとも一つの経路 (すなわち、図 2 の抵抗性デバイス 120) が常時起動されるように設計される。

10

#### 【0026】

表 3 は、9 ビットの出力インピーダンス較正ワード  $W$  の本発明に従う典型的なバイナリ加重温度符号を例示する。表 3 におけるそれぞれのビット位置は、それぞれの抵抗性デバイス 111 ~ 119 に対応する。表 3 においてビット位置が「0」として示されるときは、対応する抵抗性デバイスは接続されず、したがって回路の並列抵抗に含まれなくなる。表 3 においてビット位置が「1」として示されるときは、対応する抵抗性デバイスが接続され、したがって回路 100 の合成並列抵抗の一因となる。

20

#### 【0027】

#### 【表 3】

| $W_0$ | $W_1$ | $W_2$ | $W_3$ | $W_4$ | $W_5$ | $W_6$ | $W_7$ | $W_8$ | $W_9$                                 | アドミ<br>タンス<br>( $Y=1/Z$ )             | インピ<br>ーダン<br>ス<br>( $Z$ ) |    |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------------------------|---------------------------------------|----------------------------|----|

| 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                                     |                                       | 1                          |    |

| 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1 + . 1                               | . 9 0 9                               | 10                         |    |

| 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1 + . 2                               | . 8 3 3                               |                            |    |

| 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1 + . 3                               | . 7 6 9                               |                            |    |

| 1     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 1 + . 4                               | . 7 1 4                               |                            |    |

| 1     | 1     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 1 + . 5                               | . 6 6 7                               |                            |    |

| 1     | 0     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 1 + . 6                               | . 6 2 5                               |                            |    |

| 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 1 + . 7<br>= 1 . 7                    | . 5 8 8                               |                            |    |

| 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | (1 + . 7) * 1. 1 =<br>1. 87           | . 5 3 5                               | 20                         |    |

| 1     | 1     | 1     | 1     | 0     | 1     | 0     | 0     | 0     | (1 + . 7) * 1. 2 =<br>2. 04           | . 4 9 0                               |                            |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0     | (1 + . 7) * 1. 3 =<br>2. 21           | . 4 5 2                               |                            |    |

| 1     | 1     | 1     | 1     | 0     | 0     | 1     | 0     | 0     | (1 + . 7) * 1. 4 =<br>2. 38           | . 4 2 0                               |                            |    |

| 1     | 1     | 1     | 1     | 1     | 0     | 1     | 0     | 0     | (1 + . 7) * 1. 5 =<br>2. 55           | . 3 9 2                               |                            |    |

| 1     | 1     | 1     | 1     | 0     | 1     | 1     | 0     | 0     | (1 + . 7) * 1. 6 =<br>2. 72           | . 3 6 7                               |                            |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | (1 + . 7) * 1. 7 =<br>2. 89           | . 3 4 6                               |                            |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | ((1 + . 7) * 1. 7<br>)* 1. 1 = 3. 179 | . 3 1 5                               | 30                         |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 0                                     | ((1 + . 7) * 1. 7<br>)* 1. 2 = 3. 468 | . 2 8 8                    |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0                                     | ((1 + . 7) * 1. 7<br>)* 1. 3 = 3. 757 | . 2 6 6                    |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 1                                     | ((1 + . 7) * 1. 7<br>)* 1. 4 = 4. 046 | . 2 4 7                    |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1                                     | ((1 + . 7) * 1. 7<br>)* 1. 5 = 4. 335 | . 2 3 1                    |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 1                                     | ((1 + . 7) * 1. 7<br>)* 1. 6 = 4. 624 | . 2 1 6                    |    |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1                                     | ((1 + . 7) * 1. 7<br>)* 1. 7 = 4. 913 | . 2 0 4                    | 40 |

## 【0028】

図2に示され、また表3にも例示される本発明の典型的な実施形態は、抵抗性デバイス120を表わすビット $W_0$ が常時起動されている（すなわち、線102と線104との間の電気的接続を提供するよう常時イネーブルされる）。この脚は、低速PVTケースにおける最も高いインピーダンスを規定する。

## 【0029】

また、図2に示される本発明の典型的な実施形態によれば、第1の区分された組121は、ビット $W_1$ 、 $W_2$ 、 $W_3$ により表わされる抵抗性デバイス111、112、113を含

む。第1の抵抗性デバイス111は、アドミタンス $Y_1$ によって特徴付けられ、該アドミタンス $Y_1$ は、ビット $W_0$ により表される抵抗性デバイス120のアドミタンス $Y_0$ の値の10%である。(換言すれば、第1の抵抗性デバイス111は、FET120のインピーダンス $Z_0$ の10倍であるインピーダンス $Z_1$ により特徴付けられる。)第1の組121における抵抗性デバイス111, 112, 113のアドミタンス $Y_1, Y_2, Y_3$ は、バイナリ符号を実現すべく加重され、ここで、抵抗性デバイスFET111は、アドミタンス $Y_1$ を有する大きさとされ、抵抗性デバイスFET112は、アドミタンス $Y_2 = 2^* Y_1$ を有する大きさとされ、抵抗性デバイスFET113は、アドミタンス $Y_3 = 4^* Y_1$ を有する大きさとされる。

## 【0030】

第2の区分された組122は、ビット $W_4, W_5, W_6$ で表される抵抗性デバイス114, 115, 116を含む。組122における第1の抵抗性デバイス114は、前述のビット位置 $W_0, W_1, W_2, W_3$ により表わされる抵抗性デバイス120, 111, 112, 113の合成アドミタンス $Y_0, Y_1, Y_2, Y_3$ の値の10%であるアドミタンス $Y_4$ によって特徴付けられる。第2の組122における抵抗性デバイス114, 115, 116のアドミタンス $Y_4, Y_5, Y_6$ もまた、バイナリ符号を実現するよう加重され、ここで、抵抗性デバイスFET114は、アドミタンス $Y_4$ を有する大きさとされ、抵抗性デバイスFET115は、アドミタンス $Y_5 = 2^* Y_4$ を有する大きさとされ、抵抗性デバイスFET116は、アドミタンス $Y_6 = 4^* Y_4$ を有する大きさとされる。第1の組121におけるすべての抵抗性デバイス111, 112, 113が起動された時、かつこの時だけ、第2の組122における抵抗性デバイス114, 115, 116のうち任意のものを起動できるようになる。

## 【0031】

第3の区分された組123は、ビット $W_7, W_8, W_9$ により表される抵抗性デバイス117, 118, 119を含む。組123における第1の抵抗性デバイス117は、アドミタンス $Y_7$ によって特徴付けられており、該アドミタンス $Y_7$ は、先のビット位置 $W_0, W_1, W_2, W_3, W_4, W_5, W_6$ により表される抵抗性デバイス120, 111, 112, 113, 114, 115, 116の合成アドミタンス $Y_0, Y_1, Y_2, Y_3, Y_4, Y_5, Y_6$ の値の10%である。第3の組123の抵抗性デバイス117, 118, 119のアドミタンス $Y_7, Y_8, Y_9$ もまた、バイナリ符号を実現するよう加重され、ここで、抵抗性デバイスFET117は、アドミタンス $Y_7$ を有する大きさとされ、抵抗性デバイスFET118は、アドミタンス $Y_8 = 2^* Y_7$ を有する大きさとされ、抵抗性デバイスFET119は、アドミタンス $Y_9 = 4^* Y_7$ を有する大きさとされる。第1の組121のすべての抵抗性デバイス111, 112, 113と第2の組122のすべての抵抗性デバイス114, 115, 116が起動された時、かつこの時だけ、第3の組123の抵抗性デバイス117, 118, 119のうち任意のものを起動できるようになる。

## 【0032】

組の数、区分された各組における抵抗性デバイスの数、各組における抵抗性デバイスのそれぞれに与えられる加重が、所与の設計またはアプリケーションに従って変化させることができるということは、当業者には理解されよう。しかしながら、本発明は、抵抗性デバイスの各組が温度符号アルゴリズムに従って起動され、かつ各組内の抵抗性デバイスは純バイナリ符号アルゴリズムにより起動されるすべての変形形態に適用され、かつ該変形形態のすべてをカバーするよう意図されている。

## 【0033】

PVT可変出力駆動制御に対する新規なハイブリッド型バイナリ加重温度符号のアプローチは、より少ない制御線を用いて、可変出力インピーダンス範囲内の感度の範囲および程度を増大させることにより、従来技術を著しく改善する。例えば、表3に規定された実現において、制御可能な出力インピーダンスは、常時起動の抵抗性デバイス120のインピーダンス(すなわち、低速PVTケースの最大インピーダンス)の1倍から0.204倍にわたって変化する。制御可能な出力インピーダンス範囲内の感度の程度もまた、非常に

10

20

30

40

50

高いものとなる。

【0034】

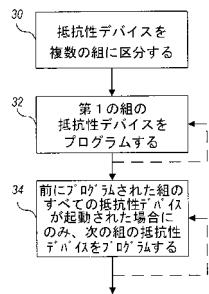

図3は、本発明の方法を例示するフローチャートである。図に示されるように、ドライバ出力と信号パッドとの間にプログラム可能なように接続可能な複数の抵抗性デバイスは、相互に排他的な複数の組へ区分される(ステップ30)。第1の組の抵抗性デバイスは、第1の組におけるゼロ個以上の抵抗性デバイスがドライバ出力と信号パッドとの間に電気的に接続されるようにプログラムされる(ステップ32)。伝送線路インピーダンス値に最も近い出力インピーダンス値を得るために、第1の組を二回以上プログラムすることができる。好ましくは、第1の組の抵抗性デバイスが、所与の較正セッション(calibration session)において二回以上プログラムされる場合、出力パッド上に見られる出力インピーダンスの変化量を減らすように、再プログラミングが、ステップごとに(逐次的に)実行される。

【0035】

第1の組における抵抗性デバイスのすべてが、ドライバ出力と信号パットとの間で電気的に接続された場合にのみ、抵抗性デバイスの次の1組が、抵抗性デバイスのまだプログラムされずに残っている組から選択され、プログラムされる(ステップ34)。再び、伝送線路インピーダンス値に最も近い出力インピーダンス値を得るために、抵抗性デバイスの選択された該次の1組を二回以上プログラムすることができ、好ましくは、抵抗性デバイスの該選択された次の1組が、所与の較正セッションにおいて二回以上プログラムされる場合、出力パッド上に見られる出力インピーダンスの変化量を減らすように、再プログラミングが、ステップごとに(逐次的に)実行される。

【0036】

出力ドライバの出力インピーダンスが、該出力ドライバが駆動する伝送線路インピーダンスに最も接近して整合するまで、ステップ34を、抵抗性デバイスのまだプログラムされていない残っている組のそれぞれについて繰り返すことができる。

【0037】

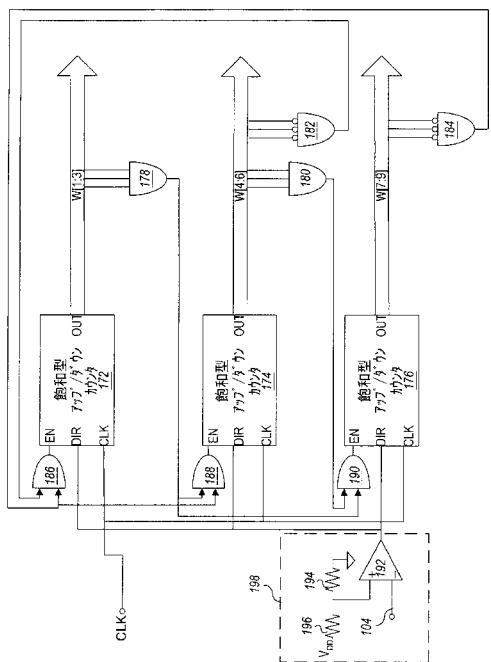

図4は、図2のインピーダンス回路100をプログラムするためのコントローラ110の概略的なブロック図である。図に示されるように、コントローラ110は3つの3ビットカウンタ172, 174, 176を含む。カウンタ172, 174, 176は、最高の出力から最低の出力へ、または最低の出力から最高の出力へ反転しないような、飽和型カウンタが好ましい。カウンタ172, 174, 176は、クロック入力CLKがストローブ(strobe)であるときの入力DIRの方向状態に従い、それぞれの出力上のバイナリ値をインクリメントし、またはデクリメントする。カウンタ172, 174, 176の出力のそれぞれは、信号W[1:3], W[4:6], W[7:9]をそれぞれ生成し、該信号のそれぞれは、インピーダンス回路100におけるそれぞれの組121, 122, 123のFETのうちの1つのゲートを駆動するのに用いられる。

【0038】

それぞれのカウンタ172, 174, 176は、イネーブル入力ENを有しており、これがアサートされると、クロック入力CLKのパルスのそれぞれについて1回、(方向入力DIRの状態に従い)カウンタは、インクリメントまたはデクリメントすることができる。組ごとに温度符号を実現することにより、次の下位のオーダー(桁)の組をプログラムする前に、それよりも高位のオーダー(桁)の組のFETのすべてをまず起動するため、それぞれのカウンタを、プログラミング処理の所定部分の間だけイネーブルすることができる。本例では、第1のカウンタ172をイネーブルすることができるのは、他のカウンタに対応する組に属するFETのいずれもが起動されない時のみである。換言すれば、カウンタ174および176によって出力されるビットW[4:9]はすべて、値“0”を有さなければならない。これに応じて、反転入力ANDゲート182および184は、ビットW[4:6]およびW[7:9]を、カウンタ174および176からそれぞれ受け取る。反転入力ANDゲート182および184の出力は、ANDゲート186の入力を駆動する。ANDゲート186の出力は、カウンタ172のイネーブル入力ENを駆

動する。これに応じて、カウンタ 172 は、ビット W [ 4 : : 9 ] がすべて “0” であるとき、イネーブルされる。

【 0039 】

また、本例では、ビット W [ 1 : 3 ] により制御される第 1 の組 121 のすべての FET が起動され、ビット W [ 7 : 9 ] により制御される第 3 の組に属する FET のいずれもが起動されないとき、カウンタ 174 を起動することができる。換言すれば、カウンタ 172 によって出力されるビット W [ 1 : 3 ] は、すべて ‘1’ をもたねばならず、カウンタ 176 によって出力されるビット W [ 7 : : 9 ] は、すべて ‘0’ をもたねばならない。これに応じて、AND ゲート 178 は、カウンタ 172 によって出力されるビット W [ 1 : 3 ] を受け取る。AND ゲート 178 および反転入力 AND ゲート 184 の出力は、AND ゲート 188 の入力を駆動する。こうして、カウンタ 172 によって出力されるビット W [ 1 : 3 ] がすべて ‘1’ で、かつカウンタ 176 によって出力されるビット W [ 7 : : 9 ] がすべて ‘0’ である時だけ、カウンタ 174 はイネーブルされる。

【 0040 】

また、この例では、ビット W [ 1 : 3 ] および W [ 4 : 6 ] により制御される第 1 の組および第 2 の組 121 および 122 の両方におけるすべての FET がそれぞれ起動された時にだけ、カウンタ 176 をイネーブルすることができる。換言すれば、カウンタ 172 および 174 によって出力されるビット W [ 1 : : 6 ] は、すべて値 ‘1’ をもたねばならない。これに応じて、AND ゲート 180 は、カウンタ 174 によって出力されるビット W [ 4 : 6 ] を受け取る。AND ゲート 178 および 180 の出力は、AND ゲート 190 の入力を駆動する。こうして、カウンタ 176 は、ビット W [ 1 : : 6 ] がすべて ‘1’ である時だけ、イネーブルされる。

【 0041 】

方向入力 DIR は、比較回路 198 により制御される。インピーダンス回路 100 出力における線 104 は、アナログ比較器 192 の反転端子に対する入力となる。アナログ比較器 192 の非反転入力は、抵抗器 194 および 196 から形成される分圧器に接続される。抵抗器 194 および 196 は、オンチップ抵抗器でよく、正電源と負電源の間に直列に接続されており、該正電源と負電源の中間ノードは、アナログ比較器 192 の非反転入力に接続されている。一実施形態では、抵抗器 194 および 196 は同じ値を有しており、これにより、アナログ比較器 192 の非反転入力における電圧が VDD / 2 となる。アナログ比較器 192 の出力は、カウンタ 172, 174, 176 のそれぞれの DIR 入力に接続されており、該 DIR 入力は、これらのカウンタがイネーブルされたとき、該カウンタがカウントする方向を制御する。

【 0042 】

比較器 192 の反転入力が、アナログ比較器 192 の非反転入力よりも低いとき、カウンタ 172, 174, 176 は、(イネーブルされた時) カウントアップし、インピーダンス回路 100 のより多くのトランジスタを導通させ、インピーダンス回路 100 のインピーダンスを減らす。このフィードバックシステムは、インピーダンス回路 100 のインピーダンスが、パッド 106 により駆動される負荷のインピーダンスとほぼ整合する時に安定する。比較器 192 の反転入力が、アナログ比較器 192 の非反転入力よりも高いとき、カウンタ 172, 174, 176 はカウントダウンする。これは、インピーダンス回路 100 のより多くのトランジスタを非導通とし、インピーダンス回路 100 のインピーダンスを増やす。

【 0043 】

図 4 の回路には、インピーダンス回路 100 の制御入力が生成される方法を例示するものとして示されている。これらの信号の特定の生成方法は、本発明を限定するものではない。しかしながら、図 4 の回路により、該システムは、(比較回路およびアップ - ダウンカウンタを介して) 較正制御ワードを連続的に更新し、出力ドライバの出力インピーダンスを更新することを可能にすることは、理解されるであろう。

【 0044 】

10

20

30

40

50

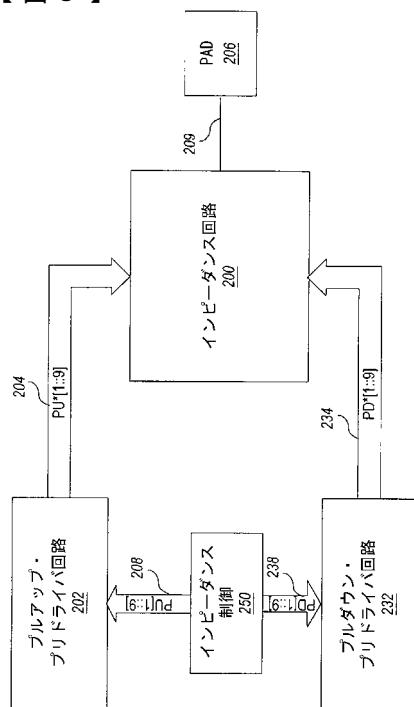

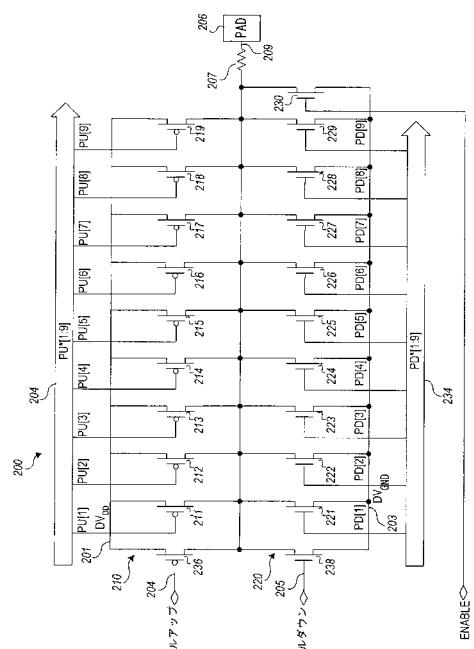

可変インピーダンス出力ドライバの代替実施形態のブロック図が、図5に示されている。本実施形態では、本発明のドライバ回路は、プルアップ・プリドライバ回路202およびプルダウン・プリドライバ回路232を有するドライバ回路環境において動作する。これらの回路は、出力信号をロー状態からハイ状態へ、およびハイ状態からロー状態へ（またはトライステート（tri-state）状態へ）駆動するようそれぞれ動作する。インピーダンス制御回路250は、較正ワードPU[1::9]およびPD[1::9]の形で制御信号208および238を生成する。これらの制御信号は、プリドライバ回路202, 232によってそれぞれデータ修飾され、修飾された較正ワードPU\* [1::9], PD\* [1::9]をそれぞれ生成する。修飾された較正ワードPU\* [1::9] 204およびPD\* [1::9] 234を用い、下記に説明するようなやり方で、本発明に従って構成された出力インピーダンス回路200を制御する。図5に示されるように、出力インピーダンス回路200の出力209は、信号パッド206に向けられる。10

#### 【0045】

ここで図6を参照すると、本発明に従って構成された出力インピーダンス回路200の好ましい実施形態が詳細に例示されている。手短に言えば、インピーダンス回路200は、Pチャネル電界効果トランジスタ（PFET）236、211～219のアレイ210を含む。アレイ210において、これらのPFETは電気的に並列接続されており、それぞれのPFETのソースノードが、それぞれの他のPFETのソースノードに電気的に接続され、それぞれのPFETのドレインノードが、それぞれの他のPFETのドレインノードに電気的に接続されている。回路200はさらに、Nチャネル電界効果トランジスタ（NFET）のアレイ220を含む。NFETは、それらのソースノードが、一緒に接続されると共にさらにPFETのアレイ210のドレインノードに接続され、それらのドレインノードが電気的に一緒に接続されるように、電気的に接続されている。20

#### 【0046】

好ましい実施形態によれば、PFETアレイ210は、10個のPFETデバイス236, 211, 212, 213, 214, 215, 216, 217, 218, および219を含む。これらのPFETデバイスのそれぞれのソースノードは、電位がDV<sub>DD</sub>にある共通信号線201上に一緒に電気的に接続される。同様に、NFETデバイスのアレイ220は、10個のNFETデバイス238, 221, 222, 223, 224, 225, 226, 227, 228, および229を含む。さらに、NFETデバイス230を出力の所に設けて、さもなくば駆動されない出力を、それがフロート（浮動）しないように少しプルダウンすることができる（CMOSデバイスではフローティング入力は望ましくないため）。複数のNFETデバイスのそれぞれのドレインノードは、電位がDV<sub>GN</sub>にある線203に一緒に電気的に接続される。30

#### 【0047】

PFETアレイ210は、プルアップ・プリドライバ回路202の出力204によって直接駆動される第1のPFET236を含む。同様に、NFETアレイ220は、プルダウン・プリドライバ回路204の出力234によって駆動される第1のNFETデバイス238を含む。2つのアレイにおけるPFETおよびNFETの残りは、ラベルPU\* [9::1]およびPD\* [9::1]によって示されるバス204および234上に供給される制御信号によって駆動される。図7と関連して図示され記述されるように、線204および234上に供給され、デジタルのデータ修飾された較正ワードPU\* [9::1]（負論理）およびPD\* [9::1]（正論理）を備える制御信号は、アレイ210および220の様々なPFETおよびNFETデバイスを選択的にオン／オフするのに用いられ、ドライバ回路の出力インピーダンスを効果的に変化させる。40

#### 【0048】

好ましい実施形態によれば、PFETおよびNFETアレイ210および220のそれらにおけるPFETおよびNFETデバイス211～219, 221～229は、複数の組241, 242, 243および244, 245, 246にそれぞれ区分される。好ましくは、それぞれのアレイ210および220は、表3に示されるバイナリ加重温度符号を50

実現する。

【0049】

特に、P F E Tアレイ210は、ビットPU\* [1], PU\* [2], PU\* [3]により表わされる抵抗性デバイス211, 212, 213を備える第1の区分された組241を含む。第1の抵抗性デバイス211は、抵抗性デバイス236のアドミタンスY<sub>0</sub>の値の10%であるアドミタンスY<sub>1</sub>により特徴付けられる。第1の組241における抵抗性デバイス211, 212, 213のアドミタンスY<sub>1</sub>, Y<sub>2</sub>, Y<sub>3</sub>は加重され、バイナリ符号を実現する。ここで、抵抗性デバイスFET211は、アドミタンスY<sub>1</sub>を有する大きさとされ、抵抗性デバイスFET212は、アドミタンスY<sub>2</sub> = 2\* Y<sub>1</sub>を有する大きさとされ、抵抗性デバイスFET213は、アドミタンスY<sub>3</sub> = 4\* Y<sub>1</sub>を有する大きさとされる。10

【0050】

第2の区分された組242は、PU\* [4], PU\* [5], PU\* [6]で表わされる抵抗性デバイス214, 215, 216を含む。第2の組242における抵抗性デバイス214, 215, 216の抵抗も加重され、バイナリ符号を実現する抵抗性デバイスFET214は、アドミタンスY<sub>4</sub>を有する大きさとされ、抵抗性デバイスFET215は、アドミタンスY<sub>5</sub> = 2\* Y<sub>4</sub>を有する大きさとされ、抵抗性デバイスFET216は、アドミタンスY<sub>6</sub> = 4\* Y<sub>4</sub>を有する大きさとされる。ビットPU [4]により表される抵抗性デバイスFET214は、起動された抵抗性デバイス236, 211, 212, 213の合成アドミタンスの10%のアドミタンスを有する大きさとされる。第1の組241におけるすべての抵抗性デバイス211, 212, 213が起動されたとき、かつその時のみ、第2の組242における抵抗性デバイス214, 215, 216を、2進増分に(

binary increment)に従って起動することができる。20

【0051】

第3の区分された組243は、ビットPU\* [7], PU\* [8], PU\* [9]により表される抵抗性デバイス217, 218, 219を含む。第3の組243における抵抗性デバイス217, 218, 219のアドミタンスも加重され、バイナリ符号を実現する。抵抗性デバイスFET217は、アドミタンスY<sub>7</sub>を有する大きさとされ、抵抗性デバイスFET218は、アドミタンス2\* Y<sub>7</sub>を有する大きさとされ、抵抗性デバイスFET219は、アドミタンス4\* Y<sub>7</sub>を有する大きさとされる。ビットPU\* [7]により表される抵抗性デバイスFET217は、起動された抵抗性デバイス211, 212, 213, 214, 215, 216の合成アドミタンスの10%のアドミタンスを有する大きさとされる。第1の組241におけるすべての抵抗性デバイス211, 212, 213および第2の組242におけるすべての抵抗性デバイス214, 215, 216が起動されたとき、かつその時のみ、第3の組243の抵抗性デバイス217, 218, 219が、2進増分に従って起動される。30

【0052】

N F E Tアレイ220は、P F E Tアレイ210と同じ原理に従って動作し、表3のバイナリ加重温度符号を実現するが、D V<sub>GND</sub>に連結されたN F E Tを用いて出力パッドをプルダウンする。40

【0053】

組の数、それぞれの区分された組における抵抗性デバイスの数、およびそれぞれの組における抵抗性デバイスのそれぞれに与えられる加重が、所与の設計またはアプリケーションに従って変化することがあるということは、当業者には理解されよう。しかしながら、本発明は、それぞれの組内の抵抗性デバイスが、純バイナリ符号アルゴリズムに従って起動され、各組の抵抗性デバイスが温度符号アルゴリズムに従って起動される、様々な変形形態に適用されることができ、また該変形形態をカバーするよう意図されている。

【0054】

本発明の好ましい実施形態に従って図6に例示される様々なトランジスタの物理的サイズ(図示のように)を規定する、下記の表4が提供される。しかしながら、本発明は、表に50

示された値に限定されず、該表が、本発明の好ましい実施形態を余すところなく開示する目的にだけ単に提供されることは、理解されるべきである。

【0055】

【表4】

| 参照番号 | 長さ (ミクロン) | 幅 (ミクロン) |

|------|-----------|----------|

| 236  | . 44      | 80       |

| 211  | . 44      | 8        |

| 212  | . 44      | 16       |

| 213  | . 44      | 32       |

| 214  | . 44      | 13. 6    |

| 215  | . 44      | 27. 2    |

| 216  | . 44      | 54. 4    |

| 217  | . 44      | 23. 12   |

| 218  | . 44      | 46. 24   |

| 219  | . 44      | 92. 48   |

| 238  | . 44      | 20       |

| 221  | . 44      | 2        |

| 222  | . 44      | 4        |

| 223  | . 44      | 8        |

| 224  | . 44      | 3. 4     |

| 225  | . 44      | 6. 8     |

| 226  | . 44      | 13. 6    |

| 227  | . 44      | 5. 78    |

| 228  | . 44      | 10. 56   |

| 229  | . 44      | 21. 12   |

10

20

30

【0056】

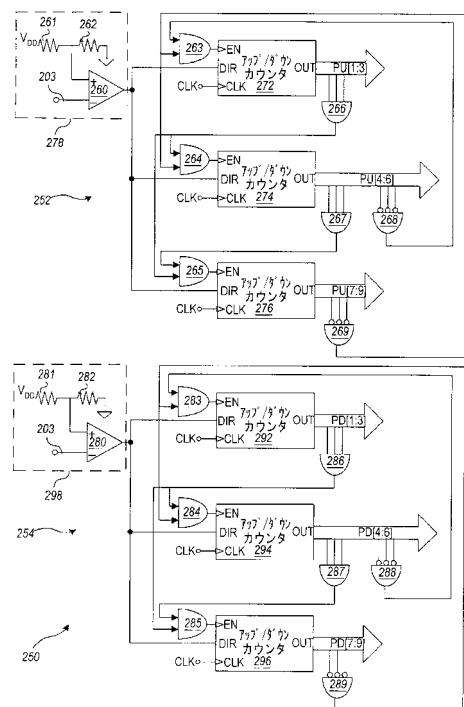

本発明の概念および教示に従い、制御回路250(図7)を、様々な方法で実現することができる。本発明の概念の目的に重要なことは、制御回路250が、FETアレイ200における様々なPFEトの状態を制御し、ドライバ回路の出力インピーダンスを変更し、これにより出力抵抗が、プロセス、電圧、および温度の様々な範囲にわたる負荷インピーダンスに実質的に等しいままでいるようにすることである。様々な構成および回路を、この広範囲の目標を達成するよう実現することができるが、図7は、そのような回路の一例を示す。

40

【0057】

図7を参照すると、一群の出力ドライバのインピーダンスが整合するよう、または外部抵抗器の何らかの倍数になるようプログラムするのに使用することのできる、2組(一方は、プルアップ・トランジスタ用であり、他方は、プルダウン・トランジスタ用)の制御信号が生成される。通常動作の間、較正ドライバPFEトアレイ210は、そこを流れる電流を有する。電流は、正電源DVDDから流れ、PFEトアレイ210を通り、静電放電(ESD)保護抵抗器207および出力パッド206を通り、外部抵抗(図示せず)を通って接地へ流れる。

【0058】

制御回路250は、プルアップ制御回路252およびプルダウン制御回路254を含み、

50

これらのそれぞれが、P F E Tアレイ210およびN F E Tアレイ220をそれぞれ制御するプルアップ制御ワードP U [ 1 : 9 ]およびプルダウン制御ワードP D [ 1 : 9 ]を生成する。

#### 【 0 0 5 9 】

プルアップ制御回路252は、P F E Tアレイ210におけるP F E Tのそれぞれの組241, 242, 243について、カウンタ272, 274, 276を含む。カウンタ272, 274, 276は、最高の出力から最低の出力へ、または最低の出力から最高の出力へ反転しない飽和型カウンタである。カウンタ272, 274, 276は、クロック入力C L Kがストローブであるとき、入力D I R<sub>P U</sub>の方向状態に従って、それらのそれぞれの出力についてバイナリ値をインクリメントし、またはデクリメントする。カウンタ272, 274, 276のそれぞれの出力は、信号P U [ 1 : 3 ], P U [ 4 : 6 ], P U [ 7 : 9 ]をそれぞれ生成し、これらのそれぞれは、P F E Tアレイ210におけるそれぞれの組241, 242, 243のF E Tのうちの1つのゲートを駆動するのに用いられる。

#### 【 0 0 6 0 】

それぞれのカウンタ272, 274, 276は、イネーブル入力E Nを有しており、該イネーブル入力E Nがアサートされたとき、カウンタは、クロック入力C L Kのそれぞれのパルスについて1回、(方向入力D I R<sub>P U</sub>の状態に従い)インクリメントまたはデクリメントすることができる。組ごとに温度符号を実現することによって、次の下位の組をプログラミングする前に、第1の組におけるすべてのP F E Tをまず起動するために、それぞれのカウンタを、プログラミング処理の所定部分の間だけイネーブルすることができる。本例では、他のカウンタ274, 276に対応する組242, 243に属するP F E Tのいずれもが起動されないとき、カウンタ272はイネーブルされる。換言すれば、カウンタ274, 276によって出力されるビットP U [ 4 : : 9 ]のすべては、値「0」をもたねばならない。これに応じて、反転入力A N Dゲート268および269は、カウンタ274および276からビットP U [ 4 : 6 ], P U [ 7 : 9 ]をそれぞれ受け取る。反転入力A N Dゲート268, 269の出力は、A N Dゲート263の入力を駆動する。A N Dゲート263の出力は、カウンタ272のイネーブル入力E Nを駆動する。それに応じて、P U [ 4 : : 9 ]がすべて「0」であるときにのみ、カウンタ272はイネーブルとされる。

#### 【 0 0 6 1 】

カウンタ274は、ビットP U [ 1 : 3 ]により制御される組241においてP F E Tのすべてが起動され、ビットP U [ 7 : 9 ]により制御される組243に属するP F E Tのいずれもが起動されていないときにのみ、イネーブルされる。換言すれば、カウンタ272により出力されるビットP U [ 1 : 3 ]はすべて値「1」をもち、カウンタ276により出力されるビットP U [ 7 : : 9 ]はすべて値「0」をもたねばならない。こうして、A N Dゲート266は、カウンタ272により出力されるビットP U [ 1 : 3 ]を受け取る。A N Dゲート266および反転入力A N Dゲート269の出力は、A N Dゲート264の入力を駆動する。こうして、カウンタ272により出力されるビットP U [ 1 : 3 ]がすべて「1」であり、カウンタ276により出力されるP U [ 7 : : 9 ]がすべて「0」であるときにだけ、カウンタ274はイネーブルされる。

#### 【 0 0 6 2 】

ビットP U [ 1 : 3 ]およびP U [ 4 : 6 ]により制御される組241, 242におけるF E Tのすべてが起動されたときにだけ、カウンタ276はイネーブルされる。換言すれば、カウンタ272および274によって出力されるビットP U [ 1 : : 6 ]は、すべて値「1」をもたねばならない。それに応じて、A N Dゲート267は、カウンタ274により出力されるビットP U [ 4 : 6 ]を受け取る。A N Dゲート266および267の出力は、A N Dゲート265の入力を駆動する。こうして、カウンタ276は、ビットP U [ 1 : : 6 ]がすべて「1」であるときにだけイネーブルされる。

#### 【 0 0 6 3 】

10

20

30

40

50

それぞれのカウンタ 272, 274, 276 の方向入力 D<sub>I</sub>R<sub>P</sub><sub>U</sub> は、比較回路 278 によって制御される。P<sub>F</sub>E<sub>T</sub>アレイ 210 および N<sub>F</sub>E<sub>T</sub>アレイ 220 のインピーダンスは、外部抵抗（図示せず）とともに分圧器を形成し、パッド 206 ノードにおいて正電源電圧を分圧する。このノードは、アナログ比較器 260 の反転端子に対する入力となる。アナログ比較器 260 の非反転入力は、抵抗器 261 および 262 で形成される分圧器に接続される。抵抗器 261 および 262 は、オンチップ抵抗器でもよく、正電源と負電源との間に直列に接続される。ここで、正電源および負電源の中間ノードは、アナログ比較器 260 の非反転入力に接続される。一実施形態では、抵抗器 261 および 262 は、同じ値を有しており、これにより、アナログ比較器 260 の非反転入力における電圧は、V<sub>DD</sub> / 2 となる。アナログ比較器 260 の出力は、デジタルのアップ / ダウンカウンタ 272, 274, 276 の D<sub>I</sub>R<sub>P</sub><sub>U</sub> 入力に接続される。アップ / ダウンカウンタ 272, 274, 276 が P<sub>F</sub>E<sub>T</sub>アレイ 210 においてイネーブルされたとき、D<sub>I</sub>R<sub>P</sub><sub>U</sub> 入力は、該カウンタがカウントする方向を制御する。

10

#### 【0064】

比較器 260 の反転入力が、アナログ比較器 260 の非反転入力よりも低いとき、カウンタ 272, 274, 276 は、（イネーブルされた時に）カウントアップし、P<sub>F</sub>E<sub>T</sub>アレイ 210 のより多くのトランジスタを導通させ、ブルアップインピーダンス回路（P<sub>F</sub>E<sub>T</sub>アレイ 210）のインピーダンスを減らす。P<sub>F</sub>E<sub>T</sub>アレイ 210 のインピーダンスが、パッド 206 によって駆動される負荷のインピーダンスにほぼ整合するとき、このフィードバックシステムは安定する。比較器 260 の反転入力が、アナログ比較器 260 の非反転入力よりも高いとき、カウンタ 272, 274, 276 は、カウントダウンする。これにより、P<sub>F</sub>E<sub>T</sub>アレイ 210 のより多くのトランジスタが非導通とされ、ブルアップ・インピーダンス回路のインピーダンスを増やす。

20

#### 【0065】

ブルダウン制御回路 254 は、N<sub>F</sub>E<sub>T</sub>アレイ 220 における N<sub>F</sub>E<sub>T</sub>のそれぞれの組 244, 245, 246 についてのカウンタ 292, 294, 296 を含む。カウンタ 292, 294, 296 は、最高の出力から最低の出力へ反転したり、最低の出力から最高の出力へ反転することのない飽和型カウンタである。カウンタ 292, 294, 296 は、クロック入力 C<sub>L</sub>K がストローブであるとき、入力 D<sub>I</sub>R<sub>P</sub><sub>D</sub> の方向状態に従って、それらのそれぞれの出力についてバイナリ値をインクリメントし、またはデクリメントする。カウンタ 272, 274, 276 の出力のそれぞれは、信号 P<sub>D</sub> [1 : 3], P<sub>D</sub> [4 : 6], P<sub>D</sub> [7 : 9] をそれぞれ生成し、これらの信号のそれぞれが、N<sub>F</sub>E<sub>T</sub>アレイ 220 におけるそれぞれの組 244, 245, 246 の F<sub>E</sub>T のうちの 1 つのゲートを駆動するのに用いられる。

30

#### 【0066】

ブルダウン制御回路 254 の動作は、ブルアップ制御回路 252 の動作と同様であり、それによって、AND ゲート 283, 284, 285, 286, 287, 288, 289 により実現される制御ロジックが、それぞれのカウンタ 292, 294, 296 のイネーブル入力を制御し、比較回路 298（比較回路 280 の非反転入力を駆動する分圧器を形成する抵抗器 281, 282 を備える）が、それぞれのカウンタ 292, 294, 296 の方向入力 D<sub>I</sub>R<sub>P</sub><sub>D</sub> を制御する。ブルダウン制御回路 254 は、ブルダウン N<sub>F</sub>E<sub>T</sub>アレイ 220 のインピーダンスを制御し、ブルダウン・インピーダンス制御ワード P<sub>D</sub> [1 : 9] を生成する。

40

#### 【0067】

繰り返しになるが、先に述べたように、図 7 の回路は、インピーダンス回路 P<sub>F</sub>E<sub>T</sub> および N<sub>F</sub>E<sub>T</sub>アレイ 210 および 220 についての制御入力を生成する方法を例示するためだけに提供されるものであり、これらの信号の生成の特定のやり方が本発明を限定することはない。しかしながら、図 7 の回路により、（比較器およびアップ - ダウンカウンタを介して）システムが連続的に較正制御ワードを更新し、出力ドライバの出力インピーダンスを更新することが可能となることは理解されたい。

50

## 【0068】

前述の説明は、例示および説明を目的に提示した。これは、本発明を開示された形態に排他的にまたは限定するように意図するものではない。明確な修正または変形が、上記の教示を考慮して可能である。例えば、組241～246の数および／または各組におけるFETの数を、アプリケーション（応用例）のニーズに従って増減できることは理解されよう。

## 【0069】

較正ワード204および234（本願明細書において、9ビットのワードとして例示される）は、異なるサイズであってもよく、9ビットよりも大きくてよいし、小さくてもよいこともまた理解されたい。

10

## 【0070】

プルアップFETおよびプルダウンFETに対する別個の独立した較正ワードを有することで、出力ドライバが、様々なプロセス、電圧、および温度の範囲にわたって正確なインピーダンス整合を提供することができるようになることもまた理解されたい。

## 【0071】

本発明は例示実施形態に関して記載したにも拘わらず、本発明の趣旨または範囲から逸脱することなく、例示の実施形態に対し様々な変更および修正が可能であることは当業者には理解されよう。本発明の範囲は、図示および説明した例示の実施形態に決して限定されず、本発明は、特許請求の範囲によってのみ限定されることを意図するものである。

## 【0072】

20

本発明は、以下の実施態様を含む。

(1) ノード(104, 209)上へ信号を駆動するよう構成された出力ドライバ回路の出力インピーダンスを、出力ドライバ制御回路を用いて可変に調整する方法であって、出力ドライバ制御回路は、複数の抵抗性デバイス(111～120, 211～219, 236, 221～229, 238)を備えており、該抵抗性デバイスのそれぞれは、第1の電源(VDD)と前記ノード(104)との間にプログラム可能なように電気的に並列接続可能であり、該方法は、

前記第1の電源と前記ノードとの間の第1の組(121)の抵抗性デバイスの電気的な接続を、2進増分的な方法でプログラムするステップ(32)と、

30

前記第1の組における前記抵抗性デバイスのすべてがイネーブルされたときだけ、前記第1の電源と前記ノードとの間に、第2の組(122)の抵抗性デバイスの電気的な接続を、2進増分的な方法でプログラムするステップ(34)と、を含む方法。

(2) 先にプログラムされた組(121, 122)における前記抵抗性デバイスのすべてがイネーブルされたときだけ、前記第1の電源と前記ノードとの間に、抵抗性デバイスの1以上の追加の組(123)の電気的な接続を、2進増分的な方法でプログラムするステップを含む、上記(1)に記載の方法。

(3) 前記第1の電源と前記ノードとの間に、前記複数の抵抗性デバイスのうちの少なくとも1つ(120, 236, 238)を、常時電気的に接続するステップをさらに含む、上記(1)または(2)に記載の方法。

## 【0073】

40

(4) 信号をノード(104, 209)上へ駆動するよう構成された可変インピーダンス出力ドライバ回路のための制御回路であって、

第1の電源(VDD)と前記ノード(104, 209)との間に、プログラム可能なように電気的に接続可能な第1の組の抵抗性デバイス(111, 112, 113, 211, 212, 213, 221, 222, 223)と、

前記第1の電源と前記ノードとの間に、プログラム可能なように電気的に接続可能な第2の組の抵抗性デバイス(114, 115, 116, 214, 215, 216, 224, 225, 226)と、

前記第1の電源と前記ノードとの間の前記第1の組(121)の抵抗性デバイスの電気的接続を、2進増分的な方法でプログラムし、前記第1組(121)の前記抵抗性デバイス

50

のすべてが前記第1の電源と前記ノードとの間に電気的に接続された時だけ、前記第1の電源と前記ノードとの間の前記第2の組(122)の抵抗性デバイスの電気的接続を、2進増分的な方法でプログラムするコントローラ(110, 250)と、

を備える、制御回路。

(5) 前記第1の電源と前記ノードとの間に、プログラム可能なように電気的に接続可能な抵抗性デバイス(117, 118, 119と217, 218, 219と227, 228, 229)の1以上の追加の組(123)を備え、

前記先にプログラムされた組(121, 122)の前記抵抗性デバイスのすべてが、前記第1の電源と前記ノードとの間に電気的に接続された時だけ、前記コントローラ(110, 250)が、前記第1の電源と前記ノードとの間の前記抵抗性デバイスの1以上の追加の組(123)のうちの少なくとも1つの電気的な接続を、2進増分的な方法でプログラムする、上記(4)に記載の制御回路。

10

(6) 少なくとも1つの抵抗性デバイス(120, 236, 238)は、前記第1の電源と前記ノードとの間に常時電気的に接続される、上記(4)または(5)に記載の制御回路。

(7) 前記第1の組(121)における前記抵抗性デバイス(111, 112, 113と211, 212, 213と221, 222, 223)は、抵抗のバイナリ加重された符号を実現する、上記(4)、(5)または(6)のいずれかに記載された制御回路。

(8) 前記第2の組(122)における前記抵抗性デバイス(114, 115, 116と214, 215, 216と224, 225, 226)は、抵抗のバイナリ加重された符号を実現する、上記(4)、(5)、(6)または(7)のいずれかに記載された制御回路。

20

#### 【0074】

(9) 前記1以上の追加の組(123)の少なくとも1つにおける抵抗性デバイス(117, 118, 119と217, 218, 219と227, 228, 229)は、抵抗のバイナリ加重された符号を実現する、上記(5)、(6)、(7)または(8)のいずれかに記載された制御回路。

#### 【0075】

(10) 前記第1の組(121)、前記第2の組(122)、前記1以上の追加の組(123)のそれぞれにおける前記抵抗性デバイスが、電界効果トランジスタを含む、上記(5)、(6)、(7)、(8)または(9)のいずれかに記載された制御回路。

30

#### 【図面の簡単な説明】

【図1】可変インピーダンス出力ドライバ回路の概略的なブロック図。

【図2】図1の可変インピーダンス出力ドライバについて、本発明に従って実現されるインピーダンス回路の回路図。

【図3】本発明に従う方法のフローチャート。

【図4】本発明に従って実現されるインピーダンス回路コントローラの概略的なブロック図。

【図5】可変インピーダンス出力ドライバの代替的な実施形態のブロック図。

【図6】図5の可変インピーダンス出力ドライバの概略図。

40

【図7】図6の可変インピーダンス出力ドライバのインピーダンスを制御するインピーダンス回路コントローラの概略的なブロック図。

#### 【符号の説明】

100 インピーダンス回路

106 信号パッド

110 制御回路

111 ~ 120 抵抗性デバイス

121 第1の組

122 第2の組

123 第3の組

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 ガイ・ハーラン・ハンフリー

アメリカ合衆国 8 0 5 2 5 コロラド州フォート・コリンズ、ロックウッド・ドライヴ 3 4 6 5、

キュー 8 3

審査官 宮島 郁美

(56)参考文献 特開2 0 0 0 - 1 5 1 3 8 4 (JP, A)

特開平0 9 - 2 7 0 6 9 8 (JP, A)

特開平0 6 - 2 6 8 5 0 5 (JP, A)

特開平0 4 - 2 4 6 9 1 0 (JP, A)

特開平0 3 - 2 7 2 1 6 7 (JP, A)

特開平1 1 - 2 7 4 9 3 5 (JP, A)

特開平9 - 8 6 7 1 (JP, A)

特開2 0 0 1 - 3 6 4 1 1 (JP, A)

特表2 0 0 4 - 5 1 1 9 4 5 (JP, A)

特開2 0 0 4 - 7 6 1 7 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

H03K19/00,19/01-19/082,19/092-19/096

H03K17/00-17/70

H04L25/00-25/66

H03M3/00-11/00