(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5337373号

(P5337373)

(45) 発行日 平成25年11月6日(2013.11.6)

(24) 登録日 平成25年8月9日(2013.8.9)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/786 (2006.01)H01L 29/78 621

H01L 29/78 617V

請求項の数 6 (全 33 頁)

(21) 出願番号 特願2007-314141 (P2007-314141)

(22) 出願日 平成19年12月5日 (2007.12.5)

(65) 公開番号 特開2008-166748 (P2008-166748A)

(43) 公開日 平成20年7月17日 (2008.7.17)

審査請求日 平成22年11月23日 (2010.11.23)

(31) 優先権主張番号 特願2006-328015 (P2006-328015)

(32) 優先日 平成18年12月5日 (2006.12.5)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 大沼 英人

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

(57) 【特許請求の範囲】

## 【請求項1】

絶縁表面上に半導体膜を形成し、

前記半導体膜上にレジストを形成し、

前記レジストをマスクとして前記半導体膜を選択的に除去して島状の半導体層を形成し、

前記レジストを残したまま、前記半導体層に対してウェット酸化を行い前記半導体層の端部に第1の絶縁層を形成し、

前記半導体層上および前記第1の絶縁層上に第2の絶縁層を形成し、

前記第2の絶縁層を介して、前記半導体層上および前記第1の絶縁層上にゲート電極を形成することを特徴とする半導体装置の作製方法。 10

## 【請求項2】

絶縁表面上に半導体膜を形成し、

前記半導体膜上にレジストを形成し、

前記レジストをマスクとして前記半導体膜を選択的に除去して島状の半導体層を形成し、

前記レジストを除去した後、前記半導体層の表面を希フッ酸で洗浄し、

洗浄した前記半導体層上に第2の絶縁層を形成し、

前記第2の絶縁層で覆われていない前記半導体層に対してウェット酸化を行い前記半導体層の端部に第1の絶縁層を形成し、

前記第2の絶縁層を介して、前記半導体層上および前記第1の絶縁層上にゲート電極を形成することを特徴とする半導体装置の作製方法。

【請求項3】

絶縁表面上に半導体膜を形成し、

前記半導体膜上に第1のレジストを形成し、

前記第1のレジストをマスクとして前記半導体膜を選択的に除去して島状の半導体層を形成し、

前記第1のレジストの側面を後退させることにより、前記半導体層の表面を部分的に覆う第2のレジストを形成し、

前記第2のレジストをマスクとして前記半導体層に対してウェット酸化を行い前記半導体層の端部及び上面の一部に第1の絶縁層を形成し、

前記第2のレジストを除去した後、前記半導体層および前記第1の絶縁層上に第2の絶縁層を形成し、

前記第2の絶縁層を介して、前記半導体層上および前記第1の絶縁層上にゲート電極を形成することを特徴とする半導体装置の作製方法。

【請求項4】

請求項2において、

前記半導体層の表面を前記希フッ酸で洗浄することにより、前記絶縁表面が部分的に除去されて前記半導体層と前記絶縁表面が接する領域に窪みが形成されることを特徴とする半導体装置の作製方法。

【請求項5】

請求項1乃至請求項4のいずれか一において、

前記第2の絶縁層は、前記第1の絶縁層より誘電率が大きいことを特徴とする半導体装置の作製方法。

【請求項6】

請求項1乃至請求項5のいずれか一において、

前記ウェット酸化は、オゾンを含む水溶液、過酸化水素を含む水溶液、硫酸を含む水溶液、ヨウ素酸を含む水溶液、または硝酸を含む水溶液を用いて行われることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその作製方法に関する。

【背景技術】

【0002】

近年、ガラス等の絶縁表面を有する基板上に薄膜トランジスタ(TFT)を形成し、当該薄膜トランジスタをスイッチング素子等として利用する半導体装置の作製が盛んに行われている。当該薄膜トランジスタは、絶縁表面を有する基板上にCVD法、フォトリソグラフィ工程等を用いて島状の半導体層を形成し、当該島状の半導体層の一部をトランジスタのチャネル形成領域として利用するように設けられている(例えば特許文献1)。

【0003】

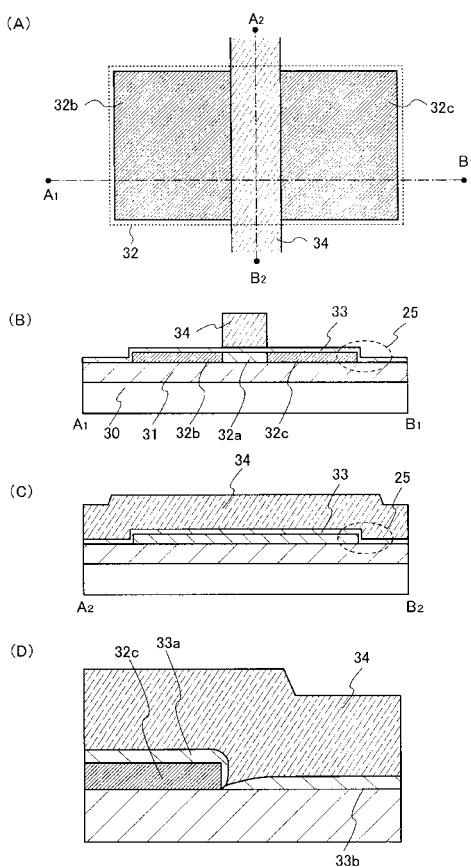

一般的な薄膜トランジスタの模式図を図24に示す。図24(A)は、薄膜トランジスタの上面図を示している。図24(B)は、図24(A)のA1とB1とを結ぶ破線における断面図を示している。図24(C)は、図24(A)のA2とB2とを結ぶ破線における断面図を示している。図24(D)は、図24(C)の半導体層32の端部25の拡大図を示している。図24(B)～(D)に示すように、薄膜トランジスタは、基板30上に下地膜として機能する絶縁層31が形成され、絶縁層31上にチャネル形成領域32a、ソース領域およびドレイン領域として機能する不純物領域32b、32cを有する半導体層32が形成され、半導体層32および絶縁層31上にゲート絶縁層として機能する絶縁層33が形成され、絶縁層33上にゲート電極として機能する導電層34が形成されて

10

20

30

40

50

いる。

#### 【0004】

図24において、選択的にエッティングされた半導体層32上にゲート絶縁層として機能する絶縁層33を形成する場合、半導体層32の端部25において絶縁層33の膜厚が不均一となり被覆不良が生じる。また、被覆不良がなくても、端部はその形状により電界強度が強くなる。絶縁層33の膜厚が薄くなった部分においては、ゲート電圧の電界強度が強くなり、薄膜トランジスタの耐圧や信頼性に悪影響を与えていた。

#### 【0005】

また、半導体層32の端部25には、基板および各薄膜の応力が集中するため、素子特性の変動を引き起こし問題となっていた。

10

#### 【0006】

この半導体層32の端部の段差に起因するゲート絶縁層の被覆性の低下を改善する手段として、活性層の端部をテーパー形状とする手段が用いられている（例えば、特許文献2）。

#### 【0007】

一方、高速動作を必要とする回路を構成する薄膜トランジスタとしては、チャネル長が短く、かつゲート絶縁層の膜厚が薄いことが好ましい。このため、ゲート絶縁層の膜厚は、数十ナノメートルと膜厚が薄くなっている。

【特許文献1】特開平08-018055号公報

【特許文献2】特開2005-167207号公報

20

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

しかしながら、半導体層の端部をテーパー形状にしても、電界や応力の集中は依然として問題となっている。

#### 【0009】

つまり、半導体層の端部をテーパー形状にしても、半導体層の端部においてゲート絶縁層の膜厚が不均一となり、ゲート絶縁層の薄い箇所において電界集中が生じてしまう。電界集中が起きることでリーク電流が増大し、デバイスの消費電力が増大する。さらに、電界集中が過度な場合にはゲート絶縁層の静電破壊が起こり、ゲートリーク不良が発生する。そのため、ゲート耐圧が低下する。これらはゲート絶縁層の膜厚を数十ナノメートルと薄くした場合に特に顕著な問題である。

30

#### 【0010】

本願発明はこのような課題を解決するための技術であり、ゲート絶縁層の膜厚が薄くなつた部分、すなわち段差部におけるゲート絶縁層の膜厚の不均一による半導体装置の特性への影響を低減し、半導体装置の信頼性を向上させることを目的とする。

#### 【課題を解決するための手段】

#### 【0011】

本発明の半導体装置は、絶縁表面上に半導体層を形成し、半導体層の端部をウェット酸化して第1の絶縁層を形成し、半導体層上および第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層を介して、半導体層上および第1の絶縁層上にゲート電極を形成することにより形成することができる。

40

#### 【0012】

なお、ここでいうウェット酸化とは、オゾンを含む水溶液、過酸化水素を含む水溶液、硫酸を含む水溶液、ヨウ素酸を含む水溶液、または硝酸を含む水溶液を用いて半導体層の表面を酸化処理することをいう。

#### 【発明の効果】

#### 【0013】

本発明において、ゲート電極下の半導体層のチャネル形成領域の端部（側面）に絶縁層を有するため、ゲート絶縁層の半導体層表面への被覆不良が半導体装置に及ぼす影響を低減

50

することができる。つまり、半導体層のチャネル形成領域の側面とゲート電極とが接するのを防ぐことができる。

【0014】

また、半導体層の端部において酸化膜とゲート絶縁層が形成されているため実効膜厚を厚くすることができ、半導体層の端部における電界集中を緩和できる。

【0015】

また、半導体層の端部と下地膜として機能する絶縁層との接する部分において、絶縁層に窪みが形成される場合があるが、半導体層の端部に選択的に絶縁層を形成することができるため、下地の絶縁層に窪みが形成されても、半導体層とゲート電極とが接することができなくなる。

10

【0016】

したがって、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることができるとなる。本発明は、ゲート絶縁層として機能する絶縁層の膜厚が数ナノメートル～数十ナノメートルのように、膜厚が半導体層の膜厚よりも薄い場合に特に効果的である。本発明により、信頼性が高い半導体装置を作製できる。

【発明を実施するための最良の形態】

【0017】

本発明の実施の形態について、図面を用いて以下に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

20

【0018】

(実施の形態1)

本実施の形態では、半導体層の端部におけるゲート絶縁層の被覆性低下によるリーク電流を抑制することが可能な半導体装置の構造について説明する。

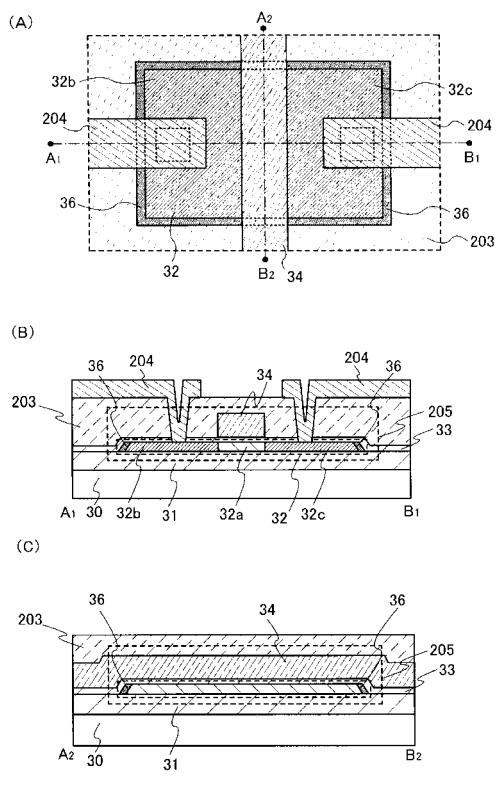

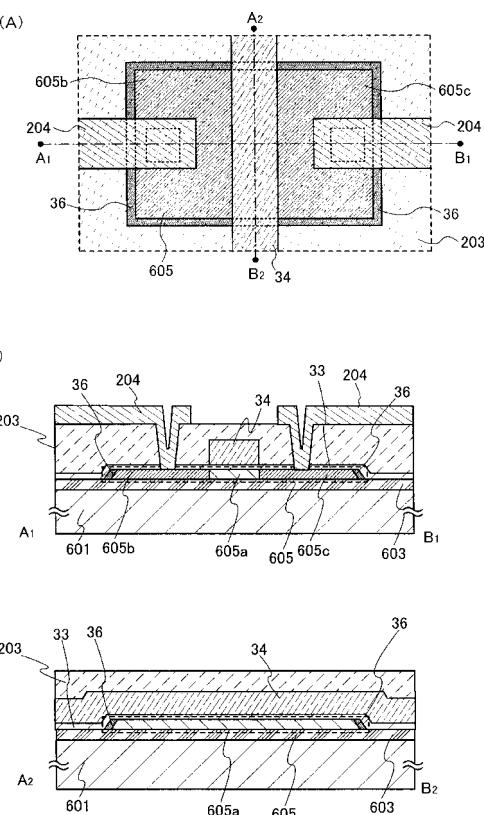

【0019】

図1は本発明に係る半導体装置の主要な構成を説明するための上面図および断面図である。図1(A)は、特に薄膜トランジスタの要部の上面図を示している。図1(B)は、図1(A)のA<sub>1</sub>とB<sub>1</sub>とを結ぶ破線における断面図を示し、図1(C)は、図1(A)のA<sub>2</sub>とB<sub>2</sub>とを結ぶ破線における断面図を示している。

30

【0020】

本実施の形態に示す半導体装置は、基板30上に絶縁層31を介して島状に設けられた半導体層32と、当該半導体層32の上方にゲート絶縁層33を介して設けられたゲート電極として機能する導電層34と、を含む薄膜トランジスタ205と、ゲート絶縁層33および導電層34を覆って設けられた絶縁層203と、絶縁層203上に設けられたソース電極またはドレイン電極として機能する導電層204と、を有している(図1(A)～(C))。なお、半導体層32は、チャネル形成領域32aと、ソース領域またはドレイン領域として機能する不純物領域32b、32cと、に加えて、半導体層32の端部、ここでは導電層34の下方のチャネル形成領域32aに接した部分に形成された絶縁層36と、を有している。なお、チャネル形成領域32a中に、不純物領域32b、32cに添加した不純物とは逆の導電型の不純物が添加されていてもよい。

40

【0021】

ここで、絶縁層36は、半導体層32を酸化することにより形成された酸化膜である。なお、半導体層の端部に形成された絶縁層36は、半導体層32の端部とゲート電極として機能する導電層34が短絡、あるいは半導体層32の端部近傍の電界強度が強くなることで、リーク電流が流れるのを抑制するために設ける。したがって、絶縁層36は、少なくとも半導体層32のチャネル形成領域32aの側面(露出している部分)に形成されなければならない。ただし、それ以外の部分に形成されていてももちろん構わない。

50

## 【0022】

本実施の形態において、基板30上に形成された絶縁層31上に半導体層を形成し、半導体層上に選択的にレジストを形成し、レジストをマスクとして半導体層をエッチングすることにより島状の半導体層32を形成できる。そして、レジストを除去する前に半導体層32の端部に対してウェット酸化することにより、半導体層32の端部に絶縁層36を形成できる。そして、レジストを除去して半導体層32および絶縁層36を覆ってゲート絶縁層33を形成し、ゲート絶縁層33上にゲート電極として機能する導電層34を形成する。

## 【0023】

ここで、ウェット酸化を用いて半導体層32の端部に絶縁層36を形成する方法について説明する。例えば、5 ppm以上、望ましくは20 ppm以上、より望ましくは100 ppm以上のオゾン( $O_3$ )を含む水溶液(代表的にはオゾン水)で半導体層32の表面を酸化処理することにより、半導体層32の露出している部分に酸化膜からなる絶縁層36を形成できる。なお、オゾンを含む水溶液にかえて、過酸化水素( $H_2O_2$ )を含む水溶液、硫酸( $H_2SO_4$ )を含む水溶液、ヨウ素酸( $HIO_3$ )を含む水溶液、または硝酸( $HNO_3$ )を含む水溶液等を用いることもできる。また、それぞれの水溶液は、酢酸やしう酸等の有機酸を含んでいてもよい。

10

## 【0024】

なお、本明細書において、上記のように水溶液を用いて半導体層32の露出した部分に酸化膜を形成する処理をウェット酸化という。

20

## 【0025】

本実施の形態に示す半導体装置は、ゲート電極下の半導体層32のチャネル形成領域32aの端部(側面)に絶縁層36を有するため、ゲート絶縁層33の半導体層32表面への被覆不良が半導体装置に及ぼす影響を低減できる。つまり、半導体層32のチャネル形成領域32aの側面はゲート電極として機能する導電層34と接しないため、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

## 【0026】

また、本実施の形態において、半導体層32の端部の露出している部分から酸化を進めることができるため、半導体層32の端部に選択的に厚く酸化膜を形成できる。よって、半導体層32の端部付近における電界集中を緩和でき、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

30

## 【0027】

また、半導体層32の端部に形成される絶縁層36より誘電率の大きな材料でゲート絶縁層33を形成することにより、ゲート絶縁層33と半導体層32の端部に形成される絶縁層36とを同程度の膜厚で形成した場合でも、ゲート絶縁層33の実効膜厚に比べて、半導体層32の端部に形成される絶縁層の実効膜厚を厚くすることができる。よって、半導体層32の端部における電界集中を緩和することができる。したがって、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

## 【0028】

半導体層32の端部に形成される絶縁層36より誘電率の大きな材料で形成されるゲート絶縁層33として、気相成長法やスパッタリング法を用いて形成された酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン( $SiO_xNy$ )( $x > y > 0$ )膜、窒化酸化シリコン( $SiNxOy$ )( $x > y > 0$ )膜、 $Hf$ 系酸化膜等を単層または積層した膜等を用いることができる。

40

## 【0029】

なお、本実施の形態において、半導体層32を形成した後に、ウェット酸化して酸素を含む雰囲気下または窒素を含む雰囲気下で半導体層32表面をプラズマ処理することにより、半導体層32表面に形成された酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン( $SiO_xNy$ )( $x > y > 0$ )膜または窒化酸化シリコン( $SiNxOy$ )( $x > y > 0$ )膜等をゲート絶縁層33として用いることもできる。

50

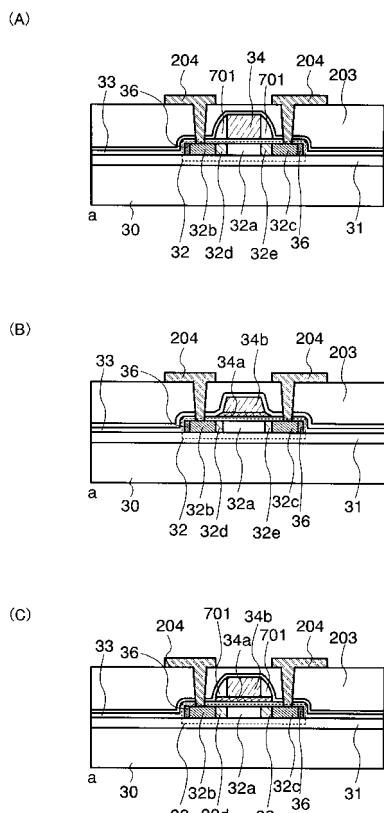

## 【0030】

なお、薄膜トランジスタの形状は図1に示すものに限られるものではなく、例えば、ゲート電極として機能する導電層34の側壁に接して、絶縁物からなるサイドウォール701を形成してもよい。また、ソース領域またはドレイン領域として機能する不純物領域32b、32cと、チャネル形成領域32aとの間に、不純物領域32b、32cより低濃度に不純物が添加された低濃度不純物領域(LDD領域)32d、32eが形成されていてもよい(図11(A))。また、薄膜トランジスタの構造として、上述した構造に限られず、チャネル形成領域が2つ形成されるダブルゲート構造または3つ形成されるトリブルゲート構造等のマルチゲート構造を用いることができる。また、ゲート電極を積層構造で設けてもよい。例えば、ゲート電極を、第1の導電層34aと、第1の導電層34a上に形成される第2の導電層34bとの2層構造とし、第1の導電層34aをテーパー状で形成し、第1の導電層34aにのみ重なるように低濃度不純物領域32d、32eを設ける構造(図11(B))としてもよい。また、ゲート電極を、第1の導電層34aと、第1の導電層34a上に形成される第2の導電層34bで設け、第2の導電層34bの側壁に接し、かつ第1の導電層34aの上方に形成されるようにサイドウォール701を設ける構造(図11(C))としてもよい。また、ソース領域またはドレイン領域として機能する不純物領域32b、32cを、Ni、Co、W等のシリサイドで形成することも可能である。

## 【0031】

## (実施の形態2)

20

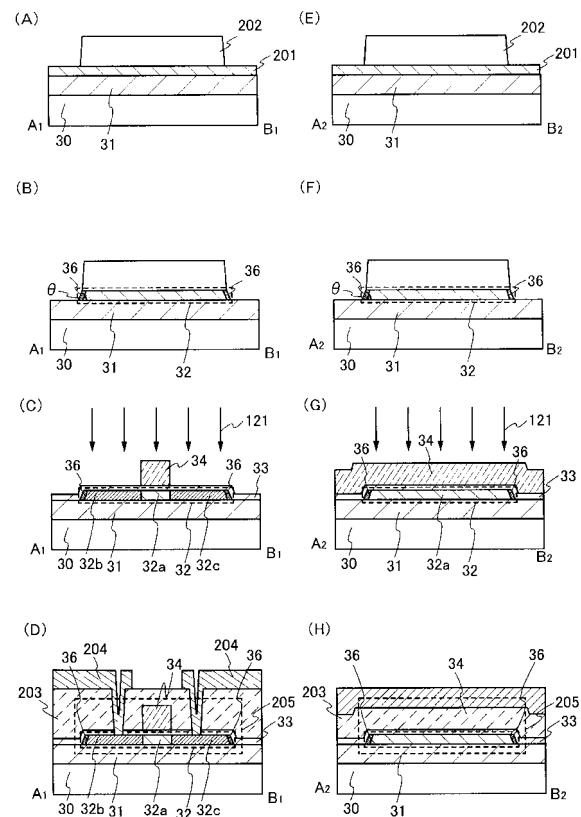

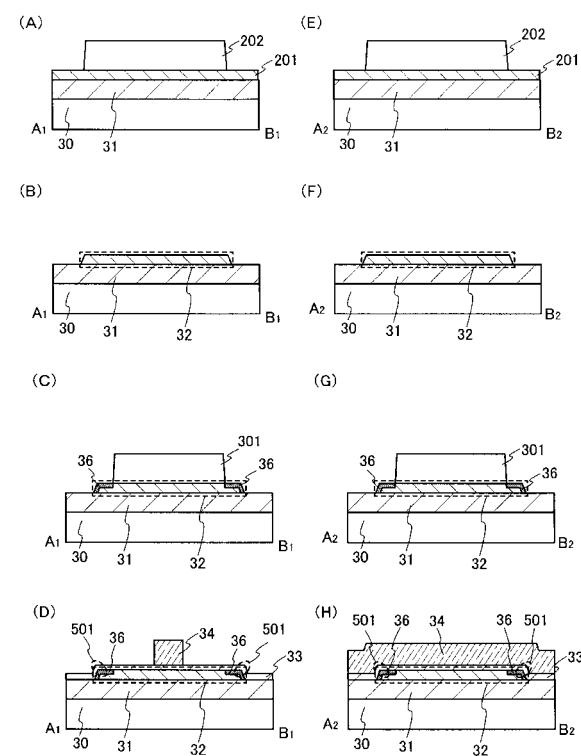

本実施の形態では、図1で示した半導体装置の作製方法の一例に関して図面を参照して説明する。なお、本実施の形態では、図1(A)のA<sub>1</sub>とB<sub>1</sub>とを結ぶ破線での断面における作製工程を図2(A)～(D)を用いて、図1(A)のA<sub>2</sub>とB<sub>2</sub>とを結ぶ破線での断面における作製工程を図2(E)～(H)を用いて説明する。

## 【0032】

まず、基板30上に絶縁層31を形成する(図2(A)、(E))。

## 【0033】

基板30は、ガラス基板、石英基板、金属基板(例えばステンレス基板など)、セラミック基板、Si基板等の半導体基板などを用いることができる。また、他にもプラスチック基板として、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)、アクリルなどの基板を選択することもできる。

30

## 【0034】

絶縁層31は、基板30からアルカリ金属などの不純物が拡散して、上に形成される素子の汚染を防ぐものであり、プロッキング層として適宜設ければよい。例えば、CVD法やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x>y>0)、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x>y>0)等の絶縁材料を用いて形成できる。例えば、絶縁層31を2層構造とする場合は、第1層目の絶縁層として窒化酸化シリコン膜を形成し、第2層目の絶縁層として酸化窒化シリコン膜を形成するとよい。また、第1層目の絶縁層として窒化シリコン膜を形成し、第2層目の絶縁層として酸化シリコン膜を形成してもよい。

40

## 【0035】

続いて、絶縁層31上に半導体層201を形成する。半導体層201は、非晶質半導体膜または結晶質半導体膜で形成できる。結晶性半導体膜としては、絶縁層31上に形成した非晶質半導体膜を熱処理やレーザ光の照射によって結晶化させたものなどを用いることができる。なお、半導体材料としては、シリコンが好ましく、その他にシリコンゲルマニウム等を用いることもできる。

## 【0036】

半導体層201は、10～200nm、好ましくは10～50nm程度、さらに好ましくは10～30nm程度の膜厚で形成するとよい。なお、50nm以下の半導体層201を

50

形成する場合、50 nm以上 の膜厚で半導体層を形成した後で、半導体層の表面をドライエッティング処理することにより10~50 nm程度の膜厚の半導体層201を形成してもよい。このときのエッティングの際のエッティングガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiC<sub>1</sub><sub>4</sub>等の塩素系のガス、CF<sub>4</sub>、NF<sub>3</sub>、SF<sub>6</sub>、CHF<sub>3</sub>等のフッ素系のガス、またはフッ素系ガスにHeやAr等の不活性ガス、O<sub>2</sub>ガス、H<sub>2</sub>ガス、を適宜加えた混合ガス等を用いることができる。なお、ドライエッティングの前に、半導体層表面を希フッ酸処理して半導体層表面に形成される自然酸化膜を除去し、その後半導体層表面をオゾン水などで処理して半導体層表面に酸化膜を形成しておいてもよい。

#### 【0037】

半導体層201を50 nm以下程度の薄膜で形成することにより、半導体層表面に形成されるゲート絶縁層の被覆不良を低減することができる。また、半導体層201を薄膜で形成することにより、TFTをより小型化することができる。また、TFTのしきい値電圧を小さくするためにチャネル形成領域への不純物元素のドープ量を増加させた場合でも、半導体層201を薄膜で形成することにより完全空乏型のTFTを作製しやすくなるため、良好なS値でしきい値電圧の小さなTFTを作製することができる。

10

#### 【0038】

また、非結晶半導体膜をレーザ光の照射によって結晶化もしくは再結晶化した膜を半導体層201として用いる場合、レーザ光の光源としてLD励起の連続発振(CW)レーザ(YVO<sub>4</sub>、第2高調波(波長532 nm))を用いることができる。特に第2高調波に限定する必要はないが、第2高調波はエネルギー効率の点で、さらに高次の高調波より優れている。CWレーザを半導体層に照射すると、連続的に半導体層にエネルギーが与えられるため、一旦半導体層を溶融状態にすると、溶融状態を継続させることができる。さらに、CWレーザを走査することによって半導体層の固液界面を移動させ、この移動の方向に沿って一方向に長い結晶粒を形成することができる。また、固体レーザを用いるのは、気体レーザ等と比較して、出力の安定性が高く、安定した処理が見込まれるためである。なお、CWレーザに限らず、繰り返し周波数が10 MHz以上のパルスレーザを用いることも可能である。繰り返し周波数が高いパルスレーザを用いると、半導体層が溶融してから固化するまでの時間よりもレーザのパルス間隔が短ければ、常に半導体層を溶融状態にとどめることができ、固液界面の移動により一方向に長い結晶粒で構成される半導体層を形成できる。また、その他のCWレーザおよび繰り返し周波数が10 MHz以上のパルスレーザを使用することもできる。例えば、気体レーザとしては、Arレーザ、Krレーザ、CO<sub>2</sub>レーザなどがある。固体レーザとして、YAGレーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、GdVO<sub>4</sub>レーザ、KGWレーザ、KYWレーザ、アレキサンンドライトレーザ、Ti:サファイアレーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、YVO<sub>4</sub>レーザなどがある。また、YAGレーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、GdVO<sub>4</sub>レーザ、YVO<sub>4</sub>レーザなどのセラミックスレーザがある。金属蒸気レーザとしてはヘリウムカドミウムレーザなどが挙げられる。また、レーザ発振器において、レーザ光をTEM<sub>00</sub>(シングル横モード)で発振して射出すると、被照射面において得られる線状のビームスポットのエネルギー均一性を上げることができるので好ましい。その他にも、パルス発振のエキシマレーザを用いてもよい。

20

#### 【0039】

30

次に、半導体層201上にレジスト202を選択的に形成する(図2(A)、(E))。なお、半導体層上に酸化膜を形成してから、レジストを形成してもよい。そして、レジスト202をマスクとして半導体層201をドライエッティングして、島状の半導体層32を形成する(図2(B)、(F))。なお、レジスト202は、エッティングの際のマスクとして用いるものであり、ポジ型のフォトレジストやネガ型のフォトレジスト等を適宜選択して用いることができる。

40

#### 【0040】

ドライエッティングのときのエッティングガスとしては、CF<sub>4</sub>、NF<sub>3</sub>、SF<sub>6</sub>、CHF<sub>3</sub>等のフッ素系のガス、または該フッ素系ガスにHeやAr等の不活性ガス、O<sub>2</sub>ガス、H<sub>2</sub>ガス、を適宜加えた混合ガス等を用いることができる。好ましくは、CF<sub>4</sub>とO<sub>2</sub>との

50

混合ガス、 $SF_6$ と $O_2$ との混合ガス、 $CHF_3$ と $He$ との混合ガス、または $CF_4$ と $H_2$ との混合ガスを用いるとよい。また、エッチングはドライエッチングに限られず、ウェットエッチングで行ってもよい。その場合、半導体層301に対し、TMAH (tetramethylammonium hydroxide、テトラメチルアンモニウムヒドロキシド) に代表される有機アルカリ系水溶液を用いてウェットエッチングすることにより、島状の半導体層32を形成できる。なお、エッチング液としてTMAH等を用いた場合、半導体層301のみが選択的にエッチングされるため、下地の絶縁層31にダメージを与えずにエッチングできる。このように、絶縁表面に形成された半導体層を島状に分離形成することで、同一基板上に複数の薄膜トランジスタと周辺回路を形成した場合に、それぞれの素子を分離できる。すなわち、10V～20V程度の電圧で書き込みや消去を行う必要のあるメモリ素子アレイと、3V～7V程度の電圧で動作してデータの入出力や命令の制御を主として行う周辺回路を同一基板上に形成した場合でも、各素子に印加する電圧の違いによる相互の干渉を防ぐことができる。

10

#### 【0041】

また、島状の半導体層32の端部の断面形状は、必ずしもテーパー状になっている必要はない。半導体層32の端部付近に形成される膜の被覆不良の低減を考慮すると、よりの角度が小さいほうが好ましいが、が $45^\circ$ ～ $95^\circ$ 程度のテーパー状や垂直形状にエッチングしてもよい。

#### 【0042】

続いて、半導体層32の端部に絶縁層36を形成する(図2(B)、(F))。ここで、絶縁層36は、実施の形態1と同様に、半導体層32の端部をウェット酸化することにより形成された酸化膜である。

20

#### 【0043】

続いて、半導体層32を覆うようにゲート絶縁層33を形成する。ゲート絶縁層33は、酸化シリコン、窒化シリコン、酸化窒化シリコン( $SiO_xNy$ )( $x > y > 0$ )、窒化酸化シリコン( $SiNxOy$ )( $x > y > 0$ )等を用いて形成できる。このような絶縁層は、気相成長法やスパッタリング法で形成できる。また、酸素を含む雰囲気下または窒素を含む雰囲気下で半導体層32表面をプラズマ処理することにより、半導体層32表面に形成された酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン( $SiO_xNy$ )( $x > y > 0$ )膜、または窒化酸化シリコン( $SiNxOy$ )( $x > y > 0$ )膜等をゲート絶縁層33として用いることもできる。

30

#### 【0044】

次に、ゲート絶縁層33上にゲート電極として機能する導電層34を形成する(図2(C)、(G))。ここでは、導電層34は単層で形成した例を示しているが、もちろん、導電性材料を2層または3層以上の積層で設けた構造としてもよい。なお、ここでは図示しないが、導電層34は、ゲート絶縁層33上を覆って形成された導電層を選択的にエッチングすることにより形成できる。

#### 【0045】

また、導電層34は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料、もしくは化合物材料で形成できる。また、リン等の不純物元素をドーピングした多結晶硅素に代表される半導体材料により形成することもできる。例えば、導電層34を第1の導電層と第2の導電層との積層構造とする場合、第1の導電層として窒化タンタルを用い、第2の導電層としてタングステンを用いて形成するとよい。なお、この組み合わせに限られず、導電層34を積層して形成する場合には、上記材料を自由に組み合わせて設けることができる。

40

#### 【0046】

続いて、導電層34をマスクとして、半導体層32に不純物元素121を導入することによって、半導体層32に不純物領域32b、32cおよび不純物元素121が導入されないチャネル形成領域32aを形成する(図2(C)、(G))。なお、ここでは、島状の

50

半導体層32を横断するように導電層34を形成した後に、不純物元素を導入するため、導電層34に覆われていない半導体層32の領域に不純物領域32b、32cが形成され、導電層34に覆われた半導体層32の領域に不純物元素121が導入されないチャネル形成領域32aが形成される。

【0047】

ここで、不純物元素121としては、n型を付与する不純物元素またはp型を付与する不純物元素を用いることができる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。例えば、不純物元素121として、リン(P)を $1 \times 10^{18} \sim 1 \times 10^{21} / \text{cm}^3$ の濃度で含むように半導体層32に導入し、n型を示す不純物領域32b、32cを形成すればよい。なお、チャネル形成領域32aと不純物領域32b、32cとの間に、不純物領域32b、32cより低濃度に不純物が添加された低濃度不純物領域(LDD領域)を形成してもよい。低濃度不純物領域を設けることにより、LDD領域側のドレイン端部の電界を緩和して、書き込みおよび消去の繰り返しによる劣化を抑制できる。

【0048】

また、チャネル形成領域32a中に、不純物領域32b、32cに添加した不純物とは逆の導電型を有する不純物元素(例えばn型TFTに対してはボロン)を添加してもよい。チャネル形成領域32a中に逆導電型の不純物を添加することにより、TFTのしきい値電圧を制御できる。なお、この不純物元素はゲート電極を介してドープすることによって添加してもよいし、ゲート電極形成前に予め添加しておいてもよい。

【0049】

次に、導電層34、ゲート絶縁層33、絶縁層31等を覆うように絶縁層203を形成する(図2(D)、(H))。その後、ゲート絶縁層33および絶縁層203にコンタクトホールを形成し、絶縁層203上にソース電極またはドレイン電極として機能する導電層204を選択的に形成する(図2(D)、(H))。ここで、導電層204は、半導体層32のソース領域またはドレイン領域として機能する不純物領域32b、32cと電気的に接続されるように設ける。

【0050】

絶縁層203は、CVD法やスパッタリング法等で形成した、酸化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x > y > 0)、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x > y > 0)などを用いることができる。また、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル、エポキシ等の有機材料、またはシロキサン樹脂等のシロキサン材料、オキサゾール樹脂等からなる単層または積層構造で設けることができる。なお、シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、アリール基)が用いられる。置換基として、フルオロ基を用いることもできる。オキサゾール樹脂は、例えば、感光性ポリベンゾオキサゾール等である。感光性ポリベンゾオキサゾールは、誘電率が低く(常温1MHzで誘電率2.9)、耐熱性が高く(示差熱熱重量同時測定(TG/DTA: Thermogravimetry-Differential Thermal Analysis)で昇温5/minで熱分解温度550)、吸水率が低い(常温24時間で0.3%)材料である。オキサゾール樹脂は、ポリイミド等の比誘電率(3.2~3.4程度)と比較すると、比誘電率が低いため(2.9程度)、寄生容量の発生を抑制し、高速に動作できる。ここでは、絶縁層203として、CVD法で形成した酸化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x > y > 0)または窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x > y > 0)を単層または積層して形成する。また、さらに、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル、エポキシ等の有機材料、シロキサン樹脂等のシロキサン材料、またはオキサゾール樹脂を積層して形成してもよい。

【0051】

10

20

30

40

50

また、導電層 204 は、アルミニウム、タングステン、チタン、タンタル、モリブデン、ニッケル、ネオジムから選ばれた 1 種の元素、または当該元素を複数含む合金からなる単層構造または積層構造を用いることができる。例えば、当該元素を複数含む合金からなる導電層 204 として、チタンを含有したアルミニウム合金、ネオジムを含有したアルミニウム合金などで形成できる。また、積層構造で導電層 204 を設ける場合、例えば、アルミニウム層もしくは前記したようなアルミニウム合金層を、チタン層で挟んで積層させた構造としてもよい。

#### 【 0052 】

以上の工程により、薄膜トランジスタ 205 を含む半導体装置を作製できる。

#### 【 0053 】

本実施の形態に示す半導体装置の作製工程を用いることにより、ゲート電極下の半導体層 32 のチャネル形成領域 32a の端部（側面）に、絶縁層 36 を有する半導体装置を作製することができる。したがって、ゲート絶縁層 33 の半導体層 32 表面への被覆不良が、半導体装置に及ぼす影響を低減できる。つまり、本実施の形態の方法を用いて作製された半導体装置は、半導体層 32 のチャネル形成領域 32a の側面がゲート電極と接することができなくなるため、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることができとなる。

#### 【 0054 】

また、半導体層 32 のチャネル形成領域 32a の端部に、選択的に厚く絶縁層を設けることができるため、半導体層 32 のチャネル形成領域 32a の端部における電界集中を緩和することができる。したがって、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることができとなる。

#### 【 0055 】

本実施の形態において、酸素を含む雰囲気下または窒素を含む雰囲気下で、半導体層 32 表面をプラズマ処理してゲート絶縁層 33 を形成する際、電子密度が  $1 \times 10^{11} \text{ cm}^{-3}$  以上であり、電子温度が 1.5 eV 以下のプラズマを用いるとよい。より詳しくは、電子密度が  $1 \times 10^{11} \text{ cm}^{-3}$  以上  $1 \times 10^{13} \text{ cm}^{-3}$  以下で、電子温度が 0.5 eV 以上 1.5 eV 以下のプラズマを用いるとよい。上記プラズマは、プラズマの電子密度が高密度であり、基板 30 上に形成された被処理物（ここでは、半導体層 32）付近での電子温度が低いため、被処理物に対するプラズマによる損傷を防止できる。また、プラズマの電子密度が  $1 \times 10^{11} \text{ cm}^{-3}$  以上と高密度であるため、プラズマ処理を用いて形成される酸化膜または窒化膜は、CVD 法やスパッタ法等により形成された膜と比較して、膜厚等が均一性に優れ、かつ緻密な膜を形成できる。また、プラズマの電子温度が 1.5 eV 以下と低いため、従来のプラズマ処理や熱酸化法と比較して低い温度で酸化または窒化処理できる。例えば、ガラス基板の歪点よりも 100 度以上低い温度でプラズマ処理を行っても十分に酸化できる。また、プラズマを形成するための周波数としては、マイクロ波（2.45 GHz）等の高周波を用いることができる。

#### 【 0056 】

なお、酸素を含む雰囲気下として、例えば、酸素（O<sub>2</sub>）と希ガス（He、Ne、Ar、Kr、Xe の少なくとも 1 つを含む）との混合ガス雰囲気下、酸素と水素（H<sub>2</sub>）と希ガスとの混合ガス雰囲気下、一酸化二窒素と希ガスとの混合ガス雰囲気下、または一酸化二窒素と水素と希ガスとの混合ガス雰囲気下でプラズマ処理できる。例えば、酸素（O<sub>2</sub>）と水素（H<sub>2</sub>）とアルゴン（Ar）との混合ガスを用いることができる。その場合、酸素を 0.1 ~ 100 sccm、水素を 0.1 ~ 100 sccm、アルゴンを 100 ~ 500 0 sccm 含んだ混合ガスを用いることができる。なお、酸素：水素：アルゴン = 1 : 1 : 100 の比率で混合ガスを導入することが好ましい。例えば、酸素を 5 sccm、水素を 5 sccm、アルゴンを 500 sccm として導入すればよい。

#### 【 0057 】

また、窒素を含む雰囲気下として例えば、窒素（N<sub>2</sub>）と希ガス（He、Ne、Ar、Kr、Xe の少なくとも 1 つを含む）との混合ガス雰囲気下、窒素と水素と希ガスとの混合

10

20

30

40

50

ガス雰囲気下、またはアンモニア (NH<sub>3</sub>) と希ガスとの混合ガス雰囲気下でプラズマ処理できる。

【0058】

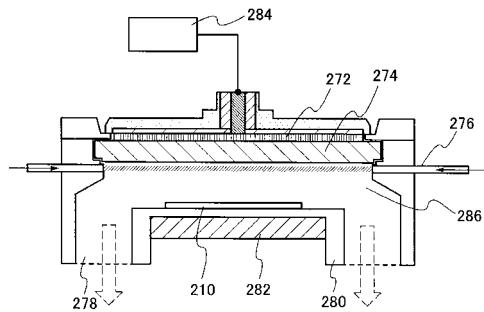

ここで、プラズマ処理するための装置の構成例について図17を用いて説明する。

【0059】

図17に示すプラズマ処理装置は、基板210を配置するための支持台280、ガスを導入するためのガス供給部276、ガスを排気するために真空ポンプに接続する排気口278、アンテナ272、誘電体板274およびプラズマ発生用のマイクロ波を供給するマイクロ波供給部284を有している。また、支持台280に温度制御部282を設けることによって、基板210の温度を制御することも可能である。

10

【0060】

以下に、プラズマ処理方法の一例について説明する。

【0061】

酸化処理もしくは窒化処理を行うには、以下のようにすればよい。まず、処理室内を真空にし、ガス供給部276から酸素または窒素を含むプラズマ処理用ガスを導入する。基板210は、室温もしくは温度制御部282により100～550に加熱する。なお、基板210と誘電体板274との間隔は、20mm～80mm（好ましくは20mm～60mm）程度である。次に、マイクロ波供給部284からアンテナ272に、マイクロ波を供給する。そしてマイクロ波を、アンテナ272から誘電体板274を通して処理室内に導入することによって、プラズマ286を生成する。マイクロ波の導入によりプラズマの励起を行うと、低電子温度（3eV以下、好ましくは1.5eV以下）で高電子密度（1×10<sup>11</sup>cm<sup>-3</sup>以上）のプラズマを生成できる。この高密度プラズマで生成された酸素ラジカル（OHラジカルを含む場合もある）および/または窒素ラジカル（NHラジカルを含む場合もある）によって、半導体基板の表面を酸化または窒化することができる。プラズマ処理用ガスにアルゴンなどの希ガスを混合させると、希ガスの励起種により酸素ラジカルや窒素ラジカルを効率良く生成できる。このプラズマ処理方法では、プラズマで励起した活性なラジカルを有效地に使うことにより、500以下の低温で固相反応による酸化処理または窒化処理ができる。

20

【0062】

上記のようなプラズマ処理による固相酸化処理または固相窒化処理を用いることで、耐熱温度が700以下ガラス基板を用いても、950～1050で形成される熱酸化膜と同等な絶縁層を得ることができる。すなわち、半導体素子、特に薄膜トランジスタや不揮発性記憶素子の絶縁層として信頼性の高い絶縁層を形成できる。

30

【0063】

例えば、図17に示すプラズマ処理装置を用いてゲート絶縁層33を形成する場合、酸化雰囲気下のプラズマ処理により、例えば、シリコンからなる半導体層32の表面を酸化して3～6nmの厚さの酸化珪素層を形成し、その後、該酸化珪素層の表面を窒素雰囲気下でプラズマ処理した窒素プラズマ処理層を形成することが好ましい。具体的には、まず、酸化雰囲気下でのプラズマ処理により、半導体層32上に3～6nmの厚さで酸化珪素層を形成する。その後、続けて窒素雰囲気下でプラズマ処理を行うことにより、酸化珪素層の表面または表面近傍に窒素濃度の高い窒素プラズマ処理層を設ける。なお、表面近傍とは、酸化珪素層の表面から概略0.5～1.5nmの深さをいう。例えば、窒素雰囲気下でプラズマ処理を行うことによって、酸化珪素層の表面から概略1nmの深さに、窒素を20～50原子%の割合で含有した構造となる。酸化珪素層表面を窒化することにより、さらに層を緻密化することができ、絶縁耐圧が高い絶縁層を形成できる。

40

【0064】

なお、本実施の形態で示すプラズマ処理装置は、半導体基板、絶縁層、導電層に対する酸化処理、窒化処理、酸窒化処理、水素化処理、表面改質処理等を行うことができる。これらの処理を行う際は、その目的に応じてガス供給部276から供給するガスを適宜選択すればよい。

50

## 【0065】

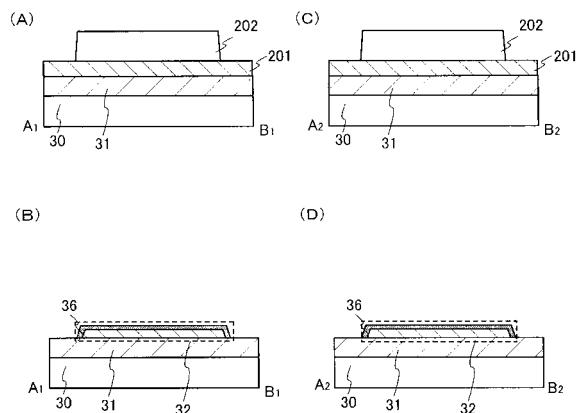

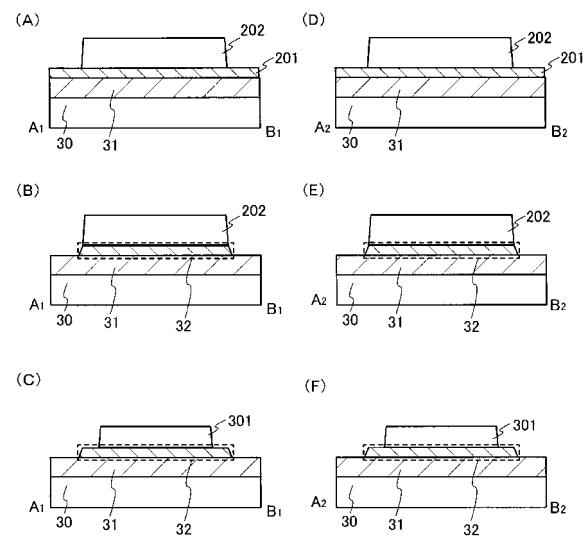

## (実施の形態3)

本実施の形態では、図1に示す半導体装置の作製方法について、実施の形態2とは異なる方法について説明する。本実施の形態では図1(A)のA<sub>1</sub>とB<sub>1</sub>とを結ぶ破線での断面における作製工程を図3(A)～(B)を用いて、図1(A)のA<sub>2</sub>とB<sub>2</sub>とを結ぶ破線での断面における作製工程を図3(C)～(D)を用いて説明する。

## 【0066】

まず、実施の形態2と同様に、基板30上に絶縁層31を形成し、絶縁層31上に半導体層201を形成し、半導体層201上にレジスト202を形成する(図3(A)、(C))。

10

## 【0067】

続いて、レジスト202をマスクとして半導体層201をエッチングすることにより、島状の半導体層32を形成する(図3(B)、(D))。

## 【0068】

続いて、レジスト202を除去した後、半導体層32表面をウェット酸化することにより、半導体層32の端部および表面に絶縁層36を形成する。

## 【0069】

以降の工程は、実施の形態2と同様に行うことにより、図1に示す半導体装置を作製できる。

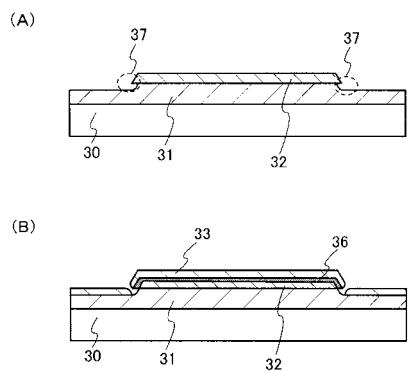

## 【0070】

なお、半導体層32の表面をウェット酸化して絶縁層36を形成する前に、必要に応じて半導体層32表面を希フッ酸等で洗浄する工程を行ってもよい。半導体層32の表面は、大気中の酸素に半導体層32が触れて酸化され自然酸化膜が形成されていたり、ゴミが付着していたりするため、洗浄することが好ましい。しかしながら、半導体層32を洗浄する際、図4(A)に示すように、半導体層32の下地膜として形成されている絶縁層31も部分的に除去され、窪み37が形成されることがある。窪み37が形成された場合に、半導体層32上にゲート絶縁層を形成すると、半導体層32および窪み37の段差を覆いきれず、ゲート絶縁層が部分的に切断されてしまうことがある。すると、半導体層32とゲート電極として機能する導電層とが接して、半導体層32およびゲート電極として機能する導電層の間でリーク電流が生じてしまう可能性がある。

20

## 【0071】

しかしながら、本実施の形態で示すように、半導体層表面をウェット酸化して、半導体層32の端部および表面に絶縁層36を形成することにより、図4(B)に示すように、窪み37部分でゲート絶縁層33の被覆不良が生じても、半導体層32のチャネル形成領域とゲート電極として機能する導電層とが接することがなくなる。

## 【0072】

また、半導体層32表面を希フッ酸処理した後、ゲート絶縁層33を形成してから、ウェット酸化してもよい。図5に、半導体層32表面を希フッ酸処理した後の素子の断面構造を示す。図5(A)、(E)は、希フッ酸処理によって絶縁層31が部分的に除去されている様子を示す。

30

## 【0073】

次に、半導体層32上に、ゲート絶縁層33を形成する(図5(B)、(F))。なお、ゲート絶縁層33は上記実施の形態のゲート絶縁層33と同様に作製することができる。ここで、絶縁層31が部分的に除去されているため、ゲート絶縁層33は半導体層32の下側には形成されない可能性がある。

## 【0074】

次に、ゲート絶縁層33の表面をウェット酸化する。ここで、半導体層32表面のゲート絶縁層33で覆われていない部分がウェット酸化されて、ゲート絶縁層33で覆われていない半導体層32表面に絶縁層36を形成できる(図5(C)、(G))。

## 【0075】

40

50

次に、ゲート絶縁層33上に、ゲート電極として機能する導電層34を形成する(図5(D)、(H))。なお、導電層34は、上記実施の形態で示した導電層34と同様に形成できる。

**【0076】**

半導体層32表面を希フッ酸処理した後、ゲート絶縁層33を形成してからさらにウェット酸化を行うことによって、ゲート絶縁層33で覆われない半導体層32表面にも絶縁層36を形成できる。したがって、半導体層32の表面は、ゲート電極として機能する導電層34と接しない構成とできる。

**【0077】**

本実施の形態に示す半導体装置の作製工程を用いることにより、ゲート電極下の半導体層32のチャネル形成領域32aの端部(側面)に、絶縁層36を有する半導体装置を作製できる。したがって、ゲート絶縁層33の半導体層32表面への被覆不良が、半導体装置に及ぼす影響を低減できる。つまり、本実施の形態の方法を用いて作製された半導体装置において、半導体層32のチャネル形成領域32aの側面は、ゲート電極と接することができないため、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

10

**【0078】**

また、半導体層32のチャネル形成領域32aの端部に選択的に厚く絶縁層を設けることができるため、半導体層32のチャネル形成領域32aの端部における電界集中を緩和できる。したがって、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

20

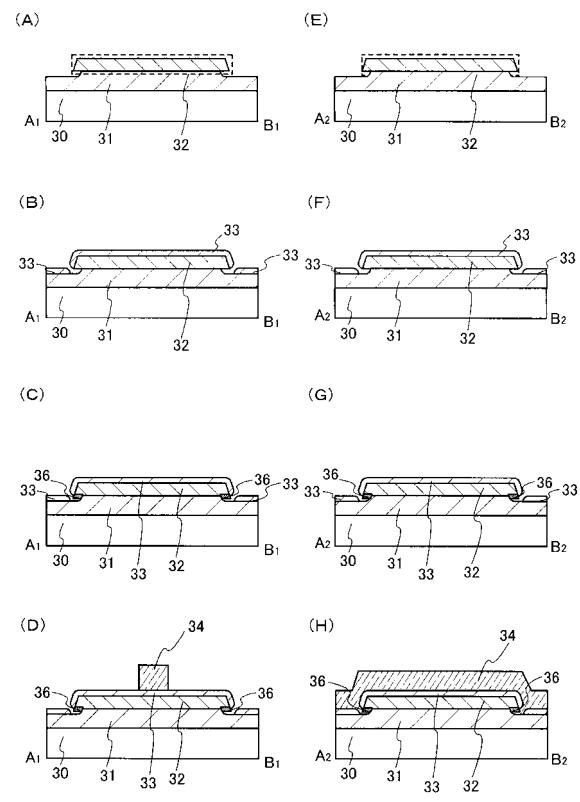

**【0079】**

(実施の形態4)

本実施の形態では、図1に示す半導体装置の作製方法について、実施の形態2または実施の形態3とは異なる方法について説明する。本実施の形態では、図1(A)のA<sub>1</sub>とB<sub>1</sub>とを結ぶ破線での断面における作製工程を図6(A)～(D)を用いて、図1(A)のA<sub>2</sub>とB<sub>2</sub>とを結ぶ破線での断面における作製工程を図6(E)～(H)を用いて説明する。

**【0080】**

まず、実施の形態2と同様に、基板30上に絶縁層31を形成し、絶縁層31上に半導体層201を形成し、半導体層201上にレジスト202を形成する(図6(A)、(E))。

30

**【0081】**

次に、レジスト202をマスクとして半導体層201をエッチングすることにより、島状の半導体層32を形成する(図6(B)、(F))。続いて、レジスト202を除去し、半導体層32表面を希フッ酸で洗浄する(図6(B)、(F))。ここで、半導体層32上に第1の絶縁層33を形成する前に、半導体層32表面を希フッ酸で処理することにより、半導体層32表面に形成される自然酸化膜を除去できる。

**【0082】**

次に、半導体層32上にレジスト301を形成する(図6(C)、(G))。ここで、レジスト301は、半導体層32より内側の領域に形成する。つまり、レジスト301は、半導体層32の表面を部分的に覆っている。

40

**【0083】**

なお、半導体層32の表面を部分的に覆うレジスト301は、半導体層201表面に形成されたレジスト202を除去せず、レジスト202を部分的にエッチングしてレジスト202の側面を後退させることにより形成してもよい。つまり、まず図6(A)、(E)と同様に基板30上に絶縁層31を形成し、絶縁層31上に半導体層201を形成し、半導体層201上にレジスト202を形成する(図7(A)、(D))。次に、レジスト202をマスクとして半導体層201をエッチングすることにより、島状の半導体層32を形成する(図7(B)、(E))。続いて、レジスト202をエッチングしてレジスト2

50

02の側面を後退させる。これにより、レジスト202の幅が細くなり、半導体層32の表面が部分的に覆われたレジスト301が形成される。

【0084】

次に、レジスト301をマスクとして半導体層32表面をウェット酸化することにより、半導体層32の端部および上面の一部に絶縁層36を形成する(図6(C)、(G))。

【0085】

次に、レジスト301を除去して、半導体層32上にゲート絶縁層33を形成する。さらに、ゲート絶縁層33上にゲート電極として機能する導電層34を形成する(図6(D)、(H))。なお、ゲート絶縁層33および導電層34はそれぞれ、上記実施の形態で説明したゲート絶縁層33および導電層34と同様に形成できる。

10

【0086】

以降、実施の形態2と同様の工程を行うことにより、図1に示すような半導体装置を作製できる。

【0087】

半導体層32の端部および上面の一部に絶縁層36が形成されているため、より電界が集中しやすい半導体層32の角部(図6(D)、(H)の領域501付近)において、導電層34下に形成される絶縁層の膜厚を厚くできる。したがって、より電界集中を防ぐことができる。

【0088】

本実施の形態に示す半導体装置の作製工程を用いることにより、ゲート電極下の半導体層のチャネル形成領域32aの端部(側面)に、絶縁層36を有する半導体装置を作製できる。したがって、ゲート絶縁層33の半導体層32表面への被覆不良が、半導体装置に及ぼす影響を低減できる。つまり、本実施の形態の方法を用いて作製された半導体装置は、半導体層32のチャネル形成領域32aの側面が、ゲート電極と接することがなくなるため、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

20

【0089】

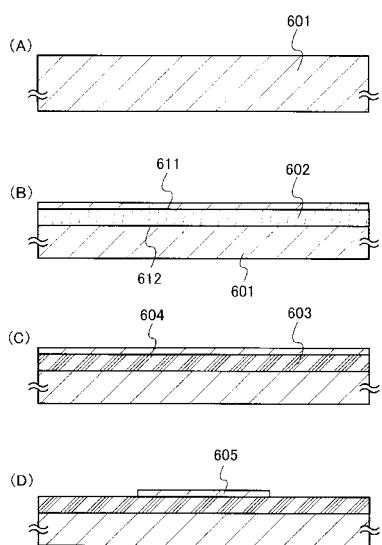

(実施の形態5)

本実施の形態では、単結晶シリコン基板上に酸化シリコンでなる酸化膜を形成し、酸化膜上に形成された単結晶半導体薄膜をチャネル形成領域として用いる半導体装置について説明する。本実施の形態では、SIMOXと呼ばれるSOI技術を用いた半導体装置について説明する。

30

【0090】

まず、単結晶シリコン層の形成材料となる単結晶シリコン基板601を用意する(図8(A))。ここではP型の単結晶シリコン基板を用いる場合を説明するが、N型の単結晶シリコン基板であってもよい。もちろん、単結晶シリコンゲルマニウム基板を用いることもできる。

【0091】

続いて、単結晶シリコン基板601に対して酸素イオンを添加し、所定の深さに酸素含有層602を形成する(図8(B))。酸素イオンは、例えば $1 \times 10^{18}$  atoms/cm<sup>2</sup>程度のドーズ量で添加すればよい。なお、酸素含有層602が形成される深さ(単結晶シリコン基板601の主表面と酸素含有層602との間の距離)は、後に形成されるTFTの活性層として機能する単結晶シリコン層の膜厚となる。

40

【0092】

次に、800~1200の温度で熱処理を行い、酸素含有層602を埋め込み絶縁層603に変化させる。酸素含有層602の深さ方向の幅は、イオン添加時の酸素イオンの分布で決まっている。酸素イオンの濃度が611から612に向かって減少していくため、単結晶シリコン基板601と酸素含有層602との界面は不明確であるが、この熱処理工程により単結晶シリコン基板601と埋め込み絶縁層603との界面は明確なものとなる(図8(B)、(C))。

【0093】

50

この埋め込み絶縁層 603 の膜厚は 10 ~ 500 nm ( 代表的には 20 ~ 50 nm ) とする。本実施の形態では、単結晶シリコン基板 601 と埋め込み絶縁層 603 の界面が安定に接合されているため、20 ~ 50 nm といった薄い埋め込み絶縁層 603 を形成することができる。

【 0094 】

こうして埋め込み絶縁層 603 が形成されると、埋め込み絶縁層 603 の上には部分的に単結晶シリコン基板の一部が残存し、単結晶シリコン層 604 が形成される。なお、単結晶シリコン層 604 の膜厚は 10 ~ 200 nm ( 好ましくは 10 ~ 50 nm 、さらに好ましくは 10 ~ 30 nm ) となるように、酸素含有層 602 が形成される深さを調節すればよい。

10

【 0095 】

次に、単結晶シリコン層 604 上に選択的にレジストを形成して、単結晶シリコン層 604 を選択的にエッチングすることにより、後に形成される TFT の活性層となる、島状の単結晶シリコン層 605 を形成する ( 図 8 ( D ) ) 。なお、本実施の形態では 1 つの島状の単結晶シリコン層しか記載していないが、同一基板上に複数個が形成されていてもよい。

【 0096 】

以降、実施の形態 2 または実施の形態 3 と同様の工程を行うことにより、図 9 に示すような半導体装置を作製することができる。なお、本実施の形態において、半導体装置として薄膜トランジスタの例を示す。図 9 ( A ) は、薄膜トランジスタの要部の上面図を示し、図 9 ( B ) は、図 9 ( A ) の A<sub>1</sub> と B<sub>1</sub> とを結ぶ破線における断面図を示し、図 9 ( C ) は、図 9 ( A ) の A<sub>2</sub> と B<sub>2</sub> とを結ぶ破線における断面図を示している。

20

【 0097 】

図 9 に示す薄膜トランジスタは、単結晶シリコン基板 601 上に埋め込み絶縁層 603 を介して設けられた島状の単結晶シリコン層 605 と、島状の単結晶シリコン層 605 上に形成されたゲート絶縁層 33 と、島状の単結晶シリコン層 605 の上方にゲート絶縁層 33 を介して設けられたゲート電極として機能する導電層 34 と、ゲート絶縁層 33 および導電層 34 を覆って設けられた絶縁層 203 と、絶縁層 203 上に設けられたソース電極またはドレイン電極として機能する導電層 204 と、を有している。なお、島状の単結晶シリコン層 605 は、チャネル形成領域 605a とソース領域またはドレイン領域として機能する不純物領域 605b 、 605c とに加えて、島状の単結晶シリコン層 605 の端部、ここでは導電層 34 の下方のチャネル形成領域 605a に接した部分に形成された絶縁層 36 を有している。なお、絶縁層 36 は、島状の単結晶シリコン層 605 の表面を、酸素を含む雰囲気中でプラズマ処理することにより形成できる。なお、チャネル形成領域 605a 中に、不純物領域 605b 、 605c に添加した不純物とは逆の導電型の不純物が添加されていてもよい。

30

【 0098 】

本実施の形態によって、ゲート電極下の単結晶シリコン層 605 のチャネル形成領域 605a の端部 ( 側面 ) に、絶縁層 36 を有する半導体装置を作製できる。したがって、ゲート絶縁層 33 の単結晶シリコン層 605 表面への被覆不良が、半導体装置に及ぼす影響を低減できる。つまり、本実施の形態の方法を用いて作製された半導体装置は、単結晶シリコン層 605 のチャネル形成領域 605a の側面がゲート電極と接しないため、電界集中が生じず、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

40

【 0099 】

また、単結晶シリコン層 605 のチャネル形成領域 605a の端部に、選択的に厚く絶縁層を設けることができるため、単結晶シリコン層 605 のチャネル形成領域 605a の端部における電界集中を緩和できる。したがって、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

【 0100 】

50

## (実施の形態 6 )

本実施の形態では、単結晶シリコン基板上に酸化シリコンでなる酸化膜を形成し、酸化膜上に形成された単結晶半導体薄膜をチャネル形成領域として用いる半導体装置について説明する。本実施の形態では、Smart-Cut法を用いて形成されるSOI基板を用いた半導体装置について説明する。

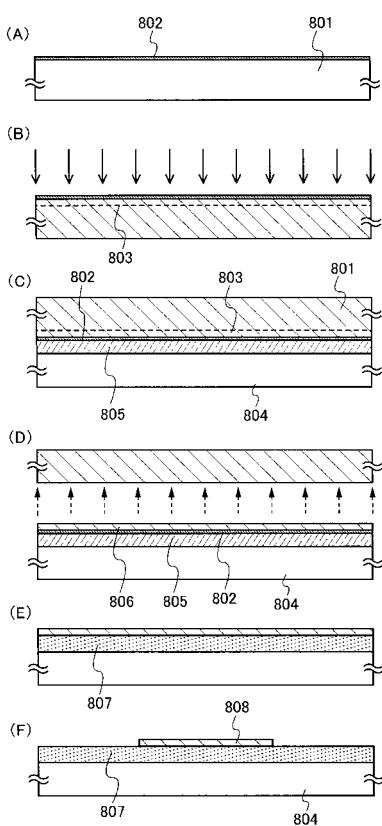

## 【0101】

まず、単結晶シリコン層の形成材料となる、単結晶シリコン基板801を用意する。ここではP型の単結晶シリコン基板を用いる場合を説明するが、N型の単結晶シリコン基板であってもよい。もちろん、単結晶シリコンゲルマニウム基板を用いることもできる。

## 【0102】

次いで熱酸化処理を行い、その主表面（素子形成面に相当する）に酸化シリコン膜802を形成する。膜厚は実施者が適宜決定すればよいが、10～500nm（代表的には20～50nm）とすればよい。この酸化シリコン膜802は、後にSOI基板の埋め込み絶縁層の一部として機能する（図10（A））。

## 【0103】

次に、単結晶シリコン基板801の主表面側から、酸化シリコン膜802を通して水素イオンを添加して、水素含有層803を形成する（図10（B））。なお、水素含有層803が形成される深さ（単結晶シリコン基板801の主表面と水素含有層803との間の距離）は、後に形成されるTFTの活性層として機能する単結晶シリコン層の膜厚となる。例えば、単結晶シリコン基板801の主表面と水素含有層803との間に50nm厚の単結晶シリコン層が残るように、イオンインプランテーション法を用いて水素イオンを $1 \times 10^{16} \sim 1 \times 10^{17}$ atoms/cm<sup>2</sup>のドーザ量で添加できる。

## 【0104】

次に、単結晶シリコン基板801と支持基板とを貼り合わせる。本実施の形態では支持基板として単結晶シリコン基板804を用い、その表面には貼り合わせ用の酸化シリコン膜805を設けておく（図10（C））。なお、単結晶シリコン基板804のかわりに、FZ法で形成されたシリコン基板、多結晶シリコン基板等を用いてもよい。また、石英基板、セラミックス基板、結晶化ガラス基板などの高耐熱性基板を用いてもよい。

## 【0105】

この時、貼り合わせ界面は親水性の高い酸化シリコン膜同士となるので、両表面に含まれた水分の反応により水素結合で接着される。

## 【0106】

次に、400～600（例えば500）の熱処理（第1熱処理）を行う。この熱処理により水素含有層803では微小空乏の体積変化が起こり、水素含有層803に沿って破断面が発生する。これにより単結晶シリコン基板801は分断され、支持基板の上には酸化シリコン膜802と単結晶シリコン層806が残される（図10（D））。

## 【0107】

次に、第2熱処理工程として1050～1150（例えば1100）の温度範囲でファーネスアニール工程を行う。この工程では貼り合わせ界面において、Si-O-Si結合の応力緩和が起こり、貼り合わせ界面が安定化する。すなわち、単結晶シリコン層806を支持基板上に完全に接着させるための工程となる。こうして貼り合わせ界面が安定化することで、埋め込み絶縁層807が形成される（図10（E））。なお、本実施の形態では、水素含有層803を形成し、水素含有層803に沿って破断面を発生させて薄膜の単結晶シリコン層806を形成しているが、単結晶シリコン層806を形成する方法はこれに限られるものではなく、水素含有層803を設けずに単結晶シリコン基板801を研磨することにより薄膜の単結晶シリコン層806を形成してもよい。

## 【0108】

次に、単結晶シリコン層806の表面を平坦化する処理を行ってもよい。平坦化にはCMP（ケミカルメカニカルポリッシング）と呼ばれる研磨工程や、還元雰囲気中で高温（900～1200程度）のファーネスアニール処理を行えばよい。

10

20

30

40

50

## 【0109】

最終的な単結晶シリコン層806の膜厚は、10～200nm（好ましくは10～50nm、さらに好ましくは10～30nm）とすればよい。

## 【0110】

次に、単結晶シリコン層806上に選択的にレジストを形成して、単結晶シリコン層806を選択的にエッチングすることにより、後に形成されるTFTの活性層となる島状の単結晶シリコン層808を形成する（図10（F））。なお、本実施の形態では1つの島状の単結晶シリコン層しか記載していないが、同一基板上に複数の島状の単結晶シリコン層が形成されていてもよい。

## 【0111】

以降、実施の形態2または実施の形態3と同様の工程を行うことにより、半導体装置として、島状の単結晶シリコン層を活性層として用いた薄膜トランジスタを形成できる。

## 【0112】

本実施の形態において作製される薄膜トランジスタは、例えば、単結晶シリコン基板804上に埋め込み絶縁層807を介して設けられた島状の単結晶シリコン層808と、島状の単結晶シリコン層808上に形成されたゲート絶縁層と、島状の単結晶シリコン層808の上方にゲート絶縁層を介して設けられたゲート電極として機能する導電層と、を有している。なお、島状の単結晶シリコン層808は、チャネル形成領域とソース領域またはドレイン領域として機能する不純物領域と、を有している。また、島状の単結晶シリコン層808の端部、ここではゲート電極として機能する導電層の下方のチャネル形成領域に接した部分には、絶縁層が形成されている。なお、チャネル形成領域に接して形成された絶縁層は、島状の単結晶シリコン層808表面を、酸素を含む雰囲気中でプラズマ処理することにより形成できる。

## 【0113】

本実施の形態によって、ゲート電極下の単結晶シリコン層のチャネル形成領域の端部（側面）に絶縁層を有する半導体装置を作製できる。したがって、ゲート絶縁層の単結晶シリコン層表面への被覆不良が半導体装置に及ぼす影響を低減できる。つまり、本実施の形態の方法を用いて作製された半導体装置は、単結晶シリコン層のチャネル形成領域の側面がゲート絶電極と接しないため、電界集中が生じず、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

## 【0114】

また、単結晶シリコン層のチャネル形成領域の端部に選択的に厚く絶縁層を設けることができるため、単結晶シリコン層のチャネル形成領域の端部における電界集中を緩和できる。したがって、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

## 【0115】

## （実施の形態7）

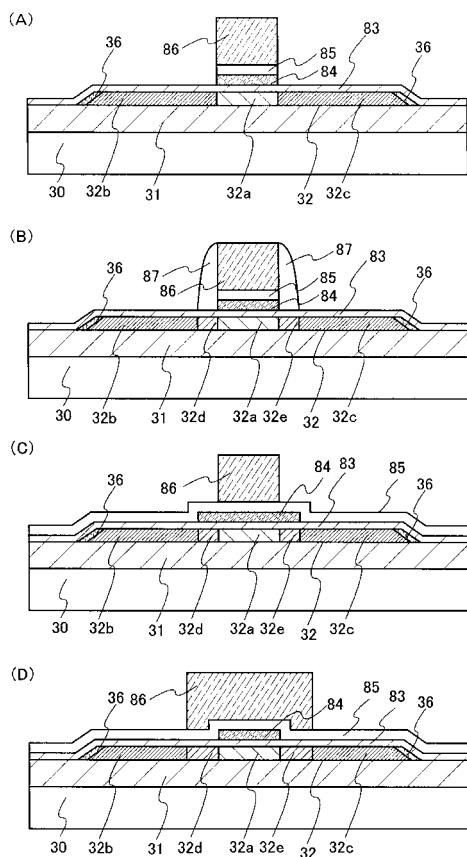

本発明の半導体装置は、薄膜トランジスタに限らず様々な形態をとることができる。本実施の形態では、本発明を適用した半導体装置の一例として、不揮発性記憶素子の構成について説明する。

## 【0116】

図12（A）に示す不揮発性記憶素子は、半導体層32上にトンネル酸化膜として機能する絶縁層83が形成され、絶縁層83上に電荷蓄積層84、コントロール絶縁膜として機能する絶縁層85およびゲート電極として機能する導電層86が形成される。また、電荷蓄積層84、コントロール絶縁膜として機能する絶縁層85およびゲート電極として機能する導電層86の端部が削っている。なお、本実施の形態における不揮発性記憶素子は、上記実施の形態で説明した方法を用いて半導体層32の端部に形成された絶縁層36を有している。また、図12（A）に示す不揮発性記憶素子は、半導体層32に低濃度不純物領域を有さず、チャネル形成領域32aおよび高濃度の不純物領域32b、32cで構成されるシングルドレイン構造である。このような不揮発性記憶素子は、低濃度不純物領域

10

20

30

40

50

を形成する工程が必要ないため、スループットを向上させることができる。

【0117】

トンネル酸化膜として機能する絶縁層83は、電荷蓄積層84に電荷を注入するためのトンネル絶縁層として用いる。絶縁層83は、実施の形態1で示すゲート絶縁層33と同様の材料および方法により形成できる。代表的には、酸化珪素、もしくは酸化珪素と窒化珪素の積層構造等で形成できる。また、図17に示す装置により高密度プラズマ処理して半導体層32の表面を酸化し、絶縁層83を形成してもよい。さらには、プラズマCVD法により酸化珪素を用いて半導体層32の表面に絶縁層を形成した後、図17に示す装置によりプラズマ処理し、酸化または窒化することにより絶縁層83を形成してもよい。この場合、酸化珪素の表面を窒化した場合は、酸化珪素層の表面または表面近傍に窒素濃度の高い窒素プラズマ処理層が設けられる。なお、表面近傍とは、酸化珪素層の表面から概略0.5~1.5nmの深さをいう。例えば、窒素雰囲気下でプラズマ処理を行うことによって、酸化珪素層の表面から概略1nmの深さに窒素を20~50原子%の割合で含有した構造となる。

【0118】

後述する電荷蓄積層84が導電層または半導体層で形成されるフローティングゲートの場合、絶縁層83は3~6nmの厚さに形成することが好ましい。例えば、ゲート長を600nmとする場合、絶縁層83は3~6nmの厚さに形成できる。また、後述する電荷蓄積層84が絶縁層で形成される場合、絶縁層83は1~10nm、好ましくは1~5nmの厚さに形成することが好ましい。例えば、ゲート長を600nmとする場合、絶縁層83は1~3nmの厚さに形成できる。

【0119】

電荷蓄積層84は、半導体材料または導電性材料の層または粒子で形成し、浮遊ゲートとできる。半導体材料としては、シリコン、シリコングルマニウム等がある。シリコンを用いる場合、アモルファスシリコンやポリシリコンを用いることができる。さらには、リンがドープされたポリシリコンを用いることができる。導電性材料としては、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)から選ばれた元素、前記元素を主成分とする合金、前記元素を組み合わせた合金膜(代表的にはMo-W合金膜、Mo-Ta合金膜)、あるいは導電性を付与した珪素膜で形成すればよい。このような材料から成る導電層の下には窒化タンタル、窒化タングステン、窒化チタン、窒化モリブデンなどの窒化物、タングステンシリサイド、チタンシリサイド、モリブデンシリサイドなどのシリサイドを形成しておいてもよい。さらには、上記半導体材料同士、導電性材料同士、または半導体材料および導電性材料の積層構造としてもよい。例えば、シリコン層およびゲルマニウム層の積層構造としてもよい。

【0120】

また、電荷蓄積層84を、絶縁性であり、電荷を保持するトラップを有する材料で形成することもできる。このような材料の代表例として、代表的にはシリコン化合物、ゲルマニウム化合物がある。シリコン化合物としては、窒化珪素、酸窒化珪素、水素が添加された酸窒化珪素等がある。ゲルマニウム化合物としては、窒化ゲルマニウム、酸素が添加された窒化ゲルマニウム、窒素が添加された酸化ゲルマニウム、酸素および水素が添加された窒化ゲルマニウム、窒素および水素が添加された酸化ゲルマニウム等のゲルマニウム化合物等がある。

【0121】

コントロール絶縁膜として機能する絶縁層85は、酸化珪素、窒化珪素、酸窒化珪素、酸化アルミニウムなどの一層もしくは複数層を、減圧CVD法やプラズマCVD法などで形成する。絶縁層85の厚さは1~20nm、好ましくは5~10nmで形成する。例えば、窒化珪素層を3nmの厚さに堆積し、酸化珪素層の厚さを5nmの厚さに堆積したものを用いることができる。

【0122】

ゲート電極として機能する導電層86としては、実施の形態2で示すゲート電極として機

10

20

30

40

50

能する導電層 3 4 の材料および作製方法を適宜用いることができる。

【 0 1 2 3 】

また、図 12 ( B ) に示すように、電荷蓄積層 8 4 、コントロール絶縁膜として機能する絶縁層 8 5 、およびゲート電極として機能する導電層 8 6 の側面に、マスク 8 7 が形成されていてもよい。また、マスク 8 7 、および低濃度不純物領域 3 2 d 、 3 2 e が、絶縁層 8 3 を介して重畳する。マスク 8 7 を形成することで、マスク 8 7 を通過して半導体層に不純物を添加することができる。すなわち、不純物を添加する工程により、半導体層 3 2 において、チャネル形成領域 3 2 a 、高濃度の不純物領域 3 2 b 、 3 2 c 、および低濃度不純物領域 3 2 d 、 3 2 e を同時に形成することが可能である。このため、スループットを向上させることができる。

10

【 0 1 2 4 】

また、図 12 ( C ) に示すように、電荷蓄積層 8 4 が、ゲート電極として機能する導電層 8 6 と比較して大きい構造であってもよい。すなわち、電荷蓄積層 8 4 が外側に突出した形状であってもよい。電荷蓄積層 8 4 において導電層 8 6 の外側に形成される領域と、低濃度不純物領域 3 2 d 、 3 2 e が、絶縁層 8 3 を介して重畳する。電荷蓄積層 8 4 およびゲート電極として機能する導電層 8 6 をこのような形状とすることで、電荷蓄積層 8 4 において導電層 8 6 の外側に形成される領域を通過して半導体層に不純物を添加することができる。すなわち、不純物を添加する工程により、半導体層 3 2 において、チャネル形成領域 3 2 a 、高濃度の不純物領域 3 2 b 、 3 2 c 、および低濃度不純物領域 3 2 d 、 3 2 e を同時に形成することが可能である。このため、スループットを向上させることができる。

20

【 0 1 2 5 】

また、図 12 ( D ) に示すように、電荷蓄積層 8 4 が、ゲート電極として機能する導電層 8 6 と比較して小さい構造であってもよい。このような構造の不揮発性記憶素子では、ゲート電極として機能する導電層 8 6 を形成する前に、低濃度に不純物を半導体層 3 2 に添加して、低濃度不純物領域 3 2 d 、 3 2 e を形成した後、ゲート電極として機能する導電層 8 6 を形成する。次に、導電層 8 6 をマスクとして半導体層 3 2 に不純物を高濃度添加することで、高濃度の不純物領域 3 2 b 、 3 2 c を形成できる。

【 0 1 2 6 】

本実施の形態において、ゲート電極下の半導体層 3 2 の端部 ( 側面 ) に、絶縁層 3 6 を有する不揮発性記憶素子を作製できる。したがって、絶縁層 8 3 の半導体層 3 2 表面への被覆不良が半導体装置に及ぼす影響を低減できる。つまり、本実施の形態の方法を用いて作製された半導体装置において、半導体層 3 2 の側面はゲート電極と接することができないため、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることができるとなる。

30

【 0 1 2 7 】

また、半導体層 3 2 の端部に選択的に厚く絶縁層を設けることができるため、半導体層 3 2 の端部における電界集中を緩和できる。したがって、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることができるとなる。

【 0 1 2 8 】

( 実施の形態 8 )

40

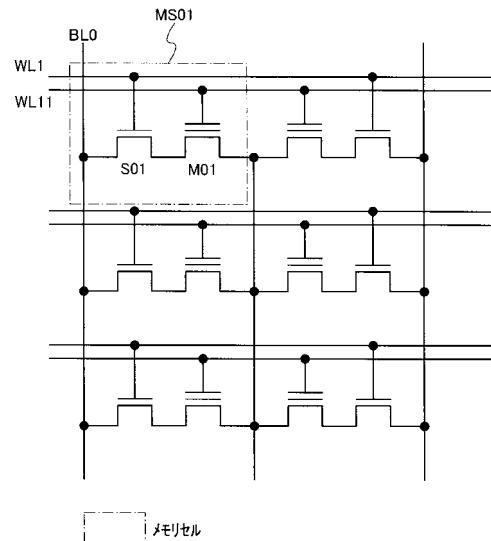

本実施の形態では、上記実施の形態で示した不揮発性記憶素子を用いたメモリセルアレイの構成について説明する。図 18 に N O R 型のメモリセルアレイの等価回路の一例を示す。1 ビットの情報を記憶するメモリセル M S 0 1 は、選択トランジスタ S 0 1 と不揮発性記憶素子 M 0 1 で構成されている。選択トランジスタ S 0 1 は、ビット線 B L 0 と不揮発性記憶素子 M 0 1 の間に直列に挿入され、ゲートがワード線 W L 1 に接続されている。また、不揮発性記憶素子 M 0 1 のゲートは、ワード線 W L 1 に接続されている。不揮発性記憶素子 M 0 1 にデータを書き込むときは、ワード線 W L 1 とビット線 B L 0 を H レベル、 B L 1 を L レベルとして、ワード線 W L 1 に高電圧を印加すればよい。すると、電荷蓄積層に電荷が蓄積される。データを消去する場合には、ワード線 W L 1 とビット線 B L 0 を H レベルとし、ワード線 W L 1 に負の高電圧を印加すればよい。

50

## 【0129】

このメモリセルMS01において、選択トランジスタS01と不揮発性記憶素子M01をそれぞれ、絶縁表面に島状に分離して形成された半導体層で形成することにより、素子分離領域を特段設けなくても、他の選択トランジスタもしくは不揮発性記憶素子との干渉を防ぐことができる。また、メモリセルMS01内の選択トランジスタS01と不揮発性記憶素子M01は共にnチャネル型なので、この両者を1つの島状の半導体層で形成することにより、この2つの素子を接続する配線を省略することができる。

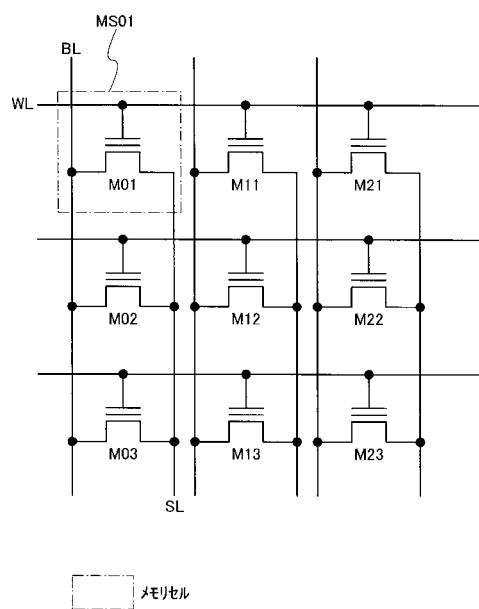

## 【0130】

図19は、ビット線に不揮発性記憶素子を直接接続したNOR型の等価回路を示している。このメモリセルアレイは、ワード線WLとビット線BLが互いに交差して配設し、各交差部に不揮発性記憶素子を配置している。NOR型は、個々の不揮発性記憶素子のドレインをビット線BLに接続する。ソース線SLには不揮発性記憶素子のソースが共通接続される。

10

## 【0131】

この場合もメモリセルMS01において、不揮発性記憶素子M01を絶縁表面に島状に分離して形成された半導体層で形成することにより、素子分離領域を特段設けなくても、他の不揮発性記憶素子との干渉を防ぐことができる。また、複数の不揮発性記憶素子（例えば、図19に示すM01～M23）を1つのブロックとして扱い、これらの不揮発性記憶素子を1つの島状に分離した半導体層で形成することにより、ブロック単位で消去動作を行なうことができる。

20

## 【0132】

NOR型の動作は、例えば、次の通りである。データ書き込みは、ソース線SLを0Vとし、データを書き込むために選択されたワード線WLに高電圧を与え、ビット線BLにはデータ”0”と”1”に応じた電位を与える。例えば、”0”と”1”に対してそれぞれHレベル、Lレベルの電位をビット線BLに付与する。”0”データを書き込むべく、Hレベルが与えられた不揮発性記憶素子ではドレイン近傍でホットエレクトロンが発生し、これが浮遊ゲートに注入される。”1”データの場合このような電子注入は生じない。

## 【0133】

”0”データが与えられたメモリセルでは、ドレインとソースとの間の強い横方向電界により、ドレインの近傍でホットエレクトロンが生成され、これが電荷蓄積層に注入される。これにより、電荷蓄積層に電子が注入されてしきい値電圧が高くなった状態が”0”である。”1”データの場合はホットエレクトロンが生成されず、電荷蓄積層に電子が注入されずしきい値電圧の低い状態、すなわち消去状態が保持される。

30

## 【0134】

データを消去するときは、ソース線SLに10V程度の正の電圧を印加し、ビット線BLは浮遊状態としておく。そしてワード線に負の高電圧を印加して（制御ゲートに負の高電圧を印加して）、電荷蓄積層から電子を引き抜く。これにより、データ”1”的消去状態になる。

## 【0135】

データ読み出しがは、ソース線SLを0Vにすると共に、ビット線BLを0.8V程度とし、選択されたワード線WLに、データ”0”と”1”的しきい値の中間値に設定された読み出し電圧を与え、不揮発性記憶素子の電流引き込みの有無を、ビット線BLに接続されるセンサアンプで判定することにより行う。

40

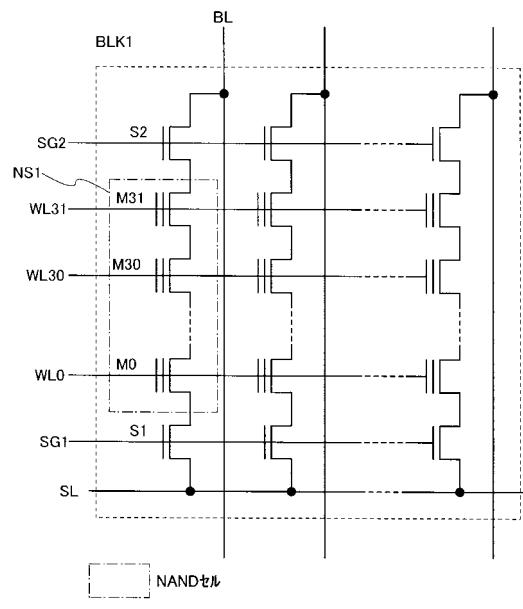

## 【0136】

図20は、NAND型のメモリセルアレイの等価回路を示す。ビット線BLには、複数の不揮発性記憶素子を直列に接続したNANDセルNS1が接続されている。複数のNANDセルが集まってブロックBLK1を構成している。図20で示すブロックBLK1のワード線は32本である（ワード線WL0～WL31）。ブロックBLK1の同一行に位置する不揮発性記憶素子には、この行に対応するワード線が共通接続されている。

## 【0137】

50

この場合、選択トランジスタ S 1、S 2 と不揮発性記憶素子 M 0 ~ M 3 1 が直列に接続されているので、これらを 1 つのまとまりとして 1 つの半導体層で形成してもよい。それにより不揮発性記憶素子を繋ぐ配線を省略することができるので、集積化を図ることができる。また、隣接する N A N D セルとの分離を容易に行うことができる。また、選択トランジスタ S 1、S 2 の半導体層と N A N D セル N S 1 の半導体層を分離して形成してもよい。それにより不揮発性記憶素子 M 0 ~ M 3 1 の電荷蓄積層から電荷を引き抜く消去動作を行うときに、その N A N D セルの単位で消去動作を行うことができる。また、1 つのワード線に共通接続する不揮発性記憶素子（例えば M 3 0 の行）を 1 つの半導体層で形成してもよい。

【 0 1 3 8 】

10

書き込み動作では、N A N D セル N S 1 を消去状態、つまり N A N D セル N S 1 の各不揮発性記憶素子のしきい値を負電圧の状態にしてから実行される。書き込みは、ソース線 S L 側のメモリ素子 M 0 から順に行う。メモリ素子 M 0 への書き込みを例として説明すると概略以下のようになる。

【 0 1 3 9 】

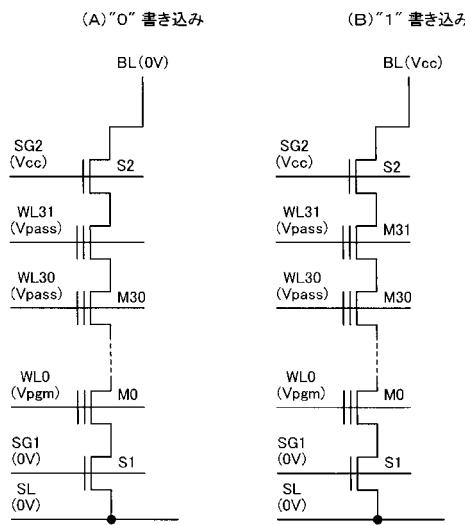

図 2 1 ( A ) は、" 0 " 書き込みをする場合、選択ゲート線 S G 2 に例えば V c c ( 電源電圧 ) を印加して、選択トランジスタ S 2 をオンにするとともに、ビット線 B L 0 を 0 V ( 接地電圧 ) にする。また、選択ゲート線 S G 1 は 0 V として、選択トランジスタ S 1 はオフとする。次に、メモリセル M 0 のワード線 W L 0 を高電圧 V p g m ( 2 0 V 程度 ) とし、これ以外のワード線を中間電圧 V p a s s ( 1 0 V 程度 ) にする。ビット線 B L の電圧は 0 V なので、選択されたメモリセル M 0 のチャネル形成領域の電位は 0 V となる。ワード線 W L 0 とチャネル形成領域との間の電位差が大きいため、メモリセル M 0 の電荷蓄積層には前述のように F - N トンネル電流により電子が注入される。これにより、メモリセル M 0 のしきい値電圧が正の状態（" 0 " が書き込まれた状態）となる。

20

【 0 1 4 0 】

一方 " 1 " 書き込みをする場合は、図 2 1 ( B ) に示すように、ビット線 B L に例えば V c c ( 電源電圧 ) を印加する。選択ゲート線 S G 2 の電圧が V c c であるため、選択トランジスタ S 2 のしきい値電圧 V t h に対して、電圧が V c c マイナス V t h ( V c c - V t h ) になると、選択トランジスタ S 2 がカットオフする。したがって、メモリセル M 0 のチャネル形成領域は、フローティング状態となる。次に、ワード線 W L 0 に高電圧 V p g m ( 2 0 V ) 、それ以外のワード線に中間電圧 V p a s s ( 1 0 V ) の電圧を印加すると、各ワード線とチャネル形成領域との容量カッピングにより、チャネル形成領域の電圧が V c c - V t h から上昇し、例えば 8 V 程度となる。チャネル形成領域の電圧が高電圧に昇圧されるため、" 0 " の書き込みの場合と異なり、ワード線 W L 0 とチャネル形成領域との間の電位差は小さい。したがって、メモリセル M 0 の浮遊ゲートには、F - N トンネル電流による電子注入が起こらない。よって、メモリセル M 3 1 のしきい値は、負の状態（" 1 " が書き込まれた状態）に保たれる。

30

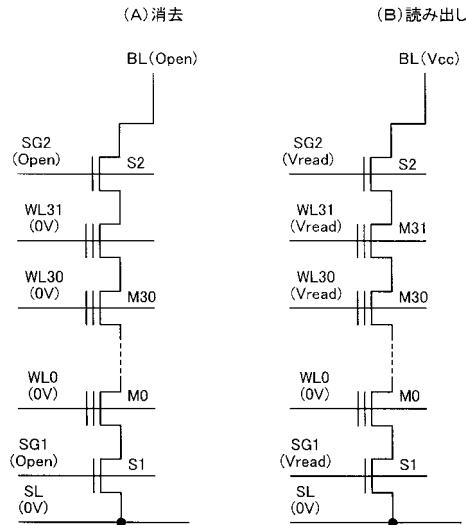

【 0 1 4 1 】

消去動作をする場合は、図 2 2 ( A ) に示すように、選択されたブロック内の全てのワード線に負の高電圧 ( V e r s ) を印加し、ビット線 B L 、ソース線 S L をフローティング状態とする。これにより、ブロックの全てのメモリセルにおいて、浮遊ゲート中の電子がトンネル電流により半導体層に放出される。この結果、これらのメモリセルのしきい値電圧が負方向にシフトする。

40

【 0 1 4 2 】

図 2 2 ( B ) に示す読み出し動作では、読み出しの選択がされたメモリセル M 0 のワード線 W L 0 の電圧を V r ( 例えば 0 V ) とし、非選択のメモリセルのワード線 W L 1 ~ 3 1 および選択ゲート線 S G 1 、 S G 2 を、電源電圧より少し高い読み出し用中間電圧 V r e a d とする。すなわち、図 2 3 に示すように、選択メモリ素子以外のメモリ素子はトランスマニアトランジスタとして働く。これにより、読み出しの選択がされたメモリセル M 0 に電流が流れるか否かを検出する。つまり、メモリセル M 3 0 に記憶されたデータが " 0 "

50

”の場合、メモリセルM0はオフなので、ビット線BLは放電しない。一方、”1”の場合、メモリセルM0はオンするので、ビット線BLが放電する。

【0143】

(実施の形態9)

本実施の形態では、上記実施の形態で示した薄膜トランジスタおよび不揮発性メモリを有する非接触でデータの入出力が可能である半導体装置の構成の一例について説明する。非接触でデータの入出力が可能である半導体装置は利用の形態によっては、RFIDタグ、IDタグ、ICタグ、ICチップ、RFタグ、無線タグ、電子タグまたは無線チップともよばれる。

【0144】

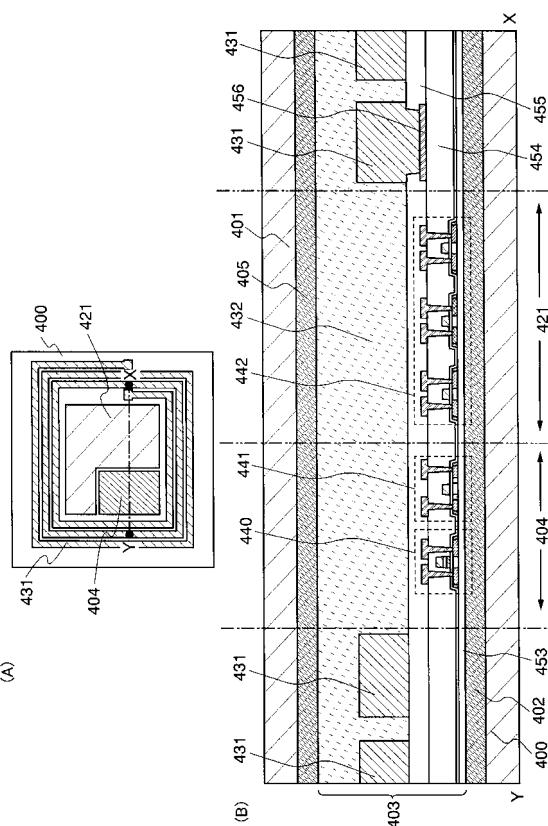

本実施の形態の半導体装置の上面図を図13(A)に、図13(A)における線Y-Xの断面図を図13(B)に示す。

【0145】

図13(A)に示すように、半導体装置は基板400上に記憶回路404、集積回路部421およびアンテナ431が設けられている。なお、上記実施の形態で示した薄膜トランジスタを用いて、記憶回路404、集積回路部421を形成できる。また、上記不揮発性半導体記憶装置を用いて記憶回路404を形成できる。

【0146】

図13(B)に示すように、半導体装置は、素子形成層403が、基板400、401によって挟持されている。また、素子形成層403と基板400、401それぞれは、接着材402、405によって固着されている。また、素子形成層403には、絶縁層453、不揮発性記憶素子440、トランジスタ441、442が形成される。また、不揮発性記憶素子440、トランジスタ441、442上に絶縁層454が形成され、絶縁層454には配線456が形成される。また、絶縁層454および配線456上にアンテナ431が形成され、アンテナ431および絶縁層455上に絶縁層432が形成される。アンテナ431は、絶縁層455に形成される開口部において、絶縁層454上に形成される配線456と接続される。配線456は集積回路部421の一部である高周波回路に接続される。また、記憶回路404には不揮発性記憶素子440、トランジスタ441を有し、集積回路部421にはトランジスタ442を有する例を示したが、その他抵抗素子、容量素子、整流素子等も有する。

【0147】

本実施の形態では、絶縁層455にポリイミド層を用いて形成し、導電層にチタン膜、アルミニウム膜、およびチタン膜が積層された導電層を用い、アンテナ431に印刷法により形成された銀合金層を導電層としてそれ用いている。絶縁層432はアンテナ431の凹凸を緩和するために形成しており、塗布法により組成物を塗布し、乾燥・焼成をして形成することが好ましい。ここでは、絶縁層432として、エポキシ樹脂層を用いて形成する。また、基板400、401にPENフィルムを用い、接着材402、405に熱可塑性樹脂を用いる。

【0148】

なお、アンテナ431は、記憶回路404に対して、重ねて設けてもよいし、重ならず周囲に設ける構造でもよい。また重なる場合も全面が重なってもよいし、一部が重なっている構造でもよい。アンテナ431と記憶回路404が重なる構造であると、アンテナ431が交信する際に信号に載っているノイズ等や、電磁誘導により発生する起電力の変動等の影響による、半導体装置の動作不良を減らすことが可能であり、信頼性が向上する。また、半導体装置を小型化できる。

【0149】

また、上述した非接触データの入出力が可能である半導体装置における信号の伝送方式は、電磁結合方式、電磁誘導方式またはマイクロ波方式等を用いることができる。伝送方式は、実施者が使用用途を考慮して適宜選択すればよく、伝送方式に伴って最適なアンテナを設ければよい。

10

20

30

40

50

## 【0150】

例えば、半導体装置における信号の伝送方式として、電磁結合方式または電磁誘導方式（例えば13.56MHz帯）を適用する場合には、磁界密度の変化による電磁誘導を利用するため、アンテナ431として機能する導電層を輪状（例えば、ループアンテナ）、らせん状（例えば、スパイラルアンテナ）に形成する。

## 【0151】

また、半導体装置における信号の伝送方式として、マイクロ波方式（例えば、UHF帯（860～960MHz帯）、2.45GHz帯等）を適用する場合には、信号の伝送に用いる電磁波の波長を考慮してアンテナ431として機能する導電層の長さ等の形状を適宜設定すればよく、例えば、アンテナ431として機能する導電層を線状（例えば、ダイポールアンテナ）、平坦な形状（例えば、パッチアンテナ）またはリボン型の形状等に形成できる。また、アンテナ431として機能する導電層の形状は線状に限られず、電磁波の波長を考慮して曲線状や蛇行形状またはこれらを組み合わせた形状で設けてもよい。

10

## 【0152】

アンテナ431として機能する導電層は、CVD法、スパッタリング法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム（Al）、チタン（Ti）、銀（Ag）、銅（Cu）、金（Au）、白金（Pt）ニッケル（Ni）、パラジウム（Pd）、タンタル（Ta）、モリブデン（Mo）から選択された元素、またはこれらの元素を主成分とする合金材料もしくは化合物材料で、単層構造または積層構造で形成する。

20

## 【0153】

例えば、スクリーン印刷法を用いてアンテナ431として機能する導電層を形成する場合には、粒径が数nm～数十μmの導電体粒子を、有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷し、乾燥・焼成することによって設けることができる。導電体粒子としては、銀（Ag）、金（Au）、銅（Cu）、ニッケル（Ni）、白金（Pt）、パラジウム（Pd）、タンタル（Ta）、モリブデン（Mo）およびチタン（Ti）等のいずれか1つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた1つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコーン樹脂等の有機樹脂が挙げられる。また、上述した材料以外にも、セラミックやフェライト等をアンテナ431に適用してもよい。

30

## 【0154】

また、電磁結合方式または電磁誘導方式を適用する場合であって、アンテナを備えた半導体装置を金属に接して設ける場合には、当該半導体装置と金属との間に透磁率を備えた磁性材料を設けることが好ましい。アンテナを備えた半導体装置を金属に接して設ける場合には、磁界の変化に伴い金属に渦電流が流れ、当該渦電流により発生する反磁界によって、磁界の変化が弱められて通信距離が低下する。そのため、半導体装置と金属との間に透磁率を備えた材料を設けることにより、金属の渦電流を抑制し、通信距離の低下を抑制することができる。なお、磁性材料としては、高い透磁率を有し高周波損失の少ないフェライトや金属薄膜を用いることができる。

40

## 【0155】

本実施例においては、素子形成層においてトランジスタ等の半導体素子と、アンテナ431として機能する導電層を直接形成した半導体装置を示したが、半導体装置の構成はこれに限定される物ではない。例えば、半導体素子とアンテナ431として機能する導電層を別々の基板上に設けた後に、電気的に接続するように貼り合わせることによって設けてもよい。

## 【0156】

本発明により、半導体層およびゲート電極間のリーク電流を抑制した素子を用いた、信頼性の高い半導体装置を作製できる。

50

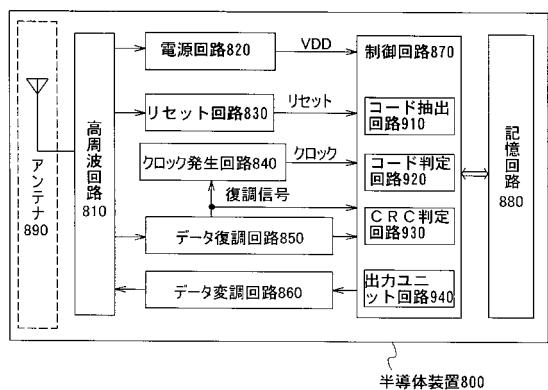

## 【0157】

図14に非接触でデータの入出力が可能である半導体装置のブロック図を示す。非接触でデータの入出力が可能である半導体装置800は、非接触でデータを交信する機能を有し、高周波回路810、電源回路820、リセット回路830、クロック発生回路840、データ復調回路850、データ変調回路860、他の回路の制御を行う制御回路870、記憶回路880およびアンテナ890を有している。なお、図14に示す記憶回路880は図13に示す記憶回路404に相当する。また、図14に示す高周波回路810、電源回路820、リセット回路830、クロック発生回路840、データ復調回路850、データ変調回路860および制御回路870は、図13に示す集積回路部421に相当する。また、図14に示すアンテナ890は、図13に示すアンテナ431に相当する。

10

## 【0158】

高周波回路810は、アンテナ890より信号を受信して、データ変調回路860より受信した信号をアンテナ890から出力する回路である。電源回路820は、受信信号から電源電位を生成する回路である。リセット回路830は、リセット信号を生成する回路である。クロック発生回路840は、アンテナ890から入力された受信信号を基に各種クロック信号を生成する回路である。データ復調回路850は、受信信号を復調して制御回路870に出力する回路である。データ変調回路860は、制御回路870から受信した信号を変調する回路である。また、制御回路870としては、例えばコード抽出回路910、コード判定回路920、CRC判定回路930および出力ユニット回路940が設けられている。なお、コード抽出回路910は、制御回路870に送られてきた命令に含まれる複数のコードをそれぞれ抽出する回路である。コード判定回路920は、抽出されたコードとリファレンスに相当するコードとを比較して命令の内容を判定する回路である。CRC判定回路930は、判定されたコードに基づいて送信エラー等の有無を検出する回路である。

20

## 【0159】

次に、上述した半導体装置の動作の一例について説明する。まず、アンテナ890により無線信号が受信される。無線信号は、高周波回路810を介して電源回路820に送られ、高電源電位（以下、VDDと記す）が生成される。VDDは、半導体装置800が有する各回路に供給される。また、高周波回路810を介してデータ復調回路850に送られた信号は、復調される（以下、復調信号と記す）。さらに、高周波回路810を介してリセット回路830およびクロック発生回路840を通った信号および復調信号は、制御回路870に送られる。制御回路870に送られた信号は、コード抽出回路910、コード判定回路920およびCRC判定回路930等によって解析される。そして、解析された信号にしたがって、記憶回路880内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は、出力ユニット回路940を通じて符号化される。さらに、符号化された半導体装置800の情報は、データ変調回路860を通じて、アンテナ890により無線信号に載せて送信される。なお、半導体装置800を構成する複数の回路においては、低電源電位（以下、VSS）は共通であり、VSSはGNDとすることができます。また、上記した半導体素子、代表的には薄膜トランジスタを用いて、高周波回路810、電源回路820、リセット回路830、クロック発生回路840、データ復調回路850、データ変調回路860、他の回路の制御を行う制御回路870、記憶回路880等を形成することができる。また、上記した不揮発性半導体記憶装置を、記憶回路880に適用することができる。本発明の半導体装置は、駆動電圧を低くすることができるため、非接触でデータを交信できる距離をのばすことが可能となる。

30

## 【0160】

このように、リーダ／ライタから半導体装置800に信号を送り、当該半導体装置800から送られてきた信号をリーダ／ライタで受信することによって、半導体装置のデータを読み取ることが可能となる。

40

## 【0161】

また、半導体装置800は、各回路への電源電圧の供給を、電源（バッテリー）を搭載せ

50

ず電磁波により行うタイプとしてもよいし、電源（バッテリー）を搭載して電磁波と電源（バッテリー）により各回路に電源電圧を供給するタイプとしてもよい。

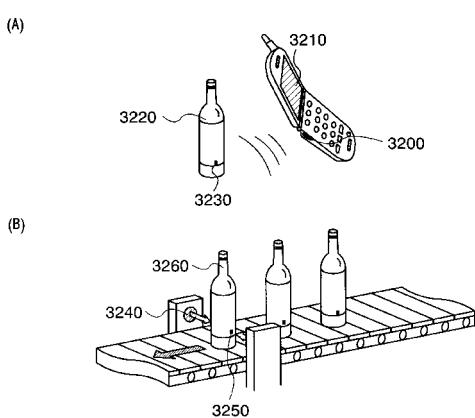

#### 【0162】

次に、非接触でデータの入出力が可能な半導体装置の使用形態の一例について説明する。表示部3210を含む携帯端末の側面には、リーダ／ライタ3200が設けられ、品物3220の側面には半導体装置3230が設けられる（図15（A））。品物3220に含まれる半導体装置3230にリーダ／ライタ3200をかざすと、表示部3210に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、さらに商品の説明等の商品に関する情報が表示される。また、商品3260をベルトコンベアにより搬送する際に、リーダ／ライタ3240と、商品3260に設けられた半導体装置3250を用いて、該商品3260の検品を行うことができる（図15（B））。このように、システムに半導体装置を活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。

#### 【0163】

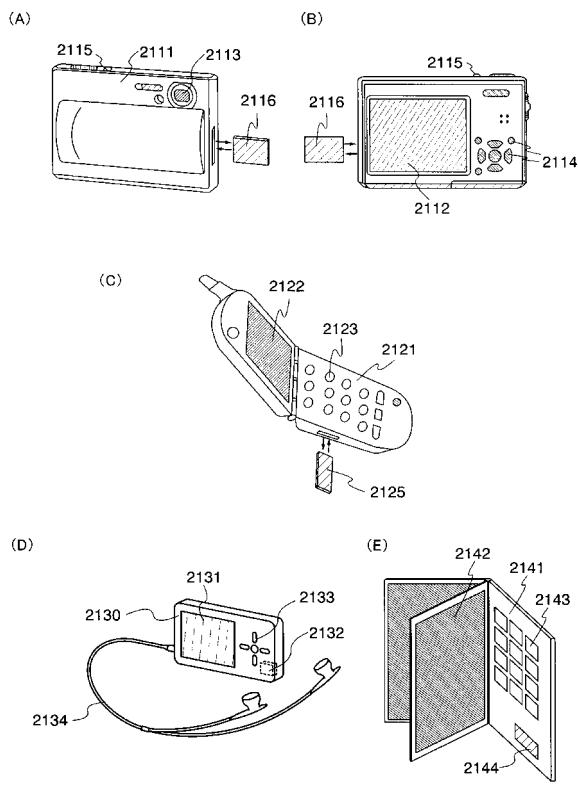

また、本発明の不揮発性半導体記憶装置は、メモリを具備したあらゆる分野の電子機器に用いることが可能である。例えば、本発明の不揮発性半導体記憶装置を適用した電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDVD（*digital versatile disc*）等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それら電子機器の具体例を図16に示す。

#### 【0164】

図16（A）、（B）は、デジタルカメラを示している。図16（B）は、図16（A）の裏側を示す図である。このデジタルカメラは、筐体2111、表示部2112、レンズ2113、操作キー2114、シャッターボタン2115などを有する。また、取り出し可能な不揮発性のメモリ2116を備えており、当該デジタルカメラで撮影したデータをメモリ2116に記憶させておく構成となっている。本発明を用いて形成された不揮発性の半導体記憶装置は、当該メモリ2116に適用することができる。

#### 【0165】

また、図16（C）は、携帯電話を示しており、携帯端末の1つの代表例である。この携帯電話は筐体2121、表示部2122、操作キー2123などを含む。また、携帯電話は、取り出し可能な不揮発性のメモリ2125を備えており、当該携帯電話の電話番号等のデータ、映像、音楽データ等をメモリ2125に記憶させ再生することができる。本発明を用いて形成された不揮発性の半導体記憶装置は、当該メモリ2125に適用することができる。

#### 【0166】

また、図16（D）は、デジタルプレーヤーを示しており、オーディオ装置の1つの代表例である。図16（D）に示すデジタルプレーヤーは、本体2130、表示部2131、メモリ部2132、操作部2133、イヤホン2134等を含んでいる。なお、イヤホン2134の代わりにヘッドホンや無線式イヤホンを用いることができる。メモリ部2132は、本発明を用いて形成された不揮発性の半導体記憶装置を用いることができる。例えば、記録容量が20～200ギガバイト（GB）のNAND型不揮発性メモリを用い、操作部2133を操作することにより、映像や音声（音楽）を記録、再生することができる。なお、表示部2131は黒色の背景に白色の文字を表示することで消費電力を抑えられる。これは携帯型のオーディオ装置において特に有効である。なお、メモリ部2132に設けられた不揮発性の半導体記憶装置は、取り出し可能な構成としてもよい。

#### 【0167】

また、図16（E）は、電子ブック（電子ペーパーともいう）を示している。この電子ブ

10

20

30

40

50

ックは、本体 2141、表示部 2142、操作キー 2143、メモリ部 2144 を含んでいる。またモデムが本体 2141 に内蔵されていてもよいし、無線で情報を送受信できる構成としてもよい。メモリ部 2144 は、本発明を用いて形成された不揮発性の半導体記憶装置を用いることができる。例えば、記録容量が 20 ~ 200 ギガバイト (GB) の NAND 型不揮発性メモリを用い、操作キー 2143 を操作することにより、映像や音声 (音楽) を記録、再生することができる。なお、メモリ部 2144 に設けられた不揮発性の半導体記憶装置は、取り出し可能な構成としてもよい。

【0168】

以上のように、本発明の不揮発性半導体記憶装置の適用範囲は極めて広く、メモリを有するものであればあらゆる分野の電子機器に用いることが可能である。

10

【図面の簡単な説明】

【0169】

【図 1】本発明の薄膜トランジスタの構成を説明する上面図および断面図。

【図 2】本発明の薄膜トランジスタの構成を説明する断面図。

【図 3】本発明の薄膜トランジスタの作製工程を説明する断面図。

【図 4】本発明の薄膜トランジスタの作製工程を説明する断面図。

【図 5】本発明の薄膜トランジスタの作製工程を説明する断面図。

【図 6】本発明の薄膜トランジスタの作製工程を説明する断面図。

【図 7】本発明の薄膜トランジスタの作製工程を説明する断面図。

【図 8】本発明の薄膜トランジスタの作製工程を説明する断面図。

20

【図 9】本発明の薄膜トランジスタの構成を説明する上面図および断面図。

【図 10】本発明の薄膜トランジスタの作製工程を説明する断面図。

【図 11】本発明の薄膜トランジスタの構成を説明する断面図。

【図 12】本発明の不揮発性記憶素子の構成を説明する断面図。

【図 13】本発明の半導体装置の構成を説明する上面図および断面図。

【図 14】本発明の半導体装置の構成を説明するブロック図。

【図 15】本発明の半導体装置の使用形態を説明する図。

【図 16】本発明の半導体装置の使用形態を説明する図。

【図 17】プラズマ処理装置の構成を説明する断面図。

【図 18】不揮発性メモリセルアレイの等価回路の一例を示す図。

30

【図 19】NOR 型不揮発性メモリセルアレイの等価回路の一例を示す図。

【図 20】NAND 型不揮発性メモリセルアレイの等価回路の一例を示す図。

【図 21】NAND 型不揮発性メモリの書き込み動作を説明する図。

【図 22】NAND 型不揮発性メモリの消去および読み出し動作を説明する図。

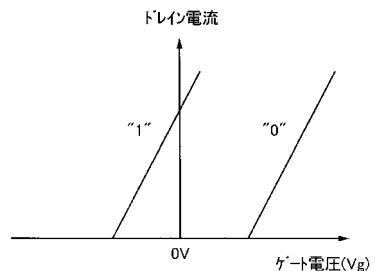

【図 23】電荷が蓄積された "0" の場合と消去された "1" の場合における不揮発性記憶素子のしきい値電圧の変化を示す図。

【図 24】従来の薄膜トランジスタの構成を説明する上面図および断面図。

【符号の説明】

【0170】

|       |          |    |

|-------|----------|----|

| 3 0   | 基板       | 40 |

| 3 1   | 絶縁層      |    |

| 3 2   | 半導体層     |    |

| 3 3   | 絶縁層      |    |

| 3 4   | 導電層      |    |

| 3 6   | 絶縁層      |    |

| 2 0 3 | 絶縁層      |    |

| 2 0 4 | 導電層      |    |

| 2 0 5 | 薄膜トランジスタ |    |

| 3 2 a | チャネル形成領域 |    |

| 3 2 b | 不純物領域    | 50 |

3 2 c 不純物領域

3 2 d 低濃度不純物領域

3 2 e 低濃度不純物領域

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

### 【図17】

【 図 1 8 】

### 【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

---

フロントページの続き

(56)参考文献 特開2006-032917(JP,A)

特開2003-017500(JP,A)

特開2000-195972(JP,A)

特開2000-037671(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786