(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5789403号

(P5789403)

(45) 発行日 平成27年10月7日(2015.10.7)

(24) 登録日 平成27年8月7日(2015.8.7)

(51) Int.Cl.

F 1

|              |           |            |       |      |

|--------------|-----------|------------|-------|------|

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 29/78 | 617V |

| HO1L 29/786  | (2006.01) | HO1L       | 29/78 | 618B |

| HO1L 21/8242 | (2006.01) | HO1L       | 29/78 | 626C |

| HO1L 27/108  | (2006.01) | HO1L       | 29/78 | 617T |

| HO1L 21/8247 | (2006.01) | HO1L       | 29/78 | 617U |

請求項の数 7 (全 59 頁) 最終頁に続く

(21) 出願番号

特願2011-95085 (P2011-95085)

(22) 出願日

平成23年4月21日(2011.4.21)

(65) 公開番号

特開2011-243975 (P2011-243975A)

(43) 公開日

平成23年12月1日(2011.12.1)

審査請求日

平成26年3月26日(2014.3.26)

(31) 優先権主張番号

特願2010-100237 (P2010-100237)

(32) 優先日

平成22年4月23日(2010.4.23)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 宇多川 勉

(56) 参考文献 特開2010-062276 (JP, A

)特開2008-060419 (JP, A

)特開2006-165531 (JP, A

)

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

第1の絶縁膜を形成し、

前記第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、前記ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、

前記酸化物半導体膜上に、第2の絶縁膜を形成し、

前記第2の絶縁膜に酸素ドープ処理を行い、

前記第2の絶縁膜上に、前記酸化物半導体膜と重なる領域を有するようにゲート電極を形成し、

前記酸素ドープ処理を行う前に第1の熱処理を行い、前記酸化物半導体膜中の水素、水または水酸基を低減し、

前記酸素ドープ処理を行った後に第2の熱処理を行い、前記第2の絶縁膜中の酸素を前記酸化物半導体膜に供給する半導体装置の作製方法。

## 【請求項2】

第1の絶縁膜を形成し、

前記第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、前記ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、

前記酸化物半導体膜上に、第2の絶縁膜を形成し、

前記第2の絶縁膜に酸素プラズマ処理を行い、

前記第2の絶縁膜上に、前記酸化物半導体膜と重なる領域を有するようにゲート電極を

10

20

形成し、

前記酸素プラズマ処理を行う前に第1の熱処理を行い、前記酸化物半導体膜中の水素、水または水酸基を低減し、

前記酸素プラズマ処理を行った後に第2の熱処理を行い、前記第2の絶縁膜中の酸素を前記酸化物半導体膜に供給する半導体装置の作製方法。

【請求項3】

前記第1の絶縁膜または前記第2の絶縁膜は、前記酸化物半導体膜の構成元素を含む絶縁膜である請求項1または請求項2に記載の半導体装置の作製方法。

【請求項4】

前記第1の絶縁膜または前記第2の絶縁膜は、前記酸化物半導体膜の構成元素を含み当該酸化物半導体膜に接して形成された第3の絶縁膜と、当該第3の絶縁膜の構成元素とは異なる元素を含む第4の絶縁膜との積層膜であり、

前記第3の絶縁膜は、前記酸化物半導体膜と前記第4の絶縁膜によって挟まれるように設けられる請求項1または請求項2に記載の半導体装置の作製方法。

【請求項5】

前記第1の絶縁膜または前記第2の絶縁膜は、酸化ガリウムを含む絶縁膜である請求項1または請求項2に記載の半導体装置の作製方法。

【請求項6】

前記第1の絶縁膜または前記第2の絶縁膜は、酸化ガリウムを含み前記酸化物半導体膜に接して形成された第3の絶縁膜と、酸化ガリウムとは異なる材料を含む第4の絶縁膜との積層膜であり、

前記第3の絶縁膜は、前記酸化物半導体膜と前記第4の絶縁膜によって挟まれるように設けられる請求項1または請求項2に記載の半導体装置の作製方法。

【請求項7】

前記ゲート電極を覆うように、窒素を含有する絶縁膜を形成する請求項1乃至請求項6のいずれか一に記載の半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路( I C )や画像表示装置(表示装置)のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

【0004】

例えば、トランジスタの活性層として、電子キャリア濃度が  $10^{18} / \text{cm}^3$  未満であるインジウム( In )、ガリウム( Ga )、及び亜鉛( Zn )を含む非晶質酸化物を用いたトランジスタが開示されている(特許文献1参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006-165528号公報

【発明の概要】

【発明が解決しようとする課題】

10

20

30

40

50

**【 0 0 0 6 】**

しかし、酸化物半導体はデバイス作製工程において、電子供与体を形成する水素や水の混入などが生じると、その電気伝導度が変化する恐れがある。このような現象は、酸化物半導体を用いたトランジスタにとって電気的特性の変動要因となる。

**【 0 0 0 7 】**

上述の問題に鑑み、酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

**【課題を解決するための手段】****【 0 0 0 8 】**

酸化物半導体膜を有するトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。少なくとも、酸化物半導体膜を有するトランジスタの作製工程において、酸素ドープ処理を行う。

10

**【 0 0 0 9 】**

開示する発明の一態様は、第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

**【 0 0 1 0 】**

20

開示する発明の別の一態様は、成分として酸素原子を含む第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜上に、成分として酸素原子を含む第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

**【 0 0 1 1 】**

上記において、化学量論比の1倍を超えて2倍までの比率の酸素原子が酸化物半導体膜に含まれるように、酸化物半導体膜および第2の絶縁膜に酸素ドープ処理を行う場合がある。また、化学量論比の1倍を超えて2倍までの比率の酸素原子が第2の絶縁膜に含まれるように、第2の絶縁膜に酸素ドープ処理を行う場合がある。また、第1の絶縁膜または第2の絶縁膜として、酸化物半導体膜の構成元素を含む絶縁膜を形成する場合がある。また、第1の絶縁膜または第2の絶縁膜として、酸化物半導体膜の構成元素を含み、酸化物半導体膜に接して形成された第3の絶縁膜と、当該第3の絶縁膜の構成元素とは異なる元素を含む第4の絶縁膜との積層膜を形成する場合がある。このとき、当該第3の絶縁膜は当該酸化物半導体膜と当該第4の絶縁膜によって挟まれるように設けられている。また、第1の絶縁膜または第2の絶縁膜として、酸化ガリウムを含む絶縁膜を形成する場合がある。

30

また、第1の絶縁膜または第2の絶縁膜として、酸化ガリウムを含み、酸化物半導体膜に接して形成された第3の絶縁膜と、酸化ガリウムとは異なる材料を含む第4の絶縁膜との積層膜を形成する場合がある。このとき、当該第3の絶縁膜は当該酸化物半導体膜と当該第4の絶縁膜によって挟まれるように設けられている。また、ゲート電極を覆うように、窒素を含有する絶縁膜を形成する場合がある。なお、本明細書において、「酸化ガリウム」の用語は、特に言及しない限り、構成元素としての酸素とガリウムを意味するものであって、酸化ガリウムの態様に限る趣旨で用いない。例えば、「酸化ガリウムを含む絶縁膜」という場合には、「酸素とガリウムを含む絶縁膜」のように読み替えることが可能である。

40

**【 0 0 1 2 】**

また、上記において、ゲート電極を覆うように、窒素を含有する絶縁膜を形成する場合が

50

ある。このように、上方に、水素の含有がない、または極めて少ない窒化シリコンなどを用いた絶縁膜を形成する場合には、添加された酸素が外部に放出されることを防ぎ、加えて、外部からの水素や水の混入を防ぐことが可能である。この点において、当該絶縁膜の重要性は高いといえる。

【0013】

なお、上記の「酸素ドープ」とは、酸素（少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む）をバルクに添加することを言う。なお、当該「バルク」の用語は、酸素を、薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、「酸素ドープ」には、プラズマ化した酸素をバルクに添加する「酸素プラズマドープ」が含まれる。

10

【0014】

上記の酸素ドープ処理によって、酸化物半導体膜の膜中（バルク中）、絶縁膜の膜中（バルク中）、酸化物半導体膜と絶縁膜の界面、のいずれかには少なくとも化学量論比をこえる量の酸素が存在する。酸素の量は、好ましくは化学量論比の1倍を超えて4倍まで（4倍未満）、より好ましくは、1倍を超えて2倍まで（2倍未満）である。ここで、化学量論比を超える酸素過剰な酸化物とは、それが、例えば、 $In_a Ga_b Zn_c Si_d Al_e Mg_f O_g$ （a, b, c, d, e, f, g 0）で表されるとき、 $2g > 3a + 3b + 2c + 4d + 3e + 2f$ 、を満たす酸化物をいう。なお、酸素ドープ処理によって添加された酸素は、酸化物半導体の格子間に存在する場合もある。

【0015】

20

また、少なくとも脱水化、脱水素化した後の酸化物半導体膜中の水素よりも添加される酸素の量が多くなるようにする。少なくとも添加される酸素の量が水素よりも多ければ、酸素が拡散し、不安定性の原因の水素と反応することにより水素を固定化（非可動イオン化）することができる。すなわち、信頼性の低下を抑制することができる。また、酸素を過剰とすることで酸素欠損に起因するしきい値電圧  $V_{th}$  のばらつきを低減すると共に、しきい値電圧のシフト量  $V_{th}$  を低減することができる。

【0016】

なお、酸化物半導体膜の膜中（バルク中）、絶縁膜の膜中（バルク中）、酸化物半導体膜と絶縁膜の界面、の2カ所以上に上述した量の酸素が存在するとより好ましい。

【0017】

30

なお、欠陥（酸素欠損）のない酸化物半導体であれば、化学量論比に一致した量の酸素が含まれていれば良いが、トランジスタのしきい値電圧の変動を抑えるなどの信頼性を確保するためには、酸化物半導体には、化学量論比を超える量の酸素が含まれていることが好ましい。同様に、欠陥（酸素欠損）のない酸化物半導体であれば、下地膜を酸素過剰の絶縁膜とする必要はないが、トランジスタのしきい値電圧の変動を抑えるなどの信頼性を確保するためには、酸化物半導体膜に酸素欠損の状態は生じ得ることを考慮して、下地膜を酸素過剰の絶縁膜とすることが好ましい。

【0018】

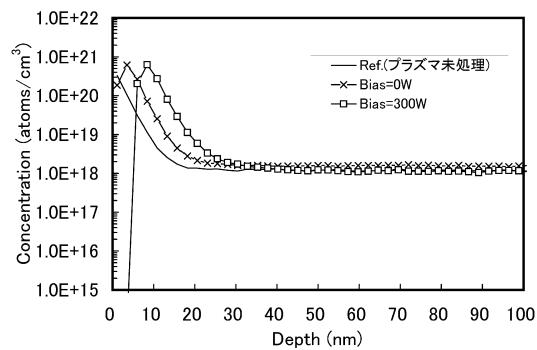

ここで、上述の「酸素プラズマドープ」処理によって、バルク中に酸素が添加される様子を示す。なお、酸素を一成分として含む酸化物半導体膜中に酸素ドープ処理を行う場合、一般に、酸素濃度の増減を確認することは困難である。よって、ここでは、シリコンウエハを用いて、酸素ドープ処理の効果を確認した。

40

【0019】

酸素ドープ処理は、誘導結合プラズマ（ICP：Inductively Coupled Plasma）方式を用いて行った。その条件は、ICP電力800W、RFバイアス電力300Wまたは0W、圧力1.5Pa、酸素ガス流量75sccm、基板温度70である。図15に、SIMS（SIMS、Secondary Ion Mass Spectrometry）分析によるシリコンウエハの深さ方向の酸素濃度プロファイルを示す。図15において、縦軸は酸素濃度を示し、横軸はシリコンウエハ表面からの深さを示す。

50

## 【0020】

図15より、RFバイアス電力が0Wの場合および300Wの場合のいずれにおいても、酸素が添加されていることが確認できる。また、RFバイアス300Wの場合は、RFバイアス0Wの場合と比較して、酸素がより深く添加されることが確認できる。

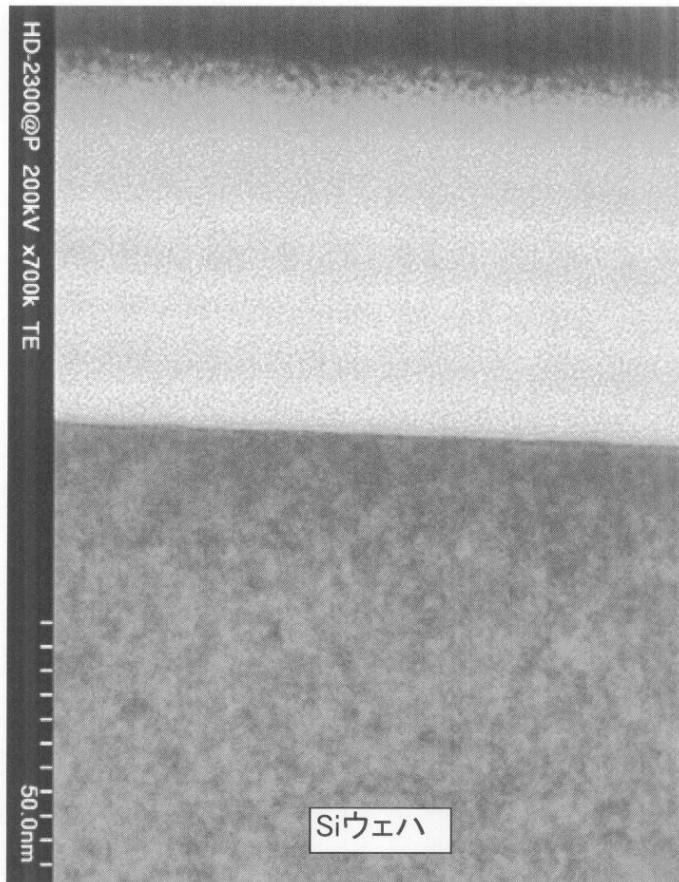

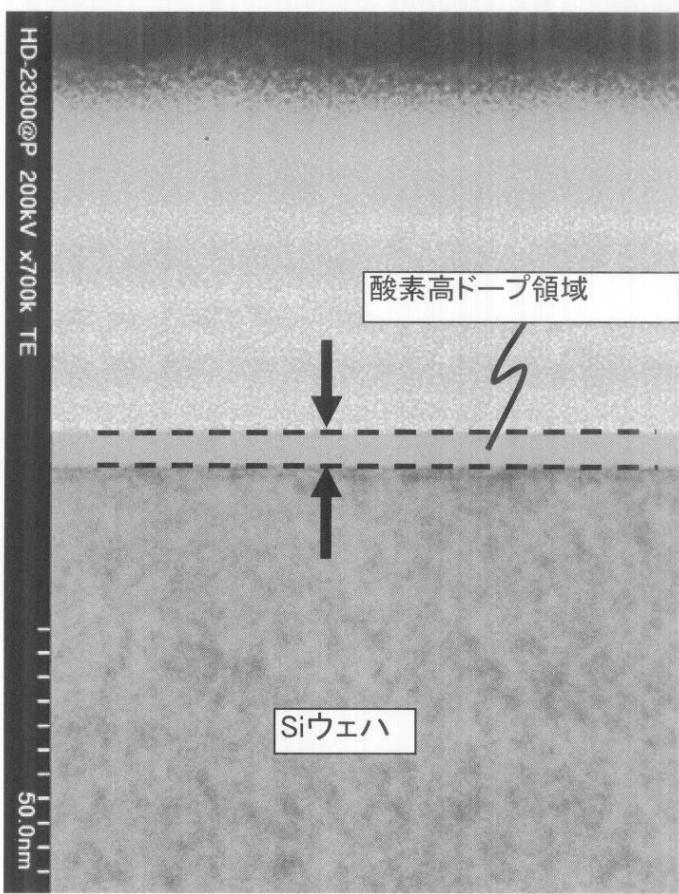

## 【0021】

次に、酸素ドープ処理を行う前と、酸素ドープを行った後のシリコンウェハの断面をSEM(Scanning Transmission Electron Microscopy)で観察した結果を図16に示す。図16(A)は、酸素ドープ処理を行う前のSEM像であり、図16(B)は、上述のRFバイアス電力300Wの条件で酸素ドープ処理を行った後のSEM像である。図16(B)に示すように、酸素ドープを行うことによって、シリコンウェハに酸素高ドープ領域が形成されていることが確認できる。10

## 【0022】

以上のように、シリコンウェハに対して酸素ドープを行うことで、シリコンウェハに酸素が添加されることが示された。この結果により、酸化物半導体膜に対して酸素ドープを行うことによっても、酸化物半導体膜に酸素を当然に添加できることが理解できる。

## 【0023】

開示する発明の一態様である上述の構成の効果は、次のように考えると理解が容易である。ただし、以下の説明は、あくまでも一考察に過ぎないことを付記する。

## 【0024】

ゲート電極にプラスの電圧を印加すると、酸化物半導体膜のゲート電極側からバックチャネル側(ゲート絶縁膜と反対側)へ電界が発生するため、酸化物半導体膜中に存在するプラスの電荷を有する水素イオンがバックチャネル側へ移動して、絶縁膜との界面近傍に蓄積する。蓄積した水素イオンから絶縁膜中の電荷捕獲中心(水素原子、水、あるいは汚染物等)へプラスの電荷が移動することによって、酸化物半導体膜のバックチャネル側にはマイナスの電荷が蓄積される。すなわち、トランジスタのバックチャネル側に寄生チャネルが発生して、しきい値電圧がマイナス側にシフトし、トランジスタがノーマリーオンの傾向を示す。20

## 【0025】

上記の通り、絶縁膜中の水素または水等の電荷捕獲中心がプラスの電荷を捕獲し、絶縁膜中へプラスの電荷が移動することによってトランジスタの電気的特性が変動するため、トランジスタの電気的特性の変動を抑制するためには、絶縁膜中にこれらの電荷捕獲中心が存在しない、またはその含有量が少ないことが重要である。したがって、絶縁膜の成膜には、成膜時に水素含有量が少ないスペッタ法を用いるのが望ましい。スペッタ法により成膜された絶縁膜は、その膜中に電荷捕獲中心が存在しない、または少なく、CVD法等によって成膜した場合と比較してプラスの電荷の移動が起こりにくい。よって、トランジスタのしきい値電圧のシフトを抑制し、トランジスタをノーマリーオフとすることができる。30

## 【0026】

なお、トップゲート型のトランジスタにおいては、下地となる絶縁膜上に酸化物半導体膜を形成した後、熱処理を行うことで、酸化物半導体膜に含まれる水または水素を除去すると同時に、絶縁膜中に含まれる水または水素をも除去することができる。よって、絶縁膜中には、酸化物半導体膜中を移動してきたプラスの電荷を捕獲するための電荷捕獲中心が少ない。このように、酸化物半導体膜への脱水化または脱水素化のための熱処理は、酸化物半導体膜に加えて、酸化物半導体膜の下層に存在する絶縁膜に対しても行われるため、トップゲート型のトランジスタにおいては、下地となる絶縁膜はプラズマCVD法等のCVD法を用いて成膜されていても構わない。40

## 【0027】

また、ゲート電極にマイナスの電圧を印加すると、バックチャネル側からゲート電極側へ電界が発生するため、酸化物半導体膜中に存在する水素イオンがゲート絶縁膜側へ移動して、ゲート絶縁膜との界面近傍へと蓄積する。また、これによりトランジスタのしきい値50

電圧はマイナス側へシフトする。

【0028】

なお、電圧を0として放置すると、電荷捕獲中心からプラスの電荷が解放され、トランジスタのしきい値電圧がプラス側へシフトして、初期状態に戻る、または、場合によっては初期状態よりもプラス側へシフトする。これらの現象は、酸化物半導体膜中に移動しやすいイオンが存在していることを示唆しており、最も移動しやすいイオンは、最も小さい原子である水素がイオン化した水素イオンであると考察することができる。

【0029】

また、酸化物半導体膜が光を吸収することによって、光エネルギーによって酸化物半導体膜中の金属元素(M)と水素原子(H)との結合(M-H結合とも表記する)が切れる。

なお、波長が400nm前後の光エネルギーと、金属元素及び水素原子の結合エネルギーと、は概略一致している。酸化物半導体膜中の金属元素と水素原子との結合が切れたトランジスタに負のゲートバイアスを加えると、金属元素から脱離した水素イオンがゲート電極側に引き寄せられるため電荷の分布が変化し、トランジスタのしきい値電圧はマイナス側にシフトして、ノーマリーオンの傾向を示す。

10

【0030】

なお、トランジスタへの光照射と負のゲートバイアスの印加によってゲート絶縁膜界面に移動した水素イオンは、電圧の印加を停止すると元に戻る。これは、酸化物半導体膜中のイオンの移動の代表的な例として理解できる。

【0031】

このような、電圧印加による電気的特性の変動(BT劣化)または光照射による電気的特性の変動(光劣化)への対策は、酸化物半導体膜から水素原子または水などの水素原子を含む不純物を徹底的に排除し、酸化物半導体膜を高純度化することが最も重要である。電荷密度が $10^{15} \text{ cm}^{-3}$ 、つまり、単位面積あたりの電荷が $10^{10} \text{ cm}^{-2}$ の場合、その電荷はトランジスタ特性に影響しないまたは影響するとしてもごく僅かである。よって、電荷密度は $10^{15} \text{ cm}^{-3}$ 以下であることが望ましい。仮に、酸化物半導体膜に含まれる水素のうち、10%の水素が酸化物半導体膜中で移動する場合、酸化物半導体膜に含まれる水素の濃度は $10^{16} \text{ cm}^{-3}$ 以下であることが望ましい。さらに、デバイス完成後に水素が外部より侵入するのを防ぐために、スパッタ法によって成膜した窒化シリコン膜をパッシベーション膜として用い、トランジスタを覆うのが好ましい。

20

【0032】

さらに、酸化物半導体膜中に含まれる水素に対して、過剰な量の酸素を含ませる((水素原子の数)(酸素ラジカルの数)または、(酸素イオンの数)とする)ことで、酸化物半導体膜から水素または水を排除することができる。具体的には、高周波(RF)を用いて酸素をプラズマ化し、基板バイアスを大きくして、酸素ラジカル、酸素イオンを基板上の酸化物半導体膜へドープまたは添加し、酸化物半導体膜中では残存する水素よりも酸素を多くする。酸素の電気陰性度は3.0と、電気陰性度が約2.0である酸化物半導体膜中の金属(Zn、Ga、In)よりも大きいため、水素に対して酸素を過剰に含有させることで、M-H基より水素を奪い、OH基を形成する。なお、このOH基は、Mと結合してM-O-H基を形成しうる。

30

【0033】

なお、酸化物半導体膜の酸素の含有量が、化学量論比よりも過剰となるようになるのがより好ましい。例えば、酸化物半導体膜としてIn-Ga-Zn-O系酸化物半導体膜を用いる場合、酸素のドープなどによって酸素の比率を化学量論比の1倍を超えて2倍まで(2倍未満)とするのがより好ましい。例えば、In-Ga-Zn-O系酸化物半導体の単結晶の化学量論比をIn:Ga:Zn:O=1:1:1:4とすると、組成がInGaZnO<sub>x</sub>で表される酸化物半導体薄膜において、Xは4を超えて8未満とするのがより好ましい。よって、酸化物半導体膜において酸素の含有量は水素の含有量より大きくなる。

40

【0034】

光エネルギーやBTストレスによって、M-H基から水素が脱離して劣化の原因となるが

50

、酸化物半導体膜中に含まれる水素に対して、過剰な量の酸素を含ませる場合、酸化物半導体膜中の酸素が水素イオンと結合してOH基となる。OH基は、結合エネルギーが大きいため、トランジスタに光照射やBTストレスが加えられても水素イオンを放出せず、また、水素イオンより質量も大きいため、酸化物半導体膜中を移動しにくい。よって、OH基は、トランジスタの劣化の原因にならないか、または劣化の原因を減らすことができる。

#### 【0035】

なお、酸化物半導体膜の膜厚を大きくする程、トランジスタのしきい値電圧のばらつきが大きくなる傾向が確認されている。これは、酸化物半導体膜中の酸素欠陥がしきい値電圧の変動の一因であり、膜厚が大きくなるほど該酸素欠陥が増加するためと推測できる。本発明の一態様に係るトランジスタにおいて、酸化物半導体膜中に含まれる水素に対して、過剰な量の酸素を含ませることは、酸化物半導体膜からの水素または水の排除のみでなく、膜中の酸素欠陥の補填に対しても有効である。よって、本発明の一態様に係るトランジスタは、しきい値電圧のばらつきも抑制することができる。

#### 【0036】

また、酸化物半導体膜を挟むように酸化物半導体膜と同種の成分でなる金属酸化物膜を設ける構成も、電気的特性の変動防止に効果的である。酸化物半導体膜と同種の成分でなる金属酸化物膜として、具体的には、酸化物半導体膜の構成元素から選択される一または複数の金属元素の酸化物を含む膜を用いるのが好ましい。このような材料を含む膜は酸化物半導体膜との相性が良く、酸化物半導体膜を挟んで該金属酸化物膜を設けることで、酸化物半導体膜との界面の状態を良好に保つことができる。つまり、上述の材料を用いた金属酸化物膜を、酸化物半導体膜と接する絶縁膜として設けることで、該金属酸化物膜と酸化物半導体膜との界面及びその近傍への水素イオンの蓄積を抑制または防止することができる。したがって、酸化物半導体膜を挟むように例えば酸化シリコン膜等の酸化物半導体膜とは異なる成分でなる絶縁膜を設けた場合と比較して、トランジスタのしきい値電圧に影響を与える酸化物半導体膜界面の水素濃度を十分に低減することができる。

#### 【0037】

なお、該金属酸化物膜としては、酸化ガリウム膜を用いるのが好ましい。酸化ガリウムは、バンドギャップ(Eg)が大きいので、酸化ガリウム膜によって酸化物半導体膜を挟むことで、酸化物半導体膜と金属酸化物膜との界面において、エネルギー障壁が形成され、その界面においてキャリアの移動は妨げられる。したがって、キャリアは酸化物半導体から金属酸化物に移動することなく、酸化物半導体膜中を移動する。一方、水素イオンは、酸化物半導体と金属酸化物との界面を通過して、金属酸化物と絶縁膜との界面付近に蓄積する。仮に、絶縁膜との界面近傍に水素イオンが蓄積されたとしても、金属酸化物膜としての酸化ガリウム膜にはキャリアが流れうる寄生チャネルが形成されないため、トランジスタのしきい値電圧への影響を与えない、またはその影響が極めて少ない。なお、酸化ガリウムとIn-Ga-Zn-O系の材料を接触させた場合のエネルギー障壁は、伝導帯側で約0.8eVとなり、価電子帯側で約0.9eVとなる。

#### 【0038】

上述のように、開示する発明の一態様に係るトランジスタは、酸素ドープ処理によって、酸化物半導体膜に接する絶縁膜中、酸化物半導体膜中、またはこれらの界面近傍の少なくともいずれか一に酸素の含有量を増大させることを技術思想とするものである。

#### 【0039】

酸化物半導体膜としてインジウムを含む酸化物半導体材料を用いる場合、インジウムと酸素の結合力は比較的弱いため、酸化物半導体膜に接する絶縁膜にシリコン等のより酸素との結合力が強い材料が含まれる場合に、熱処理によって酸化物半導体膜中の酸素が引き抜かれてしまい、酸化物半導体膜の界面近傍に酸素欠損が形成される恐れがある。しかしながら、開示する発明の一態様に係るトランジスタは、酸化物半導体膜と接する絶縁膜に過剰な酸素を供給することで、酸化物半導体膜の界面近傍における酸素欠損の形成を抑制することができる。

10

20

30

40

50

## 【0040】

ここで、トランジスタの作製工程において酸素ドープ処理を行った後では、酸化物半導体膜または酸化物半導体膜に接する絶縁膜に含有される、化学量論比より過剰な酸素の量が各層において異なる場合がある。過剰な酸素の量が異なる状態では、各層の酸素の化学ポテンシャルが異なり、化学ポテンシャルの相違はトランジスタの作製工程における熱処理等で、平衡状態へ近づく、または平衡状態となると考えられる。したがって、絶縁膜への酸素ドープ処理後には、熱処理を行うことがより好ましい。酸素ドープ処理後の熱処理によって、絶縁膜に過剰に供給された酸素を拡散させ、十分な量の酸素を酸化物半導体膜に供給することが可能である。以下では、平衡状態における酸素の分布について検討する。

## 【0041】

ある温度  $T$ 、圧力  $P$  での平衡状態とは、全系のギブスの自由エネルギー  $G$  が最小となる状態であり、以下の式(1)で表される。

## 【0042】

## 【数1】

$$G(N_a, N_b, N_c, \dots, T, P) = G^{(1)}(N_a, N_b, N_c, \dots, T, P) + G^{(2)}(N_a, N_b, N_c, \dots, T, P) + G^{(3)}(N_a, N_b, N_c, \dots, T, P) \dots \dots (1)$$

## 【0043】

式(1)において、 $G^{(1)}$ 、 $G^{(2)}$ 、 $G^{(3)}$  は、各層のギブスの自由エネルギーを表す。また、 $N_a$ 、 $N_b$ 、 $N_c$  は粒子数を表し、 $a$ 、 $b$ 、 $c$  は粒子の種類を表す。粒子  $a$  が  $i$  層から  $j$  層へ  $N_a^{(j)}$  だけ移動した場合、ギブスの自由エネルギーの変化は、以下の式(2)のようになる。

## 【0044】

## 【数2】

$$\delta G = -\frac{\partial G^{(i)}}{\partial N_a^{(i)}} \delta N_a^{(j)} + \frac{\partial G^{(j)}}{\partial N_a^{(j)}} \delta N_a^{(j)} \dots \dots (2)$$

## 【0045】

ここで  $G$  が 0、すなわち以下の式(3)が成り立つとき、系が平衡状態となる。

## 【0046】

## 【数3】

$$\frac{\partial G^{(i)}}{\partial N_a^{(i)}} = \frac{\partial G^{(j)}}{\partial N_a^{(j)}} \dots \dots (3)$$

## 【0047】

ギブスの自由エネルギーの粒子数微分は、化学ポテンシャルに相当するので、平衡状態において、粒子の化学ポテンシャルが全ての層で等しくなる。

## 【0048】

つまり、具体的には、酸化物半導体膜と比較して該酸化物半導体膜と接する絶縁膜に酸素が過剰に含まれている場合、酸化物半導体膜では酸素の化学ポテンシャルが相対的に小さく、絶縁膜では化学ポテンシャルが相対的に大きい状態となっている。

## 【0049】

そして、トランジスタの作製工程において熱処理を行うことにより、系全体(ここでは、酸化物半導体膜と、それに接する絶縁膜)が十分高温になり、原子の層内及び層間の拡散が起こるようになると、化学ポテンシャルが同じになるように酸素の移動が起こる。すなわち、絶縁膜の酸素が酸化物半導体膜に移動することで、絶縁膜の化学ポテンシャルが小さくなり、酸化物半導体膜の化学ポテンシャルが大きくなる。

10

20

30

40

50

## 【0050】

したがって、酸素ドープ処理によって絶縁膜に過剰に供給された酸素は、その後の熱処理によって系内の化学ポテンシャルを平衡状態とすることで、拡散し、酸化物半導体膜へ酸素が供給される。上述のように、酸化物半導体膜に供給された酸素は、水素イオンと結合してOH基となり、トランジスタの劣化の原因にならないか、または劣化の原因を減らすことができる。また、酸化物半導体膜に酸素を供給することは、膜中の酸素欠陥の補填に対しても有効である。

## 【発明の効果】

## 【0051】

熱処理による脱水化または脱水素化処理、および、酸素ドープ処理されたゲート絶縁膜を有するトランジスタは、バイアス-熱ストレス(BT)試験前後においてもトランジスタのしきい値電圧の変化量が低減しており、安定した電気特性を有する信頼性の高いトランジスタが実現できる。

10

## 【0052】

また、開示する発明の一態様により、電気特性が良好で信頼性の高いトランジスタを有する様々な半導体装置を作製することができる。

## 【図面の簡単な説明】

## 【0053】

【図1】半導体装置の一形態を説明する図。

20

【図2】半導体装置の作製方法の一形態を説明する図。

【図3】半導体装置の形態を説明する図。

【図4】半導体装置の作製方法の一形態を説明する図。

【図5】半導体装置の作製方法の一形態を説明する図。

【図6】半導体装置の作製方法の一形態を説明する図。

【図7】半導体装置の断面図、上面図及び回路図。

【図8】半導体装置の一形態を説明する図。

【図9】半導体装置の一形態を説明する図。

【図10】半導体装置の一形態を説明する図。

【図11】半導体装置の一形態を説明する図。

【図12】半導体装置の一態様を説明する図。

30

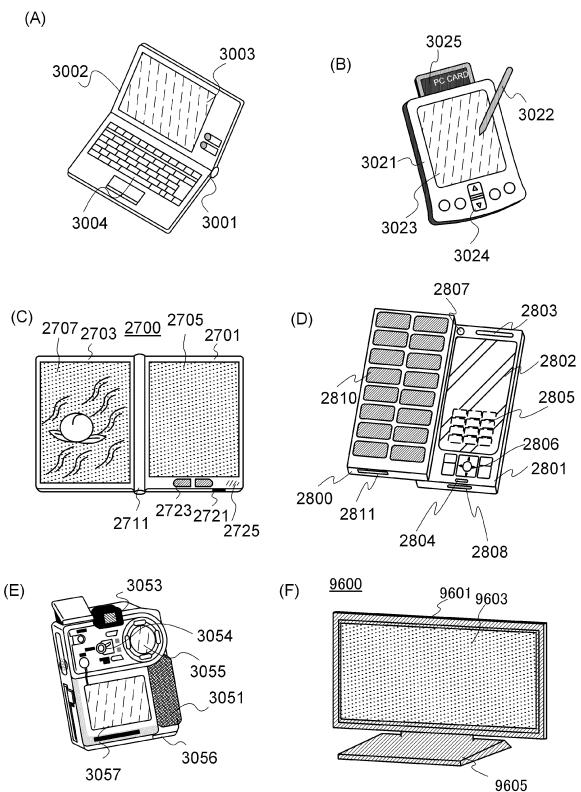

【図13】電子機器を示す図。

【図14】電子機器を示す図。

【図15】酸素ドープしたシリコンウェハのSIMS測定結果を示す図である。

【図16】断面SEM像を説明する図である。

【図17】プラズマ装置の上面図及び断面図である。

## 【発明を実施するための形態】

## 【0054】

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。ただし、本明細書に開示する発明は以下の説明に限定されず、その形態および詳細を様々な変更し得ることは、当業者であれば容易に理解される。また、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

40

## 【0055】

なお、本明細書における「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

## 【0056】

(実施の形態1)

本実施の形態では、半導体装置および半導体装置の作製方法について、図1乃至図3を用いて説明する。

## 【0057】

半導体装置の構成例

50

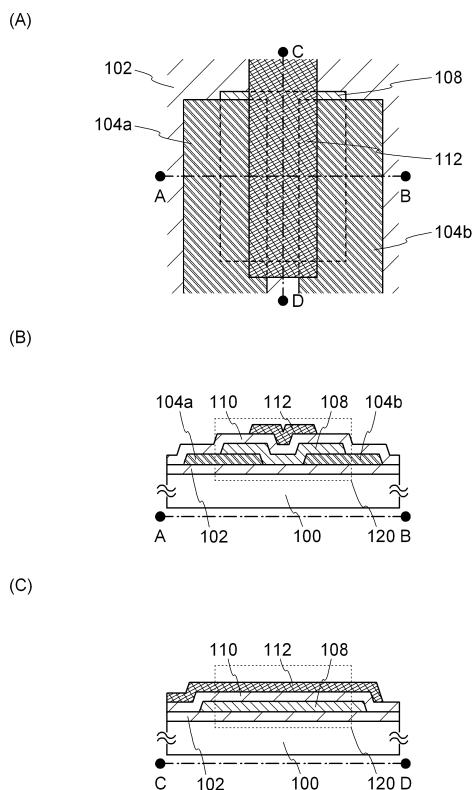

図1には、トランジスタ120の構成例を示す。ここで、図1(A)は平面図であり、図1(B)および図1(C)はそれぞれ、図1(A)におけるA-B断面およびC-D断面に係る断面図である。なお、図1(A)では煩雑になることを避けるため、トランジスタ120の構成要素の一部(例えば、ゲート絶縁膜110など)を省略している。

【0058】

図1に示すトランジスタ120は、基板100上の絶縁膜102、ソース電極104a、ドレイン電極104b、酸化物半導体膜108、ゲート絶縁膜110、ゲート電極112を含む。

【0059】

図1に示すトランジスタ120において、ゲート絶縁膜110は、酸素ドープ処理が行われた絶縁膜であり、酸素過剰領域を有する。ゲート絶縁膜110が酸素過剰領域を有することにより、酸化物半導体膜108からゲート絶縁膜110への酸素の移動を防ぐことができる。また、ゲート絶縁膜110から酸化物半導体膜108への酸素の供給を行うこともできる。よって、ゲート絶縁膜110に酸素ドープ処理を行うことにより、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができるので、信頼性が高められたトランジスタ120が実現する。

【0060】

半導体装置の作製工程例

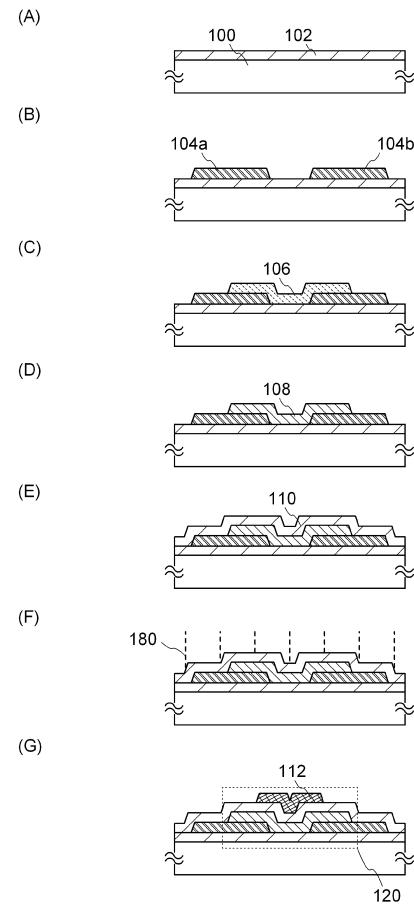

以下、図2を用いて、図1に示す半導体装置の作製工程の一例を説明する。

【0061】

まず、基板100上に絶縁膜102を形成する(図2(A)参照)。

【0062】

基板100の材質に大きな制限はないが、少なくとも、後の熱処理に耐える程度の耐熱性を有していることが必要となる。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。

【0063】

また、基板100として、可撓性基板を用いてもよい。可撓性基板上にトランジスタを設ける場合、可撓性基板上に直接的にトランジスタを作り込んでよいし、他の基板にトランジスタを形成した後、これを剥離し、可撓性基板に転置しても良い。なお、トランジスタを剥離し、可撓性基板に転置するためには、上記他の基板とトランジスタとの間に剥離層を形成すると良い。

【0064】

絶縁膜102は、下地として機能する絶縁膜である。具体的には、絶縁膜102には、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ガリウム、これらの混合材料、などを用いればよい。また、絶縁膜102は、上述の材料を含む絶縁膜の単層構造としても良いし、積層構造としても良い。

【0065】

絶縁膜102の作製方法に特に限定はない。例えば、プラズマCVD法やスパッタリング法などの成膜方法を用いて絶縁膜102を作製することができる。なお、水素や水などが混入しにくいという点では、スパッタリング法が好適である。

【0066】

なお、絶縁膜102には、後に形成される酸化物半導体膜と同種の成分でなる絶縁材料を用いると特に好ましい。このような材料は酸化物半導体膜との相性が良く、これを絶縁膜102に用いることで、酸化物半導体膜との界面の状態を良好に保つことができるからである。ここで、「酸化物半導体膜と同種の成分」とは、酸化物半導体膜の構成元素から選択される一または複数の元素を含むことを意味する。例えば、酸化物半導体膜がIn-Ga-Zn-O系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料

10

20

30

40

50

としては酸化ガリウムなどがある。

【0067】

また、絶縁膜102を積層構造とする場合には、酸化物半導体膜と同種の成分でなる絶縁材料でなる膜(以下、膜a)と、膜aの成分材料とは異なる材料を含む膜(以下、膜b)との積層構造とするとなお良い。膜aと膜bを酸化物半導体膜側から順に積層した構造とすることで、電荷は膜aと膜bとの界面の電荷捕獲中心に優先的に捕獲される(酸化物半導体膜と膜aとの界面との比較)ため、酸化物半導体膜の界面での電荷捕獲を十分に抑制することができるようになり、半導体装置の信頼性が向上するためである。

【0068】

なお、このような積層構造としては、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

【0069】

次いで、絶縁膜102上に、ソース電極およびドレイン電極(これと同じ層で形成される配線を含む)を形成するための導電膜を形成し、当該導電膜を加工して、ソース電極104aおよびドレイン電極104bを形成する(図2(B)参照)。なお、ここで形成されるソース電極104aの端部とドレイン電極104bの端部との間隔によって、トランジスタのチャネル長Lが決定されることになる。

【0070】

ソース電極104aおよびドレイン電極104bに用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜)等がある。また、Al、Cuなどの金属膜の下側または上側の一方または双方にTi、Mo、Wなどの高融点金属膜またはそれらの金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜)を積層させた導電膜を用いても良い。

【0071】

また、ソース電極104aおよびドレイン電極104bに用いる導電膜は、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ混合酸化物(ITOと略記する)、酸化インジウム酸化亜鉛混合酸化物またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

【0072】

導電膜の加工は、レジストマスクを用いたエッチングによって行うことができる。当該エッチングに用いるレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光などを用いるとよい。

【0073】

なお、チャネル長L=25nm未満の露光を行う場合には、例えば、数nm～数10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用いて、レジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。したがって、後に形成されるトランジスタのチャネル長Lを微細化することができる、回路の動作速度を高めることができる。

【0074】

また、いわゆる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成されたレジストマスクは、複数の膜厚を有する形状となり、アッシングによってさらに形状を変形させることができるために、異なるパターンに加工する複数のエッチング工程に用いることが可能である。このため、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。つまり、工程の簡略化が可能となる。

【0075】

次に、絶縁膜102上に、ソース電極104aおよびドレイン電極104bと接する酸化物半導体膜を形成し、当該酸化物半導体膜を加工して島状の酸化物半導体膜106を形成

10

20

30

40

50

する（図2（C）参照）。

【0076】

酸化物半導体膜は、水素や水などが混入しにくい方法で作製するのが望ましい。例えば、スパッタリング法などを用いて作製することができる。また、酸化物半導体膜の厚さは、3 nm以上30 nm以下とするのが望ましい。酸化物半導体膜を厚くしすぎると（例えば、膜厚を50 nm以上）、トランジスタがノーマリーオンとなってしまうおそれがあるためである。

【0077】

酸化物半導体膜に用いる材料としては、例えば、インジウムを含有する酸化物半導体材料や、インジウムおよびガリウムを含有する酸化物半導体材料などがある。

10

【0078】

また、酸化物半導体膜に用いる材料としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O系の材料や、三元系金属酸化物であるIn-Ga-Zn-O系の材料、In-Sn-Zn-O系の材料、In-Al-Zn-O系の材料、Sn-Ga-Zn-O系の材料、Al-Ga-Zn-O系の材料、Sn-Al-Zn-O系の材料や、二元系金属酸化物であるIn-Zn-O系の材料、Sn-Zn-O系の材料、Al-Zn-O系の材料、Zn-Mg-O系の材料、Sn-Mg-O系の材料、In-Mg-O系の材料、In-Ga-O系の材料や、単元系金属の酸化物であるIn-O系の材料、Sn-O系の材料、Zn-O系の材料などがある。また、上記の材料に酸化珪素を含ませてもよい。ここで、例えば、In-Ga-Zn-O系の材料とは、インジウム（In）、ガリウム（Ga）、亜鉛（Zn）を有する酸化物膜、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。

20

【0079】

また、酸化物半導体膜は、化学式 $InMO_3 (ZnO)_m (m > 0)$ で表記される材料を用いた薄膜とすることができます。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMn、またはGaおよびCoなどを用いることができる。

30

【0080】

本実施の形態では、酸化物半導体膜を、In-Ga-Zn-O系の酸化物半導体成膜用ターゲットを用いたスパッタリング法により形成する。

【0081】

In-Ga-Zn-O系の酸化物半導体成膜用ターゲットとしては、例えば、組成比として、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  [mol数比] の酸化物半導体成膜用ターゲットを用いることができる。なお、ターゲットの材料および組成を上述に限定する必要はない。例えば、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol数比] の組成比の酸化物半導体成膜用ターゲットを用いることもできる。

【0082】

また、酸化物半導体としてIn-Zn-O系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、 $In : Zn = 50 : 1 \sim 1 : 2$  (モル数比に換算すると $In_2O_3 : ZnO = 25 : 1 \sim 1 : 4$ )、好ましくは $In : Zn = 20 : 1 \sim 1 : 1$  (モル数比に換算すると $In_2O_3 : ZnO = 10 : 1 \sim 1 : 2$ )、さらに好ましくは $In : Zn = 15 : 1 \sim 1.5 : 1$  (モル数比に換算すると $In_2O_3 : ZnO = 15 : 2 \sim 3 : 4$ )とする。例えば、In-Zn-O系酸化物半導体の形成に用いるターゲットは、原子数比が $In : Zn : O = X : Y : Z$ のとき、 $Z > 1.5X + Y$ とする。

40

【0083】

酸化物半導体成膜用ターゲットの充填率は、90%以上100%以下、好ましくは95%以上99.9%以下とする。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とすることができるためである。

【0084】

成膜の雰囲気は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、または、希ガ

50

スと酸素の混合雰囲気下などとすればよい。また、酸化物半導体膜への水素、水、水酸基を有する化合物、水素化物などの混入を防ぐために、水素、水、水酸基を有する化合物、水素化物などの水素原子を含む不純物が十分に除去された高純度ガスを用いた雰囲気とすることが望ましい。

【0085】

より具体的には、例えば、酸化物半導体膜は次のように形成することができる。

【0086】

まず、減圧状態に保持された成膜室内に基板100を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板100が加熱された状態で成膜を行うことで、酸化物半導体膜に含まれる不純物濃度を低減することができるためである。また、スパッタリングによる損傷を軽減することができるためである。

10

【0087】

次に、成膜室内の残留水分を除去しつつ、水素および水などの水素原子を含む不純物が十分に除去された高純度ガスを導入し、上記ターゲットを用いて基板100上に酸化物半導体膜を成膜する。成膜室内の残留水分を除去するためには、排気手段として、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどの吸着型の真空ポンプを用いることが望ましい。また、排気手段は、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素分子や、水( $H_2O$ )などの水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)などが除去されているため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

20

【0088】

成膜条件の一例として、基板とターゲットとの間との距離を100mm、圧力を0.6Pa、直流(DC)電源を0.5kW、成膜雰囲気を酸素(酸素流量比率100%)雰囲気とすることができる。なお、パルス直流電源を用いると、成膜時の粉状物質(パーティクル、ごみともいう)の発生を軽減でき、膜厚分布も均一となるため好ましい。

【0089】

酸化物半導体膜の加工は、所望の形状のマスクを酸化物半導体膜上に形成した後、当該酸化物半導体膜をエッティングすることによって行うことができる。上述のマスクは、フォトリソグラフィなどの方法を用いて形成することができる。または、インクジェット法などの方法を用いてマスクを形成しても良い。

30

【0090】

なお、酸化物半導体膜のエッティングは、ドライエッティングでもウェットエッティングでもよい。もちろん、これらを組み合わせて用いてもよい。

【0091】

その後、酸化物半導体膜106に対して熱処理を行って、高純度化された酸化物半導体膜108を形成する(図2(D)参照)。この熱処理によって酸化物半導体膜106中の水素(水や水酸基を含む)を除去し、酸化物半導体膜の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。上記熱処理の温度は、250以上650以下、好ましくは450以上600以下、または基板の歪み点未満とする。

40

【0092】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450、1時間の条件で行うことができる。この間、酸化物半導体膜106は大気に触れさせず、水や水素の混入が生じないようにする。

【0093】

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。GRTA装置は、高温のガスを用いて熱処理を行う装置で

50

ある。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性ガスが用いられる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。

【0094】

例えば、上記熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出すG R T A 処理を行ってもよい。G R T A 処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えてても良い。酸素を含む雰囲気において熱処理を行うことで、酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減することができるためである。

10

【0095】

なお、不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6 N (99.9999%)以上、好ましくは7 N (99.99999%)以上(すなわち、不純物濃度が1 ppm以下、好ましくは0.1 ppm以下)とする。

【0096】

いずれにしても、上記熱処理によって不純物を低減し、i型(真性半導体)またはi型に限りなく近い酸化物半導体膜を形成することで、極めて優れた特性のトランジスタを実現することができる。

20

【0097】

ところで、上述の熱処理には水素や水などを除去する効果があるから、当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該脱水化処理や、脱水素化処理は、例えば、酸化物半導体膜を島状に加工する前などのタイミングにおいて行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

【0098】

次に、酸化物半導体膜108と接し、かつ、ソース電極104aおよびドレイン電極104bを覆うゲート絶縁膜110を形成する(図2(E)参照)。

30

【0099】

ゲート絶縁膜110は、絶縁膜102と同様に形成することができる。すなわち、ゲート絶縁膜110は、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ガリウム、これらの混合材料、などを用いて形成すればよい。ただし、トランジスタのゲート絶縁膜として機能することを考慮して、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>(x>0, y>0))、窒素が添加されたハフニウムアルミネート(HfAl<sub>x</sub>O<sub>y</sub>(x>0, y>0))、などの比誘電率が高い材料を採用しても良い。

40

【0100】

なお、ゲート絶縁膜110には、絶縁膜102と同様に、後に形成される酸化物半導体膜と同種の成分でなる絶縁材料を用いると特に好ましい。このような材料は酸化物半導体膜との相性が良く、これをゲート絶縁膜110に用いることで、酸化物半導体膜との界面の状態を良好に保つことができるからである。ここで、「酸化物半導体膜と同種の成分」とは、酸化物半導体膜の構成元素から選択される一または複数の元素を含むことを意味する。例えば、酸化物半導体膜がIn-Ga-Zn-O系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料としては酸化ガリウムなどがある。

【0101】

また、絶縁膜102と同様に、積層構造を採用しても良い。この場合には、酸化物半導体

50

膜と同種の成分でなる絶縁材料でなる膜（以下、膜a）と、膜aの成分材料とは異なる材料を含む膜（以下、膜b）との積層構造とするとなお良い。膜aと膜bを酸化物半導体膜側から順に積層した構造とすることで、電荷は膜aと膜bとの界面の電荷捕獲中心に優先的に捕獲される（酸化物半導体膜と膜aとの界面との比較）ため、酸化物半導体膜の界面での電荷捕獲を十分に抑制することができるようになり、半導体装置の信頼性が向上するためである。

#### 【0102】

なお、このような積層構造としては、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

#### 【0103】

上述のゲート絶縁膜110の形成後には、熱処理を行うのが望ましい。当該熱処理の温度は、250以上700以下、好ましくは450以上600以下、または基板の歪み点未満とする。

#### 【0104】

上記熱処理は、窒素、酸素、超乾燥空気（水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気）、または希ガス（アルゴン、ヘリウムなど）の雰囲気下で行えばよいが、上記窒素、酸素、超乾燥空気、または希ガス等の雰囲気には、水、水素などが含まれないことが好ましい。また、熱処理装置に導入する窒素、酸素、または希ガスの純度は、6N（99.9999%）以上（即ち不純物濃度を1ppm以下）とするのが好ましく、7N（99.99999%）以上（即ち不純物濃度を0.1ppm以下）とすると、より好ましい。

#### 【0105】

本実施の形態に係る上記熱処理においては、酸化物半導体膜108と、ゲート絶縁膜110と、が接した状態で加熱される。したがって、上述の脱水化（または脱水素化）処理によって減少してしまう可能性のある酸素を、酸化物半導体膜108へ供給することも可能である。この意味において、当該熱処理を、加酸化（加酸素化）と呼ぶこともできる。

#### 【0106】

なお、加酸化を目的とする熱処理のタイミングは、酸化物半導体膜108の形成後であれば特に限定されない。例えば、ゲート絶縁膜110に対して酸素ドープ処理を行った後に加酸化を目的とする熱処理を行っても良いし、ゲート電極の形成後に加酸化を目的とする熱処理を行っても良い。または、脱水化等を目的とする熱処理に続けて加酸化を目的とする熱処理を行っても良いし、脱水化等を目的とする熱処理に加酸化を目的とする熱処理を兼ねさせても良いし、加酸化を目的とする熱処理に脱水化等を目的とする熱処理を兼ねさせても良い。

#### 【0107】

上述のように、脱水化等を目的とする熱処理と、酸素ドープ処理または加酸化を目的とする熱処理とを適用することで、酸化物半導体膜108を不純物が極力含まれないように高純度化することができる。高純度化された酸化物半導体膜108中にはドナーに由来するキャリアが極めて少ない（ゼロに近い）。

#### 【0108】

次に、ゲート絶縁膜110に対して、酸素180による処理（酸素ドープ処理や、酸素プラズマドープ処理ともいう）を行う（図2（F）参照）。ここで、酸素180には、少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかが含まれている。ゲート絶縁膜110に酸素ドープ処理を行うことにより、ゲート絶縁膜110中、またはゲート絶縁膜110と酸化物半導体膜108との界面近傍に酸素を含有させることができる。この場合、ゲート絶縁膜110中の酸素の含有量は、ゲート絶縁膜110の化学量論比を超える程度、好ましくは、化学量論比の1倍を超えて4倍まで（1倍より大きく4倍未満）、より好ましくは、1倍を超えて2倍まで（1倍より大きく2倍未満）とする。あるいは、酸素の含有量は、ゲート絶縁膜110を構成する材料が単結晶の場合の酸素の量をYとして、Yを超える程度、好ましくは、Yを超えて4Yまでとすることもできる。あるいは、酸

10

20

30

40

50

素の含有量は、酸素ドープ処理を行わない場合の絶縁膜中の酸素の量  $Z$  を基準として、  $Z$  を超える程度、好ましくは、  $Z$  を超えて  $4Z$  までとすることもできる。

【0109】

例えば、組成が  $\text{GaO}_x$  ( $x > 0$ ) で表現される酸化ガリウムを用いる場合、単結晶の酸化ガリウムは  $\text{Ga}_2\text{O}_3$  であるので、  $x$  は  $1.5$  を超えて  $6$  まで (つまり  $\text{Ga}$  の  $1.5$  倍を超えて  $6$  倍まで)、が許容される。また、例えば、組成が  $\text{SiO}_x$  ( $x > 0$ ) で表現される酸化シリコンを用いる場合、  $\text{SiO}_2$  (すなわち  $\text{Si}$  の  $2$  倍) であれば、  $x$  は  $2$  を超えて  $8$  まで (つまり  $\text{Si}$  の  $2$  倍を超えて  $8$  倍まで) が許容される。なお、このような酸素過剰領域は、絶縁膜の一部 (界面を含む) に存在していればよい。

【0110】

10

このように、ゲート絶縁膜 110 中、またはゲート絶縁膜 110 と酸化物半導体膜 108 との界面近傍に酸素過剰領域を形成することにより、酸化物半導体膜 108 からゲート絶縁膜 110 への酸素の移動を防ぐことができる。よって、ゲート絶縁膜 110 に酸素ドープ処理を行うことにより、酸化物半導体膜 108 に水素に対して過剰な量の酸素を含有させることができる。

【0111】

さらに、上記酸素ドープ処理において、酸化物半導体膜 108 中、酸化物半導体膜 108 と絶縁膜 102 との界面近傍、または絶縁膜 102 中に酸素が供給され得る。特に、ゲート絶縁膜 110 または酸化物半導体膜 108 の膜厚が十分薄い場合や、基板に印加する電気的なバイアスが十分大きい場合や、酸素ドープ処理後に熱処理を行う場合に、酸化物半導体膜 108 中、酸化物半導体膜 108 と絶縁膜 102 との界面近傍、または絶縁膜 102 中に酸素が供給されやすくなる。

【0112】

この場合、酸化物半導体膜 108 中の酸素の含有量は、酸化物半導体膜 108 の化学量論比を超える程度、好ましくは、化学量論比の  $1$  倍を超えて  $2$  倍まで ( $1$  倍より大きく  $2$  倍未満)、とする。あるいは、酸素の含有量は、酸化物半導体膜 108 を構成する材料が単結晶の場合の酸素の量を  $Y$  として、  $Y$  を超える程度、好ましくは、  $Y$  を超えて  $2Y$  までとすることもできる。あるいは、酸素の含有量は、酸素ドープ処理を行わない場合の酸化物半導体膜中の酸素の量  $Z$  を基準として、  $Z$  を超える程度、好ましくは、  $Z$  を超えて  $2Z$  までとすることもできる。なお、上述の好ましい範囲に上限が存在するのは、酸素の含有量を多くしすぎると、水素吸蔵合金 (水素貯蔵合金) のように、酸化物半導体膜 108 が水素を取り込んでしまう恐れがあるためである。なお、酸化物半導体膜において酸素の含有量は水素の含有量より大きくなる。

【0113】

結晶構造が  $\text{InGaO}_3(\text{ZnO})_m$  ( $m > 0$ ) で表現される材料の場合、例えば、  $m = 1$  ( $\text{InGaZnO}_4$ ) の結晶構造を基準にすれば、  $\text{InGaZnO}_x$  において  $x$  は  $4$  を超えて  $8$  まで、また、  $m = 2$  ( $\text{InGaZn}_2\text{O}_5$ ) の結晶構造を基準にすれば、  $\text{InGaZn}_2\text{O}_x$  において  $x$  は  $5$  を超えて  $10$  まで、が許容される。なお、このような酸素過剰領域は、酸化物半導体の一部 (界面を含む) に存在していればよい。

【0114】

40

なお、酸化物半導体膜において、酸素は主たる成分材料の一つである。このため、酸化物半導体膜中の酸素濃度を、 SIMS (Secondary Ion Mass Spectroscopy) などの方法を用いて、正確に見積もることは難しい。つまり、酸化物半導体膜に酸素が意図的に添加されたか否かを判別することは困難であるといえる。

【0115】

ところで、酸素には  $^{17}\text{O}$  や  $^{18}\text{O}$  といった同位体が存在し、自然界におけるこれらの存在比率はそれぞれ酸素原子全体の  $0.037\%$ 、  $0.204\%$  程度であることが知られている。つまり、酸化物半導体膜中におけるこれら同位体の濃度は、 SIMS などの方法によって見積もることができる程度になるから、これらの濃度を測定することで、酸化物半導体膜中の酸素濃度をより正確に見積もることが可能な場合がある。よって、これらの濃

10

20

30

40

50

度を測定することで、酸化物半導体膜に意図的に酸素が添加されたか否かを判別しても良い。

【0116】

例えば、 $^{18}\text{O}$ の濃度を基準に用いると、酸化物半導体膜において、酸素が添加された領域における酸素の同位体の濃度D1( $^{18}\text{O}$ )と、酸素が添加されていない領域における酸素の同位体の濃度D2( $^{18}\text{O}$ )との間には、 $D1(^{18}\text{O}) > D2(^{18}\text{O})$ が成立するといえる。

【0117】

また、ゲート絶縁膜110に添加される酸素180の少なくとも一部は、酸化物半導体に供給された後、酸化物半導体中において不対結合手を有することが好ましい。不対結合手を有することにより、膜中に残存する水素と結合して、水素を固定化（非可動イオン化）することができるためである。

【0118】

このように、ゲート絶縁膜110に酸素ドープ処理を行うことにより、酸化物半導体膜108中に酸素過剰領域が形成され、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができる。

【0119】

また、絶縁膜102中、または絶縁膜102と酸化物半導体膜108との界面近傍に酸素過剰領域を形成することにより、酸化物半導体膜108から絶縁膜102への酸素の移動を防ぐことができる。

【0120】

上述の酸素180は、プラズマ発生装置やオゾン発生装置によって発生させることができる。より具体的には、例えば、半導体装置に対してエッチング処理を行うことができる装置や、レジストマスクに対してアッシングを行うことができる装置などを用いて酸素180を発生させ、酸化物半導体膜108を処理することができる。

【0121】

なお、酸素の添加をより好適に行うためには、基板には電気的なバイアスを加えておくことが望ましい。

【0122】

なお、上述の酸素ドープ処理の後には、熱処理を行うことが好ましい。この熱処理によって、水素に対して過剰な量の酸素を酸化物半導体膜に供給することができる。また、この熱処理に、上述の加酸化を目的とする熱処理を兼ねさせても良い。当該効果を得るために熱処理のタイミングは、上述の酸素ドープ処理の後であればいつでも構わない。また、酸素ドープ処理と熱処理を繰り返して行っても良い。当該処理を繰り返して行うことにより、トランジスタの信頼性をさらに高めることができる。なお、繰り返しの回数は適宜設定することができる。

【0123】

その後、ゲート電極112を形成する（図2（G）参照）。ゲート電極112は、モリブデン、チタン、タンタル、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。なお、ゲート電極112は、単層構造としても良いし、積層構造としても良い。

【0124】

なお、ゲート電極112の形成後には、絶縁膜を形成しても良い。当該絶縁膜は、例えば、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ガリウム、これらの混合材料、などを用いて形成することができる。特に、絶縁膜として窒化シリコン膜を用いる場合には、添加された酸素の外部への放出を防ぐことができると共に、酸化物半導体膜108への外部からの水素等の混入を効果的に抑制することができるため好適である。また、ソース電極104aやドレイン電極104b、ゲート電極112などと接続される配線を形成しても良い。

【0125】

10

20

30

40

50

以上の工程でトランジスタ120が形成される。

【0126】

半導体装置の変形例

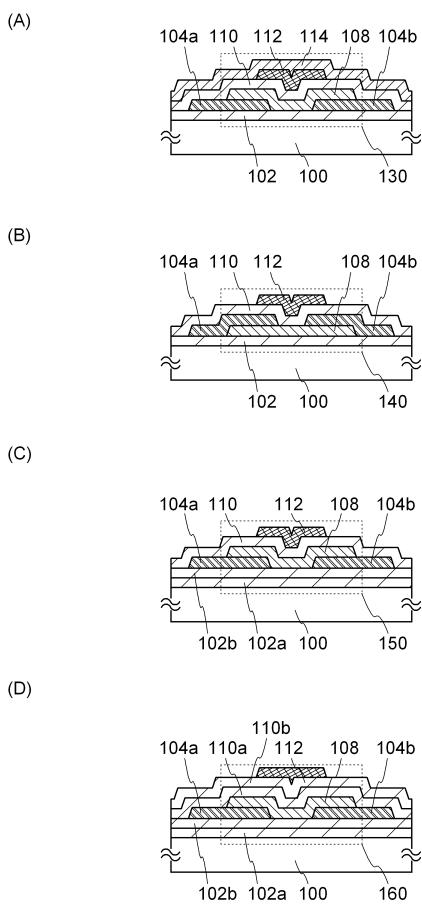

図3(A)乃至図3(D)には、図1に示すトランジスタ120の変形例として、トランジスタ130、トランジスタ140、トランジスタ150、およびトランジスタ160の断面図を示す。

【0127】

図3(A)に示すトランジスタ130は、絶縁膜102、ソース電極104a、ドレイン電極104b、酸化物半導体膜108、ゲート絶縁膜110、ゲート電極112を含む点で、トランジスタ120と共に通している。トランジスタ130とトランジスタ120との相違は、上述の構成要素を覆う絶縁膜114の有無である。すなわち、トランジスタ130は、絶縁膜114を有している。その他の構成要素については図1のトランジスタ120と同様であるから、詳細は、図1に関する記載を参照することができる。

【0128】

図3(B)に示すトランジスタ140は、上述の各構成要素を含む点で、図1に示すトランジスタ120と共に通している。トランジスタ140とトランジスタ120との相違は、ソース電極104aおよびドレイン電極104bと、酸化物半導体膜108との積層順序である。つまり、トランジスタ120では、ソース電極104aおよびドレイン電極104bが先に形成されるのに対して、トランジスタ140では、酸化物半導体膜108が先に形成される。その他の構成要素については、図1と同様である。なお、トランジスタ130のように、絶縁膜114を有する構成としても良い。

【0129】

図3(C)に示すトランジスタ150は、上述の各構成要素を含む点で、図1に示すトランジスタ120と共に通している。トランジスタ150とトランジスタ120との相違は、基板100側の絶縁膜にある。つまり、トランジスタ150では、絶縁膜102aと絶縁膜102bの積層構造を備えている。その他の構成要素については、図3(B)と同様である。

【0130】

このように、絶縁膜102aと絶縁膜102bの積層構造とすることにより、電荷は絶縁膜102aと絶縁膜102bとの界面の電荷捕獲中心に優先的に捕獲されるため、酸化物半導体膜108の界面での電荷捕獲を十分に抑制することができるようになり、半導体装置の信頼性が向上する。

【0131】

なお、絶縁膜102bは酸化物半導体膜108と同種の成分でなる絶縁材料でなる膜とし、絶縁膜102aは絶縁膜102bの成分材料とは異なる材料を含む膜とすることが望ましい。例えば、酸化物半導体膜108がIn-Ga-Zn-O系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料としては酸化ガリウムなどがある。この場合、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

【0132】

図3(D)に示すトランジスタ160は、上述の各構成要素を含む点で、図1に示すトランジスタ120と共に通している。トランジスタ160とトランジスタ120との相違は、基板100側の絶縁膜およびゲート絶縁膜にある。つまり、トランジスタ160では、絶縁膜102aと絶縁膜102bの積層構造を備え、かつ、ゲート絶縁膜110aとゲート絶縁膜110bの積層構造を備えている。その他の構成要素については、図1と同様である。

【0133】

このように、絶縁膜102aと絶縁膜102bの積層構造とし、ゲート絶縁膜110aとゲート絶縁膜110bの積層構造とすることにより、電荷は絶縁膜102aと絶縁膜102bや、ゲート絶縁膜110aとゲート絶縁膜110bの界面に優先的に捕獲されるため

10

20

30

40

50

、酸化物半導体膜 108 の界面での電荷捕獲を十分に抑制することができるようになり、半導体装置の信頼性が向上する。

【0134】

なお、絶縁膜 102b やゲート絶縁膜 110a (つまり、酸化物半導体膜 108 と接する絶縁膜) は酸化物半導体膜 108 と同種の成分でなる絶縁材料でなる膜とし、絶縁膜 102a やゲート絶縁膜 110b は、絶縁膜 102b やゲート絶縁膜 110a の成分材料とは異なる材料を含む膜とすることが望ましい。例えば、酸化物半導体膜 108 が In-Ga-Zn-O 系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料としては酸化ガリウムなどがある。この場合、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

10

【0135】

本実施の形態に係るトランジスタは、熱処理によって、水素、水、水酸基又は水素化物 (水素化合物ともいう) などの水素原子を含む不純物を酸化物半導体より排除し、かつ、不純物の排除工程において減少するおそれのある酸素を酸化物半導体に十分に含有させることによって、高純度化および i 型 (真性) 化を図った酸化物半導体膜を用いている。このように高純度化された酸化物半導体膜を含むトランジスタは、しきい値電圧などの電気的特性変動が抑制されており、電気的に安定である。

【0136】

また、酸化物半導体膜としてインジウムを含む酸化物半導体材料を用いる場合、インジウムと酸素の結合力は比較的弱いため、酸化物半導体膜に接する絶縁膜にシリコン等のより酸素との結合力が強い材料が含まれる場合に、熱処理によって酸化物半導体膜中の酸素が引き抜かれてしまい、酸化物半導体膜の界面近傍に酸素欠損が形成される恐れがある。しかしながら、開示する発明の一態様に係るトランジスタは、酸化物半導体膜と接する絶縁膜に過剰な酸素を供給することで、酸化物半導体膜からの酸素の引き抜きによる酸素欠損の形成を抑制することができる。

20

【0137】

特に、ゲート絶縁膜 110 の酸素ドープ処理によって、ゲート絶縁膜 110 が酸素過剰領域を有することにより、酸化物半導体膜 108 からゲート絶縁膜 110 への酸素の移動を防ぐことができる。これにより、酸化物半導体膜中に水素に対して過剰な量の酸素を含有させることで、電気的バイアスストレスや熱ストレスに起因する劣化を抑制し、光による劣化を低減することができる。

30

【0138】

このように、開示する発明の一態様によって、信頼性に優れたトランジスタを提供することが可能である。

【0139】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0140】

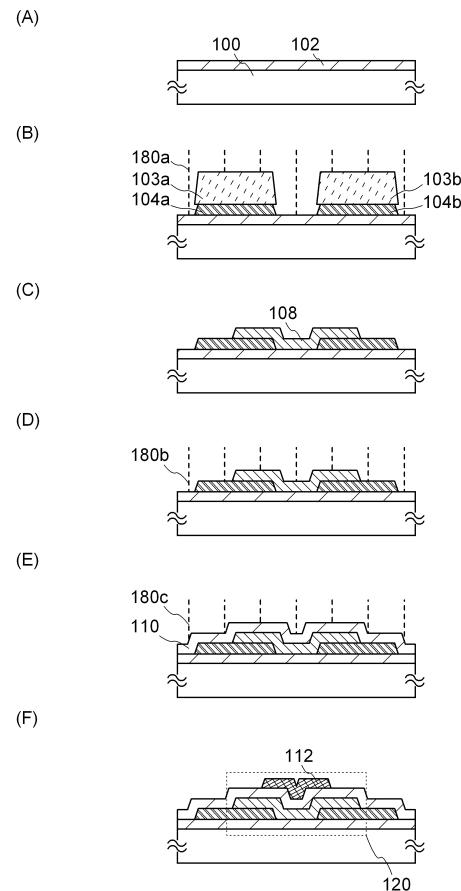

(実施の形態 2)

本実施の形態では、半導体装置の作製方法の別の例について、図 4 および図 5 を用いて説明する。

40

【0141】

半導体装置の構成例

本実施の形態の作製方法にて作製される半導体装置の構成は、先の実施の形態のトランジスタ 120 と同様である。すなわち、基板 100 上の絶縁膜 102、ソース電極 104a、ドレイン電極 104b、酸化物半導体膜 108、ゲート絶縁膜 110、ゲート電極 112 を含む (図 1 参照)。

【0142】

先の実施の形態でも説明したように、トランジスタ 120 において、ゲート絶縁膜 110 は、酸素ドープ処理が行われた絶縁膜であり、酸素過剰領域を有する。ゲート絶縁膜 11

50

0が酸素過剰領域を有することにより、酸化物半導体膜108からゲート絶縁膜110への酸素の移動を防ぐことができる。また、ゲート絶縁膜110から酸化物半導体膜108への酸素の供給を行うこともできる。さらに、本実施の形態では、酸化物半導体膜108に直接酸素ドープ処理を行い、絶縁膜102に対しても酸素ドープ処理を行うことができる。このような酸素ドープ処理によって、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができるので、さらに信頼性が高められたトランジスタ120が実現する。なお、先の実施の形態と同様に、構成を変更したトランジスタを作製することもできる(図3(A)乃至図3(D)参照)。

【0143】

半導体装置の作製工程例

10

以下、図4および図5を用いて、上述の半導体装置の作製工程の一例を説明する。

【0144】

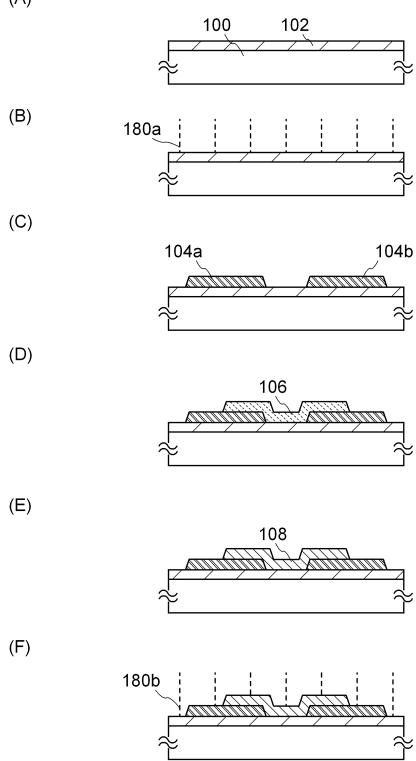

まず、基板100上に絶縁膜102を形成する(図4(A)参照)。

【0145】

基板100の材質に大きな制限はないが、少なくとも、後の熱処理に耐える程度の耐熱性を有していることが必要となる。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。

20

【0146】

また、基板100として、可撓性基板を用いてもよい。可撓性基板上にトランジスタを設ける場合、可撓性基板上に直接的にトランジスタを作り込んでよいし、他の基板にトランジスタを形成した後、これを剥離し、可撓性基板に転置しても良い。なお、トランジスタを剥離し、可撓性基板に転置するためには、上記他の基板とトランジスタとの間に剥離層を形成すると良い。

【0147】

絶縁膜102は、下地として機能する絶縁膜である。具体的には、絶縁膜102には、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ガリウム、これらの混合材料、などを用いればよい。また、絶縁膜102は、上述の材料を含む絶縁膜の単層構造としても良いし、積層構造としても良い。

30

【0148】

絶縁膜102の作製方法に特に限定はない。例えば、プラズマCVD法やスパッタリング法などの成膜方法を用いて絶縁膜102を作製することができる。なお、水素や水などが混入しにくいという点では、スパッタリング法が好適である。

【0149】

なお、絶縁膜102には、後に形成される酸化物半導体膜と同種の成分でなる絶縁材料を用いると特に好ましい。このような材料は酸化物半導体膜との相性が良く、これを絶縁膜102に用いることで、酸化物半導体膜との界面の状態を良好に保つことができるからである。ここで、「酸化物半導体膜と同種の成分」とは、酸化物半導体膜の構成元素から選択される一または複数の元素を含むことを意味する。例えば、酸化物半導体膜がIn-Ga-Zn-O系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料としては酸化ガリウムなどがある。

40

【0150】

また、絶縁膜102を積層構造とする場合には、酸化物半導体膜と同種の成分でなる絶縁材料でなる膜(以下、膜a)と、膜aの成分材料とは異なる材料を含む膜(以下、膜b)との積層構造とするとなお良い。膜aと膜bを酸化物半導体膜側から順に積層した構造とすることで、電荷は膜aと膜bとの界面の電荷捕獲中心に優先的に捕獲される(酸化物半導体膜と膜aとの界面との比較)ため、酸化物半導体膜の界面での電荷捕獲を十分に抑制することができるようになり、半導体装置の信頼性が向上するためである。

50

## 【0151】

なお、このような積層構造としては、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

## 【0152】

次に、絶縁膜102に対して、酸素180aによる処理（酸素ドープ処理や、酸素プラズマドープ処理ともいう）を行う（図4（B）参照）。酸素180aには、少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかが含まれている。絶縁膜102に酸素ドープ処理を行うことにより、絶縁膜102中に酸素を含有させることができ、後に形成される酸化物半導体膜108中、酸化物半導体膜108界面近傍、または、酸化物半導体膜108中および該界面近傍に酸素を含有させることができる。この場合、絶縁膜102中の酸素の含有量は、絶縁膜102の化学量論比を超える程度、好ましくは、化学量論比の1倍を超えて4倍まで（1倍より大きく4倍未満）、より好ましくは、1倍を超えて2倍まで（1倍より大きく2倍未満）とする。あるいは、酸素の含有量は、単結晶の場合の酸素の量をYとして、Yを超える程度、好ましくは、Yを超えて4Yまでとすることもできる。あるいは、酸素の含有量は、酸素ドープ処理を行わない場合の絶縁膜中の酸素の量Zを基準として、Zを超える程度、好ましくは、Zを超えて4Zまでとすることもできる。

## 【0153】

例えば、組成が $GaO_x$ （ $x > 0$ ）で表現される酸化ガリウムを用いる場合、単結晶の酸化ガリウムは $Ga_2O_3$ であるので、xは1.5を超えて6まで（つまりGaの1.5倍を超えて6倍まで）、が許容される。また、例えば、組成が $SiO_x$ （ $x > 0$ ）で表現される酸化シリコンを用いる場合、 $SiO_2$ （すなわちOがSiの2倍）であれば、xは2を超えて8まで（つまりSiの2倍を超えて8倍まで）が許容される。なお、このような酸素過剰領域は、絶縁膜の一部（界面を含む）に存在していればよい。

## 【0154】

このように、絶縁膜102中、または絶縁膜102と後に形成される酸化物半導体膜108との界面近傍に酸素過剰領域を形成することにより、酸化物半導体膜108から絶縁膜102への酸素の移動を防ぐことができる。よって、絶縁膜102に酸素ドープ処理を行うことにより、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができる。

## 【0155】

また、絶縁膜に添加される酸素180aの少なくとも一部は、酸化物半導体に供給された後、酸化物半導体中において未結合手を有することが好ましい。未結合手を有することにより、膜中に残存しうる水素と結合して、水素を固定化（非可動イオン化）することができるためである。

## 【0156】

上述の酸素180aは、プラズマ発生装置やオゾン発生装置によって発生させることができる。より具体的には、例えば、半導体装置に対してエッティング処理を行うことができる装置や、レジストマスクに対してアッシングを行うことができる装置などを用いて酸素180aを発生させ、絶縁膜102を処理することができる。

## 【0157】

なお、酸素の添加をより好適に行うためには、基板には電気的なバイアスを加えておくことが望ましい。

## 【0158】

次いで、絶縁膜102上に、ソース電極およびドレイン電極（これと同じ層で形成される配線を含む）を形成するための導電膜を形成し、当該導電膜を加工して、ソース電極104aおよびドレイン電極104bを形成する（図4（C）参照）。なお、ここで形成されるソース電極104aの端部とドレイン電極104bの端部との間隔によって、トランジスタのチャネル長Lが決定されることになる。

## 【0159】

ソース電極104aおよびドレイン電極104bに用いる導電膜としては、例えば、A1

10

20

30

40

50

、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）等がある。また、Al、Cuなどの金属膜の下側または上側の一方または双方にTi、Mo、Wなどの高融点金属膜またはそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）を積層させた導電膜を用いても良い。

#### 【0160】

また、ソース電極104aおよびドレイン電極104bに用いる導電膜は、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ混合酸化物（ITOと略記する）、酸化インジウム酸化亜鉛混合酸化物またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

10

#### 【0161】

導電膜の加工は、レジストマスクを用いたエッチングによって行うことができる。当該エッチングに用いるレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光などを用いるとよい。

#### 【0162】

なお、チャネル長L=25nm未満の露光を行う場合には、例えば、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて、レジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。したがって、後に形成されるトランジスタのチャネル長Lを微細化することが可能であり、回路の動作速度を高めることができる。

20

#### 【0163】

また、いわゆる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成されたレジストマスクは、複数の膜厚を有する形状となり、アッシングによってさらに形状を変形させることができるために、異なるパターンに加工する複数のエッチング工程に用いることが可能である。このため、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。つまり、工程の簡略化が可能となる。

#### 【0164】

次に、絶縁膜102上に、ソース電極104aおよびドレイン電極104bと接する酸化物半導体膜を形成し、当該酸化物半導体膜を加工して島状の酸化物半導体膜106を形成する（図4（D）参照）。

30

#### 【0165】

酸化物半導体膜は、水素や水などが混入しにくい方法で作製するのが望ましい。例えば、スパッタリング法などを用いて作製することができる。また、酸化物半導体膜の厚さは、3nm以上30nm以下とするのが望ましい。酸化物半導体膜を厚くしすぎると（例えば、膜厚を50nm以上）、トランジスタがノーマリーオンとなってしまうおそれがあるためである。

#### 【0166】

酸化物半導体膜に用いる材料としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O系の材料や、三元系金属酸化物であるIn-Ga-Zn-O系の材料、In-Sn-Zn-O系の材料、In-Al-Zn-O系の材料、Sn-Ga-Zn-O系の材料、Al-Ga-Zn-O系の材料、Sn-Al-Zn-O系の材料や、二元系金属酸化物であるIn-Zn-O系の材料、Sn-Zn-O系の材料、Al-Zn-O系の材料、Zn-Mg-O系の材料、Sn-Mg-O系の材料、In-Mg-O系の材料、In-Ga-O系の材料や、単元系金属酸化物であるIn-O系の材料、Sn-O系の材料、Zn-O系の材料などがある。また、上記の材料に酸化珪素を含ませてもよい。ここで、例えば、In-Ga-Zn-O系の材料とは、インジウム（In）、ガリウム（Ga）、亜鉛（Zn）を有する酸化物膜、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。

40

50

## 【0167】

また、酸化物半導体膜は、化学式  $In_xMO_3$  ( $ZnO$ )<sub>m</sub> ( $m > 0$ ) で表記される材料を用いた薄膜とすることができます。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMn、またはGaおよびCoなどを用いることができる。

## 【0168】

本実施の形態では、酸化物半導体膜を、In-Ga-Zn-O系の酸化物半導体成膜用ターゲットを用いたスパッタリング法により形成する。

## 【0169】

In-Ga-Zn-O系の酸化物半導体成膜用ターゲットとしては、例えば、組成比として、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  [mol数比] の酸化物半導体成膜用ターゲットを用いることができる。なお、ターゲットの材料および組成を上述に限定する必要はない。例えば、 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 2$  [mol数比] の組成比の酸化物半導体成膜用ターゲットを用いることもできる。

10

## 【0170】

また、酸化物半導体としてIn-Zn-O系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、 $In : Zn = 50 : 1 \sim 1 : 2$  (モル数比に換算すると  $In_2O_3 : ZnO = 25 : 1 \sim 1 : 4$ )、好ましくは  $In : Zn = 20 : 1 \sim 1 : 1$  (モル数比に換算すると  $In_2O_3 : ZnO = 10 : 1 \sim 1 : 2$ )、さらに好ましくは  $In : Zn = 15 : 1 \sim 1.5 : 1$  (モル数比に換算すると  $In_2O_3 : ZnO = 15 : 2 \sim 3 : 4$ ) とする。例えば、In-Zn-O系酸化物半導体の形成に用いるターゲットは、原子数比が  $In : Zn : O = X : Y : Z$  のとき、 $Z > 1.5X + Y$  とする。

20

## 【0171】

酸化物半導体成膜用ターゲットの充填率は、90%以上100%以下、好ましくは95%以上99.9%以下とする。充填率の高い金属酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とすることができます。

## 【0172】

成膜の雰囲気は、希ガス (代表的にはアルゴン) 雰囲気下、酸素雰囲気下、または、希ガスと酸素の混合雰囲気下などとすればよい。また、酸化物半導体膜への水素、水、水酸基を有する化合物、水素化物などの混入を防ぐために、水素、水、水酸基を有する化合物、水素化物などの水素原子を含む不純物が十分に除去された高純度ガスを用いた雰囲気とすることが望ましい。

30

## 【0173】

なお、酸化物半導体膜の成膜の際に、絶縁膜102中の酸素が酸化物半導体膜に供給されることがある。このように、絶縁膜102に酸素を添加しておくことで、酸素が十分に添加された酸化物半導体膜を作製することが可能である。

## 【0174】

より具体的には、例えば、酸化物半導体膜は次のように形成することができる。

## 【0175】

まず、減圧状態に保持された成膜室内に基板100を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板100が加熱された状態で成膜を行うことで、酸化物半導体膜に含まれる不純物濃度を低減するためである。また、スパッタリングによる損傷を軽減するためである。

40

## 【0176】

次に、成膜室内の残留水分を除去しつつ、水素および水などの水素原子を含む不純物が十分に除去された高純度ガスを導入し、上記ターゲットを用いて基板100上に酸化物半導体膜を成膜する。成膜室内の残留水分を除去するためには、排気手段として、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどの吸着型の真空ポンプを用いることが望ましい。また、排気手段は、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素分子や、水(

50

$H_2O$  )などの水素原子を含む化合物 (より好ましくは炭素原子を含む化合物も) などが除去されているため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

【0177】

成膜条件の一例として、基板とターゲットとの間との距離を 100 mm、圧力を 0.6 Pa、直流 (DC) 電源を 0.5 kW、成膜雰囲気を酸素 (酸素流量比率 100%) 雰囲気とすることができる。なお、パルス直流電源を用いると、成膜時の粉状物質 (パーティクル、ごみともいう) の発生を軽減でき、膜厚分布も均一となるため好ましい。

【0178】

酸化物半導体膜の加工は、所望の形状のマスクを酸化物半導体膜上に形成した後、当該酸化物半導体膜をエッチングすることによって行うことができる。上述のマスクは、フォトリソグラフィなどの方法を用いて形成することができる。または、インクジェット法などの方法を用いてマスクを形成しても良い。

【0179】

なお、酸化物半導体膜のエッチングは、ドライエッチングでもウェットエッチングでもよい。もちろん、これらを組み合わせて用いてもよい。

【0180】

その後、酸化物半導体膜 106 に対して熱処理を行って、高純度化された酸化物半導体膜 108 を形成する (図 4 (E) 参照)。この熱処理によって酸化物半導体膜 106 中の、水素 (水や水酸基を含む) を除去し、酸化物半導体膜の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。また、この熱処理によって、絶縁膜 102 中の酸素が酸化物半導体膜に供給されることがある。上記熱処理の温度は、250 以上 650 以下、好ましくは 450 以上 600 以下、または基板の歪み点未満とする。

【0181】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450 、 1 時間の条件で行うことができる。この間、酸化物半導体膜 106 は大気に触れさせず、水や水素の混入が生じないようにする。

【0182】

熱処理装置は電気炉に限らず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置等の RTA (Rapid Thermal Anneal) 装置を用いることができる。GRTA 装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。LRTA 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光 (電磁波) の輻射により、被処理物を加熱する装置である。

【0183】

例えば、上記熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出す GRTA 処理を行ってもよい。GRTA 処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。酸素を含む雰囲気において熱処理を行うことで、酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減することができるためである。

【0184】

なお、不活性ガス雰囲気としては、窒素、または希ガス (ヘリウム、ネオン、アルゴン等) を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N (99.9999%) 以上、好ましくは 7N (99.99999%) 以上 (

10

20

30

40

50

すなわち、不純物濃度が 1 ppm 以下、好ましくは 0.1 ppm 以下) とする。

【 0185 】

いざれにしても、上記熱処理によって不純物を低減し、i 型(真性半導体)または i 型に限りなく近い酸化物半導体膜を形成することで、極めて優れた特性のトランジスタを実現することができる。

【 0186 】

ところで、上述の熱処理には水素や水などを除去する効果があるから、当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該脱水化処理や、脱水素化処理は、例えは、酸化物半導体膜を島状に加工する前などのタイミングにおいて行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

10

【 0187 】

次に、酸化物半導体膜 108 に対して、酸素 180b による処理を行う(図 4(F) 参照)。酸素 180b には、少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかが含まれている。酸化物半導体膜 108 に酸素ドープ処理を行うことにより、酸化物半導体膜 108 中、酸化物半導体膜 108 界面近傍、または、酸化物半導体膜 108 中および該界面近傍に酸素を含有させることができる。

【 0188 】

このように、酸化物半導体膜 108 に酸素ドープ処理を行うことにより、酸化物半導体膜 108 中に酸素過剰領域が形成され、酸化物半導体膜 108 に水素に対して過剰な量の酸素を含有させることができる。

20

【 0189 】

また、酸化物半導体膜に添加される酸素 180b の少なくとも一部は、酸化物半導体中において未結合手を有することが好ましい。未結合手を有することにより、膜中に残存しうる水素と結合して、水素を固定化(非可動イオン化)することができるためである。

【 0190 】

上述の酸素 180b は、プラズマ発生装置やオゾン発生装置によって発生させることができる。より具体的には、例えは、半導体装置に対してエッチング処理を行うことができる装置や、レジストマスクに対してアッシングを行うことができる装置などを用いて酸素 180b を発生させ、酸化物半導体膜 108 を処理することができる。

30

【 0191 】

なお、酸素の添加をより好適に行うためには、基板には電気的なバイアスを加えておくことが望ましい。

【 0192 】

なお、酸素ドープ処理を行った酸化物半導体膜 108 に熱処理(温度 150 ~ 470)を行ってもよい。当該熱処理により、水素と酸化物半導体材料との反応によって生成された水、水酸基(OH)などを酸化物半導体膜から除去することができる。熱処理は、水、水素などが十分に低減された窒素、酸素、超乾燥空気(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が 20 ppm(露点換算で -55) 以下、好ましくは 1 ppm 以下、好ましくは 10 ppb 以下の空気)、希ガス(アルゴン、ヘリウムなど)などの雰囲気下で行えばよい。また、酸素ドープ処理と熱処理を繰り返して行っても良い。当該処理を繰り返して行うことにより、トランジスタの信頼性をさらに高めることができる。なお、繰り返しの回数は適宜設定することができる。

40

【 0193 】

次に、酸化物半導体膜 108 の一部と接し、かつ、ソース電極 104a およびドレイン電極 104b を覆うゲート絶縁膜 110 を形成する(図 5(A) 参照)。

【 0194 】

ゲート絶縁膜 110 は、絶縁膜 102 と同様に形成することができる。すなわち、ゲート絶縁膜 110 は、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、

50

酸化ガリウム、これらの混合材料、などを用いて形成すればよい。ただし、トランジスタのゲート絶縁膜として機能することを考慮して、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムアルミニート( $HfAl_xO_y$  ( $x > 0$ 、 $y > 0$ ))、などの比誘電率が高い材料を採用しても良い。

#### 【0195】

なお、ゲート絶縁膜110には、絶縁膜102と同様に、後に形成される酸化物半導体膜と同種の成分でなる絶縁材料を用いると特に好ましい。このような材料は酸化物半導体膜との相性が良く、これをゲート絶縁膜110に用いることで、酸化物半導体膜との界面の状態を良好に保つことができるからである。ここで、「酸化物半導体膜と同種の成分」とは、酸化物半導体膜の構成元素から選択される一または複数の元素を含むことを意味する。例えば、酸化物半導体膜がIn-Ga-Zn-O系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料としては酸化ガリウムなどがある。

10

#### 【0196】

また、絶縁膜102と同様に、積層構造を採用しても良い。この場合には、酸化物半導体膜と同種の成分でなる絶縁材料でなる膜(以下、膜a)と、膜aの成分材料とは異なる材料を含む膜(以下、膜b)との積層構造とするとなお良い。膜aと膜bを酸化物半導体膜側から順に積層した構造とすることで、電荷は膜aと膜bとの界面の電荷捕獲中心に優先的に捕獲される(酸化物半導体膜と膜aとの界面との比較)ため、酸化物半導体膜の界面での電荷捕獲を十分に抑制することができるようになり、半導体装置の信頼性が向上するためである。

20

#### 【0197】

なお、このような積層構造としては、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

#### 【0198】

上述のゲート絶縁膜110の形成後には、熱処理を行うのが望ましい。当該熱処理の温度は、250以上700以下、好ましくは450以上600以下、または基板の歪み点未満とする。

30

#### 【0199】

上記熱処理は、窒素、酸素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウムなど)の雰囲気下で行えばよいが、上記窒素、酸素、超乾燥空気、または希ガス等の雰囲気には、水、水素などが含まれないことが好ましい。また、熱処理装置に導入する窒素、酸素、または希ガスの純度は、6N(99.9999%)以上(即ち不純物濃度を1ppm以下)とするのが好ましく、7N(99.99999%)以上(即ち不純物濃度を0.1ppm以下)とすると、より好ましい。

#### 【0200】

本実施の形態に係る上記の熱処理においては、酸化物半導体膜108と、絶縁膜102やゲート絶縁膜110と、が接した状態で加熱される。したがって、上述の脱水化(または脱水素化)処理によって減少してしまう可能性のある酸素を、絶縁膜102やゲート絶縁膜110などから酸化物半導体膜108へ供給することも可能である。この意味において、当該熱処理を、加酸化(加酸素化)と呼ぶこともできる。

40

#### 【0201】

なお、加酸化を目的とする熱処理のタイミングは、酸化物半導体膜108の形成後であれば特に限定されない。例えば、ゲート絶縁膜110に対して酸素ドープ処理を行った後に加酸化を目的とする熱処理を行っても良いし、ゲート電極の形成後に加酸化を目的とする熱処理を行っても良い。または、脱水化等を目的とする熱処理に続けて加酸化を目的とする熱処理を行っても良いし、脱水化等を目的とする熱処理に加酸化を目的とする熱処理を兼ねさせても良いし、加酸化を目的とする熱処理に脱水化等を目的とする熱処理を兼ねさ

50

せてても良い。

【0202】

上述のように、脱水化等を目的とする熱処理と、酸素ドープ処理または加酸化を目的とする熱処理とを適用することで、酸化物半導体膜108を不純物が極力含まれないように高純度化することができる。高純度化された酸化物半導体膜108中にはドナーに由来するキャリアが極めて少ない(ゼロに近い)。

【0203】

次に、ゲート絶縁膜110に対して、酸素180cによる処理(酸素ドープ処理や、酸素プラズマドープ処理ともいう)を行う(図5(B)参照)。ここで、酸素180cには、少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかが含まれている。ゲート絶縁膜110に酸素ドープ処理を行うことにより、ゲート絶縁膜110中、またはゲート絶縁膜110と酸化物半導体膜108との界面近傍に酸素を含有させることができる。この場合、ゲート絶縁膜110中の酸素の含有量は、ゲート絶縁膜110の化学量論比を超える程度、好ましくは、化学量論比の1倍を超えて4倍まで(1倍より大きく4倍未満)、より好ましくは、1倍を超えて2倍まで(1倍より大きく2倍未満)とする。あるいは、酸素の含有量は、ゲート絶縁膜110を構成する材料が単結晶の場合の酸素の量をYとして、Yを超える程度、好ましくは、Yを超えて4Yまでとすることもできる。あるいは、酸素の含有量は、酸素ドープ処理を行わない場合の絶縁膜中の酸素の量Zを基準として、Zを超える程度、好ましくは、Zを超えて4Zまでとすることもできる。

【0204】

例えば、組成が $GaO_x$ ( $x > 0$ )で表現される酸化ガリウムを用いる場合、単結晶の酸化ガリウムは $Ga_2O_3$ であるので、xは1.5を超えて6まで(つまり $Ga$ の1.5倍を超えて6倍まで)、が許容される。また、例えば、組成が $SiO_x$ ( $x > 0$ )で表現される酸化シリコンを用いる場合、 $SiO_2$ (すなわちOがSiの2倍)であれば、xは2を超えて8まで(つまりSiの2倍を超えて8倍まで)が許容される。なお、このような酸素過剰領域は、絶縁膜の一部(界面を含む)に存在していればよい。

【0205】

このように、ゲート絶縁膜110中、またはゲート絶縁膜110と酸化物半導体膜108との界面近傍に酸素過剰領域を形成することにより、酸化物半導体膜108からゲート絶縁膜110への酸素の移動を防ぐことができる。よって、ゲート絶縁膜110に酸素ドープ処理を行うことにより、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができる。

【0206】

さらに、上記酸素ドープ処理において、酸化物半導体膜108中、酸化物半導体膜108と絶縁膜102との界面近傍、または絶縁膜102中に酸素が供給され得る。特に、ゲート絶縁膜110または酸化物半導体膜108の膜厚が十分薄い場合や、基板に印加する電気的なバイアスが十分大きい場合や、酸素ドープ処理後に熱処理を行う場合に、酸化物半導体膜108中、酸化物半導体膜108と絶縁膜102との界面近傍、または絶縁膜102中に酸素が供給されやすくなる。

【0207】

また、ゲート絶縁膜110に添加される酸素180cの少なくとも一部は、酸化物半導体に供給された後、酸化物半導体中において未結合手を有することが好ましい。未結合手を有することにより、膜中に残存しうる水素と結合して、水素を固定化(非可動イオン化)することができるためである。

【0208】

上述の酸素180cは、プラズマ発生装置やオゾン発生装置によって発生させることができる。より具体的には、例えば、半導体装置に対してエッチング処理を行うための装置や、マスクに対してアッシングを行うための装置などを用いて酸素180cを発生させ、ゲート絶縁膜110を処理することができる。

【0209】

10

20

30

40

50

なお、酸素の添加をより好適に行うためには、基板には電気的なバイアスを加えておくことが望ましい。

【0210】

なお、上述の酸素ドープ処理の後には、熱処理を行うことが好ましい。この熱処理によって、水素に対して過剰な量の酸素を酸化物半導体膜に供給することが可能である。また、この熱処理に、上述の加酸化を目的とする熱処理を兼ねさせてても良い。当該効果を得るために熱処理のタイミングは、上述の酸素ドープ処理の後であればいつでも構わない。また、酸素ドープ処理と熱処理を繰り返して行っても良い。当該処理を繰り返して行うことにより、トランジスタの信頼性をさらに高めることができる。なお、繰り返しの回数は適宜設定することができる。

10

【0211】

その後、ゲート電極112を形成する(図5(C)参照)。ゲート電極112は、モリブデン、チタン、タンタル、タンクスチール、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。なお、ゲート電極112は、単層構造としても良いし、積層構造としても良い。

【0212】

なお、ゲート電極112の形成後には、絶縁膜を形成しても良い。当該絶縁膜は、例えば、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ガリウム、これらの混合材料、などを用いて形成することができる。特に、絶縁膜として窒化シリコン膜を用いる場合には、添加された酸素の外部への放出を防ぐことができると共に、酸化物半導体膜108への外部からの水素等の混入を効果的に抑制することができるため好適である。また、ソース電極104aやドレイン電極104b、ゲート電極112などと接続される配線を形成しても良い。

20

【0213】

以上の工程でトランジスタ120が形成される。

【0214】

ここで、酸化物半導体膜108中の酸素の含有量は、酸化物半導体膜108の化学量論比を超える程度、好ましくは、化学量論比の1倍を超えて2倍まで(1倍より大きく2倍未満)、とする。あるいは、酸素の含有量は、酸化物半導体膜108を構成する材料が単結晶の場合の酸素の量をYとして、Yを超える程度、好ましくは、Yを超えて2Yまでとすることができる。あるいは、酸素の含有量は、酸素ドープ処理を行わない場合の酸化物半導体膜中の酸素の量Zを基準として、Zを超える程度、好ましくは、Zを超えて2Zまでとすることもできる。なお、上述の好ましい範囲に上限が存在するのは、酸素の含有量を多くしすぎると、水素吸蔵合金(水素貯蔵合金)のように、かえって酸化物半導体膜108が水素を取り込んでしまう恐れがあるためである。

30

【0215】

結晶構造が $InGaO_3(ZnO)_m$ ( $m > 0$ )で表現される材料の場合、例えば、 $m = 1$ ( $InGaZnO_4$ )の結晶構造を基準にすれば、 $InGaZnO_x$ において $x$ は4を越えて8まで、また、 $m = 2$ ( $InGaZn_2O_5$ )の結晶構造を基準にすれば、 $InGaZn_2O_x$ において $x$ は5を越えて10まで、が許容される。なお、このような酸素過剰領域は、酸化物半導体の一部(界面を含む)に存在していればよい。

40

【0216】

このようにして、酸化物半導体膜108中に酸素過剰領域が形成され、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができる。

【0217】

なお、上述の説明は、絶縁膜102、酸化物半導体膜108、およびゲート絶縁膜110の全てに酸素ドープ処理を適用する例についてのものだが、開示する発明の一態様はこれに限定されない。例えば、絶縁膜102およびゲート絶縁膜110に酸素ドープ処理を適用しても良いし、酸化物半導体膜108およびゲート絶縁膜110に酸素ドープ処理を適用しても良い。

50

## 【0218】

本実施の形態に係るトランジスタは、熱処理によって、水素、水、水酸基又は水素化物（水素化合物ともいう）などの水素原子を含む不純物を酸化物半導体より排除し、かつ、不純物の排除工程において減少するおそれのある酸素を供給し、酸化物半導体に水素に対して過剰な量の酸素を含有させることによって、高純度化およびi型（真性）化を図った酸化物半導体膜を用いている。このように高純度化された酸化物半導体膜を含むトランジスタは、しきい値電圧などの電気的特性変動が抑制されており、電気的に安定である。

## 【0219】

また、酸化物半導体膜としてインジウムを含む酸化物半導体材料を用いる場合、インジウムと酸素の結合力は比較的弱いため、酸化物半導体膜に接する絶縁膜にシリコン等のより酸素との結合力が強い材料が含まれる場合に、熱処理によって酸化物半導体膜中の酸素が引き抜かれてしまい、酸化物半導体膜の界面近傍に酸素欠損が形成される恐れがある。しかしながら、開示する発明の一態様に係るトランジスタは、酸化物半導体膜と接する絶縁膜に過剰な酸素を供給することで、酸化物半導体膜からの酸素の引き抜きによる酸素欠損の形成を抑制することができる。

10

## 【0220】

特に、ゲート絶縁膜110または絶縁膜102の酸素ドープ処理によって、ゲート絶縁膜110または絶縁膜102が酸素過剰領域を有することにより、酸化物半導体膜108からゲート絶縁膜110または絶縁膜102への酸素の移動を防ぐことができる。また、酸化物半導体膜108の酸素ドープ処理によって、酸化物半導体膜108に含有される酸素の量を増加させることができる。よって、酸化物半導体膜中に水素に対して過剰な量の酸素を含有させることで、電気的バイアスストレスや熱ストレスに起因する劣化を抑制し、光による劣化を低減することができる。

20

## 【0221】

このように、開示する発明の一態様によって、信頼性に優れたトランジスタを提供することが可能である。

## 【0222】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【0223】

30

## (実施の形態3)

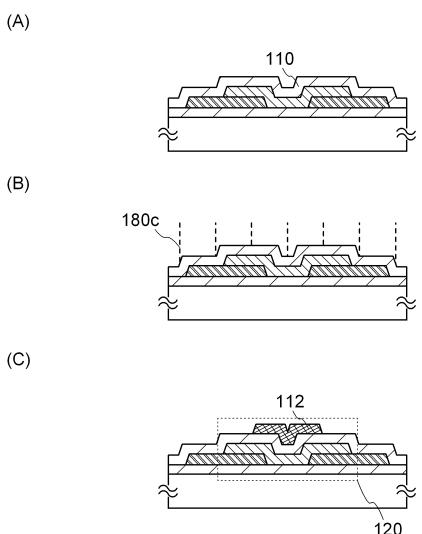

本実施の形態では、半導体装置の作製方法の別の例について、図6を用いて説明する。

## 【0224】

## 半導体装置の構成例

本実施の形態の作製方法にて作製される半導体装置の構成は、先の実施の形態のトランジスタ120と同様である。すなわち、基板100上の絶縁膜102、ソース電極104a、ドレイン電極104b、酸化物半導体膜108、ゲート絶縁膜110、ゲート電極112を含む（図1参照）。

## 【0225】

先の実施の形態でも説明したように、トランジスタ120において、ゲート絶縁膜110は、酸素ドープ処理が行われた絶縁膜であり、酸素過剰領域を有する。ゲート絶縁膜110が酸素過剰領域を有することにより、酸化物半導体膜108からゲート絶縁膜110への酸素の移動を防ぐことができる。また、ゲート絶縁膜110から酸化物半導体膜108への酸素の供給を行うこともできる。さらに、本実施の形態では、酸化物半導体膜108に直接酸素ドープ処理を行い、絶縁膜102に対して酸素ドープ処理を行うことができる。このような酸素ドープ処理によって、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができるので、さらに信頼性が高められたトランジスタ120が実現する。さらに、本実施の形態における絶縁膜102に対する酸素ドープ処理は、ソース電極104aおよびドレイン電極104bの形成に用いるマスク103aおよびマスク103bの除去の工程を兼ねている。このようなプロセスを採用することで、工程の簡略

40

50

化による製造コストの低減を図ることができる。なお、先の実施の形態と同様に、構成を変更したトランジスタを作製することもできる（図3（A）乃至図3（D）参照）。

### 【0226】

#### 半導体装置の作製工程例

以下、図6を用いて、上述の半導体装置の作製工程の一例を説明する。なお、作製工程の基本的な内容は先の実施の形態と同様であるため、以下では相違点について述べるに留める。

### 【0227】

まず、基板100上に絶縁膜102を形成する（図6（A）参照）。詳細は、図4（A）に関する記載を参酌すればよい。

10

### 【0228】

次いで、絶縁膜102上に、ソース電極およびドレイン電極（これと同じ層で形成される配線を含む）を形成するための導電膜を形成し、当該導電膜を、マスク103aおよびマスク103bを用いて加工して、ソース電極104aおよびドレイン電極104bを形成する。そして、絶縁膜102に対して、酸素180aによる処理（酸素ドープ処理や、酸素プラズマドープ処理ともいう）を行う（図6（B）参照）。ソース電極104aおよびドレイン電極104bを形成するため工程の詳細は、図4（C）に関する記載を参酌すればよい。ここで、上述の酸素ドープ処理は、マスク103aおよびマスク103bの除去工程を兼ねるものである。

### 【0229】

酸素180aには、少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかが含まれている。絶縁膜102に酸素ドープ処理を行うことにより、絶縁膜102中に酸素を含有させることができ、後に形成される酸化物半導体膜108中、酸化物半導体膜108界面近傍、または、酸化物半導体膜108中および該界面近傍に酸素を含有させることができる。この場合、絶縁膜102中の酸素の含有量は、絶縁膜102の化学量論比を超える程度、好ましくは、化学量論比の1倍を超えて4倍まで（1倍より大きく4倍未満）、より好ましくは、1倍を超えて2倍まで（1倍より大きく2倍未満）、とする。あるいは、酸素の含有量は、絶縁膜102を構成する材料が単結晶の場合の酸素の量をYとして、Yを超える程度、好ましくは、Yを超えて4Yまでとすることもできる。あるいは、酸素の含有量は、酸素ドープ処理を行わない場合の絶縁膜中の酸素の量Zを基準として、Zを超える程度、好ましくは、Zを超えて4Zまでとすることもできる。

20

### 【0230】

例えば、組成が $GaO_x$ （ $x > 0$ ）で表現される酸化ガリウムを用いる場合、単結晶の酸化ガリウムは $Ga_2O_3$ であるので、xは1.5を超えて6まで（つまりGaの1.5倍を超えて6倍まで）、が許容される。また、例えば、組成が $SiO_x$ （ $x > 0$ ）で表現される酸化シリコンを用いる場合、 $SiO_2$ （すなわちOがSiの2倍）であれば、xは2を超えて8まで（つまりSiの2倍を超えて8倍まで）が許容される。なお、このような酸素過剰領域は、絶縁膜の一部（界面を含む）に存在していればよい。

30

### 【0231】

このように、絶縁膜102中、または絶縁膜102と後に形成される酸化物半導体膜108との界面近傍に酸素過剰領域を形成することにより、酸化物半導体膜108から絶縁膜102への酸素の移動を防ぐことができる。よって、絶縁膜102に酸素ドープ処理を行うことにより、酸化物半導体膜108に水素に対して過剰な量の酸素を含有させることができる。

40

### 【0232】

また、絶縁膜に添加される酸素180aの少なくとも一部は、酸化物半導体に供給された後、酸化物半導体中において未結合手を有することが好ましい。未結合手を有することにより、膜中に残存しうる水素と結合して、水素を固定化（非可動イオン化）することができるためである。

### 【0233】

50

上述の酸素 180a は、プラズマ発生装置やオゾン発生装置によって発生させることができる。より具体的には、例えば、レジストマスクに対してアッシングを行うことができる装置などを用いて酸素 180a を発生させ、絶縁膜 102 を処理することができる。

【0234】

当該酸素ドープ処理によってマスク 103a およびマスク 103b が除去される。ただし、通常のマスク除去工程とは異なり、当該工程は酸素の添加を目的とするものであるから、基板には強めのバイアスを加えておくことが望ましい。

【0235】

また、当該酸素ドープ処理によって、絶縁膜 102 中には、酸素が高濃度に存在する領域と、酸素が低濃度に存在する領域とが形成される。具体的には、絶縁膜 102 の、ソース電極 104a およびドレイン電極 104b に覆われていない領域が、酸素が高濃度に存在する領域となり、ソース電極 104a およびドレイン電極 104b に覆われている領域が、酸素が低濃度に存在する領域となる。

【0236】

次に、絶縁膜 102 上に、ソース電極 104a およびドレイン電極 104b と接する酸化物半導体膜を形成し、当該酸化物半導体膜を加工して島状の酸化物半導体膜を形成する。そして、その後、島状の酸化物半導体膜に対して熱処理を行って、高純度化された酸化物半導体膜 108 を形成する（図 6（C）参照）。当該工程の詳細は、図 4（D）および図 4（E）に関する記載を参照すればよい。

【0237】

次に、酸化物半導体膜 108 に対して、酸素 180b による処理を行う（図 6（D）参照）。詳細は、図 4（F）に関する記載を参照すればよい。

【0238】

次に、酸化物半導体膜 108 の一部と接し、かつ、ソース電極 104a およびドレイン電極 104b を覆うゲート絶縁膜 110 を形成する。そして、その後、ゲート絶縁膜 110 に対して、酸素 180c による処理を行う（図 6（E）参照）。詳細は、図 5（A）および図 5（B）に関する記載を参照すればよい。

【0239】

その後、ゲート電極 112 を形成する（図 6（F）参照）。詳細は、図 5（C）に関する記載を参照すればよい。

【0240】

なお、ゲート電極 112 の形成後には、絶縁膜を形成しても良い。当該絶縁膜は、例えば、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ガリウム、これらの混合材料、などを用いて形成することができる。特に、絶縁膜として窒化シリコン膜を用いる場合には、添加された酸素の外部への放出を防ぐことができると共に、酸化物半導体膜 108 への外部からの水素等の混入を効果的に抑制することができるため好適である。また、ソース電極 104a やドレイン電極 104b、ゲート電極 112 などと接続される配線を形成しても良い。

【0241】

以上の工程でトランジスタ 120 が形成される。

【0242】

なお、上述の説明は、絶縁膜 102、酸化物半導体膜 108、およびゲート絶縁膜 110 の全てに酸素ドープ処理を適用する例についてのものだが、開示する発明の一態様はこれに限定されない。例えば、絶縁膜 102 およびゲート絶縁膜 110 に酸素ドープ処理を適用しても良い。

【0243】

本実施の形態に係るトランジスタは、熱処理によって、水素、水、水酸基又は水素化物（水素化合物ともいう）などの水素原子を含む不純物を酸化物半導体より排除し、かつ、不純物の排除工程において減少するおそれのある酸素を供給し、酸化物半導体に水素に対して過剰な量の酸素を含有させることによって、高純度化および i 型（真性）化を図った酸

10

20

30

40

50

化物半導体膜を用いている。このように高純度化された酸化物半導体膜を含むトランジスタは、しきい値電圧などの電気的特性変動が抑制されており、電気的に安定である。

【0244】

また、酸化物半導体膜としてインジウムを含む酸化物半導体材料を用いる場合、インジウムと酸素の結合力は比較的弱いため、酸化物半導体膜に接する絶縁膜にシリコン等のより酸素との結合力が強い材料が含まれる場合に、熱処理によって酸化物半導体膜中の酸素が引き抜かれてしまい、酸化物半導体膜の界面近傍に酸素欠損が形成される恐れがある。しかしながら、開示する発明の一態様に係るトランジスタは、酸化物半導体膜と接する絶縁膜に過剰な酸素を供給することで、酸化物半導体膜からの酸素の引き抜きによる酸素欠損の形成を抑制することができる。

10

【0245】

特に、ゲート絶縁膜110または絶縁膜102の酸素ドープ処理によって、ゲート絶縁膜110または絶縁膜102が酸素過剰領域を有することにより、酸化物半導体膜108からゲート絶縁膜110または絶縁膜102への酸素の移動を防ぐことができる。また、酸化物半導体膜108の酸素ドープ処理によって、酸化物半導体膜108に含有される酸素の量を増加させることができる。よって、酸化物半導体膜中に水素に対して過剰な量の酸素を含有させることで、電気的バイアスストレスや熱ストレスに起因する劣化を抑制し、光による劣化を低減することができる。

【0246】

さらに、本実施の形態に係る作製方法では、工程が簡略化されているため製造に係るコストを抑制することができる。

20

【0247】

このように、開示する発明の一態様によって、製造コストを低く抑えつつ、信頼性に優れたトランジスタを提供することが可能である。

【0248】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0249】

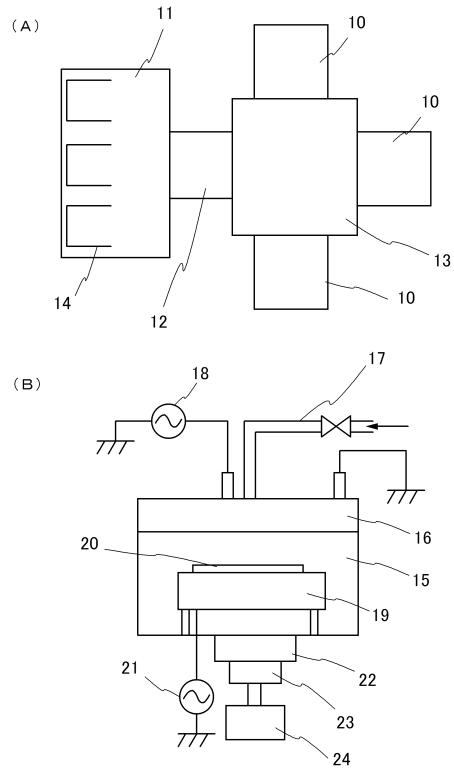

(実施の形態4)

本実施の形態では、酸素ドープ処理に用いることができるプラズマ装置(アッシング装置とも呼ぶ)の例を説明する。なお、この装置は、例えば第5世代以降の大型のガラス基板などに対応することができる点で、イオン注入装置などよりも工業的に適している。

30

【0250】

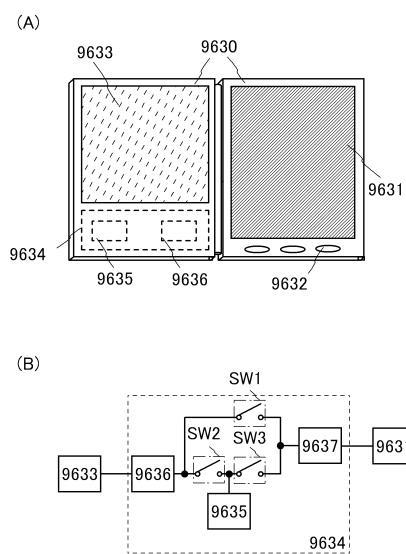

図17(A)は、枚葉式マルチチャンバー設備の上面図の一例を示す。図17(B)は、酸素プラズマドープを行うプラズマ装置(アッシング装置とも呼ぶ)の断面図の一例を示す。

【0251】

図17(A)に示す枚葉式マルチチャンバー設備は、図17(B)に示すプラズマ装置10を3つ有し、被処理基板を収容するカセットポート14を3つ有する基板供給室11や、ロードロック室12や、搬送室13などを有している。基板供給室に供給された基板は、ロードロック室12と搬送室13を介してプラズマ装置10内の真空チャンバー15に搬送されて酸素プラズマドープが行われる。酸素プラズマドープが終了した基板は、プラズマ装置10からロードロック室12と搬送室13を介して基板供給室11に搬送される。なお、基板供給室11及び搬送室13には、被処理基板を搬送するための搬送ロボットがそれぞれ配置されている。

40

【0252】

図17(B)を参照すると、プラズマ装置10は、真空チャンバー15を備える。真空チャンバー15の上部には、複数のガス吹き出し口と、プラズマ発生源であるICPコイル16(誘導結合プラズマコイル)が配置されている。

【0253】

50

ガス吹き出し口は、プラズマ装置10の上面から見て中央部分に12個配置されている。それぞれのガス吹き出し口は、酸素ガスを供給するためのガス供給源とガス流路17を介して接続されており、ガス供給源は、マスフローコントローラ等を備え、所望の流量(0より多く1000sccm以下)でガス流路17に対して酸素ガスを供給することができる。ガス供給源から供給される酸素ガスは、ガス流路17から12個のガス吹き出し口を介して真空チャンバー15内に供給される。

【0254】

ICPコイル16は、複数本の帯状の導体を螺旋状に配置してなる。各導体の一端は、インピーダンス調整のためのマッチング回路を介して第1の高周波電源18(13.56MHz)に電気的に接続され、他端は接地されている。

10

【0255】

真空チャンバーの下部には、下部電極として機能する基板ステージ19が配置されている。基板ステージ19に設けられた静電チャックなどにより、基板ステージ上に被処理基板20が着脱可能に保持される。基板ステージ19には、加熱機構としてヒータ、冷却機構としてHeガス流路を備えている。基板ステージは、基板バイアス電圧印加用の第2の高周波電源21(3.2MHz)に接続されている。

【0256】

また、真空チャンバー15には、排気口が設けられ、自動圧力制御弁22(Automatic Pressure Control valve、APCとも呼ぶ。)が備えられる。APCはターボ分子ポンプ23に接続され、さらにターボ分子ポンプ23を介してドライポンプ24に接続される。APCは真空チャンバー内の圧力制御を行い、ターボ分子ポンプ23及びドライポンプ24は、真空チャンバー15内を減圧する。

20

【0257】

次に、図17(B)に示す真空チャンバー15内にプラズマを発生させ、被処理基板20に設けられている酸化物半導体膜、下地絶縁膜またはゲート絶縁膜に酸素プラズマドープを行う一例を示す。

【0258】

まず、ターボ分子ポンプ23及びドライポンプ24などを作動させて、真空チャンバー15内を所望の圧力に保持した後、被処理基板20を真空チャンバー15内の基板ステージに設置する。なお、基板ステージに保持する被処理基板20には少なくとも酸化物半導体膜または下地絶縁膜を備えるものとする。本実施の形態では、真空チャンバー15内の圧力を1.33Paに保持する。なお、酸素ガスをガス吹き出し口から真空チャンバー15内に供給する流量を250sccmに設定する。

30

【0259】

次いで、第1の高周波電源18からICPコイル16に高周波電力を印加し、プラズマを発生させる。そして、プラズマを発生させた状態を一定時間(30秒以上600秒以下)維持する。なお、ICPコイル16に印加する高周波電力は、1kW以上10kW以下とする。本実施の形態では、6000Wとする。この際、第2の高周波電源21から基板ステージに基板バイアス電圧を印加してもよい。本実施の形態では基板バイアス電圧印加に用いる電力を1000Wとする。

40

【0260】

本実施の形態では、プラズマを発生させた状態を60秒維持した後、被処理基板20を真空チャンバー15から搬出する。こうして、被処理基板20に設けられている酸化物半導体膜、下地絶縁膜またはゲート絶縁膜に酸素プラズマドープを行うことができる。

【0261】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0262】

(実施の形態5)

本実施の形態では、半導体装置の一例として、記憶媒体(メモリ素子)を示す。本実施の

50

形態では、実施の形態1乃至3などにおいて示す酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとを同一基板上に形成する。

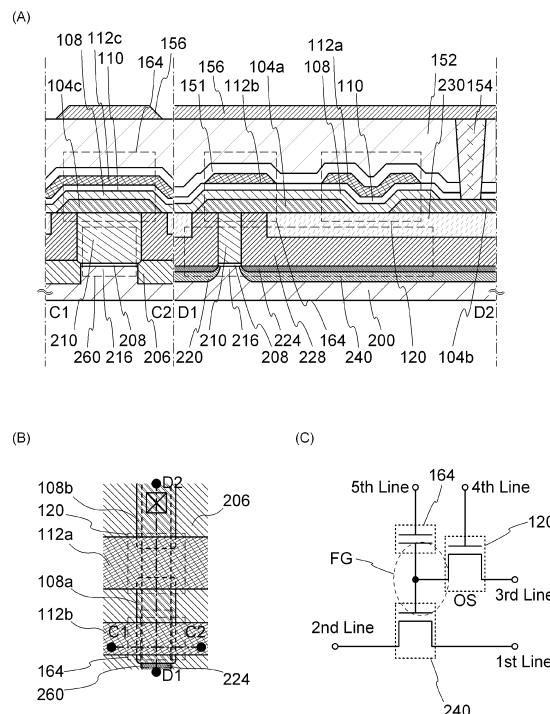

【0263】

図7は、半導体装置の構成の一例である。図7(A)には、半導体装置の断面を、図7(B)には、半導体装置の平面を、それぞれ示す。ここで、図7(A)は、図7(B)のC1-C2およびD1-D2における断面に相当する。また、図7(C)には、上記半導体装置をメモリ素子として用いる場合の回路図の一例を示す。図7(A)および図7(B)に示される半導体装置は、下部に第1の半導体材料を用いたトランジスタ240を有し、上部に実施の形態1で示したトランジスタ120を有する。なお、トランジスタ120は、第2の半導体材料として酸化物半導体を用いている。本実施の形態では、第1の半導体材料を酸化物半導体以外の半導体材料とする。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いるのが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0264】

なお、本実施の形態においては、トランジスタ120を用いて記憶媒体を構成する例を示すが、トランジスタ120に代えて、実施の形態1または2で示したトランジスタ130、トランジスタ140、トランジスタ150およびトランジスタ160等を適用可能であることは、いうまでもない。

【0265】

図7におけるトランジスタ240は、半導体材料(例えば、シリコンなど)を含む基板200に設けられたチャネル形成領域216と、チャネル形成領域216を挟むように設けられた不純物領域220と、不純物領域220に接する金属化合物領域224と、チャネル形成領域216上に設けられたゲート絶縁膜208と、ゲート絶縁膜208上に設けられたゲート電極210と、を有する。

【0266】

半導体材料を含む基板200は、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体膜が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体膜が設けられた構成の基板も含む。つまり、「SOI基板」が有する半導体膜は、シリコン半導体膜に限定されない。また、SOI基板には、ガラス基板などの絶縁基板上に絶縁膜を介して半導体膜が設けられた構成のものが含まれるものとする。

【0267】

基板200上にはトランジスタ240を囲むように素子分離絶縁膜206が設けられており、トランジスタ240を覆うように絶縁膜228および絶縁膜230が設けられている。なお、高集積化を実現するためには、図7(A)に示すようにトランジスタ240がサイドウォール絶縁膜を有しない構成とすることが望ましい。一方で、トランジスタ240の特性を重視する場合には、ゲート電極210の側面にサイドウォール絶縁膜を設け、不純物濃度が異なる領域を含む不純物領域220を設けても良い。

【0268】

トランジスタ240はシリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いて作製することができる。このようなトランジスタ240は、高速動作が可能であるという特徴を有する。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。

【0269】

トランジスタ240を形成した後、トランジスタ120および容量素子164の形成前の処理として、絶縁膜228や絶縁膜230にCMP処理を施して、ゲート電極210の上

10

20

30

40

50

面を露出させる。ゲート電極 210 の上面を露出させる処理としては、C M P 処理の他にエッティング処理などを適用することも可能であるが、トランジスタ 120 の特性を向上させるために、絶縁膜 228 や絶縁膜 230 の表面は可能な限り平坦にしておくことが望ましい。

【0270】

次に、ゲート電極 210、絶縁膜 228、絶縁膜 230 などの上に導電膜を形成し、該導電膜を選択的にエッティングして、ソース電極 104a、ドレイン電極 104b を形成する。

【0271】

導電膜は、スパッタ法をはじめとする P V D 法や、プラズマ C V D 法などの C V D 法を用いて形成することができる。また、導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、W から選ばれた元素や、上述した元素を成分とする合金等を用いることができる。Mn、Mg、Zr、Be、Nd、Sc のいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

【0272】

導電膜は、単層構造であっても良いし、2 層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された 2 層構造、窒化チタン膜上にチタン膜が積層された 2 層構造、チタン膜とアルミニウム膜とチタン膜とが積層された 3 層構造などが挙げられる。なお、導電膜を、チタン膜や窒化チタン膜の単層構造とする場合には、テーパー形状を有するソース電極 104a、およびドレイン電極 104b への加工が容易であるというメリットがある。

【0273】

上部のトランジスタ 120 のチャネル長 (L) は、ソース電極 104a、およびドレイン電極 104b の下端部の間隔によって決定される。なお、チャネル長 (L) が 25 nm 未満のトランジスタを形成する場合に用いるマスク形成の露光を行う際には、数 nm ~ 数 10 nm と波長の短い超紫外線を用いるのが望ましい。

【0274】

次に、ソース電極 104a、およびドレイン電極 104b を覆うように酸化物半導体膜を形成した後、当該酸化物半導体膜を選択的にエッティングして酸化物半導体膜 108 を形成する。酸化物半導体膜は、実施の形態 1 に示す材料及び形成プロセスを用いる。

【0275】

次に、酸化物半導体膜 108 に接するゲート絶縁膜 110 を形成する。ゲート絶縁膜 110 は、実施の形態 1 に示す材料及び形成プロセスを用いる。

【0276】

次に、ゲート絶縁膜 110 上において酸化物半導体膜 108 と重畠する領域にゲート電極 112a を形成し、ソース電極 104a と重畠する領域に電極 112b を形成する。

【0277】

ゲート絶縁膜 110 の形成後には、不活性ガス雰囲気下、または酸素雰囲気下で熱処理（加酸化などとも呼ぶ）を行うのが望ましい。熱処理の温度は、200 以上 450 以下、望ましくは 250 以上 350 以下である。例えば、窒素雰囲気下で 250 、1 時間の熱処理を行えばよい。熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減することができる。

【0278】

なお、加酸化を目的とする熱処理のタイミングはこれに限定されない。例えば、ゲート電極の形成後に加酸化を目的とする熱処理を行っても良い。また、脱水化等を目的とする熱処理に続けて加酸化を目的とする熱処理を行っても良いし、脱水化等を目的とする熱処理に加酸化を目的とする熱処理を兼ねさせてても良いし、加酸化を目的とする熱処理に脱水化等を目的とする熱処理を兼ねさせてても良い。

【0279】

10

20

30

40

50

上述のように、脱水化等を目的とする熱処理と、酸素ドープ処理または加酸化を目的とする熱処理とを適用することで、酸化物半導体膜108を不純物が極力含まれないように高純度化することができる。

【0280】

ゲート電極112aおよび電極112bは、ゲート絶縁膜110上に導電膜を形成した後に、当該導電膜を選択的にエッチングすることによって形成することができる。

【0281】

次に、ゲート絶縁膜110、ゲート電極112a、および電極112b上に、絶縁膜151および絶縁膜152を形成する。絶縁膜151および絶縁膜152は、スパッタ法やCVD法などを用いて形成することができる。また、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム等の無機絶縁材料を含む材料を用いて形成することができる。

【0282】

次に、ゲート絶縁膜110、絶縁膜151、及び絶縁膜152に、ドレイン電極104bにまで達する開口を形成する。当該開口の形成は、マスクなどを用いた選択的なエッチングにより行われる。

【0283】

その後、上記開口に電極154を形成し、絶縁膜152上に電極154に接する配線156を形成する。

【0284】

電極154は、例えば、開口を含む領域にPVD法やCVD法などを用いて導電膜を形成した後、エッチング処理やCMPといった方法を用いて、上記導電膜の一部を除去することにより形成することができる。

【0285】

配線156は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて導電膜を形成した後、当該導電膜をパターニングすることによって形成される。また、導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。Mn、Mg、Zr、Be、Nd、Scのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。詳細は、ソース電極104aまたはドレイン電極104bなどと同様である。

【0286】

以上により、高純度化された酸化物半導体膜108を用いたトランジスタ120、および容量素子164が完成する。容量素子164は、ソース電極104a、酸化物半導体膜108、ゲート絶縁膜110、および電極112b、で構成される。

【0287】

なお、図7の容量素子164では、酸化物半導体膜108とゲート絶縁膜110を積層させることにより、ソース電極104aと、電極112bとの間の絶縁性を十分に確保することができる。もちろん、十分な容量を確保するために、酸化物半導体膜108を有しない構成の容量素子164を採用しても良い。さらに、容量が不要の場合は、容量素子164を設けない構成とすることも可能である。

【0288】

図7(C)には、上記半導体装置をメモリ素子として用いる場合の回路図の一例を示す。図7(C)において、トランジスタ120のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、トランジスタ240のゲート電極とは電気的に接続されている。また、第1の配線(1st Line:ソース線とも呼ぶ)とトランジスタ240のソース電極とは、電気的に接続され、第2の配線(2nd Line:ビット線とも呼ぶ)とトランジスタ240のドレイン電極とは、電気的に接続されている。また、第3の配線(3rd Line:第1の信号線とも呼ぶ)とトランジスタ120のソース電極またはドレイン電極の他方とは、電気的に接続され、第4の配線(4th Line:第2の信号線とも呼ぶ)と、トランジスタ120のゲート電極とは、電気的に接続されてい

10

20

30

40

50

る。そして、第5の配線(5th Line:ワード線とも呼ぶ)と、容量素子164の電極の他方は電気的に接続されている。

【0289】

酸化物半導体を用いたトランジスタ120は、オフ電流が極めて小さいという特徴を有しているため、トランジスタ120をオフ状態とすることで、トランジスタ120のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、トランジスタ240のゲート電極とが電気的に接続されたノード(以下、ノードFG)の電位を極めて長時間にわたって保持することが可能である。そして、容量素子164を有することにより、ノードFGに与えられた電荷の保持が容易になり、また、保持された情報の読み出しが容易になる。

10

【0290】

半導体装置に情報を記憶させる場合(書き込み)は、まず、第4の配線の電位を、トランジスタ120がオン状態となる電位にして、トランジスタ120をオン状態とする。これにより、第3の配線の電位が、ノードFGに供給され、ノードFGに所定量の電荷が蓄積される。ここでは、異なる二つの電位レベルを与える電荷(以下、ロー(Low)レベル電荷、ハイ(High)レベル電荷という)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ120がオフ状態となる電位にして、トランジスタ120をオフ状態とすることにより、ノードFGが浮遊状態となるため、ノードFGには所定の電荷が保持されたままの状態となる。以上のように、ノードFGに所定量の電荷を蓄積及び保持させることで、メモリセルに情報を記憶させることができる。

20

【0291】

トランジスタ120のオフ電流は極めて小さいため、ノードFGに供給された電荷は長時間にわたって保持される。したがって、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となり、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

【0292】

記憶された情報を読み出す場合(読み出し)は、第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、ノードFGに保持された電荷量に応じて、トランジスタ240は異なる状態をとる。一般に、トランジスタ240をnチャネル型とすると、ノードFGにHighレベル電荷が保持されている場合のトランジスタ240の見かけのしきい値 $V_{th\_H}$ は、ノードFGにLowレベル電荷が保持されている場合のトランジスタ240の見かけのしきい値 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値とは、トランジスタ240を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を $V_{th\_H}$ と $V_{th\_L}$ の中間の電位 $V_0$ とすることにより、ノードFGに保持された電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位が $V_0 (> V_{th\_H})$ となれば、トランジスタ240は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位が $V_0 (< V_{th\_L})$ となっても、トランジスタ240は「オフ状態」のままである。このため、第5の配線の電位を制御して、トランジスタ240のオン状態またはオフ状態を読み出す(第2の配線の電位を読み出す)ことで、記憶された情報を読み出すことができる。

30

【0293】

また、記憶させた情報を書き換える場合においては、上記の書き込みによって所定量の電荷を保持したノードFGに、新たな電位を供給することで、ノードFGに新たな情報に係る電荷を保持させる。具体的には、第4の配線の電位を、トランジスタ120がオン状態となる電位にして、トランジスタ120をオン状態とする。これにより、第3の配線の電位(新たな情報に係る電位)が、ノードFGに供給され、ノードFGに所定量の電荷が蓄積される。その後、第4の配線の電位をトランジスタ120がオフ状態となる電位にして、トランジスタ120をオフ状態とすることにより、ノードFGには、新たな情報に係る

40

50

電荷が保持された状態となる。すなわち、ノード F G に第 1 の書き込みによって所定量の電荷が保持された状態で、第 1 の書き込みと同様の動作（第 2 の書き込み）を行うことで、記憶させた情報を上書きすることが可能である。

【 0 2 9 4 】

本実施の形態で示すトランジスタ 1 2 0 は、高純度化され、真性化された酸化物半導体膜 1 0 8 を用いることで、トランジスタ 1 2 0 のオフ電流を十分に低減することができる。また、酸化物半導体膜 1 0 8 を酸素過剰な層とすることで、トランジスタ 1 2 0 の電気的特性変動が抑制されており、電気的に安定なトランジスタとすることができます。そして、このようなトランジスタを用いることで、極めて長期にわたり記憶内容を保持することができるで、信頼性の高い半導体装置が得られる。

10

【 0 2 9 5 】

また、本実施の形態において示す半導体装置では、トランジスタ 2 4 0 とトランジスタ 1 2 0 を重畳させることで、集積度が十分に高められた半導体装置が実現される。

【 0 2 9 6 】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【 0 2 9 7 】

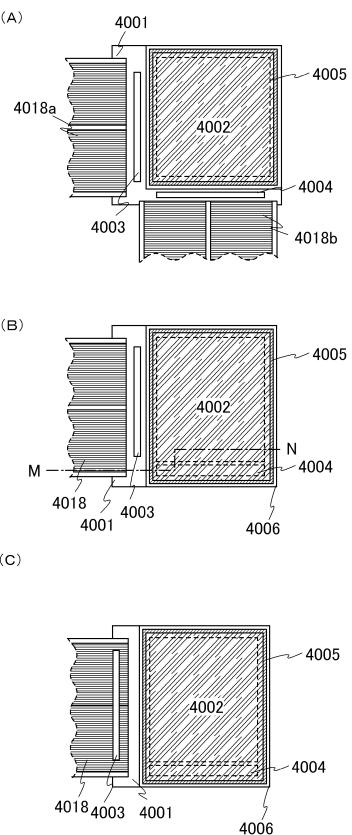

( 実施の形態 6 )

実施の形態 1 ~ 3 で例示したトランジスタを用いて表示機能を有する半導体装置（表示装置ともいう）を作製することができる。また、トランジスタを含む駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

20

【 0 2 9 8 】

図 8 ( A )において、第 1 の基板 4 0 0 1 上に設けられた画素部 4 0 0 2 を囲むようにして、シール材 4 0 0 5 が設けられ、第 2 の基板 4 0 0 6 によって封止されている。図 8 ( A )においては、第 1 の基板 4 0 0 1 上のシール材 4 0 0 5 によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された走査線駆動回路 4 0 0 4 、信号線駆動回路 4 0 0 3 が実装されている。また別途形成された信号線駆動回路 4 0 0 3 と、走査線駆動回路 4 0 0 4 または画素部 4 0 0 2 に与えられる各種信号及び電位は、F P C ( F l e x i b l e p r i n t e d c i r c u i t ) 4 0 1 8 a 、F P C 4 0 1 8 b から供給されている。

30

【 0 2 9 9 】

図 8 ( B )、図 8 ( C )において、第 1 の基板 4 0 0 1 上に設けられた画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 とを囲むようにして、シール材 4 0 0 5 が設けられている。また画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 の上に第 2 の基板 4 0 0 6 が設けられている。よって画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 とは、第 1 の基板 4 0 0 1 とシール材 4 0 0 5 と第 2 の基板 4 0 0 6 とによって、表示素子と共に封止されている。図 8 ( B )、図 8 ( C )においては、第 1 の基板 4 0 0 1 上のシール材 4 0 0 5 によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路 4 0 0 3 が実装されている。図 8 ( B )、図 8 ( C )においては、別途形成された信号線駆動回路 4 0 0 3 と、走査線駆動回路 4 0 0 4 または画素部 4 0 0 2 に与えられる各種信号及び電位は、F P C 4 0 1 8 から供給されている。

40

【 0 3 0 0 】

また、本実施の形態は図 8 ( A )乃至図 8 ( C )において示した構成に限定されない。信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

【 0 3 0 1 】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、C O G ( C h i p O n G l a s s ) 方法、ワイヤボンディング方法、或いはT A B ( T a p e A u t o m a t e d B o n d i n g ) 方法などを用いることができる。図 8 ( A )は、C O G 方法により信号線駆動回路 4 0 0 3 、走査線駆動回路 4 0 0 4 を実装する例であり、

50

図 8 ( B ) は、 C O G 方法により信号線駆動回路 4 0 0 3 を実装する例であり、 図 8 ( C ) は、 T A B 方法により信号線駆動回路 4 0 0 3 を実装する例である。

【 0 3 0 2 】

なお、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む I C 等を実装した状態にあるモジュールとを含む。

【 0 3 0 3 】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えば F P C もしくは T A B テープもしくは T C P が取り付けられたモジュール、 T A B テープや T C P の先にプリント配線板が設けられたモジュール、または表示素子に C O G 方式により I C （集積回路）が直接実装されたモジュールも全て表示装置に含むものとする。 10

【 0 3 0 4 】

また第 1 の基板上に設けられた画素部及び走査線駆動回路は、トランジスタを複数有しております、実施の形態 1 乃至 3 で例示したトランジスタを適用することができる。

【 0 3 0 5 】

表示装置に設けられる表示素子としては液晶素子（液晶表示素子ともいう）、発光素子（発光表示素子ともいう）、を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機 E L ( E l e c t r o L u m i n e s c e n c e ) 素子、有機 E L 素子等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。 20

【 0 3 0 6 】

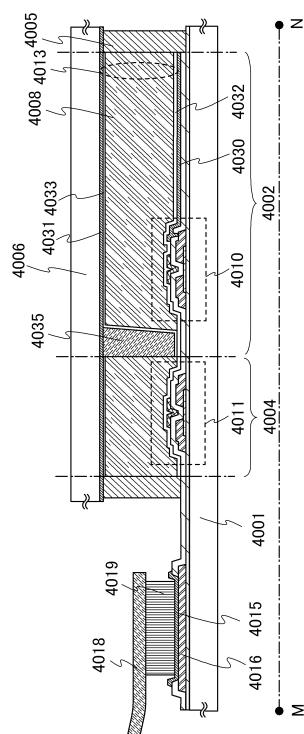

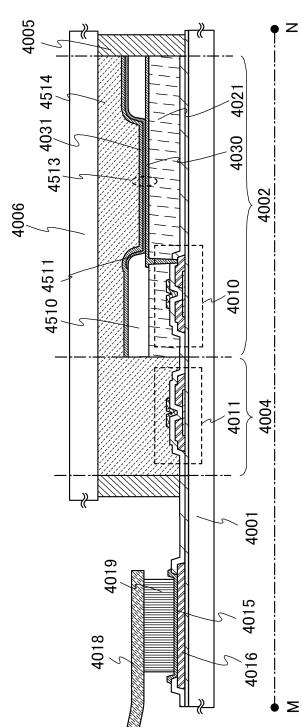

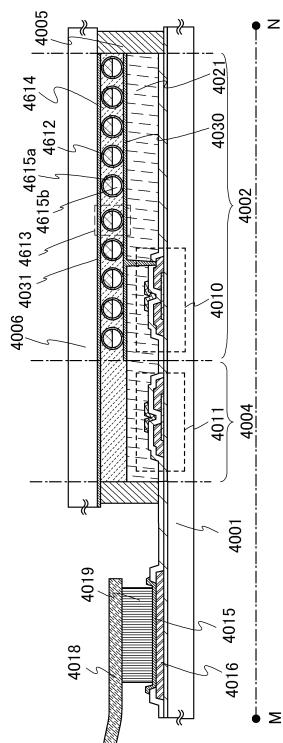

半導体装置の一形態について、図 9 乃至図 11 を用いて説明する。図 9 乃至図 11 は、図 8 ( B ) の M - N における断面図に相当する。

【 0 3 0 7 】

図 9 乃至図 11 で示すように、半導体装置は接続端子電極 4 0 1 5 及び端子電極 4 0 1 6 を有しております、接続端子電極 4 0 1 5 及び端子電極 4 0 1 6 は F P C 4 0 1 8 が有する端子と異方性導電膜 4 0 1 9 を介して、電気的に接続されている。

【 0 3 0 8 】

接続端子電極 4 0 1 5 は、第 1 の電極層 4 0 3 0 と同じ導電膜から形成され、端子電極 4 0 1 6 は、トランジスタ 4 0 1 0 、トランジスタ 4 0 1 1 のソース電極及びドレイン電極と同じ導電膜で形成されている。 30

【 0 3 0 9 】

また第 1 の基板 4 0 0 1 上に設けられた画素部 4 0 0 2 と、走査線駆動回路 4 0 0 4 は、トランジスタを複数有しております、図 9 乃至図 11 では、画素部 4 0 0 2 に含まれるトランジスタ 4 0 1 0 と、走査線駆動回路 4 0 0 4 に含まれるトランジスタ 4 0 1 1 とを例示している。図 10 及び図 11 では、トランジスタ 4 0 1 0 、トランジスタ 4 0 1 1 上に、絶縁層 4 0 2 1 が設けられている。

【 0 3 1 0 】

本実施の形態では、トランジスタ 4 0 1 0 、トランジスタ 4 0 1 1 として、実施の形態 1 乃至 3 のいずれかで示したトランジスタを適用することができる。トランジスタ 4 0 1 0 、トランジスタ 4 0 1 1 は、電気的特性変動が抑制されており、電気的に安定である。よって、図 9 乃至図 11 で示す本実施の形態の半導体装置として信頼性の高い半導体装置を提供することができる。 40

【 0 3 1 1 】

画素部 4 0 0 2 に設けられたトランジスタ 4 0 1 0 は表示素子と電気的に接続し、表示パネルを構成する。表示素子は表示を行うことができれば特に限定されず、様々な表示素子を用いることができる。

【 0 3 1 2 】

図 9 に表示素子として液晶素子を用いた液晶表示装置の例を示す。図 9 において、表示素子である液晶素子 4 0 1 3 は、第 1 の電極層 4 0 3 0 、第 2 の電極層 4 0 3 1 、及び液晶

10

20

30

40

50

層4008を含む。なお、液晶層4008を挟持するように配向膜として機能する絶縁膜4032、絶縁膜4033が設けられている。第2の電極層4031は第2の基板4006側に設けられ、第1の電極層4030と第2の電極層4031とは液晶層4008を介して積層する構成となっている。

【0313】

また、スペーサ4035は絶縁膜を選択的にエッティングすることで得られる柱状のスペーサであり、液晶層4008の膜厚(セルギャップ)を制御するために設けられている。なおスペーサの形状は、柱状に限定されるものではなく、例えば、球状のスペーサを用いていても良い。

【0314】

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スマクチック相、キューピック相、カイラルネマチック相、等方相等を示す。

【0315】

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために数重量%以上のカイラル剤を混合させた液晶組成物を液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1msec以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって液晶表示装置の生産性を向上させることができるとなる。

【0316】

また、液晶材料の固有抵抗率は、 $1 \times 10^9 \cdot \text{cm}$ 以上であり、好ましくは $1 \times 10^{11} \cdot \text{cm}$ 以上であり、さらに好ましくは $1 \times 10^{12} \cdot \text{cm}$ 以上である。なお、本明細書における固有抵抗率の値は、20で測定した値とする。

【0317】

液晶表示装置に設けられる保持容量の大きさは、画素部に配置されるトランジスタのリーアク電流等を考慮して、所定の期間、電荷を保持できるように設定される。高純度の酸化物半導体膜を有するトランジスタを用いることにより、各画素における液晶容量に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。

【0318】

本実施の形態で用いる高純度化された酸化物半導体膜を用いたトランジスタは、オフ状態における電流値(オフ電流値)を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

【0319】

また、本実施の形態で用いる高純度化された酸化物半導体膜を用いたトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に上記トランジスタを用いることで、高画質な画像を提供することができる。また、上記トランジスタは、同一基板上に駆動回路部または画素部に作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

【0320】

液晶表示装置には、TN(Twisted Nematic)モード、IPS(In-Plane-Switching)モード、FFS(Fringe Field Switching)モード、ASM(Axially Symmetric aligned)

10

20

30

40

50

Micro-cell) モード、OCB (Optical Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モードなどを用いることができる。

#### 【0321】

また、ノーマリーブラック型の液晶表示装置、例えば垂直配向 (VA) モードを採用した透過型の液晶表示装置としてもよい。ここで、垂直配向モードとは、液晶表示パネルの液晶分子の配列を制御する方式の一種であり、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ASV (Advanced Super View) モードなどを用いることができる。また、画素 (ピクセル) をいくつかの領域 (サブピクセル) に分け、それぞれ別の方向に分子を倒すよう工夫されているマルチドメイン化あるいはマルチドメイン設計といわれる方法を用いることができる。

#### 【0322】

また、表示装置において、ブラックマトリクス (遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材 (光学基板) などは適宜設ける。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

#### 【0323】

また、バックライトとして複数の発光ダイオード (LED) を用いて、時間分割表示方式 (フィールドシーケンシャル駆動方式) を行うことも可能である。フィールドシーケンシャル駆動方式を適用することで、カラーフィルタを用いることなく、カラー表示を行うことができる。

#### 【0324】

また、画素部における表示方式は、プログレッシブ方式やインターレース方式等を用いることができる。また、カラー表示する際に画素で制御する色要素としては、RGB (Rは赤、Gは緑、Bは青を表す) の三色に限定されない。例えば、RGBW (Wは白を表す)、又はRGBに、イエロー、シアン、マゼンタ等を一色以上追加したものがある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。ただし、本発明はカラー表示の表示装置に限定されるものではなく、モノクロ表示の表示装置に適用することもできる。

#### 【0325】

また、表示装置に含まれる表示素子として、エレクトロルミネッセンスを利用する発光素子を適用することができる。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

#### 【0326】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア (電子および正孔) が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

#### 【0327】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー-アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利

10

20

30

40

50

用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

【0328】

発光素子は発光を取り出すために少なくとも一対の電極の一方が透明であればよい。そして、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、どの射出構造の発光素子も適用することができる。

【0329】

図10に表示素子として発光素子を用いた発光装置の例を示す。表示素子である発光素子4513は、画素部4002に設けられたトランジスタ4010と電気的に接続している。なお発光素子4513の構成は、第1の電極層4030、電界発光層4511、第2の電極層4031の積層構造であるが、示した構成に限定されない。発光素子4513から取り出す光の方向などに合わせて、発光素子4513の構成は適宜変えることができる。

【0330】

隔壁4510は、有機絶縁材料、又は無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第1の電極層4030上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することができる。

【0331】

電界発光層4511は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0332】

発光素子4513に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4031及び隔壁4510上に保護膜を形成してもよい。保護膜としては、窒化シリコン膜、窒化酸化シリコン膜、DLC (Diamond - Like Carbon) 膜等を形成することができる。また、第1の基板4001、第2の基板4006、及びシール材4005によって封止された空間には充填材4514が設けられ密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することができる。

【0333】

充填材4514としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。例えば充填材として窒素を用いればよい。

【0334】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

【0335】

また、表示装置として、電子インクを駆動させる電子ペーパーを提供することも可能である。電子ペーパーは、電気泳動表示装置(電気泳動ディスプレイ)とも呼ばれており、紙と同じ読みやすさ、他の表示装置に比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。

【0336】

電気泳動表示装置は、様々な形態が考えられ得るが、プラスの電荷を有する第1の粒子と、マイナスの電荷を有する第2の粒子とを含むマイクロカプセルが溶媒または溶質に複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロカプ

10

20

30

40

50

セル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示するものである。なお、第1の粒子または第2の粒子は染料を含み、電界がない場合において移動しないものである。また、第1の粒子の色と第2の粒子の色は異なるもの（無色を含む）とする。

【0337】

このように、電気泳動表示装置は、誘電定数の高い物質が高い電界領域に移動する、いわゆる誘電泳動的効果を利用したディスプレイである。

【0338】

上記マイクロカプセルを溶媒中に分散させたものが電子インクと呼ばれるものであり、この電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。 10

【0339】

なお、マイクロカプセル中の第1の粒子および第2の粒子は、導電体材料、絶縁体材料、半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレクトロクロミック材料、磁気泳動材料から選ばれた一種の材料、またはこれらの複合材料を用いればよい。

【0340】

また、電子ペーパーとして、ツイストボール表示方式を用いる表示装置も適用することができる。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極層である第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせての球形粒子の向きを制御することにより、表示を行う方法である。 20

【0341】

図11に、半導体装置の一形態としてアクティブマトリクス型の電子ペーパーを示す。図11の電子ペーパーは、ツイストボール表示方式を用いた表示装置の例である。

【0342】

トランジスタ4010と接続する第1の電極層4030と、第2の基板4006に設けられた第2の電極層4031との間には黒色領域4615a及び白色領域4615bを有し、周りに液体で満たされているキャビティ4612を含む球形粒子4613が設けられており、球形粒子4613の周囲は樹脂等の充填材4614で充填されている。第2の電極層4031が共通電極（対向電極）に相当する。第2の電極層4031は、共通電位線と電気的に接続される。 30

【0343】

なお、図9乃至図11において、第1の基板4001、第2の基板4006としては、ガラス基板の他、可撓性を有する基板も用いることができ、例えば透光性を有するプラスチック基板などを用いることができる。プラスチックとしては、FRP（Fiberglass-Reinforced Plastics）板、PVF（ポリビニルフルオライド）フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。 40

【0344】

絶縁層4021は、無機絶縁材料又は有機絶縁材料を用いて形成することができる。なお、アクリル樹脂、ポリイミド、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機絶縁材料を用いると、平坦化絶縁膜として好適である。また上記有機絶縁材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層を形成してもよい。

【0345】

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタリング法、スピンコート法、ディッピング法、スプレー塗布、液滴吐出法（インクジェット法）、スク 50

リーン印刷、オフセット印刷、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

【0346】

表示装置は光源又は表示素子からの光を透過させて表示を行う。よって光が透過する画素部に設けられる基板、絶縁膜、導電膜などの薄膜はすべて可視光の波長領域の光に対して透光性とする。

【0347】

表示素子に電圧を印加する第1の電極層及び第2の電極層（画素電極層、共通電極層、対向電極層などともいう）においては、取り出す光の方向、電極層が設けられる場所、及び電極層のパターン構造によって透光性、反射性を選択すればよい。

10

【0348】

第1の電極層4030、第2の電極層4031は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITOと示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

【0349】

また、第1の電極層4030、第2の電極層4031はタンゲステン（W）、モリブデン（Mo）、ジルコニウム（Zr）、ハフニウム（Hf）、バナジウム（V）、ニオブ（Nb）、タンタル（Ta）、クロム（Cr）、コバルト（Co）、ニッケル（Ni）、チタン（Ti）、白金（Pt）、アルミニウム（Al）、銅（Cu）、銀（Ag）等の金属、又はその合金、若しくはその窒化物から一つ、又は複数種を用いて形成することができる。

20

【0350】

また、トランジスタは静電気などにより破壊されやすいため、駆動回路保護用の保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することができる。

【0351】

以上のように、実施の形態1乃至3で例示したトランジスタを適用することで、信頼性の高い半導体装置を提供することができる。

30

【0352】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

【0353】

（実施の形態7）

実施の形態1乃至3のいずれかで一例を示したトランジスタを用いて、対象物の情報を読み取るイメージセンサ機能を有する半導体装置を作製することができる。

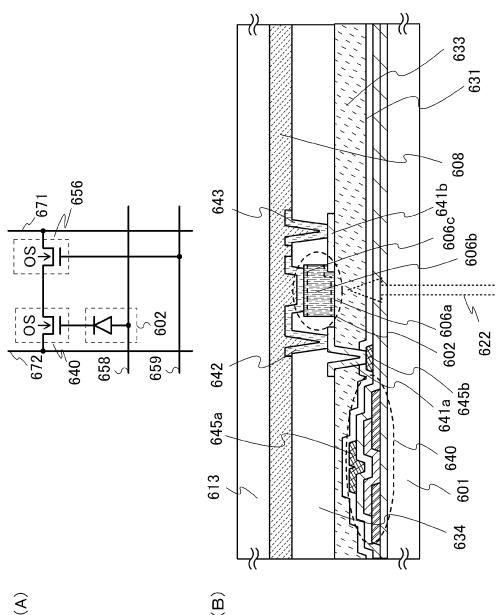

【0354】

図12（A）に、イメージセンサ機能を有する半導体装置の一例を示す。図12（A）は、フォトセンサの等価回路であり、図12（B）はフォトセンサの一部を示す断面図である。

40

【0355】

フォトダイオード602は、一方の電極がフォトダイオードリセット信号線658に、他方の電極がトランジスタ640のゲートに電気的に接続されている。トランジスタ640は、ソース又はドレインの一方がフォトセンサ基準信号線672に、ソース又はドレインの他方がトランジスタ656のソース又はドレインの一方に電気的に接続されている。トランジスタ656は、ゲートがゲート信号線659に、ソース又はドレインの他方がフォトセンサ出力信号線671に電気的に接続されている。

【0356】

なお、本明細書における回路図において、酸化物半導体膜を用いるトランジスタと明確に判明できるように、酸化物半導体膜を用いるトランジスタの記号には「OS」と記載して

50

いる。図12(A)において、トランジスタ640、トランジスタ656は酸化物半導体膜を用いるトランジスタである。

【0357】

図12(B)は、フォトセンサにおけるフォトダイオード602及びトランジスタ640に示す断面図であり、絶縁表面を有する基板601(TFT基板)上に、センサとして機能するフォトダイオード602及びトランジスタ640が設けられている。フォトダイオード602、トランジスタ640の上には接着層608を用いて基板613が設けられている。また、トランジスタ640上には絶縁膜631、第1の層間絶縁層633、第2の層間絶縁層634が設けられている。

【0358】

また、トランジスタ640のゲート電極645aと電気的に接続されるように、該ゲート電極645aと同じ層に電極層645bが設けられている。電極層645bは、絶縁膜631及び第1の層間絶縁層633に設けられた開口を介して、電極層641aと電気的に接続している。電極層641aは、第2の層間絶縁層634に形成された電極層642と電気的に接続し、電極層642は電極層641aを介してゲート電極645aと電気的に接続しているため、フォトダイオード602はトランジスタ640と電気的に接続している。

10

【0359】

フォトダイオード602は、第1の層間絶縁層633上に設けられ、第1の層間絶縁層633上に形成した電極層641bと、第2の層間絶縁層634上に設けられた電極層642との間に、第1の層間絶縁層633側から順に第1半導体層606a、第2半導体層606b、及び第3半導体層606cを積層した構造を有している。

20

【0360】

本実施の形態では、トランジスタ640として、実施の形態1乃至3のいずれかで示したトランジスタを適用することができる。トランジスタ640、トランジスタ656は、電気的特性変動が抑制されており、電気的に安定であるため、図12で示す本実施の形態の半導体装置として信頼性の高い半導体装置を提供することができる。

【0361】

ここでは、第1半導体層606aとしてp型の導電型を有する半導体層と、第2半導体層606bとして高抵抗な半導体層(i型半導体層)、第3半導体層606cとしてn型の導電型を有する半導体層を積層するpin型のフォトダイオードを例示している。

30

【0362】

第1半導体層606aはp型半導体層であり、p型を付与する不純物元素を含むアモルファスシリコン膜により形成することができる。第1半導体層606aの形成には13族の不純物元素(例えばボロン(B))を含む半導体材料ガスを用いて、プラズマCVD法により形成する。半導体材料ガスとしてはシラン(SiH<sub>4</sub>)を用いればよい。または、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>、SiHC<sub>1</sub><sub>3</sub>、SiC<sub>1</sub><sub>4</sub>、SiF<sub>4</sub>等を用いてもよい。また、不純物元素を含まないアモルファスシリコン膜を形成した後に、拡散法やイオン注入法を用いて該アモルファスシリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合にアモルファスシリコン膜を形成する方法としては、LPCVD法、気相成長法、又はスパッタリング法等を用いればよい。第1半導体層606aの膜厚は10nm以上50nm以下となるよう形成することが好ましい。

40

【0363】