(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7080660号

(P7080660)

(45)発行日 令和4年6月6日(2022.6.6)

(24)登録日 令和4年5月27日(2022.5.27)

|                        |                                    |

|------------------------|------------------------------------|

| (51)国際特許分類             | F I                                |

| H 04 N 5/3745(2011.01) | H 04 N 5/3745                      |

| H 04 N 5/369(2011.01)  | H 04 N 5/369                       |

| H 01 L 27/146(2006.01) | H 01 L 27/146 D<br>H 01 L 27/146 A |

請求項の数 15 (全51頁)

|          |                             |          |                                            |

|----------|-----------------------------|----------|--------------------------------------------|

| (21)出願番号 | 特願2018-22400(P2018-22400)   | (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日  | 平成30年2月9日(2018.2.9)         | (74)代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (65)公開番号 | 特開2019-140531(P2019-140531) | (74)代理人  | 100124442<br>弁理士 黒岩 創吾                     |

|          | A)                          | (72)発明者  | 小林 秀央<br>東京都大田区下丸子3丁目30番2号キ<br>ヤノン株式会社内    |

| (43)公開日  | 令和1年8月22日(2019.8.22)        | (72)発明者  | 中野 慎也<br>東京都大田区下丸子3丁目30番2号キ<br>ヤノン株式会社内    |

| 審査請求日    | 令和3年2月5日(2021.2.5)          | (72)発明者  | 戸塚 洋史<br>東京都大田区下丸子3丁目30番2号キ<br>最終頁に続く      |

(54)【発明の名称】 光電変換装置、撮像システム、および、移動体

## (57)【特許請求の範囲】

## 【請求項1】

第1の半導体基板と第2の半導体基板とが積層された光電変換装置であって、光電変換部、および、画素回路をそれぞれが含む複数の画素と、前記複数の画素から信号を読み出すための読み出し回路と、を備え、前記光電変換部で生じた信号電荷に基づく信号を受け、かつ、互いに差動対を構成する第1のトランジスタおよび第2のトランジスタを、前記複数の画素のそれぞれの前記画素回路は少なくとも含み、

前記第1の半導体基板に前記光電変換部と前記差動対が配され、

前記第2の半導体基板に前記読み出し回路が配され、

前記読み出し回路は前記差動対に接続されるとともに第3のトランジスタを含むカレントミラー回路と、前記差動対および前記カレントミラー回路に接続される正帰還回路およびレベルシフタ回路と、前記レベルシフタ回路に接続され、第4のトランジスタを含むメモリ回路とを備え、

前記第3のトランジスタのサイズが前記第4のトランジスタのサイズより大きいことを特徴とする光電変換装置。

## 【請求項2】

前記差動対と前記カレントミラー回路が、アナログデジタル変換回路の比較器を構成する、ことを特徴とする請求項1に記載の光電変換装置。

## 【請求項3】

前記第3のトランジスタのゲート絶縁膜の膜厚が、前記第4のトランジスタのゲート絶縁膜の膜厚より大きい、

ことを特徴とする請求項1または2に記載の光電変換装置。

【請求項4】

前記メモリ回路は、メモリセル、または、ラッチ回路である、

ことを特徴とする請求項1乃至請求項3のいずれか一項に記載の光電変換装置。

【請求項5】

前記レベルシフタ回路に含まれるトランジスタのサイズが、前記第4のトランジスタのサイズと異なる、

ことを特徴とする請求項1乃至請求項4のいずれか一項に記載の光電変換装置。

10

【請求項6】

前記第3のトランジスタのサイズ、および、前記第4のトランジスタのサイズは、それぞれ、トランジスタのチャネル長、トランジスタのチャネル幅、および、トランジスタのゲート絶縁膜の膜厚から選ばれた少なくとも1つである、

ことを特徴とする請求項1乃至請求項5のいずれか一項に記載の光電変換装置。

【請求項7】

前記第1のトランジスタのサイズより前記第3のトランジスタのサイズが小さいことを特徴とする請求項1乃至請求項6のいずれか一項に記載の光電変換装置。

【請求項8】

第1の半導体基板と、第2の半導体基板と、第3の半導体基板とが積層された光電変換装置であって、

20

光電変換部、および、画素回路をそれぞれが含む複数の画素と、

前記複数の画素から信号を読み出すための読み出し回路と、を備え、

前記光電変換部で生じた信号電荷に基づく信号を受け、かつ、互いに差動対を構成する第1のトランジスタおよび第2のトランジスタを、前記複数の画素のそれぞれの前記画素回路は少なくとも含み、

前記第1の半導体基板に前記光電変換部と前記差動対が配され、

前記読み出し回路は前記差動対に接続されるカレントミラー回路と、前記差動対あとび前記カレントミラー回路に接続される正帰還回路およびレベルシフタ回路と、前記レベルシフタ回路に接続され、第3のトランジスタを含むメモリ回路とを備え、

30

前記第2の半導体基板に前記カレントミラー回路が配され、

前記第3の半導体基板に前記メモリ回路が配され、

前記第1のトランジスタのサイズより、前記第3のトランジスタのサイズが小さく、

前記第2の半導体基板に配されたトランジスタのサイズが前記第3のトランジスタのサイズより大きい

ことを特徴とする光電変換装置。

【請求項9】

前記第2の半導体基板に前記レベルシフタ回路が配され、

前記レベルシフタ回路の含むトランジスタのサイズより、前記第3のトランジスタのサイズが小さいことを特徴とする請求項8に記載の光電変換装置。

40

【請求項10】

前記第1のトランジスタのサイズより、前記第2の半導体基板に配された前記トランジスタのサイズが小さく、前記第2の半導体基板に配された前記トランジスタより前記第3のトランジスタのサイズが小さいことを特徴とする請求項8または9に記載の光電変換装置。

【請求項11】

前記第1のトランジスタのサイズ、および、前記第3のトランジスタのサイズは、それぞれ、トランジスタのチャネル長、トランジスタのチャネル幅、および、トランジスタのゲート絶縁膜の膜厚から選ばれた少なくとも1つである、

ことを特徴とする請求項8乃至請求項10のいずれか一項に記載の光電変換装置。

【請求項12】

50

前記カレントミラー回路に供給される電源電圧より、

前記メモリ回路に供給される電源電圧が小さいことを特徴とする請求項 1 乃至請求項 1\_1 のいずれか一項に記載の光電変換装置。

**【請求項 1\_3】**

前記カレントミラー回路に供給される電源電圧より前記レベルシフタ回路に供給される電源電圧の方が小さく、

前記レベルシフタ回路に供給される電源電圧よりも前記メモリ回路に供給される電源電圧の方が小さいことを特徴とする請求項 1 乃至請求項 1\_2 のいずれか一項に記載の光電変換装置。

**【請求項 1\_4】**

請求項 1 乃至請求項 1\_3 のいずれか一項に記載の光電変換装置と、

前記光電変換装置から出力された信号を処理して画像信号を取得する処理装置と、を備えた撮像システム。

**【請求項 1\_5】**

移動体であって、

請求項 1 乃至請求項 1\_3 のいずれか一項に記載の光電変換装置と、

前記光電変換装置から出力された信号に対して処理を行う処理装置と、

前記処理の結果に基づいて前記移動体を制御する制御手段と、を有することを特徴とする移動体。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は、光電変換装置、撮像システム、および、移動体に関する。

**【背景技術】**

**【0002】**

光電変換装置、特に撮像やマシンビジョンに用いられる光電変換装置は、複数の画素を備える。特許文献 1 は、各画素が光電変換部および光電変換部で生じた電荷に基づく信号を受け、かつ、差動対を構成するトランジスタを含むことを開示している。また、特許文献 1 に記載されるように、1つの画素に含まれる回路が、複数の半導体基板に分かれて配置されることもある。

30

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【文献】** WO 2016 / 009832 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

特許文献 1 では、回路を構成するトランジスタのサイズについては考慮されていない。トランジスタのサイズとは、チャネル長、チャネル幅、チャネル幅とチャネル長との比 (W / L)、ゲート絶縁膜の厚さなどである。そのため、トランジスタの耐圧が低いために信頼性が低下したり、電気特性が低下するためにノイズが増加したりする可能性がある。

40

**【0005】**

上記の課題に鑑み、本発明は光電変換装置の性能を向上させることを目的とする。

**【課題を解決するための手段】**

**【0006】**

1つの実施形態に係る光電変換装置は、第 1 の半導体基板と第 2 の半導体基板とが積層された光電変換装置であって、光電変換部、および、画素回路をそれぞれが含む複数の画素と、前記複数の画素から信号を読み出すための読み出し回路と、を備え、前記光電変換部で生じた信号電荷に基づく信号を受け、かつ、互いに差動対を構成する第 1 のトランジスタおよび第 2 のトランジスタを、前記複数の画素のそれぞれの前記画素回路は少なくとも

50

含み、前記第1の半導体基板に前記光電変換部と前記差動対が配され、前記第2の半導体基板に前記読み出し回路が配され、前記読み出し回路は前記差動対に接続されるとともに第3トランジスタを含むカレントミラー回路と、前記差動対および前記カレントミラー回路に接続される正帰還回路およびレベルシフタ回路と、前記レベルシフタ回路に接続され第4のトランジスタを含むメモリ回路とを備え、前記第3のトランジスタのサイズが前記第4のトランジスタのサイズより大きいことを特徴とする。

【0007】

他の実施形態に係る光電変換装置は、第1の半導体基板と、第2の半導体基板と、第3の半導体基板とが積層された光電変換装置であって、光電変換部、および、画素回路をそれぞれが含む複数の画素と、前記複数の画素から信号を読み出すための読み出し回路と、を備え、前記光電変換部で生じた信号電荷に基づく信号を受け、かつ、互いに差動対を構成する第1のトランジスタおよび第2のトランジスタを、前記複数の画素のそれぞれの前記画素回路は少なくとも含み、前記第1の半導体基板に前記光電変換部と前記差動対が配され、前記読み出し回路は前記差動対に接続されるカレントミラー回路と、前記差動対および前記カレントミラー回路に接続される正帰還回路およびレベルシフタ回路と、前記レベルシフタ回路に接続され、第3のトランジスタを含むメモリ回路とを備え、前記第2の半導体基板に前記カレントミラー回路が配され、前記第3の半導体基板に前記メモリ回路が配され、前記第1のトランジスタのサイズより、前記第3のトランジスタのサイズが小さく、前記第2の半導体基板に配されたトランジスタのサイズが前記第3のトランジスタのサイズより大きい、ことを特徴とする。

【発明の効果】

【0009】

本発明に係るいくつかの実施例によれば、光電変換装置の性能を向上させることができる。

【図面の簡単な説明】

【0010】

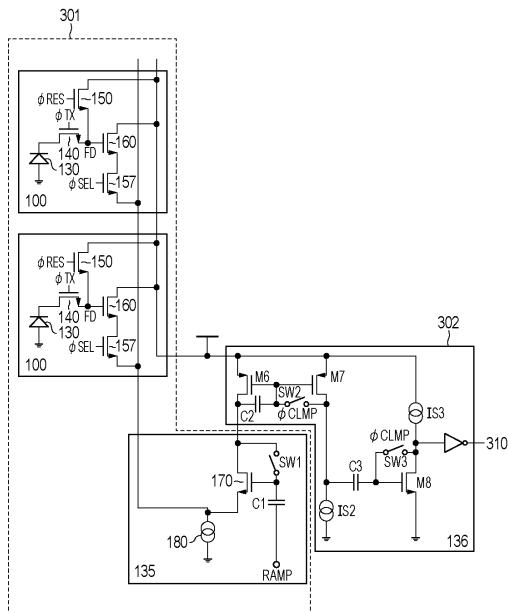

【図1】光電変換装置の構成を模式的に示す図。

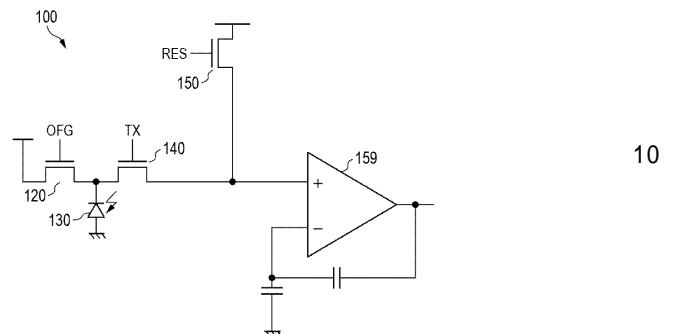

【図2】光電変換装置の画素の構成を模式的に示すブロック図。

【図3】光電変換装置の画素の等価回路を示す図。

【図4】(a)メモリ回路の構成を模式的に示したブロック図。(b)ラッチ回路およびメモリセルの等価回路図。

【図5】カウンタ回路の論理回路図。

【図6】光電変換装置の動作を説明するためのタイミングチャート図。

【図7】(a)トランジスタの断面構造を模式的に示す図。(b)トランジスタの平面構造を模式的に示す図である。

【図8】(a)トランジスタの断面構造を模式的に示す図。(b)トランジスタの平面構造を模式的に示す図である。

【図9】(a)トランジスタの断面構造を模式的に示す図。(b)トランジスタの平面構造を模式的に示す図である。

【図10】光電変換装置の画素の等価回路を示す図。

【図11】光電変換装置の画素の等価回路を示す図。

【図12】光電変換装置の画素の等価回路を示す図。

【図13】光電変換装置の構成を模式的に示す図。

【図14】光電変換装置の等価回路を示す図。

【図15】光電変換装置の動作を説明するためのタイミングチャート図。

【図16】光電変換装置の等価回路を示す図。

【図17】光電変換装置の等価回路を示す図。

【図18】光電変換装置の画素の等価回路を示す図。

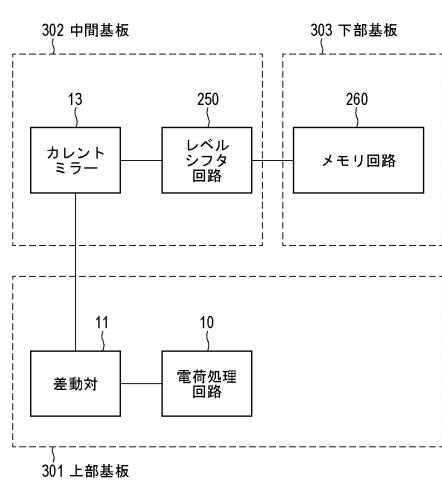

【図19】光電変換装置の画素の構成を模式的に示すブロック図。

【図20】2つのトランジスタの関係を示す図。

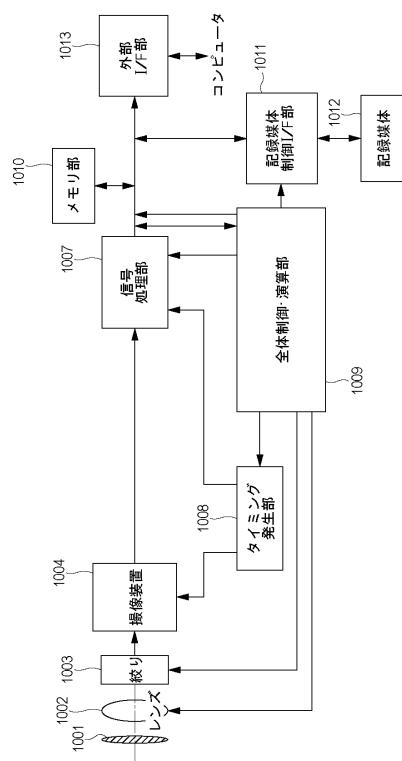

【図21】撮像システムの構成を模式的に示すブロック図。

10

20

30

40

50

【図22】車載カメラを備えた自動車の構成を模式的に示すブロック図。

【発明を実施するための形態】

【0011】

[実施例1]

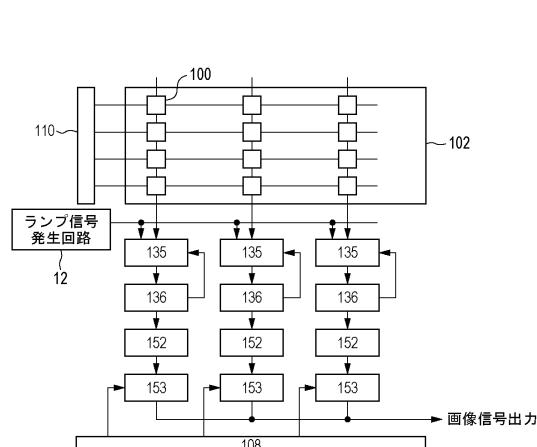

[全体構成]

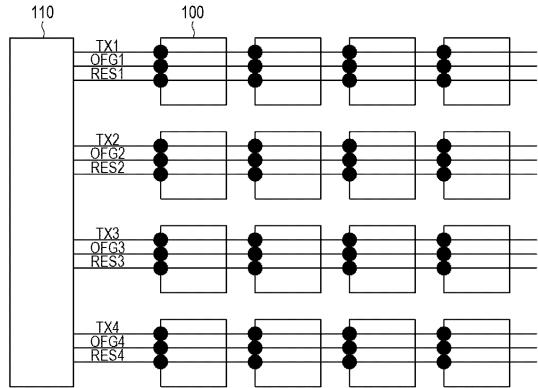

本実施例に係る光電変換装置を説明する。光電変換装置は、例えば、撮像装置である。図1は、光電変換装置の構成を模式的に示す。光電変換装置は、複数の画素100、および、複数の画素100から信号を読み出すための読み出し回路110を備える。

【0012】

画素100は、光電変換部と画素回路を含む。光電変換部は、入射光を信号電荷に変換する。光電変換部には、シリコン基板に形成されたフォトダイオード、半導体基板の上に積層された有機光電変換膜などが用いられる。画素回路は、光電変換部で生じた電荷に基づく信号を画素から出力するための回路である。本実施例の画素回路は、アナログデジタル変換回路（以下、ADC回路）を含む。典型的には、ADC回路は差動対を含む比較器を含む。つまり、本実施例の画素回路は、差動対を構成するトランジスタを含んでいる。

10

【0013】

読み出し回路110は、画素100に接続された複数の制御線に制御信号（TX1～4、OFG1～4、RES1～4）を供給する走査回路である。画素100は制御信号に応じて動作し、画素100から光電変換部で生じた電荷に基づく信号が出力される。なお、読み出し回路110は、画素100から出力された信号を処理する信号処理回路であってもよい。

20

【0014】

[画素構成]

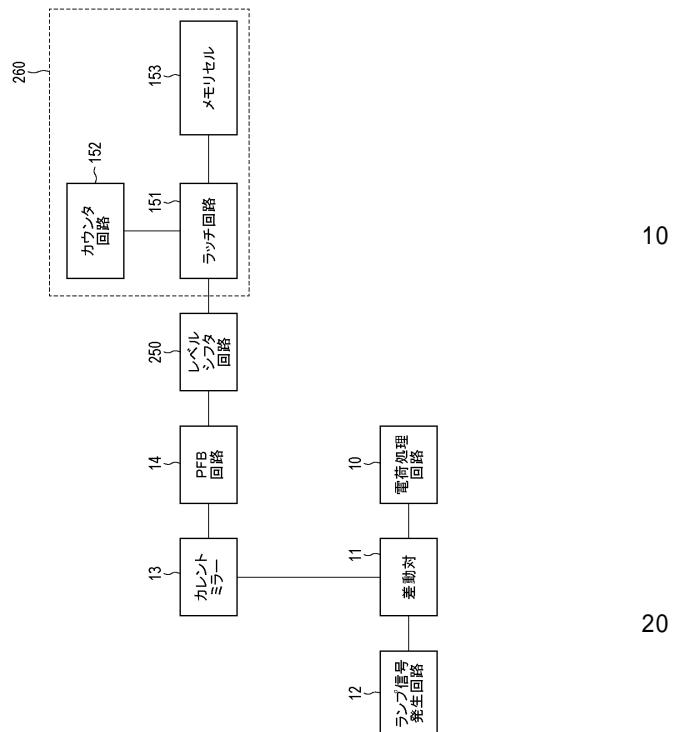

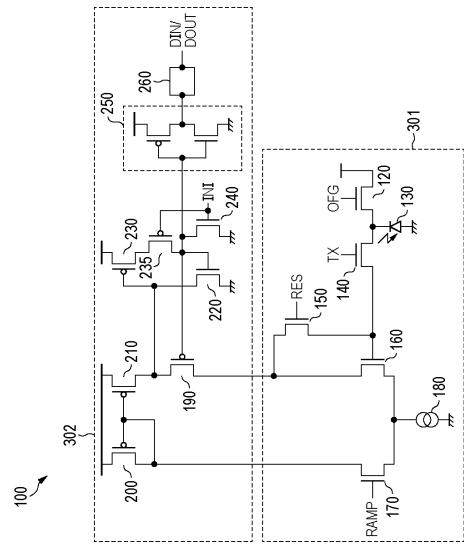

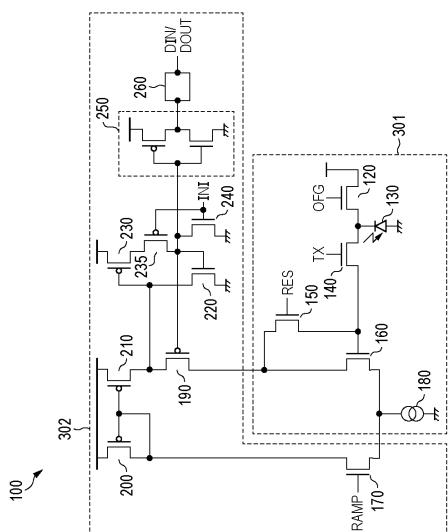

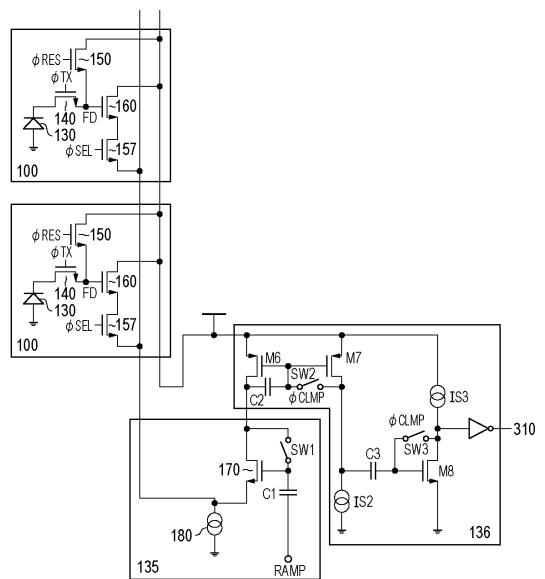

図2は、画素100の構成を模式的に示すブロック図である。画素100の画素回路は、機能的に、複数の回路ブロックにより構成される。信号電荷処理回路10は、光電変換部で生じた信号電荷の蓄積、転送、排出を行う。差動対回路11は、差動対を構成するトランジスタ、および、差動対に電流を供給する電流源を含む。ランプ信号発生回路12は、ADC回路にランプ信号を供給する。カレントミラーレベルシフタ回路13は差動対回路11に流れる電流を制御する。差動対回路11およびカレントミラーレベルシフタ回路13は、ADC回路の比較器を構成する。さらに、画素100の画素回路は、正帰還回路14（Positive Feed Back回路）、メモリ回路260を含む。正帰還回路14は、比較器の出力が反転を開始したことに応じて、立ち上がり（または立ち下がり）のより速いパルスを生成する。レベルシフタ回路250は、正帰還回路14を介して比較器から出力されるラッチ信号の振幅を小さくする。メモリ回路260は、比較器の出力するラッチ信号に基いて、デジタル信号を保持する。典型的には、差動対回路11、カレントミラーレベルシフタ回路13、および、メモリ回路260が、ADC回路を構成する。なお、本実施例において、画素100の画素回路は、1つの半導体基板に形成される。

30

【0015】

[画素回路]

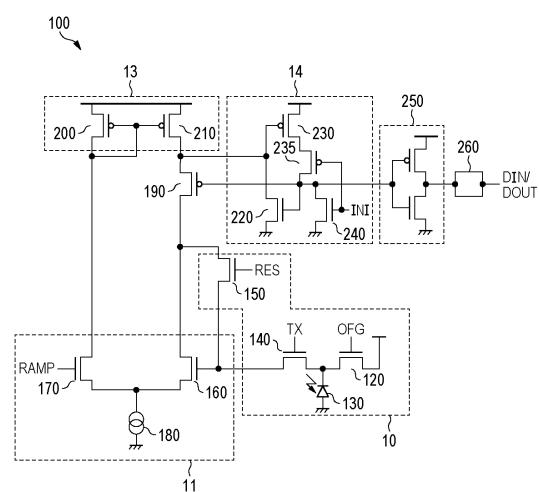

各回路ブロックの詳細な構成を説明する。図3は、画素100の等価回路を示す図である。ただし、メモリ回路260の構成は別の図を用いて説明するため、メモリ回路260はブロックで示されている。また、ランプ信号発生回路12は、画素100ごと、あるいは、複数の画素100を含む行ごと、あるいは、全ての画素100に対して共通に設けられる。そのため、図3は、ランプ信号発生回路12を示していない。

40

【0016】

信号電荷処理回路10は、電荷排出トランジスタ120、転送トランジスタ140、および、リセットトランジスタ150を含む。電荷排出トランジスタ120、転送トランジスタ140、および、リセットトランジスタ150は、それぞれ、Nチャネル型のMOSトランジスタである。回路図では、ゲートに白丸を付することでPチャネル型のMOSトラン

50

ジスタであることを示す。一方、ゲートに白丸をつけないことでNチャネル型のMOSトランジスタであることを示す。

【0017】

電荷排出トランジスタ120は、光電変換部130に接続される。電荷排出トランジスタ120は、制御信号RESに応じて光電変換部130で生じた信号電荷を排出する。転送トランジスタ140は、光電変換部130および差動対回路11の入力ノードに接続される。転送トランジスタ140は、制御信号TXに応じて光電変換部130で生じた信号電荷を差動対回路11の入力ノードに転送する。リセットトランジスタ150は、差動対回路11の入力ノードに接続される。リセットトランジスタ150は、差動対回路11の入力ノードの電圧を初期値にリセットする。本実施例では、リセットトランジスタ150のドレインは、差動対回路11の入力トランジスタ160のドレインに接続されている。本実施例の変形例では、リセットトランジスタ150のドレインは、リセット電源を供給するノードに接続される。

10

【0018】

差動対回路11は、入力トランジスタ160および参照トランジスタ170を含む。入力トランジスタ160および参照トランジスタ170は、いずれもNチャネル型のMOSトランジスタである。入力トランジスタ160のソース、および、参照トランジスタ170のソースは、共通に、電流源180に接続される。このような接続により、入力トランジスタ160および参照トランジスタ170は差動対を構成する。入力トランジスタ160は、光電変換部130で生じた信号電荷に基づく信号を受ける。つまり、入力トランジスタ160のゲートが、差動対回路11の入力ノードである。参照トランジスタ170のゲートには、不図示のランプ信号発生回路12がランプ信号を供給する。

20

【0019】

カレントミラー回路13は、トランジスタ200およびトランジスタ210を含む。トランジスタ200およびトランジスタ210は、いずれもPチャネル型のMOSトランジスタである。トランジスタ200のゲートとトランジスタ210のゲートは互いに接続されている。トランジスタ200のドレインは参照トランジスタ170に、そして、トランジスタ210のドレインは入力トランジスタ160にそれぞれ接続される。また、トランジスタ200のゲートとドレインとが接続される。

30

【0020】

図3に示す接続により、差動対回路11およびカレントミラー回路13は、比較器を構成する。入力トランジスタ160のゲートの電位と、参照トランジスタ170のゲートの電位との大小関係が反転すると、比較器の出力ノード(トランジスタ210のドレイン)の電位が変化する。入力トランジスタ160のゲートの電位が参照トランジスタ170のゲートの電位より高いときは、比較器の出力ノードの電位は低いレベルである。一方、入力トランジスタ160のゲートの電位が参照トランジスタ170のゲートの電位より低いときは、比較器の出力ノードの電位は高いレベルである。

40

【0021】

ランプ信号発生回路12の供給するランプ信号は、高い電圧から低い電圧へ変化する。そのため、ある時点で比較器の出力ノードの電位は高いレベルから低いレベルへ変化する。入力トランジスタ160のゲートの電位の高さ、つまり、光電変換部130で生じた電荷に基づく信号のレベルに応じて、ランプ信号が変化を開始してから比較器の出力ノードの電位が変化するまでの時間が決まる。当該時間をカウントすることにより、光電変換部130で生じた電荷に基づく信号をデジタル信号に変換することができる。

【0022】

リセットトランジスタ150がオン状態のときは、差動対回路11およびカレントミラー回路13はボルテージフォロア回路として機能する。そのため、入力トランジスタ160のゲートの電位を、ランプ信号の電位に応じた任意の値にリセットすることができる。

【0023】

正帰還回路14は、4つのトランジスタ220、230、235、240を含む。トラン

50

ジスタ220およびトランジスタ240は、それぞれ、Nチャネル型のMOSトランジスタである。トランジスタ230およびトランジスタ235は、それぞれ、Pチャネル型のMOSトランジスタである。

#### 【0024】

比較器の出力ノードが、トランジスタ220のドレイン、および、トランジスタ230のゲートに接続される。トランジスタ220のソースは接地される。トランジスタ230のソースは電源ノードに接続される。トランジスタ230のドレインは、トランジスタ235を介して、トランジスタ220のゲートに接続される。トランジスタ240のドレインが、トランジスタ220のゲート、および、トランジスタ235に接続される。トランジスタ235のゲート、および、トランジスタ240のゲートに、初期化信号INIが供給される。トランジスタ220のゲート、および、トランジスタ240のドレインに接続されたノードが、正帰還回路14の出力ノードである。

10

#### 【0025】

正帰還回路14の機能を説明する。正帰還回路14を動作させる前、すなわち、アナログデジタル変換(AD変換)を開始する前に、初期化信号INIがハイレベルからローレベルに遷移する。そのため、トランジスタ235はオン状態になり、一方、トランジスタ240はオフ状態になる。初期化信号INIがハイレベルの時には、トランジスタ240がオンであるため、正帰還回路14の出力ノードは低い電位(ほぼ接地電位)となっている。

#### 【0026】

AD変換の開始時には、ランプ信号の電位が入力トランジスタ160のゲートの電位(光電変換部130の電荷に基づく信号のレベル)より高い。そのため、比較器の出力ノード(トランジスタ210のドレイン)の電位は高いレベルである。そのため、トランジスタ230はオフ状態である。また、前述の通り、正帰還回路14の出力ノード(トランジスタ220のゲート)はほぼ接地電位であるため、トランジスタ220はオフ状態である。

20

#### 【0027】

比較器の出力ノードの電位が高いレベルから低いレベルへ変化すると、トランジスタ230のゲート・ソース間の電圧が大きくなる。これにより、トランジスタ230がオン状態になる。電源ノードからトランジスタ220のゲートまでが導通するため、トランジスタ220のゲートの電位が高くなる。トランジスタ220がオン状態になり、比較器の出力ノードからトランジスタ220を介して接地ノードまで電流が生じるため、比較器の出力ノードの電位の低下が加速される。比較器の出力ノードの電位の低下により、トランジスタ230のゲート・ソース間の電圧はさらに大きくなるため、ランジスタ220のゲートの電位の上昇が加速される。このように、正帰還回路14により比較器の出力ノードの電位の変化が正帰還される。結果として、入力トランジスタ160のゲートの電位と参照トランジスタ170のゲートの電位(ランプ信号)との大小関係が反転したときに、正帰還回路14の出力ノードの電位を高速に変化させることができる。

30

#### 【0028】

AD変換が終了した後、初期化信号INIがローレベルからハイレベルに遷移する。これにより、正帰還回路14の出力ノードの電位が接地電位にリセットされる。初期化信号INIがハイレベルである間、トランジスタ235はオフしている。そのため、正帰還回路14の電源ノードから接地ノードへ流れる貫通電流を低減することができる。トランジスタ235がない場合、トランジスタ230のゲートの電位に応じた貫通電流が生じうる。しかし、消費電力の制限が緩い場合は、トランジスタ235は省略してもよい。トランジスタ235が省略される場合、トランジスタ230のドレインが直にトランジスタ220のゲートに接続される。そのため正帰還回路14による高速化の効果が高くなる。

40

#### 【0029】

本実施例では、カレントミラー回路13のトランジスタ210が、電流制限トランジスタ190を介して、入力トランジスタ160に接続される。電流制限トランジスタ190は、Pチャネル型のMOSトランジスタである。電流制限トランジスタ190のゲートは、正帰還回路14の出力に接続されている。

50

## 【0030】

電流制限トランジスタ190が設けられていない場合、比較器の出力信号が反転した後、カレントミラー回路13のトランジスタ210から正帰還回路14のトランジスタ220に大きい電流が流れたままの状態となる。

## 【0031】

電流制限トランジスタ190をトランジスタ210と入力トランジスタ160との間に挿入することで、トランジスタ210から正帰還回路14のトランジスタ220に流れる電流を制限することができる。

## 【0032】

なお、正帰還回路14は必要に応じて設けられるものであり、省略されてもよい。正帰還回路14が省略された場合、比較器の出力ノードがレベルシフタ回路250に接続される。また、正帰還回路14が省略された場合、電流制限トランジスタ190も省略してもよい。

10

## 【0033】

比較器の出力ノードの信号、ならびに、正帰還回路14の出力ノードの信号は、ラッチ信号として用いられる。ラッチ信号に基づいて、メモリ回路260はカウント値を保持する。ラッチ信号をメモリ回路260に伝達するため、レベルシフタ回路250が用いられる。レベルシフタ回路250は、Nチャネル型のトランジスタおよびPチャネル型のトランジスタによって構成されたインバータ回路である。レベルシフタ回路250に供給される電源電圧に応じて、レベルシフタ回路250の出力するラッチ信号の振幅が変化する。後段のデジタル回路を高速で動作させるため、本実施例では、レベルシフタ回路250がラッチ信号の振幅を小さくしている。つまり、レベルシフタ回路250に供給される電源電圧が、比較器（差動対回路11およびカレントミラー回路13）や正帰還回路14に供給される電源電圧より低い。

20

## 【0034】

なお、レベルシフタ回路250は必要に応じて設けられるものであり、省略されてもよい。レベルシフタ回路250が省略された場合、正帰還回路14の出力ノードが、メモリ回路260に接続される。あるいは、レベルシフタ回路250が波形整形のためのインバータ回路の機能のみを担ってもよい。この場合、レベルシフタ回路250はラッチ信号の振幅を変更しない。

30

## 【0035】

## [画素回路（メモリ部）]

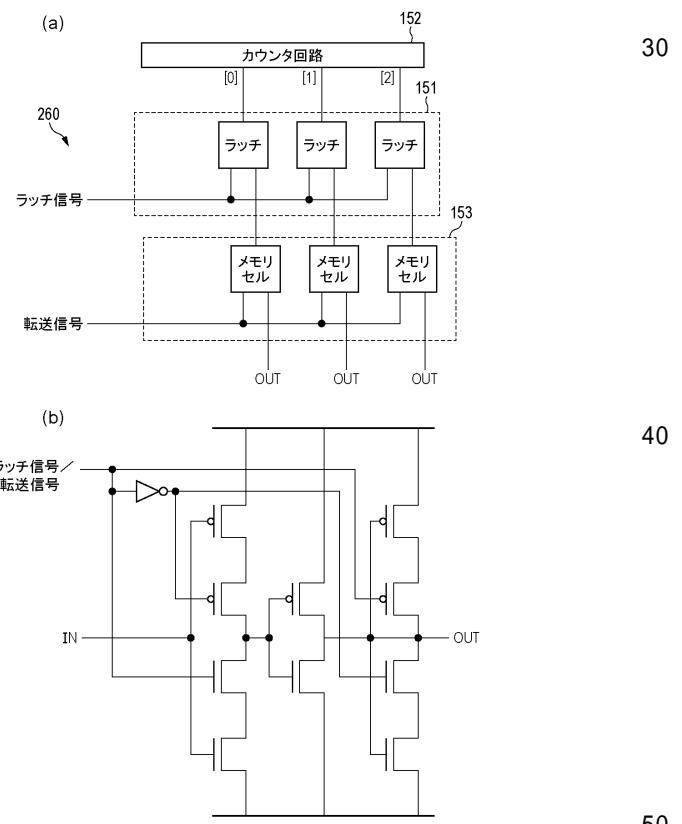

次に、メモリ回路260の構成を説明する。図4(a)は、メモリ回路260の構成をビットごとに示したブロック図である。また、図4(b)はラッチ回路およびメモリセルの等価回路図である。図4では、3ビットのメモリ回路260を示しているが、ビット数はこれに限られない。

## 【0036】

メモリ回路260は、ラッチ回路151、カウンタ回路152、メモリセル153を含む。カウンタ回路152は3ビットのカウント信号を出力する。ビット数に応じて複数のラッチ回路151が設けられる。ラッチ回路151は、カウンタ回路152の各ビットの出力線に接続される。また、ビット数に応じて複数のメモリセル153が設けられる。メモリセル153は、ラッチ回路151の出力ノードに接続される。

40

## 【0037】

ラッチ回路151は、ラッチ信号に応じて、カウンタ回路152から出力されているカウント信号を保持する。また、転送信号に応じて、ラッチ回路151が保持している信号が、メモリセル153に転送される。ラッチ回路151、および、メモリセル153は、それぞれ、図4(b)に示されるように、複数のPチャネル型のトランジスタおよび複数のNチャネル型のトランジスタにより構成される。

## 【0038】

## [画素回路（カウンタ回路）]

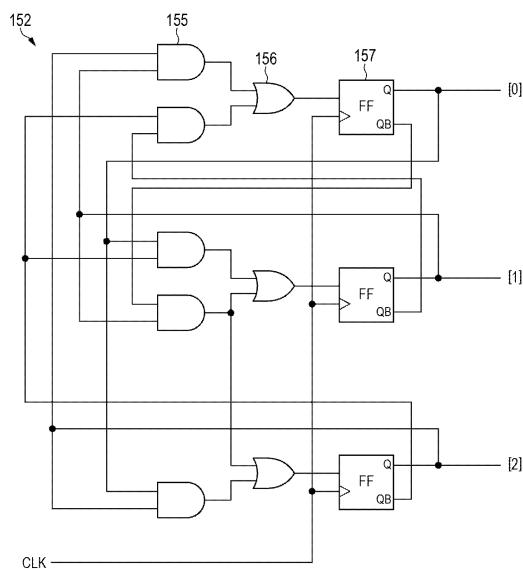

図5はカウンタ回路152の論理回路図である。図5では、3ビットのグレイコードを出

50

力するカウンタ回路 152 の例を示している。図 5 が示す通り、カウンタ回路 152 は、ビット数に応じた数のフリップフロップを含む。また、カウンタ回路 152 は、複数の AND ゲート、および、複数の OR ゲートを含む。詳細な等価回路の説明は省略するが、フリップフロップ、AND ゲート、OR ゲートは、それぞれ、トランジスタを含んで構成される。このような構成により、カウンタ回路 152 は、クロック信号 CLK に応じて、カウント信号を出力する。

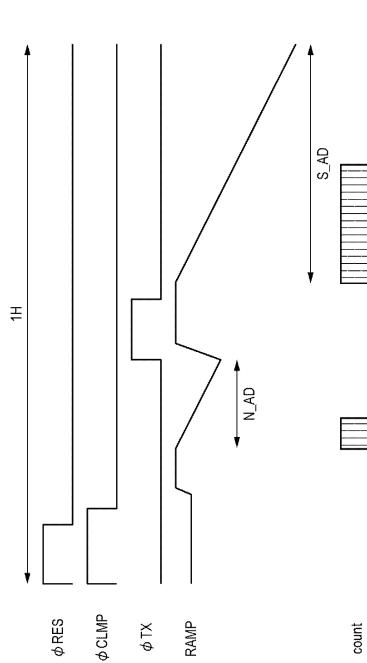

#### 【 0039 】

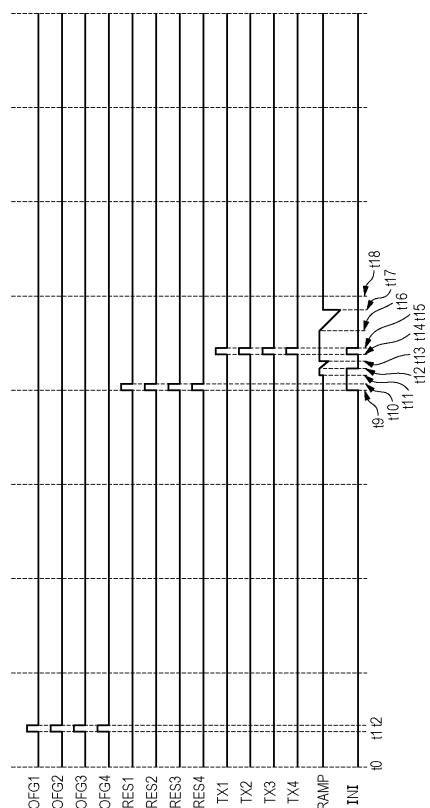

##### [ 動作 ]

続いて、本実施例の光電変換装置の動作を説明する。図 6 は、光電変換装置の動作を説明するためのタイミングチャートを示す。図 6 は、制御信号 OFG、制御信号 RES、制御信号 TX、ランプ信号 RAMP、および、初期化信号INIを示している。符号の末尾の数字は、図 1 の行番号に対応している。

10

#### 【 0040 】

時刻  $t_1$  から時刻  $t_2$  の間に、全行の光電変換部 130 の電荷の排出（リセット）を同時に行う。その後、光電変換部 130 は、入射光によって生じた信号電荷を蓄積する。続いて、時刻  $t_9$  から時刻  $t_{10}$  の間に、全ての行において、入力トランジスタ 160 のゲート（比較器の入力ノード）の電位をリセットする。

20

#### 【 0041 】

時刻  $t_{11}$  に、ランプ信号 RAMP のレベルを上げて、比較器の出力ノード（トランジスタ 210 のドレイン）の電位を電源電圧に振り切らせる。これにより、トランジスタ 230 がオフ状態になる。

20

#### 【 0042 】

その後、時刻  $t_{12}$  で初期化信号INIをローレベルにする。トランジスタ 230 がオンの状態で初期化信号INIをローレベルにすると、初期化信号INIがローレベルになった直後にトランジスタ 220 がオンする。そのため、ランジスタ 230 がオフの状態で初期化信号INIをローレベルにすることが好ましい。時刻  $t_{12}$  には、ランプ信号 RAMP の電位の変化、つまり、スロープ動作が開始される。

30

#### 【 0043 】

時刻  $t_{12}$  から時刻  $t_{13}$  の間のいずれかのタイミングで、比較器の出力ノードの電位、つまり、ラッチ信号が反転する。このときの動作は、図 3 で説明した通りである。ラッチ信号の反転に応じて、メモリ回路 260 はリセットレベル信号を保持する。リセットレベル信号は、画素 100 がリセットされた状態での比較器の入力ノードの電位に対応するデジタル信号である。

30

#### 【 0044 】

時刻  $t_{14}$  から時刻  $t_{15}$  に、光電変換部 130 から入力トランジスタ 160 のゲートへ、信号電荷が転送される。すなわち、入力トランジスタ 160 のゲートに、光電変換部で生じた信号電荷に基づく信号が入力される。この信号電荷の転送はすべての行で同時に行われる。時刻  $t_2$  から時刻  $t_{15}$  までが露光期間あるいは蓄積期間である。

40

#### 【 0045 】

時刻  $t_{16}$  から時刻  $t_{17}$  の期間で、光電変換部 130 で生じた信号電荷に基づく信号に対して AD 変換が行われる。時刻  $t_{16}$  から時刻  $t_{17}$  の間のいずれかのタイミングで、比較器の出力ノードの電位、つまり、ラッチ信号が反転する。ラッチ信号の反転に応じて、メモリ回路 260 は光レベル信号を保持する。光レベル信号は、光電変換部 130 で生じた信号電荷に基づく信号に対応するデジタル信号である。

40

#### 【 0046 】

メモリ回路 260 に保持されたリセットレベル信号は、時刻  $t_{13}$  から時刻  $t_{16}$  の間に、後段の処理部（不図示）へ転送される。また、時刻  $t_{17}$  以降に、光レベル信号が処理部へ転送される。その後、処理部は、リセットレベル信号と光レベル信号との差分処理を行い、差分信号を外部に出力する。メモリ回路 260 から処理部へのデジタル信号の転送は、行順次に行われても良いし、全画素で同時に行われてもよい。

50

## 【0047】

以上に説明した動作では、すべての行の電荷排出トランジスタ 120 が互いに同期して動作し、そして、すべての行の転送トランジスタ 140 が互いに同期して動作する。そのため、すべての行で露光期間が一致する。いわゆる、グローバル電子シャッタ動作が行われる。

## 【0048】

## [トランジスタのサイズ1]

本実施例においては、画素 100 の画素回路が入力トランジスタ 160 を含む。入力トランジスタ 160 は、光電変換部 130 で生じた信号電荷に基づく信号を受け、かつ、参照トランジスタ 170 と差動対を構成している。画素 100 の画素回路は、さらに、入力トランジスタ 160 とは別のトランジスタを含んでいる。また、図 1 の読み出し回路 110 はトランジスタを含んで構成される。ここで、入力トランジスタ 160 のサイズは、画素 100 の画素回路、または、読み出し回路 110 に含まれる、いずれかのトランジスタのサイズと異なっている。以下、便宜的に、互いに異なるサイズの 2 つのトランジスタを、トランジスタ A、および、トランジスタ B と呼ぶ。

10

## 【0049】

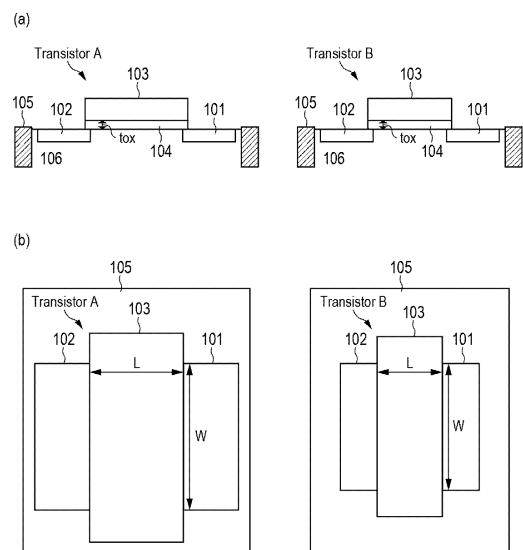

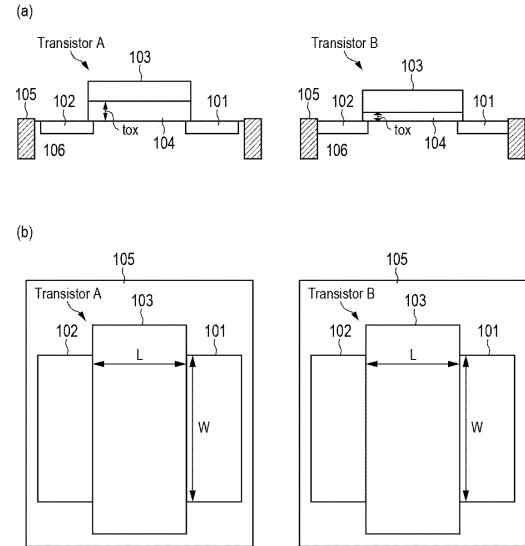

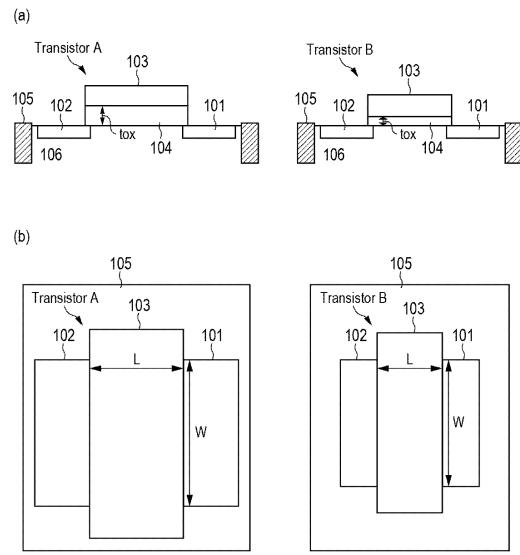

図 7 (a) は、トランジスタ A およびトランジスタ B の断面構造を模式的に示す図である。図 7 (b) は、トランジスタ A およびトランジスタ B の平面構造を模式的に示す図である。平面構造とは、半導体基板の表面に垂直な方向に沿って見たときの構造である。

20

## 【0050】

半導体基板には、LOCOS、STI、DTI などの分離部 105 が配される。分離部 105 が、トランジスタ A およびトランジスタ B が配置される活性領域 106 を規定する。トランジスタ A およびトランジスタ B のソース領域 101 およびドレイン領域 102 が、活性領域 106 に形成される。N チャネル型の場合、ソース領域 101 およびドレイン領域 102 はそれぞれ n 型の半導体領域である。P チャネル型の場合、ソース領域 101 およびドレイン領域 102 はそれぞれ p 型の半導体領域である。半導体基板の上に、ゲート絶縁膜 104 を介してゲート電極 103 が形成される。ゲート絶縁膜 104 は、シリコン酸化膜などの絶縁体で形成される。ゲート電極 103 はポリシリコンなどの導体で形成される。

30

## 【0051】

トランジスタ A およびトランジスタ B のサイズは、ゲート絶縁膜 104 の膜厚  $t_{ox}$ 、チャネル長 L、チャネル幅 W、あるいは、チャネル幅 W とチャネル長 L との比  $W/L$  のいずれかである。図 7 (a) では、ゲート絶縁膜 104 の膜厚  $t_{ox}$  が矢印で示されている。図 7 (b) では、チャネル長 L およびチャネル幅 W が矢印でそれぞれ示されている。チャネル長 L は、例えば、ゲート電極 103 の端から端までの距離で規定される。チャネル幅 W は、例えば、ゲート電極 103 に覆われた活性領域 106 の幅で規定される。換言すると、チャネル幅 W は分離部 105 の端によって規定される。

30

## 【0052】

図 7 (a) および図 7 (b) は、トランジスタ A とトランジスタ B との間で、チャネル長 L およびチャネル幅 W がそれぞれ異なる例を示している。一方、トランジスタ A の  $W/L$  およびゲート絶縁膜 104 の膜厚  $t_{ox}$  は、トランジスタ B のそれらと同じである。図 7 (b) が示すように、トランジスタ A のチャネル長 L およびチャネル幅 W が、それぞれ、トランジスタ B のチャネル長 L およびチャネル幅 W より大きい。つまり、トランジスタ A のサイズが、トランジスタ B のサイズより大きい。

40

## 【0053】

## [差動対]

サイズの異なる 2 つのトランジスタの組み合わせには、いくつかのバリエーションがある。ひとつの例では、参照トランジスタ 170 にトランジスタ A が用いられ、入力トランジスタ 160 にトランジスタ B が用いられる。すなわち、参照トランジスタ 170 のチャネル長 L およびチャネル幅 W が、それぞれ、入力トランジスタ 160 のチャネル長 L および

50

チャネル幅Wより大きい。この構成によりS/N比を向上させることが可能である。

【0054】

光電変換部130で生じた電荷を受けるトランジスタが、長いチャネル長L、および、長いチャネル幅Wを有する場合、当該トランジスタのゲートの寄生容量が大きくなる。これにより、電荷電圧変換係数が小さくなり、結果として、信号レベルが低下する。そこで、入力トランジスタ160のゲート電極のサイズを小さくすることで、S/N比を向上させることができる。

【0055】

一方、参照トランジスタ170のゲート電極には、電荷電圧変換係数の向上のためのサイズの制限は適用されない。一般に、ゲート電極のサイズを大きくすることで、1/fノイズや閾値電圧のばらつきを低下させることができる。そこで、参照トランジスタ170のサイズを大きくすることで、フリッカノイズなどの1/fノイズを低減することができる。また、閾値電圧のばらつきが小さいことで、比較器の入力ノード（入力トランジスタ160のゲート）の電位をリセットするとき、リセット電圧のばらつきを低減することができる。

10

【0056】

このように、参照トランジスタ170のチャネル長Lおよびチャネル幅Wが、それぞれ、入力トランジスタ160のチャネル長Lおよびチャネル幅Wより大きい構成によれば、S/N比を向上させることが可能である。なお、参照トランジスタ170のチャネル長Lだけが、入力トランジスタ160のチャネル長Lより大きい場合にも、同様の効果が得られる。また、参照トランジスタ170のチャネル幅Wだけが、入力トランジスタ160のチャネル幅Wより大きい場合にも、同様の効果が得られる。特に断りがないかぎり、この点は以降に述べる例でも同様である。

20

【0057】

また、参照トランジスタ170のチャネル長Lが、入力トランジスタ160のチャネル長Lより長いという構成により、熱雑音による電流ノイズを低下させることができる。

【0058】

典型的に、MOSトランジスタの熱雑音による電流ノイズは、相互コンダクタンス $g_m$ の平方根（ $g_m$ ）に比例する。差動対を構成する入力トランジスタ160および参照トランジスタ170で生じる電流ノイズを、比較器の入力ノード（入力トランジスタ160のゲート）における電圧ノイズ $V_n$ に換算すると、電圧ノイズ $V_n$ は式（1）で表される。

30

【0059】

【数1】

$$V_n \propto \sqrt{\frac{1}{g_{m1}} + \sqrt{\frac{g_{m2}}{(g_{m1})^2}}} \quad (1)$$

40

【0060】

式（1）が示すように、入力トランジスタ160の相互コンダクタンス $g_m1$ が大きくなると、電圧ノイズ $V_n$ は小さくなる。一方、参照トランジスタ170の相互コンダクタンス $g_m2$ が小さくなると、電圧ノイズ $V_n$ は小さくなる。参照トランジスタ170で生じた電流ノイズは、差動対の相手である入力トランジスタ160の電流変化を生む。そのため、参照トランジスタ170の電流ノイズと、入力トランジスタ160のゲートの電圧ノイズ $V_n$ とが、比例関係を有する。

【0061】

50

ここで、相互コンダクタンス  $g_m$  は以下の式(2)で表される。 $\mu$  はチャネル中の電荷の移動度を、 $\epsilon_{ox}$  はゲート絶縁膜の誘電率を、 $I_d$  はドレイン電流を、それぞれ表している。ゲート絶縁膜 104 の膜厚  $t_{ox}$  は、チャネル長  $L$ 、および、チャネル幅  $W$  は、図 7 に示されている。

【0062】

【数2】

$$g_m = \sqrt{2\mu \frac{\epsilon_{ox} \cdot W}{t_{ox} \cdot L} I_d} \quad (2)$$

10

【0063】

入力トランジスタ 160 のチャネル長  $L$  が短いため、入力トランジスタ 160 の相互コンダクタンス  $g_m 1$  を大きくすることができる。一方、参照トランジスタ 170 のチャネル長  $L$  が長いため、参照トランジスタ 170 の相互コンダクタンス  $g_m 2$  を小さくすることができる。結果として、熱雑音によるノイズを低下させることができる。このとき、2つのトランジスタのチャネル幅  $W$  は、どのような関係であってもよい。

20

【0064】

変形例として、入力トランジスタ 160 のチャネル幅  $W$  が、参照トランジスタ 170 のチャネル幅  $W$  より大きいことにより、熱雑音による電流ノイズを低下させることができる。この効果については、上述の式(1)および式(2)で説明した通りである。

20

【0065】

このとき、2つのトランジスタのチャネル長  $L$  は、どのような関係であってもよい。電荷電圧変換係数の向上の観点からは、入力トランジスタ 160 のチャネル長  $L$  は参照トランジスタ 170 のチャネル長  $L$  より短く、一方、入力トランジスタ 160 のチャネル幅  $W$  は参照トランジスタ 170 のチャネル幅  $W$  より大きいことが好ましい。入力トランジスタ 160 のチャネル長  $L$  が短いことにより、電荷電圧変換係数を大きくすることができる。結果として、チャネル長  $L$  の関係により信号レベルを上げ、かつ、チャネル幅  $W$  の関係によりノイズを低減することが可能になる。

30

【0066】

入力トランジスタ 160 のサイズと参照トランジスタ 170 のサイズとが互いに異なる場合も、オフセットキャンセルは可能である。リセットトランジスタ 150 をオンして比較器の入力ノード(入力トランジスタ 160 のゲート)の電位をリセットする際、ランプ信号 RAMP を所定のリセット電位  $V_r$  にする。その時の入力トランジスタ 160 のゲートの電位は、 $V_r - V_{gs}(170) + V_{gs}(160)$  で表される。このとき、 $V_{gs}(170)$  および  $V_{gs}(160)$  には、それぞれ、入力トランジスタ 160 の閾値電圧  $V_{th}$  および参照トランジスタ 170 の閾値電圧  $V_{th}$  が反映される。そのため、オフセットキャンセルを行うことが可能である。換言すると、画素 100 ごとに入力トランジスタ 160 および参照トランジスタ 170 の閾値電圧  $V_{th}$  が異なっていても、いずれの画素 100 においてもランプ信号 RAMP のレベルがリセット電位  $V_r$  になった時に比較器の出力が反転する。

40

【0067】

以上に説明した通り、入力トランジスタ 160 のサイズと、参照トランジスタ 170 のサイズとが異なることにより、電気的特性を向上させることができる。

【0068】

[入力トランジスタとリセットトランジスタ]

50

他の例では、リセットトランジスタ 150 にトランジスタ A が用いられ、入力トランジスタ 160 にトランジスタ B が用いられる。すなわち、リセットトランジスタ 150 のチャネル長 L およびチャネル幅 W が、それぞれ、入力トランジスタ 160 のチャネル長 L およびチャネル幅 W より大きい。

#### 【0069】

前述の通り、入力トランジスタ 160 のゲートのサイズが小さいことにより、電荷電圧変換係数を大きくすることができる。また、リセットトランジスタ 150 のサイズが大きいことで、リセットトランジスタ 150 の閾値電圧  $V_{th}$  のばらつきを小さくすることができる。結果として、リセット時の電圧のばらつきを小さくすることができる。

#### 【0070】

##### [入力トランジスタとデジタル回路]

他の例では、入力トランジスタ 160 にトランジスタ A が用いられ、メモリ回路 260 のトランジスタ（図 4 (b) および図 5）にトランジスタ B が用いられる。すなわち、入力トランジスタ 160 のチャネル長 L およびチャネル幅 W が、それぞれ、メモリ回路 260 のトランジスタのチャネル長 L およびチャネル幅 W より大きい。

#### 【0071】

差動対回路 11 などアナログ回路に使われるトランジスタは、大きい相互コンダクタンス  $g_m$  を持つことが好ましい。そのため、入力トランジスタ 160 のサイズを大きくする。一方、メモリ回路 260 などのデジタル回路では、トランジスタのサイズを小さくすることで、高速に動作することが好ましい。つまり、入力トランジスタ 160 のサイズが、メモリ回路 260 のトランジスタのサイズより大きいことで、結果として、ノイズを低減しつつ、かつ、高速な動作を行うことが可能となる。

#### 【0072】

他の例では、入力トランジスタ 160 にトランジスタ A が用いられ、読み出し回路 110 のトランジスタにトランジスタ B が用いられる。すなわち、入力トランジスタ 160 のチャネル長 L およびチャネル幅 W が、それぞれ、読み出し回路 110 のトランジスタのチャネル長 L およびチャネル幅 W より大きい。

#### 【0073】

読み出し回路 110 は、典型的には、論理ゲートやフリップフロップなどのロジック回路により構成される。そのため、トランジスタのサイズを小さくすることで、高速に動作することが好ましい。先ほどの例と同様に、入力トランジスタ 160 のサイズが、メモリ回路 260 のトランジスタのサイズより大きいことで、結果として、ノイズを低減しつつ、かつ、高速な動作を行うことが可能となる。

#### 【0074】

##### [トランジスタのサイズ 2]

次に、トランジスタ A、および、トランジスタ B が、互いに異なる膜厚  $t_{ox}$  のゲート絶縁膜 104 を有する例を説明する。図 8 (a) は、トランジスタ A およびトランジスタ B の断面構造を模式的に示す図である。図 8 (b) は、トランジスタ A およびトランジスタ B の平面構造を模式的に示す図である。図 7 と同じ部分には同じ符号を付している。

#### 【0075】

図 8 (a) が示すように、トランジスタ A のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、トランジスタ B のゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きい。一方、図 8 (b) が示すように、トランジスタ A のチャネル長 L およびチャネル幅 W は、それぞれ、トランジスタ B のチャネル長 L およびチャネル幅 W と等しい。

#### 【0076】

異なる膜厚  $t_{ox}$  のゲート絶縁膜 104 を持つ 2 つのトランジスタの組み合わせには、いくつかのバリエーションがある。ひとつの例では、参照トランジスタ 170 にトランジスタ A が用いられ、入力トランジスタ 160 にトランジスタ B が用いられる。すなわち、参照トランジスタ 170 のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きい。この構成により熱雑音によるノイズを低下

10

20

30

40

50

させることが可能である。

【0077】

前述の式(1)が表す通り、入力トランジスタ160の相互コンダクタンス $g_m 1$ が大きくなると、電圧ノイズ $V_n$ は小さくなる。一方、参照トランジスタ170の相互コンダクタンス $g_m 2$ が小さくなると、電圧ノイズ $V_n$ は小さくなる。そして、式(2)が表す通り、ゲート絶縁膜104の膜厚 $t_{ox}$ が小さいほど、相互コンダクタンス $g_m$ は大きくなる。

【0078】

この例では、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ が小さいため、入力トランジスタ160の相互コンダクタンス $g_m 1$ を大きくすることができる。一方、参照トランジスタ170のゲート絶縁膜104の膜厚 $t_{ox}$ が大きいため、参照トランジスタ170の相互コンダクタンス $g_m 2$ を小さくすることができる。結果として、熱雑音によるノイズを低下させることができる。

10

【0079】

なお、ノイズをさらに低下させるためには、入力トランジスタ160のチャネル長 $L$ は参照トランジスタ170のチャネル長 $L$ より短く、かつ、入力トランジスタ160のチャネル幅 $W$ は参照トランジスタ170のチャネル幅 $W$ より大きいことが好ましい。

【0080】

他の例では、入力トランジスタ160にトランジスタAが用いられ、メモリ回路260のトランジスタ(図4(b)および図5)にトランジスタBが用いられる。すなわち、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ が、メモリ回路260のトランジスタのゲート絶縁膜104の膜厚 $t_{ox}$ より大きい。

20

【0081】

差動対回路11などアナログ回路に使われるトランジスタには、比較的高い電源電圧が供給される。そのため、高い耐圧が得られるように、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ を大きくすることが好ましい。一方、メモリ回路260などのデジタル回路は、アナログ回路に対して相対的に高速に動作することが多い。また、典型的には、アナログ回路の電源電圧より低い電源電圧が供給される。そのため、ゲート絶縁膜104の膜厚 $t_{ox}$ を小さくすることで、トランジスタが高速に動作することが好ましい。つまり、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ が、メモリ回路260のトランジスタのゲート絶縁膜104の膜厚 $t_{ox}$ より大きいことで、結果として、信頼性を向上しつつ、かつ、高速な動作を行うことが可能となる。

30

【0082】

他の例では、入力トランジスタ160にトランジスタAが用いられ、読み出し回路110のトランジスタにトランジスタBが用いられる。すなわち、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ が、読み出し回路110のトランジスタのゲート絶縁膜104の膜厚 $t_{ox}$ より大きい。

【0083】

読み出し回路110は、典型的には、論理ゲートやフリップフロップなどのロジック回路により構成される。そのため、トランジスタのサイズを小さくすることで、高速に動作することが好ましい。先ほどの例と同様に、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ が、メモリ回路260のトランジスタのゲート絶縁膜104の膜厚 $t_{ox}$ より大きいことで、結果として、信頼性を向上しつつ、かつ、高速な動作を行うことが可能となる。

40

【0084】

[トランジスタのサイズ3]

次に、さらに別の変形例を説明する。図9(a)は、トランジスタAおよびトランジスタBの断面構造を模式的に示す図である。図9(b)は、トランジスタAおよびトランジスタBの平面構造を模式的に示す図である。図7あるいは図8と同じ部分には同じ符号を付している。

50

## 【0085】

図9(a)が示すように、トランジスタAのゲート絶縁膜104の膜厚 $t_{ox}$ が、トランジスタBのゲート絶縁膜104の膜厚 $t_{ox}$ より大きい。そして、図9(b)が示すように、トランジスタAのチャネル長 $L$ およびチャネル幅 $W$ が、それぞれ、トランジスタBのチャネル長 $L$ およびチャネル長 $W$ より大きい。

## 【0086】

図7および図8の例と同様に、入力トランジスタ160にトランジスタAおよびトランジスタBの一方を適用し、他のトランジスタにトランジスタAおよびトランジスタBの他方を適用することで、電気的特性の向上の効果を得ることができる。

## 【0087】

例えば、参照トランジスタ170にトランジスタAが用いられ、入力トランジスタ160にトランジスタBが用いられる。すなわち、参照トランジスタ170のチャネル長 $L$ およびチャネル幅 $W$ が、それぞれ、入力トランジスタ160のチャネル長 $L$ およびチャネル幅 $W$ より大きい。さらに、参照トランジスタ170のゲート絶縁膜104の膜厚 $t_{ox}$ が、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ より大きい。

10

## 【0088】

このような構成により、まず、比較器の入力ノード(入力トランジスタ160のゲート)の電荷電圧変換係数を大きくすることができる。さらに、参照トランジスタ170において、 $1/f$ ノイズを低減することができる。加えて、差動対で生じる熱雑音によるノイズを低減することができる。

20

## 【0089】

なお、図9では、ゲート絶縁膜104の膜厚 $t_{ox}$ 、チャネル長 $L$ 、および、チャネル幅 $W$ の各観点において、トランジスタAのサイズがトランジスタBのサイズより大きい。しかし、一部の観点において、サイズの関係が逆であってもよい。

## 【0090】

相互コンダクタンス $g_m$ を最適化するためには、参照トランジスタ170のゲート絶縁膜104の膜厚 $t_{ox}$ が、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{ox}$ より大きいことが好ましい。また、参照トランジスタ170のチャネル長 $L$ が、入力トランジスタ160のチャネル長 $L$ より大きいことが好ましい。一方で、参照トランジスタ170のチャネル幅 $W$ は、入力トランジスタ160のチャネル幅 $W$ より小さいことが好ましい。

30

## 【0091】

## [まとめ]

以上に説明した通り、画素100は、入力トランジスタ160は、光電変換部130で生じた信号電荷に基づく信号を受け、かつ、参照トランジスタ170と差動対を構成する入力トランジスタ160を含む。そして、入力トランジスタ160のサイズは、画素回路の他のいずれかのトランジスタ、または、読み出し回路のトランジスタのサイズと異なっている。このような構成により、電気的特性を向上させることができる。

## 【0092】

チャネル幅 $W$ が大きいことにより、 $1/f$ ノイズの低減、閾値電圧のばらつきの低減、入力トランジスタ160として用いられたときの熱雑音によるノイズの低減(相互コンダクタンス $g_m$ の増加)などの効果が得られる。

40

## 【0093】

一方、チャネル幅 $W$ が小さいことにより、高速動作、入力トランジスタ160として用いられたときの電荷電圧変換係数の向上、参照トランジスタ170として用いられたときのノイズの低減(相互コンダクタンス $g_m$ の低下)などの効果が得られる。

## 【0094】

チャネル長 $L$ が大きいことにより、 $1/f$ ノイズの低減、閾値電圧のばらつきの低減、参照トランジスタ170として用いたときのノイズの低減(相互コンダクタンス $g_m$ の低下)などの効果が得られる。

## 【0095】

50

一方、チャネル長  $l$  が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの電荷電圧変換係数の向上、および、熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

【0096】

ゲート絶縁膜 104 の膜厚  $t_{ox}$  が大きいことにより、耐圧の向上、参照トランジスタ 170 として用いたときのノイズの低減（相互コンダクタンス  $g_m$  の低下）などの効果が得られる。

【0097】

一方、ゲート絶縁膜 104 の膜厚  $t_{ox}$  が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

10

【0098】

これらの効果を得るために、上述した組み合わせの例の他にも、サイズの異なるトランジスタの組み合わせが選択されうる。

【0099】

【実施例 2】

本実施例に係る光電変換装置を説明する。本実施例の光電変換装置は、1つの画素 100 の回路が、2つの半導体基板に分かれて配置される。それ以外の構成は、実施例 1 と同じである。以下では、実施例 1 と異なる点を説明し、実施例 1 と同じ部分は説明を省略する。

20

【0100】

本実施例の光電変換装置の全体構成、および、画素 100 の機能ブロックは、実施例 1 と同じである。つまり、図 1 は、光電変換装置の構成を模式的に示す。また、図 2 は、画素 100 の構成を模式的に示すブロック図である。これらの図面の説明は実施例 1 と同じであるため、説明を省略する。

【0101】

図 1 は、画素 100 の等価回路を示す図である。ただし、メモリ回路 260 はブロックで示されている。図 1 が示すように、本実施例の画素 100 の等価回路は、実施例 1 (図 3) と同じである。そのため、各回路ブロックの機能についての説明は省略する。

【0102】

実施例 1 との差異は、本実施例の画素 100 の画素回路は、第 1 の半導体基板 301 および第 2 の半導体基板 302 に分かれて配置されることである。

30

【0103】

具体的に、光電変換部 130 は、第 1 の半導体基板 301 に配される。電荷排出トランジスタ 120、転送トランジスタ 140、および、リセットトランジスタ 150 を含む信号電荷処理回路 10 は、第 1 の半導体基板 301 に配される。入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を含む差動対回路 11 は、第 1 の半導体基板 301 に配される。

【0104】

これに対して、トランジスタ 200 およびトランジスタ 210 を含むカレントミラー回路 13 は、第 2 の半導体基板 301 に配される。4つのトランジスタ 220、230、235、240 を含む正帰還回路 14 は、第 2 の半導体基板 301 に配される。レベルシフタ回路 250 ならびにメモリ回路 260 は、第 2 の半導体基板 301 に配される。また、図 1 の読み出し回路 110、および、図 2 のランプ信号発生回路 12 は、それぞれ、第 2 の半導体基板 302 に配置される。

40

【0105】

2つの半導体基板の相対的な配置を説明する。本実施例では、光電変換部 130 を含む第 1 の半導体基板 301 と、画素回路の一部を含む第 2 の半導体基板 302 とが、積層される。第 1 の半導体基板 301 の表面に垂直な方向に沿って光電変換部 130 を第 2 の半導体基板 302 に射影したとき、光電変換部 130 の射影に、画素回路の少なくとも一部のトランジスタが重なる。具体的には、カレントミラー回路 13、正帰還回路 14、レベル

50

シフタ回路 250、メモリ回路 260 に含まれるトランジスタのいずれか、または、全部が、光電変換部 130 の射影と重なる位置に配置される。

【0106】

第1の半導体基板 301においては、光電変換部 130、信号電荷処理回路 10、および、差動対回路 11 を1つの単位とする複数の画素回路が、行列を成すように二次元状に配列される。第2の半導体基板 302においては、カレントミラー回路 13、正帰還回路 14、レベルシフタ回路 250、および、メモリ回路 260 を1つの単位とする複数の画素回路が、行列を成すように二次元状に配列される。

【0107】

【トランジスタのサイズ1】

10

本実施例の1つの側面は、第1の半導体基板 301 に配されたトランジスタのサイズと、第2の半導体基板 302 に配されたトランジスタのサイズが異なることである。トランジスタのサイズは、ゲート絶縁膜 104 の膜厚  $t_{ox}$ 、チャネル長  $L$ 、チャネル幅  $W$ 、あるいは、チャネル幅  $W$  とチャネル長  $L$  との比  $W/L$  のいずれかである。すなわち、図7乃至図9が、本実施例における異なるサイズを有する2つのトランジスタ（トランジスタAおよびトランジスタB）を示している。図7乃至図9に示された構造の説明は、実施例1と同様であるため、省略する。

【0108】

サイズの異なる2つのトランジスタの組み合わせには、いくつかのバリエーションがある。ひとつの例では、第1の半導体基板 301 のトランジスタに図8のトランジスタAが用いられ、第2の半導体基板 302 のトランジスタに図8のトランジスタBが用いられる。

20

【0109】

信号電荷処理回路 10 および差動対回路 11 などアナログ回路に使われるトランジスタには、比較的高い電源電圧が供給される。そのため、高い耐圧が得られるように、トランジスタのゲート絶縁膜 104 の膜厚  $t_{ox}$  は大きいことが好ましい。

【0110】

一方、メモリ回路 260 などのデジタル回路は、アナログ回路に対して相対的に高速に動作することが多い。また、典型的には、アナログ回路の電源電圧より低い電源電圧が供給される。そのため、トランジスタが高速に動作できるように、ゲート絶縁膜 104 の膜厚  $t_{ox}$  は小さいことが好ましい。

30

【0111】

このように、第1の半導体基板 301 のトランジスタのゲート絶縁膜 104 の膜厚  $t_{ox}$  が、第2の半導体基板 302 のトランジスタのゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きいことで、結果として、信頼性を向上しつつ、高速な動作を行うことが可能となる。

【0112】

また、製造プロセスの最適化のために、第1の半導体基板 301 に配されたトランジスタのサイズと、第2の半導体基板 302 に配されたトランジスタのサイズが異なっていてよい。例えば、第1の半導体基板 301 のトランジスタに図8のトランジスタAが用いられ、第2の半導体基板 302 のトランジスタに図8のトランジスタBが用いられる。すなわち、チャネル幅  $W$ 、チャネル長  $L$ 、および、ゲート絶縁膜 104 の膜厚  $t_{ox}$  のそれぞれの観点で、第1の半導体基板 301 のトランジスタのサイズが、第2の半導体基板 302 のトランジスタのサイズより大きい。

40

【0113】

第1の半導体基板 301 に比べて、第2の半導体基板 302 には多くの素子が配置される。そのため、第2の半導体基板 302 のトランジスタを製造するためにより微細なデザインルールが適用される。しかし、デザインルールが小さいプロセスほど、配線ショートなどによる歩留まり低下の課題が大きい。そこで、第1の半導体基板 301 には、より条件の緩いデザインルールを適用することで、歩留まりの低下を抑えることができる。結果として、画素 100 を小型化、ひいては、光電変換装置を小型化しつつ、高い生産性を維持することができる。

50

## 【0114】

## [トランジスタのサイズ2]

本実施例の別の側面としては、実施例1と同様に、入力トランジスタ160のサイズが、画素100の画素回路、または、読み出し回路110に含まれる、いずれかのトランジスタのサイズと異なっている。この場合、入力トランジスタ160とはサイズの異なるトランジスタは、第1の半導体基板301に配されたトランジスタであってもよいし、あるいは、第2の半導体基板302に配されたトランジスタであってもよい。

## 【0115】

サイズの異なる2つのトランジスタの組み合わせには、いくつかのバリエーションがあり、実施例1で説明したすべての組み合わせが適用される。具体的な組み合わせ、および、その時に得られる効果は、実施例1と同じである。そのため、実施例1の説明を援用し、繰り返しの説明は適宜、省略する。

10

## 【0116】

1つの例では、入力トランジスタ160のサイズと、参照トランジスタ170のサイズとが異なることにより、電気的特性を向上させることが可能である。参照トランジスタ170のチャネル長Lおよびチャネル幅Wが、それぞれ、入力トランジスタ160のチャネル長Lおよびチャネル幅Wより大きい。この構成によりS/N比を向上させることが可能である。あるいは、参照トランジスタ170のチャネル長Lが、入力トランジスタ160のチャネル長Lより長いという構成により、熱雑音による電流ノイズを低下させることができる。

20

## 【0117】

別の例では、リセットトランジスタ150のチャネル長Lおよびチャネル幅Wが、それぞれ、入力トランジスタ160のチャネル長Lおよびチャネル幅Wより大きい。このような構成により、リセット時の電圧のばらつきを小さくすることができる。

## 【0118】

このように、2つの半導体基板に分かれて画素回路が配置される場合に、同じ半導体基板に配された2つのトランジスタが互いに異なるサイズを持っていてもよい。また、実施例1と同様に、2つのトランジスタが、互いに異なる膜厚 $t_{0x}$ を有するゲート絶縁膜104を含んでいてもよい。

30

## 【0119】

以上に説明した通り、画素100の画素回路は、第1の半導体基板301と第2の半導体基板302に分かれて配置される。第1の半導体基板301のいずれかのトランジスタのサイズは、第2の半導体基板302のいずれかトランジスタのサイズと異なっている。このような構成により、電気的特性を向上させることができる。

## 【0120】

## [実施例3]

本実施例に係る光電変換装置を説明する。本実施例の光電変換装置は、1つの画素100の回路が、2つの半導体基板に分かれて配置される。それ以外の構成は、実施例1と同じである。また、実施例2では、参照トランジスタ170が第1の半導体基板301に配置されていたのに対し、本実施例では、参照トランジスタ170が第2の半導体基板302に配置される。以下では、実施例1および実施例2と異なる点を説明し、実施例1あるいは実施例2と同じ部分は説明を省略する。

40

## 【0121】

本実施例の光電変換装置の全体構成、および、画素100の機能ブロックは、実施例1と同じである。つまり、図1は、光電変換装置の構成を模式的に示す。また、図2は、画素100の構成を模式的に示すブロック図である。これらの図面の説明は実施例1と同じであるため、説明を省略する。

## 【0122】

図11は、画素100の等価回路を示す図である。ただし、メモリ回路260はブロックで示されている。図10が示すように、本実施例の画素100の等価回路は、実施例1(

50

図3)と同じである。そのため、各回路ブロックの機能についての説明は省略する。

【0123】

実施例1との差異は、本実施例の画素100の画素回路は、第1の半導体基板301および第2の半導体基板302に分かれて配置されることである。

【0124】

具体的に、光電変換部130は、第1の半導体基板301に配される。電荷排出トランジスタ120、転送トランジスタ140、および、リセットトランジスタ150を含む信号電荷処理回路10は、第1の半導体基板301に配される。

【0125】

差動対回路11の入力トランジスタ160、および、電流源180は、第1の半導体基板301に配される。これに対して、差動対回路11の参照トランジスタ170は、第2の半導体基板302に配される。本実施例は、この点で、実施例2と相違している。

10

【0126】

他は、実施例2と同様に、トランジスタ200およびトランジスタ210を含むカレントミラー回路13は、第2の半導体基板301に配される。4つのトランジスタ220、230、235、240を含む正帰還回路14は、第2の半導体基板301に配される。レベルシフタ回路250ならびにメモリ回路260は、第2の半導体基板301に配される。また、図1の読み出し回路110、および、図2のランプ信号発生回路12は、それぞれ、第2の半導体基板302に配置される。

【0127】

2つの半導体基板の相対的な配置を説明する。本実施例では、光電変換部130を含む第1の半導体基板301と、画素回路の一部を含む第2の半導体基板302とが、積層される。第1の半導体基板301の表面に垂直な方向に沿って光電変換部130を第2の半導体基板302に射影したとき、光電変換部130の射影に、画素回路の少なくとも一部のトランジスタが重なる。具体的には、カレントミラー回路13、正帰還回路14、レベルシフタ回路250、メモリ回路260に含まれるトランジスタ、ならびに、参照トランジスタ170のいずれか、または、全部が、光電変換部130の射影と重なる位置に配置される。

20

【0128】

第1の半導体基板301においては、光電変換部130、信号電荷処理回路10、および、差動対回路11(入力トランジスタ160と電流源180)を1つの単位とする複数の画素回路が、行列を成すように二次元状に配列される。第2の半導体基板302においては、参照トランジスタ170、カレントミラー回路13、正帰還回路14、レベルシフタ回路250、および、メモリ回路260を1つの単位とする複数の画素回路が、行列を成すように二次元状に配列される。

30

【0129】

本実施例の1つの側面は、実施例2と同様に、第1の半導体基板301に配されたトランジスタのサイズと、第2の半導体基板302に配されたトランジスタのサイズが異なることである。トランジスタのサイズは、ゲート絶縁膜104の膜厚 $t_{ox}$ 、チャネル長 $L$ 、チャネル幅 $W$ 、あるいは、チャネル幅 $W$ とチャネル長 $L$ との比 $W/L$ のいずれかである。すなわち、図7乃至図9が、本実施例における異なるサイズを有する2つのトランジスタ(トランジスタAおよびトランジスタB)を示している。この構成により得られる効果は、実施例2と同じであるため、説明は省略する。

40

【0130】

本実施例では、入力トランジスタ160が第1の半導体基板301に配される。そして、参照トランジスタ170が第2の半導体基板302に配される。すなわち、差動対に含まれる入力トランジスタ160と参照トランジスタ170とが、異なる半導体基板に配置される。このような構成により、簡単な製造プロセスで、両者のゲート絶縁膜104の膜厚 $t_{ox}$ を変えることが可能である。

【0131】

50

1つの半導体基板に配された2つのトランジスタの間で、ゲート絶縁膜104の厚さを変える場合、いわゆるデュアルゲートプロセスが用いられるなど、製造プロセスが複雑になりうる。例えば、一方のトランジスタのゲート絶縁膜104を成膜する工程と、他方のトランジスタのゲート絶縁膜104を成膜する工程とを別々に実施する。あるいは、半導体基板の全面に厚いゲート絶縁膜104を形成する工程の後に、当該ゲート絶縁膜の一部を薄く加工する工程を追加する。したがって、入力トランジスタ160および参照トランジスタ170が1つの半導体基板に配される場合、両者のゲート絶縁膜104の膜厚 $t_{0x}$ を異ならせるため、製造プロセスが複雑になる。

#### 【0132】

これに対して、積層された2つの半導体基板を含む光電変換装置を製造する際には、もともと、それぞれの半導体基板のトランジスタを形成するための工程がある。したがって、工程を追加することなく、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{0x}$ と、参照トランジスタ170のゲート絶縁膜104の膜厚 $t_{0x}$ とを変えることが可能である。結果として、簡易な製造プロセスで製造された光電変換装置において、電気的特性を向上させることができる。

10

#### 【0133】

差動対を構成する2つのトランジスタが、互いに異なるサイズを有することで向上させることのできる電気的特性は、実施例1で説明した通りである。例えば、参照トランジスタ170のゲート絶縁膜104の膜厚 $t_{0x}$ が、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{0x}$ より大きい。この構成により熱雑音によるノイズを低下させることができる。

20

#### 【0134】

また、チャネル長 $L$ あるいはチャネル幅 $W$ の異なる2つのトランジスタを形成する場合も、製造プロセスを別にすることが好ましい。そのため、本実施例によれば、参照トランジスタ170のチャネル長 $L$ 、または、チャネル幅 $W$ が、入力トランジスタ160のそれらと異なる構成を有する光電変換装置を、より簡易な製造プロセスで製造することができる。

#### 【0135】

以上に説明した通り、入力トランジスタ160が第1の半導体基板301に配される。そして、参照トランジスタ170が第2の半導体基板302に配される。第1の半導体基板301のいずれかのトランジスタのサイズは、第2の半導体基板302のいずれかトランジスタのサイズと異なっている。このような構成により、電気的特性を向上させることができる。

30

#### 【0136】

また、本実施例の別の側面としては、第1の半導体基板301の入力トランジスタ160のサイズが、第2の半導体基板302の参照トランジスタ170のサイズと異なっている。このような構成により、簡易な製造プロセスで製造された光電変換装置において、電気的特性を向上させることができる。

#### 【0137】

#### 【実施例4】

本実施例は、上述の実施例1乃至実施例3の変形例である。そのため、実施例1乃至実施例3と異なる点を説明する。

40

#### 【0138】

本実施例では、カレントミラー回路13を構成するトランジスタ200とトランジスタ210とが、互いに異なるサイズを有する。トランジスタ200とトランジスタ210は、図3、図10、または、図11に示されている。そのほかの構成は、実施例1乃至実施例3のいずれかと同じである。

#### 【0139】

トランジスタ200のチャネル長 $L$ に対して、相対的にトランジスタ210のチャネル長 $L$ を小さくすることで、参照トランジスタ170に流れる電流よりも入力トランジスタ160に流れる電流を大きくすることが可能となる。これにより、入力トランジスタ160

50

の相互コンダクタンス  $g_m 1$  が増加する。一方、参照トランジスタ 170 の相互コンダクタンス  $g_m 2$  が低下する。結果として、式(1)が表す通り、熱雑音によるノイズを低減することができる。

【0140】

別の例として、トランジスタ 200 のチャネル幅  $W$  に対して、相対的にトランジスタ 210 のチャネル幅  $W$  を大きくすることで、参照トランジスタ 170 に流れる電流よりも入力トランジスタ 160 に流れる電流を大きくすることが可能となる。これにより、入力トランジスタ 160 の相互コンダクタンス  $g_m 1$  が増加する。一方、参照トランジスタ 170 の相互コンダクタンス  $g_m 2$  が低下する。結果として、式(1)が表す通り、熱雑音によるノイズを低減することができる。

10

【0141】

別の例では、トランジスタ 200 のゲート絶縁膜 104 の膜厚  $t_{ox}$  に対して、相対的にトランジスタ 210 のゲート絶縁膜 104 の膜厚  $t_{ox}$  が小さい。このような構成により、参照トランジスタ 170 に流れる電流よりも入力トランジスタ 160 に流れる電流を大きくすることが可能となる。これにより、入力トランジスタ 160 の相互コンダクタンス  $g_m 1$  が増加する。一方、参照トランジスタ 170 の相互コンダクタンス  $g_m 2$  が低下する。結果として、式(1)が表す通り、熱雑音によるノイズを低減することができる。

【0142】

また、上述の効果を得るために、入力トランジスタ 160 のサイズと参照トランジスタ 170 のサイズとの関係に制約はない。ただ、参照トランジスタ 170 に流れる電流が小さくなると、参照トランジスタ 170 の  $1/f$  ノイズが増加する可能性がある。そこで、参照トランジスタ 170 のチャネル長  $L$ 、および、チャネル幅  $W$  が、それぞれ、入力トランジスタ 160 のチャネル長  $L$ 、および、チャネル幅  $W$  より大きい構成が用いられてもよい。このような構成によれば、参照トランジスタ 170 のゲート電極の面積を大きくすることができ、結果として、 $1/f$  ノイズの増加を抑制することができる。

20

【0143】

トランジスタ 200 とトランジスタ 210 とは、同じ半導体基板に配されることが、ばらつき抑制の観点からは望ましい。実施例 2 あるいは実施例 2 の変形例として、実施例の構成を採用する場合、トランジスタ 200 およびトランジスタ 210 はいずれも第 2 の半導体基板 302 に配されることが好ましい。

30

【0144】

本実施例では、トランジスタ 200 とトランジスタ 210 とが、互いに異なるサイズを有する。そのため、トランジスタ 200 およびトランジスタ 210 の少なくとも一方のサイズは、入力トランジスタ 160 のサイズと異なる。また、トランジスタ 200 とトランジスタ 210 が第 2 の半導体基板 302 に配された場合、トランジスタ 200 およびトランジスタ 210 の少なくとも一方のサイズは、第 1 の半導体基板 301 に配されたトランジスタのサイズと異なる。

【0145】

以上に説明した通り、本実施例では、カレントミラー回路 13 を構成するトランジスタ 200 とトランジスタ 210 とが、互いに異なるサイズを有する。この構成によれば、比較器で生じる熱雑音によるノイズを低減することができる。

40

【0146】

【実施例 5】

本実施例は、上述の実施例 1 乃至実施例 4 の変形例である。そのため、実施例 1 乃至実施例 4 と異なる点を説明する。

【0147】

図 12 は、画素 100 の等価回路を示す図である。実施例 1 乃至実施例 4 では、カレントミラー回路 13 のトランジスタ 210 が差動対回路 11 の入力トランジスタ 160 に接続されている(図 3)。これに対して、本実施例では、カレントミラー回路 13 のトランジスタ 200 が差動対回路 11 の入力トランジスタ 160 に接続されている。また、実施例

50

1乃至実施例4では、カレントミラー回路13のトランジスタ200が差動対回路11の参照トランジスタ170に接続されている(図3)。これに対して、本実施例では、カレントミラー回路13のトランジスタ210が差動対回路11の参照トランジスタ170に接続されている。つまり、光電変換部130で生じた電荷に基づく信号が入力されるノードと、ランプ信号RAMPが入力されるノードとが入れ替わっている。

#### 【0148】

加えて、比較器の入力ノード(入力トランジスタ160のゲート)の電位をリセットするリセットトランジスタ150は、リセット電圧を供給するノードに接続される。そのため、リセット時のリセット電圧のばらつきを低減することができる。なお、この構成は、リセットトランジスタ150の変形例として、実施例1乃至実施例4に適用されてもよい。

10

#### 【0149】

ランプ信号RAMPは、クランプ容量156を介して、参照トランジスタ170のゲートに入力される。参照トランジスタ170のゲートの電位を初期化するため、第2のリセットトランジスタ155が配される。第2のリセットトランジスタ155は、参照トランジスタ170のゲートとドレインとの間に接続される。

#### 【0150】

そのほかの回路の構成は、実施例1乃至実施例4と同じである。なお、図12においては、レベルシフタ回路250をインバータの回路記号で示している。

#### 【0151】

本実施例の1つの側面としては、実施例1と同様に、入力トランジスタ160のサイズが、画素100の画素回路、または、読み出し回路110に含まれる、いずれかのトランジスタのサイズと異なっている。サイズの異なる2つのトランジスタの組み合わせには、いくつかのバリエーションがあり、実施例1で説明したすべての組み合わせが適用される。具体的な組み合わせ、および、その時に得られる効果は、実施例1と同じである。そのため、実施例1の説明を援用し、繰り返しの説明は適宜、省略する。

20

#### 【0152】

本実施例の別の側面は、第1の半導体基板301に配されたトランジスタのサイズと、第2の半導体基板302に配されたトランジスタのサイズが異なることである。実施例2あるいは実施例3のように、画素100の画素回路が、第1の半導体基板301と第2の半導体基板302に分かれて配置されてもよい。

30

#### 【0153】

例えば、入力トランジスタ160および参照トランジスタ170が、第1の半導体基板301に配される(図10)。この場合、第2のリセットトランジスタ155、および、クランプ容量156は、第1の半導体基板301に配されることが好ましい。別の例としては、入力トランジスタ160が第1の半導体基板301に配され、一方、参照トランジスタ170が第2の半導体基板302に配される(図11)。この場合、第2のリセットトランジスタ155、および、クランプ容量156は、第2の半導体基板302に配されることが好ましい。

#### 【0154】

サイズの異なる2つのトランジスタの組み合わせには、いくつかのバリエーションがあり、実施例2および実施例3で説明したすべての組み合わせが適用される。具体的な組み合わせ、および、その時に得られる効果は、実施例2あるいは実施例3と同じである。そのため、実施例2および実施例3の説明を援用し、繰り返しの説明は省略する。

40

#### 【0155】

本実施例において、トランジスタのサイズは、ゲート絶縁膜104の膜厚 $t_{0x}$ 、チャネル長 $L$ 、チャネル幅 $W$ 、あるいは、チャネル幅 $W$ とチャネル長 $L$ との比 $W/L$ のいずれかである。すなわち、図7乃至図9が、本実施例における異なるサイズを有する2つのトランジスタ(トランジスタAおよびトランジスタB)を示している。図7乃至図9に示された構造の説明は、実施例1と同様であるため、省略する。

#### 【0156】

50

以上に説明した通り、画素 100 の画素回路は、サイズの異なる 2 つのトランジスタを含む。このような構成により、電気的特性を向上させることができる。

【 0 1 5 7 】

【 実施例 6 】

別の実施例について説明する。本実施例は、複数の画素 100 が参照トランジスタ 170 を共有する点で、実施例 1 乃至実施例 5 と異なっている。実施例 1 乃至実施例 5 と異なる点を主として説明する。

【 0 1 5 8 】

【 全体構成 】

図 13 は、本実施例の光電変換装置の全体構成を模式的に示すブロック図である。複数の画素 100 が、画素アレイを構成する。画素アレイは、複数の画素行と複数の画素列とを含む。垂直走査回路 110 は、複数の画素 100 からの信号を読み出すために、複数の画素 100 を制御する。複数の画素 100 からの信号は、例えば、画素行ごとに読み出される。

10

【 0 1 5 9 】

比較回路 135 は、画素 100 の信号と参照信号とを比較する。ランプ信号発生回路 12 によって発生されたランプ信号が、参照信号として、比較回路 135 へ入力される。比較回路 135 による比較の結果に基づく制御信号が、出力回路 136 を介して、カウンタ回路 152 へ出力される。当該比較の結果に基づく制御信号が、カウンタ回路 152 のカウント期間を制御する。カウンタ回路 152 は制御信号を受けたタイミングに対応したカウント値をメモリセル 153 へ出力する。メモリセル 153 へ出力されたカウント値が、画素 100 の信号をアナログデジタル変換（以下、A/D 変換）された結果のデジタル信号として保持される。メモリセル 153 に保持されたデジタル信号は水平走査回路 108 により、順次、光電変換装置から出力される。

20

【 0 1 6 0 】

また、出力回路 136 は、画素 100 の信号に基づく信号を、フィードバック信号として、比較回路 135 へ出力する。比較回路 135 はフィードバック信号を保持することができる。

【 0 1 6 1 】

【 画素構成 】

30

図 14 は、光電変換装置の画素 100 、比較回路 135 、および、出力回路 136 の等価回路を示している。説明を簡略にするため、図 14 は 2 つの画素 100 のみを示している。

【 0 1 6 2 】

画素 100 は、光電変換部 130 、リセットトランジスタ 150 、転送トランジスタ 140 、入力トランジスタ 160 、および、選択トランジスタ 157 を含む。リセットトランジスタ 150 のゲートには制御信号 RES 、転送トランジスタ 140 のゲートには制御信号 TX 、選択トランジスタ 157 のゲートには制御信号 SEL がそれぞれ入力される。

【 0 1 6 3 】

入力トランジスタ 160 のゲートはフローティングディフュージョンノード（以下、FD ノード）に接続されている。光電変換部 130 で生じた電荷は、転送トランジスタ 140 によって、FD ノードに転送される。つまり、入力トランジスタ 160 のゲートに、光電変換部 130 で生じた電荷に基づく信号が入力される。リセットトランジスタ 150 は、入力トランジスタ 160 のゲートの電圧をリセットする。なお、入力トランジスタ 160 のゲートが FD ノードに接続されているので、本明細書においては、入力トランジスタ 160 のゲートを FD ノードと呼ぶことがある。

40

【 0 1 6 4 】

【 差動対（比較回路）の説明 】

比較回路 135 は、参照トランジスタ 170 を含む。参照トランジスタ 170 のゲートには、ランプ信号 RAMP が入力される。ランプ信号 RAMP は、例えば、時間と共にその

50

電圧が変化する信号である。入力トランジスタ 160 および参照トランジスタ 170 は、電流源 180 に接続されることで、差動対を構成している。図 14において、電流源 180 は、例えば、ゲートに所定のバイアス電圧を印加したNチャネル型のMOSトランジスタが用いられる。入力トランジスタ 160 および参照トランジスタ 170 は、同じ導電型である。本実施例では、入力トランジスタ 160 および参照トランジスタ 170 は、いずれも、Nチャネル型のMOSトランジスタである。

#### 【0165】

比較回路 135 は、参照トランジスタ 170 のゲートの電圧を、所定の電圧にクランプするクランプ回路を含む。クランプ回路は、例えば、クランプスイッチ素子 SW1 およびクランプ容量素子 C1 を含む。クランプスイッチ素子 SW1 は、参照トランジスタ 170 のゲートに接続される。クランプスイッチ素子 SW1 は、制御信号 C L M P によって制御される。クランプスイッチ素子 SW1 がオフすることで、参照トランジスタ 170 のゲートは電気的にフローティングになる。これにより、参照トランジスタ 170 のゲートの電圧を所定の電圧にクランプすることができる。クランプ容量素子 C1 の一方の端子は、参照トランジスタ 170 のゲートに接続される。クランプ容量素子 C1 の他方の端子に、ランプ信号 R A M P が入力される。この構成により、ランプ信号 R A M P の交流成分が、クランプ容量素子 C1 を介して、参照トランジスタ 170 のゲートに入力される。

10

#### 【0166】

1つの画素列に含まれる複数の画素 100 (図 14 の 2 つの画素 100) に対して、図 14 に示された 1 つの比較回路 135 が配される。具体的には、複数の画素 100 の選択トランジスタ 157 のソースが、互いに接続され、かつ、電流源 180 に接続される。また、複数の画素 100 の画素トランジスタのドレインが互いに接続される。そして、1 つの参照トランジスタ 170 が、1 つの画素列に含まれる複数の画素 100 のそれぞれの入力トランジスタ 160 と差動対を構成する。撮像用の光電変換装置、つまり、撮像装置は、画素列と比較回路 135 の組を複数備える。

20

#### 【0167】

##### 【出力回路の説明】

出力ノード 310 を有する出力回路 136 が、参照トランジスタ 170 に電気的に接続される。出力ノード 310 は、入力トランジスタ 160 のソースおよびドレイン、ならびに、参照トランジスタ 170 のソースおよびドレインとは別のノードである。

30

#### 【0168】

出力回路 136 は、入力トランジスタ 160 のゲートの電圧に基づく電圧を参照トランジスタ 170 のゲートに出力する第 1 動作を行う。また、出力回路 136 は、参照トランジスタ 170 からの電流を受けて、入力トランジスタ 160 のゲートの電圧と参照トランジスタ 170 のゲートの電圧との比較の結果に基づく信号を出力ノード 310 に出力する第 2 動作を行う。図 14 において、「フィードバック信号」が入力トランジスタ 160 のゲートの電圧に基づく電圧を表し、「制御信号」が比較の結果に基づく信号を表している。

#### 【0169】

第 1 動作において、出力回路 136 は、参照トランジスタ 170 に電流を供給する電流源として動作してもよい。このとき、出力回路 136 は入力トランジスタ 160 および参照トランジスタ 170 による差動対が構成する演算増幅器の負荷となる。したがって、参照トランジスタ 170 のゲートとドレインとがショートされると、出力回路 136 は入力トランジスタ 160 のゲートの電圧に基づく電圧を参照トランジスタ 170 のゲートに出力する。

40

#### 【0170】

クランプスイッチ素子 SW1 をオフにすることで、クランプ回路は参照トランジスタ 170 のゲートに出力された電圧を保持する。つまり、クランプ回路は、参照トランジスタ 170 のゲートの電圧を、入力トランジスタ 160 のゲートの電圧に基づく電圧にクランプする。入力トランジスタ 160 のゲートの電圧に基づく電圧とは、例えば、入力トランジスタ 160 のゲートの電圧と実質的に等しい電圧を含む。トランジスタの特性の差、温度

50

の差、熱ノイズなどがあるため、両者は厳密に等しい電圧でなくてもよい。

【0171】

第2動作において、出力回路136は、参照トランジスタ170の電流を検出する電流検出回路として動作してもよい。電流検出回路は、参照トランジスタ170の電流の変化を、別の信号として、参照トランジスタ170のドレインとは別の出力ノード310に出力する。この機能により、出力回路136は、入力トランジスタ160のゲートの電圧と参照トランジスタ170のゲートの電圧との比較の結果に基づく信号を出力ノード310に出力する。

【0172】

例えば、参照トランジスタ170のゲートの電圧のほうが入力トランジスタ160のゲートの電圧より高い場合に、出力回路136は出力ノード310に第1の電圧を出力する。一方、参照トランジスタ170のゲートの電圧のほうが入力トランジスタ160のゲートの電圧より低い場合に、出力回路136は出力ノード310に第1の電圧とは異なる第2の電圧を出力する。

10

【0173】

上述の説明では、電流源180が接続された配線の寄生抵抗を無視している。配線の寄生抵抗は、入力トランジスタ160と参照トランジスタ170による差動対が構成する演算增幅器のオフセットとなりうる。

【0174】

[制御部(電圧変動低減部)の説明]

20

出力回路136は、上述の第2動作における参照トランジスタ170のドレインの電圧の変化量を、出力ノード310の電圧の変化量よりも小さくする制御部を含む。制御部は、特に、入力トランジスタ160のゲートの電圧の大きさと参照トランジスタ170のゲートの電圧の大きさとの関係が逆転するときの参照トランジスタ170のドレインの電圧の変化量を、出力ノード310の電圧の変化量よりも小さくする。このときの出力ノード310の電圧の変化量とは、上述の第1の電圧と第2の電圧との差である。

【0175】

制御部は、カレントミラー回路を含みうる。カレントミラー回路は、それぞれが他方のゲートに接続されたゲートを有する2つのトランジスタを少なくとも含む。当該2つのトランジスタの一方のドレインが、参照トランジスタ170に電気的に接続される。

30

【0176】

また、制御部は、当該2つのトランジスタの他方のゲートとドレインとを接続するスイッチ素子を含みうる。当該スイッチ素子によって、上述の第1動作および第2動作を切り替えることができる。

【0177】

[カレントミラー回路]

出力回路136の制御部は、Pチャネル型のMOSトランジスタM6およびPチャネル型のMOSトランジスタM7を含むカレントミラー回路を含む。トランジスタM6のドレインは、参照トランジスタ170のドレインに電気的に接続される。トランジスタM6のゲートとトランジスタM7のゲートとが互いに接続される。

40

【0178】

トランジスタM6およびM7が構成するカレントミラー回路は、出力回路136が第1動作を行うときに、トランジスタM7の電流をトランジスタM6へミラーする。また、出力回路136が第2動作を行うときに、カレントミラー回路は、トランジスタM6の電流をトランジスタM7へミラーする。

【0179】

本実施例では、第1動作において、カレントミラー回路は、トランジスタM6から参照トランジスタ170へ電流を供給する電流源として動作している。そして、第2動作において、カレントミラー回路は、参照トランジスタ170からトランジスタM6に入力される電流を、トランジスタM7へミラーする電流検出回路として動作する。

50

## 【0180】

出力回路136の制御部は、容量素子C2を含む。容量素子C2は、トランジスタM6のドレインに電気的に接続された第1端子、および、トランジスタM6のゲートに電気的に接続された第2端子を有する。容量素子C2により、トランジスタM6のドレインとゲートとが交流的に結合し、トランジスタM6の電流をトランジスタM7にミラーすることができる。

## 【0181】

出力回路136の制御部は、第1スイッチ素子SW2を含む。第1スイッチ素子SW2は、トランジスタM7のゲートとドレインとを接続する。第1スイッチ素子SW2がオンすることによって、カレントミラー回路は、トランジスタM7の電流をトランジスタM6へミラーすることができる。第1スイッチ素子SW2をオフすることによって、カレントミラー回路は、トランジスタM6の電流をトランジスタM7にミラーすることができる。つまり、第1スイッチ素子SW2が、出力回路136の第1動作と第2動作とを切り替えている。

10

## 【0182】

なお、容量素子C2の容量値は、第1スイッチ素子SW2がオフしているときの第1スイッチ素子SW2の両端の間の結合容量の容量値より大きい。第1スイッチ素子SW2がMOSトランジスタの場合、第1スイッチ素子SW2の両端は、当該MOSトランジスタのソースとドレインである。このような構成によれば、カレントミラー回路の動作を安定させることができる。

20

## 【0183】

クランプスイッチ素子SW1と第1スイッチ素子SW2とが互いに同相で動作することが好ましい。本実施形態では、クランプスイッチ素子SW1と第1スイッチ素子SW2とを共通の制御信号CLMPによって制御することで、クランプスイッチ素子SW1と第1スイッチ素子SW2とが互いに同相で動作する。

## 【0184】

本実施例の出力回路136は、出力ノード310に接続された参照電流源IS2を備える。参照電流源IS2は、トランジスタM7へ参照電流を出力する。また、出力ノード310には、インバータ回路が接続される。

30

## 【0185】

## [動作]

本実施例の光電変換装置は、図15で示された駆動信号によって駆動される。図15は、光電変換装置の駆動信号のタイミングチャートを模式的に示す図である。図15は、1回の水平走査期間(1H期間)、すなわち、1つの画素行の信号を読み出すための駆動信号を示している。駆動信号がハイレベルのとき、当該駆動信号の供給されるトランジスタはオンする。駆動信号がローレベルのとき、当該駆動信号の供給されるトランジスタはオフする。ハイレベルおよびローレベルの具体的な電圧は、トランジスタの導電型に応じて定まる。

## 【0186】

本実施形態においては、制御信号CLMPがハイレベルのときに、出力回路136は電流源として動作する。制御信号CLMPがローレベルのときに、出力回路136は電流検知回路として動作する。

40

## 【0187】

最初に制御信号RESおよび制御信号CLMPをハイレベルとする。これにより、リセットトランジスタ150およびクランプスイッチ素子SW1が導通状態になる、つまり、オンする。FDノードの電圧は、電源電圧VDDなどの所定の電圧(以下、リセットレベル)にリセットされる。同時に、出力回路136はFDノードの電圧に基づく電圧(以下、クランプレベル)を、参照トランジスタ170のゲートおよびクランプ容量素子C1に出力する。つまり、出力回路136は、入力トランジスタ160のゲートの電圧に基づく電圧を参照トランジスタ170のゲートに出力する第1動作を行う。

50

## 【0188】

制御信号 C L M P がハイレベルの期間は、クランプスイッチ素子 S W 1 と第 1 スイッチ素子 S W 2 がオンする。参照電流源 I S 2 からの参照電流が、トランジスタ M 6 および M 7 で構成したカレントミラーにより、参照トランジスタ 1 7 0 へ出力される。すなわち、トランジスタ M 6 が参照トランジスタ 1 7 0 へ電流を供給する電流源として動作する。

## 【0189】

クランプスイッチ素子 S W 1 は参照トランジスタ 1 7 0 のゲートとドレインとを接続している。そのため、入力トランジスタ 1 6 0 、参照トランジスタ 1 7 0 、電流源 1 8 0 は、トランジスタ M 6 による電流源を負荷とし、ボルテージフォロワとして動作する。これにより、F D ノードの電圧が、参照トランジスタ 1 7 0 のゲート、および、クランプ容量素子 C 1 に出力される。換言すると、出力回路 1 3 6 が、入力トランジスタ 1 6 0 のゲートの電圧に基づく電圧を参照トランジスタ 1 7 0 のゲートに出力する第 1 動作を行う。

10

## 【0190】

その後、制御信号 R E S と制御信号 C L M P を順次ローレベルとする。これにより、リセットレベルが F D ノードに保持され、クランプレベルがクランプ容量素子 C 1 にそれぞれ保持される。クランプスイッチ素子 S W 1 より先にリセットトランジスタ 1 5 0 をオフにすることで、リセットトランジスタ 1 5 0 によって生じる熱ノイズが、クランプレベルに反映されうる。クランプスイッチ素子 S W 1 がオフした直後は、F D ノード、つまり、入力トランジスタ 1 6 0 のゲートの電圧と、参照トランジスタ 1 7 0 のゲートの電圧とはほぼ等しい。

20

## 【0191】

続いて、ランプ信号 R A M P をより高い電圧へ変化させる。これにより、参照トランジスタ 1 7 0 のゲートの電圧が、入力トランジスタ 1 6 0 のゲートの電圧より高くなる。入力トランジスタ 1 6 0 および参照トランジスタ 1 7 0 は差動対を構成しているため、電流源 1 8 0 の電流の大半が参照トランジスタ 1 7 0 に流れる。

## 【0192】

次にランプ信号 R A M P のランプダウンを開始する。ランプダウンとは、ランプ信号 R A M P の電圧を下げていくことである。あるタイミングで入力トランジスタ 1 6 0 のゲートの電圧の大きさと参照トランジスタ 1 7 0 のゲートの電圧の大きさとの関係が反転する。当該関係が反転した後は、電流源 1 8 0 の電流の大半は入力トランジスタ 1 6 0 に流れる。一方、参照トランジスタ 1 7 0 の電流は小さくなる。

30

## 【0193】

出力回路 1 3 6 は参照トランジスタ 1 7 0 の電流の変化を検出する。具体的には、参照トランジスタ 1 7 0 の電流が小さくなったタイミングで、出力回路 1 3 6 は当該電流の変化が生じたことを示す信号を、制御信号として、出力ノード 3 1 0 に出力する。言い換えると、出力回路 1 3 6 は、入力トランジスタ 1 6 0 のゲートの電圧と参照トランジスタ 1 7 0 のゲートの電圧との比較の結果に基づく信号を出力ノード 3 1 0 に出力する第 2 動作を行う。

## 【0194】

制御信号 C L M P がローレベルになると、クランプスイッチ素子 S W 1 と第 1 スイッチ素子 S W 2 はオフする。その後、出力回路 1 3 6 は、入力トランジスタ 1 6 0 のゲートの電圧と参照トランジスタ 1 7 0 のゲートの電圧とを比較する第 2 動作を行う。

40

## 【0195】

上述の通り、トランジスタ M 6 のゲートとドレインとが容量素子 C 2 により交流的に結合している。そのため、参照トランジスタ 1 7 0 を流れる電流が、トランジスタ M 6 からトランジスタ M 7 へミラーされる。ミラーされた電流の大きさと参照電流源 I S 2 からの参照電流との大きさの関係によって、出力ノード 3 1 0 の電圧が変化する。つまり、出力ノード 3 1 0 に比較の結果に基づく信号が出力される。

## 【0196】

図 1 4 の光電変換装置においては、制御信号がカウンタ回路 1 5 2 を制御することにより

50

、ランプダウンの開始から電圧の大きさの関係の反転までの時間を計測している。ランプダウンの開始から所定の時間が経過した後に、リセットレベルのA D変換を終了する。リセットレベルのA D変換を行っている期間は、図15においてN\_A Dと表記されている。

#### 【0197】

この後、ランプ信号R A M Pをリセットする。制御信号T Xをハイレベルとすることにより、転送トランジスタ140がオンし、光電変換部130で発生した電荷がF Dノードに転送される。

#### 【0198】

制御信号T Xをローレベルとした後、ランプ信号R A M Pのランプダウンを開始する。その後、リセットレベルのA D変換と同様に、光信号レベルのA D変換を行う。光信号レベルのA D変換を行っている期間は、図15においてS\_A Dと表記した。

10

#### 【0199】

詳細な説明は割愛するが、光電変換装置においては、光信号レベルをA D変換したコード値からリセットレベルをA D変換したコード値を減算するデジタルC D S ( C o r r e l a t e d D o u b l e S a m p l i n g )を行ってもよい。

#### 【0200】

ここで、各部の数値例を説明する。例えば、カレントミラー回路を構成するトランジスタM 6およびM 7のサイズはほぼ等しい。また、電流源180の電流量I\_IS1と、参照電流源I\_IS2の電流量I\_IS2とが、 $I_IS1 = 2 \times I_IS2$ の関係をほぼ満たしている。

20

#### 【0201】

この条件において、第1動作においては、入力トランジスタ160および参照トランジスタ170のそれぞれに、電流源180の電流量I\_IS1をほぼ等分した量の電流、すなわち、電流量I\_IS2にはほぼ等しい量の電流が流れる。第2動作においては、参照トランジスタ170のゲートの電圧が、入力トランジスタ160のゲートの電圧より高いときは、電流源180の電流の大半は参照トランジスタ170に流れる。一方、入力トランジスタ160の電流はほぼ0になる。そのため、トランジスタM 7にはほぼ電流源180と同じ量の電流が流れる。その結果、トランジスタM 7のドレイン、つまり、出力ノード310の電圧は電源電圧V D Dに近い電圧となる。

30

#### 【0202】

参照信号がランプダウンすると、参照トランジスタ170のゲートの電圧が、入力トランジスタ160のゲートの電圧より低くなる。この時は、電流源180の電流の大半は入力トランジスタ160に流れる。一方、参照トランジスタ170の電流はほぼ0になる。したがって、トランジスタM 7の電流もほぼ0となる。その結果、トランジスタM 7のドレイン、つまり、出力ノード310の電圧は接地電圧に近い電圧となる。

#### 【0203】

このように、出力回路136は、参照トランジスタ170の電流の変化を検出している。このとき、トランジスタM 6がカレントミラー回路の入力である。参照トランジスタ170のドレインの電流が変化しても、トランジスタM 6のドレインの電圧は大きく変化しない。言い換えると、カレントミラー回路が、参照トランジスタ170のドレインの電圧の変化量を、出力ノードの電圧の変化量より小さくしている。そのため、ランプ信号R A M Pの電圧変動を低減することができる。結果として、本実施例によれば、光電変換装置が<sup>40</sup>出力する信号の精度を向上させることができる。

40

#### 【0204】

比較例として、特許文献1に記載の光電変換装置では、クランプ動作が終了した後も、P M O Sトランジスタ203が定電流源として動作する。そして、差動トランジスタ201のドレインの電圧が、出力として読み出される。そのため電圧の関係が反転したときに、差動トランジスタ201のドレイン電圧が大きく変化する。この電圧の変動が、参照信号の電圧を変動させ、結果として、画質の低下の原因になる可能性がある。

#### 【0205】

50

## 【トランジスタサイズ】

本実施例においては、画素 100 の画素回路が入力トランジスタ 160 を含む。入力トランジスタ 160 は、光電変換部 130 で生じた信号電荷に基づく信号を受け、かつ、参照トランジスタ 170 と差動対を構成している。画素 100 の画素回路は、さらに、入力トランジスタ 160 とは別のトランジスタを含んでいる。

## 【0206】

本実施例の読み出し回路は、ランプ信号発生回路 12、比較回路 135、出力回路 136、カウンタ回路 152、メモリセル 153、垂直走査回路 110、および、水平走査回路 108 を含んで構成される。これらの回路は、それぞれ、トランジスタを含んで構成される。

10

## 【0207】

ここで、入力トランジスタ 160 のサイズは、画素 100 の画素回路、または、読み出し回路に含まれる、いずれかのトランジスタのサイズと異なっている。トランジスタのサイズは、ゲート絶縁膜 104 の膜厚  $t_{ox}$ 、チャネル長  $L$ 、チャネル幅  $W$ 、あるいは、チャネル幅  $W$  とチャネル長  $L$  との比  $W/L$  のいずれかである。以下、便宜的に、互いに異なるサイズの 2 つのトランジスタを、トランジスタ A、および、トランジスタ B と呼ぶ。

## 【0208】

図 7 (a) および図 7 (b) は、本実施例において、トランジスタ A とトランジスタ B との間で、チャネル長  $L$  およびチャネル幅  $W$  がそれぞれ異なる例を示している。一方、トランジスタ A の  $W/L$  およびゲート絶縁膜 104 の膜厚  $t_{ox}$  は、トランジスタ B のそれらと同じである。図 7 (b) が示すように、トランジスタ A のチャネル長  $L$  およびチャネル幅  $W$  が、それぞれ、トランジスタ B のチャネル長  $L$  およびチャネル長  $W$  より大きい。つまり、トランジスタ A のサイズが、トランジスタ B のサイズより大きい。図 7 についての説明は、実施例 1 と同じであるため、繰り返しの説明は省略する。

20

## 【0209】

サイズの異なる 2 つのトランジスタの組み合わせには、いくつかのバリエーションがある。ひとつの例では、参照トランジスタ 170 にトランジスタ A が用いられ、入力トランジスタ 160 にトランジスタ B が用いられる。すなわち、参照トランジスタ 170 のチャネル長  $L$  およびチャネル幅  $W$  が、それぞれ、入力トランジスタ 160 のチャネル長  $L$  およびチャネル幅  $W$  より大きい。この構成により S/N 比を向上させることができる。この効果については、実施例 1 と同じであるため、繰り返しの説明を省略する。

30

## 【0210】

なお、参照トランジスタ 170 のチャネル長  $L$  だけが、入力トランジスタ 160 のチャネル長  $L$  より大きい場合にも、同様の効果が得られる。また、参照トランジスタ 170 のチャネル幅  $W$  だけが、入力トランジスタ 160 のチャネル幅  $W$  より大きい場合にも、同様の効果が得られる。特に断りがないかぎり、この点は以降に述べる例でも同様である。

## 【0211】

また、参照トランジスタ 170 のチャネル長  $L$  が、入力トランジスタ 160 のチャネル長  $L$  より長いという構成により、熱雑音による電流ノイズを低下させることができる。この効果についても実施例 1 と同じである。

40

## 【0212】

入力トランジスタ 160 のチャネル長  $L$  が短いため、入力トランジスタ 160 の相互コンダクタンス  $g_m 1$  を大きくすることができます。一方、参照トランジスタ 170 のチャネル長  $L$  が長いため、参照トランジスタ 170 の相互コンダクタンス  $g_m 2$  を小さくすることができます。結果として、式 (1) にしたがって、熱雑音によるノイズを低下させることができる。なお、このとき、2 つのトランジスタのチャネル幅  $W$  は、どのような関係であってもよい。

## 【0213】

変形例として、入力トランジスタ 160 のチャネル幅  $W$  が、参照トランジスタ 170 のチャネル幅  $W$  より大きいことにより、熱雑音による電流ノイズを低下させることができる。

50

この効果については、実施例 1 と同様である。

【0214】

このとき、2つのトランジスタのチャネル長 L は、どのような関係であってもよい。電荷電圧変換係数の向上の観点からは、入力トランジスタ 160 のチャネル長 L は参照トランジスタ 170 のチャネル長 L より短く、一方、入力トランジスタ 160 のチャネル幅 W は参照トランジスタ 170 のチャネル幅 W より大きいことが好ましい。入力トランジスタ 160 のチャネル長 L が短いことにより、電荷電圧変換係数を大きくすることができる。結果として、チャネル長 L の関係により信号レベルを上げ、かつ、チャネル幅 W の関係によりノイズを低減することが可能になる。

【0215】

入力トランジスタ 160 のサイズと参照トランジスタ 170 のサイズとが互いに異なる場合も、オフセットキャンセルは可能である。リセットトランジスタ 150 をオンして比較器の入力ノード（入力トランジスタ 160 のゲート）の電位をリセットする際、ランプ信号 RAMP を所定のリセット電位 Vr にする。その時の入力トランジスタ 160 のゲートの電位は、 $V_r - V_{gs}(170) + V_{gs}(160)$  で表される。このとき、 $V_{gs}(170)$  および  $V_{gs}(160)$  には、それぞれ、入力トランジスタ 160 の閾値電圧  $V_{th}$  および参照トランジスタ 170 の閾値電圧  $V_{th}$  が反映される。そのため、オフセットキャンセルを行うことが可能である。換言すると、画素 100 ごとに入力トランジスタ 160 および参照トランジスタ 170 の閾値電圧  $V_{th}$  が異なっていても、いずれの画素 100 においてもランプ信号 RAMP のレベルがリセット電位 Vr になった時に比較器の出力が反転する。

10

20

【0216】

以上に説明した通り、入力トランジスタ 160 のサイズと、参照トランジスタ 170 のサイズとが異なることにより、電気的特性を向上させることができるものである。

【0217】

他の例では、リセットトランジスタ 150 にトランジスタ A が用いられ、入力トランジスタ 160 にトランジスタ B が用いられる。すなわち、リセットトランジスタ 150 のチャネル長 L およびチャネル幅 W が、それぞれ、入力トランジスタ 160 のチャネル長 L およびチャネル幅 W より大きい。

【0218】

30

前述の通り、入力トランジスタ 160 のゲートのサイズが小さいことにより、電荷電圧変換係数を大きくすることができる。また、リセットトランジスタ 150 のサイズが大きいことで、リセットトランジスタ 150 の閾値電圧  $V_{th}$  のばらつきを小さくすることができる。結果として、リセット時の電圧のばらつきを小さくすることができる。

【0219】

他の例では、入力トランジスタ 160 にトランジスタ A が用いられ、カウンタ回路 152、または、メモリセル 153 のトランジスタにトランジスタ B が用いられる。すなわち、入力トランジスタ 160 のチャネル長 L およびチャネル幅 W が、それぞれ、カウンタ回路 152、または、メモリセル 153 のトランジスタのチャネル長 L およびチャネル幅 W より大きい。

40

【0220】

差動対回路 11 などアナログ回路に使われるトランジスタは、大きい相互コンダクタンス  $g_m$  を持つことが好ましい。そのため、入力トランジスタ 160 のサイズを大きくする。一方、カウンタ回路 152、および、メモリセル 153 などのデジタル回路では、トランジスタのサイズを小さくすることで、高速に動作することが好ましい。つまり、入力トランジスタ 160 のサイズが、カウンタ回路 152、または、メモリセル 153 のトランジスタのサイズより大きいことで、結果として、ノイズを低減しつつ、かつ、高速な動作を行うことが可能となる。

【0221】

他の例では、入力トランジスタ 160 にトランジスタ A が用いられ、垂直走査回路 110

50

または水平走査回路 108 のトランジスタにトランジスタ B が用いられる。すなわち、入力トランジスタ 160 のチャネル長 L およびチャネル幅 W が、それぞれ、垂直走査回路 110 または水平走査回路 108 のトランジスタのチャネル長 L およびチャネル幅 W より大きい。

#### 【 0222 】

垂直走査回路 110 または水平走査回路 108 は、典型的には、論理ゲートやフリップフロップなどのロジック回路により構成される。そのため、トランジスタのサイズを小さくすることで、高速に動作することが好ましい。先ほどの例と同様に、入力トランジスタ 160 のサイズが、メモリ回路 260 のトランジスタのサイズより大きいことで、結果として、ノイズを低減しつつ、かつ、高速な動作を行うことが可能となる。

10

#### 【 0223 】

次に、トランジスタ A、および、トランジスタ B が、互いに異なる膜厚  $t_{0x}$  のゲート絶縁膜 104 を有する例を説明する。図 8 (a) が示すように、トランジスタ A のゲート絶縁膜 104 の膜厚  $t_{0x}$  が、トランジスタ B のゲート絶縁膜 104 の膜厚  $t_{0x}$  より大きい。一方、図 8 (b) が示すように、トランジスタ A のチャネル長 L およびチャネル幅 W は、それぞれ、トランジスタ B のチャネル長 L およびチャネル幅 W と等しい。図 8 の説明は実施例 1 と同じであるため、繰り返しの説明は省略する。

#### 【 0224 】

異なる膜厚  $t_{0x}$  のゲート絶縁膜 104 を持つ 2 つのトランジスタの組み合わせには、いくつかのバリエーションがある。ひとつの例では、参照トランジスタ 170 にトランジスタ A が用いられ、入力トランジスタ 160 にトランジスタ B が用いられる。すなわち、参照トランジスタ 170 のゲート絶縁膜 104 の膜厚  $t_{0x}$  が、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{0x}$  より大きい。この構成により熱雑音によるノイズを低下させることができる。

20

#### 【 0225 】

前述の式 (1) が表す通り、入力トランジスタ 160 の相互コンダクタンス  $g_{m1}$  が大きくなると、電圧ノイズ  $V_n$  は小さくなる。一方、参照トランジスタ 170 の相互コンダクタンス  $g_{m2}$  が小さくなると、電圧ノイズ  $V_n$  は小さくなる。そして、式 (2) が表す通り、ゲート絶縁膜 104 の膜厚  $t_{0x}$  が小さいほど、相互コンダクタンス  $g_{m}$  は大きくなる。

30

#### 【 0226 】

この例では、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{0x}$  が小さいため、入力トランジスタ 160 の相互コンダクタンス  $g_{m1}$  を大きくすることができる。一方、参照トランジスタ 170 のゲート絶縁膜 104 の膜厚  $t_{0x}$  が大きいため、参照トランジスタ 170 の相互コンダクタンス  $g_{m2}$  を小さくすることができる。結果として、熱雑音によるノイズを低下させることができる。

#### 【 0227 】

なお、ノイズをさらに低下させるためには、入力トランジスタ 160 のチャネル長 L は参照トランジスタ 170 のチャネル長 L より短く、かつ、入力トランジスタ 160 のチャネル幅 W は参照トランジスタ 170 のチャネル幅 W より大きいことが好ましい。

40

#### 【 0228 】

他の例では、入力トランジスタ 160 にトランジスタ A が用いられ、カウンタ回路 152、または、メモリセル 153 のトランジスタにトランジスタ B が用いられる。すなわち、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{0x}$  が、カウンタ回路 152、または、メモリセル 153 のトランジスタのゲート絶縁膜 104 の膜厚  $t_{0x}$  より大きい。

#### 【 0229 】

差動対回路 11 などアノログ回路に使われるトランジスタには、比較的高い電源電圧が供給される。そのため、高い耐圧が得られるように、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{0x}$  を大きくすることが好ましい。一方、カウンタ回路 152、および、メモリセル 153 などのデジタル回路は、アノログ回路に対して相対的に高速に動作す

50

ることが多い。また、典型的には、アナログ回路の電源電圧より低い電源電圧が供給される。そのため、ゲート絶縁膜 104 の膜厚  $t_{ox}$  を小さくすることで、トランジスタが高速に動作することが好ましい。つまり、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、カウンタ回路 152 またはメモリセル 153 のトランジスタのゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きいことで、信頼性を向上しつつ、かつ、高速な動作を行うことが可能となる。

#### 【0230】

他の例では、入力トランジスタ 160 にトランジスタ A が用いられ、垂直走査回路 110 または水平走査回路 108 のトランジスタにトランジスタ B が用いられる。すなわち、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、垂直走査回路 110 または水平走査回路 108 のトランジスタのゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きい。

10

#### 【0231】

垂直走査回路 110 および水平走査回路 108 は、典型的には、論理ゲートやフリップフロップなどのロジック回路により構成される。そのため、トランジスタのサイズを小さくすることで、高速に動作することが好ましい。入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、垂直走査回路 110 または水平走査回路 108 のトランジスタのゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きいことで、信頼性を向上しつつ、かつ、高速な動作を行うことが可能となる。

#### 【0232】

次に、さらに別の変形例を説明する。図 9 (a) が示すように、トランジスタ A のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、トランジスタ B のゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きい。そして、図 9 (b) が示すように、トランジスタ A のチャネル長 L およびチャネル幅 W が、それぞれ、トランジスタ B のチャネル長 L およびチャネル長 W より大きい。

20

#### 【0233】

図 7 および図 8 の例と同様に、入力トランジスタ 160 にトランジスタ A およびトランジスタ B の一方を適用し、他のトランジスタにトランジスタ A およびトランジスタ B の他方を適用することで、電気的特性の向上の効果を得ることができる。

#### 【0234】

例えば、参照トランジスタ 170 にトランジスタ A が用いられ、入力トランジスタ 160 にトランジスタ B が用いられる。すなわち、参照トランジスタ 170 のチャネル長 L およびチャネル幅 W が、それぞれ、入力トランジスタ 160 のチャネル長 L およびチャネル幅 W より大きい。さらに、参照トランジスタ 170 のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きい。

30

#### 【0235】

このような構成により、まず、比較器の入力ノード（入力トランジスタ 160 のゲート）の電荷電圧変換係数を大きくすることができる。さらに、参照トランジスタ 170 において、 $1/f$  ノイズを低減することができる。加えて、差動対で生じる熱雑音によるノイズを低減することができる。

#### 【0236】

なお、図 9 では、ゲート絶縁膜 104 の膜厚  $t_{ox}$ 、チャネル長 L、および、チャネル幅 W の各観点において、トランジスタ A のサイズがトランジスタ B のサイズより大きい。しかし、一部の観点において、サイズの関係が逆であってもよい。

40

#### 【0237】

相互コンダクタンス  $g_m$  を最適化するためには、参照トランジスタ 170 のゲート絶縁膜 104 の膜厚  $t_{ox}$  が、入力トランジスタ 160 のゲート絶縁膜 104 の膜厚  $t_{ox}$  より大きいことが好ましい。また、参照トランジスタ 170 のチャネル長 L が、入力トランジスタ 160 のチャネル長 L より大きいことが好ましい。一方で、参照トランジスタ 170 のチャネル幅 W は、入力トランジスタ 160 のチャネル幅 W より小さいことが好ましい。

#### 【0238】

以上に説明した通り、画素 100 は、入力トランジスタ 160 は、光電変換部 130 で生

50

じた信号電荷に基づく信号を受け、かつ、参照トランジスタ 170 と差動対を構成する入力トランジスタ 160 を含む。そして、入力トランジスタ 160 のサイズは、画素回路の他のいずれかのトランジスタ、または、読み出し回路のトランジスタのサイズと異なっている。このような構成により、電気的特性を向上させることができる。

【0239】

チャネル幅 W が大きいことにより、 $1/f$  ノイズの低減、閾値電圧のばらつきの低減、入力トランジスタ 160 として用いられたときの熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

【0240】

一方、チャネル幅 W が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの電荷電圧変換係数の向上、参照トランジスタ 170 として用いられたときのノイズの低減（相互コンダクタンス  $g_m$  の低下）などの効果が得られる。

10

【0241】

チャネル長 L が大きいことにより、 $1/f$  ノイズの低減、閾値電圧のばらつきの低減、参照トランジスタ 170 として用いたときのノイズの低減（相互コンダクタンス  $g_m$  の低下）などの効果が得られる。

【0242】

一方、チャネル長 L が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの電荷電圧変換係数の向上、および、熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

20

【0243】

ゲート絶縁膜 104 の膜厚  $t_{ox}$  が大きいことにより、耐圧の向上、参照トランジスタ 170 として用いたときのノイズの低減（相互コンダクタンス  $g_m$  の低下）などの効果が得られる。

【0244】

一方、ゲート絶縁膜 104 の膜厚  $t_{ox}$  が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

【0245】

これらの効果を得るために、上述した組み合わせの例の他にも、サイズの異なるトランジスタの組み合わせが選択されうる。

30

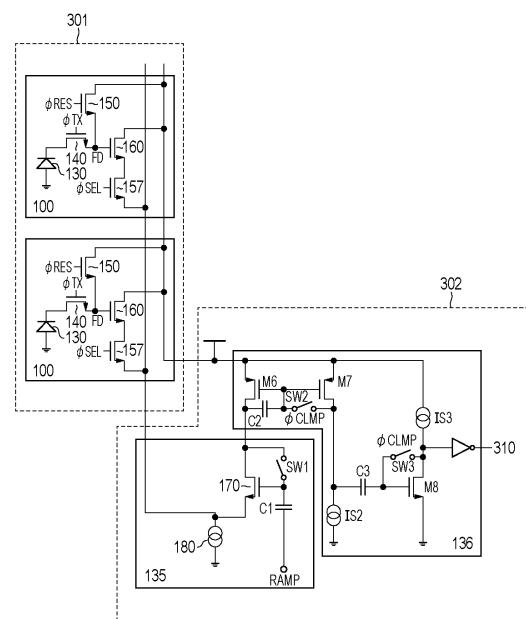

【0246】

[変形例 1]

本実施例の変形例について説明する。図 14 に示された回路は、1 つの半導体基板に配されている。変形例として、本実施例の回路が、第 1 の半導体基板 301 と第 2 の半導体基板 302 に分かれて配置される。図 15 に変形例の等価回路を示す。

【0247】

画素 100 は第 1 の半導体基板 301 に配される。具体的に、光電変換部 130、転送トランジスタ 140、リセットトランジスタ 150、および、入力トランジスタ 160 は、第 1 の半導体基板 301 に配される。

40

【0248】

これに対して、参照トランジスタ 170 および電流源 180、ならびに、クランプ回路（クランプ容量素子 C1 およびクランプスイッチ素子 SW1）を含む比較回路 135 は、第 2 の半導体基板 302 に配される。また、出力回路 136 は、第 2 の半導体基板 302 に配される。

【0249】

すなわち、図 16 に示された例は、実施例 3 と同様に、差動対を構成する入力トランジスタ 160 と参照トランジスタ 170 とが、異なる半導体基板に配置される。

【0250】

画素 100 を駆動するための垂直走査回路 110 は、第 1 の半導体基板 301 に配される

50

。一方、ランプ信号発生回路 12、カウンタ回路 152、メモリセル 153、および、水平走査回路 108 は、第 2 の半導体基板 302 に配される。なお、垂直走査回路 110 が、第 2 の半導体基板 302 に配され、画素 100 のみが第 1 の半導体基板 301 に配されていてもよい。

【0251】

第 1 の半導体基板 301 のトランジスタのサイズが、第 2 の半導体基板 302 のトランジスタのサイズと異なる点は、実施例 2、および、実施例 3 と同じである。実施例 2 および実施例 3 で説明したすべての組み合わせが、本実施例にも適用される。

【0252】

特に、図 16 の例では、第 1 の半導体基板 301 の入力トランジスタ 160 のサイズが、第 2 の半導体基板 302 の参照トランジスタ 170 のサイズと異なっている。このような構成により、簡易な製造プロセスで製造された光電変換装置において、電気的特性を向上させることができる。

【0253】

また、画素 100 のトランジスタ（例えば入力トランジスタ 160）のサイズと、出力回路 136 のトランジスタのサイズが異なっていてもよい。

【0254】

【変形例 2】

本実施例のさらに別の変形例について説明する。図 17 に変形例の等価回路を示す。本実施例の回路が、第 1 の半導体基板 301 と第 2 の半導体基板 302 に分かれて配置される。参照トランジスタ 170、電流源 180、および、クランプ回路（クランプ容量素子 C1 およびクランプスイッチ素子 SW1）を含む比較回路 135 が、第 1 の半導体基板 302 に配される点で、図 17 の例は、図 16 の例と異なっている。これに伴って、ランプ信号発生回路 12 が、第 1 の半導体基板 301 に配されてもよい。

20

【0255】

この変形例においても、第 1 の半導体基板 301 のトランジスタのサイズが、第 2 の半導体基板 302 のトランジスタのサイズと異なる点は、実施例 2、および、実施例 3 と同じである。実施例 2 および実施例 3 で説明したすべての組み合わせが、本実施例にも適用される。

【0256】

30

【実施例 7】

別の実施例を説明する。本実施例は、画素 100 がオペアンプ 159 を用いた增幅回路を含む点が、実施例 1 乃至実施例 6 と異なる。

【0257】

図 18 は画素 100 の等価回路を示す。図 3 と同じ機能を有する素子には、図 3 と同じ符号を付してある。本実施例の画素 100 は、オペアンプ 159 を含む、オペアンプ 159 は、非反転入力ノードと、反転入力ノードを有する。オペアンプ 159 の出力ノードとオペアンプ 159 の反転入力ノードとはフィードバック容量によって接続される。オペアンプ 159 の非反転入力ノードには、転送トランジスタ 140 とリセットトランジスタ 150 が接続される。光電変換部 130 で生じた信号電荷に基づく信号は、オペアンプ 159 の非反転入力ノードに入力される。

40

【0258】

オペアンプ 159 は、不図示の、入力トランジスタと参照トランジスタを含む。入力トランジスタと参照トランジスタは差動対を構成している。入力トランジスタのゲートがオペアンプ 159 の非反転入力ノードである。参照トランジスタのゲートがオペアンプ 159 の反転入力ノードである。

【0259】

本実施例において、オペアンプ 159 に含まれる入力トランジスタのサイズが、他のトランジスタのサイズと異なる。このような構成により、電気的特性の向上の効果を得ることができる。サイズの異なる 2 つのトランジスタの組み合わせは、実施例 1 乃至実施例 6 で

50

説明した組み合わせが適宜適用される。サイズの異なる2つのトランジスタの構造は、図7乃至図9に示されている。

#### 【0260】

##### 【実施例8】

別の実施例を説明する。画素100の画素回路が3つの半導体基板に分かれて配置されることが、本実施例と実施例1乃至実施例7との相違点である。

#### 【0261】

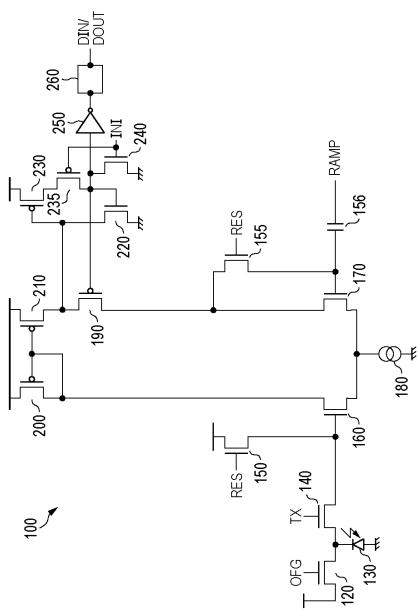

図19は、画素100の構成を模式的に示すブロック図である。画素100の画素回路は、機能的に、複数の回路ブロックにより構成される。信号電荷処理回路10は、光電変換部で生じた信号電荷の蓄積、転送、排出を行う。差動対回路11は、差動対を構成するトランジスタ、および、差動対に電流を供給する電流源を含む。カレントミラーレベルシフタ回路13は、差動対回路11に流れる電流を制御する。差動対回路11およびカレントミラーレベルシフタ回路13は、ADC回路の比較器を構成する。さらに、画素100の画素回路は、レベルシフタ回路250、メモリ回路260を含む。レベルシフタ回路250は、比較器から出力されるラッチ信号の振幅を小さくする。メモリ回路260は、比較器の出力するラッチ信号に基づいて、デジタル信号を保持する。典型的には、差動対回路11、カレントミラーレベルシフタ回路13、および、メモリ回路260が、ADC回路を構成する。

10

#### 【0262】

各回路ブロックの詳細な構成は、実施例1と同じである。すなわち、図3が本実施例の画素100の等価回路図を示している。なお、不図示のランプ信号発生回路12が、ADC回路にランプ信号を供給する。また、本実施例の画素100は、正帰還回路14を含まない。そのため、比較器の出力ノードが、直接、レベルシフタ回路250に接続される。なお、実施例1のように、画素100が正帰還回路14を含んでもよい。正帰還回路14は、比較器の出力の反転を高速化する。換言すると、正帰還回路14は、比較器の出力が反転を開始したことに応じて、立ち上がり（または立ち下がり）のより速いパルスを生成する。

20

#### 【0263】

図19が示すように、光電変換部130、信号電荷処理回路10、および、差動対回路11が第1の半導体基板301（上部基板）に配される。カレントミラーレベルシフタ回路13、および、レベルシフタ回路250が、第2の半導体基板302（中間基板）に配される。メモリ回路260は、第3の半導体基板303（下部基板）に配される。光源（被写体）に近い側から順に、第1の半導体基板301、第2の半導体基板302、および、第3の半導体基板303が積層される。

30

#### 【0264】

本実施例においては、入力トランジスタ160のサイズが、メモリ回路260のトランジスタのサイズと異なっている。それに加えて、レベルシフタ回路250のトランジスタのサイズが、メモリ回路260のトランジスタのサイズと異なっている。すなわち、第1の半導体基板301に配されたトランジスタのサイズと、第3の半導体基板303に配されたトランジスタのサイズが異なっている。さらに、第2の半導体基板302に配されたトランジスタのサイズと、第3の半導体基板303に配されたトランジスタのサイズが異なっている。サイズの異なる2つのトランジスタは、図7乃至図9に示されている。このような構成により、高い信頼性と高速動作の両立が可能である。

40

#### 【0265】

例えば、入力トランジスタ160のゲート絶縁膜104の膜厚 $t_{0x}$ が、メモリ回路260のトランジスタのゲート絶縁膜104の膜厚 $t_{0x}$ より大きい。加えて、レベルシフタ回路250のトランジスタのゲート絶縁膜104の膜厚 $t_{0x}$ が、メモリ回路260のトランジスタのゲート絶縁膜104の膜厚 $t_{0x}$ より大きい。

#### 【0266】

差動対回路11やレベルシフタ回路250はアナログ回路であり、比較的高い電源電圧が供給される。そのため、高い耐圧が得られるように、トランジスタのゲート絶縁膜104

50

の膜厚  $t_{ox}$  が大きいことが好ましい。一方、メモリ回路 260 などのデジタル回路は、アナログ回路に対して相対的に高速に動作することが多い。また、典型的には、アナログ回路の電源電圧より低い電源電圧が供給される。そのため、ゲート絶縁膜 104 の膜厚  $t_{ox}$  を小さくすることで、トランジスタが高速に動作することが好ましい。

#### 【0267】

このように、本実施例では、レベルシフタ回路 250 までの回路のトランジスタと、レベルシフタ回路 250 より後段の回路のトランジスタとが、異なる膜厚  $t_{oz}$  のゲート絶縁膜 104 を含む。そのため、高い信頼性と高速動作の両立が可能である。

#### 【0268】

さらに、入力トランジスタ 160 のサイズが、レベルシフタ回路 250 のトランジスタのサイズと異なっていてもよい。3つの半導体基板に分かれて画素回路が配置された場合、各半導体基板のトランジスタは、独立した製造プロセスにより形成される。したがって、3つの半導体基板のトランジスタが、互いに異なるサイズを有することにより、各半導体基板に対して最適なデザインルールを適用することができる。

#### 【0269】

以上に説明した通り、入力トランジスタ 160 のサイズが、メモリ回路 260 のトランジスタのサイズと異なっている。加えて、レベルシフタ回路 250 のトランジスタのサイズが、メモリ回路 260 のトランジスタのサイズと異なっている。このような構成により、高い信頼性と高速動作の両立が可能である。

#### 【0270】

もちろん、実施例 1 乃至実施例 8 の構成を、適宜、本実施例に組み合わせることで、実施例 1 乃至実施例 8 で説明した効果を得ることができる。

#### 【0271】

##### [実施例 9]

サイズの異なる 2 つのトランジスタの組み合わせについて、他の例を説明する。本実施例の説明は、実施例 1 乃至実施例 8 のそれぞれに対して、変形例として適用される。

#### 【0272】

図 20 は、トランジスタ A のサイズとトランジスタ B のサイズとの関係を示す図である。チャネル長 L、チャネル幅 W、および、ゲート絶縁膜 104 の膜厚  $t_{ox}$  の関係が示されている。例えば、図 20 (a) の表は、トランジスタ A のチャネル長 L が、トランジスタ B のチャネル長 L よりも大きいことを意味している。また、空欄は、任意の関係であることを意味している。サイズの異なるサイズの 2 つのトランジスタの構造は、図 7 から図 9 に例示される。

#### 【0273】

1 つの例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が入力トランジスタ 160 である。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【0274】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が電荷排出

10

20

30

40

50

トランジスタ 120 である。この場合、トランジスタ B は、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【0275】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が転送トランジスタ 140 である。この場合、トランジスタ B は、電荷排出トランジスタ 120、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【0276】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A がリセットトランジスタ 150 である。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【0277】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が参照トランジスタ 170 である。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフ

10

20

30

40

50

タ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【 0278 】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が電流源 180 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、および、参照トランジスタ 170 から選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

10

#### 【 0279 】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A がランプ信号発生回路 12 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

20

#### 【 0280 】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A がカレントミラー回路 13 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または

30

40

50

、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

【 0 2 8 1 】

別の例では、図 20 ( a ) から図 20 ( m ) の各表において、トランジスタ A が正帰還回路 14 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120 、転送トランジスタ 140 、リセットトランジスタ 150 、入力トランジスタ 160 、参照トランジスタ 170 、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

10

【 0 2 8 2 】

別の例では、図 20 ( a ) から図 20 ( m ) の各表において、トランジスタ A がレベルシフタ回路 250 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120 、転送トランジスタ 140 、リセットトランジスタ 150 、入力トランジスタ 160 、参照トランジスタ 170 、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、または、正帰還回路 14 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

20

【 0 2 8 3 】

別の例では、図 20 ( a ) から図 20 ( m ) の各表において、トランジスタ A がラッチ回路 151 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120 、転送トランジスタ 140 、リセットトランジスタ 150 、入力トランジスタ 160 、参照トランジスタ 170 、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

30

【 0 2 8 4 】

別の例では、図 20 ( a ) から図 20 ( m ) の各表において、トランジスタ A がカウンタ

40

50

回路 152 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【0285】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A がメモリセル 153 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【0286】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が読み出し回路 110 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、または、メモリセル 153 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【0287】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が水平走査回路 108 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14

10

20

30

40

50

を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、比較回路 135 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

#### 【 0288 】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が比較回路 135 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、出力回路 136 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

10

#### 【 0289 】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が出力回路 136 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、または、オペアンプ 159 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

20

#### 【 0290 】

別の例では、図 20 (a) から図 20 (m) の各表において、トランジスタ A が、オペアンプ 159 を構成するトランジスタである。この場合、トランジスタ B は、電荷排出トランジスタ 120、転送トランジスタ 140、リセットトランジスタ 150、入力トランジスタ 160、参照トランジスタ 170、および、電流源 180 を構成するトランジスタから選ばれるいずれかである。あるいは、トランジスタ B は、ランプ信号発生回路 12 を構成するトランジスタ、カレントミラー回路 13 を構成するトランジスタ、正帰還回路 14 を構成するトランジスタ、または、レベルシフタ回路 250 を構成するトランジスタである。あるいは、トランジスタ B は、ラッチ回路 151 を構成するトランジスタ、カウンタ回路 152 を構成するトランジスタ、メモリセル 153 を構成するトランジスタ、または、読み出し回路 110 を構成するトランジスタである。あるいは、トランジスタ B は、水平走査回路 108 を構成するトランジスタ、比較回路 135 を構成するトランジスタ、ま

30

40

50

たは、出力回路 136 を構成するトランジスタである。ここで、上述のトランジスタおよび回路は、いずれも、実施例 1 乃至実施例 8 において同じ符号が付されたトランジスタおよび回路である。

【0291】

上述の各例において、実施例 1 のように、トランジスタ A とトランジスタ B とは同じ半導体基板に形成されてもよい。あるいは、上述の各例において、トランジスタ A とトランジスタ B とは、互いに異なる半導体基板に形成されてもよい。

【0292】

トランジスタのサイズが異なることによって、次の効果を得ることができる。チャネル幅 W が大きいことにより、 $1/f$  ノイズの低減、閾値電圧のばらつきの低減、入力トランジスタ 160 として用いられたときの熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

10

【0293】

一方、チャネル幅 W が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの電荷電圧変換係数の向上、参照トランジスタ 170 として用いられたときのノイズの低減（相互コンダクタンス  $g_m$  の低下）などの効果が得られる。

【0294】

チャネル長 L が大きいことにより、 $1/f$  ノイズの低減、閾値電圧のばらつきの低減、参照トランジスタ 170 として用いたときのノイズの低減（相互コンダクタンス  $g_m$  の低下）などの効果が得られる。

20

【0295】

一方、チャネル長 L が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの電荷電圧変換係数の向上、および、熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

【0296】

ゲート絶縁膜 104 の膜厚  $t_{ox}$  が大きいことにより、耐圧の向上、参照トランジスタ 170 として用いたときのノイズの低減（相互コンダクタンス  $g_m$  の低下）などの効果が得られる。

30

【0297】

一方、ゲート絶縁膜 104 の膜厚  $t_{ox}$  が小さいことにより、高速動作、入力トランジスタ 160 として用いられたときの熱雑音によるノイズの低減（相互コンダクタンス  $g_m$  の増加）などの効果が得られる。

【0298】

【実施例 10】

撮像システムの実施例について説明する。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、カメラヘッド、複写機、ファックス、携帯電話、スマートフォン、車載カメラ、観測衛星などがあげられる。図 21 に、撮像システムの例としてデジタルスチルカメラのブロック図を示す。

【0299】

図 21において、1001 はレンズの保護のためのバリアである。1002 は被写体の光学像を撮像装置 1004 に結像させるレンズである。1003 はレンズ 1002 を通った光量を可変するための絞りである。撮像装置 1004 には、上述の実施例 1 乃至実施例 4 のいずれかで説明した撮像装置が用いられる。

40

【0300】

1007 は撮像装置 1004 より出力された画素信号に対して、補正やデータ圧縮などの処理を行い、画像信号を取得する信号処理部である。そして、図 21 において、1008 は撮像装置 1004 および信号処理部 1007 に、各種タイミング信号を出力するタイミング発生部、1009 はデジタルスチルカメラ全体を制御する全体制御部である。1010 は画像データを一時的に記憶する為のフレームメモリ部である。1011 は記録媒体に記録または読み出しを行うためのインターフェース部である。1012 は撮像データの記

50

録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体である。1013は外部コンピュータ等と通信する為のインターフェース部である。

【0301】

なお、撮像システムは少なくとも撮像装置1004と、撮像装置1004から出力された画素信号を処理する信号処理部1007とを有すればよい。その場合、他の構成はシステムの外部に配される。

【0302】

以上に説明した通り、撮像システムの実施例において、撮像装置1004には、実施例1乃至実施例9のいずれかの光電変換装置が用いられる。このような構成によれば、撮像システムの電気的特性を向上させることができる。

10

【0303】

【実施例11】

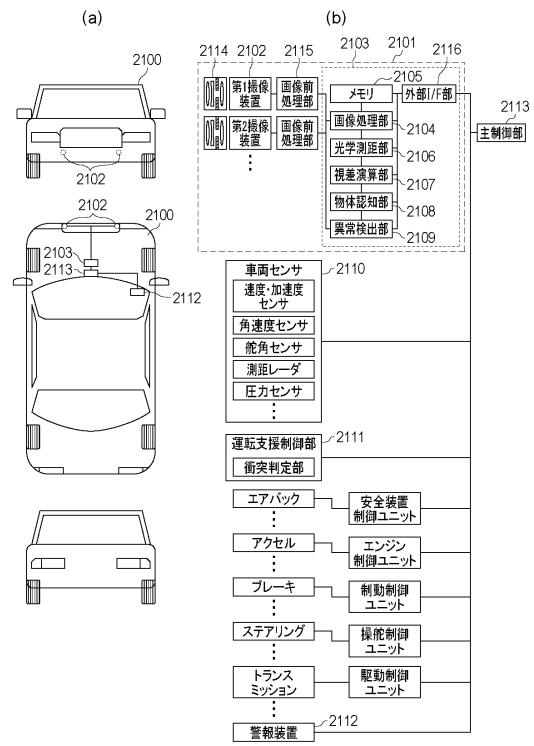

移動体の実施例について説明する。本実施例の移動体は、車載カメラを備えた自動車である。図22(a)は、自動車2100の外観と主な内部構造を模式的に示している。自動車2100は、撮像装置2102、撮像システム用集積回路(Application Specific Integrated Circuit)2103、警報装置2112、主制御部2113を備える。

【0304】

撮像装置2102には、上述の各実施例で説明した撮像装置が用いられる。警報装置2112は、撮像システム、車両センサ、制御ユニットなどから異常を示す信号を受けたときに、運転手へ向けて警告を行う。主制御部2113は、撮像システム、車両センサ、制御ユニットなどの動作を統括的に制御する。なお、自動車2100が主制御部2113を備えていなくてもよい。この場合、撮像システム、車両センサ、制御ユニットが個別に通信インターフェースを有して、それぞれが通信ネットワークを介して制御信号の送受を行う(例えばCAN規格)。

20

【0305】

図22(b)は、自動車2100のシステム構成を示すブロック図である。自動車2100は、第1の撮像装置2102と第2の撮像装置2102を含む。つまり、本実施例の車載カメラはステレオカメラである。撮像装置2102には、光学部2114により被写体像が結像される。撮像装置2102から出力された画素信号は、画像前処理部2115によって処理され、そして、撮像システム用集積回路2103に伝達される。画像前処理部2115は、S-N演算や、同期信号付加などの処理を行う。

30

【0306】

撮像システム用集積回路2103は、画像処理部2104、メモリ2105、光学測距部2106、視差演算部2107、物体認知部2108、異常検出部2109、および、外部インターフェース(I/F)部2116を備える。画像処理部2104は、画素信号を処理して画像信号を生成する。また、画像処理部2104は、画像信号の補正や異常画素の補完を行う。メモリ2105は、画像信号を一時的に保持する。また、メモリ2105は、既知の撮像装置2102の異常画素の位置を記憶していてもよい。光学測距部2106は、画像信号を用いて被写体の合焦または測距を行う。視差演算部2107は、視差画像の被写体照合(ステレオマッチング)を行う。物体認知部2108は、画像信号を解析して、自動車、人物、標識、道路などの被写体の認知を行う。異常検出部2109は、撮像装置2102の故障、あるいは、誤動作を検知する。異常検出部2109は、故障や誤動作を検知した場合には、主制御部2113へ異常を検知したことを示す信号を送る。外部I/F部2116は、撮像システム用集積回路2103の各部と、主制御部2113あるいは種々の制御ユニット等との間での情報の授受を仲介する。

40

【0307】

自動車2100は、車両情報取得部2110および運転支援部2111を含む。車両情報取得部2110は、速度・加速度センサ、角速度センサ、舵角センサ、測距レーダ、圧力センサなどの車両センサを含む。

50

## 【0308】