(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2018-510481

(P2018-510481A)

(43) 公表日 平成30年4月12日(2018.4.12)

(51) Int.Cl.

H05B 37/03 (2006.01)

H05B 37/02 (2006.01)

F 1

H05B 37/03

H05B 37/02

テーマコード(参考)

B

J 3 K 2 7 3

審査請求 未請求 予備審査請求 未請求 (全 14 頁)

(21) 出願番号 特願2017-550847 (P2017-550847)

(86) (22) 出願日 平成28年3月23日 (2016.3.23)

(85) 翻訳文提出日 平成29年10月13日 (2017.10.13)

(86) 國際出願番号 PCT/EP2016/056318

(87) 國際公開番号 WO2016/156130

(87) 國際公開日 平成28年10月6日 (2016.10.6)

(31) 優先権主張番号 15161585.3

(32) 優先日 平成27年3月30日 (2015.3.30)

(33) 優先権主張国 歐州特許庁 (EP)

(71) 出願人 516043960

フィリップス ライティング ホールディング ピー ヴィ

オランダ国 5656 アーヴー アイン

トホーフェン ハイ テク キャンパス

45

(74) 代理人 110001690

特許業務法人M&Sパートナーズ

(72) 発明者 バン ボーデグラヴェン タイメン コル

ネリス

オランダ国 5656 アーヴー アイン

トホーフェン ハイ テク キャンパス

5

最終頁に続く

(54) 【発明の名称】絶縁ドライバ

## (57) 【要約】

本発明は、負荷3に電圧及び電流を供給するコンバータモジュール21と、ドライバ2の動作中に電圧及び/又は電流を監視するフィードバック装置22と、コンバータモジュール21にコンバータ制御信号CI、CF、VCONを供給するコンバータコントローラ1とを含む絶縁ドライバ2であって、コンバータコントローラ1は、入力端子によりフィードバック装置22に接続された单一のオプトカプラ10と、オプトカプラの出力端子間の電圧が故障状態を示すとき、ドライバ2のコンバータモジュール21を低出力モードMLOにするためのコンバータ制御信号CI、CF、VCONを生成する、複数の半導体スイッチQ<sub>20</sub>、…、Q<sub>25</sub>、Q<sub>30</sub>、…、Q<sub>34</sub>を含む、オプトカプラ10の出力端子に接続されたスイッチング回路装置11と、を含む、絶縁ドライバ2を特徴付ける。本発明はさらに、主電源4からLED照明負荷3を駆動するための絶縁ドライバ2を含むLED照明装置5を特徴付ける。本発明はまた、絶縁ドライバ2用のコンバータコントローラ1と、絶縁ドライバ2を動作させる方法とを特徴付ける。

FIG. 2

## 【特許請求の範囲】

## 【請求項 1】

負荷に電圧及び電流出力を供給するコンバータモジュールと、絶縁ドライバの動作中に電圧及び/又は電流を監視するフィードバック装置と、前記コンバータモジュールにコンバータ制御信号を供給するコンバタコントローラとを含む、絶縁ドライバであって、前記コンバタコントローラは、

入力端子により前記フィードバック装置に接続された單一のオプトカプラであって、故障状態を示すために前記單一のオプトカプラの出力トランジスタが導通していない、前記單一のオプトカプラと、

前記單一のオプトカプラの出力端子の両端の電圧が故障状態を示すとき、前記絶縁ドライバの前記コンバータモジュールを低出力モードにするためのコンバータ制御信号を生成する複数の半導体スイッチを含む、前記單一のオプトカプラの出力端子に接続されたスイッチング回路装置と

を含む、絶縁ドライバ。

## 【請求項 2】

前記フィードバック装置は、前記絶縁ドライバの二次側に設けられ、前記コンバタコントローラは、前記絶縁ドライバの一次側に設けられる、請求項 1 に記載の絶縁ドライバ。

## 【請求項 3】

前記スイッチング回路装置は、故障状態に応答してコンバータ制御信号をラッチする、請求項 1 又は 2 に記載の絶縁ドライバ。

## 【請求項 4】

前記スイッチング回路装置は、所定の持続時間だけ故障状態応答を遅延させる遅延要素を含む、請求項 1 乃至 3 の何れか一項に記載の絶縁ドライバ。

## 【請求項 5】

前記單一のオプトカプラは、前記單一のオプトカプラの第 1 の出力端子が、通常動作中には低電位であり、故障状態中には高電位であるように、前記フィードバック装置に接続される、請求項 1 乃至 4 の何れか一項に記載の絶縁ドライバ。

## 【請求項 6】

前記コンバータモジュールは、集積回路を含み、前記スイッチング回路装置は、前記集積回路の対応するピンに供給するためのコンバータ制御信号を生成する、請求項 1 乃至 5 の何れか一項に記載の絶縁ドライバ。

## 【請求項 7】

コンバータ制御信号が、故障状態に応答して前記コンバータモジュールのスイッチング周波数を増大させる、請求項 1 乃至 6 の何れか一項に記載の絶縁ドライバ。

## 【請求項 8】

第 1 の故障状態に応答して第 1 のコンバータ制御信号が生成されて、前記單一のオプトカプラの前記出力端子間の上昇した電圧となり、第 2 の故障状態に応答して第 2 のコンバータ制御信号が生成されて、前記單一のオプトカプラの前記出力端子間の低下した電圧となる、請求項 1 乃至 7 の何れか一項に記載の絶縁ドライバ。

## 【請求項 9】

U L CLAS 2 ドライバとして実現される、請求項 1 乃至 8 の何れか一項に記載の絶縁ドライバ。

## 【請求項 10】

主電源から LED 照明負荷を駆動するために請求項 1 乃至 9 の何れか一項に記載の絶縁ドライバを含む、LED 照明装置。

## 【請求項 11】

絶縁ドライバのフィードバック装置に接続するための入力端子を含む單一のオプトカプラであって、故障状態を示すために前記單一のオプトカプラの出力トランジスタが導通していない、前記單一のオプトカプラと、

10

20

30

40

50

前記単一のオプトカプラの出力端子間の電圧が故障状態を示すとき、前記絶縁ドライバのコンバータモジュールを低出力モードにするコンバータ制御信号を生成する、複数の半導体スイッチを含む、前記単一のオプトカプラの前記出力端子に接続されたスイッチング回路装置と

を含む、絶縁ドライバ用のコンバータコントローラ。

【請求項 1 2】

負荷に電圧及び電力出力を供給するためのコンバータモジュールを含む、絶縁ドライバを動作させる方法であって、

前記絶縁ドライバの動作中に、電圧及び／又は電流を監視するために、フィードバック装置からフィードバック信号を供給するステップと、

前記フィードバック信号を、前記コンバータモジュールを制御するスイッチング回路装置にオプトカプラを介して転送するステップと、

故障状態を示すために前記オプトカプラの出力トランジスタが導通しないようにするフィードバック信号を供給するステップと、

前記オプトカプラの出力端子間の電圧が故障状態を示すとき、前記絶縁ドライバの前記コンバータモジュールを低出力モードにするステップと

を含む、方法。

【請求項 1 3】

前記絶縁ドライバのスタートアップ及び／又はシャットダウン間隔中は、前記スイッチング回路装置を無効にするステップを含む、請求項 1 2 に記載の方法。

10

20

30

40

50

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、絶縁ドライバと、絶縁ドライバ用のコンバータコントローラと、絶縁ドライバを動作させる方法とを特徴付けている。

【背景技術】

【0 0 0 2】

ランプ、小型家電等の低電圧デバイスは、主電源をデバイスに適した電圧及び電流に変換するための、電源又は“ドライバ”を必要とする。例えば、LED光源は、主AC電源を適切なレベルのDC出力に変換する電源から駆動され得る。保護対策が取られていないと、回路内の何れかの部品の故障は、あるポイントでの過度な電圧及び／又は電流をもたらす可能性があり、火災の危険や感電の危険がある。したがって、このようなドライバは、一般的に、（主電源に接続された）一次側が（負荷に接続された）二次側から絶縁又は分離されるように構築される。このような絶縁ドライバは、主電源分離ドライバとも呼ばれる。安全を保証するために、絶縁ドライバ又は電源は、出力電圧及び電流レベルが一定の閾値を超えないことを保証しなければならない。例えば、Underwriters Laboratories LaboratoriesのUL1310規格は、屋内及び屋外用のクラス2パワーユニットに向けられる。UL1310クラス2認定を取得するために、電源又はドライバは、出力電圧が決して60Vを超えないことと、出力電流が決して2.5Aを超えないことと、その出力が決して100Wを超えないことを保証しなければならない。これらの要件は、回路全体の部品が故障した場合でも、電源又はドライバの動作中には常に満たされなければならない。したがって、このような電源又はドライバの製造者は、一般的に、ドライバの二次側を一次側から絶縁する、何らかの保護回路を含ませる。

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 3】

しかし、先行技術の解決策は一般的に複雑であり、多くの部品を必要とし、したがって電源製品の設計労力及びコストを増大させる。さらに、いくつかの故障状態が検出されず、ドライバが完全に準拠しているとはみなされない可能性がある。先行技術の例として、

当業者は、米国特許第8,520,415号、EP 2284980又はU.S.2014/0328427を参考し得る。

【0004】

したがって、本発明の目的は、上述のタイプの絶縁ドライバの出力が、動作中、常に安全レベル内に留まることを保証する、より経済的なやり方を提供することである。

【課題を解決するための手段】

【0005】

本発明の目的は、請求項1に記載の絶縁ドライバと、請求項11に記載のコンバータコントローラと、絶縁ドライバを動作させる請求項13に記載の方法とによって、達成される。

10

【0006】

本発明による絶縁ドライバは、負荷に電圧及び電流出力を供給するコンバータモジュールと、絶縁ドライバの動作中に電圧及び/又は電流を監視するフィードバック装置と、コンバータモジュールにコンバータ制御信号を供給するコンバータコントローラとを含み、コンバータコントローラは、一対の入力端子によりフィードバック装置に接続された単一のオプトカプラであって、故障状態を示すためにオプトカプラの出力トランジスタが導通していない、単一のオプトカプラと、オプトカプラ出力端子の両端の電圧が故障状態を示すときに、絶縁ドライバのコンバータモジュールを低出力モードにするためのコンバータ制御信号を生成する複数の半導体スイッチを含む、オプトカプラの一対の出力端子に接続されたスイッチング回路装置と、を含む。

20

【0007】

本発明による絶縁ドライバの利点は、オプトカプラの出力電圧が“健全”である限り、コンバータ制御信号がコンバータを通常モードで動作し続けるが、ドライバ及び負荷を含む全体の装置のどこかに故障があるときには、コンバータモジュールが低出力モードにされることを保証することである。“低出力モード”は、出力電圧及び/又は電流が、通常動作モード中のそれらのレベルよりも低い、動作モードとして理解されよう。この安全対策は、単一のオプトカプラ及び複数の半導体スイッチのみを用いて実現され得るので、本発明による絶縁ドライバは非常に経済的に構築され得る。

【0008】

本発明によれば、絶縁ドライバ用のコンバータコントローラは、絶縁ドライバのフィードバック装置に接続するための入力端子を含む単一のオプトカプラであって、故障状態を示すためにオプトカプラの出力トランジスタが導通していない、単一のオプトカプラと、オプトカプラの出力端子間の電圧が故障状態を示すとき、ドライバのコンバータモジュールを低出力モードにするコンバータ制御信号を生成する、複数の半導体スイッチを含む、オプトカプラの出力端子に接続されたスイッチング回路装置とを含む。

30

【0009】

本発明によるコンバータコントローラの利点は、どの部品が故障したかに問らず、一次側と二次側との間の安全な絶縁を保証するために様々なドライバタイプで実施され得ることである。本発明によるコンバータコントローラは、従来の絶縁保護回路と比較して、より簡単な態様で、より少ない部品の数を使用して、実現され得る。本発明によるコンバータコントローラは、全体の装置のどこかに故障があるときには、コンバータモジュールが低出力モードにされることを保証することにより保護機能を果たすので、用語“コンバータコントローラ”と“保護回路”とは、以下において互換的に使用される。

40

【0010】

本発明によれば、負荷に電圧及び電力出力を供給するためのコンバータモジュールを有する、絶縁ドライバを動作させる方法は、絶縁ドライバの動作中に、電圧及び/又は電流を監視するために、フィードバック装置からフィードバック信号を供給するステップと、前記フィードバック信号を、コンバータモジュールを制御するスイッチング装置にオプトカプラを介して転送するステップと、故障状態を示すためにオプトカプラの出力トランジスタが導通されていないようにするフィードバック信号を供給するステップと、オプトカ

50

プラの出力端子間の電圧が故障状態を示すとき、ドライバのコンバータモジュールを低出力モードにするステップとを含む。

【0011】

本発明による方法の利点は、コンバータコントローラ又は保護回路が、ドライバの出力の電圧及び/又は電流が許容レベルを決して超えないことを常に保証し、この保護を簡単かつ費用対効果の高い態様で達成することである。

【0012】

従属請求項及び以下の説明は、本発明の特に有利な実施形態及び特徴を開示する。実施形態の特徴は適宜組み合わさることができる。1つの請求項のカテゴリのコンテキストで説明される機能は、別の請求項のカテゴリにも等しく適用できる。

10

【0013】

以下、本発明を何ら限定するものではないが、コンバータモジュールは、負荷に電圧及び電流を供給するためのスイッチモード電源(SMPS)であると仮定される。コンバータモジュールは、ハーフブリッジコンバータ、フライバックコンバータ等として実現され得る。好ましくは、本発明による絶縁ドライバは、出力電圧及び電流が決して上述の限界を超えないULクラス2ドライバとして実現される。用語“絶縁ドライバ”及び“主電源分離ドライバ”は、以下において互換的に使用される。

【0014】

絶縁ドライバのフィードバック装置の目的は、動作中の電圧及び/又は電流を監視することである。好ましくは、フィードバック装置は絶縁ドライバの二次側に設けられ、コンバータコントローラはドライバの一次側に設けられる。この好ましい装置では、フィードバック装置と、コンバータコントローラと、コンバータモジュールとの間に制御ループが確立され、それによりオプトカプラはドライバの一次側と二次側との間のガルバニック絶縁を事実上保証する。

20

【0015】

全体の装置内の何れかの任意の部品の故障により、上述のように、故障状態が発生し得る。故障状態は、ドライバ内のあるポイントでいつになく高い又は低い電圧をもたらす。フィードバック装置は、これを検出し、オプトカプラの入力端子に適切な電圧レベルを印加し得る。例えば、通常動作中、オプトカプラの一方の入力端子へのフィードバック信号は“ロー”であり得る一方で、他方の端子は永続的に“ハイ”にクランプされるので、オプトカプラダイオードに電流が流れ、オプトカプラトランジスタを導通可能にする。ドライバの二次側、コンバータモジュール、又は負荷での電気的故障中、故障状態はフィードバック装置により検出され、オプトカプラの入力端子で“ハイ”電圧レベルに変換されるので、ダイオードはもはや導通しない。このようにして、フィードバック装置は、“故障情報”をコンバータ制御ユニットに転送する。これは、コンバータを低出力動作モードにすることにより、故障状態に応答する。結果として、二次側は、フィードバック信号をその故障レベルで保持し続けるので、故障状態は事実上“ラッチ”される。この状態は、たとえ故障自体が一時的性質であったとしても、ドライバが主電源から切斷され、再始動されるまで持続する。永続的な故障は、ドライバが安全な“低出力”動作モードから永久に離れるのを防止するが、ドライバは、故障が非永続的性質であった場合、又は故障の原因が取り除かれた場合に、再起動後に通常動作を再開し得る。

30

【0016】

様々な理由から、電気回路の電圧及び/又は電流が時々、その“正しい”レベルから一時的に逸脱し、次いでこの正しいレベルに戻ることがある。このような小さな誤作動は、必ずしも故障に関連することなく、例えば電磁干渉(EMI)の結果として、いつでも発生する。コンバータモジュールが無効にされることを回避するために、すなわち、このような誤作動の場合にコンバータモジュールが低出力動作モードにされることを回避するために、スイッチング回路装置は、好ましくは、所定の持続時間だけ故障状態応答を遅延させる遅延回路部分を含む。このようにして、真の故障のみが故障応答を引き起こす。

40

【0017】

50

ドライバの一次側と二次側との間にオプトカプラを接続する、様々な態様がある。上述のように、オプトカプラは、電流がダイオードを流れる限りトランジスタが“オン”であるように、その入力端子間に接続されたダイオードと、その出力端子間に接続されたNPNバイポーラジャンクショントランジスタ(BJT)とを事実上含む。本発明の好ましい実施形態では、オプトカプラは、オプトカプラの第1の出力端子が、通常動作中には低電位であり、故障状態中には高電位であるように、フィードバック装置に接続される。この目的のために、二次側の“健全な”電圧及び/又は電流レベルにより電流がオプトカプラダイオードを流れるが、二次側の“欠陥のある”電圧及び/又は電流レベルは電流がオプトカプラダイオードを流れるのを防止するといった態様で、オプトカプラはフィードバック装置に接続される。これは、NPNトランジスタのコレクタ端子に対応するオプトカプラ出力の電圧の上昇をもたらす。この上昇した電圧は、図を参照してより詳細に説明されるように、コンバータ制御信号をラッチするために複数の半導体トランジスタをスイッチする。

10

## 【0018】

一般的に、絶縁ドライバのコンバータモジュールのSMP(Single Phase)機能は、既製の集積回路を使用して実現される。したがって、本発明の好ましい実施形態では、保護回路は集積回路の対応するピンによりコンバータ制御信号を生成する。例えば、本発明の好ましい実施形態では、コンバータ制御信号がこのようなICの適切な調整ピンに供給され得るので、故障状態が検出されると、コンバータ制御信号はSMP(Single Phase)を強制的に低出力動作モードにする。本発明のさらに好ましい実施形態では、このようなICがSMP(Single Phase)のスイッチング周波数を調整するための入力ピンを有する場合、そのピンに供給されたコンバータ制御信号は、故障に応答してスイッチング周波数を上昇し得る。上昇したスイッチング周波数により、負荷端子の出力電圧及び電流が低下する。

20

## 【0019】

上述のように、ドライバの一次側でも故障が発生し得る。また、保護回路で故障が発生するか、又はオプトカプラ自身が故障する可能性がある。したがって、本発明の好ましい実施形態では、第1の故障状態に応答して第1のコンバータ制御信号が生成されて、オプトカプラの出力端子間の上昇した電圧となり、第2の故障状態に応答して第2のコンバータ調整信号が生成されて、オプトカプラの出力端子間の低下した電圧となる。このようにして、全体の装置の何れかの任意の故障状態が検出され、応答され得る。

30

## 【0020】

ドライバのスタートアップ又はシャットダウン中、フィードバック装置又はドライバの他の何れかの電圧及び/又は電流レベルは、それらの“通常の”レベルとは異なる場合がある。したがって、本発明のさらに好ましい実施形態では、故障検出及び応答は、ドライバのスタートアップ及び/又はシャットダウン間隔中は無効にされる。これは、例えば、ドライバがスタートアップ又はシャットダウン状態にあるかどうかを判定するために、コントローラICの1つ以上の適切な出力ピンを(保護回路において)監視することにより、達成され得る。

## 【0021】

本発明のこれら等の目的及び特徴は、添付の図面と併せて考慮される以下の詳細な説明から明らかになる。しかし、図面は説明の目的のためだけにデザインされており、本発明の範囲の定義としてではないことを理解されたい。

40

## 【図面の簡単な説明】

## 【0022】

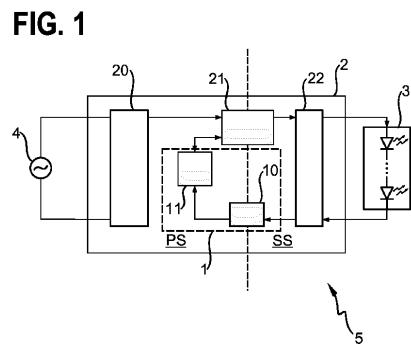

【図1】本発明によるLED照明装置の一実施形態のブロック図を示す。

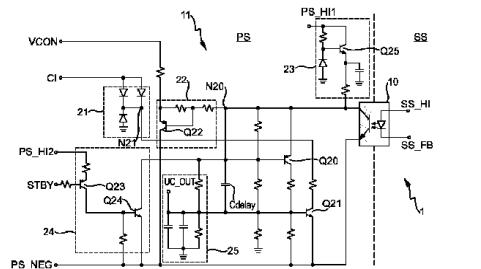

【図2】本発明による保護回路の第1の実施形態を示す。

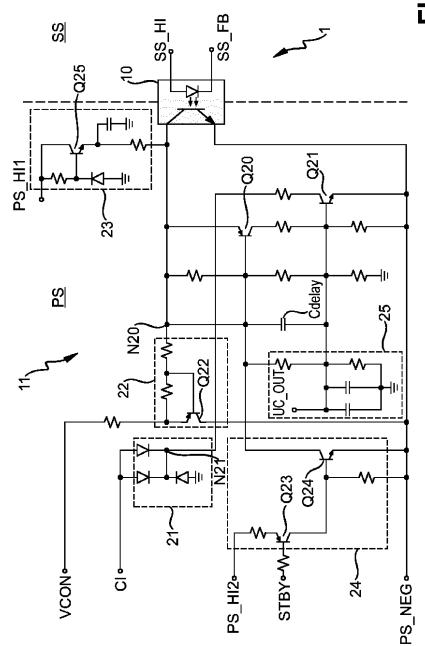

【図3】本発明による保護回路の第2の実施形態を示す。

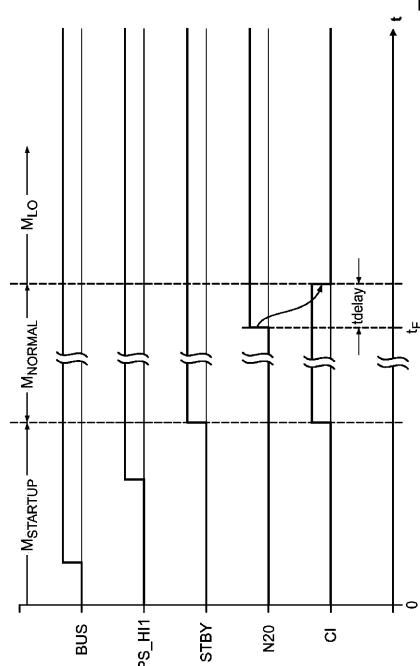

【図4】図1のLED照明装置の例示的なタイミング図を示す。

## 【0023】

図では、同様の番号は全体を通して同様のオブジェクトを示す。図中のオブジェクトは

50

、必ずしも縮尺通りに描かれていない。

【発明を実施するための形態】

【0024】

図1は、本発明によるLED照明装置5の実施形態のブロック図を示し、本発明による絶縁ドライバ2は、主電源4と負荷3との間に接続される。入力段20はAC/DC変換を行い、電力コンバータ（例えばSMPSCコンバータ）21は、DC電力をLED負荷3を駆動することに適した形式に変換する。ドライバ2のフィードバック装置22は、動作中の電圧及び電流レベルを監視するために、コンバータ21と負荷3との間に接続される。図示されていないが、一次側PS上のマイクロコントローラと二次側SS上のマイクロコントローラとは、様々な制御動作を実行するために実装され得る。ドライバ2は、（主電源4に接続された）一次側PSと（負荷3に接続された）二次側SSとに分割され、冒頭で説明されたような特定の安全基準を満たすために、これらは（破線で示されたように）互いに分離又は絶縁されなければならない。この実施形態では、保護がコンバータコントローラ1により達成され、全体の装置5中の何れかに故障が発生した場合、SMPSCコンバータ21を低出力動作モードにする。低出力動作モードでは、ドライバ2の出力の電圧及び電流は、冒頭で述べられた制限を超えない。図2と図3とを参照して説明されるように、これは、スイッチング回路装置11によりコンバータモジュール21に印加される制御信号により達成される。図は、フィードバック装置22と、オプトカプラ10と、スイッチング回路装置11と、コンバータモジュール21を通る制御ループを示す。

10

20

【0025】

図2は、本発明による保護回路1の第1の実施形態を示す。図は、ドライバの一次側PSと二次側SSとの間に単一のオプトカプラ10を示す。オプトカプラの第1の入力端子は二次側上の高電位SS\_HIに接続され、他方の入力端子SS\_FBは図1のフィードバック装置22に接続されるので、ドライバの二次側の電圧及び電流レベルが問題ない限り、オプトカプラ10の入力端子間に電流が流れる。スイッチング回路装置11は、オプトカプラ10の出力端子間に接続される。この実施形態では、信号CI、VCON、STBYは、SMPSC\_ICパッケージ21から生じる。信号CIは、SMPSC\_ICの調整ピンであり、ローに引き下げられるとSMPSCコンバータを低出力動作モードにし、信号VCONは、SMPSC\_ICの追加の調整ピンであり、信号STBYは、ドライバがスタートアップ/シャットダウンモードであるときを示す。特定のノードは、端子PS\_HI1、PS\_HI2により適切な高レベルに保持されるか、グラウンドGND又は負電位PS\_NEGへの接続により、適切な低電位に保持される。

30

【0026】

フィードバック信号SS\_FBが“健全な”低電圧に保持されている限り、オプトカプラ10のNPNトランジスタは通常動作中に導通するので、ドライバの健全な動作はノードN20の低電圧により特徴づけられる。二次側、負荷、又はコンバータモジュールの故障中は、オプトカプラダイオードに流れる電流が少なくなるか、又は電流が流れなくなるように、この端子SS\_FBに高電圧が印加され、その結果、ノードN20の電圧が上昇する。これにより、PNPトランジスタQ20がオンにされるので、NPNトランジスタQ21もオンにされ、次いでSMPSC\_ICのCIピンをノードN21を介してローレベルに引き下げる。回路部分20の遅延要素C\_dealyは、ノードN20での過渡電圧上昇が故障応答を引き起こさないことを保証する。

40

【0027】

この例示的な実施形態では、入力信号STBYはアクティブローであり、ドライバがスタートアップ/シャットダウンモード（ロー）又は通常動作モード（ハイ）にあるときを示す。したがって、ドライバのスタートアップ又はシャットダウン中に、スタンバイ回路部分24のトランジスタQ23が導通し、トランジスタQ24が導通することを保証し、次いでノードN20をローに引き下げる。これは、保護回路11を事実上無効にする。

【0028】

故障状態が発生すると、それが一時的であるか永続的であるかに関らず、コンバータを

50

“低出力”動作モードにした結果として、上述のように“ラッチ”され、次いでフィードバック装置がオプトカプラ入力端子 S S \_ F B に高電圧を維持するようにさせる。

【0029】

C I ピン回路経路に故障が発生した場合、トランジスタ Q 2 1 が導通し、したがって N 2 0 が低電位に引き下がり、結果としてトランジスタ Q 2 2 が導通する。これは、V C O N をローに引き下げるにより、S M P S I C を低出力動作モードにする効果がある。オプトカプラ 1 0 が故障した場合、回路部分 2 3 は、ノード N 2 0 の電圧が上昇することを保証し、その結果、上述のようにピン C I がローに引き下げられる。マイクロコントローラへの出力信号 U C \_ O U T は、通常動作中に故障がないときはローであり、故障状態が検出され“ラッチ”されるときはハイである。

10

【0030】

回路部分 2 1 、 2 3 、 2 5 は、コンバータ I C の接地端子を共有する一方で、回路部分 2 4 は、残りのドライバ回路と接続される。当業者は、本明細書に示される回路要素に精通し、所望の動作を達成するために適切な部品とその値とを選択し得る。

【0031】

図 3 は、本発明による保護回路 1 の第 2 の実施形態を示す。ここでは、図 2 の回路と同様に、故障中のノード N 3 0 の高電圧により、トランジスタ Q 3 0 、 Q 3 1 がオンにされるので、出力信号 C F の電圧が上昇する。この例示的な実施形態では、出力 C F は、S M P S I C の周波数調整入力ピンに接続される。このピンの電圧レベルは、S M P S I C のスイッチング周波数を判定する。故障中に出力 C F の電圧を上げることにより、S M P S のスイッチング周波数が上昇され、これにより出力電圧及び電流が低下するので、ドライバが冒頭で述べられた安全要件に準拠する。ここでもまた、遅延要素 C \_ d e l a y は、ノード N 3 0 の過渡電圧上昇が故障応答を引き起こさないことを保証する。

20

【0032】

定常状態又は通常動作中、ノード N 3 0 の電圧は、C I ピン上の電圧を、クランプ電圧以下、例えば、S M P S I C により指定される 3.2 V 以下に保つ必要がある。これは、ノード N 3 0 の最大“通常モード”電圧を判定し、故障状態“トリガレベル”は、このレベルより上でなければならない。C I ピン電流がゼロのとき、すなわち定常状態動作中に、ノード N 3 0 の電圧 U N 3 0 は、

30

【数 1】

$$U_{N30} = U_{CI\_clamp} - V_d \quad (1)$$

により与えられ、U C I \_ c l a m p は S M P S I C により指定される C I ピンのクランプ電圧であり、V d はダイオード両端の電圧降下である。

【0033】

故障のためにオプトカプラトランジスタが導通していないと、ノード N 3 0 の電圧は、C I ピンのクランプ電圧により制限される。この電圧は、

【数 2】

40

$$U_{N30} = \frac{PS\_HI1 \cdot R1 + (U_{CI\_clamp} + V_d + V_{be}) \cdot R2}{R1 + R2} \quad (2)$$

により表され得、R 1 、 R 2 は抵抗値であり、P S \_ H I 1 は一次側から供給される高電圧であり、V b e はトランジスタ Q 3 0 の両端の電圧降下である。

【0034】

ノード N 3 0 の電圧が一定のハイレベルに達すると、トランジスタ Q 3 0 が導通し始める。次いで、これは、トランジスタ Q 3 1 を駆動し、その結果、S M P S I C の C F ピン内に定義された電流が注入されることにより、スイッチング周波数が上昇される。このより高いスイッチング周波数では、出力電圧、電流、及び電力は、U L クラス 2 ドライバ

50

の限界以下に留まる。保護回路の“トリガレベル”は、式(1)と式(2)とで与えられる電圧の間にるべきであり、トリガ感度は、抵抗器R2と組み合わせてトリガ遅延を定義するキャパシタC<sub>de1ay</sub>により調整され得る。

#### 【0035】

スタートアップ段階中、C I ピンは、例えば0.38Vのような、低い電圧を有する。この電圧は、スタートアップ中の保護を防止するために、Q33を介してノードN30の電圧をクランプする。この実施形態では、ドライバマイクロコントローラから生じる信号UC\_INは、SMPSCコンバータの定常状態動作中はローである。またあるときには、この信号がハイであるので、ノードN30を低電位に引き下げるためにトランジスタQ34が導通し、スタートアップ又はシャットダウン中にC I ピンがローに引き下げられないよう、トランジスタQ30、Q31が“オフ”に留まることを保証する。例えば、シャットダウン中に、バス電圧が低下する。一定の閾値以下に低下すると、ノードN30の電圧を低レベルに保ち、スイッチオフ中の保護を防止しながら、高信号UC\_INを用いて一次側マイクロコントローラによりトランジスタQ34がオンにされる。一次側マイクロコントローラがない場合、トランジスタQ34は、当業者に知られるように、追加のスイッチを使用して制御され得る。

10

#### 【0036】

C I ピン回路経路に故障が発生した場合、トランジスタQ35が導通するので、ノードN30の電圧が低下し、その結果、回路部32のトランジスタQ32によりピンVCONが引き下げられ、結果としてSMPSC\_ICは低出力動作モードにされる。オプトカプラが故障した場合、ノードN30の電圧は入力PS\_HI1のために上昇し、その結果、上述のようなトランジスタQ30、Q31の動作によりピンC I はローに引き下げられる。

20

#### 【0037】

図4は、図2の保護回路を用いた図1のLED照明装置の例示的かつ非常に単純化されたタイミング図を示す。関連する信号のみが表示される。明確にするために、実際の信号値は示されず、代わりに各信号の最小及び最大レベルのみが示される。スタートアップモードM<sub>STARTUP</sub>中、ドライバは主電源に接続され、バス電圧はSMPSCコンバータに印加される。一次側上のマイクロコントローラが動作を開始し、電圧レベルPS\_HI1を供給する。二次側マイクロコントローラもアクティブになると、信号STBYは、ドライバが現在通常動作モードM<sub>NORMAL</sub>であることを示す。SMPSC\_ICへの調整入力C I が高いので、定格出力電圧及び電流が負荷に供給される。この動作モードM<sub>NO NORMAL</sub>は、任意の持続時間にわたって持続し得る。時刻t<sub>F</sub>に示されるように、故障が発生すると、ノードN20の電圧は“故障レベル”に上昇する。これは、例えば、オプトカプラ入力端子SS\_FBがハイに引き上げられたときに起こり得る。誤ったトリガを避けるために、(キャパシタC<sub>de1ay</sub>により判定される)遅延t<sub>de1ay</sub>の後、C I ピンはローに引き下げられる。これは、ドライバの出力の電圧及び電流がULクラス2ドライバに必要とされる閾値レベル以下である間、上述のように、ドライバを低出力モードM<sub>L0</sub>にする。この状態M<sub>L0</sub>は、上述のようにドライバが主電源から切断されるまで持続する。これについては図示されていないが、負荷をオフにすることにより通常動作が通常のやり方で閉じられると、故障保護回路を無効にするために信号STBYがローに引き下げられる間にドライバはシャットダウンモードに入り、したがって通常動作されるやり方でシステムがシャットダウンすることが可能になる。

30

#### 【0038】

本発明は、本発明についての好ましい実施形態及びバリエーションの形式で開示されているが、これらに対して、本発明の範囲から逸脱することなく、多数の追加的な修正及びバリエーションがなされ得ることが理解されるであろう。

40

#### 【0039】

明確にするために、本願全体にわたり“a”又は“an”的使用は複数を除外するものではなく、“含む”は他のステップ又は要素を除外するものではないことを理解されたい。“ユニット”又は“モジュール”的言及は、複数のユニット又はモジュールの使用を排

50

除するものではない。

【図1】

【図2】

【図3】

FIG. 3

【図4】

FIG. 4

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2016/056318

A. CLASSIFICATION OF SUBJECT MATTER

INV. H05B33/08

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H05B

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 8 520 415 B1 (KRISHNAMOORTHY RAVISHANKER [SG] ET AL) 27 August 2013 (2013-08-27) the whole document                            | 1-4,6-13              |

| Y         | -----                                                                                                                             | 5                     |

| X         | EP 2 284 983 A1 (MARVELL WORLD TRADE LTD [BB]) 16 February 2011 (2011-02-16) paragraph [0004] - paragraph [0048]; figures 1-3,6   | 1-4,6-13              |

| Y         | -----                                                                                                                             | 5                     |

| X         | US 2014/328427 A1 (CHANG KWEE CHONG [SG] ET AL) 6 November 2014 (2014-11-06) paragraph [0007] - paragraph [0065]; figures 1-3,6,7 | 1,10-12               |

| Y         | paragraph [0129] - paragraph [0138]                                                                                               | 5                     |

| Y         | WO 98/21813 A1 (THOMSON CONSUMER ELECTRONICS [US]) 22 May 1998 (1998-05-22) page 7, paragraph third; figure 1                     | 5                     |

|           | -----                                                                                                                             |                       |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

14 June 2016

21/06/2016

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Henderson, Richard

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/EP2016/056318

| Patent document cited in search report |    | Publication date | Patent family member(s) |               | Publication date |

|----------------------------------------|----|------------------|-------------------------|---------------|------------------|

| US 8520415                             | B1 | 27-08-2013       | NONE                    |               |                  |

| EP 2284983                             | A1 | 16-02-2011       | CN                      | 101997435 A   | 30-03-2011       |

|                                        |    |                  | EP                      | 2284983 A1    | 16-02-2011       |

|                                        |    |                  | US                      | 2011038184 A1 | 17-02-2011       |

| US 2014328427                          | A1 | 06-11-2014       | NONE                    |               |                  |

| WO 9821813                             | A1 | 22-05-1998       | AU                      | 5442398 A     | 03-06-1998       |

|                                        |    |                  | CN                      | 1238072 A     | 08-12-1999       |

|                                        |    |                  | DE                      | 69719207 D1   | 27-03-2003       |

|                                        |    |                  | DE                      | 69719207 T2   | 12-02-2004       |

|                                        |    |                  | EP                      | 0938771 A1    | 01-09-1999       |

|                                        |    |                  | ES                      | 2191865 T3    | 16-09-2003       |

|                                        |    |                  | JP                      | 3880071 B2    | 14-02-2007       |

|                                        |    |                  | JP                      | 2001503957 A  | 21-03-2001       |

|                                        |    |                  | KR                      | 20000053264 A | 25-08-2000       |

|                                        |    |                  | MY                      | 118078 A      | 30-08-2004       |

|                                        |    |                  | US                      | 5949154 A     | 07-09-1999       |

|                                        |    |                  | WO                      | 9821813 A1    | 22-05-1998       |

---

## フロントページの続き

(81) 指定国 AP(BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), EA(AM, AZ, BY, KG, KZ, RU, T, J, TM), EP(AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, R, O, RS, SE, SI, SK, SM, TR), OA(BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG), AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, H, N, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US

F ターム(参考) 3K273 AA09 BA27 BA35 CA02 EA06 EA07 EA25 EA35 FA07 FA14

FA22 FA32 FA40 GA02 GA14