(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0125085

(43) 공개일자 2009년12월03일

(51) Int. Cl.

*G01R 31/307* (2006.01) *G01R 31/28* (2006.01)

(21) 출원번호 10-2009-7018643

(22) 출원일자 2008년02월01일

심사청구일자 없음

(85) 번역문제출일자 2009년09월07일

(86) 국제출원번호 PCT/US2008/052754

(87) 국제공개번호 WO 2008/109213

국제공개일자 2008년09월12일

(30) 우선권주장

11/683,607 2007년03월08일 미국(US)

(71) 출원인

프리스캐일 세미컨덕터, 인크.

미합중국 텍사스 (우편번호 78735) 오스틴 월리암

캐논 드라이브 웨스트 6501

(72) 별명자

펠리, 폐리 에이치.

미국 텍사스 78726, 오스틴, 인디고 브러쉬 9606

(74) 대리인

장훈

전체 청구항 수 : 총 20 항

(54) 다수의 모듈들 또는 서브모듈들을 갖는 집적 회로를 테스트 및 제공하기 위한 시스템 및 방법

### (57) 요 약

실질적으로 동일한 기능을 각각 수행하는 복수의 모듈들(12 내지 14) 및/또는 서브모듈들(32, 33, 36 내지 39)을 갖는 집적 회로(10)에서, 결합 모듈들 및/또는 서브모듈들은 입력 테스트 패턴으로부터 테스트 시그니처(64)를 생성함으로써 결정된다. 각 모듈 및/또는 서브모듈의 출력(60)은 테스트 시그니처 및 결합 모듈들과 비교되어 (68) 결합 모듈들 및/또는 서브모듈들을 식별한다. 결합 모듈들/서브모듈들의 아이덴티티는 고객에 의한 후속 사용을 위해 집적 회로 상에 저장된다. 하나 이상의 결합 모듈들/서브모듈들을 갖는 집적 회로들은 모듈들/서브모듈들이 결함이 있는 완전한 개시로 고객들에게 판매되어(96), 제품과 연관된 양품률을 향상시킨다. 제품의 프라이싱은 덜 완전한 기능성을 갖는 제품들에 대해 할인된다.

### 대 표 도 - 도3

## 특허청구의 범위

### 청구항 1

집적 회로 상의 제 1 회로에 제 1 양호/불량 정보를 제공하는 단계;

상기 집적 회로 상의 제 2 회로에 제 2 양호/불량 정보를 제공하는 단계;

상기 집적 회로 상의 제 3 회로에 제 3 양호/불량 정보를 제공하는 단계로서, 상기 제 1 회로, 상기 제 2 회로, 상기 제 3 회로는 양호할 때의 동일한 테스트 입력에 응답하여 동일한 테스트 결과를 각각 출력하는, 상기 제 3 양호/불량 정보 제공 단계; 및

상기 제 1 양호/불량 정보, 상기 제 2 양호/불량 정보, 또는 상기 제 3 양호/불량 정보 중 적어도 하나가 상기 제 1 회로, 상기 제 2 회로, 또는 상기 제 3 회로 중 적어도 하나가 여전히 불량하고 수리되지 않음을 나타낼 때, 세일(sale)을 위해 상기 집적 회로를 제공하는 단계를 포함하는, 방법.

### 청구항 2

제 1 항에 있어서,

상기 제 1 양호/불량 정보는 상기 집적 회로 상의 비휘발성 저장 회로에 저장되는, 방법.

### 청구항 3

제 1 항에 있어서,

상기 집적 회로의 프라이싱(pricing)은 상기 집적 회로 상의 다수의 양호한 회로들의 기능인, 방법.

### 청구항 4

제 1 항에 있어서,

상기 집적 회로는 상기 제 1, 상기 제 2, 및 상기 제 3 회로들 모두가 양호하면, 제 1 가격이고, 상기 집적 회로는 상기 제 1, 상기 제 2, 또는 상기 제 3 회로 중 적어도 하나가 여전히 불량하면 제 2 가격이고, 상기 제 1 가격은 상기 제 2 가격보다 더 높은, 방법.

### 청구항 5

제 1 항에 있어서,

상기 제 1 회로가 상기 집적 회로의 작동 동안에 사용되지 않아야 하는지를 결정하기 위해 상기 제 1 회로에 대해 상기 제 1 양호/불량 정보를 사용하는 단계를 추가로 포함하는, 방법.

### 청구항 6

제 1 항에 있어서,

복수의 집적 회로들에 걸쳐 불량 회로들의 분배를 결정하는 단계를 추가로 포함하는, 방법.

### 청구항 7

제 6 항에 있어서,

상기 집적 회로의 구매자에 상기 불량 회로들의 분배를 제공하는 단계를 추가로 포함하는, 방법.

### 청구항 8

제 1 항에 있어서,

상기 제 1 회로, 상기 제 2 회로, 및 상기 제 3 회로 각각이 양호/불량인지의 여부를 결정하기 위해 적어도 하나의 테스트의 결과에 대해 보우팅(voting)하는 단계를 추가로 포함하는, 방법.

### 청구항 9

집적 회로 상의 복수의 회로들을 테스트하는 단계;

상기 복수의 회로들 각각으로부터 테스트 출력을 제공하는 단계; 및

임의의 테스트 결과가 상이하면, 상기 복수의 회로들 중 어떤 회로가 불량한지를 결정하기 위해 보우팅하는 단계를 포함하는, 방법.

#### 청구항 10

제 9 항에 있어서,

상기 보우팅 단계는:

어떤 테스트 출력이 가장 정확한 테스트 출력인지를 결정하는 단계; 및

상기 가장 정확한 테스트 출력을 갖는 상기 복수의 회로들 각각이 양호한 것으로 가정하는 단계를 추가로 포함하는, 방법.

#### 청구항 11

제 9 항에 있어서,

상기 복수의 회로들에 대한 양호/불량 정보를 상기 집적 회로 상의 비휘발성 저장 회로에 저장하는 단계를 추가로 포함하는, 방법.

#### 청구항 12

제 11 항에 있어서,

상기 비휘발성 저장 회로는 퓨즈를 포함하는, 방법.

#### 청구항 13

제 11 항에 있어서,

상기 비휘발성 저장 회로는 복수의 퓨즈들을 포함하고, 상기 복수의 퓨즈들 각각은 상기 복수의 회로들 중 하나에 대응하는, 방법.

#### 청구항 14

집적 회로에 있어서:

테스트에 응답하여 제 1 테스트 시그니처(test signature)를 제공하는 제 1 회로;

상기 테스트에 응답하여 제 2 테스트 시그니처를 제공하는 제 2 회로;

상기 테스트에 응답하여 제 3 테스트 시그니처를 제공하는 제 3 회로;

상기 제 1, 상기 제 2, 및 상기 제 3 테스트 시그니처들을 비교하고 가장 정확한 테스트 시그니처를 결정하는 보우팅 회로; 및

상기 제 1, 상기 제 2, 및 상기 제 3 테스트 시그니처들 각각을 상기 가장 정확한 테스트 시그니처와 비교하여 상기 제 1, 상기 제 2, 및 상기 제 3 회로들 각각에 대한 양호/불량 정보를 결정하는 비교기를 포함하는, 집적 회로.

#### 청구항 15

제 14 항에 있어서,

상기 제 1, 상기 제 2, 및 상기 제 3 회로들 각각에 대한 상기 양호/불량 정보를 저장하는 비휘발성 저장 회로를 추가로 포함하는, 집적 회로.

#### 청구항 16

제 14 항에 있어서,

상기 제 1, 상기 제 2, 및 상기 제 3 회로들 모두가 양호한지를 나타내는 플래그(flag)를 추가로 포함하는, 집적 회로.

### 청구항 17

제 14 항에 있어서,

상기 제 1, 상기 제 2, 및 상기 제 3 테스트 시그니처들을 저장하기 위한 저장 회로를 추가로 포함하는, 집적 회로.

### 청구항 18

제 14 항에 있어서,

상기 테스트 동안에 입력 테스트 패턴을 상기 제 1, 상기 제 2, 및 상기 제 3 회로들에 제공하기 위한 테스트 회로를 추가로 포함하는, 집적 회로.

### 청구항 19

제 14 항에 있어서,

상기 제 1, 상기 제 2, 및 상기 제 3 회로들은 동일한 유형의 데이터 프로세서인, 집적 회로.

### 청구항 20

제 14 항에 있어서,

상기 제 1 회로는 제 1 서브모듈(submodule)을 포함하고, 상기 제 2 회로는 제 2 서브모듈을 포함하고, 상기 제 3 회로는 제 3 서브모듈을 포함하는, 집적 회로.

## 명세서

### 기술 분야

<1> 본 발명은 일반적으로 반도체들에 관한 것이고 특히, 반도체들의 테스팅 및 세일(sale)에 관한 것이다.

### 배경 기술

<2> 집적 회로들은 발전하고 상당히 더 많은 량들의 회로를 통합하기 때문에, 단일 반도체 웨이퍼 상에 완전한 기능 집적 회로 제품들을 더 큰 퍼센티지들(percentages)로서 신뢰성있게 제조하기 위한 능력은 매우 어려워진다. 따라서, 웨이퍼 상에 존재하는 양호한 다이(die)의 양품률(yield)은 종종 복잡한 집적 회로에 대해 더 낮고 낮은 양품률은 제조자에 대해 상당한 수익의 손실을 초래한다.

<3> 양품률 결과들을 향상시키기 위해, 다른 제조업자들은 중복 회로(redundant circuitry)를 집적 회로로 통합한다. 중복 회로는 선택적으로 식별된 결합 회로를 대체하도록 테스트된 후에 사용된다. 그러나, 많은 양의 회로가 집적 회로로 통합되기 때문에, 결점있는 회로가 대체될 수 있음을 보증하도록 요구된 리던던시(redundancy)량이 종종 비용이나 크기 측면에서 터무니 없이 높을 수 있다. 결과적으로, 복잡한 집적 회로들의 양품률들은 종종 원하는 것보다 더 낮다.

<4> 집적 회로들이 기능적으로 진보하고 복잡하기 때문에, 다수의 데이터 프로세서들이 단일 집적 회로에 통합된다. 이러한 집적 회로들이 테스트될 때, 집적 회로 내의 데이터 프로세서들 각각은 전형적으로 할당된 순서로 직렬 테스트된다. 공지된 테스팅 방법론들을 갖는 단점들은 복잡한 집적 회로들을 테스트하기 위한 증가된 시간 및 집적 회로의 기능성을 결정하는 전기적인 테스터들과 연관된 높은 비용을 포함한다. 복잡한 집적 회로들에 대한 진단 테스팅(diagnostic testing)을 수행하기 위한 테스트 장비는 전형적으로 백만달러를 초과하고 따라서, 집적 회로 제조자에 대한 상당한 투자를 나타낸다. 테스트 시간을 감소시키기 위해, 다른 집적 회로 제조업자들은 다수의 프로세서들을 별별로 테스트한다. 이러한 테스트 방법론들에서, 다수의 프로세서들의 출력들 사이의 비교는 모든 프로세서들이 동일한 결과 또는 상이한 결과를 제공하고 있는지의 여부를 표시하도록 행해진다. 상이한 결과는 회로의 고장이 테스트 장비에 의해 주의됨을 나타낸다.

## 발명의 상세한 설명

&lt;5&gt;

실질적으로 동일한 기능을 각각 수행하는 복수의 모듈들 및/또는 서브모듈들을 갖는 집적 회로에서, 결합 모듈들 및/또는 서브모듈들은 입력 테스트 패턴으로부터 테스트 시그니처를 생성함으로써 결정된다. 각 모듈 및/또는 서브모듈의 출력은 테스트 시그니처 및 결합 모듈들과 비교되어 결합 모듈들 및/또는 서브모듈들을 식별한다. 결합 모듈들/서브모듈들의 아이덴티티는 고객에 의한 후속 사용을 위해 집적 회로 상에 저장된다. 하나 이상의 결합 모듈들/서브모듈들을 갖는 집적 회로들은 모듈들/서브모듈들이 결합이 있는 완전한 개시로 고객들에게 판매되어, 제품과 연관된 양품률을 향상시킨다. 제품의 프라이싱은 덜 완전한 기능성을 갖는 제품들에 대해 할인된다.

&lt;6&gt;

본 발명은 예로서 예시되고 동일한 참조부호들이 동일한 소자들을 나타내는, 첨부된 도면들에 의해 제한되지 않는다. 도면들의 소자들은 단순성 및 명료성을 위해 예시되고 비례적으로 도시될 필요는 없다.

## 실시 예

&lt;12&gt;

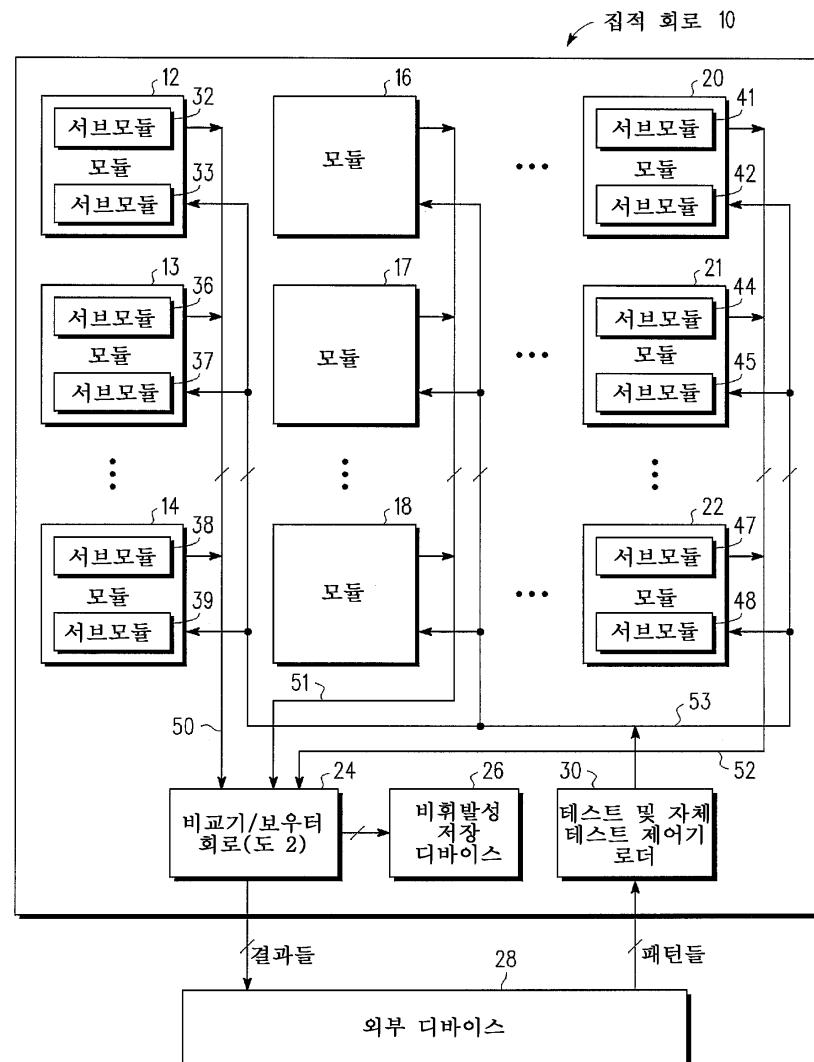

도 1은 모듈들(12)과 같은 복수의 회로 모듈들을 갖는 집적 회로(10)를 예시한 도면이다. 도 1에 도시된 바와 같은 집적 회로(10)는 구현될 수 있는 수많은 회로 아키텍처들(circuit architectures) 중 단지 하나임이 이해되어야 한다. 예시의 편리함을 위해, 집적 회로(10)의 테스트 특징들과 관련없는 집적 회로(10) 내의 다양한 회로는 상술되지 않는다. 집적 회로(10)는 모듈들(12, 13, 14, 16, 17, 18, 20, 21, 22)과 같은 복수의 모듈들을 갖는다. 모듈들은 행들 및 열들로 정렬되는 것으로서 예시되지만, 이러한 획일성(uniformity)이 요구되지 않음이 이해되어야 한다. 또한, 부가적인 모듈들은 모듈들의 각 열 및 행에 존재하는 세 개의 도트들(dots)에 의해 표시되는 것으로서 존재할 수 있다. 예를 들면, 하나의 형태에서, 64개의 모듈들이 존재할 수 있지만, 임의의 수의 모듈들이 사용될 수 있음이 잘 이해되어야 한다. 몇몇 모듈들의 내부에는 복수의 부가적인 모듈들 또는 서브모듈들이 존재한다. 예를 들면, 모듈(12)은 서브모듈(32) 및 서브모듈(33)을 갖는다. 모듈(13)은 서브모듈(36) 및 서브모듈(37)을 갖는다. 모듈(14)은 서브모듈(38) 및 서브모듈(39)을 갖는다. 모듈(20)은 서브모듈(41) 및 서브모듈(42)을 갖는다. 모듈(21)은 서브모듈(44) 및 서브모듈(45)을 갖는다. 모듈(22)은 서브모듈(47) 및 서브모듈(48)을 갖는다. 모듈들(12 내지 14) 각각은 테스트 출력 버스(50)에 접속된 출력부를 갖는다. 모듈들(16 내지 18) 각각은 테스트 출력 버스(51)에 접속된 출력부를 갖는다. 모듈들(20 내지 22) 각각은 테스트 출력 버스(52)에 접속된 출력부를 갖는다. 또 다른 형태에서, 3개의 개별적인 버스들 보다는 단일 공통 테스트 출력 버스가 사용될 수 있음이 이해되어야 한다. 모듈들(12 내지 14, 16 내지 18, 20 내지 22) 각각은 테스트 입력 버스(53)에 접속된 입력부를 갖는다. 비교기/보우터 회로(comparator/voter circuit)(24)는 테스트 출력 버스(50), 테스트 출력 버스(51), 및 테스트 출력 버스(52)에 각각 접속된 제 1, 제 2, 및 제 3 입력부들을 갖는다. 비교기/보우터 회로(24)의 제 1 출력부는 비교기/보우터 회로(24)에 의해 수행된 비교 및 보우팅 기능들의 결과에 관한 결과 정보(Results information)를 제공하기 위한 외부 디바이스(28)의 입력부에 다중 도전체 버스(multiple conductor bus)를 통해 접속된다. 비교기/보우터 회로(24)의 제 2 출력부는 비휘발성 저장 디바이스(26)의 입력부에 접속된다. 외부 디바이스(28)는 테스트 및 자체 테스트(built-in self-test; BIST) 제어기 로더(30)의 입력부에 테스트 패턴들을 다중 도전체 버스를 통해 제공하기 위한 출력부를 갖는다. 테스트 및 BIST 제어기 로더(30)는 테스트 입력 버스(53)에 접속된 출력부를 갖는다.

&lt;13&gt;

작동 시에, 집적 회로(10)는 다수의 모듈들을 갖는다. 하나의 형태에서, 모듈들은 동일한 기능을 구현한다. 예를 들면, 각 모듈은 동일한 명령 세트를 실행할 수 있는 코어 또는 데이터 프로세서일 수 있다. 또 다른 형태들에서, 각 모듈은 메모리, 변환기 또는 상태 기계와 같은 또 다른 유형의 회로일 수 있다. 다른 형태들에서, 모듈들의 단지 부분들이 동일하다. 예를 들면, 제 1 열의 모듈들(12 내지 14)은 부동 소수점 프로세싱 유닛들(floating point processing units)일 수 있는 반면에, 제 2 열의 모듈들(16 내지 18)은 고정 소수점 프로세싱 유닛들(fixed point processing units)일 수 있다. 부가적으로, 집적 회로(10)의 각 또는 대부분의 모듈들은 상이한 유형들의 회로들일 수 있다. 하나 이상의 모듈들 내에 복수의 동일한 또는 실질적으로 동일한 서브모듈들이 존재한다. 서브모듈들은 다음 논의가 집적 회로(10) 내의 동일한 기능의 모듈들의 테스팅을 설명하는 동일한 방식으로 단일 모듈 내에서의 기능성을 위해 검사 또는 테스트될 수 있다. 따라서, 용어들 "모듈(module)" 및 "서브모듈(submodule)"이 여기에서 사용될 때, 이를 용어들 각각은 더 일반적으로 "회로(circuit)"로서 식별될 수 있다.

&lt;14&gt;

설명의 목적들을 위해, 모듈들(12 내지 14, 16 내지 18, 20 내지 22)가 동일한 기능들을 구현하고 따라서, 동일한 입력들을 제공받을 때, 동일한 결과를 생성해야한다고 가정한다. 외부 디바이스(28)는 테스트 패턴들을 저장

하고 수신하는 테스트 및 BIST 제어기 로더(30)에 특정한 테스트 패턴들을 제공한다. 테스트 패턴들은 테스트 패턴들에 대해 모든 모듈들에 의한 미리 결정된 테스트 기능의 실행을 위한 모듈들 각각에 제어 회로(도시되지 않음)의 제어 하에 라우팅된다. 테스트 패턴의 일례로서, 2개의 연산수들(operands)이 모듈들 각각에 2개의 연산수들을 곱하기 위한 명령에 더하여, 테스트 패턴에 제공될 수 있다. 모듈들 각각은 테스트 패턴에 포함된 하나 이상의 테스트 작동들을 수행하고 비교기/보우터 회로(24)에 테스트 출력 버스들(50 내지 52)을 통해 전송된 "실제 테스트 시그니처(actual test signature)"로서 언급된 결과를 생성한다. 비교기/보우터 회로(24)는 모듈들로부터의 출력들 각각을 검사하고 어떤 바이너리 값이 결과로서 생성되는지 비트-바이-비트(bit-by-bit) 단위로 결정하도록 기능한다. 이 결정은 비트-바이-비트 단위로 각 모듈을 폴링함으로써 및 각 모듈이 정정 테스트 시그니처 비트(correct test signature bit)에 대해 "보우트(vote)" 하도록 허용함으로써 행해진다. 간단한 다수의 보우트는 어떤 바이너리 값이 테스트 시그니처의 모든 비트들에 대해 정정 비트 값으로서 인식되는지 결정하거나 획득한다(win). 분할 보우트(split vote)가 발생한 경우에, 디폴트 비트 값이 일정하게 사용된다. 분할 보우트의 존재는 모듈들의 절반이 발산 값들(diverging values)을 생성하고 있음을 나타내고 이것은 집적 회로가 상업적으로 실행가능하기에(viable) 너무 큰 적어도 50%의 에러 마진을 나타낸다. 따라서, 디폴트 비트의 값은 결정적이지 않다. 비교기/보우터 회로(24)가 보우팅 기능으로부터 정정 테스트 시그니처를 생성하고 그 시그니처를 모듈들에 의해 생성된 각 시그니처와 비교할 때, 테스트의 결과들은 비휘발성 저장 디바이스(26)에 저장된다. 테스트 결과들은 모듈이 양호 또는 불량인지의 여부를 나타내는 양호/불량 정보(good/bad information)를 각 모듈에 제공한다. 비휘발성 저장 디바이스(26)는 임의의 유형의 NVM 디바이스일 수 있다. 비휘발성 저장 디바이스(26)는 바람직하게 비휘발성일 수 있어, 테스트 결과들은 집적 회로의 사용자에 의한 후속 사용 또는 집적 회로(10)의 외부로부터의 후속 검사를 위해 잔존한다. 예를 들면, 각 모듈의 양호/불량 정보는 임의의 표시된 불량 모듈들이 명령 흐름에서 액세스되지 못하게 되는 명령 흐름 스레드 할당에 대해 후속적으로 사용될 수 있다. 테스팅이 집적 회로의 단일 모듈의 다수의 서브모듈들에 적용될 수 있고, 여기에 제공된 디테일들이 동일하게 적용함이 다시 언급되어야 한다.

&lt;15&gt;

하나의 형태에서, 외부 디바이스(28)는 비교기/보우터 회로(24)로부터의 결과들에 관한 통계들을 유지하는 개인용 컴퓨터 형태의 테스터(tester)임이 주의되어야 한다. 집적 회로(10)의 테스팅에 연관된 장점은 종래의 개인용 컴퓨터가 분석 및 집적 회로(10)의 테스팅을 구현하기 위해 요구된 데이터 프로세싱을 용이하게 수행할 수 있다는 것이다. 따라서, 복잡하고 비싼 테스터는 집적 회로(10)의 완전한 기능성을 결정하기 위해 요구되지 않는다. 테스트 및 BIST 제어기 로더(30)의 BIST 부분이 테스트 입력 버스(53)에 결합되는 테스트 패턴들을 독립적으로 생성할 수 있음이 또한 이해되어야 한다. 하나의 형태에서, 테스트 및 BIST 제어기 로더(30)의 BIST 부분이 집적 회로의 파워-업(power-up)으로 구동된다.

&lt;16&gt;

외부 디바이스(28)이 결과들을 수신할 때, 집적 회로(10) 내의 얼마나 많은 모듈들(또는 서브모듈들)이 양호하고 얼마나 많은 모듈들이 불량인지 쉽게 결정가능할 것이다. 얼마나 많은 모듈들이 양호한지에 따라, 집적 회로(10)는 몇 퍼센트의 다수의 모듈들이 양호한지에 기초하여 세일을 위한 제품 카테고리(product category)에 위치될 수 있다. 집적 회로(10)가 실질적인 수의 반복 모듈들(repetitive modules)을 갖기 때문에, 제품은 심지어 몇몇 불량(즉, 부정확하게 동작하는) 모듈들이 존재할 때, 여전히 상업적인 가치를 갖는다. 예를 들면, 많은 수의 프로세서들이 제공되어 제품의 사용이 심지어 모든 프로세서들이 정확하게 동작하고 있지 않을 때, 가치가 있는 수많은 애플리케이션들(applications)이 존재한다. 부정확하게 동작하는 프로세서 또는 프로세서들이 식별되어, 그것이 사용되지 않는 한, 많은 실행가능한 애플리케이션들이 불완전(less-than-fully) 기능 집적 회로에 대해 존재한다.

&lt;17&gt;

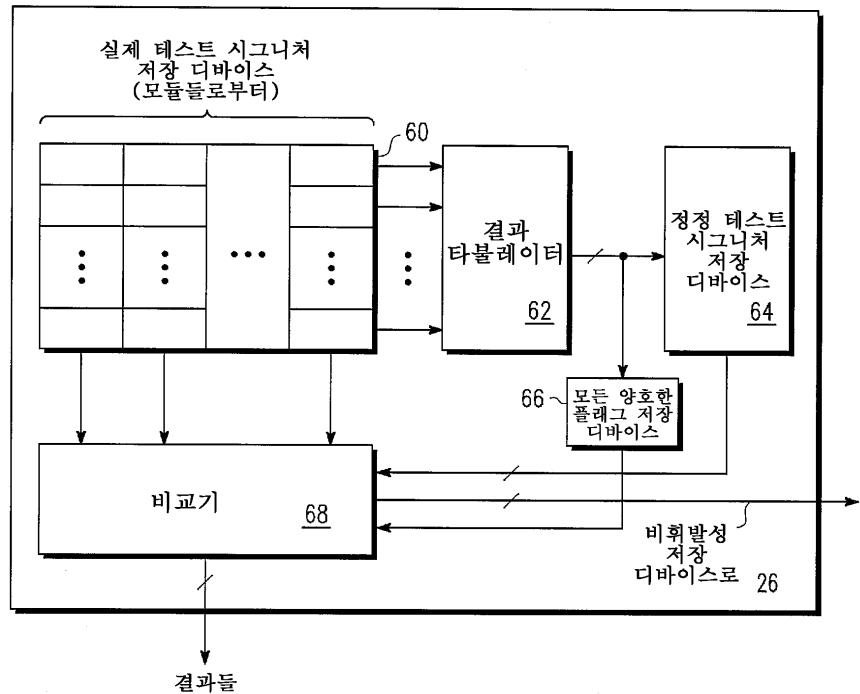

도 2는 도 1의 하나의 형태의 비교기/보우터 회로(24)의 블록도를 예시한 도면이다. 별별로 테스트되는 모듈들 각각으로부터의 실제 테스트 시그니처들을 수신하기 위한 저장 디바이스(60)가 제공된다. 각 테스트 시그니처는 외부 디바이스(28)에 의해 제공된 패턴들을 사용하여 미리 결정된 기능 작동의 출력 결과를 나타낸다. 저장 디바이스(60)는 각각의 모듈과 저장된 실제 테스트 시그니처를 용이하게 상관시키기 위해 구조적으로 구성된다. 단일 모듈의 서브모듈들로부터의 테스트 시그니처들이 다수의 모듈들로부터 테스트 시그니처들을 수신 또는 저장하기보다는 수신되고 저장될 수 있음이 다시 이해되어야 한다. 저장 디바이스(60)는 결과 타불레이터(result tabulator)(62)의 각각의 입력부들에 접속되는 다수의 출력부들을 갖는다. 결과 타불레이터(62)는 정정 테스트 시그니처 저장 디바이스(64)의 입력부와 모든 양호한 플래그 저장 디바이스(All Good Flag storage device)(66)의 입력부 둘 모두에 접속된 출력부를 갖는다. 정정 테스트 시그니처 저장 디바이스(64)의 출력부는 비교기(68)의 제 1 제어 입력부에 접속된다. 모든 양호한 플래그 저장 디바이스(66)의 출력부는 비교기(68)의 제 2 제어 입력부에 접속된다. 비교기(68)는 다수의 입력부들을 갖고, 이들 각각은 저장 디바이스(60)의 미리 결정된 출력부에 접속된다. 비교기(68)는 외부 디바이스(28)에 접속된, 결과들을 제공하기 위한 제 1 출력부 및

집적 회로(10) 내의 저장 디바이스에 결과들을 또한 제공하기 위한 상기 언급된 바와 같은, 비휘발성 저장 디바이스(26)에 접속된 제 2 출력부를 갖는다. 비교기(68)의 제 1 출력부 및 제 2 출력부에 의해 제공된 결과 정보는 어떤 모듈들(서브모듈들)이 양호한 정보를 제공했고 어떤 모듈들(서브모듈들)이 불량 정보를 제공했는지에 관한 동일한 정보를 여전히 포함하는 동안에 상이한 포맷들일 수 있음이 이해되어야 한다.

&lt;18&gt;

작동 시에, 결과 타뷸레이터(62)는 논리 회로에 의해 구현되고, 논리값(1 또는 0)이 테스트 하에서 모든 모듈들(또는 서브모듈들)에 의해 생성된 실제 테스트 시그니처들의 각 비트에 대해 가장 우세한 것임을 결정한다. 따라서, 결과 타뷸레이터(62)는 실제 테스트 시그니처들의 각 위치에 얼마나 많은 논리값(1들) 및 얼마나 많은 논리값(0들)이 존재하는지 카운트(count)하거나 타뷸레이트하도록 가능한다. 단순한 대부분은 전형적으로 어떤 비트 값이 정정 테스트 시그니처를 형성하기 위해 사용되는지를 결정하기 위해 사용된다. 따라서, 정정 테스트 시그니처는 각 실제 테스트 시그니처를 비교하기 위한 비교기(68)에 의해 후속적으로 사용될 "골든 마스터(golden master)" 시그니처로서 가능할 것이다. 비교기(68)의 출력은 실제 테스트 시그니처들이 생성된 정정 테스트 시그니처와 상이함을 나타낸다. 결과 타뷸레이터(62)가 실제 테스트 시그니처들의 모든 각각의 비트 값들이 매칭(matching)한다고 결정하는 경우에, 비트값 또는 플래그는 모든 양호한 플래그 저장 디바이스(66)에 나타내기 위해 설정된다. 모든 양호한 플래그가 어서트(assert)될 때, 비교기(68)는 실제 테스트 시그니처들 및 정정 테스트 시그니처들의 비교로부터 디스에이블(disable)되고, 모든 테스트 시그니처들이 양호한 정보임을 결과들에 직접 나타낸다. 이 바이패스 작동(bypass operation)은 테스트 작동의 속도를 높이고 그렇지 않으면, 비교기(68)에 의해 소비될 수 있는 전력을 감소시킨다. 따라서, 비교기/보우터 회로(24)는 입력 테스트 데이터로부터의 결과들을 사용하고 테스트되는 각 모듈 또는 서브모듈로부터의 출력을 개별적으로 비교하기 위해 사용되는 정정 테스트 시그니처를 생성한다.

&lt;19&gt;

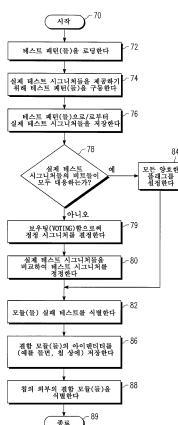

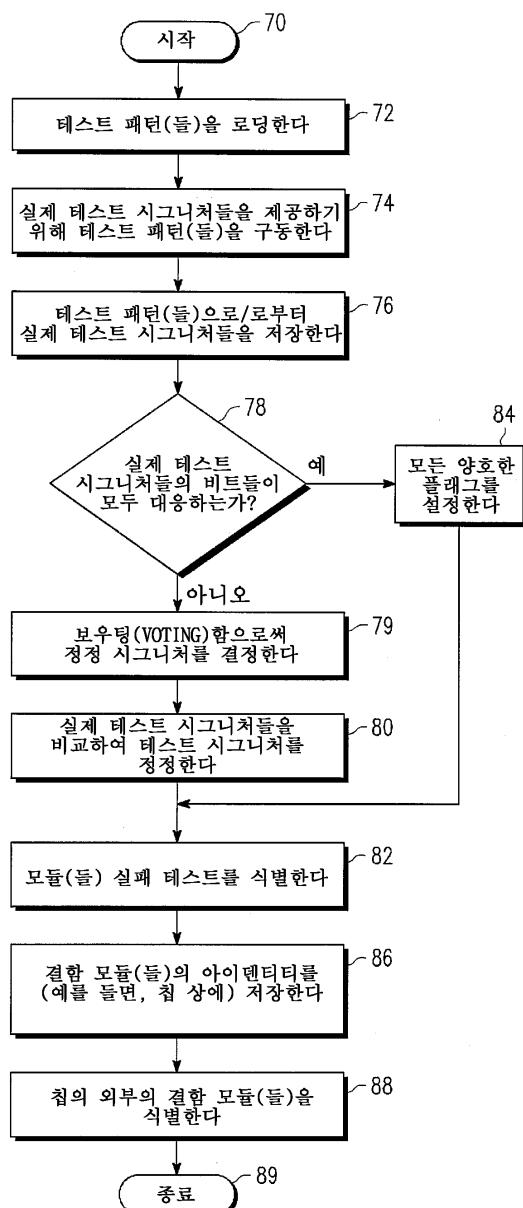

도 3은 도 1의 집적 회로(10)를 제공하기 위한 방법의 흐름도를 예시한 도면이다. 단계(70)에서, 방법은 시작 명령으로 개시된다. 단계(72)에서, 하나 이상의 미리 결정된 테스트 패턴들이 테스트 및 BIST 제어기 로더(30)에 로딩된다. 단계(74)에서, 하나 이상의 테스트 패턴들은 실제 테스트 시그니처들을 제공하기 위해 모듈들 또는 서브모듈들을 실행하게 함으로써 구동된다. 단계(76)에서, 하나 이상의 테스트 패턴들의 구동으로부터 생성된 실제 테스트 시그니처들은 저장 디바이스(60)에 저장된다. 단계(78)에서, 실제 테스트 시그니처들이 비트들이 모두 대응하는지를 결정하기 위한 비교가 행해진다. 테스트 결과들의 모든 비트들이 동일하지 않으면, 단계(79)에서 정정 테스트 시그니처가 상기 설명된 바와 같이 보우팅함으로써 결정된다. 실제 테스트 시그니처들이 단계(79)에서 결정되는 정정 테스트 시그니처와 비교되는 단계(80)가 실행된다. 단계(80)의 완료 시에, 정정 시그니처와 상이한 모듈들 또는 서브모듈들의 임의의 결과들은 단계(82)에서의 테스트의 실패(failing)로서 식별된다. 테스트 결과들의 모든 비트들이 동일하면, 모든 양호한 플래그 저장 디바이스(66)의 모든 양호한 플래그가 설정되는 단계(84)가 실행되고 단계(80)은 무시된다. 이 상황에서, 단계(82)는 '양호한 정보' 표시자를 모든 모듈들/서브모듈들에 제공하고 테스트의 실패로서 임의의 모듈/서브모듈을 식별하지 않을 것이다. 단계(82) 이후에, 임의의 결합 모듈 또는 서브모듈의 아이덴티티는 단계(86)에서 집적 회로(10) 상의 비휘발성 저장 디바이스(26)에 저장된다. 단계(86) 이후에, 임의의 결합(즉, 불량) 모듈들 또는 서브모듈들의 아이덴티티는 단계(88)에서 집적 회로(10)의 외부에 제공되고, 방법은 단계(89)로 종료된다.

&lt;20&gt;

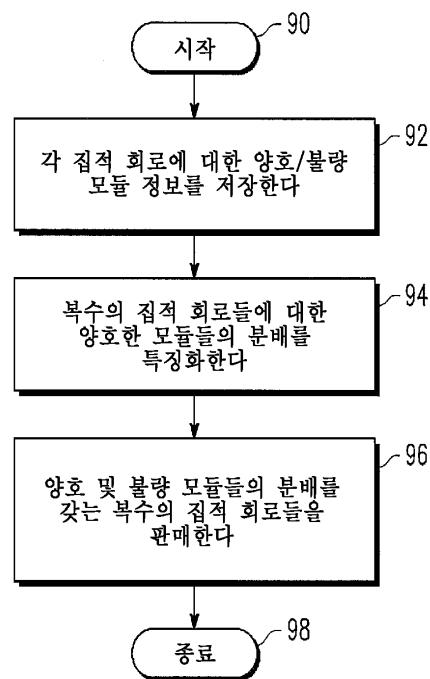

도 4는 상기 설명된 테스팅을 사용하기 위한 방법을 예시한 도면이다. 방법은 단계(90)으로 시작한다. 단계(92)에서, 양호한 모듈/서브모듈 및 불량 모듈/서브모듈 정보는 테스트되어온 모듈들 또는 서브모듈들 각각에 대해 저장된다. 후속 단계(94)에서, 양호한 모듈들의 분배는 복수의 집적 회로들에 대한 누적 양품률을 결정하기 위해 복수의 집적 회로들에 대해 특징된다. 즉, 결합 모듈들 또는 서브모듈들을 갖지 않는 양호한 모듈들의 수가 결정된다. 그 다음, 하나의 결합 모듈, 2개의 결합 모듈들, 등을 갖는 양호한 모듈들의 수가 결정된다. 단계(96)에서, 복수의 집적 회로들이 집적 회로들의 양호한 및 불량 모듈들의 개시된 분배에 기초하여 판매된다. 예를 들면, 64개의 모듈들 중 3개의 결합 모듈들이 존재할 때, 특정한 집적 회로가 애플리케이션에서 유용한지의 여부의 결정이 행해진다. 그들 애플리케이션들에 대해, 집적 회로들이 결합 모듈들의 수의 완전한 개시로 판매되고 집적 회로는 모듈들이 결합이 있다는 아이덴티티를 그 안에 저장한다. 판매되는 집적 회로 내의 불량 회로들의 분배는 집적 회로를 그들의 설계에 적용 시에 그들의 사용을 위해 고객에게 제공된다. 집적 회로들의 판매는 돈 거래, 현물 지급(in-kind) 제품의 교환, 집적 회로들에 대한 기술과 실제적인 지식(know-how) 및 다른 형태들의 보상을 포함함이 이해되어야 한다. 결과적으로, 집적 회로의 사용자는 불량 모듈들에 의해 야기될 수 있는 에러들을 회피함으로써 집적 회로를 프로그래밍 및 사용할 수 있을 것이다. 집적 회로를 수반하는 상업적인 거래의 방법은 단계(98)에서 완료된다.

&lt;21&gt;

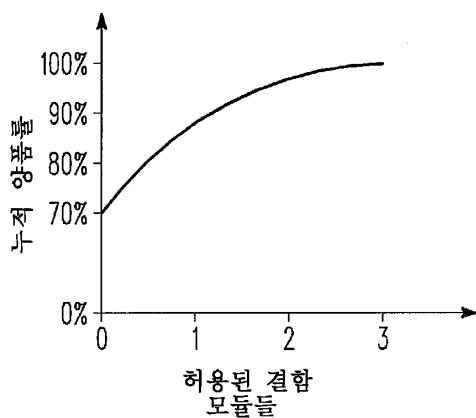

도 5는 허용된 결합 모듈들의 수가 증가함에 따라 집적 회로의 누적 양품률이 어떻게 증가하는지를 예

시한 그래프이다. 종래적으로, 하나의 결합 모듈은 비-상업적인 제품을 야기한다. 그러나, 사용자가 회피하고자 하는 결합 모듈이 식별될 때, 여기에 설명된 방법들을 사용함으로써, 제품이 유용하고 양품률이 단지 결합 모듈들을 갖지 않는 제품들을 사용함에 따라 증가한다. 유사하게, 충분하게 많은 수의 모듈들이 존재하면, 허용될 수 있는 결합 모듈들의 수가 더 많다. 이들 제품들 모두를 상업적으로 사용함으로써 양품률이 증가되고 더 많은 이익이 실현된다. 몇몇 포인트에서, 허용될 수 있는 결합 모듈들의 최대 수가 달성되고 실현된 양품률이 레벨-오프(level-off)한다. 누적 양품률의 실제 값들은 구현되는 모듈들 또는 서브모듈들의 총 수에 따른다.

<22> 이제, 테스트 특성들 및 집적 회로들의 양품률을 상당히 향상시키는 테스트 방법들 및 구조들이 제공되어왔음이 인식되어야 한다. 동일한 기능들을 실질적으로 수행하는 집적 회로에 대해 다수의 모듈들 또는 서브모듈들이 하나 이상의 테스트 패턴들과 병렬로 테스트된다. 모듈들 또는 서브모듈들 각각으로부터의 결과들은 임의의 불일치를 찾기 위해 테스트되고 유효한(valid) 시그니처 결과는 각 비트 위치에 대한 다수 디지털 값을 나타내는 비트들로 생성된다. 임의의 고장 모듈들(failing modules) 또는 서브모듈들은 각 모듈의 실제 시그니처를 유효 시그니처 결과와 비교함으로써 식별된다. 고장 모듈들 또는 서브모듈들의 아이덴티티는 모듈들 및 서브모듈들이 기능적이지 않은 고객에 대한 개시로 판매되는 집적 회로 상에 저장된다. 따라서, 집적 회로 제조의 양품률은 향상된다. 여기에 설명된 방법들은 다수의 회로 모듈들을 갖는 다른 집적 회로들 및 다수의 코어 프로세서들과 연관된 테스트 비용들을 감소시킨다. 고장 모듈들의 아이덴티티는 고장난 코어의 어드레스들(addresses)을 표시함으로써 행해질 수 있다. 고장 모듈들의 어드레스들은 비휘발성 저장 디바이스(26)와 같은 비휘발성 메모리를 사용하기보다 어떤 모듈들이 고장났는지를 표시하는 퓨즈들을 블로우링(blowing)하기 위해 사용될 수 있다. 대안적으로, 고장 주소들은 고장난 모듈의 어드레스를 나타내는 엔트리(entry)를 메모리에 기록하거나 레지스터에 기록하기 위해 사용될 수 있다.

<23> 본 발명이 특정한 도전성 유형들 또는 포텐셜들(potentials)의 극성에 관하여 설명될지라도, 당업자들은 도전성 유형들 또는 포텐셜들의 극성들이 반전될 수 있음을 인식했다. 게다가, 만약에 있다면, 설명 및 청구항들에서의 용어들 "정면(front)", "뒷면(back)", "위(top)", "밑(bottom)", "위쪽(over)", "아래쪽(under)", 등은 설명적인 목적들을 위해 사용되고 불변의 상대적인 위치들을 설명하기 위해 반드시 필요한 것은 아니다. 그렇게 사용된 용어들은 적절한 환경 하에서 상호변경가능하여, 여기에 설명된 본 발명의 실시예들이 예를 들면, 여기에 예시된 또는 그렇지 않으면 설명된 오리엔테이션들(orientations)과 다른 오리엔테이션들에서 동작할 수 있음이 이해된다.

<24> 본 발명이 특정한 실시예들을 참조하여 여기에 설명될지라도, 다양한 수정들 및 변화들이 아래의 청구항들에 기술된 바와 같이 본 발명의 범위에서 벗어나지 않고 행해질 수 있다. 예를 들면, 모듈들 및 서브모듈들에 의해 표시된 회로의 유형은 프로세서 코어들, 표준 논리, 상태 기계들, 메모리들, 및 수많은 다른 전기 회로들일 수 있다. 모듈들 및 서브모듈들의 총 수는 매우 클 수 있고 임의의 특정한 수에 제한되지 않는다. 다양한 수정들이 여기에 제공된 예들이라기보다는 고장 모듈들을 식별하기 위해 행해질 수 있다. 예를 들면, 디스플레이들(displays) 또는 다른 광학 표시자들이 사용될 수 있다. 사용될 수 있는 테스트 패턴들은 임의의 특정한 유형의 테스트 방법론에 제한되지 않는다. 여기에 설명된 모든 회로는 실리콘 또는 또 다른 반도체 재료로 구현될 수 있거나, 대안적으로 실리콘 또는 또 다른 반도체 재료의 소프트웨어 코드 표현에 의해 구현될 수 있음이 이해되어야 한다. 따라서, 명세서 및 도면들은 제한적인 센스라기보다는 예시적인 것으로서 간주되어야 하고, 모든 이러한 수정들은 본 발명의 범위 내에 포함되도록 의도된다. 임의의 이점들, 장점들, 또는 특정한 실시예들에 대해 여기에서 설명되는 문제점들에 대한 해결책들은 핵심적이고, 요구되거나, 임의의 또는 모든 청구항들의 소자 또는 필수적인 특징들로서 해석되도록 의도되지 않는다.

<25> 하나의 형태에서, 제 1 양호/불량 정보가 집적 회로 상의 제 1 회로에 제공되는 방법에 제공된다. 제 2 양호/불량 정보가 집적 회로 상의 제 2 회로에 제공된다. 제 3 양호/불량 정보가 집적 회로 상의 제 3 회로에 제공된다. 제 1, 제 2, 및 제 3 회로들은 양호할 때의 동일한 테스트 입력에 응답하여 동일한 테스트 결과를 각각 출력한다. 집적 회로는 제 1, 제 2, 또는 제 3 양호/불량 정보 중 적어도 하나가 제 1, 제 2, 또는 제 3 회로들 중 적어도 하나가 여전히 불량하고 수리되지 않음을 나타낼 때, 세일을 위해 제공된다. 또 다른 형태에서, 제 1 양호/불량 정보는 집적 회로 상의 비휘발성 저장 회로에 저장된다. 또 다른 형태에서, 집적 회로의 프라이싱(pricing)은 집적 회로 상의 다수의 양호한 회로들의 기능이다. 또 다른 형태에서, 집적 회로는 제 1, 제 2, 및 제 3 회로들 모두가 양호하면, 제 1 가격이다. 집적 회로는 제 1, 제 2, 또는 제 3 회로들 중 적어도 하나가 여전히 불량하면 제 2 가격이고, 제 1 가격은 제 2 가격보다 더 높다. 또 다른 형태에서, 제 1 양호/불량 정보는 제 1 회로가 집적 회로의 작동 동안에 사용되지 않아야 하는지를 결정하기 위해 제 1 회로에 대해 사용된다. 또 다른 형태에서, 불량 회로들의 분배는 복수의 집적 회로들에 걸쳐 결정된다. 또 다른 형태에서, 불량 회로들

의 분배는 집적 회로들의 구매자에 제공된다. 하나의 형태에서, 보우팅 작동은 각 회로가 양호/불량인지의 여부를 결정하기 위한 적어도 하나의 테스트의 결과에 대해 수행된다.

<26> 또 다른 형태에서, 방법은 집적 회로에 대한 복수의 회로들을 테스트하는 단계를 포함한다. 테스트 출력은 복수의 회로들 각각으로부터 제공된다. 임의의 테스트 출력들이 상이하면, 보우팅 작동은 복수의 회로들 중 어떤 회로가 불량한지를 결정하기 위해 수행된다. 하나의 형태에서, 보우팅은 어떤 테스트 출력이 가장 정확한 테스트 출력인지를 결정하는 단계를 포함한다. 가장 정확한 테스트 출력을 갖는 복수의 회로들 각각은 양호한 것으로 가정된다. 또 다른 형태에서, 복수의 회로들에 대한 양호/불량 정보는 집적 회로 상의 비휘발성 저장 회로에 저장된다. 또 다른 형태에서, 비휘발성 저장 회로는 퓨즈이다. 또 다른 형태에서, 비휘발성 저장 회로는 복수의 퓨즈들을 포함하고, 복수의 퓨즈들 각각은 복수의 회로들 중 하나에 대응한다.

<27> 또 다른 형태에서, 집적 회로는 테스트에 응답하여 제 1 테스트 시그니처를 제공하는 제 1 회로를 포함한다. 제 2 회로는 테스트에 응답하여 제 2 테스트 시그니처를 제공한다. 제 3 회로는 테스트에 응답하여 제 3 테스트 시그니처를 제공한다. 보우팅 회로는 제 1, 제 2, 및 제 3 테스트 시그니처들을 포함하고, 가장 정확한 테스트 시그니처를 결정한다. 비교기는 제 1, 제 2, 및 제 3 테스트 시그니처들 각각을 가장 정확한 테스트 시그니처와 비교하여 제 1, 제 2, 및 제 3 회로들 각각에 대한 양호/불량 정보를 결정한다. 또 다른 형태에서, 비휘발성 저장 회로는 제 1, 제 2, 및 제 3 회로들 각각에 대한 양호/불량 정보를 저장한다. 또 다른 형태에서, 제 1, 제 2, 및 제 3 회로들 모두가 양호한 것을 나타내기 위한 플래그가 제공된다. 또 다른 형태에서, 저장 회로는 제 1, 제 2, 및 제 3 테스트 시그니처들을 저장한다. 또 다른 형태에서, 테스트 회로는 테스트 동안에, 입력 테스트 패턴을 제 1, 제 2, 및 제 3 회로들에 제공한다. 또 다른 형태에서, 제 1, 제 2, 및 제 3 회로들은 동일한 유형의 데이터 프로세서이다. 하나의 형태에서, 제 1 회로는 제 1 서브모듈이고, 제 2 회로는 제 2 서브모듈이고, 제 3 회로는 제 3 서브모듈이다.

<28> 또한, 여기에서 사용된 바와 같은 용어들 "a" 또는 "an"은 하나 또는 하나 이상으로서 규정된다. 또한, 청구항들에서의 "적어도 하나(at least one)" 및 "하나 이상의(one or more)"와 같은 도입 구들의 사용은 부정관사들 "a" 또는 "an"에 의한 또 다른 청구항 소자의 도입이 심지어 동일한 청구항이 도입 구들 "하나 이상의" 또는 "적어도 하나" 및 "a" 또는 "an" 같은 부정관사들을 포함할 때 단지 하나의 이러한 소자를 포함하는 발명들에 대한 이러한 도입된 청구항 소자를 포함하는 임의의 특정한 청구항을 제한함을 암시하도록 해석되지 말아야 한다. 동일한 것은 정관사의 사용에 대해 진실이다.

<29> 다르게 언급되지 않는 한, "제 1(first)" 및 "제 2(second)"와 같은 용어들은 이들 용어들이 설명하는 소자들 사이를 임의적으로 구별하기 위해 사용된다. 따라서, 이들 용어들은 이러한 소자들의 일시적 또는 다른 우선순위를 표시하도록 필수적으로 의도되는 것은 아니다.

<30>

<31>

### 도면의 간단한 설명

<7> 도 1은 본 발명의 하나의 형태에 따른 다수의 모듈들을 갖는 집적 회로를 블록도 형태로 예시한 도면.

<8> 도 2는 도 1의 집적 회로의 비교 및 보우팅 회로(compare and voting circuit)를 블록도 형태로 예시한 도면.

<9> 도 3은 도 1의 집적 회로를 테스트하기 위한 방법을 흐름도 형태로 예시한 도면.

<10> 도 4는 테스팅이 수행된 이후에 도 1의 집적 회로를 제공하기 위한 방법을 흐름도 형태로 예시한 도면.

<11> 도 5는 도 1의 집적 회로의 제품 양품률과 검출된 결점들 사이의 관계를 그래프 형태로 예시한 도면.

## 도면

## 도면1

## 도면2

비교기/보우터 회로

24

## 도면3

## 도면4

## 도면5