(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3749174号

(P3749174)

(45) 発行日 平成18年2月22日(2006.2.22)

(24) 登録日 平成17年12月9日(2005.12.9)

(51) Int.C1.

F 1

|                    |                  |             |

|--------------------|------------------|-------------|

| <b>HO3M 1/78</b>   | <b>(2006.01)</b> | HO3M 1/78   |

| <b>HO3K 17/00</b>  | <b>(2006.01)</b> | HO3K 17/00  |

| <b>HO3K 17/693</b> | <b>(2006.01)</b> | HO3K 17/693 |

E

A

請求項の数 24 (全 16 頁)

(21) 出願番号 特願2001-505139 (P2001-505139)

(86) (22) 出願日 平成12年5月18日 (2000.5.18)

(65) 公表番号 特表2004-515931 (P2004-515931A)

(43) 公表日 平成16年5月27日 (2004.5.27)

(86) 國際出願番号 PCT/US2000/013650

(87) 國際公開番号 WO2000/079685

(87) 國際公開日 平成12年12月28日 (2000.12.28)

審査請求日 平成13年12月25日 (2001.12.25)

(31) 優先権主張番号 09/337,796

(32) 優先日 平成11年6月22日 (1999.6.22)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 590003940

バーブラウン・コーポレーション

B U R R - B R O W N C O R P O R A T

I O N

アメリカ合衆国アリゾナ州85706, タ

クソン, サウス・タクソン・ブルバード

6730

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100076691

弁理士 増井 忠式

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】 DAC用ラダー・スイッチ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

デジタル／アナログ変換器における抵抗性分圧ネットワークの分路抵抗器を、低基準電圧および高基準電圧のいずれかに切り換える切り替え回路であって、

(a) 前記低基準電圧を前記分路抵抗器に結合する第1スイッチMOSFETと、前記分路抵抗器を前記高基準電圧に結合する第2スイッチMOSFETと、

(b) 第1スイッチ制御回路であって、

i. 前記第1スイッチMOSFETのゲートに結合された出力を有する第1CMOS論理回路と、

ii. 前記低基準電圧に両方とも結合された第1基準抵抗器および第1制御MOSFETと、前記第1制御MOSFETのゲートに接続され更に前記第1スイッチMOSFETのゲートに前記第1CMOS論理回路を介して結合されている出力を有する第1演算増幅器であって、前記第1制御MOSFETおよび前記第1基準抵抗器の抵抗を等化し、前記第1スイッチMOSFETのオン抵抗を前記第1基準抵抗器の抵抗に比例する値に調節するように動作する第1演算増幅器と、を含む第1ブリッジ回路と、

を含む第1スイッチ制御回路と、

(c) 第2スイッチ制御回路であって、

i. 前記第2スイッチMOSFETのゲートに結合された出力を有する第2CMOS論理回路と、

ii. 第2基準抵抗器および第2制御MOSFETと、前記第2制御MOSFETのゲ

10

20

ートに接続され、更に前記第2CMOS論理回路を介して前記第2スイッチMOSFETのゲートに結合されている出力を有する第2演算増幅器であって、前記第2制御MOSFETおよび前記第2基準抵抗器の抵抗を等化し、更に前記第2スイッチMOSFETのオン抵抗を前記第2基準抵抗器の抵抗に比例する値に調節するように動作する第2演算増幅器と、を含む第2ブリッジ回路と、

を含む第2スイッチ制御回路と、

を備える切り換え回路。

#### 【請求項2】

請求項1記載の切り換え回路において、前記第1基準抵抗器の抵抗は、前記第2基準抵抗器の抵抗とは実質的に異なること、を特徴とする切り換え回路。 10

#### 【請求項3】

請求項1記載の切り換え回路において、前記第1および第2CMOS論理回路はCMOS反転器であること、を特徴とする切り換え回路。

#### 【請求項4】

請求項1記載の切り換え回路において、前記第1ブリッジ回路は、前記第1ブリッジ回路を付勢するように結合されている第1ブリッジ入力導体を含み、前記第2ブリッジ回路は、前記第2ブリッジ回路を付勢するように結合されている第2ブリッジ入力導体を含むこと、を特徴とする切り換え回路。

#### 【請求項5】

請求項4記載の切り換え回路において、前記第1ブリッジ入力導体は、第1電流源エレメントを介して前記第1基準抵抗器および前記第1演算増幅器の(-)入力に結合され、更に第2電流源エレメントを介して前記第1制御MOSFETおよび前記第1演算増幅器の(+)入力にも結合されており、前記第2ブリッジ入力導体は、第3電流源エレメントを介して前記第2基準抵抗器および前記第2演算増幅器の(-)入力に結合され、更に第4電流源エレメントを介して前記第2制御MOSFETおよび前記第2演算増幅器の(+)入力にも結合されていること、を特徴とする切り換え回路。 20

#### 【請求項6】

請求項1記載の切り換え回路であって、前記第1基準抵抗器および前記第1演算増幅器の(-)入力に結合されている第1電流源エレメントと、前記第1制御MOSFETおよび前記第1演算増幅器の(+)入力に結合されている第2電流源エレメントと、前記第2基準抵抗器および前記第2演算増幅器の(-)入力に結合されている第3電流源エレメントと、前記第2制御MOSFETおよび前記第2演算増幅器の(+)入力に結合されている第4電流源エレメントとを含むこと、を特徴とする切り換え回路。 30

#### 【請求項7】

請求項5記載の切り換え回路において、前記第1、第2、第3および第4電流源エレメントは、それぞれ、第1、第2、第3、および第4抵抗器であり、前記第1ブリッジ入力導体は、前記低基準電圧から一定量だけブーストストラップした電圧を導通させ、前記第2ブリッジ入力導体は、前記高基準電圧から別の一定量だけブーストストラップした電圧を導通させること、を特徴とする切り換え回路。

#### 【請求項8】

請求項5記載の切り換え回路において、前記第1演算増幅器の(+)入力は、第1レベル・シフト抵抗器を介して前記第1制御MOSFETのドレインに結合されており、前記第1基準抵抗器は第1複合抵抗器の一体部分であり、該第1複合抵抗器は、前記第1基準抵抗器の抵抗と直列の前記第1レベル・シフト抵抗器の抵抗に等しい第1レベル・シフト抵抗も含み、前記第2演算増幅器の(+)入力は、第2レベル・シフト抵抗器を介して前記第2制御MOSFETのドレインに結合されており、前記第2基準抵抗器は第2複合抵抗器の一体部分であり、該第2複合抵抗器は、前記第2レベル・シフト抵抗器の抵抗と直列の第2レベル・シフト抵抗も含むこと、を特徴とする切り換え回路。 40

#### 【請求項9】

請求項5記載の切り換え回路において、前記第1基準抵抗器の抵抗は、前記第2基準抵 50

抗器の抵抗よりも実質的に大きな値であって、前記第1ブリッジ回路を流れるバイアス電流を、前記第2ブリッジ回路を流れる対応のバイアス電流に対して、実質的に減少させること、を特徴とする切り換え回路。

【請求項10】

請求項1記載の切り換え回路であって、前記第1ブリッジ制御回路において、前記低基準電圧とは独立した値に前記第1ブリッジ回路を付勢する第1バイアス電流を維持する第1手段と、前記第2ブリッジ制御回路において、前記高基準電圧とは独立した値に前記第2ブリッジ回路を付勢する第2バイアス電流を維持する第2手段とを含むこと、を特徴とする切り換え回路。

【請求項11】

デジタル／アナログ変換器において、当該デジタル／アナログ変換器のデジタル入力に印加される二進入力の1ビットに対応する論理情報に応答して、 $R / 2R'$  抵抗性分圧ネットワークのレッグを、高基準電圧または低基準電圧に切り換える切り換え回路であって、

(a) 前記低基準電圧を導通させる第1導体に結合されているソースと、前記レッグの導体に結合されているドレインとを有する第1MOSFETと、前記レッグの導体に結合されているソースと、前記高基準電圧を導通させる第2基準電圧導体に結合されているドレインとを有する第2MOSFETとを含むスイッチ回路と、

(b) 第1スイッチ制御回路であって、

i. 第1給電導体および第2給電導体の間に結合され、前記論理情報を受けるように結合されている入力と、前記第1MOSFETのゲートに結合されている出力とを有する第1CMOS反転器と、

ii. 第1ブートストラップ基準電圧源と、

iii. 第1および第2入力端子と、第1および第2出力端子とを含む第1ブリッジ回路であって、前記第1ブートストラップ基準電圧源を前記第1および第2入力端子間に結合した、第1ブリッジ回路と、

iv. 前記第2入力端子および前記第1出力端子の間に結合されている第1抵抗器と、前記第1出力端子および前記第1入力端子の間に結合されている第2抵抗器と、前記第1入力端子および前記第2出力端子の間に結合されている第3抵抗器と、前記第2出力端子および前記第2入力端子の間に結合されている第4抵抗器と、前記第4抵抗器を前記第2入力端子に結合する第3MOSFETと、

v. 前記第1出力端子に結合されている第1入力と、前記第2出力端子に結合されている第2入力と、第2導体によって前記第3MOSFETのゲート電極に接続されている出力とを有する第1演算増幅器と、

を含む第1スイッチ制御回路と、

(c) 第2スイッチ制御回路であって、

i. 第3給電導体および前記第2給電導体の間に結合されており、前記二進ビット信号の相補値を受けるように接続されている入力と、前記第2MOSFETのゲートに結合されている出力とを有する第2CMOS反転器と、

ii. 第2ブートストラップ基準電圧源と、

iii. 第3および第4入力端子ならびに第3および第4出力端子を含む第2ブリッジ回路であって、前記第2ブートストラップ基準電圧源を前記第3および第4入力端子間に結合した、第2ブリッジ回路と、

iv. 前記第4入力端子および前記第3出力端子間に結合されている第5抵抗器と、前記第3出力端子および前記第3入力端子間に結合されている第6抵抗器と、前記第3入力端子および前記第4出力端子間に結合されている第7抵抗器と、前記第4出力端子および前記第4入力端子間に結合されている第8抵抗器と、前記第8抵抗器を前記第4入力端子に結合する第4MOSFETと、

v. 前記第3出力端子に結合されている第1入力と、前記第4出力端子に結合されている第2入力と、第3導体によって前記第4MOSFETのゲート電極に接続されている出

10

20

30

40

50

力とを有する第2演算増幅器であって、前記第1および第2スイッチMOSFETの各々のオン抵抗が $R_{ONi}$ に等しく、前記抵抗 $2R'$ が $2R - R_{ONi}$ に等しい、第2演算増幅器と、

を含む第2スイッチ制御回路と、

を備える切り換え回路。

【請求項12】

デジタル／アナログ変換器であって、

(a) 各々抵抗 $R$ を有する複数の直列抵抗器と、各々抵抗 $2R'$ を有する複数の分路抵抗器とを含む抵抗性分圧ネットワークと、

(b) デジタル／アナログ変換器における抵抗性分圧ネットワークの分路抵抗器を、

低基準電圧および高基準電圧のいずれかに切り換える切り換え回路であって、

10

(1) 前記低基準電圧を前記分路抵抗器に結合する第1スイッチMOSFETと、前記分路抵抗器を前記高基準電圧に結合する第2スイッチMOSFETと、

(2) 第1スイッチ制御回路であって、

i. 前記第1スイッチMOSFETのゲートに結合されている出力を有する第1CMOS論理回路と、

ii. 前記低基準電圧に両方とも結合されている第1基準抵抗器および第1制御MOSFETと、前記第1制御MOSFETのゲートに接続され、更に前記第1CMOS論理回路を介して前記第1スイッチMOSFETのゲートにも結合されている出力を有する第1演算増幅器であって、前記第1制御MOSFETおよび前記第1基準抵抗器の抵抗を等化し、前記第1スイッチMOSFETのオン抵抗を前記第1基準抵抗器の抵抗に比例する値に調節するように動作する第1演算増幅器と、を含む第1ブリッジ回路と、

20

を含む第1スイッチ制御回路と、

(3) 第2スイッチ制御回路であって、

i. 前記第2スイッチMOSFETのゲートに結合されている出力を有する第2CMOS論理回路と、

ii. 第2基準抵抗器および第2制御MOSFETと、前記第2制御MOSFETのゲートに接続され、更に前記第2CMOS論理回路を介して前記第2スイッチMOSFETのゲートにも結合されている出力を有する第2演算増幅器であって、前記第2制御MOSFETおよび前記第2基準抵抗器の抵抗を等化し、前記第2スイッチMOSFETのオン抵抗を前記第2基準抵抗器の抵抗に比例する値に調節するように動作する第2演算増幅器と、を含む第2ブリッジ回路と、

30

を含む第2スイッチ制御回路と、

を備え、

(c) 前記第1および第2スイッチMOSFETの各々のオン抵抗が $R_{ONi}$ に等しく、

前記抵抗 $2R'$ が $2R - R_{ONi}$ に等しいこと、

を特徴とするデジタル／アナログ変換器。

【請求項13】

請求項12記載のデジタル／アナログ変換器において、前記第1基準抵抗器の抵抗が、前記第2基準抵抗器の抵抗とは実質的に異なること、を特徴とするデジタル／アナログ変換器。

40

【請求項14】

請求項12記載のデジタル／アナログ変換器において、前記第1および第2CMOS論理回路はCMOS反転器であること、を特徴とするデジタル／アナログ変換器。

【請求項15】

請求項12記載のデジタル／アナログ変換器において、前記第1ブリッジ回路は、該第1ブリッジ回路を付勢するように結合されている第1ブリッジ入力導体を含み、前記第2ブリッジ回路は、該第2ブリッジ回路を付勢するように結合されている第2ブリッジ入力導体を含むこと、を特徴とするデジタル／アナログ変換器。

【請求項16】

請求項 1 5 記載のデジタル / アナログ変換器において、前記第 1 ブリッジ入力導体は、第 1 電流源エレメントを介して前記第 1 基準抵抗器および前記第 1 演算増幅器の( - )入力に結合し、更に第 2 電流源エレメントを介して前記第 1 制御MOSFET および前記第 1 演算増幅器の( + )入力にも結合し、前記第 2 ブリッジ入力導体は、第 3 電流源エレメントを介して前記第 2 基準抵抗器および前記第 2 演算増幅器の( - )入力に結合し、更に第 4 電流源エレメントを介して前記第 2 制御MOSFET および前記第 2 演算増幅器の( + )入力にも結合したこと、を特徴とするデジタル / アナログ変換器。

#### 【請求項 1 7】

請求項 1 6 記載のデジタル / アナログ変換器において、前記第 1 、第 2 、第 3 および第 4 電流源エレメントは、それぞれ、第 1 、第 2 、第 3 、および第 4 抵抗器であり、前記第 1 ブリッジ入力導体は、前記低基準電圧から一定量だけブーストアップされた電圧を導通させ、前記第 2 ブリッジ入力導体は、前記高基準電圧から別の一定量だけブーストアップされた電圧を導通させること、を特徴とするデジタル / アナログ変換器。

10

#### 【請求項 1 8】

請求項 1 6 記載のデジタル / アナログ変換器において、前記第 1 演算増幅器の( + )入力は、第 1 レベル・シフト抵抗器を介して前記第 1 制御MOSFET のドレインに結合されており、前記第 1 基準抵抗器は、第 1 複合抵抗器の一体部分であり、該第 1 複合抵抗器は、前記第 1 基準抵抗器の抵抗と直列に前記第 1 レベル・シフト抵抗器の抵抗に等しい第 1 レベル・シフト抵抗も含み、前記第 2 演算増幅器の( + )入力は、第 2 レベル・シフト抵抗器を介して前記第 2 制御MOSFET のドレインに結合されており、前記第 2 基準抵抗器は、第 2 複合抵抗器の一体部分であり、該第 2 複合抵抗器は、前記第 2 レベル・シフト抵抗器の抵抗と直列に第 2 レベル・シフト抵抗も含むこと、を特徴とするデジタル / アナログ変換器。

20

#### 【請求項 1 9】

請求項 1 6 記載のデジタル / アナログ変換器において、前記第 1 基準抵抗器の抵抗は、前記第 2 基準抵抗器の抵抗よりも実質的に大きい値にスケーリングして、前記第 1 ブリッジ回路を流れるバイアス電流を、前記第 2 ブリッジ回路を流れる対応のバイアス電流に対して実質的に減少させること、を特徴とするデジタル / アナログ変換器。

#### 【請求項 2 0】

請求項 1 2 記載のデジタル / アナログ変換器であって、前記第 1 ブリッジ制御回路において、前記低基準電圧とは独立した値に前記第 1 ブリッジ回路を付勢する第 1 バイアス電流を維持する第 1 手段と、前記第 2 ブリッジ制御回路において、前記高基準電圧とは独立した値に前記第 2 ブリッジ回路を付勢する第 2 バイアス電流を維持する第 2 手段とを含むこと、を特徴とするデジタル / アナログ変換器。

30

#### 【請求項 2 1】

請求項 1 2 記載のデジタル / アナログ変換器において、前記第 1 および第 2 基準抵抗器は、前記第 1 および第 2 制御MOSFET および前記第 1 および第 2 スイッチMOSFET のオン抵抗と同じ温度係数を有すること、を特徴とするデジタル / アナログ変換器。

40

#### 【請求項 2 2】

請求項 2 1 記載のデジタル / アナログ変換器において、前記抵抗  $R$  は単一の値であり、前記抵抗値  $2R'$  の一部が他の抵抗と異なり、オン抵抗値  $R_{ONi}$  の一部が他の抵抗と異なること、を特徴とするデジタル / アナログ変換器。

#### 【請求項 2 3】

請求項 2 2 記載のデジタル / アナログ変換器であって、全てが同じチャネル長を有する複数の第 1 スイッチMOSFET および第 2 スイッチMOSFET を含むことによって、前記デジタル / アナログ変換器の精度におけるコードに依存したばらつきを低減すること、を特徴とするデジタル / アナログ変換器。

#### 【請求項 2 4】

デジタル / アナログ変換器において用いるために適合させた抵抗性分圧ネットワーク

であつて、

(a) 各々抵抗Rを有する複数の直列抵抗器と各々抵抗 $2R'$ を有する複数の分路抵抗器とを備え、前記ディジタル／アナログ変換器が、前記抵抗性分圧ネットワークの分路抵抗器を、第1および第2基準電圧のいずれかに切り換える回路を含み、該回路が、前記低基準電圧をレッグに結合する第1スイッチMOSFETと、レッグを前記高基準電圧に結合する第2スイッチMOSFETとを含み、

(b) 前記第1および第2スイッチMOSFETの各々のオン抵抗が $R_{ONi}$ に等しく、前記抵抗 $2R'$ が $2R - R_{ONi}$ に等しく、

(c) 前記低基準電圧に両方とも結合されている第1基準抵抗器および第1制御MOSFETと、前記第1スイッチMOSFETのゲートに結合されている出力を有する第1演算増幅器であつて、前記第1基準抵抗器の抵抗に比例するよう前記第1スイッチMOSFETのオン抵抗を調節するように動作する第1演算増幅器と、を含む第1回路と、第2基準抵抗器および第2制御MOSFETと、前記第2スイッチMOSFETのゲートに結合されている出力を有する第2演算増幅器であつて、前記第2基準抵抗器の抵抗に比例するよう前記第2スイッチMOSFETのオン抵抗器を調節するように動作する第2演算増幅器と、を含む第2回路と、を備えた切り換え回路を含むこと、

を特徴とする抵抗性分圧ネットワーク。

#### 【発明の詳細な説明】

##### 【0001】

##### (発明の背景)

本発明は、ディジタル／アナログ変換器(DAC)に用いられるR/2Rラダー電圧分割ネットワークと連動するビット・スイッチ回路に関する。

##### 【0002】

最も近い従来技術は、米国特許第5,764,174号(Dempsey et al.)の図5および図9であると考えられる。図9の $V_{gp}$ および $V_{gn}$ は、制御された「供給」電圧として図5のCMOSバッファ116iおよび118iに供給される。米国特許第5,075,677号(Meaney et al.)および第4,558,242号(Tuthill et al.)も高および低基準電圧にR/2Rラダーの2R分路抵抗器を切り換える従来技術の回路を開示する。

##### 【0003】

Dempsey et al.特許の図9の制御回路は、2つの制御電圧 $V_{gp}$ および $V_{gn}$ を発生し、供給電圧として1対のCMOS反転器またはバッファ46iおよび48iにそれぞれ印加する。二進入力 $b_i$ によってCMOSバッファ46iおよび48iを制御し、MOSFET42iおよび44iをオンおよびオフに切り換える。MOSFET42iおよび44iのドレイン電極は、R/2Rラダー・ネットワークの対応するレッグに接続されている。MOSFET42iは、P-チャネルまたはN-チャネルのいずれとすることもでき(Dempsey et al.特許の図6を参照)、バッファ46iは対応して反転または非反転となる。

##### 【0004】

演算増幅器58および59は、各々、それらの(+)および(-)入力のバランスを取るように動作する。Dempsey et al.特許の図9における抵抗器54および57は、同じバイアス電流を確定し、結合したMOSFET55のオン抵抗を結合抵抗器52の抵抗に一致させ、更に結合MOSFET56のオン抵抗を結合抵抗器53の抵抗に一致させる。共通バイアス電流を生成する回路構造は、抵抗器54および57を含み、 $V_{REF+}$ が $V_{REF-}$ よりも約2ボルト以上高くない場合、Dempsey et al.の図9の回路は正確な動作が妨げられる。 $V_{REF+}$ および $V_{REF-}$ 間の差が減少するに連れて、図9の回路を通過する電流も減少し、抵抗器間の電圧低下における2つの演算増幅器のオフセット・エラーの割合が増々大きくなる。このために、動作の精度が著しく低下する。

##### 【0005】

Dempsey et al.特許の図11は、代替実施形態を開示しており、その中でMOSFETスイッチ42iおよび44iのドレインならびにR/2Rラダーの対応するレッグ間に、単位抵抗器72および74を直列に接続している。この実施形態は、MOSFETスイッ

10

20

30

40

50

チ 4 2<sub>i</sub> および 4 4<sub>i</sub> のオン抵抗を、単位抵抗器 7 2 および 7 4 の抵抗に対して制御する。

【 0 0 0 6 】

Dempsey et al.特許、および関連する従来技術の全ての制御および切り換え回路は、従来の R / 2 R 抵抗性分圧ネットワークと共に用いるように設計されており、直列抵抗器は全て抵抗 R を有し、分路抵抗器は全て抵抗 2 R を有する。

【 0 0 0 7 】

あらゆる R / 2 R 抵抗性分圧ネットワークでは、2 R 分路抵抗器を高基準電圧または低基準電圧に選択的に結合するスイッチのチャネル幅対チャネル長比 (W / L 比) を二進でスケーリングする必要がある。これは、例えば、1 2 ないし 1 6 ビットの分解能というような、分解能のビット数が大きいディジタル / アナログ変換器にとっては非常に問題である。例えば、1 6 ビット・ディジタル / アナログ変換器では、M S B スイッチのオン抵抗が 4 0 オームであるとすると、L S B スイッチのオン抵抗は 3 2 0 キロオームないし 1 . 2 0 メグオームとなる。4 0 オームのオン抵抗を得るには、非常に大きな M O S F E T が必要となる。何故なら、チャネル幅 W を非常に大きくしなければないからである。また、3 2 0 キロオームないし 1 . 2 0 メグオームのオン抵抗を得るためにも非常に大きな M O S F E T が必要となる。何故なら、チャネル長 L を非常に大きくしなければからである。したがって、R / 2 R 分圧ネットワークを用いて高精度のディジタル / アナログ変換器を実施するには、大量のチップ面積が必要となる。大量のチップ面積を回避するために、当業者は種々の「ショート・カット」を開発し、L S B ビットのための非常に大きな M O S F E T スイッチの使用を回避したが、これらの技法は精度低下を招き、約 1 2 ビットの分解能を超える分解能を有するディジタル / アナログ変換器では、この精度低下は容認することができない。

【 0 0 0 8 】

例えば、場合によっては、当業者は R / 2 R ラダーの最下位ビットに対するスイッチのサイズを二進スケーリングせず、生じたエラーを単に受け入れる場合もある。別の手法では、高抵抗薄膜抵抗器をスイッチに直列に挿入し、薄膜抵抗器の温度係数がスイッチのオン抵抗のそれとは異なるという事実を受け入れていた。Dempsey et al.特許の図 1 3 に示すように単位抵抗器を用いることは、更に別のショートカットであり、R / 2 R ラダー・ネットワークの最下位レッグに対するスイッチのオン抵抗を二進スケーリングするのを回避するために用いられている。

【 0 0 0 9 】

チャネル長 L を非常に長くすることによって M O S F E T スイッチをスケーリングし大きなオン抵抗を有することが難しいのは、オン抵抗  $R_{ON}$  を生成する有効ゲート・ソース電圧の大きさが、流れる電流に起因してチャネル領域に沿って生ずる電圧降下のために、チャネル領域の長さに沿って徐々に減少するからである。その結果、W / L 比を二進スケーリングしても、チャネル電流の全ての値に対して二進スケーリングした  $R_{ON}$  が得られない。このため、特に最下位ビット・スイッチでは、コード依存エラーが生ずる。何故なら、チャネル電流は、R / 2 R ラダーに接続されている M O S F E T スイッチでは、非常にコード依存性が高いからである。これは、高精度の高分解能ディジタル / アナログ変換器を得る際の重要な問題点である。

【 0 0 1 0 】

(1) 従来技術よりも精度が高く、(2) 外部から供給する上位および下位基準電圧間の差を小さくすることができる、ディジタル / アナログ変換器を提供することができれば非常に望ましいであろう。

(発明の摘要)

したがって、本発明の目的は、抵抗性分圧ネットワークの分路抵抗器を高基準電圧または低基準電圧のいずれかに結合する種々のビット・スイッチ・トランジスタのオン抵抗を二進スケーリングする必要性を回避した回路および技法を提供することである。

【 0 0 1 1 】

本発明の別の目的は、最も近い従来技術よりも精度が高く安価なディジタル / アナログ

10

20

30

40

50

変換器を提供することである。

本発明の別の目的は、抵抗性分圧ネットワークの分路抵抗器を高基準電圧または低基準電圧のいずれかに結合するように動作するビット・スイッチを制御するブリッジ制御回路を提供し、ブリッジ制御回路によってユーザが供給する基準電圧のばらつきに伴う精度低下を回避することである。

#### 【0012】

本発明の別の目的は、ユーザが供給する基準電圧間の差を実質的に最も近い従来技術のそれ未満とすることができますデジタル／アナログ変換器を提供することである。

#### 【0013】

本発明の別の目的は、従来技術のR / 2Rを有する高分解能デジタル／アナログ変換器において発生するコード依存精度低下を回避することである。 10

本発明の別の目的は、抵抗性ラダー・ネットワークを有するデジタル／アナログ変換器において、直列接続したビット・スイッチMOSFETの使用を回避し、長い有効チャネル長(L)を達成し、更にビット・スイッチMOSFETに要求されるチップ面積量を縮小することである。

#### 【0014】

本発明の別の目的は、米国特許第5,764,174号の図11および図13におけるように、「単位」抵抗器と直列に接続したスケーリングしたビット・スイッチの使用を回避し、二進スケーリングしたスイッチの要求オン抵抗を得るようにすることである。

#### 【0015】

端的に説明すると、本発明の一実施形態によれば、本発明は、デジタル／アナログ変換器(1)を提供し、これは、各々抵抗Rを有する複数の直列抵抗器(27i)および各々抵抗2R'を有する複数の分路抵抗器(30i)と、デジタル／アナログ変換器(1)内の抵抗性分圧ネットワーク(10)の分路抵抗器(30i)を、第1および第2基準電圧のいずれかに切り換える回路とを含む。デジタル／アナログ変換器は、低基準電圧( $V_{REFL}$ )を分路抵抗器(30i)に結合する第2スイッチMOSFET(44i)と、分路抵抗器(30i)を高基準電圧( $V_{REFH}$ )に結合する第2スイッチMOSFET(42i)とを含む。第1スイッチ制御回路(11)は、第1スイッチMOSFET(44i)のゲートに結合されている出力を有する第1CMOS反転器(39)と、低基準電圧( $V_{REFL}$ )に結合されている第1基準抵抗器(26)および第1制御MOSFET(24)と、第1制御MOSFET(24)のゲートに接続され、更に第1スイッチMOSFET(44i)のゲートに結合されている出力を有し、第1制御MOSFET(24)および第1基準抵抗器(26)の抵抗を等化し、第1基準抵抗器(26)の抵抗に比例するよう第1スイッチMOSFET(44i)のオン抵抗を調節するように動作する第1ブリッジ回路(11A)とを含む。第2スイッチ制御回路(12)は、第2スイッチMOSFET(42i)のゲートに結合されている出力を有する第2CMOS反転器(21)と、第2基準抵抗器(25)および第2制御MOSFET(23)と、第2制御MOSFET(23)のゲートに接続され更に第2スイッチMOSFET(42i)のゲートに結合されている出力を有し、第2制御MOSFET(23)および第2基準抵抗器(25)の抵抗を等化し、第2基準抵抗器(25)の抵抗に比例するよう第2スイッチMOSFET(42i)のオン抵抗を調節するように動作する第2ブリッジ回路(12A)とを含む。第1(44i)および第2(42i)スイッチMOSFETの各々のオン抵抗は $R_{ONi}$ に等しく、抵抗2R'は2R -  $R_{ONi}$ に等しい。 30

#### 【0016】

一実施形態では、本発明は、デジタル／アナログ変換器において、ビット・スイッチの二進スケーリングを行うことなく、抵抗性ラダー・ネットワークの分路抵抗器を低基準電圧( $V_{REFL}$ )または高基準電圧( $V_{REFH}$ )のいずれかに接続し、高精度を達成する技法を提供する。各分路抵抗器毎に、第1スイッチMOSFET(44i)を当該分路抵抗器と低基準電圧( $V_{REFL}$ )との間に結合し、第2スイッチMOSFET(42i)を分路抵抗器の端子と高基準電圧( $V_{REFH}$ )との間に結合する。デジタル／アナログ変換器に印 40

加するデジタル入力ワードのビット状態に応じて、第1(44<sub>i</sub>)および第2(42<sub>i</sub>)スイッチMOSFETのゲート電極に制御電圧を印加し、それぞれ各分路抵抗器に結合されている第1(44<sub>i</sub>)および第2(42<sub>i</sub>)スイッチMOSFETの一方または他方をオンに切り換え、オンに切り換えられた第1または第2スイッチMOSFETのオン抵抗を2R-2R'に等しくする。ここで、Rは抵抗性ラダー・ネットワークの複数の直列抵抗器の各々の抵抗であり、2R'は、オンに切り換えられた第1または第2スイッチを結合している分路抵抗器の抵抗である。制御電圧の大きさを制御して、オンに切り換えた第1および第2スイッチMOSFETのオン抵抗の温度係数が、抵抗性ラダー・ネットワークを構成する抵抗器の温度係数に等しくなるようにする。第1スイッチMOSFET(44<sub>i</sub>)および第2スイッチMOSFET(42<sub>i</sub>)のオン抵抗器に対する二進スケーリングは行わない。

#### (好適な実施形態の詳細な説明)

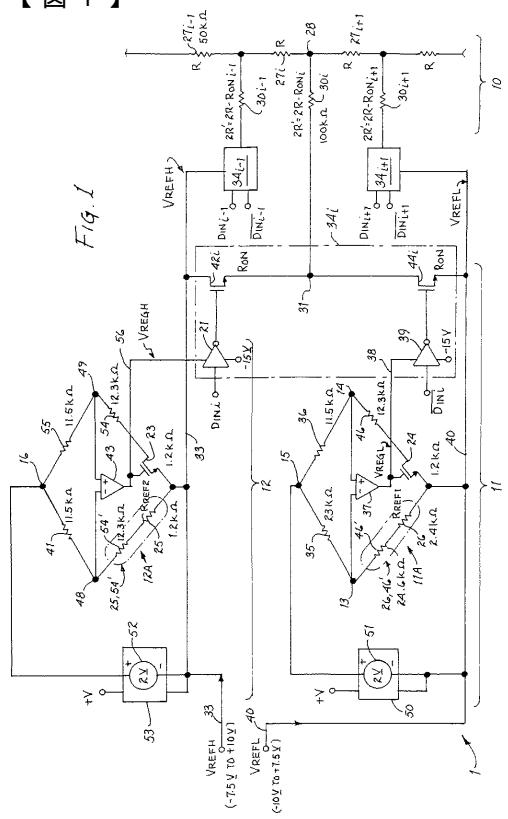

図1および図2を参照すると、16ビット・デジタル/アナログ変換器1は、抵抗Rの複数の直列抵抗器27<sub>i</sub>および各々抵抗2R'を有する複数の分路抵抗器30<sub>i</sub>を有する抵抗性分圧ネットワーク10、20個のスイッチおよびドライバ回路34<sub>i</sub>、ならびに第1および第2ブリッジ制御回路11および12を含み、iは1から20までの値である(尚、以下で説明するように、分圧ネットワーク10のいずれの分路レッグに対する2R'の値も、対応するスイッチのR<sub>ON</sub>に依存することを注記しておく。)下位ブリッジ制御回路11は、外部供給基準電圧V<sub>REF</sub>を16個のN-チャネルV<sub>REFL</sub>スイッチMOSFET44<sub>i</sub>の各々に印加し、上位ブリッジ制御回路12は、外部供給基準電圧V<sub>REFH</sub>をi個のN-チャネル「V<sub>REFH</sub>スイッチ」MOSFET42<sub>i</sub>の各々に供給する。最初の上位3ビットを除いて、各スイッチおよびドライバ回路34<sub>i</sub>におけるスイッチMOSFET42<sub>i</sub>および44<sub>i</sub>は、16ビット・デジタル入力ワードの対応する第iビットDIN<sub>i</sub>に応答して、オンおよびオフとなる。(デジタル入力コードの最初の3ビット1~3は、温度計型デコーダでは「セグメント化」即ちデコードされ、3つの入力および7つの出力が抵抗性ネットワーク・ラダーレッグの最初の7セグメントの各々に向かう。これについては、以下で図2を参照しながら説明する。これによって、デジタル入力ワードの最初の上位3ビットの8つの組み合わせ全てに対する出力が得られる。その各々は、V<sub>REFL</sub>およびV<sub>REFH</sub>間の差によって決められる電圧範囲の1/8だけ、他から分離されている。

#### 【0017】

即ち、スイッチMOSFET42<sub>i</sub>のドレインは、導体33に接続されており、導体33上は、電圧V<sub>REFH</sub>(通例では+10ボルトであるが、V<sub>REFL</sub>が-10ボルトの場合、約-9.9ボルト程度でも可能である)に維持されている。スイッチMOSFET42<sub>i</sub>のソースは、導体31によって、「修正R/2Rラダー・ネットワーク」10の分路抵抗器30<sub>i</sub>に接続されている。スイッチMOSFET44<sub>i</sub>は、そのドレインが導体31によって分路抵抗器30<sub>i</sub>に接続されており、そのソースが導体40に接続されている。導体40上には、デジタル/アナログ変換器1のユーザがV<sub>REFL</sub>を供給している。V<sub>REFL</sub>は、通例では-10ボルトの電圧を有するが、V<sub>REFH</sub>が+10ボルトの場合、+9.9ボルトでも可能である。図1の回路では、V<sub>REFH</sub>およびV<sub>REFL</sub>が変化しても、そしてこれら2つの値が非常に接近していても(例えば、100ミリボルト以内)、スイッチMOSFET42<sub>i</sub>および44<sub>i</sub>のR<sub>ON</sub>の値が非常に高い精度で得られる。

#### 【0018】

R/2R'ラダー・ネットワーク10は、分路抵抗器30<sub>i</sub>の抵抗が従来のR/2Rラダーにおけるように2Rではなく、代わりに2R'に等しいという点で、従来の(例えば、Dempsey et al.特許の図13に示すような)R/2Rラダー・ネットワークとは異なる。2R'は2R-R<sub>ONi</sub>に等しく、R<sub>ONi</sub>は、オンになっているスイッチMOSFET42<sub>i</sub>および44<sub>i</sub>の一方のチャネル抵抗である。別の言い方をすれば、本発明の抵抗性分圧ネットワークの各分路抵抗器の全抵抗「2R」は、抵抗性ネットワーク10の各分路レッグが正確に2Rの値を有する従来技術のデジタル/アナログ変換器とは異なり、対応するビット・スイッチ42<sub>i</sub>または44<sub>i</sub>のオン抵抗R<sub>ONi</sub>を含む。

10

20

30

40

50

## 【0019】

従来技術とは異なり、種々のビットのスイッチMOSFET 44<sub>i</sub>および42<sub>i</sub>のW/L比（即ち、チャネル幅対チャネル長比）は、二進スケーリングしたオン抵抗が得られるように調節されていない。代わりに、これらは、適当な小さなサイズとなり、適当なオン抵抗を有するように選択されている。R/2R'ラダー・ネットワーク10の種々の2R'抵抗の値は、種々のビットに対して別個とすることができます。この特徴は、抵抗性分圧ネットワークの全分路抵抗器の2R抵抗が必然的に2Rの値に正確に等しい、従来のR/2Rラダー・ネットワークとは異なる。

## 【0020】

スイッチMOSFET 42<sub>i</sub>および44<sub>i</sub>のオン抵抗は、ブリッジ制御回路11および12によって制御し、抵抗性分圧ネットワーク10の直列および分路抵抗器の抵抗Rおよび2R'と同じ温度係数を有するようにしている。二進スケーリングしていないスイッチMOSFET 42<sub>i</sub>および44<sub>i</sub>のオン抵抗を、抵抗性分圧ネットワーク10の分路抵抗器レッグの全抵抗2R = 2R' + R<sub>ONi</sub>に含ませることができるのは、この特性のためである。

## 【0021】

ブリッジ制御回路11および12、ならびにR/2R'分圧ネットワーク10の抵抗器は全て、ケイ化クロムまたはシクロムと呼ばれるシリコン・クロム材で形成された薄膜抵抗器であるので、MOSFET 24のオン抵抗の温度係数は、基準抵抗器26の抵抗の温度係数に追従し、MOSFET 23のオン抵抗は第2基準抵抗器25の抵抗に追従する。その結果、スイッチMOSFET 44<sub>i</sub>のオン抵抗の温度係数も、シクロム抵抗器26の抵抗ならびに分圧ネットワーク10のシクロム抵抗器Rおよび2R'の温度係数に追従する。

## 【0022】

下位ブリッジ制御回路11は、ブリッジ回路11Aを含む。ブリッジ回路11Aは、抵抗R<sub>REF1</sub>の第1基準抵抗器26を含み、その下位端子は導体40に結合され、その上位端子は抵抗器46'の一方の端子に結合されている。抵抗器46'の他方の端子は、導体13によって、演算増幅器37の(-)入力、および抵抗器35の下位端子に接続されている。抵抗器35の上位端子は、導体15によって、約2ボルトの値を有する定電圧源回路51の(+)端子、および抵抗器36の上位端子に接続されている。導体15上の電圧は、V<sub>REFL</sub>よりも2ボルト高いレベルに「ブートストラップ」されている。何故なら、定電圧源51の(-)端子がV<sub>REFL</sub>導体40に接続されているからである。定電圧回路51は、定電圧源50に含まれており、定電圧源50は、通例では、+15ボルト電源+VおよびV<sub>REFL</sub>の間に接続されている。抵抗器36の下位端子は、導体14によって演算増幅器37の(+)入力に接続され、更に抵抗器46を介してN-チャネル基準トランジスタ24に結合されている。基準トランジスタ24のゲートは、導体38によって演算増幅器37の出力に接続されている。N-チャネル基準MOSFET 24のソースは、導体40に接続されており、導体40上には外部基準電圧V<sub>REFL</sub>が供給されている。

## 【0023】

導体38上に演算増幅器37によって電圧V<sub>REGL</sub>が生成され、演算増幅器37はサーボ增幅器として動作し、必要に応じて制御MOSFET 24のゲート電圧を確立し、そのオン抵抗をR<sub>REF1</sub>に等しくし、同じゲート電圧をスイッチMOSFET 44<sub>i</sub>に供給し、そのW/L比に応じて、そのオン抵抗R<sub>ONi</sub>をR<sub>REF1</sub>に等しくするか、またはこれに対してスケーリングする。V<sub>REGL</sub>はCMOS反転器39の高電源端子に接続されており、その低供給電圧端子は、負供給電圧（通例では-15ボルト）に接続されている。したがって、CMOS反転器39の高出力電圧はV<sub>REGL</sub>に等しくなる。CMOS反転器39の出力は、スイッチMOSFET 44<sub>i</sub>のゲートに接続されている。抵抗器46および46'は、演算増幅器37のためにより多くの「ヘッド・ルーム」(head room)を設ける機能を果たす。即ち、抵抗器46および46'を通過する電流は、これらの間に等しい電圧降下を発生させ、導体13および14上の電圧を、導体40上の電圧に対して、より高いレベルにシ

10

20

30

40

50

フトさせる。これによって、演算増幅器 37 の入力段に、より多い「動作余裕」即ち「ヘッド・ルーム」が得られる。

#### 【0024】

抵抗器 46' は、実際には、単一の 27.0 キロオーム抵抗器 26、46' の中に基準抵抗器 26 と共に一体化されているが、抵抗器 46' は、発明の説明に供するために、別個の抵抗器として図示されている。

#### 【0025】

同様に、上位ブリッジ制御回路 12 は、抵抗  $R_{REF2}$  を有する同様の第 2 基準抵抗器 25 を備えたブリッジ回路 12A を含む。基準抵抗器 25 は、その下位端子が導体 33 に接続されており、導体 33 上には、通例では +10 ボルトの第 2 外部基準電圧  $V_{REFH}$  が、デイジタル / アナログ変換器 1 のユーザによって供給されている。基準抵抗器 25 の上位端子は、抵抗器 54' を介して、演算増幅器 43 の( - )入力に結合され、更に抵抗器 41 の下位端子に結合されている。抵抗器 41 の上位端子は、抵抗器 55 の上位端子に接続され、更に、 $V_{REFH}$  よりも 2 ボルトだけ高い値にブーストされた定電圧源回路 52 の( + )端子に接続されている。これによって、上位ブリッジ回路 12A 間に約 2 ボルトの電圧が生成する。定電源回路 52 の( - )端子は、導体 33 に接続されている。抵抗器 55 の下位端子は、導体 49 を介して、演算増幅器 43 の( + )入力に接続され、第 2 基準 N-チャネル MOSFET 23 のドレインに結合されている。MOSFET 23 のゲートは、導体 56 によって、演算増幅器 43 の出力に接続されている。(ブーストされた電圧源 51 および 52 は、各々、従来の定電流源を含み、抵抗性素子および / またはダイオード素子を介して定電流を供給する。その間には 2 ボルトの電圧降下が生ずる。)

演算増幅器 43 は、導体 56 上に基準電圧  $V_{REGH}$  を生成する。演算増幅器 43 は、サーボ増幅器として動作し、必要に応じて制御 MOSFET 23 のゲート電圧を確立し、そのオン抵抗を  $R_{REF2}$  に等しくし、更に同じゲート電圧をスイッチ MOSFET 42' に供給して、その W/L 比に応じて、そのオン抵抗  $R_{ONi}$  を  $R_{REF2}$  に等しくするか、またはこれに対してスケーリングする。 $V_{REGH}$  は、CMOS 反転器 21 の高供給電圧端子に接続されている。その結果、CMOS 反転器 21 の高出力電圧は  $V_{REGH}$  に等しくなる。CMOS 反転器 45 の低供給電圧端子は -15 ボルトに接続されている。基準 MOSFET 23 のソースは導体 33 に接続されている。抵抗器 54 および 54' は、演算増幅器 43 により多くのヘッド・ルームを設ける機能を果たす。即ち、抵抗器 54' および 46' を通過する電流は、これらの間に電圧降下を発生させ、導体 48 および 49 上の電圧を、導体 33 上の電圧に対して、より高いレベルにシフトさせる。これによって、演算増幅器 43 の入力段により多くの「動作余裕」即ち「ヘッド・ルーム」が得られる。尚、抵抗器 54' は、実際には、単一の 13.5 キロオーム抵抗器 25、54' の中に基準抵抗器 25 と共に一体化されているが、抵抗器 54' は、発明の説明に供するために、別個の抵抗器として図示されている。

#### 【0026】

本発明によれば、下位ブリッジ回路 11A の基準抵抗器 26 の抵抗  $R_{REF1}$  を、ブリッジ回路 12A 内の基準抵抗器 25 に対してスケーリングし、下位ブリッジ回路 11A における電力消費を低減する。例えば、 $R_{REF1}$  は、2.4 キロオームとすることができ、これは、上位ブリッジ回路 12A における基準抵抗器 25 の抵抗  $R_{REF2}$  である 1.2 キロオームの 2 倍とすることができます。この例では、下位ブリッジ制御回路 11 の抵抗器 35 および 36 の公称値は、それぞれ、23 キロオームおよび 11.5 キロオームであり、上位ブリッジ制御回路 12 の抵抗器 41 および 55 の抵抗は、双方とも 11.5 キロオームである。

#### 【0027】

したがって、下位ブリッジ制御回路 11 では、抵抗器 46' および 46 の抵抗の比は 2 に等しく、抵抗器 35 および 36 の抵抗の比も 2 に等しい。ブリッジ 11A の抵抗器 35 、抵抗器 46' 、および基準抵抗器 26 は、分圧器を形成し、導体 13 を通じて演算増幅器 37 の( - )入力に電圧を印加する。抵抗器 36 、抵抗器 46' 、および基準 MOSFET

10

20

30

40

50

T 2 4 は、分圧器を形成し、導体 1 4 を通じて演算増幅器 3 7 の(+)入力に電圧を印加する。演算増幅器 3 7 は、導体 3 8 を通じて電圧を印加し、MOSFET 2 4 のチャネル抵抗  $R_{ON}$  を調節し、導体 1 4 上の電圧が導体 1 3 上の電圧と等しくなるようにする。この導体 1 3 および 1 4 上の電圧の等化は、MOSFET 2 4 の  $R_{ON}$  抵抗に対する  $R_{REF1}$  (2.4 キロオーム) の比率も 2 に等しく調節したとき、即ち、 $R_{ON}(24)$  が 1.2 キロオームに等しいときに得られる。また、MOSFET 2 4 の  $R_{ON}$  を 1.2 キロオームに等しくするために必要な同じ電圧  $V_{REGL}$  は、導体 3 8 および CMOS 反転器 3 9 を介して MOSFET 4 4<sub>i</sub> のゲートにも印加され、MOSFET 4 4<sub>i</sub> のチャネル抵抗を  $R_{REF1}$  に等しくしている（または  $R_{REF1}$  に対して適当にスケーリングする）。

## 【0028】

10

上位ブリッジ制御回路 1 2 では、抵抗器 5 4 および 5 4' の抵抗は等しく、スケーリングしない。また、抵抗器 4 1 および 5 5 の抵抗も等しい。ブリッジ制御回路 1 2 A の抵抗器 4 1、抵抗器 5 4' 、および基準抵抗器 2 5 は分圧器を形成し、導体 4 8 を通じて演算増幅器 4 3 の(+)入力に電圧を印加する。抵抗器 5 5、抵抗器 5 4' 、および基準MOSFET 2 3 は分圧器を形成し、導体 4 9 を介して演算増幅器 4 3 の(-)入力に電圧を印加する。

## 【0029】

20

演算増幅器 4 3 は、導体 5 6 を通じて電圧を印加し、基準MOSFET 2 3 のチャネル抵抗  $R_{ON}$  を調節して、導体 4 9 上の電圧を導体 4 8 上の電圧に等しくする。これは、MOSFET 2 3 の  $R_{ON}$  抵抗が  $R_{REF2}$  に等しくなるときに生ずる。MOSFET 2 3 の  $R_{ON}$  抵抗を  $R_{REF2}$  に等しくするために必要な同じ電圧  $V_{REGH}$  を、導体 5 6 および CMOS 反転器 2 1 を介して MOSFET 4 2<sub>i</sub> のゲートに印加し、MOSFET 4 2<sub>i</sub> のチャネル抵抗を  $R_{REF2}$  に等しくするか、または  $R_{REF2}$  に対して適当にスケーリングする。

## 【0030】

このように、スイッチMOSFET 4 4<sub>i</sub> および 4 2<sub>i</sub> のオン抵抗は、異なる抵抗値に等しくなる（またはスケーリングする）。

尚、図 1 におけるブリッジ回路 1 1 A および 1 2 A の種々のノード電圧は、抵抗性分圧によって決定されるので、抵抗器のいずれでも「基準抵抗器」として見なすことができ、これに対して対応する MOSFET 4 4<sub>i</sub> および 4 2<sub>i</sub> のオン抵抗を制御することは理解されよう。これは、ブリッジ回路 1 1 A および 1 2 A における種々のノード電圧およびプランチ電流についても言えることである。したがって、ブリッジ回路 1 1 A および 1 2 A におけるノード電圧のいずれでも、またはプランチ電圧のいずれでも、「基準値」と見なすことができ、これに対して対応するスイッチMOSFET 4 4<sub>i</sub> または 4 2<sub>i</sub> のオン抵抗を制御する。

30

## 【0031】

前述のように下位ブリッジ制御回路 1 1 のブリッジ回路 1 1 A の左側および右側における対応する抵抗の比率を決定することにより、内部のバイアス電流が低下する。このため、こうしなければ更に高い電圧消散が、下位ブリッジ制御回路 1 1 において低減する。下位ブリッジ制御回路 1 1 における電力消散は、定電圧源回路 5 0 に印加する +15 ボルト供給電圧と、通例では -10 ボルトである  $V_{REFL}$  との間の大きな電圧差を、内部のバイアス電流に乘算した値に等しい。

40

## 【0032】

更に、前述の構造では、下位ブリッジ制御回路 1 1 および上位ブリッジ制御回路 1 2 に別個で独立したバイアス回路を用いており、 $V_{REFH}$  および  $V_{REFL}$  を互いの電圧のわずか 1 / 10 以内にすることができる。これは、前述の Dempsey et al. 特許の図 9 の回路について先に述べた約 2.0 ボルトより遙かに低い。

## 【0033】

50

デジタル / アナログ変換器における (R / 2 R ラダー・ネットワークではなく) 前述の R / 2 R' ラダー・ネットワークの使用による重要な結果は、 $R_{ONi}$  スイッチの抵抗が、R / 2 R' ラダー・ネットワークの 2 R' 抵抗と同じ温度係数を正確に有することであ

る。これは、基準抵抗器 26、46' および 25、54' を、ラダー・ネットワーク抵抗器を構成するのと同じ材料（例えば、シクロム）で構成しているはずであるからである。尚、これは、前述の Dempsey et al. 特許に開示されている回路を含む、従来技術の R / 2 R ラダー・ネットワークおよび MOSFET スイッチ制御回路には当てはまらないことを注記しておく。

#### 【0034】

前述の構造は、Dempsey et al. 特許の図 7 および図 9 の組み合わせにおいて開示されるものとは、完全に別個で独立した上位および下位ブリッジ回路を設けることに相違がある。即ち、図 1において、上位ブリッジ回路 12 は、下位ブリッジ回路 11 から切断されており、これと独立している。これは、抵抗器 52 およびトランジスタ 55 を含む上位ブリッジ回路が、抵抗器 53 およびトランジスタ 56 を含む下位ブリッジ回路と共にソース抵抗器 54 および 57 を共有する図 9 の Dempsey et al. 回路とは対照的である。

10

#### 【0035】

また、図 1 では、トランジスタ 23 および 24 をそれぞれ演算増幅器 43 および 37 によって制御し、それぞれ、 $R_{REF2}$  および  $R_{REF1}$  に正確に一致するようにしている。これらは、それぞれ、抵抗器 54' および 46' を含む、より大きな抵抗器の「隠れた」部分である。対照的に、Dempsey et al. 特許の図 9 では、演算増幅器 58 は、トランジスタ 55 の複合抵抗を複合抵抗 52 と正確に一致させるように動作する。図 1 の下位ブリッジ回路 11 では、左側レッグ 35 および 46'、26 の抵抗を右側レッグ 36、24 の抵抗に対してスケーリングし、電流の削減、したがって電力消散の削減を図っている。更に、図 1 の回路は、R / 2 R' 型のラダー・ネットワークとのみ動作し、2 R' は  $2R - R_{ON}$  に等しく、 $R_{ON}$  はスイッチ・トランジスタ 42<sub>i</sub> および 44<sub>i</sub> のオン抵抗であるが、一方 Dempsey et al. 特許では、回路は従来の R / 2 R ラダー・ネットワークに対する高精度の変換を行うに過ぎない。

20

#### 【0036】

最後に、図 1 は、2 つの追加のスイッチおよびドライバ回路 34<sub>i-1</sub> および 34<sub>i+1</sub> を、前述のスイッチおよびドライバ回路 34<sub>i</sub> の両側に示す。ドライバ・ネットワーク 10 の残りの部分を図 2 に示す。

#### 【0037】

図 2 を参照すると、抵抗性分圧ネットワーク 10 は、7 つの等しいセグメント S1, 2, ..., 7 を有する第 1 セクション 10A を含む。ここで、デジタル入力ワードの上位 3 ビットが温度計コードを構成し、これをデコードして 8 つの等しい電圧セグメントを得て、デジタル / アナログ変換器 1 の上位 3 ビット（ビット 1 ~ 3）とする。7 セグメント・セクション 10A の 2 R' 分路抵抗器 30 の各々の右端に接続されている導体 58 は、デジタル / アナログ変換器 1 の出力電圧  $V_{OUT}$  を導通させる。図 2 における各分路レッグは、100 キロオームの抵抗を有し、抵抗器 2 R' および連動するスイッチの  $R_{ON}$  を含む。また、抵抗性分圧器 10 は、ビット 4 ~ 16 に対する R / 2 R' ラダー・ネットワークを含む第 2 セクション 10B も含み、各直列抵抗器 27<sub>4</sub>, 5, ..., 15 は値 R を有する。各分路抵抗器 30<sub>4</sub>, 5, ..., 16 は、 $2R - R_{ONi}$  に等しい値 2 R' を有し、 $R_{ONi}$  は、対応するスイッチ 42<sub>i</sub> および 44<sub>i</sub> のオン抵抗である。セクション S1 ~ S7 の 7 つのセグメント抵抗器 2 R' は、（例えば）100 キロオームに等しく、MOSFET スイッチ 42<sub>s1-7</sub> および 44<sub>s1-7</sub> のオン抵抗を含む。これは 75 オームとすることができます。ビット B4 に対するオン抵抗スイッチの抵抗は、150 オームとすることができます。ビット B5 ~ 9 に対するスイッチのオン抵抗は、300 オームとすることができます。ビット B10 ~ 16 に対するオン抵抗は 600 オームとすることができます。尚、これらのオン抵抗は任意であることを注記しておく。オン抵抗の値が低いと、MOSFET スイッチの全てを、同じ短いチャネル長で用いることが可能となり、前述の  $R_{ON}$  におけるコードに依存したばらつきは比較的少ない。

30

#### 【0038】

前述のデジタル / アナログ変換器 1 の主な利点は、スイッチ MOSFET 42<sub>i</sub> およ

び $4\frac{1}{4}$ のオン抵抗を二進スケーリングする必要がなく、したがって従来技術のMSBスイッチMOSFETおよびLSBスイッチMOSFETよりもサイズを遥かに小さくできることにある。この利点は、前述の回路において、制御MOSFET $2\frac{3}{4}$ および $2\frac{1}{4}$ のオン抵抗が、分圧ネットワーク10の抵抗器と同じ材料で構成した基準抵抗器に追従することによるものである。16ビット以上の分解能およびそれに対応する精度は、以前に用いられていた前述の「ショート・カット」技法のいずれに頼ることもなく達成することができ、ディジタル／アナログ変換器の最下位ビットを精度高く実現するためには必要であった、非常に大型のスイッチ・トランジスタの使用を回避することができる。

#### 【0039】

更に、ブリッジ制御回路11および12の独立性により、そのバイアス電流の比率を変えることができる、下位ブリッジ制御回路11を通過する電流を、上位ブリッジ制御回路12を通過する電流よりも遥かに少なくすることができる。10

#### 【0040】

また、ディジタル／アナログ変換器1の最上位および最下位ビット・グループに対するスイッチMOSFET $4\frac{1}{2}$ および $4\frac{1}{4}$ のサイズを大幅に小型化することによって、チップ・サイズの縮小およびコスト削減がもたらされる。上位および下位ブリッジ制御回路11および12の独立性によって、外部供給基準電圧間の差を小さくすることができる。

#### 【0041】

以上いくつかの特定実施形態を参照しながら本発明について説明したが、本発明の真の精神および範囲から逸脱することなく、前述の発明の実施形態に対して当業者は種々の変更を行うことができよう。あまり相違がない、即ち、ほぼ同じ機能をほぼ同じように実行して、特許請求の範囲におけると同じ成果を得るエレメントまたはステップは、その全てが本発明の範囲に該当することとする。例えば、図1の抵抗器35、36、41および55は、適当な定電流源と交換すれば、ブーストストラップ電圧源回路50および53を省略することができる。上位スイッチ $4\frac{1}{2}$ をP-チャネルMOSFETとすることもでき、その場合バッファ21は非反転バッファとなる。反転器 $4\frac{1}{2}$ および $4\frac{1}{4}$ を含むバッファ回路は、論理相補信号を不要とするように構成することも可能である。別の例として、図1のブリッジ回路12Aは、ブリッジ回路12Aの鏡像であるブリッジ回路と置換することも可能である。これは導体33の下に示してあり、電圧源52の極性を逆にし、N-チャネルMOSFET $2\frac{3}{4}$ を同等のP-チャネルMOSFETと置換している。あるいは、N-チャネルMOSFET $2\frac{3}{4}$ を用いることも可能であり、その際そのソースおよびドレイン電極を逆にして、演算増幅器43の(+)および(-)入力も逆にする。同様に、下位ブリッジ回路11Aを、その鏡像で置換することも可能である。2030

#### 【図面の簡単な説明】

【図1】 図1は、本発明のビット・スイッチ制御回路およびR/2R'抵抗性分圧ネットワークを含むディジタル／アナログ変換器の概略図である。

【図2】 図2は、図1に含まれるR/2R'抵抗性分圧ネットワーク10の更に詳細な構成図である。

【図1】

---

フロントページの続き

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100120112

弁理士 中西 基晴

(72)発明者 ネイラー, ジミー・アール

アメリカ合衆国アリゾナ州85711, タクソン, イースト・ケーパー 4873

(72)発明者 カルトフ, ティモシー・ブイ

アメリカ合衆国アリゾナ州85730, タクソン, イースト・エスカランテ・ロード 11141

772

(72)発明者 ジョンソン, ジェフリー・ディー

アメリカ合衆国アリゾナ州85741, タクソン, ウエスト・カレ・ルシンド 3025

審査官 柳下 勝幸

(56)参考文献 実開昭61-107235(JP, U)

特開平07-193504(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M1/00-1/88