(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3973250号

(P3973250)

(45) 発行日 平成19年9月12日(2007.9.12)

(24) 登録日 平成19年6月22日(2007.6.22)

(51) Int.C1.

F 1

G 11 C 11/401 (2006.01)

G 11 C 11/34 362 H

請求項の数 16 (全 109 頁)

(21) 出願番号 特願平8-171229

(22) 出願日 平成8年7月1日(1996.7.1)

(65) 公開番号 特開平9-73774

(43) 公開日 平成9年3月18日(1997.3.18)

審査請求日 平成15年5月28日(2003.5.28)

(31) 優先権主張番号 特願平7-167358

(32) 優先日 平成7年7月3日(1995.7.3)

(33) 優先権主張国 日本国(JP)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が行および列のマトリクス状に配列される複数のメモリセルを有するとともに、互いに独立にメモリセル行選択動作およびメモリセル列選択動作の活性化および非活性化の制御が可能な複数のアレイブロック、

前記複数のアレイブロックに共通に配設され、外部入出力データのビット幅に対応するビット幅を有し、外部からのアクセス時に書きまたは読み出データを転送する共通データバス、

アドレス信号に従って、前記複数のアレイブロックのうちの1つのアレイブロックを選択し、さらに該選択されたアレイブロックから前記ビット幅と同じ数のメモリセルを並行して選択して、該選択されたメモリセルのデータを前記共通データバスへ読み出すアレイ制御手段、および

転送指示と転送アドレス信号とに応答して、前記アレイ制御手段により前記共通データバスへ読み出されたメモリセルのデータを前記転送アドレス信号が指定するアレイブロックへ転送する転送手段、

前記アドレス信号と前記転送アドレス信号とをリンクして格納する格納手段、

外部からのアドレス信号と前記格納手段の格納するアドレス信号の一一致 / 不一致を判別する手段、および

前記判別手段の一一致検出時に前記格納手段の対応の転送アドレス信号を選択しつつ前記判別手段の不一致検出時に前記外部からのアドレス信号を選択して前記アドレス信号とし

て与える手段を備える、半導体記憶装置。

**【請求項 2】**

前記複数のアレイブロックの各々は、各行に対応して配置され、各々に対応の行のメモリセルが接続される複数のワード線と、各列に対応して配置され、各々に対応の列のメモリセルが接続される複数のビット線対と、各列に対応して配置され、対応のビット線対上の電位を検知、増幅、およびラッチする複数のセンスアンプとを有し、

前記アレイ制御手段は、

前記アドレス信号が指定するアレイブロックの前記アドレス信号が指定する行に対応して配置されるワード線を選択状態へ駆動した後、該アレイブロックのセンスアンプを活性化する手段と、

前記アドレス信号に応答して、前記選択アレイブロックの対応の列のセンスアンプを前記共通データバスへ結合する列選択手段とを含み、

前記転送手段は、

前記転送アドレス信号に応答して、前記転送アドレス信号が指定するアレイブロックの列のセンスアンプを前記共通データバスに結合する手段と、

前記転送指示に応答して、前記転送アドレス信号が指定するアレイブロックのセンスアンプを活性化する手段とを備える、請求項 1 記載の半導体記憶装置。

**【請求項 3】**

前記複数のアレイブロックそれぞれに対応して設けられ、各々が前記共通データバスと同じビット幅を有する複数のローカルデータバスをさらに備え、

前記アレイ制御手段は、前記アドレス信号が指定するアレイブロックの対応の列のセンスアンプを該対応のローカルデータバスへ接続する手段と、

前記アドレス信号に従って、前記対応のローカルデータバスを前記共通データバスへ接続する手段とを含み、

前記転送手段は、

前記転送アドレス信号に従って、前記転送アドレス信号が指定するアレイブロックのローカルデータバスを前記共通データバスに接続する手段と、

前記転送アドレス信号に従って、前記転送アドレス信号が指定するアレイブロックの対応の列のセンスアンプを該対応のローカルデータバスへ接続する手段とを備える、請求項 1 または 2 に記載の半導体記憶装置。

**【請求項 4】**

前記転送手段は、前記転送指示と前記転送アドレス信号とに応答して、前記転送アレイブロックのセンスアンプの活性化前に、前記転送アドレス信号が指定する行のワード線を選択状態へ駆動する手段を備える、請求項 1 ないし 3 のいずれかに記載の半導体記憶装置。

**【請求項 5】**

前記転送手段は、前記転送指示と前記転送アドレス信号とに応答して、前記転送アレイブロックのワード線を非選択状態に維持する手段を備える、請求項 1 ないし 3 のいずれかに記載の半導体記憶装置。

**【請求項 6】**

各列に対応して配置されるビット線対と対応のセンスアンプとの間に配置される接続ゲートをさらに備え、

前記転送手段は、前記転送指示と前記転送アドレス信号とに応答して、前記転送アレイブロックの接続ゲートを非導通状態に維持する手段をさらに備える、請求項 5 記載の半導体記憶装置。

**【請求項 7】**

前記共通データバス上のデータを増幅して出力バッファへ伝達するためのリードドライバと、

前記リードドライバの出力信号を受けるように結合される入力部を有し、入力バッファから前記入力部へ与えられたデータをバッファ処理して前記共通データバスへ伝達するた

10

20

30

40

50

めのライトドライバと、

前記転送指示に応答して、前記ライトドライバを活性化する手段をさらに備える、請求項1ないし6のいずれかに記載の半導体記憶装置。

**【請求項8】**

前記転送手段は、前記転送指示に応答して、前記転送アドレス信号が指定するアレイブロックのセンスアンプと対応のローカルデータバスとの接続および前記対応のローカルデータバスと前記共通データバスとの接続の確立の後、前記転送アドレス信号が指定するアレイブロックのセンスアンプを活性化する手段を含む、請求項3記載の半導体記憶装置。

**【請求項9】**

前記転送手段は、前記転送指示に応答して、前記転送アドレス信号が指定するアレイブロックのセンスアンプの活性化の後、前記ライトドライバを活性化する手段を含む、請求項7記載の半導体記憶装置。 10

**【請求項10】**

容量手段、

各前記アレイブロックのセンスアンプに対応して配置されるセンスアンプ活性化信号線

、

アドレス信号に応答して、前記アドレス信号が指定するアレイブロックのセンスアンプの活性化から非活性化への移行時、該アレイブロックのセンスアンプ活性化信号線を前記容量手段へ所定期間結合する手段、および

前記転送アドレス信号と前記転送指示とに応答して、前記転送アドレス信号が指定するアレイブロックのセンスアンプ活性化信号線を、該転送アドレス信号が指定するアレイブロックのセンスアンプの非活性化から活性化への移行時に所定期間前記容量手段へ結合する手段をさらに備える、請求項2ないし9のいずれかに記載の半導体記憶装置。 20

**【請求項11】**

前記転送手段は、前記転送指示と同時に与えられる保持指示の活性化に応答して、前記転送アドレス信号が指定するアレイブロックのセンスアンプを活性状態に保持する手段をさらに備える、請求項1ないし10のいずれかに記載の半導体記憶装置。

**【請求項12】**

外部から一定のパルス幅を有する周期的に与えられるクロック信号に同期して、前記複数のアレイブロックのうちのアレイブロックを指定するブロックアドレス信号、該アレイブロックの行を指定する行アドレス信号、および該アレイブロックの列を指定する列アドレス信号を同時に取込んで内部アドレス信号を生成する手段をさらに備える、請求項1ないし11のいずれかに記載の半導体記憶装置。 30

**【請求項13】**

前記複数のアレイブロックそれぞれに対応して配置され、前記クロック信号に同期して与えられるチップ活性化信号に応答して活性化されて前記内部アドレス信号をラッチする手段を含み、前記ラッチ手段は、前記内部アドレス信号が対応のアレイブロックを指定するときのみ与えられた内部アドレス信号をラッチする、請求項12記載の半導体記憶装置。

。

**【請求項14】**

前記クロック信号に同期して、外部から与えられる制御信号を取り込み内部制御信号を生成する制御信号入力バッファをさらに備える、請求項12または13に記載の半導体記憶装置。 40

**【請求項15】**

前記アドレス信号により指定される選択アレイブロックの前記アレイ制御手段は、対応のアレイブロックを、前記チップ活性化信号の活性化から所定の時間活性状態に維持する、請求項13記載の半導体記憶装置。

**【請求項16】**

各々が、行および列のマトリクス状に配列されるメモリセルと、各列に対応して配置され、各々に対応の列のメモリセルが接続される複数のビット線対と、各行に対応して配置 50

され、各々に対応の行のメモリセルが接続される複数のワード線と、各列に対応して配置され、各々が対応の列のビット線対のデータを検知、増幅、およびラッチする複数のセンスアンプとを有する複数のアレイブロック、

前記複数のアレイブロックの隣接するアレイブロックの各列に対応して配置されるビット線対の間に配置され、対応の隣接アレイブロックのビット線対を相互接続するための複数のゲート、

第1のアドレス信号と転送指示とに応答して、前記第1のアドレス信号が指定する選択アレイブロックのメモリセル行を選択する第1の選択手段、

前記第1のアドレス信号と前記第1の選択手段とに応答して、前記選択アレイブロックのセンスアンプを活性化する手段、

前記第1のアドレス信号と前記転送指示とに応答して、前記選択アレイブロックと隣接するアレイブロックの間のゲートを導通状態とする接続手段、

第2のアドレス信号と前記転送指示とに応答して、前記隣接するアレイブロックのメモリセル行を選択する第2の選択手段、

前記第2のアドレス信号と前記転送指示とに応答して、前記隣接するアレイブロックのセンスアンプを活性化する手段、および

リフレッシュ指示とリフレッシュアドレスとに従って、リフレッシュアドレスが指定するアレイブロックに隣接するアレイブロックに対してビット線対をフローティング状態として前記ゲートを導通状態として、前記リフレッシュアドレスが指定するアレイブロックのセンスアンプに保持されているデータを前記隣接するアレイブロックに転送して、前記ゲートを非導通状態とし、前記リフレッシュアドレスが指定するアレイブロックにおいてリフレッシュを実行し、前記リフレッシュ指示の非活性化への移行時、前記隣接するアレイブロックのデータを前記選択アレイブロックのセンスアンプへ返送し、該センスアンプを活性状態とするリフレッシュ制御手段を備える、半導体記憶装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は半導体記憶装置に関し、特に、高速でアクセスすることのできるダイナミック型半導体記憶装置に関する。

##### 【0002】

##### 【従来の技術】

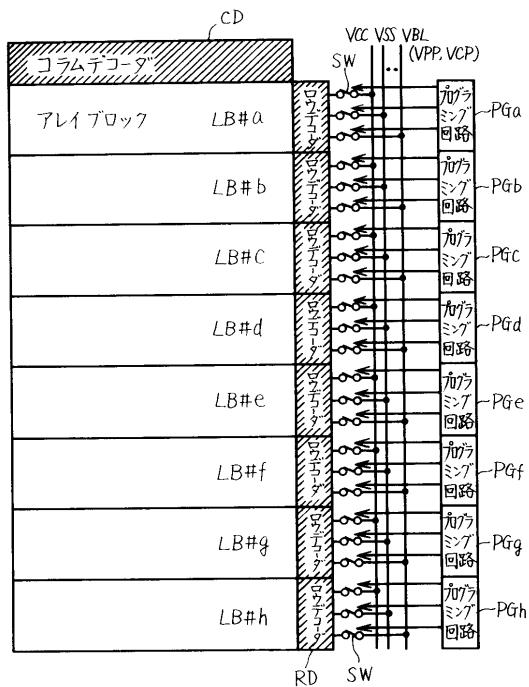

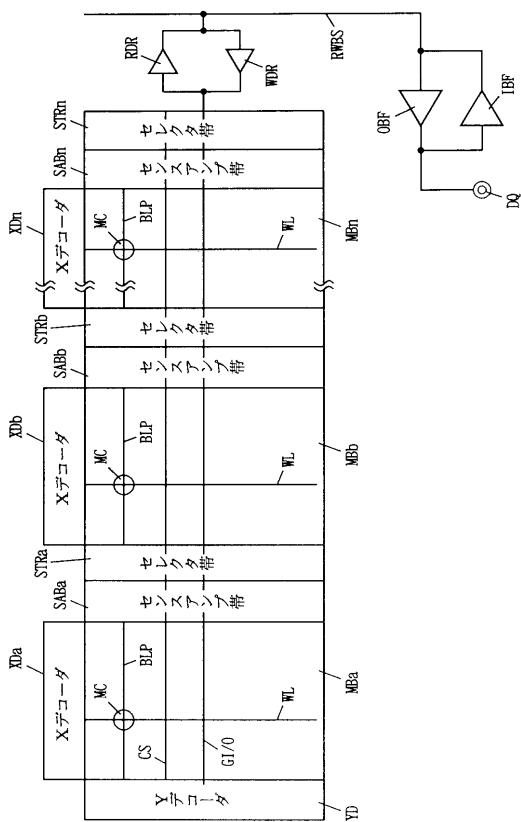

図97は、従来の半導体記憶装置の要部の構成を概略的に示す図である。図97において、半導体記憶装置は、複数のアレイブロックMBa～MBnを含む。アレイブロックMBa～MBnの各々は、行列状に配置される複数のメモリセルMCと、各行に対応して配置され、各々に対応の行のメモリセルが接続される複数のワード線WLと、各列に対応して配置され、各々に対応の列のメモリセルが接続される複数のビット線対BLPを含む。図97においては、アレイブロックMBa～MBn各々において、1本のワード線WLと1つのビット線対BLPを代表的に示す。

##### 【0003】

アレイブロックMBa～MBnそれぞれに対応して、XデコーダXDa～XDn、センスアンプ帯SABA～SABnおよびセレクタ帯STRa～STRnが配置され、またアレイブロックMBa～MBnに共通にYデコーダYDおよびグローバルI/O線GIOが設けられる。

##### 【0004】

XデコーダXDa～XDnは活性化時、与えられた行アドレス信号（この経路は示さず）をデコードし、対応のアレイブロックMBa～MBnのアドレス指定された行に対応して配置されたワード線を選択状態へと駆動する。

##### 【0005】

センスアンプ帯SABA～SABnは、対応のアレイブロックMBa～MBnの各列（ビット線対BLP）に対応して配置されるセンスアンプを含み、活性化時、対応のビット線

10

20

30

40

50

対 B L P 上に現れたメモリセルデータを検知し増幅しラッチする。

**【 0 0 0 6 】**

Yデコーダ Y D は、与えられた列アドレス信号をデコードし、アドレス指定された列を選択する列選択信号を列選択信号線 C S 上に伝達する。セレクタ帯 S T R a ~ S T R n は、Yデコーダ Y D から列選択信号線 C S 上に伝達された列選択信号と図示しないアレイブロック選択信号とに応答して、アレイブロック選択信号の指定するアレイブロックのアドレス指定された列（ビット線対 B L P ）をグローバル I / O バス G I / O へ接続する。

**【 0 0 0 7 】**

グローバル I / O バス G I / O には、データ読出時に活性化され、グローバル I / O バス G I / O 上のデータを増幅して内部リード / ライトバス R W B S 上へ伝達するリードドライバ R D R と、データ書込時に活性化され、内部リード / ライトバス R W B S 上のデータをバッファ処理してグローバル I / O バス G I / O へ伝達するライトドライバ W D R が設けられる。

**【 0 0 0 8 】**

リード / ライトバス R W B S とデータ入出力端子 D Q との間に、データ読出時に活性化され、内部リード / ライトバス R W B S 上のデータをバッファ処理してデータ入出力端子 D Q へ出力する出力バッファ O B F と、データ書込時に活性化され、データ入出力端子 D Q へ与えられたデータ信号から内部書込データを生成して内部リード / ライトバス R W B S へ伝達する入力バッファ I B F が設けられる。

**【 0 0 0 9 】**

図 9 7 に示す半導体記憶装置においては、複数のアレイブロック M B a ~ M B n のうち 1 つのアレイブロックのみが活性化される。ここで、「アレイ活性化」は、アレイにおいてワード線が選択状態とされ、この選択されたワード線に接続されるメモリセルのデータが各ビット線対 B L P 上に読出されてセンスアンプにより増幅される状態を示す。アレイブロック選択信号により指定されたアレイブロックに対してのみデータの書込 / 読出が行なわれる。

**【 0 0 1 0 】**

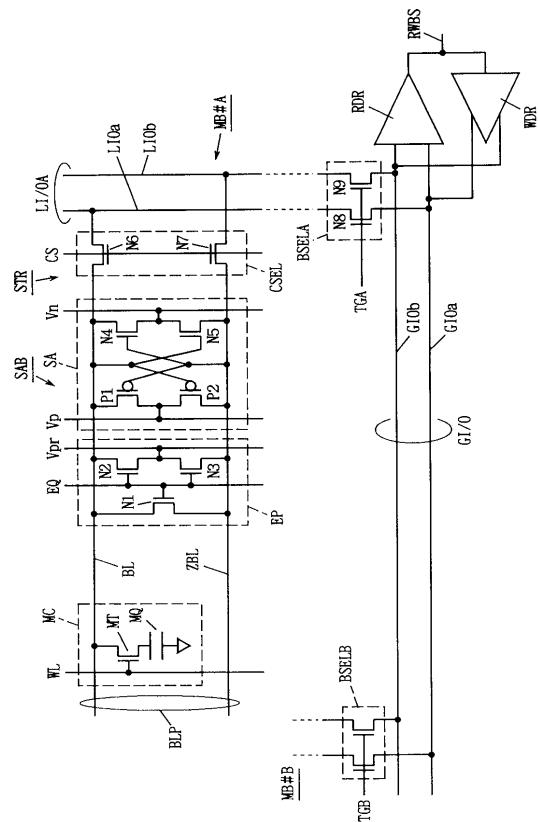

図 9 8 は、図 9 7 に示すアレイブロック M B a ~ M B n の内部構成を詳細に示す図である。図 9 8 においては、1 つのアレイブロックの 1 列に関連する部分の構成を代表的に示す。また、1 本のワード線 W L のみが示される。

**【 0 0 1 1 】**

図 9 8 において、ビット線対 B L P は、互いに相補なデータ信号を伝達するビット線 B L および Z B L を含む。ビット線 B L とワード線 W L の交差部に配置されるメモリセル M C は、データを電荷の形態で格納するキャパシタ M Q と、ワード線 W L 上の信号電位に応答して、メモリキャパシタ M Q をビット線 B L へ接続する n チャネル M O S トランジスタで構成されるアクセストランジスタ M T を含む。

**【 0 0 1 2 】**

センスアンプ帯 S A B に含まれるセンスアンプ S A は、ビット線 B L に接続される一方導通端子と、ビット線 Z B L に接続されるコントロールゲートと、センスアンプ活性化信号 V p を受ける他方導通端子とを有する p チャネル M O S トランジスタ P 1 と、ビット線 Z B L に接続される一方導通端子と、ビット線 B L に接続されるコントロールゲートと、センスアンプ活性化信号 V p を受ける他方導通端子とを有する p チャネル M O S トランジスタ P 2 と、ビット線 B L に接続される一方導通端子と、ビット線 Z B L に接続されるコントロールゲートと、センスアンプ活性化信号 V n を受ける他方導通端子とを有する n チャネル M O S トランジスタ N 4 と、ビット線 Z B L に接続される一方導通端子と、ビット線対 B L に接続されるコントロールゲートと、センスアンプ活性化信号 V n を受ける他方導通端子とを有する n チャネル M O S トランジスタ N 5 を含む。

**【 0 0 1 3 】**

p チャネル M O S トランジスタ P 1 および P 2 は、フリップフロップを構成し、センスアンプ活性化信号 V p の活性化時（ハイレベル）、ビット線 B L および Z B L のうちの電位

10

20

30

40

50

の高いビット線をハイレベルへ駆動する。nチャネルMOSトランジスタN4およびN5も、フリップフロップを構成し、センスアンプ活性化信号Vnの活性化時（ローレベル）、ビット線BLおよびZBLの低電位のビット線をローレベルへ駆動する。

#### 【0014】

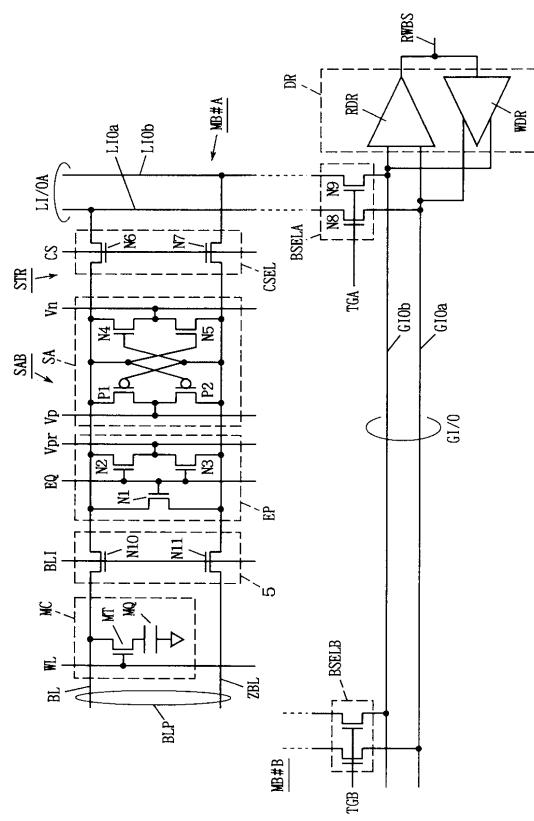

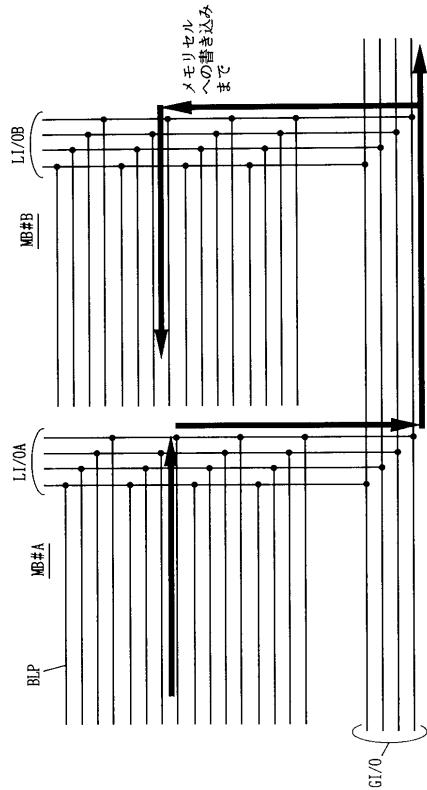

アレイブロックMB-A（MBa～MBnのいずれか）に対しては、ローカルI/O線LI\_OaおよびLI\_ObからなるローカルI/OバスLII\_OAが配置される。

#### 【0015】

セレクタ帯STRはビット線BLおよびZBLに対して設けられ、列選択信号CS（図97に示す列選択信号線上に伝達される信号であり、同じ符号で示す）に応答してビット線BLおよびZBLをローカルI/O線LI\_OaおよびLI\_Obへ接続する列選択ゲートCSELと、アレイブロック選択信号TGAに応答してローカルI/O線LI\_OaおよびLI\_ObをグローバルI/OバスGII\_Oを構成するグローバルI/O線GIOaおよびGIObへそれぞれ接続するブロック選択ゲートBSEL\_Aを含む。列選択ゲートCSELは、ビット線BLとローカルI/O線LI\_Oaの間に配置されるnチャネルMOSトランジスタで構成されるトランスファゲートN6と、ビット線ZBLとローカルI/O線LI\_Obの間に配置されるnチャネルMOSトランジスタで構成されるトランスファゲートN7を含む。ブロック選択ゲートBSEL\_Aは、ローカルI/O線LI\_OaとグローバルI/O線GIOaの間に配置されるnチャネルMOSトランジスタで構成されるトランスファゲートN8と、ローカルI/O線LI\_ObとグローバルI/O線GIObの間に配置されるnチャネルMOSトランジスタで構成されるトランスファゲートN9を含む。

10

#### 【0016】

図98においては、また別のアレイブロックMB-Bに対して設けられるブロック選択ゲートBSEL\_Bを示す。このブロック選択ゲートBSEL\_Bは、ブロック選択信号TGBに応答して、このアレイブロックMB-Bに対して配置されるローカルI/O線をグローバルI/OバスGII\_Oへ接続する。

#### 【0017】

リードドライバRDRは、このグローバルI/OバスGII\_O上に現れた相補的な信号を差動増幅して内部リード/ライトバスRWBSへ伝達する。ライトドライバWDRは、内部リード/ライトバスRWBS上の信号を増幅して相補書き込みデータを生成してグローバルI/Oバス線GIOaおよびGIOb上に伝達する。

30

#### 【0018】

ビット線BLおよびZBLには、イコライズ信号EQに応答してビット線BLおよびZBLを所定のプリチャージ電位Vprにプリチャージしかつイコライズするプリチャージ/イコライズ回路EPが設けられる。このイコライズ/プリチャージ回路EPは、イコライズ信号EQに応答してビット線BLおよびZBLを接続するnチャネルMOSトランジスタN1と、イコライズ信号EQに応答してプリチャージ電位Vprをビット線BLへ伝達するnチャネルMOSトランジスタN2と、イコライズ信号EQに応答してプリチャージ電位Vprをビット線ZBLへ伝達するnチャネルMOSトランジスタN3を含む。イコライズ信号EQは、この半導体記憶装置のスタンバイサイクル時において活性状態のハイレベルとされる。次に動作について説明する。

40

#### 【0019】

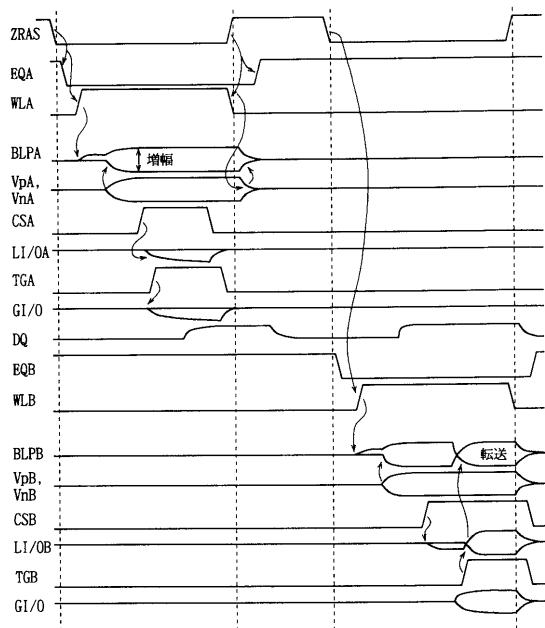

今、画像データ処理などにおいてよく行なわれる、ある画素データを別の画素データで書換える動作を考える。このような動作は、画像の複製の処理などにおいて実行される。今、特に、1つのアレイブロックMB-Aから別のアレイブロックMB-Bへ画素データを転送する動作をその動作波形図である図99を参照して説明する。図99においては、アレイブロックMB-Aに関連する制御信号およびローカルI/Oバスは、その末尾に文字「A」を付し、アレイブロックMB-Bについての制御信号およびローカルI/O線等については、その末尾に「B」を付して示す。

#### 【0020】

ロウアドレスストローブ信号ZRASがハイレベルの非活性状態においては、イコライズ

50

信号 E Q A および E Q B はともに活性状態のハイレベルにある。アドレスストローブ信号 Z R A S がローレベルの活性状態とされると、この半導体記憶装置のメモリセル選択動作が始まる。今、外部から与えられるアドレス信号（図示せず）がアレイブロック M B A を指定しているため、このアレイブロック M B A に対してのイコライズ信号 E Q A がローレベルとされ、イコライズ／プリチャージ回路 E P が非活性状態とされる。これにより、アレイブロック M B A においてピット線 B L および Z B L はプリチャージ電位 V p r でフローティング状態とされる。続いて、図 9 7 に示す X デコーダによりロウアドレスストローブ信号 Z R A S の立下がり時に与えられたアドレス信号に従って、アレイブロック M B A においてワード線 W L A が選択され、ワード線 W L A 上の電位が上昇する。これにより、ピット線対 B L P A 上に、この選択ワード線 W L A に接続されるメモリセルのデータが読み出され、ピット線対 B L P A の電位がこの選択メモリセルデータに応じて変化する。図 9 9 においては、ハイレベルのデータが読み出された場合の波形が一例として示される。

。

#### 【 0 0 2 1 】

次いで、所定時間が経過し、ピット線対 B L P A のピット線 B L A および Z B L A の電位差が十分に大きくなると、センスアンプ活性化信号 V p および V n が活性状態とされて、センスアンプ帯 S A B A に含まれるセンスアンプ S A が、このピット線対 B L P A 上の電位を差動的に増幅する。

#### 【 0 0 2 2 】

センスアンプ S A により、ピット線 B L および Z B L の電位差が十分に拡大した後、Y デコーダ Y D からの列選択信号 C S A が選択状態を示すハイレベルに立上がり、列選択ゲート C S E L が導通し、ピット線 B L および Z B L がローカル I / O 線 L I O a および L I O b に接続される。

#### 【 0 0 2 3 】

次いで、図示しないブロックデコーダからのブロック選択信号 T G A が選択状態を示すハイレベルとされ、ブロック選択ゲート B S E L A が導通し、ローカル I / O 線 L I O a および L I O b がグローバル I / O 線 G I O a および G I O b に接続される。これにより、センスアンプ S A により検知増幅された選択メモリセルデータがグローバル I / O バス G I / O 上に伝達される。

#### 【 0 0 2 4 】

この後、リードドライバ R D R が活性化され、このグローバル I / O バス G I / O 上に与えられた信号を差動増幅し、内部読み出データを生成して内部リード／ライトバス R W B S 上に伝達する。この内部リード／ライトバス R W B S 上の内部読み出データは、出力バッファ O B F ( 図 9 7 参照 ) を介してデータ入出力端子 D Q へ伝達される。この読み出されたデータは、半導体記憶装置の別のアレイブロックに再書き込みするため、一旦レジスタなどの外部に設けられたデータ保持手段に格納される。半導体記憶装置においては別のワード線を選択するためにアレイプリチャージ動作が行なわれる。すなわち、ロウアドレスストローブ信号 Z R A S を非活性状態のハイレベルとし、選択アレイブロック M B A の選択ワード線 W L A を非選択状態とし、メモリセル M C に含まれるアクセストランジスタ M T を非導通状態とする。この後、センスアンプ活性化信号 V p および V n を非活性状態とし、次いでイコライズ信号 E Q A をハイレベルとして、イコライズ／プリチャージ回路 E P を活性化して、ピット線対 B L P A のピット線 B L および Z B L を中間電位 V p r にプリチャージする。このときまた、列選択信号 C S A はローレベルの非選択状態とされており、ピット線対 B L P A とローカル I / O 線 L I / O A とは切離され、またローカル I / O バス L I / O A とグローバル I / O バス G I / O も切離される。またデータ入出力端子 D Q の出力バッファ O B F が非活性状態とされ、出力ハイインピーダンス状態とされる。

#### 【 0 0 2 5 】

次に、アレイブロック M B B を選択するためにロウアドレスストローブ信号 Z R A S が再び活性状態のローレベルとされる。このとき同時にアドレス信号が与えられ、アレイブロック M B B の指定およびアレイブロック M B B におけるワード線 W L B の指定が行

10

20

30

40

50

なわれる。これにより、指定されたアレイブロック M B Bにおいて、イコライズ信号 E Q B がローレベルとされ、イコライズ／プリチャージ回路 E P が非活性状態とされる。ビット線対 B L P B に選択メモリセルデータが現れた後、センスアンプ活性化信号 V p B および V n B が活性状態とされ、ビット線対 B L P B の電位が選択メモリセルデータに応じて変化する。次いで列選択信号 C S B がハイレベルとされ、このビット線対 B L P B がローカル I / O バス L I / O B に接続される。一方、データ書込のため、入力バッファ I B F を介して、先に読出されて一旦保持されているデータが書込まれ、ライトドライバ W D R を介して書込データがグローバル I / O バス上に伝達される。

#### 【0026】

グローバル I / O バス上のデータが伝達されると、次いでアレイブロック選択信号 T G B 10 がハイレベルとされ、ブロック選択ゲート B S E L B が導通し、グローバル I / O バス G I / O とローカル I / O バス L I / O B が接続されてローカル I / O バス L I / O B に書込データが伝達され、次いで列選択ゲート C S L E B を介して選択ビット線対 B L P B へ書込データが伝達される。ライトドライバ W D R の駆動力は、センスアンプ S A のラッチ力も大きいため、ビット線対 B L P B に設けられたセンスアンプ S A のラッチデータが書込データに対応するデータとなる。

#### 【0027】

書込動作が完了すると、再びロウアドレスストローブ信号 Z R A S がハイレベルの非活性状態とされ、アレイブロック M B B における選択ワード線が再び非活性状態とされ、センスアンプ活性化信号 V p B および V n B が非活性状態とされ、セレクタ S T R B も非導通状態とされ、ローカル I / O バス L I / O B とグローバル I / O バス G I / B も切離される。これにより、アレイブロック M B B のプリチャージ状態とされる。 20

#### 【0028】

**【発明が解決しようとする課題】**

メモリアレイが複数のアレイブロックに分割され、1つのアレイブロックのみが活性状態とされるアレイ分割構造の半導体記憶装置において、1つのアレイブロックのメモリセルのデータを別のアレイブロックのメモリセルへ転送する場合、2つの Z R A S サイクル（ロウアドレスストローブ信号 Z R A S についてのサイクル）が必要とされる。すなわち、1つのアレイブロックのメモリセルを選択し、この選択メモリセルのデータを装置外部を読み出すサイクルと、別のアレイブロックのメモリセルを選択し、この選択メモリセルへ外部に読み出されたデータを書込むサイクルとが必要とされる。このため、アレイブロック間データ転送を高速で行なうことができないという問題が生じる。特に、画像処理用途にこの半導体記憶装置を用いる場合、複製処理などの画像処理を高速で行なうことができず、データ処理速度（描画速度）が低下し、処理システムの性能が低下する。 30

#### 【0029】

また、データ転送時において、ビット線の充放電が1つのアレイブロックと別のアレイブロックとにおいて合計2回行なわれる。このビット線充放電はセンスアンプ活性化信号 V p および V n を伝達する信号線を介して行なわれる。このため、センスアンプ駆動のための電流消費が大きくなるという問題が生じる。

#### 【0030】

また、アレイ分割構造の半導体記憶装置において1つのアレイブロックから別のアレイブロックへアクセス先を変更する場合、半導体記憶装置を一旦プリチャージ状態（非選択状態）へ駆動する必要がある（アレイブロックは互いに独立に駆動することができないため）。このため、アレイブロック変更時において最小限 R A S プリチャージ時間と呼ばれる時間が必要とされ、アクセス時間が長くなり、高速アクセスすることができなくなるという問題が生じる。 40

#### 【0031】

また、1つのアレイブロックにおいてページモードでアクセスする場合、ページ切換（選択ワード線の切換）においては、選択ページ（選択ワード線）を一旦非選択状態へ駆動した後次のページ（ワード線）を選択状態へ駆動する必要があり、この場合においても、R 50

A S プリチャージ時間と呼ばれる時間が最小限必要とされ、応じてページ切換を高速で行なうことができず、高速アクセスがすることができなくなるという問題が生じる。

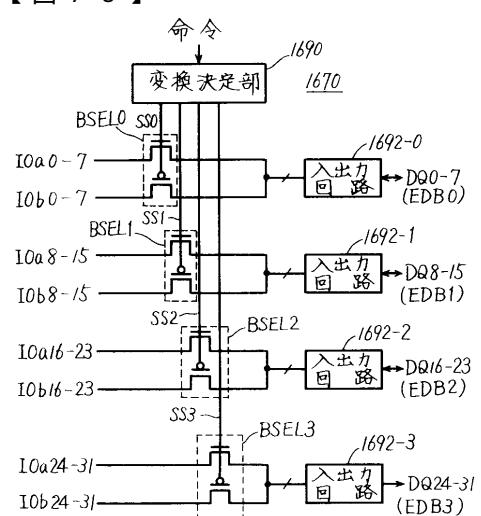

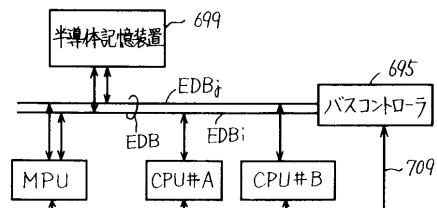

【0032】

さらに、従来の半導体記憶装置の場合、内部データバスすなわち入出力バッファと外部データバスのバス線と接続は固定的に1対1対応で定められている。ある種のCPU(中央演算処理装置)においては、バイトスワップ機能が設けられており、たとえば16ビットデータバスのうち上位または下位の8ビットデータバスを用いてデータ転送を行なうことにより、16ビット処理システムにおいて、8ビットデータを格納する8ビットメモリおよび8ビットデータを利用可能としている。しかしながら、このバイトスワップ機能においては、単に、CPUバスとメモリバスとの間の接続が上位バイトと下位バイトで切換えられるが、切換様式は、各メモリに対し固定的に定められている。たとえば、1つの8ビットメモリは、CPUバスの8ビット上位バスまたは下位8ビットバスのみと接続されている。たとえば、この8ビットメモリのデータ書き込み時および読み出し時において利用されるCPUバスを変更することはできず、処理用途に応じてこの8ビットメモリから読み出された8ビットデータをCPUバスの上位バスまたは下位バスへ選択的に接続することはできず、したがってCPUの内部レジスタでその演算処理内容に応じて適宜データを格納することができず、CPUが内部で再びその演算処理内容に応じて8ビットデータの格納位置を変更しており、CPUの処理操作が煩雑となるという欠点が生じる。

またこのバイトスワップ機能を用いてデータ転送を行なう場合、利用されていないデータバスは空き状態であり、バス利用効率が低いという問題が生じる。

【0033】

それゆえ、この発明の目的は、アレイブロック間のデータ転送を高速かつ低消費電流で行なうことのできる半導体記憶装置を提供することである。

【0034】

この発明の他の目的は、低消費でセンスアンプを駆動することのできる半導体記憶装置を提供することである。

【0035】

この発明の他の目的は、複数のブロック間にわたって高速でアクセスすることのできる半導体記憶装置を提供することである。

【0036】

この発明のさらに他の目的は、ページ変更を高速で行なうことのできる半導体記憶装置を提供することである。

【0037】

この発明のさらに他の目的は、高速かつ効率的にデータ転送を外部処理装置とメモリ半導体記憶装置との間で行なうことのできる半導体記憶装置を提供することである。

【0038】

【課題を解決するための手段】

この発明は、要約すれば、複数のアレイブロックを互いに独立に駆動可能とするとともに、センスアンプ活性化信号線を選択的に容量に結合し、この容量の充電電圧をセンスアンプ活性化信号として利用するものである。

【0039】

すなわち、請求項1に係る半導体記憶装置は、各々が行および列のマトリクス状に配列される複数のメモリセルを有するとともに互いに独立にメモリセル行選択動作およびメモリセル列選択動作の活性化および非活性化の制御が可能な複数のアレイブロックと、これらの複数のアレイブロックに共通に配設され外部入出力データのビット幅に対応するビット幅を有する共通データバスと、アドレス信号に従ってこれら複数のアレイブロックのうちの1つのアレイブロックを選択し、この選択されたアレイブロックから共通データバスのビット幅と同じ数のメモリセルを選択し、かつ選択メモリセルデータを共通データバスへ読み出すアレイ制御手段と、転送指示と転送アドレス信号とに応答して、アレイ制御手段により共通データバスへ読み出されたメモリセルデータをこの転送アドレス信号が指定する

10

20

30

40

50

アレイブロックへ転送する転送手段と、アドレス信号と転送アドレス信号とをリンクして格納する格納手段と、外部からのアドレス信号と格納手段の格納するアドレス信号の一一致／不一致を判別する手段と、この判別手段の一致検出時に格納手段と対応の転送アドレス信号を選択しつつ判別手段の不一致検出時に外部からのアドレス信号を選択してアドレス信号として与える手段とを備える。

#### 【0040】

請求項2に係る半導体記憶装置は、アレイブロックの各々が、メモリセルの行に対応して配置される複数のワード線と、メモリセルの各列に対応して配置される複数のビット線対と、各列に対応して配置される複数のセンスアンプとを有する。このアレイ制御手段は、アドレス信号が指定するアレイブロックのセンスアンプを活性化する手段と、このアドレス信号に従って、選択アレイブロックの対応の列のセンスアンプを共通データバスへ接続する列選択手段とを含み、また転送手段が、転送アドレス信号に応答して共通データバス線を転送アドレス信号が指定する転送アレイブロックの列に接続する手段と、転送指示と転送アドレス信号に応答して、この転送アレイブロックのセンスアンプを活性化する手段とを備える。10

#### 【0041】

請求項3に係る半導体記憶装置は、請求項1または2に係る半導体記憶装置において、アレイブロックそれぞれに対応して配置され、共通データバスと同一ビット幅のローカルデータバスをさらに備え、列選択手段が対応のアレイブロックの列のセンスアンプを対応のローカルデータバス線へ接続する手段と、アドレス信号に応答してこの対応のローカルデータバスを共通データバスへ接続する手段とを含み、転送手段は、転送アドレス信号に従って、共通データバスを転送アレイブロックのローカルデータバスに接続する手段と、この転送アドレス信号の指定する転送アレイブロックの列のセンスアンプをこのローカルデータバス線に接続する手段とを含む。20

#### 【0042】

請求項4に係る半導体記憶装置は、転送手段が、転送指示と転送アドレス信号とに応答して、転送アドレス信号が指定する転送アレイブロックのセンスアンプ活性化前にこの転送アドレス信号が指定する行のワード線を選択状態へ駆動する手段を備える。

#### 【0043】

請求項5に係る半導体記憶装置は、転送手段が、上記転送指示と上記転送アドレス信号とに応答して、この転送アドレス信号が指定する転送アレイブロックのワード線を非選択状態に維持する手段を備える。30

#### 【0044】

請求項6に係る半導体記憶装置は、請求項5の半導体記憶装置において、各列のビット線対とセンスアンプとの間に配置される接続ゲートをさらに備え、転送手段が、転送指示と転送アドレス信号とに応答して、転送アレイブロックの接続ゲートを非導通状態に維持する手段を備える。

#### 【0045】

請求項7に係る半導体記憶装置は、請求項1ないし6のいずれかの半導体記憶装置が、共通データバス上のデータを増幅して出力バッファへ伝達するリードドライバと、このリードドライバの出力信号を受けるように結合される入力部を有し、入力バッファからのデータをバッファ処理して共通データバスへ伝達するライトドライバと、転送指示に応答してこのライトドライバを所定期間活性化する手段とを備える。40

#### 【0046】

請求項8に係る半導体記憶装置は、請求項3の半導体記憶装置の転送手段が、転送指示に応答して転送アレイブロックのセンスアンプと対応のローカルデータバスとの接続およびこのローカルデータバスと共通データバスとの接続の確立の後、転送アレイブロックのセンスアンプを活性化する手段とを含む。

#### 【0047】

請求項9に係る半導体記憶装置は、請求項7の転送手段が、転送指示に応答して転送アレ50

イブロックのセンスアンプの活性化の後ライトドライバを活性化する手段を含む。

**【0048】**

請求項10に係る半導体記憶装置は、請求項2ないし9のいずれかの半導体記憶装置が、さらに、容量手段と、センスアンプの各アレイブロックに対応して配置されるセンスアンプ活性化信号線と、アドレス信号に従ってこのアレイブロックのセンスアンプの活性化から非活性化への移行時にアレイブロックのセンスアンプ活性化信号線を容量手段へ結合する手段と、転送アドレス信号と転送指示とに応答して転送アレイブロックのセンスアンプ活性化信号線をこの転送アレイブロックのセンスアンプの非活性化から活性化への移行時に容量手段へ所定期間結合する手段を備える。

**【0051】**

請求項1\_1に係る半導体記憶装置は、請求項1ないし1\_0のいずれかの転送手段が、転送指示と同時に与えられる保持指示に応答して、この転送アレイブロックのセンスアンプを保持指示の活性期間中、活性状態に維持する手段をさらに備える。

**【0053】**

請求項1\_2に係る半導体記憶装置は、請求項1ないし1\_1のいずれかの半導体記憶装置が、外部から周期的に与えられる一定のパルス幅を有するクロック信号に同期して、外部から与えられる行および列アドレス信号を同時に取込んで内部アドレス信号を生成する手段を備える。

**【0054】**

請求項1\_3に係る半導体記憶装置は、請求項1\_2の半導体記憶装置が、アレイブロック各々に対応して配置され、クロック信号に同期して与えられるチップ活性化信号によりインペブルされて内部アドレス信号をラッチするラッチ手段を含む。このラッチ手段は、内部アドレス信号が対応のアレイブロックを指定するときに、その与えられた内部アドレス信号をラッチする。

**【0055】**

請求項1\_4に係る半導体記憶装置は、請求項1\_2または1\_3の半導体記憶装置が、クロック信号に同期して、外部から与えられる内部動作指定用制御信号を取込んで内部制御信号を発生する手段を含む。

**【0056】**

請求項1\_5に係る半導体記憶装置は、請求項1\_3の半導体記憶装置のアレイ制御手段は、アドレス信号により指定される選択アレイブロックを、チップ活性化信号の活性化から所定の時間のみ選択アレイブロックを活性状態に維持する手段を含む。

**【0057】**

請求項1\_6に係る半導体記憶装置は、請求項1ないし1\_5の半導体記憶装置がアドレス信号と転送アドレスとをリンクして格納する格納手段と、外部から与えられるアドレス信号とこの格納手段の格納されたアドレス信号の一一致／不一致を判別する手段と、この判別手段の一致検出時には格納手段の対応の転送アドレスを選択し、かつ不一致検出時には外部から与えられるアドレス信号を選択してアドレス信号として各アレイブロックへ与える手段をさらに備える。

**【0059】**

請求項1\_6に係る半導体記憶装置は、各々が、行列状に配列される複数のメモリセルと、各列に対応して配置される複数のビット線対と、各行に対応して配置される複数のワード線と、各列に対応して配置される複数のセンスアンプとを有する複数のアレイブロックと、これら複数のアレイブロックの隣接アレイブロックの各列を相互接続するための複数のゲートと、第1のアドレス信号と転送指示とに応答して、第1のアドレス信号が指定するアレイブロックのメモリセルを選択する第1の選択手段と、この第1のアドレス信号と第1の選択手段とに応答して、この第1のアドレス信号が指定する選択アレイブロックのセンスアンプを活性化する手段と、第1のアドレス信号と転送指示とに応答して、選択アレイブロックと隣接アレイブロックとの間のゲートを導通状態とする接続手段と、第2のアドレス信号と転送指示とに応答して、該隣接アレイブロックのセンスアンプを活性化す

10

20

30

40

50

る手段を備える。

【0060】

請求項1\_6の半導体記憶装置は、さらに転送アレイブロックのセンスアンプの活性化時、リフレッシュ指示とリフレッシュアドレス信号とに従って、リフレッシュアドレス信号が指定するアレイブロックに隣接するアレイブロックに対してビット線対をフロー・ティング状態として対応のゲートを導通状態としてリフレッシュアドレスが指定するアレイブロックのセンスアンプの保持データを該隣接アレイブロックに転送してゲートを非導通状態とし、リフレッシュアドレス信号に従ってリフレッシュを実行し、リフレッシュ指示の活性化から非活性化への移行時、この異なるアレイブロックのセンスアンプの保持データを転送アレイブロックのセンスアンプへ返送し、該センスアンプを活性状態としつつ異なるアレイブロックのセンスアンプを非活性状態とする手段をさらに備える。10

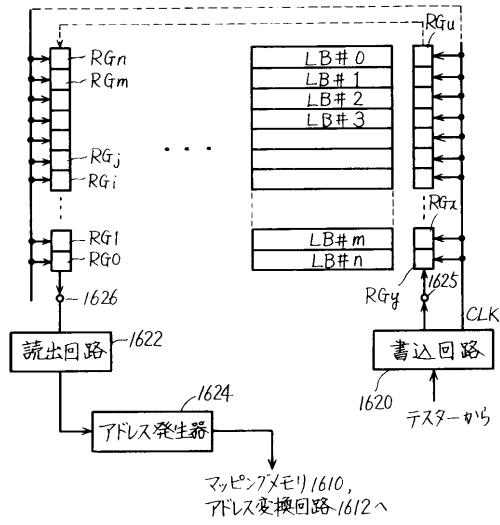

【0082】

請求項1に係る半導体記憶装置においては、アレイ制御手段により共通データバス線上に読み出されたメモリセルデータが、転送手段により転送先のアレイブロックへ転送されるため、メモリセルデータを、データ転送のために装置外部へ読み出す必要がなく、高速でアレイブロック間のデータ転送を行うことができる。また、アドレス信号と対応の転送アドレス信号とをリンクして格納し、外部アドレス信号と格納アドレス信号との一致／不一致に従って外部アドレス信号および転送アドレス信号の一方を選択しており、センスアンプをキャッシュとして利用することができ、高速アクセスが可能となる。

【0083】

請求項2に係る半導体記憶装置においては、転送先のアレイブロックのセンスアンプを活性化しており、確実に選択メモリセルのデータを転送先へ転送し、そこにラッチすることができる。

【0084】

請求項3に係る半導体記憶装置においては、アレイブロック各々にローカルI/Oバスが配置されており、ローカルI/Oバス線から共通データバスを介して転送先のアレイブロックのローカルI/Oバスを介してデータを転送しており、余分のデータ転送経路を新たに設ける必要がない。

【0085】

請求項4に係る半導体記憶装置においては、転送アレイブロックのセンスアンプの活性化前にワード線を選択状態としており、センスアンプ活性化時に、メモリセルのデータをこの転送先のアレイブロックのメモリセルへ書込むことができる。

【0086】

請求項5に係る半導体記憶装置においては、ワード線は非選択状態を維持しており、センスアンプに転送データがラッチされる。これにより、センスアンプをキャッシュとして利用することができる。

【0087】

請求項6に係る半導体記憶装置においては、データ転送時に、転送先のアレイブロックのビット線対をセンスアンプと切離しており、センスアンプのセンスノードの容量を小さくすることができ、このセンスアンプのセンスノードの電位を転送データに応じて変化させることができ、確実にセンスアンプによる転送データの検知、増幅およびラッチを行なわせることができる。40

【0088】

請求項7に係る半導体記憶装置においては、リードドライバで増幅されたデータがライトドライバを活性化して共通データバスへ伝達しているため、転送先のアレイブロックの対応の列へ確実に転送データを書込むことができる。

【0089】

請求項8に係る半導体記憶装置においては、転送先のアレイブロックの対応のセンスアンプと共にデータバスとの接続の後センスアンプを活性化しており、データ転送のために大きな駆動力を有するドライバを新たに設けて用いる必要がなく、対応のセンスアンプのセ50

ンスノードの電位をこの共通データバス上に伝達された転送データに応じて確実に変化させることができる。

**【0090】**

請求項9に係る半導体記憶装置においては、転送先のアレイブロックのセンスアンプの活性化の後、ライトドライバを活性化しており、余分のデータ転送用のドライバを用いることなく通常のデータ書込動作と同様の動作シーケンスで転送データを転送アレイブロックの対応の列へ書込むことができる。

**【0091】**

請求項10に係る半導体記憶装置においては、センスアンプ活性化信号線が容量に選択的に所定期間結合されるため、センスアンプ活性化信号線の充放電電流を容量に保存して次のセンスアンプ活性化信号の活性化時に再利用することができ、センスアンプ駆動部の消費電流を低減することができる。

**【0094】**

請求項1\_1に係る半導体記憶装置においては、保持指示に応答して、転送アレイブロックのセンスアンプを活性状態に維持するように構成しているため、この転送先のアレイブロックのセンスアンプをキャッシュとして利用することができる。

**【0096】**

請求項1\_2に係る半導体記憶装置においては、クロック信号に同期して行および列アドレス信号を取込んでおり、行選択系回路および列選択系回路を互いに独立に駆動することができ、複数のアレイブロックを重複的に活性状態としてデータ転送を行なうことができる。

**【0097】**

請求項1\_3に係る半導体記憶装置においては、アレイブロック各々に対応してアドレスラッチが配置されており、各アレイブロックにおいて互いに独立にアドレス指定を行なうことができる。

**【0098】**

請求項1\_4に係る半導体記憶装置においては、内部動作を指定する制御信号が外部クロック信号に同期して与えられており、信号取込タイミングおよび内部動作開始タイミングを容易に確立することができる。

**【0099】**

請求項1\_5に係る半導体記憶装置においては、各アレイブロックの活性化期間は、チップ活性化信号の活性化から所定期間とされており、各アレイブロックの活性化を重複して行なう際のアレイブロック活性化の制御が容易となる。

**【0102】**

請求項1\_6に係る半導体記憶装置においては、転送指示が与えられると、ゲートを用いて隣接アレイブロック間のビット線対を接続しており、高速で1行のメモリセルのデータを隣接アレイブロックへ転送することができる。

**【0108】**

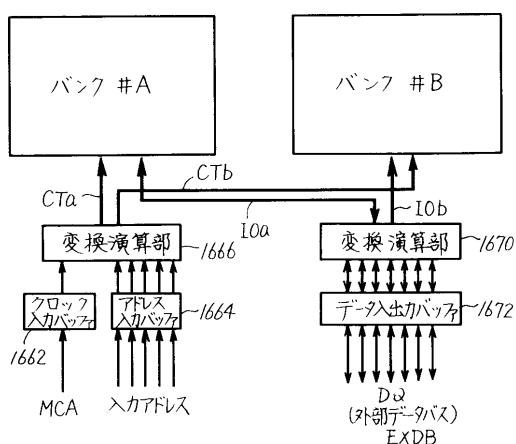

**【発明の実施の形態】**

**[実施の形態1]**

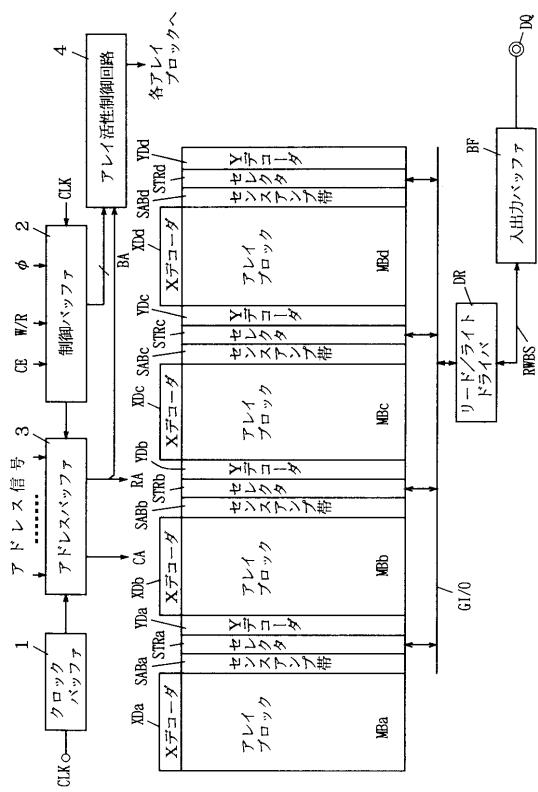

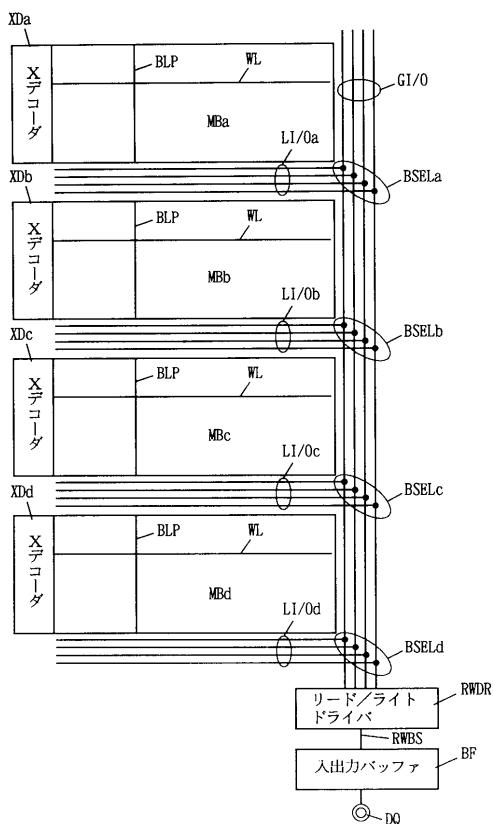

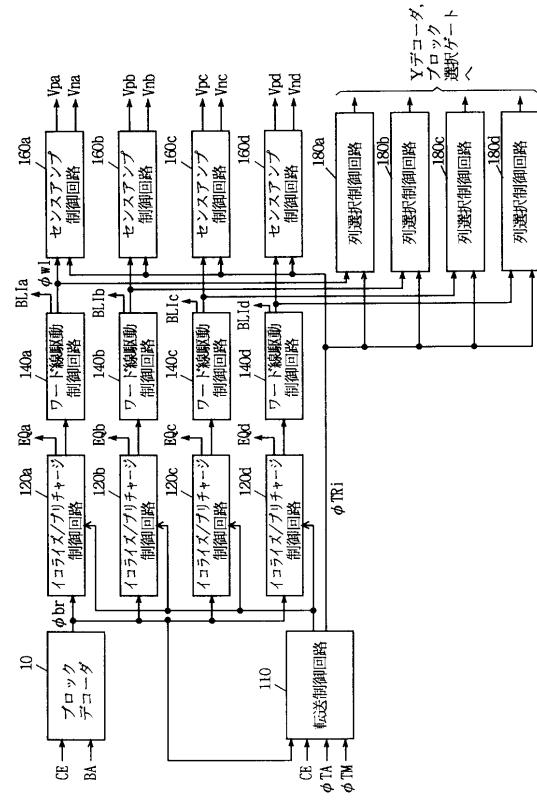

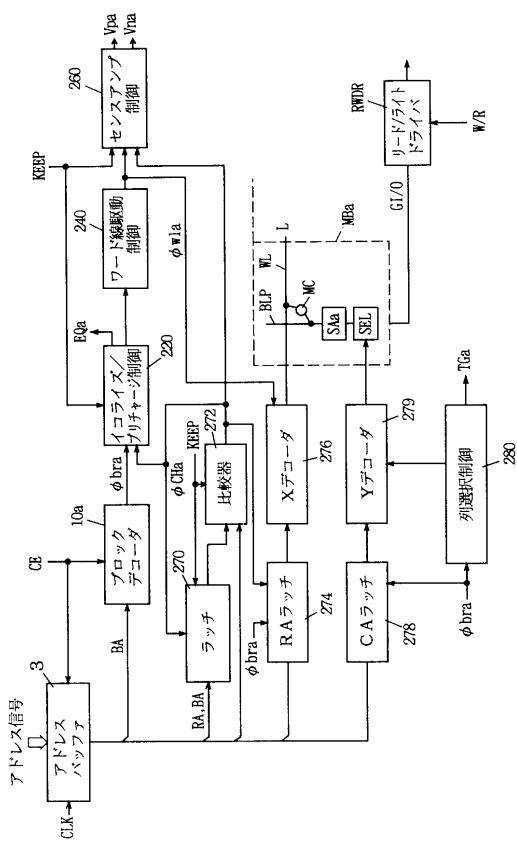

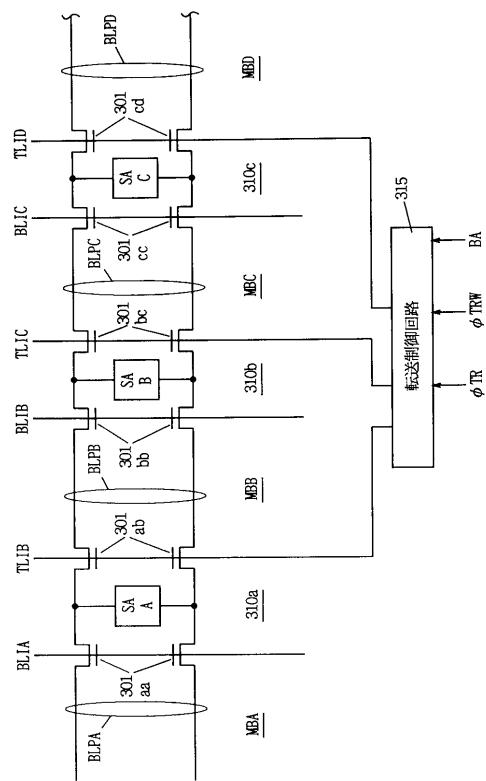

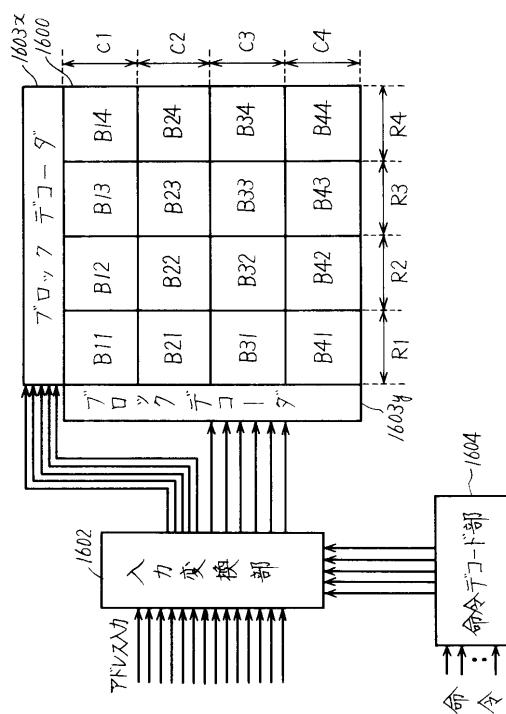

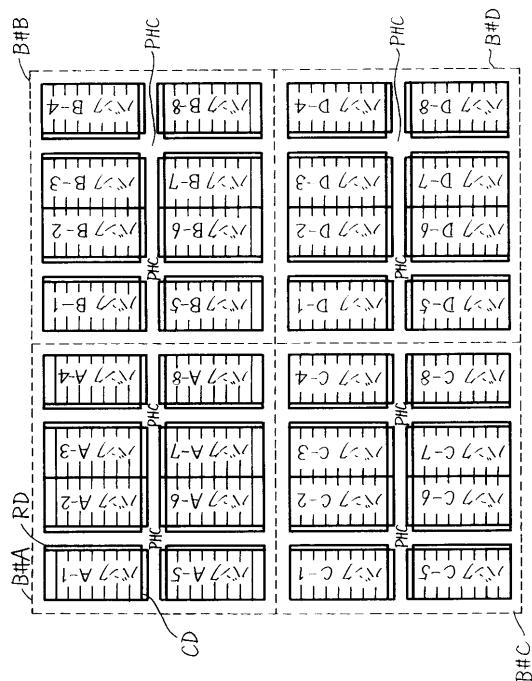

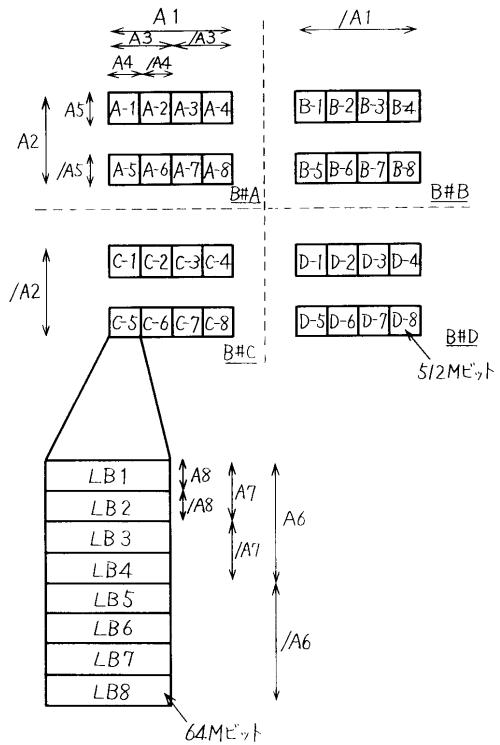

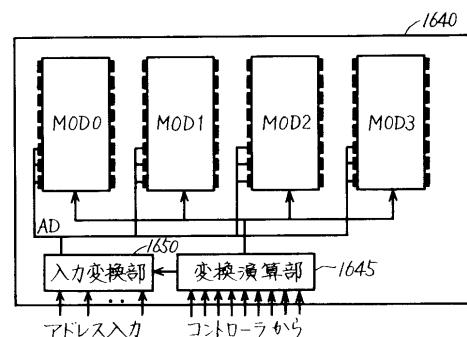

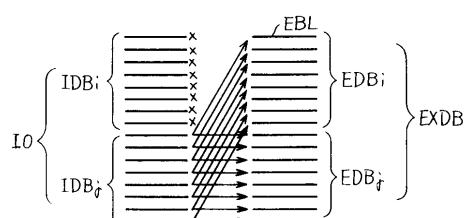

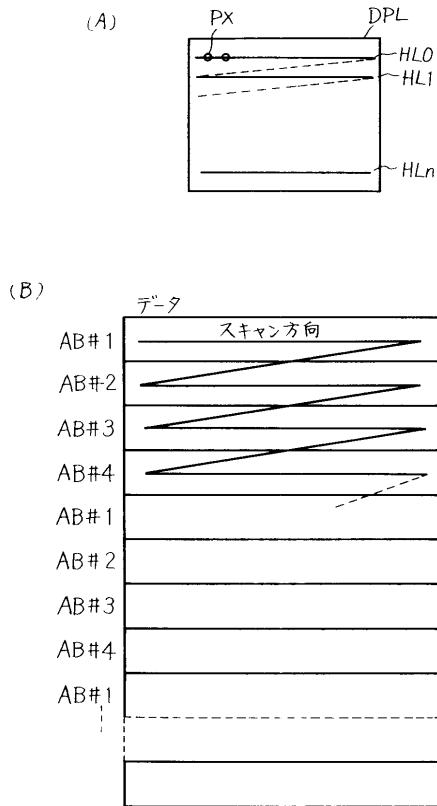

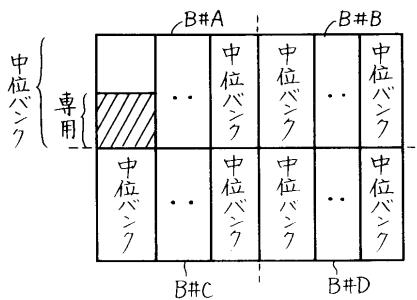

図1は、この発明の第1の実施の形態である半導体記憶装置の全体の構成を概略的に示す図である。図1において、半導体記憶装置は、1つのデータ入出力端子DQに対し4つのアレイブロックMBa～MBdを一例として含む。このアレイブロックの数は複数個であればよく、さらに多く設けられてもよい。

**【0109】**

アレイブロックMBa～MBdの各々は、後にその構成は詳細に説明するが、行および列状に配置される複数のメモリセルと、各行に対応して配置される複数のワード線と、各列に対応して配置される複数のビット線対を含む。

**【0110】**

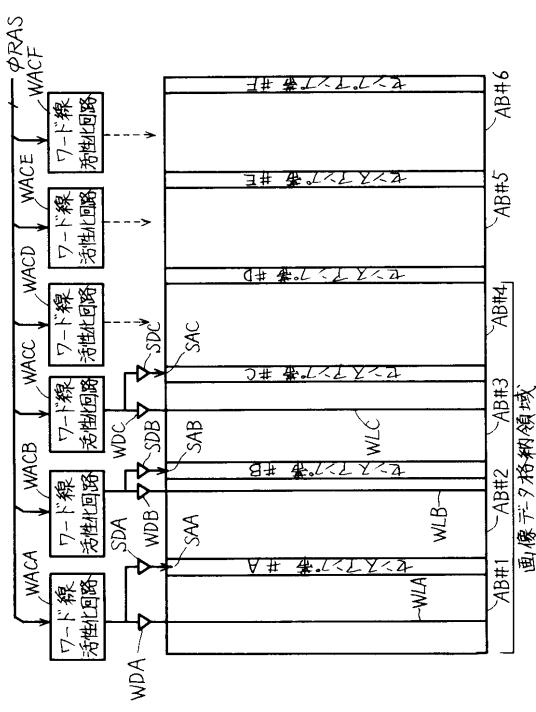

アレイブロックMBa～MBdそれぞれに対応して、活性化時、与えられた行アドレス信

10

20

30

40

50

号をデコードし、対応のアレイブロック M B a ~ M B d のワード線を選択する X デコーダ X D a ~ X D d と、対応のアレイブロックのビット線対それぞれに対応して配置され、対応のビット線対上の電位を検知し増幅しかつラッチする複数のセンスアンプを含むセンスアンプ帯 S A B a ~ S A B d と、列選択信号に従って、対応のアレイブロックの対応の列に配置されたセンスアンプをグローバル I / O バス G I / O へ接続するセレクタ S T R a ~ S T R d が設けられる。

#### 【 0 1 1 1 】

この図 1 に示す構成において、アレイブロック M B a ~ M B d それぞれに対応して、活性化時、列選択信号を発生するための Y デコーダ Y D a ~ Y D d が設けられる。 Y デコーダ Y D a ~ Y D d は、活性化時、対応のアレイブロックに対応して設けられたセレクタに対してのみ列選択信号 ( C S ) を出力する。グローバル I / O バス G I / O に対しては、リード / ライトドライバ D R が設けられ、またリード / ライトドライバ D R は、内部リード / ライトバス R W B S を介して入出力バッファ B F に接続される。入出力バッファ B F は、データ入出力端子 D Q とデータの授受を行なう。

#### 【 0 1 1 2 】

図 1 に示す半導体記憶装置はさらに、外部から周期的に与えられる一定のパルス幅を有するクロック信号 C L K を受けて内部クロック信号を生成するクロックバッファ 1 と、このクロックバッファ 1 からの内部クロック信号に同期して外部から与えられる制御信号 C E , W / R および を取込み内部制御信号を発生する制御回路 2 と、クロックバッファ 1 からの内部クロック信号と制御回路 2 からの指示信号に従って外部から与えられるアドレス信号を取り込み内部アドレス信号 B A 、 R A および C A を生成するアドレスバッファ 3 を含む。制御信号 C E は、チップイネーブル信号であり、クロック信号 C L K の立上がり時に活性状態のハイレベルとされると、内部での行選択動作が開始される。信号 W / R は、データの書き / 読出を示す信号であり、チップイネーブル信号 C E の活性化時に同時にデータの書き / 読出を示す状態に設定される。制御信号 は、内部動作を指定する制御信号信号を総称的に示す信号であり、後に詳細に説明するが、転送指示、データ書換指示、データ保持指示などの各種制御信号を含む。制御信号 C E , W / R および をクロック信号 C L K に同期して取込み内部動作を開始することにより、通常のアレイ分割構造の異なり、1つのアレイブロックが活性状態にあるときに、これと独立に別のアレイブロックを活性化することが可能となる。

#### 【 0 1 1 3 】

アドレスバッファ 3 は外部から与えられるアドレス信号を取り込み、行アドレス信号 R A および列アドレス信号 C A を同時に生成する。行アドレス信号 R A および列信号 C A をチップイネーブル信号 C E の活性化時に同時に生成することにより、各アレイブロックにおいて行選択系回路および列選択系回路の動作を互いに独立に制御することができ、かつセンスアンプの活性 / 非活性をワード線の選択 / 非選択と独立に制御することができる。

#### 【 0 1 1 4 】

半導体記憶装置は、さらに、この制御回路 2 からの内部制御信号とアドレスバッファ 3 から与えられるブロックアドレス B A に従って、このブロックアドレス B A が所定するアレイブロックに対し、必要な制御信号を与えるアレイ活性制御回路 4 を含む。

#### 【 0 1 1 5 】

このアレイ活性制御回路 4 は、後のその構成については詳細に説明するが、アレイブロック M B a ~ M B d 各々を互いに独立に活性化 / プリチャージする。すなわち、制御バッファ 2 から与えられるチップイネーブル信号 C E の活性化に応答して、アドレスバッファ 3 から与えられるブロックアドレス B A が指定するアレイブロックを一定の期間活性状態とする。アレイ活性制御回路 4 により、アレイブロック M B a ~ M B d を、互いに独立に駆動する構成とすることにより、1つのアレイブロックにおいて選択されたメモリセルのデータを高速で他のアレイブロックへ伝達することができる。

#### 【 0 1 1 6 】

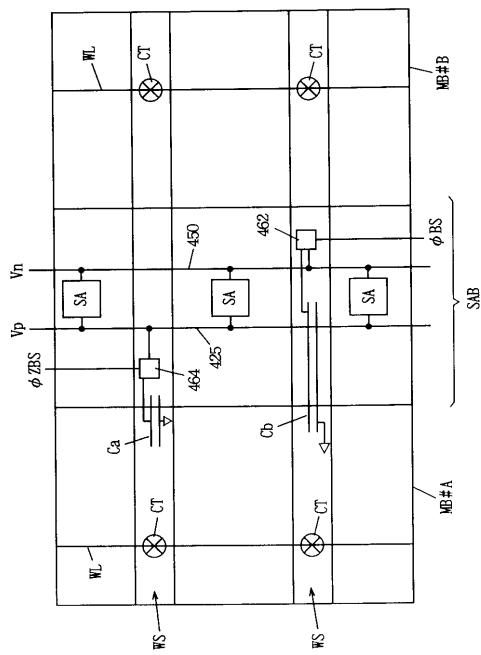

図 2 は、図 1 に示すアレイブロックの構成をより詳細に示す図である。図 2 において、図

10

20

30

40

50

55に示す従来の半導体記憶装置の構成要素と対応する構成要素には同一の参照符号を付し、それらの詳細説明は省略する。

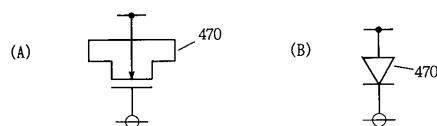

#### 【0117】

図2において、ビット線対B L Pそれぞれに対し、メモリセルM Cが配置される部分とプリチャージ／イコライズ回路E PおよびセンスアンプS Aを含むビット線周辺回路との間に、ビット線分離信号B L Iに応答して選択的に非導通状態とされるビット線分離ゲート5が配置される。このビット線分離ゲート5は、ビット線B Lに対して設けられるnチャネルMOSトランジスタN 10と、ビット線Z B Lに対して設けられるnチャネルMOSトランジスタN 11を含む。これらのMOSトランジスタN 10およびN 11のゲートへビット線分離信号B L Iが与えられる。このビット線分離ゲート5を各ビット線対B L Pに設けることによりメモリセルデータを別のアレイブロックへ転送するときに他のアレイブロックのセンスアンプをキャッシュとして利用することが可能となる（これについては後に詳細に説明する）。

#### 【0118】

リード／ライトドライバD Rは、従来と同様、リードドライバR D RおよびライトドライバW D Rを含む。次に動作について、その動作波形図である図3を参照して説明する。

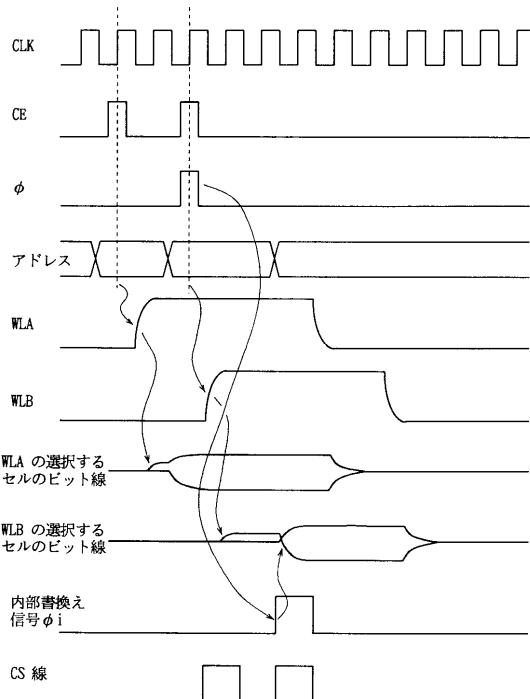

#### 【0119】

今、アレイブロックM B A（アレイブロックM B a～M B dのいずれか）から他のアレイブロックM B Bへのデータ転送動作について説明する。

#### 【0120】

クロックバッファ1へは、半導体記憶装置へのアクセスの有無にかかわらず、常時クロック信号C L Kが印加される。アクセス時においては、チップイネーブル信号C Eをワンショットのパルスの形で制御バッファ2へ与える。制御バッファ2は、クロック信号C L Kの立上がり時にチップイネーブル信号C Eを取り込み、内部チップイネーブル信号をアドレスバッファ3およびアレイ活性制御回路4へ与える。アドレスバッファ3は、この制御バッファ2からの内部チップイネーブル信号の活性化時、与えられたアドレス信号を取り込み内部アドレス信号B A、R AおよびC Aを出力する。アレイ活性制御回路4は、この制御バッファ2からの内部チップイネーブル信号の活性化時活性化され、アドレスバッファ3からのロックアドレス信号B Aを取り込み、このロックアドレス信号B Aが指定するアレイブロックに対して設けられたXデコーダX Dを活性化する。

#### 【0121】

ロックアドレス信号B Aが指定するアレイブロックM B Aにおいては、対応のXデコーダX D A（X D a～X D dのいずれか）が活性化され、アドレスバッファ3からの内部行アドレス信号R Aをデコードし、アレイブロックM B Aにおいてアドレス指定されたワード線W L Aを選択状態へ駆動する。これにより、アレイブロックM B Aにおいては、この選択ワード線W L Aに接続されるメモリセルデータが各ビット線対B L P上に読み出される。ここで、図3においては、ワード線W L Aに接続するメモリセルのハイレベルのデータがビット線対B L P Aに読み出された状態が一例として示される。このチップイネーブル信号C Eの活性化時において書換指示信号が非活性状態のローレベルを維持しており、アレイ活性制御回路4の制御のもとに、この選択アレイブロックM B Aのセンスアンプ帯S A B Aの各センスアンプが所定のタイミングで活性状態とされ、選択されたワード線に接続されるメモリセルのデータの検知、増幅およびラッチが行なわれる。

#### 【0122】

選択アレイブロックM B Aでのセンスアンプ活性化と並行してまたはその活性化の完了の後、新たにチップイネーブル信号C Eがワンショットのパルス形態で印加され、制御バッファ2により、クロック信号C L Kの立上がり時にチップイネーブル信号C Eがハイレベルの活性状態であり、新たなアクセス動作が指定されたと判定され、内部チップイネーブル信号C Eがアドレスバッファ3およびアレイ活性制御回路4へ与えられる。制御バッファ2は、またこのとき書換指示信号がワンショットのパルス形態で印加されるため、同様、クロック信号C L Kが立上がりで、このハイレベルの活性状態にある書換指示信号

10

20

30

40

50

を取り込み、アレイ活性制御回路4へ与える。アドレスバッファ3は、制御バッファ2からの内部チップイネーブル信号に応答して活性化され、クロック信号CLKの立上がり時に与えられたアドレス信号RAおよびCAならびにロックアドレス信号BAを取り込み内部アドレス信号を発生する。後に詳細に説明するが、アドレスバッファ3から新たに内部アドレス信号が与えられても、先に選択状態とされているアレイブロックMB-Aに対して設けられたXデコーダXD-Aは、先に与えられたアドレス信号をラッチしており、この新たに与えられたアドレス信号によりそのラッチした、アドレス信号が変化するのは防止される。

#### 【0123】

アレイ活性制御回路4は、この制御バッファ2からの書換指示信号に応答して、このアクセスサイクルで与えられたアドレス信号は、先に選択されたアレイブロックのメモリセルデータを転送するアレイブロックのメモリセルを指定するアドレスであると判定する。この状態においては、アレイ活性制御回路4の制御のもとに、新たにアドレス指定されたアレイブロック（転送アレイブロック）MB-Bにおいて、ワード線選択が行なわれ、このアレイブロックMB-Bにおいて選択されたワード線WLBの接続するメモリセルのデータが各対応のビット線対BLP上に伝達される。

#### 【0124】

一方、アレイ活性制御回路4は、先に指定されたアレイブロックMB-Aに対し所定のタイミングでYデコーダYD-Aを活性化する。活性化されたYデコーダYD-Aは、既にラッチしていた列アドレス信号CAをデコードし、選択アレイブロックMB-Aの対応の列すなわちビット線対BLPを選択するための列選択信号CSを活性状態とする。これにより、アレイブロックMB-AのセレクタSTRの列選択ゲートが導通し、選択ビット線対BLPがローカルI/OバスLIA/OAに接続される。同様に、ロックアドレス信号BAに従ってロック選択ゲートBSELが導通状態とされ、このローカルI/OバスLIA/OAがグローバルI/OバスGIA/Oに接続される。これにより、選択アレイブロックMB-Aのアドレス指定されたメモリセルデータがグローバルI/OバスGIA/O上に伝達される。

#### 【0125】

アレイ活性制御回路4は、制御バッファ2から与えられた活性状態の書換指示信号に応答して、転送先アレイブロックにおいては、センスアンプの活性化タイミングを遅らせる。グローバルI/OバスGIA/O上に転送されるべきメモリセルデータが現われるのを保証するためである。

#### 【0126】

次いで、この書換指示信号が与えられてから所定期間経過後、内部書換信号 $i$ が活性状態とされる。この内部書換信号 $i$ の活性化に応答して、転送アレイブロックのセレクタがYデコーダYD-Bの出力信号および図示しないロックデコーダの出力信号に従って導通し、アドレス指定された列のセンスアンプがグローバルI/OバスGIA/Oに接続される。この後、転送アレイブロックMB-Bのセンスアンプが活性状態とされ、選択メモリセルへ転送メモリセルデータが書き込まれる。アレイブロックMB-AおよびMB-Bにおいては、チップイネーブル信号CEの活性化から所定期間経過後、アレイ活性制御回路4の制御のもとにアレイプリチャージ動作が実行される。

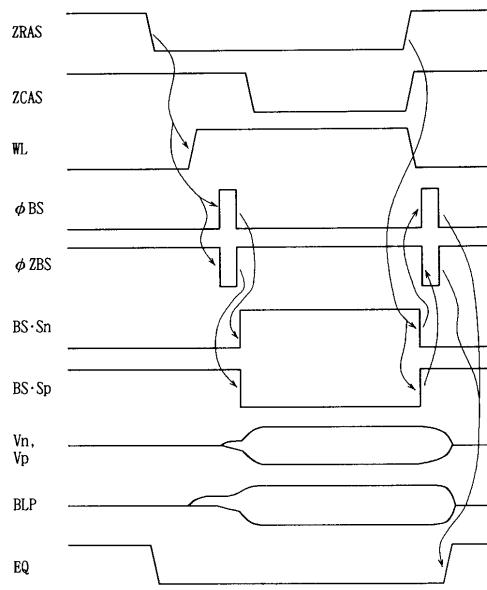

#### 【0127】

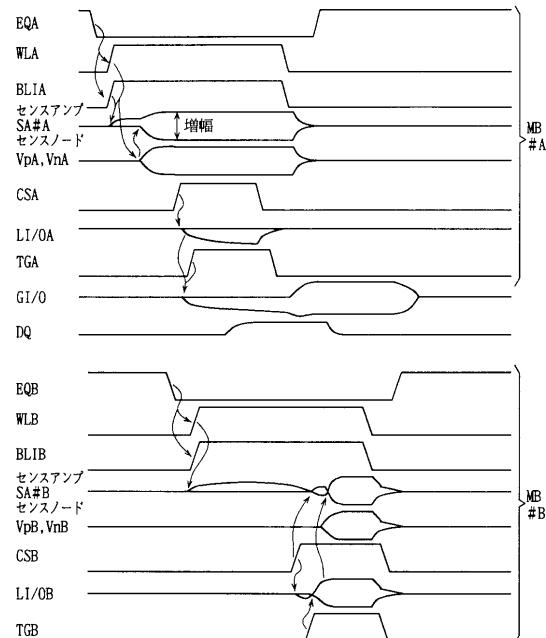

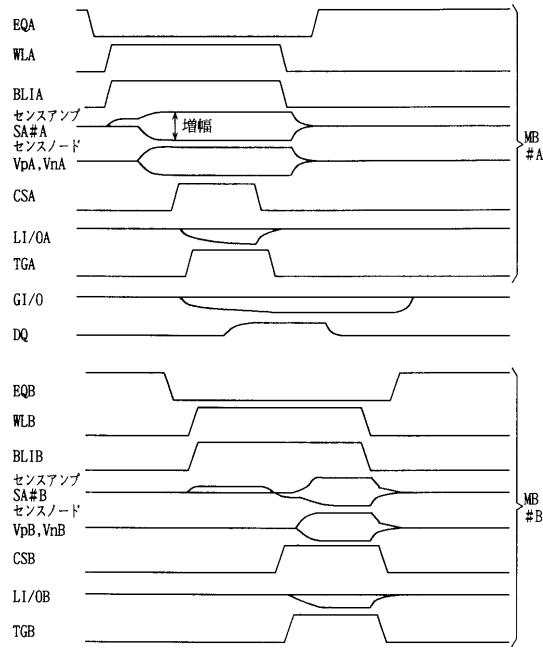

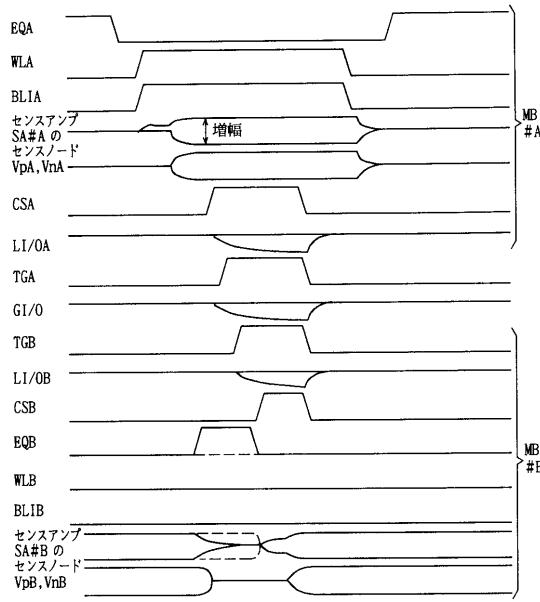

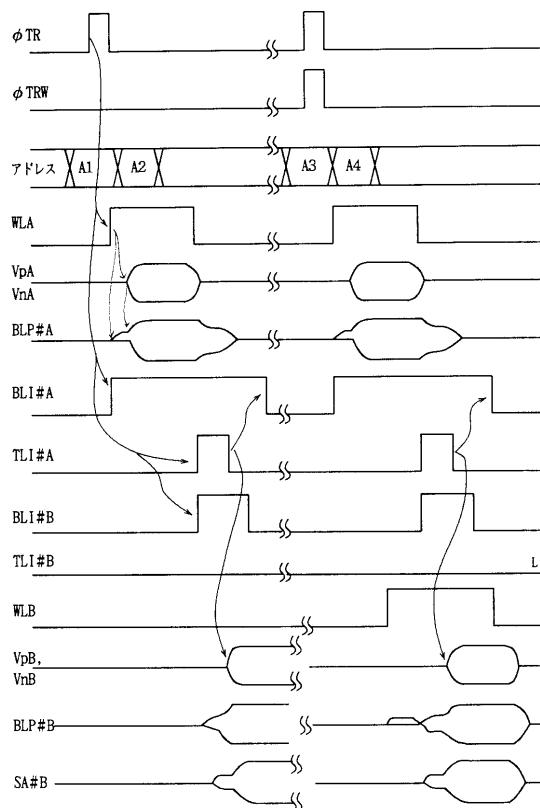

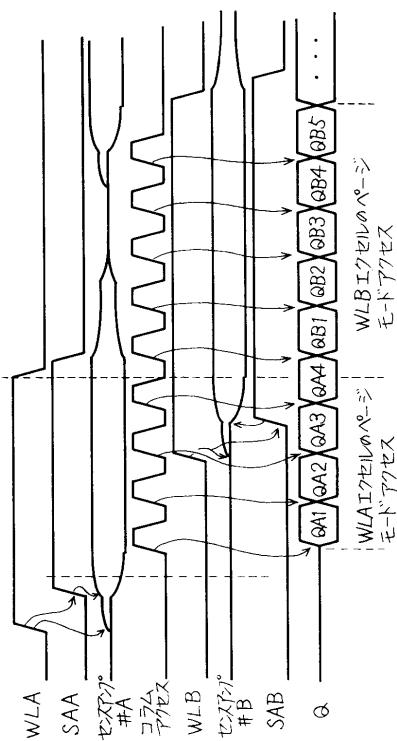

図4は、この発明の第1の実施の形態のデータ転送動作をより詳細に示す波形図である。以下、図4を参照してより具体的にデータ転送動作について説明する。

#### 【0128】

アレイブロックMB-Aにおいては、チップイネーブル信号CEの活性化に応答して、イコライズ信号EQ-Aがローレベルの非活性状態とされ、イコライズ/プリチャージ回路が非活性状態とされる。次いで、ビット線分離指示信号BLIAがハイレベルとなり、ビット線対BLPAがセンスアンプSA-Aのセンスノードに結合される。ここで、センスアンプのセンスノードとは、交差結合されたセンスアンプのMOSトランジスタのゲートと

10

20

30

40

50

ドレインが接続されるノードを示す。次いで、行アドレス信号 R A に従ってワード線が選択され、選択ワード線 W L A の電位が立上がり、センスアンプ S A A のセンスノードの電位がこの選択ワード線 W L A に接続されるメモリセルデータに応じて変化する。センスノードの電位が十分に拡大した後、センスアンプ活性化信号 V p A および V n A が活性状態のハイレベルおよびロー・レベルとされ、このセンスアンプ S A A のセンスノードの電位が増幅される。センスアンプ S A A のセンスノードの電位が十分に増幅され後、Y デコーダ Y D A の出力する列選択信号 C S A がハイレベルとなり、この列選択信号 C S A が指定する列がローカル I / O バス L I / O A に接続され、ローカル I / O バス L I / O A の電位が変化する。次いでブロック選択ゲート B S E L A がブロック選択信号 T G A に活性化に従って導通し、ローカル I / O バス L I / O A がグローバル I / O バス G I / O に接続され、グローバル I / O バスの電位が変化する。

10

#### 【 0 1 2 9 】

クロック信号 C L K の立上がり時に与えられたリード / ライト信号 W / R に従って、リードドライバ R D R および出力バッファ O B F が活性化され、このグローバル I / O バス G I / O 上のデータが増幅されてデータ入出力端子 D Q へ出力される。

#### 【 0 1 3 0 】

一方、このアレイブロック M B A へのアクセス動作と並行して、アレイブロック M B B において、転送アドレス信号に従ってビット線分離信号 B L I B がハイレベルとなり、また選択ワード線 W L B の電位がハイレベルとなる。これにより、センスアンプ S A B のセンスノードへ、選択ワード線 W L B に接続されるメモリセルのデータが伝達され、センスアンプ S A B のセンスノード電位が変化する。書換指示信号 i が活性状態とされているため、アレイブロック M B B のセンスアンプ活性化は、内部書換信号 i 活性状態とされるまで待合せられる。グローバル I / O バス G I / O 上のデータが確定状態とされた後にセンス動作を行なうためである。

20

#### 【 0 1 3 1 】

内部書換信号 i が活性状態とされると、まずライトドライバが活性状態とされ、グローバル I / O バス G I / O 上の電位が増幅される。図 2 に示すように、内部リード / ライトバス R W B S はリードドライバ R D R の出力部に接続されかつライトドライバ W D R の入力部に接続されている。したがって、グローバル I / O バス G I / O 上の電位は、アレイブロック M B A において選択されたメモリセルのデータをさらに増幅した電位レベルとされる。次いでアレイブロック M B B において、列選択信号 C S B が活性状態となり、対応の列のビット線対 B L P B (センスアンプ S A B のセンスノード) がローカル I / O バス L I / O B に接続される。ローカル I / O バス L I / O B とビット線対との接続により、このセンスアンプ S A B のセンスノードの電位が変動しても、このセンスアンプ S A B のセンスノードの電位は、アレイブロック M B A からの転送データで書換えられるため、何ら問題は生じない。

30

#### 【 0 1 3 2 】

次いでアレイブロック M B B に対するブロック選択信号 T G B がハイレベルの活性状態となり、ブロック選択ゲート B S E L B が導通し、ローカル I / O バス L I / O B がグローバル I / O バス G I / O に接続され、ローカル I / O バス L I / O B の電位がライトドライバ W D R から与えられた電位に従って変化し、応じてセンスアンプ S A B のセンスノード電位も変化する。次いでアレイブロック M B B のセンスアンプを活性化し、選択メモリセルへのデータの書き込みおよび選択ワード線 W L B に接続される残りのメモリセルデータのリストア動作を行ない、所定期間が経過した後に、データ転送サイクルが終了する。

40

#### 【 0 1 3 3 】

以上のように、アレイブロックを互いに独立して駆動可能とすることにより、1つのアレイブロックが活性状態とされているときに、別のアレイブロックを活性状態とすることができます、ロウアドレスストローブ信号 Z R A S の2サイクル期間よりもはるかに短い期間でアレイブロック間のデータ転送を行なうことができる。

50

## 【0134】

[転送動作の変更例]

図5は、この発明の第1の実施の形態である半導体記憶装置のデータ転送動作の第1の変更例を示す波形図である。

## 【0135】

図5に示すデータ転送動作において、アレイブロックMB\_AからアレイブロックMB\_Bへのデータ転送が行なわれる。この場合、アレイブロックMB\_Aにおける動作は、先の図4に示す動作と同様の動作が行なわれる。書換指示信号<sub>i</sub>が与えられても、ライトドライバの活性化は行なわれず、したがってグローバルI/OバスG\_I/O上の電位は、アレイブロックMB\_Aから読出されたデータの電位を維持する。

10

## 【0136】

アレイブロックMB\_Bにおいては、転送アドレス信号に従って、ワード線W\_L\_Bが選択状態とされ、またビット線分離信号B\_L\_I\_Bもハイレベルの活性状態とされる。これにより、選択ワード線W\_L\_Bに接続されるメモリセルのデータが各ビット線対B\_L\_P\_Bを介してセンスアンプSA\_Bのセンスノードへ伝達される。書換指示信号<sub>i</sub>に応答して、所定時間経過後に、YデコーダY\_D\_Bからの列選択信号C\_S\_Bおよび図示しないブロックデコーダからのブロック選択信号T\_G\_Bがハイレベルとされる。これにより、選択列に対応して配置されたセンスアンプSA\_BのセンスノードがグローバルI/OバスG\_I/Oに接続される。センスアンプSA\_Bは非活性状態であるため、そのセンスノードの電位がグローバルI/OバスG\_I/O上の電位に従って変化する。この後、センスアンプ活性化信号V\_p\_BおよびV\_n\_Bが活性状態とされ、センスアンプSA\_Bのセンスノードの電位が増幅され、メモリセルに書き込まれる。センスアンプSA\_BのセンスノードがローカルI/OバスL\_I/O\_Bに接続されたとき、センスアンプSA\_Bのセンスノード電位が不定状態となつても、この不定データはグローバルI/OバスG\_I/O上の電位により書換えられるデータであり、センスアンプ活性化信号V\_p\_BおよびV\_n\_Bの活性化前に、センスアンプSA\_Bのセンスノードの電位がグローバルI/OバスG\_I/O上の電位に応じて変化すれば何ら問題は生じない。列選択信号C\_S\_Bおよびブロック選択信号T\_G\_Bの活性化は、いずれが先に行なわってもよい。またワード線W\_Lとビット線分離信号B\_L\_I\_Bは、いずれが先に活性状態とされてもよい。

20

## 【0137】

30

この図5に示すように、ライトドライバW\_D\_Rをデータ書換時において非活性状態に維持しても、転送アレイブロックのセンスアンプSA\_Bの活性化を、グローバルI/OバスG\_I/Oとセンスノードとの接続の後に行なうことにより正確にデータを転送することができる。

## 【0138】

[周辺回路の構成]

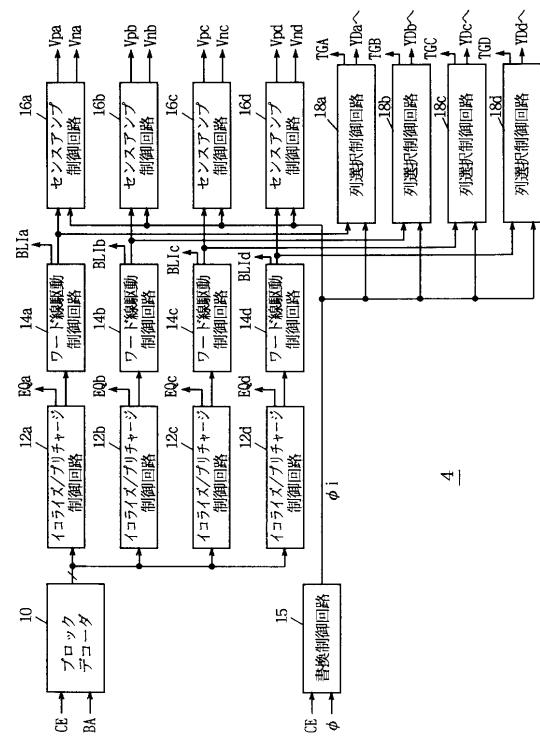

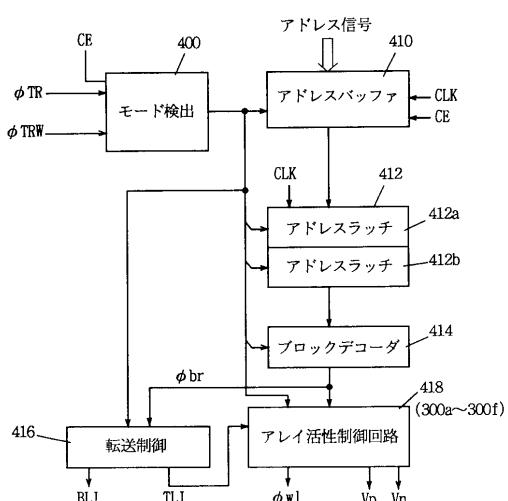

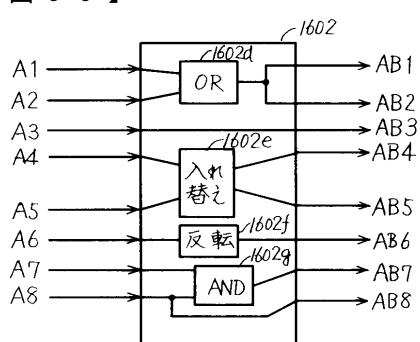

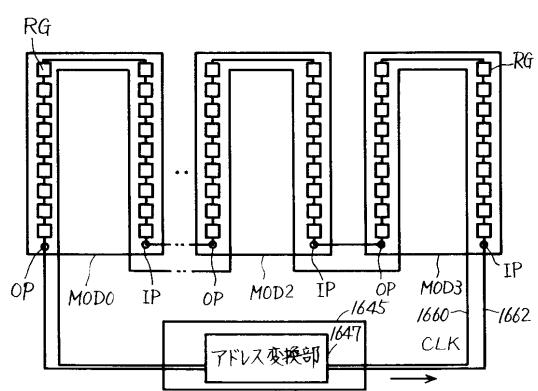

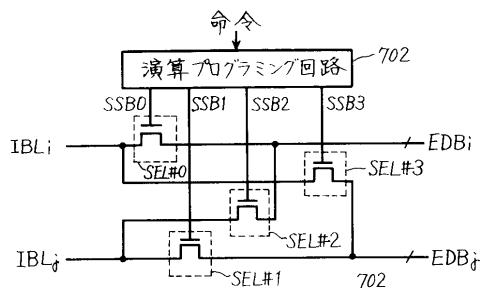

アレイ活性制御回路：

図6は、図1に示すアレイ活性制御回路4の内部構成を概略的に示すブロック図である。図4において、アレイ活性制御回路4は、アレイブロックM\_B\_a～M\_B\_dを互いに独立に駆動するために、アレイブロックM\_B\_a～M\_B\_dそれぞれに対応して設けられるアレイ活性化/プリチャージ制御回路を含む。すなわち、アレイ活性制御回路4は、チップイネーブル信号C\_Eに応答して活性され、ブロックアドレス信号B\_Aをデコードし、アドレス指定されたアレイブロックを指定する信号を出力するブロックデコーダ10と、ブロックデコーダ10からのブロック指定(活性化)信号に応答して活性化されて、活性化時、対応のアレイブロックのイコライズ回路を非活性状態とするイコライズ/プリチャージ制御回路12a～12dと、イコライズ/プリチャージ制御回路12a～12dによるイコライズ動作非活性化に応答して、対応のアレイブロックのワード線選択動作を活性化するワード線駆動制御回路14a～14dと、チップイネーブル信号C\_Eと書換指示信号<sub>i</sub>とに応答して所定のタイミングで内部書換信号<sub>i</sub>を出力する書換制御回路15と、ワード線駆動制御回路14a～14dからの出力信号と書換制御回路15からの内部書換指示信号<sub>i</sub>

40

50

$i$  とに応答して、対応のアレイブロックのセンスアンプを活性化するセンスアンプ活性化信号  $V_p$  および  $V_n$  を出力するセンスアンプ制御回路 16a ~ 16d と、ワード線駆動制御回路 14a ~ 14d からのワード線選択動作開始指示信号と書換制御回路 15 からの内部書換指示信号  $i$  とに応答して対応のアレイブロックの列選択動作を開始する列選択制御回路 18a ~ 18d を含む。

#### 【0139】

イコライズ／プリチャージ制御回路 12a ~ 12d は、ブロックデコーダ 10 からのブロック指定信号の活性化時、対応のアレイブロックに対し所定の時間期間イコライズ信号  $E_QA$  ~  $E_QD$  を非活性状態とする。ワード線駆動制御回路 14a ~ 14d の各々は、対応のイコライズ／プリチャージ制御回路 12a ~ 12d の出力信号の変化に応答して、ビット線分離信号  $BLIA$  ~  $BLID$  を所定期間活性状態のハイレベルとともに、後にその構成を説明する X デコーダを所定期間活性状態とする。

#### 【0140】

センスアンプ制御回路 16a ~ 16d は、内部書換指示信号  $i$  の非活性化時には、ワード線駆動制御回路 14a ~ 14d からのワード線選択動作開始指示信号に応答して所定期間所定のタイミングで対応のアレイブロックに対しセンスアンプ活性化信号  $VpA$ ,  $VnA$  ~  $VpD$ ,  $VnD$  を活性状態とする。内部書換指示信号  $i$  の活性化時には、センスアンプ制御回路 16a ~ 16d は、この内部書換指示信号  $i$  の活性化に応答して対応のセンスアンプ活性化信号  $VpA$ ,  $VnA$  ~  $VpD$ ,  $VnD$  を所定期間活性状態とする。

#### 【0141】

列選択制御回路 18a ~ 18d は活性化時、所定のタイミングでブロック選択信号  $TGA$  ~  $TGD$  を所定期間活性状態とともに、対応の Y デコーダを活性状態とする。内部書換指示信号  $i$  の活性化時には、列選択制御回路 18a ~ 18d は、この内部書換指示信号  $i$  に応答してブロック選択信号  $TGA$  ~  $TGD$  を活性化し、また対応の Y デコーダ  $YDA$  ~  $YDD$  からの列選択信号を活性状態とする。

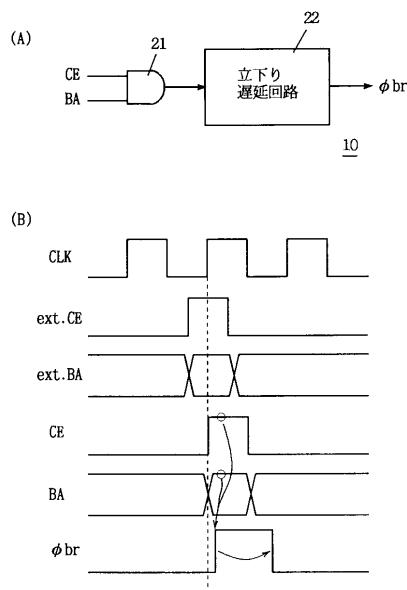

#### 【0142】

図 7 は、図 6 に示すブロックデコーダ 10 の構成および動作を示す図である。図 7 (A)において、ブロックデコーダ 10 は、制御バッファ 2 からの内部チップイネーブル信号  $C_E$  およびアドレスバッファ 3 からのブロックアドレス信号  $BA$  をデコードするデコード回路 21 と、デコード回路 21 からの活性化信号（ハイレベル信号）の立下がりを所定時間遅延する立下がり遅延回路 22 を含む。この立下がり遅延回路 22 から対応のアレイブロックを活性化するブロック活性化信号  $b_r$  が出力される。

#### 【0143】

デコード回路 21 は、たとえば AND 型回路で構成され、内部チップイネーブル信号  $C_E$  およびブロックアドレス信号  $BA$  (2 ビットのアドレス信号：アレイブロックが 4 つの場合) がすべてハイレベルのときに選択状態を示すハイレベルの信号を出力する。立下がり遅延回路 22 は、パルス幅を拡張する機能を備える回路であれば任意の回路構成を利用することができる。次に図 7 (B) を参照して、この図 7 (A) に示すブロックデコーダ 10 の動作について説明する。

#### 【0144】

外部のクロック信号  $CLK$  の立下がり時に外部チップイネーブル信号  $extCE$  がハイレベルとされ、外部から与えられるブロックアドレス信号  $ext.BA$  が確定状態とされる。この状態において、チップアクセスが指定され、内部チップイネーブル信号  $C_E$  がクロック信号  $CLK$  の立上がりに応答して所定期間ハイレベルとされ、また内部のブロックアドレス信号  $BA$  も所定期間確定状態とされる。デコーダ回路 21 は、この確定状態とされた内部チップイネーブル信号  $C_E$  および内部ブロックアドレス信号  $BA$  をデコードし、ブロックアドレス信号  $BA$  が指定するアレイブロックにハイレベルの信号を出力する。これにより、立下がり遅延回路 22 から出力されるブロック活性化信号  $b_r$  が、デコード回路 21 の出力信号の立上がりから所定期間ハイレベルの活性状態とされる。立下がり遅延回路 22 を用いてブロック活性化信号  $b_r$  のパルス幅を十分な広さとすることにより、

10

20

30

40

50

クロック信号 C L K のパルス幅が短く、内部のチップイネーブル信号 C E およびブロックアドレス信号 B A の確定期間が短い場合においても、アドレス指定されたアレイブロックを確実に活性状態とする信号を出力することができる。

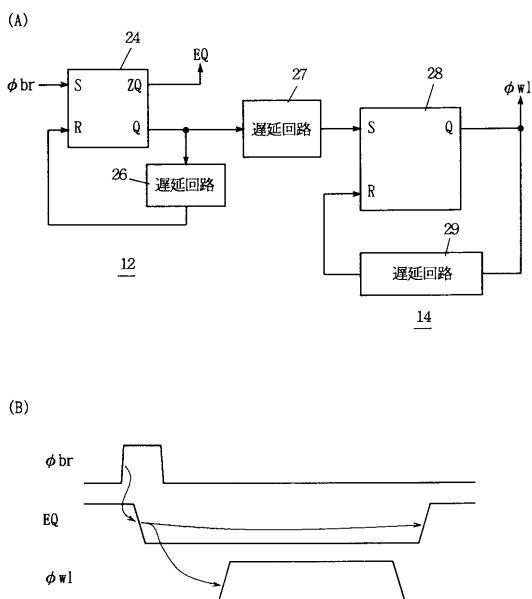

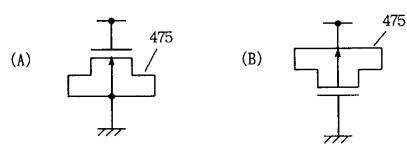

#### 【 0 1 4 5 】

図 8 ( A ) は、図 6 に示すイコライズ / プリチャージ制御回路 1 2 a ~ 1 2 d およびワード線駆動制御回路 1 4 a ~ 1 4 d の構成の一例を示す図である。図 8 ( A ) においては、1 つのアレイブロックに対するイコライズ / プリチャージ制御回路 1 2 およびワード線駆動制御回路 1 4 の構成を示す。図 8 ( A ) において、イコライズ / プリチャージ制御回路 1 2 は、ブロック活性化信号 b r の活性化に応答してセットされるリセット優先型セット / リセットフリップフロップ 2 4 を含む。このフリップフロップ 2 4 の補出力 Z Q からイコライズ E Q が出力される。フリップフロップ 2 4 の真出力 Q からの出力信号は、遅延回路 2 6 を介してリセット入力 R へフィードバックされる。遅延回路 2 6 の与える遅延時間によりイコライズ信号 E Q の非活性化期間が決定される。10

#### 【 0 1 4 6 】

ワード線駆動制御回路 1 4 は、イコライズ / プリチャージ制御回路 1 2 に含まれるフリップフロップ 2 4 の真出力 Q からの出力信号を所定時間遅延する遅延回路 2 7 と、この遅延回路 2 7 の出力信号の活性化 ( ハイレベル ) 時にセットされるリセット優先型フリップフロップ 2 8 を含む。フリップフロップ 2 8 から、ワード線選択動作活性化信号 w 1 が出力される。このフリップフロップ 2 8 の出力信号 w 1 は、また遅延回路 2 9 を介してフリップフロップ 2 8 のリセット入力 R へフィードバックされる。遅延回路 2 9 の有する遅延時間により、このワード線選択動作活性化信号 w 1 の活性化期間が決定される。次にこの図 8 ( A ) に示す回路の動作を、その動作波形図である図 8 ( B ) を参照して説明する。20

#### 【 0 1 4 7 】

ブロック活性化信号 b r の立上がりに応答してフリップフロップ 2 4 がセットされ、その補出力 Z Q からのイコライズ信号 E Q がローレベルとされる。フリップフロップ 2 4 の真出力 Q の出力信号は遅延回路 2 6 を介してフリップフロップ 2 4 のリセット入力 R へフィードバックされる。したがって、イコライズ E Q がローレベルの非活性状態とされてから所定時間経過後、このフリップフロップ 2 4 がリセットされ、イコライズ信号 E Q がハイレベルへ復帰する。30

#### 【 0 1 4 8 】

一方、ワード線駆動制御回路 1 4 においては、フリップフロップ 2 4 の真出力 Q の出力する信号が遅延回路 2 7 を介してフリップフロップ 2 8 のセット入力 S へ与えられる。したがって、このイコライズ信号 E Q がローレベルの非活性状態とされてから遅延回路 2 7 が与える遅延時間が経過した後、フリップフロップ 2 8 の真出力 Q からの信号 w 1 がハイレベルの活性状態とされ、ワード線選択動作が行なわれる。この信号 w 1 が活性状態とされてから遅延回路 2 9 が与える遅延時間が経過した後、このフリップフロップ 2 8 のリセット入力 R へ与えられる信号がハイレベルの活性状態とされ、フリップフロップ 2 8 がリセットされ、信号 w 1 がローレベルの非活性状態とされる。

#### 【 0 1 4 9 】

各アレイブロックにおいて、ワード線選択期間をそれぞれ所定期間とする構成を用いることにより、アレイブロックそれぞれ独立にアレイブロックの活性化 / プリチャージを行なうことができる。40

#### 【 0 1 5 0 】

なお、図 8 ( A ) に示す構成において、遅延回路 2 9 の出力信号が遅延回路 2 6 の入力部へ与えられてもよい。この場合には、遅延回路 2 6 の有する遅延時間を小さくすることができ、装置回路規模を低減することができる。また、確実にワード線選択動作が完了した後にイコライズ信号 E Q をハイレベルとしてイコライズ / プリチャージ回路を活性化することができる。

#### 【 0 1 5 1 】

10

20

30

40

50

なおこの信号  $w_1$  は、ビット線分離信号 B L I として利用されてもよい。

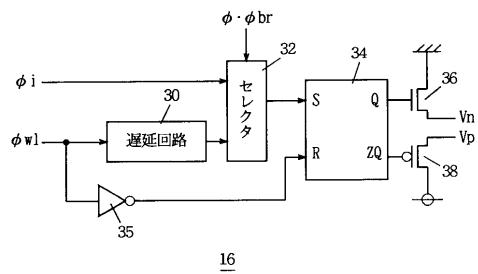

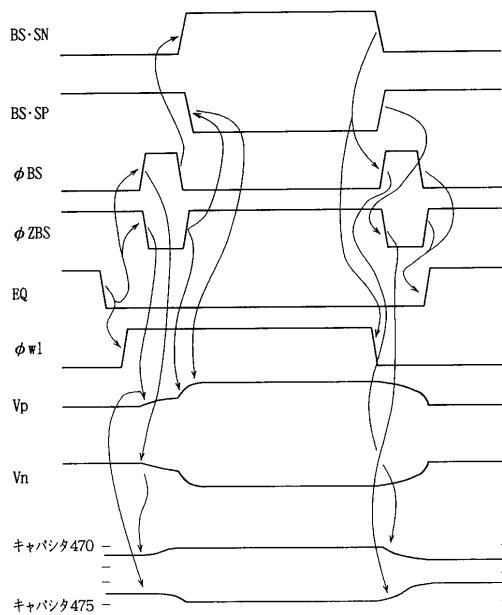

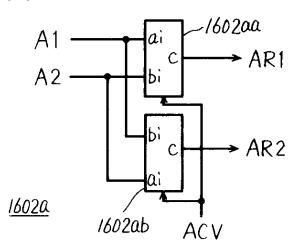

図 9 は、図 6 に示すセンスアンプ制御回路 16 の構成を概略的に示す図である。図 9においては、センスアンプ制御回路 16 a ~ 16 d それぞれは同一の構成を備えるため、1つのセンスアンプ制御回路 16 を代表的に示す。図 9において、センスアンプ制御回路 16 は、ワード線選択動作活性化信号  $w_1$  を所定時間遅延する遅延回路 30 と、書換指示信号  $b_r$  とブロック活性化信号  $b_r$  の論理積信号  $\cdot b_r$  に応答して、内部書換信号  $i$  と遅延回路 30 の出力信号の一方を選択するセレクタ 32 と、セレクタ 32 の出力信号の活性化時にセットされるリセット優先型フリップフロップ 34 を含む。フリップフロップ 34 のリセット入力 R へは、ワード線選択動作活性化信号  $w_1$  を受けるインバータ 35 の出力信号が与えられる。10

#### 【 0 1 5 2 】

センスアンプ制御回路 16 は、さらに、フリップフロップ 34 の真出力 Q の出力信号に応答して導通し、センスアンプ活性化信号  $V_n$  を接地電位レベルへと駆動するセンスアンプ活性化トランジスタ 36 と、フリップフロップ 34 の補出力 ZQ の出力信号に応答して導通し、センスアンプ活性化信号  $V_p$  を電源電圧または高電圧レベルのハイレベルへ駆動するセンスアンプ活性化用トランジスタ 38 を含む。

#### 【 0 1 5 3 】

セレクタ 32 は、書換指示信号  $b_r$  がハイレベルの活性状態にあり、かつアレイブロック活性化信号  $b_r$  がハイレベルの活性化のときに、内部書換信号  $i$  を選択する。すなわち、転送アレイブロックとして指定されたアレイブロックに対しては、センスアンプの活性化タイミングは内部書換信号  $i$  に従って決定される。信号  $\cdot b_r$  がローレベルの非活性化時には、セレクタ 32 は、遅延回路 30 の出力信号を選択する。フリップフロップ 34 は、セット入力 S へ与えられる信号がハイレベルとされると、その真出力 Q をハイレベル、補出力 ZQ をローレベルとする。フリップフロップ 34 は、リセット入力 R へ与えられる信号がハイレベルへ立上がるときにリセットされて、真出力 Q をローレベルに、補出力 ZQ をハイレベルとする。したがって、センスアンプ活性化信号  $V_n$  および  $V_p$  の活性化から非活性化への移行は、ワード線選択動作活性化信号  $w_1$  の非活性化への移行により決定される。20

#### 【 0 1 5 4 】

この図 9 に示す構成を利用することにより、転送アレイブロックにおいてのみセンスアンプの活性化タイミングを内部書換信号に従って決定することができる。30

#### 【 0 1 5 5 】

図 6 に示す列選択制御回路 18 a ~ 18 d も、この図 9 に示すセンスアンプ制御回路 16 と同様の構成を備える。フリップフロップ 34 の出力部に設けられたトランジスタ 36 および 38 が用いられないだけである。フリップフロップの出力信号（出力 Q および ZQ いずれでもよい）に従って列選択動作（セレクタ S T R の導通 / 非導通の制御）が行なわれる。

#### 【 0 1 5 6 】

図 6 に示す書換制御回路 15 は、チップイネーブル信号 C E および書換指示信号  $b_r$  がともにハイレベルの活性状態のとき、所定時間経過後に、所定の幅を有する内部書換信号  $i$  を出力する。この構成は、ワンショットパルス発生回路と遅延回路を用いることにより容易に実現できる。40

#### 【 0 1 5 7 】

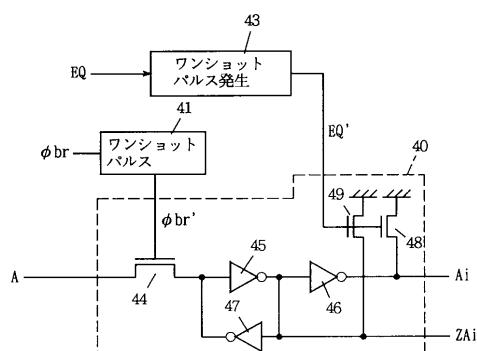

図 10 は、アレイブロックそれぞれに対応して配置されるアドレスラッチの構成の一例を示す図である。図 10においては、1つのアレイブロックに対応して配置されるアドレスラッチを示し、参照番号 40 で総称的にアドレスラッチを示す。

#### 【 0 1 5 8 】

図 10において、アドレスラッチ 40 は、アドレスバッファから与えられる内部アドレス信号 A（行および列アドレス信号 R A および C A 両者を含む）をワンショットパルス発生回路 41 からの取込指示信号  $b_r$  により取込み、かつワンショットパルス発生回路 450

3からのショットパルスに従って、その内部アドレス  $A_i$  をリセットする。ワンショットパルス発生回路 4 1 は、アレイブロック活性化信号  $b_r$  の立上がりに応答して所定パルス幅を有するアドレス取込指示信号  $b_r$  を発生する。ワンショットパルス発生回路 4 3 は、対応のアレイブロックのイコライズ信号  $E_Q$  の非活性化に従って所定期間ローレベルとされるパルス信号  $E_Q$  を出力する。

#### 【0159】

アドレスラッチ 4 0 は、アドレス取込指示信号  $b_r$  に応答して導通し、アドレスバッファから与えられるアドレス信号  $A$  を通過させる  $n$  チャネル MOS トランジスタでたとえば構成されるトランスファゲート 4 4 と、トランスファゲート 4 4 を介して与えられたアドレス信号を増幅する 2 段の継続接続されたインバータ 4 5 および 4 6 と、インバータ 4 5 の出力信号を受けて反転してインバータ 4 5 の入力部へ伝達するインバータ 4 7 を含む。インバータ 4 7 の駆動力はインバータ 4 5 のそれよりも小さくされる。インバータ 4 6 から内部アドレス信号  $A_i$  が出力され、インバータ 4 5 から内部アドレス信号  $Z_A_i$  が出力される。

#### 【0160】

アドレスラッチ 4 0 は、さらに、ワンショットパルス発生回路 4 3 からのパルス信号  $E_Q$  に応答して、内部アドレス信号  $A_i$  および  $Z_A_i$  をローレベルにリセットするリセットトランジスタ 4 8 および 4 9 を含む。次に、この図 10 に示すアドレスラッチ 4 0 の動作を、その動作波形図である図 11 を参照して説明する。

#### 【0161】

クロック信号  $C_LK$  の立上がり時に内部チップイネーブル信号  $C_E$  がハイレベルの活性状態とされ、そのときに与えられたアドレス信号  $A$  が確定状態とされる。このチップイネーブル信号  $C_E$  の立上がりに応答して、図 6 に示すロックデコーダ 1 0 から、アドレス指定されたアレイブロックに対して、ロック活性化信号  $b_r$  が出力される。このロック活性化信号  $b_r$  の活性化に応答して、ワンショットパルス発生回路 4 1 が、所定の時間幅（ロック活性化信号  $b_r$  のパルス幅よりも短いパルス幅）を有する信号  $b_r$  を出力する。この信号  $b_r$  のハイレベルへの移行に応答して、トランスファゲート 4 4 が導通し、そのときに与えられているアドレス信号  $A$  を通過させてインバータ 4 5 の入力部へ与える。一方、ワンショットパルス発生回路 4 3 は、また図 8 (A) に示すイコライズ / プリチャージ制御回路からのイコライズ信号  $E_Q$  に応答してパルス信号  $E_Q$  が所定期間ローレベルとし、リセット用トランジスタ 4 8 および 4 9 が非導通状態とされる。これにより、内部アドレス  $A_i$  および  $Z_A_i$  がそのときに与えられたアドレス信号  $A$  に従って変化し、インバータ 4 5 および 4 7 によりラッチされる。

#### 【0162】

トランスファゲート 4 4 は、信号  $b_r$  がローレベルとなると、非導通状態とされる。これにより、アレイブロックに対して、有効状態とされたアドレス  $A_i$  および  $Z_A_i$  (互いに相補なアドレス信号) が持続的に出力される。アドレスラッチ 4 0 が内部アドレス信号  $A_i$  および  $Z_A_i$  のラッチ中に、次の転送アドレスが与えられても、この場合には、ワンショットパルス発生回路 4 1 の出力する信号  $b_r$  は転送アレイブロックに対してのみハイレベルの活性状態とされるため、先にアドレス指定されたアレイブロックにおいては何ら影響を受けることなく内部アドレス信号  $A_i$  および  $Z_A_i$  が継続してラッチされる。

#### 【0163】

信号  $E_Q$  がローレベルに立下がってから所定時間が経過すると、この信号  $E_Q$  がハイレベルに立上がり、リセットトランジスタ 4 8 および 4 9 が導通し、内部アドレス信号  $A_i$  および  $Z_A_i$  がともにローレベルとされる。この信号  $E_Q$  がハイレベルとされてから所定期間経過後にイコライズ信号  $E_Q$  がハイレベルとなる。

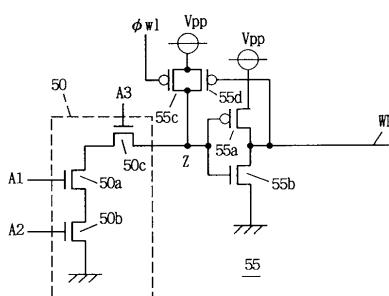

#### 【0164】

図 12 は、図 1 に示す X デコーダ X D の具体的構成を示す図である。図 12 において 1 本のワード線  $W_L$  に対して設けられる X デコーダ回路の構成を代表的に示す。図 12 におい

10

20

30

40

50

て、Xデコーダ回路は、内部アドレス信号をデコードし、対応のワード線を指定する行選択信号を生成するロウデコード回路50と、このロウデコード回路50の出力信号に従って対応のワード線WLを選択状態へと駆動するためのワードドライバ55を含む。ロウデコード回路60は、内部ノードZと接地ノードとの間に直列に接続され、それぞれが内部アドレス信号A1～A3をゲートに受けるnチャネルMOSトランジスタ50a, 50bおよび50cを含む。ロウデコード回路50は、NAND型デコード回路である。このロウデコード回路50の構成において、アドレス信号A3は、複数のワード線（たとえば4本）のワード線に対して設けられたロウデコード回路に対し共通に与えられてもよい。この4本のうちのワード線のうちの1本が残りのアドレス信号A1およびA2により選択される。

10

#### 【0165】

ワードドライバ55は、高電圧Vppを受けるノードと接地ノードの間に接続され、そのゲートが内部ノードZに接続されるpチャネルMOSトランジスタ55aおよびnチャネルMOSトランジスタ55bを含む。MOSトランジスタ55aおよび55bはインバータを構成し、内部ノードZ上の電位がローレベルのときに、対応のワード線WL Aへ高電圧Vppを伝達する。内部ノードZ上の電位がハイレベルのときには、対応のワード線WLは非選択状態のローレベルとされる。

#### 【0166】

ワードドライバ55は、さらに、ワード線選択動作活性化信号w1の非活性化時に導通し、内部ノードZへ高電圧Vppを伝達するpチャネルMOSトランジスタ55cと、ワード線WL上の電位がローレベルのとき導通し、内部ノードZへ高電圧Vppを伝達するpチャネルMOSトランジスタ55dを含む。ワード線選択動作が行なわれるときには、信号w1はハイレベルであり、MOSトランジスタ55cは非導通状態である。この場合には、ロウデコード回路50の出力信号に従って内部ノードZの電位が決定されて、この内部ノードZ上の電位に従ってワード線WLの電位が決定される。信号w1がローレベルとされると、ワード線選択動作が完了し、MOSトランジスタ55cが導通し、内部ノードZが高電圧Vppレベルに充電される。このときには、アドレス信号A1～A3はすべてローレベルにリセットされており（図10のアドレスラッチ参照）、ロウデコード回路50は出力ハイインピーダンス状態とされる。内部ノードZを高電圧Vppレベルに保持することにより、MOSトランジスタ55aを確実に非導通状態とし、非選択状態のワード線WLをMOSトランジスタ55bを介して接地電位レベルに保持する。

20

#### 【0167】

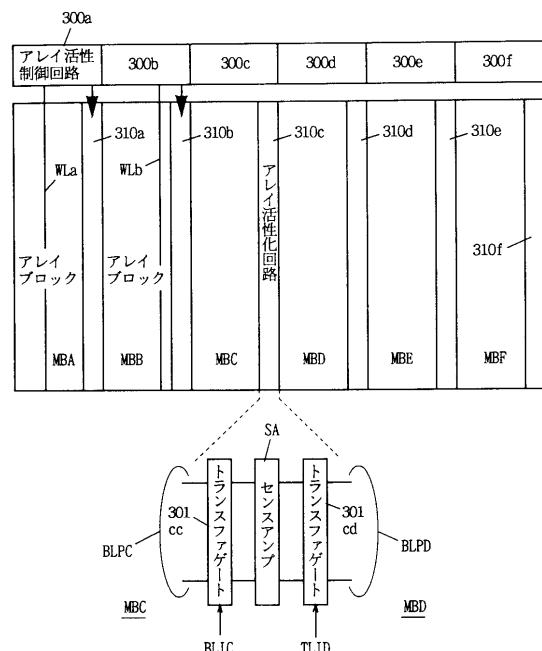

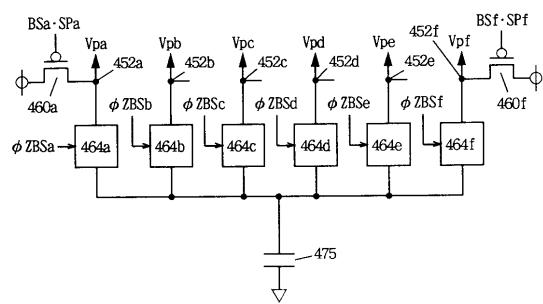

##### [アレイの変更例]

図13は、この発明の第1の実施の形態の変更例の構成を示す図である。図13において、半導体記憶装置のアレイおよびデータ伝達のためのI/Oバスを概略的に示す。図13に示す構成において、アレイブロックMBa～MBdそれぞれに対応して複数ビット（図13において4ビット）のデータを伝達するためのローカルI/OバスLI/Oa～LID/I/Odが配置される。これらの4ビットローカルLI/Oa～LID/I/Odに共通に、4ビットのグローバルI/OバスG I/Oが配置される。ローカルI/OバスLI/Oa～LID/I/OdとグローバルI/OバスG I/Oの交差部には、それぞれブロック選択ゲートBSELa～BSELdが配置される。これらのブロック選択ゲートBSELa～BSELdの構成は、先の図2において示すものと同じである。

30

#### 【0168】

グローバルI/OバスG I/Oに対し、1ビットのデータの入出力を行なうためのリード/ライトドライバRWDRが配置される。このリード/ライトドライバRWDRは、内部リード/ライトバスRWB Sを介して入出力バッファBFに結合される。

40

#### 【0169】

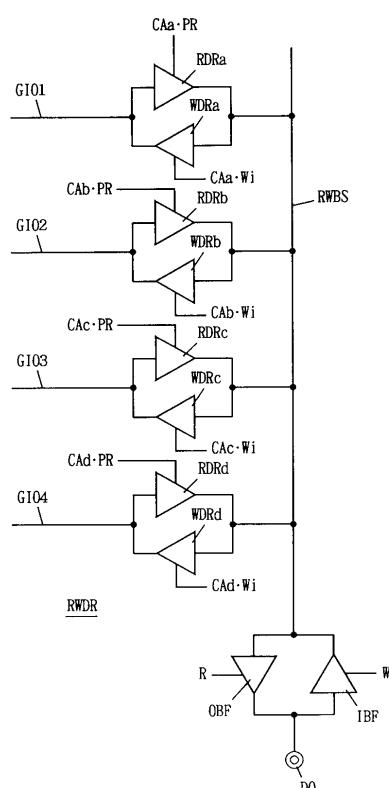

図14は、この図13に示すリード/ライトドライバRWDRの構成を概略的に示す図である。図14において、リード/ライトドライバRWDRは、グローバルI/OバスGI/O1に対して設けられるリードドライバRDRaおよびライトドライバWDRaと、グロ

50

ーバル I / O バス G I O 2 に対して設けられるリードドライバ R D R b およびライトドライバ W D R b と、グローバル I / O バス G I O 3 に対して設けられるリードドライバ R D R c およびライトドライバ W D R c と、グローバル I / O バス G I O 4 に対して設けられるリードドライバ R D R d およびライトドライバ W D R d を含む。リードドライバ R D R a は、アレイブロック M B a を指定するブロックアドレス信号 B A a とプリアンプイネーブル信号（内部読出指示信号）P R がともに活性状態のときに活性状態とされてグローバル I / O バス G I O 1 上のデータを增幅して内部リード / ライトバス R W B S 上に伝達する。ライトドライバ W D R a は、ブロックアドレス信号 B A a と内部書込指示信号 W i がともに活性状態のときに活性化され、リード / ライトバス R W B S 上のデータを増幅してグローバル I / O バス G I O 1 上に伝達する。

10

#### 【 0 1 7 0 】

リードドライバ R D R b は、アレイブロック M B b を指定するブロックアドレス信号 B A b とプリアンプイネーブル信号 P R がともに活性状態のときに活性状態とされてグローバル I / O バス G I O 2 上のデータを増幅して内部リード / ライトバス R W B S 上に伝達する。ライトドライバ W D R b は信号 W i および B 4 b の活性化時に活性化される。

#### 【 0 1 7 1 】

リードドライバ R D R c は、アレイブロック M B c を指定するブロックアドレス信号 B A c とプリアンプイネーブル信号 P R がともに活性状態のときに活性化され、グローバル I / O バス G I O 3 上のデータを増幅して内部リード / ライトバス R W B S 上に伝達する。ライトドライバ W D R c は、ブロックアドレス信号 B A c と内部書込指示信号 W a がともに活性状態のときに活性化され、内部リード / ライトバス R W B S 上のデータを増幅してグローバル I / O バス G I O 3 上に伝達する。リードドライバ R D R d は、アレイブロック M B d を指定するブロックアドレス信号 B A d とプリアンプイネーブル信号 P R の活性化時に活性化され、グローバル I / O バス G I O 4 上のデータを増幅して内部リード / ライトバス R W B S 上に伝達する。ライトドライバ W D R d は、ブロックアドレス信号 B A d と内部書込指示信号 W i がともに活性状態のときに活性化され、内部リード / ライトバス R W B S 上のデータを増幅してグローバル I / O バス G I O 4 上に伝達する。

20

#### 【 0 1 7 2 】

入出力バッファは、読出指示信号 R に応答して活性化されて内部リード / ライトバス R W B S 上のデータを増幅してデータ出力端子 D Q へ伝達する出力バッファ O B F と、書込指示信号 W の活性化時に活性化され、データ入出力端子 D Q 上のデータを増幅して内部リード / ライトバス R W B S 上に伝達する入力バッファ I B F を含む。

30

#### 【 0 1 7 3 】

この図 13 および図 14 に示す構成によればリード / ライトドライバ R W D R に含まれるライトドライバ W D R a ~ W D R d をデータ転送時用いない場合には、図 5 に示す動作波形図に従って、4 ビットのメモリセルデータを 1 つのアレイブロックから他のアレイブロックへ伝達することができる。データ転送時にライトドライバを用いる場合、転送元のアレイブロックにおいて列選択信号を非活性状態とすることにより、元のデータの書換を伴なうことなく、4 ビットのうちの 1 ビットのメモリセルデータを転送先アレイブロックへ転送することができる。この 4 ビットのうちの 1 ビットの選択は、たとえば最下位 2 ビットの列アドレスをデコードすることにより生成される。1 つのアレイブロックにおいて、4 つのビット線対が同時に選択状態とされるため、この同時に選択状態とされる 4 つのビット線対のうちの 1 対を選択する。この場合、図 4 に示す動作波形に従ってデータ転送が行なわれる。列選択信号 C S A および C S B が同時に選択状態となるのを避けることによりデータ読出と並行してデータ転送を行なうことができる。

40

#### 【 0 1 7 4 】

##### [ アレイの変更例 2 ]

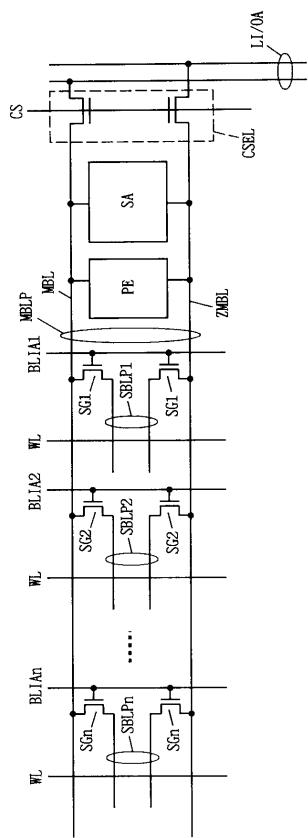

図 15 は、この発明の第 1 の実施の形態である半導体記憶装置の第 2 の変更例を示す図である。図 15 において、1 つのアレイブロックの 1 列のメモリセルに関連する部分の構成のみを示す。図 15 に示す構成においては、ビット線がメインビット線とサブビット線の

50

階層構造とされる。すなわち、メインビット線 MBL および ZMBL からなるメインビット線対 MBLP に対し、複数のサブビット線対 SBLP<sub>1</sub> ~ SBLP<sub>n</sub> が配置される。サブビット線対 SBLP<sub>1</sub> が、ビット線分離信号 BLIA<sub>1</sub> に応答して導通する選択ゲート SG<sub>1</sub> を介してメインビット線対 MBLP に接続される。サブビット線対 SBLP<sub>2</sub> が、ビット線分離信号 BLIA<sub>2</sub> を通して導通する選択ゲート SG<sub>2</sub> を介してメインビット線対 MBLP に接続される。サブビット線対 SBLP<sub>n</sub> は、ビット線分離信号 BLIA<sub>n</sub> に応答して導通する選択ゲート SG<sub>n</sub> を介してメインビット線対 MBLP に接続される。メインビット線対 MBLP には、センスアンプ SA およびプリチャージ / イコライズ回路 PE が配置される。このメインビット線対 MBLP が列選択ゲート CSEL を介してローカル I/O バス LIOA に接続される。サブビット線対 SBLP<sub>1</sub> ~ SBLP<sub>n</sub> それぞれとワード線との交差部にメモリセル（図示せず）が配置される。メインビット線対 MBLP にはメモリセルは直接接続されない。したがって、このメモリセルの有する寄生容量はメインビット線対 MBLP には接続されず、メインビット線対 MBLP の寄生容量を低減することができる。10

#### 【0175】

動作時においては、選択ワード線を含むサブビット線対 SBLPi ( i = 1 ~ n のいずれか ) のみがメインビット線対 MBLP に接続される。この図 15 に示すような階層ビット線の構成を備える半導体記憶装置であっても、上述の実施の形態と同様にして、1つのアレイブロックから別のアレイブロックへデータ転送を行なうことができる。先の実施の形態におけるビット線分離信号 BLIA を、サブビット線対とメインビット線対とを接続する信号として利用すればよい。他の動作は全く同様にしてデータ転送を行なうことができる。20

#### 【0176】

以上のように、この発明の第 1 の実施の形態に従えば、アレイブロックをそれぞれ個々独立に駆動可能とし、かつクロック信号に同期して外部制御信号およびアドレス信号を取込むように構成しているため、複雑なタイミング制御を伴うことなく高速でアレイブロック間のデータ転送を行なうことができる。

#### 【0177】

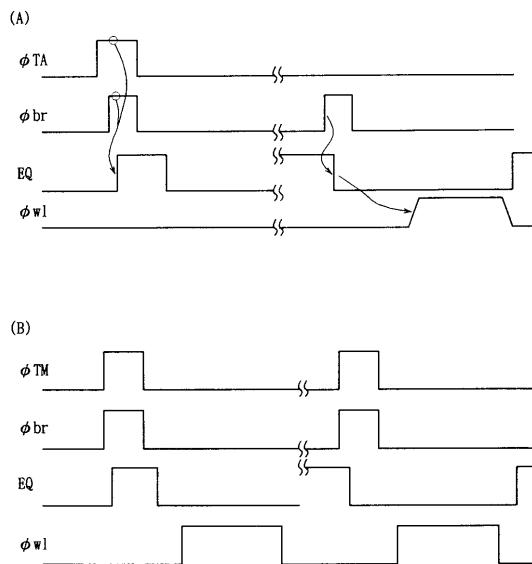

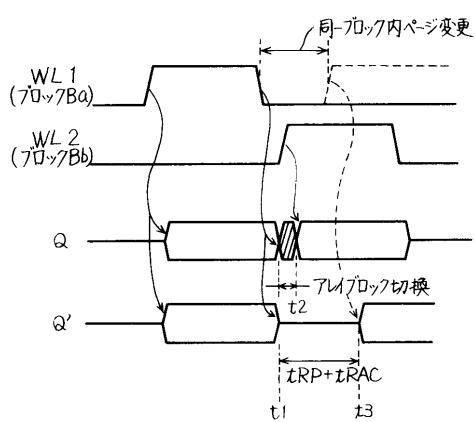

##### [実施の形態 2]

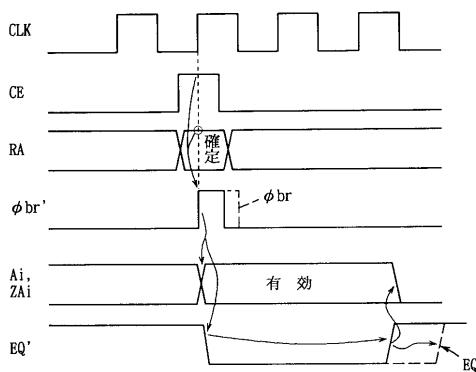

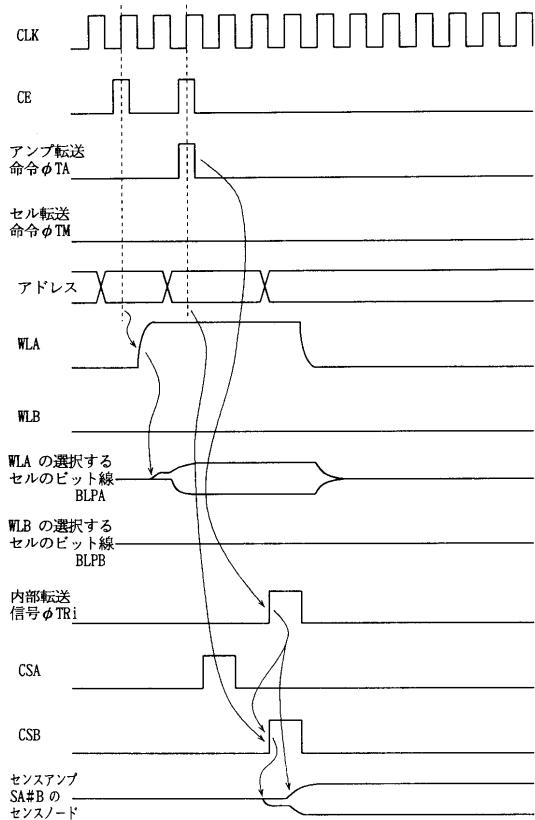

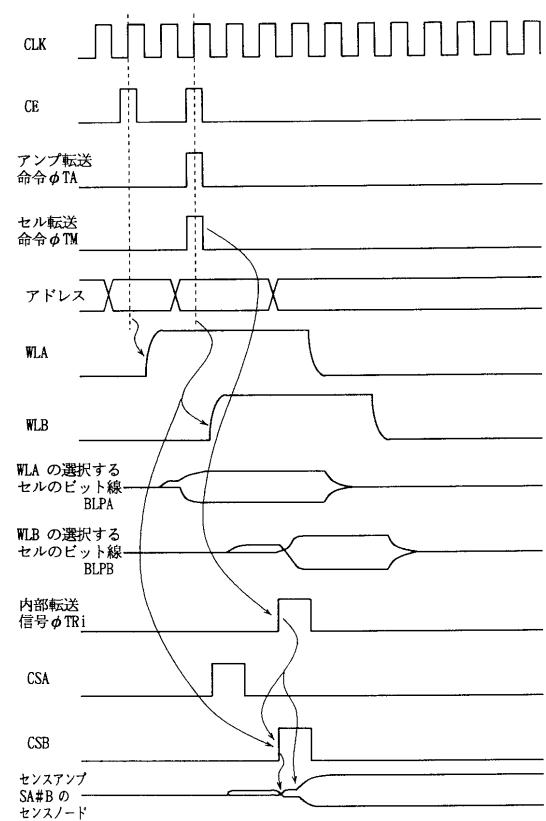

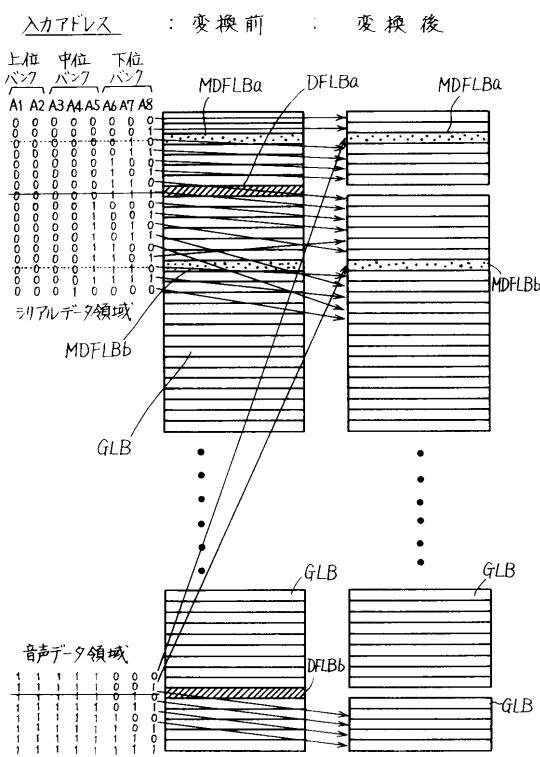

図 16 は、この発明の第 2 の実施の形態である半導体記憶装置の動作を示す信号波形図である。まずこの発明に従う第 2 の実施の形態の半導体記憶装置の動作について説明し、次いで、この動作を実現するための構成について説明する。30

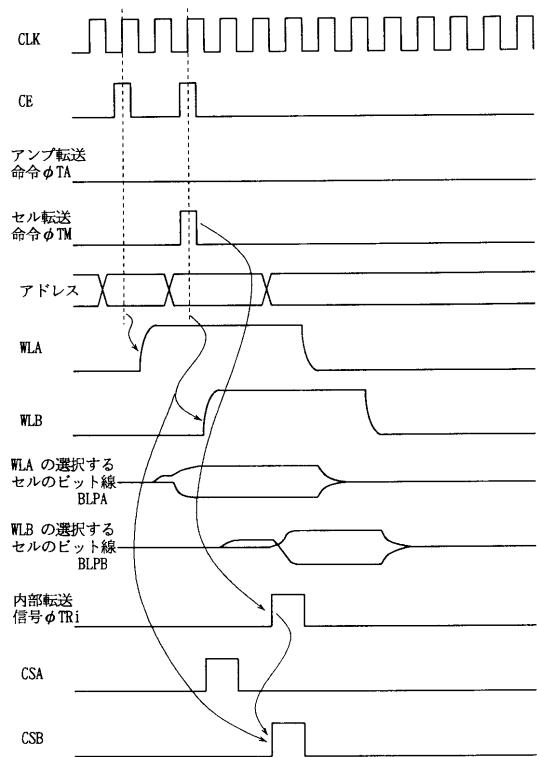

#### 【0178】

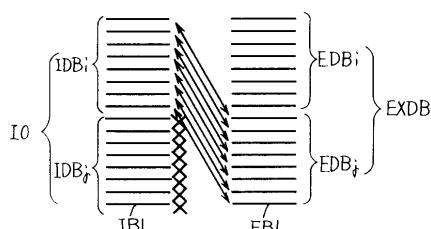

この発明の第 2 の実施の形態において、2つの命令、すなわちアンプ転送命令 TA およびセル転送命令 TM が用いられる。アンプ転送命令 TA は、1つのアレイブロックのメモリセルのデータを、別のアレイブロックのセンスアンプに転送し、そこでラッチさせる命令である。セル転送命令 TM は、1つのアレイブロックのメモリセルのデータを別のアレイブロックのメモリセルへ転送しそこに書込む命令である。アンプ転送命令 TA を用いた場合には、転送先のアレイブロックのメモリセルへのデータ書き込みが行なわれず、センスアンプによるラッチのみが行なわれる。これにより、センスアンプを常時活性化することによりセンスアンプをキャッシュとして利用することができ、また1つのアレイブロックのメモリセルデータを別のアレイブロックのセンスアンプに退避させておくことができる。あるメモリセルのデータを外部で加工し、その加工したデータを元のメモリセルに書込むとともに、加工前のデータを別のアレイブロックのセンスアンプに保持しておく。必要なときに、加工前のデータを取出すことができ、たとえば演算処理において、同一の係数データを用いて連続して加算または乗算などの演算を行なうことができる。40

#### 【0179】

図 16において、クロック信号 CLK の立上がりにチップイネーブル信号 CE が活性状態のハイレベルとされる。この状態においては、アンプ転送命令 TA およびセル転送命令 TM はともに非活性状態のローレベルである。このときには通常のアクセス動作が行な50

われ、このクロック信号 C L K の立上がり時に与えられたアドレス信号が取込まれ、アドレス指定されたアレイロックにおいて行および列の選択動作が行なわれる。すなわちアレイロック (M B A とする) において、アドレス指定されたワード線 W L A が選択され、この選択ワード線 W L A の電位が上昇する。これに応答して、選択ワード線 W L A に接続するメモリセルデータが各対応のビット線対 B L P A に伝達され、ビット線対 B L P A の電位が変化する。次いで、適当な間隔をもいて、チップイネーブル信号 C E が再びクロック信号 C L K の立上がり時に活性状態のハイレベルとされる。このとき、併せてアンプ転送命令 T A が活性状態のハイレベルとされる。アンプ転送命令 T A の活性化においては、このときに取込まれたアドレス信号の行アドレスを指定する部分は無視され、アレイロックにおけるワード線選択は行なわれず、非選択状態を維持する。ブロックアドレス信号と列アドレス信号のみが利用される。10

#### 【0180】

一方、アレイロック M B A においては、通常動作時と同様にして、列選択信号が列アドレス信号のデコード結果に従って活性状態のハイレベルとされ、対応のメモリセルのデータがグローバル I / O 線上に伝達される。この後、アンプ転送命令 T A の活性化に応答して所定のタイミングで（列選択信号 C S A の活性化の後）内部転送信号 T R i がハイレベルの活性状態とされる。この内部転送信号 T R i に応答して、転送先のアレイロック (M B B とする) において Y デコーダが活性化され、列選択信号 C S B がハイレベルとされ、先にグローバル I / O 線 G I / O 上に読み出されたアレイロック M B A からのデータがセンスアンプ S A B のセンスノードに伝達され、このセンスノードの電位が変化する。このとき、まだセンスアンプ S A B は活性化されていない。これにより、容易にセンスアンプ S A B のセンスノード電位がグローバル I / O 線上の電位に従って変化する。次いで内部転送信号 T R i が活性化されてから所定の期間が経過した後、その転送先アレイロック M B B のセンスアンプ S A B の活性化が行なわれる。センスノードに現われた電位差（転送データ）の増幅およびラッチが行なわれる。上述の一連の動作により、アレイロック M A A のメモリセルデータが別のアレイロック M A B のセンスアンプ S A B のセンスノードにラッチされる。20

#### 【0181】

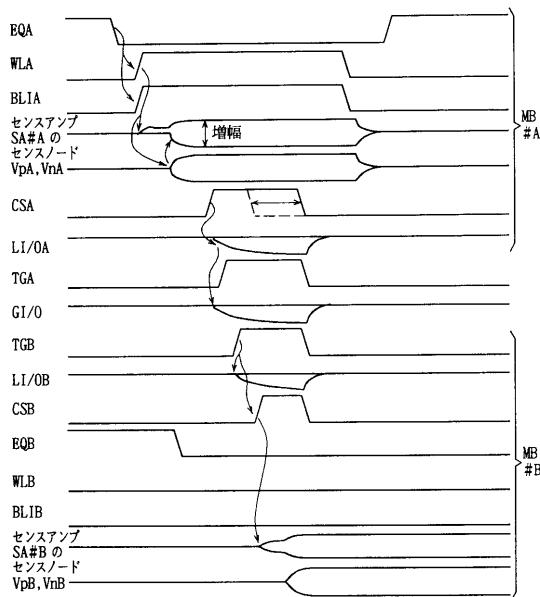

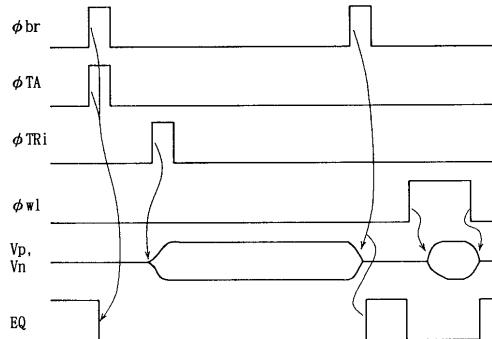

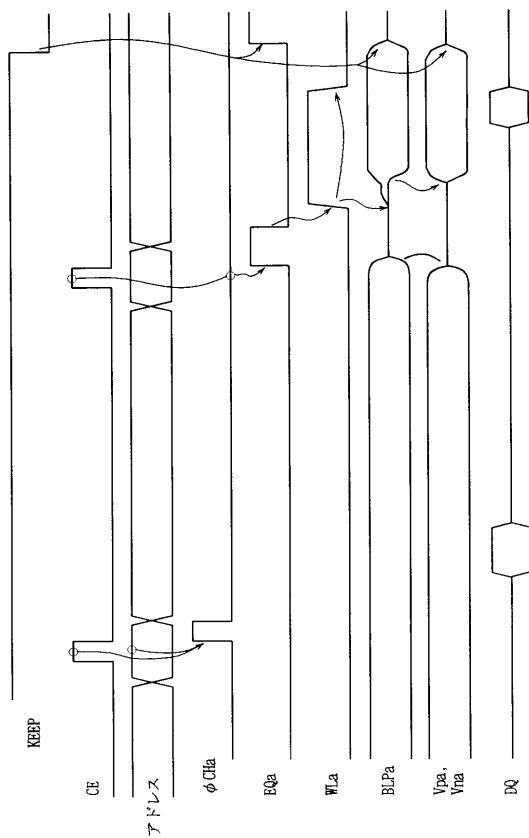

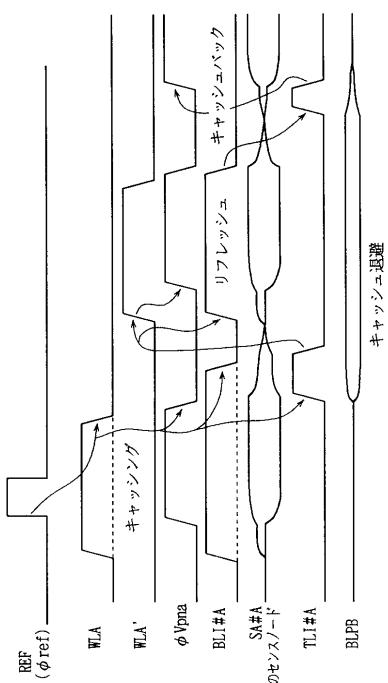

図 17 は、アンプ転送動作時における内部信号を示す波形図である。以下、図 17 を参照してアレイの内部動作についてより詳細に説明する。30

#### 【0182】

まず図 16 に示すように、最初にチップイネーブル信号 C E が活性状態とされると、アレイロック M B A において、メモリセルの選択動作が実行される。すなわちイコライズ信号 E Q A が非活性状態のローレベルとされ、次いでワード線 W L A が選択されてその電位が上昇する。このときまたビット線分離信号 B L I A もハイレベルとされ、選択メモリセルのデータがセンスアンプ S A A のセンスノードへ伝達される。次いで、そのセンスアンプ S A A のセンスノードの電位が十分に拡大されると、センスアンプ活性化信号 V p A , V n A が活性状態とされ、センスアンプ S A A のセンスノードの電位が差動的に増幅される。その後、Y デコーダからの列選択信号 C S A がハイレベルとされ、センスアンプ S A A のセンスノードの電位がローカル I / O バス L I / O A 上に伝達される。次いでブロック選択ゲート B S E L A がブロック選択信号 T G A に従って導通し、このローカル I / O バス L I / O A 上の電位がグローバル I / O バス G I / O 上に伝達される。40

#### 【0183】

アレイロック M B B においては、このアレイロック M B B のメモリセル選択動作およびデータの読み出動作と並行して、イコライズ信号 E Q B の非活性化が行なわれる。このとき、アンプ転送命令 T A により、ワード線選択が行なわれず、またビット線分離信号 B L I B も非活性状態のローレベルを維持する。アンプ転送命令 T A が与えられてから所定期間が経過すると内部転送信号 T R i に応答して、列選択信号 C S B およびブロック選択信号 T G B が所定期間ハイレベルの活性状態とされ、グローバル I / O バス上に伝達されたデータがセンスアンプ S A B のセンスノードへ伝達され、センスアンプ S A 50

B のセンスノードの電位が変化する。このとき、ビット線分離信号 B L I B はローレベルの非活性状態を維持しており、センスアンプ S A B のセンスノードの寄生容量は小さく、容易にこのセンスアンプ S A B のセンスノードの電位はグローバル I / O バス上の電位に従って変化する。センスアンプ S A B のセンスノード電位が変化し、この電位差が十分拡大されると、センスアンプ活性化信号 V p B および V n B が活性状態とされ、このセンスアンプ S A B のセンスノードの電位が活性化されたセンスアンプ S A B により増幅されてラッチされる。以後、この状態を維持する。

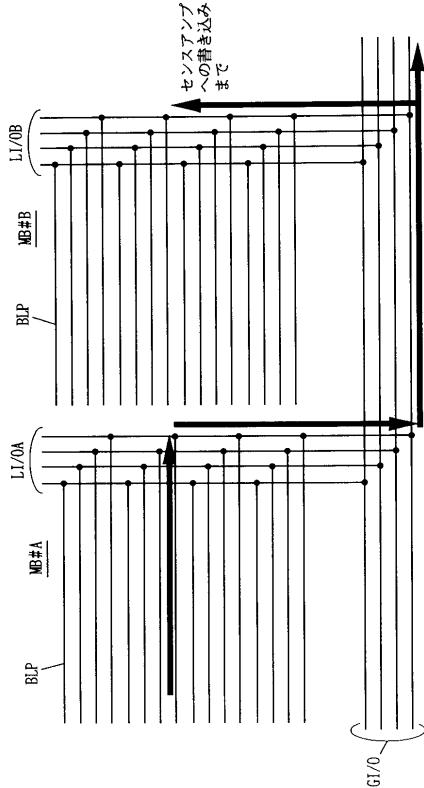

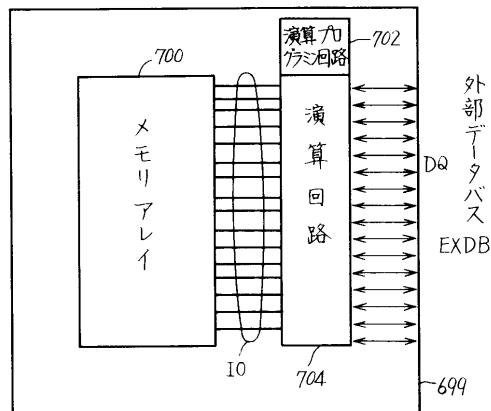

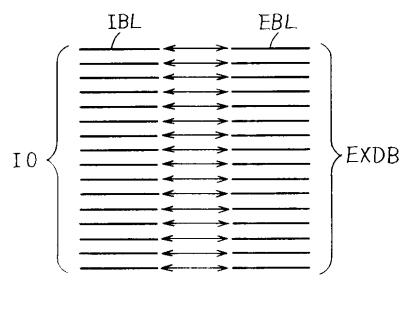

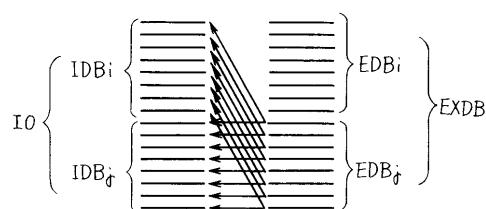

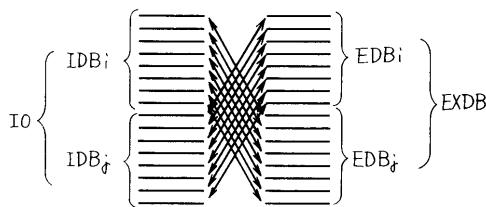

#### 【 0 1 8 4 】

図 18 は、このアンプ転送動作時におけるメモリセルデータの転送経路を模式的に示す図である。この図 18 に示す半導体記憶装置の構成においては、ローカル I / O バス L I / O A および L I / O B およびグローバル I / O バス G I / O は、すべて 4 ビットの幅を備える構成が一例として示される。アレイブロック M B A において同時に選択された 4 ビットのメモリセルデータがグローバル I / O バス G I / O を介して転送されて外部に読出され（1 ビットのみが読出されてもよく、また 4 ビットデータが読出されてもよい）、これと同時に、アレイブロック M B B のローカル I / O バス L I / O B を介してこのアレイブロック M B B のセンスアンプへ転送されてここでラッチされる。なおこの図 18 に示す構成においては、先の図 14 に示す構成と同様、アレイブロック M B B のセンスアンプへは、1 ビットのデータのみが転送されてもよい。

#### 【 0 1 8 5 】

図 19 は、セル転送時における動作を示す信号波形図である。セル転送命令 T M の活性化時においては、転送先アレイブロックにおいて、ワード線の選択が行なわれる。このときには、クロック信号 C L K の立上がり時に活性状態とされたチップイネーブル信号 C E と同期して与えられたアドレス信号は行アドレス信号、列アドレス信号、およびブロックアドレス信号すべてが利用される。この場合、すでに、先に与えられたチップイネーブル信号 C E とそれと一緒に与えられたアドレス信号に従ってアレイブロック M B A においては、先のアンプ転送動作時と同様にワード線選択およびメモリセルの選択動作が実行される。

#### 【 0 1 8 6 】

セル転送命令 T M の活性化時においては、まず転送アレイブロック M B B において、ワード線選択が行なわれ、選択ワード線 W L B の電位が立上がる。このとき、また後に説明するが、ビット線分離信号 B L I B もハイレベルの活性状態とされ、この選択ワード線 W L B に接続されるメモリセルのデータがセンスアンプにより増幅される。アレイブロック M B A において、列選択信号 C S A がハイレベルに立上がり、選択メモリセルデータがグローバル I / O バス G I / O へ転送された後、アレイブロック M B B においては、内部転送信号 T R i の活性化に応答して、列選択動作が行なわれ、選択された列に対する列選択信号 C S B がハイレベルとなり、グローバル I / O バス G I / O がこのアレイブロック M B B のセンスアンプ S A B のセンスノードに接続される。センスアンプ S A

B はまだ活性状態とされていないため、アレイブロック M B B の選択メモリセルデータが伝達されても、センスアンプ S A B のセンスノードの電位（ビット線対 B L P B の電位）は、容易にこのグローバル I / O バス G I / O 上の電位に従って変化する。センスアンプ S A B のセンスノードの電位が十分変化した後、センスアンプ活性化信号（図 19 には示さず）が活性状態とされ、センスアンプ S A B がセンス動作を行ない、このグローバル I / O バス G I / O から伝達されたメモリセルデータを検知し増幅し、選択メモリセルへ書込む。これら一連の動作により、アレイブロック M B A の選択メモリセルデータがアレイブロック M B B のメモリセルへ書込まれる。

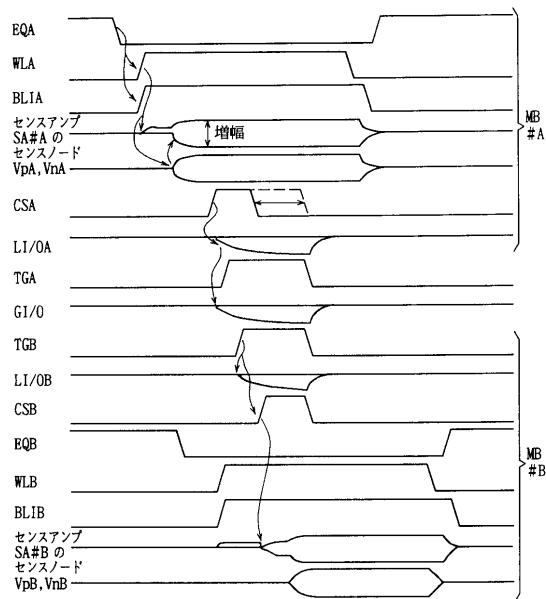

#### 【 0 1 8 7 】

図 20 は、セル転送動作時における内部信号波形を示す図である。アレイブロック M B A においては、イコライズ信号 E Q A が立上がってから、選択ワード線 W L A およびビット線分離信号 B L I A がハイレベルに立上がり、この選択ワード線 W L A に接続されるメモリセルデータがセンスアンプ S A A のセンスノードへ伝達される。次いで、所定のタ

10

20

30

40

50

イミングでセンスアンプ活性化信号  $V_{pA}$  および  $V_{nA}$  が活性状態とされ、次いで、列選択信号  $C_{SA}$  がハイレベルとされ、このセンスアンプ  $SA_A$  のセンスノードの電位がローカル  $I/O$  バス  $L_I/O_A$  へ伝達される。この後、ブロック選択信号  $TGA$  がハイレベルとされ、このローカル  $I/O$  バス  $L_I/O_A$  上のデータがグローバル  $I/O$  バス  $G_I/O$  上に伝達される。

#### 【0188】

一方、このアレイブロック  $MB_A$  でのメモリセルデータの検知増幅およびグローバル  $I/O$  バス  $G_I/O$  への伝達と並行して、アレイブロック  $MB_B$  において同様にメモリセルの選択動作が行なわれる。すなわち、イコライズ信号  $EQB$  がローレベルとされた後、ワード線  $WLB$  およびビット線分離信号  $BLIB$  がハイレベルに立上がり、選択メモリセルのデータがセンスアンプ  $SA_B$  のセンスノードへ伝達される。この後、内部転送信号の活性化に従ってブロック選択信号  $TGB$  および列選択信号  $C_{SB}$  がハイレベルとされ、グローバル  $I/O$  バス  $G_I/O$  上のデータがローカル  $I/O$  バス  $L_I/O_B$  を介してセンスアンプ  $SA_B$  のセンスノードへ伝達される。このときまだセンスアンプ  $SA_B$  は活性化されていないため、センスアンプ  $SA_B$  のセンスノードは、グローバル  $I/O$  バス  $G_I/O$  から伝達されたデータに応じて変化する。この後、センスアンプ活性化信号  $V_{pB}$  および  $V_{nB}$  が活性化され、選択メモリセルのデータがこのアレイブロック  $MB_B$  の選択メモリセルへ書き込まれる。次いで選択ワード線  $WLB$  の電位が立上がり、イコライズ信号  $EQB$  がハイレベルとされ、ビット線対の電位およびセンスアンプ  $SA_B$  のセンスノードのイコライズが行なわれた後、ビット線分離信号  $BLIB$  がローレベルとされる。

10

#### 【0189】

なお、図20において、列選択信号  $C_{SA}$  は、アレイブロック  $MB_B$  の列選択信号  $C_{SB}$  と重なり合わないタイミングで活性化されているが、これは図20において破線で示すように、互いに重なり合うタイミングで活性状態を維持するように構成されてもよい。

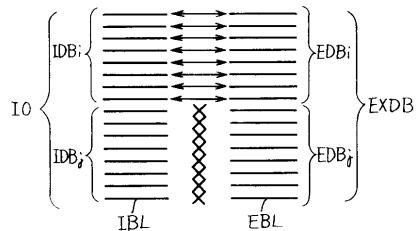

#### 【0190】

上述の一連の動作を行なうことにより、図21に示すように、アレイブロック  $MB_A$  において選択されたメモリセルデータがローカル  $I/O$  バス  $L_I/O_A$ 、グローバル  $I/O$  バス  $G_I/O$ 、およびローカル  $I/O$  バス  $L_I/O_B$  を介してアレイブロック  $MB_B$  のメモリセルへ伝達されてそこに書き込まれる。このときまたアレイブロック  $MB_A$  の選択メモリセルのデータが外部に読み出される。なお、図21においては、4ビットのメモリセルが1つのアレイブロックにおいて同時に選択される構成が一例として示されている。この場合、4ビットのメモリセルデータがアレイブロック  $MB_A$  からアレイブロック  $MB_B$  へ伝達されてもよい。

30

#### 【0191】

図22は、この発明の第2の実施の形態の別の動作波形を示す図である。この図22においては、アンプ転送命令  $TA$  およびセル転送命令  $TM$  両者が活性状態とされる。この状態においては、アレイブロック  $MB_A$  において選択されたメモリセルのデータがアレイブロック  $MB_B$  のメモリセルへ書き込まれるとともに、センスアンプで持続的にラッチされる。すなわち先のアンプ転送動作およびセル転送動作両者が組合せて実行される。

#### 【0192】

40

#### [センス保持データ書換動作]

図23は、センス転送動作により保持されたデータを書き換える際の動作を示す信号波形図である。図23において、アレイブロック  $MB_B$  においては、センスアンプが、センス転送動作による転送データを保持している。この状態において、再びアレイブロック  $MB_A$  または別のアレイブロックからアレイブロック  $MB_B$  の同一のアドレス位置へデータが転送される。この場合、アレイブロック  $MB_A$  においては、先の動作と同様にして、ワード線  $WLA$  の選択およびビット線分離信号  $BLIA$  の活性化が行なわれ、次いでセンスアンプ  $SA_A$  による検知増幅が行なわれて、この検知増幅されたデータがローカル  $I/O$  バス  $L_I/O_A$  およびグローバル  $I/O$  バス  $G_I/O$  へ伝達される。センス転送命令が活性状態とされかつそのときの転送アドレスが先に与えられた転送アドレスと同じ場

50

合、アレイブロック M B Bにおいては、センスアンプ活性化信号 V p B および V n B が非活性状態とされかつイコライズ信号 E Q B が活性状態とされ、センスアンプ S A B のセンスノードのイコライズが行なわれる。次いで、イコライズ信号 E Q B を非活性状態とした後、列選択信号 C S B およびブロック選択信号 T G B がハイレベルとされ、グローバル I / O バス G I / O 上のデータがセンスアンプ S A B のセンスノードへ伝達される。この後、センスアンプ活性化信号 V p B および V n B が活性状態とされ、このグローバル I / O バス G I / O から伝達されたデータがセンスアンプ S A B のセンスノードにおいて増幅されかつラッチされる。

#### 【 0 1 9 3 】

なお、図 2 3において破線で示すように、センス転送動作時に、アレイブロック M B B のイコライズ信号 E Q B を非活性状態のローレベルに維持し、かつセンスアンプ活性化信号 V p B および V n B を所定期間非活性状態とする構成が利用されてもよい。この場合、センスアンプ S A B のセンスノードが、その保持データに対する電位でフローティング状態とされる。この状態で、グローバル I / O バス G I / O とセンスアンプ S A B のセンスノードと接続すれば、このセンスアンプ S A B のセンスノードの電位はグローバル I / O バス G I / O からの信号電位に応じて変化する。センスアンプ S A B のセンスノードの容量は、グローバル I / O バスの容量に比べて十分小さく、したがってセンスアンプ S A B のセンスノード電位は十分このグローバル I / O バス G I / O からのデータ信号（電荷）に従って充放電されてその電位を変化させることができる。

#### 【 0 1 9 4 】

なおこの図 2 3 に示す動作波形図において、メモリセルへのデータ書き込みが行なわれるセル転送動作が併せて行なわれる場合には、図 2 3 に示す信号波形図において、ワード線 W L B およびピット線分離信号 B L I B がイコライズ信号 E Q B の非活性化の後センスアンプ S A B の活性化の前に活性状態のハイレベルとされる。

#### 【 0 1 9 5 】

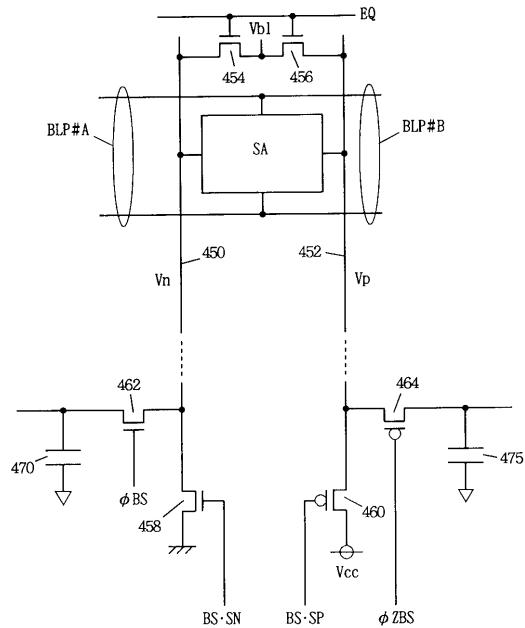

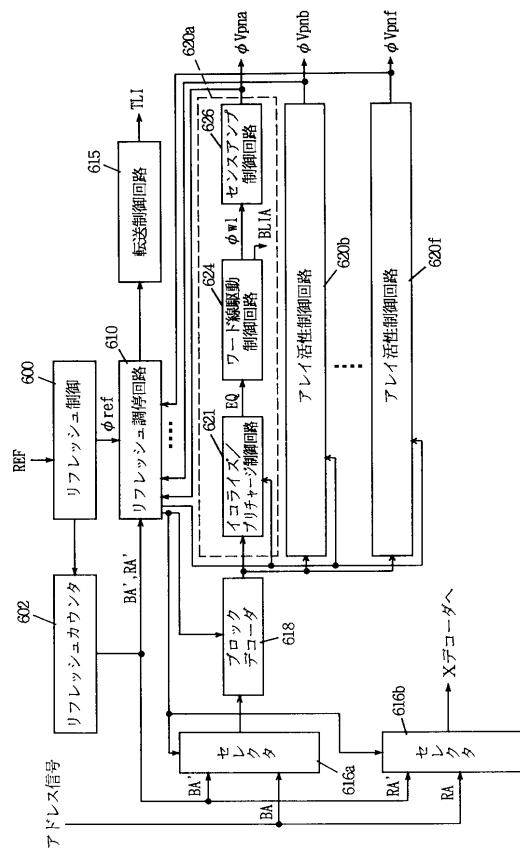

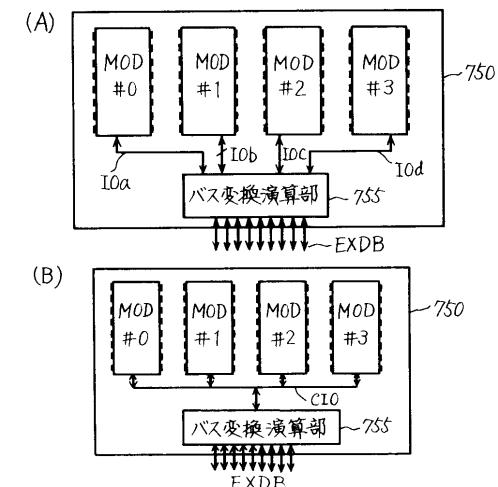

##### [ 制御回路 ]

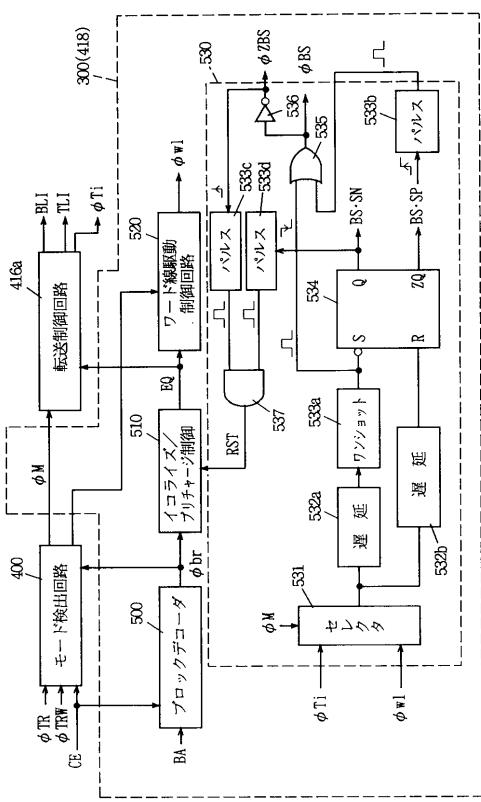

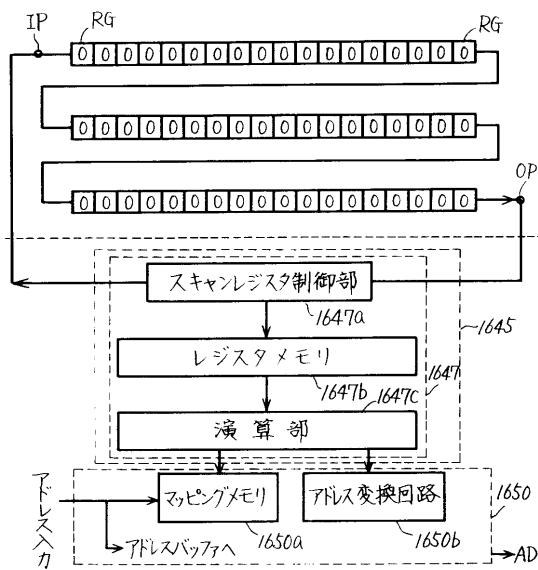

図 2 4 は、この発明の第 2 の実施の形態である半導体記憶装置のアレイ活性制御部の構成を概略的に示すブロック図である。この第 2 の実施の形態に従う半導体記憶装置の全体の構成は、図 1 に示す構成と同じである。

#### 【 0 1 9 6 】

図 2 4 において、アレイ活性制御部は、内部チップイネーブル信号 C E の活性化時に活性化され、内部ブロックアドレス信号 B A をデコードし、アドレス指定されたアレイブロックを活性化するためのブロック活性化信号 b r を出力するブロックデコーダ 1 0 を含む。このブロック活性化信号 b r が、各アレイブロックそれぞれに対応して発生される。活性状態とされたブロック活性化信号 b r ( b r a ~ b r d ) のアレイブロックのみが活性状態とされる。

#### 【 0 1 9 7 】

アレイ活性制御部は、さらに、ブロックデコーダ 1 0 からのブロック活性化信号 b r と内部チップイネーブル信号 C E とセンスアンプ転送指示信号（アンプ転送命令） T A とメモリセル転送指示信号（セル転送命令） T M を受けて、内部転送指示信号 T R i を所定のタイミングで出力しつつイコライズ／プリチャージ制御回路 1 2 0 a ~ 1 2 0 d のイコライズ／プリチャージ動作を制御する信号を発生する転送制御回路 1 1 0 を含む。イコライズ／プリチャージ制御回路 1 2 0 a ~ 1 2 0 d は、アレイブロック M A a ~ M A d それぞれに対応して設けられ、活性化時対応のアレイブロックのイコライズ／プリチャージ動作を実行する。アレイ活性制御部は、さらに、アレイブロック M A a ~ M A d それぞれに対応して配置されるワード線駆動制御回路 1 4 0 a ~ 1 4 0 d 、センスアンプ制御回路 1 6 0 a ~ 1 6 0 d 、および列選択制御回路 1 8 0 a ~ 1 8 0 d を含む。これらの回路部分の機能自体は先の実施の形態 1 において示したものと同じであるが、その内部構成が、転送指示信号 T R i を受けるため異なる。この構成については後に説明する。

#### 【 0 1 9 8 】

10

20

30

40

50

次に各部の具体的構成について説明する。

ロックデコーダ10の構成は、先の図7において示すものと同じであり、クロック信号CLKの立上がりに同期して発生された内部チップイネーブル信号CEに従って活性化され、そのときに与えられたロックアドレス信号BAをデコードし、アドレス指定されたアレイロックに対し所定の時間幅を有するロック活性化信号b\_r(b\_ra~b\_rd)を出力する。

#### 【0199】

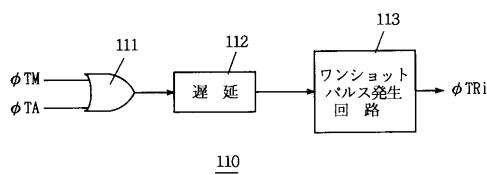

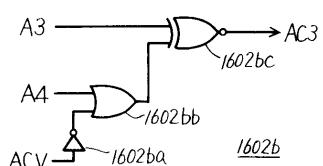

図25は、図24に示す転送制御回路110の構成を概略的に示す図である。この図25においては、転送制御回路110のうちの、内部転送指示信号を発生する部分の構成を示す。残りの部分(センスアンプ制御回路160a~160dを制御する部分およびイコライズ/プリチャージ制御回路120a~120dを制御する部分)の構成については後に各部分の構成と組合せて説明する。

10

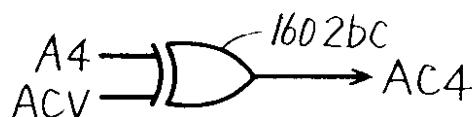

#### 【0200】

図25において、転送制御回路110は、センスアンプ転送指示信号TAとメモリセル転送指示信号TMを受けるORゲート111と、ORゲート111の出力信号を所定時間遅延する遅延回路112と、遅延回路112の出力信号の立上がりに応答して、所定の時間幅を有するワンショットのパルスを発生するワンショットパルス発生回路113を含む。このワンショットパルス発生回路113は、先に説明したフリップフロップおよび遅延回路の構成を用いて実現されればよい。

#### 【0201】

20

この図25に示す転送制御回路110においては、転送指示信号TAおよびTMの少なくとも一方がハイレベルの活性状態とされたときに、ワンショットパルス発生回路113から、所定のタイミングでデータ転送を指示するワンショットのパルス信号TRiが発生される。

#### 【0202】

##### [イコライズ/プリチャージ制御回路およびワード線駆動制御回路の構成]

図26は、この発明の第2の実施の形態である半導体記憶装置のイコライズ/プリチャージ制御回路120(120a~120d)およびワード線駆動制御回路140(140a~140d)の構成を示す図である。図26において、ワード線駆動制御回路140は、先の第1の実施の形態において図8において示した構成と同じ構成を備え、対応する部分には同一の参照番号を付す。

30

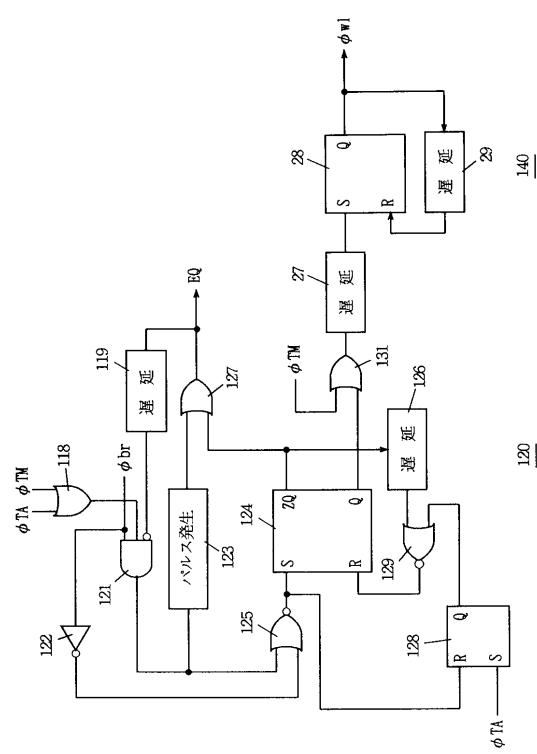

#### 【0203】

イコライズ/プリチャージ制御回路120は、信号TAおよびTMを受けるORゲート118(ORゲート111に対応)と、イコライズ信号EQ(EQa~EQd)を所定時間遅延する遅延回路119と、遅延回路119の出力信号を偽入力に受け、ロック活性化信号b\_rおよびORゲート118の出力信号を真入力に受けるゲート回路121と、ゲート回路121の出力信号がハイレベルのときに所定期間ハイレベルとなるパルス信号を発生するパルス発生回路123と、ロック活性化信号b\_rを反転するインバータ122と、ゲート回路121の出力信号とインバータ122の出力信号を受けるNORゲート125と、NORゲート125の出力信号の立上がりに応答してセットされるリセット優先型セット/リセットフリップフロップ124を含む。

40

#### 【0204】

このプリチャージ/イコライズ制御回路120は、さらに、フリップフロップ124の補出力ZQからの出力信号とパルス発生回路123からの出力信号とを受けるOR回路127と、フリップフロップ124の補出力ZQからの出力信号を所定時間遅延する遅延回路126と、NOR回路125の出力信号に応答してリセットされ、かつセンスアンプ転送指示信号TAに応答してセットされるセット/リセットフリップフロップ128と、フリップフロップ128の真出力Qからの出力信号と遅延回路126の出力信号とを受けるNOR回路129を含む。NOR回路129の出力信号はフリップフロップ124のリセット入Rへ与えられる。フリップフロップ124のQ出力からの信号は、信号TMを一

50

方入力に受けるOR回路131を介して遅延回路27へ与えられる。次にこのプリチャージ／イコライズ制御回路120の動作についてその動作波形図である図27(A)および(B)を参照して説明する。

#### 【0205】

図27(A)において、ブロック活性化信号  $b_r$  が指定するアレイブロックが既にセンスアンプにデータを保持している場合、イコライズ信号  $E_Q$  はローレベルにある。この状態において、新たにこのセンスアンプにデータを保持している状態においてさらにセンスアンプ転送指示信号が活性状態とされると、ゲート回路121の出力信号がハイレベルとなり、パルス発生回路123から所定期間ハイレベルとなるパルス信号が出力される。このときゲート回路121の出力信号はハイレベルであり、NOR回路125の出力信号はローレベルに固定され、フリップフロップ124のセット動作は禁止される。したがってOR回路127からのイコライズ信号  $E_Q$  が所定時間の間ハイレベルに立上がる。フリップフロップ124はリセット状態を維持している。この状態においては、信号  $T_M$  はローレベルであり、ワード線駆動制御回路140においてワード線選択動作活性化信号  $w_1$  はローレベルを維持しており、この転送アレイブロックにおいてのワード線選択動作は禁止される。

#### 【0206】

遅延回路119が設けられているのは、このイコライズ信号  $E_Q$  のローレベルからハイレベルへの移行時にゲート回路121の出力信号がローレベルとされ、フリップフロップ124がセット状態とされるのを防止するためである。

#### 【0207】

転送アレイブロックがセンスアンプにデータを保持していない場合においては、イコライズ信号  $E_Q$  はハイレベルにある。この状態においては、ゲート回路121の出力信号はローレベルにあり、パルス発生回路123のパルス発生動作は禁止される。この場合、NOR回路125がインバータとして機能し、ブロック活性化信号  $b_r$  に応答して、ハイレベルの信号を出力する。これにより、フリップフロップ124がセットされ、かつフリップフロップ128がリセットされる。このとき、センスアンプ転送指示信号  $T_A$  も活性状態にあり、このセット／リセットフリップフロップ128は、セット優先型の構成を備えており、そのセット入力  $S$  およびリセット入力  $R$  に活性状態の信号が与えられたときは、セット状態とされ、その真出力  $Q$  からの出力信号はハイレベルに設定される。これにより、NOR回路129の出力信号はローレベルに固定され、フリップフロップ124のリセットが禁止される。フリップフロップ124がセットされて、その真出力  $Q$  からの出力信号がハイレベルに立上がると、遅延回路27の出力信号が所定時間経過後に立上がり、フリップフロップ28がセットされ、ワード線選択動作活性化信号  $w_1$  が所定時間ハイレベルの活性状態とされる。

#### 【0208】

図27(B)に示すメモリセル転送動作時においては、信号  $T_A$  がローレベルであり、ブロック活性化信号  $b_r$  がハイレベルである。この場合には、メモリセル転送指示信号  $T_M$  がハイレベルであり、OR回路118の出力信号がハイレベルとされ、ゲート回路121の出力信号は、イコライズ信号  $E_Q$  がローレベルのときにはハイレベル、イコライズ信号  $E_Q$  がハイレベルのときにはローレベルとなる。したがって、転送アレイブロックがセンスアンプにデータを保持しているか否かに従ってイコライズ信号  $E_Q$  の活性／非活性が制御される。転送アレイブロックが既にセンスアンプにデータを保持している場合には、このメモリセル転送指示信号  $T_M$  とフリップフロップ124の真出力  $Q$  の出力信号を受けるOR回路131の出力信号がハイレベルとされ、遅延回路27の出力信号によりフリップフロップ28がセットされて所定期間ワード線選択動作活性化信号  $w_1$  が活性状態とされる。これにより、転送アレイブロックがセンスアンプにデータを保持しているか否かにかかわらず、メモリセル転送指示信号  $T_M$  が与えられると、転送アレイブロックにおいてワード線選択動作が実行される。

#### 【0209】

10

20

30

40

50

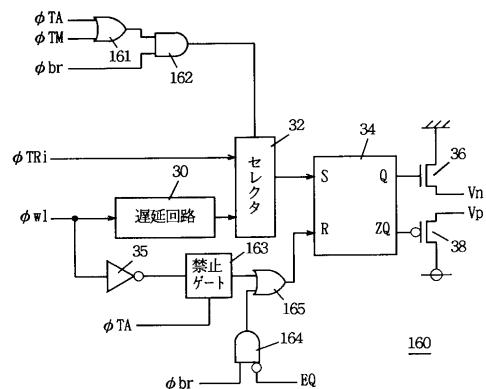

[ センスアンプ制御回路の構成 ]

図28は、図24に示すセンスアンプ制御回路の構成の一例を示す図である。図28において、センスアンプ制御回路160は、転送指示信号TAおよびTMを受けるOR回路161と、OR回路161の出力信号とブロック活性化信号brを受けるAND回路162とを含む。回路161および162は、図24に示す転送制御回路150に含まれてもよい。この図28に示すセンスアンプ制御回路160は、図9に示すセンスアンプ制御回路の構成に加えて、さらに、センスアンプ転送指示信号TAの活性化時ワード線選択動作活性化信号w1を受けるインバータ35の出力信号の伝達を禁止する禁止ゲート163と、ブロック活性化信号brおよびイコライズ信号EQを受けるゲート回路164と、禁止ゲート163の出力信号とゲート回路164の出力信号を受けるOR回路165をさらに含む。他の構成は、先に図9において示したセンスアンプ制御回路の構成と同じであり、対応する部分には同一の参照番号を付す。

【 0 2 1 0 】

禁止ゲート163はセンスアンプ転送指示信号TAの活性化時、その出力信号をローレベルの非活性状態に固定的に設定する。この禁止ゲート163には、たとえば、センスアンプ転送指示信号TAに応答して非導通状態とされ、信号w1の非活性化に応答して導通状態とされるラッチ回路を利用することができる。ゲート回路164は、イコライズ信号EQがローレベルにあり、かつブロック活性化信号brがハイレベルのときハイレベルの信号を出力する。

【 0 2 1 1 】

この図28に示す構成は、残りの構成は図9に示すセンスアンプ制御回路の構成と同じであり、対応する部分には同一の参照番号を付す。次に動作について図29を参照して説明する。

【 0 2 1 2 】

ブロック活性化信号brおよびセンスアンプ転送指示信号TAがともにハイレベルにあり、イコライズ信号EQがハイレベルのときには、先に図26を参照して説明した回路部分により、イコライズ信号EQがローレベルとされる。このときフリップフロップ34は、OR回路165の出力信号により、リセットされる可能性はあるが、この場合、既にフリップフロップ34はリセット状態にあり、何ら問題は生じない。

【 0 2 1 3 】

またこのとき、OR回路161およびAND回路162の出力信号がハイレベルとされ、セレクタ32は、内部転送指示信号TRiを選択する状態に設定される。内部転送指示信号TRiが活性状態とされると、セレクタ32を介してフリップフロップ34のセット入力Sに活性状態の信号が与えられてフリップフロップ34がセットされ、トランジスタ36および38が導通し、センスアンプ活性化信号VnおよびVpが活性状態とされる。信号TAの活性化に応答して禁止ゲート163は、インバータ35の出力信号の伝達を禁止しているため、フリップフロップ34のリセットは行なわれず、フリップフロップ34はセット状態を維持する。これにより、センスアンプ活性化信号VpおよびVnは活性状態を維持する。

【 0 2 1 4 】

次いでこの状態で、このアレイブロックに対し再びアクセスが行なわれる場合には、イコライズ信号EQがローレベルのため、ゲート回路164の出力信号がブロック活性化信号brの活性化に応答してハイレベルに立上がり、OR回路165を介してフリップフロップ34がリセットされる。これにより、センスアンプ活性化信号VpおよびVnが非活性状態とされる。ここで、イコライズ信号EQがローレベルから所定期間ハイレベルとなる構成は図26に示す構成により実現される。

【 0 2 1 5 】

次いで、通常アクセス動作時においては、所定時間経過後にワード線選択動作活性化信号w1がハイレベルとされ、セレクタ32を介してフリップフロップ34がセットされてセンスアンプ活性化信号VpおよびVnが活性状態とされる。ワード線選択動作活性化信号w1がローレベルに立上がり、OR回路165を介してフリップフロップ34がリセットされる。

10

20

30

40

50

号  $w_1$  が非活性状態とされると、禁止ゲート 163 は、信号 TA の非活性化のためインバータ 35 の出力信号を通過させ、フリップフロップ 34 が OR 回路 165 の出力信号に従ってリセットされ、センスアンプ活性化信号  $V_p$  および  $V_n$  が非活性状態とされる。

#### 【0216】

メモリセル転送動作時においては、信号 TM がハイレベルとされ、ゲート回路 162 の出力信号がハイレベルとなり、セレクタ 32 は、内部転送指示信号 TRi を選択する状態に設定される。この場合においては、センスアンプ活性化信号  $V_p$  および  $V_n$  は、内部転送指示信号 TRi の活性化に応答して活性状態とされる。その非活性化は、信号  $w_1$  の活性状態から非活性状態への移行に応答して行なわれる（メモリセル転送動作時においては、信号  $w_1$  は活性状態とされる）。

10

#### 【0217】

X デコーダの構成は、先の第 1 の実施の形態の図 12 に示す構成と同じである。またアドレスラッチの構成は、図 10 に示す第 1 の実施の形態のアドレスラッチの構成を利用することができる。

#### 【0218】

以上のように、この発明の第 2 の実施の形態に従えば、各アレイブロックを互いに独立に駆動可能とし、かつ 1 つのアレイブロックから他のアレイブロックのセンスアンプまたはメモリセルヘデータを転送するように構成したため、処理用途に応じてメモリセルデータの退避、キャッシュ化を実現することができ、汎用性の高い半導体記憶装置を実現することができる。

20

#### 【0219】

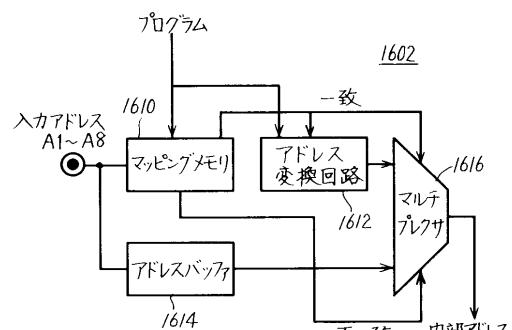

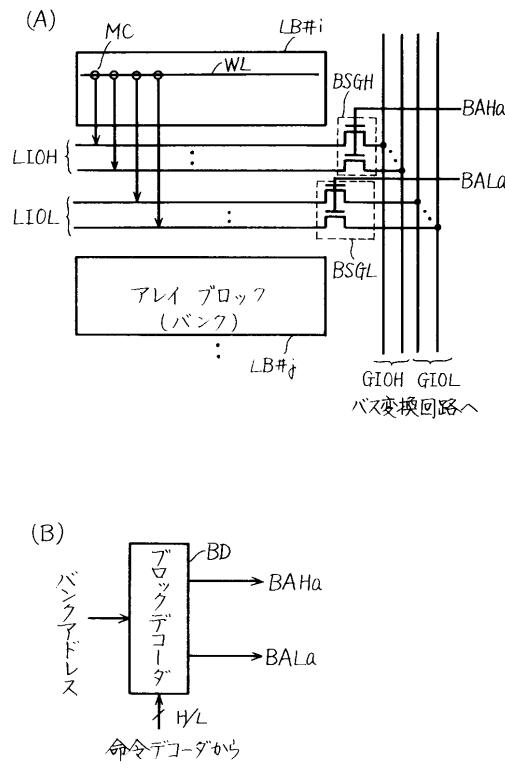

##### [実施の形態 3]

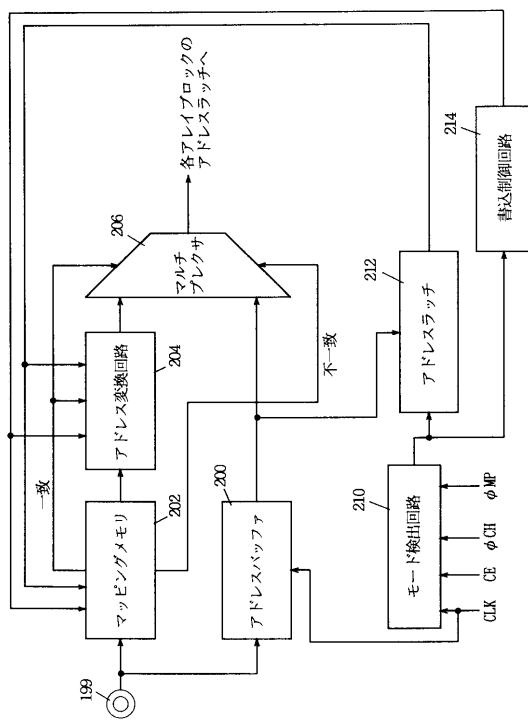

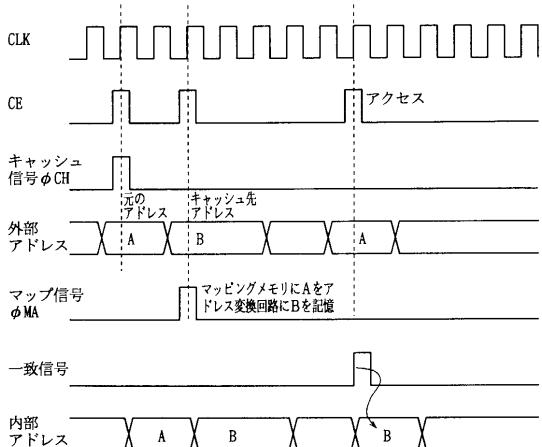

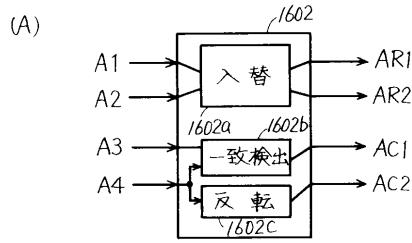

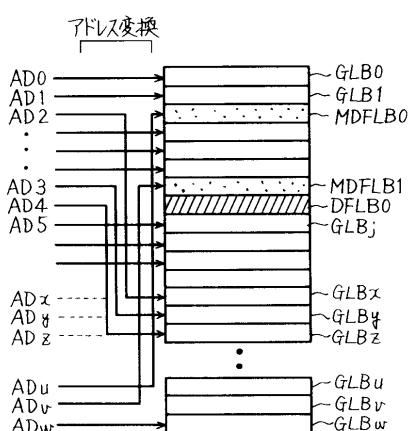

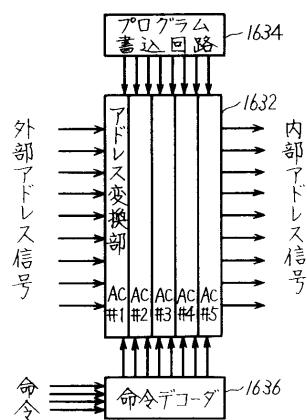

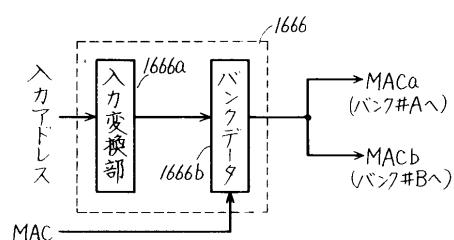

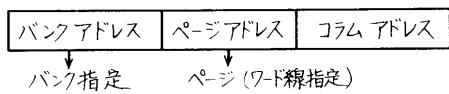

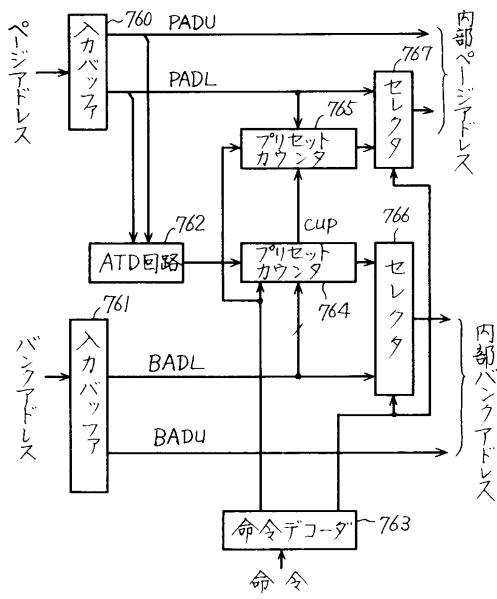

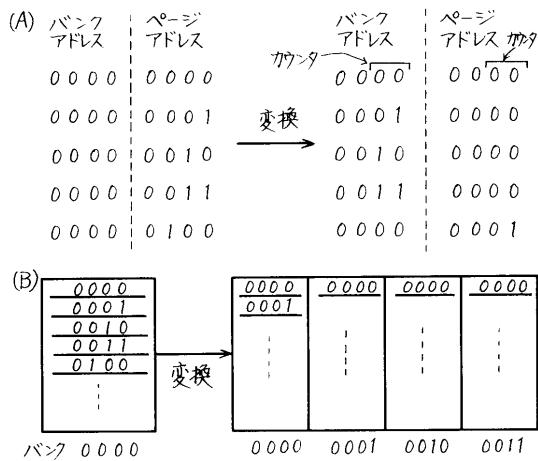

図 30 は、この発明の第 3 の実施の形態である半導体記憶装置の要部の構成を示す図である。この図 30 においては、アドレス入力部の構成が示される。この図 30 に示すアドレス入力部から出力される内部アドレス信号が先の実施の形態 1 および実施の形態 2 で示したブロックデコーダおよび各アレイブロックの行選択回路へ与えられる。

#### 【0220】

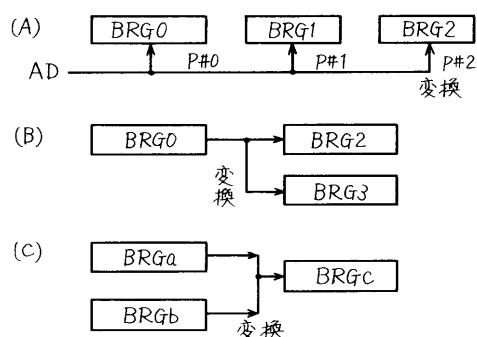

図 30 において、アドレス入力部は、アドレス入力端子 199 へ与えられるアドレス信号をクロック信号 CLK に同期して取込むアドレスバッファ 200 と、メモリセルデータの転送前のアドレスを格納するマッピングメモリ 202 と、マッピングメモリ 202 に格納された転送前のアドレス信号のデータ転送後のアドレス信号を各転送前のアドレス信号に対応して格納するアドレス変換回路 204 と、アドレスバッファ 200 およびアドレス変換回路 204 の一方のアドレス信号を通過させ、内部アドレス信号を生成するマルチプレクサ 206 を含む。マッピングメモリ 202 は、たとえば連想メモリ（CAM）で構成され、アドレス変換回路 204 は、たとえばレジスタで構成される。

30

#### 【0221】

このマッピングメモリ 202 およびアドレス変換回路 204 へのデータの格納を制御するために外部からのクロック信号 CLK、チップイネーブル信号 CE、キャッシュ信号 CH、およびマップ信号 MP を受けて、指定されたモードを検出するモード検出回路 210 と、モード検出回路 210 の制御のもとに、アドレスバッファ 200 から与えられたアドレス信号をそれぞれラッチするアドレスラッチ 212 と、モード検出回路 210 の制御のもとに、このアドレスラッチ 212 に格納されたアドレスをマッピングメモリ 202 およびアドレス変換回路 204 へ書込む書込制御回路 214 を含む。アドレスラッチ 212 は、転送前のアドレスと転送後のアドレスを格納する。次に動作についてその動作波形図である図 31 を参照して説明する。

40

#### 【0222】

クロック信号 CLK の立上がり時にチップイネーブル信号 CE がハイレベルの活性状態とされ、またデータ転送を指定するキャッシュ信号 CH がハイレベルの活性状態とされる。これにより、データ転送が指定されて、転送されるべきメモリセルのアドレス（A）がモード検出回路 210 の制御のもとにアドレスラッチ 212 に格納される。この状態にお

50

いては、マルチプレクサ 206 は、モード検出回路 210 の制御のもとに、アドレスバッファ 200 から与えられる元のアドレスすなわち転送前のアドレスを選択して各アレイブロックのアドレスラッチへ与える。

#### 【0223】

次いで、転送先を指定するアドレス B が与えられ、チップイネーブル信号 C E およびマップ信号 M A がクロック信号 C L K の立上がり時にハイレベルの活性状態とされる。モード検出回路 210 は、このチップイネーブル信号 C E およびマップ信号 M A に従って、転送先アドレスが与えられたことを検知し、アドレスバッファ 200 から与えられたアドレス信号をアドレスラッチ 212 に格納する。この場合においても、マルチプレクサ 206 は、モード検出回路 210 の制御のもとに、アドレスバッファ 200 からのアドレス信号を選択して各アレイブロックへ与え、データ転送動作が行なわれる。10

#### 【0224】

一方、書き制御回路 214 は、このモード検出回路 210 の制御のもとにマッピングメモリ 202 およびアドレス変換回路 204 に対し書きアドレスを発生し、アドレスラッチ 212 に格納された元のアドレス（転送前アドレス）およびキャッシュ先アドレス（転送アドレス）を格納する。

#### 【0225】

以後の動作時において、チップイネーブル信号 C E がクロック信号 C L K の立上がり時ににおいて活性状態とされ、アドレス入力端子 199 に元のアドレス（A）が与えられたとき、マッピングメモリ 202 は、この与えられたアドレスと格納している元のアドレス（キャッシュアドレスと称す）とを比較し、その比較結果を示す信号を出力する。かつこのマッピングメモリ 202 は、一致時においては、アドレス変換回路 204 から、対応の転送先アドレス（キャッシュ先アドレス）を読み出してマルチプレクサ 206 へ与える。マルチプレクサ 206 は、マッピングメモリ 202 からの一致信号に従ってアドレス変換回路 204 から与えられたアドレス信号を選択して各アレイブロックのアドレスラッチへ与える。これにより、外部から与えられたキャッシュアドレス（A）に対して、転送先アドレス（B）が内部アドレスとして指定される。アレイブロックにおいてセンスアンプがデータをラッチしている場合には、このセンスアンプをキャッシュとして利用して、転送アドレスに格納されたデータの読み出または書きを行なうことができる。20

#### 【0226】

上述のようにマッピングメモリ 202 およびアドレス変換回路 204 を利用することにより、別のアレイブロックのセンスアンプにデータが転送されている場合、その転送されたデータを高速で読み出すことができる。30

#### 【0227】

図 32 は、図 30 に示すマッピングメモリ 202 およびアドレス変換回路 204 の構成を概略的に示す図である。図 32 において、マッピングメモリ 202 は、各エントリが元のアドレス信号を格納する複数の連想メモリセルエントリ ENT 1 ~ ENT n を含む。連想メモリセルエントリ ENT 1 ~ ENT n の各々には、一致線 C H L 1 ~ C H L n が接続される。一致線 C H L 1 ~ C H L n は、それぞれ対応の連想メモリセルエントリ ENT 1 ~ ENT n の格納するアドレス信号と、外部から与えられるアドレス信号の一致したときにハイレベルの活性状態とされる。40

#### 【0228】

アドレス変換回路 204 は、マッピングメモリ 202 の各エントリ ENT 1 ~ ENT n に対応して設けられるレジスタ R E G 1 ~ R E G n と、レジスタ R E G 1 ~ R E G n それぞれに対応して設けられ、一致線 C H L 1 ~ C H L n の活性化時、対応のレジスタの内容を読み出データ線 R D 上に伝達するリードゲート R G 1 ~ R G n を備える。このアドレス変換回路 204 は、さらに、転送アドレス信号書き時に、書き制御回路の制御のもとにアドレスラッチにラッチされたデータを書込むためのライトゲート W G 1 ~ W G n を含む。これらのライトゲート W G 1 ~ W G n はレジスタ R E G 1 ~ R E G n それぞれに対応して設けられ、書き制御回路からの活性化信号に従って選択的に活性状態とされ、対応のレジスタ50

REG<sub>1</sub> ~ REG<sub>n</sub> を書きデータバスWDに接続する。書き制御回路は、明確には示さないが、アドレスカウンタなどのアドレス発生器を備えており、アドレスラッチ212に格納されたアドレスをマッピングメモリ202およびアドレス変換回路204へ格納する。連想メモリセルエントリENT<sub>1</sub> ~ ENT<sub>n</sub>へのデータ書きは、通常の手法を用いて行なわれる。すなわちエントリ選択信号線(ワード線)を選択状態として、元のアドレス信号をこのマッピングメモリへ与えることにより、選択された連想メモリセルエントリへ元のアドレス信号が格納される。

#### 【0229】

一致信号は、一致線CHL<sub>1</sub> ~ CHL<sub>n</sub>上の信号を受けるORゲート215から出力される。一致線CHL<sub>1</sub> ~ CHL<sub>n</sub>のいずれかが活性状態とされると一致信号が活性状態とされる。このとき、一致を示す一致線に対応して設けられたリードゲートが導通し、対応のレジスタの内容が読み出されてマルチプレクサへ与えられる。10

#### 【0230】

アドレスラッチ212としては、単にモード検出回路210の制御のもとに、それぞれ元のアドレス信号および転送アドレス信号格納領域に、与えられたアドレス信号を格納する構成が用いられればよい。

#### 【0231】

以上のように、この発明の第3の実施の形態の構成に従えば、元のアドレス信号と転送先アドレス信号とをリンクして(対応付けて)格納し、与えられた信号がこの登録された元のアドレス信号と一致するときには、転送アドレス信号を内部アドレス信号として出力するように構成しているため、この半導体記憶装置において転送先のメモリセルへ容易にアクセスすることができ、たとえばあるメモリセルのデータの加工時に退避された加工前のデータを再びアクセスすることができる。また転送先アレイブロックのセンスアンプをキヤッシュとして利用することができ、高速アクセスが可能となる。20

#### 【0232】

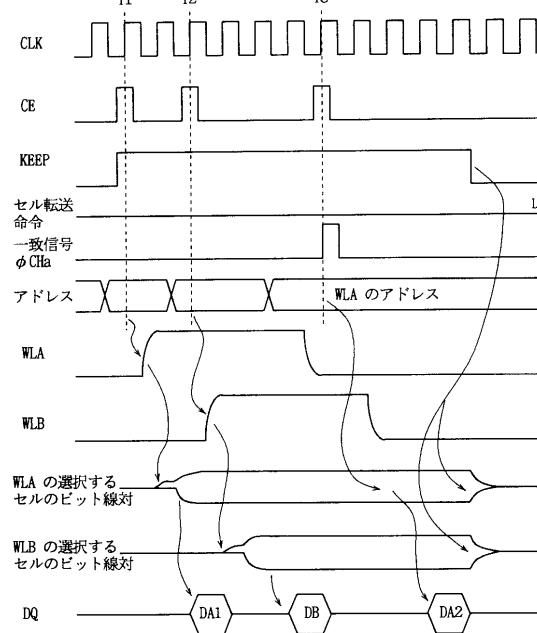

##### [実施の形態4]

図33は、この発明の第4の実施の形態である半導体記憶装置の動作を示す波形図である。以下、図33に示す波形図を参照してこの発明の第4の実施の形態である半導体記憶装置の動作について説明する。

#### 【0233】

クロック信号CLKの立ち上がり時に、チップイネーブル信号CEをハイレベルとし、かつデータ保持指示信号KEEPをハイレベルとする。この状態においては、時刻T1において与えられたアドレス信号に従って、アレイブロックにおいてワード線WLAが選択され、この選択ワード線WLAに接続されるメモリセルのデータがビット線上に読み出され、次いでセンスアンプが活性状態とされ、次いで列選択が行なわれ、データDA1が読み出される。データ保持指示信号KEEPがハイレベルであるため、所定期間経過後にワード線WLAがローレベルに立下がっても、この選択アレイブロックにおいて、センスアンプは活性状態を維持する。30

#### 【0234】

時刻T2において再びチップイネーブル信号CEが与えられると、その時点において与えられたアドレス信号に従って別のアレイブロックにおいてワード線WLBが選択され、このワード線WLBの電位が立ち上がり、選択ワード線WLBに接続されるメモリセルのデータがビット対上に読み出され、次いで列選択動作が行なわれ、このワード線WLBに接続するメモリセルのうち選択列上に配置されるメモリセルのデータDBが読み出される。40

#### 【0235】

時刻T3において、時刻T1に与えられたアドレスと同じ行アドレスを指定するアドレス信号が与えられて、ワード線WLAが指定された場合、信号KEEPにより、このワード線WLAのデータはセンスアンプにより保持されているため、行選択動作は行なわれず、列選択動作のみが行なわれ、このワード線WLAに接続するメモリセルのうちの対応のメモリセルのデータDA2が読み出される。以降、信号KEEPがハイレベルのある間、選択50

アレイブロックにおいては、すべてセンスアンプが活性状態を維持しており、いずれかのアレイブロックにおいて選択動作が指定された場合には、列選択動作のみが行なわれ、対応のメモリセルのデータが読出される。

#### 【0236】

上述の一連の動作により、この半導体記憶装置を信号 K E E P に従ってこの半導体記憶装置をキャッシュとして利用することができるため、選択ワード線を再度アクセスする場合に、行選択動作が必要とされず、高速でデータの読出が可能となる。

#### 【0237】

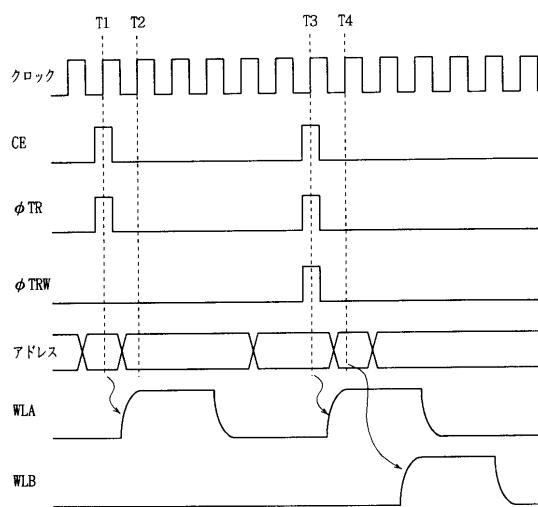

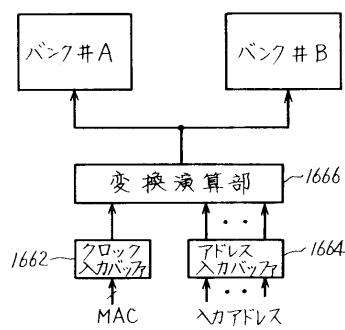

図 34 は、この発明の第 4 の実施の形態である半導体記憶装置のアレイ活性制御部の構成を示す図である。図 34 において、アレイブロック M B a のアレイ活性制御部の構成のみを示す。残りのアレイブロック M B b ~ M B d に対しても同様の構成が用いられる。

10

#### 【0238】

図 34 において、アレイ活性制御部は、チップイネーブル信号 C E に応答して活性化され、アドレスバッファ 3 からのブロックアドレス信号 B A をデコードし、ブロック活性化信号 b r a を出力するブロックデコーダ 10 a と、ブロックデコーダ 10 a からのブロック活性化信号 b r a と後に説明する比較器 272 からの一致信号 I H a に応答して、イコライズ信号 E Q a を選択的に活性 / 非活性状態とするイコライズ / プリチャージ制御回路 220 と、イコライズ / プリチャージ制御回路 220 からのイコライズ信号 E Q a の立下がりに応答して、所定期間活性状態とされるワード線選択動作活性化信号 w 1 a を出力するワード線駆動制御回路 240 と、データ保持信号 K E E P とワード線駆動制御回路 240 の出力する信号 w 1 a と、比較器 272 からの一致信号 I H a に応答して、センスアンプ活性化信号 V p a および V n a を選択的に活性状態にするセンスアンプ制御回路 260 を含む。イコライズ / プリチャージ制御回路 220 およびセンスアンプ制御回路 260 の内部構成については後に説明する。ワード線駆動制御回路 240 の構成は、先の第 2 の実施の形態において説明したものと同様である。

20

#### 【0239】

アレイ活性制御部はさらに、比較器 272 の出力信号 I H a とデータ保持信号 K E E P に応答して、アドレスバッファ 3 から与えられた内部行アドレス信号 R A および内部ブロックアドレス信号 B A をラッチするラッチ 270 を含む。このラッチ 270 は、データ保持信号 K E E P の活性化時（ハイレベル）のとき、一致信号 I H a が不一致を示す場合には、そのときに与えられた行アドレス信号 R A およびブロックアドレス信号 B A をラッチする。またラッチ 270 は、データ保持信号 K E E P の非活性化時（ハイレベルからローレベルへの移行時）、そのラッチデータがリセットされる。

30

#### 【0240】

比較器 272 は、データ保持信号 K E E P の活性化時、このラッチ 270 にラッチされたアドレス信号とアドレスバッファ 3 から与えられる行およびブロックアドレス信号とを比較し、その比較結果に従って一致信号 I H a を活性状態または非活性状態に駆動する。

#### 【0241】

X デコーダ 276 に対しては、ブロック活性化信号 b r a と一致信号 I H a に従ってアドレスバッファ 3 からの内部行アドレス信号をラッチする R A ラッチ 274 が設けられる。Y デコーダ 279 に対しては、ブロック活性化信号 b r a に応答してアドレスバッファ 3 から与えられる内部列アドレス信号をラッチする C A ラッチ 278 が設けられる。X デコーダ 276 は、ワード線駆動制御回路 240 からのワード線選択動作活性化信号 w 1 a に応答して活性化される。R A ラッチ 274 は、比較器 272 からの一致信号 I H a が一致を示す場合にはブロック活性化信号 b r a が活性状態とされてもリセット状態を維持する。Y デコーダ 279 は、ブロック活性化信号 b r a に応答して活性化される列選択制御回路 280 によりそのデコード開始タイミングが決定される。列選択制御回路 280 はまた、ブロック活性化信号 b r a に応答して、所定のタイミングでブロック選択信号（ローカル I / O 線とグローバル I / O 線とを接続するゲート）を導通を制御するブロック選択信号 T G A を活性状態とする。

40

50

## 【0242】

Xデコーダ276からの出力信号（ワード線駆動信号）は、アレイブロックM B aに配設されるワード線W L上に伝達される。Yデコーダ279の出力信号は、アレイブロックM B aに対して配設されたビット線対B L Pに設けられた列選択ゲートS E Lへ与えられる。このアレイブロックM B aの各ビット線対B L Pに設けられたセンスアンプS A aは、センスアンプ制御回路260からのセンスアンプ活性化信号V p aおよびV n aに応答して活性状態とされる。次にこの図34に示す制御の動作をその動作波形図である図35および図36を参照して説明する。

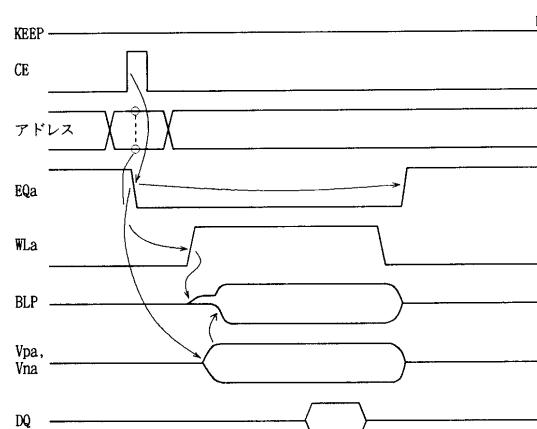

## 【0243】

図35は、通常動作時の動作を示す波形図である。通常動作時においては、データ保持信号K E E Pは非活性状態のローレベルを維持する。この場合には、比較器272は非活性状態とされ、その比較動作が禁止され、一致信号I H aはローレベルに固定される。チップイネーブル信号C Eの活性化に応答して、アドレスバッファ3からのブロックアドレス信号B Aがブロックデコーダ10aでデコードされ、ブロック活性化信号b r aが活性状態とされる。これに応答して、イコライズ／プリチャージ制御回路220からのイコライズ信号E Q aが非活性状態のローレベルとされる。ワード線駆動制御回路240は、このイコライズ／プリチャージ制御回路220からのイコライズ信号E Q aの非活性化に応答して、所定時間経過後、ワード線選択動作活性化信号w l aを活性状態として、Xデコーダ276へ与える。R Aラッチ274は、一致検出信号I H aが非活性状態にあるため、ブロック活性化信号b r aに応答して、アドレスバッファ3から与えられた内部行アドレス信号R AをラッチしてXデコーダ276へ与える。Xデコーダ276は、ワード線駆動制御回路240からの信号w l aに応答して活性化され、このR Aラッチ274から与えられたアドレス信号をデコードし、ワード線W L aを所定期間選択状態へと駆動する。このワード線W L aが選択状態とされる期間は、ワード線駆動制御回路240から出力される信号w l aにより決定される。選択ワード線W L aに接続されるメモリセルデータがビット線対B L Pへ与えられ、その電位差が十分に拡大されると、センスアンプ制御回路260からのセンスアンプ活性化信号V p aおよびV n aが活性状態とされ、ビット線対B L Pのデータが増幅される。

## 【0244】

一方、C Aラッチ278は、ブロック活性化信号b r aの活性化に応答して、アドレスバッファ3から与えられた内部列アドレス信号をラッチしている。Yデコーダ279が列選択制御回路280の制御のもとに活性化され、このC Aラッチ278のラッチする内部列アドレス信号をデコードし、列選択信号を出力する。これにより、選択列に対応するビット線対B L Pが列選択ゲートおよびブロック選択ゲート（S E Lで示す）を介してグローバルI / O線に接続される。この後リード／ライトドライバR W D Rがリード／ライト信号W / Rへ応答して所定のタイミングで活性化され、入出力バッファを介してデータの出力が行なわれる。

## 【0245】

図36は、データ保持信号が活性状態のときの動作を示す波形図である。データ保持信号K E E Pがハイレベルの活性状態のときには、既に、センスアンプ活性化信号V p aおよびV n aは活性状態を維持している。チップイネーブル信号C Eが活性状態とされると、アドレスバッファ3からの内部アドレス信号が確定状態とされる。比較器272が、このラッチ270にラッチされている行アドレス信号R Aおよびブロックアドレス信号B Aとアドレスバッファ3から与えられた内部行アドレス信号およびブロックアドレス信号を比較する。両者が同じ場合、すなわちアレイブロックM B aの同じワード線が選択状態とされる場合には、この比較器272からの一致信号I H aが活性状態とされる。この一致信号I H aの活性化に応答して、イコライズ／プリチャージ制御回路220はその動作が禁止され、前のサイクルの状態、すなわち、非活性状態のローレベルを維持する。したがってこの状態においては、ワード線駆動制御回路240からのワード線選択動作活性化信号w l aは非活性状態を維持し、R Aラッチ274およびXデコーダ276による、

10

20

30

40

50

新たなワード線の選択動作は禁止される。センスアンプ制御回路260は、この比較器272からの活性状態の一致信号IH<sub>a</sub>に応答して、センスアンプ活性化信号V<sub>p a</sub>およびV<sub>n a</sub>を活性状態に維持する。

#### 【0246】

CAラッチ278が、このチップイネーブル信号CEと同時に与えられたアドレス信号から内部列アドレス信号をラッチし、Yデコーダ279が列選択制御回路280の制御のもとに活性化される。これにより、既に選択状態とされているセンスアンプSAaにラッチされている1行のメモリセルデータのうち内部列アドレス信号が指定するメモリセルのデータが選択されてグローバルI/OバスG<sub>I/O</sub>上に伝達されて、次いでリード/ライトドライバRWDRを介して入出力バッファ(図示せず)へ与えられる。

10

#### 【0247】

チップイネーブル信号CEの活性化時に与えられるアドレス信号がセンスアンプに保持されているメモリセルの行アドレスと異なる行アドレスを指定する場合には、比較器272の出力信号は非活性状態を維持する。この場合には、イコライズ/プリチャージ制御回路220は、ブロックデコーダ10aからのブロック活性化信号b<sub>r a</sub>の活性化に応答して、所定期間イコライズ信号EQ<sub>a</sub>をハイレベルに維持する。このときまた、センスアンプ制御回路260が比較器272からの非活性状態の一致信号IH<sub>a</sub>に応答して、センスアンプ活性化信号V<sub>p a</sub>およびV<sub>n a</sub>を非活性状態に維持する。これにより、センスアンプSAaに保持されていたメモリセルのデータがリセットされる。次いで、ワード線駆動制御回路240が、このイコライズ信号EQ<sub>a</sub>の立下がりに応答して、所定のタイミングで信号w<sub>l a</sub>を活性状態とする。

20

#### 【0248】

RAラッチ274は、比較器272の非活性状態の一致検出信号IH<sub>a</sub>とブロック活性化信号b<sub>r a</sub>の活性化とに応答して、アドレスバッファ3からの内部行アドレス信号RAをラッチしてXデコーダ276へ伝達する。Xデコーダ276が、このワード線選択動作活性化信号w<sub>l a</sub>に応答して所定期間活性状態とされ、新たにアドレス指定された行に対応するワード線を選択状態とする。

#### 【0249】

このワード線選択動作活性化信号w<sub>l a</sub>の活性化に応答して、センスアンプ制御回路260が、一定のタイミングでセンスアンプ活性化信号V<sub>p a</sub>およびV<sub>n a</sub>を活性状態とする。これにより、新たにアドレス指定された行のメモリセルのデータがセンスアンプSAaにより検知、增幅され、かつラッチされる。次いで、CAラッチ278にラッチされた内部列アドレス信号がYデコーダ279でデコードされ、対応の列を指定する列選択信号が活性状態とされる。これにより、新たにアドレス指定されたメモリセルのデータがグローバルI/OバスG<sub>I/O</sub>上に伝達される。データ保持信号KEEPのハイレベルのとき、センスアンプ制御回路260は、ワード線駆動制御回路240からの信号w<sub>l a</sub>が非活性状態とされても、センスアンプ活性化信号V<sub>p a</sub>およびV<sub>n a</sub>を活性状態に維持する。Xデコーダ276は、この信号w<sub>l a</sub>の非活性化に応答してプリチャージ状態とされる。

30

#### 【0250】

またラッチ270は、比較器272からの非活性状態の一致検出信号IH<sub>a</sub>に応答して、アドレスバッファ3から与えられた内部行アドレス信号RAおよび内部ブロックアドレス信号BAをラッチする。これにより、選択状態とされているワード線を示すアドレス信号の更新が行なわれる。

40

#### 【0251】

データ保持信号KEEPが非活性状態のローレベルとされると、ラッチ270のラッチするアドレス信号がリセットされ、またセンスアンプ制御回路260からのセンスアンプ活性化信号V<sub>p a</sub>およびV<sub>n a</sub>も非活性状態とされ、イコライズ信号EQ<sub>a</sub>がハイレベルへ立上がる。

#### 【0252】

50

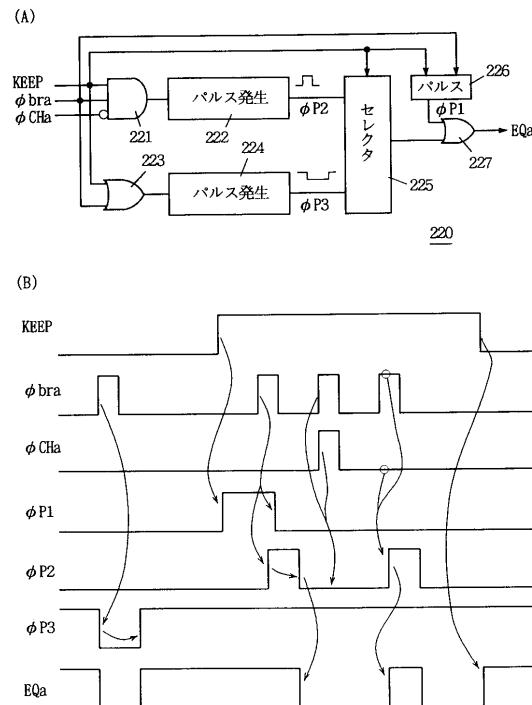

[イコライズ / プリチャージ制御回路の構成]

図37は、図34に示すイコライズ / プリチャージ制御回路の構成および動作を示す図である。図37(A)において、プリチャージ / イコライズ回路220は、信号KEEPおよびbraを真入力に受け、信号IH<sub>a</sub>を補入力に受けるゲート回路221と、ゲート回路221の出力信号の立上がりに応答して、所定の時間幅を有するパルス信号を発生するパルス発生回路222と、信号KEEPおよびbraを受けるOR回路223と、OR回路223の出力信号の立上がりに応答して、所定期間ローレベルとなるパルス信号を発生するパルス発生器224と、信号KEEPに応答してパルス発生器222および224の一方を選択的に低下させるセレクタ225と、信号KEEPの立上がりに応答して立上がりかつ信号braの立上がりに応答して立下がるパルス信号を発生するパルス発生器226と、パルス発生器226の出力信号とセレクタ225の出力を受けるOR回路227を含む。OR回路227からイコライズ信号EQ<sub>a</sub>が出力される。次にこの図37に示すイコライズ / プリチャージ制御回路220の動作をその動作波形図である図37(B)を参照して説明する。

【0253】

信号KEEPがローレベルのとき、ゲート回路221の出力信号はローレベルに固定される。セレクタ225は、パルス発生器224からのパルス信号p3を選択する状態に設定される。パルス発生器226は、信号KEEPがローレベルに固定されるため、パルスを発生しない。

【0254】

OR回路223は、バッファ回路として機能し、信号braをバッファ処理してパルス発生器224へ与える。パルス発生器224は、このOR回路223からの信号の立上がりに応答して、所定期間ローレベルとされるパルス信号p3を発生する。セレクタ225はこのパルス発生器224からのパルス信号p3を選択して通過させる。OR回路227はいま、バッファ回路として機能しており(パルス発生器226出力信号はローレベル)、イコライズ信号p3がイコライズ信号EQ<sub>a</sub>として出力される。

【0255】

一方、信号KEEPがハイレベルに立上ると、この立上がりに応答してパルス発生器226が出力信号p1をハイレベルに立上げる。これにより、OR回路227からのイコライズ信号EQ<sub>a</sub>がハイレベルとされる。アレイロックMB<sub>a</sub>がプリチャージ状態にあれば、イコライズ信号EQ<sub>a</sub>はハイレベルを維持するだけであり、何ら状態変化は生じない。

【0256】

この状態でブロック活性化信号braが活性状態とされると、最初のサイクルにおいては、比較器(図34参照)の出力する一致信号IH<sub>a</sub>は不一致を示すローレベルである(図34に示すラッチ270は、信号KEEPの立上がりに応答してリセットされており、いずれの行をも指定していない)。これに応答して、ゲート回路221の出力信号がハイレベルに立上がり、パルス発生器222からのパルス信号p2が所定期間ハイレベルとされる。セレクタ225は信号KEEPに従ってパルス発生器222の出力信号を選択している。パルス発生器226からのパルス信号p1は、ブロック活性化信号braの立上がりに応答してローレベルとされる。パルス信号p1およびp2は、そのハイレベルの期間が互いに重なり合うようにタイミングが設定される。したがって、イコライズ信号EQ<sub>a</sub>が、所定期間経過後、ハイレベルからローレベルとされ、ワード線選択動作が開始される。

【0257】

次いでアクセスが行なわれ、ブロック活性化信号braおよび一致信号IH<sub>a</sub>がともにハイレベルとされると、この場合には、ゲート回路221の出力信号はローレベルであり、パルス発生器222からのパルス信号p2はローレベルを維持する。したがってイコライズ信号EQ<sub>a</sub>もローレベルを維持する。

【0258】

10

20

30

40

50

次に再びブロック活性化信号  $b_{ra}$  がハイレベルとなり、一致信号  $IHa$  がローレベルのときには、パルス発生器 222 からのパルス信号  $p_2$  が発生され、イコライズ信号  $EQa$  が所定期間ハイレベルとされ、アレイブロック MBa のプリチャージが行なわれる。この後、ワード線が選択され、新たなメモリセルデータの選択が行なわれる。信号  $KEEP$  がローレベルとされると、セレクタ 225 がパルス発生器 224 からのハイレベル状態にあるパルス信号  $p_3$  を選択し、応じてイコライズ信号  $EQa$  がハイレベルに立上がる。

#### 【0259】

ワード線駆動制御回路の構成は、先の第 1 の実施の形態と第 2 の実施の形態において用いた構成を利用することができます。

10

#### 【0260】

##### [センスアンプ制御回路の構成]

図 38 は、図 34 に示すセンスアンプ制御回路の構成および動作を示す図である。

#### 【0261】

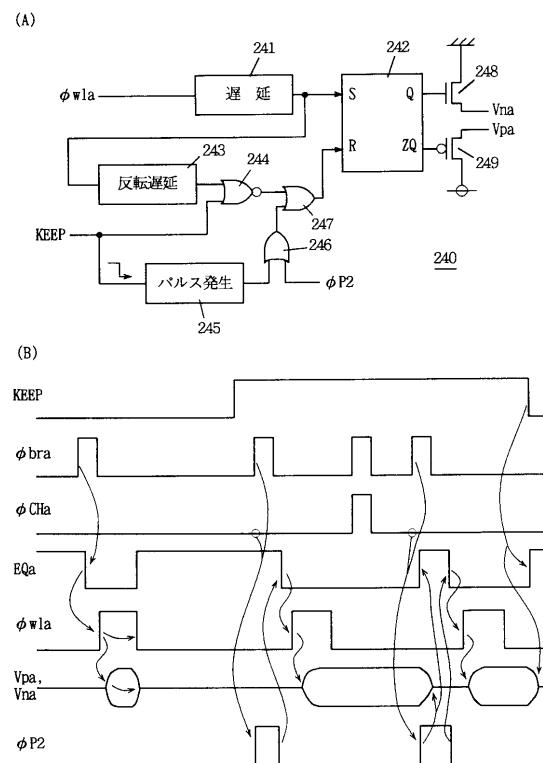

図 38 (A)において、センスアンプ制御回路 240 は、ワード線選択動作活性化信号  $w_{1a}$  を所定時間遅延する遅延回路 241 と、遅延回路 241 の出力信号の立上がりに応答してセットされるセット／リセットフリップフロップ 242 と、遅延回路 241 の出力信号を所定時間遅延させかつその出力信号を反転する反転遅延回路 213 と、データ保持信号  $KEEP$  と反転遅延回路 243 の出力信号とを受ける NOR 回路 244 と、信号  $KEEP$  の立下がりに応答して所定時間ハイレベルとされるパルス信号を発生するパルス発生器 245 と、パルス発生器 245 の出力信号と、図 37 に示すパルス信号  $p_2$  を受ける OR 回路 246 と、NOR 回路 244 の出力信号と OR 回路回路 246 の出力信号とを受ける OR 回路 247 とを含む。フリップフロップ 242 は、この OR 回路 247 の出力信号の立上がりに応答してリセットされる。

20

#### 【0262】

フリップフロップ 242 の補出力  $ZQ$  からの出力信号は、センスアンプ活性化信号  $Vpa$  を出力する  $p$  チャネル MOS トランジスタ 249 のゲートへ与えられる。フリップフロップ 242 の  $Q$  出力からの出力信号は、センスアンプ活性化信号  $Vna$  を出力する  $n$  チャネル MOS トランジスタ 248 のゲートへ与えられる。次に図 38 (B) に示す動作波形図を参照してこの図 38 (A) に示すセンスアンプ制御回路動作について説明する。

30

#### 【0263】

信号  $KEEP$  がローレベルのとき、NOR 回路 244 は、インバータとして機能する。フルロック活性化信号  $b_{ra}$  がハイレベルとされると、イコライズ信号  $EQa$  がハイレベルからローレベルへ立下がり、このイコライズ信号  $EQa$  の立下がりに応答して、所定期間ワード線選択動作活性化信号  $w_{1a}$  がハイレベルとされる。この信号  $w_{1a}$  の立上がりに応答して、フリップフロップ 242 が遅延回路 241 の出力信号に従ってセットされ、次いで反転遅延回路 243、NOR 回路 244 および OR 回路 247 により、所定時間経過後にリセットされる。これにより、センスアンプ活性化信号  $Vpa$  および  $Vna$  が所定時間活性化状態とされる。

#### 【0264】

40

データ保持信号  $KEEP$  がハイレベルとされると、パルス信号  $p_2$  が所定期間ハイレベルされ、OR 回路 246 および 247 を介してフリップフロップ 242 がリセットされる。このときには、センスアンプ活性化信号  $Vna$  および  $Vpa$  はリセット状態（非活性状態）にあり、何ら問題は生じない。パルス信号  $p_2$  がローレベルに立下がると、イコライズ信号  $EQa$  がハイレベルからローレベルに立下がり、応じてワード線選択動作活性化信号  $w_{1a}$  が所定期間ハイレベルの活性状態とされる。このワード線選択動作活性化信号  $w_{1a}$  の立上がりに応答して、フリップフロップ 242 が所定時間経過後にセットされ、センスアンプ活性化信号  $Vna$  および  $Vpa$  が活性状態とされる。信号  $KEEP$  がハイレベルであり、NOR 回路 244 の出力信号はローレベルに固定されるため、このフリップフロップ 242 のリセットが禁止され、センスアンプ活性化信号  $Vna$  および  $Vpa$

50

は活性状態を維持する。

**【0265】**

信号  $b_{r,a}$  および  $I_{H,a}$  がともにハイレベルの活性状態とされる場合、イコライズ信号  $E_{Q,a}$  はローレベルを維持しており、センスアンプ活性化信号  $V_{n,a}$  および  $V_{p,a}$  も活性状態を維持している。

**【0266】**

信号  $b_{r,a}$  がハイレベルであり、信号  $I_{H,a}$  がローレベルのとき、パルス信号  $p_2$  がハイレベルとされ、フリップフロップ 242 がリセットされ、センスアンプ活性化信号  $V_{p,a}$  および  $V_{n,a}$  が非活性状態とされる。イコライズ信号  $E_{Q,a}$  がパルス信号  $p_2$  に従ってハイレベルからローレベルとされると、ワード線選択動作活性化信号  $w_{l,a}$  が所定期間ハイレベルとされ、新たなワード線選択動作が行なわれる。このワード線選択動作活性化信号  $w_{l,a}$  の立上がりに応答して、フリップフロップ 242 が所定時間経過後にセットされ、センスアンプ活性化信号  $V_{p,a}$  および  $V_{n,a}$  が活性状態とされる。以降、上述の動作が繰返される。信号  $K_{E,E,P}$  がハイレベルからローレベルへ立下がると、パルス発生器 245 が所定時間幅を有するパルス信号を出力し、OR 回路 246 および 247 を介してフリップフロップ 242 がリセットされ、センスアンプ活性化信号  $V_{n,a}$  および  $V_{p,a}$  が非活性状態とされる。

**【0267】**

以上のように、この発明の第4の実施の形態に従えば、アレイブロックをそれぞれ独立に駆動可能とし、かつ各アレイブロックにおいてセンスアンプにデータを保持するように構成しているため、各アレイブロックをキャッシュとして利用することができ、高速アクセスが可能となる。

**【0268】**

なお、この第4の実施の形態において、ビット線対とセンスアンプとの間にビット線分離ゲートが設けられており、センスアンプの活性化 / 非活性化に応じてビット線対とセンスアンプとの接続 / 分離が行なわれる構成が用いられてもよい。この場合、ビット線分離信号  $B_{L,I}$  の活性 / 非活性の制御は、ワード線選択動作活性化信号  $w_{l,a}$  に従って行なわればよい。

**【0269】**

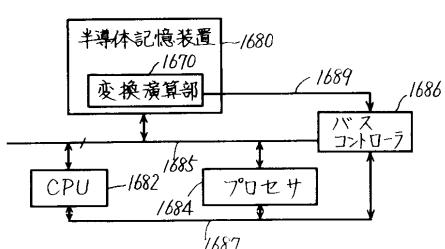

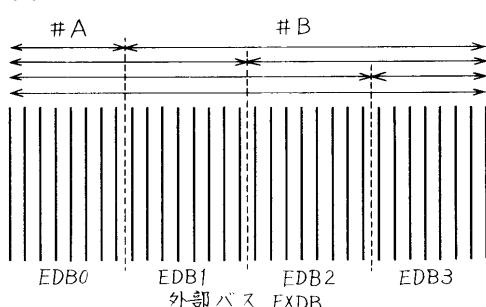

**[実施の形態 5]**